# DESIGN AND ANALYSIS OF UNIVERSAL 4-BIT BARREL SHIFTER USING LOW POWER MULTIPLEXERS

A DISSERTATION REPORT  $\label{eq:submitted} \text{SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS}$  FOR THE AWARD OF THE DEGREE

OF

## MASTER OF TECHNOLOGY IN VLSI DESIGN & EMBEDDED SYSTEMS

SUBMITTED BY

NISHANT KUMAR 2K18/VLS/08

UNDER THE SUPERVISION OF

Dr. POORNIMA MITTAL

ASSOCIATE PROFESSOR

#### **ELECTRONICS & COMMUNICATION ENGINEERING**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi -110042

AUGUST, 2020

**ELECTRONICS & COMMUNICATION**

**ENGINEERING**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CANDIDATE'S DECLARATION**

I, (Nishant Kumar), Roll No. 2K18/VLS/08 student of MTech (VLSI design & Embedded

systems), hereby declare that the project Dissertation titled "Designing of Universal 4-bit

Barrel Shifter" which is submitted by me to the Department of Electronics and

Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the

requirement for the award of the degree of Master of Technology, is original and not copied

from any source without proper citation. This work has not previously formed the basis for the

award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: Delhi

NISHANT KUMAR

Date: Aug 28, 2020

i

**ELECTRONICS & COMMUNICATION**

**ENGINEERING**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CERTIFICATE**

I hereby certify that the Project Dissertation titled "Designing of Universal 4-bit Barrel

Shifter" which is submitted by Nishant Kumar 2K18/VLS/08, Electronics & Communication

Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for

the award of the degree of Master of Technology, is a record of the project work carried out by

the student under my supervision. To the best of my knowledge this work has not been

submitted in part or full for any Degree or Diploma to this University or elsewhere.

Joinna

Place: Delhi

Date: Aug 28, 2020

Dr. Poornima Mittal

Supervisor

**Associate Professor**

Department of ECE, DTU

ii

ACKNOWLEDGEMENT

Foremost, I would like to express my sincere gratitude to my mentor **Dr. Poornima Mittal** for

helping me on each step of this research, due to her continuous help and support I completed

this research. Her patience, motivation, enthusiasm and vast knowledge helped me in all the

time of this research and in writing of this dissertation. Without her guidance, I could not have

imagined of completing this research. Her suggestions and the way of managing the work were

the most important key points, which made my path clear. She helped me use my full potential

because of that I tried my best to get the maximum for this project. I am extremely thankful for

guiding me throughout the project.

I am thankful to Electronics Department and faculties for helping me, and also thankful to my

friends who helped me directly and indirectly in my research.

**Nishant Kumar**

2K18/VLS/08

M.Tech: VLSI Design and Embedded System

(2018-2020)

iii

#### **ABSTRACT**

This report highlights a comparative analysis of eight diverse techniques for 2×1 multiplexer. The functionality is similar but diversity achieved in terms of dynamic power consumption, delay and power delay product. Thereby enabling the designer to pick out the best fit technique for a specific application in keeping with their design requirement. The techniques that have been analysed are TG, GDI, PT, MSL, Static CMOS, CPL, CVSL and MTCMOS CVSL. For power application, GDI based multiplexer is the best suit as it reports minimum power consumption of 1.72 fW. While PT based technique has holistic power dissipation as the maximum and minimum power consumption is moderate at 198.53 nW and 0.2196 nW respectively. It also has least average power dissipation of 110.9 nW. If the timing plays a more crucial role for an application, then GDI is the fastest of all. It has the least input to output transmission time of 1.65 ps. While the power delay product is best for PT at 0.395 aJ. In terms of static power dissipation, the best performance is demonstrated by GDI based technique at 0.2199 nW. The multiplexers are designed at 90 nm technology node and simulated at supply voltage of 1 V.

FinFET device is one of the most advance devices by which any logic circuit can be designed and will give better performance compare to MOSFET. Comparison is completed between MOSFET and FinFET based multiplexers and analysis of delay and power. Switching and scaling is also an important factor by which analyses of devices can be done. Switching of the signals causes the changes in the overall power dissipation. If signal is switching at same time instance power dissipation will be more and if switching at different time instance power dissipation will be less. Devices are getting smaller in size, using of same power supply will lead to more power consumption. Scaling of power supply will improve the overall performance of the device. MOSFET is analysed at 1V, 0.8V, 0.6V and FinFET is analysed at 0.8V, 0.6V, 0.4V. The designing and simulation are done using MOSFET at 90nm technology node and by using FinFET at 10 nm technology on cadence virtuoso.

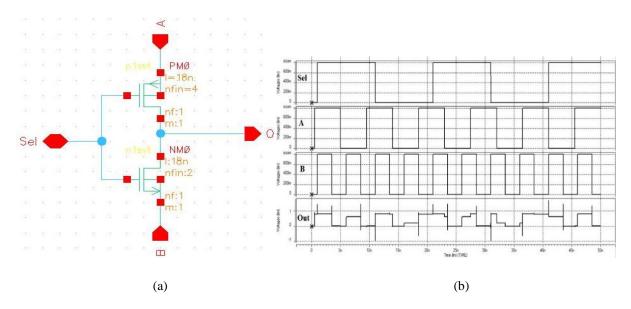

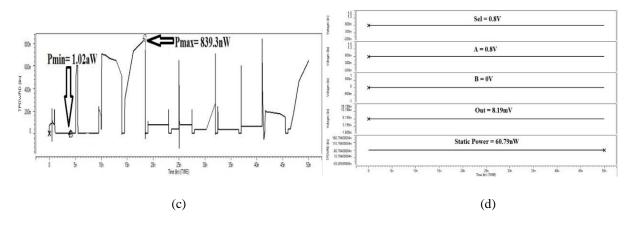

A comparison is made between FINFET based Gate Diffusion Input (GDI) and Pass Transistor (PT) based 2:1 Multiplexers in terms of delay, average power dissipation, and Power delay product (PDP). Both the multiplexers are designed using an 10nm technology node and functional at 0.8V supply voltage. GDI based mux consumes very less power dissipation of 839.3nW, which is 88.08% lesser than the PT based Mux. If the user requirement is of fast operation than GDI based Mux meets the criteria. It takes 0.0107ps to pass the signal at the

output, which is 165.42 times faster than PT based Mux. PDP of GDI and PT based Mux is 0.00029aJ and 0.1aJ. Additionally, GDI based Mux demonstrates better performance with 3.15nW power dissipation. The multiplexers can be used in many combinational circuits, therefore, if the performance of the multiplexer is improved, the complete circuit is bound to give better performance.

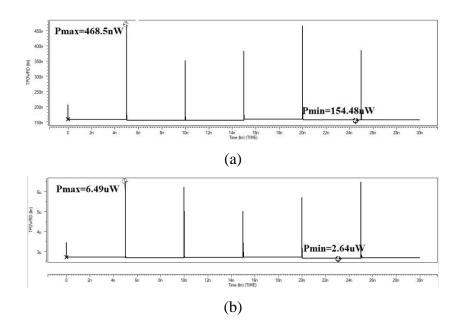

Finally, GDI and PT techniques are used to design barrel shifters for MOSFET as well as FinFET technology. Using FinFET based technology designing of barrel shifter is achieved, in both Barrel Shifter GDI based Barrel shifter shows the better performance, maximum power dissipation of GDI based barrel shifter is 468.5nW which is 13.85 times less than PT based barrel shifter. Whereas minimum power dissipation is 154.48nW. GDI based barrel shifter takes 47.27ps to pass the input to the output, it is 15.23ps less compare to PT based barrel shifter. Analysis states that GDI based Universal Barrel Shifter shows the better performance.

### **CONTENTS**

| Candidate'                 | s Declaration                            | i    |

|----------------------------|------------------------------------------|------|

| Certificate.               | ••••••                                   | ii   |

| Acknowled                  | gement                                   | iii  |

| Abstract                   |                                          | iv   |

| Contents                   |                                          | vi   |

| List of Figu               | res                                      | viii |

| List of Tab                | andidate's Declaration                   |      |

| List of Abb                |                                          |      |

| CHAPTER                    | I: INTRODUCTION                          | 1    |

| 1.1 Introd                 | luction                                  | 1    |

|                            |                                          |      |

| 1.3 Object                 | ctive of Work                            | 3    |

| 1.4 Organ                  | nization of Report                       | 4    |

| CHAPTER                    | II: LITERATURE REVIEW                    | 6    |

| 2.1 Previous Reported Work |                                          | 6    |

| 2.2 Tech                   | nical Gap                                | 10   |

| CHAPTER                    | III: SCHEMATIC DIVERSITY OF MULTIPLEXERS | 11   |

| 3.1 Diffe                  | rent Multiplexers                        | 11   |

| 3.1.1                      | TG based Multiplexer                     | 11   |

| 3.1.2                      | GDI based Multiplexer                    | 12   |

| 3.1.3                      | PT based Multiplexer                     | 13   |

| 3.1.4                      | MSL based Multiplexer                    | 14   |

|                            | 1                                        | 15   |

|                            | 1                                        |      |

|                            | •                                        |      |

|                            | •                                        |      |

|                            |                                          |      |

| 3.3 Delay                  | and Power Analysis                       | 25   |

| CHAPTER                    | IV: POWER ANALYSIS                       | 28   |

|                            | •                                        | 28   |

| 4.2 Switc                  |                                          | 30   |

| 4.2.1                      | Scaling of Power Supply                  | 31   |

| 4.2.2                      | Switching of the Signals                 | 34   |

| 4.2        | 2.2.1 GDI based Multiplexer                        | 35 |

|------------|----------------------------------------------------|----|

| 4.2        | 2.2.2 PT based Multiplexer                         | 36 |

| CHAPTER    | R V: FINFET BASED MULTIPLEXERS                     | 38 |

| 5.1 Multi  | iplexers                                           | 38 |

| 5.1.1      | PT based Multiplexer                               | 38 |

| 5.1.2      | GDI based Multiplexer                              | 40 |

| 5.2 Delay  | y and Power Analysis                               | 42 |

| 5.3 Scali  | 42                                                 |    |

| 5.4 Swite  | ching of the Signals                               | 46 |

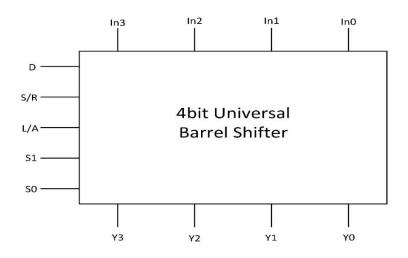

| CHAPTER    | R VI: UNIVERSAL 4-BIT BARREL SHIFTER               | 49 |

| 6.1 Intro  | 49                                                 |    |

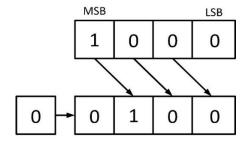

| 6.1.1      | Shift Right Logical                                | 51 |

| 6.1.2      | Shift Right Arithmetic                             | 51 |

| 6.1.3      | Rotate Right                                       | 52 |

| 6.1.4      | Shift Left Logical                                 | 53 |

| 6.1.5      | Shift Left Arithmetic                              | 53 |

| 6.1.6      | Rotate Left                                        | 54 |

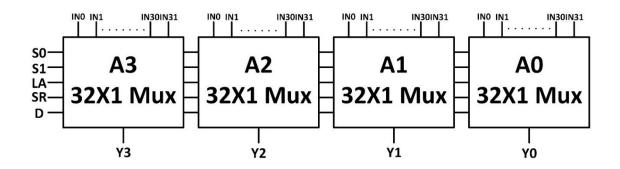

| 6.2 Design | gning of Universal 4-bit Barrel Shifter            | 56 |

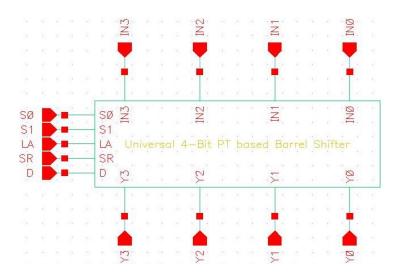

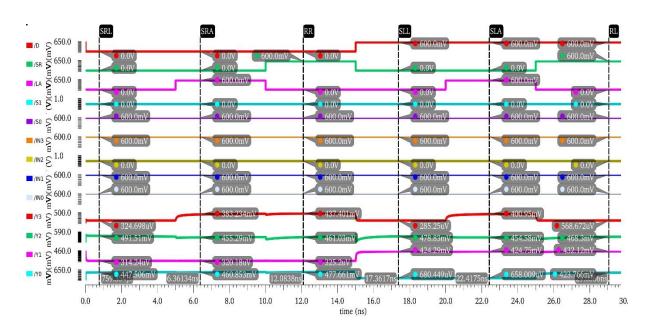

| 6.2.1      | Universal 4-bit Barrel Shifter using PT based Mux  | 58 |

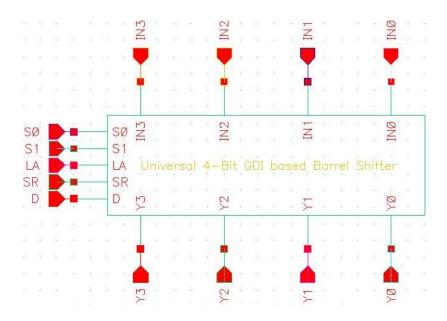

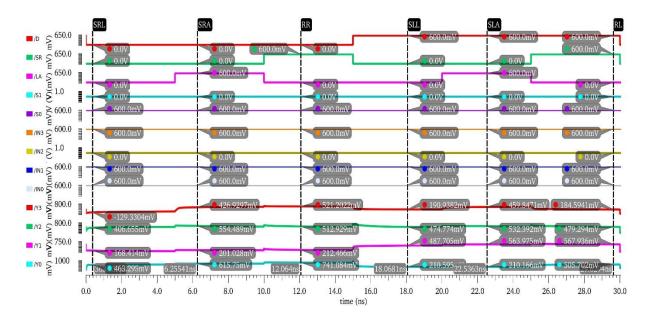

| 6.2.2      | Universal 4-bit Barrel Shifter using GDI based Mux | 60 |

| 6.2.3      | Delay and Power Analysis                           | 62 |

| 6.3 Univ   | ersal 4-bit Barrel Shifter using FinFET            | 65 |

| 6.3.1      | Universal 4-bit GDI based Barrel Shifter           | 65 |

| 6.3.2      | Universal 4-bit PT based Barrel Shifter            | 67 |

| 6.3.3      | Delay and Power Analysis                           | 69 |

| CHAPTER    | R VII: CONCLUSION AND FUTURE SCOE                  | 72 |

| 7.1        | Conclusion                                         | 72 |

| 7.2        | Future Scope                                       | 74 |

| REFEREN    | CES                                                | 75 |

| LIST OF P  | PUBLICATIONS                                       | 78 |

#### LIST OF FIGURES

- 1.1 Schematic of 2x1 Multiplexer

- 3.1 Schematic of TG based Multiplexer

- 3.2 Schematic of GDI based Multiplexer

- 3.3 Schematic of PT based Multiplexer

- 3.4 Schematic of MSL based Multiplexer

- 3.5 Schematic of static CMOS based Multiplexer

- 3.6 Schematic of CPL based Multiplexer

- 3.7 Schematic of CVSL based Multiplexer

- 3.8 Schematic of MTCMOS CVSL based Multiplexer

- 3.9 Characteristic plot of TG based Mux (a) Output Response with Total Power Dissipation, (b) Total Power Dissipation, and GDI based Mux (c) Output Response with Total Power Dissipation, (d) Total Power Dissipation.

- 3.10 Characteristic plot of PT based Mux (a) Output Response with Total power Dissipation, (b) Total Power Dissipation, and MSL based Mux (c) Output Response with Total Power Dissipation, (d) Total Power Dissipation.

- 3.11 Characteristic plot Static CMOS based Mux (a) Output Response with Total power Dissipation, (b) Total Power Dissipation, and CPL based Mux (c) Output Response with Total Power Dissipation, (d) Total Power Dissipation.

- 3.12 Characteristic plot CVSL based Mux (a) Output Response with Total power Dissipation, (b) Total Power Dissipation, and MTCMOS CVSL based Mux (c) Output Response with Total Power Dissipation, (d) Total Power Dissipation.

- 4.1 Static power dissipation plot for (a) TG based Mux (b) GDI based Mux (c) PT based Mux (d) MSL based Mux.

- 4.2 Static power dissipation plot for (a) Static CMOS based Mux (b) CPL based Mux (c) CVSL based Mux (d) MTCMOS CVSL based Mux.

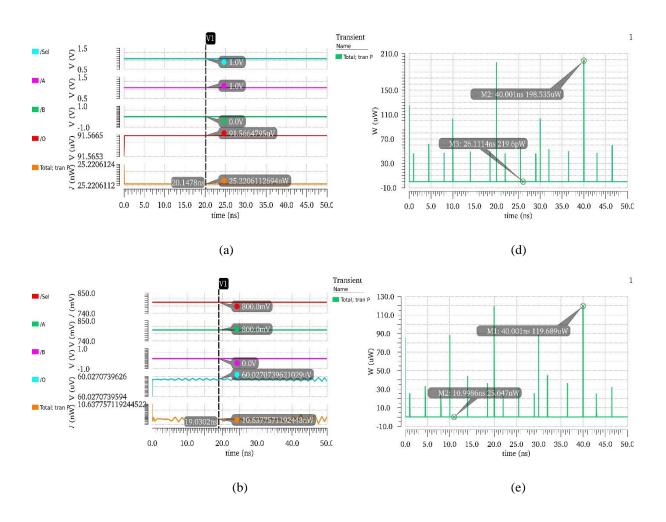

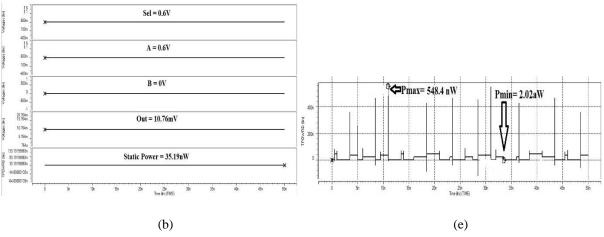

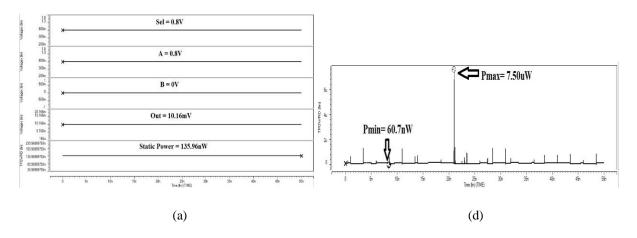

- 4.3 Static Power Dissipation of GDI based Multiplexer at (a) Vdc=1V, (b) Vdc=0.8V and (c) Vdc=0.6V. Total Power Dissipation of GDI based Mux (d) Vdc=1V, (e) Vdc=0.8V and (f) Vdc=0.6V.

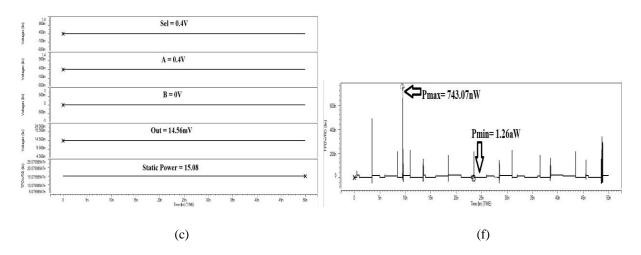

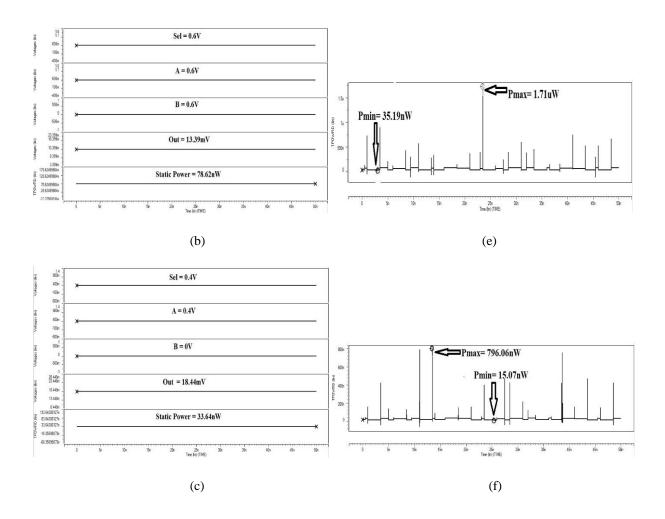

- 4.4 Static Power Dissipation of PT based Multiplexer at (a) Vdc=1V, (b) Vdc=0.8V and (c) Vdc=0.6V. Total Power Dissipation of PT based Mux (d) Vdc=1V, (e) Vdc=0.8V and (f) Vdc=0.6V.

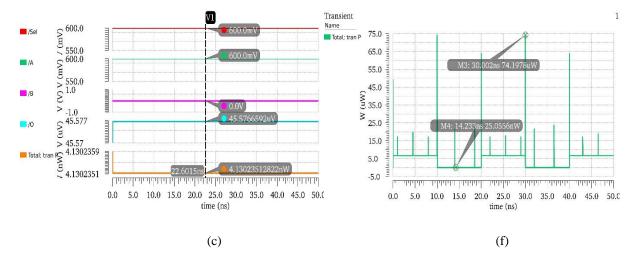

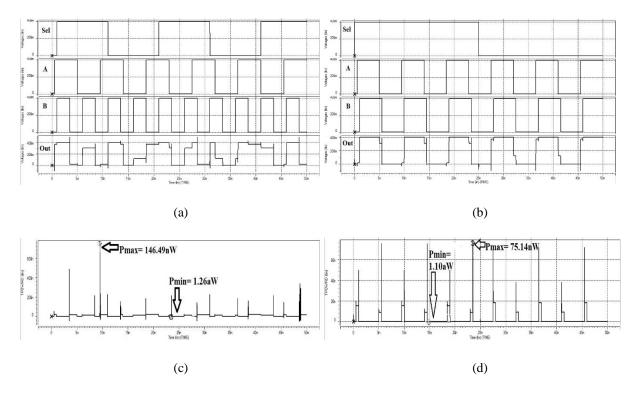

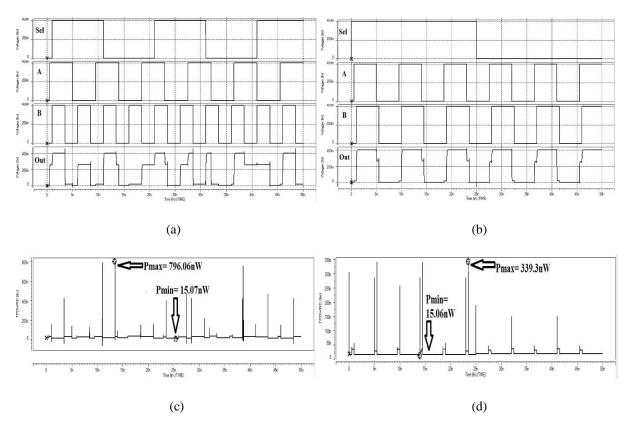

- 4.5 GDI based Multiplexer (a) Output plot at Same Time Switching, (b) Output Plot at Different Time Switching, (c) Total Power Dissipation at Same Switching, (b) Total Power Dissipation at Different Time Switching.

- 4.6 PT based Multiplexer (a) Output plot at Same Time Switching, (b) Output Plot at Different Time Switching, (c) Total Power Dissipation at Same Switching, (b) Total Power Dissipation at Different Time Switching.

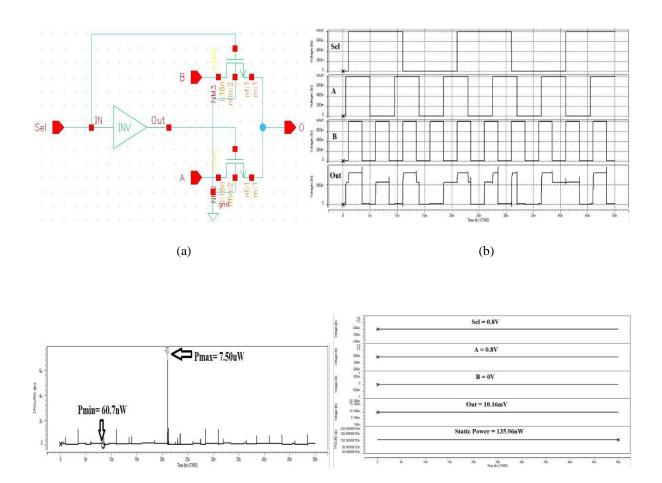

- 5.1 PT based Multiplexer using FinFET (a) Schematic, (b) Output with Total power dissipation, (c) Total Power Dissipation and (d) Output with Static Power Dissipation.

- 5.2 GDI based Multiplexer using FinFET (a) Schematic, (b) Output with Total power dissipation, (c) Total Power Dissipation and (d) Output with Static Power Dissipation.

- 5.3 GDI based Multiplexer using FinFET (a) Schematic, (b) Output with Total power dissipation, (c) Total Power Dissipation and (d) Output with Static Power Dissipation.

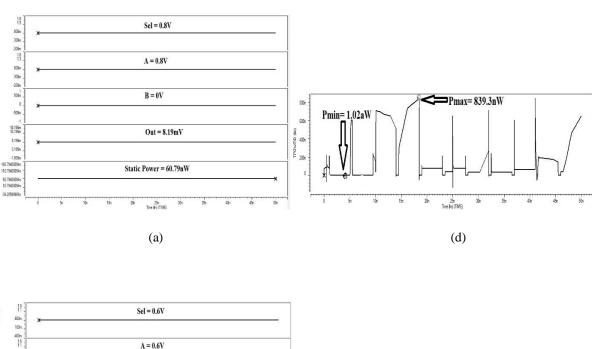

- 5.4 Static Power Dissipation of PT based Multiplexer using FinFET at (a) Vdc=0.8V, (b) Vdc=0.6V and (c) Vdc=0.4V. Total Power Dissipation of PT based Mux using FinFET at (d) Vdc=0.8V, (e) Vdc=0.6V and (f) Vdc=0.4V.

- 5.5 FinFET GDI based Multiplexer (a) Output plot at Same Time Switching, (b) Output Plot at Different Time Switching, (c) Total Power Dissipation at Same Switching, (b) Total Power Dissipation at Different Time Switching.

- 5.6 FinFET PT based Multiplexer (a) Output plot at Same Time Switching, (b) Output Plot at Different Time Switching, (c) Total Power Dissipation at Same Switching, (b) Total Power Dissipation at Different Time Switching.

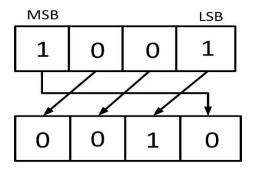

- 6.1 Schematic of Barrel Shifter

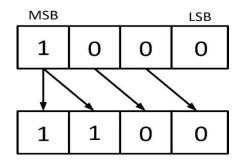

- 6.2 Shift Right Logical 1-bit shift

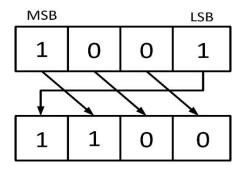

- 6.3 Shift Right Arithmetic 1-bit shift

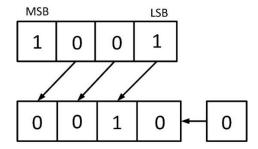

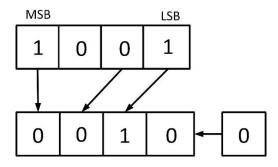

- 6.4 Rotate Right by 1-bit

- 6.5 Shift Left Logical 1-bit shift

- 6.6 Shift Left Arithmetic 1-bit shift

- 6.7 Rotate Left by 1-bit

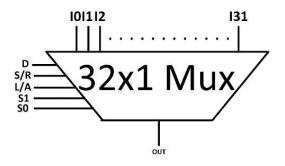

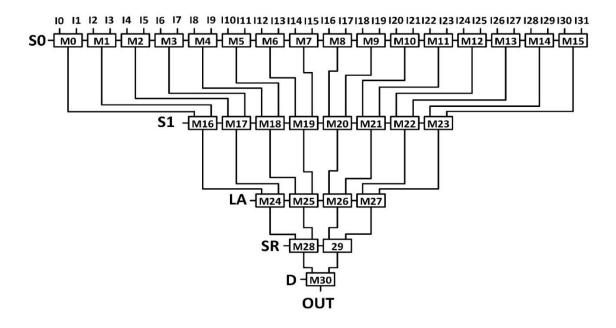

- 6.8 32x1 Multiplexer

- 6.9 Schematic 32x1 Multiplexer

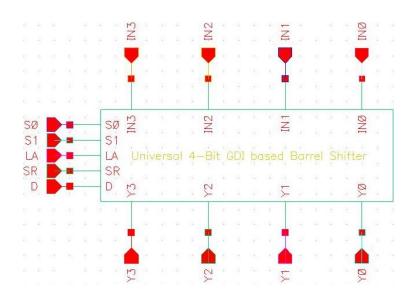

- 6.10 Schematic of Universal 4-bit Barrels Shifter

- 6.11 Schematic of Universal 4-bit PT based Barrel Shifter

- 6.12 Outputs of Universal 4-bit PT based Barrel Shifter

- 6.13 Universal 4-bit GDI based Barrel Shifter

- 6.14 Output of Universal 4-bit GDI based Barrel Shifter

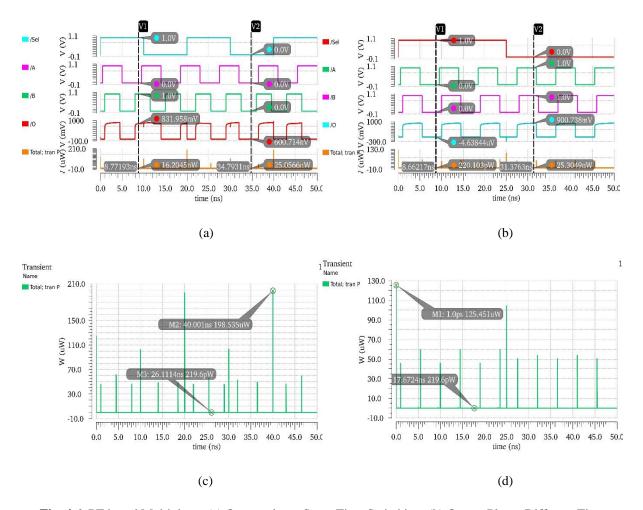

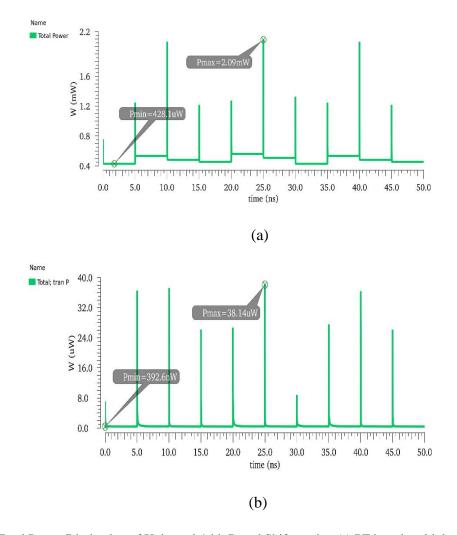

- 6.15 Total Power Dissipation of Universal 4-bit Barrel Shifter using (a) PT based multiplexer, (b) GDI based Multiplexer

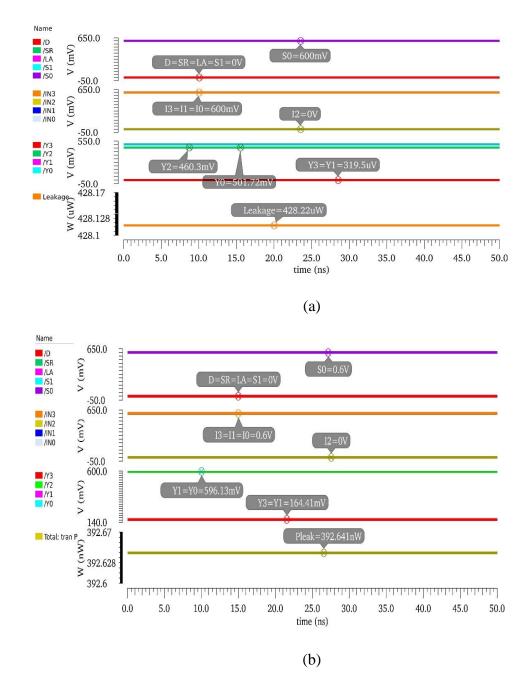

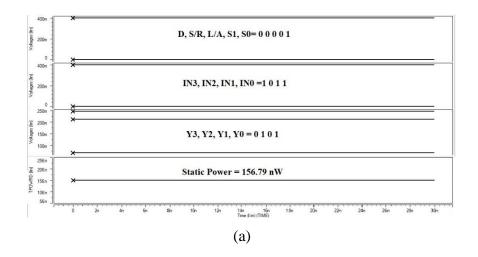

- 6.16 Static Power Dissipation of Universal 4-bit (a) PT, (b) GDI based Barrel Shifter

- 6.17 FinFET based Universal 4-bit Barrel Shifter

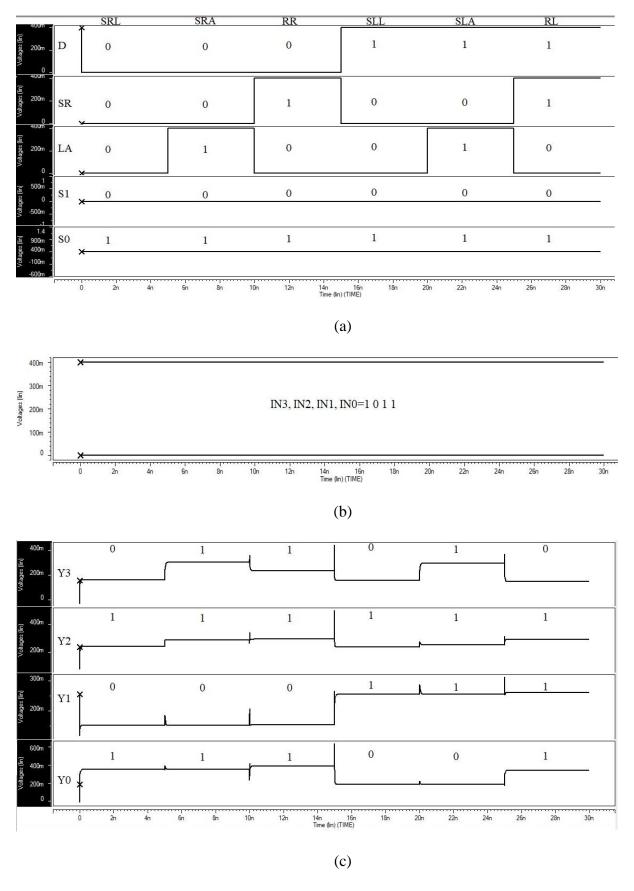

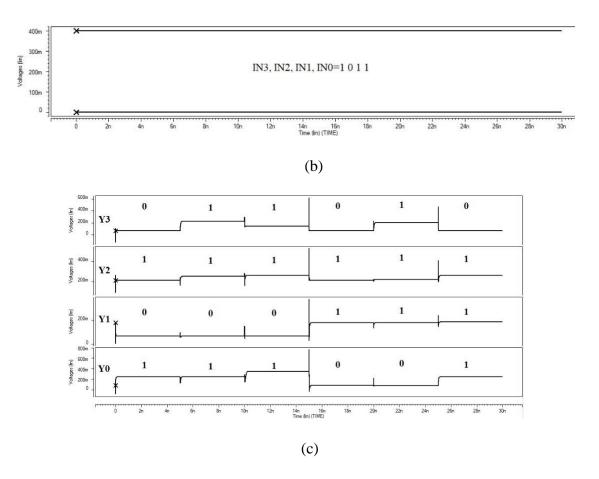

- 6.18 Output plot of GDI based Universal 4-bit Barrel Shifter

- 6.19 Output plot of PT based Universal 4-bit Barrel Shifter

- 6.20 Total Power Dissipation of (a) GDI based and (b) PT based Universal 4-bit Barrel Shifter

- 6.21 Static Power Dissipation of (a) GDI and (b) PT based Universal 4-bit Barrel Shifter

#### LIST OF TABLES

- 3.1 Various Logic Functions of GDI cell for Different Input Combinations

- 3.2 Timing details of Sel, A, B

- 3.3 Delay, Average Power, PDP and Static Power Dissipation Analysis.

- 4.1 Scaling on GDI based Mux and PT based Mux

- 5.1 Summary of Power and Average Power

- 5.2 Delay, Average Power, PDP (Power Delay Product) and Static Power Dissipation.

- 5.3 Scaling of GDI and PT based Multiplexer.

- 6.1 Truth Table of Barrel Shifter

- 6.2 List of all the Operations-

- 6.3 Example of all Operations

- 6.4 Connections of Inputs in Barrel Shifter

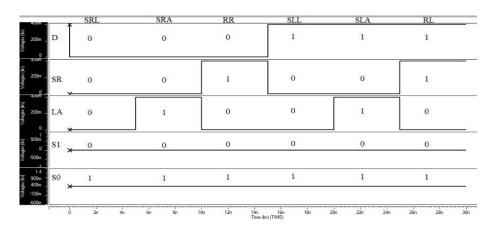

- 6.5 Timing Values

- 6.6 Total Power Dissipation of Universal 4-bit PT and GDI based Barrel Shifter

- 6.7 Delay, Average, PDP and Static Power Dissipation

- 6.8 Total Power Dissipation of Universal 4-bit PT and GDI based Barrel Shifter

- 6.9 Delay, Average, PDP and Static Power Dissipation

#### LIST OF ABBREVIATIONS

**TG-** Transmission Gate

GDI- Gate Diffusion Input

PTL- Pass Transistor Logic

MSL- Multiplexer Single with Level Restoration

CPL- Complementary Pass Transistor Logic

CVSL- Cascode Voltage Switch Logic

MD- Multiplexer Double

MDL- Multiplexer Double with Level Restoration

DCVSL- Differential Cascode Voltage Switch Logic

CNTFET- Carbon Nano Tube Field Effect Transistor

SISO- Serial in Serial Out

SIPO- Serial in Parallel Out

PISO- Parallel in Serial Out

PIPO- Parallel in Parallel Out

PDP- Power Delay Product

#### **CHAPTER-1**

#### INTRODUCTION

#### 1.1 INTRODUCTION

Combination logic is an integral part of digital circuit design. It is implemented using Boolean circuits where the output is exclusively dependent on the present state of input combination. Whereas in case of sequential circuits the output is dependent on the present inputs and the history of inputs. To store the pervious input combinations a sequential logic circuit needs a memory element while combinational logic circuit does not rely on the memory unit. Over the past decades, scaling of CMOS technology has been driving the electronics industries and providing a path for complex and faster integration. As the size of the transistor is decreasing, IC's getting more complex and denser. Power consumption for integrated-circuits (ICs) has always been an important factor. Voltage down-scaling technique has been quite helpful in bring down the power consumption of ICs. For some applications, such as medical devices, portable wireless devices, and sensor network nodes, if power supply is reduced just higher than the threshold voltage, results the reduction in power [1][2][3]. The necessity for low power devices has caused a significant effect on Daily life, whereas the power dissipation has become the important factor to improve the performance [2].

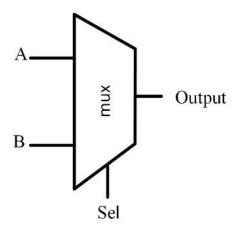

2×1 Mux is an elementary unit of the "switch logic". The principle of switch logic is to implement the logic circuits as a combination of switches, rather than as a logic gate. Multiplexers are used as programmable logic machines, in telecommunications, in computer networks, and in digital video, in digital semiconductors also in CPUs and graphics controllers. Often named Multiplexer as data selector. A multiplexer is a hybrid circuit that selects and directs binary information from one to several input lines to a single output line [1]. 2×1 multiplexer circuit has one output, two inputs and one input selection. The selection of particular input line is controlled by a set of selection lines as illustrated in Fig. 1. The line of selection decides which bit of the input is transmitted to the output.

Fig. 1.1. Schematic of 2:1 Multiplexer.

Through advancements in large-scale automation, millions of transistors can be placed on a single chip for robust circuitry implementation. It depends on Moore's law however, According to the Moore's law the number of transistors on IC has doubled at every two years [2] As a consequence of having too many transistors in such a limited room, significant heat dissipation and power consumption issues have been introduced into the picture. Work to address these problems was done [3]. Solutions have been suggested to decrease transistor power supply voltage, switching frequency and capacitance reliant on the usage, the type of circuit to be applied, and the design methodology used, different performance considerations become relevant, disallowing the formulation of uniform rules for optimum logic types. In [4] author have analysed the different techniques of multiplexers circuits for low power applications, Analysis of GDI based Mux is performed by the author in [6]. CPL based Design is illustrated in [7] with their power analysis. In [11] author have designed and analysed the different pass transistor-based circuits.

In view of optimize the performance of 2×1 Mux, here different configurations including GDI (Gate Diffusion input), PT (Pass Transistor), MSL (Multiplexer single with level Restoration), TG (Transmission), Static CMOS, CPL (Complementary Pass Logic), CVSL (Cascode Voltage Switch Logic) and MTCMOS CVSL (Multi Threshold CMOS CVSL) are designed using MOSFET at 90 nm technology node. Further, their performance is analysed and compared by means of output response and dynamic power dissipation using Cadence virtuoso software. Additionally, power and delay are also analysed to find the best mux amongst all the configurations. After that designing of Universal 4-bit barrel shifter is done by using best performance 2x1 multiplexer.

#### 1.2 MOTIVATION:

Due to the scaling of the device, dissipation of the energy has improved very significantly with new technology node, because there are billions of transistors are integrated on the chip. So, the power dissipation factor is important to consider the device efficient. One of the significant reasons behind the extensive usage of this barrel shifter is, it can perform multiple bit shifting operation in a single cycle. Further, area of this barrel shifter is small, so this barrel shifter demonstrates the optimum performance.

Barrel shifter is often used in many devices and designs like microprocessors, ARM processors, Digital signal processing, ALU, and many others. Fast Barrel shifter increases the performance of devices, so desired barrel shifter with optimum performance is required. Barrel shifter is a digital circuit to shift data by specific number of bits. It can shift n-bit data in a single cycle. N-bit Barrel Shifter can perform any shifting operation like right sift, left shift, rotate by N-1bits. The old version of shifter is shift register, these shift resistors are SISO, SIPO, PISO and PIPO in which right, left and rotation operation is possible but requires more than one cycle to perform the operation. Further research is conducted to design the efficient barrel Shifter, which can perform shifting operation with a smaller number of cycles. Unidirectional shifter came out after shift register, which can shift the data bus using single cycle, but it is not able to perform shifting operation in both left and right direction. For bidirectional shifting operation new design is constructed, this can perform the shifting operation in both left and right direction. Designing of these shifters is done using MOSFET with different technology node after that FinFET is used to increase the performance and speed of the design and also requires less area compared to MOSFET. This motivates me to design barrel shifter, which gives better performance in terms of delay, area and power. In this thesis barrel shifter is designed using FinFET at 10nm technology node.

#### 1.3 OBJECTIVE OF WORK:

Aim of this thesis is to design and simulate different 2x1 multiplexer using MOSFET at 90nm technology node, further analysis of delay and power is done, which gives the best performance multiplexer. After that best multiplexers are designed using FinFET to analyse the performance which further will be used for designing of Universal 4-bit barrel shifter using FinFET at 10nm technology node.

- Designing of different multiplexers is done using MOSFET at 90nm technology node, with their delay and power analysis. This analysis helps us to understand each aspect of the multiplexers design by which we can understand which multiplexer is showing better performance and why.

- When device is in stable condition it should not or dissipate less power compare to the condition when inputs are changing, this analysis is also done to find out which multiplexer dissipates minimal power. Switching is also another factor by which variation of power dissipation at different switching is analysed.

- After designing of different multiplexer using MOSFET at 90nm technology node, some of the multiplexer which demonstrates better performance in terms of delay and power are constructed using FinFET at 18nm technology node.

- Multiplexer which shows better performance designed using MOSFET and FinFET is

used to construct the universal 4-bit barrel shifter. Further delay and power analysis is

done.

#### 1.4 ORGANIZATION OF REPORT:

This report has been organized into 7 chapters. Chapter 1 deals with the introduction of different multiplexers, it also includes the Motivation and aim of the report. Chapter 2 is about the previous work on designs and technical gap. Chapter 3 is related to the Schematic diversity and delay & power dissipation analysis of different multiplexers. Chapter 4 illustrates the static power dissipation and effect of switching on power dissipation. Designing and analysis of FinFET based multiplexers are done in Chapter 5, further delay and power analysis is also done in this section. Main aim of this report is to design the optimum universal barrel shifter using best performance multiplexer is illustrated in Chapter 6. Chapter 7 is about the conclusion and future scope.

- Chapter 1- Introduction of the design and operation of basic multiplexer is done with Motivation, Aim and organization of the report is illustrated in this chapter.

- Chapter 2- This chapter explains the previous work done on multiplexer and barrel shifter. SISO, SIPO, PISO and PIPO are the shift registers, which uses more than one cycle to shift and rotate the data, increases the power dissipation. After, Further research designing of unidirectional shifter is done, requires only one cycle to shift and rotate the data but its limited to the single direction either left or right. Unidirectional barrel

- shifter can perform the shifting and rotating operation in both left or right direction using single clock

- Chapter 3- Designing of TG, GDI, PT, MSL, Static CMOS, CPL, CVSL and MTCMOS

CVSL based multiplexer is done. Further, delay and power analysis are also done to

find the finest multiplexer in terms of delay and power.

- Chapter 4- Static power dissipation is an important factor, which gives the information about the power dissipation when all the inputs are static. This chapter explains the static power dissipation of all the multiplexers. Variation in the switching of the input signals shows variation in power dissipation, if switching is occurring at the same time power dissipation will be more and if switching is at the different time then there will be less power dissipation. This chapter also illustrates the power dissipation of the multiplexer at different switching.

- Chapter 5- This chapter illustrates the design of PT and GDI based multiplexer, these both multiplexers shows finest performance when designing with MOSFET, so designing of these multiplexers with FinFET will increase the performance of multiplexer. Further, delay and power analysis are also accomplished.

- Chapter 6- Purpose of this report is to design the best performance universal 4-bit barrel shifter. This is done by improving the basic element of barrel shifter which is 2x1 multiplexer. In previous chapters different type of multiplexer have analysed in terms of delay and power, where two of them PT and GDI based multiplexers shows better performance. These two optimum multiplexers are further used in universal 4-bit barrel shifter. Designing and analysis of barrel shifter using MOSFET and FinFET is achieved in this chapter.

- Chapter 7- Conclusion of this report and future scope of this barrel shifter explained in this chapter

In the last of this report references are mentioned, which helped me a lot to complete my thesis and improved my knowledge in this domain.

#### **CHAPTER II**

#### LITERATURE REWIEW

#### 2.1 PREVIOUS REPORTED WORK:

This section illustrates the work done on the multiplexers using MOSFET and FinFET. It also exemplifies the barrel shifter.

R. Avudaiammam, A. Rode V and D. Devi S [1], In this paper author designed and explained different 2x1 multiplexers using MOSFET at 180nm technology node. Various logic families are used to design multiplexers such as Pseudo NMOS logic, Static CMOS logic, Domino Logic and dual rail domino. Delay and power analysis of these multiplexers illustrates that Domino logic-based mux is the most efficient design because it shows 20.06% average power dissipation and 20.1% power delay product less than other techniques.

Z. Yan, W. Zhigong and L. Wei [5], have proposed the design of 80Gb/p 2x1 multiplexer using BICMOS at 130nm technology node. In this paper analysis and design multiplexer is done, this analysis shows that performance speed of this multiplexer is fast and can drive a high load of  $50 \Omega$  load. Working frequency of this design is 106GHz, Analysis demonstrates that it provides the highest data rate.

Z. Changchun, W. Zhigong, S. Shi and M. Peng [6], In this paper author presents the 5 Gb/s half rate multiplexer using MOSFET at 180nm technology node. Supply voltage used to analyse the design is 1.8V. In this design total power consumption is 70mW, where mux can work appropriately without any external clock because of CE (Clock Extraction).

M. Vyas, S. K. Manna, S. Akashe [7], this paper presents the design and simulation of different 2x1 multiplexers and comparison with the conventional multiplexer. Designing is done using FinFET at 45nm technology node and some designing is done using 120nm technology node to attain the operational speed of 34Gb/s with 0.7V power supply. Using of FinFET for multiplexer reduced some parameters like, dynamic power dissipation and leakage while increasing the performance of the design. Noise of the circuit is reduced about 60% whereas power dissipation and leakage are 40% and 50% respectively. So, designing of mux using FinFET provide the efficient and better performance compare to CMOS.

V. K. Agrawal, M. Guduri, A. Islam [8], have proposed the design and comparison of Static CMOS, CVSL, CPL, EEPL, SRPL and TG based multiplexers using FinFET at 16nm

technology node. Author has done the delay and power analysis of different multiplexers, this analysis states that CMOSTG multiplexer shows the better performance. Therefore, designing of this CMOSTG mux is done using CNFET. Designing of multiplexer using CNFET further reduced the power and leakage of the circuit. For CMOSTG average power dissipation is 17.97pW and for CNFET it is 7.67pW, which is 57.31% less than CMOSTG based mux.

A. Morgenshtein, V. Yuzhaninov, A. Kovshilovsky, A. Fish [9], in this paper analysis of low power CLA adder is done using GDI (Gate Diffusion Logic) at 40nm technology node. Simulation results shows the twice in area reduction and 5 times improvement in the dynamic power dissipation and 4 times decrement in the leakage with only 24% degradation in the performance. GDI cell consumes vert less area because of less number of transistor used, less transistor leads to less switching which causes less power dissipation compare the other logic.

A. Morgenshtein, A. Fish, I. A. Wagner [10], this paper completely based on the basic of GDI cell and its performance and how many operations this cell can performance. Author analysed the various logic functions of GDI cell for different input. GDI cell only uses two transistors and which can perform AND, OR, NOT, Mux and other functions also. Comparing with TG logic, 45% reduction is achieved in GDI cell. So, any complex CMOS design can be implemented using GDI cell with less delay, area and power dissipation.

K. Yano, T. Yamanaka, T. Nishida, M. Saito, K. Shimohigashi, A. Shimizu [11], In this paper author proposed the CMOS based 16x16-b multiplier using CPL (Complementary Pass-Transistor Logic) at 4v power supply. CPL is twice as fast as compared to conventional CMOS and this can be improved further to 2.6ns using 60mW. Total power consumption in CPL very less compare to CMOS due to less input capacitances.

J.H. Pasternak, A. S. Shubat, C. A. T. Salama [12], This paper illustrates the design and analysis of CMOS differential pass-transistor logi0063 (DPTL). By using this logic technique designing of any circuit offers better area efficiency, higher operating speed, less power dissipation and designing of circuits is simple compare to conventional PT logic. Sequential circuits can also take benefits from this DPTL logic. Possibility of programming of these pass arrays is less in proposed layout technique.

M. Suzuki, N. Ohkubo, T. Yamanaka, A. Shimizu, K. Sasaki [13], Author has proposed the circuit techniques for a high-speed adder using Pass- Transistor logic. DPL (Double Pass-Transistor) logic is used to improve the performance of the design with less usage of power supply voltage. It improves the gate speed without increasing of the input capacitance. By using

this technique time taken by the addition in 32-b ALU can be reduced by 30% compare to the conventional CMOS based ALU. Designing of this ALU is done at 250nm technology node at 2.5V supply voltage and it is capable of adding data in 1.5ns.

K. Yano, Y. Sasaki, K. Rikino, K. Seki [14], In this paper author proposed the design and analysis of Pass-Transistor logic. To clarify the potential of PT logic, construction of PT based cell library and synthesis tool are done. This method is called LEAP (Lean Integration with Pass-Transistor). Comparison is done between the, very simple cell library which have only 7 cells combined with synthesis tool named as "Circuit inventor" with the conventional CMOS library which includes more than 60 cells, combined with state-of-the-art logic synthesis. Result of this analysis states that area, power and delay all are improved by using this LEAP method and value cost ratio is also improved. Autor also have found that at low voltage supply nMOS based Pass transistor logic shows the better performance in comparison conventional CMOS circuits at 1V.

B.P. Singh, N. Arora, I. Gupta [15], This paper based in the, design, simulation and analysis of 2x1 multiplexer at 90nm technology node using Tanner EDA Tool. There comparative analysis with other multiplexer is done in terms of power, operating frequency, supply voltage, area and load capacitances. Different 2x1 multiplexers are NMOS based, CMOS, MSL (Multiplexer single with level restoration), MD (Multiplexer Double), MDL (Multiplexer double with level restoration), DCVSL (Differential Cascode Voltage Switch Logic), MDCVSL based multiplexers. Result of the complete analysis of multiplexers is that MDCVSL based multiplexer demonstrations the less power dissipation, output load capacitance and delay is also less. NMOS circuit reveals the better operating frequency, whereas MDCVSL shows the smallest amount of PDP (Power Delay Product).

A. Pahadia, U. R. Bhatt, V. Bhat [16], This paper illustrates the review on high performance multiplexers. Analysis of different 2x1 multiplexer is done using Tanner EDA tool and designing and analysis of the improved multiplexer is also done at microwind 3.5 version tool. Analysed multiplexers are NMOS CPL logic, CMOS, MSL, MD, MDL, DCVSL and MDCVSL based multiplexers. After analysing of all these multiplexers, it is concluded that MDCVSL shows the better performance in terms of dynamic and static power dissipation.

I. Hussain, A. Sing, S. Chaudhary [17], Aim of this paper is to design and analyse the CPL (Complementary Pass Transistor Logic) using both CMOS and CNTFET model at 90nm and 32nm technology for CMOS and 32nm technology node for CNTFET. In this analysis shows

that CMOS logic style performs better operation compare to Bulk-Si MOS technology. In CNTFET technology some basic gates such as NOR, NAND and Mux, for this CMOS logic style performs the better operation than CPL logic style. Another observation is that while scaling down the Bulk-Si MOS technology, overall performance of the design starts degrading and leakage is also increased which leads to more power consumption. This analysis states that CNTFET is better than other technology because static power dissipation and leakage is very less and area consideration is also very minimum.

- K. Mishra, S. Akashe [18], Focus of this paper is to improve the performance and reduce are area and power consumption of the 2x1 multiplexers. Different configurations are used are designed using diverse technology methods such as CMOS, TG (Transmission Gate), PT (Pass Transistor) using FinFET based. Several analyses are done such as leakage power, leakage current, operating power, operating current, optimum power, optimum current and delay atnm technology node with 0.7 supply voltage. All the analysis is done at different temp 10, 27 and 50 degree Celsius. After taking consideration of CMOS based mux and PT based Mux, in both of them pass transistor-based mux provides the better performance in terms of area, power and performance. It also shows the high-performance speed with less static power dissipation.

- P. Mandal, S. Malani, Y. Gudepkar, S. Singhi, P. M. Palsodkar [23], have proposed the design of barrel shifter using 2x1 multiplexer and its VLSI implimentation. In this paper four module have been designed which are, CMOS inverter, CMOS AND Gate, CMOS 2x1 mux and CMOS 4x1 mux. These all modules are used to design the barrel shifter, by which 4bit and 8bit barrel shifter can be designed.

- S. Kotiyal, H. Thapliyal, N. Ranganathan [24], have designed the barrel shifter using Fredkin gate which can perform both shift and rotating operation. Barrel shifter which can perform both shifting and rotation is very for computational purpose. In this paper proposed design consist of both reversible Fredkin and Feynman gates to design barrel shifter, where Fredkin gate is used to design the reversible logical and arithmetic barrel shifter, while Feynman gate is used to evade the fanout because fanout is not acceptable in reversible logic.

- J. H. Saho, N. K. Rout [25], This paper illustrates the comparative study of low power barrel shifter and rotator at 45nm technology node. In this paper initially barrel shifter and rotator is designed using CMOS logic and then different low power circuit is also used using cadence virtuoso tool. Used low power techniques to improve the design of barrel shifter are PTL (Pass Transistor Logic), LECTOR technique and DFAL Logic, where proposed design is Double

gate DFAL logic. Analysis shows that proposed design shows the better and efficient performance in terms of delay and power in comparison to other techniques at 0.8, 0.7 and 0.6V.

S. Devamane, A. Hanchate, U. Vagare, S. Ujagare, P. Teggelli [26], have designed and analysed the FPGA based barrel shifter. Int this paper the author has proposed the 8-bit and 16-bit barrel shifter and designing and analysis is done using Verilog code. Designing of barrel shifter is done using multiplexer which can perform the right shift and right rotate operation at single clock.

R. Pappachan, V. Vijayakumar, T. Ravi, V. Kannan [27], have proposed the design of 4-bit low power barrel shifter at 20nm FinFET technology node. This barrel shifter can perform the both shifting and rotating operation such as, SRL (Shift Right Logical), SRA (Shift Right Arithmetic), RR (Rotate Right), SLL (Shift Left Logical), SLA (Shift Left Arithmetic) and RL (Rotate Left). Analysis of this FinFET based universal barrel shifter states that, FinFET based barrel shifter outperform the MOSFET based barrel shifter in terms of all three factors area, power and delay. So, designing of FinFET based barrel shifter performs the better performance.

#### 2.2 TECHNICAL GAP

After analysing each points and factors in the previous researches and papers, there was a technical gap in the work. All the research was done on universal barrel shifter using MOSFET based technology which can be further improved by using the FinFET model at 10nm based technology node. Using MOSFET it increases the use of power and also requires more area to fabricate, whereas FinFET consumes very less power and requires minimal area in comparison to MOSFET. In terms of dynamic and static power dissipation FinFET dissipates many times lesser than MOSFET and the performance speed is also much faster than MOSFET.

Choosing FinFET over MOSFET improves the overall performance of the universal barrel shifter, which also overcomes all the short channel effects which occurs in the MOSFET while scaling down.

#### **CHAPTER III**

#### SCHEMATIC DIVERSITY OF MULTIPLEXERS

#### 3.1 DIFFERENT MULTIPLEXERS

Multiplexers are defined as the data selectors in which large numbers of inputs are produced at the single output terminal on the basis of their respective turn, which is decided through selection line. In this section, different types of 2×1 multiplexer are designed and analysed. These multiplexers are different by means of structural configuration, delay, power dissipation and area. Some designs depict lesser area that too with low power dissipation but a degradation in output is observed. On the contrary, some designs are liable for non-degraded output but consumes more power and larger delay, as well. The schematic designs of different multiplexers are discussed in subsequent subsections.

#### 3.1.1 TG Based Multiplexer

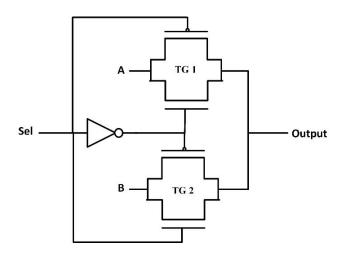

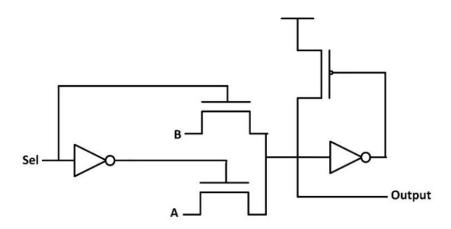

Transmission gate logic is designed using two pairs of NMOS and PMOS transistors (TG1 and TG2) wherein, the source and drain terminals of transistors are connected in parallel, as illustrated in Fig. 2. Additionally, the gate terminals of PMOS and NMOS are connected at input and output terminals of an inverter in TG1 and the connections are reversed in TG2 [7]. Both NMOS and PMOS permit the same input simultaneously and thus it is transferred at the output node through this transmission gate without any deterioration.

Fig. 3.1. Schematic of TG based Multiplexer

At high input signal, the NMOS gives a weak 1 at the output, however, PMOS provides a strong 1 at the same time. Similarly, at low input, the PMOS produces a weak 0 but NMOS a strong 0 at the output. This is a conventional  $2\times1$  Mux, where total 6 transistors are used; 4 for two transmission gates and 2 for inverter. The gates; TG1 and TG2 are used to pass the input signal A and B, respectively. While Select signal; Sel is kept high, both PMOS and NMOS of TG1 remain OFF. On the contrary, the TG2 section is ON and thus the input signal B reaches at the output. The case is reversed at Sel = 0 and signal A is passed at the output terminal. Use of TG is not limited to multiplexer only; this is used as the basic building block for designing of logic circuits as it can isolate the components and signals/data from being transmitted to the other nodes without using any other hardware.

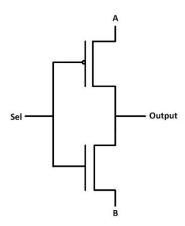

#### 3.1.2 GDI Based Multiplexer

Gate Diffusion Input logic allows the user to design complex logic circuits using a smaller number of transistors. This is an appropriate technique for designing of fast and low power circuits using lesser number of transistors, as compared to CMOS and PTL techniques. The basic GDI cell is shown in Fig. 3, which resembles a CMOS inverter at first glance. Nevertheless, it is different in terms of accessing the inputs, which are applied at the coupled gate terminal (Sel signal) and source terminals of two transistors (inputs A and B) [8-9]. If Sel is 1, the NMOS transistor operates in ON mode and input signal B will pass to the output. On the other side, output receives the input signal A, when Sel is maintained at 0.

Fig. 3.2. Schematic of GDI based Multiplexer

Logic functions corresponding to various input combinations for GDI cell are summarised in Table 1. Several advantages associated with GDI technique are minimal transistors requirement, low power dissipation and fast operation. However, some limitations are also exhibited - (1) If A is equal to 0, then PMOS being a weak 0 will not pass a perfect 0 at the output, (2) The complementary is applicable for B = 1, as NMOS is weak 1. The major advantage that GDI has over other techniques is its low area requirement for implementation.

| <b>Table 3.1.</b> Various Logic Functions of GDI Cell for Different Input Combin |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

| Inputs |   | Selection input | Output | Function |  |

|--------|---|-----------------|--------|----------|--|

| A      | В | Sel             |        |          |  |

| 0      | Q | P               | P'Q    | F1       |  |

| Q      | 1 | P               | P'+Q   | F2       |  |

| 1      | Q | P               | P+Q    | OR       |  |

| Q      | 0 | P               | PQ     | AND      |  |

| R      | Q | P               | P'Q+PR | MUX      |  |

| 0      | 1 | P               | P'     | NOT      |  |

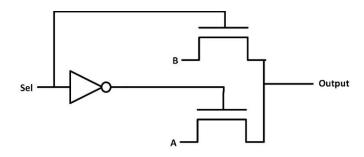

#### 3.1.3 PT Based Multiplexer

Pass Transistor Logic (PTL) uses two NMOS transistors in pass transistor configuration. The inputs are connected at the sources of the NMOS. The drain ends are shorted and the output is sensed at the drain end. The gates of the two NMOS are controlled using select signal, Sel and complement of Sel [10-11]. This logic is different from CMOS design as the source side of logic network is connected to the input signal instead of power supply [12-13]. The schematic for the same is depicted in Fig. 4.

Fig. 3.3. Schematic of PT Based Multiplexer

When the Sel signal is low; then the lower NMOS is in ON state that leads the value at A to be appears at the output terminal. Whereas, when Sel signal is high the value at B gets passed to the output. The upsides to PTL are high speed, low power consumption and low interconnect effect. But the factors that limit the use of PTL technique are slow operation and reduced voltage swing owing to the inability of NMOS to pass a strong 1. Therefore, at conditions such as, Sel=1 and B=1 or Sel=0 and A=1, the output is obtained as a weak 1. Transmission Gate logic can be used to implement a wide range of functions using lesser transistors.

#### 3.1.4 MSL Based Multiplexer

MSL based multiplexer is an improved version of PT based multiplexer. In this design, additional to the PT based multiplexer configuration a PMOS transistor is used to restore the output level. The gate of the PMOS is driven by an inverter controlled by the output of the PT based mux [14]. The gate and drain of PMOS are connected to the output and input of the second inverter, respectively as indicated in the Fig. 5. Similarly, gate terminals of both NMOS transistors are connected to the input and the output of the first inverter.

Fig. 3.4. Schematic of MSL Based Multiplexer

The purpose of designing MSL based mux is that it overcomes the major drawback of output deterioration in PT based multiplexer by using an inverter and a PMOS. When Sel is high and B = 1, the NMOS produces a weak 1 as has been explained in the previous subsection. To rectify the same MSL based mux converts the 1 to 0 through the inverter. This inverter then drives the PMOS to ON state, thereby making the output signal a strong 1. It also shows other advantages such as, fast operation and maximum output swing (nearly  $V_{DD}$  and 0). Also,

complemented input is not needed in this design. However, as it consists of more transistors in comparison to PT based design, it shows greater power dissipation and lower speed.

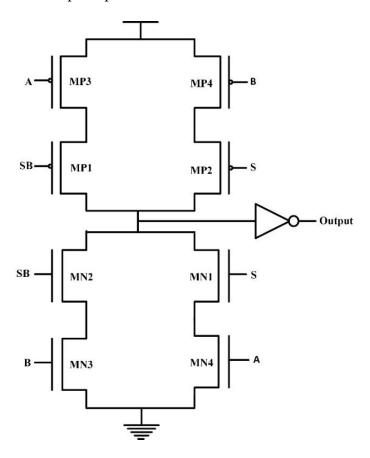

#### 3.1.5 Static CMOS Based Multiplexer

Static CMOS based mux uses eight transistors, wherein four PMOS transistors forms the pull up network and the other four NMOS transistors form the pull-down network. An inverter is used to get the actual output, as illustrated in Fig. 6 [15]. When S is low and B = 0 or SB = 1 and A=1/0, the MP2, MP4, MN2 are ON and MN1, MN3, MP1 are OFF thus output becomes 0. There is some leakage due to MN2 and MN4 of pull-down network. Similar observations are achieved for SB=B=1 or S=0 and A=0/1 wherein, MP2, MN2, MN3 remain ON and MN1, MP1, MP4 are OFF thus input of the inverter gets connected to the ground through pull down network and 1 is produced at the output. This operation also shows some leakage because of MP1 and MP4 transistors in pull up network.

Fig. 3.5. Schematic of static CMOS based Multiplexer

Further, when S is high and A = 1 or SB = 0 and B=0/1, the transistors MN1, MN4, MP1 remain in ON condition and MN2, MP2, MP3 are in OFF. Consequently, the input of inverter

gets connected to the ground through pull down network makes the output equal to 1. With similar phenomena, a zero output is produced for SB = A = 0 or S=1 and B=0/1. In such condition, the leakage occurs through MN2 and MN4 of pull-down network. This analysis concludes that the input B/A gets produced at the output for S=0/1.

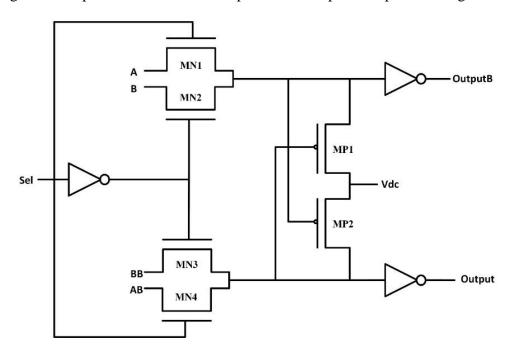

#### 3.1.6 CPL Based Multiplexer

Complementary Pass Transistor Logic (CPL), comprises of three inverters and six transistors of which four are NMOS transistors and two are PMOS transistors. The NMOS transistors are connected in pairs as pass transistors. A pair of NMOS is used to pass the input signal while the other pair is used to provide inverted input. The PMOS pair is used for the purpose of level restoration. The inverters are used to invert the select signal and the output. In this logic circuit, half of the gates are used to pull-up while other half to pull-down the logic [16] and thereby providing both complemented and non-complemented output as depicted in Fig. 7.

Fig. 3.6. Schematic of CPL based Multiplexer

When Sel is in low state, transistors MN2-MN3 are turned ON and pass the input signal B and BB (Complement of input B) to output and outputB respectively. If input B = 0 (i.e. BB = 1), MP2 is ON therefore  $V_{DC}$  gets connected to the output of MN3 and restore the logic level 1 hence 0 is produced at the output of the inverter. Now if B=1 (BB=0), transistor MP1 is ON at that moment  $V_{DC}$  gets connected to the output of MN2 and logic level 1 is restored accordingly outputB (complement of output) is 0. Correspondingly, when Sel=1, then MN1-MN4 are ON

and passes input signal A, AB (complement of input A) respectively. With similar condition When A=0 (AB=1), then MP2 is ON and  $V_{DC}$  gets connected to the output of MN4 and restores the logic level 1 thus makes the 0 at the output, however if A=1 (AB=0) then MP1 switches ON and output of MN1 gets connected to  $V_{DC}$  as a result restores the logic level 1 thus gets the 0 at the outputB. This technique exhibits advantages like presence of both inverting and non-inverting logics at the output, fast operation and restoration of output level. But its high-power dissipation and larger circuit size serve as limiting elements.

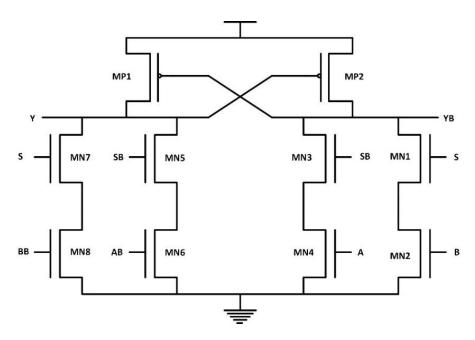

#### 3.1.7 CVSL Based Multiplexer

Cascode Voltage Switch Logic (CVSL) refers to a CMOS-type logic family. The logic function and its inverse are simultaneously implemented in this technique. The NMOS logic forms the pull-down network and generates the complementary logic. CVSL can be divided into two parts: a differential latching circuit and a cascaded complementary logic array. Therefore, this logic family is also acknowledged as Differential Cascode Voltage Switch Logic (DCVS or DCVSL) [14-15]. The schematic for 2×1 mux using this technique is illustrated in Fig. 8. As can be seen from the schematic a total of ten transistors are used, wherein, 4-4 NMOS transistors are used for input-select signals and one pair of PMOS is kept to restore the output logic level.

Fig. 3.7. Schematic of CVSL based Multiplexer

When S is low and A= 0, transistor MN3, MN5 and MN6 are ON, henceforth, the output Y and gate of MP2 gets connected to the ground terminal through transistor MN5 and MN6. Thus, the output obtained at Y is 0 (YB = 1). While, for S = 0 and A= 1, transistor MN3, MN4 and MN5 are ON and the ground gets connected to the output; YB through MN3 and MN4. Thereby making the output YB = 0 and Y = 1 as it gets connected to  $V_{DC}$  owing to the ON state of MP1. Similarly, while S is high and B = 0 transistor MN1, MN7 and MN8 turn ON and output Y and YB are obtained as 0 and 1 respectively. This configuration exhibits an advantage of elimination of large PMOS from each logic function leading to a significant area reduction.

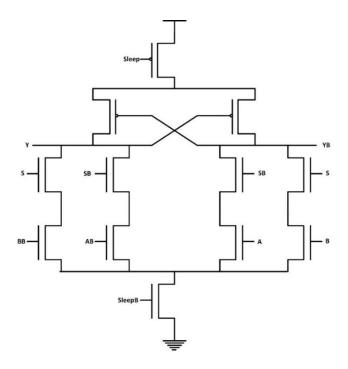

#### 3.1.8 MTCMOS CVSL Based Multiplexer

The functionality of multi threshold CMOS cascode voltage switch logic (MTCMOS CVSL) based mux is similar to the CVSL based mux. This technique is used to reduce the leakage in the circuit in static condition. In this configuration, one pair of PMOS-NMOS is used, wherein, PMOS isolates the logic circuit from  $V_{DC}$  and NMOS isolates the ground, as shown in Fig. 9. MTCMOS technique separates the circuit from the power supply and ground to prevent power dissipation in static state.

Fig. 3.8. Schematic of MTCMOS CVSL based Multiplexer

Here, two complemented sleep signals; sleep and sleepB are used to control the gates of PMOS and NMOS respectively. When sleep is low and sleepB is high, the circuit works as a standard CVSL based mux however, for the complementary case i.e. sleep = 1 and sleepB = 0, the circuit

gets disconnected from the supply and ground terminals which results in quite lesser static power dissipation than that of CVSL based multiplexer.

### 3.2 CHARACTERISTIC RESPONSE OF DIFFERENT MULTIPLEXERS

In this section, the output responses corresponding to different multiplexer techniques that have been discussed in the previous section are discussed and showcased. The common timing values used to generate output for the multiplexer techniques are given in Table 2. All the multiplexers are simulated for 50 ns to achieve the output waveform.

Table 3.2: Timing details of Sel, A, B

|                  | Sel | A   | В   |

|------------------|-----|-----|-----|

| Time period (ns) | 20  | 9   | 7   |

| Duty cycle (ns)  | 10  | 4.5 | 3.5 |

| Delay (ns)       | 0   | 0.5 | 1   |

In an ideal scenario, the generated output waveform will attain 0 V and 1V level as per the input combination and select line configuration. If the output waveform is unable to attain a perfect 0 V or 1 V level, it is a non-ideal waveform. The output waveforms generated for all mux techniques is discussed here.

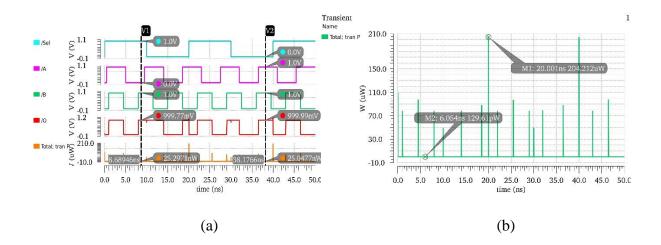

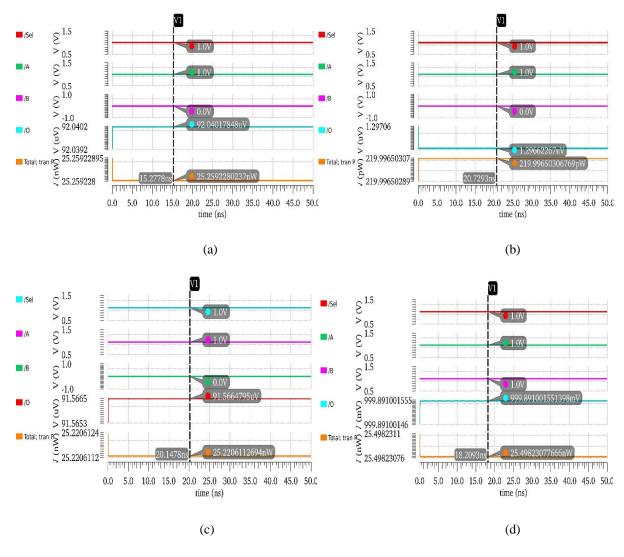

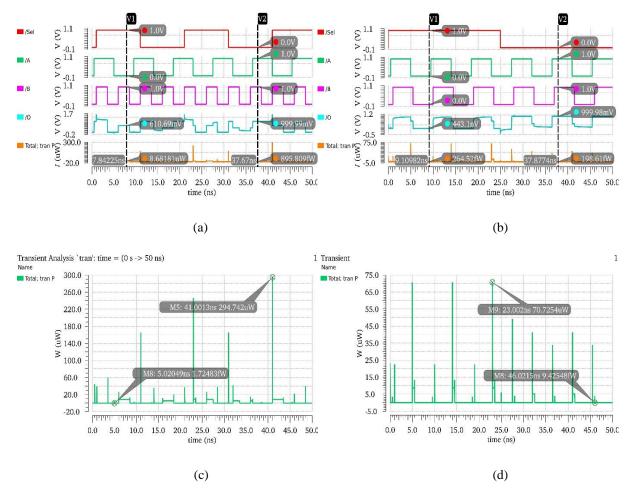

**Fig. 3.9.** Characteristic plot of TG based Mux (a) Output Response with Total Power Dissipation, (b) Total Power Dissipation, and GDI based Mux (c) Output Response with Total Power Dissipation, (d) Total Power Dissipation.

In TG based Mux all the signals transmitted through the Transmission Gate where both PMOS and NMOS is used. If input is 1 then PMOS will provide the strong 1 at the output and if input is 0 then NMOS will provide the strong 0 to the output. So, output in any case will not degrade as we can see in Fig. 10 (a). if Sel is 1, A is 1 and B is 0 then output is nearly 0 and if Sel is 0, A is 1, B is 0 then output is almost 1. This figure also shows the information about total power dissipation, at the time of switching power dissipation is more. Fig. 10 (b) shows the Total power dissipation, here the maximum power dissipation is 204.21uW and minimum power dissipation is 129.61pW.

In GDI based Mux only two MOSFET are used one PMOS and one NMOS. There is a drawback of degraded output in this type of Mux, when Sel is then PMOS will ON and if input is then PMOS will not be able to provide 0 at the output completely because PMOS gives weak 0, as we can see in Fig. 10 (c). whenever there will be switching in signals power dissipation will be more as we can see in Fig. 1 (c). Fig. 10 (d) shows the Total Power Dissipation where maximum power dissipation is 294.74uW and minimum power dissipation is 1.724fW.

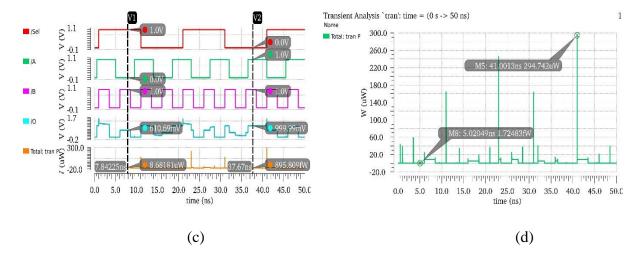

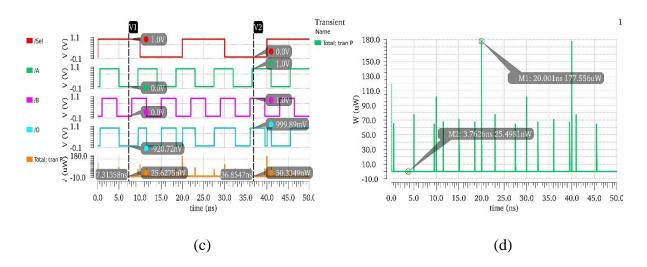

**Fig. 3.10.** Characteristic plot of PT based Mux (a) Output Response with Total power Dissipation, (b) Total Power Dissipation, and MSL based Mux (c) Output Response with Total Power Dissipation, (d) Total Power Dissipation.

In PT based Mux only two NMOS is used to pass the input signals to the output and one inverter decides which input will pass to output. Using NMOS as a switch to pass the input signal will increase the speed and area will be less in comparison to PMOS but there is a drawback of using NMOS, it gives weak 1 at the output. If Select signal is 1 and then Input B will pass to the output and if B is 0 then output will be 0 and if input B is 1 then output will not be completely 1 as shown in Fig. 11 (a), when Sel, B is 1 then output is nearly is 831.95mV. If Sel is 0 then input A will pass to the output and if A is 0 then output is 600.71nV which is nearly 0V. Total power dissipation in PT based Mux is shown in Fig. 11 (b) where maximum power dissipation is 198.535uW and minimum power dissipation is 219.6pW.

IN MSL based mux there is no level degradation problem because here one PMOS and one inverter is used in PT based Mux to restore the output level as shown in Fig. 11 (c). When Select signal is 1 then input A will pass to the output and if input A is 1 then output is nearly 1 and if input A is 0 then output is almost, so there is no drop of the signal level at the output. Same for input signal B, output will not degrade whatever the input signal. In MSL based Mux total power dissipation is shown in Fig. 11 (d), maximum power dissipation in MSL based Mux is less than PT based Mux which is 177.55uW and minimum power dissipation is more than PT based Mux which is 25.49nW.

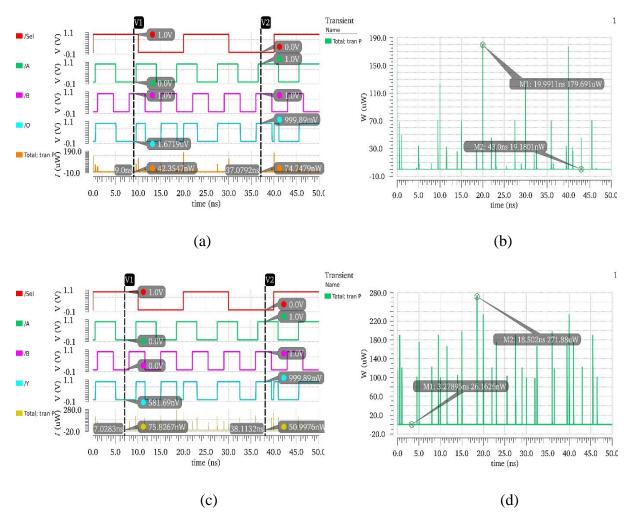

**Fig. 3.11.** Characteristic plot Static CMOS based Mux (a) Output Response with Total power Dissipation, (b) Total Power Dissipation, and CPL based Mux (c) Output Response with Total Power Dissipation, (d) Total Power Dissipation.

In Static CMOS based Mux both pull-up and pull-down network is used to perform the multiplexer operation. Total 8 MOS is used in which 4 for pull-down and 4 for pull-up network. It gives the complemented output, so one inverter is used to get the original output. Static CMOS based Mux requires both inverting and non-inverting input signals and one inverter to invert the select signal. If select signal is 1 then only A signal will pass to the output and if A is 1 then output is nearly 999.82 mV and if input signal A is 0 then output is 1.67uV which is nearly 0V as shown in Fig. 12 (a). Same case when select signal is 0 then input signal B will pass to the output. Output is not degraded in this type of Mux but it requires more numbers of MOS in compare to others. Power dissipation in Static CMOS based Mux is more compare to others because of a greater number of transistors used, maximum power dissipation is 179.69uW and minimum power dissipation is 19.18nW which is shown in Fig. 12 (b).

CPL based Mux provides both non-inverting and inverting output, when select signal is 1 then input signal A will pass to the output, if A is 1 then output Y will be 999.8mV approximately and YB will be nearly 0 as shown in Fig. 12 (c) and same case for when select signal is 0 then input signal B will pass to the output. Total power dissipation of CPL based Mux is shown in Fig. 12 (d), where maximum power dissipation is 271.88uW and minimum power dissipation is 26.16nW.

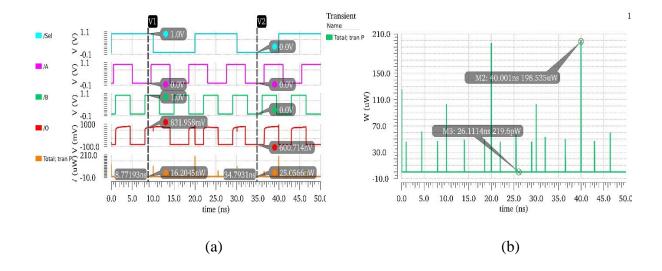

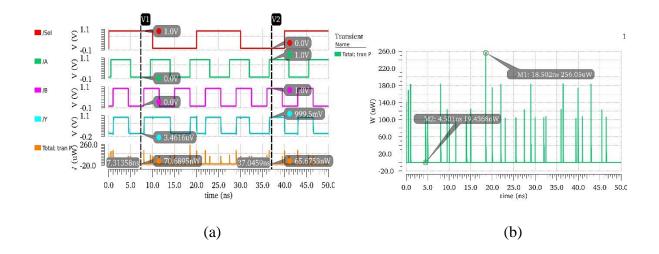

**Fig. 3.12.** Characteristic plot CVSL based Mux (a) Output Response with Total power Dissipation, (b) Total Power Dissipation, and MTCMOS CVSL based Mux (c) Output Response with Total Power Dissipation, (d) Total Power Dissipation.

CVSL based Mux stands for Cascode voltage switch logic. In this method both pull-up and pull-down network is used, in pull-down network 8 NMOS is used to pass the inverting and non-inverting signal of A, B and Sel but in pull-up network only two PMOS is used. By this CVSL based Mux both inverting and non-inverting output can be generated. When select signal is 0 then input signal A will pass to the output as shown in Fig. 13 (a), if A is 0 then output signal Y is almost 1.32uV and YB is 999.89mV and if input signal A is 1 then output Y is 999.89mV and YB is almost 1.30uV. Same condition for case when Select signal is 1 then input signal B will pass to the output, if B is 0 then output Y is 1.39uV And YB is 999.89mV, if B is 1 then output Y is 999.9mV and YB is nearly 43.75nV. Total power dissipation is consumed by CVSL based Mux is shown in Fig. 13 (b), here maximum power dissipation is 256.05uW and minimum power dissipation is 19.43nW.

MTCMOS CVSL based Mux is better than CVSL based Mux in terms of power dissipation. MTCMOS technique is used to reduce the static power dissipation when circuit is in idle condition. In MTCMOS technique two extra MOS is used one PMOS to isolate the power supply and one NMOS to isolate the ground to the main circuit because if there will be no connection of the circuit to the power supply then there will be no or very less power dissipation. Sleep signal is applied to those two extra MOS to reduce the consumption of power when there is no need of circuit. When sleep signal is 0 then circuit will work normal and if sleep signal is 1 then circuit will isolate form supply and also from the ground so, power dissipation will be less. When sleep signal is ON then output should be stable, there should not

be any change in the output by changing the input of the circuit because entire circuit is disconnected from the supply and ground as shown in Fig. 13 (c). Fig. 13 (d) shows the power dissipation analysis of the MTCMOS CVSL based Mux. Maximum power dissipation is 206.81uW, which is approximately 50uW less than CVSL based Mux and minimum power dissipation is 931.8pW, which is nearly 18nW less than CVSL based Mux.

#### 3.3 DELAY AND POWER ANALYSIS

Use of multiplexer depends on some basic requirements like how much time it will take to pass the input signal to the output, how much power it will consume when inputs are switching, what is its average power dissipation and how much power it will dissipate when input are not switching means all are in static condition. If requirement is that multiplexer should be very fast in operation than we will use different multiplexer and if requirement is that it should dissipate very less power than multiplexer will be different. Below Table 3 shows the analysis of Delay, Average Power, PDP and Leakage. Expressions for power calculation is

$$P = V_{dd} \times I_{avg} \tag{1}$$

This is the total power consumption of the circuit. Where  $V_{dd}$  represents supply voltage and  $I_{avg}$  is the average current. Total power dissipation is the summation of Static and Dynamic power dissipation

$$P_{total} = \text{Static Power} \times \text{Dynamic Power}$$

(2)

This equation is represented by,

$$P(t) = V_{dd} \times I(t) \tag{3}$$

Static Power Dissipation (Leakage) is,

$$P = I \times V_{dd} \tag{4}$$

Dynamic Power Dissipation is,

$$P = C \times \alpha \times V_{dd} \times 2f \tag{5}$$

Where c is the capacitance,  $\alpha$  is the switching activity,  $V_{dd}$  is the supply voltage, f is the frequency and I is the static current.

Table 3.3: - Delay, Average power, PDP and Static power dissipation analysis.

| Mux               | Delay           | Average Power | PDP    | Static Power |

|-------------------|-----------------|---------------|--------|--------------|

|                   | (s)             |               | (J)    | Dissipation  |

| Conventional TG   | 3.844p (A to O) | 158.9nW       | 0.61a  | 25.25nW      |

| MUX               | 4.832p (B to O) |               |        |              |

| GDI Based Mux     | 1.65p (A to O)  | 1.64uW        | 2.7a   | 219.99pW     |

|                   | 2.42p (B to O)  |               |        |              |

| PT Based Mux      | 3.57p (A to O)  | 110.9nW       | 0.395a | 25.22nW      |

|                   | 4.60p (B to O)  |               |        |              |

| MSL Based Mux     | 17.65p (A to O) | 792.4nW       | 13.98a | 25.49nW      |

|                   | 16.22p (B to O) |               |        |              |

| Static CMOS based | 34.87p (A to O) | 605.29nW      | 21.1a  | 25.48nW      |

| Mux               | 35.55p (B to O) |               |        |              |

| CPL based Mux     | 47.57p (A to O) | 1.42uW        | 67.54a | 101.07nW     |

|                   | 47.47p (B to O) |               |        |              |

| CVSL Based MUX    | 64.40p (A to O) | 1.16uW        | 74.7a  | 65.85nW      |

|                   | 65.42p (B to O) |               |        |              |

| MTCMOS CVSL       | 172.0p (A to O) | 736.4nW       | 126.6a | 63.83nW(S=0) |

| based Mux         | 171.7p (B to O) |               |        | 25.51nW(S=1) |

By analysing the delay and power of different multiplexer it is clear that performance of each mux is different and two of them showing better performance compare to others in terms of delay, power and leakage. In Table 3 it is clear that delay of GDI based Mux is 1.65ps which is fast compare to all other Mux, if there is a requirement of fast operation then GDI based Mux should be used. In some scenario when circuit is in idle condition that's mean input signals are not changing at that time leakage will occur. For static condition GDI based Mux shows the best performance, it dissipates 219.99pW in idle condition. PT based Mux is little bit slower than the GDI based Mux and has the lowest Average power dissipation 110.9nW, if we want mux which should have less average power dissipation than PT based Mux is the best option. In some of the condition we check that PDP of the circuit should be minimum for better operation, for that PT based Mux shows the optimum performance. PDP of PT based Mux is 0.395aJ.

The Delay of the circuit represents the time taken by the signal to reach from the input to output. Higher the delay more time required by the circuit to reach the output.

$$\tau_{delay} = \frac{\tau_{PLH} + \tau_{PHL}}{2} \tag{6}$$

$\tau_{PLH}$  = time for the fall to rise of the signal.

$\tau_{PHL}$  = time for the rise to fall of the signal.

After the power and delay calculation power delay product are calculated, which is the multiplication of both delay and power, represented by PDP.

$$PDP = Delay \times Power \tag{7}$$

These calculations of the circuits help the designer and user to understand the performance of the circuit.

#### **IMPORTANT OUTCOMS:**

- Designing and analysis of different type of multiplexers is accomplished.

- All the designing is done using MOSFET at 90nm technology node at 1V.

- Analysis shows that in all different multiplexers GDI and PT based multiplexers provides the best and efficient performance.

- In both GDI and PT based mux delay of GDI is less and consumes less static power dissipation

# **CHAPTER IV**

## **POWER ANALYSIS**

## 4.1 STATIC POWER DISSIPATION ANALYSIS

In this section static power dissipation is analysed of different type of mux. Static power analysis is done when all the input signals are stable to either one or zero. Timing values used for analysis of static power dissipation is, Sel, input signal A is 1 and B is 0.

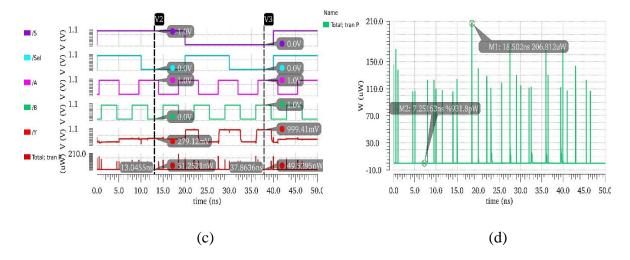

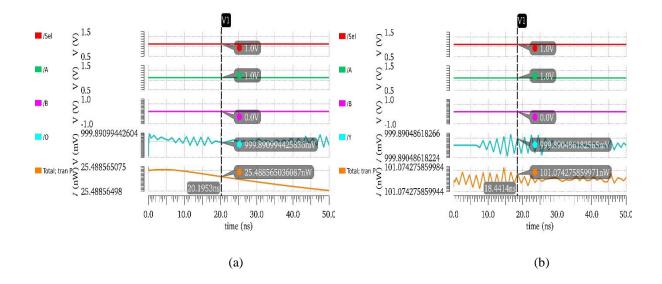

**Fig. 4.1.** Static power dissipation plot for (a) TG based Mux (b) GDI based Mux (c) PT based Mux (d) MSL based Mux.

TG based mux is a conventional type mux, where two transmission gates is used to pass the input signal and select signal is used to decide which input will pass to the output. Main power supply is only connected to the inverter which will invert the select signal. So, the static power dissipation which is also call leakage is 25.25nW as shown in Fig. 14 (a). GDI based mux looks like CMOS inverter but in GDI based mux both source of PMOS source of NMOS is connected to the input signals rather than connected to the power supply and the ground. In GDOI based cell only two MOS is used so static power dissipation in this mux is 219.99pW as shown in Fig. 14 (b) which is very less compare to others multiplexers. In PT based Mux two NMOS is used to pass the input signals to the output but contrary to GDI in PT based mux both MOS are NMOS and one inverter is also used to decide which input will pass to the output. In PT based Mux static power dissipation shown in Fig. 14 (c) is 25.22nW. Working and design of MSL based Mux is same as PT based mux with some extra hardware but. The advantage of MSL based mux over PT based Mux is that it overcome the drawback of low voltage swing. In PT based mux NMOS b pass the input signal to the output, if input is 1 then output will be less than 1 because NMOS gives weak 1 at the output. This problem can be solved by the MSL based Mux. Because of the use of extra circuit to overcome the drawback of PT based Mux static power dissipation is increased, as shown in the Fig. 14 (d) static power dissipation is 50.54nW

**Fig. 4.2.** Static power dissipation plot for (a) Static CMOS based Mux (b) CPL based Mux (c) CVSL based Mux (d) MTCMOS CVSL based Mux.

In static CMOS based Mux both pull-up and pull-down network is used, because of more than one transistor in series leakage path resistance is high which will reduce the leakage in this circuit, Fig. 15 (a) shows the static power dissipation 25.48nW. CPL stands for complementary pass transistor logic, in which NMOS pass transistor is used to pass the input signals with PMOS and inverter to restore logic level at the output of the pass transistors. When select, A is 1 and B is 0, then static power dissipation is 101.07nW depicted in Fig. 15 (b). In Cascode voltage switch logic only two PMOS is used rather than using dual of NMOS. Both PMOS are connected back to back, because to this method output will not degrade and in static input condition leakage will be less as shown in Fig. 15 (c). Static power dissipation is 65.85nW. MTCMOS CVSL based Mux is modified version of CVSL based Mux. MTCMOS technique is used to reduce the leakage in the circuit for this one NMOS is used to isolate the ground and one PMOS is used to isolate the supply. As we can see clearly that in MTCMOS CVSL based Mux static power dissipation is 25.51nW as shown in Fig. 15 (d). which is 40.34nW less than CVSL based Mux.

#### 4.2 SWITCHING AND SCALING

This section illustrates the importance and details of scaling of the power supply and switching. Scaling of the power supply affects the dissipation of power in both dynamic and static condition. Less power supply causes less power dissipation, contrary is also true. Whereas,

switching of the signal also have an effect on power dissipation. If switching of the signals occurs at same time, then it increases the power dissipation.

## **4.2.1** Scaling of Power Supply:

Voltage Scaling is an essential part of VLSI (Very Large-Scale Integration) to increase the performance of the devices, demand and success of the industries. Voltage Scaling directly affects power dissipation. Scaling down the power supply leads to less power dissipation with the condition of not affecting the output. If by scaling down the voltage causing the wrong output, then it's the limit at which further scaling down is not possible. In this section, voltage scaling is done on multiplexers to get an analysis of power dissipation at the different power supply. MOS is a basic building block for any logic circuits and scaling of voltage in MOS improves its performance. After a complete analysis of delay, power dissipation, and leakage of the multiplexers it is found that two of them show better performance compared to others. Voltage Scaling of both multiplexers is shown in Table 4.

Table 4.1. Scaling on GDI based Mux and PT based Mux

| Multiplexer     | Scaling of | Maximum     | Minimum     | Average     | Leakage  |

|-----------------|------------|-------------|-------------|-------------|----------|

|                 | supply     | Power       | Power       | Power       |          |

|                 |            | Dissipation | Dissipation | Dissipation |          |

|                 |            |             |             |             |          |

| GDI based       | 1V         | 294.7uW     | 1.725fW`    | 1.73uW      | 219.9pW  |

| Mux             | 0.8V       | 230.1uW     | 1.58fW      | 166.6nW     | 87.88pW  |

|                 | 0.6V       | 157.5uW     | 9.51fW      | 22.13nW     | 32.74pW  |

| PT based<br>Mux | 1V         | 198.5uW     | 219.6pW     | 110.9nW     | 25.22nW  |

| Mux             | 0.8V       | 119.7uW     | 25.04nW     | 223.2nW     | 10.637nW |

|                 | 0.6V       | 74.2uW      | 25.05nW     | 4.05uW      | 4.13nW   |

Above Table 4 clearly states that when we reduce the value of supply voltage there are some considerable amount of reduction in both dynamic and static power dissipation. Here up to at 3 level voltage power is analysed.

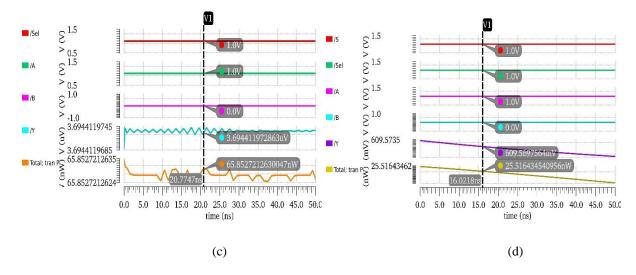

**Fig. 4.3.** Static Power Dissipation of GDI based Multiplexer at (a) Vdc=1V, (b) Vdc=0.8V and (c) Vdc=0.6V. Total Power Dissipation of GDI based Mux (d) Vdc=1V, (e) Vdc=0.8V and (f) Vdc=0.6V.

In GDI based Mux at Vdc=1V maximum power dissipation is 294.7uW and average power dissipation is 1.73uW but when we reduce the power supply from 1V to 0.6V maximum power dissipation is also reduced to 157.5uW which is 46.55% less than of maximum power

dissipation at 1V and average power dissipation reduced to 22.13nW at 0.6V which is 98% less than of average power dissipation at 1V as shown in Table 4. leakage is also 85.11% reduced from 219.9pW at 1V to 32.74pW at 0.6V as shown in Fig. 16 (a), (b), (c). While reducing the supply voltage output is not degrading but power dissipation is reduced which will improve the performance. Fig. 16 (d), (e), (f) shows the analysis of total power dissipation at different voltage node.

**Fig. 4.4.** Static Power Dissipation of PT based Multiplexer at (a) Vdc=1V, (b) Vdc=0.8V and (c) Vdc=0.6V. Total Power Dissipation of PT based Mux (d) Vdc=1V, (e) Vdc=0.8V and (f) Vdc=0.6V.

In PT based Multiplexers maximum power dissipation is reduces from 198.5uW at 1V to 74.2uW at 0.6V which is 62.61% less than maximum power dissipation at 1V shown in Table 4. 15. When circuit is static condition, leakage (static power dissipation) is also 83.62% reduced from 25.22nW at 1V to 4.13nW at 0.6V as shown in Fig. 17 (a), (b), (c). Analysis and variation of total power dissipation at different voltage level is shown in Fig. 17 (d), (e), (f).

#### **4.2.2** Switching of the signals:

Switching at different time instances shows different power dissipation. If signals are switching at the same time than power dissipation will be more and if switching of the signals is happening at different time instances then power dissipation will be less. Two different Timing values which is being used in this analysis one for same time switching and one for different switching time. (1) Different Time Switching- for select signal Time period= 20ns, Duty cycle= 10ns and Delay= 0ns, for input signal A Time period=9ns, Duty cycle=4.5ns and Delay=0.5ns and for input signal B Time period=50ns, Duty cycle=25ns and Delay= 0ns, for input signal A Time period=9ns, Duty cycle=4.5ns and Delay= 0.5ns and for input signal B Time period=9ns, Duty cycle=4.5ns and Delay= 1ns.

Table: Timing Values

| Timing    | Signals | Time Period | Duty Cycle | Delay |

|-----------|---------|-------------|------------|-------|

|           |         | (ns)        | (ns)       | (ns)  |

| Different | Select  | 20          | 10         | 0     |

| Timing    | A       | 9           | 4.5        | 0.5   |

|           | В       | 7           | 3.5        | 1     |

| Same Time | Select  | 50          | 25         | 0     |

|           | A       | 9           | 4.5        | 0.5   |

|           | В       | 9           | 4.5        | 1     |

## 4.2.2.1 GDI based Multiplexer

In this multiplexer only two MOS is used to pass the input signals. Switching at different time and same time will change the power dissipation. Same switching more power dissipation and different switching less power dissipation.

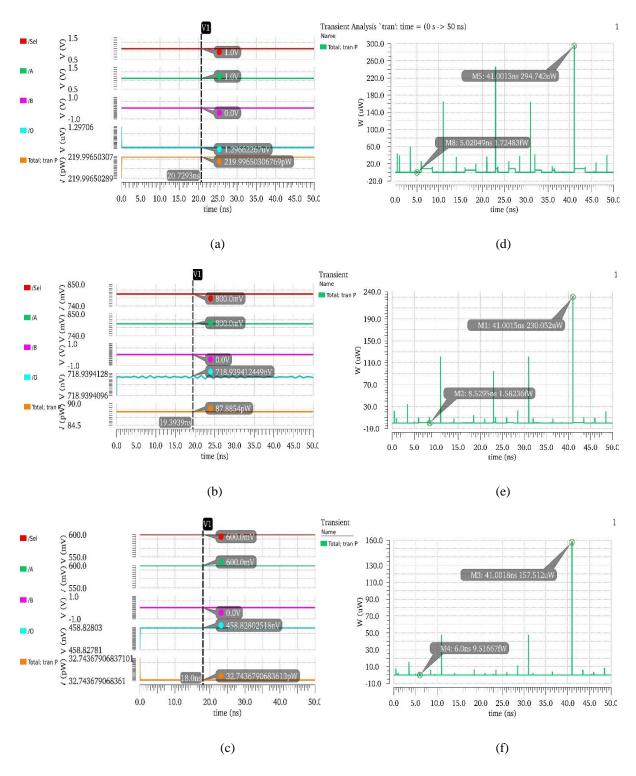

**Fig. 4.5.** GDI based Multiplexer (a) Output plot at Same Time Switching, (b) Output Plot at Different Time Switching, (c) Total Power Dissipation at Same Switching, (b) Total Power Dissipation at Different Time Switching.