# DESIGN OF CONTINUOUS TIME CIRCUITS USING CURRENT MODE BUILDING BLOCKS

Thesis Submitted to the Delhi Technological University for the Award of Degree of

# **DOCTOR OF PHILOSOPHY**

in

# **Electronics and Communication Engineering**

by

# Priyanka Gupta

(Enrollment No.- 2K14/PHD/EC/10)

Under the supervision of

Prof. Rajeshwari Pandey

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(FORMERLY DELHI COLLEGE OF ENGINEERING)

DELHI-110042, INDIA

**JULY 2020**

© DELHI TECHNOLOGICAL UNIVERSITY- 2020 ALL RIGHTS RESERVED **CANDIDATE'S DECLARATION**

I hereby declare that the thesis entitled "Design of Continuous Time Circuits using

Current Mode Building Blocks" is an original work carried out by me under the

supervision of Dr. Rajeshwari Pandey, Professor, Department of Electronics and

Communication Engineering, Delhi Technological University, Delhi. This thesis has

been prepared in conformity with the rules and regulations of the Delhi Technological

University, Delhi. The research work reported and results presented in the thesis has

not been submitted either in part or full to any other university or institute for the award

of any other degree or diploma.

(Priyanka Gupta)

2K14/PhD/EC/10

Research Scholar

Department of ECE

Delhi Technological University

Delhi-110042

Date: 13 July 2020

Place: New Delhi

i

## **CERTIFICATE**

Time Circuits using Current Mode Building Blocks" by Priyanka Gupta (2K14/PhD/EC/10) in partial fulfillment of requirements for the award of Degree of DOCTOR OF PHILOSOPHY in Department of Electronics and Communication Engineering, Delhi Technological University is an authentic record of student's own work carried by her under my supervision. In my opinion, the thesis has reached the standards fulfilling the requirements of the regulations relating to the degree. This is further certified that this work has not been submitted to any other Institute or University for the award of any other diploma or degree.

(Dr. Rajeshwari Pandey)

Professor

Department of ECE

Delhi Technological University

Delhi- 110042

#### **ACKNOWLEDGMENT**

The work presented in this thesis would have not been possible without the support of many people.

First and foremost it is my pleasure to express a deep sense of gratitude and indebtedness to my learned guide Prof. Rajeshwari Pandey for her invaluable guidance, encouragement and patient review. Her continuous inspiration has made me complete this thesis. I owe her lots of gratitude for having me. I am really glad to be associated with her. Her enthusiasm and her mission for providing high quality work, has made a deep impression on me. I was not only provided with a research environment but also academically and emotionally through the rough road to finish this thesis. And during the most difficult times in my Ph.D, she gave me the freedom that I needed to move on.

I sincerely thank Prof. N.S. Raghava, Head, Department of ECE, Prof. S. Indu, for providing all the necessary facilities for the completion of my work. My special words of thanks should also go to Prof. Neeta Pandey for her time to time advice, support and help on various occasions and to other faculty members of Department of ECE, DTU, Delhi for their encouragement and guidance.

I am also grateful to Prof. Yogesh Singh, Vice-Chancellor, DTU, Delhi, for providing the research environment in the university.

I am thankful to my friends Dr. K Gurumurhty, Parveen Rani, Anshita and lab staff of the Electronics and Communication Department for their support and motivation.

My special regards to my teachers because of whose teaching at different stages has made it possible for me to see this day.

I owe my deepest gratitude towards my husband Dr. Sidharth for his eternal support and

understanding of my aspirations. His infallible love and support have always been my

strength. Without his help, it would not have been possible to complete much of what I

have done. I am thankful to my daughter Deetya Bansal for being my strength and for

teaching me the meaning of selfless love. I dedicate this work to her.

My heartfelt regards and respects go to my father Sh. Ishwar Chand Gupta for his

motivation during the duration of my Ph.D. He taught me to always move ahead, what

may be the situation. A heartfelt thanks to my mother Smt. Kamla Gupta. Her endless

love, prayers and sacrifices help me in every situation.

I am also thankful to my numerous friends and family members whose names I haven't

added here but have helped me in my research and I will always be obliged for their

guidance and support.

Finally, I thank my God, for letting me through all the difficulties. You are the one who

let me finish. Thank you Lord.

(Priyanka Gupta)

iv

## **ABSTRACT**

The information being processed in electric networks may be denoted through node voltages or through branch currents. An analog circuit is termed as voltage mode (VM) circuit when the information is expressed through voltage levels at different nodes, whereas if branch currents represent the signal, the circuit are termed as a current mode (CM) circuit. Current mode processing has received significant attention in the field of analog circuit design due to advantages offered over voltage mode circuits. This has resulted in emergence of various current mode analog building blocks which is evident from vast available literature. Voltage differencing buffered Amplifier (VDBA) is an active block of relatively recent origin which uses voltage differencing as input stage. In circuit implementation of VDBA its transconductance (*g<sub>m</sub>*) can be controlled through bias current which helps in electronic tuning of design parameters of the applications build around this active block. This leads to ease of circuit integration. The VDBA, therefore, has evolved as a promising choice for analog applications and this has led the author to explore analog circuit designing using VDBA.

A variety of VDBA implementations are available in literature but a VDBA providing high transconsuctance gain (g<sub>m</sub>) and bandwidth (BW) with low power consumption has not been explored and leads to a significant research gap. So a low power, high performance VDBA using differential flipped voltage followers is presented.

In consumer and industrial applications variety of physical quantities are measured using transducers as input unit. The low level differential output of transducer is to be amplified faithfully, eliminating the common mode noise, for further processing. This is accomplished by using instrumentation amplifiers (IA) at input stage. The IAs are always designed for high differential gain along with high common mode rejection ratio

(CMRR). A high CMRR voltage mode IA employing single VDBA is proposed which works on much lower power supply as compared the existing designs.

Electronic filters are essential building blocks of electronic systems. In this thesis, three applications namely (i) a first order APF (ii) a SISO multifunctional filter and (iii) a MISO universal filter are proposed. An APF in inverting/non-inverting configuration using a VDBA has been proposed which provides voltage output at low impedance with electronically tunable voltage gain. A second order VM multifunction generalized filter topology employing single VDBA is presented next which can be configured to provide low pass, high pass, and band pass responses with appropriate admittance selection. The proposed topology is a suitable choice for high quality factor implementation. The third filter topology is a MISO universal biquad filter designed using two VDBAs, two capacitors and a grounded resistor.

Non-linear signal processing applications have also been explored in this thesis. A four quadrant analog multiplier (FQAM) using the quarter square algebraic identity is proposed first. A low power squaring is the next proposition which is followed by a low power square rooting circuit.

Sinusoidal oscillators are the integral part of electronic circuit design. The oscillators find extensive usage in communication systems, control systems, measurement and instrumentation systems. In this work, a single phase, three quadrature phase and two multiphase sinusoidal oscillators have been proposed using VDBA/DO-VDBA.

All the proposed designs are functionally verified through the virtuoso ADE tool or SPICE environment is used for simulation work. Some of the propositions are verified experimentally also.

# **TABLE OF CONTENTS**

|     | CANDIDATE'S DECLARATION    | i     |

|-----|----------------------------|-------|

|     | CERTIFICATE                | ii    |

|     | ACKNOWLEDGMENT             | . iii |

|     | ABSTRACT                   | V     |

|     | TABLE OF CONTENTS          | vii   |

|     | LIST OF FIGURES            | xi    |

|     | LIST OF TABLES             | xvi   |

|     | ABBREVIATIONSx             | vii   |

| CHA | APTER 1                    | 1     |

| 1.1 | Introduction               | 1     |

| 1.2 | Available Literature       | 3     |

| 1.2 | 2.1 VDBA Implementations   | 3     |

| 1.2 | 2.2 VDBA Applications      | 5     |

| 1.3 | Objectives                 | . 11  |

| 1.4 | Thesis Organization        | . 11  |

| CHA | APTER 2                    | .14   |

| 2.1 | Introduction               | . 14  |

| 2.2 | The Ideal VDBA and DO-VDBA | . 14  |

| 2.3 | Non-Ideal Model            | . 16  |

| 2.4 | Implementation of VDBA     | . 17  |

| 2.4 | 4.1 Simulation Results     | .21   |

|     | 2.4.1.1 DC Characteristics | .22   |

|     | 2.4.1.2 AC Characteristics | .23   |

| 2.5 | Implementation of DO-VDBA  | . 24  |

| 2.5 | 5.1 Simulation Results     | .27   |

|     | 2.5.1.1 DC Characteristics | .27   |

|     | 2.5.1. | 2 AC Characteristics               | 28 |

|-----|--------|------------------------------------|----|

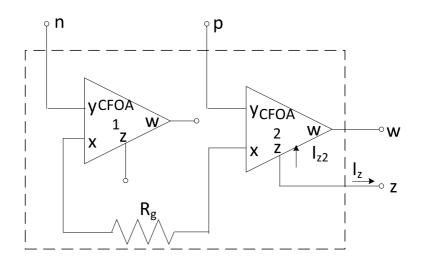

| 2.6 | The    | CFOA based Implementation of VDBA  | 29 |

| 2   | .6.1   | Simulation Results                 | 31 |

|     | 2.6.1. | 1 DC Characteristics               | 32 |

|     | 2.6.1. | 2 AC Characteristics               | 33 |

| 2.7 | The    | NMOS Based Resistor Realization    | 34 |

| 2.8 | Con    | clusion                            | 36 |

| СН  | APTE   | R 3                                | 37 |

| 3.1 | Intro  | oduction                           | 37 |

| 3.2 | Diff   | Perential Flipped Voltage Follower | 37 |

| 3.3 | Prop   | posed Structure                    | 38 |

| 3   | .3.1   | Small Signal Analysis              | 40 |

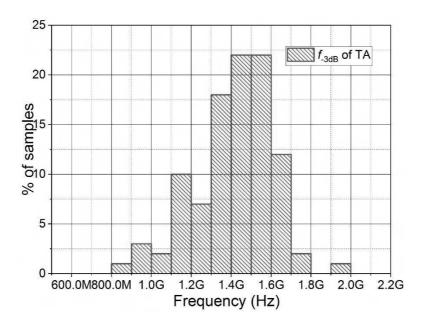

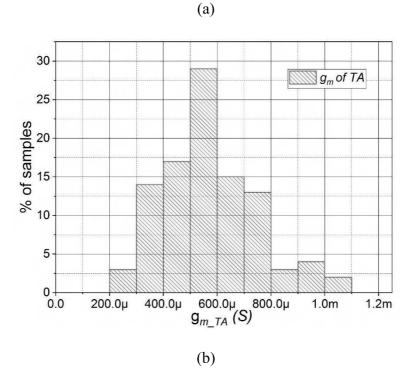

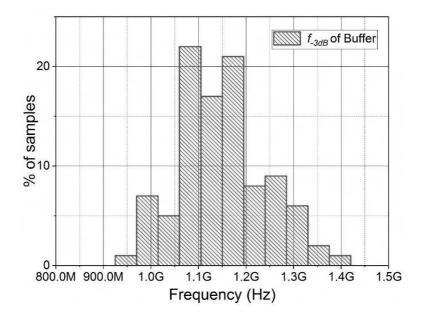

| 3   | .3.2   | Simulation Results                 | 44 |

| 3.4 | Con    | clusion                            | 59 |

| СН  | APTE   | R 4                                | 61 |

| 4.1 | Intro  | oduction                           | 61 |

| 4.2 | Instr  | rumentation Amplifier              | 61 |

| 4   | .2.1   | Proposed IA                        | 64 |

|     | 4.2.1. | 1 Non-Ideal Analysis               | 64 |

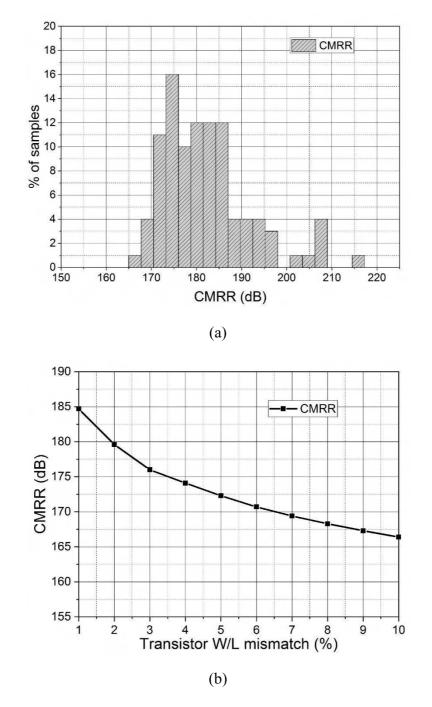

|     | 4.2.1. | 2 Noise Analysis                   | 66 |

|     | 4.2.1. | 3 Simulation Results               | 68 |

| 4.3 | Elec   | etronics Filters                   | 77 |

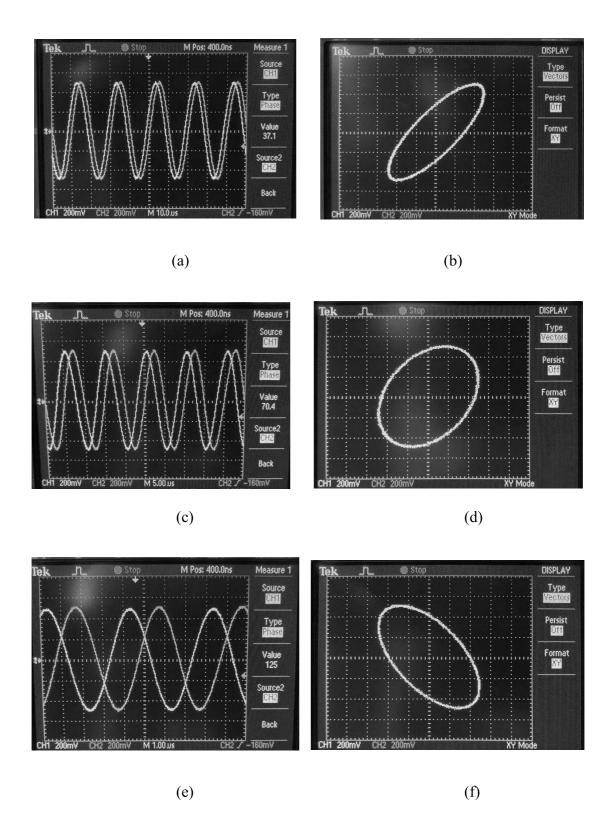

| 4   | .3.1   | Proposed First Order APF           | 77 |

|     | 4.3.1  | 1 Non-Ideal Analysis               | 79 |

|     | 4.3.1. | 2 Simulation Results               | 81 |

|     | 4.3.1. | 3 Experiment Results               | 87 |

| 4   | .3.2   | Proposed SISO Multifunction Filter | 89 |

|     | 4.3.2.1 Sensitivity Analysis           | 91  |

|-----|----------------------------------------|-----|

|     | 4.3.2.2 Non-Ideal Analysis             | 92  |

|     | 4.3.2.3 Simulation Results             | 94  |

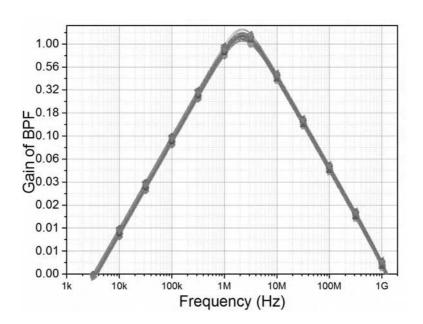

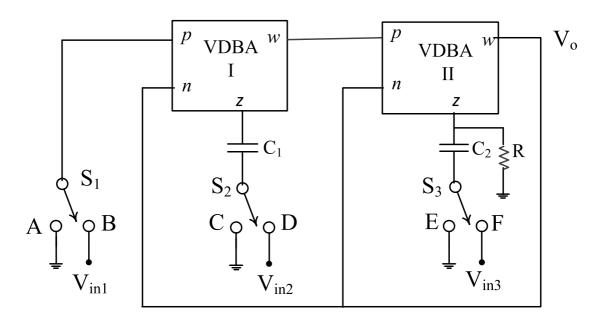

| 4   | .3.3 Proposed MISO Universal Filter    | 100 |

|     | 4.3.3.1 Sensitivity Analysis           | 102 |

|     | 4.3.3.2 Non-Ideal Analysis             | 102 |

|     | 4.3.3.3 Simulations Results            | 104 |

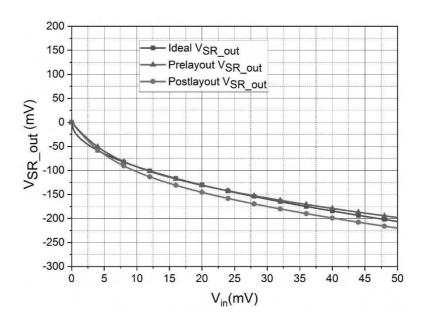

|     | 4.3.3.4 Post Layout Simulation Results | 109 |

| 4.4 | Conclusion                             | 111 |

| СН  | APTER 5                                | 113 |

| 5.1 | Introduction                           | 113 |

| 5.2 | Analog Multiplier                      | 113 |

| 5   | .2.1 Proposed FQAM                     | 115 |

|     | 5.2.1.1 Non-Ideal Analysis             | 121 |

|     | 5.2.1.2 Simulation Results             | 122 |

|     | 5.2.1.3 Applications of Proposed FQAM  | 126 |

| 5.3 | Squaring Circuit                       | 130 |

| 5   | .3.1 Proposed Squaring Circuit         | 132 |

|     | 5.3.1.1 Non-Ideal Analysis             | 134 |

|     | 5.3.1.2 Simulation Results             | 136 |

| 5.4 | Square Rooting Circuit                 | 143 |

| 5   | .4.1 Proposed Square Rooting Circuit   | 144 |

|     | 5.4.1.1 Non-Ideal Analysis             | 146 |

|     | 5.4.1.2 Simulation Results             | 148 |

| 5.5 | Conclusion                             | 153 |

| СН  | APTER 6                                | 155 |

| 6 1 | Introduction                           | 155 |

| 6.2 | Basi     | c Principle                      | 155   |

|-----|----------|----------------------------------|-------|

| 6.3 | Sing     | le Phase Oscillator (SPO)        | 156   |

| 6   | 3.1      | Simulation Results               | .157  |

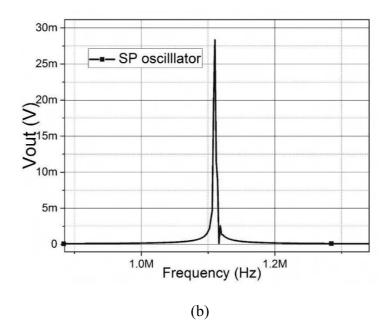

| 6   | 3.2      | Experimental Results             | 158   |

| 6.4 | Quad     | drature Phase Oscillator (QPO)   | .159  |

| 6.  | 4.1      | Topology I                       | 160   |

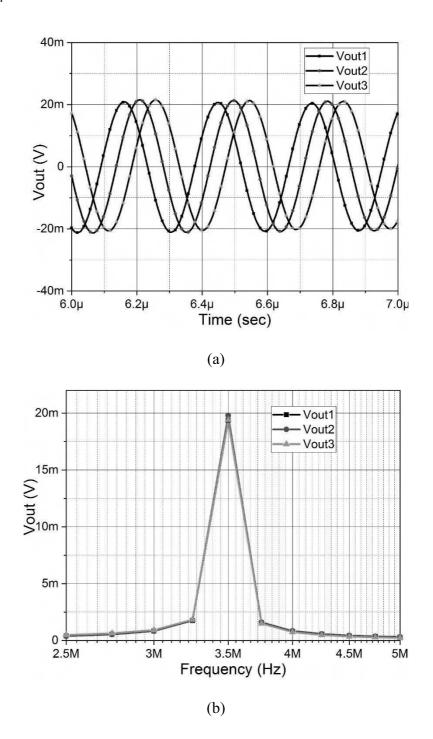

|     | 6.4.1.   | 1 Simulation Results             | 161   |

| 6.  | 4.2      | Topology II                      | 162   |

|     | 6.4.2.   | 1 Simulation Results             | 163   |

|     | 6.4.2.2  | 2 Experiment Results             | 165   |

| 6.4 | 4.3      | Topology III                     | 166   |

|     | 6.4.3.   | 1 Simulation Results             | 167   |

|     | 6.4.3.2  | 2 Experiment Results             | 169   |

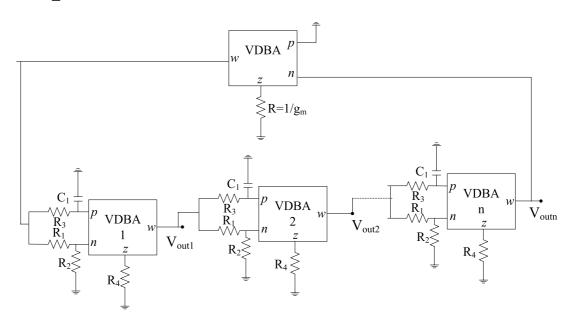

| 6.5 | Mult     | tiphase Oscillator (MPO)         | . 170 |

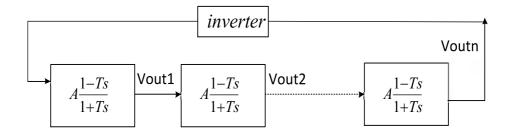

| 6   | 5.1      | Generic Approach                 | .171  |

| 6.  | 5.2      | Topology I                       | 173   |

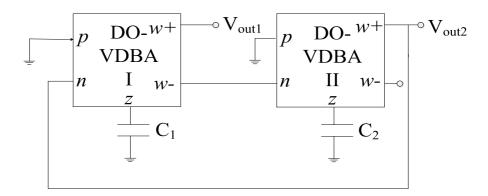

|     | 6.5.2.   | 1 Simulation Results             | 174   |

|     | 6.5.2.2  | 2 Experiment Results             | 175   |

| 6   | 5.3      | Topology II                      | 176   |

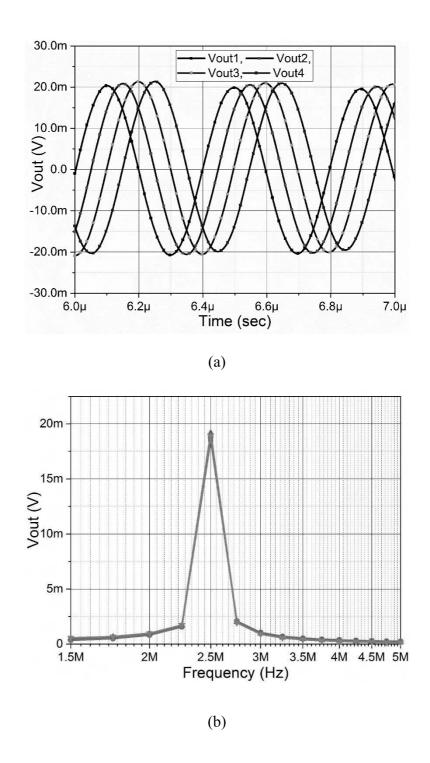

|     | 6.5.3.   | 1 Simulation Results             | 176   |

| 6.6 | Cond     | elusion                          | 181   |

| CHA | APTE     | R 7                              | 182   |

| 7.1 | Sum      | mary of work done in this Thesis | 182   |

| 7.2 | Futu     | re Scope                         | 185   |

| DET | ים כו כו | NCEC                             | 107   |

# LIST OF FIGURES

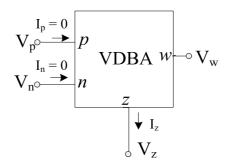

| Figure 2.1 Symbol of VDBA                                                                        | 14    |

|--------------------------------------------------------------------------------------------------|-------|

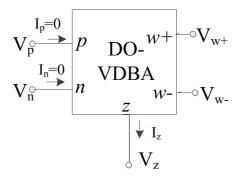

| Figure 2.2 Symbol of DO-VDBA                                                                     | 15    |

| Figure 2.3 Non-ideal model of VDBA                                                               | 17    |

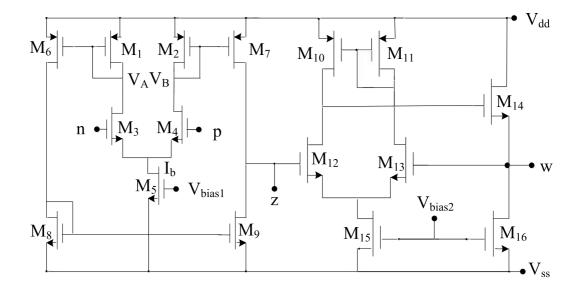

| Figure 2.4 CMOS VDBA [33]                                                                        | 18    |

| Figure 2.5 Small signal equivalent of (a) TA and (b) buffer                                      | 18    |

| Figure 2.6 DC characteristics of (a) TA and (b) buffer                                           | 23    |

| Figure 2.7 AC characteristics of (a) TA and (b) buffer                                           | 24    |

| Figure 2.8 CMOS implementation of the DO-VDBA [61]                                               | 25    |

| Figure 2.9 Small signal equivalent model of (a) TA and (b) inverting buffer                      | 25    |

| Figure 2.10 DC characteristics of (a) TA and (b) buffer                                          | 28    |

| Figure 2.11 AC characteristics of (a) TA and (b) buffer                                          | 29    |

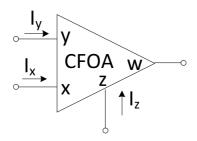

| Figure 2.12 CFOA symbol.                                                                         | 30    |

| Figure 2.13 Proposed CFOA based VDBA                                                             | 30    |

| Figure 2.14 DC characteristics of (a) TA and (b) buffer                                          | 32    |

| Figure 2.15 AC characteristics of (a) TA and (b) buffer                                          | 33    |

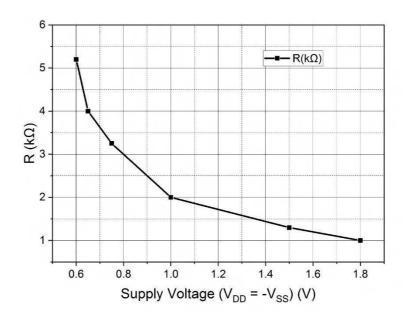

| Figure 2.16 The NMOS based resistor (R) realization                                              | 35    |

| Figure 2.17 R Vs Supply voltage                                                                  | 36    |

| Figure 3.1 The DFVF structure [95]                                                               | 38    |

| Figure 3.2 Proposed VDBA                                                                         | 40    |

| Figure 3.3 Small signal model of TA                                                              | 41    |

| Figure 3.4 Small signal model of buffer                                                          | 42    |

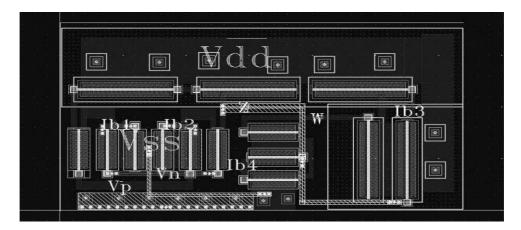

| Figure 3.5 The layout of the proposed VDBA                                                       | 44    |

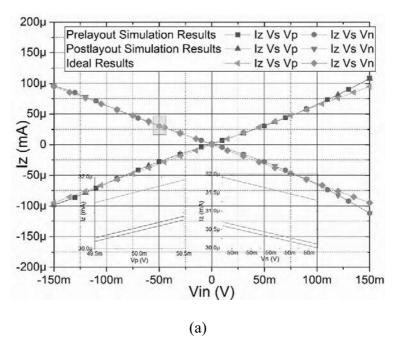

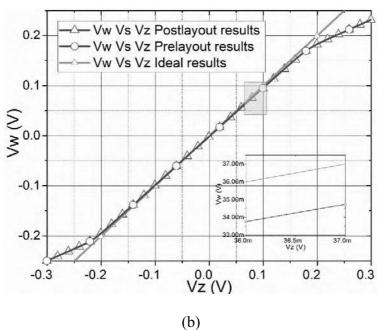

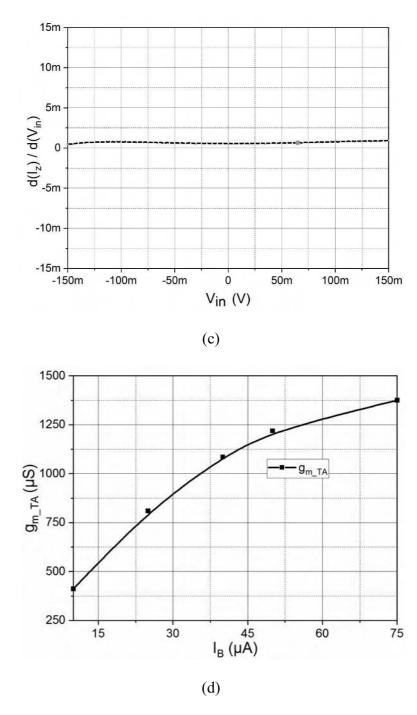

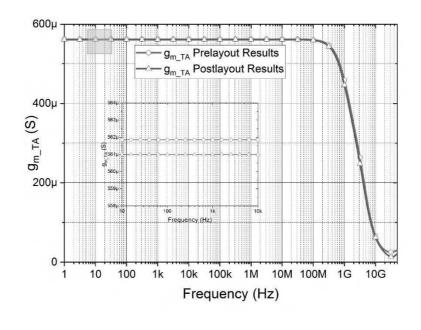

| Figure 3.6 The DC characteristics (a) $I_z$ variation w.r.t $V_p$ and $V_n,$ (b) $V_w$ variation | w.r.t |

| $V_z$ , (c) the ICMR plot and (d) the $g_m$ variation w.r.t $I_B$                                | 46    |

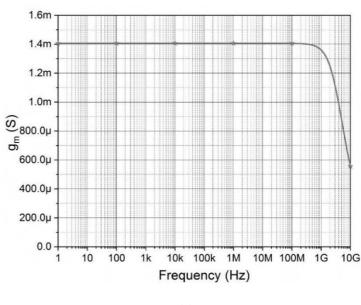

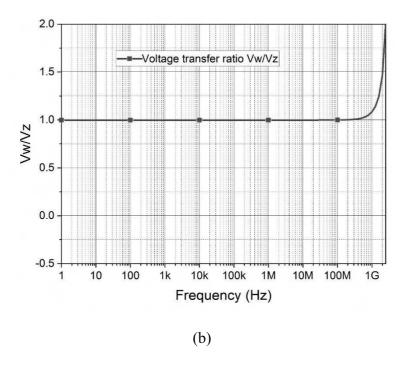

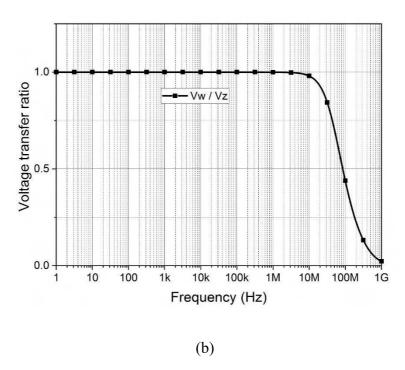

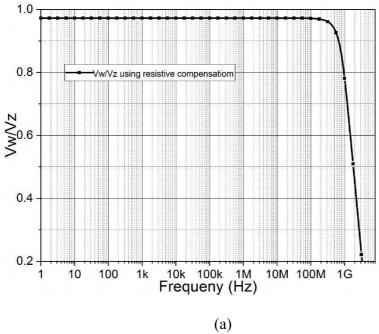

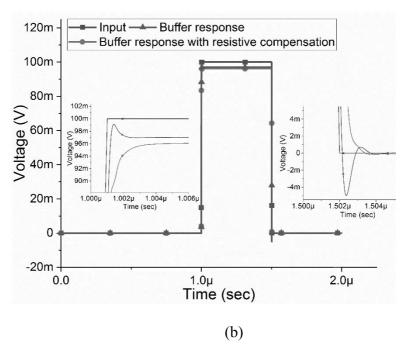

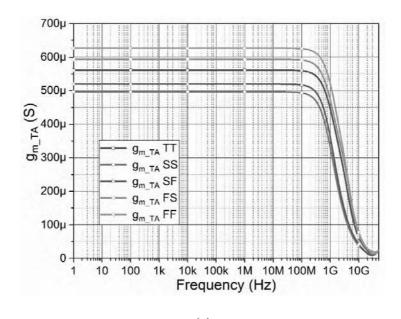

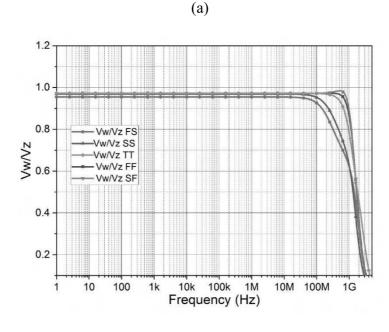

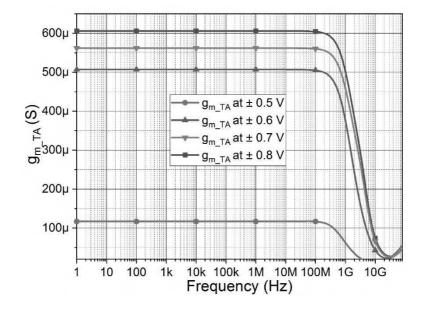

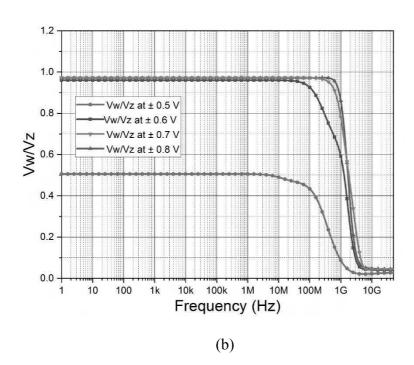

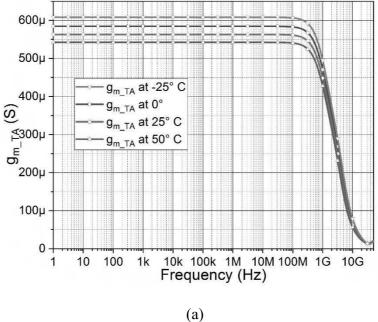

| Figure 3.7 The frequency response of the (a) TA and (b) buffer                                   | 47    |

| Figure 3.8 High frequency small signal model of uncompensated/compensated                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| buffer                                                                                                                                                                                                                        |

| Figure 3.9 (a) Frequency response and (b) Step response of the compensated buffer 54                                                                                                                                          |

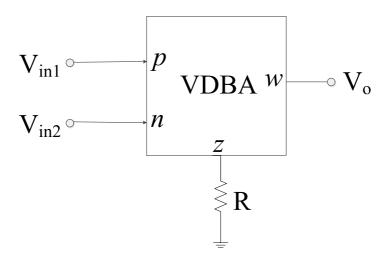

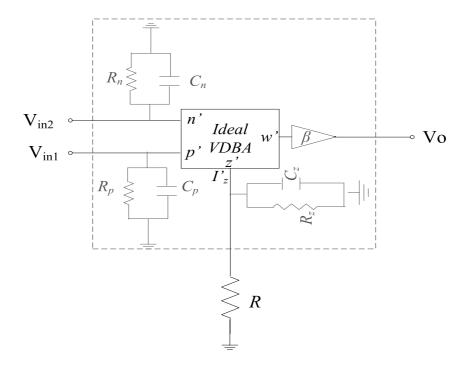

| Figure 4.1 The proposed IA                                                                                                                                                                                                    |

| Figure 4.2 Non-ideal IA 65                                                                                                                                                                                                    |

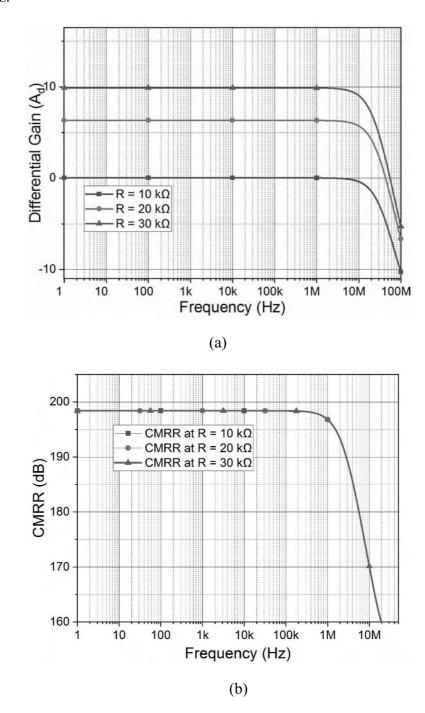

| Figure 4.3 (a) Differential gain and (b) CMRR69                                                                                                                                                                               |

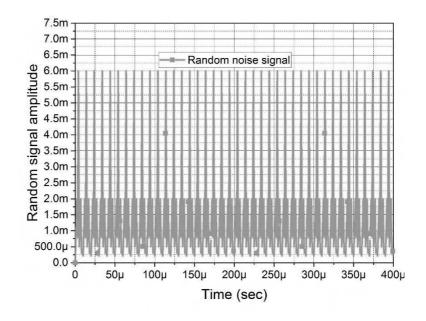

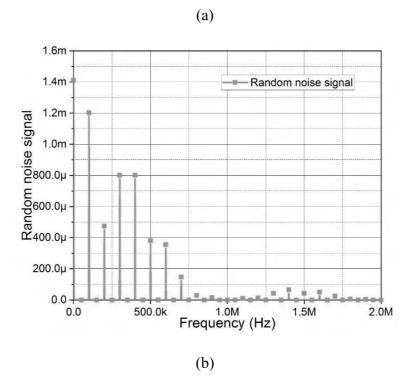

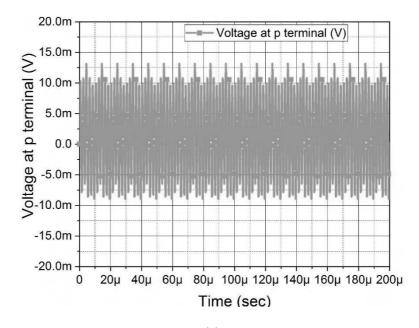

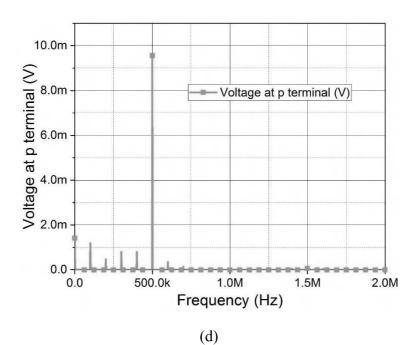

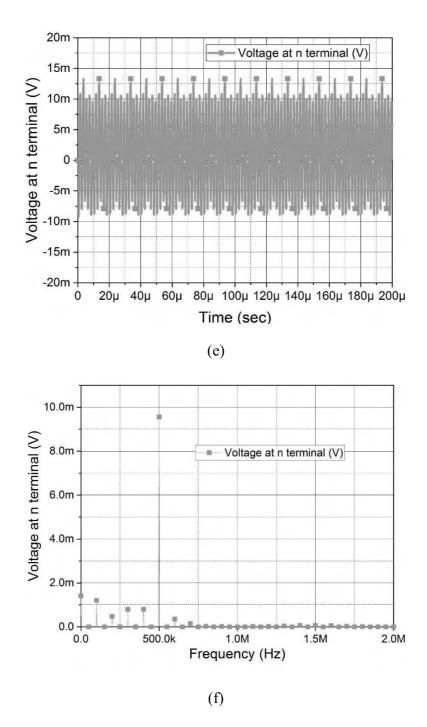

| Figure 4.4 Input signal (a) Random Noise Transient, (b) Noise Frequency spectrum:  Overall signal at p terminal (c) Transient, (d) Frequency spectrum; and Overall signal at n terminal (e) Transient, (f) Frequency spectrum |

| Figure 4.5 Output signal (a) transient and (b) frequency spectrum                                                                                                                                                             |

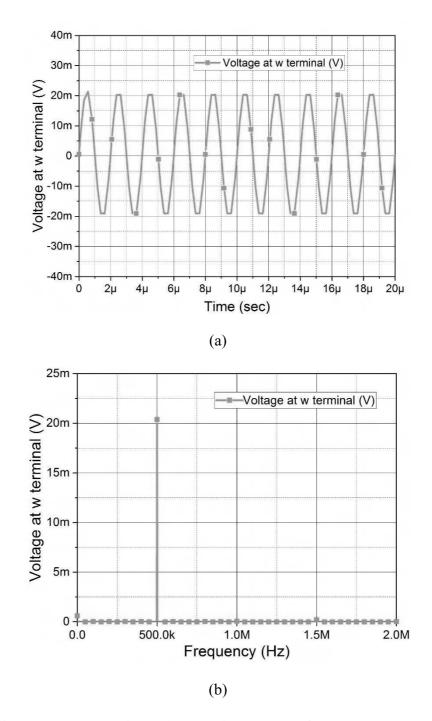

| Figure 4.6 (a) Input Noise and (b) Output Noise                                                                                                                                                                               |

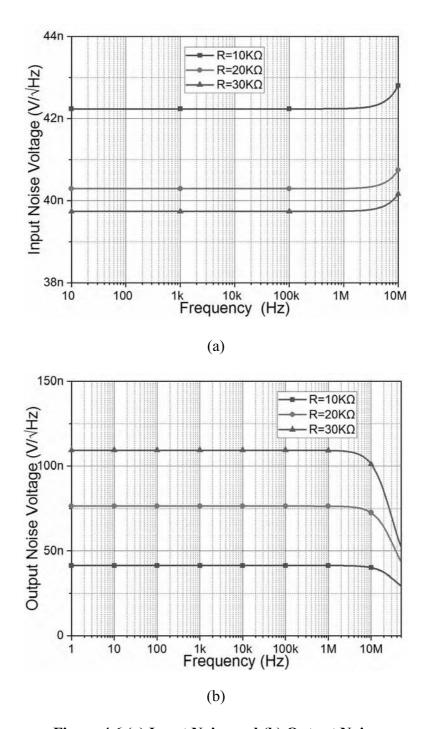

| Figure 4.7 (a) Monte Carlo Analysis for CMRR and (b) CMRR Vs W/L mismatch of M <sub>3</sub> and M <sub>4</sub>                                                                                                                |

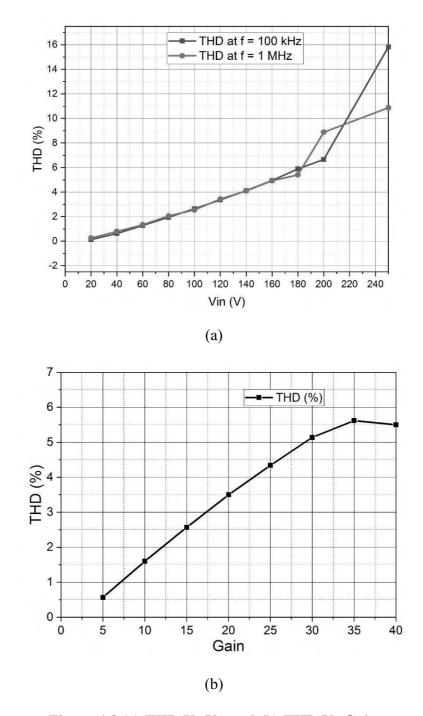

| Figure 4.8 (a) THD Vs V <sub>in</sub> and (b) THD Vs Gain                                                                                                                                                                     |

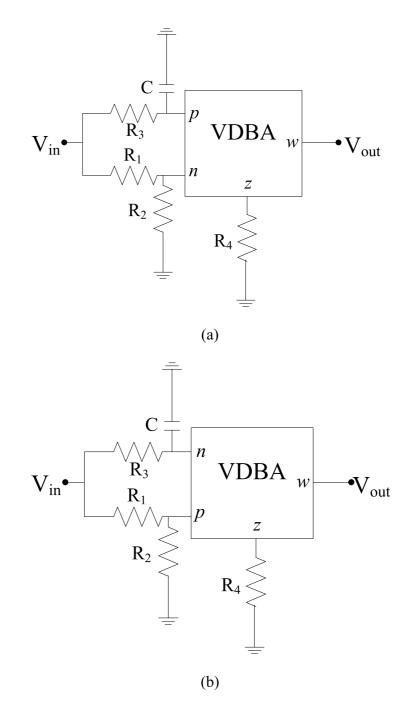

| Figure 4.9 The proposed First order (a) non-inverting and (b) inverting APF configurations                                                                                                                                    |

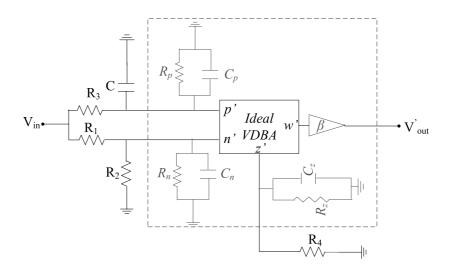

| Figure 4.10 Non-Ideal structure of non-inverting APF                                                                                                                                                                          |

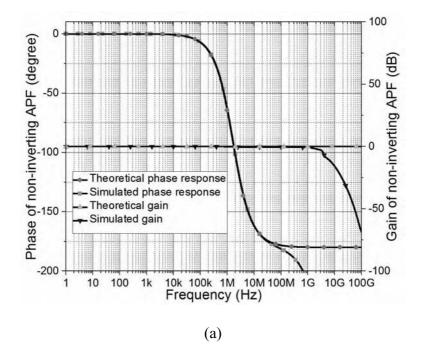

| Figure 4.11 The frequency response of (a) non-inverting APF and (b) inverting APF                                                                                                                                             |

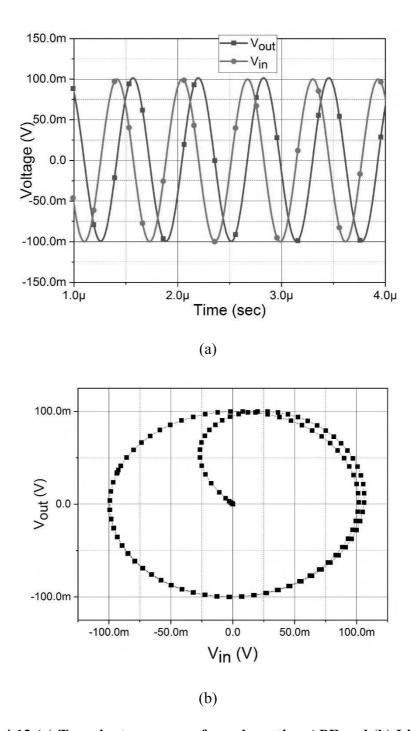

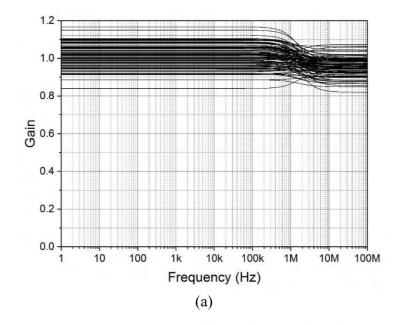

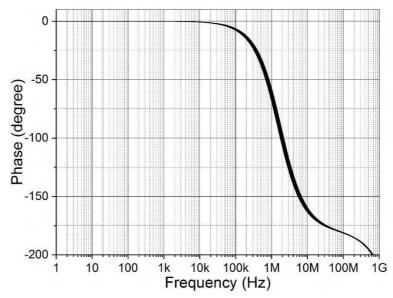

| Figure 4.12 (a) Transient response of non-inverting APF and (b) Lissajous pattern at right phase frequency                                                                                                                    |

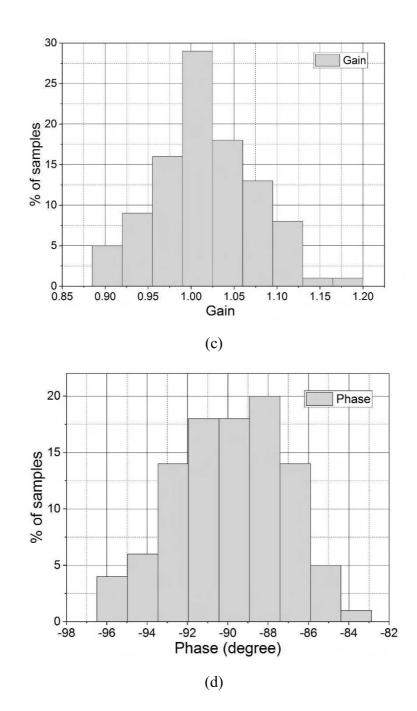

| Figure 4.13 Monte Carlo analysis for (a) gain and (b) phase responses; Monte Carlo histograms for (c) gain and (d) phase of the proposed non-inverting APF85                                                                  |

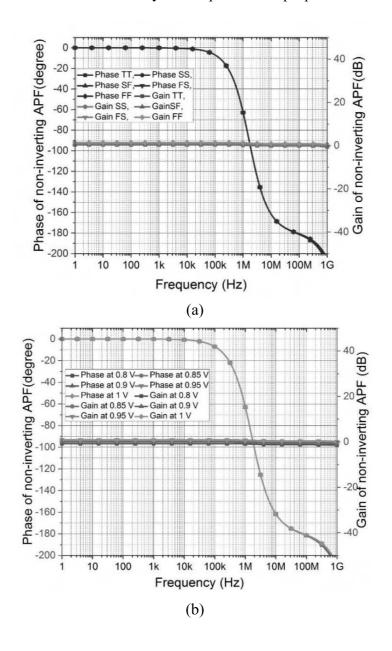

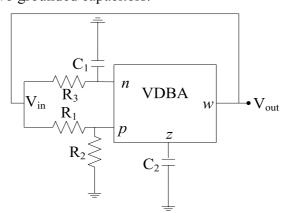

| Figure 4.14 Gain and Phase response of non-inverting APF at different (a) corners, (b) supply voltages and (c) temperatures                                                                                                   |

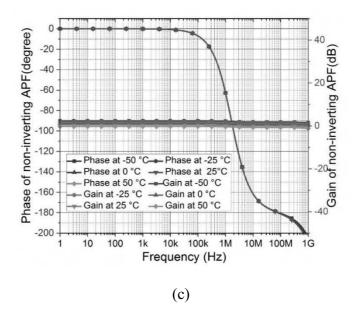

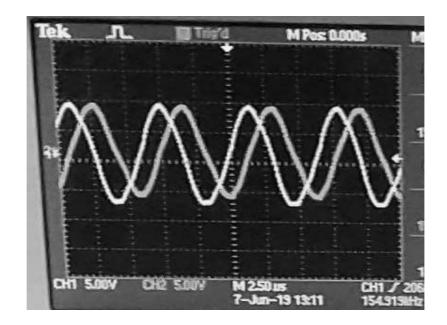

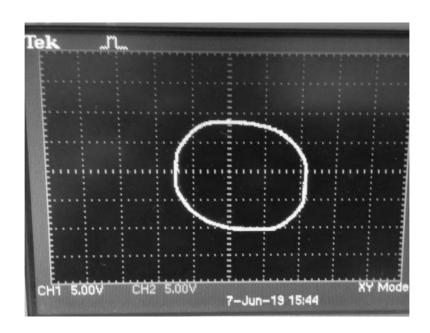

| Figure 4.15 Time domain responses and corresponding Lissajous patterns obtained experimentally at frequencies of (a) and (b) 50 kHz, (c) and (d) 100 kHz and (e) and (f) 250 kHz.                                             |

| Figure 4-16 The proposed SISO multifunction filter 89                                                                                                                                                                         |

| Figure 4.17 Non-ideal structure of SISO multifunction filter                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

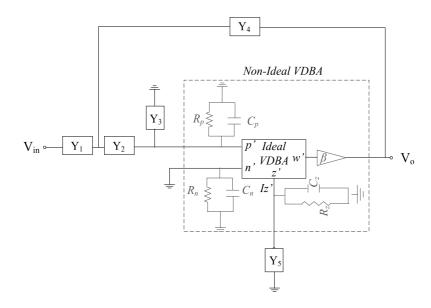

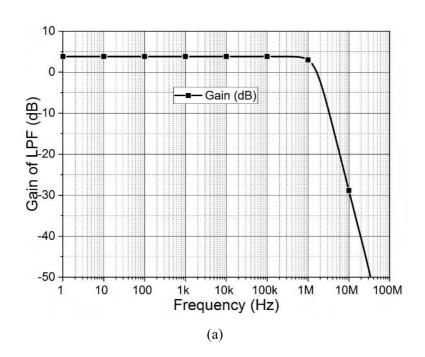

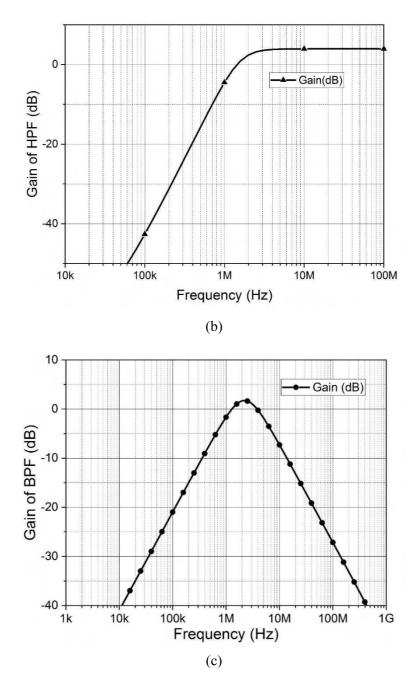

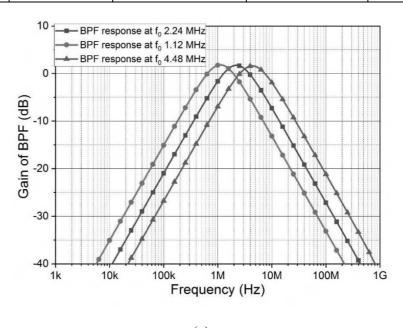

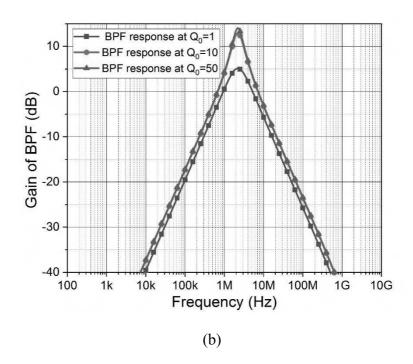

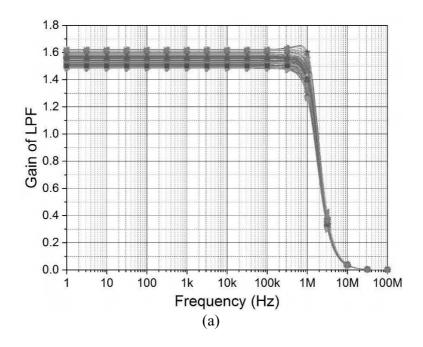

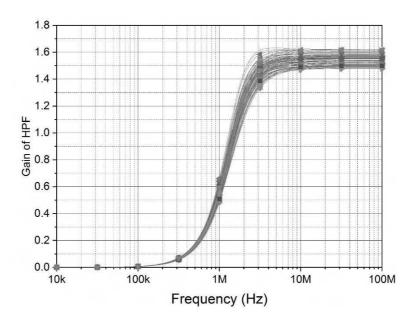

| Figure 4.18 Frequency responses of proposed (a) LPF, (b) HPF and (c) BPF95                                                                                                |

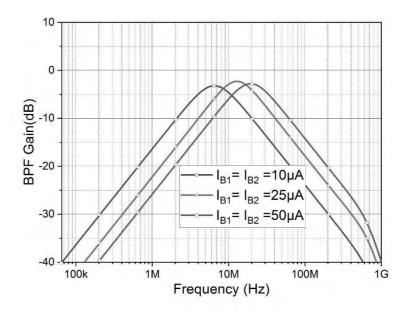

| Figure 4.19 (a) BPF response for independent tunability of (a) $f_0$ and (b) $Q_0$ 97                                                                                     |

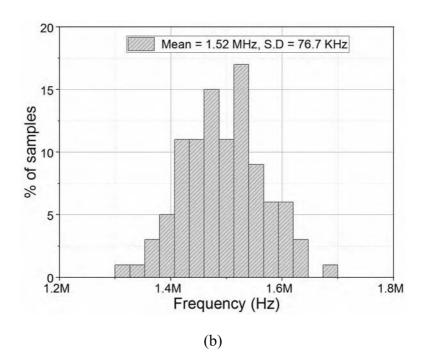

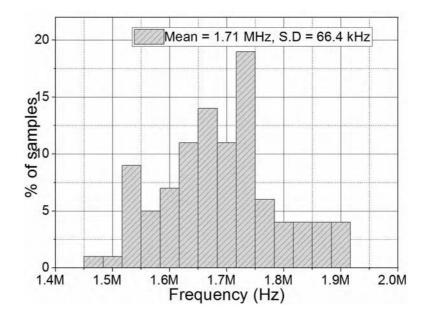

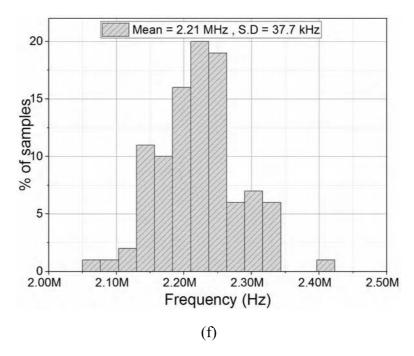

| Figure 4.20 Monte Carlo analysis, Frequency response and corresponding histogram of (a) and (b) LPF, (c) and (d) HPF, (e) and (f) BPF                                     |

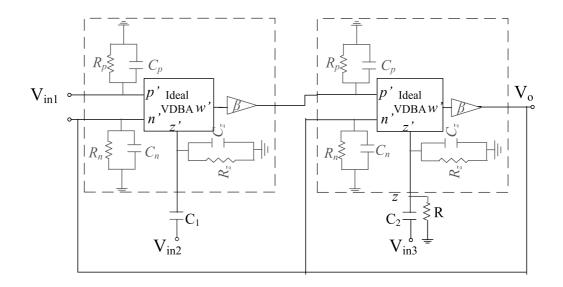

| Figure 4.21 Proposed universal MISO filter                                                                                                                                |

| Figure 4.22 Non-ideal structure of proposed VM universal MISO filter                                                                                                      |

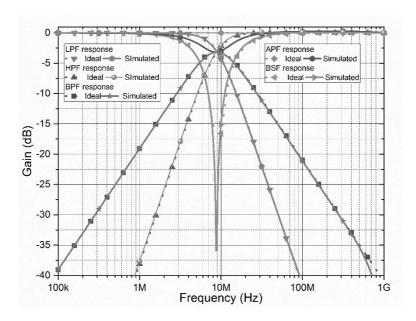

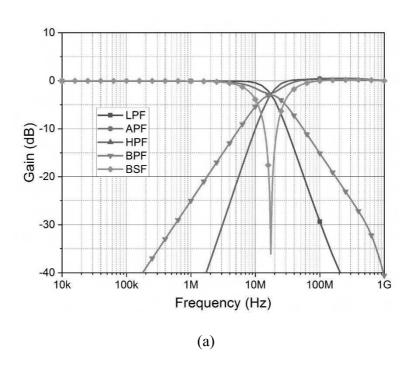

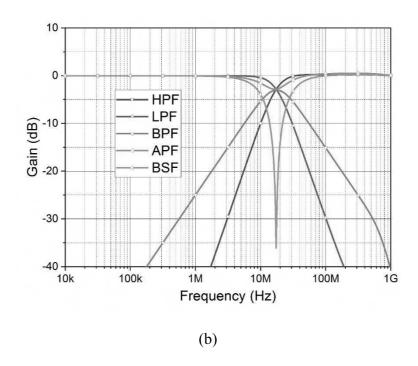

| Figure 4.23 Frequency response of VM MISO universal filter                                                                                                                |

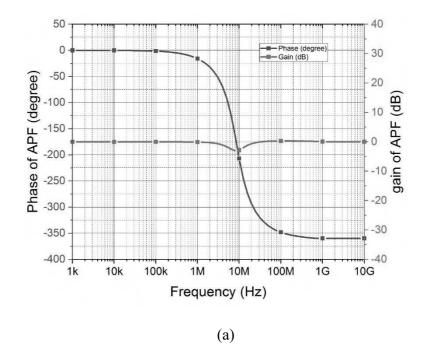

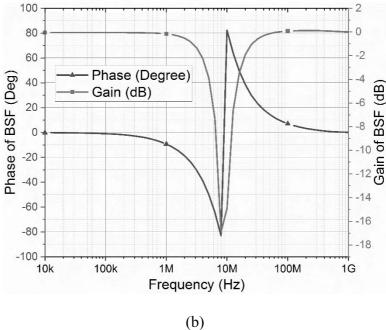

| Figure 4.24 Gain and phase responses of the (a) APF and (b) BSF105                                                                                                        |

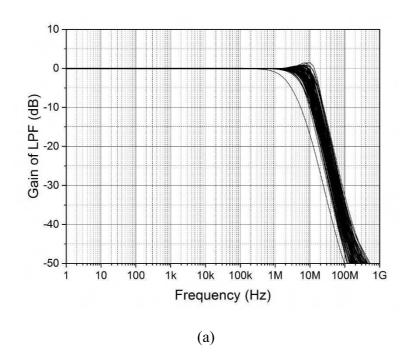

| Figure 4.25 (a) BPF response depicting electronic tunability of $f_0$ , (b) The $Q_0$ variation with capacitor ratio ( $C_2/C_1$ ) and (c) The $f_0$ variation with $I_B$ |

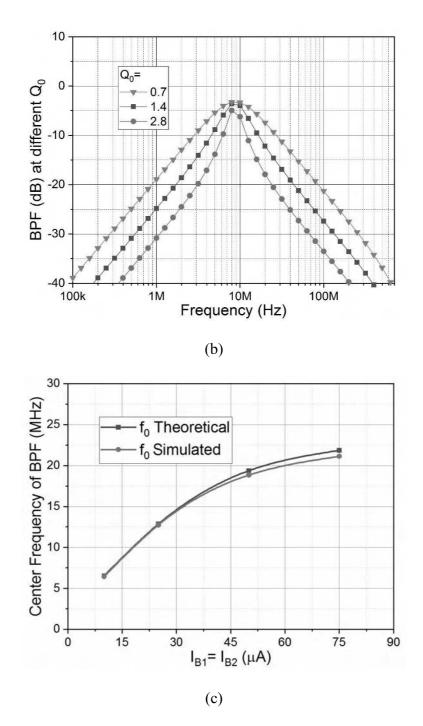

| Figure 4.26 (a) Transient input and output of HPF and (b) spectrum of input and output of HPF                                                                             |

| Figure 4.27 Monte Carlo (a) Frequency response of LPF and (b) Histogram 109                                                                                               |

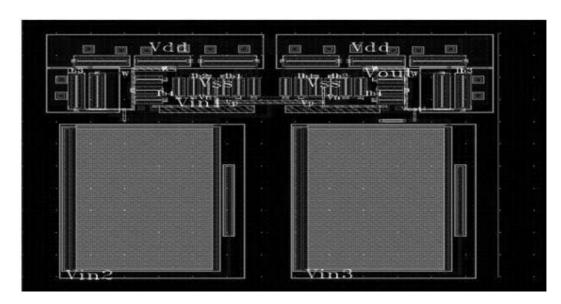

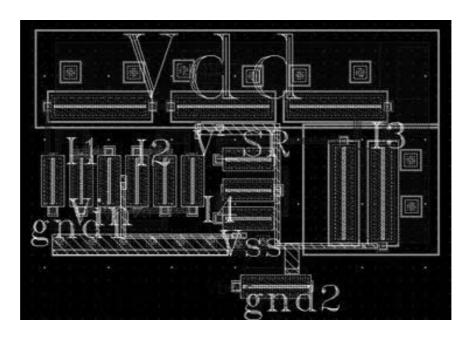

| Figure 4.28 Layout of the proposed MISO universal filter                                                                                                                  |

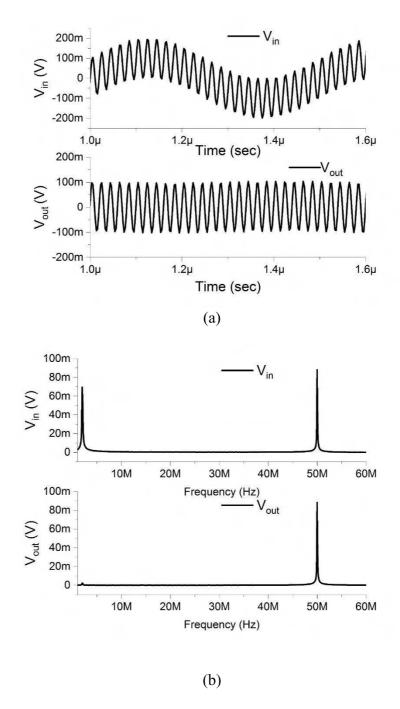

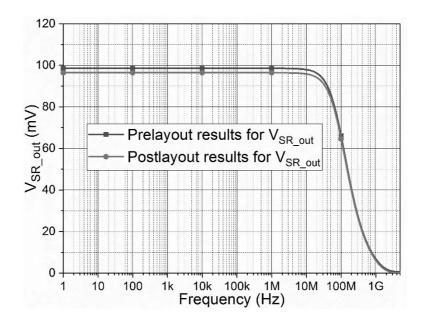

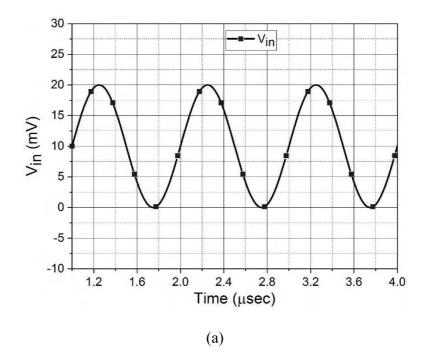

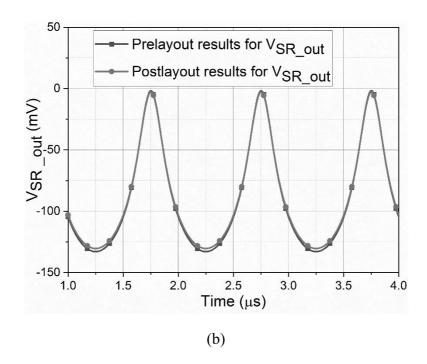

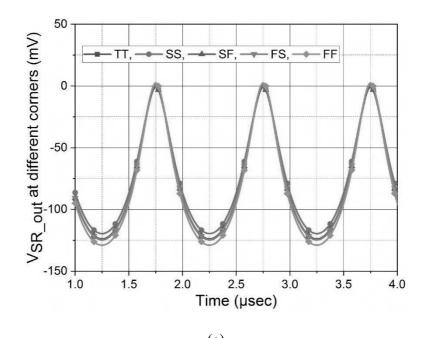

| Figure 4.29 (a) Pre layout and (b) Post layout, frequency response of proposed MISO universal filter                                                                      |

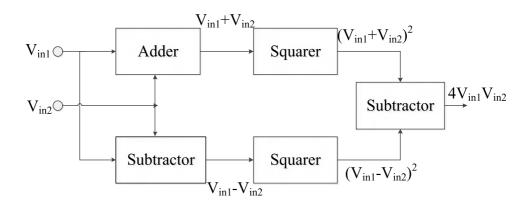

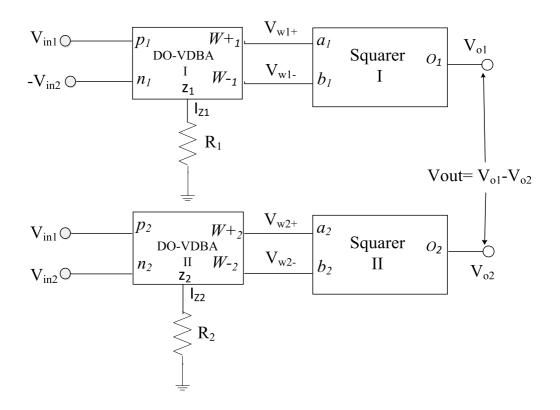

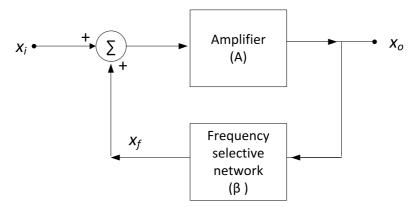

| Figure 5.1 Block diagram of quarter square algebraic identity                                                                                                             |

| Figure 5.2 Proposed VDBA based FQAM                                                                                                                                       |

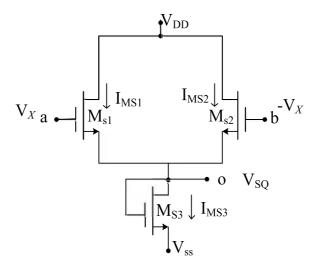

| Figure 5.3 Squarer circuit [128]                                                                                                                                          |

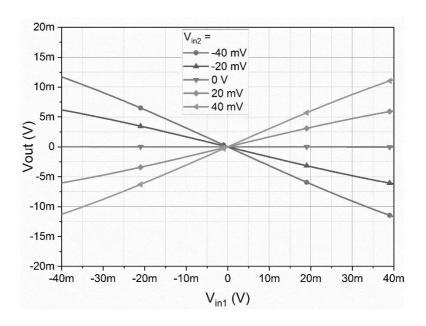

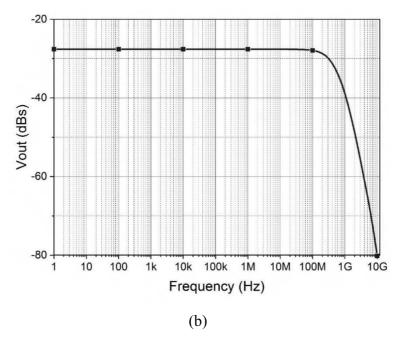

| Figure 5.4 (a) DC characteristics and (b) AC characteristics                                                                                                              |

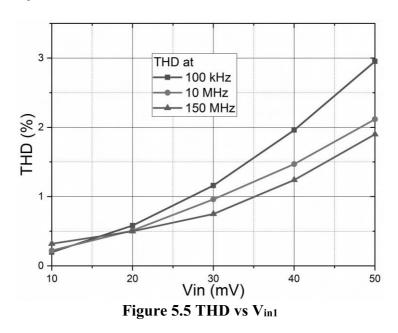

| Figure 5.5 THD vs V <sub>in1</sub>                                                                                                                                        |

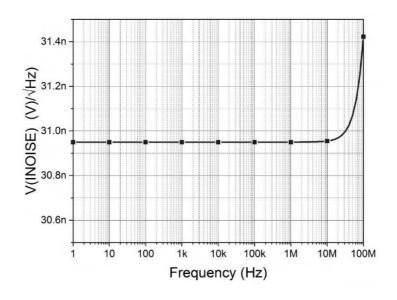

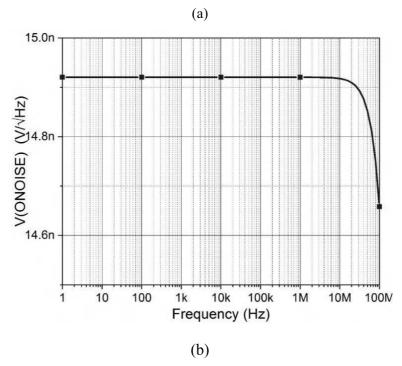

| Figure 5.6 (a) Input Noise and (b) Output Noise                                                                                                                           |

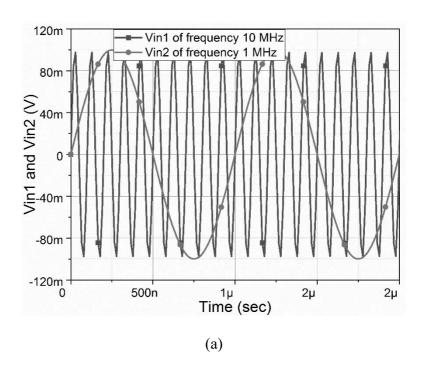

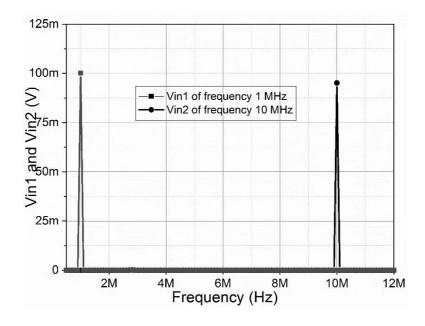

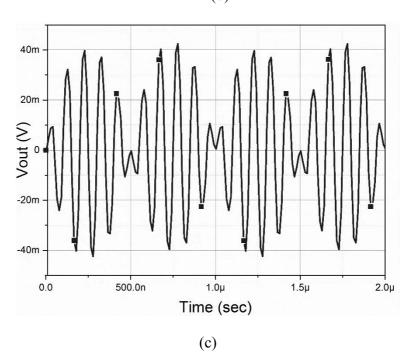

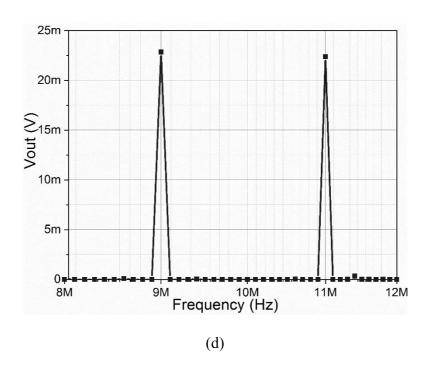

| Figure 5.7 (a) Input transient, (b) Frequency spectrum of input signal, (c) Output transient and (d) Frequency spectrum of output signal                                  |

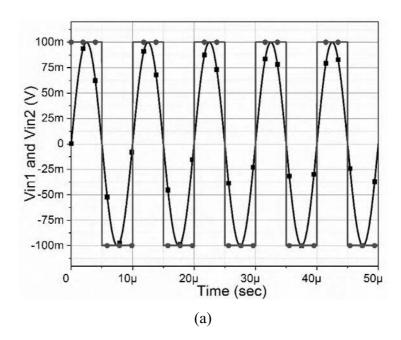

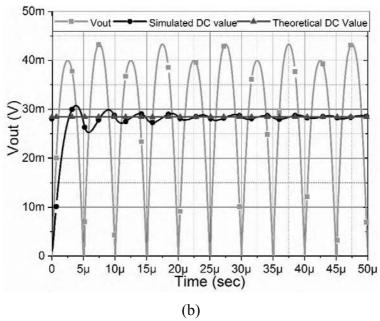

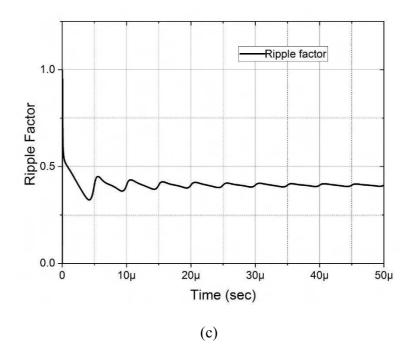

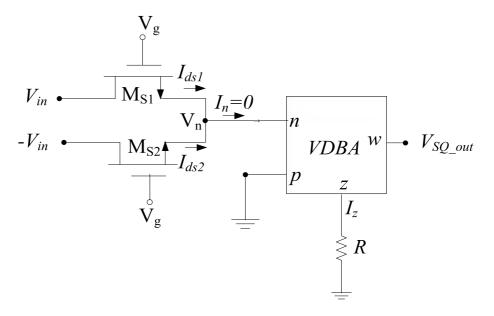

| Figure 5.8 Time domain representation of (a) input signals, (b) output signal and (c) ripple factor                                                                       |

| Figure 5.9 Proposed squaring circuit                                                                                                | 32 |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.10 Non-ideal model of squaring circuit                                                                                     | 35 |

| Figure 5.11 Layout of squaring circuit                                                                                              | 37 |

| Figure 5.12 DC characteristics of squaring circuit                                                                                  | 37 |

| Figure 5.13 AC characteristics of squaring circuit                                                                                  | 38 |

| Figure 5.14 (a) Sinusoidal input, (b) spectrum of the input, (c) transient output and (the output spectrum for the squaring circuit |    |

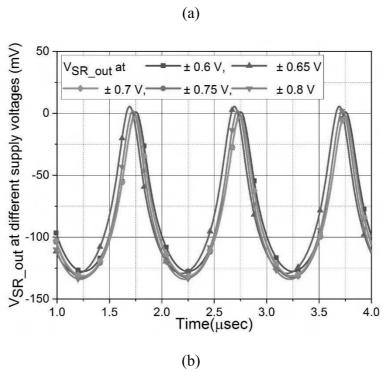

| Figure 5.15 Transient output of squaring circuit at different (a) corners, (b) supprolates and (c) temperatures                     |    |

| Figure 5.16 (a) THD Vs V <sub>in</sub> and (b) THD Vs R                                                                             | 43 |

| Figure 5.17 Proposed square rooting circuit                                                                                         | 45 |

| Figure 5.18 The non-ideal model for the square rooting circuit                                                                      | 46 |

| Figure 5.19 Layout of proposed square rooting circuits                                                                              | 49 |

| Figure 5.20 DC characteristics of square rooting circuit                                                                            | 49 |

| Figure 5.21 AC characteristics of square rooting circuit                                                                            | 50 |

| Figure 5.22 (a) Sinusoidal input and (b) the corresponding output of the square rooti circuit                                       | Ī  |

| Figure 5.23 Transient output of square rooting circuit at different (a) corners, (b) supprolates and (c) temperature                |    |

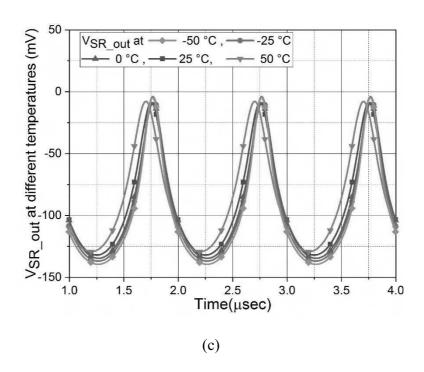

| Figure 6.1 Block diagrammatic representation of the sinusoidal oscillators                                                          | 55 |

| Figure 6.2 Proposed SP oscillator                                                                                                   | 56 |

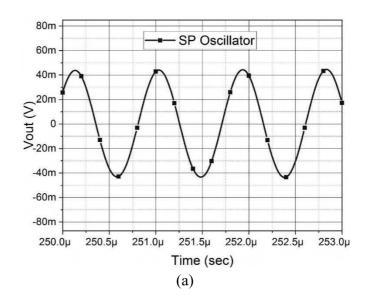

| Figure 6.3 (a) Steady state output and (b) Spectrum of SP oscillator1                                                               | 58 |

| Figure 6.4 (a) Steady state response and (b) Spectrum of SP oscillator1                                                             | 59 |

| Figure 6.5 Proposed QP topology I                                                                                                   | 60 |

| Figure 6.6 (a) Steady state output, (b) Spectrum and (c) Lissajous pattern of C topology I                                          |    |

| Figure 6.7 Proposed OP topology II                                                                                                  | 63 |

| Figure 6.8 (a) Steady state output, (b) spectrum and (c) Lissajous pattern of QP topology  II  |

|------------------------------------------------------------------------------------------------|

| Figure 6.9 (a) Steady state response and (b) Lisssajous pattern of QP topology II 166          |

| Figure 6.10 The QP Topology III                                                                |

| Figure 6.11 (a) Steady state output, (b) Spectrum and (c) Lissajous pattern of QP topology III |

| Figure 6.12 (a) Steady state response and (b) Lisssajous pattern of QP topology III 170        |

| Figure 6.13 Generic Approach of MPO                                                            |

| Figure 6.14 MP topology I                                                                      |

| Figure 6.15 (a) Steady state output and (b) Spectrum of MP topology I175                       |

| Figure 6.16 Steady state response of MSO                                                       |

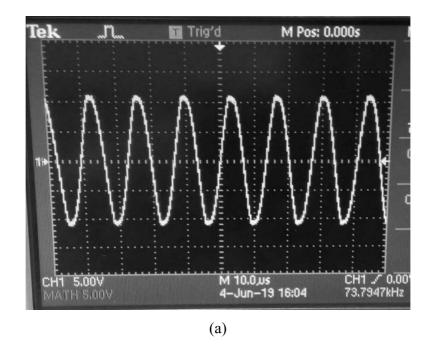

| Figure 6.17 MP topology II                                                                     |

| Figure 6.18 (a) Time domain output and (b) spectrum of 3 phase MP topology II 177              |

| Figure 6.19 (a) Time domain output and (b) spectrum of 4 phase MP topology II178               |

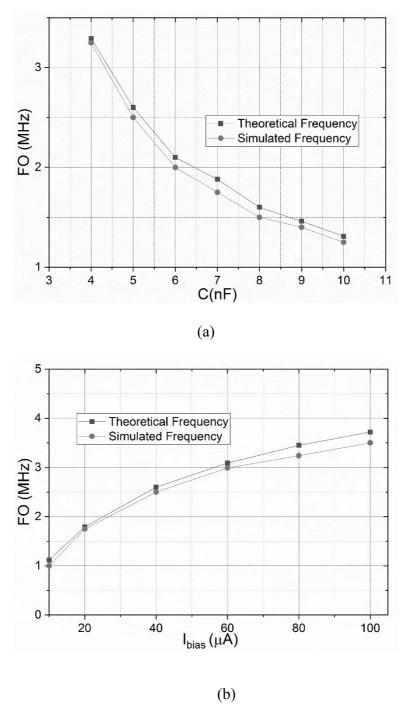

| Figure 6.20 (a) FO Vs C and (b) FO Vs I <sub>bias</sub>                                        |

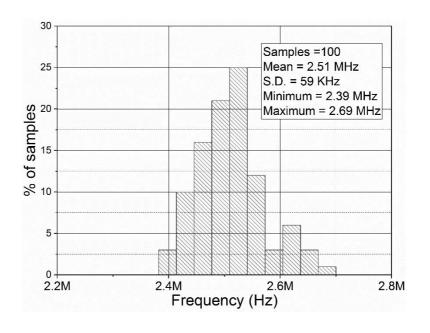

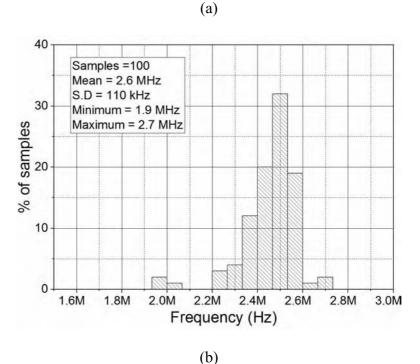

| Figure 6.21 Monte Carlo simulation results                                                     |

# LIST OF TABLES

| Table 1.1 Literature summary of different VDBA structures                           | 4   |

|-------------------------------------------------------------------------------------|-----|

| Table 1.2 Literature summary for filters using VDBA                                 | 7   |

| Table 1.3 Literature summary for oscillator using VDBA                              | 10  |

| Table 2.1 Aspect ratio of VDBA of Figure 2.4.                                       | 22  |

| Table 2.2 Aspect ratio of DO-VDBA of Figure 2.8                                     | 27  |

| Table 2.3 Parameters of VDBA and DO-VDBA                                            | 34  |

| Table 3.1 Dimensions of the MOS transistors used                                    | 44  |

| Table 4.1 Comparison of the proposed work with the previously reported work         | 62  |

| Table 4.2 Statistical results observed through Monte Carlo histograms               | 85  |

| Table 4.3 The frequency settings and corresponding results                          | 87  |

| Table 4.4 Selection of admittance for specific filter response                      | 90  |

| Table 4.5 Parameters of the specific filter response for equal component values     | 91  |

| Table 4.6 Passive Sensitivity Analysis                                              | 91  |

| Table 4.7 Component values chosen for various responses                             | 94  |

| Table 4.8 Component values used for f <sub>0</sub> tunability                       | 96  |

| Table 4.9 Component values used for independent tunability of Q <sub>0</sub>        | 96  |

| Table 4.10 Selection of input for specific filter response                          | 101 |

| Table 4.11 Component values for independent Q <sub>0</sub> tunability               | 106 |

| Table 4.12 The bias current and g <sub>m</sub> values for f <sub>0</sub> tunability | 106 |

| Table 5.1 Comparison of previously reported analog multipliers                      | 114 |

| Table 5.2 Comparison of existing VM squaring circuits                               | 131 |

| Table 5.3 Comparison of existing VM square rooting circuits                         | 144 |

| Table 7.1 Summary of work presented in the thesis                                   | 185 |

#### **ABBREVIATIONS**

**APF**

all pass filter

**OTA** operational transconductance amplifier analog building blocks **ABBs** ADE analog design environment band pass filter **BPF BSF** band stop filter bandwidth BWcommon mode rejection ratio **CMRR** condition of oscillation CO current controlled CDBA CC-CDBA current controlled CDTA **CCCDTA CCC** current controlled current conveyor current controlled current through transconductance amplifier **CCCTTA**

current conveyor CC

current differencing buffered amplifier CDBA

current differencing transconductance amplifier CDTA

current feedback operational amplifier CFOA

current follower CF

current follower transconductance amplifier CFTA

current mode CM

current mode instrumentation amplifier CMIA

current through transconductance amplifier CTTA

design rule check DRC

differential difference amplifier DDA

differential difference OFA DDOFA

differential flip voltage follower DFVF

dual output VDBA DO-VDBA

dynamic threshold MOSFET DTMOS

flip voltage follower FVF

floating gate MOSFET FGMOS

four quadrant analog multiplier FQAM

four terminal floating nullor FTFN

frequency of oscillation FO

fully balanced VDBA FB-VDBA

fully differential flip voltage follower FD-FVF

high pass filter HPF

input common mode range ICMR

instrumentation amplifier IA

layout vs. schematic check LVS

low pass filter LPF

multiphase MP

multiple inputs multiple output MIMO

multiple inputs single output MISO

Number of inputs and outputs: single input single output SISO

operational floating amplifier OFA

operational transresistance amplifier OTRA

quadrature phase QP

single input multiple outputs SIMO

single phase SP

total harmonic distortion THD

transadmittance mode TAM

transadmittance mode IA TAMIA

transconductance amplifier TA

transfer function TF

transimpedance IA TIMIA

transimpedance mode TIM

unity gain BW UGB

voltage differencing buffered amplifier VDBA

voltage differencing inverted buffered amplifier VDIBA

voltage differencing transconductance amplifier VDTA

voltage mode VM

voltage mode instrumentation amplifier VMIA

Z copy VDBA ZC-VDBA

#### 1.1 Introduction

Nowadays in electronic systems, storage and signal processing are done in digital domain [1]. However, the real-world signals are represented in the analog domain and therefore analog signal processing serves as an interfacing medium between the two. The analog signal processing requires a number of applications such as filters, amplifiers, comparators, sample and holding circuit, digital-analog convertor and analog-digital convertor.

In lumped electric networks, the information being processed may be denoted through node voltages or through branch currents [1]. An analog circuit is termed as voltage mode (VM) circuit when the information is expressed through voltage levels at different nodes, whereas if branch currents represent the signal, the circuit is termed as a current mode (CM) circuit [2]. A VM circuit is supposed to deliver large swing in output voltage keeping minimum power consumption. It results into a high impedance node design. The parasitic capacitance in the VM circuit needs charging and discharging with the full swing for signal processing, which confines the slew rate and speed [3]. The CM circuit is a low impedance node network, making it a low time constant circuit that improves speed and slew rate. It is well established in the literature [1], [2], [4] that a CM circuit may function with lower voltage supply [5] and at a given supply, the CM circuit possess higher dynamic range in comparison to its VM counterpart. The simple architecture of CM circuits makes it more attractive compared to VM circuits. It leads to smaller die area.

These advantages led researchers to explore CM circuits which are manifested in the form of several analog building blocks (ABBs) and are presented in [1], [5]–[53] and

references cited therein. The current conveyor (CC) [6] is an amalgam of current/voltage circuit and is most widely explored ABB. The different generations of CC were named as CCI, CCII [7], [34]–[39] and CCIII [8]. They were introduced in the years 1968, 1970 and 1995 respectively and the three generations of CC differ in terms of terminal characteristics. A variety of modifications in the basic conveyor structure, for more effective utilization, led to the introduction of various CC based newer elements [9]–[19]. An operational transconductance amplifier (OTA) [20], is a three terminal block and the output current is the multiplication of transconductance gain and difference of input voltages. To be compatible with VM circuits, it becomes essential to translate the output current into a voltage signal. A four terminal block having port relations analogous to CCII followed by a voltage buffer is the current feedback operational amplifier (CFOA) [21], [22], [41]. The operational floating amplifier (OFA) [24], differential difference amplifier (DDA) [26], differential difference OFA (DDOFA) [25] and four terminal floating nullor (FTFN) [23] are few examples of fully balanced structures and hence are more immune to noise. The circuit element operational transresistance amplifier (OTRA) [5], [42], [43] is a three terminal ABB and a current controlled voltage source. A simplified version of the OTRA is current differencing buffered amplifier (CDBA) [27], consisting of a current differencing unit [52] and a voltage buffer. Another block having current differencing unit as an input section and being explored widely is the current differencing transconductance amplifier (CDTA) reported in [29]. In current controlled CDBA (CC-CDBA) [28] and current controlled CDTA (CCCDTA)[30], [53], the circuit parameters are controlled electronically. In the current follower transconductance amplifier (CFTA) [31], the current follower (CF) is followed by a transconductance amplifier (TA) and is suited for CM circuits as its input and output signals are current. A different

class of CM ABBs has evolved recently, having a TA as the input stage. One block of this class is voltage differencing transconductance amplifier (VDTA) [32]. The second important block receiving great attention for circuit designing is voltage differencing buffered amplifier (VDBA) [33].

The VDBA was first conceptualized by Biolek *et al.* [1] as a block consisting of a TA followed by a buffer. This block can provide both current and voltage outputs at an appropriate impedance level thereby providing design flexibility. Additionally, incircuit implementation of VDBA, its transconductance ( $g_m$ ) can be controlled through bias current which helps in the electronic tuning of design parameters of the applications build around this ABB. This leads to ease of circuit integration. The VDBA, therefore, has evolved as a promising choice for analog applications [33], [54]–[67] and this has led the author to explore analog circuit designing using VDBA.

#### 1.2 Available Literature

An extensive literature review is carried out which advises that the available literature on VDBA may be categorized as the work associated with

- VDBA Implementations [33], [54]–[67]

- VDBA Applications [33], [54]–[91]

#### 1.2.1 VDBA Implementations

Various implementation of VDBA and its variants are available in the literature. The CMOS implementation of VDBA has been presented in [33] and [65]. The floating gate MOSFET (FGMOS) based VDBA implementation is proposed by Ninawe *et al.* [55] and a dynamic threshold MOSFET (DTMOS) based VDBA structure is presented in [56] which operates at ultra low power supply (0.2 V). To further enhance the versatility

of these blocks, some modifications in the internal structure have been proposed by researchers leading to its variants like voltage differencing inverted buffered amplifier (VDIBA) [57]–[60]. In VDIBA the output unit consists of an inverted voltage buffer. In dual output VDBA (DO-VDBA) [61] alteration is done to get the output voltages in inverted/non-inverted forms simultaneously. Another amendment is done to have the current and voltage outputs with both signs and the circuit is termed as a fully balanced VDBA (FB-VDBA) [61]–[63]. One more variant termed as Z copy VDBA (ZC-VDBA) is reported by Guney *et al.* in [64], in which two z terminals of same polarity exists. The VDBA using BiCMOS technology is implemented by Onjan *et al.* [66]. Design and analysis of tunable VDIBA with enhanced performance is presented in [67]. These structures along with their salient features have been summarized in Table 1.1.

Table 1.1 Literature summary of different VDBA structures

| Reference No. | Block | Technology (µm)           | Power Supply (V) | No of transistors +<br>passive components  | Linear input voltage range of TA (V) | Linear input voltage<br>range of<br>Buffer (V) | Transconductance (μS) at bias current (IB) (μA) | Buffer transfer ratio | 3 dB BW of TA<br>(MHz)   | 3 dB BW of Buffer (MHz)  | Power consumption (µW)    |

|---------------|-------|---------------------------|------------------|--------------------------------------------|--------------------------------------|------------------------------------------------|-------------------------------------------------|-----------------------|--------------------------|--------------------------|---------------------------|

| [33]          | VDBA  | 0.35                      | ±1.5             | 16 MOS                                     | ± 0.2                                | -1.5<br>to 1.1                                 | 748<br>I <sub>B</sub> not<br>reported           | 1                     |                          | -                        | 970                       |

| [54]          | VDBA  | 0.18                      | ±2               | 29 MOS<br>+<br>2Resistor<br>+1<br>Capaitor |                                      | ± 0.25                                         | $79$ at $I_B =$ $120$                           | 1                     | 69                       | 49.5                     | 1.4×1<br>0 <sup>3</sup>   |

| [55]          | VDBA  | 0.18                      | ±1.3             | 12 MOS<br>+4FGM<br>OS                      | ± 0.4                                |                                                | 483 I <sub>B</sub> not reported                 | 0.97                  | 385                      |                          | 745                       |

| [56]          | VDBA  | 0.18                      | ±<br>0.2         | 7 MOS<br>+9<br>DTMOS                       | 0.145<br>to 0.                       | - 0.145<br>to 0.2                              | 0.064<br>I <sub>B</sub> not<br>reported         | 1                     | 3.7<br>×10 <sup>-3</sup> |                          | 6.22<br>×10 <sup>-3</sup> |

| [57]          | VDIBA | 0.09                      | ±<br>0.6         | 12 MOS<br>+3<br>Resistor                   | ±<br>0.05                            | - 0.5<br>to 0.2                                | $3.58 \times 10^3$ at $I_B = 220$               | 0.94<br>4             | 334                      | 3.75<br>×10 <sup>3</sup> | 4.54<br>×10 <sup>3</sup>  |

| [58]          | VDIBA | Com<br>meri<br>cal<br>ICs | ± 5              |                                            |                                      | -1                                             |                                                 |                       |                          | I                        |                           |

| [59] | VDIBA | 0.18 | ±0.7 | 5 MOS    | ±0.25 | -0.75      | 582                    | 0.98        | 92.47            | 1.58             | 1.5×1   |

|------|-------|------|------|----------|-------|------------|------------------------|-------------|------------------|------------------|---------|

|      |       |      | 5    | +1       |       | to 0.5     | at I <sub>B</sub> =100 | 5           |                  | $\times 10^{3}$  | $0^{3}$ |

|      |       |      |      | FGMOS    |       |            |                        |             |                  |                  |         |

| [60] | VDIBA | 0.18 | ±    | 13 MOS   | ±0.3  | -0.4       | 223                    | 0.98        | 1.124            | 2.35             | 569     |

|      |       |      | 0.4  | +2       |       | to 0.16    | at I <sub>B</sub> =50  | 1           | ×10 <sup>3</sup> | ×10 <sup>3</sup> |         |

| 5647 |       | 0.10 |      | FGMOS    | . 0.4 |            |                        | 0.06        | 1.00             |                  |         |

| [61] | DO-   | 0.18 | ±    | 8 MOS    | ±0.1  | $\pm 0.25$ | 500                    | 0.96        | 160              |                  |         |

|      | VDBA  |      | 1.2  |          |       |            | at $I_B = 50$          | 2/          |                  |                  |         |

|      |       |      |      |          |       |            |                        | 0.92        |                  |                  |         |

|      |       |      |      |          |       |            |                        | 6 at<br>two |                  |                  |         |

|      |       |      |      |          |       |            |                        | outp        |                  |                  |         |

|      |       |      |      |          |       |            |                        | uts         |                  |                  |         |

|      | FB-   | 0.18 | ±    | 16 MOS   | ±0.1  |            | $1.025 \times 10^3$    |             | 51               |                  | _       |

|      | VDBA  |      | 1.2  | 1011100  | 0.12  |            | at $I_B = 50$          |             |                  |                  |         |

|      |       |      |      |          |       |            |                        |             |                  |                  |         |

| [62] | FB-   | Com  | ±5   |          |       |            | 0.1×10 <sup>6</sup>    |             |                  |                  |         |

|      | VDBA  | mer  |      |          |       |            | I <sub>B</sub> not     |             |                  |                  |         |

|      |       | cial |      |          |       |            | reported               |             |                  |                  |         |

|      |       | ICs  |      |          |       |            |                        |             |                  |                  |         |

| [63] | FB-   | 0.35 | ±0.7 | 10 MOS   | ±     | $\pm 0.4$  | $3.5 \times 10^3$      | 0.98        | 23               | 1.3×1            | 1.6×1   |

|      | VDBA  |      | 5    | + 14 BJT | 0.05  |            | at I <sub>B</sub> =100 | 6           |                  | 03               | 03      |

| [64] | ZC-   | 0.18 | ±    | 28 MOS   | ± 0.5 | - 0.5      | 50                     | 0.95        | 884/             | 487              | 690.3   |

|      | VDBA  |      | 0.9  |          |       | to 0.7     | at $I_B = 47$          | 3           | 926              |                  |         |

|      |       |      |      |          |       |            |                        |             | at               |                  |         |

|      |       |      |      |          |       |            |                        |             | two              |                  |         |

|      |       |      |      |          |       |            |                        |             | outpu            |                  |         |

|      |       |      |      |          |       |            |                        |             | ts               |                  |         |

| [65] | VDBA  | 0.25 | ± 2  | 17       | 土     | ± 0.10     | 500                    | 0.99        |                  | 145              |         |

| []   | _     |      |      |          | 0.10  |            | at I <sub>B</sub> =40  | 1           |                  | -                |         |

| [66] | DO-   | 0.35 | ±0.7 | 7        |       |            | 580                    |             |                  |                  |         |

|      | VDBA  |      | 5    | MOS+6    |       |            | at I <sub>B</sub> =15  |             |                  |                  |         |

|      |       |      |      | BJT      |       |            |                        |             |                  |                  |         |

| [67] | VDIBA | 0.18 | ±    | 12 MOS   | ±     |            | 1024 at                | 1.07        | 263              |                  | 560     |

|      |       |      | 0.6  | + 2      | 0.50  |            | $I_{\rm B}=150$        |             |                  |                  |         |

|      |       |      |      | Resistor |       |            |                        |             |                  |                  |         |

It may be observed from Table 1.1 that though a variety of VDBA structures exist but a VDBA providing high  $g_m$  and bandwidth (BW) with low power consumption has not been explored and leads to a significant research gap.

## 1.2.2 VDBA Applications

In the available literature VDBA is used for designing numerous signal processing and generating applications as summarized below:

- i) Active immittance simulators [68]–[77]

- ii) Filters [33], [54]–[60], [62]–[68], [78]–[84]

- iii) Signal generators [61], [82], [85]–[91]

#### i) Active immittance simulators

An inductor is an essential and integral part of any electronic circuit. But due to large area requirement, weight, cost and electronic tunabilty, on chip design of inductor is not possible. This can be fixed by simulating the inductor using the ABBs. A VDBA with two passive elements are used to realize a lossless grounded inductance simulator in [68]. A grounded lossy parallel inductance simulation is presented in [69]. A resistorless floating inductance simulator employing two VDBAs with a capacitor is presented in [70]. One series and one parallel active floating lossy inductance simulators are presented by [71]. A floating lossy series type inductance simulator having electronic tunability, using two VDBAs is presented in [72]. A variable lossy series inductance simulator using a single VDBA is presented in [73].

Further, to obtain large valued capacitors using small capacitors, few capacitance multiplier structures have also been presented in the literature. A capacitance multiplier using single VDBA, a capacitor and a grounded resistor is proposed in [74]. Two capacitance multipliers with a grounded capacitor and a VDBA having electronic tunability are realized in [55] and [56]. Tunable floating capacitance multiplier using single FB-VDBA, a capacitor and a resistor is realized in [77].

#### ii) Filters

Filters find widespread usage in communication and instrumentation systems and are the essential building block in analog signal processing. These are frequency selective networks that allow a specified range of frequencies to be passed known as filter pass band, while attenuate frequencies outside this range known as filter stop band. In literature, the categorization of filters is done in several ways as:

- -Filter transmission characteristic: low pass filter (LPF), high pass filter (HPF), band pass filter (BPF), band stop filter (BSF) and all pass filter (APF),

- -Slope of the stop band: first, second and higher order filters,

- -Input and output signals: CM, VM, or transimpedance mode (TIM) or transadmittance mode (TAM) filters,

- -Number of inputs and outputs: single input single output (SISO), single input multiple outputs (SIMO), multiple inputs single output (MISO) and multiple inputs multiple output (MIMO).

A number of filter applications exists in literature using VDBA and its variants [33], [54]–[60], [62]–[68], [78]–[84]. The available literature on filters using VDBA and its variant is summarized in Table 1.2.

Table 1.2 Literature summary for filters using VDBA

| Reference | No. of ABB | Order | Type | Standard filter<br>Function   | Mode | Passive elements<br>(R+C) | Supply voltage (V) | Independent 000 and<br>Q0 | Output impedance | Power Consumption (mW) | Technology used          |

|-----------|------------|-------|------|-------------------------------|------|---------------------------|--------------------|---------------------------|------------------|------------------------|--------------------------|

| [57]      | 3<br>VDIBA | 3     | SISO | LPF                           | VM   | 0+3                       | 0.6                |                           | Low              | 12.3                   | 0.09 μm<br>CMOS          |

| [58]      | 1<br>VDIBA | 2     | MISO | LPF, BPF,<br>HPF, APF,<br>BSF | VM   | 1+2                       | 0.9                | No                        | High             |                        | 0.18 μm<br>CMOS          |

| [59]      | 2<br>VDIBA | 2     | MISO | LPF, BPF,<br>HPF, APF,<br>BSF | VM   | 0+2                       | 0.75               | No                        | Low              | 2.8                    | 0.18 μm<br>CMOS<br>FGMOS |

| [60]      | 2<br>VDIBA | 2     | MISO | LPF, BPF,<br>HPF              | VM   | 0+2                       | 0.4                | No                        | Low              | 1.1                    | 0.18 μm<br>FGMOS         |

| [67]      | 2<br>VDIBA | 2     | MISO | LPF, BPF,<br>HPF, APF,<br>BSF | VM   | 1+2                       | 0.6                | Yes                       | Low              |                        | 0.18 μm<br>CMOS          |

| [79]      | 1<br>VDIBA | 2     | MISO | LPF, BPF,<br>HPF, APF,<br>BSF | VM   | 1+2                       | 0.9                | No                        | High             | 10.5                   | 0.18 μm<br>CMOS          |

| [82]      | 1<br>VDIBA | 1     | SISO | APF                           | VM   | 0+1                       |                    | Yes                       | Low              |                        | OPA860                   |

| [84] | 2<br>VDIBA    | 2 | MISO   | BPF, HPF               | VM    | 1+2   | 0.6  | No  | Low  |      | 0.045 μm<br>CMOS   |

|------|---------------|---|--------|------------------------|-------|-------|------|-----|------|------|--------------------|

| [0+] | VDIDA         |   | MISO   | LPF, BPF,              | V 1V1 | 1 1 2 | 0.0  | 110 | Low  |      | CMOS               |

|      | 2             |   | Mac    | HPF, APF,              | 773.f | 0.12  | 1.5  |     |      | 0.07 | 0.18 μm            |

|      | VDBA          | 2 | MISO   | BSF                    | VM    | 0+2   | 1.5  | No  | Low  | 0.97 | CMOS               |

|      | 2             |   |        | LPF, BPF,<br>HPF, APF, |       |       |      |     |      |      | 0.18 µm            |

| [33] | VDBA          | 2 | MISO   | BSF                    | VM    | 1+2   | 1.5  | Yes | Low  | 0.97 | CMOS               |

|      |               |   |        | LPF, BPF,              |       |       |      |     |      |      | 0.18 μm            |

|      | 2             |   |        | HPF, APF,              |       |       |      |     | _    |      | CMOS               |

| [55] | VDBA          | 2 | MISO   | BSF                    | VM    | 1+2   | 1.35 | No  | Low  | 1.5  | FGMOS              |

|      | 2             |   |        | LPF, BPF,              |       |       |      |     |      | 13x  | 0.18 μm<br>CMOS    |

| [56] | VDBA          | 2 | MISO   | HPF, BSF               | VM    | 2+2   | 0.2  | No  | Low  | 10-6 | DTMOS              |

|      | 1             |   |        | ĺ                      |       |       |      |     |      |      | 0.25 μm            |

| [65] | VDBA          | 1 | SISO   | APF                    | VM    | 0+2   | 2    |     | Low  |      | CMOS               |

|      |               |   |        |                        |       |       |      |     |      |      | 0.35 μm            |

| [(() | 2             | 2 | CICO   | ADE                    | N/M   | 0+2   | 0.75 | Van | Т    |      | CMOS               |

| [66] | VDBA<br>1     |   | SISO   | APF                    | VM    | 0+2   | 0.75 | Yes | Low  |      | BiCMOS             |

| [68] | VDBA          | 2 | SISO   | BPF                    | VM    | 2+2   | 5    | Yes | Low  |      | OPA 860            |

|      | 1             |   |        | LPF, BPF,              |       |       |      |     |      |      | 0.18 μm            |

| [78] | VDBA          | 2 | MISO   | HPF                    | VM    | 2+2   | 0.9  | No  | High | 0.45 | CMOS               |

|      | _             |   |        | LPF, BPF,              |       |       |      |     |      |      |                    |

| [83] | 2<br>VDBA     | 2 | MISO   | HPF, APF,<br>BSF       | VM    | 1+2   | 0.6  | No  | Low  |      | OPA860             |

| [65] | 3 ZC-         |   | MISO   | HPF,BPF,               | V IVI | 1 1 2 | 0.0  | 110 | LOW  |      | 0.18 μm            |

| [54] | VDBA          | 2 | SIMO   | LPF                    | VM    | 0+2   | 2    | No  | Low  | 4.2  | CMOS               |

|      | 2 ZC-         |   |        | LPF, BPF,              |       |       |      |     |      |      | 0.18µm             |

| [64] | VDBA          | 2 | SIMO   | HPF                    | CM    | 0+2   | 0.9  | No  | High | 1.48 | CMOS               |

|      | 4 ED          |   |        | I DE DDE               |       |       |      |     |      |      | SPICE              |

| [62] | 2 FB-<br>VDBA | 2 | SIMO   | LPF, BPF,<br>HPF       | VM    | 4+2   | 5    | No  | Low  |      | Model of<br>OPA860 |

| [02] | 1 FB-         |   | SHVIO  | III I                  | A TAT | 712   | , ,  | 110 | LOW  |      | 0.35 μm            |

| [63] | VDBA          | 1 | SISO   | APF                    | VM    | 1+1   | 0.75 |     | Low  | 1.6  | CMOS               |

|      | 1 FB-         |   |        |                        |       |       |      |     |      |      |                    |

| [81] | VDBA          | 1 | SISO   | APF                    | VM    | 1+1   | 5    |     | Low  |      | OPA860             |

|      | 1.00          |   |        | LPF, BPF,              |       |       |      |     |      |      |                    |

| [80] | 1 DO-<br>VDBA | 2 | SIMO   | HPF, APF,<br>BSF       | СМ    | 2+2   | 1.2  | No  | Low  |      | OPA860             |

| [OO] | 1001          | _ | DIIVIO | DOI                    | C171  | 4.4   | 1.2  | 110 | LOW  | l    | 0171000            |

From the existing literature, it is observed that all the structures are VM except those presented in [64] and [82] which are CM filters. Filters proposed in [57], [63], [65], [66], [68], [81], [82] provide only single response, those in [54], [56], [60], [62], [64], [78] provide multiple responses and the structures of [33], [55], [58], [59], [79] are universal filters. The voltage output in [64], [78], [79] is available at high impedance, not a suitable choice for cascading purpose. Further, only a few configurations [33], [66] provide independent tuning of pole frequency ( $\omega_0$ ) and quality factor ( $Q_0$ ). The filters proposed in [33], [54], [55], [59], [62], [64], [66], [78], [79], [82] are designed using off shelf ICs and use large supply voltage.

Circuit structures using single ABB lead to low power designs. Circuit design with moderate component spread is always a preferred choice from the integration viewpoint. Further, independent tuning of  $\omega_0$  and  $Q_0$  is a desirable feature. It is observed from Table 1.2 that limited structures qualify for all the above features and this led the author to explore such filter structures.

A universal filter provides all five responses using a single circuit. From Table 1.2, it is observed that few universal structures are available. The structures of [33], [55], [59], [67], [79], [80], [82], [83] are MISO and the availability of output voltage at low impedance node is desirable with the independent tuning of  $\omega_0$  and  $Q_0$ . From Table 1.2, it is seen that only a few structures met up with these requirements which motivated the author to explore such design.

An APF, also termed as phase shifter, is a two port network that allows all input signal frequencies to pass with altered phases. Though a variety of first order APF using different ABBs exist but limited literature is available on VDBA based first order APF [65], [81], [82]. This gap was tapped as a possibility to explore new VDBA based APF design.

#### iii) Oscillators

Sinusoidal oscillators are the integral part of electronic circuit design. The oscillators find extensive usage in communication systems, control systems, measurement and instrumentation systems. In literature, the sinusoidal oscillators are classified on the basis of:

- Phase: single phase (SP) oscillator, quadrature phase (QP) oscillator or a multiphase (MP) oscillator,

- Order of characteristic equation: second order and higher order oscillators.

Circuits which provide sinusoidal oscillations at a single frequency and at a single output are termed as SP oscillators. The QP oscillators provide two quadrature phased outputs at single frequency and find vast application in communication. The MP oscillators provide multiple equally phased oscillations of a single frequency. The widespread usage of the MP oscillators [34]–[53] in telecommunication systems; power electronics, instrumentation and control systems are well known. Few sinusoidal oscillators using VDBA and its variant [61], [82], [85]–[91] have been proposed in literature which are summarized below in Table 1.3.

Table 1.3 Literature summary for oscillator using VDBA

| Reference No. | No. of ABB    | Order | Passive<br>components<br>R+C | Independent<br>control of FO<br>and CO | Supply<br>Voltage (V) | Output phase                          | Output node<br>impedance                | Technology<br>used |

|---------------|---------------|-------|------------------------------|----------------------------------------|-----------------------|---------------------------------------|-----------------------------------------|--------------------|

| [90]          | 2 VDIBA       | 2     | 1+2                          | Yes                                    | 0.9                   | SP                                    | Low                                     | CMOS<br>0.18 μm    |

| [87]          | 1 VDBA        | 3     | 2+3                          | Yes                                    | 1.5                   | QP                                    | Low                                     | CMOS<br>0.35 μm    |

| [88]          | 2 VDBA        | 3     | 1+3                          | Yes                                    | 1.5                   | QP                                    | Low                                     | CMOS<br>0.18 μm    |

| [89]          | 2 VDBA        | 3     | 1+3                          | Yes                                    | 0.9                   | QP                                    | One phase –<br>High ,One<br>Phase - Low | CMOS<br>0.18 μm    |

| [91]          | 2 VDBA        | 2     | 1+2                          | Yes                                    | 1.5                   | QP                                    | Low                                     | CMOS<br>0.35 μm    |

| [85]          | 2 FB-VDBA     | 2     | 7+4                          | Yes                                    |                       | QP                                    | Low                                     | OPA860             |

| [86]          | 1 FB-VDBA     | 2     | 1+2                          | Yes                                    | 5                     | QP                                    | Low                                     | OPA860             |

| [61]          | 2 DO-<br>VDBA | 2     | 3+2                          | Yes                                    | 1.2                   | MP                                    | Low                                     | OPA860             |

| [82]          | 2 VDIBA       | 2     | 0+2                          | Yes                                    |                       |                                       | 1 phase –<br>High,<br>1 Phase –<br>Low  | CMOS<br>0.18 μm    |

|               |               |       | 1+2                          | Yes                                    | 0.9<br>MP             | 2 Phase –<br>High<br>2 Phase –<br>low |                                         |                    |

<sup>\*</sup>FO- Frequency of oscillation, CO- Condition for oscillation.

It may be noted that very limited literature is available on oscillators; therefore, additional topologies may be explored.

## 1.3 Objectives

Following objectives are set after identifying the research gaps through extensive literature review:

- 1. To design a low power VDBA that provides high transconductance gain (g<sub>m</sub>) with high bandwidth (BW).

- 2. To develop VDBA based high CMRR instrumentation amplifier.

- 3. To develop a new filter configuration using single ABB with moderate component spread; having independent tuning of  $\omega_0$  and  $Q_0$ . Further, to explore the possibility of designing universal filter configuration and first order all pass filter.

- 4. To realize non-linear functions like multiplication, squaring and square rooting using VDBA.

- 5. To design sinusoidal oscillators.

#### 1.4 Thesis Organization

#### Chapter 1

This chapter presents a brief on the evolution of CM ABBs and their significance in signal processing applications. Further, a detailed review of existing literature on VDBA, its variants and their applications are presented to identify the research gap.

#### Chapter 2

In this chapter detailed study of CMOS based VDBA and DO-VDBA is presented to lay the ground for further reported work. Characterization of CMOS VDBA and DO-VDBA circuits has been carried out through SPICE simulations using  $0.18~\mu m$  CMOS technology node. These realizations are used for functional verification of proposed

work in the thesis. The VDBA realization using commercially available IC AD844 is presented further to be is used for experimental verification of proposed structures.

#### Chapter 3

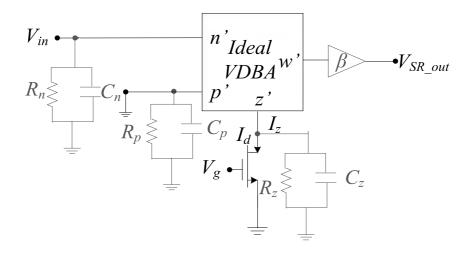

A low power VDBA structure is presented in this chapter. Detailed DC and AC analyses of the proposed structure are presented. The structure is further verified through pre and post layout simulations and is tested for its robustness and sensitivity through PVT and Monte Carlo analyses.

#### Chapter 4

This chapter presents VDBA based linear applications. A high CMRR instrumentation amplifier using a single VDBA is presented first which is followed by filter applications. Three filter applications are developed out of which the first order APF and second order SISO multifunction filter are designed using single ABB whereas the MISO universal filter is designed using two VDBAs. The effect of device non-ideality on instrumentation amplifier and filter parameters has been analyzed. Sensitivity analyses are also carried out to find the dependence on the passive elements. The workability of all propositions is verified through simulations.

#### Chapter 5

This chapter is devoted to non-linear applications of VDBA. A multiplier, a squaring circuit and a square rooting circuit are developed wherein the multiplier employs two DO-VDBAs while the later ones use single VDBA only. The functionality of all three propositions is confirmed through simulations. Post layout simulations are also included for squaring and square rooting circuits.

## Chapter 6

This chapter delves into the designing of signal generators. A new structure for the realization of a single phase sinusoidal oscillator using a single VDBA is presented first. Three quadrature phase and two multiphase sinusoidal oscillators are also proposed. The functionality of proposed structures is tested through simulation and experimental work.

## Chapter 7

In Chapter 7, the presented work is summarized and concluded with a thought on the prospective future scope.

#### 2.1 Introduction

The conceptual model of VDBA was first proposed in [1] by biolek et.al. The VDBA consists of an input voltage differencing stage and the output current is equal to transcoductance times the voltage difference of stage one. Further a voltage terminal at low impedance is also available, thus adding design flexibility. Thus it can be understood as a tansconductance amplifier (TA) followed by a voltage buffer. Bias dependent transcoductance adds the feature of electronic tunability of circuit parameters. Thus the VDBA has emerged as a promising choice for both VM and CM analog applications in recent past.

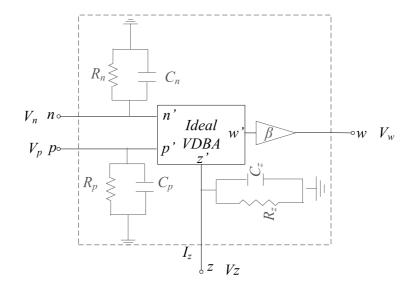

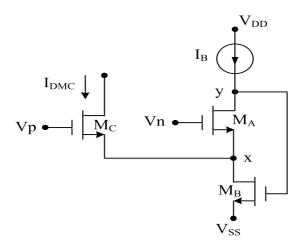

In this chapter, ideal VDBA and DO-VDBA are discussed first followed by their non-ideal models. A detailed analysis of the CMOS realizations of VDBA [33] and DO-VDBA [61] which are used in this thesis is presented next. In this chapter, a CFOA based implementation of VDBA is also proposed. All these VDBA structures are characterized using SPICE simulations. The MOSFET based resistor realization [92] has also been presented which is utilized in some of the proposed structures.

#### 2.2 The Ideal VDBA and DO-VDBA

The VDBA is a four terminal block as shown in Figure 2.1 which is ideally characterized by the matrix (2.1).

Figure 2.1 Symbol of VDBA

(2.1)

It may be observed from (2.1) that the p and n are the high impedance voltage input terminals whereas the z is the high impedance current output terminal providing a current which is  $g_m$  times input voltage difference. The w terminal replicates the voltage of z terminal at low impedance.

The VDBA can be modified to DO-VDBA simply by the addition of a voltage inverter. This adds flexibility to circuit design and is useful for differential mode signal operations. The symbol for DO-VDBA is shown in Figure 2.2.

Figure 2.2 Symbol of DO-VDBA

Terminal characteristics of DO-VDBA may be expressed as

(2.2)

### 2.3 Non-Ideal Model

The VDBA and DO-VDBA characterized by (2.1) and (2.2) respectively describe their ideal behavior and do not account for various non-idealities associated with the active blocks.

The non-idealities in a VDBA may arise from:

- i. The parasitic related to p, n and z terminals

- ii. Tracking error in transconductance gain

- iii. Tracking error in unity voltage transfer ratio from port z to w

The non-ideal model of VDBA is shown in Figure 2.3 wherein the parasitic resistance and capacitance associated with a terminal 'i' are denoted as  $R_i$  and  $C_i$  respectively such that 'i' may represent any of p, n and z terminals. Considering the non-idealities, the VDBA terminal characteristics get modified as

$$\begin{bmatrix} I_z \\ V_w \\ I_p \\ I_n \end{bmatrix} = \begin{bmatrix} 1/Z_z & 0 & \alpha g_m & -\alpha g_m \\ \beta & 0 & 0 & 0 \\ 0 & 0 & 1/Z_p & 0 \\ 0 & 0 & 0 & 1/Z_n \end{bmatrix} \begin{bmatrix} V_z \\ I_w \\ V_p \\ V_n \end{bmatrix}$$

(2.3)

Where  $\alpha$  and  $\beta$  represent the non-ideal transconductance gain and non-ideal buffer transfer ratio respectively and should ideally be equal to unity.

Figure 2.3 Non-ideal model of VDBA

Taking the non-idealities due to tracking errors into consideration the DO-VDBA terminal characteristics get modified as

(2.4)

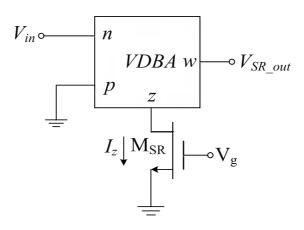

# 2.4 Implementation of VDBA

In this section, the CMOS implementation of VDBA [33] which is used for verification of applications proposed in this work is discussed.

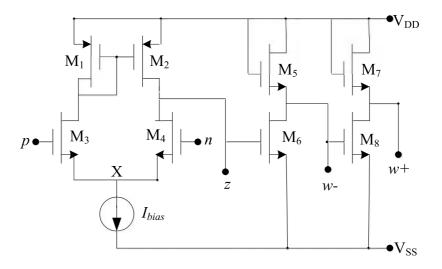

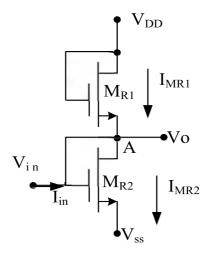

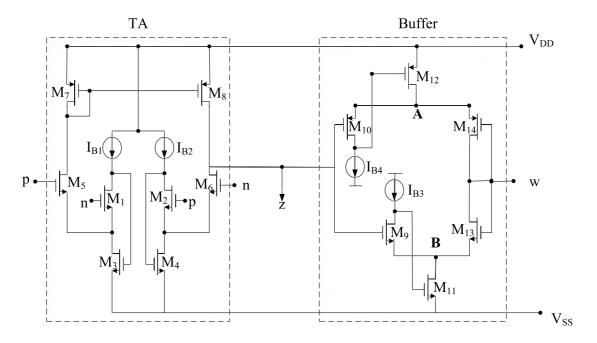

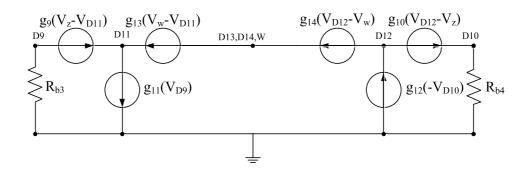

The complete schematic of the VDBA [33] is shown in Figure 2.4 wherein the circuit consisting of transistors ( $M_1$ - $M_9$ ) represents the TA unit and that consisting of ( $M_{10}$ - $M_{16}$ ) is the voltage buffer circuit.

Figure 2.4 CMOS VDBA [33]

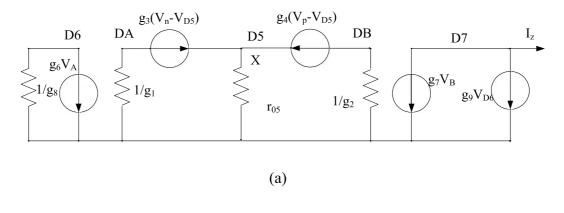

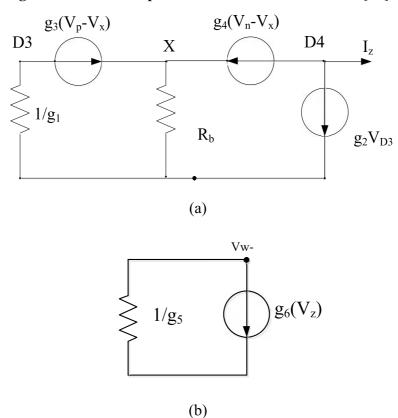

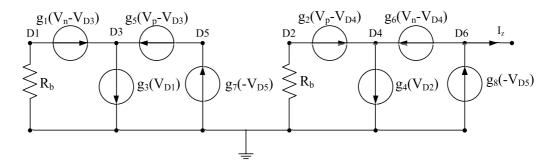

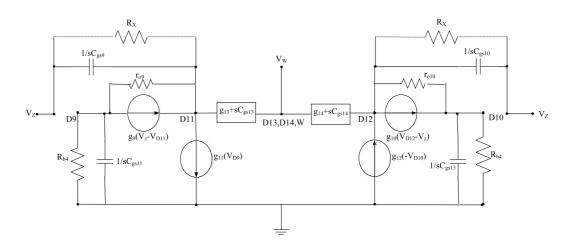

The small signal equivalent of CMOS VDBA of Figure 2.4 is drawn in Figure 2.5. The small signal equivalent circuits of TA and buffer are shown in Figures 2.5 (a) and (b) respectively, where  $D_i$  represents the drain of  $i^{th}$  transistor and  $g_i$  is corresponding transconductance.

Figure 2.5 Small signal equivalent of (a) TA and (b) buffer

The nodal equations at nodes D5, DA, DB, D6 and D7 can be expressed by (2.5)-(2.9) respectively.

$$g_3 V_n + g_4 V_p = (g_3 + g_4) V_X$$

(2.5)

$$-g_1V_A = g_3(V_n - V_X)$$

$$(2.6)$$

$$-g_{2}V_{B} = g_{4}(V_{p} - V_{X})$$

(2.7)

$$-g_{8}V_{D6} = g_{6}V_{A} \tag{2.8}$$

$$-g_{7}V_{B} - g_{9}V_{D6} = I_{z}$$

(2.9)

Substituting V<sub>D6</sub> from (2.8), (2.9) modifies to

$$-g_{7}V_{B} + \frac{g_{6}g_{9}}{g_{8}}V_{A} = I_{z}$$

(2.10)

By considering  $g_2 = g_7$  and  $g_6 = g_9 = g_8 = g_1$ , and using (2.6) and (2.7) and (2.10), the  $I_z$  may be expressed as

$$g_4(V_p - V_x) - g_3(V_n - V_x) = I_z$$

(2.11)

From (2.5) and (2.11), the  $I_z$  may be expressed as

$$g_4 V_p - g_3 V_n + \frac{(-g_4 + g_3)(g_3 V_n + g_4 V_p)}{(g_4 + g_3)} = I_z$$

(2.12)

$$I_z = \frac{2g_3g_4}{(g_3 + g_4)}(V_p - V_n)$$

(2.13)

Thus the g<sub>m</sub> may be obtained as

$$g_{m} = \frac{I_{z}}{(V_{p} - V_{n})} = \frac{2g_{3}g_{4}}{(g_{3} + g_{4})}$$

(2.14)

Further the small signal analysis of buffer can be carried out to establish relation between  $V_{\rm w}$  and  $V_{z_{\rm c}}$

The nodal equation at node D16 of Figure 2.5 (b) is expressed as

$$g_{14}r_{016}V_{D12} = (1 + g_{14}r_{016})V_{w}$$

(2.15)

Assuming  $g_{14}r_{016} >> 1$ , (2.15) may be rewritten as

$$V_{D12} = V_w$$

(2.16)

Similarly, the nodal equations at node D15, D12, D13 can be respectively expressed as

$$g_{12}(V_z - V_{D15}) = -g_{13}(V_w - V_{D15})$$

(2.17)

$$-g_{10}V_{D13} = g_{12}(V_z - V_{D15})$$

(2.18)

$$-g_{11}V_{D13} = g_{13}(V_w - V_{D15})$$

(2.19)

From (2.18) and (2.19)

$$\frac{g_{12}}{g_{10}}(V_z - V_{D15}) = \frac{g_{13}}{g_{11}}(V_w - V_{D15})$$

(2.20)

Considering  $g_{10}=g_{11}$  and  $g_{12}=g_{13}$ , and substituting the value of  $V_{D15}$  from (2.17)

$$V_z - \frac{V_z + V_w}{2} = V_w - \frac{V_z + V_w}{2}$$

(2.21)

$$V_z = V_w$$

### 2.4.1 Simulation Results

The functionality of VDBA is verified through SPICE simulations using TSMC 0.18  $\mu$ m process parameters. The supply voltages are set to  $\pm$  0.9 V. The bias voltages  $V_{bias1}$  and  $V_{bias2}$  are taken as 0.5 V and -0.25 V respectively. The VDBA shown in Figure 2.4 is simulated for the aspect ratios listed in Table 2.1.

Table 2.1 Aspect ratio of VDBA of Figure 2.4

| Transistor                                                                                           | W(μm)/L(μm) |

|------------------------------------------------------------------------------------------------------|-------------|

| M <sub>1</sub> -M <sub>4</sub> , M <sub>12</sub> -M <sub>13</sub> , M <sub>15</sub> -M <sub>16</sub> | 3.6/0.18    |

| M <sub>5</sub>                                                                                       | 1.8/0.36    |

| M <sub>6</sub> -M <sub>7</sub>                                                                       | 10.8/0.36   |

| M <sub>8</sub> -M <sub>9</sub>                                                                       | 3.6/0.36    |

| M <sub>10</sub> -M <sub>11</sub> , M <sub>14</sub>                                                   | 7.2/0.18    |

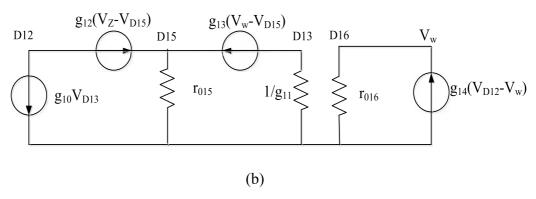

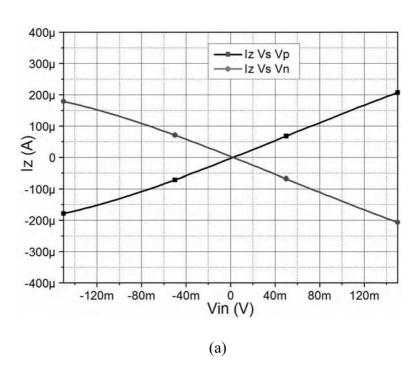

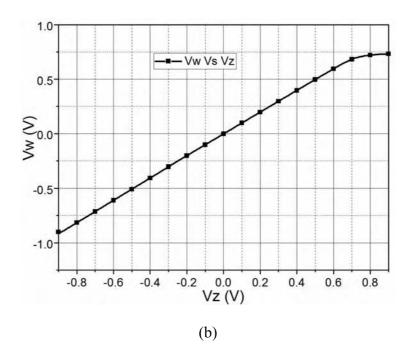

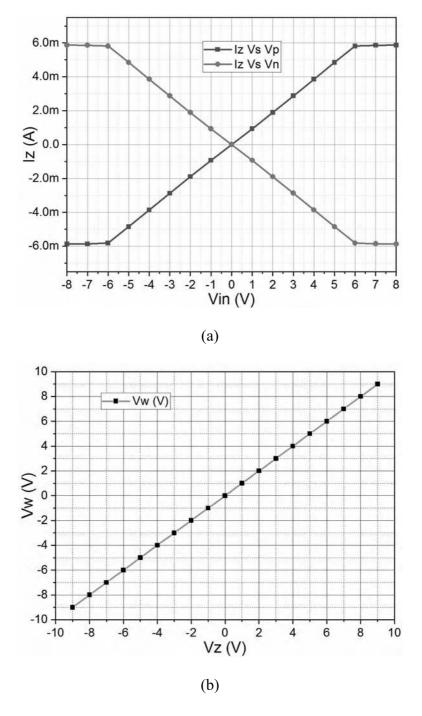

# 2.4.1.1 DC Characteristics

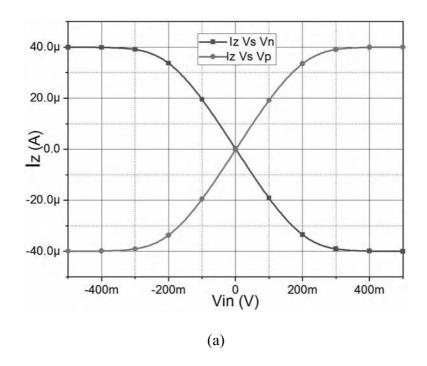

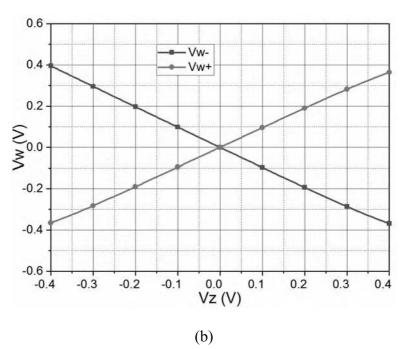

The DC characteristics obtained from the simulations are depicted in Figure 2.6. The variation of  $I_z$  with  $V_p$  and  $V_n$  is shown in Figure 2.6 (a). Similarly, the variation in  $V_w$  with respect to (w.r.t)  $V_z$  is depicted in Figure 2.6 (b). It may be witnessed that  $V_w$  follows  $V_z$  linearly for a voltage range of (-0.7 V to 0.7 V). Thus the terminal relations of VDBA are verified.

Figure 2.6 DC characteristics of (a) TA and (b) buffer

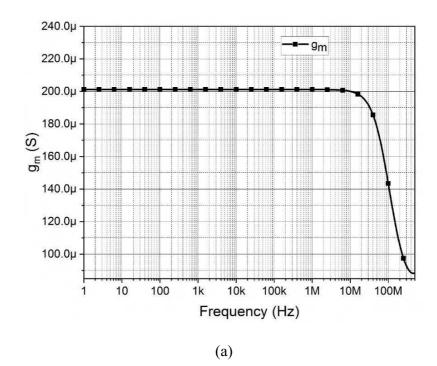

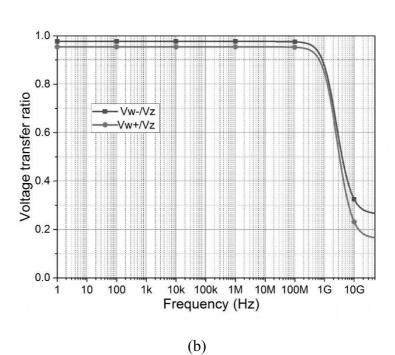

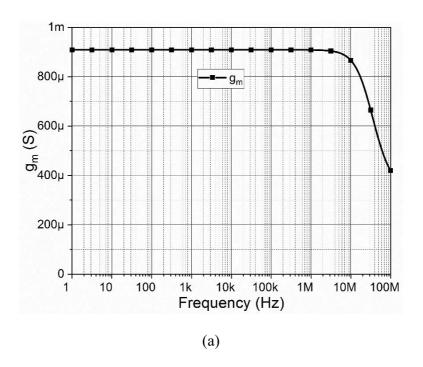

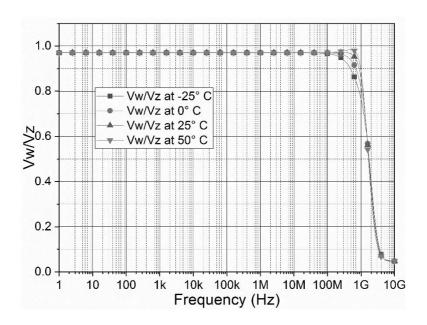

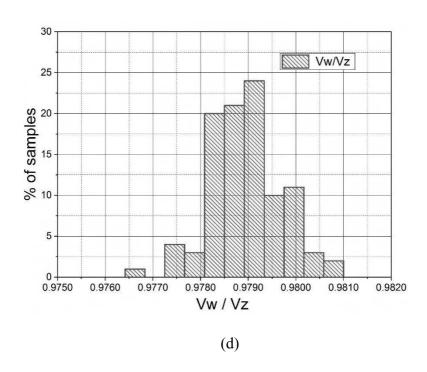

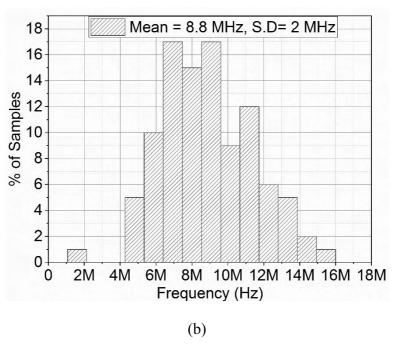

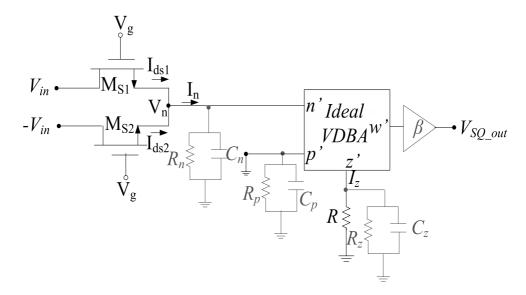

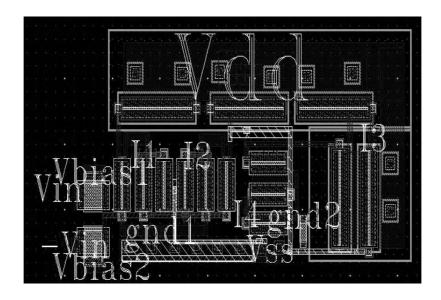

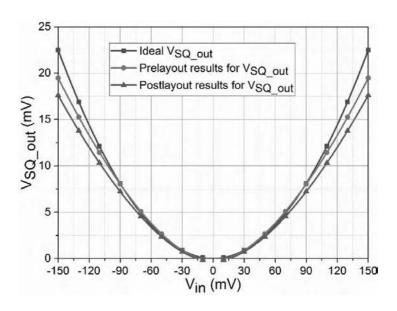

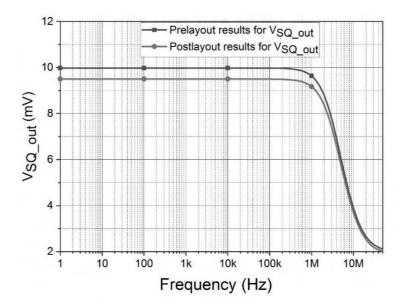

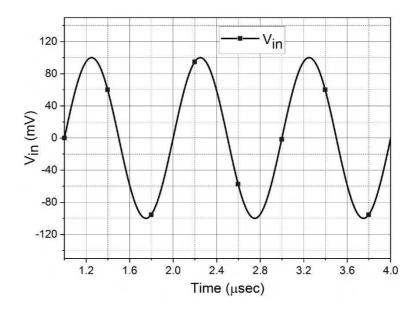

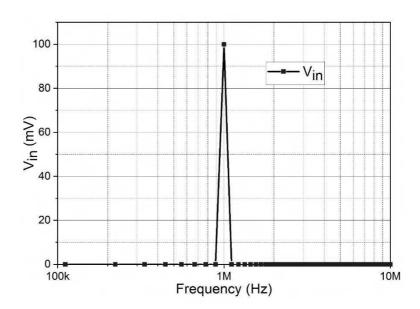

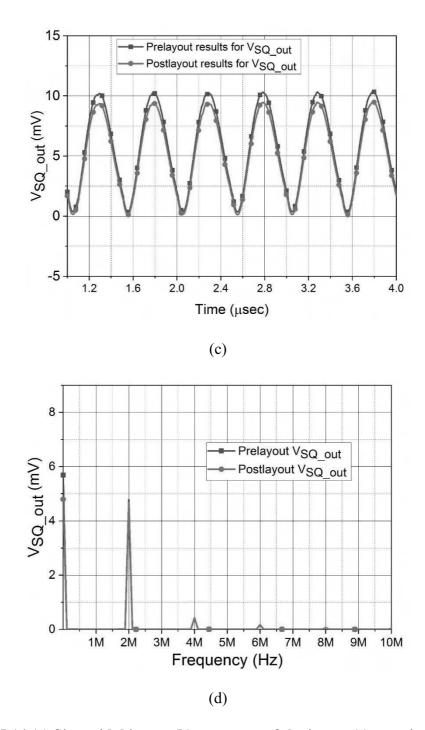

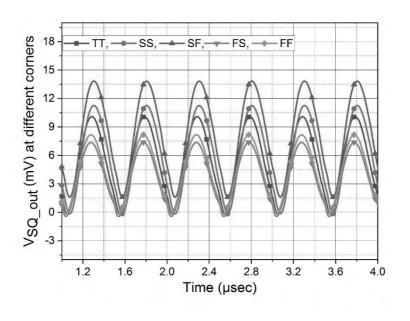

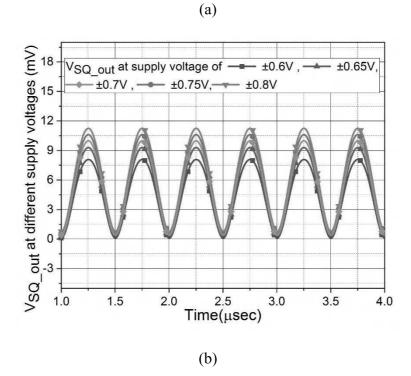

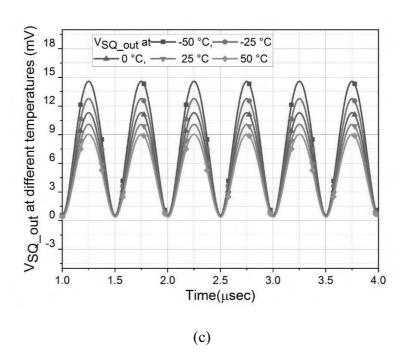

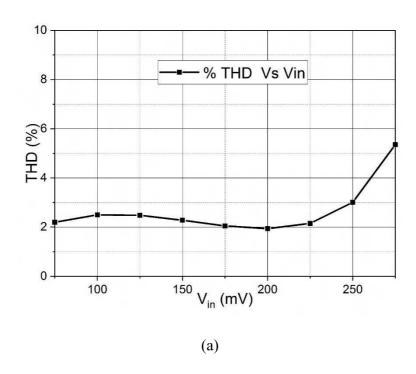

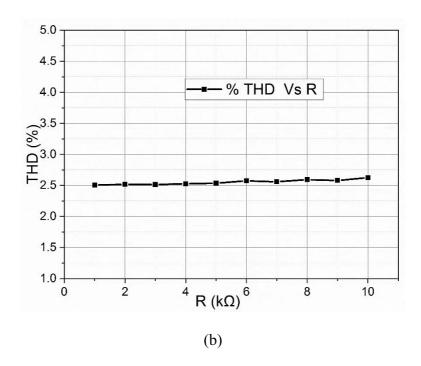

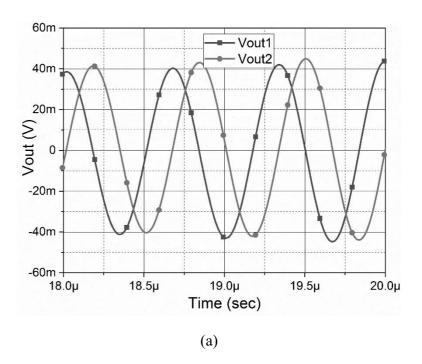

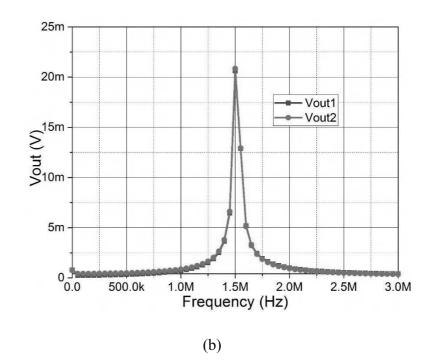

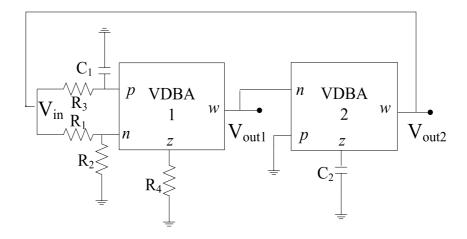

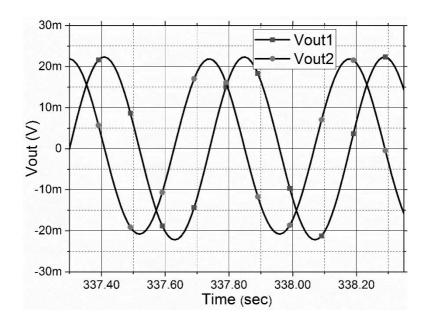

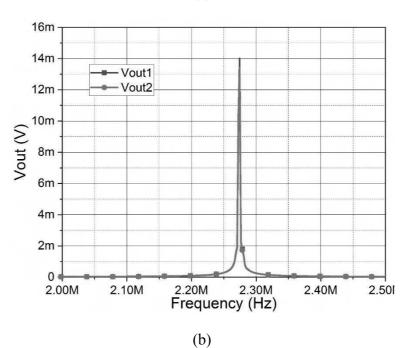

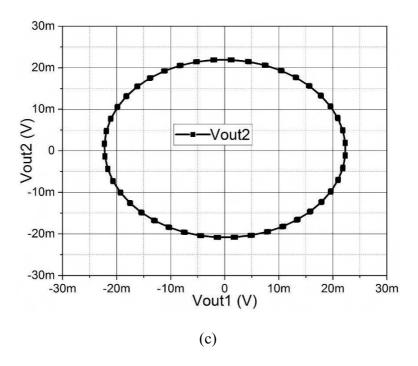

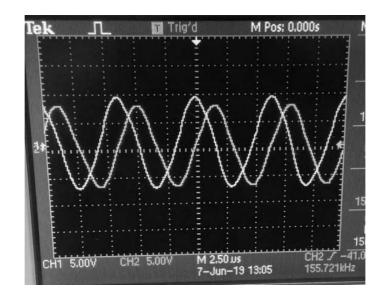

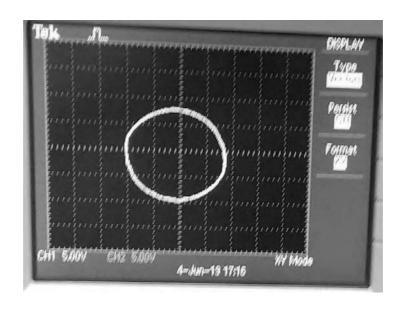

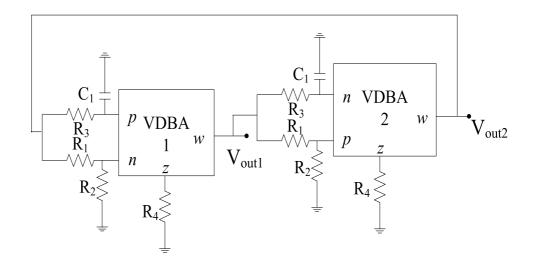

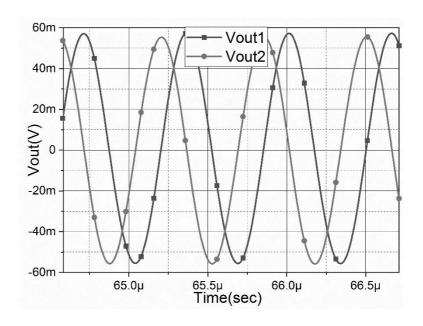

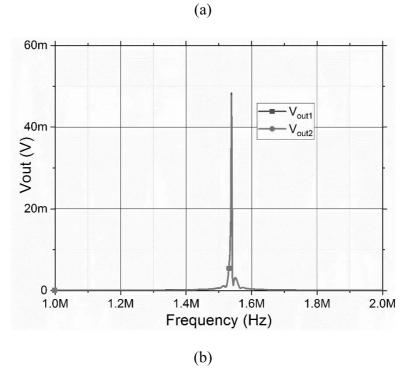

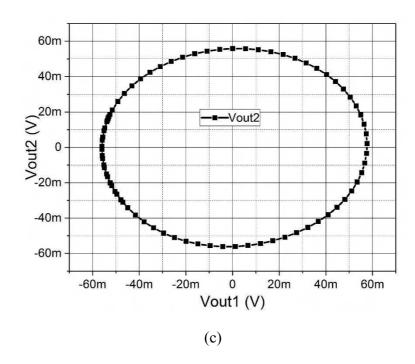

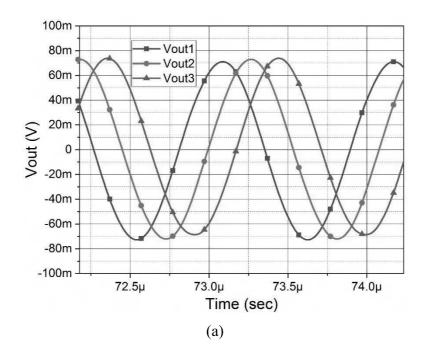

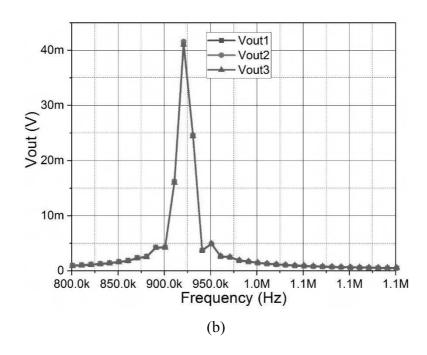

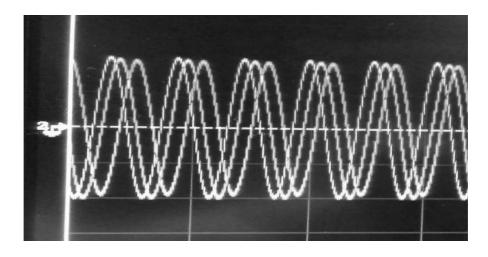

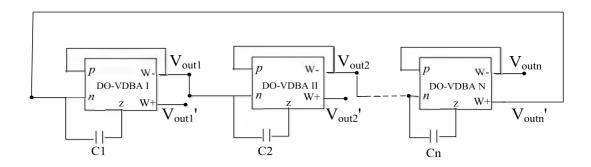

### 2.4.1.2 AC Characteristics