# **OTRA based Signal Generators and**

### their Performance Analysis

Thesis Submitted to the Delhi Technological University

for the Award of Degree of

### **Doctor of Philosophy**

in

**Electronics and Communication Engineering**

by Komanapalli Gurumurthy

(Enrollment No.: 2K14/Ph.D/EC/06)

Under the Supervision of

Prof. Rajeshwari Pandey &

**Prof. Neeta Pandey**

Department of Electronics & Communication Engineering Delhi Technological University Delhi-110042, India. December 2019

© Delhi Technological University-2019

All Rights Reserved

Delhi Technological University

*Formerly Delhi College of engineering* Shahbad Daulatpur, Bawana Road, Delhi-110042

### CERTIFICATE

This is to certify that the thesis entitled "**OTRA based Signal Generators and their Performance Analysis**" submitted by **Komanapalli Gurumurthy** (2K14/PHD/EC/06) to the Department of Electronics and Communication Engineering, Delhi Technological University for the award of the degree of Doctor of Philosophy is based on the original research work carried out by him under our guidance and supervision. In our opinion, the thesis has reached the standards fulfilling the requirements of the regulations relating to the degree. It is further certified that the work presented in this thesis is not submitted to any other university or institution for the award of any degree or diploma.

#### **Prof. Neeta Pandey**

Supervisor, Department of ECE Delhi Technological University Delhi-110042, India.

#### Prof. Rajeshwari Pandey

Supervisor, Department of ECE Delhi Technological University Delhi-110042, India.

**Prof. N.S. Raghava** Head of Department, Department of ECE Delhi Technological University Delhi-110042, India.

I hereby certify that the research work, which is being presented in the thesis, titled,

"**OTRA based Signal Generators and their Performance Analysis**" in fulfillment of requirements of the award of the degree of Doctor of Philosophy is an authentic record of my research work carried under the supervision of Prof. Rajeshwari Pandey and Prof. Neeta Pandey. The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for the award of any degree.

> Komanapalli Gurumurthy (2K14/PHD/EC/06)

### ACKNOWLEDGMENTS

The support and expert advice of my supervisors, Prof. Rajeshwari Pandey and Prof. Neeta Pandey Department of Electronics and Communication Engineering, Delhi Technological University (DTU), are greatly acknowledged with gratitude. I always availed of their priceless supervision, continuous motivation and ever-unforgettable humanitarian considerations.

My sincere thanks to Prof. N.S. Raghava, Head, ECED, DTU, Delhi and Prof. S. Indu for providing me all the necessary facilities for the completion of my work. I am thankful to all the faculty members of the department, with special mention of Prof. D.R. Bhaskar for their time-to-time advice, support and help on various occasions.

I am also grateful to Prof. Yogesh Singh, Vice-Chancellor, DTU, Delhi, for providing the research environment in the institute.

I would like to thank my friends Sirish Oruganti, Dr. Divyesh Sachan, Priyanka Gupta, Rakesh Verma, Dr. P.K.Verma, Rahul Bansal, Parveen Rani, Damyanti Singh, Ajishek, Garima Varshney, Sweta chowdary and lab staff of the electronics department for their support.

I express my deep sense of respect and gratitude to my father, Sh. Satyanarayana and my mother, Smt. Parvathi. Their scarifies and endless prayers helped me throughout my life. The support of my loving wife, Sai Sudha, has consistently been there throughout my research work. I would like to dedicate this work to my little angel, Pavishna Vedhya. A special thanks to my in-laws for their patience shown to me during my research. Finally, I would like to thank my brothers Prof. K.V.L Narayana and Dr. K. Sunil Kumar for their understanding and boosting me at every stage of Ph.D. work.

Komanapalli Gurumurthy

### ABSTRACT

The reduction of the minimum feature size of MOS transistor for digital very-large-scale integration (VLSI) circuits has been ongoing for the past few decades. As the channel length is scaled down into deep sub-micrometer dimensions, the lower power supply voltage is required to ensure the device reliability. To be compatible with digital VLSI technologies, analog integrated circuits, which can operate at low supply voltages, also, received significant attention. The current mode signal processing emerged as low voltage design technique for analog circuits which was manifested in proposition of numerous current mode analog building blocks for the realization of various signal processing and generation circuits. The Operational transresistance amplifier (OTRA), a current-controlled voltage source, is one among those. Due to its inherent pros like bandwidth independent of closed loop gain, high slew rate and simplicity in assimilating the effect of parasitic capacitances at the input ports OTRA is being used widely for signal processing and generating applications.

Sinusoidal oscillators are extensively used in the field of communication, instrumentation, testing and measurements. Versatility of oscillators in electronic applications coupled with advantages of OTRA and availability of limited literature has led the author of the thesis to explore the area of OTRA based signal generation. In this work several OTRA based sinusoidal oscillators that provide additional features not available in previously known OTRA oscillators have been presented.

It is useful to minimize the number of active blocks and passive elements in the oscillator topologies from power consumption optimization, reduction in parasitic

effects and area efficient design viewpoint. Therefore, sinusoidal oscillator design with single OTRA is given due consideration and three second order oscillators are presented. Additionally, the viability of oscillators providing low frequencies oscillations is also examined. Another significant contribution is development of single OTRA based third order SO having smaller component spread in condition of oscillation compared to available topologies, which is a desirable feature from IC fabrication viewpoint.

Quadrature oscillators find widespread applications in the field of communication. In this work, five new structures (one second order and four third order designs) are presented. Out of these five circuits, three third order topologies are derived from a generic structure. The second order design also qualifies for low frequency operations.

Further, four new oscillators are presented that are capable of generating a wide range of frequencies from very low to high. All the topologies provide electronic tuning, independent control of frequency of oscillations without disturbing the condition of oscillation. One of the configurations provides linear tuning, which is suitable for measurement and instrument applications.

Finally, a new OTRA based Wein bridge oscillator with wider tuning range is proposed in this work. A detailed mathematical formulation of harmonic distortion analysis is also presented to ascertain the linearity of the proposed design.

The non-ideal behavior of all proposed configurations is studied by considering nonidealities of OTRA and various performance analyses such as sensitivity, frequency stability, harmonic and phase noise analysis as applicable are carried out. Functionality of all propositions is verified through simulations using SPICE/Cadence Virtuoso spectre ADE tool using 0.18  $\mu$ m CMOS process parameters. Further, few circuits are verified experimentally also and post layout simulation results are included for rest.

# TABLE OF CONTENTS

| CAND   | IDATE'S DECLARATION                                    | v     |

|--------|--------------------------------------------------------|-------|

| ACKN   | OWLEDGMENTS                                            | vii   |

| ABSTR  | RACT                                                   | ix    |

| TABLE  | E OF CONTENTS                                          | xi    |

| LIST C | OF FIGURES                                             | XV    |

| LIST C | OF TABLES                                              | xxi   |

| ABBRI  | EVATIONS                                               | xxiii |

| Chapte | er 1 INTRODUCTION                                      | 1     |

| 1.1    | Background                                             | 2     |

| 1.2    | Related Literature and Scope of Work                   | 6     |

| 1.3    | Objectives                                             | 9     |

| 1.4    | Organization of the Dissertation                       | 9     |

| Chapte | er 2 OPERATIONAL TRANSRESISTANCE AMPLIFIER (OTRA       | ) 13  |

| 2.1    | Introduction                                           | 14    |

| 2.2    | Basics of OTRA                                         | 14    |

| 2.3    | Nonideal Analysis                                      | 16    |

| 2.4    | OTRA Implementation                                    | 17    |

| 2.4    | 4.1 CFOA based Implementation and its Characterization | 17    |

| 2.4    | 4.2 CMOS based Implementation and its Characterization | 21    |

| 2.5    | Active Resistor Realization in OTRA based Circuits     |       |

| 2.6    | Concluding Remarks                                     |       |

| Chapte | er 3 SINGLE OTRA BASED SINUSOIDAL OSCILLATORS          |       |

| 3.1    | Introduction                                           |       |

| 3.2    | Single OTRA based Second Order SOs                     | 33    |

| 3.2    | 2.1 Proposed Topology I                                |       |

| 34 |

|----|

| 35 |

| 36 |

| 37 |

| 39 |

| 40 |

| 47 |

| 49 |

| 50 |

| 50 |

| 51 |

| 52 |

| 57 |

| 59 |

| 61 |

| 62 |

| 62 |

| 64 |

| 64 |

| 65 |

| 65 |

| 66 |

| 68 |

| 74 |

| 75 |

| 76 |

| 76 |

| 78 |

| 78 |

| 78 |

| 80 |

| 83 |

| 84 |

|    |

|        | 4.3.9.1 MOS -C Implementations               |             |

|--------|----------------------------------------------|-------------|

|        | 4.3.9.2 Nonideal Analysis                    |             |

|        | 4.3.9.3 Sensitivity Analysis                 |             |

|        | 4.3.9.4 Frequency Stability                  |             |

|        | 4.3.9.5 Phase Noise Analysis                 |             |

|        | 4.3.9.6 Functional Verification              |             |

| 4.4    | Conclusion                                   |             |

| Chapte | er 5 GENERIC OSCILLATOR STRUCTURE FOR WID    | E FREOUENCY |

| _      | NG                                           |             |

| 5.1    | Introduction                                 |             |

| 5.2    | Proposed Oscillators                         |             |

| 5.2    | 2.1 MOS Resistor based Implementation        | 111         |

| 5.2    | 2.2 Nonideal Analysis                        |             |

| 5.2    | 2.3 Sensitivity Analysis                     |             |

| 5.2    | 2.4 Frequency Stability                      |             |

| 5.2    | 2.5 Phase Noise Analysis                     |             |

| 5.3    | Simulation Results                           |             |

| 5.4    | Conclusion                                   |             |

| Chapte | er 6 OTRA BASED WIEN BRIDGE OSCILLATOR AND I | TS HARMONIC |

|        | YSIS                                         |             |

| 6.1    | Introduction                                 |             |

| 6.2    | Proposed Oscillator                          |             |

| 6.2    | 2.1 Nonideal Analysis                        |             |

| 6.3    | Harmonic Distortion Analysis                 |             |

| 6.4    | Simulation Results                           |             |

| 6.4    | 4.1 Experimental Results                     |             |

| 6.5    | Conclusion                                   |             |

| Chapte | er 7 CONCLUSION AND FUTURE SCOPE             |             |

| 7.1    | Summary of Work done in this Thesis          |             |

| 7.2    | Future Scope                                 |             |

| DIMER  | -                                            |             |

| KEFEI  | RENCES                                       |             |

| PUBLI  | ICATIONS                                     |             |

# LIST OF FIGURES

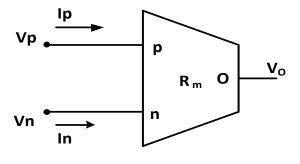

| Figure 2.1. (a) Schematic symbol representation of OTRA (b) Equivalent of OTRA | . 15 |

|--------------------------------------------------------------------------------|------|

| Figure 2.2. Equivalent circuit model of a practical OTRA                       | . 16 |

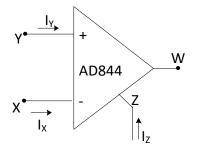

| Figure 2.3. Symbol of IC AD 844                                                | . 17 |

| Figure 2.4. IC AD 844 based OTRA [189]                                         | . 18 |

| Figure 2.5. DC characteristics of CFOA based OTRA                              | . 19 |

| Figure 2.6. Frequency response of CMOS based OTRA (a) Magnitude (b) Phase      | . 20 |

| Figure 2.7. The input resistance of CFOA based OTRA                            | . 20 |

| Figure 2.8. CMOS implementation of OTRA [32]                                   | . 21 |

| Figure 2.9. The complete physical layout of OTRA                               | . 22 |

| Figure 2.10. DC characteristics of CMOS based OTRA                             | . 23 |

| Figure 2.11. Frequency response of CMOS based OTRA (a) Magnitude (b) Phase     | . 24 |

| Figure 2.12. Frequency response of CMOS based OTRA at different corner paramet | ters |

|                                                                                | . 24 |

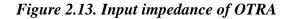

| Figure 2.13. Input impedance of OTRA                                           | . 25 |

| Figure 2.14. MOS implementation of resistance [35]                             | . 27 |

| Figure 2.15. MOS implementation of a linear resistance                         | . 27 |

| Figure 2.16. Differential gate controlling voltage versus transistor current   | . 28 |

| Figure 3.1. Proposed single OTRA SO topology I                                 | . 33 |

| Figure 3.2. Proposed single OTRA SO topology II                                | . 34 |

| Figure 3.3. Proposed single OTRA SO topology III                               | . 35 |

| Figure 3.4. MOS-C implementation of proposed topology-I                        | . 36 |

| Figure 3.5. Timing waveform of proposed topology I                             | . 40 |

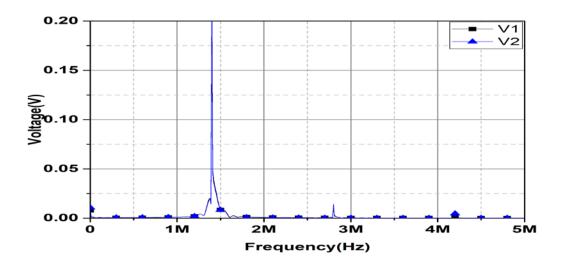

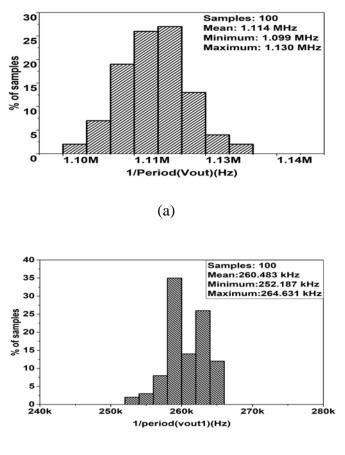

| Figure 3.6. Frequency spectrum of proposed SO topology-I41                           |

|--------------------------------------------------------------------------------------|

| Figure 3.7. Variation of frequency with respect to n41                               |

| Figure 3.8. Histogram of Proposed SO-I after Monte Carlo simulation                  |

| Figure 3.9. (a) Timing waveform and (b) frequency spectrum of proposed SO topology I |

|                                                                                      |

| Figure 3.10. (a) Transient waveform and (b) frequency spectrum of proposed SO-II44   |

| Figure 3.11. Histogram of proposed SO-II after Monte Carlo simulation                |

| Figure 3.12. (a) Transient waveform and (b) frequency spectrum of proposed SO-II45   |

| Figure 3.13. (a) Transient waveform and (b) frequency spectrum of proposed SO-III46  |

| Figure 3.14. Histogram of Proposed SO-III after Monte Carlo simulation47             |

| Figure 3.15. Experimental results of Figure 3.147                                    |

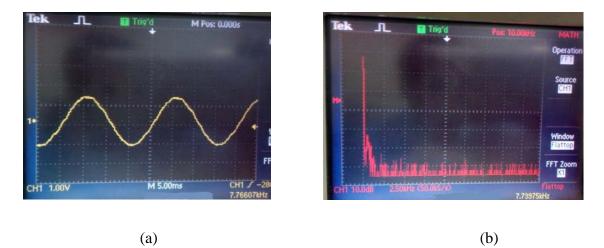

| Figure 3.16. Measured outputs of SO-II                                               |

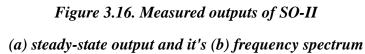

| Figure 3.17. Measured outputs of SO-III                                              |

| Figure 3.18. Proposed TOSO circuit                                                   |

| Figure 3.19. MOS resistor implementation of proposed TOSO50                          |

| Figure 3.20. (a) Transient Output and (b) frequency spectrum of proposed TOSO53      |

| Figure 3.21. Monte Carlo simulation (a) Transient output (b) Histogram of FO54       |

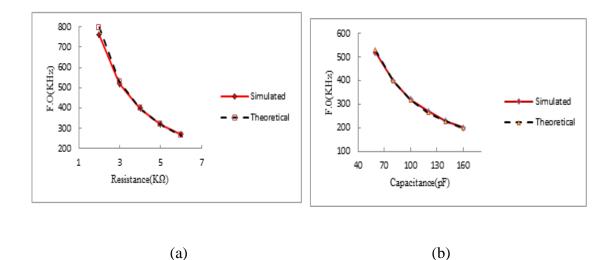

| Figure 3.22. (a) Frequency Tuning with (a) Resistance (b) with Capacitance for       |

| proposed TOSO55                                                                      |

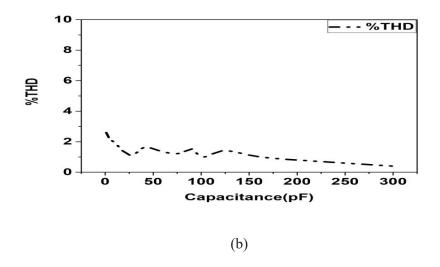

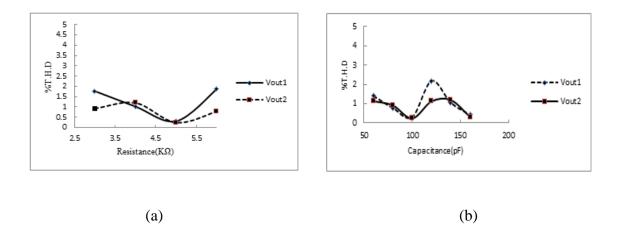

| Figure 3.23. The % THD variation with (a) Resistance (b) Capacitance                 |

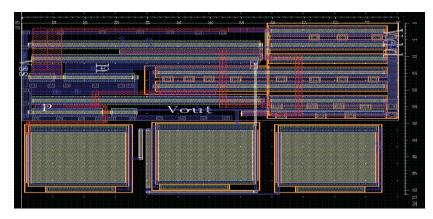

| Figure 3.24. The complete physical layout of proposed TOSO                           |

| Figure 3.25. (a) Simulated Output waveform and (b) frequency spectrum of proposed    |

| TOSO                                                                                 |

| Figure 3.26. Experimental (a) steady-state output and it's (b) frequency spectrum58  |

| Figure 3.27. (a) Frequency Tuning with R and C (b) % THD variation with R and C59    |

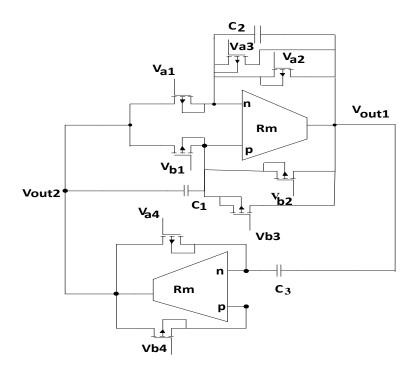

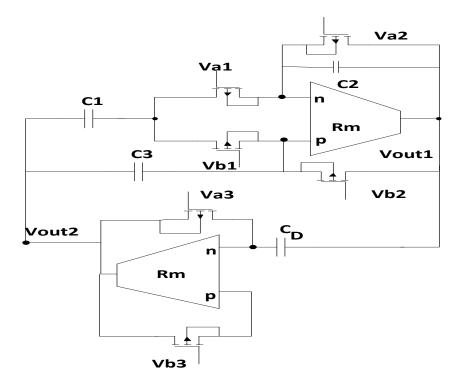

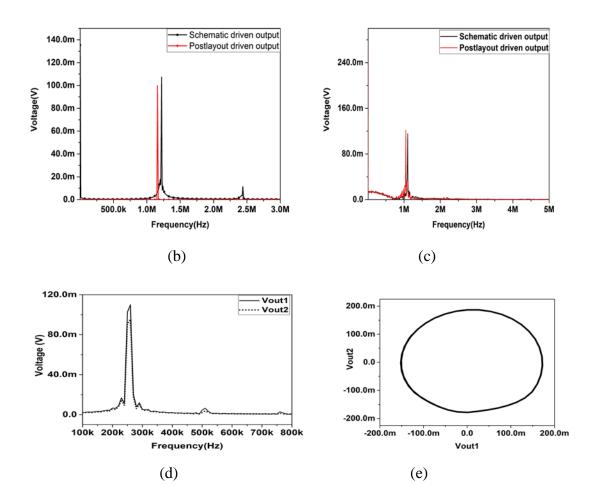

| Figure 4.1. Proposed second order LFQO                                                   |

|------------------------------------------------------------------------------------------|

| Figure 4.2. Complete MOS-C implementation of proposed second order LFQO 64               |

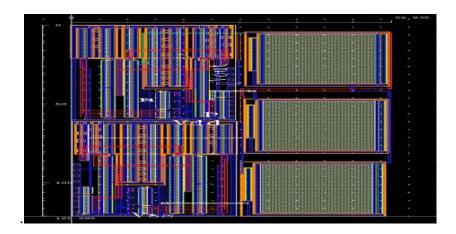

| Figure 4.3. The complete physical layout of proposed LFQO                                |

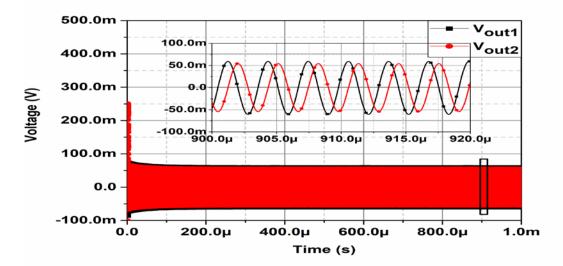

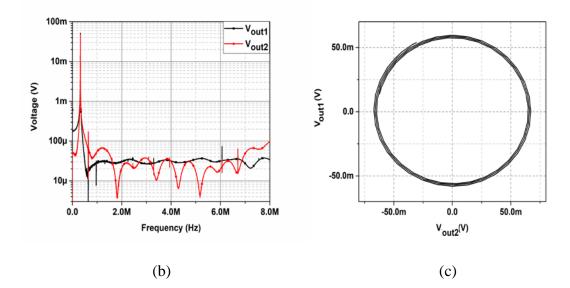

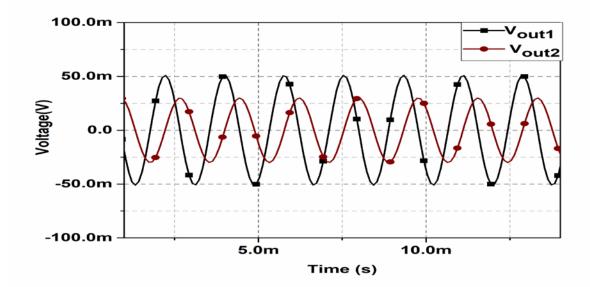

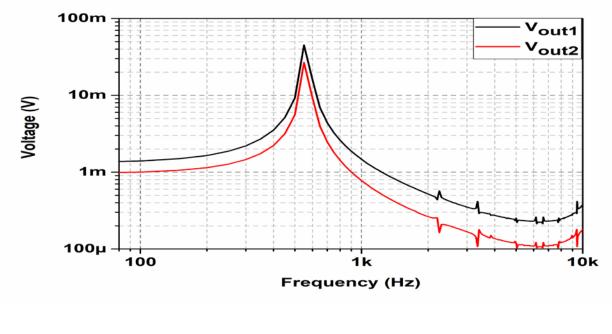

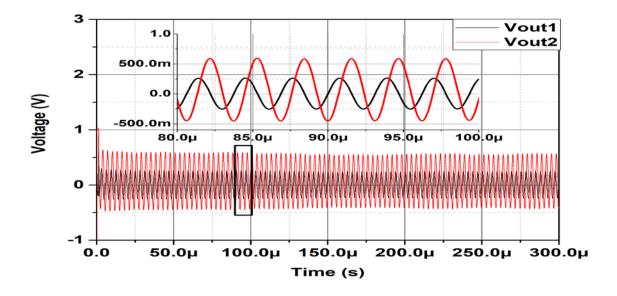

| Figure 4.4. Post layout results of proposed LFQO (a) simulated transient Response (b)    |

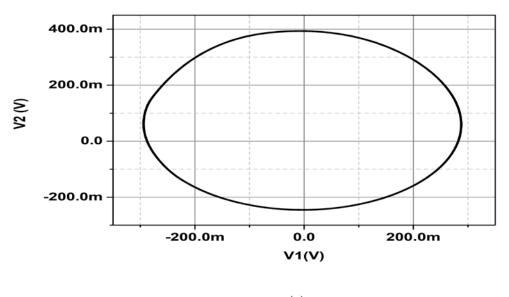

| FFT spectrum (c) Vout1 versus Vout2                                                      |

| Figure 4.5. Histogram of proposed LFQO70                                                 |

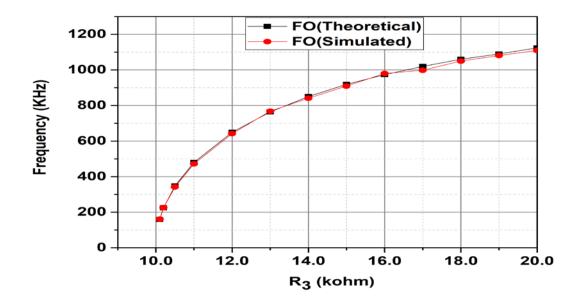

| Figure 4.6. Variation of FO with Resistance R371                                         |

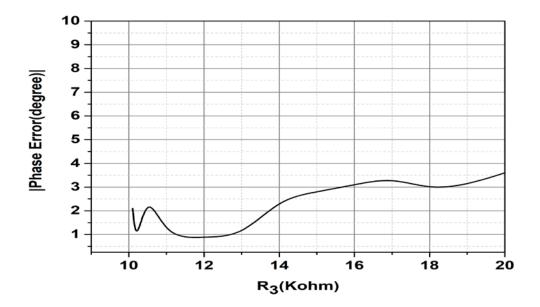

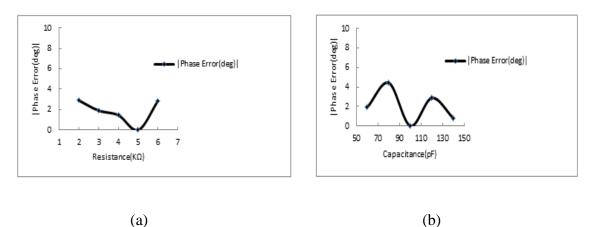

| Figure 4.7. Variation of phase error between Vout1 and Vout2 with Resistance R371        |

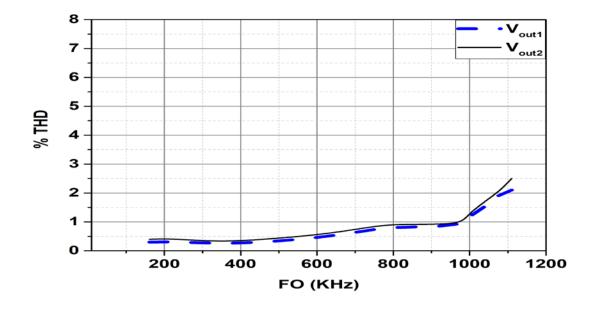

| Figure 4.8. Variation of %THD with Resistance R372                                       |

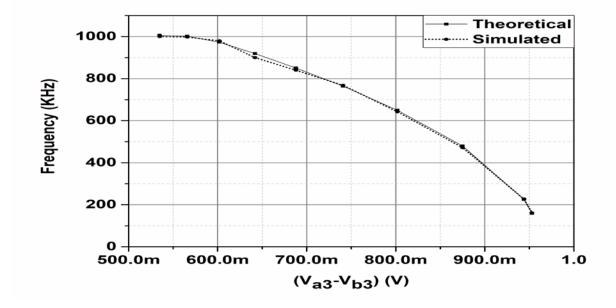

| Figure 4.9. Variation of FO with resistance $R_3$ by changing (Va3 – Vb3)73              |

| Figure 4.10. Schematic driven simulated results of proposed LFQO-I (Figure 4.1)74        |

| Figure 4.11. Proposed TOQO-I75                                                           |

| Figure 4.12. The MOS resistor based implementation of proposed TOQO-I76                  |

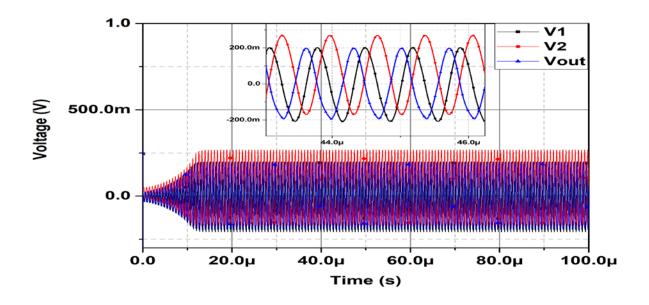

| Figure 4.13. (a) Transient output (b) frequency spectrum and (c) plot of Vout1 vs. Vout2 |

| of proposed TOQO topology-I                                                              |

| Figure 4.14. Histogram of proposed third order QO-I                                      |

| Figure 4.15. Frequency tuning of proposed QO (Figure 4.12)                               |

| Figure 4.16. The % THD variation with (a) Resistance (b) Capacitance                     |

| Figure 4.17. Phase error between Vout1 and Vout2                                         |

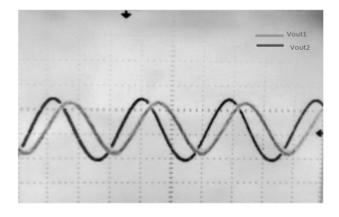

| Figure 4.18. Transient Response of Proposed TOQO-I on CRO                                |

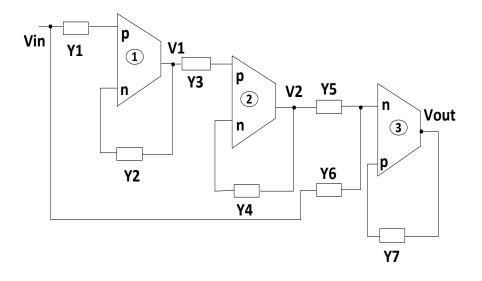

| Figure 4.19. Proposed generalized third order IF                                         |

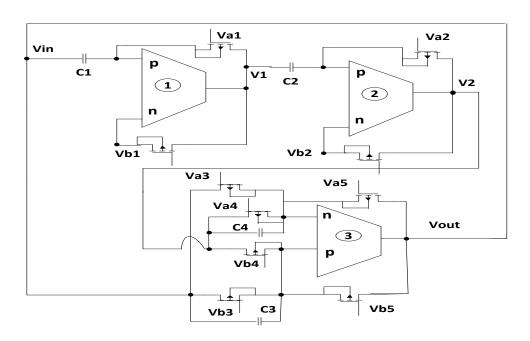

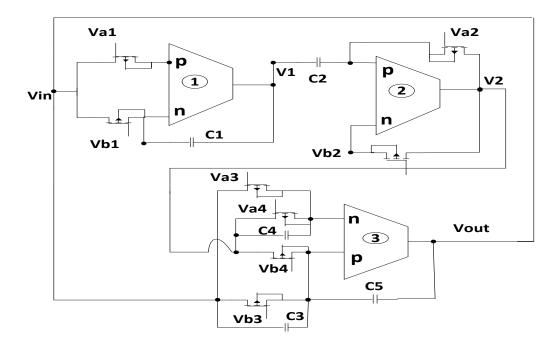

| Figure 4.20. Complete MOS-C implementations of proposed IF based TOQOs                   |

| Figure 4.21. (a) Complete physical layout of ILPF and its (b) frequency response95       |

| Figure 4.22. (a) Complete physical layout out IHPF and its (b) frequency response96      |

| Figure 4.23. (a) Complete physical layout out IBPF and its (b) frequency response 97     |

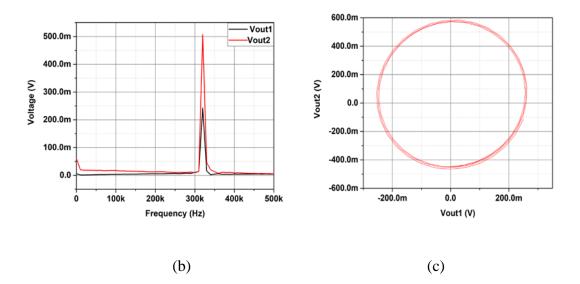

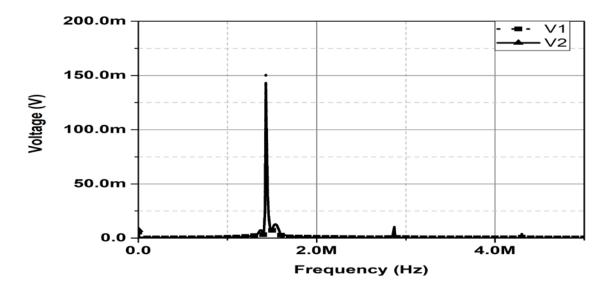

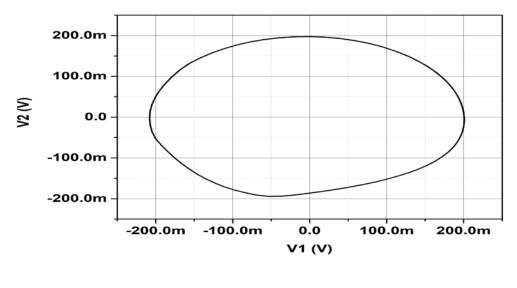

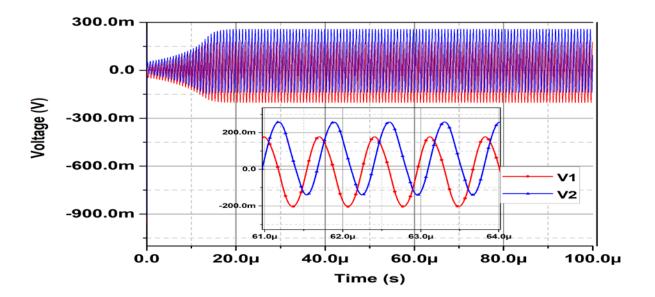

| Figure 4.24. (a) Transient / steady-state response (b) FFT and (c) V1 versus V2 graphs |

|----------------------------------------------------------------------------------------|

| for proposed ILP_SO                                                                    |

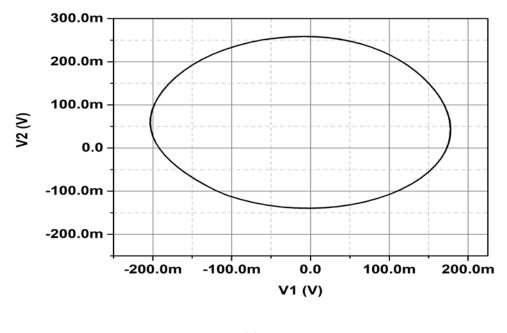

| Figure 4.25. (a) Transient / steady-state response (b) FFT and (c) V1 versus V2 graphs |

| for proposed IHP_SO100                                                                 |

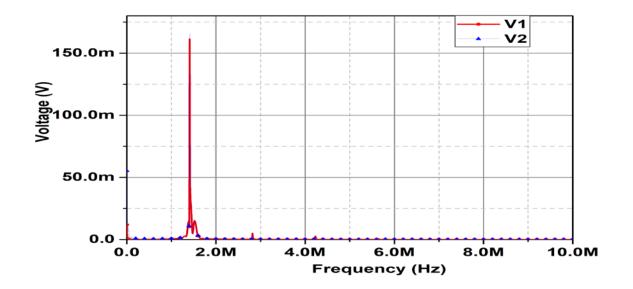

| Figure 4.26. (a) Transient / steady-state response (b) FFT and (c) V1 versus V2 graphs |

| for proposed IBP_SO102                                                                 |

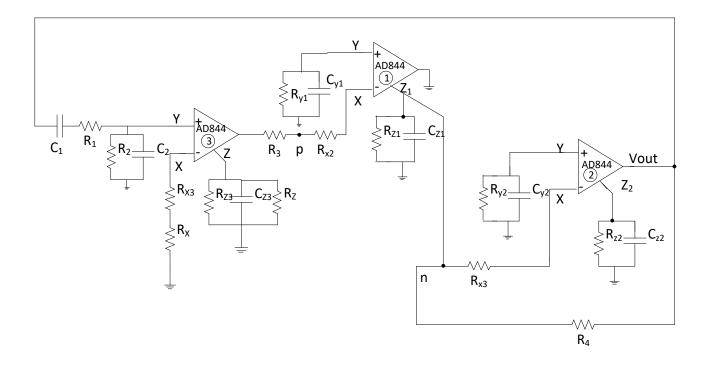

| Figure 5.1. Generalized representation of forward path106                              |

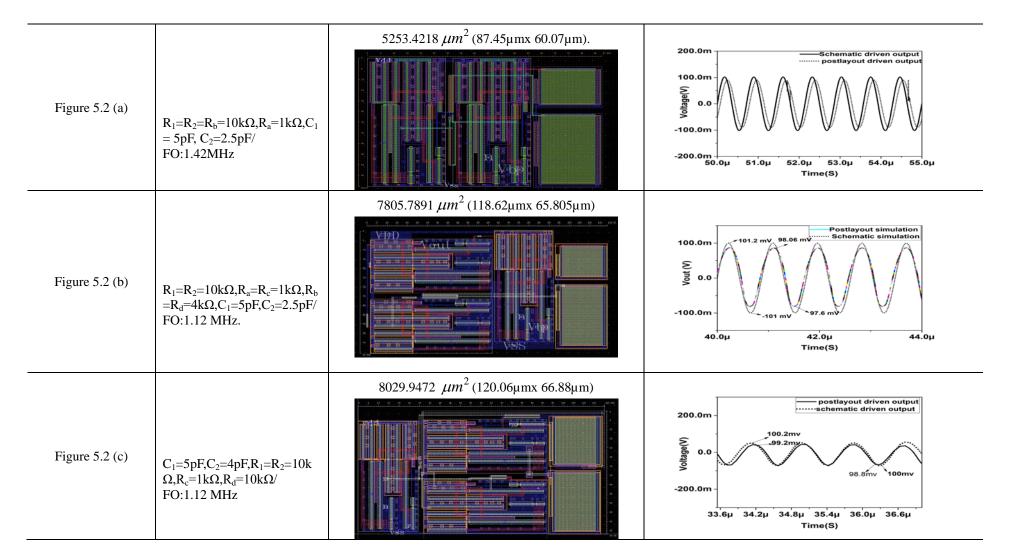

| Figure 5.2. Proposed sinusoidal configurations109                                      |

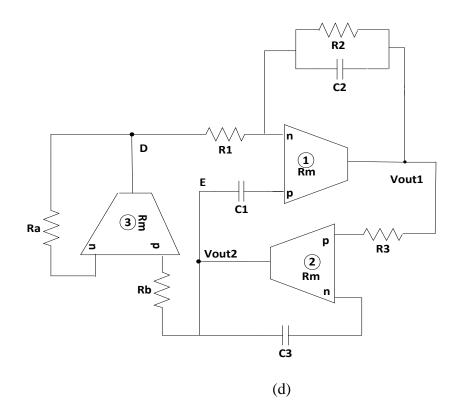

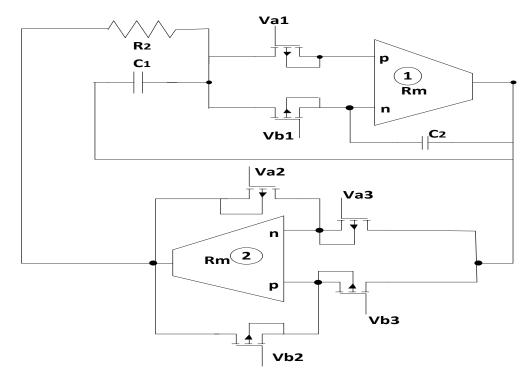

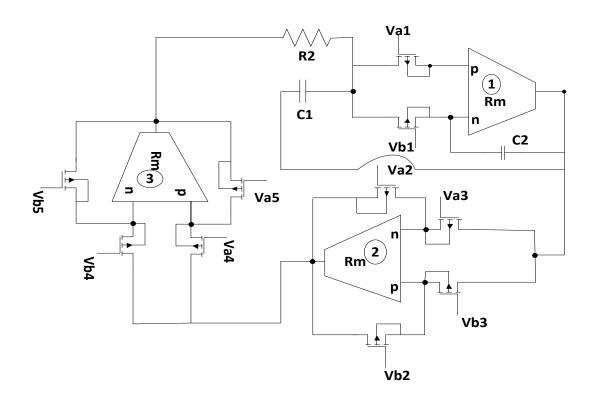

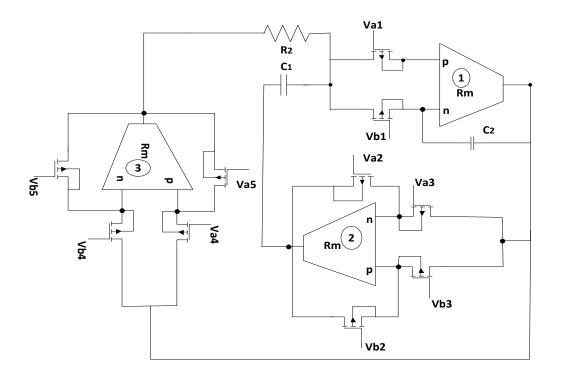

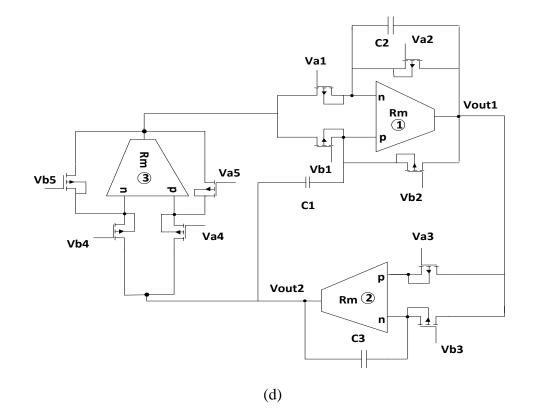

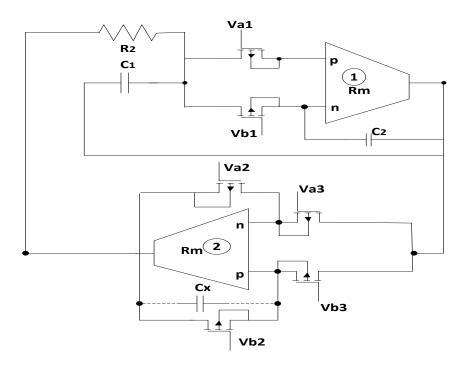

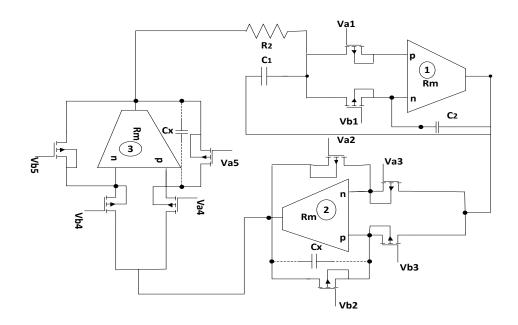

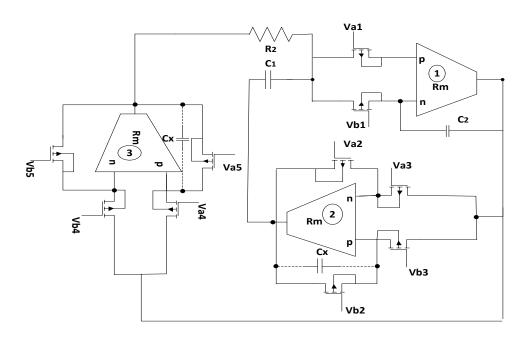

| Figure 5.3. (a)-(d) Electronically tunable realizations of proposed SOs113             |

| Figure 5.4. (a)-(d) Passive compensated proposed SOs118                                |

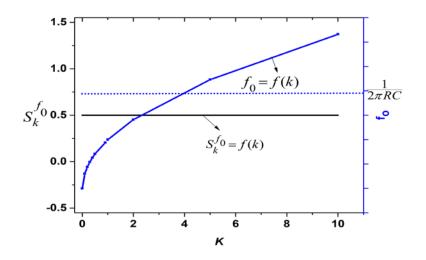

| Figure 5.5. $f_0$ and $S_k^{f_0}$ as a function of k for proposed topologies           |

| Figure 5.6. (a)-(d) FFT spectrums of Figure 5.2 (a)-(d) and (e) Vout1 versus Vout2     |

| graph for proposed QO (Figure 5.2 (d))125                                              |

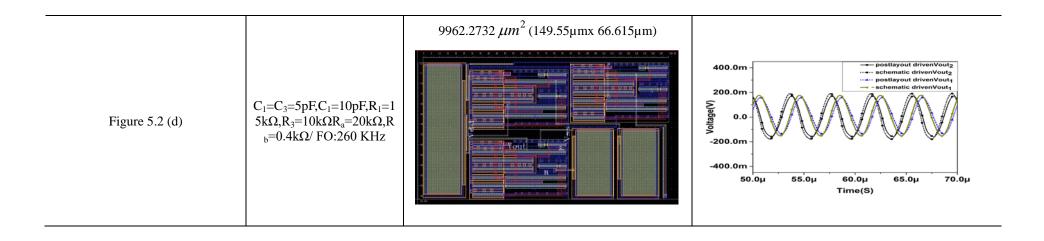

| Figure 5.7. Variation of FO with R for SO of Figure 5.2 (b)                            |

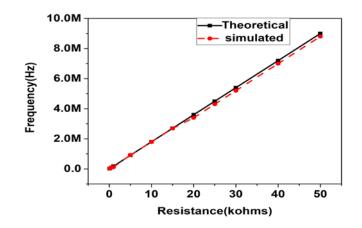

| Figure 5.8. Simulated output waveforms at 260 KHz for proposed SO (Figure 5.3 (d))     |

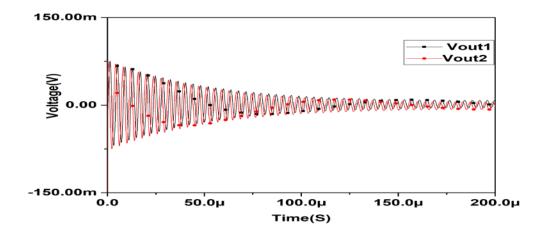

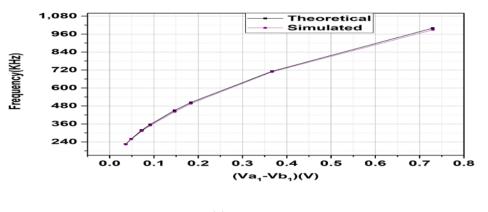

| (a) growing oscillations (b) decay of oscillations (c) variation of FO with $R_1$ by   |

| changing (V <sub>a1</sub> -V <sub>b1</sub> )                                           |

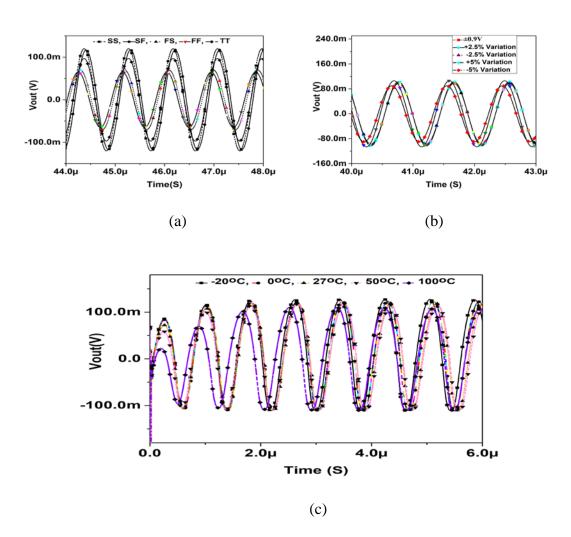

| Figure 5.9. Output waveforms of PVT analysis corresponding to (a) process variations   |

| (b) supply voltage Variations, (c) variations in temperature                           |

| Figure 5.10. (a) Simulated transient waveform, (b) FFT spectrum                        |

| Figure 5.11. Histogram of the proposed circuits                                        |

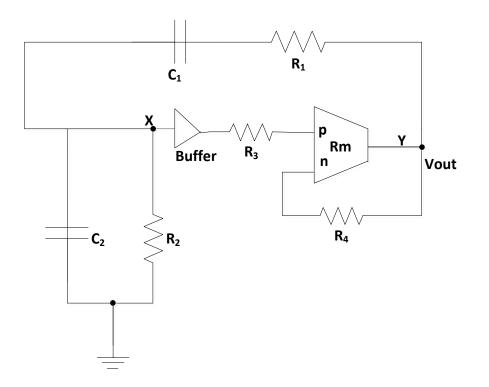

| Figure 6.1. OTRA based Wien bridge Oscillator                                          |

| Figure 6.2. IC AD 844 based Buffer implementation                                      |

| Figure 6.3. Proposed oscillator including Nonidealities140                             |

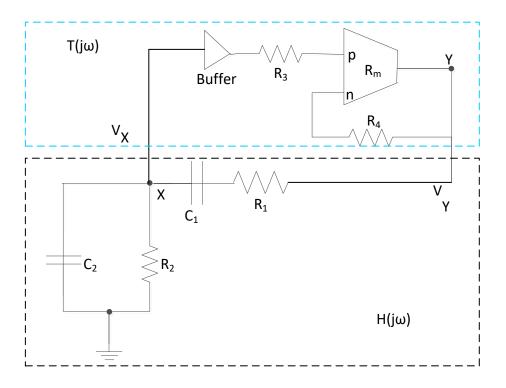

| Figure 6.4. Generic block diagram representation of proposed circuit141                |

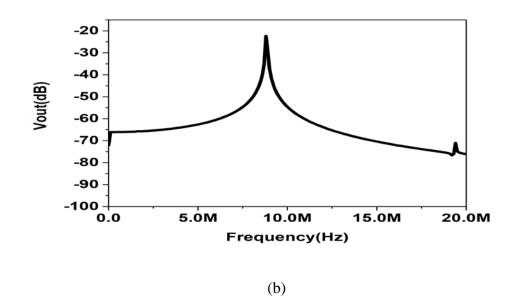

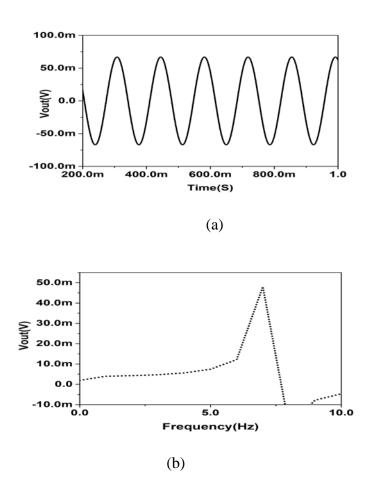

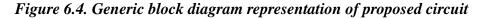

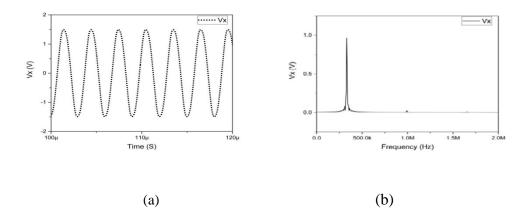

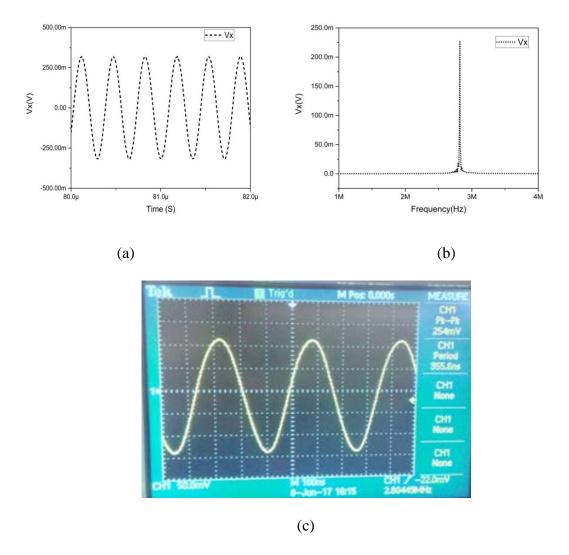

| Figure 6.5. (a) Transient output (b) Frequency spectrum                                 | 148     |

|-----------------------------------------------------------------------------------------|---------|

| Figure 6.6. Simulated waveforms for $V_X$ and $V_Y$ (Settings of S. No. 1 of Table 6.   | 1) with |

| (a) R4/R3 = 10.1 (b) R4/R3= 11                                                          | 148     |

| Figure 6.7. Simulated waveforms for $V_X$ and $V_Y$ (Settings of S. No. 2 of Table 6.7) | 1) with |

| (a) $R4/R3 = 5.1$ (b) $R4/R3 = 6$                                                       | 149     |

| Figure 6.8. Simulated waveforms for $V_X$ and $V_Y$ (Settings of S. No. 3 of Table 6.   | 1) with |

| (a) R4/R3 = 3.1 (b) R4/R3 = 4                                                           | 149     |

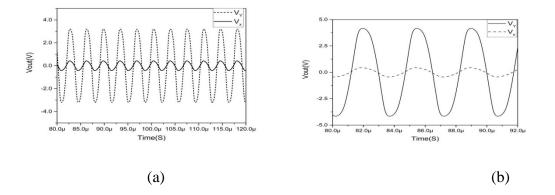

| Figure 6.9. (a) Simulated transient output waveform and (b) its frequency sp            | ectrum  |

| (c) Experimental output waveform                                                        | 150     |

# LIST OF TABLES

| Table 2.1. Aspect Ratios of Transistors                                           | 2 |

|-----------------------------------------------------------------------------------|---|

| Table 2.2. Parameters of CMOS OTRA circuit    2                                   | 5 |

| Table 2.3. Gate controlling voltages for different resistor values implementation | 8 |

| Table 4.1. Proposed IF transfer functions and their parameters       80           | 6 |

| Table 4.2. Frequency of oscillation and condition of oscillation of proposed QC   | С |

| topologies                                                                        | 7 |

| Table 4.3. Nonideal FO and CO of proposed IF based QO topologies       9          | 1 |

| Table 4.4. Sensitivity calculations for proposed IF based TOQOs       92          | 2 |

| Table 4.5. Frequency stability factors for proposed topologies       92           | 3 |

| Table 5.1. Sensitivity calculations for proposed circuits    119                  | 9 |

| Table 5.2. Frequency stability factors for proposed topologies       120          | 0 |

| Table 5.3. Pre and Post layout results    120                                     | 6 |

| Table 6.1. Example design parameters                                              | 8 |

| Table 6.2. Theoretical and Simulated values of HD2 and HD3                        | 9 |

| Table 7.1. Salient features of proposed structures    150                         | 6 |

# ABBREVATIONS

| ABB    | Analog building block                                            |

|--------|------------------------------------------------------------------|

| ADE    | Analog design Environment                                        |

| CCII   | Second generation current conveyor                               |

| CCCII  | Second generation current controlled conveyor                    |

| CCVS   | Current controlled voltage source                                |

| CCCDTA | Current controlled current difference transconductance amplifier |

| CDTA   | Current difference transconductance amplifier                    |

| CCCCTA | Current controlled current conveyor transconductance amplifier   |

| CDBA   | Current differencing buffered amplifier                          |

| CFOA   | Current feedback amplifier                                       |

| СМ     | Current-mode                                                     |

| СО     | Condition of oscillation                                         |

| DAC    | Digital-to-analog convertor                                      |

| DDCC   | Differential difference current conveyor                         |

| DRC    | Design Rule Check                                                |

| DVCC   | Voltage current conveyor                                         |

| DVCCTA | Differential voltage current conveyor transconductance amplifier |

| FFT    | Fast Fourier transform                                           |

| FO     | Frequency of oscillation                                         |

| HD      | Harmonic distortion                                                     |

|---------|-------------------------------------------------------------------------|

| IF      | Inverse filter                                                          |

| IBP     | Inverse bandpass filter                                                 |

| ILP     | Inverse lowpass                                                         |

| IHP     | Inverse Highpass                                                        |

| LFSOs   | Low frequency sinusoidal oscillators                                    |

| LVS     | Layout vs. Schematic check                                              |

| MCCCFTA | Modified current controlled current follower transconductance amplifier |

| MDCC    | Modified differential current conveyor                                  |

| OTA     | Operational transconductance amplifier                                  |

| OTRA    | Operational Transresistance Amplifier                                   |

| pFTFN   | Positive four terminals floating nullor                                 |

| QO      | Quadrature oscillators                                                  |

| SO      | Sinusoidal oscillator                                                   |

| THD     | Total harmonic distortion                                               |

| TOSO    | Third order sinusoidal oscillators                                      |

| UVC     | Universal voltage conveyor                                              |

| VLF     | Very low frequency                                                      |

| VM      | Voltage mode                                                            |

| VDTA    | Voltage difference transconductance amplifier                           |

# CHAPTER 1 INTRODUCTION

### 1.1 Background

Tremendous advancement in analog circuit design has occurred over the last few decades, mainly due to rapid growth in very large scale integration (VLSI) technology. One of the main driving forces that ensured this continuous growth and interest in analog circuit design is the grown need for fully integrated systems, which are compatible with CMOS technology encompassing a larger number of digital as well as analog circuits on a single chip. Analog circuits such as continuous time filters, oscillators, current and voltage amplifiers, voltage comparators, rectifiers, digital to analog and analog to digital converters, disk drive electronics, etc. are inevitable analog circuits, which cannot be accomplished by digital techniques. Moreover, new applications continue to appear where high performance and low power requirements are being treated with equal importance.

Voltage mode (VM) operational amplifier has been in the mainstay for decades and considered to be the most prominent and dominant analog building block (ABB) in the area of analog signal processing. The limitations imposed by opamp based topologies in their high-frequency operations due to lower slew rate and constant gain-bandwidth product made analog designers and researchers to search for the alternative approach.

More recently, current-mode (CM) signal processing is widely considered to be the viable design technique to overcome the limitations imposed by VM counterparts [1]-[6]. In contrast to the conventional VM, current-mode signal representing the information being processed is in the form of electric current. These circuits are low impedance node networks, hence result in a low time constant, thereby improving system performance in terms of speed and slew rate. Thus, the CM technique has resulted in the emergence of numerous CM ABBs. The literature has thus addressed voluminous blocks, which may run into an equally voluminous bibliography, which is beyond the scope of the present work and hence limited to some important selected works.

The CM building blocks, such as first-generation current conveyor (CCI) [7], secondgeneration CCII [8], third-generation CCIII [9], have drawn significant attention of the circuit designers and researchers. The CC based structures were being proposed in abundance since 1970 onwards, with different alterations in the basic CC structure, a number of newer elements have been introduced for better utilization [10]-[23]. To encompass both electronic tunability and for CMOS integration, the operational transconductance amplifier (OTA)-C [24] configurations were also significantly inspected beyond 1985. The topologies using current feedback operational amplifier (CFOA) [25] and its variants such as current controlled current feedback amplifier (CC-CFA) [26] differential voltage current feedback amplifier (DVCFA) [27] and differential difference complementary current feedback amplifier (DDCCFA) [28] came in prominence around 1990 onwards to maintain compatibility with the existing voltage mode topologies. The need for the floating output in some applications led to the design four terminal floating nullor (FTFN) [29] and its variants, fully balanced four-terminal floating nullor (FBFTFN) and operational floating amplifier (OFA) are presented in [30] and [31] respectively.

The operational transresistance amplifier (OTRA) [32]-[35] implements a current control voltage source and its generalization is current differencing buffered amplifier (CDBA) [36]. Another interesting, current mode ABB, which is well suited for on-chip implementation, is current differencing transconductance amplifier (CDTA) [37]. Differential voltage current conveyor (DVCC) [38] and its variants such as differential

voltage current conveyor transconductance amplifier (DVCCTA), current controlled current conveyor transconductance amplifier (CCCCTA) are reported in [39] and [40] respectively. Current controlled current follower transconductance amplifier (CFTA) [3] and its variant modified current MC-CFTA [41] provides parasitic resistance R<sub>f</sub> that can be controlled by the bias current. Differential-difference current conveyor (DDCC) [42], differential voltage controlled current source (DVCCS) [43], differential difference amplifier (DDA) [44], differential difference OFA (DDOFA) [45], universal voltage conveyor (UVC) [46] are some other ABBs available in the literature. These active blocks are used for the realization of various signal processing and generation circuits. Signal generators can be divided into two categories; function generators and arbitrary waveform generators (AWGs). Function generators are designed to generate periodic waveforms at precise frequencies, whereas AWGs, is designed to generate large and often complex waveforms. The function generators can broadly be classified as (i) linear generators (ii) nonlinear generators. A linear generator can generate oscillations which are sinusoidal and periodic, whereas nonlinear generators provide pulses, ramp and sawtooth waveform, etc. Unlike function generators, AWGs can generate any arbitrarily defined waveshape as their output.

Sinusoidal oscillators (SOs) find numerous applications in various fields such as applications in communication such as signal generators, spectrum analyzers, A/D converters, etc., measurement and instrumentation systems [47]-[49]. This electronic function provides standard test and carrier signals for communication and instrumentation circuits and also acts as the starting signal for the generation of several other types of test signals. Therefore, these topologies acquired ample attention among various researchers and inspired to develop new topologies, with better performance than earlier known circuits, that are most suited for these applications. These new SO

topologies have been realized employing a variety of ABBs such as op-amps [47], [50]-[56], CCII [57]-[65], OTA [57], [66]-[67], CCCII [68]-[70]. The designs proposed in [59], [71]-[80] use CFOA. The structures proposed in [38], [81]-[82] use DVCC, whereas the design of [83] utilizes DVCCTA. The CDTA based SOs are available in [84]-[85], while CCCCTA based oscillator is presented in [86]. The VDTA and MCCCFTA based oscillators are discussed in [87]-[88] and [41], [89]respectively. The structure of [90] is designed using OTA and CCCCTA, whereas [42] uses OTA and DDCC. Combination of OTA and current controlled current difference transconductance amplifier (CCCDTA) is reported in [91]. Reference [92] proposes DDCC and VDTA based SO and the oscillator presented in [93] is based on CCII and UVC.

The OTRA [32] is a high gain current input, voltage output amplifier and has gained much consideration from several researchers, due to its inherent pros like bandwidth independent of closed-loop gain, higher slew rate and simplicity in assimilating the effect of parasitic capacitances at the input ports. The parasitic impedances at input and output terminals of OTRA are low and have a negligible effect on circuits. As the output of OTRA can be used without a buffering device so these circuits can easily be cascaded. Therefore, OTRA has been explored in the recent past to develop various applications [94] such as immitance simulators [95]-[103], filters [35], [104]-[139], inverse filters [140], analog multipliers and dividers [141]-[142], relaxation oscillators and multivibrators [143]-[148] and various other applications such as instrumentation amplifier [149], proportional derivative controller [150], pulse width modulator [151], digital-to-analog converter (DAC) [152], field-programmable analog array (FPAA) [153], PID controller [154], semi-Gaussian shaper [155], time marker generator [156], voltage transfer characteristics generator [157], and linear signal generation circuits (SOs) etc.

In this work, OTRA is chosen for the development of sinusoidal oscillators.

### **1.2 Related Literature and Scope of Work**

The available literature on SO designed using OTRA can be categorized based on 1) number of OTRAs used in the topology 2) a number of output phases 3) order of the circuit 4) tuning law of the oscillation frequency.

The available literature on SO designed using OTRA can be classified into four categories as detailed below:

- 1) Category I- on the basis of number of OTRAs used in the topology.

- 2) Category II- on the basis of number of output phases.

- 3) Category III- on the basis of the order of the circuit.

- 4) Category IV- on the basis of tuning law of the oscillation frequency.

#### Category I

On the basis of the number of OTRAs used the literature is further classified as (i) single OTRA based oscillators [158]-[170], (ii) two OTRA based SOs [35], [166]-[167], [170]-[181] and (iii) SOs using three OTRAs [182]-[183]. A further delving revealed that most of the single OTRA based SOs are second order structures [158]-[159], [161]-[166] and only single topology [160] is a third order SO (TOSO). It is worth noticing that in the TOSO of [160], the capacitive component spread in oscillation condition is large, which is not favorable for IC implementation. It may, therefore, be concluded that there is a lean presence of single ABB based TOSO in literature, which led authors to present a single ABB based TOSO structure.

#### Category II

On the basis of number of output phases the SOs can be divided in (i) single-phase oscillators [158]–[165], [167]-[170], [178]-[180] (ii) quadrature oscillators (QO) [35], [166]-[167], [171]-[178], [181]-[183] and (iii) multiphase sinusoidal oscillators (MSO) [184]–[186]. Among several kinds of oscillators, QO (sinusoidal signals with 90° phase difference) has acquired ample attention by circuit designers because of its wide range of applications in telecommunications, measurements, etc. Therefore, many QO topologies based on OTRA are designed and readily found in the literature [166]-[167], [171]-[178], [182]-[183]. Among these topologies, no OTRA based QO qualifies for generating low frequency (LF) quadrature outputs. In this work, a new OTRA based electronically tunable low frequency quadrature oscillator (LFQO) is presented. To the best of the author's knowledge, this is the first OTRA based LFQO.

Further, from a literature survey, it reveals that several third order QO designs [171]-[173], [182]-[183] are also available. These QOs are in general based on forming closed loop using lossy and lossless integrators and can be classified in particular as those using (i) two lossy and one lossless integrators [183], (ii) one lossy and two lossless integrators [183] (iii) a second order low pass filter followed by an integrator [172] (iv) three lowpass filters and gained feedback around the loop (v) High pass filter and differentiator [171]. The structures of [173], [182] are based on intuitive design methods. However, for controlling the FO, the topology [172] suffers from the tracking problems inherent in dual-element control and topology in [173] has capacitive FO control, which is not suitable IC integration viewpoint. The SOs discussed in [183] (Figure 2) lack independent tuning. New realizations of third order QOs are designed in this work that adds to the present repertoire of OTRA based QOs.

#### Category III

Based on order of the SO topologies they can be divided in to second order [35], [158]-[159], [161]–[170], [174]–[181] and third order oscillators [160], [171]-[173], [182]-[183].

#### Category IV

Based on the tuning expression OTRA based SOs can be divided into oscillators having tuning expression in the form of  $1/2\pi$ RC [35], [158]-[165], [167]-[187] and SOs are having tuning law of the form  $\frac{\sqrt{|1-k|}}{2\pi RC}$  where *K* is resistor ratio [166]. On the other hand, the structures presented in [35], [158]-[187] are suitable for achieving medium to high frequencies. The topology in [166] uses two OTRAs having tuning law of the form  $\frac{\sqrt{|1-k|}}{2\pi RC}$ . This type of tuning law used to generate LF oscillations by employing less passive component spread, which ultimately reduces significant area overhead in IC implementation. Further, most of the second order SOs [158]-[159], [161]-[165] have an expression for the frequency of oscillation (FO) of form  $1/2\pi$ RC, which is suitable for generating frequencies ranging from medium frequencies (MF) to high frequencies (HF).

However, to ensure a wide range of frequencies (very low frequencies (VLF) to high frequencies) with less sensitivity to passive component variations at all frequencies, FO should be of the form  $\sqrt{k/2\pi}RC$  where k is resistive gain. This has motivated the development of SOs having an oscillation frequency of the form  $\sqrt{k/2\pi}RC$ . An extensive literature survey suggests that although numerous OTRA based SOs have been advanced, the evaluation of non-linearity and harmonic distortion (HD) factors of SOs have not been carried out. To fill this void OTRA based mathematical formulation HD analysis is carried out in this work by proposing Weinbridge SO topology.

### 1.3 Objectives

This work presents several OTRA based SO topologies which provide additional features and advantages not available in previously known OTRA oscillator circuits. Based on the literature survey and identified research gaps following objectives are set:

- i. To design new single OTRA based second order SOs

- ii. To develop a single OTRA based TOSO topology with the reduced component spread in the condition of oscillation (CO).

- iii. To design oscillator topologies with a wide frequency range.

- iv. To develop OTRA based QOs having independent CO, FO tuning feature

- v. To design OTRA based Wien bridge oscillator and to carry out its harmonic analysis

### 1.4 Organization of the Dissertation

The following section presents the sequencing of chapters in the thesis:

#### Chapter 1:

This chapter takes a detailed look at the significance of signal generation circuits and presents a review of existing literature available on OTRA based sinusoidal oscillators.

#### Chapter 2:

Characterization of OTRA realizations using (i) commercially available AD844 (CFOA) ICs and (ii) CMOS based integrated circuit implementation is presented in this chapter to set the groundwork for the material that follows. Functional verification of CMOS OTRA circuit has been carried out through simulations using Cadence Virtuoso analog design Environment (ADE) spectre tool at 0.18µm CMOS technology node. The schematic driven and post layout simulation results have been presented in this chapter.

#### Chapter 3:

This chapter is devoted to the design of single OTRA based sinusoidal oscillators. Two new second order SOs and one TOSO each employing one OTRA and few passive components have been presented in this chapter. The functionality of all proposed structures is verified through simulations as well as experimentation using CFOA based realization of OTRA.

#### Chapter 4:

This chapter of the thesis extends into the designing of quadrature oscillators and in all five QO topologies have been proposed. The first one is a second order structure and it qualifies for low frequency operations as well without having large component spread. One of the third order quadrature oscillator (TOQO) topology adapts the scheme of using second order high pass filter and a differentiator in a feedback loop whereas the other three topologies are derived from an inverse filter based generalized structure.

#### Chapter 5:

This chapter presents four new electronically tunable sinusoidal oscillators. Each of the proposed SO consists of forward path derived from a generic structure along with one/two OTRA based resistive gain stages or integrator in its feedback path. All the proposed SOs enjoy independent tuning of the FO through resistors without affecting the CO. One of the structures also provides a quadrature output. The proposed SOs have been successfully implemented and verified in 0.18µm CMOS technology node using Cadence Virtuoso ADE spectre tool. Both schematic driven and post-layout simulation results have been included.

#### Chapter 6:

This chapter presents an OTRA based Wien bridge oscillator. The mathematical formulation of harmonic analysis is presented to characterize the linear performance of

the proposed oscillator. The workability of the proposed Wien bridge oscillator is verified through SPICE simulations followed by experimental results.

### Chapter 7:

This chapter presents a summary of the work presented in the thesis and future scope.

# CHAPTER 2 OPERATIONAL TRANSRESISTANCE AMPLIFIER (OTRA)

## 2.1 Introduction

The CM signal processing has grown rapidly in the past few decades and demonstrated to be a viable design technique to provide efficient solutions to circuit design problems. This evolution has resulted in the emergence of numerous CM analog building blocks [3], [5].

The OTRA [32], [34], [188] is one among these blocks and has gained much consideration from several researchers, due to its inherent pros like bandwidth independent of closed-loop gain, higher slew rate and simplicity in assimilating the effect of parasitic capacitances at the input ports. As a result, OTRA is being used widely for signal processing and generating applications [94] and the references cited therein.

It is interesting to note that topologies developed employing OTRA as ABB has an advantage from the current processing capabilities at the input terminals and can directly drive the existing VM signal processing circuits, thus eliminating the requirement of additional circuitry and associated power consumption, at the output. In this chapter, OTRA characterization, using CFOA and CMOS, has discussed in detail, followed by nonideal analysis using a single pole and active resistor realization in OTRA based Circuits.

## 2.2 Basics of OTRA

OTRA is a high gain current input voltage output analog building block [32]. The input terminals of OTRA are internally grounded, thereby eliminating response limitations due to parasitic capacitances and resistances and hence is a suitable choice for high-frequency applications. The circuit symbol of OTRA is shown in Figure 2.1 (a) and the port characteristics are given by (2.1), which signifies the output voltage ( $V_0$ ) is equal to

the product of the difference of input currents  $(I_p, I_n)$  and transresistance gain  $R_m$ . For ideal operations, the  $R_m$  of OTRA approaches infinity and forces the input currents to be equal.

$$\begin{bmatrix} V_{p} \\ V_{n} \\ V_{o} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ R_{m} & -R_{m} & 0 \end{bmatrix} \begin{bmatrix} I_{p} \\ I_{n} \\ I_{o} \end{bmatrix}$$

(2.1)

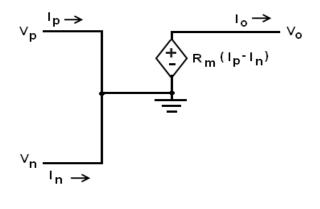

*Figure 2.1. (a) Schematic symbol representation of OTRA (b) Equivalent of OTRA* An equivalent circuit model of OTRA is illustrated in Figure 2.1(b). The equivalent circuit model of a practical OTRA is depicted in Figure 2.2, where  $R_p$  and  $R_n$  characterize the terminal resistances of p and n ports, respectively.

Figure 2.2. Equivalent circuit model of a practical OTRA

## 2.3 Nonideal Analysis

Nonideal analysis of OTRA using a single-pole is presented in this section, which will come handy to analyze the behavior of proposed circuits in this work in the presence of OTRA nonidealities.

The performance of the proposed OTRA designs may deviate from the original results because of the OTRA nonidealities. As already discussed, because of internally grounded input terminals, most of the parasitics affecting the performance of OTRA can be ignored. Ideally, R<sub>m</sub> is assumed to approach infinity. However, practically, its value is frequency-dependent.

Considering a single-pole model, R<sub>m</sub> can be expressed as

$$R_m(s) = \left(\frac{R_o}{1 + \frac{s}{\omega_o}}\right)$$

(2.2)

Where  $R_o$  represents the dc transresistance gain. For high-frequency applications, the  $R_m(s)$  reduces to

$$R_m(s) = \frac{1}{sC_p} \tag{2.3}$$

where C<sub>p</sub> in (2.3) designates the parasitic capacitance of OTRA ;  $C_p = \frac{1}{R_0 \omega_0}$

# 2.4 OTRA Implementation

In this section, OTRA implementations that are used in the proposed work are presented. These implementations are based on:

(i) Using commercially available AD844 (CFOA) ICs [189].

(ii) Using integrated circuit implementations [27], [36]-[40].

#### 2.4.1 CFOA based Implementation and its Characterization

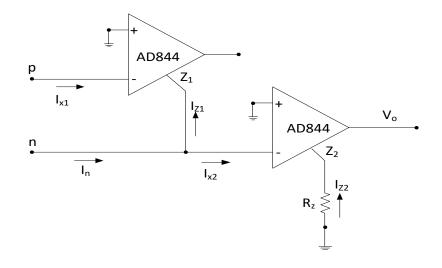

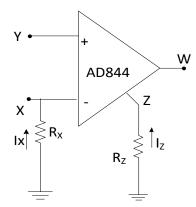

The symbol of the CFOA is shown in Figure 2.3. An OTRA can be realized using two AD844 ICs [189] connected, as depicted in Figure 2.4.

Figure 2.3. Symbol of IC AD 844

By using terminal equations of CFOA  $V_X = V_Y$ ;  $I_Y = 0$ ;  $I_Z = I_X$ ;  $V_W = V_Z$ , Figure 2.4 may be analyzed to verify the terminal characteristics of OTRA, as given below. The voltages at different ports can be written as

$$V_p = V_{X1} = V_{Y1} = 0 (2.4)$$

$$V_n = V_{X2} = V_{Y2} = 0 \tag{2.5}$$

17

$$V_{o1} = V_{Z1} = V_{2n} = V_{2p} = 0 (2.6)$$

From Figure 2.4 the currents can be evaluated as

$$I_{Z_1} = I_{X_1} = I_p \tag{2.7}$$

$$I_{Z_2} = I_{X_2} = I_n - I_{Z_1} = I_n - I_p$$

(2.8)

From above-quoted equations, the output port voltage (V<sub>o</sub>) can be yielded as

$$V_o = V_{Z2} = -I_{Z2} \cdot R_Z = -R_Z \left( I_n - I_p \right)$$

(2.9)

$$V_o = R_Z \left( I_n - I_p \right) \tag{2.10}$$

Figure 2.4. IC AD 844 based OTRA [189]

It may be observed that (2.10) is similar to (2.1) provided that the value of  $R_Z$  be very high. To have large resistance gain, the resistance  $R_Z$  at Z terminal of the second AD844 is kept high.

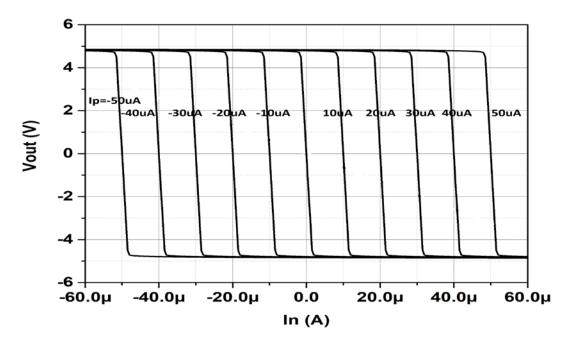

The functionality of the OTRA has been verified through SPICE simulations, where the OTRA is realized using commercially available IC AD844N. The supply voltages are chosen as  $\pm$  8.5V.

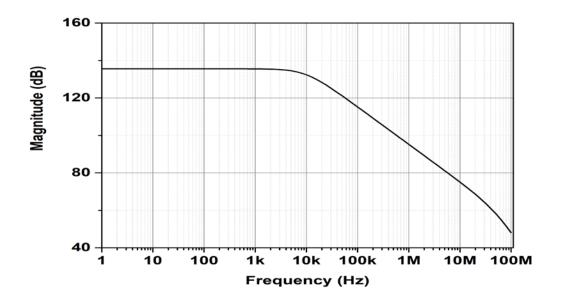

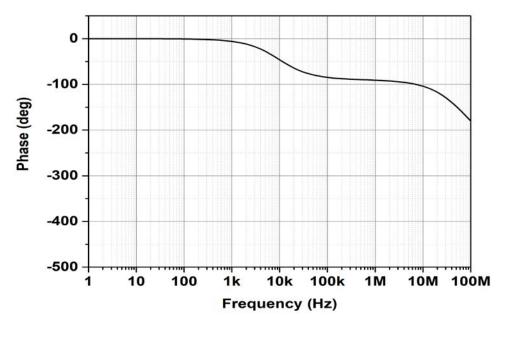

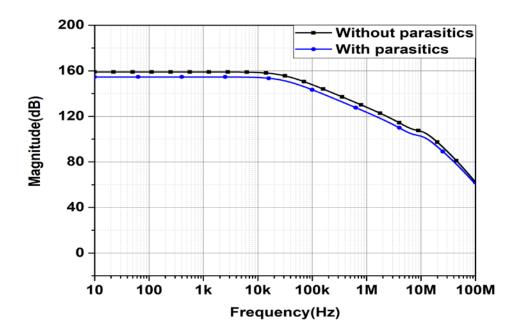

The DC characteristics of CFOA based OTRA are plotted in Figures 2.5. The offset current is obtained as 0.1  $\mu$ A. The magnitude and phase responses are depicted in Figures 2.6 (a) and (b), respectively. The DC open loop transresistance gain (R<sub>o</sub>) for OTRA is obtained as 136 dB $\Omega$ .

Figure 2.5. DC characteristics of CFOA based OTRA

(a)

(b)

Figure 2.6. Frequency response of CMOS based OTRA (a) Magnitude (b) Phase

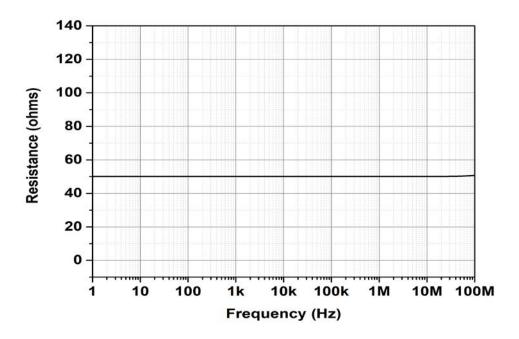

The input resistance is plotted in Figure 2.7 and its value is observed to be 50  $\Omega$ .

Figure 2.7. The input resistance of CFOA based OTRA

#### 2.4.2 CMOS based Implementation and its Characterization

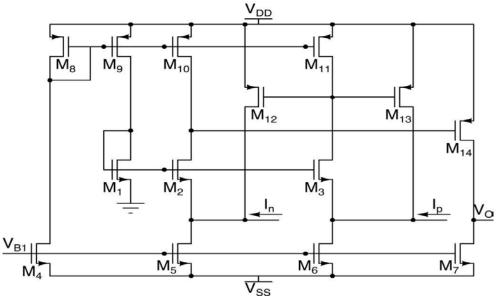

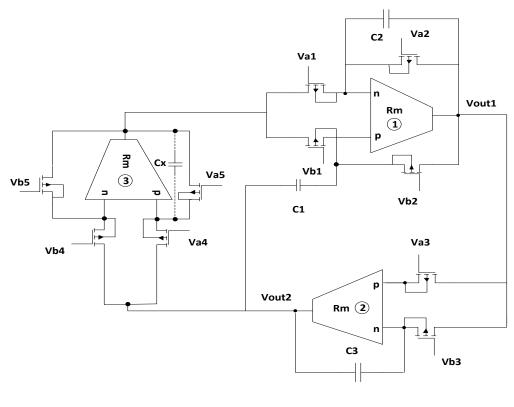

The CMOS realization of OTRA [32] is shown in Figure 2.8. It is based on the cascaded connection of the modified differential current conveyor (MDCC) and a common source amplifier.

Figure 2.8. CMOS implementation of OTRA [32]

Assuming that all transistors operate in saturation region and each of the groups of the transistors ( $M_1$ - $M_3$ ), ( $M_5$  and  $M_6$ ), ( $M_8$ - $M_{11}$ ) and ( $M_{12}$  and  $M_{13}$ ) are matched, the circuit operation can be explained as follows. The current mirrors formed by ( $M_8$ - $M_{11}$ ) force equal currents ( $I_B$ ) in the transistors  $M_1$ ,  $M_2$  and  $M_3$ . This operation drives the gate to source voltages of  $M_1$ ,  $M_2$  and  $M_3$  to be equal and in turn, forces the two input terminals to be virtually grounded.

The current mirrors formed by the transistor pairs ( $M_{10}$  and  $M_{11}$ ) and ( $M_{12}$  and  $M_{13}$ ) provide the current differencing operation, whereas the common source amplifier (M7,  $M_{14}$ ) serves as high gain stage.

| Transistor | W(μm)/L( μm) |

|------------|--------------|

| M1-M3      | 36/0.9       |

| M4         | 3.6/0.9      |

| M5, M6     | 10.8/0.9     |

| M7         | 3.6/0.9      |

| M8-M11     | 18/0.9       |

| M12,M13    | 36/0.9       |

| M14        | 18/0.18      |

Table 2.1. Aspect Ratios of Transistors

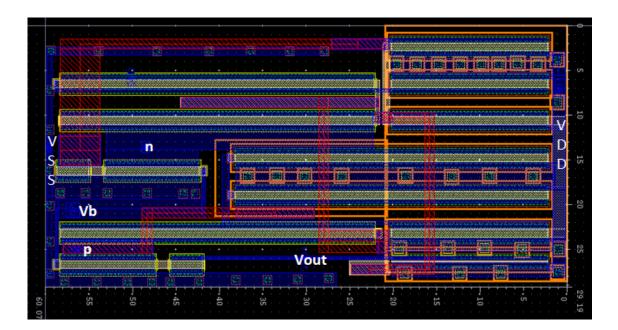

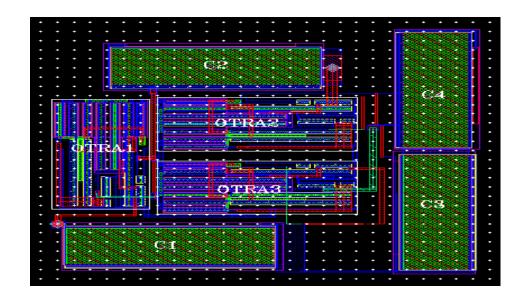

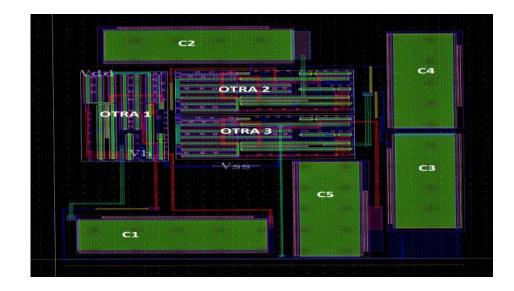

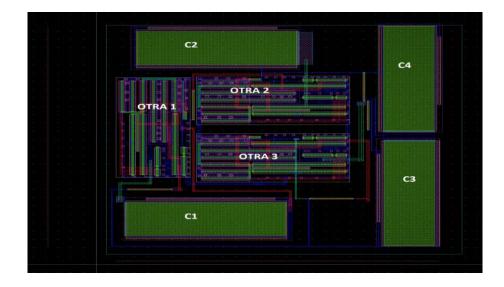

The functionality of CMOS OTRA [32] is verified through the Cadence Virtuoso ADE spectre tool using 0.18 $\mu$ m parameters. Supply voltages are taken as ±1 V and bias voltage as -0.3 V. The aspect ratios of transistors are given in Table 2.1. The Complete layout of CMOS OTRA is shown in Figure 2.9 and the total die area is about 1753.4433  $\mu$ m<sup>2</sup> (29.19 $\mu$ mx 60.07 $\mu$ m).

#### Figure 2.9. The complete physical layout of OTRA

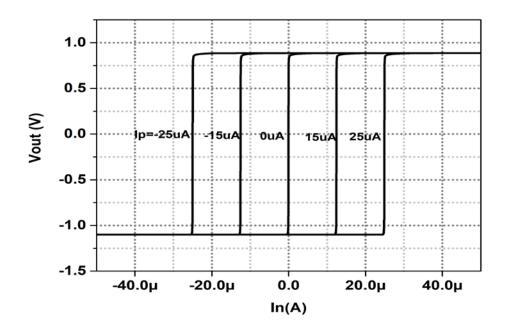

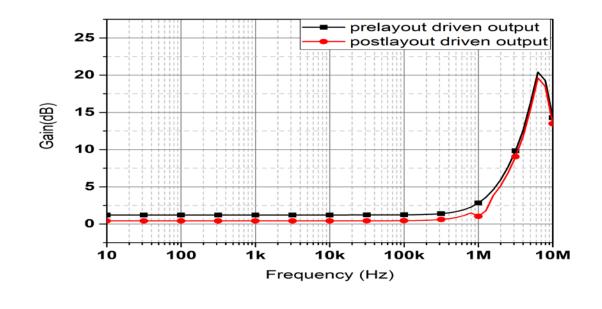

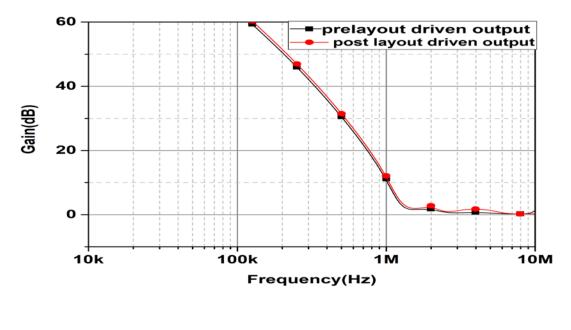

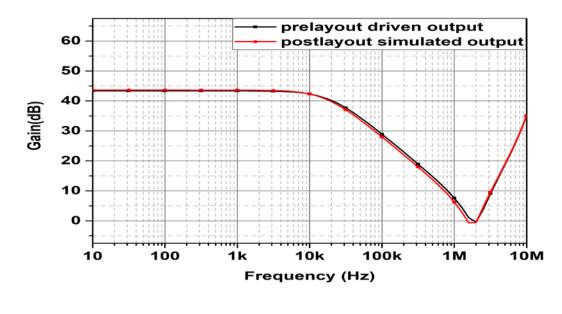

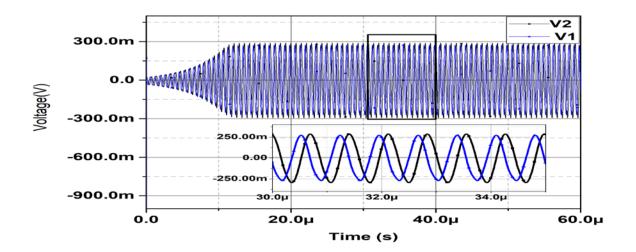

The DC characteristics of the simulated OTRA are shown in Figure 2.10, which shows that the input differential current range is  $-25\mu$ A to  $25\mu$ A. The pre and post-layout magnitude and phase responses are depicted in Figures 2.11 (a) and (b), respectively.

Figure 2.10. DC characteristics of CMOS based OTRA

(a)

(b)

*Figure 2.11. Frequency response of CMOS based OTRA (a) Magnitude (b) Phase* The layout implemented is verified by physical verification checks [190] such as Design Rule Check (DRC), Layout vs. Schematic check (LVS) and RC parasitic extraction. Due to the inclusion of parasitics, the post layout simulated magnitude response is slightly in deviation from one obtained from schematic driven simulation.

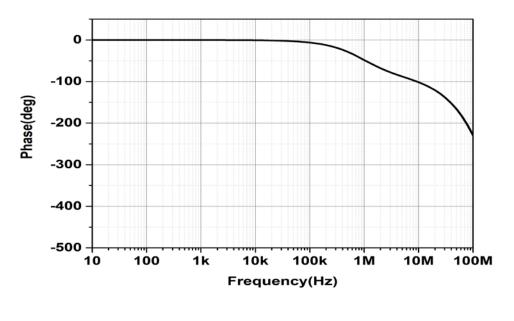

Figure 2.12. Frequency response of CMOS based OTRA at different corner parameters

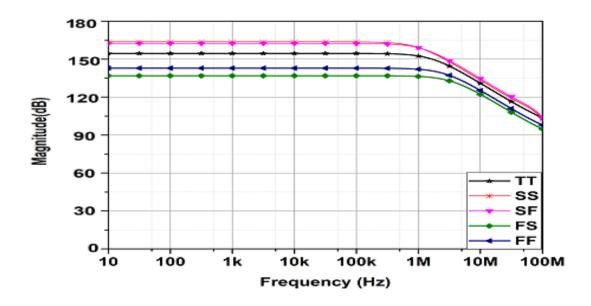

The postlayout DC transresistance gain is observed to 157 dB $\Omega$  as against 160 dB $\Omega$  prelayout value. Figure 2.12 shows the effect of different process corners (SS, SF, TT, FS, FF) on the output waveform. The input resistance is plotted in Figure 2.13 and its value is observed to be 3.8  $\Omega$  till 2 MHz.

The gain-bandwidth product, parasitic capacitance and power dissipation are obtained as 440 GHz. $\Omega$ , 5.03 fF and 226.26  $\mu$ W respectively. These results are summarized in Table 2.2.

| Technology                        | 0.18µm CMOS      |

|-----------------------------------|------------------|

| DC open loop transresistance gain | 157 dBΩ          |

| Gain bandwidth product            | 440 GHz $\Omega$ |

| Power dissipation                 | 226.26 µW        |

| Parasitic capacitance             | 5.03fF           |

| Input resistance                  | 3.8Ω             |

| Offset current                    | 71.2nA           |

#### Table 2.2. Parameters of CMOS OTRA circuit

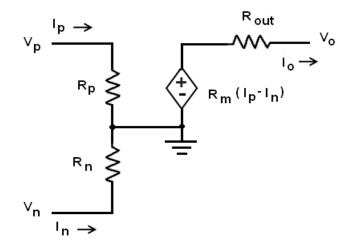

## 2.5 Active Resistor Realization in OTRA based Circuits

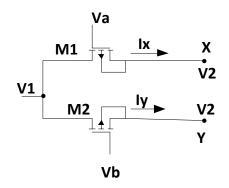

The current differencing property of the OTRA makes it feasible to realize the resistors connected to the input terminals of OTRA, using MOSFETs with complete nonlinearity cancellation [35]. Each resistor implementation requires two matched NMOS transistors, as shown in Figure 2.14.

Essentially, both the transistors should operate in the ohmic region. Figure 2.15 shows a typical MOS based implementation of resistance connected at the inverting terminal of OTRA, where nodes X and Y need to be connected to inverting and non-inverting terminals of the OTRA, respectively. The currents flowing into the two transistors can be specified as

$$I_{x} = k_{n}(V_{a} - V_{T})V_{DS1} + x_{1}V_{DS1}^{2} + x_{2}V_{DS1}^{3} + \dots$$

$$= k_{n}(V_{a} - V_{T})(V_{1} - V_{2}) + x_{1}(V_{1} - V_{2})^{2} + x_{2}(V_{1} - V_{2})^{3} + \dots$$

(2.11)

$$I_{y} = k_{n}(V_{b} - V_{T})V_{DS2} + x_{1}V_{DS2}^{2} + x_{2}V_{DS2}^{3} + \dots$$

$$= k_{n}(V_{b} - V_{T})(V_{1} - V_{2}) + x_{1}(V_{b} - V_{2})^{2} + x_{2}(V_{b} - V_{2})^{3} + \dots$$

(2.12)

Since the transistors  $M_1$  and  $M_2$  are perfectly matched and have the same drain to source voltages, the difference of the currents flowing into the two transistors can be computed as

$$(I_x - I_y) = k_n (V_a - V_b)(V_1 - V_2)$$

=  $\frac{1}{R} \cdot (V_1 - V_2)$  (2.13)

The resistance value can thus be expressed as

$$R = \frac{1}{\mu_n C_{ox} (W / L) (V_a - V_b)}$$

(2.14)

where  $\mu_n$  = electron Mobility;  $C_{ox}$  = Oxide capacitance per unit area; W/L = Effective channel width/ Effective channel length and  $V_a$ ,  $V_b$  are the gate voltages.

Figure 2.14. MOS implementation of resistance [35]

Figure 2.15. MOS implementation of a linear resistance connected between negative and output terminals of OTRA

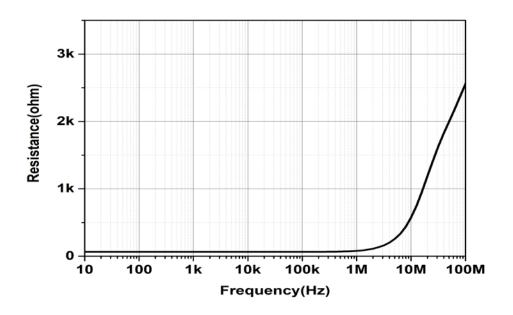

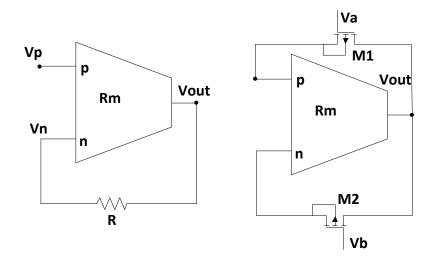

Further, different values of resistors have been realized using MOSFETs by setting W/L as 1  $\mu$ m/2.5  $\mu$ m. Table 2.3 lists the difference of gate controlling voltages required for implementing different resistor values. It also shows the current flowing through corresponding resistors.

| R(kΩ) | $(V_a-V_b)(V)$ | $I_R(\mu A)$ |

|-------|----------------|--------------|

| 10.1  | 0.963          | 95.3         |

| 10.2  | 0.953          | 93.4         |

| 10.3  | 0.944          | 91.6         |

| 11    | 0.875          | 79.5         |

| 12    | 0.802          | 66.8         |

| 13    | 0.741          | 57           |

| 14    | 0.688          | 49.1         |

| 15    | 0.642          | 42.8         |

| 16    | 0.602          | 37.6         |

| 17    | 0.566          | 33.29        |

| 18    | 0.535          | 29.7         |

Table 2.3. Gate controlling voltages for different resistor values implementation

Figure 2.16. Differential gate controlling voltage versus transistor current

The graph between gate controlling voltages and its current is depicted in Figure 2.16.

# 2.6 Concluding Remarks

In this chapter, CFOA and CMOS based OTRAs are characterized. Nonidealities of practically realized OTRA are also discussed, which would be helpful in performance evaluation of any OTRA based circuit. The active resistor realization in OTRA based circuits is also presented in this chapter.

# CHAPTER 3 SINGLE OTRA BASED SINUSOIDAL OSCILLATORS

The content and results of the following papers have been reported in this chapter

[1] K. Gurumurthy, R. Pandey and N. Pandey, "Minimum component count Low frequency sinusoidal oscillator based on Single OTRA," *IJCTA*, vol. 9, pp. 181–7, 2016.

(SCOPUS)

[2] K. Gurumurthy, N. Pandey and R. Pandey, "Single OTRA Based Low frequency Sinusoidal Oscillator Realization," *IOP: Materials Science and Engineering*; vol. 225, 2017. (SCOPUS)

[3] K. Gurumurthy, N. Pandey and R. Pandey, "New realization of third order sinusoidal oscillator using single OTRA," *Int J Electron Commun (AEÜ)*, vol. 93, pp. 182–90, 2018. (SCI) (IF: 2.82)

## **3.1 Introduction**

Sinusoidal oscillators (SOs) play a vital role in control, power electronics, instrumentation, measurement, standard test and carrier signals for communications and other electronic systems [47]–[49]. These oscillators may generate signals of various frequencies ranging from very low to very high.

Low frequency (LF) oscillators are a specific class of oscillators, which produce periodic waveforms at a very low frequency generally in (0-20 Hz) range. These are very commonly used for music and speech synthesis and also find applications in various other fields such as testing of various servomechanisms, geophysical systems, biological and biomedical fields [53], [76], [191]. The oscillators, which can produce medium to high frequencies, can be easily designed by implementing tuning expression of the form 1/RC, whereas, designing of LF oscillators with lower passive component

spread needs a special tuning function of the form  $\frac{\sqrt{|1-n|}}{2\pi RC}$ .

The SOs are most commonly designed using a forward active network of single/multiple ABBs based amplifiers/filters and passive networks placed in the feedback loop. The oscillator topologies with a reduced number of ABBs and passive components lead to power and area efficient designs wherein the parasitic effects are also reduced. Therefore, this chapter is devoted to the design of single OTRA based SOs. It is pertinent to mention here that with reference to harmonic distortion performance, the TOSOs are always preferred over second order oscillators. This led us to present a third order SO (TOSO) also in this chapter.

# 3.2 Single OTRA based Second Order SOs

This section elaborates on the proposed second order SO topologies. Each topology is described first, which is followed by its MOS resistor based realization. The effect of nonidealities of OTRA on these structures is analyzed in the subsequent section.

## 3.2.1 Proposed Topology I

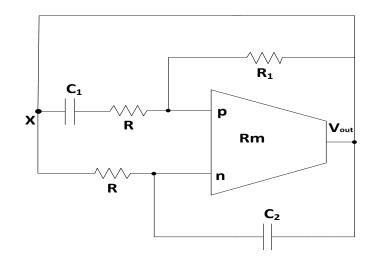

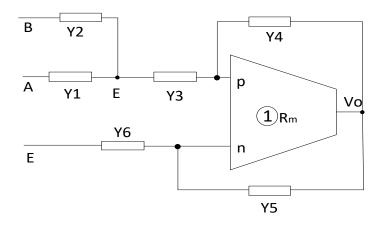

The proposed topology I is shown in Figure 3.1, using routine analysis the characteristic equation (CE) of the SO can be expressed as

$$s^{2}C_{1}C_{2} + s\left(\frac{C_{2}}{R} - \frac{C_{1}}{R_{1}}\right) - \frac{1}{R_{1}R} + \frac{1}{R^{2}} = 0$$

(3.1)

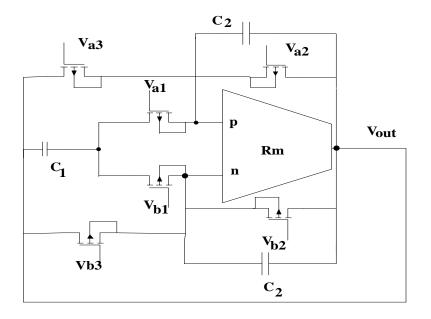

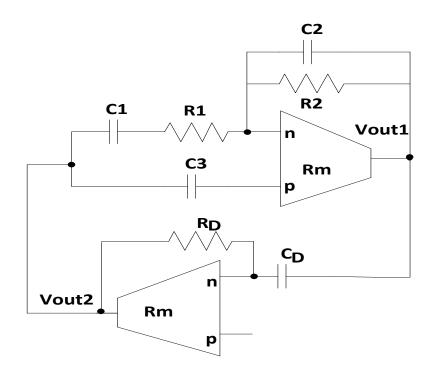

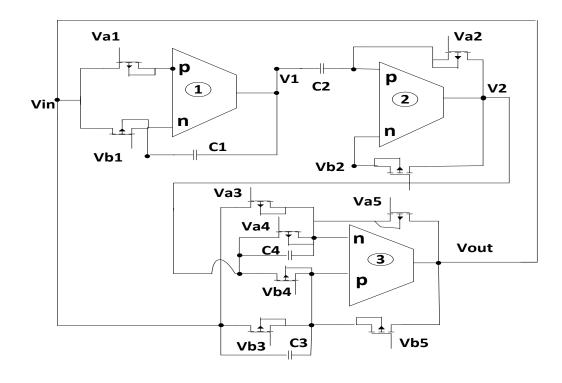

Figure 3.1. Proposed single OTRA SO topology I

The CO and FO ( $f_o$ ) for topology I from CE are given as

CO:

$$C_2 R_1 = C_1 R$$

FO:  $f_o = \frac{1}{2\pi R \sqrt{C_1 C_2}} [1 - n]^{\frac{1}{2}}$ ; where  $n = \frac{R}{R_1}$  (3.2)

By choosing the appropriate value of n, the proposed oscillator can provide low to medium frequencies.

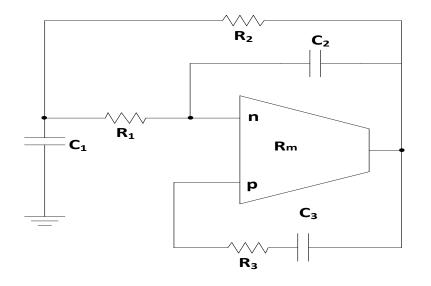

# 3.2.2 Proposed Topology II

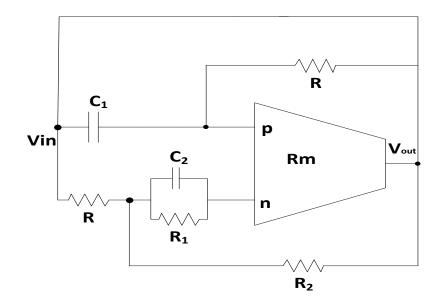

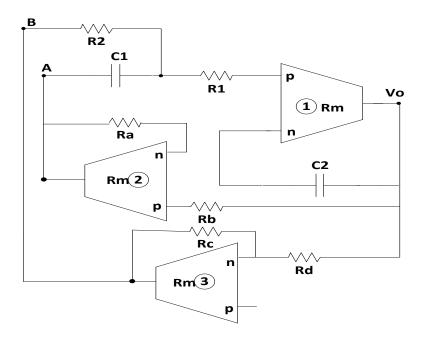

The proposed topology II is depicted in Figure 3.2 and its CE is expressed as

Figure 3.2. Proposed single OTRA SO topology II

$$\begin{cases} s^{2}C_{1}C_{2}R^{2}R_{1}R_{2} + s\left[C_{1}R_{1}R_{2}R + C_{1}R^{2}(R_{1} + R_{2}) - C_{2}R^{2}R_{1}\right] \\ +R_{1}R_{2} - R^{2} + RR_{1} = 0 \end{cases}$$

(3.3)

The CO and FO may be obtained as

$$CO: C_1 R_2 (R + R_1) = RR_1 (C_2 - C_1)$$

FO:  $f_o = \frac{1}{2\pi R \sqrt{C_1 C_2}} \left[ 1 + \left( \frac{R}{R_2} - \frac{R^2}{R_1 R_2} \right) \right]^{\frac{1}{2}} \right]$  (3.4)

The FO can further be written as

$$f_o = \frac{1}{2\pi R \sqrt{C_1 C_2}} \left[ K \right]^{\frac{1}{2}}$$

(3.5)

Where K = 1 + n and n denotes the resistor ratio  $\left(\frac{R}{R_2} - \frac{R^2}{R_1R_2}\right)$ .

The multiplication factor *K* can be selected to be greater than or less than unity by choosing the appropriate values of *R*,  $R_1$ ,  $R_2$ . By making  $\frac{R}{R_1} < 1$  the *K* value may be chosen to be greater than unity, whereas if  $\frac{R}{R_1} > 1$  the *K* value is set to be less than one. Thus, the proposed oscillator can provide frequencies ranging from LF to MF by simply adjusting *K*.

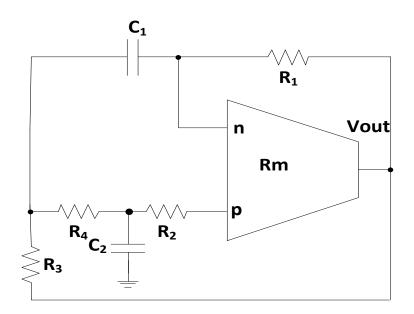

## 3.2.3 Proposed Topology III

The proposed topology III is presented in Figure 3.3 and the CE is given by (3.6).

$$\begin{cases} s^{2} + \frac{s}{C_{1}C_{2}} \left( C_{2} \left( \frac{1}{R_{3}} + \frac{1}{R_{4}} \right) + \frac{C_{1}}{R_{2}} + \frac{C_{1}(1-K)}{R_{4}} \right) + \frac{1}{C_{1}C_{2}} \left( \frac{1}{R_{3}R_{4}} + \frac{1}{R_{2}R_{4}} + \frac{1}{R_{2}R_{3}} \right) \\ - \frac{K}{R_{3}R_{4}C_{1}C_{2}} = 0 \end{cases}$$

(3.6)

where  $K = \frac{R_1}{R_2}$ ; by considering equal capacitances, the FO and CO are computed as

FO:

$$f_o = \frac{1}{2\pi C} \sqrt{\frac{1}{R_2 R_4} + \frac{1}{R_2 R_3} - \frac{2}{R_3 R_4}}$$

(3.7)

$$CO: \frac{1}{R_2} + \frac{1}{R_3} = \frac{1}{R_4}; K = 3$$

(3.8)

# 3.2.4 MOS-C implementation of Proposed Topology-I

The current differencing property of the OTRA makes it feasible to realize the resistors connected to the input terminals of OTRA, using MOSFETs with complete nonlinearity cancellation [35], as explained in chapter 2.

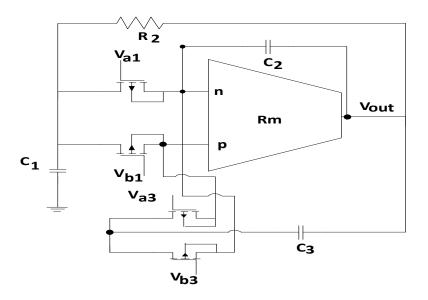

# Figure 3.4. MOS-C implementation of proposed topology-I

A thorough inspection of proposed topology-I suggests that all the resistors of Figure 3.1 are MOS realizable and the resulting structure is shown in Figure 3.4. The resistance values can be tuned with the help of gate voltages and thus, the FO can be tuned electronically.

#### 3.2.5 Nonideal Analysis

The performance of the proposed oscillators may deviate from the ideal results because of the OTRA nonidealities. Ideally,  $R_m$  is assumed to approach infinity. However, practically, its value is frequency-dependent.

Considering a single-pole model single-pole mode of OTRA in Figure 3.1, the CE of (3.1) modifies to

$$s^{2}C_{1}(C_{2}+C_{p})R^{2}+s[(C_{2}+C_{p})R-C_{1}\frac{R^{2}}{R_{1}}]-\frac{R}{R_{1}}+1=0$$

(3.9)

The modified CO and FO are computed as

CO:

$$R_1(C_2 + C_p) = C_1 R$$

FO:  $\hat{f}_o = \frac{1}{2\pi (C_2 + C_p) \sqrt{RR_1}} [1 - n]^{\frac{1}{2}}$  (3.10)

For, Figure 3.2, the CE of (3.2) changes to (3.11) by considering the nonidealities.

$$s^{2} (C_{1} + C_{p})C_{2}R^{2}R_{1}R_{2} + s \begin{bmatrix} (C_{1} + C_{p})R_{1}R_{2}R + (C_{1} + C_{p})R^{2}(R_{1} + R_{2}) \\ -C_{2}R^{2}R_{1} \end{bmatrix}$$

(3.11)

$$-R^{2} + R_{1}R_{2} + RR_{1} = 0$$

The altered CO and FO are computed as

$$CO: (C_1 + C_p)R_2(R + R_1) = RR_1(C_2 - (C_1 + C_p))$$

FO:

$$\hat{f}_{o} = \frac{1}{2\pi R \sqrt{(C_{1} + C_{p})C_{2}}} \left[ 1 + \left( \frac{R}{R_{2}} - \frac{R^{2}}{R_{1}R_{2}} \right) \right]^{\frac{1}{2}}$$

(3.12)

From (3.10) and (3.12), it is observed that there is a slight deviation in FO in the presence of nonidealities. The effect of parasitic capacitances  $C_p$  can be eliminated by preadjusting  $C_1$  and  $C_2$ , thus achieving self-compensation.

Considering the nonidealities of OTRA, the CE of Figure 3.3 changes to

$$X_1 s^2 + Y_1 s + Z_1 = 0 (3.13)$$

where coefficients  $X_1$ ,  $Y_1$  and  $Z_1$  are represented respectively as

$$X_{1} = C_{1}C_{2}\left(1 + sC_{p}R_{1} + \frac{C_{p}}{C_{1}}R_{1}\left(\frac{1}{R_{3}} + \frac{1}{R_{4}}\right) + \frac{C_{p}}{C_{2}}R_{1}\left(\frac{1}{R_{2}} + \frac{1}{R_{4}}\right)\right)$$

(3.14)

$$Y_{1} = C_{1}C_{2}\left(\frac{1}{C_{1}}\left(\frac{1}{R_{3}} + \frac{1}{R_{4}}\right) + \frac{1}{R_{2}C_{2}} + \frac{(1-K)}{R_{4}C_{2}} + \frac{C_{p}R_{1}}{C_{1}C_{2}}\left(\frac{1}{R_{2}R_{4}} + \frac{1}{R_{2}R_{3}} + \frac{1}{R_{3}R_{4}}\right)\right)$$

(3.15)

$$Z_1 = \left(\frac{1}{R_2 R_4} + \frac{1}{R_2 R_3} + \frac{1}{R_3 R_4}\right) - \frac{K}{R_3 R_4}$$

(3.16)

It is clear that the CE modifies in the presence of nonidealities. However, the effect may practically be ignored by choosing oscillator frequency much below  $1/C_pR_1$  and selecting external capacitors of value much higher than  $C_p$ . In such a situation, the coefficients X<sub>1</sub>, Y<sub>1</sub> and Z<sub>1</sub> modify to

$$X_1 \approx C_1 C_2; \tag{3.17}$$

$$Y_{1} \approx C_{1}C_{2} \left( C_{2} \left( \frac{1}{R_{3}} + \frac{1}{R_{4}} \right) + \frac{C_{1}}{R_{2}} + \frac{C_{1}}{R_{4}} (1 - K) \right)$$

(3.18)

$$Z_{1} = \left(\frac{1}{R_{2}R_{4}} + \frac{1}{R_{2}R_{3}} + \frac{1}{R_{3}R_{4}}\right) - \frac{K}{R_{3}R_{4}}$$

(3.19)

By substituting (3.17), (3.18) and (3.19) in (3.13), the CE given by (3.13) reduces to (3.6) and FO, CO are given by (3.7) and (3.8) respectively.

### 3.2.6 Sensitivity Analysis

The sensitivity is an important performance criterion for any circuit, which enables analog IC designers to choose which elements should be carefully designed to maintain high circuit performance. The sensitivity of FO is calculated with respect to all passive components [48] may be calculated as

$$S_X^{f_o} = \frac{X}{f} \cdot \frac{\partial f_o}{\partial X}$$

(3.20)

where X refers to various elements used.

The sensitivity of  $f_o$  for Figure 3.1 with respect to circuit components is computed as

$$\left|S_{C_{1}}^{f_{o}}\right| = \left|S_{C_{2}}^{f_{o}}\right| = \frac{1}{2}; \left|S_{R_{1}}^{f_{o}}\right| = \frac{R}{2(R_{1}-R)}; \left|S_{R}^{f_{o}}\right| = \frac{2R_{1}+R}{2\left(1-\frac{R}{R_{1}}\right)}$$

(3.21)

The sensitivities of  $f_o$  for Figure 3.2 with respect to C<sub>1</sub>, C<sub>2</sub>, R<sub>2</sub>, R<sub>1</sub>, R are

$$\begin{cases} \left| S_{C_{1}}^{f_{o}} \right| = \left| S_{C_{2}}^{f_{o}} \right| = \frac{1}{2}; \left| S_{R_{2}}^{f_{o}} \right| = \frac{R(R - R_{1})}{2\left[ R_{1}(R + R_{2}) - R^{2} \right]}; \\ \left| S_{R_{1}}^{f_{o}} \right| = \frac{R^{2}}{2\left[ R_{1}(R + R_{2}) - R^{2} \right]}; \left| S_{R}^{f_{o}} \right| = \frac{R_{1}(2R_{2} + R)}{2\left[ R_{1}(R + R_{2}) - R^{2} \right]} \end{cases}$$

(3.22)

The sensitivities of  $f_o$  for Figure 3.3 with respect to C, R<sub>2</sub>, R<sub>3</sub>, R<sub>4</sub> are

$$\begin{cases} \left| S_{C}^{f_{o}} \right| = 1; \left| S_{R_{3}}^{f_{o}} \right| = \frac{1}{2 \left[ 1 + R_{3} / (R_{4} - 2R_{2}) \right]}; \left| S_{R_{4}}^{f_{o}} \right| = \frac{1}{2 \left[ 1 + R_{4} / (R_{3} - 2R_{2}) \right]} \\ \left| S_{R_{2}}^{f_{o}} \right| = \frac{1}{2 \left[ 1 - 2R_{2} / (R_{3} + R_{4}) \right]}; \end{cases}$$

(3.23)

39

From (3.21) to (3.23), it can be seen that all the sensitivities with respect to passive components and parasitic capacitances are less than unity in magnitude.

#### 3.2.7 Simulation Results

The workability of the proposed structures is tested using SPICE simulations and the CMOS implementation [32] of OTRA is used. The process parameters are taken as 0.18  $\mu$ m provided by MOSIS (AGILENT) for the transistors used in OTRA. Supply voltages  $V_{SS}$  and  $V_{DD}$  used are  $\pm$  1.5V.

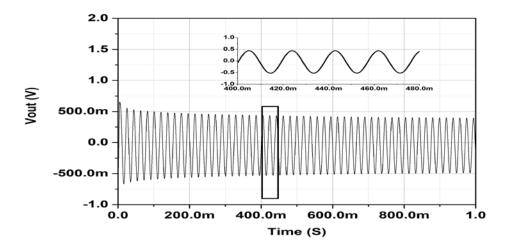

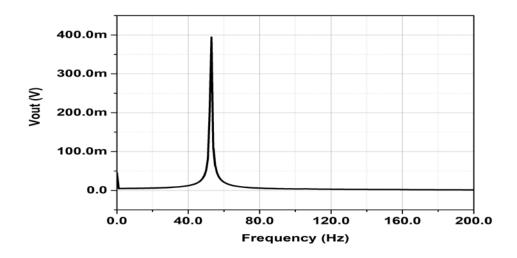

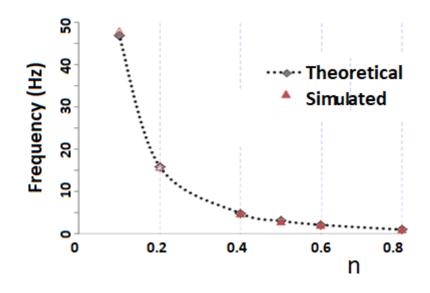

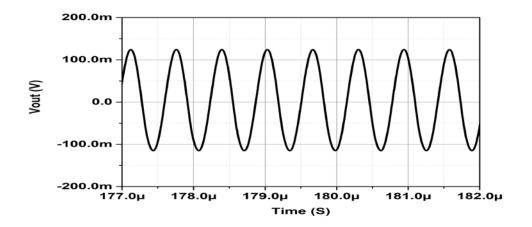

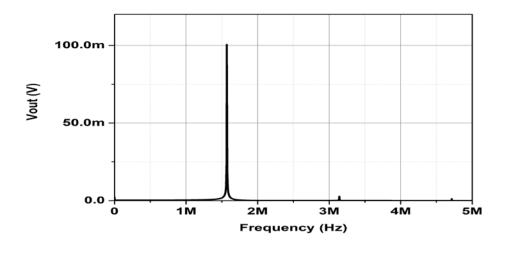

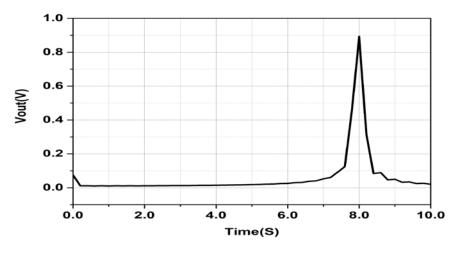

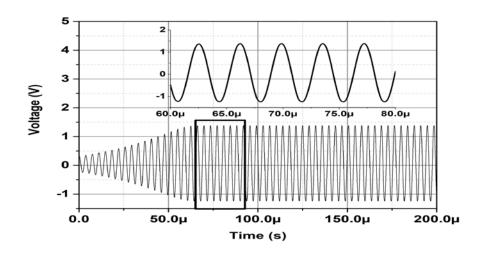

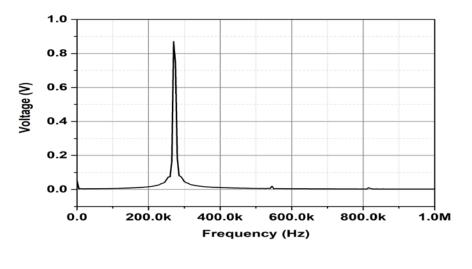

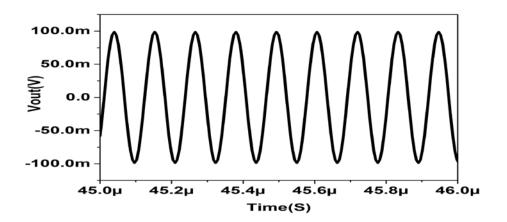

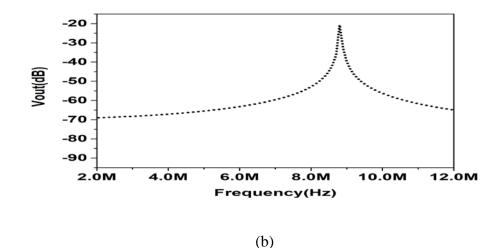

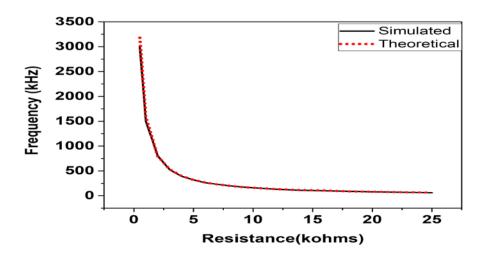

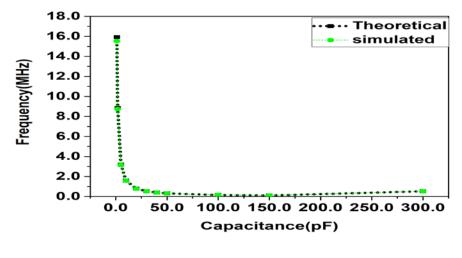

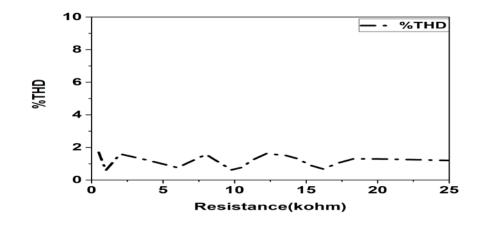

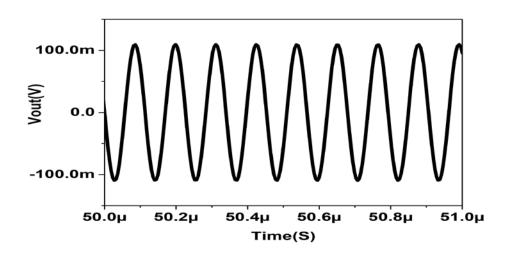

For topology in Figure 3.1 simulations are carried out for f = 45 Hz by selecting R<sub>1</sub>= 11 k $\Omega$ , R= 10 k $\Omega$ , C<sub>1</sub>= 110 nF, C<sub>2</sub>= 100 nF. The corresponding timing waveform and its frequency spectrums are depicted in Figure 3.5 and Figure 3.6, respectively. The Total harmonic distortion (THD) is observed to be 2.24%. Figure 3.7 shows the variation of frequency with resistor ratio '*n*'. At *n* = 0.8 the frequency is 1 Hz.

Figure 3.5. Timing waveform of proposed topology I

Figure 3.6. Frequency spectrum of proposed SO topology-I

Figure 3.7. Variation of frequency with respect to n

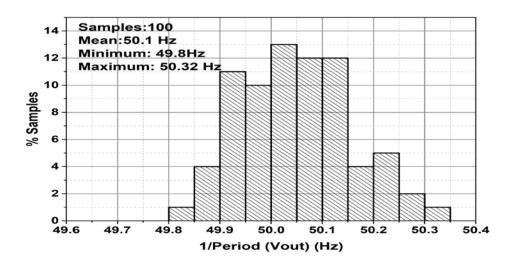

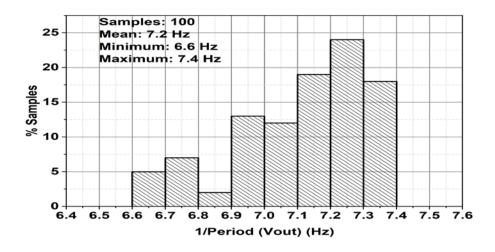

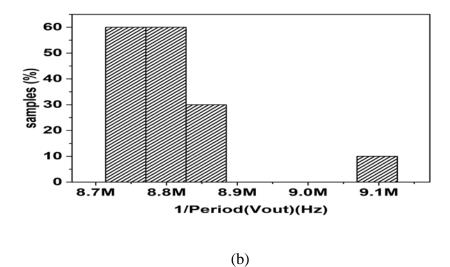

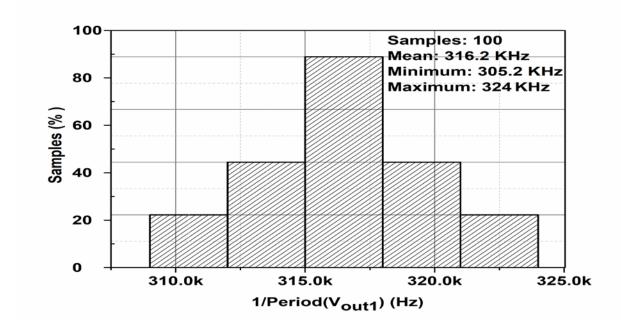

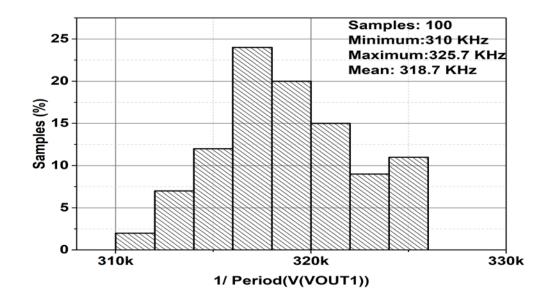

Figure 3.8. Histogram of Proposed SO-I after Monte Carlo simulation

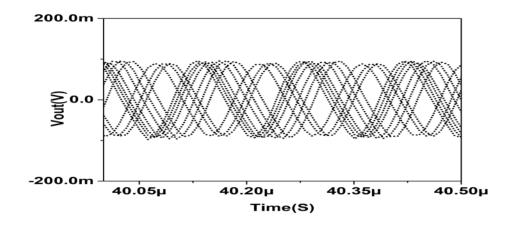

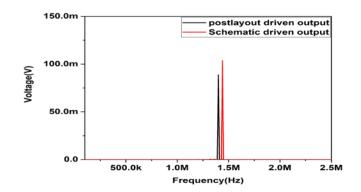

The robustness of the proposed circuit is examined through Monte Carlo simulations by considering hundred samples with 5% variations in all passive components. Figure 3.8 shows the histogram in which the value of FO remains close to its theoretical value of 45 Hz. The proposed topology in Figure 3.1 also provides oscillations at higher frequencies. To illustrate this point, the oscillator was designed for a FO of 1.59 MHz by selecting component values as  $R= 1 \ k\Omega$ ,  $R_1= 2 \ k\Omega$ ,  $C_1= 100 \ pF$ ,  $C_2= 50 \ pF$ . The simulated timing waveform and its frequency spectrum are plotted in Figure 3.9 (a) and (b), respectively. The THD is observed as 0.47% at FO of 1.59 MHz.

(b)

Figure 3.9. (a) Timing waveform and (b) frequency spectrum of proposed SO topology I

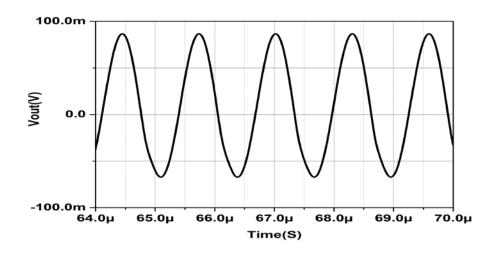

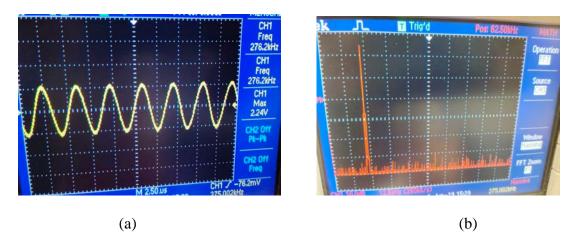

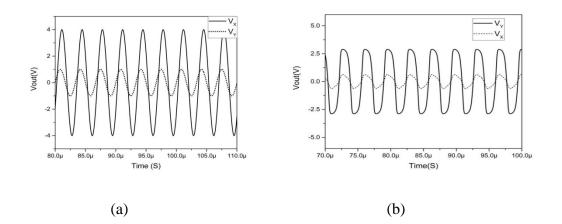

Simulations are performed for oscillator topology in Figure 3.2 at FO of 7.96 Hz by selecting R= 50 k $\Omega$ , R<sub>1</sub>= R<sub>2</sub>= 100 k $\Omega$ , C<sub>1</sub>= 100 nF, C<sub>2</sub>= 400 nF. The simulated transient response and its corresponding frequency spectrum are shown in Figure 3.10 (a) and (b), respectively. The robustness of the proposed SO topology II is examined through Monte Carlo simulations by considering hundred samples with 5% variations in all passive components.

(b)

Figure 3.10. (a) Transient waveform and (b) frequency spectrum of proposed SO-II

Figure 3.11. Histogram of proposed SO-II after Monte Carlo simulation

Figure 3.11 shows the histogram in which the value of FO remains close to its standard value of 7.9 Hz. By adjusting the multiplication factor *K* in (3.5), the proposed structure can provide higher frequency oscillations. To verify this fact, the oscillator was tested at 796 KHz by choosing component values as  $R= 0.5 \text{ k}\Omega$ ,  $R_1=R_2=1 \text{ k}\Omega$ ,  $C_1=100 \text{ pF}$ ,  $C_2=400 \text{ pF}$ .

(b)

Figure 3.12. (a) Transient waveform and (b) frequency spectrum of proposed SO-II

The simulated transient response and corresponding frequency spectrum are plotted in Figure 3.12 (a) and (b), respectively. The THD is observed as 2.14% for 7.96 Hz oscillation and 0.6% at 796 KHz.

(b)

*Figure 3.13. (a) Transient waveform and (b) frequency spectrum of proposed SO-III* For simulation of circuit of Figure 3.3, the component values are chosen as  $R_1$ = 5.4 kΩ,  $R_2$ = 1.8 kΩ,  $R_3$ = 7.2 kΩ,  $R_4$ = 1.44 kΩ and capacitor values are taken as 300 pF. The simulated transient response and corresponding frequency spectrum are shown in Figure 3.13 (a) and (b), respectively. The simulated FO is obtained to be 273 KHz and THD is observed to be 3.27%.

Figure 3.14. Histogram of Proposed SO-III after Monte Carlo simulation.

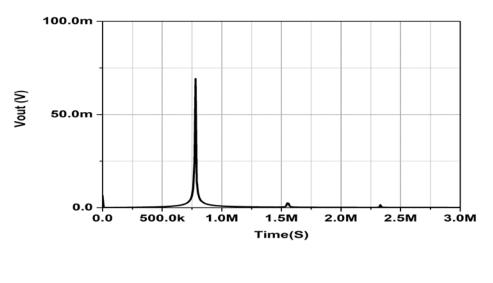

The robustness of the proposed SO topology III is examined through Monte Carlo simulations by considering fifty samples with 5% variations in all passive components. Figure 3.14 shows the histogram in which the value of FO remains close to its standard value of 273 KHz.

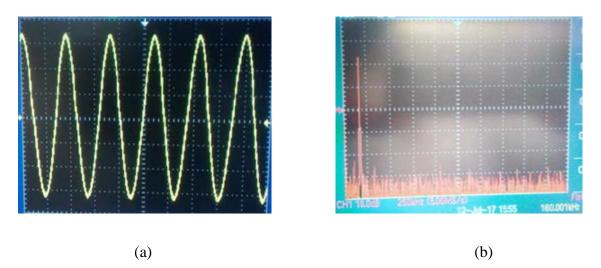

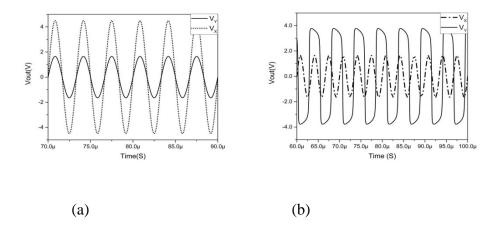

## 3.2.8 Experimental Results

The proposed SOs are also verified experimentally by breadboarding AD844IC based implementation of OTRA [181] and supply voltages of  $\pm$  8V are used.

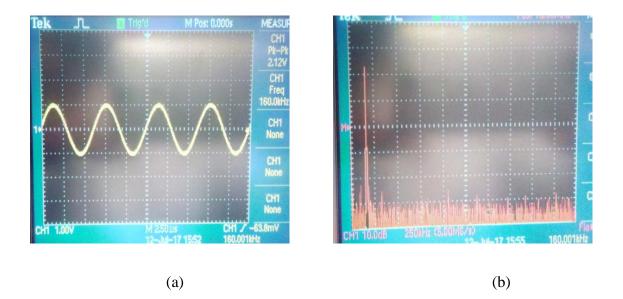

Figure 3.15. Experimental results of Figure 3.1 (a) steady-state output and it's (b) frequency spectrum

The resistor and capacitor values taken are  $R_1$ = 10.1 k $\Omega$ , R= 10 k $\Omega$ ,  $C_1$ = 10 pF,  $C_2$ = 10.1 pF. Figures 3.15 (a) and (b) show the observed oscillations and FFT spectrums at 160 KHz for topology in Figure 3.1. Figure 3.2 is designed at 7 KHz ( $R_1$ = 10 k $\Omega$ ,  $R_2$ = 1.2 k $\Omega$ , R= 11 k $\Omega$ ;  $C_2$ = 100 pF,  $C_1$ = 436 pF) and the corresponding steady-state response and FFT spectrum are depicted in Figure 3.16 (a) and (b), respectively.

Figure 3.17. Measured outputs of SO-III (a) steady-state output and it's (b) frequency spectrum

Figure 3.3 is modeled at 275 KHz ( $R_1$ = 5.4 k $\Omega$ ,  $R_2$ = 1.8 k $\Omega$ ,  $R_3$ = 7.2 k $\Omega$ ,  $R_4$ = 1.44 k $\Omega$ ). Its steady-state response and corresponding frequency spectrum are depicted in Figure 3.17 (a) and (b), respectively.

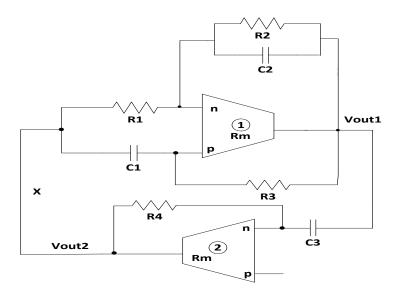

## 3.3 Proposed TOSO Configuration

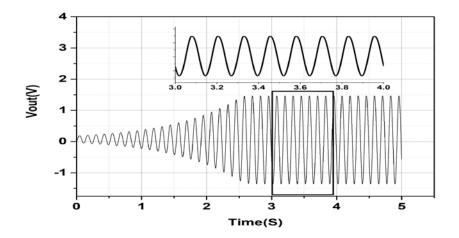

The literature review, as presented in chapter 1, suggested that only a single topology [160] of TOSO using single OTRA is available. It is worth noting that in the TOSO of [160], the capacitive component spread in the oscillation condition is large, which is not favorable for IC implementation.

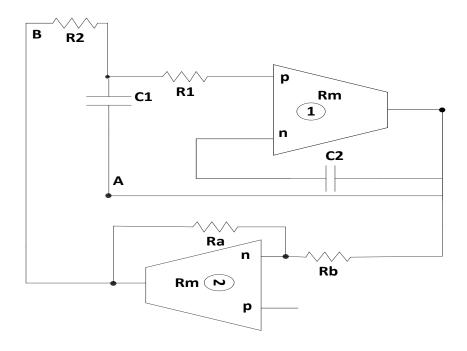

The proposed TOSO is shown in Figure 3.18. It uses a single OTRA and six passive components. The CE is obtained by performing routine analysis, assuming ideal OTRA and is given by

$$\begin{cases} s^{3}C_{1}C_{2}C_{3}R_{1}R_{2}R_{3} + s^{2} \begin{bmatrix} C_{1}C_{2}R_{1}R_{2} + C_{2}C_{3}R_{1}R_{3} + \\ C_{2}C_{3}R_{2}R_{3} - C_{1}C_{3}R_{1}R_{2} \end{bmatrix} + \\ s[C_{2}R_{1} + C_{2}R_{2} + C_{3}R_{3} - C_{3}R_{1} - C_{3}R_{2}] + 1 = 0 \end{cases}$$

(3.24)

Assuming  $C_1 = C_2 = C_3 = C$ ,  $R_1 = R_2 = R$  the CE (3.24) reduces to

$$s^{3}C^{3}R^{2}R_{3} + 2s^{2}C^{2}RR_{3} + sCR_{3} + 1 = 0$$

(3.25)

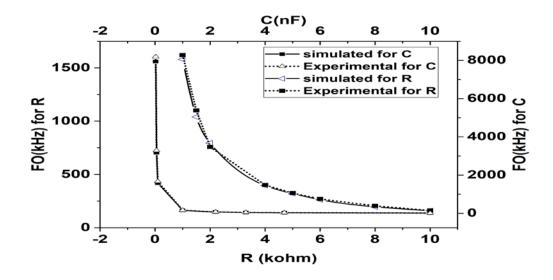

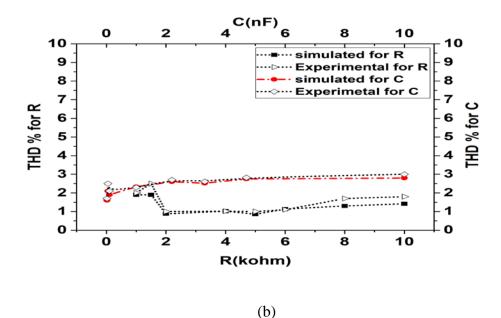

Therefore FO and CO are given by

FO:

$$f_o = \frac{1}{2\pi RC}$$

CO:  $2R_3 = R$  (3.26)

From (3.26), it is clear that FO can be tuned using C without affecting CO. Similarly, CO can be adjusted using  $R_3$ . In practice, frequency tuning via capacitor variation is difficult. However, the capacitors may be replaced by a capacitor bank formed by a parallel connection of a capacitor and a series switch. The value of capacitance may be varied by appropriate switch settings.

Figure 3.18. Proposed TOSO circuit

## 3.3.1 MOS resistor based Implementation

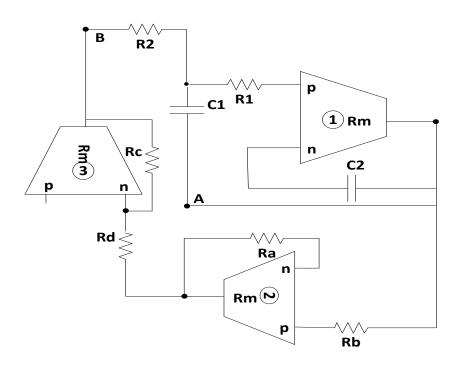

A thorough inspection of Figure 3.18 reveals that all the resistors except  $R_2$  can be realized using MOSFETs. The MOS resistor based implementation of proposed TOSO is shown in Figure 3.19.

## Figure 3.19. MOS resistor implementation of proposed TOSO 3.3.2 Nonideal Analysis

Using a single-pole model for  $R_m$  the CE given in (3.24) modifies to

$$s^{3}C_{1}C_{3}R_{1}R_{2}R_{3}(C_{2}+C_{p})+s^{2}\left[(C_{2}+C_{p})\left(C_{3}R_{3}(R_{1}+R_{2})+C_{1}R_{1}R_{2}\right)-C_{1}C_{3}R_{1}R_{2}\right]+s\left[(R_{1}+R_{2})\left(C_{2}+C_{p}\right)-C_{3}\left(R_{1}+R_{2}-R_{3}\right)\right]+1=0$$

(3.27)

and the FO and CO change to

FO:

$$\hat{f}_{o}^{\Lambda} = \frac{1}{2\pi} \sqrt{\frac{(R_{1} + R_{2})(C_{2} + C_{p}) - C_{3}(R_{1} + R_{2} - R_{3})}{C_{1}C_{3}R_{1}R_{2}R_{3}(C_{2} + C_{p})}}$$

(3.28)

CO:

$$\begin{cases} \left[ \frac{(R_1 + R_2)(C_2 + C_p) - C_3(R_1 + R_2 - R_3)}{C_1 C_3 R_1 R_2 R_3 (C_2 + C_p)} \right] = \\ \frac{1}{(C_2 + C_p)(C_3 R_3 (R_1 + R_2) + C_1 R_1 R_2) - C_1 C_3 R_1 R_2} \end{cases}$$

(3.29)

The effect of  $C_p$  can be eliminated by pre-adjusting the value of capacitor  $C_2$ , thus achieving self-compensation. By choosing equal capacitance and resistor values except for  $R_3$ , the FO and CO are reduced to (3.26).

#### 3.3.3 Sensitivity Analysis

The sensitivity of FO ( $f_o$ ) for the circuit of Figure 3.18 with respect to R and C are given as

$$\left|S_{C}^{f_{o}}\right| = \left|S_{R}^{f_{o}}\right| = 1; \left|S_{R_{3}}^{f_{o}}\right| = 0$$

(3.30)

From (3.31), it is observed that all passive sensitivities are less than or equal to unity in magnitude. Therefore, it ensures that the sensitivity performance is satisfactory. Sensitivities of the proposed TOSO structure by considering nonidealities and component setting of  $C_1 = C_2 = C_3 = C$ ,  $R_1 = R_2 = R$  are given by

$$\begin{vmatrix} S_{R}^{\Lambda} \\ = \frac{RC_{p} + R_{3}C}{2RC_{p} + R_{3}C}; & S_{R_{3}}^{\Lambda} \\ = \frac{2RC_{p}}{2RC_{p} + R_{3}C}; \\ S_{C}^{\Lambda} \\ = \frac{R_{3}C(C + C_{p}) - (2RC_{p} + R_{3}C)(3C + 2C_{p})}{2(2RC_{p} + R_{3}C)(C + C_{p})}; \\ S_{C}^{\Lambda} \\ = \frac{RC_{p}(C + C_{p}) - (2RC_{p} + R_{3}C)(C + C_{p})}{(2RC_{p} + R_{3}C)(C + C_{p})};$$

(3.31)

It is found that with  $C_p \rightarrow 0$  the above passive sensitivities reduce to as given in (3.31)