# DESIGN AND IMPLEMENTATION OF CMOS LNA FOR BLUETOOTH AND BLE APPLICATIONS

A Dissertation

Submitted In Partial Fulfillment Of The Requirements For The Award Of The Degree Of

> Master of Technology In Microwave and Optical Communication

> > Submitted by:

# Diksha Singh (2K17/MOC/04)

Under the supervision of

# Dr Malti Bansal

Assistant Professor Department of Electronics and Communication Engineering Delhi Technological University

Department of Electronics and Communication Engineering Delhi Technological University (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042 2017- 2019

Department Of Electronics And Communication Engineering Delhi Technological University (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# **Candidate's Declaration**

I, Diksha Singh, 2K17MOC/04, student of M.Tech(Microwave and Optical Communication Engineering), hereby declare that the project Dissertation entitled "Design and Implementation of CMOS LNA for Bluetooth and BLE applications", which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirements for the award of the degree of Master of Technology in Microwave and Optical Communication Engineering is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: New Delhi Date: Diksha Singh (2K17/MOC/04)

Department of Electronics and Communication Engineering Delhi Technological University (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# Certificate

I hereby certify that the Project Dissertation entitled "Design and Implementation of CMOS LNA for Bluetooth and BLE Applications" which is submitted by Diksha Singh (2K17/MOC/04), Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirements for the award of the degree of Master of Technology(Microwave and Optical Communication Engineering), is a bonafide record of the project work carried out by her under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: New Delhi Date:

Dr Malti Bansal Project Supervisor Assistant Professor Department of Electronics and Communication Engineering Delhi Technological University

# Acknowledgement

I thank GOD almighty for guiding me throughout the semester. I would like to thank all those who have contributed to the completion of my project and helped me with valuable suggestions for improvement. I am extremely grateful to Dr. Malti Bansal ,Assistant Professor, Department of Electronics and Communication Engineering , for providing me with best facilities and atmosphere for the creative work guidance and encouragement. I have been extremely lucky to have a supervisor who cared so much about my work and who responded to my questions and queries so promptly. Above all I would like to thank my parents without whose blessings, I would not have been able to accomplish my goal.

Diksha Singh (2K17/MOC/04)

# Abstract

Low Noise Amplifier (LNA) is an important component of transceivers and is also widely used in wireless applications. LNA is the first active element in the receiving chain. Its NF and gain play a significant role in the overall performance of the receiver. With the increasing need for the Internet of things (IoT), Bluetooth low energy (BLE) technology has become a popular solution for wireless devices. When compared to classic bluetooth, BLE has an advantage of low power consumption. Hence it will be apt for IoT based applications. BLE may replace Bluetooth as it is ought to have a low power consumption which gives BLE an upper edge over Bluetooth. We will study the different topologies used to implement LNA for BLE applications and analyze their performance parameters. Our aim is to design an LNA which is able to provides better performance in terms of all parameters and is apt to be used in Bluetooth and BLE applications. We perform all the simulations in Advanced Design System(ADS).

# **List of Published Papers**

- Malti Bansal, Diksha Singh, "Low Noise Amplifier for Neural Applications ", International Journal of Computer & Mathematical Sciences IJCMS ISSN 2347 – 8527 Volume 6, pp -74-81, Issue 11, November 2017

- 2. Malti Bansal, Diksha Singh, "Low Noise Amplifier In Bluetooth And Bluetooth Low Energy (Ble) Applications", In Proceedings Of National Conference On Emerging Trends in Electronics and Communication-2019,pp.110-113

- 3. Malti Bansal, Diksha Singh, "Design and Implementation of Low Noise Amplifier in Neural Signal Analysis", in proceedings of International Conference on Information, Communication and Computing Technology ICCICT 2019,pp. 1-11

- 4. Malti Bansal, Diksha Singh, "Cascode Common Source LNA With Inductive Degeneration Topology Utilizing Different Output Matching Circuits In 45nm CMOS Technology ", in proceedings of International Conference in Communications and Electronics Systems(ICCES 2019), pp. 594-598

- 5. Malti Bansal, Diksha Singh, "Different Input Impedance Matching Circuits For Cascode Common Source LNA With Inductive Degeneration Topology In 45nm CMOS Technology", in proceedings of International Conference in Communications and Electronics Systems(ICCES 2019), 589-593

# List of Contents

| Candidates Declaration                           | ii       |

|--------------------------------------------------|----------|

| Certificate                                      | iii      |

| Acknowledgement                                  | iv       |

| Abstract                                         | V        |

| List of Published Papers                         | vi       |

| List of Contents                                 | vii-viii |

| List of Figures                                  | ix-xi    |

| List of Tables                                   | xii      |

| List of Abbreviations                            | xiii     |

| CHAPTER 1 INTRODUCTION                           | 1-30     |

| 1.1 Bluetooth and BLE                            | 3        |

| 1.2 Applications                                 | 5        |

| 1.3 Low Noise Amplifier                          | 6        |

| 1.4 LNA Applications                             | 10       |

| 1.5 LNA Design Process                           | 11       |

| 1.6 LNA Design Parameters                        | 14       |

| 1.7 Noise Considerations                         | 19       |

| 1.8 LNA Topologies                               | 22       |

| CHAPTER 2 LITERATURE SURVEY                      | 31-43    |

| CHAPTER 3- EXPERIMENTAL WORK AND RESULTS         | 44-78    |

| 3.1 LNA with L-matching at input and RLC as load | 45       |

| 3.2 LNA with L-matching and R as load            | 52       |

| 3.3 LNA with L-matching and tank circuit as load | 58       |

| 3.4 LNA with L-matching and inductor as load63             |                                     | 63    |

|------------------------------------------------------------|-------------------------------------|-------|

| 3.5 LNA with LC as load and T- matching                    |                                     | 68    |

| 3.6 LNA with new matching network and tank circuit as load |                                     | 74    |

| CHAPTER 4 CON                                              | CLUSION AND FUTURE SCOPE            | 77-78 |

| Bibliography                                               |                                     | 79    |

| Appendix- I                                                | List of Publications                |       |

| Appendix-II                                                | <b>Certificates of Publications</b> |       |

# LIST OF FIGURES

| Fig. No.        | Figure Name                                        | Page No. |

|-----------------|----------------------------------------------------|----------|

| Fig.1.1 Part o  | of a receiver system                               | 2        |

| Fig.1.1 Scatter | ring Matrix                                        | 15       |

| Fig.1.2 S-Para  | ameters                                            | 15       |

| Fig.1.3 Input   | Third Order Intercept Point(IIP3)                  | 17       |

| Fig.1.4 1 dB (  | Compression Point                                  | 18       |

| Fig.1.5 Thevr   | nin and Norton model of resistor thermal noise     | 20       |

| Fig.1.6 Induct  | ively loaded Common Source stage                   | 23       |

| Fig.1.7 Induct  | ively loaded Common Source stage – Input Impedance | 23       |

| Fig.1.8 Induct  | or $L_F$ to neutralise the effect of $C_F$         | 24       |

| Fig.1.9 CS Sta  | age with resistive feedback                        | 24       |

| Fig.1.10 Com    | mon Gate Stage                                     | 24       |

| Fig.1.11 Case   | ode common gate stage                              | 25       |

| Fig.1.12 Input  | TImpedance in presence of C <sub>GD</sub>          | 26       |

| Fig.1.13 Impe   | dance in presence of pad capacitance               | 28       |

| Fig.1.14 Addi   | tion of L for impedance matching                   | 28       |

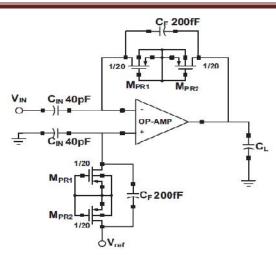

| Fig.1.15 Nois   | se cancelling LNA                                  | 29       |

| Fig.1.16 Reac   | tance Cancelling LNA topology                      | 30       |

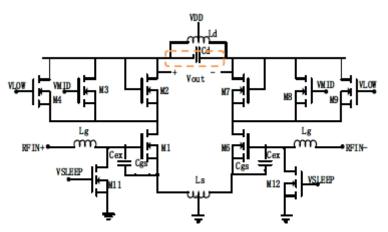

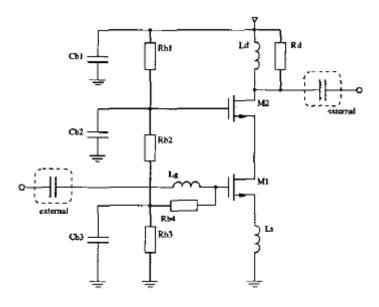

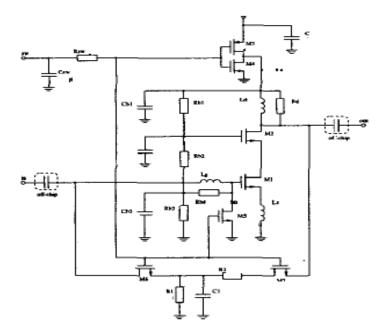

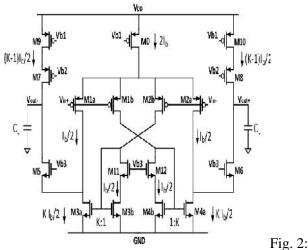

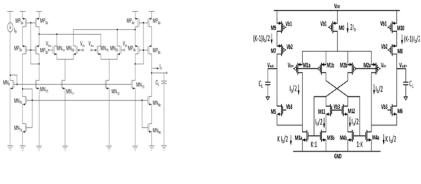

| Fig.2.1 LNA     | with multigrain control(reproduced from[33])       | 31       |

| Fig.2.2 Differ  | ential Common Gate LNA                             | 32       |

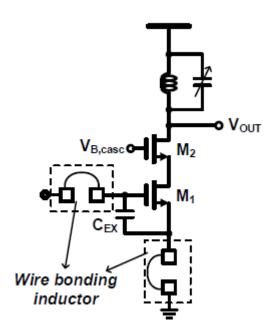

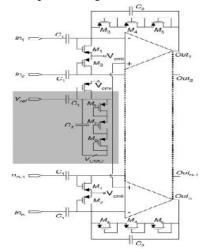

| Fig.2.3 Casco   | de stage based LNA (reproduced from [36])          | 33       |

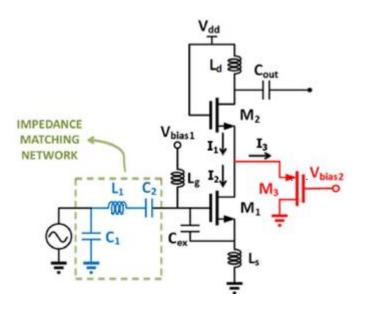

| Fig.2.4 CS sta  | ge LNA (reproduced from [39])                      | 34       |

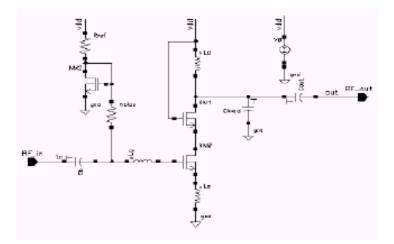

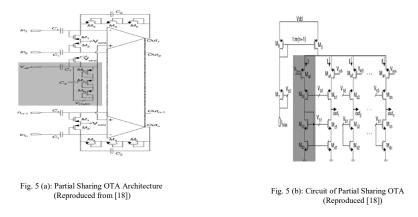

| Fig.3.5 Schem   | natic of LNA( reproduced from [40])                | 35       |

| Fig.2.6 Schem   | natic of LNA (reproduced from [41])                | 36       |

| Fig.2.7 (a) Ga  | in Vs Frequency                                    | 37       |

| Fig.2.7 (b) No  | ise Figure Vs Frequency                            | 37       |

| Fig.2.8 Schem   | natic of LNA(reproduced from [43])                 | 38       |

| Fig.2.9 Schem   | natic of core LNA                                  | 39       |

| Fig.2.10 Schematic of switched LNA                                             | 40     |

|--------------------------------------------------------------------------------|--------|

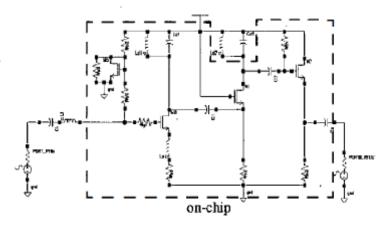

| Fig.2.11 Schematic of LNA (reproduced from [45])                               | 41     |

| Fig.2.12 Circuit showing single ended LNA                                      | 42     |

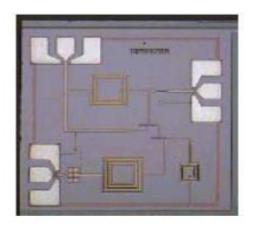

| Fig.2.13 LNA die after fabrication                                             | 43     |

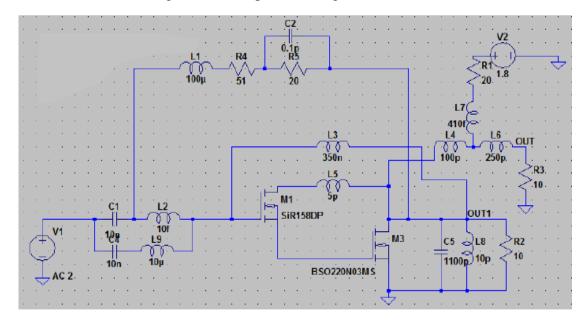

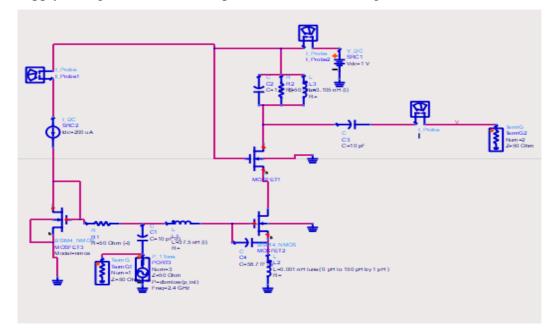

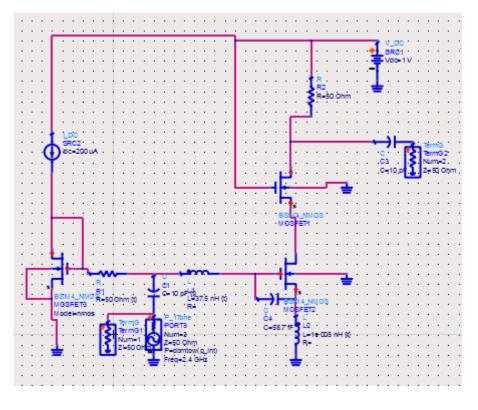

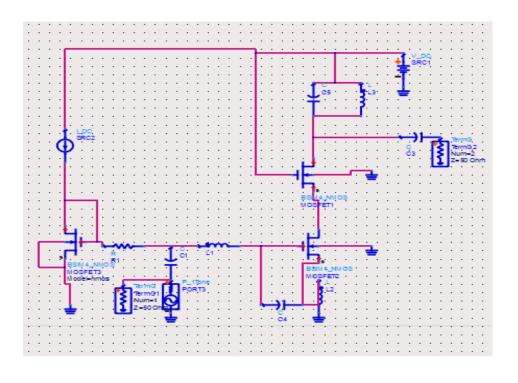

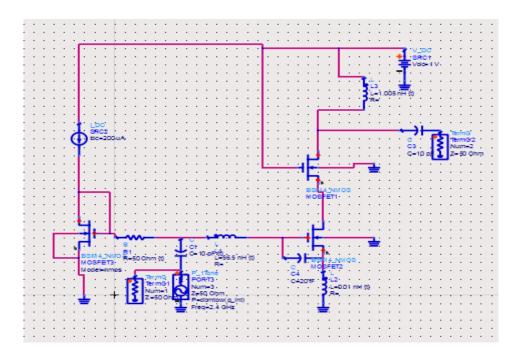

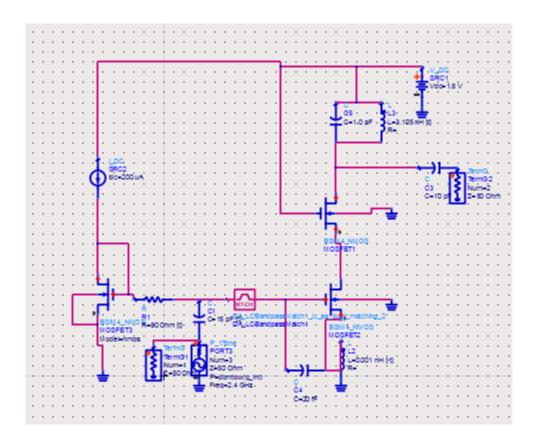

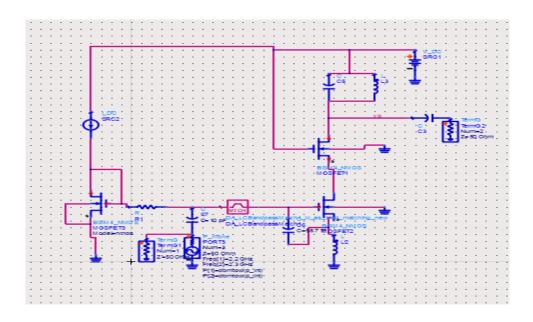

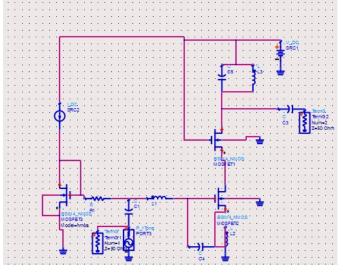

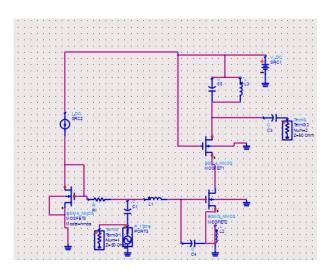

| Fig.3.1 Schematic of LNA (Circuit 1) implemented in ADS                        | 45     |

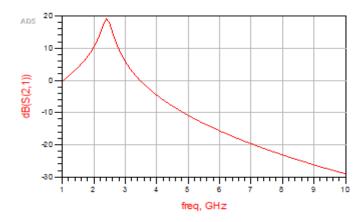

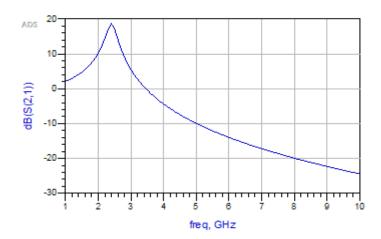

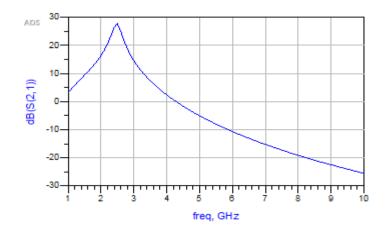

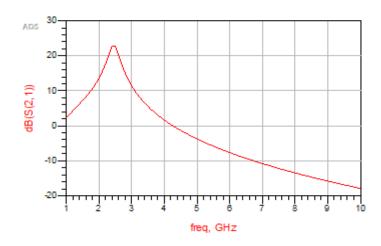

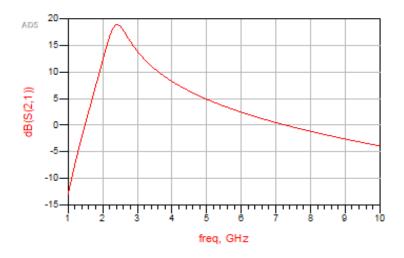

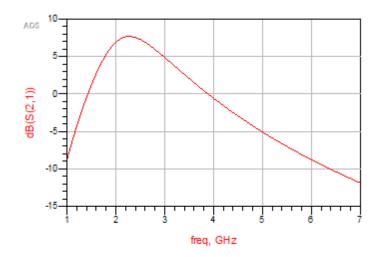

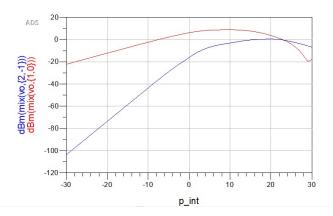

| Fig.3.2 S <sub>21</sub> (Gain) of LNA (Circuit 1)                              | 46     |

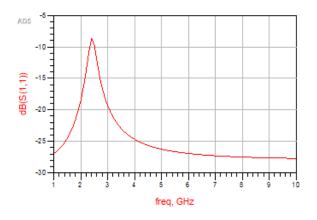

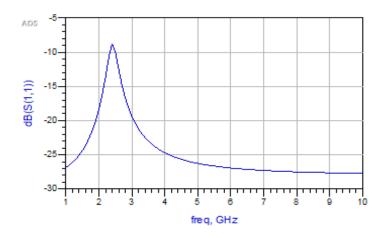

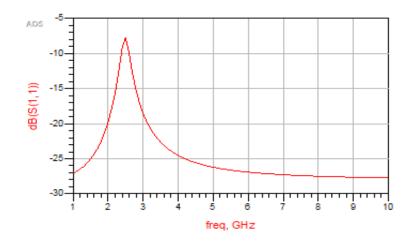

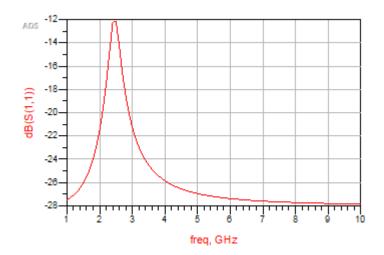

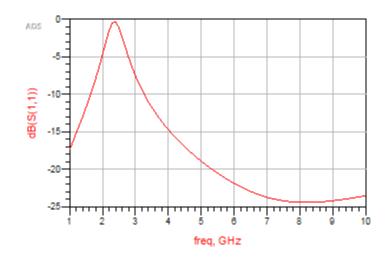

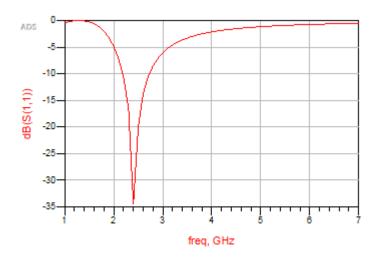

| Fig.3.3 S <sub>11</sub> (Input Return Loss) of LNA (Circuit 1)                 | 47     |

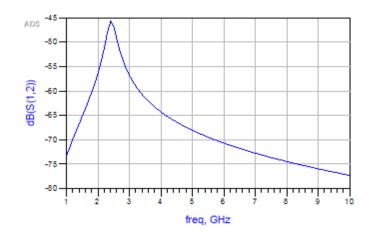

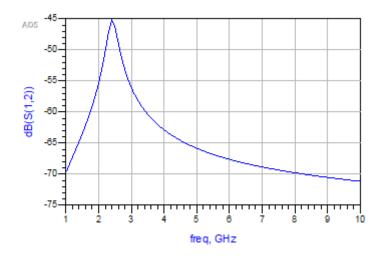

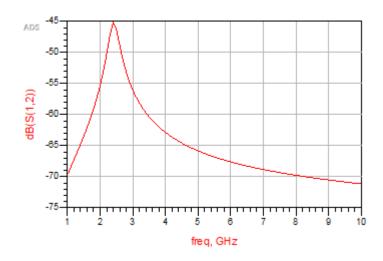

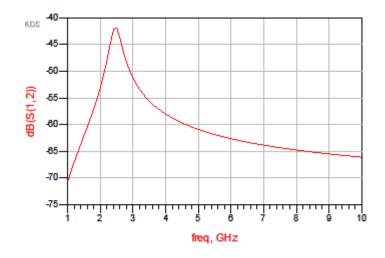

| Fig.3.4 S <sub>12</sub> (Reverse Gain) of the LNA (Circuit 1)                  | 48     |

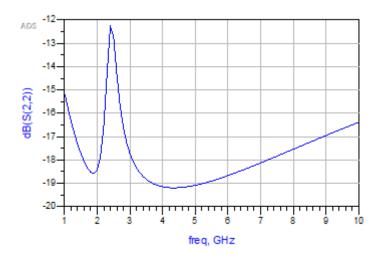

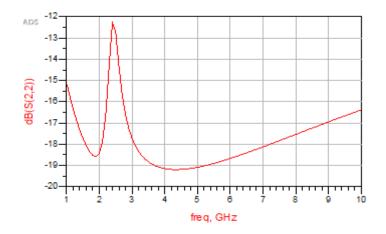

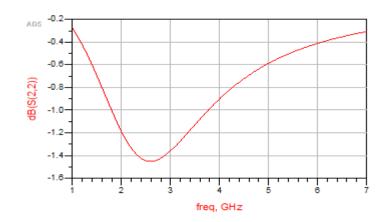

| Fig.3.5 S <sub>22</sub> (Output Reflection Coefficient) of LNA (Circuit 1)     | 48     |

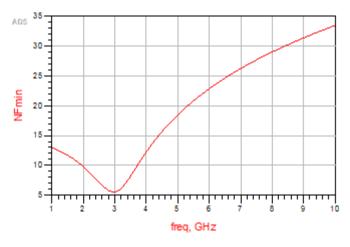

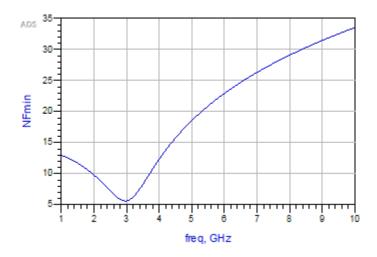

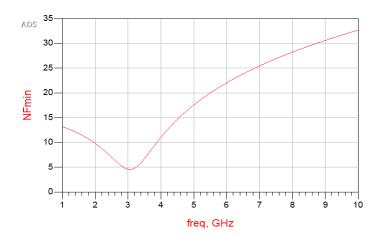

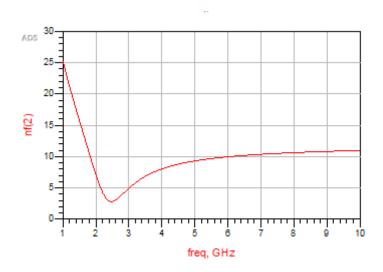

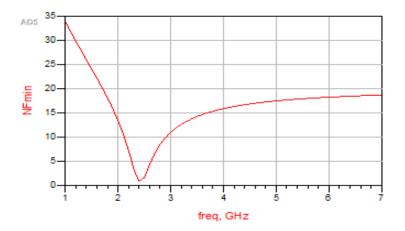

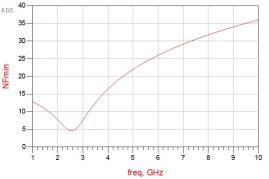

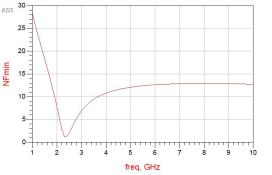

| Fig.3.6 NF (Noise Figure) of LNA (Circuit 1)                                   | 49     |

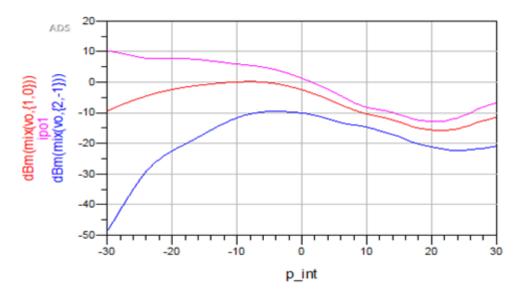

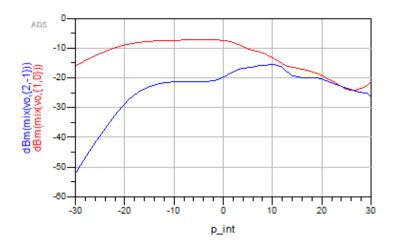

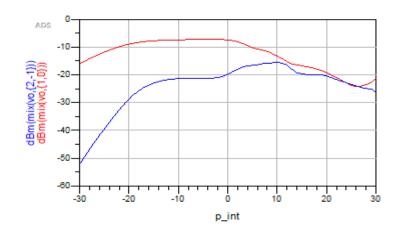

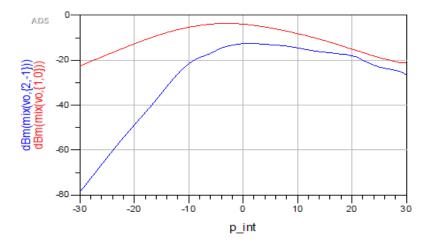

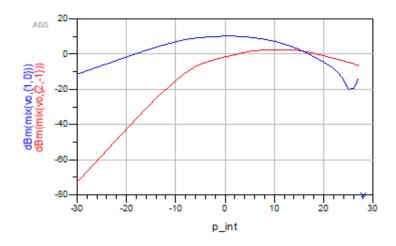

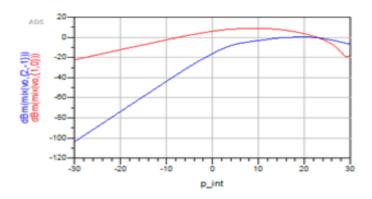

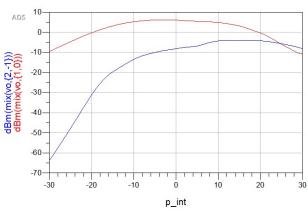

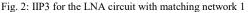

| Fig.3.7 Fundamental Harmonic and Third order harmonic curves for LNA (Circuit  | 1) 49  |

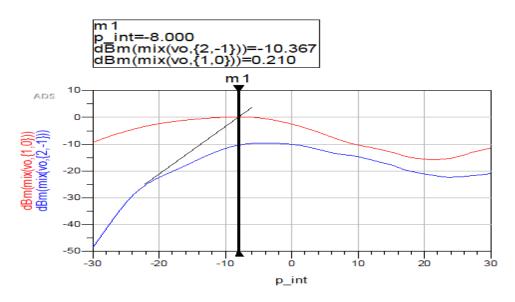

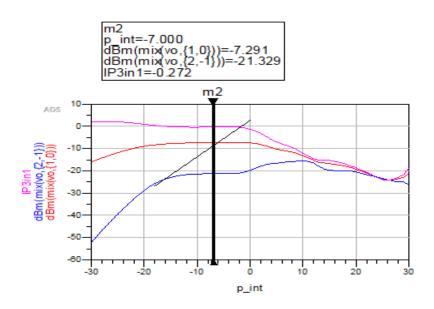

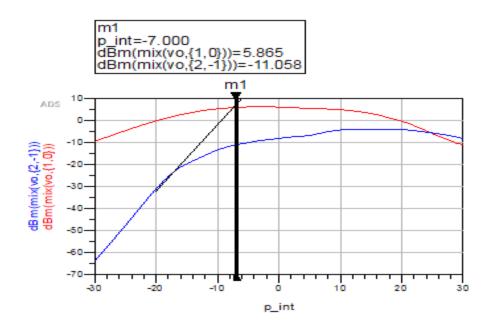

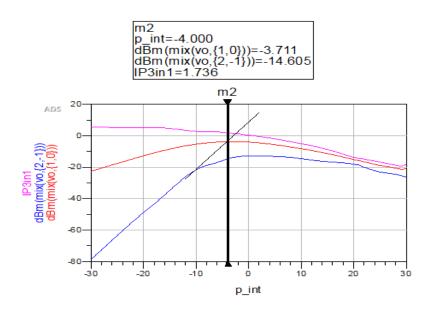

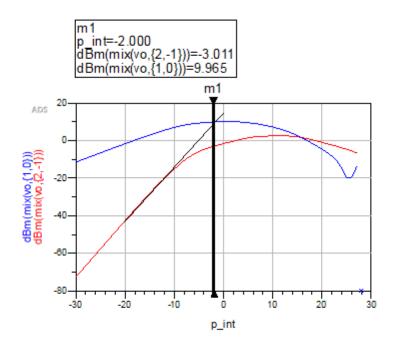

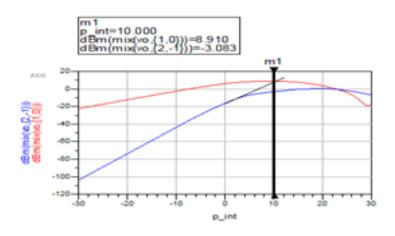

| Fig.3.8 Calculation of IIP3 for LNA(Circuit 1)                                 | 51     |

| Fig.3.9 Schematic of LNA (Circuit 2)                                           | 51     |

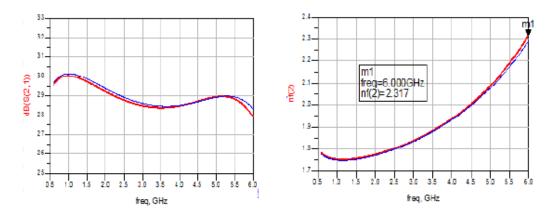

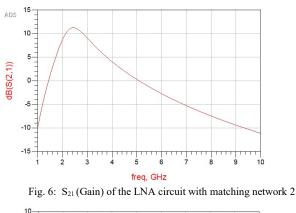

| Fig.3.10 S <sub>21</sub> (Gain) of LNA (Circuit 2)                             | 52     |

| Fig.3.11 S <sub>11</sub> (Input Return Loss) of LNA (Circuit 2)                | 52     |

| Fig.3.12 S <sub>12</sub> (Reverse Gain) of the LNA (Circuit 2)                 | 53     |

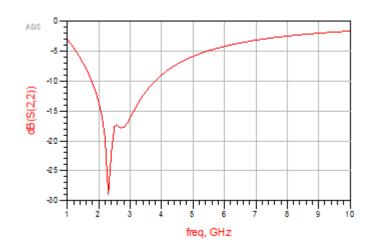

| Fig.3.13 S <sub>22</sub> (Output Reflection Coefficient) of LNA (Circuit 2)    | 53     |

| Fig.3.14 NF (Noise Figure) of LNA (Circuit 2                                   | 54     |

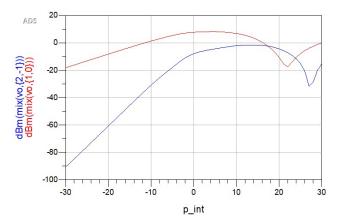

| Fig.3.15 Fundamental Harmonic and Third order harmonic curves for LNA (Circuit | t 2)55 |

| Fig.3.16 Calculation of IIP3 for LNA(Circuit)                                  | 56     |

| Fig.3.17 Schematic of LNA (Circuit 3)                                          | 56     |

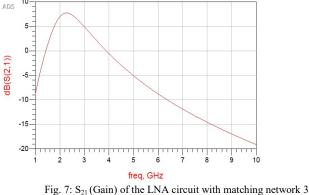

| Fig.3.18 S <sub>21</sub> (Gain) of LNA (Circuit 3)                             | 57     |

| Fig.3.19 S <sub>11</sub> (Input Return Loss) of LNA (Circuit)                  | 57     |

| Fig.3.20 S <sub>12</sub> (Reverse Gain) of the LNA (Circuit 3)                 | 58     |

| Fig.3.21 S22 (Output Reflection Coefficient) of LNA (Circuit 3)                | 58     |

| Fig.3.22 NF (Noise Figure) of LNA (Circuit 3)                                  | 59     |

| Fig.3.23 Fundamental Harmonic and Third order harmonic curves for LNA (Circuit | t 3)59 |

| Fig.3.24 Calculation of IIP3 for LNA(Circuit)                                  | 59     |

| Fig.3.25 Schematic of LNA (Circuit 4)                                          | 60     |

| Fig.3.26 S <sub>21</sub> (Gain) of LNA (Circuit 4)                             | 61     |

| Fig.3.27 S <sub>11</sub> (Input Return Loss) of LNA (Circuit 4)                | 61     |

|                                                                                |        |

| Fig.3.28 S <sub>12</sub> (Reverse Gain) of the LNA (Circuit 4)                | 62      |

|-------------------------------------------------------------------------------|---------|

| Fig.3.29 S <sub>22</sub> (Output Reflection Coefficient) of LNA (Circuit 4)   | 62      |

| Fig.3.30 NF (Noise Figure) of LNA (Circuit 4)                                 | 63      |

| Fig.3.31 Fundamental Harmonic and Third order harmonic curves for LNA (Circui | t 4)63  |

| Fig.3.32 Calculation of IIP3 for LNA(Circuit 4                                | 64      |

| Fig.3.33 Matching Network for the LNA (Circuit 4)                             | 65      |

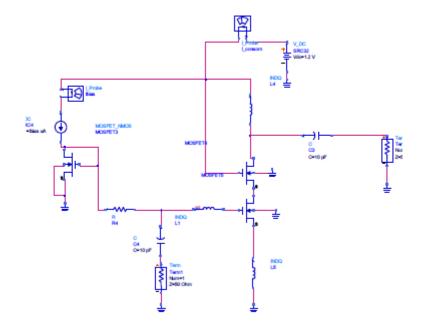

| Fig.3.34 Schematic of LNA (Circuit 5)                                         | 66      |

| Fig.3.35 S <sub>21</sub> (Gain) of LNA (Circuit 5)                            | 67      |

| Fig.3.36 S <sub>11</sub> (Input Return Loss) of LNA (Circuit 5)               | 67      |

| Fig.3.37 S <sub>12</sub> (Reverse Gain) of the LNA (Circuit 5)                | 68      |

| Fig.3.38 S <sub>22</sub> (Output Reflection Coefficient) of LNA (Circuit 5)   | 68      |

| Fig.3.39 NF (Noise Figure) of LNA (Circuit 5)                                 | 69      |

| Fig.3.40 Fundamental Harmonic and Third order harmonic curves for LNA (Circui | t 5) 69 |

| Fig.3.41 Calculation of IIP3 for LNA (Circuit 5                               | 70      |

| Fig.3.42 New Matching Circuit used in LNA (Circuit 6)                         | 70      |

| Fig.3.43 Schematic of LNA (Circuit 6)                                         | 71      |

| Fig.3.44 S <sub>21</sub> (Gain) of LNA (Circuit 6)                            | 71      |

| Fig.3.45 S <sub>11</sub> (Input Return Loss) of LNA (Circuit 6)               | 72      |

| Fig.3.46 S <sub>12</sub> (Reverse Gain) of the LNA (Circuit 6)                | 72      |

| Fig .3.47 S <sub>22</sub> (Output Reflection Coefficient) of LNA (Circuit 6)  | 73      |

| Fig .3.48 NF (Noise Figure) of LNA (Circuit 6)                                | 73      |

| Fig.3.49 Fundamental Harmonic and Third order harmonic curves for LNA (Circui | t 6) 74 |

| Fig .3.50 Calculation of IIP3 for LNA (Circuit 6)                             | 74      |

|                                                                               |         |

# LIST OF TABLES

| Table No. | Title of the table           | Page No. |

|-----------|------------------------------|----------|

|           |                              |          |

| Table 2.1 | Comparison Table             | 42       |

| Table 3.1 | Parameter values (Circuit 1) | 50       |

| Table 3.2 | Parameter values (Circuit 2) | 55       |

| Table 3.3 | Parameter values (Circuit 3) | 60       |

| Table 3.4 | Parameter values (Circuit 4) | 64       |

| Table 3.5 | Parameter values (Circuit 5) | 70       |

| Table 3.6 | Parameter values (Circuit 6) | 74       |

| Table 4.1 | Combined Comparison table    | 75       |

# LIST OF ABBREVIATIONS

| IoT  | Internet of Things                                |

|------|---------------------------------------------------|

| BLE  | Bluetooth Low Energy                              |

| VLSI | Very Large Scale Integration                      |

| CMOS | Complimentary Metal Oxide Semiconductor           |

| RF   | Radio Frequency                                   |

| LNA  | Low Noise Amplifier                               |

| IIP3 | Input Third Order Intercept                       |

| IEEE | Institute of Electrical and Electronics Engineers |

| GFSK | Gaussian Frequency Shift Keying                   |

| ECG  | Electrocardiogram                                 |

| NILM | Non-Intrusive Load Monitoring                     |

| SNR  | Signal to Noise Ratio                             |

| NF   | Noise Figure                                      |

| CAD  | Computer Aided Design                             |

| ADS  | Advanced Design Systems                           |

| PSD  | Power Spectral Density                            |

| CS   | Common-Source                                     |

| CG   | Common-Gate                                       |

| IMD  | Inter-modulation Distortion                       |

| SoC  | System on Chip                                    |

#### **CHAPTER-1**

#### **INTRODUCTION**

Wireless communication has become an important necessity of today's world. Demand of technologies that are compatible with changing trends in technology is increasing and end-users desire that their devices should be versatile enough and support new technologies i.e. WiMax, 3G, 4G and so on. Household devices may not be connected to wireless devices at this time but in coming future this will also become possible as Internet of Things (IoT) is the hottest topic of research today. This increases the necessity of designing RF circuits that can be implemented for wireless communications meeting the present standards. This increases the cost of the devices as well as maximises the circuit complexity i.e. integrating a large no of elements on a single chip. All these challenges when considered in designing a circuit can contribute to bright future of RF circuits.

With advancements in technologies, devices which provide better efficiency at a lower cost have been in demand nowadays. Internet of Things (IoT) has also created a tremendous scope for research in many fields which includes wireless networks, sensors, low power operating devices, energy-efficient devices. The next generation devices which intend to turn IoT into a reality require operating on ultra low –power and working for several years. Integration of the elements on-chip is also a critical challenge that needs to be overcome by researchers.

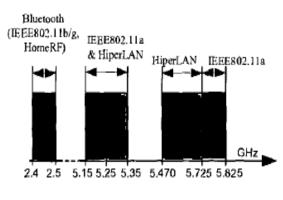

If we restrict to wireless communication, the operating frequency gets fixed to 2.4 GHz because it is the only available frequency which does not require a license. Bluetooth technology also works on the same frequency. When compared to classic Bluetooth, BLE has an advantage of low power consumption. As a consequence of extensive research in the area of Internet of Things (IoT), Bluetooth low energy (BLE) technology seems to provide an apt solution for wireless devices. Hence it will be appropriate for IoT based applications in the coming future.

Designing of RF circuits requires a good understanding of many disciplines that include understanding of RF and microwave theory, VLSI and other basic concepts of RF circuits. RF circuits have created a tremendous scope of research and this comes due to advancements in semiconductor technologies which makes system level integration more flexible. These have also gained popularity due to its low cost which makes it most attractive technology to work on. CMOS technology advancements have proved to be beneficial for both analog and digital circuits. However redesign of digital circuits for a newer technology is an uncomplicated process it is not so in case of redesigning analog circuit for a newer technology. It is a challenge to redesign analog circuits for newer technologies. [1] With brisk increase in communication technology, additional burden of larger integration also follows up. Better performance delivering Integrated Circuits are in demand with spectacular improvements in technology. CMOS scaling technologies are also improving day by day which is able to provide better performance at a lower cost and lower chip area. These developments in CMOS process technologies have made realizing a System on Chip feasible, for use in almost all domains of life. [2]

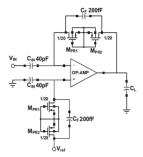

Ability to communicate by the means of wireless medium is the most important feature required in the systems nowadays. For this we require a receiver which should be capable of providing an optimum performance when implemented in real-time systems. Transceiver is one of the basic components of RF circuits required in wireless communications. The transceiver is responsible for transmitting as well as receiving information at the same point of time i.e. it performs the work of a transmitter as well as a receiver. Designing a receiver for different applications that should support different range of frequencies is a tedious task. At the receiver end generally the first important functional block is a Low Noise Amplifier (LNA) that is specifically designed to provide a better noise performance than the other amplifiers.

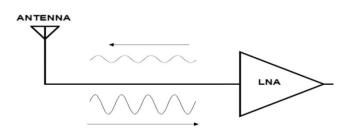

Fig.1.1 Parts of a receiver system

Designing an LNA which is best in terms of performance parameters increases the efficiency of the receivers system. However with expeditious growth in wireless communication industry, manufacturers aim to design a circuit which is able to deliver best results among the already available hardware at present. In case of LNA performance, target is to achieve a low noise figure, high gain, low loss, high Input Third Order

#### Intercept (IIP3).[3]

We try to analyze the pervious works in the field of LNA design and try to design a new LNA with features that would be compatible with the devices designed keeping new advancements in concern.

LNA'S are being widely used in designing receivers for Bluetooth as well as BLE. However the basic difference lies in the fact that the power consumption is drastically low in BLE applications.BLE has an advantage of low power consumption which makes it suitable for device to device communication. BLE devices can last for years once placed in machine and makes it suitable for IoT devices. Higher speed may not be obtained but longer battery life is a surely obtained. BLE is discussed in detail un the next section.

# **1.1 BLUETOOTH AND BLE**

Many wireless technologies are available for use in healthcare applications which include ANT, ZigBee, and Bluetooth. Out of these available technologies Bluetooth is considered to be the most versatile technology as far as compatibility is concerned. However in the era of IoT low power consuming devices are in demand which limits its applications nowadays.

Bluetooth is also a form of wireless communication which is more prevalent and everybody is more familiar with this form of wireless communication. For Bluetooth communication also we need a transmitter and receiver and the receiver end utilises an LNA as the first block of the system. LNA for this particular application will have different characteristics than the LNA for other forms of communication as LNA parameters depend on the application for which they are being designed. More specifically a LNA for Bluetooth applications should provide a higher gain and consume less power than others. To cope up with the requirements on new generation wireless technologies, Bluetooth was modified and a newer version of Bluetooth is more prevalent in devices now. Bluetooth v4.0 is specially designed to consume less power than the pre-existing Bluetooth version. This version named as Bluetooth Low Energy (BLE) was announced in 2010 and since then it is chosen over other wireless technologies as it overcomes the disadvantages of other wireless technologies. Bluetooth Low Energy (BLE) focuses on reducing the power consumption of the circuit and is apt for IoT applications. BLE devices can work for longer hours as they consume less power.

Bluetooth Low Energy is also known as Bluetooth Smart and was in the specification IEEE 802.15.1. It is apt for applications requiring low power consumption, ability to connect more no of users on a single network, reduced cost and simple implementation. BLE modules are available that can be used in many applications and the users do not have to design the system for BLE implementation by themselves. Being a promising candidate in all aspects, BLE has become a part of many systems that are being utilised in smart phones, wireless sensor networks , medical applications, industrial equipments.[4]

Bluetooth is widely used for short range communications. Bluetooth is known to work at a frequency of 2.4 GHz and provides us with data connectivity upto a range of 50m. Maximum data rate that is achieved in bluetooth is upto 440 Kbps. Bluetooth connections setup should adhere to specifications which are already listed Bluetooth specifications . These specification provide with the allowable range of carrier frequency, modulation, transmitted power etc. Bluetooth standard states that the modulation scheme used should be GFSK with index prescribed in the specifications.[5][6]

Though BLE devices have a lower power requirement they are not capable of transmitting data at very high rates. However BLE devices are not required to have large data transfer rates so lower data rates do not effect its performance . For example, if we wish to control air-conditioner or other home appliances, we do not desire higher data rates. We only need to signal it to switch it on/off or control the settings of the appliance which does not involve large data It simply needs to send the data conveying the required message to turn on/off or vay the temperature to the device and vice-versa to the transmitter.. On the contrary , if the consumer uses a smartphone to run a live video pr television through a wireless connection, it will not be a small amount of data conveying a single task ; instead, it will be a large data that must be smoothly achieved. Otherwise, the user will never replace the wired connection with wireless.

Depending on the application requirement Bluetooth emerged to have different modes of operations. If devices need to operate for longer time we cannot achieve higher data rates and if higher data rates are desired power consumption will increase. A trade-off always exists in higher data rates and power consumption of the circuit. When we intend to use BLE in our systems we must follow the specifications stated by IEEE for BLE. Operating frequency of BLE is fixed at 2.4 GHz which is standard for most of the wireless technologies as well. For transmission of data BLE uses GFSK (Gaussian Frequency Shift Keying) technique of modulation. It consists of a total 40 channels which were 79 in Classic Bluetooth, resulting in a reduced interference from adjacent channels. The channels are 2 MHz wide and out of the available 40 channels 3 are dedicated to send and receive short messages broadcast. Other remaining channels are dedicated to transfer data packets. [7]

LNA in BLE puts a constraint on power consumption of the circuit and it is a difficult task to adhere to power consumption specifications as well as fulfil other system specifications.[8]

#### **1.2 APPLICATIONS**

Bluetooth as well as BLE because of its specifications has opened a plethora of applications in almost every domain. It includes healthcare, smart homes, smart driving, security systems etc. Systems operating on this technology are being reported everyday which aim to provide better efficiency than the previously reported ones.

#### **1.2.1 BIOMEDICAL APPLICATION**

With improvements in technologies and everything moving towards automation physical activities of humans have reduced which makes it necessary to keep a record of one's health regularly and people have begun to pay attention to their health . Most important measure of one's health can be predicted by measuring blood pressure and it proves to be an important step in self-health management. Smart-phones are also being used in healthcare and this has further increased the versatility of smart-phones in human life. [9] Keeping a record of a patient blood pressure values assists the doctors also to provide proper treatment to the patient.[10] Further with improvement in wireless technology, application of wireless communication in monitoring health has become an important topic of research and many systems based on wireless monitoring of signals have been proposed.

BLE based electrocardiogram (ECG) monitoring system was also reported in [11]. BLE based blood pressure monitoring systems was also reported after the announcement of BLE.[12] This device was designed to detect the blood pressure signals and convert

them into equivalent BP readings using standard algorithms and then transmit the readings to smart phone using BLE.

With BLE announcements a tremendous increase has been observed in devices utilising this wireless technology specifically in wearable fitness devices. BLE is apt for these devices as its low energy allows it to be compact in size and it can be implemented using a coin size battery only. Moreover BLE works on a simple protocol that can be easily implemented and is suitable for adoption in smart phones. [13]

Conventionally wired electrodes are used to acquire signals and then monitor them which restrict their mobility. Using wireless technology in monitoring these signals has a lot of advantages over conventional methods. Wireless sensors can be implanted very easily as compared to wired ones and these do not create discomfort to the patient and signal can be monitored in any environment. Doctors can easily access these and provide medical assistance to those in need.

### 1.2.2 LOAD MONITORING SYSTEMS

Energy consumption of households have shoot up because of increase in no of electrical appliances in houses. These results in overload and it can be reduced by judicious use of appliances. This can be monitored using smart sensors which can assist in achieving an increase in energy efficiency. If there is no person in room smart sensors will detect the situation and appliances will be turned off. [14] Information about a user's energy consumption may assist the user in improving energy consumption habits of the family. To improve energy usage by the appliance Non-Intrusive Load Monitoring (NILM) algorithm can be applied which segregates the energy consumed by different appliances. [15][16]

### 1.2.3 SMART SECURITY SYSTEM

BLE is also used in implementing smart security system A smart security system was reported which allowed the user to control the appliances un home via a webpage even if the user is not physically present at home.[17]

### **1.2.4 OTHER APPLICATIONS**

BLE was also implemented in smart farming i.e. data related to soil was transmitted to the cloud and required operations were performed on the data and again it was transmitted to the microcontroller. In this process BLE was used to transfer data to the microcontroller. [18]

Other researcher reported using BLE in VANET applications, which was used for smart driving and this was achieved by using a smart phone equipped with BLE radio. This smart phone was used to transmit information between vehicles. [19]

#### **1.3 LOW NOISE AMPLIFIER**

In wireless communication message signal is transmitted via free space i.e. the transmitter directs the desired signal in free space and the signal then passes through free space and is received by the intended receiver antenna. When this signal is received at the antenna a lot of noise gets added to the signal which reduces the Signal-to-Noise ratio of the signal. This signal received at the antenna needs to be processed further which includes filtering out the undesired frequencies, amplifying the signal, conversion from analog to digital domain if required. As the signal passes through these blocks additional noise gets added to them which further degrades the SNR of the desired signal. Hence we need devices which do not degrade the SNR of the signal and reduce the effect of noise on the signal. Low Noise Amplifier (LNA) serves this purpose perfectly i.e. it amplifies the signal up-to a sufficient level and the noise added by the components of the amplifier is very low.

$$OUTPUT SNR = \frac{INPUT SIGNAL * GAIN}{(INPUT NOISE * GAIN) + SYSTEM NOISE}$$

LNA is designed such that the system noise added by it is very less which provides a better value of SNR than provided by other amplifiers. There are many sources of noise in a device which will be discussed later. LNA is designed to provide better noise performance and is generally placed at the first stage of the receiver system. After LNA other blocks are also present in the receiver system which is connected in cascade for further signal processing. Placing LNA at the first stage improves the noise performance of the complete receiver system because the noise performance of a system with many blocks connected in cascade is given by the formula:

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2 G_3} + \dots + \frac{F_n - 1}{G_1 G_2 G_3 \cdots G_{n-1}}$$

(1)

From the above formula it can be seen that the Noise Figure (NF) of the first stage dominates the NF of the completer receiver system. Therefore placing LNA the initial stages of the receiver reduces the overall cascaded effect of noise on the receiver system and the NF of the LNA determines the performance of the transceiver.

Wireless communication is generally limited to short distances as compared to other forms of communication. Designing a LNA for short distance communication (up-to 10m) is a smooth process in comparison to design a LNA for long distance communication (more than 10 m). LNA for long distance communication where the distance between the transmitter and receiver is more than the specified range requires high sensitivity which in turn leads to increase in complex design process. LNA for short distance communication where the distance between the transmitter and receiver module is less than 10 m drives the next block into compression because of the signal at the input being strong in amplitude. This signal needs leads to a output signal which is distorted. In this scenario we need a LNA that can overcome this problem by suppressing the input signal to prevent this condition.[20]

LNA with all parameters perfectly within the limit cannot be designed as trade-off always exists between the different parameters of a circuit. Based on our application area we need to focus on the parameter to be optimised and accordingly the LNA design procedure is carried out further.

Most of the LNA's are generally single band LNA i.e. they are designed to operate at a single frequency. However multiple band LNA's are also being introduced i.e. they are capable of operation at more than one frequency. Operating a single LNA over multiple frequencies increases the complexity of the circuit but it also makes it versatile for multi-standard applications. However LNA's are reported that operate at two frequencies i.e. they are dual band LNA's. Multiple band LNA's are less common as achieving optimum performance at multiple frequencies increase the overhead of increase in cost of the LNA. Moreover it also results in increase in power requirements of the circuit as well as increase in the chip area occupied by the circuit.[21]

If we wish to design a broadband LNA we generally use a single transistor which is being used in common-source configuration. [22] Darlington amplifier is used in case of broadband applications i.e. optimum performance over a larger bandwidth.[23] Application of LNA also decides the components that can be utilised in the circuit design. If we require a system on chip we should avoid components which occupy larger chip area. If we wish to have a higher gain again we can contain connect multiple stages in cascade with each other, they will provide an optimised gain with reduced performance in terms of other parameters. If we wish to optimise chip area occupied by the amplifier we should use a single stage amplifier because increasing the number of stages increases the chip area that is being occupied. We should also avoid using bulk elements i.e. the elements which occupy larger chip area. If we wish to have lower power consumption we should avoid using multiple stages in our amplifier. The parameter that is to be optimised plays important role in design specification and the amplifier is to be designed accordingly.

### **1.4 LNA APPLICATIONS**

LNA finds applications in many domains which include biomedical domain, neural applications, wireless communications etc.

#### **1.4.1 NEURAL APPLICATION**

Brain activities are also studied by analyzing the neural signals produced in our brain. These neural signals produced are very weak signals and noise gets added as they are passed through various components which are used in their analysis. Noise degrades the signal to noise ratio of these neural signals and as a consequence of addition of noise, it becomes difficult to study brain activity pertaining to these signals. To analyze these signals in an appropriate manner, they need to be amplified up to a certain threshold level without much noise being added to them. Low Noise Amplifiers are best suited to analyze these weak signals and achieve this function. LNA amplifies the signal received at the input; and very less noise is added due to its components to the received signal. Hence, the SNR of the signal is maintained at an appropriate level which is suitable for analysis of neural signals. LNA can be utilized for neural signal analysis with different design techniques to improve the performance of LNA.

Detailed examination of neural signals produced in our brain helps us to understand the brain activities. Detailed analysis also provides a better understanding of disorders related to brain i.e. Parkinson's disease, Alzheimer's disease and various

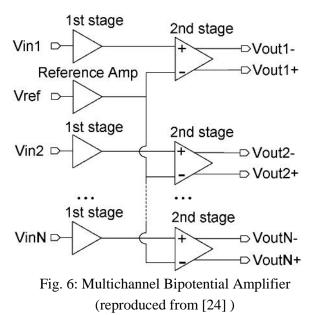

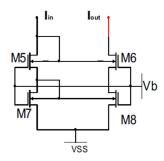

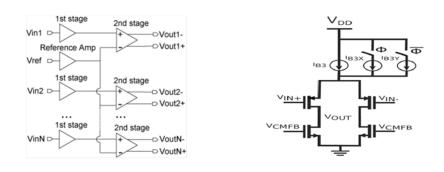

others.[24][25]. Electrodes are used for interfacing these with the tissues present in the brain[26] .Multiple sites can also be observed at the same point of tine i.e. activities in different parts of brain can be studied by using multichannel neural amplifiers. Multichannel LNA are capable of observing multiple neuron activities at the same instance but the area occupied by these amplifiers is increased because multiple amplifiers are to be fabricated on a single chip. However, many multi-channel amplifiers reported so far were also found to use a very small chip area.

Neural signals lie in the range of few millivolts and are therefore considered as very weak signals and they may get degraded if more noise gets added to them. LNA is suitable for analysis of these signals because the noise added by this type of amplifier is very less and does not degrade the SNR of the signal. Power consumption is a very crucial factor in case of neural amplifiers as high power may result in increase of temperature and this may damage the brain tissues. An important requirement for the use of LNA for neural applications is that they should be designed in such a way that power consumed by them for operation is very low.

Neurons may generate a rhythmic pattern of action potentials or spikes and if they generate action potentials in sync, this gives rise to local field potentials. Neural signal can also be considered as superimposition of action potentials or spikes on low frequency local field potentials. Frequency range for these signals is different .Action potentials lie in higher frequency range (300-6000 Hz) in comparison to local field potentials (1-200 Hz)[27]. LNA's are specially designed to study these signals separately in their respective frequency band. Some configurations focus on action potential analysis and some on local field potential analysis; because of the different frequency range .However some amplifiers used filters which filtered out the desired frequencies to handle Action potentials as well as local field potential simultaneously. In any circumstances ,the gain of the LNA should be high because the signals associated are always weak signals.

Design phase of LNA should be properly executed because before fabrication LNA needs to be designed for certain specifications which are solely dependent on the application it is being designed for. Conventionally LNA design are carried out by trial and error process or using simulation tools which increase the chances of error in design as it requires human intervention. CAD( Computer Aided Design) tools have made the work easier and error free nowadays and are being utilised in LNA design. [28]

#### **1.5 LNA DESIGN PROCESS**

LNA is used in a wide range of applications including biomedical domain as well. Designing an LNA is specifically dependent on the application for which it is being designed. Application domain of the device determines the factors that should be considered while designing a circuit and the parameters that are to be enhanced. The parameters to be enhanced play a high-priority role in the design process of LNA. However the basic steps remain the same inattentive of the application it is being designed for. Basic steps involved in design of LNA can be divided into five parts:

- Transistor Selection

- Biasing network

- Matching networks

- Topology

- Stability

Designing a circuit meeting the required standards involves proper investigation of these design steps and then proceeding with the design of the circuit and analysis of the results obtained.

### **1.5.1 TRANSISTOR SELECTION**

Initial step in LNA design is choosing a proper transistor that would be apt for operation at high frequency. Transistor should be chosen such that it is able to work properly at microwave and higher frequencies and keeping in mind the trade-offs regarding the device operation. Choice of transistor may not affect the performance of the circuit in simulating environment to great extent but it affects the real-time performance of the circuit by a significant amount. Hence we need to be cautious while making the choice of transistor to be used in our circuit. A wide variety of transistor choices are available nowadays. Pseudomorphic High Electron Mobility Transistor (PHEMT) was being used while designing a wideband LNA that is capable of providing a high gain over a wide range of frequencies. These transistor types are also suitable for designing microwave monolithic circuits and also for circuits intended for operation at higher frequencies. Amplification property of the MOS transistor is determined by the value of transconductance denoted by g<sub>m</sub>. Appropriate value of g<sub>m</sub> should be availed and it depends on many parameters. Bias current plays an important role in determining

the value of transconductance and the width and length of the transistor also determine the value of the transconductance. The size of the transistor is also crucial in LNA's design process. Transit frequency of the transistor being used is a major parameter that affects the values of other parameters of the circuit as well. The transit frequency  $f_T$ helps to identify the value of inductance required to achieve input matching.

# **1.5.2 BIASING NETWORK**

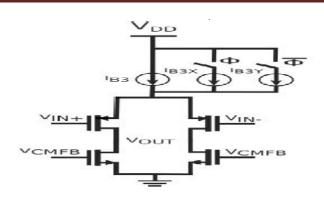

Once your circuit design is complete you also need to provide proper biasing to your circuit to give it a stable bias point of operation. Biasing can be provided using many different techniques which have their own benefits as well as negative aspects. Choice needs to be made between biasing network to be chosen for a particular circuit. However the technique should be chosen so as to be suitable for the application of LNA. Few techniques that are being used for providing biasing include voltage divider biasing, transistor biasing, current mirror biasing etc. Out of the entire techniques available current mirror biasing is the most widely used biasing in circuits. Voltage divider resistive biasing was used in some LNA circuits which were intended to be used as wide-band LNA i.e. for a wider range of frequencies. Using current mirror biasing has an advantage of providing a reduced chip area when the device is fabricated for practical applications.

### **1.5.3 MATCHING NETWORKS**

LNA is implemented as a part of a larger receiver system that consists of other blocks as well. These blocks are connected in cascade which together forms the receiver system. When devices are connected in cascade maximum power transfer does not take place from one stage to another due to loading effect. Loading effect tends to decrease gain of the device because of impedance mismatch at the input or output stage. Accordingly we need to employ matching circuits at the input and output terminals of the circuit to achieve maximum power transfer to the subsequent stages and minimise the loading effect to a large extent.

In the receiver block, LNA is generally placed after the antenna which denotes an impedance of  $50\Omega$ . For maximum power transfer between two stages the output impedance of the first stage should be matched with the input impedance of the second stage. If impedance mismatch occurs between the two stages maximum power transfer

will not take place and reflections are ought to occur. Hence LNA's input impedance needs to be matched with antenna's impedance to achieve complete power transfer. This can be achieved by using an input matching network that performs this task of matching the input impedance and it is very crucial for LNA's performance. Matching networks also have different topology and numerous components are available that can provide matching between two stages. However choosing a proper matching network that enhances the performance of the circuit is a tedious task to be done properly. A change in matching network affects the circuit performance and hence a comparison can be done to find which matching network is best for our circuit design.

Similar to the input stage, output matching also needs to be accomplished in order to transfer maximum power to the next stage after the LNA in the receiver block. Different output matching circuits also affect circuit performance

#### **1.5.4 TOPOLOGY**

LNA's utilise configurations that are being used traditionally to design amplifiers. Other than configuration additional steps are to be taken to achieve the desired performance. It can be obtained by introducing a change in the biasing network or it can be through a change in matching networks being used. Most common LNA topologies are common-gate, common-source, cascode etc. Each of the above topology has its own advantages and disadvantages. In-spite of their own merits and demerits the cascode configuration in the most common configuration used in implementing LNA. Topology to be used to design LNA is decided by the applications it is being designed for. Parameters that are to be optimised are application dependent and hence topology must be properly chosen so as to obtain better results.

# **1.5.5 STABILITY**

A device is of no practical use if it is not stable at the required operating frequencies and other conditions which include temperature as well. An amplifier is considered as stable if it is able to resist conditions which may destroy the system. A system should be designed such that is able to overcome conditions which cause hindrance to proper operations of the circuit. LNA may become unstable due to ground and other parasitic capacitances and inductances which arise during fabrication and packaging of the circuit. For example if a large series inductance appears across gate terminal of a transistor operating in common-gate topology it may create a sufficient amount of feedback in the circuit which may result in instability of the circuit.

# **1.6 LNA DESIGN PARAMETERS**

LNA's performance is characterised by the values of LNA parameters obtained after completion of our design. These values can be obtained by performing simulations using tools which are used for studying behaviour of our circuit at higher frequencies. Before fabrication of our device we need to analyze our design using simulations to get an idea f how the design will perform in real-time environment.

### **1.6.1 S PARAMETERS**

When we move towards analysing circuits at higher frequencies that are in the rage of microwave frequencies port parameters such as Z-parameters, ABCD parameters cannot be evaluated. At higher frequencies these port parameters cannot be obtained because of the following reasons:

- (i) Open circuit and short circuit conditions are difficult to achieve at these frequencies

- Sophisticated equipments are not available at higher frequencies to correctly measure the voltage and current in the ports

- (iii) When dealing with wave propagation open circuit and short circuit conditions introduce reflections which may damage the device under test

At higher frequencies we define parameters called scattering parameters or Sparameters which act as a tool which makes the analysis of the circuit possible at higher frequencies without creating damage to the device under test. S parameters help us in studying the input-output relations between the different ports of a device in terms of power incident or reflected. S-parameters are usually displayed in a matrix format, with the number of rows and columns equal to the number of ports. For the S-parameter  $S_{ij}$  the j subscript stands for the port that is excited (the input port), and the "i" subscript is for the output port.

Sij= Power reflected from port j / Power incident at port i

Thus  $S_{11}$  refers to the ratio of the amplitude of the signal that reflects from port one to the amplitude of the signal incident on port one.

$$\begin{cases} b_1 \\ b_2 \end{cases} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{cases} a_1 \\ a_2 \end{cases}$$

#### Fig.1.2 Scattering Matrix

The matrix [S] is called scattering matrix, where  $[S_{11}]$  is the input reflection coefficient,  $[S_{12}]$  the reverse transmission coefficient,  $[S_{21}]$  is the forward transmission coefficient, and  $[S_{22}]_{is}$  the output reflection coefficient. The S parameters can be calculated individually by using given expressions:

$$S_{11} = \frac{b_1}{a_1}\Big|_{a2=0} = \frac{reflected \ power \ wave \ at \ port1}{incident \ power \ wave \ at \ port1}$$

$$S_{21} = \frac{b_2}{a_1}\Big|_{a2=0} = \frac{transmitted \ power \ wave \ at \ port2}{incident \ power \ wave \ at \ port1}$$

$$S_{22} = \frac{b_2}{a_2}\Big|_{a1=0} = \frac{reflected \ power \ wave \ at \ port2}{incident \ power \ wave \ at \ port2}$$

$$S_{12} = \frac{b_1}{a_2}\Big|_{a1=0} = \frac{transmitted \ power \ wave \ at \ port1}{incident \ power \ wave \ at \ port2}$$

Fig. 1.3 S-Parameters

#### **1.6.2 NOISE FIGURE**

Noise figure of an LNA directly affects the performance of the receiver; however other components of the receiver also affect the performance because we really design an LNA in isolation from other blocks of the receiver. The low noise figure requirement of an LNA generally restricts the circuit topologies that can be used for designing a LNA because as we increase the number of circuit elements the noise contribution also increases. Hence we have to limit our circuit design to a less no of transistors. This is done so that there are a few elements which are a dominant contributor to noise figure. Few configurations provide a higher noise figure which is not desirable.

Typical Noise Figure offered by an LNA is around 2-3 dB. Noise Figure of the LNA affects the performance of the receiver system directly.

### 1.6.3 GAIN

Gain offered by the LNA should be high enough to overcome the effect of noise from subsequent stages of the receiver system.

Gain of the LNA is desired to be high because LNA is placed at the front end of the receiver and it should provide a gain which is sufficient enough to suppress the noise contribution of the subsequent stages. However a higher gain makes the circuit non-linear. There is a trade-off between higher gain and a high linearity which should be kept in mind.

## **1.6.4 INPUT RETURN LOSS**

LNA is placed at the initial stages of the receiver but before LNA receiver system also consists of antenna and a filter placed before the LNA. Interfacing LNA with the antenna requires analysis of many factors which should be incorporated in the design.

If we consider LNA as a voltage amplifier we would prefer the input impedance of the antenna to be very high whereas if we want to obtain better noise performance we will have to precede the LNA with a transformation network. To transfer maximum power we would wish to provide conjugate matching between the LNA and the antenna. However we will have to make choice between these factors which should minimise reflection in the system.

(1) If a filter is placed before the LNA it should be properly matched with the input impedance of the LNA. Generally a filter is designed with a 50 $\Omega$  termination and if the input impedance of the antenna deviates from the standard 50 $\Omega$  impedance the filter may exhibit ripples in the pass band and will not produce required response.

(2) Even if filter is not used, antenna is also designed with certain load impedance which should be kept in mind while designing LNA and interface of LNA with antenna can be managed to provide conjugate matching between the two stages.

(3) In practical circuit implementation, the signal after being received from the antenna should travel a certain distance on the circuit board before reaching the receiver block. If proper matching is not provided it leads to attenuation and losses in the signal. This matching is significant at only the LNA antenna interface. Design of other components of the receiver need not focus on this parameter. They should focus on maximising output swings rather than power transfer.

Input return loss is a measure of input match and is expressed in dB.

#### **1.6.5 LINEARITY**

One important parameter at high frequency is the linearity of the circuit. When we

operate in small signal range we approximate the circuit by small signal models of its circuit elements. However non-linearity is also a factor of circuit performance and it may lead to certain interesting phenomena. If we apply a sinusoidal signal to a non-linear system, the output consists of harmonics of the input frequency. The harmonics generated may dominate the fundamental harmonic due to which the desired signal may get suppressed. We need to reduce the non-linearity i.e. we need to reduce the effect of harmonics on the fundamental frequency component.

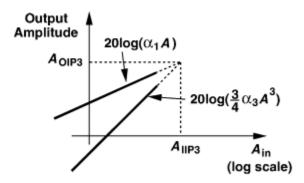

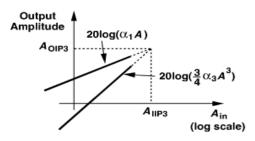

A measure of non-linearity of an amplifier can be estimated by calculating IIP3 i.e. Input Third Order Intercept. A circuit with higher value of IIP3 is said to be more linear as compared to a circuit with lower value of IIP3. However a better IIP3 value is achieved at the cost of reduced gain.We need to make a choice between a highly linear circuit and a circuit with the high gain, we can only optimise one of these parameters. IIP3 can be depicted graphically as:

Fig.1.4 Input Third Order Intercept Point (IIP3)

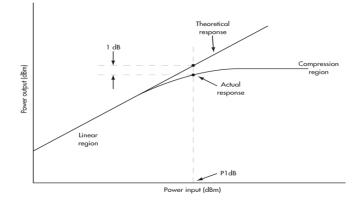

To calculate the value of IIP3 for any circuit amplifier we use two tone tests in Advanced Design System(ADS). However we can also carry out theoretical calculations for IIP3 using relevant formulae. The result obtained during theoretical calculation is an approximate value of IIP3 as it assumes that only third order nonlinearity exists and it ignores the higher harmonics. When we consider the non-linear behaviour of the elements we observe that the gain decreases as we increase the input power level. Here we observe a new parameter i.e. 1dB compression point. It is defined as that input level which decreases the output gain by 1dB. Its graphical representation is given below:

Fig.1.5 1 dB Compression Point

In most of the cases LNA does not limit the linearity of the receiver.

### **1.6.8 BANDWIDTH**

Bandwidth of an LNA defines the frequency range over which the LNA provides desired performance. It may not necessarily be at a single frequency rather it can be a range of frequencies depending on the application domain. LNA must provide a flat response in the frequency range of interest and the gain variation should not be more than 1 dB. We intend to provide a larger 3 dB bandwidth than the actual band required to constraint the gain variation within 1 dB. Instead of referring to 3-dB bandwidth we refer to a circuit's fractional bandwidth.

'fractional bandwidth' =

$$\frac{3 \, dB \, bandwidth}{center \, frequency \, of \, the \, band}$$

For example IEEE 802.11g LNA should have a fractional bandwidth greater than 0.0328. LNA application which needs larger fractional bandwidth can employ a technique which can change the centre frequency of operation which in turn will improve the fractional bandwidth of the circuit.

#### **1.6.9 POWER DISSIPATION**

There is a trade-off between noise figure, linearity and the power dissipation of a circuit. However LNA consumes only a small portion of total receiver power. Hence we can improve the noise performance of the LNA as it is more critical for receiver performance. So we do not need to be more specific about the power consumption of the circuit. However for applications in IoT power consumption of the circuit is the most important factor that should be optimised to make it compatible with the newer technologies.

Demand for devices consuming less power is increasing and Bluetooth communication itself requires less power consuming devices which can facilitate longer working hours. Recent research topic IoT and other low power applications have increased the utility of BLE devices as well which are designed to consume less power and are capable of operating on low cost batteries. Power consumption of LNA becomes a crucial factor in determining the application of LNA. LNA designed for application in Bluetooth and BLE should have low power design if it is to be made suitable for practical implementation.

#### **1.7 NOISE CONSIDERATIONS**

Noise affects the performance of the RF systems. If noise was absent receiver sensitivity would be very high i.e. receiver will be able to detect very weak signals as well. Noise analysis of a circuit is necessary and it can be done using time domain techniques as well as frequency domain techniques. Time domain analysis of noise is capable of providing limited information about the effect on noise i.e. noise power. However analysis in frequency domain provides a deeper insight into the effect of noise. Power Spectral Density needs to be defined for easier analysis of noise produced in a circuit. Choosing PSD for noise analysis helps us to apply operations that can be applied on random signals as noise is random in nature. If PSD at the input of a system is known PSD at the output can be determined easily if the system's response in known beforehand. Noise is random in nature i.e. its instantaneous value cannot be predicted

In order to analyze noise performance of circuits, we need to create a model which represents all the elements connected in the circuit by modelling noise of these constituent elements. We should know the equivalent noise model of all the elements being used in our circuit.

### **1.7.1 THERMAL NOISE**

Thermal noise is caused by random agitation of electrons in a conducting material. This agitation is caused by heat or temperature.

# **1.7.1.1 THERMAL NOISE IN RESISTORS**

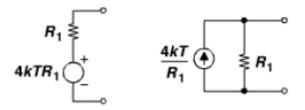

Resistors are employed in almost every circuit and they are a source of thermal noise as well. Charge carrier exhibit random motion with increase in temperature. Due to ambient temperature also the charge carriers in resistors get agitated and they follow a random path. Because of random nature we study noise in terms of its Power Spectral Density (PSD). Noise in a resistor can be modelled by a voltage source with PSD of 4KTR<sub>1</sub>. Norton equivalent can also be used for modelling which will be represented by a current source in parallel with PSD of 4KT/R<sub>1</sub>.

If we can model a circuit in terms of resistance we can represent the noise of the circuit by the equivalent formula by replacing the resistance by the equivalent resistance. This model is not only applicable to lumped elements but it can be applied to antenna as well

Fig.1.6 Thevnin and Norton model of resistor thermal noise

where the resistance denotes the radiation resistance of the antenna. PSD of the antenna will be given by:

$$(V_{n, ant})^2 = 4KTR_{Rad}$$

Where  $R_{Rad}$  is the radiation resistance of the antenna.

### **1.7.1.2 THERMAL NOISE IN MOSFETS**

Mostly we operate mosfet in saturation region in our circuit. In saturation region noise in mosfet can be modelled by a current source connected between the source and drain terminals of the device.

$$I_n^2 = 4 \text{KT} \gamma g_m$$

Where  $\gamma$  is the excess noise coefficient and  $g_m$  is the transconductance of the MOS. Value of  $\gamma$  is determined by many factors. It depends on the channel length of the MOS being used and also depends on CMOS technology being used.  $\gamma$  takes vale 2/3 for long channel devices and takes higher values for devices with shorter channel. It may take value 2 for short channel devices. Another component of thermal noise is also present in MOS that arises from gate and it increases with decrease in gate length. Gate resistance is given by:

$$R = \frac{W}{L} * R'$$

Where W is the width and L is the length. R' denotes the sheet resistance of the polysilicon used in fabrication of the device. This gate resistance is distributed over the entire width of the transistor which makes analysis of noise contribution from this resistance difficult. It can be made easier by representing it by a lumped model which has a gate resistance of  $R_G/3$ . [30] PSD of noise due to gate resistance can then be given by the formula:

$$V_n^2 = 4KT * \frac{R_G}{3}$$

A device is preferred if the noise added by it is always less than the channel noise. RF circuits are intended to work at higher frequencies which in turn affect the noise in the device. Thermal noise current at higher frequencies becomes the source of an additional noise component which is known as 'gate induced noise current'. [31] However this current is generally ignored in simulations and practical calculations as well because it is no significant to the device performance.

#### **1.7.2 FLICKER NOISE**

Flicker noise is also observed in MOS devices. As thermal noise can be modelled flicker noise can also be modelled in a MOS by placing a voltage source in series in with the gate terminal on the MOS. PSD of this noise is given by:

$$V_n^2 = \frac{K}{WLC_{ox}} \frac{1}{f}$$

Where K is process-dependent constant and it is lower for PMOS devices and has a higher value for NMOS devices. Value of K is lower in PMOS because it carries charge carriers well below the surface and hence has a less no dangling bonds.[32] This noise component is larger for noise components which vary slowly because of 1/f dependence. PSD of flicker noise may intercept PSD of thermal noise of a device at some frequency which is termed as corner frequency. Flicker noise has 1/f dependency which reduces its significance at higher frequencies.

#### **1.8 LNA TOPOLOGIES**

Parameters which should be kept in mind while designing an LNA provides an important lead so as to which topology should be chosen to design an LNA circuit. LNA determines the receiver performance, designing a LNA with consideration of all parameters within specified limits presents a demanding situation for all the researchers .Out of all the available topologies we have to analyze which topology is better in terms of these design parameters. LNA's utilise configurations that are being used traditionally to design amplifiers. Other than configuration additional steps are to be taken to achieve the desired performance. It can be obtained by introducing a change in the biasing network or it can be through a change in matching networks being used.

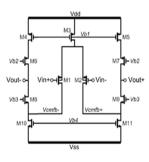

Most common LNA topologies are common-gate, common-source, cascode etc. Each of the above topology has its own advantages and disadvantages. In-spite of their own merits and demerits the cascode configuration in the most common configuration used in implementing LNA.

#### **1.8.1 COMMON-SOURCE STAGE WITH RESISTIVE LOAD**

This configuration is rarely used in practical applications. This configuration is not adequate to be used in practical applications as it is not able provide proper matching which is the most important factor in the design of LNA. Improper matching gives rise to reflections and most of the power is reflected back if the matching is not proper. This reflected power creates a hindrance to the proper operation of the other circuit components as well. Moreover LNA's are designed to be implemented at high frequencies and this design is not desirable for operation at high frequencies which further restricts its practical applications.

Gain offered by this topology is dependent on the supply voltage being used in the circuit. If we reduce the supply voltage the gain offered by this configuration will be reduced. In the latest CMOS technology this circuit provides a very poor performance as the supply voltage gets reduced with the CMOS technology.

$$|A_V| = g_{m.}R_D$$

Where,

A<sub>V</sub> is the voltage gain

$$|A_{V}| = \frac{2.V_{RD}}{V_{GS}-V_{TH}}$$

22

Where,

$g_m$  is the transconductance,  $V_{RD}$  is the voltage drop across the resistor

For new technologies we work on lower voltages and hence the gain further reduces if we use resistance in our circuit. This dependency is observed if we consider the channel length modulation to be negligible and do not include it in our calculations. If the channel length modulation is also taken into account the gain is further lowered

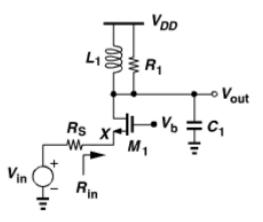

# **1.8.2 COMMON SOURCE STAGE WITH INDUCTIVE LOAD**

In order to evade the disadvantages of the configuration using Resistance as load we employ an inductor as a load in the configuration. Using an inductor as a load also felicitates the high frequency operation of the circuit. This topology offers provision of operating the circuit at lower supply voltage and high frequency. Operation at lower supply voltage is possible because inductor sustains a lower voltage drop than a resistor. Inductor as a load helps to achieve impedance matching as well as it resonates with the capacitor placed at the output terminal of the circuit.

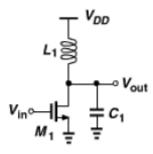

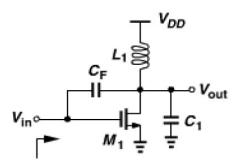

Fig.1.7 Inductively loaded Common Source stage

Along-with output matching we also need to analyze the input matching provided by this configuration.  $C_F$  is the capacitor that denotes the gate-drain overlap capacitance of the MOS. Other overlap capacitances are ignored as they are insignificant. On the basis of below circuit we can analyze the circuit for input matching.

Fig.1.8 Inductively loaded Common Source stage – Input Impedance On replacing the MOS by its equivalent circuit the circuit can be studied and we can

obtain the value of the input impedance. Impedance obtained has a real part and a imaginary part. Component values can be chosen accordingly and the real part can be made equal to 50  $\Omega$  and the imaginary can be equated to 0 to obtain the desired component values. When we try to achieve impedance matching at a frequency we end up having negative resistance at other frequency. If this frequency falls in region of interest it affects the functioning of the circuit and cause instability to the circuit as well.

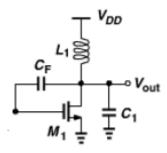

To achieve optimum performance the effect of the capacitance  $C_F$  can be nullified by placing an inductor in parallel with it. Placing an inductor in parallel with this capacitance attains parallel resonance and neutralizes the effect of capacitance. However the capacitance  $C_F$  is small we need to place an inductor with large value in parallel with it to satisfy condition of resonance. Use of large inductors introduces parasitic capacitances at the input and output nodes which degrade the performance of the circuit significantly. Hence this configuration is not suitable for use in practical applications.

Fig.1.9 Inductor L<sub>F</sub> to neutralise the effect of C<sub>F</sub>

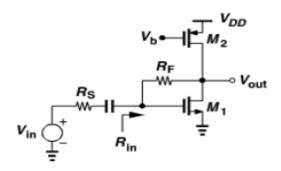

## **1.8.3 COMMON SOURCE STAGE WITH RESISTIVE FEEDBACK**

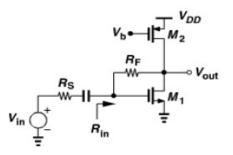

Circuit design process gets altered if the frequency of operation gets changes. If the frequency of operation of circuit is a magnitude lower than transit frequency  $(f_T)$  of the transistor. Common Source with resistive feedback can be considered for implementing LNA in such scenario.

#### Fig.1.10 CS Stage with resistive feedback

In above configuration MOS M2 operates as a current source. Feedback resistor  $R_F$  provides feedback from the output to the input of the circuit. It senses the voltage at the output of the circuit and then sends a current signal in response to the voltage sensed. On simplifications gain of the above circuit comes out to be:

$$|\mathbf{A}_{\mathbf{V}}| = \frac{-R_F}{R_S}$$

Where  $R_F$  is the feedback resistor,  $R_S$  is input resistance.

As indicated by the above formula gain of this configuration is not dependent on the supply voltage. Hence this configuration evades the disadvantage of resistively loaded CS stage. Noise figure of this configuration is observed to be a bit higher. Noise figure of this configuration is given by:

$$NF = 1 + \frac{4R_S}{R_F} + \gamma + \gamma g_{m2} R_S$$

Where symbols have their usual meanings.

Even if we consider  $\gamma = 1$ , Noise Figure if this configuration will exceed 3 dB which is relatively large value of NF.

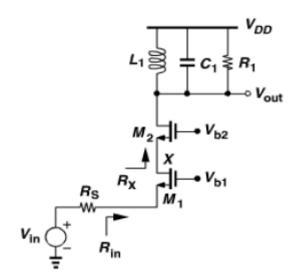

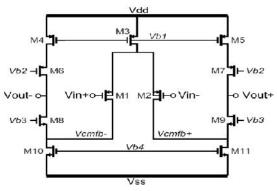

### **1.8.4 COMMON GATE STAGE**

Apart from Common Source configuration, Common Gate configuration is also a possible candidate for implementing LNA. This configuration is striking for LNA design owing to low input impedance of Common Gate stage. In this configuration resistance is not preferred as load the reason being the same as discussed earlier. Inductively loaded Common Gate configuration is used and the inductor at the load resonates with the capacitance connected the output terminals. MOS is used in Common Gate configuration and the parameters of MOS are chosen such that it is able to provide an input impedance of 50  $\Omega$ .

### Fig.1.11 Common Gate Stage

In above calculations we neglect the channel length modulation of the MOS. As stated before the input impedance of CG stage is low but this happens only when we assume the channel length modulation to absent. If we consider the channel length modulation, input impedance of this configuration is very high which is a drastic change in the circuit parameter . Techniques have been proposed which tend to deal with this condition as well. One such technique is to use a cascode Common Gate stage to lower the input impedance of the above configuration which came into existence because of the channel length modulation.

Fig.1.12 Cascode common gate stage

In order to account for noise inefficiency CG configuration generally employ an inductor in their bias networks. Introducing an inductor also helps to neutralize the input capacitance of the circuit. Because of addition of a new circuit component an inductor additional noise gets added to the circuit, Additional noise can be removed by using a proper biasing network for the circuit. This biasing should be provided such that is removes the effect of noise added by the inductor as well as resolves the problem of input matching. Moreover in new technologies inductors can be easily fabricated on chip which makes the implementation of circuits with inductors trouble free.

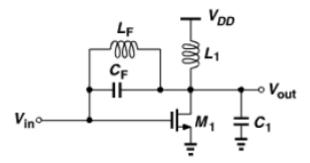

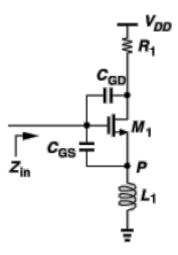

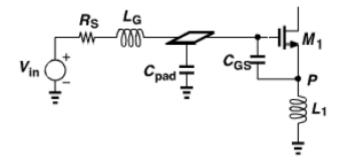

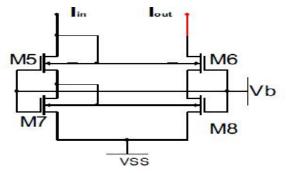

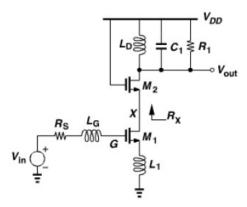

# **1.8.5 CASCODE STAGE WITH INDUCTIVE DEGENERATION**

We observed that using a capacitor to achieve input matching creates a problem of negative resistance at certain frequencies. We require a configuration that should be able to address this issue and provide a reliable solution to this. We need a configuration that

should provide isolation between the input and output which helps to remove the effect due to feedback and an alternate method of achieving input impedance other than the gatedrain overlap capacitance which is the root of all these problems.

To achieve input matching we prefer a circuit with active devices rather than using passive devices to reduce the noise contribution from circuit components. This configuration is one of the methods to do so. The input impedance of the configuration can be given by the expression:

$$Z_{in} = \frac{1}{s.C_{GS1}} + L_{1.S} + \frac{g_m L_1}{C_{GS1}}$$

The input impedance of the configuration contains a frequency dependent part and a frequency independent part. The frequency independent part can be made equal to  $50\Omega$  by choosing appropriate values of the components. Typically the value of inductor used comes in the range of pH. To realise  $50\Omega$  input impedance, inductor with value in pH need to be implemented. Inductors are implemented using bond wires because they need to included in design and cannot be realised off-chip. Degeneration inductor cannot be placed off-chip under any circumstances as it is a part of the circuit. Using bond wires realising an inductor within pH range is very tedious task. Even after using technique to obtain minimum inductance, we achieve an inductance value in nH which is much larger than required value. If we realise inductor using bond wires and input impedance greater than  $50\Omega$  is achieved which disturbs the input impedance match.

To obtain an input impedance of  $50\Omega$  as well as realise it using bond-wire inductors we need to reduce the transit frequency of the mosfet. It can be done by increasing the channel length of the transistor or placing a capacitor in parallel with the C<sub>GS</sub>. We calculate the above impedance values by neglecting C<sub>GD</sub> and C<sub>SB</sub>.

If we include the effect of  $C_{GD}$  in our calculations we observe that the input impedance is further lowered if  $C_{GD}$  is included.

Fig.1.13 Input Impedance in presence of CGD

We observe that the input resistance falls by a factor of  $(1 - \frac{2C_{GD}}{c_{GS}})$  which becomes 1 if effect of C<sub>GD</sub> is neglected.

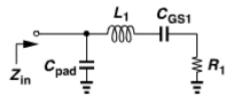

With  $C_{GD}$ , input pad capacitance of MOSFET also lowers the input impedance which should also be taken care of.

Fig.1.14 Impedance in presence of pad capacitance

On inclusion of pad capacitance we observe that the degeneration inductor is not sufficient enough to resonate with the capacitance to provide an input matching of 50 $\Omega$ . Hence we place an inductor in series to achieve the required inductance value to achieve impedance matching.

Fig.1.15 Addition of L for impedance matching Noise figure of above configuration is computed to be :

NF= 1 +

$$g_{m.}R_{S.}\gamma.\left(\frac{w_o}{w_t}\right)^2$$

Where  $w_0$  is the frequency of interest,  $w_t$  is the transit frequency.

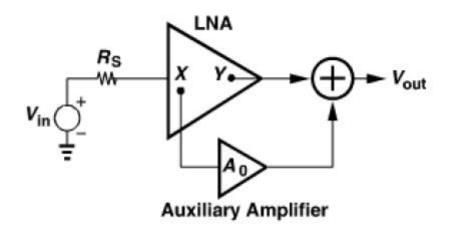

# **1.8.6 NOISE CANCELLING LNA**

In calculations related to noise figures of the above configuration we obtained terms signifying the noise because of resistor  $R_s$ , noise due to load resistor and the noise contribution of the transistor. The noise added because of the resistor cannot be removed as the charge carriers will exhibit random agitation in presence of ambient heat. In noise cancelling LNA's we aim to reduce the effect of noise added by the input transistor. These LNA's work on the principle that if two signals with opposite polarities are added they cancel each other's effect and if two signals with same polarity are added the resultant signal has an increased strength.. We identify two nodes in LNA where the required signal appears at opposite polarity and noise appears with same polarity. We can scale up the signals at the available nodes and add them further such that the signal components add up and the noise components cancel each other.

Fig.1.16 Noise cancelling LNA

We observe that CS stage with resistive feedback provides two nodes within the circuit with required polarities between the signal and the noise. Two nodes available are the gate and drain of the transistor. Noise current of the resistors appear at the gate and drain terminal with the same polarity whereas the signal reaching the nodes experience inversion.

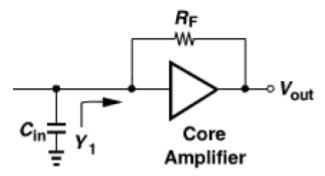

## **1.8.7 REACTANCE CANCELLING LNA**

This configuration is designed such that it cancels the effect of its own input capacitance.

This configuration is designed by the idea that input inductive impedance can be exploited to cancel the effect of input capacitance. The methodology used for obtaining input matching holds for frequencies up to the frequency of interest i.e. input matching provided depends on the frequency of interest as well.

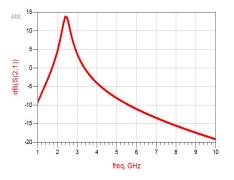

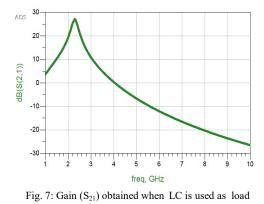

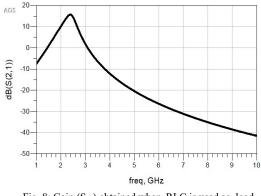

Fig.1.17 Reactance Cancelling LNA topology