# DESIGN & IMPLEMENTATION OF CMOS LNA FOR WIRELESS APPLICATIONS

A Dissertation

Submitted In partial Fulfilment of the Requirements For The Award of the Degree of

Master of Technology (2017-19) In Microwave & Optical Communication Engineering (MOCE)

Submitted by:

# Gaurav Srivastava (2K17/MOC/012)

Under the Supervision of

## Dr. Malti Bansal

Assistant Professor Department of Electronics & Communication Engineering Delhi Technological University (DTU)

Department of Electronics & Communication Engineering Delhi Technological University (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

2017-19

Department of Electronics & Communication Engineering Delhi Technological University (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **Candidate's Declaration**

I GAURAV SRIVASTAVA, Roll No. 2K17/MOC/12 student of M.Tech (Microwave & Optical Communication), hereby declare that the project Dissertation titled "Design & Implementation of CMOS LNA for Wireless Applications" which is being submitted by me to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology in Microwave & Optical Communication, is original and bonafide record without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: New Delhi Date: GAURAV SRIVASTAVA (2K17/MOC/12)

Department of Electronics & Communication Engineering Delhi Technological University (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# Certificate

I hereby certify that the Project Dissertation titled "Design & Implementation of CMOS LNA for Wireless Applications" which is being submitted by GAURAV SRIVASTAVA, Roll No (2K17/MOC/12) Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is a bonafide record of the project work carried out by the student under my supervision. To the best of my knowledge, this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: New Delhi Date:

Dr. Malti Bansal Project Supervisor Assistant Professor Department of Electronics &Communication Engineering Delhi Technological University

## Acknowledgement

Someone wise had once said, "If the destination is beautiful, don't ask about the pains of the journey, and if the journey is beautiful don't ask to which destination it will lead." And I have a lot of people to thank who have made my study journey and destination both beautiful. This dissertation is the result of work of almost two years, whereby I have been accompanied and supported by many people, to whom I would like to express my gratitude.

I would like to express my deep gratitude to my supervisor, **Dr**. **Malti Bansal** assistant professor department of Electronics and Communication Engineering, DTU Delhi who has provided me with guidelines for my work and supported me with valuable advice throughout my studies. I would like to take this opportunity to express my appreciation to all my friends and colleagues in Electronics and Communication Engineering Department, Delhi Technological University.

The two people to whom I believe I owe all and saying just 'Thanks' will be insufficient, are my parents. I would like to thank them and my siblings for believing in me and supporting me.

GAURAV SRIVASTAVA Roll no: 2K17/MOC/12

#### Abstract

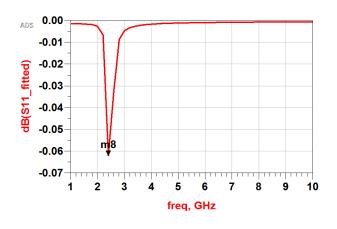

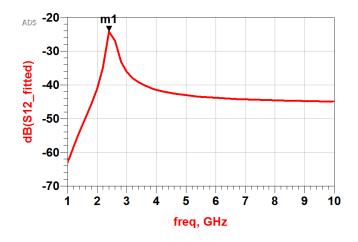

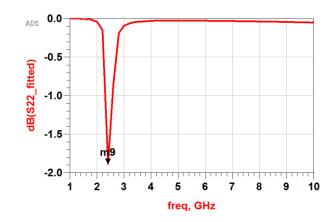

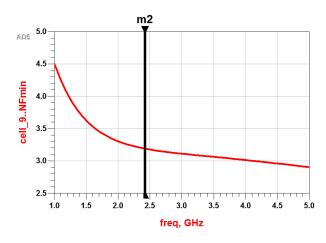

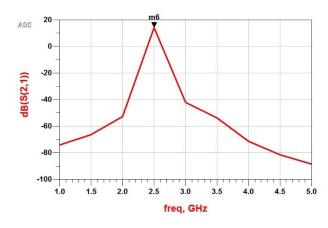

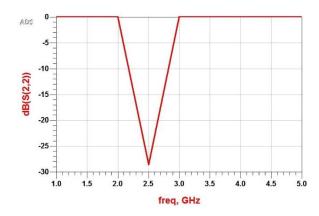

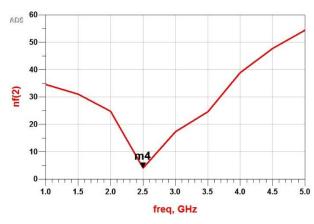

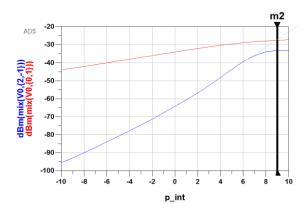

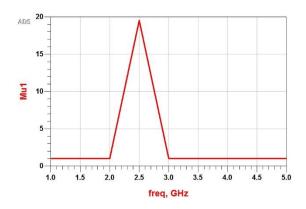

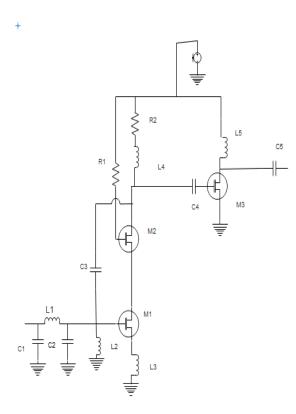

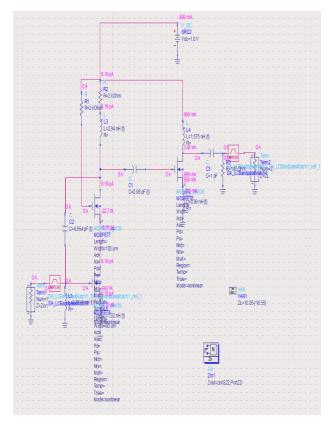

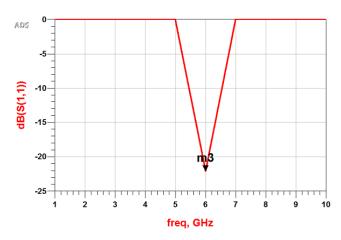

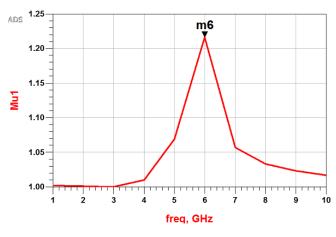

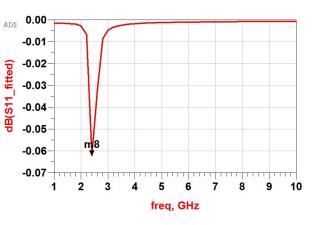

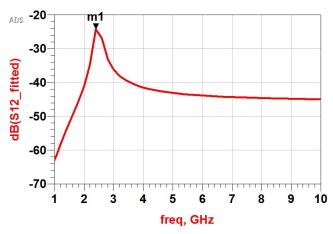

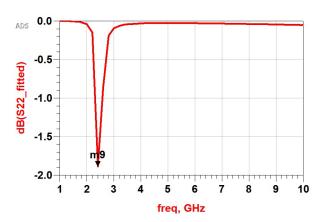

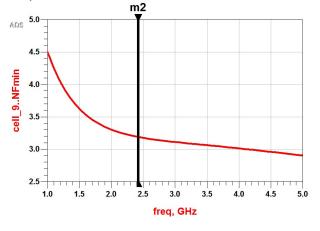

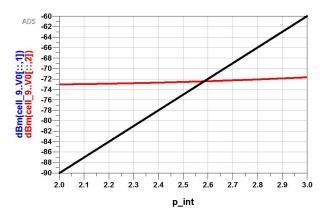

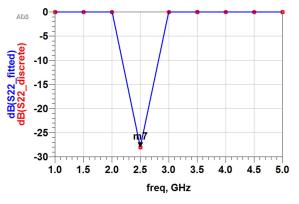

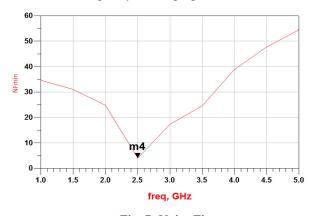

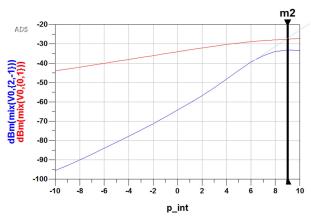

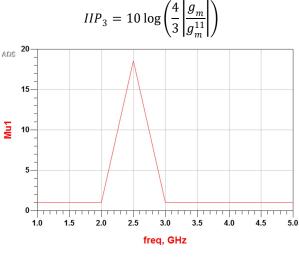

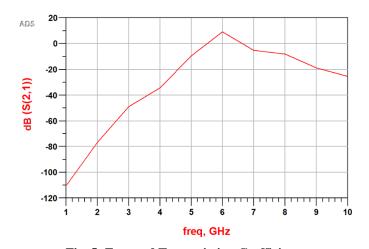

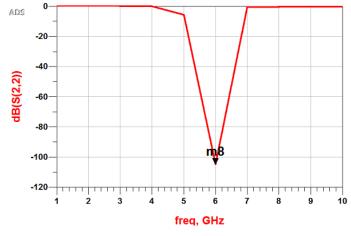

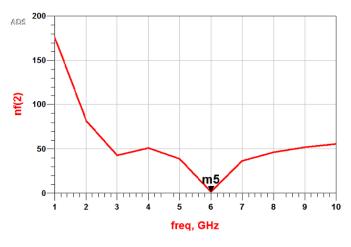

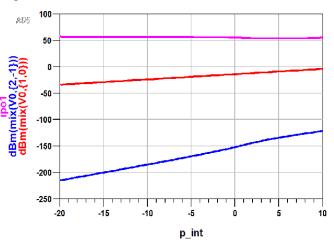

In recent years the advancement in the wireless communication technologies especially in the RF range including all the major applications like (satellite communication, mobile communication, IOTs). The basic characteristics of the RF transceiver system is determined by the major components which includes mixer, LNA, Filters, ADC and DAC converters. However, the properties of RF transceiver is mainly affected by the designing of Mixers and LNA. In this thesis LNA for 2.4 GHz ISM band that is (Industrial, Scientific and Medical band) for RF transceiver system is designed and implemented. The basic parameters of LNA includes low power consumption, small supply voltage and low chip area. Apart from this LNA should have high matching network for (minimum return loss), low noise figure, optimum gain and high linearity. The LNA is implemented in 180 nm and 45nm TSMC Technology on Advance Designing Software (ADS). The LNA is implemented using major topologies like Common source, Common gate and Cascoded Topology. The mode of implementation of LNA with CS or CG depends upon the mode of applications. The most common and efficient topology is common source with inductor degenerate cascoded with Common gate topology. The LNA attains the NF of 1.23 and third order intercept point (IIP3) (measure of linearity) of 56.85 dBm which is best so far.

## **List of Published Papers**

- 1. Malti Bansal, Gaurav Srivastava, "LNA for Biomedical Applications," International Journal of Engineering Technology Science & Research (IJESTR) ISSN 2394-3386, Volume 4 pp- 295-300, Issue 11, November 2017.

- 2. Malti Bansal, Gaurav Srivastava, "High Linearity and Low Power Cascode CMOS LNA for RF Front-End Applications," in proceedings of Third International conference on Intelligent Computing and Control Systems(ICICCS-2019),pp-1-4.

- 3. Malti Bansal, Gaurav Srivastava, "Design and Implementation of LNA for Biomedical Applications", in proceedings of International Conference on Intelligent Computing ,Information and Control Systems(ICICCS-2019),pp-151-160.

## **List of Communicated Papers**

- **1.** Malti Bansal, Gaurav Srivastava, "High Linearity High Stability Cascode CMOS LNA for RF Front-End Applications.

- 2. Gaurav Srivastava, Malti Bansal, "A High Linearity Shunt Capacitive Feedback LNA for Wireless Applications

## **TABLE OF CONTENTS**

- **Candidate Declaration**

- Certificate

- Acknowledgement

Abstract

List of Published & Communicated Papers

Contents

**List of Figures**

**List of Tables**

List of Abbreviations

#### **CHAPTER 1 INTRODUCTION**

- 1.1 Background

- 1.2 Types of RF Receivers

- **1.3 Amplifier Basics**

- 1.4 LNA Basics

- 1.5 Parameters of LNA

- 1.6 Different Topologies of LNA

- 1.7 Use of LNA in Biomedical Applications

## **CHAPTER 2 LITERATURE REVIEW**

#### **CHAPTER 3 EXPERIMENTAL WORK AND RESULTS**

- 3.1 Source Degenerate Feedback

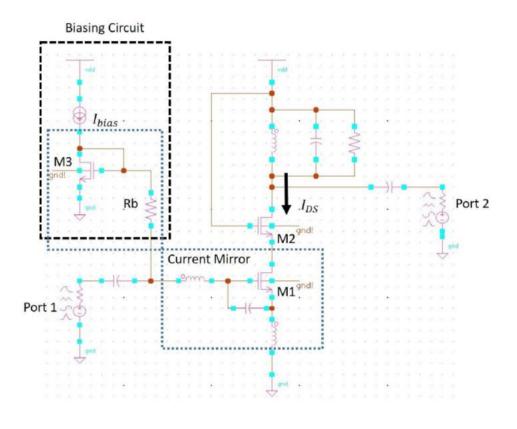

- 3.2 Biasing Circuits Using Current Mirror

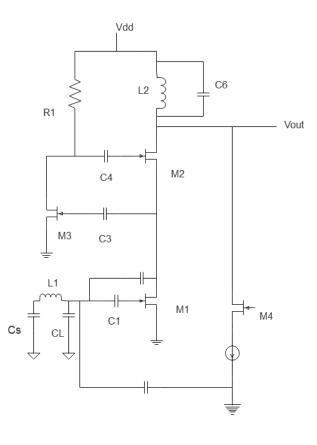

- 3.3 Cascode LNA

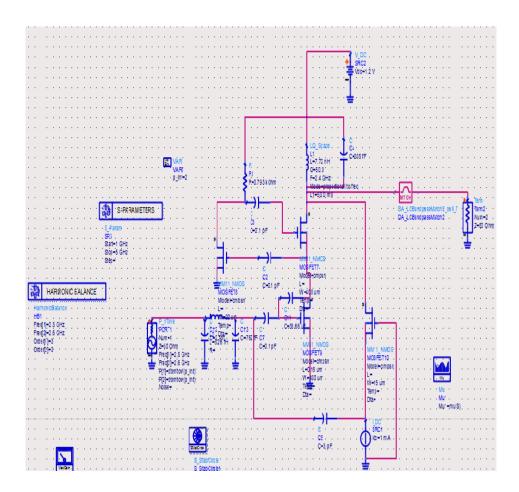

- 3.4 Circuit Design

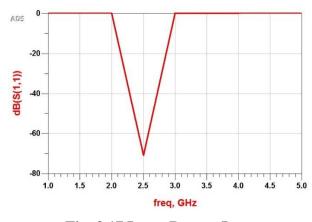

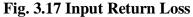

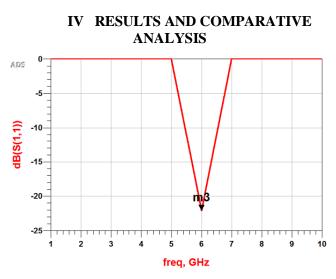

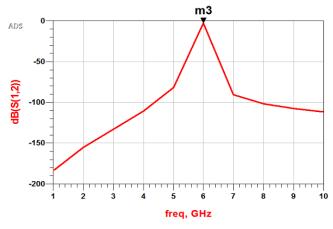

- 3.5 Simulation Results & Comparisons

- **3.6** Conclusions

- 3.7 Design Methodology

- 3.8 Circuit Design

- **3.9** Conclusions

## **CHAPTER 4 CONCLUSION & FUTURE SCOPE**

## BIBLIOGRAPHY

Appendix: (1) List of Published Papers

(2) List of Communicated Papers

# **LIST OF FIGURES**

| Figure No.      | Title                                           | Page No. |

|-----------------|-------------------------------------------------|----------|

| Figure No.1.1   | Block Diagram of RF Transceiver System          | 1        |

| Figure No.1.2   | LNA for Universal RF Receivers                  | 2        |

| Figure No.1.3   | RF Transceiver System                           | 4        |

| Figure No.1.4   | Tuned Frequency Receivers(TRF)                  | 5        |

| Figure No.1.5   | Super Regenerative Receivers                    | 5        |

| Figure No.1.6   | Super Heterodyne Receivers                      | 6        |

| Figure No.1.7   | Basic Amplifier Circuits                        | 7        |

| Figure No.1.8   | Basic BJTs & MOS Circuit                        | 8        |

| Figure No.1.9   | Common Source Amplifier                         | 9        |

| Figure No.1.10  | Common Drain Amplifier                          | 9        |

| Figure No. 1.11 | Basic LNA                                       | 11       |

| Figure No.1.12  | Port n/w with Voltage source V1 and V2          | 12       |

| Figure No.1.13  | Port n/w with Incident wave $(a_1 \& a_2)$ and  | 14       |

|                 | $(b_1 \& b_2)$                                  |          |

| Figure No.1.14  | Reflection Coefficient Representation           | 15       |

| Figure No. 1.15 | 2 Port n/w indicates measurement from source    | 15       |

|                 | To Load                                         |          |

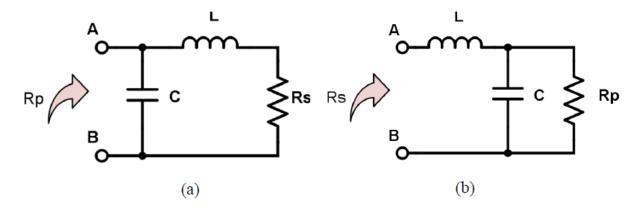

| Figure No.1.16  | RF simplified RLC series Circuits               | 16       |

| Figure No.1.17  | Parallel to series Transformation Circuits      | 17       |

| Figure No.1.18  | L- Match Circuit i.) Upward ii.) Downward       | 17       |

| Figure No.1.19  | High Pass L-Match Circuit i.) Upward ii.)       | 18       |

|                 | Downward                                        |          |

| Figure No.1.20  | pie matching with two L-matching Circuits       | 19       |

| Figure No.1.21  | Transformation from i.) R-L series circuit ii.) | 19       |

|                 | RL- parallel circuit                            |          |

| Figure No.1.23  | Noise Spectral Density                          | 23       |

| Figure No.1.24  | P-1dB Compression Point                         | 26       |

| Figure No.1.26  | Measure of Third – Order Intercept point        | 27       |

| Figure No.1.27  | CS with Resistive Termination                      | 30 |

|-----------------|----------------------------------------------------|----|

| Figure No.1.28  | CS I/P stage with source inductive degenerate      | 31 |

| Figure No.1.29  | CS I/P stage with Shunt F/B                        | 32 |

| Figure No.1.30  | I/P impedance with C <sub>F</sub>                  | 33 |

| Figure No.1.31  | Neutralising C <sub>F</sub> by L <sub>F</sub>      | 33 |

| Figure No.1.32  | Common Gate LNA                                    | 34 |

| Figure No.1.33  | I/P impedance in presence of r <sub>0</sub>        | 35 |

| Figure No.1.34  | I/P with Resonant Load                             | 35 |

| Figure No.1.37  | Cascoded Amplifier                                 | 37 |

| Figure No.1.38  | Schematic representation of Inductor               | 38 |

| Figure No.1.39  | BALUN Rx I/P                                       | 39 |

| Figure No.1.40  | Basic Balun Amplifier Circuit                      | 39 |

| Figure No.1.41  | Paddling Capacitor                                 | 40 |

| Figure No.1.42  | Differential CG LNA                                | 41 |

| Figure No.1.43  | Differential CS LNA                                | 42 |

| Figure No. 1.44 | Differential CS stage Transconductance             | 42 |

| Figure No. 1.45 | BASN n/w                                           | 46 |

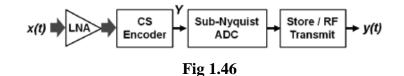

| Figure No. 1.46 | An Analog Domain CS Transmitter                    | 47 |

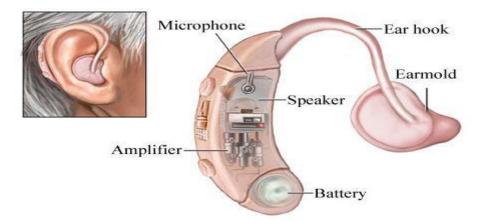

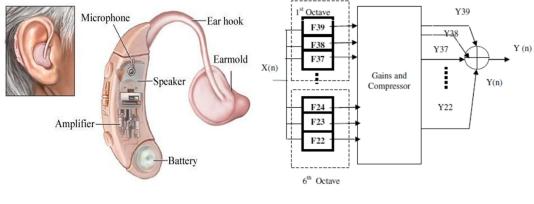

| Figure No. 1.47 | LNA in Hearing Aids Applications                   | 48 |

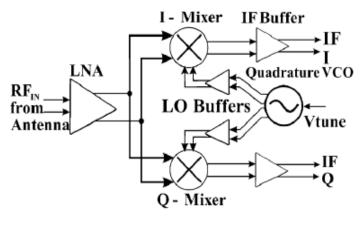

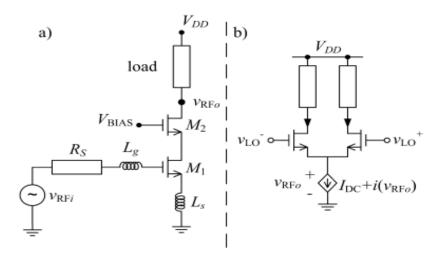

| Figure No. 2.1  | Direct Conversion Front-End Diagram                | 50 |

| Figure No. 2.2  | RF Transceiver System                              | 51 |

| Figure No. 2.3  | Cascode LNA with Inductor Degenerate               | 53 |

|                 | 2.) Balanced Mixer                                 |    |

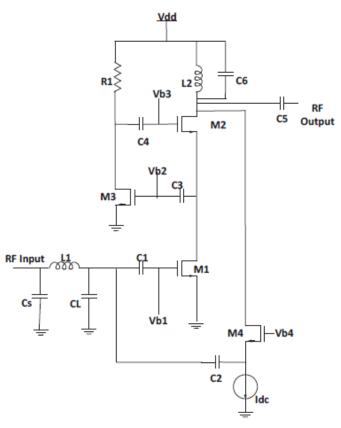

| Figure No.2.4   | Schematic of Proposed LNA Ref [40]                 | 54 |

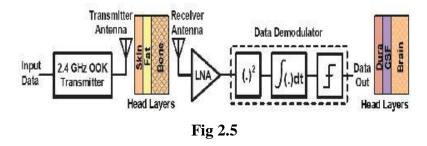

| Figure No.2.5   | Conceptual Diagram of Wireless Link                | 55 |

|                 | (Transmitter, Antenna, Head tissue, LNA            |    |

|                 | And OOK- demodulator)                              |    |

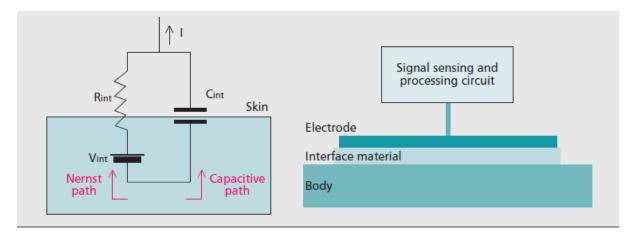

| Figure No.2.6   | Body equivalent Circuit modal and electrode        | 56 |

|                 | Body interface                                     |    |

| Figure No.2.7   | Nyquist ADC followed by Digital Compression        | 57 |

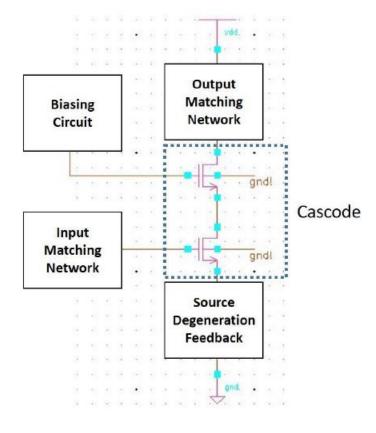

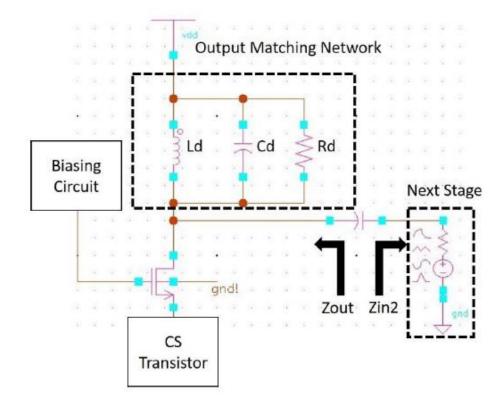

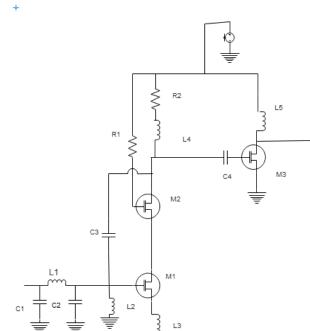

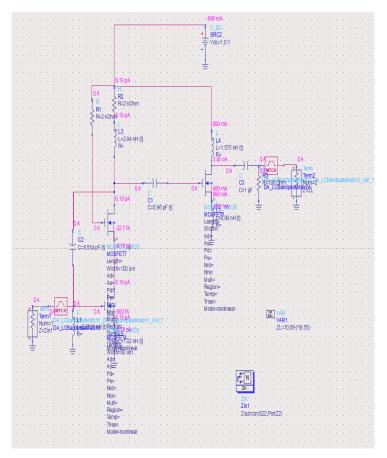

| Figure No.3.1   | structure of Cascode LNA with different Functional | 59 |

|                 | Block                                              |    |

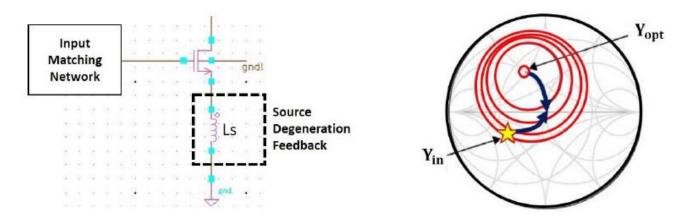

| Figure No.3.2  | I/P matching with Source Degenerate ii.) Smith chart |    |

|----------------|------------------------------------------------------|----|

|                | Optimising admittance (Yopt)                         |    |

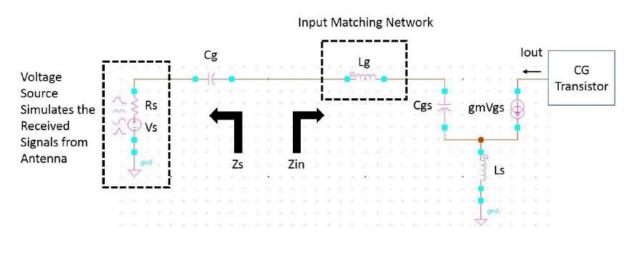

| Figure No.3.3  | I/P Matching N/W of LNA                              | 60 |

| Figure No.3.4  | O/P Matching N/W of LNA                              | 61 |

| Figure No. 3.5 | Small Signal Modal of LNA                            | 62 |

# **LIST OF TABLES**

| Table No.   | Title                                  | Page No. |

|-------------|----------------------------------------|----------|

| Table 1.3.1 | Types of Amplifiers                    | 7        |

| Table 1.3.2 | Comparison Table                       | 10       |

| Table 1.6.1 | Different Types of Topologies of LNA   | 29       |

| Table 1.6.2 | Design Specifications                  | 29       |

| Table 1.6.3 | Characteristics of the Amplifiers      | 42       |

| Table 1.7.1 | Comparison of Work                     | 49       |

| Table 2.1   | Comparison of Different Topologies     | 52       |

| Table 3.1   | Comparison of LNA with other Published | 69       |

|             | Work                                   |          |

| Table 3.2   | Comparison of Proposed LNA with other  | 76       |

|             | Published Work (schematic 2)           |          |

| Table 3.4   | Comparison of Proposed LNA with other  | 83       |

|             | Published Work (schematic 3)           |          |

| Table 3.5   | Conclusion                             | 84       |

## **LIST OF ABBREVIATIONS**

| Abbreviations | Full Form                               |

|---------------|-----------------------------------------|

| VLSI          | Very Large Scale Integration            |

| RFIC          | Radio Frequency Integrated Circuits     |

| CDMA          | Code Division Multiple Access           |

| GSM           | Global System for Mobile Communications |

| LAN           | Local Area Network                      |

| LTE           | Long Term Evolution                     |

| ISM           | Industrial, Scientific and Medical      |

| RF            | Radio Frequency                         |

| IC            | Integrated Circuits                     |

| LNA           | Low Noise Amplifier                     |

| ADC           | Analog to Digital Converter             |

| IIP3          | Third Order Intercept Point             |

| SNR           | Signal to the Noise Ratio               |

| IR            | Infrared Radiations                     |

| AM            | Amplitude Modulation                    |

| SSB           | Single Side Band                        |

| QPSK          | Quadrature Phase Shift Keying           |

| QAM           | Quadrature Amplitude Modulation         |

| BJTs          | Bipolar Junction Transistors            |

| MOSFETs       | Metal Oxide Semiconductor Field         |

|               | Effect Transistor                       |

| FET           | Field Effect Transistors                |

| WSN           | Wireless Switching Network              |

| ITU           | International Telecommunication Union   |

| NFC           | Near Field Communication                |

| GHz           | Gigahertz                               |

| CCRLNA        | Complementary Current Reuse Low Noise   |

|      | Amplifier.                              |

|------|-----------------------------------------|

| CMRR | Common Mode Rejection Ratio             |

| OTA  | Operational Transistor Amplifier        |

| FIFO | First Input First Output                |

| FPGA | Field Programmable Gate Array           |

| DSP  | Digital Signal Processor                |

| CMOS | Complementary Metal Oxide Semiconductor |

| SOC  | Silicon on Chip                         |

| UWB  | Ultra-Wideband                          |

#### **CHAPTER 1 INTRODUCTION**

#### **1.1 BACKGROUND**

The need of wireless communication is pushing many VLSI Designers to continue research in RFICs design and transceivers systems. Different wireless standards CDMA ,GSM, wireless LAN(IEEE 802.11a),Bluetooth, Zigbee, wimax and LTE are operated at different frequencies with different modulation methods which has exponentially increased the use of wireless application devices. The concept of IEEE 802.15.4 provides data rate of 250kbps over a distance of 10m. The band of 802.15.4 corresponds to the license free radio band which are available all across the globe. The 2.4 GHz (ISM band) or unlicensed band are the internationally reserved radio spectrum intended for scientific ,medical and industrial requirements. Nowadays, wireless devices are designed keeping important parameters like compact size, less power dissipation and less cost.[1] Current mobile phones and handsets having RF transceiver system consisting of complex circuitry includes amplifiers, mixers, oscillators fabricated on a single chip. Thus, occupying a large chip area on a single IC and consuming more power so, For controlling these parameters single wideband RF front end devices supporting all wireless communication standards are favoured. Therefore, designing of LNA plays a crucial and important role in determining the performance of an RF transceiver system.

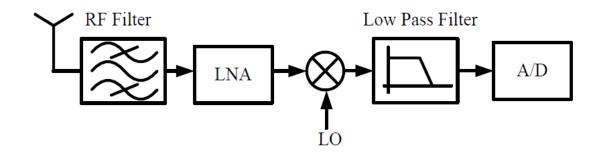

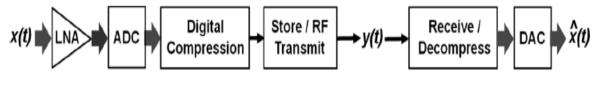

Fig 1.1 Block Diagram of RF Transceiver System

All RF transceiver systems are being integrated on a single chip consisting of hardware components and wires having parasitic effects [2]. The receiver having such effects are called as universal receiver. Ideal RF transceiver system cannot be designed because of its tough designing requirements of (ADC) (Analog to Digital converters). the main components of ADC consist of mixers and LNA. The LNA[3] are calibrated on the basis of noise figure, gain ,linearity and IIP3 parameters. Hence, LNA plays a important role

in any RF receivers. The design of LNA is still a challenging task. Presently, the amplifiers designed for specific wireless standards consumes more power and is having a high cost. In fig 1.1 [2] the system consist of RF filter which filters frequency of specific range the LNA used for amplifying the signal by adding a very little noise to the system. Since the system cannot be the ideal one therefore LNA adds very little noise and SNR obtain is approximately equals to 1. The local oscillator causes the up conversion or down conversion of the frequency. The low pass filter selects the required frequency. In addition[4],LNA is matched to the output of the filters to prevent the back and forth signal reflection between the LNA and antenna, Other parameters in designing of the LNA includes topologies with efficient input matching, biasing circuits, source degenerate feedback circuit and output matching circuits. Further, designing of LNA involves resistors, inductors and capacitors circuit theory.

| T   | 1 | •    |

|-----|---|------|

| HIO |   | · 7. |

| 115 |   | • –  |

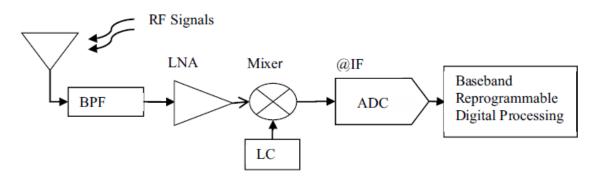

The above figure represents designing of LNA for universal RF receiver which is a difficult process. But the universal receiver has the key advantage over the superhetrodyne receiver such as low complexity, no image frequency as compared to superhetrodyne receiver. [5]The RF receiver is implemented using digital and analog. The components like mixers and filters are replaced by digital counterpart but these are found to be having high sampling rate and high SNR, therefore the SNR of the input signal need to be increased. Analog RF receiver [3] is implemented by the method of discrete fourier transform between the antenna and digital signal processor. A software defined ratio selects (SDR) a required frequency from channel bandwidth but system still suffer from the problem of high sampling rate.

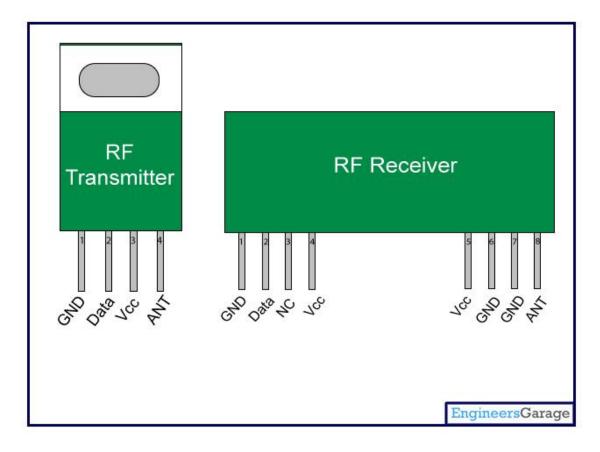

The RF module stands for radio frequency as the name suggests. the range of frequency for RF module ranges from 30 KHz to 300 GHz. the information is carried in the form of

digital data represented as variation of amplitudes in carrier waves. This type of modulation scheme is called as amplitude shift keying (ASK). The other modulation schemes consist of frequency shift keying (FSK) phase shift keying(PSK) in which frequency and phases are varied. The modulation method carries the actual information in the form of audio, video or data. the receiver need to perform number of actions so that the information can be processed and deciphered. Receivers need to perform effectively even in the presence of noise and interfering signals. Therefore, selectivity and sensitivity are the important characteristics of the receivers.

Transmission through RF is more convenient then IR mode due to many reasons. signals through RF are capable of travelling long distances they can even travel with the obstruction between the transmitter and receiver. these are generated at high frequency so highly directive and strong at specific frequency. The IR mostly operates in line of sight mode so they get affected by the obstruction in there path. The IR emitting sources are not as effective as RF module.

The RF Transceiver module consist of RF transmitter and RF receiver. The transmission and reception takes place at specific frequency the RF transmitter receives serial data and transmit wirelessly through RF antenna. The transmission occour at a rate around 1-100(kbps). Depending upon the mode of frequency band and sampling rate. The data transmitted at the receiver is at the same frequency as that of the transmitter.

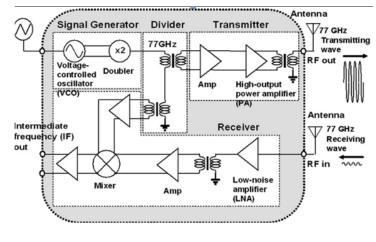

Fig 1.3 RF Transceiver System

#### **1.2 TYPES OF RF RECEIVERS**

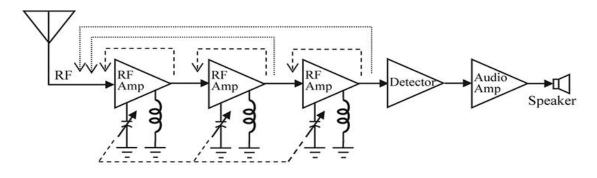

a)**Tuned Radio Frequency**(**TRF**) **Receiver-** the mixed signal obtained from antenna is filtered extracting the desired signal. It consisted of three stages 1. Filtering 2. Tuning 3.Selectivity provided at the Radio frequency stages. Previous TRF Receivers used crystal sets having tuned network consisting of numbers of coils tuning in this stage is provided by simple crystal or diode detector. It consisted of three stages

1.) Tuned Radio Frequency Stages- it consists of one or more amplifying tuning stages .

2.) Signal Detector- enabling extraction of the audio signals from amplitude modulation. the system consisted of a envelope detection and diode for rectifying signal.

3.)Audio amplifier Stage- Audio stage to provide audio amplification.

Fig 1.4 Tuned Frequency Receiver (TRF)

b.) **Regenerative Receivers**-it consisted of small number of valves or tubes providing high level of gain and selectivity. the main supply was batteries therefore minimising the number of stages was key. the positive feedback in the receiver circuit increased the gain and selectivity of the system. The received signal is in same phase with the input signal which increased the gain by 1000 or more which causes the quality factor to be multiplied thus, circuit have high selectivity.it consist of three stages 1.) **AM Reception** 2.) **Morse/CW reception** 3.) **SSB Reception.**

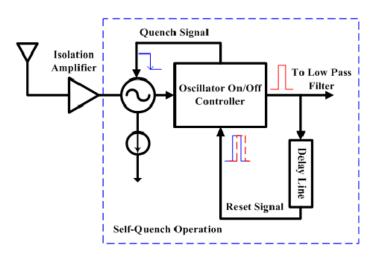

c.) **Super regenerative Receiver-** the super regenerative receiver works on regeneration of the stage further.it consist of second low frequency oscillator that quenches the regenerative loop of the main RF oscillation. It works around audio range of 25 kHz to 100 KHz. Although the gain of the amplifier is fixed some of the output is fed back to the input node in phase. It consist of negative resistance reducing the overall resistance of the circuit and quality factor of the circuit is also improved. The quenching oscillation causes RF signal to build up to a very high value.

Fig 1.5 Super Regenerative Receiver

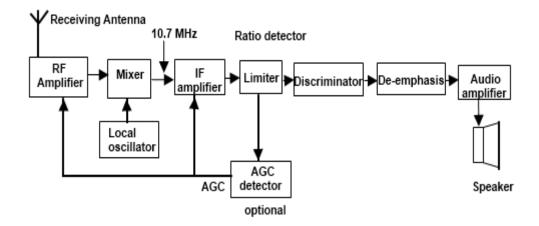

**Super Heterodyne Receivers**-The superheterodyne receiver involves the process of mixing of two signals together. the up conversion and down conversion results in the modulation of the signal. the mixing of RF and local oscillator frequency results in infrared frequency(IF) frequency and varying the frequency of the local oscillator causes the tuning of the circuit to different frequencies.it suffers from the problem of image frequency in the IF stage which is removed by selecting only required range of frequency. Therefore, good image rejection ratio is one of the key features of radio receivers.

Fig 1.6 Super Heterodyne Receivers

**Direct Conversion Receiver-** This type of receiver are based on radio formats for converting signals directly to the baseband frequency. The previous method used AM, FSK modulation methods for transmission of the signal but now digital communication transmission method PSK , BPSK ,QPSK methods are used for transmission of the message signal the IQ demodulators of QPSK takes the advantages over PSK and QAM scheme.

Many of theses widespread radio receivers are used today. Each radio receiver has its own characteristics that leads to a particular application.

#### **1.3 AMPLIFIER BASICS**

An amplifier is a general term which describes a circuit producing an increased or amplified version of an input signal. However, all amplifier circuits are different based on the modes of operation and circuit configuration[6]. In electronics, designing of an amplifier starts from small signal amplifier at low frequency having the ability to amplify a relatively small input signal for eg. Transducer used in microphones, power amplifier, sensors in photo-devices amplifying a signal into an output signal.

| Types of Signal | Types of         | Classification     | Frequency of      |

|-----------------|------------------|--------------------|-------------------|

|                 | Confrigation     |                    | operation         |

| Small Signal    | Common Emitter   | Class A amplifier  | Direct Current    |

| Large signal    | Common Base      | Class B amplifier  | Audio Frequencies |

|                 |                  |                    | (AF)              |

|                 | Common Collector | Class AB amplifier | Radio             |

|                 |                  |                    | Frequencies(RF)   |

|                 |                  | Class C amplifier  | VHF,UHF,and SHF   |

|                 |                  |                    | frequencies       |

Table 1.3.1 Types of Amplifiers

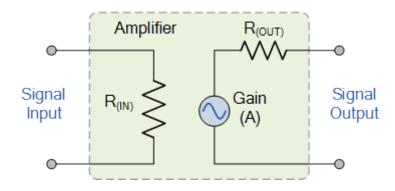

Amplifiers are simple box containing amplifying devices BJTs, field effect transistors or operational amplifiers(op-Amps) having two input and output terminals. An ideal amplifier has three main properties input resistance ,( $R_{IN}$ ), output resistance( $R_{out}$ ) and amplification factor gain or A.

Fig 1.7 Basics Amplifier

**Amplifier Gain-** It is defined as the ratio of output signal and input signal. there are three different types of Voltage  $Gain(A_v)$ , Amplifier gain, Current gain (Ai) and power gain (Ap) depending upon the measurement of quantity.

Voltage Gain (A<sub>v</sub>) =

$$\frac{Vout}{Vin}$$

Eq 1.3.1

Current Gain (A<sub>i</sub>)=

$$\frac{lout}{lin}$$

Eq 1.3.2

Power amplifier Gain  $(A_p) = A_v * A_I$

The power gain A<sub>p</sub> or power levels of the amplifier can be expressed in Decibels(dB).

The most commonly used mode of operation of BJT amplifiers are Common Emitter, Common collector and Common base mode of configuration. Whereas in MOSFETs common gate Common source and Common Drain configuration are the different modes of configuration used for amplification.

Fig 1.8 Basic BJT & MOS Circuit

Different modes of MOSFET configuration-

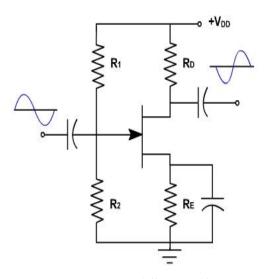

a.) Common Source- this is most widely and commonly used FET circuit. The circuit produces medium input and output impedances. Current and the voltage gain have 180<sup>o</sup> phase change.

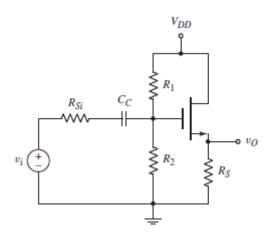

Fig 1.9 CS Amplifier

Eq 1.3.3  $A_v = -gmR_D ||r_0$ To keep the device in the saturation mode of operation Eq 1.3.4  $V_{DS} = V_{DD}$ -  $I_DR_D > V_{DS, Sat}$

b.) Common Drain- this type of FET [7]is also called as source follower circuit as it provides a high level of buffering and input impedance. The input resistance of FET is very high which means that the circuit is capable of providing excellent performance as a buffer. The voltage gain is unity and current gain is high and at the O/P the input and output signals are in phase.

Fig 1.10 Common Drain Amplifier

Eq 1.3.5

$$A_v = \frac{gmRs}{1+gmRs} = 1$$

.9

However to drive the device into saturation the amount of threshold voltage applied should be greater than the device work function

$$I_{DS} = \mu C_{ox} \frac{W}{L} \frac{1}{2} (V_{GS} - V_T)^2$$

Eq 1.3.7

$$V_{GS} = V_T + \sqrt{\frac{2I_{DS}}{\mu C_{ox}} \frac{W}{L}}$$

Weak  $I_{DS}$  dependence

Eq 1.3.8

$$V_{Tn} = V_{TOn} + \gamma_n \left[ \sqrt{(V_{OUT} - V) - 2\phi_p} - \sqrt{2\phi_p} \right]$$

Eq 1.3

c.) Common Gate- The common gate amplifier [7] is also called as current buffer amplifier because the amplifier is having a low input resistance and output resistance of the amplifier is found to be high. The other parameters like current gain of the amplifier is low and therefore, the power gain of the amplifier is also low as compared to other FET configuration circuits. The input and output are also found in phase.

$$A_v = g_m R_D \qquad \qquad Eq \ 1.3.10$$

| FET                | COMMON | COMMON | COMMON           |

|--------------------|--------|--------|------------------|

| CONFIGURATION      | GATE   | DRAIN  | SOURCE           |

| VOLTAGE GAIN       | High   | Low    | Medium           |

| CURRENT GAIN       | Low    | High   | Medium           |

| POWER GAIN         | Low    | Medium | High             |

| INPUT RESISTANCE   | Low    | High   | Medium           |

| OUTPUT             | High   | Low    | Medium           |

| RESISTANCE         |        |        |                  |

| I/P PHASE RELATION | 00     | 00     | 180 <sup>0</sup> |

#### **1.4 LNA BASICS**

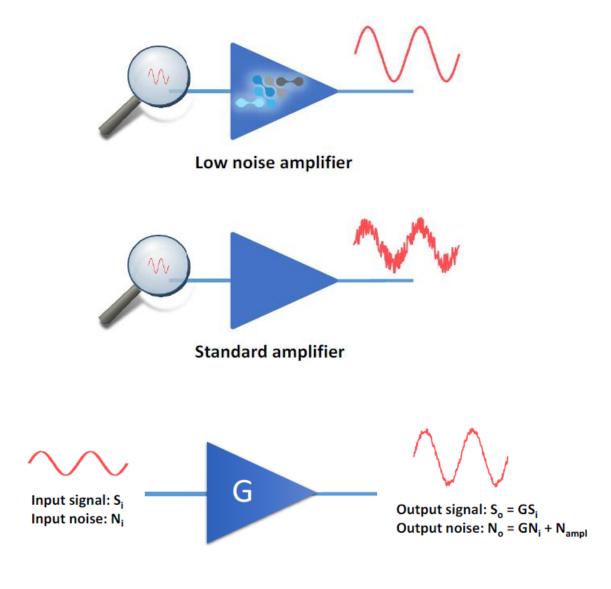

The low noise amplifier (LNA) are devices capable of amplifying extremely weak signals and providing voltage levels for analog to digital conversion or further analog processing[8]. These are employed in the circuit consisting of transducer and antenna. When the strength of the signal is low system is dominated by noise and gain introduced in the first stage. Thus, selection of the LNA is an important factor for complete experimental setup. Consider ,LNA with a gain (G) the desired signal S<sub>i</sub> represents the input signal having an unavoidable noise N<sub>i</sub> at the output both the signal and noise are amplified by a factor of G. the parasitic effect and thermal effect results in generation of additional noise factor N<sub>ampl</sub> for amplifying a low level signal.

Fig 1.11 Basic LNA

The objective of my thesis is to design a low noise amplifier for IEEE standard 802.15.a and RF front end application. The designing of LNA is determined by input and output matching network and determination of some common parameters like S parameters, noise figure, IIP<sub>3</sub> linearity and stability factor. The optimal value of these parameters determines the stability and efficient performance of the system.

#### **1.5 PARAMETERS OF LNA**

The front end of the transceiver system consist of transmitting and receiving path while transmission the perseverance of exiting signal or the wanted signal is required. This clarifies the designing of transmitting end and issues such as interference rejection, noise and selectivity can be ignored. Thus, designing of receiver is complicated as it involves the factors like S parameters, input and output matching networks noise figure, stability, sensitivity and linearity.

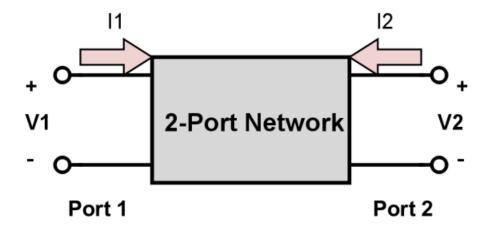

2-port network- a two-port network represents a universal way of analysing RF circuits.it consist of "black box" discussing the flow of the voltages and currents from port 1 to port2. this determines the characteristics of the system without analysing the whole circuit.

| $I_1 = Y_{11}V_1 + Y_{12}V_2$ | Eq 1.4.1 |

|-------------------------------|----------|

|-------------------------------|----------|

$$I_{2} = Y_{21}V_1 + Y_{22}V_2 Eq 1.4.2$$

Fig 1.12 Port N/W with Voltage Source V1 & V2

In the above network the  $I_1$  and  $I_2$  are the independent parameters  $V_1$  and  $V_2$  are the dependent parameters. The analysis is made by considering either of the port as short or open circuit considering only one at a time. These parameters are crucial at low frequency

analysis at high frequency the transmission coefficients, reflection coefficient, forward gain, reverse gain become significant. Therefore, the role of S parameters becomes significant and analysis are made considerably.

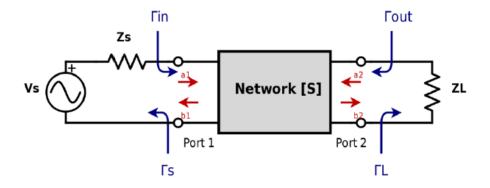

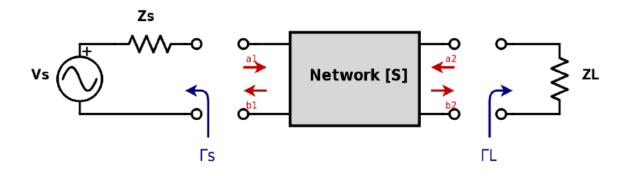

S parameters also called as scattering parameters that relays the information of the travelling waves. Theses waves are scattered back and forth when transmission line is introduced in an n-port networks. S parameters are widely used in the analysis of amplifier, active devices and transistor circuit. For eg- these are measured when the instruments and RF circuits are embedded between a source and a 50  $\Omega$  load.

S parameters are a common way of describing a network . unlike V and I, it do not change at the terminals of the circuits. The changes are obtained along the length of the transmission line whenever a mismatch between the load and source load is observed. However, at high frequency parasitic effects causes the change in the load impedances.

The two port network defining S parameters consist of variables a<sub>1</sub> and a<sub>2</sub> as normalised incident voltages.

$$a_{1} = \frac{V_{1} + I_{1}Z_{0}}{2\sqrt{Z_{0}}} = \frac{\text{voltage wave incident on port 1}}{\sqrt{Z_{0}}} = \frac{V_{i1}}{\sqrt{Z_{0}}}$$

$$a_{2} = \frac{V_{2} + I_{2}Z_{0}}{2\sqrt{Z_{0}}} = \frac{\text{voltage wave incident on port 2}}{\sqrt{Z_{0}}} = \frac{V_{i2}}{\sqrt{Z_{0}}} \text{Eq 1.5.1}$$

Where  $Z_0$  refers to the single positive real impedances.

While the b<sub>1</sub> and b<sub>2</sub> are the normalised reflected voltage coefficients

$$b_{1} = \frac{V_{1} - I_{1}Z_{0}}{2\sqrt{Z_{0}}} = \frac{\text{voltage wave reflected on port 1}}{\sqrt{Z_{0}}} = \frac{V_{r1}}{\sqrt{Z_{0}}}$$

$$b_{2} = \frac{V_{2} - I_{2}Z_{0}}{2\sqrt{Z_{0}}} = \frac{\text{voltage wave reflected on port 2}}{\sqrt{Z_{0}}} = \frac{V_{r2}}{\sqrt{Z_{0}}}$$

Eq 1.5.2

Now the S parameter equation for two port network is given by as-

$$b_1 = S_{11}a_1 + S_{12}a_2 Eq1.5.3$$

$$b_2 = S_{21}a_1 + S_{22}a_2$$

Eq 1.5.4

the S parameters coefficients are given by-

$S_{11} = \frac{b_1}{a_1}$  when  $a_2=0$  (Port 1 reflection coefficient when port 2 is terminated by a matched load  $Z_L=Z_0$ )

$$S_{12} = \frac{b_1}{a_2}$$

when a<sub>1</sub>=0 (Reverse transmission gain when port 1 is terminated by a

matched load)

$$S_{21} = \frac{b_2}{a_1}$$

when a<sub>2</sub>=0(Forward transmission gain when port 2 is terminated by a

matched load)

$$S_{22} = \frac{b_2}{a_2}$$

when a<sub>1</sub>=0 (Port 2 reflection coefficient when port 1 is terminated by a

matched load)

Overall, S parameters help the designers to predict the nature and desired performance of the system.

Considering the load and the source coefficients  $\Gamma_s$  and  $\ \Gamma_L \$  given by

$$\Gamma_s = \frac{Z_s - Z_0}{Z_s + Z_0}$$

$$\Gamma_L = \frac{Z_L - Z_0}{Z_L + Z_0}$$

Eq1.5.5

Fig 1.14 Reflection Coefficient Representation

$$\Gamma_{in} = \frac{b_1}{a_1} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}$$

$$\Gamma_{out} = \frac{b_1}{a_2} = S_{22} + \frac{S_{12}S_{21}\Gamma_s}{1 - S_{11}\Gamma_s}$$

Eq 1.5.6

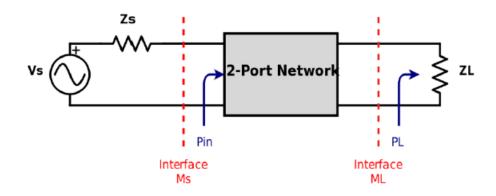

The power gain of the system is defined as ratio of the power delivered to the load end to the power available from the source end  $P_{in}$

$$G_p = \frac{P_L}{P_{in}}$$

$$P_L = \frac{1}{2} |b_2|^2 (1 - |\Gamma_L|^2)$$

$$P_{in} = \frac{1}{2} |a_1|^2 (1 - |\Gamma_{in}|^2)$$

Eq 1.5.7

$$G_p = \frac{1}{1 - |\Gamma_{in}|^2} |S_{21}|^2 \frac{1 - |\Gamma_L|^2}{|1 - S_{22}\Gamma_L|^2}$$

Eq 1.5.8

Finally, the available power gain  $G_a$  is defined as output network power available to the ratio of the source power available.the mismatch factor  $M_L$  is defined as mismatch between load and the output.

$$G_a = \frac{1 - |\Gamma_s|^2}{|1 - S_{11}\Gamma_s|^2} |S_{21}|^2 \frac{1}{1 - |\Gamma_{out}|^2}$$

Eq 1.5.9

The above equation gives the expression for available power gain G<sub>a</sub>.

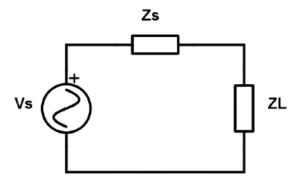

2.)MATCHING INPUT AND OUTPUT IMPEDANCES- Power gain at low frequency is obtained using the venin equivalent and maximum power transfer theorem. But, due to power lossess the power gain of the circuit is usually deficient which is observed from one stage to the other because of thermal resistance and load impedance. therefore, RF circuit designing mainly focuses on impedance matching assuming RF circuit is represented by a simple voltage source having a source impedance ( $Z_s$ ) and a load impedance ( $Z_L$ ).

Fig 1.16 RF Simplified Series RLC Circuits

It is considered that the component losses are minimum but the parasitic effects are considered. For matching we consider the different combinations of R, L and C. the source impedance  $Z_s$  can be written as source resistance  $R_s$  in series with the impedance  $X_s$ , while the load impedances can be expressed load  $R_L$  in series with  $X_L$ , therefore maximum power transfer can be represented as

$$P_L = \frac{V_L^2}{R_L} = \frac{R_L V_s^2}{(R_L + R_s)^2 + (X_L + X_s)^2}$$

Eq 1.5.10

When the load  $X_L$  is equal to  $X_s$  imaginary terms cancel out  $R_L$  should be equal to  $R_s$ . for maximum power transfer. At high frequency circuits we have three types of matching circuits L matching, T matching and pie matching circuits.

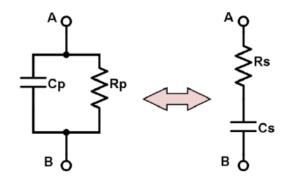

L -Matching Circuits- For the L- matching circuit the concept of series and parallel transformation is necessary. Like for example the impedance  $Z_{AB}$  can be transformed as

Fig 1.17

$$R_p = R_s (1+Q^2)$$

Eq 1.5.11

$$X_P = X_s(\frac{1+Q^2}{Q^2})$$

Eq 1.5.12

Where X<sub>s</sub> denotes  $\frac{1}{\omega c_s}$  and X<sub>P</sub> denotes  $\frac{1}{\omega Cp}$  in the L matching circuit the load

impedances can be expressed as upward or downward and  $R_s$  and  $R_p$  can be transformed into each other.

**Fig 1.18**

The quality factor serves as the measurement of reactivity of the circuit and is defined as the ratio of energy stored in the elements and energy dissipated by the components.

$$Q = \frac{x_L}{R_L}$$

Eq 1.5.13

$$Q = \frac{w \cdot L}{R_L}$$

or  $Q = \frac{1}{\omega c R_L}$  Eq 1.5.14

Therefore, the quality factor can be written as the ratio of  $R_L/R_S$

$$Q \cong \sqrt{\frac{R_P}{R_s}}$$

Eq 1.5.15

The conjugate matching results in the cancellation of reactive terms therefore, the effect of inductor and capacitor becomes insignificant. Therefore, the designer can manipulate the positions of impedances to obtain the low pass or high pass circuit.

**Fig 1.19**

The quality factor of the circuit is obtained by a particular value of  $R_L$  and  $R_S$  due to which quality factor of the circuit is fixed and design of the circuit gets frozen meaning no more changes can be made providing only one degree of freedom.

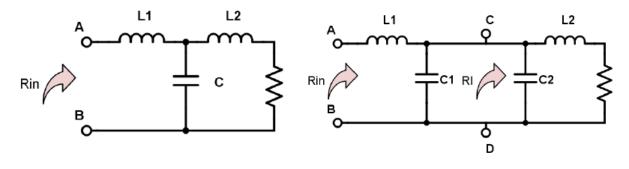

$\prod$  or pie matching circuit- it improves the limitation of L- matching circuits. The limiting factor consist of Q, impedance transformation ratio and centre frequency. L matching circuit consist of only two manipulative components whereas  $\prod$  or T matching circuit adds extra components giving a designer a extra degree of freedom for optimising the circuits.

Adding the component or making it T or pie adds extra degree of freedom controlling the value of Q added to the circuit. Adding extra components causes bandwidth improvements while decreases the value of Q. adding inductance in series makes the circuit more inductive in nature and adding C capacitive in parallel causes the circuit to become more capacitive in nature.

$$Q_{CD} = \frac{\omega_0 L_2}{R_I} = \sqrt{\frac{R_P}{R_I} - 1}$$

Eq 1.5.16

Where the ratio of  $\frac{R_P}{R_I}$  is the transformation ratio.

T- matching circuits- this matching circuit consist[9] of connecting two L matching circuits back to back. The capacitor  $C_1$  and  $C_2$  are connected in parallel combination. The formulas of Q,L and C can be derived from pie matching circuit.

**Fig 1.21**

$$Q_{ov} = Q_{AB} + Q_{CD} = \omega_0 R_I (C_1 + C_2) = \sqrt{\frac{R_I}{R_{in}} - 1} + \sqrt{\frac{R_I}{R_S} - 1}$$

$$C_1 + C_2 = \frac{Q_{ov}}{\omega_0 R_I}$$

$$L_1 = \frac{Q_{AB} R_{in}}{\omega_0}$$

$$L_2 = \frac{Q_{CD} R_S}{\omega_0}$$

Eq 1.5.17

These are used when the source and load impedances are inductive in nature. these are capable of absorbing parasitic inductor of the matching circuit and are preferred when high quality factor is desirable.

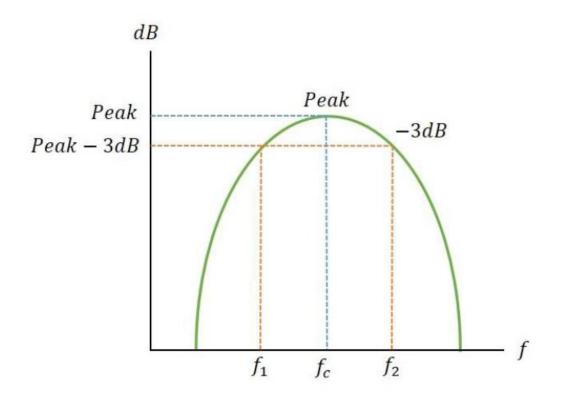

**BANDWIDTH**- It is the crucial factor for designing of RF circuits. Different WSN have different frequency ranges. For eg- the Bluetooth technology has a frequency range from 2.40 GHz to 2.438 GHz. Estimating the bandwidth of RF circuits with hand calculations is very difficult as it requires one to find (peak frequency) fpeak and also -3dB points of the circuits.for finding these values the total impedances of the circuits must be calculated first. It involves the impedances both at the output and input ends consisting of parasitic resistances and imaginary components (like inductor and capacitors).however, conventional ways of finding the impedances is called as open circuit time constant (OTC) or zero value time constants.

Fig 1.22 3-dB Bandwidth with Peak frequency

OCT gives the bandwidth of the system obtained by inspecting from nodes. OCT specifies the elements and factor causing bandwidth limitations.

$$\frac{V_o(s)}{V_i(s)} = \frac{a_0}{(\tau_1 s + 1)(\tau_2 s + 1)\dots(\tau_n s + 1)}$$

Eq 1.5.18

The Industrial, Scientific and medical (ISM) frequency band are designed for radio frequency bands defined by ITU regulations. These frequency bands are used for RF applications other then telecommunication. Telecommunication equipment's operating at such frequency are interrupted by microwave ovens, electromagnetic interference (EMI),RF heating devices.

The most common use of the ISM band are low power, short range telecommunications such as Bluetooth ,Zigbee Wifi, Wireless Telephones NFC and RFID. In recent times, ISM band [10] is also shared with (non-ISM) license free-tolerant communication devices like (WSN) in 915 MHz and 2.4 GHz and 5.8 GHz in cordless and wireless LANs applications.

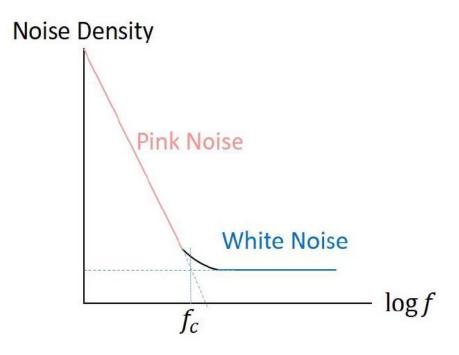

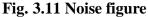

**NOISE FIGURE**-noise is defined as unavoidable and undesirable effect occurring in electronics and RF circuits. It is expressed as spectral density in voltage or current/Hz

that is  $V^2/Hz$  or  $A^2/Hz$ . The spectral density specifies the noise parameters. The characteristics equation representing a noise source is integrated over a frequency for specifying the spectral density of a noisy source. Therefore, differentiating a noisy source and its cause is required for minimizing its effects to an acceptable degree. In electronics circuit we have five types of noise effecting the performance of the amplifiers. These are thermal noise, shot noise, flicker noise burst noise and avalanche noise.

THERMAL NOISE-this type of noise is generated due to the random motion of the electrons. The agitation in the charge carrier due to applied voltages causes generation of the electrons within the electrical conductors. The vibration of the charge carriers about their mean position is only effected by the temperature variation higher the temperature more will be the agitation resulting in high thermal noise. The noise power generated is proportional to the bandwidth. Therefore, the generalised expression of thermal noise is given by-

$$V_n^2 = 4KT \int_{f1}^{f2} R \, df$$

Eq 1.5.19

Where  $V_n$  represent the integrated rms voltages between frequency  $f_1$  and  $f_2$

R denotes the resistive components in  $\Omega$  (impedances) and T is measured in degrees kelvin. The equation is further simplified as where  $\Delta f$  is the bandwidth in Hz.

$$V_n = \sqrt{4KT\Delta fR}$$

Eq 1.5.20

SHOT NOISE- it is caused due to the current flow generated when a large number of charge carrier crosses a potential barrier, which is a random event. Thus, the instantaneous current I, represents a large number of random motions of the independent currents having average value I<sub>D</sub>. the charge carriers consist of discrete sets of bundles in discontinuous form of currents. This is observed when electrons crosses energy barriers and the difference in the arrival time.

$$I_n^2 = 2qI_{DC}\Delta f$$

Eq 1.5.21

Where  $I_n$  represents the rms current having bandwidth.q is the charge  $I_{DC}$  represents the current through an energy barrier and  $\Delta$  f is the bandwidth.

FLICKER NOISE- it is defined as inversely proportional to the frequency. It is found in all active devices. It is always associated with the DC current. It is mainly found in carbon composite resistors in addition to the thermal noise. Since it is proportional to the d.c. current when the current is low system is dominated by thermal noise. The shot noise and thermal noise dominates the high frequency regions. As it is inversely proportional to frequency it is expressed as

$$N^2 = \frac{K}{f^n} \Delta f$$

Eq 1.5.22

Where N represent the RMS noise signal which is either in the form of voltage or current, K is the empirical device parameters and  $\Delta f$  is bandwidth in Hz.

Fig 1.23 Noise Spectral Density

NOISE FIGURE – It is defined as the noise performance of a two port network.it is defined as the ratio of output noise power to the noise power of the input source. When expressed in decibels it is called as noise figure.

$$SNR = \frac{P_{signal}}{P_{noise}}$$

$$F = \frac{SNR_{in}}{SNR_{out}} = \frac{\frac{S_i}{N_i}}{\frac{S_o}{N_o}}$$

$$NF = 10 \log F \quad \text{Eq 1.5.23}$$

Where  $S_i$  and  $S_0$  are the signal power at the input and output source and  $N_i$  and  $N_0$  are noise power at the input and the output port .

For an ideal case  $SNR_{in}$  and  $SNR_{out}$  should be equal. This is due to the desired signal and noise are amplified by the same gain. So therefore,  $SNR_{in}$  and  $SNR_{out}$  are having the same values. When the signal is allowed to pass through system. The receiving circuit generate its own noise by components and degrades SNR. Additional noise signal ( $N_a$ ) and network gain(G) are related as

$$F = \frac{\frac{S_i}{N_i}}{\frac{S_o}{N_o}} = \frac{\frac{S_i}{N_i}}{\frac{GS_i}{N_a + GN_i}} = \frac{N_a + GN_i}{GN_i}$$

$$F = \frac{N_a + KT_0BG}{KT_0BG}$$

Eq 1.5.24

Where K is  $1.38*(10)^{-23}$  Joules/K<sup>0</sup>

B is network bandwidth in Hz.

G is the gain.

The noise figure of the multistage amplifier is expressed as

$$NF_{tot} = 1 + (NF_1 - 1) + \frac{NF_2 - 1}{A_{p1}} + \dots + \frac{NF_m - 1}{A_{p1} \dots A_{p(m-1)}}$$

Eq 1.5.25

The first stage of the RF system contributes major portion of the overall noise. Therefore, the first stage of amplifier circuit mainly consist of LNA which plays a crucial role in overall noise figure calculations.

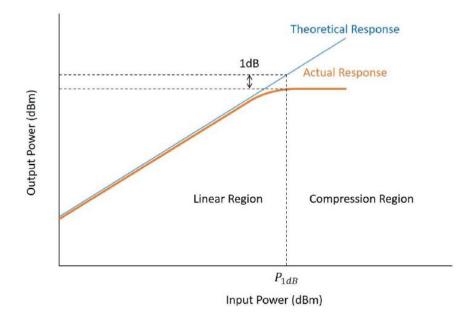

**LINEARITY**- If the nature of the system does not change with time and all the initial conditions are found to be zero then the system is called as a linear system. Linearity is an important factor in the designing of LNA. LNA must uphold, property of linearity

when the signal is weak or strong even in the presence of interfering signal[11]. There are two types of linearity 1-dB compression point and third order intercept point (IIP<sub>3</sub>) which improves the performance of LNA.

**1 dB- Compression point**- the input and output power is found to be linear at a specific frequency for the amplifier having a solid gain. The slope represents the power gain in dBm. For the gradual increase in the input power at one point output power saturates. 1 dB compression point is defined as that point where the output power saturates for the increase in the input power signifying that when the signal is received by the amplifier it becomes non-linear causing signal distortion, as a result harmonics are produced due to intermodulation distortion.

Assume that sinusoidal input signal is applied to a non-linear system. For the explanations of  $P_{1dB}$  compression point. The output signal can be represented by

$$x(t) = A \cos \omega t$$

$$y(t) = \alpha_1 A \cos \omega t + \alpha_2 A^2 \cos^2 \omega t + \alpha_3 A^3 \cos^3 \omega t$$

$$y(t) = \frac{\alpha_2 A^2}{2} + (\alpha_1 A + \frac{3\alpha_3 A^3}{4}) \cos \omega t + \frac{\alpha_2 A^2}{2} \cos 2\omega t + \frac{\alpha_3 A^3}{4} \cos 3\omega t$$

Eq 1.5.26

In above the desired signal is *coswt*. Byproducts of the input signal in eq() are also called as harmonic distortion. The signal coefficients  $\alpha_1\alpha_3$  signifies the characteristics of amplifier. If the coefficient  $\alpha_1\alpha_3>0$  then the output is increasing with the increase in the input signal. This phenomena is mainly observed in BJTs since MOSFETs saturates at certain point. Therefore,  $\alpha_1\alpha_3<0$  is considered for comprehensive characteristics which are more suitable for LNA design.

Fig 1.24 P1-dB compression Point

Finally,  $P_{1dB}$  is 1 dB below expected output power by giving the input signals

$$10 \log \left| \alpha_1 + \frac{3\alpha_3 A^2}{4} \right| = 10 \log |\alpha_1| - 1dB$$

Eq 1.5.27

where:

$\alpha_1 + \frac{3\alpha_3 A^2}{4}$  is actual power response

$\alpha_1$  is expected power response

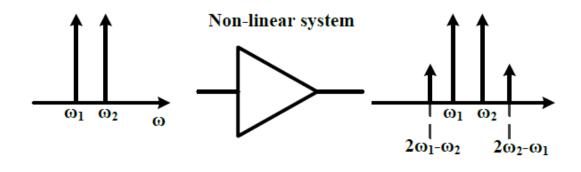

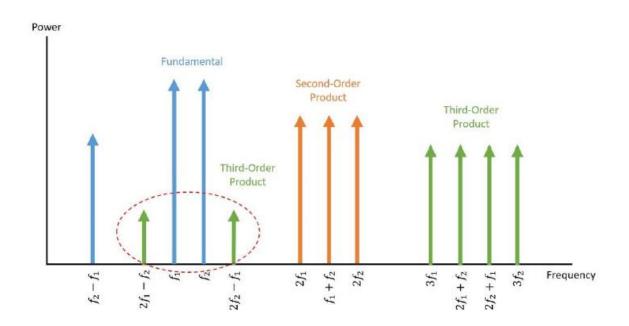

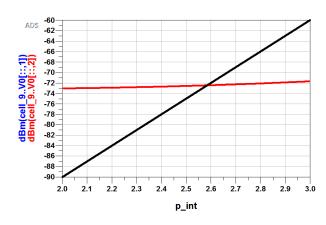

Third- order intercept point (IIP<sub>3</sub>)- assuming [2] the input signal of the amplifier is a sinusoidal signals when amplifier becomes non-linear it consist of harmonics of  $\cos 2wt$  and  $\cos 3wt$ . the highest harmonics are insignificant since the system consist of finite bandwidth . however, non-linearity produces two signals because of intermodulation distortion.

The sum and the difference of the frequencies at the receiving end are called as intermodulation products. The interfering signals are not filtered out since it consist of desired signal. Several methods like signal levels, biasing control and other factor ensures the linearity and significantly reducing the intermodulation distortion (IMD) products.

However, at the receiving end  $w_1$  and  $w_2$  produces  $w_1 + w_2$  and  $w_1 - w_2$  and  $2w_1 + w_2$ and  $2w_2 - w_1$ . These sets of frequency ranges produces second, third and fourth harmonics of the interfering signals. The IP3 is defined as the point where the first order of the input signal is found to be equal to the third harmonics of the desired signal.

$$|\alpha_1 P_{IIP3}| = \left|\frac{3\alpha_3 P_{IIP3}^3}{4}\right|$$

Fig 1.26 Measure of Third order Intercept point

$$P_{IIP3} = \sqrt{\frac{4}{3} \left| \frac{\alpha_1}{\alpha_3} \right|}$$

Eq 1.5.28

Note IP3 is a theortical concept that is never obtained in present scenario. However, it's a tool in determining the linearity of the amplifier.

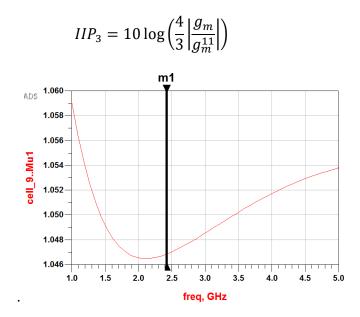

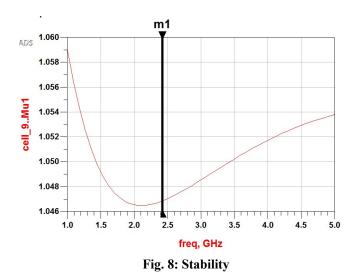

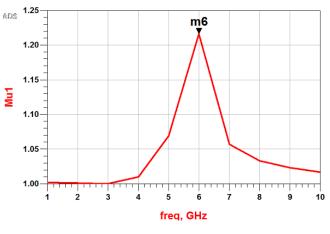

**STABILITY FACTOR**-it is defined as immunity against spurious oscillations. The circuit becomes unstable for specific combination of source and load impedances. An LNA designed oscillate at extreme of voltage variation for low or high frequency. Therefore, the stability of an amplifier is given by two factors K and  $\Delta$  where K denotes rollet's stability factor or stern stability factor.

For unconditionally stable system K>1 and  $\Delta$ <1. The points considered under such region denotes that the circuit do not oscillate for any combination of source and load impedances.

Eq 1.5.29

$$k = \frac{1 - |s_{22}|^2 - |s_{11}|^2 + |\Delta|^2}{2|s_{12}s_{21}|} > 1$$

Where

$$\Delta_s = S_{11}S_{22} - S_{12}S_{21}$$

**SENSITIVITY**- it is defined as minimum signal level detected by a receiver with "acceptable quality" when the signal is interrupted by noise it carries little information. Acceptable quality is defined as sufficient signal to noise ratio depending upon the type of modulation and corruption that signal can tolerate. Typically, (SNR) ranges from 6 to 25 dB.

$$P_{sig} = P_{RS}. F. SNR_{out}$$

Eq 1.5.30

When the signal is distributed both side of the channel the equation is integrated over the bandwidth so the mean square power is given by-

$$P_{sig,tot} = P_{RS}. F. SNR_{out}. B$$

Eq 1.5.31

Therefore, the overall sensitivity of the system includes the channel bandwidth, NF, SNR expressed in dB and the channel bandwidth B in Hz.

$$P_{sig,\min |dB} = P_{RS|dB/Hz} + NF + SNR_{out,\min |dB} + 10logB$$

Eq 1.5.32

Where P<sub>sig,min</sub> is the minimum power achieving SNR<sub>out,min</sub> in dB.

| BASIC LNA                | ALTERNATE LNA            | NONLINEARITY OF           |

|--------------------------|--------------------------|---------------------------|

| TOPOLOGIES               | TOPOLOGIES               | LNAs                      |

| CS stage using Inductive | Types of CS LNA          | Nonlinearity Calculations |

| load                     |                          |                           |

| CS stage implemented     | Noise- Cancellation LNAs | Differential and Quasi-   |

| with Resistive Feedback  |                          | Differential LNAs         |

| CS stage with Inductive  | Differential LNAs        |                           |

| Degeneration             |                          |                           |

TABLE 1.6.1 DIFFERENT TYPES OF TOPOLOGIES OF LNA

In this section LNA is divided into five parts topologies, I/P and O/P matching circuits, source degenerate feedback, biasing circuits. Further, the key factors such as S parameters, Stability factor, Noise figure is estimated and presented with schematic in chapter 3 for RF front end applications.

## **Table 1.6.2 Common Design Specifications**

| PARAMETERS                      | SPECIFICATIONS |

|---------------------------------|----------------|

| a.) Power Supply                | 1-3 (V)        |

| b.) Power Dissipation           | 1-20 (mW)      |

| c.) Input and Output Impedances | 50 Ω           |

| d.) NF                          | <3(dB)         |

| e.) Gain                        | < 10(dB)       |

| f.) IIP3                        | (-10)(dBm)     |

LNA is implemented mainly using three topologies which are common source, common gate and cascode topology which provides the perfect input output isolation and increases the stability of the system.

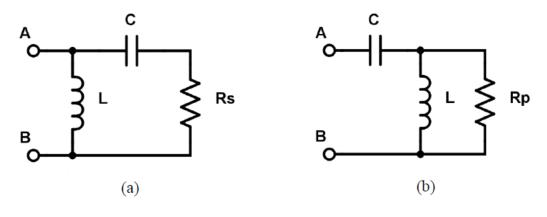

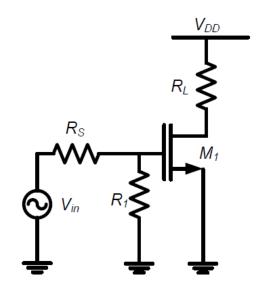

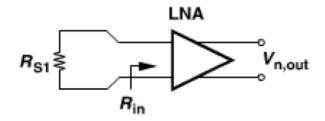

1.6.1 **COMMON SOURCE TOPOLOGY-** LNA[12] implemented with a common source topology provides proper input/output matching network. The common source with resistive termination provides  $50\Omega$  input impedances. For this R<sub>1</sub> is placed in parallel with the input matching network of LNA. However, this confrigation is less preferred because of the tradeoff between voltage gain and supply voltage. Furthermore, the o/p node becomes inappropriate as the resistor generates noise.

**Fig 1.27**

The noise figure calculation of the circuit is given by

$$F = \frac{\overline{v_{n,out}^2}}{\overline{v_{n,o,Rs}^2}} = \frac{\overline{v_{n,o,Rs}^2} + \overline{v_{n,o,R1}^2} + \overline{v_{n,o,M1}^2}}{\overline{v_{n,o,Rs}^2}}$$

Eq 1.6.1

$$=\frac{4kT(R_s//R_1)g_m^2R_L^2\Delta f + \iota_{n,d}^2R_L^2}{\frac{1}{4}g_m^2R_L^2}\frac{1}{4kTR_s\Delta f}$$

Eq 1.6.2

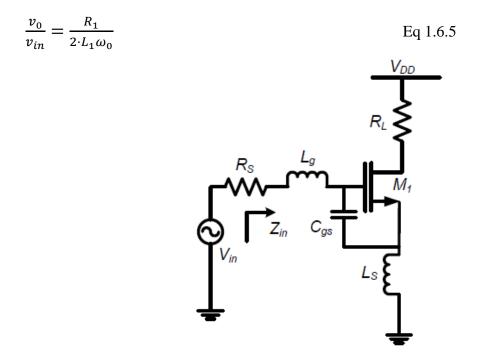

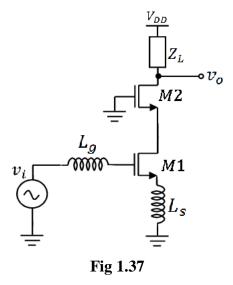

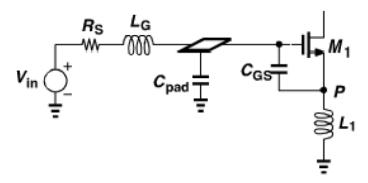

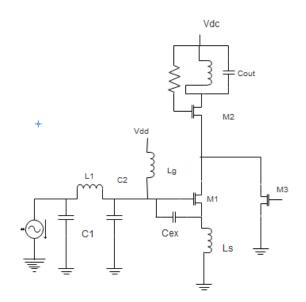

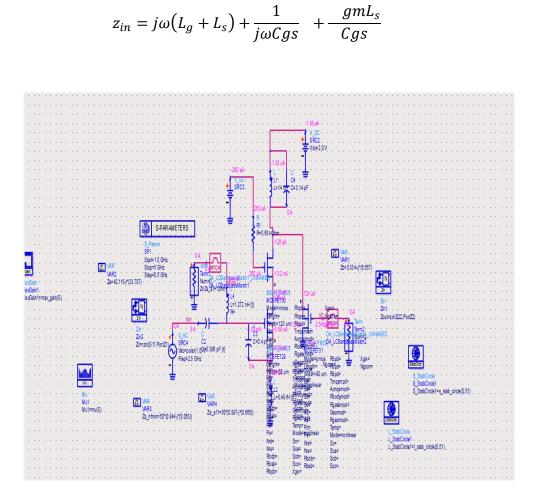

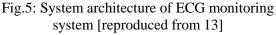

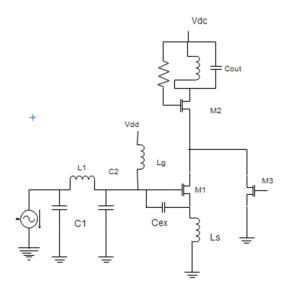

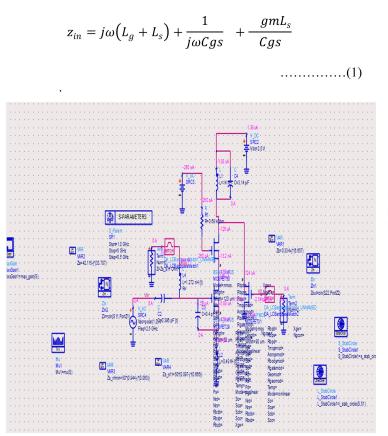

1.6.2**COMMON SOURCE WITH INDUCTIVE DEGENERATE TOPOLOGY**-This is the most preferred topology[13] as it provide the most efficient I/P and O/P matching. Introducing a inductor at the source of the mosfets improves the linearity of circuit. In this configuration the high value of the inductor is not preferred as it causes the circuit to have low gain. The input impedance has a resistive term which shows that resistance is directly proportional to inductor and the circuit do not generate thermal noises like other resistive networks and circuit of reactance becomes noiseless. The 50 $\Omega$  input impedances is equal to  $g_m L_s/C_{gs}$  controlling the value of the transconductance of amplifier so high value of  $g_m$  causes the mosfet to leave linear mode of operation.

$Zin = g_m L_s / C_{gs}$

$$\omega_0 = \frac{1}{\sqrt{(L_g + L_s)C_{gs}}}$$

Eq 1.6.3

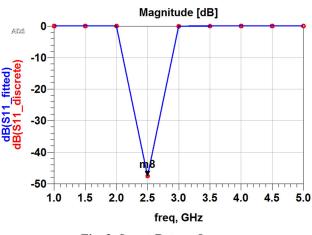

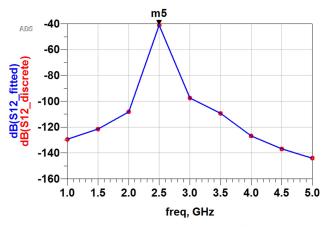

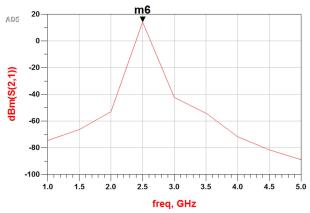

$$z_{in} = j\omega(L_g + L_s) + \frac{1}{j\omega Cgs} + \frac{gmL_s}{Cgs}$$

Eq 1.6.4

So therefore the equation for voltage gain is given by as-

Fig 1.28

1.6.3 **COMMON SOURCE STAGE WITH SHUNT FEEDBACK LNA**- in this [14] the  $R_{fB}$  acts as a feedback element. The circuit is having a 50  $\Omega$  input impedances. The input impedances is expressed as from miller theorem

$$Z_{in} \approx R_{fb} / (1 + |A_v|)$$

Eq 1.6.6

Where  $R_{fB}$  denotes the feedback resistor and  $A_v$  denotes the voltage gain of the circuit. The voltage gain is equal to

$$\left[1 - g_m \left(R_L / / R_{fb}\right)\right]$$

Eq 1.6.7

And the noise factor of the circuit is expressed as-

$$F = 1 + \left(\frac{G_s + G_{fb}}{g_m - G_{fb}}\right)^2 R_s (G_L + \gamma g_{d0}) + \left(\frac{G_s + g_m}{g_m - G_{fb}}\right)^2 R_s G_{fb}$$

Eq 1.6.8

$$I = 1 + \left(\frac{G_s + G_{fb}}{g_m - G_{fb}}\right)^2 R_s G_{fb}$$

Eq 1.6.8

Fig 1.29

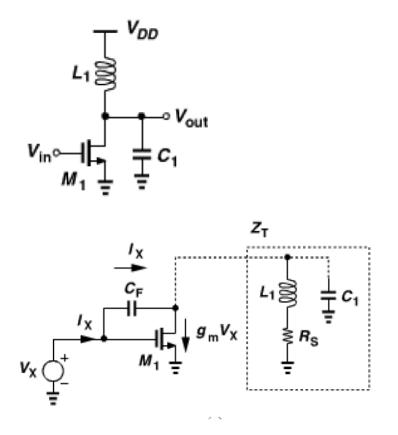

b.) **COMMON SOURCE STAGE WITH INDUCTIVE LOAD**- it operates at a very low frequency with low supply voltage as the inductor sustains a small d.c. drop as the resistors [15]. Moreover, the inductor oscillate with capacitors at the output node capable of operating at high frequency than does the resistively loaded counterparts. The common source topology with inductive load is considered as it generates the required number of poles and zeros. The gain of this circuit is given by

$$Av = g_m R_D Eq 1.6.9$$

When the overdrive voltages are considered  $\frac{2v_{RD}}{v_{g_S} - v_{th}}$  Eq 1.6.10

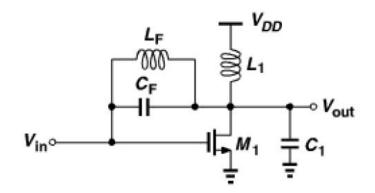

Fig 1.30 Input Impedance with C<sub>F</sub>

When the effect of Cgd overlapping capacitance is considered ignoring the effect of gate to source capacitances. The losses across the inductor is modelled by a series resistance Rs in parallel to the capacitance  $C_1$ . However, for the purpose of nullifying the effects of capacitor  $C_F$  a parallel inductor  $L_F$  is considered.

Fig 1.31 Neutralising the C<sub>F</sub> by L<sub>F</sub>

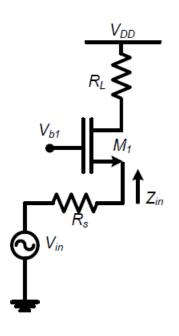

b.) **COMMON GATE TOPOLOGY**- the common gate (CG-LNA) is [16] widely used for wide band applications. The voltage gain and input impedances of CG LNA is given by as-

$$A = g_m R_L$$

Eq 1.6.11

$$Z_{in} = \frac{1}{g_m}$$

Eq 1.6.12

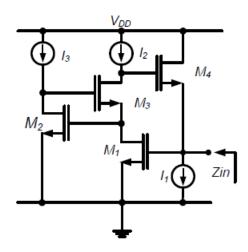

For matching the input matching network  $g_m$  is equal to  $1/R_s$  due to which the load resistance  $R_L$  is a design variable. For the matching networks, the transconductance of the input transistor cannot be made high thus optimised or low value of noise factor is obtained. The noise factor is proportional to  $\gamma/\alpha$  which is reasonable and acceptable however, the other factor like gate induced noise and substrate noise can degrade the performance of the circuit substantially. The load contribute thermal noise and biasing causes shot noises when these effects are considered gain of the system decreases so a common gate with cascode topology is mostly preferred.

Fig 1.32 Common Gate LNA

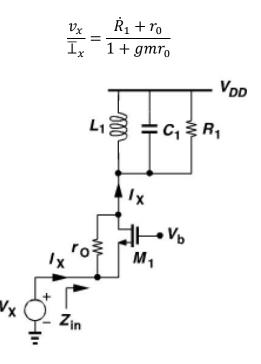

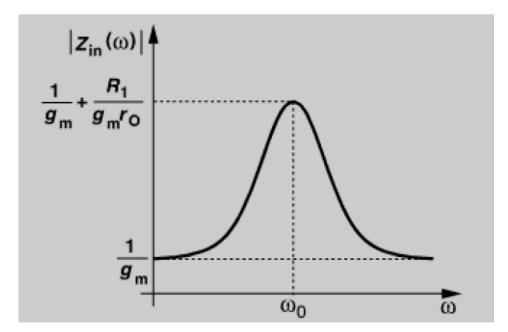

1.6.7 COMMON GATE STAGE WITH RESISTIVE FEEDBACK TOPOLOGY- In this[2] topology resistance is used as a feedback element. At deep micron, CMOS technology channel length modulation significantly effects the behaviour of the common gate stage. The positive feedback through  $r_0$  raises the input impedances. Since the drain

source currents of  $M_1$  is equal to  $-g_m V_x$ . the net amount of current flowing through the  $r_0$  is equal to  $(I_x - g_m V_x)$ . across it. The current Ix flowing through the output loop or tank circuit causes a voltage drop of Ix $R_1$ . This causes the voltage drop across  $r_0$  to be equal to

Fig 1.33 Input Impedance in the presence of r<sub>0</sub>

Therefore the net input resistance of the circuit increases which can be compensated by using cascode topology which consist of common gate with resistive feedback connected to cascaded CG stage.

Fig 1.34

## Fig 1.35 Cascode CG Stage

Therefore the overall input impedances of the circuit reduces to

$$R_{in} = \frac{1}{g_m} + \frac{R_1}{g_{m_1} r_{01} g_{m_2} r_{0_2}} + \frac{1}{g_{m_1} r_{0_1} g_{M_2}}$$

Which finally becomes equal to  $1/g_m$ .

Eq 1.6.13

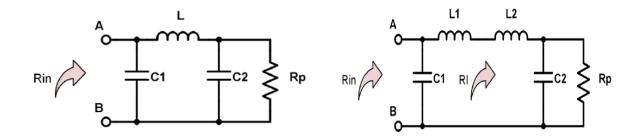

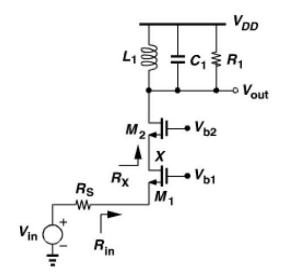

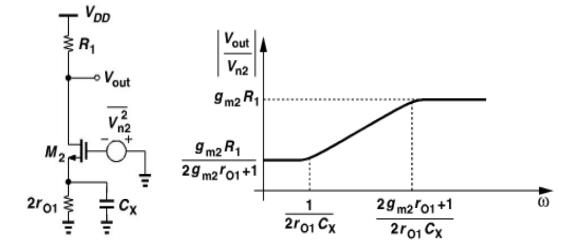

Fig 1.36 Cascoded Transistor Noise and Frequency Response

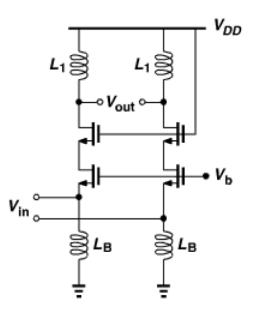

1.6.8 **CASCODE TOPOLOGY**- in amplifier designing cascode topology is preferred which means adding a transistor or mosfets which means isolating the input from the

output. This isolation between the output and the input end stabalises the circuit. The advantages of cascode topology are-

- Better stability

- Better noise figure

- High gain

- Better reverse isolation

- Input and output matching network

Spiral inductors are less preferred due to the limitation of occupying a large chip area, capacitive and resistive losses. Therefore, active inductor can be implemented with reasonable good physical size. Traditionally, active inductor [17] are implemented using high gain operational amplifier with a negative feedback but these are unsuitable for operating in frequencies of GHz. Another type of active inductor are implemented by considering parasitic capacitances. However, varying the value of  $I_1$  and  $I_2$  the optimised value of the inductor is obtained. This circuit has two limitation 1.) the circuit has poor linearity 2.) the circuit has poor noise performance. The active inductors are always more noisier then the parasitic devices due to parasitic effects.

Fig 1.38 Schematic representation of Inductor

**ULTRA LOW POWER LNA DESIGN-** the conventional L-CS LNA are widely used for narrow band applications having high gain and low noise figure. For low power consumption different topologies are used. But, for obtaining low noise figure design of amplifier becomes stringent. For eg, cascode CS source with inter stage inductor can enhance the gain of the amplifier at the input stage. LNA with a low power of 0.8mW and noise figure of 4.1 dB is obtained. However, due to the requirement of on chip inductors the design results in large chip area. The technique like gm boosting or gain boosting technique enhances the gain of the amplifier and reduces the noise figure. Therefore, it [18] is used for narrow band applications. But this LNA consumes 6.48 mW of dc power and have a noise figure of 3 dB. Therefore this is considered for low power consumption

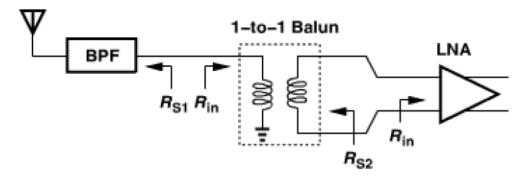

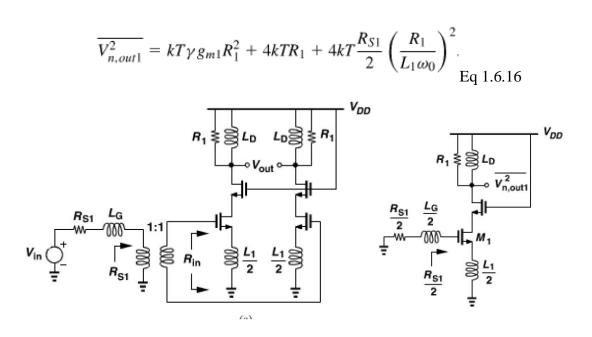

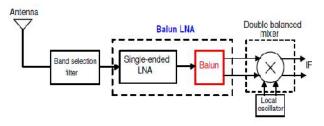

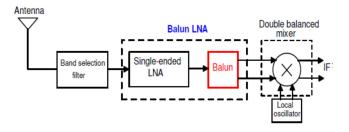

Even order distortion significantly degrades the performance of direct of direct conversion Rx. The circuit realised in differential form, exhibits a high IP<sub>2</sub> having mixers and LNA effecting the design of receivers in amplifiers. The noise figure of the circuits gets converted to the differential form. Since the antenna and preselect filters are typically single ended therefore, transformer precedes the LNA to perform single-to-differential conversion. A cascade processes the signal differential from the input port to the end of baseband section of LNA. This transformer is called "balun" balanced to unbalanced conversion when its two ports are swapped.

Fig 1.39 Balun Rx I/P

Fig 1.40 Basic Balun Amplifier Circuit

In addition lowering the value of Cgd the input pad capacitance also lowers the values of input resistance. For formulating these effects we consider the circuit consisting of Cgs<sub>1</sub>, L<sub>1</sub> and R<sub>1</sub>. From the analysis,[19] the observations like lowering the value of  $f_T$  is not required for matching impedances R<sub>1</sub>=50 $\Omega$ . Second , the degenerate inductors Rin=50 $\Omega$  is insufficient to resonate with Cgs<sub>1</sub> + C<sub>padd</sub>. Therefore, another inductor is placed in series with the gate where Lg acts as a off chip inductors.

Fig 1.41 Padding of Capacitance

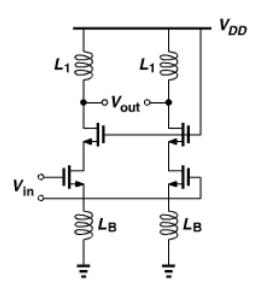

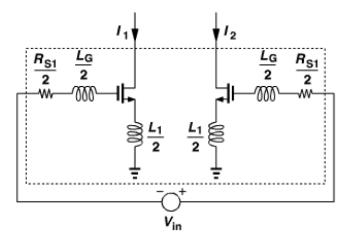

1.6.9 **DIFFRERENTIAL CG LNAs-** After the circuit gets converted into differential form the impedances between each I/P and the ground becomes equals to  $Rs_1/2$ . That means each CG transistor is providing an input resistance of 25 $\Omega$ . Now from the symmetry of the circuit the o/p noise is given by summation of each half circuits. The

the CG half circuits. Now, the output noise consist of 1.) input transistor 2.)load resistance contributions ,3.) the source impedances contributions.

Fig 1.42 Differential CG LNA

the output noise is given by  $V_{n,out}^2 = V_{n1,out}^2 + V_{n2,out}^2$

$$\overline{V_{n,out1}^2} = kT\gamma \frac{R_1^2}{R_{51}/2} + 4kTR_1 + 4kT\frac{R_{51}}{2} \left(\frac{R_1}{\frac{2R_{51}}{2}}\right)^2.$$

Eq 1.6.14

$$NF = \frac{\overline{V_{n,out}^2}}{A_v^2} \cdot \frac{1}{4kTR_{51}}$$

$$= 1 + \gamma + \frac{2R_{51}}{R_1}.$$

Eq 1.6.15

1.6.10 **COMMON SOURCE DIFFERENTIAL AMPLIFIERS**- the properties of common source differential LNA is different from its common gate counterparts . the i/p resistance of each halves circuits is equal to  $L_1w_T$ . the voltage gain of the circuit is equal to  $R_1/(2L_1w_0)$  is doubled. Assuming that the width and bias current of each transistor is same as those of single ended LNAs. However, when the i/p is matched half of the noise current from input flows to the o/p node. The transistor contribution is halved due to  $g_m$  and hence, the transistor noise currents remain unchanged. When the transconductance of

the circuit gets doubled. The differential output currents contains noise currents of both M1 and M2 equals to  $2(KT\gamma gm_1)$ .

Fig 1.43 Differential CS LNA

Fig 1.44 Differential CS stage Transconductor

Table 1.6.3 Characteristics of Amplifier

| CHARACTERSTICS       | COMMON<br>SOURCE      | COMMON<br>GATE                      | CASCODE<br>TOPOLOGY |

|----------------------|-----------------------|-------------------------------------|---------------------|

| NF                   | Lowest                | Lowest Rises rapidly with frequency |                     |

| LINEARITY            | Moderate              | High                                | Highest             |

| GAIN                 | Moderate              | Lowest                              | Broad               |

| BANDWIDTH            | Narrow                | Fairly broad                        | Higher              |

| STABILITY            | Requires compensation | Higher                              | Higher              |

| REVERSE<br>ISOLATION | Low                   | Higher                              | Higher              |

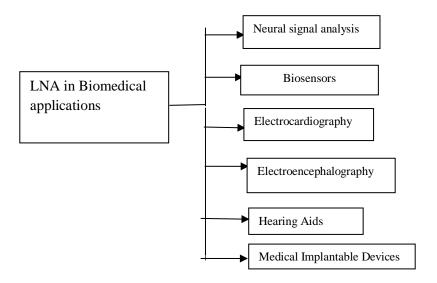

## **1.7 USE OF LNA IN BIOMEDICAL APPLICATIONS**

it is defined as combining biomedical and engineering applications into one common domain or reducing the gap between engineering and medicine.

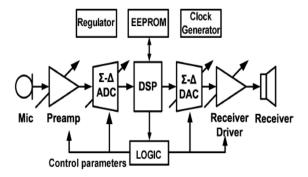

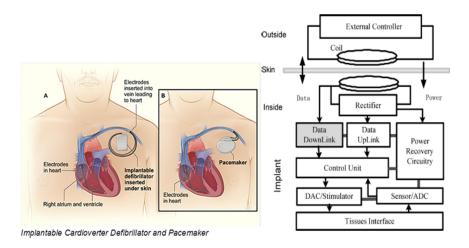

In biomedical applications we deal with weak signals LNA implemented with many topologies like cascode degenerate topology achieves low noise figure and high gain. LNA is required to have low power consumption and small size. For eg- LNA with inductor degenerate topology are less preferred due to large chip area. In[20] full differential RF front end amplifier is designed on 0.13µm CMOS technology for obtaining low power and direct conversion of short range radio signal at low cost.the RF signal is down converted to a baseband signal containing dc offsets and flicker noise corrupting the SNR.therefore (CG-LNA) is used instead of (CS-LNA).Eliminating on chip inductor and provides a good input matching it also improves stability, linearity and provides robustness against PVT variation in CS topology of small size and low power consumption are preferred in biomedical application. therefore [21] LNA using gm boost technique is implemented on a 130nm IBM technology and processed providing a good matching of  $600\Omega$  and current consumption up to  $500\mu$ A. in ultra-low power design. LNA with CG topology is preferred as it consumes less power and resistance attaining less sensitivity. In [21] RF front end for biomedical is implemented using ultra low power 401-406 MHz medical Device Radio communication service designed for biomedical quantization application implemented on 0.18µm technology. It uses single ended compatible current-reuse (LNA). Capable of achieving a power gain of 20 dB with IIP3 of -8.1dBm and noise figure of 2.8dB.the RF front end consist of coupling CCRLNA with quadrature folded mixer with local oscillator buffer achieves a conversion gain of 28.7dB and NF of 5.5dB consuming less power of  $500\mu$ W with chip area of 0.7mm<sup>2</sup>.

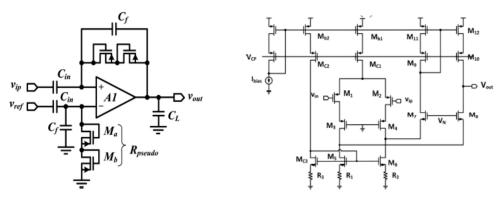

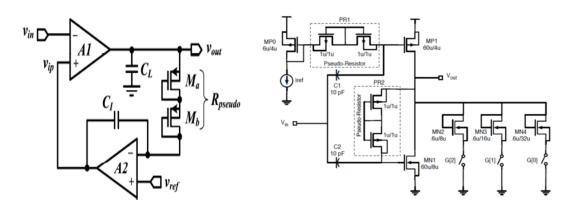

LNA IN NEURAL APPLICATIONS- In biomedical application neural signals are dealt with the learning and comprehensive study of brain function and its healing, curative prosthetic application. Neural signal are interfaced in large number of channels for the study of neurons specifically for brain microcircuits. The entire system consists of dealing with important parameters like noise performance, CMRR and power consumptions. The entire system consist of action potential carrying information to the neural cells.these are formed by the process of polarisation and depolarisation occurring across neural cell membrane or these are caused due to the fast movements of ions across cell membrane. In animal cells the ion's like Na<sup>+</sup>/K<sup>+</sup>are powered by ATP molecules forming basic building blocks in animal cells. Whenever channel consist of ions are activated electrically or biochemically through mechanisms like depolarisation causes voltage sensitivity resulting in the opening of ions membrane containing  $Na^+$  to open first the arrival of large number of positive charges across cell increases potential rapidly. However, the balance is obtained by the inflow of K<sup>+</sup> ions across the cell membrane. For getting sneak peak for action potential an amplifying method is required.the neural amplifier should reject the dc offsets of the resulting signal amplitudes. The amplifier should have have high (SNR) and proper CMRR and PSRR.the majority of neural amplifier successfully extracts I/P referred noise between 3-7µVrms. Without the controlling mechanism the system is dominated by noise. . the main component of noise are mainly from muscle contraction affecting neural recording and intensifying brain activity environmental noise includes the noise from radio and electrical signals which degrades the performance drastically. The main noise are thermal and flicker noise caused by intrinsic property of the semiconductor. The LNA implemented with (OTA) topology with two stage op-amps and current mirror OTA's. the folded cascaded combinations. is implemented in different modes should have considerably large phase margin and swing margin. The LNA implemented with capacitive feedback topology. These are optimized with very low noise power. These are operated through a dedicated circuit design topology. the desired architecture achieved a gain of 39.5dB, power consumption of 80µW and NEF of 4. In [22] achieved a modified and optimized capacitor feedback topology having a power consumption of 7.92µw and I/P reffered noise of 3.5µV<sub>rms</sub>. LNA implemented with Active feedback topology a segment of filtered signal is used as a feedback for suppressing a signal component. this is one of the efficient way of extracting the low frequency component of a signal which makes it a very stable system. This topology is mainly used in EEG biomedical application. LNA implemented with a MOS bipolar pseudo resistor(implemented using a cross coupled configuration) are used for implementing AC coupling and rejecting the large DC offsets caused due to contact potential.every transistor in MOS diode is connected such that a parasitic source-bulk diode is obtained in anti-parallel now if the voltage across the device is small then neither of the diode conducts since the effective resistance is very large.>(10G $\Omega$ ) so for minimizing the I/P reffered noise two strategy are adopted.first amplifier is reduced to a single branch which is operating at a full current.the reference current so obtained is found to be 10 times the amplifier bias current which do not contributes in the total power consumption.

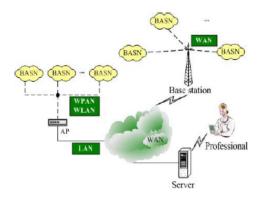

LNA IN BIOSENSORS APPLICATIONS - The term 'Biosensor' is a short for "biological sensor" the device consist of transducer and biological elements consisting of enzymes, antibody or nucleic acids. The bioelements interact with the analyte being tested and biological response are converted to electrical signal by transducers the biological response of biosensors obtained are examined by biocatalytic membrane achieving the conversions of reactant to the product. Immobilised enzymes provides a large number of advantages making them applicable for biological systems. These can be reused ensuring catalytic activity for a series of analyses. thus, biosensors are widely used in the field of healthcare, medical diagnosis, etc. in [23] CMOS on chip sensor is used for measuring the dielectric constant of an organic chemicals .the dielectric constants is measured by changes observed in the tank capacitance producing LC oscillation in VCO due to the exposure to the liquid. VCO is placed in a frequency synthesisers frequency change causes change in the voltage measured using on chip digitised analog to digital converter.the calibration of sensor is used for the measurements of dielectrics.the measurements are made in frequency ranging from 7-9GHz. The advancement in wireless communication and network technologies has lead to the significant advancement in wearable and implantable sensors creating an impact on e-health and telemetry systems. m-health biosensors comprises of mobile computing, medical sensors and communication technologies.for diagonsis and monitoring of diseases .for eg diseases like diabities a large number of biosensors are worn and implanted.the interconnection

are made inside a human body and the entire system is called BASN body area sensor network performing two operations.

- 1.) The transmitting of processed data.

- A secured channel for transmitting of data between human body and biosensors placed at the same node.

The BASN differentiates between the individual based on their pyscological and behavioural characteristics.

The BASN differentiates between the individual based on their pyscological and behavioural characteristics.

Fig 1.45 BASN Network

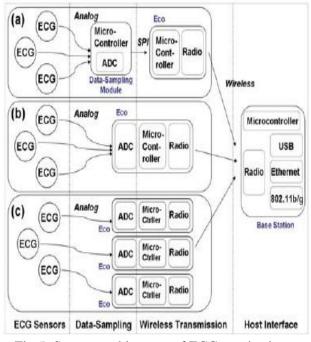

**LNA IN ECG SIGNALS**- Biomedical signals is the study of physiological activities of organism produced by gene and protein sequences observed in neural and cardiac pattern. the well known biosignals are (ECG),(EEG),(EMG) and (MMG). ECG is the acquisition of electrical activity observed from the heart captured by the electrodes attached to the skin. these are very weak signal produced during strenuous or ambulatory conditions and because of this weak nature noise gets added for which signal processing is required. The ECG or electrocardiography signals are produced due to the potential difference between the two electrodes and since these are recorded for long time the compression of data is required both at transmitting and receiver ends. The contraction of the muscles and cardiac pattern ECG signals are coupled with noise.therefore filtering is not possible.

To solve ensembled averages techniques for time aligning heartbeats and reducing muscle noise is used. The three algorithm applied are

- Stress testing

- Ambulatory monitoring

• Intensive care monitoring

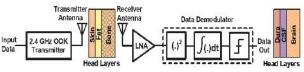

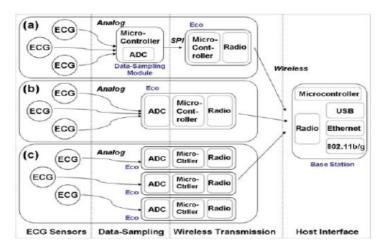

For the purpose of monitoring ECG signals. In [24] The low power and compact wearable sensors are designed. The signals are wirelessly transmitted and monitored using ECG filtering and QRS detection methods which carries less number of bits for transmission. LNA with differential topology is implemented using successive approximations(SAR) ADC using 2 SPI interfaces and on chip SRAM having central control unit of 8 Kbits.

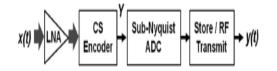

The ECG signals are sampled at a rate of 256Hz using QRS complexes and the ECG signals are then continuously wrote on asynchronous FIFO and are forwarded to CPU thus consuming less power. In [25] the bio signals obtained with Nyquist rate are reproduced without degrading the characteristics of the bio signals the low power bio signal is provided at analog front ends of the amplifiers having a bandwidth with a dynamic range of (40-70 dB).

The conditioned bio signal is received by the encoder from a low noise amplifier and compression of N I/P sample gives M O/P samples which are digitised and transmitted using ADC.the RF front elements are made to operate at Nyquist having a conversion factor of [N/M] which is greater then 1 and these signals are down converted at O/P y(t).

**LNA IN EEG APPLICATIONS-** The EEG signal which stands for electroencephalogram is a signal produced due to the electrical activity of the brain and recorded from the scalp. the recorded waveform consist of cortial, electrical activity. These are very weak signal and measured in microvolts. The main frequency of the human EEG wave consist of

- Delta[frequency of 3 Hz or below]

- Theta[frequency of 3.5Hz and 7.5Hz]

- Alpha [frequency between 7.5 and 13Hz]

- Beta [frequency> 14 Hz]

Since these are weak signal the voltage fluctuation measured at the electodes are very small, the recorded data is digitised and sent to LNA. The LNA processes data which is then displayed as a sequence of voltage values. This is one of the fastest imaging techniques having high sampling rate.