# **Current Differencing Current Conveyor and its Applications**

A thesis submitted in fulfillment of the requirements for the award of the

**Degree**

of

**Doctor of Philosophy**

by

## Alok Kumar Singh Roll No. 2K11/Ph.D/EC/12

Under the Supervision of

Prof. Pragati Kumar

Department of Electrical Engg.

Delhi Technological University

(Formerly DCE)

New Delhi

Prof. Raj Senani

Division of Electronics and Commun. Engg.

Netaji Subhas University of Technology

(Formerly NSIT)

New Delhi

# Department of Electronics and Communication Engineering Delhi Technological University Shahabad Daulatpur, Main Bawana Road

Shahabad Daulatpur, Main Bawana Road Delhi-110042

September, 2018

Copyright © Delhi Technological University-2018 All rights reserved.

### Certificate

Certified that the thesis entitled, 'Current Differencing Current Conveyor and Its Applications', which is being submitted by Shri Alok Kumar Singh for the award of Doctor of Philosophy in Electronics and Communication Engineering, Delhi Technological University, Delhi, is a record of student's own work carried out by him under our supervision and guidance. The matter embodied in this thesis has not been submitted for any other degree.

Prof. Pragati Kumar

Department of Electrical Engg.

Delhi Technological University

(Formerly DCE)

New Delhi

Prof. Raj Senani

Division of Electronics and Commun. Engg.

Netaji Subhas University of Technology

(Formerly NSIT)

New Delhi

गुशब्दस्त्वन्धकारः स्यात् रुशब्दस्तन्निरोधकः। अन्धकारनिरोधित्वात् गुरुरित्यभिधीयते॥ १६॥

The syllable *gu* means darkness, the syllable *ru*, he who dispels them, Because of the power to dispel darkness, the guru is thus named.

— Advayataraka Upanishad, Verse 16

गुरुर्ब्रह्मा गुरुर्विष्णु गुरुर्देवो महेश्वरः गुरु साक्षात परब्रह्मा तस्मै श्रीगुरवे नमः

Guru is the Creator (Brahma), Guru is the Preserver(Vishnu), GuruDeva is Destroyer(Maheshwara)

Guru is the absolute (singular) Lord himself, Salutations to that Sri Guru.

गुरू पारस को अन्तरों, जानत हैं सब संत। वह लोहा कंचन करें, ये करि लेय महंत।।

पारस मणी के विषय जग विख्यात है कि उसके स्पर्श से लोहा सोने का बन जाता है। All the wise men know the difference between Guru and Paras. The subject of Paras Mani, the world is famous that with its touch iron becomes gold. किन्तु गुरु भी इतने महान हैं कि अपने गुण-ज्ञान मे ढालकर शिष्य को अपने जैसा ही महान बना लेते हैं। But the gurus are so great that they can make the disciple as great as their own in their knowledge.

## **Acknowledgement**

No thesis is solely the creative work of the person whose name is on the cover. It is the joint exertion of everyone, who is associated with me directly or indirectly at various stages of the research. I wish to regard my thanks to following indispensable persons, who contributed beyond measures.

It gives me an immense pleasure to have this opportunity to express my heart felt Gratitude and acknowledgement to my Supervisors Prof. Pragati Kumar and Prof. Raj Senani. I am grateful to them for the interest shown by them in the work and overall supervision which enabled me to complete the work. Their way of supervision has convinced me that unless one carries out research work, one cannot be an effective teacher.

Sincere appreciation and thanks extended to Prof. S. Indu, Professor and Head, Department of Electronics and Communication Engineering, Delhi Technological University, Delhi to provide me this opportunity and for their immense help during the course of this work.

I also want to extend my sincere thanks to Prof. Neeta Pandey and Prof. Rajeshwari Pandey, Department of Electronics and Communication Engineering, Delhi Technological University, Delhi for their exemplary quidance, motivation, constant encouragement and for their immense help during the course of this work.

I especially thank Prof Asok Bhattacharyya (Ex Director/Principal of DCE and Ex HOD of ECE department) for giving me the opportunity of teaching, EC304 (Linear Integrated Circuits) course to V semester students of DCE and EC314 (Bipolar and MOS Analog Integrated Circuits) course to VI semester students of DCE. Without hesitation I can claim that the later course, which was introduced by Prof. Raj Senani, in DIT (renamed as NSIT subsequently) and DCE as early as 1989-1990, is among the most modern courses being-offered in any UG curriculum anywhere in the world. I was always influenced by these stalwarts.

The Analog Signal Processing Research Lab of NSIT where the present work has been carried out is a true GURUKUL, where the 'guru shishya parampara' is to be seen, to be believed! I thank all my senior

research co-workers in the lab namely Prof. D.R. Bhaskar, Prof. V.K. Singh, (IET, Lucknow), Dr. Abdhesh Kumar Singh, Dr. S.S. Gupta (Ministry of Commerce and Industry, Government of India, New Delhi) and Prof. R.K. Sharma (Ambedkar Institute of Advanced Communication Technologies and Research, Delhi). I have received their help at each and every stage of my research work.

I would also like to acknowledge the help rendered by Sh. Rajendra, Sh. Sunil Kumar, Sh. Baljit and Sh. Sanjeev Mishra of Electronics & Communication Engineering Department of DTU during the course of my research work.

During the course of the present work, apart from learning and relearning many concepts, I had the opportunity of learning so many interesting developments not only in the field of Analog Circuits through anecdotes but also in the field of Hindi film music, in both of which Prof. Raj Senani is, a walking encyclopedia! The discussions in the lab were always centered around the works of legendary Professors like Prof. R. W. Newcomb, Prof. S. C. Dutta Roy, Prof. Chris Toumazou, Prof. David Haigh, Prof. Mohammad Ismail, Prof Allain Fabre, Prof. A.M. Soliman, Prof. S.I. Liu and others.

I also thank my colleagues in the Department of Electronics and communication Engineering, DCE namely Prof. Asok De, Prof. J.Panda, Prof. N.S. Raghava, Prof. Rajesh Rohilla, Prof. Dinesh, Dr. D.K, Vishkarma, Dr. Sudipta Majumdar, Dr. M.S. Chaudhary, Dr. N. Jayanthi, Dr. Malti Bansal, Mr. Devanand, Mr. Rajesh Birok, Mr Ajai Gautam for the concerns shown by them for my research work. Special thanks are due to Prof. Rajiv Chaudhary and Prof R. C. Singh (my colleagues in Mechanical Engineering Department of DTU) for their co-operation and motivation at every stage of my research work.

I also thank my colleagues in the Department of Electrical Engineering, DTU namely Prof. Madhusudan Singh (HOD Electrical Engineering Department), Mr. Ram Bhagat, Mrs. Garima, Mr. Manoj Kumar (G. B. Pant Engineering College, Pauri-Garhwal, Uttarakhand) and Sh. Ajishek Raj for the concerns shown by them for my research work. Special thanks are due to Sh. Upendra, Sh. Jagbir and other persons available

in Analog Integrated Laboratory of Electrical Engineering Department for their co-operation during the research work. At last but not the least I would like to convey my thanks to all the people who directly or indirectly involve in this work.

My parents (late), In-laws, siblings and their spouses have always been a source of inspiration to me and it is because of this inspiration that I have been able to complete the present work.

Last but not the least, I convey my gratitude to my wife Vibha Singh and my son Abhishek Singh who have endured me and my long hours spent in the laboratory with patience and encouraged me to carry out my research work.

(Alok Kumar Singh)

# Index

| Cer  | tificate                                                                                                                  | i    |

|------|---------------------------------------------------------------------------------------------------------------------------|------|

| Ack  | nowledgements                                                                                                             | ii   |

| Ind  | ex                                                                                                                        | vi   |

| List | of Figures                                                                                                                | ix   |

| List | of Tables                                                                                                                 | XV   |

| List | of Abbreviations used in the thesis                                                                                       | xvii |

| Cha  | pter 1: Introduction                                                                                                      | 1    |

| 1.1  | Introduction                                                                                                              | 2    |

| 1.2  | Active building blocks available as Off-the-shelf ICs                                                                     | 3    |

| 1.3  | Other active elements                                                                                                     | 5    |

| 1.4  | Novel Active Elements                                                                                                     | 7    |

| 1.5  | The Current Differencing Current Conveyor (CDCC)                                                                          | 13   |

|      | 1.5.1 CMOS implementation of the CDCC                                                                                     | 14   |

|      | 1.5.2 Characterization of the CMOS CDCC                                                                                   | 19   |

| 1.6  | Z-copy current follower current conveyor                                                                                  | 21   |

|      | 1.6.1 CMOS implementation of Z-copy current follower current conveyor                                                     | 23   |

|      | 1.6.2 Characterization of the ZC-CFCC                                                                                     | 23   |

| 1.7  | Scope of the present work                                                                                                 | 25   |

| 1.8  | References                                                                                                                | 25   |

| Cha  | npter 2: A Novel Fully Differential Current Mode Universal Filter                                                         | 30   |

| 2.1  | Introduction                                                                                                              | 31   |

| 2.2  | CDCC-based fully-differential current-mode universal filter with independently tunable gain, pole frequency and bandwidth | 33   |

| 2.3  | Non-ideality analysis                                                                                                     | 36   |

| 2.4  | Simulation results                                                                                                        | 38   |

| 2.5  | Fully-differential current-mode filter with limited tunability of parameters                                              | 42   |

|      | 2.5.1 Fully-differential current-mode universal filter with independent tunability of gain and pole frequency             | 42   |

|      | 2.5.1.1 Simulation results                                                                                                | 43   |

|      | 2.5.2 Fully-differential current-mode universal filter with fixed gain, fixed pole frequency and tunable gain             | 45   |

|            | 2.5.2.1 Simulation results                                                                                                       | 46  |

|------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

|            | 2.5.3 Fully-differential current-mode universal filter with fixed pole frequency, fixed bandwidth and tunable gain               | 47  |

|            | 2.5.3.1 Simulation results                                                                                                       | 48  |

|            | 2.5.4 Fully-differential current-mode universal filter with fixed gain, fixed bandwidth and independently tunable pole frequency | 49  |

|            | 2.5.4.1 Simulation results                                                                                                       | 50  |

| 2.6        | Concluding remarks                                                                                                               | 51  |

| 2.7        | References                                                                                                                       | 52  |

| Cha        | pter 3: Grounded Immittance Simulators Employing a Single CFCC                                                                   | 54  |

| 3.1        | Introduction                                                                                                                     | 55  |

| 3.2        | Current follower current conveyor (CFCC)                                                                                         | 60  |

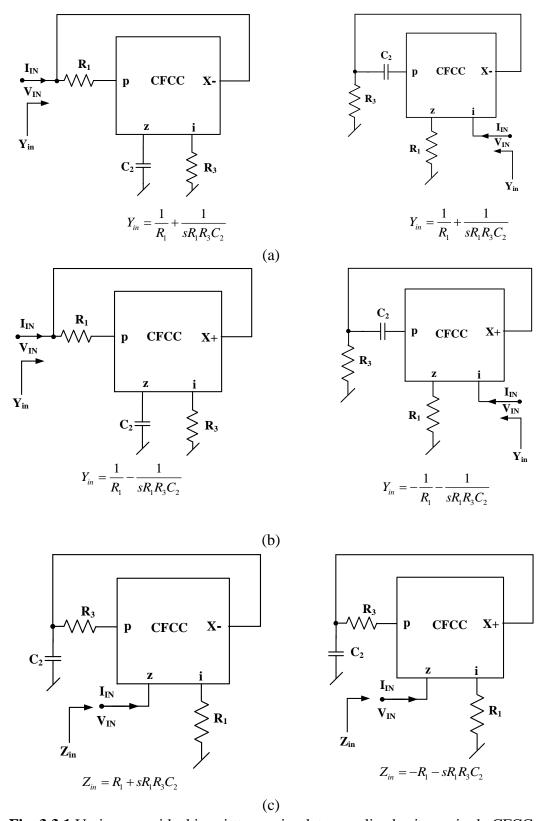

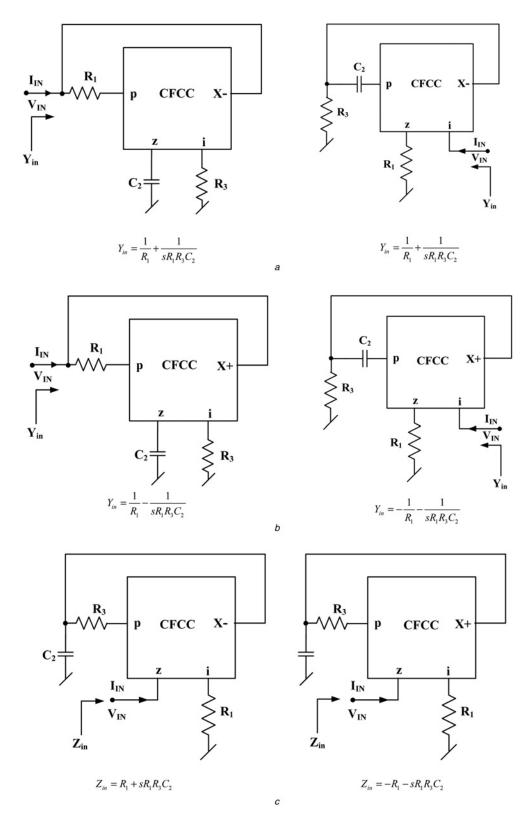

| 3.3        | Proposed CFCC-based immittance simulators                                                                                        | 61  |

| 3.4        | Non-ideal analysis                                                                                                               | 64  |

|            | 3.4.1 Non-ideal analysis of the lossy inductor                                                                                   | 64  |

|            | 3.4.2 Non-ideal analysis of the lossless inductor                                                                                | 66  |

|            | 3.4.3 Non-ideal analysis of the FDNR                                                                                             | 66  |

| 3.5        | SPICE simulation results                                                                                                         | 67  |

| 3.6        | Comparison with recently published grounded inductance simulators                                                                | 75  |

| 3.7        | Concluding remarks                                                                                                               | 78  |

| 3.8        | Appendix                                                                                                                         | 78  |

| 3.9        | References                                                                                                                       | 79  |

|            | pter 4: Electronically-tunable Grounded/floating Inductance Simulators                                                           |     |

|            | using z-copy CFCCC                                                                                                               | 84  |

| 4.1        | Introduction                                                                                                                     |     |

| 4.2        | Electronically-tunable grounded inductor                                                                                         |     |

| 4.3        | Electronically-tunable floating inductor                                                                                         |     |

| 4.4        | SPICE simulations, application examples and results                                                                              |     |

| 4.5        | Comparison with previously published circuits                                                                                    |     |

| 4.6        | Concluding remarks                                                                                                               |     |

| 4.7        | References                                                                                                                       | 103 |

| Cha        | pter 5: Fully-differential Current-mode Higher order Filters Using all                                                           | 40= |

| <b>.</b> . | Grounded Passive Elements                                                                                                        |     |

| 5.1        | Introduction                                                                                                                     | 108 |

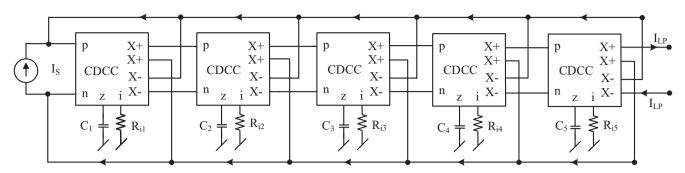

| 5.2        | Realization of CDCC-based fully-differential current-mode higher order                                                           | 111 |

| 5.3  | Design examples                                                        | 114 |

|------|------------------------------------------------------------------------|-----|

|      | 5.3.1 Fifth order lowpass Butterworth filter design                    | 115 |

|      | 5.3.2 Fifth order lowpass Chebyshev filter design                      | 121 |

| 5.4  | Concluding remarks                                                     | 125 |

| 5.5  | References                                                             | 126 |

| Chaj | pter 6: Current-Mode Quadrature Oscillators                            | 131 |

| 6.1  | Introduction                                                           | 132 |

| 6.2  | CFCC-based realization of the current-mode quadrature oscillator       | 133 |

| 6.3  | CFCC-based current-mode quadrature oscillator with grounded capacitors | 135 |

| 6.4  | Non-ideal consideration                                                | 137 |

| 6.5  | PSPICE simulation results                                              | 139 |

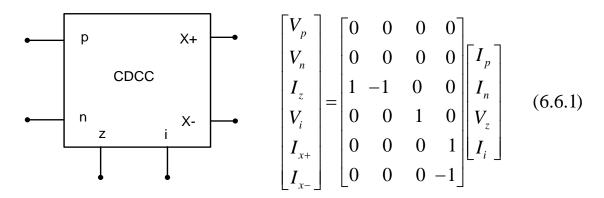

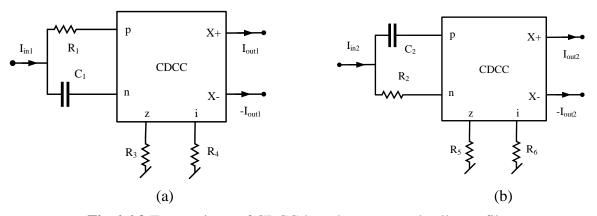

| 6.6  | CDCC-based realization of current-mode quadrature oscillator           | 141 |

| 6.7  | Non-ideal consideration                                                | 144 |

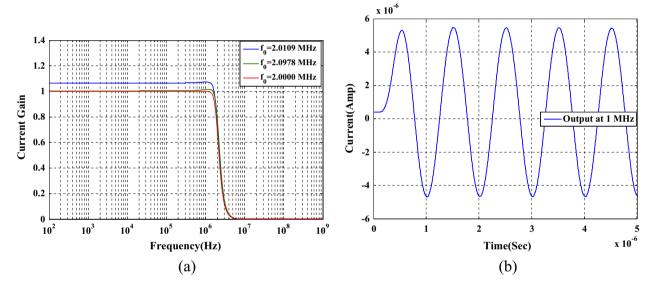

| 6.8  | PSPICE simulation results                                              | 146 |

| 6.9  | Experimental results                                                   | 148 |

| 6.10 | Concluding remarks                                                     | 151 |

| 6.11 | References                                                             | 151 |

| Chaj | pter 7: Conclusions                                                    | 154 |

| 7.1  | Summary of the work presented in the thesis                            | 156 |

| 7.2  | Some suggestions for further work                                      | 159 |

| List | of Research Papers                                                     | 161 |

|      |                                                                        |     |

**Copy of Research papers (Reprints)**

Biography

# **List of Figures**

| Fig.1.5.1    | (a) Circuit symbol of CDCC (b) Behavioral model (c) Modified                                                                                                                                                                                             |    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | behavioral model considering parasitics                                                                                                                                                                                                                  | 14 |

| Fig. 1.5.1.1 | Translinear voltage buffer                                                                                                                                                                                                                               | 15 |

| Fig.1.5.1.2  | Equivalent circuit of translinear voltage buffer                                                                                                                                                                                                         | 16 |

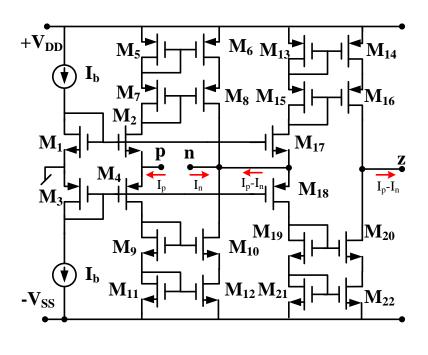

| Fig.1.5.1.3  | Current differencing unit (CDU)                                                                                                                                                                                                                          | 17 |

| Fig.1.5.1.4  | MOCCII                                                                                                                                                                                                                                                   | 18 |

| Fig.1.5.1.5  | Proposed CMOS implementation of CDCC                                                                                                                                                                                                                     | 19 |

| Fig. 1.5.2.1 | (a) DC Current transfer from Ip and In to Iz (b) DC Voltage Transfer from $V_z$ to $V_i$ (c) DC current Transfer characteristics for proposed CDCC from Ii to Ix+ and Ix- (d) Frequency Response of Ix+/ Ii and Ix-/Ii for proposed CDCC                 | 20 |

| Fig. 1.5.2.2 | CDCC as an amplifier                                                                                                                                                                                                                                     | 21 |

| Fig.1.5.2.3  | (a) Frequency response of fully-differential amplifier (b) Transient Response of fully-differential amplifier                                                                                                                                            | 21 |

| Fig.1.6.1    | Symbolic notation of CFCC                                                                                                                                                                                                                                | 22 |

| Fig.1.6.2    | Symbolic notation of (a) ZC-CFCC and (b) behavioral model                                                                                                                                                                                                | 22 |

| Fig.1.6.1.1  | Proposed CMOS implementation of ZC-CFCC                                                                                                                                                                                                                  | 23 |

| Fig. 1.6.2.1 | (a) DC Current transfer from $I_p$ to $I_z$ and $I_{zc}$ (b) DC Voltage Transfer from $V_z$ (c) DC Transfer characteristics between $I_i$ and $I_{x+}$ and $I_{x-}$ (d) Frequency response of $I_{x+}$ / $I_i$ and $I_{x-}$ / $I_i$ for proposed ZC-CFCC | 24 |

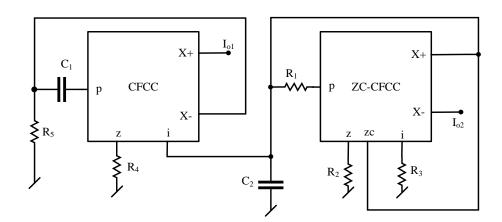

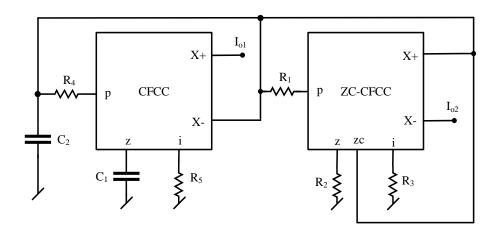

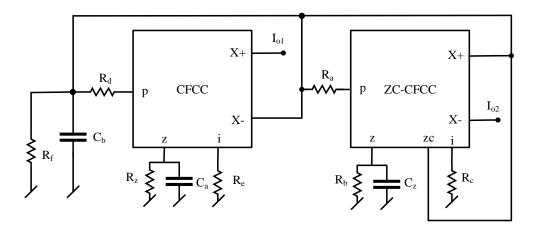

| Fig.2.2.1    | Symbolic notation of the CDCC                                                                                                                                                                                                                            | 33 |

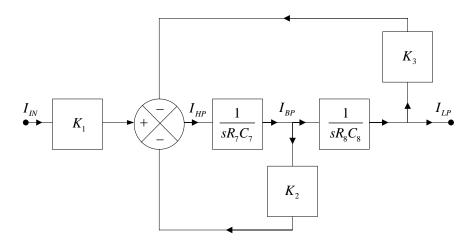

| Fig.2.2.2    | Block diagram representation of the single ended two-integrator loop                                                                                                                                                                                     | 34 |

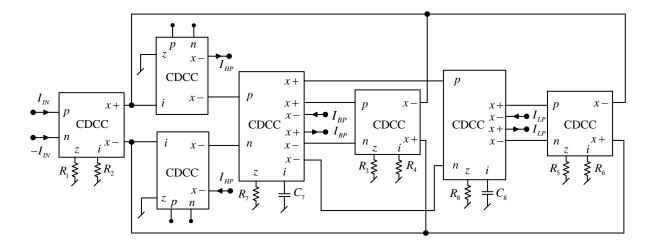

| Fig.2.2.3    | Fully-differential current- mode universal filter with independently tunable gain, bandwidth and pole frequency                                                                                                                                          | 34 |

| Fig.2.4.1    | CMOS implementation of the CDCC                                                                                                                                                                                                                          | 38 |

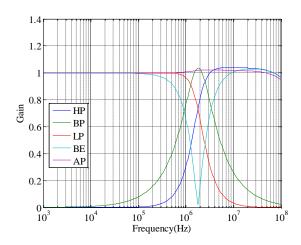

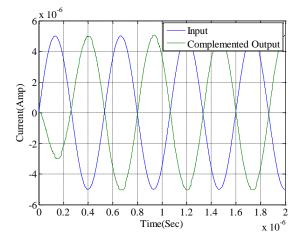

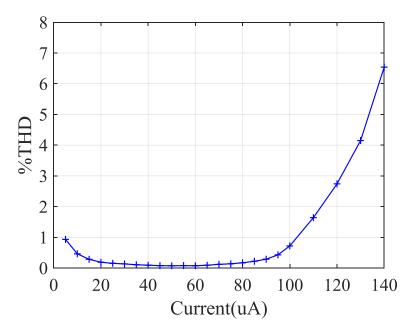

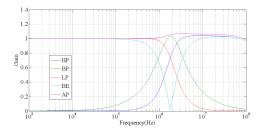

| Fig.2.4.2    | (a) Magnitude response of HP, BP, LP, AP and BE filters for a pole frequency of 1.8759 MHz (b) Time response of the BP filter for an                                                                                                                     |    |

|              | input current of $5\mu A$ at 1.8759 MHz (c) Variation of THD with applied input Current for Fully- differential BP filter at 1.8759 MHz                                                                                                                     | 39 |

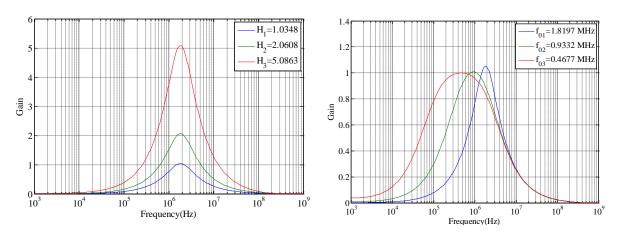

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

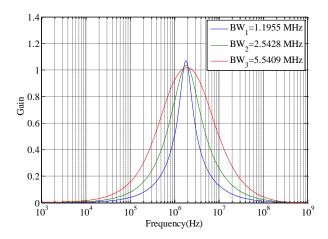

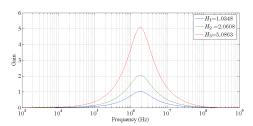

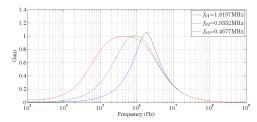

| Fig.2.4.3    | (a) Magnitude response showing tunability of gain (b) Magnitude response showing tunability of pole frequency (c) Magnitude response showing tunability of bandwidth                                                                                        | 40 |

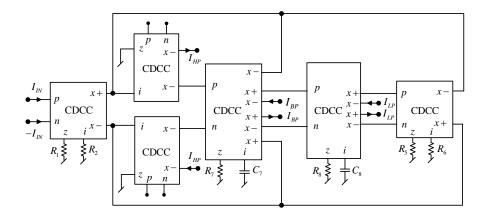

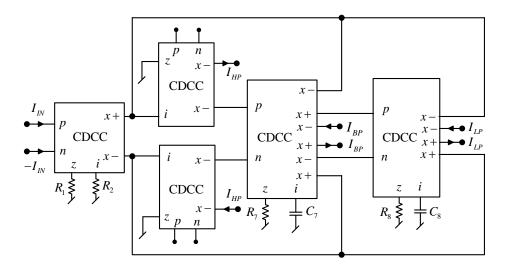

| Fig.2.5.1.1  | FDCMUF employing six- CDCC both independently tunable gain and pole frequency with fixed bandwidth                                                                                                                                                          | 42 |

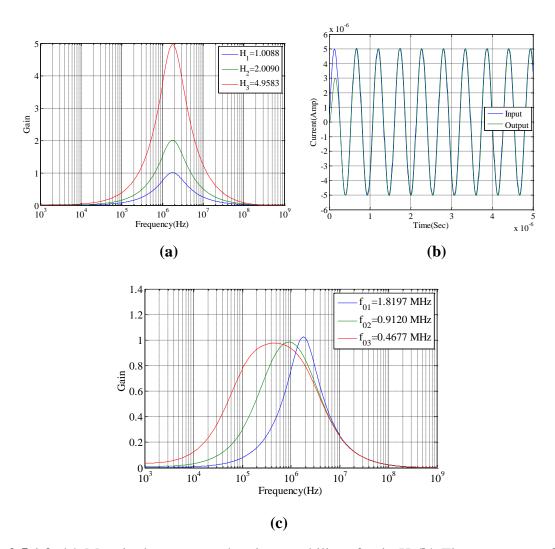

| Fig. 2.5.1.2 | (a) Magnitude response showing tunability of gain (b) Time response of the Bandpass filter for an input of $5\mu A$ at 1.8759 MHz for the circuit of Fig.2.5.1.1 (c) Magnitude response showing tunability of pole frequency for the circuit of Fig.2.5.1.1 | 44 |

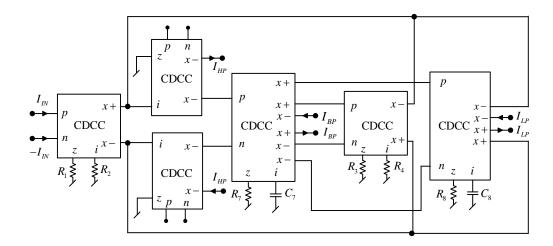

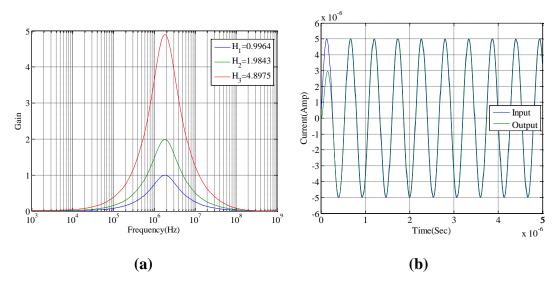

| Fig.2.5.2.1  | FDCMUF employing six CDCC wth independently tunable bandwidth for fixed pole frequency and fixed gain                                                                                                                                                       | 45 |

| Fig. 2.5.2.2 | (a) Magnitude response showing tunability of bandwidth (b) Time response of the Bandpass filter for an input of $5\mu A$ at 1.8759 MHz for the circuit of Fig. 2.5.2.1                                                                                      | 47 |

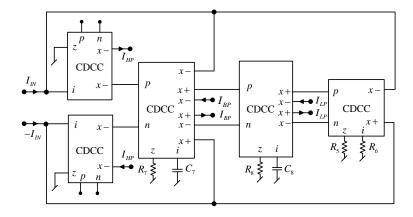

| Fig.2.5.3.1  | FDCMUF employing five CDCC with fixed bandwidth, fixed pole frequency and independently tunable gain                                                                                                                                                        | 47 |

| Fig. 2.5.3.2 | (a) Magnitude response showing tunability of gain (b) Time response of the bandpass filter for an input of $5\mu A$ at 1.8759 MHz for the circuit of Fig.2.5.3.1                                                                                            | 49 |

| Fig.2.5.4.1  | FDCMUF employing five CDCC with fixed bandwidth, fixed gain and independently tunable pole frequency                                                                                                                                                        | 49 |

| Fig. 2.5.4.2 | (a) Magnitude response showing tunability of the pole frequency $f_0$<br>(b) Time response of the bandpass filter for an input of $5\mu A$ at 1.8759 MHz for the circuit of Fig.2.5.4.1                                                                     | 51 |

| Fig.3.2.1    | Symbolic notation of the CFCC                                                                                                                                                                                                                               | 60 |

| Fig.3.2.2    | CMOS implementation of ZC-CFCC                                                                                                                                                                                                                              | 61 |

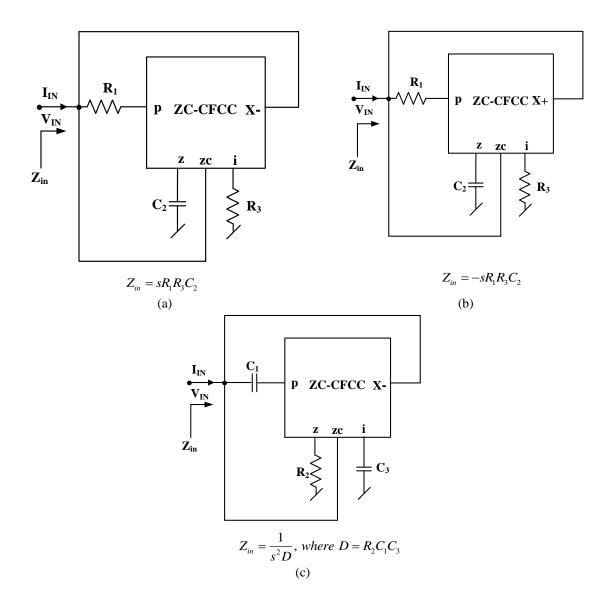

| Fig. 3.3.1   | Various non-ideal immitttance simulators realized using a single                                                                                                                                                                                            | 62 |

| Fig. 3.3.2 | Various ideal immitttance simulators realized using a single ZC-CFCC                                                                                                                                      | 63 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

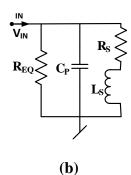

| Fig. 3.4.1 | (a) Non-ideal equivalent circuit of the ZC-CFCC with additional zc terminal (b) Passive equivalent circuit for lossy and lossless inductor                                                                |    |

| Fig. 3.5.1 | of Fig. 3.3.1(a) and Fig. 3.3.2(a)                                                                                                                                                                        | 65 |

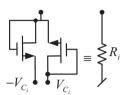

|            | inductive and resistive part with frequency (c) Magnitude and phase response of the proposed grounded inductor (d) CMOS VCR                                                                               | 68 |

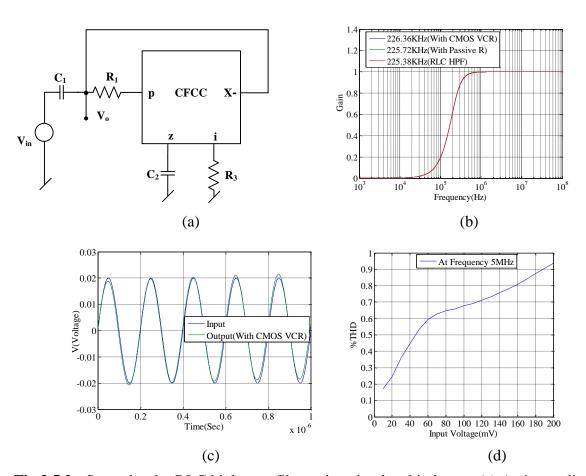

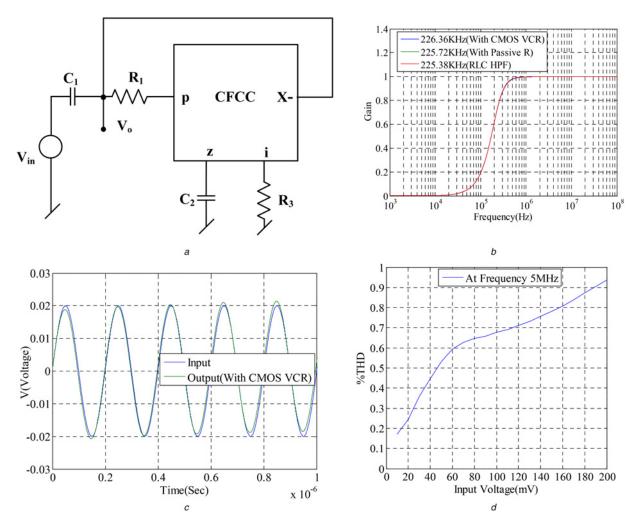

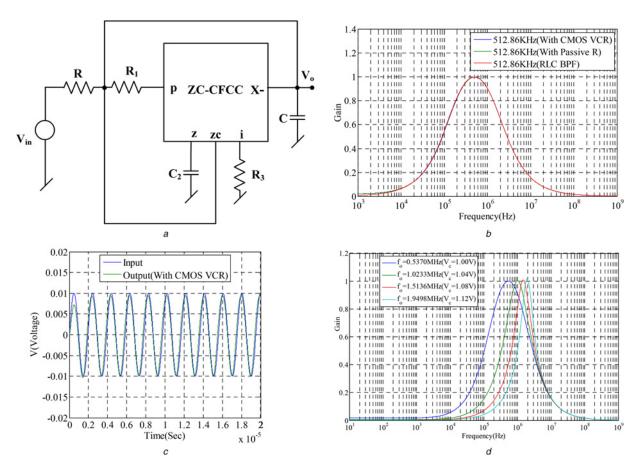

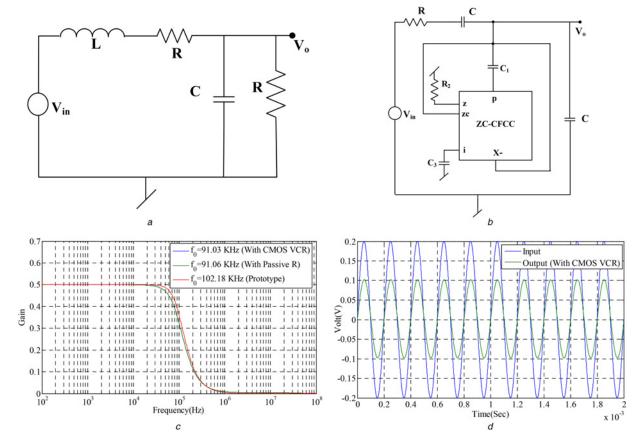

| Fig.3.5.2  | Second order RLC high pass filter using simulated inductor (a)  Active realization (b) Magnitude response for the circuit (c)  Transient Response (d) Variation of THD with applied input voltage at 5MHz | 69 |

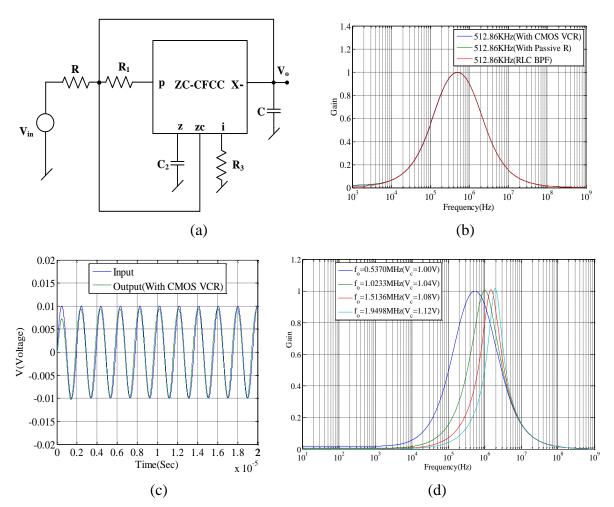

| Fig. 3.5.3 | Second order RLC band pass filter realization (a) Active realization (b) Magnitude response for the circuit (c) Transient Response (d) Tunability of the pole frequency with control voltage              | 71 |

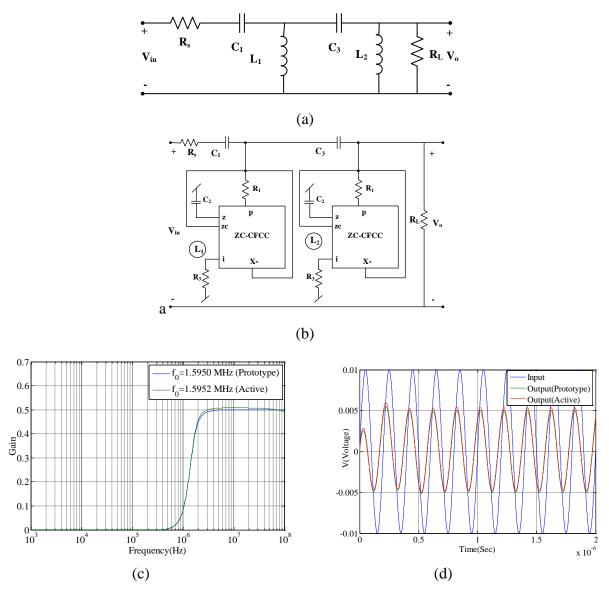

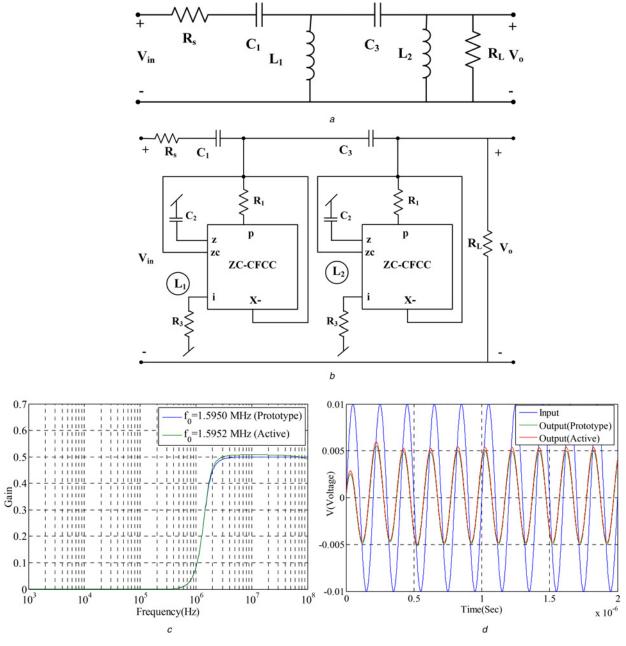

| Fig. 3.5.4 | Fourth order high pass Butterworth filter realization (a) Prototype (b) Active realization (c) Magnitude response for the circuit (d) Transient response                                                  | 73 |

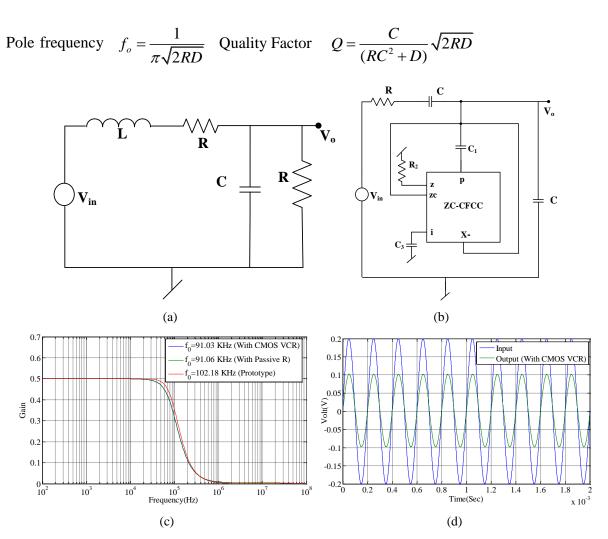

| Fig. 3.5.5 | Second order RCD low pass filter realization (a) Prototype (b)  Active realization (c) Magnitude response for the circuit (d)  Transient response                                                         | 74 |

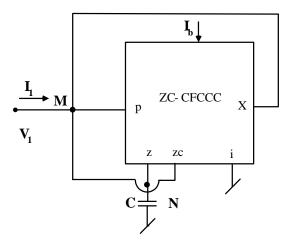

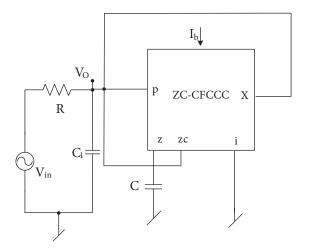

| Fig. 4.2.1 | An exemplary CMOS implementation of the ZC-CFCCC                                                                                                                                                          | 86 |

| Fig.4.2.2  | The proposed new electronically-tunable grounded inductor                                                                                                                                                 | 87 |

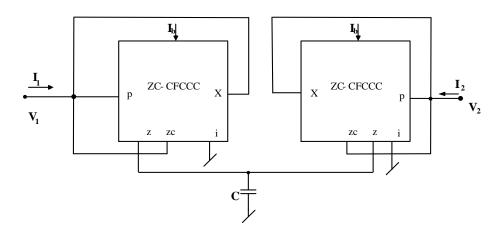

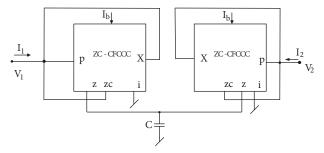

| Fig.4.3.1  | The proposed new electronically-tunable floating inductor                                                                                                                                                 | 89 |

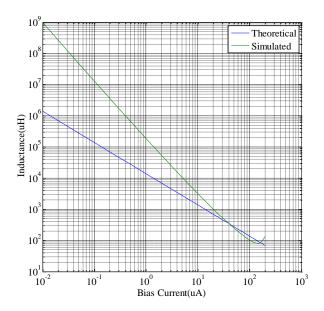

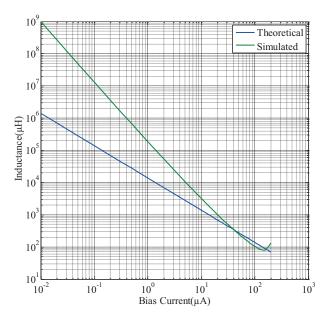

| Fig.4.4.1  | Variation of inductance with bias current                                                                                                                                                                 | 92 |

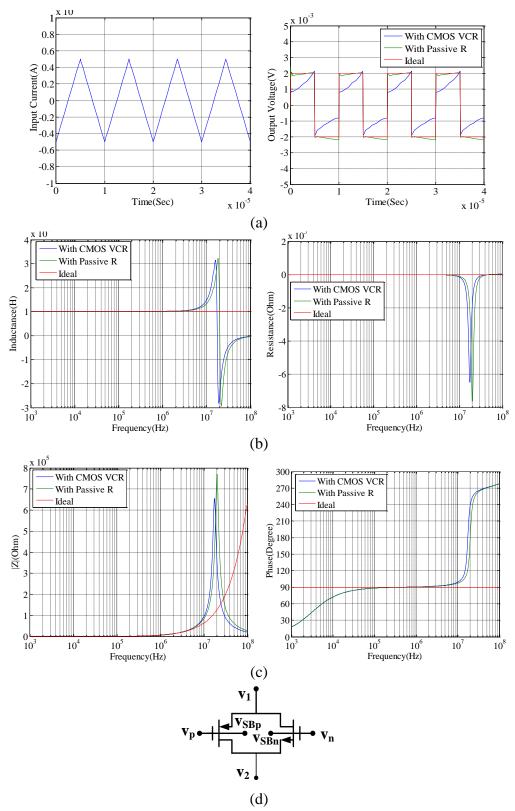

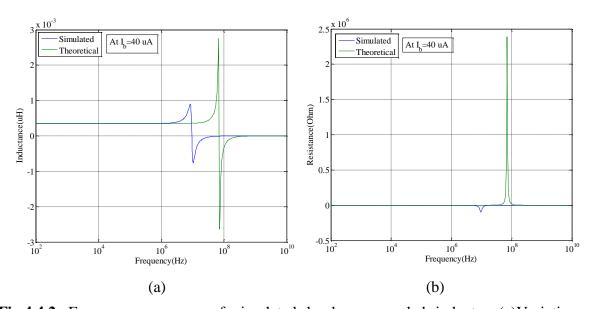

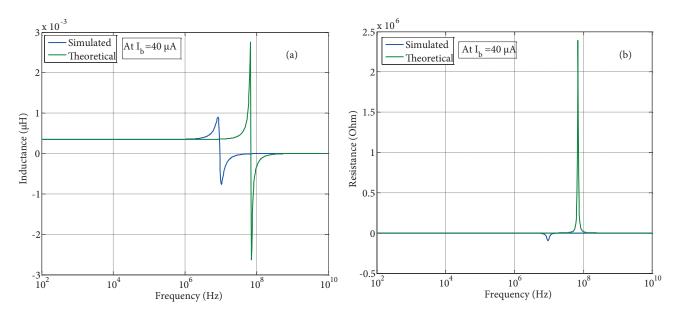

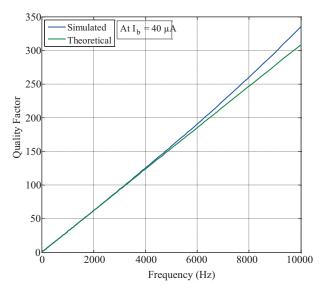

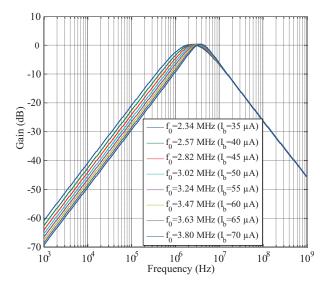

| Fig.4.4.2  | Frequency response of simulated lossless grounded inductor (a)  Variation of inductance value with frequency (b) Variation of                                                                             |    |

| E' 442     | parasitic resistance with frequency                                                                                                                                                                       |    |

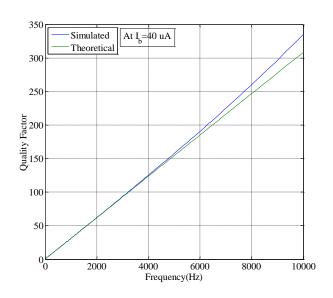

| Fig.4.4.3  | Variation of quality factor with frequency                                                                                                                                                                | 93 |

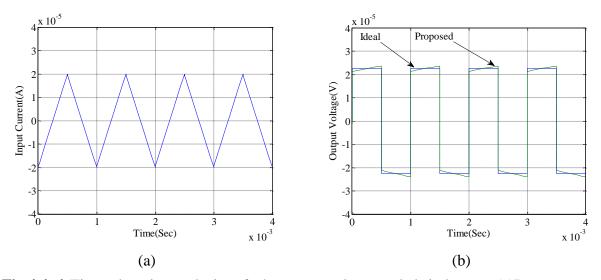

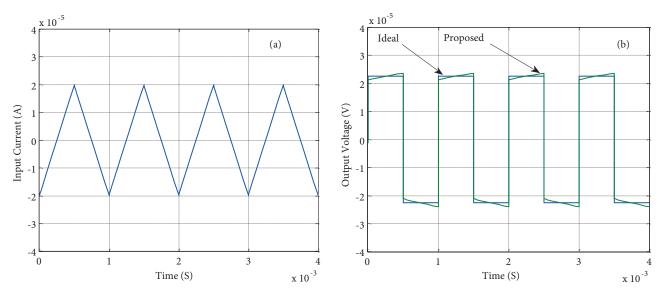

| F1g.4.4.4    | current waveform (b) output voltage waveform                                                                                                                                                                                                              | 94  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

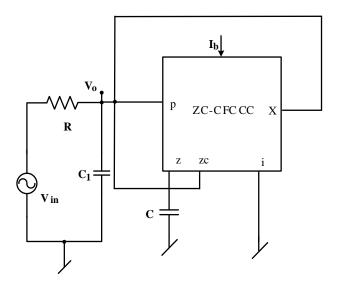

| Fig.4.4.5    | Tunable second order RLC band pass filter                                                                                                                                                                                                                 | 94  |

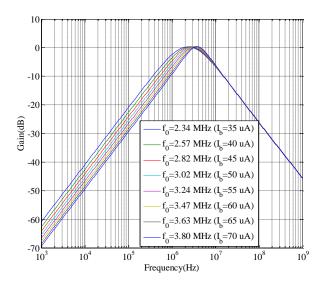

| Fig. 4.4.6   | Frequency response of second order BPF for different values of bias current                                                                                                                                                                               | 95  |

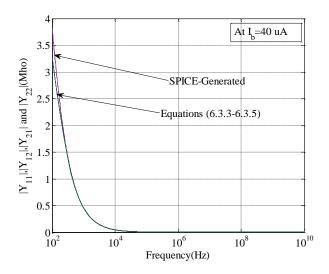

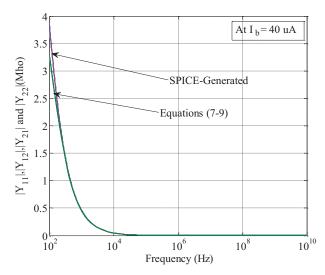

| Fig.4.4.7    | Frequency response of the y parameters of the simulated floating inductor                                                                                                                                                                                 | 96  |

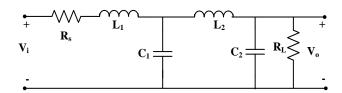

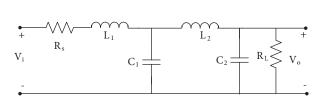

| Fig. 4.4.8   | Prototype fourth order low pass Butterworth filter                                                                                                                                                                                                        | 96  |

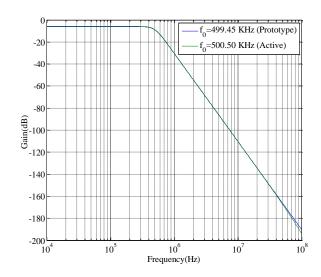

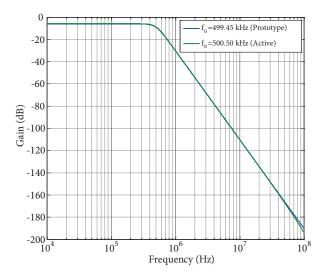

| Fig.4.4.9    | Frequency response of the fourth order low pass Butterworth filter                                                                                                                                                                                        | 97  |

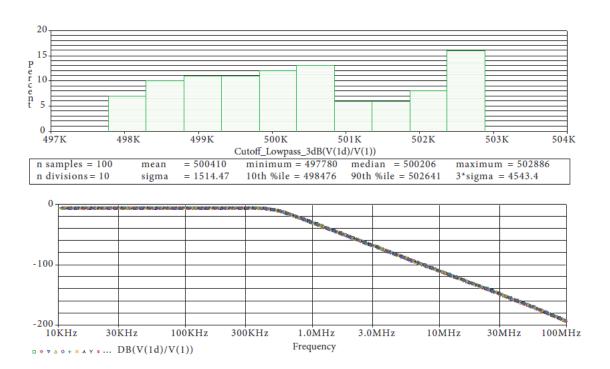

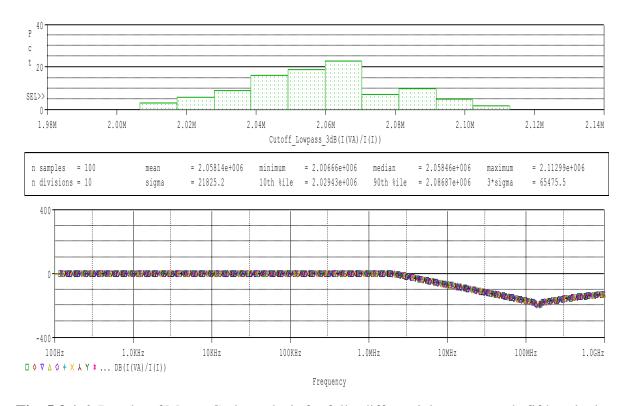

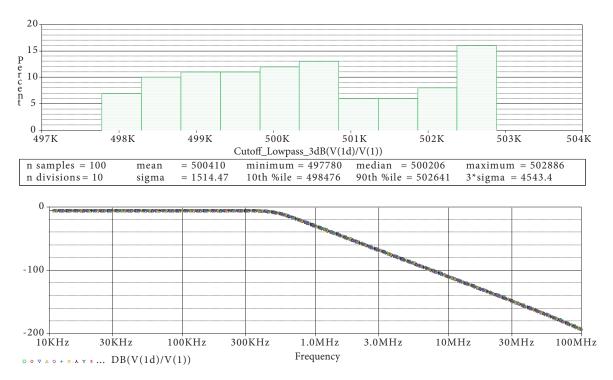

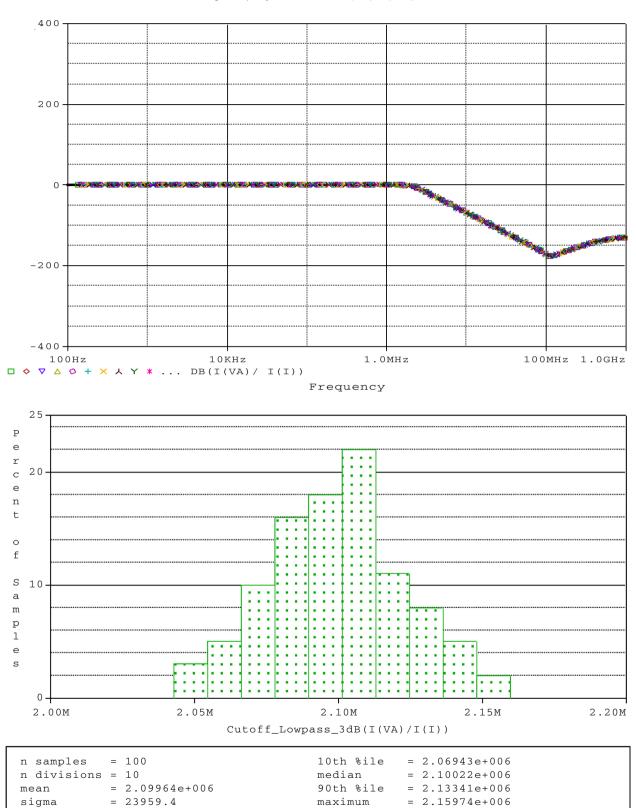

| Fig.4.4.10   | Simulation results of Monte Carlo analysis for fourth order low pass  Butterworth filter                                                                                                                                                                  | 98  |

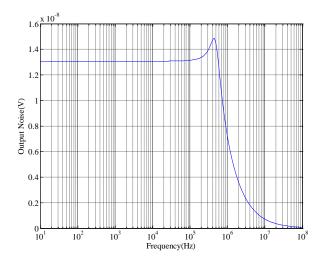

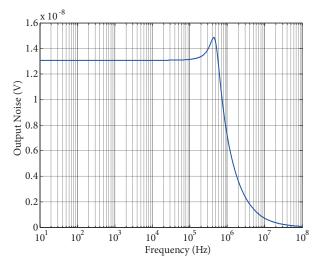

| Fig.4.4.11   | Output noise variation for fourth order low pass Butterworth filter                                                                                                                                                                                       | 98  |

| Fig. 5.2.1   | Symbolic notation and port-relations of the CDCC                                                                                                                                                                                                          | 112 |

| Fig. 5.2.2   | The general configuration to realize a scalar, lossless integrator or lossy integrator                                                                                                                                                                    | 112 |

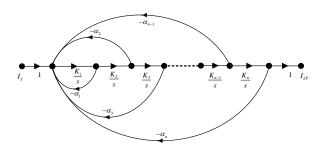

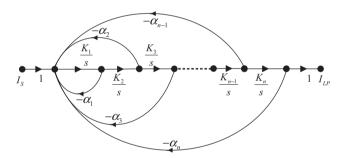

| Fig.5.2.3    | Signal flow graph corresponding to an nth-order all pole transfer function                                                                                                                                                                                | 113 |

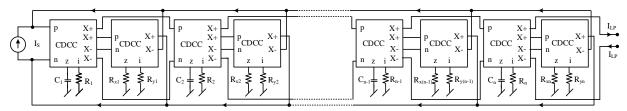

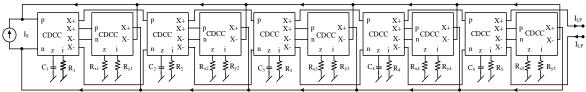

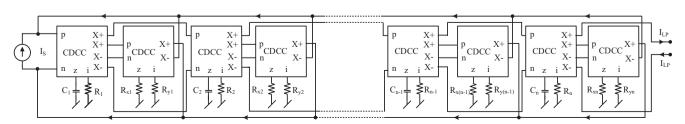

| Fig. 5.2.4   | n <sup>th</sup> order fully-differential current-mode transfer function realization                                                                                                                                                                       | 113 |

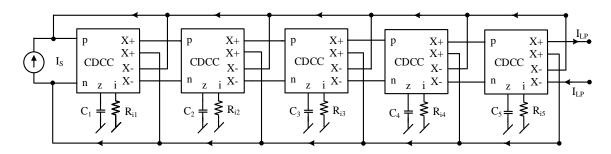

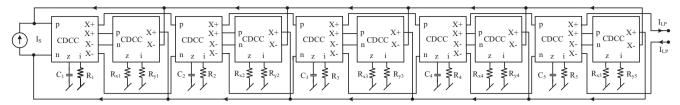

| Fig. 5.3.1.1 | Fifth order fully-differential current-mode lowpass filter                                                                                                                                                                                                | 115 |

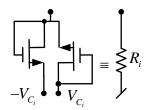

| Fig. 5.3.1.2 | The MOS VCR adopted from [50]                                                                                                                                                                                                                             | 116 |

| Fig. 5.3.1.3 | CMOS implementation of the CDCC                                                                                                                                                                                                                           | 117 |

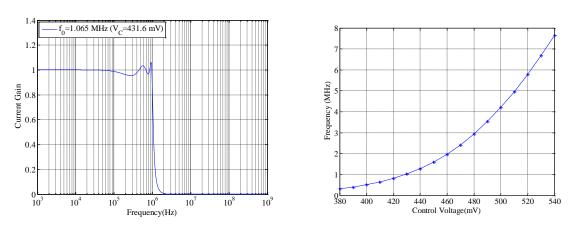

| Fig. 5.3.1.4 | PSPICE simulation results of the fully-differential current-mode fifth order lowpass Butterworth Filter (a) Frequency response (i) Normal (ii)Using pre-distorted resistor values at ports `i` (iii) Ideal (obtained using MATLAB) (b) Transient response | 119 |

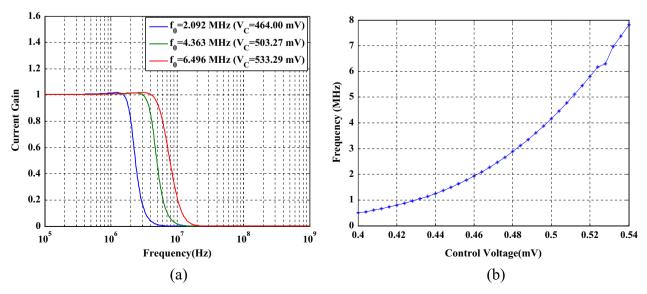

| Fig. 5.3.1.5 | PSPICE simulation results (a) Tunability of cut-off frequency with Control Voltage and (b) Variation of the cut-off frequency with control voltage Vc                                                                                                     | 120 |

| Fig. 5.3.1.6 | Results of Monte Carlo analysis for fully-differential current-mode fifth order low pass Butterworth filter                                                                                                                                 | 120 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.3.1.7 | Fifth order fully-differential CM lowpass filter with reduced-component-count                                                                                                                                                               | 121 |

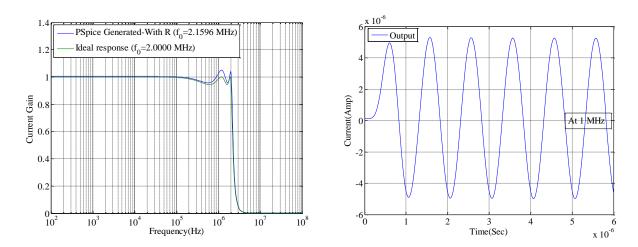

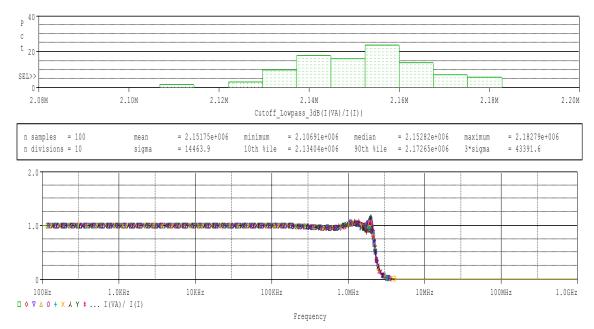

| Fig. 5.3.2.1 | PSPICE simulation results of the fully-differential current-mode fifth order lowpass Chebyshev Filter (a) Frequency response (i)-Using pre-distorted resistor values at ports `i` (iii)Ideal (obtained using MATLAB) (b) Transient response | 123 |

| Fig. 5.3.2.2 | PSPICE simulation results (a) Tunability of cut-off frequency with Control Voltage and (b) Variation of the cut-off frequency with control voltage Vc                                                                                       | 124 |

| Fig. 5.3.2.3 | Results of Monte Carlo analysis for fully-differential current-mode fifth order low pass Chebyshev filter.                                                                                                                                  | 124 |

| Fig.6.2.1    | Symbolic notation of the ZC-CFCC                                                                                                                                                                                                            | 134 |

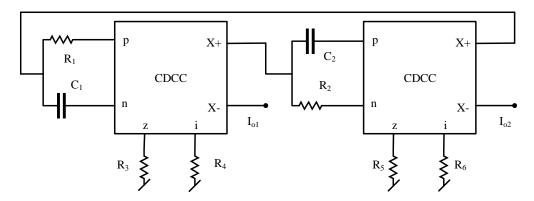

| Fig.6.2.2    | The proposed CFCC-based current mode quadrature oscillator                                                                                                                                                                                  | 134 |

| Fig.6.3.1    | CFCC-based current mode quadrature oscillator with grounded capacitors                                                                                                                                                                      | 135 |

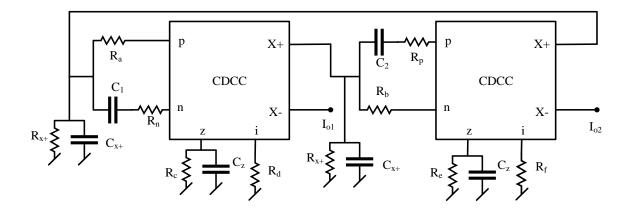

| Fig.6.4.1    | Non-ideal model of CFCC- based current mode quadrature oscillator                                                                                                                                                                           | 137 |

| Fig.6.5.1    | An exemplary CMOS implementation of the ZC-CFCC                                                                                                                                                                                             | 140 |

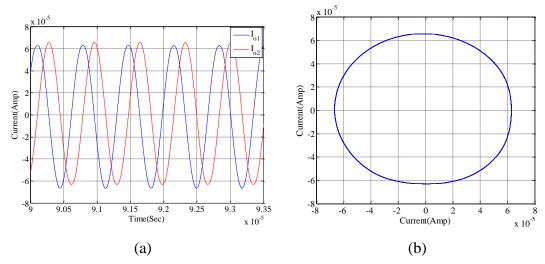

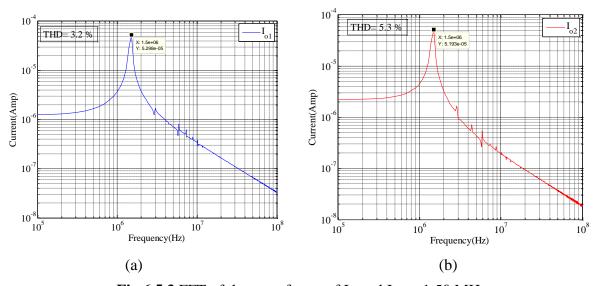

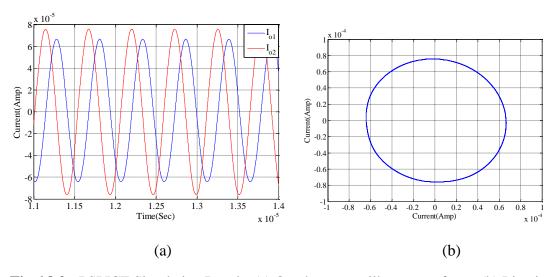

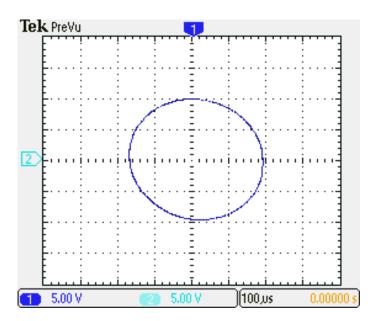

| Fig.6.5.2    | PSPICE Simulation Results (a) Quadrature oscillator waveforms (b)  Lissajous pattern                                                                                                                                                        | 141 |

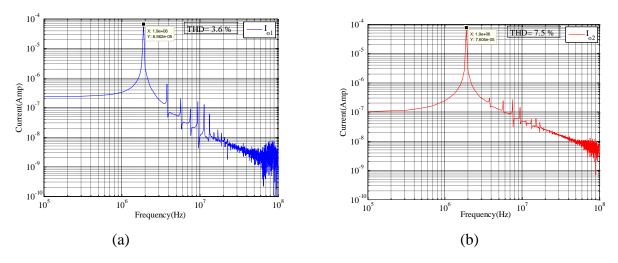

| Fig.6.5.3    | FFT of the waveforms of $I_{o1}$ and $I_{o2}$ at 1.50 MHz                                                                                                                                                                                   | 141 |

| Fig.6.6.1    | Symbolic notation and port-relations of the CDCC                                                                                                                                                                                            | 142 |

| Fig.6.6.2    | Two variants of CDCC-based current mode all pass filters                                                                                                                                                                                    | 142 |

| Fig.6.6.3    | Proposed CDCC-based current mode quadrature oscillator                                                                                                                                                                                      | 143 |

| Fig.6.7.1    | Non-ideal model of CDCC based current mode quadrature oscillator                                                                                                                                                                            | 144 |

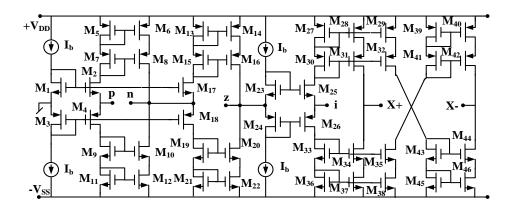

| Fig.6.8.1    | CMOS implementation of the CDCC [28]                                                                                                                                                                                                        | 147 |

| Fig.6.8.2    | PSPICE Simulation Results (a) Quadrature oscillator waveforms (b) Lissajous pattern                                                                                                                                                         | 147 |

| Fig.6.8.3     | FFT response of designed oscillator at 2 MHz                         | 148 |

|---------------|----------------------------------------------------------------------|-----|

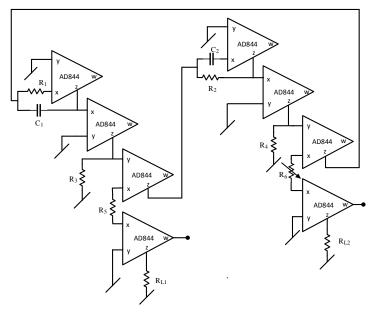

| Fig. 6.9.1(a) | Schematic realization of the proposed CDCC-based oscillator using    |     |

|               | AD844 ICs                                                            | 149 |

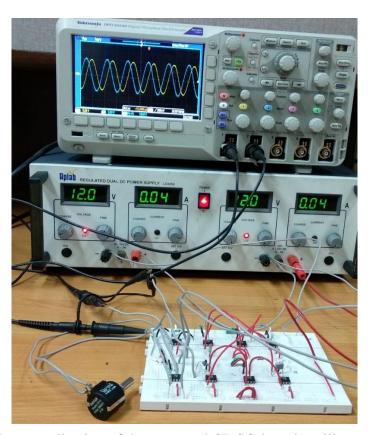

| Fig. 6.9.1(b  | ) Hardware realization of the proposed CDCC-based oscillator using   |     |

|               | AD844 ICs                                                            | 149 |

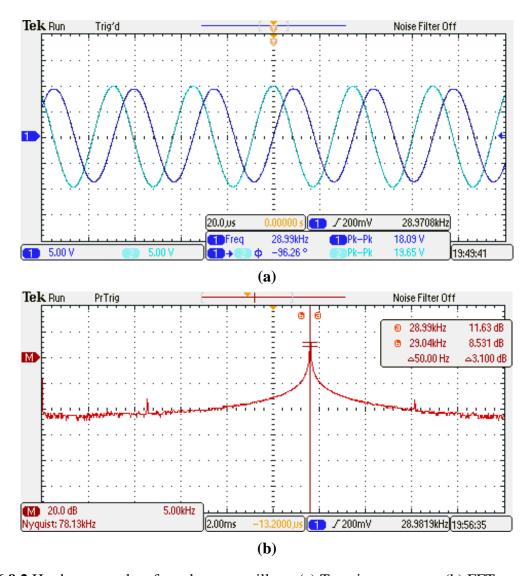

| Fig.6.9.2     | Hardware results of quadrature oscillator (a) Transient response (b) |     |

|               | FFT waveform                                                         | 150 |

| Fig.6.9.3     | Lissajous pattern of proposed quadrature oscillator                  | 150 |

# **List of Tables**

| Table 1.2.1   | Basic Active Element (available as off-the -shelf ICs)                                                                             | 5   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 1.3.1   | Some other active elements                                                                                                         | 8   |

| Table 1.4.1   | Novel active elements                                                                                                              | 10  |

| Table 1.5.2.1 | Aspect ratios of MOSFETs used in CDCC realization.                                                                                 | 19  |

| Table 1.6.2.1 | Aspect ratios of MOSFETs used in ZC-CFCC                                                                                           | 23  |

| Table 2.4.1   | Aspect ratios of MOSFETs used in CDCC realization                                                                                  | 38  |

| Table 2.4.2   | Summary of results obtained from calculations and simulations                                                                      | 41  |

| Table 2.5.1   | Summary of the filter parameters for the circuits of six and five CDCC-based FDCMUF                                                | 51  |

| Table 3.5.1   | Aspect ratios of MOSFETs used in ZC-CFCC given in Fig. 3.2.2                                                                       | 67  |

| Table 3.6.1   | Comparison with other recently published grounded inductors realized with single active building block                             | 75  |

| Table 3.8.1   | Characteristic parameters of ZC-CFCC                                                                                               | 78  |

| Table 4.4.1   | Characteristic parameters of ZC-CFCCC                                                                                              | 91  |

| Table 4.4.2   | Aspect ratios of MOSFETs used in ZC-CFCCC realization                                                                              | 92  |

| Table 4.5.1   | Comparison with other previously published lossless grounded and floating inductors realized with synthetic active building blocks | 101 |

| Table 5.1.1   | An overview of fully-differential higher order filter structures using different ABBs                                              | 109 |

| Table 5.1.2   | Comparison of the proposed methodology with the existing general methodologies for nth order fully-differential CM filters.        | 111 |

| Table 5.3.1.1 | Aspect ratios of the various MOSFETs used in CDCC realization                                                                      | 117 |

| Table 5.3.1.2 | The SPICE-measured values of the various parasitics of the CMOS CDCC                                                               | 117 |

| Table 6.4.1   | The SPICE-measured values of the various parasitics of the CMOS ZC-CFCC                                                            | 138 |

| Table 6.5.1   | Aspect ratios of the MOSFETs used in the ZC-CFCC realization                                                                       | 140 |

| Table 6.7.1 | The SPICE-measured values of the various parasitics of the CMOS |     |  |

|-------------|-----------------------------------------------------------------|-----|--|

|             | CDCC                                                            | 145 |  |

| Table 6.8.1 | Aspect ratios of MOSFETs used in CDCC realization               | 147 |  |

### List of abbreviations used in the thesis

ABBs Active Building Blocks

**ASIC** Application Specific IC

**BP** Band Pass

**CA** Current Amplifier

**CBTA** Current Backward Transconductance Amplifier

**CCCCTA** Current Controlled Current Conveyor Transconductance Amplifier

**CCCDTA** Current Controlled Current Differencing Transconductance Amplifier

**CC-CFA** Current Controlled Current Feedback Amplifier

**CCCFCC** Current Controlled Current Follower Current Conveyor

**CCCFTA** Current Controlled Current Follower Transconductance Amplifier

**CCCII** Second–Generation Current Controlled Conveyor

CCII Second–Generation Current Conveyor

CCIII Third–Generation Current Conveyor

**CCII-TA** Second-Generation Current Conveyor Transconductance Amplifier

CDBA Current Differencing Buffered Amplifier

CDCC Current Differencing Current Conveyor

**CDDIBA** Current Differencing Differential Input Buffered Amplifier

**CDDIDOBA** Current Differencing Differential Input Differential Output Buffered

**Amplifier**

**CDDITA** Current Differencing Differential Input Transconductance Amplifier

**CDDOBA** Current Differencing Differential Output Buffered Amplifier

**CDOA** Current Differencing Operational Amplifier

**CDTA** Current Differencing Transconductance Amplifier

**CDU** Current Differencing Unit

**CF** Current Followers

**CFBCCII** Current-Controlled Fully Balanced Second Generation Current Conveyor

**CFCC** Current Follower Current Conveyor

**CF-MOCC** Current Follower Multiple-Output Current Conveyor

**CFOA** Current Feedback Operational Amplifier

**CFTA** Current Follower Transconductance Amplifier

CI Current Inverter

**CICC** Current Inverter Current Follower

CM Current Mode

CM Current Mirror

CMOS Complementary Metal Oxide Semiconductor

CTTA Current Through Transconductance Amplifier

CVBA Current Voltage Buffered Amplifier

CVCC Current Voltage Current Conveyor

CVDIBA Current Voltage Differential Input Buffered Amplifier

CVDOBA Current Voltage Differential Output Buffered Amplifier

CVTA Current Voltage Transconductance Amplifier

**DACA** Digitally Adjustable Current Amplifier

**DBTA** Differential-Input Buffered Transconductance Amplifier

**DCCII** Differential Current Conveyor

**DDA** Differential Differential Amplifier

**DIBOCOA** Differential Input Balanced Output Current Operational Amplifier

**DVCC** Differential Voltage Current Conveyor

**DVCCCTA** Differential Voltage Current-Controlled Conveyor Transconductance

**Amplifier**

DXCCII Dual X Second–Generation Current ConveyorFBDDA Fully Balanced Differential Difference Amplifier

**FBFTFN** Fully Balanced Four-Terminal Floating Nullor **FBFTFNs** Fully Balanced Four Terminal Floating Nullor

**FDCCII** Fully Differential Second Generation Current Conveyor

**FD-CF** Fully-Differential Current Follower

**FDCFOA** Fully Differential Current Feedback Operational Amplifier

**FDCMUF** Fully-Differential Current-Mode Universal Filter

**FDNR** Frequency Dependent Negative Resistance

**FTFN** Four-Terminal Floating Nullor

**GVCCIII** Gain–Variable Third-Generation Current Conveyor

**LP** Low Pass

MCDTA Modified Current Differencing Transconductance Amplifier

MCFOA Modified Current Feedback Operational Amplifier

MICCI Modified Inverting First-Generation Current Conveyor

MO-CCCDTA Multiple-Output Current Controlled Current Differencing

Transconductance Amplifier

MOCCII Multi-Output Second Generation Current Conveyor

MO-CFCC Multiple-Output Current Follower Current Conveyor

MO-CFTA Multiple-Output-Current Follower Transconductance Amplifier

MO-CICC Multiple-Output-Current Inverter Current Conveyor

MO-CITA Multiple-Output Current Inverter Transcondctance Amplifier

MOTA Multi- Output Operational Transconductance Amplifier

OTA Operational Transconductance Amplifier

OTRA Operational Trans-Resistance Amplifier

**S-E** Single-Ended

**SIMO** Single Input Multi-Output

**TSMC** Taiwan Semiconductor Manufacturing Compancy

VCR Voltage Controlled Resistors

**VDBA** Voltage Differencing Buffered Amplifier

**VDCC** Voltage Differencing Current Conveyor

**VD-DIBA** Voltage Differencing-Differential Input Buffered Amplifier

**VDIBA** Voltage Differencing Inverting Voltage Buffered Amplifier

**VDTA** Voltage Differencing Transconductance Amplifier

**VDU** Voltage Differencing Unit

**VF** Voltage Follower

**ZC CFCCC** Z-Copy Current Follower Current Controlled Conveyor

**ZC-CDBA** Z-Copy CDBA

**ZC-CDTA** Z-Copy CDTA

**ZC-CFTA** Z-Copy Current Follower Transconductance Amplifier

# Chapter 1

## Introduction

After reviewing the evolution of the various active circuit elements in a historical perspective, it has been pointed out that the current differencing current conveyor (CDCC) or any variant of this have not received much attention in the literature in the context of the synthesis and design of analog electronic circuits. It has been pointed out that this void has been the main reason for exploring the characterisation and applications of the CDCC for the research reported in this thesis.

#### 1.1 Introduction

This thesis deals with a new analog circuit building block known as Current Differencing Current Conveyor (CDCC) and its variants and their applications in circuit synthesis and design.

In modern integrated circuits, analog and digital signal processing circuits both are required to be integrated on the same chip. In contrast to the conventional voltage mode, which utilizes electric voltages, the current mode circuits can exhibit under certain conditions among other things higher bandwidth and better signal linearity. Moreover, there is continued demand for the circuits to operate on lower power supplies, because of which low voltage analog design with wide dynamic range and high linearity is challenging. This is one of the main reasons for a lot of research work being carried out in the current mode (CM) circuits in which the principal signals are in the form of currents, rather than voltages [1]. The CM circuits offer one or more of the following attractive features in several applications: superior bandwidth, lower operating voltages, enhanced linearity, low power consumption, and simple architecture. Apart from using discrete transistors, analog signal processing was traditionally carried out with the help of Integrated circuit amplifiers (Operational Amplifiers, Operational Transconductance Amplifiers etc.). With the introduction of current conveyor and current feedback amplifier ICs (CCII01, PA630, AD844) these ICs are also being used in analog signal processing.

More recently, the advent of CM signal processing alongwith developments in modern IC fabrication technology, has seen a new trend in analog signal processing research wherein new active building blocks (ABBs) comprised of a combination of current conveyor blocks, transconductance blocks, current differencing blocks, voltage buffers and current buffers, current mirrors have emerged. Since the work presented in this thesis deals with a modern active building block named CDCC, it is worthwhile to present a brief overview of the

evolution of the various new active building blocks since the time of introduction of the integrated circuit operational amplifiers.

#### 1.2 Active building blocks available as Off-the-shelf ICs

The introduction of the integrated circuit operational amplifier in mid-sixties was a natural consequence of the developments taking place in semiconductor fabrication technology and the advantages offered by ICs (reduction in size, power consumption, economy of scales etc.). Though operational amplifiers had come around early 40s, these were vacuum tube based and occupied very large space. The first mass produced IC operational amplifier was Fairchild's µA741 which came around 1966-67. It was an internally compensated voltage amplifier with differential-input but single-ended output. Internal frequency compensation was provided by an on-chip compensating capacitor of typical value in the range 25pF-30pF. The amplifier had a unity gain bandwidth of around 1MHz. Several excellent text books have appeared in literature in which details of the architecture of this amplifier, its analysis and its various applications have been presented [2]- [5].

Another very important integrated circuit amplifier, CA 3080 which became very popular with analog circuit designers was introduced in 1969 at RCA. It was a transconductance amplifier whose gain could be controlled externally by changing its bias current.

The current-mode approach in analog signal processing had started gaining currency during this time and appearance of an integrated circuit amplifier with a current output became very handy in implementing a number of current-mode circuits. The front end of this amplifier was a differential amplifier and thus the linear range of this amplifier was restricted to less than  $\pm 2V_T$ . In later versions of this IC such as LM13600/13700 diode linearization scheme was used to enhance its linear range. Applications of this amplifier in analog signal processing have been well documented. Some of these may be found in [6]-[11] and the references cited therein.

The second half of sixties witnessed a lot of research and development activities in analog signal processing. The introduction of current conveyors [12], [13] by Sedra and Smith was one such development. The current conveyors have attracted lot of attention from the analog signal processing community worldwide and it is also available in integrated circuit form from several semiconductor manufactures namely CCII01 from LTP Electronics, PA630 from Phototronics Limited and AD844 from Analog devices. Though AD844 is not available by the name of current conveyor but it contains a CCII+ whose terminals are externally accessible. The current conveyor can also be thought of as among the first active building blocks which combined the characteristics of two functionally independent blocks, namely, a voltage follower and a current follower. The current conveyor IC had one very low impedance input terminal 'x' and a very high impedance terminal 'y'. Its output current is available at a very high output impedance terminal 'z'. Like the operational transconductance amplifier, the current conveyor and its numerous variants have been used to implement all kinds of analog signal processing/generation circuits. A research monograph on current conveyors containing most of the important implementations, applications and other related aspects has appeared in literature recently [14].

The development of truly complementary bipolar process with PNP and NPN transistors having comparable performance characteristics led to the introduction of a new amplifier architecture, namely, the trans-impedance amplifier, alternatively referred to as current feedback amplifier. This nomenclature was assigned to this structure so as to distinguish it from the conventional voltage amplifier architecture in which the feedback employed was voltage. This architecture offered several advantages over the conventional voltage feedback amplifier viz. (i) very high slew rate (ii) constant bandwidth operation for medium to moderately large values of the closed loop gain. Typical values of slew rate attainable are in the range 2000-9000V/us. The first integrated circuit current feedback op-amps (CFOA) were AD844 from

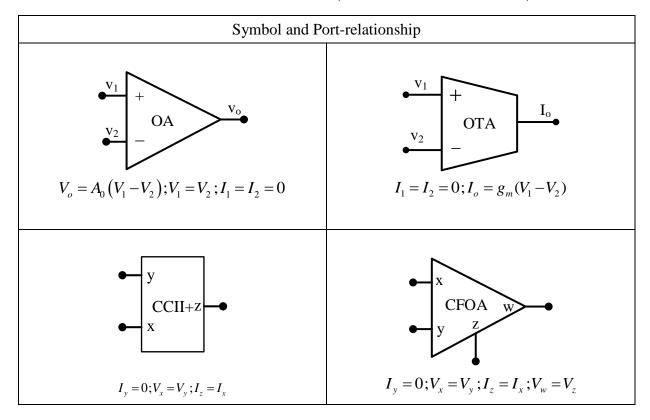

Analog Devices Inc. (Designed by Barrie Gilbert) introduced in 1984 and the other one introduced by Elantec in 1987. A CFOA is functionally equivalent to a CCII+ followed by a voltage buffer. The external compensation pin available separately in AD844 makes possible the use of this IC as second generation current conveyors of both kinds (CCII+ using one AD844 and CCII- using two AD844s). If the compensation pin is left open, then this IC is pin-compatible with µA741 type integrated circuit operational amplifiers. Different Bipolar/CMOS architectures of the current feedback amplifiers and their numerous applications in analog circuits have been given in [15]. The Table 1.2.1 given below gives the terminal equations and the standard symbols used to describe these active building blocks.

**Table 1.2.1** Basic Active Elements (available as off-the-shelf ICs)

#### 1.3 Other active elements

The developments in the semiconductor fabrication technology, largely on account of concurrent developments in fast processors and industrial applications of computers and

microcontrollers during the last couple of decades have led to many developments in the field of analog signal processing. Application specific ICs (ASIC) are a reality now. The simultaneous integration of analog and digital circuits on the same piece of silicon requires ever decreasing supply voltages for these ICs to be used in various portable applications. Newer techniques and ideas for processing of analog signals are needed to keep pace with such developments. Various new active building blocks, integrable versions of which (both CMOS and Bipolar) have been proposed by researchers, came up in response to either overcome some of the major limitations of the existing building blocks e.g. very small value of slew rate of voltage operational amplifiers or its gain-bandwidth conflict, very small linear range of operation of transconductance amplifiers or specific signal processing problems (e.g. realisation of a particular filter configuration with all grounded passive elements and independently tunable parameters, realisation of a harmonic oscillator with fully decoupled control of condition of oscillation and frequency of oscillation etc.). Some of the important active building blocks so developed are now described briefly.

**OTRA**: Chen, Tsao and Chen in 1992 introduced the new active building block namely, Operational Trans-resistance Amplifier (OTRA). The CMOS implementation of the OTRA did not suffer from the gain-bandwidth conflict. Inverting amplifier, non-inverting amplifier and MOSFET-C differentiator realizations using the OTRA have been presented in [16].

**CDBA**: In 1999, Acar and Özoğuz proposed Current Differencing Buffered Amplifier (CDBA) as a versatile active building block useful for realization of analog filters. Its CMOS realization and an alternate realization using commercially available ICs (AD844) have been presented in [17].

**CDTA**: Biolek, in 2003, presented the Current Differencing Transconductance Amplifier (CDTA) as a versatile active building block especially suitable for current-mode signal

processing. It had currents as the input and output variables. Several application examples using CDTA in realization of current-mode filters were also presented in [18].

CTTA: The active building block Current through Transconductance Amplifier (CTTA), presented in [19] was also introduced by Biolek and Gubek in 2004. This amplifier had characteristics similar to that of the CDTA except the input current differencing unit which was replaced by a current 'through' unit which presented a short circuit to the input current. The application of CTTA in realization of current controlled impedance has been presented in [19]. The difficulties in realization of the 'current through unit' led to the development of CCTA, the Current Conveyor Transconductance Amplifier by Prokop and Musil [20] in 2005. In CCCTA, a current controlled conveyor is used to sense the input current.

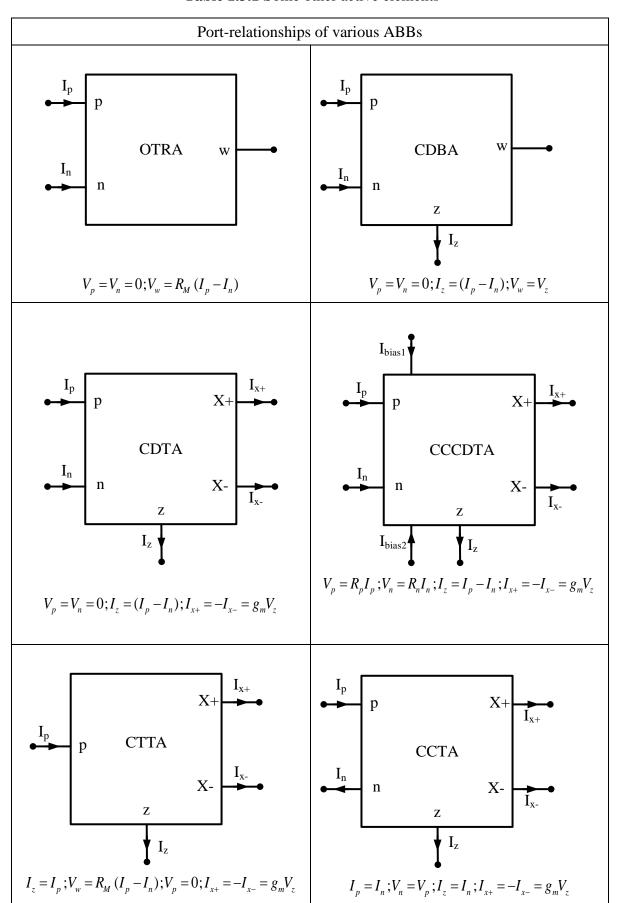

Like several variants of the basic current conveyors, numerous variants of CDBA, CDTA and CCTA have appeared in literature for use in various kinds of signal processing and generation circuits. A detailed discussion of these variants and their applications is beyond the scope of this thesis and hence has not been attempted here. Table 1.3.1 shows the symbols and terminal/port relations of the active building blocks described above.

#### 1.4 Novel Active Elements

In 2008 Biolek, Senani, Biolkova, and Kolka,[21] presented a very comprehensive review of the developments of various active building blocks employed in analog signal processing. They had given a different perspective to the development of the existing active building blocks in terms of fundamental building blocks viz. voltage followers (VF), current followers (CF), voltage differencing units (VDU), current differencing units (CDU), current inverters (CI) and current mirrors (CM). The terminal equations of most of the existing active building blocks were shown to be derivable from an interconnection of these fundamental blocks.

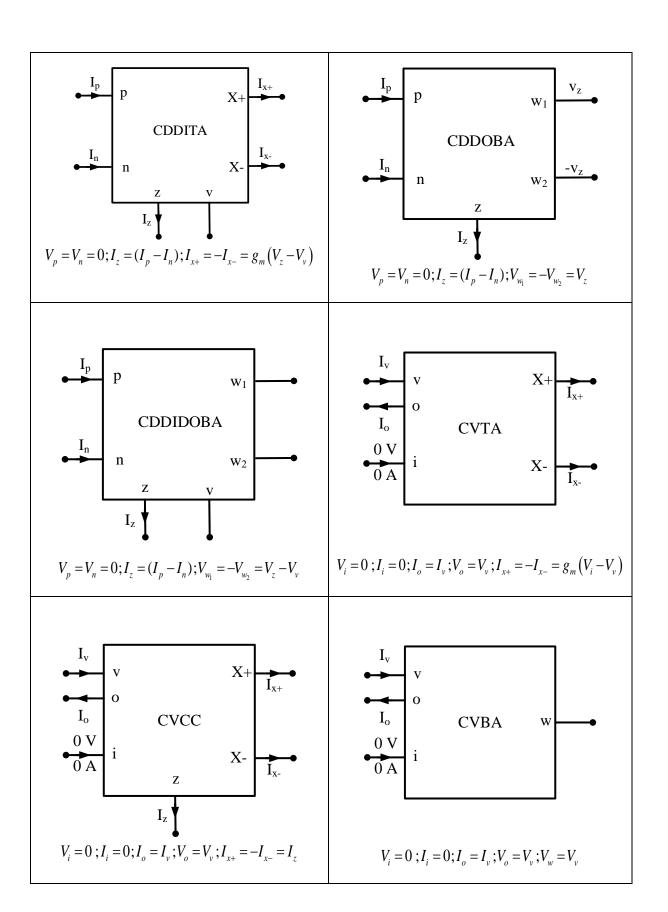

**Table 1.3.1** Some other active elements

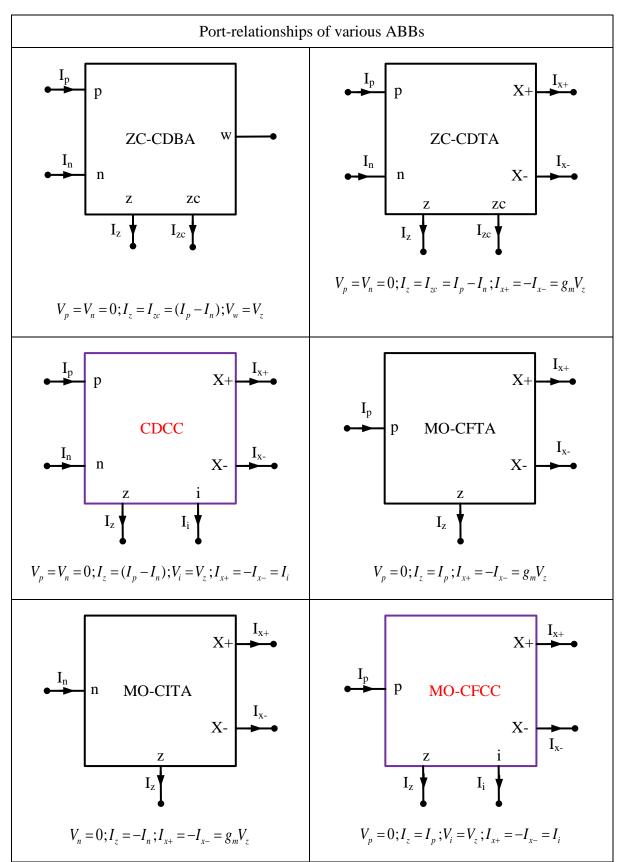

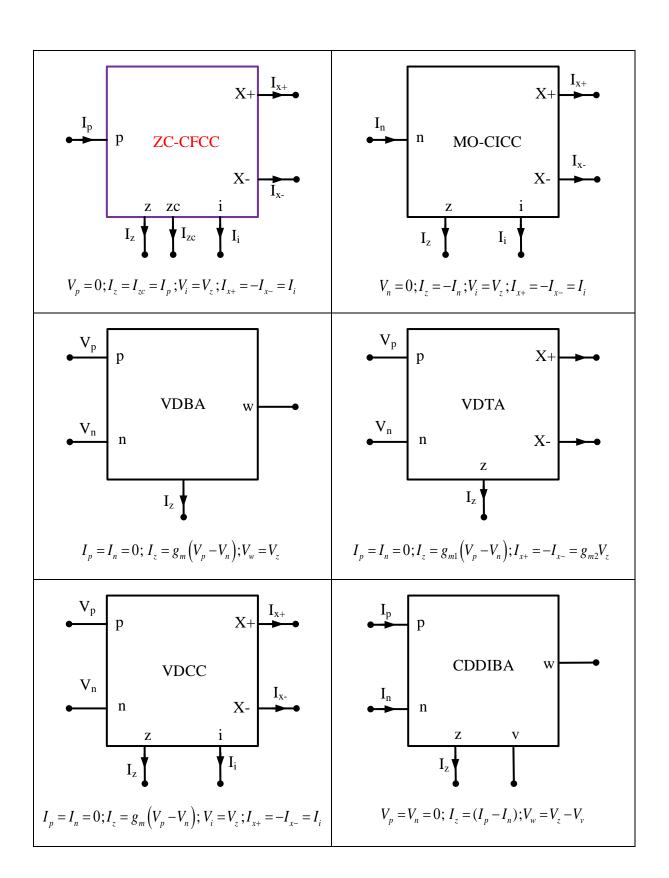

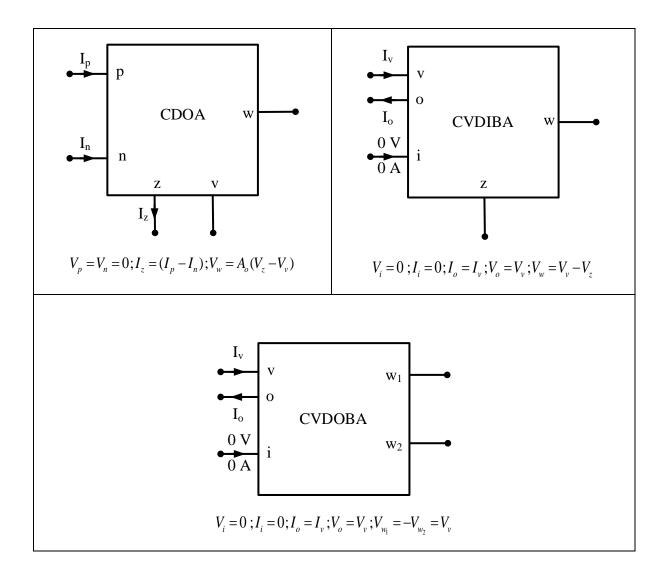

In addition, they also took cognisance of the existence of standard amplifiers like operational amplifiers, operational transconductance amplifiers, current conveyors and current feedback amplifiers etc. and proposed a set of new active building blocks in which these amplifier configurations and combinations of VF/CF/VDU/CDU/CI/CM have been used. The following novel elements were proposed in this paper: Z-copy CDBA (ZC-CDBA), Z-Copy CDTA (ZC-CDTA), current differencing external transconductance amplifier (CDeTA), current differencing current conveyor (CDCC), multiple-output-current follower transconductance amplifier (MO-CFTA), multiple-output current inverter transcondctance amplifier (MO-CITA), multiple-output current follower current conveyor (MO-CFCC), multiple-outputcurrent inverter current conveyor (MO-CICC), voltage differencing buffered amplifier (VDBA), voltage differencing transcoductance amplifier (VDTA), voltage differencing current conveyor (VDCC), current differencing differential input buffered amplifier (CDDIBA), current differencing differential input transconductance amplifier (CDDITA), current differencing differential output buffered amplifier (CDDOBA), current differencing differential input differential output buffered amplifier (CDDIDOBA), current voltage transconductance amplifier (CVTA), current voltage current conveyor (CVCC), current voltage buffered amplifier (CVBA), current differencing operational amplifier (CDOA), current voltage differential input buffered amplifier (CVDIBA) and current voltage differential output buffered amplifier (CVDOBA). The terminal relation-ships of these ABBs are given in Table 1.4.1.

Many of these newly proposed active building blocks and other similar blocks have been used by various researchers in various signal processing and signal generation applications (see [22-48] and the references cited therein).

**Table 1.4.1** Novel active elements introduced in [21]

#### 1.5 The Current Differencing Current Conveyor (CDCC)

From the literature survey it was found that amongst the proposed novel active elements given in Table 1.4.1, CDCC and its variants viz. CFCC/ZC-CFCC had not received any attention in open literature as compared to other building blocks till the time the work proposed in the thesis started (November 2011)<sup>1</sup>. It was thus decided to investigate the CDCC and some of its variants (CFCC/ZC-CFCC) and their applications for the work reported in this thesis.

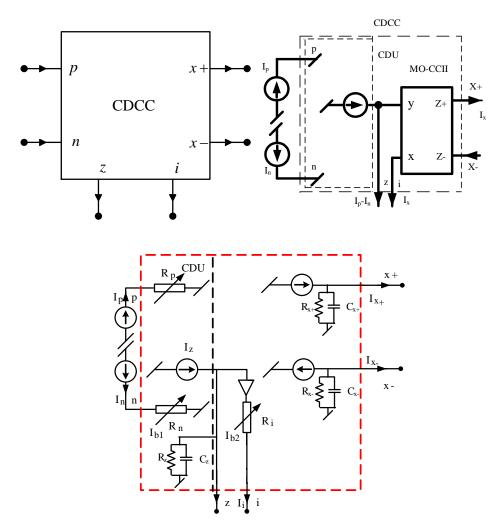

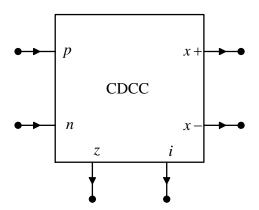

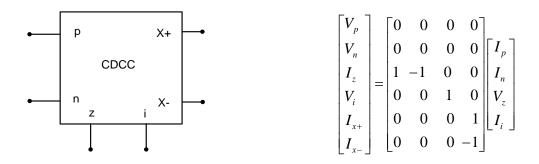

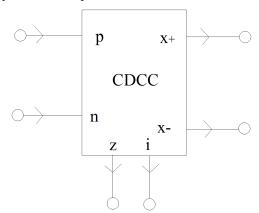

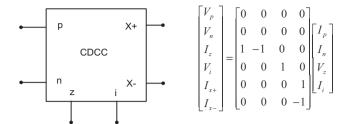

The behavioural model of the current differencing current conveyor (CDCC) was given in [21] and is shown below in Fig.1.5.1

Although two publications on CDCC [49], [50] did appear later during the course of this work (November, 2011-September, 2018).

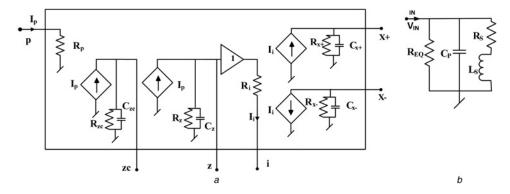

**Fig.1.5.1** (a) Circuit symbol of CDCC (b) Behavioural model [21] (c) Modified behavioural model considering parasitics

The port relationship of the CDCC can be described by equation (1.5.1)

## 1.5.1 CMOS implementation of the CDCC

From the behavioural model of the CDCC shown in Fig.1.5.1 it may be noted that the CMOS implementation of this block will require (i) a current differencing unit and (ii) a multiple

output current conveyor. Both the units can be realized using translinear voltage buffer(s) and current mirrors/ cross coupled current mirrors.

**Translinear Voltage Buffer:** A translinear voltage buffer is shown below in Fig. 1.5.1.1.

Fig.1.5.1.1 shows the voltage buffer based on translinear loop formed by transistors. We now present an analysis of this circuit [51]. KVL in the loop comprising  $M_1 - M_4$  gives:

$$V_{xy} = V_{GS1} - V_{GS2} = V_{GS3} - V_{GS4}$$

(1.5.1.1*a*)

where  $V_{GSi}$  (i = 1,2,3,4) represent gate to source voltage of transistor  $M_i$ . KCL at node x gives (as  $I_2 = I_{D2} = I_{S2}$  and  $I_4 = I_{D4} = I_{S4}$ )

$$i_x = I_4 - I_2$$

(1.5.1.1b)

Fig.1.5.1.1 Translinear Voltage buffer

Assuming saturation region operating region of all the transistors, (1.5.1.1a) can be written as

$$V_{xy} \cong \sqrt{\frac{I_b}{\frac{1}{2}\mu_n C_{ox} \frac{W_n}{L_n}}} - \sqrt{\frac{I_2}{\frac{1}{2}\mu_n C_{ox} \frac{W_n}{L_n}}}$$

$$V_{xy} \cong \sqrt{\frac{I_4}{\frac{1}{2}\mu_p C_{ox} \frac{W_p}{L_n}}} - \sqrt{\frac{I_b}{\frac{1}{2}\mu_p C_{ox} \frac{W_p}{L_n}}}$$

$$(1.5.1.2a)$$

=where  $I_b$ ,  $I_2$  and  $I_4$  represent bias current and drain currents of transistor  $M_2$  and  $M_4$  respectively.

Therefore, from (1.5.1.2a) and (1.5.1.2b)

$$i_{x} = V_{xy}^{2} \frac{C_{ox}}{2} \left( \frac{\mu_{p} W_{p}}{L_{p}} - \frac{\mu_{n} W_{n}}{L_{n}} \right) + V_{xy} \sqrt{2I_{b}C_{ox}} \left( \sqrt{\frac{\mu_{p} W_{p}}{L_{p}}} + \sqrt{\frac{\mu_{n} W_{n}}{L_{n}}} \right)$$

(1.5.1.3)

If we select the aspect ratios of the MOSFETs as per the following equation

$$\frac{\mu_p W_p}{L_p} \cong \frac{\mu_n W_n}{L_n} \tag{1.5.1.4}$$

then the equation 1.5.1.3 can be expressed as

$$V_{x} \cong V_{y} + \frac{i_{x}}{\sqrt{2I_{b}C_{ox}} \left(\sqrt{\frac{\mu_{p}W_{p}}{L_{p}}} + \sqrt{\frac{\mu_{n}W_{n}}{L_{n}}}\right)}$$

$$(1.5.1.5)$$

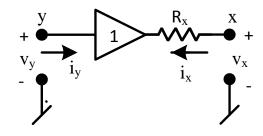

$$V_x \cong V_y + i_x R_x \tag{1.5.1.6}$$

where  $R_x$  is the output resistance of the voltage buffer as shown in Fig. 1.5.1.2.

$$R_{x} \cong \frac{1}{\sqrt{2I_{b}C_{ox}} \left(\sqrt{\frac{\mu_{p}W_{p}}{L_{p}}} + \sqrt{\frac{\mu_{n}W_{n}}{L_{n}}}\right)}$$

$$(1.5.1.7)$$

If  $i_x \leq \leq \sqrt{2I_b}$  then

$$V_{x} \cong V_{y} \tag{1.5.1.8}$$

Fig.1.5.1.2 Equivalent circuit of translinear voltage buffer

**Current Differencing Unit**: The current differencing unit is shown in Fig.1.5.1.3.

$$V_p = V_n = 0; I_z = I_p - I_n$$

Fig. 1.5.1.3 Current differencing unit (CDU)

It uses two translinear voltage buffers formed by  $(M_1, M_2, M_3, M_4)$  and  $(M_1, M_3, M_{17}, M_{18})$ . The input terminals of both the buffers (junction of S1 and S3) is connected to ground resulting in a virtual ground at the p and n terminal of the CDU. Further, the CDU uses four cascode current mirrors formed by transistors  $(M_5-M_8)$ ,  $(M_9-M_{12})$ ,  $(M_{13}-M_{16})$  and  $(M_{19}-M_{23})$ . We have used cascode configuration of current mirrors to have a higher value of output resistance of the CDU. A routine analysis of the circuit, assuming no channel length modulation in all the MOSFETs, by writing KCL at p, n and z nodes gives

$$i_p = I_4 - I_2 \tag{1.5.1.9}$$

**Multiple output Current Conveyor**: A multiple output current conveyor can be realized by a voltage buffer, and current mirrors as shown below in Fig. 1.5.1.4 The x terminal of the current conveyor is available at the output of the voltage buffer (junction of S2 and S4), y terminal at the input of the voltage buffer (junction of S1 and S3) while the positive output terminal and

the negative output terminals are available at the junction of (drain of  $M_{10}$  and  $M_{12}$ ) and (drain of  $M_{20}$  and  $M_{22}$ ) respectively. For ix<< $I_b$  as discussed above, the voltage at x terminal tracks the voltage at the z terminal with a very small error. The current flowing into x terminal is replicated at  $z_+$  through cascode mirrors formed by transistors  $M_5$ ,  $M_6$ ,  $M_8$ ,  $M_9$  and  $M_{11}$ ,  $M_{12}$ ,  $M_{14}$ ,  $M_{15}$ . The inverted current at z- terminal is transferred through cross coupled current mirror formed by transistors  $M_{17} - M_{20}$  and  $M_{21} - M_{24}$ .

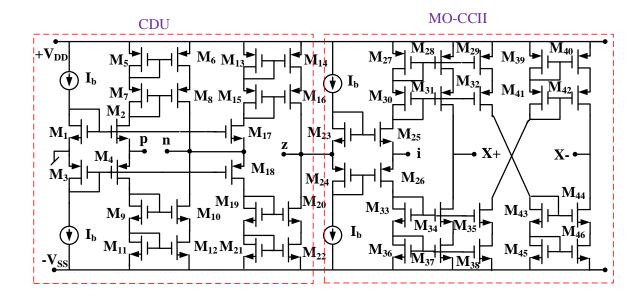

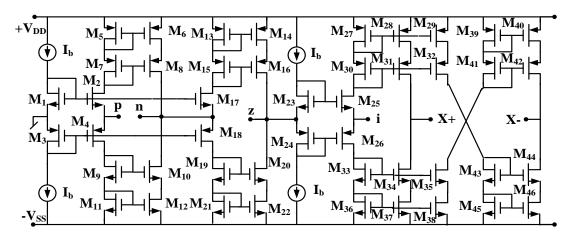

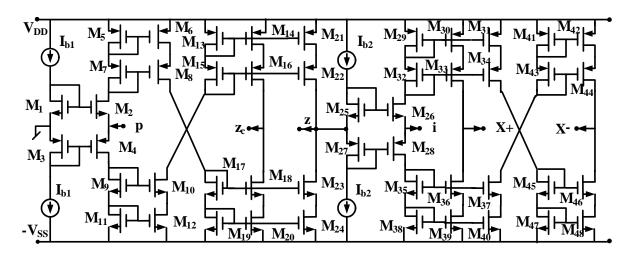

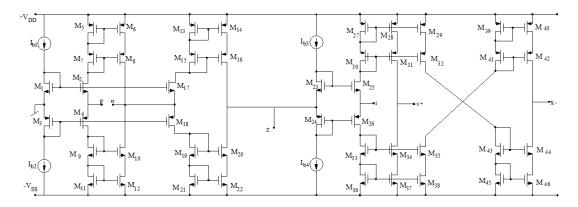

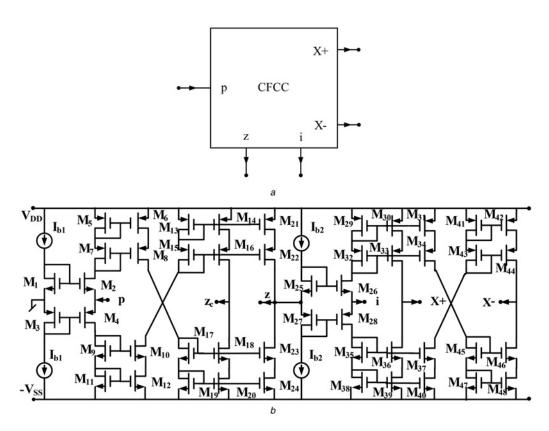

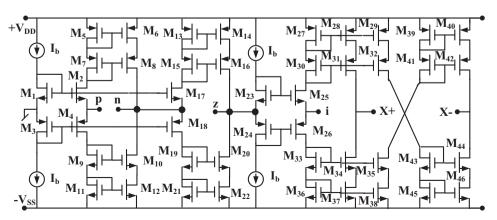

The complete CDCC can thus be implemented by simply interconnecting these constitutive sub-blocks appropriately as specified in the behavioral model shown in Fig. 1.5.1. Fig.1.5.1.5 shows the complete CMOS realization of the CDCC.

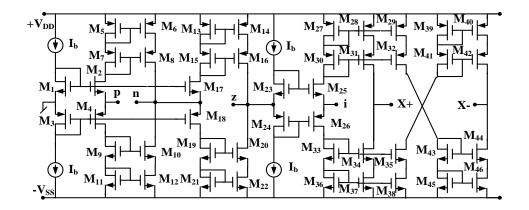

In this implementation, the transistors  $M_1 - M_{22}$  realize the CDU while the multiple-output current conveyor comprises of the transistors  $M_{23} - M_{46}$ . The aspect ratios details are given in Table 1.5.2.1.

$I_y = 0; V_x = V_y; I_{z+} = I_x; I_{z-} = -I_x$

**Fig.1.5.1.4 MOCCII**

Fig.1.5.1.5 Proposed CMOS implementation of CDCC

# 1.5.2 Characterization of the CMOS CDCC

The CMOS CDCC was implemented with TSMC CMOS 0.35  $\mu m$  technology parameters. Bias current and  $I_b$  and bias voltages  $V_{SS}$  and  $V_{DD}$  were taken as 80  $\mu A$ , -5V and +5V respectively. The aspect ratios of the MOSFETs are given below in Table 1.5.2.1.

Table 1.5.2.1 Aspect ratios of MOSFETs used in CDCC realization

| MOSFETs                   | W/L(µm/µm) |

|---------------------------|------------|

| M1,M2,M17,M23,M25         | 50/0.5     |

| M3,M4,M18,M24,M26         | 100/0.5    |

| M5- M16,M19- M22,M27- M46 | 3.33/0.5   |

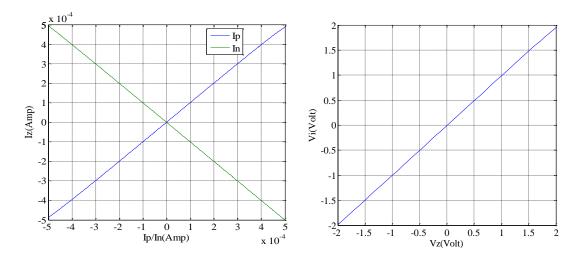

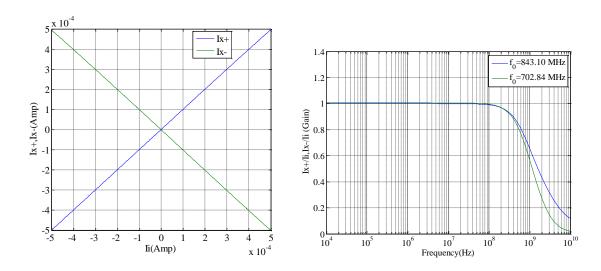

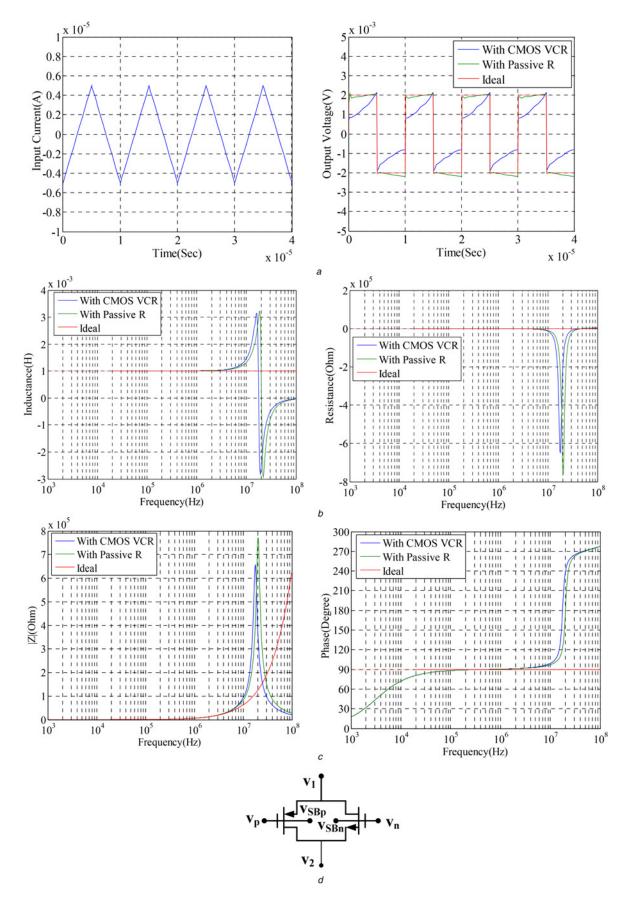

**Voltage and current transfer characteristics**: The DC current transfer characteristic are given in Fig. 1.5.2.1 (a) obtained when one input of CDCC is open circuited (i.e. either p or n). The various voltage and current transfer characteristics are shown below in Fig.1.5.2.1.

Fig. 1.5.2.1(a) DC Current transfer from I<sub>p</sub> and I<sub>n</sub> to I<sub>z</sub> (b) DC Voltage Transfer from V<sub>z</sub> to V<sub>i</sub>

**Fig. 1.5.2.1** (c) DC current transfer characteristics from  $I_i$  to  $I_{x+}$  and  $I_{x-}$  (d). Frequency Response of  $I_{x+}/I_i$  and  $I_{x-}/I_i$  for proposed CDCC

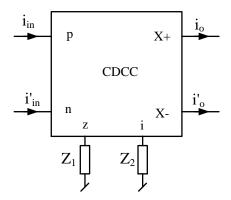

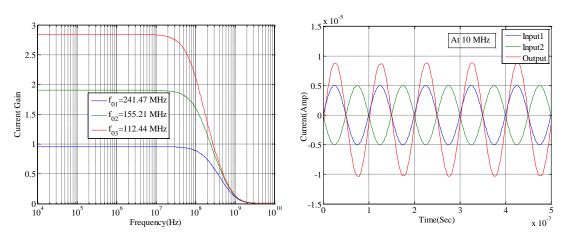

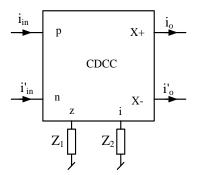

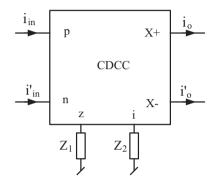

**CDCC** as an **Amplifier**: CDCC was configured as a fully differential current amplifier to verify the workability of this active building block as shown in Fig.1.5.2.2 where the z and i terminals of the CDCC are terminated into impedances  $Z_1$  and  $Z_2$ . By straight forward analysis, the output currents are given by

$$i_0 = -i_0' = \frac{Z_1}{Z_2} \left( i_{in} - i_{in}' \right) \tag{1.5.2.1}$$

Fig. 1.5.2.2 CDCC as an amplifier

If  $Z_1$  and  $Z_2$  are pure resistances than this will work as a fully differential amplifier with a gain of  $\frac{Z_1}{Z_2}$ .

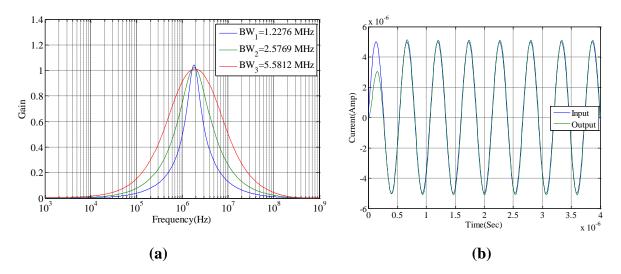

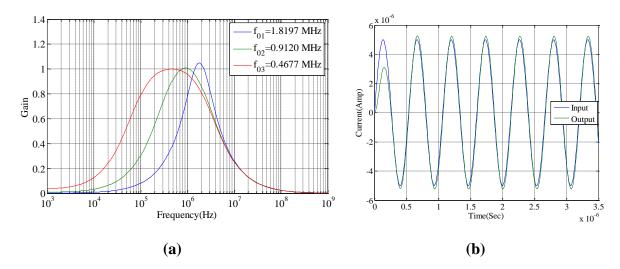

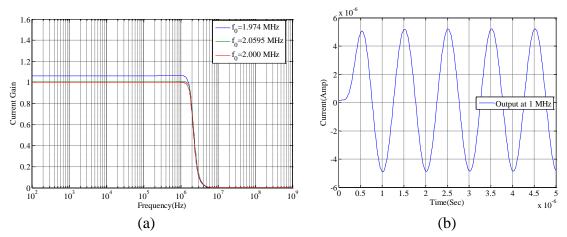

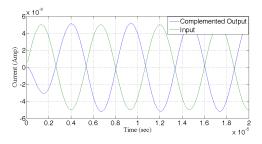

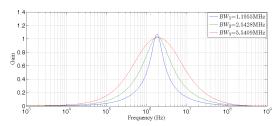

In Fig.1.5.2.2 terminal i is terminated with  $10 \text{K}\Omega$  and z terminal is terminated with  $10 \text{ k}\Omega$ ,  $20 \text{ k}\Omega$  and  $30 \text{ k}\Omega$  respectively. The frequency response of differential current gain is shown in Fig.1.5.2.3 (a). Transient response for an input current of 5  $\mu$ A and -5 $\mu$ A when the gain is 1 ( $Z_1 = Z_1 = 10 \text{K}\Omega$ ) is shown in Fig. 1.5.2.3(b).

Fig. 1.5.2.3. (a) Frequency response of fully-differential amplifier (b) Transient Response

# 1.6 Z-copy current follower current conveyor

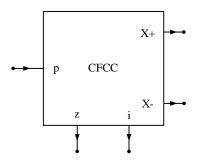

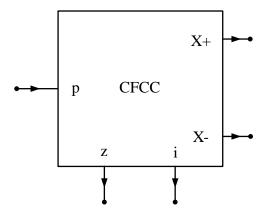

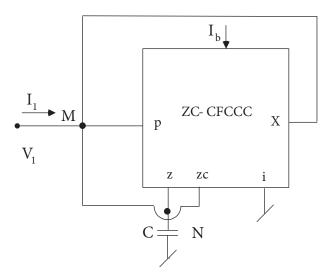

The CDCC structure is a very comprehensive structure; if we use only one of the input terminals, then the device can be termed as current follower current conveyor (CFCC) or current inverter current follower (CICC) [21]. CFCC thus turns out to be a five-port active building block whose symbolic notation is shown in Fig. 1.6.1

Fig.1.6.1 Symbolic notation of CFCC

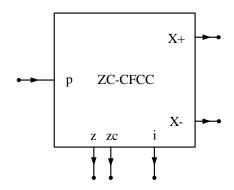

The current at the z terminal is an inverted copy of the input current at 'p' terminal. The terminal 'i' tracks the potential at the terminal z. Two complementary currents at the output terminals are available which are copies of the current at the 'i' terminal. To provide addition functionality to the CFCC a copy of the current at the 'z' terminal may also be provided resulting in the Z-copy CFCC. The symbolic notation and behavioral model of ZC-CFCC is shown in Fig.1.6.2.

Mathematically, a ZC-CFCC can be characterized by the following matrix equation:

$$\begin{bmatrix} V_{p} \\ I_{z} \\ V_{i} \\ I_{x-} \\ I \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & -1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} I_{p} \\ V_{z} \\ I_{i} \\ V_{x+} \\ V_{x-} \\ V_{x-} \end{bmatrix}$$

$$(1.6.1)$$

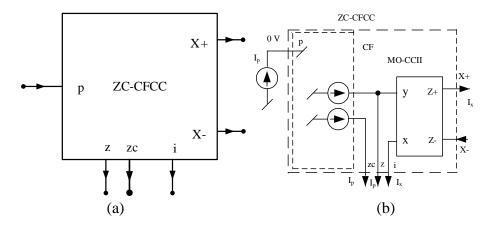

Fig.1.6.2 Symbolic notation of (a) ZC-CFCC and (b) behavioral model [21]

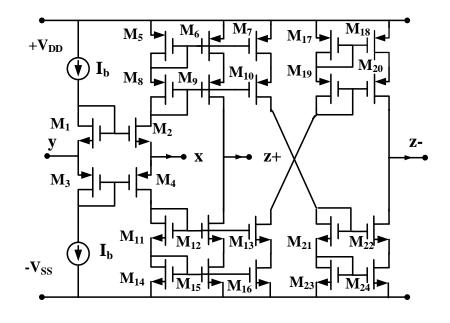

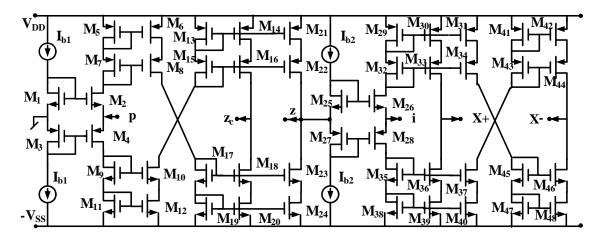

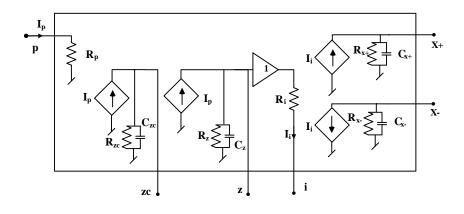

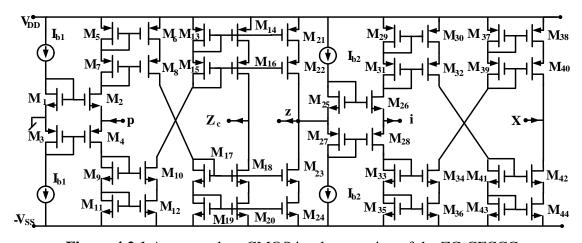

### 1.6.1 CMOS implementation of Z-copy current follower current conveyor

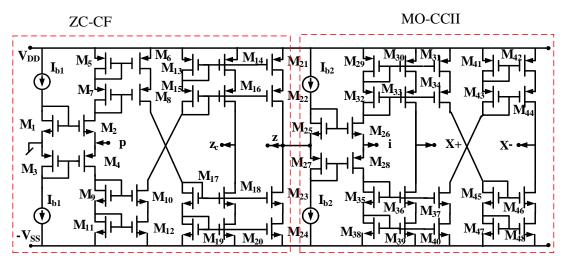

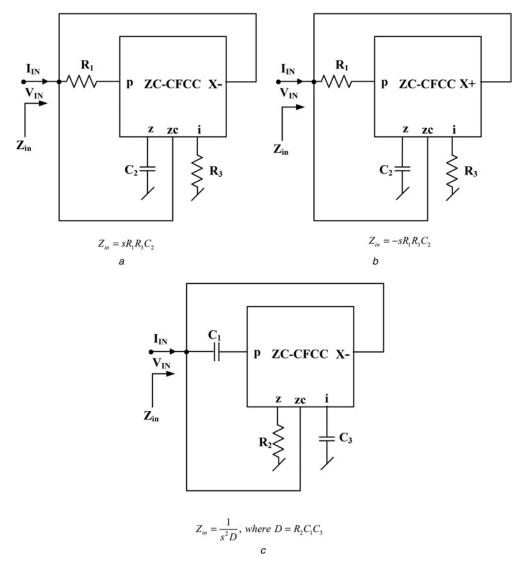

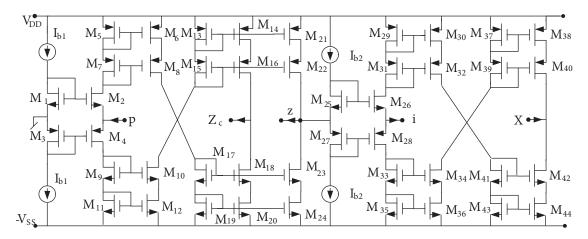

Using the behavioral model of the Z-copy CFCC, we have developed its CMOS implementation by appropriately interconnecting the basic cells discussed in section 1.6.1. The complete CMOS realization of the ZC-CFCC is shown in Fig.1.6.1.1. In this realization, the transistors  $M_1 - M_{24}$  realize the Current follower (CF) and an additional copy of Current (ZC-CF) while the multiple-output current conveyor (MO-CII) comprises of the transistors  $M_{25} - M_{48}$ .

Fig.1.6.1.1 Proposed CMOS implementation of ZC-CFCC

### 1.6.2 Characterization of the ZC-CFCC

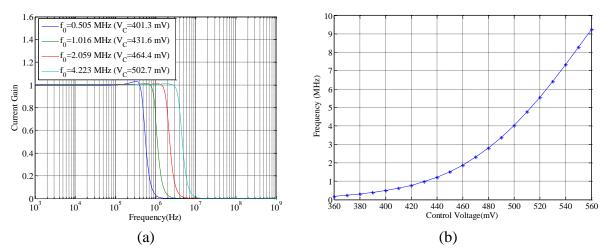

The CMOS implementation of the ZC-CFCC shown in Fig. 1.6.1.1 has been used to verify the workability of the ZC-CFCC based circuits developed in this thesis. The circuit was implemented with MOSFETS using 0.18 micron TSMC CMOS technology. The aspect ratios of the MOSFETS employed are given in Table 1.6.2.1 .The values of the DC bias currents and voltages were taken as  $40~\mu A$  and  $\pm 2.5 V$  respectively.

**Table** 1.6.2.1 Aspect ratios of MOSFETs used in ZC-CFCC

| MOSFETs                                                             | W/L (µm/µm) |  |

|---------------------------------------------------------------------|-------------|--|

| $M_1, M_2, M_{25}, M_{26}$                                          | 25/0.25     |  |

| M <sub>3</sub> , M <sub>4</sub> , M <sub>27</sub> , M <sub>28</sub> | 50/0.25     |  |

| M <sub>5</sub> - M <sub>24</sub> , M <sub>29</sub> -M <sub>48</sub> | 2.5/0.25    |  |

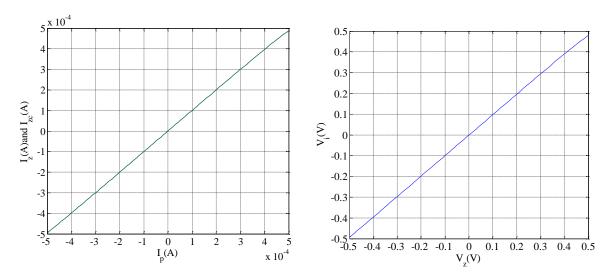

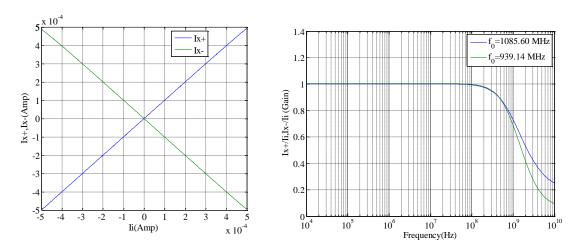

**DC** and **AC** transfer characteristics: The DC current transfer characteristic are given in Fig. 1.6.2.1 (a) obtained when current is applied at p terminal of ZC-CFCC and output current is measured at z and zc terminals. The input stage transfers the current with good accuracy. The DC voltage transfer characteristics of  $V_i$  against  $V_z$  is shown in Fig. 1.6.2.1 (b). The current transfers  $I_{x+}$  and  $I_{x-}$  with respect to  $I_i$  are given in Fig. 1.6.2.1 (c). The AC characteristics of the ZC-CFCC, namely, frequency response  $I_{x+}/I_i$  and  $I_{x-}/I_i$  are shown in Fig. 1.6.2.1 (d).

Fig. 1.6.2.1 (a) DC Current transfer from  $I_p$  to  $I_z$  and  $I_{zc}$  (b) DC Voltage Transfer from  $V_z$  to  $V_i$

**Fig. 1.6.2.1** (c) DC Transfer characteristics between  $I_i$  and  $I_{x+}$  and  $I_{x-}$  (b)Frequency response of  $I_{x+}/I_i$  and  $I_{x-}/I_i$  for proposed ZC-CFCC

### 1.7 Scope of the present work

As pointed out earlier, till the time the work reported in this thesis began (Nov.2011) nothing had appeared in open literature on CDCC hence, it was taken up for detailed investigation for applications in (i) immittance simulation (ii) design of alternative topologies of biquad and higher order filters (in fully differential form) and (iii) harmonic oscillators. The work presented in the thesis has been organized as follows:

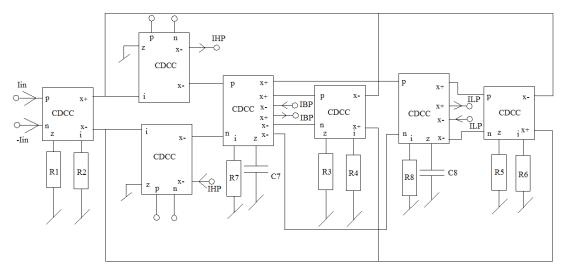

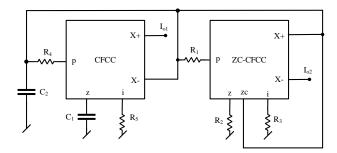

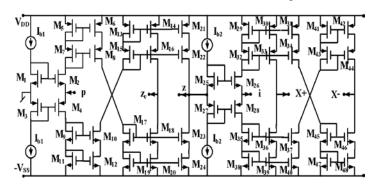

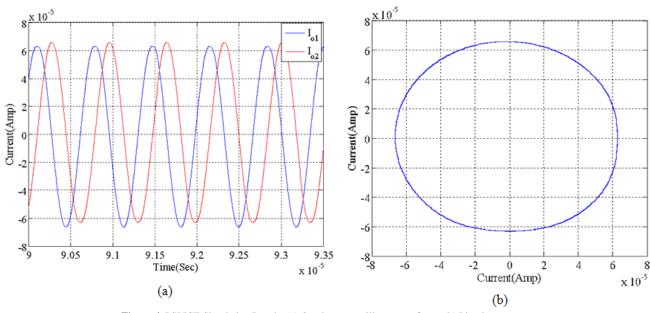

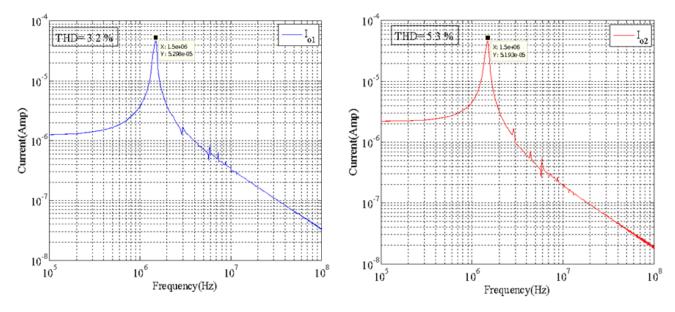

**Chapter 2** presents realization of fully differential current mode universal biquad filter configurations using CDCC.