# LC LADDER BUTTERWORTH FILTER DESIGN USING VOLTAGE DIFFERENCING TRANSCONDUCTANCE AMPLIFIER

A DISSERTATION SUBMITTED TOWARDS THE PARTIAL FULFILMENT OF THE REQUIREMENT FOR THE AWARD OF DEGREE OF

> MASTER OF TECHNOLOGY IN CONTROL & INSTRUMENTATION (ELECTRICAL ENGINEERING)

> > SUBMITTED BY

SANGITA SARKAR (2K16/C&I/17)

UNDER THE SUPERVISION OF

**RAM BHAGAT (Associate Professor)**

AND

**BHAVNESH JAINT (Assistant Professor)**

**Department of Electrical Engineering**

**DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Bawana Road, Delhi 110042 2016-2018

#### DELHI TECHNOLOGICAL UNIVERSITY

Established by Govt. Of Delhi vide Act 6 of 2009 (formerly Delhi College Of Engineering) Shahbad Daulatpur,Bawana Road,Delhi-110042

# CERTIFICATE

This is to certify that the dissertation title "LC LADDER BUTTERWORTH FILTER DESIGN USING VOLTAGE DIFFERENCING TRANSCONDUCTANCE AMPLIFIER" submitted by **Ms. Sangita Sarkar, Roll. No. 2K16/C&I/17** in partial fulfillment for the award of degree of Master Of Technology in "Control and Instrumentation(C&I)", run by department of Electrical Engineering in Delhi Technological University during the year 2016-2018, is a bonafide record of student's own work carried out by her under my supervision and guidance in the academic session 2016-2018. To the best of my belief and knowledge the matter embodied in dissertation has not been submitted for the award of any other degree or certificate in this or any other university or institute.

**Ram Bhagat**

Associate Professor (EE)

Delhi Technological University

**Bhavnesh Jaint**

Assistant Professor (EE)

Delhi Technological University

# DECLARATION

I hereby declare that all the information in this document has been obtained and presented in accordance with academic rules and ethical conduct. This report is my own work to the best of my belief and knowledge. I have fully cited all material by others which I have used in my work. It is being submitted for the degree of Master of Technology in Control and Instrumentation at Delhi Technological University. To the best of my belief and knowledge it has not been submitted before any degree or examination in any other university.

Sangita Sarkar

M.Tech (C&I)

2k16/C&I/17

Date: July,2018

Place: Delhi Technological University, Delhi

# ACKNOWLEDGEMENT

I would like to express my gratitude towards all the people who have contributed their precious time and effort to help me without whom it would not have been possible for me to understand and complete the project.

I would like to thank Mr. Ram Bhagat, Associate Professor of Electrical Engineering Department, DTU and Mrs. Bhavnesh Jaint, Assistant Professor of Electrical Engineering department, DTU, my Project supervisors for the support, motivation and encouragement throughout, the period this work was carried out. Their readiness for consultation at all times, educative comments, concern and assistance even with practical things have been invaluable.

Finally, I want to thank my parents, family and friends for always believing in my abilities and showering their invaluable love and support.

Sangita Sarkar M.Tech.(C&I) 2K16/C&I/17

#### ABSTRACT

This paper deals with the LC ladder Butterworth filter design using VDTA. As we know, there are many approaches to realize the LC ladder filter. We have adopted the element replacement method where the inductor in the LC ladder filter is replaced by the active element, i.e. VDTA as inductor cannot be realized physically due to its large size and other complexity associated with it. The non-ideal effect of VDTA is also taken into consideration. The LC ladder filter has an excellent feature of having low sensitivity to parameter variation and Butterworth filter has the maximally flat response in its pass-band so the attenuation or ripple is very less. So, these filters combine the advantages of both features. Here, I have realized low-pass, high-pass, band-pass and band-stop filters using VDTA. Its response curve is observed and transient response of output input has been checked to see the proper working of the filters designed. I also realized the inductor, floating and grounded both, and after checking its inductive equivalent characteristics, then I used it in the main filter design. The power consumption and THD% is also checked in simulation.

# CONTENTS

| CERTIFICATE                                                                                                     | i                |

|-----------------------------------------------------------------------------------------------------------------|------------------|

| DECLARATION                                                                                                     | ii               |

| ACKNOWLEDGEMENT                                                                                                 | iii              |

| ABSTRACT                                                                                                        | iv               |

| CONTENTS                                                                                                        | v                |

| LIST OF FIGURES                                                                                                 | viii             |

| LIST OF TABLES                                                                                                  | xii              |

| LIST OF ABBREVIATIONS                                                                                           | xiii             |

| CHAPTER – 1 INTRODUCTION                                                                                        | 1                |

| <ol> <li>INTRODUCTION</li> <li>ORGANIZTION OF THESIS</li> <li>STATE OF ART</li> <li>THESIS OBJECTIVE</li> </ol> | 1<br>2<br>3<br>5 |

| CHAPTER-2 LITERATURE REVIEW                                                                                     | 7                |

| 2.1. INTRODUCTION                                                                                               | 7                |

| 2.2. DIFFERENT RESEARCH METHODOLOGIES FOR LC LADDER FILTER                                                      | 8                |

| 2.2.1. LC LADDER FILTER SIMULATION USING ELEMENT REPLACEM                                                       | IENT             |

| METHOD                                                                                                          | 8                |

| 2.2.2. GYRATOR                                                                                                  | 9                |

| 2.2.3. LC LADDER METHODOLOGIES                                                                                  | 12               |

| CHAPTER-3 VOLTAGE DIFFERENCING TRANSCONDUCTAN<br>AMPLIFIER                                                                                                                                                                                                                                                                                                                                                            | NCE<br>16                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                     | 16                               |

| 3.2. VDTA (VOLTAGE DIFFERENCING TRANSCONDUCTANCE AMPLIFIER)                                                                                                                                                                                                                                                                                                                                                           | 17                               |

| 3.3. CMOS IMPLEMENTATION OF VDTA                                                                                                                                                                                                                                                                                                                                                                                      | 19                               |

| 3.4. VDTA REALIZATION USING OPERATIONAL TRANSCONDUCTAL AMPLIFIER USING OTA                                                                                                                                                                                                                                                                                                                                            | NCE<br>21                        |

| 3.5. TRANSFER CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                         | 21                               |

| <ul> <li>CHAPTER-4 REALISATION OF GROUNDED INDUCTOR A FLOATING INDUCTOR USING VDTA</li> <li>4.1. INTRODUCTION</li> <li>4.2. GROUNDED INDUCTOR USING VDTA</li> <li>4.2.1. NON-IDEALITY AND SENSITIVITY PERFORMANCE FOR GROUNDE INDUCTANCE VICTIMIZATION VDTA</li> <li>4.3. FLOATING INDUCTOR USING VDTA</li> <li>4.3.1. NON-IDEALITY AND SENSITIVITY PERFORMANCE FOR FLOATING INDUCTANCE VICTIMIZATION VDTA</li> </ul> | 23<br>23<br>24<br>ED<br>29<br>30 |

| <b>CHAPTER-5 LC LADDER FILTER REALIZATION USING VDTA</b><br>5.1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                         | <b>40</b>                        |

| 5.2. LC LADDER FILTER DESIGN                                                                                                                                                                                                                                                                                                                                                                                          | 40                               |

| 5.3. SYNTHESIS PROCEDURE                                                                                                                                                                                                                                                                                                                                                                                              | 41                               |

| 5.3.1. TRANSFORMATION OF COMPONENTS                                                                                                                                                                                                                                                                                                                                                                                   | 46                               |

| 5.4. PROJECT WORK                                                                                                                                                                                                                                                                                                                                                                                                     | 48                               |

| REFERENCES                                                      | 90          |

|-----------------------------------------------------------------|-------------|

| CHAPTER-6 CONCLUSION AND FUTURE SCOPE                           | 89          |

| 5.4.7. 10TH ORDER LC LADDER BUTTERWORTH BAND REJECT FILTER VDTA | USING<br>85 |

| 5.4.6. EIGHTH ORDER LC LADDER BUTTERWORTH BANDPASS FILTER VDTA  | USING<br>80 |

| 5.4.5. SIXTH ORDER LC LADDER BUTTERWORTH HIGHPASS FILTER VDTA   | USING<br>73 |

| 5.4.4. SIXTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER VDTA    | USING<br>66 |

| 5.4.3. FIFTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER VDTA    | USING<br>60 |

| 5.4.2. FOURTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER VDTA   | USING<br>54 |

| 5.4.1. THIRD ORDER LC LADDER BUTTERWORTH LOWPASS FILTER VDTA    | USING<br>48 |

| APPENDIX | 10 |

|----------|----|

| APPENDIX | 10 |

# LIST OF FIGURES

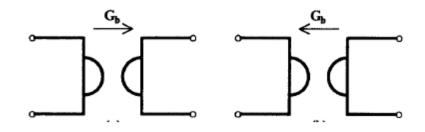

| 2.1         | GYRATOR                                                                            | 10        |

|-------------|------------------------------------------------------------------------------------|-----------|

| 2.2         | OTA BASED INDUCTOR                                                                 | 11        |

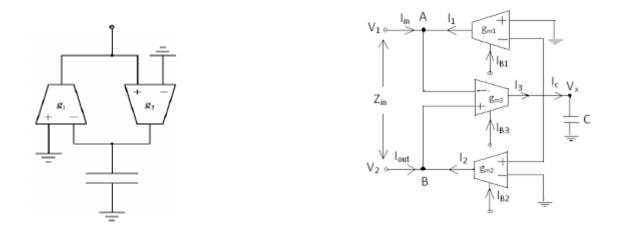

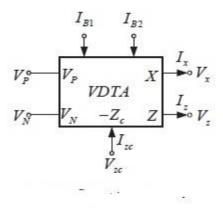

| 3.1         | CIRCUIT SYMBOL OF VDTA                                                             | 17        |

| 3.2         | CMOS IMPLEMENTATION OF VDTA                                                        | 19        |

| 3.3         | VDTA REALIZATION USING OTA                                                         | 21        |

| 3.4         | TRNSFER CHARACTEISTICS OF VDTA                                                     | 22        |

| 4.1         | GROUNDED INDUCTOR USING VDTA                                                       | 24        |

| 4.2         | INDUCTOR VS FREQUENCY FOR GROUNDED INDUCTOR USING VDTA                             | 26        |

| 4.3         | BANDPASS FILTER USING VDTA BASED GROUNDED INDUCTOR                                 | 27        |

| 4.4         | RLC CIRCUIT                                                                        | 27        |

| 4.5         | FREQUENCY RESPONSE OF BANDPASS FILTER USING VDTA BASED                             |           |

|             | GROUNDED INDUCTOR                                                                  | 28        |

| 4.6         | NON IDEAL STRUCTURE OF VDTA BASED GROUNDED INDUCTOR                                | 30        |

| 4.7         | FLOATING INDUCTOR USING VDTA                                                       | 31        |

| 4.8(        | a) VDTA BASED FLOATING INDUCTOR WITH $V_2$ SHORTED i.e. $V_2=0$                    | 32        |

| 4.8(        | b) VDTA BASED FLOATING INDUCTOR WITH V <sub>1</sub> SHORTED i.e. V <sub>1</sub> =0 | 33        |

| 4.9         | INDUCTANCE VS FREQUENCY FOR VDTA BASED FLOATING INDUCTOR                           | R         |

|             |                                                                                    | 35        |

| 4.10        | BANDPASS FILTER USING VDTA BASED FLOATING INDUCTOR                                 | 36        |

| 4.11        | RLC SERIES CIRCUIT                                                                 | 36        |

| 4.12<br>FLC | 2 FREQUENCY RESPONSE FOR BANDPASS FILTER USING VDTA BAS<br>DATING INDUCTOR         | SED<br>37 |

| 4.13        | NON IDEAL STRUCTURE OF FLOATING INDUCTOR USING VDTA                                | 39        |

|             |                                                                                    |           |

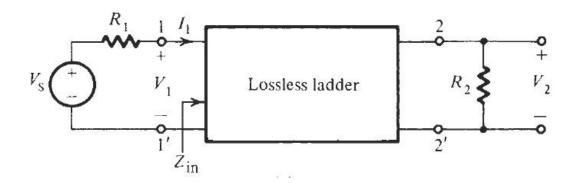

| 5.1 DOUBLY RESISTIVELY TERMINATED LC LADDER LOSSLESS FILTER                                                     | 41       |

|-----------------------------------------------------------------------------------------------------------------|----------|

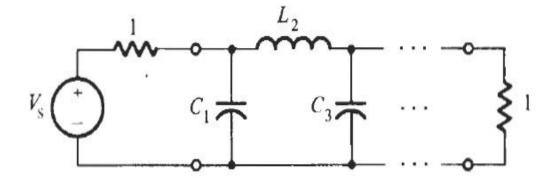

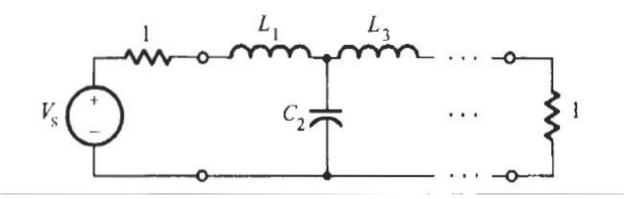

| 5.2 (a) LC LADDER LOWPASS FILTER IN GENERALISED FORM (i)                                                        | 45       |

| 5.2 (b) LC LADDER LOWPASS FILTER IN GENERALISED FORM (ii)                                                       | 46       |

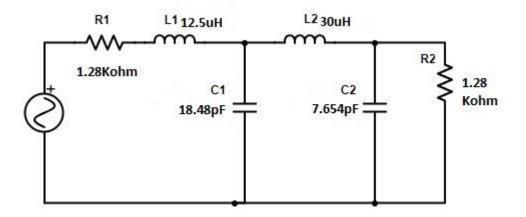

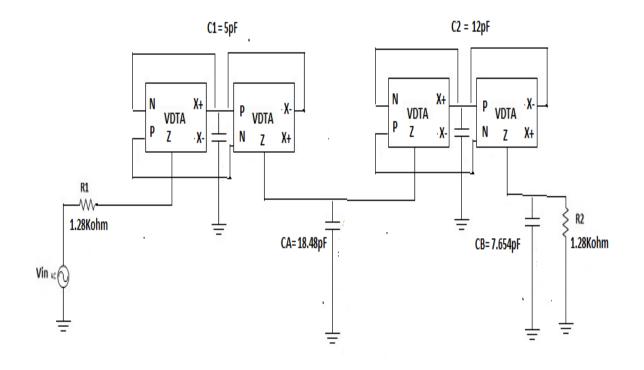

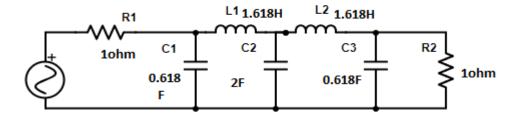

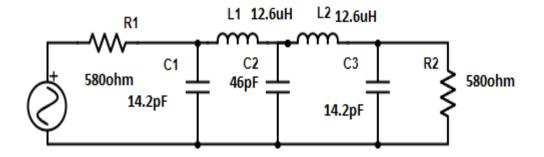

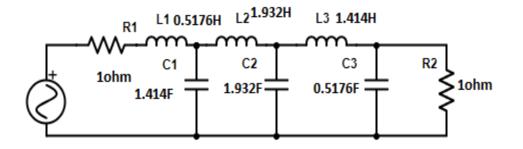

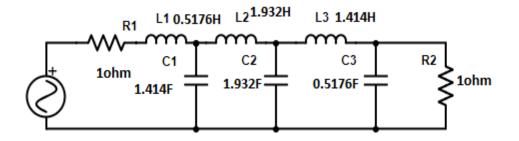

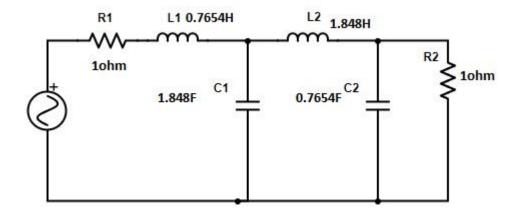

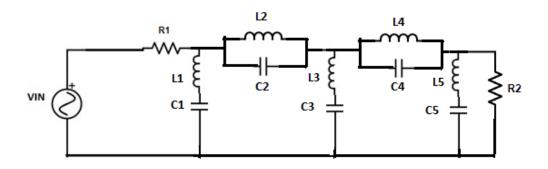

| 5.3 THIRD ORDER LC LADDER BUTTERWORTH LOWPASS FILTER                                                            | 49       |

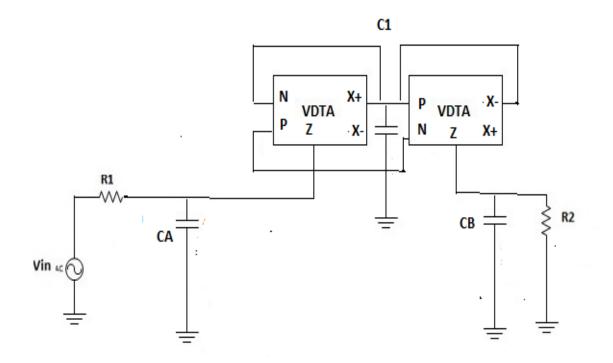

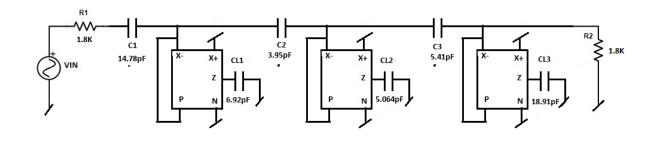

| 5.4 THIRD ORDER LC LADDER BUTTERWORTH LOWPASS FILTER USING VDT                                                  | ГA       |

|                                                                                                                 | 51       |

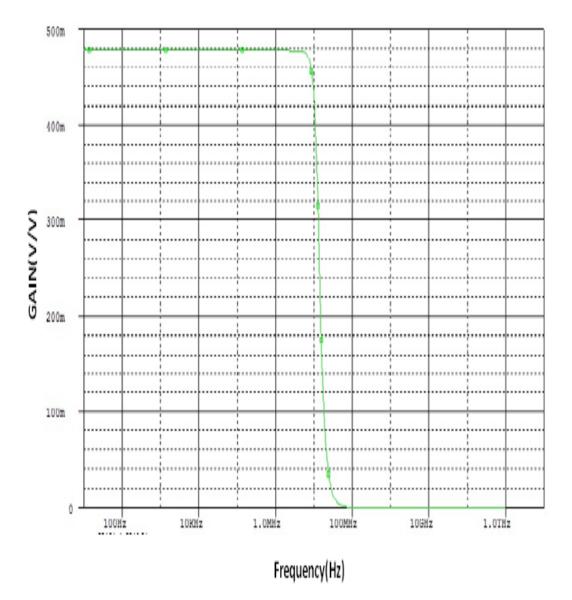

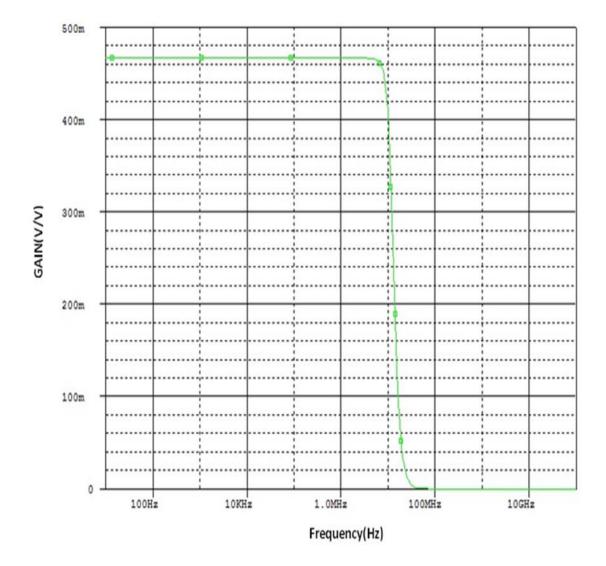

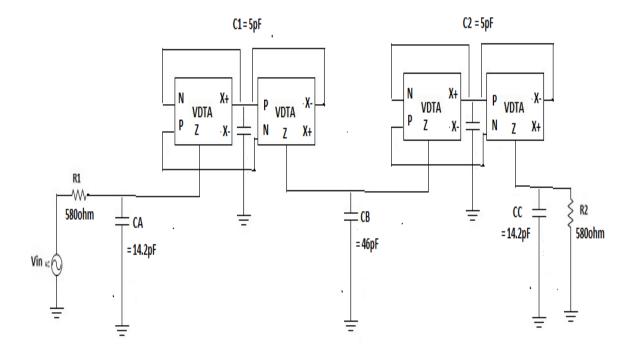

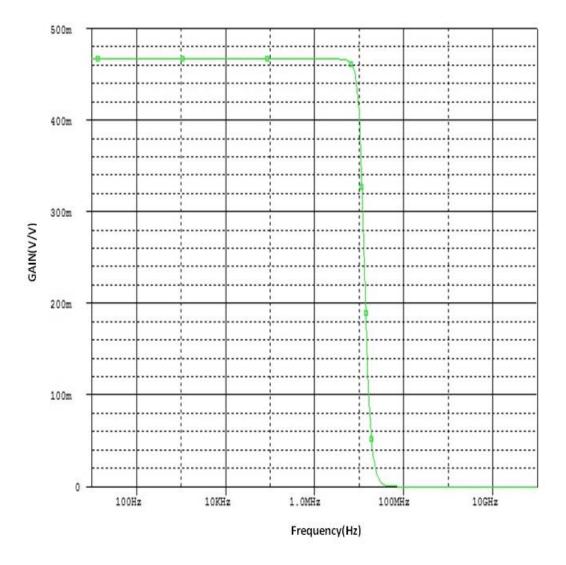

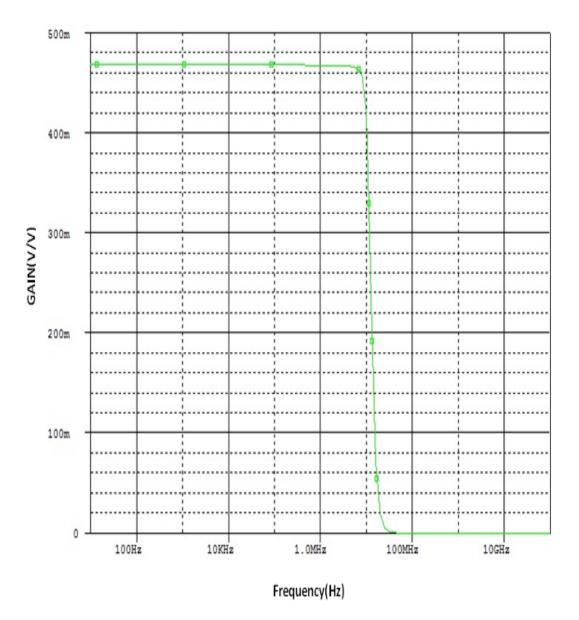

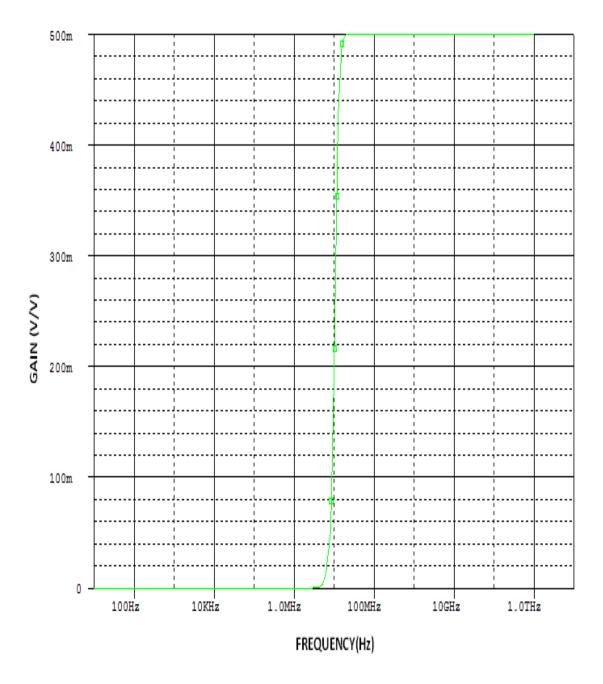

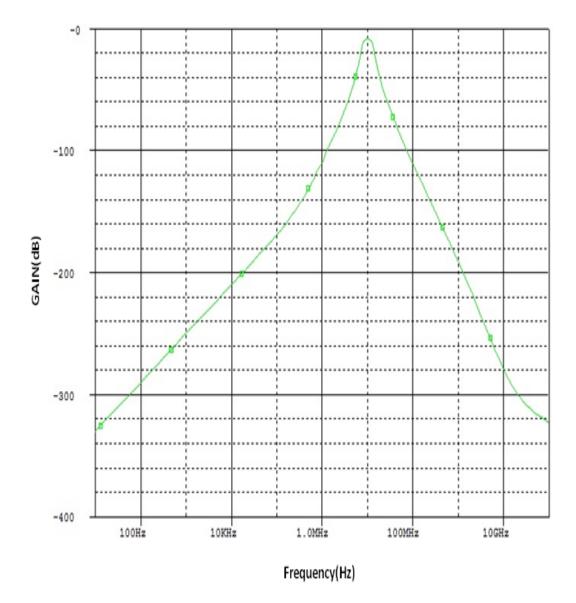

| 5.5 FREQUENCY (AC) RESPONSE OF MAGNITUDE GAIN FOR THIRD ORDER ELADDER BUTTERWORTH LOWPASS FILTER USING VDTA     | LC<br>52 |

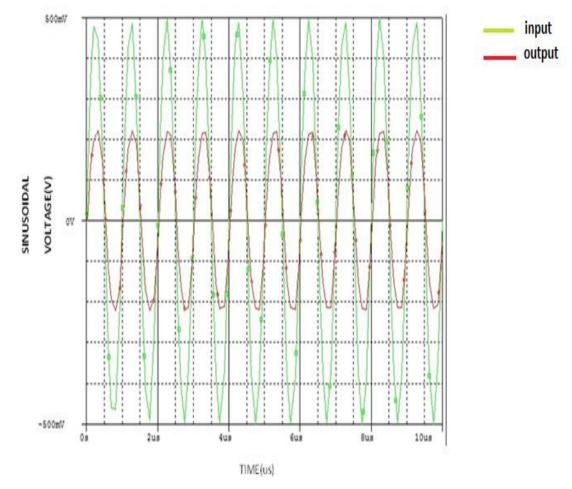

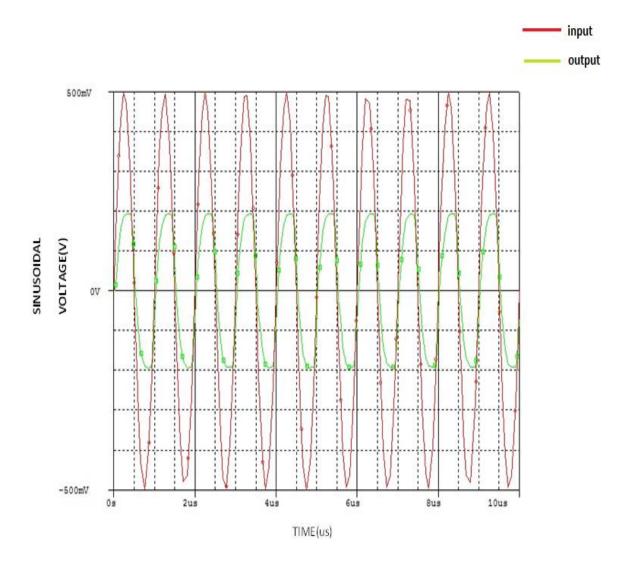

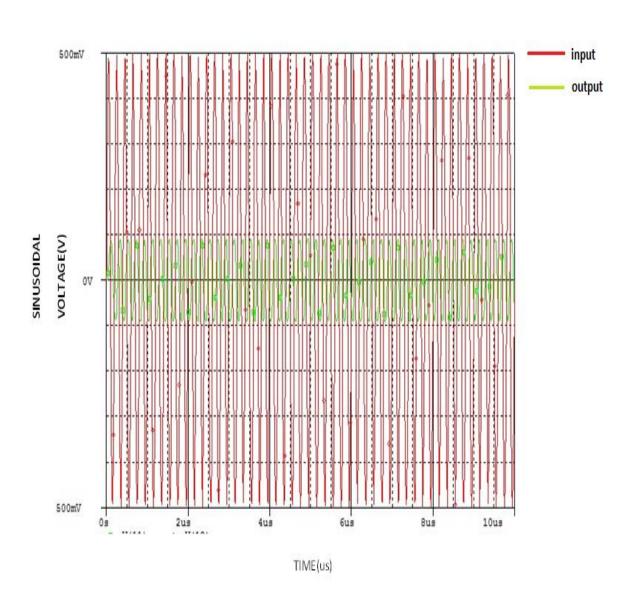

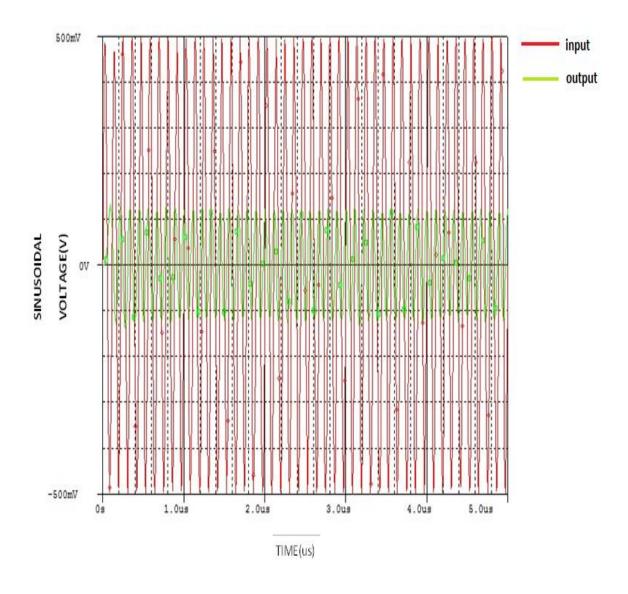

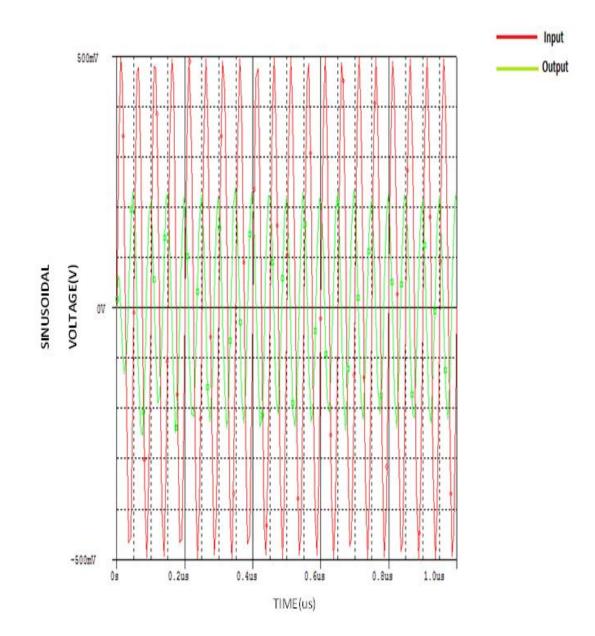

| 5.6 TRANSIENT RESPONSE FOR INPUT AND OUTPUT FOR THIRD ORDER LADDER BUTTERWORTH LOWPASS FILTER USING VDTA        | LC<br>53 |

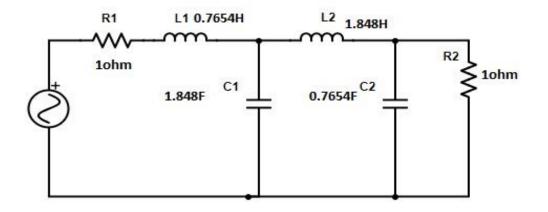

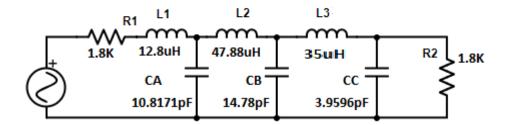

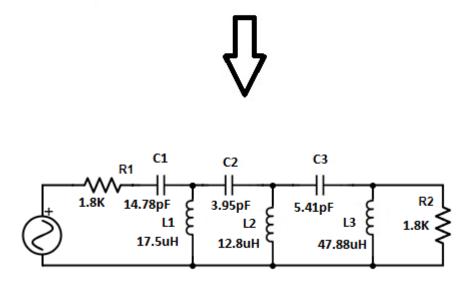

| 5.7(a) FOURTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER                                                        |          |

| (FOR NORMALISED FREQUENCY ω=1rad/sec)                                                                           | 55       |

| 5.7(b) FOURTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER                                                        |          |

| (FOR DENORMALISED FOR FREQUENCY f=10MHz)                                                                        | 55       |

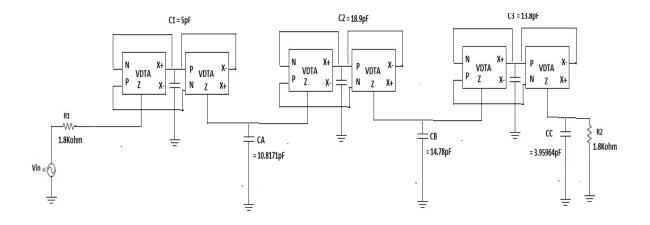

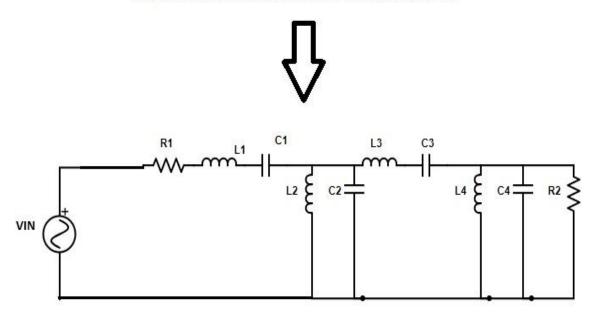

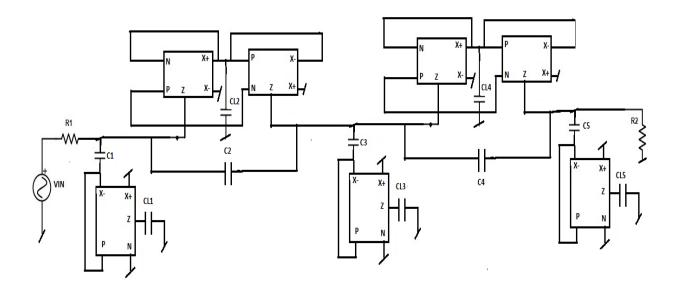

| 5.8 FOURTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER USIN VDTA                                                 | NG<br>57 |

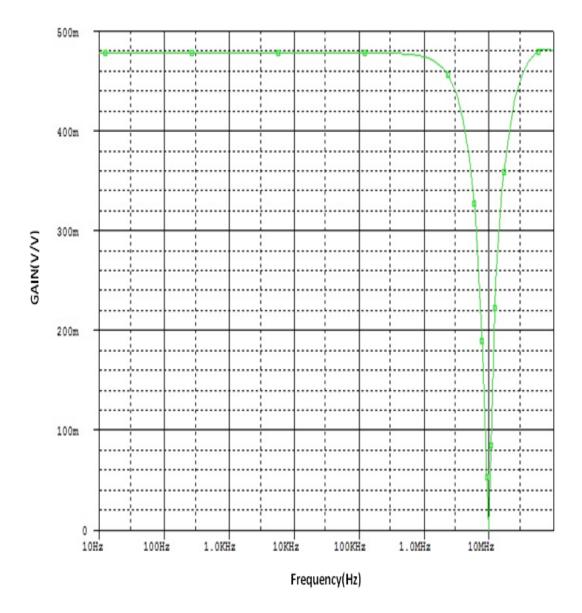

| 5.9 FREQUENCY (AC) RESPONSE OF MAGNITUDE GAIN FOR FOURTH ORD<br>LC LADDER BUTTERWORTH LOWPASS FILTER USING VDTA | ER<br>58 |

| 5.10 TRANSIENT RESPONSE FOR INPUT AND OUTPUT FOR FOURTH ORDER LADDER BUTTERWORTH LOWPASS FILTER USING VDTA      | LC<br>59 |

| 5.11(a) FIFTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER (FONORMALISED FREQUENCY $\omega$ =1rad/sec)            | OR<br>60 |

| 5.11(b) FIFTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER (FOR DENORMALISED FOR FREQUENCY f=10MHz)               | OR<br>61 |

| 5.12 FIFTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER USIN VDTA                                                 | NG<br>63 |

| 5.13 FREQUENCY (AC) RESPONSE OF MAGNITUDE GAIN FOR FIFTH ORD<br>LC LADDER BUTTERWORTH LOWPASS FILTER USING VDTA | ER<br>64 |

ix

5.14 TRANSIENT RESPONSE FOR INPUT AND OUTPUT FOR FIFTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER USING VDTA 65 5.15.(a) SIXTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER (FOR NORMALISED FREQUENCY  $\omega = 1 \text{ rad/sec}$ ) 67 5.15.(b) SIXTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER (DENORMALISED FOR FREOUENCY f=10MHz) 67 5.16 SIXTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER USING VDTA 70 5.17 FREQUENCY (AC) RESPONSE OF MAGNITUDE GAIN FOR SIXTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER USING VDTA 71 5.18 TRANSIENT RESPONSE FOR INPUT AND OUTPUT FOR SIXTH ORDER LC LADDER BUTTERWORTH LOWPASS FILTER USING VDTA 72 5.19. SIXTH ORDER HIGHPASS FILTER DESIGNED FOR FREQUENCY 10MHz FROM ITS EQUIVALENT LOWPASS PROTOTYPE 74

5.20. 6th ORDER LC LADDER BUTTERWORTH HIGHPASS FILTER USING VDTA

77

5.21FREQUENCY (AC) RESPONSE OF MAGNITUDE GAIN FOR SIXTH ORDERLC LADDER BUTTERWORTH HIGHPASS FILTER USING VDTA78

5.22. TRANSIENT RESPONSE FOR INPUT AND OUTPUT FOR SIXTH ORDER LC LADDER BUTTERWORTH HIGHPASS FILTER USING VDTA 79

5.23 8th ORDER BANDPASS FILTER DESIGNED FOR FREQUENCY 10MHz FROM ITS EQUIVALENT LOWPASS PROTOTYPE 81

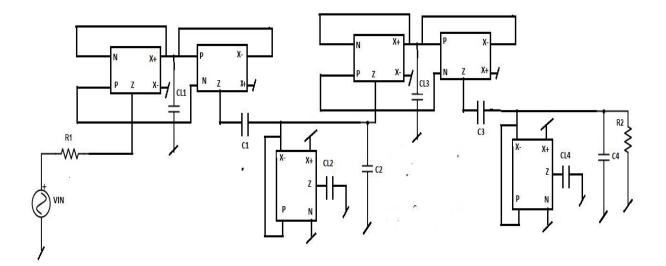

5.24 8<sup>th</sup> ORDER LC LADDER BUTTERWORTH BANDPASS FILTER USING VDTA

82

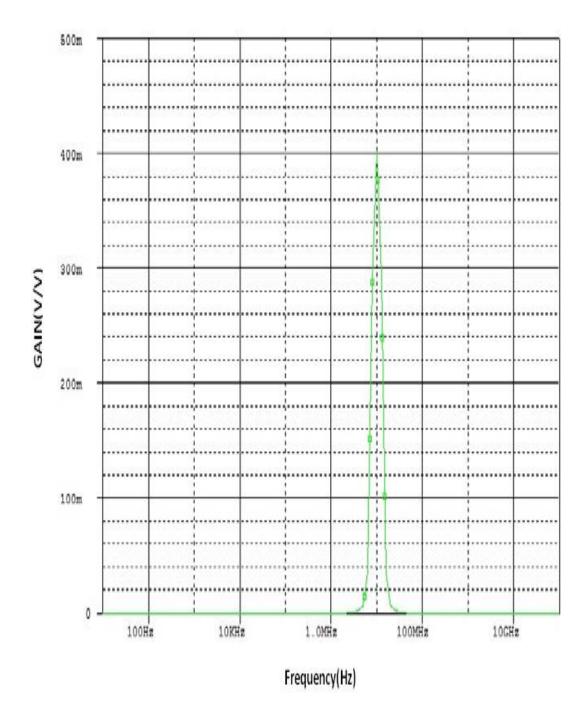

5.25 FREQUENCY (AC) RESPONSE OF MAGNITUDE GAIN FOR 8th ORDER LC LADDER BUTTERWORTH BANDPASS FILTER USING VDTA 83

5.26 FREQUENCY (AC) RESPONSE OF MAGNITUDE GAIN FOR 8<sup>TH</sup> ORDER LC LADDER BUTTERWORTH BANDPASS FILTER USING VDTA(IN LOGARITHMIC SCALE) 84

5.27 10th ORDER BANDREJECT FILTER DESIGNED FOR FREQUENCY 10MHzFROM ITS EQUIVALENT LOWPASS PROTOTYPE86

5.28 10th ORDER LC LADDER BUTTERWORTH BAND-REJECT FILTER USING VDTA 87

5.29 FREQUENCY (AC) RESPONSE OF MAGNITUDE GAIN FOR 10th ORDER LC LADDER BUTTERWORTH BAND-REJECT FILTER USING VDTA 88

# LIST OF TABLES

3.1. ASPECT RATIOS OF THE CMOS USED IN VDTA IMPLEMENTATION 22

5.1 TABLE OF ELEMENT VALUES FOR DOUBLY TERMINATED BUTTERWORTH FILTERS FOR N=2 TO N=10 NORMALIZED TO HALF-POWER FREQUENCY OF 1rad/s 45

5.2 LC FILTERS

46

#### LIST OF ABBREVIATIONS

- VDTA Voltage Differencing Trans-conductance Amplifier

- g<sub>m</sub> Trans-conductance gain

- $Z_{\text{in}}$  Input Impedance

- OTA Operational Trans-conductance Amplifier

- MO-OTA- Multiple Output Operational Trans-conductance Amplifier

- VC-Voltage Conveyor

- CC- Current Conveyor

- DCVC+ Differential Current Voltage Conveyor

- CCII Second Generation Current Conveyor

- DO-CCII- Dual Output Second Generation Current Conveyor

- CDBA- Current Differencing Buffered Amplifier

- CDTA-Current Differencing Trans-conductance Amplifier

- FDNR-Frequency Dependent Negative Resistor

- **OTRA-** Operational Trans-resistor Amplifier

- SFG- Signal Flow Graph

- L<sub>equ</sub> Equivalent Inductance

- CFTA- Current Feedback trans-conductance Amplifier

- CFOA- Current Feedback Operational Amplifier

- **OPAMP-** Operational Amplifier

- FI- Floating Inductor

- GI- Grounded Inductor

- **OMA-** Operational Mirrored Amplifier

R- resistor

L- inductor

C- capacitor

Iin –Input Current

Vin-Input Voltage

CCCII- Current Controlled Conveyor II

Biquad – Biquadratic Filter

## **CHAPTER** – 1

### **INTRODUCTION**

#### **1.1. INTRODUCTION**

We use filters generally [1] to select a particular frequency band or reject a particular frequency range. Voltage mode and Current mode filters are getting popularity as it has an excellent feature in terms of low power consumption, less circuitry, less complexity, larger bandwidth and wide dynamic range and linearity. Some of the current mode active building blocks are Current conveyors [2] which combines all three generations and Current Feedback Operational Amplifier.

In past years, many new active building blocks have been introduced which has brought revolution in terms of using less number of components used and also all the other parameters what a designer should take care of to have a performance of good quality. But still there are need of realizing new active building blocks to meet the requirements and specification what a designer is looking for while designing filters and also the advantages in terms of all the features listed above, are also being considered.

Now a days, researchers are giving emphasis on Current Mode Active Building Block as it has overcome the problems associated with the Voltage mode filter design in terms of Bandwidth and slew rate. So, many new prototypes of active building blocks have come into existence in analog filter design, design of sinusoidal oscillator or multi-vibrators. The proposed circuit is basically working on the current mode where the source is the voltage mode based.

The thesis is basically on the analog active block VDTA and how it can be used for LC ladder filter design. VDTA is generally operated at low voltage. In electronic integrated circuit and mobile communication system, it is desired to have a circuit that will exhibit high speed, low power consumption and the ideal performance. So, the analog designers are

trying to design filters to fulfill aforesaid features using LV methodology. The proposed circuit is basically having bulk CMOS driven architecture.

#### **1.2. ORGANIZTION OF THESIS**

The thesis is organized as follows:

Chapter one presents the overall introduction regarding the project and offers overall summary regarding a number of the active building blocks. This additionally consists of the objectives of the thesis and organization of the thesis work.

Chapter two presents the literature review that is on the previous work of the research scholars in the relevant field. VDTA is utilized in this thesis for realizing different kind of LC ladder Butterworth filters. This Chapter additionally introduces works outlined to this point.

In Chapter three, the new architecture of Voltage Differencing Trans-conductance amplifier is discussed and DC transfer characteristics of VDTA is also presented. The CMOS implementation is also given here.

In Chapter four, it is focusing on synthesis of floating and grounded inductor that is going to be utilized in LC ladder filter simulation. I adopted the element replacement methodology in simulation of LC ladder filter in which we have a tendency to exploit the idea of gyrator.

In Chapter five, it focuses on the main thesis work i.e. the simulation of various sort of LC ladder Butterworth filter (3rd , 4th , 5th, 6<sup>th</sup> LC ladder low-pass, 6<sup>th</sup> order high-pass filter, 8<sup>th</sup> order band-pass and 10<sup>th</sup> order band-reject filter). This chapter presents different analysis of the proposed filters.

In Chapter six, the conclusion and future scope are discussed. Different methodologies, which are being adopted and how these methods are having an effect on different parameters of the filters such as noise and also non ideality of the filter, is mentioned.

#### **1.3. STATE OF ART**

Due to disadvantages of standard inductors that were utilized in past decades, active element-based inductor came into existence. Throughout the previous few years or say decades, different floating inductors are simulated using different active building blocks. That's the explanation behind replacement of standard inductors by synthesis of passive LC ladder filters. These filters have a unique feature of low sensitivity to parameter variation.

Current conveyors are basically used in analog signal processing in current mode. It was first introduced in late 60's [5]. After some time, second generation current conveyor came [6], and in the middle of 90's, third-generation current conveyor came into existence [7]. Current conveyors have an excellent performance as an amplifier, used in current mode in analog signal processing. These current conveyors gained much popularity compared to the conventional op-amp. It is useful for amplifiers as it does not require high precision passive components and it has the better performance in terms of gain, response, speed, bandwidth and accuracy. In recent year with the growing diffusion of current mode approach as a way to design LV LP circuits, current conveyors have gained an increased popularity.

The necessity of the emergence of a current conveyor, having more than one output, current conveyor with light-emitting diode leads to the invention of DO-CCII (Dual-Output CCII), which is the combination of both positive and negative second generation current conveyors, as it gives the z terminal current in both direction [8]. If each current has identical polarity, the device are essentially leads to the fabrication of Current Follower CCII,( both p and n type wherever p or n symbolizes positive or negative current conveyor) [9]. Other variety is the Differential Voltage Current Conveyor [10], these devices is flexible to be used in any mode of signal processing, be it current mode, voltage mode or mixed mode.

Operational Trans-conductance Amplifier (OTA) [11] falls below one of the mostly used active parts, employed for on-chip module fabrication of filters that exhibit excellent frequency response. This device is essentially a device that based on voltage source and

generates signal in the form of current. Electronic tune-ability can be achieved by adjusting trans-conductance value.

Recently, Multiple Output Operational Transconductance amplifier abbreviated as MO-OTA has been come into existence. It is a replica, described by bipolar OTA and this is very useful for the design of bi-quad filters [12], [13]. But, the shortcomings of these element implementations aren't stressed. Many of such factors have been mentioned in [14]: But, these elements have high sensitivity to the matching error constraints in comparison to those of the conventional ones.

The voltage conveyor (VC) has come into existence in 1981 [15], in the documentation of current conveyors, all varieties of voltage conveyors have been discussed in [15], [16], [17], [18]. The one of the popular Voltage conveyor is positive differential current voltage conveyor (DCVC+) [19] that's usually referred as differentiated and buffered current type of amplifier termed as Current Differencing Buffered Amplifier (CDBA) [20].

By introducing some of changes in CDBA or substituting Voltage Follower by the OTA [21], CDTA has been published [22].

A change has been made on the already existing active building blocks to consider changes in the voltage at the input terminals instead of considering the current, which leads to the introduction of VDTA [23].

Recently, many works were proposed regarding passive ladder filter simulation via employing different active elements discussed so far. Direct simulation by adopting replacement method of either inductor or capacitor by synthesizing it by some of the active block, wave active filter using scattering phenomenon and indirect simulation via Bruton's frequency transformation of passive resistively terminated LC block and its further approach to FDNR implementation, which leads to leap-frog structured filter, is used to realize LC ladder filter.

In such circuits, active parts used are CDBA [24-26], Current Amplifiers [27], Multi-Output CCCIIs [28], CDTAs [29-31], OTRAs (Operational Trans-resistance Amplifier) [32], Differential Voltage Current Conveyor [33], Second generation current conveyors and current feedback amplifier [34], [35], DO-OTA (Differential-Output OTAs) [36], MO-OTAs (Multiple-Output OTA) [37], and a combination of conventional Operational Amplifiers and Operational trans-conductance amplifiers [38]. The disadvantage it has is that it leads to the complexity in circuitry. The filter may have a bulk number of components to realize the floating or grounded immittance synthesis technique, which only adds to the complexity to the proposed filter. This problem can be overcome using CBTA to exploit ordinal order of ladder filter realization [39], [40].

The above discussion clearly states crux of simulation of ladder filters exploitation in such a way that it will employ active blocks that might encourage artificial synthesis of passive elements (inductors in most of cases). Throughout this thesis, VDTA is implemented to synthesize the inductor in artificial way, then it is used in LC ladder filter implementation.

#### **1.4. THESIS OBJECTIVE**

- To outline VDTA (Voltage Differencing Trans-conductance Amplifier) for the effective synthesis of filter simulating LC ladder structure. The CMOS implementation of VDTA is adopted and its DC transfer characteristic is determined.

- 2. The second aim is to perform synthesis. The thesis deals with LC ladder simulation on the principle of element replacement by artificial electrical device (GIC is used basically in this case where GIC is realized with the help of VDTA and in GIC, the input resistance is inversely proportional to the load impedance). The floating inductor is synthesized via newly introduced VDTA that is intended in the first part of the thesis. All the methods are cross-checked in two steps: in the beginning, the theoretical analyses are done . To verify the complicated behavior of the projected circuits, PSPICE simulations are performed in PSpice AD, utilizing transistor-level models of active parts (CMOS during this case). For this,

DC transfer Characteristics are observed and tested with PSPICE to verify the theoretical results with the simulation ones. For all the filters that are simulated in this thesis work, the calculation part is done to get the required cutoff frequency, and it's then matched with the simulation result to envision the error. Our objective is to have the error to be smallest. In filter synthesis, the result of attenuation in the pass-band is taken into account to have the ripple as low as possible so the LC ladder filters, employing the inductor synthesized by VDTA, showing the low sensitivity to component tolerances that is our prime goal to get.

3. To get the proposed floating and grounded inductor that is utilized in LC ladder implementation. For this it's expected to verify whether or not the synthesized component works as inductor or not. It is verified by the behavior of its reactive behavior with the change in frequency. The inductive behavior of the synthesized part by active element can be verified by using it in a RLC circuit in the place of inductor and obtaining its frequency response, that is ought to be just like that of a band pass filter with the desired center frequency and bandwidth.

#### **CHAPTER-2**

#### LITERATURE REVIEW

#### **2.1. INTRODUCTION**

Different strategies like element replacement method ( it is either synthesized resistance, inductance or capacitor) and wave technique (where scattering parameters are thought of to imagine voltage and current as wave) are prototyped for his or her active LC realization. In the first procedure, a symbolic graph (SFG) is intended from the relationship between voltage and current of this epitome ladder. Lossy and lossless, both type of integrators are used to implement SFG simulation. Lossless integrators is troublesome to comprehend, owing to non-ideal parasitic effect resulted from already used active and passive elements. The complexness of the structure will increase because the order of filter will increase. In the second procedure, part substitution method, the inductors of the filters are substituted by resistance or capacitive simulators using blocks like voltage differencing trans-conductance amplifier (VDTA) [49], current follower trans-conductance amplifier (CFTA) [50] and current backward trans-conductance amplifier (CBTA) [51] and so on. The requirement for floating capacitance in the synthesized filter topology makes the performance of the filter not appropriate in high frequency. In wave filter technique [52,53], that is that the third technique, filter realization depends on the representation of incident and reflected voltage wave that is resolved by explanation and determination of scattering matrix. Every part of element of filter is substituted by its equivalent wave form. The benefits of aforesaid method are-the filter module is standard in design. It also employs solely measuring device that is not lossless in nature. There are options that have light-emitting diode. Researchers want to implement wave active filter structure using different active components. Amplifiers [52, 53], operational trans-conductance amplifier (OTA) [54], CFOA [55], DVCCTA [56], DVCCCTA [57], CCDDCCTA [58], OTRA [59], VDTA [60] are used to design higher order filters being supported by this approach.

Most of the works of LC ladder filter in the literature is subjected to the first design technique adopted by Darlington, Cauer, Bader etc., which might be delineated as follows: ranging from a driving-point resistance of respective LC two-port network or another equivalent demonstration, remove low-order realizable lossless sub-networks. Every sub network is employed to comprehend a selected transmission zero. The strategy of extracting a sub network typically is predicated on the name of the transmission zero that is being extracted. Once every extraction step is finished, the rest resistance is achieved. The entire method is being perennial till the rest resistance becomes exhausted.

# 2.2. DIFFERENT RESEARCH METHODOLOGIES FOR LC LADDER FILTER

#### 2.2.1. LC LADDER FILTER SIMULATION USING ELEMENT REPLACEMENT METHOD

Element replacement technique is often performed with the help of three methods:

- 1. Using Gyrator (General Impedance Converter abbreviated as GIC)

- 2. Gorski-Popiel's Embedding Technique

- 3. Bruton's FDNR transformation technique

Element replacement technique is performed by replacement of the inductance which might not be realized physically due to its large size and different difficulties that emerge beside it. It is often done either by using Gyrator, where the load resistance is inversely proportional to the supply resistance. Thus, if we use capacitor at the load, we'll get the inductive resistance at the supply terminal. Another approach is FDNR, where we tend to perform scaling of the transfer function by s (simply by dividing) and thereby get the Frequency Dependent Negative Resistance (FDNR), which is realized by VDTA.

A few years back, Reddy [61] presented, which is said to Hilberman's theorem [62], two lossless FI circuits that used 3 op amps. After some times, in [63], Rathore and Singhi

introduced a method to synthesize general floating impedances. Recently, GRM [64] has been devised subjected to adopting FI configuration.

Many approaches are adopted to simulate floating, grounded and FDNR.

Floating and grounded inductors are realized using many different approaches. I adopted the approaches depicted in [65], [66], [67].

The inductances, each floating and grounded are realized. Conjointly, the non ideal implementation of the inductors is also taken into consideration.

#### **2.2.2. GYRATOR**

The gyrator, or could also be termed as positive resistance electrical converter, could be a terribly enticing development enforced on two-port, as a result of it are often adopted to simulate inductance. Its image and transmission matrix is represented in Fig. 3.3. This definition of gyrator through its transmission matrix, with  $g_1 \neq g_2$  and positive, denotes the active gyrator. However, if  $g_1 = g_2 = g$ , it refers to the gyrator of having passive two-port. Clearly, the gyrator could be a unreciprocated two-port device, since

$$a_{11}a_{22} - a_{12}a_{21} \neq 1 \tag{2.1}$$

It is necessary for network synthesis from the side that, if it's terminated at port two by a capacitance  $C_L$ , the resistance are often seen on port one, consistent with atomic weight. (2.2), is

$$Z_{i} = G_{b}sC_{L} = s\frac{c_{L}}{g_{1}g_{2}} = sL_{eq}$$

(2.2)

Fig.2.1. Gyrator [92]

i.e., the resistance of a similar inductance is given as

$$L_{eq} = \frac{c_L}{g_1 g_2} \tag{2.3}$$

The gyrator is often synthesized using totally different active building blocks. There are several approaches being adopted to simulate inductance. A perfect negative-impedance invertor (Lundry type) that uses a voltage-controlled voltage supply is outlined. This is configured using an operational amplifier in [68].

It's utilized in a mixture of negative-impedance convertors to implement new gyrator circuits. An alternative configuration for a gyrator that is realized from 2 commercially available trans-impedance operational amplifiers (OPAMPs) and three passive elements that is described in [69].

A new resistive capacitive circuit which is active in nature is depicted to get implementd. Floating inductance which is lossless in nature in [70] realized using three opamps as gain summers having magnitude equal to one, three resistors and one capacitance. In contrast to different 3 amplifiers, the new circuit realizes inductance that's controlled through one resistance.

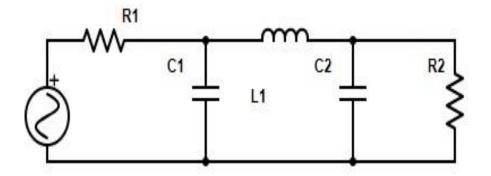

OTA based implementation of inductance is represented in [71]. The parasitic result and open loop information is being taken into account. OTA-based inductance which might be thought of to be each grounded and floating topologies is depicted as shown below in Fig 2.2.

Fig.2.2. OTA Based Inductor [71]

In [72], two structures for realizing inductance, capacitance and frequency-dependent negative resistance (FDNR) simulators (all are floating type), simulated by the passive elements, are being introduced. This can be done by employing the active building block namely modified current feedback operational amplifier (MCFOA). This requires also a very few number of passive components to realize the filter. Proposed floating inductor and Farm Credit System employ a capacitance (basically grounded one) therefore the proposed circuits suited to completely computer circuit (IC) design. Also, the projected circuits does not need any reasonably important passive element matching conditions, therefore reduces matching error and/or cancellation constraints.

Four operational mirrored amplifier (OMA) based floating resistance configurations are presented in [73] that use a minimum range of (three) OMAs in contrast to four OMAs depicted in the antecedently documented circuits, having all advantageous features over its earlier implementation using four OMAs.

Three newly published active RC artificial FIs is described in [74] that depicts lossless floating inductance and series and parallel RL resistance, using current conveyors of second generation (CCII) as major components for this purpose. The unique key-points of this newly introduced prototype is stated as under

- 1. It is distinctive to already existing typical op-amps for floating inductors, the prototype mentioned in the above discussion don't ought to select element matching to obtain the required realization;

- 2. All the circuits that have been introduced in the past and also in recent times, the magnitude of inductance is controlled by varying one resistance. Thus electronic tunability and suppleness are often obtained.

- 3. These circuits employ a very few number of passive elements (generally 2 resistors and a capacitor). Therefore, the circuit complexity is less.

#### 2.2.3. LC LADDER METHODOLOGIES

The objective of the thesis is to simulate LC ladder filter using VDTA. Apart from VDTA, several approaches are done so far using totally different active building block to simulate LC Ladder Butterworth Filter. In [75], the idea of LC Ladder Filter using OTA has been projected. This contributes to a unique feature to reduce noises for the applications which is operated at high frequency to own a better performance.

The step by step procedure for synthesizing low-pass and band-pass ladder filters having leapfrog structure is bestowed in [76]. The projected design uses 2 typical active elements, i.e., employing op-amps and a Current Controlled Conveyor II (CCCII), which does not comprise of any reasonably external passive part.

In [77], Operational Trans-Resistance amplifier (OTRA) based implementation of LCladder filter is mentioned. This projected configuration uses a technique that is taken into account to be a scientific approach to the design of LC-ladder filter having leap frog structure. Operational trans-resistor amplifier is essentially an active element having low resistance at both input and output ports. This energized part is often chosen for realizing voltage output filter. An insight into Butterworth Filter is bestowed in [78] where four parameters in an elaborated way is mentioned i.e. attenuation in pass-band, attenuation in stop band and frequency at which passing and stopping of signal happens.

Switched capacitance filters are being used to simulate LC Ladder Filter as mentioned in [79]. The LC ladder works on primarily by extracting LC network from research tables and reworking it into a similar switched capacitance configuration. It has the advantage is that it has least sensitivity to method variation, however has the disadvantage that it's difficult to design a filter that's not delineated during a look-up table. The strategy is widely used owing to its doubly terminated terminals with resistors. LC ladder structure that focuses on its behavior with respect to the pass-band magnitude sensitivity, though it is observed that this quite often goes beyond normal range by sensitivity in terms of phase i.e. the variation due to the phase change is not of good quality.

Another technique for doubly resistive terminated ladder filters synthesis was bestowed in [80]. Constantinides and Dimopoulos proposed a new method that is predicted on the implementation of voltage mode instead of current mode to realize doubly resistive terminated LC ladder filters. There are a variety of realizations of passive components adopting another technique which are discussed. An elaborated illustration of a 3<sup>rd</sup> order low-pass filter has been done with the proposed technique and comparison is made with the ideas proposed by Rathor and Khott.

In [81], discussions are made on a scientific approach for designing a wave active filter realization employing voltage differencing trans-conductance amplifier. This structure does not need the use of any resistor. This proposed filter employs only a capacitance that is grounded and conjointly having the feature of electronic tunability of cut-off frequency just by adjusting bias current.

In [82], a scientific technique for explaning the RLC filter has been proposed; which is CFOA based filter employing capacitors. All capacitors are grounded. This filter is useful in current mode analog signal processing. It is based on the operational simulation of filter

where we are more interested in modeling circuit equations and the voltage current relationships of the element. This approach basically focuses on the operation rather than its components. This method can also be utilized in realizing LC ladder filter operated in voltage mode. These filters use a very few number of capacitors that contributes to very less amount to the total capacitance. Such filters are very useful for the design of IC circuits and also contribute to the design of computer architecture.

In [83], it represents a simplified scattering synthesis procedure and its application within the development of a bug for synthesizing LC ladder networks. The new approach relates to the scattering transfer matrix theory that has never been applied earlier to ladder synthesis technique. The primary step during this synthesis procedure is trying to find the determination of a scattering synthesis strategy for choosing the sequence of extracting transmission zero.

In [84], another synthesizing technique is taken into account to simulate LC ladder filter in leap frog structure. The incorporation of general simulations of LC ladder networks offers matched correspondence between reactive components, thereby reducing matching error related constraints. This is achieved by maintaining integrators by introducing special type of "port reciprocators" that depicts the active parts that can be depicted by signal flow graph procedure and a variety of thumb-rules to interconnect the elements constructs a whole active synthesis technique.

In [85], another replacement frequency technique is introduced that is taken into account to be a compensation technique of the second generation current conveyors, that is used to synthesize floating inductor. To obtain the desired electronic tunability of the proposed inductor, a trans-linear CCII is employed where its series parasitic resistance at its X terminal is being compensated to reduce the non-ideality of the filter. After getting the desired frequency characteristics of this prototype, some restrictions have been imposed on frequency of the conventional second generation current conveyor based simulated adjustable floating type of inductor, that doesn't depend upon standardization current, is being analyzed. To root out this drawback, a pole or zero cancellation technique has been

adopted. Hence an external resistor of  $650\Omega$  has been used in series and it outlined a negative resistor, suggested by that of the current conveyors. Simulation results exhibit that this cancellation method enhances the standardization range of varying proposed inductor. Moreover, a special arrangement is presented so the cancellation method isn't sensitive to the fluctuation of current that's used for standardization the inductance value.

In [86], some work has been done for having relation between magnitude and phase sensitivity, that is a prime tool to measure in a qualitative manner to see how these parameters have an impact on element variation and parasitic loss due to non-ideal phenomenon associated with the circuit, that may have an effect to get a deviated response from the nominal filter response.

In [87], the popular leap frog structure was no more found useful in designing LC ladder filter as it has the finite range of transmission zeros. This design was having some drawbacks in the application of the strategy to comprehend high pass and band stop filters. Hence, these issues are often sorted through the active RC filter synthesis technique, that is predicated on emulating mesh current of RLC ladder filters. In this work, a singular relevance model that incorporates coupled feed-forward Tow-Thomas bi-quadric filter is adopted. This design has been used to simulate all categories of LC low pass and high pass ladder filters. All type of filters can easily be realized just by applying the frequency transformation technique implemented on the nominal low pass filter prototypes and frequency scaling are performed afterward to get the frequency range for which the filter is expected to operate.

In [88], a widely known leap frog structure has been projected to simulate LC ladder filter by using MO-CCCII and grounded passive capacitors. Electronic tunability is taken into account and matching constraints is not taken into account for the design part.

#### **CHAPTER-3**

# VOLTAGE DIFFERENCING TRANSCONDUCTANCE AMPLIFIER

#### **3.1. INTRODUCTION**

Active parts have a widespread use in signal processing in analog domain, adore filters design, resonators modeling, oscillators and inductance synthesizing etc. Several active parts were used for this purpose due to the fact that they're having vital options with relevancy one another, adore i/p and/or o/p terminal having similar or dissimilar options, any of the parameters will be controlled by the adjustment of external voltage or current etc. New approaches are being proposed by researchers with these newly introduced active parts. At present, active parts are being considered under review and several other new parts are being enforced and synthesized. However, the implementation of the newly introduced active parts doesn't seem to be declared. One amongst those newly introduced active parts is VDTA. It may be compared with its typical current mode counterpart, Current Differencing Transconductance Amplifier, where the input is considered to be current signals. CDTA is an antecedently projected non-passive element. In CDTA, difference of input currents (I<sub>p</sub>, I<sub>n</sub>) is translated to a proportional current via first transconductance g<sub>m1</sub> at Z port. In VDTA, in the place of input currents, difference of input voltage (V<sub>p</sub>,V<sub>n</sub>) is being considered. These voltages applied at input terminal is translated to current at the terminal Z by multiplying the difference of voltage with 1st trans-conductance gain  $g_{m1}$  and therefore proportional voltage produced at the terminal Z (due to the current at Z terminal) is copied to current at the terminals X+ and X- ports by multiplying it with second transconductance gain (g<sub>m2</sub>). The trans-conductance can be varied by changing external bias currents. If comparisons are made, alternative non-passive building blocks, the advantages VDTA is having is that it offers two completely different values of trans-conductance so many applications like design of bi-quad filters (e.g, KHN Biquads, Tow-Thomas Biquads), oscillator, inductance and FDNR (frequency dependent negative resistor) circuitry will be made with the help of one active block using one or two capacitors. In alternative words, these implementation need less range of passive parts thereby reducing the circuit complexity and additionally helps in reducing power consumption. Another advantage, this block has is that, it will be used simply at trans-conductance mode applications which implies that voltage is applied at the input terminal and current is taken out from the output terminal. In this paper, an illustration has been stated to show how CMOS can be used to design VDTA. By choosing input terminal voltages, this formation or orientation of VDTA will generate any reasonably normal filter functions. No parameter matching condition is needed in this case.

# 3.2. VDTA(VOLTAGE DIFFERENCING TRANSCONDUCTANCE AMPLIFIER)

The voltage differencing trans-conductance amplifier (VDTA) is the main active block for designing proposed filter. It was introduced in 2012 by Yesil et al. Its symbol is illustrated in Fig.3.1. The input voltage at P and N terminals ( $V_P$  and  $V_N$ ) are applied and then its difference is taken and it is copied to be current at z terminal ( $I_z$ ) using 1st trans-conductance ( $g_{m1}$ ). This trans-conductance is set as per the 1st input bias current ( $I_{B1}$ ).

Fig.3.1. Circuit Symbol Of VDTA [89]

To make associated degree of extension to the employment of VDTA, the output current, specifically z copy terminal ( $Z_c$ ) is employed. At  $Z_c$  terminal, ( $I_{zc}$ ) is translated from current at z terminal. The voltage at z terminal ( $V_z$ ), is translated to be current using second transconductance ( $g_{m2}$ ) that is electronically adjusted by varied  $I_{B2}$ . As voltage being the input and current being the output, this active part is attributed to act as a trans-conductance amplifier. The voltage and current relationship at input and output terminal is shown by equivalent (3.1)

$$\begin{bmatrix} I_{Z} \\ I_{X+} \\ I_{X-} \end{bmatrix} = \begin{bmatrix} g_{m1} & -g_{m1} & 0 \\ 0 & 0 & g_{m2} \\ 0 & 0 & -g_{m2} \end{bmatrix} \begin{bmatrix} V_{P} \\ V_{N} \\ V_{Z} \end{bmatrix}$$

(3.1)

which refers to,

$I_{Z} = gm1(V_{P} - V_{N}) \tag{3.2}$

$$I_{X+} = g_{m2} V_Z \tag{3.3}$$

$$I_{X-} = -g_{m2} V_Z \tag{3.4}$$

As a consequence, the above describing-equations, the input stage and output stage will be merely employed by floating current sources. As per input terminals, the proportional output current at Z terminal is obtained. The intermediate voltage of Z terminal is then translated to output currents. In this paper, VDTA is thought to be an active analog building block, attributable to the subsequent reasons:

#### (i) The straightforward implementation of VDTA using CMOS,

(ii) There use of two trans-conductance amplifiers that offers resistance less realization,

(iii) The trans-conductance gain of VDTA which may be modified via varied bias current, thus providing the electronic tunability and suppleness to designed filter.

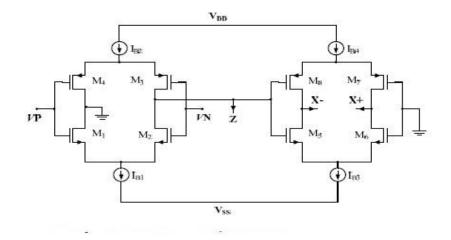

#### 3.3. CMOS IMPLEMENTATION OF VDTA

The intermediate voltage at Z terminal is copied to output currents. The new CMOS implementation of the VDTA is shown in Fig. 3.2.

Fig 3.2. CMOS Implementation Of VDTA [89]

The above figure demonstrates the CMOS implementation of the VDTA block. NMOS  $M_1$  and  $M_2$  and PMOS  $M_3$  and  $M_4$  form the primary main active a part of VDTA.  $M_1$ ,  $M_4$ , and  $M_3$ ,  $M_2$  forms the first CMOS differential amplifier. Another differential amplifier, that is identical to first differential amplifier by using NMOS  $M_5$  and  $M_6$  and PMOS  $M_7$  and  $M_8$ , is used. The circuit operation starts operating as follows: in the presence of CMOS differential amplifier, the output is obtained at port z, which is mainly due to the difference between the input signals at port p and port n. This is then amplified in the 1st amplifier. The output voltage obtained at port z is then taken to be fed into the secondary amplifier where one terminal that's grounded, guaranteeing that there's no loss in signal. Finally, the amplified output is taken out at port x+ and x-. With the help of differential input voltage, there's an increase in trans-conductance gain in the primary block i.e.,  $g_{m1}$  gets magnified. There's associated degree of magnified feed of output in the secondary block, is largely due to the secondary trans-conductance  $g_{m2}$ , there's final increase in output current as a result of what finally offers associated degree of overall gain and signal amplification.

The newly introduced circuit uses two Arbel-Goldminz trans-conductance. Input and output trans-conductance parameters of VDTA part in the circuit is determined by the trans-conductance of outputs transistors. Associated degree approximation will be written as

$$g_{m1} = \left(\frac{g_3 + g_4}{2}\right) \tag{3.5}$$

$$g_{m2} = \left(\frac{g_5 + g_8}{2}\right)$$

Or,

$$g_{m1} = \left(\frac{g_6 + g_7}{2}\right) \tag{3.6}$$

where  $g_j$  is the transconductance value of *j*th transistor described by

$$g_j = \sqrt{I_{Bj} \mu_j C_{OX} \left[\frac{W}{L}\right]_j}$$

(3.7)

$\mu_j$  is (j = n, p) the quality of the carrier for NMOS (n) and PMOS (p) transistors, C<sub>OX</sub> is that the capacitance between gate-oxide per unit space, W is that the effective channel-width, L is that the effective channel-length and I<sub>Bj</sub> is bias current of j<sup>th</sup> semiconductor.

# 3.4. VDTA REALIZATION USING OPERATIONAL TRANSCONDUCTANCE AMPLIFIER USING OTA

For the broad perspective, we need to understand the design of VDTA using OPERATIONAL TRANSCONDUCTANCE AMPLIFIER (OTA) as shown in the 3.3.

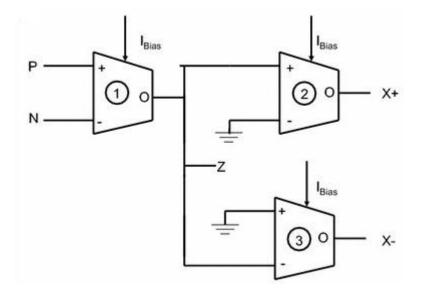

Fig.3.3. VDTA Realization Using OTA [89]

The output of the primary OTA is thought to be Z terminal of VDTA, current at which is proportional to the differential voltage applied to the non-inverting and inverting terminal of the OTA. This current at Z terminal creates proportional differential voltage that is fed to two alternative OTAs as inputs in second stage and eventually produces Ix+ and Ix- proportional to applied voltage. Throughout the structure, we must always take into account the biasing current that is provided to every OTAs to form the active building block to work properly.

#### **3.5. TRANSFER CHARACTERISTICS**

We perform the simulation by PSPICE AD program with TSMC CMOS 0.18µm method parameters. The aspect ratios of the CMOS transistors used in the design is given in Tab. 1.

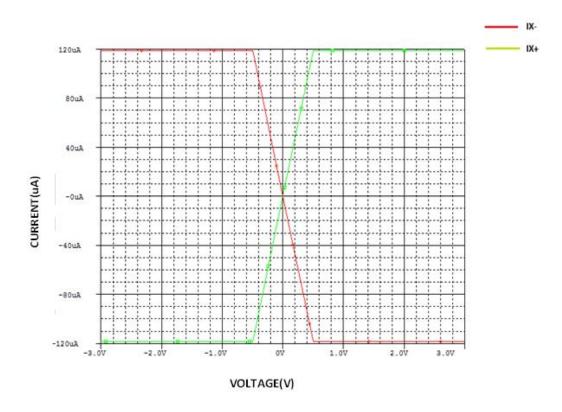

Supply voltages are  $V_{DD} = -V_{SS} = 0.9$  V and  $I_{B1} = I_{B2} = I_{B3} = I_{B4} = 150$  µA biasing currents which are used. Simulation results depict that this selection yields trans-conductance values of VDTA to be  $g_{m1} = g_{m2} = 631.8$  µA/V. The DC transfer characteristic of  $I_{X+}$  and  $I_{X-}$  against  $V_Z$  for final output stage of projected VDTA is shown in Fig. 3.4.

| Transistors                                                       | W(µm) | L(µm) |

|-------------------------------------------------------------------|-------|-------|

| M <sub>1</sub> , M <sub>2</sub> , M <sub>3</sub> , M <sub>6</sub> | 3.6   | 0.36  |

| M <sub>3</sub> , M <sub>4</sub> , M <sub>7</sub> , M <sub>8</sub> | 16.64 | 0.36  |

TABLE 3.1. Aspect Ratios Of The CMOS Used In VDTA Implementation [89]

Fig. 3.4. Transfer Characteistics Of VDTA

# **CHAPTER-4**

# REALISATION OF GROUNDED INDUCTOR AND FLOATING INDUCTOR USING VDTA

#### **4.1. INTRODUCTION**

In this chapter, electronically adjustable lossless grounded inductance and floating inductance simulators using active building block Voltage Differencing Trans-conductance amplifier (VDTA) and one capacitor are synthesized.

One of the standard problems in designing frequency (RF) circuits is expounded to the idea of integrated inductors with high quality factor. It's okay with the fact that, using common semiconductor method, it also suffers from comprehending passive inductors that exhibit the same value of quality factor (e.g. Q>10) and high inductance value(e.g. a few nH) in the fabrication method.

Inspite of the many circuits and methodologies that were already presented and investigated, the term active (AIs) had appeared in the title in early 70's. Later, economical realizations of selective active filters on semiconductor, i.e., bipolar technology, were projected in 90's.

Many simulated grounded inductors (GI) and Floating Inductors using different active blocks consist of op-amps, CCs, CFOAs, FTFNs, CDBAs, CFTAs, however they suffer from following disadvantages:

- 1. Demand for additional variety of passive parts,

- 2. Needs additional variety of active parts,

- 3. Synthesized inductance is lossy.

Recently VDTA is introduced and it will be operated in each voltage mode and current mode applications. In the following discussion, we will have a review of some important works on grounded and floating inductance using Voltage Differencing Trans-conductance amplifier (VDTA).

#### **4.2. GROUNDED INDUCTOR USING VDTA**

Fig. 4.1. Grounded Inductor Using VDTA [90]

The grounded inductance will be accomplished employing a single VDTA and a capacitor. [90].

We have to work out the input resistance of the circuit where  $V_1$  is applied at terminal one. Applying KCL at node one, we have a tendency to get

$I_1 + I_x = 0$ i.e.  $I_x = -I_1$  (4.1) We know

$$Ix = -g_{m2}V_Z$$

Therefore,

$$I_1 = g_{m2} V_Z$$

(4.3)

Now,

$$V_Z = \frac{I_Z}{sC}$$

Therefore

$$I_{1} = g_{m2} \frac{Iz}{sC} = \frac{gm1gm2Vp}{sC} = \frac{gm1gm2V1}{sC}$$

(4.5)

So the input impedance,

$$\frac{V1}{I1} = \frac{sC}{gm1gm2}$$

which is nothing but the expression for inductor,

Where

$$L_{Equ} = \frac{C}{gm1gm2}$$

(4.7)

(4.6)

Now the experiment is applied employing a 0.01nF capacitor, we are able to get the magnitude of grounded inductance as

$$L_{Equ} = \frac{C}{gm1gm2} = \frac{0.01nF}{\frac{631\mu A}{V}x627\frac{\mu A}{V}} = 25.27\mu H$$

The simulation of  $L_{equ}$  Vs Frequency is shown in Fig 4.2, wherever we have a tendency to get the inductance worth as 25.39  $\mu$ H.

Error=

$$\frac{25.39 - 25.27}{25.27} x\ 100\% = 0.47\%$$

Fig 4.2. Inductor Vs Frequency for Grounded Inductor Using VDTA

Response of the new simulated inductors was verified by SPICE simulations. CMOS-based VDTA from was accustomed confirming the frequency responses of the grounded simulated inductors. The subsequent values were used for grounded inductor:  $C_{L2} = .01nF$ ,  $g_{m1} = g_{m2} = 631.7 \mu A/V$ . From the frequency response of the simulated floating inductance (Fig 4.1), the inductance value remains constant up to 10MHz.

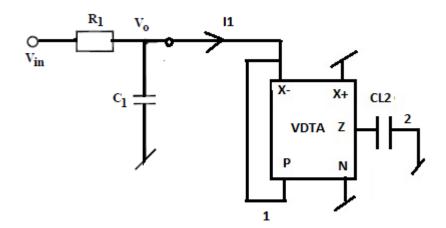

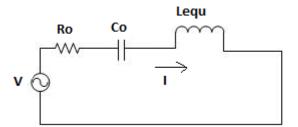

Fig 4.3. Band-pass Filter Using VDTA Based Grounded Inductor [66]

Here in fig 4.1, the  $L_{equ}$ = 23.27  $\mu H$  as discussed earlier. Now the circuit will be behaved as the RLC circuit shown in figure 4.4, we can have similar circuit just by replacing the inductor by the simulated VDTA based grounded inductor as shown in Fig 4.3.

Fig 4.4. RLC Circuit

The Transfer Function of the circuit shown in Fig 4.4, will be,

$$\frac{V_o(s)}{Vin(s)} = \frac{\frac{1}{RC}s}{s^2 + \frac{1}{RC}s + \frac{1}{LC}}$$

Where center frequency,  $\omega_0 = \frac{1}{\sqrt{LC}} rad/sec$

Therefore,

$$f_0 = \frac{1}{2\pi\sqrt{LCo}} = \frac{1}{2\pi\sqrt{\frac{C_{L2}}{gm1gm2}C1}}$$

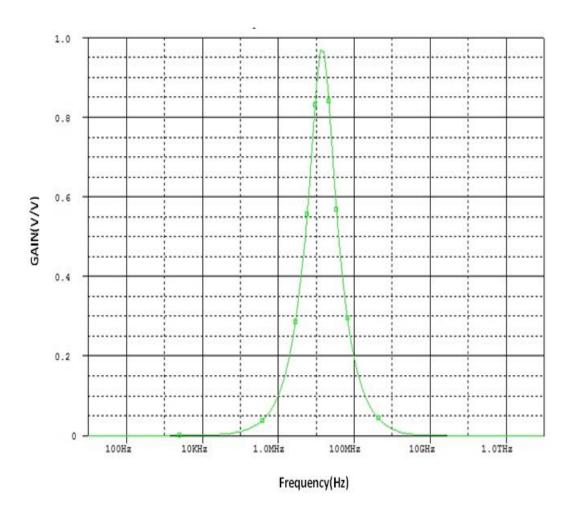

The theoretical value of the band-pass filter is calculated as 14.75MHz

By simulation as shown in Fig 4.5, we get 15.955MHz

So the error will be,  $\frac{15.955 - 14.75}{14.75} \times 100\% = 8.16\%$

Fig 4.5. Frequency Response Of Bandpass Filter Using VDTA Based Grounded Inductor

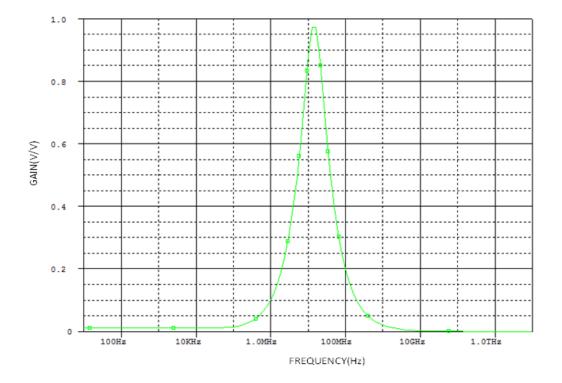

# 4.2.1. NON-IDEALITY AND SENSITIVITY PERFORMANCE FOR GROUNDED INDUCTANCE VICTIMIZATION VDTA

Considering VDTA non-ideal parasitic i.e., the finite X-terminal parasitic electrical resistance consisting of a resistance Rx in parallel with capacitance 110 and therefore the parasitic electrical resistance at the Z-terminal consisting of a resistance Rz in parallel with capacitance Cz.

The non-ideal input electrical resistance for the circuit shown in Figure 4.6, is given by

$$Zin(s) = \frac{s(C + C_x) + \frac{1}{R_x}}{s^2 C_z (C + C_x) + s \left\{ \frac{(C + C_x)}{R_z} + \frac{C_z}{R_x} \right\} + \frac{1}{R_x R_z} + g_{m1} g_{m2}}$$

(4.8)

From Equation (4.8) a non-ideal equivalent circuit of the grounded inductance is derived that is shown in Fig.4.6.

Where

$$L_{GI} = \frac{(C+C_x)R_xR_z}{1+g_{m1}g_{m2}R_xR_z}, \quad R' = \frac{(C+C_x)R_xR_z}{(C+C_x)R_x+CzR_z}, \quad C' = \frac{(C+C_x)R_x+CzR_z}{R_z}, \\ R'' = \frac{R_z}{1+g_{m1}g_{m2}R_xR_z} \text{ and } R'' = \frac{R_z}{R_z}$$

$$\mathbf{D} = (C + C_x) R_x R_z \tag{4.9}$$

From the on top of, the sensitivities of  $L_{GI}$  with relevance varied active and passive parts are found to be

$$S_{C}^{L_{GI}} = \frac{c}{(c+cx)}, S_{Cx}^{L_{GI}} = \frac{cx}{(c+cx)}, S_{R_{x}}^{L_{GI}} = S_{R_{x}}^{L_{GI}} = \frac{1}{1+g_{m1}g_{m2}R_{x}R_{z}}, S_{g_{m1}}^{L_{GI}} = S_{g_{m1}}^{L_{GI}} = -\frac{g_{m1}g_{m2}R_{x}R_{z}}{1+g_{m1}g_{m2}R_{x}R_{z}}$$

Fig 4.6. Non Ideal Structure Of VDTA Based Grounded Inductor [66]

#### **4.3. FLOATING INDUCTOR USING VDTA**

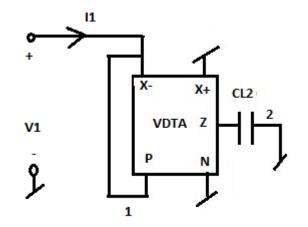

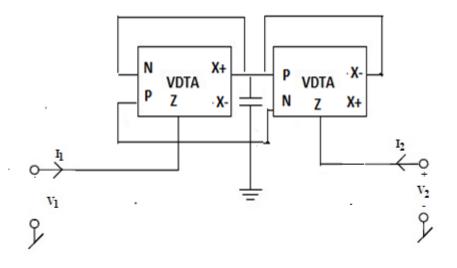

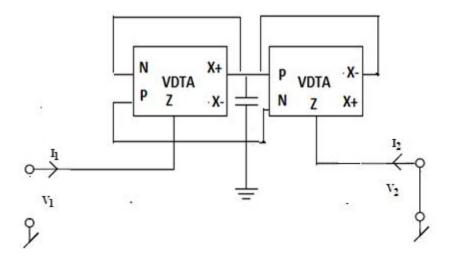

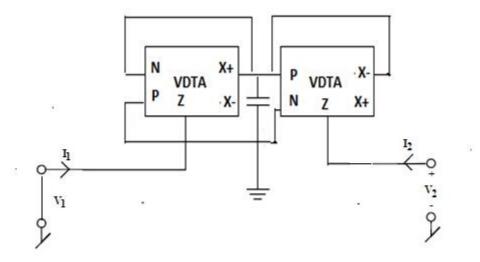

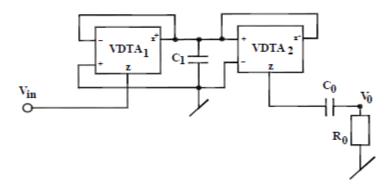

Floating inductance using VDTA [65] is shown in figure 4.7. The Floating inductance is realized using two VDTA and one single capacitor. The transfer function of floating inductance is illustrated below

Fig 4.7. Floating Inductor Using VDTA [66]

The y matrix of the fig 4.7, is written as

$$I_1 = y_{11} V_1 + y_{12} V_2 \tag{4.11}$$

And  $I_2 = y_{21}V_1 + y_{22}V_2$  (4.12)

Where

$$y_{11} = \frac{I1}{V1} | V_2 = 0$$

$y_{12} = \frac{I1}{V2} | V_1 = 0$

$y_{21} = \frac{I2}{V1} | V_2 = 0$

$y_{22} = \frac{I2}{V2} | V_1 = 0$

Fig 4.8(a) VDTA Based Floating Inductor with V2 Shorted i.e. V2=0

To derive y matrix of the circuit we short  $V_2$  first as shown in figure 4.8(a), so that  $V_2=0$ . We need to derive the value of  $y_{11}$  and  $y_{21}$ .

Applying nodal analysis at node 1 we get,

$$sC_1V_N = ix + = g_{m2}V_1$$

Or,

$$V_N = \frac{\text{gm}2\text{V1}}{\text{sC1}}$$

(4.13)

Now,

$$I_1 = -i_{Z1} = g_{m1}V_N = \frac{gm1gm2V1}{sC}$$

(4.14)

Therefore

$$y_{11} = \frac{I_1}{V_1} | V_2 = 0 = \frac{sC}{gm_1 gm_2}$$

(4.15)

Now

$$I_2 = -i_{z2} = -g_{m1}V_p$$

(4.16)

Now

$$sCV_p = i_{x+} = g_{m2}V_1$$

(4.17)

Or,

$$i_2 = \frac{-g_{m1}g_{m2}V_1}{sC}$$

(4.18)

Now,

$$y_{21} = \frac{v_1}{i_2} | v_2 = 0 = \frac{sC}{gm_1 gm_2}$$

(4.19)

Now we short  $V_1$  terminal as shown in figure 4.8(b), so that V1=0. We need to derive  $y_{12}$  and  $y_{22}$ .

Fig 4.8(b) VDTA Based Floating Inductor With  $V_1$  Shorted i.e.  $V_1=0$

Applying nodal analysis at node 1, we get,

$$sCV_{\rm P} = ix - g_{\rm m2}V_2$$

$$_{\text{Or},}Vp = \frac{-gm2V2}{sC} \tag{4.20}$$

Now,

$$I_2 = -i_{z2} = -g_{m1}V_p = \frac{gm1gm2V2}{sC}$$

(4.21)

Therefore

$$y_{22} = \frac{I2}{V2} | V_1 = 0 = \frac{sC}{gm1gm2}$$

(4.22)

Now

$$I_1 = -i_{z1} = g_{m1} V_N$$

(4.23)

Now

$$sCV_N = i_{x-} = -g_{m2}V_2$$

(4.24)

Or,

$$i_1 = \frac{-gm1gm2V2}{sC}$$

(4.25)

Now,

$$y_{12} = \frac{v_2}{i_1} | v_1 = 0 = -\frac{sC}{gm_1 gm_2}$$

(4.26)

So the y matrix of the circuit in Fig is described as

$$\begin{bmatrix} I_1\\I_2 \end{bmatrix} = \frac{gm1gm2}{sC} \begin{bmatrix} +1 & -1\\-1 & +1 \end{bmatrix} \begin{bmatrix} V1\\V2 \end{bmatrix}$$

(4.27)

which proves that the circuit behaves as a floating lossless, that is electronicallycontrollable inductance with the inductance worth given by  $g_{m1}$  and  $g_{m2}$  that is controlled by biasing current  $I_{bias}$ .

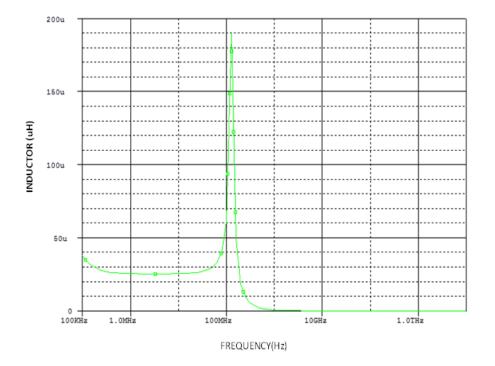

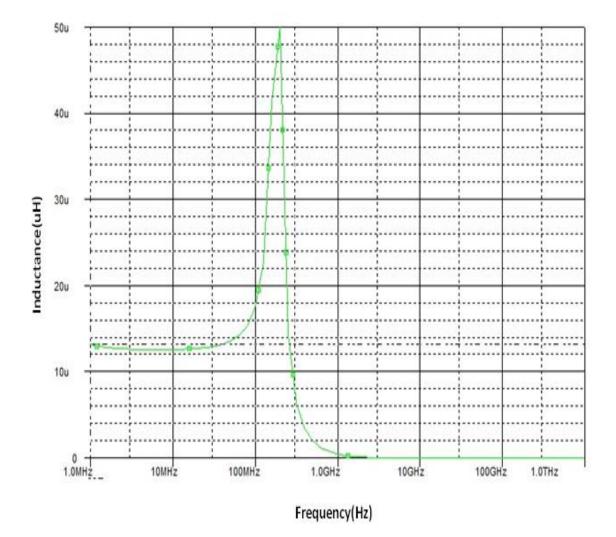

Now the experiment is carried out using a 5pF capacitor. We can get the magnitude of floating inductance as,

$$L_{Equ} = \frac{C}{gm1gm2} = \frac{5pF}{\frac{631\mu A}{V}x627\frac{\mu A}{V}} = 12.6\mu H$$

The simulation of  $L_{equ}$  Vs Frequency is shown in Fig 4.9, where we get the inductance value as 13.14  $\mu$ H.

So error=

$$\frac{13.4 - 12.6}{12.6}X100\% = 4.28\%$$

Fig 4.9. Inductance Vs Frequency For VDTA Based Floating Inductor

Performance of the new simulated inductors was verified by SPICE simulations. CMOSbased VDTA from [35] was accustomed to confirm the frequency responses of the floating simulated inductors. The subsequent values were used for grounded in addition as floating inductor:  $C_1 = 5pF$ ,  $g_{m1} = g_{m2} = 631.7 \mu A/V$ . From the frequency response of the simulated floating inductance (Figure 4.7), the inductance value remains constant up to 10MHz.

Fig 4.10. Bandpass Filter Using VDTA Based Floating Inductor [66]

Here in fig 4.10, the  $L_{equ}=12.6 \,\mu H$  as discussed earlier is used in band-pass filter configuration. Now the circuit will be behaved as the RLC series circuit shown in figure 4.11.

Whose Transfer Function is written as,

$$\frac{I(s)}{V(s)} = \frac{\frac{1}{L}s}{s^2 + \frac{R}{L}s + \frac{1}{LC}}$$

That is the expression of band pass filter.

Fig 4.11. RLC Series Circuit

Where center frequency

$$\omega_0 = \frac{1}{\sqrt{LC}}$$

rad/sec therefore fo  $= \frac{1}{2\pi\sqrt{LCo}} = \frac{1}{2\pi\sqrt{\frac{C1}{gm1gm2}Co}}$

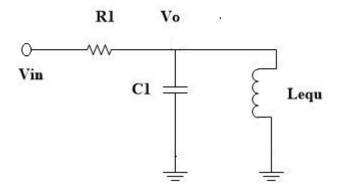

The theoretical value of the band-pass filter is calculated as 14.17MHz

By simulation, we get 12.67MHz as shown in figure 4.12.

So the error will be,

$$\frac{12.67 - 14.17}{14.17} X100\% = -10.58\%$$

Fig 4.12. Frequency Response for Band-pass Filter Using VDTA Based Floating Inductor

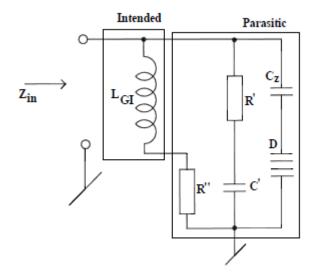

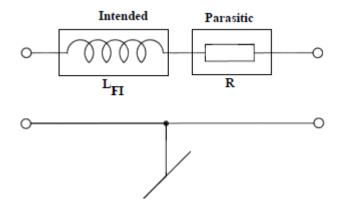

### 4.3.1. NON-IDEALITY AND SENSITIVITY PERFORMANCE FOR FLOATING INDUCTANCE VICTIMIZATION VDTA

Considering VDTA non-ideal parasitic i.e., the finite X-terminal parasitic electrical resistance consisting of a resistance Rx in parallel with capacitance 110 and therefore the parasitic electrical resistance at the Z-terminal consisting of a resistance Rz in parallel with capacitance Cz

The non-ideal equivalent circuit of floating inductance of Figure 4.7 is derived from Equation (4.28) and is shown in Figure 4.13. Similarly, for the circuit shown in Figure 4.7, the input-output current and voltage relationships are given by:

$$\begin{bmatrix} I_{1} \\ I_{2} \end{bmatrix}$$

$$= \frac{gm1gm2}{s(C+2Cx) + \frac{2}{Rx}} \begin{bmatrix} 1 + \left\{ s(C+2Cx) + \frac{2}{Rx} \right\} \left( sCz + \frac{1}{Rz} \right) & -1 \\ -1 & 1 + \left\{ s(C+2Cx) + \frac{2}{Rx} \right\} \left( sCz + \frac{1}{Rz} \right) \end{bmatrix}$$

$$\begin{bmatrix} V_{1} \\ V_{2} \end{bmatrix}$$

Where

$$L_{FI} = \frac{(C+2Cx)}{gm1gm2}R = \frac{2}{Rxgm1gm2}$$

The various sensitivities of  $L_{FI}$  with respect to active and passive elements are:

$$S_C^{LFI} = \frac{C}{(C+2Cx)} S_{Cx}^{LFI} = \frac{Cx}{(C+2Cx)}$$

$$S_{gm1}^{LFI} = -1 \ S_{Cgm2}^{LFI} = -1$$

(4.29)

Fig 4.13. Non Ideal Structure of Floating Inductor Using VDTA [66]

# **CHAPTER-5**

# LC LADDER FILTER REALIZATION USING VDTA

#### **5.1. INTRODUCTION**

In the previous chapter we presented the realization as well as floating inductor using active building blocks VDTA.

In the present chapter we have realized 3<sup>rd</sup>, 4<sup>th</sup>, 5<sup>th</sup>, 6<sup>th</sup> order low-pass and high-pass filters, 8<sup>th</sup> order band-pass filter and 10<sup>th</sup> order band reject Butterworth filters. We have adopted the aforesaid filters using synthesis technique described in.

#### **5.2. LC LADDER FILTER DESIGN**

The LC ladder filter is having an excellent circuit with very less sensitivity to component tolerances. Because of the low sensitivity to component values that characterizes the doubly terminated LC ladders, these circuits are majorly used in filter applications. LC ladder is used as a model for circuits that employ active elements to simulate inductors, resistors and other elements. To obtain transfer of signal power, the ladder has a source  $V_s$ , as a rule with a source resistor  $R_1$ , and is terminated with a load resistor  $R_2$  that dissipates the output signal energy and where the output signal is being measured. We will have keen interest in lossless ladders for the following reasons:

- 1. Even though the design of LC filters has its roots in antiquity, lossless ladders has its widespread use in this day for high frequency applications or where no power is available to drive the active devices.

- 2. LC ladder filters form prototype models that are simulated by active circuits, both with discrete components and in fully integrated form on an on-board integrated

circuit chip. The goal is to develop the active circuit in such a way that the simulation inherits the excellent sensitivity properties of lossless passive ladders.

3. Finally if we get success in developing an active simulation of the passive ladder, we will be able to make use of a bulk number of design information and tables that are readily available for LC ladders.

The low sensitivity property that we are interested in is valid for doubly terminated ladders. Sensitivities can be shown to exhibit poor response when either or both terminations are not present for example, source resistance=0 and/or load resistance= $\infty$ . We therefore are left only with ladders working between two resistors.

Fig 5.1. Doubly Resistively Terminated LC Ladder Lossless Filter [91]

#### **5.3. SYNTHESIS PROCEDURE**

In the doubly terminated [91] circuits in Fig 5.1 we have seen the current from the source,  $I_1$ , and its reference flowing direction, and  $Z_{in}$  seen as the input impedance of the RLC circuit what consists of the lossless ladder terminated by  $R_2$ . We assume that the circuit is under working condition in sinusoidal steady state. The input impedance is having both a real and imaginary component

$$Zin = Rin + JXin \tag{5.1}$$

And the current at the input terminal is

$$I_1 = \frac{V_S}{R_1 + Z_{in}}$$

(5.2)

Now since the LC circuit acts as lossless, we may make the average power equating to the circuit,  $P_1$ , equation, to that of the load. Thus,

$$P_1 = R_{in} |I_1(j\omega)|^2 = \frac{|V_2(j\omega)|^2}{R_2}$$

(5.3)

Substituting Eq.(2) for  $I_1$  into this equation provides us

$$\frac{R_{in}|V_s(j\omega)|^2}{|R_1 + Z_{in}|^2} = \frac{|V_2(j\omega)|^2}{R_2}$$

(5.4)

From this equation, we have a tendency to get the magnitude square of the required transfer perform

$$\left|\frac{V_2(j\omega)}{V_S(j\omega)}\right|^2 = |T(j\omega)|^2 = \frac{R_2 R_{in}}{|R_1 + Z_{in}|^2}$$

(5.5)

To make this expression relate to the transfer function H(s) that we represent to use for LC filter and if we take the ratio of power, we get,

$$|H(j\omega)|^{2} = \frac{P_{2}}{P_{1,max}} = \frac{4R_{1}}{R_{2}} \left| \frac{V_{2}(j\omega)}{V_{S}(j\omega)} \right|^{2} = \frac{4R_{1}}{R_{2}} \frac{R_{2}R_{in}}{|R_{1}+Z_{in}|^{2}} \le 1$$

(5.6)

With Eq.(1) we obtain,

$$|H(j\omega)|^{2} = 1 - \frac{|R_{1} - Z_{in}|^{2}}{|R_{1} + Z_{in}|^{2}} = 1 - |\rho(j\omega)|^{2}$$

(5.7)

where the auxiliary function  $\rho(s)$  is termed as the reflection coefficient. P(s) is a measure to know how well R<sub>1</sub> and Z<sub>in</sub> are matched ; we have always  $|\rho(j\omega)|^2 \le 1$  and for matching purpose,  $\rho(s)=0$ . Evidently,  $\rho(s)$  is described as

$$|\rho(j\omega)|^{2} = |\rho(s)|\rho(-s)||_{s=j\omega} = \frac{|R_{1}-Z_{in}|^{2}}{|R_{1}+Z_{in}|^{2}}$$

(5.8)

From this equation, we can see that  $\rho(s)$  may be separated from  $\rho(-s)$  to give the result as

$$\rho(s) = \pm \frac{R_1 - Z_{in}(s)}{R_1 + Z_{in}(s)}$$

(5.9)

Clearly, this equation may be deduced for  $Z_{in}$  in terms of  $\rho(s)$  and  $R_1$ . The final result is

$$Z_{in} = R_1 \frac{1 - \rho(s)}{1 + \rho(s)} \tag{5.10}$$

Or

$$Z_{in} = R_1 \frac{1 - \rho(s)}{1 + \rho(s)}$$

(5.11)

Observe that these expressions result into two reciprocal impedances. Now, since  $\rho$  is described in terms of the prescribed transfer function H, we have reduced the problem to determining a lossless circuit terminated in a resistor R<sub>2</sub> from a defined Z<sub>in</sub>. Sidney Darlington (1939) showed in his classic publication that this was always possible, and so the circuit may be designed from a given Z<sub>in</sub>. To depict the implementation of the strategy, consider the problem to determine circuits which have a Butterworth response where there are equal terminations with R<sub>1</sub>=R<sub>2</sub>=1, a normalized value that may later be magnitude scaled by de-nomalizing the element parameters to obtain the desired cutoff or centered frequency.

The Butterworth response is expressed as:

$$|H(j\omega)|^2 = \frac{1}{1+\omega^{2n}}$$

(5.12)

Note that this magnitude-squared function is less than or equal to unity and so it satisfies the condition of Eq. (6). Since the magnitude-squared function is

$$|H(j\omega)|^{2} = |H(s)|H(-s)||_{s=j\omega}$$

(5.13)

Then

$$|H(j\omega)|^{2} = \frac{K_{H}}{|D(j\omega)|^{2}} = \left|\frac{K_{H}}{|D(s)|D(-s)|}\right|_{s=j\omega}$$

(5.14)

The constant K<sub>H</sub> relates to the constant K by  $K_H = 2\sqrt{\frac{R_1}{R_2}}K$ , and D(s) is known from our study of the Butterworth response function.

We may determine from Eq. (5.7) the auxiliary function of Eq.(5.9), We have

$$|\rho(j\omega)|^2 = 1 - \frac{1}{1 + \omega^{2n}} = \frac{\omega^{2n}}{1 + \omega^{2n}}$$

(5.15)

Since

$$\omega^{2n}|_{\omega^2 = -s^2} = s^n (-s)^n \tag{5.16}$$

We see that

$$\rho(s) = \frac{s^n}{D(s)} \tag{5.17}$$

Substituting this value of  $\rho(s)$  into Eqs. (10) and (11), we get,

$$Z_{in} = R_1 \left[ \frac{1 - \rho(s)}{1 + \rho(s)} \right]^{\pm} = R_1 \left[ \frac{D(s) - s^n}{D(s) + s^n} \right]^{\pm}$$

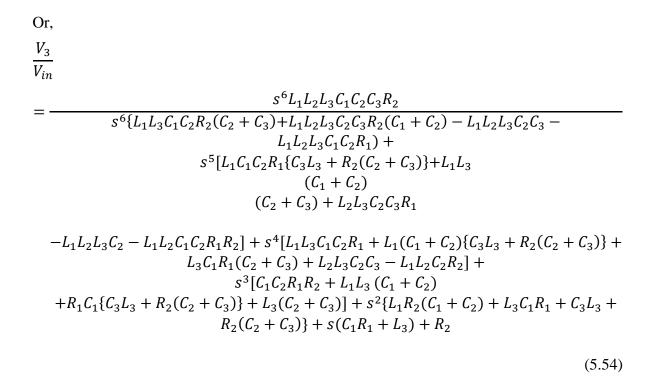

(5.18)