# FGMOS based Instrumentation Amplifier for Healthcare Applications

A Dissertation

submitted in partial fulfillment of the requirements for the award of the degree of

## Master of Technology in VLSI Design &Embedded Systems

Submitted by:

# **ROSHAN DEEP RANJAN**

## 2K16/VLS/19

under the supervision of

# Dr. MALTI BANSAL

Assistant Professor Department of Electronics and Communication Engineering, DTU

Department of Electronics & Communication Engineering DELHI TECHNOLOGICAL UNIVERSITY

> (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

> > 2016-2018

# FGMOS based Instrumentation Amplifier for Healthcare Applications

## A PROJECT REPORT

submitted in partial fulfillment of the requirements for the award of the degree of

## Master of Technology in VLSI Design &Embedded Systems

Submitted by:

# **ROSHAN DEEP RANJAN**

## 2K16/VLS/19

Under the supervision of

# Dr. MALTI BANSAL

Assistant Professor Department of Electronics and Communication engineering, DTU

**Electronics & Communication Engineering DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

2016-2018

Electronics & Communication Engineering DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CANDIDATE'S DECLARATION**

I ROSHAN DEEP RANJAN, Roll No. 2K16/VLS/19 student of M.Tech (VLSI & Embedded System), hereby declare that the project Dissertation titled "FGMOS based Instrumentation Amplifier for Healthcare Applications" which is being submitted by me to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology in VLSI Design & Embedded Systems, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: New Delhi

ROSHAN DEEP RANJAN (2K16/VLS/19)

## **Electronics & Communication Engineering**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CERTIFICATE**

I hereby certify that the Project Dissertation titled "FGMOS based Instrumentation Amplifier for Healthcare Applications" which is being submitted by ROSHAN DEEP RANJAN, Roll No 2K16/VLS/19 Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge, this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: New Delhi Date:

### Dr. MALTI BANSAL

Assistant Professor Department of Electronics & Communication Engineering Delhi Technological University **Electronics & Communication Engineering** DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **ACKNOWLEDGEMENT**

Someone wise had once said, "If the destination is beautiful, don't ask about the pains of the journey, and if the journey is beautiful don't ask to which destination it will lead." And I have a lot of people to thank who have made my study journey and destination both beautiful. This dissertation is the result of work of almost two years, whereby I have been accompanied and supported by many people, to whom I would like to express my gratitude.

I would like to express my deep gratitude to my supervisor, **Dr**. **Malti Bansal** assistant professor department of Electronics and Communication Engineering, DTU Delhi who has provided me with guidelines for my work and supported me with valuable advice throughout my studies.

I would like to take this opportunity to express my appreciation to all my friends and colleagues in Electronics and Communication Engineering Department, Delhi Technological University.

The two people to whom I believe I owe all and saying just 'Thanks' will be insufficient, are my parents. I would like to thank them and my siblings for believing in me and supporting me.

#### **ROSHAN DEEP RANJAN**

Roll no: 2K16/VLS/19 M.TECH. (VLSI Design and Embedded Systems) Department of Electronics & Communication Engineering Delhi Technological University Delhi – 110042

### **ABSTRACT**

This thesis presents a new FGMOS based instrumentation amplifier for bio-medical applications. Instrumentation amplifier is an essential block for most of the bio-medical applications as it extracts out weak potential signals that may lie between microvolt to millivolt from human body. To extract weak potential signal, an instrumentation amplifier is needed to have very high common mode rejection ratio (CMRR) so that it can minimise the effect of common mode noise and hence desired signal can be extracted out. An instrumentation amplifier with high CMRR, high gain and low power dissipation is essentially required. To operate circuit on low voltage, FGMOS is used. FGMOS is a multi-input floating gate MOSFET used to reduce threshold voltage and hence operated on low supply voltage which results in lower power dissipation. Here, FGMOS is used to simulate two stage operational amplifier and hence, by using operational amplifier, instrumentation amplifier is drawn. The main purpose of using FGMOS in the circuit is its smaller threshold voltage compared to the normal MOSFET and having threshold voltage tuning ability. Threshold voltage can be changed by changing capacitance ratio at the gate terminal. Because lower threshold voltage is required for the circuit operation, it consumes low power and is hence suitable for battery powered portable devices. The two stage operational amplifier is designed in virtuoso 90nm technology and operated on 1.8V supply. Also, the two stage operational amplifier based on FGMOS is operated on 1.35V (the minimum voltage requirement of FGMOS based circuit so that all the MOSFET remains in saturation region). Technological parameters table of two stage operational amplifiers are charted out using FGMOS and with conventional MOS.

## **CONTENTS**

| Candidate's Declaration | i   |

|-------------------------|-----|

| Certificate             | ii  |

| Acknowledgement         | iii |

| Abstract                | iv  |

| Contents                | v   |

| List of Figures         | vii |

| List of Tables          | ix  |

| List of abbreviations   | х   |

|                         |     |

### **CHAPTER 1 INTRODUCTION**

- 1.1 Motivation

- 1.2 History of Operational Amplifier

- 1.3 Operational Amplifier Basics

- 1.4 Different Parameters of Operational Amplifier

- 1.5 Ideal and Practical Values of Operational Amplifier

- 1.6 Different Parameter Test Circuit

- 1.7 Conventional CMOS Operational Amplifier

- 1.8 Simulation Results of Conventional Operational Amplifier

- 1.9 Organization of Thesis

## **CHAPTER 2 LITERATURE SURVEY**

- 2.1Introduction

- 2.2 FGMOS history

- 2.3 Device Characteristics

- 2.4 Charge Accumulation

- 2.5 Challenges of Using FGMOS in Nanometer Technologies

- 2.5.1 Gate direct tunneling in sub 100nm technologies

- 2.5.2 Previous modelling of gate tunneling current in NMOS transistors

- 2.6 FGMOS Simulation Model

- 2.7 Summary

### **CHAPTER 3 EXPERIMENTAL WORK**

- 3.1 Schematic of Conventional Operational Amplifier

- 3.2 Schematic of FGMOS based Operational Amplifier

- 3.2.1 Simulated values of fgmos operational amplifier

- 3.3Transistor Dimension of Conventional and FGMOS based Operational Amplifier

### 3.4 Instrumentation Amplifier

3.4.1 Simulated parameters of instrumentation amplifier

## **CHAPTER 4 RESULTS AND CONCLUSION**

- 4.1 Problems Faced in FGMOS Model for Nanometer Technologies

- 4.2 A New Model for FGMOS Transistor in Nanometer Technologies

## **CHAPTER 5 FUTURE SCOPE**

Appendix: (i) List of Published Papers

(ii) List of Communicated Papers

## LIST OF FIGURES

| Figure No   | Title                                                     | Page No. |

|-------------|-----------------------------------------------------------|----------|

| Figure 1.1  | Basic block diagram of operational amplifier              | 4        |

| Figure 1.2  | Symbol of operational amplifier                           | 6        |

| Figure 1.3  | Circuit for measuring open loop gain                      | 7        |

| Figure 1.4  | Test circuit for CMRR                                     | 7        |

| Figure 1.5  | Test circuit for PSRR                                     | 8        |

| Figure 1.6  | Test circuit for slew rate                                | 8        |

| Figure 1.7  | Conventional two stage op amp                             | 9        |

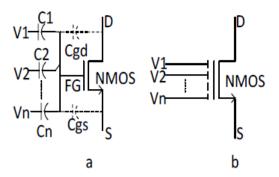

| Figure 2.1  | N- type FGMOS using double poly structure                 | 15       |

| Figure 2.2  | n- input FGMOSET (a) equivalent circuit, (b) the symbolic | 15       |

|             | representation                                            |          |

| Figure 2.3  | Equivalent circuit of FGMOS                               | 16       |

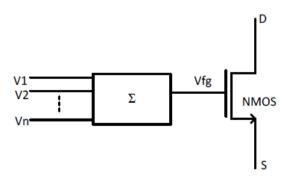

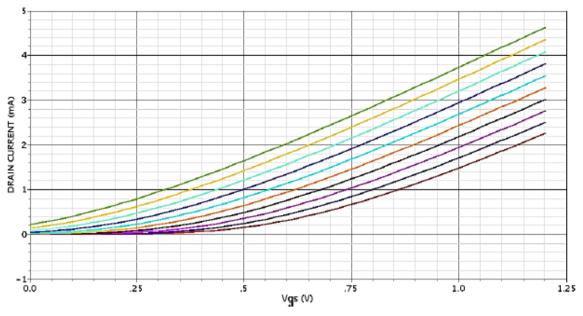

| Figure 2.4  | A comparison between FGMOS and standard MOS drain         | 17       |

|             | current                                                   |          |

| Figure 2.5  | FGMOS threshold voltage programmability by sweeping       | 18       |

|             | one of the input voltage                                  |          |

| Figure 2.6  | The mechanism of gate tunneling current in CMOS           | 20       |

|             | transistor                                                |          |

| Figure 2.7  | Direct tunneling gate current components for NMOS         | 21       |

|             | transistor                                                |          |

| Figure 2.8  | Direct tunneling gate current micro model                 | 21       |

| Figure 2.9  | Micro model for gate tunneling for circuit simulation     | 22       |

| Figure 2.10 | Gate direct tunneling model for circuit simulation        | 22       |

| Figure 2.11 | Multiple inputs FGMOS simulation model                    | 23       |

| Figure 2.12 | FGMOS simulation model                                    | 25       |

| Figure 2.13 | Simulation model for FGMOS transistor                     | 25       |

| Figure 3.1  | Gain and phase plot of conventional two stage op amp      | 29       |

| Figure 3.2  | UGB and phase margin plot of conventional two stage op    | 30       |

|             | amp                                                       |          |

| Figure 3.3  | FGMOS based two stage op amp                              | 31       |

| Figure 3.4  | Gain and phase plot of FGMOS based two stage op amp       | 33       |

| Figure 3.5  | UGB and phase margin plot of FGMOS based two stage op  |    |

|-------------|--------------------------------------------------------|----|

|             | amp                                                    |    |

| Figure 3.6  | CMRR plot of FGMOS based two stage op amp              | 35 |

| Figure 3.7  | Instrumentation amplifier based on FGMOS two stage op  | 36 |

|             | amp                                                    |    |

| Figure 3.8  | Instrumentation amplifier gain and phase plot at Rg=10 | 38 |

|             | ohms                                                   |    |

| Figure 3.9  | Instrumentation amplifier UGB and phase margin plot at | 39 |

|             | Rg=10  ohms                                            |    |

| Figure 3.10 | Instrumentation amplifier gain and phase plot at Rg= 1 | 40 |

|             | Kohms                                                  |    |

| Figure 4.1  | The structure of N type FGMOS simulation model for     | 44 |

|             | nanometer technologies                                 |    |

## LIST OF TABLES

| Table No. | Title                                                     | Page No. |

|-----------|-----------------------------------------------------------|----------|

| Table 1   | Comparison between ideal and practical parameters of op   | 6        |

|           | amp                                                       |          |

| Table 2   | Technological parameters of conventional two stage op amp | 28       |

| Table. 3  | Technological parameters of FGMOS based two stage op      | 32       |

|           | amp                                                       |          |

| Table 4   | FGMOS and conventional op amp transistor dimensions       | 32       |

| Table 5   | Resistor Values of instrumentation amplifier              | 37       |

| Table 6   | Technological parameters of FGMOS based                   | 37       |

|           | instrumentation amplifier                                 |          |

## LIST OF ABBREVIATIONS

| Abbreviation      | Full form                                         |

|-------------------|---------------------------------------------------|

| AHDL              | Analog Hardware Duscription Language              |

| BW                | Bandwidth                                         |

| Cox               | Oxide Capacitance                                 |

| CMOS              | Complementary Metal Oxide Semiconductor           |

| DT                | Direct Tunneling                                  |

| EPROM             | Erasable Programmable Read Only Memory            |

| ECB               | Electron Conduction band                          |

| EVB               | Electron Valence band                             |

| FGMOS             | Floating Gate Metal Oxide Semiconductor           |

| IC                | Integrated Circuit                                |

| MOSFET            | Metal Oxide Semiconductor Field Effect Transistor |

| PM                | Phase Margin                                      |

| SiO2              | Silicon Oxide                                     |

| tox               | Silicon Oxide thickness                           |

| Vth               | Threshold Voltage                                 |

| V <sub>THFG</sub> | Floating gate Threshold Voltage                   |

| HVB               | Hole Valence Band                                 |

| UGB               | Unity Gain Bandwidth                              |

| SR                | Slew Rate                                         |

| ICMR              | Input Common Mode Range                           |

| CMRR              | Common Mode Rejection Ratio                       |

| PSRR              | Power Supply Rejection Ratio                      |

| IA                | Instrumentation Amplifier                         |

| Rout              | Output Resistance                                 |

| Rin               | Input Resistance                                  |

| DC                | Direct Current                                    |

| Op amp            | Operational Amplifier                             |

|                   |                                                   |

### **CHAPTER-1**

### **INTRODUCTION**

#### **1.1 Motivation :**

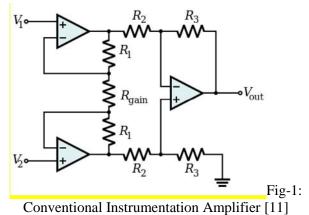

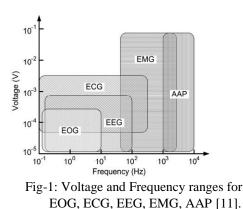

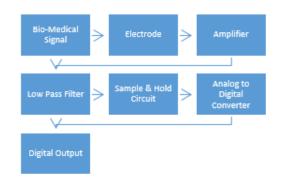

The instrumentation amplifier is one of the most important block in signal acquisition system. To extract weak potential signal, highly efficient instrumentation amplifier is required. Due to growing demand of portable battery powered devices, low power consumption is essentially required. The performance of an instrumentation amplifier depends upon its technological parameters i.e., CMRR, gain, noise, power dissipation etc. Different topologies are available in the literature to increase CMRR, gain etc. and also different topologies are available to reduce power dissipation that directly depends on supply voltage. The growing demands of low power portable devices makes the designer to investigate and present new low power circuits. Due to above requirement, in this thesis FGMOS is used due to which supply voltage requirement decreases and hence power dissipation.

The need of high performance systems from the last decade had grown rapidly. That's why the transisitor density has beenincreasing subsequently which also demands an expensive cooling &packaging technologies which give rise to some drawbacks. The voltages are scaleddownto minimize the effect of drawbacks which also affects current driving capability.

Due to smallerthreshold voltage ( $V_{TH}$ ) because of scaling, results in exponential rise of subthreshold leakage current and causes leakage (static) power dissipation( $P_{Static}$ ). Static power dissipation is now dominating and become a major concern indeep submicron technologies which results in inferior battery life.

[1-2] discusses about leakage power dissipation forbetterbattery life,that also requires advanced design techniques. $P_{Static}$  is predominantly dominated byleakage current components flowing in the transistor or CMOS circuits during idle or standby mode. It is anticipated and described in [2] that theleakage power ( $P_{Static}$ ) could rise by 32 times per device by 2020.

The four main roots of leakage currentin a CMOS transistor are:

- i) Reverse-biased PN-junction leakage current

- ii) Gate induced drain leakagecurrent

- iii) Gate direct-tunnelling leakage current

- iv) Subthreshold(weak inversion) leakage current  $(I_{SUB})$ .

The subthreshold leakage current( $I_{SUB}$ ) mainly doinatesamong all the leakage currentsources and has become extremely challenging research in current and for future silicon technologies. The gate direct-tunneling leakage current is dominate in FGMOS in sub-micron technologies and hence degrades the circuit performance. From last two decades, analog designers starts using FGMOS based circuit in computational design due to the features of multi-input FGMOS and threshold voltage programmability.

In the structure of FGMOS where there is no path for DC grounding, a modified simulation model is used in order to get correct result.

### **1.2 History of Operational Amplifier**

Operational amplifier is very important block in analog and mixed signal circuits. It plays vital role in analog circuits as because with the help of this, one can perform most of the mathematical operations like addition, subtractions, logrithms, integration, differentiation etc. John R. Ragazzinidesigned it in 1947 and shows a unique kind of amplifier by selecting external components appropriately. The first& early applications of operational amplifier was in analog computer [23].

### **1.3 Op amp Basics**

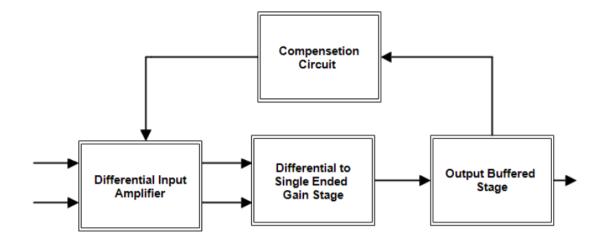

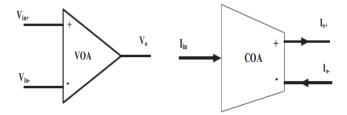

Basically op amp is a voltage amplifier and hence having very high input resistance and extremely low output resistance. The op amp has very high open loop gain and hence when used in negative feedback configuration, overall transfer function becomes independent of open loop gain and this property is very useful and hence used in most of the analog circuits. op amp in open loop configuration used as comparator, in positive feedback used as a wave generater circuit and in negative feedback used as a amplifier along with different mathematical operations and filtering. The essential requirement of an op ampis that it must have very high open loop gain to implement negative feedback configuration. Due to the frequent use of op amp is IC, two stage op amp technique need to be simple and efficient. In an op amp, the differential signal is applied and whose output is amplified versiondifferential input. The op amp is a basic differential amplifier having input stage and the output stages. The output stage of op amp is a single ended & hence, op amp is a differential to single ended circuit. As to get high swing at the output, a buffer stage is used since op amp has low output impedance. Compensation circuitry is used to make close loop op amp stable.

The block diagram of basic closed loop op amp shown in figure (1.1). The input stage is called differential amplifier. As its name suggests it processes the difference between the two input signals. It helps to remove common mode signal applied. As because most of the common mode signals are filtered out therefore, noise as well as bias voltage are also negated out. Though differential amplifier filtered out most of the common mode signal, still some common mode signal left out at the output of differential amplifier [23]. The output of differential amplifier is given by:

$$V_{out} = A_d(Vin^+ - Vin^-) + A_C((Vin^+ - Vin^-)/2)$$

(2.1)

Ideally,  $A_C = 0$

$$V_{out} = A_d(Vin^+ - Vin^-)$$

(2.2)

Where,  $A_C$  is the Common mode gain due to common mode signal and  $A_d$  is the differential mode gain of the amplifier due to differential input.

Differential amplifier helps to minimize common mode signal and left out small common mode voltage which is good and can be handeled comfortably.

Figure 1.1 – Basic block diagram of op amp.

The CMRR of a differential amplifer specifies the common mode rejection ability of an amplifier. And ideally it should be infinite. Mathematically, CMRR is given by:

$$CMRR = \frac{Ad}{Ac}$$

(2.3)

Single ended output differential amplifer is used in CMOS technology [24]. Also, from figure 1.1, it can be seen that differential to single ended gain stage is used in cascade with differential amplifier as because single ended output is used in CMOS technology. A output buffer stage is used in the output stage to get voltage output with high swing. A common source amplifier is used in the output stage as a buffer. A compensation circuit is used in the feedback to get improved performance, it improves phase margin.

### **1.4 Different Parameters of Operational Amplifier**

Anop amp is characterized by its technological parameters and its parameters are as follows:

DC Gain: It signifies the open loop gain of the Operatioal amplifier. The ideal open loop DC gain of an Op-amp is infinite, practically it lies in between 60 dB to 100 dB.

ICMR: It is the range of common mode input voltage at which all the transistors remains in saturation & results in constant gain.

CMRR: It is defined as the ratio of differential mode gain to the common mode gain of an amplifier. Ideally, an op amp should have very high CMRR value & it would be infinite, practically CMRR should be more than 60 dB. CMRR is one of the important parameter of the op amp for biomedical system.

PSRR: It is defined as the product of ratio of the change in supply to change in output voltage of the amplifier due to the change in the power supply and open loop gain of the op amp. It also indicates how efficiently an op amp maintaining to the deviation of power

supply (both positive supply & negative supply which also might be considered as ground). Less variation at the output of an op amp corresponding to the variation of power supply results in higher PSRR. An op amp is need to have very high PSRR & practically it should be greater than 60 dB.

Slew Rate: It is defined as the maximum rate of change of output voltage with respect to time. It is expressed in terms of V/us. A good op amp should have high slew rate. It determines by the charging and discharging of output capacitor by current available. Slew rate is completely depends on the current sourcing or sinking capability of the input stage rather than the output.

Settling time: It is the minimum time taken by the system to reach the steady state. For a typical op amp this value is less than 1us.

Phase Margin: It is defined as the excess of phase required to make the system marginally stable at the unit gain frequency. It is a measure of stability for close loop system.

$$PM = 180 + \phi \tag{2.4}$$

$\phi$  = Phase of system when gain is 0 dB.

Practically for a well designed op amp this value is around 60 degree.

For a becoming a system stable the phase margin and gain margin both are need to be positive. However, the consideration of a phase margin is very vital because it affects the transient response such as the settling time, slew rate, rise time, fall time and overshoot. Input offset voltage: It defined as the voltage that must be applied between the two input terminals of an op amp to null or zero the output voltage.

#### **1.5 Ideal and Practical Values of Op Amp Parameters**

Table 1 shows the comparison of different Practical and Ideal technological parameters of an operational amplifier. Getting ideal values of parameters for an op amp is very tough.

| IDEALLY                | PRACTICALLY                                        |

|------------------------|----------------------------------------------------|

| $R_{IN} = infinite$    | $R_{IN}$ is very high (in terms of M $\Omega$ )    |

| R <sub>OUT</sub> =zero | $R_{OUT}$ is a low value (in terms of K $\Omega$ ) |

| DC GAIN = infinite     | $DC GAIN \ge 60 dB$                                |

| BANDWIDTH =infinite    | BANDWITH is very high value (in terms of MHz)      |

| CMRR = infinite        | $CMRR \ge 60 dB$                                   |

| PSRR = infinite        | $PSRR \ge 60 dB$                                   |

| OFFSET = zero          | OFFSET $\neq$ zero (in order of millivolts)        |

| SLEW RATE = infinite   | SLEW RATE $\geq$ 5 V/us                            |

Table 1: Comparison between Ideal and Practical parameters of op amp

### **1.6 Different Parameter Test Circuit**

To find different technological parameter of an op amp, different test circuits have been in this section. Schematic configuration are also present in this section.

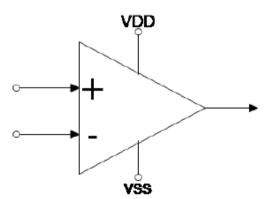

Figure 1.2- Symbol of op amp [23].

The figure 1.2 is a symbolic representation of a three terminal op amp. The left side two terminal are used to apply differential input signal and right side terminal provides amplified output. The input terminal signed as negative is known as inverting terminal & the positive indicating input terminal is known as non-inverting terminal. The op amp has a single ended output. The supply voltages are shown by the pin VDD and VSS. The op amp

generally uses dual power supply and hence, positive power supply is shown by  $V_{DD}$  & negative power supply is shown by VSS, in some cases VSS terminal is replaced by ground.

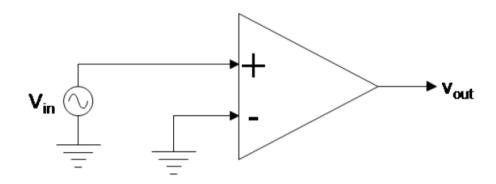

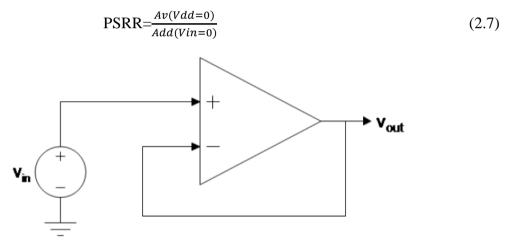

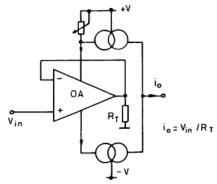

Figure 1.3- Circuit for measuring open loop gain [25].

From figure 1.3, we can find the open loop gain of operational amplifier. From the above figure 1.3, we can see that an AC signal  $V_{in}$  is applied on its non-inverting terminal & inverting terminal is AC grounded with op amp having supply voltages of VDD and VSS and AC analysis is carried out. The ratio of output to input will the open loop gain or DC gain of an op amp. Same configuration is used to findthe UGB, phase margin, 3dB bandwidth of etc.

Mathrmatically,

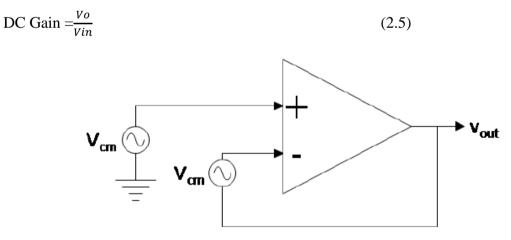

Figure 1.4- Test circuit for CMRR [25].

Figure 1.4 is used to find CMRR of an op amp. By finding differential mode gain and common mode gain, we can find CMRR. The ratio of differential mode gain to the common mode gain will give CMRR. The configuration shown above having two identical AC signal source Vcmand are tied in series with the inputs. The CMRR from above figure is given by:

$$\frac{Vout}{Vcm} = \frac{1}{CMRR}$$

(2.6)

Also, from equation (2.3), we can get CMRR.

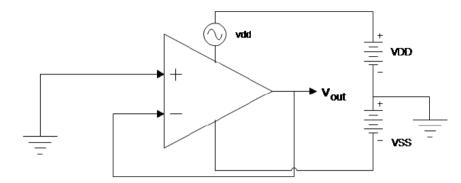

Figure 1.5- Test circuit for PSRR [25].

The figure 1.5 shown above is a configuration used to find PSRR of an op amp. To measure PSRR, an AC signal vdd is connected in series with supply VDD. An AC analysis gives out the PSRR of an op amp. From equation (2.7) we can calculate PSRR [25].

Figure 1.6- Test circuit for slew rate [25].

Figure 1.6 is used to find slew rate & settling time of an op amp. It is a basic unit gain buffer amplifier having negative feedback configuration. By applying a step input at non inverting terminal, we can find slew rate of the op amp. After a transient time, we can find the settling time, the time at which ringing settles down. Slew rate is determined by the slope of the output signal during rise or fall time.

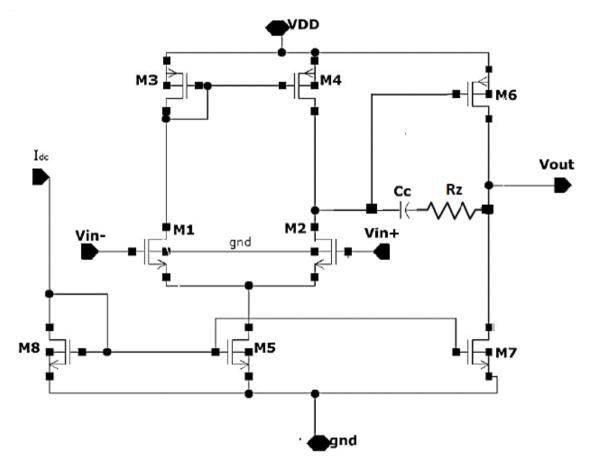

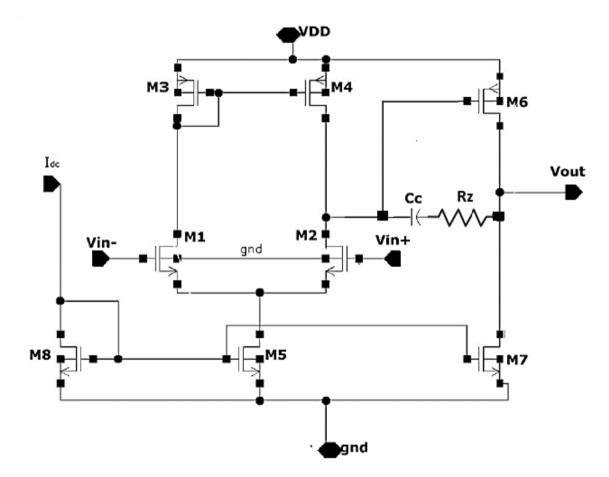

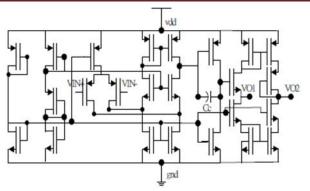

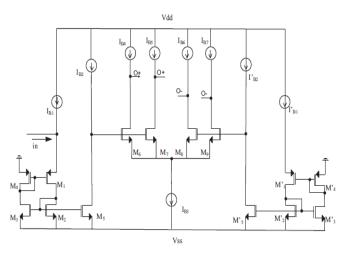

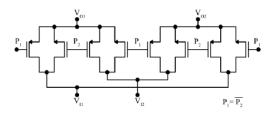

#### **1.7 Conventional CMOS Operational Amplifier**

Figure 1.7 shows a conventional two stage operational amplifier based on CMOS technology. Transistors M1-M5 & M8 constitutes first stage circuit and the second stage of the circuit is consists of transistor M6-M7. The Miller compensating capacitor C<sub>c</sub>and a

nulling resister is used between the output and input of the second stage. All transistors used in the circuit are biased in saturation region.

In first stage, the differential signal is applied into the transistor M1 & M2 from the pin  $V_{in}^{-1}$  and  $V_{in}^{+}$  the gate terminal respectively. M1 and M2 are two NMOS transistorwhich is used to drive the circuit and converts the differential voltage to differential current, these differential currents are further processed byPMOScurrent mirroredload transistor M3 and M4. The transistor M5 and M8 forms a current mirror and are used to provide reference current to the differential stage. The differential stage output is a single ended and it providesconstant gain with difference of the input signals. The single ended output of the first stage is then applied to the gate of the M6. Transistor M6 &M7 forms a second stage which is a common source configuration and offers high gain. The output of the second stage is taken from the drain terminal of the M6 [25].

Figure 1.7- Conventional two stage op amp [25].

The design relationships for the two stage op amp are from [25] is given by: The first stage DC gain is given by:

$$A_1 = \frac{-gm1}{gds2 + gds4} \tag{2.8}$$

The second stage DC gain is given by:

$$A_2 = \frac{-gm6}{gds6+gds7} \tag{2.9}$$

The overall gain of an operational amplifier from [25] is given by:

$$A_{V} = A_{1}.A_{2}$$

(2.10)

Therefore,

$$A_{V} = \frac{gm1gm6}{(gds2+gds4)(gds6+gds7)}$$

(2.11)

Slew Rate of two stage op amp is given by from [25]:

$$SR = \frac{I5}{Cc}$$

(2.12)

Where,  $I_5$  the current flowing through of transistor M5 & is the bias current of the first stage.

The gain bandwidth product of two stage op amp is given by from [25] is:

$$GB = \frac{gm1}{cc}$$

(2.13)

Positive ICMR

$$V_{in(max)} = V_{DD} - \sqrt{(I_5/\beta_3)} - |V_{T03}|_{(max)} + V_{T1(min)}$$

(2.14)

Negative ICMR

$$V_{in(min)} = V_{SS} + \sqrt{(I_5/\beta_1) + V_{T1(max)} + V_{DS5(sat)}}$$

(2.15)

For 60° phase margin, it is required that  $gm_6 = 2.2gm_2(CL/Cc)$  provided all other roots are greater than or equal to 10GB [25].

#### **1.8 Simulation Results of Conventional Op Amp**

Figure 1.7 shows a conventional two stage op amp based on CMOS technology and is designed in gpdk 90 nm technology having supply voltage of 1.8V along with a bias current IDC of 15 uA. This op amp is simulated in Cadence circuit simulator.

All the experimental work and results are elaborated in chapter 3. Also, all the conclusion drawn from circuits are explained in chapter 4.

#### **1.9 Organisation of Thesis:**

This thesis presents a comparison study between FGMOS based two stage operational amplifier and conventional two stage operational amplifier. Also technological parameters table is charted out. The thesis emphasized on design of instrumentation amplifier based on Floating-Gate MOS two stage operational amplifier. Chapter 2 deals with literature survey and the experimental work i.e., conventional operational amplifier is simulated in chapter 3 along with FGMOS based two stage operational amplifier and instrumentation amplifier. Problem associated with sub-micron technologies in FGMOS and its possible solution is discussed in chapter 4. Also chapter 4, presents result and conclusion. Future scope is reported in chapter 5.

### **CHAPTER-2**

### LITERATURE SURVEY

#### **2.1 Introduction**

In this chapter, the floating gate transistor is dicussed. FGMOS characteristics and the problem associated with submicron technology is also discussed like, the gate leakage current that cannot be tolerated and has a significantimpact on the transistor's performance. From last one decade huge amount of research is going on in analog FGMOS based circuit.Researchers are doing enormous effort to develop circuits based on FGMOS and minimizing the leakage current in sub-micron technology.This segment comprises of the various associated research themes.

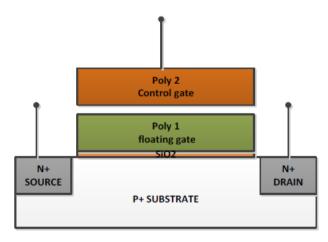

D. Kahng& S. M. Sze[3], introduced the concept of "floating gate MOS" in 1967. They proposed the circuit and simulation results which shows that floating gate can store charge for long duration and hence suitable as a memory element.

L. Richard Carley [4], describes in 1989 about electrically programmable FGMOS analog memory circuit for both positive as well as negative voltage changes & suitable for fabrication in a standard CMOS IC.

T. Shibata and T. Ohmi [5], presents a new type of MOS device based on FGMOS in 1992 and called it as "neuron MOSFET" because it perform fuctions more intelligently than conventional MOS. This transistor calculates the weighted sum of all the input voltage signal and controls the ON and OFF state of transistor based on the weighted sum result.

Y. Berg & T.S. Lande [6], described novel technique for threshold programmability using FGMOS for low power operation in 1997. The threshold voltage shifting was possible with the cost of extra polysilicon layer and the programmability in FGMOS transistor was possible by UV light activation and this gives rise to a new device called FGUVMOS transistor and is suitable for low power supply.

Y. Berg & T.S. Lande [7], presented a paper in 1999 showing area efficient threshold tuning technique for FGMOS circuits. The FGMOS is programmed by supply voltage rails & UV light, and hence additional programming circuitary is not required.

Antonio Lopez-Martin, J. Ramirez-Angulo [8], In 1999, presented a noval DAC converter the ability of the multiple input FGMOS transistor. A 6-bit DAC conversion is designed by the authors using multiple input FGMOS technique.

K. Nandhasri and J. Ngarmnil [9], in 2001, presented analog & digital comparator based on the threshold voltage characteristics of FGMOS transistor to produce a hysteresis that results in analog voltage comparator and analog comparator then used to develop digital comparator.

E. Rodríguez-Villegas, A. Rueda, and A. Yúfera [10], presented in 2001, a FGMOS transistor based translinear circuits for low voltage and low power. The technique used in [10] allows supply voltage reduction in strong inversion mode and hence suitable for low power applications.

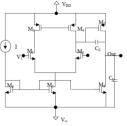

B. A. Minch [11], presented a folded FGMOS differential pair in 2000, which is capable of providing both rail to rail input common mode range & output voltage swing with low supply voltage.

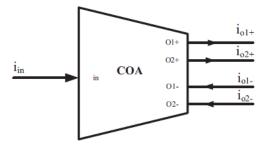

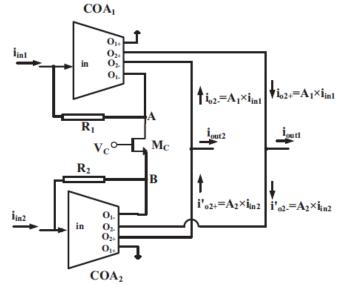

K. Moolpho. J. Ngarmnil and K. Nandhasri [12], presented wide swing FGMOS based current amplifier operated on low voltage. In [12] authors used a class AB structure which is designed with CMOS inverter and an analog inverter based on FGMOS transistor.

S. Sharma, S.S. Rajput, L.K. Magotra, and S.S. Jamuar [13], presented FGMOS based current mirror and its low power applications in 2002. It has wide operating current range and also has very high bandwidth. It also offers high output impedance, more than one megaohm for higher bias current and circuit is suitable for both N-type & P-type current mirror.

12

Rodriguez-Villegas and Esther [14], presented a paper in 2003, discussed about charge storage problem in FGMOS and possible solution to get rid of accumulated charge.

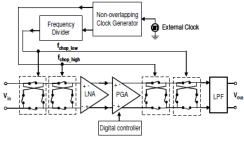

D. Yates, E. López-Morillo, R. G. Carvajal, J. Ramirez-Angulo and E. Rodriguez-Villegas [15] had presented a low power front end circuit for werarable biomedical systems using quasi-floating gate MOS in 2007 which rejects low frequency noise and provides higher SNR.

Patricia Mejía-Chávez, Juan C. Sánchez-García and José Velázquez-López [16], presented a differential difference amplifier based on FGMOS for ECG signal acquisition. Due to the use of FGMOS, DC offset reduced significantly.

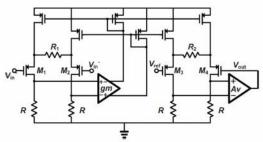

N. G. Lopez-Martinez, A. S. Medina-Vazquez and M. A. Gurrola-Navarro [17,] presented multiple input transconductance amplifier in common source configuration based on FGMOS in 2015.

Guoqiang Hang and Guoquan Zhu [18], in 2015 presented a Schmitt trigger with adjustable hysteresis based on FGMOS threshold inverter.

Sherif M. Sharroush [19], presented a novel variable gain amplifier using FGMOS suitable for radio frequency receivers where variable gain is needed.

P. Chandrakasan,[20] introduced "Low-power CMOS digital design," in 1992. The work was carried out by keeping the things in mind thatportable and battery-operated applications were emerging rapidly, the techniques allowslowers power consumption in CMOS digital circuits.

Gu, R.X and M.I Elmasry[21], presented a paper in 1996 wherethey evaluated stand-by as well as switching power dissipation in deep submicron technologies and a logical representation was elaborated.

A. Keshavarzi, K. Roy and C. F. Hawkins [22], presented a paper in 1997 in which they investigated various sources of leakage power in MOS device and their behavior with scaling.

### 2.2 FGMOS History

In 1967, FGMOS had been introduced by Sze et.al., [3] &has been used in memories widely like, EPROMs, EEPROMs, and flash because of their charge storing capabilities for long time. These charges can be controlled by:

(a) Exposing the chip on ultra violet (UV) light for finite duration of time.(b) For tunnelling electrons through the oxide, it is required to add a high potential voltage across gate capacitor.

(c) By using hot electron injection [26] to add electrons.

FGMOS still used in digital memories but from last couple of decades, it extended to analog design [27] also. As because of FGMOS threshold voltagetenability, it is being used in analog design environment to design analog circuits that can operate at smaller supply voltage than that of the standard MOS (for same process). Also, due to multiple input feature of FGMOS transistor, the designers are havingadvantage of designing different analog applications like, multipliers, integrators, amplifiers [28-30] etc. due to sum operation at the gate.

#### **2.3 Device Characteristics**

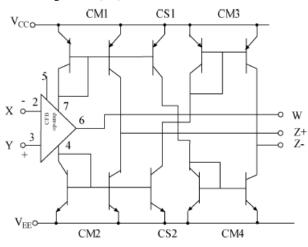

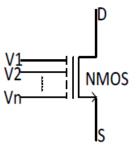

A Floating Gate MOS transistor is similar to standard MOS transistor, but it does not have any resistive connections to its gate & also numbers of inputs that are connected above the floating gate. The multiple inputs of floating gate are only capacitively connected. Double poly structure is used in the fabrication of FGMOS in which, the first poly is the floating gate & control gate is on second poly where rest of the inputs are deposited as shown in figures 2.1 and 2.2.As there is no DC path to ground at the gate of FGMOS transistor, and having multiple inputs which are capacitively connected, has changes the DC characteristics significantly from the standard MOSFET.

Figure 2.1- N-type FGMOS using double poly structure.

Figure 2.2- n-inputs FG MOSFET: a- equivalent circuit, b- the symbolic representation.

As because gate is electrically isolated from body due to the basic nature of FGMOS, there is no DC path to ground and hence, charge gets stored in the FG and this property of FGMOS is directly affects the drain current as well as the threshold voltage. This property of FGMOS helps in analog memories like Field Programmable Analogue Array (FPAA) [31].

The floating gate voltage is given by the weighted sum of all the capacitivelycoupled inputs voltages connected at the gate. By taking an assumption that there is no leakage current [32] flowing through gate terminal due to strong SiO<sub>2</sub> insulator at the gate, the FG voltage is given by:

$$V_{FG} = \sum_{i=1}^{N} \frac{CiVi}{CT} + \frac{QFG}{CT}$$

(3.1)

$$C_{T} = \sum_{i=1}^{N} Ci + Cgs + Cgd$$

(3.2)

By assumuing that, zero charge is accumulated at the gate, equation (3.1) can be re-written as:

$$V_{FG} = \frac{C1V1}{CT} + \frac{C2V2}{CT} + \frac{C3V3}{CT} + \dots + \frac{CnVn}{CT}$$

(3.3)

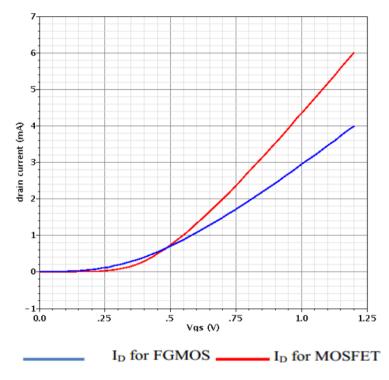

From Equation (3.3), we can conclude that, FGMOS reduces complexity in certain circuitsthat require adders & also it minimizes the power requirement & noise in such circuits [33] as shown in below figure 2.3.

Figure 2.3-Equivalent circuit for floating gate transistor [33].

For FGMOS in saturation region, the current equations can be written as:

$$I_D = \mu_N C_{OX} \frac{W}{2L} (V_{FG} - V_T)^2$$

(3.4)

By assume zero Q<sub>FG</sub> and replacing V<sub>FG</sub>in Equation (3.1), will result in

$$I_{\rm D} = \mu_{\rm N} \operatorname{Cox} \frac{W}{2L} (\sum_{i=1}^{N} \frac{CiVi}{CT} - V_{\rm T})^2 (3.5)$$

$$I_{\rm D} = \mu_{\rm N} \operatorname{Cox} \frac{W}{2L} \beta (\sum_{i=1}^{N} Vi - (\frac{CT}{Ci}) V_{\rm T})^2$$

(3.6)

$$I_{\rm D} = \mu_{\rm N} C_{\rm OX} \frac{W}{2L} \beta \left( \sum_{i=1}^{N} V_{i-1} V_{\rm THFG} \right)^2$$

(3.7)

Where,

$$\beta = \sum_{i=1}^{N} (\frac{Ci}{CT})^2$$

and,  $V_{\text{THFG}} = \sum_{i=1}^{N} (\frac{CT}{Ci}) V_{\text{T}}$

From above equations, it can be seen that, drain current of FGMOS is a function of the capacitor ratio and it is the ratio of effective input voltage to the total capacitance at the gate.

Let's assume that  $V_1$  is the effective input, then, the drain current can be written as :

$$I_{\rm D} = \mu_{\rm N} C_{\rm OX} \frac{W}{2L} \beta (V_1 - (\frac{CTVT}{C1} - \frac{C2V2}{C1} - \frac{C3V3}{C1} - \dots - \frac{CnVn}{C1}))^2$$

(3.8)

In this case,

$$\beta = \left(\frac{c_1}{c_T}\right)^2$$

$$V_{\text{THFG}} = \left(\frac{c_{TVT}}{c_1} - \frac{c_{2V2}}{c_1} - \frac{c_{3V3}}{c_1} - \dots - \frac{c_{nVn}}{c_1}\right)$$

$$I_D = \mu_N C_{\text{OX}} \frac{W}{2L} \beta (V_1 - V_{\text{THFG}})^2 (3.10)$$

$$gm_i = \frac{c_i}{c_T}$$

(3.11)

where, i= 1, 2, -----, N

Where, Ci are the input capacitors connected at the gate,  $C_{gs}\&C_{gd}$  are the parasitic capacitors,Vi are input voltages, V<sub>FG</sub> is the floating gate voltage,V<sub>THFG</sub> the threshold voltage of floating gate MOSFET&V<sub>T</sub> is the threshold of standard MOS threshold voltage. L is the channel length, W is the channel width, $\mu_N$  is the mobility, C<sub>OX</sub> is the oxide capacitance per unit area, N is the number of inputs voltages at the gate, Q<sub>FG</sub> indicating charges trapped in floating gate during fabrication and, gm is the FGMOS transconductance.

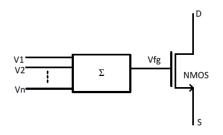

From equation (3.10), we conclude that FGMOS behaves as a programmable threshold voltagedevice in which the effective threshold voltage of floating gate  $V_{THFG}$ can be reduced zero or minimum i.e., to negative value compared to standard MOS threshold as shown in figure (2.4).

Figure (2.5) indicating the tuning ability of FGMOS by taking two inputs into consideration. By sweeping one input voltage and keeping the other. By increasing the numbers of input the gate or the input capacitors ratio,  $V_{THFG}$  can be further reduced. This is the one of the important specification of FGMOS that made this technique suitable for low power applications and also tunable circuit that used to compensate mismatches.

From equation (3.10) & (3.11), it can be seen that, the drain current  $I_D$ & the transconductance - gm of FGMOS is smaller than that of standard MOS transistor, as it can be seen from figure 2.4, due to the scalingwhich is a function of the coupling capacitors ratio for the effective input. These are some demerits of floating gate transistor. However, analog designers overcomes them & they used this transistor in other circuits.

Figure 2.4- A comparison between standard MOS and FGMOS drain currents.

Figure 2.5- FGMOS threshold voltage programmability by sweeping one of the input voltages.

### 2.4 Charge Accumulation

In FGMOS, because of silicon is surrounded by gate oxide, the charge carries may be accumulated during the fabrication process and therefore, these charges affects the threshold voltage of FGMOS directly and it is indeterminate. Theaccumulated charges may result in change in fundamental operations of the circuits and hence, these charges need to be eliminated in order to work FGMOS properly.

To resolve this problem, different solutions have been reported in the literature like, as shown in [34], FGMOS is exposed to ultra voilet light to get rid of the accumulated charges at the gate. The problem associated with technology is that it is not compatible with CMOS technology since, in order to activate lighttransition in FGMOS, the passivation layer hasto be removed.

Another proposed solution as described in [35] is suggests a Fowler–Nordheimtunnelling (FN) current to remove the charges from the floating gate. As  $SiO_2$  is an insulator that kept the electrons and hence, this electrons need high energy to cross through it, as oxide works as a barrier and therefore a high voltage applied in order to tunnel the trapped electrons through the barrier to the silicon below it. As the applied voltage is inversely proportional totheoxide thickness, a very high voltage is required, since the oxide thickness is very small.

A technique to get rid of trapped charges is reported in [14], this technique suggests that charges from the floating gate is eliminated by adding dummy contacts at the gate. This technique is highly efficient and simple. Also, it does not requires any extra circuitry and hence, has been widely used in FGMOS analog circuits.

### 2.5 Challenges of Using FGMOS in Nanometer Technologies

Analog designers are facing problems when they use FGMOS in submicron technology. The direct tunneling gate current is a serious concern in FGMOS transistor thatoccurs in sub 100nm technologies where oxide thickness is very small and due to this the electrons and holes tunnel through it. This DT leakage current degrades thetransistor performance in CMOS & in FGMOS specifically. The other problem is due to the nature of FGMOS that, the need of a model it in order to carry out thesimulations in any industry simulator due to the convergence problem.

In the next sections previously simulated models for FGMOS as well as the gate leakage current will be discussed.

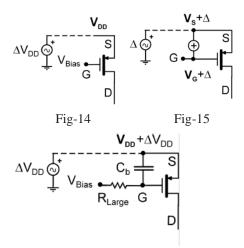

#### 2.5.1 Gate Direct Tunneling in sub 100nm Technologies

From last two decades, the CMOS technology has been scaled down significantly to meet the industry demand. Scaling of CMOS technology has improved the performance by reducing the power dissipation, small chip size, increased the speed etc., however, the scaling in transistor sizes also brings different challenges for a design engineer to predict the transistor performance.

Silicon oxide thickness has reduced to few nanometers due to continuous scaling in CMOS technology. Due to the small gate thickness oxide layer, direct tunneling (DT) current has become a growing issue foranalog designers. Tunneling of charge carriers (electronsand holes) from the gate through the oxide to the bulk and source / drain region respectively results in gate DT current.

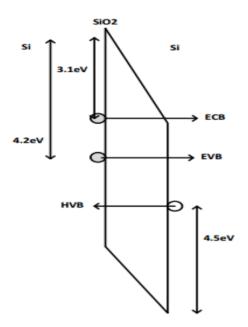

Figure 2.6, showsa DT mechanism in NMOS transistor. Tunneling of carriers from three bands result in DT current in which, the first tunneling is due to the tunneling of electrons of the conductions band (ECB) in the gate. The second tunneling is due to electrons in the valence band (EVB) and the third is due to the tunneling of holes through thevalence band to the gate (HVB). Direct tunneling is NMOS devices is dominated by ECB and EVB whereas in PMOS is by HVB.

Figure 2.6- The mechanism of gate tunneling current in CMOS transistor.

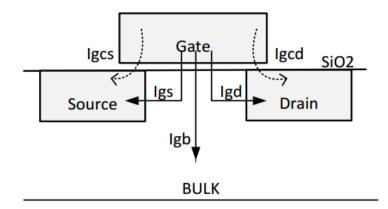

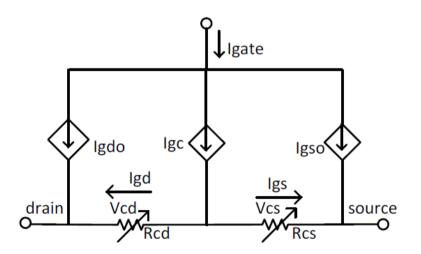

TheDT gate current has three components, 'Igb'the current between gate & substrate as shown in figure 2.7.also, the channel current 'Igc'. The channel current is further divided into two current components i.e., the current between the gate & the source 'Igcs' and the current between the gate & the drain 'Igcd' respectively. The total tunneling gate current thus can be written as:

$$I_{G} = I_{gcs} + I_{gcd} + I_{gs} + I_{gd} + I_{gb}$$

(3.12)

Where, Igs&Igd are the dominantfunction of gate source and gate drain terminals voltages respectively.

DT gate current for a NMOS device is one order of magnitude higher than the PMOS device because the holes in PMOS need high energy to cross the barrier than the electrons in NMOS for same value of oxide thickness and power supply [36].

Figure 2.7- DT gate current components for NMOS [37].

#### 2.5.2 Previous modeling of gate tunnelingcurrent in NMOS

Due to gate DT current, the circuit performance degrades. Also, static power dissipation increases due to it. Many papers in gate DT currenteffect on circuits have been reported along with simulation result [36, 38, 39].

In [36], it is described that, DT gate current increases exponentially as thickness oxide decreases, also when the gate voltage increase as because, DT gate current is an exponential function of thickness oxide as well as the potential across it.

$$I_{gs} = \frac{127.04 \cdot Leff \cdot e^{(5.606 \cdot Vgs - 10.6 \cdot tox^{-2.5})}}{2}$$

(3.13)

$$I_{gd} = \frac{127.04 \cdot Leff \cdot e^{(5.606 \cdot Vgd - 10.6 \cdot tox^{-2.5})}}{2}$$

(3.14)

An empirical gate leakage model is described in [36]. In themodel shown in figure 2.8,voltage dependent current sources(VCCS) is used to describe gate to source (Igs) &gate to drain (Igd)currentsbetweengate to source & gate to drain.

Figure 2.8- DT gate current micro model proposed in[36].

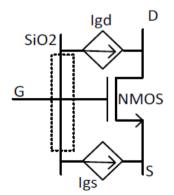

Figure 2.9 illustrates a model based on [38] for circuit simulation where three terminal transistor with the parasitic capacitors like Cgs,Cgd and Cgb are included along with the gate tunneling. Again, VCCS is used to describe the gate current as shown in below figure 2.9asIgs,Igd andIch.

Figure 2.9- Micro model for gate tunneling for circuit simulation proposed in [38].

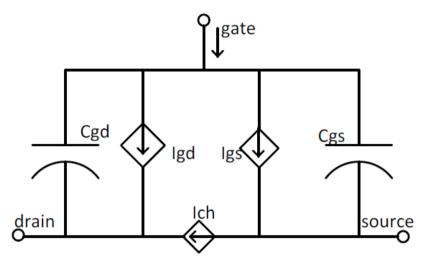

Figure 2.10 showing another model for the gate DT leakage current as reported in [39]. It also having voltage dependent current sources as shown in figure below and they are a function of terminal voltages. The channel current is partitioned into to Igs and Igd and it is represented using variable resistors.

$$I_{gc} = I_{gs} + I_{gd} \tag{3.15}$$

$$\mathbf{R}_{cd} = \frac{v_{cd}}{l_{cd}} \& \ \mathbf{R}_{cs} = \frac{v_{cs}}{l_{cs}}$$

(3.16)

Figure 2.10- Gate DT model for circuit simulation suggested in [15].

### **2.6 FGMOS Simulation Models**

In order the simulator to converge on a solution, simulator needs to have atleat one path to ground, also an initial conditions in each point of the circuit. As FGMOS transistor has no DC path to ground, a DC model is required to simulate it.

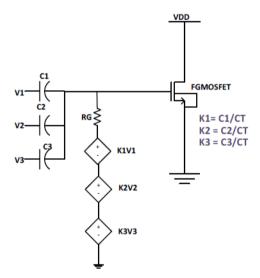

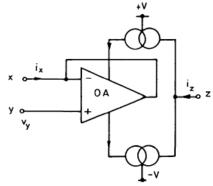

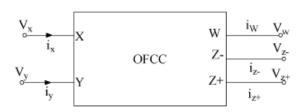

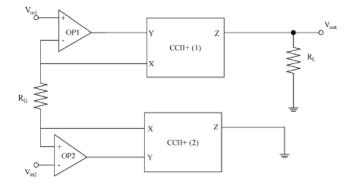

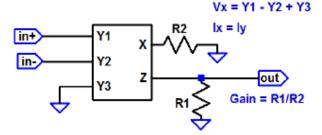

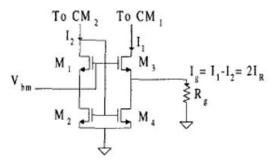

Some authors have presented a simulation model to solve the convergence problem. In [32], authors J. Ramirez-Anguloet. al., have presented a simulation model in which FGMOS is suggested where a standard MOSFET is used with multiple inputs capacitively coupled to floating gate along with a large value resistor&dependant voltage source which is voltage controlled voltage source (VCVS), to provide a DC path to ground. The value of VCVS is determined by the ratio of coupling capacitors seen from the gatefor each inputs (Ci/CT) as shown in figure 2.11.

The model shown below in figure 2.11 has widely been used in simulations for simulating floating gate. The drawback of this circuit is that this circuit is unable to represent the movement of charge due to gate leakage.

Figure 2.11- multiple inputs FGMOS simulation model proposed in [32]. Where RG is in Megaohms.

$$V_{FG} = \sum_{i=1}^{N} \frac{CiVi}{CT} + \frac{CgsVs}{CT} + \frac{CgdVD}{CT} + \frac{QFG}{CT}$$

(3.17)

$$C_{T} = \sum_{i=1}^{N} C_{i} + C_{gs} + C_{gd}$$

(3.18)

$$K_{i} = \sum_{i=1}^{N} \frac{c_{i}}{c_{T}}$$

(3.19)

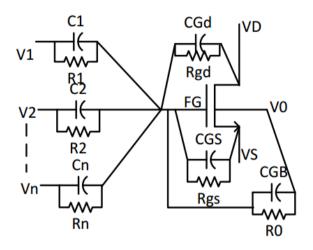

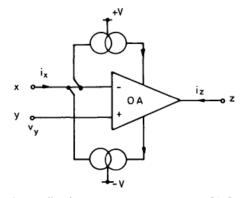

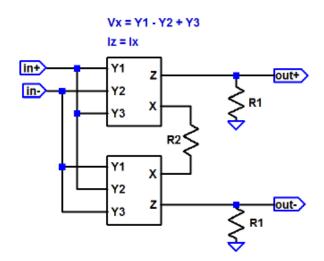

In [40], Liming Yin et. al., have present a model for simulating FGMOS by taking parasitics into consideration along with input coupling capacitors as infigure 2.12. In this model, a resistor is connected in parallel with each of the input capacitosr in order to resolve the convergence problem. It is necessary to have the RC product of each input pair branch equal.

Also, the input resistors must have very high resistance value in order not to have any effect onAC simulation. If any charge traps in the floatinggate, a voltage source is connected to the floating gate.

Where,  $V_Q = Q / C_T$ .

$$R_i = \frac{1}{KCi}$$

(3.20)

$$G_i = \frac{1}{Ri}$$

(3.21)

Where i=1, 2, 3 .... n and k is a constant quantity chosen to make R very large.

$$R_i C_i = R_{GD} C_{GD} = R_{GS} C_{GS} = R_{GB} C_{GB}$$

$$(3.22)$$

$$V_{fg} = \frac{CGBV0 + CGsVs + CGdVd + C1V1 + C2V2 + - - -CnVn}{CT}$$

(3.23)

Where,Ri indicates the input resistors and Ci indicates the input capacitors, Vfgis floating gate voltage andV1, V2,----Vn are the control input voltages. V0 indicates the substrate voltage. Also,  $C_{GS}\&C_{GD}$  are the parasitic capacitors and  $V_S\&V_D$  are the source & drain voltages respectively.

This model also have the same drawback as the model shown in [32] by Ramírez-Angulo et. al. i.e., this model also incapable of accounting the amount of charge movement through gate which results in gate leakage.

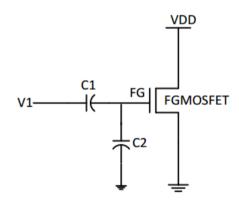

In [41],Ai Chen Lowet. al., also have presented a model for FGMOS using multiple input capacitors as shown in figure 2.13. In this model, there is no DC path to ground as well as there is no parasitic capacitors is assumed to have in the FGMOS transistor. Therefore an initial voltage has been connected to the input capacitors to resolve the convergence problem.Addition of a initial positive voltage to capacitor connected to floating gate through thenegative terminal signifies removal of charges from FG, while addition of a negative

initial voltage signifies to addition of charges to floating gate.

$$V_{fg} = \frac{C1}{C1 + C2} V1$$

(3.24)

Figure 2.12- FGMOS simulation model in [40].

Figure 2.13- simulation model for FG transistor proposed in [41].

## 2.7Summary

It should be noted that, all the previous models discussed for simulating floating gate are used to model the functionality of floating gate transistor & hence, it solves the convergence problem in simulation. It should be also noted that, all the previous models did not includes gate current in there construction because, initially FGMOS transistors was fabricated using double poly technique which was having thick gate oxide i.e., thicknessis

more than 3nm and hence, gate DT current was negligible and hence has no much impact on FGMOS performance.

It is very crucial & important to model FGMOS transistor in submicron technologies using single poly layer where tox is less than 3nm.

# **CHAPTER-3**

# **EXPERIENTAL WORK**

## 3.1 Schematic of Conventional Op Amp Circuit

In this chapter, all the experimental work will be presented like conventional two stage op amp followed by two stage op amp using FGMOS and instrumentation amplifier based on FGMOS. This chapter will also present the limitation in Ramirez-Angelo's FGMOS model which is one of the most efficient &promising models available in the literature. A gate current impact on FGMOS behavior is also discussed in floating gate operational amplifier. Simulation results and comparison are also included.

Figure 1.7- Conventional two stage op amp [25].

Figure 1.7 shown above is a schematic of conventional two stage op amp in which all the transistors are operating in a saturation region. It can be seen from above circuit that, Cc is the coupling capacitor used along with Rz which is a nulling resistor to nullify the effect of

zero from circuit and hence, increases the phase margin of the circuit. The table 2, shown be will give all the technological parameter values of conventional op amp.

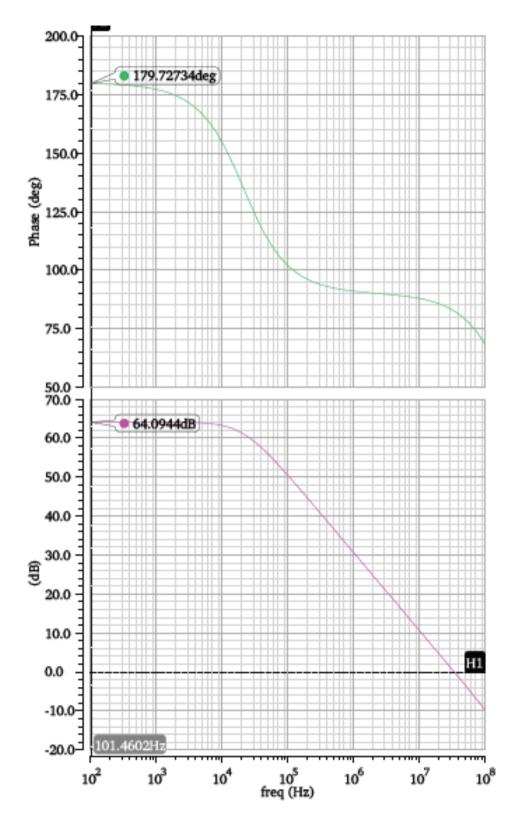

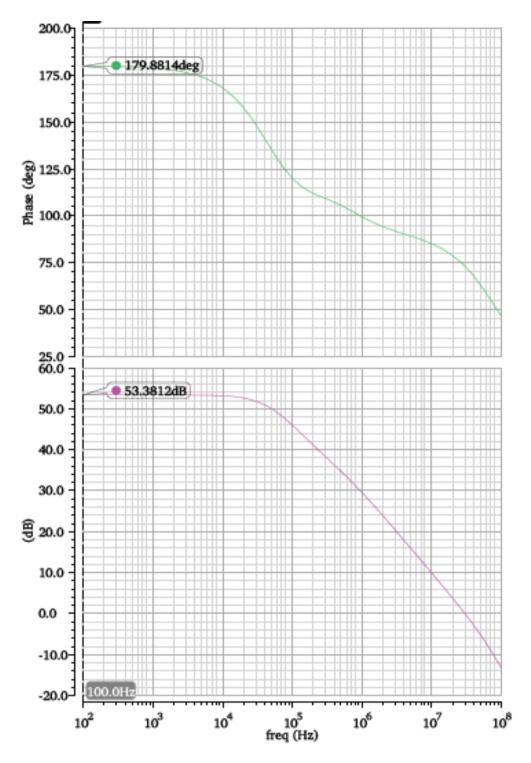

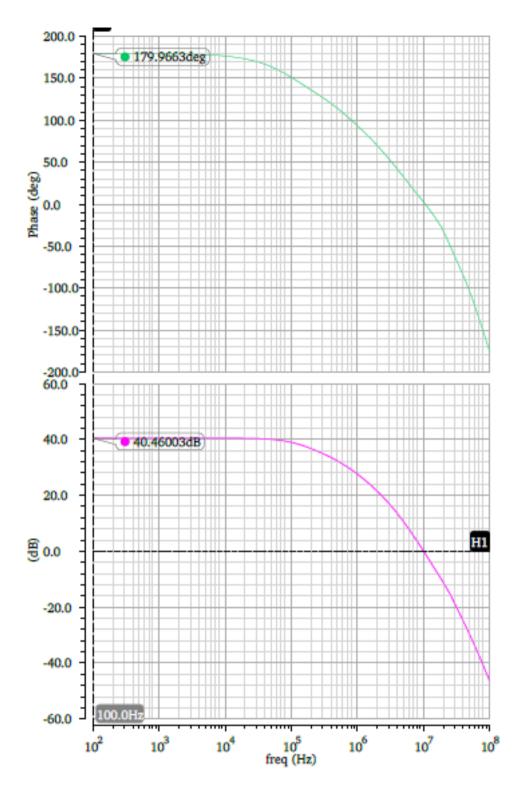

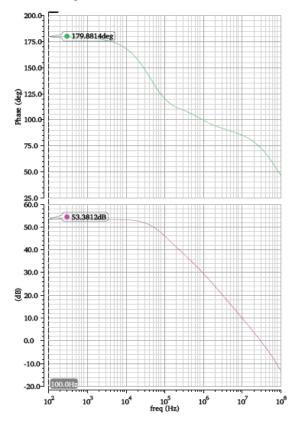

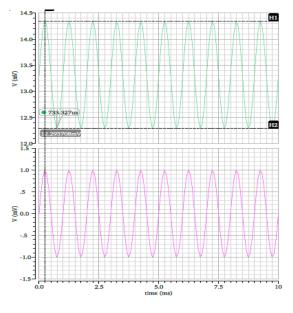

Figure 3.1 shows the gain as well as phase characteristics plot of the conventional op amp circuit shown in figure 2.7. A sinusoidal signal of 1mV and a frequency of 1 kHz is applied at the non-inverting input of an op amp with common mode voltage of 1.6V. We found a DC gain of 64.0944 dB and having maximum phase of 179.72 degree. The phase margin of 82.69 degree is reported along with a UGB is 33.7 MHz is shown in figure 3.2.

#### 3.1.1 Simulated values of conventional op amp

| S. No. | Parameters              | Values       |

|--------|-------------------------|--------------|

| 1.     | DC Gain                 | 64 dB        |

| 2.     | Maximum Phase at 100 Hz | 179.7 degree |

| 3.     | UGB                     | 33.7 MHz     |

| 4.     | Phase Margin            | 82.6 degree  |

| 5.     | Slew Rate               | 25 V/us      |

| 6.     | ICMR-                   | 0.8 V        |

| 7.     | ICMR+                   | 1.2 V        |

| 8.     | Common mode voltage     | 0.8V         |

| 9.     | Supply Voltage          | 1.8 V        |

| 10.    | Power Dissipation       | 436uW        |

| 11.    | CMRR                    | 104 dB       |

Table 2- Technological parameters of conventional two stage op amp.

Figure 3.1- Gain and Phase plot of conventional two stage op amp.

Figure 3.2- UGB and phase margin plot of conventional two stage op amp.

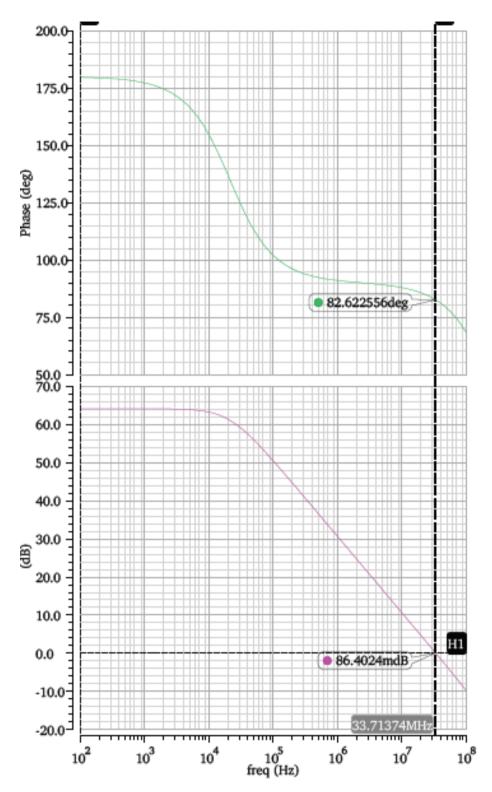

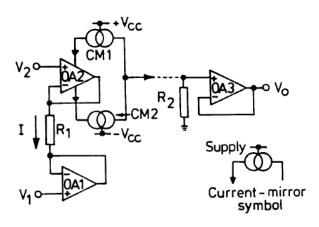

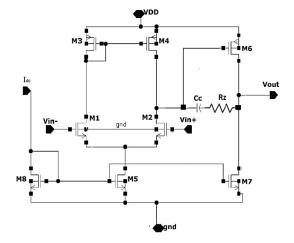

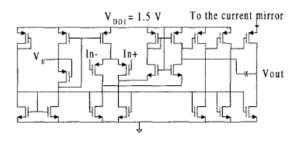

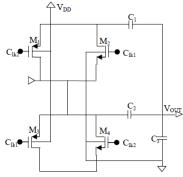

## 3.2 Schematic of FGMOSBbased Op amp Circuit

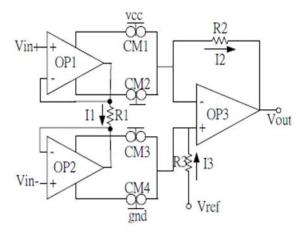

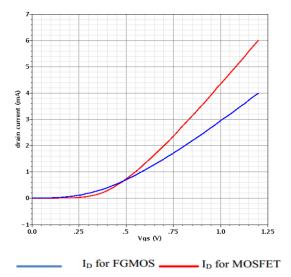

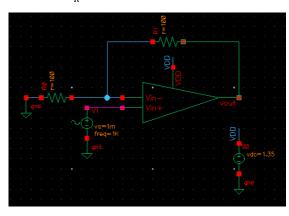

Figure 3.3- FGMOS based two stage op amp.

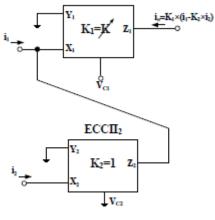

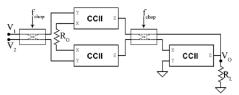

Figure 3.3 shown above is a two stage op amp based on FGMOS with DC input path to ground constraint taken into consideration. Here, K1V1 and K2V2 are voltage dependent voltage sources used with a large resistor to provide DC path to ground that helps to resolve convergance problem, where K is the capacitance ratio i.e., C1/CT=K1 and C2/CT= K2. Here, C1 & C2 is given as 500 femtoFarad& V1 as well as V2 is 0.67V.Hence, the resultant of K1V1 & K2V2 is given by 0.67V & resistance is given as one megaohm.

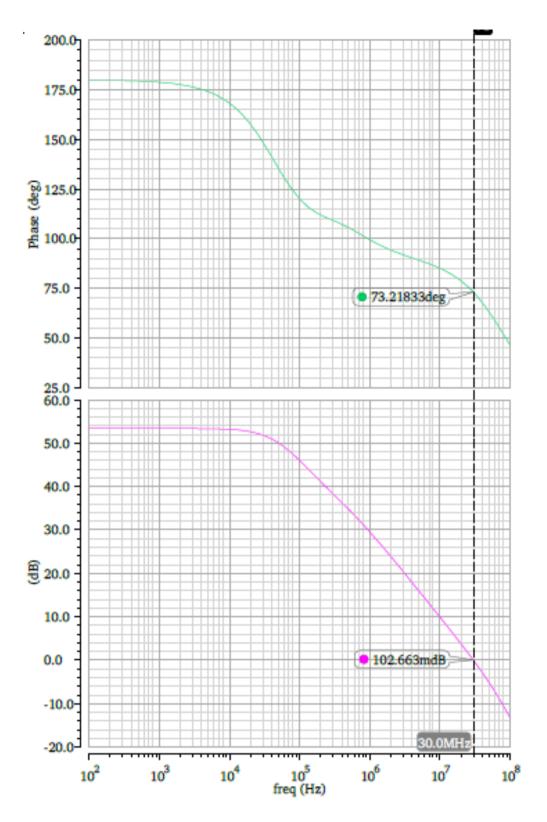

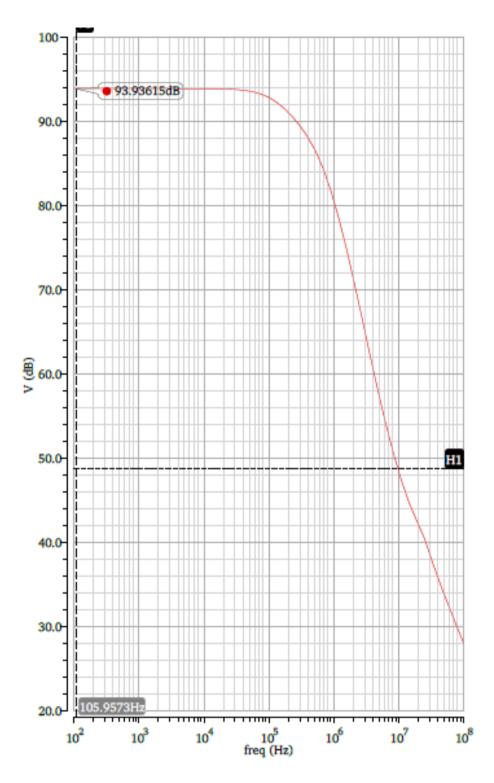

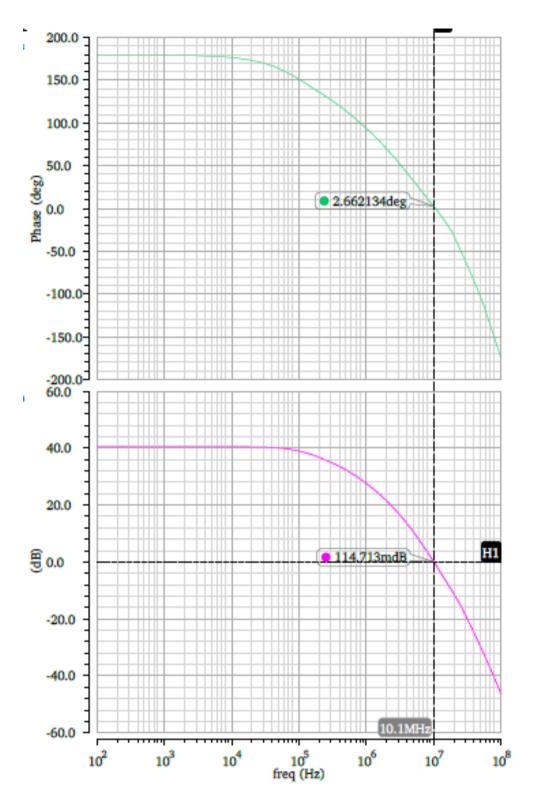

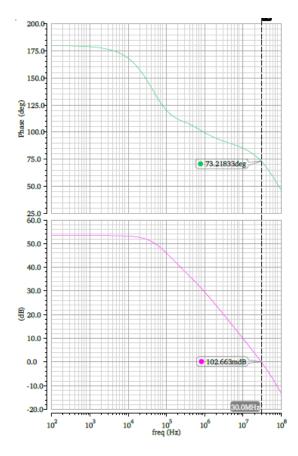

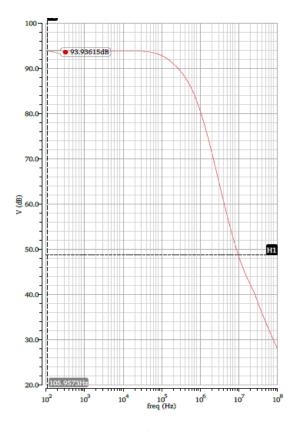

The gain of this op amp is given by 53.3 dB and has a phase margin of 73.2 degree as shown in figure 3.4, that indicates highly stable system. The UGB of this op amp is given by 30 MHz as shown in figure 3.5. also, from figure 3.6, it can be seen that the CMRR of this op amp is 93.9 dB. Table 3 shown below describes about transistor dimensions for conventional op amp and FGMOS based op amp. Also, table 3 gives all the technological parameter of FGMOS based op amp.

# 3.2.1 Simulated Values of FGMOS Op Amp

| S. No. | Parameters              | Values       |

|--------|-------------------------|--------------|

| 1.     | DC Gain                 | 53 dB        |

| 2.     | Maximum Phase at 100 Hz | 179.8 degree |

| 3.     | UGB                     | 30 MHz       |

| 4.     | Phase Margin            | 73 degree    |

| 5.     | Slew Rate               | 50 V/us      |

| 6.     | PSRR                    | 73 dB        |

| 7.     | CMRR                    | 93.9 dB      |

| 8.     | Common mode voltage     | 0.6 V        |

| 9.     | Supply Voltage          | 1.35 V       |

| 10.    | Power Dissipation       | 290uW        |

Table 3- Technological parameters of FGMOS based two stage op amp.

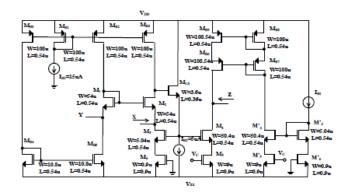

# 3.3 Transistor Dimensions of Conventional and FGMOS Based Op Amp.

Table 4- FGMOS and conventional op amp transistor dimensions.

| Transistor | Width (W) | Channel    |  |

|------------|-----------|------------|--|

|            |           | Length (L) |  |

| M1         | 3.36 um   | 480 nm     |  |

| M2         | 3.36 um   | 480 nm     |  |

| M3         | 890 nm    | 400 nm     |  |

| M4         | 890 nm    | 400 nm     |  |

| M5         | 480 nm    | 400 nm     |  |

| M6         | 25.6 um   | 480 nm     |  |

| M7         | 7.2 um    | 480 nm     |  |

| M8         | 480 nm    | 400 nm     |  |

Figure 3.4- Gain and Phase plot of FGMOS based two stage op amp.

Figure 3.5- UGB and phase margin plot of FGMOS based two stage op amp.

Figure 3.6- CMRR plot of FGMOS based two stage op amp.

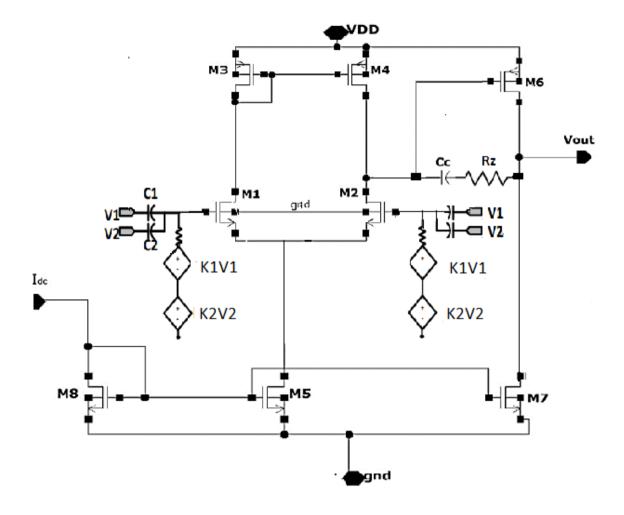

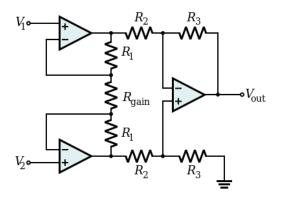

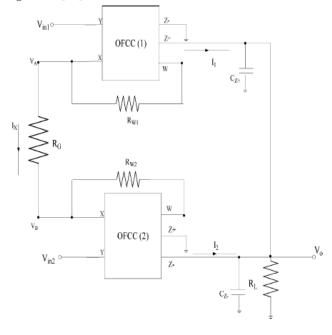

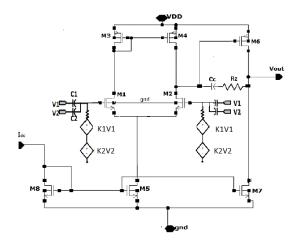

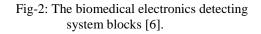

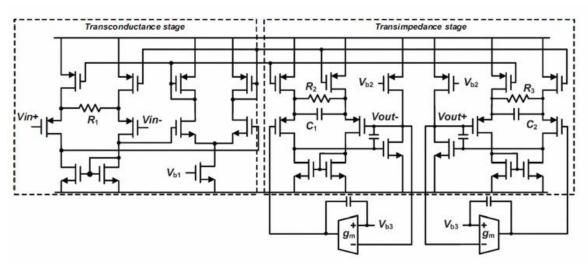

## **3.4 Instrumentation Amplifier**

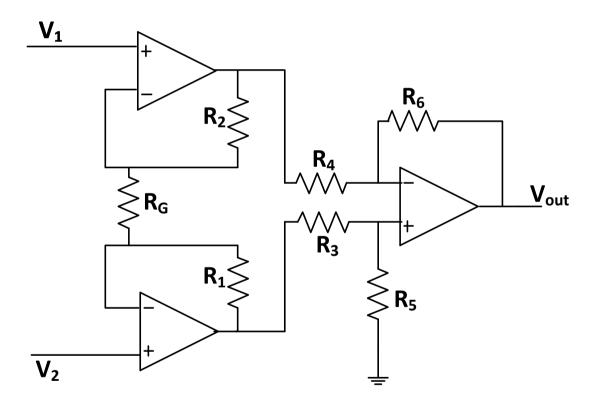

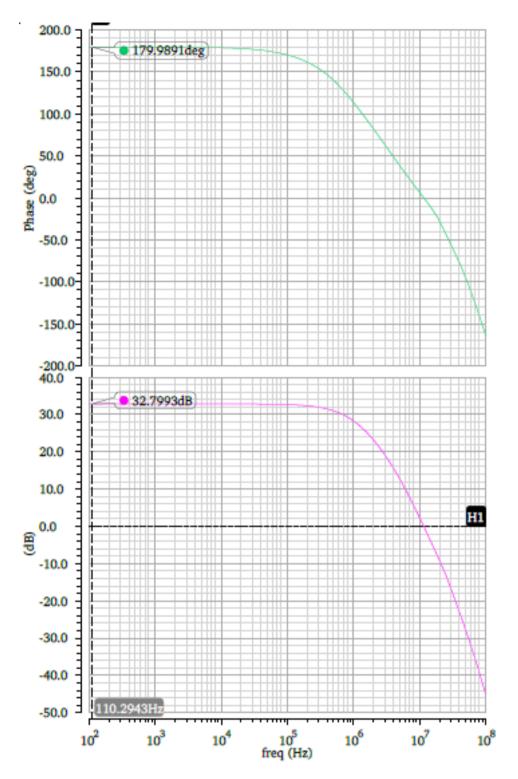

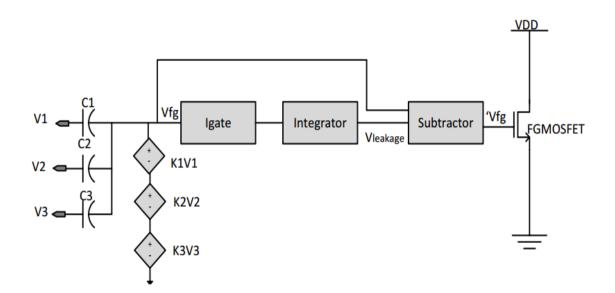

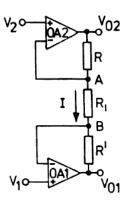

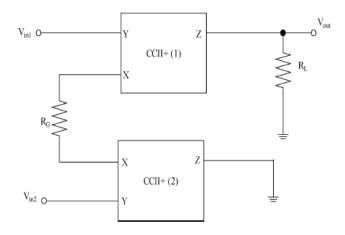

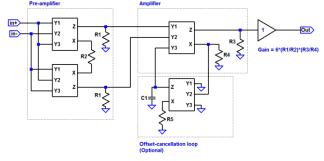

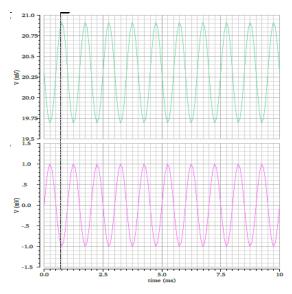

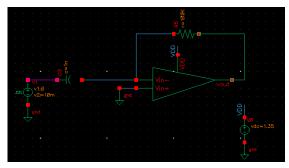

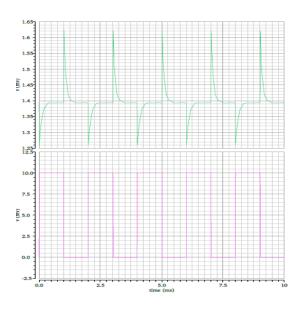

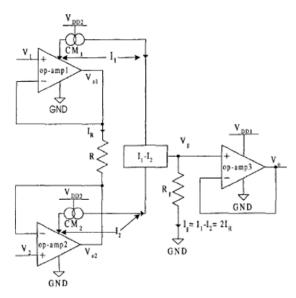

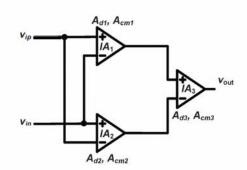

Figure 3.7, illustrates instrumentation amplifier based on FGMOS transistor. An instrumentation amplifier is a circuit which extracts out weak potential signal and hence, it is very useful circuit for bio medical applications. This instrumentation amplifier is voltage mode amplifier. By keeping all the op amp in transistor in saturation region, op amp is drawn. This instrumentation amplifier is remains stable upto large value of gain varying resistor i.e., it remains stable upto 10Kohm of Rg. Figure 3.9 shows that phase margin of this instrumentation amplifier is more than one degree and hence, closed loop system is stable. The necessary condition for closed loop system to be stable is that, its phase margin should be more than zero degree i.e., it should have positive phase margin. Table 5 shown below gives all the technological parameters of instrumentation amplifier shown in figure 3.7.

Figure 3.7- Instrumentation amplifier based on FGMOS two stage op amp.

| S. No. | Resistor              | Value                 |

|--------|-----------------------|-----------------------|

| 1.     | R <sub>G</sub>        | Gain varying resistor |

| 2.     | <b>R</b> <sub>1</sub> | 30 Kohms              |

| 3.     | R <sub>2</sub>        | 30 Kohms              |

| 4.     | <b>R</b> <sub>3</sub> | 10 Kohms              |

| 5.     | <b>R</b> <sub>4</sub> | 10 Kohms              |

| 6.     | R <sub>5</sub>        | 22 Kohms              |

| 7.     | <b>R</b> <sub>6</sub> | 22 Kohms              |

Table 5 – Resistor Values of instrumentation amplifier.

# 3.4.1 Simulated Parameters of Instrumentation Amplifier

## Table 6- Technological parameters of FGMOS based instrumentation amplifier.

| S.  | Parameters              | For Rg= 10 | For Rg= 100 | For Rg= 1 |  |

|-----|-------------------------|------------|-------------|-----------|--|

| No. |                         | ohms       | ohms        | Kohms     |  |

| 1.  | Difference<br>mode gain | 40.46 dB   | 39.5 dB     | 32.8 dB   |  |

| 2.  | CMRR                    | 86.7 dB    | 80 dB       | 58 dB     |  |

| 3.  | 3dB<br>frequency        | 200 kHz    | 239.5 kHz   | 834.3 kHz |  |

| 4.  | Gain<br>Bandwidth       | 10 MHz     | 10.5 MHz    | 11.5 MHz  |  |

| 5.  | Power<br>dissipation    | 719 uW     | 721 uW      | 727 uW    |  |

\* all the parameters are calculated at common mode voltage of 1V.

Figure 3.8- IA gain and phase plot based on FGMOS at Rg=10 ohms.

Figure 3.9- IA UGB and phase margin plot based on FGMOS at Rg=10 ohms.

Figure 3.10- IA gain and phase plot based on FGMOS at Rg=1K ohms.

# CHAPTER- 4 RESULTS AND CONCLUSION

After studying the FGMOS, simulation models and graphs were plotted in chapter 3. In this chapter we will evaluate the result and will arrive to a possible conclusion from the data given in chapter 3.

As it can be seen from section 3.1 that, conventional op amp is simulated in virtuoso gpdk 90nm simulator. This conventional op amp is offering high unity gain bandwidth of 33MHz and having phase margin of 82.6 degree which is indicating highly stable system. The condition for a two stage op amp to be stable, its phase margin is need to have 45-60 degree.

The technological parameter for a conventional two stage op amp is charted out in table 2.

Section 3.2 of chapter 3 describes about FGMOS based op amp. Table 3 illustrates all the technological parameter of FGMOS based op amp. By comparing conventional op amp and two stage op amp, it is noted that, FGMOS based op amp offering significant power reduction for the same value of aspect ratio. The aspect ratio of both FGMOS and conventional op amp is charted out in table 4. The main advantage of using FGMOS in two stage op amp is that, it offers tuning of threshold voltage and also low power requirement.

Section 3.4 illustrates instrumentation amplifier based on FGMOS op amp. This op amp offers high CMRR and hence suitable for bio medical applications. For bio medical applications, it is required to have CMRR more than 60dB. Also, this circuit is consumes less power and hence suitable for portable powered devices.

The limitations of this op amp is that, it requires resistor trimming to get high CMRR. Also, from figure 3.7, it can be seen that, it is three op amp instrumentation amplifier and hence, requires a large chip area. Table 5 shown above gives all the technological parameters of IA.

The next section 3.5 will deal with possible challenges faced by the technology scaling to the nanometer region. Also, in section 3.5, a newsimulation model is discussed for FGMOS that will be used in simulating FGMOS in nanometer scale technologies.

#### 4.1 Problem Faced in FGMOS Model for Nanometer Technologies

The result based on above model of FGMOS discussed above in chapter 3 is not accurate and hence there must be some change in parameter will occur. As it cannot be applied for submicron technologies due to thin gate oxide of transistors which leads to gate leakage current.

A new model for submicron i.e., sub 100nm CMOS technologies is derived. The analysis is conducted by considerating gate leakage current into account & also the way FGMOS structure responds to it.

Gate leakage current is due tocharge movement at the oxide. It also depends on the type of transistor & the polarity across the insulator, and it can be found as:

$$Q_{\text{leakage}} = C_{\text{T}} V_{\text{leakage}} \tag{4.1}$$

$$\frac{dQleakage}{dt} = C \frac{dVleakage}{dt}$$

(4.2)

$$I_{\text{leakage}} = C_{\text{T}} \frac{dV \text{leakage}}{dt}$$

(4.3)

$$\frac{dVleakage}{dt} = \pm \frac{1}{CT} \mathbf{I}_{\text{leakage}}$$

(4.4)

$$V_{\text{leakage}} = \frac{1}{CT} \int I leakagedt$$

(4.5)

Equation (4.4) shown above suggests that, the charge movement in FGMOS oxide due to leakage can be into or out of gate oxide due to voltage change can be negative and positive quantity. Hence, floating gate voltage can increase or decrease as a function of time based charge flow & thecapacitors values and can be written as:

$$\frac{dVFG}{dt} = \frac{C1}{CT}\frac{dV1}{dt} + \frac{C2}{CT}\frac{dV2}{dt} + \dots + \frac{Cn}{CT}\frac{dVn}{dt} \pm \frac{1}{CT}I_{\text{leakage}}$$

(4.6)

$$V_{FG} = \sum_{i=1}^{N} \frac{C1V1}{CT} + \frac{C2V2}{CT} + \dots + \frac{CnVn}{CT} \pm V_{leakage}$$

(4.7)

The condition to keep the transistor in saturation region is  $V_{FG} > V_{TH}$ , and by aplying  $V_1$  as the effective input, the result is given as:

$$V_1 > \frac{CTVT}{C1} - \frac{C2V2}{C1} - \dots - \frac{CnVn}{C1} \pm \frac{CT}{C1} V_{leakage}$$

(4.8)

Hence, the equivalent threshold voltage for floating gate transistor innanometers technologies is given by:

$$V_{\text{THFG}} > \frac{CTVT}{C1} - \frac{C2V2}{C1} - \dots - \frac{CnVn}{C1} \pm \frac{CT}{C1} V_{\text{leakage}}$$

(4.9)

Equation (4.8) showing very important implication of gate leakage current because this leakage current will increase the effective threshold voltage in NMOS transistors.

Equation (4.10) shows below showing that, the threshold voltage of a FGMOS is a function of gate leakagecurrent due to tunneling effect. The gate current is an exponential function of gate voltage and also technology dependent parameters A and B.

$$\mathbf{I}_{\mathbf{G}} = \mathbf{A} \cdot \boldsymbol{e}^{BVG} \tag{4.10}$$

Where B and A are the technology and biasing conditions dependent parameters that are extracted out from fitting the simulation data in TSMC 90nm for gate current using BSIM4. These parameters will futherincrease as the technology scaled down to 65nm, 45nm or 28nm.

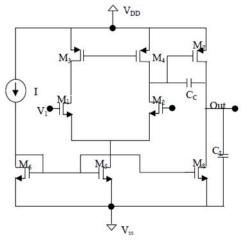

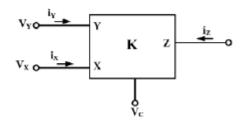

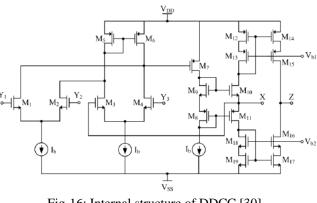

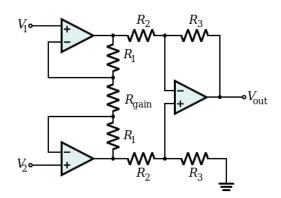

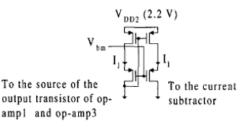

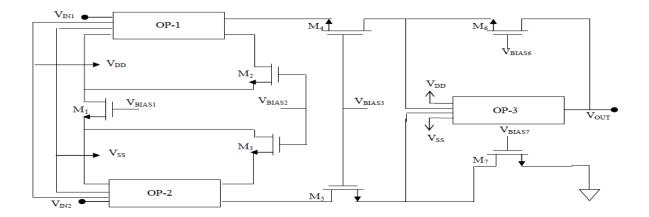

#### 4.2 A New Model for FGMOS Transistor in Nanometer Technologies

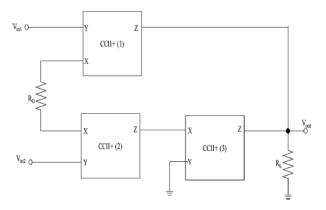

To test the floating gate circuit without actually fabricating it, a new model is proposed. This model is arises by keeping the things in mind that the CMOS technologies continue shrinking down as tox scaled down proportionally and this causes more gate leakage current.

This new simulation model is proposed for FGMOS that are suitable for submicron technologies. This model also includes gate leakage current and is compatible with simulators likeSpectre and SPICE.

To built this model, a standard transistor from the industry i.e., TSMC 90nm with two cells from analog hardware description language AHDL library is used along with one block of verilog code to describe the gate tunneling.

As described in [36-37], the new model uses voltage dependant current source in its implemented in Verilog code embedded under Cadence / Spectretol& it is described as a function of V<sub>gs</sub>terminal. As shown in figure 4.1, the circuit also includes an integrator

along with subtractor, integrator integrates the gate tunneling current to generate a voltage which is fed intosubtractor.

The model shown in below figure 4.1 is suitable with any submicron technology oxidethickness less than 3nm& suffers gate leakage current with no change in the model itself is required. However, to comply with thetechnology parameters where the gate tunnelling current exponentially increases as tox decreases, some changes need to be done to the gate tunneling cell. By addinginitial condition to the leakage current integrator, this model can be used for transient and DC simulations.

Figure 4.1: The structure of N-type FGMOS simulation model for nanometer (sub 100nm) technologies.

# CHAPTER- 5 FUTURE SCOPE

In this thesis, a three op amp based IA is simulated based on the FGMOS opamp. FGMOS based op amp is derived from conventional two stage op amp in which a nulling resistor is used to nullify the effect of zero in the transfer function which increases the phase margin of the circuit. In the circuit shown in figure 1.7, where a passive resistor is used as a nulling resistor. Further modification can be done by replacing passive resistance with MOS transistor, this will help in reducing total chip area, as passive resistor is not preferred in IC. Using MOS transistor will also increase total transistor count but total chip area is less than that of passive resistor.

The instrumentation amplifier drawn above is a voltage mode IA and hence resistor trimming is required to get high CMRR which is a major drawback of this IA. Further modification can be done by replacing this IA with current mode IA. Also, passive reistance in buffer stage can be replaced by the current mirror which also helps to avoid resistor trimming constraint. As IA is a fundamental block for all the biomedical applications, it is need to have smaller chip area and also it is required to operate for longer time. Hence, current mode IA will be best suited for this.

Also, the problem with submicron technologies also taken into consideration in chapter 4. Hence, a new IA can be drawn based on that in which charge leakage can be easily controlled. All the analog devices can be futher implemented in submicron technologies based on that. It helps to get over DT leakage current problem. By taking DT leakage current into consideration, an enhanced circuit can be drawn.

# REFERENCES

- V.De and S.Borkar, "Technology and design challenges for low power and high performance," in Proc. Int. Symp. Low Power Electroics and Design, 1999, pp.163-168.

- K.Roy and S.C.Prasad, "Low-power CMOS VLSI ciruit design". New York: Wiley, 2000, ch. .5, pp.214-219.

- 3. D. Kahng and S. M. Sze, "A floating-gate and its application to memory devices", The Bell System Technical Journal, vol. 46, no. 4, 1967, pp. 1288–1295.

- L. R. Carley, "Trimming analog circuits using floating-gate analog MOS memory," IEEE J. Solid-state Circuits, vol. 24, pp. 1569-1575, Dec. 1989.

- T. Shibata and T. Ohmi, "A functional MOS transistor featuring gate-level weighted sum and threshold operations", IEEE Transactions on Electron Devices, vol. 39, no. 6, 1992, pp. 1444–1455.

- Y. Berg and T.S. Landc. Programmable Floating-Gate Mos Logic for Low-Power Operation., ISCAS97, june. 1997.

- Y. Berg, T.S. Lande, "Area efficient circuit tuning with floating-gate techniques", Circuits and Systems 1999. ISCAS '99. Proceedings of the 1999 IEEE International Symposium on, vol. 2, pp. 396-399 vol.2, 1999.

- Antonio Lopez-Martin, J. Ramirez-Angulo, "D/A conversion based on multipleinput floating-gate MOST," IEEE International Midwest Symposium on Circuits and Systems, pp. 149-152, Aug. 1999.

- 9. K. Nandhasri and J. Ngarmnil, "Design of analog and digital comparators with FGMOS," in Proc. ISCAS, vol. 1, pp. 25–28, 2001.

- E. Rodríguez-Villegas, A. Rueda, and A. Yúfera, "A 1.25-V FGMOS filter using translinear circuits," in Proc. IEEE Int. Symp. Circuits and Systems, pp. 61– 64,2001.

- 11. B. A. Minch, "A Folded Floating-Gate Differential Pair for Low-Voltage Applications," in Proc. 2000 IEEE Internotional Symposium on Circuits and Systems, Geneva, Switzerland, vol. 4, pp. 253-256, May 28-31, 2000.

- 12. K. Moolpho. J. Ngarmnil, K. Nandhasri. "A low-voltage wide-swing FGMOS current amplifier". Proc. ISCAS2002. Phoenix, pp.713-716, May 2002.

- 13. S. Sharma, S.S. Rajput, L.K. Magotra, and S.S. Jamuar, "FGMOS based wide range low voltage current mirror and its applications," in Asia-Pacific Conf. on Circuits and Systems (APCCAS '02), Denpasar, Indonesia, pp. 331-334, 2002.

- Rodriguez-Villegas, Esther, "Solution to trapped Charge in FGMOS Transistors", Electronics Letters, Volume 39, Issue 19, pp. 1416 – 1417, Sept. 2003.

- 15. D. Yates, E. López-Morillo, R. G. Carvajal, J. Ramirez-Angulo and E. Rodriguez-Villegas, "A Low-Voltage Low-Power Front-End for Wearable EEG Systems," Proceedings of the 29th Annual International Conference of the IEEE EMBS LiteInternationale, Lyon, France august 23-26, 2007.

- Patricia Mejía-Chávez; Juan C. Sánchez-GarcíaandJosé Velázquez-López, "Differential difference amplifier FGMOS for electrocardiogram signalacquisition" 2011 8th International Conference on Electrical Engineering, Computing Science and Automatic Control, pp. 1-5, 2011.

- 17. N. G. Lopez-Martinez, A. S. Medina-Vazquez and M. A. GurrolaNavarro, "Experimental analysis of a transconductor-amplifier based on a mi-fgmos transistor," Electrical Engineering, Computing Science and Automatic Control (CCE), 2015 12th International Conference on, Mexico City, 2015, pp. 1-4.

- Guoqiang Hang and Guoquan Zhu, "A new Schmitt trigger with adjustable hysteresis using FGMOS threshold inverter" 2015 IEEE 11th International Conference on ASIC (ASICON), pp. 1-4, 2015.

- SherifSharroush' "A novel variable-gain amplifier based onan FGMOS transistor,

2016 5th International Conference on Electronic Devices, Systems and

Applications (ICEDSA), pp. 1-4, 2016.

- 20. A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, "Low-power CMOS digital design," IEEE J. Solid-State Circuits, vol. 27, no. 4, pp.473–484, Apr. 1992.

- Gu, R.X and M.I Elmasry, "Power dissipation analysis and optimization of deep sub-micron CMOS digital circuits," IEEE journal of solid-state circuits, vol. 31, pp.707-713, 1996.

- A. Keshavarzi, K. Roy and C. F. Hawkins, "Intrinsic leakage in low power deep submicron CMOS ICs," Test Conference, 1997. Proceedings., International, Washington, DC, 1997, pp. 146-155. doi: 10.1109/TEST.1997.639607, 1997.

- 23. S. Franco, Design with Operational Amplifire and Analog integrated Circuit, NewYork : Tata McGraw Hill, 2002.

- 24. B. Razavi, Design of a Analog CMOS Integrated Circuit, New Delhi: Tata McGraw-Hill, 2012.

- 25. P. E. Allen and D. R. Holberg, CMOS analog circuit design, I. S. Edition, Ed., Oxford: Oxford University press, 2009.

- 26. P. Hasler and T. S. Lande. Overview of floating-gate devices, circuits, and systems. Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions On48(1),pp. 1-3. 2001.

- P. Hasler, B. A. Minch and C. Diorio. Floating-gate devices: They are not just for digital memories any more. Presented at Circuits and Systems, 1999. ISCAS '99.

Proceedings of the 1999 IEEE International Symposium On. 1999.

- 28. J. Ramirez-Angulo. Highly linear four quadrant analog BiCMOS multiplier for ±1.5 V supply operation. Presented at Circuits and Systems, 1993., ISCAS '93, 1993 IEEE International Symposium On. 1993.

- 29. T. Inoue, H. Nakane and Y. Fukuju. A low-voltage fully-differential current-mode analog CMOS integrator using floating-gate MOSFETs. Presented at Circuits and Systems, 2000. Proceedings. ISCAS 2000 Geneva. the 2000 IEEE International Symposium On. 2000.

- 30. F. Munoz, A. Torralba, R. G. Carvajal, J. Tombs and J. Ramirez-Angulo. Floating-gate-based tunable CMOS low-voltage linear transconductor and its application to HF gm-C filter design. Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions On 48(1), pp. 106-110. 2001.

- S. J. Rapp, "A Comprehensive Simulation Model for Floating Gate Transistors," 2010.

- 32. J. Ramirez-Angulo, G. Gonzalez-Altamirano and S. C. Choi"Modeling multipleinput floating-gate transistors for analog signal processing" presented at Circuits and Systems, 1997. ISCAS '97., Proceedings of 1997 IEEE International Symposium On. 1997.

- 33. E. Rodriguez-Villegas, "Low Power and Low Voltage Circuit Design with the FGMOS Transistor", 2006.

- 34. D. A. Kerns, J. E. Tanner, M. A. Sivilotti and J. Luo. CMOS UV-writable nonvolatile analog storage. Presented at Proceedings of the 1991 University of California/Santa Cruz Conference on Advanced Research in VLSI, 1991.