# ON SOME ASPECTS OF GRID SYNCHRONIZATION FOR SINGLE PHASE AND THREE PHASE SYSTEMS

## A DISSERTATION

## SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

# MASTER OF TECHNOLOGY IN POWER SYSTEM

Submitted by:

# SHIKHA PILANIA

# 2K16/PSY/16

Under the supervision of

Dr. ALKA SINGH

# **ELECTRICAL ENGINEERING**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

JULY, 2018

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# **CANDIDATE'S DECLARATION**

I, Shikha Pilania, Roll No. 2K16/PSY/16 student of M.Tech Power System, hereby declare that the project Dissertation titled "**On Some Aspects of Grid Synchronization for Single Phase and Three Phase systems**" which is submitted by me to the Department of Electrical Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associate ship, Fellowship or other similar title or recognition.

Place: Delhi Date: 30/08/2018

#### SHIKHA PILANIA

ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# **CERTIFICATE**

I hereby certify that the Project Dissertation titled "On Some Aspects of Grid Synchronization for Single Phase and Three Phase systems" which is submitted by Shikha Pilania, Roll No. 2K16/PSY/16, Electrical Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: 30/08/2018 Dr. ALKA SINGH SUPERVISOR DELHI TECHNOLOGICAL UNIVERSITY

## ABSTRACT

This thesis discusses the design, modeling and performance evaluation of various synchronization techniques. The techniques discussed in the thesis comprises phase locked loop (PLL) techniques applicable to single phase and three phase systems. Additionally, frequency locked loop (FLL) techniques applicable to single phase and three phase systems have also been studied and their performance has been compared. Moreover, experimental results have been obtained for a few single phase PLL techniques. Grid synchronization is a challenging task especially when the utility signal is polluted with disturbances such as harmonics or distorted frequency. Design, modeling and simulation of the complete system along with the controller have been carried out in MATLAB/SIMULINK environment. The focus of this thesis is to review these synchronizing techniques on the basis of frequency variations, voltage amplitude variations, phase angle variations and harmonics particularly for grid integration of renewable distributed power generating systems based on phase locked loop (PLL) and FLL.

## ACKNOWLEDGEMENT

I express my heartfelt obligation towards the people who have spared their valuable time and effort helping me to complete this thesis. Gratitude is also accorded to DTU for providing all the necessary facilities to complete the research work.

I truly understand that discovering, analyzing and presenting something unique is to venture on an untrodden territory and for me this won't have been possible without the cooperation, encouragement, motivation and able guidance of my mentor, Dr. Alka Singh, Department of Electrical Engineering (Delhi Technological University). I am highly indebted to her for giving me this golden opportunity to work on this thesis and her kind patronization.

Special thanks are also extended to all of faculties of Department of EEE and my colleagues for their kind inspiration. Finally a very special expression of appreciation is extended to my parents, without their encouragement, patience, and understanding this endeavor would not have been possible. Last but not the least I am thankful to everyone who was involved directly or in-directly throughout the journey of my M.Tech research work.

SHIKHA PILANIA

# CONTENTS

| Candidate's Declaration ii                               |                                                       |    |                          |                   |   |

|----------------------------------------------------------|-------------------------------------------------------|----|--------------------------|-------------------|---|

| Certificate                                              |                                                       |    |                          |                   |   |

| Acknowledgement<br>Abstract<br>Contents<br>List of Table |                                                       |    |                          |                   |   |

|                                                          |                                                       |    | List of Figures x        |                   |   |

|                                                          |                                                       |    | List of abbreviations xv |                   |   |

|                                                          |                                                       |    | CHAPTI                   | ER 1 INTRODUCTION | 1 |

| 1.1                                                      | Overview of Thesis                                    | 1  |                          |                   |   |

| 1.1.1                                                    | Need of Synchronization Techniques                    | 1  |                          |                   |   |

| 1.1.2                                                    | Grid Core Requirements                                | 2  |                          |                   |   |

| 1.1.3                                                    | Basics of PLL                                         | 3  |                          |                   |   |

| 1.1.4                                                    | Basic Points about PLL                                | 3  |                          |                   |   |

| 1.1.5                                                    | Structure of a PLL                                    | 4  |                          |                   |   |

| 1.1.6                                                    | Introduction to Frequency Locked Loops (FLL)          | 6  |                          |                   |   |

| 1.2                                                      | Literature Review                                     | 6  |                          |                   |   |

| 1.3                                                      | Motivation of Thesis                                  | 8  |                          |                   |   |

| 1.4                                                      | Organization of Thesis                                | 9  |                          |                   |   |

| CHAPTI                                                   | ER 2 PHASED LOCKED LOOP TECHNIQUES FOR                | 11 |                          |                   |   |

| A SINGI                                                  | LE PHASE SYSTEM                                       |    |                          |                   |   |

| 2.1                                                      | Introduction                                          | 11 |                          |                   |   |

| 2.2                                                      | Types of Phase Locked Loop Techniques Applicable to a | 12 |                          |                   |   |

|                                                          | Single Phase System                                   |    |                          |                   |   |

| 2.2.1                                                    | Transport Delay PLL                                   | 12 |                          |                   |   |

| 2.2.1.1                                                  | Analysis                                              | 12 |                          |                   |   |

| 2.2.1.2                                                  |                                                       | 13 |                          |                   |   |

| 2.2.2                                                    | Adaptive transport Delay PLL                          | 14 |                          |                   |   |

| 2.2.2.1                                                  | Analysis                                              | 16 |                          |                   |   |

| 2.2.2.2                                                  | Simulation Results                                    | 17 |                          |                   |   |

| 2.2.3                                                    | Enhanced PLL                                          | 19 |                          |                   |   |

| 2.2.3.1                                                  | Analysis                                              | 22 |                          |                   |   |

| 2.2.3.2                                                  | Simulation Results                                    | 23 |                          |                   |   |

| 2.2.4                                                    | Second Order Generalized Integrator (SOGI) PLL        | 26 |                          |                   |   |

| 2.2.4.1                                                  | Analysis                                              | 26 |                          |                   |   |

| 2.2.4.2                                                  | Simulation Results                                    | 28 |                          |                   |   |

| 2.2.5                                                    | Inverse Park PLL                                      | 30 |                          |                   |   |

vi

| 2.2.5.1 | Analysis                                               | 31        |

|---------|--------------------------------------------------------|-----------|

| 2.2.5.2 | Simulation Results                                     | 32        |

| 2.2.6   | Power PLL (pPLL)                                       | 34        |

| 2.2.6.1 | Analysis                                               | 35        |

| 2.2.6.2 | Simulation Results                                     | 37        |

| 2.2.7   | Double Frequency Amplitude Compensation (DFAC) PLL     | 39        |

| 2.2.7.1 | Analysis                                               | 40        |

| 2.2.7.2 | Simulation Results                                     | 42        |

| 2.3     | Comparison                                             | 44        |

| 2.4     | Conclusions                                            | 47        |

| CHAPT   | ER 3 PHASE LOCKED LOOP TECHNIQUES FOR A                | 49        |

| THREE   | PHASE SYSTEM                                           |           |

| 3.1     | Introduction                                           | 49        |

| 3.2     | Types of Phase Locked Loop Techniques Applicable to a  | 49        |

|         | Three Phase System                                     |           |

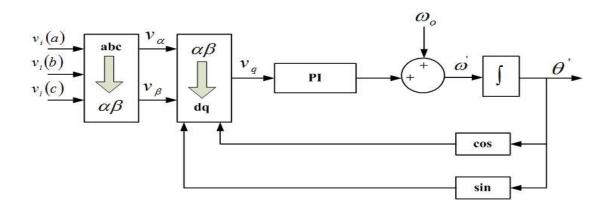

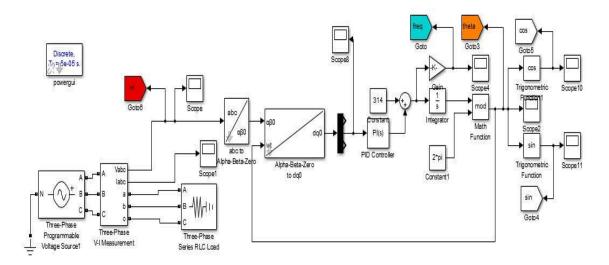

| 3.2.1   | Three Phase Synchronous Frame (SRF) PLL                | 50        |

| 3.2.1.1 | Analysis                                               | 50        |

| 3.2.1.2 | Simulation Results                                     | 52        |

| 3.2.2   | Three Phase Enhanced PLL (EPLL)                        | 55        |

| 3.2.2.1 | Analysis                                               | 56        |

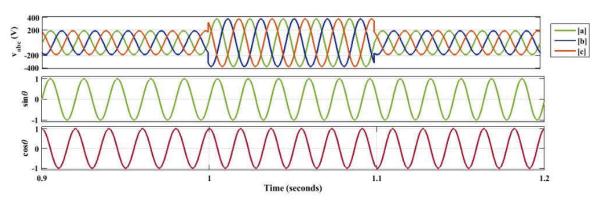

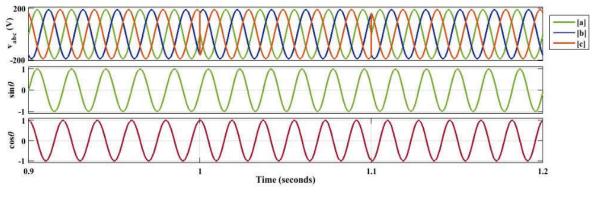

| 3.2.2.2 | Simulation Results                                     | 57        |

| 3.2.3   | Three Phase Inverse Park PLL                           | 60        |

| 3.2.3.1 | Analysis                                               | 60        |

| 3.2.3.2 | Simulation Results                                     | 62        |

| 3.2.4   | Three Phase pPLL                                       | 64        |

| 3.2.4.1 | Analysis                                               | 65        |

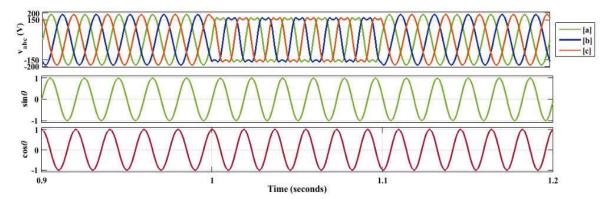

| 3.2.4.2 | Simulation Results                                     | 66        |

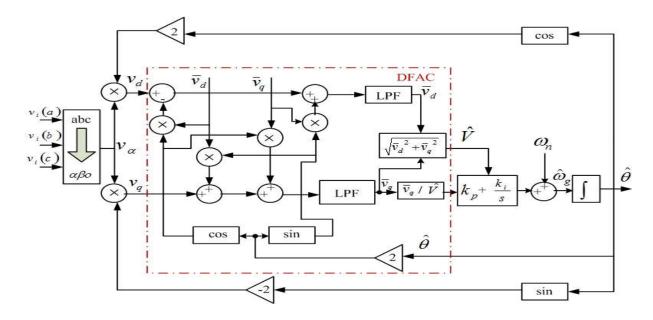

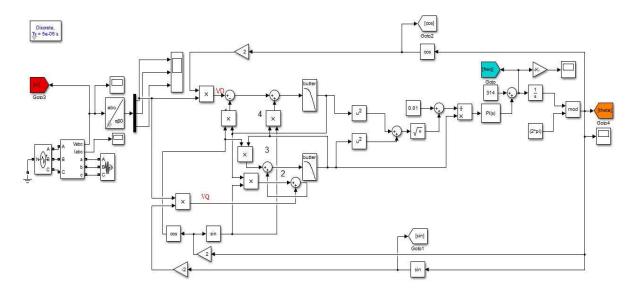

| 3.2.5   | Three Phase DFAC PLL                                   | <b>68</b> |

| 3.2.5.1 | Analysis                                               | 69        |

| 3.2.5.2 | Simulation Results                                     | 71        |

| 3.3     | Comparison                                             | 73        |

| 3.4     | Conclusions                                            | 75        |

|         | ER 4 FREQUENCY LOCKED LOOP TECHNIQUES                  | 76        |

|         | ABLE TO SINGLE PHASE SYSTEMS AND THREE                 |           |

|         | SYSTEMS                                                |           |

| 4.1     | Introduction                                           | 76        |

| 4.2     | Frequency Locked Loop (FLL) Techniques Applicable to a | 77        |

|         | Single Phase System                                    |           |

| 4.2.1   | Single Phase SOGI Based FLL                            | 77        |

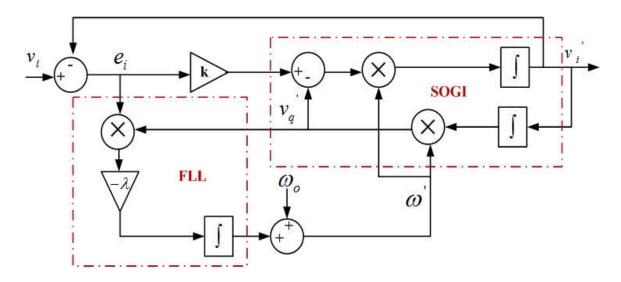

| 4.2.1.1 | Analysis                                               | 77        |

| 4.2.1.2             | Simulation Results                                    | 80        |

|---------------------|-------------------------------------------------------|-----------|

| 4.2.2               | Single Phase SOGI Based FLL with Gain Normalization   | 81        |

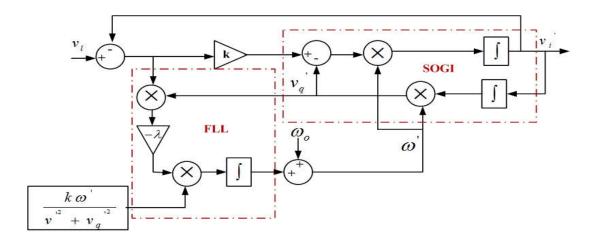

| 4.2.2.1             | Analysis                                              | 82        |

| 4.2.2.2             | Simulation Results                                    | 83        |

| 4.3                 | Frequency Locked Loops (FLL) Techniques Applicable to | 83        |

|                     | a Three Phase System                                  |           |

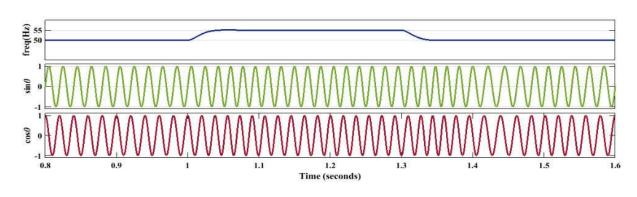

| 4.3.1               | Three Phase Standard FLL                              | 84        |

| 4.3.1.1             | Analysis                                              | 84        |

| 4.3.1.2             | Simulation Results                                    | 85        |

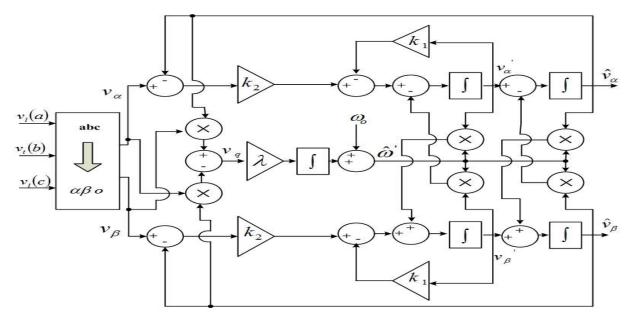

| 4.3.2               | Three Phase FLL with Enhanced DC Offset Rejection     | 86        |

| 4.3.2.1             | Analysis                                              | 87        |

| 4.3.2.2             | Simulation Results                                    | 87        |

| 4.3.3               | Three Phase Complex Band Filter (CBF) FLL 1           | 88        |

| 4.3.3.1             | Analysis                                              | 89        |

| 4.3.3.2             | Simulation Results                                    | 90        |

| 4.3.4               | Three Phase Complex Band Filter (CBF) FLL 2           | 91        |

| 4.3.4.1             | Analysis                                              | 91        |

| 4.3.4.2             | Simulation Results                                    | 93        |

| 4.4                 | Comparison                                            | 93        |

| 4.5                 | Conclusions                                           | 96        |

| CHAPTI              | ER 5 EXPERIMENTAL RESULTS                             | 97        |

| 5.1                 | Introduction                                          | 97        |

| 5.2                 | Experimental Results                                  | <b>98</b> |

| 5.2.1               | Transport Delay PLL                                   | <b>98</b> |

| 5.2.2               | EPLL                                                  | 100       |

| 5.2.3               | SOGI PLL                                              | 103       |

| 5.3                 | Comparison                                            | 105       |

| 5.4                 | Conclusion                                            | 105       |

| CHAPTI              | ER 6 CONCLUSIONS                                      | 106       |

| CHAPTI              | ER 7 FUTURE SCOPE OF WORK                             | 109       |

| List of Publication |                                                       |           |

| REFERENCES          |                                                       | 111       |

# **List of Tables**

- TABLE 2.1PI CONTROLLER GAINS

- TABLE 2.2COMPARISON OF SINGLE PHASE PLL SCHEMES

- TABLE 3.1PI CONTROLLER GAINS FOR A THREE PHASE SYSTEM

- TABLE 3.2COMPARISON OF THREE PHASE PLL SCHEMES

- TABLE 4.1COMPARISON OF SINGLE PHASE FLL SCHEMES

- TABLE 4.2COMPARISON OF THREE PHASE FLL SCHEMES

- TABLE 5.1COMAPRISON OF SINGLE PHASE PLL BASED ON<br/>EXPERIMENTAL RESULTS

### **List of Figures**

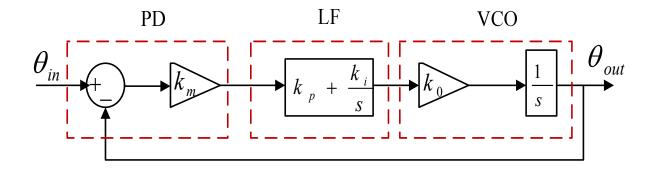

- Figure 1.1: Block diagram of a basic Phase locked loop system

- Figure 2.1: Schematic diagram of a Transport Delay PLL

- Figure 2.2: Simulation model of a transport delay PLL in MATLAB/SIMULINK environment

- Figure 2.3 Transport Delay PLL (frequency change)

- Figure 2.4 Transport Delay PLL (voltage amplitude change)

- Figure 2.5 Transport Delay PLL (phase angle change)

- Figure 2.6 Transport Delay PLL (effect of harmonics)

- Figure 2.7: Schematic diagram of an Adaptive Transport Delay PLL

- Figure 2.8 Simulation model of an adaptive transport delay PLL in MATLAB/SIMULINK environment

- Figure 2.9: Adaptive transport delay PLL (frequency change)

- Figure 2.10: Adaptive transport delay PLL (voltage amplitude change)

- Figure 2.11: Adaptive transport delay PLL (phase angle change)

- Figure 2.12: Adaptive transport delay PLL (effect of harmonics)

- Figure 2.13: Schematic diagram of an Enhanced PLL

- Figure 2.14 Simulation model of enhanced PLL in MATLAB/SIMULINK environment

- Figure 2.15: Enhanced PLL (frequency change)

- Figure 2.16: Enhanced PLL (voltage amplitude change)

- Figure 2.17: Enhanced PLL (phase angle change)

- Figure 2.18: Enhanced PLL (effect of harmonics)

- Figure 2.19: Schematic diagram of an SOGI PLL

- Figure 2.20 Simulation model of SOGI PLL in MATLAB/SIMULINK environment

- Figure 2.21: SOGI PLL (frequency change)

- Figure 2.22: SOGI PLL (voltage amplitude change)

- Figure 2.23: SOGI PLL (phase angle change)

- Figure 2.24: SOGI PLL (effect of harmonics)

- Figure 2.25: Schematic diagram of an Inverse Park PLL

- Figure 2.26 Simulation model of Inverse park PLL in MATLAB/SIMULINK environment

- Figure 2.27: Inverse park PLL (frequency change)

- Figure 2.28: Inverse park PLL (voltage amplitude change)

- Figure 2.29: Inverse park PLL (phase angle change)

- Figure 2.30: Inverse park PLL (effect of harmonics)

- Figure 2.31: Schematic diagram of pPLL

- Figure 2.32 Simulation model of pPLL in MATLAB/SIMULINK environment

- Figure 2.33: pPLL (frequency change)

- Figure 2.34: pPLL (voltage amplitude change)

- Figure 2.35: pPLL (phase angle change)

- Figure 2.36: pPLL (effect of harmonics)

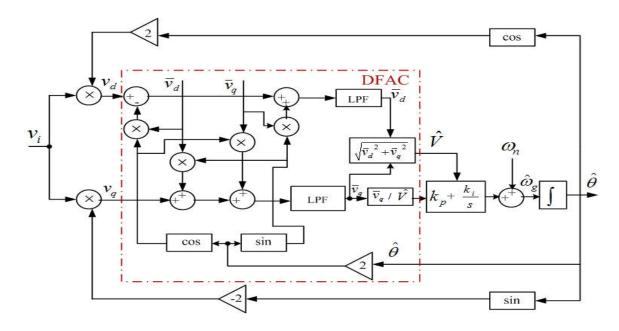

- Figure 2.37: Schematic diagram of DFAC PLL

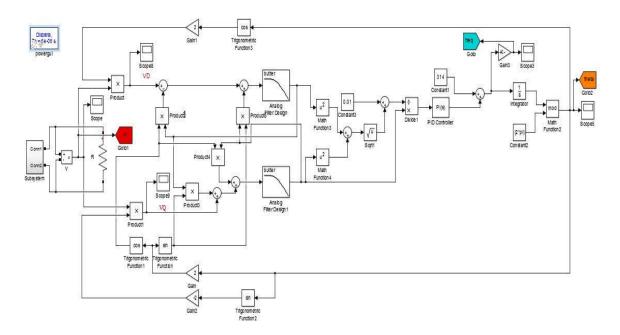

- Figure 2.38 Simulation model of DFAC PLL in MATLAB/SIMULINK environment

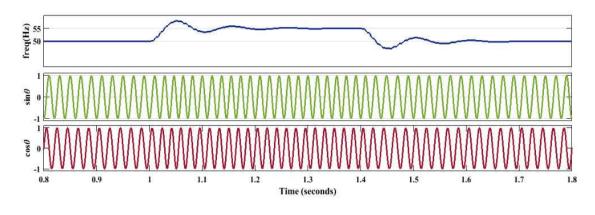

- Figure 2.39: DFAC PLL (frequency change)

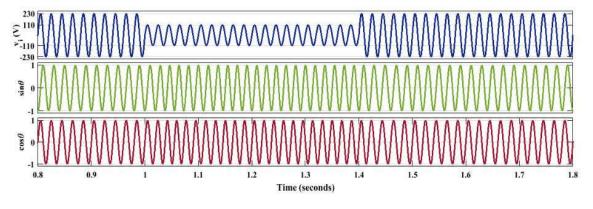

- Figure 2.40: DFAC PLL (voltage amplitude change)

- Figure 2.41: DFAC PLL (phase angle change)

Figure 2.42: DFAC PLL (effect of harmonics)

- Figure 3.1: Schematic diagram of three phase SRF PLL

- Figure 3.2 Simulation model of three phase SRF PLL in MATLAB/SIMULINK environment

- Figure 3.3: Three phase SRF PLL (frequency change)

- Figure 3.4: Three phase SRF PLL (voltage amplitude change)

- Figure 3.5: Three phase SRF PLL (phase angle change)

- Figure 3.6: Three phase SRF PLL (effect of harmonics)

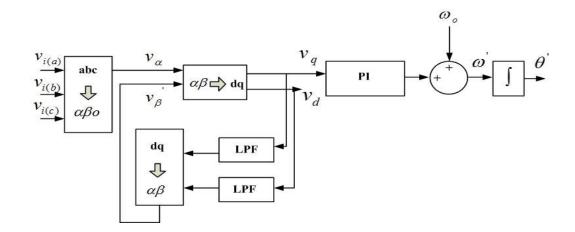

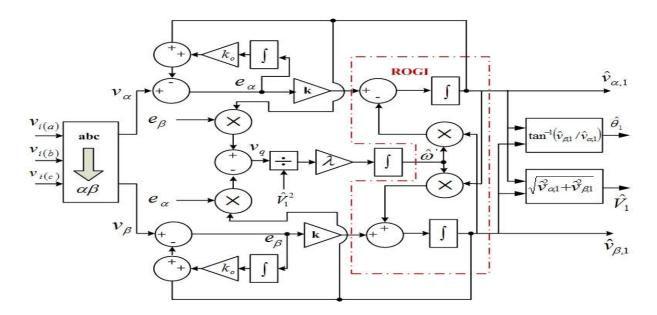

- Figure 3.7: Schematic diagram of three phase EPLL

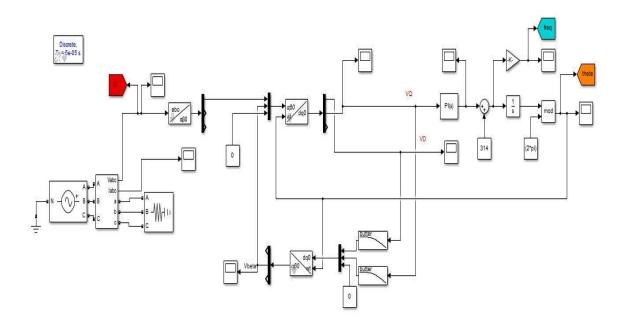

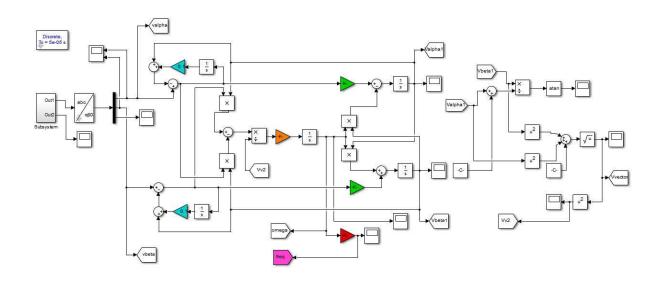

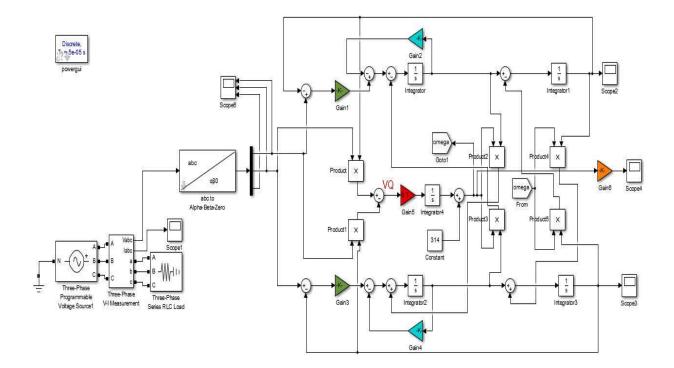

- Figure 3.8 Simulation model of three phase EPLL in MATLAB/SIMULINK environment

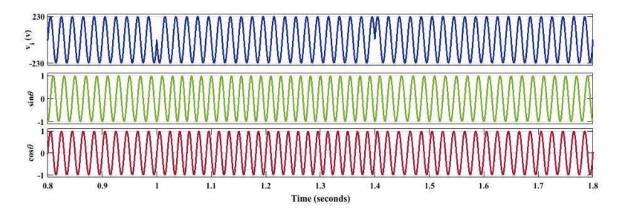

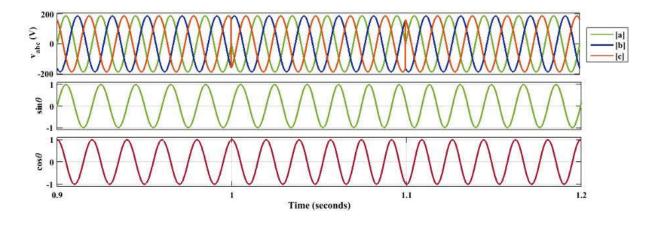

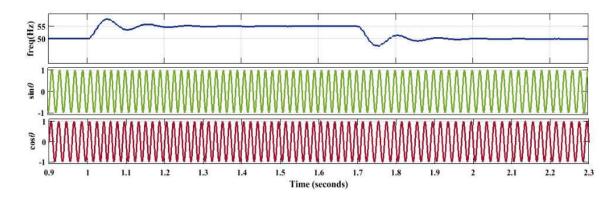

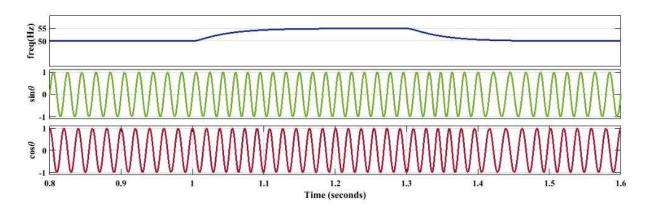

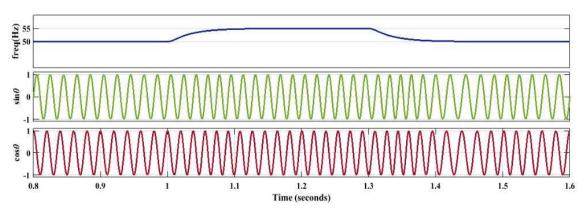

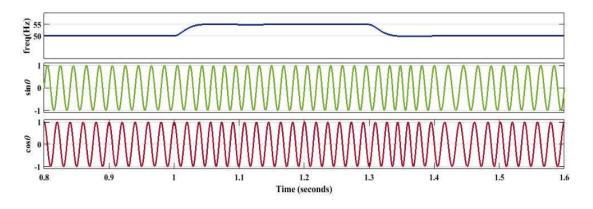

- Figure 3.9: Three Phase EPLL (Frequency Change)

- Figure 3.10: Three Phase EPLL (voltage amplitude Change)

- Figure 3.11: Three Phase EPLL (phase angle change)

- Figure 3.12: Three Phase EPLL (effect of harmonics)

- Figure 3.13: Schematic diagram of a three phase Inverse park PLL

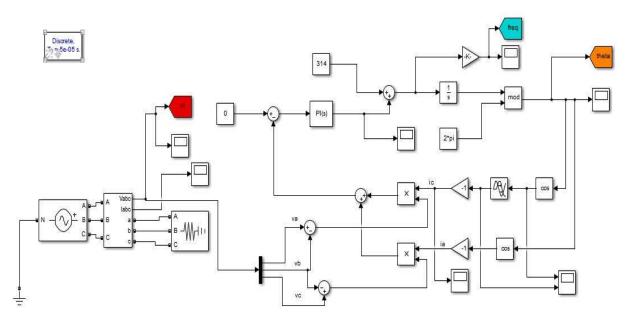

- Figure 3.14 Simulation model of a three phase inverse park PLL in MATLAB/SIMULINK environment

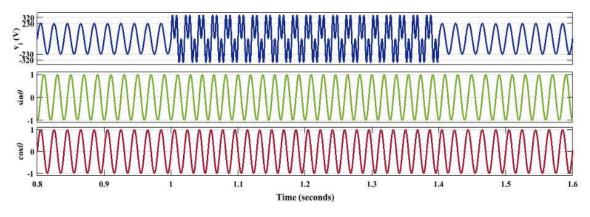

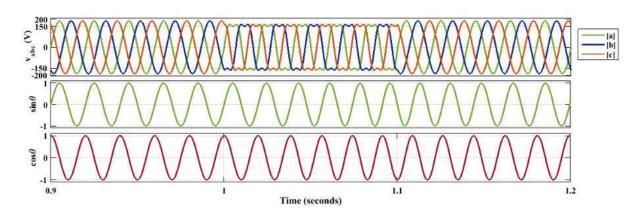

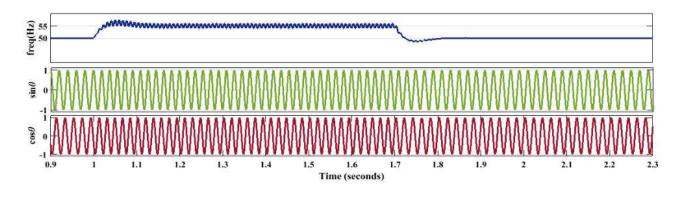

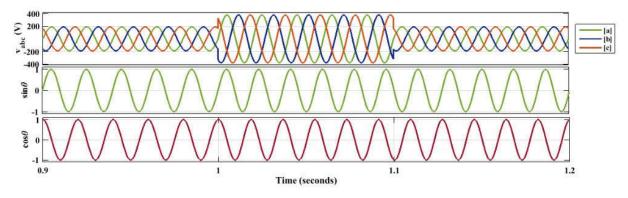

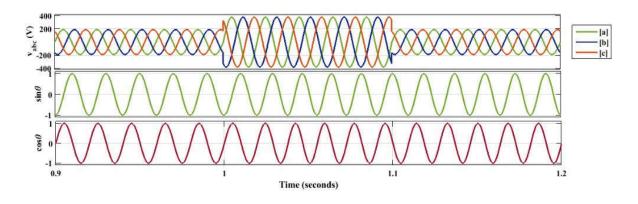

- Figure 3.15: Three Phase inverse park PLL (frequency change)

- Figure 3.16: Three Phase inverse park PLL (voltage amplitude change)

- Figure 3.17: Three Phase inverse park PLL (phase angle change)

- Figure 3.18: Three Phase inverse park PLL (effect of harmonics)

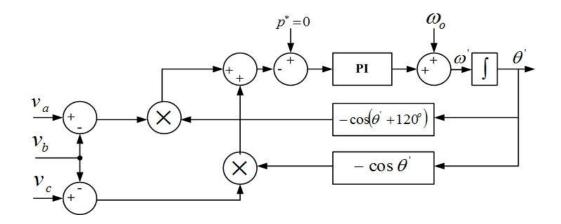

- Figure 3.19: Schematic diagram of three phase pPLL

- Figure 3.20 Simulation model of three phase pPLL in MATLAB/SIMULINK environment

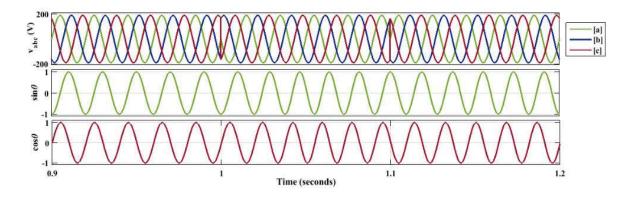

- Figure 3.21: Three Phase pPLL (frequency change)

- Figure 3.22: Three Phase pPLL (voltage amplitude change)

- Figure 3.23: Three Phase pPLL (phase angle change)

- Figure 3.24: Three Phase pPLL (effect of harmonics)

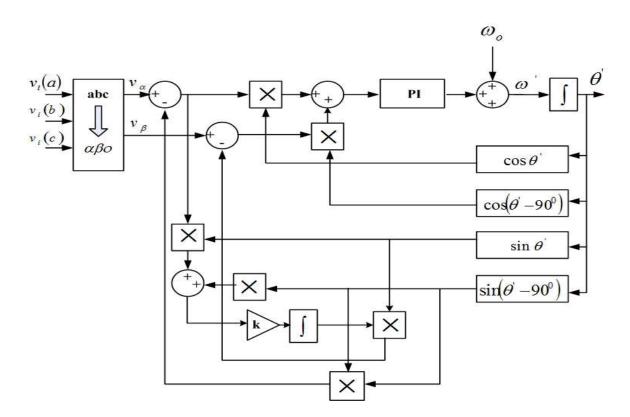

- Figure 3.25: Schematic diagram of three phase DFAC PLL

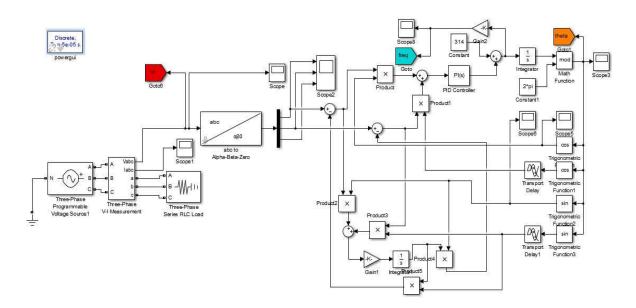

- Figure 3.26 Simulation model of three phase DFAC PLL in MATLAB/SIMULINK environment

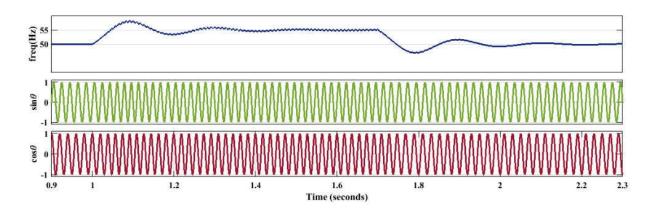

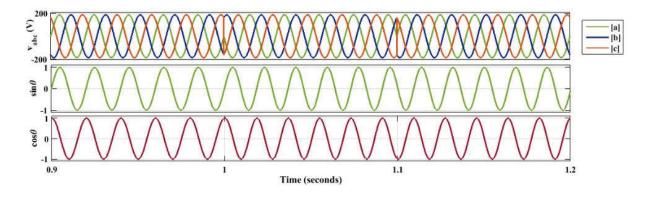

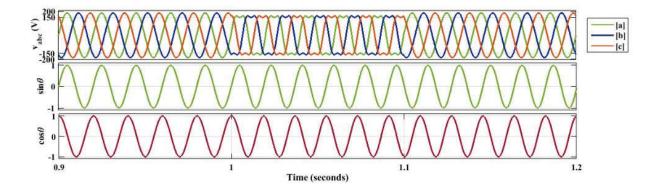

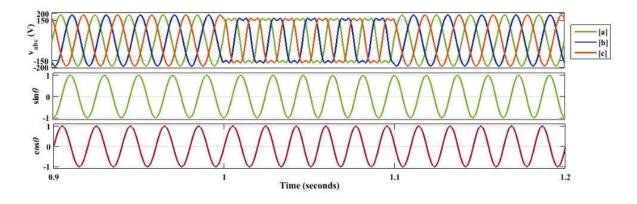

- Figure 3.27: Three Phase DFAC PLL (frequency change)

- Figure 3.28: Three Phase DFAC PLL (voltage amplitude change)

- Figure 3.29: Three Phase DFAC PLL (phase angle change)

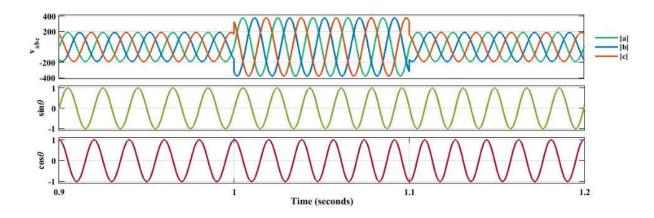

- Figure 3.30: Three Phase DFAC PLL (effect of harmonics)

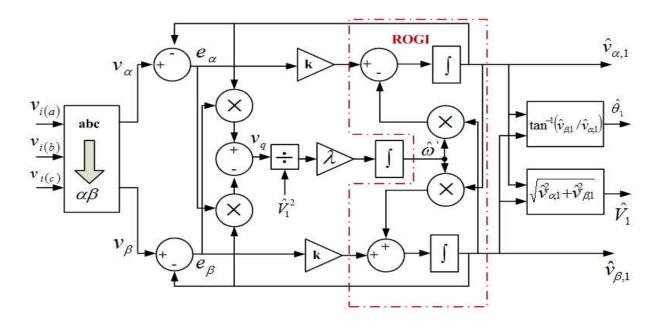

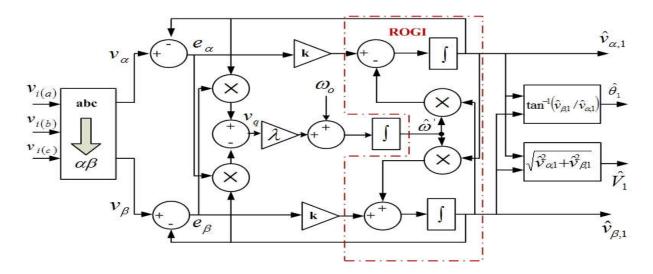

- Figure 4.1: Schematic diagram of single phase SOGI based FLL

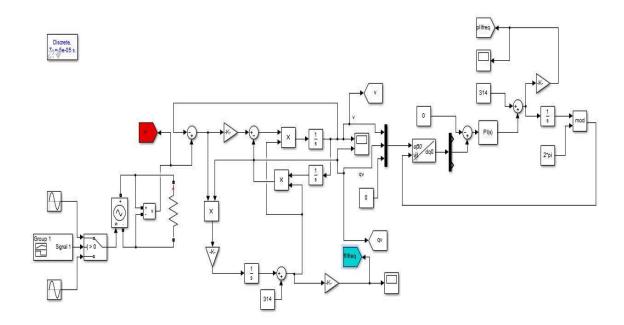

- Figure 4.2: Simulation model of a single phase SOGI based FLL in MATLAB/SIMULINK environment

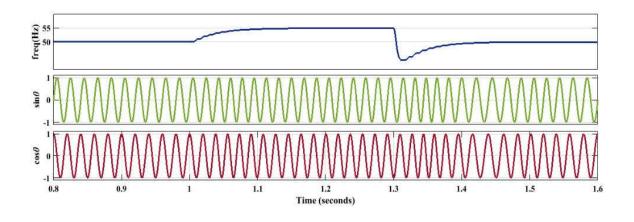

- Figure 4.3: Single phase SOGI based FLL (frequency change)

- Figure 4.4: Schematic diagram of single phase SOGI based FLL with gain normalization

- Figure 4.5: Simulation model of a single phase SOGI based FLL with gain normalization in MATLAB/SIMULINK environment

- Figure 4.6: Single phase SOGI based FLL with gain normalization (frequency change)

- Figure 4.7: Schematic diagram of three phase standard FLL

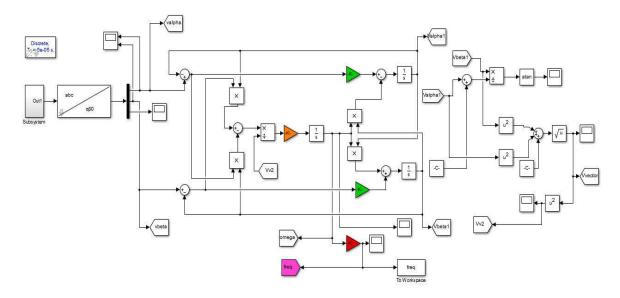

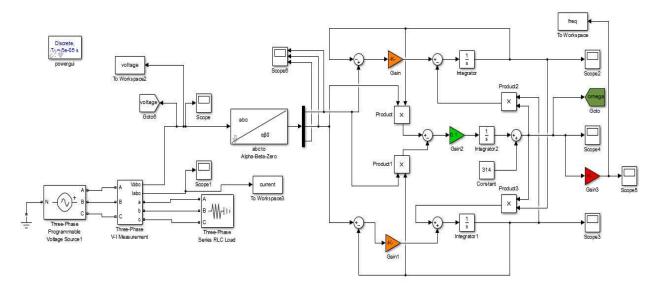

- Figure 4.8: Simulation model of a three phase standard FLL in MATLAB/SIMULINK environment

- Figure 4.9: Three phase standard FLL (frequency change)

#### Figure 4.10: Schematic diagram of three phase FLL with DC offset rejection

- Figure 4.11: Simulation model of a three phase standard FLL with DC offset rejection in MATLAB/SIMULINK environment

- Figure 4.12: Three phase standard FLL with DC offset rejection (frequency change)

- Figure 4.13: Schematic diagram of three phase CBF FLL 1

- Figure 4.14: Simulation model CBF FLL 1 in MATLAB/SIMULINK environment

- Figure 4.15: Three phase CBF FLL 1

- Figure 4.16: Schematic diagram of three phase CBF FLL 2

- Figure 4.17: Simulation model CBF FLL 2 in MATLAB/SIMULINK environment

- Figure 4.18: Three phase CBF FLL 2 (frequency change)

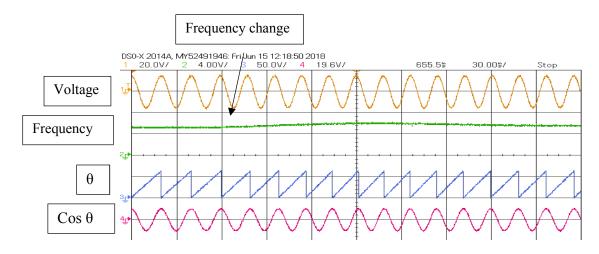

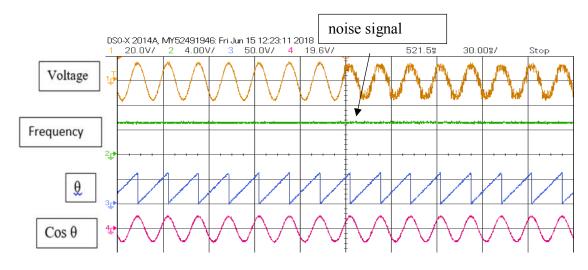

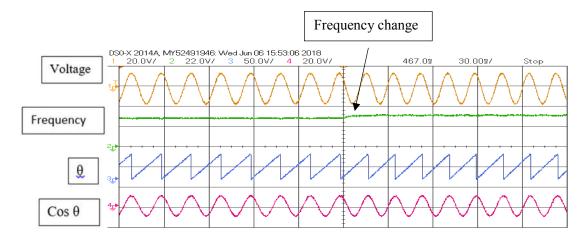

- Figure 5.1: Experimental observation of transport delay PLL on DSO (frequency change)

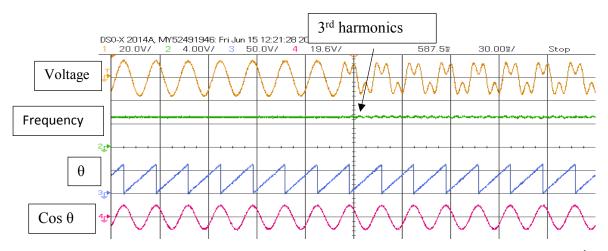

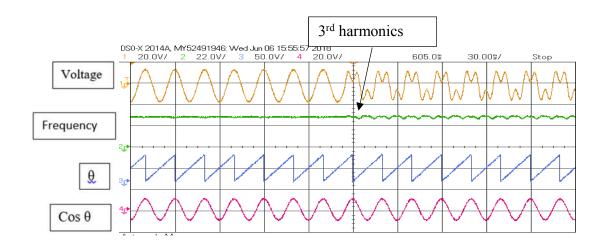

- Figure 5.2: Experimental observation of transport delay PLL on DSO (introduction of 3rd harmonics

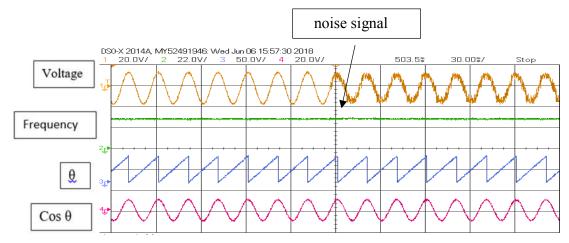

- Figure 5.3: Experimental observation of transport delay PLL on DSO (introduction of noise)

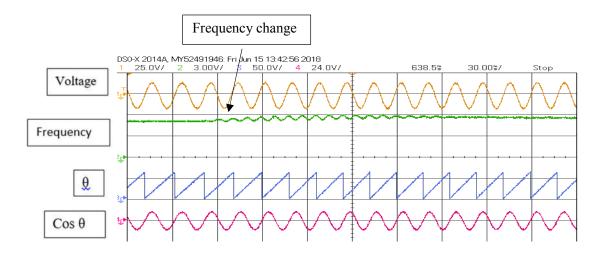

- Figure 5.4: Experimental observation of EPLL on DSO (frequency change)

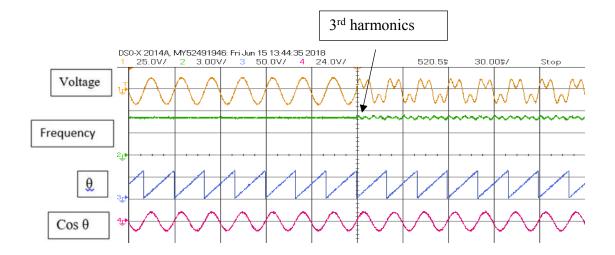

- Figure 5.5: Experimental observation of EPLL on DSO (introduction of 3rd harmonics)

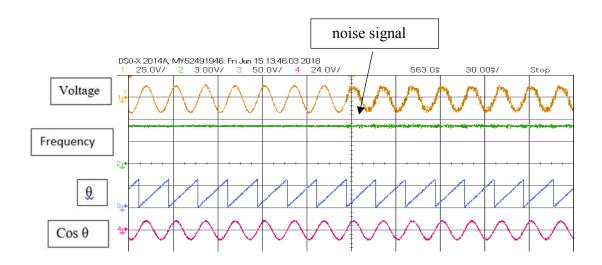

- Figure 5.6: Experimental observation of EPLL on DSO (introduction of noise)

- Figure 5.7: Experimental observation of SOGI PLL on DSO (frequency change)

- Figure 5.8: Experimental observation of SOGI PLL on DSO (introduction of 3rd harmonics)

- Figure 5.9: Experimental observation of SOGI PLL on DSO (introduction of noise)

# List of abbreviations

| 1. PLL        | Phase locked loops                                |

|---------------|---------------------------------------------------|

| 2. FLL        | Frequency locked loops                            |

| 3. DG         | Distributed generators                            |

| 4. ZCD        | Zero crossing detector                            |

| 5. IEEE       | Institute of Electrical and Electronics Engineers |

| 6. PCC        | Point of common coupling                          |

| 7. DC         | Direct current                                    |

| 8. AC         | Alternating current                               |

| 9. VCO        | Voltage controlled oscillator                     |

| 10. PD        | Phase detector                                    |

| 11. pPLL      | power Phase locked loops                          |

| 12. QSG-PLL   | Quadrature signal generator Phase locked loops    |

| 13. LPF       | Low pass filter                                   |

| 14. CBF       | Complex band filter                               |

| 15. SRF PLL   | Synchronous reference frame Phase locked loops    |

| 16. EPLL      | Enhanced Phase locked loops                       |

| 17. DDSRF PLL | Decoupled double SRF PLL                          |

| 18. SOGI PLL  | Second order generalized integrator PLL           |

| 19. DSOGI PLL | Dual SOGI PLL                                     |

| 20. ISC       | Instantaneous symmetric components                |

| 21. DSC PLL   | Delayed signal cancellation Phase locked loops    |

| 22. DSP       | Digital signal processor                          |

| 23. PLO       | Phase locked oscillator                           |

| 24. ANF       | Adaptive notch filter                             |

| 25. PV        | Photo voltaic                                     |

| 26. OSG       | Orthogonal signal generator                       |

| 27. DFAC pPLL | Double frequency amplitude compensation pPLL      |

| 28. ATD PLL   | Adaptive transport delay Phase locked loops       |

| 29. PI       | Proportional-Integral                        |

|--------------|----------------------------------------------|

| 30. GI       | Generalized integrator                       |

| 31. ROGI     | Reduced order generalized integrator         |

| 32. CBF FLL1 | Complex band filter Frequency locked loops 1 |

| 33. CBF FLL2 | Complex band filter Frequency locked loops 2 |

| 34. kVA      | kilo volt amperes                            |

| 35. DSO      | Digital scope oscilloscope                   |

| 36. dq       | direct quadrature                            |

| 37. freq     | frequency                                    |

| 38. rms      | root mean square                             |

| 39. Hz       | Hertz                                        |

| 40. s        | Seconds                                      |

xvii

## CHAPTER 1

## **INTRODUCTION**

#### **1.1 OVERVIEW OF THESIS**

Conventionally, the sources of energy consumed for the production of power comprises coal, hydro, diesel and so on. These sources of energy are depleting in nature and therefore, there is an inevitable need to switch to renewable sources of energy such as solar, wind, etc. The power plants in existence are hence being utilized for the generation of green energy (i.e. the energy produced using renewable sources of energy). The integration of power plants such as solar plant with the conventional power plants faces various problems. The major problem faced is of synchronization of the two grids (or plants). Therefore, there was a need to devise suitable synchronization techniques that could synchronize the grids under several disturbances such as harmonics, frequency deviation, etc.

#### 1.1.1 NEED OF SYNCHRONIZATION TECHNIQUES

In recent years, the single-phase power converters have received a considerable attention because of emerging applications/requirements such as the grid integrating of small scale renewable energy sources (particularly rooftop photovoltaic panels), vehicle-to-grid and grid-to-vehicle connections, low-power-rating uninterruptible power supplies, and small-scale power quality conditioners [1]–[5]. Converter interfaced distributed generator (DG) units must be synchronized with the utility system. Grid synchronization is a challenging task especially when the utility signal is polluted with disturbances and harmonics or is of a distorted frequency. A phase detecting technique provides a reference phase signal synchronized with the grid voltage that is required to control and meet the power quality standards. This is critical in converter interfaced DG units where the synchronization scheme should provide a high degree of insensitivity to power system disturbances,

unbalances, harmonics, voltage sags, and other types of pollutions that exist in the grid signal . In general, a good synchronization scheme must i) proficiently detect the phase angle of the utility signal, ii) Track the phase and frequency variations smoothly, and iii) forcefully reject disturbances and harmonics. These factors, together with the implementation simplicity and the cost are all important when examining the credibility of a synchronization scheme.

There are several ways through which synchronization can be implemented. Few of the methods include, but not limited to,

- 1. Zero Crossing detector (ZCD) method

- 2. Phase locked loop (PLL)

- 3. Frequency locked loop (FLL)

#### **1.1.2 GRID CODE REQUIREMENTS:**

A grid code is a specification which defines the parameters a facility connected to an electric network has to meet to ensure safe, secure and proper economic functioning of the electric system. These include voltage regulation, reactive power supply and power factor limits, response to a system fault (short-circuit), response to changes in the frequency on the grid, and requirement to "ride through" short interruptions of the connection. The full revision of IEEE Standard 1547 and the corresponding 2030 documents under IEEE SCC21 have established new requirements, recommended practices, and guidance for advanced DER interconnections and interoperability with the grid, now including transmission-level effects in addition to the distribution grid [56].

A few terms associated with the grid code are as follows:

- 1. Voltage regulation: This means that by the connecting the DG, the voltage at the PCC shall not be outside a specified range.

- Frequency Deviation: In the same way the frequency deviations shall also not go outside a specified range.

- 3. Synchronization: While synchronizing a DG with a utility grid it shall not cause a voltage fluctuation of more than  $\pm$  5% of the existing voltage level at the Point of Common Coupling (PCC).

- Monitoring Systems: A DG system of rating 250 kW or more shall have provisions for the monitoring of connection status and real and reactive power outputs at the point of DG connection.

- 5. Isolation system: Whenever required by utility grid operating practice for making or breaking the connection, an isolation device shall be located between the DG unit and the utility grid.

- 6. Harmonics: The allowable voltage harmonic distortion is specified at the PCC. It is normally required that the maximum voltage total harmonic distortion is 5% and maximum individual frequency voltage harmonic is 3% of the fundamental component.

- 7. DC current injection: A DG and its interconnection system shall not inject dc current greater than 0.5% of its rated output current into the utility grid at the PCC.

- 8. Flicker: A DG must not create objectionable flicker for customers on the Utility grid.

#### **1.1.3 BASICS OF PLL**

PLL stands for Phase locked loop. A phase-locked loop is a control system that generates an output signal whose phase is related to the phase of an input signal. Though there are numerous types of PLLs, it is easy to first envisage it as an electronic circuit consisting of a variable frequency oscillator (VCO) and a phase detector (PD). The VCO produce a periodic signal, and the phase detector compares the phase of that signal with the phase of the input periodic signal, regulating the oscillator to keep the phases harmonized. As the output of VCO is given back to the phase detector, it is called a feedback signal [6].

Keeping the input and output phase in lock step also implies keeping the input and output frequencies the same. Consequently, in addition to synchronizing signals, a phaselocked loop can track an input frequency, or it can generate a frequency that is a multiple of the input frequency. These properties are used for computer clock synchronization, demodulation, and frequency synthesis.

### **1.1.4 BASIC POINTS ABOUT PLL:**

- 1. PLL is a circuit that locks the phase of the output to the input.

- 2. PLL is a negative feedback control system where the output frequency tracks the input frequency.

- 3. PLL is a circuit synchronizing an output signal with a reference or input signal in frequency as well as in phase.

- 4. In the synchronized or "locked" state, the phase error between the oscillator's output signal and the reference signal is zero, or it remains constant.

- 5. If a phase error builds up, a control mechanism acts on the oscillator to reduce the phase error to a minimum so that the phase of the output signal is actually locked to the phase of the reference signal. This is why it is called a phase-locked loop.

#### **1.1.5 STRUCTURE OF A PLL**

PLL has three basic components [6] i.e.:

- 1. Phase detector

- 2. Loop filter

- 3. A VCO (Voltage controlled oscillator)

Figure 1.1: Block diagram of a basic Phase locked loop system

Phase, amplitude and frequency of the utility voltage are critical information for the operation of the grid-connected power conditioning and power generating equipment. In such applications, an accurate and fast detection of the phase angle of the utility voltage is essential to assure the correct generation of the reference signals. The phase-locked loop (PLL) structure is a feedback control system that automatically adjusts the phase of a locally generated signal to match the phase of an input signal. The purpose of the PLL in a grid connected system is to synchronize the inverter current angle,  $\theta_{out}$ , with the angle of the grid voltage,  $\theta_{in}$ , in order to obtain a power factor as close to unity as possible. The angle  $\theta_{out}$ , is used to calculate the reference current that is compared to the actual output current of the inverter. The main idea in the PLL is that it changes the inverter current frequency,  $\omega_{out}$ , if the inverter current and the grid voltage are out of phase. If the inverter current lags the grid voltage the PLL will decrease  $\omega_{out}$ , until the inverter current is in phase with the grid voltage. On the other hand, if the inverter current leads the grid voltage,  $\omega_{out}$ , is increased until they are in phase. In order to be able to synchronize  $\theta_{out}$  with  $\theta_{in}$  it is necessary somehow to measure  $\theta_{in}$ . This has been done by detecting the zero crossing on the grid voltage. Most recently, there has been an increasing interest in Phase-Locked-Loop (PLL) topologies for grid-connected systems. In order to use a PLL method in single-phase systems an artificial orthogonal voltage system should be created. It is well known that in single-phase systems there are less information than in three-phase systems regarding the grid condition, so more

advanced methods should be considered in order to create an orthogonal voltage system. Also using a PLL structure the grid voltage parameters can be monitored such as grid voltage amplitude and frequency. This grid voltage monitoring is used to ensure that the performances of the investigated methods comply with the standard requirements for operation under common utility distortions such as line notching/harmonics, voltage sags/swells/loss, frequency variations and phase jumps. A large number of single-phase PLLs have been developed and proposed in the literature. Here, they are classified into two major categories: power-based PLLs (pPLLs) [7]–[19] and quadrature signal generation-based PLLs (QSG-PLLs) [20]– [54].

#### **1.1.6 INTRODUCTION TO FREQUENCY LOCKED LOOPS (FLL)**

The closed-loop synchronization techniques can be broadly classified into two major categories: phase-locked loops (PLLs) and frequency-locked loops (FLLs). In their standard structures, both PLLs and FLLs have a limited filtering capability [34],[35]. To deal with this problem, many efforts have been made by different researchers. The majority of these efforts have been concentrated on PLLs, and a little work has been conducted on FLLs. The reason behind this probably lies in the reference frame in which PLLs and FLLs are implemented. The PLLs are implemented in the synchronous reference frame. Therefore, their filtering capability can easily and effectively be improved by including additional low-pass filters (LPFs) and/or notch filters into their structure. The FLLs, however, are realized in the stationary reference frame using generalized integrators [36],[37] or complex bandpass filters (CBFs) [51–[54]. Consequently, designing additional filters for incorporating into their structure is more difficult.

An FLL locks the frequency of the grid voltage instead of the phase angle, and the phase angle is calculated outside the loop. Due to inherent differences between the FLL and PLL, where bandpass filtering characteristics are required to extract the fundamental components and attenuate/eliminate the other harmonics in the FLL system, the in-loop low-passing filters (MAF, CDSC filter, repetitive filter, etc.) that are widely used in PLLs, cannot be directly applied to the FLLs. Therefore, in order to adapt FLLs for adverse grid systems, multiple notch filters are often employed. These FLLs provide good filtering ability, but suffer from heavy computational burden.

## **1.2 LITERATURE REVIEW**

Different synchronization techniques have been proposed in the literature. A popular strategy is using a phase-locked loop (PLL). The PLL can be single phase [7]-[27] or three phase [29]-[33]. The PLL, in simple words, is a closed-loop control system that locks its output to its input with a constant phase error (ideally zero) [6]. All PLLs, regardless of their differences, have three basic parts [6]. The first one is the phase detector (PD), which generates a phase error signal, i.e., a signal that contains the error between real and estimated phases. The second part is the loop filter (LF), which is mainly responsible for suppressing disturbances inside the PLL control loop. The dynamic response, tracking characteristics, and stability properties of the PLL are also mainly dictated by the LF. In energy and power applications, the LF is often a proportional-integral (PI) controller. The third part is the voltage-controlled oscillator (VCO), which is responsible for generating the synchronized signal with the PLL input. A large number of single-phase and three phase PLLs have been developed and proposed in the literature. Here, they are classified into two major categories: power-based PLLs (pPLLs) [22]-[24] and quadrature signal generation-based PLLs (QSG-PLLs) [8]-[21]. This classification is mainly based on the PD of PLLs because the main difference between single-phase PLLs lies in their PD. The pPLLs are characterized by having a product-type PD [22], [23]. A by-product of such PD is a double-frequency disturbance term, which results in double-frequency oscillatory errors and, therefore, an offset error in the estimated quantities by the standard pPLL. To tackle this issue, several advanced pPLLs have been designed in the recent years [22]-[25]. The main difference between them lies in the filtering strategy they use for rejecting the double-frequency disturbance term. The QSG-PLLs can be understood as the single-phase version of the conventional synchronous reference frame PLL (SRF-PLL), which is a standard PLL in three-phase applications. What almost all QSG-PLLs have in common is a unit for creating a fictitious quadrature signal, which is required for transferring the information into the dq frame. This unit can be implemented using different filters/circuits/algorithms [20]-[45]. A member of this class that looks different from others, at least at first glance, is the enhanced PLL (EPLL) [8]–[13]. This PLL, which has been developed based on an optimization perspective, has a close connection with some QSG-PLLs [11]. For this purpose, it has been subsumed under the category of QSG-PLLs.

The three phase synchronous reference frame phase-locked loops (SRFPLLs) [29]-[33] are the most widely used on synchronization techniques. The SRF-PLL yields a satisfactory performance in terms of the phase/frequency tracking capability and the dynamic response under ideal grid conditions. However, when the grid voltage is unbalanced or harmonically distorted, it presents a degraded performance: high amplitude steady-state oscillations in the estimated phase/frequency arise (Yang et al. 2013). This problem can be mitigated by reducing the SRF-PLL's bandwidth at the expense of the dynamic response; however, this measure may not be an effective solution in some applications. Many advanced PLLs have been proposed in literature. For instance, the decoupled double synchronous reference frame PLL (DDSRF PLL) is proposed in (Rodriguez et al. 2007), it employs two SRFs and a decoupling network to separate the positive and negative sequence components, and extracts the fundamental positive-sequence and negative sequence component of grid voltage. Therefore the approach can prevent the double-frequency detection errors caused by the fundamental frequency negative-sequence component. Because there are four low-pass filters, the system is complex. In (Rodriguez et al. 2006), Rodriguez P et al. proposed a dual second-order generalized integrator based PLL (DSOGI-PLL), which is based on the instantaneous symmetrical components (ISC) theory in the stationary reference frame. The approach achieves frequency self-adaptation, but the orthogonal property of output is sensitive to direct current biasing voltage of input. Delayed signal cancellation-based PLL (DSC-PLL) is applied in order to eliminate the negative sequence component in unbalanced grids and also to cancel any given harmonics (Wang et al. 2011), (Liccardo et al. 2011), but improper sampling rate or system frequency shift could result in estimation deviations and their complexity always require multiple digital signal processors. A three-phase PLL algorithm based on signal reforming is presented by Liu, Baoquan et al. (Liu et al. 2015). It focuses on the reforming of the primary signals before phase estimation, and dedicates to eliminate the negative sequence of the three-phase imbalances. Although the aforementioned PLL methods show good performance, the implementation of these algorithms is quite complicated, and requires multiple digital signal processors (DSPs) to reduce the execution time of the algorithms (Xu et al. 2007). Several types of PL that can be applied to three phase systems other than the conventional SRF PLL have also been studied in the literature. Few of the prior art includes three phase EPLL [40]-[41] which is categorized under QSG based PLL, three phase power PLL which is quite similar to the single phase power PLL [22]-[25].

### **1.3 MOTIVATION OF THESIS**

The Environmental friendly renewable energy technologies such as wind and solar energy systems are among the fleet of new generating technologies driving the demand for distributed generation of electricity. Power Electronics has initiated the next technological revolution and enables the connection of distributed generation (DG) systems to the grid. Thus the increasing power demand will be met by Distributed Generation (DG) system which are based on renewable energy sources such as solar power, wind power, small hydro power etc. [1]-[2]. These systems need to be controlled properly in order to ensure synchronization of the grid. Grid connected inverter plays a vital role in maintaining voltage at the point of common coupling (PCC) constant. For the reliable operation of utility grid based on DG system, the power plant operators should satisfy the grid code requirements such as fault ride through, grid stability, grid synchronization and power control etc. The major issue associated with DG system is their synchronization with utility voltage vector [4]. Various synchronization methods have therefore been analyzed to meet the synchronization requirements of the grid.

#### **1.4 ORGANIZATION OF THESIS**

The thesis is organized into five chapters including the introduction in the Chapter 1. Each of these is summarized below:

CHAPTER 1: Chapter 1 deals with the topics such as need of synchronization techniques, various synchronization techniques, detailed explanation of phase locked loop system, introduction to frequency locked loop system and so forth.

CHAPTER 2: Chapter 2 deals with various single phase phase locked loop systems. Furthermore, the chapter includes the analysis of PLL techniques, the estimation of PLL performance on application of various disturbances such as, frequency change, voltage amplitude change, phase angle change and introduction to harmonics. Additionally, the performance of single phase phase locked loop techniques has been compared with respect to frequency change introduced in the system and formulated in a table.

CHAPTER 3: Chapter 3 deals with various three phase phase locked loop systems. Furthermore, the chapter includes the analysis of PLL techniques, the estimation of PLL performance on application of various disturbances such as, frequency change, voltage amplitude change, phase angle change and introduction to harmonics. Additionally, the performance of three phase phase locked loop techniques has been compared with respect to frequency change introduced in the system and formulated in a table.

CHAPTER 4: Chapter 4 deals with various single phase and three phase frequency locked loop systems. Furthermore, the chapter includes the analysis of FLL techniques, the estimation of FLL performance on application of frequency change. Additionally, the performance of single phase and three phase frequency locked loop techniques has been compared with respect to frequency change introduced in the system and formulated in a table.

CHAPTER 5: Chapter 5 includes experimental results conducted on a few single phase phase locked loop techniques based on frequency change, effect of harmonics and noise. The PLLs were examined for the maintenance of locked state under the mentioned disturbances.

## **CHAPTER 2**

# PHASE LOCKED LOOP TECHNIQUES FOR A SINGLE PHASE SYSTEM

### **2.1 INTRODUCTION**

Several techniques such as zero crossing detection (ZCD), phase locked oscillator (PLO), EPLL [14-16] have been mentioned in the literature for implementing grid synchronization. Some newer techniques are also being researched for this purpose which includes PLLs based on adaptive notch filters (ANF), weighted least squares estimation techniques, and artificial neural network based controllers. Moreover, PLL less synchronization is also gaining importance. The use of different PLLs for single phase as well as three phase systems for PV interfaced grid connected systems is gaining high importance and studied thoroughly [28]. High significance is assigned to designing simpler and effective synchronization schemes that will work well in harmonically polluted grid systems. Fast tracking ability should be ensured by the designed PLL under all varied conditions.

Here in this chapter, various synchronization techniques based on phase locked loop applicable to a single phase system have been discussed. Design, modeling and simulation of the complete system along with the controller have been carried out in MATLAB/SIMULINK environment. Simulation results for different cases have been investigated which include the performance of these single phase PLL under (i) Voltage amplitude change, (ii) Frequency change (iii) Phase change and (iv) effect of harmonics. Comparative results have been tabulated for the different PLL schemes. PLL techniques are gaining importance worldwide and the research conducted on synchronization techniques have been mentioned in the literature review in the chapter 1.

# 2.2 TYPES OF PHASE LOCKED LOOP TECHNIQUES APPLICABLE TO A SINGLE PHASE SYSTEM

In this chapter few of the single phase PLL techniques have been discussed. The most commonly used single phase PLL techniques are based on quadrature signal generation. The quadrature signal generation is used to obtain a signal which is in quadrature with the original signal. There are a few methods which can be used to obtain the quadrature signal. Some of the methods have been discussed below:

#### 2.2.1 TRANSPORT DELAY PLL

The transport delay PLL is one of the easiest methods to obtain a quadrature signal from the grid voltage. The objective of using transport delay block is to generate a signal which is in quadrature with the grid voltage. The signal in quadrature implies that if the grid voltage has a time period of T s, then second signal is generated after the delay block will be (T/4) s.

Figure 2.1: Schematic diagram of a Transport Delay PLL

#### 2.2.1.1 ANALYSIS

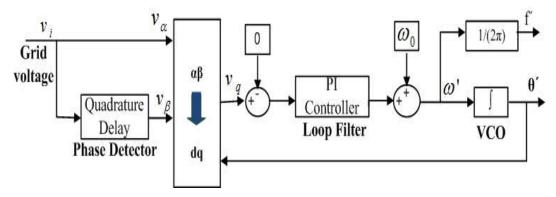

Figure 2.1 shows the schematic diagram of the transport delay PLL. This is one of the simplest PLLs and uses Park transformation (i.e.  $\alpha\beta$  to dq) for computation of frequency and phase angle [7]-[11]. To realize this transformation, the  $\beta$  variable is in-quadrature with the grid voltage i.e. shifted from the supply voltage by 90<sup>0</sup>.

Let the grid voltage be  $v_i$ ,

$$v_i(t) = v_i \cos(\theta) = v_i \cos(\omega t + \phi_o)$$

(2.1)

Considering the grid signal frequency is 50 Hz, the time period T will be 1/50 s i.e. 0.02 s. Consequently, there will be a phase shift between  $v_i$  and  $v_\beta$ .

The  $\alpha$  and  $\beta$  components so obtained are then converted into direct and quadrature (dq) components using Park's transformation described below:

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = \begin{bmatrix} \cos \theta' & \sin \theta' \\ -\sin \theta' & \cos \theta' \end{bmatrix} \begin{bmatrix} v_a \\ v_\beta \end{bmatrix}$$

(2.2)

The generated signal is now passed through the loop filter which is represented by the PI controller. The further stages include passing it through Voltage controlled Oscillator (VCO). As it a closed loop system, the output of VCO is fed back to the transformation stage as the derived angle. The delay PLL works satisfactorily under normal operating conditions. However, if the input grid voltage is not completely sinusoidal and not at rated frequency, the delayed signal will not be in exact quadrature with the input signal. This will cause problems in the synchronization. Overall, this technique is quite hassle free and can be used to extract phase angle in single phase applications without much distortions.

Due to the problems faced by this method of synchronization, another method was proposed i.e. Adaptive transport Delay PLL technique which has been discussed in the next section.

#### **2.2.1.2 SIMULATION RESULTS**

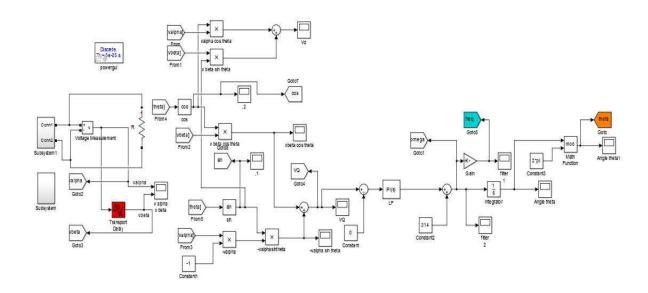

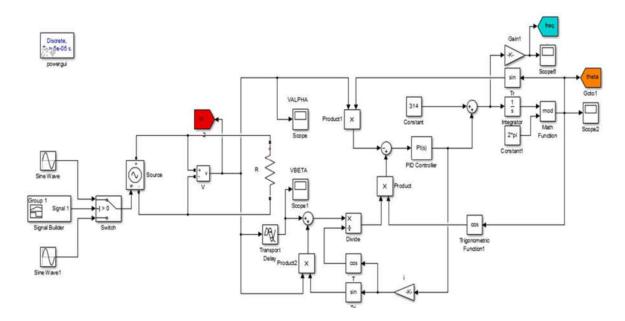

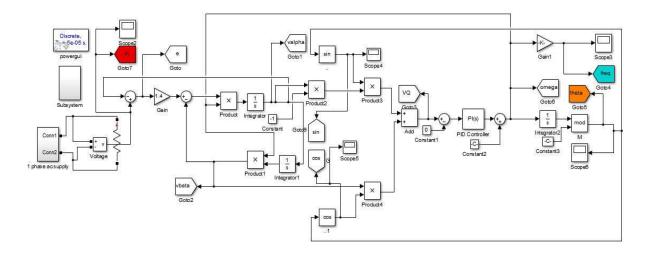

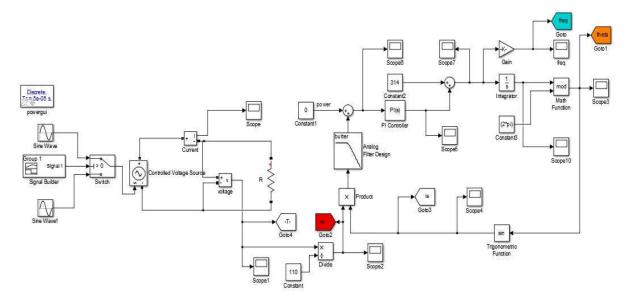

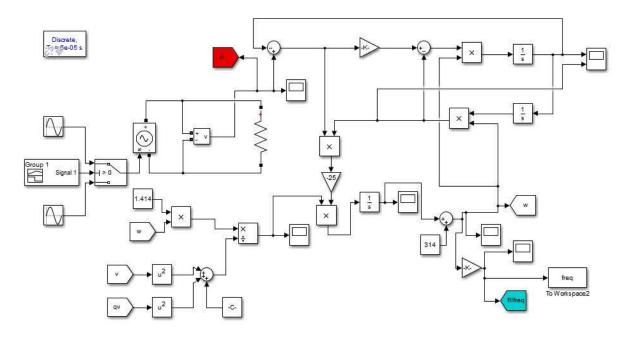

Figure 2.2 shows a simulation model of a transport delay PLL in MATLAB/SIMULINK environment. In the SIMULINK model, single phase system is devised and transport delay PLL is implemented. Various changes have been made at an interval to check if the devised model shows synchronism under disturbances.

The results have been taken for frequency change, voltage amplitude change, phase angle change and effect of harmonics.

Figure 2.2: Simulation model of a transport delay PLL in MATLAB/SIMULINK environment

The changes have been made at intervals t = 1 s till t = 1.4 s. The working of the PLL has been investigated in case of various disturbances.

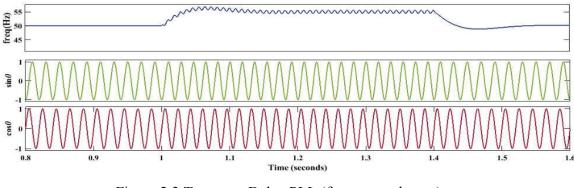

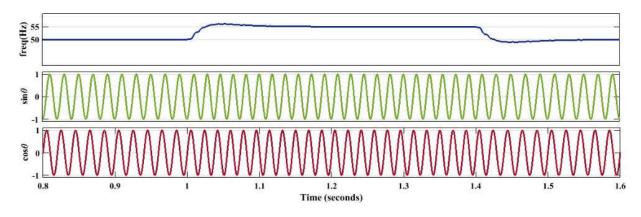

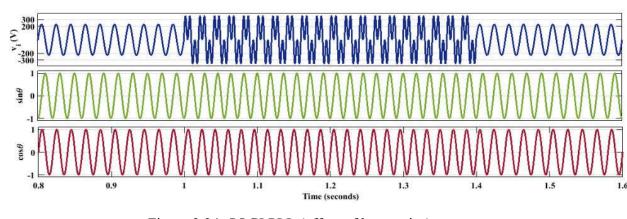

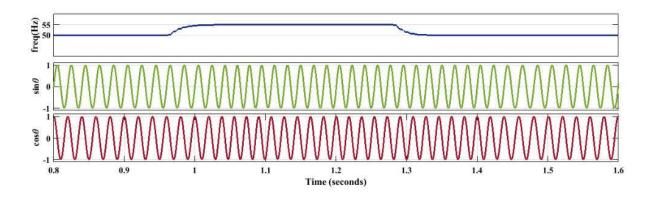

## (a) FREQUENCY CHANGE

The frequency is changed from 50 Hz to 55 Hz. It has been observed that the PLL takes nearly 6-7 cycles to settle at 55 Hz and after t = 1.4 s the frequency reaches again to 50 Hz. It can be concluded that in case of frequency deviation, the transport delay PLL is able to maintain synchronism after a few cycles.

Figure 2.3 Transport Delay PLL (frequency change)

### (b) VOLTAGE AMPLITUDE CHANGE

The voltage change has been made from 230 V to 110 V between t = 1 s till t = 1.4 s. It can be noted that the PLL tracks voltage and settles to 230 V after t = 1.4 s. It can be observed that the grid voltage is in phase with  $\cos\theta$ .

Figure 2.4 Transport Delay PLL (voltage amplitude change)

#### (c) PHASE ANGLE CHANGE

Phase angle change has been introduced between t = 1 second to t = 1.4 s. Phase angle has been changed from 0 radians to pi radians.

Figure 2.5 Transport Delay PLL (phase angle change)

#### (d) EFFECT OF HARMONICS

Third harmonics has been introduced between t = 1 s till t = 1.4 s. It can be observed that perfect sin  $\theta$  and cos  $\theta$  are maintained in case of harmonics in the system.

Figure 2.6 Transport Delay PLL (effect of harmonics)

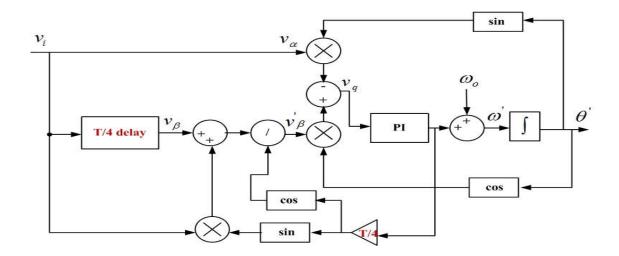

#### 2.2.2 ADAPTIVE TRANSPORT DELAY PLL

Adaptive transport delay PLL is quite similar to the transport delay PLL only with a few modifications. Whenever there is a frequency drift in the system, it results in the lack of orthogonality between  $v_{\alpha}$  and  $v_{\beta}$  components which causes double-frequency oscillatory errors and offset errors in the predicted quantities of the Transport Delay PLL. Therefore, there was a need to eliminate the abovementioned problem. So a modification to the conventional transport delay PLL was introduced [12]-[13].

Figure 2.7: Schematic diagram of an Adaptive Transport Delay PLL

#### 2.2.2.1 ANALYSIS

Figure 2.7 shows the schematic diagram of an adaptive transport delay PLL. Mathematical analysis of the Adaptive transport delay PLL has been shown below:

$$v_i(t) = v_\alpha(t) = V_i \cos \theta_i \tag{2.3}$$

$$\theta_i = \omega_i t + \varphi_i \tag{2.4}$$

where,

$V_i$  is the voltage amplitude of the grid,

$\omega_i$  is the grid frequency,

$\varphi_i$  is the initial phase angle of the grid, and

$\theta_i$  is the phase angle of the grid.

Let the grid frequency be denoted as:

$$\omega_i = \omega_{nf} + \Delta \omega_i \tag{2.5}$$

where,

$\omega_{nf}$  is the actual value of the grid frequency, and

$\Delta \omega_i$  is the deviation of grid frequency from its actual value.

Using equation 2.3 and equation 2.5, the fictitious quadrature signal  $v_{\beta}$  can be defined as:

$$v_{\beta}(t) = v_{\alpha}\left(t - \frac{T}{4}\right) = V_i \cos(\theta_i - \omega_i \frac{T}{4}) = V_i \sin(\theta_i - \Delta \omega_i \frac{T}{4})$$

(2.6)

Equations 2.3 and 2.6 demonstrates that  $v_{\alpha}$  and  $v_{\beta}$  are orthogonal signals only when  $\Delta \omega_i$ = 0 (i.e. when there is no deviation of the actual grid frequency in the system). The lack of orthogonality between  $v_{\alpha}$  and  $v_{\beta}$  components in the case of frequency drifts results in double-frequency oscillatory errors and offset errors in the predicted quantities of the Transport Delay PLL.

By the use of equation 2.6, the quadrature signal produced by the transport delay block can be expressed as:

$$v_{\beta}(t) = \underbrace{V_{i}\sin(\theta_{i})}_{v_{\beta}'}\cos\left(\Delta\omega_{i}\frac{T}{4}\right) - \underbrace{V_{i}\cos(\theta_{i})}_{v_{\alpha}}\sin\left(\Delta\omega_{i}\frac{T}{4}\right)$$

(2.7)

Using equation 2.7,  $v_{\beta}$  which is the needed orthogonal signal, can be acquired as:

$$\nu_{\beta}' = \frac{\nu_{\beta}(t) + \nu_{\alpha}(t)\sin\left(\Delta\omega_{i}\frac{T}{4}\right)}{\cos\left(\Delta\omega_{o}\frac{T}{4}\right)}$$

(2.8)

As equation 2.8 demonstrates, the generation of  $v_{\beta}$  requires information about the frequency deviation in the system  $\Delta \omega_i$ . The output of Proportional Integral (PI) controller, imparts an estimation of the change in frequency  $\Delta \omega_i$ . Therefore, orthogonal signal  $v_{\beta}$  can be produced as shown in equation 2.9:

$$v_{\beta}'(t) = \frac{v_{\beta}(t) + v_{\alpha}(t)\sin\left(\Delta\omega_{o}\frac{T}{4}\right)}{\cos\left(\Delta\omega_{o}\frac{T}{4}\right)}$$

(2.9)

The analysis shows that the adaptive transport delay PLL is an advancement over the conventional transport delay PLL which is basically an SRF PLL employed for a single phase system.

Figure 2.8 Simulation model of an adaptive transport delay PLL in MATLAB/SIMULINK environment

#### **2.2.2.2 SIMULATION RESULTS**

Figure 2.8 shows a simulation model of an adaptive transport delay PLL in MATLAB/SIMULINK environment. In the SIMULINK model, single phase system is devised and adaptive transport delay PLL is implemented. Various changes have been made at an interval to check if the devised model shows synchronism under disturbances. The results have been taken for frequency change, voltage amplitude change, phase angle change and effect of harmonics. The working of the PLL has been investigated in case of various disturbances.

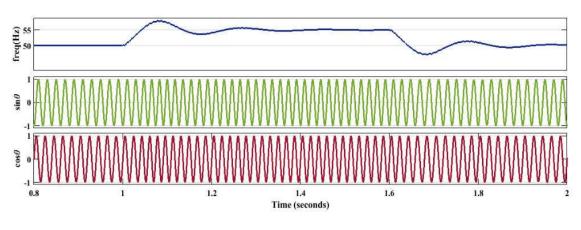

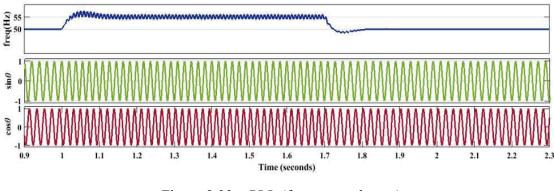

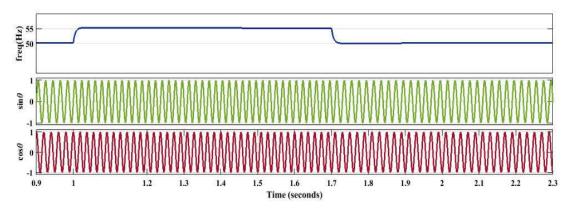

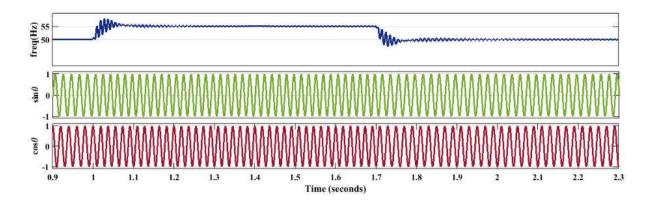

#### (a) FREQUENCY CHANGE

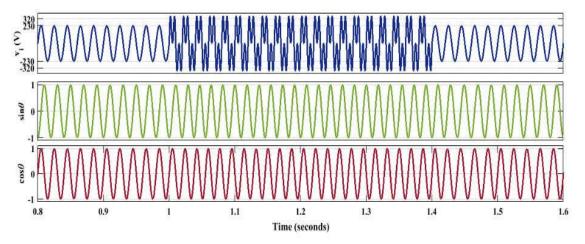

The frequency is changed from 50 Hz to 55 Hz. It can be noted that the PLL takes nearly 10-11 cycles to settle at 55 Hz and after t = 1.6 s the frequency reaches again to 50 Hz. It can

be concluded that the PLL tracks the frequency and remains in synchronism during frequency deviation.

Figure 2.9: Adaptive transport delay PLL (frequency change)

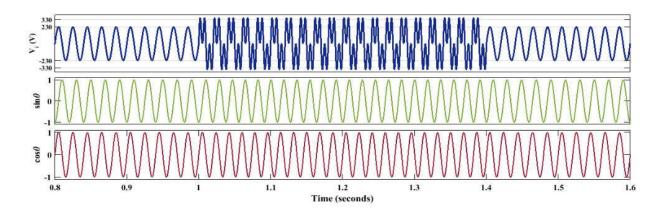

## (b) VOLTAGE AMPLITUDE CHANGE

The voltage change has been made from 230 V to 110 V between t = 1 s till t = 1.6 s. It can be observed that the PLL tracks voltage and settles to 230 V after t = 1.6 s. Additionally, it can be seen that the grid voltage is in phase with  $\cos \theta$ .

Figure 2.10: Adaptive transport delay PLL (voltage amplitude change)

# (c) PHASE ANGLE CHANGE

Phase angle change has been introduced between t = 1 second to t = 1.4 s. Phase angle has been changed from 0 rad to pi rad in the 0.4 s interval. The grid voltage maintains synchronism and comes in phase with  $\cos \theta$  when the phase angle is again changed to 0 rad.

Figure 2.11: Adaptive transport delay PLL (phase angle change)

### (d) EFFECT OF HARMONICS

Third harmonics has been introduced between t = 1 second till t = 1.4 s. It can be observed that perfect sin  $\theta$  and cos  $\theta$  are maintained in case of harmonics in the system.

Figure 2.12: Adaptive transport delay PLL (effect of harmonics)

#### 2.2.3 ENHANCED PLL

EPLL is a frequency adaptive non linear synchronization method, which uses an adaptive filter (AF) and a sinusoidal multiplier [14]-[16]. One of the most significant characteristics of an EPLL is that it can be used for locking the grid voltage amplitude and the phase angle both. The EPLL becomes free of any oscillations after a certain time period.

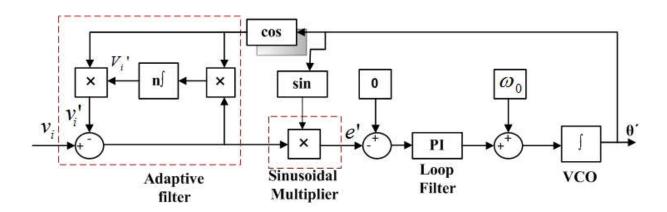

Figure 2.13: Schematic diagram of an Enhanced PLL

# 2.2.3.1 ANALYSIS

The phase detector of the EPLL is efficient and quite flexible which helps in presenting more information about several attributes of the system vis-à-vis fundamental components, phase components, frequency components, etc. The expected grid voltage amplitude  $v_i$  can be shown as:

$$v_i' = n \int e \cos \theta' \tag{2.10}$$

where n : control parameter and

$$e = v_i - v_i' \tag{2.11}$$

$$e' = e\sin\theta' \tag{2.12}$$

$$V_i' = \cos\theta' = v_i' \tag{2.13}$$

The block diagram for the basic EPLL is shown in Fig.2.13. The input grid voltage  $v'_i$  is passed through various stages i.e. Adaptive filter, Loop filter incorporated as a PI controller and a voltage controlled oscillator. The derived angle  $\theta'$  is fed to cosine and sinusoidal functions which are given to the adaptive filter and the sinusoidal multiplier respectively.

Figure 2.14 Simulation model of enhanced PLL in MATLAB/SIMULINK environment

#### **2.2.3.2 SIMULATION RESULTS**

Figure 2.14 shows a simulation model of enhanced PLL in MATLAB/SIMULINK environment. In the SIMULINK model, single phase system is devised and enhanced PLL is implemented. Various changes have been made at an interval to check if the devised model shows synchronism under disturbances.

The results have been taken for frequency change, voltage amplitude change, phase angle change and effect of harmonics.

The changes have been made at intervals t = 1 s till t = 1.4 s.

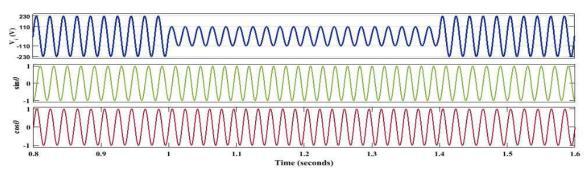

#### (a) FREQUENCY CHANGE

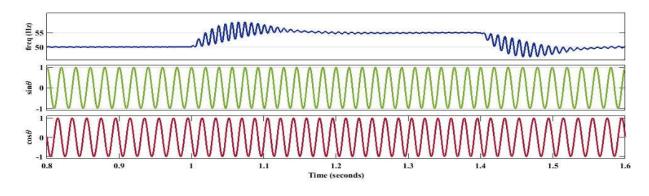

The frequency is changed from 50 Hz to 55 Hz. It can be observed that the PLL takes nearly 11-12 cycles to settle at 55 Hz along with a few oscillations and after t = 1.4 s the frequency reaches again to 50 Hz.

Figure 2.15: Enhanced PLL (frequency change)

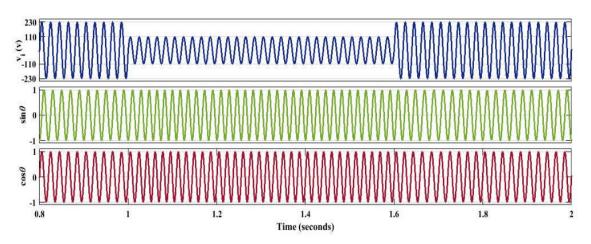

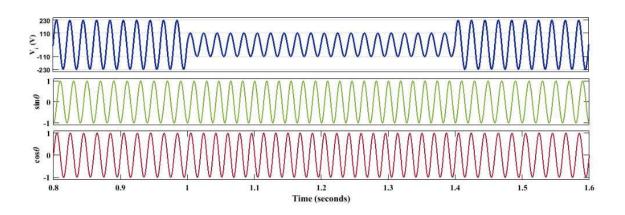

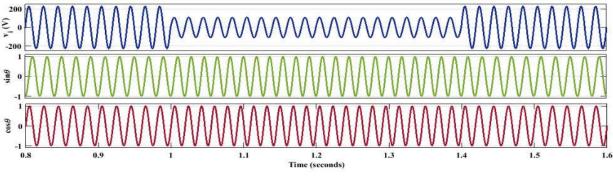

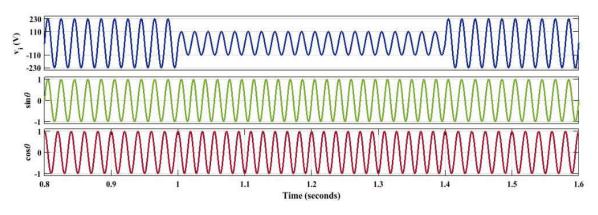

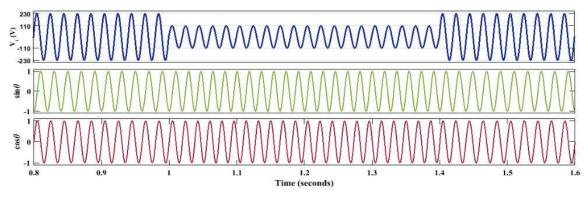

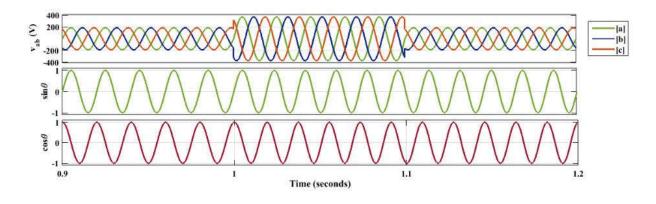

# (b) VOLTAGE AMPLITUDE CHANGE

The voltage change has been made from 230 V to 110 V between t = 1 s till t = 1.4 s. It can be seen that the PLL tracks voltage and settles to 230 V after t = 1.4 s. Additionally, it can be seen that the grid voltage is in phase with  $\cos \theta$ .

Figure 2.16: Enhanced PLL (voltage amplitude change)

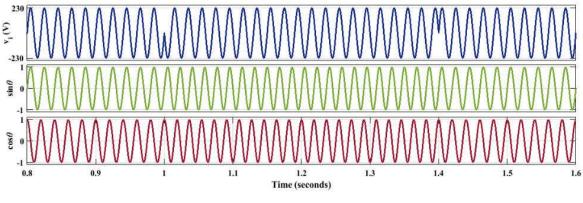

## (c) PHASE ANGLE CHANGE

Phase angle change has been introduced between t = 1 s to t = 1.4 s. Phase angle has been changed from 0 rad to pi rad. The grid voltage maintains synchronism and comes in phase with  $\cos \theta$  when the phase angle is again changed to 0 rad.

Figure 2.17: Enhanced PLL (phase angle change)

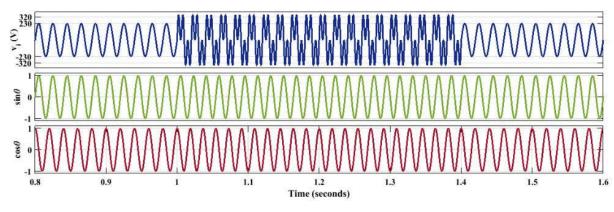

# (d) EFFECT OF HARMONICS

Third harmonics has been introduced from t= 1 s till t= 1.4 s. It can be observed that perfect sin  $\theta$  and cos  $\theta$  are maintained in case of harmonics in the system.

Figure 2.18: Enhanced PLL (effect of harmonics)

#### 2.2.4 SECOND ORDER GENERALIZED INTEGRATOR (SOGI) PLL

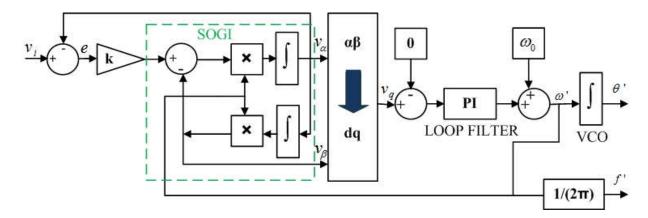

SOGI PLL stands for second order generalized integrator PLL. The drawback of using enhanced PLL system is that it uses only one adaptive weight in its realization. Hence, it will take some time period for the transients to die out and the error signal to come into a zero steady state error zone. This zero steady state tracking of the input signal is realized using only one weight adaptive filter. A further improved PLL has been introduced namely SOGI PLL [17-18]. The characteristic feature of SOGI PLL is that it uses a second order adaptive notch filter. The adaptive notch filter in SOGI PLL behaves like a Sinusoidal integrator. Thus, a SOGI PLL behaves like a Sinusoidal integrator whose basic block diagram has been shown in the Fig.2.19.

Figure 2.19: Schematic diagram of an SOGI PLL

#### 2.2.4.1 ANALYSIS

It is clear that the SOGI PLL does not employ the typical sin and cosine blocks. This is because it inherently contains the sin and cosine blocks. For an undamped SOGI-PLL system, its transfer function (T.F.) can be defined as:

When in-phase:

$$T. F. = \frac{\omega_0 s}{s^2 + \omega_0^2}$$

(2.14)

When in quadrature:

$$T. F. = \frac{\omega_o^2}{s^2 + \omega_o^2}$$

(2.15)

There is an inherent problem of resonance in using the Equations (2.14-2.15). Hence, the transfer function of the SOGI PLL can be described by adding a feedback control parameter, k as:

$$\begin{bmatrix} \nu_{\alpha}(s) \\ \nu_{\beta}(s) \end{bmatrix} = \begin{bmatrix} \frac{k\omega's}{s^2 + k\omega's + {\omega'}^2} \\ \frac{k\omega'}{s^2 + k\omega's + {\omega'}^2} \end{bmatrix} V_i(s)$$

(2.16)

where k is the control parameter usually taken as  $\sqrt{2}$  for accuracy.Now in SOGI PLL, it can be noted that there are two feedback variables. One is the output of the PI controller added to  $\omega_o$ , let us say  $\omega'$ . The other one is the output of VCO i.e.  $\theta'$ . Both the variables are of utmost importance as  $\omega'$  is used for filteration and  $\theta'$  for the Park Transform. This leads to the inference that the realization of SOGI PLL is more complicated than the other two schemes discussed in the previous sections. SOGI PLL gives us relatively good results in terms of harmonic rejection capability, therefore it can have added advantage in applications involving distorted single phase systems also.

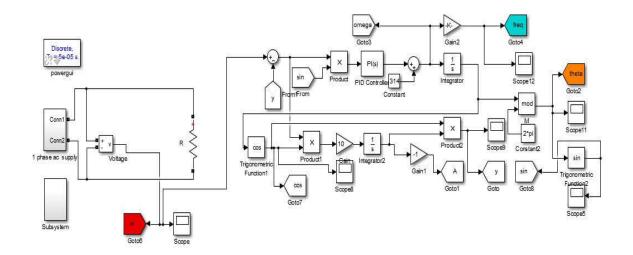

Figure 2.20 Simulation model of SOGI PLL in MATLAB/SIMULINK environment

#### 2.2.4.2 SIMULATION RESULTS

Figure 2.20 shows a simulation model of SOGI PLL in MATLAB/SIMULINK environment. In the SIMULINK model, single phase system is devised and SOGI PLL is implemented. Various changes have been made at an interval to check if the devised model shows synchronism under disturbances.

The results have been taken for frequency change, voltage amplitude change, phase angle change and effect of harmonics.

The changes have been made at intervals t = 1 s till t = 1.4 s.

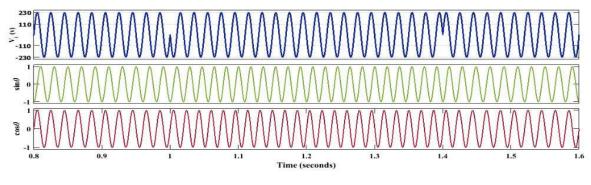

## (a) FREQUENCY CHANGES

The frequency is changed from 50 Hz to 55 Hz. It can be noted that the PLL takes nearly 3-4 cycles to settle at 55 Hz and after t = 1.4 s the frequency reaches again to 50 Hz. It can be concluded that in case of frequency deviation, the SOGI PLL is able to maintain synchronism after a few cycles.

Figure 2.21: SOGI PLL (frequency change)

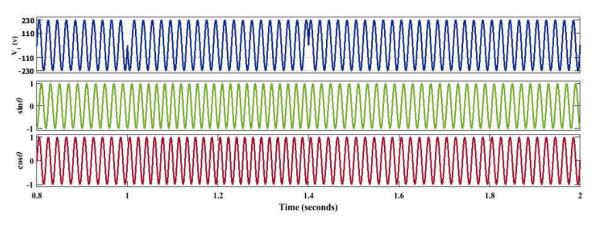

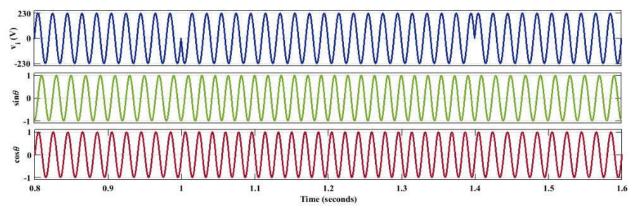

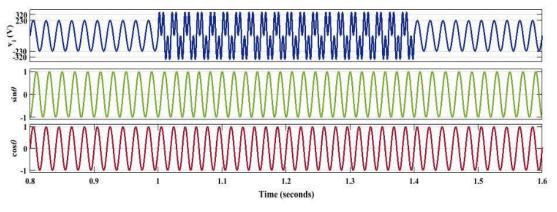

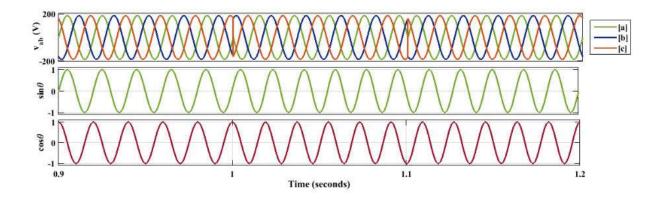

#### (b) VOLTAGE AMPLITUDE CHANGE

The voltage change has been made from 230 V to 110 V between t = 1 s till t = 1.4 s. It can be noted that the PLL tracks voltage and settles to 230 V after t = 1.4 s. The grid voltage is in phase with  $cos \theta$ .

Figure 2.22: SOGI PLL (voltage amplitude change)

# (c) PHASE ANGLE CHANGE

Phase angle change has been introduced between t = 1 s to t = 1.4 s. The grid voltage maintains synchronism and comes in phase with  $\cos \theta$  when the phase angle is again changed to 0 rad.

Figure 2.23: SOGI PLL (phase angle change)

# (d) EFFECT OF HARMONICS

Third harmonics has been introduced between t= 1 s till t= 1.4 s. It can be observed that perfect  $\sin \theta$  and  $\cos \theta$  are maintained in case of harmonics in the system.

Figure 2.24: SOGI PLL (effect of harmonics)

### 2.2.5 INVERSE PARK PLL

Inverse park PLL can be employed in single phase systems which is implemented by using park transform. The computational burden of this PLL is quite high as the transformations have to be done twice. Inverse park PLL can be categorized as a QSG based PLL as the motive of using park transform is to generate a component which is in quadrature with the grid voltage.

Figure 2.25: Schematic diagram of an Inverse Park PLL

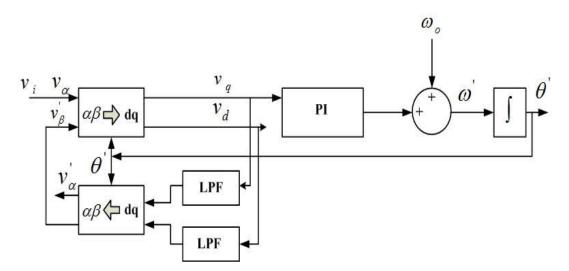

#### 2.2.5.1 ANALYSIS

In this method to build an orthogonal signal generator, which is supposed to generate the ' $\beta$ ' component, a loop consisting of direct as well as indirect Park's transform supported by two low pass filters is created [19]-[21] as shown in Fig.2.25. But here the condition is the PLL should be perfectly tuned to the input frequency to make  $v_{\alpha}$  to be in phase with  $v_{\alpha}$  and in quadrature with  $v_{\beta}$ . Also the nonlinear inner loop must be fast enough to generate the ' $\beta$ ' component. The whole technique can be described by these set of equations:

$$v_{dq}(s) = \begin{bmatrix} v_d(s) \\ v_q(s) \end{bmatrix} = T_p \begin{bmatrix} v_i(s) \\ v'_\beta(s) \end{bmatrix}$$

(2.17)

$$v_{\alpha\beta}(s) = \begin{bmatrix} v'_{\alpha}(s) \\ v'_{\beta}(s) \end{bmatrix} = T_p^{-1} \begin{bmatrix} v'_d(s) \\ v'_q(s) \end{bmatrix}$$

(2.18)

$$\begin{bmatrix} v_d'(s) \\ v_q'(s) \end{bmatrix} = G_L(s) \begin{bmatrix} v_d(s) \\ v_q(s) \end{bmatrix} = \frac{\omega}{s + \omega_L} \begin{bmatrix} v_d(s) \\ v_q(s) \end{bmatrix}$$

(2.19)

where

$$T_p$$

is

$$\begin{bmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{bmatrix}$$

(2.20)

Two LPFs are employed to filter out unwanted parts of dq components. The filtered components are used to produce the quadrature signal with respect to the grid signal. The q component is fed to the PI controller and the output of PI controller is fed to the VCO.

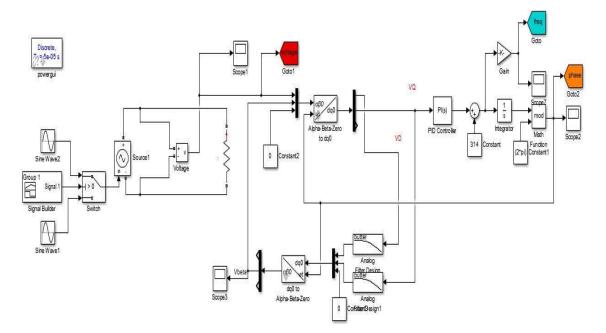

Figure 2.26 Simulation model of Inverse park PLL in MATLAB/SIMULINK environment

# 2.2.5.2 SIMULATION RESULTS

Figure 2.26 shows a simulation model of inverse park PLL in MATLAB/SIMULINK environment. In the SIMULINK model, single phase system is devised and inverse park PLL is implemented. Various changes have been made at an interval to check if the devised model shows synchronism under disturbances.

The results have been taken for frequency change, voltage amplitude change, phase angle change and effect of harmonics.

The changes have been made at intervals t = 1 s till t = 1.4 s.

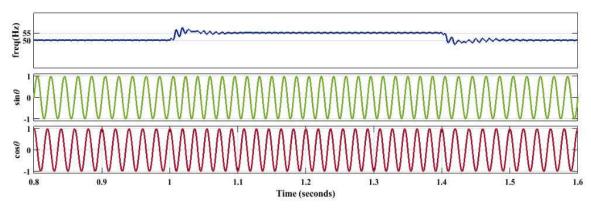

# (a) FREQUENCY CHANGE

The frequency is changed from 50 Hz to 55 Hz. It can be observed that the PLL takes nearly 6-7 cycles to settle at 55 Hz and after t = 1.4 s the frequency reaches again to 50 Hz. It can be concluded that the PLL tracks the frequency and remains in synchronism during frequency deviation.

Figure 2.27: Inverse park PLL (frequency change)

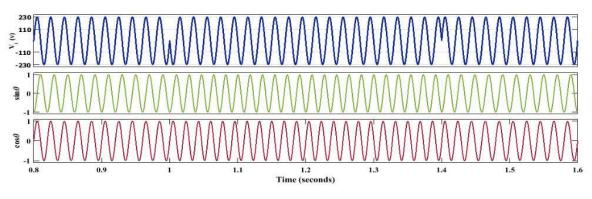

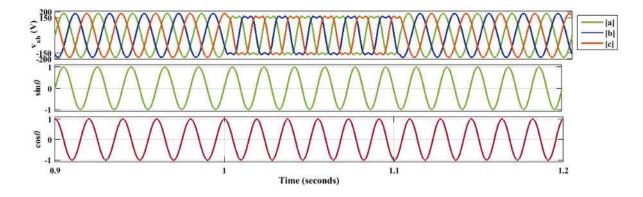

# (b) VOLTAGE AMPLITUDE CHANGE

The voltage change has been made from 230 V to 110 V between t = 1 s till t = 1.4 s. It can be noted that the PLL tracks voltage and settles to 230 V after t = 1.4 s. The grid voltage is in synchronism with sin  $\theta$ .

Figure 2.28: Inverse park PLL (voltage amplitude change)

# (c) PHASE ANGLE CHANGE

Phase angle change has been introduced between t = 1 s to t = 1.4 s. Phase angle has been changed from 0 rad to pi rad. The grid voltage maintains synchronism and comes in phase with sin  $\theta$  when the phase angle is again changed to 0 rad.

Figure 2.29: Inverse park PLL (phase angle change)

# (d) EFFECT OF HARMONICS

Third harmonics has been introduced between t= 1 s till t= 1.4 s. It can be observed that perfect sin  $\theta$  and cos  $\theta$  are maintained in case of harmonics in the system.

Figure 2.30: Inverse park PLL (effect of harmonics)

# 2.2.6 POWER PLL (pPLL)

pPLL is one of the simplest PLL techniques for synchronization. There has been ample amount of research on pPLL [22]-[25]. pPLL is one of the oldest methods used for synchronization.

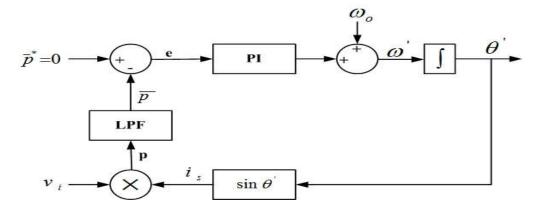

Figure 2.31: Schematic diagram of pPLL

#### 2.2.6.1 ANALYSIS

The input voltage and  $\sin \theta$  are multiplied which gives us the power. This power is fed to a low pass filter which is used to extract mean power  $(\overline{p})$ , which is the first term of the equation (2.23) i.e.  $\overline{p} = \frac{v}{2} \sin(\theta' - \theta)$ .

Let

$$v_i = V \cos\theta$$

(2.21)

$$p = V\cos\theta\sin\theta' \tag{2.22}$$

$$p = \frac{v}{2}\sin(\theta' - \theta) + \frac{v}{2}\sin(\theta' + \theta)$$

(2.23)

Suppose  $\theta = \omega t + \emptyset$ ;  $\theta' = \omega' t + \emptyset'$  and  $\omega' \cong \omega$ ; for small phase differences  $\emptyset - \emptyset'$ ,  $\overline{p}$  can be estimated as:

$$\bar{p} = \frac{v}{2}(\phi' - \phi) \tag{2.24}$$

The above equation demonstrates the small signal static Phase detector gain. If we consider only a slight difference variation between  $\theta$  and  $\theta'$ , equation (2.23) can be segregated into two parts:

$$\frac{v}{2}\sin(\theta'-\theta) \tag{2.25}$$

which is a minute dc term and provides information about the phase difference between input signal and the output signal.

and

$$\frac{V}{2}\sin(\theta' + \theta) \tag{2.26}$$

which is a double frequency disturbance term comprising of high-amplitude. It is extremely important to filter this double frequency component to keep up the phase jittering within an acceptable range. To cancel out the undesired double-frequency component from the fictitious power p, one can use either a first- (or second-) order LPF with a low cutoff frequency or a high-order LPF with a higher cutoff frequency. In addition to stability problems, using a high-order LPF imposes a high computational load on the control system. On the other hand, using a low-order LPF with a low cutoff frequency, significantly degrades the transient performance of the PLL. Another approach is to use a notch filter tuned at twice the input voltage fundamental frequency. Because of the grid frequency variations, the notch filter should be adaptive, which increases the system cost and complexity. Some improvements to the pPLL have been suggested in [7]-[21]. In these techniques, referred to as orthogonal signal generation (OSG)-based techniques, the fundamental component of the input voltage is shifted by 90° to generate a fictitious phase signal, thus making it possible to represent the single phase system as a pseudo two-phase ( $\alpha\beta$ ) system. Applying the wellknown park ( $\alpha\beta \rightarrow dq$ ) transformation to the two phase ( $\alpha\beta$ ) system, yields the phase error information without generating the undesired double-frequency component. It should be noticed that the main difference among different OSG-based techniques lies in how the fictitious orthogonal signal is generated. In spite of their differences, all OSG-based techniques suffer from some common drawbacks, such as high sensitivity to the grid frequency variations, and relatively high complexity. To filter out the undesired steady-state double-frequency oscillations without degrading the stability and the transient performance of the PLL and, at the same time, to compensate for the input voltage amplitude variations, an effective method, called the DFAC method, is presented in the next section.

Figure 2.32 Simulation model of pPLL in MATLAB/SIMULINK environment

#### **2.2.6.2 SIMULATION RESULTS**

Figure 2.32 shows a simulation model of pPLL in MATLAB/SIMULINK environment. In the SIMULINK model, single phase system is devised and pPLL is implemented. Various changes have been made at an interval to check if the devised model shows synchronism under disturbances.

The results have been taken for frequency change, voltage amplitude change, phase angle change and effect of harmonics.

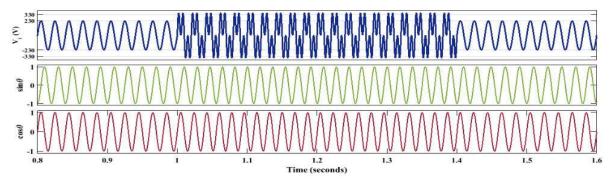

# (a) FREQUENCY CHANGE

The frequency is changed from 50 Hz to 55 Hz. It can be noted that the PLL takes nearly 6-7 cycles to settle at 55 Hz and after t = 1.4 s the frequency reaches again to 50 Hz. It can be concluded that the PLL tracks the frequency and remains in synchronism during frequency deviation.

Figure 2.33: pPLL (frequency change)

## (b) VOLTAGE AMPLITUDE CHANGE

The voltage change has been made from 230 V to 110 V between t = 1 second till t = 1.4 s. It can be noted that the PLL tracks voltage and settles to 230 V after t = 1.4 s.

Figure 2.34: pPLL (voltage amplitude change)

#### (c) PHASE ANGLE CHANGE

Phase angle change has been introduced between t = 1 s to t = 1.4 s. Phase angle has been changed from 0 radians to pi radians. The grid voltage maintains synchronism and comes in phase with  $\cos \theta$  when the phase angle is again changed to 0 rad.

Figure 2.35: pPLL (phase angle change)

# (d) EFFECT OF HARMONICS

Third harmonics has been introduced between t= 1 s till t= 1.4 s. It can be observed that perfect sin  $\theta$  and cos  $\theta$  are maintained in case of harmonics in the system.

Figure 2.36: pPLL (effect of harmonics)

# 2.2.7 DOUBLE FREQUENCY AMPLITUDE COMPENSATION (DFAC) PLL

DFAC PLL is an advancement over conventional pPLL. The main advantage of having a DFAC PLL is that is eliminates the double frequency term which is associated with the conventional pPLL technique [26]-[27].

Figure 2.37: Schematic diagram of DFAC PLL

# 2.2.7.1 ANALYSIS

Fig.2.37 displays the basic scheme of the proposed phase detection unit, where  $v_d$  and  $v_q$  are obtained as expressed in the following equation:

$$\begin{bmatrix} v_d(t) \\ v_q(t) \end{bmatrix} = \begin{bmatrix} \cos\theta' & \sin\theta' \\ -\sin\theta' & \cos\theta' \end{bmatrix} \begin{bmatrix} 2v_i(t) \\ 0 \end{bmatrix}$$

(2.27)

Substituting  $v_i = V \cos \theta$  into equation (2.27)

$$v_d(t) = V\cos(\theta - \theta') + V\cos(\theta + \theta')$$

(2.28)

$$v_q(t) = V \sin(\theta - \theta') - V \sin(\theta + \theta')$$

(2.29)

Considering  $\theta_e = \theta - \theta'$  and after some simple mathematical manipulations, equations (2.28) and (2.29) can be written as :

$$v_d(t) = V\cos(\theta_e) + V\cos(2\theta' + \theta_e)$$

(2.30)

$$v_q(t) = Vsin(\theta_e) - Vsin(2\theta' + \theta_e)$$

(2.31)

Expanding the  $2^{nd}$  terms on the right hand side of the equations (2.30) and (2.31), yields:

$$v_d(t) = V\cos(\theta_e) + V\cos(\theta_e)\cos(2\theta') - V\sin(\theta_e)\sin(2\theta')$$

(2.32)

$$v_a(t) = V \sin(\theta_e) - V \sin(\theta_e) \cos(2\theta') - V \cos(\theta_e) \sin(2\theta')$$

(2.33)

For a small angle difference  $\theta_e$ , the first terms on the right hand side of the equations (2.32) and (2.33) (i.e.,  $V \cos(\theta_e)$ , and  $V \sin(\theta_e)$  respectively) are almost dc components. It is also clear from the equations (2.32) and (2.33) that the amplitudes of the double-frequency components depend on these dc components. Thus, the perfect cancellation of the undesired double-frequency components can be easily achieved by injecting double-frequency signals with the same amplitude but an opposite angle into  $v_d$  and  $v_q$ , as shown in Fig 2.37. The proposed DFAC strategy consists of two main parts: a double-frequency cancellation block, and an amplitude compensation block. The low pass filter (LPF) block is considered as a first-order filter.

The LPF is as follows:

$$LPF(s) = \frac{\omega_p}{s + \omega_p} \tag{2.34}$$