# DESIGN AND IMPLEMENTATION OF ANALOG CIRCUITS USING CURRENT MODE BUILDING BLOCKS

**A THESIS**

SUBMITTED TO THE DELHI TECHNOLOGICAL UNIVERSITY

FOR THE AWARD OF THE DEGREE OF

## **DOCTOR OF PHILOSOPHY**

IN

## **Electronics and Communication Engineering**

SUBMITTED BY

**DEVA NAND**

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

DELHI- 110042 (INDIA)

2018

# DESIGN AND IMPLEMENTATION OF ANALOG CIRCUITS USING CURRENT MODE BUILDING BLOCKS

BY

## **DEVA NAND**

SUBMITTED TO THE DELHI TECHNOLOGICAL UNIVERSITY IN PARTIAL FULFILMENTS OF THE REQUIREMENTS FOR THE DEGREE OF

## DOCTOR OF PHILOSOPHY

IN

## ELECTRONICS AND COMMUNICATION ENGINEERING

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

DELHI- 110042 (INDIA)

2018

**CANDIDATE DECLARATION**

I hereby certify that the research work which is being presented in this thesis entitled

"Design and Implementation of analog circuits using current mode building blocks"

in fulfilment of requirements of the award of degree of Doctor of Philosophy, is an

authentic record of my own research work carried out under the supervision of Prof. Neeta

Pandey.

The matter presented in this thesis has not been submitted elsewhere in part or fully

to any other University or Institute for award of any degree.

**Deva Nand**

2K11/PhD/EC/07

Department of Electronics and Communication Engineering

Delhi Technological University

Delhi, India-110042.

i

**CERTIFICATE**

This is to certify that the thesis entitled "Design and Implementation of analog circuits

using current mode building blocks" being submitted by Mr. Deva Nand (Reg. No.:

2K11/PhD/EC/07) for the award of degree of Doctor of Philosophy to the Delhi

Technological University is based on the original research work carried out by him. He has

worked under my supervision and has fulfilled the requirements that to our knowledge have

reached the requisite standard for the submission of this thesis. It is further certified that

the work embodied in this thesis has neither partially nor fully submitted to any other

university or institution for the award of any degree or diploma.

**Prof. Neeta Pandey**

(Supervisor)

Department of Electronics and Communication Engineering

Delhi Technological University, Delhi

India-110042

ii

**ACKNOWLEDGEMENT**

I owe my debt and would like to express deep feelings of gratitude to accomplish the

research program with the support and direction of several persons. This challenging and

rewarding experience definitely helped me to grow in character as well as academically. It

is a pleasant aspect that I have now the opportunity to express my gratitude for all of them.

First and foremost, I would like to thank my supervisor, Prof. Neeta Pandey for

insightful advices, conversations and suggestions during PhD work. Her support and trust,

together with genuine interest in the research subject, turned my research work into a great

experience. Words cannot express my gratitude to her for her patience and support.

Special thanks to DRC chairman/HOD, ECE Prof. S. Indu and Dean academics

(PG) Prof. H. C. Taneja for all the administrative support that made the journey smoother.

Heartfelt thanks to Prof. Rajeshwari Pandey for her unconditional support, discussions and

encouragement all the time. Words cannot express my gratitude to her. I will be thankful

to my colleagues for all their helps and comments throughout. I wish to pay high regards

to my parents, in-laws, my wife and my children for their invaluable support, best wishes

and encouragements.

Last but not least, I would like to thanks my all faculty colleague and friends who

supported me during this period directly or indirectly.

Date:

(Deva Nand)

Place: Delhi

iii

## **ABSTRACT**

Rapid advancements in semiconductor technology has made integration of millions of transistors on a single die. The analog – digital boundaries are diminishing and integrated solutions for complete system are in vogue where both analog and digital subsystems are placed on single die. Though in last two decades' electronic circuit design has a paradigm shift from analog to digital domain yet analog circuit design is going to remain in mainstay. For signal acquisition and processing, amplifiers, filters, sample and hold circuits, signal comparators, analog to digital converter (ADC) and digital to analog converter (DAC) are required. Further, new applications continue emerging and require high performance analog interface circuits.

There are challenges in designing analog circuits due to continual scaling of device dimensions and also the power supply voltages. The lowering in power supply lead to reduction in input common mode range, linearity and output voltage swing. It is well known that signal processing may be done by manipulating node voltages or branch currents. The analog circuits are termed as voltage mode (VM) or current mode (CM) if the information medium is represented by the nodal voltages or branch currents. The performance parameters of VM circuits such as dynamic range, slew rate and common mode range are severely affected by scaling. The CM circuits show advantageous features such as improved slew rate due to smaller time constant, wider bandwidth, as transistors in current amplifiers may be used till unity gain bandwidth. Further as current depends nonlinearly on voltage, a smaller voltage swing allows larger current change, thus improving dynamic range. Further, these circuits may be compact as addition of current can done by simply joining branches. To exploit the advantages of CM signal processing, a wide variety of analog building blocks have been developed. Operational floating current conveyor (OFCC) is one

among these building block which combines the features of current conveyor and the current feedback operational amplifier along with additional current outputs that adds flexibility in the circuit design. It can readily be used for processing and providing both current and voltage at appropriate impedance levels.

Numerous OFCC based signal processing applications such as basic amplifiers, filters, oscillators, instrumentation amplifiers (IAs), variable/programmable gain amplifiers (VGA/PGA), read out circuits, wheat-stone bridge and logarithmic amplifier, as available in open literature. The main focus of the work presented in this thesis is to develop circuits which are more versatile, modular, integrable and can provide better quality response.

A first order Transadmittance mode (TAM) filters is presented that processes signal from voltage sensor and provide current output for further processing. It provides three responses i.e. low pass, high pass and all pass at high impedance. A feature that is gainfully used for developing an oscillator without using any extra active blocks. Second order CM SIMO filter is put forward that can provide low pass, high pass, band pass and notch responses simultaneously. The filter parameters can be adjusted independently. As an application a CM shadow bandpass filter is developed for controlling filter parameters through an amplifier gain. Electronic tunability of filter parameters is achieved via MOS based resistors.

Instrumentation amplifier (IA) is widely used in applications pertaining to medical instrumentation, sensor read out integrated circuits, data acquisition systems, industrial process control, automotive transducers, bio-potential acquisition systems and linear position sensing. Two generalized structure of IA is put forward and its usefulness is shown through OFCC. These structures are termed as: Structure-I and Structure-II. Each structure is used to generate IA topologies operating in VM, CM, TIM and TAM, thus eight IAs are generated in total. A

modification to Structure I and Structure II are suggested to obtain IA topologies with reduced resistor count. Considering the modifications, six more topologies are put forward. The input and output impedance of all proposed topologies are proper therefore no additional active block is needed for interfacing.

Amplifiers, in particular PGA, find applications in instrumentation, photodiode circuits, ultrasound preamplifiers, sonar, wide dynamic range sensors, driving ADCs and automatic gain control (AGC) loops. A new OFCC based PGA is the key contribution towards such amplifiers which offers programmable gain feature.

The rectifiers are widely used in applications pertaining to telecommunication, instrumentation and measurement. OFCC based CM half wave rectifiers (HWRs) and full wave rectifier (FWR) are put forward. These rectifiers do not use diode and are thus suitable for low voltage rectification. It is pertinent to mention here that all proposed rectifiers use single active block and are resistor-less.

The behavior of all the proposed circuits under the influence of nonidealities of OFCC is also examined. The functionality of proposed circuits is verified through SPICE simulations and/or through experimental observations.

## TABLE OF CONTENT

| CANDIDATE DECLARATION                                                                                                                                                                                                                                                                                   | i        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| CERTIFICATE                                                                                                                                                                                                                                                                                             | ii       |

| ACKNOWLEDGEMENT                                                                                                                                                                                                                                                                                         | iii      |

| ABSTRACT                                                                                                                                                                                                                                                                                                | iv       |

| TABLE OF CONTENT                                                                                                                                                                                                                                                                                        | vii      |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                         | X        |

| LIST OF TABLES                                                                                                                                                                                                                                                                                          |          |

| CHAPTER 1 INTRODUCTION                                                                                                                                                                                                                                                                                  | 1        |

| CHAPTER I INTRODUCTION                                                                                                                                                                                                                                                                                  | 1        |

| 1.1 Background                                                                                                                                                                                                                                                                                          | 3        |

| 1.2 Available literature and scope of work                                                                                                                                                                                                                                                              | 5<br>11  |

| CHAPTER 2 CURRENT MODE BUILDING BLOCK                                                                                                                                                                                                                                                                   | 13       |

| 2.1 Introduction                                                                                                                                                                                                                                                                                        | 15       |

| 2.2 Operational floating current conveyor                                                                                                                                                                                                                                                               | 16       |

| 2.3 Effect of nonidealities                                                                                                                                                                                                                                                                             | 16       |

| 2.3.1 Effect of finite transimpedance gain                                                                                                                                                                                                                                                              |          |

| 2.5.1 Effect of finite transmipedance gain                                                                                                                                                                                                                                                              |          |

| 2.3.2 Effect of voltage and current tracking errors                                                                                                                                                                                                                                                     | 17       |

| 2.3.2 Effect of voltage and current tracking errors 2.4 OFCC realization                                                                                                                                                                                                                                | 17<br>18 |

| 2.3.2 Effect of voltage and current tracking errors 2.4 OFCC realization                                                                                                                                                                                                                                |          |

| 2.3.2 Effect of voltage and current tracking errors 2.4 OFCC realization                                                                                                                                                                                                                                |          |

| 2.3.2 Effect of voltage and current tracking errors 2.4 OFCC realization                                                                                                                                                                                                                                |          |

| 2.3.2 Effect of voltage and current tracking errors.  2.4 OFCC realization.  2.4.1 CMOS based implementation.  2.4.2 CFOA based implementation.  2.5 Basic applications of OFCC.  2.5.1 Voltage amplifier.                                                                                              |          |

| 2.3.2 Effect of voltage and current tracking errors.  2.4 OFCC realization.  2.4.1 CMOS based implementation.  2.4.2 CFOA based implementation.  2.5 Basic applications of OFCC.  2.5.1 Voltage amplifier.  2.5.2 Current amplifier.                                                                    |          |

| 2.3.2 Effect of voltage and current tracking errors.  2.4 OFCC realization.  2.4.1 CMOS based implementation.  2.4.2 CFOA based implementation.  2.5 Basic applications of OFCC.  2.5.1 Voltage amplifier.  2.5.2 Current amplifier.  2.5.3 Transadmittance amplifier.                                  |          |

| 2.3.2 Effect of voltage and current tracking errors.  2.4 OFCC realization.  2.4.1 CMOS based implementation.  2.4.2 CFOA based implementation.  2.5 Basic applications of OFCC.  2.5.1 Voltage amplifier.  2.5.2 Current amplifier.  2.5.3 Transadmittance amplifier.  2.5.4 Transimpedance amplifier. |          |

| 2.3.2 Effect of voltage and current tracking errors.  2.4 OFCC realization.  2.4.1 CMOS based implementation.  2.4.2 CFOA based implementation.  2.5 Basic applications of OFCC.  2.5.1 Voltage amplifier.  2.5.2 Current amplifier.  2.5.3 Transadmittance amplifier.                                  |          |

| CHAPTER 3 OFCC BASED TA MODE FIRST ORDER FILTER           | 33           |

|-----------------------------------------------------------|--------------|

| 3.1 Introduction                                          | 35           |

| 3.2 Literature review                                     |              |

| 3.3 Proposed first order TAM filter                       | 37           |

| 3.3.1 Filter structure                                    |              |

| 3.3.2 Non ideal analysis                                  |              |

| 3.3.2.1 Finite transimpedance gain                        |              |

| 3.3.2.2 Tracking error                                    |              |

| 3.3.3 Filter application                                  |              |

| 3.4 Simulation results.                                   |              |

| 3.5 Concluding remarks                                    |              |

| CHAPTER 4 OFCC BASED CM SECOND ORDER FILTER               | 49           |

| 4.1 Introduction                                          | 51           |

| 4.2 Literature review of CM SIMO filters                  |              |

| 4.3 Proposed CM SIMO filter                               | 54           |

| 4.3.1 Proposed OFCC based CM SIMO Filter                  |              |

| 4.3.2 Non ideal analysis                                  |              |

| 4.3.2.1 Effect of finite transimpedance gain              |              |

| 4.3.2.2 Effect of tracking errors                         | 57           |

| 4.3.2.3 Effect of parasites                               |              |

| 4.4 Proposed OFCC based CM shadow band pass filter        |              |

| 4.5 Simulation results                                    |              |

| 4.6 Concluding remarks.                                   |              |

| CHAPTER 5 OFCC BASED INSTRUMENTATION AMPLIFIER            | 71           |

| 5.1 Introduction                                          | 73           |

| 5.2 Literature review.                                    |              |

| 5.3 Proposed generalized IA structures                    |              |

| 5.3.1 Proposed generalized IA structures                  |              |

| 5.3.2 IA topologies derived from Structure I              |              |

| 5.3.3 IA topologies derived from Structure II             |              |

| 5.3.4 Non ideal analysis                                  |              |

| 5.3.4.1 Effect of the finite transimpedance gain          |              |

| 5.3.4.2 Tracking errors                                   |              |

| 5.3.5 Simulation results                                  |              |

| 5.3.6 Experimental results                                |              |

| 5.4 OFCC based IA topologies with reduced component count |              |

| 5.4.1 IA topologies derived from modified Structure I     |              |

| 5.4.2 IA topologies derived from modified Structure II    |              |

| 5.4.3 Non ideal analysis                                  |              |

| 5.4.4 Simulation results.                                 |              |

| V. I. I DIIIIMMUUI I VUUIUU                               | , <i>.</i> O |

| 5.5 Performance comparison                     | 98    |

|------------------------------------------------|-------|

| 5.6 Concluding remarks                         |       |

| CHAPTER 6 OFCC BASED TRANSIMPEDANCE MODE PO    | GA103 |

| 6.1 Introduction                               | 105   |

| 6.2 Literature survey                          | 106   |

| 6.3 Proposed OFCC based PGA                    | 108   |

| 6.4 Simulation and Experimental results        | 112   |

| 6.4.1 Simulation results                       | 112   |

| 6.4.2 Experimental results                     | 116   |

| 6.5 Concluding remarks                         | 117   |

| CHAPTER 7 OFCC BASED CM RECTIFIER              | 119   |

| 7.1 Introduction                               | 121   |

| 7.2 Literature survey                          |       |

| 7.3 Proposed OFCC based rectifiers             |       |

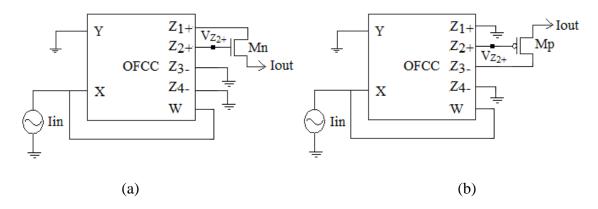

| 7.3.1 Proposed CM HWRs                         |       |

| 7.3.2 Proposed CM FWR                          |       |

| 7.4 Simulation results                         |       |

| 7.5 Concluding remarks                         |       |

| CHAPTER 8 CONCLUSION AND FUTURE SCOPE          | 133   |

| 8.1 Conclusion.                                | 135   |

| 8.2 Summary of work carried out in this thesis |       |

| 8.3 Future scope                               |       |

| REFERENCES                                     | 141   |

| LIST OF PUBLICATIONS                           | 159   |

| AUTHOR'S BIOGRAPHY                             | 161   |

## LIST OF FIGURES

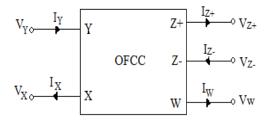

| Fig. 2.1 OFCC Circuit symbol.                                                           | 16 |

|-----------------------------------------------------------------------------------------|----|

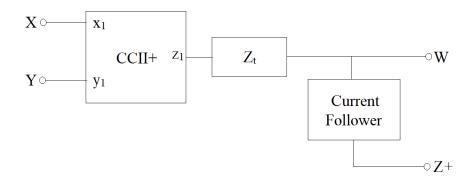

| Fig. 2.2 Implementation scheme for OFCC block [13]                                      | 19 |

| Fig. 2.3 CMOS schematic of OFCC block [13]                                              | 19 |

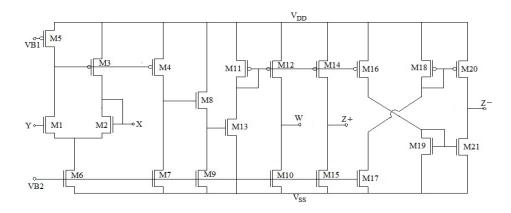

| Fig. 2.4 Frequency response of (a) current transfer (b) voltage transfer                |    |

| characteristics of OFCC                                                                 | 20 |

| Fig. 2.5 (a) Circuit symbol of AD844 [170] (b) AD844 based                              |    |

| OFCC implementation                                                                     | 21 |

| Fig. 2.6 Voltage amplifier using OFCC.                                                  | 22 |

| Fig. 2.7 Frequency response of voltage amplifier                                        | 23 |

| Fig. 2.8 Current amplifier using OFCC                                                   | 23 |

| Fig. 2.9 Frequency response of current amplifier                                        | 24 |

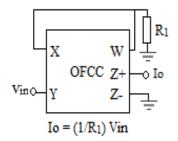

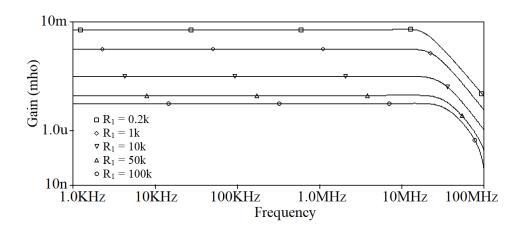

| Fig. 2.10 Transadmittance amplifier                                                     | 25 |

| Fig. 2.11 Frequency response of transadmittance amplifier                               | 26 |

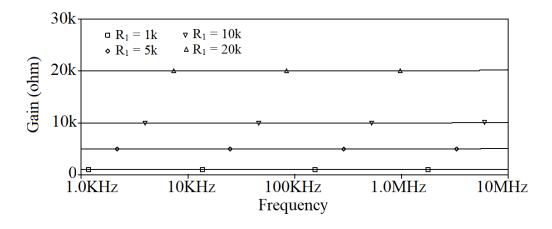

| Fig. 2.12 Transimpedance amplifier                                                      | 26 |

| Fig. 2.13 Frequency response of transimpedance amplifier                                | 27 |

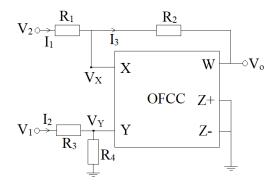

| Fig. 2.14 Voltage Difference Amplifier.                                                 | 29 |

| Fig. 2.15 Frequency response of voltage difference amplifier with (a) gain=1 (b) gain=5 | 30 |

| Fig. 2.16 MOS based resistor implementation [169]                                       | 31 |

| Fig. 3.1 TA mode first order filter circuit.                                            | 38 |

| Fig. 3.2 Proposed filter (a) with integrator (b) as an oscillator                       | 43 |

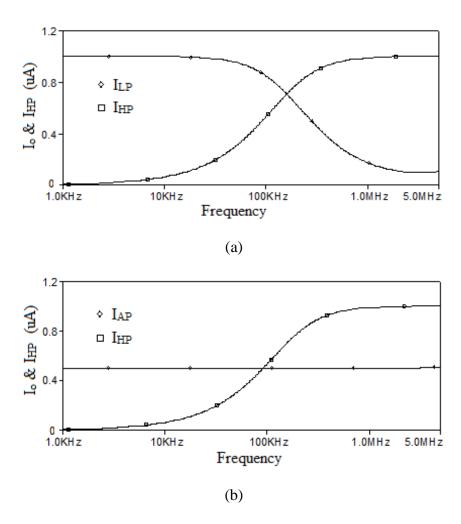

| Fig.3.3 Frequency response of first order (a) LP and HP (b) AP and HP filter            | 44 |

| Fig. 3.4 Phase response of first order AP filter.                                       | 44 |

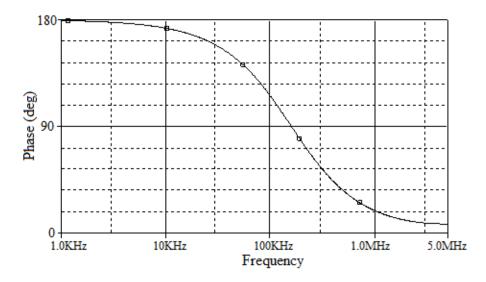

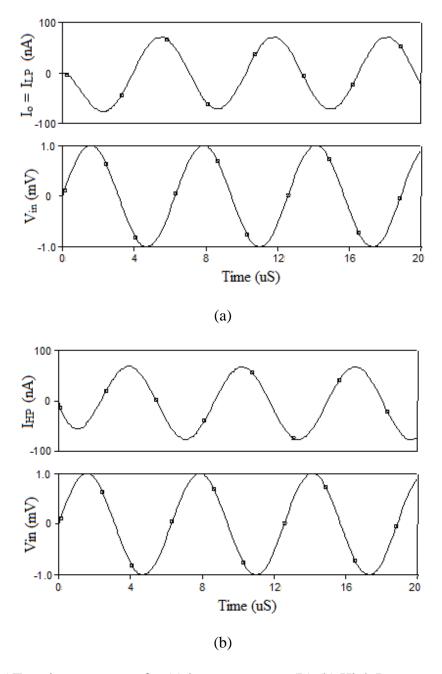

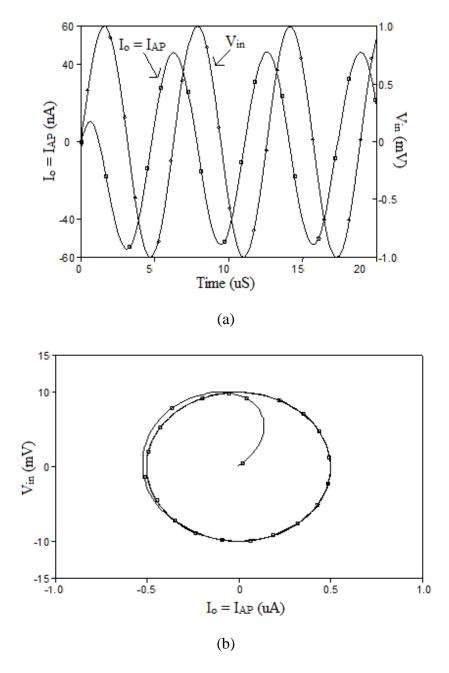

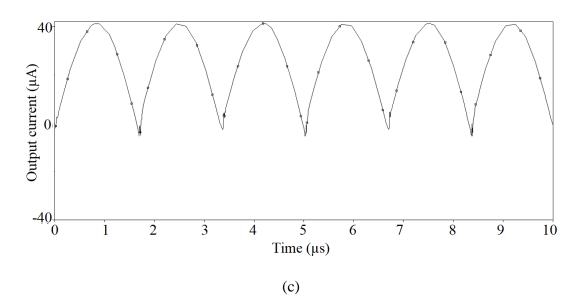

| Fig.3.5 Transient responses for (a) low pass output $(I_0)$ (b) High Pass output $(I_{HP})$ 4 | 5 |

|-----------------------------------------------------------------------------------------------|---|

| Fig. 3.6 (a) Transient response and (b) corresponding Lissagous figure for all pass filter4   | 6 |

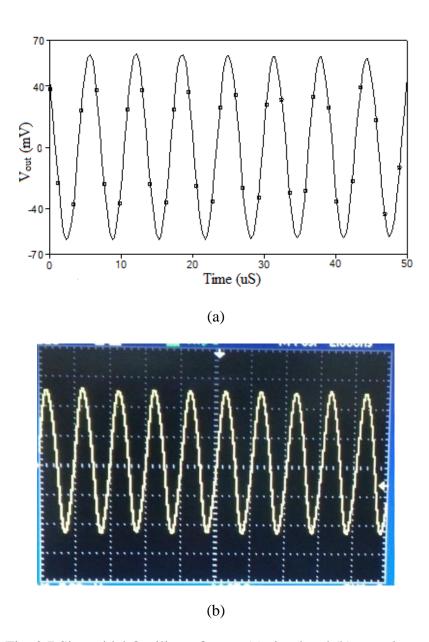

| Fig. 3.7 Sinusoidal oscillator output (a) simulated (b) experimental                          | 7 |

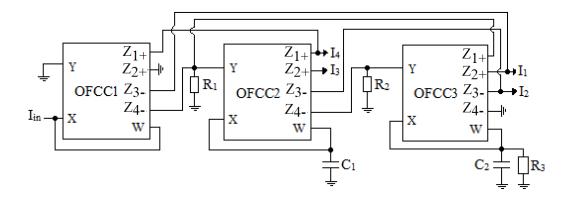

| Fig. 4.1 Proposed OFCC based CM SIMO Filter5                                                  | 4 |

| Fig. 4.2 Proposed OFCC based CM SIMO filter with parasites                                    | 8 |

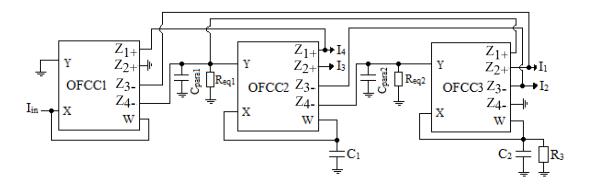

| Fig.4.3 (a) Generalized scheme of shadow filter [81], (b) Proposed OFCC based                 |   |

| CM shadow band pass filter60                                                                  | 0 |

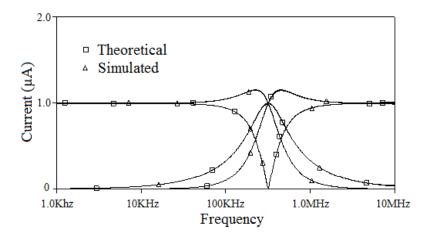

| Fig. 4.4 Theoretical and simulated responses of CM SIMO filter                                | 3 |

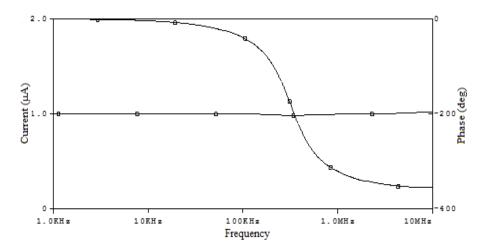

| Fig. 4.5 Simulated magnitude and phase plots of all pass response                             | 4 |

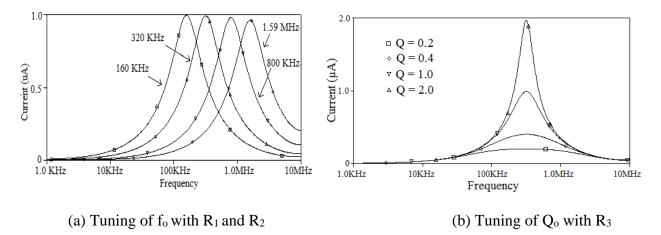

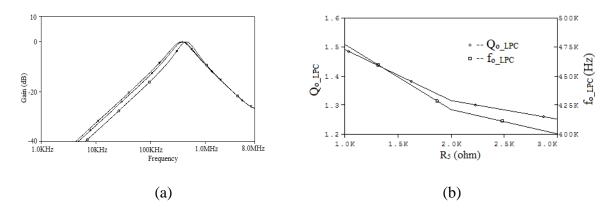

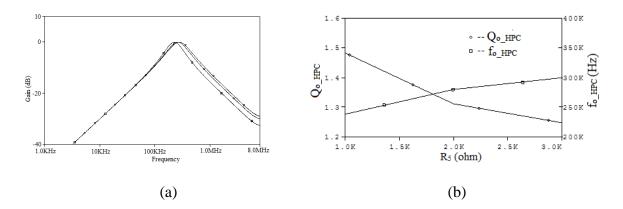

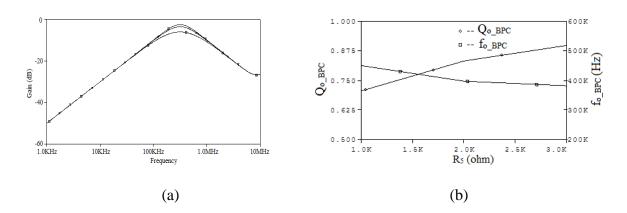

| Fig. 4.6 Tuning of fo and Qo6                                                                 | 5 |

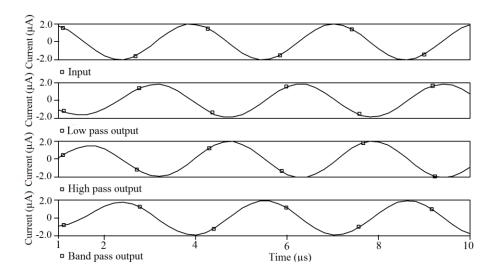

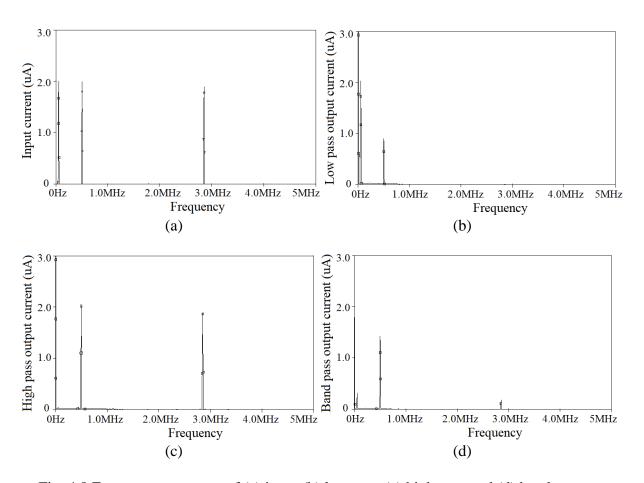

| Fig. 4.7 Transient responses for Sinusoidal current input of 2μA, 500 KHz6                    | 5 |

| Fig. 4.8 Frequency spectrum of (a) input (b) low pass (c) high pass and                       |   |

| (d) band pass output6                                                                         | 6 |

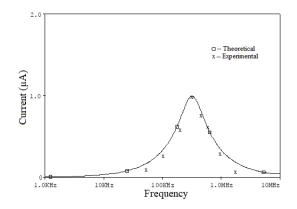

| Fig. 4.9 Simulated and experimental bandpass frequency response                               | 6 |

| Fig. 4.10 LP controlled shadow BP response                                                    | 7 |

| Fig. 4.11 HP controlled shadow BP response                                                    | 8 |

| Fig. 4.12 BP controlled shadow BP response                                                    | 8 |

| Fig. 4.13 LP controlled shadow BP response with bandwidth (BW_LPC)                            |   |

| independent of $\omega_{o\_LPC}$ and $Q_{o\_LPC}$ 6                                           | 8 |

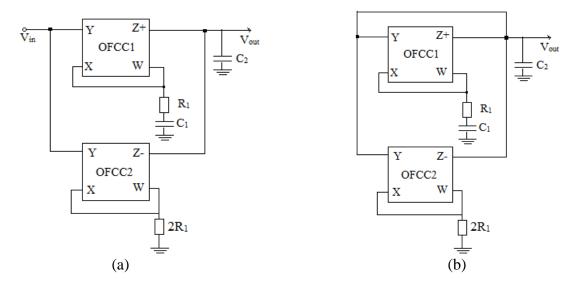

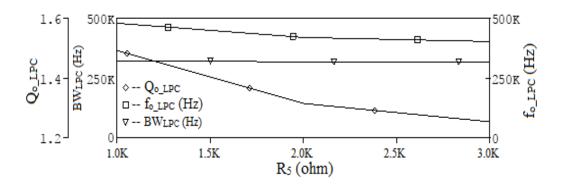

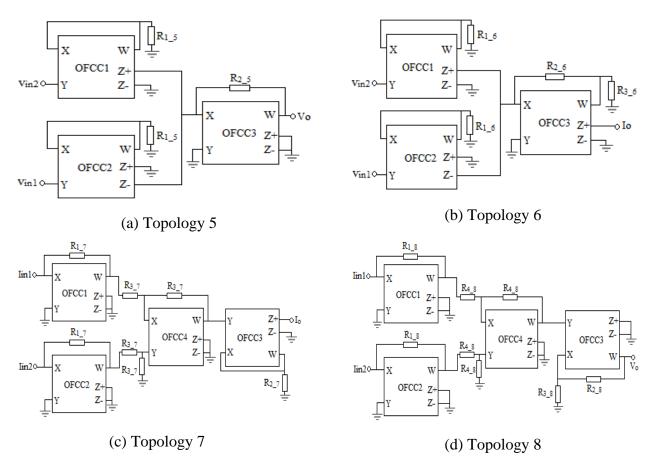

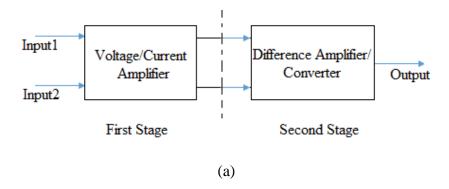

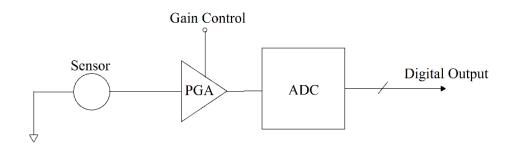

| Fig. 5.1 Generalized Block Diagrams (a) Structure I (b) Structure II                          | 6 |

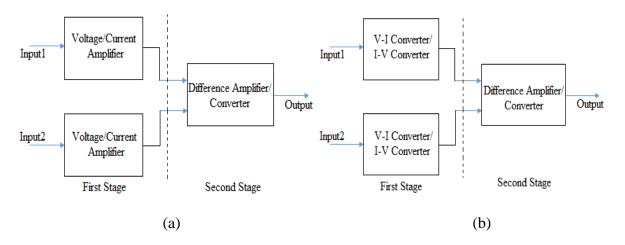

| Fig 5.2 Proposed (a) VM (b) TAM (c) CM and (d) TIM IA topologies generated                    |   |

| from Structure I7                                                                             | 8 |

| Fig 5.3 Proposed (a) VM (b) TAM (c) CM and (d) TIM IA topologies generated       |

|----------------------------------------------------------------------------------|

| from Structure II79                                                              |

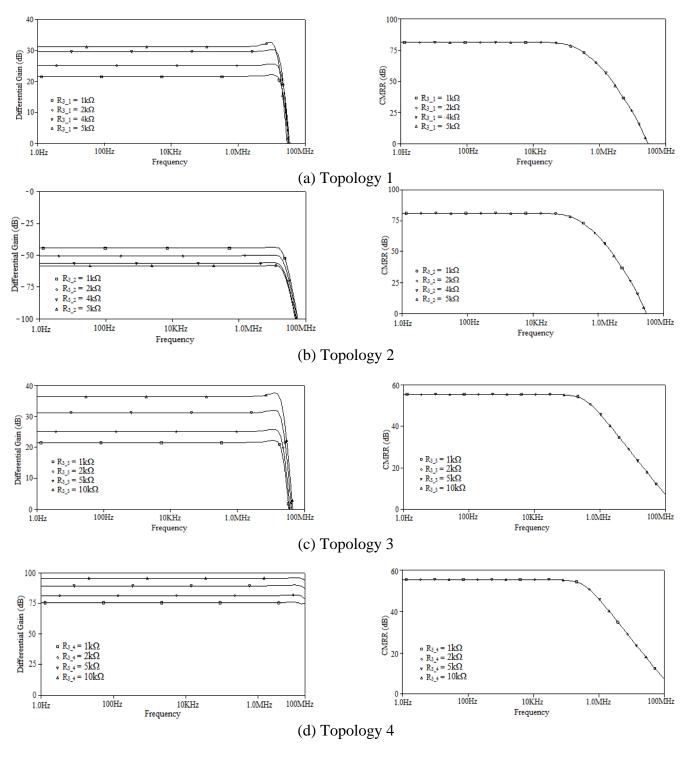

| Fig. 5.4 Simulated frequency responses for differential gain and CMRR for        |

| (a) topology 1 (b) topology 2 (c) topology 3 (d) topology 486                    |

| Fig. 5.5 Simulated frequency responses for differential gain and CMRR for        |

| (a) topology 5 (b) topology 6 (c) topology 7 (d) topology 8                      |

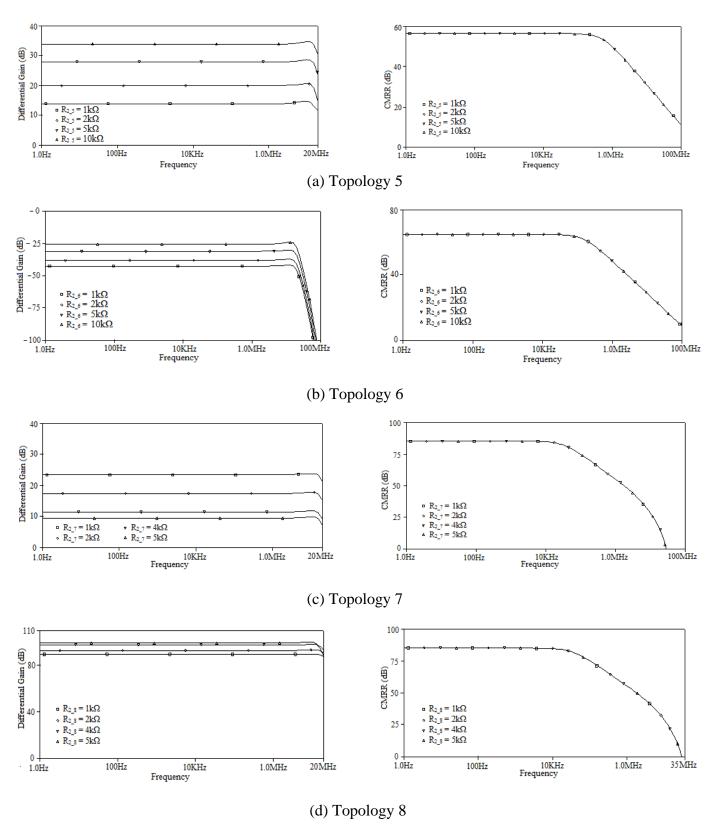

| Fig. 5.6 Observed output responses for input frequencies (a) 100 KHz (b) 1 MHz89 |

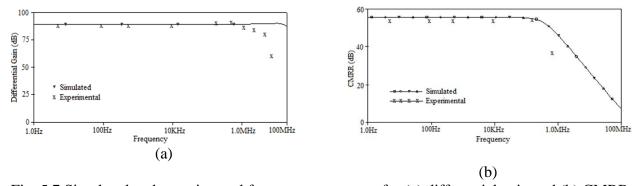

| Fig. 5.7 Simulated and experimental frequency responses for                      |

| (a) differential gain and (b) CMRR89                                             |

| Fig. 5.8 Generalized block diagram of IAs (a) modified Structure I               |

| (b) modified Structure II91                                                      |

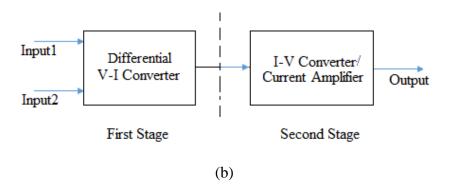

| Fig. 5.9 Proposed (a) VM (b) TAM (c) CM and (d) TIM IA topologies generated      |

| from Structure I91                                                               |

| Fig. 5.10 Proposed (a) VM (b) TAM IA topologies generated from Structure II93    |

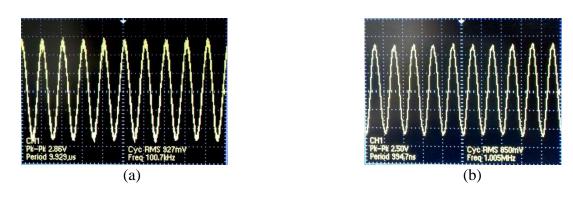

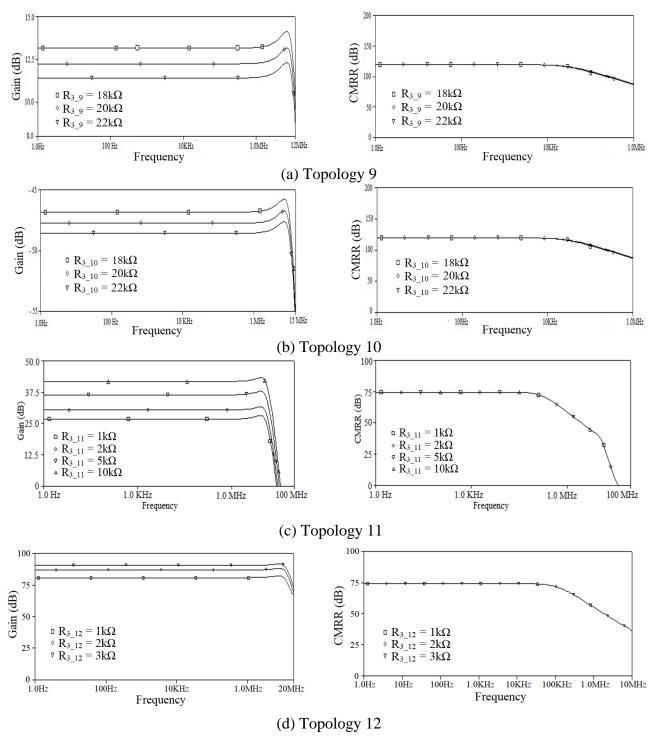

| Fig. 5.11 Simulated frequency responses for differential gain and CMRR for       |

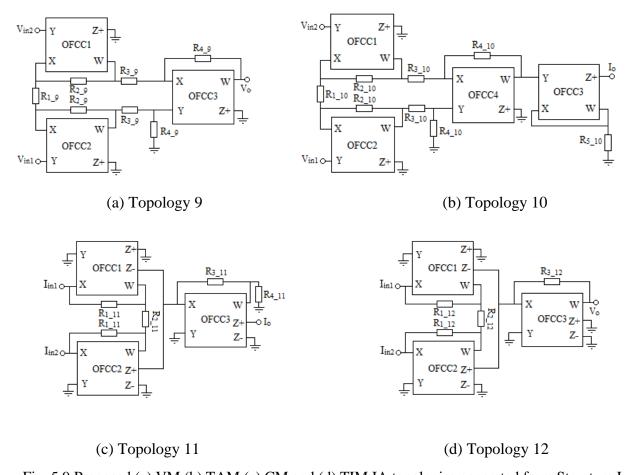

| (a) topology 9 (b) topology 10 (c) topology 11 (d) topology 1296                 |

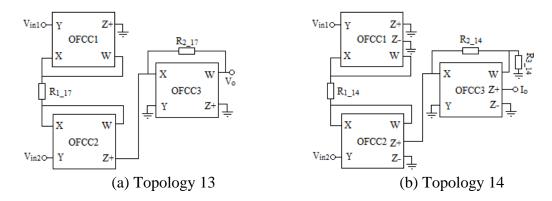

| Fig. 5.12 Simulated frequency responses for differential gain and CMRR for       |

| (a) topology 13 (b) topology 1497                                                |

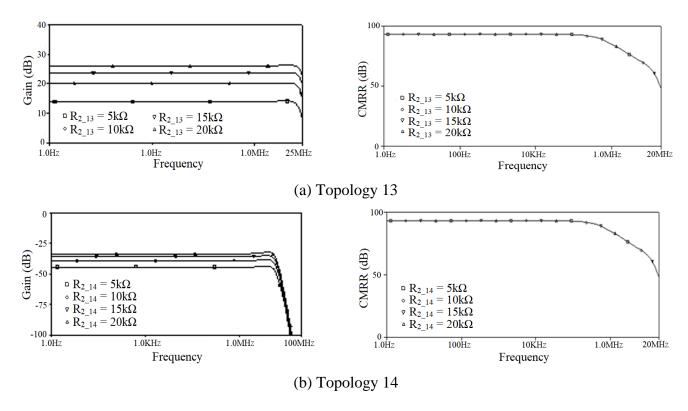

| Fig. 6.1 PGAs in data acquisition systems [121]                                  |

| Fig. 6.2 Block diagram of proposed Programmable Gain Amplifier                   |

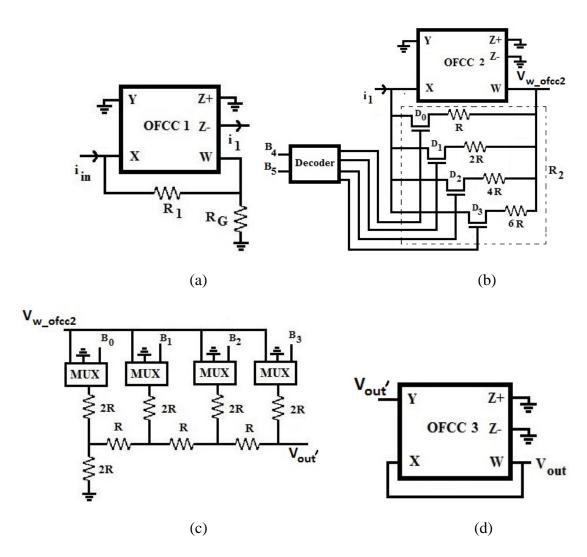

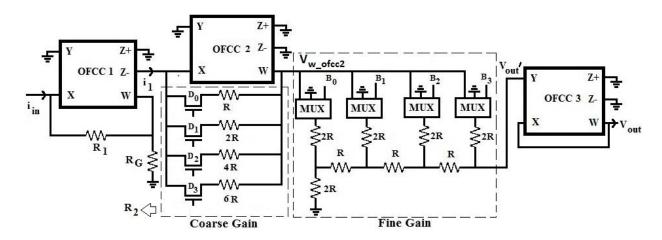

| Fig. 6.3 (a) Current gain block (b) digitally controlled I-V converter           |

| (c) R-2R ladder network (d) voltage buffer                                       |

| Fig. 6.4 Circuit level realization proposed Programmable Gain Amplifier          |

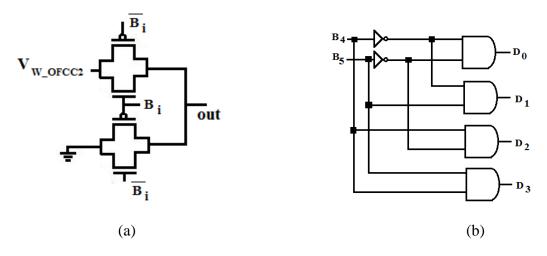

| Fig. 6.5 Schematic of (a) 2x1 multiplexer using transmission gates               |

| (b) 2x4 decoder                                                                        |

|----------------------------------------------------------------------------------------|

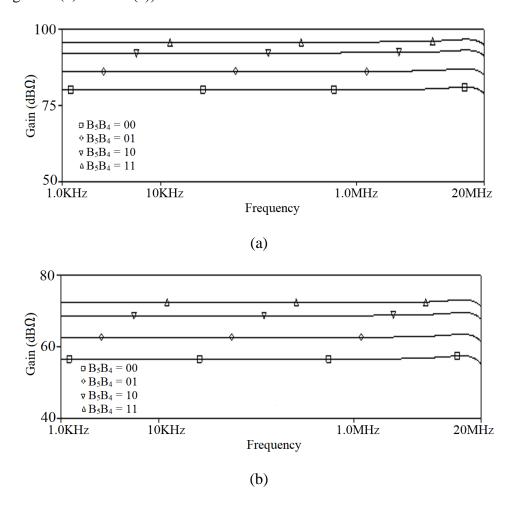

| Fig. 6.6 Frequency response of proposed PGA with coarse gain setting of                |

| (a) 1111 (b) 0001112                                                                   |

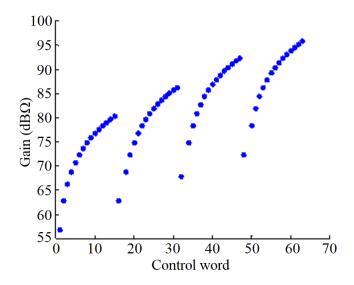

| Fig. 6.7 Variation in gain with respect to control word of the proposed PGA113         |

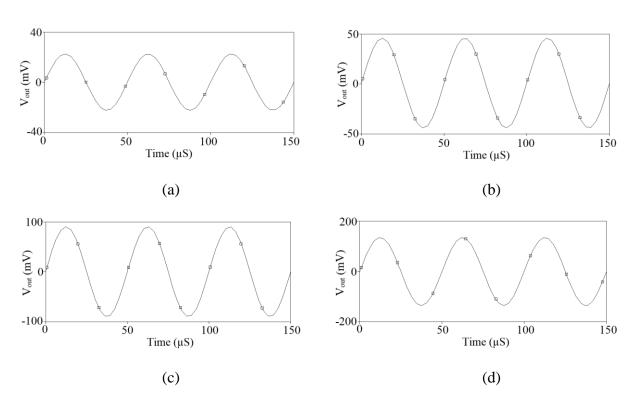

| Fig. 6.8 Transient responses of proposed PGA with $B_3$ – $B_0$ = 1111 and $B_5B_4$ as |

| (a) 00 (b) 01 (c) 10 (d) 11                                                            |

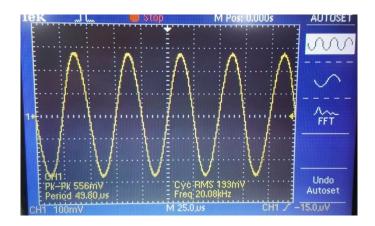

| Fig. 6.9 Experimental output response                                                  |

| Fig. 7.1 Proposed Half wave rectifiers circuit                                         |

| Fig. 7.2 Proposed Full wave rectifier circuit                                          |

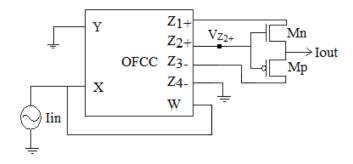

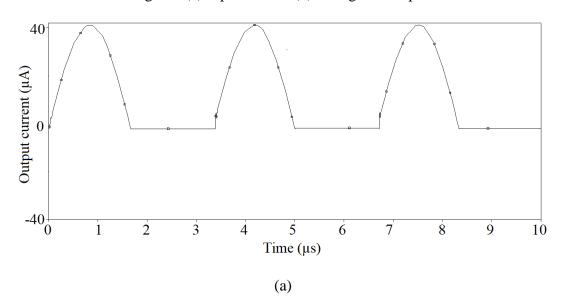

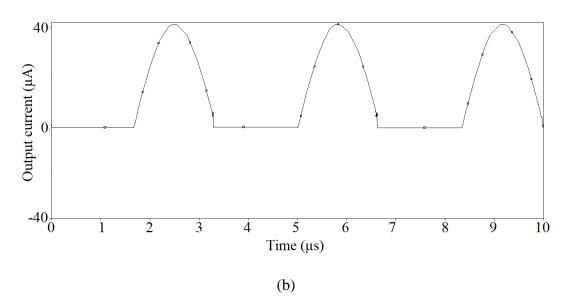

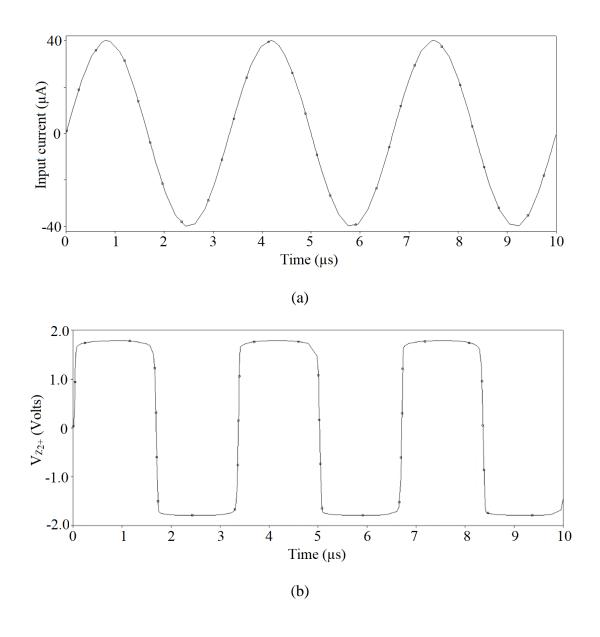

| Fig. 7.3 (a) Input current (b) Voltage at Z <sub>2+</sub> port                         |

| Fig. 7.4 HW rectified outputs for (a) positive cycle of input current                  |

| (b) negative cycle of input current                                                    |

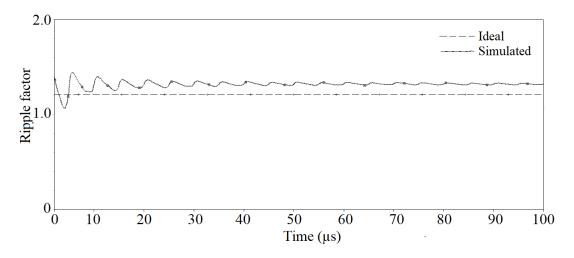

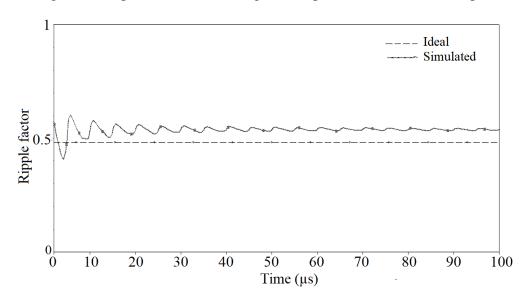

| Fig. 7.5 Ripple factor of HW rectifier under sinusoidal excitation                     |

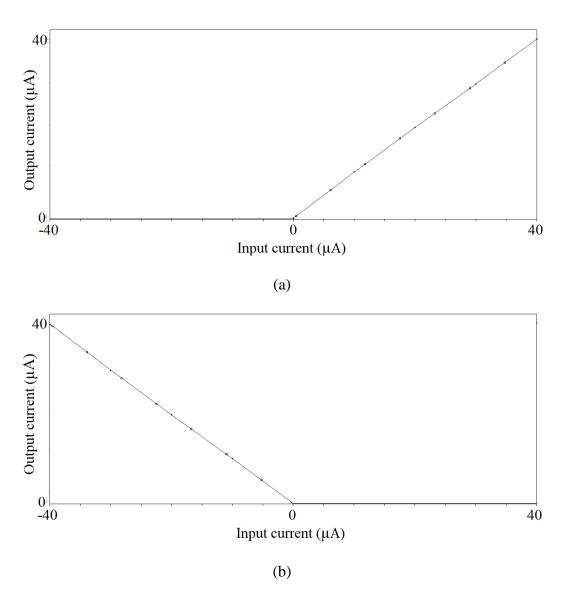

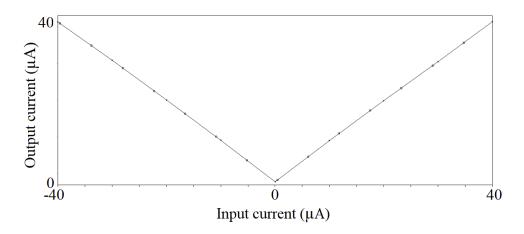

| Fig. 7.6 DC response of the proposed HW rectifiers circuit for                         |

| (a) positive current and (b) negative current transfers                                |

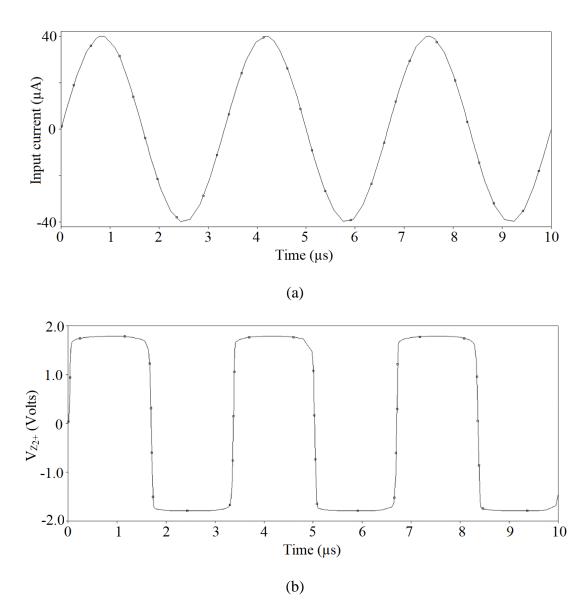

| Fig.7.7 (a) Input current (b) Voltage at Z <sub>2+</sub> port (c) FW rectified output  |

| Fig. 7.8 Ripple factor of proposed FWR under sinusoidal excitation                     |

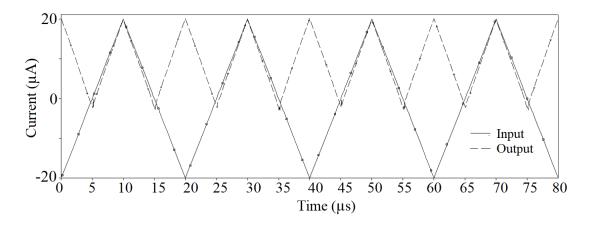

| Fig. 7.9 Input and output waveform under triangular excitation for proposed FWR130     |

| Fig. 7.10 DC response of the proposed FWR                                              |

## LIST OF TABLES

| Table 2.1 Transistor's aspect ratios [13]                                                   |

|---------------------------------------------------------------------------------------------|

| Table 2.2 Simulated values of MOS based resistance [169]                                    |

| Table 3.1 Available TA mode first order filters                                             |

| Table 4.1 Comparative analysis of CM SIMO Filters53                                         |

| Table 4.2 Simulation settings for independent adjustment of filter parameters64             |

| Table 4.3 Tuning of shadow filter parameters                                                |

| Table 5.1 Characteristics of available Instrumentation Amplifiers                           |

| Table 5.2 Stage Description                                                                 |

| Table 5.3 Differential gain, common mode gain and CMRR with finite transimpedance gain (Zt) |

| Table 5.4 Differential gain, common mode gain and CMRR with tracking errors85               |

| Table 5.5 Summary of simulation results for IA topologies 1-8                               |

| Table 5.6 Differential gain, common mode gain and CMRR with finite transimpedance           |

| gain (Z <sub>t</sub> )94                                                                    |

| Table 5.7 Differential gain, common mode gain and CMRR with tracking                        |

| errors95                                                                                    |

| Table 5.8 Differential gain, common mode gain and CMRR with finite transimpedance           |

| gain $(Z_t)$ and tracking errors95                                                          |

| Table 5.9 Summary of simulation results for new IA topologies 9-1499                        |

| Table 5.10 Comparison of performance parameters of available and                            |

| proposed IAs100                                                                             |

| Table 6.1 Literature Survey on previously reported PGAs                                     |

| Table 6.2 Truth Table for 2x1 Multiplexer                        | 111  |

|------------------------------------------------------------------|------|

| Table 6.3 Truth Table for 2 to 4 Decoder.                        | .111 |

| Table 6.4 Performance analysis of previously reported PGAs       | .115 |

| Table 6.5 Experimental measurement results and error calculation | .117 |

| Table 7.1 Literature survey of available rectifiers              | .122 |

## CHAPTER - 1 INTRODUCTION

## 1.1 BACKGROUND

The advancements in VLSI technology has made it possible to integrate millions of transistors on a single die [1]. The analog – digital boundaries are diminishing and integrated solutions for complete system are in vogue where both analog and digital subsystems are placed on single die. Though in last two decades' electronic circuit design has a paradigm shift from analog to digital domain yet analog circuit design is going to remain in mainstay [2]. For signal acquisition and processing, amplifiers, filters, sample and hold circuits, signal comparators, analog to digital converter (ADC) and digital to analog converter (DAC) are required. Further, new applications continue emerging and require high performance analog interface circuits.

The analog circuits are broadly classified as voltage mode (VM) if the information medium is represented by the nodal voltages of the circuits, else as current mode (CM) if the information is represented by time varying currents. The VM circuits are widely employed in applications in comparison to their CM counterparts. This can be attributed to – ease in nodal voltage measurement than branch current (additional circuitry is required); very large input impedance at gate of MOS transistor; and availability of circuit topologies for high voltage gain. The quest for putting more and more circuitry on same die area has led to aggressive scaling of device dimensions, threshold and supply voltage. Some of the after effects of scaling on performance of VM circuits are dynamic range reduction, slew rate, and common mode range. Impact of scaling is less severe in CM circuits as these work on branch currents instead of nodal voltages. Though the performance of any circuit depends on characteristics of the device, current mode circuits may prove advantageous in terms of bandwidth, linearity, slew rate, power consumption and accuracy

for specific applications. Further, these circuits may be compact as addition of current can be done by simply joining branches.

To exploit the advantages of CM signal processing, a wide variety of analog building blocks have been proposed in the literature. Current conveyor (CC) [3, 4, 106, 147] is one among these blocks which is widely explored. It can process both voltage and current signals appropriately and is called voltage/current hybrid circuit. The advantageous features of CC have culminated into development of its extended versions namely first generation current conveyor (CCI) [4], second generation current conveyor (CCII) [5, 35, 65, 96, 102-104, 113, 124, 135, 153, 155, 158, 160, 161, 164, 166] and third generation current conveyor (CCIII) [6, 39, 44, 45, 54, 78]. These blocks share some common port characteristics while other port characteristics slightly differ from one another. Subsequently, extended versions of current conveyors namely differential voltage current conveyor (DVCC) [38, 52, 79, 154, 155, 159], differential difference current conveyor (DDCC) [40], z-copy voltage differencing current conveyor (ZC-VDCC) [49], second generation current controlled current conveyor (CCCII) [56, 70, 71, 76, 107, 111, 150, 162], multiple output current conveyor (MOCC) [57, 62, 63, 66], multiple output second generation current controlled conveyor (MOCCCII) [64], dual output current conveyor (DO-CCII) [58, 67, 74], dual output inverting CCII (DO-ICCII) [75], dual output third generation current conveyor (DO-CCIII) [67], Digitally Programmable CCII (DPCCII) [122], Digitally Controlled Fully Differential CCII (DCFDCCII) [123], Fully Differential CCII (FDCCII) [136], Extra-X second generation current conveyor (EXCCII) [148], dual-X second generation current conveyor (DXCCII) [149, 152] are developed. Operational floating current conveyor (OFCC) [7-33, 50] is another variant of CC family that offer more flexibility and additional current output options. Operational Transconductance Amplifier (OTA) [59, 78, 141, 142, 159, 163] is yet another block that processes

voltage input and provides current output. Its properties are combined with differential input buffer, current conveyor, current follower, current inverter and current difference to result in fully differential input output operational transconductance amplifier (FDIO-OTA) [151], differential input buffered transconductance amplifier (DBTA) [47, 48], current conveyor transconductance amplifier (CCTA) [53, 73], current follower transconductance amplifier (CFTA) [55, 77], Z-copy current follower transconductance amplifier (ZC-CFTA) [60, 72] and Z-copy current inverter transconductance amplifier (ZC-CITA) [61], current difference transconductance amplifier (CDTA) [41, 156, 157] respectively. Few other active blocks are modified current backward transconductance amplifier (MCBTA) [46], multiple output current follower (MO-CF) [69], operational transresistance amplifier (OTRA) [117], operational conveyors (OC) [110], operational amplifier (OPAMP) [97-101, 105, 106, 108, 109, 112, 114, 116, 119, 143-145], current feedback operational amplifier (CFOA) [118, 125] and its variant such as Fully Differential Current Feedback Op Amp (FDCFOA) [126], current difference buffered amplifier (CDBA) [165] and floating current source (FCS) [167]. The topologies [128, 129, 132, 133, 137, 140] employ differential amplifier where along with differential amplifier [128] using current mode feedback (CMFB) and [140] using flipped voltage follower (FVF). A review of available active blocks is presented in [168] along with possible future directions.

## 1.2 AVAILABLE LITERATURE AND SCOPE OF WORK

Numerous applications such as filters, oscillators, instrumentation amplifiers, programmable gain amplifiers, multivibrators and rectifiers have been developed using active blocks. The circuit topologies, based on the type of input signal processed and output signal provided, are classified as voltage mode (VM), current mode (CM), transimpedance mode (TIM) and transadmittance

mode (TAM). The VM and TAM mode circuits process voltage signal whereas CM and TIM mode circuits process current signal. The voltage output is available in VM and TIM mode circuits while CM and TAM mode provide current output.

There is widespread use of filters in instrumentation and communication systems. The filter comprises of interconnection of passive components (inductors, capacitors and resistors) and active devices such as controlled sources, amplifiers, transistor etc. [34]. Low pass, high pass, bandpass and band reject/notch are typical filter categories when magnitude is of prime concern while all pass filter or delay equalizers is important when phase or delay specifications are to be met while keeping magnitude constant. Other classifications are - first, second or higher order depending upon the roll off characteristics, single input single output (SISO), single input multiple output (SIMO), multiple input single output (MISO) and multiple input multiple output (MIMO) depending upon number of inputs being processed and output provided.

The first order low pass and high pass filters find applications in communication systems while all pass filter is commonly used analog filter offering capability to modify phase of the input signal with unity magnitude for all frequencies. Over the desired frequency range, phase varies from 0° to 180°, due to this frequency dependent time displacement property first order all pass filters may be used in radio systems, communication subsystems such as reconstruction filters and signal generation using multiphase sinusoidal oscillators and quadrature oscillators [35]. First order VM, CM and TAM mode filters are presented in [35-40, 47-49], [39, 41-43, 49, 50] and [44-49] respectively. The structures reported in [38, 39] provide low pass, high pass and all pass responses simultaneously. First order filters with low pass, high pass and all pass functions are reported in VM [38, 39] and CM [39] only. First order TAM filters [44-49] provide all pass response only.

Thus literature survey suggests that no first order TAM filter was present in open literature that provide low pass, high pass and all pass responses simultaneously. This has led to development of TAM filter capable of providing all three responses.

A wide variety of second order CM SIMO filters presented in [29, 30, 52-79] and references cited therein. The features of CM SIMO filters [29, 30, 52-79] differ in terms of number of active blocks and passive elements used; types of active blocks used; input/output impedances; simultaneous availability of output responses; and independent adjustment of the filter parameters. Single active blocks is used in filters reported in [53, 54 (Fig. 2, 3), 77] whereas multiple active blocks of different and similar types are employed in [56, 67, 68, 71, 76, 78] and [55, 60, 65 (Fig. 5a, 9a), 70 (Fig. 3)] respectively. The number of simultaneously available responses are two in [54, 55], three in [29, 52, 53, 57-59, 61-69, 72-75, 77-79], four in [30] and all the five in [56, 60, 70 (Fig.3 & 4), 71, 76]. Few responses are available through components in [30, 53, 54 (Fig.2, 3), 59, 77]. The desired condition of low input impedance in CM filters is not maintained in [29, 52-54, 59, 63, 64, 73, 77, 79]. The configurations [54, 57, 65, 69, 79] use floating passive elements which are not suitable from fabrication viewpoint. Therefore, additional active blocks would be required to process output further. References [29, 30, 52, 54, 55, 59, 61-67, 69, 70, 77] do not support independent adjustment of filter parameters. The parameters adjustment is possible in [55, 56, 60, 68, 71-73, 76] and [53, 58, 65 (sec. 2.2, 3.2), 74, 75, 78, 79] through transconductance (g<sub>m</sub>) or internal resistance of active block. It is clear from above discussion that only one SIMO filter [60] is available that uses similar active blocks and provides four or more output responses at high output impedance; and allows independent adjustment of filter parameters. This configuration, however, uses four active blocks.

Thus, single SIMO filter [60] is available that uses similar active blocks and provides four or more output responses at high output impedance. This configuration, however, uses four active blocks. Alternate topology that uses reduced number of similar active blocks may therefore be explored.

The instrumentation amplifier (IA) is used as an input stage in variety of applications such as medical instrumentation [87,88], sensor read out integrated circuits [89], data acquisition systems [2, 90], industrial process control [91], automotive transducers [92], bio-potential acquisition systems [93], [94] and linear position sensing [95]. Numerous IA are available in the literature [14, 96-119] and are classified on the basis of active block employed for implementation. Conventionally the operational amplifier based IAs are termed as voltage mode IAs (VMIA) [97-101, 112, 114, 116, 119] whereas current mode building block based IAs are referred as current mode IAs (CMIA) [14, 96, 102-111, 113, 118]. Most of the available IAs [14, 96-114] can process data sensed by voltage sensor but need current to voltage converter for processing current sensors' data. The IAs [96,115-118] are suitable to process data available from current sensor and provide current [115,118] and voltage outputs [96,116,117]. The IAs may be categorized as VM, CM, TAM and TIM depending on the basis of input and output signals. Accordingly, the IAs presented in [14, 96-114, 119], [107], [115,118] and [96,116,117] are VM, TAM, CM and TIM IAs respectively. Though the input impedance of VM IA topologies [14, 96-114] is high, the output is not available at low impedance [14, 96, 102-104, 106, 107, 110, 111, 113]. It is therefore necessary to place a buffer at the output for isolation. The CM and TAM IA topologies with proper impedance level are put forward in [115] and [107] respectively. The output impedance of TIM IA topologies [116, 117] is proper but former has high input impedance. The IAs [97-101, 112, 114, 116] are designed using operational amplifier and therefore exhibit narrow and gain Page | 8

dependent bandwidth. The gain is independent of band width in [14, 96, 102-104, 107, 110, 111, 113, 115, 117, 118] as current mode active blocks namely OFCC [14], CCII [96, 102-104, 113], CCCII [107, 111], OC [110], OTRA [117] and CFOA [118] are being used. The IA topologies presented in [105, 106, 108, 109, 119] employ both voltage and current mode active blocks, their bandwidth will be decided by the bandwidth of voltage mode active block.

Though a variety of CM active blocks based VM IA topologies are available, yet none of these provide output at low impedance. Additional active block is required to satisfy impedance requirement. Generalized IA topology is not available. Also, OFCC based CM, TAM and TIM mode IA are not available.

Amplifiers, in particular programmable gain amplifiers (PGAs), find applications in instrumentation, photodiode circuits, ultrasound preamplifiers, sonar, wide dynamic range sensors, driving ADCs (some ADCs have on-chip PGAs), automatic gain control (AGC) loops [120, 121]. Typically, PGA [121] in data acquisition system is placed between a sensor and analog to digital converter (ADC). Additional signal processing circuitry, as per demand of application, may be placed before or after the PGA. Former location is, however, preferred as it allows to condition a larger signal. Typically, operational amplifiers are employed in designing PGAs. The PGA designs [13, 122-143] provide voltage output and process data from voltage sensor. A current to voltage converter is needed if data is sensed from current sensor. The PGA design [122] processes data sensed from current sensor and provides current output. A current to voltage converter is required in case there is a need of interfacing it with circuit having input as voltage. Different active blocks such as CCII [124, 135] and its variants such as DPCCII [122], DCFDCCII [123] and FDCCII [136]; CFA [125] and its variant such as FDCFOA [126]; OFCC is used in [13]; the topologies [128, 132, 133, 137, 140] employ differential amplifier; CMOS based simple single ended and

fully differential gate driven variable gain amplifier (VGA) with programmable gain is also reported in [138, 139]; few topologies with OTA is reported in [141, 142]; whereas [143] employs op-amp for PGA design. The input and output impedances are proper in [13, 125, 127, 129, 130, 133, 138-140, 143] while additional active block is needed in [122-124, 126, 128, 131, 132, 134-137, 141, 142] to satisfy impedance condition. Gain tuning is achieved through current division networks (CDN) [123, 124, 134], weighted transistor arrays [122, 133], potentiometer [125, 126, 132, 136] or switches [13, 127-129, 131]; and digitally controlled exponential function [130] or current mirrors [135]; 4-bit Digitally controlled look up table and pre-calibration method [137]; DAC gain control (dB linear/digital) [138]; 4-bit and 5-bit digitally programmable VGA [139]; source degenerated capacitor array [140]; two stacked transistors [141]; switched capacitor array [142]; and resistor array with MOS switches [143]. Explicit mechanism for fine and coarse gain tuning is applied in [13, 124] and [143].

The discussion of available PGA indicates non-availability of TIM PGA which may be useful when input is sensed in form of current and a voltage output is needed for either further processing or display.

The rectifiers are widely used in applications pertaining to telecommunication, instrumentation and measurement [144-147]. Some of the applications are ac voltmeter, averaging circuits, peak value detectors, clipper circuits, amplitude-modulated signal detectors, signal-polarity detectors etc. Various current mode blocks are also incorporated in rectifiers such as OPAMP [144, 145], CCIICS [146], CC [147], EXCCII [148], DXCCII [149, 152], CCCII [150, 162], FDIO-OTA [151], CCII [153, 155, 158, 160, 161, 164, 166], DVCC [154, 155, 159], CDTA [156, 157], OTA [159], DO-OTA [163], CDBA [165] and FCS [167]. Available rectifiers operate in VM [144 - 147, 149 – 155, 160, 161, 163, 164, 166, 167], CM [148, 156-159, 165] and TAM

[162]. More than one active block is reported in [144 – 147, 152, 154, 155, 158, 161, 162, 164, 166]. VM rectifiers [144-147, 151, 154, 161, 163, 164, 166, 167] and CM rectifiers in [156-159, 165] use diodes to achieve rectification. The input and output impedance of VM rectifier [144, 146, 147, 149-153, 155, 161, 164, 167] and CM rectifier [157] are not proper hence additional active block is required. Resistances and MOS transistors are also used in [144-147, 150-157, 159-163, 166, 167] and [148-150, 152, 153, 155, 164] respectively.

## 1.3 THESIS ORGANIZATION

The thesis is organized in eight chapters where Chapter 3 to Chapter 7 constitutes the main body of the thesis.

**Chapter 1** titled "Introduction" presents introduction to current mode approach and current mode signal processing including review of various current mode building blocks. An extensive literature survey is also presented with the scope of work.

Chapter 2 titled "OFCC current mode building block" presents description of OFCC and its behavior in presence of nonidealities. Schematic used for verification of proposals through simulations and experimentation are discussed next. The study of basic applications of OFCC such as amplifier configurations are detailed in this thesis and used extensively in this work. The MOS based resistor implementation is also studied and utilized to show electronic tuning in proposed circuits.

Chapter 3 titled "OFCC based TA mode first order filter" presents a new first order TA mode filter is put forward in this chapter. Literature survey for TA mode first order filters followed by proposed filter description including filter structure and its routine analysis using nonidealities is presented. One filter application as an oscillator is also developed.

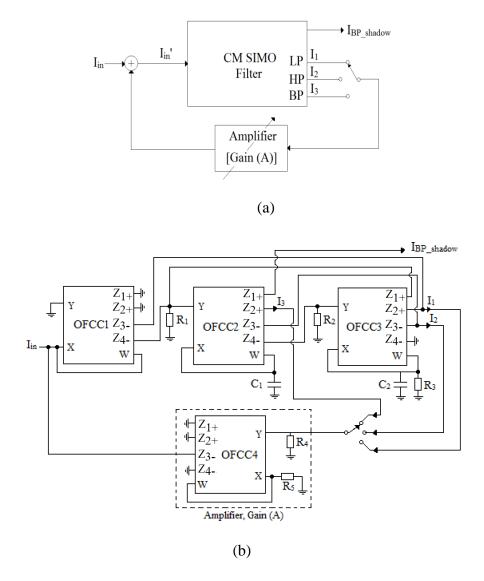

Chapter 4 titled "OFCC based CM second order filter" deals with literature review followed by CM SIMO filter description. Proposed CM SIMO filter is also analyzed for nonidealities namely finite transimpedance gain, tracking errors and parasites offered by the OFCC. As an application a CM shadow bandpass filter is developed and both proposals verified through simulations while CM SIMO filter is prototyped for bandpass response.

Chapter 5 titled "OFCC based Instrumentation Amplifier" presents generalized structure of IA. This generalized structure is categorized into two structures: Structure-I and Structure-II. Using these structures generalized IA topologies 1-8 are proposed which can operate in VM, CM, TIM and TAM modes. To reduce the number of passive components the structures I and II are modified. Six more IA topologies are derived from modified structures. The effect of non-idealities of OFCC has been analyzed. A thorough comparison of all proposed topologies with existing one is also put forward in a tabulated format for better comparison.

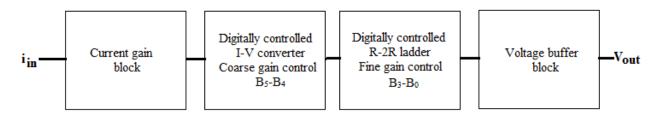

Chapter 6 titled "OFCC based transimpedance mode PGA" presents new OFCC based PGA. It operates in TIM i.e. it receives current signal as input and provides voltage as output. It uses four blocks – a current amplifier, digitally controlled transimpedance amplifier, digitally controlled R-2R ladder network and a voltage buffer. Digital coarse and fine gain tuning is the key feature of proposed PGA which is achieved by control bits (B<sub>5</sub>-B<sub>0</sub>).

Chapter 7 titled "OFCC based CM rectifier" presents single OFCC based CM half wave rectifiers (HWRs) and full wave rectifier (FWR). These rectifiers do not use diode and are thus suitable for low voltage rectification. It is pertinent to mention here that all proposed rectifiers use single active block and are resistor-less.

**Chapter 8** titled "Conclusion and Future scope" presents concluding remarks and future scope of the discussed work.

## CHAPTER - 2 OFCC CURRENT MODE BUILDING BLOCK

## 2.1 INTRODUCTION

The development of current mode circuits has received growing interest over voltage mode circuits due to high frequency limitations of voltage mode circuits just because of constant gain bandwidth product and low slew rate of op-amps. Therefore, current mode approach results in significant improvement in signal linearity, bandwidth and power consumption. It's also in consonance with the trend of operating circuits at lower supply voltages where the current mode concept is more useful. In current mode circuits the operation of the circuit is decided by current which enables the system design having wider dynamic range [1-3]. These circuits are also simple and compact as current addition/subtraction does not require additional circuit blocks. Owing to the advantages of current mode blocks considerable research has directed towards development of active blocks and the realization of current mode signal processing and generation circuits. Current conveyor (CC) [3,4] is one among these CM blocks and CCI [4], CCII [5], CCIII [6] are the basic variants, which is widely explored throughout the literature. The operational floating current conveyor (OFCC) [7,8,10] is yet another variant of CC which combines the features of current conveyor and the current feedback opamp along with additional current outputs that adds flexibility in the circuit design.

This chapter describes OFCC and its behavior in presence of nonidealities. The schematic used for simulation and experimentation verification are discussed next. The VM, CM, TAM and TIM amplifier configurations and difference amplifier are used extensively in this work and are detailed. The MOS based resistor implementation [169] is also presented towards end of this chapter which is utilized to introduce electronic tuning feature in proposed circuits.

## 2.2 OPERATIONAL FLOATING CURRENT CONVEYOR

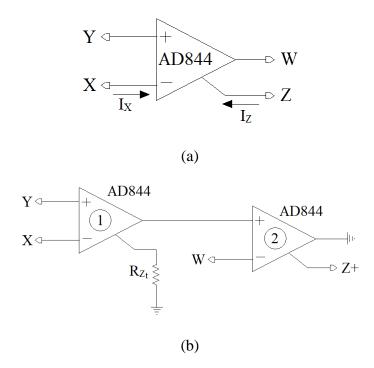

The circuit symbol of OFCC [7,8,10] is shown in Fig. 2.1. The port labeled as X is low impedance current input and Y is a high impedance voltage input port. The voltage at port W is multiplication of input current at port X and open loop transimpedance gain  $Z_t$ . Ports  $Z_t$  and  $Z_t$  are high impedance current output ports.

Fig. 2.1 OFCC Circuit symbol

The port X tracks the voltage of Y port and current at port W is copied to ports Z+ and Z-in phase and out of phase respectively. The port relationships of the OFCC are described by matrix given in (2.1).

$$\begin{bmatrix} I_{Y} \\ V_{X} \\ V_{W} \\ I_{Z+} \\ I_{Z-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 \\ 0 & Z_{t} & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & -1 & 0 & 0 \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{X} \\ I_{W} \\ V_{Z+} \\ V_{Z-} \end{bmatrix}$$

$$(2.1)$$

## 2.3 EFFECT OF NONIDEALITIES

The behavior of the proposed topologies may deviate from the ideal one due to nonidealities of OFCC which are classified in two categories. The first type of nonidealities is due to the finite transimpedance gain while the second type is due to non-ideal voltage and current transfers. The later type is manifested in terms of voltage and current tracking errors. The following sub sections describe the effect of these two nonidealities.

## 2.3.1 Effect of finite transimpedance gain

Ideally the transimpedance gain  $Z_t$  is assumed to approach infinity. However, in practice  $Z_t$  is a frequency dependent finite value. Therefore, using single pole model the transimpedance gain  $(Z_t(s))$  can be obtained as

$$Z_t(s) = \frac{Z_{to}}{1 + S/\omega_{tc}} \tag{2.2}$$

Here  $Z_{to}$  is the dc open loop transimpedance gain and  $\omega_{tc}$  is the transimpedance cut off frequency. For high frequency applications, the transimpedance gain  $(Z_t(s))$  is approximated as

$$Z_t(s) \cong \frac{1}{s_{/(Z_{to}\omega_{tc})}} = \frac{1}{sC_p}$$

(2.3)

where

$$C_p = \frac{1}{Z_{to}\omega_{tc}} \tag{2.4}$$

represents the parasitic capacitance of OFCC.

### 2.3.2 Effect of voltage and current tracking errors

The port relationship of OFCC in practice, differ from (2.1) due to voltage and current tracking errors and is represented as

$$\begin{bmatrix} I_{Y} \\ V_{X} \\ V_{W} \\ I_{Z^{+}} \\ I_{Z^{-}} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ \beta & 0 & 0 & 0 & 0 \\ 0 & Z_{t} & 0 & 0 & 0 \\ 0 & 0 & \alpha & 0 & 0 \\ 0 & 0 & -\gamma & 0 & 0 \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{X} \\ I_{W} \\ V_{Z^{+}} \\ V_{Z^{-}} \end{bmatrix}$$

$$(2.5)$$

where  $\beta = (1 - \varepsilon_V)$ ,  $\alpha = (1 - \varepsilon_{i+})$  and  $\gamma = (1 - \varepsilon_{i-})$  are errors in voltage transfer from Y to X port and error in current transfer from W port to Z+ and Z- ports respectively. Here  $\varepsilon_V$  represents voltage tracking error, whereas  $\varepsilon_{i+}$  and  $\varepsilon_{i-}$  are current tracking errors. The effect of tracking errors

is strongly topology dependent, e.g. the voltage tracking error does not affect the response if Y port of OFCC is grounded and the same is true for current tracking errors if Z+ or Z- ports are not used.

## 2.4 OFCC REALIZATION

The OFCC implementations are based on

- CMOS schematic [13]

- CFOA [170].

## **2.4.1 CMOS based implementation**

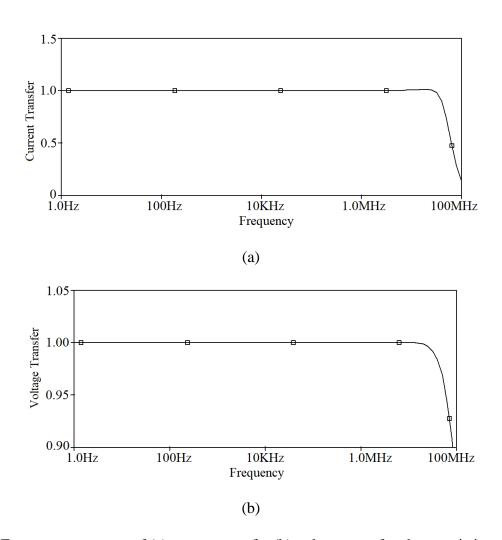

The CMOS based implementation of OFCC are given in [13]. This subsection describes the CMOS implementation used to validate different proposals in the work. Simulations are carried out using implementation scheme [13] of Fig. 2.2. It uses a plus type second generation current conveyor (CCII+), a transimpedance amplifier block (Z<sub>t</sub>) and a current follower. The CMOS schematic of OFCC [13] based on this implementation scheme is depicted in Fig. 2.3. It uses matched transistor pairs (M1 and M2), (M3 and M4), (M10 and M15) and (M11, M12 and M14). Considering the saturation region operation of all the transistors, the functioning of the circuit may be elucidated as follows. Port X follows voltage of W port through transistors (M1 - M7) which form CCII+. The cross coupled current mirror formed by transistors (M16 - M21) provide negative current transfer from W port to Z- port. Voltage at port W is produced by multiplication of current input at X port with transimpedance gain (Z<sub>t</sub>) provided by amplifier formed by transistors M8 - M13. The set of transistors (M10, M12, M14 and M15) forms current follower and provides current tracking between ports W and Z+.

Fig. 2.2 Implementation scheme for OFCC block [13]

Fig. 2.3 CMOS schematic of OFCC block [13]

To verify the operation of the circuit of Fig. 2.3, SPICE simulations are carried out using MOSIS (AGILENT) 0.5  $\mu$ m CMOS process technology parameters. The aspect ratios of various transistors are listed in Table 2.1. The power supplies  $V_{DD}$  and  $V_{SS}$  are taken as 1.5 V and -1.5 V, while bias voltage  $V_{B1}$  and  $V_{B2}$  of  $\pm$  0.8 V are considered.

Table 2.1 Transistor's aspect ratios [13]

| Transistor                                                     | $W(\mu m)/L(\mu m)$ |

|----------------------------------------------------------------|---------------------|

| M1, M2                                                         | 50/1                |

| M3, M4, M11, M12, M14,                                         | 50/2.5              |

| M16, M18, M20                                                  |                     |

| <i>M</i> 5, <i>M</i> 7, <i>M</i> 10, <i>M</i> 15, <i>M</i> 17, | 20/2.5              |

| M19, M21                                                       |                     |

| M6, M8                                                         | 40/2.5              |

| M9, M13                                                        | 100/2.5             |

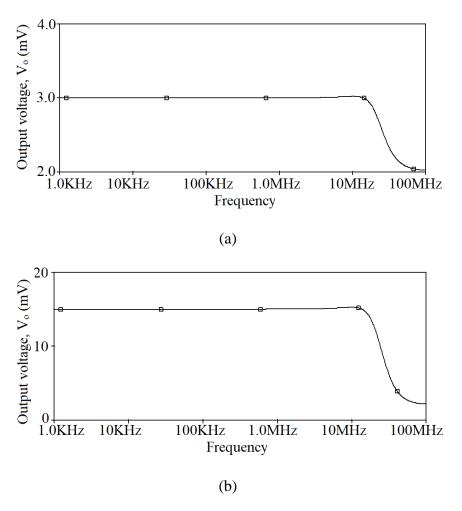

Simulated frequency response for current and voltage transfer characteristics of OFCC is shown in Fig. 2.4 (a) and (b) respectively. These current transfer characteristic is showing current transfer property of OFCC existing in between port Z and W. It is found that current transfer value is 0.998 and is less than unity due to current tracking error ( $\varepsilon_i$ ). Similarly, the voltage transfer characteristic shows voltage transfer property of OFCC existing in between port Y and X. The voltage transfer value is 0.999 and any deviation is represented by voltage tracking error ( $\varepsilon_v$ ).

Fig. 2.4 Frequency response of (a) current transfer (b) voltage transfer characteristics of OFCC

#### 2.4.2 CFOA based implementation

The circuit symbol of AD844 is given in Fig. 2.5 (a). Its port relationship is expressed as

$$I_Y = 0, I_Z = I_X, V_X = V_Y, V_W = V_Z$$

(2.6)

The AD844 based implementation of OFCC is given in Fig. 2.5 (b). The experimental verification of various proposals in this work is done using this implementation based on commercially available CFOA AD844 IC. It uses two AD844 ICs. The first IC provides voltage transfer between Y and X ports. The second IC is used for current transfer from W to Z+ port.

Fig. 2.5 (a) Circuit symbol of AD844 [170] (b) AD844 based OFCC implementation

#### 2.5 BASIC APPLICATIONS OF OFCC

The OFCC based voltage amplifier, current amplifier, transadmittance amplifier, transimpedance amplifier and voltage difference amplifier are extensively used in this work. These are briefly described in the following subsections.

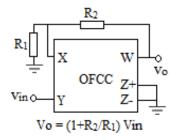

#### 2.5.1 Voltage Amplifier

The voltage amplifier configuration using OFCC [13] is shown in Fig. 2.6. Assuming transimpedance approaches infinity, the gain of the amplifier (Av) is computed as

$$A_V = \frac{V_0}{V_{in}} = 1 + \frac{R_2}{R_1} \tag{2.7}$$

Fig. 2.6 Voltage amplifier using OFCC

Considering the nonidealities described in section 2.3, the gain  $(A_{v\_fz})$  in presence of finite  $Z_t$ , is recalculated as

$$A_{V_{-}fz} = \left. \frac{v_o}{v_{in}} \right|_{fz} = \left( 1 + \frac{R_2}{R_1} \right) \varepsilon_V(s) \tag{2.8}$$

where,  $\varepsilon_{v}(s)$  is the error function and is given by

$$\varepsilon_V(s) = \frac{1}{1 + sC_p R_2} \tag{2.9}$$

Hence, for high frequency application, compensation method is needed to take the error function into account.

Similarly, if tracking errors are taken into consideration then (2.7) modifies to

$$A_{V_{-}tr} = \left. \frac{V_o}{V_{in}} \right|_{tr} = \beta \left( 1 + \frac{R_2}{R_1} \right) \tag{2.10}$$

where A<sub>v\_tr</sub> is voltage gain in presence of tracking errors.

The operation of OFCC based voltage amplifier is examined through simulation using schematic of Fig. 2.3. Fig. 2.7 depicts simulated frequency response of voltage amplifier with

component values  $R_1=1~k\Omega$  and  $R_2=1~k\Omega$ ,  $5~k\Omega$ ,  $10~k\Omega$  and  $20~k\Omega$ . Simulated gain values are found as 6 dB, 15dB, 20 dB and 26 dB for these settings. Corresponding theoretical gain values are computed as 6.02 dB, 15.56 dB, 20.82 dB and 26.44 dB which verify the functionality of voltage amplifier.

Fig. 2.7 Frequency response of voltage amplifier

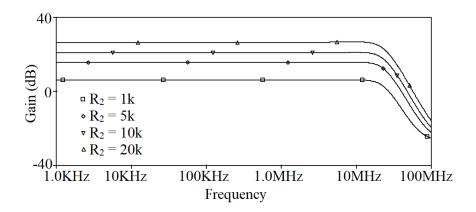

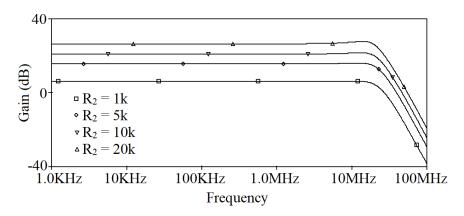

#### 2.5.2 Current Amplifier

The current amplifier configuration using OFCC [13] is shown in Fig. 2.8 and using routine analysis, the gain of the amplifier (A<sub>I</sub>) can be obtained as

Fig. 2.8 Current amplifier using OFCC

Considering the nonidealities described in section 2.3, the gain  $(A_{I\_fz})$  in presence of  $Z_t$ , is recalculated as

$$A_{I_{fz}} = \frac{I_0}{I_{in}}\Big|_{fz} = -\left(1 + \frac{R_2}{R_1}\right)\varepsilon_I(s)$$

(2.12)

where,  $\varepsilon_I(s)$  is the error function and is given by

$$\varepsilon_I(s) = \frac{1}{1 + sC_p R_2} \tag{2.13}$$

Hence, for high frequency application, compensation method is needed to take the error function into account.

Similarly, if tracking errors are taken into consideration then (2.11) modifies to

$$A_{I_{-}tr} = \frac{I_0}{I_{in}}\Big|_{tr} = -\alpha \left(1 + \frac{R_2}{R_1}\right) \tag{2.14}$$

where A<sub>I\_tr</sub> corresponds to current gain in presence of tracking error.

The operation of OFCC based current amplifier is examined through simulation using schematic of Fig. 2.3. Fig. 2.9 depicts simulated frequency response of current amplifier with component values  $R_1 = 1 \text{ k}\Omega$  and  $R_2 = 1 \text{ k}\Omega$ ,  $5 \text{ k}\Omega$ ,  $10 \text{ k}\Omega$  and  $20 \text{ k}\Omega$ . Simulated gain values are found as 6 dB, 15dB, 20 dB and 26 dB while theoretical gain values are as 6.02 dB, 15.56 dB, 20.82 dB and 26.44 dB for these settings which verify the functionality of current amplifier.

Fig. 2.9 Frequency response of current amplifier

#### 2.5.3 Transadmittance Amplifier

The transadmittance amplifier configuration using OFCC [13] is shown in Fig. 2.10 and using routine analysis, gain of the amplifier ( $A_{TA}$ ) can be obtained as

$$A_{TA} = \frac{I_0}{V_{in}} = \left(\frac{1}{R_1}\right) \tag{2.15}$$

Fig. 2.10 Transadmittance amplifier

Considering the nonidealities described in section 2.3, the gain in presence of  $Z_t$  ( $A_{TA\_fz}$ ) is recalculated as

$$A_{TA\_fZ} = \frac{I_o}{V_{in}}\Big|_{fZ} = \left(\frac{1}{R_1}\right)\varepsilon_{TA}(s) \tag{2.16}$$

where,  $\varepsilon_{TA}(s)$  is the error function and is given by

$$\varepsilon_{TA}(s) = \frac{1}{1 + sC_pR_1} \tag{2.17}$$

Hence, for high frequency application, compensation method is needed to take the error function into account.

Similarly, if tracking errors are taken into consideration then (2.15) modifies to

$$A_{TA\_tr} = \frac{I_o}{V_{in}}\Big|_{tr} = \alpha\beta\left(\frac{1}{R_1}\right) \tag{2.18}$$

where (A<sub>TA\_tr</sub>) is transadmittance gain in presence of tracking errors.

The operation of OFCC based transadmittance amplifier is examined through simulation using schematic of Fig. 2.3. Fig. 2.11 depicts simulated frequency response of transadmittance

amplifier with component values  $R_1=0.2~k\Omega$ ,  $1~k\Omega$ ,  $10~k\Omega$ ,  $50~k\Omega$  and  $100~k\Omega$ . Simulated gain values are found as 4.99 m-mho, 0.99 m-mho,  $100.01~\mu$ -mho,  $20.02~\mu$ -mho and  $10.02~\mu$ -mho for these settings. Corresponding theoretical gain values are computed as 5 m-mho, 1~m-mho,  $100~\mu$ -mho,  $20~\mu$ -mho and  $10~\mu$ -mho which verify the functionality of transadmittance amplifier.

Fig. 2.11 Frequency response of transadmittance amplifier

#### 2.5.4 Transimpedance Amplifier

The transimpedance amplifier configuration using OFCC [13] is shown in Fig. 2.12 and using routine analysis, gain of the amplifier ( $A_{TI}$ ) can be obtained as

$$A_{TI} = \frac{v_o}{l_{in}} = -(R_1)$$

$$\begin{array}{c} R_1 \\ \hline \\ X \\ \hline \\ V \\ \hline \end{array}$$

$$\begin{array}{c} R_1 \\ \hline \\ V \\ \hline \end{array}$$

$$\begin{array}{c} C \\ C \\ C \\ \hline \end{array}$$

$$\begin{array}{c} C \\ C \\ C \\ \hline \end{array}$$

$$\begin{array}{c} C \\ C \\ C \\ C \\ \hline \end{array}$$

$$\begin{array}{c} C \\ C \\ C \\ C \\ \hline \end{array}$$

Fig. 2.12 Transimpedance amplifier

Considering the nonidealities described in section 2.3, the gain in presence of  $Z_t$  ( $A_{TI\_fz}$ ) is recalculated as

$$A_{TI\_fZ} = \frac{v_o}{l_{in}}\Big|_{fZ} = -(R_1)\varepsilon_{TI}(s) \tag{2.20}$$

where,  $\varepsilon_{TI}(s)$  is the error function and is given by

$$\varepsilon_{TI}(s) = \frac{1}{1 + sC_p R_1} \tag{2.21}$$

Hence, for high frequency application, compensation method is needed to take the error function into account.

Similarly, if tracking errors are taken into consideration then gain of transimpedance amplifier remains unchanged and is given as (2.19).

The operation of OFCC based transimpedance amplifier is examined through simulation using schematic of Fig. 2.3. Fig. 2.13 depicts simulated frequency response of transimpedance amplifier with component values  $R_1 = 1 \text{ k}\Omega$ ,  $5 \text{ k}\Omega$ ,  $10 \text{ k}\Omega$  and  $20 \text{ k}\Omega$ . Simulated gain values are found as  $1 \text{ k}\Omega$ ,  $5 \text{ k}\Omega$ ,  $10 \text{ k}\Omega$  and  $20 \text{ k}\Omega$  for these settings. Corresponding theoretical gain values are computed as  $1 \text{ k}\Omega$ ,  $5 \text{ k}\Omega$ ,  $10 \text{ k}\Omega$  and  $20 \text{ k}\Omega$  which verify the functionality of transimpedance amplifier.

Fig. 2.13 Frequency response of transimpedance amplifier

#### 2.5.5 Voltage difference Amplifier

The voltage differencing principle used in opamp [121] is applied to arrive at OFCC based voltage difference circuit of Fig. 2.14. The voltage difference amplifier configuration using OFCC is shown in Fig. 2.14 and using routine analysis, the currents I<sub>1</sub>, I<sub>2</sub> and I<sub>3</sub> in Fig. 2.14 may be written as

$$I_1 = \frac{V_2 - V_X}{R_1}$$

,  $I_2 = \frac{V_1 - V_Y}{R_3}$  and  $I_3 = \frac{V_X - V_O}{R_2}$  (2.22)

where  $V_X$  and  $V_Y$  are voltages at X and Y ports of OFCC.

As  $V_X = V_Y$ , then voltage at terminal  $(V_Y)$  is computed as

$$V_Y = V_1 \left( \frac{R_4}{R_3 + R_4} \right) \tag{2.23}$$

Now, if  $V_1 = 0$  then

$$V_o(V_1 = 0) = -V_2\left(\frac{R_2}{R_1}\right)$$

(2.24)

If  $V_2 = 0$ , then

$$V_o(V_2 = 0) = V_1 \left(\frac{R_4}{R_3 + R_4}\right) \left(\frac{R_1 + R_2}{R_1}\right) \tag{2.25}$$

and output will be  $V_0 = V_0$  ( $V_1 = 0$ ) +  $V_0$  ( $V_2 = 0$ ) therefore  $V_0$  may be obtained as

$$V_o = -V_2 \left(\frac{R_2}{R_1}\right) + V_1 \left(\frac{R_4}{R_3 + R_4}\right) \left(\frac{R_1 + R_2}{R_1}\right) \tag{2.26}$$

If equal resistor values i.e.  $R_1=R_2=R_3=R_4$  are taken, then the amplifier will become unity gain voltage difference amplifier and the output expression can be obtained as  $V_0=(V_1-V_2)$ . However, if  $R_1=R_3=R_A$  and  $R_2=R_4=R_B$  then output voltage is computed as

$$V_0 = {\binom{R_B}{R_A}} (V_1 - V_2) \tag{2.27}$$

and gain of the amplifier (A<sub>VDA</sub>) can be obtained as

$$A_{VDA} = \frac{V_0}{(V_1 - V_2)} = \binom{R_B}{R_A} \tag{2.28}$$

Thus circuit performs operation of difference amplifier with gain.

Fig. 2.14 Voltage Difference Amplifier

Considering the nonidealities described in section 2.3, the gain in presence of  $Z_t$ , is recalculated as

$$A_{VDA\_fZ} = \left. \frac{V_o}{(V_1 - V_2)} \right|_{fZ} = \left. \left( \frac{R_B}{R_A} \right) \varepsilon_{VDA}(s)$$

(2.29)

where,  $\varepsilon_{VDA}(s)$  is the error function and it is given by

$$\varepsilon_{VDA}(s) = \frac{1}{1 + sC_p R_B} \tag{2.30}$$

Hence, for high frequency application, compensation method is needed for taking the error function into account.

Similarly, if tracking errors are taken into consideration then (2.27) modifies to

$$V_{o\_tr} = \left(\frac{R_B}{R_A}\right) (\beta V_1 - V_2) \tag{2.31}$$

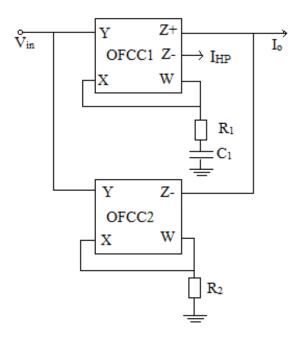

The operation of OFCC based voltage difference amplifier is examined through simulation using schematic of Fig. 2.3. Simulated frequency responses of voltage difference amplifier for input voltage  $V_1 = 5$  mV,  $V_2 = 2$  mV with component values  $R_1 = R_2 = R_3 = R_4 = R_B = 1$  k $\Omega$  to set the unity gain value while  $R_1 = R_3 = R_A = 1$  k $\Omega$  and  $R_2 = R_4 = R_B = 5$  k $\Omega$  to set the gain value of 5, are depicted in Fig. 2.15 (a) and (b) respectively.

Fig. 2.15 Frequency response of voltage difference amplifier with (a) gain=1 (b) gain=5

Simulated values are found as 3 mV and 15 mV respectively for both of these settings. Corresponding theoretical values are computed as 3 mV and 15 mV, which verify the functionality

of voltage difference amplifier. Similarly, by varying R<sub>A</sub> and R<sub>B</sub> to another values the gain can be varied accordingly and amplified voltage difference output is achieved.

#### 2.6 MOS BASED RESISTOR IMPLEMENTATION

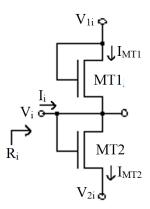

This section briefly describes grounded resistor implementation based on two diode connected MOS transistors as shown in Fig. 2.16 [169].

Fig. 2.16 MOS based resistor implementation [169]

Assuming MOS transistor structure operating in saturation region and equal aspect ratios of MT1 and MT2, the KCL at input node may be written as

$$I_i = I_{MT2} - I_{MT1} (2.32)$$

$$I_{i} = \frac{1}{2} \mu_{n} C_{ox} (W/L) (V_{i} - V_{2i} - V_{T})^{2} - \frac{1}{2} \mu_{n} C_{ox} (W/L) (V_{1i} - V_{i} - V_{T})^{2}$$

(2.33)

where  $\mu_n$ ,  $C_{ox}$  and  $V_T$  represent mobility, oxide capacitance and threshold voltage respectively.

Taking  $V_{1i} = -V_{2i}$ , input resistance (R<sub>i</sub>) may be computed by simplifying (2.33) as

$$R_i = \frac{V_i}{I_i} = \frac{1}{2\mu_n C_{ox}(W/I_i)(V_{1i} - V_T)}$$

(2.34)

So by varying  $V_{1i}$  the resistance may be electronically tuned. Simulated values of MOS based resistance are shown in Table 2.2.

Table 2.2 Simulated values of MOS based resistance [169]

| Resistance b | oias voltages | Resistance value             |  |

|--------------|---------------|------------------------------|--|

| $V_{1i}(V)$  | $V_{2i}(V)$   | $R_{i}\left( k\Omega\right)$ |  |

| 1.310        | -1.310        | 1                            |  |

| 0.869        | -0.869        | 2                            |  |

| 0.726        | -0.726        | 5                            |  |

| 0.711        | -0.711        | 10                           |  |

#### 2.7 CONCLUDING REMARKS

In this chapter, the description of OFCC as a CM block, its circuit symbol, port matrix and port relationships are given. OFCC implementation using CMOS based schematic and commercially available IC AD844, is provided in next section. It is used for simulation and experimental purpose respectively throughout the complete study. The current and voltage transfer characteristics of OFCC is also verified to check the functionality of the block. The basic amplifier configurations such as voltage, current, transadmittance, transimpedance and voltage difference amplifier followed by their respective responses and derivations are given. These responses confirm the behavior of OFCC as an amplifier. Nonidealities of OFCC is also analyzed and discussed. The MOS based resistor implementation is also studied and utilized wherever required in proposed circuits to provide electronic tunability.

### CHAPTER - 3

## OFCC BASED TA MODE FIRST ORDER FILTER

This chapter includes various details, analysis and simulated results of following published paper:

Deva Nand, Neeta Pandey, "Transadmittance Mode First Order LP/HP/AP Filter and its Application as an Oscillator" IOP Conf. Ser.: Mater. Sci. Eng. Vol. 225 (012150), 2017. DOI: 10.1088/1757-899X/225/1/012150 (Scopus indexed)

#### 3.1 INTRODUCTION

There is widespread use of filters in instrumentation and communication systems. The filter comprises of interconnection of passive components (inductors, capacitors and resistors) and active devices such as controlled sources, amplifiers, transistor etc. [34]. Low pass, high pass, bandpass and band reject/notch are typical filter categories when magnitude is of prime concern while all pass filter or delay equalizers is important when phase or delay specifications are to be met while keeping magnitude constant. Low pass filter passes frequencies (passband) from dc to cut off frequencies while higher frequencies are attenuated. High pass filter attenuates frequencies below cut off frequencies while passing all frequencies above it. Band pass (reject) filter passes (attenuates) passband of frequencies while attenuating (passing) remaining frequencies. In general, the transfer function of first order transfer filter is given by