## REALIZATION OF NON-LINEAR SIGNAL PROCESSING BLOCKS, STANDARD FUNCTIONS AND APPLICATION TO CRYPTOGRAPHY

## A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

## MASTER OF TECHNOLOGY IN CONTROL & INSTRUMENTATION

Submitted by:

# **ANKUR SINGH**

# 2K16/C&I/04

Under the supervision of

# PROF. PRAGATI KUMAR

## DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

# JULY, 2018

# DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

### CANDIDATE'S DECLARATION

I, Ankur Singh, Roll No. 2K16/C&I/04 student of M.Tech. (Control & Instrumentation), hereby declare that the Dissertation titled "Realization of Non-Linear Signal Processing Blocks, Standard Functions and Application to Cryptography" which is submitted by me to the Department of Electrical Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: Delhi Date:

#### ANKUR SINGH

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CERTIFICATE**

I hereby certify that the Dissertation titled "**Realization of Non-Linear Signal Processing Blocks, Standard Functions and Application to Cryptography**" which is submitted by Mr. Ankur Singh, Roll No 2K16/C&I/04 Electrical Engineering Department, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the students under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: PROF. PRAGATI KUMAR SUPERVISOR Professor

### **ABSTRACT**

Non-Linear signal processing circuits are used in various streams of engineering such as telecommunication, control system, digital design, biomedical, information security etc. Various types of signal processing methods such as analog or digital are used according to applications and requirements. CMOS non-linear signal processing circuits consume less power whereas bipolar non-linear circuits provide faster response and also provide wide operating range.

In this dissertation linear term generator and higher order non-linear blocks such as squarer generator, cubic generator, power four generator and power five generator blocks have been implemented.

The functions like sine, cosine, exponential, logarithmic, tangent hyperbolic inverse functions and the other two functions viz. Gaussian and sigmoid, which are extensively used in artificial neural network are also implemented in this dissertation. These functions are implemented in current mode since this mode is found to be more advantageous as compared to voltage mode implementation.

The analog implementation of elliptic curve using these non-linear blocks is also presented in this dissertation which can be further used in Cryptography.

### **ACKNOWLEDGEMENT**

First and foremost, I express my deep sense of gratitude to my supervisor, counselor and advisor **Prof. Pragati Kumar**, Professor, department of Electrical Engineering for his constant guidance, support, motivation and encouragement throughout the period this work was carried out. His readiness for consultation at all times, his educative comments, his concern and assistance has been invaluable.

I want to thank **Prof. Madhusudan Singh,** Head of Electrical Department for building this platform and creating such an energetic environment for research work.

I want to thank **Mr. Ajishek Raj** (Research Scholar) for his guidance and support and all the staff of the Non-Linear Signal Processing Lab, Electrical Engineering Department for their fullest cooperation.

I would like to thank my friends and all those who have directly or indirectly helped me in completion of the thesis well in time.

Finally, I wish to thank my parents for their moral support and confidence showed in me to pursue M. Tech at an advanced stage of my academic career.

#### ANKUR SINGH

## **CONTENTS**

| CANDIDATE'S DECLARATION                     | ii         |  |  |  |

|---------------------------------------------|------------|--|--|--|

| CERTIFICATE                                 | iii        |  |  |  |

| ABSTRACT i                                  |            |  |  |  |

| ACKNOWLEDGEMENT                             |            |  |  |  |

| VONTENTS                                    |            |  |  |  |

| LIST OF FIGURES                             | xi         |  |  |  |

| LIST OF TABLES                              | xiv        |  |  |  |

| LIST OF SYMBOLS, ABBREVIATION               | XV         |  |  |  |

| CHAPTER 1 INTRODUCTION                      | 1          |  |  |  |

| 1.1 INTRODUCTION                            | 1          |  |  |  |

| 1.2 ANALOG VS DIGITAL SIGNAL PROCESSING     | 2          |  |  |  |

| 1.3 VOLTAGE MODE, CURRENT MODE AND MIXED MO | ODE SIGNAL |  |  |  |

| PROCESSING                                  | 3          |  |  |  |

| 1.3.1 VOLTAGE MODE SIGNAL PROCESSING        | 3          |  |  |  |

| 1.3.2 CURRENT MODE SIGNAL PROCESSING        | 4          |  |  |  |

| 1.3.3 MIXED MODE SIGNAL PROCESSING          | 4          |  |  |  |

| 1.4 CRYPTOGRAPHY AND NETWORK SECURITY       | 4          |  |  |  |

| 1.5 ORGANISATION OF THE THESIS              | 5          |  |  |  |

| REFRENCES                                   | 6          |  |  |  |

| CHAPTER 2 NON LINEAR BLOCKS AND FUNCTION    | ONS 7      |  |  |  |

| 2.1 INTRODUCTION                            | 7          |  |  |  |

| 2.2 TRANSLINEAR PRINCIPLE                   | 7          |  |  |  |

| 2.3 TRANSLINEAR BASED CIRCUITS              | 9          |  |  |  |

| 2.3.1 SQUARER AND LINEAR BLOCK              | 9          |  |  |  |

| 2.3.2 ANALYSIS OF LINEAR AND SQUARE GEN     | ERATOR 10  |  |  |  |

| 2.3.3 DEVIATION FROM IDEAL CHARACTERST      | ICS 12     |  |  |  |

| 2.3.4 SIMULATION                            | 12         |  |  |  |

| 2.3.5 STANDARD SQUARER CIRCUIT              | 16         |  |  |  |

| 2.4 LOG AND EXPONENTIAL BLOCKS              | 18         |  |  |  |

|     | 2.4.1 | LO     | OGARITH   | MIC BI | .OCK    |         |       |       |          |      | 18 |

|-----|-------|--------|-----------|--------|---------|---------|-------|-------|----------|------|----|

|     | 2.4.2 | A      | NALYSIS ( | OF LOO | GARITH  | MIC BL  | OCK   |       |          |      | 19 |

|     | 2.4.3 | EZ     | XPONENT   | IAL BL | .OCK    |         |       |       |          |      | 21 |

|     | 2.4.4 | A      | NALYSIS ( | OF EXI | PONENT  | TIAL BL | OCK   |       |          |      | 22 |

| 2.5 | TRAN  | ISLIN  | EAR PRIN  | CIPLE  | BASED   | CURRE   | NT M  | ODE   | SQUARE   |      |    |

|     | ROOT  | TING I | BLOCK     |        |         |         |       |       |          |      | 24 |

|     | 2.5.1 | DER    | IVATION   | AND    | SIMUL   | ATION   | OF    | TRAN  | ISLINEAR | BAS  | ED |

|     |       | SQU    | ARE ROO   | Г BLO  | CK      |         |       |       |          |      | 25 |

| 2.6 | SQU   | ARE F  | ROOT BLO  | CK US  | ING CM  | IOS     |       |       |          |      | 27 |

|     | 2.6.1 | IN     | IPLEMEN   | ΓΑΤΙΟ  | N OF SÇ | UARE I  | ROOT  | BLO   | CK       |      | 27 |

| 2.7 | SIGM  | 10IDA  | AL FUNCT  | ION    |         |         |       |       |          |      | 29 |

| 2.8 | CON   | CLUS   | ION       |        |         |         |       |       |          |      | 33 |

| REI | FREN  | CES    |           |        |         |         |       |       |          |      | 34 |

| CH  | APTE  | R 3    | STAN      | NDARI  | D MOD   | ULES    | FOR   | APP   | ROXIMAT  | ION  | OF |

| FUI | NCTIC | ONS    |           |        |         |         |       |       |          |      | 36 |

| 3.1 | INTR  | ODU    | CTION     |        |         |         |       |       |          |      | 36 |

| 3.2 | NON   | INVEI  | RTING CU  | RREN   | Γ MIRR( | OR AND  | INVE  | ERTIN | G CURREN | ΝT   |    |

|     | MIRR  | OR     |           |        |         |         |       |       |          |      | 36 |

|     | 3.2.1 | N      | ON INVER  | TING   | CURREN  | NT MIRI | ROR   |       |          |      | 37 |

|     | 3.2.2 | IN     | VERTING   | CURR   | ENT MI  | RROR    |       |       |          |      | 38 |

| 3.3 | LINE  | AR T   | ERM GENI  | ERATO  | OR/BLOO | СК      |       |       |          |      | 39 |

|     | 3.3.1 | ID     | EAL ANA   | LYSIS  | OF LIN  | EAR TE  | RM G  | ENER  | ATOR     |      | 40 |

|     | 3.3.2 | EZ     | XACT ANA  | ALYSIS | OF LIN  | EAR TE  | ERM ( | GENEI | RATOR    |      | 41 |

|     | 3.3.3 | DC     | TRANSF    | ER (   | CHARA   | CTERST  | ICS   | OF    | LINEAR   | TE   | RM |

|     |       | GEN    | ERATOR    |        |         |         |       |       |          |      | 45 |

|     | 3.3.4 | TI     | RANSIENT  | ANAI   | LYSIS O | F LINEA | AR BL | OCK   |          |      | 45 |

|     | 3.3.5 | A      | C ANALYS  | SIS OF | LINEAF  | R BLOCI | X     |       |          |      | 47 |

|     | 3.3.6 | C      | OMPARITI  | VE AN  | ALYSIS  | S WITH  | IDEA  | L CHA | ARACTERI | STIC | 49 |

| 3.4 | SQU   | ARE T  | TERM GEN  | ERAT   | OR/BLO  | СК      |       |       |          |      | 50 |

|     | 3.4.1 | ID     | EAL ANA   | LYSIS  | OF SQU  | ARE TE  | ERM ( | GENEI | RATOR    |      | 50 |

|     | 3.4.2 | EZ     | XACT ANA  | ALYSIS | S OF SQ | UARE T  | ERM   | GENE  | RATOR/BI | LOCK | 52 |

|     | 3.4.3 | DC     | TRANSF    | ER C   | CHARAC  | TERIST  | TICS  | OF    | SQUARE   | TE   | RM |

|     |       | GEN    | ERATOR    |        |         |         |       |       |          |      | 55 |

viii

| 3.4.4 TRANSIENT ANALYSIS OF SQUARE BLOCK 56                 |

|-------------------------------------------------------------|

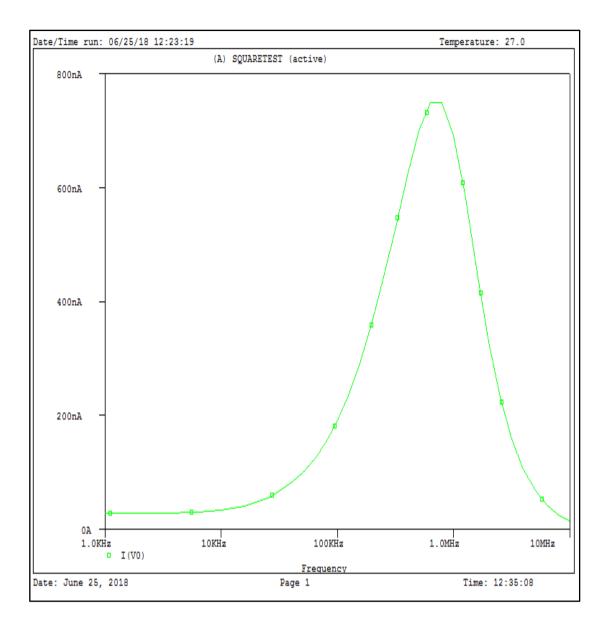

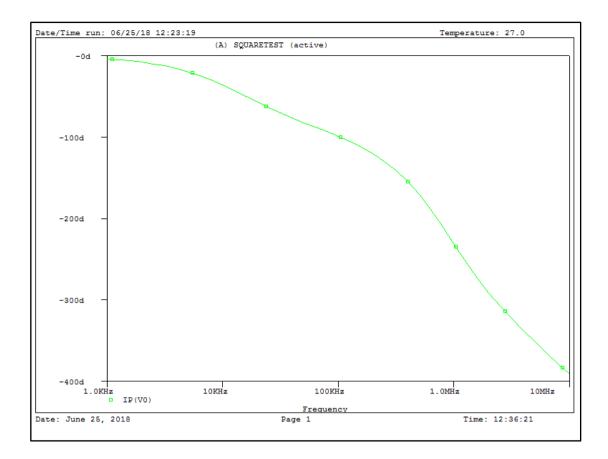

| 3.4.5AC ANALYSIS OF SQUARE GENERATOR/BLOCK57                |

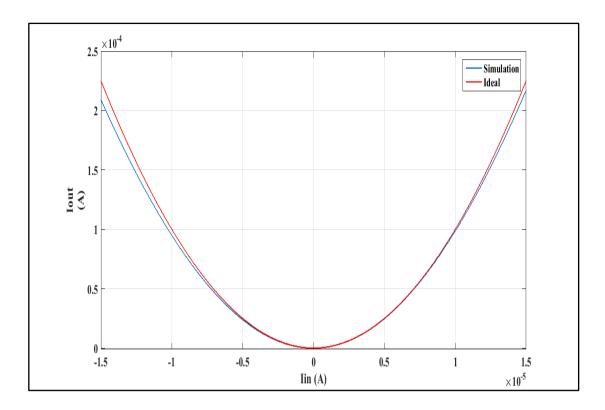

| 3.4.6 COMPARITIVE ANALYSIS WITH IDEAL SQUARE                |

| CHARACTERISTICS 59                                          |

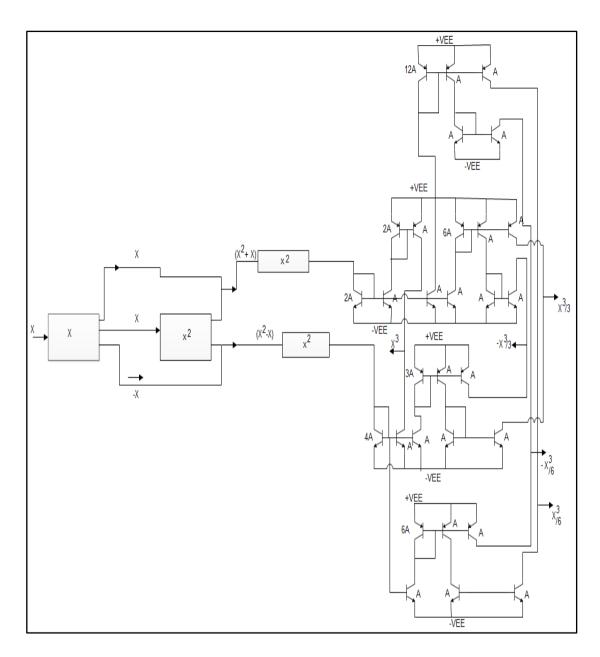

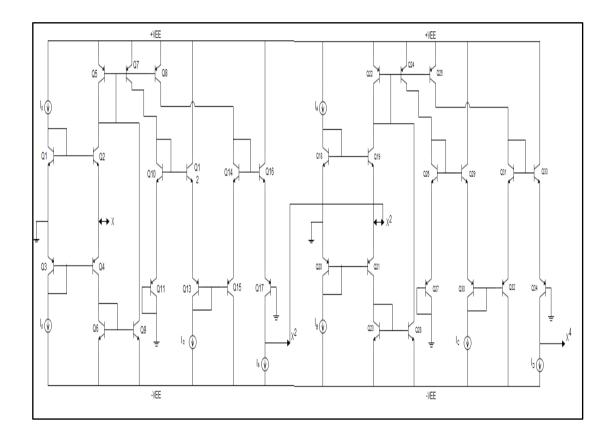

| 3.5 CUBIC TERM GENERATOR/BLOCK 60                           |

| 3.5.1 EXACT ANALYSIS OF CUBIC TERM GENERATOR 63             |

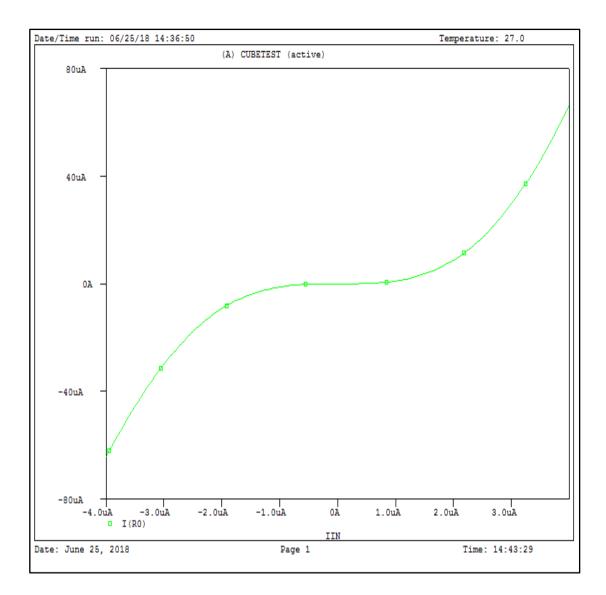

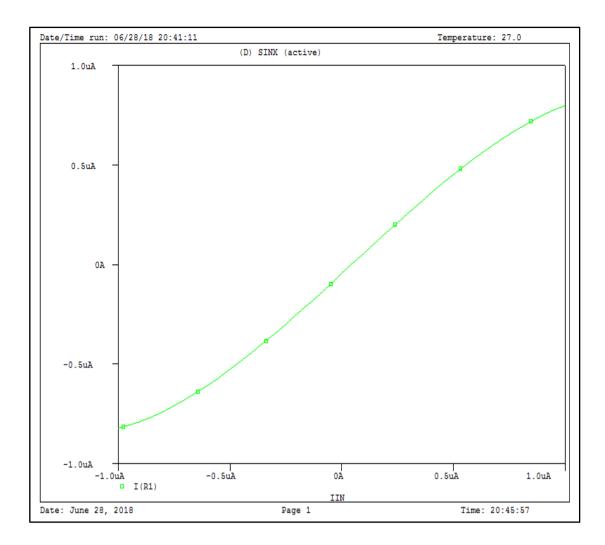

| 3.5.2 DC TRANSFER CHARACTERISTICS OF CUBIC BLOCK 64         |

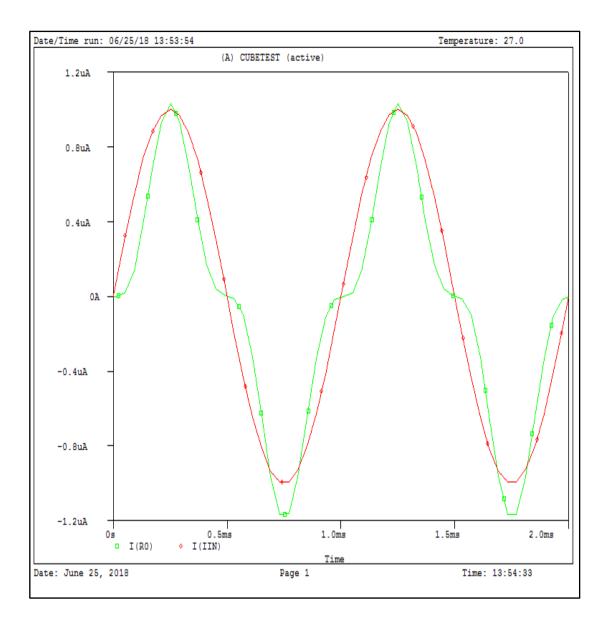

| 3.5.3 TRANSIENT ANALYSIS OF CUBIC GENERATOR/BLOCK 65        |

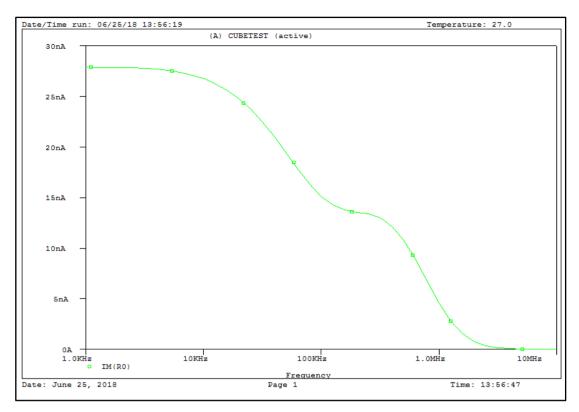

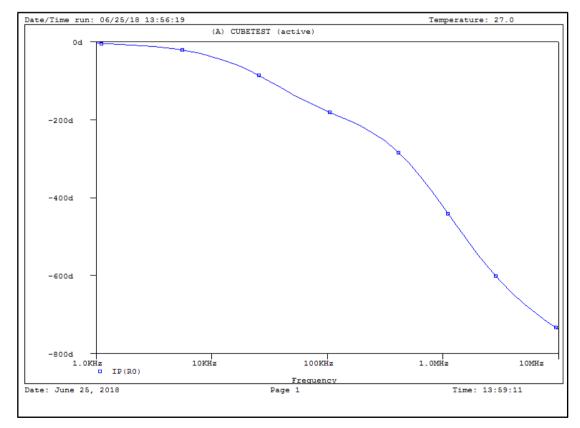

| 3.5.4 AC ANALYSIS OF CUBIC GENERATOR/BLOCK 66               |

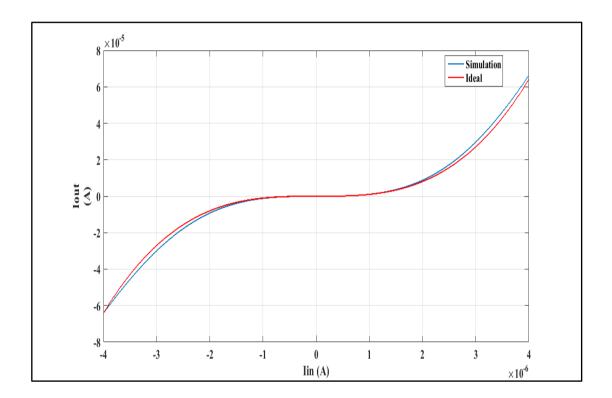

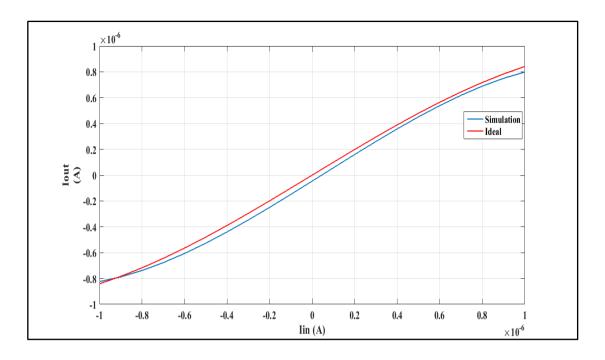

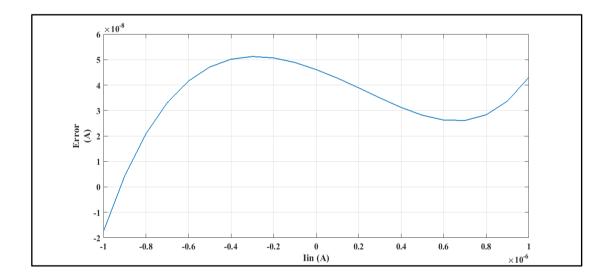

| 3.5.5 COMPARITIVE ANALYSIS WITH IDEAL BEHAVIOR 68           |

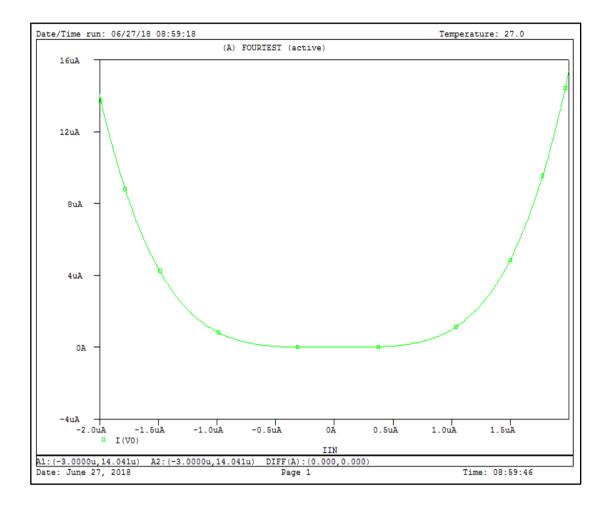

| 3.6 FOURTH ORDER GENERATOR BLOCK 68                         |

| 3.6.1 DC TRANSFER CHARACTERISTICS OF FOURTH ORDER           |

| GENERATOR BLOCK 69                                          |

| 3.6.2 TRANSIENT ANALYSIS FOR FOURTH TERM GENERATOR 70       |

| 3.6.3 AC ANALYSIS FOR FOURTH TERM GENERATOR/BLOCK 71        |

| 3.6.4 COMPARITIVE ANALYSIS FOURTH ORDER TERM GENERATOR      |

| WITH IDEAL CHARACTERISTICS 73                               |

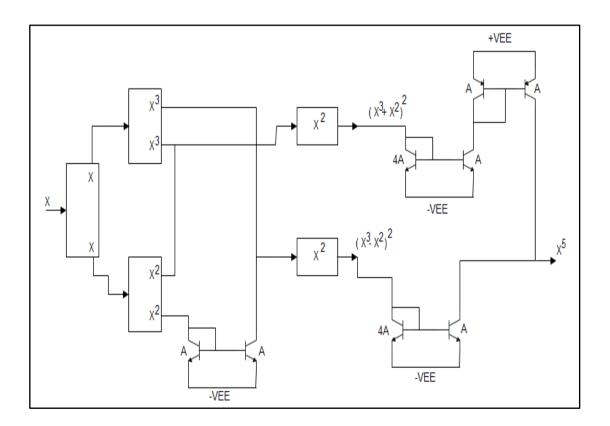

| 3.7 FIFTH ORDER TERM GENERATOR/BLOCK74                      |

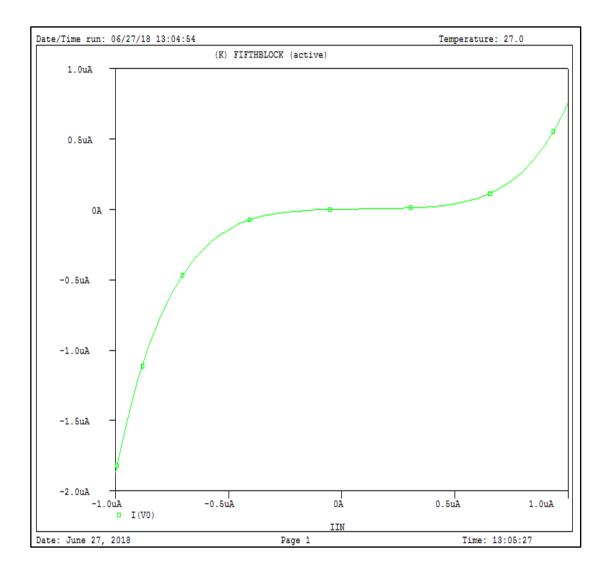

| 3.7.1 DC TRANSFER CHARACTERSTICS OF FIFTH ORDER             |

| GENERATOR/BLOCK 75                                          |

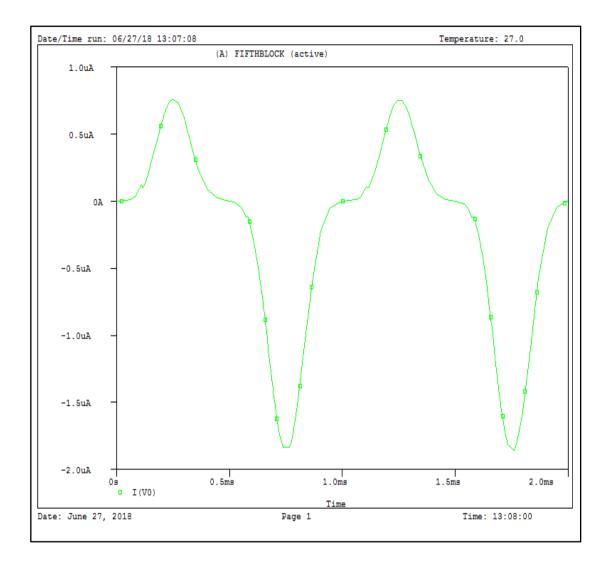

| 3.7.2 TRANSIENT ANALYSIS OF THE FIFTH ORDER                 |

| GENERATOR/BLOCK 76                                          |

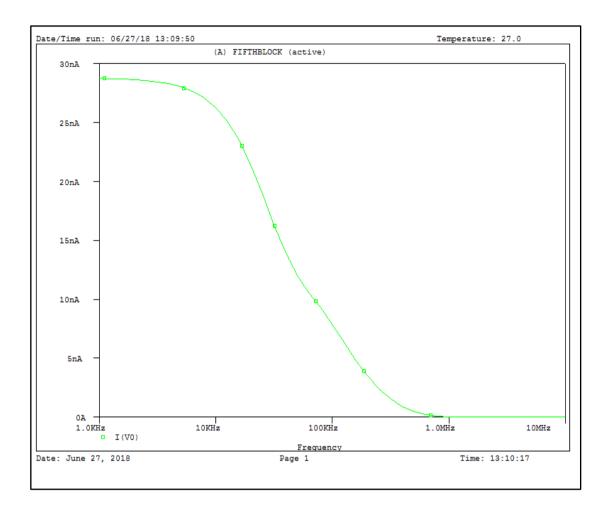

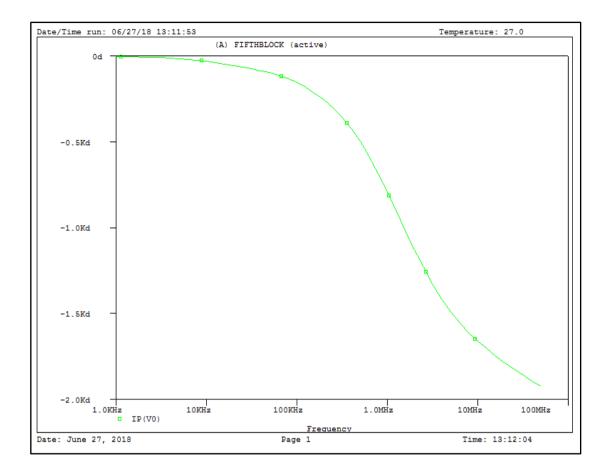

| 3.7.3 AC ANALYSIS OF FIFTH ORDER GENERATOR/BLOCK 76         |

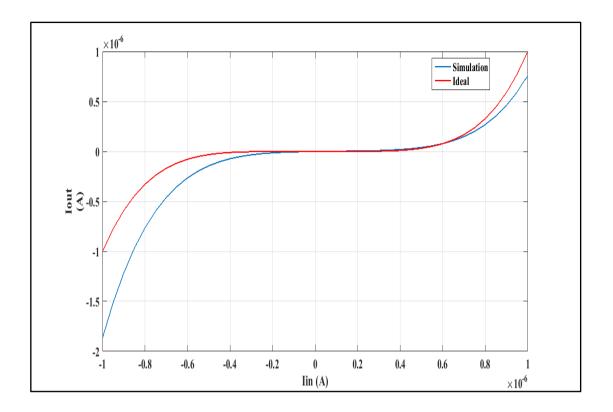

| 3.7.4 COMPARISON WITH IDEAL CHARACTERISTIC FOR FIFTH        |

| ORDER TERM 78                                               |

| 3.8 CONCLUSION 79                                           |

| REFRENCES 80                                                |

| CHAPTER 4 BIPOLAR IMPLEMENTATION OF NON LINEAR FUNCTIONS 81 |

| 4.1 INTRODUCTION 81                                         |

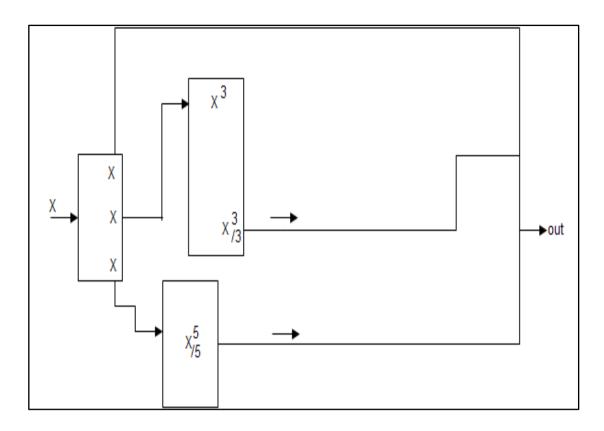

| 4.2 TAYLOR SERIES EXPANSION 81                              |

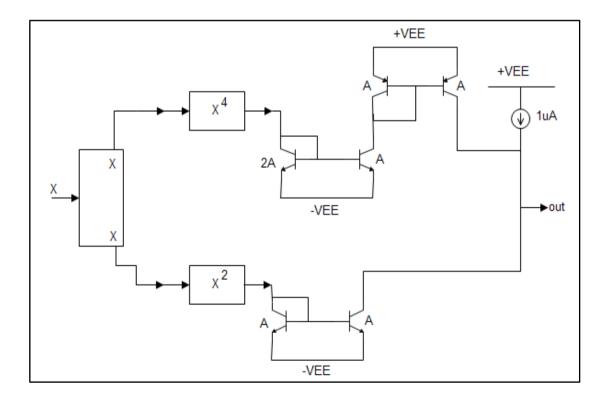

| 4.3 GENERATION OF GAUSSIAN FUNCTION82                       |

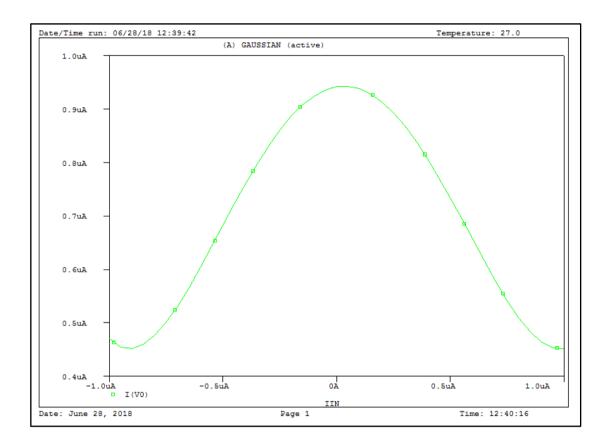

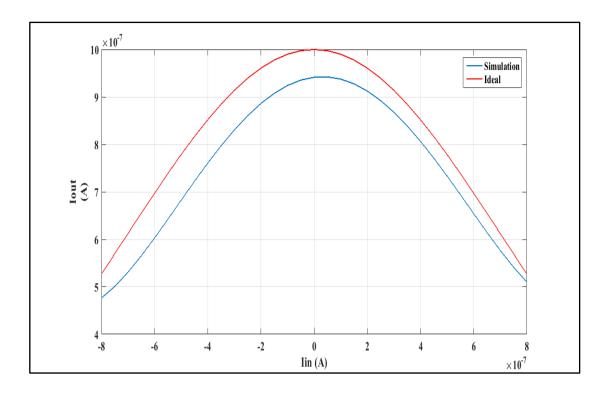

| 4.3.1 DC TRANSFER CHARACTERISTICS OF GAUSSIAN BLOCK 83      |

| 4.3.2COMPARISON WITH IDEAL CHARACTERISTIC83                 |

| 4.3.3 APPLICATION OF GAUSSIAN FUNCTION                | 85     |

|-------------------------------------------------------|--------|

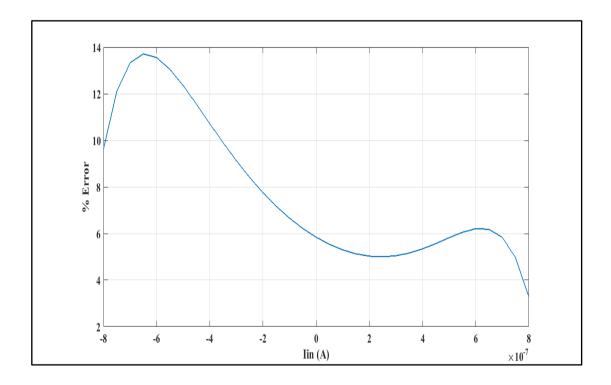

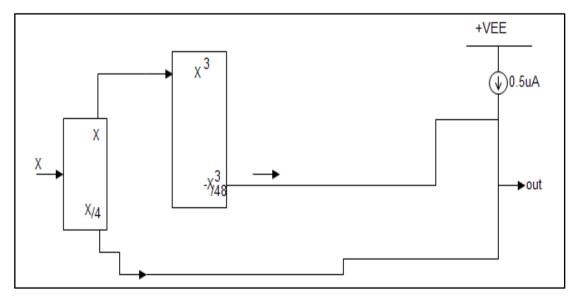

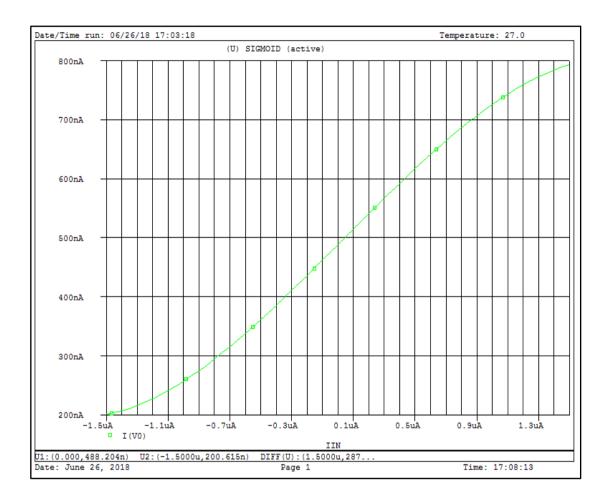

| 4.4 GENERATION OF SIGMOID FUNCTION                    | 85     |

| 4.4.1 DC TRANSFER CHARACTERISTIC OF SIGMOID BLOCK     | K 86   |

| 4.4.2 COMPARISION WITH IDEAL CHARACTERISTICS          | 86     |

| 4.4.3 APPLICATION OF SIGMOID FUNCTION                 | 88     |

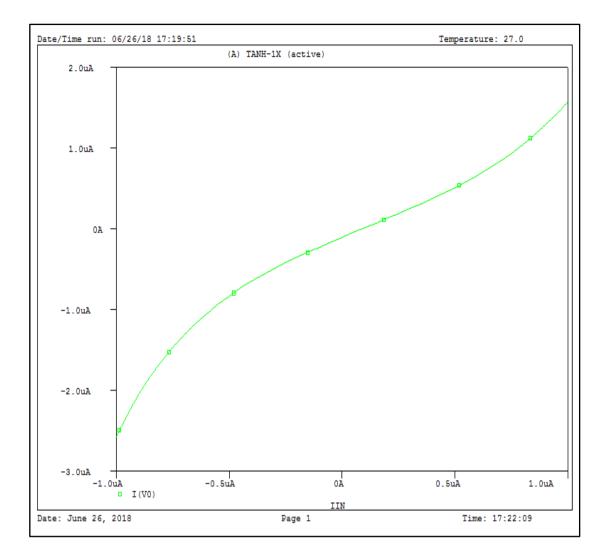

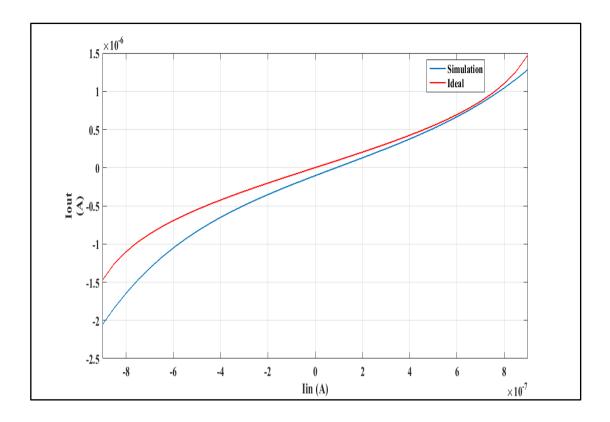

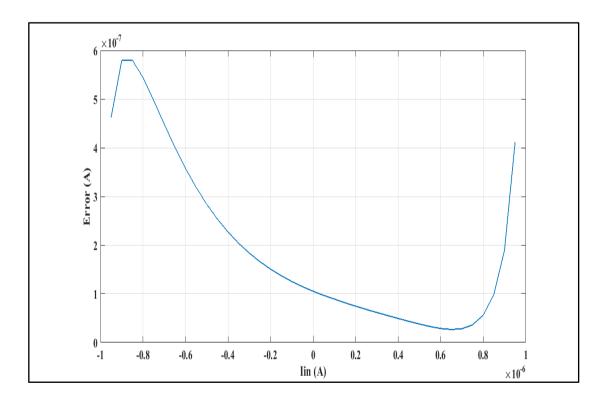

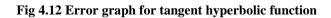

| 4.5 GENERATION OF TANGENT HYPERBOLIC INVERSE FUNCTION | N 88   |

| 4.5.1 DC TRANSFER CHARACTERISTICS OF TANGENT HYPE     | RBOLIC |

| INVERSE FUNCTION                                      | 89     |

| 4.5.2 COMPARISON OF TANGENT HYPERBOLIC INVERSE FU     | NCTION |

| WITH ITS IDEAL CHARACTERISTIC                         | 90     |

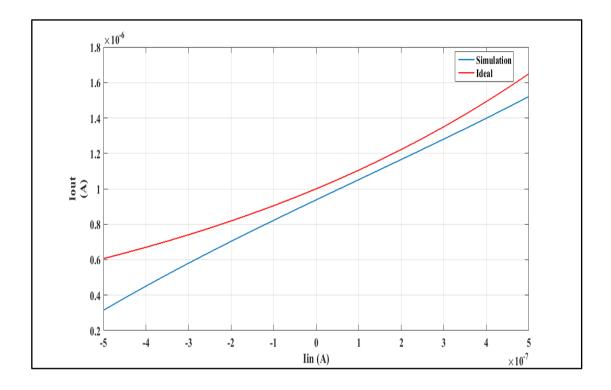

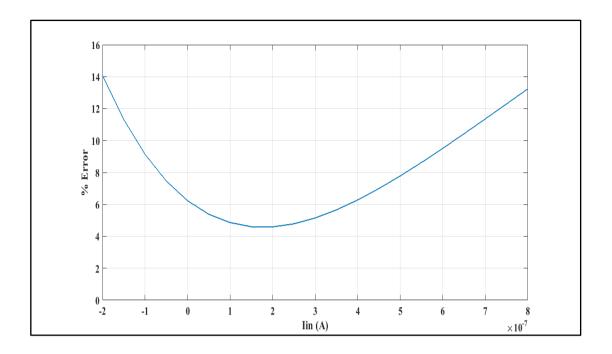

| 4.6 GENERATION OF EXPONENTIAL FUNCTION                | 92     |

| 4.6.1 DC TRANSFER CHARACTERISTICS OF THE EXPON        | ENTIAL |

| BLOCK                                                 | 93     |

| 4.6.2 COMPARISON WITH IDEAL CHARACTERISTIC            | FOR    |

| EXPONENTIAL FUNCTION                                  | 94     |

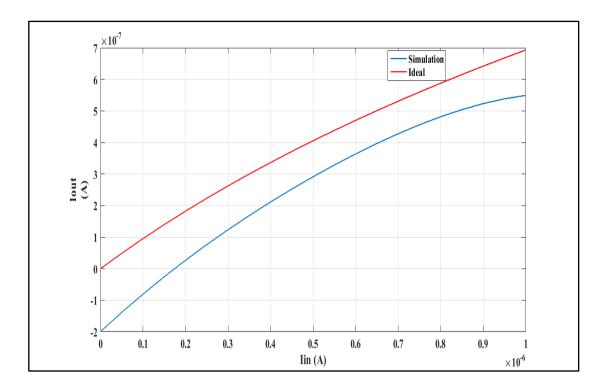

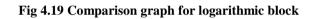

| 4.7 GENERATION OF LOGARITHMIC FUNCTION                | 95     |

| 4.7.1 DC TRANSFER CHARACTERISTIC OF THE LOGAR         | ITHMIC |

| BLOCK                                                 | 96     |

| 4.7.2 COMPARISON WITH IDEAL LOGARITHMIC FUNCTION      | N 97   |

| 4.8 GENERATION OF SINE FUNCTION USING BASIC MODULES   | 99     |

| 4.8.1 SINE FUNCTION DC ANALYSIS                       | 99     |

| 4.8.2 COMPARISON WITH IDEAL CHARACTERSTIC FO          | R SINE |

| FUNCTION                                              | 100    |

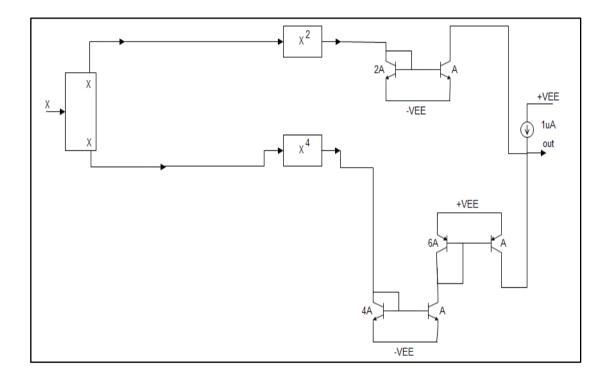

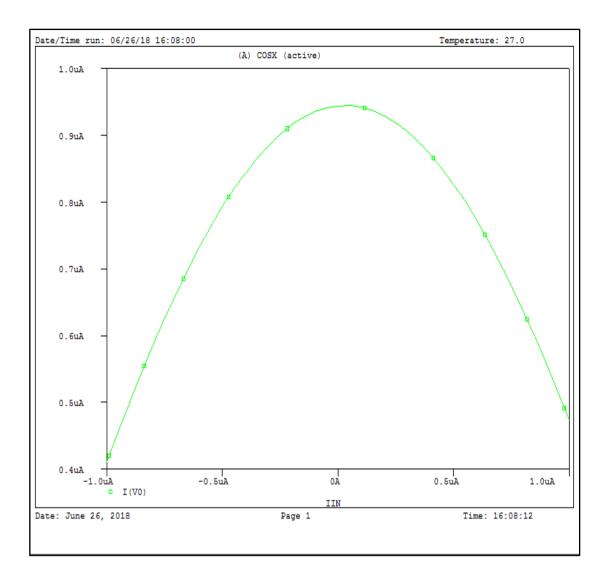

| 4.9 GENERATION OF COSINE FUNCTION                     | 102    |

| 4.9.1 DC TRANSFER CHARACTERISTICS OF COSINE BLOCK     | X 102  |

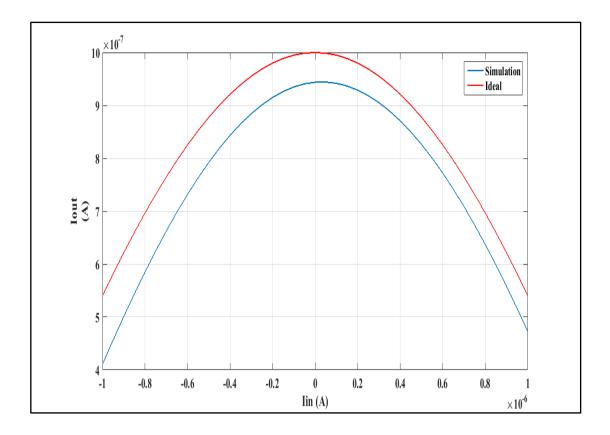

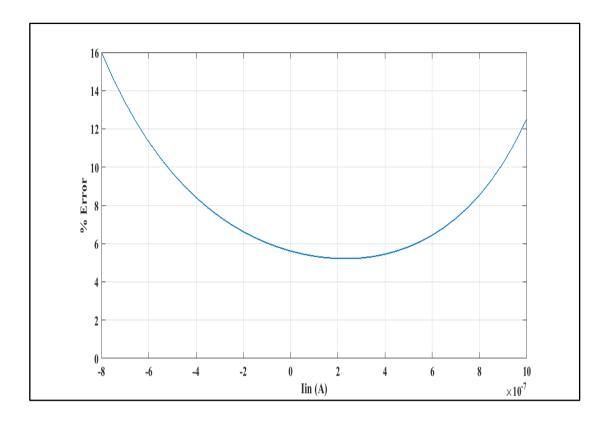

| 4.9.2 COMPARISON OF IMPLEMENTED BLOCK WITH IDEAL      | COSINE |

| FUNCTION                                              | 103    |

| 4.10 CONCLUSION                                       | 105    |

| REFRENCES                                             | 106    |

| CHAPTER 5 BIPOLAR IMPLEMENTATION OF ELLIPTIC CUR      | VE FOR |

| CRYPTOGRAPHY                                          | 107    |

| 5.1 INTRODUCTION                                      | 107    |

| 5.2 ELLIPTIC CURVE                                    | 107    |

ix

|     | 5.2.1   | PROPERTIES OF ELLIPTIC CURVE                | 108 |

|-----|---------|---------------------------------------------|-----|

| 5.3 | IMPLEN  | MENTATION OF ELLIPTIC CURVE IN CRYPTOGRAPHY | 110 |

| 5.4 | ANALO   | G IMPLEMENTATION OF THE ELLIPTIC CURVE      | 111 |

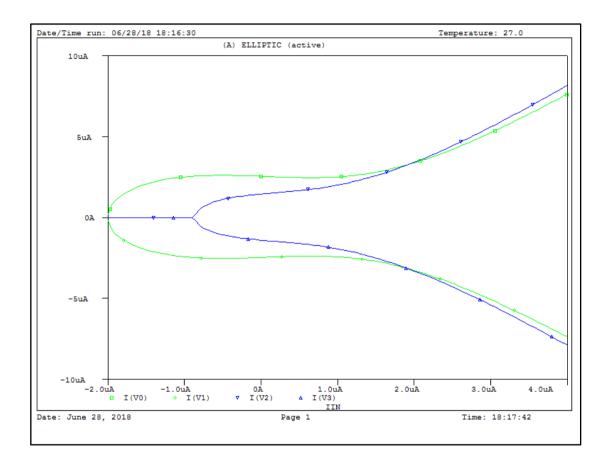

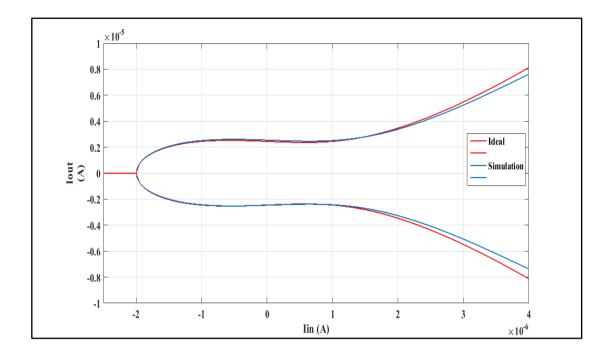

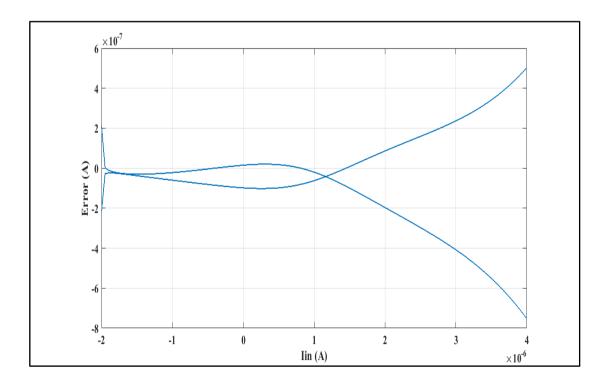

|     | 5.4.1   | DC ANALYSIS OF ELLIPTIC CURVE               | 111 |

|     | 5.4.2   | COMPARISON WITH IDEAL ELLIPTIC CURVE        | 112 |

| 5.5 | CONCL   | USION                                       | 114 |

| RE  | FERENCI | ES                                          | 115 |

| CH  | APTER 6 | 5 SUMMARY AND FUTURE SCOPE                  | 116 |

| 6.1 | SUMMA   | ARY                                         | 116 |

| 6.2 | FUTUR   | E SCOPE                                     | 117 |

| API | PENDICE | ES                                          | 118 |

| API | PENDIX  | 1                                           | 118 |

| API | PENDIX  | 2                                           | 120 |

## **LIST OF FIGURES**

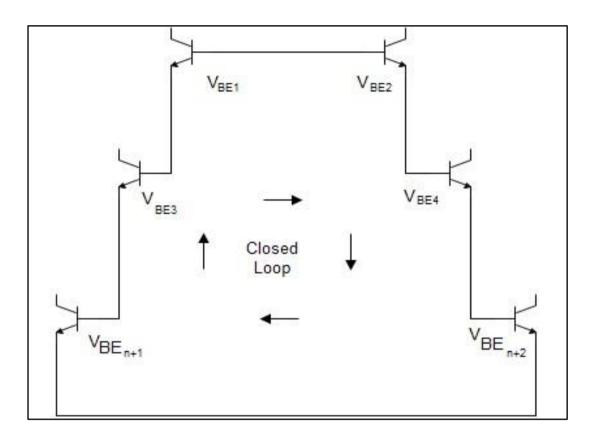

| Fig 2.1 Translinear Loop                                         | 8  |

|------------------------------------------------------------------|----|

| Fig 2.2 Linear And Square Block                                  | 10 |

| Fig 2.3 Output of linear term for long channel length            | 13 |

| Fig 2.4 Square results for long channel length                   | 14 |

| Fig 2.5 Square result for Short channel length                   | 15 |

| Fig 2.6 Linear result for short channel length                   | 15 |

| Fig 2.7 Standard Square Circuit                                  | 16 |

| Fig 2.8 DC characteristics of Standard square block              | 18 |

| Fig 2.9 Logarithimic Block                                       | 19 |

| Fig 2.10 Logarithmic simulated result                            | 21 |

| Fig 2.11 Exonential Circuit                                      | 22 |

| Fig 2.12 DC characteristics of exponential block                 | 24 |

| Fig 2.13 Translinear Based square root circuit                   | 25 |

| Fig 2.14 DC characteristics of Square root circuit               | 26 |

| Fig 2.15 CMOS Square root circuit                                | 27 |

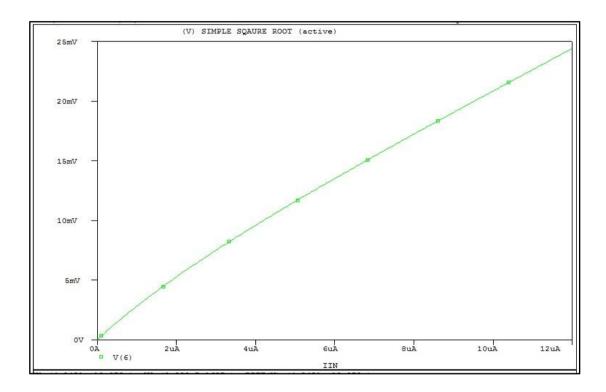

| Fig 2.16 Simulated result for CMOS square root circuit           | 29 |

| Fig 2.17 Sigmoid Function Generator                              | 30 |

| Fig 2.18 DC transfer characterstics of Sigmoid function          | 33 |

| Fig 3.1 Non Inverting Current mirror                             | 37 |

| Fig 3.2 Inverting Current Mirror                                 | 39 |

| Fig 3.3 Linear Term Generator/block                              | 40 |

| Fig 3.4 DC characterstics of Linear Term generator               | 45 |

| Fig 3.5 Transient response of positive linear term generator     | 46 |

| Fig 3.6 Transient Result for negative linear term generator      | 47 |

| Fig 3.7 Gain magnitude versus frequncy response for linear block | 48 |

| Fig 3.8 Phase angle versus frequency for linear block            | 48 |

| Fig 3.9 Comparison with Ideal Characteristics                    | 49 |

| Fig 3.10 Square Term Generator Circuit                           | 50 |

| Fig 3.11 DC characteristics for square term generator/block      | 56 |

| Fig 3.12 Transient analysis for square block                     | 57 |

| Fig 3.13 Gain Magnitude versus frequency for Square Block58             |

|-------------------------------------------------------------------------|

| Fig 3.14 Phase angle versus frequency for Square Block59                |

| Fig 3.15 Comparison graph for square block with ideal characteristic60  |

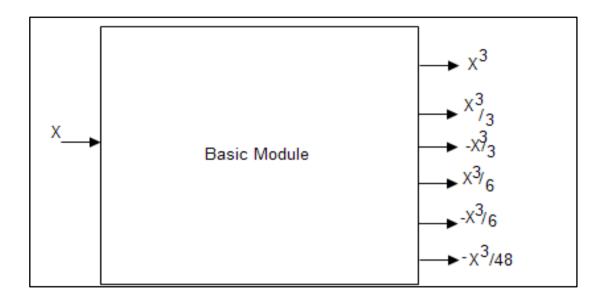

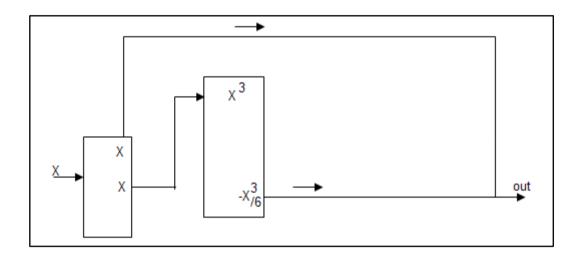

| Fig 3.16 Cubic term generator Block62                                   |

| Fig 3.17 Block Diagram For cubic generator block63                      |

| Fig 3.18 DC characteristic of Cube term generator                       |

| Fig 3.19 Transient response for Cube term generator/block66             |

| Fig 3.20 Gain magnitude versus frequency for Cubic generator67          |

| Fig 3.21 Phase angle versus frequency for cubic generator67             |

| Fig 3.22 Comparison between Ideal and simulated results68               |

| Fig 3.23 Fourth term generator circuit69                                |

| Fig 3.24 DC transfer characteristics for fourth term generator70        |

| Fig 3.25 Transient response for Fourth term generator/block71           |

| Fig 3.26 Gain Magnitude versus frequency graph for fourth term          |

| generator/block                                                         |

| Fig 3.27 Phase angle versus frequency graph for fourth term             |

| generator/block                                                         |

| Fig 3.28 Comparison graph between Simulated and Ideal values for fourth |

| order term73                                                            |

| Fig 3.29 Fifth Order Generator/Block74                                  |

| Fig 3.30 DC characteristics for fifth order term generator75            |

| Fig 3.31Transient analysis of fifth order block76                       |

| Fig 3.32 Gain magnitude versus frequency for fith order block77         |

| Fig 3.33 Phase angle versus frequency for Fifth order block78           |

| Fig 3.34 Comparison between Ideal and Simulated result for fifth order  |

| term generator                                                          |

| Fig 4.1 Gaussian Block                                                  |

| Fig 4.2 Gaussian Function Plot                                          |

| Fig 4.3 Comparison graph with Ideal Characteristics                     |

| Fig 4.4 Percentage error graph                                          |

| Fig 4.5 Sigmoid Block                                                   |

| Fig 4.6 DC characteristics of Sigmoid Block                             |

| Fig 4.7 Sigmoid comparison graph with ideal characteristics             |

| Fig 4.8 Percentage Error Graph for sigmoid function       |     |

|-----------------------------------------------------------|-----|

| Fig 4.9 Tangent Hyperbolic Inverse Block                  | 89  |

| Fig 4.10 Tangent Hyperbolic Inverse Function Plot         | 90  |

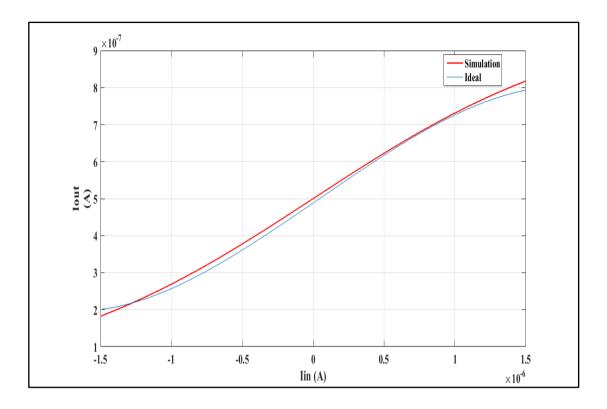

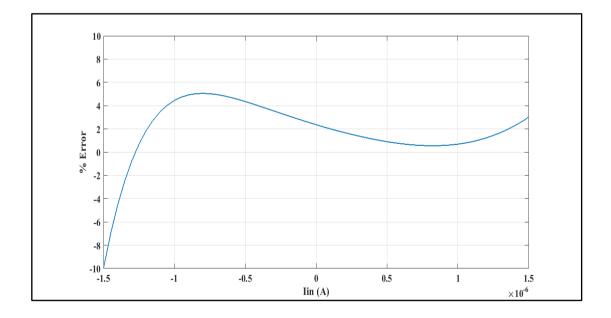

| Fig 4.11 Comparison Graph with Ideal Characteristics      | 91  |

| Fig 4.12 Error graph for tangent hyperbolic function      | 91  |

| Fig 4.13 Exponential Block                                | 92  |

| Fig 4.14 DC transfer characteristics of exponential block | 93  |

| Fig 4.15 Comparison graph for exponential function        | 94  |

| Fig 4.16 Percentage error graph for exponential function  | 95  |

| Fig 4.17 Logarithmic block                                | 96  |

| Fig 4.18 Logarithmic Block DC characteristic plot         | 97  |

| Fig 4.19 Comparison graph for logarithmic block           | 98  |

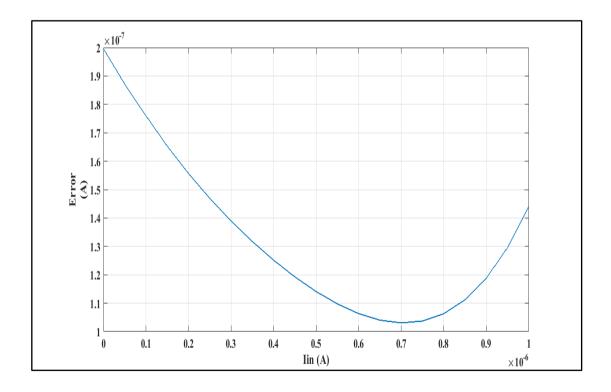

| Fig 4.20 Error plot for Logarithmic block                 | 98  |

| Fig 4.21 Sine Function Generator Block                    | 99  |

| Fig 4.22 Sine function plot                               |     |

| Fig 4.23 Comparison Plot for Sine Function                |     |

| Fig 4.24 Error graph for Sine Function                    | 101 |

| Fig 4.25 Cosine block                                     |     |

| Fig 4.26 Cosine DC transfer characteristics               |     |

| Fig 4.27 Comparison Graph for Cosine function             | 104 |

| Fig 4.28 Percentage error graph for Cosine function       |     |

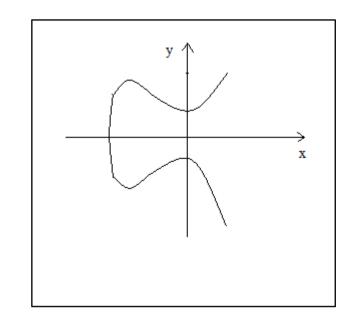

| Fig 5.1 Elliptic Curve                                    |     |

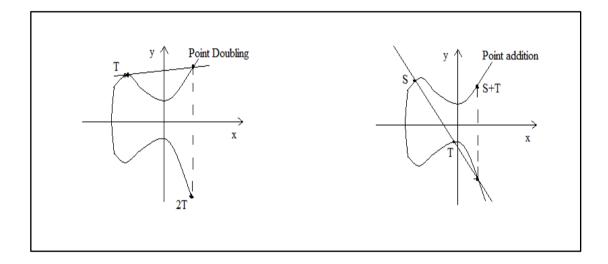

| Fig 5.2 Properties Of Elliptic Curve                      | 109 |

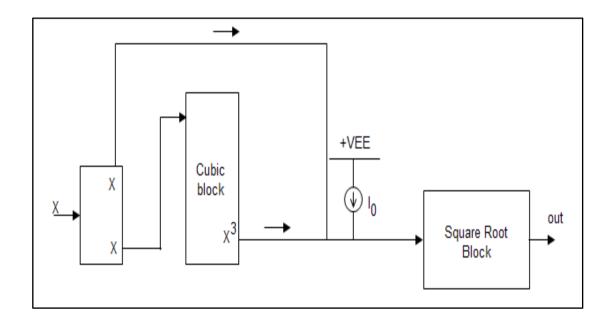

| Fig 5.3 Elliptic Curve Generator Block                    | 111 |

| Fig 5.4 DC Transfer characteristic for Elliptic Curve     | 112 |

| Fig 5.5 Comparison with Ideal elliptic curve              | 113 |

| Fig 5.6 Error graph for Elliptic curve                    | 113 |

## LIST OF TABLES

| Table 2.1 Operating Region                                       |

|------------------------------------------------------------------|

| Table 2: W/L Ratio for CMOS Linear and Squarer Circuit for long  |

| channel length                                                   |

| Table 3: W/L ratio for CMOS Linear and Squarer circuit for Short |

| Channel Length                                                   |

| Table 4: W/L Ratio for CMOS Square Rooting Block121              |

| Table 5: W/L Ratio for CMOS Sigmoid Function Generator121        |

## LIST OF SYMBOLS, ABBREVIATION

V<sub>GS</sub> – Gate to Source Voltage V<sub>SG</sub> – Source to Gate Voltage I<sub>D</sub> – Drain Current  $\mu_n$  – Mobility of Electron  $\mu_p$  – Mobility of Holes W/L - Aspect Ratio  $I_o, I_p, I_q, I_s, I_a, I_b, I_\alpha$  – Biasing Current  $+V_{cc}$ ,  $V_{DD}$ ,  $+V_{EE}$  – Positive Power Supply  $-V_{cc}$ ,  $V_{SS}$ ,  $-V_{EE}$  – Negative Power Supply  $M_i - i^{th} MOSFET$ Q<sub>i</sub> - i<sup>th</sup> Bipolar Transistor V<sub>o</sub> – Output Voltage I<sub>S</sub> – Reverse Saturation Current V<sub>BE</sub> – Base Emitter Voltage V<sub>EB</sub> – Emitter Base Voltage V<sub>T</sub> – Thermal Voltage V<sub>B</sub> – Base Voltage I<sub>C</sub> – Collector Current I<sub>B</sub> – Base Current I<sub>E</sub> – Emitter Current  $\beta_n$  – Collector-Base Current Gain for npn Transistor

$\beta_p$  – Collector-Base Current Gain for pnp Transistor

V<sub>in+</sub> – Positive Input Voltage

V<sub>in-</sub> – Negative Input Voltage

Iout – Output Current

Iin - Input Current

Vt - Threshold Voltage of NMOS and PMOS

V<sub>G</sub> – Gate Voltage

$\lambda$  – Process technology parameter

k<sub>n</sub> - Transconductance for N-Channel MOSFET

k<sub>p</sub>-Transconductance for P-Channel MOSFET

$S_{i}\mbox{-}Aspect$  Ratio of NMOS and PMOS

A<sub>i</sub> – Area of Bipolar Transistor

$\beta$  –Collector-Base Current Gain for both npn and pnp bipolar transitors

$\phi$ ,  $\rho$ ,  $\Upsilon$ ,  $\sigma$ ,  $\mu$ ,  $\gamma$  – Ratios of Collector-Base Current Gain

It - Counter-Clockwise Collector Current

I<sub>W</sub> – Clockwise Collector Current

I<sub>Dt</sub> – Counter-Clockwise Drain Current

IDW- Clockwise Drain Current

C<sub>OX</sub> – oxide capacitance

CMOS - Complementary Metal Oxide Semiconductor

CCII - Current Conveyor Second

## **CHAPTER 1**

## INTRODUCTION

## **1.1 INTRODUCTION**

The presented work describes the design and implementation of currentmode non-linear signal processing blocks and their applications in implementation of some non-linear functions like sine, cosine,  $e^x$ , Gaussian function, ln(1+x) etc. Lot of research work is going in the field of data security and in this dissertation an attempt has also been made to introduce analog implementation of Elliptic curve which may be used in Cryptography to enhance security.

Because of advances made in CMOS technology there has been a significant reduction in the cost of digital hardware which has led to increased use of digital systems. Digital systems offer several advantages over analog systems but the fact which cannot be ignored is that all signals available in natural world are analog. To match with the fast growing digital part, extensive research has been carried out in the field of non linear signal processing in current mode and voltage but current mode approach was found to have some advantages like higher frequency operating range, more accurate, greater value of slew rate, less consumption of power and better linearity [1].

Before going into the detail of implemented work we will first go through the basic concepts associated with signal processing.

## **1.2 ANALOG VS DIGITAL SIGNAL PROCESSING**

The signal processing operations involved in many applications like communication systems, control systems, instrumentation, biomedical signal processing etc can be implemented in two different ways

- 1) Analog or continuous time method and

- 2) Digital or discrete time method.

The analog approach to signal processing was dominant for many years and it use analog circuit element such as resistors, capacitors, transistors, diodes etc. With the advent of digital computer and later microprocessor, the digital signal processing has become dominant now a days. The analog signal processing is based on natural ability of the analog system to solve differential equations that describe a physical system. The solutions are obtained in real time. In contrast digital signal processing relies on numerical calculations. The method may or may not give result in real time. The digital approach has two main advantages over analog approach (1) Flexibility: Same hardware can be used to do various kind of signal processing operation, while in the core of analog signal processing one has to design a system for each kind of operation. (2). Repeatability: The same signal processing operation can be repeated again and again giving same results, while in analog systems there may be parameter variation due to change in temperature or supply voltage [2]. Added to these, digital signal processing has many advantages added to its list like, better noise immunity than analog signals. They are compact and much cheaper than their analog counterpart. Digital signals can be encrypted so that only the intended receiver can decode it. It enables transmission of signals over a long distance and it enables multi-directional transmission simultaneously [3].

Taking these advantages into the account, the designers are forced to look for digital solutions rather than analog in VLSI systems. Even then, analog circuits are fundamentally necessary in many of the today's complex, high performance systems. This is caused by the reality that naturally occurring signals are analog. Practically all signals in the physical world are continuous in both amplitude and time, and hence always analog techniques will be required for conditioning of such signals before they can be processed by digital processing circuits. Therefore analog circuits act as a bridge between the real world and digital systems. Another important reason for the existence of analog signal processing is the bandwidth, which can be some order of magnitudes higher, if the signal is processed in analog circuits than in digital.

## 1.3 VOLTAGE MODE, CURRENT MODE AND MIXED MODE SIGNAL PROCESSING

Over the past couple of decades, the area of analog signal processing has been viewed in terms of the dominant variables of the circuit viz. voltage and current. The signal processing of any electronic and electrical circuits where voltages and currents are important variables. The main cause of using voltage and current in signal processing is that the active devices which are operate usually with resistances or conductances [4].

#### 1.3.1 VOLTAGE MODE SIGNAL PROCESSING

In signal processing circuits, there are two main parameters that are mostly considered: either voltage or current. While others are considered as an unwanted parasitic. In the past, voltage has been considered as the main variable in signal processing. Approach in terms of voltages instead of current is very easier and simpler for the designers [4]. The input impedance of voltage mode device is very high, ideally it is infinite, so that there is no loss of signal power. Through this arrangement, it is possible to connect more input terminals parallel with only signal output terminal. The output impedance of the terminals of voltage mode device are ideally zero. Having low output impedance makes it possible to drive heavy load by single output [4]. There are parasitic resistances as well as capacitances present at input terminals of voltage mode circuit, which can affect performance of the circuit. These parasitic also affect output terminals, which is not allowed to drive heavy load at output terminal. The effect of inductances parasitic has not significant meaning in VLSI processing. The main advantage of voltage mode circuits that a single voltage-output terminal could supply more input terminals which are connected parallel.

### 1.3.2 CURRENT MODE SIGNAL PROCESSING

In current mode signal processing, the dominant variable is current (both input as well as output). The devices used (amplifiers) have very low input impedance, ideally zero and very high output impedance, ideally infinite. As a result, cascading of inputs and outputs with voltage device are not possible. These devices are characterized by very small voltage swings which result in fast speed. Also, the signal processing circuitry becomes simpler and lesser number of components are required (for adding currents no extra amplifiers is needed). Another very important feature of the current mode device is large dynamic range of the input quantity. [5] [6] [7].

#### **1.3.3 MIXED MODE SIGNAL PROCESSING**

In this mode of signal processing both current and voltage variables are the integral part of the signal space of the application and help in matching the impedance levels at the input and output side.

## **1.4 CRYPTOGRAPHY AND NETWORK SECURITY**

To ensure the security of network by implementing the security for data we require a technique called Cryptography. Cryptosystems using neural network provide higher security. Neural network is formed of neuronal or activation function along with weights and these functions with weights could be the key or code for our security purpose which could be difficult to estimate. Decryption of messages without having the knowledge of encryption technique used i.e. a hit and trial method falls under Cryptanalysis [8] [9].

Encryption, the process to convert the information which is in plaintext form into incomprehensible text called cipher text or encrypted message. The reverse of it is decryption i.e. breaking out the plaintext from cipher text. Security services provided by protocol layer of communicating open systems gives data integrity, confidentiality, authenticity, and non-repudiation. Major applications of Cryptography are in systems like ATMs, electronic commerce and passwords for computers. Development in World Wide Web has resulted in major use of Cryptography for e-commerce and applications in business [9].

## **1.5 ORGANISATION OF THE THESIS**

In Chapter 2, we have briefly discussed translinear circuit principle and some of the important existing non linear analog blocks and derived functions.

In Chapter 3, the Translinear principle based basic modules used in various approximations have been discussed.

In Chapter 4, some applications of our basic modules are presented as realization of various approximated functions and their applications.

In Chapter 5, the discussion on Elliptic curve along with its properties and along with its analog implementation in Cryptography for network security.

In Chapter 6, Summary of whole thesis is done along with Future scope has been discussed.

### REFERENCES

- [1] J. Huijsing, R. van de Plassche, W. Sansen (Eds.), "Analog circuit design: Lownoise, low-power, low-voltage, Mixed-mode design with Cad Tools Voltage, Current and Time References," *Kluwer*, 1996, pp. 269-352.

- [2] nptel(2018) analog versus digital signal processing, Available at: <u>http://nptel.ac.in/courses/Webcourse-contents/IIT-</u> <u>KANPUR/Digi\_Sign\_Pro/lecture1/images/node3.html</u> (Accessed: 5 July 2018).

- [3] nptel(2018) *digital* system advantages, Available at: <u>http://nptel.ac.in/courses/117103064/2</u> (Accessed: 4 July 2018)

- [4] Igor M.,"New Circuit Principle of Integrated Circuits," Part 2: Special Function Blocks for Analog current signal processing, PhD Thesis, Brno University of Technology,2010.

- [5] Toumazou C., Lidgey F.J., Haigh D.G. (Eds.), "Analogue IC design: The currentmode approach," *IEE Circuits and Systems Series* 2, Perigrinus Press, 1990

- [6] J. W. HASLETT, M. K. N. RAO, "A High Quality Controlled Current Source," *IEEE Trans. Instrumentation and Measurement*, vol. IM-28, No. 2, 1979.

- [7] Groza R., M. Cirlugia, "Current mode configurational analog block," *IEEE transaction*,978-1-5090-3748-3,2016.

- [8] W. Stallings, Cryptography And Network Security Principles and Practices, *PrenticeHall*,2012.

- [9] S.N. Kumar, "Review on Network Security and Cryptography," *International Transaction Of Electrical and Computer Engineers System*, 2015 3 (1),pp1-11.

## **CHAPTER 2**

## NON LINEAR BLOCKS AND FUNCTIONS

## 2.1 INTRODUCTION

Since the presented work deals with analog circuit realization of some non linear functions, it is worthwhile to present a review of the basic building blocks used in the realization of these non-linear functions. The building blocks used are

- 1. Logarithmic block

- 2. Exponential block

- 3. Square rooting block

- 4. Linear block

Most of these blocks utilize the translinear circuit principle [1] proposed by Gilbert for bipolar transistors or its CMOS version. We first present the TCP (Translinear circuit principle) in the following section.

## 2.2 TRANSLINEAR PRINCIPLE

A closed loop circuit consisting of even number of transistors and all having their base emitter junction forward biased, along with arranged in such a fashion that half of them having clockwise polarity and half of them having anticlockwise polarity then the sum of forward biased base emitter junction in clockwise is equal to forward biased base emitter junction in counter clockwise [1], as shown in Fig 2.1 below.

Fig 2.1 Translinear Loop

From above Fig 2.1, it can expressed as,

$$\sum_{t=1}^{n+1} V_{BEt} = \sum_{w=2}^{n+2} V_{BEw}$$

(2.1)

Where, left hand side of above equation is sum of voltages in counter clockwise direction and right hand side is sum of voltages in clockwise direction.

Therefore,

$$\prod_{t=1}^{n+1} I_t = \prod_{w=2}^{n+2} I_w \tag{2.2}$$

Since,

$$V_{BE} = V_T \ln \left(\frac{I_C}{I_S}\right)$$

The above relation in equation 2.3 is for translinear loop formed with the help of bipolar transistors. Similar analysis can be done for translinear loop consisting of MOSFETs, in which all transistors are made to operate in saturation region. The relation for such case is given as follow:

$$\sum_{t=1}^{n+1} V_{GSt} = \sum_{w=2}^{n+2} V_{GSw}$$

(2.3)

Or,

$$\sum_{t=1}^{n+1} \sqrt{\frac{I_{Dt}}{K_t(W/L)_t}} = \sum_{w=2}^{n+2} \sqrt{\frac{I_{Dw}}{K_w(W/L)_w}}$$

(2.4)

### 2.3 TRANSLINEAR BASED CIRCUITS

Among the various analog multiplier circuits that can be used as squarer block and some CMOS based squarer circuits presented in [2] [3] [4] [5] we have analyzed one of the blocks that has been presented in the following section.

### 2.3.1 SQUARER AND LINEAR BLOCK

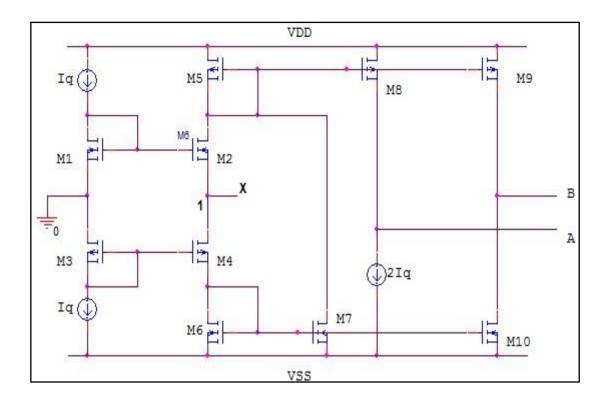

The application of the principle of translinear loop is shown in Fig 2.2, which results in scaled squarer and inverted linear term. In the following CMOS circuit the very important parameter is the matching of the transistors with their W/L ratios along with keeping in mind the relationship between electron mobility ( $\mu_n$ ) and hole mobility ( $\mu_p$ ) [5].

Fig 2.2 Linear And Square Block

## 2.3.2 ANALYSIS OF LINEAR AND SQUARE GENERATOR

Transistors M1-M4 form a translinear loop such that sum of voltages in clockwise direction equals the sum of voltages in anti-clockwise direction around the loop. It is assumed that transistors M1-M2 and M3-M4 are matched and all operate in saturation region. The equation leading to squarer and linear term as derived as follows:

$$V_{GS1} + V_{SG3} = V_{GS2} + V_{SG4} (2.5)$$

$$\sqrt{\frac{I_{D1}}{\mu_n(W/L)_1}} + \sqrt{\frac{I_{D3}}{\mu_p(W/L)_3}} = \sqrt{\frac{I_{D2}}{\mu_n(W/L)_2}} + \sqrt{\frac{I_{D4}}{\mu_p(W/L)_4}}$$

(2.6)

But since transistors are matched and their transconductance are equal i.e.  $\beta_n = \beta_{p.}$  Hence,

$$2\sqrt{I_{D1}} = \sqrt{I_{D2}} + \sqrt{I_{D4}}$$

(2.7)

But,  $I_{D1} = I_q$ , thus we have

$$2\sqrt{I_q} = \sqrt{I_{D2}} + \sqrt{I_{D4}}$$

(2.8)

Now at node 1, we have

$$I_{D2} + x = I_{D4} (2.9)$$

After solving equation (2.8) and (2.9) we get,

$$I_{D2} = I_q - \frac{x}{2} + \frac{x^2}{16I_q}$$

(2.10)

$$I_{D4} = I_q + \frac{x}{2} + \frac{x^2}{16I_q}$$

(2.11)

Adding equation (2.10) and (2.11) results gives,

$$I_{D2} + I_{D4} = 2I_q + \frac{x^2}{8I_q}$$

(2.12)

From figure 2.2 we have,

$$I_{D5} = I_{D2} + I_{D4} (2.13)$$

Now current  $I_{D5}$  is copied with the help of M8 transistor and  $2I_q$  is subtracted from this current value such that at node A we get,

$$I_A = \frac{x^2}{8I_q} \tag{2.14}$$

Now scaling of current  $I_{D5}$  is done by the factor of 2 which gives,

$$\frac{I_{D5}}{2} = I_q + \frac{x^2}{16I_q} \tag{2.15}$$

Copying this current through transistor M9 and subtracting  $I_{D4}$  from equation (2.15) with the help of copier transistor M10 gives,

$$\frac{I_{D5}}{2} - I_{D4} = -\frac{x}{2} \tag{2.16}$$

Which is done at node B, giving current I<sub>B</sub> as,

$$I_B = -\frac{x}{2} \tag{2.17}$$

Equation (2.14) and equation (2.17) i.e.  $I_A$  and  $I_B$  can be used to approximated functions up to second order.

The above circuit has been simulated by the author [5] in 0.8um CMOS technology. But the drawbacks of the above circuit are mismatch in transconductances of transistors when short channel length is considered which is analyzed below. Also matching of transistor's aspect ratio is also tedious task.

## 2.3.3 DEVIATION FROM IDEAL CHARACTERSTICS

Since in above block it has been assumed that the transistors hold exact square law equation and transconductances are equal. But as we come to small channel length transistors our assumptions deviates from ideal condition due to second order effects that plays their role which are channel-length modulation, velocity saturation, body effect and decrement in mobility. These above parameters results in transconductance mismatch and contribute in error [5].

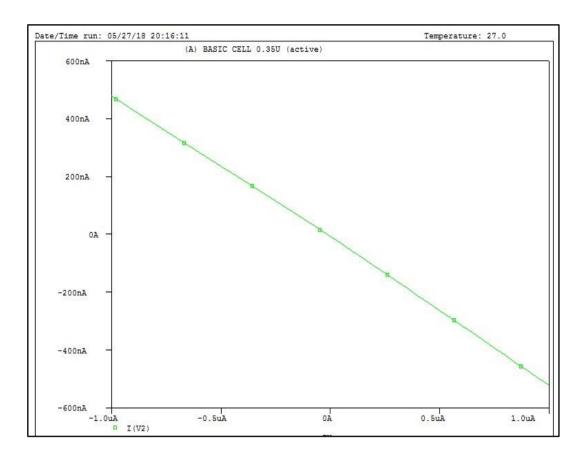

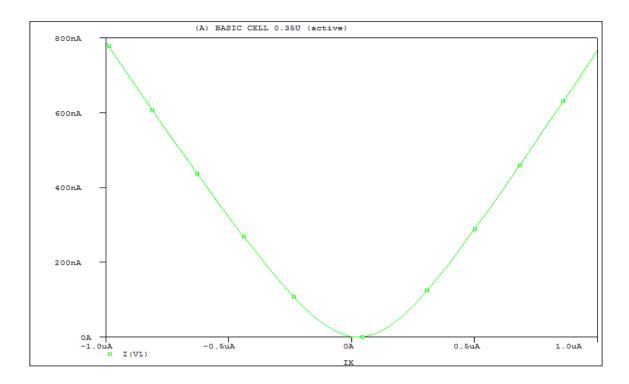

#### 2.3.4 SIMULATION

The above circuit is simulated for large channel condition and deviation from ideal behavior for its short channel length is observed and its less maximum operation range have been shown in the simulation below in Fig 2.3, Fig 2.4, Fig 2.5 and Fig 2.6 using 0.35um CMOS technology in PSPICE A/D. Keeping in mind that at room temperature electron mobility is approximately twice that of hole mobility in extrinsic semiconductor, transistor's aspect ratio has been chosen accordingly. The biasing currents  $I_q$  have been made equal to 0.125uA in order to make scaled square term equal to simple square term. The circuit is tested at power supply of  $\pm 1V$ .

Fig 2.3 Output of linear term for long channel length

Fig 2.4 Square results for long channel length

One of the drawbacks of this circuit can be observed from Fig 2.4 that there is loss of signal i.e. as we move towards  $\pm 1$ uA there is lose in its output. Also this circuit is tested for its maximum operating range then it results in great loss of signal for exceeding input current more than  $\pm 2$ uA. Following graphs will present the output for short channel lengths, and deviations will be observed significantly.

Fig 2.5 Square result for Short channel length

Fig 2.6 Linear result for short channel length

Now it can be easily observed from Fig 2.5 and Fig 2.6 that as we implement short channel length transistors matching of transistors comes into role because of short channel length parameters like channel length modulation etc. and it can be observed in Fig 2.5 that there is significant loss of signal as we increase its input range.

This is the major reason why in this dissertation bipolar circuits are implemented in latter chapter. But before we move to work implemented there are few more circuits that have been reviewed and used for implementation of functions that are implemented.

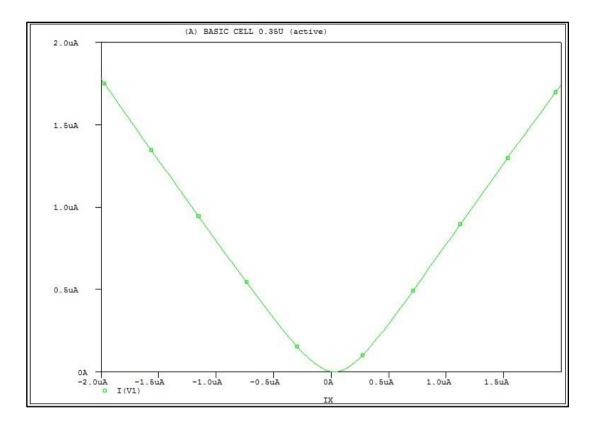

#### 2.3.5 STANDARD SQUARER CIRCUIT

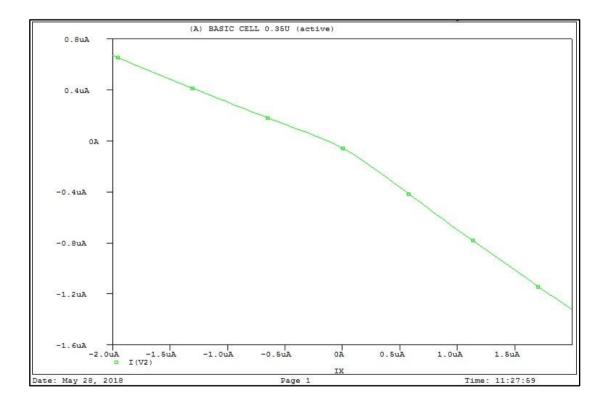

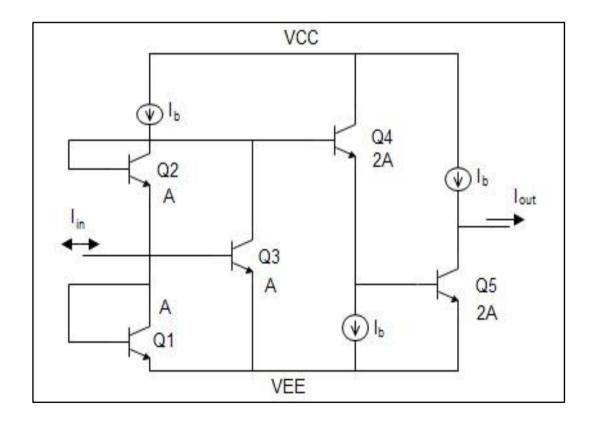

The analysis of this block presented in [6] is performed below for literature review purpose and for comparison purpose with the presented block in chapter 3.

Fig 2.7 Standard Square Circuit

It should be noted here that Q4 and Q5 have double the area of Q1-Q3.

Considering the translinear loop containing Q1, Q2, Q4 and Q5, we have

$$I_{C1}I_{C2} = \frac{I_{C4}I_{C5}}{2}$$

(2.18)

$$I_{C1} = I_{C2} \pm I_{in} = I_{C3} \tag{2.19}$$

And,

$$I_{C2} = I_b - I_{C3} (2.20)$$

$$I_{C4} = I_b \tag{2.21}$$

$$I_{C5} = I_b - I_{out} (2.22)$$

Adding equations we get,

$$I_{C2} = \frac{I_b \mp I_{in}}{2}$$

and  $I_{C1} = \frac{I_b \pm I_{in}}{2}$

Placing the value of  $I_{C2}$  and  $I_{C1}$ , also  $I_{C4}$  and  $I_{C5}$  in equations we get,

$$I_{out} = \frac{I_{in}^2}{I_b}$$

(2.23)

The above equation is derived by neglecting the effect of commonemitter gain and base current equal to zero.

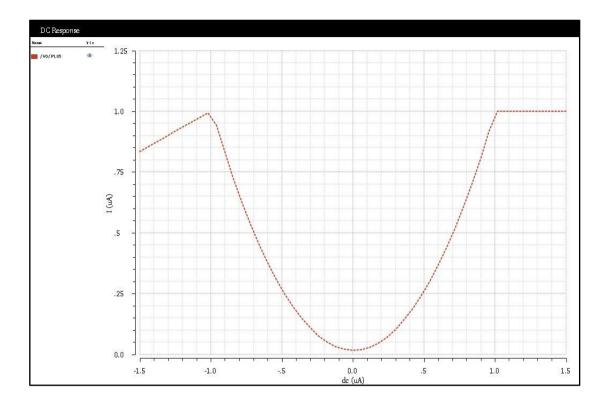

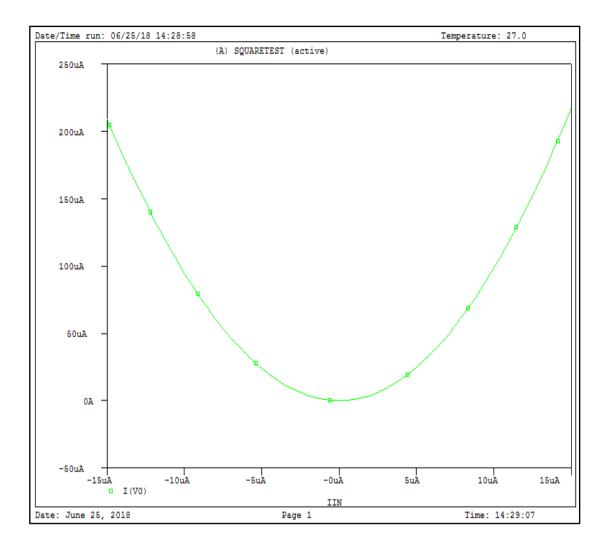

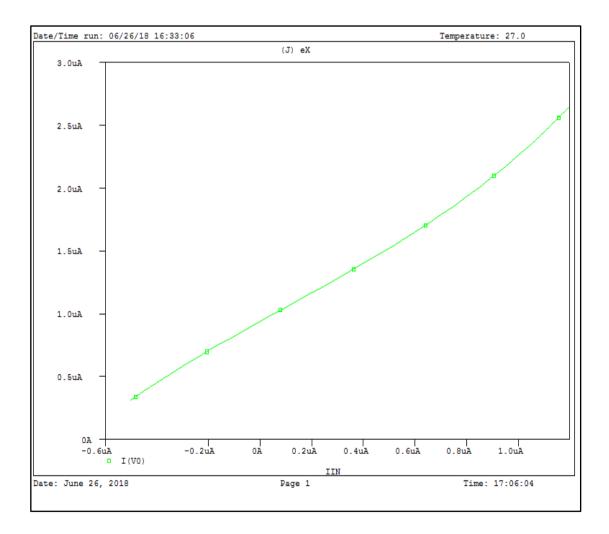

The PSPICE simulation results for this circuit is shown in Fig 2.8 below where we have used transistors NR200N and PR200N of ALA400 transistor array of AT&T company. Keeping the value of bias current  $I_b = 1$ uA and input current range to ±1.5uA.

Fig 2.8 DC characteristics of Standard square block

It can be easily observed that the circuit output saturates at 1uA in both the quadrants. This drawback of maximum operating range is over came in proposed circuit in chapter 3.

## 2.4 LOG AND EXPONENTIAL BLOCKS

Several logarithmic and exponential blocks have been presented in [7] [8] [9]. Out of which logarithmic and exponential blocks are presented in [7] with bipolar implementation is discussed below.

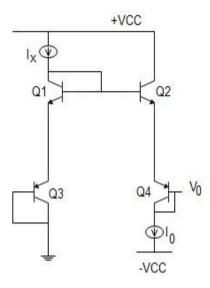

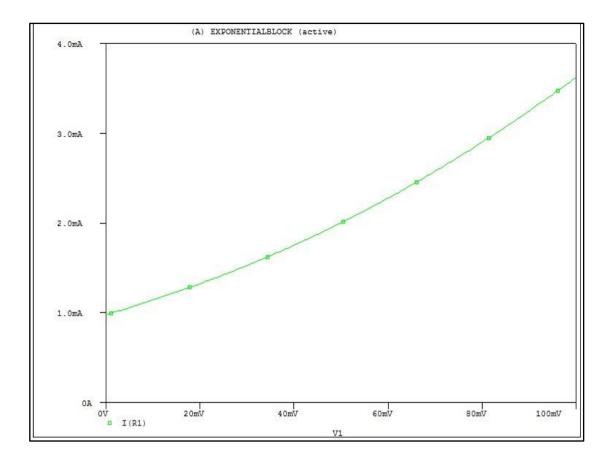

#### 2.4.1 LOGARITHMIC BLOCK

It consists of four bipolar transistors Q1-Q4, as shown in Fig 2.9, where input to this circuit is current and output is taken to be in voltage [7]. Derivation of input-output relationship and simulation part is shown in following part.

Fig 2.9 Logarithimic Block

## 2.4.2 ANALYSIS OF LOGARITHMIC BLOCK

Since emitter of transistors Q1 and Q3 are at same potential and similarly emitter of transistors Q2 and Q4 are also at same potential thus  $V_{E1} = V_{E3}$  and  $V_{E2} = V_{E4}$ . Keeping this in mind we start with the derivation as follows:

$$I_X = I_S exp\left(\frac{V_{BE1}}{V_T}\right)$$

(2.24)

Also,

$$I_X = I_S exp\left(\frac{V_{EB3}}{V_T}\right) \tag{2.25}$$

But  $V_{B3} = 0$ , hence

$$V_{E3} = V_T \ln\left(\frac{l_X}{l_S}\right) = V_{E1}$$

(2.26)

Therefore,

$$V_{B1} = 2V_T \ln\left(\frac{I_X}{I_S}\right) = V_{B2}$$

(2.27)

Now  $V_{B4} = V_0$ , thus

$$V_{E4} = V_T \ln\left(\frac{I_0}{I_S}\right) + V_0 = V_{E2}$$

(2.28)

And

$$V_{B2} - V_{E2} = V_T \ln\left(\frac{I_0}{I_S}\right)$$

(2.29)

From equations we get:

$$V_0 = 2V_T \ln\left(\frac{I_X}{I_0}\right) \tag{2.30}$$

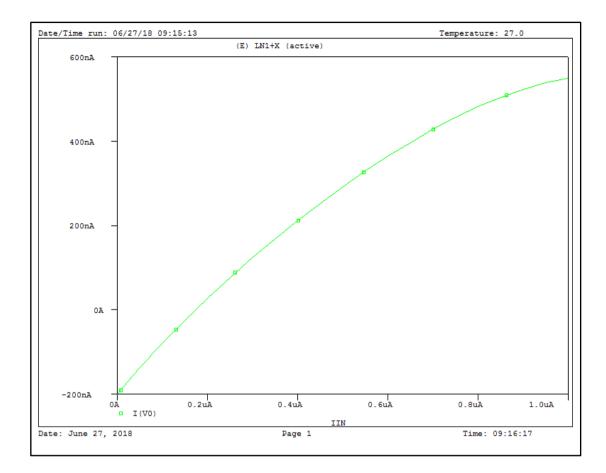

Equation (2.30) gives the relationship between voltage and current in logarithmic form. Its simulation is done in PSPICE A/D with  $I_0 = 1$ mA and using bipolar transistors NR200N and PR200N of ALA400 transistor array of AT&T company. Fig 2.10 below shows the DC transfer characteristics.

Fig 2.10 Logarithmic simulated result

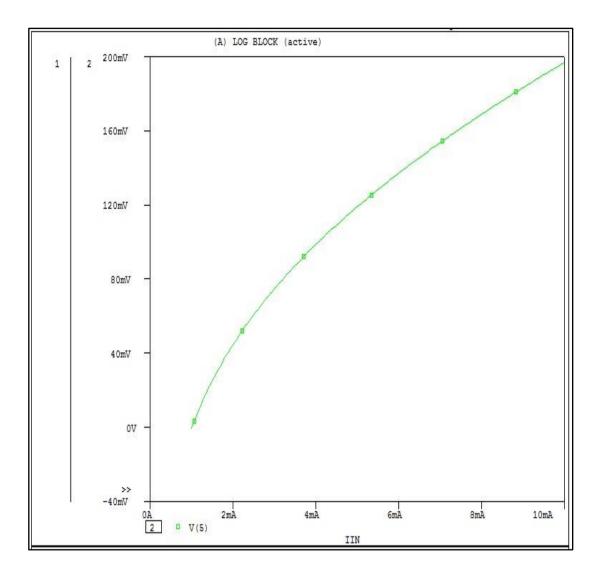

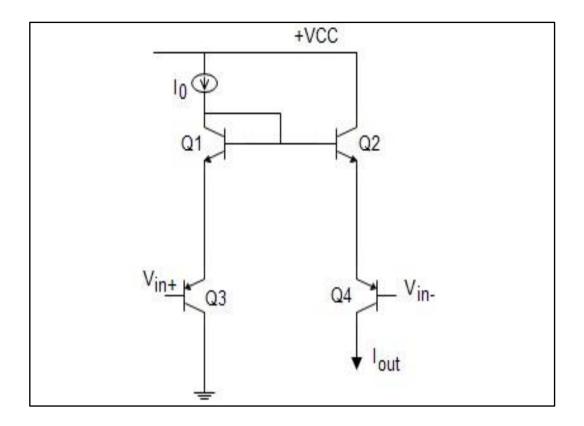

### 2.4.3 EXPONENTIAL BLOCK

It consists of four transistors Q1-Q4 as shown in Fig 2.11 such that the relationship between input and output parameters i.e. differential voltage and current respectively is exponential. The input signal can be made single ended voltage by making one of the voltages to ground and the other to voltage signal [7]. The relationship and simulation part of the exponential block in shown below.

Fig 2.11 Exonential Circuit

### 2.4.4 ANALYSIS OF EXPONENTIAL BLOCK

Before moving to derivation part it is very important to keep it in mind from Fig 2.11 that emitter voltages of transistors Q1 and Q3 are equal as well as emitter voltages of transistors Q2 and Q4 are also equal.

From the fig 2.11 we have,

$$I_0 = I_S exp\left(\frac{V_{BE1}}{V_T}\right)$$

(2.31)

$$V_{B1} = V_T \ln\left(\frac{I_0}{I_S}\right) + V_{E1}$$

(2.32)

Or,

$$V_{B1} = V_T \ln\left(\frac{I_0}{I_S}\right) + V_{in+} + V_T \ln\left(\frac{I_0}{I_S}\right)$$

(2.33)

Since,  $V_{E1} = V_{E3}$

Therefore,

$$V_{B1} = 2V_T \ln\left(\frac{l_0}{l_s}\right) + V_{in+}$$

(2.34)

Similarly,

$$V_{E4} = V_T \ln\left(\frac{I_{0ut}}{I_S}\right) + V_{in-}$$

(2.35)

And,

$$V_{B2} - V_{E2} = V_T \ln\left(\frac{I_{out}}{I_S}\right)$$

(2.36)

But  $V_{B2} = V_{B1}$  and  $V_{E2} = V_{E4}$ , keeping the value of  $V_{B1}$  in place of  $V_{B2}$  in equation (2.36) from equation (2.34) and also the value of  $V_{E4}$  in place of  $V_{E2}$  in equation (2.36) from equation (2.35) we get relationship as follows:

$$I_{out} = I_0 exp\left(\frac{V_{in+}-V_{in-}}{2V_T}\right)$$

(2.37)

The simulation of the above circuit is performed in PSPICE A/D, using transistors NR200N and PR200N parameters of ALA400 transistor array from AT&T company, with VCC at 1.7V,  $I_0 = 1$ mA, and varying the positive input voltage from 0mV to 100mV, and keeping negative terminal voltage to ground potential. The DC characteristic of the circuit is shown in Fig 2.12 below:

Fig 2.12 DC characteristics of exponential block

# 2.5 TRANSLINEAR PRINCIPLE BASED CURRENT MODE SQUARE ROOTING BLOCK

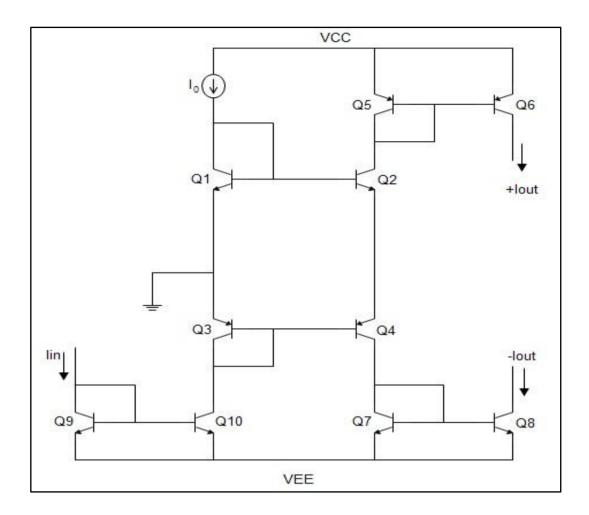

The circuit used for finding out square root of the given value is based on translinear principle [1], this circuit [10] consists of bipolar transistors as shown in Fig 2.13 below. This circuit is made up of translinear loop from Q1-Q4. Current mirrors are used to generate the square root of current with symmetry about x-axis. This block will be used latter in realization of elliptic curve which is one of the major applications of this dissertation which is an important technique for security in Cryptography.

Fig 2.13 Translinear Based square root circuit

# 2.5.1 DERIVATION AND SIMULATION OF TRANSLINEAR BASED SQUARE ROOT BLOCK

From translinear loop Q1-Q4, we have

$$V_{BE1} + V_{EB3} = V_{BE2} + V_{EB4} (2.38)$$

Therefore,

$$V_T \ln\left(\frac{l_0}{l_s}\right) + V_T \ln\left(\frac{l_{in}}{l_s}\right) = V_T \ln\left(\frac{l_{out}}{l_s}\right) + V_T \ln\left(\frac{l_{out}}{l_s}\right)$$

(2.39)

Thus,

$$I_0 I_{in} = (I_{out})^2 (2.40)$$

Hence,

$$I_{out} = \pm \sqrt[2]{I_{in}I_0}$$

(2.41)

Equation (2.41) gives us the output current as square root of product of input current and biasing current in both  $1^{st}$  and  $4^{th}$  quadrant.

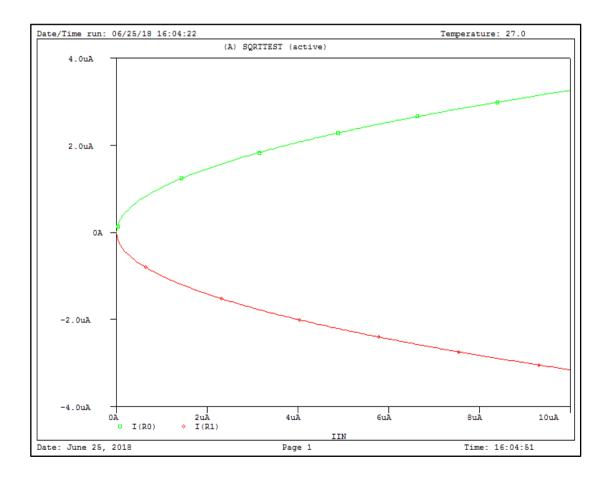

Keeping all transistor's emitter width equal and keeping  $I_0 = 1uA$  along with VCC = +3.65V and VEE = - 3.65V, the simulation is performed in PSPICE A/D using NR200N and PR200N model of ALA400 transistor array from AT&T company. The simulation is shown below in Fig 2.14.

It can be observed that the circuit has large operating range as the input current is varied from 0uA to 10uA and we have received significant output for its square root shown in Fig 2.14.

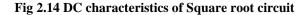

#### 2.6 SQUARE ROOT BLOCK USING CMOS

The circuit shown below consists on NMOS and PMOS transistors which is not based on translinear loop principle [1], circuit is mainly the application of current mirror, in this circuit the relationship between input and output is between voltage and current, where as current is the input and voltage as output. The circuit [11] is shown in Fig 2.15 and its simulation is shown in Fig 2.16 below.

Fig 2.15 CMOS Square root circuit

Derivation of relationship between input and output and simulation results is shown below in following section.

#### 2.6.1 IMPLEMENTATION OF SQUARE ROOT BLOCK

It can be observed from Fig 2.15 that transistors M1, M2 and M4 form a current mirror circuit, thus the same current  $I_{in}$  flows through transistor M4, and eventually through transistor M2, and M2 is connected to transistor M3 leading to same flow of current  $I_{in}$ , now transistors M3 and M7 also forms a current mirror

circuit, thus the M7 also flows current  $I_{in}$ . To be noted here is that transistor M5 aspect ratio is kept is scaled by the factor of 4 than other transistors in order to get square root relationship at node  $V_0$ .

It should be kept in mind that all the transistors operate in saturation region to follow the square law characteristic.

We have,

$$V_A = V_T + V_{SS} + \sqrt{\frac{I_{in}}{K_3}}$$

(2.42)

And

Where

$$K_1 = K_2 = \dots = K_7 = K = \mu C_{ox}(W/L)/2$$

(2.43)

$$\frac{1}{4} \left(\frac{W}{L}\right)_5 = \left(\frac{W}{L}\right)_6 \tag{2.44}$$

$$V_B = V_T + \sqrt{\frac{4I_{in}}{K_5}}$$

(2.45)

$$I_{D6} = K_6 (V_B - V_0 - V_T)^2$$

(2.46)

$$I_{D7} = K_7 (V_A - V_{SS} - V_T)^2$$

(2.47)

And

$$I_{D6} = I_{D7}$$

(2.48)

Equating equations (2.46) and (2.47) and putting values from equation (2.42) and (2.45), we get

$$V_0 = \sqrt{\frac{I_{in}}{K}} \tag{2.49}$$

Equation (2.49) gives us the voltage as the square root of current with scaling factor K.

Simulation of this circuit is performed in PSPICE A/D using 0.35um CMOS technology keeping bias giving VDD = 1.75V and VSS = -1.75V, varying input range from 0uA to 12uA, a resistor of 1Kohm is connected at output node V<sub>0</sub> in order to observe the output. The characteristic observed is DC transfer characteristics shown in Fig 2.16, the aspect ratio and parameter model files for level 7 0.35um CMOS technology is presented in Appendix 1 and 2.

Fig 2.16 Simulated result for CMOS square root circuit

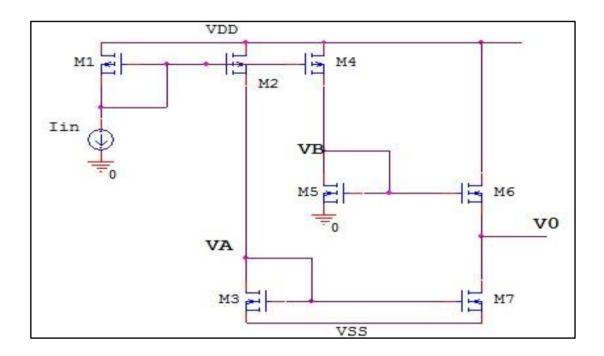

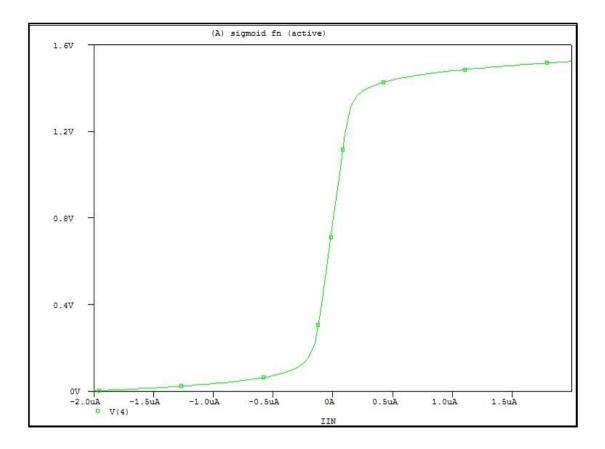

# 2.7 SIGMOIDAL FUNCTION

A Sigmoid Function [12] is a very useful non-linear signal processing element used extensively in artificial neural networks. These functions may be implemented using digital hardware which requires more power, more chip area as compared to analog implementation of the same [13]-[16]. An analog circuit implementation of the same has been presented in [12].

It is called resistive type because of its input-output characteristics which have current as input and voltage as output. There are other resistive type sigmoid function which were proposed earlier than this one [17] in which the transistors were operating only off or saturation region due to sudden switching from off to saturation and vice-versa noise spikes was introduced. In this work [12] transistors are made operative in triode and saturation regions making it more smooth result and with very much precision.

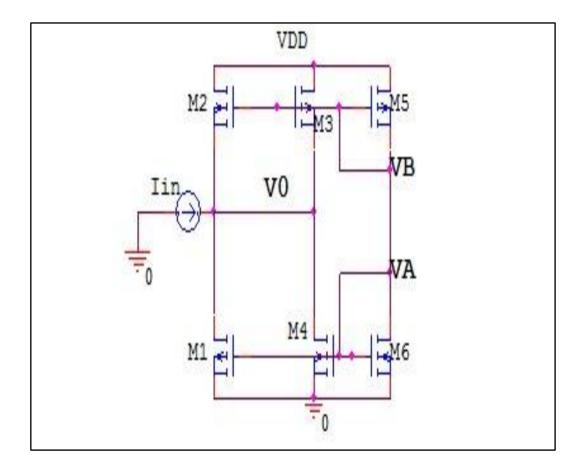

Sigmoid function is generated using the following circuitry shown in Fig 2.17 consisting of six transistors M1-M6 where M5 and M6 are used to generate the gate voltage equal to half of the supply voltage i.e. VCC/2, there sizing is done accordingly. And rest four transistors are used to give sigmoid function.

Fig 2.17 Sigmoid Function Generator

| Region | Iin | Vout                                         | M1  | M2  | M3     | M4     |

|--------|-----|----------------------------------------------|-----|-----|--------|--------|

| Ι      | < 0 | $0 \le V_{out} \le V_G - V_{in}$             | off | sat | sat    | Triode |

| Π      | < 0 | $V_G - V_t \le V_{out} \le V_G$              | off | off | sat    | Sat    |

|        | = 0 | $\mathbf{V}_{out} = \mathbf{V}_{\mathbf{G}}$ |     |     |        |        |

|        | >0  | $V_G \leq V_{out} \leq V_G +  V_t $          |     |     |        |        |

|        |     |                                              |     |     |        |        |

| III    | >0  | $V_{G} +  V_t  \leq V_{out} \leq V dd$       | sat | off | triode | Sat    |

**Table 2.1 Operating Region**

In region I, the direction of current is outward causing very low voltage at output node. Thus making transistor M1 to turn off, M4 in triode and M2 and M3 is saturation region. Thus the relationship in this region is as follows:

$$I_{in} = -\frac{1}{2}k_n S_2 (V_G - V_{out} - V_t)^2 (1 + \lambda (V_{dd} - V_{out})) - \frac{1}{2}k_p S_3 (-V_G + V_{dd} - V_t)^2 (1 + \lambda (V_{dd} - V_{out})) + k_n S_4 ((V_G - V_t) V_{out} - \frac{1}{2} V_{out}^2)$$

$$(2.50)$$

Where S is defined as (W/L)

Changes in operating region can be observed with the increase in input current, as M3-M4 switches to saturation region and other two are off entering into region II, which can be divided into three sub regions. First sub threshold region is when the current in negative, i.e. current coming out of M3 is more than the M4 sinking the current at output node. Now with the increase in output voltage, current through M3 decreases and through M4 increases resulting to voltage reaching at

$V_{dd}/2$ , at this point no current flows in i.e. when input current is zero. In third sub region current becomes positive and the equation is followed as follows:

$$I_{in} = \frac{1}{2}k_n S_4 (V_G - V_t)^2 (1 + \lambda V_{out}) - \frac{1}{2}k_p S_3 (V_{dd} - V_G - V_t)^2 (1 + \lambda (V_{dd} - V_{out}))$$

$$(2.51)$$

The circuit enters into third region now where current is always positive. The output voltage corresponding to increase in current results in M1 to move into saturation and M3 to move into triode region but keeping rest of the two transistors in same regions as earlier. The equation in this region is as follows:

$$I_{in} = -k_p S_3 \left( (V_{dd} - V_G - V_t) (V_{dd} - V_{out}) - \frac{1}{2} (V_{dd} - V_{out})^2 \right) + \frac{1}{2} k_p S_1 (V_{out} - V_G - V_t)^2 (1 + \lambda V_{out}) + \frac{1}{2} k_n S_4 (V_G - V_t)^2 (1 + \lambda V_{out})$$

(2.52)

Note that for  $I_{in}$  equal to zero when  $V_{out} = V_{dd}/2$ ,  $k_p S_3 = k_n S_4$ . And  $S_2 = 2S_4$ ,  $3S_1 = 4S_3$ . This is done to keep the symmetry around  $I_{in} = 0$ .

The simulation is performed in PSPICE A/D using the 0.35um CMOS technology keeping the power supply VDD = 1.5V, and varying input current from - 2uA to 2uA with the step size of 0.05uA, the aspect ratio and parameter model files for level 7 0.35um CMOS technology is presented in Appendix 1 and 2. The input – output characteristics of the implemented sigmoid function is shown in Fig 2.18 below. This circuit's improved version is shown in latter chapter 4, which is operated in current mode and is framed using Taylor series approximation.

Fig 2.18 DC transfer characterstics of Sigmoid function

# 2.8 CONCLUSION

In this chapter we have presented various non linear blocks along with their simulation and operating range as an literature review, which have been already implemented. One of the blocks i.e. translinear based square rooting will be helpful in latter chapter as our major application of elliptic curve used in Cryptosystems.

#### REFERENCES

- [1] B. Gilbert, "Translinear circuits: a proposed classification," *Electronics Letters*, vol.11,no.1,pp.14-16,1975.

- [2] A. Naderi, A. Khoei, Kh. Haddi, H. Ghasemzadeh, "A New High Speed and Low Power Four-Quadrant CMOS Analog Multiplier in Current-Mode," *International Journal of Electronics and Communications (AEU)*, vol. 63, no. 9, pp. 769-775, 2009.

- [3] H. Sajjadi-Kia, "An Analog Cell and Its Applications in Analog Signal Processing," *International Journal of the Circuit theory and Applications*, vol. 39, no.2,pp.195-201,2011.

- [4] S. Minaei, E. Yuce, "New Squarer Circuits and a Current-Mode Full Wave Rectifier Topology Suitable for Integration," *Radioengineering*, vol. 19, no. 4, pp. 657-661,2010.

- [5] M.T. Abuelma'atti, M.A. Alabsi, "A CMOS Analog Cell and its Applications in Analog Signal Processing," *International Journal Of Electronics*, vol. 93, No.4,2006,251-267.

- [6] B. Gilbert, "A Precise Four-Quadrant Multiplier with Subnanosecond Response," *IEEE J. Solid – State Circuits*, vol. SC-3, 365-373,1968.

- [7] R. Groza, L. Festila, E. Szopos, "Four Quadrant Log-Domain Analog Current Multiplier," *IEEE Int. Conf. on Automation, Quality and Testing, Robotics*, Cluj-Napoca, Romania, 2008, pp.1-4244-2577-8/08.

- [8] W. Liu, S.I. liu, "CMOS Exponential Function Generator," *Electronics Letters*, vol. 39, pp. 1-2,2003

- [9] A. Motamed, C. Hwang, M. Ismail, "CMOS exponential Current-to-Voltage converter," *Electronics Letters*, vol. 33, pp. 998-1000,1997.

- [10] M. Kumngern, K. Dejhan, "A New Translinear-Based Dual-Output Square-Rooting Circuit," Active and Passive Electronic Components, 2008, Article ID623970.

- [11] C. Sakul, "A CMOS Square Rooting Circuit," International Technical Conference on Circuits/Systems, Computers and Communications, 2008, pp-537-540.

- [12] G. Khodabandehloo, M. Mirhassani, M. Ahmadi, "Analog Implementation of a Novel Resistive-Type Sigmoidal Neuron," *IEEE trans. On VLSI sytems*, vol. 20,

No.4,2012.

- [13] M.T. Tommiska, "Efficient digital implementation of the sigmoid function for reprogrammable logic," *IEE Proc. Comput. Digit. Techn.*, vol. 150, no. 6, pp. 403-411,2003.

- [14] A.H. Namin, K. Leboeuf, R. Muscedere, H. Wu, M. Ahmadi, "Efficient hardware implementation of the hyperbolic tangent sigmoid function," *Proc. IEEE Int. Symp.CircuitsSyst.*,2009,pp.2117-2120.

- [15] M. Mirhassani, M. Ahmadi, A. Jullien, "Robust low –sensitivity adaline neuron based on continuous valued number system," J. Analog Integr. Circuit Signal Process., vol. 56, pp. 223-231, 2008.

- [16] S.M. Gowda, B.J. Sheu, J. Choi, C.G. Hwang, J.S. Cable, "Design and characterization of analog VLSI neural network modules," *IEEE J. Solid –State Circuits*,vol.28,no.3,pp.301-313,1993.

- [17] H. Djahanshahi, M. Ahmadi, G.A. Jullien, W.C. Miler, "Sensitivity study and improvements on a nonlinear resistive-type neuron circuit," *IEE Proc. – Circuits, DevicesSyst.*, vol.147,no.4,pp.237-242,2000.

# **CHAPTER 3**

# STANDARD MODULES FOR APPROXIMATION OF FUNCTIONS

#### 3.1 INTRODUCTION

In the previous chapter we had presented a brief review of analog circuit realization of the non-linear building blocks along with basics of translinear circuit principle that will be helpful in further realization of blocks.

In current chapter we start with current mirrors and inverting current mirrors [1]. They have major application in developing the standard modules and approximated functions [2] discussed in this chapter and later in chapter 4. Realization of additional non linear building blocks has been done which have been used for functional approximation in later chapters. All blocks are realized in current mode which is advantageous as highlighted in earlier chapters. All the blocks are implementation of bipolar transistors hence provides the faster response. And have wide operating range. In this chapter we have also done exact analysis along with ideal analysis for the purpose of comparison. The DC transfer characteristics, transient analysis and AC analysis are done using PSPICE A/D simulation. The each block's comparison with ideal characteristic performed in MATLAB.

# 3.2 NON INVERTING CURRENT MIRROR AND INVERTING CURRENT MIRROR

Current mirrors are also known as current copier, which copies the input current at output transistor with some constant C, and whose value can be a positive integers or some fractional value except zero to maximum until the transistors remain in operating region. Non inverting current mirror have same direction of both input current and output current which are either in inward or outward direction, whereas inverting current mirror have opposite direction of input and output currents. The relation among input-output current and basic concept is discussed below.

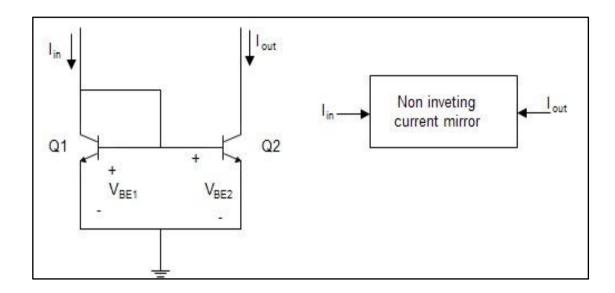

#### 3.2.1 NON INVERTING CURRENT MIRROR

It is also known as current copier which copies the input current in the same direction with some constant which is ratio of two transistor's area as shown in Fig 3.1 below.

Fig 3.1 Non Inverting Current mirror

Base of two NPN transistors Q1 and Q2 are connected together and both transistor's emitter are at zero potential. Thus base-emitter voltage of both the transistors is equal.

$$V_{BE1} = V_{BE2} \tag{3.1}$$

And

$$V_{BEi} = V_T \ln \left(\frac{I_{Ci}}{I_{Si}}\right)$$

where

$I_{Ci}$  = Collector current of transistor

$I_{Si} \propto A_i$ , reverse saturation current proportional to area or emitter width.

Thus

$$V_T \ln\left(\frac{l_{C1}}{l_{S1}}\right) = V_T \ln\left(\frac{l_{C2}}{l_{S2}}\right) \tag{3.2}$$

And  $I_{C1} = I_{in}$  ,  $I_{C2} = I_{out}$

$$I_{out} = \frac{A_2}{A_1} I_{in} \tag{3.3}$$

Or,

$$I_{out} = CI_{in} \tag{3.4}$$

Where C = area ratio of bipolar transistors

The value of C can be chosen by varying the emitter width of transistors. And it can be easily observed that the direction of output current is also inward as that of input hence named as non-inverting current mirror or current copier.

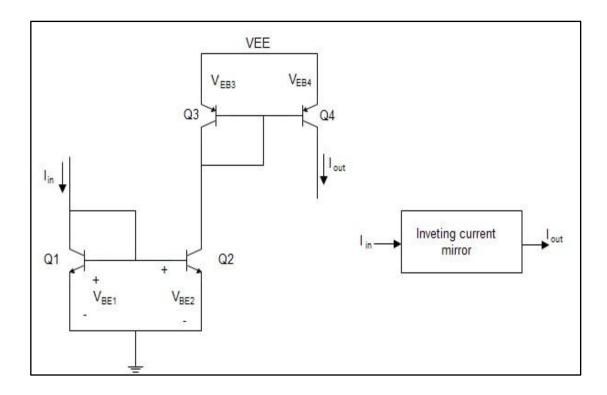

#### 3.2.2 INVERTING CURRENT MIRROR

It is composed of four transistors, two NPN and other two PNP. Both similar transistors forming a current mirror pair, the basic objective of this Configuration is to invert the direction of input current. It also has a constant value  $C_K$ , which is ratio of product of transistors. The inverting configuration is shown in Fig 3.2 below.

Fig 3.2 Inverting Current Mirror

From Fig 3.2 we have input-output current relation as follows:

$$I_{out} = \frac{A_2}{A_1} \frac{A_4}{A_3} I_{in}$$

(3.5)

Where

$$C_K = \frac{A_2}{A_1} \frac{A_4}{A_3}$$

The value of  $C_K$  can modified accordingly with the variation in emitter width of four transistors defined as ratio of area of bipolar transistors.

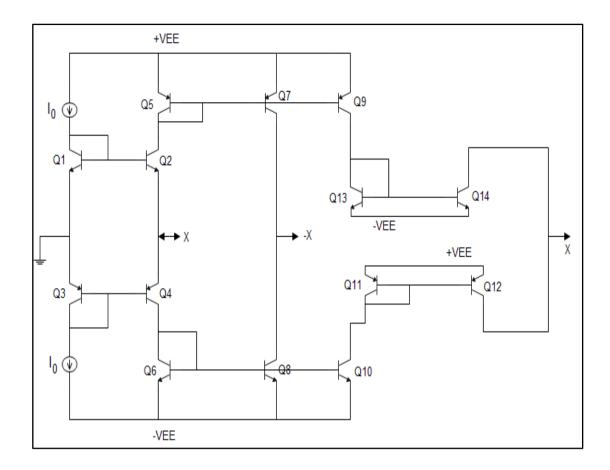

# 3.3 LINEAR TERM GENERATOR/BLOCK

Inspired from current conveyors circuits as proposed in [3], that module can be used as one of the building block for generation of various functions. CCII has linear relation between input current and output current. The basic for the development of this circuit is translinear principle [4]. The circuit is shown in Fig 3.3 and the relation is derived in following part.

Fig 3.3 Linear Term Generator/block

#### 3.3.1 IDEAL ANALYSIS OF LINEAR TERM GENERATOR

From the translinear loop shown above in Fig 3.3 we can write as,

$$V_{BE1} + V_{EB3} = V_{BE2} + V_{EB4} ag{3.6}$$

Therefore,

$$I_0 I_0 = I_{C2} I_{C4} \tag{3.7}$$

And at input node,

$$I_{C4} = I_{C2} \pm X \tag{3.8}$$

From equation 3.7 and 3.8 we have,

$$I_{C2}^2 \pm X I_{C2} = I_0^2 \tag{3.9}$$

Or,

$$I_{C2} = \frac{\mp X \pm \sqrt{X^2 + 4I_0^2}}{2} \tag{3.10}$$

Now from equation 3.8 and 3.10 we have,

$$I_{C4} = \frac{\pm X \pm \sqrt{X^2 + 4I_0^2}}{2} \tag{3.11}$$

At output node we have,

$$I_{out\,1} = I_{C7} - I_{C8} \tag{3.12}$$

$$I_{out\,2} = I_{C12} - I_{C14} \tag{3.13}$$

From equation 3.14, 3.15, 3.16 and 3.17, we get result as,

$$I_{out\,1} = \mp X \text{ and } I_{out\,2} = \pm X \tag{3.14}$$

### 3.3.2 EXACT ANALYSIS OF LINEAR TERM GENERATOR

The effect of  $\beta$  (common-emitter current gain or collector to base current ratio) can be observed as the deviation from the ideal linear characteristics at higher values of input signal. Its effect is theoretically analyzed in the following part. With the help of translinear principle in above Fig 3.3 we have,

$$V_{BE1} + V_{EB3} = V_{BE2} + V_{EB4} aga{3.15}$$

Therefore,

$$I_{C1}I_{C3} = I_{C2}I_{C4} \tag{3.16}$$

Also,

$$I_0 = I_{C1} + \frac{I_{C1}}{\beta_n} + \frac{I_{C2}}{\beta_n}$$

(3.17)

And,

$$I_0 = I_{C3} + \frac{I_{C3}}{\beta_p} + \frac{I_{C3}}{\beta_p}$$

(3.18)

Also,

$$I_{E4} = I_{E2} \pm X \tag{3.19}$$

That is,

$$I_{C4} + \frac{I_{C4}}{\beta_p} = I_{C2} + \frac{I_{C2}}{\beta_n} \pm X$$

(3.20)

After solving equations 3.16, 3.17, 3.18 and 3.20 we get  $I_{\rm C2}$  and  $I_{\rm C4}$  as follows in terms of  $\beta.$

$$I_{C2} = \mp \frac{1}{2} \left[ \frac{\beta_n}{1 + \beta_n} \right] X \pm \frac{\beta_n \sqrt{X^2 + 4I_0^2}}{2(1 + \beta_n)}$$

(3.21)

$$I_{C4} = \pm \frac{1}{2} \left[ \frac{\beta_p}{1 + \beta_p} \right] X \pm \frac{\beta_p \sqrt{X^2 + 4I_0^2}}{2(1 + \beta_p)}$$

(3.22)

From exact analysis of current mirrors formed by transistor pairs Q5-Q7-Q9 and Q6-Q8-Q10, gives us the collector current relation as,

$$I_{C7} = I_{C9} = \left(1 + \frac{2}{\beta_p}\right) I_{C5} = \left(1 + \frac{2}{\beta_p}\right) I_{C2}$$

(3.23)

$$I_{C8} = I_{C10} = \left(1 + \frac{2}{\beta_n}\right)I_{C6} = \left(1 + \frac{2}{\beta_n}\right)I_{C4}$$

(3.24)

And,

$$I_{out\,1} = I_{C7} - I_{C8} \tag{3.25}$$

$$I_{out\,2} = I_{C12} - I_{C14} \tag{3.26}$$

Solving for  $I_{out1}$  and  $I_{out2}$  we get,

$$I_{out\,1} = \mp \left( \left( 1 + \frac{2}{\beta_p} \right) \frac{1}{2} \left[ \frac{\beta_n}{1 + \beta_n} \right] + \left( 1 + \frac{2}{\beta_n} \right) \frac{1}{2} \left[ \frac{\beta_p}{1 + \beta_p} \right] \right) X \ \mp \left( \left( 1 + \frac{2}{\beta_n} \right) \frac{\beta_p \sqrt{X^2 + 4l_0^2}}{2(1 + \beta_p)} - \left( 1 + \frac{2}{\beta_p} \right) \frac{\beta_n \sqrt{X^2 + 4l_0^2}}{2(1 + \beta_n)} \right)$$

(3.27)

$$I_{out\,1} = \pm \left(1 + \frac{2}{\beta_p}\right) \left(1 + \frac{2}{\beta_n}\right) \left(\frac{1}{2} \left[\frac{\beta_n}{1+\beta_n}\right] + \frac{1}{2} \left[\frac{\beta_p}{1+\beta_p}\right]\right) X \pm \left(1 + \frac{2}{\beta_n}\right) \left(1 + \frac{2}{\beta_p}\right) \left(\frac{\beta_p \sqrt{X^2 + 4I_0^2}}{2(1+\beta_p)} - \frac{\beta_n \sqrt{X^2 + 4I_0^2}}{2(1+\beta_n)}\right)$$

(3.28)

Considering,

$$\sigma = \left( \left(1 + \frac{2}{\beta_p}\right) \frac{1}{2} \left[\frac{\beta_n}{1 + \beta_n}\right] + \left(1 + \frac{2}{\beta_n}\right) \frac{1}{2} \left[\frac{\beta_p}{1 + \beta_p}\right] \right)$$

$$\varphi = \left( \left(1 + \frac{2}{\beta_p}\right) \left(1 + \frac{2}{\beta_n}\right) \frac{1}{2} \left[\frac{\beta_n}{1 + \beta_n}\right] + \left(1 + \frac{2}{\beta_p}\right) \left(1 + \frac{2}{\beta_n}\right) \frac{1}{2} \left[\frac{\beta_p}{1 + \beta_p}\right] \right)$$

And,

$$\delta(x) = \left( \left( 1 + \frac{2}{\beta_n} \right) \frac{\beta_p \sqrt{X^2 + 4I_0^2}}{2(1 + \beta_p)} - \left( 1 + \frac{2}{\beta_p} \right) \frac{\beta_n \sqrt{X^2 + 4I_0^2}}{2(1 + \beta_n)} \right)$$

$$\omega(x) = \left(1 + \frac{2}{\beta_n}\right) \left(1 + \frac{2}{\beta_p}\right) \left(\frac{\beta_p \sqrt{X^2 + 4I_0^2}}{2(1 + \beta_p)} - \frac{\beta_n \sqrt{X^2 + 4I_0^2}}{2(1 + \beta_n)}\right)$$

We can rewrite the equation 3.27 and 3.28 as,

$$I_{out\,1} = \mp \sigma X \ \mp \delta(x) \tag{3.29}$$

$$I_{out\,2} = \pm \varphi X \pm \omega(x) \tag{3.30}$$

As we know,

$$\left(1+\frac{2}{\beta_p}\right) \cong \left[\frac{1+\beta_n}{\beta_n}\right] \cong \left(1+\frac{2}{\beta_n}\right) \cong \left[\frac{1+\beta_p}{\beta_p}\right] \approx 1$$

(3.31)

Hence  $\delta(x) = \omega(x) \approx 0$ , thus we have,

$$I_{out\,1} = \mp \sigma X \text{ and } I_{out\,2} = \pm \varphi X$$

(3.32)

Where  $\sigma \approx 1$ ,  $\phi \approx 1$ .

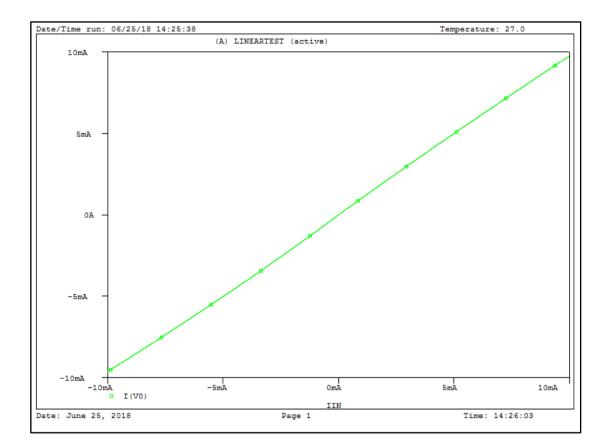

# 3.3.3 DC TRANSFER CHARACTERSTICS OF LINEAR TERM GENERATOR

The simulation is performed in PSPICE A/D using bipolar transistors NR200N and PR200N of ALA400 transistor array from AT&T company, the value of power supply is kept at  $\pm 3.65$ V, and I<sub>0</sub> = 1uA. This circuit is analyzed for operating range of  $\pm 10$ mA. The DC transfer characteristic is shown in Fig 3.4 as below.

Fig 3.4 DC characterstics of Linear Term generator

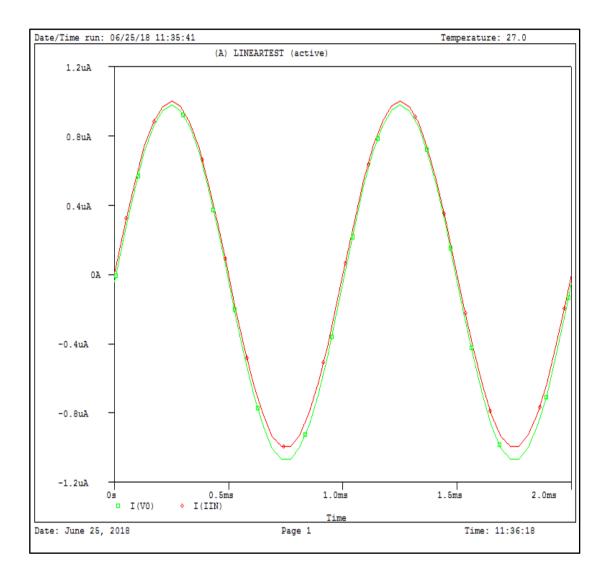

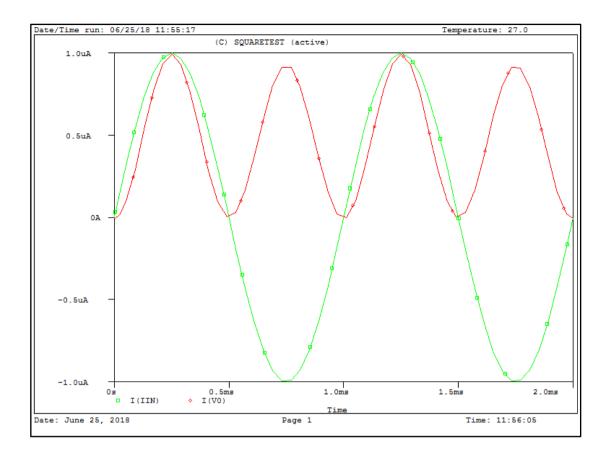

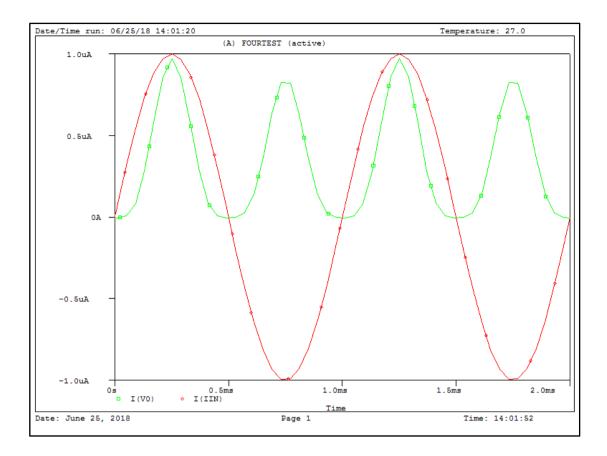

#### 3.3.4 TRANSIENT ANALYSIS OF LINEAR BLOCK

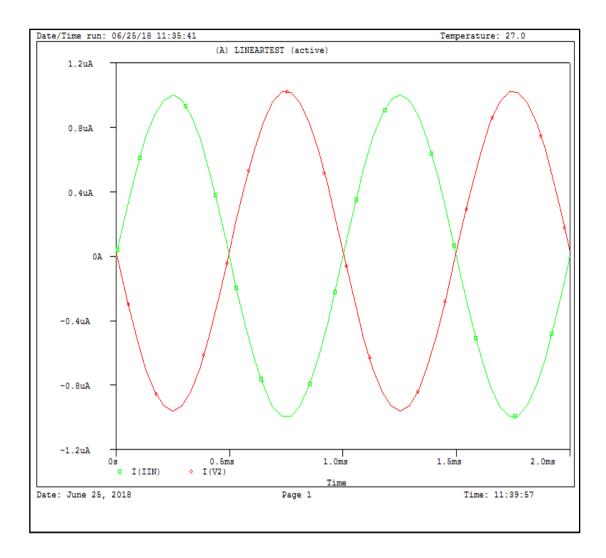

The transient analysis is performed in PSPICE A/D with power supply voltage equal to  $\pm 3.65$  V. The NR200N and PR200N transistor models of ALA400 transistor array from AT&T company are used for simulation. Transient analysis is done for varying the time from 0ms to 2ms, and applying the input signal at

frequency 1KHz and amplitude 1uA. Fig 3.5 and Fig 3.6 below shows the analysis for both positive linear term and negative linear term.

Fig 3.5 Transient response of positive linear term generator

Fig 3.6 Transient Result for negative linear term generator

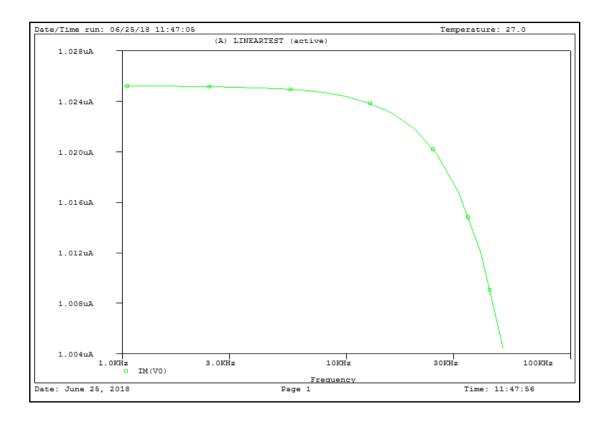

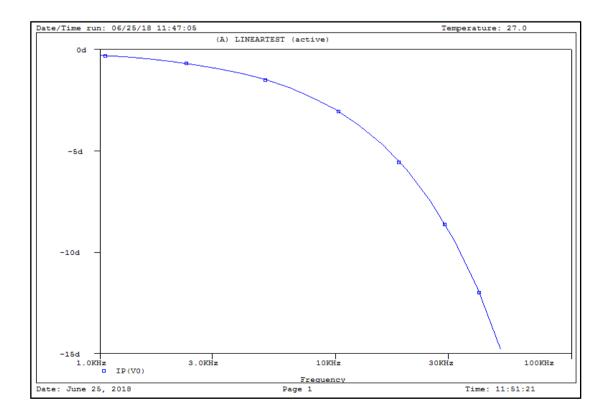

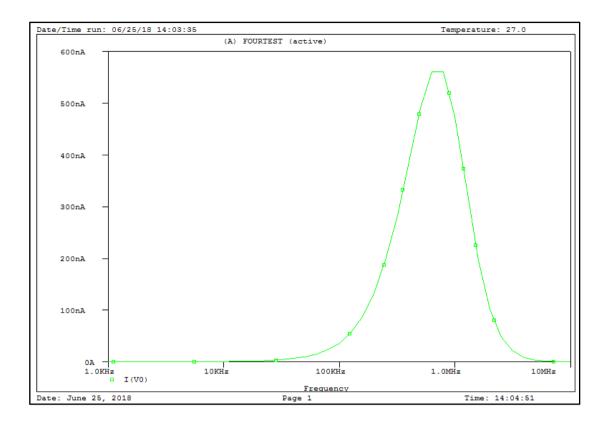

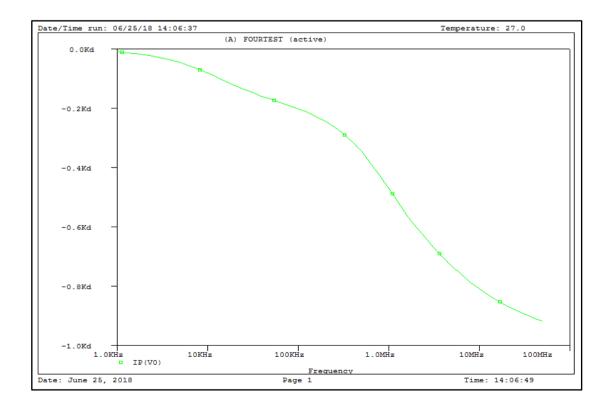

# 3.3.5 AC ANALYSIS OF LINEAR BLOCK

The AC analysis is performed in PSPICE A/D, using the same transistor models NR200N and PR200N of ALA400 transistor array from AT&T company, its magnitude versus frequency and phase versus frequency graph is shown below in Fig 3.7 and Fig 3.8 with the varying frequency 1KHz to 50KHz.

Fig 3.7 Gain magnitude versus frequency response for linear block

It can be observed from the above Fig 3.7 that the gain of the linear block is nearly equal to unity for wide range of frequencies i.e. up to 10KHz.

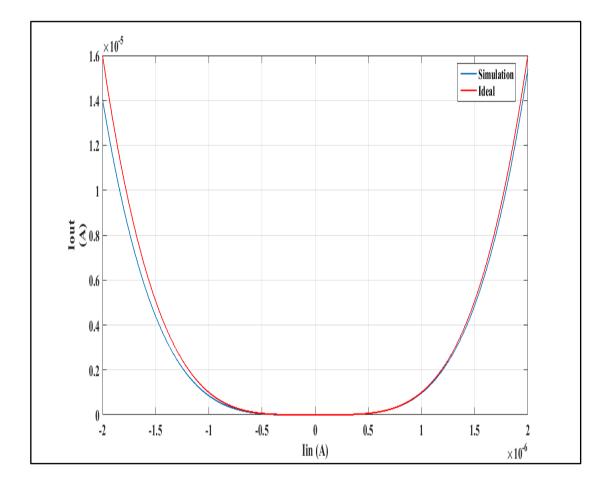

#### 3.3.6 COMPARITIVE ANALYSIS WITH IDEAL CHARACTERISTIC

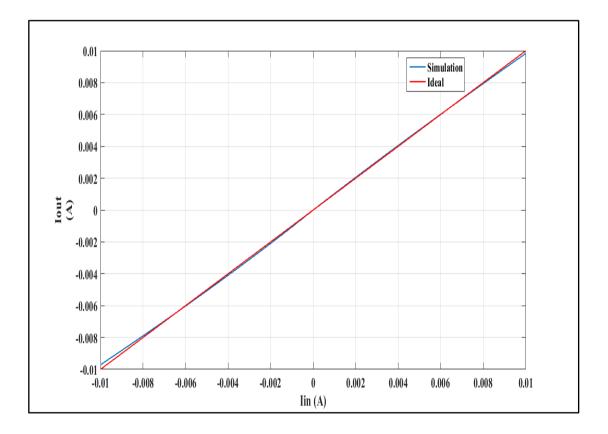

This block's comparison is performed in MATLAB with ideal linear function behavior. The analysis between ideal and simulated results is shown by plotting the comparison graph as shown below in Fig 3.9, where blue line represents the simulated results and red line represents the ideal results. The maximum error for negative values of input is at input current signal of -10mA which is equal to 4% and maximum error for positive values of input is at input current signal of +10mA with value equal to 2%.

Fig 3.9 Comparison with Ideal Characteristics

#### 3.4 SQUARE TERM GENERATOR/BLOCK

The second order term i.e. squarer term, which will be used in realizing the functions with Taylor series expansion in chapter 4, is generated and analyzed in this section. In this dissertation, the squarer term is realized using bipolar transistors and comparison with ideal behavior is also presented in this section.

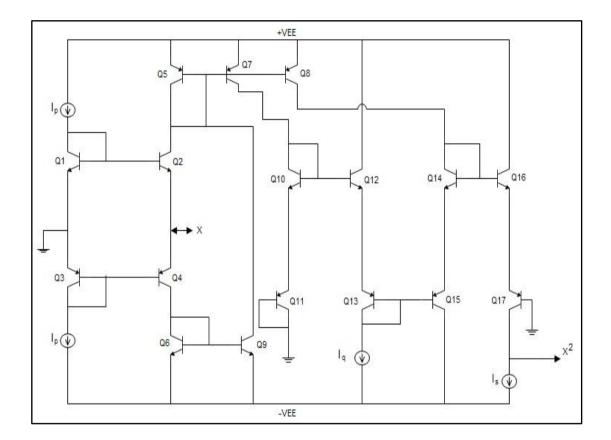

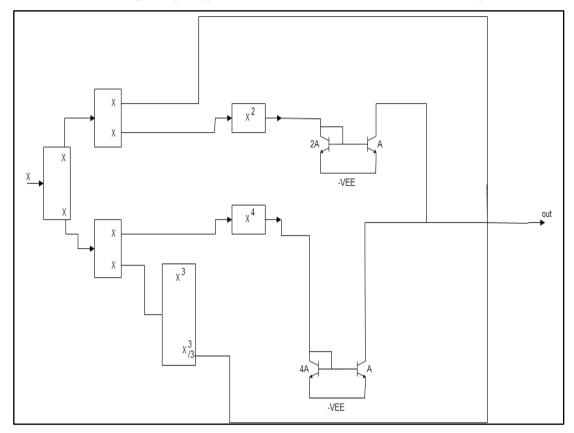

This circuit is implemented using log-antilog blocks proposed in [5], this circuit is also based on translinear principle. The circuit diagram for square generator is shown in Fig 3.10 below with the derivation and results under this section.

Fig 3.10 Square Term Generator Circuit

#### 3.4.1 IDEAL ANALYSIS OF SQUARE TERM GENERATOR

Considering all the bipolar transistors to be ideal i.e. neglecting the effect of  $\beta$ , the above circuit shown in Fig 3.10 can be analyzed as below. From the translinear loop formed by Q1-Q4, we have:

$$V_{BE1} + V_{EB3} = V_{BE2} + V_{EB4} ag{3.33}$$

Thus,

$$I_p I_p = I_{C2} I_{C4} (3.34)$$

And,

$$I_{C4} = I_{C2} \pm X \tag{3.35}$$

Hence,

$$I_{C2} = \frac{\mp x \pm \sqrt{x^2 + 4l_p^2}}{2}$$

(3.36)

$$I_{C4} = \frac{\pm X \pm \sqrt{X^2 + 4I_p^2}}{2}$$

(3.37)

$$I_{C5} = I_{C2} + I_{C9} \tag{3.38}$$

And  $I_{C9} = I_{C6} = I_{C4}$

Therefore,

$$I_{C5} = \pm \sqrt{X^2 + 4I_p^2} \tag{3.39}$$

And

$$I_{C7} = I_{C8} = I_{C5} = \pm \sqrt{X^2 + 4I_p^2}$$

Now Q10-Q17 form a one quadrant analog multiplier [5], and its output can be derived from logarithmic and exponential block explained in chapter 2. Using those results expressed in equations 2.24 and 2.31, we get

$$V_{B13} = 2V_T \ln\left(\frac{I_{C10}}{I_q}\right)$$

(3.40)

And,

$$I_{C17} = I_{C14} exp\left(\frac{V_{B13}}{2V_T}\right)$$

(3.41)

Also,

$$I_{C10} = I_{C14} = \pm \sqrt{X^2 + 4I_p^2}$$

(3.42)

We have,

$$I_{out} = I_{C17} - I_S \tag{3.43}$$

Solving for equations 3.41 gives,

$$I_{out} = \frac{X^2 + 4I_p^2}{I_q} - I_s \tag{3.44}$$

Keeping  $I_p = I_q = 1uA$  and  $I_s = 4uA$ , we get

$$I_{out} = X^2 \tag{3.45}$$

# 3.4.2 EXACT ANALYSIS OF SQUARE TERM GENERATOR/BLOCK

From above Fig 3.10, considering the effect of common-emitter gain  $\beta$ , the exact analysis can be done as follows:

$$V_{BE1} + V_{EB3} = V_{BE2} + V_{EB4} ag{3.46}$$

Therefore,

$$I_{C1}I_{C3} = I_{C2}I_{C4} \tag{3.47}$$

Also,

$$I_p = I_{C1} + \frac{I_{C1}}{\beta_n} + \frac{I_{C2}}{\beta_n}$$

(3.48)

And,

$$I_p = I_{C3} + \frac{I_{C3}}{\beta_p} + \frac{I_{C3}}{\beta_p}$$

(3.49)

Also,

$$I_{E4} = I_{E2} \pm X \tag{3.50}$$

That is,

$$I_{C4} + \frac{I_{C4}}{\beta_p} = I_{C2} + \frac{I_{C2}}{\beta_n} \pm X$$

(3.51)

After solving equations we get  $I_{C2}$  and  $I_{C4}$  as follows in terms of  $\beta.$

$$I_{C2} = \mp \frac{1}{2} \left[ \frac{\beta_n}{1 + \beta_n} \right] X \pm \frac{\beta_n \sqrt{X^2 + 4I_p^2}}{2(1 + \beta_n)}$$

(3.52)

$$I_{C4} = \pm \frac{1}{2} \left[ \frac{\beta_p}{1 + \beta_p} \right] X \pm \frac{\beta_p \sqrt{X^2 + 4I_p^2}}{2(1 + \beta_p)}$$

(3.53)

$$I_{C5} = I_{C2} + I_{C9} \tag{3.54}$$

Therefore,

$$I_{C5} = \mp \frac{1}{2} \left[ \frac{\beta_n}{1 + \beta_n} \right] X \pm \frac{\beta_n \sqrt{X^2 + 4I_p^2}}{2(1 + \beta_n)} + \left( 1 + \frac{2}{\beta_n} \right) \left( \pm \frac{1}{2} \left[ \frac{\beta_p}{1 + \beta_p} \right] X \pm \frac{\beta_p \sqrt{X^2 + 4I_p^2}}{2(1 + \beta_p)} \right)$$

(3.55)

And,

$$I_{C7} = I_{C8} \cong \pm \frac{1}{2} \left( 1 + \frac{2}{\beta_p} \right) \left[ \frac{\beta_n}{1 + \beta_n} + \frac{\beta_p}{1 + \beta_p} \left( 1 + \frac{2}{\beta_n} \right) \right] \sqrt{X^2 + 4I_p^2}$$

(3.56)

Now considering the multiplier block Q10-Q17, Exact analysis follows the results as

$$V_{B13} = 2V_T \ln\left(\frac{I_{C7} - \frac{I_q}{1 + \beta_n}}{I_q}\right)$$

(3.57)

And,

$$I_{C17} = \frac{\left(\frac{\beta_p}{1+\beta_p}\right) \frac{1}{I_q} I_{C7}^2 - \frac{\beta_p}{1+\beta_p (1+\beta_n)} I_{C7}}{1 + \frac{I_{C7}}{I_q (1+\beta_n)} - \frac{1}{(1+\beta_n)^2}}$$

(3.58)

Since,

$$1 + \beta_n \gg 1 \text{ and } \left(1 + \frac{2}{\beta_p}\right) \cong \left[\frac{1 + \beta_n}{\beta_n}\right] \cong \left(1 + \frac{2}{\beta_n}\right) \cong \left[\frac{1 + \beta_p}{\beta_p}\right] \approx 1$$

We get,

$$I_{out} = \frac{\gamma \frac{X^2 + 4I_p^2}{I_q} \mp \alpha \sqrt{X^2 + 4I_p^2}}{1 + \theta \sqrt{X^2 + 4I_p^2}} - I_s$$

(3.59)

Where  $\gamma \approx 1$ ;  $\alpha \ll 1$ ;  $\theta \ll 1$

Therefore,

$$I_{out} \approx \gamma \frac{X^2 + 4I_p^2}{I_q} - I_s \tag{3.60}$$

Keeping  $I_p = I_q = 1uA$  and  $I_s = 4uA$ , we get

$$I_{out} \approx \gamma X^2 + \rho \tag{3.61}$$

Where  $\rho \ll 1$

The above equation 3.61 is derived while considering the effect of common-emitter gain for both pnp and npn bipolar transistors. The little bit deviation can be observed in the comparison plot with ideal characteristics below.

# 3.4.3 DC TRANSFER CHARACTERISTICS OF SQUARE TERM GENERATOR