# MICROGRID OPERATION AND CONTROL

# ASHUTOSH TRIVEDI

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042, INDIA

**JUNE-2018**

# MICROGRID OPERATION AND CONTROL

by

### ASHUTOSH TRIVEDI

**Department of Electrical Engineering**

Submitted

## In fulfillment of the requirements of the degree of

### DOCTOR OF PHILOSOPHY

to the

## DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042, INDIA

**JUNE-2018**

सा विद्या या विमुक्तये !

### CERTIFICATE

This is to certify that the thesis entitled "Microgrid Operation and Control" being submitted by Mr. Ashutosh Trivedi for the award of degree of Doctor of Philosophy in the Department of Electrical Engineering, Delhi Technological University, Delhi, is the record of student's own work carried out by him under my supervision. The contents of this research work have not been submitted in part or full to any other university or institute for award of any degree.

Date \_\_\_\_/\_\_\_/\_\_\_\_

Prof. Mukhtiar Singh Department of Electrical Engineering Delhi Technological University, Delhi Shahbad Daulatpur, Delhi-110042 India

#### ACKNOWLEDGEMENT

I wish to express my sincere appreciation to those who have contributed to this thesis and supported me in one way or the other during this amazing journey of my research.

Firstly, I would like to express my sincere gratitude to my advisor Prof. Mukhtiar Singh for his continuous support during my Ph.D. study and related research. His patience, motivation, and immense knowledge have been an inspiration and guiding light for me. His guidance helped me in all the time during this research work and writing of this thesis. I could not have imagined having a better advisor and mentor than him for my Ph.D study.

Besides my advisor, I would like to thank Prof. D.K. Jain, Dr. Jaipal, Prof. M.M.Tripathi and Prof. Kapil Sharma for helping me wherever required and provided me continuous motivation during my research.

I also want to specially mention about our Head of Department (EE), Prof. Madhusudan Singh and Prof. Dheeraj Joshi (OIC) who provided me an opportunity to do research and gave access to the laboratory and research facilities.Without their precious support, it would not be possible to conduct this research.

I thank my seniors & colleagues, Dr. Manoj Badoni, Vivek Raiwani, Abhishek Sinha, Neeraj Meena and Sandeep Prajapati who were always present there with me during my lab work not only for all their help and useful suggestions but also for being there to listen when I needed an ear and also for all the stimulating discussions.

I would especially like to thank our Power Electronics Labaratory staff Mr.Vinod Kumar, Ms. Renu, Ms. Vandana and Mr. Raju for their continuous support and help during my research work.

At Last but not least, I would like to thank my family and close ones for supporting me spiritually and emotionally throughout my research work and writing this thesis.

Date \_\_\_\_/\_\_\_/\_\_\_\_

Ashutosh Trivedi (2K13/PHD/EE/02)

### ABSTRACT

Due to everlasting electricity demand, the worldwide power system networks are under tremendous pressure and there is very strong need of strengthening our infrastructure related to power generation and transmission capabilities. However, with rising concern about the environmental issues of conventional generation and their limited resources, a lot of emphasis is being given to renewable energy sources (RES) based distributed generation (DG). As per the nomenclature the DG'S are to be integrated to main grid at distribution level and this eliminate the need of installing newer centralized power generation facilities and corresponding transmission line infrastructure. The integration of RES at distribution level has its own demerits primarily related to their intermittency and control. Recently, the concept of Microgrid is gaining lot of attention worldwide, as it can be very helpful in controlling the RES both in grid tie mode as well as in island mode. Thus, the microgrid may have its own generation and load, where it can remain grid tie in case of normal operation while it can isolate itself and keeps on feeding the localized load in case of any fault on grid side. However, microgrid has many issues regarding their operation, stability, power quality and protection. Moreover, most of the microgrid technology involves power electronics based interface which makes it almost inertia less system. Thus, the inherent advantage of transient stability by virtue of inertia is lost in case of microgrid. Therefore, to achieve stable operation of microgrid with enhanced power quality under intermittent generation and dynamic load conditions are one of the major issues. In modern distribution system, most of the loads are non-linear in nature and draw harmonic current. The variable load with the non-linear characteristics may distort the output voltage and degrade the power quality. Hence, major requirements of microgrid is to keep on feeding its connected load at regulated voltage and frequency with stable operation in transient condition, which are difficult to achieve especially in inverter based microgrid. The various control methodologies and control layers (Primary, secondary and tertiary etc.) have been used in past literature to overcome these issues. Therefore, the proposed research mainly deals with the two problems, first one is improvement of power quality under harmonic and unbalance load condition

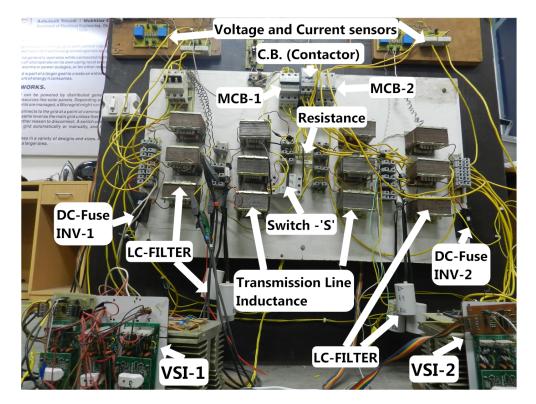

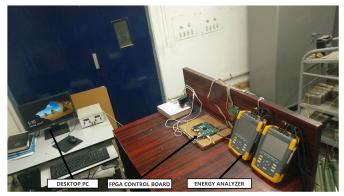

and second is the stable operation of microgrid having reconfigurable architecture which leads to huge variation in grid parameters. For the first problem, a novel repetitive control has been used to enhance power quality of voltage source inverters in droop based microgrid while for second problem a  $L_1$  based droop controller has been proposed. It is well known that variation in grid parameters may not be easily handled by conventional droop controllers which are mainly designed while assuming fixed grid configuration. However, these assumptions become invalid for a microgrid having small mesh network with reconfigurable structure. Therefore, it is most important for a microgrid to remain stable not only during various changes in droop characteristics but also during dynamic topological changes. For validation of methods and control strategy, real world hardware prototype has been developed. The hardware consists of two inverters (3-ph) with battery sources connected via variable transmission line impendences. Various types of load are connected to output of inverters and common points. These inverters are controlled by FPGA development board.

### Contents

| $\mathbf{C}$ | ERTI   | FICATE                                                  | i  |

|--------------|--------|---------------------------------------------------------|----|

| A            | CKN    | OWLEDGEMENTS i                                          | ii |

| A            | BSTI   | RACT                                                    | v  |

| $\mathbf{C}$ | onter  | ts v                                                    | ii |

| Li           | ist of | Figures xi                                              | ii |

| Li           | ist of | Tables xi                                               | х  |

| Li           | ist of | Symbols and Abbreviations xx                            | ci |

| 1            | INT    | RODUCTION                                               | 1  |

|              | 1.1    | Microgrid and its Requirement                           | 2  |

|              | 1.2    | Role of RES in Microgrid                                | 4  |

|              | 1.3    | Microgrid Worldwide                                     | 7  |

|              | 1.4    | Microgrid in India                                      | 9  |

|              | 1.5    | Type of Microgrid and their Structures                  | 1  |

|              |        | 1.5.1 AC Microgrid 1                                    | 1  |

|              |        | 1.5.2 DC Microgrid                                      | 3  |

|              |        | 1.5.3 Hybrid Microgrid                                  | .4 |

|              | 1.6    | IEEE 1547 Standards and Cigre WG C6.22 for Microgrids 1 | 5  |

|              | 1.7    | Scope of the Research Work                              | .6 |

|              | 1.8    | Thesis Structure                                        | 7  |

| 2 | AC  | MICR   | OGRID OPERATION AND PROTOTYPE DEVEL-             |    |

|---|-----|--------|--------------------------------------------------|----|

|   | OP  | MENT   | 1                                                | 19 |

|   | 2.1 | Opera  | tional Goals of Microgrid                        | 19 |

|   |     | 2.1.1  | Economic Benefits                                | 19 |

|   |     | 2.1.2  | Environmental Benefits                           | 20 |

|   |     | 2.1.3  | Value Addition                                   | 20 |

|   | 2.2 | Micro  | grid's Renewable Energy Sources                  | 20 |

|   |     | 2.2.1  | Solar PV                                         | 20 |

|   |     | 2.2.2  | Micro Hydro:                                     | 22 |

|   |     | 2.2.3  | Fuel Cell                                        | 23 |

|   |     | 2.2.4  | Biomass                                          | 23 |

|   |     | 2.2.5  | Wind                                             | 23 |

|   | 2.3 | Opera  | ting Modes                                       | 24 |

|   |     | 2.3.1  | Grid Connected Operations:                       | 24 |

|   |     | 2.3.2  | Island Operations                                | 25 |

|   |     | 2.3.3  | Black Start & Synchronization                    | 25 |

|   |     | 2.3.4  | Power Quality Improvement                        | 26 |

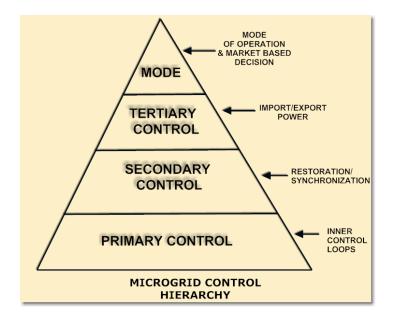

|   | 2.4 | Microg | grid Control Layers                              | 26 |

|   |     | 2.4.1  | Primary Control (Level 1)                        | 27 |

|   |     | 2.4.2  | Secondary Control (Level 2)                      | 27 |

|   |     | 2.4.3  | Tertiary Control (Level 3)                       | 27 |

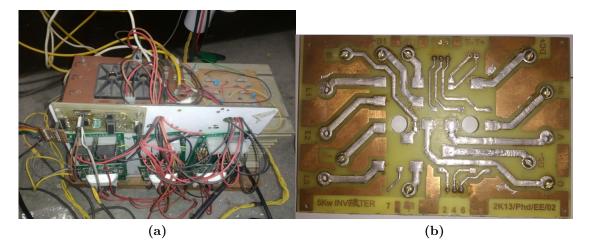

|   | 2.5 | Develo | opment of Microgrid Prototype                    | 27 |

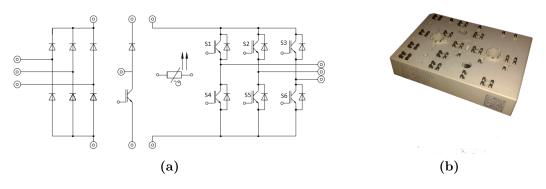

|   |     | 2.5.1  | IGBT Module & Drivers Configuration              | 28 |

|   | 2.6 | Outpu  | t Power Filter for PWM Inverter                  | 29 |

|   |     | 2.6.1  | Design of LC Filter                              | 31 |

|   |     | 2.6.2  | Filter Attenuation Constant and Inductance Value | 31 |

|   |     | 2.6.3  | Resonant Peak & Capacitor Selection              | 32 |

|   |     | 2.6.4  | Passive Damping                                  | 33 |

|   |     | 2.6.5  | Inductor Design                                  | 33 |

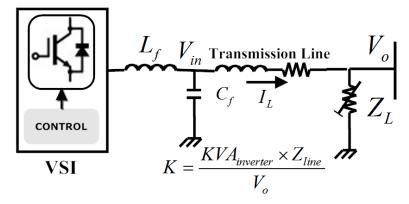

|   |     | 2.6.6  | Transmission Line/ Variable Impedance:           | 34 |

|   |     | 2.6.7  | Sensors & ADC:                                   | 35 |

|   |     | 2.6.8  | Battery Bank                                     | 37 |

# $\mathbf{2}$

|   |     | 2.6.9   | Linear, Nonlinear and Unbalance Load                                                           | 37     |

|---|-----|---------|------------------------------------------------------------------------------------------------|--------|

|   |     | 2.6.10  | Fuses, Circuit breaker and other Protective Circuits                                           | 38     |

|   | 2.7 | Conclu  | sion $\ldots$ | 38     |

| 3 | DRO | DOP C   | CONTROL OF MICROGRID                                                                           | 41     |

|   | 3.1 | Droop   | Control                                                                                        | 42     |

|   |     | 3.1.1   | Static Voltage Source Inverter (VSI) vs Synchronous Gen-                                       |        |

|   |     |         | erator (SG)                                                                                    | 43     |

|   |     | 3.1.2   | Power Sharing Parallel VSI                                                                     | 44     |

|   |     | 3.1.3   | Power sharing using Dedicated Communication Link:                                              | 44     |

|   |     | 3.1.4   | Power sharing using droop control:                                                             | 44     |

|   | 3.2 | Paralle | el Operation using Droop Control                                                               | 45     |

|   | 3.3 | Concep  | ot of Droop Control in Microgrid                                                               | 46     |

|   | 3.4 | Small s | signal Modeling and Stability analysis of microgrid                                            | 49     |

|   |     | 3.4.1   | Power controller and Inverter Model $\ . \ . \ . \ . \ . \ .$                                  | 50     |

|   |     | 3.4.2   | Network and Load Model                                                                         | 53     |

|   | 3.5 | Effect  | of Droop Coefficient in Microgrid                                                              | 55     |

|   | 3.6 | Primar  | ry Control in Microgrid                                                                        | 56     |

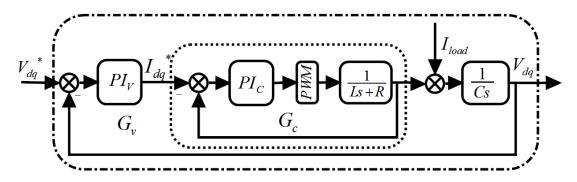

|   |     | 3.6.1   | Controller design:                                                                             | 58     |

|   |     | 3.6.2   | Design of Voltage and Current Controller:                                                      | 59     |

|   | 3.7 | Simula  | tion of Droop Control for VSI's in Microgrid                                                   | 61     |

|   |     | 3.7.1   | Simulation of Parallel Operation of VSI with Linear Droop .                                    | 62     |

|   |     | 3.7.2   | Effect of Droop Coefficient:                                                                   | 64     |

|   |     | 3.7.3   | SOC Based Droop Control:                                                                       | 64     |

|   |     | 3.7.4   | Grid Tie Mode:                                                                                 | 69     |

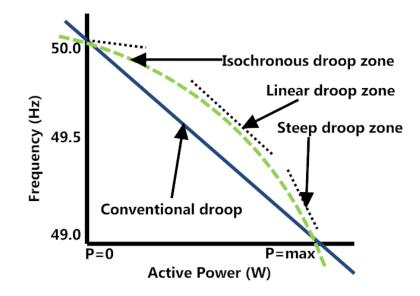

|   | 3.8 | A Mod   | lified Droop Control                                                                           | 71     |

|   | 3.9 | Conclu  | sion                                                                                           | 72     |

| 4 | REI | PETIT   | IVE CONTROLLER FOR DROOP BASED MICROGE                                                         | RID 75 |

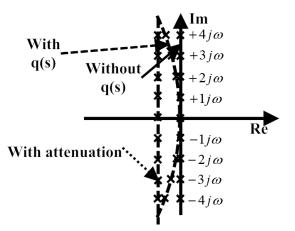

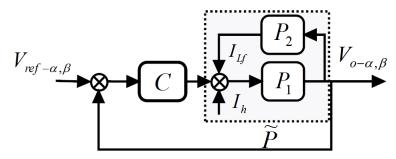

|   | 4.1 | Multi-  | loop Control Strategy of Microgrid                                                             | 76     |

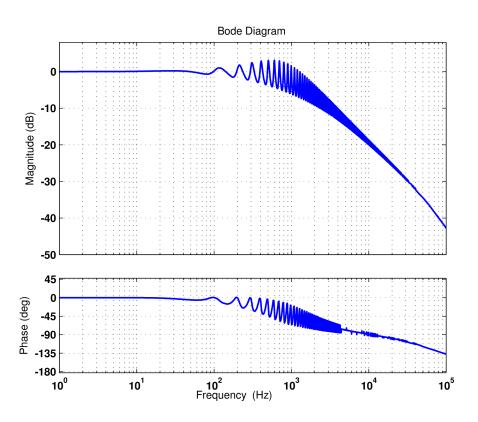

|   | 4.2 | Design  | of Repetitive Controller                                                                       | 78     |

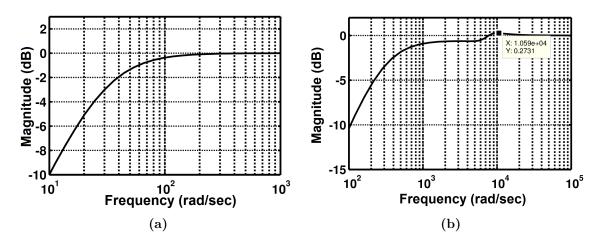

|   |     | 4.2.1   | Design of Voltage Controller:                                                                  | 81     |

|   |     | 4.2.2   | Design of Current Controller                                                                   | 84     |

|          |         | 4.2.3    | Response of Designed Controllers:                                       |

|----------|---------|----------|-------------------------------------------------------------------------|

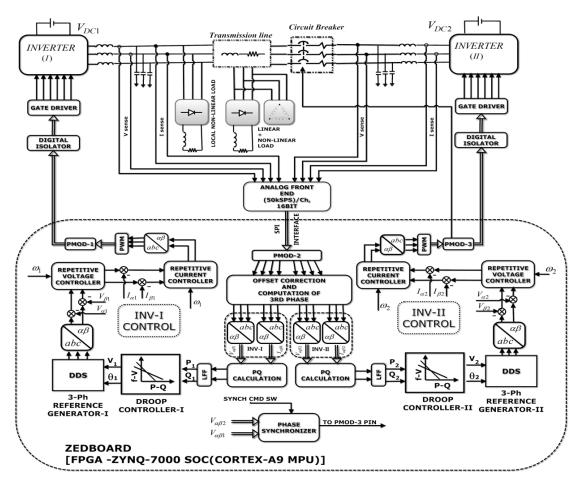

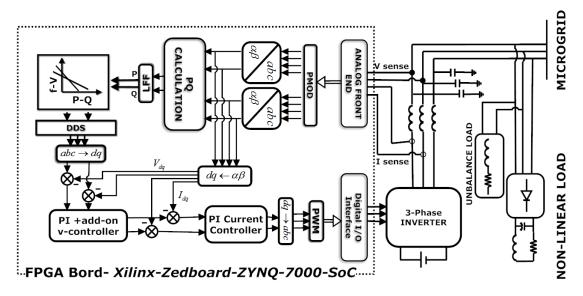

|          | 4.3     | Impler   | nentation in Real Time Hardware                                         |

|          | 4.4     | Simula   | ation and Experimental Results                                          |

|          |         | 4.4.1    | Performance of RC with Non-Linear Load: 90                              |

|          |         | 4.4.2    | Performance of RC in power sharing                                      |

|          | 4.5     | Conclu   | usion                                                                   |

| <b>5</b> | REF     | PETIT    | IVE ADD-ON CONTROLLER FOR UNBALANCE                                     |

|          | COI     | MPEN     | SATION IN MICROGRID 99                                                  |

|          | 5.1     | Voltag   | e Unbalance and Harmonics                                               |

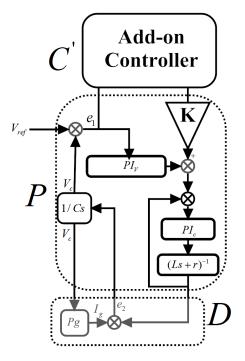

|          | 5.2     | Repeti   | tive Controller for Unbalance and Harmonics                             |

|          |         | 5.2.1    | Design of controller:                                                   |

|          |         | 5.2.2    | Proportional gain for effort sharing:                                   |

|          |         | 5.2.3    | RC Implementation in FPGA:                                              |

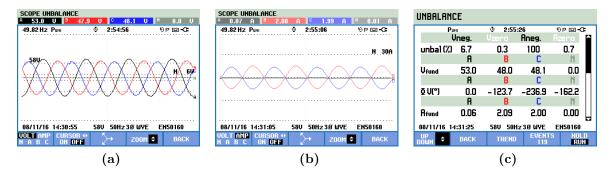

|          | 5.3     | Experi   | imental and Simulation Results                                          |

|          |         | 5.3.1    | Performance of controller:                                              |

|          |         | 5.3.2    | Implementation Cost:                                                    |

|          | 5.4     | Conclu   | usion                                                                   |

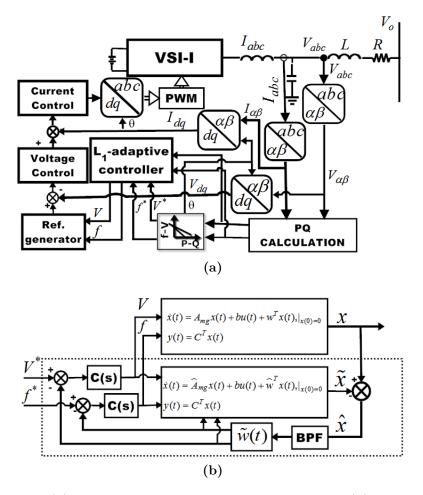

| 6        | $L_1$ A | DAP      | TIVE DROOP CONTROL FOR MESH MICROGRID115                                |

|          | 6.1     | Genera   | alized Average Modeling of VSI in Microgrid                             |

|          | 6.2     | $L_1$ Ad | aptive Droop Control                                                    |

|          |         | 6.2.1    | $L_1$ Adaptive control Theory:                                          |

|          |         | 6.2.2    | Design of $L_1$ Droop Controller                                        |

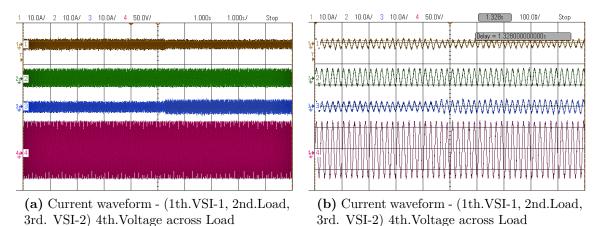

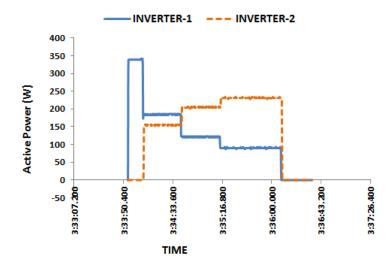

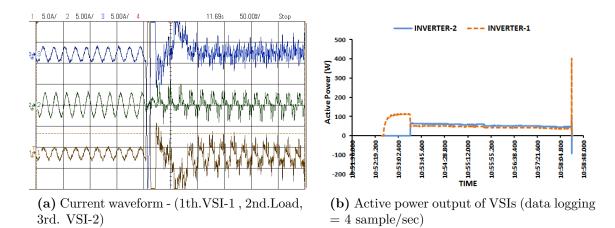

|          |         | 6.2.3    | Hardware Description and Results                                        |

|          |         | 6.2.4    | Eigen Value Analysis                                                    |

|          |         | 6.2.5    | Simulation                                                              |

|          | 6.3     | Real T   | Time Hardware Verification:                                             |

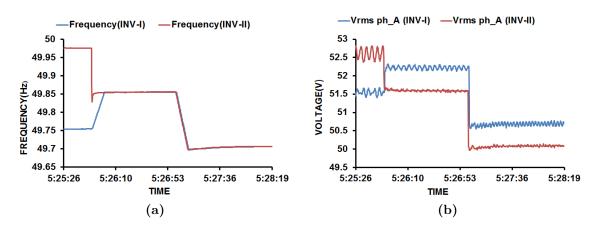

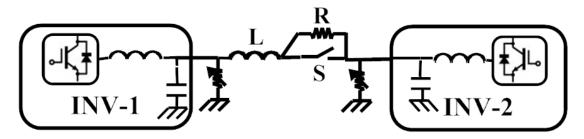

|          |         | 6.3.1    | Case 1: Variation in Droop Coefficients with High R/X 127               |

|          |         | 6.3.2    | Case 2: Increasing R/X Ratio Instantaneously $\ldots \ldots \ldots 129$ |

|          | 6.4     | Conclu   | usion                                                                   |

### 7 IMPLEMENTATION OF CONTROL WITH FPGA 133

|   | 7.1                                                                                                   | FPGA Overview                                                                                                                                                                                                                                                                                                                                                  | . 134                                                                                                                                        |

|---|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

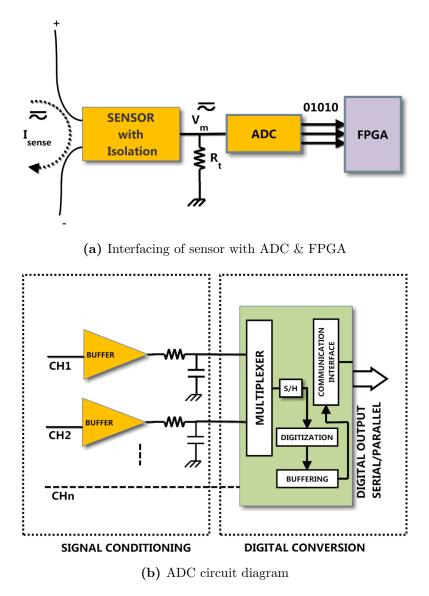

|   | 7.2                                                                                                   | ADC Design & Interfacing with FPGA                                                                                                                                                                                                                                                                                                                             | . 137                                                                                                                                        |

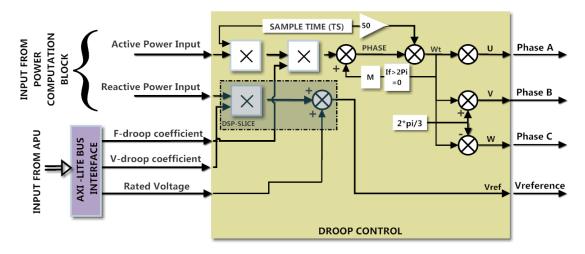

|   | 7.3                                                                                                   | Droop Control                                                                                                                                                                                                                                                                                                                                                  | . 139                                                                                                                                        |

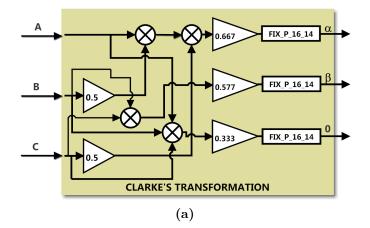

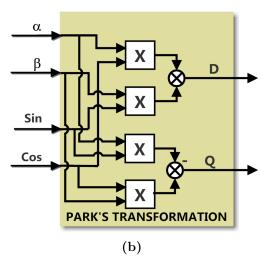

|   | 7.4                                                                                                   | Transformation Block                                                                                                                                                                                                                                                                                                                                           | . 141                                                                                                                                        |

|   | 7.5                                                                                                   | Power Calculation and Filters                                                                                                                                                                                                                                                                                                                                  | . 141                                                                                                                                        |

|   | 7.6                                                                                                   | Synchronization Block                                                                                                                                                                                                                                                                                                                                          | . 142                                                                                                                                        |

|   | 7.7                                                                                                   | Overcurrent Protection Block                                                                                                                                                                                                                                                                                                                                   | . 144                                                                                                                                        |

|   | 7.8                                                                                                   | Three Phase Reference Voltage Generation                                                                                                                                                                                                                                                                                                                       | . 145                                                                                                                                        |

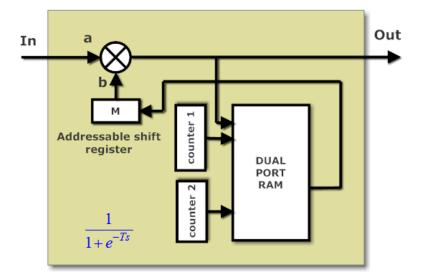

|   | 7.9                                                                                                   | RC Block                                                                                                                                                                                                                                                                                                                                                       | . 145                                                                                                                                        |

|   | 7.10                                                                                                  | PI Regulator Block                                                                                                                                                                                                                                                                                                                                             | . 147                                                                                                                                        |

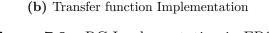

|   | 7.11                                                                                                  | Overclocking                                                                                                                                                                                                                                                                                                                                                   | . 147                                                                                                                                        |

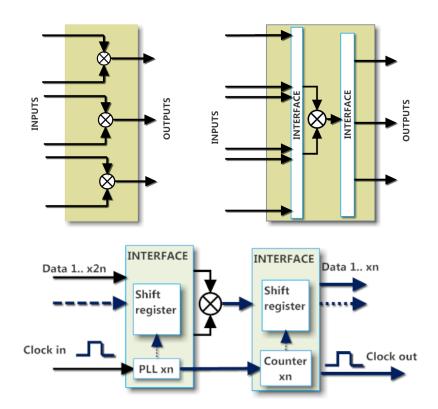

|   | 7.12                                                                                                  | Time Division Multiplexing                                                                                                                                                                                                                                                                                                                                     | . 149                                                                                                                                        |

|   | 7.13                                                                                                  | Fixed Point Computation                                                                                                                                                                                                                                                                                                                                        | . 150                                                                                                                                        |

|   | 7.14                                                                                                  | Programing Soft Core (Software Development)                                                                                                                                                                                                                                                                                                                    | . 151                                                                                                                                        |

|   | 7.15                                                                                                  | Conclusion                                                                                                                                                                                                                                                                                                                                                     | . 152                                                                                                                                        |

|   |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              |

| 8 | COI                                                                                                   | NCLUSION & FUTURE WORK                                                                                                                                                                                                                                                                                                                                         | 153                                                                                                                                          |

|   |                                                                                                       | NCLUSION & FUTURE WORK                                                                                                                                                                                                                                                                                                                                         | 153<br>159                                                                                                                                   |

|   |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                | 159                                                                                                                                          |

|   | SYS                                                                                                   | STEM PARAMETERS AND TRANSFORMATIONS                                                                                                                                                                                                                                                                                                                            | <b>159</b><br>. 159                                                                                                                          |

|   | <b>SYS</b><br>A.1                                                                                     | STEM PARAMETERS AND TRANSFORMATIONS                                                                                                                                                                                                                                                                                                                            | <b>159</b><br>. 159<br>. 159                                                                                                                 |

|   | <b>SYS</b><br>A.1                                                                                     | STEM PARAMETERS AND TRANSFORMATIONS         SYSTEM PARAMETERS         REFERENCE FRAME THEORY                                                                                                                                                                                                                                                                   | <b>159</b><br>. 159<br>. 159<br>. 159<br>. 159                                                                                               |

|   | <b>SYS</b><br>A.1                                                                                     | STEM PARAMETERS AND TRANSFORMATIONS         SYSTEM PARAMETERS         REFERENCE FRAME THEORY         A.2.1 dq0 Transformation                                                                                                                                                                                                                                  | <b>159</b><br>. 159<br>. 159<br>. 159<br>. 159<br>. 161                                                                                      |

|   | <b>SYS</b><br>A.1<br>A.2                                                                              | STEM PARAMETERS AND TRANSFORMATIONS         SYSTEM PARAMETERS         REFERENCE FRAME THEORY         A.2.1 $dq0$ Transformation         A.2.2 $\alpha\beta0$ Transformation                                                                                                                                                                                    | <b>159</b><br>. 159<br>. 159<br>. 159<br>. 159<br>. 161                                                                                      |

| A | <b>SYS</b><br>A.1<br>A.2                                                                              | STEM PARAMETERS AND TRANSFORMATIONS         SYSTEM PARAMETERS $\qquad$ REFERENCE FRAME THEORY $\qquad$ A.2.1 dq0 Transformation $\qquad$ A.2.2 $\alpha\beta0$ Transformation $\qquad$ A.2.3 Instantaneous Power Calculation $\qquad$                                                                                                                           | <ol> <li>159</li> <li>159</li> <li>159</li> <li>159</li> <li>161</li> <li>162</li> <li>165</li> </ol>                                        |

| A | SYS<br>A.1<br>A.2                                                                                     | STEM PARAMETERS AND TRANSFORMATIONS         SYSTEM PARAMETERS $\ldots$ REFERENCE FRAME THEORY $\ldots$ A.2.1 dq0 Transformation $\ldots$ A.2.2 $\alpha\beta0$ Transformation $\ldots$ A.2.3 Instantaneous Power Calculation $\ldots$ MPUTATION OF $L_1$ NORM                                                                                                   | <ol> <li>159</li> <li>159</li> <li>159</li> <li>161</li> <li>162</li> <li>165</li> </ol>                                                     |

| A | SYS<br>A.1<br>A.2<br>COI<br>B.1                                                                       | STEM PARAMETERS AND TRANSFORMATIONS         SYSTEM PARAMETERS                                                                                                                                                                                                                                                                                                  | <b>159</b> . 159 . 159 . 159 . 161 . 162 <b>165</b> . 165                                                                                    |

| в | <ul> <li>SYS</li> <li>A.1</li> <li>A.2</li> <li>CON</li> <li>B.1</li> <li>B.2</li> <li>B.3</li> </ul> | STEM PARAMETERS AND TRANSFORMATIONS         SYSTEM PARAMETERS         REFERENCE FRAME THEORY         A.2.1 $dq0$ Transformation         A.2.2 $\alpha\beta0$ Transformation         A.2.3 Instantaneous Power Calculation         MPUTATION OF $L_1$ NORM $L_P$ Spaces         Computation of $L_1$ -Norm                                                      | <b>159</b> . 159 . 159 . 159 . 161 . 162 <b>165</b> . 165                                                                                    |

| в | <ul> <li>SYS</li> <li>A.1</li> <li>A.2</li> <li>CON</li> <li>B.1</li> <li>B.2</li> <li>B.3</li> </ul> | STEM PARAMETERS AND TRANSFORMATIONS         SYSTEM PARAMETERS         REFERENCE FRAME THEORY         A.2.1 $dq0$ Transformation         A.2.2 $\alpha\beta0$ Transformation         A.2.3 Instantaneous Power Calculation         MPUTATION OF $L_1$ NORM $L_P$ Spaces         Computation of $L_1$ -Norm         Computation for $L_1$ -Controller Parameters | <ol> <li>159</li> <li>159</li> <li>159</li> <li>161</li> <li>162</li> <li>165</li> <li>165</li> <li>165</li> <li>167</li> <li>169</li> </ol> |

Bibliography

### List of Figures

| 1.1  | Renewal Power Generation Capacities by Share (World)                       | 7  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | Power Generation Capacity Share in India (by type of source) $\ . \ . \ .$ | 8  |

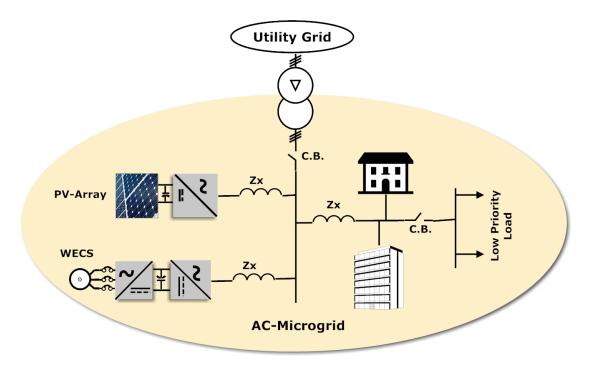

| 1.3  | AC Microgrid Schematic                                                     | 12 |

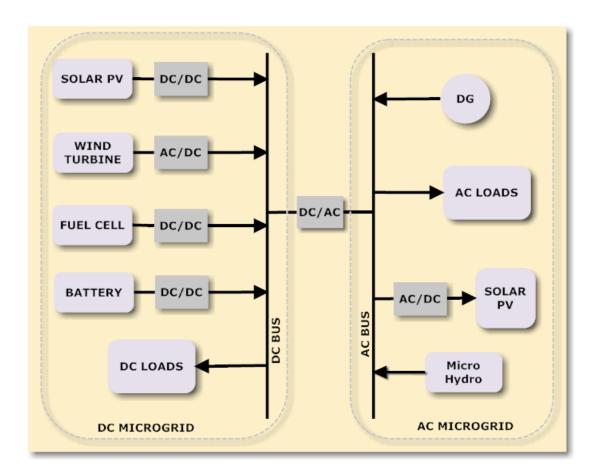

| 1.4  | Hybrid Microgrid                                                           | 14 |

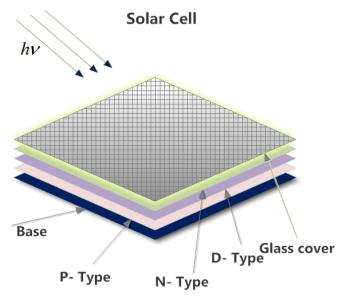

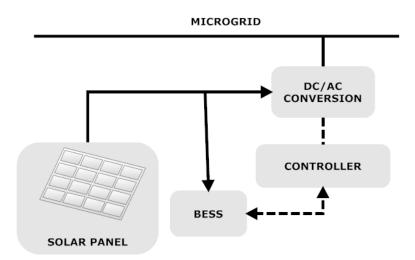

| 2.1  | Soler Cell                                                                 | 21 |

| 2.2  | Solar panel connected to microgrid                                         | 21 |

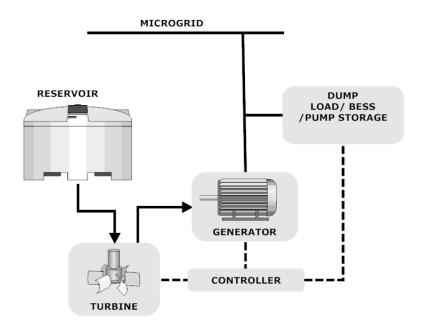

| 2.3  | Micro-hydro plant in microgrid                                             | 22 |

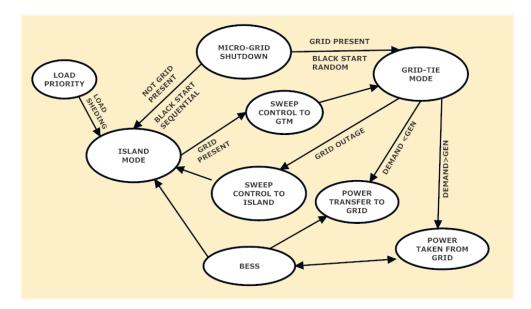

| 2.4  | State Diagram of Microgrid Operation                                       | 24 |

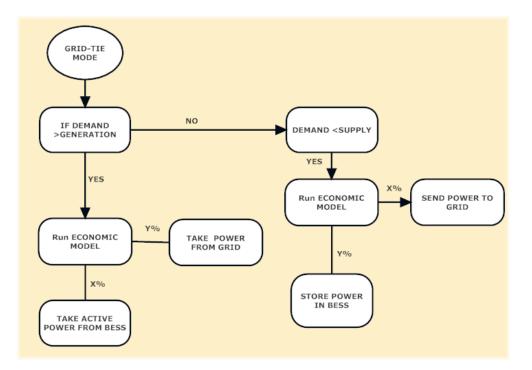

| 2.5  | Grid tie mode operation diagram                                            | 25 |

| 2.6  | Hierarchical Control of Microgrid                                          | 26 |

| 2.7  | Inverter Module Schematic and a Picture of Physical Device                 | 28 |

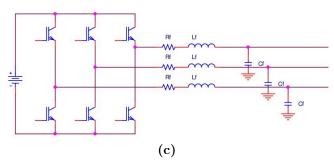

| 2.8  | 3-ph Inverter with Driver and other Circuitry                              | 29 |

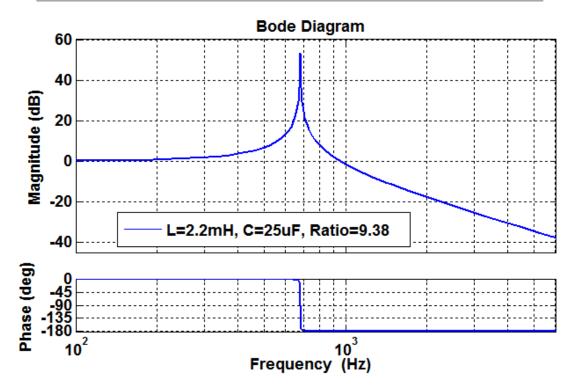

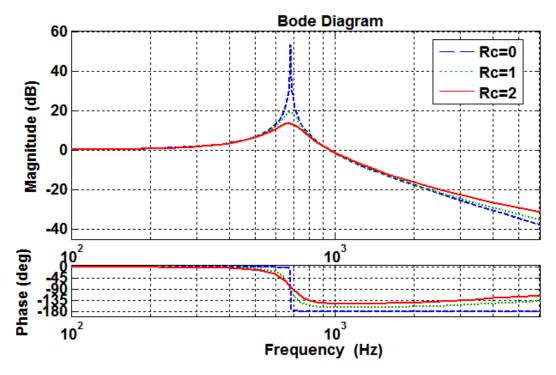

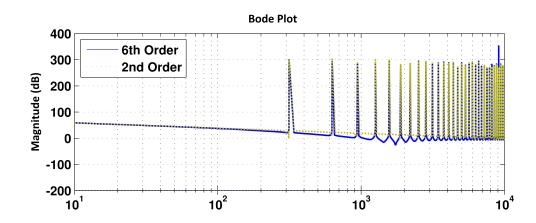

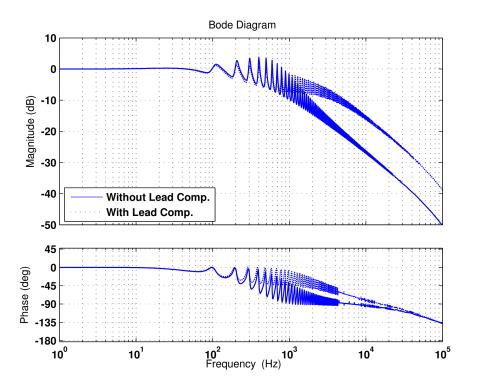

| 2.9  | Bode Plot of Designed Filter                                               | 34 |

| 2.10 | Bode Plot of Filter with Passive Damping                                   | 35 |

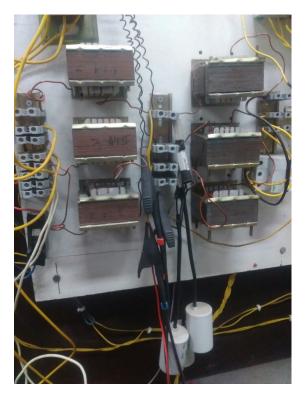

| 2.11 | LC Filter in Circuit                                                       | 36 |

| 2.12 | Switchover Circuit for Variable Transmission Line                          | 36 |

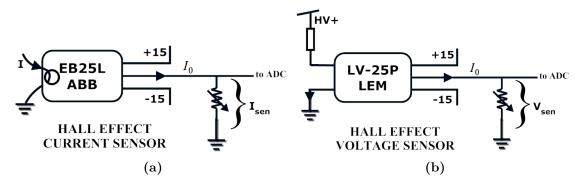

| 2.13 | Schematic Diagram of Sensors                                               | 37 |

| 2.14 | In Circuit Current and Voltage Sensors                                     | 37 |

| 2.15 | Battery Bank                                                               | 38 |

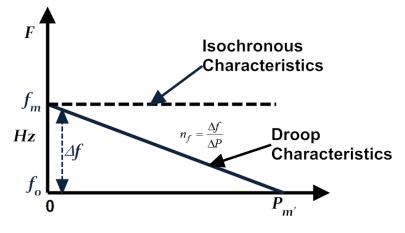

| 3.1  | Governor Characteristics Curve                                             | 43 |

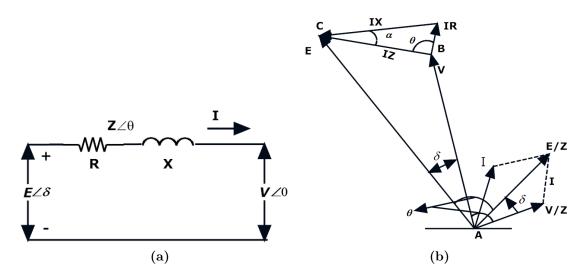

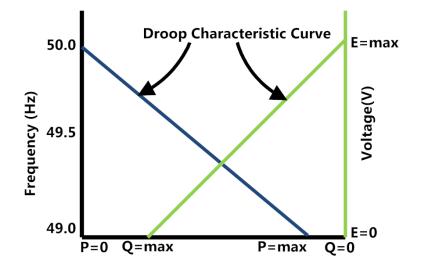

| 3.2  | Equivalent Circuit & Phasor Diagram of Network                             | 47 |

| 3.3  | Voltage and Frequency Droop Characteristicss                               | 48 |

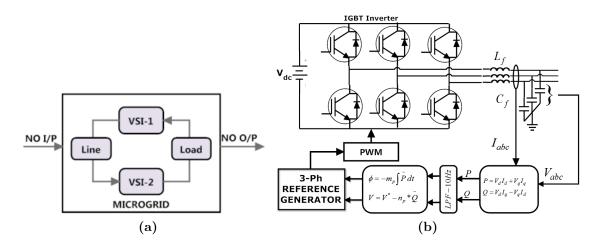

| 3.4  | Island Microgrid & Inverter interface                                      | 49 |

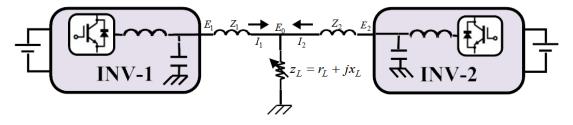

| 3.5  | Network and Load Model                                                     | 53 |

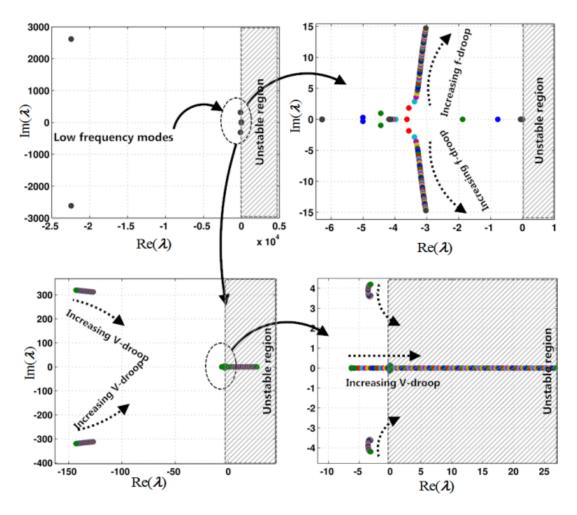

| 3.6  | Effect on modes of microgrid due to variation in different droop para-   |    |

|------|--------------------------------------------------------------------------|----|

|      | meters                                                                   | 57 |

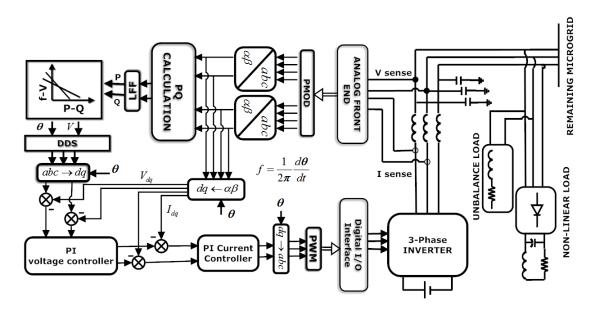

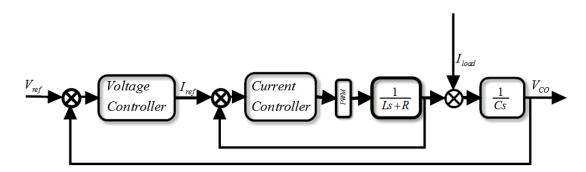

| 3.7  | Basic Control Stretegy forVSI in microgrid                               | 58 |

| 3.8  | Basic structure of PI voltage and current controllers                    | 59 |

| 3.9  | Controller Responses                                                     | 60 |

| 3.10 | Control Schematic                                                        | 61 |

| 3.11 | Output Voltage and Frequency in Droop Control                            | 62 |

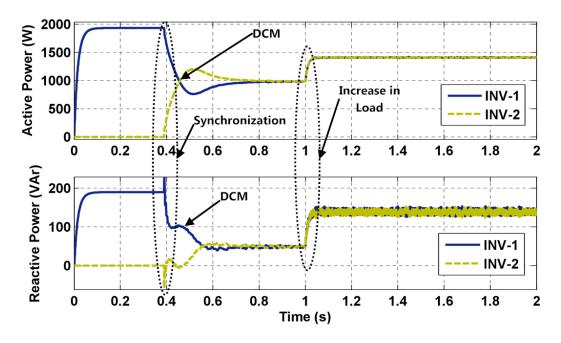

| 3.12 | Output Powers in Droop Control                                           | 63 |

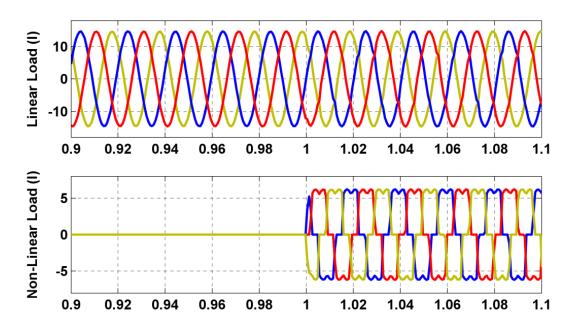

| 3.13 | Load Current Profile                                                     | 63 |

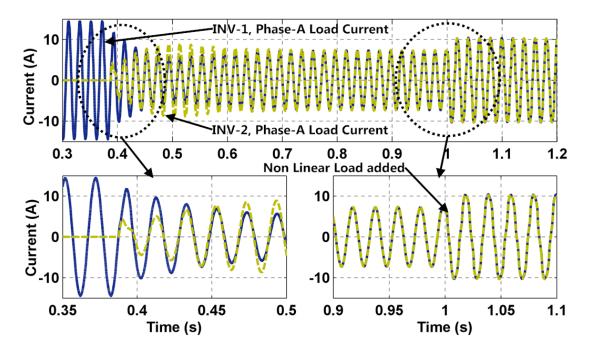

| 3.14 | Inverters Output Curernt During Parallel Operation                       | 64 |

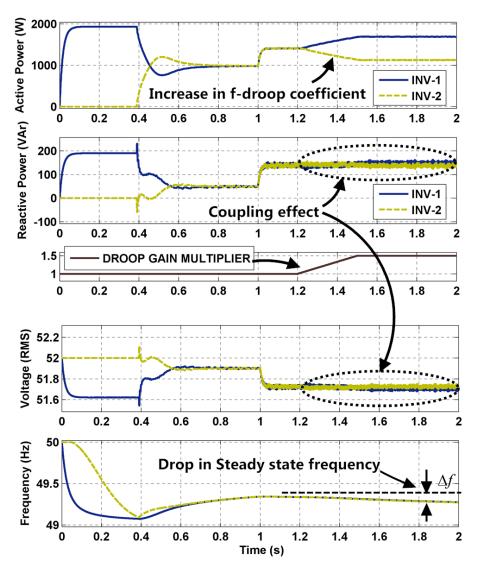

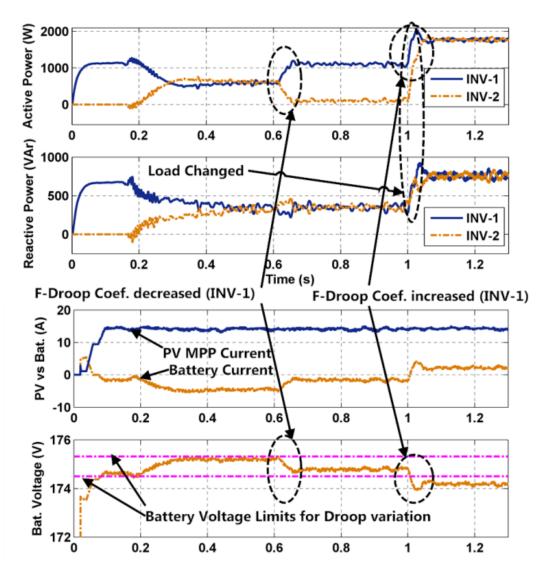

| 3.15 | Inverters Output with Varying $f$ -Droop Coefficient                     | 65 |

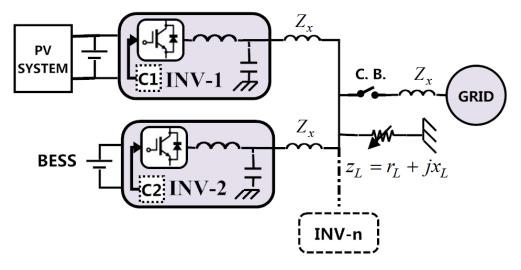

| 3.16 | Microgrid with PV System with BESS                                       | 65 |

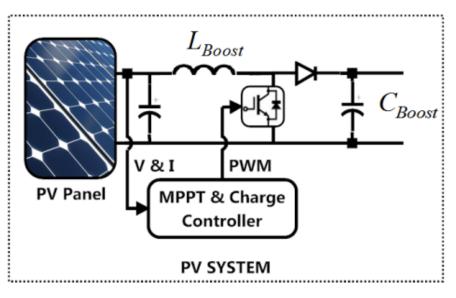

| 3.17 | PV System Diagram with MPPT                                              | 66 |

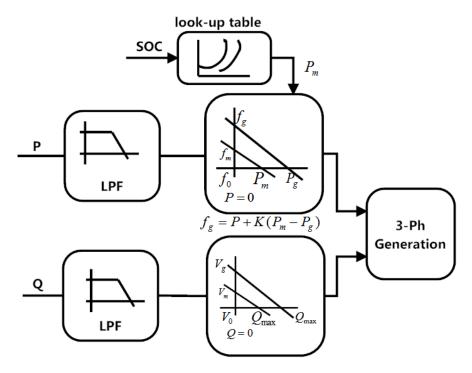

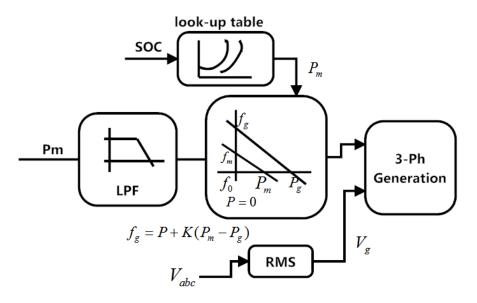

| 3.18 | SoC Based Droop Controller                                               | 66 |

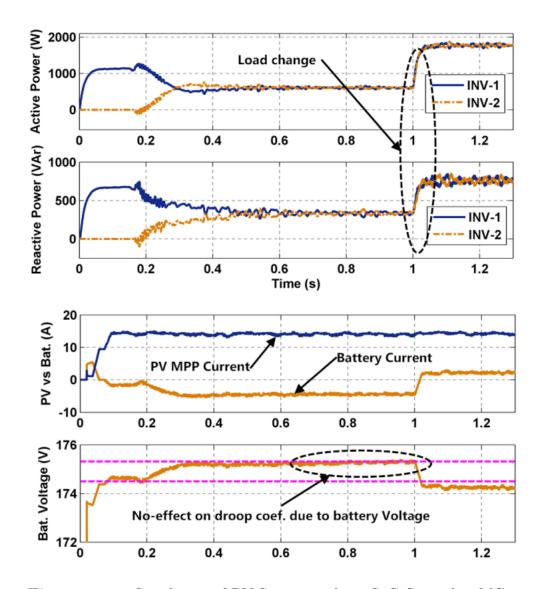

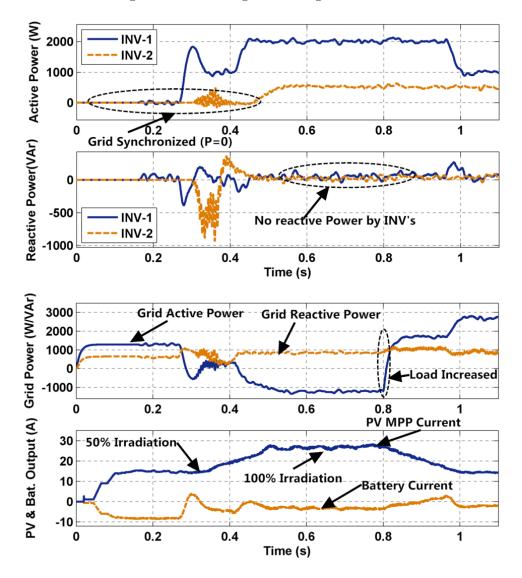

| 3.19 | Simulation of PV System without SoC Control in MG                        | 67 |

| 3.20 | Simulation of PV System with SoC Control in MG                           | 68 |

| 3.21 | Grid Tie Mode of Control                                                 | 69 |

| 3.22 | Simulation of PV System in Grid Tie mode                                 | 70 |

| 3.23 | Non-linear Droop Characterstics                                          | 71 |

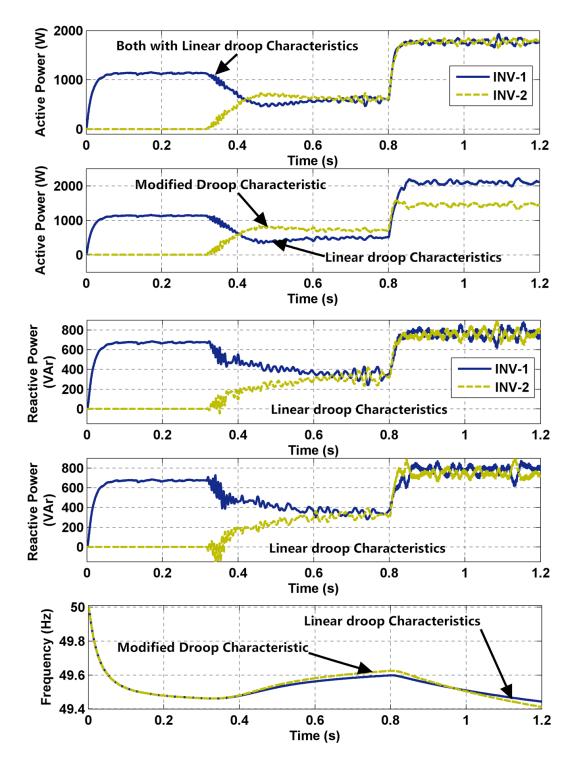

| 3.24 | Simulation of Modified Droop Control                                     | 73 |

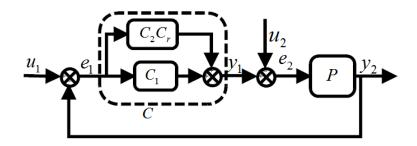

| 4.1  | Basic inner loop control                                                 | 77 |

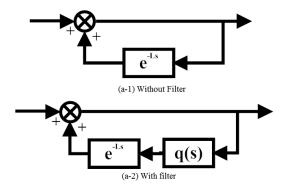

| 4.2  | Internal Model of Feedback Time Delay                                    | 78 |

| 4.3  | Poles of the Time delay system                                           | 78 |

| 4.4  | Unity feedback RC                                                        | 79 |

| 4.5  | Plant Diagram                                                            | 82 |

| 4.6  | Bode plot of (a) Sensitivity shaping function $1/W_1$ (b) System sensit- |    |

|      | ivity with $C_v$                                                         | 83 |

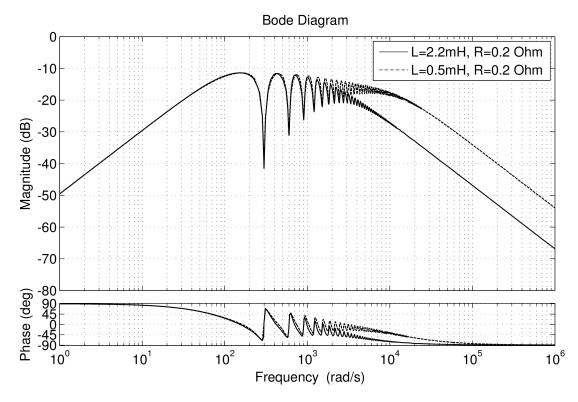

| 4.7  | Frequency Response of Voltage RC                                         | 83 |

| 4.8  | Frequency Response of Current RC                                         | 85 |

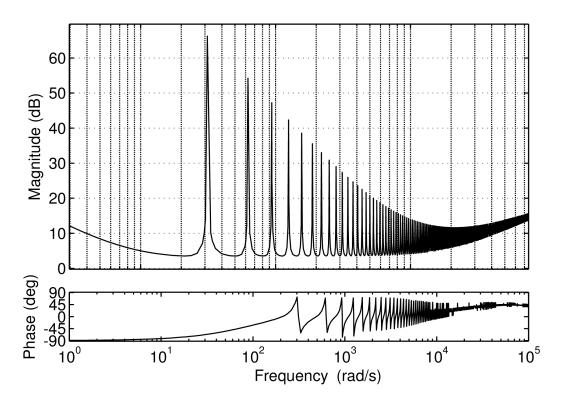

| 4.9  | Frequency Response of Current RC with different filter inductance        | 85 |

| 4.10 | Performance Test Digram of RC                                            | 86 |

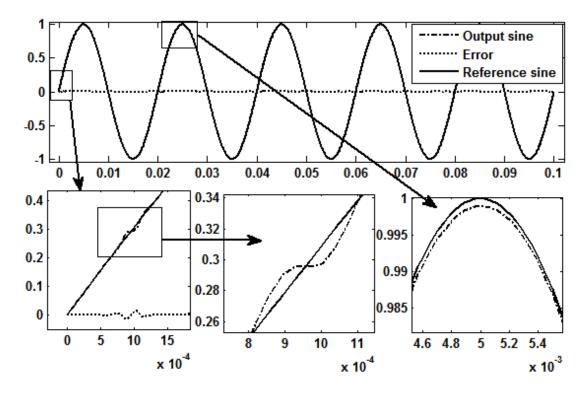

| 4.11 | Reference tracking of RC controller with Sin input                                   | 86  |

|------|--------------------------------------------------------------------------------------|-----|

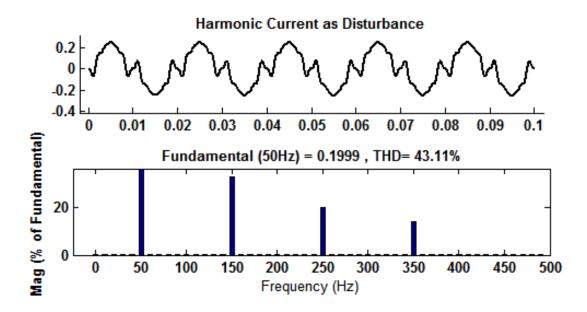

| 4.12 | Disturbance input and its THD (Simulating Non-linear Load) $\ . \ . \ .$             | 87  |

| 4.13 | Real Time System Schematic                                                           | 88  |

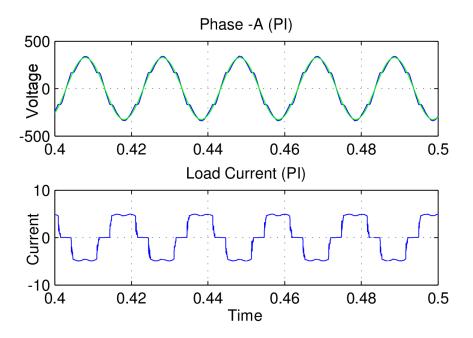

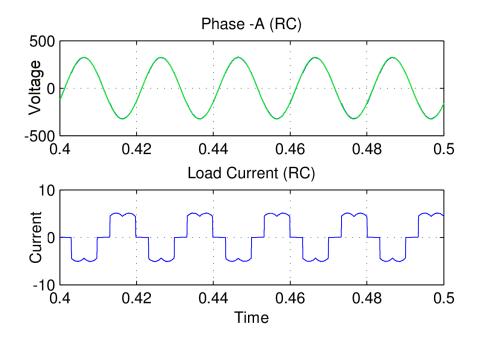

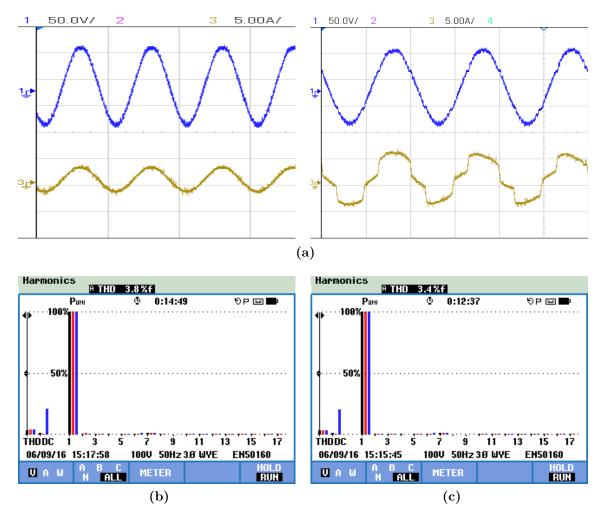

| 4.14 | With PI control : Output Voltage, Reference Voltage and load current                 | 90  |

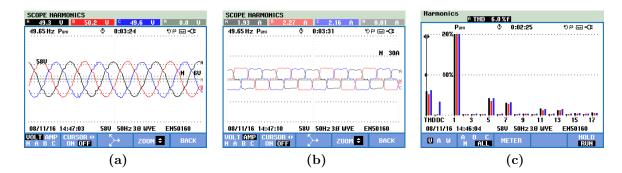

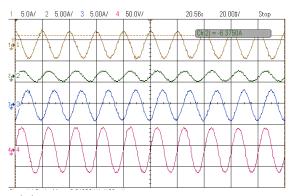

| 4.15 | With RC: Output Voltage, Reference Voltage and load current                          | 91  |

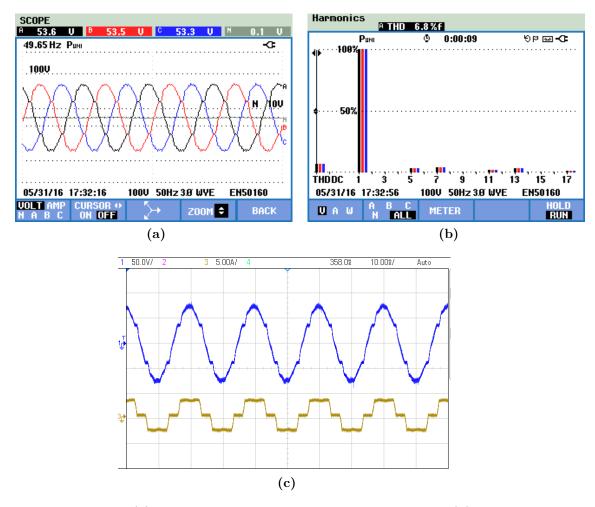

| 4.16 | (a) 3-Phase voltage waveform with PI control (b) Harmonics profile of                |     |

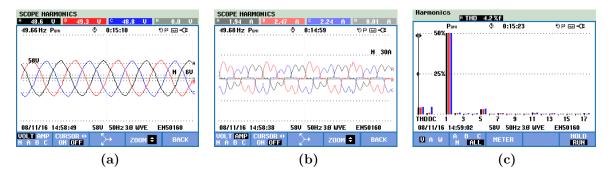

|      | voltage (6.8% THD) (c) Voltage and Non-linear load current profile $\ . \ .$         | 92  |

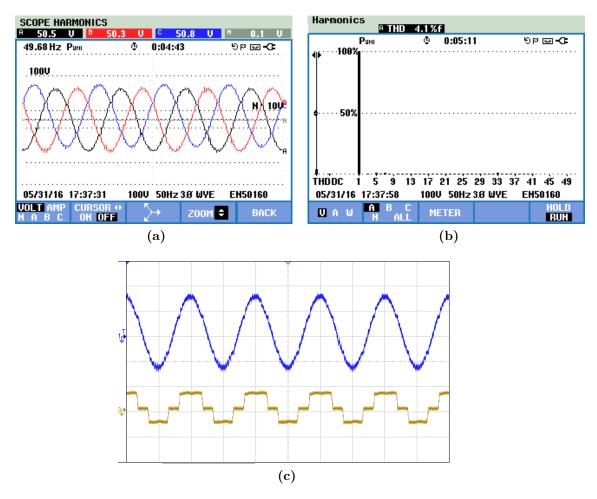

| 4.17 | (a) Voltage waveform with RC control (b) Harmonics profile of voltage                |     |

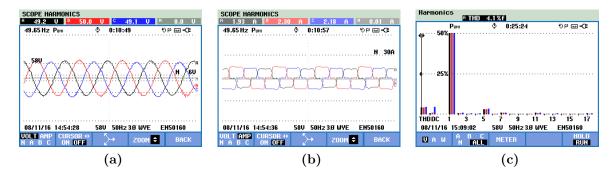

|      | (4.1% THD) (c) Voltage and Non-linear load current $\hdots$                          | 93  |

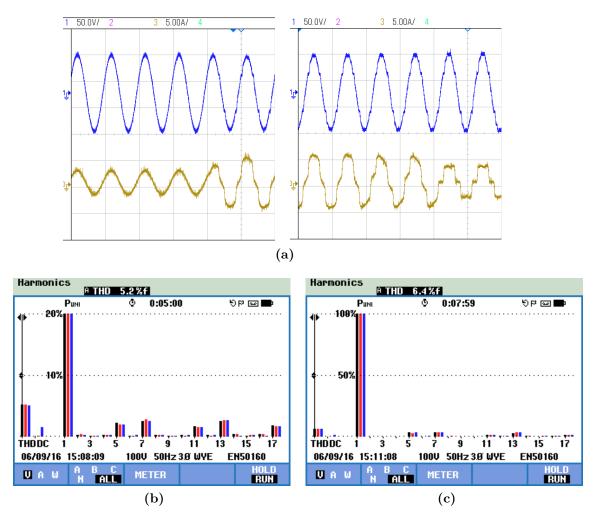

| 4.18 | a) Voltage and current under different load condition with PI (b) Har-               |     |

|      | monic profile of voltage under linear plus non-linear loading(c) Har-                |     |

|      | monic profile of voltage under non-linear loading                                    | 94  |

| 4.19 | (a) Voltage and current under different load condition with RC (b)                   |     |

|      | Harmonic profile of voltage under linear plus non-linear loading (c)                 |     |

|      | Harmonic profile of voltage under non-linear loading                                 | 95  |

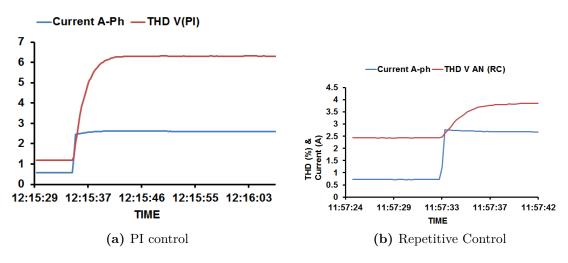

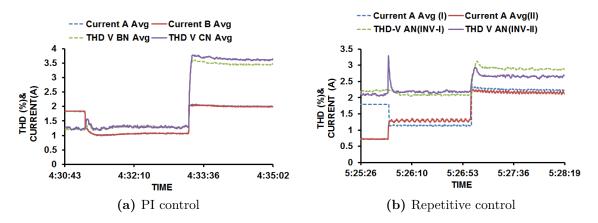

| 4.20 | THD comparison with Load Current                                                     | 95  |

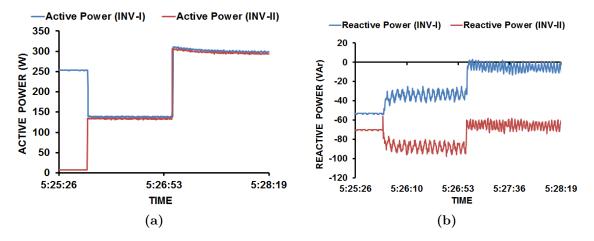

| 4.21 | (a) Frequency and (b) Voltage of both inverters $\ldots \ldots \ldots \ldots \ldots$ | 96  |

| 4.22 | (a) Frequency and (b) Voltage of both inverters                                      | 96  |

| 4.23 | THD vs Load Current diagram during parallel operation of both the                    |     |

|      | inverters                                                                            | 96  |

| 5.1  | Voltage current control loop                                                         | 102 |

| 5.2  | System with Add-on Controller                                                        | 102 |

| 5.3  | System response with modified RC                                                     | 103 |

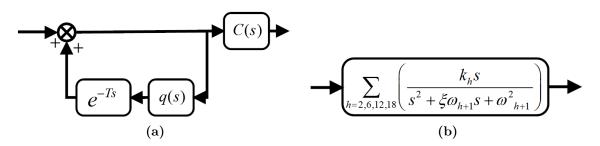

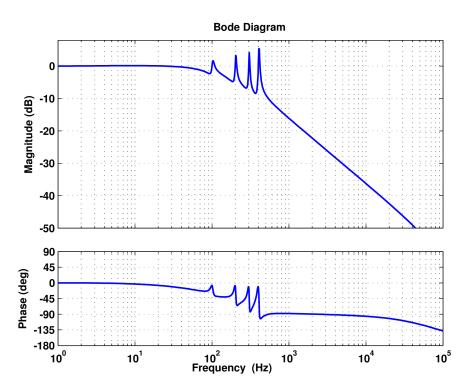

| 5.4  | Effect of Lead Compensator                                                           | 104 |

| 5.5  | Add-on multi Resonant Controller                                                     | 105 |

| 5.6  | System response with add-on SOGI Resonant controller                                 | 105 |

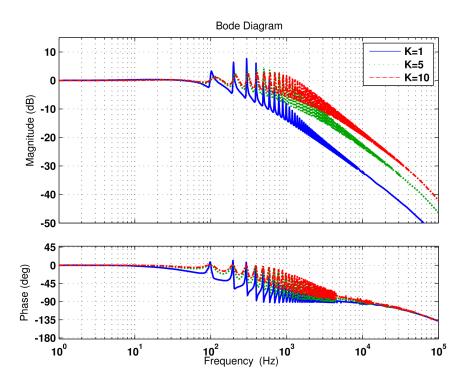

| 5.7  | System response with different value of K                                            | 106 |

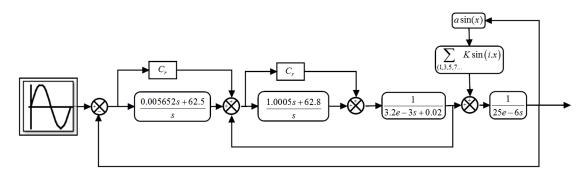

| 5.8  | System diagram                                                                       | 107 |

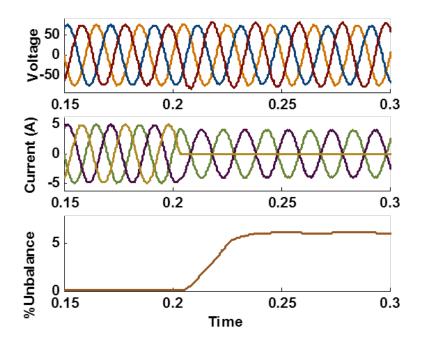

| 5.9  | Output Voltage without add-on RC controller (Simulation) 1                           | 108 |

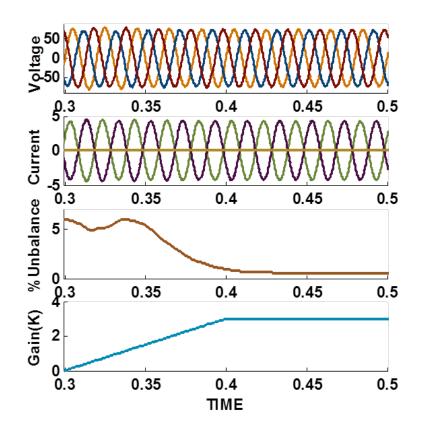

| 5.10 | Unbalance mitigation with varying K (Simulation)                                     | 109 |

|      |                                                                                      |     |

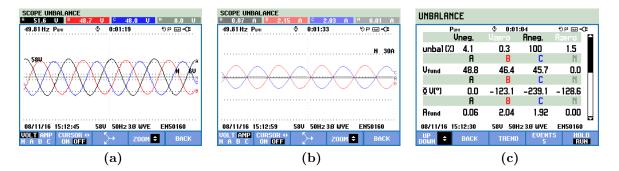

| 5.11  | (a) Output Voltage, (b) Load Current (c) Unbalance without add-on<br>controller                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.12  | (a) Output Voltage, (b) Load Current (c) Unbalance with add-on res-<br>onant controller                                                                            |

| 5.13  | (a) Output Voltage, (b) Load Current (c) Unbalance with add-on Re-                                                                                                 |

| F 1 / | petitive controller $\dots \dots \dots$                            |

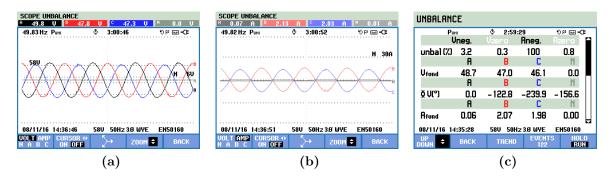

|       | <ul><li>(a) Output Voltage, (b) Load Current (c) THD without add-on controller111</li><li>(a) Output Voltage, (b) Load Current -RL(c) THD with add-on RC</li></ul> |

|       | under Rectifeid RL load                                                                                                                                            |

| 5.16  | (a) Output Voltage, (b) Load Current -RLC(c) THD with add-on RC                                                                                                    |

|       | under Rectifeid RLC load                                                                                                                                           |

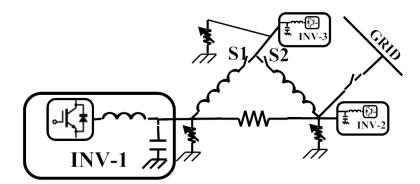

| 6.1   | Microgrid with small mesh network                                                                                                                                  |

| 6.2   | (a) Adaptive control system of an Inverter (b) Adaptive Controller                                                                                                 |

|       | diagram                                                                                                                                                            |

| 6.3   | Schematic of Two VSI forming microgrid with Line Changeover Switch $124$                                                                                           |

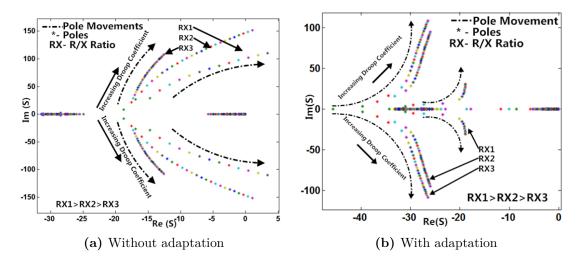

| 6.4   | Variation in low frequency modes of two inverter microgrid                                                                                                         |

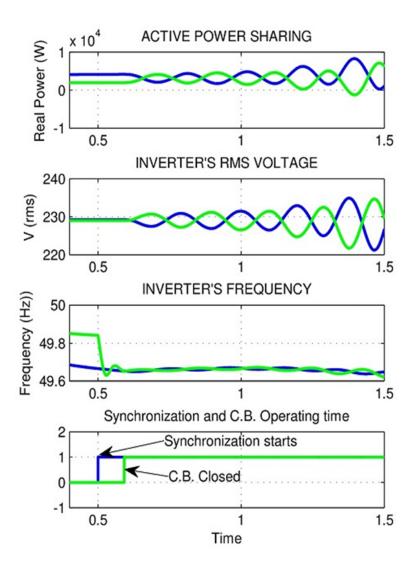

| 6.5   | Parallel operation with High R/X (Simulation) without adaptive control<br>126 $$                                                                                   |

| 6.6   | Parallel operation with adaptive control with High R/X $(>7)$ and In-                                                                                              |

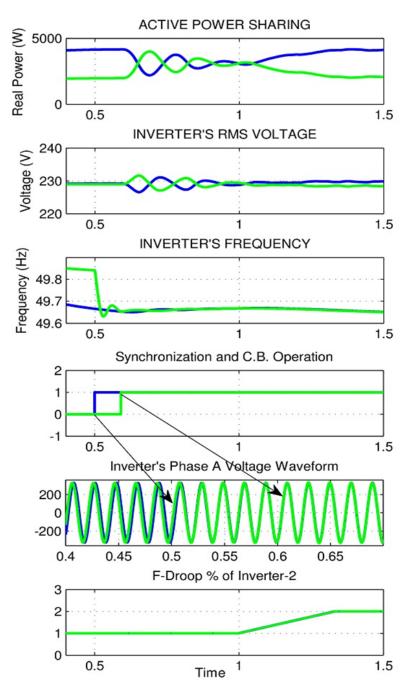

|       | creased f-droop coefficient                                                                                                                                        |

| 6.7   | Increasing droop (up-to 200%) with high R/X ratio (>=2) without                                                                                                    |

|       | adaptive control                                                                                                                                                   |

| 6.8   | Increasing droop (up-to 200%) with high R/X ratio (>=7) with ad-                                                                                                   |

|       | aptive control                                                                                                                                                     |

| 6.9   | Power sharing while Increasing droop (up-to 200%) with high $R/X$<br>ratio (>=7) with adaptive control                                                             |

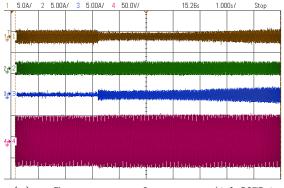

| 6.10  | Instantaneous Change of $R/X$ from 0.3 to 7 without adaptation 129                                                                                                 |

|       | With adaptive Control R/X increased from 0.3 to 7                                                                                                                  |

|       | Power sharing with adaptive Control R/X increased from 0.3 to 7 131                                                                                                |

| 7.1   | Xlinx FPGA Slice                                                                                                                                                   |

| 7.2   | ZYNQ FPGA SOC Design                                                                                                                                               |

| 7.3   | ADC-FPGA Interface                                                                                                                                                 |

| 7.4  | GUI of Component IP ADC                                                                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.5  | Droop Control Design for FPGA                                                                                                                                                             |

| 7.6  | Transforation block FPGA (3ph- 2ph)                                                                                                                                                       |

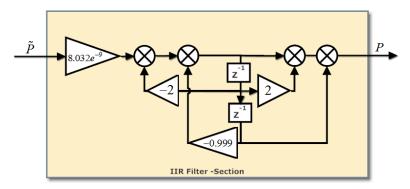

| 7.7  | Power filter Block                                                                                                                                                                        |

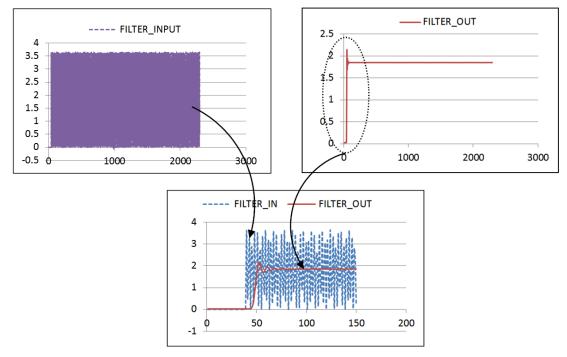

| 7.8  | Synchronization Block                                                                                                                                                                     |

| 7.9  | RC Implementation in FPGA                                                                                                                                                                 |

| 7.10 | Over clocking (a) Without Overclocking (b) With Overclocking $\ . \ . \ . \ 147$                                                                                                          |

| 7.11 | 3-Ph generation using DDS with TDM                                                                                                                                                        |

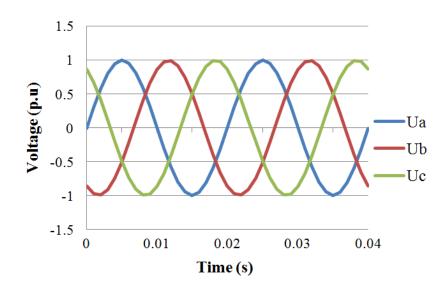

| A.1  | 3-phase AC source waveform                                                                                                                                                                |

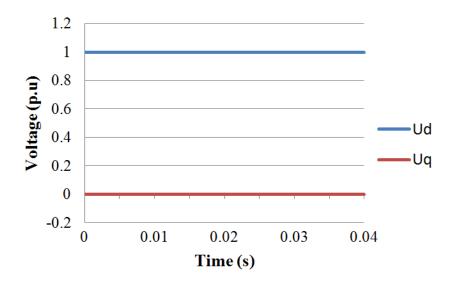

| A.2  | Output waveform after $dq_0$ transformation                                                                                                                                               |

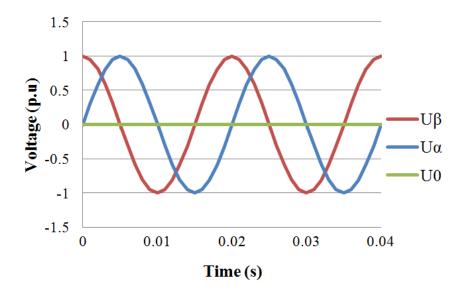

| A.3  | Output of waveform of $\alpha\beta$ transformation $\ldots \ldots \ldots$ |

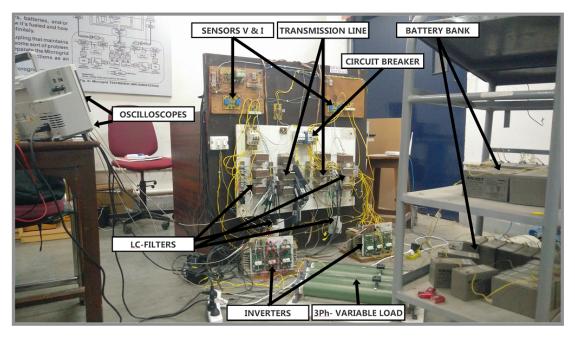

| C.1  | Complete Hardware Setup                                                                                                                                                                   |

| C.2  | Hardware Description                                                                                                                                                                      |

| C.3  | Setup Component                                                                                                                                                                           |

### List of Tables

| 1.1  | WIND ENERGY GENERATION -WORLD                     |

|------|---------------------------------------------------|

| 1.2  | SOLAR PV GENERATION-WORLD                         |

| 1.3  | HYDRO ELECTRIC GENERATION -WORLD                  |

| 1.4  | HYDRO ELECTRIC GENERATION -WORLD 6                |

| 2.1  | L & C Values with Different Ratio                 |

| 3.1  | Intitial Condtions                                |

| 3.2  | Modes of Microgrid at Different $f$ -Droop Values |

| 5.1  | Comparison of FPGA Resources                      |

| 7.1  | FPGA- ZYNQ-7000-SOC (xc7z020clg484-1) Resources   |

| 7.2  | Example of Q15 &Q16 Fixed point number            |

|      |                                                   |

| 11.4 |                                                   |

### List of Symbols and Abbreviations

| lphaeta              | Direct and Quadrature Axis Transformed Quantities in Fixed Reference Frame       |

|----------------------|----------------------------------------------------------------------------------|

| δ                    | Power Angle                                                                      |

| $\omega_c$           | Corner frequency of Filter                                                       |

| ω                    | Frequency in radian / second                                                     |

| $\theta$             | Phase angle                                                                      |

| $C_f$                | Capacitance in a Filter                                                          |

| dq                   | Direct and Quadrature Axis Transformed Quantities in Synchronous Reference Frame |

| E                    | Sending End Voltage                                                              |

| $f_s$                | Swtiching Frequency                                                              |

| $L_1, L_2, L_\infty$ | Norms in Lebesgue space                                                          |

| $n_v, n_f$           | Voltage and Frequency Droop Coefficent Respectively                              |

| Р                    | Active Power (if not specified) , Plant Transfer Function                        |

| Q                    | Reactive Power                                                                   |

| $R_c$                | Resistance in Series of Capacitor in a Filter                                    |

| $R_f$                | Equivelent Series Resister of Inductor in a Filter                               |

| V                    | Receiving End Voltage                                                            |

$V_{a,b,c}, I_{a,b,c}$  Three Phase Voltage and Current Quantiteis

| X      | Reactance (if not specified), States in Variable or Function |

|--------|--------------------------------------------------------------|

| Ζ      | Complex Impedance                                            |

| AC, DC | Alternating Current and Direct Current                       |

| ADC    | Analog to Digital Converter                                  |

| AMI    | Advance Metering Infrastructure                              |

| CERTS  | Consortium for Electric Relibility Technology Solutions      |

| CHP    | Combined Heat and Power                                      |

| CIGRE  | International Council on Large Electric Systems              |

| CT     | Current Transformer                                          |

| DDS    | Direct Digital Synthesis                                     |

| DEM    | Demand Energy Management                                     |

| DG     | Distributed Generators                                       |

| DR     | Distributed Resources                                        |

| DSP    | Digital Signal Processor                                     |

| FPGA   | Field Programble Gate Array                                  |

| GOI    | Government of India                                          |

| IEEE   | Institute of Electrical and Electronics Engineers            |

| IGBT   | Insulated-Gate Bipolar Transistor                            |

| IMP    | Internal Model Principle                                     |

| LV     | Low Voltage                                                  |

| MCB    | Miniature Circuit Breaker                                    |

| MG     | Microgrid                                                    |

| MNRE   | Ministry of New and Renewable Energy, India                  |

- PCC Point of Comon Coupling

- PHC Primery Health Centre

- PI Proportional plus Integral

- PR Proportional plus Resonant

- PT Potential Transformer

- PWM Pulse Width Modulation

- RAM Random Access Memory

- RC Repetitive Controller

- REDCO Renewable Energy Development Cooperative

- RES Renewable Energy Resources

- SOC State of Charge

- SPV Solar Photo Voltaic

- SRF Synchronous Reference Frame

- TDD Total Demand Distortion

- THD Total Harmonic Distortion

- TPDDL Tata Power Delhi Distribution

- UPS Unintruptable Power Supply

- VHDL Very high-speed integrated circuit Hardware Description Language

- VSI Voltage Source Inverter

- EPS Electric Power System

,

### CHAPTER 1

### INTRODUCTION

Electricity is the most useful and efficient form of energy amongst various other forms of available energies owing to its various advantages such as, transmittability, controllability, storability, ease of use and clean in use etc. Conventionally, electricity is generated by burning of fossil fuels (e.g. coal, gas or petroleum) in thermal power plants or by water in hydro power plants. In thermal power plants superheated steam produced by combustion of fossil fuels is used to run steam turbines which in turn run the electromagnetic energy conversion devices such as synchronous generators. Whereas, in hydro power plants the potential energy of stored water in the dam is used to run the hydro turbine coupled with the generator. The availability of fossil fuels is the main constraint for the thermal power plant while availability of site with huge water resources or continuous availability of water is the main hindrance in the development of these plants. So, generally these power plants are away from load centers. The generated power from these plants is transported to the distant load centers through an interconnected network of transmission lines known as Electric Power System (EPS) or widely known as grid. The operation of EPS or grid is dynamic and have to continuous control its generation in order to meet the variable load demand. Any mismatch between supply and demand beyond a permissible limit may endanger the healthy state of the grid in terms of voltage and frequency. Rotating mass of generators plays a vital role in stabiliging grid by absorbing small mismatch in demand and supply. The kinetic energy stored in rotating mass may be released quickly to meet the sudden increase in load demand with slight decrease in speed. similarly it can absorb some energy by increasing its speed whenever a big load is suddenly switched off

[1]. So, it is evident that larger the number of interconnected generators, greater is the inertia and hence, greater is the stability provided by cushioning effect of inertia. Moreover, the electric power generated by sources reaches to the load in a unidirectional way which makes the system behaviour more predictive and less complex in terms of operation and control of EPS. Fault detection and protection schemes become more reliable and accurate. Since, conventional generation has been in use over a long time and due to their vast utilization or exploitation, the demerits of conventional generation have almost outweigh their merits. It can better be understood in terms of wide spread threat of global warming and visualizing the global warming and excessive environmental pollution caused by burning of fossil fuels. Depletion of conventional resources is also another matter of concern for the sustainable growth of society while discharging our duty in saving scarce fossil resources for our future generation. Recent technological advancement has made it possible to harness the renewable energy and thereby can provide the substitute of conventionally generated power. Renewable resources are intermittent in nature [2]. Use of energy storage devices such as battery and Combined Heat and Power (CHP) can compensate the intermittency effect of renewable resources. Electric power taped from Solar photo voltaic (SPV) systems and from Wind Conversion Energy Systems can together be used to meet the local load demand. These sources can be interconnected with the conventional grid along with loads. This interconnected network of renewable energy resources and loads is known as microgrid. A microgrid can be used to supply a local load only or can be connected to the conventional grid for the bidirectional transfer of power in case of deficit / excess of power generated from DRs. This bidirectional flow of power makes the EPS operation, protection and control more complex.

#### 1.1 Microgrid and its Requirement

Owing to intermittent nature of renewable resources they fail to provide a reliable power to the load [3]. That is why DRs mainly work in support of main EPS and not as a backup facility. With the advancement of energy storage technologies interconnected DRs can be used to cater the local load demand in the case of unavailibvilty or failure of main grid. This operation is known as autonomous or stand-alone operation of microgrid. Microgrids are able to serve a load fully or partially thereby reducing power demand from the conventional grid. In case power generated through DRs exceeds the local demand, it can be exported to main grid, when connected to main grid. Thus, the operation of microgrid reduces the demand from the main grid. The reduced power demand from the main grid will certainly reduce the use of conventional resources like fossil fuels. Development of microgrids can empower the society in various aspects. The salient features and future aspects of microgrids towards the development of society could be as follows:

- a) Improved Reach: Renewable energy resources are available everywhere in abundance. Sunshine is available through the day while wind may be available round the clock. So, a microgrid can be formed near to local load. This can help the rural areas or societies where main grid is still a distant dream. Otherwise also if main grid is available, formation of a microgrid enhances the relaibility of service in addition to meet the local load demand. Therefore, forming a microgrid in a metropolitan or at a far remote place is equally realizable and beneficial in addition to meet the demand locally.

- b) Economics: The monetary aspects regarding the formation, operation and maintenance of microgrids are equally important. Economics can better be understood by considering the fact that electricity demand is increasing day by day and to meet this increased demand from conventional generation, it needs augmentation in generation capacity and reinforcement of existing transmission lines to transfer the increased amount of power. These additional provisions will require additional capital cost. Whereas the initial cost of forming a microgrid is somewhat high but in fact this cost is very economical because running and maintenance costs are very less. Furthermore, the life span of energy conversion devices is considerable longer, Internal Rate of Return (IRR) becomes high. Consumers can participate in generation

so as they also can manage their economies and practically it results in a flat load demand curve paving the way for establishment of ideal trade based market.

- c) Social Inclusion and Welfare: Renewable energies are available freely to all mankind irrespective of rich or poor. The societies living away from main grid can be empowered to develop themselves through operation and management of renewable energy resources through cooperative efforts. Availability of power to such areas will generate sources of living by creating small markets having facilities like ICT, glossary shops with cold or hot preservation systems, vaccine preservation through refrigerators etc. Local people can be encouraged to form and operate microgrids through community based ownership management. In nutshell microgrids can prove a boon for the development of under privileged societies living without access to electricity.

- d) **Future Grid:** Pertaining to the numerous advantages, government agencies are promoting the use of renewable resources to meet energy demands. The most burgeoning issue of environmental and ecology degradation necessitates the use of renewable energies to save the earth. Recently MNRE GOI has proposed setting up of 1000 microgrids across India. With the pace of advancement in the field of energy conversion techniques, power electronics devices and storage energy techniques, it can rightly be said that microgrids have the potential to become a important component of the future grid.

#### 1.2 Role of RES in Microgrid

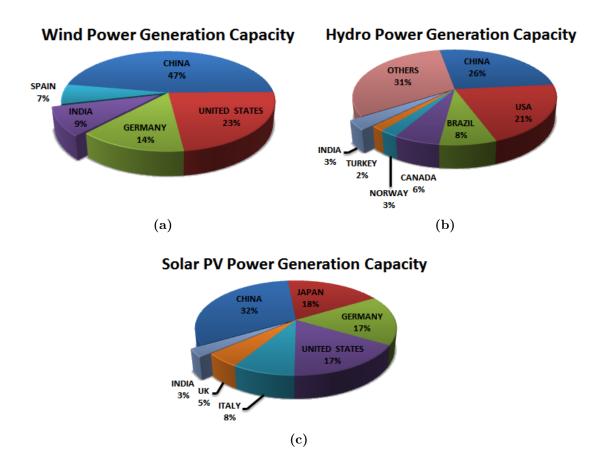

In Microgrid all type of sources can be incorporated including conventional fossil fuel types and non-conventional renewables. However, inclusion of higher number of RES will increase the efficiency of microgrid and reduce the carbon emission for energy generation. The new trend in electric power generation shows that more number of countries are promoting RES in their distribution system. These countries are also promoting microgrid based on RES to integrate all the sources to improve reliability and additional benefits. Table 1.1 to Table 1.3 show that RES capacity / generation share in world's major countries. The RES share shows a considerable increase in total electric power generation. China tops in all segment of power generation and has maximum share of RES capacity in the world. India is ranked at 4th position in wind energy generation far behind from USA and China but having growth of 12% per year which is slightly behind from china [4, 5, 6].

| S.No. | NAME OF THE   | TOTAL              | TOTAL                 |

|-------|---------------|--------------------|-----------------------|

|       | COUNTRY       | CAPACITY(2015)     | CAPACITY(2016)        |

| 1     | CHINA         | $145 \mathrm{GW}$  | $168.4 \ \mathrm{GW}$ |

| 2     | UNITED STATES | $75 \mathrm{GW}$   | 83.2 GW               |

| 3     | GERMANY       | $45 \mathrm{GW}$   | $50 \mathrm{GW}$      |

| 4     | INDIA         | $30 \ \mathrm{GW}$ | $33.6 \mathrm{GW}$    |

| 5     | SPAIN         | -                  | $23 \ \mathrm{GW}$    |

Table 1.1 – WIND ENERGY GENERATION - WORLD

Table 1.2 – SOLAR PV GENERATION-WORLD

| S.No. | NAME OF THE   | TOTAL               | TOTAL                |

|-------|---------------|---------------------|----------------------|

|       | COUNTRY       | CAPACITY(2015)      | CAPACITY(2016)       |

| 1     | CHINA         | $43 \; \mathrm{GW}$ | $77.5 \ \mathrm{GW}$ |

| 2     | JAPAN         | $35 \ \mathrm{GW}$  | 43.6 GW              |

| 3     | GERMANY       | $40 \ \mathrm{GW}$  | 41.5 GW              |

| 4     | UNITED STATES | $26 \mathrm{GW}$    | 40.8 GW              |

| 5     | ITALY         | 19 GW               | 21 GW                |

| 6     | UK            | 10 GW               | 12 GW                |

| 7     | INDIA         | $3~\mathrm{GW}$     | 7.1 GW               |

|       |               |                     |                      |

Table 1.3 – HYDRO ELECTRIC GENERATION -WORLD

| S.No. | NAME OF THE | TOTAL              | TOTAL                 |

|-------|-------------|--------------------|-----------------------|

|       | COUNTRY     | CAPACITY(2015)     | CAPACITY(2016)        |

| 1     | CHINA       | $300  \mathrm{GW}$ | 306.9 GW              |

| 2     | BRAZIL      | $238  \mathrm{GW}$ | $243.3 \ \mathrm{GW}$ |

| 3     | TURKEY      | $75 \mathrm{GW}$   | $75.8  \mathrm{GW}$   |

| 4     | VIETNAM     | 38 GW              | 39.1 GW               |

| 5     | INDIA       | 41.6 GW-           | $42.78 \mathrm{GW}$   |

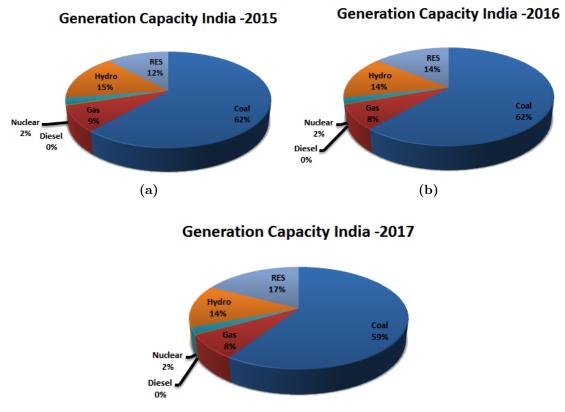

Figure 1.1 shows a pie-chart of renewable energy sources capacity. It can be seen from wind source pie-chart that China ranks 1st among all the countries with wind generation capacity of 168.4 GW in the year 2016. The countries United States, Germany, India and Spain are also in the list of top five countries with wind generation capacity of 83.2GW, 50GW, 33.6GW and 23 GW in 2016. In 2016 solar PV generation, China is again at the first position in worldwide with 77.5 GW capacity. India got the 7th rank worldwide in solar-PV generation with 7.1 GW capacity. Also in hydro power generation, China ranks ahead of all the countries with 308.9 GW capacity. India is on 5th position with 42.78 GW of hydro power capacity. Figure 1.2 shows a pie-chart of power generation capacity share in India. In 2015, only 27% power generation is achieved through renewable energy sources and remaining 73% generation from fossil fuels (like diesel, nuclear, gas, coal). But in 2016, share of renewable energy sources is increased to about 1% and reached at 28% and reduces fossil fuel generation from 73% to 72%. Nowadays ,use of renewable energy sources increases which provide clean energy and these sources are available in abundance. As in 2017, this increase of RES power generation reached to 31% and non-renewable sources generation decreases from 72 % to 69%. So in future, there is a large scope of RES power generation due to their number of advantages. In view of this, Indian government's (MNRE) has targeted to build 10,000 number of microgrid in India for rural electrification using only RES by 2021 [5].

| S.No. | NAME OF THE | TOTAL                 | TOTAL                 | TOTAL CAPA-          |

|-------|-------------|-----------------------|-----------------------|----------------------|

|       | COUNTRY     | CAPACITY              | CAPACITY              | CITY(2016)           |

|       |             | (2016) HYDRO          | (2016) WIND           | SOLAR PV             |

|       | BRAZIL      | 98.1 GW               |                       |                      |

|       | CANADA      | 79.3 GW               |                       |                      |

|       | CHINA       | 331.9 GW              | $168.4 \ \mathrm{GW}$ | $77.5 \ \mathrm{GW}$ |

|       | GERMANY     |                       | $50 \ \mathrm{GW}$    | $41.5 \ \mathrm{GW}$ |

|       | INDIA       | $42.7 \mathrm{GW}$    | $33.6 \ \mathrm{GW}$  | 7.1 GW               |

|       | ITALY       |                       |                       | 21.0 GW              |

|       | JAPAN       |                       |                       | 43.6 GW              |

|       | NORWAY      | 31.4 GW               |                       |                      |

|       | SPAIN       |                       |                       |                      |

|       | TURKEY      | $23.66 \mathrm{GW}$   |                       |                      |

|       | UK          |                       |                       | $12.0 \ \mathrm{GW}$ |

|       | USA         | $265.8 \ \mathrm{GW}$ | 83.2 GW               | 40.8 GW              |

|       | OTHERS      | 396 GW                | 111.1 GW              | $53.7 \ \mathrm{GW}$ |

| -     |             |                       |                       |                      |

Table 1.4 – HYDRO ELECTRIC GENERATION -WORLD

**Figure 1.1** – Renewal Power Generation Capacities by Share (World)

#### 1.3 Microgrid Worldwide

With the boost in renewable energy generation and affordable technology, microgrids are becoming more efficient and economically viable. Furthermore, recently a number of major blackouts have occurred in some countries which virtually left the affected areas in a state of chaos [7, 8, 9, 10]. The lack of electric power revealed one common fact that our modern society is highly dependent on electricity. It can be visualized from these blackouts that may cripple the life severely. Electrical transport system, financing activity, academic institutions, industries and health services with no emergency or standby generation, public and residential lighting and even some communication systems may fail to operate. These failures sudden raise the requirement of microgrid to supply electricity to the local area. According to a report of Navigant research, a consulting company, there were 1869 microgrid projects worldwide having a total capacity of 20.7 GW till the year 2017. These projects were analyzed across 123 countries in

(c)

Figure 1.2 – Power Generation Capacity Share in India (by type of source)

which majority of were small-scale with the exception of only one project of 2.2 GW Microgrids installed at Saudi Aramco gas-oil separation plant in Shaybah, Saudi Arabia. In regards to the geographic distribution of microgrid projects, Asia-Pacific and North America followed the way, accounting for almost 75% of all installed microgrid capacity. It is expected that global microgrid capacity will be increased up to 7.6 GW by 2024. In 2013, North America ranks first among all the countries worldwide by taking overall market share with total capacity of 2GW. After that Europe with 384 MW capacities and Asia-pacific with 303 MW capacities take the 2nd and 3rd place. But it is planned that North America will reach up to 5.9 GW and Asia Pacific jump on to 2nd place with 2GW capacity and Europe reached to third place with 694 MW (approx.8% market share) capacity by 2020. The global growth of microgrids has occurred across six key microgrid segments i.e. Commercial and Industrial (C&I), Community, Utility distribution, Institutional / campus, Military and Remote rural areas. Here is brief account of

state of the art microgrid in world:

- a) 1.0 MW SOLAR-PV Microgrid, Monolo Island, Fiji: This, microgrid combines with 1 MW solar –array with 20 Tesla power packs, having a total energy storage capacity of 4MWh.It is installed in Monolo Island, Fiji in 2016 by Tesla.

- b) 15.0 KW PV-BASED Microgrid, Ocracoke Island, North Carolina, US: This microgrid is located in Ocracoke island ,North Carolina,US in 2016 by North Carolina Electric Membership Corp.Tideland Electric Membership Corporation.It includes a PV array of 15 KW, 10 power packs and 150 Ecobee smart thermostats.

- c) 4.6 MW Hybrid Microgrid, Marshall Islands: A 4.6 MW hybrid microgrid installed at Marshall Island by IRENA in 2017. This includes solar-PV assets and lithium-ion batteries as the storage devices.

- d) UC San Diego 42MW Microgrid: This microgrid is installed in University of California, San Diego consists of 2.8 MW fuel cell, 1.5 MW of photovoltaic array(PV) and a 30KW/30KWh PV fully integrated storage system. Total capacity of this microgrid is 42 MW. This microgrid supplies power to about 45,000 people of university. According to university, this provides approximately 95% of their heating & cooling load and 92% of its annual load.

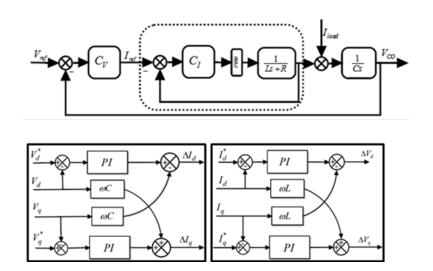

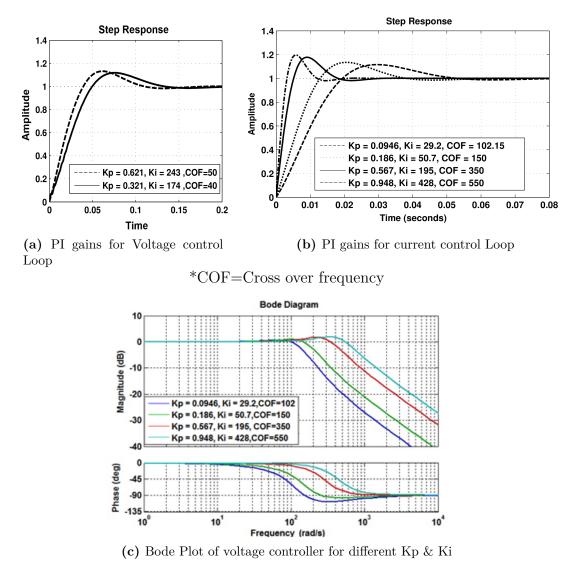

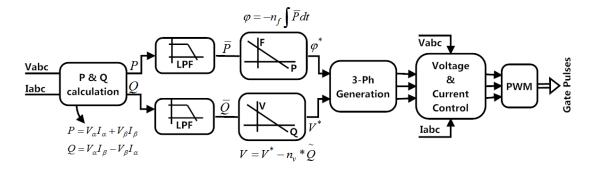

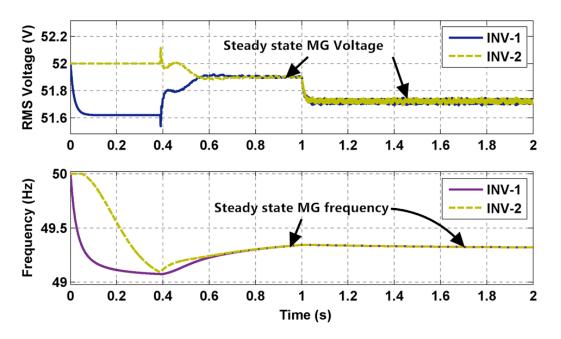

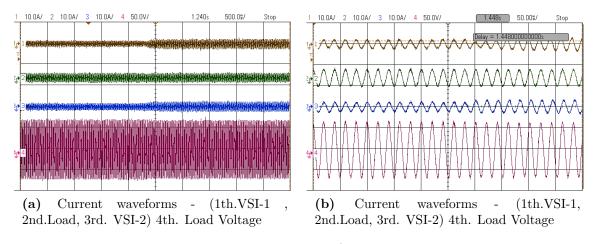

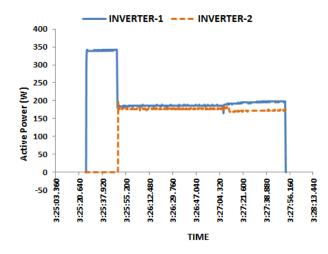

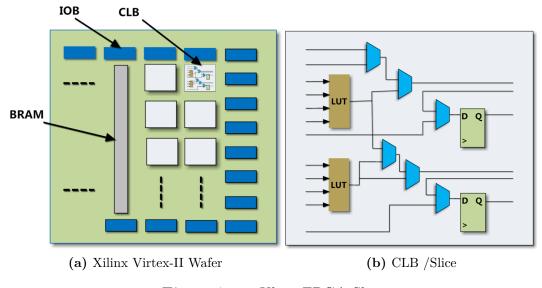

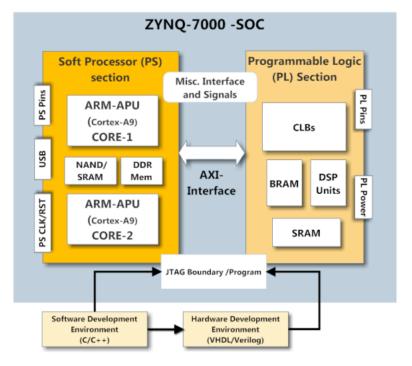

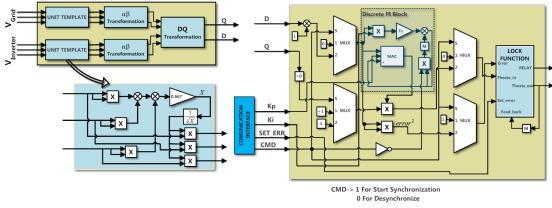

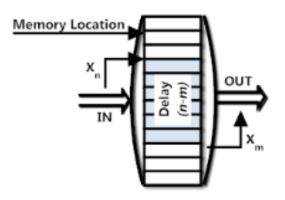

#### 1.4 Microgrid in India