# REALIZATION OF DXCCII BASED HALF WAVE AND FULL WAVE RECTIFIER

### A DISSERTATION

#### SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

## MASTER OF TECHNOLOGY IN VLSI DESIGN & EMBEDDED SYSTEMS

Submitted by:

## VISHWAJEET SINGH

## 2K15/VLS/20

Under the supervision of

Mr.DEVA NAND Assistant Professor

## **ELECTRONICS & COMMUNICATION ENGINEERING** DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042 2015-2017

### ELECTRONICS & COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

## **CANDIDATE'S DECLARATION**

I, (Vishwajeet Singh), Roll No. 2K15/VLS/20 student of M.Tech (VLSI design & Embedded systems), hereby declare that the project Dissertation titled "Realization of DXCCII based Half wave and Full wave rectifier" which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: Delhi Date: (VISHWAJEET SINGH)

## ELECTRONICS & COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

### **CERTIFICATE**

I hereby certify that the Project Dissertation titled "Realization of DXCCII based Half wave and Full wave rectifier" which is submitted by Vishwajeet Singh, 2K15/VLS/20, Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date:

## (**Mr. DEVA NAND**) Supervisor Assistant Professor, Deptt. of ECE, DTU

### **ABSTRACT**

Rectification is a demanding aspect when it comes to electronic equipment. The demand of low supply voltage and high speed devices has increased the demand of such rectifiers which can process low amplitude signals with high efficiency and can operate at high frequencies. Such rectifiers are called as the precision rectifiers which are used for signal processing, measurement and control of the low level signals.

In the past operational amplifiers have been used to develop the precision rectifiers but they failed to operate at high frequencies due to their slew rate limitations. They also needed passive devices such as diodes and matching resistors which offered difficulties in their integration. The employment of current mode techniques either by using current conveyors or by creating dedicated CMOS circuits have fruitfully resolved the conventional limitations by providing much enhanced performance of precision rectifiers.

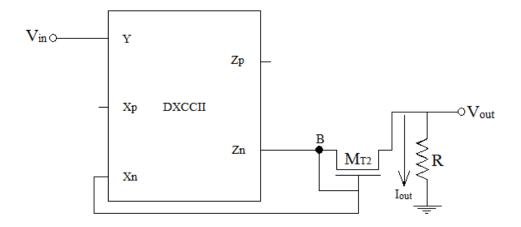

Concerned about the above mentioned issues, three newly proposed circuits are presented to serve the applications of precision rectification. Each circuit employs single Dual-X Second Generation Current Conveyor (DXCCII) as the active building block and uses one or two NMOS transistors for the switching purposes.

The first two proposed circuits are voltage mode precision half wave rectifiers. The first proposed precision half wave rectifier rectifies the positive half cycles of the input AC (Alternating Current) voltage signal while the second proposed precision half wave rectifier rectifies the negative half cycles of the input AC voltage signal. The third proposed circuit is a voltage mode precision full wave rectifier that provides the full wave rectification of the input AC voltage signal.

Further two voltage mode digital modulators have been proposed i.e. Binary Amplitude Shift Keying (BASK) and Binary Phase Shift Keying (BPSK). BASK uses one DXCCII and one NMOS transistor. BPSK uses one DXCCII, one NMOS transistor and one PMOS transistor.

All the above proposed circuits have the advantage of having proper input impedance and use of grounded resistor. The rectifiers provide additional advantage of using no diodes for rectification, rather NMOS transistors are used.

All the proposed circuits have been simulated with SPICE using  $0.35\mu$ m CMOS technology parameters. The supply voltage of  $\pm 1.8V$  is used. Much satisfactory results have been obtained with all the proposed circuits.

#### **ACKNOWLEDGEMENT**

I express my deepest gratitude to my project guide **Mr. Deva Nand**, Asstt. Prof., Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, whose encouragement, guidance and support from the initial to the final level enabled me to develop an understanding of the research work. His suggestions and ways of summarizing the things made me to go for independent studying and trying my best to get the maximum for my project, this made my circle of knowledge very vast. I am highly thankful to him for guiding me in this project.

I also express my profound sense of gratitude to **Prof. S. Indu** (H.O.D., ECE), for giving encouragement and opportunity to complete my project smoothly.

I would love to express immense thankfulness to my all dearest and beloved friend **Jayesh Trivedi**, Scientist B, Space Center, Ahmedabad, whose presence in my life is truly a blessing of GOD for me. His warmth of friendship, valuable ideas, guidance and constant moral support kept me motivated and made this project more fruitful and worthwhile.

I also express my thanks to all staff of VLSI laboratory to provide me all facilities to complete this research.

(Vishwajeet Singh) 2K15/VLS/20 M.Tech.: VLSI Design and Embedded Systems (2015-2017)

## TABLE OF CONTENTS

| CANDIDATE'S DECLARATION                                                  | i       |

|--------------------------------------------------------------------------|---------|

| <u>CERTIFICATE</u>                                                       | ii      |

| <u>ABSTRACT</u>                                                          | iii-iv  |

| ACKNOWLEDGEMENT                                                          | v       |

| TABLE OF CONTENTS                                                        | vi-ix   |

| LIST OF FIGURES                                                          | x-xii   |

| LIST OF TABLES                                                           | xiii    |

| LIST OF ABBREVIATIONS AND SYMBOLS                                        | xiv-xvi |

|                                                                          |         |

| CHAPTER 1: <u>INTRODUCTION</u>                                           | 1-8     |

| 1.1 OVERVIEW                                                             | 1       |

| 1.2 CURRENT MODE VERSUS VOLTAGE MODE                                     | 3       |

| 1.2.1 DEFINING CURRENT MODE AND VOLTAGE MODE APPROACHES                  | 3       |

| 1.2.2 THE DOMINANCE OF VOLTAGE MODE                                      | 3       |

| 1.2.3 COMPARISON BETWEEN THE CURRENT MODE AND<br>VOLTAGE MODE TOPOLOGIES | 5       |

| 1.3 THESIS STRUCTURE                                                     | 7       |

| CHAPTER 2:      | HISTORY OF CURRENT CONVEYORS                | 9-17  |

|-----------------|---------------------------------------------|-------|

| 2.1 THE FIRST G | ENERATION CURRENT CONVEYOR (CCI) [45], [46] | 9     |

| 2.2 THE SECOND  | GENERATION CURRENT CONVEYOR (CCII) [46]     | 10    |

| 2.3 THE THIRD C | ENERATION CURRENT CONVEYOR (CCIII) [47]     | 12    |

| 2.4 VERSIONS OF | F CURRENT CONVEYORS                         | 14    |

| 2.5 ADVANTAGE   | ES OF CURRENT CONVEYOR                      | 16    |

| 2.6 APPLICATION | NS OF CURRENT CONVEYORS                     | 17    |

|                 |                                             |       |

| CHAPTER 3:      | THE DUAL-X CURRENT CONVEYOR (DXCCII)        | 18-34 |

| 3.1 INTRODUCTI  | ON OF DXCCII [34]                           | 18    |

| 3.2 CMOS IMPLE  | MENTATION OF DXCCII [35]                    | 20    |

| 3.3 NON IDEAL N | MODEL OF DXCCII [35]                        | 21    |

| 3.4 PARASITIC M | IODEL OF DXCCII [35]                        | 24    |

| 3.5 ADVANTAGE   | ES OF DXCCII                                | 25    |

| 3.6 APPLICATION | NS OF DXCCII                                | 26    |

| 3.7 SIMULATION  | RESULTS OF DXCCII                           | 28    |

|                 |                                             |       |

| CHAPTER 4:      | <u>RECTIFIERS</u>                           | 35-66 |

| 4.1 INTRODUCTI  | ON OF RECTIFIERS                            | 35    |

| 4.2 CLASSIFICAT | TION OF RECTIFIERS                          | 38    |

| 4.3 SWITCHING   | DEVICES USED IN RECTIFIERS                  | 39    |

| 4.4 SYNCHRONC   | US RECTIFIER: ACTIVE RECTIFIER              | 42    |

| 4.5 FULL WAVE   | RECTIFIER ADVANTAGES AND DISADVANTAGES      | 43    |

| 4.5.1 FULL WAVE RECTIFIER ADVANTAGES                                                              | 43 |

|---------------------------------------------------------------------------------------------------|----|

| 4.5.2 FULL WAVE RECTIFIER DISADVANTAGES                                                           | 43 |

| 4.6 APPLICATIONS OF RECTIFIER                                                                     | 44 |

| 4.7 LITERATURE SURVEY OF VOLTAGE MODE FULL WAVE RECTIFIERS                                        | 45 |

| 4.8 PROPOSED PRECISION HALF WAVE RECTIFIER (POSITIVE HALF CYCLE)                                  | 52 |

| 4.8.1 OPERATION OF THE PROPOSED PRECISION HALF WAVE RECTIFIER<br>FOR POSITIVE HALF CYCLE          | 52 |

| 4.8.2 SIMULATION RESULTS OF THE PROPOSED PRECISION HALF WAVE<br>RECTIFIER FOR POSITIVE HALF CYCLE | 55 |

| 4.9 PROPOSED PRECISION HALF WAVE RECTIFIER (NEGATIVE HALF CYCLE)                                  | 57 |

| 4.9.1 OPERATION OF THE PROPOSED PRECISION HALF WAVE RECTIFIER<br>FOR NEGATIVE HALF CYCLE          | 57 |

| 4.9.2 SIMULATION RESULTS OF THE PROPOSED PRECISION HALF WAVE<br>RECTIFIER FOR NEGATIVE HALF CYCLE | 59 |

| 4.10 PROPOSED PRECISION FULL WAVE RECTIFIER                                                       | 61 |

| 4.10.1 OPERATION OF THE PROPOSED PRECISION FULL WAVE RECTIFIER                                    | 61 |

| 4.10.2 SIMULATION RESULTS OF THE PROPOSED PRECISION FULL WAVE<br>RECTIFIER                        | 64 |

|                                                                                                   |    |

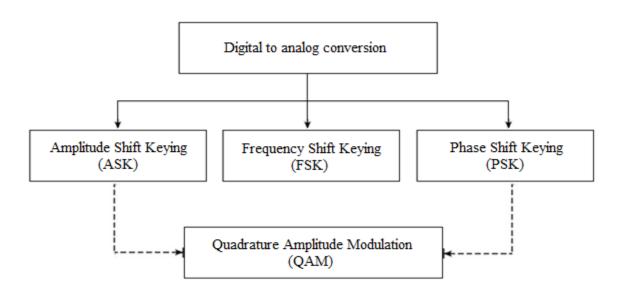

| CHAPTER 5: DIGITAL MODULATORS      | 67-91 |

|------------------------------------|-------|

| 5.1 DIGITAL MODULATION             | 67    |

| 5.2 TYPES OF DIGITAL MODULATION    | 67    |

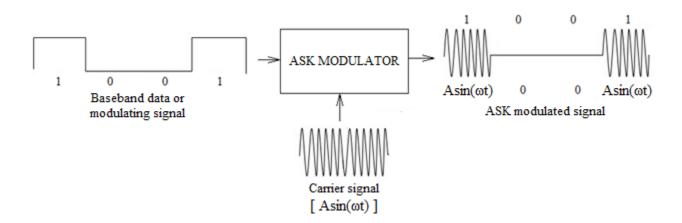

| 5.2.1 AMPLITUDE SHIFT KEYING (ASK) | 68    |

| 5.2.1.1 ADVANTAGES OF ASK          | 69    |

| 5.2.1.2 DISADVANTAGES OF ASK       | 69    |

|                                    |       |

| 5.2.1.3 APPLICATIONS OF ASK                             | 69 |

|---------------------------------------------------------|----|

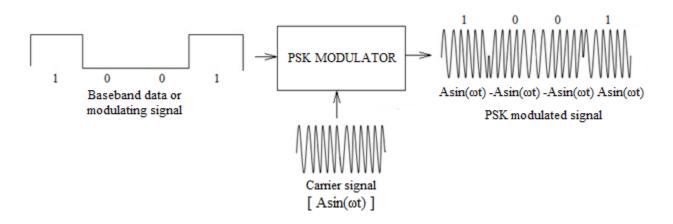

| 5.2.2 PHASE SHIFT KEYING (PSK)                          | 70 |

| 5.2.2.1 ADVANTAGES OF PSK                               | 71 |

| 5.2.2.2 DISADVANTAGES OF PSK                            | 71 |

| 5.2.2.3 APPLICATIONS OF PSK                             | 71 |

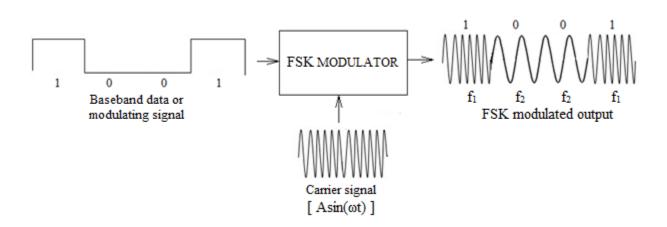

| 5.2.3 FREQUENCY SHIFT KEYING (FSK)                      | 71 |

| 5.2.3.1 ADVANTAGES OF FSK                               | 73 |

| 5.2.3.2 DISADVANTAGES OF FSK 73                         |    |

| 5.2.3.3 APPLICATIONS OF FSK                             | 73 |

| 5.3 LITERATURE SURVEY OF DIGITAL MODULATORS             | 74 |

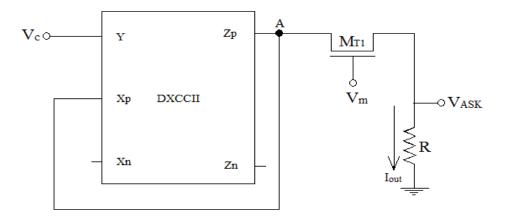

| 5.4 PROPOSED BASK MODULATOR                             | 77 |

| 5.4.1 OPERATION OF THE PROPOSED BASK MODULATOR          | 77 |

| 5.4.2 SIMULATION RESULTS OF THE PROPOSED BASK MODULATOR | 81 |

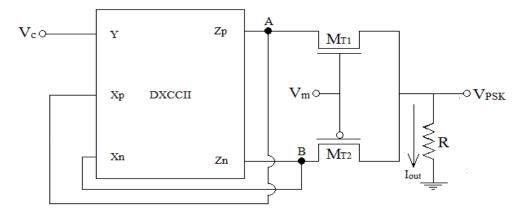

| 5.5 PROPOSED BPSK MODULATOR                             | 83 |

| 5.5.1 OPERATION OF THE PROPOSED BPSK MODULATOR          | 83 |

| 5.5.2 SIMULATION RESULTS OF THE PROPOSED BPSK MODULATOR | 89 |

|                                                         |    |

| CHAPTER 6: <u>CONCLUSION AND FUTURE SCOPE</u>           | 92 |

## **REFERENCES**

93-97

## **LIST OF FIGURES**

| 9  |

|----|

| 11 |

| 11 |

| 13 |

| 18 |

| 20 |

| 24 |

| 28 |

| 28 |

| 29 |

| 29 |

| 30 |

| 31 |

| 31 |

| 32 |

| 32 |

| 33 |

| 33 |

| 34 |

| 52 |

|    |

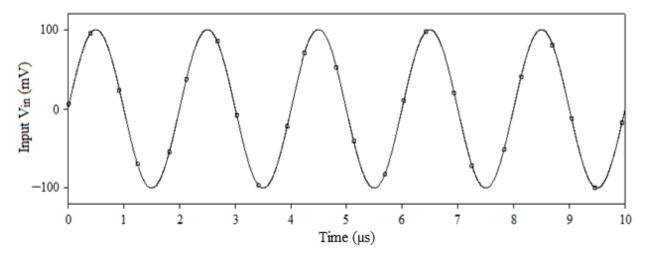

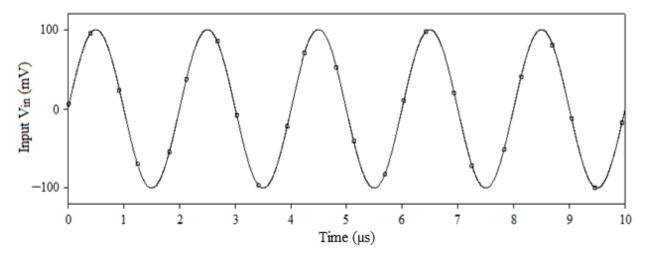

| 20. Waveform of the input voltage V <sub>in</sub>                                                    | 55 |

|------------------------------------------------------------------------------------------------------|----|

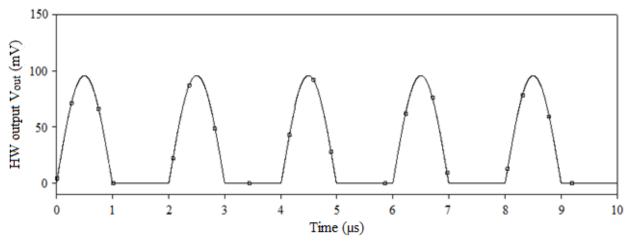

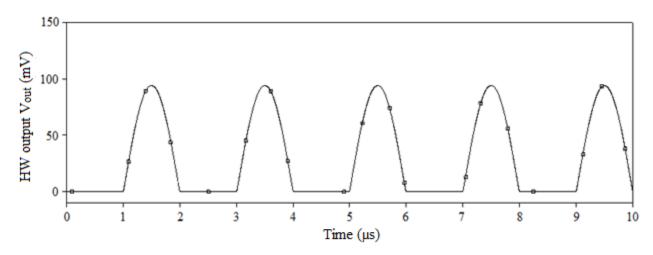

| 21. Half wave rectified output $V_{out}$ for the positive cycle of the input voltage $V_{in}$        | 55 |

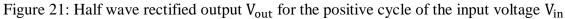

| 22. DC transfer characteristics of the proposed precision half wave rectifier for the positive cycle | 56 |

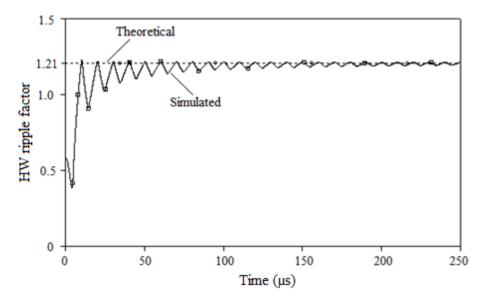

| 23. Waveform for the ripple factor of the proposed precision half wave rectifier for positive cycle  | 56 |

| 24. Proposed precision half wave rectifier for negative half cycle                                   | 57 |

| 25. Waveform of the input voltage $V_{in}$                                                           | 59 |

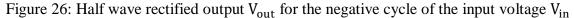

| 26. Half wave rectified output $V_{out}$ for the negative cycle of the input voltage $V_{in}$        | 59 |

| 27. DC transfer characteristics of the proposed precision half wave rectifier for the negative cycle | 60 |

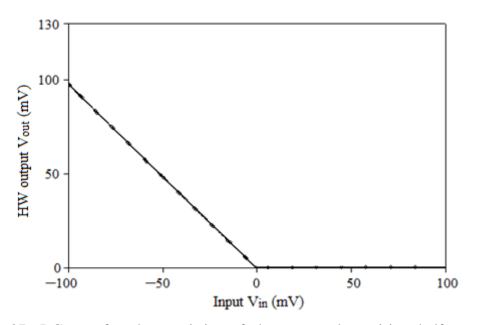

| 28. Waveform for the ripple factor of the proposed precision half wave rectifier for negative cycle  | 60 |

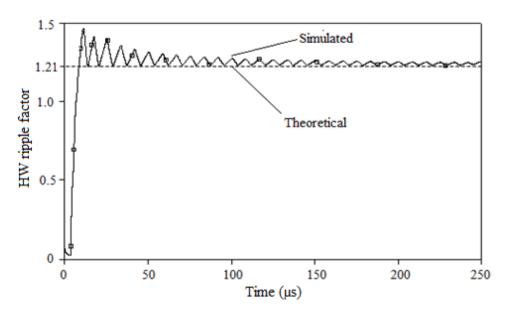

| 29. Proposed precision full wave rectifier                                                           | 61 |

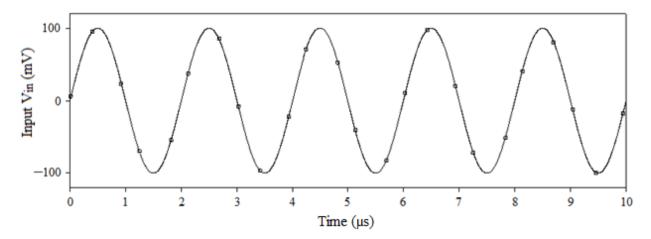

| 30. Waveform of the input voltage V <sub>in</sub>                                                    | 64 |

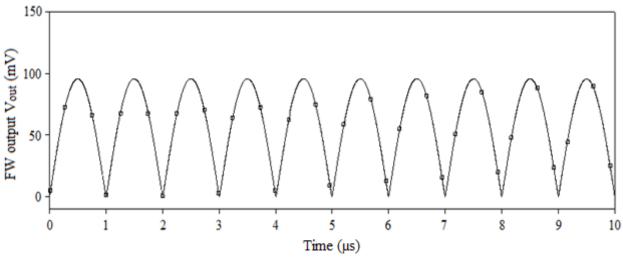

| 31. Full wave rectified output $V_{out}$ for the input voltage $V_{in}$                              | 64 |

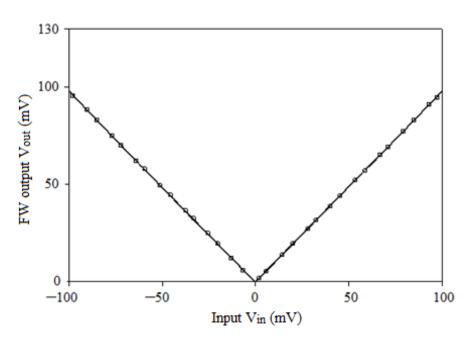

| 32. DC transfer characteristics of the proposed precision full wave rectifier                        | 65 |

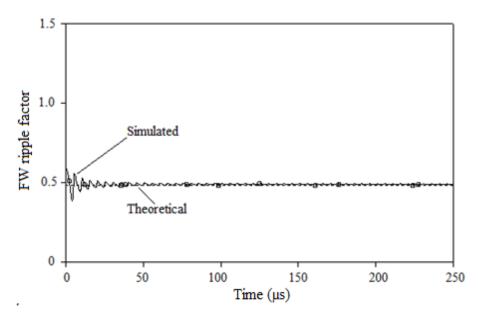

| 33. Waveform for the ripple factor of the proposed precision full wave rectifier                     | 65 |

| 34. Types of digital modulation                                                                      | 67 |

| 35. Block diagram of BASK modulator                                                                  | 68 |

| 36. Block diagram of BPSK modulator                                                                  | 70 |

| 37. Block diagram of BFSK modulation process                                                         | 72 |

| 38. Proposed BASK modulator                                                                          | 77 |

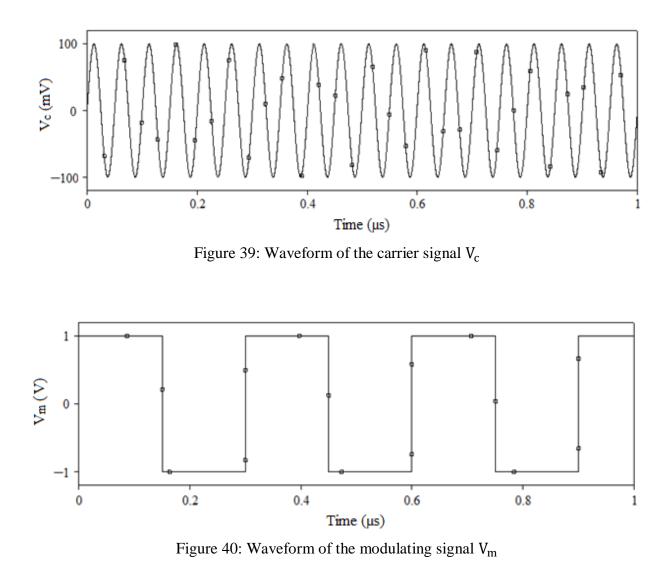

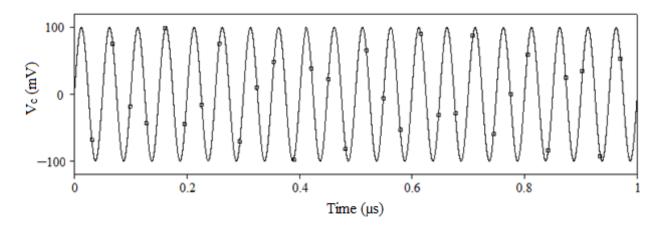

| 39. Waveform of the carrier signal $V_c$                                                             | 81 |

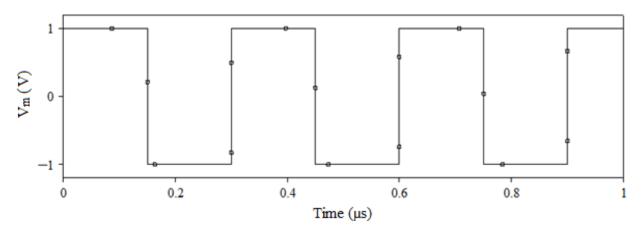

| 40. Waveform of the modulating signal $V_m$                                                          | 81 |

xi

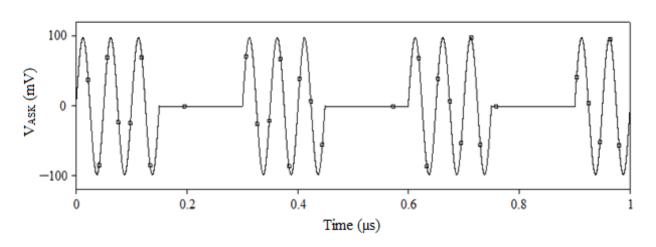

| 41. ASK modulated output voltage V <sub>ASK</sub> | 82 |

|---------------------------------------------------|----|

| 42. Proposed BPSK modulator                       | 83 |

| 43. Waveform of the carrier signal $V_c$          | 89 |

| 44. Waveform of the modulating signal $V_{\rm m}$ | 89 |

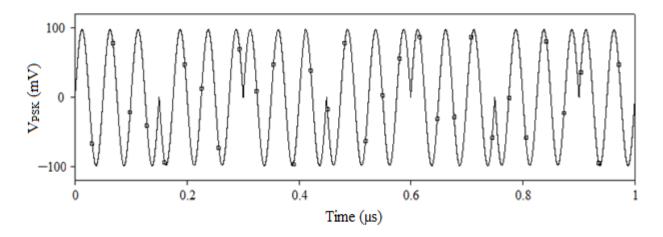

| 45. PSK modulated output voltage V <sub>PSK</sub> | 90 |

## **LIST OF TABLES**

| 1. (W/L) Ratio of CMOS used in the DXCCII [35]                                | 21 |

|-------------------------------------------------------------------------------|----|

| 2. Comparison of various voltage mode precision full wave rectifiers          | 50 |

| 3. Summary of outputs of the proposed precision half and full wave rectifiers | 66 |

| 4. Comparison of the various digital modulators                               | 76 |

| 5. Summary of outputs of the proposed BASK and BPSK modulators                | 91 |

## LIST OF ABBREVIATIONS AND SYMBOLS

| [1] CC       | : Current Conveyor                                                  |

|--------------|---------------------------------------------------------------------|

| [2] CCI      | : First Generation Current Conveyor                                 |

| [3] CCII     | : Second Generation Current Conveyor                                |

| [4] CCII+    | : Positive type Second Generation Current Conveyor                  |

| [5] CCII-    | : Negative type Second Generation Current Conveyor                  |

| [6] CCIII    | : Third Generation Current Conveyor                                 |

| [7] CCIII+   | : Positive type Third Generation Current Conveyor                   |

| [8] CCIII-   | : Negative type Third Generation Current Conveyor                   |

| [9] CCCS     | : Current Controlled Current Source                                 |

| [10] VCVS    | : Voltage Controlled Voltage Source                                 |

| [11] VCCS    | : Voltage Controlled Current Source                                 |

| [12] CCVS    | : Current Controlled Voltage Source                                 |

| [13] NIV     | : Negative Impedance Inverter                                       |

| [14] INIC    | : Inverting Negative Impedance Converter                            |

| [15] Op-Amp  | : Operational Amplifier                                             |

| [16] DO-CCII | : Dual Output Second Generation Current Conveyor                    |

| [17] CFCCII  | : Current Follower Second Generation Current Conveyor               |

| [18] CFCCIIp | : Positve type Current Follower Second Generation Current Conveyor  |

| [19] CFCCIIn | : Negative type Current Follower Second Generation Current Conveyor |

| [20] DVCCII  | : Differential Voltage Second Generation Current Conveyor           |

| [21] DVCCC   | : Differential Voltage Complementary Current Conveyor               |

|              |                                                                     |

- [22] ICCII : Inverting Second Generation Current Conveyor

- [23] DDCC : Differential Difference Current Conveyor

- [24] DCC : Differential Current Conveyor

- [25] MDCC : Modified Differential Current Conveyor

- [26] DXCCII : Dual-X Second Generation Current Conveyor

- [27] FDCCII : Fully Differential Second Generation Current Conveyor

- [28] FBCCII : Fully Balanced Second Generation Current Conveyor

- [29] MCCII : Modified Second Generation Current Conveyor

- [30] OFC : Operational Floating Conveyor

- [31] UCC : Universal Current Conveyor

- [32] CCCII : Current Controlled Second Generation Current Conveyor

- [33] CGCCII : Current Gain Second Generation Current Conveyor

- [34] EXCCII : Extra-X Second Generation Current Conveyor

- [35] DV-DXCCII : Differential Voltage Dual-X Second Generation Current Conveyor

- [36] MO-DXCCII : Multiple Output Dual-X Second Generation Current Conveyor

- [37] MO-CCCII : Multiple Output Current Controlled Second Generation Current Conveyor

- [38] OTRA : Operational Trans Resistance Amplifier

- [39] CFOA : Current Feedback Operational Amplifier

- [40] UVC : Universal Voltage Conveyor

- [41] OTA : Operational Transconductance Amplifier

- [42] DO-OTA : Dual Output Operational Transconductance Amplifier

- [43] FCS : Floating Current Source

- [44] ZCD : Zero Crossing Detector

#### [45] TE : Transconductance Element

- [46] CCIICS : Current Conveyor Based on Current Steering Output Stage

- [47] FDNR : Frequency Dependent Negative Resistance

- [48] IC : Integrated Circuit

- [49] RF : Radio Frequency

- [50] IR : Infrared

- [51] RFID : Radio Frequency Identifier

- [52] SR : Slew Rate

- [53] SNR : Signal to Noise Ratio

- [54] RMS : Root Mean Square

- [55] P<sub>e</sub> : Probability of Error

- [56] BER : Bit Error Rate

- [57] AWGN : Additive White Gaussian Noise

- [58] CM : Current Mirror

- [59] MOS-R : MOS Resistor

- [60] BJT : Bipolar Junction Transistor

- [61] MOSFET : Metal Oxide Semiconductor Field Effect Transistor

- [62] JFET : Junction Field Effect Transistor

### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1 OVERVIEW**

Designing of the analog circuits itself has been through the evolution process, together with the evolution in the technology and the performance requirements. Today, for the development of microelectronic industry, there is a need of electronic circuits which can operate on extremely low supply voltages consuming the least amount of power. Also, there is a need of extreme speed of operation along with the high accuracy. However, it has still not been possible to satisfy all the needs simultaneously, to improve one performance parameter the other parameter has to be compromised, therefore many trade off solutions are employed in practice.

There is a big range of applications of analog signal processing where there is a need of an active building block, hence the development and improvement of the active elements also is of prime concern in today's generation. Within the last decade, many active analogue building blocks or elements have been introduced which offers the feature of electronic tunability. The behavior or response of the active building block can therefore be controlled electronically. Such devices offer facility of single parameter control for example the input impedance, trans resistance, trans conductance, voltage gain and current gain can be controlled electronically. Recently, many methods have been proposed for multi parameter control also i.e. they allow control of more than one parameter simultaneously hence make the active block more versatile and efficient.

In the development process, a new trend emerged to describe the circuit that is called as the current mode approach. The current mode processing may be defined as the processing environment where signals in the voltage form are irrelevant and processing is done in the form of current signals to determine the performance of the circuits. This is particularly used in the case of a circuit that has low impedance nodes and voltage swing is small and time constant is small. Therefore, usually to describe an electronic circuit the two terms are often used, i.e. the current mode circuit or the voltage mode circuit. Although, there is no clear cut definition of current mode or voltage mode available in the literature, but a working definition can be, that a current mode circuit is that in

which the state variables are represented in the form of currents, and in the dual sense, a voltage mode circuit is that in which the state variables are represented in the form of voltages [51]. A voltage mode circuit can be transformed in to a current mode circuit using a theorem known as the adjoint network theorem [52], where the modelling of circuits is done in the form of passive network segments and the controlled sources. Also a current mode circuit can be obtained from their voltage mode equivalent circuit by interchanging the position of nullators and norators [53]. With the emergence of the current mode applications, mixed mode circuits also gained attention to fulfil the optimization requirement of the interfaces in between the sub blocks of a system that operate in different modes.

With the advancement in time, CMOS VLSI technology has become more popular and much efforts have been devoted to reduce the dimensions of CMOS devices in order to reduce the area requirements and to make them operate on as low power supply as possible to reduce the power requirements. This led to an aggressive decrement in the supply voltage and a moderate decrement in the threshold voltage of the CMOS technology. Therefore when it comes to the CMOS based voltage mode circuits, these changes have greatly affected their performance. The performance of CMOS based voltage mode circuits has degraded because of these changes, for example, there has been a reduction in the dynamic range, an increment in the propagation delay and reduction in the noise margins. However when it comes to the current mode circuits, the impact of these changes in CMOS technology on their performance is less severe when compared to voltage mode circuits. This is due to the reason that in a current mode circuit the design emphasis is on the currents in the branches of the circuit rather than the voltages at the nodes of the circuit. The more immunity of the current mode circuits over voltage mode circuits towards the difficulties being born because of the reduction in the supply voltage of CMOS technology and increment in the operational speed has captured much attention of both the industry and the academia recently, thus has increased the popularity of current mode circuits. The design principles of the voltage mode and the current mode circuits are different, as in case of a voltage mode circuit, the design focus is on the intrinsic characteristics of the nodal voltages, while in case of a current mode circuit, the design focus is on the intrinsic characteristics of the currents flowing in the branches of the circuit.

### **1.2 CURRENT MODE VERSUS VOLTAGE MODE**

#### **1.2.1 DEFINING CURRENT MODE AND VOLTAGE MODE APPROACHES**

A current mode technique is that technique which tends to reduce the voltage swing or voltage variation and deal with the current, whereas, a voltage mode technique is that technique which tends to reduce the current swing or current variation and deal with the voltage [55].

The information contained in an electronic circuit can be represented either by the nodal voltages or by the branch currents of the circuit. When nodal voltages are used to describe a circuit's equations and information, it is called as the voltage mode circuit while if branch currents are used to describe the information and equations of a circuit, it is called as the current mode circuit.

A voltage mode circuit often uses high loop gain and is more complex while a current mode circuit often uses less loop gain and is less complex [56].

For a voltage mode circuit, the input impedance must be high while the output impedance must be low. And for a current mode circuit the input impedance must be low while the output impedance must be high. When voltage mode and current mode are taken together, the behavior of a circuit can be characterized completely.

#### **1.2.2 THE DOMINANCE OF VOLTAGE MODE**

Although, the concept of an ideal current mode circuit similar to that of an ideal voltage mode circuit had been introduced like four decades ago, still, voltage mode circuits became more popular and found much more number of applications than the current mode counterparts. This can be seen by the fact that countless texts are available on voltage mode circuits but comparatively very little literature is available for the current mode circuits.

The reasons for high popularity of the voltage mode circuits can be described as follows

- In voltage mode, the voltages at various nodes can be measured easily using voltmeters and there is no need to modify the circuit topology for this purpose. Whereas in the current mode, it is not easy to measure the currents flowing in the branches of a circuit and it mostly needs to change the circuit topology or needs an additional circuitry.

- 2) The impedance of the gate terminal of a MOSFET is infinite and it makes MOSFETs the ideal choice to realize a voltage mode circuit, especially in configuration employing cascading of different blocks, for example a multi stage voltage amplifier.

- It is easy to get the high voltage gain in case of a voltage mode circuit by using certain techniques for example cascodes, regulated cascodes etc.

- 4) In the past high supply voltages were available, so designing of a circuit with a low voltage power supply was not a critical concern.

- 5) As high supply voltage was available, therefore switching noise was not a big issue to be concerned about.

- 6) In the past there were low speed requirements, it allowed the charging and discharging times of the nodal capacitors to be large.

The analog signal processing was considered superior in the voltage mode topology, but since the development of CMOS technology, the supply voltage greatly reduced and this has adverse effect on the performance of the voltage mode circuits. Whereas the negative effect on the current mode circuits performance is much less than compared to that of voltage mode circuits. Therefore, lately, the current mode topology has gained much interest of the circuit designers because of the advantages they offer over the voltage mode circuits. However, in reality, there is no single

topology among the voltage mode and current mode topologies that can be used to satisfy all the required performance parameters. To satisfy some parameters, other parameters have to be compromised and a tradeoff solution has to be considered where the parameters of less importance are compromised and the important performance parameters are given more attention regarding improvement in the performance. Therefore one must analyze the performance parameters first and then decide which topology among the voltage mode topology and current mode can be considered optimum to get the required performance of a certain application.

## 1.2.3 COMPARISON BETWEEN THE CURRENT MODE AND VOLTAGE MODE TOPOLOGIES

Below is the relative comparison between the current mode and voltage mode topologies [57].

- 1) Delay and power dissipation: With the shrinking technology there has been an increment in the interconnect delays and it has become a dominant transistor gate delay. As the delay has increased the speed has therefore decreased and also, delays can give rise to a faulty output which is undesired. With signaling in the voltage mode, insertion of buffer comes out to be very effective in delay reduction but it needs extra chip area for the buffer and also the power dissipation of buffer leads to an increment in the overall power dissipation of the circuit. But when it comes to the current mode interconnects, a low impedance is there at the output and it is found that these circuits give less delay when compared to that of voltage mode interconnect circuits, as it is limited by the signal to noise ratio (SNR) required in the application. But in case of the current mode circuits, the charging and discharging currents can be increased and it results in delay reduction and therefore the current mode circuits.

- 2) Voltage swing reduction: When compared to the voltage mode circuits, the current mode circuits can operate at the lower voltage swings of the input signal. The output of a voltage mode circuit directly varies with the variations in the input signal, the output thus gets

distorted or noisy when the input voltage swings are reduced. As mentioned above that the voltage swing can't be decreased in voltage mode circuits below a certain level, as it is limited by the SNR required in the application, it therefore results in the slow response offered by the circuit.

- **3) Supply voltage reduction:** The voltage mode circuits have an adverse effect on their performance because of the reduction in the input supply voltage and also because of the ground fluctuations. This is due to the direct linear relation of the output signal with the input signal. However in current mode circuits the output is in the form of current signal and the attenuation on the circuit performance due to the decrement in the input supply voltage is very less.

- 4) Bandwidth improvement: The bandwidth offered by the current mode circuits is higher than the bandwidth offered by the voltage mode circuits. Therefore the signals in the current mode can be transmitted faster thus offering higher speed of operation than the voltage mode circuits.

- 5) Electrostatic discharge (ESD): As with the advancement in CMOS technology size of the device is reducing, the gate oxide thickness is also getting reduced. Due to this there is an increment in the electrostatic discharge induced failures in the MOSFET. This occurs due to the breakdown of the insulators used in the gate oxide of MOSFETs. Because of the high impedance available at the input of the voltage mode circuits, electrostatic charge accumulates at the input terminal which is basically the gate of the MOSFET, the voltage mode devices are therefore in a more vulnerable condition to such failures than the current mode circuits. The input impedance of the current mode circuit is low and it doesn't allow the electrostatic charge to accumulate at the input terminal and therefore the current mode circuits are much immune to such failures and offers a safer design approach.

Therefore in summary it can be concluded that with the increased popularity of the CMOS technology, performance of the voltage mode circuits degraded and the current mode circuits gained more interest of the designers therefore increasing its popularity in the recent times. The

current mode circuits are favored because they provide efficient solutions to various problems occurred in the circuit designing and because of having advantages as mentioned in the literature like the potential to reach at higher frequencies, lower power consumption even at these high frequencies, better linearity, high slew rate availability, better accuracy, smaller chip area requirement, high immunity to the voltage fluctuations, increased speed of operation, less switching noise, low cross talk and suitability for the low voltage and low power applications. But these advantages are often fulfilled at the cost of increment in the distortion and higher gain variations [56].

#### **1.3 THESIS STRUCTURE**

<u>**CHAPTER 1:**</u> Gives introduction about the increasing demand of low power devices, increased popularity of the current mode technique, advancements in the CMOS VLSI technology and their impact on voltage mode circuits. Then explains the current mode and voltage mode approaches. It also gives the thesis structure.

<u>**CHAPTER 2:</u>** Explains the history of Current Conveyors (CCs), about their invention and their three generations. Explains the growth in popularity of the Second Generation Current Conveyor (CCII) and brief introduction about their various versions evolved with time.</u>

<u>**CHAPTER 3:</u>** Gives introduction about the Dual-X Current Conveyor (DXCCII). Explains ideal and non ideal behavior and its parasitic model. Simulation results have also been provided at the end to justify the theory.</u>

**<u>CHAPTER 4:</u>** Gives introduction to the precision rectifiers, various limitations of conventional Operational Amplifier (Op-Amp) based precision rectifiers. Gives a literature review about various voltage mode full wave rectifiers reported in the open literature along with a concluding summary table. Then proposed topologies of precision half and full wave rectifiers using DXCCII are explained in detail along with the simulations results.

<u>**CHAPTER 5:</u>** Introduces the various digital modulation schemes. Gives a literature survey of the reported digital modulators along with the summary table. Further, proposed BASK and BPSK modulators are explained in detail along with the simulation results.</u>

**<u>CHAPTER 6</u>**: Concludes the overall work described in this thesis with possible future improvements. The thesis work ends with this chapter.

### **CHAPTER 2**

#### **HISTORY OF CURRENT CONVEYORS**

#### 2.1 THE FIRST GENERATION CURRENT CONVEYOR (CCI) [45], [46]

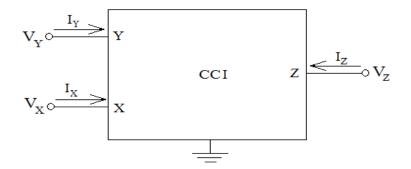

The concept of Current Conveyor (CC) was first proposed by K. C. Smith and A. Sedra in the year 1968 [45]. The current conveyor's circuit implementation of first order was also presented. It employed three matched npn Bipolar Junction Transistors (BJTs), two matched pnp BJTs and three matched resistors. The current conveyor has three terminals named as X, Y and Z. A voltage applied at the input terminal Y is reflected at the other input terminal X as if there is a virtual short circuit between the two terminals. In the dual manner, if some current is forced at the input terminal X is also conveyed to the output terminal Z. Because of its current conveying property it was therefore named as the current conveyor. This was later called as the first generation current conveyor (CCI) [46]. Figure 1 represents the block diagram of the current conveyor [46]. The relations between the input variables of the current conveyor are given in matrix (1) below [46].

Figure 1: CCI block diagram [46]

$$\begin{bmatrix} V_{X} \\ I_{Y} \\ I_{Z} \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ \pm 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} I_{X} \\ V_{Y} \\ V_{Z} \end{bmatrix}$$

(1)

Page | 9

The matrix can be written in equation form also as below.

$$V_{\rm X} = V_{\rm Y} \tag{2}$$

$$I_{Y} = I_{X} \tag{3}$$

$$I_{Z} = \pm I_{X} \tag{4}$$

The input terminal X has low impedance while the output terminal Z has high impedance, hence its current conveying action is also called as the transfer of current from a low impedance level to a high impedance level. The impedance of input terminal Y is low. The X and Z terminals if taken together can be called as the Current Controlled Current Source (CCCS) where terminal Z is working as the current source and terminal X is controlling it with the use of current.

Because of the current characteristics, the current conveyor CCI was used in several instrumentation and communication systems. Because of its voltage characteristics, it was used as voltage to current converter, digital to analog converter with current source output and used in DC offset control of the wide band signals. It was also used as negative impedance converter and as an amplifier whose gain could be controlled electronically. Because of its current mode operation it offered high speed along with reasonable accuracy [45].

#### 2.2 THE SECOND GENERATION CURRENT CONVEYOR (CCII) [46]

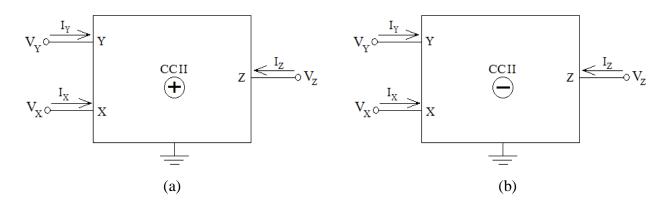

The upgradation of current conveyor was done and therefore a new version of current conveyor known as the second generation current conveyor (CCII) was proposed, again by K. C. Smith and A. Sedra in the year 1970 [46]. The limitation of CCI is the low input impedance of the input terminal Y. In many applications it is considered undesirable. But in CCII there is no such limitation and all terminals are at the proper impedance level. The block diagram of CCII is same

CCI as shown below in figure 2, but the port matrix is a bit different. The port matrix [46] is given in (5) below.

Figure 2: (a) The positive type second generation current conveyor (CCII+) [46](b) The negative type second generation current conveyor (CCII-) [46]

$$\begin{bmatrix} V_{X} \\ I_{Y} \\ I_{Z} \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ 0 & 0 & 0 \\ \pm 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} I_{X} \\ V_{Y} \\ V_{Z} \end{bmatrix}$$

(5)

The matrix can thus be written in equation form as below.

$$V_{\rm X} = V_{\rm Y} \tag{6}$$

$$I_{\rm Y} = 0 \tag{7}$$

$$I_{Z} = \pm I_{X} \tag{8}$$

Page | 11

The difference between CCI and CCII is the huge difference in the input impedance level of the input Y terminal. The impedance of input Y terminal of CCI is very low, while that of CCII the impedance of input Y terminal is very high. Therefore CCII can be used in more number of applications than CCI as CCII has all the terminals at the proper impedance levels. The terminal Y can be used only as the input terminal for the voltage input signal. But the terminal X can be used both ways i.e. as an input terminal for the current input signal and as an output terminal for the voltage output signal.

Further in [46], the current conveyors are also classified as the positive type current conveyor and the negative type current conveyor. If the current direction at the input X terminal and the output Z terminal is same than it is called as the positive type current conveyor (CCII+), however if the direction of currents at the input terminal X and the output terminal Z is different than the current conveyor is called as the negative type current conveyor (CCII-). Also, taking the voltage and current characteristics together, the CCII can be called as the combination of a voltage follower and a current follower.

Several applications of the CCII have also been reported in [46], they include the use of CCII in realization of the Voltage Controlled Voltage Source (VCVS), Voltage Controlled Current Source (VCCS), Current Controlled Current Source (CCCS), Current Controlled Voltage Source (CCVS), Negative Impedance Inverter (NIV), Inverting Negative Impedance Converter (INIC) and the gyrator. The application of current conveyor as the element of analog computer is also reported. For analog computation it can be used to realize various current mode functional elements, i.e. current amplifier, current differentiator, current integrator, current summer and weighted current summer.

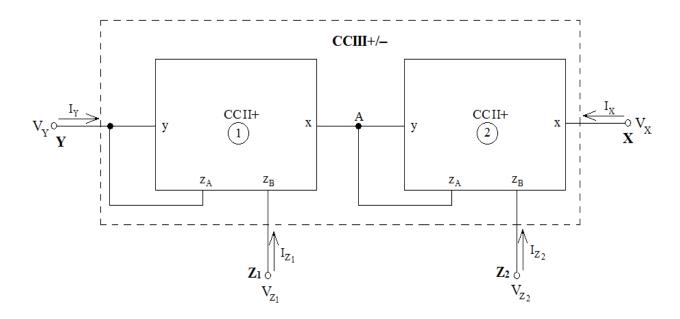

#### 2.3 THE THIRD GENERATION CURRENT CONVEYOR (CCIII) [47]

In the year 1995, a further updated version of the current conveyor called as the third generation current conveyor (CCIII) was introduced by A. Fabre [47]. The CCIII is all similar to the CCI in terms of the impedances of the three terminals X, Y and Z but is different from CCII when it comes

to the direction of the current at terminal Y. The direction of current flowing in terminal Y of CCIII is exactly opposite to the direction of the current flowing in terminal Y of the CCII. This is also represented in the below port matrix (9) of CCIII. The CCIII too is classified as the positive type third generation current conveyor (CCIII+) and the negative type third generation current conveyor (CCIII-).

Figure 3: Block diagram of CCIII [47]

The reported block diagram [47] of the CCIII is shown above in figure 3. It employs two CCII+s with each current conveyor CCII+ having two output terminals named as  $z_A$  and  $z_B$  having the same direction of current flowing through them. The CCIII thus obtained also has the two output terminals named as  $Z_1$  and  $Z_2$ , where currents flowing through both terminals are 180° out of phase with one another. Thus the CCIII provides both the output currents simultaneously i.e. the non inverted current as well as the inverted current or it can be concluded that the CCIII performs the operation of CCIII+ and CCIII- simultaneously.

The terminals voltage and current relations are mentioned in the matrix (9) below

$$\begin{bmatrix} V_{X} \\ I_{Y} \\ I_{Z} \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ -1 & 0 & 0 \\ \pm 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} I_{X} \\ V_{Y} \\ V_{Z} \end{bmatrix}$$

(9)

The matrix can thus be written in equation form as below.

$$V_{\rm X} = V_{\rm Y} \tag{10}$$

$$\mathbf{I}_{\mathbf{Y}} = -\mathbf{I}_{\mathbf{X}} \tag{11}$$

$$I_Z = \pm I_X \tag{12}$$

The CCIII can be employed in the input section of the probes and in the current measuring devices [47].

#### 2.4 VERSIONS OF CURRENT CONVEYORS

Although in the beginning, the current conveyor was not preferred in many applications because the advantages of current conveyor were not appreciated widely over the advantages of the conventional operational amplifier (Op-Amp) and there was no commercial availability of the integrated circuit (IC) implementation of the current conveyor. However, later in the year 1989 an IC for current conveyor was finally introduced by Wadsworth [48]. It was named as PA630, its mass production was carried out by Phototronics Ltd. of Canada. And almost at the same time when the current conveyor's IC was introduced, the operational transimpedance amplifier's IC named AD844 was recognized to be internally consisting of CCII+ following a voltage follower [49].

Since the year 1995 particularly, there has come many modifications and improvements in the basic CCII so that it can be used more efficiently and can be employed in more number of applications. With time there increased a demand of availability of current conveyor with multiple output, hence a Dual Output Second Generation Current Conveyor (DO-CCII) was introduced which is a combination of both the CCII+ and CCII-, so that the output current in both directions can be provided. If the dual output current conveyor has the same direction of both the output currents then it is called as the Current Follower Second Generation Current Conveyor (CFCCII). Depending on the direction of the output currents, it also has its positive type and negative type versions denoted as CFCCIIp and CFCCIIn respectively [50].

Then, with the further evolution, there came many versions of current conveyors [50]. They are the Differential Voltage Second Generation Current Conveyor (DVCCII), the Differential Voltage Complementary Current Conveyor (DVCCC), the Inverting Second Generation Current Conveyor (ICCII), the Differential Difference Current Conveyor (DDCC) which is an upgradation of the current conveyor DVCCII, the Differential Difference Complementary Current Conveyor (DDCCC) which is an upgraded version of DDCC with an extra output Z terminal to provide the output current in both directions, Differential Current Conveyor (DCC) which is a current conveyor CCII with two X terminals, the modified version of DCC i.e. Modified Differential Current Conveyor (MDCC), the Dual X Second Generation Current Conveyor (DXCCII) which is a combination of CCII and ICCII, Fully Differential Second Generation Current Conveyor (FDCCII) in which the three terminals (X,Y,Z) occur in pairs, Fully Balanced Second Generation Current Conveyor (FBCCII), Modified Second Generation Current Conveyor (MCCII), Operational Floating Conveyor (OFC) which is obtained by joining the two CCII-s, Universal Current Conveyor (UCC), Modified Current Conveyor Third generation (MCCIII), Current Controlled Second Generation Current Conveyor (CCCII), Current Gain Second Generation Current Conveyor (CGCCII) [50].

The most recent version of current conveyor is the Extra X Second Generation Current Conveyor (EXCCII) [59] which has two identical input X terminals. It is much similar to DXCCII, the only difference is that in EXCCII both the X terminals produces the non inverting voltage applied at the input.

Among the various version of current conveyor, a version named as the DXCCII has been used in this thesis to propose two precision half wave rectifiers, one precision full wave rectifier, a BASK modulator and a BPSK modulator.

#### 2.5 ADVANTAGES OF CURRENT CONVEYOR

Lately the current conveyor has gained the consideration of being a universal analog active building block as it offers several advantages as follows

- More versatility

- Low power

- More accuracy

- Availability of very high slew rates

- Availability of wider bandwidth

- Offers large dynamic range

- And the most important is the availability of the integration.

#### 2.6 APPLICATIONS OF CURRENT CONVEYORS

It can used in a number of applications employing the current mode, voltage mode and the mixed mode operations. However its features make it more preferable for the current mode applications.

The applications of current conveyors mostly include realization of

- Filters

- Oscillators

- Precision rectifiers

- Gyrators

- Analog computation circuits

- Transfer function realization

- Inductor simulation circuits

- Frequency Dependent Negative Resistance (FDNR) device

- Grounded capacitance multiplier

- Four quadrant multiplier

- Vector summation circuit etc.

### **CHAPTER 3**

#### THE DUAL-X CURRENT CONVEYOR (DXCCII)

#### 3.1 INTRODUCTION OF DXCCII [34]

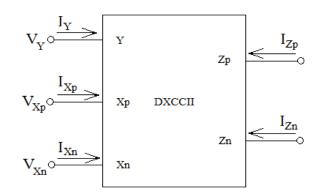

Since the CCII was first introduced [32], it had gained much attention in designing of the integrated continuous time filters. These filters required tuning in order to compensate for the behavioral deviations that occurred due to the process tolerances, effect of parasitics, effect of temperature and aging etc. But the RC filters based on the CCII failed to provide the needed tunability. Therefore, the requirement of the needed tunability for these continuous time filters led to the invention of the new active block named as the dual-X second generation current conveyor (DXCCII) [34]. The DXCCII, conceptually, is a combination of CCII [32] and ICCII [33]. It is therefore more versatile building block as it has the features of both the current conveyors i.e. CCII and ICCII.

The block diagram of DXCCII [34] is shown below in figure 4. It has 5 terminals named as Y, Xp, Xn, Zp and Zn. Xp is called as the non inverting X terminal while Xn is called as the inverting X terminal. Y is an input terminal with high impedance. Xp and Xn are terminals with low impedance while Zp and Zn are terminals with high impedance.

Figure 4: Block diagram of DXCCII [34]

When a voltage is applied at the Y terminal the current drawn by Y terminal is zero ideally. With the application of the voltage at Y terminal, an equal and in phase voltage is generated at the Xp terminal, and an equal but 180° out of phase voltage is generated at the Xn terminal. The current developed at Zp terminal is equal to the current developed at the Xp terminal and the current developed at Zn terminal is equal to the current developed at the Xn terminal but the currents developed at the Zp and Zn terminals have no direct relation with each other. Mathematically, it can be expressed in the matrix form [34] as mentioned below in (13).

$$\begin{bmatrix} I_{Y} \\ V_{Xp} \\ V_{Xn} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ -1 & 0 & 0 \\ I_{Zp} \\ I_{Zn} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ -1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{Xp} \\ I_{Xn} \end{bmatrix}$$

(13)

The terminal voltage and current relations can also be written in the equation form as written below

$$I_{\rm Y} = 0 \tag{14}$$

$$V_{Xp} = V_Y \tag{15}$$

$$V_{Xn} = -V_Y \tag{16}$$

$$I_{Zp} = I_{Xp} \tag{17}$$

$$I_{Zn} = I_{Xn} \tag{18}$$

Where,  $V_Y$  is the voltage applied at Y terminal.  $V_{Xp}$  and  $V_{Xn}$  are the voltages developed at Xp and Xn terminals respectively.  $I_{Xp}$ ,  $I_{Xn}$ ,  $I_{Zp}$  and  $I_{Zn}$  are the currents developed at Xp, Xn, Zp and Zn terminals respectively.

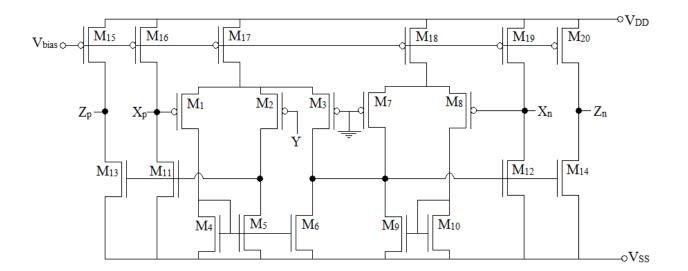

## 3.2 CMOS IMPLEMENTATION OF DXCCII [35]

Figure 5 shows the CMOS implementation of DXCCII. As mentioned already, it has cascading of the inverting and non inverting second generation current conveyors. The inversion of voltage from terminal Y to terminal Xn is done in the same way as it is done in the inverting second generation current conveyor. In order to provide the copy of the current generated at non inverting X terminal Xp to the Zp terminal, a non inverting current mirror is used. While to provide the copy of the current generated at the inverting X terminal Xn to the Zn terminal, an inverting current mirror has been used. The terminal Y needs to have high impedance and zero current drawn by it as the port matrix of DXCCII says. So in order to satisfy these needs the gate terminal of the MOSFET is used as the Y terminal, since the gate of MOSFET has very high resistance and therefore ideally no current is drawn by it. Also an NMOS transistor  $M_{13}$  and a PMOS transistor  $M_{15}$  are employed additionally in order to transfer the current generated at the Xp terminal to the Zp terminal. The total count of transistors used is twenty, out of which eleven are PMOS transistors and the remaining nine transistors are NMOS transistors.

Figure 5: CMOS implementation of DXCCII [35]

The aspect ratio of transistors used in the implementation of DXCCII are given in table 3 [35].

| Transistor                                        | W(µm) | L(µm) |

|---------------------------------------------------|-------|-------|

| M <sub>1</sub> , M <sub>2</sub>                   | 1.4   | 0.7   |

| M <sub>3</sub> , M <sub>7</sub> , M <sub>8</sub>  | 2.8   | 0.7   |

| M4, M5                                            | 2.4   | 0.7   |

| M <sub>6</sub> , M <sub>9</sub> , M <sub>10</sub> | 4.8   | 0.7   |

| M <sub>11</sub> to M <sub>20</sub>                | 9.6   | 0.7   |

Table 1: (W/L) Ratio of CMOS used in the DXCCII [35]

## 3.3 NON IDEAL MODEL OF DXCCII [35]

Four parameters are introduced which describe the non ideal behavior of the DXCCII. These are, the voltage transfer gains i.e.  $\alpha_p$  and  $\alpha_n$ , and the current transfer gains i.e.  $\beta_p$  and  $\beta_n$ . Ideally value of all these parameters is unity. But practically they are not exactly unity but much close to unity for a very high range of frequencies i.e. in Giga hertz (GHz) range [35].

Because of the non idealities in the DXCCII, the port matrix [35] can therefore be modified as shown below in (19).

$$\begin{bmatrix} I_{Y} \\ V_{Xp} \\ V_{Xn} \\ I_{Zp} \\ I_{Zn} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ \alpha_{p} & 0 & 0 \\ -\alpha_{n} & 0 & 0 \\ 0 & \beta_{p} & 0 \\ 0 & 0 & \beta_{n} \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{Xp} \\ I_{Xn} \end{bmatrix}$$

(19)

The terminal voltage and current relations in the equation form is also modified then, as written below

$$I_{\rm Y} = 0 \tag{20}$$

$$V_{Xp} = \alpha_p V_Y \tag{21}$$

$$V_{Xn} = -\alpha_n V_Y \tag{22}$$

$$I_{Zp} = \beta_p I_{Xp} \tag{23}$$

$$I_{Zn} = \beta_n I_{Xn} \tag{24}$$

## Here

$\begin{array}{l} \alpha_p \text{ is the voltage transfer gain from Y to Xp terminal.} \\ \alpha_n \text{ is the voltage transfer gain from Y to Xn terminal.} \\ \beta_p \text{ is the current transfer gain from Xp to Zp terminal.} \end{array}$

$\beta_n$  is the current transfer gain from Xn to Zn terminal.

$\alpha_p,\,\alpha_n,\,\beta_p,\,\beta_n$  are given by the following equations below.

$$\alpha_{\rm p} = 1 - \varepsilon_{\rm Vp} \tag{25}$$

$$\alpha_{\rm n} = 1 - \varepsilon_{\rm Vn} \tag{26}$$

$$\beta_{\rm p} = 1 - \varepsilon_{\rm Ip} \tag{27}$$

$$\beta_{\rm n} = 1 - \varepsilon_{\rm In} \tag{28}$$

### Where

$\varepsilon_{Vp}$  is the voltage tracking error at Xp terminal.  $\varepsilon_{Vn}$  is the voltage tracking error at Xn terminal.  $\varepsilon_{Ip}$  is the current tracking error at Zp terminal.  $\varepsilon_{In}$  is the current tracking error at Zn terminal.

$\varepsilon_{Vp}$ ,  $\varepsilon_{Vn}$ ,  $\varepsilon_{Ip}$ ,  $\varepsilon_{In}$  are zero ideally but practically they are much smaller than one, i.e.

$$\varepsilon_{Vp} \ll 1$$

(29)

$$\varepsilon_{Vn} \ll 1$$

(30)

$$\varepsilon_{Ip} \ll 1$$

(32)

$$\varepsilon_{\text{In}} \ll 1$$

(32)

Theoretically  $\alpha_p$ ,  $\alpha_n$ ,  $\beta_p$ ,  $\beta_n$  are also defined by the following equations below.

$$\alpha_{\rm p} = \frac{V_{\rm Xp}}{V_{\rm Y}} \tag{33}$$

$$\alpha_{n} = \left| \frac{V_{Xn}}{V_{Y}} \right| \tag{34}$$

$$\beta_{\rm p} = \frac{I_{\rm Zp}}{I_{\rm Xp}} \tag{35}$$

$$\beta_n = \frac{I_{Zn}}{I_{Xn}} \tag{36}$$

## Where

$V_{Y}$  is the voltage applied at Y terminal.

$V_{Xp}$  and  $V_{Xn}$  are the voltages developed at Xp and Xn terminals respectively.

$I_{Xp}$ ,  $I_{Xn}$ ,  $I_{Zp}$  and  $I_{Zn}$  are the currents developed at Xp, Xn, Zp and Zn terminals respectively.

## 3.4 PARASITIC MODEL OF DXCCII [35]

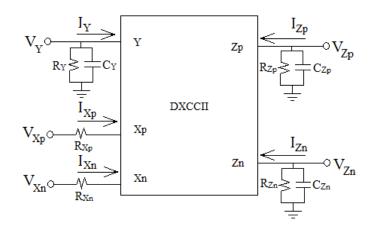

There are various parasitic resistances and capacitances at the terminals of DXCCII. The two X terminals have only parasitic resistance associated with them while the Y terminal and the two Z terminals have both, the parasitic resistance as well as the parasitic capacitance associated with them. The block diagram of DXCCII revealing its associated parasitics is shown in figure 6 [35].

Figure 6: DXCCII parasitic model [35]

It can be observed from the block diagram that for the terminals Y, Zp and Zn, the respective parasitic resistance and the parasitic capacitance appears in parallel combination with each other, this parallel combination being connected between the respective terminal and the ground.

The notation of the various parasitic resistances and capacitances shown in the above block diagram are described as follows.

$R_{Xp}$  and  $R_{Xn}$  are the parasitic resistances of the Xp and Xn terminals respectively.

$R_{Y}$  and  $C_{Y}$  are the parasitic resistance and capacitance of the Y terminal.

$R_{Zp} \mbox{ and } C_{Zp}$  are the parasitic resistance and capacitance of the Zp terminal.

$R_{Zn} \mbox{ and } C_{Zn}$  are the parasitic resistance and capacitance of the Zn terminal.

The parasitic resistances of X terminal i.e  $R_{Xp}$  and  $R_{Xn}$  are much smaller in magnitude. While the parasitic resistances of Y, Zp and Zn terminals i.e.  $R_Y$ ,  $R_{Zp}$  and  $R_{Zn}$  are much higher in magnitude. Further, this assumption is taken in to consideration that the circuits employing DXCCII are restricted to perform correctly only for the frequencies which are much lower than the corner frequencies of the various voltage and current gains i.e.  $\alpha_p$ ,  $\alpha_n$ ,  $\beta_p$ ,  $\beta_n$ . Also, practically the parasitic resistances at Y, Zp and Zn terminals are assumed to be much higher in value than the value of the external resistors used in the DXCCII based circuit, but the value of these external resistors is assumed to be much higher than the parasitic resistances value of the Xp and Xn terminals [35].

## **3.5 ADVANTAGES OF DXCCII**

DXCCII basically consists of the main advantages of CCII and ICCII. With the addition of a triode MOSFET efficient tunability is provided without affecting the high linearity for the large signals. This tunability helps to compensate for the behavioral deviations that occurred due to the process tolerances, effect of parasitics, effect of temperature, aging etc. The dual-X terminals provides the added features such as inverting input voltage is also available at its Xn terminal other than the non inverting input voltage at its Xp terminal, therefore these added features helped to reduce the elements count used in the continuous time filters [34].

Also, like the other current mode active blocks, the DXCCII provides some superior features over its voltage mode equivalent [37]. These features are as follows

- The usable gain is higher.

- At the sensitive nodes the voltage excursion is further reduced.

- Greater linearity.

- Power dissipation is less.

- Wider bandwidth.

- Accuracy is better.

- Larger dynamic range.

## **3.6 APPLICATIONS OF DXCCII**

There are a variety of applications employing the DXCCII as the active block as reported in the open literature such as a tunable gyrator, current mode biquad filter using tunable gyrator, grounded inductance design, oscillator design, and filter design etc. Some of these applications are mentioned below.

- After the DXCCII was proposed, it was first employed in the applications to make a tunable transconductor, voltage mode lossless and lossy integrator, current mode lossless and lossy integrator, current mode lossless and lossy integrator, current mode Tow Thomas filter and a current mode sinusoidal oscillator [34].

- The four quadrant analog multiplier have been proposed with two topologies, the first one uses one DXCCII while the second one uses two DXCCII [36].

- A precision voltage mode full wave rectifier has been proposed with only one DXCCII and three NMOS transistors. It has high input impedance which supports its easy cascading [37].

- Further a new CMOS implementation of DXCCII has been reported to improve its performance and a vector summation circuit is proposed which uses two DXCCIIs along with seven MOS transistors [38].

- The hardware realization of DXCCII with commercially available ICs has been reported.

Fourteen hardware implementations are proposed. Seven implementations employ only

AD844 ICs and the other seven implementations employ AD843 opamps ICs and AD844s

ICs. The total number of ICs used is every proposed implementation is four. Also all of these implementations have additional advantage of availability of the buffered voltage outputs, which is not provided in the conventional DXCCII. A quadrature oscillator has been also been proposed with these hardware implementation. Further feature enhancement is done of DXCCII and thus a gain variable DXCCII has been proposed [39].

- A tunable grounded capacitance multiplier has been presented, it uses only one DXCCII block [40].

- A new CMOS DXCCII has been proposed and it is used to realize a FDNR (Frequency Dependent Negative Resistance) element [41].

- Differential Voltage Dual-X second generation Current Conveyor (DV-DXCCII) has been used in the proposed all pass filter of first order, it gives both inverting and non inverting responses [42].

- First and second order current mode all pass filter has been proposed using a multiple output DXCCII (MO-DXCCII). Four Z terminals are there in the MO-DXCCII. [43]

- Differential Voltage Dual-X Current Conveyor (DV-DXCCII) has been used to propose a fully differential first order all pass filter [44].

- Recently a digital modulator circuit has also been proposed which can perform BASK and BPSK modulation processes simultaneously. The modulator uses only one DXCCII along with two NMOS transistors and three grounded resistors [59].

## **3.7 SIMULATION RESULTS OF DXCCII**

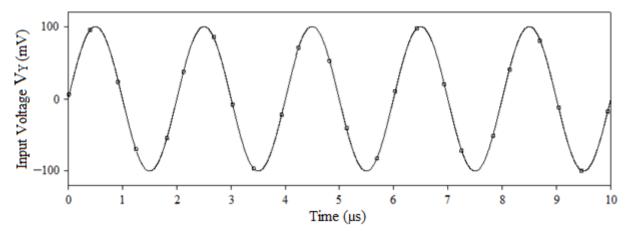

The various characteristics of DXCCII are simulated using PSpice software. 0.35 $\mu$ m CMOS technology parameters are used. The supply voltage for the active block DXCCII [35] is taken as  $\pm 1.8V$  and the voltage V<sub>bias</sub> is set to 1.05V.

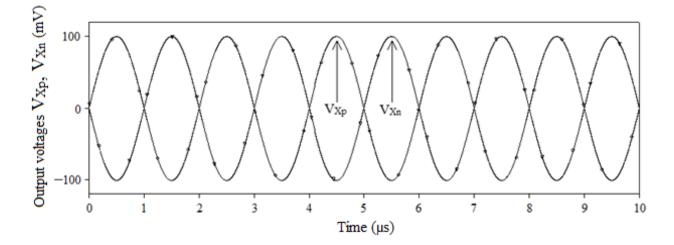

The transient response of the terminals Xp and Xn for a sinusoidal excitation with a frequency of 500KHz at the input terminal Y (figure 7) is shown in figure 8. It can be observed that the non inverted and inverted input voltage signal are produced at the terminal Xp and Xn respectively.

Figure 7: Input voltage, V<sub>Y</sub>

Figure 8: Output voltages, V<sub>Xp</sub>, V<sub>Xn</sub>

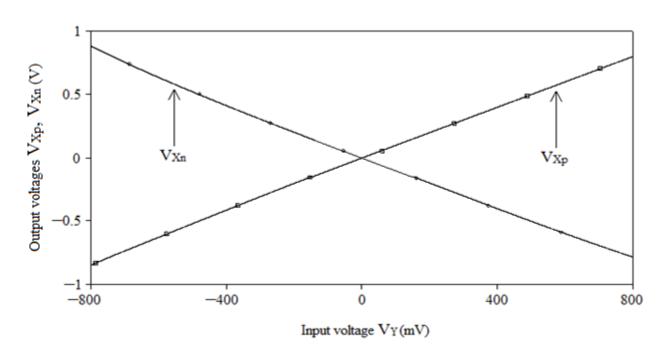

Figure 9: DC voltage characteristics of terminals Xp and Xn

Figure 9 shows the DC voltage characteristics of terminals Xp and Xn. It can be observed that as the input voltage signal applied at terminal Y varies, the output voltages at the terminals Xp and Xn also varies linearly.

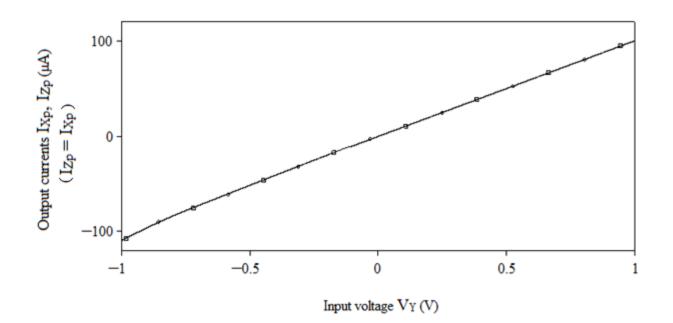

Figure 10: Variation in the output currents,  $I_{\rm Xp}$  and  $I_{\rm Zp}$  with input voltage,  $V_{\rm Y}$

Figure 10 shows the linear variation in the output currents at terminals Xp and Zp with the variation in the input voltage at terminal Y. It also shows that currents at the terminals Xp and Zp are equal.

Input voltage VY (V)

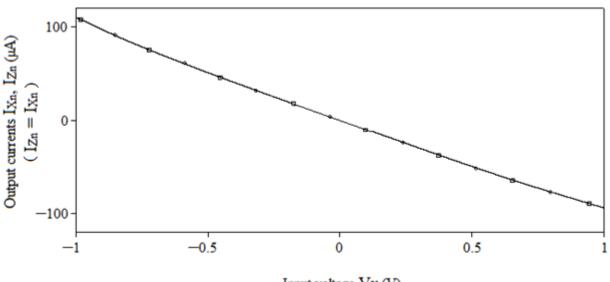

Figure 11: Variation in the output currents,  $I_{Xn}$  and  $I_{Zn}$  with input voltage,  $V_Y$

Figure 11 shows the linear variation in the output currents at terminals Xn and Zn with the variation in the input voltage at terminal Y. It also shows that currents at the terminals Xn and Zn are equal.

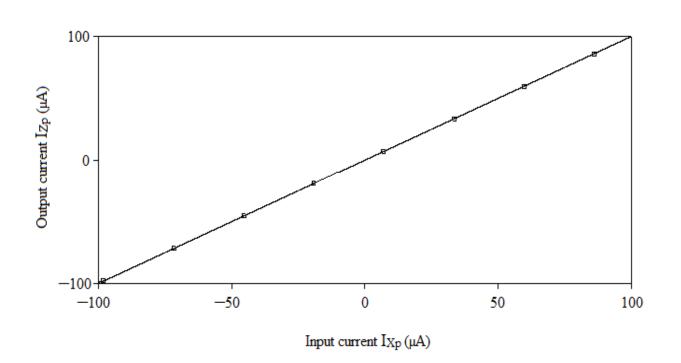

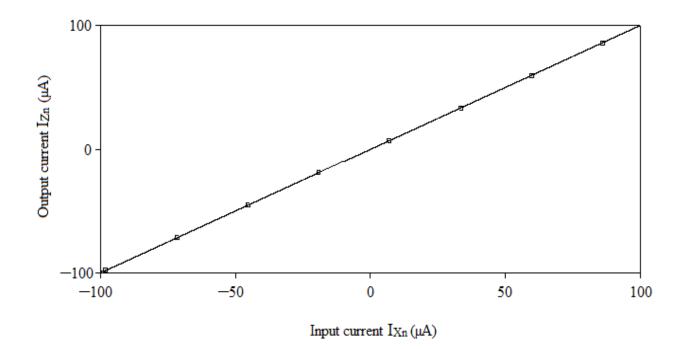

Figure 12 shows the DC current characteristic of terminal Zp. It can be observed that the output current at terminal Zp is exactly same as the applied input current at terminal Xp.

Figure 13 shows the DC current characteristic of terminal Zn. Here also it can be observed that the output current at terminal Zn is the exact copy of the input current applied at the terminal Xn.

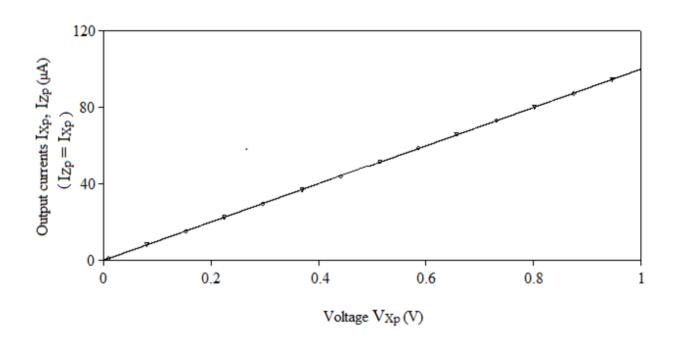

Figure 14 shows the linear variation in the output currents,  $I_{Xp}$  and  $I_{Zp}$  with the voltage,  $V_{Xp}$ .

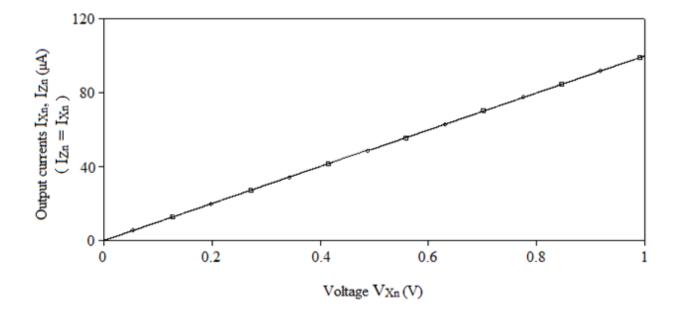

Figure 15 shows the linear variation in the output currents,  $I_{Xn}$  and  $I_{Zn}$  with the voltage,  $V_{Xn}$ .

Figure 12: DC current characteristic of terminal Zp

Figure 13: DC current characteristic of terminal Zn

Figure 14: Variation in the output currents,  $I_{\text{X}p}$  and  $I_{\text{Z}p}$  with the voltage,  $V_{\text{X}p}$

Figure 15: Variation in the output currents,  $I_{\text{Xn}}$  and  $I_{\text{Zn}}$  with the voltage,  $V_{\text{Xn}}$

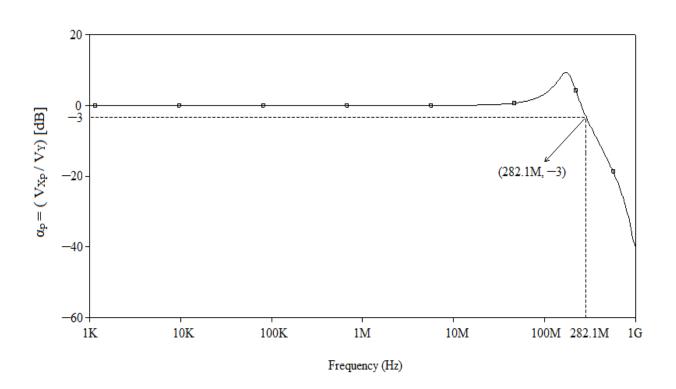

Figure 16: Simulated frequency response of the voltage gain,  $\alpha_p$  from terminal Y to terminal Xp

Page | 33

Figure 16 above shows the simulated frequency response of the voltage gain,  $\alpha_p$  from terminal Y to terminal Xp. The simulated 3 dB cut off frequency for the voltage gain,  $\alpha_p$  is observed to be 282.1 MHz.

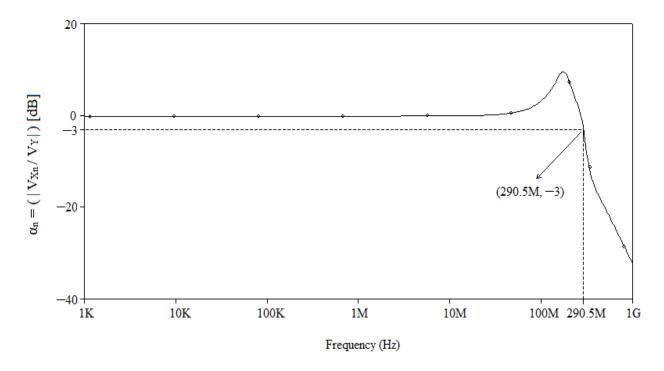

Figure 17 above shows the simulated frequency response of the voltage gain,  $\alpha_n$  from terminal Y to terminal Xn. The simulated 3 dB cut off frequency for the voltage gain,  $\alpha_n$  is observed to be 290.5 MHz.

Figure 18: Simulated frequency response of the current gain,  $\beta_p$  from terminal Xp to terminal Zp

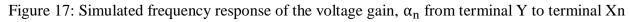

The simulated frequency response curve for the current gain,  $\beta_p$  from terminal Xp to terminal Zp is shown above in figure 18. The 3 dB cut off frequency is observed to be 1.57 GHz.

## **CHAPTER 4**

## **RECTIFIERS**

## **4.1 INTRODUCTION OF RECTIFIERS**

The rectifier is a device that converts AC (Alternating Current) signal that periodically reverses direction into the pulsating DC (Direct Current) signal that flows only in one direction. This process of conversion of a bidirectional signal in to a unidirectional signal is known as rectification.

For large signals the concept of rectification is well developed. However, with time there has been a growth in the demand of portable circuits that can operate on low supply voltages. This therefore raised the need of such circuits that can process naturally occurring very small analog signals and can handle the frequencies associated with them. One such circuit is precision rectifier. Much research studies have now been focused on designing such rectifiers which can rectify very small signals, these rectifiers are referred as the precision rectifiers.

In the conventional rectifiers, simply diodes can be used for rectification. But these conventional diode rectifiers fail to rectify those signals whose amplitudes are below the cut in voltage of the diode. For example, the semiconductor silicon (Si) diode has a cut in voltage of 0.7 V and germanium (Ge) diode has a cut in voltage of 0.3 V, therefore the rectifier using silicon diodes fails to rectify the signals in the range from -0.7 V to 0.7 V while the rectifier using germanium diodes fails to rectify the signals in the range from -0.3 V to 0.3 V [26]. Therefore the conventional diode only rectifiers, for example half wave rectifier, full wave bridge rectifier and full wave center tapped rectifier, are employed in those applications only where rectification in the range of cut in voltages of the diodes is of less importance, for example in Radio Frequency (RF) demodulation, in DC voltage supplies etc. Since the cut in voltages of the semiconductor diodes don't allow the conventional rectifiers to be used in those cases where rectification of low level voltage signals is needed, precision rectifiers using active elements have to be employed.

In the last few decades such precision rectifiers have been developed using operational amplifier (Op-Amp) and passive components such as diodes and resistors, often with the matching conditions of these resistors, and many of these external passive components are in the floating condition. Many precision rectifiers employing Op-Amp, passive components such as diodes and resistors have been reported in the open literature. In these rectifiers the diodes are connected directly to the output terminal of the active block [26], [31].

But there are certain limitations of the precision rectifiers making use of Op-Amps. Due to the voltage mode processing of the operational amplifiers, their Slew Rate (SR) is limited. This gives rise to a classical problem known as the corner distortion. It's a distortion that occurs during the zero crossings of the input signal because the diodes and Op-Amp have to recover during the transition from the conducting state to the non conducting state and vice versa with in finite small signal slew rate. This distortion is more for the low level signals. The employment of high slew sate Op-Amps does not solve this problem either, since this problem is a small signal transient problem [6]. These limitations therefore restricts the correct operation of the conventional Op-Amp based precision rectifiers to low frequencies only. These low frequencies are much lower than the gain bandwidth product of the operational amplifier used. Also, since these conventional precision rectifiers use Op-Amp and resistors, these are therefore not suitable for the IC fabrication. These conventional precision rectifier circuits also give rise to noise problems associated with the resistors used in them.

An improvement in the precision rectification of high frequency signals has been achieved by using the current mode technique [10]. Current mode or current sensing approach has several advantages over the voltage mode counterparts, for example current mode approach offers higher frequency of operation, larger dynamic range, wider bandwidth, and also the offset value is lower at the zero crossing areas of the input signal. Therefore high frequency rectification could be achieved using current mode technique.

Although the current mode circuits provide the advantage of high frequency precision rectification, some of the reported precision rectifiers which achieved this improvement employing the CCs are not ideal for the IC fabrication because they make use of either grounded or floating resistors. In

addition to this, some of the precision rectifiers need two identical CCs. Mismatching of these affects the output of the full wave precision rectifier, that is, the amplitude of the first half cycle may be different than the amplitude of the second half cycle of the full wave rectified output waveform [10].

In general, it can be said that the precision rectifier circuits have been developed with diodes, active analog building blocks, for example CCIIs, Op-Amps, etc. or both [1-3, 5, 7, 9-18, 20, 27]. CCIIs provides a very high Slew Rate and bandwidth in comparison to the conventional Op-Amp. This makes CCIIs of primary importance when it comes to the design of modern analog ICs.

Other rectifiers have been developed with different active building blocks for example precision rectifiers making use of the Operational Trans conductance Amplifiers (OTAs) [19, 22, 23] provide the attractive feature of IC implementation, some of them nevertheless suffer from the application of a large number of active components and limitation to the high frequency performance.

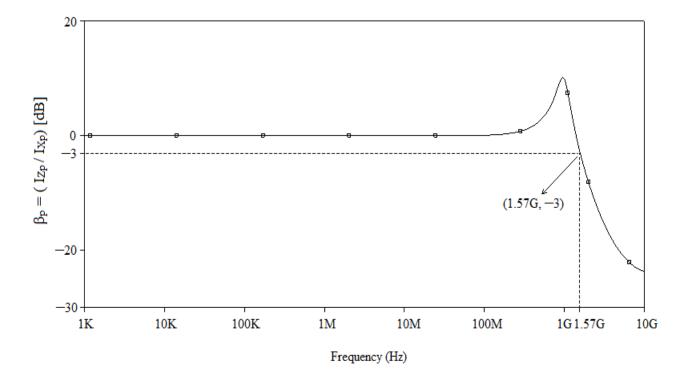

Recently efforts have been made to replace diode with active elements, for example a MOS transistor is employed in place of diode for switching purpose. In this thesis also two MOS transistors are employed in the newly proposed precision full wave rectifier using DXCCII as the active building block. In addition, there have been several rectifiers reported in the literature that make use of only MOS transistors and no passive element is used in their construction. Such precision rectifiers are very suitable for the Complementary Metal Oxide Semiconductor (CMOS) technology IC implementation. One benefit of the IC precision rectifiers developed by making use of the simple active blocks such as Op-Amps, CCs and active or passive elements such as transistors, diodes and resistors as components, is that they can be fabricated in many countries.

## **4.2 CLASSIFICATION OF RECTIFIERS**

- They are basically of two types when the alternating voltage used as input is concerned. They are:

- 1) Single phase rectifiers

- 2) Poly-phase rectifiers (for example: 3-phase rectifier)

- When the switching device used is taken in to account the rectifiers have two categories, that is:

- 1) Uncontrolled rectifiers

- 2) Controlled rectifiers

Also, as per the of functionality limitation of the switching device is concerned there can be a sub division also named as half controlled rectifiers.

- When the period of conduction is concerned rectifiers have two categories. They are:

- 1) Half-wave rectifiers

- 2) Full-wave rectifiers

Full wave rectifiers can further have two classifications when the nature of the circuit connections is concerned. They are:

- 1) Centre tapped full-wave rectifier

- 2) Bridge full-wave rectifier

Synchronous rectifiers: When the active element is employed for switching purposes

instead of diodes than the rectifier is called as the synchronous rectifier or active rectifier.

To overcome the diode losses active elements are used in place of diodes and it

significantly improves the efficiency levels also.

In view of the availability of a variety of different types of rectifier circuits, there is often a good choice available to the user of which type of rectifier to use. In many cases it depends on the level of performance required, and usually a type of full wave rectifier is required. Usually bridge full wave rectifier is the cheapest option as it is available with low cost rather than center taped transformer type full wave rectifier where less diodes are used in comparison with bridge rectifier but it requires a center taped transformer which is expensive. Now in the modern power supplies which require high level of efficiency, the designers are looking to employ the synchronous or active rectifiers. Though synchronous or active rectifiers are more complicated and therefore are more costly, but still this increased cost often gives the returns in terms of increasing the level of efficiency.

## **4.3 SWITCHING DEVICES USED IN RECTIFIERS**

One of the most important component that needs to be considered in power electronics before designing of any circuit is the switching device. It is assumed that switching device will behave as an ideal switch but it is not practically true. There can be two groups when it comes to the classification of the switching devices. They are

#### 1) Uncontrolled Switching Device

An example of uncontrolled switching device is diode whose state completely depends on the power circuit that is connected externally to it. Ideally a diode has two states of operation, first is ON state (or forward biased state) where diode is considered to be an on switch or closed switch and second is OFF state (or reverse biased state) where diode is considered as an off switch or open switch. During forward-biased condition of the diode, ideally the voltage across its terminals is zero, no matter what amount of current is flowing through it. While during reverse-biased state of the diode, ideally no current flows through it or say the current flow through the diode is zero no matter what the voltage across its terminals is, provided the reversed biased voltage doesn't exceed the reverse breakdown voltage of the diode. Diodes find applications in the designing of rectifiers, voltage clipper, voltage clamper, schmitt trigger, constable multivibrator, voltage multiplier etc.

#### 2) Controlled switching device

In this category, there are semi-controllable and fully-controllable switches. Semicontrollable switches are like thyristors and fully-controllable switches are like BJT (Bipolar Junction Transistor), JFET (Junction Field Effect Transistor), MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) etc.

Below is a brief introduction of various types of active devices used in the rectifiers.

Thyristors - There are three terminals in a thyristor called as anode terminal, cathode terminal and gate terminal. It is made up with four semiconductor material layers. There can be three modes or states of operation of a thyristor called as reverse blocking mode or state, forward blocking mode or state and forward controlling mode or state.

When the thyristor is operated in the reverse blocking mode, the direction of application of voltage across thyristor is same as the direction of voltage applied in a reversed biased diode and no current flows through it. When the thyristor is operated in forward blocking mode or state, the application of voltage applied across it has the same direction as the direction of voltage applied in a forward biased diode is, and still the current flow through it is zero and there is a control on the trigger of the thyristor into conduction state via its gate terminal. And during the forward conducting mode of operation, the thyristor is made to conduct by triggering it with its gate terminal and current begins to flow through it and voltage drop across it reduces to a very small value, now it will turn off only when the

current flowing through it is made to fall below a certain threshold value called as the holding current.

Thyristors have many types, for example - SCR, MOS-controlled thyristor, optically triggered thyristor, static induction thyristor.

- 2) BJT (Bipolar Junction Transistor) BJT is a current-controlled switch and can be considered as combination of two diodes connected in as way where the anode terminals of both diodes are shorted. BJT has three terminals named as the base, collector and the emitter terminal. The base current is required to be supplied to turn on the BJT. The input resistance of the BJT is low and it is a temperature sensitive device. In a BJT the internal current is due to both electrons and holes i.e. it is bipolar while the external current is only due to electrons i.e. it is unipolar. BJTs are now being replaced by MOSFETs for they have better efficiency, more thermal stability and low power dissipation.