# INTELLIGENT CONTROL ALGORITHMS FOR DSTATCOM AND ITS APPLICATIONS

A Thesis Submitted to the Delhi Technological University For the Award of Doctor of Philosophy In Electrical Engineering

Submitted By

MD. TAUSIF AHMAD (2K11/PhD/EE/03)

Under the Supervision of: **Prof. Narendra Kumar and Prof. Bhim Singh**

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042, INDIA 2018

### CERTIFICATE

This is to certify that the thesis entitled "Intelligent Control Algorithms for DSTATCOM and its Applications" which is being submitted by Mr. Md. Tausif Ahmad for the award of degree of Doctor of Philosophy in Electrical Engineering, Delhi Technological University, Delhi, is a record of student's own work carried out by him under our supervision and guidance. The matter embodied in this thesis has not been submitted in part or full to any other university or institute for award for any others degree.

Date 16/04 / 2018

Prof. Bhim Singh (Supervisor) Electrical Engineering Department Indian Institute of Technology Delhi Hauz Khas, New Delhi-110016, India

Navenary

Prof. Narendra Kumar (Supervisor) Electrical Engineering Department Delhi Technological University Delhi Shahbad Daulatpur, Delhi-110042, India

#### ACKNOWLEDGEMENTS

First and foremost, I thank the Almighty who is at the helm of everything and at whose command dances the successes and failures of life.

Next, I express my profound sense of gratitude to my supervisors and motivators **Prof. Bhim Singh**, Electrical Engineering Department, Indian Institute of Technology Delhi and **Prof. Narendra Kumar**, Electrical Engineering Department, Delhi Technological University for their invaluable suggestions, co-operation and help in providing necessary facilities and resources during the entire period of my research work. I thank them for encouraging me to stay in the laboratory for long hours. Their wide knowledge and logical way of thinking have helped me to complete my research work. They always made themselves available to clarify my doubts despite their busy schedules and I consider it as a great opportunity to do my doctoral programme under their guidance and to learn from their research expertise.

I also thank them not only for their continued morale-boosting efforts and support towards the completion of my research work but also for their fatherly attitude towards me throughout my association. Thank you very much Sirs, for all your help and support.

In the same vein, I also acknowledge **Prof. Madhusudan Singh**, Head of the Department, Electrical Engineering, Delhi Technological University (formerly Delhi College of Engineering) who enlightened me during my research.

I especially thank **Dr. M. Rizwan**, Assistant Professor, for always standing beside me through my thick and thin, personally and professionally.

I also would like to thank **Prof. Suman Bhowmick** for his immense support and valuable guidance during the entire work of this thesis. I also express my thanks to SRC members mainly **Prof. G. Bhuwneshwari**, Professor, Electrical Engineering Department, IIT Delhi and **Prof. Mini S. Thomas**, Professor, Electrical Engineering Department, Jamia Millia Islamia, New Delhi who have given me valuable guidance and advice to improve quality of my research work. I am also very grateful to Prof. Vishal Verma who helped me in numerous ways during various stages of my Ph.D. I also extend my sincere thanks to Prof. Pragati Kumar, Prof. Narendra Kumar I, Prof. Rachna Garg, Prof. Alka Singh, Dr. Priya Mahajan and other faculties of the Electrical Engineering, Delhi Technological University, Delhi, for their encouragement and moral support for the completion of this thesis.

I am also thankful to IIT Delhi for permitting me to access old issues of international journals and reference books related with my research work. I also would like to thank to all the personnel of Electrical Engineering Utilization Laboratory for their enormous support and help during my research work. I also thank the office staff of Central Library and Central Computer Centre for their valuable cooperation and support.

I extend my personal thanks to my friends and colleagues specially, Priyanka Chaudhary, Imran Ahmad Quadri, Prakash Chittora, Ramesh Singh, Arshad Hussain Quadri, Dr. Manoj Badoni, Dr. Amritesh Kumar, Ambrish Devanshu, Nikita Gupta, Astitva Kumar for their valuable support and reminding me to complete my work at the earliest.

I would like to offer my sincere thanks to **Dr. Sabha Raj Arya**, who has guided me to develop hardware setup at initial stage and support me in many ways. His vast knowledge of control algorithms for shunt compensator and research publications guided me always to carry out my research work. I am also grateful to Dr. Arun Kumar, and Dr. Ikhlaque Hussain, for their valuable support to drive my hardware setup.

The assistance of the valuable staffs in Electrical Energy Utilization Laboratory of Delhi Technological University is gratefully acknowledged. I am especially thankful to Mr. Vickey Kumar Prasad, Mr. TPS Rana and Mrs. Komal for their substantial technical assistance and companionship during development and tests of prototype system.

Moreover, every bit of mine would always remain indebted to my loving parents whose blessings have been and will always be an inseparable part of every stride of my life. I'm also thankful to my brothers and sisters for their support and encouragement.

And finally, of course, worthy of appreciation is my wife Dr. Shagufta Khan, who gave her unconditional support and continued to be a source of inspiration during my research.

Date: \_ /\_ /\_

Place: Delhi

Md. Tausif Ahmad (2k11/Ph.D/EE/03)

#### ABSTRACT

Power quality in power distribution systems has been the topic of much research with the significant benefits and advancements in the applications of power electronics at utility appliances due to its compactness; energy efficient and reliability. In a threephase distribution system, all possible situations are included, which deviate the quality of waveform of voltage or current at the point of common coupling (PCC) from the sinusoidal waveform with amplitude corresponding to the rated root mean square (RMS) value at rated frequency for all three phases have been included. This lures to a decrease of power transfer and a poor power factor. However, distribution systems do not behave in an ideal power quality limit. The systems react dynamically to changes in active and reactive powers, influencing the magnitude of the voltage and power factor of the distribution systems. Quite often, it gives rise to a myriad of losses and operational problems; the power distribution operator has to intervene to try to achieve power redistribution with good quality. The distribution static compensator (DSTATCOM) is one of the custom power devices used to enhance the quality and reliability of power delivered to customers. The functions of DSTATCOM solely depend on developed control algorithms. The developed intelligent control algorithms for the DSTATCOM open up new opportunities for controlling and enhancing power quality without and as well as with integrated renewable sources in power distribution systems. The opportunities arise through the ability of DSTATCOM to control the interrelated parameters that govern the operation of harmonics elimination, load balancing, voltage regulation and power factor improvement. The DSTATCOM integrated distribution system is effectively examined and investigations have been made to mitigate the power quality issues under balanced and unbalanced loads.

## **TABLE OF CONTENTS**

| CERTIFICATE                                                  | i         |

|--------------------------------------------------------------|-----------|

| ACKNOWLEDGEMENTS                                             | ii-iv     |

| ABSTRACT                                                     | V         |

| TABLE OF CONTENTS                                            | vi-x      |

| LIST OF FIGURES                                              | xi-xvi    |

| LIST OF TABLES                                               | xvii      |

| LIST OF SYMBOLS                                              | xviii-xix |

| ABBREVIATIONS                                                | XX        |

|                                                              |           |

| CHAPTER 1 INTRODUCTION                                       | 1-13      |

| 1.1 GENERAL                                                  | 1         |

| 1.2 STATE OF THE ART ON POWER QUALITY                        | 2         |

| 1.3 TRANSITION TO SMART POWER DISTRIBUTION SYSTEM            | 4S 3      |

| 1.3.1 Limitations of CPDs                                    | 4         |

| 1.3.2 Concept of Intelligent CPDs                            | 5         |

| 1.4 SCOPE OF THE WORK                                        | 6         |

| 1.4.1 Control Strategy for DSTATCOM                          | 7         |

| 1.4.1.1 Sensing of signals                                   | 7         |

| 1.4.1.2 Reference currents generation                        | 8         |

| 1.4.1.3 Switching pulse generation                           | 8         |

| 1.4.2 Fast Multilayer Neural Network Based Control Algorithm | n 9       |

| 1.4.3 Generalized Neural Network based Control Algorithm     | 9         |

| 1.4.4 Nonlinear Adaptive Filter based Control Algorithm      | 10        |

| 1.5 OUTLINE OF CHAPTERS                                      | 10        |

| CHAPTER 2 LITERATURE REVIEW                                  | 14-25     |

| 2.1 INTRODUCTION                                             | 14        |

| 2.2 POWER QUALITY ISSUES AND THEIR MITIGATION                | 14        |

| 2.2.1 Equipments Sensitive to Voltage Disturbances           | 15        |

| 2.2.2 Equipments Cause Voltage Disturbances                  | 15        |

| 2.2.3 Standardization and Performance Criteria               | 16        |

| 2.3 POWER QUALITY STANDARDS                                  | 17        |

| 2.4 | POWI    | ER QUALITY MONITORING                             | 17    |

|-----|---------|---------------------------------------------------|-------|

|     | 2.4.1 0 | Utilities Demand for Good Power Supply            | 18    |

|     | 2.4.2   | Good Power Supply                                 | 18    |

|     | 2.4.3 1 | Measurements of Power Quality                     | 18    |

| 2.5 | INVE    | STIGATIONS ON PERFORMANCE OF DSTATCOM             | 18    |

|     | 2.5.1 I | Principle of Operation and Control of DSTATCOM    | 20    |

|     | 2.5.2 ( | Classification of DSTATCOM Configurations         | 21    |

| 2.6 | REQU    | JIREMENT OF CONTROL ALGORITHMS IN DSTATCOM        | A 21  |

|     | 2.6.1 1 | nvestigations on Control Algorithms of DSTATCOM   | 22    |

| 2.7 | IDEN'   | TIFIED RESEARCH AREAS                             | 23    |

| 2.8 | PROB    | LEM FORMULATION                                   | 23    |

| 2.9 | CONC    | CLUSIONS                                          | 24    |

| CH  | APTER   | <b>3 DESIGN AND DEVELOPMENT OF DSTATCOM</b>       | 26-62 |

| 3.1 | INTR    | ODUCTION                                          | 26    |

| 3.2 | CONF    | FIGURATION OF DSTATCOM                            | 27    |

| 3.3 | PRIN    | CIPLE, OPERATION AND CONTROL OF DSTATCOM          | 28    |

|     | 3.3.1 I | Load Compensation using DSTATCOM                  | 28    |

|     | 3.3.2   | Voltage Regulation using DSTATCOM                 | 31    |

| 3.4 | DESI    | GN OF DSTATCOM                                    | 31    |

|     | 3.4.1   | Mathematical Modeling of DSTATCOM                 | 32    |

|     | 3.4.2   | Design of DC Bus Voltage                          | 34    |

|     | 3.4.3   | Design of DC Bus Capacitor                        | 36    |

|     | 3.4.4   | Design of AC Interfacing Inductors                | 37    |

|     | 3.4.5   | Design of Passive High Pass Ripple Filters        | 37    |

|     | 3.4.6   | Selection of Voltage and Current Ratings of IGBTs | 38    |

| 3.5 | DEVE    | ELOPMENT OF PROTOTYPE OF DSTATCOM                 | 38    |

|     | 3.5.1   | Development of Voltage Source Converter (VSC)     | 39    |

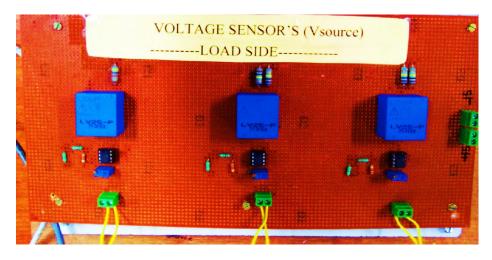

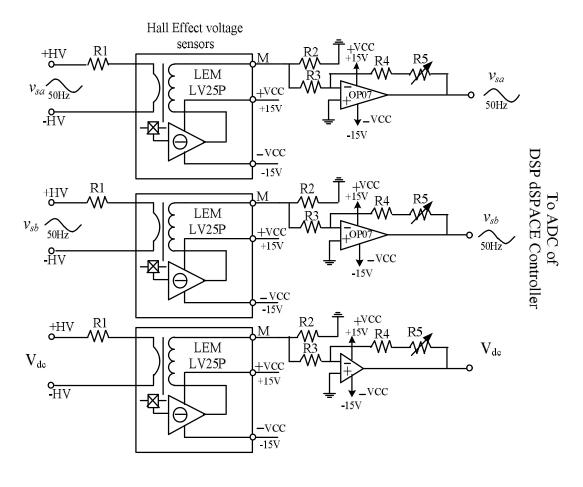

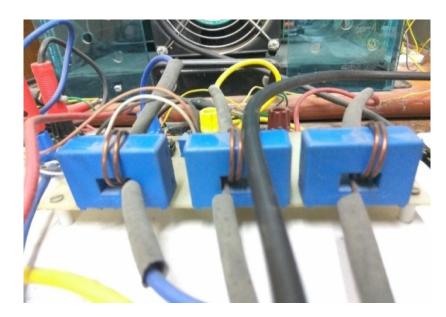

|     | 3.5.2   | Development of Voltage Sensors Circuit            | 44    |

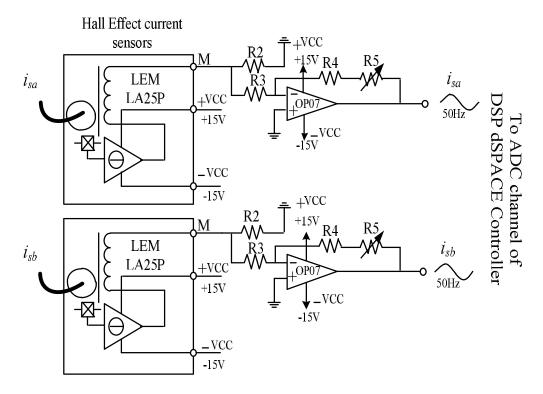

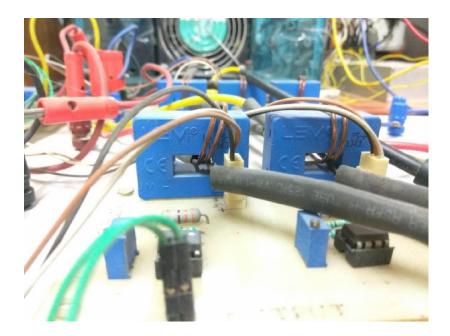

|     | 3.5.3   | Development of Current Sensors Circuit            | 46    |

|     | 3.5.4   | Development of AC Interfacing Inductors           | 48    |

|     | 3.5.5   | Development of Gate Driver Circuit                | 50    |

|     | 3.5.6   | Development of Passive High Pass Ripple Filters   | 51    |

| 3.6 | RESU    | LTS AND DISCUSSION                                | 51    |

|     | 3.6.1   | Test Results of Prototype of DSTATCOM             | 51    |

|     |         |                                                   |       |

|   |         | 3.6.1.1 Test results of voltage sensors                                       | 53           |

|---|---------|-------------------------------------------------------------------------------|--------------|

|   |         | 3.6.1.2 Test results of source current sensors                                | 55           |

|   |         | 3.6.1.3 Test results of load current sensors                                  | 56           |

|   |         | 3.6.1.4 Test results of interfacing inductors                                 | 57           |

|   |         | 3.6.1.5 Test results of gate driver circuit                                   | 58           |

|   | 3.6.2   | 2 Hardware Results with DSP                                                   | 59           |

|   |         | 3.6.2.1 Hardware results of voltage sensors                                   | 59           |

|   |         | 3.6.2.2 Hardware results of current sensors                                   | 60           |

|   |         | 3.6.2.3 Hardware results of gate driver circuit                               | 61           |

| - | 3.7 CON | ICLUSIONS                                                                     | 62           |

| ( | СНАРТЕ  | CR 4 FAST MLPNN BASED CONTROL ALGORITHM<br>DSTATCOM                           | FOR<br>63-96 |

| Z | 4.1 INT | RODUCTION                                                                     | 63           |

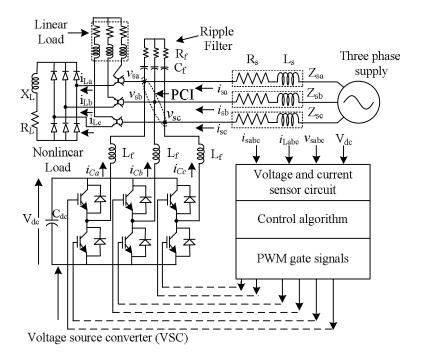

| Z | 4.2 SYS | TEM CONFIGURATION                                                             | 64           |

| Z | 4.3 STA | ANDARD BACKPROPAGATION ALGORITHM                                              | 65           |

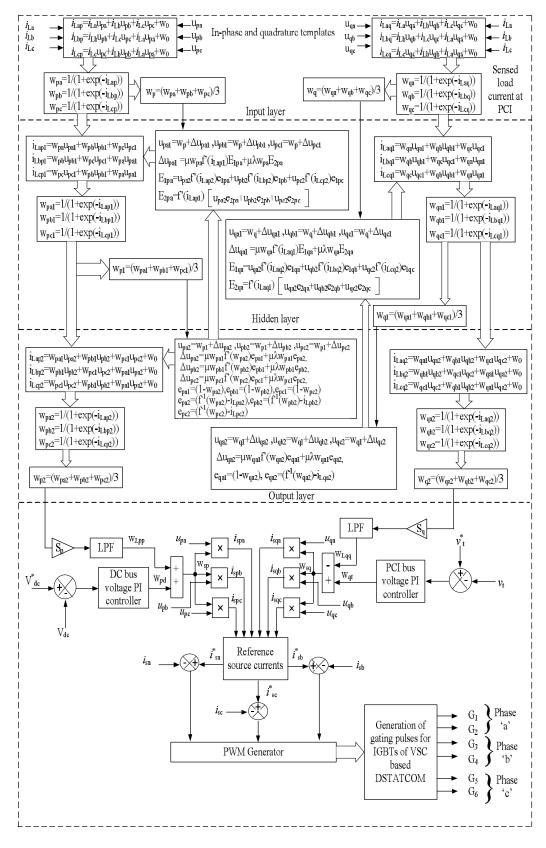

| Z | 4.4 FAS | T MLPNN BASED CONTROL OF DSTATCOM                                             | 66           |

| Ζ |         | THEMATICAL MODELLING OF FAST MLPNN<br>GORITHM                                 | 68           |

| Z |         | IMATION OF FUNDAMENTAL REFERENCE<br>JRCE CURRENTS                             | 71           |

|   | 4.6.1   | Amplitude Estimation of Fundamental Load Active Current Components            | 71           |

|   | 4.6.2   | 2 Active Power Current Components Amplitude of<br>Reference Source Currents   | 77           |

|   | 4.6.3   | 3 Amplitude Estimation of Fundamental Load Reactive<br>Current Components     | 78           |

|   | 4.6.4   | 4 Reactive Power Current Components Amplitude of<br>Reference Source Currents | 81           |

|   | 4.6.5   | 5 Generation of Switching Gate Pulses of DSTATCOM                             | 81           |

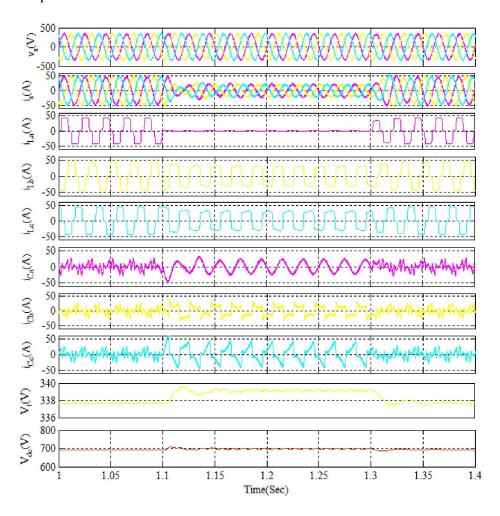

| Z | 4.7 RES | ULTS AND DISCUSSION                                                           | 82           |

|   | 4.7.1   | Performance of DSTATCOM in PFC Mode                                           | 82           |

|   |         | 4.7.1.1 Simulation results at nonlinear load conditions                       | 82           |

|   |         | 4.7.1.2 Simulation results at linear load conditions                          | 86           |

|   | 4.7.2   | 2 Performance of DSTATCOM in ZVR mode                                         | 88           |

|   |         | 4.7.2.1 Simulation results at linear load conditions                          | 88           |

|   |         | 4.7.2.2 Simulation results at nonlinear load conditions                       | 89           |

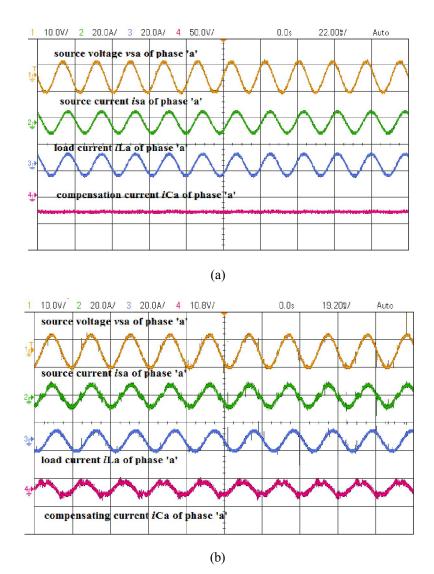

|     | 4.7.3 Experimental Results in PFC Mode                                     | 93      |

|-----|----------------------------------------------------------------------------|---------|

| 4.8 | CONCLUSIONS                                                                | 96      |

| CHA | APTER 5 GENERALISED NEURAL NETWORK BASED<br>CONTROL ALGORITHM FOR DSTATCOM | 97-131  |

| 5.1 | INTRODUCTION                                                               | 97      |

| 5.2 | THREE PHASE DISTRIBUTION SYSTEM TEST MODEL                                 | 97      |

| 5.3 | FUNDAMENTAL CONCEPT OF GENERALIZED<br>NEURAL NETWORK (GNN)                 | 99      |

| 5.4 | MATHEMATICAL MODELING OF GNN ALGORITHM                                     | 101     |

|     | 5.4.1 Estimation of Weights for Active Current Components                  | 102     |

|     | 5.4.2 Estimation of Weights for Reactive Current Components                | 104     |

| 5.5 | GNN BASED CONTROL ALGORITHM FOR DSTATCOM                                   | 105     |

|     | 5.5.1 Estimation of Amplitude of Active Current Components                 | 106     |

|     | 5.5.2 Estimation of Amplitude of Reactive Current Components               | 109     |

|     | 5.5.3 Estimation of Switching Gate Pulses for DSTATCOM                     | 111     |

| 5.6 | RESULTS AND DISCUSSION                                                     | 111     |

|     | 5.6.1 Performance of DSTATCOM in PFC mode                                  | 112     |

|     | 5.6.1.1 Simulation results at nonlinear load conditions                    | 112     |

|     | 5.6.1.2 Simulation results at linear load conditions                       | 114     |

|     | 5.6.2 Performance of DSTATCOM in ZVR mode                                  | 117     |

|     | 5.6.2.1 Simulation results at linear load conditions                       | 117     |

|     | 5.6.2.2 Simulation results at nonlinear load conditions                    | 118     |

|     | 5.6.3 Experimental results in PFC mode                                     | 122     |

|     | 5.6.3.1 Performance of DSTATCOM at nonlinear load                          | 122     |

|     | 5.6.3.2 Performance of DSTATCOM at linear load                             | 127     |

| 5.7 | CONCLUSIONS                                                                | 131     |

| CHA | APTER 6 AVSF BASED CONTROL ALGORITHM<br>FOR DSTATCOM                       | 132-174 |

| 6.1 | INTRODUCTION                                                               | 132     |

| 6.2 | TEST MODEL CONFIGURATION                                                   | 132     |

| 6.3 | CONCEPT OF NONLINEAR ADAPTIVE FILTER                                       | 134     |

| 6.4 | MATHEMATICAL MODELING OF AVSF<br>BASED CONTROL ALGORITHM                   | 138     |

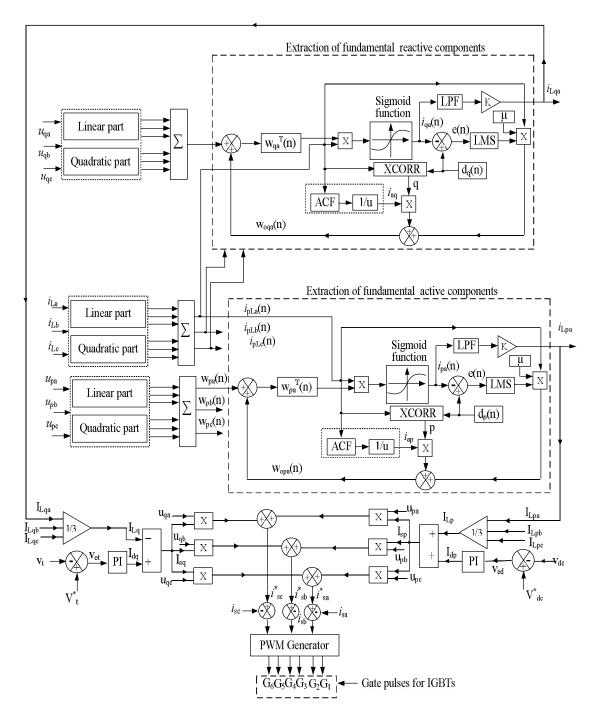

| 6.5 | ESTIMATION OF FUNDAMENTAL REFERENCE<br>SOURCE CURRENTS                     | 140     |

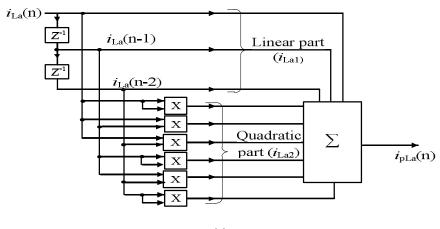

|      |         | Amplitude Estimation of Fundamental Load<br>Active Current Components   | 141     |

|------|---------|-------------------------------------------------------------------------|---------|

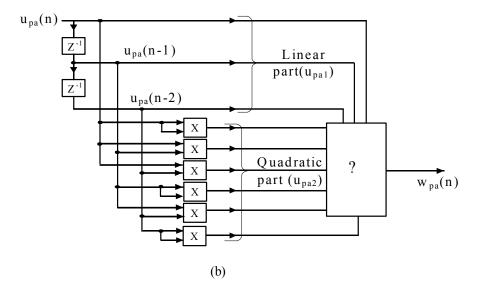

|      |         | Amplitude Estimation of Fundamental Load<br>Reactive Current Components | 149     |

|      | 6.5.3 ( | Generation of Switching Gate Pulses for DSTATCOM                        | 152     |

| 6.6  | RESU    | LTS AND DISCUSSION                                                      | 152     |

|      | 6.6.1   | Performance of DSTATCOM in PFC Mode                                     | 153     |

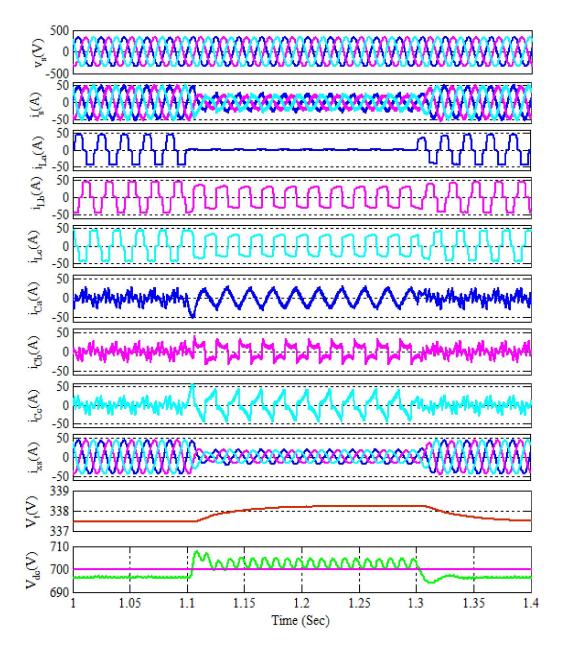

|      |         | 6.6.1.1 Simulation results at nonlinear load conditions                 | 153     |

|      |         | 6.6.1.2 Simulation results at linear load conditions                    | 154     |

|      | 6.6.2   | Performance of DSTATCOM in ZVR Mode                                     | 158     |

|      |         | 6.6. 2.1 Simulation results at nonlinear load conditions                | 158     |

|      |         | 6.6.2.2 Simulation results at linear load conditions                    | 160     |

|      | 6.6.3   | Experimental Results in PFC Mode                                        | 164     |

|      |         | 6.6.3.1 Test performance of DSTATCOM at nonlinear load                  | 164     |

|      |         | 6.6.3.2 Test performance of DSTATCOM at linear load                     | 170     |

| 6.7  | CONC    | CLUSIONS                                                                | 173     |

| CHA  | APTER   | 7 MAIN CONCLUSIONS AND SUGGESTIONS FOR<br>FURTHER WORK                  | 175-180 |

| 7.1  | GENE    |                                                                         | 175     |

| 7.2  | MAIN    | CONCLUSIONS                                                             | 176     |

| 7.3  | SUGG    | ESTIONS FOR FURTHER WORK                                                | 180     |

|      |         |                                                                         |         |

| REF  | ERENC   | CES                                                                     | 181-197 |

| APP  | ENDIX   |                                                                         | 198     |

| LIST | T OF PU | JBLICATIONS                                                             | 199-200 |

| CUR  | RICUL   | JUM VITAE                                                               | 201     |

### **LIST OF FIGURES**

| Fig. No. | Captioning of the Figures                                                        | Page No. |

|----------|----------------------------------------------------------------------------------|----------|

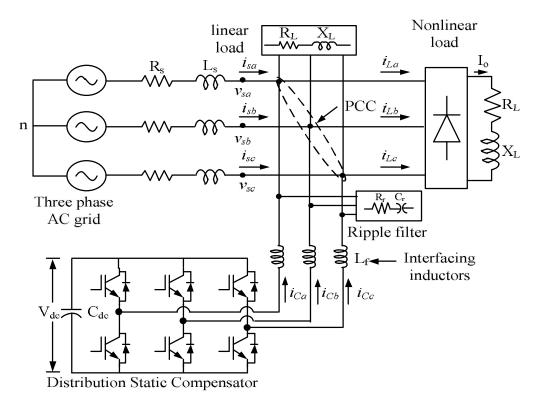

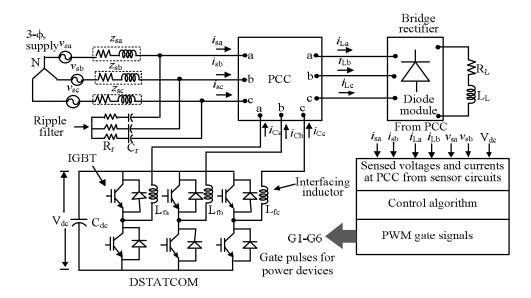

| 3.1      | DSTATCOM in a three phase distribution system                                    | 27       |

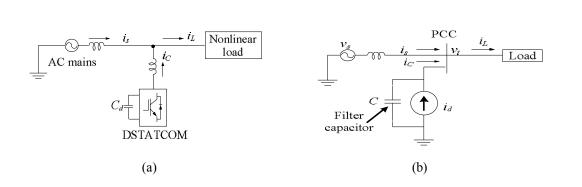

| 3.2 (a)  | Schematic diagram of current compensation                                        | 29       |

| 3.2 (b)  | Ideal load compensation                                                          | 29       |

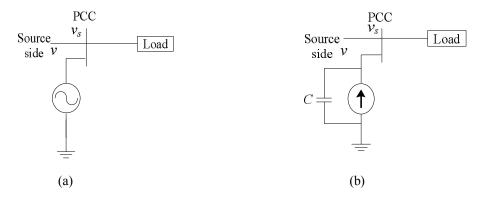

| 3.3 (a)  | Ideal voltage controller                                                         | 31       |

| 3.3 (b)  | Practical realization                                                            | 31       |

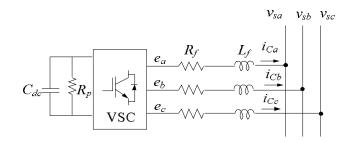

| 3.4      | Equivalent circuit of DSTATCOM                                                   | 32       |

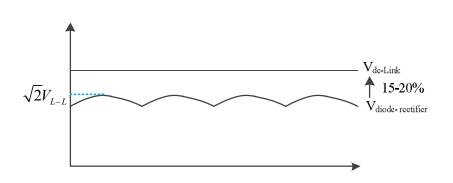

| 3.5      | DC link voltage condition                                                        | 35       |

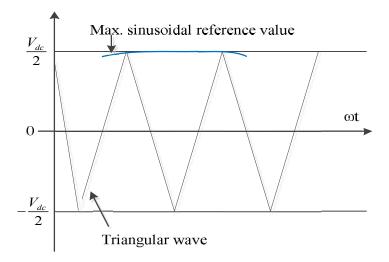

| 3.6      | Maximum sinusoidal reference voltage (converter voltage -) for sinusoidal PWM    | 35       |

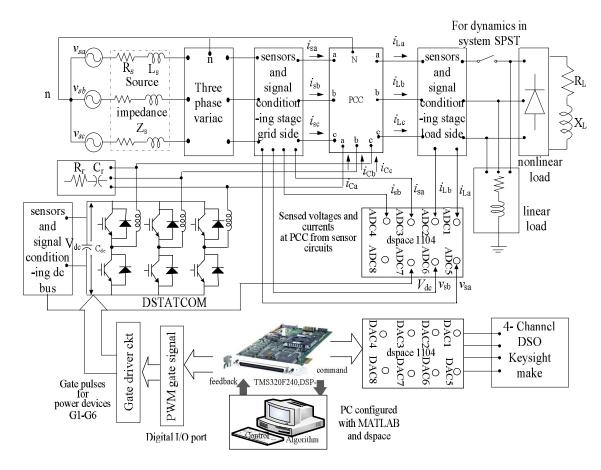

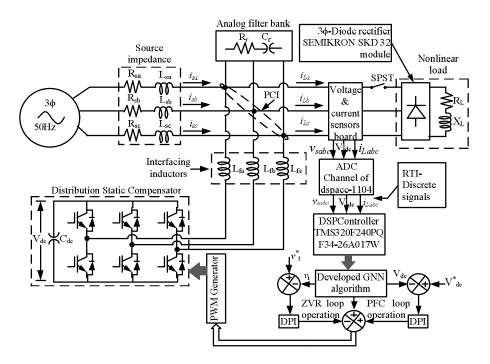

| 3.7      | Functional block diagram of developed hardware prototype DSTATCOM                | 40       |

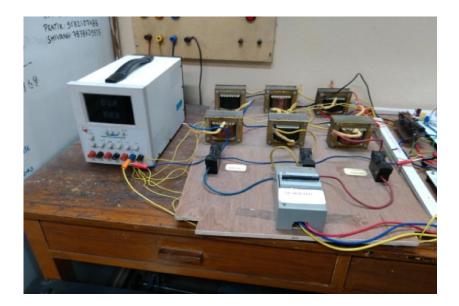

| 3.8      | Experimental prototype developed of DSTATCOM in the laboratory                   | 41       |

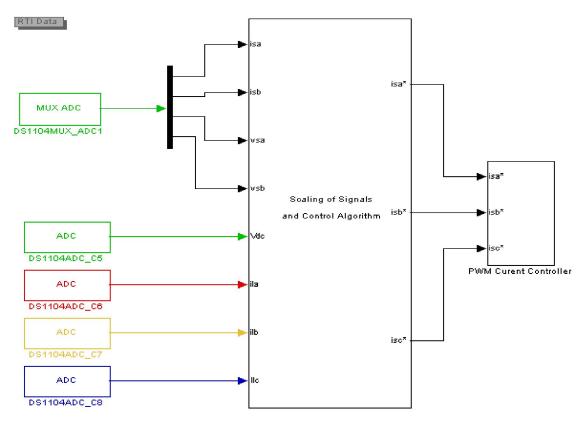

| 3.9      | MATLAB based real time interface (RTI) control of DSTATCOM on DSP implementation | 42       |

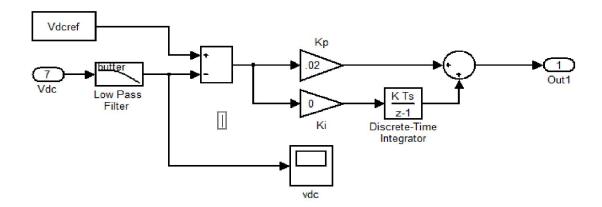

| 3.10     | Implementation of DC bus PI controller                                           | 42       |

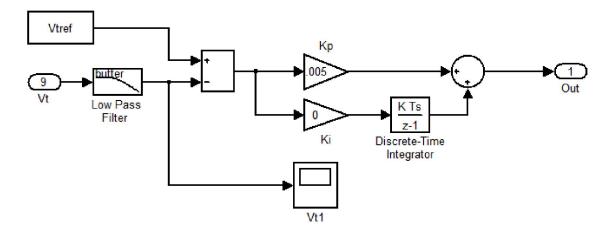

| 3.11     | Implementation of AC bus PI controller                                           | 42       |

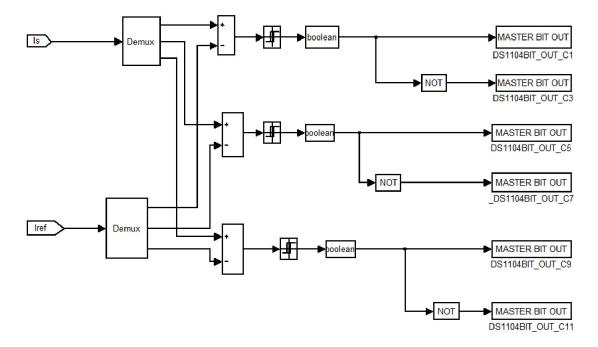

| 3.12     | Implementation of Hysteresis PWM current controller                              | 43       |

| 3.13     | IGBTs (SEMIKRON MAKE) based VSC                                                  | 44       |

| 3.14 (a) | Developed prototype test model                                                   | 45       |

| 3.14 (b) | Schematic diagram of voltage sensors with power signal conditioner               | 45       |

| 3.15 (a) | Snapshot of sensed grid currents                                                 | 46       |

| 3.15 (b) | Schematic diagram of current sensors and signal conditioner circuit              | 47       |

| 3.15 (c) | Snapshot of sensed load currents                                                 | 47       |

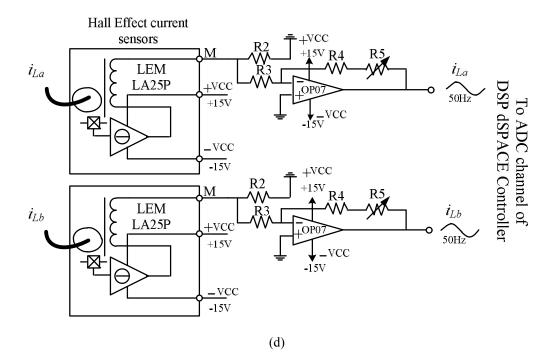

| 3.15 (d) | Schematic diagram of load currents with buffer circuit                           | 48       |

| 3.16     | RTI interface of the sensed parameters using dSAPCE-1104                         | 48       |

| 3.17            | Developed interfacing inductors                                                                          | 49 |

|-----------------|----------------------------------------------------------------------------------------------------------|----|

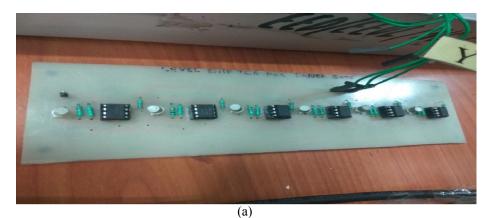

| 3.18 (a)        | Snapshot of developed gate driver                                                                        | 50 |

| 3.18 (b)        | Schematic diagram of gating circuit                                                                      | 50 |

| 3.19            | Development of resistive capacitive (R-C) ripple filters                                                 | 51 |

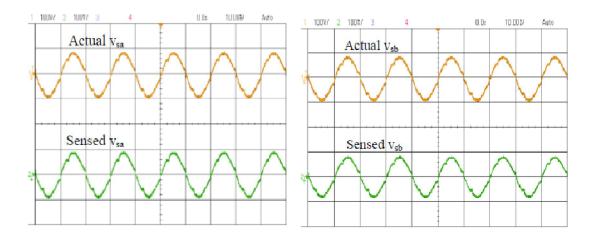

| 3.20<br>(a)-(b) | Actual and sensed voltages at PCC corresponding to phase 'a' and 'b'                                     | 55 |

| 3.20 (c)        | Balanced three phase voltages                                                                            | 55 |

| 3.20 (d)        | Actual and sensed DC bus voltage                                                                         | 55 |

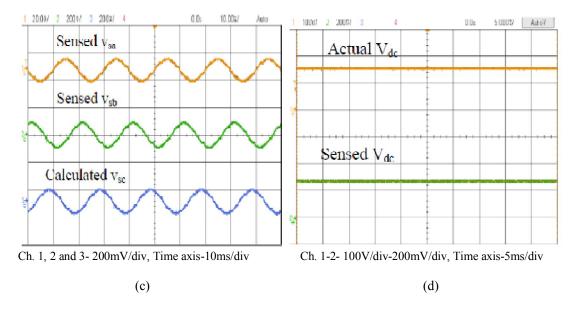

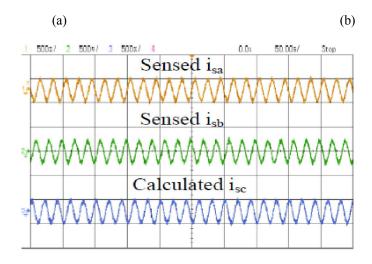

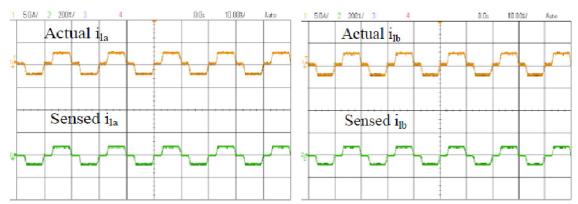

| 3.21<br>(a)-(b) | Actual and sensed supply currents,                                                                       | 56 |

| 3.21 (c)        | Calculated supply current                                                                                | 56 |

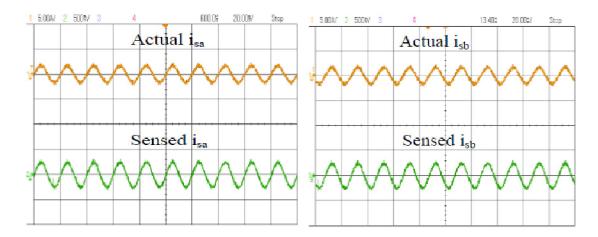

| 3.22<br>(a)-(b) | Actual and sensed load currents of phase 'a' and 'b'                                                     | 57 |

| 3.22 (c)        | Calculated load currents (`)                                                                             | 57 |

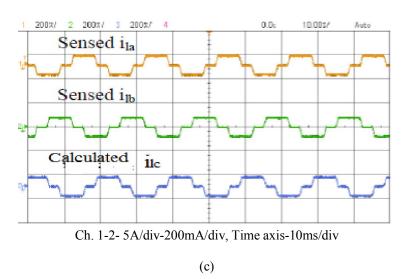

| 3.23            | Variation of inductance value with current                                                               | 58 |

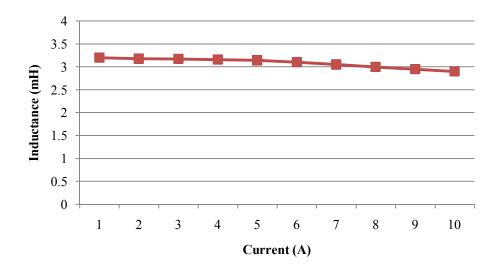

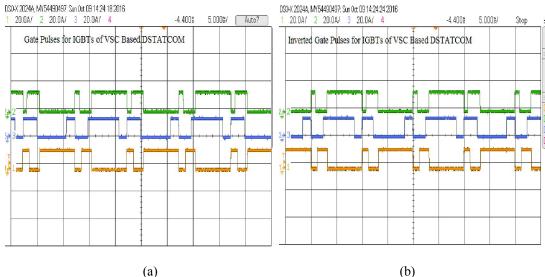

| 3.24 (a)        | Gating pulses for three phase VSC                                                                        | 59 |

| 3.24 (b)        | Inverted gating pulses for three phase VSC                                                               | 59 |

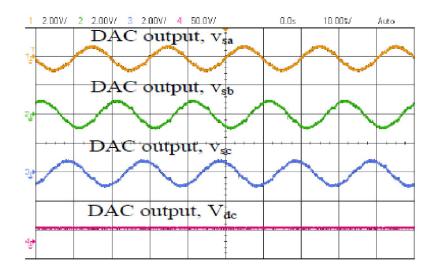

| 3.25            | Sensed PCC voltages $(1 \dots , 1 \dots $ and $1 \dots )$ and DC bus voltage $( \swarrow )$              | 59 |

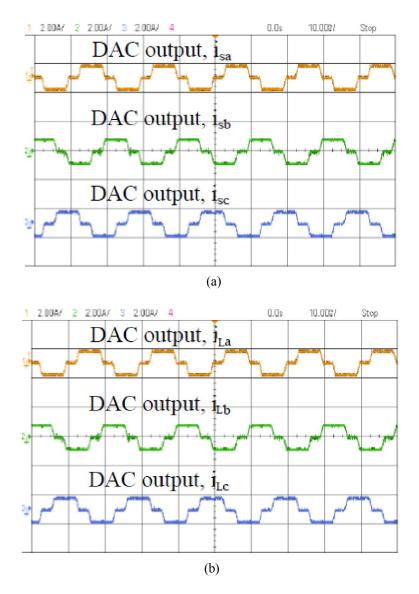

| 3.26 (a)        | Sensed supply currents (`, ` and `)                                                                      | 60 |

| 3.26 (b)        | Sensed load currents ( $f_{ff}$ , $f_{ff}$ and $f_{fl}$ )                                                | 60 |

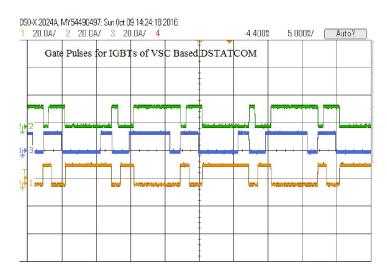

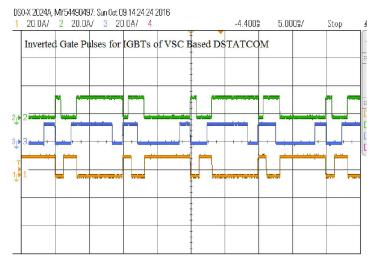

| 3.27 (a)        | Generated PWM pulses using HCC from I/O ports of DSP dSPACE                                              | 61 |

| 3.27 (b)        | Generated inverted PWM pulses using HCC from I/O ports of DSP dSPACE                                     | 61 |

| 4.1             | Three-phase test system schematic diagram                                                                | 64 |

| 4.2             | Functional block diagram of MLPNN algorithm                                                              | 70 |

| 4.3             | Proposed three-stage MLPNN model of the weighted fundamental active current components                   | 71 |

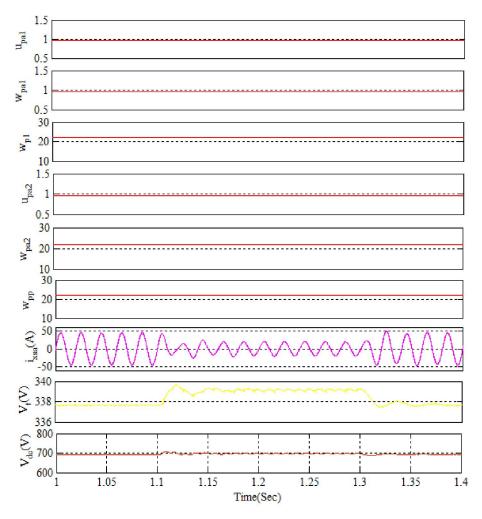

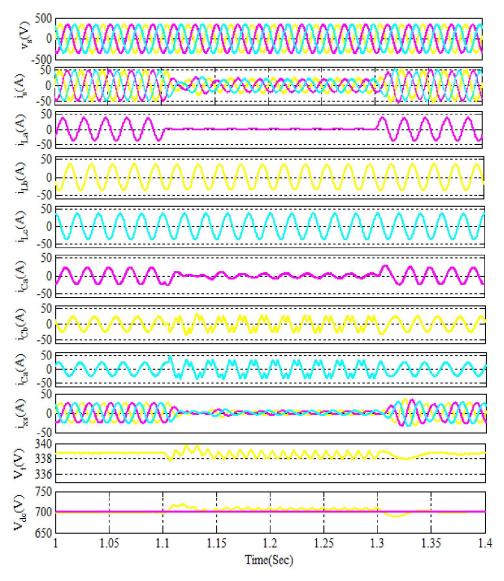

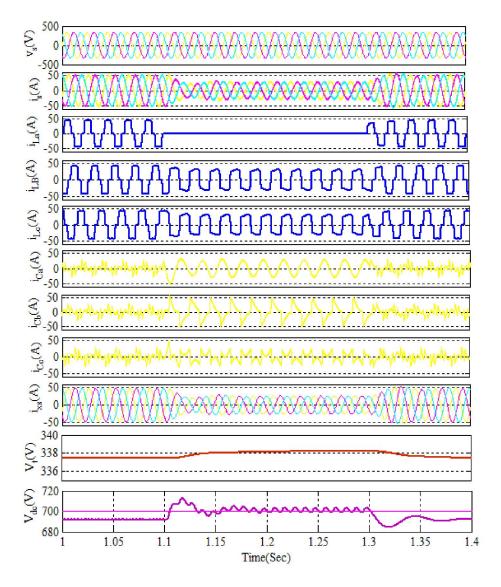

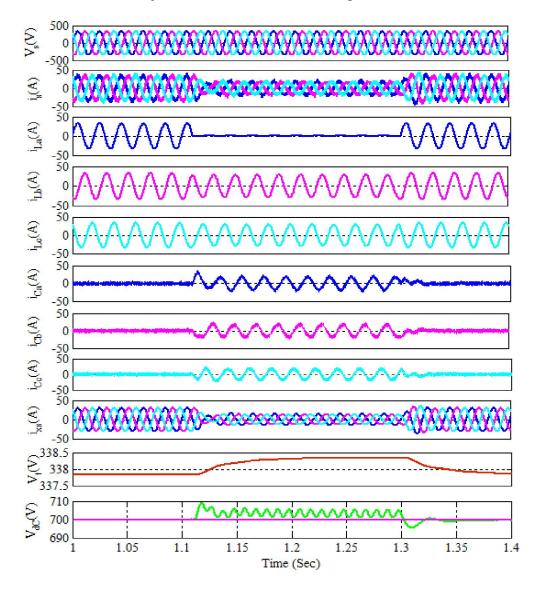

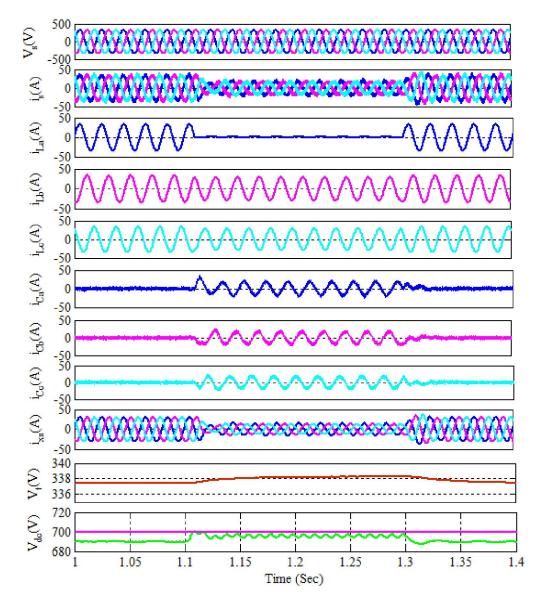

| 4.4             | Simulated performance of DSTATCOM at nonlinear load in PFC mode                                          | 83 |

| 4.5             | Intermediate signals of MLPNN algorithm in PFC mode                                                      | 84 |

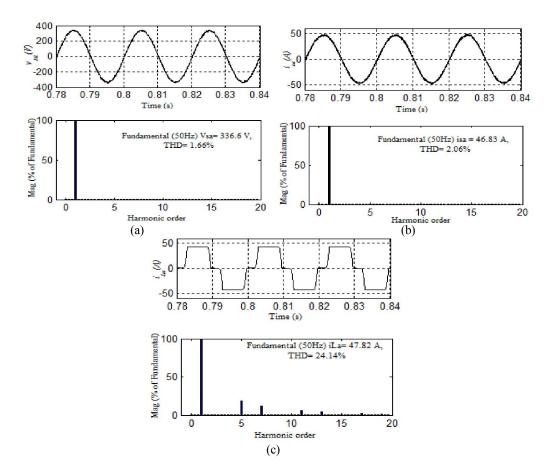

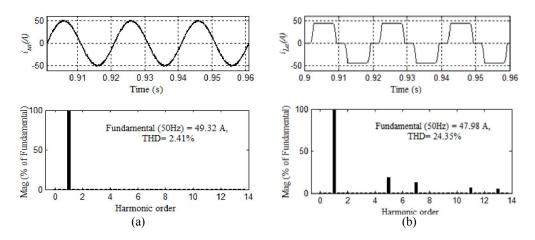

| 4.6             | Waveforms and harmonic spectra of (a) PCI voltage, (b) source current, and (c) load current of phase 'a' | 86 |

| 4.7             | Simulated performance of DSTATCOM at linear load in PFC mode                                             | 87 |

| 4.8     | Performance parameters of phase 'a' in PFC mode of DSTATCOM                                                                                                                                                       | 88    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

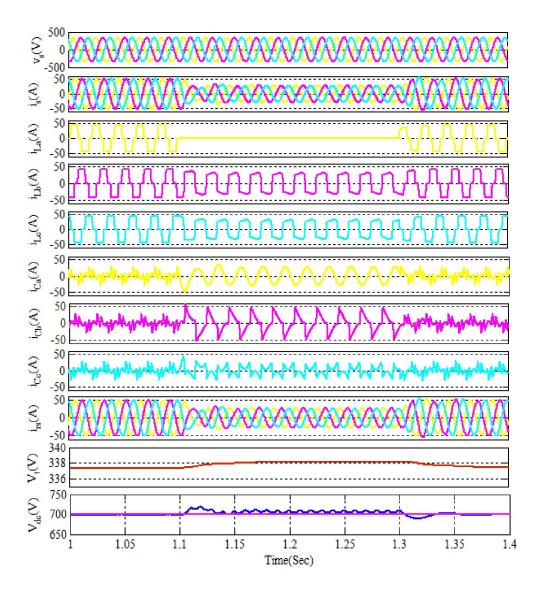

| 4.9     | Simulated performance of DSTATCOM at linear load in ZVR mode                                                                                                                                                      | 89    |

| 4.10    | Simulated performance of DSTATCOM at nonlinear load in ZVR mode                                                                                                                                                   | 90    |

| 4.11    | Intermediate signals of MLPNN algorithm in ZVR mode                                                                                                                                                               | 91    |

| 4.12    | Waveforms and harmonic spectra of (a) PCI voltage, (b) source current, and (c) load current, of phase 'a'                                                                                                         | 92    |

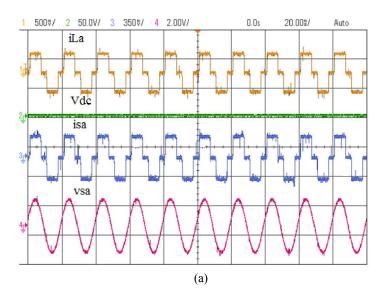

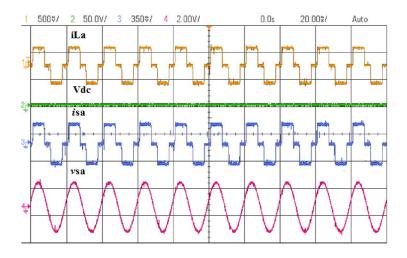

| 4.13(a) | Load current (`), dc link voltage ( $\nearrow$ ), source current (`) and source voltage (1) of phase 'a' when DSTATCOM is in OFF state                                                                            | 93    |

| 4.13(b) | Compensating current ( ${}^{\circ}_{fl^{\circ}}$ ), dc link voltage ( $\nearrow$ ), source current ( ${}^{\circ}_{\cdot \cdot}$ ) and source voltage (1 $\cdot \cdot$ ) of phase 'a' when DSTATCOM is in ON state | 94    |

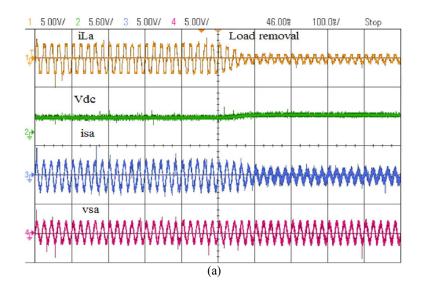

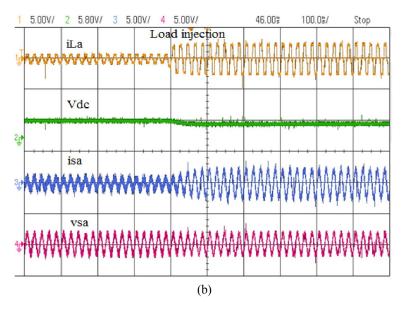

| 4.14    | Dynamics of unbalancing load by (a) load removal (b) injecting load in phase 'a'                                                                                                                                  | 94-95 |

| 5.1     | DSTATCOM for three phase distribution system                                                                                                                                                                      | 98    |

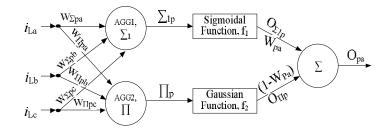

| 5.2     | Summation type GNN model for amplitude estimation of active current component of phase 'a'                                                                                                                        | 109   |

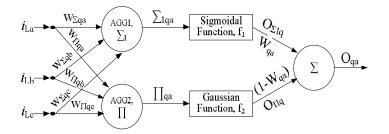

| 5.3     | GNN model for amplitude estimation of reactive current component of phase 'a'                                                                                                                                     | 109   |

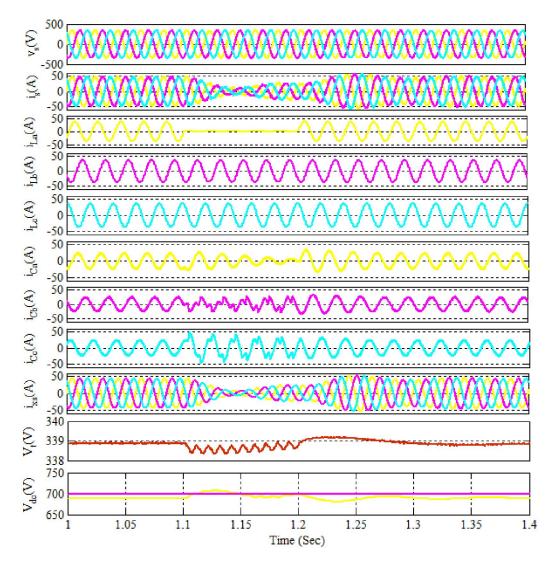

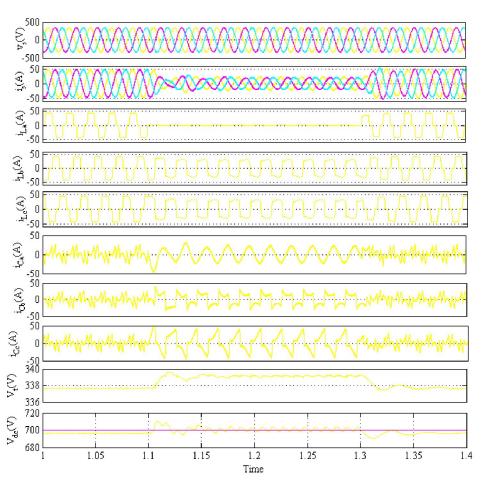

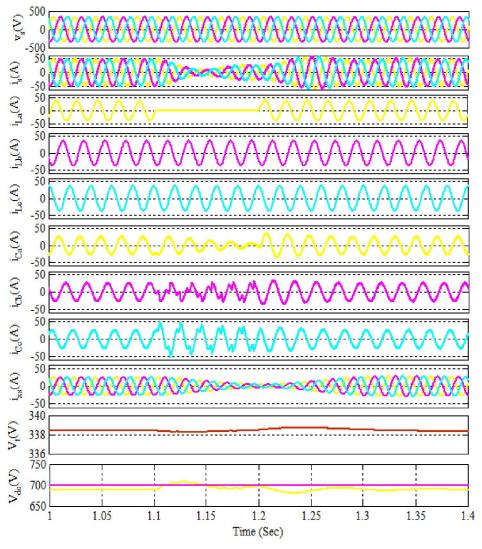

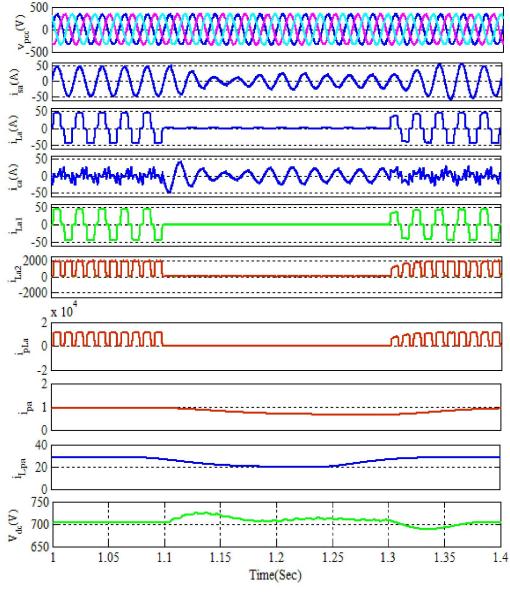

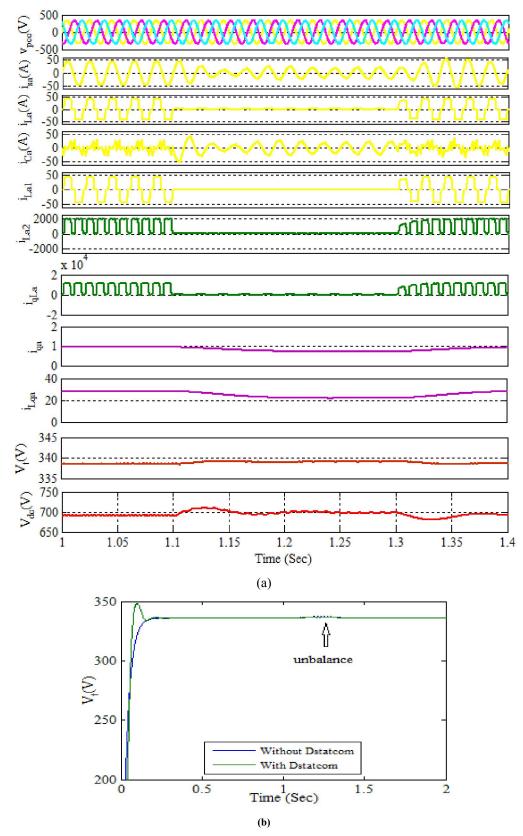

| 5.4     | Simulated performance of DSTATCOM at nonlinear load                                                                                                                                                               | 113   |

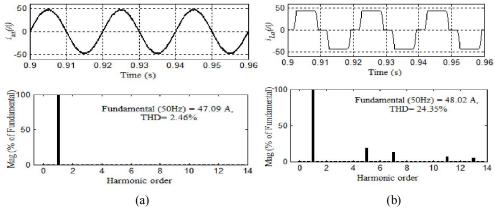

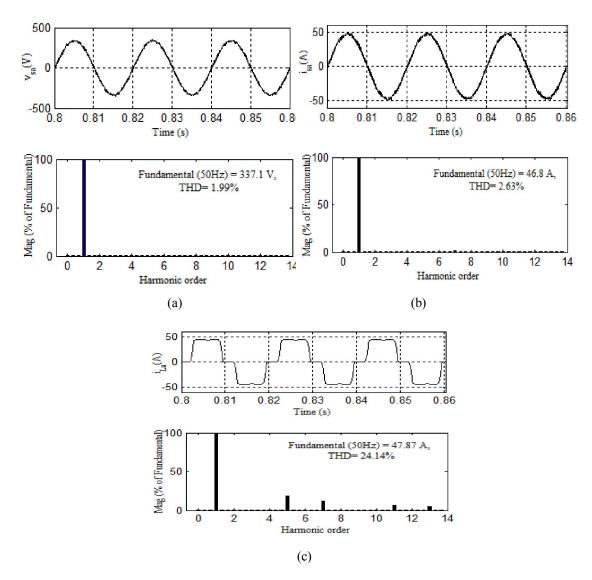

| 5.5     | Waveforms and harmonic spectra of (a) Source current (b) Load current in PFC mode of phase 'a'                                                                                                                    | 113   |

| 5.6     | Performance of DSTATCOM at linear load                                                                                                                                                                            | 114   |

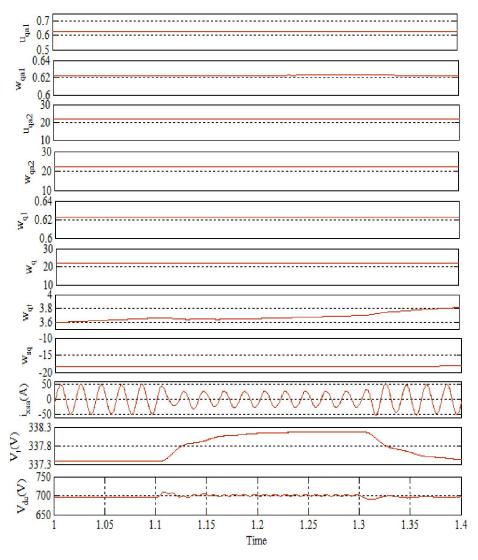

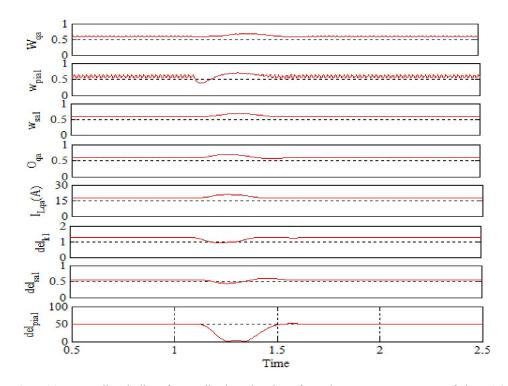

| 5.7     | Intermediate indices for amplitude estimation of active current component of phase 'a'                                                                                                                            | 116   |

| 5.8      | Performance parameters of phase 'a' in PFC mode of DSTATCOM                                                                                                                                                           | 117 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.9      | Simulated performance of DSTATCOM at linear load                                                                                                                                                                      | 118 |

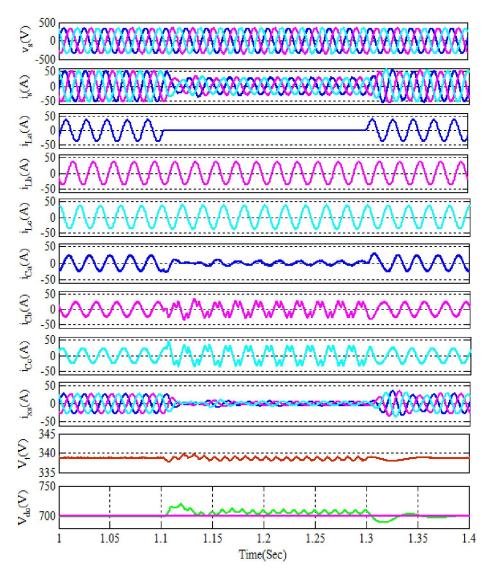

| 5.10     | Simulated performance of DSTATCOM at nonlinear load                                                                                                                                                                   | 119 |

| 5.11     | Intermediate indices for amplitude estimation of reactive current component of phase 'a'                                                                                                                              | 121 |

| 5.12     | Waveforms and harmonic spectra of (a) source current<br>and (b) load current at PCI of phase 'a' in zero voltage<br>regulation mode                                                                                   | 120 |

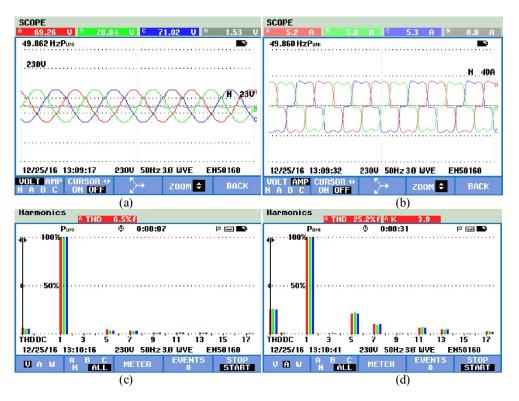

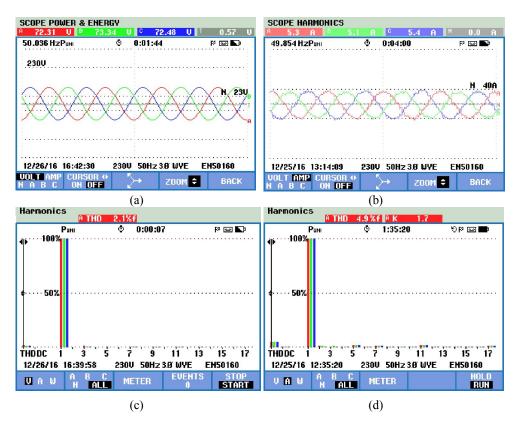

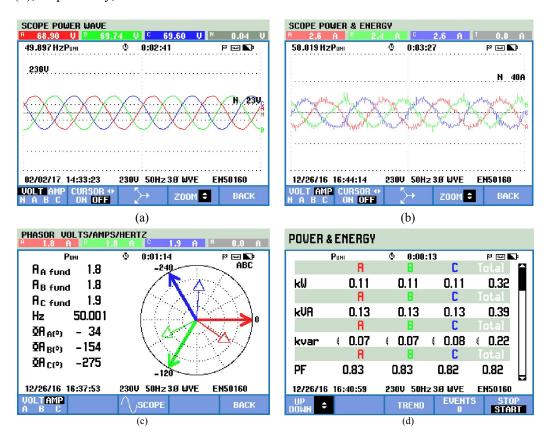

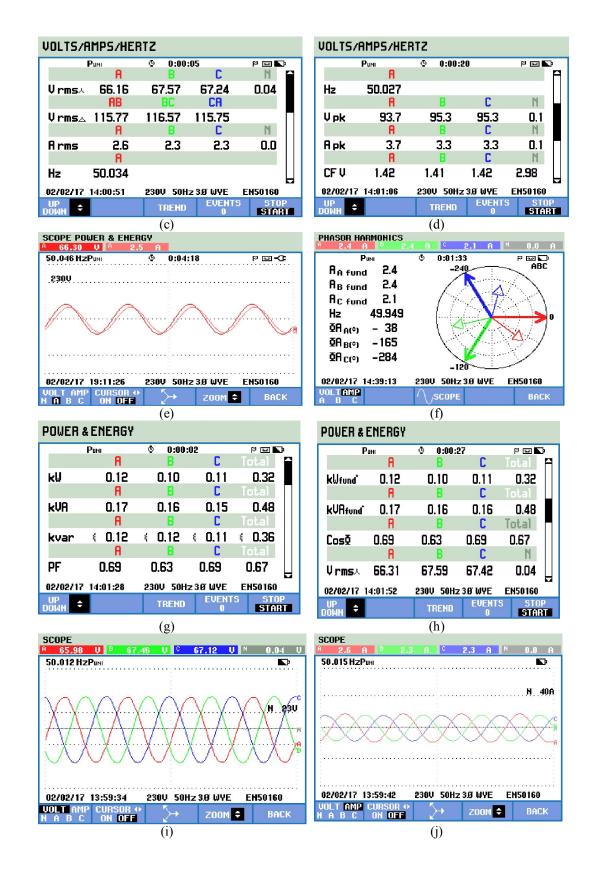

| 5.13     | Performance of DSTATCOM (a) Source voltages 1 - (b)<br>Source currents -, (c)-(d) Harmonics spectra, for all<br>phases during OFF state of DSTATCOM                                                                   | 123 |

| 5.14     | Performance of DSTATCOM (a) Source voltages 1- (b)<br>Source currents -, (c)-(d) Harmonics spectra, for all<br>phases during ON state of DSTATCOM                                                                     | 124 |

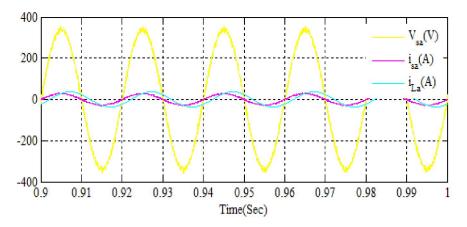

| 5.15     | <ul> <li>(a) Source voltage sa and source current of phase 'a'</li> <li>(b) Phasor diagram of source voltages and currents, after switching ON DSTATCOM</li> </ul>                                                    | 124 |

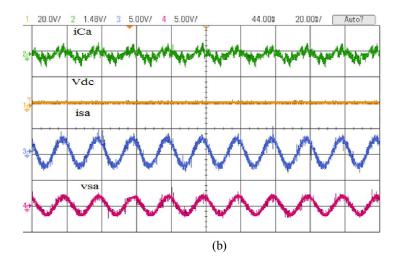

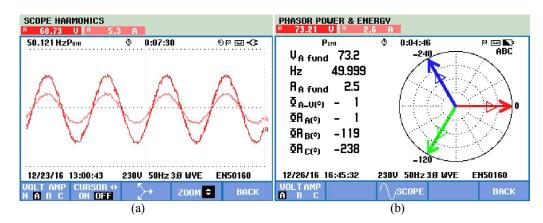

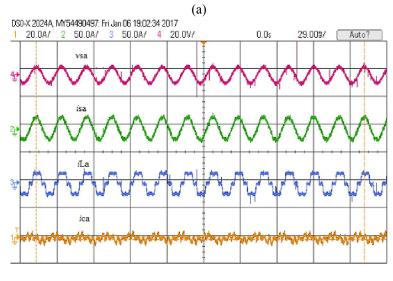

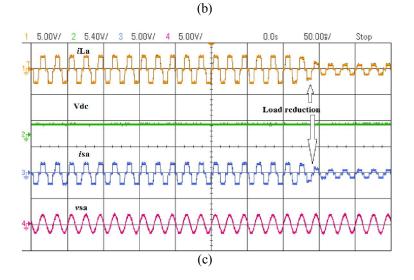

| 5.16 (a) | Performance parameters: Load current $\cdot$ , DC-bus voltage $/$ , source current $\cdot$ , and source voltage $1 \cdot \cdot$ , under static condition                                                              | 125 |

| 5.16 (b) | Performance parameters:, , and 1 under varying load condition when DSTATCOM is OFF                                                                                                                                    | 125 |

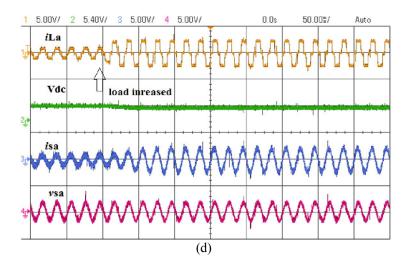

| 5.17 (a) | Performance parameters: Load current $\cdot$ , compensating current $\cdot_{fl}$ , source current $\cdot$ and source voltage $1 \cdot \cdot$ , when DSTATCOM is in ON state under varying load condition of phase 'a' | 126 |

| 5.17 (b) | Performance parameters: Load current $\cdot$ , DC bus voltage $/$ , source current $\cdot$ and source voltage $1 \cdot \cdot$ , when DSTATCOM is in ON state under varying load condition of phase 'a'                | 126 |

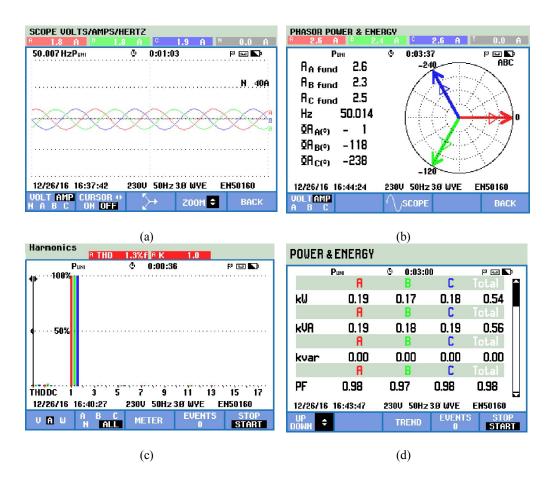

| 5.18 | Performance of DSTATCOM (a) Source voltages $1 \cdot (b)$<br>Source currents $\cdot (c)$ Phasor diagram of $1 - \cdot (d)$ Power<br>and power factor, when DSTATCOM is in OFF state                                                   | 127 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.19 | Performance parameters (a) source currents $\cdot$ , (b) Phasor diagram $1 - \cdot$ (c) Harmonics spectra of $\cdot$ (d) Power and power factor, when DSTATCOM is switched ON                                                         | 128 |

| 6.1  | Three phase distribution system with a DSTATCOM                                                                                                                                                                                       | 133 |

| 6.2  | Nonlinear adaptive model of Volterra filter                                                                                                                                                                                           | 138 |

| 6.3  | Decomposition of (a) Load current $\because$ (b) In-phase unit template $l_{\tilde{Z}^{*}}$ of phase 'a'                                                                                                                              | 143 |

| 6.4  | Functional layout of the proposed AVSF based control algorithm to generate reference template for switching DSTATCOM                                                                                                                  | 147 |

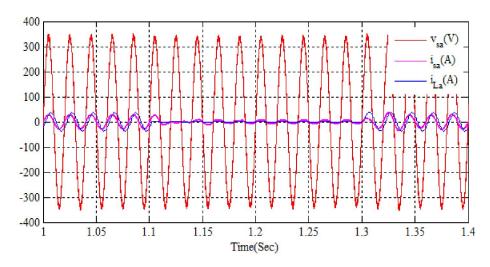

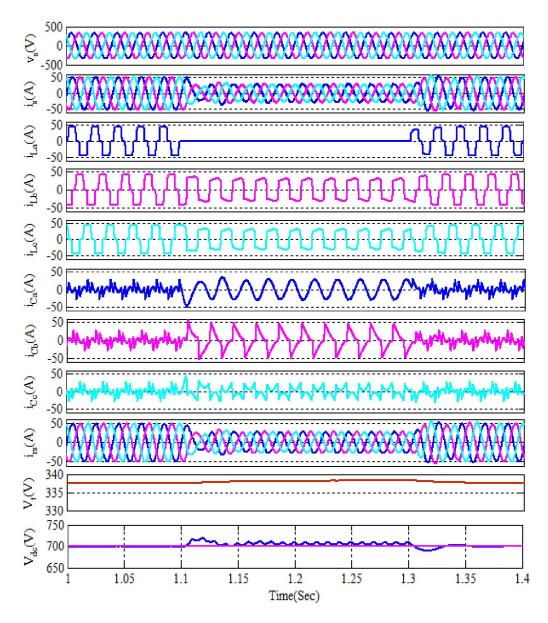

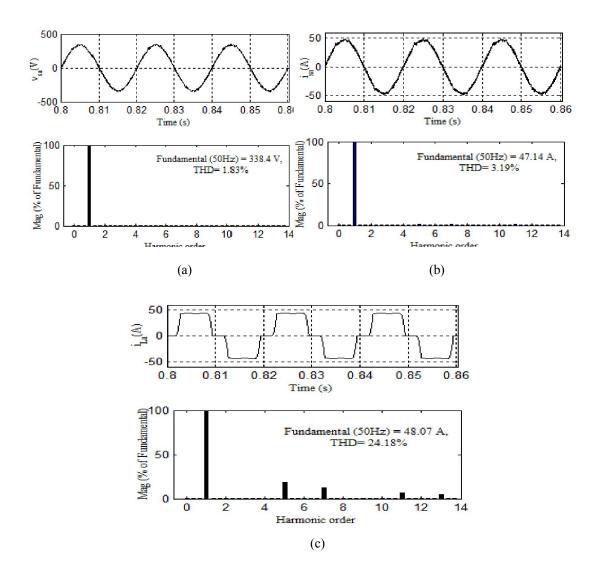

| 6.5  | Performance of DSTATCOM at nonlinear load                                                                                                                                                                                             | 154 |

| 6.6  | Performance of DSTATCOM at linear load                                                                                                                                                                                                | 155 |

| 6.7  | Intermediate signals at nonlinear load                                                                                                                                                                                                | 156 |

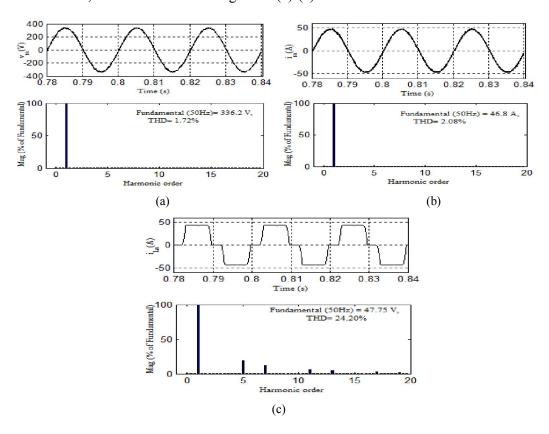

| 6.8  | Waveforms and harmonic spectra of (a) Source voltage $1 \cdots$ (c) Source current $\cdots$ (c) Load current $\cdots$ , of Phase 'a',                                                                                                 | 157 |

| 6.9  | Performance indices of DSTATCOM at nonlinear load                                                                                                                                                                                     | 159 |

| 6.10 | Performance indices of DSTATCOM at linear load                                                                                                                                                                                        | 160 |

| 6.11 | Performance parameters of DSTATCOM (a) Intermediate signals (b) Voltage regulation of AC bus voltage with and without DSTATCOM                                                                                                        | 162 |

| 6.12 | Waveforms and harmonic spectra (a) Source voltage 1<br>(b) Source current (c) Load current, of phase 'a'                                                                                                                              | 163 |

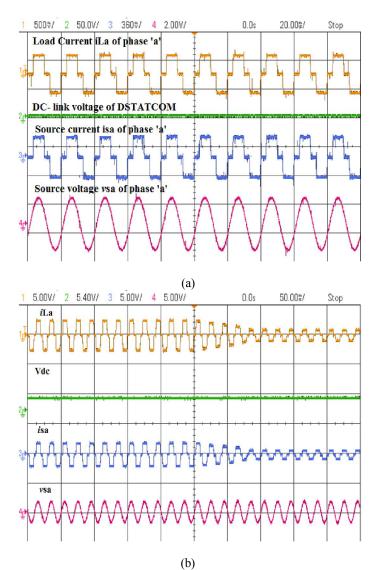

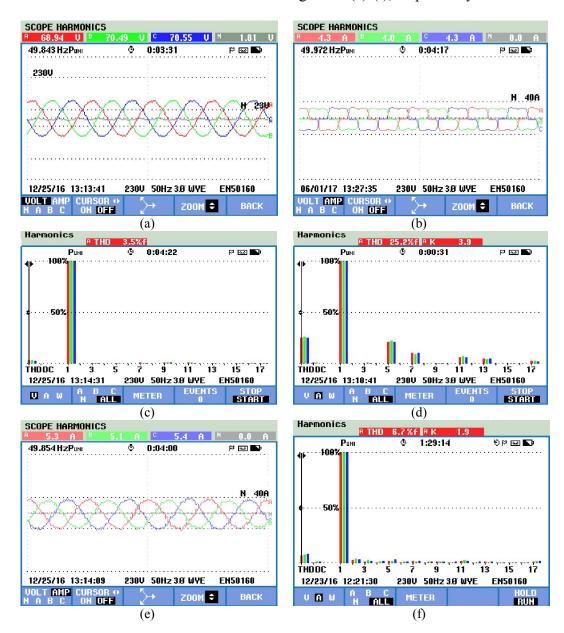

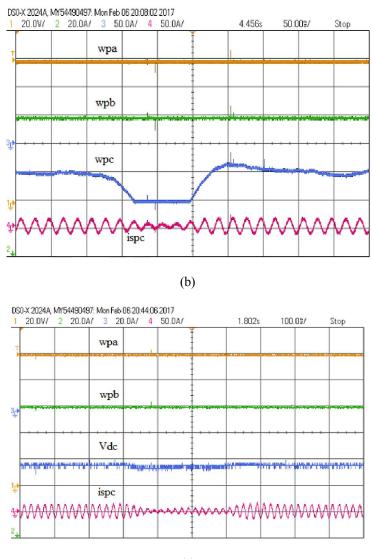

| 6.13 | Performance parameters of test system (a) Source voltages 1 · (b) Source currents · (c) %THDs of 1 · (d) %THDs of ·, for all phases, when DSTATCOM is in OFF state (e) Source currents · (f) %THDs of ·, when DSTATCOM is switched ON | 165 |

| 6.14 | Performance parameters (a) $\cdot \cdot \cdot , \cdot \cdot \cdot \cdot \cdot$ and $1 \cdot \cdot \cdot \cdot (b) 1 \cdot \cdot , \cdot \cdot$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 167-168 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 6.15 | (a) Intermediate control signals $\check{z}^{*}$ , $\check{z}^{*}$ , $\check{z}^{*}$ , $\check{z}^{*}$ , and $\check{z}_{\check{Z}}$<br>(b) Weights of each phase $\check{z}^{*}$ , | 168-169 |

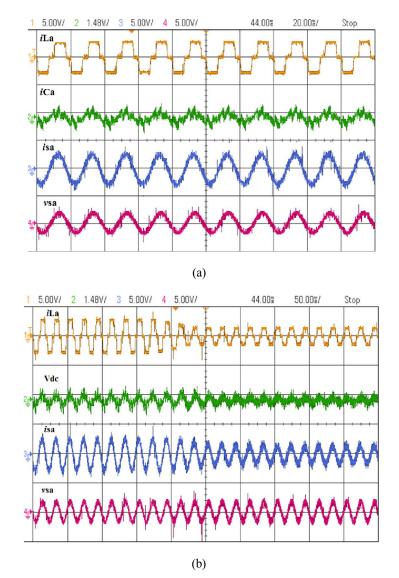

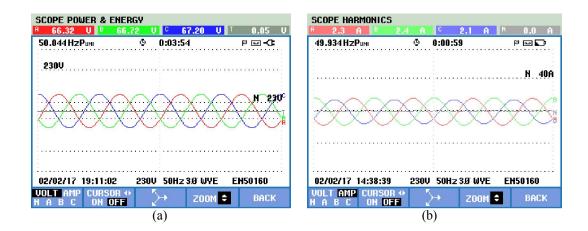

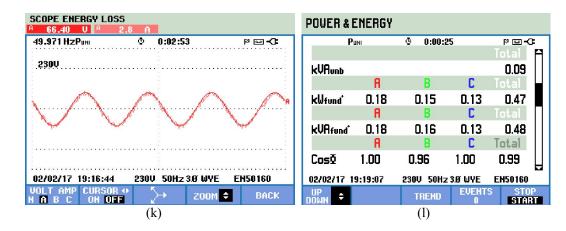

| 6.16 | Performance parameters of test system (a) Source<br>voltages 1. (b) Source currents . (c)-(d) Power and<br>power factor (e) Waveforms of voltage 1 and current<br>of phase 'a' (f) Phasor diagram, when DSTATCOM<br>is in OFF state, (g) Source voltages 1. (h) Source currents<br>, RMS values, (i) Source voltages 1. (j) Source<br>currents . (k) voltage 1 and current, of phase 'a'<br>(l) Power and power factor, when DSTATCOM is<br>switched ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 170-172 |

| 6.17 | Voltage and currents waveforms of phase 'a' (a) Before<br>switching ON DSTATCOM (b) After switching ON<br>DSTATCOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 173     |

## LIST OF TABLES

| Table no. | Title                                                                                  | Page no. |

|-----------|----------------------------------------------------------------------------------------|----------|

| 3.1       | System Parameters of DSTATCOM for Simulation                                           | 52       |

| 3.2       | System parameters of developed DSTATCOM                                                | 53       |

| 4.1       | Design specifications of the developed test model of a three-phase distribution system | 65       |

| 4.2       | Performance parameters of DSTATCOM                                                     | 95       |

| 5.1       | Parameters of developed $3-\phi$ distribution system                                   | 98       |

| 5.2       | Comparison of ANN and GNN based controllers                                            | 129      |

| 5.3       | Performance parameters of DSTATCOM                                                     | 130      |

| 6.1       | Configuration parameters and design specifications of test system                      | 134      |

| 6.2       | Simulated performance results of AVSF based control algorithm                          | 158      |

## LIST OF SYMBOLS

| 1 •• ,1 •″ ,1 •                                                                      | Phase-a, b, c PCC voltages                                           |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| · · · · · · · · · · · · · · · · · · ·                                                | Phase-a, b, c supply currents                                        |

| · · · · · · · · · · · · · · · · · · ·                                                | Phase-a, b, c load currents                                          |

| fl°, fl″, fl                                                                         | Phase-a, b, c compensating currents components                       |

| " - and #-                                                                           | Source resistance and inductance                                     |

| \$ <sub>1</sub>                                                                      | DC bus capacitance of voltage source converter                       |

| 1.                                                                                   | DC bus voltage of voltage source converter                           |

| # <sub>%</sub>                                                                       | Inductance of interfacing inductor                                   |

| " %                                                                                  | Resistance of interfacing inductor                                   |

| " $_8$ and $S_8$                                                                     | Resistance and capacitance of ripple filter                          |

| $\dot{I}_{\check{Z}^{\circ}}, \dot{I}_{\check{Z}^{''}}, \dot{I}_{\check{Z}_{\circ}}$ | Unit inphase templates                                               |

| ł··, ł·", ł·                                                                         | Unit quadrature templates                                            |

| (                                                                                    | Terminal voltage amplitude of AC bus at PCC                          |

| )/*                                                                                  | Cross-correlation vector                                             |

| "*                                                                                   | Correlation matrix of input data                                     |

| μ                                                                                    | Step size parameter                                                  |

| ! <sub>`Ž</sub> , ! <sub>´Ž</sub> , ! <sub>,Ž</sub>                                  | Fundamental active power weights of phase a, b ,c of load currents   |

| ! • ' , ! ″ ' , ! ౖ'                                                                 | Fundamental reactive power weights of phase a, b ,c of load currents |

|                                                                                      |                                                                      |

| +,                                         | Summation neuron                                                                       |

|--------------------------------------------|----------------------------------------------------------------------------------------|

| <b>,</b> .                                 | Summation neuron of active current components                                          |

| π                                          | Product neuron                                                                         |

| λ                                          | Weighted convergence coefficient                                                       |

| η                                          | Weight learning parameter                                                              |

| γ                                          | Stabilization factor                                                                   |

| α                                          | Momentum                                                                               |

| ! /,. 0, ! /,. 1,<br>! / 2                 | Summation neuron weight of phase 'a', 'b' and 'c'                                      |

| ! <u>3.</u> 0,! <u>3.</u> 1, ! <u>3.</u> 0 | Product neuron weight of phase 'a', 'b' and 'c'                                        |

| $\boldsymbol{\omega}$ and $\boldsymbol{g}$ | Network parametric weights                                                             |

| $S$ , $S_1$ and $S_2$                      | Total set of parameters, set of premise parameters<br>and set of consequent parameters |

## **ABBREVIATIONS**

| ANN      | Artificial neural network                  |

|----------|--------------------------------------------|

| ADALINE  | Adaptive linear neuron                     |

| BP       | Back-propagation                           |

| DPI      | Discrete proportional-integral             |

| DSTATCOM | Distribution static compensator            |

| DVR      | Dynamic voltage restorer                   |

| GD       | Gradient descent                           |

| GDM      | Gradient descent with momentum             |

| GNN      | Generalized neural network                 |

| HB       | Hysteresis bandwidth                       |

| HPF      | High pass filter                           |

| IGBT     | Insulated-gate bipolar junction transistor |

| IRP      | Instantaneous reactive power               |

| LMS      | Least mean square                          |

| LPF      | Low pass filter                            |

| MLPNN    | Multilayer perceptron neural network       |

| NN       | Neural network                             |

| OLS      | Optimum least square                       |

| PCC      | Point of common coupling                   |

## CHAPTER 1 INTRODUCTION

#### **1.1 GENERAL**

With the growth and development of technologies, power distribution systems and the loads, have increasingly concentrated on the quality of power supply. In the recent years, various highly sensitive medical equipments, high-speed motors, and computer-controlled processing plants, require the power source of high quality and good reliability. Over the last decade, substantial research has been carried out on power distribution systems to overcome most severe power disturbances such as harmonics elimination, mitigation of voltage sags, load balancing, voltage regulation and interruptions of renewable resources [1]. The required techniques have been developed to analyze, predict, and mitigate these disturbances in system-equipment interactions [2]-[3]. To assess and to maintain the good quality of power in power distribution systems, presently electrical supply industries are becoming efficient without compromising the quality of power supply service [4]-[5]. Providing new solutions for this newly power quality paradigm in distribution systems by custom power devices (CPDs) has reduced the complexity, costs and has increased the reliability of power supply [6]-[11].

In addition, the demand for electricity is increasing due to urbanization and growth of population. Renewable energy resources integration is playing an important role to meet the demand in distribution systems. However, issues of power delivery quality of the supply voltage or current from the sinusoidal waveform with the amplitude at rated frequency, have deviated the quality of waveforms.

#### **1.2 STATE OF THE ART ON POWER QUALITY**

The power quality problems in the distribution systems are mainly due to the proliferation of different types of nonlinear loads, unplanned expansion of the distribution system, etc [12]-[13]. Therefore, power quality is quantified in terms of voltage, current, or frequency deviation of the supply system, which may result in failure or mal-operation of customer's equipment [8]. The degradation of power quality leads to low power factor, low efficiency, over heating of transformers, and so on. In distribution systems, the power quality problems can reduce the power supplied to the customers from its nominal value. The utility and the users are responsible in polluting the supply network due to operating large loads [14]-[15]. Power quality has taken an increasing importance in view of the widespread use of power electronic equipment [16]-[18]. Power quality problems related to the voltage, are voltage harmonics, surge, sag/dip, spikes, notches, unbalance, swell, fluctuations, and so on at the point of common coupling (PCC) where various loads are connected. However, some power quality problems related to the currents drawn from the AC mains, are poor power factor, reactive power burden, harmonic currents, unbalanced currents, and an excessive neutral current in poly-phase systems due to unbalancing and harmonic currents generated by some nonlinear loads. In distribution systems, power quality issues related to voltage and current drawn from AC mains at point of common coupling (PCC) like unbalanced voltages supply, active and reactive power demands, are affecting performance of customer equipment [19]-[21]. A power quality problem is any occurrence manifested in voltage, current, or frequency deviations, which are major impacts to a distribution system that result in failure of customer equipment [22]-[27]. These aspects become important when power supply is not ideal

i.e., it deals with unbalance, harmonics, faults and fluctuations in frequency [28], [29]. The mitigation of power quality issues has been provided by filters such as passive, active and hybrid in series, shunt or combination of both [30]-[50]. Power electronics based controllers have played a vital role to enhance the quality and reliability of power delivered by electric distribution system. These devices can be shunt connected, series connected or a combination of both series and shunt connected at PCC [51]-[61]. A number of international standards are developed by various organizations such IEEE (Institute of Electrical and Electronics Engineers) and IEC (International Electrotechnical Commission) to specify the permissible limit of power quality problems and to provide guidelines for the end users, manufacturers and utilities to improve the quality of power [62]-[68]. The critical and sensitive loads are protected from power quality problems by monitoring these power quality events. The objectives of power quality monitoring, are prediction of performance of the load and the selection of power quality mitigation system [69]-[79].

Further, with the deregulation of the power industry, competitive pressure forces electric utilities to cut cost, which sometimes affects power quality and reliability. Hence, it must be ensured by suitable regulations that customers do not suffer from reduced power quality and reliability.

#### **1.3 TRANSITION TO SMART POWER DISTRIBUTION SYSTEMS**

With the help of intelligent custom power devices (CPDs) in distribution systems such as distribution static compensators (DSTATCOMs), dynamic voltage restorers (DVRs), and unified power quality conditioners (UPQCs), power quality problems arising due to various disturbances in the system or due to the presence of various nonlinear loads such as furnaces, uninterruptible power supplies (UPSs), and adjustable speed drives (ASDs), which have evolved inherently, can be monitored and mitigated. These intelligent CPDs make the power distribution systems smart [30]-[36]. Intelligent CPDs use experiential knowledge about the process that generally produces a model in terms of input-output behaviour. The acceptable controller to mitigate current related power quality problems at distribution level is distribution static compensator (DSTATCOM), which is also named as an active shunt compensator or filter [52]-[61]. The DSTATCOM is used for mitigation of current related power quality problems such as harmonics distortion, poor power factor, load unbalancing and voltage regulation etc. Tremendous progress in the field of power semiconductor devices and signal processing, has made the cost effective implementation of DSTATCOM [50]-[58]. The research in this area has led to the developments in the area of different configurations and control algorithms for control of the shunt compensator. The DSTATCOM is configured based on the number of switching devices, the use of isolation transformer and the use of type of transformer for neutral current compensation. Mainly DSTATCOM configurations are divided into two major categories such as three phase three wire and three phase four wire [69]-[79].

#### **1.3.1** Limitations of CPDs

The ability of the DSTATCOM as a compensator is impaired by control algorithms of the following steady-state and dynamic-state limitations. The control algorithm should have fast response and stable operation in both steady state and dynamic conditions. The selection of a control algorithm depends upon processing time, mathematical complexity, fast response, stable operation and easy implementation. The primary objectives of the DSTATCOM in a distribution system are:

- DC link voltage control: Maintaining desired level of voltage, prevention of transient under dynamic condition of load and fast response under steady state.

- Power flow control: Increased power factor, minimization of loop flows and voltage regulation.

- Load balancing: During, transient, steady-state and dynamic state.

- Harmonics elimination: Reduction in losses, reduction in overload capacity and increase in efficiency of utility equipments.

#### **1.3.2** Concept of Intelligent CPDs

The modeling of intelligent CPDs to be computationally efficient to deal with the power quality problems is related to the current drawn from the AC mains. There are three basic approaches to intelligent controls [80].

- Knowledge-based systems

- Fuzzy logic

- Neural networks.

Knowledge-based systems utilize a collection of information in different forms such as facts, heuristics, common sense and other forms of knowledge and use reasoning methods to inferences. In this approach, measurements, process modeling and control can never be exact for real and complex processes. Moreover, there are uncertainties such as incompleteness, randomness, and ignorance of data in the process model [81]-[85]. Fuzzy logic can incorporate certain types of unknown nonlinearity from imprecise and incomplete information by giving definitions to vague terms and allowing construction of knowledge-base in form of rules [86]-[89].

Neural network based control has received considerable interest over the last two decades because neural networks have been shown to be able to approximate any nonlinear function defined on a compact set of data to a specified accuracy and secondly most control systems exhibit certain types of unknown nonlinearity, which suits neural networks as an appropriate control technology [85]-[95].

#### **1.4 SCOPE OF THE WORK**

After carrying out a brief literature survey on control algorithms of the CPDs like UPQC, DVR and DSTATCOM, it has been identified that the advanced intelligent control of DSTATCOM builds the distribution system smart and intelligent. The aspects of advanced intelligent control strategies comprise of different issues that include the speed of response, convergence, computational burden, complexity, static error, robustness and stable operation in the steady state and dynamic conditions with verification by an experimental prototype.

The main objectives of the proposed research work are as follows:

- To design and develop a prototype configuration of three-phase distribution system with DSTATCOM in the laboratory.

- To develop the mathematical model of the proposed control algorithms and their experimental realization through the digital signal processor (DSP).

- To investigate the implication on real-time application to mitigate the power quality issues of the configuration taken under consideration.

• To assess the effectiveness of the developed advanced intelligent control algorithms based on neural network and nonlinear adaptive filter under different operating conditions.

The proposed research work has been carried out as follows:

#### **1.4.1 Control Strategy for DSTATCOM**

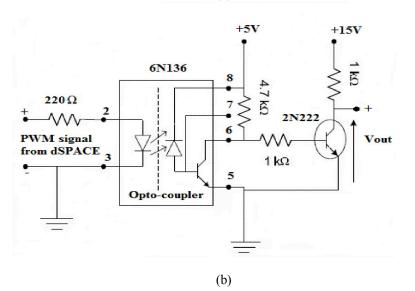

The control strategy for DSTATCOM is implemented in three stages, which are required for implementing developed control algorithms. In the first stage, current and voltage signals are sensed using Hall Effect sensors (LEM make) to take system parameters. In the second stage, developed model of control algorithms on MATLAB Simulink platform, are used to drive the DSTATCOM to deliver current compensation signals in order to mitigate current related issues of power quality. In the third and last stage, the gating signals for controlled switches (IGBTs) are driven using hysteresis current controller (HCC) logic based pulse width modulation (PWM) control technique. To design the control part in real time, digital signal processor (DSP) based on dSpace-1104 is used. Earlier this work has been carried out through complex analog and digital circuits.

#### 1.4.1.1 Sensing of signals

For implementing control algorithm, instantaneous voltage and current signals are sensed. These signals are used to evaluate various parameters like THDs, power factor, crest factor, active and reactive power, etc. The Hall Effect voltage sensors (LV-25P) are used to sense the voltage signals such as phase voltages of AC supply at PCC and DC bus voltage of VSC based DSTATCOM. The Hall Effect current sensors (LA-25) are used to sense current signals such as load currents, supply currents at PCC. Current and voltage

signals have to be filtered to avoid any noise or interference problems using R-C series low pass filter (LPF). The required levels of sensed signals are maintained by dSPACE, which has DSP based platform, by passing through power conditioning circuits. In hardware, the ripple filters are designed using analog circuit.

#### **1.4.1.2** Reference currents generation

The generation of the reference currents comprises of extracted fundamental active and reactive current components of the load current, respectively. The switching has been initiated by taking the error of sensed and reference fundamental currents that results into injecting compensating current signals. To draw compensating current signals, some control algorithm based on either frequency domain or time domain has to be designed.

In frequency domain, Fourier analysis is generally used to extract fundamental current components, for which switching frequency for the device is kept twice of highest frequency component for accurate and effective compensation. Fourier transform has a disadvantage of producing large response time in the system.

In time domain, instantaneous values of compensation currents or voltages are generally derived from polluted currents or voltages signals. Here, a number of control methods have been derived such as synchronous reference frame, instantaneous active and reactive power theory, adaptive filter based techniques etc.

#### **1.4.1.3** Switching pulse generation

The error signal of fundamental current is passed to PWM based hysteresis current control method that generates required gate signals at a frequency of around 10 kHz.

#### 1.4.2 Fast Multilayer Neural Network Based Control Algorithm

The back-propagation learning has various drawbacks such as slowness in learning, stuck in local minima, and requires functional derivative of aggregation and threshold functions to minimize error function. Various researchers have suggested a number of improvements in simple back-propagation learning algorithm [96]-[120]. On the primary objectives of advanced intelligent control, fast multilayer neural network based control algorithm is developed that has enhanced the convergence speed of the developed backpropagation (BP) algorithm in three-phase three-wire distribution system using three-leg VSC for reactive power compensation, harmonics eliminations, and load balancing. The developed algorithm is validated experimentally in the laboratory on the developed prototype of DSTATCOM.

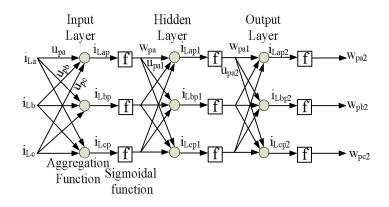

#### 1.4.3 Generalized Neural Network based Control Algorithm

In the available ANN based algorithms, the sigmoid threshold function and ordinary summation or product as aggregation functions in the existing models, fail to cope with the nonlinearities present in the AC supply current or voltage sinusoidal waveforms. To deal with such nonlinearities, the proposed generalized neuron has both sigmoid and Gaussian functions with weight sharing. The generalized neuron has flexibility at both the aggregation and threshold function level to cope with the nonlinearity present in the sinusoidal waveforms [121]-[145]. This new concept has reduced the complexity of multilayer into single layer, which reduces the computational time. GNN has reduced network problem and learning complexity on training of input signals in three-phase three-wire distribution system using DSTATCOM for reactive power compensation,

harmonics eliminations, and load balancing. The developed algorithm is validated experimentally in the laboratory on the developed prototype of DSTATCOM.

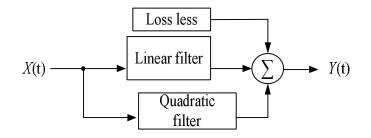

#### 1.4.4 Nonlinear Adaptive Filter based Control Algorithm

In the literature survey, the applications of non-linear filter based control algorithms for DSTATCOM, are rarely available. However, linear filter based control algorithms, are effective in a variety of performances improvement of DSTATCOM [146]-[165]. Moreover, in nonlinear signal processing where linear filters do not give satisfactory performance, nonlinear filtering techniques are able to provide better performance. Performance of these control algorithms are analyzed in three-phase three-wire system using three-leg VSC for reactive power compensation, harmonics eliminations and load balancing.

#### **1.5 OUTLINE OF CHAPTERS**

This thesis consists of seven chapters including introduction, literature review, design and development of DSTATCOM in a three phase distribution system, which deals with the control strategy for DSTATCOM, realization of developed advanced intelligent control algorithms such as fast multilayer neural network based control of DSTATCOM, generalized neural network based control of DSTATCOM, nonlinear adaptive Volterra second order filter (AVSF) based control of DSTATCOM, main conclusions and suggestions for further work followed by references.

**Chapter-1:** This chapter covers introductory concepts of power quality issues and their mitigation in a distribution system and transition to smart power distribution system integrated with custom power devices and their control techniques. The scope of work includes advanced intelligent control algorithms for improving power quality problems

such as harmonics, reactive power and load unbalancing. This classification of control algorithms, includes fast multilayer neural network based control algorithm, generalized neural network based control algorithm, and nonlinear adaptive filter based control algorithm.

**Chapter-2:** The brief literature review on power quality standards, issues, monitoring and their mitigation in the distribution system, is described in this chapter. Further, a comprehensive literature review on multifunction operation and control of DSTATCOM is also reported in detail. The performance of DSTATCOM on configurations and control algorithms for load compensation, is also discussed in this chapter. Based on the exhaustive literature review, identified research areas are presented at the end of this chapter.

**Chapter-3:** This chapter deals with the design and development of DSTATCOM in a three phase distribution system. Mathematical modeling and selection of various components of DSTATCOM such as VSC, DC bus voltage, DC bus capacitance, interfacing inductors, and ripple filter are presented. Design and testing of voltage sensor circuits, current sensor circuits, and gate driver circuits with signal conditioning for generation of pulses for control of VSC, are discussed here. In addition, the interfacing inductors are also designed in the laboratory for the hardware of prototype of DSTATCOM.

**Chapter-4:** This chapter addresses the mathematical modeling and analysis of the proposed fast multilayer neural network based control algorithm for DSTATCOM. Mathematical formulation, MATLAB modeling and DSP based implementation of the proposed control algorithms, are discussed in detail. Simulation and test results of the

11

proposed algorithm are also given in detail. Test configuration of DSTATCOM, has been simulated and validated with the experimental results for linear/nonlinear loads under various conditions.