# SIMULATION AND ANALYSIS OF GATE ALL AROUND TUNNEL FET FOR HIGH PERFORMANCE ANALOG AND RF APPLICATIONS

Thesis submitted by

# JAYA MADAN

# In Partial Fulfillment of the Requirements for the Degree of **DOCTOR OF PHILOSOPHY**

Under the Supervision of

Dr. RISHU CHAUJAR

Department of Applied Physics, Delhi Technological University Bawana Road, Delhi-110042, India

December-2017.

**Delhi Technological University**

(Govt. of National Capital Territory of Delhi) Bawana Road, Delhi-110042

# **CERTIFICATE**

This is to certify that the thesis titled "Simulation and Analysis of Gate All Around Tunnel FET For High Performance Analog and RF Applications" is being submitted by Miss. JAYA MADAN with registration number 2K13/PHDAP/02 to the Delhi Technological University for the award of the degree of Doctor of Philosophy in Applied Physics. The work embodied in this thesis is a record of bonafide research work carried out by me in the Microelectronics Research Lab, Applied Physics Department, Delhi Technological University (Formerly Delhi College of Engineering), New Delhi under the guidance of Dr. RISHU CHAUJAR. It is further certified that this work is original and has not been submitted in part or fully to any other University or Institute for the award of any degree or diploma.

Jaya Madan Candidate Roll No. 2K13/PHDAP/02

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

Dr. Rishu Chaujar

Supervisor (Asst. Professor) Department of Applied Physics Delhi Technological University Delhi, India

ECHN

**Prof. S. C. Sharma** Head, Department of Applied Physics Delhi Technological University Delhi, India

# **ACKNOWLEDGEMENTS**

This four year journey of my research work has been a very great and learning experience. I would like to thank all those people who guide and support me in this tremendous journey, may be without them, completion of this thesis could be a tough task. I'm highly obliged to take this opportunity to acknowledge them for being there for me.

At the very inception, I would like to express my cordial thanks and hat tip to my overseer, my mentor **Dr. Rishu Chaujar** for her steadfast support, encouragement and enlightenment at each and every point of my research expedition. She provided me every opportunity to prove myself and my potential. I predominantly, thank her for her true and valuable reviews for my work. Being a Chivalrous Person, she guided me as my curator. It was a pleasure working under her supervision. She will always be an inspiration for me. I truly appreciate the optimism which gave me positive vibes, which made my research successful.

It was an immense pleasure to work with my academic Professor, **Prof. R.S. Gupta**, Department of Electronics and Communication Engineering, Maharaja Agrasen Institute of Technology, India, for his intuitive treasure of Knowledge and Heirloom comments. His nature of distant cognition helped me a lot to improve my understanding of the research work. I am grateful to him for his prompt reading and keen observation.

I am thankful to **Prof. S. C. Sharma**, Head of Department, Applied Physics DTU and **Honorable Prof. Yogesh Sharma**, Vice Chancellor, DTU for their munificent support and providing the abundant core for executing the research work efficiently. I further thank SRC and DRC members **Prof. S.C. Sharma** (chairman DRC), **Prof. Anurag Sharma** (External Expert), **Dr. Navneet Kaushik** (External Expert) for taking their momentous time serving in my committee and giving their priceless endorsement on my thesis.

I wish to express my gratitude benevolently to **Mr. Rahul Pandey** (Research Fellow) and **Ms. Nisha Deopa** (Research Fellow) for their important prospect, suggestions and support which heighten the value of my research work. Their continuous moral support made this research work possible. I would explicitly appreciate my research group mates **Ajay Kumar** and **Neha Gupta**, for their continuous support throughout my research days. I am also behold to my colleagues and friends Kamal Arora, Lucky Krishnia, Reetu Singh, Vinay Yadav, Sonam Rewari, Ratneshwar Kumar Ratnesh, Ardhman Kaur, Swati Aggarwal, Ritika Khatri, Deepika Sandil, Kanika Sharma, Nishant Shankhwar, Dr. Kamal Kishor, Aman Prashad, Sumandeep Kaur, Jyotsna Panwar, Ravi Gupta, Neha Gupta, Kaushal Jha and Harpreet Kaur for the discussions we had, both technical and vice-versa.

I am candidly obliged to **Skanda Shekhar** (B. Tech Student) and **Henika Arora** (Scientist-C, SSPL, DRDO and sponsored M.Tech Student) for their accessibility and invaluable ideas during my research period.

My colleagues and friends always swayed me with lots of positivity and strength which helped me complete my research effectively. It was a great experience and fun to work with all of them.

I would also like to convey my utmost thanks to all my faculty members and technical staff of Department of Applied Physics for their valuable backing.

I also thank and acknowledge University Grant Commission (UGC) for their financial support during my Ph.D.

Last but not the least, I cordially thank my family, my father (Avani Madan), my mother (Meera), my loving sister (Mrs. Komal Bhardwaj) and my brother-in-law (Rahul Bhardwaj) for helping and supporting me spiritually to complete my research work and my life in general. They always motivated me to be a positive soul and their priceless love, affection and boundless sacrifices always helped me give my best to complete this expedition of my life.

(Jaya Madan) New Delhi, December 2017.

# **ABSTRACT**

# SIMULATION AND ANALYSIS OF GATE ALL AROUND TUNNEL FET FOR HIGH PERFORMANCE ANALOG AND RF APPLICATIONS

Steeper subthreshold swing (SS) and lower OFF-state current ( $I_{OFF}$ ) accessible by Tunnel FET offers great potentials in low power electronics applications. In this thesis, gate all around Tunnel FET's performance has been studied and various efforts have been done to overcome the major roadblock of TFET such as the lower ON-state current ( $I_{ON}$ ), ambipolar conduction, higher threshold voltage ( $V_{th}$ ) and the higher miller capacitance.

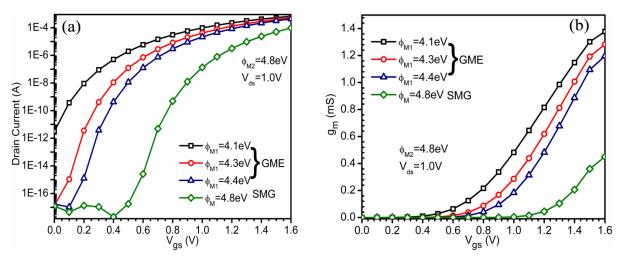

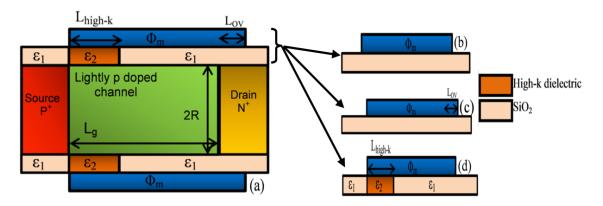

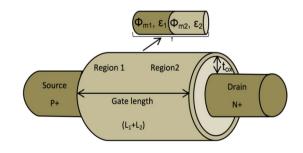

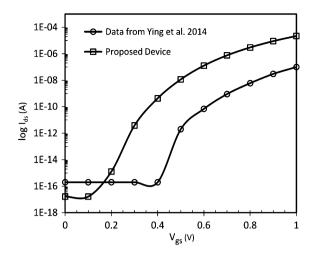

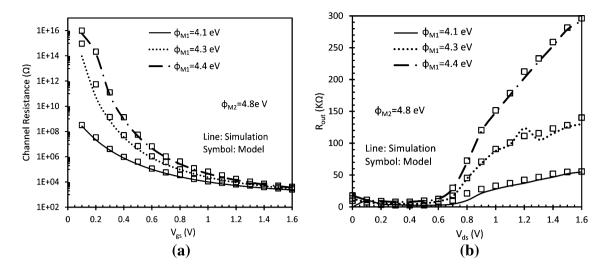

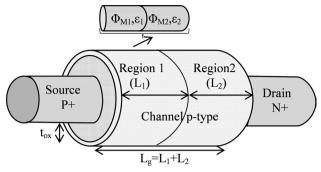

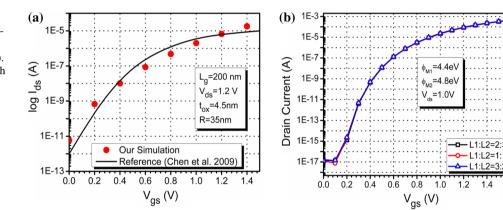

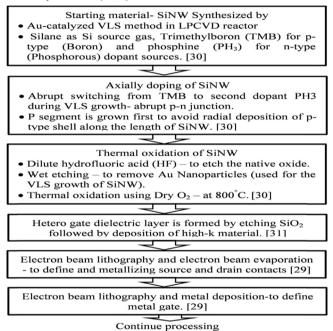

In this regard, firstly hetero gate dielectric (HD) and gate metal engineering (GME) are integrated simultaneously on a gate all around TFET i.e. HD-GME-GAA-TFET has been proposed. An analytical model for the proposed HD-GME-GAA-TFET has also been developed for its in-depth inspection. First and foremost, a drain current model for the proposed device is developed, and for the authentication of the developed model, the analytical results so obtained are matched with simulation results. For developing a drain current model, Poisson's equation is solved by using appropriate boundary conditions and continuity equations to obtain a surface potential profile, lateral electric field and finally by using the generation rate and tunneling barrier width, the drain current is obtained. Developed analytical model and the extensive simulations are used to determine the optimum value of hetero gate dielectrics and dual material gate work functions for acquiring best characteristics of the device. It is analyzed that the  $I_{\text{ON}}$  of GAA-TFET is enhanced from an order of  $10^{\text{-8}}\text{A}$  to  $10^{-4}$ A with the amalgamation of HD and GME. Furthermore, the SS of 49mV/decade at a V<sub>th</sub> of 0.5V has been acquired. Moreover, the influence of gate and drain bias has also been analyzed on the electrical and analog performance of the proposed device. Further, the impact of gate oxide thickness has also been enlightened. It is analyzed that the SS of the proposed device in each case throughout the study, is much lesser compared to 60mV/decade (fundamental limit on the SS of a conventional MOSFET), proving that the proposed device can be used for high performance switching applications in the future.

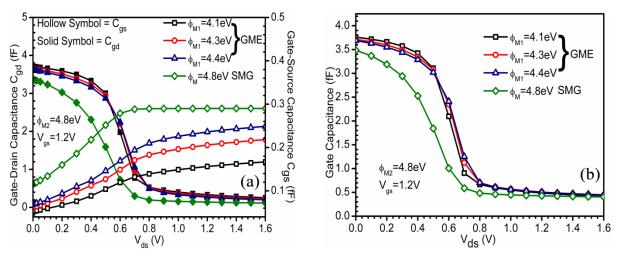

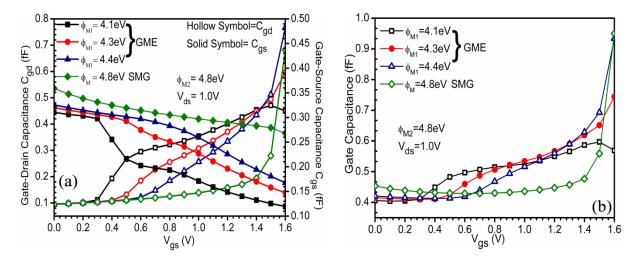

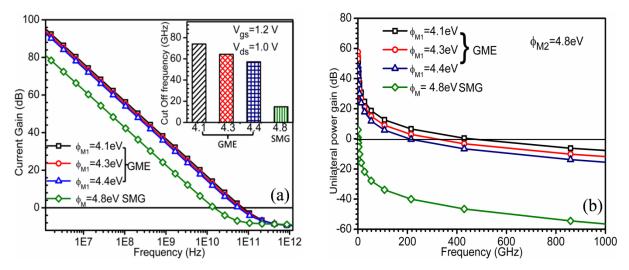

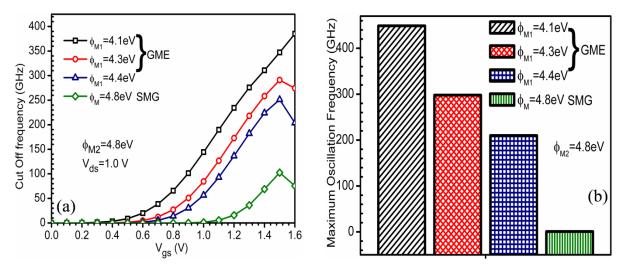

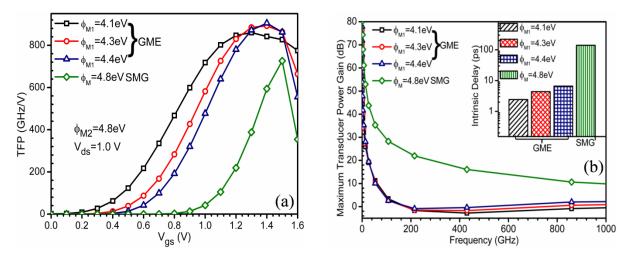

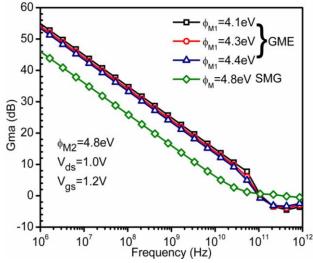

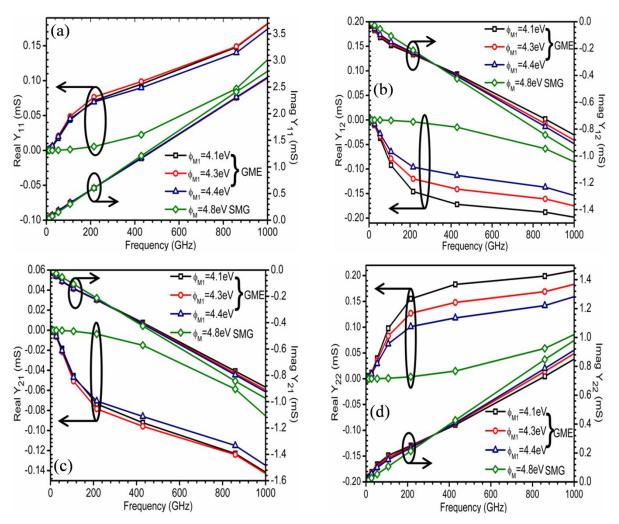

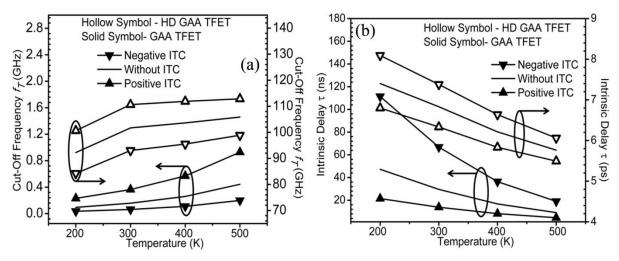

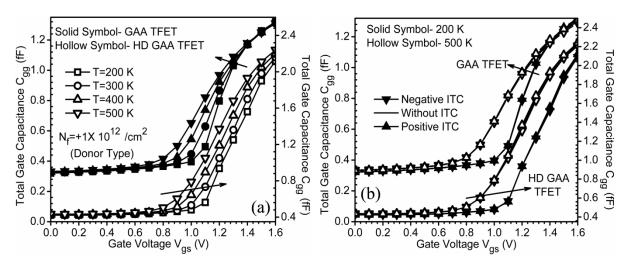

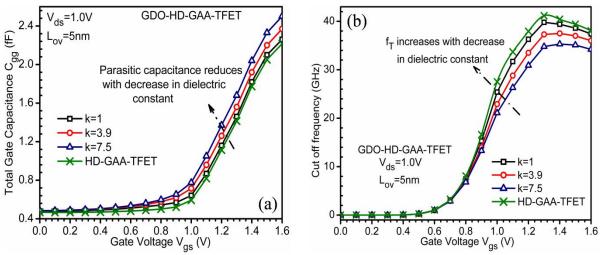

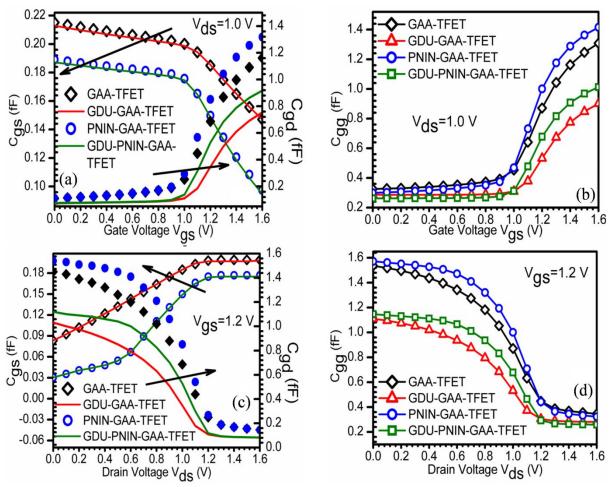

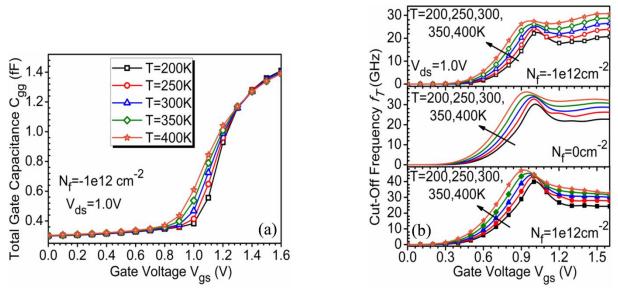

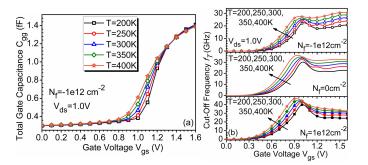

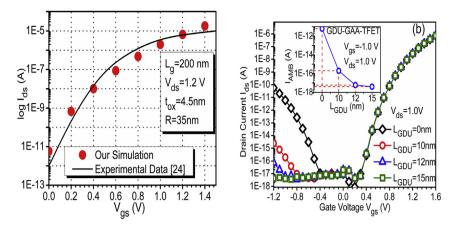

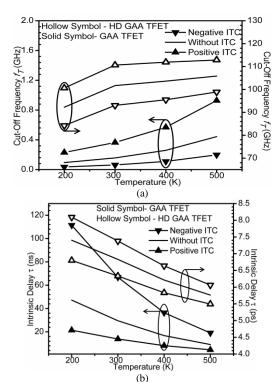

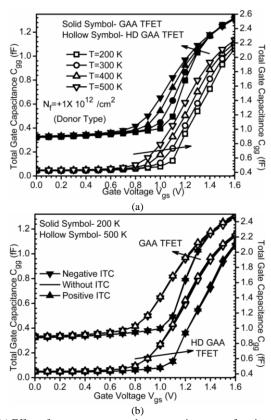

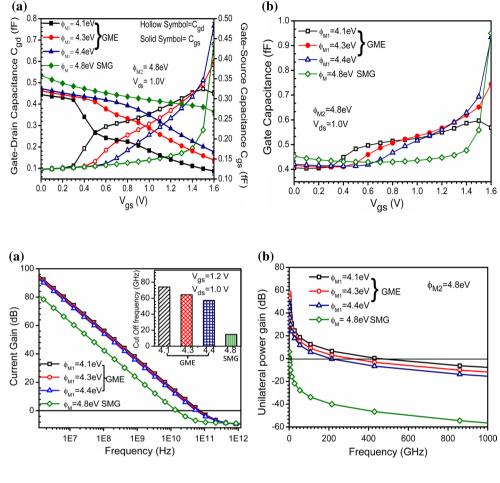

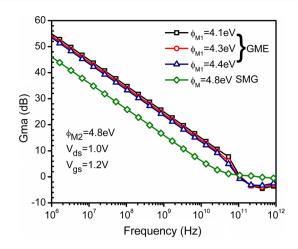

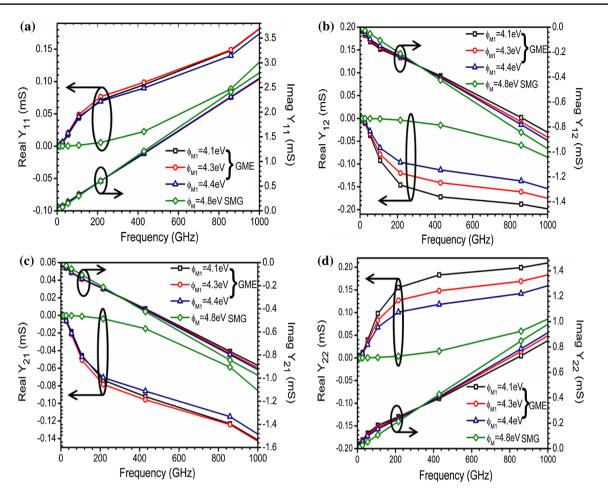

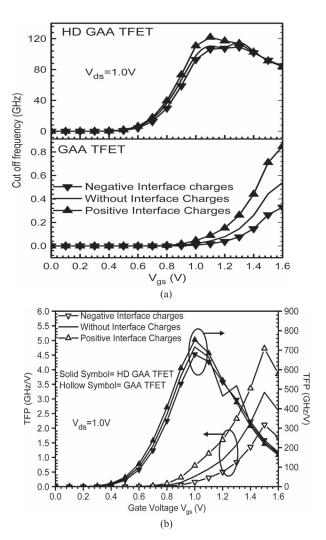

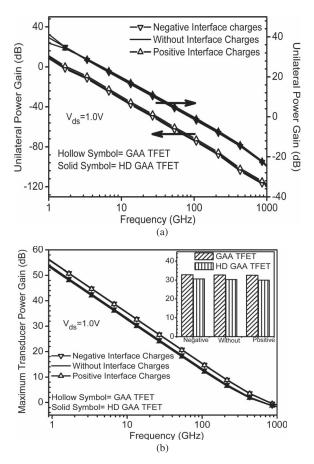

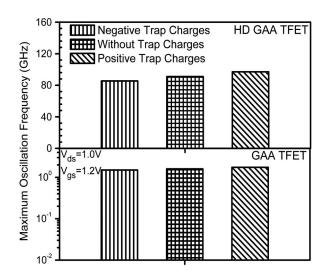

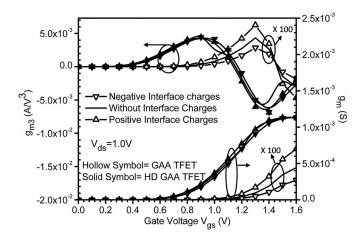

After analyzing the analog characteristics of HD-GME-GAA-TFET, and to account for the response time, switching speed and active power dissipation; the bias dependent intrinsic parasitic capacitances have been analyzed. The bias dependent parasitic capacitances have been examined under various gate bias, drain bias and also for different metal work function configuration of GME design. Further, for comprehensive RF analysis of GAA-TFET and its effectiveness at high frequency, various RF Figure of Merits (FOMs) such as maximum available power gain, maximum transducer power gain, cut-off frequency ( $f_{T}$ ), maximum oscillation frequency ( $f_{MAX}$ ) and intrinsic delay has also been studied for different gate metal work functions of GME engineering scheme integrated on GAA-TFET. The analyzed data would be beneficially providing detailed knowledge about the RF parameters of HD-GME-GAA-TFET at such aggressively scaled dimensions.

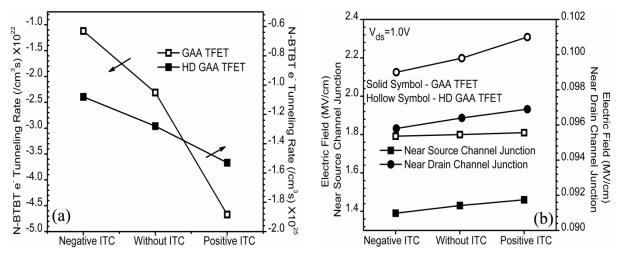

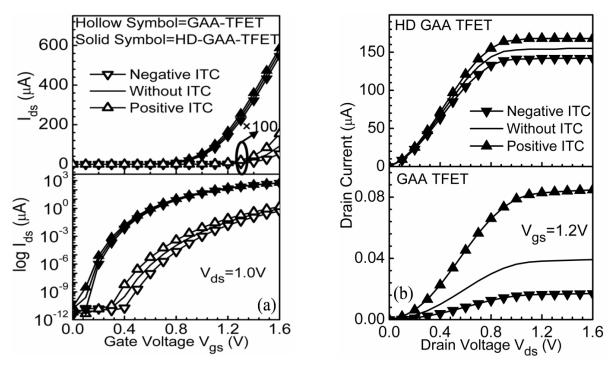

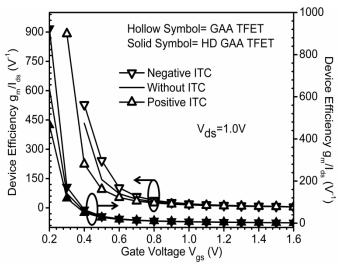

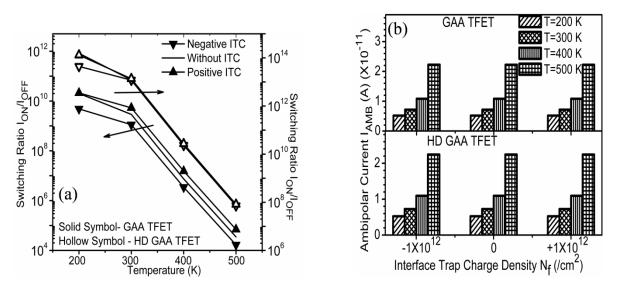

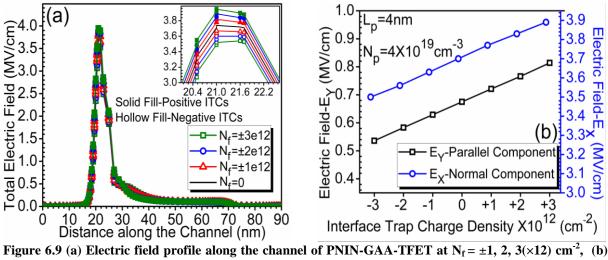

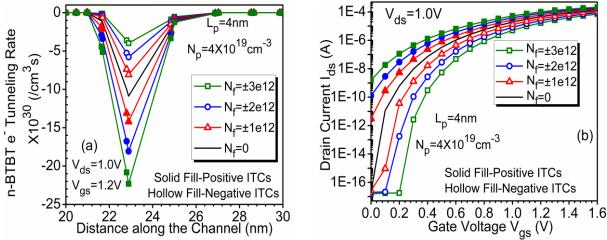

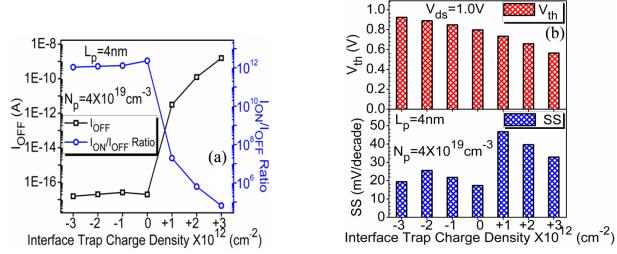

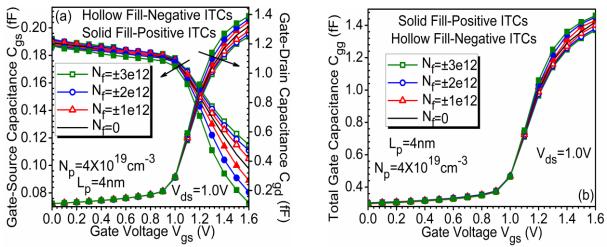

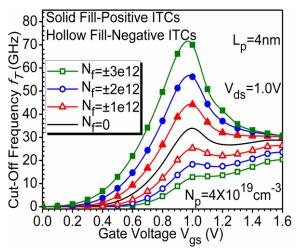

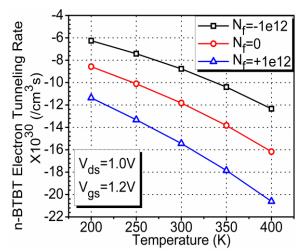

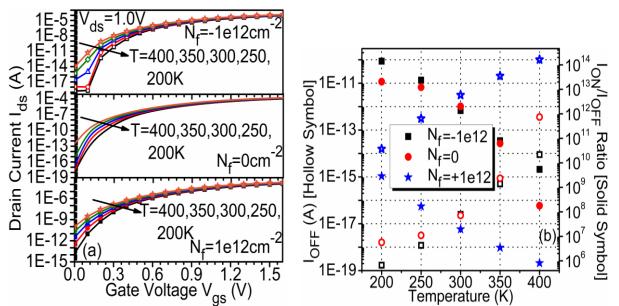

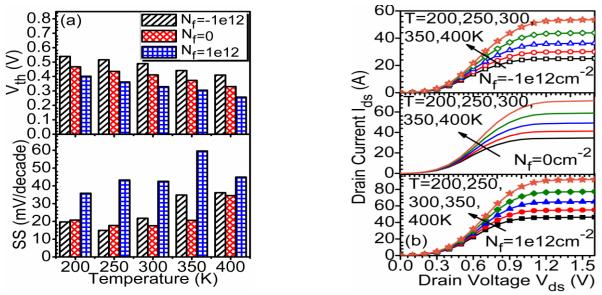

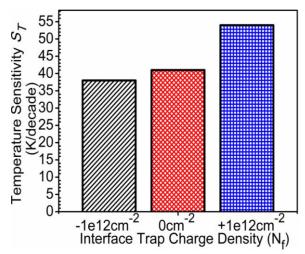

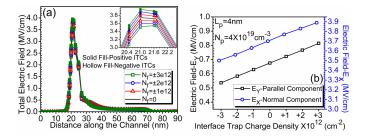

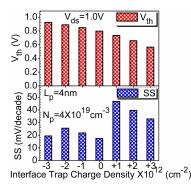

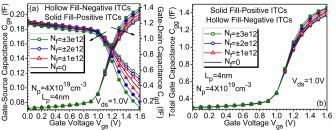

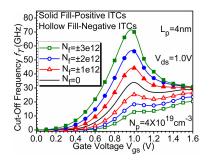

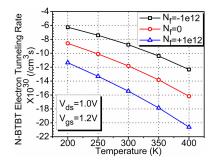

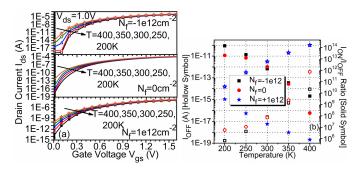

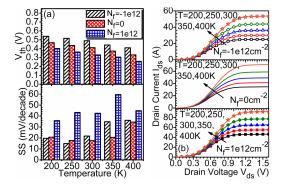

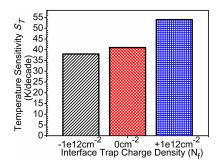

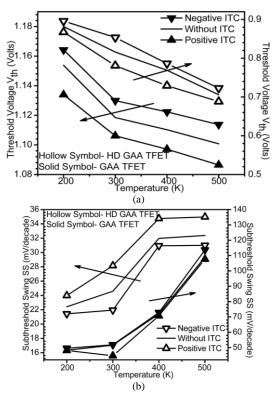

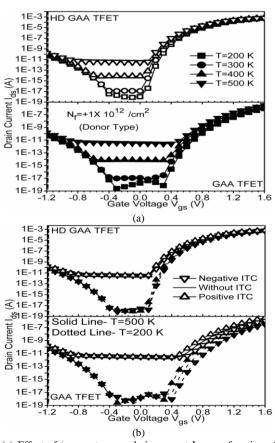

With the miniaturization of CMOS devices that marks in considerably high integration, the fabrication process damage, stress-induced damage and radiation damage at sub-nm regime result in solemn device reliability issues. These damages originate various interface trap charges (ITCs) at the Si-SiO<sub>2</sub> interface and thereby alters the ideal predicted device characteristics and is thus a serious issue that must be scrutinized before circuit designing. Thus, to account for the reliability of HD-GAA-TFET, the device is analyzed under the presence of ITCs of various polarity and density and the results are simultaneously compared with the ideal case in which the interface is free from defects. A comparative analysis of GAA-TFET and HD-GAA-TFET has been done in terms of various analog, RF and linearity parameters to inspect the impact of ITCs and thus the reliability. Results show that the integration of high-k dielectric near source side (to upgrade the device characteristics) concurrently leads to better immunity against the ITCs. Further, to find the pertinence of HD-GAA-TFET in wide temperature range ambience, the temperature robustness is also analyzed. Again the device analog and RF characteristics have been investigated at wide temperature range and it is realized that the HD-GAA-TFET and GAA-TFET have bias dependent temperature. Moreover, a severe degradation in IOFF has been obtained at elevated temperatures, whereas at low temperatures (as compared to room temperature), the I<sub>OFF</sub> reduces appreciably. Thus, the immunity against the ITCs and the marginally increased drain

current (in ON-state) marks the HD-GAA-TFET an efficient candidate for low power switching applications.

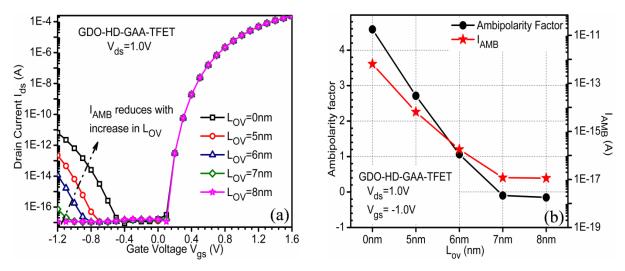

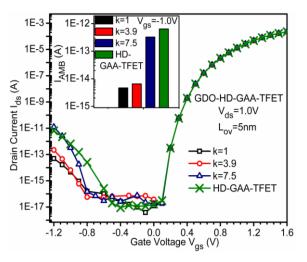

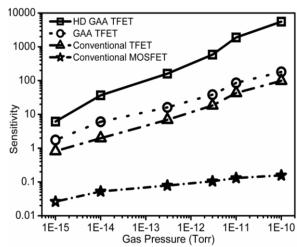

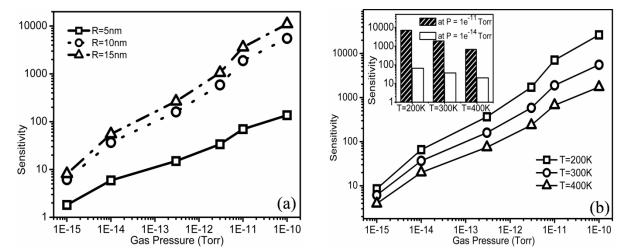

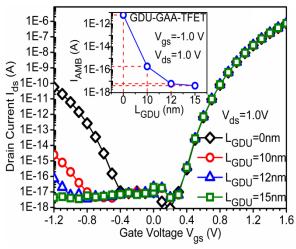

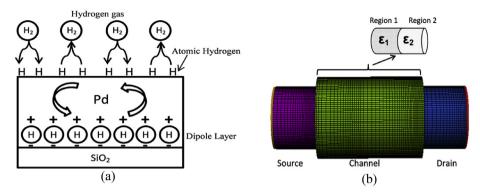

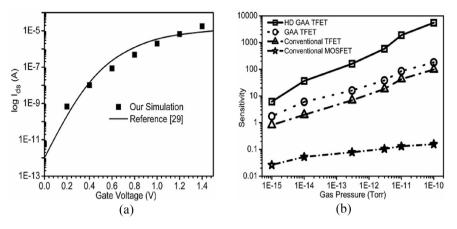

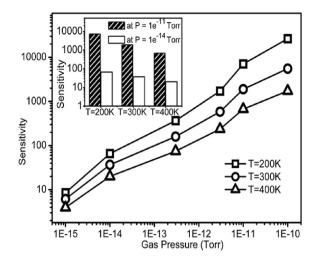

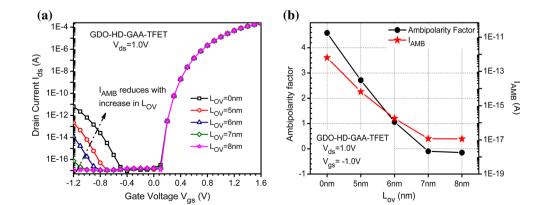

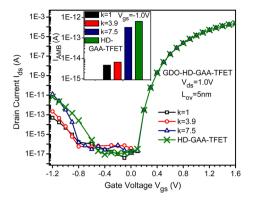

Afterwards, for comprehensively upgrading the performance of HD-GAA-TFET, the gate metal is overlapped near drain side that suppresses the ambipolar conduction. Extensive device simulations have been done to examine an optimum gate-drain overlap length ( $L_{ov}$ ) at which the ambipolar current ( $I_{AMB}$ ) is reduced efficiently. It is obtained that by overlapping the gate metal over the drain, the  $I_{AMB}$  is reduced to an order of  $10^{-17}$ A. Additionally, the applicability of the HD-GAA-TFET as a Hydrogen gas sensor has been suggested by utilizing a Palladium (Pd) metal gate. Primarily, the Pd supported SiO<sub>2</sub> is used as a sensing media and sensing relies on the interaction of hydrogen gas molecules with Pd-SiO<sub>2</sub>-Si. The sensitivity of the proposed gas sensor is compared with its conventional counterparts and it is obtained that the proposed design of gas sensor has appreciably high sensitivity. Further, the stability of the sensor with respect to temperature affectability has also been studied, and it is found that the device is reasonably stable and highly sensitive over the bearable temperature range. The successful utilization of HD-GAA-TFET in gas sensors may open a new door for the development of novel nanostructure gas sensing devices with a sensitivity of the order of  $10^{-3}$  i.e. considerably higher than as obtained for a conventional MOSFET.

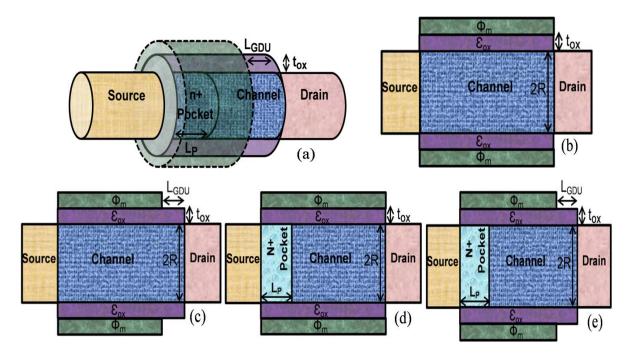

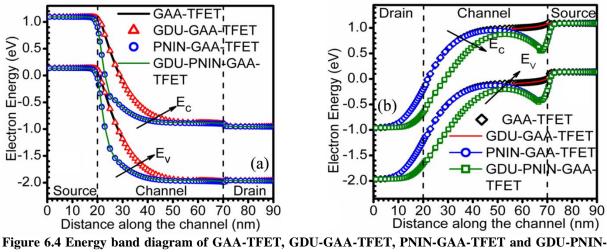

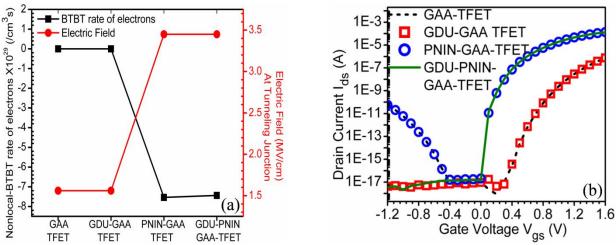

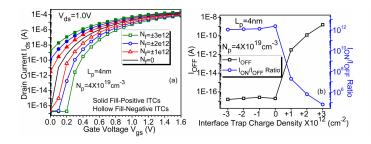

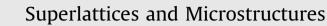

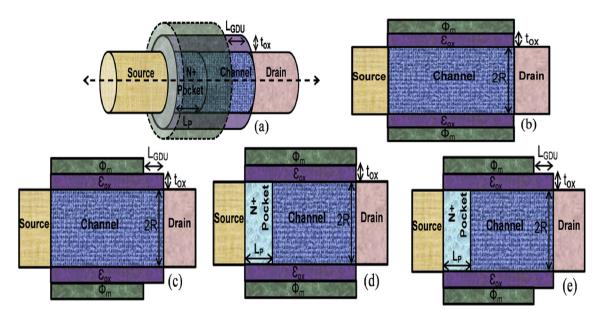

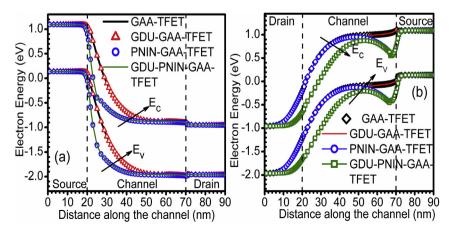

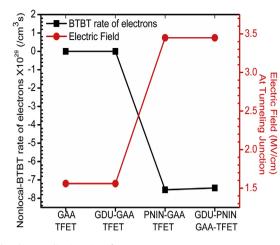

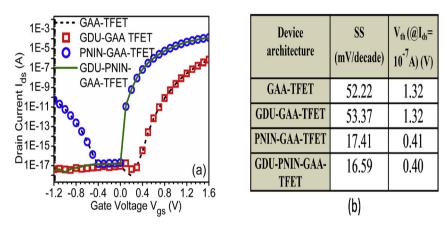

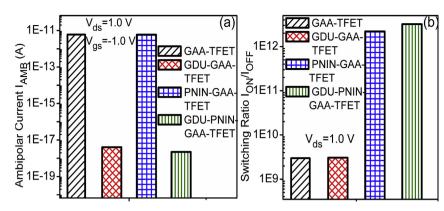

Another effort to overcome the major shortcoming of conventional TFET is done by integrating the efficient engineering schemes i.e. a  $n^+$  source pocket and gate-drain underlapping (GDU) on GAA-TFET that form GDU-PNIN-GAA-TFET. The  $n^+$  source pocket improves the analog and RF characteristics; on the other hand, the GDU controls the ambipolar conduction. Thereby, the GDU-PNIN-GAA-TFET gathers the collective merits of GDU (reduces the  $I_{AMB}$ ) and  $n^+$  source pocket (enhances  $I_{ON}$ ). Hence, GDU-PNIN-GAA-TFET results in an up-gradation in the overall performance and offers a SS of 17mV/decade at a V<sub>th</sub> of 0.4V,  $I_{AMB}$  of  $10^{-18}$ A, and  $I_{ON}/I_{OFF}$  ratio of the order of  $10^{12}$ .

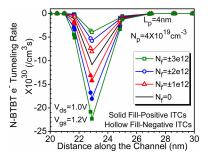

Furthermore, the reliability issues of the PNIN-GAA-TFET have also been discussed. To study the reliability issues, at first, the effect of ITCs polarity, which is common during the pre and post-fabrication process, has been studied on the device analog/RF characteristics followed by the influence of ITCs density. Additionally, to examine the temperature robustness of the PNIN-GAA-TFET various electrical, analog and high-frequency parameters have been examined under different trap charge density and polarity at wide temperature

range. It is revealed that the donor traps are much hazardous in comparison to acceptor traps. In fact, at substantially higher density of donor traps, the subthreshold characteristics are found to be degraded tremendously that reduces the current switching ratio from an order of  $10^{12}$  to  $10^5$ . The temperature associativity reveals that PNIN-GAA-TFET has positive temperature coefficient in contrast to MOSFET. Moreover, the PNIN-GAA-TFET promises bearable immunity against ITCs along with stability to employ under wide temperature range.

Thus, the lower SS, high current switching ratio, lower  $I_{OFF}$ , superior RF performance, temperature robustness, and better reliability in terms of ITCs makes HD-GAA-TFET and PNIN-GAA-TFET, a promising candidate for employing in a low power, high switching speed and high performance applications even at wide temperature range.

# LIST OF FIGURES

| <b>Figure 1.1</b> (a) Schematic view of basic n-Type TFET (b) energy band diagram of 100nm n-Type TFET in OFF, ON and ambipolar state, with 100nm channel length; the n <sup>+</sup> doped region is positive biased and p <sup>+</sup> doped region is grounded ( <i>Wang et al., 2004</i> ) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Schematic representation of a p-type DMG-TFET (Vishnoi and Kumar, 2014)9                                                                                                                                                                                                           |

| Figure 1.3 Schematic representation of a hetero gate dielectric TFET ( <i>Choi and Lee, 2010</i> )10                                                                                                                                                                                          |

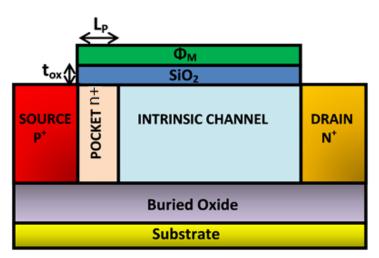

| Figure 1.4 Schematic device structure of n <sup>+</sup> source pocket PIN-TFET or PNIN-TFET11                                                                                                                                                                                                 |

| Figure 1.5 Schematic view of gate-drain overlapped TFET (GDO-TFET) (Abdi and Kumar, 2014)13                                                                                                                                                                                                   |

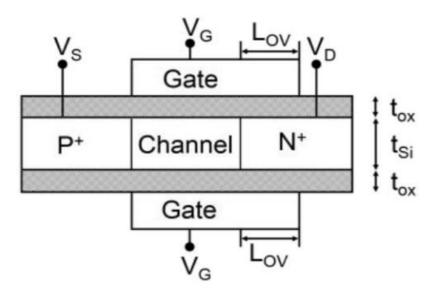

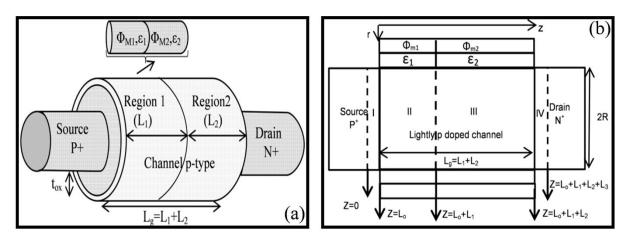

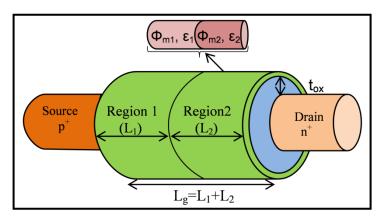

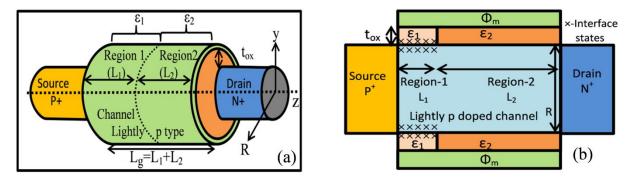

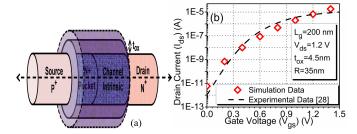

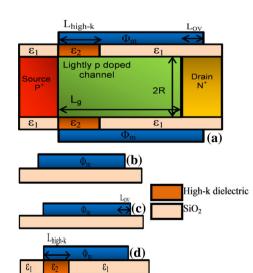

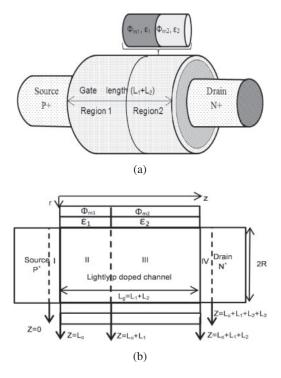

| Figure 2.1 Structure of n-type Heterogate Dielectric- Gate Metal Engineered-Gate all Around-Tunnel<br>FET (HD-GME-GAA-TFET) (a) simulated 3D view (b) schematic two-dimensional cross-<br>sectional view (Madan et al., 2015a, Madan et al., 2016)                                            |

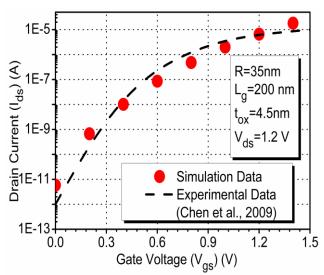

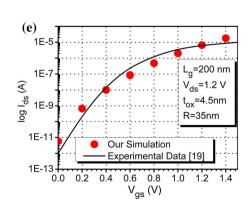

| Figure 2.2 Comparison of experimental published result ( <i>Chen et al., 2009</i> ), and simulated I <sub>ds</sub> -V <sub>gs</sub> characteristics of 200nm gate length SiNW-TFET at V <sub>ds</sub> =1.2V, T <sub>ox</sub> =4.5nm, diameter=70nm of GAA-TFET                                |

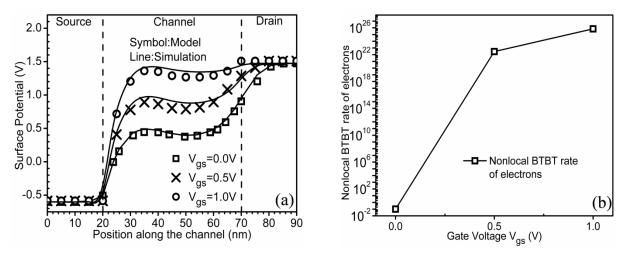

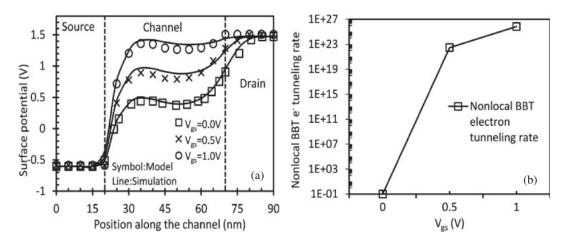

| Figure 2.3 (a) Surface Potential along the channel length from source to drain, for V <sub>gs</sub> =0.0 V, 0.5 V and 1.0 V at V <sub>ds</sub> =1V. (b) Nonlocal BTBT electron tunneling rate as a function of V <sub>gs</sub> ( <i>Madan et al.</i> , 2015a)                                 |

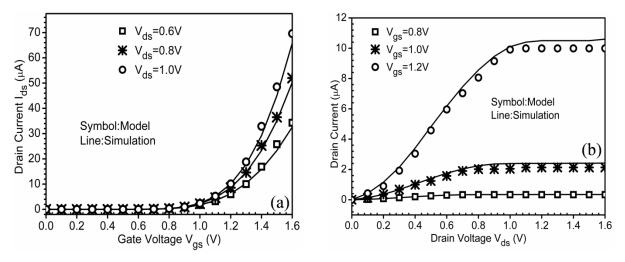

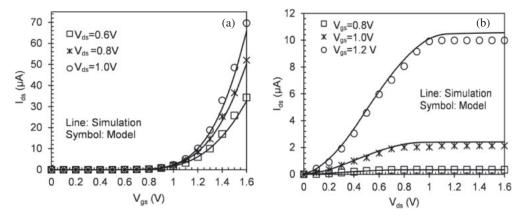

| Figure 2.4 Impact of (a) drain bias on transfer characteristics and (b) gate bias on output characteristics ( <i>Madan et al., 2015a</i> )                                                                                                                                                    |

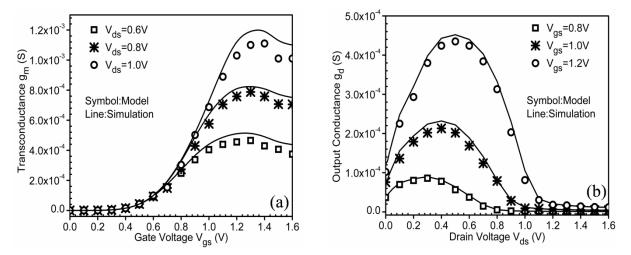

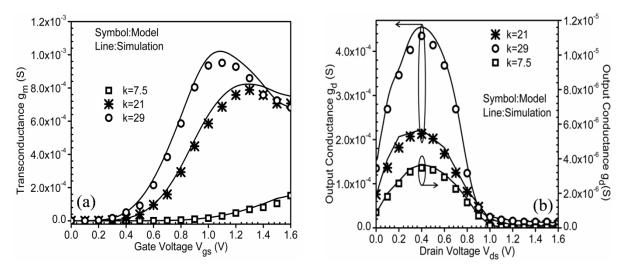

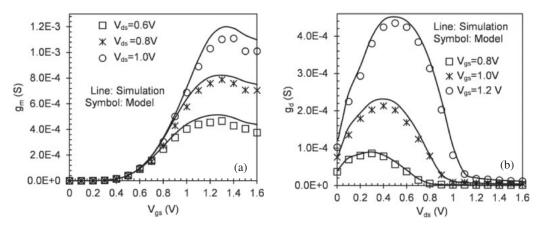

| Figure 2.5 Impact of (a) drain bias on transconductance and (b) gate bias on output conductance (Madan et al., 2015a)                                                                                                                                                                         |

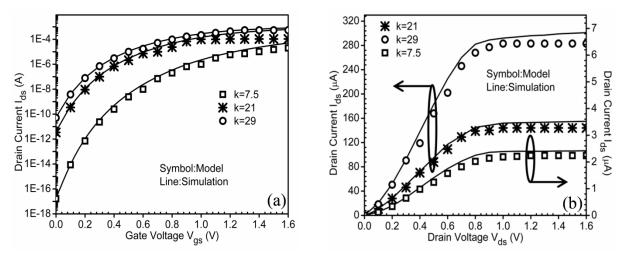

| <b>Figure 2.6</b> (a) Drain current as a function of $V_{gs}$ for different high-k dielectric at $V_{ds}$ =0.8V. (b) Drain current as a function of $V_{ds}$ for different high-k dielectric at $V_{gs}$ =1.0V ( <i>Madan et al.</i> , 2015a)                                                 |

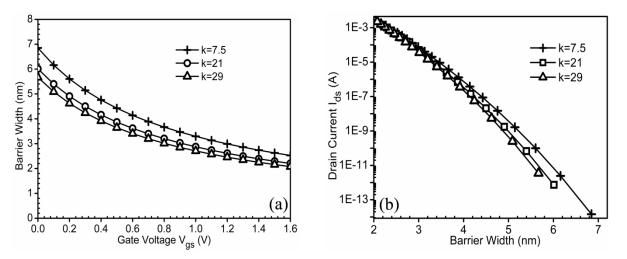

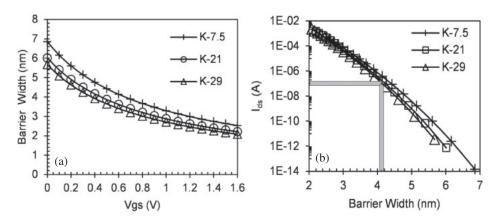

| <b>Figure 2.7</b> (a) Barrier width as a function of $V_{gs}$ for different high-k dielectric, (b) Drain current as a function of barrier width for different high-k dielectric ( <i>Madan et al., 2015a</i> )45                                                                              |

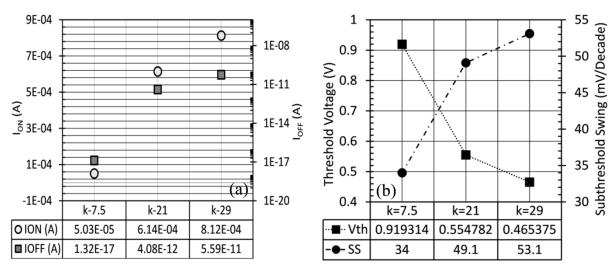

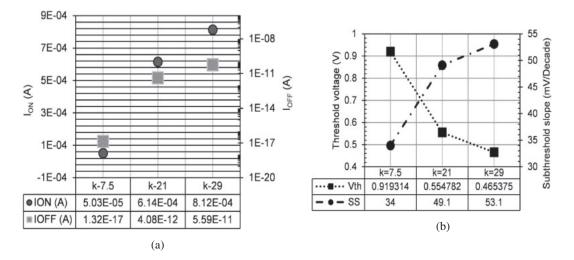

| <b>Figure 2.8</b> (a) Tunneling Current I <sub>ON</sub> and I <sub>OFF</sub> (b) V <sub>th</sub> and SS of HD-GME-GAA-TFET for various high-k ( <i>Madan et al., 2015a</i> )                                                                                                                  |

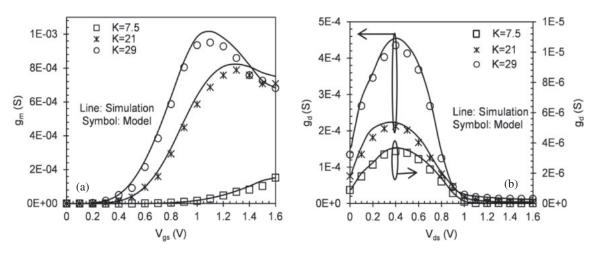

| Figure 2.9 (a) g <sub>m</sub> as a function of gate bias for different high-k dielectric. (b) g <sub>d</sub> as a function of V <sub>ds</sub> for different high-k dielectric ( <i>Madan et al.</i> , 2015a)                                                                                  |

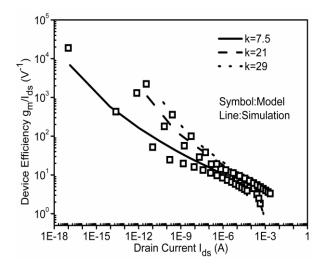

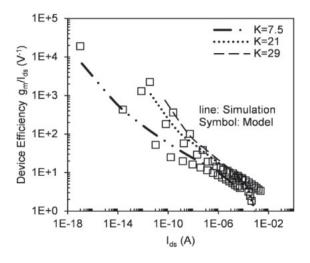

| Figure 2.10 Device efficiency as a function of tunneling current for different high-k dielectric (Madara et al., 2015a).                                                                                                                                                                      |

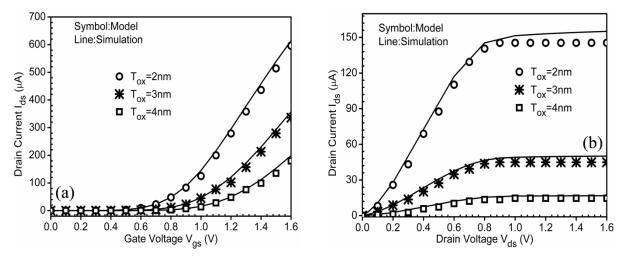

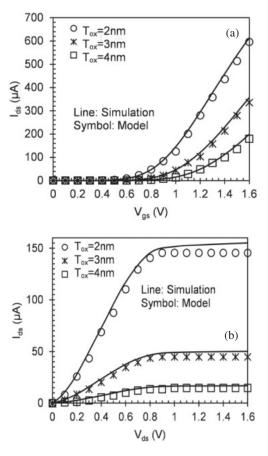

| <b>Figure 2.11</b> (a) Drain current as a function of $(V_{gs})$ for different $T_{ox}$ at $V_{ds}$ =0.8V. (b) Drain current as a function of $(V_{ds})$ for different $T_{ox}$ at $V_{gs}$ =1.0V ( <i>Madan et al.</i> , 2015a)                                                              |

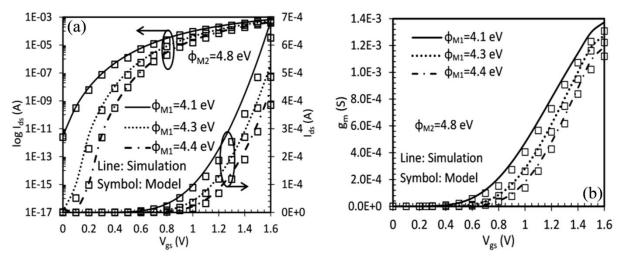

| Figure 2.12 (a) Transfer characteristics $(I_{ds}-V_{gs})$ in log and linear scale (b) Transconductance (g | g <sub>m</sub> ) as a |

|------------------------------------------------------------------------------------------------------------|-----------------------|

| function of $V_{gs}$ for different metal work function for HD-GME-GAA-TFET at c                            | onstant               |

| V <sub>ds</sub> =1.0 V ( <i>Madan et al.</i> , 2016)                                                       | 50                    |

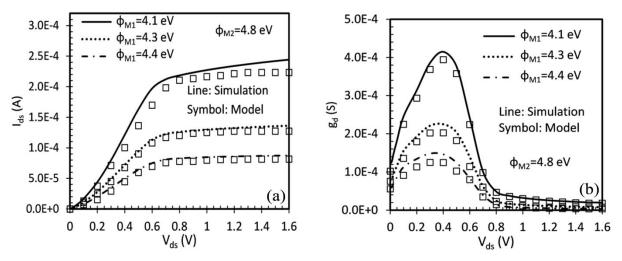

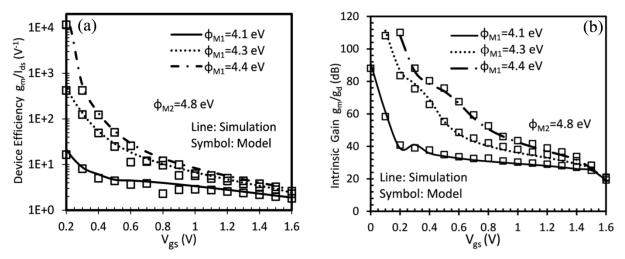

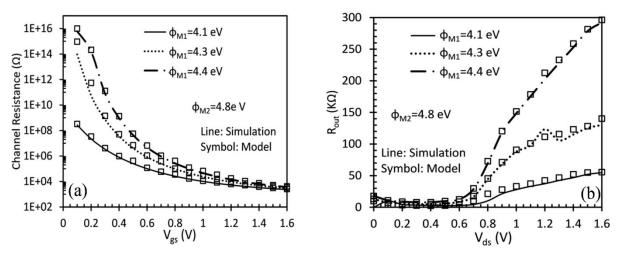

**Figure 2.14** (a) Output characteristics ( $I_{ds}$ - $V_{ds}$ ) and (b) output conductance ( $g_d$ ) for different metal work function of HD-GME-GAA-TFET at constant  $V_{gs}$ =1.2 V (*Madan et al., 2016*). ......51

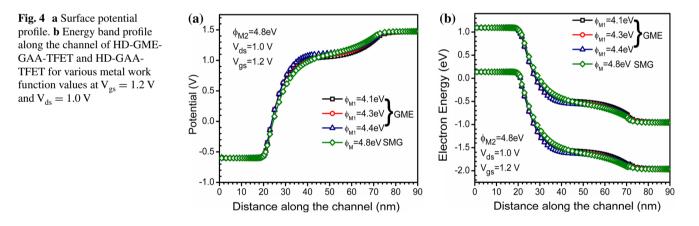

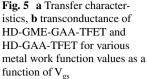

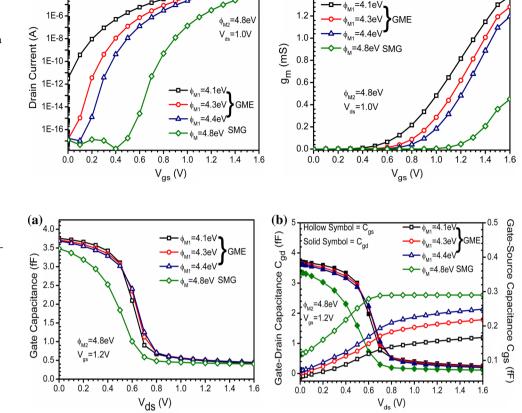

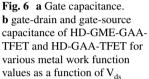

- **Figure 3.2** (a) Transfer characteristics (b) Transconductance of HD-GME-GAA-TFET and HD-GAA-TFET for various metal work function values as a function of V<sub>gs</sub> (*Madan et al., 2016*)...63

- **Figure 3.9** Y-parameters of HD-GME-GAA-TFET and HD-GAA-TFET as a function of frequency at  $V_{gs}=1.2V$  and  $V_{ds}=1.0V$ . (a)  $Y_{11}$ , (b)  $Y_{12}$ , (c)  $Y_{21}$ , (d)  $Y_{22}$  (*Madan et al., 2016*)......70

| Figure 4.1 | (a)   | Structure of    | n-typ | pe Heterogei | neous gate Diele | ctric-GA | A-' | ГFET (HD- <b>C</b> | GAA-TFET) | used |

|------------|-------|-----------------|-------|--------------|------------------|----------|-----|--------------------|-----------|------|

|            | for   | simulation      | (b)   | Schematic    | cross-sectional  | view     | of  | cylindrical        | HD-GAA-   | ГFET |

|            | illus | strating the IT | ГCs ( | Madan and    | Chaujar, 2016, 1 | Madan a  | nd  | Chaujar, 201       | 17)       | 78   |

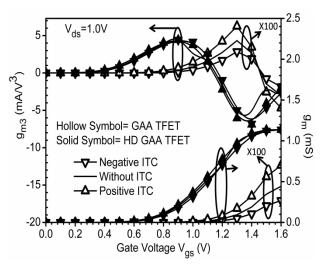

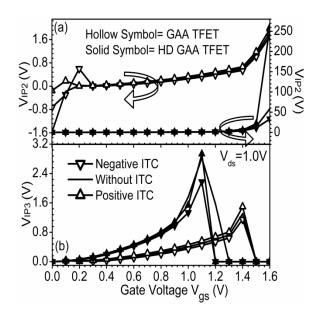

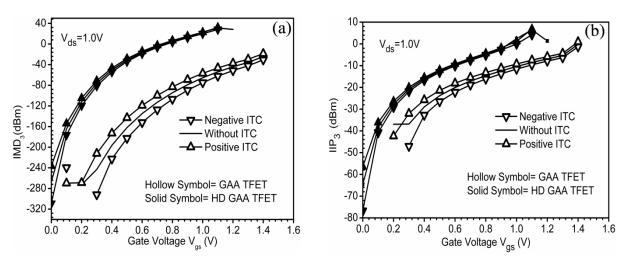

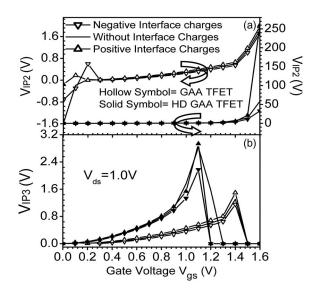

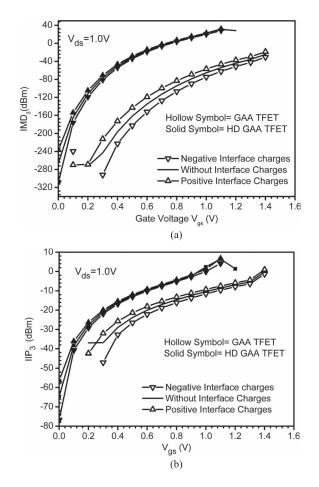

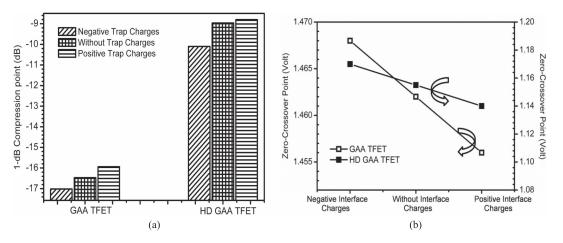

Figure 4.11 (a) IMD3 and (b) IIP3 as a function of gate bias of HD-GAA-TFET and GAA-TFET for various types of ITCs (*Madan and Chaujar*, 2016)......90

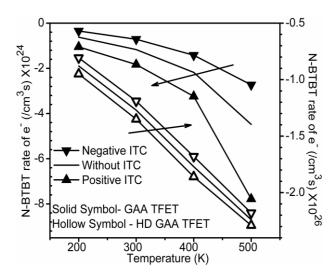

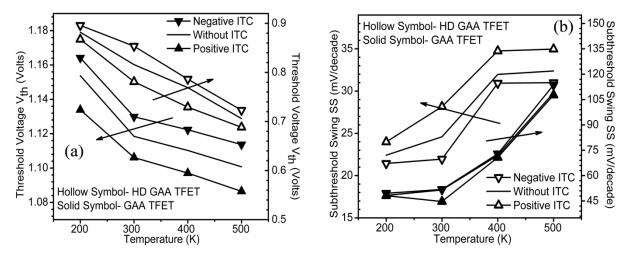

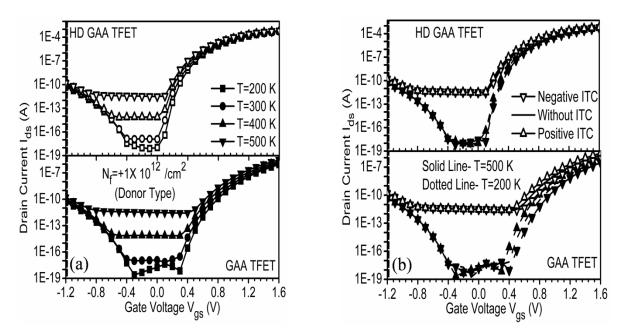

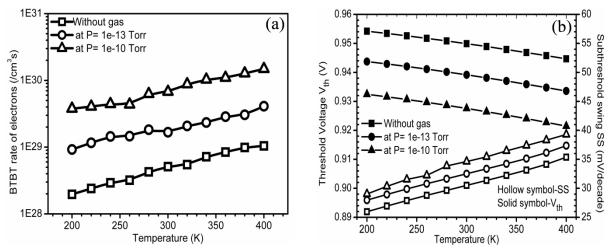

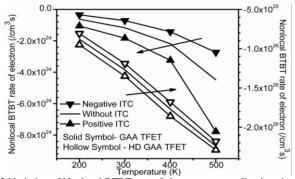

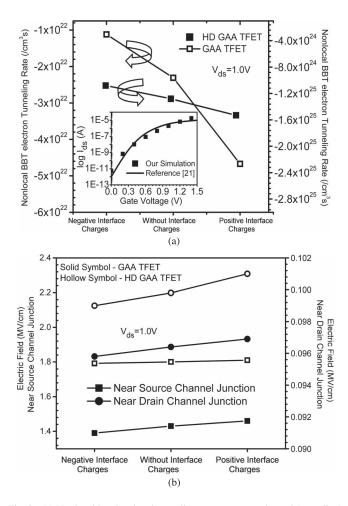

Figure 4.13 Variation of Nonlocal BTBT rate of electrons at tunneling junction with respect to temperature at  $V_{gs}$ =1.2 V and  $V_{ds}$ =1.0 V, for GAA-TFET and HD-GAA-TFET for fixed ITC density,  $N_f = \pm 1 \times 10^{12}$  cm<sup>-2</sup>, and absence of ITC (*Madan and Chaujar, 2017*). ......92

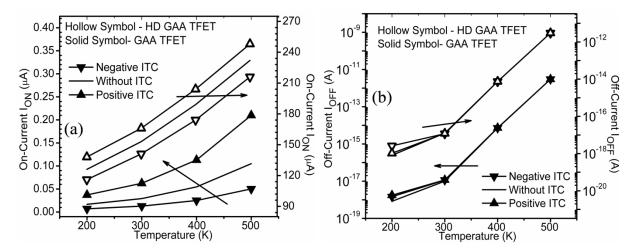

- Figure 4.16 Impact of temperature and ITCs on (a) ON-state current (at  $V_{gs}=1.2V$  and  $V_{ds}=1.0V$ ) and, (b) OFF-state current (at  $V_{gs}=0V$  and  $V_{ds}=1.0V$ ) of GAA-TFET and HD-GAA-TFET for fixed ITC density,  $N_f=\pm 1\times 10^{12}$  cm<sup>-2</sup>, and absence of ITC (*Madan and Chaujar, 2017*).....96

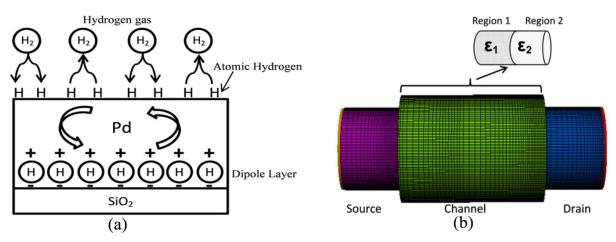

- Figure 5.2 (a) Schematic of adsorption of H<sub>2</sub> gas molecules, diffused through Pd films and formation of dipoles at the Pd-SiO<sub>2</sub> interface. (b) Meshed structure of HD-GAA-TFET gas sensor (Madan and Chaujar, 2016b).

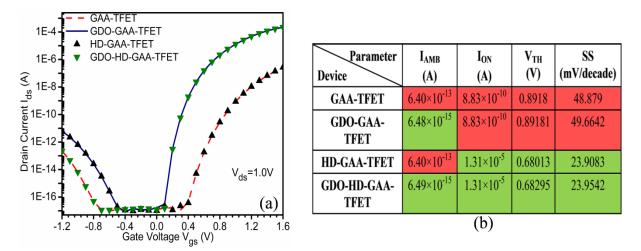

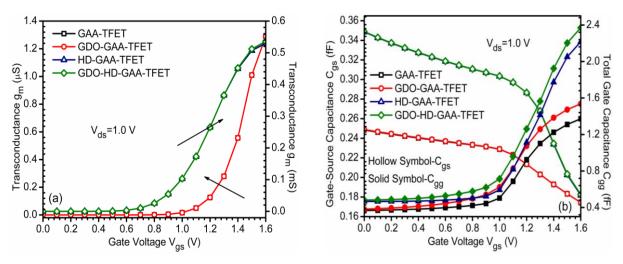

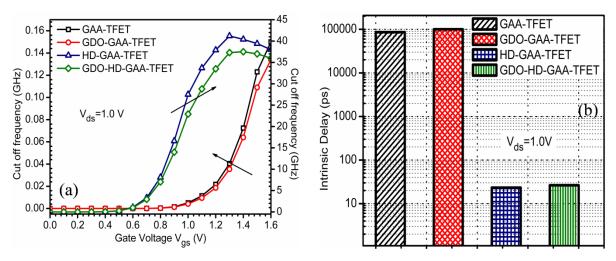

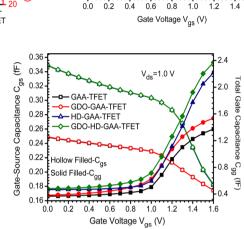

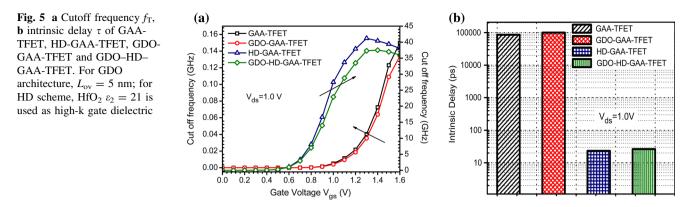

- **Figure 5.5** (a) Cut off frequency ( $f_T$ ), (b) intrinsic delay ( $\tau$ ) of GAA-TFET, HD-GAA-TFET, GDO-GAA-TFET, and GDO-HD-GAA-TFET. For GDO architecture,  $L_{ov}$ =5nm; for HD scheme, HfO<sub>2</sub>  $\mathcal{E}_2$ =21 is used as high-k gate dielectric (*Madan and Chaujar, 2016a*). ..... 116

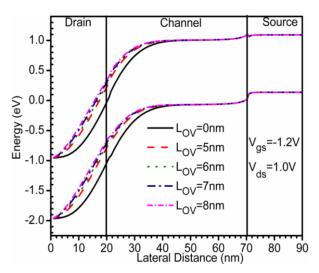

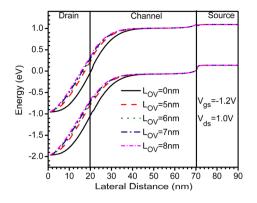

- Figure 5.7 Energy band diagram along the channel length of GDO-HD-GAA-TFET at constant  $V_{ds}$ =1.0V and  $V_{gs}$ =-1.2V for various  $L_{OV}$ =0, 5, 6, 7 and 8nm (Madan and Chaujar, 2016a).

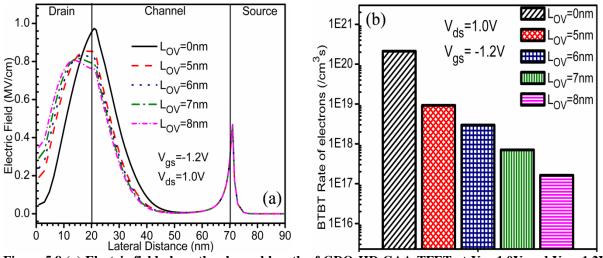

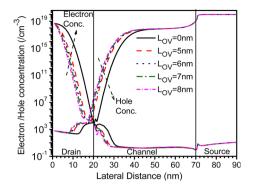

- Figure 5.8 (a) Electric field along the channel length of GDO-HD-GAA-TFET at V<sub>ds</sub>=1.0V and V<sub>gs</sub>=-1.2V for various L<sub>OV</sub>=0, 5, 6, 7 and 8nm (b) BTBT rate of electrons at the drain channel junction for all the cases (*Madan and Chaujar, 2016a*)......119

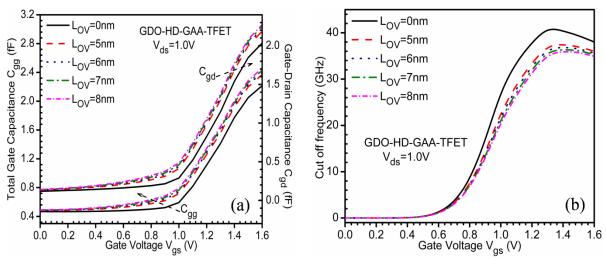

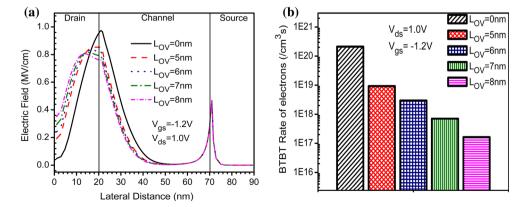

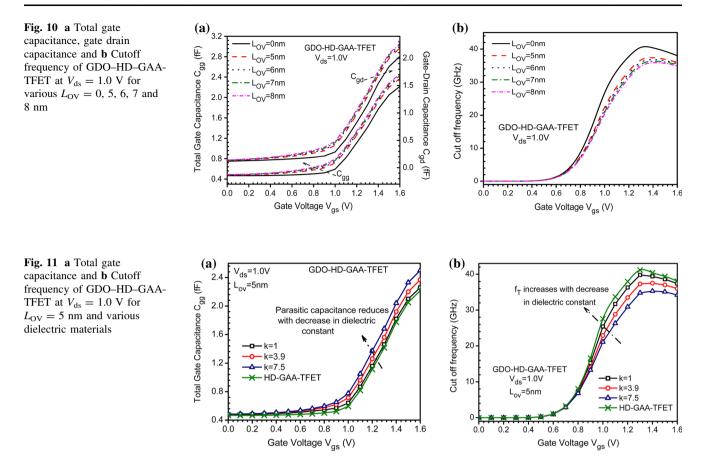

- **Figure 5.9** (a) Total gate capacitance, gate-drain capacitance and (b) Cut-off frequency of GDO-HD-GAA-TFET at V<sub>ds</sub>=1.0V for various L<sub>OV</sub>=0, 5, 6, 7 and 8nm (*Madan and Chaujar, 2016a*).

- Figure 5.10 (a) Total gate capacitance and (b) Cut-off frequency of GDO-HD-GAA-TFET at  $V_{ds}$ =1.0V for L<sub>OV</sub>=5nm and various dielectric materials (*Madan and Chaujar, 2016a*)...121

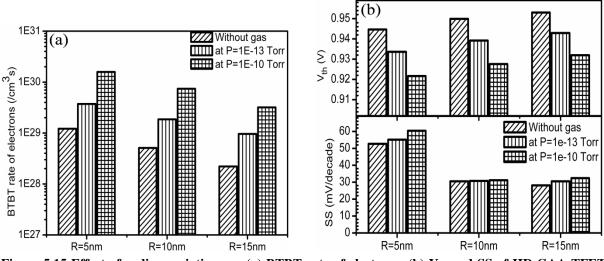

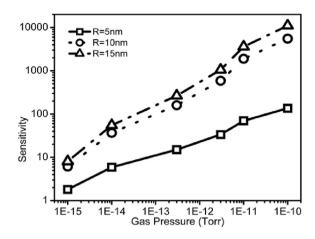

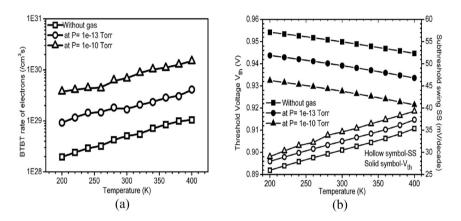

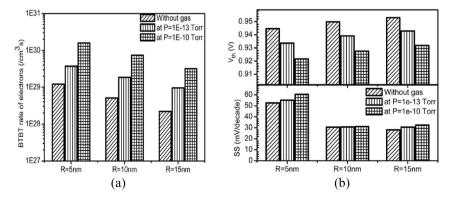

- Figure 5.13 Sensitivity comparison of HD-GAA-TFET as a function of gas pressure at (a) different radius (b) various temperatures. *Inset:* Sensitivity at constant pressures values at temperature= 200K, 300K and 400K for HD-GAA-TFET (*Madan and Chaujar, 2016b*).

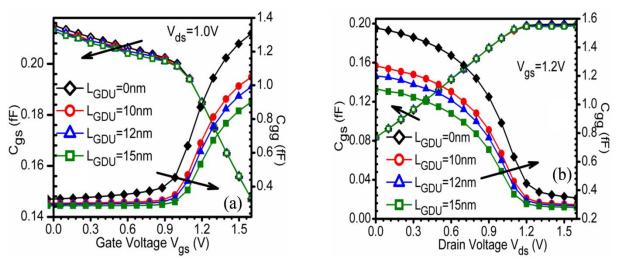

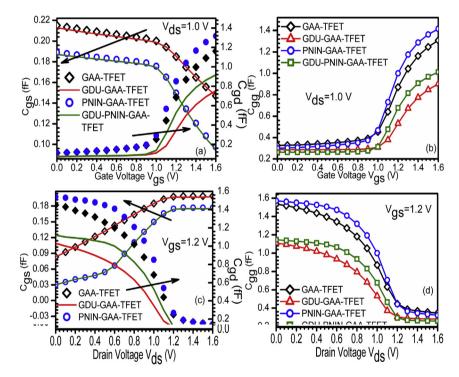

- **Figure 6.3** C<sub>gs</sub> and C<sub>gg</sub> of GDU-GAA-TFET as a function of (a) V<sub>gs</sub> at V<sub>ds</sub>=1.0V (b) V<sub>ds</sub> at V<sub>gs</sub>=1.2V at various L<sub>GDU</sub> L<sub>GDU</sub>=0nm signifies GAA-TFET (*Madan and Chaujar*, 2017a).....138

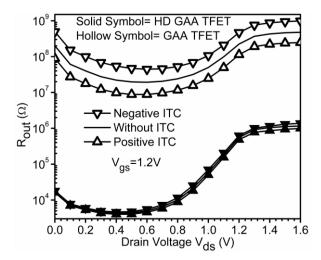

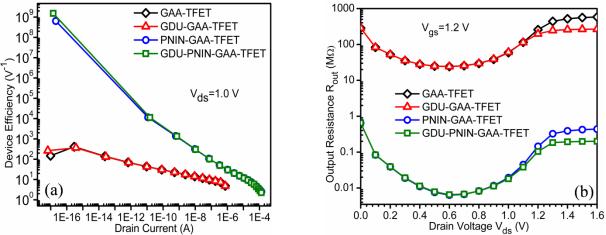

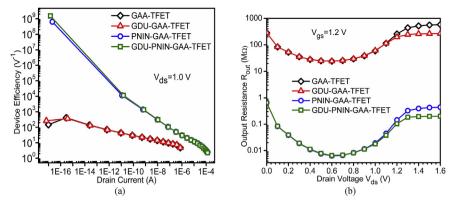

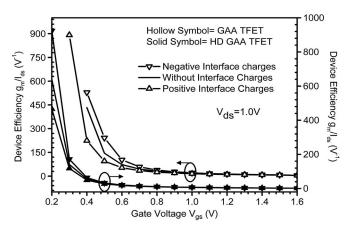

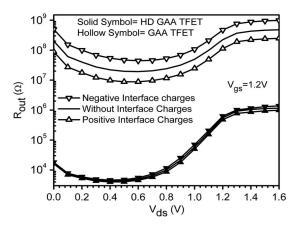

- **Figure 6.6** (a) Device efficiency at V<sub>ds</sub>=1.0V, (b) Output resistance (R<sub>out</sub>) at V<sub>gs</sub>=1.2V of GAA-TFET, GDU-GAA-TFET, PNIN-GAA-TFET and GDU-PNIN-GAA-TFET (*Madan and Chaujar*, 2017a).

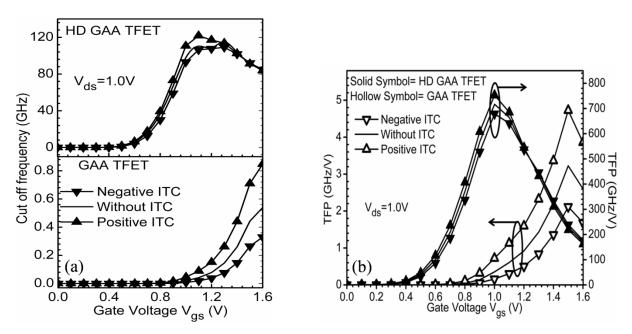

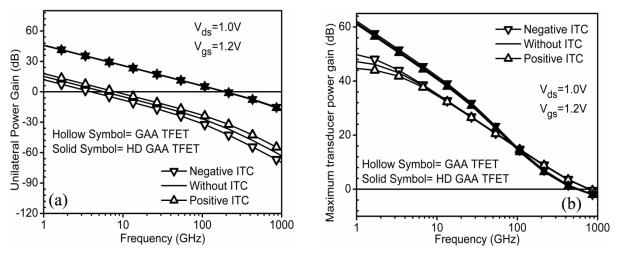

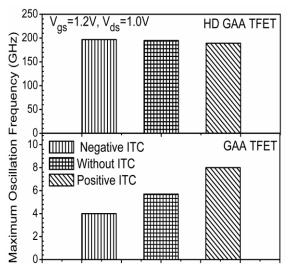

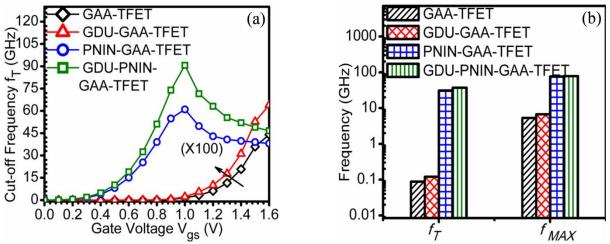

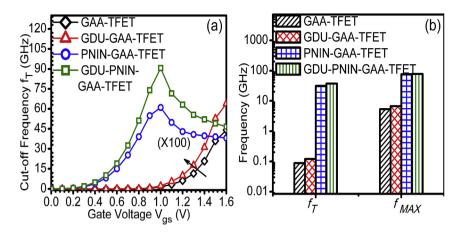

**Figure 6.8** (a)  $f_T$  as a function of gate bias, at constant  $V_{ds}=1.0V$  (b)  $f_T$  and  $f_{Max}$  at  $V_{gs}=1.2V$  and  $V_{ds}=1.0V$  of GAA-TFET, GDU-GAA-TFET, PNIN-GAA-TFET and GDU-PNIN-GAA-TFET (Madan and Chaujar, 2017a).

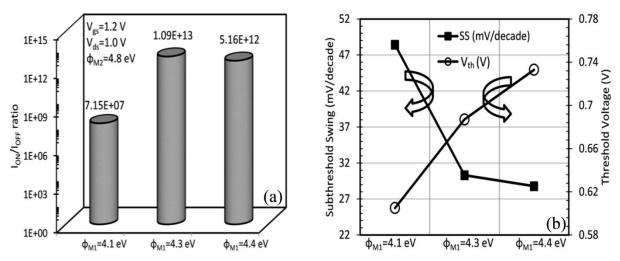

- **Figure 6.11** Impact of ITC density on (a)  $I_{OFF}$  and switching ratio (b)  $V_{th}$  and SS of PNIN-GAA-TFET at  $N_f = \pm 1, 2, 3(\times 12) \text{ cm}^{-2}$  (*Madan and Chaujar, 2017b*)......148

- Figure 6.14 Variation of n-BTBT rate of electrons at the tunneling junction as a function of temperature of PNIN-GAA-TFET at  $N_f = \pm 1 \times 12 \text{ cm}^{-2}$  (Madan and Chaujar, 2017b)......151

- Figure 6.15 (a) Drain current (b)  $I_{OFF}$  and current switching ratio as a function of temperature (200-400K) of PNIN-GAA-TFET at  $N_f = \pm 1 \times 12$  cm<sup>-2</sup>(*Madan and Chaujar, 2017b*)......152

- **Figure 6.16** (a)  $V_{th}$  and SS as a function of temperature (b) output characteristics at  $V_{gs}$ =1.2V, for temperature range of (200-400K) of PNIN-GAA-TFET (*Madan and Chaujar*, 2017b)...153

# LIST OF TABLES

| Table 2.1 Device Geometrical Parameters and the Default Values Used in the Analysis (Madan et al., 2015a).                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

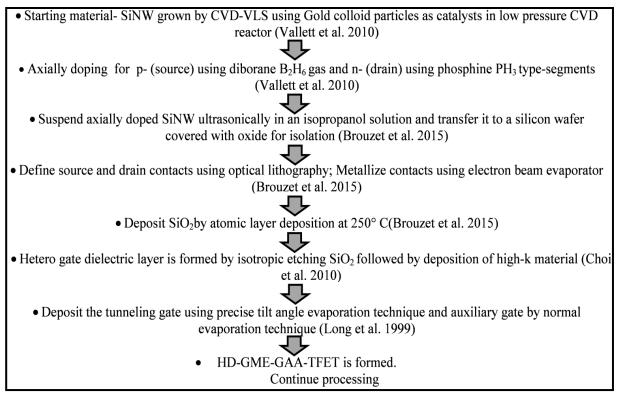

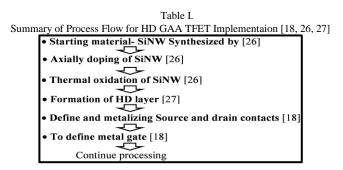

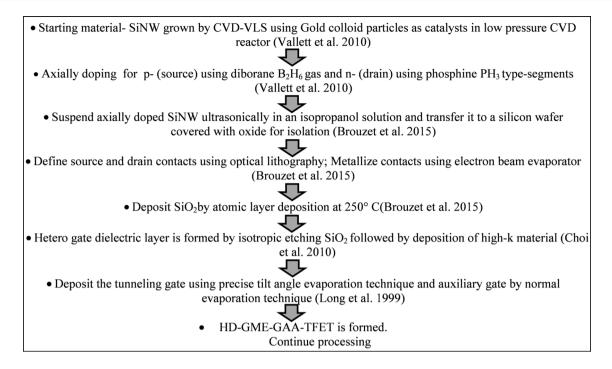

| Table 2.2 Summary of Fabrication Process Flow for HD-GME-GAA-TFET Implementation (Brouzed et al., 2015, Choi and Lee, 2010, Long et al., 1999, Vallett et al., 2010).                                                                                                                                 |

| Table 2.3 List of Constant Parameters (Madan et al., 2016)    38                                                                                                                                                                                                                                      |

| Table 5.1 Device Parameters and Values (Madan and Chaujar, 2016a)                                                                                                                                                                                                                                     |

| Table 5.2 Default Structural Parameters for all the Devices Based Gas Sensors (Madan and Chaujar, 2016b).         112                                                                                                                                                                                 |

| Table 6.1 Device Default Design Parameters Used in Simulations (Madan and Chaujar, 2017a)136                                                                                                                                                                                                          |

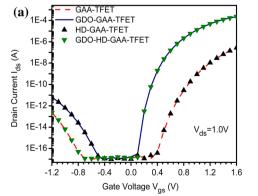

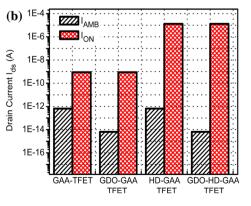

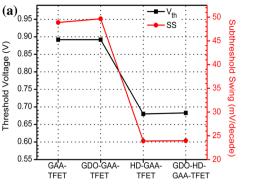

| <b>Table 6.2</b> Ambipolar Current ( $I_{amb}$ ) at $V_{gs}$ =-1.0V, Current switching ratio ( $I_{on}/I_{off}$ ), Threshold voltage ( $V_{th}$ ) and Subthreshold swing (SS) of GAA-TFET, GDU-GAA-TFET, PNIN-GAA-TFET and GDU-PNIN-GAA-TFET at $V_{ds}$ =1.0V ( <i>Madan and Chaujar</i> , 2017a)141 |

# LIST OF PUBLICATIONS

### CHAPTER'S CONTRIBUTED IN BOOKS (1)

1. **J. Madan** and R. Chaujar, "Effect of Nanoscale Structure on Reliability of Nano Devices and Sensors," in Outlook and Challenges of Nano Devices, Sensors, and MEMS, T. Li and Z. Liu, Eds., ed Cham: Springer International Publishing, 2017, pp. 239-270.

#### ARTICLES IN INTERNATIONAL REFEREED JOURNALS (10)

- J. Madan and R. Chaujar, "Numerical Simulation of N+ Source Pocket PIN-GAA-Tunnel FET: Impact of Interface Trap Charges and Temperature," *IEEE Transactions on Electron Devices*, vol. 64, pp. 1482-1488, 2017. (*I.F.-2.605*)

- 2. J. Madan and R. Chaujar, "Gate Drain Underlapped-PNIN-GAA-TFET for Comprehensively Upgraded Analog/RF Performance," *Superlattices and Microstructures*, vol. 102, pp. 17-26, Feb. 2017. (*I.F.-2.123*)

- J. Madan and R. Chaujar, "Temperature Associated Reliability Issues of Heterogeneous Gate Dielectric - Gate All Around - Tunnel FET," *IEEE Transactions on Nanotechnology*, 2017, DOI: 10.1109/TNANO.2017.2650209. (I.F.-2.485)

- 4. J. Madan, R. Gupta, and R. Chaujar, "Mathematical modeling insight of hetero gate dielectricdual material gate-GAA-tunnel FET for VLSI/analog applications," Microsystem Technologies, vol. 23, pp. 4091-4098, September 01 2017. (*I.F.-1.195*)

- 5. J. Madan, R. Gupta, and R. Chaujar, "Performance investigation of heterogeneous gate dielectric-gate metal engineered–gate all around-tunnel FET for RF applications," Microsystem Technologies, vol. 23, pp. 4081-4090, September 01 2017. (*I.F.-1.195*)

- 6. J. Madan and R. Chaujar, "Interfacial Charge Analysis of Heterogeneous Gate Dielectric-Gate All Around-Tunnel FET for Improved Device Reliability," *IEEE Transactions on Device and Materials Reliability*, vol. 16, pp. 227-234, 2016. (*I.F.-1.575*)

- J. Madan and R. Chaujar, "Palladium gate all around-Hetero dielectric-tunnel FET based highly sensitive hydrogen gas sensor," *Superlattices and Microstructures*, vol. 100, pp. 401-408, 2016. DOI: http://dx.doi.org/10.1016/j.spmi.2016.09.050. (*I.F.-2.123*)

- 8. **J. Madan** and R. Chaujar, "Gate drain-overlapped-asymmetric gate dielectric-GAA-TFET: a solution for suppressed ambipolarity and enhanced ON state behavior," *Applied Physics A*, vol. 122, p. 973, 2016. (*I.F.-1.455*)

- 9. J. Madan, R. Gupta, and R. Chaujar, "Analytical drain current formulation for gate dielectric engineered dual material gate-gate all around-tunneling field effect transistor," *Japanese Journal of Applied Physics*, vol. 54, p. 094202, 2015. (*I.F.-1.384*)

- J. Madan, R.S Gupta, R. Chaujar. "Influence of Heterogeneous Gate Dielectric on Hetero-Dielectric-DMG-GAATFET for improved tunneling current," *International Journal of Advanced Technology in Engineering and Science*, 2(1), September 2014, pp.-41-47. (*I.F.-2.870*)

#### ARTICLES COMMUNICATED IN INTERNATIONAL JOURNALS (1)

1. **J. Madan** and R. Chaujar, "PNIN - Gate All Around - TFET Employed to Nose Diverse Organic Vapors: - A Simulation Study," IEEE Sensors Journal.

#### ARTICLES IN INTERNATIONAL CONFERENCES (12)

- 1. J. Madan, S. Shekhar and R. Chaujar, "Gate Metal Engineered Heterojunction DG-TFETs for Superior Analog Performance and Enhanced Device Reliability", in Conference on Information and Communication Technology CICT-2017, IIITM Gwalior, India, November 3-5, 2017.

- 2. J. Madan, S. Shekhar, and R. Chaujar, "PNIN-GAA-tunnel FET with palladium catalytic metal gate as a highly sensitive hydrogen gas sensor," in *Simulation of Semiconductor Processes and Devices* (SISPAD), 2017 International Conference on, 2017, pp. 197-200.

- 3. J. Madan, S. Shekhar and R. Chaujar, "Source Material Assessment of Heterojunction DG-TFET for Improved Analog Performance", in International Conference on Microelectronics Devices, Circuits and Systems (ICMDCS 2017), VIT University, Vellore India, 10-12<sup>th</sup> August 2017.

- 4. H. Arora, **J. Madan** and R. Chaujar, "Impact on Analog and Linearity performance of nanoscale AlGaN/GaN HEMT with variation in surface passivation stack", in International Conference on Advanced Nano Material, University of Aveiro-Portugal, July 19-21, 2017.

- 5. J. Madan, R. Pandey and R. Chaujar, "Gate Drain Underlapping: A Performance Enhancer for HD-GAA-TFET", in International Conference on Advanced Nano Material, University of Aveiro-Portugal, July 19-21, 2017.

- J. Madan and R. Chaujar, "Influence of Temperature Variations on Radio Frequency Performance of PNIN Gate All Around Tunnel-FET", in International Conference on 2<sup>nd</sup> IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT - 2017), pp. 1110-1114, Bengaluru, India, 19-20 May 2017, DOI: 978-1-5090-3704-9.

- J. Madan and R. Chaujar, "Temperature associated reliability issues of heterogeneous gate dielectric-gate all around-tunnel FET," in Nanoelectronics Conference (INEC), 2016 IEEE International, Chengdu, China, 9-11 May, 2016, pp. 1-2, DOI: 10.1109/INEC.2016.7589278.

- 8. J. Madan, R.S. Gupta and R. Chaujar, "Impact of Heterogeneous Gate Dielectric and Gate Metal Engineering on Analog and RF Performance of GAA TFET," in 18<sup>th</sup> International Workshop on Physics of semiconductor devices,(IWPSD-2015), 7-10<sup>th</sup> December, 2015.

- J. Madan, R.S Gupta, R. Chaujar. "Capacitive Analysis of Heterogeneous Gate Dielectric-Gate Metal Engineered–Gate All Around-Tunnel FET for RF Applications," in 2<sup>nd</sup> International Conference on Microelectronics, circuits and systems, Micro-2015, Vol. 1, pp.6-10, Kolkata, 11-12th July, 2015, ISBN-81-85824-46-0.

- 10.J. Madan, R.S Gupta, R. Chaujar. "Drain current Analysis of Hetero Gate Dielectric-Dual Material Gate–GAA-Tunnel FET," in 2<sup>nd</sup> International Conference on Microelectronics, circuits and systems, Micro-2015, Vol. 2, pp.57-61, Kolkata, 11-12th July, 2015, ISBN-81-85824-46-0.

- 11.J. Madan, R.S Gupta, R. Chaujar, "TCAD Analysis of Small Signal Parameters and RF Performance of Heterogeneous Gate Dielectric-Gate All Around Tunnel FET," Tech Connect World Innovation Conference and Expo, Chapter 6, "Nanoelectronics, Materials and Devices",

pp.189-192, June 14-17, 2015, Gaylord National Resort and Convention Center, National Harbor, Maryland, just outside of Washington, D.C., U.S.A.

12.J. Madan, R.S Gupta, R. Chaujar, "Threshold voltage model of a Hetero Gate Dielectric Dual Material Gate GAA Tunnel FET," Tech Connect World Innovation Conference and Expo, Chapter 7, "Modeling and Simulation of Microsystems", pp.254-257, June 14-17, 2015, Gaylord National Resort and Convention Center, National Harbor, Maryland, just outside of Washington, D.C., U.S.A.

#### ARTICLES IN NATIONAL CONFERENCES (1)

J. Madan and R. Chaujar. "Source Pocket Parameters Assessment of PNIN-GAA-TFET for Improved Analog Performance and High Switching Speed Applications," in 2<sup>nd</sup> Second National Conference on Recent Developments in Electronics (NCRDE-2017), Delhi, pp. 77-83, 17<sup>th</sup> to 18<sup>th</sup> February, 2017.

# TABLE OF CONTENTS

# Page No.

| Certificate                                                       | <i>i</i>      |

|-------------------------------------------------------------------|---------------|

| ACKNOWLEDGEMENTS                                                  | <i>ii-iii</i> |

| ABSTRACT                                                          | iv-vii        |

| LIST OF FIGURES                                                   | viii-xiii     |

| LIST OF TABLES                                                    | xiv           |

| LIST OF PUBLICATIONS                                              | xv-xvii       |

| CHAPTER 1                                                         | 1             |

| INTRODUCTION                                                      | 1             |

| 1.1 Background                                                    | 2             |

| 1.2 Tunnel Field Effect Transistor (TFET)                         | 4             |

| 1.2.1 Operating Principle                                         | 4             |

| 1.2.2 Merits of TFET                                              | 6             |

| 1.2.3 Challenges Confronted by TFET                               | 7             |

| 1.2.4 Device Engineering Techniques for Overwhelming Challenges F | aced by TFET8 |

| 1.3 Reliability Issues of CMOS Devices                            | 14            |

| 1.3.1 Interface Trap Charges                                      | 14            |

| 1.3.2 Reliability of Tunnel FET                                   | 16            |

| 1.4 Research Gaps                                                 | 16            |

| 1.5 Possible Solutions                                            | 17            |

| 1.6 Objective of Thesis                                           |               |

| 1.7 Thesis Overview                                               | 19            |

| 1.8 References                                                    | 22            |

| CHAPTER 2                                                         | 27            |

| ANALYTICAL MODELING AND DEVICE SIMULATION OF HD-GME               |               |

| ELECTRICAL AND ANALOG PERFORMANCE                                 |               |

| 2.1 Introduction                                                  |               |

| 2.2 Device Structure and Parameters                               |               |

| 2.3 Model Validation                                                                                                                    | 33    |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2.4 Fabrication Process Flow of HD-GME-GAA-TFET                                                                                         | 34    |

| 2.5 Model Formulation for HD-GME-GAA-TFET                                                                                               | 35    |

| 2.6 Results Verification and Discussion                                                                                                 | 41    |

| 2.6.1 Impact of Gate and Drain Bias                                                                                                     | 41    |

| 2.6.2 Impact of High-k Dielectric                                                                                                       | 43    |

| 2.6.3 Impact of Scaling Oxide Thickness                                                                                                 | 48    |

| 2.6.4 Impact of Gate Metal Work function                                                                                                | 48    |

| 2.7 Summary                                                                                                                             | 53    |

| 2.8 References                                                                                                                          | 54    |

| CHAPTER 3                                                                                                                               | 58    |

| SMALL SIGNAL BEHAVIOR AND RF PERFORMANCE OF HD-GME-GAA-TFET                                                                             | 58    |

| 3.1 Introduction                                                                                                                        | 59    |

| 3.2 Simulation Methodology                                                                                                              | 61    |

| 3.3 Results Verification and Discussion                                                                                                 | 62    |

| 3.4 Summary                                                                                                                             | 70    |

| 3.5 References                                                                                                                          | 72    |

| CHAPTER 4                                                                                                                               | 74    |

| TEMPERATURE ASSOCIATED RELIABILITY ISSUES OF HETEROGENEOUS<br>DIELECTRIC-GATE ALL AROUND TUNNEL FET                                     |       |

| 4.1 Introduction                                                                                                                        | 75    |

| 4.2 Device Structure and Parameters                                                                                                     | 78    |

| 4.3 Simulation Methodology                                                                                                              | 78    |

| 4.4 Results Verification and Discussion                                                                                                 | 80    |

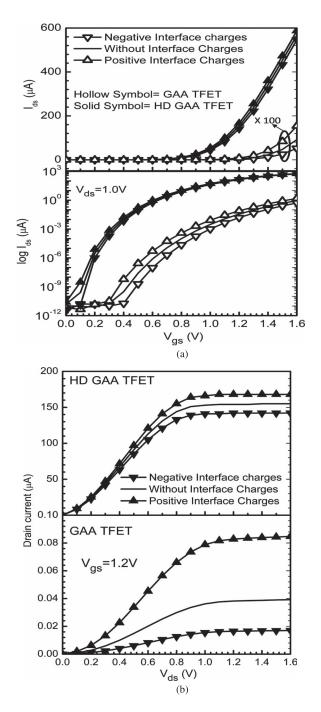

| 4.4.1 Impact of ITC on Analog and RF Performance                                                                                        | 80    |

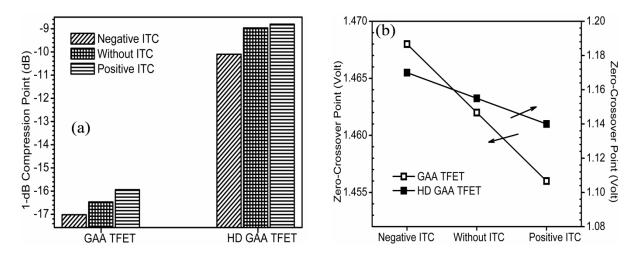

| 4.4.2 Effect of ITCs on Linearity and Distortion Performance                                                                            | 87    |

| 4.4.3 Impact of Temperature and ITCs on Analog and RF Performance                                                                       | 91    |

| 4.5 Summary                                                                                                                             | 101   |

| 4.6 References                                                                                                                          | 102   |

| CHAPTER 5                                                                                                                               | 106   |

| GATE-DRAIN ENGINEERING IN HETERO GATE DIELECTRIC GAA-TFET<br>Suppressed Ambipolar Conduction and its Application as a Hydroge<br>Sensor | n Gas |

| 5.1 Introduction                                                                                                   | 107                      |

|--------------------------------------------------------------------------------------------------------------------|--------------------------|

| 5.2 Device Structure and Parameters                                                                                | 110                      |

| 5.2.1 Suppressing Ambipolar Conduction                                                                             | 110                      |

| 5.2.2 Hydrogen Gas Sensor                                                                                          | 111                      |

| 5.3 Results Verification and Discussion                                                                            | 113                      |

| 5.3.1 Suppressing Ambipolar Conduction                                                                             | 113                      |

| 5.3.2 H <sub>2</sub> Gas Sensor: - Sensitivity Analysis                                                            | 122                      |

| 5.3.3 H <sub>2</sub> Gas Sensor: -Static Performance Analysis                                                      | 125                      |

| 5.4 Summary                                                                                                        | 127                      |

| 5.5 References                                                                                                     | 128                      |

|                                                                                                                    |                          |

| CHAPTER 6                                                                                                          |                          |

| <b>PNIN-GAA-TFET: - INTEGRATION OF GDU FOR COMPREHENSIVELY</b><br>ANALOG/RF PERFORMANCE AND ITS RELIABILITY ISSUES |                          |

| 6.1 Introduction                                                                                                   | 132                      |

| 6.2 Device Structure and Parameters                                                                                | 135                      |

| 6.3 Results Verification and Discussion                                                                            | 137                      |

| 6.3.1 Impact of GDU Length: - An Optimization Study                                                                | 137                      |

| 6.3.2 Impact of Gate-Drain Underlapping and Source Pocket                                                          | 139                      |

| 6.3.3 Impact of Interface Trap Charges- Density and Polarity                                                       | 146                      |

| 6.3.4 Temperature Affectability                                                                                    | 150                      |

| 0.5.4 Temperature Affectability                                                                                    |                          |

| 6.4 Summary                                                                                                        |                          |

|                                                                                                                    | 155                      |

| 6.4 Summary                                                                                                        | 155<br>156               |

| <ul><li>6.4 Summary</li><li>6.5 References</li></ul>                                                               | 155<br>156<br><b>160</b> |

### **REPRINTS OF JOURNAL PUBLICATIONS**

# **CHAPTER 1**

# INTRODUCTION

First and foremost, this chapter discusses the background of the work that primarily describes the MOSFET and the quest for steeper subthreshold devices. In this regard, the chapter introduces the tunnel field effect transistor, i.e., TFET and continues to illustrate the fundamental operating principle of TFET. Thereafter, the significant merits offered by TFET are discussed that is extended with the major challenges faced by the conventional TFET. Also, the chapter describes the various engineering schemes that are reported to overcome the challenges faced by TFET to make it suitable for various analog and RF applications. In the next section, the chapter describes the reliability issues of CMOS devices. In this respect, the origin of interface trap charges, that are inevitably present in any practical device is discussed and is followed by the discussion of the reliability of TFET. Further, the chapter describes the research gaps that are found while literature survey and is followed by the several possible solutions to overcome these gaps. Thereafter, the chapter describes the primary objective of this thesis followed by an overview of all the chapters.

### **1.1 BACKGROUND**

Since the invention of the first Metal Oxide Semiconductor Field Effect Transistor (MOSFET) in early 1960's at Bell labs, MOS transistors have become the core of the integrated circuits (ICs) (Shockley, 1976). Moreover, the Complementary MOSFET (CMOS) technology forms the heart of global electronic industry (Hu, 2011). The unrelenting ever increasing demand for high speed and dense ICs is the driving force for scaling down the CMOS technology to nanometer nodes that has resulted into transforming the state of art of designing the IC, by providing the stability of operation, low static power dissipation and noise immunity to devices (Heyns and Tsai, 2009, Moore, 1975, Moore, 2003). The great triumph of the CMOS devices is necessarily offered by the enhanced drive current and the higher cut off frequency acquired by scaling down the CMOS devices. The scaling of the CMOS devices follows the well-known Moore's law proposed by Gordon Moore (the cofounder of Intel Corporation) in 1960's that predicts that the number of transistors per IC would double approximately every 18 months (Moore, 1975, Moore, 2003). Aggressive scaling of MOSFET down to nanometer regime is administered by the need of higher packing density, low operating power and high switching speed. The constant scaling of MOSFET enhances its switching speed and also the cut-off frequency to Giga-Hertz regime and thus makes it appropriate for wireless and high-frequency applications.

However, the aggressive scaling of MOSFET fallouts into several critical issues such as various short channel effects (SCEs) (*Chaudhry and Kumar*, 2004). These SCEs degrades the performance of MOSFET and also increases the subthreshold swing (SS) to a value greater than the fundamental limit of MOSFET, i.e., 60mV/decade. Moreover, the SCEs increases the leakage current, while the supply voltage can no longer be scaled down, both of which result in increased power consumption. Along with various SCEs, with the reduced channel length, the passive power density approaches the active power density (in magnitude). To mitigate the standby power dissipation, lower OFF-state current (I<sub>OFF</sub>) is required. However, the leakage current increases exponentially because the SS of MOSFET has a minimum value of 60mV/decade at room temperature. To overcome these flaws, various novel device architectures and materials engineering have been proposed such as multi-gate architectures of MOSFET, new gate dielectric materials, asymmetric channel doping engineering and much more (*Ferain et al., 2011, Park et al., 1998, Kranti et al., 2004*). Since MOSFET is employed as a switch in digital applications; thus, the prime requirement for switching applications is steeper ON/OFF transitions, i.e., lower SS and higher current switching ratio, i.e.,  $I_{ON}/I_{OFF}$  ratio. The lower SS reduces the static power dissipation whereas, the higher  $I_{ON}/I_{OFF}$  ratio determines the performance level of the device. However, the variously reported device architectures for MOSFET successfully enhances the  $I_{ON}/I_{OFF}$  ratio, but the fundamental limit of MOSFET put constraints on SS and limit SS to 60mV/decade. Thus, the MOSFET has a fundamental limitation on SS to 60mV/decade at room temperature that is primarily offered by its current switching process, i.e., thermionic (temperature dependent) injection of electrons over the energy barrier. This fundamental limit on SS restricts further scaling of supply voltage below 1V due to the increased leakage current and various SCEs (*Sakurai, 2004, Bernstein et al., 2010, Seabaugh and Zhang, 2010*).

These fundamental limitations have inspired researchers to explore other paradigms of transistor construction that differ from MOSFETs in the underlying mechanism of carrier injection, and yet preserve the qualities that make MOSFET a successful candidate in the first place (Ionescu and Riel, 2011, Madan and Chaujar, 2017c). Another critical factor that must be taken into account is the compatibility of the device under consideration with the existing CMOS architecture (Gandhi et al., 2011). A promising candidate in this regard is the Tunnel Field Effect Transistor (TFET). A TFET is a gated p-i-n junction that is operated in reverse bias (Madan and Chaujar, 2016b, Madan and Chaujar, 2017a, Madan and Chaujar, 2017b, Boucart and Ionescu, 2007, Chen et al., 2009, Choi et al., 2007). Majority carriers are injected from the source into the channel through quantum mechanical Band-to-Band Tunneling (BTBT) which is a result of finite, but non-zero, probability of tunneling through a potential barrier. This lifts the aforementioned fundamental limitation of a minimum SS of 60 mV/decade, allowing TFETs to have SS as low as 20 mv/decade (Khatami and Banerjee, 2009). Apart from TFET, there are many other devices whose working principle is not governed by the drift-diffusion mechanism as in the case of MOSFET. These steeper subthreshold devices comprise: impact ionization-MOS or I-MOS (Björk et al., 2007), nanoelectro-mechanical FETs or NEMS FETs (Kam et al., 2005) and suspended gate MOSFETs (Abelé et al., 2005). However, the work in this thesis encompasses the TFET for low power high switching analog and RF performance.

# **1.2 TUNNEL FIELD EFFECT TRANSISTOR (TFET)**

### **1.2.1 OPERATING PRINCIPLE**

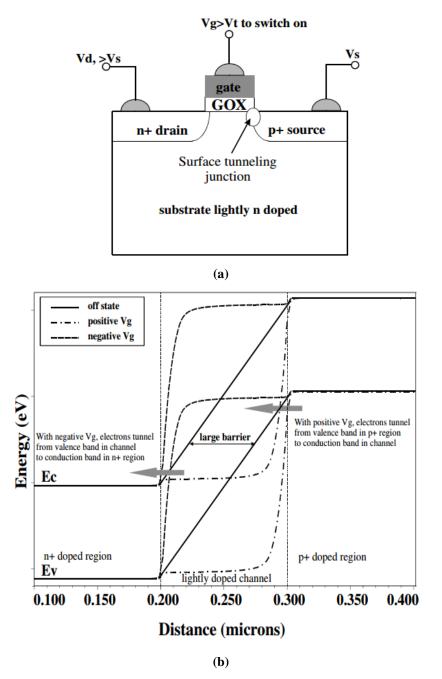

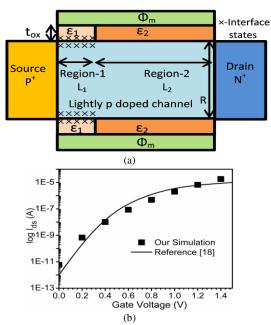

The fundamental TFET is a metal-gated p-i-n structure with the metallic gate deposited at the entire intrinsic channel region, and the p and n region is doped degenerately that principally acts as a source and drain respectively in case of n-TFET. The applied bias at the gate metal essentially controls the BTBT at the source and channel junction. Figure 1.1(a) depicts the schematic view of n-type TFET and its corresponding energy band diagram in ON, OFF and ambipolar state is represented in **Figure 1.1(b)**. It is worth mentioning that TFET works in reverse bias conditions to get the ultra-low leakage current. In comparison to MOSFET, the device structure of TFET is similar to MOSFET, with an exception that in TFET, the source and drain doping are asymmetric. Specifically, for an n (p)-type TFET, the source is  $p^+(n^+)$  doped and drain is  $n^+(p^+)$  doped. This asymmetric source/drain doping results into a staircase like energy band profile in TFET. Moreover, the Quantum Mechanical BTBT is the primary carrier injection mechanism in TFETs as opposed to thermal carrier injection in MOSFETs (Ionescu and Riel, 2011, Khatami and Banerjee, 2009, Nagavarapu et al., 2008, Choi and Lee, 2010). In TFETs, BTBT takes place at the source-channel interface due to the bending of energy bands owing to the applied voltages (Madan and Chaujar, 2016a, Madan and Chaujar, 2017a). In case of n-TFET,

- i. For a reverse biased p-i-n junction and  $V_{gs}=0$  V, i.e., the OFF state of TFET, the energy bands are aligned in such a way that there is a large tunneling barrier width present at the source channel (tunneling) junction. This wide barrier width and the barrier for thermal emission restrict the tunneling of electrons and this inherent physics of TFET upshots into a very low subthreshold leakage current (generally of the order of femto Amperes). Ideally, the tunneling barrier width at  $V_{gs}=0$  V is identical to the channel length.

- ii. For an increase in positive voltage at the gate metal, i.e., for  $V_{gs}>0$ , an accumulated or inverted n-channel is formed. This pushes down the energy bands in the channel region, and subsequently, the valence band of the p<sup>+</sup> overlaps with the conduction band of the channel that reduces the tunneling barrier width. This results in the formation of a surface tunnel junction at the p<sup>+</sup> and channel junction as illustrated in **Figure 1.1(a)**. The resultant electron energy band diagram is presented in **Figure**

**1.1(b)**. The reduced barrier width allows the tunneling of electrons from the valence band of the  $p^+$  region to the conduction band of the channel. After tunneling to channel region via BTBT mechanism, electrons transport to drain via drift-diffusion, resulting in drain current.

Figure 1.1 (a) Schematic view of basic n-Type TFET (b) energy band diagram of 100nm n-Type TFET in OFF, ON and ambipolar state, with 100nm channel length; the  $n^+$  doped region is positive biased and  $p^+$  doped region is grounded (*Wang et al., 2004*).

iii. For applied negative gate bias, i.e., for  $V_{gs}$ <0, an inverted or accumulated p-channel is formed. This leads to lifting the energy bands of the channel region upwards and consequently moves the surface tunnel junction at the n<sup>+</sup> and channel junction. Furthermore, it leads to narrower barrier width at the drain and channel junction that becomes favorable for tunneling and thereby results in an ambipolar conduction in TFET. Principally, in this case, electrons tunnel from the valence band of the channel to the conduction band of the n<sup>+</sup> region (drain). The holes generated in the channel flows to the p<sup>+</sup> region (source). Consequently, in this case, the p<sup>+</sup> region acts as drain (drain of holes) and the n<sup>+</sup> region acts as source. Thus, TFET does not turn OFF for the negative gate bias as opposed to n-MOSFET which has a negligible current for negative gate bias. This conduction of TFET for negative gate bias is the ambipolar conduction of TFET.

#### **1.2.2 MERITS OF TFET**

The significant impediments of MOSFET while scaling down to the sub-nanometer regime is the SCEs, that has been overwhelmed by the intrinsic tunneling barrier width present at the source channel junction of TFET and makes TFET insusceptible to SCEs. However, at very short channel lengths, the drain potential can affect the tunneling junction which can be resolved by reducing the  $V_{ds}$  that is primarily enabled by the lower SS of TFET. The insusceptibility of TFET to SCEs allow further downscaling of TFET, prolonging the Moore's Law and thereby poses it to be a superior candidate for ultra-low power era (Choi et al., 2007). Moreover, TFET works on BTBT as its inherent transport mechanism instead of drift-diffusion of charge carrier as in case of MOSFET. Thus, the independence of tunneling on temperature results in the weak temperature dependence of TFET characteristics (Mookerjea et al., 2010). Hence, TFET overcomes the fundamental limitations of MOSFET that limits its SS at 60mV/decade at 300K. In other words, the SS of TFET can be smaller than 60mV/decade, and thus allows further downscaling of the supply voltage, due to the lower SS, the supply voltage required for operating TFET is lower, that turns in lower static and dynamic power dissipations (Khatami and Banerjee, 2009). Additionally, as the gate controls the tunneling barrier width, accordingly at lower gate voltages, the broad tunneling width at the source channel junctions inhibits the tunneling of electrons, and there is only feeble current  $\sim 10^{-15}$ A (lesser than the I<sub>OFF</sub> of MOSFET). This lower I<sub>OFF</sub> translates into lower static power dissipation. Furthermore, TFET has compatibility with already existing standard CMOS fabrication technology that ensures the viability of TFETs fabrication and also its costeffectiveness (*Moselund et al., 2016*). These benefits of TFET make it a potential candidate to replace MOSFET, as TFET would contribute to the goal of reducing the operational speed (instigated by lower  $V_{dd}$ ) along with the standby power, which has sturdy implications on electrical power consumption today.

#### **1.2.3 CHALLENGES CONFRONTED BY TFET**

In the previous subsection, the significant merits of TFET have been discussed, and this section continues to summarize the problems confronted by TFET. It is essential to tackle these challenges to employ TFET for wide scale applications. Heretofore, it is reported in various research articles that the lower tunneling probability in TFET leads to inferior ON current ( $I_{ON}$ ) of TFET in comparison with MOSFET. This lower  $I_{ON}$  limits the device speed and also translates in higher threshold voltage ( $V_{th}$ ). Thus, the primary challenge in TFET to outperform CMOS transistors is to realize high  $I_{ON}$  without any degradation in the  $I_{OFF}$  (*Anghel et al., 2010*). Various device and material engineering schemes have been reported for enhancing the tunneling rate of electrons, that thereby conquer the lower  $I_{ON}$  and higher  $V_{th}$  of TFET and will be extensively discussed in the next part of this chapter.

Moreover, in contrast with the n-MOSFET, (which is switched ON for a  $V_{gs}>0$  and is switched OFF for  $V_{gs}<0$ ), TFET works as both n-type and p-type for positive and negative  $V_{gs}$ . Specifically, for an n-TFET with a positive bias applied to the drain, the electrons tunnels from p<sup>+</sup> source to channel for  $V_{gs}>0$  (tunneling at the source channel junction). Additionally, for  $V_{gs}<0$ , with the same drain bias, the holes will tunnel from the n<sup>+</sup>-drain to channel (tunneling at the drain channel junction) and constitute drive current mostly of the same order of magnitude as for  $V_{gs}>0$ . This is primarily the ambipolar conduction of TFET, that is undesirable for logic devices specifically inverters that demands the unipolar behavior i.e. for perfect levels of OFF and ON states (*Wang et al., 2004*). Briefly, ambipolar conduction is caused by the lowering of barrier width at the drain-channel junction for negative gate bias (for the case of n-TFET). The various previously reported device design architectures and material engineering schemes for suppressing the ambipolar conduction have also been discussed in the next section of this chapter. Further, one more challenge of TFET is the pronounced miller effect attributed by the dominant gate to drain capacitance in comparison with gate to source capacitance that collectively contributes to the total gate capacitance (*Gnani et al., 2015, Mookerjea et al., 2009*). The inherent BTBT negligibly contributes to the inversion charge density thereby the gate to source capacitance contributes negligibly to total gate capacitance in comparison with gate to drain capacitance.

# 1.2.4 Device Engineering Techniques for Overwhelming Challenges Faced by TFET

### 1.2.4.1 Heterostructure TFET

To enhance  $I_{ON}$ , the concept of different source material other than channel is proposed and is known as the heterostructure TFET. The source material is chosen such as it must have a smaller energy bandgap as compared to the bandgap of channel material. The small bandgap material in source region radically reduces the tunneling barrier width between the source and channel junction that in turn enhances the tunneling probability and thereby the drain current (*Hanna et al., 2015, Moselund et al., 2016, Hanna and Hussain, 2015*). For example - a Ge-Si heterostructure TFET, in which source is of Ge that has a lower bandgap, with Si used as channel and drain. With the Ge source, the band bending at the tunneling junction is molded such as the barrier width is reduced that translate into higher tunneling rate of electrons.

# 1.2.4.2 DUAL MATERIAL GATE (DMG) OR GATE METAL ENGINEERED (GME) OR HETEROMATERIAL GATE (HMG) TFET

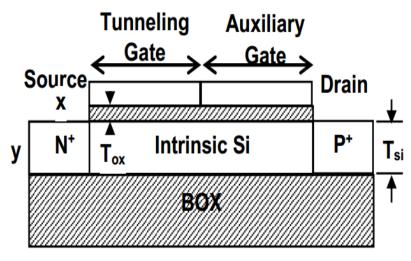

To acquire a simultaneously up-gradation in ON and OFF-state characteristics (without affecting the chip density), a Dual Material Gate TFET is proposed by Vishnoi et al. (*Vishnoi and Kumar, 2014*). In DMG-TFET, the gate metal is divided into two parts viz. the tunneling gate (near the source side) and the auxiliary gate (near the drain side) as depicted in **Figure 1.2**. For n-channel TFET, the metal near the source, i.e., the tunneling metal has lower work function and the metal near the drain, i.e., the auxiliary gate has higher work function. The aim of implementing a lower work function metal near source is to enhance the tunneling rate owing to the reduced flatband voltage that lowers the barrier width at

comparatively lower gate bias. Subsequently, the higher tunneling rate enhances the drain current and also reduces the  $V_{th}$ . Moreover, by using a higher metal work workfunction material near the drain, the subthreshold characteristics of TFET are controlled.

Figure 1.2 Schematic representation of a p-type DMG-TFET (Vishnoi and Kumar, 2014).

# 1.2.4.3 High-k Dielectric TFET and Hetero gate Dielectric TFET (HD-TFET)

To increase the  $I_{ON}$  and also to reduce  $V_{th}$ , the high-k gate dielectric has been introduced as opposed to conventional SiO<sub>2</sub> (*Boucart and Ionescu, 2007*). The high-k material such as Hafnium dioxide (HfO<sub>2</sub>) with k~21, Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>) with k~7.5, Zirconium dioxide or Zirconia (ZrO<sub>2</sub>) with k~25, etc. can be implemented as the gate oxide in TFET. The high-k dielectric material as gate oxide primarily increases the surface potential as inferred by Equation 1.1

$$V_{gs} = -\frac{q_s t_{ox}}{\varepsilon_{ox}} + \phi_s \tag{1.1}$$

Where;

q<sub>s</sub> is the charge density per unit area,

tox is the gate oxide thickness,

$\varepsilon_{ox}$  is the permittivity of the gate oxide material and,

$\phi_s$  is the surface potential.

It is deduced from Equation 1.1 that at a constant gate bias, the surface potential has a direct reliance on the high-k dielectric. For higher tunneling rate, lower barrier width and

thereby steeper band bending are required that demands for high surface potential and thus for a high-k gate oxide. The lower barrier width at the source channel junction offered by the high-k gate oxide enhances the tunneling rate and henceforth mitigates the major roadblocks of TFET, i.e., lower  $I_{ON}$  along with higher  $V_{th}$ .

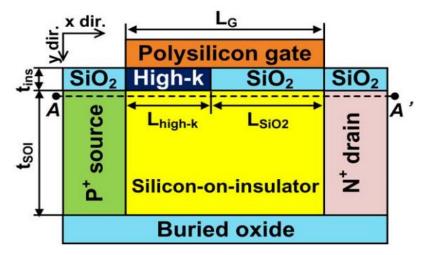

However, the concomitant challenge with high-k gate dielectric is the simultaneous increase in the ambipolar current (I<sub>AMB</sub>). Thus, to overwhelm this, i.e., to acquire higher I<sub>ON</sub> without any increase in the  $I_{AMB}$ , a hetero gate dielectric (HD) engineering scheme is proposed by Choi et al. (Choi and Lee, 2010). In HD engineering scheme, a high-k material is locally implanted in the oxide near the source-channel junction as shown in **Figure 1.3**. The high-k material located partially in the oxide near the source side over the channel induces a local minimum in the conduction band at the tunneling junction. However, the rest oxide, i.e., the dielectric near the drain side consists of conventional  $SiO_2$  that prevents the ambipolar conduction. Therefore, in HD-TFET, the I<sub>ON</sub> is enhanced by the high-k dielectric material and is substantially followed by the TFET with high-k dielectric at entire gate oxide. Simultaneously, the I<sub>AMB</sub> is followed by the case as that of TFET with SiO<sub>2</sub> as gate dielectric that thereby inhibits the ambipolar conduction. Consequently, HD-TFET concurrently employs the welfare of both SiO<sub>2</sub> dielectric (in ambipolar state and OFF-state) and high-k dielectric (in ON-state), thus offers lower IOFF and higher ION respectively. Apart from improved I<sub>ON</sub> and suppressed I<sub>AMB</sub>, HD-TFET also offers lesser gate to drain capacitance (w.r.t. the case of high-k dielectric TFET) that is desirable for higher switching speed of any transistor.

Figure 1.3 Schematic representation of a hetero gate dielectric TFET (Choi and Lee, 2010).

### 1.2.4.4 TUNNEL SOURCE P-N-P-N TFET

One of the approaches for mitigating the issues of lower  $I_{ON}$  and also higher  $V_{th}$  is implantation of a n<sup>+</sup> pocket in the channel region adjacent to the source side proposed by Nagavarapu et al. (*Nagavarapu et al., 2008*). The schematic view of an n<sup>+</sup> source pocket PNIN-TFET is displayed in **Figure 1.4**. The critical parameters for designing an optimised PNIN-TFET are the source pocket doping and the source pocket width. Additionally, tilt angled implantation process can fabricate the n<sup>+</sup> pocket that ensures its fabrication feasibility. The up-graded parameters such as higher  $I_{ON}$ , lower V<sub>th</sub> and lower SS can be acquired by implanting a n<sup>+</sup> pocket in the channel near source side owing to the formation of a local minima in the conduction band that subsequently, narrows the barrier width (*Madan and Chaujar, 2017a, Jhaveri et al., 2011*). The narrow tunneling barrier enhances the tunneling generation rate and thereby overcome the issues of lower  $I_{ON}$  and simultaneously reduces the V<sub>th</sub> of TFET.

Figure 1.4 Schematic device structure of n<sup>+</sup> source pocket PIN-TFET or PNIN-TFET.

## 1.2.4.5 MULTI-GATE TFET

Apart from the above engineering schemes that account for the alterations in the gate oxide, gate metal and channel engineered; multigate architectures TFET has also been reported such as the double gate TFET (DG-TFET), FINFET, Triple gate (or  $\pi$ -gate), Omega gate ( $\Omega$ -gate) and the Gate All Around TFET (GAA-TFET). In DG-TFET, there are two independent gates fabricated in such a way that the channel is sandwiched between them. Moreover, the gate oxide thickness and metal work workfunction of both the gate metals are

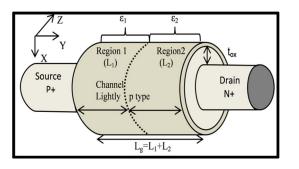

same, i.e., both the gates are symmetric with a common gate bias that tied them together. The primary idea of designing DG-TFET is to enhance the gate controllability over the channel and thereby, the effective electric field at the tunneling junction increases that is followed by the steeper band bending that enhances the tunneling rate of electrons and hence, increases the drain current. The DG-TFET is substantially similar to the design of DG-MOSFET that was proposed by T. Sekigawa et al. in 1984 (Sekigawa and Hayashi, 1984). Thereafter, in 1987 Balestra et al. (Balestra et al., 1987), have reported the concept of volume inversion in DG-MOSFET that results in an advantage in scaling about two times. Further, a gate all around MOSFET (or the surrounding gate MOSFET or Wrap around gate MOSFET) in which the gate surrounds the entire silicon beam is reported (Colinge et al., 1990, Takato et al., 1991, Leobandung et al., 1997, Auth and Plummer, 1997). It is worth mentioning that the silicon beam may be wide or narrow, square, rectangular or circular and of any of the orientation. It is investigated by Leobandung et al. that GAA-MOSFET can be scaled further about 50% in comparison with DG-MOSFET owing to the extra degree of electrostatic confinement offered by the GAA architecture (Leobandung et al., 1997). Furthermore, the GAA architectures ensure the merits of extremely high packing density that is desirable for proper memory storage. Primarily, the GAA geometry increases the electrostatic control and thereby allows further gate length scalability. Among all the geometries of GAA, the cylindrical gate geometry is of ultimate importance as it provides further gate length scalability. The cylindrical GAA-TFET enhances the tunneling volume and thus lifts the tunneling probability that leads to improved I<sub>ON</sub>. These abundant merits of GAA-TFET are the key motivating force for exploring it and thereby the entire research work done in this thesis is principally based on cylindrically GAA-TFET.

#### 1.2.4.6 SHORT GATE TFET OR GATE-DRAIN UNDERLAPPED (GDU) TFET

Verhulst et al. (*Verhulst et al.*, 2007) have introduced the concept of gate metal underlapping near drain side also stated as the short gate TFET. In short gate engineering, the gate metal is not over the entire channel length and is underlapped near drain side or is limited to the source (*Verhulst et al.*, 2007, *Chattopadhyay and Mallik*, 2011). In doing so, the underlapped gate metal near drain side limits the charge carrier (that is built-up underneath the gated region) to the gated region or restricts its extension towards the underlapped region. Hence, the short metal gate controls the ambipolar conduction (*Wang et al.*, 2014). Besides

reducing the  $I_{AMB}$ , the GDU-TFET also decreases the intrinsic gate to drain capacitance ( $C_{gd}$ ) that is one of the major hindrances while designing TFET circuitry. Moreover, GDU is of prime importance due to its viability offered by the simple fabrication process.

#### 1.2.4.7 GATE-DRAIN OVERLAPPED TFET

The gate-drain overlapping (GDO) scheme is also one of the engineering used to suppress the ambipolar conduction. Conventionally, the gate metal exists only over the channel region. However in GDO, the gate metal is extended towards the drain region beyond the channel such that it overlaps the drain region as illustrated in **Figure 1.5**. It is reported that the overlapped gate metal over drain side limits the gate to control only the source channel junction irrespective of the gate bias polarity (*Abdi and Kumar, 2014*). For n-type TFET, with the integration of GDO, the band bending at the source channel junction remains same as for the case when gate metal is not overlapped over the drain. But with overlapping gate metal over the drain and applying a negative gate bias, the effect of gate bias is primarily same on drain channel junction as that of the channel region. This result in broadening of barrier width at the drain channel junction and thereby controls the ambipolar conduction. Moreover, it is worth mentioning that the GDO doesn't alter the device characteristics for the positive gate bias region (*Shaker et al., 2015*). For processing of GDO, the electron beam lithography is used for patterning of the gate metal, and then the electron beam evaporation is used for gate metallization (*Madan and Chaujar, 2016a*).

Figure 1.5 Schematic view of gate-drain overlapped TFET (GDO-TFET) (Abdi and Kumar, 2014).

### 1.2.4.8 ASYMMETRIC SOURCE/DRAIN DOPING

To alleviate the ambipolar conduction, the viewpoint is to decrease the tunneling at the drain channel junction such that the tunneling at the source channel junction remains unaltered. The most straightforward engineering approach reported for suppressing the ambipolar conduction or to acquire unipolarity, is an asymmetrically doped source and drain TFET. It has been reported that by employing an asymmetry such that the drain doping is less than the source doping efficiently reduces the ambipolarity with insignificant alteration in  $I_{ON}$  (*Wang et al., 2004*).

### **1.3 Reliability Issues of CMOS Devices**

### **1.3.1 INTERFACE TRAP CHARGES**

With intensification in the complexity and density of VLSI chips, the assessment of the long-term reliability of CMOS devices becomes compulsory. The reliability of MOS devices is very much affected by the quality of interface of semiconductor and oxide. Precisely, the Si-SiO<sub>2</sub> interface may be associated with four types of charges viz. fixed oxide charges, mobile oxide charges, oxide trapped charges and interface states. Moreover, these charges inevitably appear during the fabrication of the MOS devices. Although the number of such charges has been reduced significantly with continuous improvements in fabrication technology, still they cause a substantial degradation in the operation of the device due to the high packing density of transistors in microchips today.

The origin of these interface states are primarily offered by the high electric field present at the source channel junction (in case of TFET) for the positive gate and drain bias, that is generated in TFET by the steeper band bending at the source channel junction. The charge carriers that tunnel through the source channel junction get across this considerably high electric field, and thereby gain an expressively enormous amount of energy between two scattering events. Few of these energetic charge carriers may gain enough energy (about 1.12eV) that generate the electrons and holes by impact ionization. However, a small fraction of charge carriers gain even large energy ( $\sim 3.2eV$  for electrons and 4.7eV for holes), that they may surmount the interface of Si-SiO<sub>2</sub> and may penetrate inside the SiO<sub>2</sub> and may constitute the gate leakage current. Among these penetrated charge carriers few of them may remain trapped in the oxide and if they are still energetic enough, they may subsequently

break some of the Si-H or similar weak bonds in the SiO<sub>2</sub>. This penetration may translate to a permanent modification of the characteristics of the device and thereby degrades the functioning of integrated circuits. Additionally, the passage of ionizing radiation in the oxide may also turn to generate the trapped charges in the oxide layer. The electron-hole pair thereby created may recombine or move in the electric field of oxide; such that the generated holes move towards the metallic gate and the electron travels toward the interface of Si and SiO<sub>2</sub>. The holes moving towards the metallic gate may be trapped in the oxide and leads to the generation of a positive charge in the oxide. Besides, the generation of trapped charges, the ionization radiation may produce new energy levels in the bandgap at Si-SiO<sub>2</sub> interface that may be occupied by the charge carriers depending on the Fermi level position at the interface and the oxide charge will be added/subtracted to the correspondingly charge value (*Oldham and McLean, 2003, Neamen, 2003*).

The most critical factors accountable for the device damage complications are: process induced damage (*Poindexter, 1989*), radiation-induced damage (*Lho and Kim, 2005*), stress-induced damage (*Trabzon and Awadelkarim, 1998*) and hot carrier induced damage (*Naseh et al., 2006*). In the era of sub-100nm, device designing plasma etching used for pattern transfer process may produce electrical and processing damage (falls under the category of stress-induced damage), and thereby damage the Si-oxide interface along with the oxide and consequently degrades the performance, yield, and reliability of the device.

Mostly the interface trap charges are of two types; viz. the acceptor type and donor type interface state. The acceptor type interface states behave as electrically neutral when it is empty, and it comes to be negatively charged when filled with an electron. Whereas, the donor type interface states behave electrically neutral when filled with an electron and turn into positively charged when it is empty (*Madan and Chaujar, 2016b, Madan and Chaujar, 2017b*). Apart from donor/acceptor, a specific interface state is also characterized by (i) the exact energy level in the bandgap i.e. measured in eV from the valence band edge, (ii) its spatial location in the device, for example distance from the source side and (iii) its density i.e. the number of states/cm<sup>2</sup> for discrete states.

The position of the Fermi level in the energy band gap accounts the net charge quantitatively in the respective interface state (*Neamen, 2003*). It is reported by Neamen (*Neamen, 2003*) that the acceptor (donor) states lie in the upper (lower) half of the energy bandgap. Moreover, these interface states act as a fixed positive/negative charge as if in case

the acceptor interface trap will accept an electron if the trap level is beneath the Fermi level and so the interface state will behave as a negative fixed charge. Similarly, a donor type interface trap acts as a positive fixed charge and thereby in this thesis, these interface traps are accounted as effective positive and negative fixed interface charges.

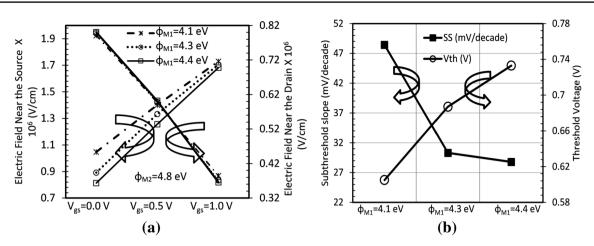

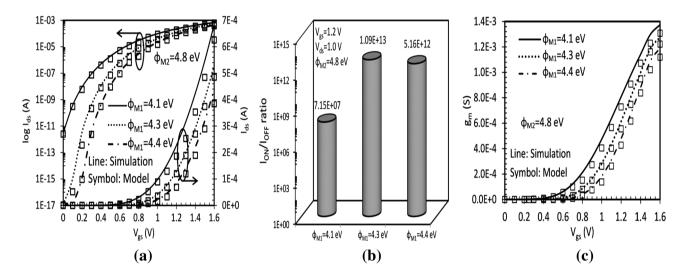

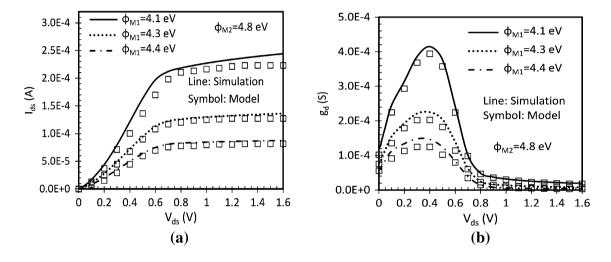

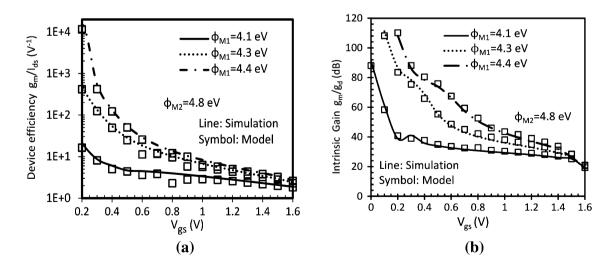

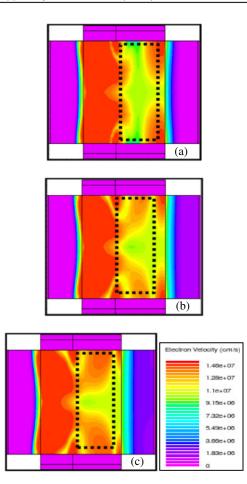

#### 1.3.2 Reliability of Tunnel FET