# IMPEMENTATION AND ANALYSIS OF ADDER CIRCUITS USING MODIFIED GLITCH FREE CASCADABLE ADIABATIC LOGIC

Submitted in partial fulfilment of the requirements for the award of the degree of

**Master of Technology**

in

**VLSI Design and Embedded Systems**

bv

Neha Raghav

(University Roll No. 2K15/VLS/11)

Under the guidance of

Dr. Malti Bansal Assistant Professor,

Department of Electronics and Communication Engineering, Delhi Technological University

2015-2017

Department of Electronics and Communication Engineering, Delhi Technological University, Delhi-110042, India.

#### Certificate

This is to certify that the work done in the thesis entitled "Implementation and Analysis of Adder Circuits using Modified Glitch Free Cascadable Adiabatic Logic" has been carried out by Ms. Neha Raghav, Roll No. 2K15/VLS/11 under my supervision, in partial fulfilment of the requirements for the award of the degree of Master of Technology (M.Tech.) in VLSI Design and Embedded systems, at Delhi Technological University, Delhi.

Date:

Dr. Malti Bansal

Assistant Professor

Department of Electronics and Communication Engineering

Delhi Technological University

Delhi- 110042

## Candidate's Declaration

The work in this thesis entitled "Implementation and Analysis of Adder Circuits using Modified Glitch Free Cascadable Adiabatic Logic" is a record of original research work carried out by me under the guidance of Dr. Malti Bansal, Assistant Professor, Department of Electronics and Communication Engineering, Delhi Technological University, in partial fulfilment of the requirements for the award of the degree of Master of Technology in VLSI Design and Embedded systems at Delhi Technological University, Delhi. Neither this thesis nor any part of it has been submitted for the award of any other degree or diploma elsewhere.

Date:

Neha Raghav (2K15/VLS/11)

## Acknowledgement

To be candid, this project would never have been successful without the good wishes and hard work of few people. My primary debt of thanks is to my mentor **Dr. Malti Bansal**, Assistant Professor, Department of Electronics and Communication Engineering, Delhi Technological University, for giving me complete freedom to express my views and for her challenging questions and thoughtful feedback, as it clarified and strengthened the ideas. Also, for providing me a unique environment to conduct my thesis research work and for providing encouragement and institutional support from the start, allowing us to closely entwine into our project. I would also like to acknowledge people with whom I made this gracious journey of two years: my college colleagues who contributed to the ideas, provided intellectual boost and energy.

Last but not the least, my parent's constant trust and faith on my abilities was like a giant shadow that sheltered me to complete this project successfully. This has been one of the greatest experiences of my life.

Neha Raghav

(2K15/VLS/11)

# **Refereed Publications arising from this Thesis**

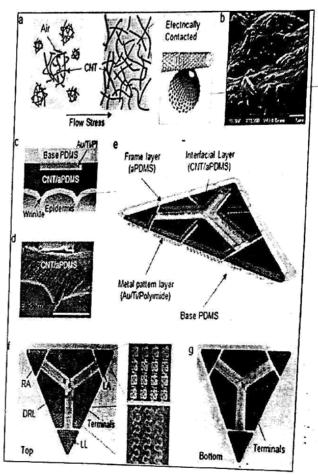

- 1. Malti Bansal, Neha Raghav, "Flexible & Dry ECG Electrodes based on Carbon Nanotubes for Long- Term & Continuous Recording of Bio- signals," in *Proceedings of 3<sup>rd</sup> International Conference on Emerging Electronics (ICEE)*, IIT Bombay.

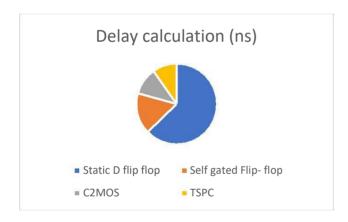

- 2. Neha Raghav, Malti Bansal, "Analytical Study of High Performance Flip-flop Circuits Based on Performance Measurements.", *International Conference on Computing, Communication and Automation (ICCCA 2017)*, pp. 1574- 1579.

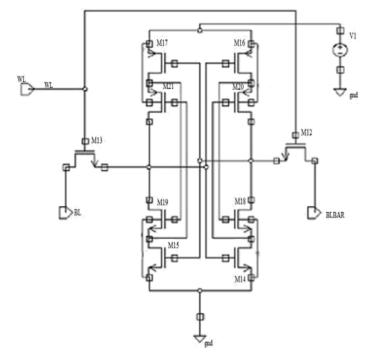

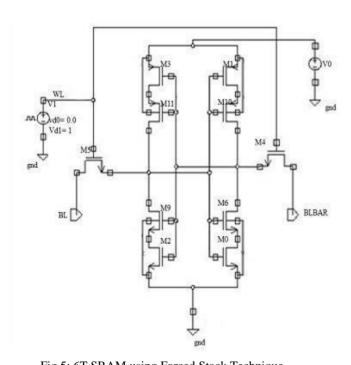

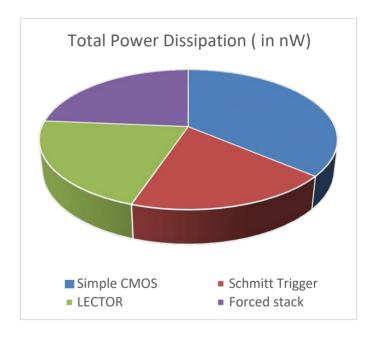

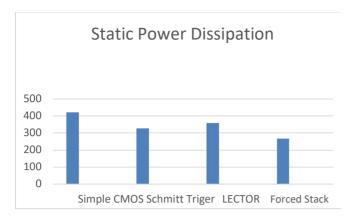

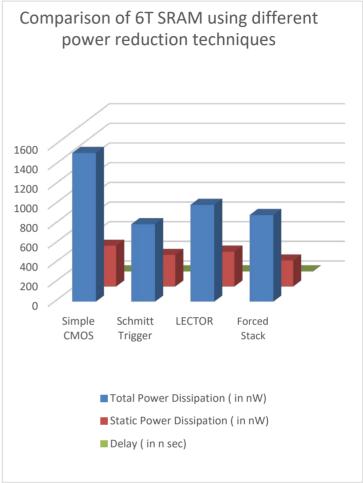

- 3. Neha Raghav, Malti Bansal, "Analysis of Power Efficient 6-T SRAM Cell with Performance Measurements.", accepted in International Conference on Innovations in Control and Information Systems (ICICCI), 2017.

# Table of Contents

| Declaration                                    |     |

|------------------------------------------------|-----|

| Acknowledgement                                |     |

| Refereed publications arising from this thesis |     |

| Table of Contents                              | v   |

| List of Figures                                | ix  |

| List of Tables                                 | xii |

| Abbreviations                                  | XV  |

| Abstract                                       | 1   |

| Chapter 1: INTRODUCTION                        |     |

| 1.1 MOTIVATION                                 | 2   |

| 1.2 DEMAND OF LOW POWER VLSI DESIGN            | 4   |

| 1.3 RESEARCH OBJECTIVE                         | 6   |

| 1.4 ORGANIZATION OF THESIS                     | 7   |

| Chapter 2: POWER CONSUMPTION IN VLSI CIRCUIT   | ΓS  |

| 2.1 POWER DISSIPATION IN CMOS CIRCUITS         | 9   |

| 2.1.1 DYNAMIC POWER                            | 9   |

| 2.1.2 HAZARD AND GLITCH POWER                  | 11  |

| 2.1.3 SHORT CIRCUIT POWER DISSIPATION          | 11  |

| 2.1.4 LEAKAGE POWER DISSIPATION                | 13  |

| 2.2 LOW POWER DESIGN TECHNIQUES                | 15  |

| 2.2.1 TRANSISTOR SIZING                        | 16  |

| 2.2.2 TECHNOLOGY SCALING                                 | 16 |

|----------------------------------------------------------|----|

| 2.3 DYNAMIC POWER REDUCTION                              | 17 |

| 2.3.1 ACTIVITY REDUCTION                                 | 17 |

| 2.3.2 SUPPLY VOLTAGE REDUCTION                           | 17 |

| 2.4 LEAKAGE REDUCTION                                    | 18 |

| 2.4.1 DUAL THRESHOLD VOLTAGE TECHNIQUE                   | 18 |

| 2.4.2 STACKING TECHNIQUE                                 | 19 |

| 2.4.3 SUPPLY GATING                                      | 19 |

| 2.4.4 SYSTEM AND ARCHITECTURE LEVEL POWER REDUCTION      | 19 |

| 2.5 ADIABATIC OR CHARGE RECOVERY BASED CIRCUIT DESIGN    | 19 |

| Chapter 3: ADIABATIC LOGIC: An Introduction              |    |

| 3.1 ADIABATIC PRINCIPLE                                  | 22 |

| 3.1.1 CONVENTIONAL SWITCHING                             | 23 |

| 3.1.2 ADIABATIC SWITCHING                                | 24 |

| 3.2 POWER CLOCK USED FOR ADIABATIC SWITCHING             | 25 |

| 3.3 CLASSIFICATION OF ADIABATIC LOGIC FAMILIES           | 27 |

| 3.3.1 2N- 2P LOGIC                                       | 28 |

| 3.3.2 2N 2N- 2D LOGIC                                    | 30 |

| 3.3.3 EFFICIENT CHARGE RECOVERY LOGIC (ECRL)             | 31 |

| 3.3.4 COMPLEMENTARY ENERGY PATH ADIABATIC LOGIC (CEPAL)  | 32 |

| 3.3.5 TWO PHASE ADAIABATIC STATIC CLOCKED LOGIC (2PASCL) | 34 |

| 3.3.6 QUASI STATIC ENERGY RECOVERY LOGIC (QSERL)         | 35 |

| 3.3.7 GLITCH- FREE CASCADABLE ADIABATIC LOGIC (GFCAL)    | 36 |

| 3.4 OVERVIEW                                             | 38 |

| 2.5 ADDI ICATION OF ADIADATIC LOGIC                      | 20 |

# **Chapter 4: MODIFIED GLITCH FREE CASCADABLE ADIABATIC LOGIC (MGFCAL)**

| 4.1 BASIC STRUCTURE OF MGFCAL                                           | 4          |

|-------------------------------------------------------------------------|------------|

| 4.2 OPERATION OF MGFCAL CIRCUIT                                         | 42         |

| 4.3 MATHEMATICAL MODEL OF THE INVERTER CIRCUIT USING MGFCAL CIRCUIT     | 43         |

| 4.4 CASCADABILITY                                                       | 45         |

| Chapter 5: APPLICATION OF MFCAL IN VARIOUS CIRCUITS                     |            |

| 5.1 BASIC INVERTER BLOCK USING MGFCAL                                   | 47         |

| 5.2 BASIC AND GATE BLOCK USING MGFCAL                                   | 18         |

| 5.3 BASIC OR GATE BLOCK USING MGFCAL                                    | 19         |

| 5.4 BASIC NAND GATE USING MGFCAL                                        | 50         |

| 5.5 BASIC NOR GATE USING MGFCAL                                         | 51         |

| 5.6 BASIC XOR GATE USING MGFCAL                                         | 52         |

| 5.7 BASIC HALF ADDER BLOCK USING MGFCAL5                                | 53         |

| 5.8 PROPOSED ADDER CIRCUITS APPLICATIONS USING MGFCAL                   | 54         |

| 5.8.1 APPLICATION OF FULL ADDER STRUCTURE USING MGFCAL                  | 55         |

| 5.8.2 APPLICATION OF HALF ADDER BASED FULL ADDER STRUCTURE USING MGFCAL |            |

| 5.8.3 APPLICATION OF RIPPLE CARRY ADDER USING MGFCAL5                   | <b>i</b> 7 |

| 5.8.4 APPLICATION OF LOOK AHEAD CARRY ADDER STRUCTURE USING MGFCAL      | 8          |

| 5.8.5 APPLICATION OF CARRY SELECT ADDER USING MGFCAL6                   | 0          |

| 5 8 6 APPLICATION OF HYBRID ADDER STRUCTURE USING MGFCAL                | 2.         |

# **Chapter 6: SIMULATION AND ANALYSIS**

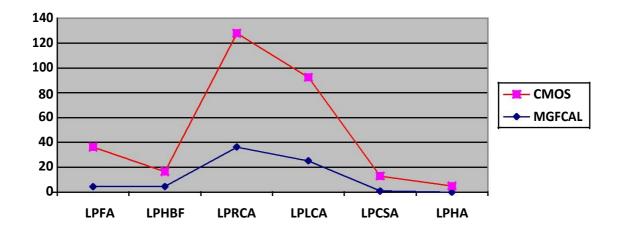

| APPENDIX- I: Comparison in Terms of Power Dissipation                   | 20  |

|-------------------------------------------------------------------------|-----|

| BIBLIOGRAPHY1                                                           |     |

| 7.2 FUTURE SCOPE1                                                       | 05  |

| 7.1 CONCLUSION1                                                         | 04  |

| Chapter 7: CONCLUSION AND FUTURE SCOPE                                  |     |

| 6.8.6 LOW POWER HYBRID ADDER (LPHA) BLOCK USING MGFCAL1                 | 00  |

| 6.8.5 LOW POWER CARRY SELECT ADDER (LPCSA) BLOCK USINGMGFCAL            | 97  |

| 6.8.4 LOW POWER LOOK AHEAD CARRY ADDER (LPLCA) BLOCK USING MGFCAL       | 94  |

| 6.8.3 LOW POWER RIPPLE CARRY ADDER (LPRCA) BLOCK USING MGFCAL9          | 91  |

| 6.8.2 LOW POWER HALF ADDER BASED FULL ADDER (LPHBF) BLOCK USING MGFCAL. |     |

| 6.8.1 LOW POWER FULL ADDER (LPFA) BLOCK USING MGFCAL                    | 85  |

| 6.8 PROPOSED ADDERS USING MGFCAL TECHNIQUE                              | 85  |

| 6.7 LOW POWER HALF ADDER BLOCK USING MGFCAL                             | .82 |

| 6.6 LOW POWER XOR GATE BLOCK USING MGFCAL                               | 79  |

| 6.5 LOW POWER NAND GATE BLOCK USING MGFCL                               | .76 |

| 6.4 LOW POWER NOR GATE BLOCK USING MGFCAL                               | 73  |

| 6.3 LOW POWER OR GATE BLOCK USING MGFCAL                                | 70  |

| 6.2 LOW POWER AND GATE BLOCK USING MGFCAL                               | 67  |

| 6.1 LOW POWER NOT GATE BLOCK USING MGFCAL                               | 64  |

# LIST OF FIGURES

| Fig.                                                   | Name                                                 | Page     |

|--------------------------------------------------------|------------------------------------------------------|----------|

| No.                                                    |                                                      | No.      |

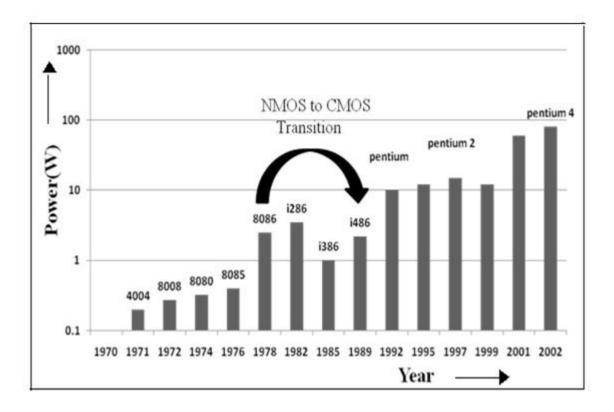

| 1.1: Maximum power c                                   | onsumption of lead Intel Microprocessor              | 5        |

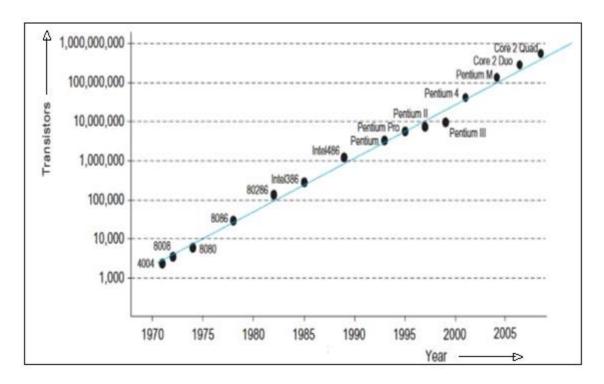

| 1.2: Total number of Tr                                | ransistors In Intel microprocessors                  | 6        |

| 2.1: Static hazard exam                                | ple                                                  | 10       |

| 2.2: Dynamic hazard ex                                 | ample                                                | 11       |

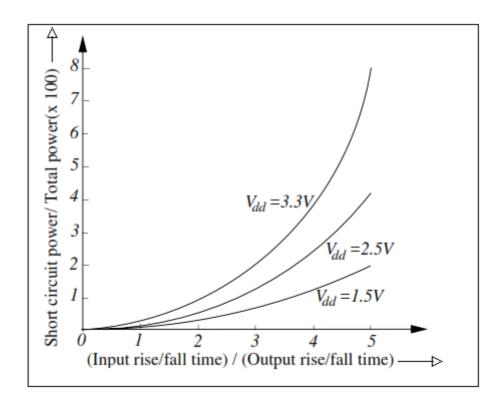

| 2.3: Short circuit power                               | dissipation versus input rise/ fall time             | 12       |

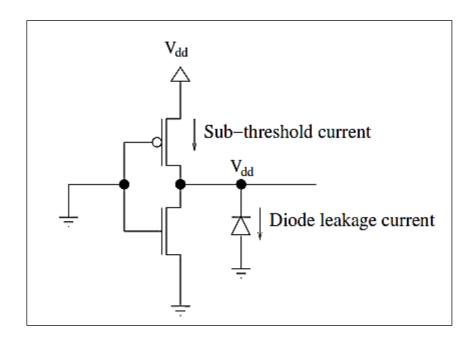

| 2.4: Leakage current in                                | an inverter                                          | 13       |

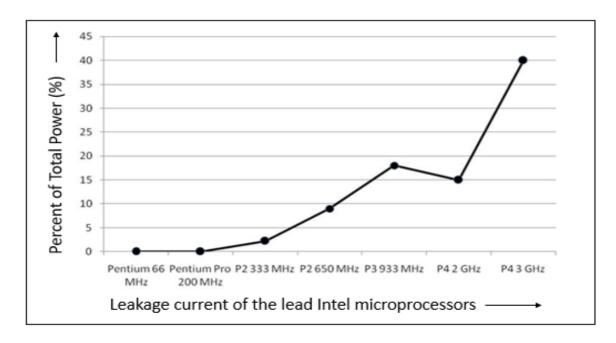

| 2.5: Increasing contribu                               | tions of leakage currents to the total power consump | ption of |

| the lead Intel mic                                     | roprocessors                                         | 14       |

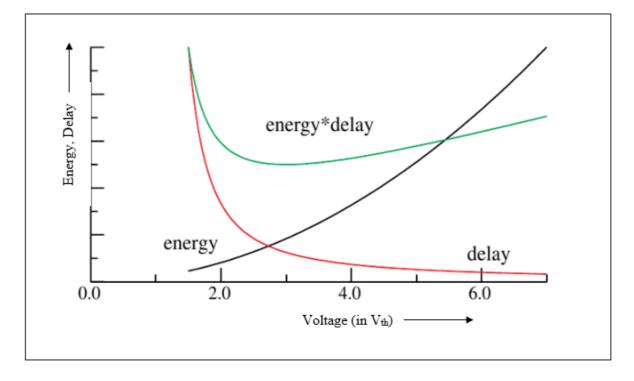

| 2.6: Energy, delay Vs.                                 | Voltage                                              | 15       |

| 2.7: Scaling of static voltage using multiple supplies |                                                      | 18       |

| 3.1: Conventional CMC                                  | OS switching                                         | 23       |

| 3.2: Adiabatic switchin                                | g circuit                                            | 24       |

| 3.3: One cycle of power clock in adiabatic technique   |                                                      | 26       |

| 3.4: Basic 2N- 2P diffe                                | rential inverter/ buffer                             | 28       |

| 3.5: Timing for 2N- 2P                                 | inverter/ buffer                                     | 29       |

| 3.6: 2N2N-2D inverter/                                 | buffer                                               | 31       |

| 3.7: ECRL inverter/buf                                 | fer                                                  | 32       |

| 3.8: Complementary En                                  | nergy Path Adiabatic logic                           | 32       |

| 3.9: Inverter Circuit usi                              | ng 2PASCL                                            | 34       |

| 3.10: QSERL logic blo                                  | ek                                                   | 35       |

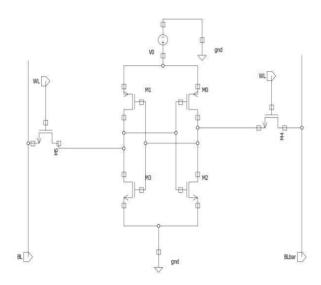

| 3.11: GFCAL inverter                                                         | 37 |

|------------------------------------------------------------------------------|----|

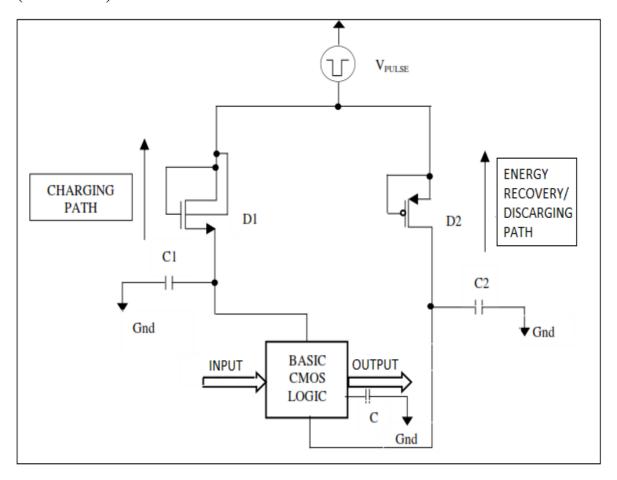

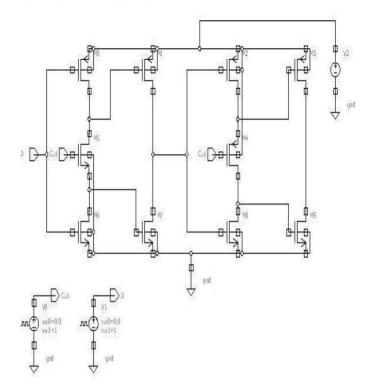

| 4.1: Modified Glitch Free Cascadable Adiabatic Logic                         | 41 |

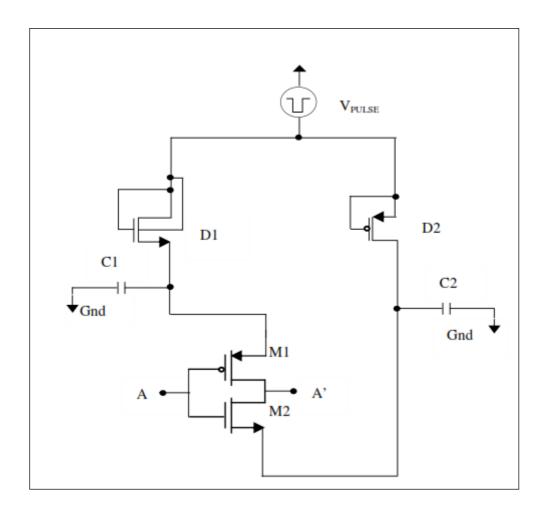

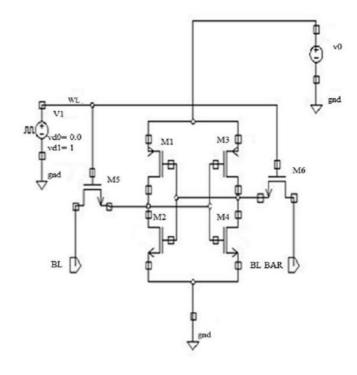

| 4.2 Low Power Inverter block using MGFCAL                                    | 42 |

| 5.1: Low Power Inverter block using MGFCAL.                                  | 47 |

| 5.2: Low Power AND gate block using MGFCAL.                                  | 48 |

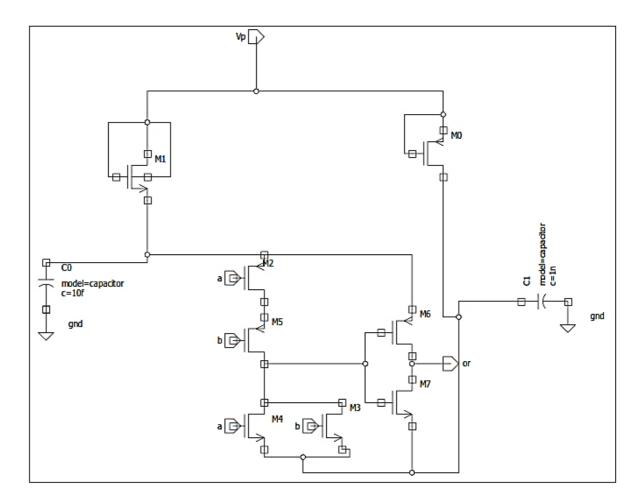

| 5.3: Low Power OR gate block using MGFCAL                                    | 49 |

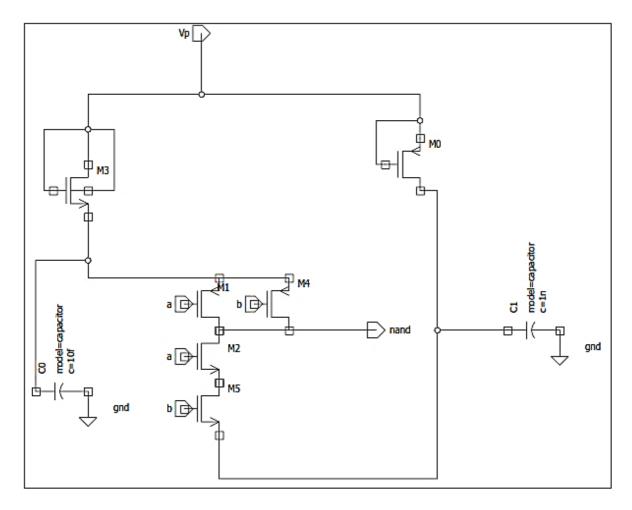

| 5.4: Low Power NAND gate block using MGFCAL                                  | 50 |

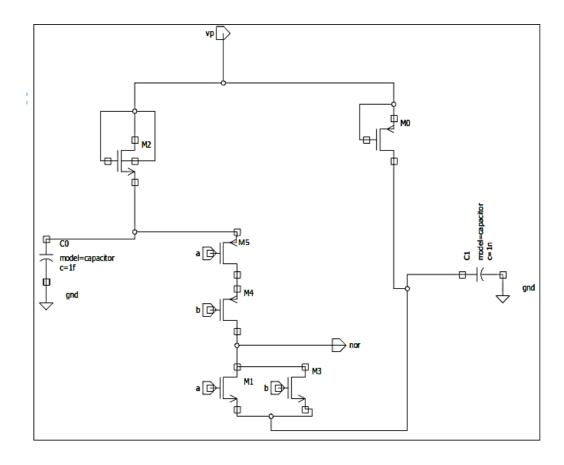

| 5.5: Low Power NOR gate block using MGFCAL                                   | 51 |

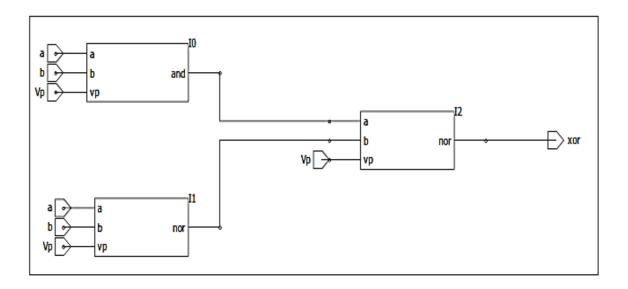

| 5.6 : Low Power XOR gate block using MGFCAL                                  | 52 |

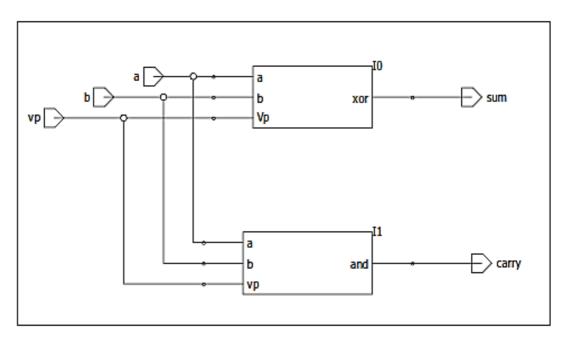

| 5.7: Low Power Half Adder block using MGFCAL                                 | 53 |

| 5.8 Low Power Full Adder block using MGFCAL                                  | 54 |

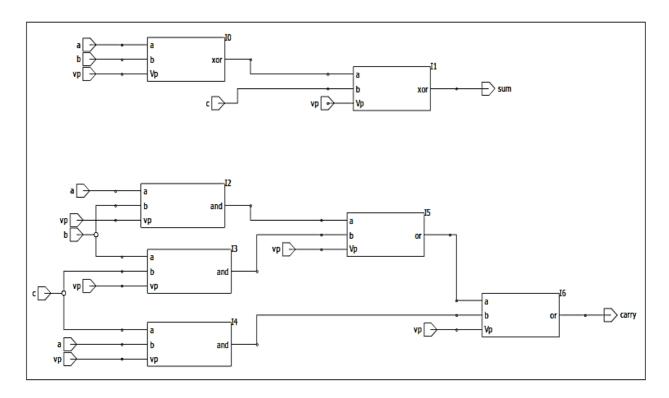

| 5.9: Low Power Half adder based Full Adder block using MGFCAL                | 56 |

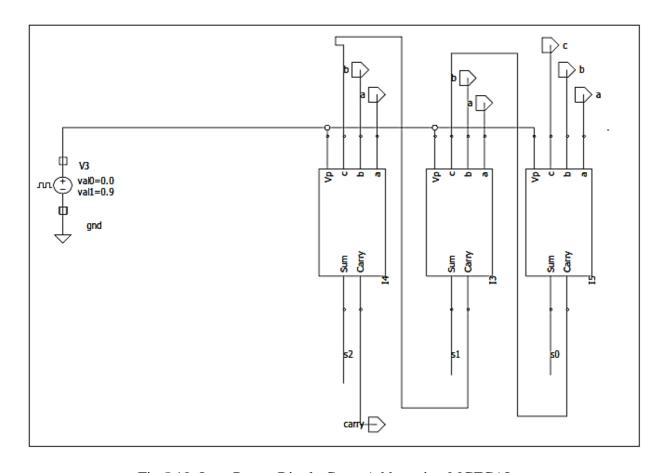

| 5.10: Low Power Ripple Carry Adder using MGFCAL                              | 57 |

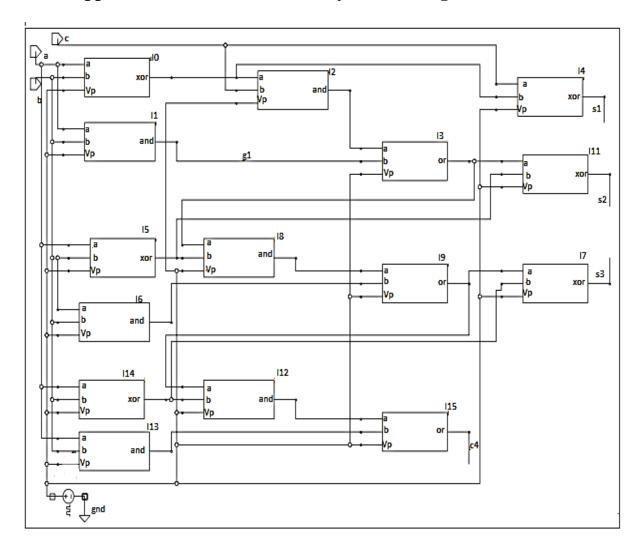

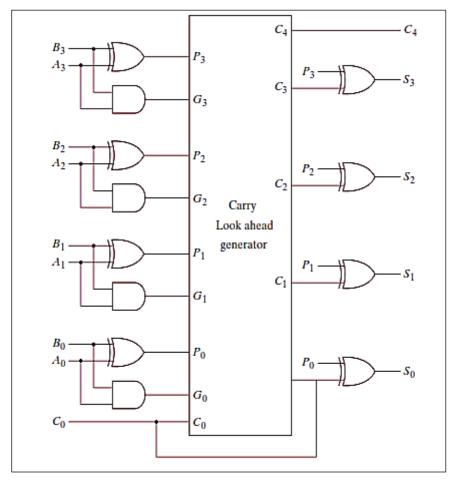

| 5.11: Low Power Look Ahead Carry Adder using MGFCAL                          | 58 |

| 5.12: : Basic Logic diagram of 4- bit Look Ahead Carry Adder                 | 59 |

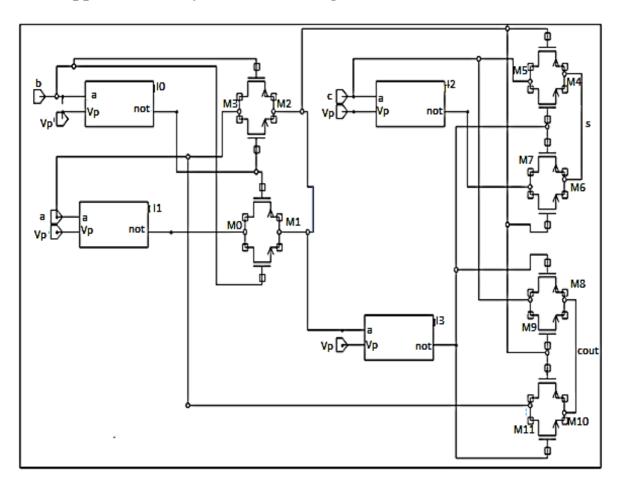

| 5.13: Low Power Carry Select Adder using MGFCAL                              | 60 |

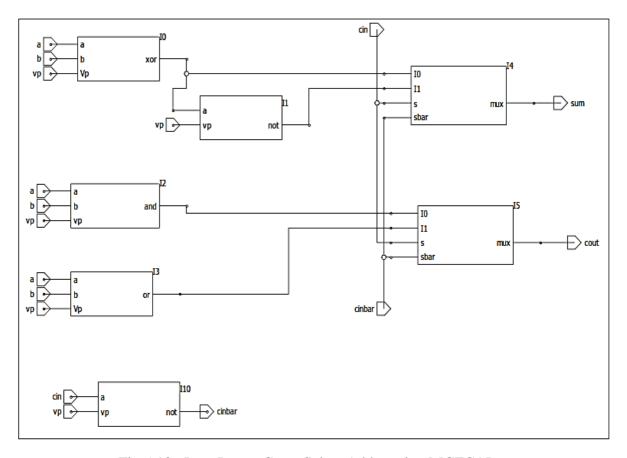

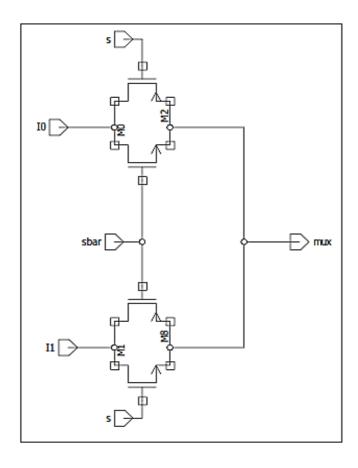

| 5.14: Logic Diagram of MUX used in Low power Carry Select Adder using MGFCAL | 61 |

| 5.15: Low Power hybrid Adder using MGFCAL                                    | 62 |

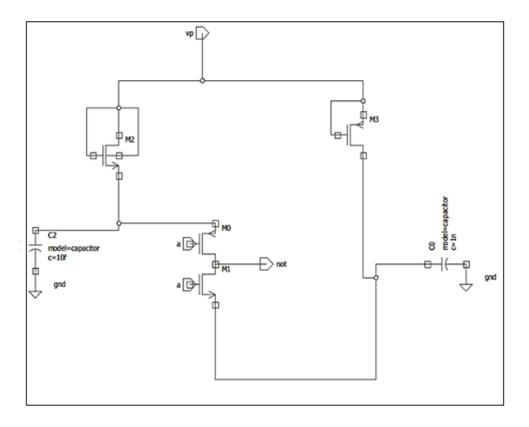

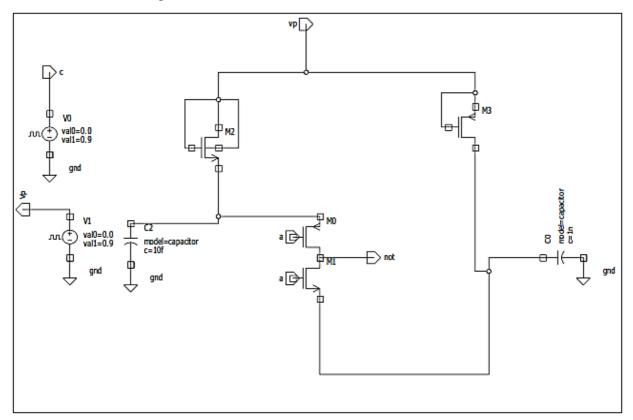

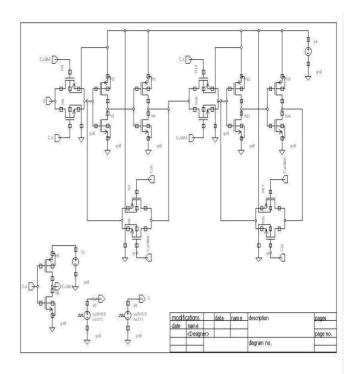

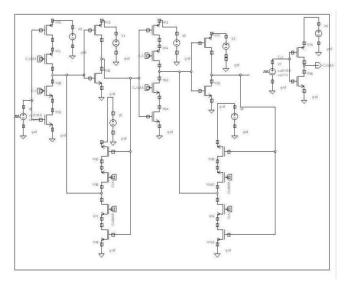

| 6.1 : Schematic of Low Power NOT gate block                                  | 64 |

| 6.2: Output waveform of Low Power NOT gate block.                            | 65 |

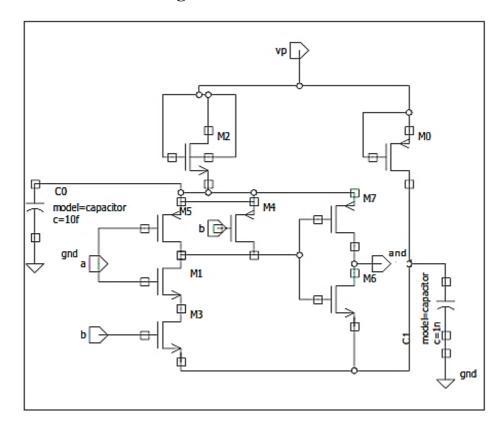

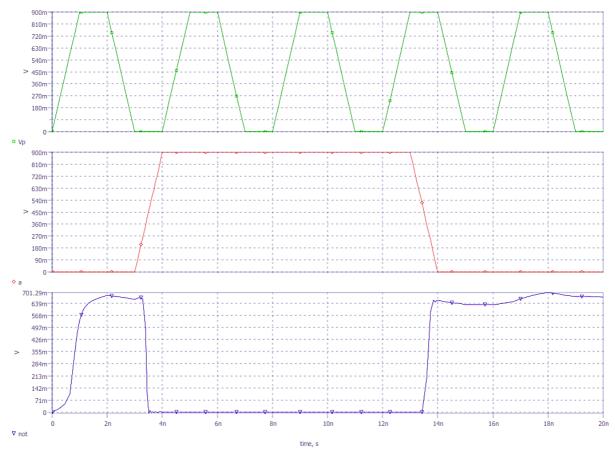

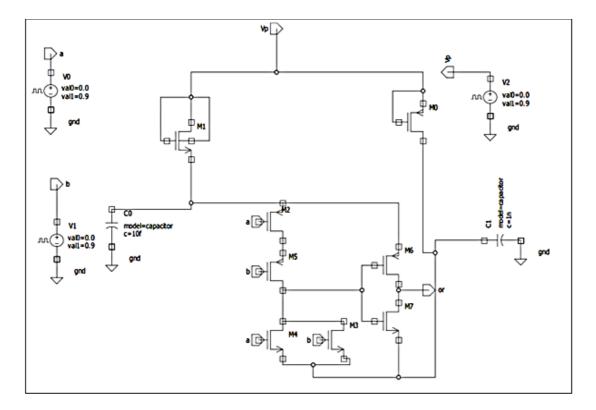

| 6.3: Low power AND gate block using MGFCAL                                   | 67 |

| 6.4: Output waveform of Low Power AND gate block.                            | 68 |

| 6.5: Low power OR gate block using MGFCAL.                           | 70  |

|----------------------------------------------------------------------|-----|

| 6.6: Output waveform of Low Power OR gate block                      | 71  |

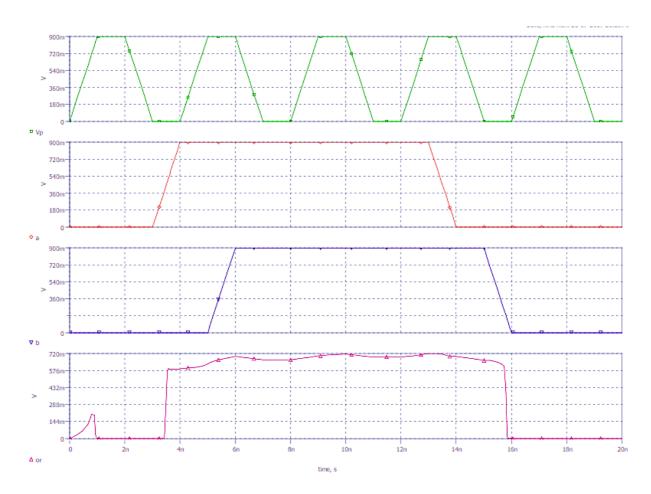

| 6.7: Low power NOR gate block using MGFCAL.                          | 73  |

| 6.8: Output waveform of Low Power NOR gate block                     | 74  |

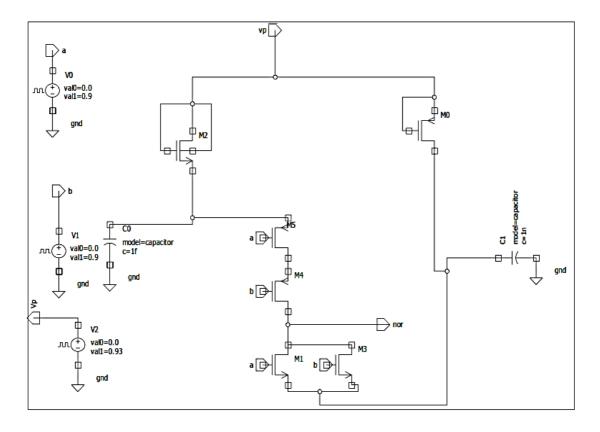

| 6.9: Low power NAND gate block using MGFCAL.                         | 76  |

| 6.10: Output waveform of Low Power NAND gate block.                  | 77  |

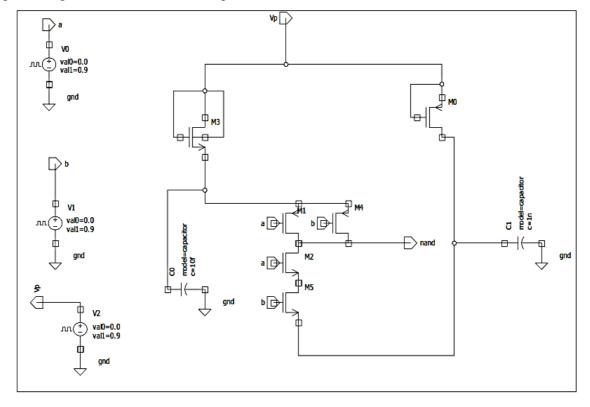

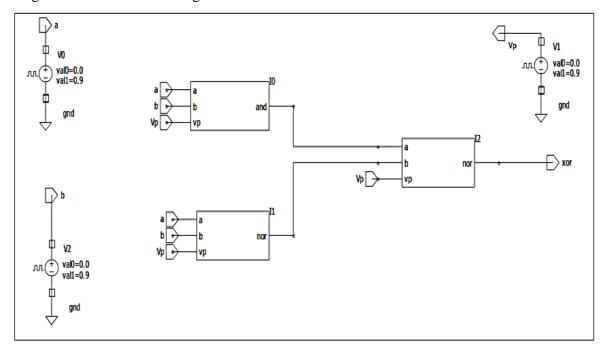

| 6.11: Low power XOR gate block using MGFCAL.                         | 79  |

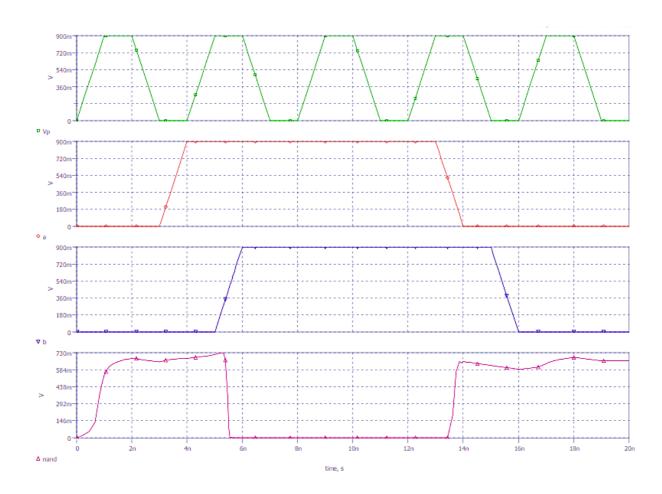

| 6.12: Output waveform of Low Power XOR gate block                    | 80  |

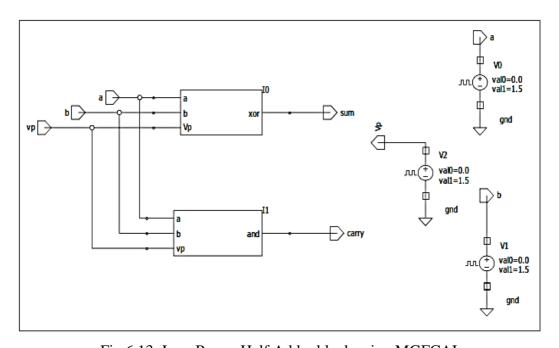

| 6.13: Low power Half Adder block using MGFCAL.                       | 82  |

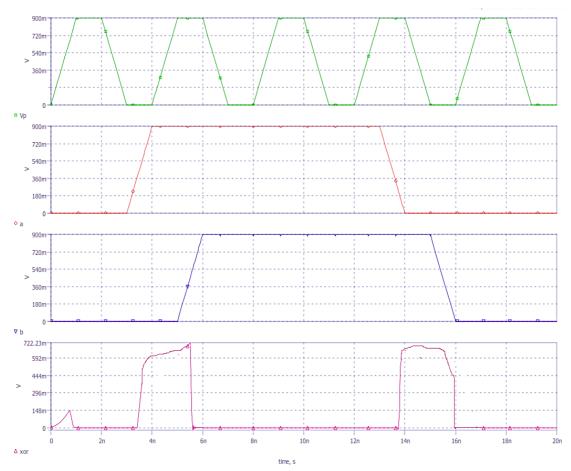

| 6.14: Output waveform of Low Power Half Adder block                  | 83  |

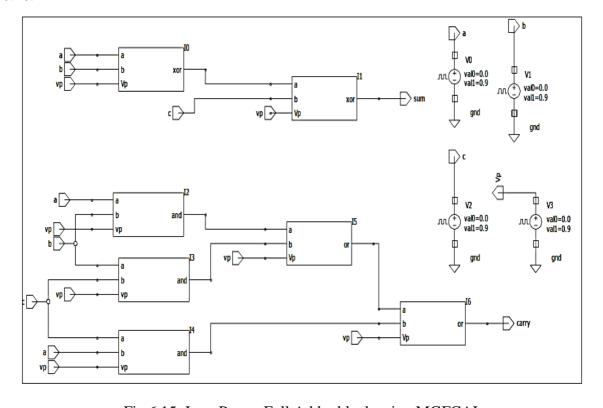

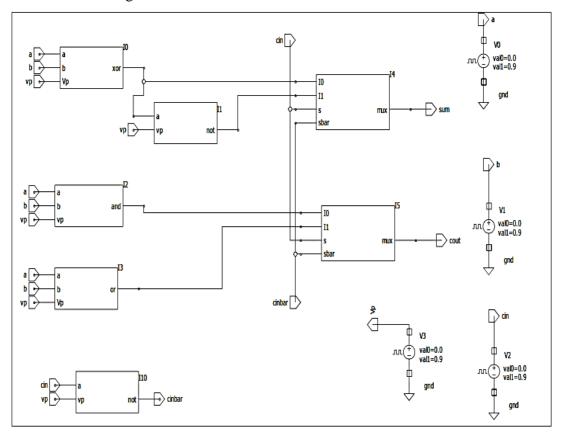

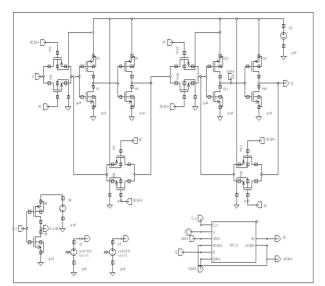

| 6.15: Low power Full Adder block using MGFCAL                        | 85  |

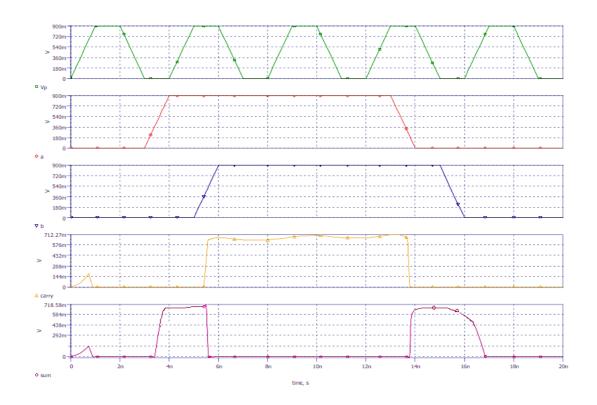

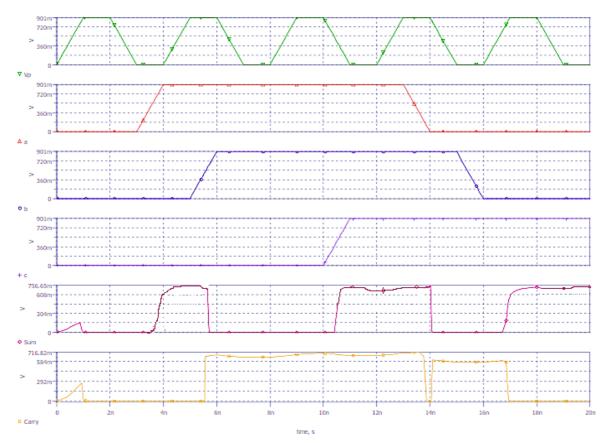

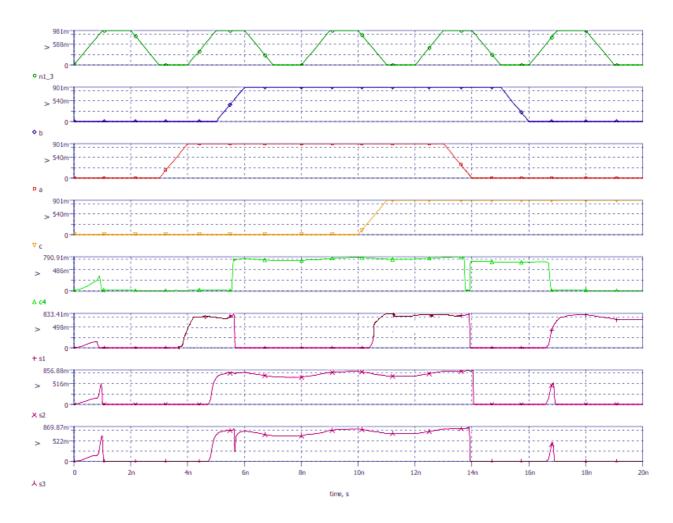

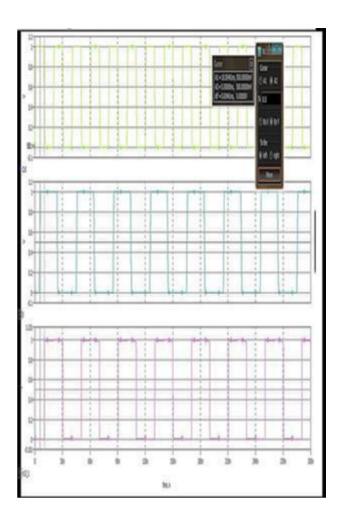

| 6.16: Output waveform of Low Power Full Adder block                  | 86  |

| 6.17: Low power Half Adder based Full Adder block using MGFCAL       | 88  |

| 6.18: Output waveform of Low Power Half Adder based Full Adder block | 89  |

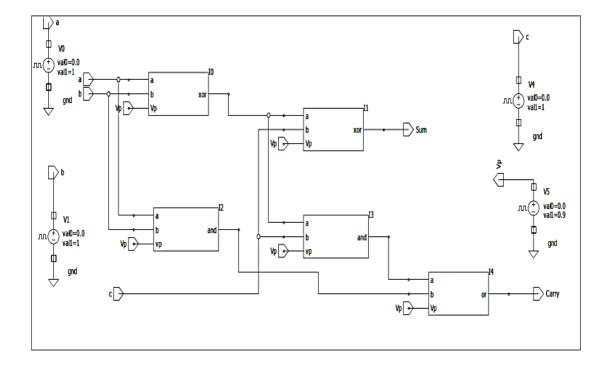

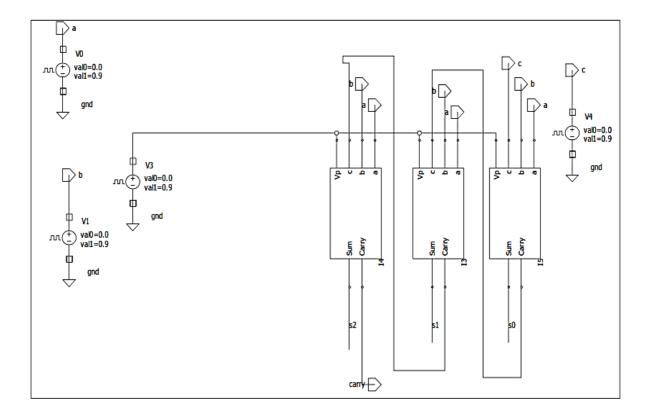

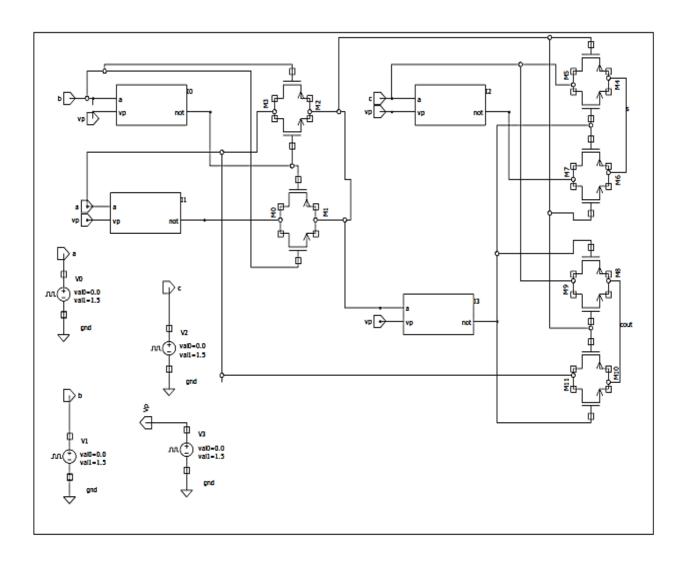

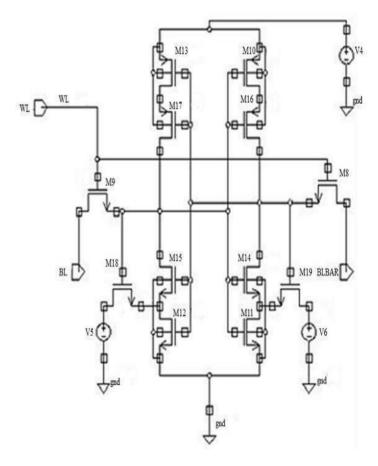

| 6. 19: Low power Ripple Carry Adder block using MGFCAL               | 91  |

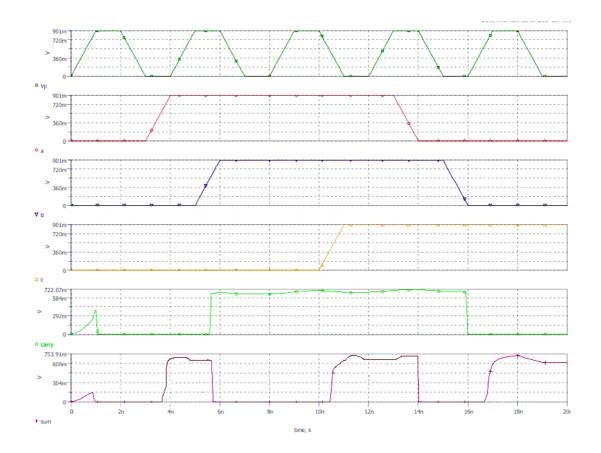

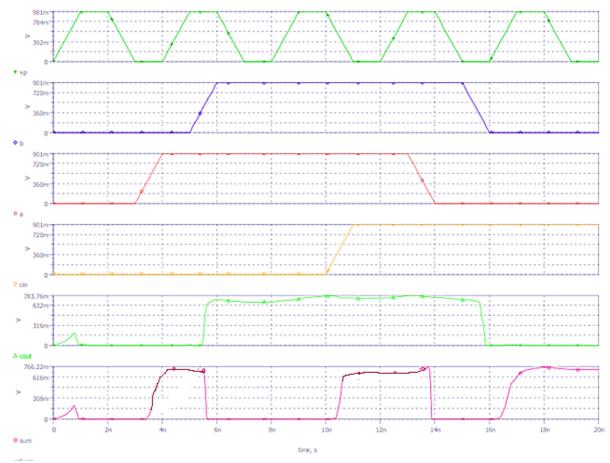

| 6.20: Output waveform of Low Power Ripple Carry Adder block          | 92  |

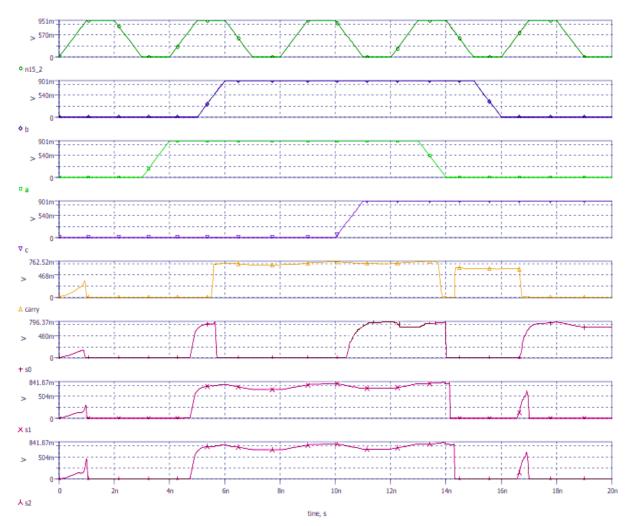

| 6.21: Low power Look Ahead Carry Adder block using MGFCAL            | 94  |

| 6.22: Output waveform of Low Power Look Ahead Carry Adder block      | 95  |

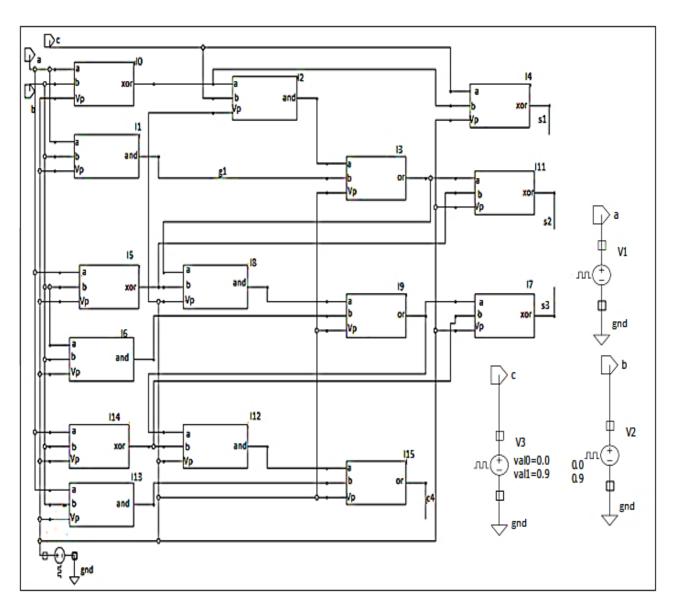

| 6.23: Low power Carry select Adder block using MGFCAL                | 97  |

| 6.24: Output waveform of Low Power Carry Select Adder block          | 98  |

| 6.25: Low power Hybrid Adder block using MGFCAL                      | 100 |

| 6.26: Output waveform of Low Power Hybrid Adder block                | 102 |

# LIST OF TABLES

| Table              | Name                                             | Page |

|--------------------|--------------------------------------------------|------|

| No.                |                                                  | No   |

| 5.1. Touch Table   |                                                  | 52   |

| 5.1: Truth Table   | of Half Adder                                    | 53   |

| 5.2: Truth Table   | of Full Adder                                    | 56   |

| 5.3: Low Power     | Carry Select Adder Truth Table                   | 62   |

| 6.1 (a): Delay cal | culation of NOT gate block using MGFCAL          | 65   |

| 6.1 (b): Performa  | nce parameter of NOT gate block using MGFCAL     | 66   |

| 6.2 (a): Delay cal | culation of NOT gate block using CMOS logic      | 66   |

| 6.2 (b): Performa  | nce parameter of NOT gate block using CMOS logic | 67   |

| 6.3 (a): Delay cal | culation of AND gate block using MGFCAL          | 68   |

| 6.3 (b): Performa  | nce parameter of AND gate block using MGFCAL     | 69   |

| 6.4 (a): Delay cal | culation of AND gate block using CMOS logic      | 69   |

| 6.4 (b): Performa  | nce parameter of AND gate block using CMOS logic | 70   |

| 6.5 (a): Delay cal | culation of OR gate block using MGFCAL           | 71   |

| 6.5 (b): Performa  | nce parameter of OR gate block using MGFCAL      | 72   |

| 6.6 (a): Delay cal | culation of OR gate block using CMOS logic       | 72   |

| 6.6 (b): Performa  | nce parameter of OR gate block using CMOS logic  | 73   |

| 6.7 (a): Delay cal | culation of NOR gate block using MGFCAL          | 74   |

| 6.7 (b): Performa  | nce parameter of NOR gate block using MGFCAL     | 75   |

| 6.8 (a): Delay cal | culation of NOR gate block using CMOS logic      | 75   |

| 6.8 (b): Performance parameters of NOR gate block using CMOS logic                 | 76 |

|------------------------------------------------------------------------------------|----|

| 6.9 (a): Delay calculation of NAND gate block using MGFCAL                         | 77 |

| 6.9 (b): Performance parameters of NAND gate block using MGFCAL                    | 78 |

| 6.10 (a): Delay calculation of NAND gate block using CMOS logic                    | 78 |

| 6.10 (b): Performance parameters of NAND gate block using CMOS logic               | 79 |

| 6.11 (a): Delay calculation of XOR gate block using MGFCAL                         | 80 |

| 6.11 (b): Performance parameters of XOR gate block using MGFCAL                    | 81 |

| 6.12 (a): Delay calculation of XOR gate block using CMOS logic                     | 81 |

| 6.12 (b): Performance parameters of XOR gate block using CMOS logic                | 82 |

| 6.13(a): Delay calculation of Half adder block using MGFCAL                        | 83 |

| 6.13 (b): Performance parameters of Half adder block using MGFCAL                  | 84 |

| 6.14 (a): Delay calculation of Half adder block using CMOS logic                   | 84 |

| 6.14 (b): Performance parameters of Half adder block using CMOS logic              | 85 |

| 6.15(a): Delay calculation of Full adder block using MGFCAL                        | 86 |

| 6.15 (b): Performance parameters of Full adder block using MGFCAL                  | 87 |

| 6.16 (a): Delay calculation of Full adder block using CMOS logic                   | 87 |

| 6.16 (b): Performance parameters of Full adder block using CMOS logic              | 88 |

| 6.17(a): Delay calculation of Half adder based full adder block using MGFCAL       | 89 |

| 6.17 (b): Performance parameters of Half adder based full adder block using MGFCAL | 90 |

| 6.18 (a): Delay calculation of Half adder based full adder block using CMOS logic  | 91 |

| 6.18 (b): Performance parameters of Half adder based full adder using CMOS logic   | 92 |

| 6.19(a): Delay calculation of Ripple Carry adder block using MGFCAL                | 93 |

| 6.19 (b): Performance parameters of Ripple Carry adder block using MGFCAL          | 93 |

| 6.20 (a): Delay calculation of Ripple Carry adder block using CMOS logic           | 93 |

| 6.20 (b): Performance parameters of Ripple carry adder using CMOS logic            | 94 |

| 6.21 (a): Delay calculation of Look ahead carry adder block using MGFCAL      | 95  |

|-------------------------------------------------------------------------------|-----|

| 6.21 (b): Performance parameters of Look ahead carry adder block using MGFCAL | 96  |

| 6.22 (a): Delay calculation of Look ahead carry adder block using CMOS logic  | 96  |

| 6.22 (b): Performance parameters of Look ahead carry adder using CMOS logic   | 97  |

| 6.23(a): Delay calculation of carry select adder block using MGFCAL           | 98  |

| 6.23 (b): Performance parameters of carry select adder block using MGFCAL     | 99  |

| 6.24 (a): Delay calculation of carry select adder block using CMOS logic      | 99  |

| 6.24(b): Performance parameters of carry select adder using CMOS logic        | 101 |

| 6.25(a): Delay calculation of Hybrid adder block using MGFCAL                 | 102 |

| 6.25 (b): Performance parameters of Hybrid adder block using MGFCAL           | 102 |

| 6.26 (a): Delay calculation of Hybrid adder block using CMOS logic            | 102 |

| 6.26 (b): Performance parameters of Hybrid adder using CMOS logic             | 103 |

## LIST OF ABBREVIATIONS

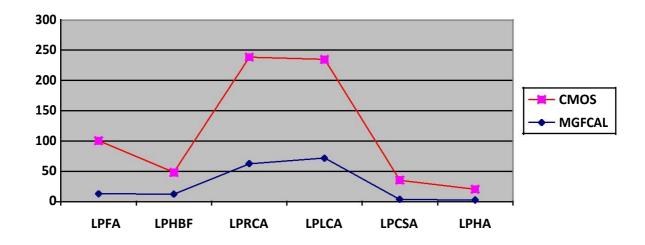

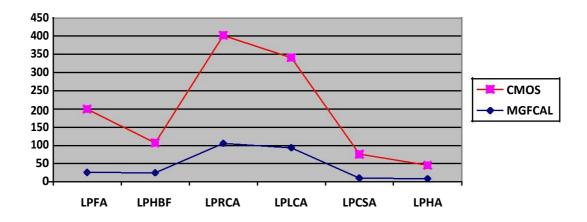

MGFCAL : Modified Glitch Free Cascadable Adiabatic Logic

LPFA : Low Power Full Adder

LPHBF : Low Power Half Adder based Full Adder

LPRCA : Low Power Ripple Carry Adder

LPLCA : Low Power Look ahead Carry Adder

LPCSA : Low Power Carry Select Adder

LPHA : Low Power Hybrid Adder

TIPS : Tera Instructions per second

IC : Integrated Circuits

CMOS : Complementary Metal Oxide Semiconductor Field Effect Transistors

Ni-MH : Nickel- Metal Hydride

NiCd: Nickel Cadmium

ULSI : Ultra Large-Scale Integration

C<sub>L</sub> : Load Capacitance

CPU : Central Processing Unit

GND : Ground

IoT : Internet of Things

RFID : Radio Frequency Identification

MUX : Multiplexer

## **ABSTRACT**

Nowadays, power dissipation is among the most dominant concerns in designing VLSI circuits. Endless improvement in technology has points to an increased requirement for devices which have the basic characteristic of low power consumption. Hence, power has turned into a demanding design parameter in low power and high-performance applications. The Adiabatic logic technique is becoming a solution to the dilemma of power dissipation. The expression 'Adiabatic' indicates to the change of state that takes place without any loss or gain of heat. The power dissipation at the time of switching events can be reduced to a greater extent by using the adiabatic switching technique. Adiabatic logic is a promising design paradigm for low power circuits since the energy which is to be dissipated is recycled and reused back. In most of the digital circuits, digital signal processing and communication systems, multipliers play a major role where adders constitute the basic blocks. Adders with huge power consumption affect the overall efficiency of the system.

The research in this thesis unfolds the rising gravity of the issue of the power dissipation and explores different ways to curtail the problem.

This thesis includes in depth study of causes of power dissipation, ways of removing a power dissipation in the circuit by using modified GFCAL circuits, along with the proposed application of modified GFCAL technique in various adder circuits. Then, the comparison is made between the conventional CMOS circuit and the modified GFCAL circuit. The functionality and effectiveness of all proposed architectures are confirmed through intensive simulations on SYMICA Development Environment at 90nm technology parameters. All the above introduced circuits are simulated with supply voltage = 0.9 V, 1.2 V and 1.8 V to analyse the pattern followed with supply variation. Similarly, the calculation of delay is performed for temperature values of 27°C, 55°C and 120°C at 90nm technology. Effect of proposed applications on the delay of the circuit has been analysed as well.

#### INTRODUCTION

#### 1.1 Motivation

In this generation of digital world, electronic gadgets with fast applications are in incredible demand. Combined with this is the demand of compact gadgets like cell phone and tablet. In these devices, there is limited power budget. The recent approach to deal with this requirement is to move towards the lower technology node called scaling but this is not so straightforward and needs lot of optimization. According to Moore law, the number of transistors doubles almost every 18 months [1]. The current pattern of expanding the quantity of transistors within the same area prompts complex circuits, which is having conflicting impact on power and performance of a given circuit.

In the previous couple of decades, the electronics industry has been encountering an unpredictable spurt in the growth, because of the utilization of incorporated circuits in processing, broadcast communications and customer electronics gadgets. We have made some amazing progress from the single transistor period in 1958 to the present day ULSI (Ultra Large-Scale Integration) frameworks with more than 50 million transistors in a solitary chip [2].

The steadily growing number of transistors coordinated on a chip and the continuous increasing transistors exchanging speed in recent decades has empowered awesome performance changes in computer system by a few orders. On the contrary, such amazing execution changes have been joined by an expansion in power and increase in energy dissipation of the digital circuits. Higher power dissipation in digital VLSI circuits require more costly bundling and cooling techniques along with a significant increase in cost, and thus makes the system less reliable. In any case, the power and energy dissipation of highly reliable systems with better performance will be a basic plan requirement [3].

There are basically 2 significant types of power dissipation present in VLSI domain: -

- (i) Static power dissipation

- (ii) Dynamic power dissipation [1].

Static Power dissipation is mainly due to the internal leakage that is present in the device, when the circuit is in OFF state [4]. Dynamic power dissipation occurs when switching takes place in the circuit and is mainly due to the energy loss at the time of charging and discharging of the output node capacitance of a transistor. Therefore, static power dissipation and dynamic power dissipation have been the dominant matter for the designers [5] For the proper power reduction in the circuits, various divergent technologies have been popularised over the years which are sub-threshold logic technique [6], multi-threshold logic technique [7] and adiabatic logic technique [8]. For instance, high end microprocessors in 2010 are anticipated to utilize 100 crores of transistors at clock rates more than 30GHz to accomplish TIPS (Tera Instructions per seconds) execution [2]. These high number of transistors, influence the power dissipation to thousands of Watts. This thesis explores the power dissipation in various CMOS adder circuits and proposes and analyse the techniques to reduce the power dissipation to a greater extent.

The basic component behind the VLSI designing is the digital CMOS based ICs for better performance and other different operations related to science and innovation. But right now, with the development of energy efficient gadgets [9] and biomedical field related applications that desires extremely low power consumption without affecting the other performance parameters to a greater extent, so a modern and different way need to be investigated so that the need for power saving is fulfilled [10].

Thus, nowadays, the requirement for decreasing the power dissipation is the significant matter for advanced digital devices. Also, utilization of adiabatic logic technique is the appealing answer for the most common issue of the advanced digital circuits for decreasing the dynamic power, which utilizes ramping supply voltage sources to recuperate the energy which would somehow or another be dissipated as a loss [11-12]

#### 1.2 Demand of Low Power VLSI Design:

In VLSI chip design, power dissipation is customarily a disregarded subject. Earlier, the functional frequency as well as the device density were sufficiently low that it was not an obliging aspect in the chips. As the device density enhances, more transistors, speedier and littler than their antecedents, are being integrated onto a chip, which further prompt increment in power dissipation of the device [1]. The multiplication in Transistor count in Intel microprocessors is shown in fig 1.1[13] Further, it is estimated the leakage power is going to increment 32 times for each device by the year 2020 in view of the present situation [14]. The rate of energy delivered from the source to the device is known as the power dissipation of the device. Nowadays, Power dissipation is turning into an imperative limitation in a design. A few reasons underline the developing of this issue. Among them some are exhibited here:

The demand for battery powered systems such as laptop, computers, etc. desires that they have extended battery life. Numerous versatile applications for the small size portable devices utilize the rechargeable Nickel Cadmium (NiCd) batteries. Despite the fact that the battery business has been trying endeavours to create batteries with higher energy limit than that of NiCd, a fast increment does not appear to be impending. The normal change expectation of the energy density is 40% by the turn of approximately 100 years. Indeed, even with the new innovations in the battery, for example, Nickel-Metal Hydride (Ni-MH) which give energy density qualities (30 Watt-hour/pound), the average lifespan of battery is still considerably on the lower side. Since battery innovation has offered a restricted change, low power design procedures are basic for versatile portable gadgets and devices [2]. Low power is required for compact applications as well as to diminish or considerably lower the power of superior performance circuits. With huge number of transistors on a single chip and enhanced speed of operation, designs with larger clock frequencies are rising. These efficient designs are utilizing fast processors and related circuits which increment the power utilization. The cost related with cooling, bundling and fans required by these modules or design to expel the heat because of increased power dissipation, is expanding fundamentally. Thus, a need for low power devices is the major requirement in today's era.

As shown in Figure 1.1, the power utilization of the lead Intel microchips has been expanding fundamentally for approximately every generation in the course of recent years. The changes amid this period in terms of frequency is from a few MHz to 3 GHz. So, the figure shown below states that at higher frequencies, the power dissipation is excessive.

Figure - 1.1 Maximum power consumption of lead Intel Microprocessor [15]

Ultra Large- Scale Integration (ULSI) unwavering quality is yet another worry which focuses to the need of low power plan. There is a very great relationship between the power dissipation of circuits and reliability issues, for example, electro migration, heating problem in the device, requirement of excess cooling pads, etc Therefore, it can be stated the lowering of energy consumption is additionally urgent for reliable quality improvement. Fig 1.2 shows the total number of transistors in Intel microprocessors within a long span of time. The figure shows that there is great increment in the total number of transistors used as the years pass by. And with the ever-increasing number of transistors, further results in increase in total power dissipation of the circuits, it is for this reason power reduction in the device module is the main concern nowadays.

But the practices which are utilized to accomplish low power utilization in compact portable digital systems traverse an ample field, from device level to process level to algorithm level, device components used, sizing of transistors, interconnects used, voltage supply used along with the other parameters plays a vital role in minimizing the total power dissipated from the circuit. Circuit level and architecture level outline measures are basically utilized to accomplish low power utilization in the digital design circuits.

So certainly, a total power consumption by the digital circuits can be lessened by an appropriate choice of information handling algorithms, particularly to limit the quantity of switching in the given design.

Fig 1.2:- Total number of Transistors in Intel microprocessors [16]

## 1.3 Research Objective:

The fundamental inspiration to continue with this specific research is to execute a significant examination of circuit level techniques to balance the ever-increasing Power dissipation in the circuit with better advances and technologies and finally came up with a Modified Glitch Free Cascadable Adiabatic Logic Technique-A Technique of the adiabatic logic family and shows its applications in different VLSI design adder circuits. Adiabatic circuits are low power circuits which utilize "reversible logic" to preserve energy, it is for this reason it offers certain

points of interest over logic implementation utilizing ordinary CMOS logic style and consequently is on the brighter side. Limiting the power dissipation is the fundamental concern these days, it is for this reason designing those circuits which save power to a greater extent serves the purpose. This thesis is an endeavour to unfurl the power dissipation issue in digital adder circuits and propose new adder circuits which can be utilized as a part of advanced VLSI configuration circuits and save the power to a greater extent as compared to the conventional CMOS circuits. The goals of doing this thesis work are as follows:

- To cautiously study the patterns of dissipated power with fast innovation progress of technology.

- In depth study of several circuit level power reduction adiabatic logic technique.

- Appropriately applying the knowledge of CMOS Technique in various full adder circuits.

- In depth analysis of modified glitch free cascadable adiabatic logic.

- To analyse various logic gates circuit based upon MGFAL so that the power is reduced to the greater extent in the circuit.

- To introduce various adders like full adder, half adder based full adder, parallel adder, look ahead carry adder, carry select adder and the hybrid adder using MFCAL.

- Authentication of proposed adder structures by performing in depth simulation on SYMICA development environment at 180nm, 90nm, 65nm and 45nm technologies.

- Performing temperature variations and voltage supply variation for the proposed adder structures.

#### 1.4 Organization of Thesis

The essential objective of this thesis is to establish a circuit level approach, for adoption in those designs which request outrageous low power dissipation. The content of this thesis is wrapped into seven major parts:

#### Chapter 1 i.e., the **Introduction**

This chapter introduces power consumption issues in the area of VLSI. This chapter also summarizes the need of low power design in the today's era of scaling down of technologies and nanotechnology. Finally, this chapter concludes with the research objective behind this thesis followed by the brief organisation of thesis.

Chapter 2 i.e., the **Power Consumption in VLSI Circuits** introduces about the types of power dissipation in the circuit along with the already existing techniques to mitigate or lessen that power dissipation in a circuit.

Chapter 3, i.e., the Adiabatic Logic Technique explains about the adiabatic logic technique along with merits and demerits of already existing quasi or partially adiabatic logic.

Chapter 4, i.e., **the Modified Glitch Free Cascadable Adiabatic Logic (MGFCAL)**, gives the brief introduction about the MGFCAL technique used in the proposed application for a power reduction in a circuit to a greater extent.

Chapter 5, i.e., **The Application of MGFCAL in various circuits**. This chapter explains the proposed adder circuits implemented through the MGFCAL technique.

Chapter 6, i.e., **Simulation and Analysis**. This chapter presents the proposed adder circuits which in turns reduces the total power dissipation in the circuit up to a greater extent along with this the comparison of the proposed circuits with the conventional CMOS circuit is also shown in terms of basic performance parameters like power, delay etc.

Chapter 7, i.e., the Conclusion and Future Scope, this chapter finally concluded the thesis work along with the future scope in which the proposed work can be used and is useful for the use in future aspects.

#### POWER CONSUMPTION IN VLSI CIRCUITS

#### 2.1 Power dissipation in CMOS Circuit

In this chapter, the essential components of power dissipation in CMOS circuits is reviewed, which is followed by the techniques that were earlier used for the power reduction in the circuit. Excessive power consumption is an essential confinement to the further improvement in semiconductor industry. Distinguishing between the causes of power consumption is basic for creating power reduction methods at the manufacture fabrication technology, circuit level or at architecture level. There are fundamentally three sources of power dissipation in digital CMOS circuits.

- Dynamic Power

- Short- circuit Power

- Leakage power

So, the total power consumption of a CMOS circuit is shown in eq. 2.1:

$$P_{total} = P_{dynamic} + P_{leakage} + P_{short\text{-}circuit} \qquad (2.1)$$

#### 2.1.1 Dynamic Power

The main cause dynamic power in the VLSI circuits is due to charging and discharging of the  $C_L$  (load capacitance). This capacitance comprises of gate internal capacitance, capacitance of the gate terminal of the transistor being disciplined by the fanout net and the value of capacitance of wire of the fanout net. The dynamic switching power does not depend on the type of switching gates, type of input waveform, neither on the rise and fall time of the input signal. On the contrary, it only depends on the voltage supply, the switching frequency of the circuit, and on the value of capacitance of a switching node [17].

The dynamic power can be determined by the equation shown below [18-19].

$$P_{dynamic} = \frac{1}{2}C_{load}V_{dd}^2fD....(2.2)$$

where,

P<sub>dynamic</sub>= Total dynamic power dissipation

$C_{load}$  = Capacitance of the load Terminal

f= Clock frequency

D = Transition density of the output

V<sub>dd</sub>= Supply voltage

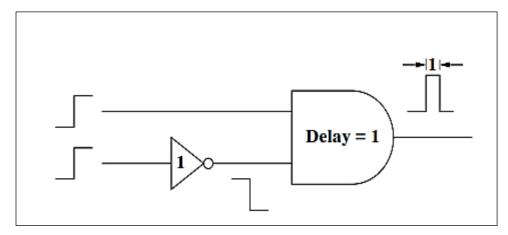

Fig 2.1: Static hazard example

All the while along a clock cycle, the average number of transitions is termed as Transition Density [20]. Thus, we can say that the total dynamic power dissipation present in the circuit is directly proportional to the total number of transitions present in the circuit. Earlier, the dynamic power contributed to majority of portion of power dissipation in the circuit but with the advancement in the deep sub- micron technology, the leakage current or we can say the static power dissipation is also considered as the important aspect [21]. The transition occurs in the circuit because of two main reasons:

- (i) Switching activity which is quite essential for the correct working of the circuit.

- (ii) Due to unnecessary transitions. The main cause of unnecessary transitions in the circuits is basically due to the unbalanced paths present in the circuit, and this is known as the glitching power.

#### 2.1.2 Hazard and Glitch Power:

As depicted in equation 2.1, power consumption is increased to a greater extent by the increment in the count of transitions in the circuit and the resulted power consumption is termed as glitch power. These unwanted transitions are known as glitches. The basic cause of glitches in the circuit is due to the variation or we can say difference in the reaching time of the input signals at the input of any logic. Glitch power in the circuit ranges from 20% to as large as 70% present in the circuits like combinational adder circuits [22].

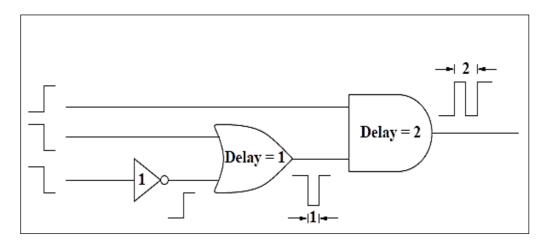

Figure 2.2: Dynamic hazard example

Because of the variation in the timing of the signal reaching the input of the AND gate, a sudden glitch is observed in the output which is of 1-unit width, which is equivalent to the delay of inverter and this is called as static hazard. As depicted in figure 2.2, the outcome of OR gate produces a static hazard of 1 unit. The transient at the output comprises of 2 rising and one falling edge, that is a sum total of three edges. And thus, we can say that it is a dynamic hazard with a width of 2 units.

A gate which is producing the hazard has greater than 1 input and has a non-zero greatest variation in the arrival time of the inputs of the gate. The amount of time in which the output changes after the change in the input is known as Inertial delay and it is contributed as a noteworthy part in altering the glitch that is produced in the circuit [23].

#### 2.1.3 Short circuit power dissipation:

In static CMOS circuits, there is a period amid the transition of the input signals when both the pull up as well as the pull-down system transistors are all the while ON, subsequently it results

in a DC current path between the power supply and ground. The conduction of DC current by a CMOS circuit amid an input signal transient just because of non-zero value of rise time and fall times of the input signal is known as the short circuit current [24-25].

The short circuit power dissipation at the input of inverter is given by:

$$P_{short-circuit} = \frac{\beta}{12} (V_{dd} - 2V_T)^3 \frac{\tau}{T} \qquad (2.3)$$

where,

$V_{dd}$  = Supply voltage.

$V_T$  = Absolute threshold temperature of NMOS and PMOS transistors

$\tau$  = Rise time or fall time of the input

T = Period of the signal

$\beta$  = Gain factor of the inverter

Fig. 2.3: Short circuit power dissipation versus input rise/fall time [1].

Figure shown above depicts the graph between the short circuit power dissipation and the ratio of input rise/ fall time to the output rise/ fall time. [26.] Larger the value of ratio on the x- axis,

higher the value of short circuit power (average) incremented in the circuit.

#### 2.1.4 Leakage Power Dissipation:

Leakage currents are mainly categorized into two parts:

- (i) Reverse biased leakage current

- (ii) Sub-threshold leakage current

The leakage current that flows through the parasitic diode amid the source and the body terminal is termed as reverse biased leakage current. On the contrary, the leakage current which flows through the channel of the device is termed as sub threshold leakage current [1]. Furthermore, added objection such as that of process variation, leads to tremendous increment in the leakage power [27-29].

Fig 2.4: Leakage current in an inverter [28].

Diode leakage current occurs when the transistor is turned OFF, and another active device charge up or discharges the drain with respect to the former's bulk potential. Let us consider the above figure, when the input applied is low, then the PMOS is turned ON While the NMOS is turned OFF. And output charges to  $V_{dd}$ . The parasitic diode from output to the NMOS bulk is reverse biased with voltage  $V_{dd}$ .

This diode has a current to the substrate given by:

$$I_{\text{leakage}} = I_s \left( e^{\frac{qV}{kT}} - 1 \right) \qquad (2.4)$$

where,

I<sub>s</sub>= Reverse saturation current n the diode

V = Reverse biased voltage

$q = charge on electron (1.602 \times 10-19 C)$

k = Boltzmann's constant

T = Temperature in Kelvin

So, as presented in Figure 2.3, leakage current will turn into the main cause of power dissipation in the coming years.

Fig.: 2.5 Increasing contributions of leakage currents to the total power consumption of the lead Intel microprocessors [30]

Also, the decrement in the threshold voltage results in increment in leakage power [31-34].

#### 2.2 Low Power Design Techniques:

The low power design of the circuit can be realized at either at the circuit level by changing the circuit configuration without changing the desired result, or at the architecture level or at the programming level, where the programming of the whole circuit module is optimized. Sometimes a blend of one or more of these of approaches are utilized to save the overall power dissipation of the circuit design. The circuit level optimization for low power in the circuit includes lowering any one of the components as shown in eq. (2.1) and this is the most difficult task at circuit level for low power optimization. In the coming section, a concise study on various strategies used to get low power configuration are shown. The power per operation can also be lowered down by reducing the supply voltage, as the value of capacitance and threshold voltage still remains constant in the circuit, but on the contrary, it has one drawback that by increasing the value of supply voltage the value of delay is decreased. It has been shown in [35] that the relation between the delay, threshold voltage and the output capacitance is as follows:

$$t_d = \frac{k(CV)}{(V - V_{th})^2}$$

.....(2.5)

Fig 2.6: Energy, delay vs. Voltage [1]

By properly scaling of voltage, Figure 2.6, demonstrates a plot among energy, delay and energy delay product. At voltage level, much greater than the threshold voltage, decreasing the supply voltage decreases the overall power dissipation of the circuit without affecting the delay to much greater extent. On the contrary, at voltage level near the threshold of the device, even with a slight shift in the supply voltage, leads to great variation in the delay value along with the modest revision in the value of total power dissipation. At  $V_{dd} = 3V_{th}$ , a minima is noticed and varying the value of supply voltage at this point does not disturb the energy-delay product to a greater extent. From the value  $V_{dd} = 1.5V_{th}$  toward  $V_{dd} = 6V_{th}$  there is a change of 8 in energy element that can be traded for delay without affecting the energy delay product largely.

#### 2.2.1 Transistor Sizing:

By properly reducing the device size in the circuit, the value of the total power dissipation in the circuit can be decreased and by decreasing the dimensions of the device in the circuit, the value of capacitance due to gates of transistors is also decreased which further reduces the overall power consumption of the circuit. But scaling of the device size results in reduction in the current driving capability of the logic gates, which reduces the response time of the circuit to a greater extent along with increasing the delay of the circuit. But like in [35], using circuits which have smaller device size, contribute to low power design but on the contrary, it does not guarantee the energy efficient design as it affects other parameters also.

## 2.2.2. Technology Scaling:

One different way to correct the energy-delay product can be done by the technology enhancement process. In ideal scaling; by a scaling factor of  $\gamma(<1)$ , all the dimensions which are linear along with all voltages are decreased [36-37]. As the scaling does not affect the electric field along with the wires present in the device, so the total current in the device as well as the capacitances of wire are also scaled by a factor of  $\gamma$ . As the scaling factor of  $\gamma$  is applied in voltage also, so the switching energy (CV²) per transition also scaled by  $\gamma^3$ . So, the delay of individual logic gate enhances by  $\gamma$  (td  $\approx$  CV/i ) . It is for this reason, there is the reduction by factor  $\gamma^4$  in the energy-delay product. This concludes that if a scaling of 0.7 is introduced, then a chip can give the same performance at (0.7)  $4 \approx 0.25$  of the previous power consumption. But in ideal scaling, the threshold voltage  $V_{th}$  does not scale in tune with the supply voltage. Static power dissipation caused by leakage current through the off transistors

will limit how low the threshold voltage can be scaled. Even with constant voltage scaling, the reduced capacitance improves both the energy and delay, so their product scales as  $\gamma^2$ .

#### 2.3 Dynamic Power Reduction:

There are two methods of reducing active power or dynamic power. They are:

## 2.3.1. Activity Reduction:

The total energy consumed is directly proportional to the frequency and the value of capacitance. This signifies that the power consumption in the circuit can be reduced by reducing the number of transitions that is there must be minimum switching activity in the circuit. For example: In the processor, a unit named program counter generally utilizes the binary code; that is on an average two bits are changed for each and every state transition. On the contrary, if gray codes are used in place of binary codes, then with each state transition only a single bit is changed. this result is energy saving in the circuit. Many such coding strategies have been accounted for in literature that yield different power saving in the circuit [38]. To reduce activity in synchronous logic, click gating [39] is used. Clock signal to a logic block is gated by a control signal, disabling clock when the particular logic block is not in use, thereby reducing the click signal activity and thus the overall active power consumption.

## 2.3.2 Supply Voltage Reduction:

Since power utilization decreases quadratically along the supply voltage, supply voltage cut back can bring about generous power saving in the circuit. There are mainly two approaches for the supply voltage cutback without trading off other performance parameters of the circuit; they are the static approach and dynamic approach [40]. In dynamic approach, the chip is intended to convey greatest performance at maximum value of supply voltage. For some applications, the performance parameter need not to be up to the mark, in those applications the chip can be operated at lower voltage which further results in reduction of power consumption by the circuit. The frequency and supply voltage can also be varied accordingly in respect to the performance need by the chip [41]. Let's consider an example of a mobile microprocessor unit. It identifies peaks in the waveform and according to the performance requirement it adjust the frequency and supply voltage to deliver the necessary performance parameter and in this way, saves power.

#### 2.4 Leakage Reduction:

This commits finally to the total power dissipation of the circuit. As the leakage current is present in the circuit even when the device is turned OFF or is in idle state. With the advancement in the newer technologies in the present era, the leakage power is becoming a significant part in the total power dissipation of the circuit. Some of the techniques for decreasing leakage power are as follows:

#### 2.4.1 Dual Threshold Voltage Technique:

The main motive behind using this technique is to minimize the sub threshold leakage power [42]. In this, the process technology adds 2 categories of transistors like:

- (i) High threshold voltage (High V<sub>t</sub>)

- (ii) Low threshold voltage (Low V<sub>t</sub>).

The high  $V_t$  transistors provide slower logic with minimal value of leakage. On the other hand, the low  $V_t$  transistors provide faster logic, but higher (about 10 times the slower ones) leakage. Thus, a proper use of low and high  $V_t$  transistors will provide better performance with lower leakage.

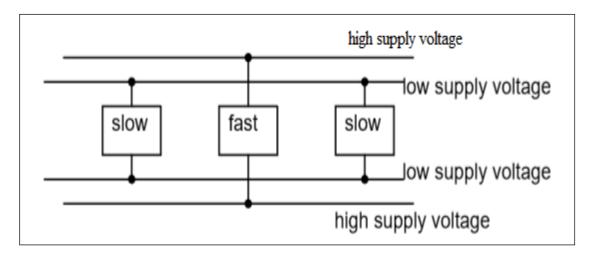

Fig 2.7: Scaling of static voltage using multiple supplies [42]

#### 2.4.2 Stacking Technique:

This strategy is utilized to decrease the standby leakage power. It utilizes the evidence that an "off" transistor stack has lower sub threshold leakage magnitude in comparison to the individual transistor. To accomplish stack effect in standby mode, the logic block need to be placed in a state where all stacked transistors are turned OFF. This should be possible physically by the future tools improvements. A 1.5X to 2.5X dimensions has been accounted for utilizing this procedure [43].

#### 2.4.3. Supply Gating:

This technique is also termed as "sleep transistor" technique. This method is utilized for the reduction of both active and standby leakage power [44]. This technique is quite comparable to the clock gating in which the power supply is "gated" by employing a high  $V_t$  transistor, so that the power can be cut off in a logic block. This method can lower the leakage currents by 1000X; along with the disadvantage of numerous unwanted issues in the circuit. First, the high  $V_t$  transistor in series with the supply causes performance degradation. Second, the noise immunity is also reduced to a greater extent in the circuit.

## 2.4.4. System and Architecture Level Power Reduction:

The previously mentioned circuit design techniques for power decrements in the circuit attempt to limit any one or more components of power dissipation as illustrated in eq. (2.1). The other approach for the power reduction can be done at the system level, where by properly altering the algorithm and data encoding, the power dissipation can be reduced to a greater extent. [45] For example, in reading a data block from the memory, requires signals to be sent from the CPU to the main memory. This signalling is decreased by implementing altered algorithms and employing cache memory structures which try to get the data as far as possible from the CPU registers or from the cache.

#### 2.5. Adiabatic or Charge Recovery based Circuit Design:

Aside from the previously mentioned circuit level approaches, one especially fascinating method is the Adiabatic Circuit Design Technique [46]. Here the primary concern is the reusing of the charge that has been stored on the capacitive nodes at the output. Normally in ordinary CMOS circuits, the output capacitance either charged to power supply level  $V_{dd}$  at the logic 1

state or at the ground level at logic 0 state. Switching from logic 1 to logic 0 or vice versa during the discharging or charging of output capacitive node is merely a wastage of power in the circuit. Each time an output capacitance C is discharged from voltage  $V_{dd}$  to GND, an energy equivalent to  $\frac{1}{2}CV^2$  is lost. Adiabatic circuits attempt to reuse this stored charge that inspite of discharging to ground, is sent back to the power supply. The basic principle behind adiabatic logic is the charge recycling the charging procedure and the charge recovery process are efficient just when the charging voltage is gradually or slowly changing one. In the following chapter, the essentials of adiabatic circuits viz., The charging and releasing procedure of a capacitor in RC circuit and the power calculations are examined. Later a short depiction on the effectively existing adiabatic logic styles with their benefits and negative marks is given.

3

#### ADIABATIC LOGIC: AN INTRODUCTION

Adiabatic technique can be considered as a thermodynamic method which implies there is no gain and no loss of energy in the circuit. Adiabatic circuits utilize trapezoidal power clock unlike CMOS which has very short fall time and rise time [47]. In adiabatic logic, the energy can again be used in the power supply with the help of capacitors. The basic logic behind adiabatic technique is that it never allows both NMOS and PMOS to turn ON or OFF simultaneously. The term originates from the way that an adiabatic procedure is one in which the total heat or energy remains consistent in the system. For perfectly implementing adiabatic logic in CMOS structure, two essential principles are as follows:

- 1) The condition for the transistor to be ON is when both drain and source are at the same potential level.

- 2) When a current is flowing through the transistor, it never turns OFF the transistor [48].

The above mentioned two rules are realized to ensure that step variations of current are absent and in this way irrelevant energy dissipation can be avoided to a greater extent in the circuit. Energy stored in transistor switch is given by  $\frac{1}{2}C_LV_{dd}^2$  [49-51].

where,

$V_{dd}$  = constant voltage supply

$C_L$  = load capacitance

For power dissipation, this is the minimal limit in the CMOS circuit, although adiabatic technique works on lower limit. Power clock is an oscillatory voltage supply which is charging and discharging by ramp voltage so that the voltage drop is decreased across the switching transistor.

Adiabatic Techniques are basically categorized into two main types:

- (i) Fully adiabatic logic

- (ii) Quasi adiabatic logic or Partially adiabatic logic

In quasi or partially adiabatic logic, some portion of power is sent to the ground which implies some heat is disseminated from the circuit and some piece of the energy is reusable by sending it back to the power supply [52]. On the contrary, in fully adiabatic logic, no part of energy is wasted and all energy of the circuit is fed back to the power supply as all charges are recovered on capacitor and this saves the mere wastage of energy in the circuit and these types of logics are termed as fully adiabatic logic. The disadvantages of fully adiabatic logic are that the speed of operation of circuit is slower and it contributes to the more complex circuitry as compared to the partially adiabatic logic. Basically, adiabatic circuits works on the principle of "reversible logic" to conserve power and it is for this reason they are used in the circuit where low power is the major requirement [53].

In conventional CMOS level-restoring logic, with rail-to-rail output voltage swing the switching event of circuits results in an energy transfer from the power supply to the output node or from the output node to the ground which results in increased value of power dissipation in the circuit. On the contrary, it is not in the case of adiabatic logic, so we can say that Adiabatic Logic have accomplished noteworthy power saving as compared with traditional CMOS circuits [54].

Tremendous circuit designs based upon adiabatic logic have been proposed throughout the years [55-69]. At the circuit nodes, to reuse the energy, adiabatic techniques use AC control clock as the power clock, which has four distinct periods of operation. In these adiabatic circuits, the charge flows back to the power supply rather than flowing from output capacitance to ground. In this manner, the charge or energy can be reused in the circuit [59], [70].

## 3.1 Adiabatic Principle:

The basic operation of adiabatic logic gate is partitioned into two specific stages: one phase is utilized for logic evaluation or assessment; while the other stage is utilized to reset the gate output logic value [71]. In the following section, conventional switching and adiabatic switching are discussed in detail.

#### 3.1.1 Conventional Switching:

The two- noteworthy source of power scattering in traditional CMOS circuits are static power dissipation and dynamic power dissipation. The main cause of dynamic power dissipation in the circuit is due to the switching in the circuit from high to low and low to high. On the contrary, static power dissipation is administered by the logic states of the circuit. Switching in the circuit has no effect on the static power dissipation of the circuit. Static power dissipation arises in the circuit because of diode leakage currents, gate oxide leakage currents and subthreshold leakage currents.

Controlling Leakage power is a critical issue as it is dominating active leakage power components in deep submicron technology. The equation for leakage power is as follows:

$$P_{lkg} = I_{lkg} \times V_{dd} \quad \dots (3.1)$$

where,

P<sub>lkg</sub> = Leakage power

$I_{lkg}$  = Leakage Current

$V_{dd} = Supply Voltage$

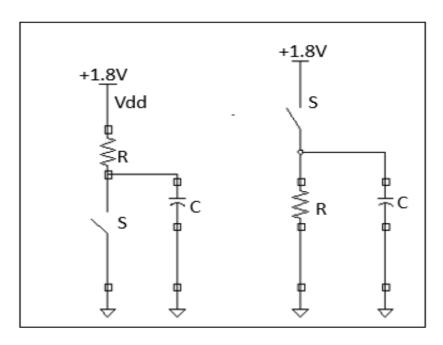

The switching depicted in Fig. 3.1, illustrates about the conventional CMOS switching.

Fig 3.1: Conventional CMOS switching [72].

Dynamic power dissipation occurs due to switching in the circuit because of the charging and discharging of capacitance. At the time of charging the energy drawn from the power supply is equivalent to  $CV_{dd}^2$ . Half of this is dissipated instantly in the PMOS transistors and its interconnect and the other half is stored at the load capacitance C which gets dissipated over the NMOS and its interconnect. The main cause of short circuit is the slow transition of input signal from 0 to  $V_{dd}$  and  $V_{dd}$  to 0 volts. Subsequently, this results in the flow of short circuit current between the  $V_{dd}$  supply and the ground terminal [72]. The equivalent circuits of CMOS logic for charging and discharging is illustrated in Figure 3.1. The expression for total power dissipation is shown in eq. 3.2

$$P_{total} = \alpha C V_{dd}^2 f_{clk} + I_{sc} V_{dd} + I_{lkg} V_{dd} \dots (3.2)$$

#### 3.1.2 Adiabatic Switching:

An adiabatic technique is another appropriate answer to the biggest problem of power dissipation in the digital logic. The energy stored in the output capacitance is send back to the power in case of discharging in this way it saves the circuit power to a greater extent. The adiabatic switching circuit is illustrated in fig. 3.2.

Fig 3.2: Adiabatic switching circuit [73].

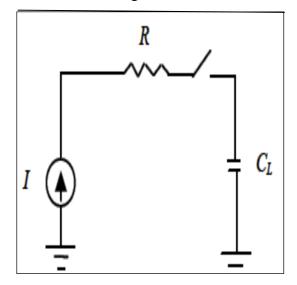

Let RC be the time constant of the circuit, T be the voltage ramp period. The value of time constant of the circuit is kept much smaller than the voltage ramp period i.e., RC << T.

So, the voltage at the capacitor strictly follows the supply voltage, so the potential difference measured across the resistor R is very close to zero. So, it implies that the voltage at the capacitor  $V_c$  is also a constant ramp signal with slope V/T.

where,

V= Supply voltage swing

T = Power-clock phase period.

The charging current of the adiabatic circuit can be given as

$$I_{c} = C \frac{dV_{c}}{dt} = \frac{cV}{T} \qquad (3.3)$$

And the energy dissipated in the resistor can be evaluated using equation 3.4.

$$E = i_c^2 RT = (\frac{CV}{T})^2 RT = (\frac{RC}{T}) CV^2$$

.....(3.4)

The equivalent circuit for discharging is also completely same as that of the charging circuit, the only difference is that the supply voltage ramps down in the discharging circuit.

As we know that, RC << T, so we have

$$E = \left(\frac{RC}{T}\right)CV^2 \ll \frac{1}{2}CV^2 \qquad (3.5)$$

The equation (3.5) signifies that the energy dissipated by the resistor during charging and discharging is less than the energy stored in the capacitor. So, this concludes that at the time of discharging, some part of energy which is stored in the capacitor is actually send back to the energy source. [72]

## 3.2 Power Clock used for Adiabatic Switching:

The noteworthy part of the entire adiabatic system is the structure of its power clock generator. The power clock utilized here is a mixture of power supply and a clock. This signifies that it comprises of both frequency and voltage levels. In adiabatic circuits, the power clock is multiphase in nature [74.].

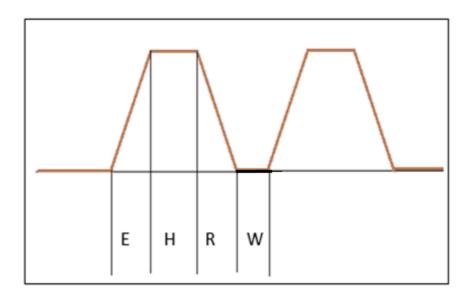

The power clock of the adiabatic process is broadly classified into four phases. These phases signifies a different levels used for the specific operations performed in the circuit. The basic structure of the power clock is illustrated in fig. 3.3.

Fig 3.3: One cycle of power clock in adiabatic technique. [73]

Power clock used in adiabatic technique shown in figure 3.3, comprises of four different phases. These are:

- (i) Evaluate (E)

- (ii) Hold (H)

- (iii) Recovery (R)

- (iv) Wait (W)

In E interval, i.e., in the evaluation phase, the outputs get evaluated from the stable input signal.

During H interval, i.e., the Hold phase, the output is kept stable to provide input to the next stage.

During R interval, i.e., the recovery phase, the energy gets recovered and

W interval, i.e., the wait interval provides symmetry.

#### 3.3 Classification of Adiabatic Logic Families:

There are basically two types of adiabatic logic families:

- (i) Partially Adiabatic or quasi adiabatic logic family.

- (ii) Fully Adiabatic logic families.

In partially adiabatic or quasi adiabatic circuits, a portion of charge is sent to the ground, that is some heat is dissipated in the circuit. And the other portion of energy is recovered and is sent back to the supply. The advantage of using the partially or quasi adiabatic logic circuit is that the implementation of circuits is easy as compared to the fully adiabatic logic families.

On the contrary, in fully adiabatic logic, no part of energy is wasted and all energy of the circuit is fed back to the power supply as all charges are recovered on capacitor and fed back to the power supply and this saves the mere wastage of energy in the circuit and these types of logics are termed as fully adiabatic logic. The disadvantages of fully adiabatic logic are that the speed of operation of circuit is slower and it contributes to the more complex circuitry as compared to the partially adiabatic logic.

A few partially or quasi adiabatic logic families are as follows: -

- (i) 2N-2P Adiabatic logic

- (ii) 2N-2N 2D Adiabatic Logic

- (iii) Efficient Charge Recovery Logic (ECRL)

- (iv) Complementary Energy Path Adiabatic Logic (CEPAL)

- (v) Two Phase Adiabatic Static Clocked Logic (2PASCL)

- (vi) Quasi- Static Energy Recovery Logic (QSERL)

- (vii) Glitch Free Cascadable Adiabatic Logic (GFCAL)

A few fully adiabatic logic families are as follows: -

- (i) Pass Transistor Adiabatic Logic (PAL)

- (ii) Two Phase Adiabatic Static CMOS Logic (2PASCAL)

- (iii) Split-Rail Charge Recovery Logic (SCRL)

Some of the already existing quasi or partially adiabatic logic techniques are discussed here

### 3.3.1 2N- 2P Logic:

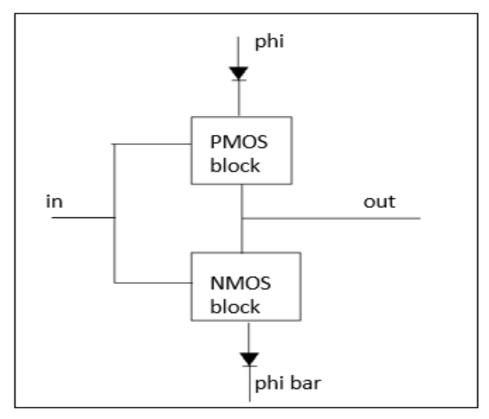

This 2N- 2P adiabatic logic was proposed by Denker et. al[75]. The name of the technique is derived from the total number of transistors in a gate. Each input needs 2 NMOS and the overhead for each complete gate is 2 PMOS transistors. Both differential input and differential output are used in tis circuit. So, both polarity of input is required at the input of the gate and the output of the gate produces both the logic function as well as its complement.

The basic circuit for an inverter-buffer is shown in figure 3.4.

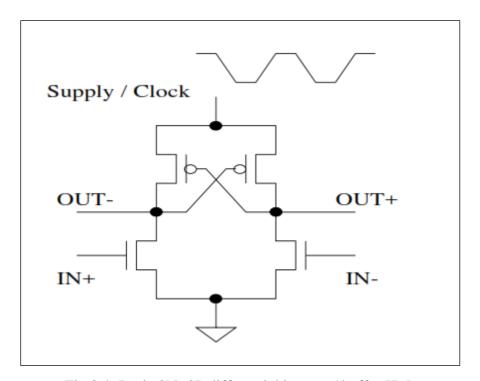

Fig 3.4: Basic 2N- 2P differential inverter/ buffer [76].

Each NMOS input gets the corresponding positive and negative polarity inputs and the cross-coupled PMOS are connected to the power clock. The timing and logical operation of fig. 3.4 is illustrated here. The basic circuit operation can be sub-categorized into 4 phases depending on the clock and input conditions. The NMOS inputs gets the positive and the negative polarity inputs and the PMOS are connected to the power supply. The timing diagram for the 2N-2P buffer/ inverter is illustrated in the fig 3.5

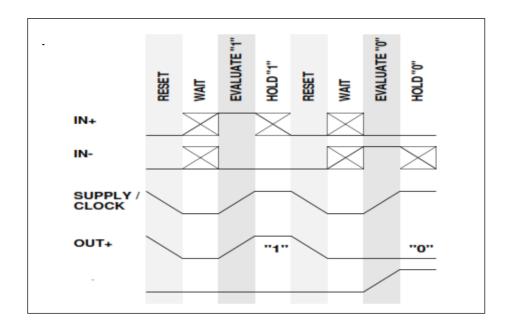

Fig. 3.5: Timing for 2N-2P inverter/ buffer [76]

#### Phase-1: RESET PHASE

The inputs are low, the outputs are in the manner that one output is low and other output is high and the power supply ramps down. As the PMOS is held in ON state by the low output, so the high output, will follow the clock down so that at the end of the reset phase both outputs will be low or at logic 0.

#### **Phase- 2: WAIT PHASE**

Power-supply is at the low level or at logic 0, so the output is kept low (as it is the crucial condition for the next logical gate, which suffer a delay by a quarter cycle, so that the reset operation is performed for the next logical gate and the inputs are evaluated. Because the gate is "powered down", so the evaluation of the inputs has no consequence on the state of the gate.

#### **Phase- 3: EVALUATE PHASE**

In this phase, the power supply ramps up and the outputs will evaluate to a complementary state. The half-gate with its input as logic 1 will have its output held low while the half-gate which have their input as low or at logic 0, will follow the ramp up. At the end of this phase, the outputs will always be complementary. This situation is assured by the inverse logic of the two half gates and their cross coupled PMOS's and this is the main reason behind the 2N- 2P logic to be differential.

#### **Phase- 4: HOLD PHASE**

This is the last phase. In this complete phase, the power supply clock is high while the inputs ramp down to logic 0 and the gate outputs continues to be valid for the entire phase. Because there are four phases to the timing, there must be four quadrature clocks in a complete system, each clock 90 degrees in advance of the previous clock. In this way, each logic phase in the system holds its outputs valid while its successor is evaluating (ramping up) and its predecessor is resetting (ramping down) and waits with its outputs both low while its successor is resetting (down) and its successor is evaluating (up) [76].

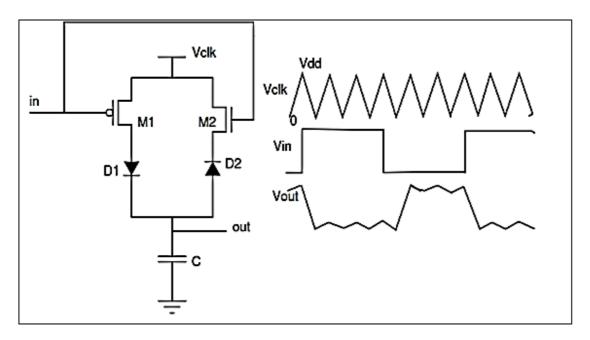

#### 3.3.2 2N 2N-2D Logic:

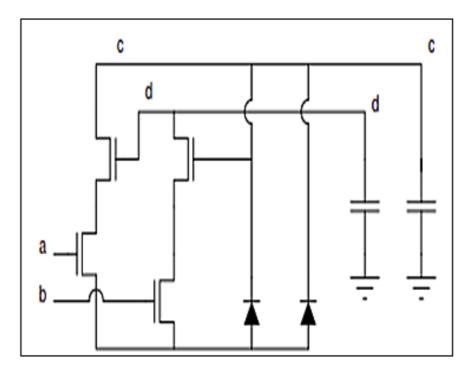

This 2N 2N- 2D logic utilizes differential signalling and it is for this reason each signal is represented in two forms- its normal form and its complemented form. Downward pulse on c signifies logic 0 and downward pulse on d signifies logic 1. This technique also utilize the four stage power clock cycle. Fig 3.6, illustrates the 2N 2N - 2D inverter/ buffer circuit. At the start of the cycle the clock is at V<sub>dd</sub>. When the clock changes from 0 to V<sub>dd</sub>, the circuit starts operating in the evaluation phase. During the evaluation phase, the inputs must be held constant. Let us assume the case when a= 0 and b =1. Since a=0, no current flows in that branch and the output c remains high. But as both b and c are 1, so all transistors in the right evaluation made are ON. And signal d follows the clock down. The next phase is the HOLD PHASE. In this phase, the output is a valid logic signal and in this phase the value of input needs not to be constant as both and the signal are at the lower value in this phase and the condition of the right evaluation branch whether ON or OFF, does not affect the output. In the same manner, as signal d is low, it turns OFF the left evaluation branch and output d is set at 1, no matter what the value of the inputs are. Then the circuit operate in the recharge phase when the clock ramps up to V<sub>dd</sub> and due to the presence of diodes, whichever output was low follows the clock to a logical high. Cascading such logic gates requires the second gate to be operated from a different clock as the output is valid only during the hold phase while the inputs are required to be valid during the evaluation phase [77 - 78].

Fig 3.6: 2N2N-2D inverter/buffer [77].

## 3.3.3 Efficient Charge Recovery Logic (ECRL):

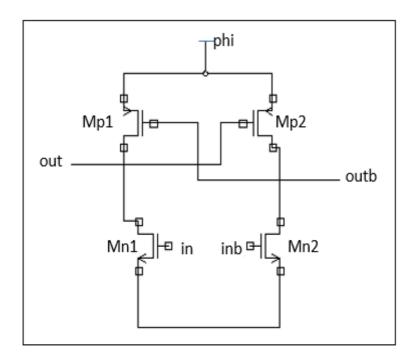

The ECRL adiabatic logic style was proposed by Yong Moon et. al [79-80]. A simple inverter circuit implementation using the ECRL adiabatic logic is shown in the figure 3.7. ECRL Technique also utilizes differential signalling, that is at the input terminal both the normal input as well as its complimented form is required. Let us consider a situation when the input "in" is at logic 1, so the compliment of the input "inb" is at logic 0, at the start of a cycle, when the clock phi ascends, the output terminal "out" stays at logic 0 level since "in" turn on MN2.So, "outb" follows phi1 through Mp1. The output will hold the valid logic as long as the phi1 is high for the utilization of these values in the next stage. While phi1 get back down to a ground level, charge on 'outb' send back its energy to phil. As there is no utilization of diodes, but still 4 phase clocking power is used for the appropriate pipelining of different stages.

Fig 3.7: ECRL inverter/buffer [80]

# 3.3.4 Complementary Energy Path Adiabatic Logic (CEPAL):

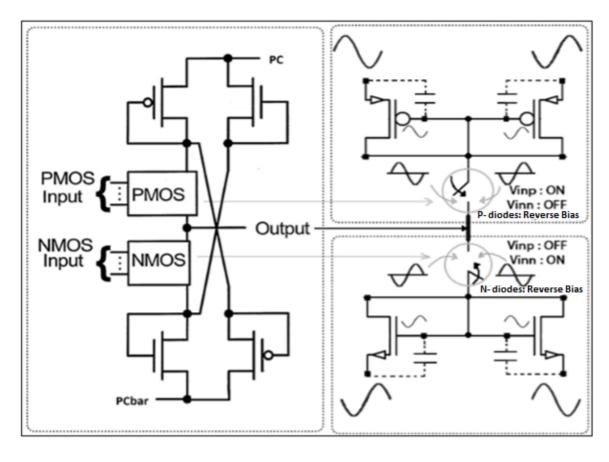

Fig 3.8: Complementary Energy Path Adiabatic logic[81].

The basic Structure and working of the CEPAL is shown in figure 3.8 [82-83]. As illustrated in figure 3.8, it basically comprises of a pair of charging and discharging transistors; A pull up network (p-network) and a pull-down network (n-network).

This CEPAL logic utilizes two sinusoidal power clocks, PC and PC bar, that are just complementary of one another. Let us assume a condition when V<sub>in</sub> is low, i.e. logic 0 at the input terminal makes the P- network ON and turns OFF the N- network, V<sub>out</sub> follows the power clock PC or PC bar which ever swings to the high level. As the power clock used in the CEPAL Adiabatic Logic is sinusoidal in nature, so when it ramps down, it makes the V out to follow it and in this way a floating node is generated in the circuit. This condition can be avoided by the complementary clock which swings high, thus eliminating this weak high signal and also eliminating the hold state seen in two phase clock operated circuits. Similarly, the weak low signal is also eliminated by the complementary clock [84-86].

Assume the other case in which V out is high with the P-network ON and the N-network is OFF. So, the value of Vout will remain high until there is some change in the input. In comparison to the QSERL technique, CEPAL technique has two extra diodes, but the two extra diodes do not affect the power dissipation adversely, as they are only meant for the charging and the discharging purpose and turning ON of these diodes takes place only at a particular instant of time. The advantages of the CEPAL logic over the QSERL logic is that the driving capability as well as the robustness is reduced to a greater extent in the circuit. The throughput of the CEPAL logic is not affected by the frequency ratio and the throughput is twice as better as the QSERL circuit. The disadvantages of using the CEPAL logic over the QSERL logic is that the two extra diodes in the charging discharging path, results in larger area on the chip [87].

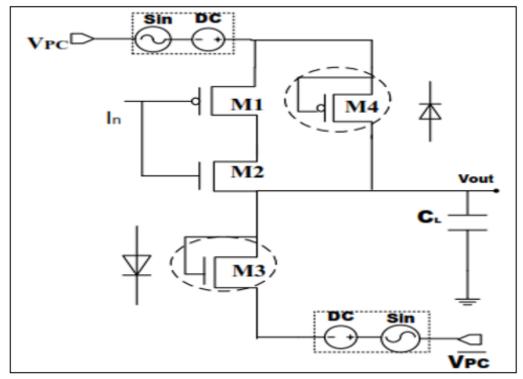

### 3.3.5 Two Phase Adiabatic Static Clocked Logic (2PASCL):

Fig 3.9: Inverter Circuit using 2PASCL [84].

The inverter circuit using 2PASCL is illustrated in figure 3.9. [84] In 2PASCL, at the time of charging, the flow of current is only via the PMOS transistor as there is no diode in the charging path. This will lower down the nun-adiabatic losses because of the cut in voltage of diodes. 2PASCL discussed here is quite different from the other quasi or partially adiabatic logic because in normal partially adiabatic logic ramp or sinusoidal power clocks are used. On the contrary, in the 2PASCL logic two split level sinusoidal power clocks are used.

The advantage of using this clock is that it results in the decrement in the voltage difference between the electrodes, which further results in decrement of the dissipated power. But the main disadvantage of this technique is that the performance is very much degraded by using this technique because the diodes are connected in parallel with the PMOS device and in series below the NMOS transistors for the purpose of recycling of charge [88-89].

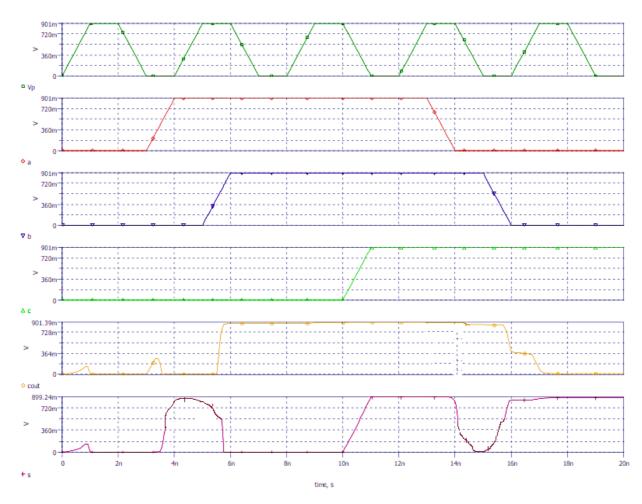

#### 3.3.6 Quasi Static Energy Recovery Logic (QSERL):