# Design and Analysis of LNA for 2.4 GHz ISM Band using 0.13 µm CMOS Technology

Submitted in partial fulfillment of the requirements for the award of the degree of Master of Technology

In

# **Microwave and Optical Communication Engineering (MOCE)**

by Aditi (2K15/MOC/03)

under the guidance of **Dr. Malti Bansal** Assistant Professor Department of Electronics and Communication Engineering, Delhi Technological University

Department of Electronics and Communication Engineering, Delhi Technological University, Shahbad Daulatpur, Bawana Road, Delhi-110042, India

## Certificate

This is to certify that the work done in the thesis entitled '**Design and Analysis of LNA for 2.4 GHz ISM Band using 0.13 \mum CMOS technology**' has been carried out by Ms. Aditi, under my supervision in partial fulfillment of the requirements for the award of the degree of Master of Technology (M.Tech) in Microwave and Optical Communication Engineering (MOCE) at Delhi Technological University, Delhi.

Date:

Dr. Malti Bansal Assistant Professor Department of Electronics and Communication Engineering Delhi Technological University Delhi-110042

## **Candidate's Declaration**

The work in the thesis entitled 'Design and Analysis of LNA for 2.4 GHz ISM Band using 0.13  $\mu$ m CMOS technology' is a record of original research work carried out by me under the guidance of Dr. Malti Bansal, Assistant Professor, Department of Electronics and Communication, Delhi Technological University, in partial fulfillment of the requirement for the award of the degree of Master of Technology in Microwave and Optical Communication Engineering (MOCE), at Delhi Technological University, Delhi. Neither this thesis nor any part of it has been submitted for the award of any other degree or diploma elsewhere.

Date:

Aditi (2K15/MOC/03)

# Acknowledgement

To be candid, this project would never have been successful without the good wishes and hard work of few people. My primary debt of thanks is to my mentor **Dr. Malti Bansal**, Assistant Professor, Department of Electronics and Communication, Delhi Technological University, for giving me complete freedom to express my views and for her challenging questions and thoughtful feedback as it clarified and strengthened the ideas. Also, for providing me a unique environment to conduct my thesis research work and for providing encouragement and institutional support from the start, allowing us to closely entwine into our project.

I would also like to acknowledge people with whom I made this gracious journey of two years: my college colleagues who contributed to the ideas, provided intellectual boost and energy.

Last but not the least, my parent's constant trust and faith on my abilities was like a giant shadow that sheltered me to complete this project successfully. This has been one of the greatest experiences of my life.

Aditi (2K15/MOC/03)

## Abstract

Due to rapid developments in communication industry, the requirement of more and different kinds of wireless communication systems has increased. It is desired that these wireless communication systems have characteristics such as low noise figure, low input/output return losses, a high IIP3 and, low power consumption. The main aim of the manufacturers of the wireless communication systems is to achieve low power. In these wireless communication systems, the RF front-end circuit is LNA which is one of the crucial elements of RF receivers. They amplify RF signal to a particular level so that the sensitivity requirements of other components in RF receivers such as filters are met by RF signal as the signal received by the antenna is very small. Hence, it is important to amplify the signal as much as possible without noise addition and also; attaining good linearity, high gain and low power consumption at the same time. For designing of LNA, the most optimum tradeoff between various parameters has to be achieved. Also, the size of communication devices and power consumption should be as minimum as possible, which is possible nowadays because of advancements in integrated circuit (IC) technology. In this thesis, low noise amplifier topologies have been proposed to achieve high linearity while keeping the noise performance as good as possible and gain as high as possible. To achieve input impedance matching of 50  $\Omega$ , a pi-matched circuit is used at input. The proposed low noise amplifier topologies are designed for 2.4 GHz frequency. The circuits are implemented using 0.13 µm CMOS technology and is simulated using Advanced Design Simulation Software.

## **Refereed Publications arising from this Thesis**

- 1. Malti Bansal, Aditi, "Mobile and Real-Time Sensing Electronic Nose based on Carbon Nanotubes," in *Proceedings of 3rd International Conference on Emerging Electronics (ICEE)*, IIT Bombay, 2016, pp. 326-331.

- 2. Aditi, Malti Bansal, "A High Gain and Moderate Linearity Inductively Degenerated Cascode CMOS LNA for 2.4GHz ISM Band," in *Proceedings of International Conference on Innovations in Information, Embedded and Communication Systems (ICIIECS)*, Coimbatore, 2017, vol. 5, no. 71, pp. 382-385.

- 3. Aditi, Malti Bansal, "A High Linearity and Moderate Gain LNA for Receiver Front-End Applications in 2.4GHz ISM Band," accepted in International Conference on Innovations in Control and Information Systems (ICICCI), 2017.

- 4. Aditi, Malti Bansal, "A High Gain, High Linearity and Low Noise LNA for IEEE 802.15.4 ZigBee Standard in 2.4 GHz ISM Band," accepted in International Conference on Innovations in Control, Communication and Information Systems (ICICCI), 2017.

- 5. Aditi, Malti Bansal, "High Linearity and Low Noise Shunt Resistive Feedback CMOS LNA in 2.4GHz ISM Band," accepted in Recent Developments in Control, Automation and Power Engineering (RDCAPE), 2017.

- 6. Aditi, Malti Bansal, "High Linearity and High Input Impedance Matching Common Gate CMOS LNA in 2.4GHz ISM Band," *accepted in Recent Developments in Control, Automation and Power Engineering (RDCAPE)*, 2017.

- 7. Aditi, Malti Bansal, "Design, Analysis and Comparison of LNA topologies for IEEE 802.15.4 Zigbee Standard," accepted in Conference on Information and Communication Technology (CICT), 2017.

- 8. Aditi, Malti Bansal, "A High Linearity and Low Noise Shunt Resistive Feedback UWB LNA," accepted in Conference on Information and Communication Technology (CICT), 2017.

- 9. Frequency Dependent LNA Design: A Review (Communicated).

# **List of Figures**

| Fig. No. | Name                                                                            | Page |

|----------|---------------------------------------------------------------------------------|------|

| 1.1      | Two port network                                                                | 2    |

| 1.2      | Basic Components of Amplifier with input/output of amplifier (two-port network) | 4    |

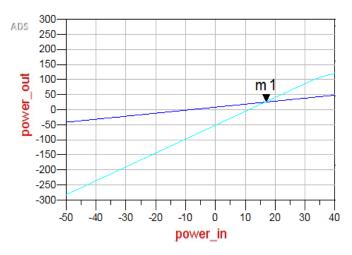

| 1.3      | P1 dB (logarithmic scale)                                                       | 6    |

| 1.4      | Third order intercept (logarithmic scale)                                       | 7    |

| 1.5      | Common Source with resistive termination LNA                                    | 8    |

| 1.6      | Common Gate LNA                                                                 | 9    |

| 1.7      | Common Source with shunt feedback LNA                                           | 9    |

| 1.8      | Common Source with inductive source degeneration LNA                            | 10   |

| 1.9      | Cascode Common Source with inductive source degeneration LNA                    | 10   |

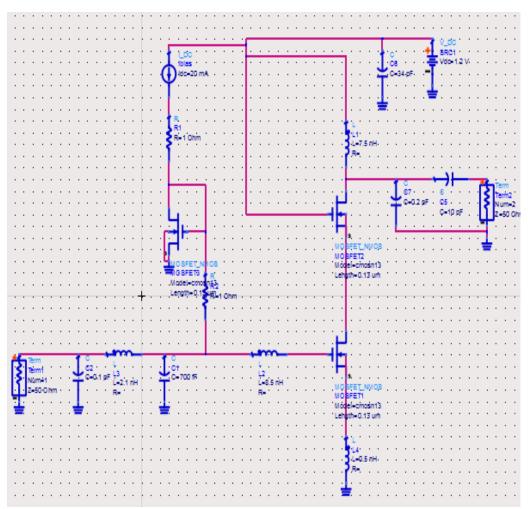

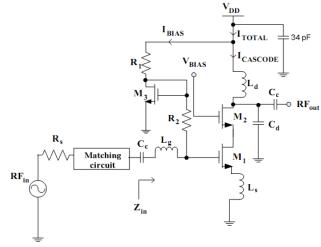

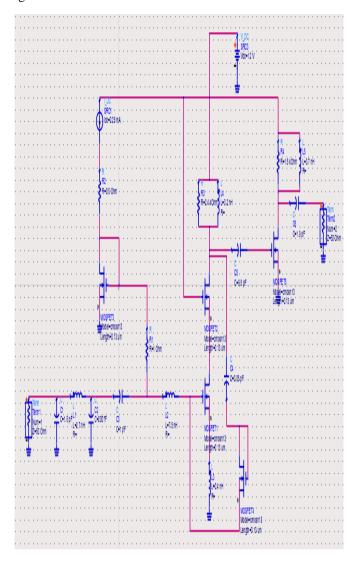

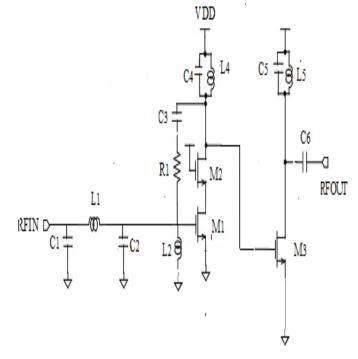

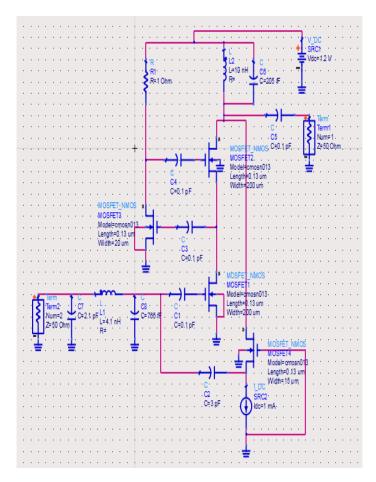

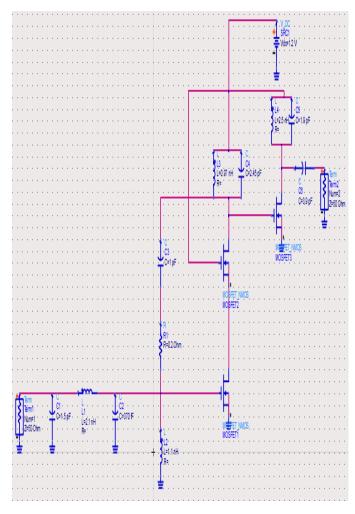

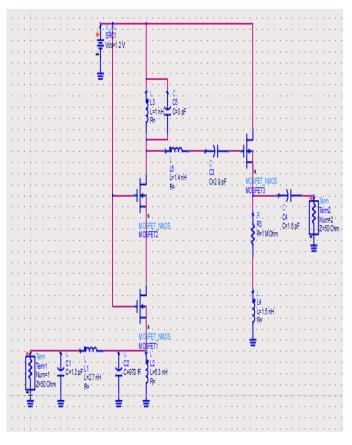

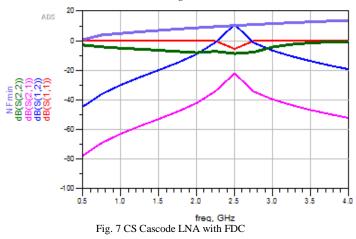

| 4.1      | Proposed Cascode CS CMOS LNA with FDC                                           | 36   |

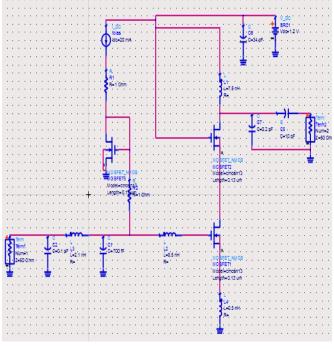

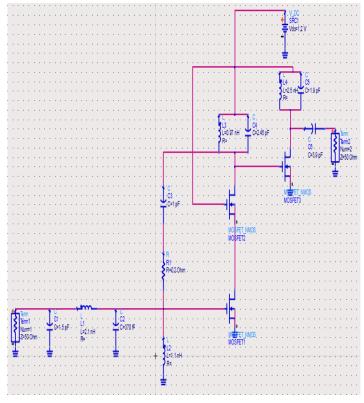

| 4.2      | Schematic of Proposed Cascode CS CMOS LNA with FDC                              | 37   |

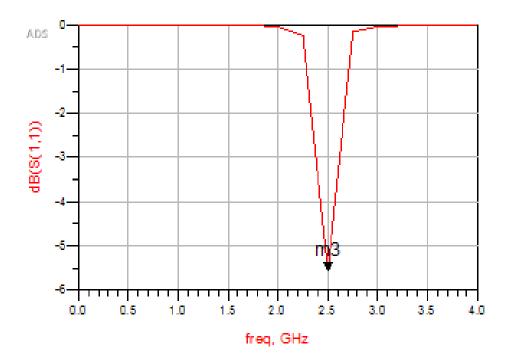

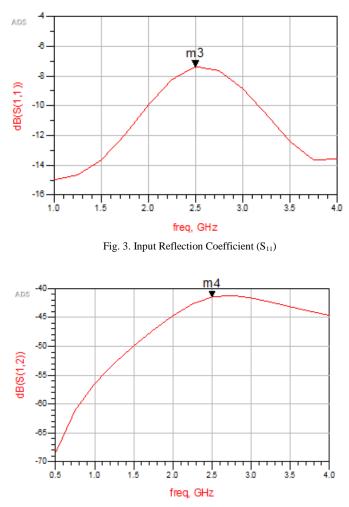

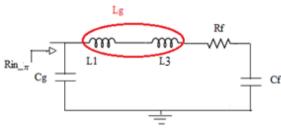

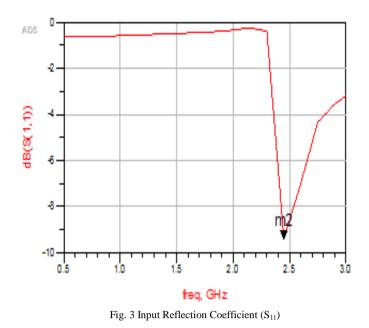

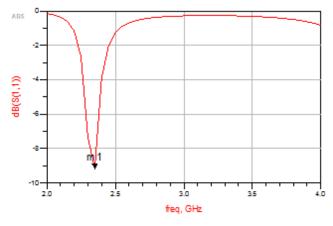

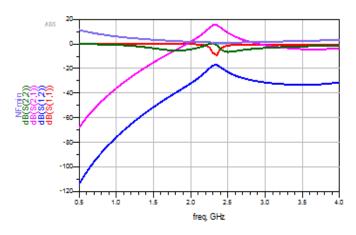

| 4.3      | Input Return Loss (S <sub>11</sub> )                                            | 38   |

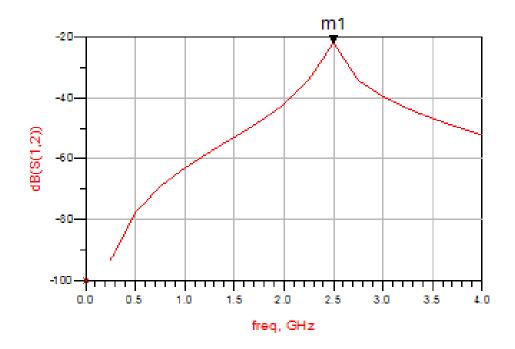

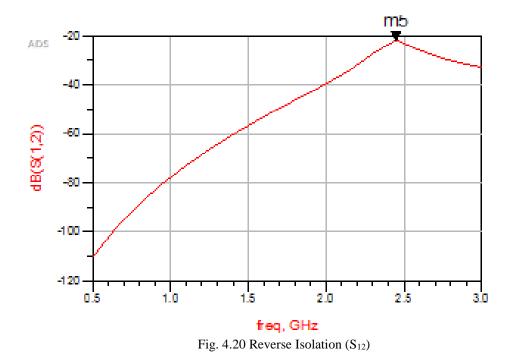

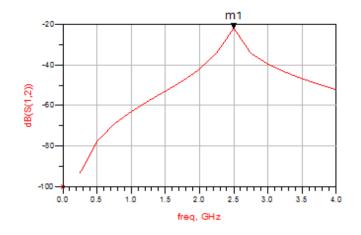

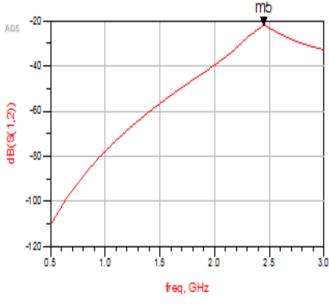

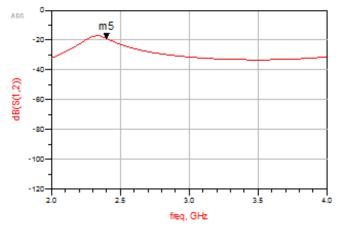

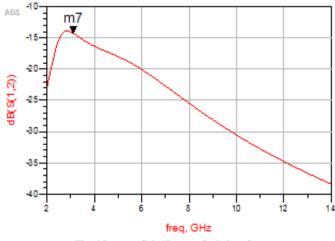

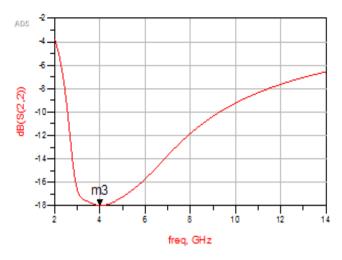

| 4.4      | Reverse Isolation (S <sub>12</sub> )                                            | 39   |

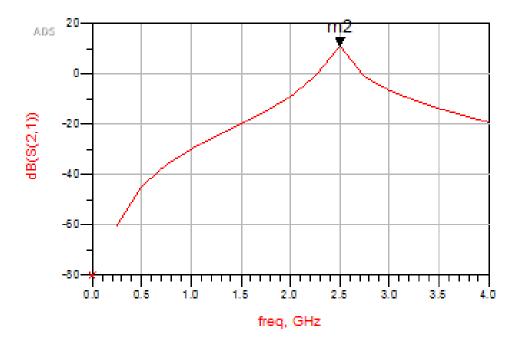

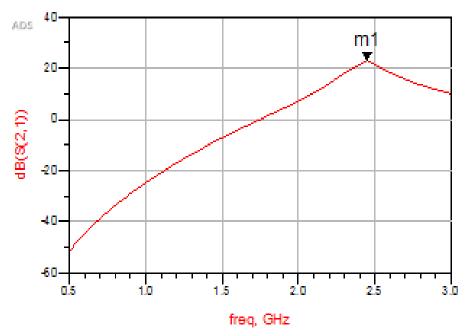

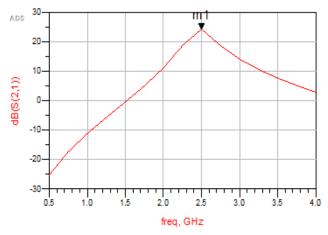

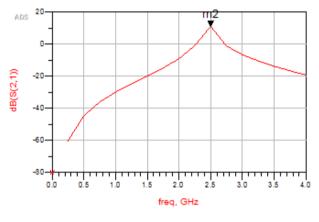

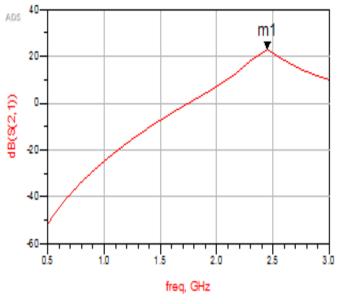

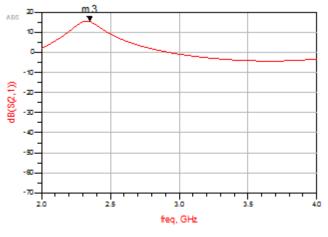

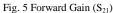

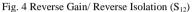

| 4.5  | Forward Gain (S <sub>21</sub> )                                                              | 39 |

|------|----------------------------------------------------------------------------------------------|----|

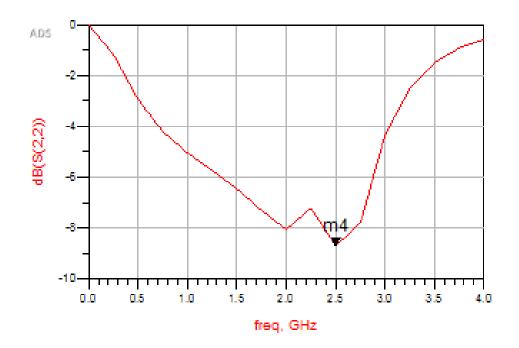

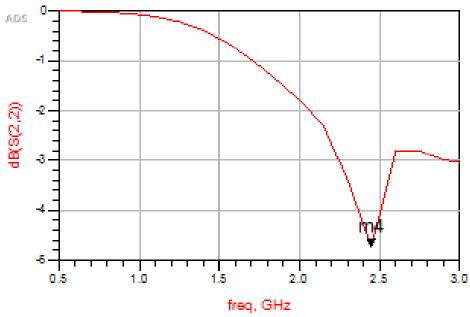

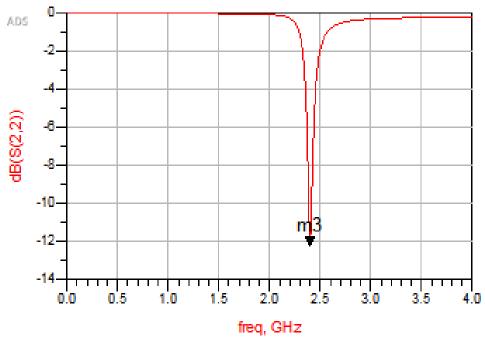

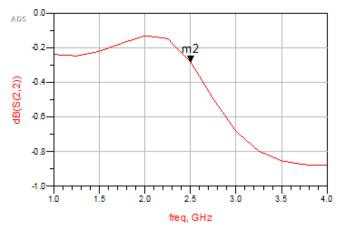

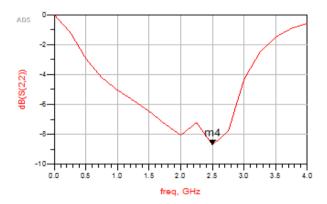

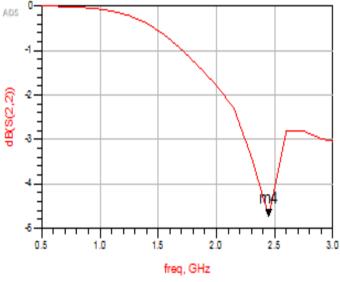

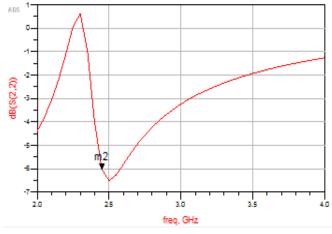

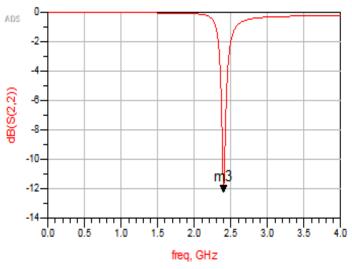

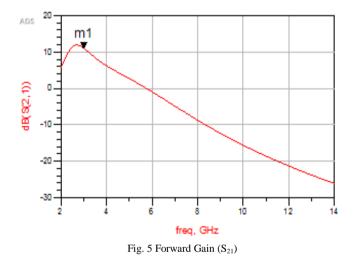

| 4.6  | Output Return Loss (S <sub>22</sub> )                                                        | 40 |

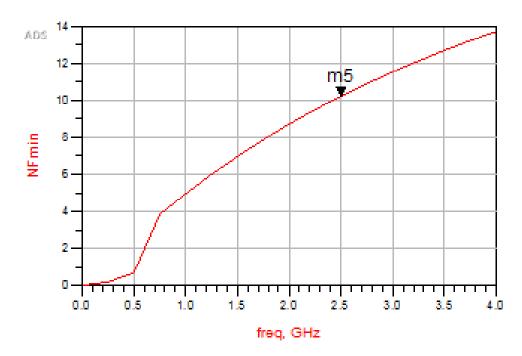

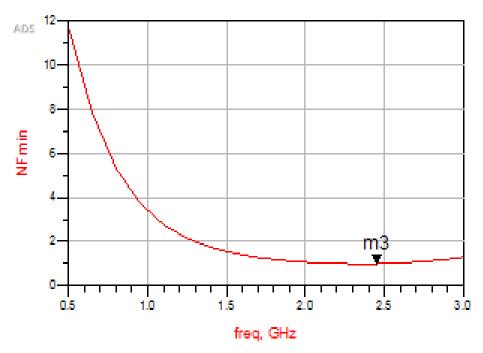

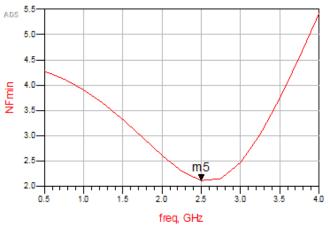

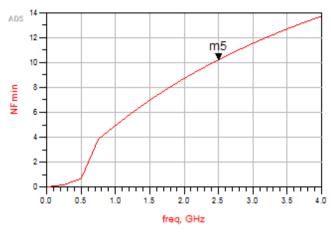

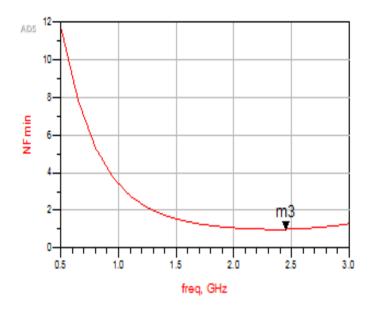

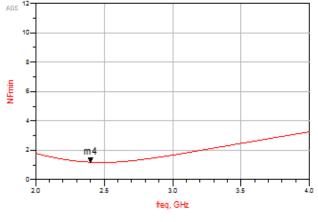

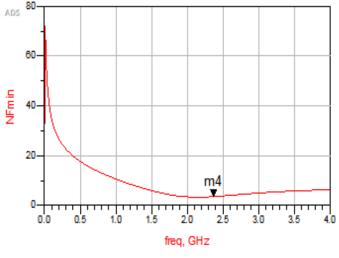

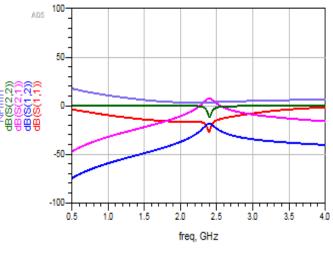

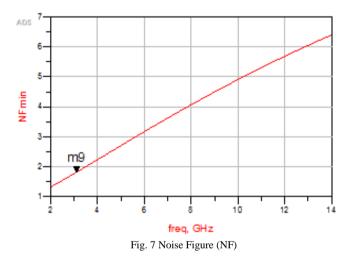

| 4.7  | Noise Figure                                                                                 | 40 |

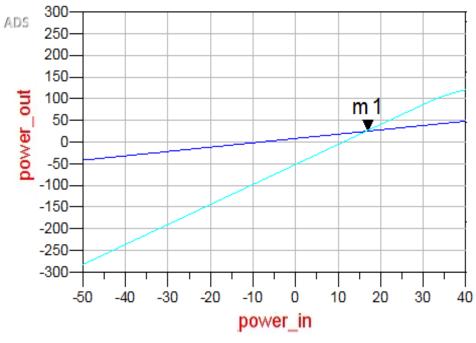

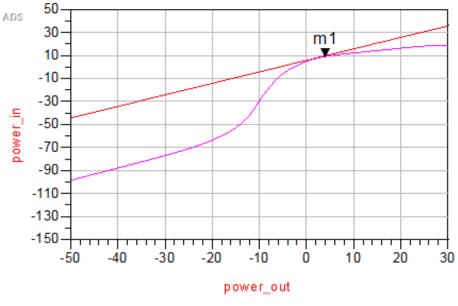

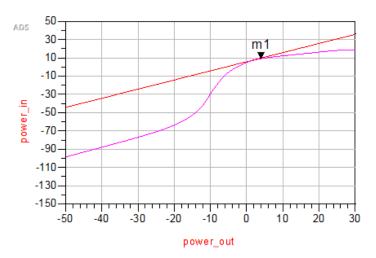

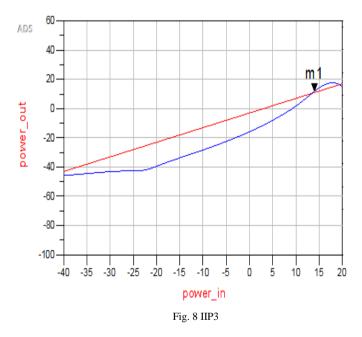

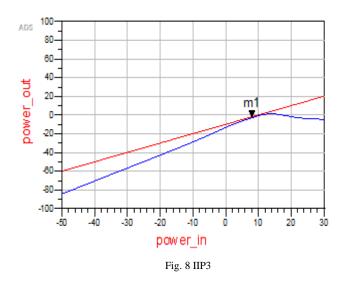

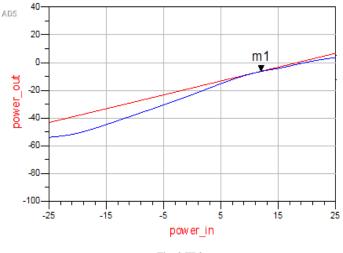

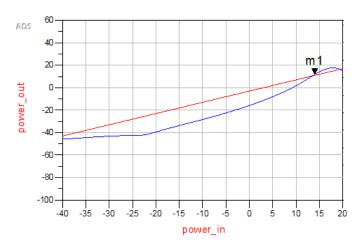

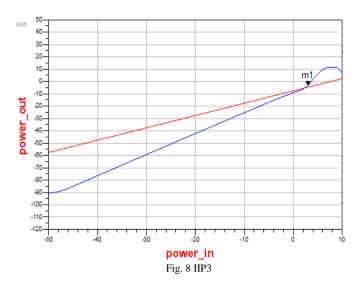

| 4.8  | IIP3                                                                                         | 41 |

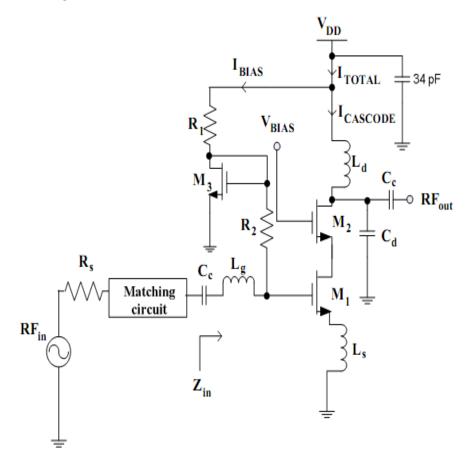

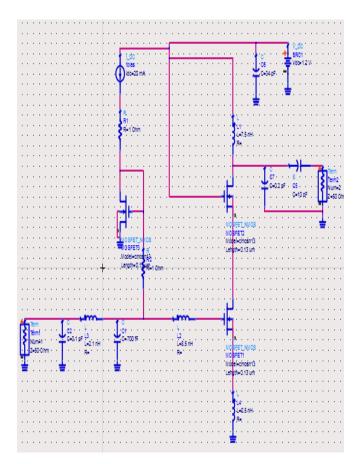

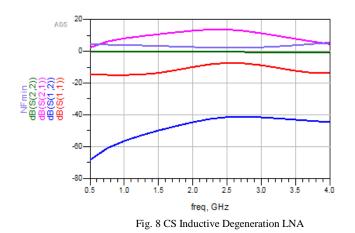

| 4.9  | Proposed Cascode Common Source Inductively-Degenerated CMOS LNA                              | 42 |

| 4.10 | Schematic of Proposed Cascode Common Source Inductively-Degenerated CMOS LNA                 | 43 |

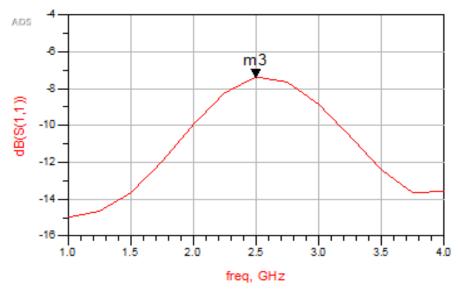

| 4.11 | Input Return Loss (S11)                                                                      | 44 |

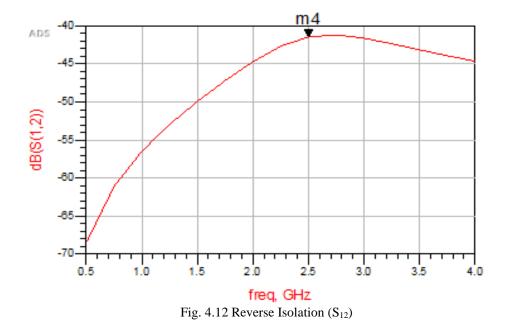

| 4.12 | Reverse Isolation (S <sub>12</sub> )                                                         | 44 |

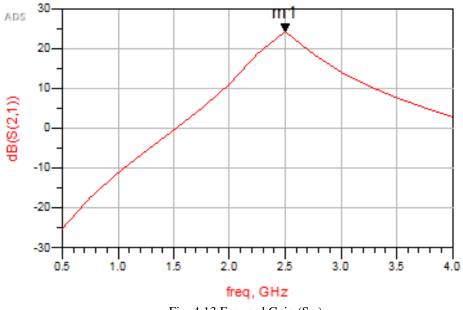

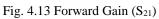

| 4.13 | Forward Gain (S <sub>21</sub> )                                                              | 45 |

| 4.14 | Output Return Loss (S <sub>22</sub> )                                                        | 45 |

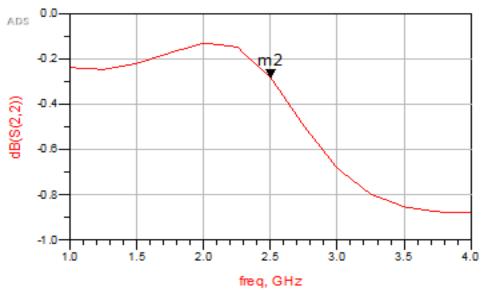

| 4.15 | Noise Figure                                                                                 | 46 |

| 4.16 | IIP3                                                                                         | 46 |

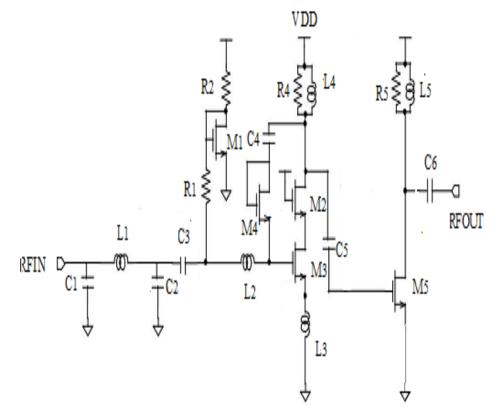

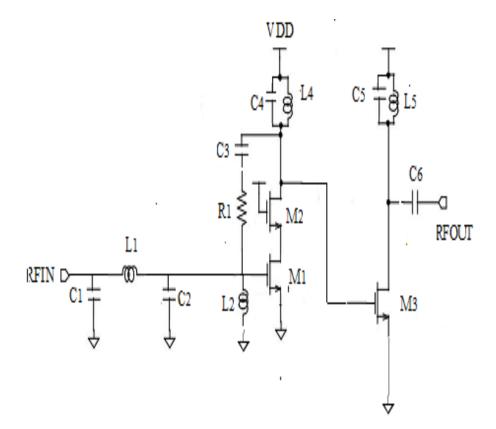

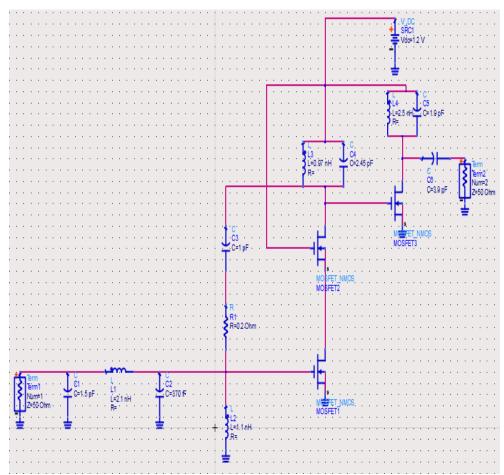

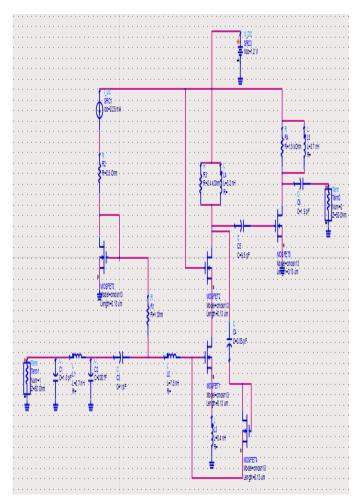

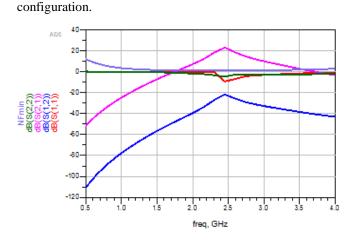

| 4.17 | Proposed Cascode Common Source Inductively-Degenerated CMOS LNA with FDC                     | 47 |

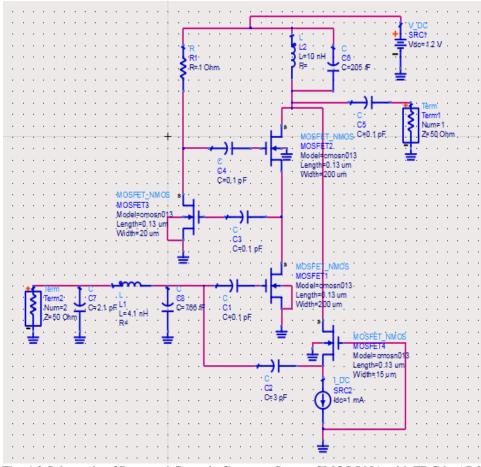

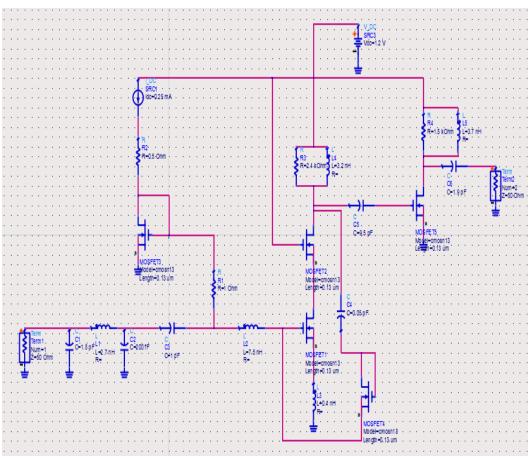

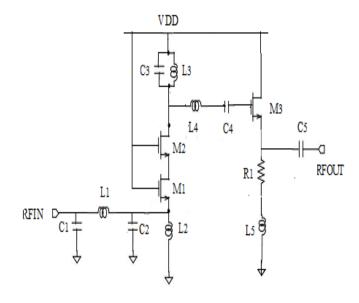

| 4.18 | Schematic of Proposed Cascode Common Source Inductively-Degenerated CMOS LNA with FDC in ADS | 48 |

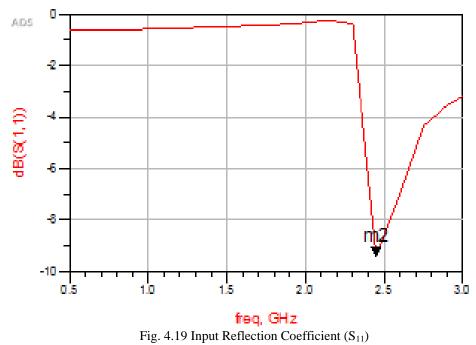

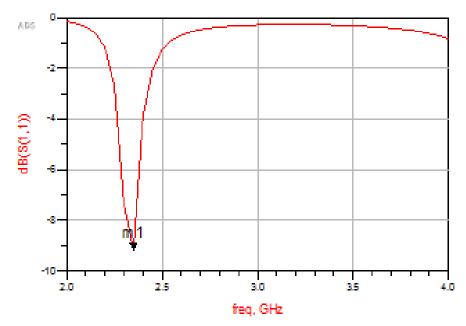

| 4.19 | Input Return Loss (S11)                                                                      | 49 |

| 4.20 | Reverse Isolation (S <sub>12</sub> )                                                         | 49 |

| 4.21 | Forward Gain (S <sub>21</sub> )                                                              | 50 |

| 4.22 | Output Return Loss (S <sub>22</sub> )                                        | 50 |

|------|------------------------------------------------------------------------------|----|

| 4.23 | Noise Figure                                                                 | 51 |

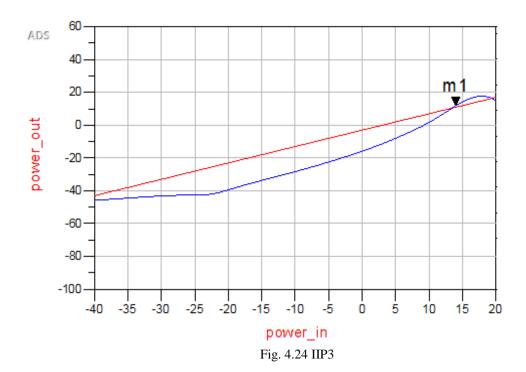

| 4.24 | IIP3                                                                         | 51 |

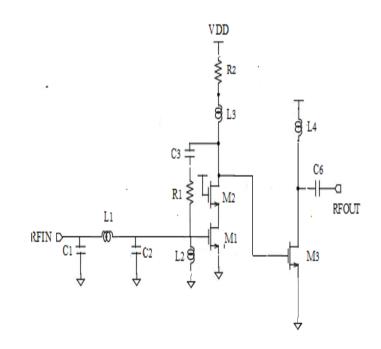

| 4.25 | Proposed Common Source Shunt Resistive Feedback CMOS LNA                     | 52 |

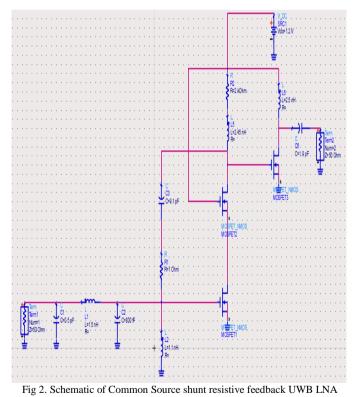

| 4.26 | Schematic of Proposed Common Source Shunt Resistive Feedback CMOS LNA in ADS | 53 |

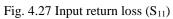

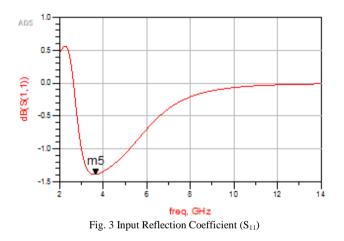

| 4.27 | Input Return Loss (S <sub>11</sub> )                                         | 54 |

| 4.28 | Reverse Isolation (S <sub>12</sub> )                                         | 54 |

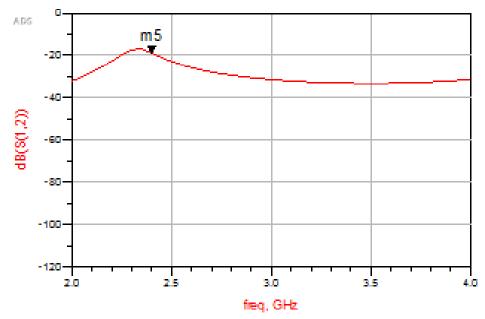

| 4.29 | Forward Gain (S <sub>21</sub> )                                              | 55 |

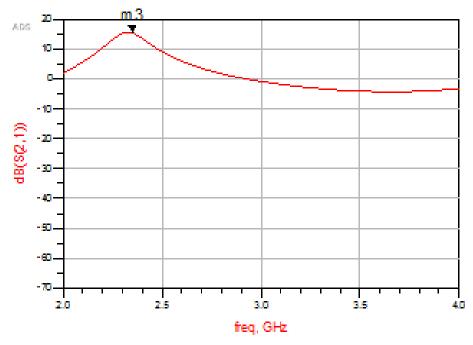

| 4.30 | Output Return Loss (S <sub>22</sub> )                                        | 55 |

| 4.31 | Noise Figure                                                                 | 56 |

| 4.32 | IIP3                                                                         | 56 |

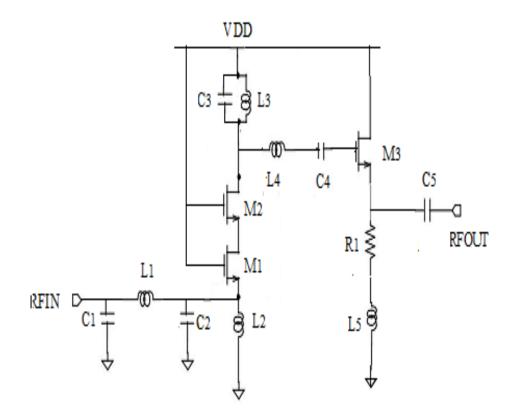

| 4.33 | Proposed Common Gate CMOS LNA                                                | 57 |

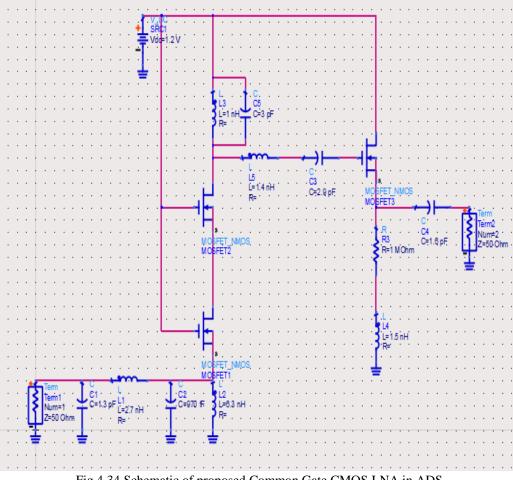

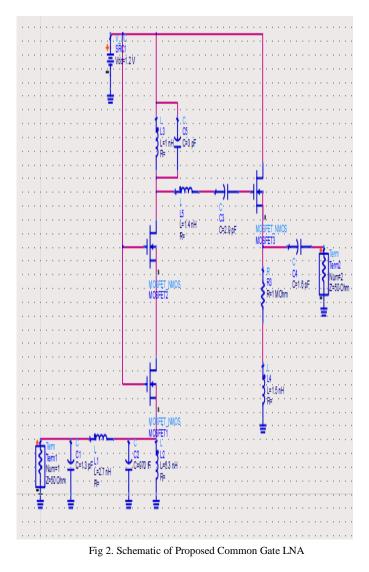

| 4.34 | Schematic of Proposed Common Gate CMOS LNA in ADS                            | 58 |

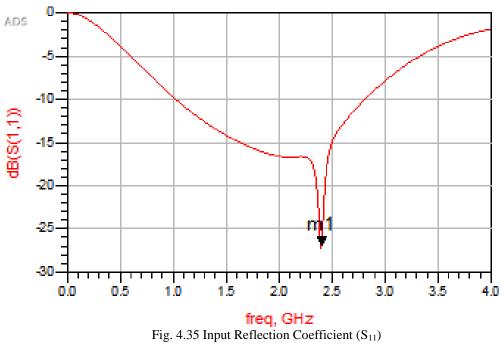

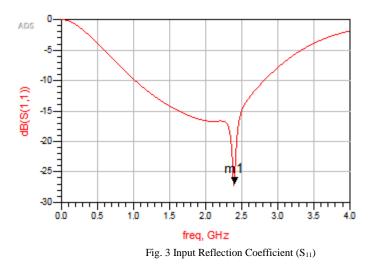

| 4.35 | Input Return Loss (S <sub>11</sub> )                                         | 59 |

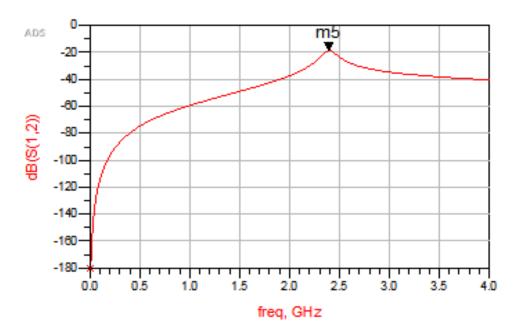

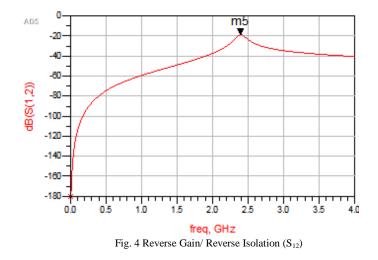

| 4.36 | Reverse Isolation (S <sub>12</sub> )                                         | 59 |

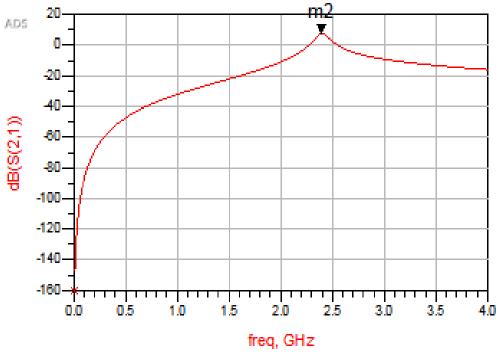

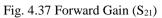

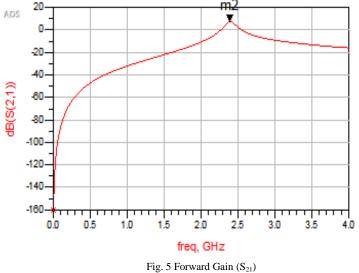

| 4.37 | Forward Gain (S <sub>21</sub> )                                              | 60 |

| 4.38 | Output Return Loss (S <sub>22</sub> )                                        | 60 |

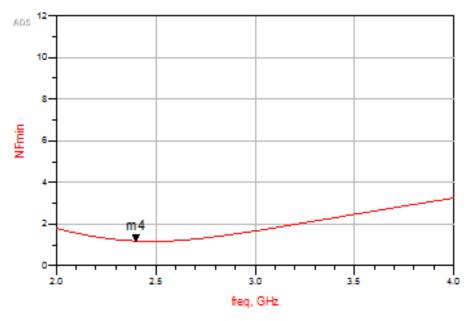

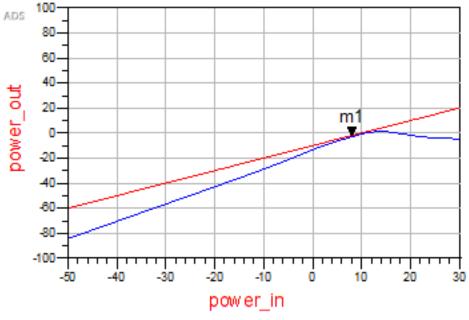

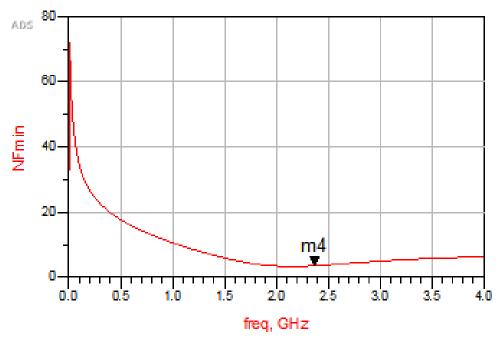

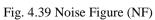

| 4.39 | Noise Figure | 61 |

|------|--------------|----|

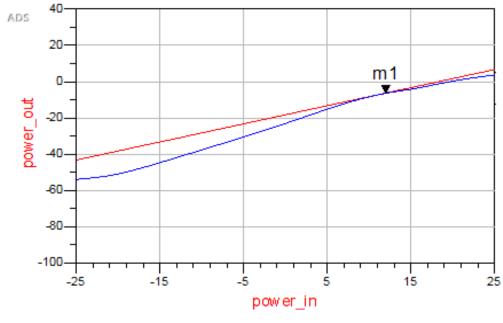

| 4.40 | IIP3         | 61 |

# List of Tables

| Table | Name                               | Page  |

|-------|------------------------------------|-------|

| 1.1   | Comparison of LNA Topologies       | 11    |

| 3.1   | Comparison of LNA at 900 MHz       | 15    |

| 3.2   | Comparison of LNA at 1 GHz         | 16    |

| 3.3   | Comparison of LNA at 1.5 GHz       | 19    |

| 3.4   | Comparison of LNA at 1.8 GHz       | 20    |

| 3.5   | Comparison of LNA at 1.9 GHz       | 21    |

| 3.6   | Comparison of LNA at 2 GHz         | 23    |

| 3.7   | Comparison of LNA at 2.4 GHz       | 28-29 |

| 3.8   | Comparison of LNA at 5 GHz         | 31    |

| 3.9   | Comparison of LNA at 5.2 GHz       | 32    |

| 3.10  | Comparison of LNA at 5.8 GHz       | 33    |

| 3.11  | Comparison of LNA at 24 GHz        | 34    |

| 3.12  | Comparison of LNA for 3.1-10.6 GHz | 35    |

| 5.1   | Comparison of Experimental Work    | 58    |

# List of Abbreviations

| SNR  | Signal to noise ration                  |

|------|-----------------------------------------|

| F    | Noise Factor                            |

| NF   | Noise Figure                            |

| IIP3 | Input third order intercept point       |

| OIP3 | Output third order intercept point      |

| LNA  | Low Noise Amplifier                     |

| RF   | Radio Frequency                         |

| CS   | Common Source                           |

| CG   | Common Gate                             |

| GSM  | Global System for Mobile                |

| GPS  | Global Positioning System               |

| LAN  | Local Area Network                      |

| WLAN | Wireless Local Area Network             |

| IM   | Intermodulation Distortion              |

| MIM  | Metal Insulator Metal                   |

| CMOS | Complementary Metal Oxide Semiconductor |

| Si   | Silicon                                 |

| GHz  | Giga-Hertz                              |

| MHz  | Mega-Hertz                              |

| KHz  | Kilo-Hertz                              |

| μm   | Micrometer                              |

| nm      | Nanometer                                       |

|---------|-------------------------------------------------|

| ADS     | Advanced Design Simulation Software             |

| EDA     | Electronic Design Automation                    |

| TSMC    | Taiwan Semiconductor Manufacturing Company      |

| Bi-CMOS | Bipolar Complementary Metal-Oxide Semiconductor |

# **Table of Contents**

| 1. | Introduc   | tion                                                         | 1  |

|----|------------|--------------------------------------------------------------|----|

|    | 1.1 Motiv  | vation                                                       | 1  |

|    | 1.2 S-para | ameter                                                       | 1  |

|    | 1.2.1      |                                                              |    |

|    | 1.2.2      | S <sub>12</sub>                                              | 2  |

|    | 1.2.3      | S <sub>21</sub>                                              | 2  |

|    | 1.2.4      | S <sub>22</sub>                                              |    |

|    | 1.3 Low 1  | Noise Amplifier                                              | 3  |

|    | 1.4 Low 1  | Noise Amplifier Parameters                                   | 3  |

|    | 1.4.1      | Input matching network                                       |    |

|    | 1.4.2      | Main amplifier section                                       | 4  |

|    |            | 1.4.2.1 Power Gain                                           | 5  |

|    |            | 1.4.2.2 Noise Figure                                         | 5  |

|    |            | 1.4.2.3 Linearity                                            | 6  |

|    | 1.4.3      | Output matching network                                      | 7  |

|    | 1.5 Low I  | Noise Amplifier Basic Topologies                             |    |

|    | 1.5.1      | Common Source with Resistive Termination LNA                 |    |

|    | 1.5.2      | Common Gate LNA                                              | 8  |

|    | 1.5.3      | Common Source with Shunt Feedback LNA                        | 9  |

|    | 1.5.4      | Common Source with Inductive Source Degeneration LNA         | 9  |

|    | 1.5.5      | Cascode Common Source with Inductive Source Degeneration LNA | 10 |

| 2. | History    |                                                              | 12 |

| 3. | Literatur  | e Survey                                                     | 13 |

|    |            | wband LNA                                                    |    |

|    | 3.1.1      | 900 MHz                                                      |    |

|    | 3.1.2      | 1 GHz                                                        | 15 |

|    | 3.1.3      | 1.5 GHz/GPS application                                      | 16 |

|    | 3.1.4      | 1.8 GHz                                                      | 19 |

|    | 3.1.5      | 1.9 GHz/GSM application                                      | 20 |

|    | 3.1.6      | 2 GHz                                                        | 22 |

|    | 3.1.7      | 2.4 GHz                                                      | 23 |

|    | 3.1.8      | 5 GHz/WLAN application                                       |    |

|    | 3.1.9      | 5.2 GHz                                                      | 31 |

|    | 3.1.10     | 5.8 GHz                                                      |    |

|    | 3.1.11     | 24 GHz                                                       | 33 |

|    | 3.2 Ultra- | wideband LNA                                                 |    |

| 4. |            | ental Work                                                   |    |

|    |            | de Common Source LNA with FDC                                |    |

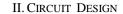

|    | 4.1.1     | Circuit Design                                        |    |

|----|-----------|-------------------------------------------------------|----|

|    | 4.1.2     | Simulation                                            |    |

|    | 4.2 Casco | Decommon Source Inductively Degenerated LNA           | 42 |

|    | 4.2.1     | Circuit Design                                        | 42 |

|    | 4.2.2     | Simulation                                            | 43 |

|    | 4.3 Casco | de Common Source Inductively Degenerated LNA with FDC | 47 |

|    | 4.3.1     | Circuit Design                                        | 47 |

|    | 4.3.2     | Simulation                                            | 48 |

|    | 4.4 Comr  | non Source Shunt Resistive Feedback LNA               | 52 |

|    | 4.4.1     | Circuit Design                                        |    |

|    | 4.4.2     | Simulation                                            | 53 |

|    | 4.5 Comr  | non Gate                                              | 57 |

|    | 4.5.1     | Circuit Design                                        |    |

|    | 4.5.2     | Simulation                                            |    |

| 5. | Conclus   | ion                                                   | 62 |

| 6. | Future D  | Directions                                            | 63 |

| 7. | Bibliogr  | aphy                                                  | 64 |

| 8. | -         | ces                                                   |    |

|    | 11        | ndix I: Published Papers                              |    |

|    |           | ndix II: Accepted Papers                              |    |

|    |           | ndix III: Communicated Papers                         |    |

|    |           | ndix IV: ADS (Advanced Design Simulation Software)    |    |

|    |           | ndix V: 802.15.4 and Zigbee                           |    |

|    | ··· ···   |                                                       |    |

# INTRODUCTION

## 1.1 Motivation

The electromagnetic spectrum's part that covers high frequencies in GHz range is the radio frequency range. Signals received by and transmitted from the antenna are RF signals. People's demand for wireless applications has become more sophisticated i.e., requiring a small power of radiation, large converging area, and higher speed because of the rapid development of communication technology.

Wireless telecommunication systems are used in reception and transmission of radio waves, which includes Wi-Fi, mobile phones, and two-way radios. Because of the communication industry's rapid developments, the requirement of more and different kinds of wireless communication systems has increased. It is desired that these wireless communication systems have characteristics such as low noise figure, low input/output return losses, a high IIP3 and, low power consumption. The main aim of the manufacturers of the wireless communication systems is to achieve low power. The demand of small radiation power, large converging area, and high speed are fulfilled due to the low-cost, low-rate, and low-power network; IEEE 802.15.4 ZigBee standard.

The license free frequency bands are 2400 MHz, 920 MHz, and 860 MHz, used by IEEE 802.15.4 ZigBee standard. The design in this thesis is mainly concentrated on the 2.4GHz band because of global operation in this band as is used by router, cordless phone, Bluetooth device, baby monitor and etc.

## 1.2 S-parameter

A two port networks performance can be described in many different ways such as using Y parameters, Z parameters, ABCD parameters and T parameters for low frequency. Linear electrical network behavior is described by these parameters by using open circuit and short circuit conditions. However, at high frequency it is difficult to realize these terminations and hence, cannot be used for high frequency analysis. Therefore, S parameter is used for high frequency analysis i.e. also for RF range.

Load termination measurement and matching is achieved by S-parameter by utilizing incident wave and reflected wave at the input port and the output port. A two port network is shown in figure 1.1.

Fig 1.1 Two port network [1]

where,

a1 and a2 are incident wave b1 and b2 are reflected wave

The relationship between a1, a2, b1 and b2 is described by s parameter as follows:

$$\begin{bmatrix} b1\\b2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12}\\S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a1\\a2 \end{bmatrix} = \begin{bmatrix} S \end{bmatrix} \begin{bmatrix} a1\\a2 \end{bmatrix}$$

(1.1)

The matrix [S] is called the scattering matrix. Its parameters are as follows:

1.2.1. S<sub>11</sub>

$S_{11}$  is input reflection coefficient or input return loss. In order to measure  $S_{11}$ , a signal is injected at input port and its reflected signal is measured. In this case, no signal is injected into output port. So, it represents the measure of matching of the input impedance to the reference impedance. It is given by:

$$S_{11} = \frac{b_1}{a_1} \Big|_{a2} = 0 \tag{1.2a}$$

1.2.2 S<sub>12</sub>

$S_{12}$  is reverse transmission coefficient or reverse isolation as it measures how much the input signal is reflected back. In  $S_{12}$ , a signal is injected into output port, and signal power leaving port is measured.

$$S_{12} = \frac{b_1}{a_2} \Big|_{a1} = 0$$

(1.2b)

#### 1.2.3 S<sub>21</sub>

$S_{21}$  is forward transmission coefficient or forward gain. If  $S_{21}$  is to be measured, a signal is injected at the input port, and the resulting signal power exiting output port is measured. It measures how well the signal goes from input to output.

$$S_{21} = \frac{b^2}{a_1} \Big|_{a^2 = 0}$$

(1.2c)

### 1.2.4 S<sub>22</sub>

$S_{22}$  is output reflection coefficient or output return loss. For  $S_{22}$  measurement, a signal at output port is injected and its reflected signal is measured. So, it represents the measure of matching of the output impedance to load impedance.

$$S_{21} = \frac{b2}{a2} \Big|_{a1} = 0$$

(1.2d)

## 1.3 Low Noise Amplifier

In these wireless communication systems, the RF front-end circuit is low noise amplifier which is one of the crucial elements of RF receivers. They amplify RF signal to a particular level so that the sensitivity requirements of other components in RF receivers such as filters are met by RF signal.

Since, the low-noise amplifier (LNA) is the first stage of receiver and is an important component of wireless telecommunication systems. Firstly, its main function is to overcome the noise of subsequent stages (such as mixers) by providing enough gain, i.e., it should have high gain. Secondly, minimize the effect of the overall noise performance by adding as little noise as possible, i.e., it should have low noise figure itself. Thirdly, large signals should be accommodated without distortion by an LNA, i.e., it should provide good linearity. A specific impedance of 50 ohms must be provided by LNA to the input source and output load. Also, low power consumption should be there especially in portable systems.

## 1.4 Low Noise Amplifier Design Parameters

The low noise amplifier is the first active and also, an essential block in the receiver chain of communication system. It is used at the front end of the receiver, is connected directly to the antenna. So, the noise performance of low noise amplifier directly impacts the overall noise performance of the receiver. Crucial design specification i.e., noise figure (NF) has trade-offs with other design specifications such as gain, power consumption and third order intercept point (IIP3). So, LNA design consists of trade-offs between gain, noise figure, linearity, input and output matching, and power consumption. However, to achieve good overall system performance, several desired parameters are required such as low power consumption, high gain, high third order intercept point, low noise figure and good input and output impedance matching.

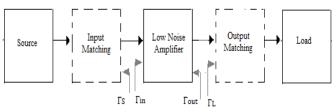

Fig. 1.2 Basic Components of Amplifier with input/output of amplifier (two-port network)

where,

$\Gamma_{\rm s}$  is reflection coefficient of source of two-port network,  $\Gamma_{\rm L}$  is reflection coefficient of load of two-port network,  $\Gamma_{\rm in}$  is reflection coefficient at input of the amplifier and,  $\Gamma_{\rm out}$  is reflection coefficient at output of amplifier.

Combination of following three stages form low noise amplifier

### 1.4.1 Input matching network.

The input matching network is present so that the input return loss or input reflection coefficient (S<sub>11</sub>) is minimum without additional noise introduction. The ideal value of the input impedance is infinite if the low noise amplifier is considered as voltage amplifier. So, to obtain minimum noise figure, a transformation network is required before low noise amplifier, if viewed from noise point of view while conjugate matching between antenna and low noise amplifier is required, if viewed from signal point of view. Each of the above choices has its own advantages and disadvantages however, the latter is commonly used in today's systems. Therefore, LNA is designed such that it has input impedance equal to 50  $\Omega$  resistance.

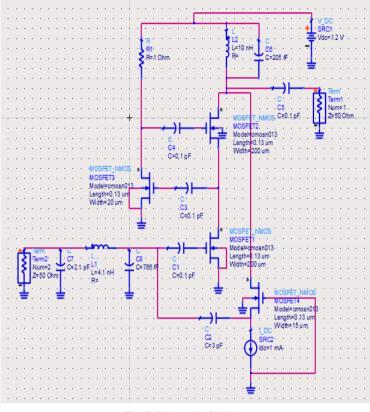

The LNA is designed to make gain and linearity as high as possible and make noise figure as low as possible. However, gain and linearity are the two parameters which are poles apart and it is difficult to balance them i.e., gain will be affected while trying to improve the linearity and vice versa. Gain is enhanced in pi-matching when compared to T-matching. So, in order to obtain reasonable linearity at low power, pi-matching is used and hence, is adopted in this thesis.

### 1.4.2 Main amplifier section

Amplifier section ensures maximum gain and linearity and also, minimum noise figure and power consumption. It also provides input impedance matching at the same time.

#### 1.2.4.1 Power Gain

In figure 1.2, the input/output power gain of low noise amplifier i.e. a two port network is shown. Power gain is defined as the ratio of the power dissipated in the load i.e., output power to the power supplied to the amplifier i.e., input power. The power gain mathematically, can be expressed as:

$$G = \frac{P_{out}}{P_{in}} \tag{1.3}$$

$$G = \frac{(1 - |\Gamma_L|^2) |S_{22}|^2}{(1 - S_{22} |\Gamma_L|^2) (1 - |\Gamma_L|^2)}$$

(1.4)

#### 1.2.4.2 Noise Figure

The basic definition of noise is everything except the desired signal. All the communication systems are sensitive to the noise. The signal to noise ratio (SNR) is used for measurement of the noise present in the system.

The degradation of SNR by the circuit is indicated by the noise factor. Noise performance of the system is measured by noise figure. Noise Factor is the ratio of the signal to noise ratio of the input port to that of output port and is larger than 1 dB and is given by:

$$F = \frac{SNR_{out}}{SNR_{in}} \tag{1.5}$$

Noise factor expressed in dB unit is called noise figure and is given by:

$$NF = 10\log \frac{SNR_{out}}{SNR_{in}}$$

(1.6)

For the single-stage amplifier, its noise figure is seen as follows:

$$F = F_{min} + \frac{4r_n |\Gamma_S - \Gamma_{opt}|}{(1 - |\Gamma_S|^2) |1 + \Gamma_{opt}|^2}$$

(1.7)

In the formula, Fmin is the minimum noise figure. Fopt,  $r_n$  and  $\Gamma$ s are the best source reflection coefficient, the equivalent noise resistance of the transistor and the input reflection coefficient of the transistor when Fmin is obtained.

For multi-stage amplifier, the entire system noise is contributed by each stage. So, the total noise factor of the system is given by the Friis formula:

$$NF = F_1 + \frac{F_2 - 1}{G_{A1}} + \frac{F_3 - 1}{G_{A2}} + \dots$$

(1.8)

where,

Fn is the noise figure of the first n-amplifier and Gn is the gain of the first n-amplifier.

1.2.4.3 Linearity

The highest value of signal that can accepted at the input of the system is defined as linearity of that system. LNA along with amplification of signal and good noise performance, should be linear even when the signal is strong. Hence, during designing of LNA, linearity is an important consideration. Several methods are used to find the linearity of the system. However, the most commonly used methods are:

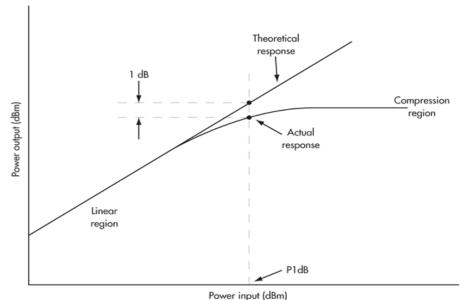

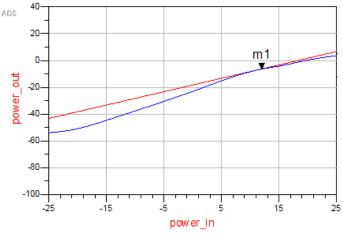

#### A. 1 dB Compression Point (P1dB)

For a specified frequency range the linear amplifier have a fixed gain. The slope of the line in the output power vs input power plot is called gain. However, after some point the gain decreases as the input power is increasing continuously and the point at where the output power is not increased further when input power is increasing, the amplifier enters into compression i.e. becomes saturated. Hence, distortion occurs due to non-linear response. The input signal is restricted to the point where compression begins to occur to avoid distortion. The value of the point is the input power where the gain is decreased by 1 dB from the normal linear gain or the output power where the 1 dB decreased gain drop occurs.

rener inper (abili)

Fig 1.3 P1 dB (logarithmic scale)

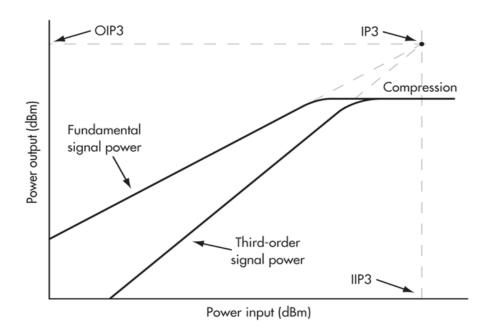

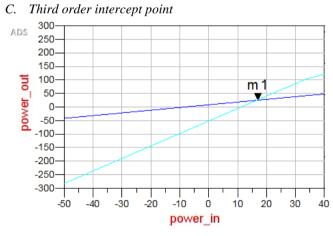

B. Third Order Intercept Point (IP3)

The amplified input produces harmonics when the amplifier becomes nonlinear. All the harmonics except the first or fundamental harmonic is present outside the bandwidth of the amplifier. Moreover, if the signal harmonics are close in the frequency then their sum and difference frequencies are also present in the bandwidth and are difficult to filter out. These frequencies are called intermodulation products.

If the graph between output power and input power is plotted then a graph similar to 1 dB is obtained and is the first order plot. Third order product signal's graph is also plotted in the same plot. The point at which gain flattens in both the graph is called compression point and if the linear region of both the graphs are extended then they meet at a point where third order signal to the first order signal. This point is called third order intercept point. It is called IIP3 if the third order point is read from input axis and is called OIP3 if the third order point is read from output axis.

Fig 1.4 Third order intercept (logarithmic scale)

#### 1.4.3 Output matching network

The output matching network is present to guarantee that the output impedance is 50  $\Omega$ .

#### **1.3 Low Noise Amplifier Basic Topologies**

The important goals in the designing of LNA are low NF, high gain, low power consumption, and 50  $\Omega$  input impedance. For achieving all these goals, different LNA architectures are available as follows: Common-Source (CS) stage with resistive termination, Common-Gate (CG) LNA, Common-Source with shunt feedback, Common-Source with inductive source degeneration and Common-Source with cascode inductive source degeneration.

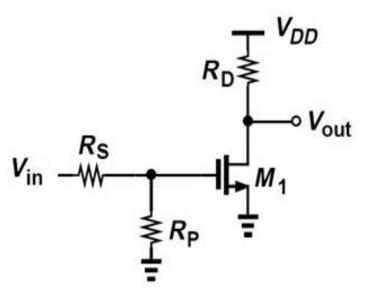

#### 1.5.1 Common Source with Resistive Termination

For termination at the input port a resistor is used, to provide 50  $\Omega$  input impedance in the resistive termination CS amplifier. In order to realize input matching, a resistor of 50  $\Omega$  is connected in parallel to the input, leading to a high NF. This architecture is undesirable where good input matching as well as low noise is desired.

Fig. 1.5 Common Source with Resistive Termination LNA [1]

#### 1.5.2 Common Gate

The transconductance (gm) value should be fixed at  $\frac{1}{R_S}$  for the input matching in the Common Gate LNA, therefore, the only design variable is RL. The input transistor's transconductance of cannot be high due to the input matching. However, this topology is well known for wideband applications and also, the noise factor is quite reasonable and acceptable.

Fig 1.6 Common Gate LNA [1]

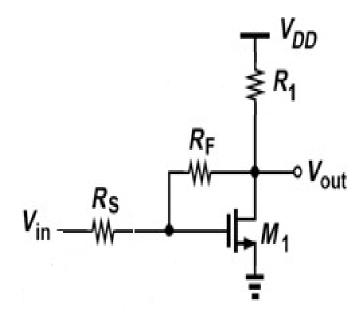

#### 1.5.3 Common Source with Shunt Feedback

The Common Source stage with shunt feedback, as compared to the conventional Common Gate LNA, achieves lower noise figure and higher power dissipation.

Fig. 1.7 Common Source with Shunt Feedback LNA [1]

#### 1.5.4 Common Source with Inductive Source Degeneration

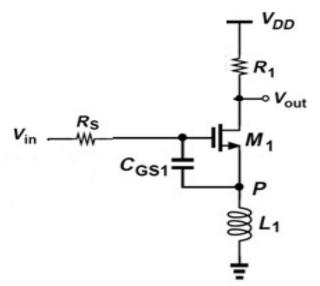

In Common Source with inductive source degeneration LNA, thermal noise is not generated like an ordinary resistor. So, the input matching requirement is achieved without introduction of the additional noise due to real resistor. Also, compared to other architectures, this topology consumes less power, making it suitable for low power applications. However, this topology has disadvantages like low gain, low linearity and high noise figure.

Fig. 1.8 Common Source with Inductive Source Degeneration LNA [1]

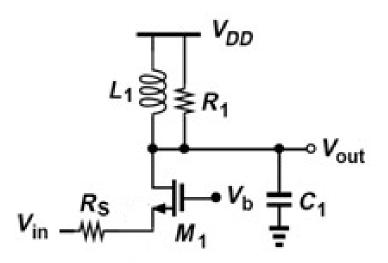

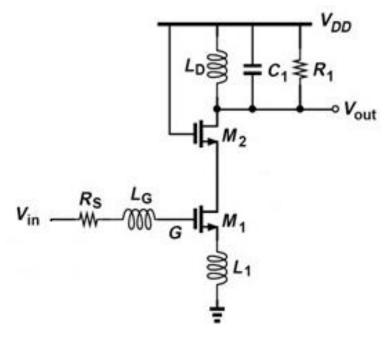

#### 1.5.5 Cascode Common Source with Inductive Source Degeneration

The Common Source with cascode inductive source degeneration LNA has high reverse isolation and high stability. However, the inductors  $L_S$  and  $L_G$  have to be adjusted to keep the input impedance to 50  $\Omega$  as the generated noise power from the cascode stage increases when the width of the cascode stage increases.

Fig. 1.9 Cascode Common Source with Inductive Source Degeneration LNA [1]

The various LNA topologies are compared in table 1.1 shown below.

| Topology                                                       | Advantages                                                            | Disadvantages                                                                                              |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|

| Resistive termination<br>common source LNA                     | Broadband amplifier.<br>Good input matching.                          | Addition of noise from the<br>resistor.<br>High noise figure.                                              |  |  |  |

| Common gate LNA                                                | Well known for wide band<br>applications.<br>Low power consumption.   | Weak noise performance.                                                                                    |  |  |  |

| Common source with<br>shunt feedback                           | Broadband amplifier.<br>Has good input and output<br>characteristics. | High power dissipation.                                                                                    |  |  |  |

| Common source with<br>inductive source<br>degeneration         | Suitable for low power applications.                                  | Low gain, low linearity and high noise figure.                                                             |  |  |  |

| Cascode Common source<br>with inductive source<br>degeneration | High reverse isolation<br>and high stability.                         | The noise power generated<br>from cascode stage increases<br>when the width of cascode<br>stage increases. |  |  |  |

TABLE 1.1 COMPARISON OF BASIC LNA TOPOLOGIES

## Chapter-2

## HISTORY

Almost, 20 years ago, the most valuable device present to function as low noise amplifier at high frequency were only travelling wave tubes or vacuum tubes which were fabricated in various laboratories [2]. However, the noise temperature of travelling wave tube was around 3000K. Thus, making its amplification limited by noise in the circuit [3]. The tunnel diode was also used as low noise amplifier which provides amplification by using negative conductance effect but shot noise is present in the dc current that flows during the amplification operation and is major source of noise, contributing as the drawback of using tunnel diode for amplification [4]. The maser standing for microwave amplification by stimulated emission of radiation, having extremely low noise figure replaced vacuum tubes and tunnel diodes but unfortunately it had its own drawback of working at low temperature environment, resulting in use of costly and highly complicated equipment. Therefore, could be used only in sophisticated systems for specialized applications [5]. Parametric amplifier formed from semiconductor diode was also a low noise amplifier because is purely reactive ideally and hence, no noise is present. Low bandwidth is the shortcoming if a single diode is used so, to increase the bandwidth multiple pair of identical diodes are used. Requiring high quality identical diodes is the serious disadvantage of the above technique [6]. Large size and unable to fabricate the device on chip made the above discussed devices less favorable to be used for low noise amplification. So, transistors such as bipolar junction transistor (BJT) or field effect transistor (FET) were used as a low noise amplifier [7][8]. However, the tradeoffs between noise figure, gain, linearity and stability in both the above transistors were different. So, the design of low noise amplifier depends on the transistor technology which is incorporated such as if Gallium arsenide high-mobility electron transistor (GaAs HEMT) is used, excellent linearity and noise figure is obtained compared to Silicon Germanium Heterojunction bipolar transistor (SiGe HBT) but on the other hand, low power consumption, high gain and good noise figure is obtained by SiGeHBT. Since, the area on chip required by BJT and FET is large, CMOS technology are used being used. The complementary MOS (CMOS) transistor is used in low noise amplifiers because of its good characteristics. High immunity against noise and static power are two of the important characteristics of CMOS transistors. Moreover, CMOS technology are used to fabricate in-chip low noise amplifiers because of high level of integration [9]. The internal structure of CMOS contains a NMOS and PMOS transistor in series. So, the power is drawn by the series combination momentarily when there is switching between ON and OFF states, because one of the transistor in the series connection is always OFF. Hence, the heat produced by CMOS devices is less as compared to other logic families such as transistor transistor logic (TTL), NMOS, etc.

Number of new devices capable of giving better performance substantially is present during these recent times. So, from the past 20 years and more, there are continuous and rapid development of low noise amplifiers due to discovery of new and advanced devices for fabrication of low noise amplifier. Moreover, the advancement in technique to reduce noise is also responsible for low noise amplifier development. Therefore, for implementation of low noise amplifier, CMOS is one of the competitive technology because of high level of integration, low cost and technology scaling. Furthermore, ultra-high level of integration (UHI) is achieved due to advancement in technology scaling. Currently, most of the low noise amplifier are designed using 0.18  $\mu$ m or 0.13  $\mu$ m technology.

## LITERATURE SURVEY

Our knowledge in the field of low noise amplifier cannot be updated without studying the earlier work done by the researchers/scientists because the earlier concepts and techniques given are helpful to study and analyze present technology concepts and techniques as there is increasing and constant demand to make the devices smaller, portable, consuming less power and operating for large frequency band. A brief review of the earlier work done in the designing of low noise amplifier by simple current reuse technique, common source cacode amplifier topology, common sou5rce inductive degeneration amplifier topology, cross couple capacitor technique and, etc. in various CMOS technology (90 nm, 35 nm, 0.18  $\mu$ m, 0.13  $\mu$ m) for microwave frequency i.e. frequency ranging from 300 MHz unto 300 GHz is discussed in the following literature review.

## 3.1 Narrowband LNA

#### 3.1.1 900 MHz

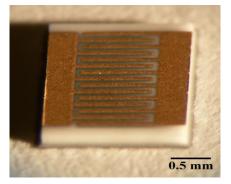

This paper [10] proposes and designed first CMOS LNA that integrates input and output matching network for 900 MHz ISM Band. The LNA is formed by two stage amplifier, the first stage of which is a cascaded amplifier having inductor-capacitor resonator as load so as to improve gain and noise performance while the second stage is a CS amplifier having capacitor transformer and resistor as a load. Therefore, improved reverse isolation and simplifying the matching because of input and output decoupling are the advantages of using two stage amplifier. It also includes series inductive feedback, bias circuit and capacitive transformer. The LNA is designed on a chip of size  $0.74x0.72 \text{ mm}^2$  using  $0.8 \mu \text{m}$  CMOS technology. A supply of 3 V is used for drawing current of 8.6 mA from first stage and 2 mA from second stage. Maximum power gain of 14.3 dB, minimum noise figure of 4.5 dB and P<sub>1dB</sub> of +5 dBm is observed.

A LNA for 900 MHz is designed using 0.5  $\mu$ m CMOS technology. Current reuse technique is used to increase overall LNA gain. The LNA design approach utilizes two stage amplifier. The forward gain is achieved from stage 1 of the amplifier and unity buffer is achieved from stage 2. Also, each stage employs bias feedback amplifier to establish Q point for each stage by setting dc output voltage of each stage to bias reference. Output of first stage is directly coupled to input of second stage. A minimum noise figure of 1.9 dB, gain of 15.6 dB, IIP3 of -3.2 dB and power consumption of 20 mW is obtained when a supply of 2.7 V is given to LNA. Chip of size 0.7 mm x 0.4 mm is designed [11].

In the paper [12], broadband inductorless LNA design at 900 MHz is explored as LC tanks which are highly tuned and have high Q value are not used i.e. on chip

providing overdrive capabilities are not exploited. The LNA consists of three NMOS gain stages in cascode. Also, multistage topology is used by the LNA so that at low or zero intermediate frequency the circuit has critical reverse isolation. To reduce power consumption, current reuse technique is used and to improve linearity the last two LNA stages are degenerated. For the input stage, open loop structure is used to avoid noise generated by the feedback system and the output buffer is degenerated cascode amplifier. A 9 dB gain, 2.3-3.3 dB NF, >-41 dB S<sub>21</sub> and -4.7 dBm IIP3 has been observed by 900 MHz designed using 0.5  $\mu$ m CMOS process while current of 3.4 mA is drawn from 3 V supply. A die area of 1.0 x 1.2 mm<sup>2</sup> has been used in total and the largest part occupied only by de-coupling capacitors while die are of 0.4x0.3 mm<sup>2</sup> is occupied only by active core.

A 900 MHz LNA is implemented in the paper [13] fabricated using three level metal 0.8  $\mu$ m CMOS process and SOIC like package used for packing. Amplifier design topology is cascode topology having only single stage for improvement of linearity, 1 dB compression point and minimization of power dissipation and also uses inductive degeneration at the source. The cacsode stage is used to improve reverse isolation and eliminate Miller effect and source inductive degeneration is used to achieve input matching and noise matching simultaneously. Only one external inductor is required. The area occupied by the chip is 720x720  $\mu$ m2. The LNA provides NF of 1.2 dB at 30 mW, 1.5-dB at 13.5 mW, and 2-dB at 6.3 mW. Also, a NF of less than 2 dB is provides at less than 10 mW power. Moreover, an IIP3's of -1 dBm is obtained at 30 mW and -3.8 dBm at 6.3 mW. A high S<sub>11</sub>, S<sub>22</sub> is below -10 dB and S<sub>12</sub> is more than 42 dB.

A full integrated 900 MHz CMOS LNA has been fabricated with 0.35  $\mu$ m minimum channel length. To provide wide dynamic range and low noise a single stage cascoded inductive degeneration configuration is used. Single stage is used in order to limit power consumption and improve reverse isolation of the LNA. Also, LC networks is used to achieve 50  $\Omega$  matching. The CMOS LNA of three different version is fabricated in [14] with the main transistor width (W) of 225 $\mu$ m, 450 $\mu$ m, and 675 $\mu$ m, are C225, C450, C675 respectively and is mounted of TQFP48 package. C225 is measure on dedicated application board and packed components are soldered on the board while C675 is measured on test board and packaged chip is plugged in Johnstech socket. C450 is measured on dedicated application and test board. The best configuration is C450 having 16 dB NF at 12 mA and 1.5 dB NF at 20 mA, along with VSWRin less than or equal to 2.5. For good matching conditions i.e. for VSWRin less than or equal to 2, the NF≤1.75 dB, IIP3≤3 dBm and gain equal to 10 dB.

A 900 MHz LNA using 0.35  $\mu$ m CMOS process has been fabricated. A single stage cascode LNA configuration is used. Here, to reduce power consumption single stage is used and to reduce Miller effect and to improve reverse isolation cacscode configuration is used. Transistor of width (W) of 450 mm is used. The LNA is housed into TQFP48 package. A power gain of 14 dB, NF of 0.9 dB, S<sub>11</sub> of -10 dB, S<sub>22</sub> of -27 dB and IIP3 0f 0 dBm is obtained at 18 mW power while a NF of 1.05

dB is also obtained at 9 mW power along with power gain of 12 dB, S<sub>11</sub> of -8.7 dB, IIP3 of -2 dBm [15].

The LNA working at 900 MHz and to be used as mobile CDMA receiver, that works on 824-894 MHz has been proposed and fabricated in the paper [16]. The LNA circuit uses the current reuse technique so as to achieve transconductance of that of device but by using less current. The inductors in LC network that is used as the load and are tuned at operating frequency, has high quality factor. The quality of inductor is high if the substrate resistivity is higher. This, the performance of inductor depends on the doping of substrate. The LNA is implemented using 0.35  $\mu$ m CMOS process. The dimensions of the LNA are 1541  $\mu$ m x 850  $\mu$ m and the total area occupied is 1.31 mm<sup>2</sup>. A NF of 1.8 dB, gain of 15 dB, IP3 of -3 dBm and compression point of -11 dBm is obtained.

|                      | [10] | [11] | [12]    | [13]  | [14]  | [15]  | [16] |

|----------------------|------|------|---------|-------|-------|-------|------|

| Technology<br>(µm)   | 0.8  | 0.5  | 0.5     | 0.8   | 0.35  | 0.35  | 0.35 |

| Supply (V)           | 3    | 2.7  | 3       | -     | -     | -     | -    |

| S <sub>21</sub> (dB) | 14.3 | 15.6 | 9       | -     | 10    | 14    | 15   |

|                      |      |      |         |       |       | @18mW |      |

| NF (dB)              | 4.5  | 1.9  | 2.3-3.3 | 1.2 @ | ≤1.75 | 0.9   | 1.8  |

|                      |      |      |         | 30mW  |       | @     |      |

|                      |      |      |         |       |       | 18mW  |      |

| IIP3 (dBm)           | -    | -3.2 | -4.7    | -1@   | ≤3    | 0     | -3   |

|                      |      |      |         | 30mW  |       | @18mW |      |

TABLE 3.1 COMPARISON OF LNA AT  $900\ MHz$

#### 3.1.2 1 GHz

Single ended two 1 GHz LNAs has been designed in the paper [17] with and without ac coupled inductor. Both the LNAs utilizes single stage cascode topology along with pull up resistive load without no chip inductor. However, the second LNA topology uses an additional ac coupled inductive load. Thus, forming inductive degeneration cascode topology. The active inductor working in GHz is built from CMOS gyrator as it can form large value inductor (20-40 nH) on chip using an area less than used by on chip spiral inductor. However, has poor linearity compared to on chip spiral inductor. A 0.5  $\mu$ m CMOS technology is used in designing of the LNA. The circuit uses 2 V supply. The active inductor LNA provides a gain of 12.2 dB, IIP3 of -21 dB and NF of 2-2.3 dB for long channel model and 2.7-3.1 dB for short channel model consuming a power 17 mW while the inductorless LNA provides a gain of 10.7 dB, IIP3 of -3.8 dBm and NF of 2-2.2 dB for long channel model and 2.6-2.9 dB for short channel model consuming a power of 16 mW. The input return loss is -10 dB and reverse isolation is higher

than 45 dB for the both the LNA while the output matching is less than -10 dB for active inductor LNA. Therefore, out of both the LNA design, active inductor LNA is more selective and image reject filter requirements are relaxed with the help of series resonance.

A 0.5  $\mu$ m RF CMOS LNA using current reuse technology and CS inductive degeneration topology is proposed in [18]. The first stage of LNA has a PMOS and a NMOS, CS amplifier in cascode configuration followed by a CG stage. Another transistor in CS configuration is present before the cascode to set the dc bias of transistor in cascode stage while a transistor in CG configuration is present at the end as buffer stage to provide output matching of LNA. The on chip inductor i.e. the degenerated inductor have quality factor of 5 while the off chip inductors i.e. input and output inductors have quality factor of 50. The proposed LNA at 1GHz gives a S<sub>11</sub> of -31.8 dB, S<sub>21</sub> of 21.6 dB, S<sub>12</sub> of 42 dB, S<sub>22</sub> of 42.1 dB, NF of 2.7 dB and IIP3 of 18.8 dB. Also, a current of 20.3 mW is consumed from 2.2 V supply.

A 1 GHz CMOS LNA which uses cascode configuration but in modified form is proposed in the [19]. Here, the LNA circuit uses a CS amplifier which is inductively degenerated in the first stage of LNA followed by CG amplifier, which forms a cascode configuration. A CS amplifier before stage 1 is used to bias the amplifier in first stage and a CG amplifier is used at the end as a buffer stage to achieve output matching. The inductor on chip is a degenerated inductor having quality factor of 5 and the input and output inductors are off chip inductor having a quality factor of 50. 0.5  $\mu$ m CMOS technology is used to design the LNA circuit. An input reflection coefficient of -33.64 dB, forward gain of 18.6 dB, reverse isolation coefficient of -45.5 dB, output reflection coefficient of -35.22 dB, NF of 1.62 dB and IIP3 of -23 dBm is observed. A power of 12.5 mW is consumed from 1 V supply.

|                 | [        | 17]          | [18] | [19] |

|-----------------|----------|--------------|------|------|

| Technology (µm) | 0.5      |              | 0.5  | 0.5  |

| Supply (V)      | 2        |              | 2.2  | 1    |

|                 | Active   | Inductorless | 21.6 | 18.6 |

|                 | inductor |              |      |      |

| $S_{21}(dB)$    | 12.2     | 10.7         |      |      |

| NF (dB)         | 2-2.3    | 2-2.2        | 2.7  | 1.62 |

| IIP3 (dBm)      | -21      | -3.8         | 18.8 | -23  |

TABLE 3.2 COMPARISON OF LNA AT 1 GHZ

#### 3.1.3 1.5 GHz/GPS

For GPS receiver a 1.5 GHz LNA is implemented in 0.6  $\mu$ m CMOS technology by employing inductive source degeneration topology along with input tuning so that 50  $\Omega$  narrow band input impedance is achieved, to convert the MOS device reactive

input impedance into real resistance. Although, dual-feedback and resistive termination could also have been used but each have its own drawback; of being used when loop gain requirement can be satisfied easily at low frequency and on the NF lower bound of 3dB is placed respectively. A gain of 22 dB, NF of 3.5 dB and IIP3 of -9.3 dB is obtained while from 1.5 V, a power of 30mW is consumed [20].

A 1.5 GHz LNA for GPS receiver, front-end applications has been designed with one poly and two metal layers only in 0.35 µm CMOS process. For better on chip rejection, a differential architecture is selected but consumes twice the power consumed by single ended architecture to achieve same noise figure. The architecture of LNA consists of two stage, the stage 1 is cascoded so that reverse isolation improves, stability is maintained as spiral inductor is used to tune stage 1 output and the influence gate to drain overlap capacitance is reduced on input impedance i.e. Miller effect is mitigated. Moreover, by reusing the bias current of stage 2 in the stage 1, the power factor is decreased by a factor of two. So, a common mode feedback technique is used. At the source of two transistors the inductive degeneration is employed so that output of the RF filter present before the LNA is properly matched to input impedance of LNA. Baluns are used to interface to single ended test instrumentation since, the circuit is differential. A total die area of 0.84 mm<sup>2</sup> is used to fabricate a LNA and a mixer on a single chip. The gain of LNA is 17 dB, NF is 3.8 dB and IIP3 is -6 17 dBm and reverse gain is 52 17 dB, while dissipating a power of 12mW and using 1.5 V supply [21].

A 0.35 µm differential CMOS LNA has been fabricated for GPS application in [22]. Inductive degeneration topology in differential form is used at the input stage and LC network is used as load where the quality factor of the inductor is 7. Transistor in cascode also present between input stage and LC load to reduce Miller effect and increase reverse isolation. At the gate of the input stage transistor, the spiral inductor is integrated in series so that level of integration is increased. Since, the telecommunication signal is narrowband, narrowband RF signal processing is required. Here, the input stage is intrinsically narrowband because maximum power transfer occurs at carrier frequency because at carrier frequency only the source and input impedance match and, out of band signal components is filtered out and in band thermal noise is minimized because of LC feedback. The LNA has been realized by 5 metal layer while spiral inductor itself is realized by upper thicker metal layer. The simulated LNA has 26 dB gain, NF of 3.6 dB, IIP3of -3 dBm and current of 5 mA flows from 2.8 V supply.

A two stage LNA has been designed using 0.6  $\mu$ m CMOS for 1.57 GHz. The LNA is design consists of cascode configuration in first stage so that input resonant circuit and output resonant circuit are decoupled followed by source follower present in the second stage. A coupling capacitor is used to separate the two stages. Current mirror is used to bias the input transistor so that minimum noise is coupled between the biasing resistor and the signal path. A separate circuit is used to bias the second stage. So, power consumption is less. The results observed for 1.8 V

power supply is that the circuit dissipates a power of 17 mW with a NF of 2 dB, gain of 19 dB,  $S_{11}$  of -30 dB,  $S_{22}$  of -32 dB,  $S_{12}$  of -57 dB and IIP3 of 10 dB. Moreover, in paper [23] noise rejection behavior of proposed design's single ended and differential LNA has been studied and it is indicated that for the same gain differential LNA produces more noise compared to single ended LNA but is less prone to common mode noise.

A LNA for GPS receiver has been designed using 0.25  $\mu$ m CMOS process in [24]. The LNA circuit uses two stage differential structure, in the stage 1 two CS amplifier are present in cascode configuration to reduce Miller effect and to improve reverse isolation, and also degenerated inductor is employed at the source to achieve stable input impedance. Spice using level 49 CMOS parameter is used for simulation of LNA, giving a NF of -5.6 dB and gain of 22 dB. The LNA circuit dissipates a power of 35 mW and uses 3 V supply. The LNA layout is designed using Cadence and area of the layout is 0.27x0.33 mm<sup>2</sup>.

A two stage LNA has been designed using  $0.18 \ \mu m$  CMOS process in [25]. The first and second stage of the LNA consists of CS amplifier with inductively degenerated inductors at the source. The output of the first stage is provided at the gate of the amplifier in the second stage. Another CS configuration transistor is present before the first stage to bias the in the amplifier in the first stage. Inductors are used as load for the two stages. The circuit is simulated using Cadence Spectre RF and uses 1 V supply. A NF of 2.0 dB, gain of 28.7 dB and IIP3 of -16.0599 dBm is obtained.

A LNA based on noise optimization technique has been designed [26] for 1.5 GHz. The LNA circuit has single stage having two CS amplifier. Also having 1 nH bond wire inductor as the degenerated inductor at the source of the first amplifier. LC network is used at the load so that is optimized at the operating frequency. The circuit is designed using 0.13  $\mu$ m CMOS process. The simulated LNA has input reflection coefficient of about -17 dB, gain of 12.9 dB and NF of 0.55 dB. A current of 1 mA is drawn from a supply of 1 V.

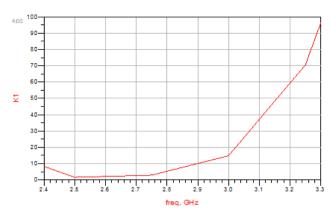

A cascode CS inductive degeneration topology is used in designing of the LNA using 90 nm CMOS technology. The gate inductor and degenerated source inductor is used for input impedance matching as at the resonant frequency are acted like series resonant circuit. Another transistor is present in current mirror formation with the CS stage transistor in cascode configuration. The load of cascode architecture is LC circuit which is used to achieve output impedance matching. Cadence spectre RF is used for simulation of the LNA circuit. The input return loss, reverse isolation, power gain, NF and IIP3 are -9.9 dB, -35.68 dB, 30.942 dB, 0.533 dB and 2.9140 dB respectively. The circuit uses a supply of 1.5 V and dissipates a power of 8.7 mW [27].

|                      | [20] | [21]  | [22] | [23] | [24] | [25]     | [26] | [27]   |

|----------------------|------|-------|------|------|------|----------|------|--------|

| Technology<br>(µm)   | 0.6  | 0.35  | 0.35 | 0.6  | 0.25 | 0.18     | 0.13 | 90 nm  |

| Supply (V)           | 1.5  | 1.5   | 2.8  | 1.8  | 3    | 1        | 1    | -      |

| S <sub>21</sub> (dB) | 22   | 17    | 26   | 19   | 22   | 28.7     | 12.9 | 30.942 |

| NF (dB)              | 3.5  | 3.8   | 3.6  | 2    | -5.6 | 2        | 0.55 | 0.533  |

| IIP3 (dBm)           | -9.3 | -6.17 | -3   | 10   | -    | -16.0599 | -    | 2.9    |

TABLE 3.3 COMPARISON OF LNA AT 1.5 GHZ

#### 3.1.4 1.8 GHz/ Direct Conversion Radio Receiver

A 1.8 GHz LNA for direct conversion radio receiver, that can drive a capacitive input mixer, has been designed in the paper [28]. In the front-end subsampling, aliasing problem is reduced by limiting LNA noise band with output resonator and integrated passive component's extracted models is used for optimizing the resonator, including on chip coupling capacitor to overcome the problem of second order non-linarites in down conversion of direct conversion receiver. Also, to optimize system noise figure output resonator is used, by limiting input noise bandwidth of mixer. The LNA uses cascaded input and inductive degeneration topology. A high quality factor of 4 is used in designing of circuit, else small change in component value will increase the NF significantly. A 0.5 µm CMOS technology is used to design LNA. DC coupling which has low sensitivity to parasitic effect is realized with an on chip structure as is an essential function of direct conversion. A gain of 17 dB, S<sub>11</sub> of -11 dB, IIP3 of +9 dBm and NF of 3.4 dB is obtained while consuming a power of 48mW from a 3 V supply. Therefore, a method to implement modern integrated receiver having CMOS LNA in GHz range using capacitor inputs instead of 50  $\Omega$  resistor matching is designed.

A two stage LNA is designed in [29] which is based on LC resonance that uses spiral inductor on chip. The LNA uses differential structure so that even order distortion gets eliminated and also uses common mode inductive coupling because it is desired for direct conversion receivers. The common mode inductive coupling can be assumed as the extension of CS topology with a spiral inductors present on chip for applications in narrowband frequency and current source for biasing. The cascode structure is also used. The inductive load are used instead of resistive load and is of 7 nH having a quality factor of 4.5. Positive feedback circuit is also present to generate negative resistance which cancels out the series resistance present in the inductive load. A 0.8  $\mu$ m with two poly and two metal CMOS process is used for designing of the LNA. The LNA exhibit a power gain of 18 dB, NF of 2.1 dB and IIP3 of -5 dBm wile dissipating a power of 48 mW from 3 V supply.

A LNA working at 1.8 GHz, using double poly triple metal 0.35  $\mu$ m CMOS technology is designed and is presented in [30]. The LNA circuit uses a two stage

cascaded configuration to provide good gain and isolation between input port and output port simultaneously. In the stage 1, CS inductive degeneration topology is used to match input impedance to 50  $\Omega$  followed by stage 2 which is a buffer stage present to match output to 50  $\Omega$ . The LNA layout occupies an area of 1025 x 1345  $\mu$ m<sup>2</sup>. The S-parameter is measured using HP 8719ES network analyzer and a resultant S<sub>11</sub> parameter value is -8.4 dB, S<sub>12</sub> is -41.7 dB, S<sub>21</sub> is 10.5 dB and S<sub>22</sub> is -6.6 dB. A NF of 4 dB and IIP3 of -2.4 dB is also observed. The circuit is operated using 2.5 V supply dissipates a power of 40 mW.

A two stage architecture LNA circuit having input stage as the first stage uses CG amplifier so as to achieve lower NF and uses CS stage as the second stage so as to achieve high gain along with good reverse isolation is designed in [31]. A capacitor present for dc blocking and an inductor is present between CG and CS amplifiers to provide biasing network to CS amplifier and for matching AC power so as to achieve maximum power transfer. Therefore, the capacitor and the inductor act as interstage matching network. Spectre RF is used for the simulation of the LNA. The resultant input reflection coefficient value is -6.4 dB, output reflection coefficient is -31.8 dB, power gain is 17.4 dB, reverse isolation of -66 dB, NF is 1.07 dB and IIP3 is -9 dBm while OIP3 is 8.1 dBm. The LNA circuit is designed using 0.35  $\mu$ m CMOS process and a power supply of 1.2 V.

|                      | [28] | [29] | [30] | [31] |

|----------------------|------|------|------|------|

| Technology (µm)      | 0.5  | 0.8  | 0.35 | 0.35 |

| Supply (V)           | 3    | 3    | 1.8  | 1.2  |

| S <sub>21</sub> (dB) | 17   | 18   | 10.5 | 17.4 |

| NF (dB)              | 3.4  | 2.1  | 4    | 1.07 |

| IIP3 (dBm)           | 9    | -5   | -2.4 | -9   |

TABLE 3.4 COMPARISON OF LNA AT 1.8 GHz

#### 3.1.5 1.9 GHz/GSM

A spiral inductor of high quality has been employed in the paper [32] having 8.5-12.5 quality factor along with optimized active device layout and bias condition. The LNA is a two-stage amplifier, CS with inductive source degeneration is present in the stage-1so as to match noise and power gain. For high linearity and gain, the second stage's bias condition is chosen. A 0.8  $\mu$ m CMOS technology LNA, fabricated on high resistivity Si substrate. Using on-wafer RF probes and HP8510C Network Analyzer measurements are carried out and a chip area of 0.93x0.93 mm2 is occupied. Linear simulator is used to simulate the LNA and ATN setup is used to measure noise parameters for 0.3-3 GHz, giving a NF of 2.8 dB at 1.9 GHz. Also, a gain of 15 dB, input reflection coefficient of -16.4 dB and output reflection

coefficient of -7 dB is observed at 1.9GHz, while consuming 15 mA from 3.6 V supply.

A quantitative analysis of LNA in cascode configuration is done in [33] in 0.35  $\mu$ m CMOS process. A single stage LNA having two transistor namely M1 and M2 is present in cascode. Degenerated inductor is present at the source of M1 and also input is applied to the gate of M1. The cascode structure is present to achieve input impedance matching and to avoid thermal noise. The noise performance of the LNA is dominated by the first MOSFET transistor i.e. M1 while the more linarites are contributed by second MOSFET transistor i.e. M2. So, using 0.35  $\mu$ m CMOS process the M1 is designed such that it gives optimum noise performance and M2 is designed to optimize linearity. The simulation of 1.9 GHz LNA is conducted in Agilent Advanced Design System (ADS) giving a minimum NF of 1.6 dB, gain of 17.5 dB, OIP3 of 10.7 dBm using a supply of 1.5 V and dissipating a power of 9 mW. Therefore, from both theoretical analysis and simulation results it is shown that the noise performance is dominated by the first MOSFET for the LNA in cascode configuration.

A 1.9 GHz LNA has been designed in [34] using 0.35  $\mu$ m CMOS technology. In the two stage LNA design, the first stage is in cascode configuration and LC tank circuit is present as the load of the cascode architecture so as to tune to 1.9 GHz. Moreover, another inductor is present at the source of the first transistor. This stage is followed by an output stage consisting of one transistor, also having LC circuit as load. Also, a current mirror is formed with before the cascode stage with first transistor of cascode stage. Inductors are placed on chip if have value lesser than 10 nH while are placed off chip if the inductor have value greater than 10 nH. For TSMC CMOS 0.35  $\mu$ m, BSIM3 transisitor model is used. The circuit is simulated using HSPICE and Cadence giving a gain of 21 dB, NF of 1.4 dB at 1.9 GHz and OIP3 of -14dBm, input reflection coefficient of -35dBm and output reflection of - 32dBm. A supply of 1.5 V is used and power dissipated is 6.5 mW. A die of active area 5 10  $\mu$ m x 250  $\mu$ m is also formed.

|                      | [32] | [33] | [34] |

|----------------------|------|------|------|

| Technology (µm)      | 0.8  | 0.35 | 0.35 |

| Supply (V)           | 3.6  | 1.5  | 1.5  |

| S <sub>21</sub> (dB) | 15   | 17.5 | 21   |

| NF (dB)              | 2.8  | 1.6  | 1.4  |

| OIP3 (dBm)           | -    | 10.7 | -14  |

#### 3.1.6 2 GHz

A 2 GHz LNA has been designed using 0.6 µm CMOS process in [35]. The LNA circuit design is based on two stage cascode topology which is narrowband LC tuned. The first stage uses CS cascode inductive degeneration topology followed by CS configuration which has LC network as load because in wireless communications RF signals are narrowband usually. The cascode architecture is used to improve reverse isolation and also to provide forward gain. The circuit uses 3.3 V supply. A NF of 2.3 dB, gain of 18 dB, reverse isolation of -44.79 dB and IIP3 of -4.94 dBm is observed as the simulation results. Also, power of 33.94 mW is dissipated.

A 0.35 µm CMOS LNA is designed in [36]. The LNA design is a two stage amplifier design, it uses conventional cascode topology. An inductor is present between the CS amplifier and CG amplifier in the cascode stage. So, inductor is used as the interstage matching network. The cascode stage is succeeded by a CS stage which along with resistors are used to bias the amplifiers in the cascode stage. The inductors used have quality factor around 5. The simulation of 2 GHz LNA using an interstage inductor is done in Agilent Advanced Design System (ADS). The simulated results are, NF of value 1.97 dB, gain of 13.7 dB. Dissipating a power of 7.5 mW from 1.5 V supply.

A 2 GHz LNA designed using 0.18  $\mu$ m CMOS process has been implemented in [37]. The LNA circuit has three parts, the first part uses CS inductively degenerated topology, the second part is realized using differential pair acting as a low pass filter and the last part is the biasing circuit formed by using pn junction of PMOS as it provides steady voltage because of the large width of the transistor. The circuit uses 1 V supply and is implemented using 0.18  $\mu$ m CMOS process. A LNA of size 175  $\mu$ m x 50  $\mu$ m is obtained. Moreover, the simulated results shows that the input reflection coefficient is -25 dB, gain is 11 dB, NF is 1.8 dB and IIP3 is 0 dBm.

A high linearity LNA circuit has been designed using 0.25  $\mu$ m CMOS technology in [38]. The LNA circuit utilizes inductively degenerated topology in balanced differential mode. A superior noise performance is obtained from inductively degenerated topology because of signal swing and hence is used. However, because of the signal swing the linearity is degraded. Thus, the linearity improvement technique is required. For differential signals two balun transformers are used. The LNA circuit uses a supply voltage of 2.5 V. At 2 GHz a maximum gain obtained is 15.2 dB, NF obtained is 2.8 dB and IIP3 obtained is 14.7 dBm and the maximum IIP3 of 16 dBm is obtained at 2.2 GHz. The size of the fabricated chip is 900  $\mu$ m x 900  $\mu$ m.

|                 | [35]  | [36] | [37] | [38] |

|-----------------|-------|------|------|------|

| Technology (µm) | 0.6   | 0.35 | 0.18 | 0.25 |

| Supply (V)      | 3.3   | 1.5  | 1    | 2.5  |

| S21 (dB)        | 18    | 13.7 | 11   | 15.2 |

| NF (dB)         | 2.3   | 1.97 | 1.8  | 2.8  |

| IIP3 (dBm)      | -4.94 | -    | 0    | 16   |

TABLE 3.6 COMPARISON OF LNA AT 2 GHZ

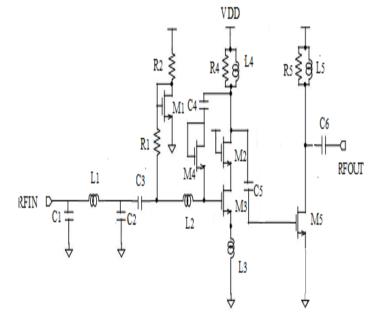

#### 3.1.7 2.4 GHz/Wireless Sensor Network/Bluetooth

A two stage 2.4 GHz LNA is presented in the paper [39][40]. The first stage has transistors in cascode configuration with resistor in parallel to capacitor as load. Here, resistor is present to set bias circuitry current to generate bias voltage at gate of first transistor in second stage; in second stage transistors are present in cascode having matching inductor between the stage such that the transistors in cascode are considered as different individual stage. So, the inter stage inductor is added between CS and CG stage. Inductor is added to increase the gain and decrease the noise of the system. The capacitor is used to provide AC ground at the gate of second transistor in second stage. A LNA using 0.5  $\mu$ m CMOS technology is designed using a 3 V supply. A power gain of 19 dB, NF of 2.4 dB and input reflection coefficient of -10 dB is observed while drawing a current of 3mA.

A 2.4 GHz two stage cascade topology LNA using 0.35  $\mu$ m CMOS process has been proposed in the paper [41]. The LNA using cascade topology uses series interstage resonance. So, it is a current sharing amplifier. Here, the two common source amplifiers are not cascaded directly but an inductor in series resonance with capacitor is present. The series resonance provides low impedance at the drain of the first transistor in the cascade stage so that common source stage of the first transistor does not experience Miller effect. A supply of 2 V is and a power gain of 21 dB along with NF of 1.24 dB has been observed. A current of 2.5 mA is drawn by the circuit.

Two CMOS LNA has been designed in the paper [42] one is single ended LNA while the other is differential LNA and fully integrated without off chip components. In the single ended LNA cascode topology is used and a degenerative inductor is also present at the source of the first amplifier in cascode architecture. Here, the input matching is obtained by the two inductor present at the gate of first amplifier present in cascode topology while the output matching is obtained by tuning of the load inductor and output capacitor. The simulation results of single ended LNA is input reflection coefficient of -17 dB, reverse isolation of -24 dB, gain of 15 dB, output reflection coefficient of -23 dB, NF of 2.2 dB. Also, a power dissipation of 4.8 mW is obtained from 3.3 V supply. In the differential LNA

architecture, the single ended LNA architecture is present in differential form. The differential LNA architecture is studied because the single ended LNA architecture is sensitive to ground parasitic inductance while the differential LNA is not affected by the common mode interference. The simulation results of differential LNA is input reflection coefficient of -19 dB, reverse isolation of -35 dB, gain of 20 dB, output reflection coefficient of -21 dB, NF of 2.4 dB. A power of 7.2 mW is dissipated from 3.3 V supply. The layout is designed using 0.25  $\mu$ m CMOS process and the layout area of single ended LNA is 2.05 mm x 1.28 mm while the layout area of differential LNA is 1.62 mm x 1.28 mm, which is smaller than the single ended LNA.

The LNA designed using  $0.35 \ \mu m$  CMOS uses the conventional cascode LNA topology with degenerated inductor in differential form [43]. Since, the mismatch occurs at CS and CG amplifier present in cascode topology the spiral inductor is present between the amplifiers in the cascode stage so as to improve the matching. At the output two source follower namely (M6 and M7) transistor along with a resistor form a current source and also, current mirror is formed by another transistor (M5) with M6. The LNA circuit is simulated for 2.4GHz and using a supply of 2 V. A power gain of 19.9 dB, reverse isolation of -47.8 dB, NF of 2.5 dB and IIP3 of 2 dBm is obtained with a power dissipation of 14.7 mW.

A 2.4 GHz fully differential LNA is proposed in [44]. The LNA circuit core has a cascode design so as to remove the Miller effect and improve the reverse isolation. The linearity of the LNA is required such that if the user is close to the transmitter the linearity from minimum detectable signal to -12 dBm is achieved. However, the LNA is able to meet these specifications but the signals overdrive the subsequent stage. So, to overcome this problem the LNA in this paper is designed to have a low gain so that it could suppress input signals that have large level to desired level. Moreover, so that linearity is improved and current is reduced. A network of NMOS devices are used which acts as bypass switches along with cascode architecture to implement low gain stage and to avoid feedback that causes unstable condition. A 0.25 µm CMOS process is used to design the LNA architecture. NF, gain, input return loss, output return loss, reverse isolation and IIP3 observed are 2.88 dB, 14.7 dB, >7 dB, >10 dB, >25 dB and -1.5 dBm respectively for a high gain mode whereas for low gain or for bypass mode the NF, gain, input return loss, output return loss, reverse isolation and IIP3 observed are 14.2 dB, -14.2 dB, >9 dB, >10 dB, 14.2 dB and 19 dBm. A current of 11.4 mA is consumed in high gain mode while no current is consumed in low gain mode.

A conventional cascode LNA with degenerated inductor is used in the LNA circuit to be operated at 2.4 GHz [45][46]. The circuit also contains additional capacitor in parallel to the gate capacitor of the CS amplifier present in cascode topology so that low power is dissipated and noise performance is optimized. An additional interstage inductor is present between CS and CG stage so that matching is improved and also gain is increased. This circuit is implemented using TSMC 0.18  $\mu$ m CMOS process. 1.2 V power supply is used in the circuit and power dissipation

of 2.4 mW is observed. Also,  $S_{11} = -22.4 \text{ dB}$ ,  $S_{12} = -48.9 \text{ dB}$ ,  $S_{21} = 12.9 \text{ dB}$ ,  $S_{22} = -21.6 \text{ dB}$  and a NF of 0.76 dB is observed.

A two stage LNA using 0.18  $\mu$ m CMOS process has been designed in the paper [47]. The first stage is in CS inductively degenerated cascode configuration followed by second stage which is source follower. In the first stage the input transistor is the main noise contributor while the second transistor contributes to the linearity more than first transistor or input transistor. The circuit uses a supply of 1 V and dissipates a power of 13 mW. The S<sub>11</sub> obtained is -16.8 dB, S<sub>12</sub> obtained is -51.7 dB, S<sub>21</sub> obtained is 23 dB, S<sub>22</sub> obtained is -10.2 dB, NF obtained is 3.8 dB and IIP30btained is -9.1 dBm.

A LNA operated at 2.4 GHz, with improved matching has been proposed in the paper [48]. The LNA circuit utilizes conventional cascode topology with degenerated inductor at the input. Here, to improve the input matching a capacitor is placed at the gate of the first MOS device present in cascode topology. The circuit is implemented using 0.18  $\mu$ m CMOS process. The value of the degenerated inductor is 0.17 nH if capacitor is not present i.e. the circuit is not improved while the value of inductor reduces to 0.5 nH is the circuit is improved. The gain and NF of the circuit with traditional input stage is 24 dB and 0.24 dB while of the modified circuit is 21 dB and 0.39 dB.