#### **A DISSERTATION**

on

# VOLTAGE DIFFERENCING TRANSCONDUCTANCE AMPLIFIER (VDTA) AND ITS APPLICATIONS

Submitted in partial fulfillment of the requirement for the award of Degree of

#### MASTER OF TECHNOLOGY

in

#### **VLSI Design and Embedded Systems**

Submitted by

**Dhruv Pratap Singh**

(Roll No.: 2K15/VLS/05)

**Under the esteemed Guidance of:**

Mr. A. K Singh

**Associate Professor**

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSI TY

(Formerly Delhi College of Engineering)

(Govt. of National Capital Territory of Delhi)

Bawana Road, Delhi – 110042

(2015-2017)

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

**DELHI TECHNOLOGICAL UNIVERSITY**

(Govt. of National Capital Territory of Delhi)

BAWANA ROAD, DELHI – 110042

Date: .....

**CERTIFICATE**

This is to certify that the dissertation titled "Voltage Differencing Transconductance

Amplifier (VDTA) and its Applications" has been completed by me, submitted in partial

fulfillment of the requirement for the award of degree of Master of Technology in VLSI

**Design and Embedded Systems**. Further it is declared that the work done in this thesis has

not been published/submitted earlier in any conference, publication or in any institution and

is my own original and authentic work.

**Name: Dhruv Pratap Singh**

**Roll No. 2K15/VLS/05**

M.Tech.: VLSI Design and Embedded Systems

This is a record of his own work carried out by him under my supervision and support. He

has completed his dissertation work with utmost sincerity and diligence.

(Mr. A. K Singh) **Associate Professor** (Project Guide)

Deptt. of ECE, DTU.

ii

**ACKNOWLEDGEMENT**

I express my deepest gratitude to my project guide Mr. A. K Singh, Associate Professor,

Department of Electronics and Communication Engineering, Delhi Technological University,

Delhi, whose encouragement, guidance and support from the initial to the final level enabled

me to develop an understanding of the research work. His suggestions and ways of

summarizing the things made me to go for independent studying and trying my best to get the

maximum for my project, this made my circle of knowledge very vast. I am highly thankful

to him for guiding me in this project.

I also express my profound sense of gratitude to Dr. S. Indu (H.O.D., ECE), for giving

encouragement and opportunity to complete my project smoothly.

I also express my thanks to all staff of VLSI laboratory to provide me all facilities to

complete this research.

2K15/VLS/05

(Dhruv Pratap Singh)

M.Tech.: VLSI Design and Embedded Systems

(2015-2017)

iii

#### **ABSTRACT**

Analog VLSI is playing an important part in technology now a days. A vast range of circuits (Amplifers, Filters, Comparators, Oscillators, Multipliers, PLL, Voltage/Current References, Sample-And-Hold Circuits, A/D and D/A Converters, High speed IO Interface etc.) are being introduced now a days for new applications for the purpose of information processing like speech recognition, integrated sensors, handwriting recognition, image processing etc.

In this report an Analog Building Block, Voltage Differencing Transconductance Amplifier (VDTA). The realization of which is given in 2011 is simulated using TSMC 0.18 µm CMOS Technology process parameters. VDTA has two different values of transconductances which eliminate the need of external resistors for most of the applications based on VDTA. Also, the application of VDTA as filter, parallel R-L impedance, controller and oscillator has been simulated and presented in this report.

Submitted by: Dhruv Pratap Singh

(2K15/VLS/05)

## TABLE OF CONTENTS

| 1. Introduction                  | 1  |

|----------------------------------|----|

| 1.1 Voltage Mode Circuits        | 1  |

| 1.2 Current Mode Circuits        | 2  |

| 1.3 Analog Building Blocks       | 4  |

| References                       | 5  |

| 2. Literature Review             | 6  |

| References                       | 9  |

| 3. VDTA                          | 11 |

| 3.1 Introduction                 | 11 |

| 3.2 Description of Circuit       | 11 |

| 3.3 Simulation Results           | 16 |

| References                       | 19 |

| 4. Filters using VDTA            | 21 |

| 4.1 Introduction                 | 21 |

| 4.2 VDTA based Filter Topologies | 22 |

| 4.2.1 Topology A                 | 23 |

| Simulation Results               | 24 |

| 4.2.2 Topology B                 | 28 |

| Simulation Results               | 30 |

| 4.2.3 Topology C                 | 33 |

| Simulation Results               | 35 |

| 4.2.4 Topology D                 | 39 |

| Simulation Results               | 41 |

| 4.2.5 Topology E                 | 46 |

| Simulation Results               | 48 |

| 4.2.6 Topology F                     | 52 |

|--------------------------------------|----|

| Simulation Results                   | 54 |

| 4.2.7 Topology G                     | 58 |

| Simulation Results                   | 60 |

| References                           | 65 |

| 5. Oscillator using VDTA             | 66 |

| 5.1 Introduction                     | 66 |

| 5.2 Topology A                       | 68 |

| Simulation Results                   | 69 |

| References                           | 73 |

| 6. Parallel R-L Impedance using VDTA | 74 |

| 6.1 Introduction                     | 74 |

| 6.2 Parallel R-L Impedance           | 74 |

| Simulation Results                   | 76 |

| References                           | 80 |

| 7. Conclusion                        | 81 |

| Appendix A                           | 82 |

| Appendix B                           | 84 |

## LIST OF FIGURES

| Figure 1: Circuit symbol of VDTA                                                          | 12 |

|-------------------------------------------------------------------------------------------|----|

| Figure 2: CMOS implementation of VDTA                                                     | 14 |

| Figure 3: CMOS implementation of VDTA showing current mirrors in place of current sources | 14 |

| Figure 4 : Implementation of VDTA using OTA                                               | 15 |

| Figure 5 : PSPICE circuit diagram of VDTA to plot DC characteristics                      | 17 |

| Figure 6: DC characterstics of VDTA                                                       | 17 |

| Figure 7 : PSPICE circuit diagram of VDTA to plot AC characteristics                      | 18 |

| Figure 8 : AC characteristics of VDTA                                                     | 18 |

| Figure 9 : Biquad Filter (Topology A)                                                     | 23 |

| Figure 10 : PSPICE circuit diagram of Topology A (V1 = Vin and V2 = 0)                    | 25 |

| Figure 11 : Gain-Frequency response of Voltage mode Band Pass Signal                      | 26 |

| Figure 12 : Gain-Frequency response of Voltage mode Low Pass Signal                       | 26 |

| Figure 13 : PSPICE circuit diagram of Topology A (V1 = 0 and V2 = Vin)                    | 27 |

| Figure 14 : Gain-Frequency response of Voltage mode High Pass Signal                      | 27 |

| Figure 15 : Gain-Frequency response of Voltage mode Band Pass Signal                      | 28 |

| Figure 16 : Current mode Biquad Filter (Topology B)                                       | 29 |

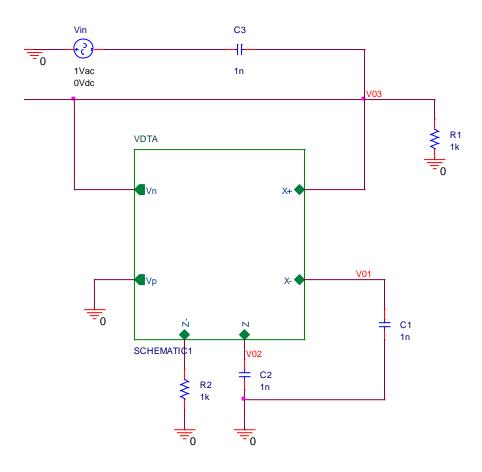

| Figure 17 : PSPICE circuit diagram of Topology B                                          | 31 |

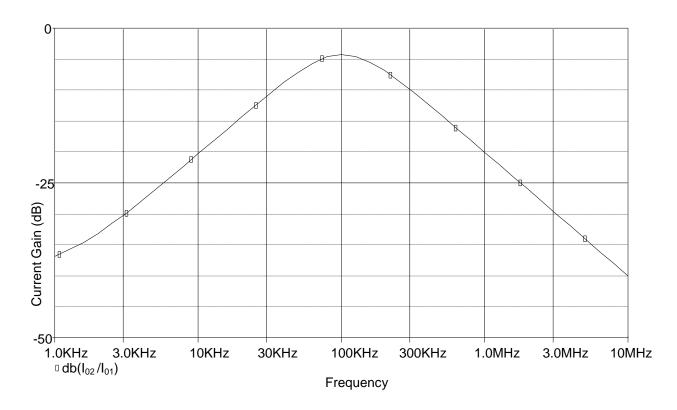

| Figure 18 : Simulated Band Pass response for filter of Topology B                         | 31 |

| Figure 19 : Simulated High Pass Response for filter of Topology B                         | 32 |

| Figure 20 : Simulated Low Pass Response for filter of Topology B                          | 32 |

| Figure 21 : Current Mode Biquad Filter (Topology C)                       | 33 |

|---------------------------------------------------------------------------|----|

| Figure 22 : PSPICE circuit diagram of Topology C                          | 36 |

| Figure 23 : Simulated Low Pass response of filter of Topology C           | 36 |

| Figure 24 : Simulated Band Pass response of filter of Topology C          | 37 |

| Figure 25 : Simulated High Pass response of Topology C                    | 37 |

| Figure 26 : Simulated Notch response of filter of Topology C              | 38 |

| Figure 27 : Simulated All Pass magnitude response of filter of Topology C | 38 |

| Figure 28 : Simulated All Pass phase response of filter of Topology C     | 39 |

| Figure 29 : Current Mode Universal Filter (Topology D)                    | 40 |

| Figure 30 : PSPICE circuit diagram of Topology D (case 1)                 | 43 |

| Figure 31 : Simulated Low Pass response of Topology D                     | 43 |

| Figure 32 : Simulated Band Pass response of Topology D                    | 44 |

| Figure 33 : Simulated High Pass response of Topology D                    | 44 |

| Figure 34 : Simulated Band Stop response of Topology D                    | 45 |

| Figure 35 : Simulated All Pass response of Topology D                     | 45 |

| Figure 36 : Voltage Mode Universal Biquad filter (Topology E)             | 46 |

| Figure 37 : PSPICE circuit diagram of Topology E (case 1)                 | 49 |

| Figure 38 : Simulated Low Pass response of Topology E                     | 49 |

| Figure 39 : Simulated Band Pass response of Topology E                    | 50 |

| Figure 40 : Simulated High Pass response of Topology E                    | 50 |

| Figure 41 : Simulated Band Stop response of Topology E                    | 51 |

| Figure 42 : Simulated All Pass response of Topology E                     | 51 |

| Figure 43 : Current Mode Universal filter (Topology F)                    | 52 |

| Figure 44 : PSPICE circuit diagram of Topology F                       | 55 |

|------------------------------------------------------------------------|----|

| Figure 45 : Simulated Low Pass response of Topology F                  | 55 |

| Figure 46 : Simulated Band Pass response of Topology F                 | 56 |

| Figure 47 : Simulated High Pass response of Topology F                 | 56 |

| Figure 48 : Simulated High Pass response of Topology F                 | 57 |

| Figure 49 : Simulated All Pass response of Topology F                  | 57 |

| Figure 50 : Dual Mode Biquadratic filter (Topology G)                  | 58 |

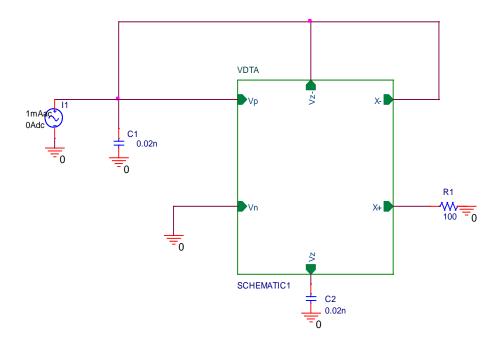

| Figure 51: PSPICE circuit diagram of Topology G for the current mode   | 61 |

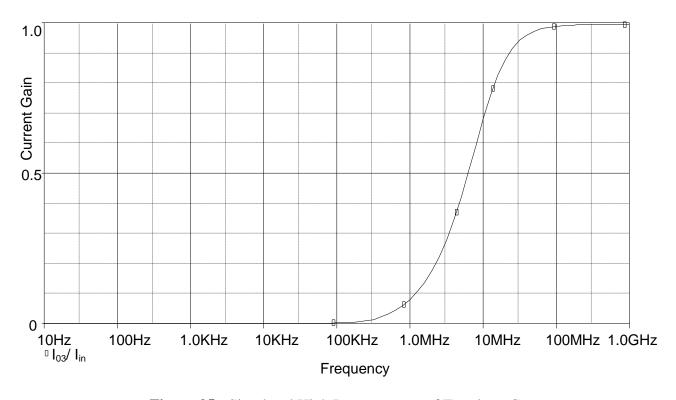

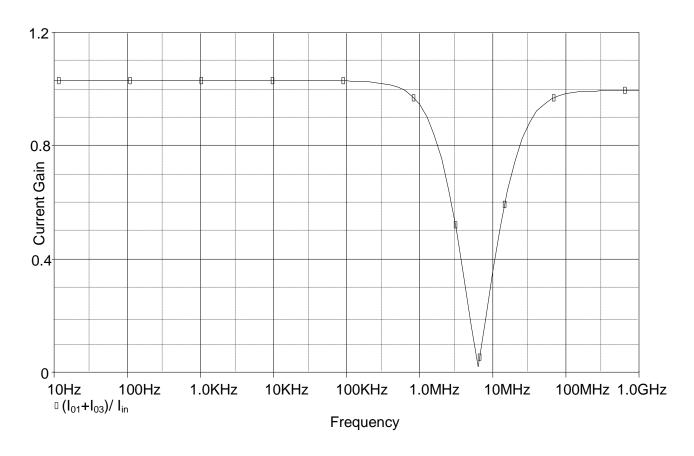

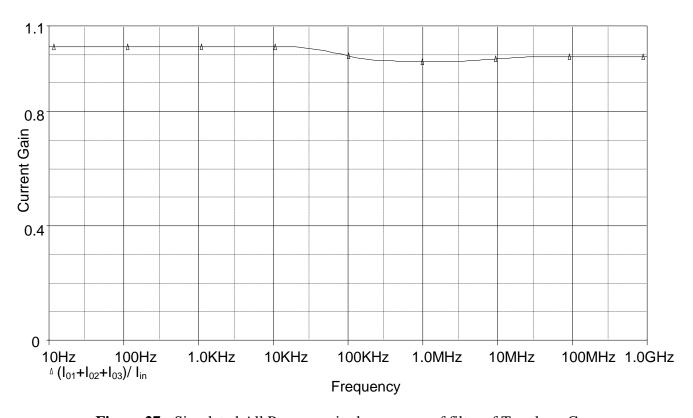

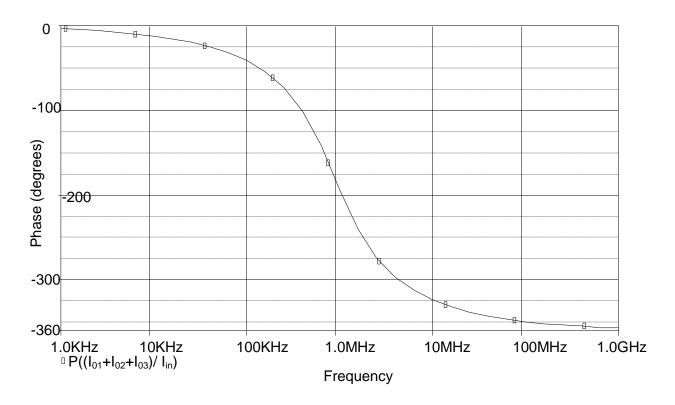

| Figure 52 : Simulated Low Pass response of Topology G in current mode  | 61 |

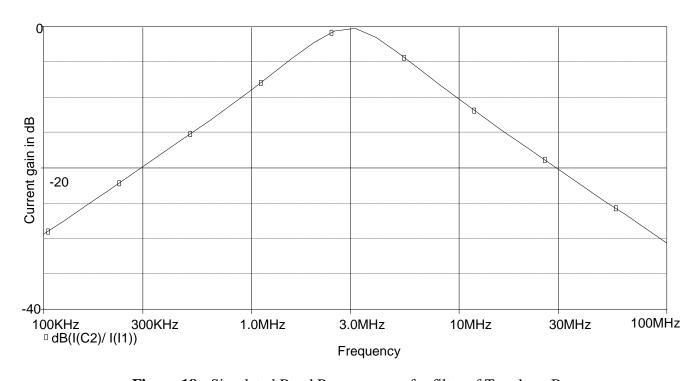

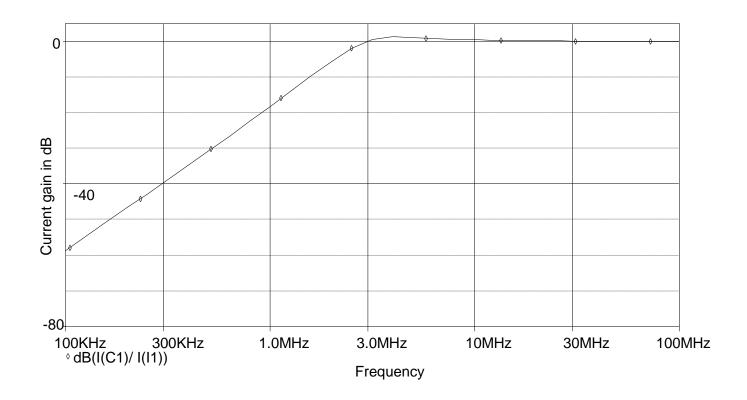

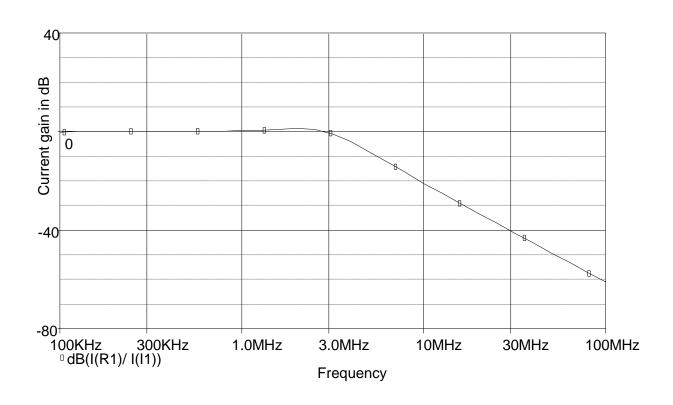

| Figure 53 : Simulated Band Pass response of Topology G in current mode | 62 |

| Figure 54 : Simulated High Pass response of Topology G in current mode | 62 |

| Figure 55 : PSPICE circuit diagram of Topology G for the Voltage mode  | 63 |

| Figure 56 : Simulated Low Pass response of Topology G in voltage mode  | 63 |

| Figure 57 : Simulated Band Pass response of Topology G in voltage mode | 64 |

| Figure 58 : Simulated High Pass response of Topology G in voltage mode | 64 |

| Figure 59 : Basic structure of an oscillator                           | 67 |

| Figure 60 : Current mode third order quadrature oscillator             | 69 |

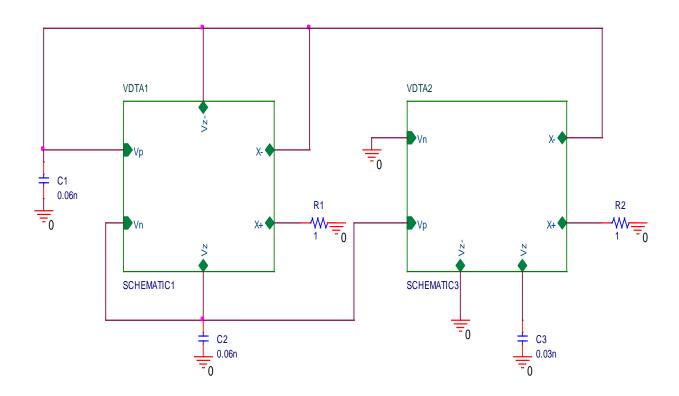

| Figure 61 : PSPICE circuit diagram of the Topology A                   | 70 |

| Figure 62: Transient Response of Topology A (rising output)            | 71 |

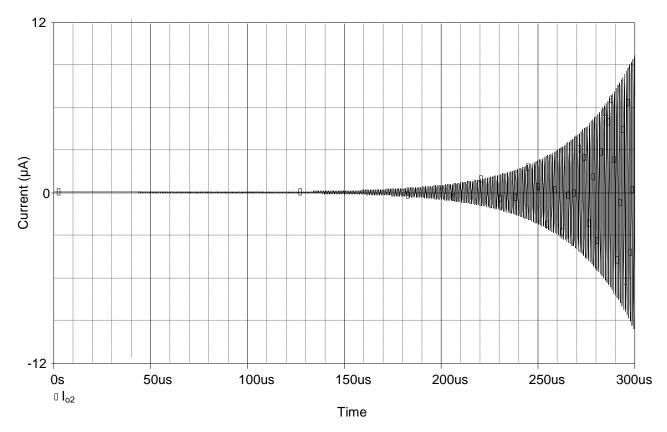

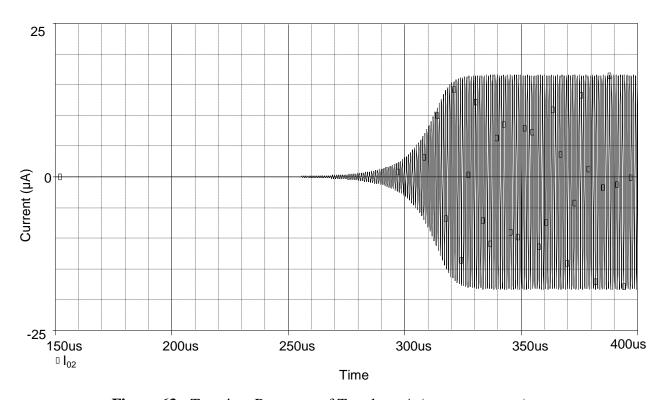

| Figure 63: Transient Response of Topology A (constant output)          | 71 |

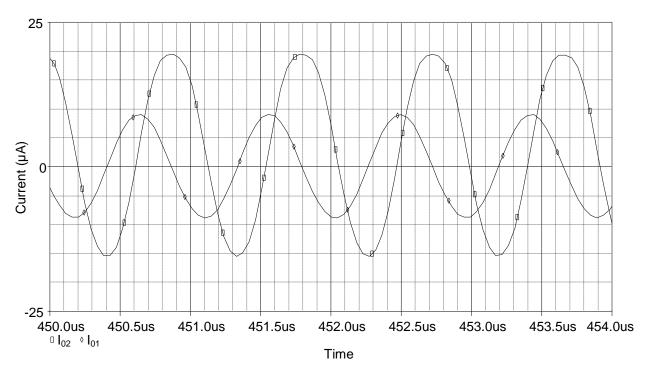

| Figure 64: Quadrature current output waveforms                         | 72 |

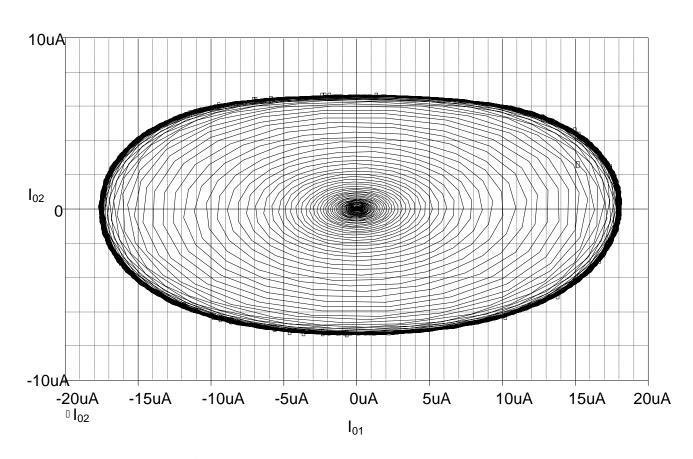

| Figure 65 : Lissagous Figure for Topology A                            | 72 |

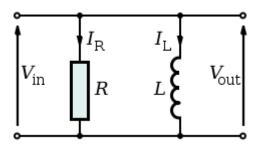

| Figure 66 : Parallel R-L Impedance                                     | 74 |

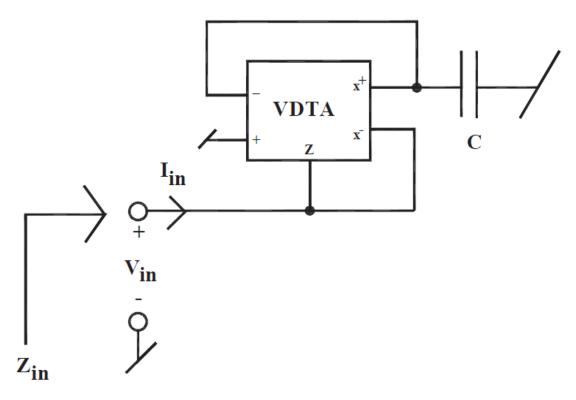

| Figure 67: Parallel R-L Impedance Configuration using VDTA              | 75 |

|-------------------------------------------------------------------------|----|

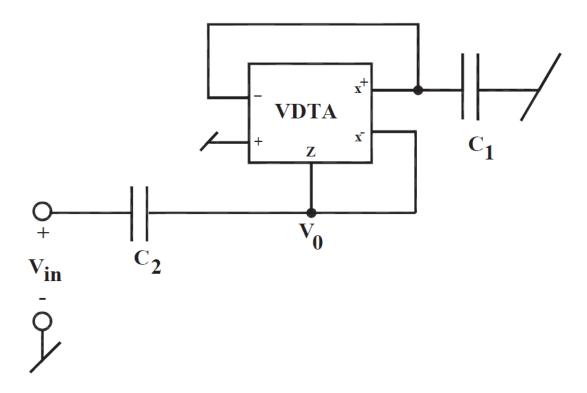

| Figure 68: High Pass Filter using Parallel R-L Impedance                | 76 |

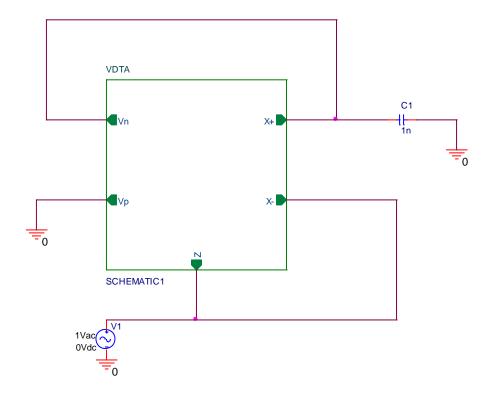

| Figure 69 : PSPICE circuit diagram of R-L Impedance                     | 77 |

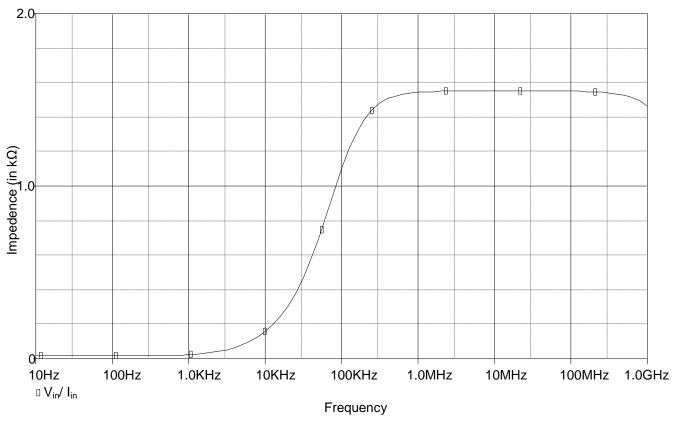

| Figure 70 : Variation of Impedance with frequency for R-L Circuit       | 78 |

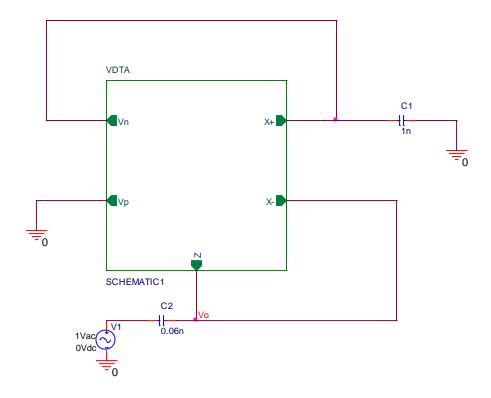

| Figure 71 : PSPICE circuit diagram High Pass Filter using R-L Impedance | 78 |

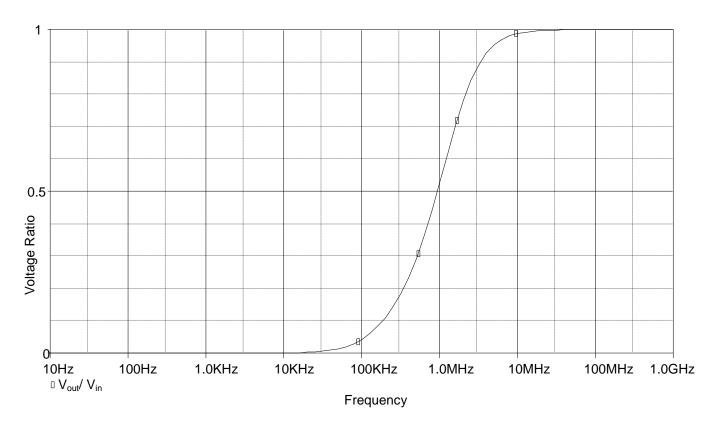

| Figure 72: Frequency Response of High Pass Filter using R-L Impedance   | 79 |

## LIST OF TABLES

| Table 1 : Aspect ratios of Transistors for VDTA (0.18 μm)                       | 16 |

|---------------------------------------------------------------------------------|----|

| Table 2 : Aspect ratios of Transistors for VDTA structure of Figure 3 (0.35 μm) | 30 |

|                                                                                 |    |

#### LIST OF ABBREVIATIONS

AC**Alternating Current BOCCII** Balanced Output Current Conveyor Second Generation CCI First Generation Current Conveyor **CCII** Second Generation Current Conveyor **CCIII** Third Generation Current Conveyor **CCTA** Curent Conveyor Transconductance Amplifier **CDTA** Current Differencing Transconductance Amplifier **CMOS** Complementary Metal Oxide Semiconductor **CTTA Current Through Transconductance Amplifier** dB Decibel **DCCII** Differential Current Conveyor Second Generation **DDCC** Differential Difference Current Conveyor **DDCCTA** Differential Difference Current Conveyor Transconductance Amplifier **DOICCII** Dual Output Inverting Current Conveyor Second Generation Dual X Current Conveyor Second Generation **DXCCII FDCCII** Fully Differential Current Conveyor Second Generation Fully Differential Operational Amplifier FD Op-Amp Fully Differential Operational Feedback Amplifier FD OFA FD OTA Fully Differential Operational Transconductance Amplifier FD OTRA Fully Differential Operational Transresistance Amplifier FDVCCII-Fully Differential Voltage Second Generation Inverting Current Conveyor IC **Integrated Circuit** MHz Mega Hertz **MOCCCA** Current Controlled Current Amplifier with Multi Outputs

**MOCCI** Multiple Output First Generation Current Conveyor **MOCCII** Multiple Output Second Generation Current Conveyor **MOCCIII** Multiple Output Third Generation Current Conveyor N- Channel Metal Oxide Semiconductor **NMOS OFA** Operational Feedback Amplifier **OFCC Operational Floating Current Conveyor OPAMP** Operational Amplifier OTA Operational Transconductance Amplifier **OTRA** Operational Transresistance Amplifier **PMOS** P- Channel Metal Oxide Semiconductor **PSPICE** Personal Simulated Program with Integrated Circuit Emphasis QO Quadrature Oscillator **VDTA** Voltage Differencing Transconductance Amplifier

#### **CHAPTER 1**

## **INTRODUCTION**

Analog circuit design is one of the important areas of the present day research and development. For designing an analog circuit two modes are commonly used which are current mode and voltage mode. In the case of voltage mode circuits, the state variables used in the equation that is used to define the circuit is always a voltage. Thus, it can be said that signal states of a voltage mode circuit is determined completely and without any ambiguity by its node voltage. In a similar way, currents are used as state variables in case of current mode circuits. Thus, it can again be said that signal state of a current mode circuit is determined completely without any ambiguity using its branch currents. Theoretically, it is said that voltage mode and current mode circuits are dual of each other [1]. So realising a function in voltage mode or current mode is almost the same thing. Due to certain constraints it may not be possible to fulfil every practical requirement. Thus using a single topology for designing all applications is not possible. Further, high performance supplies are designed using the voltage mode designs. Later in this chapter both the advantage and disadvantage of current and voltage mode designs are discussed. These can be used to find a topology, either voltage or current or mixed topology to satisfy the requirements of the design in the best possible way.

#### 1.1 VOLTAGE MODE CIRCUITS

Earlier all the circuits used voltage mode topology or only the voltage signals were used for the processing purposes. For the ease of understanding of the voltage mode circuits let us take the case of voltage power supply. Voltage power supply is required to maintain a constant output voltage irrespective of load current that is allowed to vary from zero to full rated current of the supply, which means the concern here is the voltage of the output terminals not the current. It is quite clear that in practical scenario, no circuit operates in ideal fashion. For this operation of supplying constant output voltage switched capacitor circuits and charge coupled devices are used whose performance are quite close to the required one. From the basic definition of the voltage we can say that it is the ratio of energy and charge. Since the

energy needed for taking an electron out of the valence band to the conduction band and the charge of electron both are constant. Thus voltage has invariant value providing reliable voltage reference, for a given technology.

#### **ADVANTAGES:**

- O AC dynamic range in case of voltage mode circuits is determined by internal noise voltage which is generated by Noise currents. The WB NSD is dependent on device parameters and biasing. Total noise is dependent on the absolute frequency range and bandwidth [2].

- Measurement of voltage by different instruments and its accurate display can easily be done without creating any kind of disturbance for circuit elements. These circuits have a finite impedence but they can easily drive compatible circuits with only a very small effect on magnitude. That is the reason these circuits are of great importance both for digital circuit design and analog circuit design [2].

- These circuits provide a very good cross regulation and the reason for this quality is that these circuits offer low impedences at output terminals in case of supply with multiple output.

- Design and Analysis in case of these circuits is easier as these circuits use single feedback loop.

#### **DISADVANTAGES:**

When any kind of changes in the output are sensed, then for the sake of correction a feedback loop is used that result in slowing down of the circuit. The requirement of dominant pole or a zero is added to compensate for the filter output that results in addition of 2 poles in control loop. It also results in complication of compensation as the loop gain varies with the variation in the input.

#### 1.2 CURRENT MODE CIRCUITS

Historically the signal processing was dominated by voltage signals, but with development of submicron power technologies, there emerges the need of using low power voltage supply.

But meeting this requirement using voltage mode circuits poses the constraint of linearity and dynamic range as it becomes difficult at submicron technology to design a circuit with high linearity and dynamic range. To resolve this problem either we have to use CMOS technology having the low threshold voltage and also as another option we can opt for standard CMOS technology along with low voltage circuit techniques. These suggested methods are quite expensive, so current mode processing emerged over last few decades as an alternative design technique. The characterisation of current mode circuit is done by low terminal impedence, which makes these circuits suitable for fast response. With the use of current as a signal in current mode circuits we increase the output swing and hence making these circuits to be a better choice for using them under low supply voltage. Thus it can be said that for a fixed supply current mode circuit's dynamic range is larger than the voltage mode circuits. In terms of applications like addition/subtraction, these circuits provide a simplicity over voltage mode circuits as these operations in current mode can simply be performed by joining the terminals at a single point.

#### **ADVANTAGES:**

- One of the most significant benefits that the current mode design provides is wide Bandwidth.

- o Even at high frequencies the power requirement is low.

- o It allows us to shrink the feature size.

- o Speed is high.

- O Some applications may require current mode interfaces such as in power measurement system in fiber-optics, the input required from photodiode is current [2].

- Without components in the feedback path controlled gain can be achieved.

- Switching Noise is low and the dynamic range is large.

#### **DISADVANTAGES:**

- Distortion is high.

- Gain variation is high.

Thus, after looking at advantages and disadvantages of both the voltage mode and current mode circuits we can decide that which circuit is fulfilling our practical requirements to the best possible level and depending on that we can decide the mode to be used in our design.

#### 1.3 ANALOG BUILDING BLOCKS

The demand for analog building blocks is increasing because of advancements in technology which poses new practical requirements, hence motivating towards the development of new building blocks. Some of those blocks are named as follows.Op-Amp, OFA, OTA, OTRA, COA etc. are the operational amplifiers of different types and CCI, CCII, CCIII, DOCCI, DOCCII, DOCCIII are the current conveyors of different types and have been reported in [3]. VDTA, CDTA are again important active elements. The discussion regarding the behavioural models of FD Op-Amp, FD OFA, FD OTRA, FD OTA, FD OCA, FD OFC, DCCII, DXCCII, DDCC etc. is done in [4]. The representation of BOCCII, DOICCII, DDCC and FDCCII by nuller-floating mirror elements.

#### **REFERENCES**

- 1. Toumazou, C., Lidgey, F.J., Haigh, D., 'Analogue IC design: the current mode approach', Presbyterian Publishing Corp(1990)

- 2. Gilbert, B.: 'Current mode, Voltage mode or free mode? A few sage suggestions', Analog Integrated Circuits and Signal Processing. (Springer, 2004)

- 3. López, C.S., Fernández, F.V., Cuautle, E.T., Tan, S.X.D., 'Pathological Element-Based Active Device Models and their Application to Symbolic Analysis', *IEEE Transactions on Circuits and Systems-I*:2011, vol. 58, pp. 1382-1395.

- 4. López, C.S., 'Pathological Equivalents of Fully-Differential Active Devices fir Symbolic Nodal Analysis', *IEEE Transactions on Circuits and Systems-I*: 2013, vol. 60, pp. 603-615.

#### **CHAPTER 2**

## **LITERATURE REVIEW**

In the past few years, analog building blocks have been proved to be one of the most important circuit elements to be used. Since the modern analog building blocks are CMOS based structures, so they meet two most important requirements of present day circuits which are power consumption and limitation of space. CMOS structures reduce the power consumption to a large extent. Along with this they reduce the space utilised in designing the circuit as the passive elements can be implemented using the CMOS design only. Continuous developments are being made in the field of CMOS technology which further helps in achieving the present time motives i.e integration of as many circuit elements as possible on a single chip.

A lot of analog building blocks have been proposed, implemented and used in various applications till now. However this report deals with VDTA which was proposed by Yesil as shown in the literature [18]. This report also shows the simulation of some of its applications as filter, oscillator and parallel R-L inductance. Prior to the proposal of VDTA, a lot of active blocks have been proposed. A review of some of those along with the reference of the literature in which they were proposed is being given in this chapter.

Current Conveyor, which proved to be one of the most important active blocks introduced in [1] and it proved to be an important element especially in instrumentation applications [2], [3]. [1] introduces the current conveyor as the three port network and gives the circuit implementation for the same.

In [4], CCII is introduced. CCII has a different terminal relationship as compared to CCI as introduced in [1]. This also presents the way CCII can be used for the applications namely current amplifier, differentiator, integrator, summer and the weighted current summer. The text also says that if the current is taken as the variable for the computation in an analog signal computer, then current conveyor is going to prove to be a fundamental unit of such computer.

In continuation with [4], Fabre proposed CCIII as given in [5]. This was proposed with the change in terminal relationships current conveyors as given in [1], [4] but still the number of

terminals remained three only. The usefulness of this block as a floating current sensing device is given in [5]. An implementation of CCIII using two CCII's is also given.

In [6], a new block DDCC has been introduced. The paper also presents a CMOS circuit for the implementation of DDCC. It also shows the implementation of block DDCC as frequency selective circuit, multiplier, square rooter and squarer.

In [7], a new realization using CMOS technology for DVCC is given. It is also referred to be an important building block for applications like impedance converter and an instrumentation amplifier operating in the current mode.

In [8], positive and negative floating resistors which are electronically tunable are developed using an OTA designed using CMOS. The circuit have used two OTAs which are balanced and a fully differential OTA. Thus in total it uses three OTAs and the resistance which is realised in this paper has a linear control by the external biasing current and that too over a range greater than three decades.

In [9], CDBA is proposed. It is explained as an active block with two inputs and two outputs. It is implemented practically using CFA which is available in the market as AD844.

In [10], a FDCCII is introduced. The blocks finds its utility in the applications which require mixed mode operation along with a fully differential signal processing.

In [11], a DXCC is proposed and its usefulness for filtering in continuous time domain is also given. The linearity of the device is also high when the input applied to the device is a large signal. This also helps in reducing the total number of MOSFET resistors and total number of active devices in MOSFET-C filters which operates in continuous time domain.

In [12], CDTA is introduced and an implementation of this block using two CCIIs and one OTA is given. This device is introduced with two current inputs and two current outputs.

In [13], a survey is presented for the elements that are used for the current mode signal processing. All the elements surveyed in this paper are implemented using CDTA and CTTA.

In [14], CCTA is proposed and its implementation using CMOS technology is given. This element can be used not only in the current mode circuits but also in voltage mode and mixed mode circuits.

In [15], an active block FB-VDBA is proposed. In the input stage of this element a fully differential OTA is present and to each output of OTA, a voltage buffer is connected.

In [16], three different realisations using the CMOS technology for FDVCCII- are proposed. The realisation which is given first has a limitation of the input range and rest of the two realizations are provided with a rail to rail input range and they are very good in terms of Bandwidth and linearity. A floating gyrator as an application for FDVCCII- is also proposed in this paper, which is used to realize a floating inductor which in turn is used to realize a second order low pass filter.

In [17], an analysis of active elements that are used in voltage mode, current mode and mixed mode analog signal processing applications is given. It also refers to problems involved in utilising these elements in linear applications. It also proposes a method to generate various new active elements having utilization in signal processing.

#### **REFERENCES**

- 1. Smith, K. C., Sedra, A., 'The Current Conveyor A new circuit building block', *Proc. IEEE* (Letters), 1968, pp. 1368-1369.

- 2. Sedra, A., Smith, K. C., 'Design of computer controllable instrumentation', Presented at 6<sup>th</sup> National Conference of the Computer Society of Canada, 1968.

- 3. Smith, K. C., Sedra, A., 'A new simple wide-band current measuring device', *IEEE Transactions on Instrumentation and Measurement*, 1969, vol. IM-18, pp. 125-128.

- 4. Sedra, A. S., Smith, K. C., 'A second generation current conveyor and its application', *IEEE Transactions on Circuit Theory*, 1970, vol. 17, no. 1, pp. 132-134.

- 5. Fabre, A., 'Third generation current conveyor: A new helpful active element'. *Electronics Letters*, 1995, vol. 31, no. 5, pp. 338-339.

- 6. Chiu, W., Liu, S. I., Tsao, H. W., Chen, J. J., 'CMOS differential difference current conveyors and their applications'. *IEE Proceedings Circuits, Devices and Systems*, 1996, vol. 143, no. 2, pp. 91-96.

- 7. Elwan, H. O., Soliman, A. M., 'Novel CMOS differential voltage current conveyor and its applications'. *IEE Proceedings Circuits, Devices and Systems*, 1997, vol. 144, no. 3, pp. 195-200.

- 8. Kaewdang, K., Kumwachara, K., Surakampontorn, W., 'Electronically Tunable Floating CMOS resistor using OTA', *IEEE International Symposium on Communications and Information Technology ISCIT 2005*. Bejing (China) 2005, pp. 729-732.

- 9. Acar, C., Ozoguz, S., 'A new versatile building block: Current differencing buffered amplifier suitable for analog signal processing filters', *Microelectronics Journal*, 1999, vol. 30, no. 2, pp. 157-160.

- 10. El-Adawy, A., Soliman, A. M., Elwan, H. O., 'A novel fully differential current conveyor and applications for analog VLSI', *IEEE Transactions on Circuits and Systems-II: Analog and Signal Digital Processing*, 2000, vol. 47, no. 4, pp. 306-313.

- 11. Zeki, A., Toker, A., 'The dual-X cuurent conveyor (DXCCII): a new active device for tunable continuous time filters', *International Journal of Electronics*, 2002, vol. 89, no. 12, pp. 913-923.

- 12. Biolek, D., 'CDTA Building block for current mode analog signal processing'. In *Proceedings of the ECCTD03*, Krakow (Poland), 2003, pp. 397-400.

- 13. Biolek, D., Gubek, T., 'New circuit elements for current-mode signal processing', *Elektrorevue*, 2004/28. [Online] Cited 2004-05-03. Available at: http://www.elektrorevue.cz.

- 14. Prokop, R., Musil, V., 'New modern circuit block CCTA and some of its applications', In *Proceedings of the 14<sup>th</sup> International Scientific and Applied Science Electronics ET'2005*. Sozopol (Bulgaria), 2005, pp. 93-98.

- 15. Biolkova, V., Kolka, Z., Biolek, D., 'Fully balanced voltage differencing buffered amplifier and its applications', In 52<sup>nd</sup> IEEE International Midwest Symposium on Circuits and Systems MWSCAS'09. Cancum (Mexico), 2009, pp. 45-48.

- 16. Ehab, A., Sobhy, I., Soliman, A.M., 'Realizations of fully differential voltage second generation current conveyor with an application', *International Journal of Circuit Theory and App.*, 2000, vol. 38, pp. 441-452.

- 17. Biolek, D., Senani, R., Biolkova, V., Kolka, Z., 'Active elements for analog signal processing: Classification, review, and new proposals', *Radioengineering*, 2008, vol. 17, no. 4, pp. 15-32.

- 18. Yesil, A., Kacar, F., Kuntman, H., 'New Simple CMOS Realization of Voltage Differencing Tranconductance Amplifier and Its RF Filter Applications', *Radioengineering*, 2011, vol. 20, no. 3, pp. 632-637.

#### **CHAPTER 3**

#### **VDTA**

#### 3.1 INTRODUCTION

Analog signal processing that forms the base of modern day technology widely uses active elements and the example of which can be seen in filters, oscillators etc. Many of the active elements have been proposed [1] - [13] because every active element have some important and unique features as compared to the other one such as input or output terminals. In [14] all the active elements are reviewed and many new elements are introduced whose realisations have not been given yet.

VDTA is an acronym used for Voltage Differencing Transconductance Amplifier. In case of VDTA, voltage at the differential input  $(V_{VP}, V_{VN})$  results into the current leaving the terminal Z by one transconductance gain and the voltage at Z results into the current at the terminals X+ and X- by another transconductance gain. The external bias current is capable of electronically controlling both the transconductance gains. If we compare VDTA with other active blocks [1] – [8], the advantageous feature that VDTA shows is that it has 2 different transconductance values , so a lot of applications such as oscillator, inductance, biquad filters can be realised with a single active block used in addition to one or two capacitors. One other important feature is the capability of this block to be used in transconductance mode applications because of the reason that voltage is at input terminals and on the other hand current is at the output terminals.

#### 3.2 DESCRIPTION OF CIRCUIT

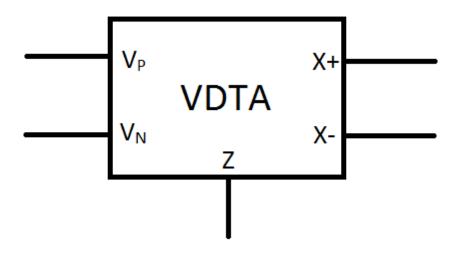

The symbol that is used to represent the circuit of VDTA [15] is given in Figure 1. Here  $V_P$  and  $V_N$  are the terminals at which input is applied and Z, X+, X- are the terminals where output is obtained. A high impedence value is exhibited by all these terminals. For an ideal VDTA, the terminal relationship can be described by the matrix given below.

$$\begin{bmatrix} I_{Z} \\ I_{X+} \\ I_{X-} \end{bmatrix} = \begin{bmatrix} g_{m1} & -g_{m1} & 0 \\ 0 & 0 & g_{m2} \\ 0 & 0 & -g_{m2} \end{bmatrix} \begin{bmatrix} V_{VP} \\ V_{VN} \\ V_{Z} \end{bmatrix}$$

Matrix equation representing the terminal relationship of VDTA [15]

Figure 1: Circuit symbol of VDTA[15]

Using the above matrix equation the terminal relations in simple mathematical equations can be expressed as

$$I_z = g_{m1}(V_{VP} - V_{VN}) (3.1)$$

$$I_{X+} = g_{m2}V_Z (3.2)$$

$$I_{X-} = -g_{m2}V_Z (3.3)$$

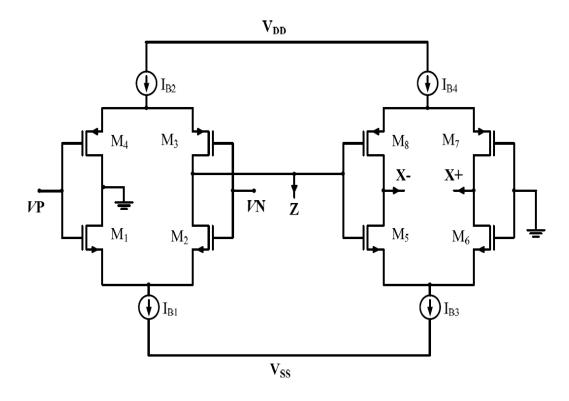

The implementation of input and output stage can be done using floating current sources. The voltage applied at the input terminals results into an output current at terminal Z. The voltage present at the terminal Z further results into output current at terminals X+ and X-. CMOS realisation of VDTA [15] is given in Figure 2. The transconductance at input and output terminals of VDTA element described in the circuit in Figure 2 is given by output transistors transconductances. The approximated expressions for the transconductances are

$$g_{m1} = \frac{g_3 + g_4}{2} \tag{3.4}$$

$$g_{m2} = \frac{g_5 + g_8}{2}$$

or (3.5)

$$g_{m2} = \frac{g_6 + g_7}{2} \tag{3.6}$$

Here  $g_i$  represents the value of transconductance for  $i^{th}$  transistor .

The value of the transconductance for a transistor is given by

$$g_i = \sqrt{I_{Bi}\mu_i C_{ox} \left(\frac{W}{L}\right)_i}$$

(3.7)

Here,

$\mu_i$  represents the carrier mobility for NMOS or PMOS transistor depending on whether i is p or n , where p is for PMOS and n is for NMOS transistor.

$C_{ox}$  is the gate capacitance per unit area.

W is the value of effective channel width.

L is the value of effective channel length.

$I_{Bi}$  is the bias current for the i<sup>th</sup> transistor.

Figure 2 : CMOS implementation of VDTA [15]

The CMOS implementation of VDTA shown above when used in practical applications, sometimes have a different looking structure which uses few more MOSFET's, the reason

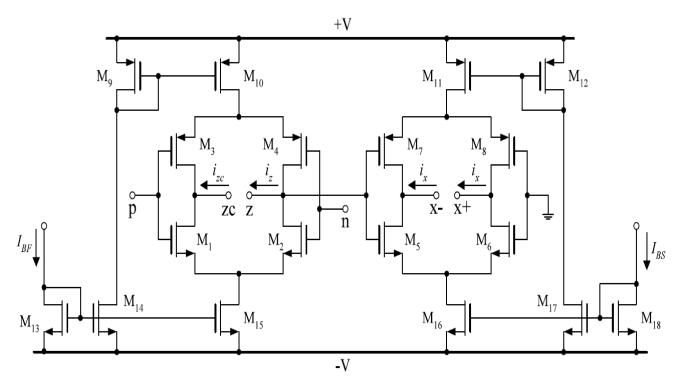

**Figure 3**: CMOS implementation of VDTA showing current mirrors in place of current sources [16]

being the current sources shown in the above figure are replaced by the current mirror structures. The design using the MOSFET's instead of current sources is shown in Figure 3.

In Figure 3, we can easily see that  $M_9$  and  $M_{10}$  are forming a current mirror and  $M_{13}$  and  $M_{14}$  as well as  $M_{13}$  and  $M_{15}$  also form a current mirror. IBF acting as a driving current for these current mirrors and these pair of current mirrors fulfil the requirement of current sources  $I_{B1}$  and  $I_{B2}$  in Figure 2. Similarly the functioning of  $I_{B3}$  and  $I_{B4}$  of Figure 2 is done in Figure 3 with the help of current mirrors formed using the MOSFETs  $M_{11}$ ,  $M_{12}$ ,  $M_{16}$ ,  $M_{17}$  and  $M_{18}$ .

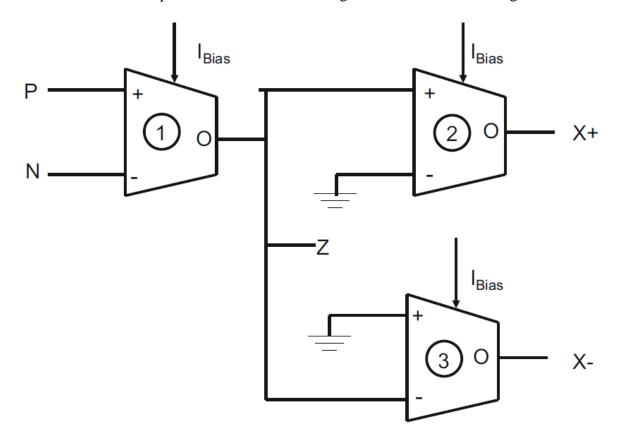

When it comes to the practical implementation of VDTA [17], it can easily be implemented using an already available IC LM13700 [18]. LM13700 is an IC manufactured by Texas Instruments. It consists of two current controlled transconductance amplifiers, each having differential inputs and push-pull outputs, it also provides a feature of adjustable transconductance. The implementation of VDTA using LM13700 is shown in Figure 4.

Figure 4: Implementation of VDTA using OTA [17]

#### 3.3 SIMULATION RESULTS

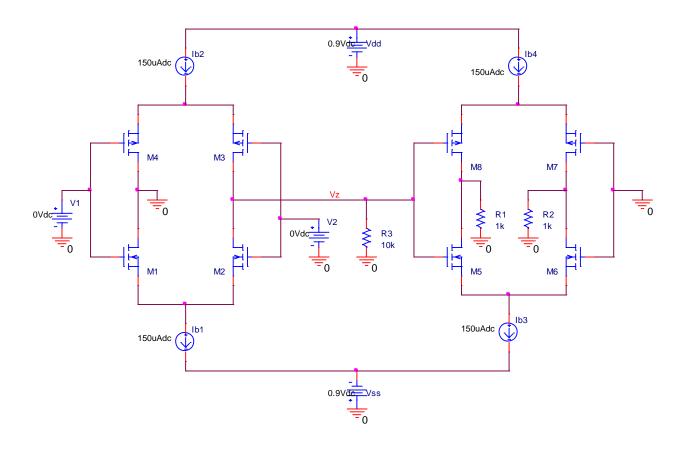

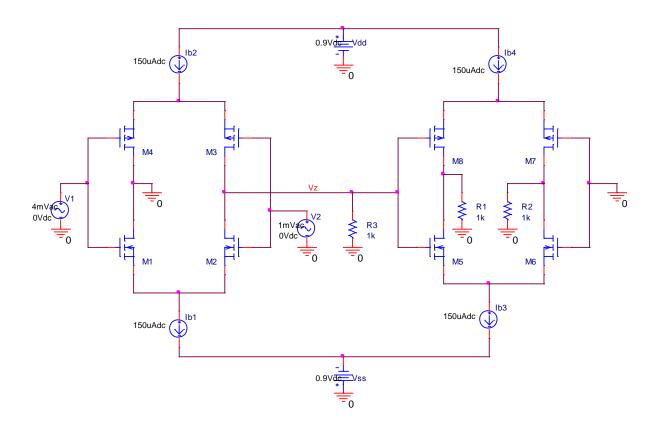

CMOS implementation of VDTA as described above in Figure 2 is simulated using PSPICE software with TSMC CMOS 0.18µm process parameters. Different Aspect ratios for NMOS and PMOS have been used. These aspect ratios for the different transistors are shown in Table 1.

| Transistors          | Width (µm) | Length (µm) |

|----------------------|------------|-------------|

| $M_1, M_2, M_5, M_6$ | 3.6        | 0.36        |

| $M_3, M_4, M_7, M_8$ | 16.64      | 0.36        |

**Table 1**: Aspect ratios of Transistors for VDTA [15]

The supply voltage shown in Figure 2 as  $V_{DD}$  and  $V_{SS}$  are taken to be  $V_{DD} = -V_{ss} = 0.9$  V and the bias currents are taken to be  $I_{B1} = I_{B2} = I_{B3} = I_{B4} = 150\mu\text{A}$ . The value of the biasing current and the aspect ratios of the transistors that have been chosen here results in the transconductance values of VDTA which were represented by  $g_{m1}$ ,  $g_{m2}$  to be both equal to  $636.3\mu\text{A/V}$ .

VDTA is here simulated for obtaining both the DC and the AC characteristics of the active block.

The circuit diagram of VDTA used in PSPICE for plotting the DC Characteristics is as given in Figure 5.

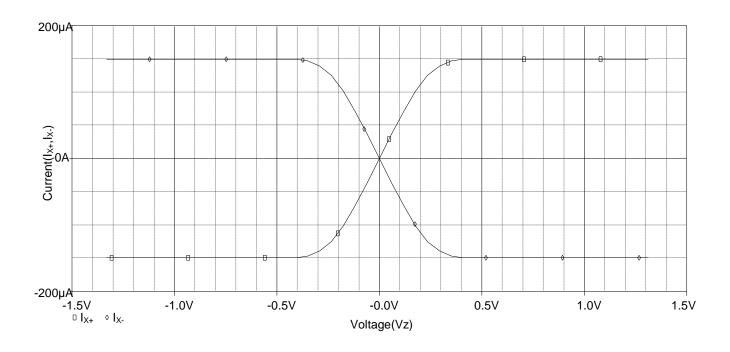

The DC characteristics of VDTA that have been obtained after simulation are given in Figure 6. DC characteristics is a plot showing the variation of  $I_{X+}$  and  $I_{X-}$  with respect to  $V_Z$ .

The circuit diagram of VDTA used in PSPICE for plotting the AC Characteristics is as given in Figure 7.

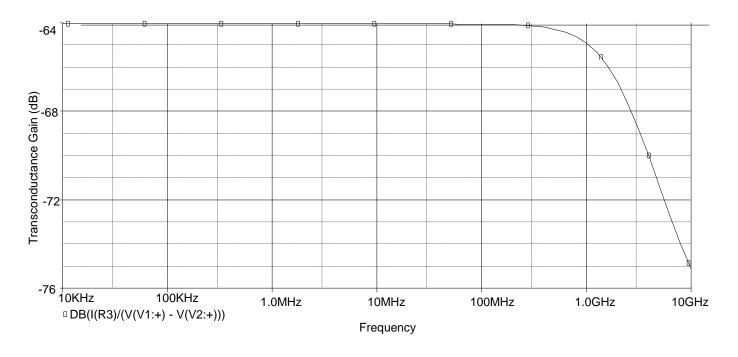

The AC Characteristics of VDTA that have been obtained after simulating the circuit in Figure 7 are given in Figure 8. The AC characteristics show the variation of transconductance gain with respect to the frequency. The simulation results show that transconductance gain drops by 3db at 2.163GHz.

Figure 5 : PSPICE circuit diagram of VDTA to plot DC characteristics

Figure 6 : DC characteristics of VDTA

Figure 7: PSPICE circuit diagram of VDTA to plot AC characteristics

Figure 8: AC characteristics of VDTA

#### REFERENCES

- 19. Sedra, A. S., Smith, K. C., 'A second generation current conveyor and its application', *IEEE Transactions on Circuit Theory*, 1970, vol. 17, no. 1, pp. 132-134.

- 20. Fabre, A., 'Third generation current conveyor: A new helpful active element'. *Electronics Letters*, 1995, vol. 31, no. 5, pp. 338-339.

- 21. Chiu, W., Liu, S. I., Tsao, H. W., Chen, J. J., 'CMOS differential difference current conveyors and their applications'. *IEE Proceedings Circuits, Devices and Systems*, 1996, vol. 143, no. 2, pp. 91-96.

- 22. Elwan, H. O., Soliman, A. M., 'Novel CMOS differential voltage current conveyor and its applications'. *IEE Proceedings Circuits, Devices and Systems*, 1997, vol. 144, no. 3, pp. 195-200.

- 23. Kaewdang, K., Kumwachara, K., Surakampontorn, W., 'Electronically Tunable Floating CMOS resistor using OTA', *IEEE International Symposium on Communications and Information Technology ISCIT 2005*. Bejing (China) 2005, pp. 729-732.

- 24. Acar, C., Ozoguz, S., 'A new versatile building block: Current differencing buffered amplifier suitable for analog signal processing filters', *Microelectronics Journal*, 1999, vol. 30, no. 2, pp. 157-160.

- 25. El-Adawy, A., Soliman, A. M., Elwan, H. O., 'A novel fully differential current conveyor and applications for analog VLSI', *IEEE Transactions on Circuits and Systems-II: Analog and Signal Digital Processing*, 2000, vol. 47, no. 4, pp. 306-313.

- 26. Zeki, A., Toker, A., 'The dual-X cuurent conveyor (DXCCII): a new active device for tunable continuous time filters', *International Journal of Electronics*, 2002, vol. 89, no. 12, pp. 913-923.

- 27. Biolek, D. 'CDTA Building block for current mode analog signal processing'. In *Proceedings of the ECCTD03*, Krakow (Poland), 2003, pp. 397-400.

- 28. Biolek, D., Gubek, T., 'New circuit elements for current-mode signal processing', *Elektrorevue*, 2004/28. [Online] Cited 2004-05-03. Available at: http://www.elektrorevue.cz.

- 29. Prokop, R., Musil, V., 'New modern circuit block CCTA and some of its applications', In *Proceedings of the 14<sup>th</sup> International Scientific and Applied Science Electronics ET'2005*. Sozopol (Bulgaria), 2005, pp. 93-98.

- 30. Biolkova, V., Kolka, Z., Biolek, D., 'Fully balanced voltage differencing buffered amplifier and its applications', In 52<sup>nd</sup> IEEE International Midwest Symposium on Circuits and Systems MWSCAS'09. Cancum (Mexico), 2009, pp. 45-48.

- 31. Ehab, A., Sobhy, I., Soliman, A.M., 'Realizations of fully differential voltage second generation current conveyor with an application', *International Journal of Circuit Theory and App.*, 2000, vol. 38, pp. 441-452.

- 32. Biolek, D., Senani, R., Biolkova, V., Kolka, Z., 'Active elements for analog signal processing: Classification, review, and new proposals', *Radioengineering*, 2008, vol. 17, no. 4, pp. 15-32.

- 33. Yesil, A., Kacar, F., Kuntman, H., 'New Simple CMOS Realization of Voltage Differencing Tranconductance Amplifier and Its RF Filter Applications', *Radioengineering*, 2011, vol. 20, no. 3, pp. 632-637.

- 34. Satansup, J., Pukkalanum, T., Tangsrirat, W., 'Electronically Tunable Single-Input Five-Output Voltage-Mode Universal Filter using VDTAs and Grounded Passive Elements', *Circuits, Systems and Signal Processing*, 2013, vol. 32, pp. 945-957.

- 35. Pandey, N., Kumar, P., Paul, S. K., 'Voltage differencing transconductance amplifier based resistorless and electronically tunable wave active filter', *Analog Integrated Circuits and Signal Processing*, 2015, vol. 84, pp. 107-117.

- 36. Data sheet of LM13700 released by Texas Instruments, SNOSBW2F November 1999 Revised November 2015. Available at: http://www.ti.com.

#### **CHAPTER 4**

## **FILTERS USING VDTA**

#### 4.1 INTRODUCTION

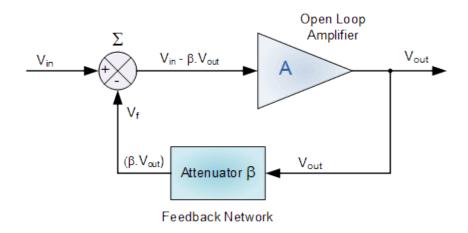

The networks that are used to process the signals taking into consideration the frequency of a signal are known as filters. The explanation of the filters can be given simply by explaining the variation in impedence of capacitors and inductors. If we consider the example of voltage divider in which the element present in shunt leg is a reactive impedence. As soon as there arises a change in frequency, there occurs a change in reactive impedence, so as a result of this the ratio appearing across the voltage divider also changes. This process results into a change in the transfer function at input/output depending on the frequency and this variation of transfer function with frequency is defined as the frequency response.

There are a lot of practical applications of filters. One of the application is the stabilisation of Amplifiers at high frequencies by rolling off gain because at such high frequencies oscillations may occur as a result of excessive phase shift. For this purpose low pass filter is used. Other general application of the filter is to improve response of high gain amplifiers and this is done by blocking the dc offset. For this purpose a high pass filter is used. Filters have the capability to separate the signals on the basis of frequency or in other words they have the capability to pass the signals of interest and block the unwanted frequencies.

A radio receiver can be considered as one of the above said application of filters, it passes the frequencies which we want to process and block the rest of the frequencies or the unwanted frequencies. In data conversion, the elimination of the aliasing effect is done using the filters in A/D systems. At the output of D/A converter, the elimination of higher frequency components which are mainly in this case harmonics of sampling frequency is done using filters, thus filters help in signal reconstruction at output of D/A converter.

If we consider the case of an ideal filter, the amplitude response in the pass band is one or unity and it is zero in the stop band. The point where pass band and stop band of a filter intersect is cut-off frequency. In practical filters, the cut-off frequency is defined as the frequency where the amplitude response of a filter falls below 3-dB point or becomes less than 0.707 times of the maximum value. The variation or changes in the pass band response

are said to be pass band ripples. The steepness or the slope of line joining the pass band and stop band depends on the order of the filter. Order of a filter is equal to the number of poles or number of roots of the denominator of the transfer function.

To represent the filter's frequency domain behaviour mathematically, we define the ratio of output voltage to input voltage in s-domain and it is called as voltage transfer function and is given by

$$H(s) = \frac{V_{OUT}(s)}{V_{IN}(s)} \tag{4.1}$$

Here  $V_{OUT}(s)$  is laplace transform of output voltage signal and  $V_{IN}(s)$  is laplace transform of input voltage signal.

Now if we replace s by  $j\omega$  in the equation 4.1 then we can represent the ratio in terms of magnitude and phase response, Magnitude response is written as

$$\left| H(j\omega) = \frac{V_{OUT}(j\omega)}{V_{IN}(j\omega)} \right| \tag{4.2}$$

And phase response can be written as

$$\arg H(j\omega) = \arg \frac{V_{OUT}(j\omega)}{V_{IN}(j\omega)} \tag{4.3}$$

The quality factor of a circuit is also represented sometimes by  $\alpha$  and it is given as

$$\alpha = \frac{1}{Q} \tag{4.4}$$

#### 4.2 VDTA BASED FILTER TOPLOGIES

Filters have been designed using all the active building blocks defined so far. VDTA proves to be a flexible active block in the realisation of different mode filters. The advantage that we have here is that transconductance can be adjusted with the help of bias currents so we do not rely on external resistors for this purpose. Here in this part of the chapter seven different topologies of filters are presented some of them being in current mode and some of them being in Voltage mode. Some of them are capable of realizing all the filters i.e Band Pass, Low Pass, High Pass, All Pass and Notch filters and some on the other hand are capable of realizing only the Low Pass, Band Pass and High Pass filters. After presenting these filter the

transfer functions of all the filters that are being realised using that topology is given and later on the results of all the simulations that have been done for that particular topology are presented.

#### 4.2.1 TOPOLOGY A

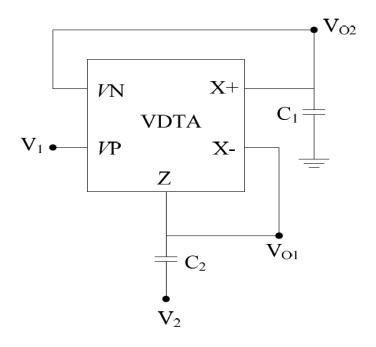

The filter topology presented as topology 1 was introduced in 2011 [1]. This circuit is using only one VDTA and two capacitors and is capable of realizing High Pass, Low Pass and Band Pass filters. The filter presented by this topology is a voltage mode biquad filter. The circuit of this filter is shown in Figure 9.

Figure 9: Biquad Filter (Topology A) [1]

As we can see in figure 9, input can be supplied at the terminals named as  $V_1$  and  $V_2$  and the output is taken from the terminals indicated by  $V_{01}$  and  $V_{02}$ . The transfer functions that are obtained after the analysis clearly show the way in which these filters can be implemented. When  $V_2$  terminal is grounded and input is supplied at  $V_1$ , then Band Pass and Low Pass filter topologies can be realized. The Band Pass output is obtained at  $V_{out1}$  terminal and Low Pass output is obtained at  $V_{out2}$  terminal . The transfer functions are written as given in the equations 4.5 and 4.6.

If

$$V_1 = V_{in}$$

and  $V_2 = 0$ , then

Band Pass

$$\rightarrow \frac{V_{out1}}{V_{in}} = \frac{s C_1 g_{m1}}{s^2 C_1 C_{2T} + s C_1 g_{m2} + g_{m1} g_{m2}}$$

(4.5)

Low Pass

$$\rightarrow \frac{V_{out2}}{V_{in}} = \frac{g_{m1}g_{m2}}{s^2 C_1 C_{2T} + s C_1 g_{m2} + g_{m1}g_{m2}}$$

(4.6)

When  $V_1$  is grounded and  $V_2$  is supplied with the input voltage, then High Pass output is available at  $V_{out1}$  and Band Pass output is available at  $V_{out2}$  terminal. The transfer functions are written as given in equations 4.7 and 4.8.

If  $V_2 = V_{in}$  and  $V_1 = 0$ , then

High Pass

$$\rightarrow \frac{V_{out1}}{V_{in}} = \frac{s^2 C_1 C_2}{s^2 C_1 C_{2T} + s C_1 g_{m2} + g_{m1} g_{m2}}$$

(4.7)

Band Pass

$$\rightarrow \frac{V_{out2}}{V_{in}} = \frac{s C_2 g_{m2}}{s^2 C_1 C_{2T} + s C_1 g_{m2} + g_{m1} g_{m2}}$$

(4.8)

The natural frequency  $(\omega_0)$  of this topology [1] is given in equation 4.9 and the Quality factor (Q) for the same [1] is given in equation 4.10.

$$\omega_0 = \sqrt{\frac{g_{m1}g_{m2}}{C_1 C_{2T}}} \tag{4.9}$$

$$Q = \sqrt{\frac{C_{2T} g_{m1}}{C_1 g_{m2}}} \tag{4.10}$$

# **SIMULATION RESULTS:**

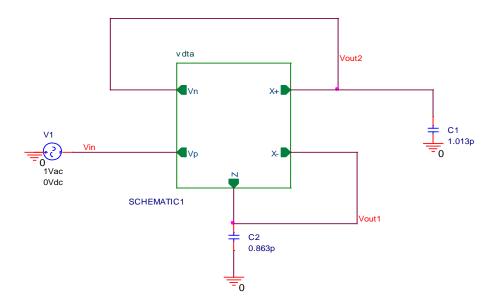

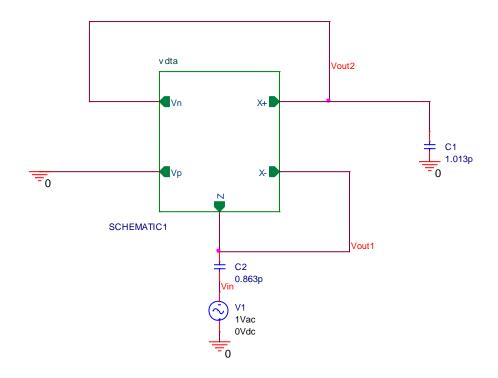

CMOS implementation of VDTA is as described in Figure 2. The circuit used here which is the circuit of topology 1 is simulated using PSPICE software with TSMC CMOS 18 $\mu$ m process parameters. The aspect ratios for the different transistors used are given in Table 1. The values of capacitors shown in Figure 9 used during this simulation are  $C_1$ =1.013pF and  $C_2$ =0.863pF.

First of all taking the case:  $V_1 = V_{in}$  and  $V_2 = 0$ .

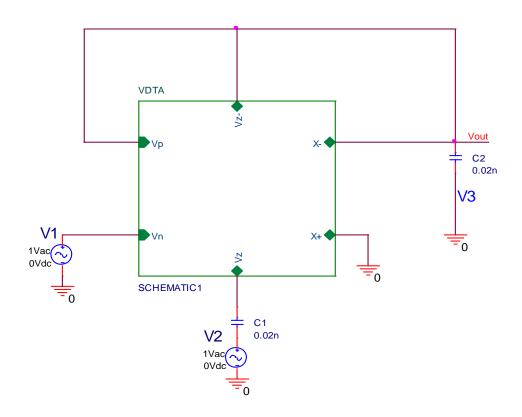

The circuit diagram used for the simulation of the filter of topology A for the case given above is shown in Figure 10.

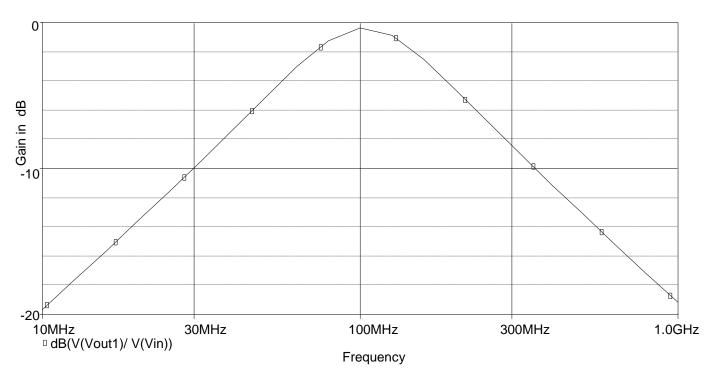

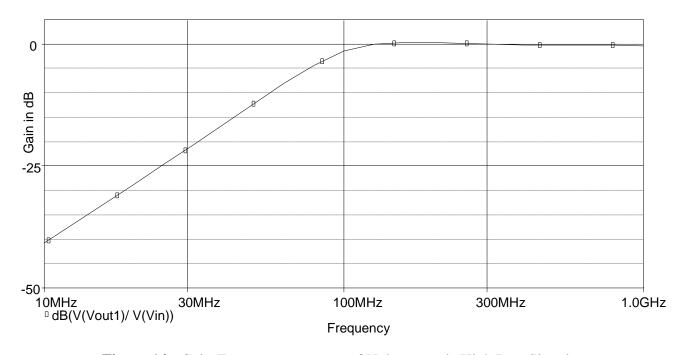

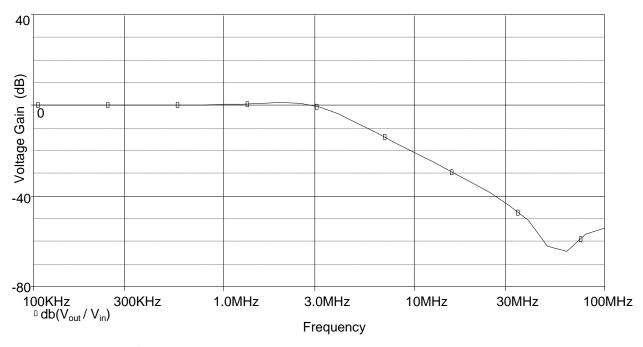

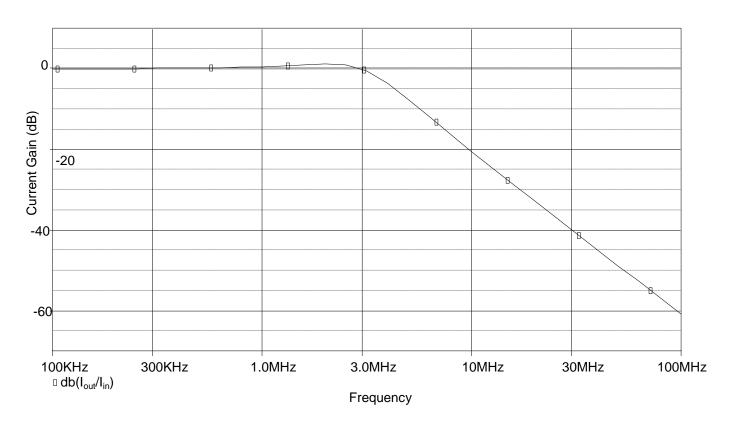

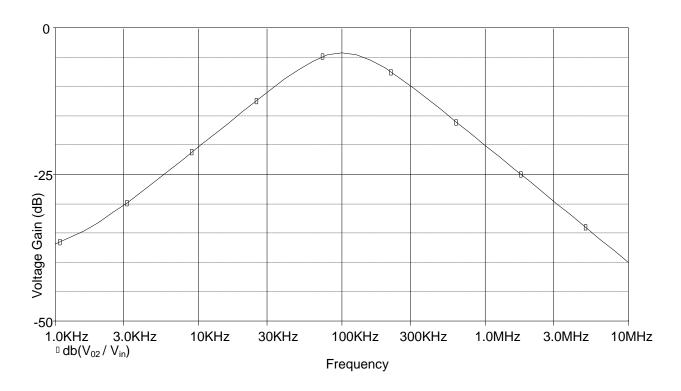

Figure 11 shows the output at the node  $V_{01}$  which comes out to be a Band Pass filter as mentioned in the equation 4.5. The bandwidth that has been obtained here is approximately 103.24 MHz and the lower cut off frequency is 63.566 MHz and the upper cut off frequency is 166.329MHz.

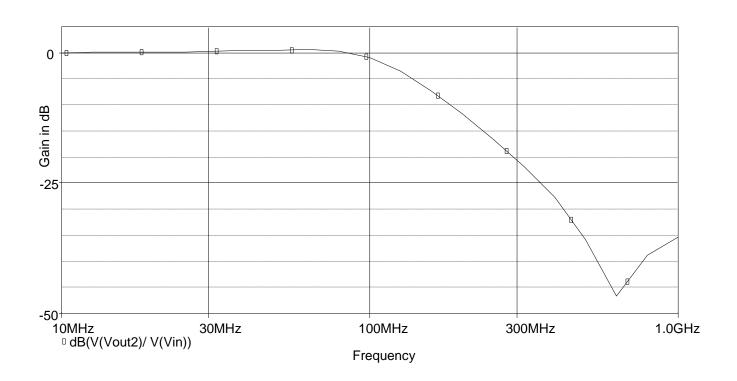

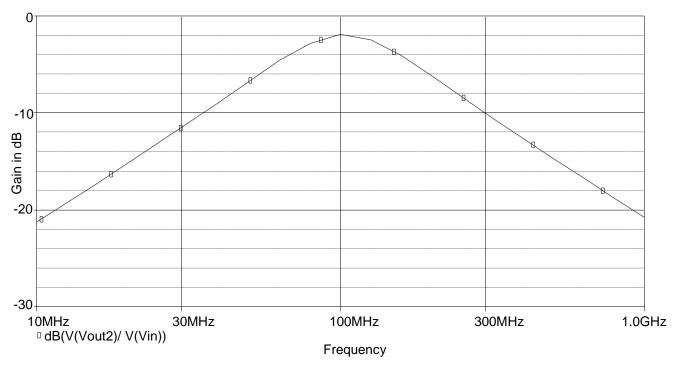

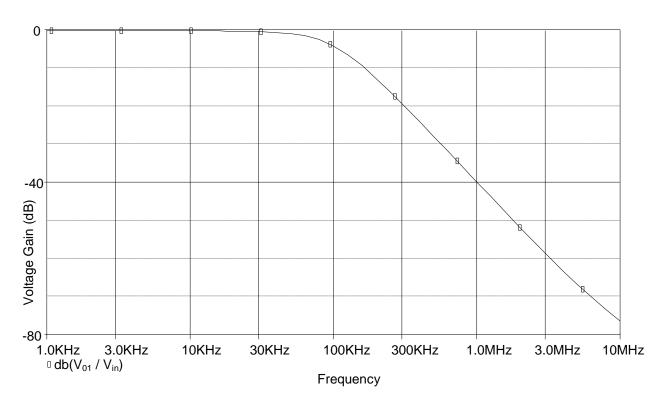

Figure 12 shows the output at the node  $V_{02}$  which comes out to be a Low Pass filter as already mentioned in the equation 4.6. The bandwidth that has been obtained here is 120.405 MHz.

Now taking the case:  $V_2 = V_{in}$  and  $V_1 = 0$ .

The circuit diagram used for the simulation of the filter of topology A for the case mentioned above is shown in Figure 13.

Figure 14 shows the output at the node  $V_{01}$  which comes out to be a High Pass Filter as mentioned in the equation 4.7. The cut off frequency that has been obtained here is 88.466MHz.

Figure 15 shows the output at the node  $V_{02}$  which comes out to be a Band Pass Filter as mentioned in the equation 4.8. The Bandwidth that has been obtained here is approximately 115MHz. The upper cutoff frequency obtained here is 175.206MHz and the lower cutoff frequency obtained here is 60.346MHz. So using this topology we are able to realise the High Pass, Low Pass and the Band Pass Filters with cutoffs as mentioned above.

**Figure 10 :** PSPICE circuit diagram of Topology A ( $V_1 = V_{in}$  and  $V_2 = 0$ ).

Figure 11: Gain-Frequency response of Voltage mode Band Pass Signal.

Figure 12: Gain-Frequency response of Voltage mode Low Pass Signal

Figure 13 : PSPICE circuit diagram of Topology A ( $V_1 = 0$  and  $V_2 = V_{in}$ ).

Figure 14: Gain-Frequency response of Voltage mode High Pass Signal.

**Figure 15 :** Gain-Frequency response of Voltage mode Band Pass Signal.

### 4.2.2 TOPOLOGY B

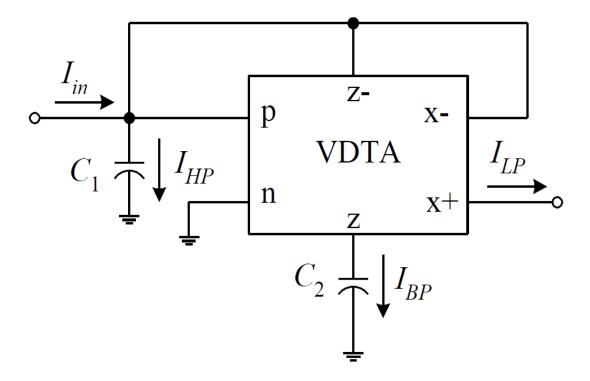

The filter topology here named as Topology B was introduced in 2012[2]. This topology shows a current mode filter. It consists of one input node and three output nodes and at each node one filter output is available. This circuit is capable of implementing Low Pass, High Pass and Band Pass output. This circuit uses one VDTA block and two capacitors for its functioning. The circuit used to implement VDTA for this topology is shown in Figure 3. So here two opposite outputs for z in terms of  $z_c$  and z are made available as compared to the output z of circuit of VDTA as shown in Figure 2. The circuit used for this topology is shown in Figure 16. In Figure 16,  $I_{in}$  indicates the input current supplied by the source,  $I_{LP}$  indicates the Low Pass output of the filter,  $I_{BP}$  indicates the Band Pass output of the filter and  $I_{HP}$  indicates the High Pass output of the filter. After analysis is performed over the circuit in Figure 16, the equations of the output at different terminals obtained are as follows.

Low Pass Output

$$\rightarrow$$

LP(s) =  $\frac{I_{LP}(s)}{I_{in}(s)} = \frac{(\frac{g_{mF}g_{mS}}{C_1C_2})}{D(s)}$  (4.11)

High Pass Output

$$\rightarrow$$

HP(s) =  $\frac{I_{HP}(s)}{I_{in}(s)} = \frac{s^2}{D(s)}$  (4.12)

Band Pass Output

$$\Rightarrow$$

BP(s) =  $\frac{I_{BP}(s)}{I_{in}(s)} = \frac{\left(\frac{g_{mF}}{C_1}\right)s}{D(s)}$  (4.13)

where,

$$D(s) = S^2 + \left(\frac{g_{mF}}{C_1}\right)S + \left(\frac{g_{mF}g_{mS}}{C_1C_2}\right)$$

(4.14)

Figure 16: Current mode Biquad Filter (Topology B)[2].

Equation 4.11 shows the ratio of the output at terminal  $I_{LP}$  and the input terminal  $I_{in}$  and since the numerator does not contain the term s, so it can easily be said that the output obtained at this terminal is Low Pass output. In a similar manner we can see that numerator in equation 4.12 contains the  $s^2$  term included in itself, so it can be said that the output current at the terminal  $I_{HP}$  indicates the High pass output and the equation 4.13 contains only the s term in the numerator so again it can clearly be understood that the output at the terminal  $I_{BP}$  indicates the Band Pass output.

The natural frequency  $\omega_0$  for this topology [2] is given in equation 4.15 and the Bandwidth for this topology [2] is given in equation 4.16.

$$\omega_0 = \sqrt{\frac{g_{mF} g_{mS}}{C_1 C_2}} \tag{4.15}$$

$$BW = \frac{g_{mF}}{C_1} \tag{4.16}$$

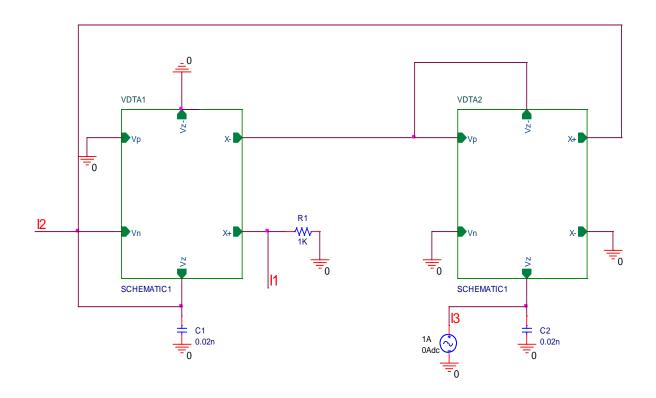

### **SIMULATION RESULTS:**

For this simulation, CMOS implementation of VDTA given in Figure 3 is used. The simulation is done on PSPICE using  $0.35\mu m$  TSMC CMOS process parameters. The aspect ratios for the PMOS and NMOS structures is given in Table 2. Supply voltages used for providing the biasing for the given circuit are +V = -V = 2 volts. The value of the capacitances indicated by  $C_1$  and  $C_2$  in Figure 16 are  $C_1 = C_2 = 20 pF$ .

| Transistors      | W(µm) | L(µm) |

|------------------|-------|-------|

| M1-M2, M5-M6     | 16.1  | 0.7   |

| M3-M4 , M7-M8    | 28    | 0.7   |

| M9-M12           | 21    | 0.7   |

| M13-M16          | 7     | 0.7   |

| M14-M15, M17-M18 | 8.5   | 0.7   |

Table 2: Aspect ratios of Transistors for VDTA structure of Figure 3 (0.35 μm) [2].

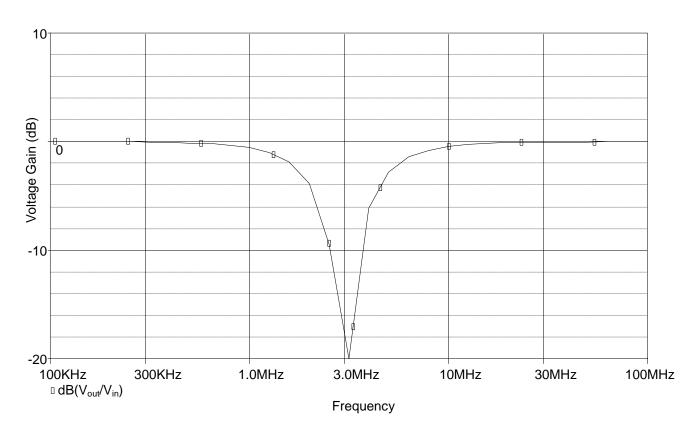

For this topology, the natural frequency of the filter for which simulations are done is selected to be  $f_0=3.03$  MHz and the Quality factor is chosen to be Q=1. For achieving these values of natural frequency and Quality factor the two transconductance values of VDTA are selected to be  $g_{mF}=g_{mS}=381\mu\text{A/V}$  [2]. For this purpose the biasing currents are taken to be  $I_{BF}=I_{BS}\approx 40\mu\text{A}$  [2].

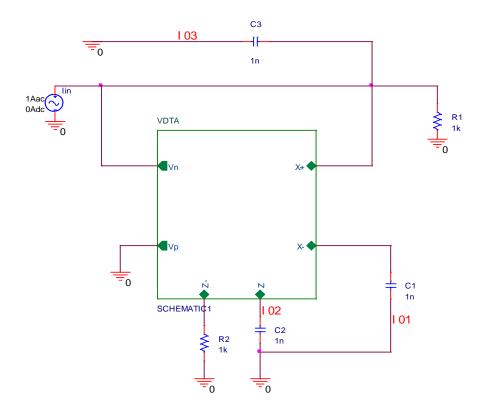

The circuit used for the simulation in PSPICE software is given in Figure 17.

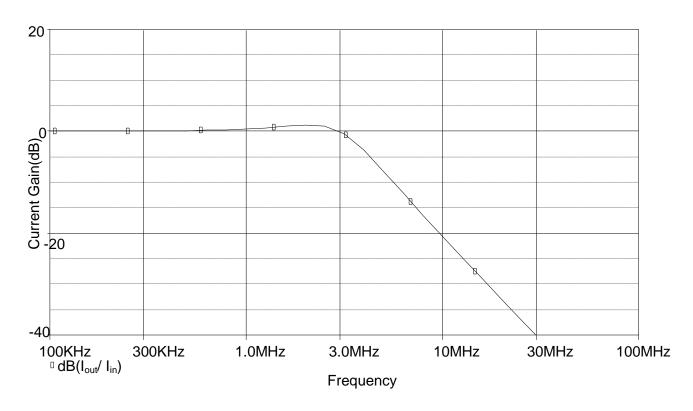

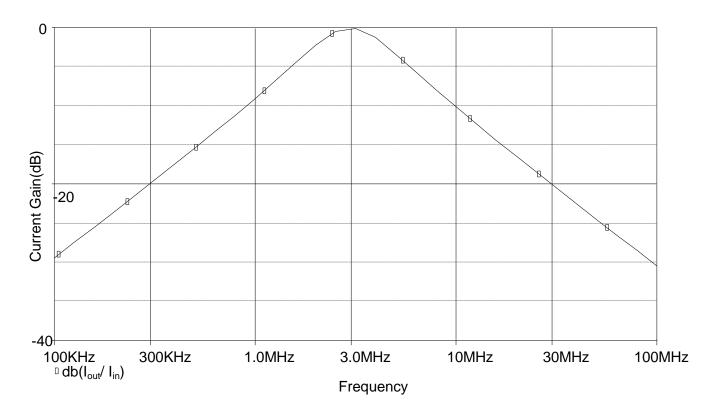

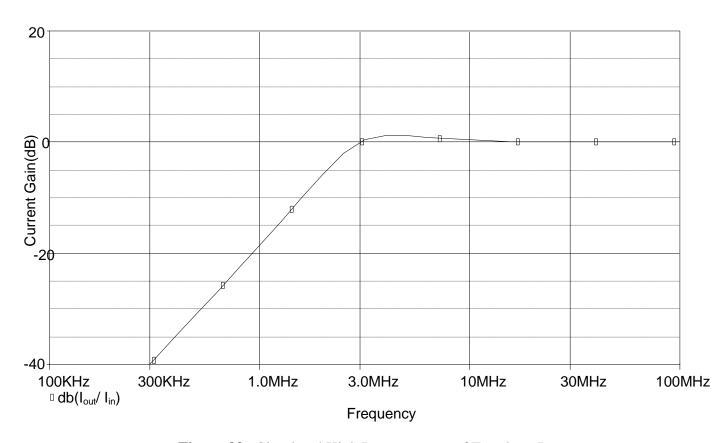

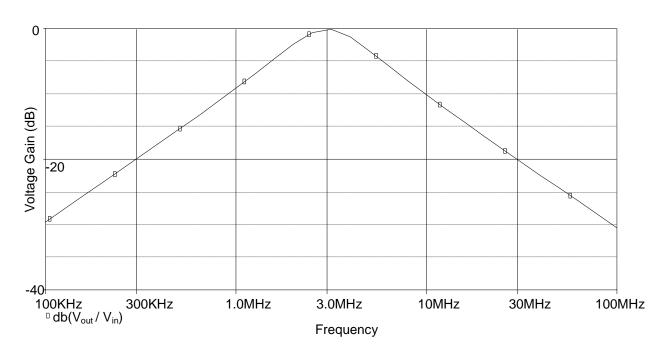

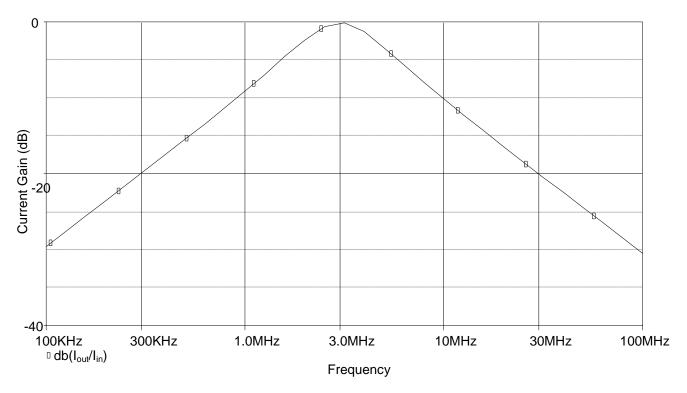

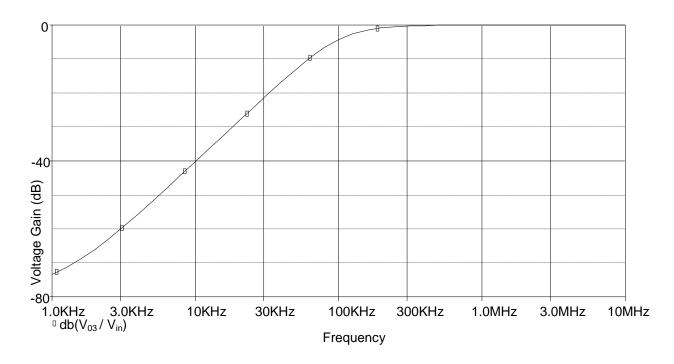

Figure 18 indicates the results of simulation which are obtained at the capacitor  $C_2$  which is a Band Pass response. The lower cut off frequency obtained after simulation is equal to 1.849MHz and the higher cut off frequency is equal to 4.676 MHz. The Bandwidth of the filter is obtained to be 2.827 MHz.

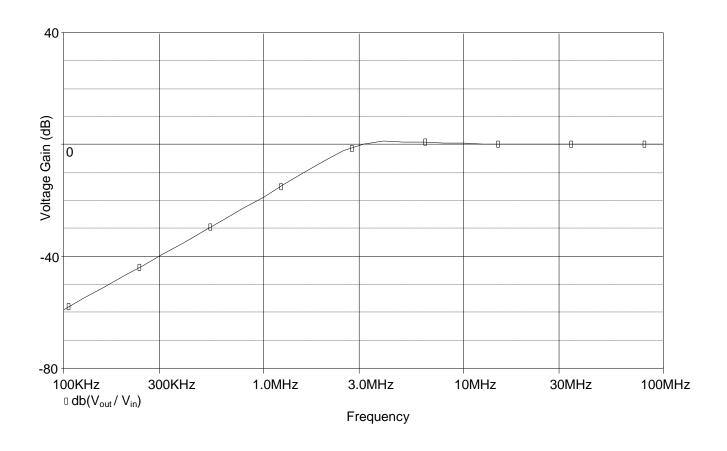

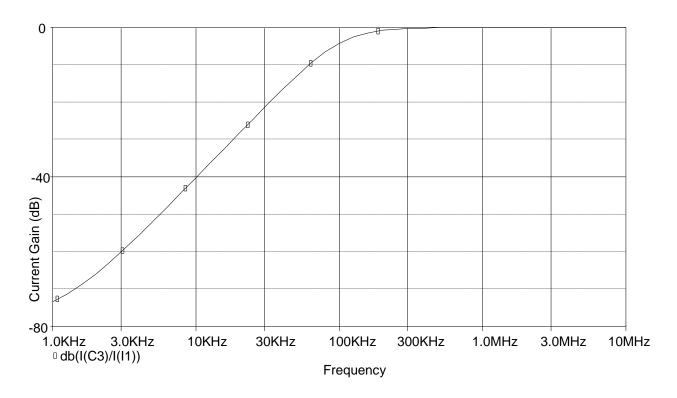

Figure 19 indicates the results of simulation that are obtained at the capacitor  $C_1$  which is a High Pass response. The cut off frequency of the filter is obtained to be 2.352 MHz.

Figure 20 indicates the results of simulation that are obtained at the terminal X+ which is a low pass response. The Bandwidth of the filter is obtained to be 3.677 MHz.

Figure 17: PSPICE circuit diagram of Topology B

Figure 18: Simulated Band Pass response for filter of Topology B

Figure 19: Simulated High Pass Response for filter of Topology B

Figure 20: Simulated Low Pass Response for filter of Topology B

# 4.2.3 TOPOLOGY C

The filter topology here named as Topology C was introduced in 2013 [3]. In this topology the filter shown is a current-mode filter. This filter has single input terminal and multiple output terminals. The filter uses a single VDTA, two capacitors which are grounded and a resistor which is also grounded. This circuit implements all the filter functions i.e Low Pass, High Pass, Band Pass, Notch and All Pass filter functions. So here we can see that as compared to previous filters this can implement all the filters implemented by previous two topologies and in addition to that it is implementing Band Stop and All Pass filter functions. Here in this filter the natural frequency and the Bandwidth are independently tunable. The CMOS implementation of VDTA that has been used by this topology is given in Figure 2 and the aspect ratios for the MOS transistors are clearly given in Table 1. The circuit used for this topology is given in Figure 21.

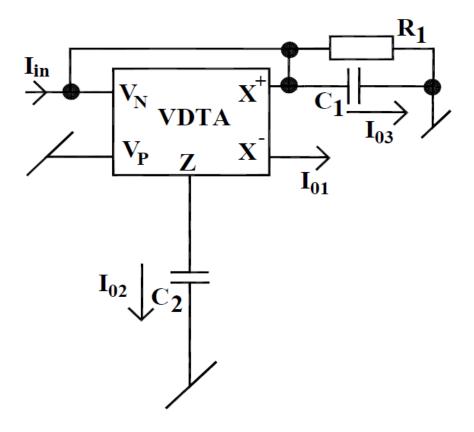

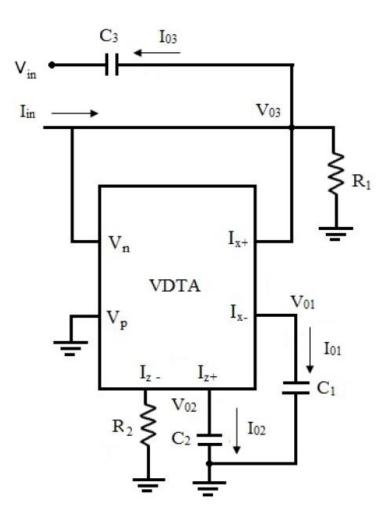

Figure 21: Current Mode Biquad Filter (Topology C) [3]

Here  $I_{in}$  refers to the input current signal which as shown in Figure 21 is applied at  $V_N$  terminal. After the proper analysis of the circuit of Figure 21, the expression that is obtained at  $I_{01}$  terminal is given in equation 4.17. Equation 4.18 gives the expression for the current at

the terminal  $I_{02}$  and equation 4.19 gives the expression for the current at the terminal  $I_{03}$ . The equations that are obtained at different terminals are [3]

$$\frac{I_{01}}{I_{in}} = \frac{g_{m1}g_{m2}}{D(s)} \tag{4.17}$$

$$\frac{I_{02}}{I_{in}} = -\frac{s \left(\frac{g_{m1}}{C_1}\right)}{D(s)} \tag{4.18}$$

$$\frac{I_{03}}{I_{in}} = \frac{s^2}{D(s)} \tag{4.19}$$

The absence of the s term in the numerator of the equation 4.17 indicate that the signal obtained at the terminal indicated by  $I_{01}$  in Figure 21 is a Low Pass signal. In a similar way, upon seeing the presence of s term in the numerator of the equation 4.18 we can clearly state that signal represented by  $I_{02}$  in Figure 21 is a Band Pass signal. The presence of  $s^2$  in the numerator of the equation 4.19 reveals that the signal indicated by  $I_{03}$  is a high pass signal. Now performing some operations on the equations 4.17, 4.18 and 4.19 we can obtain the equations 4.20 and 4.21. Out of these, equation 4.20 is a notch filter expression that is obtained after the addition of equations 4.17 and equation 4.19 whereas equation 4.21 is an All Pass filter expression and is obtained after the addition of all the three equations i.e equation 4.17, 4.18 and 4.19. The expression of the function D(s) that is used in all the expressions here is given in 4.22.

$$\frac{I_{01} + I_{03}}{I_{in}} = \frac{s^2 + \frac{g_{m1}g_{m2}}{C_1C_2}}{D(s)} \tag{4.20}$$

$$\frac{I_{01} + I_{02} + I_{03}}{I_{in}} = \frac{s^2 - s(\frac{gm_1}{C_1}) + \frac{gm_1gm_2}{C_1C_2}}{D(s)}$$

(4.21)

Where

$$D(s) = S^{2} + \left(\frac{1}{R_{1}C_{1}}\right)S + \left(\frac{g_{m1} g_{m2}}{C_{1} C_{2}}\right)$$

(4.22)

The expression for the natural frequency ( $\omega_0$ ) of this topology [3] is given in equation 4.23, the expression for Bandwidth (BW) [3] is given in equation 4.24 and the expression for the Quality factor ( $Q_0$ ) [3] is given in equation 4.25.

$$\omega_0 = \sqrt{\frac{g_{m1} g_{m2}}{C_1 C_2}} \tag{4.23}$$

$$BW = \frac{1}{R_1 C_1} \tag{4.24}$$

$$Q_0 = \sqrt{\frac{g_{m1} g_{m2} c_1 R_1^2}{c_2}} \tag{4.25}$$

### **SIMULATION RESULTS:**

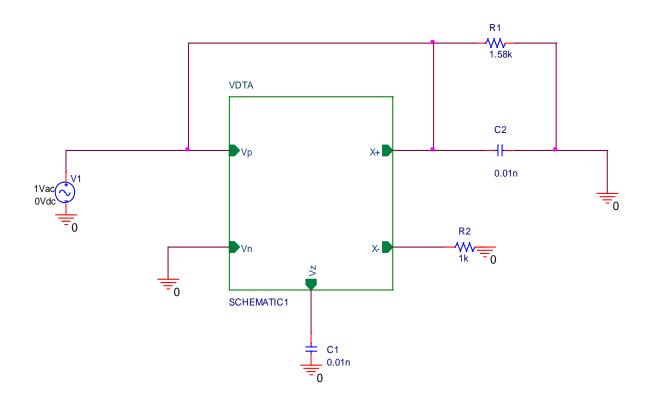

For this simulation, CMOS implementation of VDTA given in Figure 2 is used. The simulation is done on PSPICE using 0.18µm TSMC CMOS process parameters. The aspect ratios for the PMOS and NMOS structures is given in Table 1. Supply voltages used for providing the biasing for the given circuit are  $+V_{DD}=-V_{SS}=1$  volts. The value of the biasing currents used are  $I_{B1}=I_{B2}=150\mu A$  and  $I_{B3}=I_{B4}=42.38~\mu A$  [3]. The values of the passive elements are chosen to be  $C_1=C_2=0.01$  nF and  $R_1=1.58K\Omega$  [3].

The circuit used for the simulation in PSPICE software is given in Figure 22.

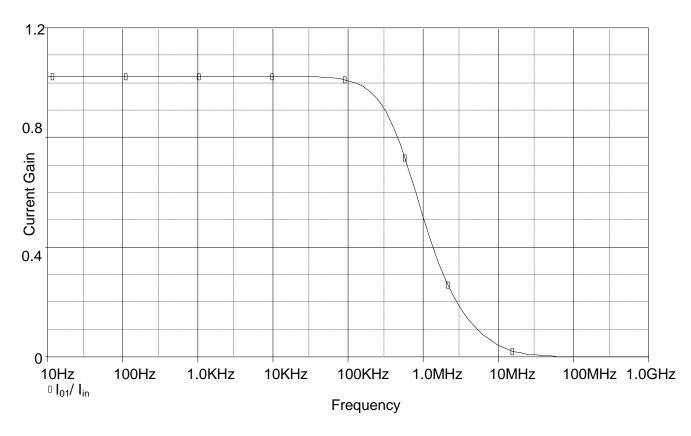

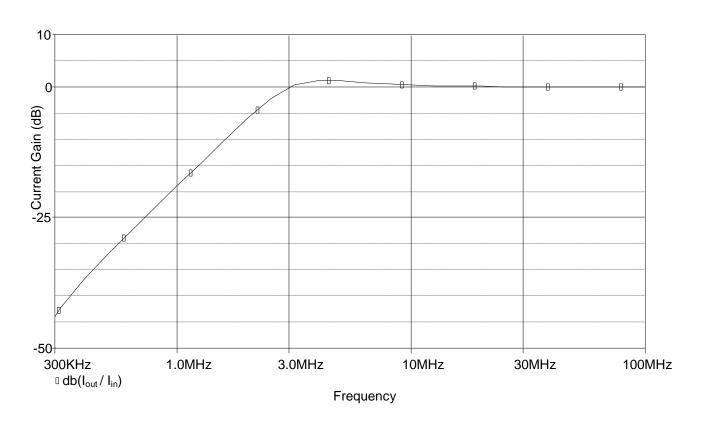

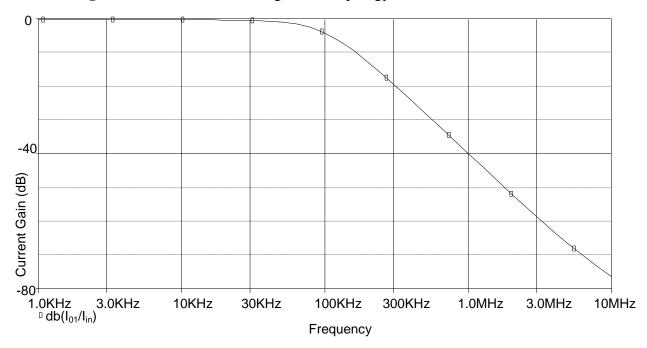

Figure 23 indicates the results of simulation which are obtained at the X- terminal which is a Low Pass response. The cut off frequency of the filter is obtained to be MHz.

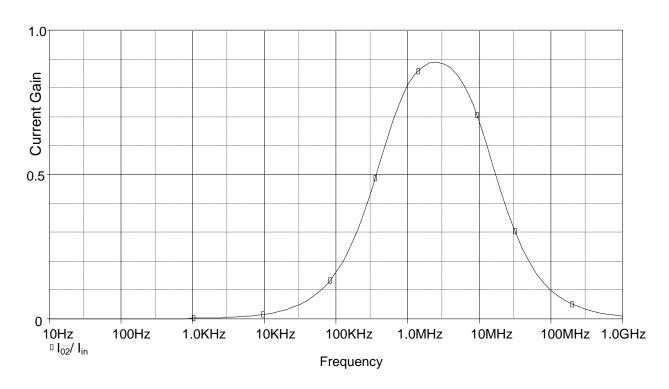

Figure 24 indicates the results of simulation that are obtained at the terminals of capacitor  $C_2$  which is a Band Pass response. The lower cut off frequency obtained after simulation is equal to 1.849MHz and the higher cut off frequency is equal to 4.676 MHz. The Bandwidth of the filter is obtained to be 2.827 MHz.

Figure 25 indicates the results of simulation that are obtained at the terminals of capacitor  $C_1$  which is a High Pass response. The cut off of the filter is obtained to be 3.677 MHz.

Figure 26 indicates the results of simulation for the Notch response of the above filter in accordance with equation 4.20.

Figure 27 indicates the results of simulation for the All Pass response of the above filter in accordance with equation 4.21.

Figure 22 : PSPICE circuit diagram of Topology C

Figure 23: Simulated Low Pass response of filter of Topology C

**Figure 24 :** Simulated Band Pass response of filter of Topology C

Figure 25: Simulated High Pass response of Topology C

**Figure 26 :** Simulated Notch response of filter of Topology C

Figure 27: Simulated All Pass magnitude response of filter of Topology C

Figure 28: Simulated All Pass phase response of filter of Topology C

### 4.2.4 TOPOLOGY D

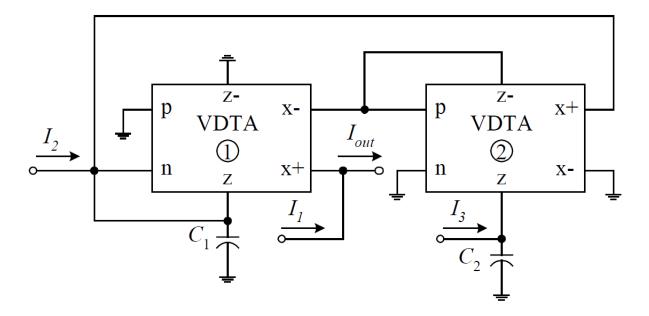

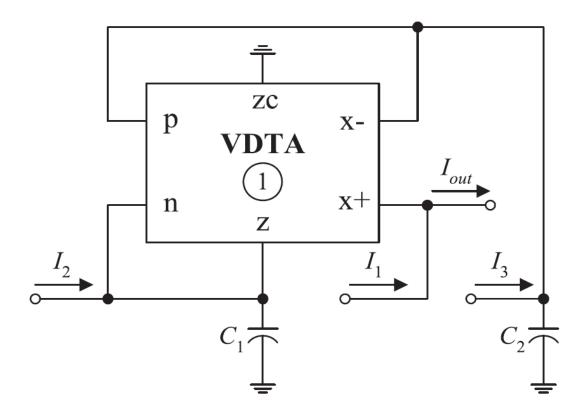

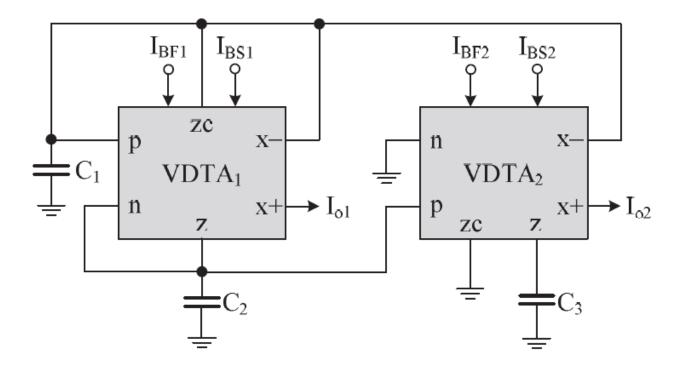

The filter topology here named as Topology D was introduced in 2013 [4]. This topology here shows a filter that works in current mode but the working of this topology is quite different from the previous one. Here only one output terminal is present but there is a presence of three input terminals along with it. So the output that we get depends on the terminal on which input is applied. This topology is capable of implementing all the filters i.e Low Pass, Band Pass, High Pass, Band Stop and All Pass filters. This filter uses two VDTA's and two capacitors which are grounded. The CMOS implementation of VDTA that is used here is given in Figure 3 and the aspect ratios of both the NMOS and PMOS transistors that are used here are given in Table 2. The circuit used for this topology is given in Figure 29. Here we can see that there is no need of any external passive resistor which is one of the benefits of this topology. This filter is capable of giving an independent control to both the angular frequency  $(\omega_0)$  and the Quality factor (Q). This control is provided through the transconductances of VDTA's.

In the Figure 29, the terminals represented by  $I_1$ ,  $I_2$  and  $I_3$  are the input terminals and the terminal represented by  $I_{out}$  is the only output terminal. The filter that is implemented on the output terminal is dependent on the input terminal at which input is being applied.

Figure 29: Current Mode Universal Filter (Topology D) [4]

Upon the analysis of the above circuit, the representation in s - domain [4] can be done as

$$I_{out} = \frac{D(s)I_1 + \left(\frac{g_{mS1}}{C_1}\right)sI_2 + \left(\frac{g_{mS1}g_{mS2}}{C_1C_2}\right)I_3}{D(s)}$$

(4.26)

$$D(s) = s^{2} + \left(\frac{g_{mF1}}{c_{1}}\right)s + \left(\frac{g_{mS1}g_{mS2}}{c_{1}c_{2}}\right)$$

(4.27)

So using above equation transfer function of any filter can be realised, so as to realise all the filters there are five different conditions [4] for the application of the input signal at the input terminals where each condition is going to realize a different function at the output terminal and are obtained using the equation 4.26.

- 1. If the current signal is being applied to the  $I_3$  input terminal and the rest two terminals are devoid of any input signal i.e  $I_3 = I_{in}$  and  $I_1 = I_2 = 0$ , then the response obtained at  $I_{out}$  is Low Pass and the gain obtained in the Pass Band is unity.

- 2. If the input current signal is supplied to the  $I_2$  terminal and the rest two terminals are devoid of any input signal i.e  $I_2 = I_{in}$  and  $I_1 = I_3 = 0$ , then the response obtained at  $I_{out}$  is Band Pass and the gain obtained in Pass Band is  $g_{mS1}/g_{mF1}$  where  $g_{mS1}$  and  $g_{mF1}$  are  $g_{mS}$  and  $g_{mF}$  of the first VDTA, where  $g_{mF}$  and  $g_{mS}$  are given as

$$g_{mF} = \frac{g_1 g_2}{g_1 + g_2} + \frac{g_3 g_4}{g_3 + g_4} \cong (g_{1,2} + g_{3,4})/2$$

(4.28)

$$g_{mS} = \frac{g_5 g_6}{g_5 + g_6} + \frac{g_7 g_8}{g_7 + g_8} \cong (g_{5,6} + g_{7,8})/2 \tag{4.29}$$

Where  $g_i$  is the transconductance value of the i<sup>th</sup> transistor of Figure 3.

- 3. If the input terminal is supplied at  $I_1$  and the opposite of that signal is supplied at  $I_2$  and  $I_3$  terminal i.e  $I_1 = -I_2 = -I_3 = I_{in}$  and  $g_{mF1} = g_{mS1}$ , the response obtained at  $I_{out}$  is High Pass and the gain obtained in the Pass Band is unity.

- 4. If  $I_1$  is supplied with the current input signal and  $I_2$  is supplied with the exact opposite of this signal i.e  $I_1 = -I_2 = I_{in}$  and also  $g_{mF1} = g_{mS1}$ . Here  $I_3$  is not supplied with any input i.e  $I_3 = 0$ , the response obtained at  $I_{out}$  is a Band Stop response and the gain obtained in the Pass Band is unity.

- 5. If the input is supplied at  $I_1$  and  $I_2$  is supplied with double of the input inverted at the terminal  $I_1$  i.e  $I_1 = -I_2/2 = I_{in}$ , no input is given at  $I_3$  i.e  $I_3 = 0$  and  $g_{mF1} = g_{mS1}$ . Here the response obtained at  $I_{out}$  is an All Pass Response and the pass band gain is obtained to be unity.

For all of the above conditions,  $g_{mF1}$  and  $g_{mS1}$  are defined in equations 4.28 and 4.29.

The equations for the Quality factor and Angular frequency [4] are given as

$$Q = \frac{1}{g_{mF1}} \sqrt{\frac{g_{mS1}g_{mS2}C_1}{C_2}} \tag{4.30}$$

$$\omega_0 = \sqrt{\frac{g_{mS1}g_{mS2}}{c_1c_2}} \tag{4.31}$$

Now for the sake of simplicity, if we go on to substitute  $g_{mS1} = g_{mS2} = g_{m2}$  and  $C_1 = C_2 = C$  in equations 4.30 and 4.31, the equations that we obtain[4] are

$$Q = \frac{g_{m2}}{g_{mF1}} \tag{4.32}$$

$$\omega_0 = \frac{g_{m2}}{C} \tag{4.33}$$

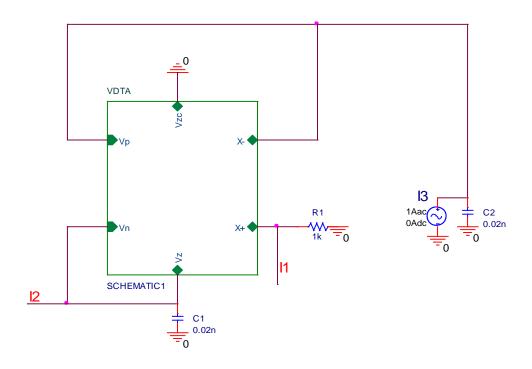

# **SIMULATION RESULTS:**

For this simulation, CMOS implementation of VDTA given in Figure 3 is used. The simulation is done on PSPICE using 0.35µm TSMC CMOS process parameters. The aspect

ratios for the PMOS and NMOS transistor are given in Table 2. Supply voltages used for providing the biasing for the given circuit are  $+V_{DD}=-V_{SS}=2$  volts. The values of the passive elements are chosen to be  $C_1=C_2=20$  pF [4]. The natural frequency of the filter is chosen to be 3.03 MHz and Quality factor is chosen to be 1 [4]. For achieving these values the transconductance values are chosen [4] to be  $g_{mF1}=g_{mS1}=g_{mF2}=g_{mS1}=381\mu\text{A/V}$ . For achieving these values the biasing currents are chosen [4] to be  $I_{BF1}=I_{BS1}=I_{BF2}=I_{BS2}=40\mu\text{A}$ .

The circuit used for the simulation in PSPICE software is given in Figure 30. However this circuit is used only for case 1 indicated above and for the rest of the cases the changes on the three terminals is done as written above in those five points.

Figure 31 indicates the results of simulation which are obtained at the  $I_{out}$  terminal following the input conditions given in point no 1 and it is a Low Pass response. The cut off frequency of the filter is obtained to be 3.7488 MHz.

Figure 32 indicates the results of simulation that are obtained at the terminal  $I_{out}$  following the input conditions given in point no 2 and it is a Band Pass response. The lower cut off frequency obtained after simulation is equal to 1.8596 MHz and the higher cut off frequency is equal to 4.872 MHz. The Bandwidth of the filter is obtained to be 3.0124 MHz.

Figure 33 indicates the results of simulation that are obtained at the terminal I<sub>out</sub> following the input conditions given in point no 3 and it is a High Pass response. The cut off of the filter is obtained to be 2.368 MHz.

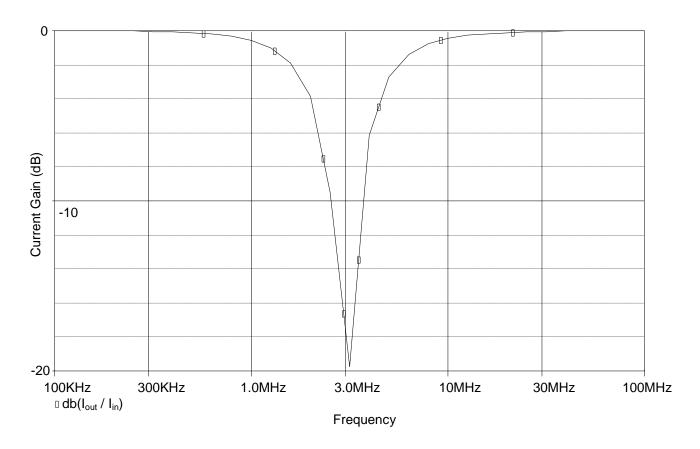

Figure 34 indicates the results of simulation that are obtained at the terminal  $I_{out}$  following the input conditions given in point no 4 and it is a Band Stop response. Frequency at the notch is obtained to be 3.157 MHz. The first 3-dB point is obtained at 1.798 MHz, the second 3-dB point is obtained at 4.934 MHz and the Bandwidth of the stop band is 3.136 MHz.

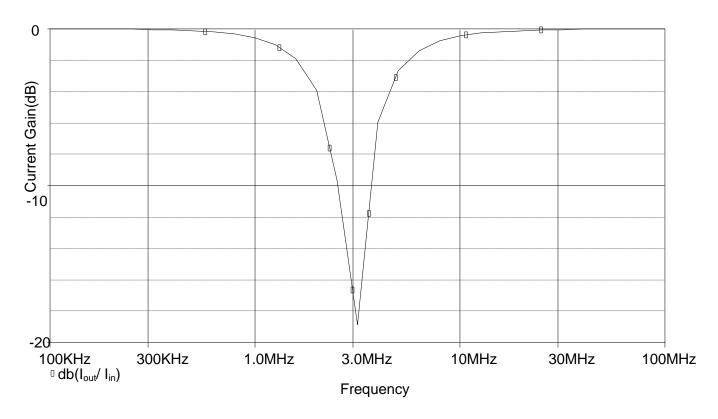

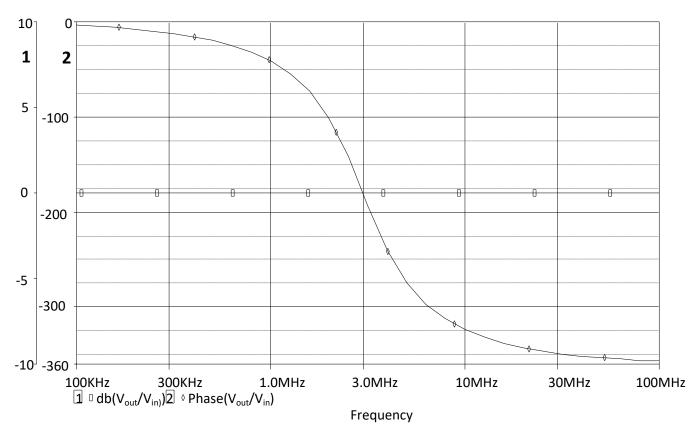

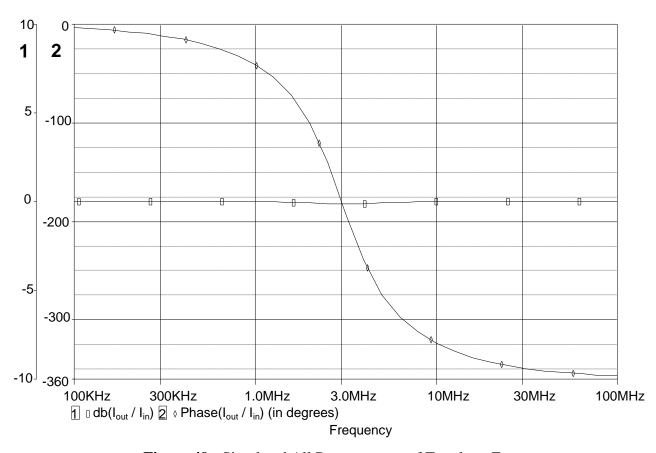

Figure 35 indicates the results of simulation that are obtained at the terminal  $I_{out}$  following the input conditions given in point no 3 and it is a All Pass response. This figure indicates both the phase and magnitude response of All Pass filter in the same graph.

Figure 30 : PSPICE circuit diagram of Topology D (case 1)

Figure 31: Simulated Low Pass response of Topology D

Figure 32: Simulated Band Pass response of Topology D

Figure 33 : Simulated High Pass response of Topology D

Figure 34: Simulated Band Stop response of Topology D

Figure 35: Simulated All Pass response of Topology D

# 4.2.5 TOPOLOGY E

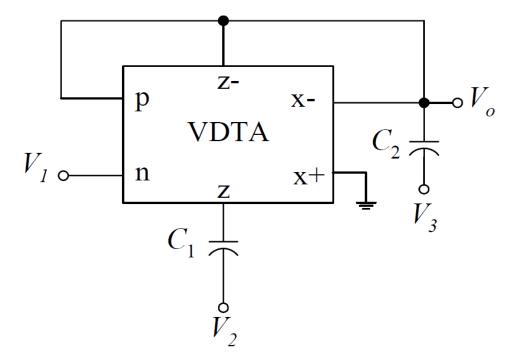

The filter topology here named as Topology E was introduced in 2012 [5]. This topology here shows a filter that works in voltage mode but the working of this topology is almost same as the previous one, only difference is that the previous topology is a current mode circuit. The filter here implemented is a Voltage Mode universal Biquad filter. Here also only one output terminal is present but there is a presence of three input terminals along with it. So the output that we get depends on the terminal on which input is applied. This topology is capable of implementing all the filters i.e Low Pass, Band Pass, High Pass, Band Stop and All Pass filters. This filter uses two VDTA's and two capacitors which are grounded. The CMOS implementation of VDTA that is used here is given in Figure 3 and the aspect ratios of both the NMOS and PMOS transistors that are used here are given in Table 2. The circuit used for this topology is given in Figure 36. Here we can see that there is no need of any external passive resistor which is one of the benefits of this topology. The angular frequency and the Bandwidth of the filter implemented in this topology can be independently tuned electronically.

In the Figure 36, the terminals represented by  $V_1$ ,  $V_2$  and  $V_3$  are the input terminals and the terminal represented by  $V_{out}$  is the only output terminal. The filter that is implemented on the output terminal is dependent on the input terminal at which input is being applied.

Figure 36: Voltage Mode Universal Biquad filter (Topology E) [5]

Upon the analysis of the above circuit, the representation in s - domain [5] can be done as

$$V_{out} = \frac{s^2 V_3 - \left(\frac{g_{mS}}{C_2}\right) s V_2 + \left(\left(\frac{g_{mF}}{C_2}\right) s + \frac{g_{mS}g_{mF}}{C_1C_2}\right) I_3}{D(s)}$$

(4.34)

Where

$$D(s) = s^2 + \left(\frac{g_{mF}}{c_1}\right)s + \left(\frac{g_{mS}g_{mF}}{c_1c_2}\right)$$

(4.35)

So using above equation transfer function of any filter can be realised, so as to realise all the filters there are five different conditions [5] for the application of the input signal at the input terminals where each condition is going to realize a different function at the output terminal and are obtained using the equation 4.34.

- 1. If the voltage signal is being applied at both the input terminals  $V_1$  and  $V_2$  i.e  $V_1 = V_2$  =  $V_{in}$  and no signal is applied at the terminal  $V_3$  or in other words  $V_3$  is grounded i.e  $V_3$ =0 and also both the transconductances are equal i.e  $g_{mF}$ = $g_{mS}$  then the output obtained at  $V_{out}$  is a low pass response.

- 2. If the input is applied at the  $V_2$  terminal i.e  $V_2 = V_{in}$  and  $V_1$  and  $V_3$  both the terminals are grounded i.e  $V_1 = V_3 = 0$ , then the response obtained at the  $V_{out}$  terminal is a Band Pass response.

- 3. If the input is applied only at the  $V_3$  terminal and both the  $V_1$  and  $V_2$  terminal are grounded i.e  $V_1 = V_2 = 0$ , then the response obtained at the  $V_{out}$  terminal is a High Pass response.

- 4. If the input is applied at all the three input terminals i.e  $V_1 = V_2 = V_3 = V$ in and also both the transconductances are equal i.e  $g_{mF}=g_{mS}$  then the output obtained at  $V_{out}$  is a Band Stop response.

- 5. If the voltage signal is being applied at both the input terminals  $V_1$  and  $V_3$  and half of the input voltage is applied at the  $V_3$  terminal i.e  $V_1 = 2V_2 = V_3 = V_{in}$  and also both the transconductances are equal i.e  $g_{mF}=g_{mS}$  then the output obtained at  $V_{out}$  is a All Pass response.

For all of the above conditions,  $g_{mF}$  and  $g_{mS}$  are defined in equations 4.28 and 4.29.

The equations for the Angular frequency and the Bandwidth [5] are given as

$$\omega_0 = \sqrt{\frac{g_{mF}g_{mS}}{C_1C_2}} \tag{4.36}$$

$$Q = \frac{g_{mF}}{c_2} \tag{4.37}$$

# **SIMULATION RESULTS:**

For this simulation, CMOS implementation of VDTA given in Figure 3 is used. The simulation is done on PSPICE using  $0.35\mu m$  TSMC CMOS process parameters. The aspect ratios for the PMOS and NMOS transistor are given in Table 2. Supply voltages used for providing the biasing for the given circuit are  $+V_{DD}=-V_{SS}=2$  volts. The values of the passive elements are chosen to be  $C_1=C_2=20$  pF [5]. The natural frequency of the filter is chosen to be 3.03 MHz and Quality factor is chosen to be 1 [5]. For achieving these values the transconductance values are chosen [5] to be  $g_{mF1}=g_{mS1}=g_{mF2}=g_{mS1}=381\mu A/V$ . For achieving these values the biasing currents are chosen [4] to be  $I_{BF1}=I_{BS1}=I_{BF2}=I_{BS2}=40\mu A$ .

The circuit used for the simulation in PSPICE software is given in Figure 37. However this circuit is used only for case 1 indicated above and for the rest of the cases the changes on the three terminals is done as written above in those five points.

Figure 38 indicates the results of simulation which are obtained at the  $V_{out}$  terminal following the input conditions given in point no 1 and it is a Low Pass response. The cut off frequency of the filter is obtained to be 3.782 MHz.

Figure 39 indicates the results of simulation that are obtained at the terminal  $V_{out}$  following the input conditions given in point no 2 and it is a Band Pass response. The lower cut off frequency obtained after simulation is equal to 1.886 MHz and the higher cut off frequency is equal to 4.808 MHz. The Bandwidth of the filter is obtained to be 2.929 MHz.

Figure 40 indicates the results of simulation that are obtained at the terminal  $V_{out}$  following the input conditions given in point no 3 and it is a High Pass response. The cut off of the filter is obtained to be at 2.3913 MHz.

Figure 41 indicates the results of simulation that are obtained at the terminal  $V_{out}$  following the input conditions given in point no 4 and it is a Band Stop response. Frequency at the notch is obtained to be 3.237 MHz. The first 3-dB point is obtained at 1.808 MHz, the second 3-dB point is obtained at 4.945 MHz and the Bandwidth of the stop band is 3.136 MHz.

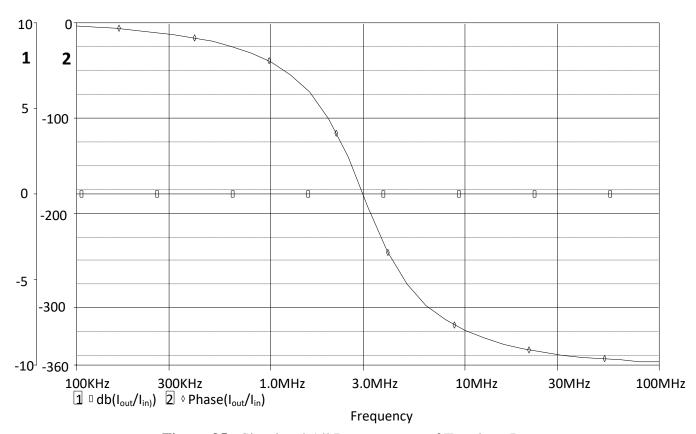

Figure 42 indicates the results of simulation that are obtained at the terminal  $V_{out}$  following the input conditions given in point no 3 and it is a All Pass response. This figure indicates both the phase and magnitude response of All Pass filter in the same graph.

Figure 37: PSPICE circuit diagram of Topology E (case 1)

Figure 38: Simulated Low Pass response of Topology E

Figure 39: Simulated Band Pass response of Topology E

**Figure 40 :** Simulated High Pass response of Topology E

Figure 41: Simulated Band Stop response of Topology E

Figure 42: Simulated All Pass response of Topology E

# 4.2.6 TOPOLOGY F

The filter topology here named as Topology F was introduced in 2014 [6]. This topology here shows a filter that works in current mode. Here only one output terminal is present but there is a presence of three input terminals along with it. So the output that we get depends on the terminal on which input is applied. This topology is capable of implementing all the filters i.e Low Pass, Band Pass, High Pass, Band Stop and All Pass filters. This filter uses two VDTA's and two capacitors which are grounded. The CMOS implementation of VDTA that is used here is given in Figure 3 and the aspect ratios of both the NMOS and PMOS transistors that are used here are given in Table 2. The circuit used for this topology is given in Figure 43. Here we can see that there is no need of any external passive resistor which is one of the benefits of this topology. This filter is capable of giving an independent control to both the angular frequency  $(\omega_0)$  and the Quality factor (Q). This control is provided through the transconductances of VDTA's.