# LEAKAGE POWER REDUCTION IN DYNAMIC DCVSL USING ONOFIC APPROACH

### DISSERTATION SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### MASTER OF TECHNOLOGY IN VLSI DESIGN AND EMBEDDED SYSTEM

BY

Jayesh Trivedi (2K15/VLS/08)

**Under the guidance of**

Dr. Neeta Pandey Associate Professor, Electronics and Communication Engineering Department, DTU

2015-2017

ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

DELHI TECHNOLOGICAL UNIVERSITY, DELHI-110042, INDIA

Electronics and Communication Engineering Department Delhi Technological University Delhi-110042

# **CERTIFICATE**

This is to certify that the dissertation titled "Leakage Power Reduction in Dynamic DCVSL using ONOFIC Approach" is a bonafide record of work done by Jayesh Trivedi, Roll No. 2K15/VLS/08 at Delhi Technological University for partial fulfilment of the requirements for the award of degree of Master of Technology in VLSI and Embedded Systems Engineering. This project was carried out under my supervision and has not been submitted elsewhere, either in part or full, for the award of any other degree or diploma to the best of my knowledge and belief.

Date:

(Dr. Neeta Pandey) Associate Professor Department of Electronics and Communication Engineering Delhi Technological University

# **ACKNOWLEDGEMENT**

First and foremost, I would like to express my deepest gratitude and sincerest appreciation to my Project Guide, **Dr. Neeta Pandey**, Associate Professor, Department of Electronics and Communication Engineering, Delhi Technological University for her guidance and tremendous support throughout the course of this project. Her knowledge and expertise have been really helpful in this research work. Her ideas for approaching each problem statement in a different manner have been extremely useful.

I would like to thank all my professors for their thoughtful teaching during my M.Tech. course. I would also like to thank all the other faculty members and non-teaching staff of the Department of ECE for helping me directly or indirectly in completion of this project.

(Jayesh Trivedi)

University Roll no: 2K15/VLS/08

M.Tech. (VLSI Design and Embedded System)

**Department of Electronics and Communication Engineering**

**Delhi Technological University**

# **CONTENTS**

| Certificate    | •••••               |                                                | •••••          |

|----------------|---------------------|------------------------------------------------|----------------|

| Acknowledge    | ement               |                                                | •••••          |

| Contents       | • • • • • • • • • • |                                                | •••••          |

| List of figure | S                   |                                                |                |

| List of tables |                     |                                                | •••••          |

| Abstract       | •••••               |                                                |                |

| Chapter 1:     | Intro               | luction                                        | {1-4}          |

|                | (1.1)               | Topic Overview                                 | (1)            |

|                | (1.2)               | Thesis Structure                               | (4)            |

| Chapter 2:     | Differ              | ential Cascode Voltage Switch Logic            | {5-10}         |

|                | (2.1)               | Operation                                      | (5)            |

|                | (2.2)               | Advantages of DCVSL                            | (6)            |

|                | (2.3)               | Disadvantages of DCVSL                         | (7)            |

|                | (2.4)               | Dynamic DCVSL                                  | (8)            |

|                |                     | • Operation                                    | (8)            |

|                |                     | Advantages of Dynamic DCVSL                    | (9)            |

|                | (2.5)               | Idea of Leakage in Dynamic DCVSL               | (9)            |

| Chapter 3:     | Dynai               | mic DCVSL Variations                           | <b>{11-40}</b> |

|                | • In                | troduction                                     | (11)           |

|                | (3.1)               | Sample-Set Differential Logic (SSDL)           | (11)           |

|                |                     | • Operation                                    | (12)           |

|                |                     | • Schematic                                    | (12)           |

|                |                     | Simulation Results                             | (13)           |

|                |                     | Performance Measurement                        | (15)           |

|                | (3.2)               | Modified Sample-Set Differential Logic (MSSDL) | (16)           |

|                |                     | • Operation                                    | (17)           |

|                |                     | • Schematic                                    | (17)           |

|            | Simulation Results                                                                                           | (18)                  |

|------------|--------------------------------------------------------------------------------------------------------------|-----------------------|

|            | Performance Measurement                                                                                      | (20)                  |

|            | (3.3) Enable/Disable CMOS Differential Logic (ECDL                                                           | <i>.</i> ) (21)       |

|            | • Operation                                                                                                  | (21)                  |

|            | Schematic                                                                                                    | (22)                  |

|            | Simulation Results                                                                                           | (23)                  |

|            | Performance Measurement                                                                                      | (25)                  |

|            | (3.4) Differential Current Switch Logic (DCSL)                                                               | (26)                  |

|            | • Operation                                                                                                  | (26)                  |

|            | Schematic                                                                                                    | (27)                  |

|            | Simulation Results                                                                                           | (28)                  |

|            | Performance Measurement                                                                                      | (29)                  |

|            | <ul> <li>(3.5) Enhanced Differential Cascode<br/>Voltage Switch Logic (EDCVSL)</li> <li>Operation</li> </ul> | ( <b>30</b> )<br>(31) |

|            | • Schematic                                                                                                  | (32)                  |

|            | Simulation Results                                                                                           | (33)                  |

|            | Performance Measurement                                                                                      | (34)                  |

|            | (3.6) NP- Mixed DCVSL                                                                                        | (35)                  |

|            | • Operation                                                                                                  | (35)                  |

|            | • Schematic                                                                                                  | (35)                  |

|            | Simulation Results                                                                                           | (36)                  |

|            | Performance Measurement                                                                                      | (38)                  |

|            | • Summary                                                                                                    | (39)                  |

| Chapter 4: | LECTOR incorporated Dynamic DCVSL Variations                                                                 | {41-63}               |

|            | • Introduction                                                                                               | (41)                  |

|            | Operation                                                                                                    | (42)                  |

| (4.1) | LECTOR incorporated Sample-Set<br>Differential Logic (L-SSDL)                        | (44) |

|-------|--------------------------------------------------------------------------------------|------|

|       | • Schematic                                                                          | (44) |

|       | Simulation Results                                                                   | (45) |

|       | Performance Measurement                                                              | (46) |

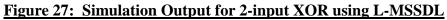

| (4.2) | LECTOR incorporated Modified<br>Sample-Set Differential Logic (L-MSSDL)              | (47) |

|       | • Schematic                                                                          | (47) |

|       | Simulation Results                                                                   | (48) |

|       | Performance Measurement                                                              | (49) |

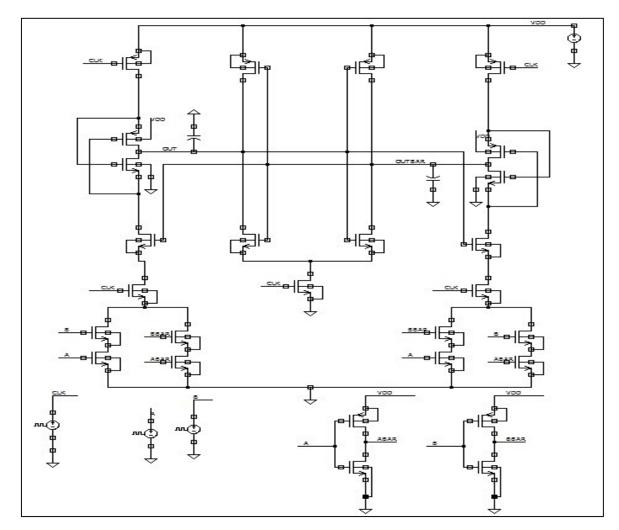

| (4.3) | LECTOR incorporated Enable/Disable<br>CMOS Differential Logic (L-ECDL)               | (50) |

|       | • Schematic                                                                          | (50) |

|       | Simulation Results                                                                   | (51) |

|       | Performance Measurement                                                              | (52) |

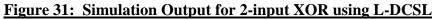

| (4.4) | LECTOR incorporated Differential Current<br>Switch Logic (L-DCSL)                    | (53) |

|       | • Schematic                                                                          | (53) |

|       | Simulation Results                                                                   | (54) |

|       | Performance Measurement                                                              | (55) |

| (4.5) | LECTOR incorporated Enhanced Differential<br>Cascode Voltage Switch Logic (L-EDCVSL) | (56) |

|       | • Schematic                                                                          | (56) |

|       | Simulation Results                                                                   | (57) |

|       | Performance Measurement                                                              | (58) |

| (4.6) | LECTOR incorporated NP- Mixed<br>DCVSL (L-NP-Mixed)                                  | (59) |

|       | • Schematic                                                                          | (59) |

|       | Simulation Results                                                                   | (60) |

|       |                                                                                      |      |

|            | Performance Meas                                         | urement (61)               |

|------------|----------------------------------------------------------|----------------------------|

|            | • Summary                                                | (62)                       |

| Chapter 5: | ONOFIC incorporated Dynamic                              | c DCVSL Variations {64-86} |

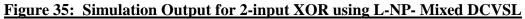

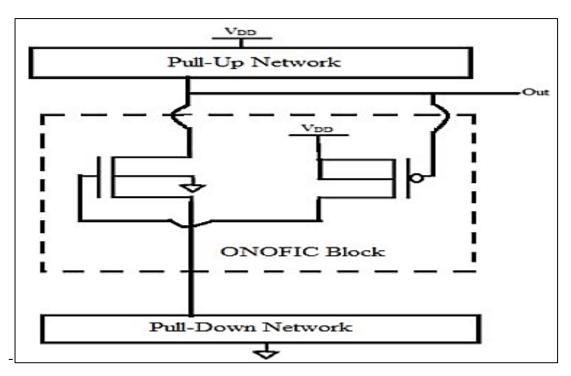

|            | <ul><li>Introduction</li><li>Operation</li></ul>         | (64)<br>(65)               |

|            | (5.1) ONOFIC incorporated S<br>Differential Logic (O-SS) | -                          |

|            | • Schematic                                              | (67)                       |

|            | Simulation Results                                       | (68)                       |

|            | Performance Meas                                         | urement (69)               |

|            | (5.2) ONOFIC incorporated M<br>Sample-Set Differential I |                            |

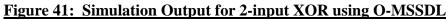

|            | • Schematic                                              | (70)                       |

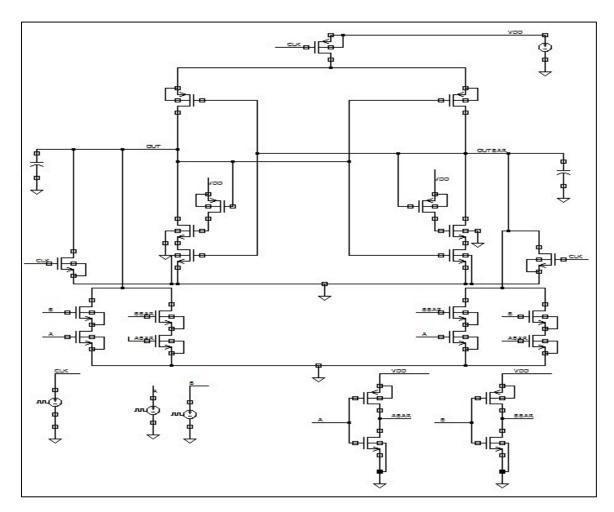

|            | Simulation Results                                       | (71)                       |

|            | Performance Meas                                         | urement (72)               |

|            | (5.3) ONOFIC incorporated E<br>CMOS Differential Logic   |                            |

|            | • Schematic                                              | (73)                       |

|            | • Simulation Results                                     | (74)                       |

|            | Performance Meas                                         | urement (75)               |

|            | (5.4) ONOFIC incorporated D<br>Switch Logic (O-DCSL)     | Differential Current (76)  |

|            | • Schematic                                              | (76)                       |

|            | Simulation Results                                       | (77)                       |

|            | • Performance Meas                                       | urement (78)               |

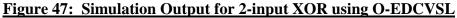

|            | (5.5) | ONOFIC incorporated Enhanced Differential<br>Cascode Voltage Switch Logic (O-EDCVSL) | (79)            |

|------------|-------|--------------------------------------------------------------------------------------|-----------------|

|            |       | • Schematic                                                                          | (79)            |

|            |       | Simulation Results                                                                   | (80)            |

|            |       | Performance Measurement                                                              | (81)            |

|            | (5.6) | ONOFIC incorporated NP- Mixed<br>DCVSL (O-NP-Mixed)                                  | (82)            |

|            |       | • Schematic                                                                          | (82)            |

|            |       | Simulation Results                                                                   | (83)            |

|            |       | Performance Measurement                                                              | (84)            |

|            | •     | Summary                                                                              | (85)            |

| Chapter 6: | Relat | ive Performance Analysis                                                             | <b>{87-98</b> } |

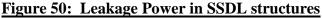

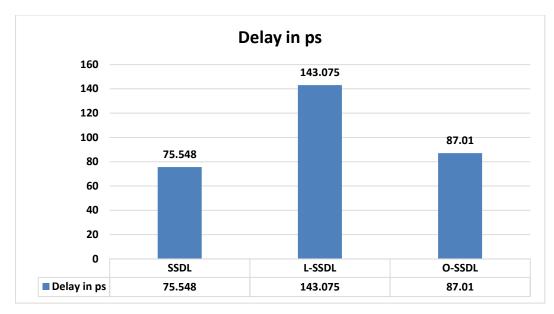

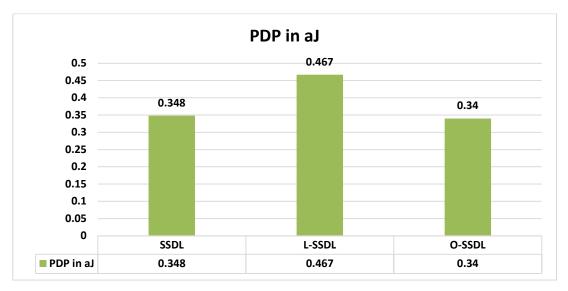

|            | (6.1) | SSDL vs. L-SSDL vs. O-SSDL                                                           | (87)            |

|            | (6.2) | MSSDL vs. L-MSSDL vs. O-MSSDL                                                        | (89)            |

|            | (6.3) | ECDL vs. L-ECDL vs. O-ECDL                                                           | (91)            |

|            | (6.4) | DCSL vs. L-DCSL vs. O-DCSL                                                           | (93)            |

|            | (6.5) | EDCVSL vs. L-EDCVSL vs. O-EDCVSL                                                     | (95)            |

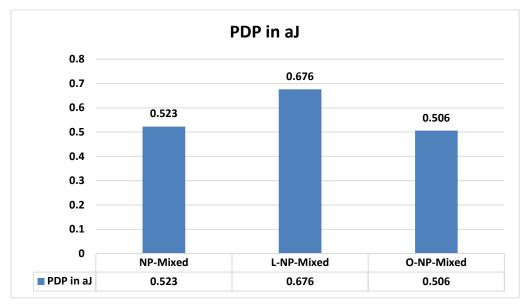

|            | (6.6) | NP-Mixed vs. L- NP-Mixed vs. O-NP-Mixed                                              | (97)            |

| Chapter 7: | Concl | lusion                                                                               | <b>{99-100}</b> |

# **LIST OF FIGURES**

| Figure 1:  | Power Dissipation in VLSI Circuits                        | (1)  |

|------------|-----------------------------------------------------------|------|

| Figure 2:  | Leakage Power significance at lower technology nodes [12] | (2)  |

| Figure 3:  | Basic DCVSL Circuit [2]                                   | (5)  |

| Figure 4:  | DCVSL: (a) Static version, and (b) Dynamic version [3]    | (8)  |

| Figure 5:  | SSDL Schematic [11]                                       | (11) |

| Figure 6:  | 2-input XOR using SSDL architecture                       | (13) |

| Figure 7:  | Simulation Output for 2-input XOR using SSDL              | (14) |

| Figure 8:  | MSSDL Schematic [2]                                       | (16) |

| Figure 9:  | 2-input XOR using MSSDL architecture                      | (18) |

| Figure 10: | Simulation Output for 2-input XOR using MSSDL             | (19) |

| Figure 11: | ECDL Schematic [2]                                        | (21) |

| Figure 12: | 2-input XOR using ECDL architecture                       | (23) |

| Figure 13: | Simulation Output for 2-input XOR using ECDL              | (24) |

| Figure 14: | DCSL Schematic [2]                                        | (26) |

| Figure 15: | 2-input XOR using DCSL architecture                       | (27) |

| Figure 16: | Simulation Output for 2-input XOR using DCSL              | (28) |

| Figure 17: | EDCVSL Type - I Structure [6]                             | (30) |

| Figure 18: | EDCVSL Type - II Structure [6]                            | (31) |

| Figure 19: | 2-input XOR using EDCVSL architecture                     | (32) |

| Figure 20: | Simulation Output for 2-input XOR using EDCVSL            | (33) |

| Figure 21: | 2-input XOR using NP- Mixed DCVSL architecture            | (36) |

| Figure 22: | Simulation Output for 2-input XOR using NP- Mixed DCVSL   | (37) |

| Figure 23: | LECTOR incorporated CMOS 2-input NAND gate [8]            | (42) |

| Figure 24: | 2-input XOR using L-SSDL architecture                     | (44) |

| Figure 25: | Simulation Output for 2-input XOR using L-SSDL            | (45) |

| Figure 26: | 2-input XOR using L-MSSDL architecture                    | (47) |

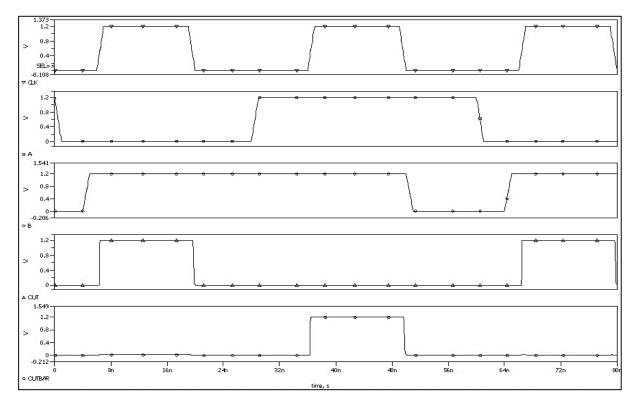

| Figure 27: | Simulation Output for 2-input XOR using L-MSSDL           | (48) |

| Figure 28: | 2-input XOR using L-ECDL architecture                     | (50) |

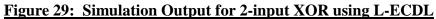

| Figure 29: | Simulation Output for 2-input XOR using L-ECDL            | (51) |

| Figure 30: | 2-input XOR using L-DCSL architecture                     | (53) |

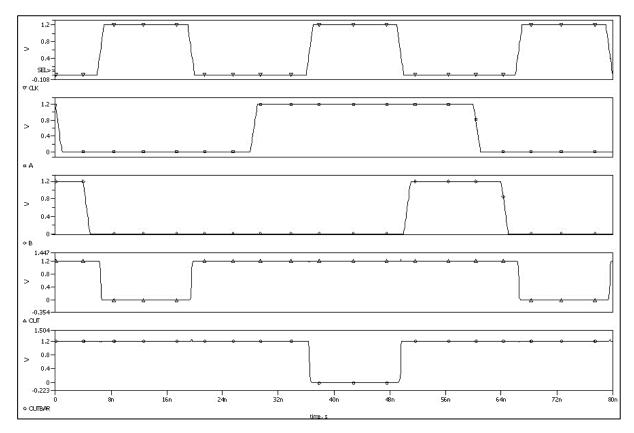

| Figure 31: | Simulation Output for 2-input XOR using L-DCSL            | (54) |

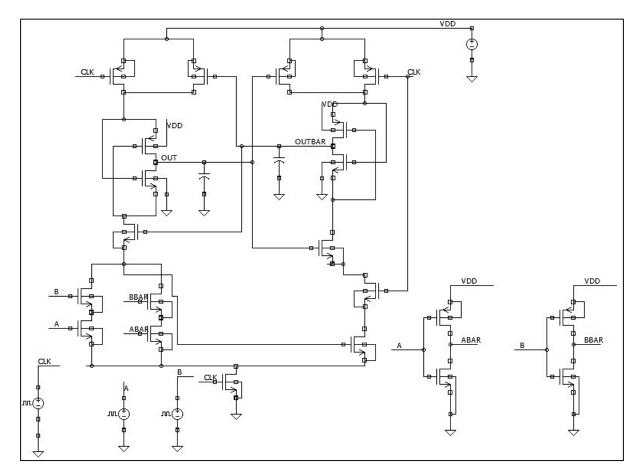

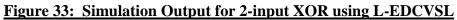

| Figure 32: | 2-input XOR using L-EDCVSL architecture                   | (56) |

|------------|-----------------------------------------------------------|------|

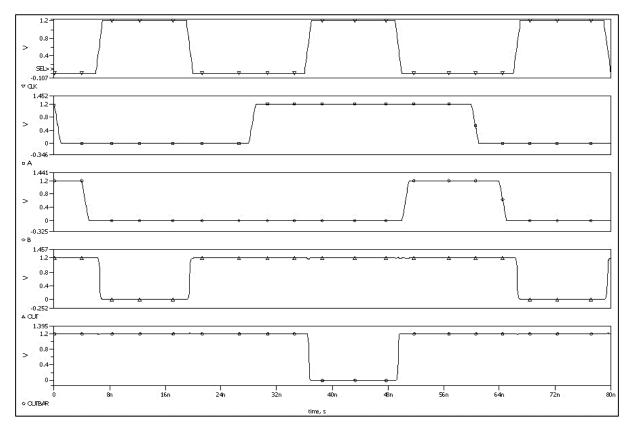

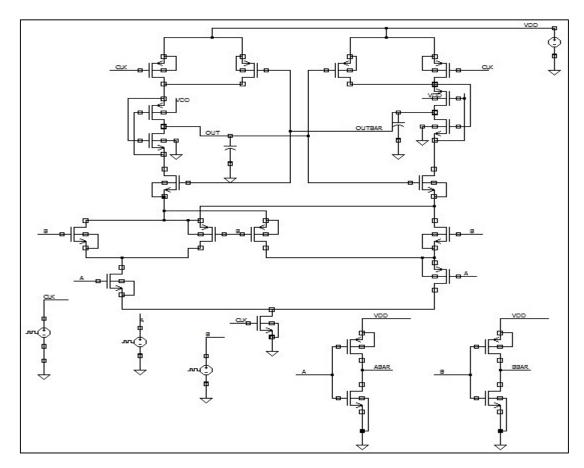

| Figure 33: | Simulation Output for 2-input XOR using L-EDCVSL          | (57) |

| Figure 34: | 2-input XOR using L-NP- Mixed DCVSL architecture          | (59) |

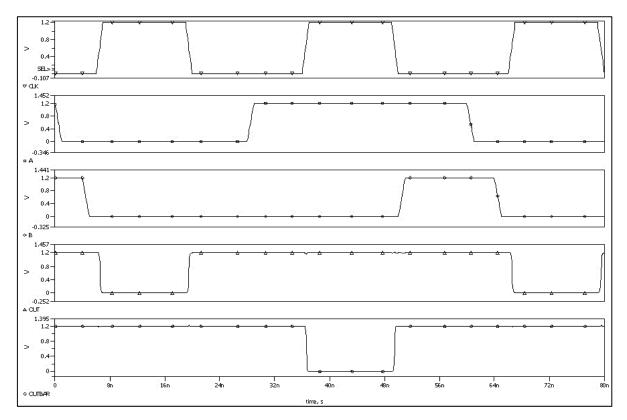

| Figure 35: | Simulation Output for 2-input XOR using L-NP- Mixed DCVSL | (60) |

| Figure 36: | ONOFIC Schematic [1]                                      | (64) |

| Figure 37: | ONOFIC 2-input NAND Schematic                             | (65) |

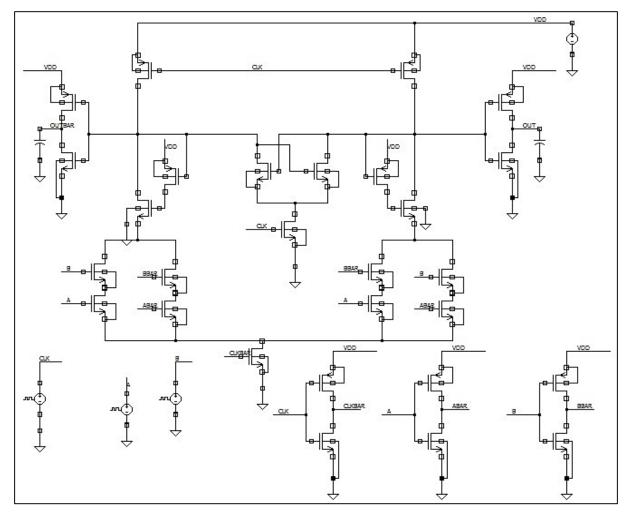

| Figure 38: | 2-input XOR using O-SSDL architecture                     | (67) |

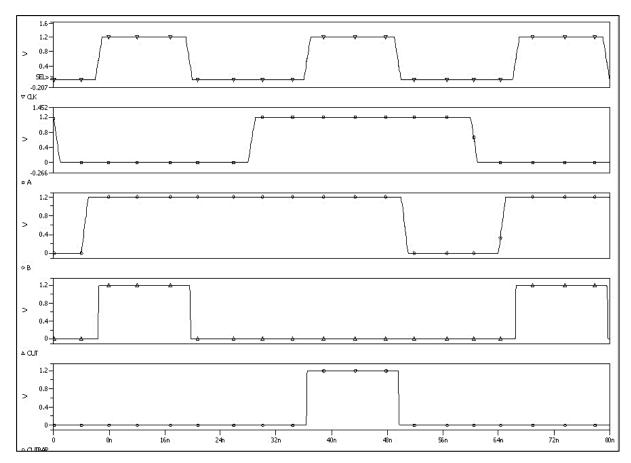

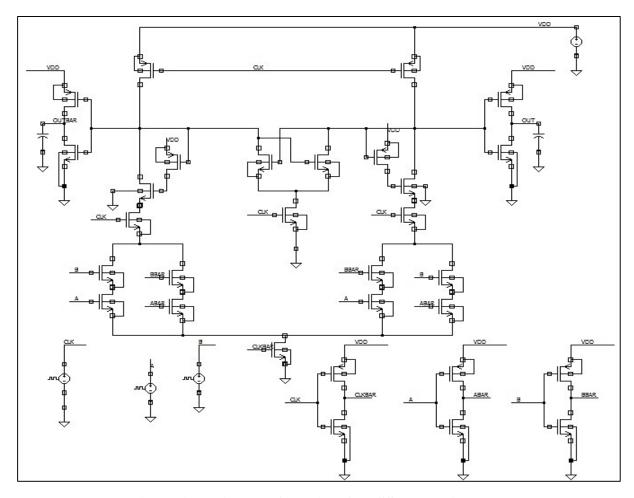

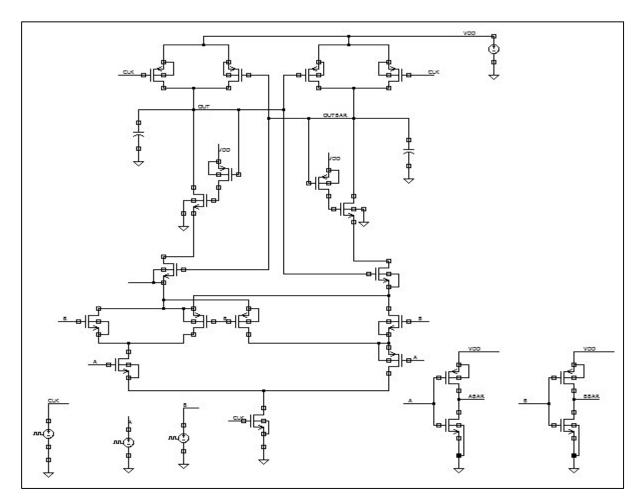

| Figure 39: | Simulation Output for 2-input XOR using O-SSDL            | (68) |

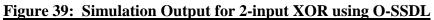

| Figure 40: | 2-input XOR using O-MSSDL architecture                    | (70) |

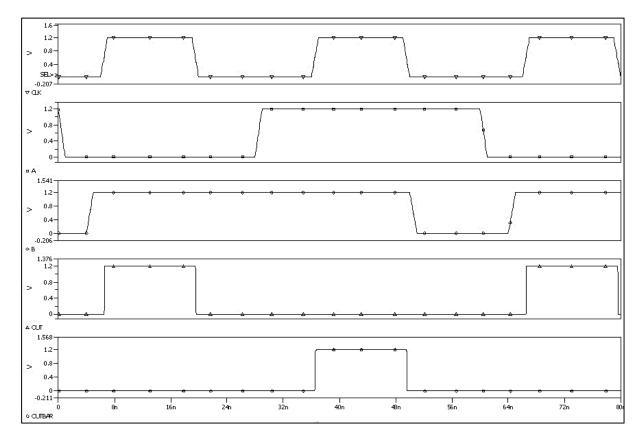

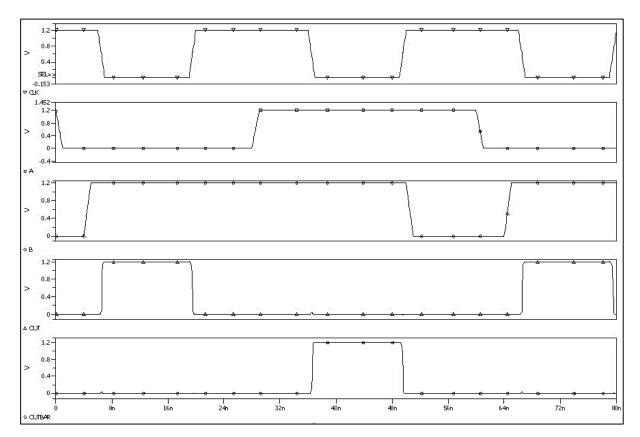

| Figure 41: | Simulation Output for 2-input XOR using O-MSSDL           | (71) |

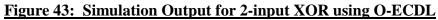

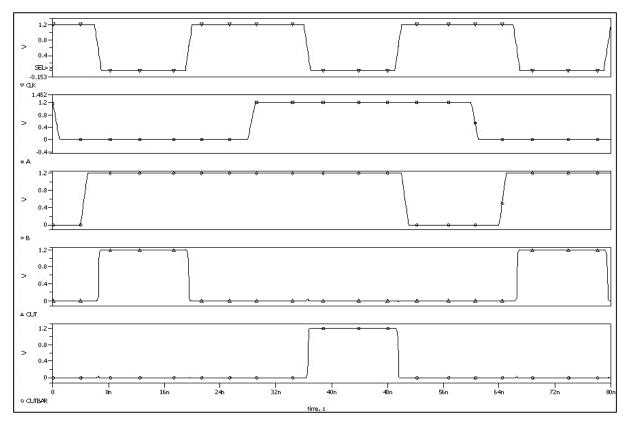

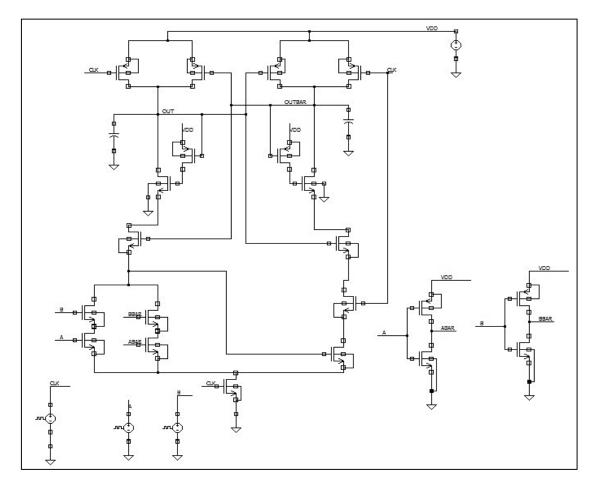

| Figure 42: | 2-input XOR using O-ECDL architecture                     | (73) |

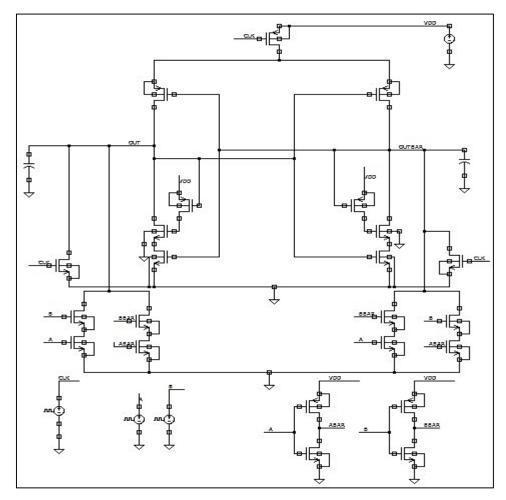

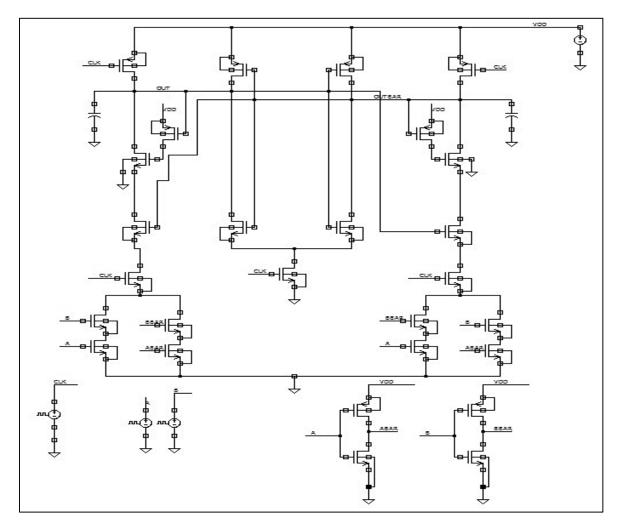

| Figure 43: | Simulation Output for 2-input XOR using O-ECDL            | (74) |

| Figure 44: | 2-input XOR using O-DCSL architecture                     | (76) |

| Figure 45: | Simulation Output for 2-input XOR using O-DCSL            | (77) |

| Figure 46: | 2-input XOR using O-EDCVSL architecture                   | (79) |

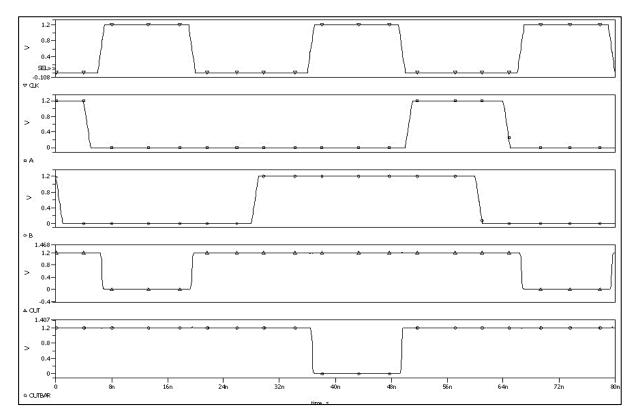

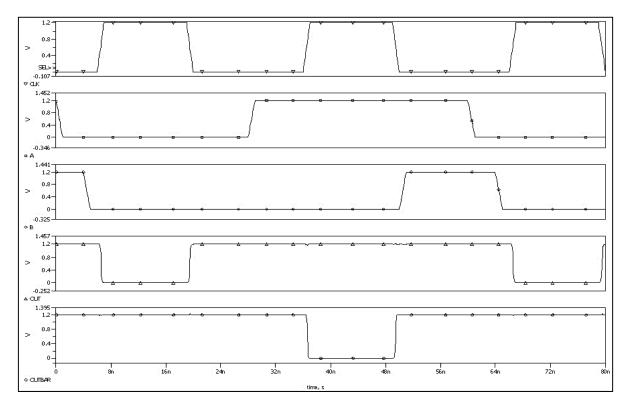

| Figure 47: | Simulation Output for 2-input XOR using O-EDCVSL          | (80) |

| Figure 48: | 2-input XOR using O-NP- Mixed DCVSL architecture          | (82) |

| Figure 49: | Simulation Output for 2-input XOR using O-NP- Mixed DCVSL | (83) |

| Figure 50: | Leakage Power in SSDL structures                          | (87) |

| Figure 51: | Delay in SSDL structures                                  | (88) |

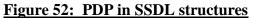

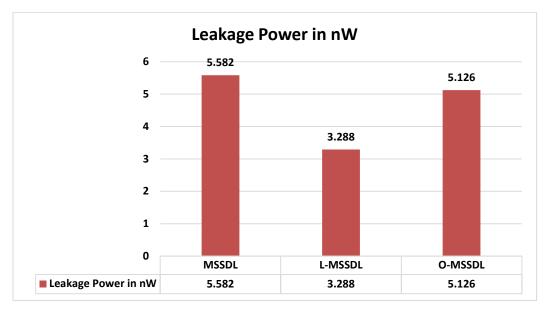

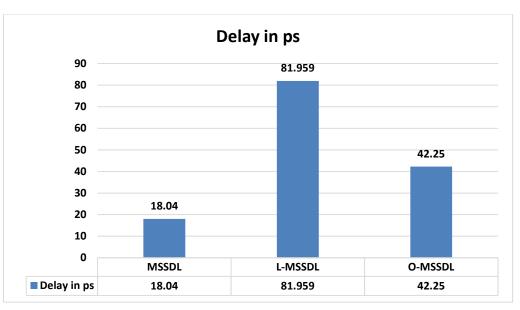

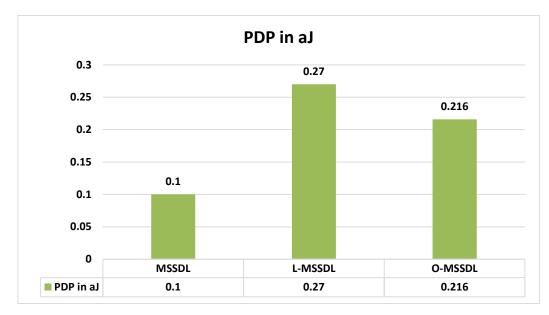

| Figure 52: | PDP in SSDL structures                                    | (88) |

| Figure 53: | Leakage Power in MSSDL structures                         | (89) |

| Figure 54: | Delay in MSSDL structures                                 | (90) |

| Figure 55: | PDP in MSSDL structures                                   | (90) |

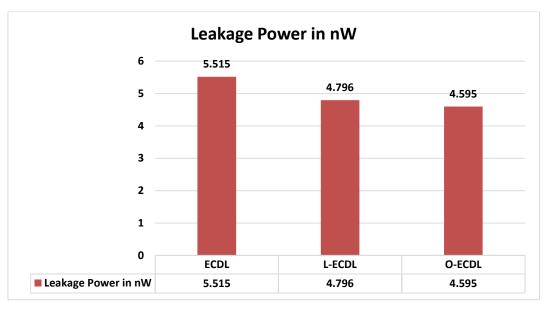

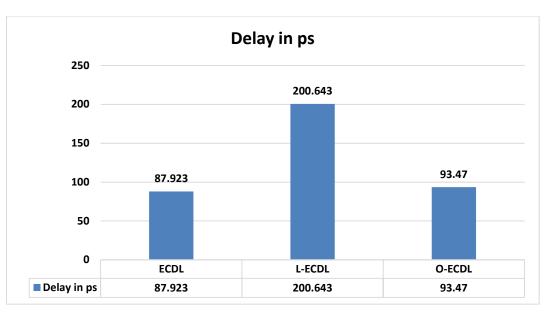

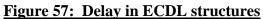

| Figure 56: | Leakage Power in ECDL structures                          | (91) |

| Figure 57: | Delay in ECDL structures                                  | (92) |

| Figure 58: | PDP in ECDL structures                                    | (92) |

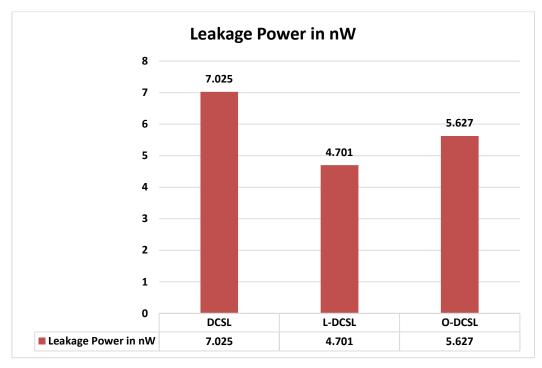

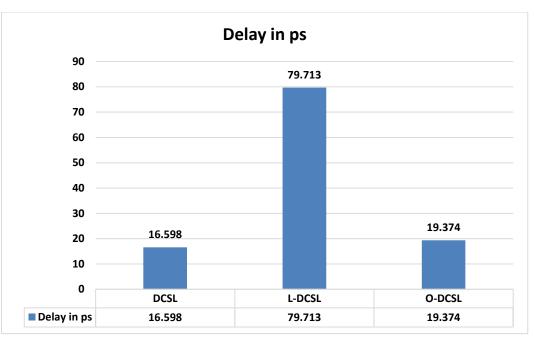

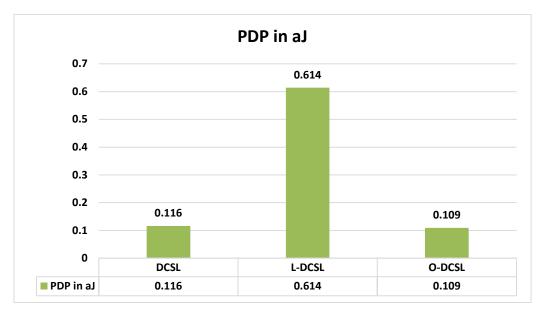

| Figure 59: | Leakage Power in DCSL structures                          | (93) |

| Figure 60: | Delay in DCSL structures                                  | (94) |

| Figure 61: | PDP in DCSL structures                                    | (94) |

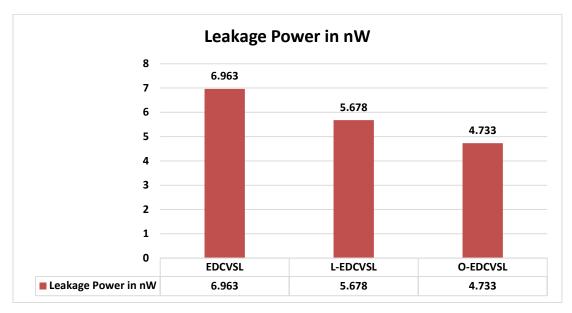

| Figure 62: | Leakage Power in EDCVSL structures                        | (95) |

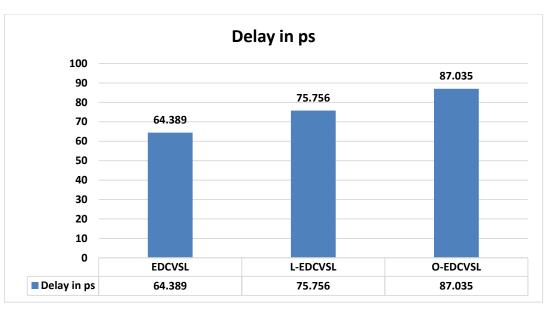

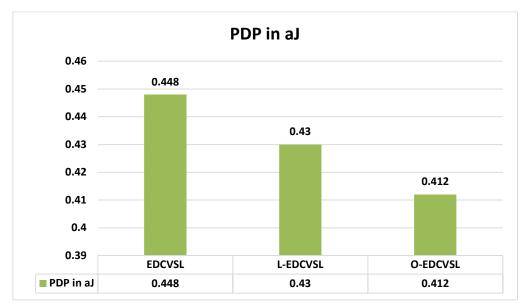

| Figure 63: | Delay in EDCVSL structures                                | (96) |

| Figure 64: | PDP in EDCVSL structures                                  | (96) |

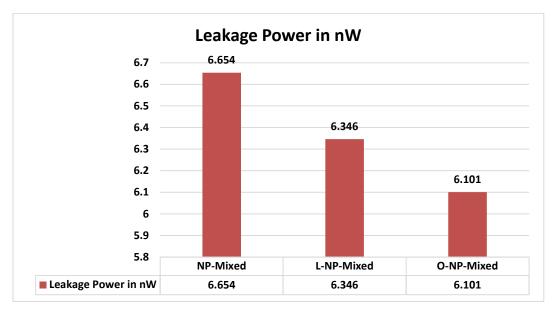

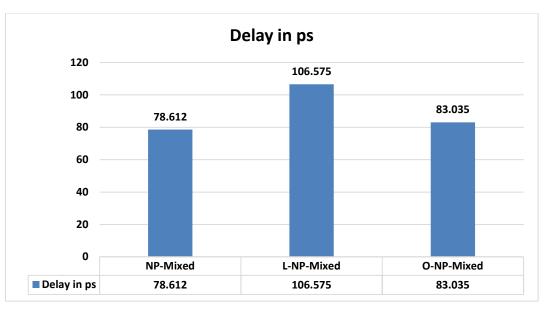

| Figure 65: | Leakage Power in NP-Mixed structures                      | (97) |

| Figure 66: | Delay in NP-Mixed structures | (98) |

|------------|------------------------------|------|

| Figure 67: | PDP in NP-Mixed structures   | (98) |

# **LIST OF TABLES**

| Table 1:          | Leakage current is input dependent in Dynamic DCVSL: 4 cases | (10) |

|-------------------|--------------------------------------------------------------|------|

|                   | possible in evaluation case (CLK= '1') for 2- input XOR      |      |

| <u>Table 2</u> :  | Clock and Input Pulse Parameters                             | (14) |

| Table 3:          | Leakage Power in SSDL                                        | (15) |

| Table 4:          | Delay in SSDL                                                | (15) |

| Table 5:          | Clock and Input Pulse Parameters                             | (19) |

| <u>Table 6</u> :  | Leakage Power in MSSDL                                       | (20) |

| <u>Table 7</u> :  | Delay in MSSDL                                               | (20) |

| <u>Table 8</u> :  | Clock and Input Pulse Parameters                             | (24) |

| <u>Table 9</u> :  | Leakage Power in ECDL                                        | (25) |

| <u>Table 10</u> : | Delay in ECDL                                                | (25) |

| <u>Table 11</u> : | Clock and Input Pulse Parameters                             | (28) |

| <u>Table 12</u> : | Leakage Power in DCSL                                        | (29) |

| <u>Table 13</u> : | Delay in DCSL                                                | (29) |

| <u>Table 14</u> : | Clock and Input Pulse Parameters                             | (33) |

| <u>Table 15</u> : | Leakage Power in EDCVSL                                      | (34) |

| <u>Table 16</u> : | Delay in EDCVSL                                              | (34) |

| <u>Table 17</u> : | Clock and Input Pulse Parameters                             | (37) |

| <u>Table 18</u> : | Leakage Power in NP- Mixed DCVSL                             | (38) |

| <u>Table 19</u> : | Delay in NP- Mixed DCVSL                                     | (38) |

| <u>Table 20</u> : | Summarized Results of Chapter 3                              | (39) |

| <u>Table 21</u> : | State Matrix of LECTOR incorporated 2-input NAND Gate        | (43) |

| <u>Table 22</u> : | Clock and Input Pulse Parameters                             | (45) |

| <u>Table 23</u> : | Leakage Power in L-SSDL                                      | (46) |

| <u>Table 24</u> : | Delay in L-SSDL                                              | (46) |

| <u>Table 25</u> : | Clock and Input Pulse Parameters                             | (48) |

| <u>Table 26</u> : | Leakage Power in L-MSSDL using L-SSDL                        | (49) |

| <u>Table 27</u> : | Delay in L-MSSDL                                             | (49) |

| <u>Table 28</u> : | Clock and Input Pulse Parameters                             | (51) |

| <u>Table 29</u> : | Leakage Power in L-ECDL                                      | (52) |

| Table 30:          | Delay in L-ECDL                                             | (52)  |

|--------------------|-------------------------------------------------------------|-------|

| <u>Table 31</u> :  | Clock and Input Pulse Parameters                            | (54)  |

| <u>Table 32</u> :  | Leakage Power in L-DCSL                                     | (55)  |

| <u>Table 33</u> :  | Delay in L-DCSL                                             | (55)  |

| <u>Table 34</u> :  | Clock and Input Pulse Parameters                            | (57)  |

| Table 35:          | Leakage Power in L-EDCVSL                                   | (58)  |

| <u>Table 36</u> :  | Delay in L-EDCVSL                                           | (58)  |

| <u>Table 37</u> :  | Clock and Input Pulse Parameters                            | (60)  |

| Table 38:          | Leakage Power in L-NP- Mixed DCVSL                          | (61)  |

| Table 39:          | Delay in L-NP- Mixed DCVSL                                  | (61)  |

| Table 40:          | Summarized Results of Chapter 4                             | (62)  |

| Table 41:          | Operating Status of transistors in ONOFIC 2-input NAND gate | (66)  |

| Table 42:          | Clock and Input Pulse Parameters                            | (68)  |

| Table 43:          | Leakage Power in O-SSDL                                     | (69)  |

| <u>Table 44</u> :  | Delay in O-SSDL                                             | (69)  |

| Table 45:          | Clock and Input Pulse Parameters                            | (71)  |

| <u>Table 46</u> :  | Leakage Power in O-MSSDL                                    | (72)  |

| Table 47:          | Delay in O-MSSDL                                            | (72)  |

| Table 48:          | Clock and Input Pulse Parameters                            | (74)  |

| <u>Table 49</u> :  | Leakage Power in O-ECDL                                     | (75)  |

| T <u>able 50</u> : | Delay in O-ECDL                                             | (75)  |

| <u>Table 51</u> :  | Clock and Input Pulse Parameters                            | (77)  |

| <u>Table 52</u> :  | Leakage Power in O-DCSL                                     | (78)  |

| T <u>able 53</u> : | Delay in O-DCSL                                             | (78)  |

| <u>Table 54</u> :  | Clock and Input Pulse Parameters                            | (80)  |

| <u>Table 55</u> :  | Leakage Power in O-EDCVSL                                   | (81)  |

| <u>Table 56</u> :  | Delay in O-EDCVSL                                           | (81)  |

| <u>Table 57</u> :  | Clock and Input Pulse Parameters                            | (83)  |

| Table 58:          | Leakage Power in O-NP- Mixed DCVSL                          | (84)  |

| Table 59:          | Delay in O-NP- Mixed DCVSL                                  | (84)  |

| <u>Table 60</u> :  | Summarized Results of Chapter 5                             | (85)  |

| Table 61:          | Final Results                                               | (100) |

# **ABSTRACT**

Differential logic styles have been becoming popular over conventional CMOS logic because of they promise lower power consumption and high computational speed. DCVSL promises the advantages of both traditional CMOS logic and pseudo NMOS logic thus offering high speed area effective rail to rail swing logic option. The dynamic DCVSL logic family has been explored and leakage power and delay has been considered. Various dynamic versions of DCVSL logic have been introduced and their leakage power and delay have been studied.

Leakage power is an important issue in dynamic circuits and a leakage control technique (LECTOR) has been explored in context of two variations of dynamic DCVSL structures. The LECTOR technique is applied to other variants of dynamic DCVSL structures and performance in terms of leakage power dissipation, propagation delay time, power delay product, transistor number is examined.

In this thesis, a relatively new leakage reduction technique known as ONOFIC technique has been successfully proposed in various DCVSL structures. Various performance related parameters and transistor count has been reported.

This thesis includes relative performance comparison of dynamic DCVSL structures in their conventional format and with the introduction of LECTOR and ONOFIC approach.

The effectiveness and functionality of all dynamic DCVSL structures and proposed architectures are confirmed through intensive simulations on Symica Design Environment. The structures were implemented using Symica Design Environment (Symica DE) using 90 nm PTM model technology at 1.2V to analyse the variation in leakage power and delay.

# **Chapter 1**

# **Introduction**

### (1.1) <u>Topic Overview</u>

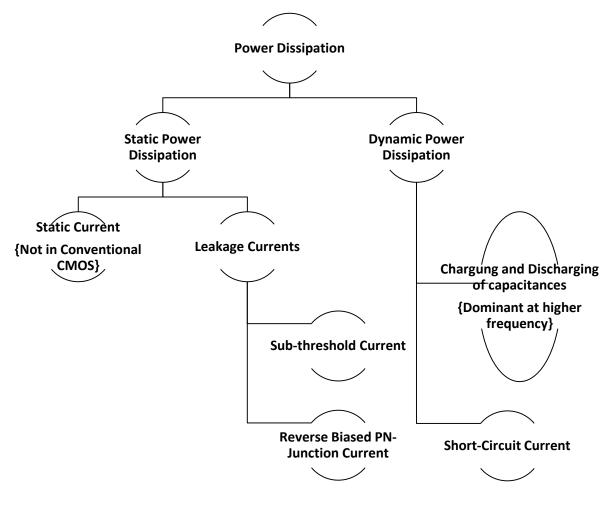

Power dissipation in a MOS circuit can be classified in two types- Static Power Dissipation and Dynamic Power Dissipation. Dynamic Power Dissipation can be due to charging or discharging of capacitance (dominant at higher frequency) and power dissipation due to short-circuit current. While Static Power Dissipation can be due to Static Current and due to Leakage Currents. This is shown in Fig. 1.

Figure 1: Power Dissipation in VLSI Circuits

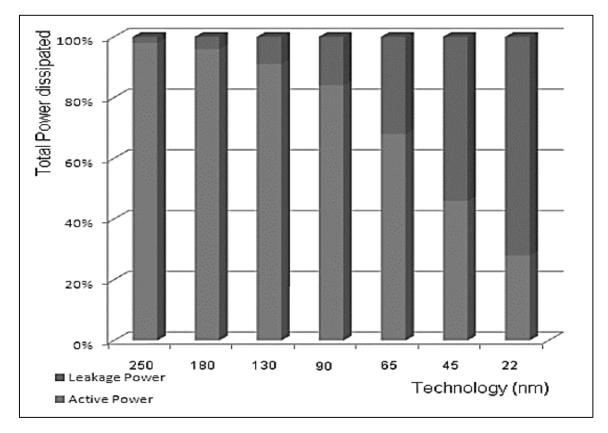

With the technology scaling in nanometre regime, static power consumption (due to leakage current) has become a major concern. Along with technology scaling down (for higher operating speeds and higher device density) leakage current which constitutes reverse biased PN- junction current and sub-threshold current are becoming significant. This is shown in Fig. 2.

Figure 2: Leakage Power significance at lower technology nodes [5]

In recent years, differential logic design has emerged as a very promising alternative to standard CMOS logic. Several differential logic styles have been reported in the literature, since including the differential cascode voltage switch logic (DCVSL). There are many factors that make the differential logic design more preferable compared to the standard CMOS design:

- High fan-in complex gates can be implemented using a single differential tree network. This results in reduced delay time and lower transistor count.

- Only NMOS devices are requires to perform a logic function which results in reduction in input loads.

- The differential circuits are preferred for self-timed architectures since the existence of complementary outputs makes the evaluation phase easily detectable.

Differential Cascode Voltage Switch Logic (DCVSL) is a widely known logic design style. DCVSL style offers several advantages over the conventional static CMOS logic design approach. The number of transistors required to implement an 'N' input logic in CMOS logic is '2N'. Subsequently, immense no. of transistors will be required to implement a complex logic.

Ratioed logic style seems an alternative to decrease the required transistor count. However, it suffers from a major drawback of static power dissipation (due to static current) and reduced logic swing because the pull up transistor is 'ON' unconditionally.

A potential ratioed logic style that totally eliminates static currents and offers rail-to-rail swing can be created. The potential logic design style combines two concepts: *differential logic* and *positive feedback*. A differential structure receives complementary inputs and generates complementary outputs. Through positive feedback mechanism the load device gets turned off when not required. *Differential Cascode Voltage Switch Logic* (or DCVSL) is an example of such a logic family.

Lot of literature on Leakage power reduction in CMOS logic approach has been already present. But study on leakage power aspect of DCVSL family specially their dynamic versions (due to the obvious advantages of dynamic circuits) is somewhat limited till date. Therefore, a sincere attempt has been made to explore various DCVSL structures and their performance is explored.

As the LECTOR technique has been investigated on only two variants of dynamic DCVSL structures [3], other variants are also examined. Also a relatively new leakage power reduction approach i.e. ONOFIC approach has been implemented in these structures.

The effectiveness and functionality of all dynamic DCVSL structures and proposed architectures are confirmed through intensive simulations on Symica Design Environment. The structures were implemented using Symica Design Environment (Symica DE) using 90 nm PTM model technology at 1.2V at a temperature of 27°C.

### (1.2) Thesis structure

| Chapter 1 | introduces the topic, discusses about the importance of DCVSL logic and |

|-----------|-------------------------------------------------------------------------|

|           | gives thesis structure.                                                 |

- <u>Chapter 2</u> starts with the details of the Differential Cascode Voltage Switch Logic (DCVSL), it shows the basic structure of DCVSL circuit and explains its operation. Apart from that, dynamic DCVSL is introduced and concept of leakage is explained.

- <u>Chapter 3</u> introduces various types of dynamic DCVSL structures, explains their operation. Simulation results has been reported to justify the functionality and various performance parameters has provided.

- <u>Chapter 4</u> introduces various dynamic DCVSL structures with LECTOR power reduction approach. Simulation results have been provided to justify the functionality and various performance related results are mentioned.

- <u>Chapter 5</u> explains a relatively new leakage power reduction ONOFIC approach, which promises a better power-delay product. This approach has been proposed in dynamic DCVSL structures. Detail study of each of these DCVSL structures, with parameters such as leakage power consumption, temperature, delay, PDP and transistor count has been done. Simulation results have been provided to justify the functionality and various performance related results are mentioned.

- <u>Chapter 6</u> provides relative performance analysis of conventional, LECTOR incorporated and proposed ONOFIC incorporated dynamic DCVSL structures.

- <u>Chapter 7</u> concludes the overall work done in this thesis. This chapter ends the thesis work.

# Chapter 2

# **Differential Cascode Voltage Switch Logic**

Differential Cascode Voltage Switch Logic (DCVSL) is a widely known differential logic design style. It offers several advantages courtesy of being a differential logic design - higher fan-in complex gates implementation by using a single differential tree network, requirement of only NMOS devices to perform a logic function, and are more preferable for self-timed architectures. DCVSL offers several other advantages which are mentioned in section (2.2).

### (2.1) **Operation**

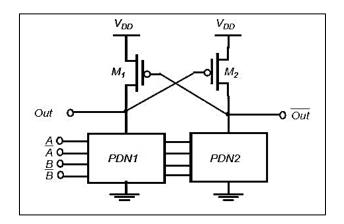

DCVSL logic design style is an amalgamation of two concepts: *differential logic* and *positive feedback*. Here, a differential gate is fed with complementary inputs which in turn generates complementary outputs. Positive feedback mechanism ensures that the load device gets turned off when not required.

A basic DCVSL logic gate is given in Fig. 3. The pull-down networks namely *PDN1* and *PDN2* are implemented using NMOS transistors only and are mutually exclusive (i.e. both are never 'ON' at the same time). This ensures such that the desired logic function and its complement are simultaneously realized by providing complementary inputs.

Figure 3: Basic DCVSL Circuit [1]

- We begin by assuming Out and  $\overline{Out}$  at logic '1' and '0' respectively.

- Now, suppose that an input combination is applied such that *PDN1* turns 'ON' thus providing a discharge path to *Out*. *Out* which is at '0' initially is keeping M<sub>1</sub> turned 'ON'. This creates a contention between M<sub>1</sub> and *PDN1* and Out is not able to discharge completely during this phase. But, still discharging of *Out* starts at slower pace.

- As soon as *Out* falls below  $(V_{DD} |V_{TP}|)$ , M<sub>2</sub> turns 'ON' which is driven by *Out*. Now, charging path is provided by M<sub>2</sub> to  $\overline{Out}$ . As *PDN1* and *PDN2* are mutually exclusive and implement differential logic functions, therefore *PDN2* is 'OFF'. Thus, there is no discharge path for  $\overline{Out}$ . This results in M<sub>2</sub> successfully charging  $\overline{Out}$  to V<sub>DD</sub>.

- As  $\overline{Out}$  exceeds (V<sub>DD</sub>-V<sub>T</sub>), M<sub>1</sub> turns off resulting in cutting of path between V<sub>DD</sub> and ground. This eliminates any static power loss. Now *PDN1* can efficiently complete the discharge of *Out*. Eventually, both *Out* and  $\overline{Out}$  attain correct logic state.

By sharing of common transistors among the two differential pull-down networks *PDN1* and *PDN2* (for realizing complex logic), implementation overhead can be reduced. The DCVSL circuit shows rail-to-rail swing, and there is an elimination of static power dissipation: in steady state, none of the stacked pull-down networks and load devices is in conduction mode simultaneously.

However, the DCVSL circuit is still ratioed logic and sizing of pull up transistors relatively to pull down devices critically affects both the performance as well as the functionality of the circuit.

### (2.2) Advantages of DCVSL

- i. High fan-in complex gates can be implemented using a single differential tree network. This results in reduced delay time and lower transistor count.

- ii. Only NMOS devices are requires to perform a logic function which results in reduction in input loads.

- iii. The differential circuits are preferred for self-timed architectures since the existence of complementary outputs makes the evaluation phase easily detectable.

- iv. There is a speed improvement in DCVSL circuits similar to that in case of domino circuits due to the reduction in the parasitic capacitances at the output nodes (logic function is implemented using only pull down network which consists only NMOS transistors that provides a quicker response.

- v. Static power consumption is reduced by employing positive feedback which is provided by two cross-connected PMOS transistors that ensures that pull up transistor and PDN are never on simultaneously.

- vi. DCVSL allows sharing of the common transistors by both the PDN networks for implementing complex circuits. Provision for sharing of transistors by both PDN and requirement of only PDNs to implement logic function ensures significant saving of chip area when compared to conventional CMOS logic.

- vii. Generations of output and its complement results in the elimination of inverting stage. This eliminates the problem of clock skew.

For E.g.: Using an inverter to complement the *Clock* signal when *Clock* and  $\overline{Clock}$  are needed simultaneously will result in clock skew problem due to delay introduced by inverter.

### (2.3) Disadvantages of DCVSL

Every design style has its merits and drawbacks and the case with DCVSL is no different. The advantages mentioned in section (2.2) comes at a price.

- i. Additional area overhead.

- ii. Additional complexity associated with differential logic networks which involve complementary signals.

- iii. To add to above disadvantages, during transition, state of contention exists for a period of time when both PMOS and PDN are turned 'ON' simultaneously, producing a short circuit path. Therefore, it might be possible that static DCVSL circuit consume slightly more power than conventional CMOS circuits because of the dependency of charging and discharging times on the Turn-ON and the Turn-OFF paths within the DCVSL tree and these are usually asymmetrical.

- iv. Asymmetry in rise and fall times resulting in extension of period of time for which current flows through the latch of the DCVSL circuit during the transient state increases the power dissipation.

Therefore, there is a need to employ circuit level power reduction techniques in the mainly very useful DCVSL circuits to achieve faster circuits while consuming less power.

### (2.4) Dynamic DCVSL

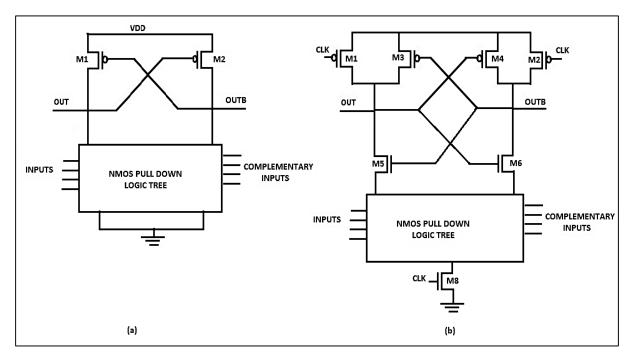

The basic dynamic version of DCVSL is shown in Fig. 4 (b) along with basic version of static DCVSL. The dynamic DCVSL consists of two complementary PDNs and has positive feedback which is in the form of the two cross-coupled PMOS PUTs.

### **Operation**

- When CLK signal is low, OUT and  $\overline{\text{OUT}}$  are pre-charged to  $V_{DD}$ . This is called pre-charge phase.

- When CLK rises to logic high, NMOS pull down logic tree evaluates to its true and complementary output state on the basis of assertion of complimentary input signals. Positive feedback ensures proper switching of the logic gate which is being applied to PMOS PUTs (M3 and M4).

- M5 and M6 are used to improve the performance of the dynamic DCVSL gate.

Figure 4: DCVSL: (a) Static version, and (b) Dynamic version [4]

#### Advantages of Dynamic DCVSL over Static DCVSL

- Dynamic DCVSL has an upper hand over static DCVSL in field of power dissipation. It consumes relatively lesser power over static DCVSL counterpart.

- The state of contention during switching as in case of static DCVSL does not occur in Dynamic DCVSL.

#### Explanation:

- In static DCVSL, Gate terminal of either of the PUTs is at logic '1' and other one is at logic '0' since they are connected to complementary output nodes. Referring Fig. 4 (a) consider the case when OUT has to switch from '1' to '0' (OUT has to make a switch from '0' to '1'). On assertion of inputs, PDN1 turns ON and trying to discharge OUT. But this task of discharging is made difficult by PUT1 which is still 'ON' since OUT is at logic '0'. This results in a state of conflict between PUT1 and PDN1. Consequence of contention is the undesired static power dissipation within that duration.

- In case of dynamic DCVSL, OUT and  $\overline{OUT}$  are both charged to V<sub>DD</sub> during pre-charge cycle. This implies that PUT1 and PUT2 both are initially 'OFF'. In the evaluation stage, PUTs get turned ON conditionally (depending upon input combination). Thus, the problem of contention is eliminated.

### (2.5) Idea of Leakage in Dynamic DCVSL

Leakage Power is the power dissipation which is due to currents which flows in those portions of DCVSL logic which are logically 'OFF'. These current comprises of sub-threshold current and reverse biased PN-Junction current which ideally should not flow. This leakage current contributes in static power dissipation. There is no problem of contention, hence there is no static current in dynamic DCVSL.

This leakage current is dependent on input combinations. Consider the case when certain input combinations cause OUT at logic '1' and  $\overline{OUT}$  at logic '0' in dynamic DCVSL shown in Fig. 4 (b) during evaluation (i.e. when CLK='1'). In this case, the current flowing from OUT node to ground and from V<sub>DD</sub> to  $\overline{OUT}$  constitute leakage current. In this thesis work leakage current during evaluation phase is only reported since during evaluation both OUT and  $\overline{OUT}$  are at logic '1' and M8 is OFF. Thus, there is no path from OUT and  $\overline{OUT}$  to ground.

In the thesis work, 2-input XOR with inputs 'A' and 'B' is used as a test circuit for performance analysis. In evaluation phase CLK= '1', therefore, before the active CLK edge inputs 'A' and 'B' should be stable. Since, leakage has been reported for evaluation phase in this thesis work, therefore 4 cases are possible as shown in Table 1.

### Table 1

### Leakage current is input dependent in Dynamic DCVSL: 4 cases possible in evaluation case (CLK= '1') for 2- input XOR

| Α | В |

|---|---|

| 0 | 0 |

| 0 | 1 |

| 1 | 0 |

| 1 | 1 |

# Chapter 3

# **Dynamic DCVSL Variations**

#### **Introduction**

The basic dynamic DCVSL introduced in section (2.4) provides the basis for several alternative differential CMOS logic design styles. Although these circuits have evolved from the DCVSL structure, they have features that make them unique. In subsequent sections, various dynamic DCVSL variations are described and simulations are carried out to verify their functionality and performance in terms leakage power and delay is observed.

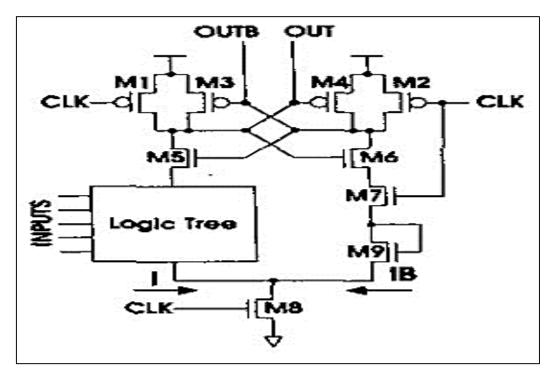

### (3.1) Sample-Set Differential Logic (SSDL)

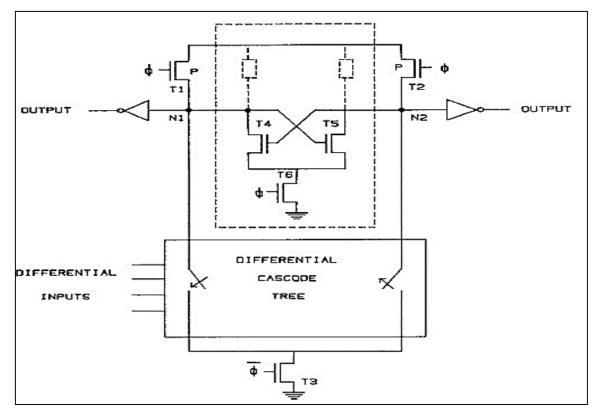

**Sample-Set Differential Logic (SSDL)** is a clocked differential logic style circuit. Its schematic is shown in Fig. 5. It consists of the differential logic tree, three sample transistors, a latching sense amplifier, two buffers, and two optional resistors as can be seen from the schematic.

Figure 5: SSDL Schematic [6]

#### **Operation**:

The operation of SSDL circuit consists of a sample and a set phase.

- During the sample phase (precharge phase), clock → is high and thus NMOS T3 and PMOS T1 and T2 are turned 'ON' creating a path exists from either N1 or N2 to ground through one side of the differential tree only determined by the input combination. Thus, either node N1 or N2 will be at *VDD* or at a voltage less than *VDD*.

- In the next phase of operation i.e. the set phase (evaluation phase), where T1, T2, and T3 are 'OFF' and the portion consisting of the sense amplifier is turned 'ON' through T6. Now, the node (N1 or N2) at the lower voltage will get discharged quickly to ground. This discharge is rapid because of the large driving capabilities of the sense amplifier.

- There is a speed advantage of SSDL circuits over the domino and DCVSL circuits. This occurs because the node (N1 or N2), which has to go low, goes low through a large transistor (T4 or T5) in the SSDL circuit in contrast to a series connection of many transistors in the domino and DCVSL circuits. The differential gain of the sense amplifier used also assists this transition. In other words, the complexity of the logic circuitry has no effect to play on the evaluation time. This makes the idea of SSDL design very attractive to achieve high circuit density.

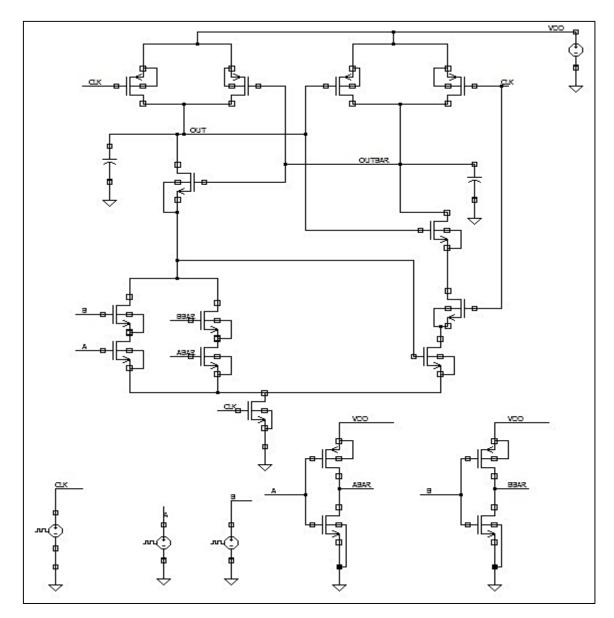

#### <u>Schematic</u>:

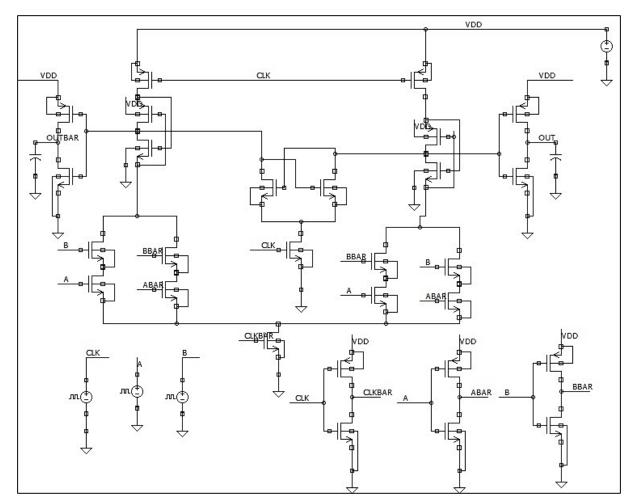

A 2-input XOR is used as a design example throughout this thesis to test as well as to compare the functionality and performance of various DCVSL variations. Fig. 6 shows the schematic for 2-input XOR with inputs 'A' and 'B' and clock 'CLK' using 90nm technology node at  $V_{DD} = 1.2V$ . The W/L for NMOS and PMOS are (135n/90n) and (337.5n/90n) respectively.

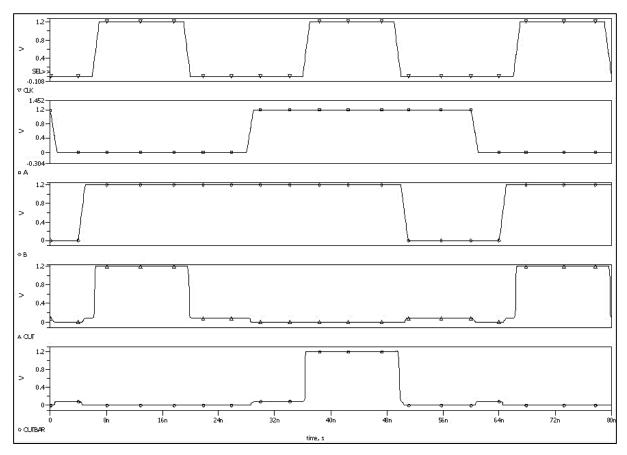

Figure 6: 2-input XOR using SSDL architecture

#### Simulation Results:

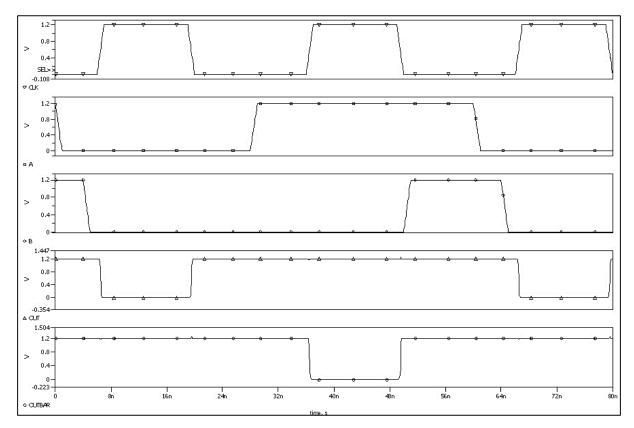

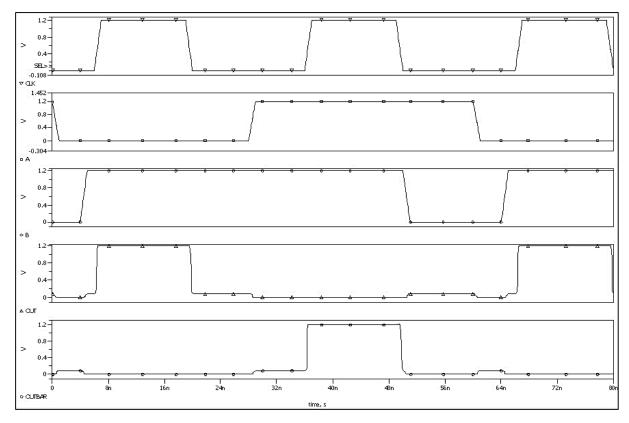

Fig. 7 shows the waveform of 'OUT' and ' $\overline{OUT}$ ' on the application of input 'A' and 'B'. Table 2 specifies simulation settings for 'CLK', 'A' and 'B' where the different parameter definition is given below.

- v1- Initial Voltage Level at t=0ns

- v2- Voltage Level after delay of td

- **per-** Period of the pulse

- td- Delay after which pulse makes first transition from v1 to v2

- tr- Rise Time of the pulse

- tf- Fall Time of the pulse

- **pw-** Pulse Width of the pulse

# Table 2:Clock and Input Pulse Parameters

| Parameters | CLK  | Α    | В    |

|------------|------|------|------|

| v1         | 0    | 1.2  | 0    |

| v2         | 1.2  | 0    | 1.2  |

| per        | 30ns | 60ns | 60ns |

| td         | бns  | Ons  | 4ns  |

| tr         | 1ns  | 1ns  | 1ns  |

| tf         | 1ns  | 1ns  | 1ns  |

| рw         | 12ns | 27ns | 45ns |

Figure 7: Simulation Output for 2-input XOR using SSDL

#### Performance Measurement:

• Table 3 shows the leakage power for the 2-input XOR SSDL structure for various input combinations in evaluation phase. These results are carried out for 90nm technology node at a temperature of 27°C.

| CLK | Α | В | Ουτ | OUT | Leakage Current<br>(nA) | Leakage Power<br>(nW) |

|-----|---|---|-----|-----|-------------------------|-----------------------|

| 0   | X | X | 0   | 0   | _                       | _                     |

| 1   | 0 | 0 | 0   | 1   | 3.86                    | 4.632                 |

| 1   | 0 | 1 | 1   | 0   | 3.756                   | 4.5072                |

| 1   | 1 | 0 | 1   | 0   | 3.894                   | 4.6782                |

| 1   | 1 | 1 | 0   | 1   | 3.848                   | 4.6176                |

## Table 3: Leakage Power in SSDL

• The delay performance of the 2-input XOR using SSDL structure is summarized in Table 4. The input should be stable before the active edge of CLK so that the OUT in evaluation stage is correct. In precharge phase, OUT= 0 in SSDL. Therefore, delay will be '0' if OUT remains '0' in evaluation phase.

### Table 4:

### **Delay in SSDL**

| СLК | Α | В | OUT | Delay (ps) |

|-----|---|---|-----|------------|

| 0   | х | х | 0   | _          |

| 1   | 0 | 0 | 0   | 0          |

| 1   | 0 | 1 | 1   | 74.242     |

| 1   | 1 | 0 | 1   | 76.853     |

| 1   | 1 | 1 | 0   | 0          |

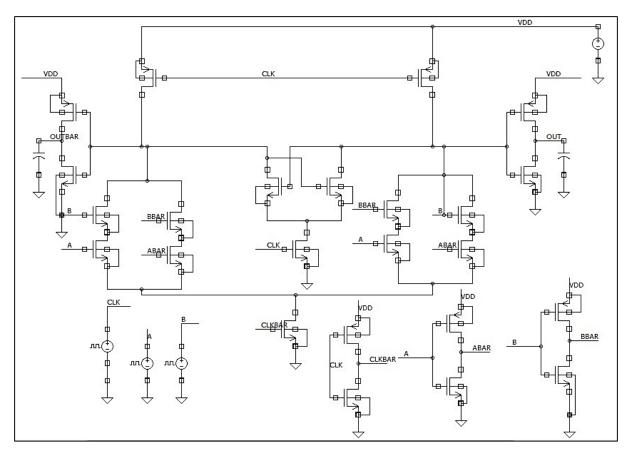

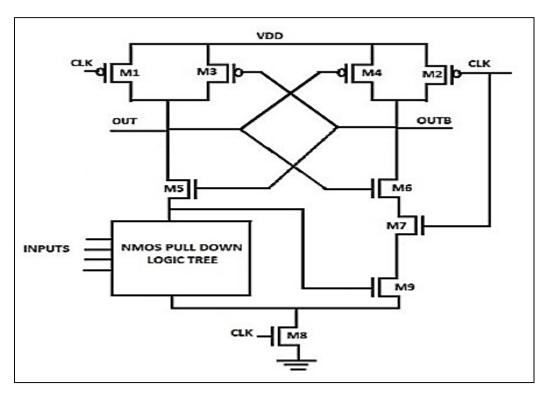

### (3.2) Modified Sample-Set Differential Logic (MSSDL)

The obvious problem with the SSDL circuit as described in Section 3.1 is the presence of a DC current flow path between the power supply  $(V_{DD})$  and ground during the precharge phase resulting in power dissipation during that period. But this is an important aspect to the design, reducing voltage on one of the latch nodes which is required for proper operation during the evaluation phase.

Thus, a variation in the SSDL circuit is required (to prevent DC power dissipation). This feature is provided by **Modified Sample-Set Differential Logic (MSSDL**). Its schematic is shown in Fig. 8. In this approach, static RAM cell, which is made up of two static inverters, replaces the dynamic latch. Extra clocking transistors  $M_{n4}$  and  $M_{n5}$  are introduced to control the DC current flow paths.

Figure 8: MSSDL Schematic [1]

#### **Operation**:

- When  $\phi = 0$  (precharge phase), both the output nodes (V<sub>1</sub> and V<sub>2</sub>) try to attain charge equal to V<sub>DD</sub> which is not a stable state of the circuit.

- During this time, the logic array is disconnected from the circuit because of  $M_{n4}$  and  $M_{n5}$ . In other words, the RAM will be in an unstable state.

- When the clock, φ makes a transition from '0' to '1', the logic tree switches into the circuit. The logic tree decides which side discharges to 0.

- Thus, the MSSDL circuit try to preserve the speed while lowering the power dissipation.

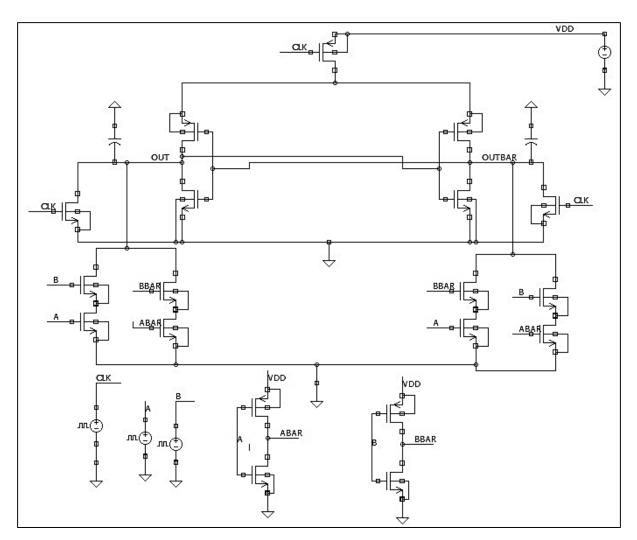

#### Schematic:

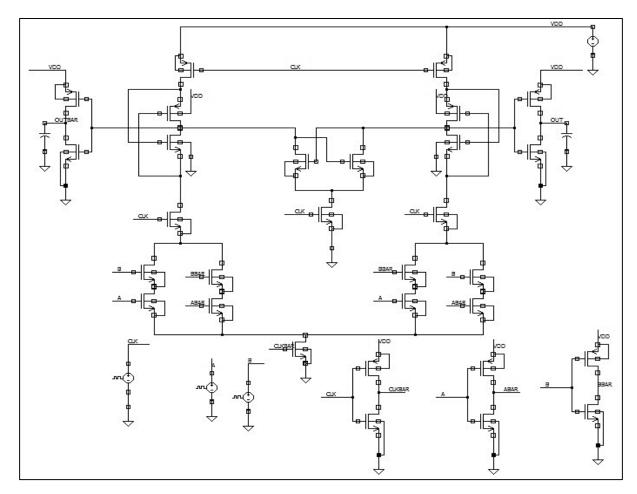

A 2-input XOR is used as a design example throughout this thesis to test as well as to compare the functionality and performance of various DCVSL variations. Fig. 9 shows the schematic for 2-input XOR with inputs 'A' and 'B' and clock 'CLK' using 90nm technology node at  $V_{DD} = 1.2V$ . The W/L for NMOS and PMOS are (135n/90n) and (337.5n/90n) respectively.

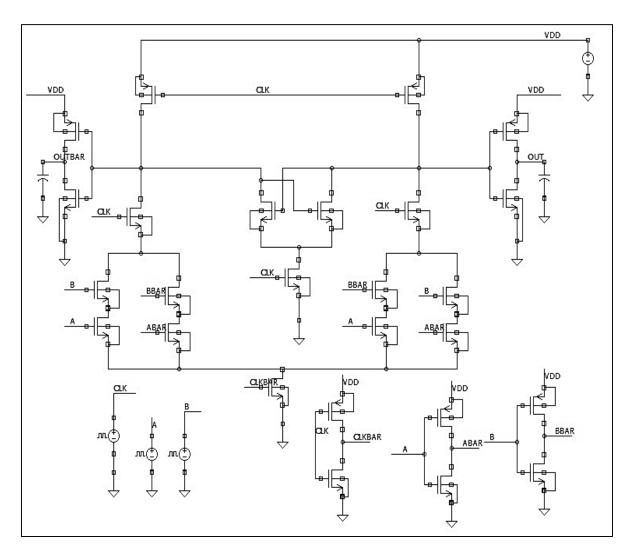

Figure 9: 2-input XOR using MSSDL architecture

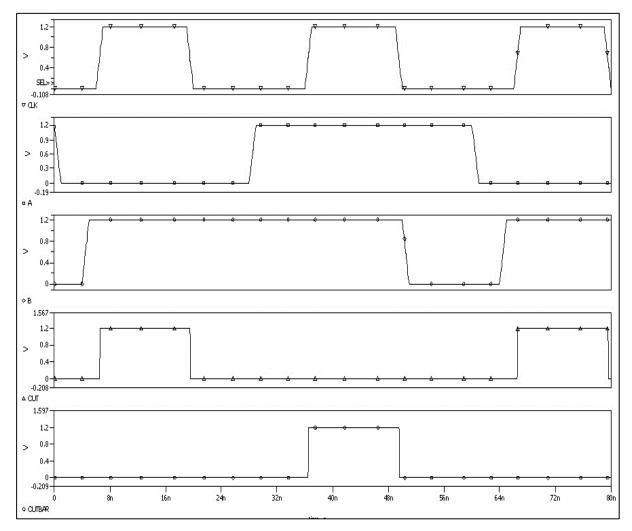

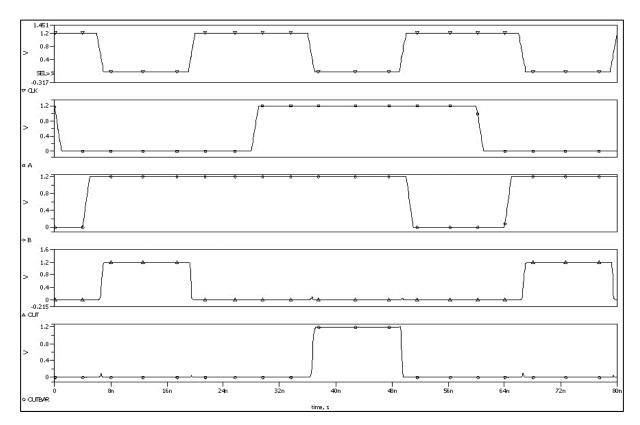

### Simulation Results:

Fig. 10 shows the waveform of 'OUT' and ' $\overline{OUT}$ ' on the application of input 'A' and 'B'. Table 5 specifies simulation settings for 'CLK', 'A' and 'B'.

## <u>Table 5:</u> <u>Clock and Input Pulse Parameters</u>

| Parameters | CLK  | Α    | В    |

|------------|------|------|------|

| v1         | 0    | 1.2  | 0    |

| v2         | 1.2  | 0    | 1.2  |

| per        | 30ns | 60ns | 60ns |

| td         | бns  | Ons  | 4ns  |

| tr         | 1ns  | 1ns  | 1ns  |

| tf         | 1ns  | 1ns  | 1ns  |

| pw         | 12ns | 27ns | 45ns |

#### Performance Measurement:

• Table 6 shows the leakage power for the 2-input XOR MSSDL structure for various input combinations in evaluation phase. These results are carried out for 90nm technology node at a temperature of 27°C.

| CLK | Α | В | OUT | OUT | Leakage Current<br>(nA) | Leakage Power<br>(nW) |

|-----|---|---|-----|-----|-------------------------|-----------------------|

| 0   | X | X | 0   | 0   | _                       | _                     |

| 1   | 0 | 0 | 0   | 1   | 4.423                   | 5.3076                |

| 1   | 0 | 1 | 1   | 0   | 4.791                   | 5.7492                |

| 1   | 1 | 0 | 1   | 0   | 4.944                   | 5.9328                |

| 1   | 1 | 1 | 0   | 1   | 4.45                    | 5.340                 |

### <u>Table 6:</u> Leakage Power in MSSDL

The delay performance of the 2-input XOR using MSSDL structure is summarized in Table 7. The input should be stable before the active edge of CLK so that the OUT in evaluation stage is correct. In precharge phase, OUT= OUT = 0 in MSSDL. Therefore, delay will be '0' if OUT remains '0' in evaluation phase.

# <u>Table 7:</u>

### **Delay in MSSDL**

| CLK | Α | В | OUT | Delay (ps) |

|-----|---|---|-----|------------|

| 0   | х | х | 0   | _          |

| 1   | 0 | 0 | 0   | 0          |

| 1   | 0 | 1 | 1   | 18.026     |

| 1   | 1 | 0 | 1   | 18.054     |

| 1   | 1 | 1 | 0   | 0          |

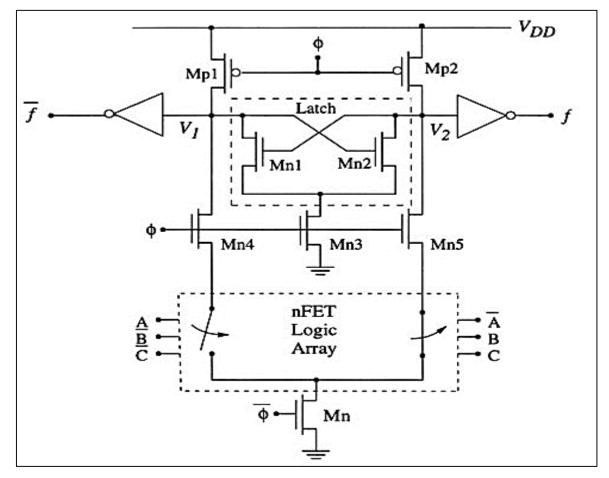

### (3.3) Enable/Disable CMOS Differential Logic (ECDL)

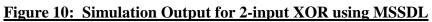

**Enable/disable CMOS Differential Logic (ECDL)** is another DCVSL variation. This design approach was developed to eliminate the static power dissipation problem in SSDL (eliminating the DC current flow path) and to reduce the transistor count. The general schematic of ECDL circuit is shown in Fig. 11.

Figure 11: ECDL Schematic [1]

#### **Operation**:

- The latching action is provided by a pair of cross-coupled static inverters which is basically an SRAM storage cell.

- The clock  $\phi$  controls the precharge transistor  $M_p$  that connects the power supply  $V_{DD}$  to the latch.

- Two additional NMOS transistors  $M_{n1}$  and  $M_{n2}$  are included at the outputs to provide enable/disable feature.

- Let the clock  $\phi = 1$  initially. This makes both  $M_{n1}$  and  $M_{n2}$  active, thus disabling the latch by making both output nodes as 0V i.e., resets the state of the circuit to ground.

- When the clock  $\phi$  makes a transition to logic '0', transistors  $M_{n1}$  and  $M_{n2}$  gets turned 'OFF', allowing the output nodes to achieve other voltages. During this time, PMOS  $M_p$  conducts and supplies power to the latching circuit. Thus, the state of the logic array determines the state that the latch will settle in.

- The circuit eliminates the DC current flow path between the V<sub>DD</sub> and ground, but the downside is that the circuit is designed to discharge the output nodes every half-cycle during the reset phase. This increases the dynamic power dissipation.

- In addition to the above drawback, the circuit relies on logic chains to discharge one of the output nodes, so that the RC delays may be a limiting factor.

- It has the advantage of being simple to design with reduced interconnect requirements. It also do not require inverted clock.

#### Schematic:

A 2-input XOR is used as a design example throughout this thesis to test as well as to compare the functionality and performance of various DCVSL variations. Fig. 12 shows the schematic for 2-input XOR with inputs 'A' and 'B' and clock 'CLK' using 90nm technology node at  $V_{DD} = 1.2V$ . The W/L for NMOS and PMOS are (135n/90n) and (337.5n/90n) respectively.

Figure 12: 2-input XOR using ECDL architecture

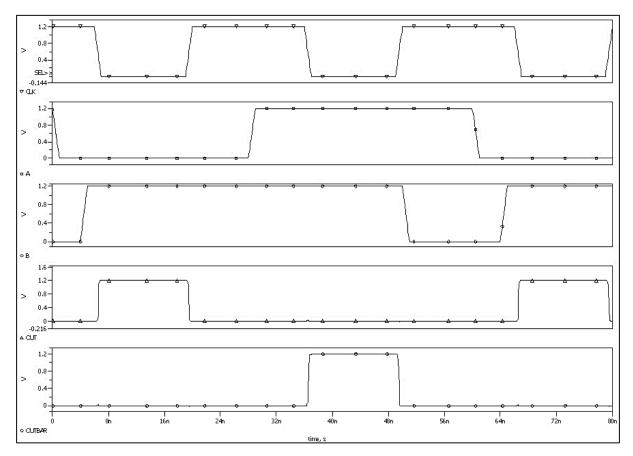

Fig. 13 shows the waveform of 'OUT' and ' $\overline{OUT}$ ' on the application of input 'A' and 'B'. Table 8 specifies simulation settings for 'CLK', 'A' and 'B.

## **Table 8:**

## **<u>Clock and Input Pulse Parameters</u>**

| Parameters | CLK  | Α    | В    |

|------------|------|------|------|

| v1         | 1.2  | 1.2  | 0    |

| v2         | 0    | 0    | 1.2  |

| per        | 30ns | 60ns | 60ns |

| td         | 6ns  | Ons  | 4ns  |

| tr         | 1ns  | 1ns  | 1ns  |

| tf         | 1ns  | 1ns  | 1ns  |

| рw         | 12ns | 27ns | 45ns |

Figure 13: Simulation Output for 2-input XOR using ECDL

Table 9 shows the leakage power for the 2-input XOR ECDL structure for various input combinations in enable phase. These results are carried out for 90nm technology node at a temperature of 27°C.

| CLK | Α | В | OUT | OUT | Leakage Current<br>(nA) | Leakage Power<br>(nW) |

|-----|---|---|-----|-----|-------------------------|-----------------------|

| 1   | X | X | 0   | 0   | -                       | _                     |

| 0   | 0 | 0 | 0   | 1   | 4.648                   | 5.5776                |

| 0   | 0 | 1 | 1   | 0   | 3.95                    | 4.74                  |

| 0   | 1 | 0 | 1   | 0   | 4.529                   | 5.4348                |

| 0   | 1 | 1 | 0   | 1   | 5.257                   | 6.3084                |

<u>Table 9:</u> Leakage Power in ECDL

The delay performance of the 2-input XOR using ECDL structure is summarized in Table 10. The input should be stable before the active edge of CLK (-ve edge) so that the OUT in enable stage is correct. In disable phase, OUT= OUT = 0 in ECDL. Therefore, delay will be '0' if OUT remains '0' in enable phase.

## **Table 10:**

#### **Delay in ECDL**

| CLK | Α | В | OUT | Delay (ps) |

|-----|---|---|-----|------------|

| 1   | х | х | 0   | _          |

| 0   | 0 | 0 | 0   | 0          |

| 0   | 0 | 1 | 1   | 87.953     |

| 0   | 1 | 0 | 1   | 87.892     |

| 0   | 1 | 1 | 0   | 0          |

#### (3.4) <u>Differential Current Switch Logic (DCSL)</u>

**Differential Current Switch Logic (DCSL)** is another variation of DCVSL that came into picture as a low-power approach to dual rail CMOS logic. Low power objective is met by limiting the voltage swings on internal nodes. Its drawback is that it requires a relatively high transistor count. Also the circuits are sensitive to circuit imbalances and noise. Different version of DCSL exist that offers trade-off in power and delay. Fig. 14 shows the schematic of one of DCSL version.

Figure 14: DCSL Schematic [1]

#### **Operation**:

- There is a static latch in the centre made of cross-coupled invertors.

- Several clocking transistors have been added to the output nodes.

- $M_{p1}$  and  $M_{p2}$  are precharge devices (governed by clock  $\phi$ ).

- M<sub>n</sub> is a latch enable FET, and M<sub>n3</sub> and M<sub>n4</sub> are used to control the current between the latch and logic array. M<sub>n</sub>, M<sub>n3</sub> and M<sub>n4</sub> are controlled by clock φ.

- $M_{n1}$  and  $M_{n2}$  which are unique to this design and are controlled by the state of the latch. They help to limit the internal voltages which in turn reduces the power dissipation.

- Inverting clock is not required.

#### <u>Schematic</u>:

A 2-input XOR is used as a design example throughout this thesis to test as well as to compare the functionality and performance of various DCVSL variations. Fig. 15 shows the schematic for 2-input XOR with inputs 'A' and 'B' and clock 'CLK' using 90nm technology node at  $V_{DD} = 1.2V$ . The W/L for NMOS and PMOS are (135n/90n) and (337.5n/90n) respectively.

Figure 15: 2-input XOR using DCSL architecture

Fig. 16 shows the waveform of 'OUT' and ' $\overline{OUT}$ ' on the application of input 'A' and 'B'. Table 11 specifies simulation settings for 'CLK', 'A' and 'B'.

# Table 11:Clock and Input Pulse Parameters

| Parameters | CLK  | Α    | В    |

|------------|------|------|------|

| v1         | 0    | 1.2  | 1.2  |

| v2         | 1.2  | 0    | 0    |

| per        | 30ns | 60ns | 60ns |

| td         | бns  | Ons  | 4ns  |

| tr         | 1ns  | 1ns  | 1ns  |

| tf         | 1ns  | 1ns  | 1ns  |

| pw         | 12ns | 27ns | 45ns |

• Table 12 shows the leakage power for the 2-input XOR DCSL structure for various input combinations in evaluation phase. These results are carried out for 90nm technology node at a temperature of 27°C.

| CLK | Α | В | OUT | OUT | Leakage Current<br>(nA) | Leakage Power<br>(nW) |

|-----|---|---|-----|-----|-------------------------|-----------------------|

| 0   | X | X | 1   | 1   | _                       | _                     |

| 1   | 0 | 0 | 0   | 1   | 5.679                   | 6.8148                |

| 1   | 0 | 1 | 1   | 0   | 6.201                   | 7.4412                |

| 1   | 1 | 0 | 1   | 0   | 5.994                   | 7.1928                |

| 1   | 1 | 1 | 0   | 1   | 5.542                   | 6.6504                |

## <u>Table 12:</u> Leakage Power in DCSL

The delay performance of the 2-input XOR using DCSL structure is summarized in Table 13. The input should be stable before the active edge of CLK so that the OUT in evaluation stage is correct. In precharge phase, OUT= OUT = 1 in DCSL. Therefore, delay will be '0' if OUT remains '1' in evaluation phase.

## **Table 13:**

#### **Delay in DCSL**

| СЦК | Α | В | OUT | Delay (ps) |

|-----|---|---|-----|------------|

| 0   | х | х | 1   | _          |

| 1   | 0 | 0 | 0   | 15.265     |

| 1   | 0 | 1 | 1   | 0          |

| 1   | 1 | 0 | 1   | 0          |

| 1   | 1 | 1 | 0   | 17.931     |

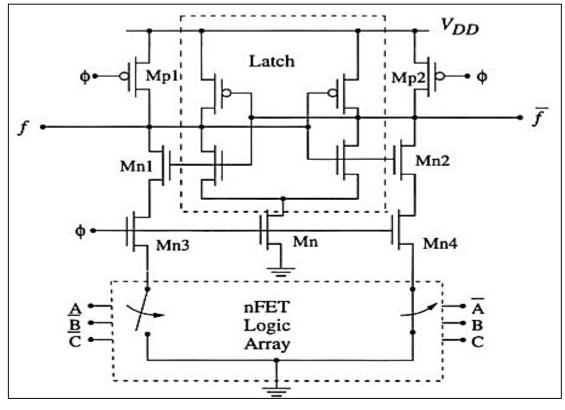

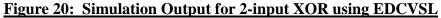

## (3.5) Enhanced Differential Cascode Voltage Switch Logic (EDCVSL)

Enhanced Differential Cascode Voltage Switch Logic (EDCVSL) as its name suggests is an improved version of dynamic DCVSL. EDCVSL circuits are basically have two versions. The two versions are called EDCVSL Type I and EDCVSL Type II. The two versions are shown in Fig. 17 and Fig. 18. In this thesis work, we have concentrated on EDCVSL Type II.

Figure 17: EDCVSL Type - I Structure [7]

Figure 18: EDCVSL Type - II Structure [7]

#### **Operation**:

- The EDCVSL Type II has been considered in this thesis work for performance analysis.

- In pre-charge phase, when CLK=0, output nodes OUT and OUTB gets precharged up to V<sub>DD</sub> through transistors M1 and M2.

- The feedback transistors M3 and M4 are 'OFF' during this phase since their gates are logic high.

- During evaluation i.e. when CLK=1, the pre-charge transistors Ml and M2 get turned OFF.

- The transistors M7 and M8 that are driven by CLK signal get turned ON which builds a path from output nodes OUT and OUTB to ground via EDCVSL logic tree depending upon the inputs asserted.

- The feedback transistors M3 and M4 are used for speeding up the evaluation and helps in maintaining the correct logic levels.

- The complete complementary input network on the other differential rail is replaced by a single transistor M9. This transistor is controlled by voltage level at the intermediate output node i.e. source of transistor M5.

#### <u>Schematic</u>:

A 2-input XOR is used as a design example throughout this thesis to test as well as to compare the functionality and performance of various DCVSL variations. Fig. 19 shows the schematic for 2-input XOR with inputs 'A' and 'B' and clock 'CLK' using 90nm technology node at  $V_{DD} = 1.2V$ . The W/L for NMOS and PMOS are (135n/90n) and (337.5n/90n) respectively.

Figure 19: 2-input XOR using EDCVSL architecture

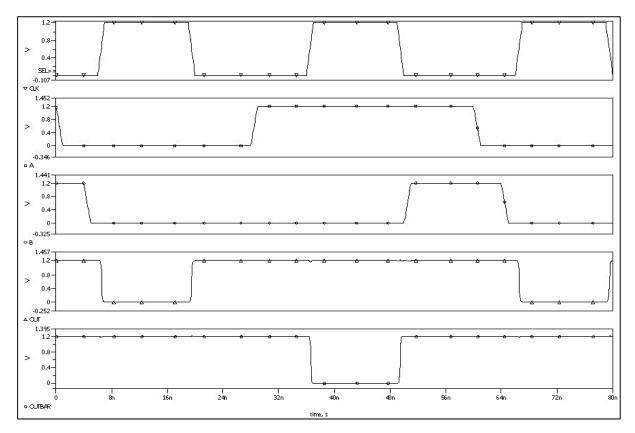

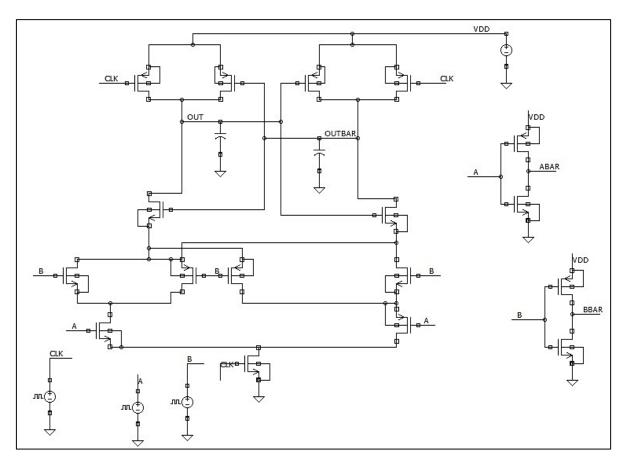

Fig. 20 shows the waveform of 'OUT' and ' $\overline{OUT}$ ' on the application of input 'A' and 'B'. Table 14 specifies simulation settings for 'CLK', 'A' and 'B'.

# Table 14: Clock and Input Pulse Parameters

| Parameters | CLK  | Α    | В    |

|------------|------|------|------|

| v1         | 0    | 1.2  | 1.2  |

| v2         | 1.2  | 0    | 0    |

| per        | 30ns | 60ns | 60ns |

| td         | бns  | Ons  | 4ns  |

| tr         | 1ns  | 1ns  | 1ns  |

| tf         | 1ns  | 1ns  | 1ns  |

| pw         | 12ns | 27ns | 45ns |

Table 15 shows the leakage power for the 2-input XOR EDCVSL structure for various input combinations in evaluation phase. These results are carried out for 90nm technology node at a temperature of 27°C.

| CLK | Α | В | OUT | OUT | Leakage Current<br>(nA) | Leakage Power<br>(nW) |

|-----|---|---|-----|-----|-------------------------|-----------------------|

| 0   | x | x | 1   | 1   | -                       | _                     |

| 1   | 0 | 0 | 0   | 1   | 6.4                     | 7.68                  |

| 1   | 0 | 1 | 1   | 0   | 5.796                   | 6.9552                |

| 1   | 1 | 0 | 1   | 0   | 6.056                   | 7.2672                |

| 1   | 1 | 1 | 0   | 1   | 4.9605                  | 5.9526                |

# Table 15: Leakage Power in EDCVSL

The delay performance of the 2-input XOR using EDCVSL structure is summarized in Table 16. The input should be stable before the active edge of CLK so that the OUT in evaluation stage is correct. In precharge phase, OUT= OUT = 1 in EDCVSL. Therefore, delay will be '0' if OUT remains '1' in evaluation phase.

## <u> Table 16:</u>

### **Delay in EDCVSL**

| CLK | Α | В | OUT | Delay (ps) |

|-----|---|---|-----|------------|

| 0   | х | х | 1   | _          |

| 1   | 0 | 0 | 0   | 64.704     |

| 1   | 0 | 1 | 1   | 0          |

| 1   | 1 | 0 | 1   | 0          |

| 1   | 1 | 1 | 0   | 64.0743    |

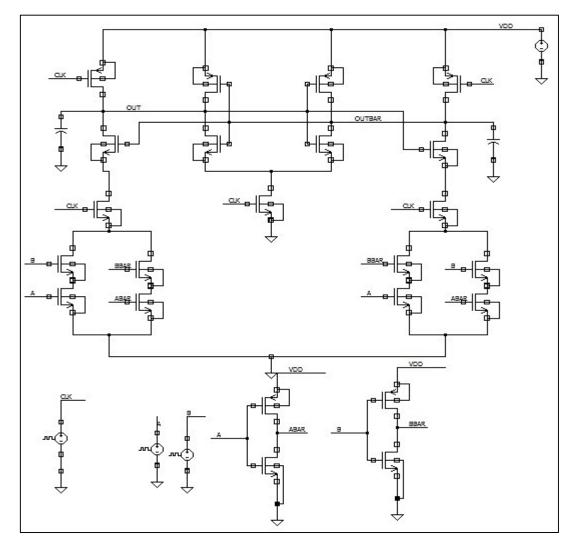

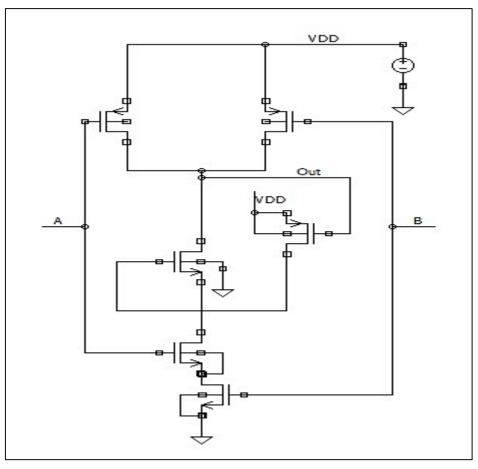

## (3.6) <u>NP- Mixed DCVSL</u>

**NP- Mixed DCVSL** a technique that uses both N and P type transistors to build pull-down network. The reason behind introducing PMOS transistors in the logic is because PMOS transistors have relatively lesser sub threshold and gate oxide leakage currents i.e. PMOS transistors are far less leaky than NMOS transistors. But this advantage comes at a cost of decrease in speed.

A conventional DCVSL circuit can be converted into NP mixed DCVSL circuit by replacing those NMOS transistors (having complementary inputs) with PMOS transistors with their gate connected to true signal input instead of their complement. Thus, the extra inverters required to complement the original signals are not required which results in reducing power consumption contributed by these inverters. Also, inverted clock is also not required.

#### Schematic:

A 2-input XOR is used as a design example throughout this thesis to test as well as to compare the functionality and performance of various DCVSL variations. Fig. 21 shows the schematic for 2-input XOR with inputs 'A' and 'B' and clock 'CLK' using 90nm technology node at  $V_{DD} = 1.2V$ . The W/L for NMOS and PMOS are (135n/90n) and (337.5n/90n) respectively.

Figure 21: 2-input XOR using NP- Mixed DCVSL architecture

Fig. 22 shows the waveform of 'OUT' and ' $\overline{OUT}$ ' on the application of input 'A' and 'B'. Table 17 specifies simulation settings for 'CLK', 'A' and 'B'.

## **Table 17:**

## **<u>Clock and Input Pulse Parameters</u>**

| Parameters | CLK  | Α    | В    |

|------------|------|------|------|

| v1         | 0    | 1.2  | 1.2  |

| v2         | 1.2  | 0    | 0    |

| per        | 30ns | 60ns | 60ns |

| td         | бns  | Ons  | 4ns  |

| tr         | 1ns  | 1ns  | 1ns  |

| tf         | 1ns  | 1ns  | 1ns  |

| рw         | 12ns | 27ns | 45ns |

Figure 22: Simulation Output for 2-input XOR using NP- Mixed DCVSL

Table 18 shows the leakage power for the 2-input XOR NP- Mixed DCVSL structure for various input combinations in evaluation phase. These results are carried out for 90nm technology node at a temperature of 27°C.

| CLK | Α | В | OUT | OUT | Leakage Current<br>(nA) | Leakage Power<br>(nW) |

|-----|---|---|-----|-----|-------------------------|-----------------------|

| 0   | X | X | 1   | 1   | _                       | _                     |

| 1   | 0 | 0 | 0   | 1   | 5.343                   | 6.4116                |

| 1   | 0 | 1 | 1   | 0   | 5.722                   | 6.8664                |

| 1   | 1 | 0 | 1   | 0   | 5.784                   | 6.9408                |

| 1   | 1 | 1 | 0   | 1   | 5.331                   | 6.3972                |

# Table 18:Leakage Power in NP- Mixed DCVSL

The delay performance of the 2-input XOR using NP- Mixed DCVSL structure is summarized in Table 19. The input should be stable before the active edge of CLK so that the OUT in evaluation stage is correct. In precharge phase, OUT= OUT = 1 in EDCVSL. Therefore, delay will be '0' if OUT remains '1' in evaluation phase.

# <u>Table 19:</u> Delay in NP- Mixed DCVSL

| СLК | Α | В | OUT | Delay (ps) |

|-----|---|---|-----|------------|

| 0   | х | х | 1   | _          |

| 1   | 0 | 0 | 0   | 78.893     |

| 1   | 0 | 1 | 1   | 0          |

| 1   | 1 | 0 | 1   | 0          |

| 1   | 1 | 1 | 0   | 78.331     |

#### Summary

In this chapter, variations of dynamic DCVSL are studied and their performance parameters are examined. Different DCVSL structure has their own merits and demerits [1] [6] [7] [13]. As an example, MSSDL decreases the delay of SSDL while sacrificing power dissipation area requirement [1] [6]. This can also be seen from results from Table 20. ECDL circuit eliminates the DC current flow path between V<sub>DD</sub> and ground, but the downside is that the circuit is designed to discharge the output nodes very half-cycle during the reset phase. This increases the dynamic power dissipation. In addition to the above drawback, the circuit relies on logic chains to discharge one of the output nodes, so that the RC delays may be a limiting factor. It has the advantage of being simple to design with reduced interconnect requirements. It also do not require inverted clock [1]. In EDCVSL, the feedback transistors M3 and M4 are used for speeding up the evaluation and helps in maintaining the correct logic levels. Also, the complete complementary input network on the other differential rail is replaced by a single transistor [7]. In NP-Mixed DCVSL, the extra inverters required to complement the original signals are not required which results in reducing power consumption contributed by these inverters. Also, inverted clock is also not required.

2-input XOR is implemented in various dynamic DCVSL structures to test their functionality. The performance results depend on circuit topology (here 2-input XOR), so these results may not show similar trend always. Yet, these results gives an idea as to utilise a particular structure depending on design requirements. Table 20 tries to summarize results of this chapter.

#### <u>Table 20:</u>

| 2-input<br>XOR<br>using | No. of TransistorsNMOSPMOSTotal |   | <u>Leakage</u><br><u>Power</u><br><u>(nW)</u> | <u>Delay</u><br>(ps) | PDP<br>(aJ) | <u>Remarks</u> |                                                                                                                                              |

|-------------------------|---------------------------------|---|-----------------------------------------------|----------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| SSDL                    | 17                              | 7 | 24                                            | 4.609                | 75.548      | 0.348          | <ul> <li>Improvement in evaluation time<br/>over conventional DCVSL and<br/>domino structures.</li> <li>Clock inversion required.</li> </ul> |

| MSSDL                   | 19                              | 7 | 26                                            | 5.582                | 18.04       | 0.1            | <ul> <li>Improves delay over SSDL.</li> <li>Leakage Power and transistor count increases.</li> </ul>                                         |

## **Summarized Results of Chapter 3**

|              |    |   |    |       |          |          | <ul> <li>Overall PDP improves.</li> <li>Clock inversion required.</li> <li>Simple to design with reduced</li> </ul>                                                                                                               |              |              |              |                                                                                                                              |

|--------------|----|---|----|-------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------|

| ECDL         | 14 | 5 | 19 | 5.515 | 19 5.515 | 19 5.515 | 5.515 87.923                                                                                                                                                                                                                      | 87.923 0.485 | 87.923 0.485 | 87.923 0.485 | <ul> <li>interconnect.</li> <li>Increased dynamic power<br/>dissipation.</li> <li>Inverted clock is not required.</li> </ul> |

| DCSL         | 17 | 6 | 23 | 7.025 | 16.598   | 0.116    | <ul> <li>NMOS transistor introduced in<br/>PDN helps in limiting node<br/>voltages.</li> <li>Delay reduced significantly<br/>offering good PDP.</li> <li>Inverting clock is not required.</li> </ul>                              |              |              |              |                                                                                                                              |

| EDCVSL       | 11 | 6 | 17 | 6.963 | 64.389   | 0.448    | <ul> <li>Transistor count decreases<br/>significantly.</li> <li>Complete complementary input<br/>network is replaced by a single<br/>transistor.</li> <li>Inverting clock is not required.</li> <li>Complex to design.</li> </ul> |              |              |              |                                                                                                                              |

| NP-<br>Mixed | 8  | 9 | 17 | 6.654 | 78.612   | 0.523    | <ul> <li>Transistor count decreases<br/>significantly.</li> <li>Inverting clock is not required.</li> <li>Delay increases significantly.</li> <li>Complex to design.</li> </ul>                                                   |              |              |              |                                                                                                                              |

# Chapter 4

# **LECTOR Incorporated Dynamic DCVSL Variations**

#### **Introduction**

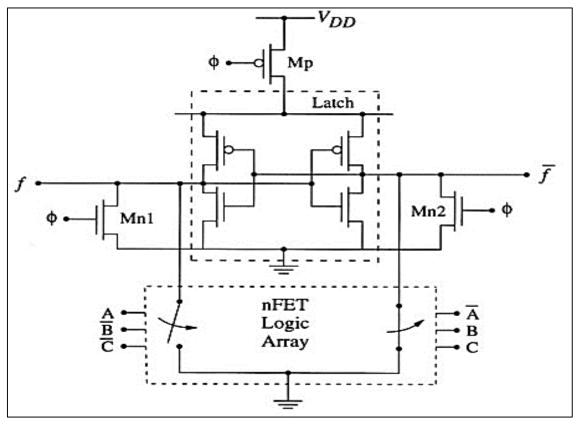

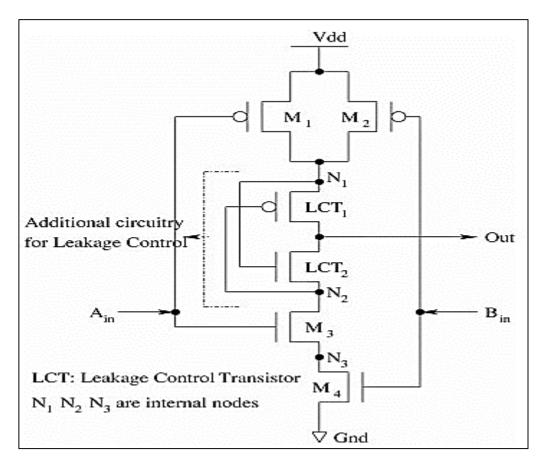

To achieve reduction in leakage power in a circuit, the idea is to assemble transistors from supply  $V_{DD}$  to ground. LECTOR technique uses this idea by incorporating two leakage control transistors (LCTs), a PMOS and a NMOS that are positioned in between the PUN and PDN. The gate terminal of one LCT is controlled by the source terminal of other. Thus, there is no need of external circuit as these LCTs are self-controlled. The arrangement of these two LCTs ensures that one of the LCTs remains in "near cut-off region" for any possible combination of inputs. This increases resistance between V<sub>DD</sub> and ground, thereby reducing the leakage current.

The most noteworthy feature of LECTOR technique that makes it one of the most popular leakage reduction technique is that it manages to have leakage suppression effectively in both active and idle states of the circuit. Making high  $V_{th}$  LCTs helps to achieve additional leakage control. Fig. 23 shows a NAND gate incorporated with LCTs to give the idea of this technique.

LECTOR technique is one of the most effective technique in reducing leakage power reduction. This is the reason this technique is used in this thesis to compare performance with the proposed ONOFIC approach for dynamic DCVSL to make a fair competition.

Figure 23: LECTOR incorporated CMOS 2-input NAND gate [9]

#### **Operation**

- Let the LECTOR incorporated CMOS 2-input NAND gate given in Fig. 23 is fed with input combination of  $(A_{in}, B_{in}) = (1, 0)$ . This results in M<sub>1</sub> and M<sub>4</sub> turning 'OFF' and M<sub>2</sub> and M<sub>3</sub> turning 'ON'.

- The node voltages at  $N_1$ ,  $N_2$ , Out and  $N_3$  determines the status of LCT<sub>1</sub> and LCT<sub>2</sub>.

- $N_1$  is at  $V_{DD}$ . LCT<sub>1</sub> being a PMOS passes good  $V_{DD}$  to 'Out' node.

- LCT<sub>2</sub> being a NMOS passes weak  $V_{DD}$  making  $N_2$  at voltage  $V_{DD}$ - $V_{th}$ .