# DESIGN OF UNIVERSAL FILTER AND OSCILLATOR USING DIFFERENTIAL DIFFERENCE CURRENT CONVEYOR TRANSCONDUCTANCE AS ACTIVE BLOCK

Dissertation submitted in

Partial fulfillment of the requirement For the award of the degree of

#### **Master of Technology**

In

#### VLSI and Embedded System Design

By

#### **RASHMIKA RAI**

#### University Roll No. 2K15/VLS/13

Under the guidance of

Dr. S. Indu

Professor,

**Electronics and Communication Engineering Department, DTU**

2015-2017

ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042, INDIA

# Department of Electronics and Communication Engineering Delhi Technological University (DTU)

(Formerly Delhi College of Engineering, DCE)

Govt. of NCT of Delhi

Bawana Road, Delhi-110042

# CERTIFICATE

This is to certify that the dissertation entitled "Design of Universal Filter and Oscillator using Differential difference current conveyor as active Block" is a bona-fide record of work done by RASHMIKA RAI, Roll No. 2K15/VLS/13 at Delhi Technological University for partial fulfillment of the requirements for the award of degree of Master of Technology in VLSI and Embedded systems Engineering. This project was carried out under my supervision and has not been submitted elsewhere, either in part or full, for the award of any other degree or diploma to the best of my Knowledge and belief.

Place-Delhi

Date-

Dr S. Indu (Professor) ECE Department Delhi Technological University

# **CANDIDATE DECLARATION**

I ,Rashmika Rai , Roll No-2k15/VLS/13,student of M.Tech (VLSI and Embedded System),hereby declare that the dissertation title "**Design of oscillator and Universal filter using Differential Difference Current Conveyor active block**", under the supervision of S.Indu , Professor in Electronics and Communication Engineering Department, Delhi Technological University, in partial fulfillment of the requirement for the award of the degree of Master of Technology, has not been submitted elsewhere for the award of any degree.

I hereby solemnly and sincerely affirm that all the particulars stated above by me are true and correct to the best of my knowledge and belief.

Place: Delhi

Date:

Rashmika Rai

2k15/VLS/13

# **ACKNOWLEDGEMENT**

I express my deepest gratitude to my project guide Mrs S.Indu (Professor) Department of Electronics and Communication Engineering, Delhi Technological University whose encouragement, guidance and support from the initial to the final level enabled me to develop an understanding of the subject. Her suggestions and ways of summarizing the things made me to go for independent studying and trying my best to get the maximum in my topic, this made my circle of knowledge very vast. I am highly thankful to her for guiding me in this project.

Finally, I take this opportunity to extend my deep appreciation to my family and friends, for all that they meant to me during the crucial times of the completion of my project.

Date-

Rashmika Rai Roll No. 2K15/VLS/13 M. Tech. (VLSI)

# **ABSTRACT**

Biquadratic filter which operates in voltage mode, and oscillator is presented in the thesis. The circuit of biquadratic filter is used to implement low pass, high pass, band pass, band stop, notch filters and all pass filter simultaneously. In the design of universal filter the circuit used two differential difference current conveyor transconductance blocks .It also uses passive component such as resistor and capacitor. It used two resistor and capacitor in the implementation of universal filter. The main benefit of this circuit is that it can derive low pass, high pass, band pass ,band stop ,all pass and notch filter concurrently. In the realization of all pass filter it does not require matching in the passive component. Maximum power supply used for the design is set to .9Volts, 180 nm parameter file used in the size of a transistor. Biasing voltage is set to be .7Volt.Using one block of differential difference current conveyor and grounded resistor and capacitor an oscillator has been designed. It is quadrature oscillators where two voltage source obtain both are in the ninety degree phase shift with respect to each other. By changing the value of passive component controlled oscillation frequency is provided in the oscillator. Oscillation frequency is directly proportional to a square root of transconductance and this transconductance can be change by changing the value of biasing current .Therefore oscillation frequency can be varied by varying the value of the biasing current.

# **LIST OF FIGURES**

## LIST OF FIGURES

| Figure No | Caption                                                                                    |    |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------|----|--|--|--|--|

|           |                                                                                            |    |  |  |  |  |

| 1.1       | Block Diagram of Voltage controlled current source                                         | 3  |  |  |  |  |

| 2.1       | Block Diagram of Voltage controlled current source                                         |    |  |  |  |  |

| 2.2       | Differential Amplifier Common Mode Input Output characteristics for small and large signal |    |  |  |  |  |

| 2.3 (a)   | (a) Characteristics of Output for Differential Input                                       |    |  |  |  |  |

| (b)       | (b) Characteristics of Differential Gain                                                   |    |  |  |  |  |

| 2.4       | Differential Amplifier with R <sub>SS</sub> as Biasing load                                | 10 |  |  |  |  |

| 2.5       | Current Mirror Circuit                                                                     | 11 |  |  |  |  |

| 2.6       | MOS Current Steering Circuit                                                               | 11 |  |  |  |  |

| 2.7       | Cascode Current Mirror Circuit.                                                            | 14 |  |  |  |  |

| 2.8       | Wilson Current Mirror                                                                      | 14 |  |  |  |  |

| 2.9       | Modified Wilson Current Mirror                                                             | 15 |  |  |  |  |

| 2.10      | Active Load MOS differential pair circuit                                                  | 15 |  |  |  |  |

| 2.11      | Current Conveyor using MOS Transistor.                                                     | 17 |  |  |  |  |

| 2.13      | Block Diagram of Differential Difference Amplifier                                         | 19 |  |  |  |  |

| 2.14      | MOS implementation of Differential Difference Amplifier                                    | 22 |  |  |  |  |

| 2.15      | Block Diagram of Fully Differential Amplifier                                              | 22 |  |  |  |  |

| 2.16      | Block Diagram of Fully Differential Current Conveyor                                       | 24 |  |  |  |  |

| 2.17      | Block Diagram of operational floating Current Conveyor                                     | 26 |  |  |  |  |

| 3.1       | Block diagram of differential difference current conveyor                                  | 30 |  |  |  |  |

| 3.2       | Circuit using MOS of Differential Difference Amplifier                                     | 31 |  |  |  |  |

| 4.1       | Frequency Response of Low Pass ,High Pass ,Band Pass, Notch                                | 35 |  |  |  |  |

| 4.2       | Block Diagram of Universal Filter                                                          | 37 |  |  |  |  |

| 4.3.1  | Frequency Response of Band Pass Filter   | 38 |

|--------|------------------------------------------|----|

| 4.3.2  | Phase Response of Band Pass Filter       | 40 |

| 4.3.3  | Frequency Response of Low Pass Filter    | 41 |

| 4.3.4  | Phase Response of Low Pass Filter        | 42 |

| 4.3.5  | Gain response of High Pass Filter        | 43 |

| 4.3.6  | Phase Response of High Pass Filter       | 44 |

| 4.3.7  | Gain Response of Notch Filter            | 45 |

| 4.3.8  | Phase Response of Notch Filter           | 46 |

| 4.3.9  | Gain and Phase Response of Notch Filter  | 47 |

| 4.3.10 | Gain Response of All Pass Filter         | 48 |

| 4.3.11 | Phase Response of All Pass Filter        | 49 |

| 4.4.1  | Block Diagram of Oscillator              | 50 |

| 4.4.2  | Block Diagram of Oscillator using DDCCTA | 51 |

## LIST OF SYMBOL AND ABBREVIATION

| Symbols_       | Abbreviation                                              |

|----------------|-----------------------------------------------------------|

|                |                                                           |

| BW             | Bandwidth                                                 |

| BPF            | Band Pass Filter                                          |

| CC             | Current Conveyor                                          |

| CCC            | Current Controlled Conveyor                               |

| CC11           | Second Generation Current Conveyor                        |

| CDBA           | Current Differential Buffer Amplifier                     |

| CDTA           | Current Differential Transconductance Amplifier           |

| CFOA           | Current Feedback Operational Amplifier                    |

| CFTA           | Current Follower Transconductance Amplifier               |

| CMRR           | Common Mode Rejection Ratio                               |

| CMOS           | Complementary Metal Oxide Semiconductor                   |

| СМ             | Current Mode                                              |

| DDCC           | Differential Difference Current Conveyor                  |

| DDCCTA         | Difference Current Conveyor<br>Transconductance Amplifier |

| DVCC           | Differential Voltage Current Conveyor                     |

| DXCC11         | Dual-X Current Conveyor                                   |

| Fo             | Pole Frequency or 3Db frequency                           |

| g <sub>m</sub> | Transconductance                                          |

| HPF              | High Pass Filter                       |

|------------------|----------------------------------------|

| I <sub>in</sub>  | Input Current                          |

| I <sub>out</sub> | Output Current                         |

| IC               | Integrated Circuit                     |

| I <sub>b</sub>   | Bias Current                           |

| LPF              | Low Pass Filter                        |

| MISO             | Multiple Input Single Output           |

| MIMO             | Multiple Input Multiple Output         |

| ΟΤΑ              | Operational Transconductance Amplifier |

| OP-AMP           | Operational Amplifier                  |

| Q                | Quality Factor                         |

| SIMO             | Single Input Multiple Output           |

| SR               | Slew Rate                              |

| THD              | Total Harmonic Distortion              |

| Vin              | Input Voltage                          |

| Vout             | Output Voltage                         |

| Vss              | Source Supply Voltage                  |

| Vdd              | Drain Supply Voltage                   |

| VDCC             | Voltage Differential Current Conveyor  |

| VM               | Voltage Mode                           |

| Zin              | Input Impedance                        |

| Zout             | Output Impedance                       |

# **INDEX**

| Certificate                                                                      | Ι    |

|----------------------------------------------------------------------------------|------|

| Candidate Declaration                                                            | III  |

| Acknowledgement                                                                  | IV   |

| Abstract                                                                         | V    |

| List of Figure                                                                   | VI   |

| List of Symbols, abbreviation                                                    | VIII |

| Contents                                                                         |      |

| Chapter 1 Introduction                                                           | 1-6  |

| 1.1. Background                                                                  | 1    |

| 1.2. Current Conveyors                                                           | 1    |

| 1.3. Operational amplifier                                                       | 2    |

| 1.4. Operational Transconductance Amplifier                                      | 3    |

| 1.5. current mode and voltage mode signal processing                             | 3    |

| 1.6. processing of signal in analog and digital mode                             | 4    |

| 1.7. organization of thesis                                                      | 5    |

| Chapter 2 Literature Survey various constituent Circuit in analog circuit design | 7-26 |

| 2.1. Differential amplifier                                                      | 7-10 |

| 2.1.1. Simple differential circuit                                               | 8    |

| 2.1.2. Basic differential pair                                                   | 9    |

| 2.1.3. Input/output characteristics                                              | 9    |

| 2.1.4. Common Mode Gain and CMRR                                                 | 10   |

| 2.2. Current M   | irror                                                                                 | 11-13 |

|------------------|---------------------------------------------------------------------------------------|-------|

| 2.2.1. Out       | put characteristic of the current source and the Current mirror                       | 11    |

| 2.2.2. MO        | S Current-Steering Circuits                                                           | 12    |

| 2.3. Active load | 1                                                                                     | 13    |

| 2.4. Modified 0  | Current Mirror                                                                        | 13-15 |

| 2.4.1. Case      | code current mirror                                                                   | 13    |

| 2.4.2. Wils      | son current mirror                                                                    | 15    |

| 2.5. The active  | loaded MOS differential pair                                                          | 15-16 |

|                  |                                                                                       | 16-19 |

| 2.6. current co  | nveyor                                                                                | 16    |

| 2.6.1. First     | t generation current conveyor                                                         | 17    |

| 2.6.2. Imp       | lementation of Current Conveyor using MOS                                             | 18    |

| 2.6.3. Sec       | ond generation current conveyor                                                       | 19    |

| 2.6.4. Thir      | d generation current conveyor                                                         | 20-21 |

| 2.7. Differentia | l difference amplifier (DDA)                                                          | 21-26 |

| 2.8. derivative  | of current conveyors                                                                  | 21    |

| 2.8.1. DDC       | CC (Differential Difference Current Conveyor)                                         | 22    |

| 2.8.2. MO        | S implementation of differential                                                      | 22    |

| 2.8.3. Diff      | erence amplifier Fully Differential current conveyor                                  | 23    |

| 2.8.4. Dua       | I-X Current Conveyor                                                                  | 23    |

| 2.8.4.1.         | Schematic of dual-x current conveyor                                                  | 24    |

| 2.8.4.2.         | Current Conveyor Voltage Graph at Xn, Xp and Y                                        | 25    |

| 2.8.5. Ope       | rational Floating Current Conveyor                                                    |       |

| -                | ation and Analysis of Differential Difference Current<br>conductance Amplifier Block. | 28-34 |

| 3.1. Introductio | on                                                                                    | 28    |

| 3.2. The DDCC    | rA symbol analysis                                                                    | 30    |

| 3.3. Schematic   | of differential difference Current Conveyor transconductance                          | 31    |

| amplifier        |                                                                                       |       |

xi

| 3.4. The aspect ratio of transistor                 | 31 |

|-----------------------------------------------------|----|

| 3.5. Graph of the voltage at terminal Y1, Y2, Y3, X | 32 |

| 3.6. Graph of current at terminal X and $I_{Z1}$    | 33 |

| 3.7. Graph of current at terminal X and $I_{Z1}$    | 34 |

## **Chapter 4 Design of Filter and Oscillator**

35-524.1. Introduction354.2. Filter Configuration364.3. Block diagram of universal filter374.4. Simulation Result384.5. Design of Oscillator494.5.1. Block Diagram of Oscillator and simulation result51

| Chapter 5 Conclusion and Future directions | 53-54 |

|--------------------------------------------|-------|

| Appendix                                   | 55-58 |

| References                                 | 59-62 |

#### **CHAPTER-1**

#### 1.1 Background

The work presented here deals with building block ,which operates in active mode ,known as Differential Difference Current Conveyor Transconductance Amplifier and it has applications in analog circuit design such as in signal processing. In the present microelectronics technology, the electronic circuits require low power consumption , low power supply and long term durable device. All of these demand strive to fulfill simultaneously but this is problematic and comes with several challenges.

Analog Signal Processing of Active Element evolved in two Part –In first part modification of active element such as OTA (Operational Transconductance Amplifier), CFA (Current Feedback Amplifier), VFA (Voltage Feedback Amplifier).Designers are strive to increase the potential application of the circuit. Structure of active element should be such that power consumption should be as low as possible and speed should be as high as possible. In second part, designer strive for entirely new active element in order to develop new technology and circuit.

#### **1.2 Current Conveyors**

K. C.Smith and A. S. Sedra published the first-generation current conveyor in 1968. They describe the basic principle of current conveyor. Two year later ,second-generation CCII comes into picture and then third generation form of current conveyor comes in 1995.Current conveyor used in current mode as well as the voltage mode .Initially current conveyor did not find any application because of the existence of operational transconductance amplifier. Current conveyor used in wide-spread application .Therefore it is also known as the universal building block. Its feature finds application mostly in current mode. In the current conveyor Voltage of the Y input terminal in grounded and current ,flowing through terminal X is copied to terminal Z. Arithmetic operation is performed in the current conveyor as the operational amplifier. Operational amplifier has a limitation on gain and bandwidth whereas current conveyor provides huge signal bandwidth irrespective of the signal swing. In the words large signal is not going to affect the operating bandwidth of the signal. Although the operation transconductance

amplifier provides tunability but there is voltage swing and sensitivity issue .Therefore ,current conveyor used in place of the operational amplifier. Current Conveyor also used for the design of oscillator, multiplier , filter ,Amplifier and provides adaptability and flexibility in the design.

Current conveyor attracts the user because it provide huge bandwidth ,higher linearity, low power consumption as compare to the operational amplifier.

#### **<u>1.3 Operational amplifier</u>**

Design of first operational amplifier was proposed 68 years ago. First commercial operational amplifier Manufactured 56 year ago. Operational Amplifier evolved in two forms –Voltage feedback amplifier and Current feedback amplifier. Behavior of the operational amplifier in both the form are same in ideal mode.

Operational amplifier provides amplification of differential voltage vp-vn with the help of negative feedback .Amplifier becomes operational if it provides negative resistance. Enormous operation can be done using this, that's way it is called operational. Idea Op-Amp has infinite differential gain but in practice, it has very high differential gain, Ideal Op-Amp has zero common mode signal gain but in reality, it has common mode gain of around 120dB. Ideal Op-Amp has zero bias current but in reality, it has the bias current as high as in micro amp to be as low as Fermi Amp. Ideal Op-Amp has zero offset voltage but in reality, it has offset voltage in range of mV to be as low as microvolt. There is a huge demand of the linear device with single supply voltage that used in computer application, laptop, camera, set-top box which performs same as dual supply voltage. Due to single supply voltage input and output signal range reduces. Therefore device become more sensitive to noise and disturbance. Due to single supply voltage power consumption is reduced.Opamp is used to convert data to reference voltage, oscillator and many other application include multiplier, used to shape different signal, generation of different function but the disadvantage of op-amp is it has limited gain bandwidth product.

#### **<u>1.4 Operational Transconductance Amplifier</u>**

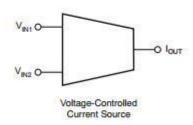

For on chip implementation of fast frequency filter, Operational Transconductance Amplifier are most widely used. It provide electronic tunability. It finds enormous application in biquadratic filter. Operational Transconductance Amplifier operates as the current source which is controlled by voltage. Circuit of OTA is the self bias .By using OTA it is possible to reduce component count. Linearity of OTA is better than any other transistor.

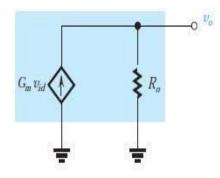

#### Fig 1.1 Block Diagram of Voltage controlled current source.

Operational Transconductance Amplifiers provide behavioral representation. Its basic function is to convert differential voltage into a current. Mainly use in oscillator design ,gain with variable value, design of filter with current and voltage controlled. Value of input impedance , output impedance, transconductance gain is independent of applied voltage and dependent on controlled current linearly. Operational a transconductance amplifier is the current source which is controlled by voltage whereas operational amplifier is the voltage source which is controlled by voltage. Value of output current

#### Iout = $g_m(Vin_1-Vin_2)$

Operation transconductance amplifier has very high output impedance because it is current source. Whereas Operational Amplifier has low output impedance because it is voltage source. Low output impedance has an advantage of having low loading effect. With the operational transconductance amplifier it is possible to design circuit without employing negative feedback. In operational transconductance amplifier has transconductance parameters which work as same as negative feedback to reduce sensitivity of the circuit. Whereas in Op-Amp we use resistor and capacitor as a control parameter which increases device size.

## <u>1.5 SIGNAL PROCESSING IN VOLTAGE MODE AND IN CURRENT</u> <u>MODE</u>

It is very difficult to find circuit which is an entirely current mode. Current mode circuit usually operates at low voltage, due to this power consumption is reduce. Circuit always behaves

according to applied voltage and current. Current decides the circuit behavior in the current mode circuit .Normally parasitic does not going to significantly affect the performance of circuit. Therefore voltage mode circuit change to current mode circuit in order to operates at voltage and hence power consumption is reduce .Building block of the current source act as constant current source and active load in amplifier stage. It provides the copy of reference current. Its input impedance is very high .Therefore it reduces loading effect. It offers high output impedance. It can generate constant current over a wide range of voltage. In the signal processing voltage and current varies with time due to the movement of the charge carrier.

In the active device only voltage or current is used because it is used to design resistance or conductance which can be controlled in the signal processing. The circuit then becomes compatible to convert voltage into current and current into voltage. Initially most of the circuit circuit operates in Voltage mode circuit .Voltage mode processing is easier as compare to current mode processing. Voltage can be use as the main variable for signal processing.

The main difference between device function in voltage process and current process is that in current mode only single input is applied and only single output we can get. Whereas in voltage mode by applying single input ,we can get multiple output. It is impossible to connect serial connection in current processing block. Therefore if we want to get multiple outputs giving the same output in current mode, we required more input terminal. While the single output terminals can supply more input voltage terminals by using parallel connection in voltage mode.

The mode is very important for the design of active block. If the signal applied to the input terminal is voltage and getting current in the output terminal then the amplifier is called transconductance and If the applied signal to the input terminal is the current and getting voltage at the output terminal then block is called transimpedance block.

#### **1.6 PROCESSING OF SIGNAL IN ANALOG AND DIGITAL MODE**

Signal is said to be medium for information so it acts as a carrier. Signals represent mathematically in information processing. In the processing of signals, there is processor to extract information. System is used to process the signal, it can be electronics, mechanical or computer type system. There is enormous application where processing of signals is performed. These processing is implemented in either analog or digital mode. If the processing of signal is in

analog mode, then used component like transistor, capacitor, resistor. In digital signal processing microprocessor, digital computer are used. In the analog signal processing there is effect of temperature variation, supply voltage. Therefore for the given same input pattern we get different output but in the digital signal processing system for the same given set of input, we get same output irrespective of parameter size, temperature and supply voltage.

#### **1.7 ORGANIZATION OF THESIS**

In the organization of the thesis ,the fundamental concept in the design of universal filter and oscillator using current conveyor operating in differential difference mode is covered and it working is illustrated as an active building building block. This need led to brief study of different type of current conveyor and study of differential difference amplifier. In this section, the circuit using voltage mode is designed. The circuit designed is the analog circuit which can be used in many analog signal processing applications.

In the chapter 2 in order to design the active building block basic components are discussed in detail .Basic building block like operational transconductance amplifier ,design of Active load using MOS transistor ,Design of Differential Amplifier, Design of voltage buffer, First ,second and current conveyor in the third generation ,Derivative of current conveyor like differential difference type current conveyor, Operational floating current conveyor ,Dual-X type current conveyor, Fully Differential type current conveyor etc are discussed.

In the chapter 3, the schematic of Differential Differential current conveyor Transconductance Amplifier and Transient analysis of differential difference current conveyor transconductance amplifier has been shown. Different graph of voltage mode and current mode is plotted and the arithmetic operations are verified through the graph obtained at terminal X. Current coping capability of the circuit has also been shown through a graphs.

In the chapter 4, Active block named Differential Difference current conveyor transconductance amplifier block is used for the designing of universal filter and oscillator. Transconductance part of the differential difference current conveyor is used to provide tunability in the circuit by changing bias current through the circuit.

In chapter 5, the future scope behind the designing of the circuit is briefly described followed by the summary of the entire thesis work.

#### **CHAPTER-2**

#### 2.1 LITERATURE SURVEY OF VARIOUS CONSTITUENT CIRCUIT IN ANALOG CIRCUIT DESIGN

A lot of work has been done in the field of integrated circuit in the past four decade. Nowadays circuit design using analog component and system plays a very crucial role in the electronics world. Designers are challenged to develop simple and basic analog solutions with the demand of compact system, fewer noisy system, broadband and wireless communications, mingled industry. Thus hundreds of bipolar /CMOS active building blocks has been proposed. After a brief study of these blocks and their crucial implementation, it is obvious that these blocks comprise of one or more of the following basic constituent blocks.

- 1. Operational Transconductance amplifier

- 2. Differential amplifier

- 3. Current mirror

- 4. Active load

- 5. Voltage buffer

As it is observed that these block is compulsory for many other active analog device, therefore this chapter focuses on these constituent blocks and their important features.

#### **<u>2.1-Differential amplifier</u>**

Differential amplifier is most important circuit invention, it used as an active element of the input stage of many analog block and analog circuit. BJTs or MOSFETs used in the implementation of Differential amplifier .In the differential mode ,it multiplies the difference of voltage between positive and negative terminal of inputs (Vin+ - Vin-) by ingredient differential gain(Ad) and in common mode multiplies common mode voltage between two inputs (Vin+ + Vin-)/2 by factor Ac. The signal which is common to both input, acts as the noise is rejected by the differential amplifier. Hence it is the powerful tool for rejection of noise in the circuit. Many circuit ,mostly with voltage input uses the differential pair. In this thesis work the DDCCTA block also uses differential pair as input stage .With the evolution of integrated circuit popularity of Differential amplifier increase in both BJT and MOS technology,

it rejects the noise which is common for both input and has the high gain as compare to its single ended counterpart. The Matching between the circuit parameter of the transistor on the two sides of the differential pair decides its performance. Its important advantage is higher immunity to environment noise.

#### **2.1.1Simple differential circuit**

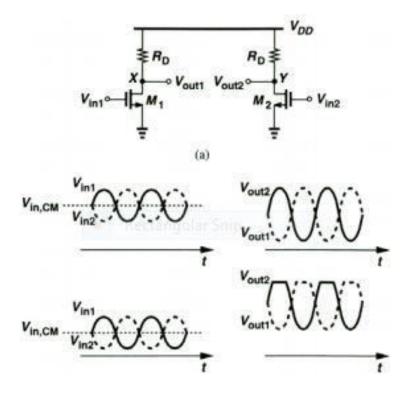

Fig 2.1 Differential Amplifier Common Mode Input Output characteristics for small and large signal

Due to the current source  $I_{SS}$ , It is possible to make ID1 + ID2 independent of *Vin*, cm. If the voltage applied at both input terminals are equal i.e Vin1 = Vin2 then bias current will be equally divided in each of the transistors. The common-mode gain is decreased by this, and The common-mode rejection ratio(CMRR) is increased by this. The drain (collector) voltages change in response to a common-mode input signal, but the difference between the drain voltages remains essentially zero if there is no mismatch present to the circuit. The differential gain is increased by the multiplying factor of 2 because output is the difference between two voltages of equal magnitude and opposite sign.

#### 2.1.2 Basic differential pair

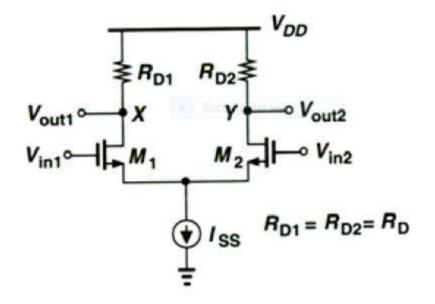

Fig 2.2 Basic Differential Amplifier with Iss as bias Load

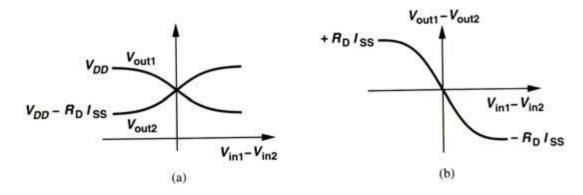

Voltage at terminal X is  $Vout_1=V_{dd}-I_{D1}R_{D1}$  and Voltage at terminal Y is  $Vout_2=V_{dd}-I_{D2}R_{D2}$ . As input voltage at terminal X increases Vout\_1 decreases ,in the same way as input voltage at terminal Y increases Vout\_2 decreases. The relationship between input and output can be given below.

#### 2.1.3 Input/output characteristics

2.3 (a)-Characteristics of Output for Differential Input

(b)-Characteristics of Differential Gain

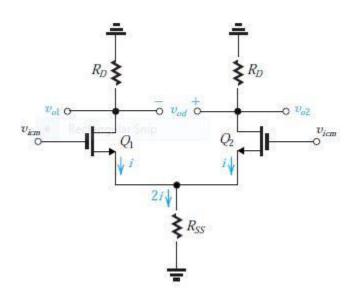

#### 2.1.4 Common-Mode Gain and CMRR

The response of the differential amplifier is only to a differential input signal and rejects a common-mode signal. The changes in input common mode signal over a wide range results in no change in the voltage at either of the two drains. It is expected that the bias current *I* is an ideal. If the current source that bias the current have a finite output resistance, the common-mode gain will no longer be zero.MOS differential amplifier biased with a current source having  $R_{ss}$  output resistance. This common mode input signal can represent an interference signal or noise that is picked up by both inputs and this interference signal or noise is totally undesirable.

Fig 2.4 Differential Amplifier with R<sub>SS</sub> as biasing load

As it is seen from the graph that Vicm is applied to both the input terminal of transistor Q1 and Q2.Vod appears in the output is due to noise and interference.

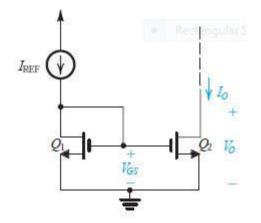

#### **2.2 - CURRENT MIRROR**

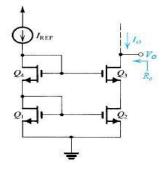

Fig 2.5 Current Mirror Circuit

Io is influenced by the reference current ( $I_{ref}$ ) by the aspect ratios of the Transistors which is due to particular connection of Q1 and Q1.Relationship between  $I_O$  and  $I_{REF}$  depends upon the size of the transistor, which is given by

$$\frac{I_O}{I_{\text{REF}}} = \frac{(W/L)_2}{(W/L)_1}$$

Current Mirror circuit provides copy of reference current at the Io.

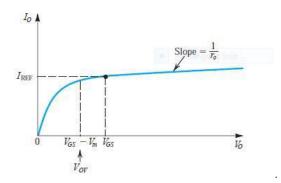

# **2.2.1** The current source and the current mirror Output characteristic can be given as

Fig 2.6 Current Mirror output characteristics

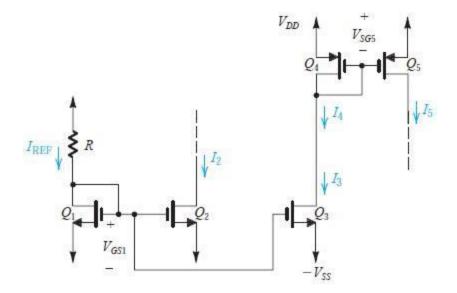

#### **2.2.2 MOS Current-Steering Circuits**

Current steering function is device using the current conveyor. Q1 accompanied by R makes a decision about the value of reference current and work as current mirror having two output, Transistors Q3,Q2 and Q3 combined to form circuit and work as current mirror having two output.

$I_2 = I_{\text{REF}}(W/L)2/(W/L)$  1  $I_3 = I_{\text{REF}}(W/L)2/(W/L)$  1

current sources and current sinks are important in integrated circuit design. In the function of current source, Current Mirror is used with several other building blocks. Two important parameter need to consider when the current mirror is use-

1-Current transfer capability of current source.

2- The current source output resistance.

2.6 MOS Current Steering Circuit

$V_{D2}, V_{D3} > -V_{SS} + V_{GS1} - V_{m}$

By the transistor Q5,Q4 work in PMOS mode the current  $I_5$  is hand over to the input side of the transistor .

$I_5 = I_4 (W/L) _5/(W/L) _4$

Q5 acts as current source because it pushes the current I<sub>5</sub>, whereas Q2 acts as a current sink because it pulls the current I2

#### 2.3 Active load

Transistors output resistance *ro* are important parameter for the operation of active-load amplifiers. After finding ro, calculate differential gain *vol vid* of the active-load MOS differential pair. If differential amplifier is not symmetric, then virtual ground will not develops in the common source terminal. The figure shown below gives the value of  $G_m$ . Here the value of gain(GmR<sub>O)</sub> is detected by finding output resistance R<sub>o</sub> and transconductance Gm obtained by short circuit.

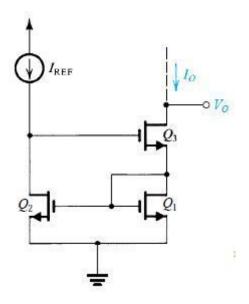

#### 2.4.1 Cascode current mirror

The figure shows the basic cascade current mirror. It consists of diode connected transistor Q1 and combination of Q1 and Q2 form the current mirror.Q4 is used to provide appropriate bias for the gate of CASCODE transistor Q3. In order to determine output resistance at the drain of Q3, assuming voltage across Q1 and Q4 is constant and therefore voltage at the gate of Q2 and Q3 is zero. Due to current source transistor having finite output resistance, error arises in current source. The Finite output resistance results in fluctuation of output current with voltage in the basic current mirror. Output resistance in cascode current mirror is higher than basic current

mirror. The current mirror in the cascade form has twice basic current mirror which is configured using Q3 and Q4 transistor and Q1 and Q2 transistor.Q3, Q4 and Q1, Q2 are connected in series.

Fig 2.7 Cascode Current Mirror Circuit.

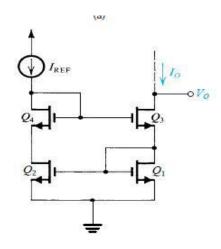

#### 2.4.2 Wilson current mirror

The figure shows Wilson's mirror using MOS. In wilson current mirror error does not exist. The main advantage of Wilson current mirror is that, it increases output resistance. In order to determine output resistance Iref has to set to zero. Apply test voltage Vx to the output node, Ro = vx/ix

Fig 2.8 Wilson Current Mirror

Modified version of Wilson current mirror is shown below

Fig 2.9 Modified Wilson Current Mirror

As it can be seen that in Wilson current mirror ,there is increase in output resistance by gm3ro3 and the same result is obtained in the cascade mirror

#### **2.5 The Active-Loaded MOS Differential Pair**

In IC technology where chip area is constrain, there is a technique where the resistor is simulated using CMOS and other active block such as OTA, This reduces chip area and circuit efficiency. Such type of active load also provides electronic tunability which is an additional advantage. A single ended differential current mirror is shown in the circuit, where the active load is provided by PMOS.

Fig 2.10 Active Load MOS differential pair circuit

differential pair is formed by the MOS transistors Q1 and Q2 whereas Q3, Q4 act as current mirror load, The value of current in the transistor Q1 and Q2 is equal under perfectly matched condition. Current pass through the drain of Q1 is I/2 and it acts as source current for the input transistor Q3,Copy of the current in Q3 is provided in transistor Q4. ). For the perfectly match condition of the two transistor the voltage of one transistor track the voltage of the other transistor.

#### **2.6 CURRENT CONVEYOR**

Current conveyor is the useful building block for high frequency current mode application. It is a three terminal device. When the device is connected to other electronic circuits ,it is use for the analog signal processing .The function of current conveyor is very much similar to op-amp. Initially function of analog circuit is highly dependent on OP-AMP, but current conveyor presents an additional method for implementation of analog circuit. Current conveyor improves accuracy ,bandwidth and it is very convenient to use. Hence current conveyor abstracts an alternative manner of abstracting complex circuit function. A lot of work had been done to implement current conveyor thus many applications of current conveyor had been proposed by researchers. Basics of current conveyor and its application has discussed.

After many different application of current conveyor has been published by different people, still after so many research, current conveyor is not available in the form of IC, due to this reason this active block could not be used in many analog circuit and system design application by many developers. Some OP-Amp based on current conveyor is available, which have high speed and wide band in the form of integrated such as OPA660,AD840, AD844. Some common type of current conveyor has discussed in the following text.

#### **2.6.1 CURRENT CONVEYOR IN FIRST GENERATION**

In the initial stage of the current conveyor also known as first generation there is no need of the filter type elements in the feedback. It is maintaining high output impedance .Therefore, without any filter element it allows the feedback in the response. In a first generation current conveyor if

voltage source V is connected at input terminal Y, then same voltage appear at another input terminal X. Potential at X is set up by Y terminal and is independent of current at X terminal.

A current of value I is applied to X terminal then same amount of current will flow through Y terminal. And the same current will flow through Z terminal such that terminal Z has very high impedance .In other words, it acts as current source.

Relationship between input outputs can be given in a matrix.

$$\begin{bmatrix} i_y \\ v_x \\ i_z \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_y \\ i_x \\ v_z \end{bmatrix}$$

$i_x = i_y$

$v_x = v_y$

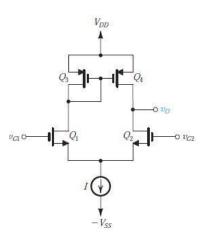

#### **2.6.2 Implementation of Current Conveyor using MOS**

MOS transistor M1 and M2 form the current mirror. Due to this current mirror ,drain current of M3 and M4 is equal and due to this drain current ,voltage at X terminal and Y terminal are also equal

Fig 2.11 Current Conveyor using MOS Transistor.

#### **2.6.3 CURRENT CONVEYOR IN SECOND GENERATION**

Current conveyor in Second generation have different and versatile characteristics. Its symbol is shown. This active block can further be classify into two classes, which is based on direction of output current at Z terminal ,and hence they can be termed as CC11+ and CC11-..

In CC11, the applied potential at Y is appear at terminal X and high input impedance appeared at input Y terminal. At the output Z terminal, appeared current is same as the input current Ix, which is used as high impedance as a current source. The following matrix is used to represent current conveyor in second generation.

| $\begin{bmatrix} i_y \end{bmatrix}$ |   | 0 | 0  | 0 | $\begin{bmatrix} v_y \end{bmatrix}$ |

|-------------------------------------|---|---|----|---|-------------------------------------|

| $v_x$                               | = | 1 | 0  | 0 | $i_x$                               |

| $\lfloor i_z \rfloor$               |   | 0 | ±1 | 0 | $v_z$                               |

The current conveyor in second generation has been introduced as a block that is convenient and easy approach to design general linear analog circuit and system.

The current at Y terminal which is represented by terminal Iy is zero.

Vx=Vy

Iz=Ix or -Ix

Impedance appeared at the terminal of the circuit are finite .While designing the circuit impedance must be taken into consideration. As there is virtual short circuit in the OP-Amp in the same why voltage applied at Y terminal appeared at X terminal.

#### **Block diagram of CC11 is shown below**

Fig 2.12 Block Diagram of second generation current conveyor

#### **2.6.4 CURRENT CONVEYOR IN THIRD GENERATION**

Fibre proposed the concept of current conveyor in Third generation .Its has a functionality which is very much similar to the first generation current conveyor with an exception that current at terminal X and Y flows in the opposite direction. It can be used as the current controlled current source with unity gain. It provides high output impedance and good dynamic swing which make it favorable for cascade system. Another advantage of third generation current conveyor is that it has low gain error ,high accuracy, high linearity and wide frequency response.

## MATRIX REPRESENTATION OF THIRD GENERATION CURRENT CONVEYOR

$$\begin{bmatrix} i_{y} \\ v_{x} \\ i_{z} \end{bmatrix} = \begin{bmatrix} 0 & -1 & 0 \\ 1 & 0 & 0 \\ 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_{y} \\ i_{x} \\ v_{z} \end{bmatrix}$$

#### 2.7 Differential difference amplifier (DDA)

Differential difference amplifier acts as OP-AMP with 4 input. It can use both in voltage mode and current mode. It can also use as single input. In voltage mode it has infinite input resistance. Differential Difference Amplifier is an extended application of Operational Amplifier. Since operational Amplifier can apply one differential input whereas Differential Difference Amplifier can employ two differential input.

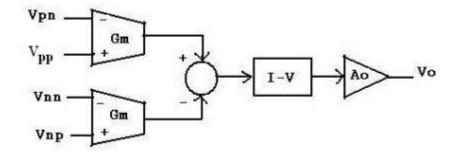

#### Fig 2.13 Block Diagram of Differential Difference Amplifier

Here ,from the block diagram it is shown that it uses two voltage to current convertor .In other words, two transconductance amplifier , which converts the applied differential voltage into a current .After that ,mixer is use which performs arithmetic operation ,here subtraction is use .Then this current is converted into voltage and this particular voltage is amplified by the amplifier.There is no virtual ground exist but in case of operational amplifier there exist virtual ground.

First, operational amplifiers are not designed for large differential voltage to be overdriven. Second, the open loop gain of first two differential amplifiers should match. The region of

interest in the DDA covers all the benefits of the Op-Amp in terms of impedances higher value of the input side and lower value of the output side.

Other than these favorable points, it requires fewer passive components in the realization of the circuits. Further it provides the huge variety of approach like filter realization, mathematical operations, oscillators and many others.

#### **2.8 DERIVATIVE OF CURRENT CONVEYORS**

In order to enhance the functionality of current conveyor lots of research has been done and therefore ,modifies the basic structure of current conveyor. Adding new technique provides versatility in the current conveyor. It is used in variety of the circuit in voltage and current form.

#### 2.8.1 DDCC (Differential Difference Current Conveyor)

It is based on second generation current conveyor and Differential Difference Amplifier. Differential Difference amplifier is particularly frequency selective circuit. Many non linear building blocks such as square , square root and multiplier have been developed. It offers the advantage of circuit simplicity, low power consumption, greater bandwidth, greater linearity, wider dynamic range. In voltage mode, it offers high input impedance. Using Differential Difference amplifier one can perform arithmetic operation. Instrumental amplifier can design using three operational amplifiers but this process is impossible in differential difference amplifier because operation amplifier is not suitable for large differential gain and open loop gain of first two differential pair should match. It has an enormous advantage compare to operational amplifier in terms of high input impedance , low output impedance, very high gain. It uses fewer passives component in the realization of the signal processing circuit.

# 2.8.2 MOS IMPLEMENTATION OF DIFFERENTIAL DIFFERENCE AMPLIFIER

2.14 MOS implementation of Differential Difference Amplifier

Transistor M1 ,M1 and M3,M4 converts the differential voltage into current ,then these current are subtracted .This obtain current apply to active load M5,M6 afterward. This obtain voltage is amplified in the next stage.

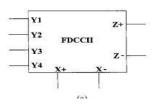

#### 2.8.3 Fully Differential current conveyor-

Block diagram of fully differential current conveyor can be shown as

Fig-2.15 Block Diagram of Fully Differential Amplifier

It works as an active block which cancelled even harmonics and unwanted common mode signal and therefore, it extends dynamic range of the circuit. Fully differential current conveyor has eight port. Relationship between ports through the matrix in Fully Differential Amplifier can be given as-

| $V_{X+1}$                                                            |     | ٢0 | 0 | 1  | -1 | 1 | ר0 | $I_X$    |

|----------------------------------------------------------------------|-----|----|---|----|----|---|----|----------|

| $\begin{bmatrix} V_{X+} \\ V_{X-} \\ I_{Z+} \\ I_{Z-} \end{bmatrix}$ | 3   | 0  | 0 | -1 | 1  | 0 | 1  | $V_{Y1}$ |

| $I_{Z+}$                                                             | - 2 | 1  | 0 | 0  | 0  | 0 | 0  | VY2      |

| $I_{Z-}$                                                             |     | LO | 1 | 0  | 0  | 0 | 0  | VY3      |

From the given matrix it can be said that

V<sub>X+</sub>=V<sub>Y1</sub>-V<sub>Y2</sub>+V<sub>Y3</sub>

$V_{X} = V_{Y2} - V_{Y1}$

$$I_{Z+}=I_{Z-}=0$$

Fully differential current conveyor is a block to realize fully differential signal. Circuit which uses the fully differential current conveyor can operate at low power supply voltage therefore power consumption is reduced in the circuit. Main advantage of using this is it reduces non linearity and noise on the circuit.

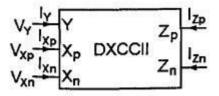

#### 2.8.4 Dual-X Current Conveyor

By using dual-X current conveyor it is possible to reduce the size of the active device by using MOSFET operated in the linear region along with dual-X current conveyor it is possible to achieve tunability in the circuit. It is the combination of inverted current conveyor and normal current conveyor.

$$\begin{bmatrix} I_Y \\ V_{\chi_p} \\ V_{\chi_n} \\ I_{Z_p} \\ I_{Z_n} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ -1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} V_Y \\ I_{\chi_p} \\ I_{\chi_n} \end{bmatrix}$$

From the matrix shown below it can be seen the it has two terminal X and Y. In the given matrix Xp stands for terminal at X, which is not inverted and Xn stands for terminal at X, which is

inverted. Current corresponds to Xp is copied to Zp and the current corresponds to Xn is copied to Zn terminal.

Symbol of Dual-X current conveyor can be given as

Fig. 2.16 Block Diagram of Fully Differential Current Conveyor

#### 2.8.4.1 SCHEMATIC OF DUAL-X CURRENT CONVEYOR

Above schematic is drawn by selecting .5micro meter file. Supply voltage of the above circuit is chosen to be +2.5 V and biasing voltage is chosen to be .6V and biasing current is chosen to be 25milli Amp.

#### 2.8.4.2 Current Conveyor Voltage Graph at Xn , Xp and Y

Graph 1 shows voltage at terminal Xn

Graph 2 shows voltage at terminal Xp

Graph 3 shows voltage at terminal Y

As per the differential current conveyor property voltage at terminal Y is exactly same as terminal Xp ie Y=Xn

Y = -Xp

Dual-X current conveyor provides negative voltage gain of negative value, in other words, it provides unity negative voltage gain. Therefore, it enhances the use of second generation current conveyor by providing extra unity negative gain. Due to its flexibility, it is used for various kinds of signal processing application. Dual-X current conveyor works in current mode. In an integrated circuit fabrication, it is useful. The main advantage of dual-X current conveyor

compares to normal second generation current conveyor is that when implementing second generation current conveyor in integrated circuit it depends on floating resistor and also capacitor, due to this packaging density is reduced in the circuit and it also introduces parasitic's capacitor which adds area in the integrated circuit and due to change in the temperature its functionality varies. On the other hand, dual-X current conveyor uses a Metal oxide semiconductor which is designed to function in the ohmic region required for several operation where non ideality and noise canceled out due to its operation in the differential mode.

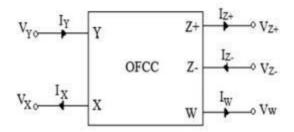

#### **<u>2.8.5 Operational Floating Current Conveyor</u>**

Floating current conveyor consists of five terminal .In its basic circuit ,it has current feedback operational amplifier, current conveyor of second generation .For realization of CC11+ and CC11- only single block of operational floating current conveyor is needed. It is also used to realize like Voltage Amplifier ,Current Amplifier, Transconductance Amplifier, Transresistance Amplifier. Circuit symbol of operational floating current conveyor is given below-

Fig 2.17 Block Diagram of operational floating Current Conveyor

Terminal X provides current input .Terminal X has very low resistance. Terminal Y provide voltage input port and it has high impedance. Terminal Z+ and Z- provide output in current mode and it is in high impedance state. At terminal W, there appear voltage  $V_W$  which is equal to product of current at X terminal and transconductance gain of the block. The relationship of various constituent operational floating current conveyors can be given as

$$\begin{bmatrix} I_{Y} \\ V_{X} \\ V_{W} \\ I_{Z+} \\ I_{Z-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 \\ 0 & Z_{t} & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & -1 & 0 & 0 \end{bmatrix} = \begin{bmatrix} V_{Y} \\ I_{X} \\ I_{W} \\ V_{Z+} \\ V_{Z-} \end{bmatrix}$$

Port X provides the voltage which is copy of voltage at terminal Y. Port Z port the copy of current of port W. Port Z+ provide in phase copy of current of port W and Port Z- provide out of phase copy of current of port W.

## **CHAPTER -3**

# SIMULATION AND ANALYSIS OF DIFFERENTIAL DIFFERENCE CURRENT CONVEYOR TRANSCONDUCTANCE AMPLIFIER BLOCK

### **3.1 Introduction**

Since the magnitude of current flowing through the circuit and voltage appeared at any branch in the electronics circuit decides the electronics device property. Kirchhoff's voltage law and Kirchhoff current law use for the determination of amount of current flowing through the circuit and value of voltage appeared across the circuit. DC analysis verifies the active block property of copying current and voltage at the particular terminal and set all the transistor size, in other words ,set the value of length and width of the transistor according to the size of parameter file and set the temperature according to the circuit suitable performance .Using this DC active block it is used for the design of filter and the oscillator.

Filter are often realized in the time domain but filters also have time base response to a pulse input .The universal filter which provides five output with only single input is applied is designed here. It is based on differential difference current conveyor transconductance amplifier (DDCCTA).It is a voltage-mode device. It has the property of high-input impedance and it does not required component matching constrain which are passive or it does not have any restrictions on input signals. The circuit simultaneously provide a response of band pass, low pass, high pass, band stop and all pass filtering which is a voltage mode by applying single input signal. Here passive and active sensitivity of the circuit is very low and this circuit provides high-input impedance, capacitors and resistors used is grounded.

The main block is a filter in the signal processing in the analog circuit. The filter which obtained for the analog circuit can be used for the modulation and demodulation ,self starting system ,transmission of voice, microphone, broadband system. The filter obtained in the analog circuit are widely used in processing of signals, voice transmission, controlling the system as required and telemetry system .The analog circuit can have multiple input and single output or single input and multiple output according to this its operation is divided. Single input multiple output has the advantage as compare to multiple input single output is that in preceding case we need one voltage source but we are getting different type of output while in another case the different voltage source is required in order to obtain only single output.

If we want a system which allows to pass only low frequency component while suppressing high frequency signal to the user and allows to pass high frequency signal and suppressed low frequency signal to second user and allows to pass band of frequency to third user and allows all frequency band to fourth user and do not allow to pass the band of frequency to the fifth user. This kind of filter is very useful because it do not require additional circuit according to different type of requirement of the user. Here we don't need more than one input to find more than one output. The filter obtained from the dc block implementation of active block used in the tuning in communication system, modulation and demodulation in various processes to transmit the information and phase locked loop implementation.

By cascading the differential difference current conveyor and transconductance amplifiers the Difference Difference Current Conveyor Transconductance is formed. Using differential difference current conveyor transconductance amplifiers (DDCCTAs) several Active Filter transfer function can be realized. Hence for different analogue functionality of circuit it is implemented on monolithic chip. DDCCTAs has the capability to generate various circuits therefore it provide electronic tunability. Implementation of the DDCCTA and using this as an active block all types of filter have been designed and simulated ,which operates in voltage mode . Transconductance of the DDCCTA block can be change by changing the bias current therefore it is electronically tunable.

Using the simulated active block it can provide application where we can change quality factor and natural frequency and they both are independent of each other, therefore it is controlled device. This circuit requires minimum no of passive component to realize. The simulated Difference Difference Current Conveyor Transconductance Amplifier (DDCCTA) operated in the voltage mode, it is basically biquard. In the given circuit by providing single input, the outputs at five terminals are obtained. In designed block, there is no need to worry about matching the component to find the waveform of low pass filter, band pass filter ,high pass filter, band stop filter and all pass filter. This simulated design does not require componentmatching condition to find the waveform of all pass filter as most of the circuit required matching.

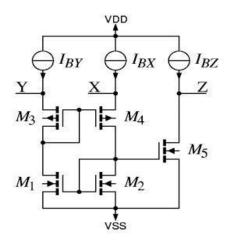

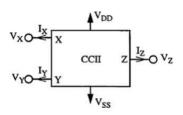

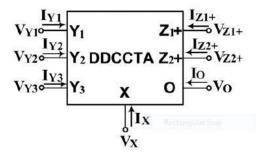

### **3.2 The DDCCTA symbol**

Fig.3.1 Block diagram of differential difference current conveyor

Relationship between ports can be characterized by the following way-

$Iy_{1=}0, Iy_{2=}0, Iy_{3=}0$   $Vx=Vy_{1-}Vy_{1}+Vy_{1}$   $Iz_{1}=Iz_{2=}Ix$  $Io=g_m=Vz_{1+}$

It can be written in Matrix form as-

Here current through the terminal Y1, Y2 and Y3 is zero ,hence it offers high impedance terminal and current at X terminal is finite ,hence it offers low impedance terminal. Port X follows the voltage difference of port Y1 and Y2 and summation of voltage at port X. The current at Z1+ duplicates the current of port X in positive magnitude. The Z2+ port has a current which is dulpicated of current at  $Z_1$ + port. Current at  $Z_2$ + is an extended output. Here  $g_m$  is transconductance which acts as a transfer function and convert voltage at  $Z_1$ + port to be the

current at  $I_o$  port. Since  $g_m$  is controlled by external bias current  $I_B$ , therefore it is electronically tunable which is very useful in variety of circuit implementation while designing a circuit.

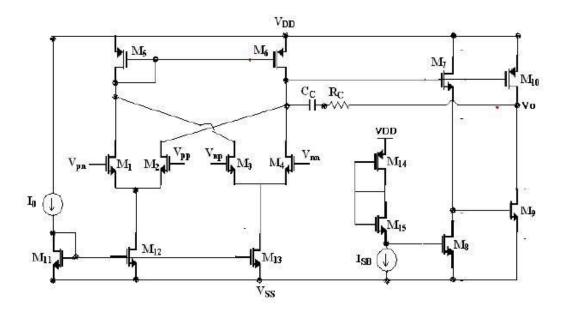

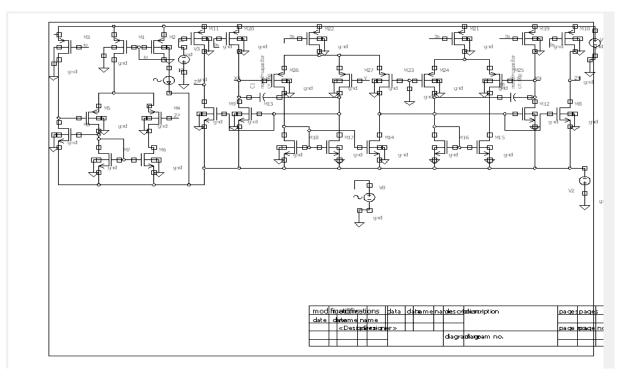

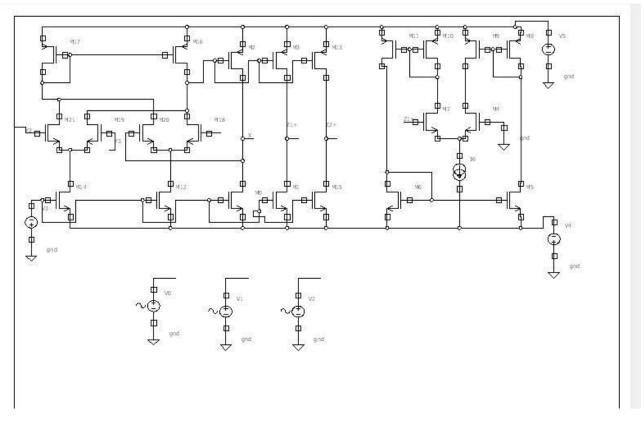

# 3.3-SCHEMATIC OF DIFFERENTIAL DIFFERENCE CURRENT CONVEYOR TRANSCONDUCTANCE AMPLIFIER

Fig 3.2 Circuit using MOS of Differential Difference Amplifier

# 3.4 IN THE DIFFERENTIAL DIFFERENCE CURRENT CONVEYOR IMPLEMENTATION FOLLOWING ARE THE ASPECT RATIO OF TRANSISTOR

| TRANSISTOR              | LENGTH IN MICROMETER | WIDTH IN MICROMETER |

|-------------------------|----------------------|---------------------|

|                         |                      |                     |

| M18-M21                 | .35um                | 8.75 um             |

| M13 ,M16 , M17 ,M2 , M3 | .18um                | 17.5um              |

| M0 ,M12 ,M14 ,M15       | .18um                | 8.75um              |

| M7,M4                   | .8um                 | 10um                |

| M8, M9, M10, M11        | .8um                 | 25um                |

| M5 , M6                 | .8um                 | 8um                 |

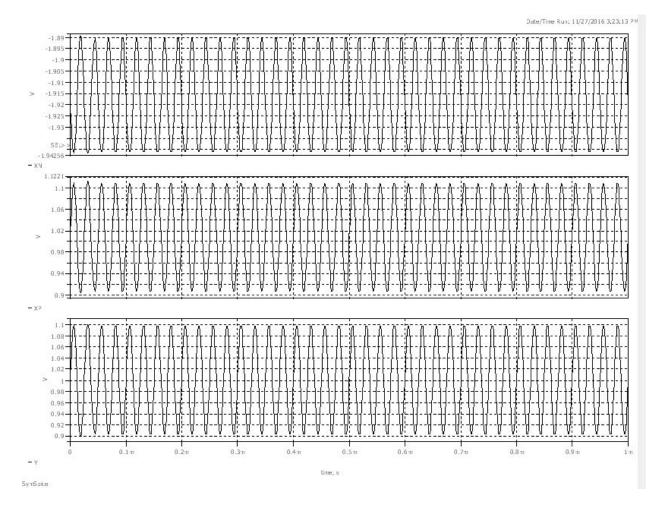

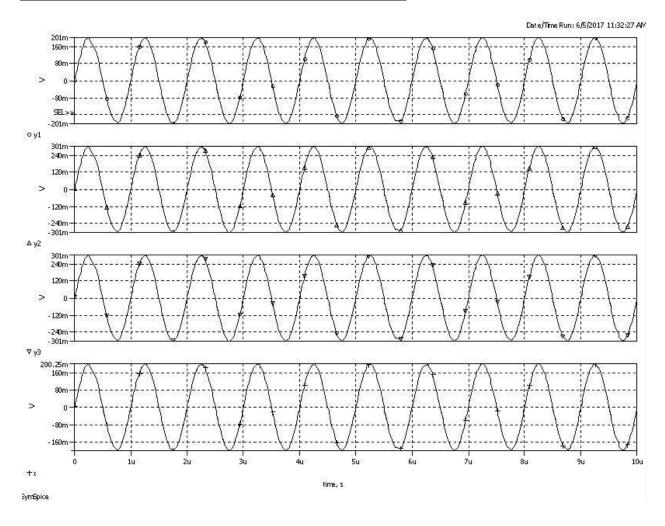

#### 3.5 Graph of the voltage at terminal Y1,Y2,Y3,X

#### Above waveform shows voltage at Y1, Y2, Y3 and X.

Voltage at Y1 is sinusoidal of peak value 200milli volt and frequency of 1Mega Hz, Voltage at Y2 is sinusoidal of peak value 300milli volt and frequency of 1Mega Hz; Voltage at Y3 is sinusoidal of peak value 300milli volt and frequency of 1Mega Hz. It can be seen from the graph that the voltage at X satisfies the equation as  $V_x=V_{Y1}-V_{Y2}+V_{Y3}$ . Here bias current is set to be 68.65uAmp.

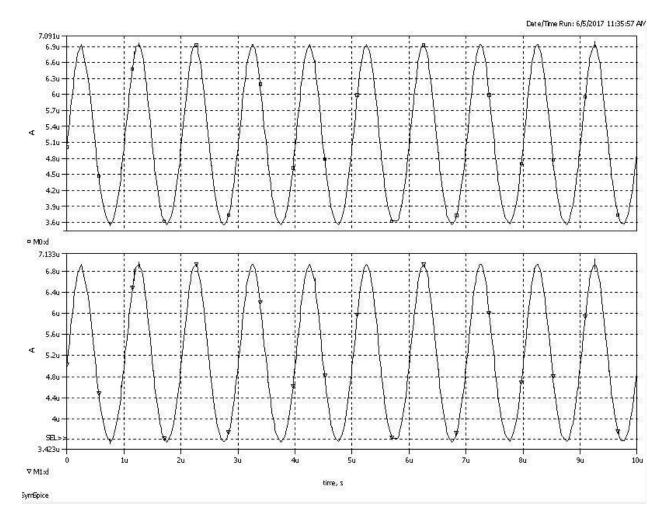

#### 3.6 Graph of current at terminal X and IZ1+

M0:d current is current at X terminal

M1:d current is current at Z1+ terminal

The graph shows that current at X terminal copy the current of Z1+ terminal.

Here bias current is set to be 68.65uAmp.

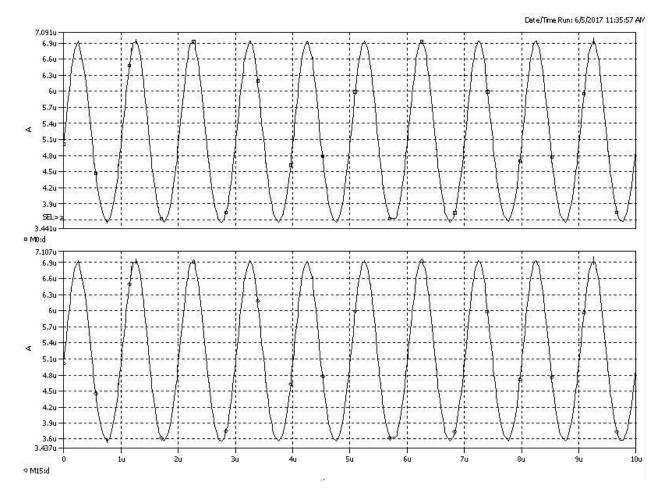

#### 3.7 Graph of current at terminal X and IZ1-

M0:d current is current at X terminal

M15:d current is current at Z2+ terminal

The graph shows that current at  $I_{z2}$  terminal copy the current of X terminal.

Here bias current is set to be 68.65uAmp.

•

## **CHAPTER-4**

### **DESIGN AND SIMULATION OF FILTER AND OSCILLATOR**

#### **4.1 Introduction**

Nowadays massive electronics tools use the filter. It is almost impossible to design an electronics system without use of filter. They use in all the area of electronics system ranging from mobile phone ,broadband network to demodulation and tuning of filter, loudspeaker. The main characteristic of filter is, it allows passing specific range of frequency and blocking the frequency other than desired frequency. Filter can be divided into many types-

1-Digital Filter and Anaog Filter

2-Radio frequency filter and Audio frequency filter

3-Passive Filter and Active Filter.

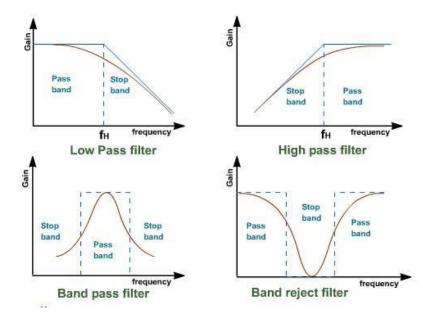

Passive Filters are those filter that use passive component like capacitor and resistor while Active filters are those filter which uses operational amplifier and transistor etc. Audio frequency is the low frequency signal that uses resistor and capacitor for filter implementation while radio frequency signals are high frequency signal that uses inductor and capacitor for filter implementation. Characteristics of various is shown below

Fig 4.1 Frequency Response of Low Pass, High Pass, Band Pass, Notch

From the diagram shown, it can be seen that in Low Pass Filter it allows to pass the frequency within the range from zero to  $f_H$  and attenuates the frequency greater that  $f_H$ . At the frequency of  $f_H$  gain is reduced by 3dB in logarithmic scale. In the High pass filter it allows to pass the frequency greater than  $f_H$  and suppressed the frequency less than  $f_H$ . And at the frequency  $f_H$  the gain is reduced by 3db of its maximum value. In the band pass filter, it allows to pass band of frequency and suppressed the signal at low frequency and high frequency. While in band reject filter also known as Notch filter it does not allow to pass though the filter. According to the listener sometimes it is required to amplify some range of frequency while sometimes it is required to attenuate some frequency component so filter provide to do so. In many case non linearity are present in the source of power supply and therefore, it create the series of harmonics in the system that add up, but through the filter these harmonics can be eliminated and only fundamental component if retrieve in the system. Filter Characteristics are best revealed in the frequency domain. As such, the following terms are often used as a way of describing the major properties of filter-

1-Break frequency-The frequency at which the amplitude drops by 3dB .In other words , amplitude drop by 70.7 % of the maximum amplitude of filter.

2-Rolloff-The rate at which the amplitude drops in dB per decade

3-Centre frequency-The frequency at which amplitude is at peak or tough.

4-Bandwidth- The range of frequency that falls between the peak and -3dB levels.

#### **4.2 Filter Configuration**

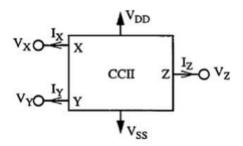

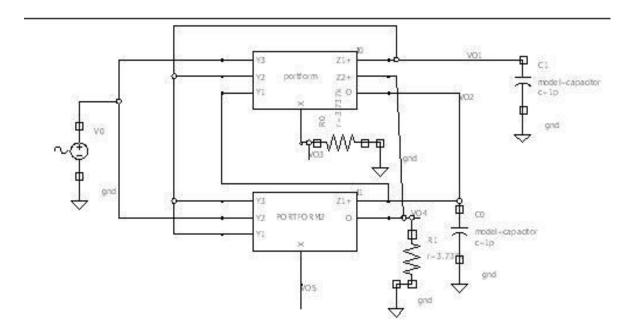

The circuit in the filter uses two Differential Difference Current Conveyor Transconductance Amplifier and two capacitor and resistor respectively. The capacitor and resistor which used here is grounded. Since the grounded capacitor compensates for stray capacitance at their port therefore it is attractive from monolithic integrated circuit prospective .Grounded resistor can be replaced by electronic resistor using MOS device. It uses SIMD i.e single input multiple output. The block describe is voltage mode differential difference current conveyor transconductance amplifier. It has high input impedance.

#### **4.3 BLOCK DIAGRAM OF UNIVERSAL FILTER**

Fig 4.2 Block Diagram of Universal Filter

The figure shown above is the schematic of universal filter where at port V01 band pass filter is obtained and at port V02 Low pass filter is obtained and at port V03 High pass filter is obtained and at port V04 Notch Filter is obtained and at port V05 All Pass Filter is obtained. It uses 180 nm technology PTM file for the circuit components dimension. It uses two grounded capacitor and two grounded resistor .Due to grounded component in the circuit parasitic effect is minimized in the circuit. Gain plot and phase plot is plotted using symica DE tools. Value of resistor and capacitor are adjusted to provide band pass filter for different resonance frequency and different quality factor. It uses two blocks of Difference Difference Current Conveyor Transconductance Amplifier. Connection between two active blocks is provided to obtain

Universal Filter. Biasing current in the active block known as Difference Difference Current Conveyor Transconductance Transconductance is adjusted to provide tunability in the circuit.

#### **4.4 Simulation Result**

Normally, Filter are design to concentrate on amplitude response but phase response also plays a very important role for the design of filter. The transient response of the filter is affected by the phase shift .It also effect group delay, impulse response and step response of system. Hence filter will change the phase of the signal as well as the amplitude.

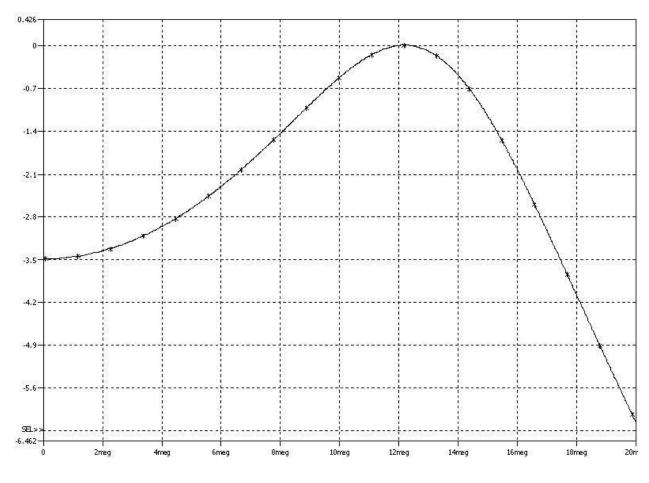

#### **4.4.1 Band Pass Filter Gain Response**

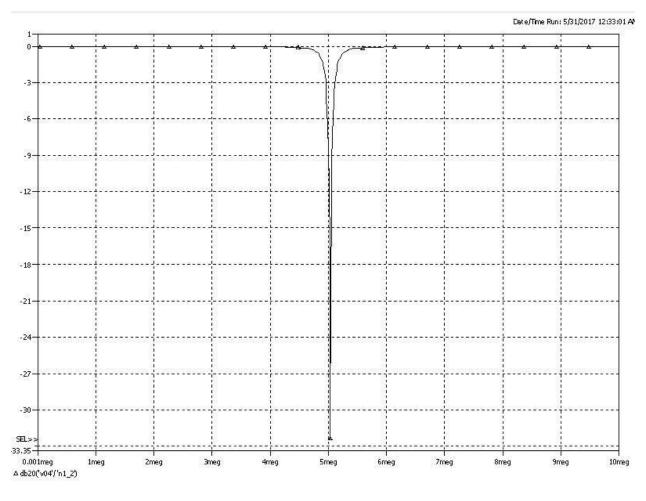

Fig 4.3.1 Gain Response of Band Pass Filter

From the graph of band pass filter response, it is shown that Centre frequency (fo) =12.4031MegaHz. This graph is drawn by taking transconductance of both Differential

Difference Current Conveyor Transconductance block as 267.53559uA/V. This value is calculated by applying .3V at the X terminal and calculate the value of  $V_{Z1+}$ , Io and the value of  $V_{Z1+}/Io$  is transconductance of the transconductance block by taking bias current as 68.65uA

By using formula

$$Q = \sqrt{\frac{g_{\rm m1}R_1C_1}{C_2}},$$

Where gm1=267.53uA/V

$R_1=6.5Kohm$

$C_1=1pF$

$C_{2=}1pF$

By putting value of gm1,  $R_1$ ,  $C_1$ ,  $C_2$  in above formula Quality Factor come out is 1.3186.

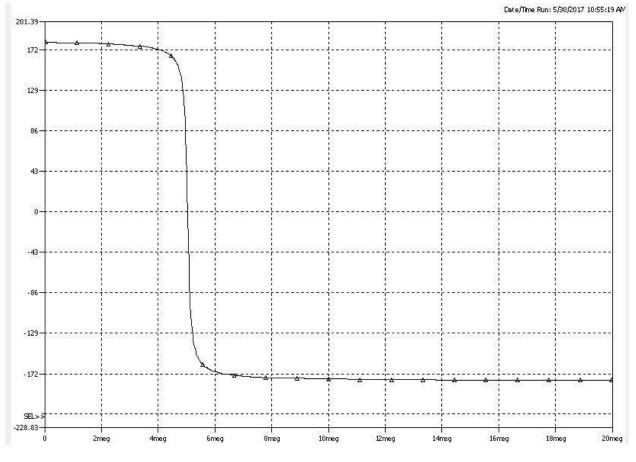

## 4.4.2 Band Pass Filter Phase response

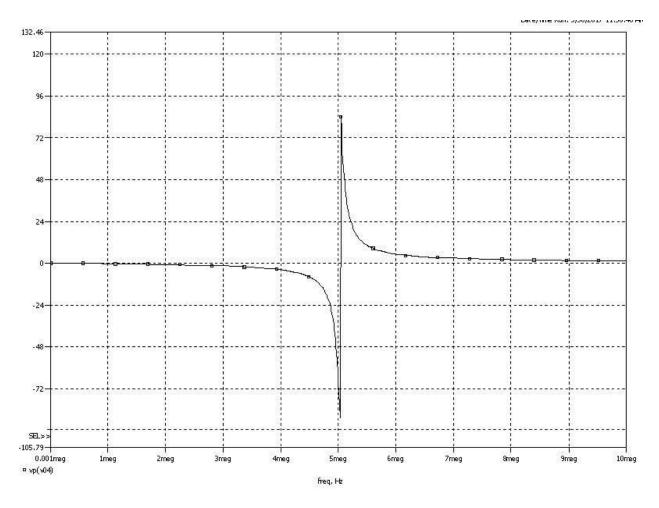

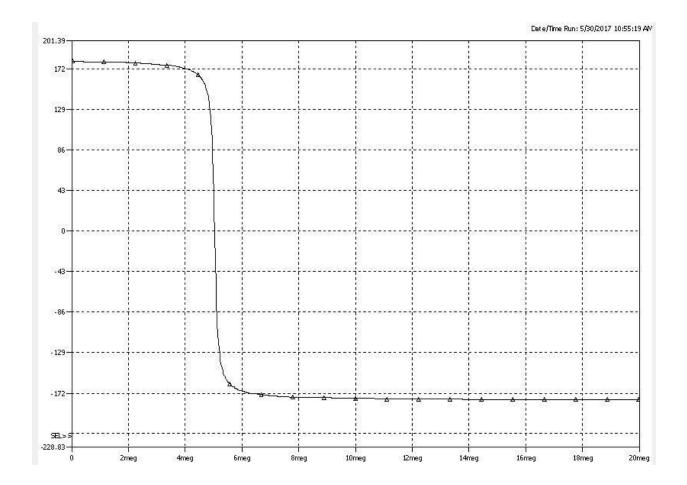

Fig 4.3.2 .Phase Response of Band Pass Filter

From the above graph of phase response of band pass filter it can be seen that at very low frequency phase of the response is 180 degree and very high frequency value of the phase response is -180 degree. At the value around 5 mega Hz frequency there is transition of frequency from 180 degree to -180 degree.

## **4.4.3 Low Pass Filter Gain Plot**

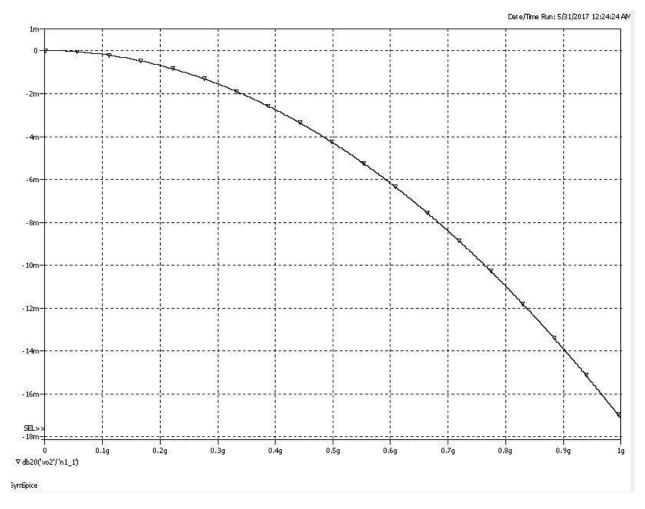

Fig 4.3.3 Gain Response of Low Pass Filter

The above graph shows gain response of the low pass filter. At low frequency it allows to pass all signal and high frequency component are attenuated in the low pass filter. The point were gain is less than 3 db of the maximum value of gain in the graph is called 3 db point and 3db point of the simulated Low Pass Filter is at 4.1847 Mega Hz.

### **4.4.4- Low Pass Filter Phase response**

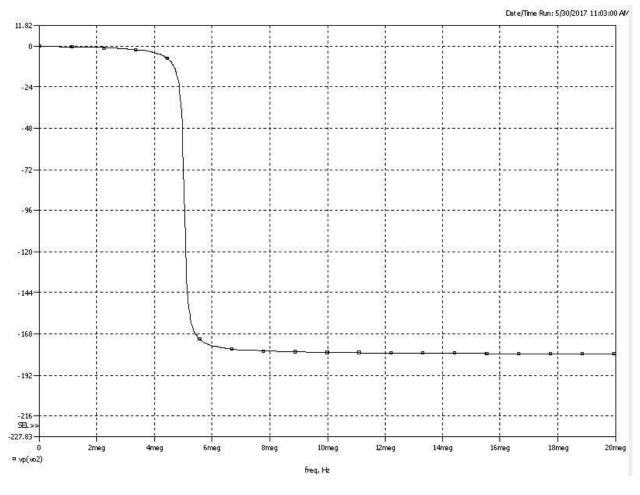

Fig 4.3.4 Phase Response of Low Pass Filter

The above graph shows the phase response of the low pass filter where phase is zero at the low frequency and as the frequency increases at the frequency around 5 Mega Hz there is jump in the phase from 0 degree to -180 degree. At the high frequency phase of the low pass filter is -180.

### 4.4.5 High Pass filter Gain Response

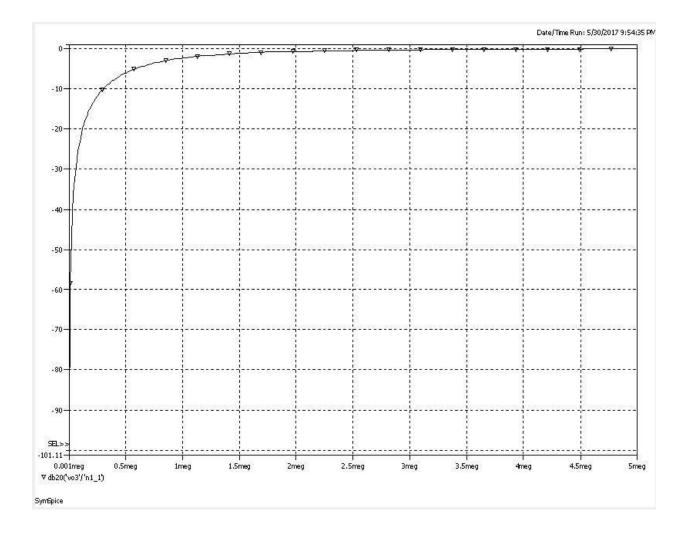

Fig 4.4.5 Gain response of High Pass Filter

The above graph shows the gain response of the high pass filter .High pass filter allows to pass high frequency contents but low frequency components are attenuated. At the point where the gain response is reduced by 3db of its maximum value is call 3db Point. From the graph shown above of the High Pass Filter is the value of 3 db point is 852.5509 KHz.

## **4.4.6- High Pass Filter Phase response**

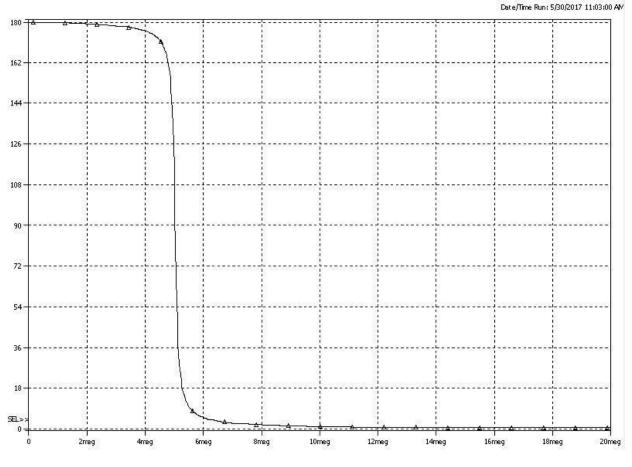

Fig .4.3.6 Phase Response of High Pass Filter

The above graph shows the phase response of the high pass filter .Where at very low frequency value of phase is 180 degree and as the frequency increases somewhere around 5 mega Hz phase response drops from 180 degree to 0 degree and after that at high frequency greater than 5 mega Hz phase is dropped to zero degree.

# 4.4.7-Gain Plot of notch filter

Fig 4.3.7 Gain Response of Notch Filter

The above graph shows the gain response of the notch filter where where it allows to pass all low and high frequency contents and block the band of frequency around 5 mega Hz.

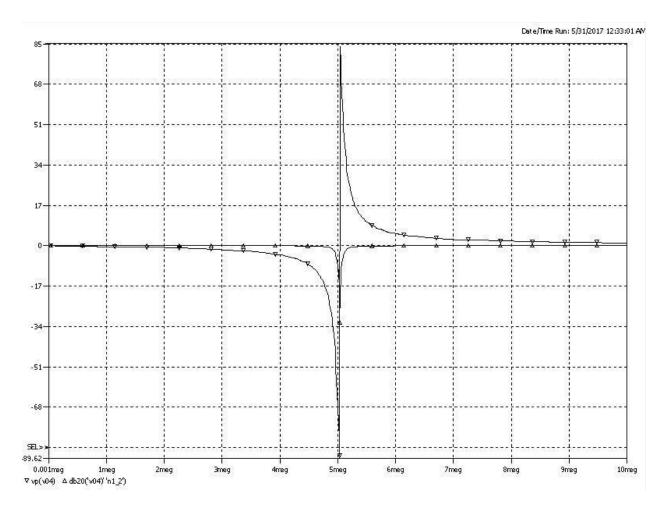

# 4.4.8-Phase response of Notch Filter

Fig 4.3.8 Phase Response of Notch Filter

The above graph shows the phase response of the notch filter where phase is almost zero at all the frequency except the frequency around 5 Mega Hz where there is transition of phase from - 90 degree to +90 degree , in other words at frequency around 5 mega Hz the is 180 phase shift in the signal.

# 4.4.9 Combined Gain and Phase Plot of Notch Filter

Fig 4.3.9 Gain and Phase Response of Notch Filter

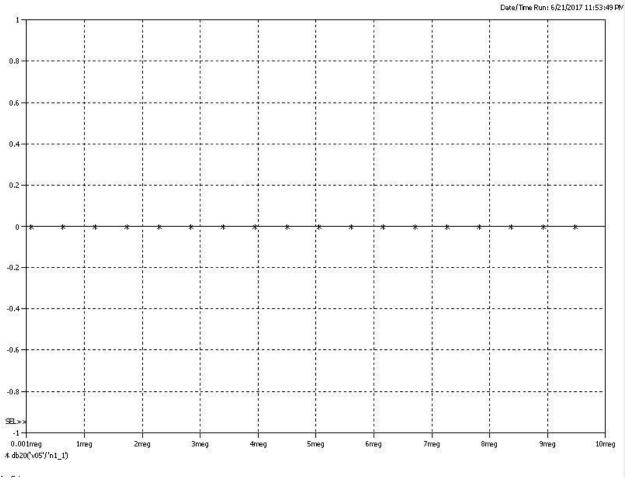

# 4.4.10-Gain response of All Pass Filter

Fig 4.3.10 Gain Response of All Pass Filter

Above graph shows the gain response of all pass filter at the terminal V05 of the filter response. Here all pass filter response allows to pass all the frequency component.

### 4.4.11-Phase response of All Pass Filter

#### Fig 4.3.11 Phase Response of All Pass Filter

The above graph shows the phase response of the all pass filter which allows to pass all frequency components. This varies in the phase from 180 degree to -180 degree.

#### 4.5 Design of Oscillator

Oscillator function is to change or alter the voltage. Oscillator does not require apply a signal for it function, only power supply is needed for its functionality whereas in amplifier it requires the input for its functionality and for the conversion of energy. Oscillator is also divided according to the type of signal obtain for the output .If the appeared voltage across the output is sinusoidal

then it is called sinusoidal oscillator and if obtained voltage at output is not sinusoidal but saw tooth wave or square or triangular then it is called relaxatation oscillator. In the design of oscillator, it consists of two type of component which are active and passive .Passive component may include resistor ,capacitor and inductor etc. While active component includes metal oxide semiconductor field effect transistor .The used capacitor is used to store electrical energy whenever voltage appears across it and inductor is used to store magnetic field whenever current is pass through it. Simple method of oscillation production is to provide positive feedback. As it can be shown from the diagram.

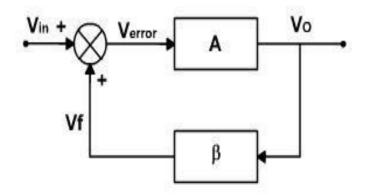

Fig 4.4.1Basic Block Diagram of Oscillator

Since the amplifier which used here provide 180 degree phase shift. If the feedback loop is not applied then relationship between input and output can be given as

Now if the feedback signal is applied then feedback factor provides 180 degree phase shift therefore total phase shift between input and output will add up to 360 degree. Here output is feedback to input and it continuously regenerates .Total Phase shift from input to the output is zero and magnitude of product of forward gain and feedback gain is unity. The relationship between an output and input when feedback signal is applies can be given as -

$$Vo = A (Vin + \beta Vo)$$

Vo/Vin=A/(1-A  $\beta$ )

When the value A  $\beta$ =1 then value of Vo/Vin=infinite, this condition is called barckhasun criteria.

### 4.5.1 Block Diagram of Oscillator

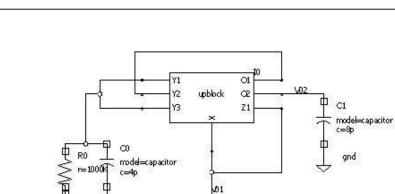

Fig 4.4.2 Block Diagram of Oscillator using DDCCTA

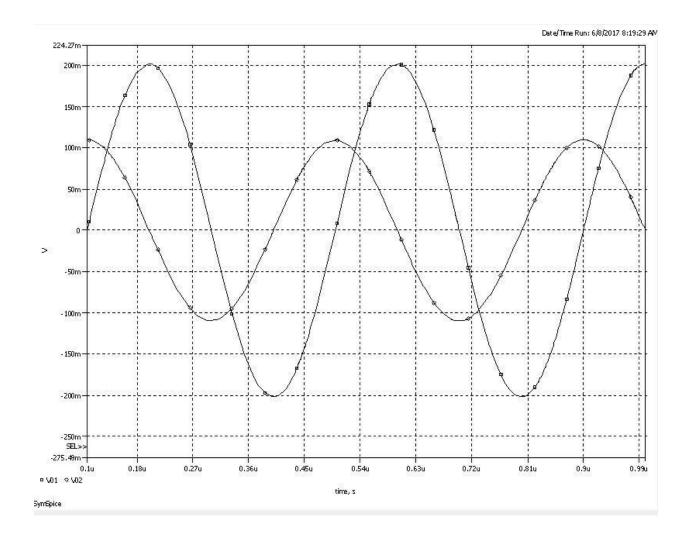

Through Symica DE Tool oscillator circuit tested on PTM 180nm Technology. Power supply in the circuit is set to be  $V_{dd}$ =- $V_{SS}$ =.9V.Oscillator is designed using one block of Differential Difference Current Conveyor Transconductance Amplifier and two capacitor of value 8pF and 4PF and Bias current are set to be 65micor Amp. During the simulating I obtain sinusoidal waveform at V01 and V02 of amplitude 202mV and 110mV respectively with the frequency of 2.5MHz .V01 and V02 are in the quadrature phase shifts with respect to each other. Bias current in the active block is set to be 65uamp.

## 4.5.2Waveform obtain at V01 and V02

From the above waveform it can be seen that sinusoidal Voltage of value of 202mvolt is obtain at port V01 and sinusoidal voltage of value 110mVolt is obtain at port V02.Both the voltages are of time period .4u second ,or in other words frequency of 2.5Mhz ,Both the voltage are in quadrature phase shift with respect to each other.

#### **CHAPTER -5**

### **CONCLUSION AND FUTURE DIRECTIONS**

#### 5.1 Conclusion

Basic circuit component of the active block implementation is thoroughly discussed in chapter 2. These components are differential mode differential amplifier, common mode differential amplifier, conventional current mirror design ,Wilson current mirror ,Wildar current mirror, Active load circuits which are used to overcome the disadvantage of resistor, current source and sink circuit design. Different types of current conveyor are CCI, CCII, CCIII. As the research goes on and on ,different derivatives of current conveyor is derived such as fully differential current conveyor ,operational floating current conveyor, Differential difference current conveyor. This derivative are used in the designing of various devices in the domain of signal processing such as high pass filter, low pass filter ,band pass filter, all pass filter ,multiplier ,smith triggered ,oscillator, amplifier etc.

Block of differential difference current conveyor transconductance amplifier is discussed in chapter 3. DC and AC analysis of the block has been done on symica DE software. The circuit has been simulated ,and the analysis is done by plotting the curve of voltage and current of the circuit. Using this plot, it is shown that the current at Z1+ and Z1- terminal copied the current of port X. The value of voltage at X terminal is voltage due to arithmetic operation of voltage at Y1, Y2,Y3. Electronics tunability is provided and transconductance of the circuit is also calculated .

Circuit design of low pass filter ,High pass filter ,Band pass filter ,all pass filter and notch filter are explored briefly in chapter 4.The circuit consists of two differential difference current conveyor transconductance amplifier block both are configured using two capacitor and two register . This circuit simultaneously realize Low pass filter, High pass filter, band pass filter, all pass filter, Notch filter. Gain response and phase response has been plotted on symica DE software .

Then the quadrature oscillator block is discussed using one differential difference current conveyor transconductance amplifier.

#### **5.2 SCOPE FOR FUTURE WORK**

In the thesis Differential Difference Current Conveyor Transconductance Amplifier has been discussed. It is very sophisticated and versatile building block where only single inputs is provided and simultaneously low pass filter, High pass filter, band pass filter, band stop filter, notch filter can be obtained. Using electronic tunability property of the circuit, band pass filter is simulated on symica DE software by fixing Q factor and varying resonance frequency  $W_0$ . In the same way, band pass filter is simulated by fixing resonance frequency  $W_0$  and varying Q factor. Hence this block is tunable and used in various circuits.

There is scope of improvement over the design of block. MOSFET used for the device will work on the smaller dimension in order to increase the chip density. If MOSFET use in the device will work on smaller dimension then power dissipation also reduces and circuit work efficiently without any power loss. If the power dissipation is minimize then circuit can works on small power supply.

A lots of work has been done on integrated circuit chip design. IC available in the market are AD 844, LM 13600 implemented using differential difference transconductance amplifier and differential difference transconductance amplifier current conveyor .As the circuit is smaller in size, so it results in the advantage of proper implementation of the IC also. Similarly a lot of work can be done on possible realization of differential difference current conveyor transconductance amplifier using different type of current conveyor and operational transconductance amplifier.