# TCAD ANALYSIS AND SIMULATION OF GATE ELECTRODE WORKFUNCTION ENGINEERED (GEWE) SILICON NANOWIRE MOSFET FOR HIGH PERFORMANCE ANALOG AND RF APPLICATIONS

Thesis Submitted to

Delhi Technological University for the Award of Degree Of

DOCTOR OF PHILOSOPHY

*in* DEPARTMENT OF APPLIED PHYSICS

# By **NEHA GUPTA**

Under the supervision of

# DR. RISHU CHAUJAR

DELHI TECHNOLOGICAL UNIVERSITY BAWANA ROAD, DELHI- 110042 INDIA

March 2017

# DELLECH COMOLOGICAL UNIT

# **DELHI TECHNOLOGICAL UNIVERSITY**

(Govt. of National Capital Territory of Delhi) BAWANA ROAD, DELHI – 110042

# CERTIFICATE

This is to certify that the thesis entitled "*TCAD Analysis and Simulation of Gate Electrode Workfunction Engineered (GEWE) Silicon Nanowire MOSFET for High Performance Analog and RF Applications*" submitted by <u>Miss. NEHA GUPTA</u> with registration number (2K12/Ph.D. AP/02) to Delhi Technological University, Delhi for the award of degree of Doctor of Philosophy. The work is based on original research work carried out by me under the supervision of <u>Dr. Rishu Chaujar</u>. It is further certified that the work embedded in this thesis has neither partially nor fully submitted to any other university or institution for the award of any degree or diploma.

#### NEHA GUPTA

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

## Dr. Rishu Chaujar

(Supervisor)

Assistant Professor Department of Applied Physics Delhi Technological University (DTU) Shahbad Daulatpur, Bawana Road Delhi-110042, INDIA

# **Prof. Suresh C. Sharma** (Head of Department)

Department of Applied Physics Delhi Technological University (DTU) Shahbad Daulatpur, Bawana Road Delhi-110042, INDIA

# ACKNOWLEDGMENTS

During four years of my research work, several people support with their valuable suggestions and make my research a wonderful journey. I would like to take this opportunity to acknowledge them.

First and foremost, I would like to express my sincere gratitude to my RISHU CHAUJAR. supervisor, mentor **Dr**. for her constant encouragement, support and guidance at every stage of my research period. She provided me every opportunity to present my work at important conferences and in industry. I especially thank her for prompt reading and careful review of my thesis.

I am thankful to **Prof. S.C. Sharma**, HOD, Applied Physics, DTU and **Prof. Yogesh Sharma**, Vice Chancellor, Delhi Technological University for their generous support and providing ample infrastructure to carry out my research work. I further thanks to SRC and DRC members Professor S. C. Sharma (Chairman DRC), Prof. Anurag Sharma (External Expert), Prof. R.S. Gupta (External Expert), for taking their decisive time serving in my committee and giving me treasured recommendations on my thesis.

I wish to express my deepest gratitude to Mr. Ajay Kumar (Research Fellow) for his important, perceptive comments and suggestions which enhance the quality of my research work. It was his continuous moral support and encouragement without which this thesis would not have been possible. I also express my gratefulness to Ms. Jaya Madan, Mr. Rahul Pandey and Mr. Aditya Jain for the various discussions we had, both technical and otherwise. It was fun to be part of this research group and share the time in the laboratory

My colleagues, associates and friends continuously influenced me in a positive way and have an important impact on my thinking. I will always remain grateful to them for their selfless support. I want to thank Deepshika Rathore, Preeti Rani, Ravi Gupta, Ashish Gupta and Dr. Savita Sharma.

To each and every one whom I have met during my time at Microelectronics Research Laboratory: Priyanka Bhati, Bharat Chowdhary, Anuj Sinha, Pawan Singh, Arshiya Vohra, Apurva Jain, Henika Arora(Scientist-C, SSPL, DRDO), Ardhman Kaur, and Bharti Taneja.

I would also like to convey my extreme thanks to all the faculty members and technical staff of Department of Applied Physics for their continuous support.

I would like to thank University Grant Commission (UGC), New Delhi, for providing the financial support to carry out the research work. I would also like to acknowledge the support of **Department of Science and Technology (DST)** for travel grant to attend the 27<sup>th</sup> ESREF-2016 conference held at Handel Halle (Saale), Germany (September 2016).

Last but not least, my mother (Rajkumari Gupta), brother (Nikhil Gupta), sister-in-law (Diksha Gupta), my nephew (Reyansh Gupta), all my relatives and well-wishers, have always encouraged me and have been by my side in every challenging and tough situation. I am highly grateful towards my parents who have sacrificed boundlessly to make this thesis a success. Also, I would like to thank Dr. Rajeev Gupta (Associate Professor, UPES, Dehradun) for his constant support and motivation during my research work.

Lastly, I would like to pay my heartiest gratefulness to my father (**Lt. Sh. Rakesh Chand Gupta**) who developed eagerness and passion in me to come at this stage in my career. Unfortunately, he was not with me during this treasured time of my life but I know his blessings are always with me without which I couldn't complete my research work.

Above all, my final words of thanks are for my **Lord Krishna**, for his continuous support and companionship through all chaos of my life.

(NEHA GUPTA) New Delhi, March 2017

# ABSTRACT

# TCAD Analysis and Simulation of Gate Electrode Workfunction Engineered (GEWE) Silicon Nanowire MOSFET for High Performance Analog and RF Applications

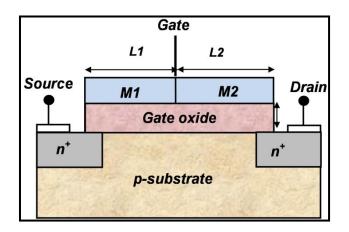

MOSFETs beyond sub-nm gate lengths is extremely Scaling challenging using planar device architecture due to the stringent criteria required for the transistor switching. The development of three dimensional devices like Multi-gate MOSFETs, ultra-thin SOI MOSFETs, FinFETs, Silicon Nanowires, Nanotubes etc. become important for the further advancement in the integrated chip industry. The top-down fabricated, gate-all-around architecture with a Si nanowire channel is a promising candidate among these for future technology generations. The gate-all-around geometry enhances the electrostatic control and hence gate length scalability and also suppress short channel effects effectively. Silicon nanowire MOSFET in gate all around configuration has proved to be good candidate due to its ability to suppress short channel effects. In nanoscale MOSFET, to improve speed and performance of a device, several engineering schemes have been proposed but the main problem associated is gate transport efficiency. As dual gate-MOSFET and Split Gate-MOSFET structures cannot improve both carrier transport efficiency and shortchannel effect. Gate Electrode Workfunction Engineering structure opens a new way to improve device performance. To eliminate polysilicon depletion width effects and polysilicon dopant penetration, polysilicon gates need to be replaced by metal gates. In 1997, Wei

Long and Ken K. Chin proposed a novel structure the Dual Material Gate MOSFET, which suppress short channel effects and enhance carrier velocity. In the DMG-MOSFET, the gate consists of two contacting materials with different work functions. The metal with higher work function is close to source and metal with lower work function is close to drain, and hence threshold voltage  $V_{T1}$ > $V_{T2}$  which improve the carrier transport efficiency. It is observed the step potential profile in the channel region because of two metal gates of different work function, which ensures reduction in short channel effects without sacrificing other device characteristics, unlike in dual gate or other gate structures.

In this dissertation, gate metal workfunction engineering scheme is amalgamated onto SiNW MOSFET and its Hot-Carrier fidelity and DIBL are studied to scrutinize its efficacy in high power CMOS applications. It is found that with k = 21 (HfO<sub>2</sub>) as gate oxide, device performance in terms of hot-carrier reliability further enhanced due to increased capacitance and thus offer its effectiveness in subnm range analog applications. Extensive device simulation results shows that GEWE-SiNW MOSFET exhibit improved RF performance in terms of high cut-off and maximum oscillator frequency and its performance further intensified with tuning of device parameters such as gate length, radius of nanowire, oxide thickness and workfunction of gate metals. Thus, providing detailed knowledge about the device's performance at such aggressively scaled dimensions. RF For comprehensive RF analysis of GEWE-SiNW MOSFET and its effectiveness at HF, the small signal behaviour in terms of scattering parameters is also discussed. This would be useful for evaluating the microwave performance of the device in terms of forward and reverse gains. In addition, noise metrics have also been evaluated which affects the device performance at HF. The RF investigation carried over is circumscribed to intrinsic components of MOSFET only. However,

at GHz frequency range, the importance of extrinsic component (the part outside the channel region) dominates to that of its intrinsic counterpart. Therefore, there is a need for an RF model which should consider the behaviour of both the intrinsic and the extrinsic components of a device for achieving accurate and predictive results in the simulation of designed circuit. Thus, the extrinsic and intrinsic parameters of GEWE-SiNW MOSFET and numerical modelling of small signal parameters such as Z and Y parameters are also studied in this work.

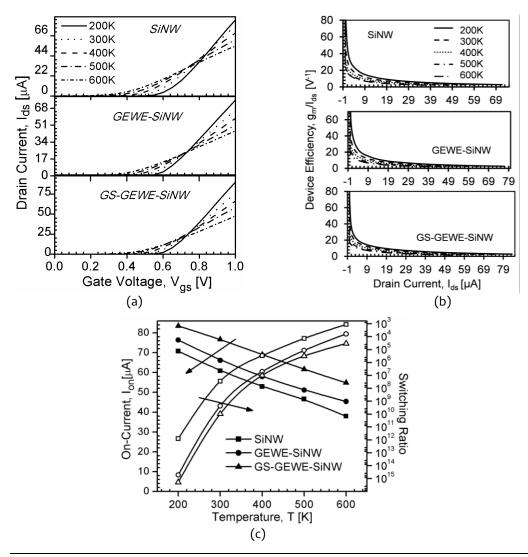

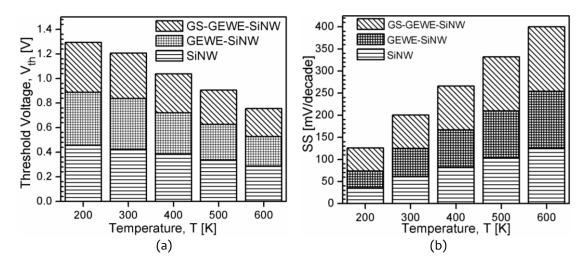

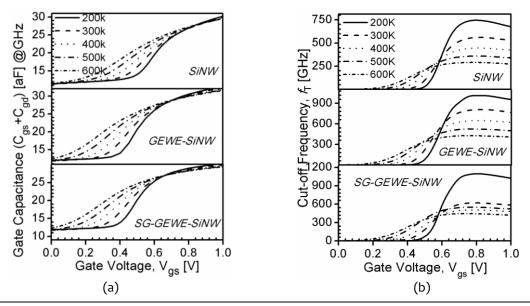

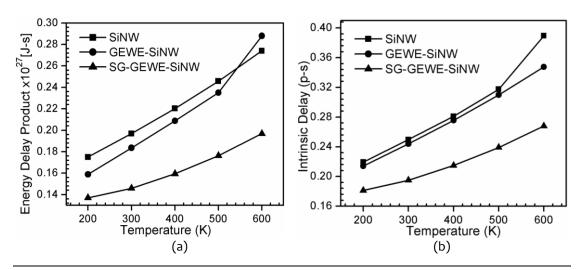

Furthermore, as oxide thickness scales down to 1.5 nm or below, the leakage current increases up to  $1 \text{ A/cm}^2$  at 1 V due to direct tunneling of carriers which, consequently increases the static power and hence affect the circuit operation. So, high-k films are proved to be the most promising solution. Though, these films result in high fringing fields from gate to source/drain regions and thus degrading the device performance. This constraint can be overcome by using gate stack architecture consisting of SiO<sub>2</sub> layer as a passivation between high-k films and bulk by keeping the effective oxide thickness (EOT) constant, high-k dielectrics permit the increase in physical oxide thickness to prevent gate tunneling and thus improves the carrier efficiency. Thus, stack gate (SG) is amalgamated onto GEWE-SiNW MOSFET to examine its performance in terms of analog and linearity FOMs. It is observed that SiNW MOSFET modeled with HfO<sub>2</sub> as a gate stack over SiO<sub>2</sub> interfacial layer, and gate metal workfunction difference ( $\Delta W$ ) of 4.4 eV can be considered as a promising potential for low power switching component in ICs and Linear RF amplifiers. Moreover, a reliability issue of Stacked Gate Electrode Workfunction Engineered (GEWE)-Silicon (SG)-Gate Nanowire (SiNW) MOSFET is examined over a wide range of ambient temperatures (200-600 K). It is observed that at low temperature SG-

GEWE-SiNW shows improved Analog/RF performance in terms of  $I_{on}/I_{off}$ , Subthreshold Swing (SS), device efficiency,  $f_{T}$ , noise conductance and noise figure and also unveil highly stable linearity performance owing to reduced distortions. The results so obtained can be serving as a worthy design tool for circuits operating at wide range of temperatures.

Immunity against SCEs, high current driving capability, optimum high frequency performance and suitability at low temperature makes GEWE-SiNW MOSFET a promising device for low power, high performance CMOS applications.

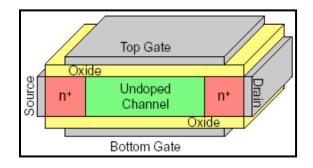

# LIST OF FIGURES

### Page No.

=

| Figure 1.01: Moore's Law predicting the downscaling of device features.                                                                                                                                                                                                                                                                                                                           | 2  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.02: Principles of constant-electric-field scaling for MOSFETs and integrated circuits.                                                                                                                                                                                                                                                                                                   | 4  |

| Figure 1.03: Drain Induced Barrier Lowering.                                                                                                                                                                                                                                                                                                                                                      | 6  |

| Figure 1.04: Cross-Sectional View of n-channel MOSFET showing Injection of Hot-<br>Carriers due to shortening of channel length.                                                                                                                                                                                                                                                                  | 7  |

| Figure 1.05: Different schemes to alleviate SCEs in nano-scale MOSFET.                                                                                                                                                                                                                                                                                                                            | 8  |

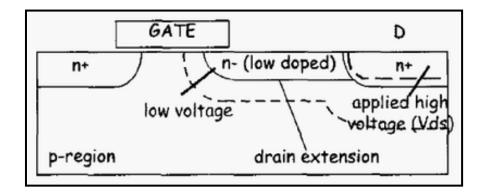

| Figure 1.06: Cross-Section of n-type MOSFET considering low doped extension from drain side.                                                                                                                                                                                                                                                                                                      | 9  |

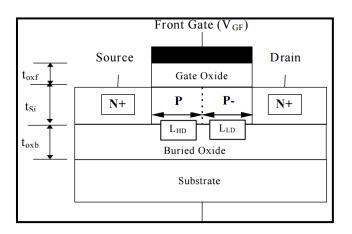

| Figure 1.07: Schematic View of n-channel SOI-MOSFET showing graded channel doping.                                                                                                                                                                                                                                                                                                                | 10 |

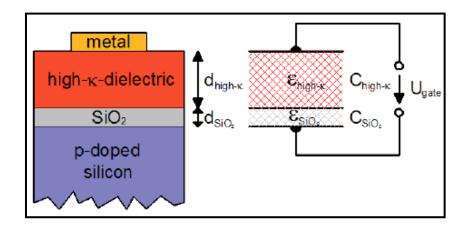

| Figure 1.08: Schematic structure of a gate stack with a high-k dielectric layer. A series capacitance has to be taken into account to evaluate the dielectric constant of the high-k material.                                                                                                                                                                                                    | 11 |

| Figure 1.09: Schematic Structure of Dual Material Gate MOSFET.                                                                                                                                                                                                                                                                                                                                    | 12 |

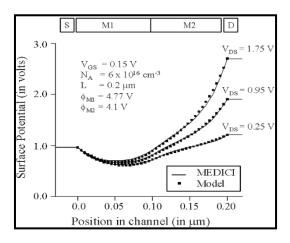

| Figure 1.10: Surface channel potential profiles of a fully depleted DMG SOI MOSFET.                                                                                                                                                                                                                                                                                                               | 12 |

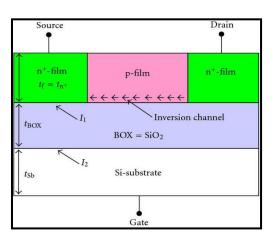

| Figure 1.11: Schematic view of n-channel SOI MOSFET.                                                                                                                                                                                                                                                                                                                                              | 14 |

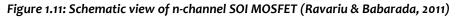

| Figure 1.12: Schematic view of n-channel Double gate MOSFET.                                                                                                                                                                                                                                                                                                                                      | 15 |

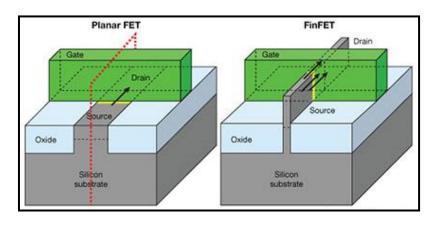

| Figure 1.13: Schematic view of both planar MOSFET and FinFETs.                                                                                                                                                                                                                                                                                                                                    | 16 |

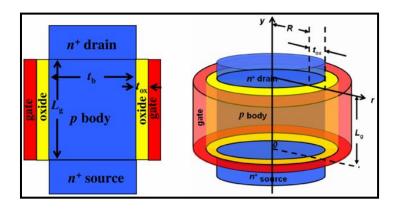

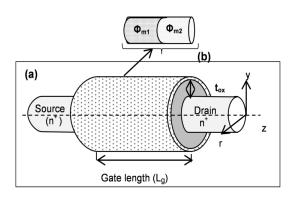

| Figure 1.14: Cross-sectional view of cylindrical gate MOSFET with the coordinate system.                                                                                                                                                                                                                                                                                                          | 16 |

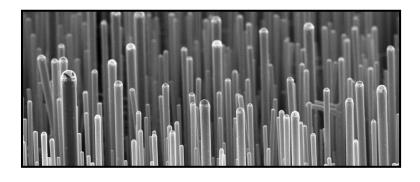

| Figure 1.15: SEM image of silicon nanowires (SiNW)                                                                                                                                                                                                                                                                                                                                                | 19 |

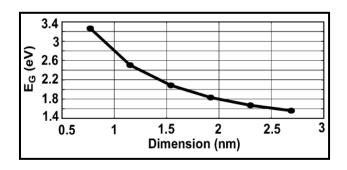

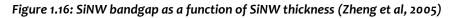

| Figure 1.16: SiNW bandgap as a function of SiNW thickness.                                                                                                                                                                                                                                                                                                                                        | 20 |

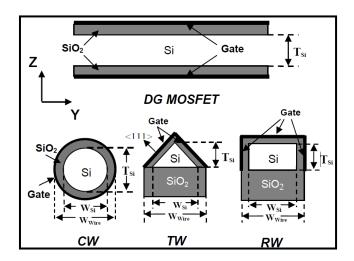

| Figure 1.17: Various cross-sections of silicon nanowire transistor.                                                                                                                                                                                                                                                                                                                               | 22 |

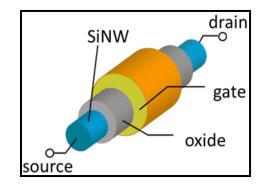

| Figure 1.18: Cross-sections of silicon nanowire transistor                                                                                                                                                                                                                                                                                                                                        | 22 |

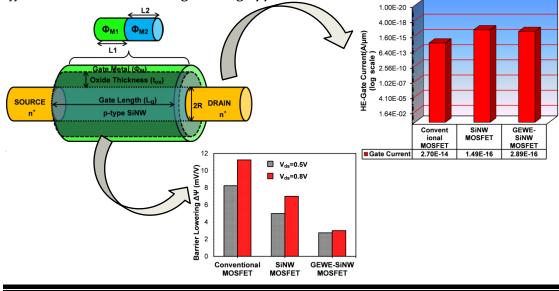

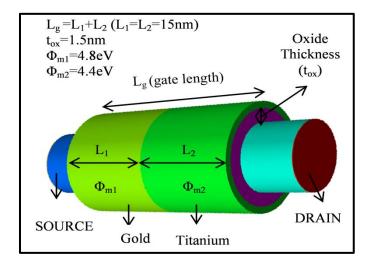

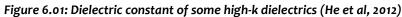

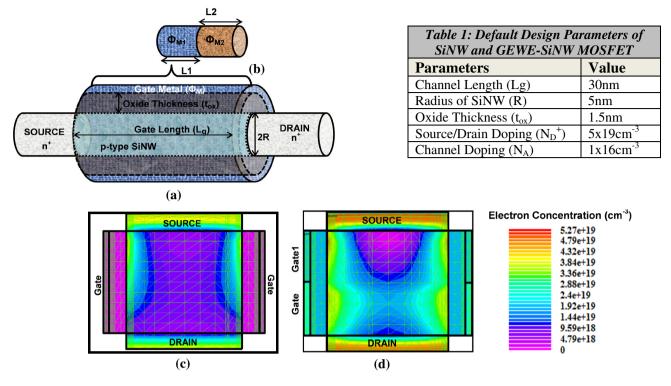

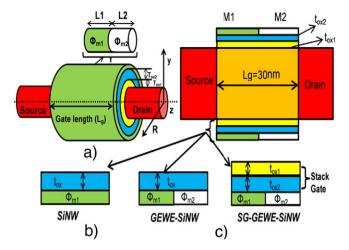

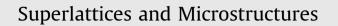

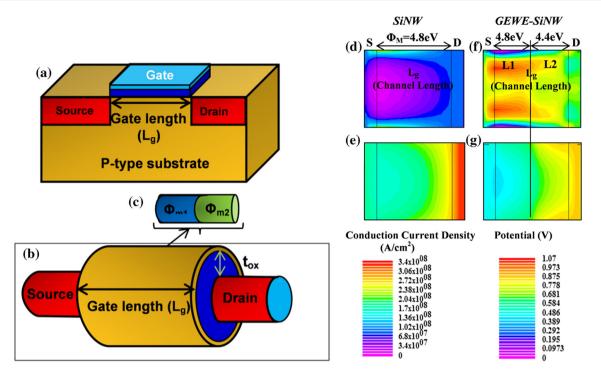

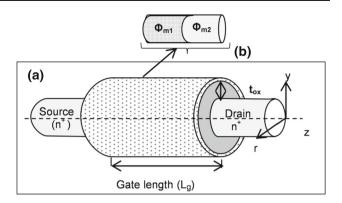

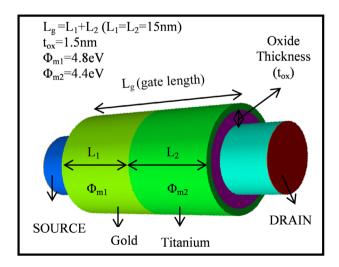

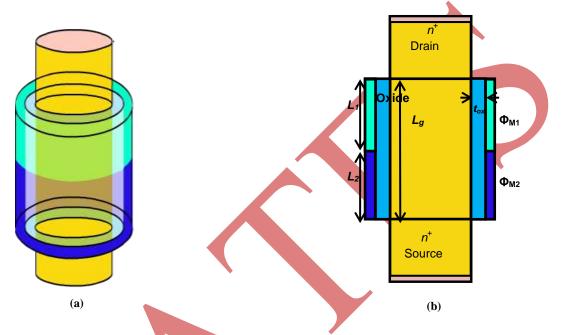

| Figure 2.01: Simulated 3-D structure of GEWE-SiNW MOSFET. Default device<br>parameters are: Channel Length ( $L_g$ ) =30nm, Oxide thickness ( $t_{ox}$ ) =1.5nm,<br>Radius of Silicon pillar (R) = 5nm, Source/Drain Doping ( $N_D$ ) =5x10 <sup>19</sup> cm <sup>-3</sup> ,<br>Channel Doping ( $N_A$ ) =1x10 <sup>16</sup> cm <sup>-3</sup> , Gate Metal workfunction ( $\Phi_{M1}$ ) = 4.8 eV. | 41 |

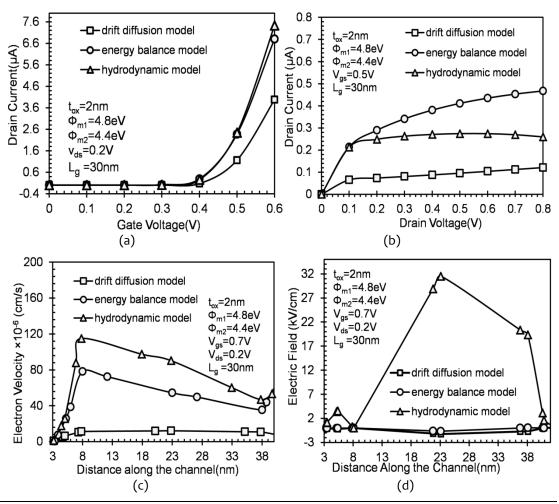

| Figure 2.02: | (a) Transfer Characteristics, (b) Output Characteristics of GEWE-SiNW MOSFET for different transport models. (c) Electron Velocity, (d) Electric Field as a function of position along the channel for GEWE-SiNW MOSFET at $V_{ds}$ =0.2 V and $V_{gs}$ =0.7 V for different transport models.          | 42 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

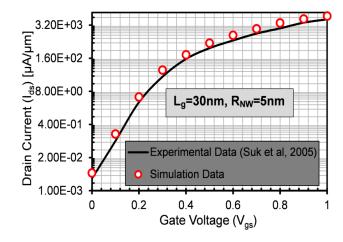

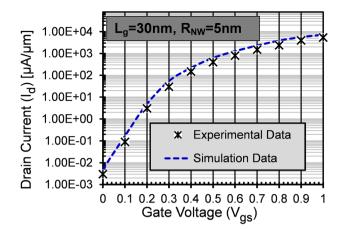

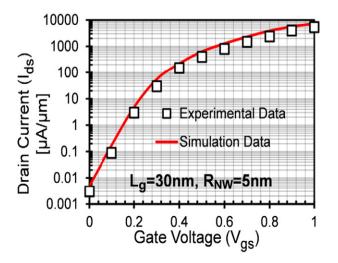

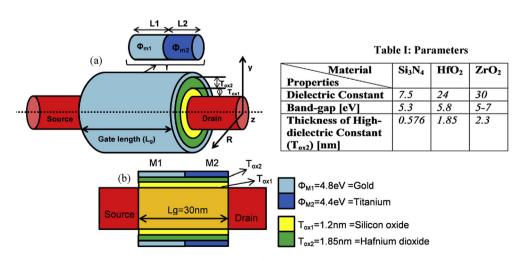

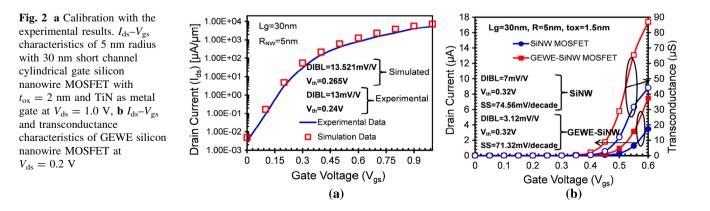

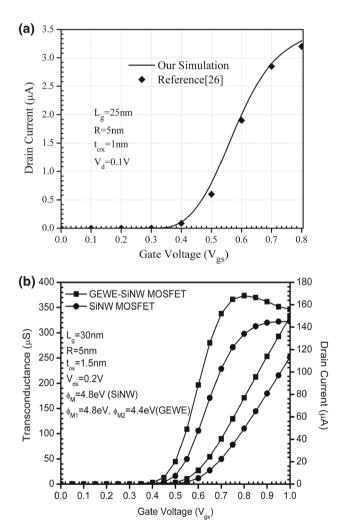

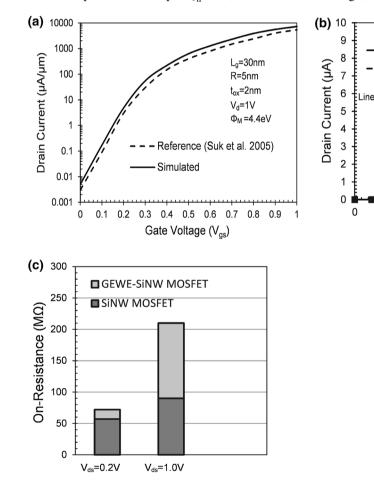

| Figure 2.03: | Calibration with the experimental result, $I_{ds}$ - $V_{gs}$ characteristics of SiNW MOSFET.                                                                                                                                                                                                           | 45 |

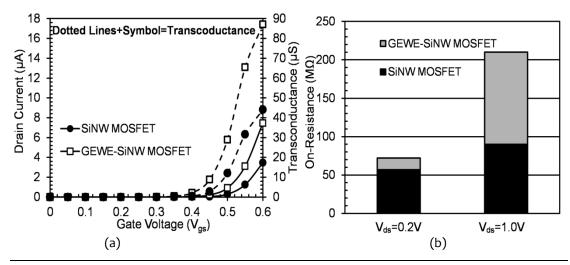

| Figure 2.04: | (a) Transfer and Transconductance characteristics of silicon nanowire and GEWE-SiNW MOSFET at $V_{ds}$ =0.4 V respectively. (b) On-resistance of SiNW and GEWE-SiNW MOSFET in active and a saturation region.                                                                                           | 47 |

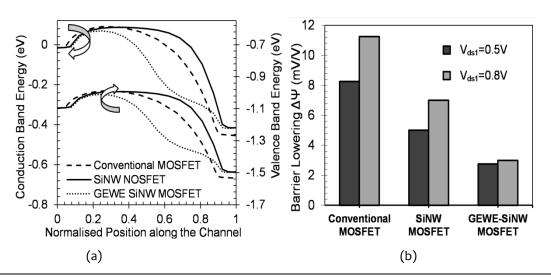

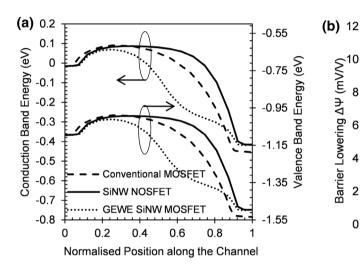

| Figure 2.05: | (a) Conduction band energy and Valence band energy variation along the channel for $V_{gs}$ =0.4V for Conventional, SiNW and GEWE-SiNW MOSFET at $V_{ds}$ =0.6 V (b) DIBL versus $V_{ds}$ variation for Conventional, SiNW and GEWE-SiNW MOSFET at $V_{gs}$ =0V for two different values of $V_{ds1}$ . | 48 |

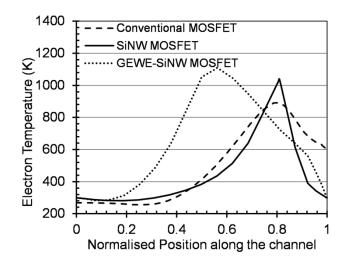

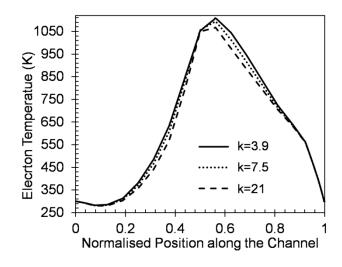

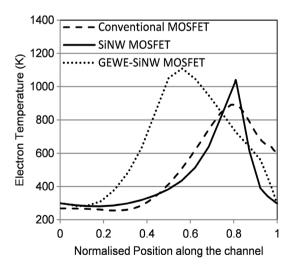

| Figure 2.06: | Electron temperature variation along the channel for Conventional, SiNW and GEWE-SiNW MOSFET at $V_{ds}$ =0.6 V, $V_{gs}$ =0.4V.                                                                                                                                                                        | 49 |

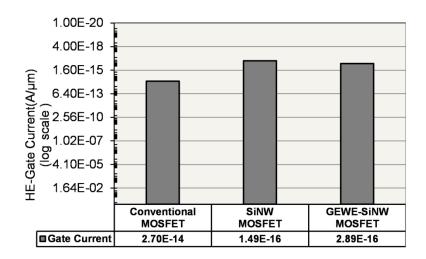

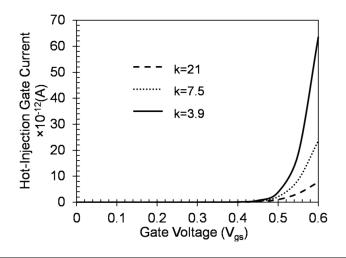

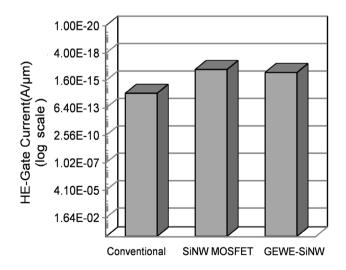

| Figure 2.07: | HE gate current for conventional MOSFET, SiNW and GEWE-SiNW MOSFET at $V_{ds}$ =0.6V.                                                                                                                                                                                                                   | 50 |

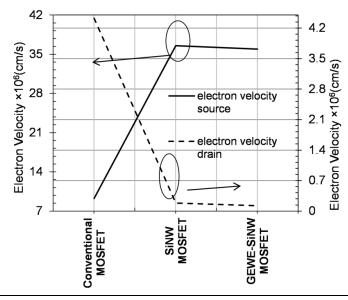

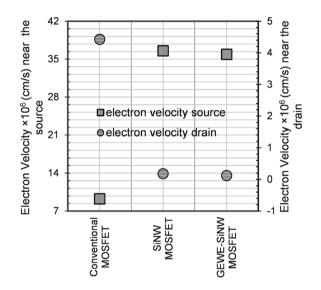

| Figure 2.08: | Electron velocity for source and drain side for conventional MOSFET, SiNW and GEWE-SiNW MOSFET at $V_{ds}$ =0.6V, $V_{gs}$ =0.4.                                                                                                                                                                        | 51 |

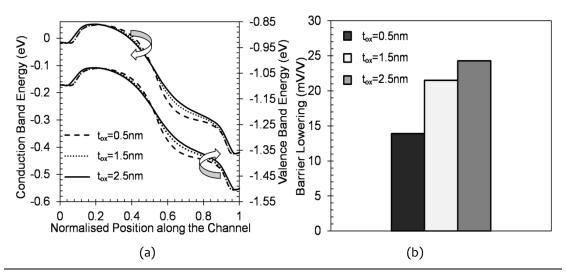

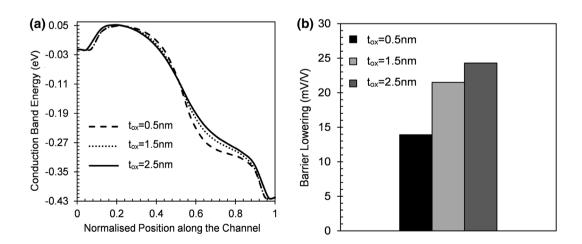

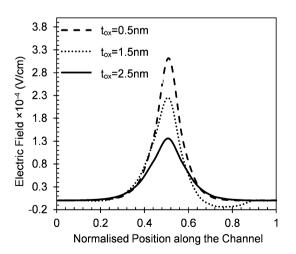

| Figure 2.09: | (a) Conduction Band Profile for GEWE-SiNW MOSFET at different values of oxide thickness. (b) Barrier Lowering for GEWE-SiNW MOSFET at different values of oxide thickness.                                                                                                                              | 52 |

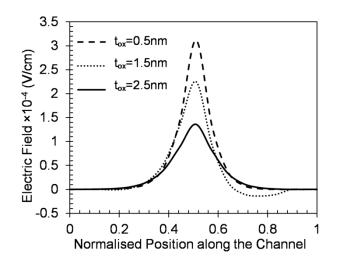

| Figure 2.10: | Electric Field for GEWE-SiNW MOSFET at different values of oxide thickness.                                                                                                                                                                                                                             | 52 |

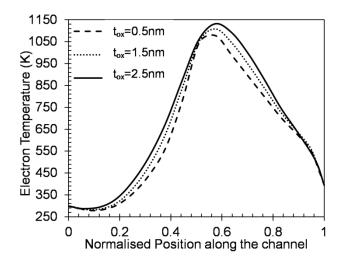

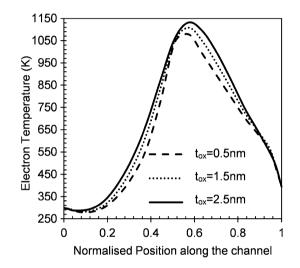

| Figure 2.11: | Electron Temperature for GEWE-SiNW MOSFET for $V_{gs}$ =0.6V and $V_{ds}$ =0.4 at different values of oxide thickness.                                                                                                                                                                                  | 53 |

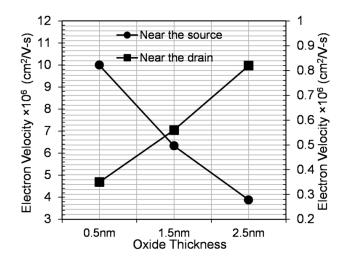

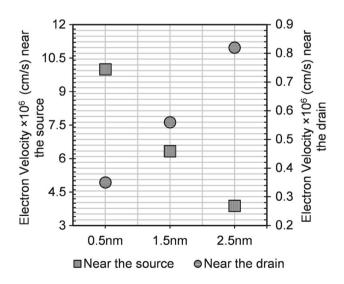

| Figure 2.12: | Electron velocity for source and drain side for GEWE-SiNW MOSFET for $V_{gs}$ =0.6V and $V_{ds}$ =0.4 at different values of oxide thickness.                                                                                                                                                           | 54 |

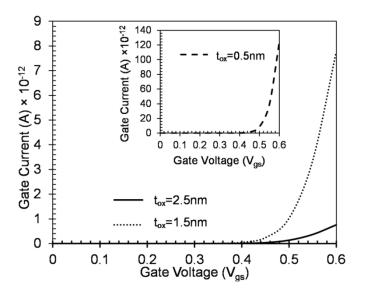

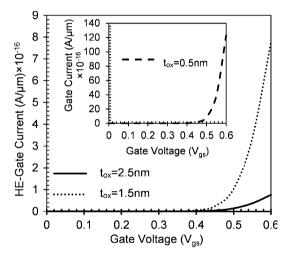

| Figure 2.13: | Hot-Electron Injection Gate Current for GEWE-SiNW MOSFET at different values of oxide thickness.                                                                                                                                                                                                        | 54 |

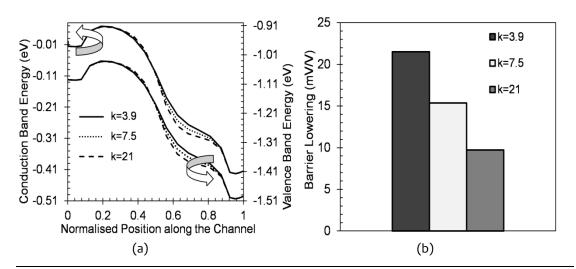

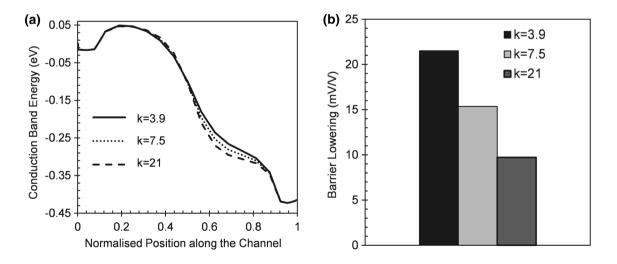

| Figure 2.14: | (a) Conduction band and Valence band energy variation along the channel for GEWE-SiNW MOSFET at different values of oxide thickness. (b) DIBL variation for GEWE-SiNW MOSFET for $V_{gs}$ =0.6V and $V_{ds}$ =0.4 at various values of High-k.                                                          | 55 |

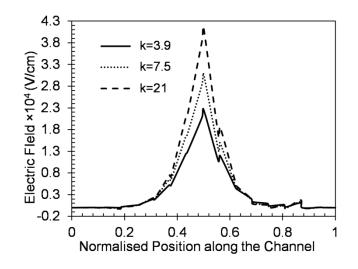

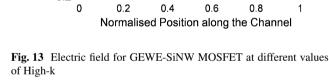

| Figure 2.15: | Electric field for GEWE-SiNW MOSFET at different values of High-k.                                                                                                                                                                                                                                      | 56 |

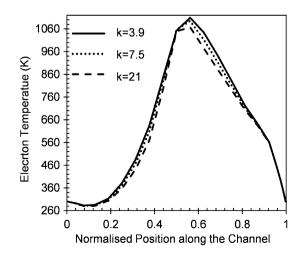

| Figure 2.16: | Electron Temperature variation along the channel for GEWE-SiNW MOSFET for $V_{gs}$ =0.6V and $V_{ds}$ =0.4 at different values of High-k.                                                                                                                                                               | 57 |

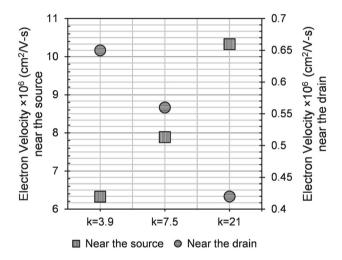

| Figure 2.17: | Electron velocity for source and drain side for GEWE-SiNW MOSFET for $V_{gs}$ =0.6V and $V_{ds}$ =0.4 at different values of High-k.                                                                                                                                                                    | 58 |

x

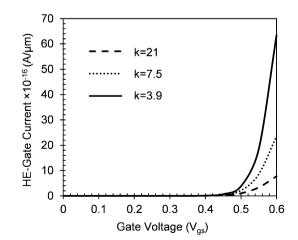

| Figure 2.18: Hot-Electron Injection Gate Current for GEWE-SiNW MOSFET at various values of High-k.                                                                                                                                                                                                                                                                                                                                           | 58 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.01: Simulated 3-D structure of GEWE-SiNW MOSFET. Default device<br>parameters are: Channel Length ( $L_g$ )=30nm, Oxide thickness ( $t_{ox}$ )=1.5nm,<br>Radius of Silicon pillar (R)=5nm, Source/Drain Doping ( $N_D$ )=5x10 <sup>19</sup> cm <sup>-3</sup> ,<br>Channel Doping ( $N_A$ )=1x10 <sup>16</sup> cm <sup>-3</sup> , Gate Metal workfunction ( $\Phi_{M1}$ )=4.8 eV,<br>Gate Metal workfunction ( $\Phi_{M2}$ )=4.4 eV. | 71 |

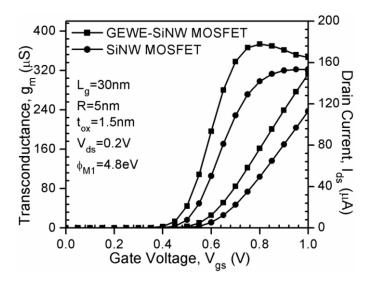

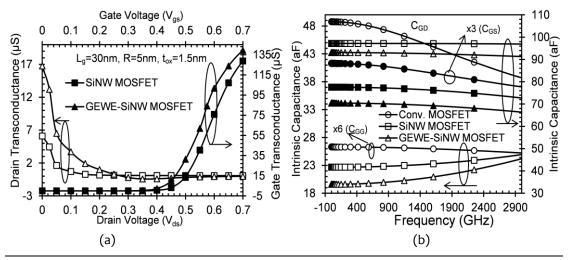

| Figure 3.02: Transfer and Transconductance characteristics of SiNW and GEWE-SiNW MOSFET at $V_{ds}$ =0.2V respectively.                                                                                                                                                                                                                                                                                                                      | 75 |

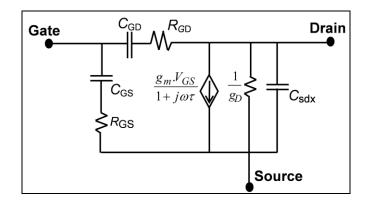

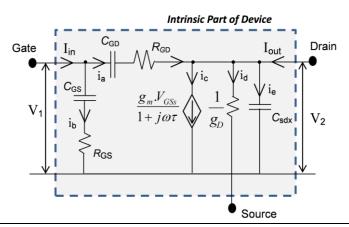

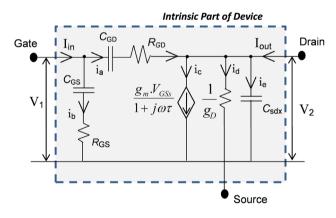

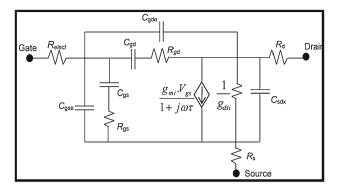

| Figure 3.03: Non-quasi-static (NQS) equivalent circuit model of SiNW MOSFET at RF region operating in the strong inversion region.                                                                                                                                                                                                                                                                                                           | 76 |

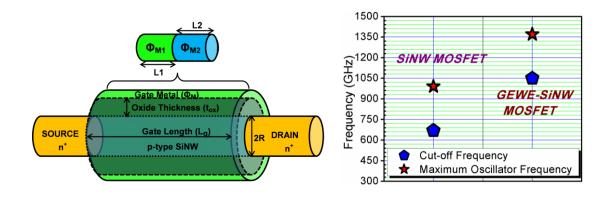

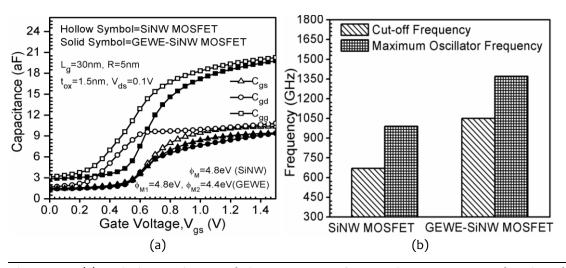

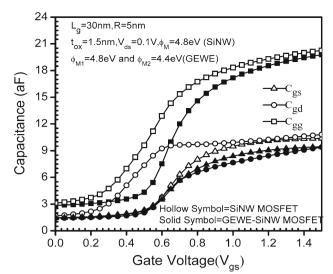

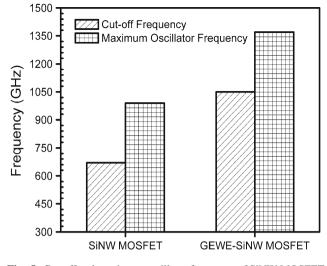

| Figure 3.04: (a) Intrinsic capacitances of SiNW MOSFET and GEWE-SiNW MOSFET as<br>a function of V <sub>gs</sub> , (b) Cut-off and Maximum Oscillator Frequency of SiNW<br>MOSFET and GEWE-SiNW MOSFET at V <sub>gs</sub> =0.7V and V <sub>ds</sub> =0.2V.                                                                                                                                                                                    | 78 |

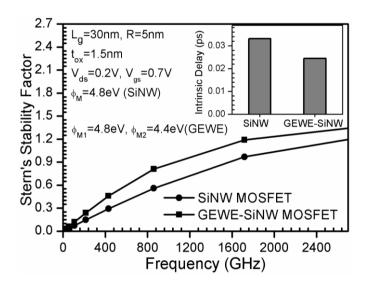

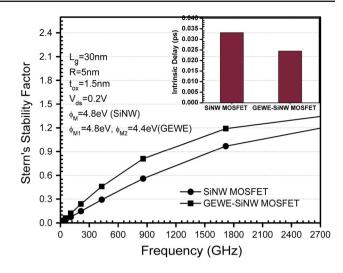

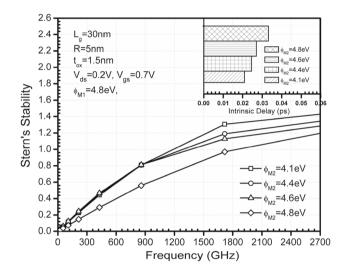

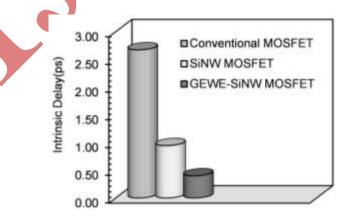

| Figure 3.05: Stern's Stability factor of SiNW and GEWE-SiNW MOSFET. Inset:<br>Intrinsic delay of SiNW and GEWE-Silicon Nanowire MOSFET at V <sub>ds</sub> =0.2V.                                                                                                                                                                                                                                                                             | 80 |

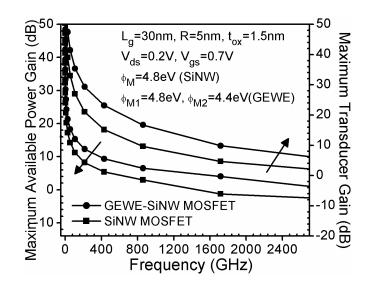

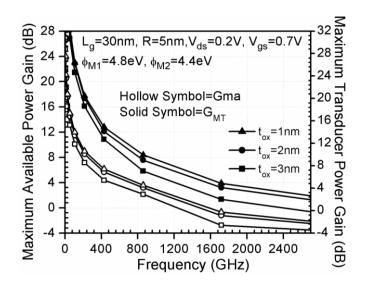

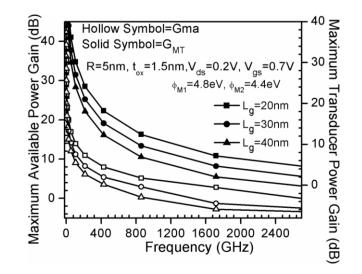

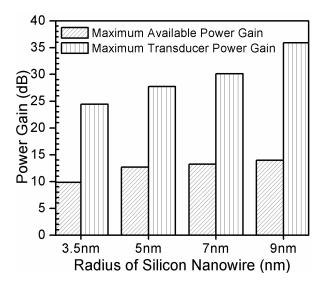

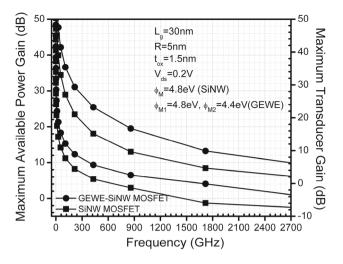

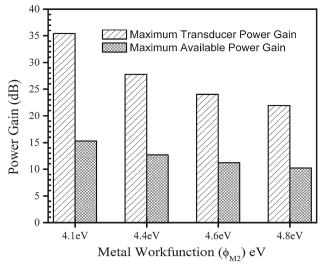

| Figure 3.06: Maximum Available Power Gain and Maximum Transducer Power Gain of SiNW and GEWE-SiNW MOSFET at $V_{ds}$ =0.2V and $V_{gs}$ =1.0V.                                                                                                                                                                                                                                                                                               | 81 |

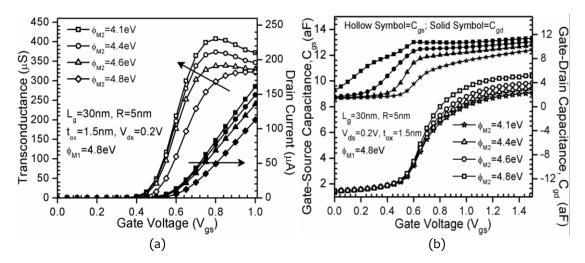

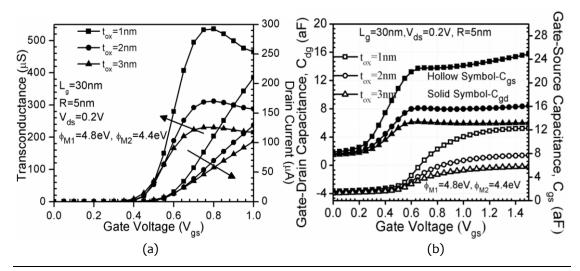

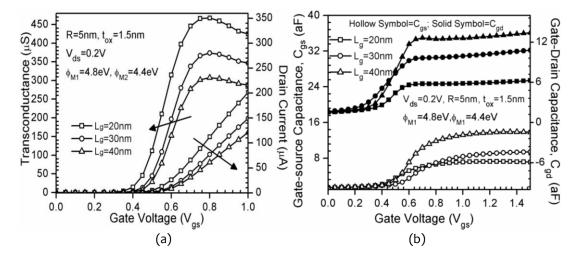

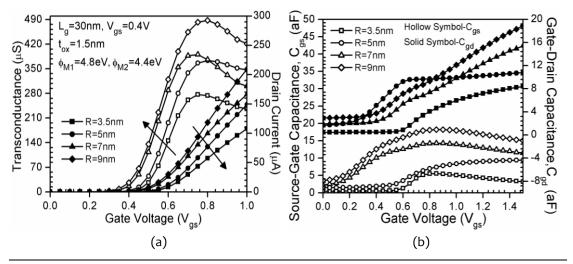

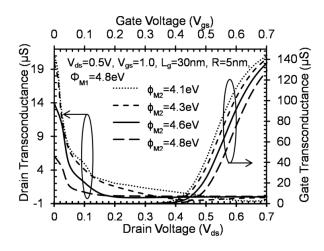

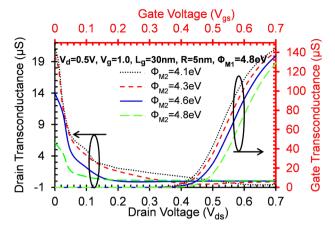

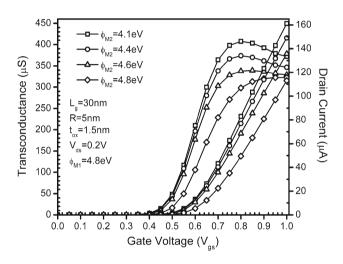

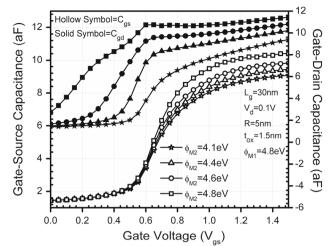

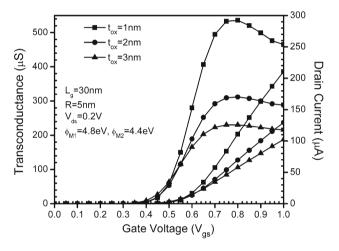

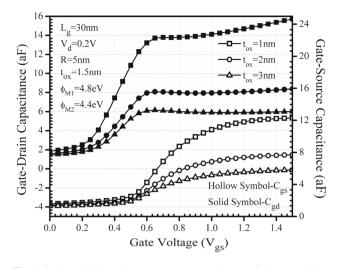

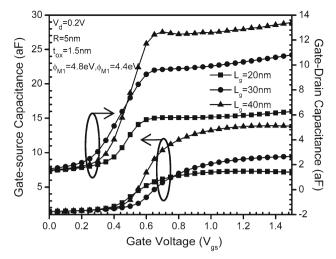

| Figure 3.07: (a)Transfer and transconductance characteristics of GEWE-SiNW MOSFET at $V_{ds}$ =0.2V, (b) Gate-Source and Gate-Drain Capacitance of GEWE-SiNW MOSFET as a function of gate voltage for various metal workfunction values at $V_{ds}$ =0.2V.                                                                                                                                                                                   | 82 |

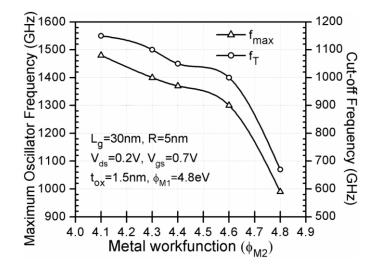

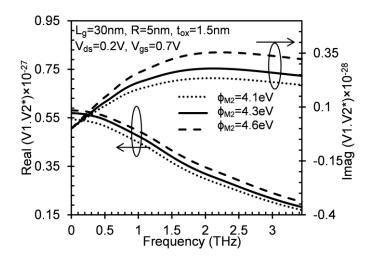

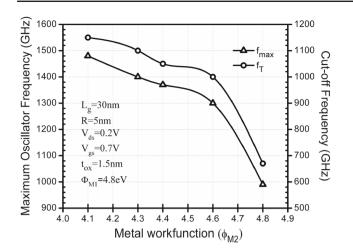

| Figure 3.08: Cut-off and Maximum Oscillator Frequency of GEWE-SiNW MOSFET for various metal workfunction values ( $\Phi_{M2}$ ).                                                                                                                                                                                                                                                                                                             | 83 |

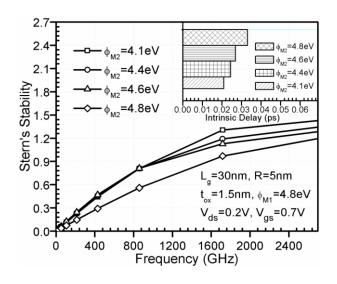

| Figure 3.09: Stern's Stability factor of GEWE-SiNW MOSFET for various metal<br>workfunction values. Inset: Intrinsic delay of GEWE-SiNW MOSFET for<br>various metal workfunction values.                                                                                                                                                                                                                                                     | 84 |

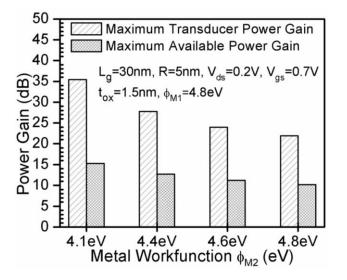

| Figure 3.10: Maximum Available power gain and Maximum Transducer Power Gain of GEWE-SiNW MOSFET as a function of $\Phi_{M2}$ .                                                                                                                                                                                                                                                                                                               | 84 |

| Figure 3.11: (a) Transfer and transconductance characteristics of GEWE-SiNW MOSFET<br>at V <sub>ds</sub> =0.2V for different oxide thickness, (b) Gate-Drain and Gate-Source<br>Capacitance of GEWE-SiNW MOSFET as a function of gate voltage for<br>different oxide thickness.                                                                                                                                                              | 85 |

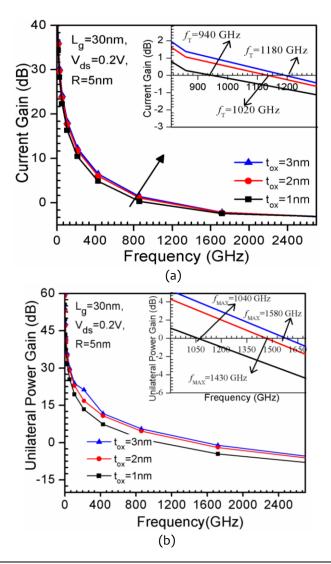

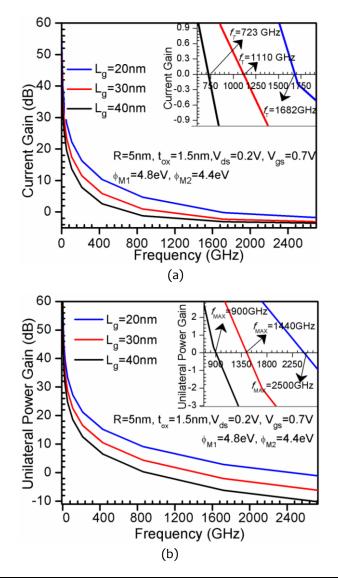

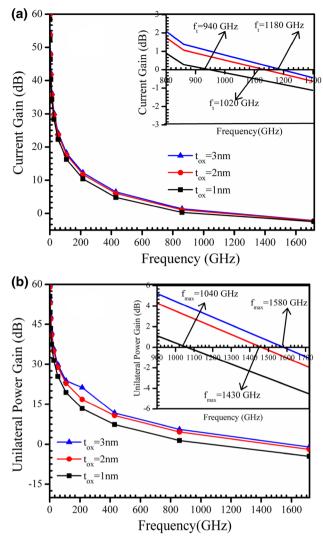

| Figure 3.12: (a) Cut-off frequency of GEWE-SiNW MOSFET at V <sub>ds</sub> =0.2V for different<br>oxide thickness as a function of gate voltage, (b) Current Gain of GEWE-<br>SiNW MOSFET for different oxide thickness.                                                                                                                                                                                                                      | 86 |

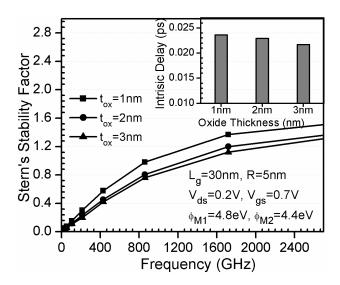

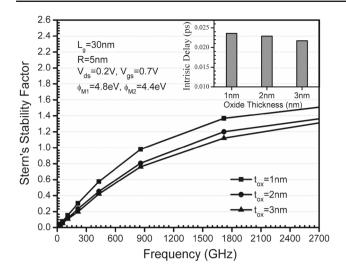

| Figure 3.13: Stern's Stability Factor of GEWE-SiNW MOSFET for various metal workfunction values. Inset: Intrinsic delay of GEWE-SiNW MOSFET at V <sub>ds</sub> =0.2V for different oxide thickness.                                                                                                                                                                                                                                          | 87 |

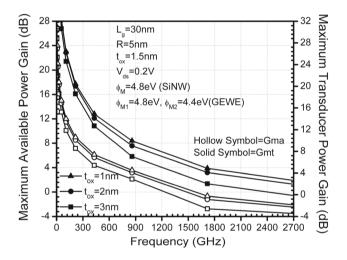

| Figure 3.14: Maximum Available and Maximum Transducer Power Gain of GEWE-<br>SiNW MOSFET for different oxide thickness.                                                                                                                                                                                                            | 88  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

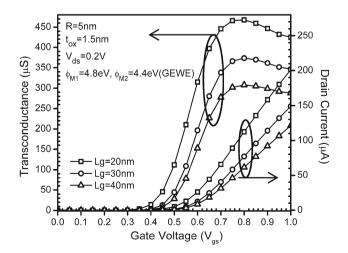

| Figure 3.15: Transfer and Transconductance characteristics of GEWE-SiNW MOSFET<br>for different channel lengths, (b) Gate-Source and Gate-Drain Capacitance<br>of GEWE-SiNW MOSFET as a function of gate voltage for different<br>channel lengths.                                                                                 | 89  |

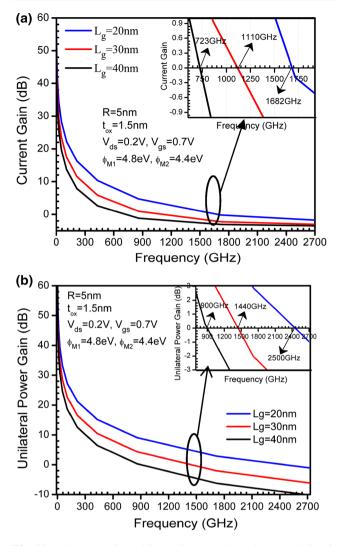

| Figure 3.16: (a) Current Gain and (b) Maximum Unilateral Power Gain of GEWE-SiNW MOSFET V <sub>ds</sub> =0.2V for different channel lengths.                                                                                                                                                                                       | 90  |

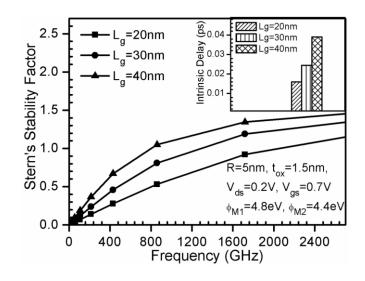

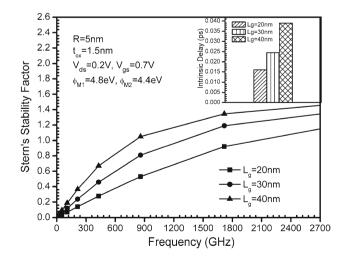

| Figure 3.17: Stern's Stability Factor of GEWE-SiNW MOSFET for different channel lengths. Inset: Intrinsic delay of GEWE-SiNW MOSFET at V <sub>ds</sub> =0.2V for different channel lengths.                                                                                                                                        | 91  |

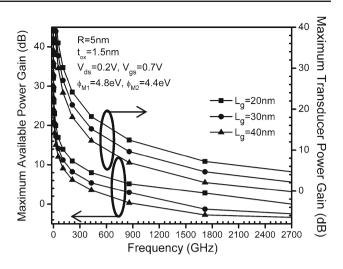

| Figure 3.18: Maximum Available and Maximum Transducer Power Gain of GEWE-<br>SiNW MOSFET at $V_{ds}$ =0.2V for different channel lengths.                                                                                                                                                                                          | 91  |

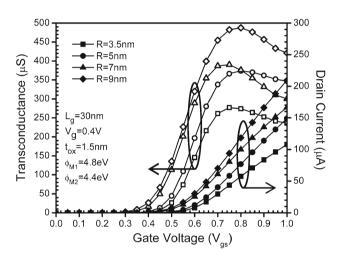

| Figure 3.19: (a) Transfer and transconductance characteristics of GEWE-SiNW MOSFET<br>for different radius of SiNW, (b) Gate-Drain and Gate-Source Capacitance of<br>GEWE-SiNW MOSFET as a function of gate voltage for different radius of<br>SiNW                                                                                | 92  |

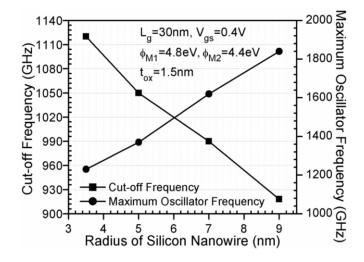

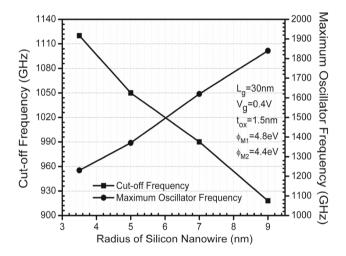

| Figure 3.20: Cut-off and Maximum Oscillatory Frequency of GEWE-SiNW MOSFET for<br>different radius of silicon nanowire.                                                                                                                                                                                                            | 93  |

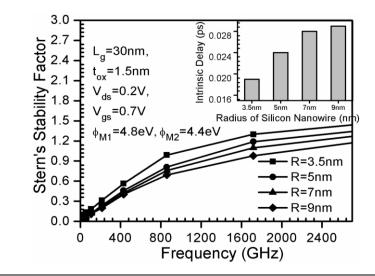

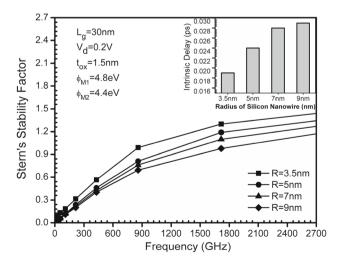

| Figure 3.21: Stern's Stability Factor of GEWE-SiNW MOSFET for different channel radius. Inset: Intrinsic delay of GEWE-SiNW MOSFET                                                                                                                                                                                                 | 93  |

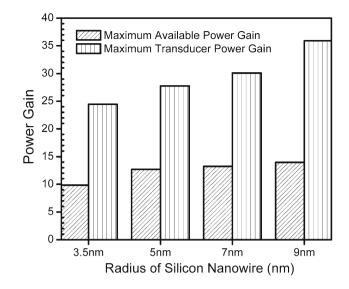

| Figure 3.22: Maximum Available Power Gain and Maximum Transducer Power Gain of GEWE-SiNW MOSFET at V <sub>ds</sub> =0.2V for different silicon nanowire radius.                                                                                                                                                                    | 94  |

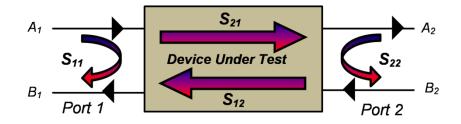

| Figure 4.01: A two port S-parameters showing reflection and transmission coefficients.                                                                                                                                                                                                                                             | 103 |

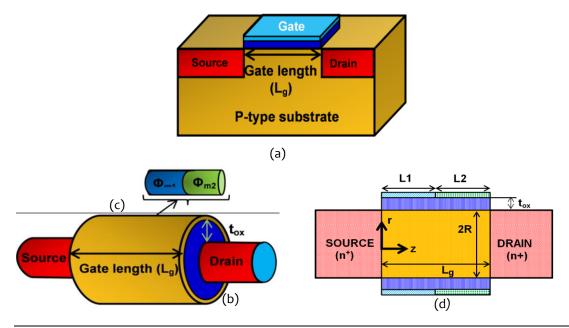

| Figure 4.02: Simulated Device Structure of (a) Conventional MOSFET, (b) SiNW<br>MOSFET, (c) GEWE-SiNW MOSFET and (d) Schematic Cross-sectional<br>view of GEWE-SiNW MOSFET.                                                                                                                                                        | 105 |

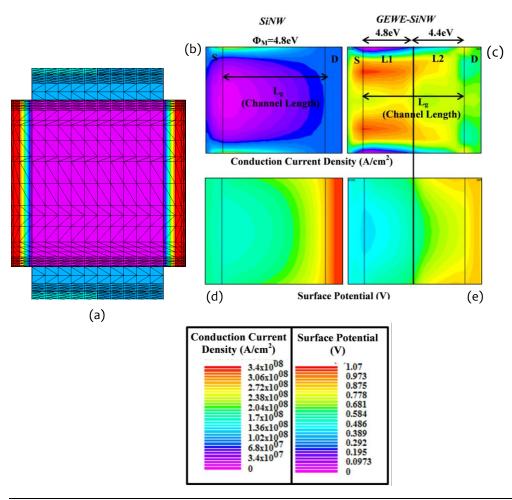

| Figure 4.03: (a) 2-D Cross-sectional view of Meshed Structure of GEWE SiNW<br>MOSFET, (b-c) Contours distribution of Conduction current density<br>and (d-e) Surface Potential along the channel for SiNW and GEWE-SiNW<br>MOSFET respectively.                                                                                    | 106 |

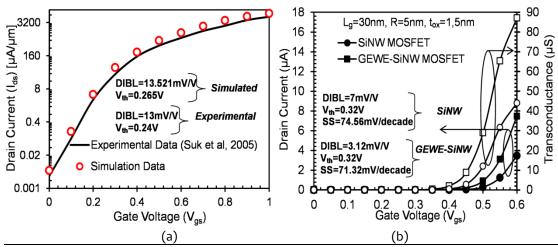

| Figure 4.04: (a) Calibration with the experimental results. $I_{ds}$ - $V_{gs}$ characteristics of 5nm radius with 30nm short channel cylindrical gate SiNW MOSFET with $t_{ox}$ =2nm and TiN as metal gate at $V_{ds}$ =1.0V, (b) $I_{ds}$ - $V_{gs}$ and transconductance characteristics of GEWE-SiNW MOSFET at $V_{ds}$ =0.2V. | 107 |

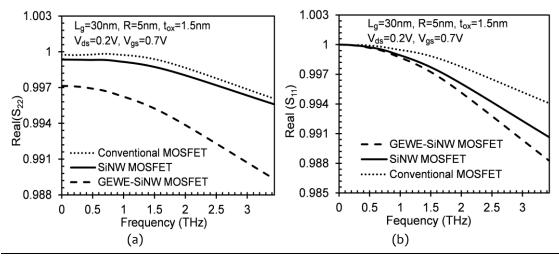

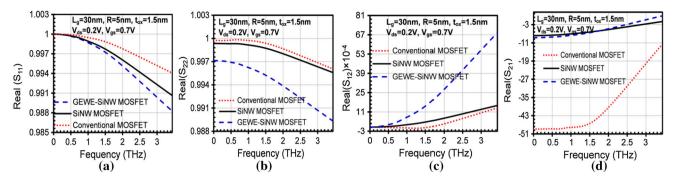

| Figure 4.05: (a) Real part of input reflection coefficient, (b) Real part of output reflection coefficient as a function of frequency for Conventional, SiNW and GEWE-SiNW MOSFET at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.                                                                                                          | 109 |

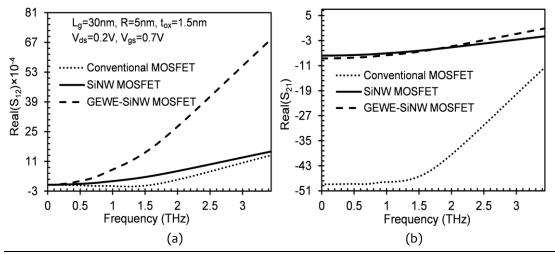

| Figure 4.06: (a) Real part of reverse transmission coefficient, (b) Real part of forward<br>transmission coefficient as a function of frequency for Conventional,<br>SiNW and GEWE-SiNW MOSFET at V <sub>gs</sub> =0.7 V and V <sub>ds</sub> =0.2 V.                                                                           | 110 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

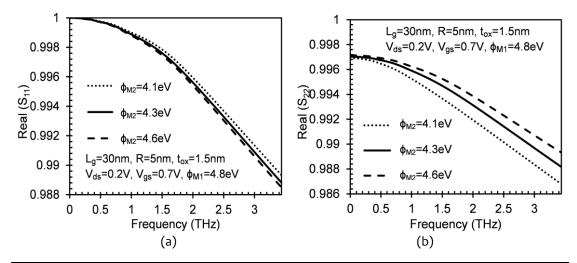

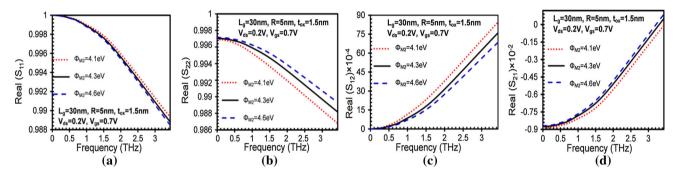

| Figure 4.07: (a) Real part of input reflection coefficient, (b) Real part of output reflection coefficient as a function of frequency for different metal gate workfunction at the drain side at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.                                                                                          | 112 |

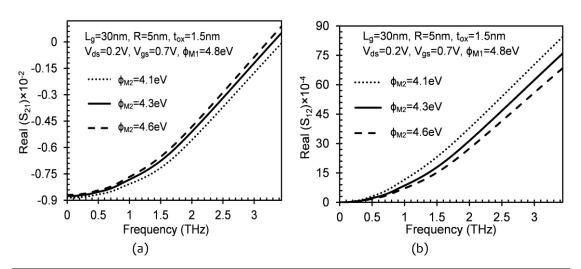

| Figure 4.08: (a-b) Real part of reverse transmission coefficient, (b) Real part of forward transmission coefficient as a function of frequency for different metal gate workfunction at the drain side at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.                                                                                 | 112 |

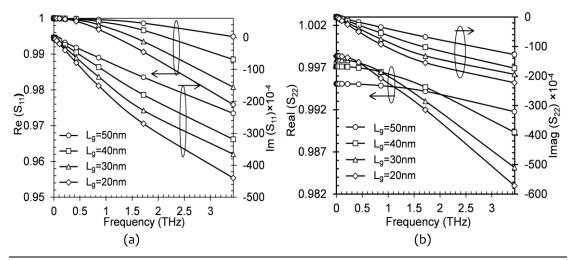

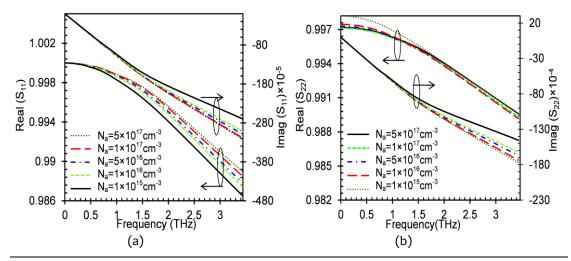

| Figure 4.09: (a) Real and Imaginary part of input reflection coefficient $(S_{11})$ , (b) Real and<br>Imaginary part of output reflection coefficient $(S_{22})$ as a function of<br>frequency for GEWE-SiNW MOSFET at different channel length $(L_g)$<br>at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.                             | 113 |

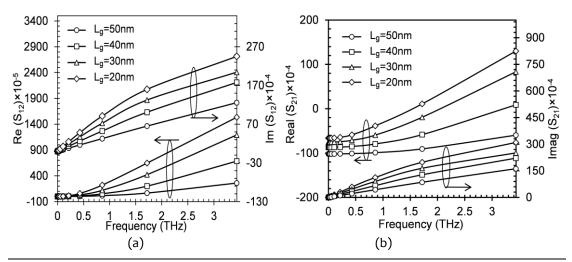

| Figure 4.10: (a) Real and Imaginary part of reverse transmission coefficient (S <sub>21</sub> ) and (b)<br>Real and Imaginary part of forward transmission coefficient (S <sub>22</sub> ) as a<br>function of frequency for GEWE-SiNW MOSFET at different channel<br>length at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.            | 114 |

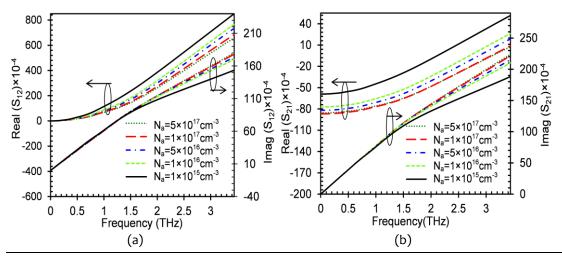

| Figure 4.11: (a) Real and Imaginary part of input reflection coefficient ( $S_{11}$ ) and (b) Real and Imaginary part of output reflection coefficient ( $S_{22}$ ) as a function of frequency for GEWE-SiNW MOSFET at different channel doping at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.                                        | 115 |

| Figure 4.12: (a) Real and Imaginary part of reverse transmission coefficient ( $S_{12}$ ), (b) Real and Imaginary part of forward transmission coefficient ( $S_{21}$ )as a function of frequency for GEWE SiNW MOSFET at different channel doping at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.                                     | 116 |

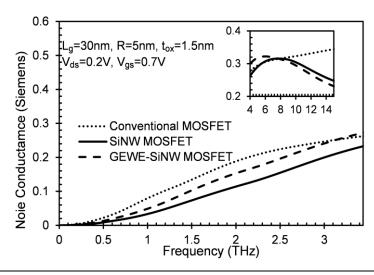

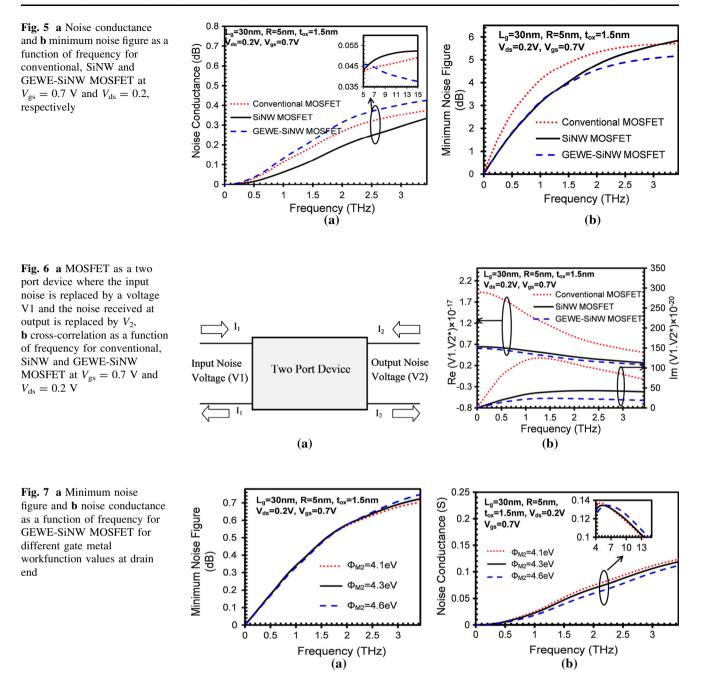

| Figure 4.13: Noise Conductance as a function of frequency for Conventional, SiNW and GEWE-SiNW MOSFET at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.                                                                                                                                                                                  | 117 |

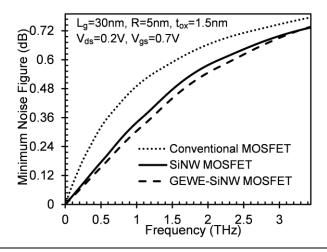

| Figure 4.14: Minimum Noise Figure as a function of frequency for Conventional, SiNW and GEWE-SiNW MOSFET at $V_{gs}$ =0.7 V and $V_{ds}$ =0.2 V.                                                                                                                                                                               | 118 |

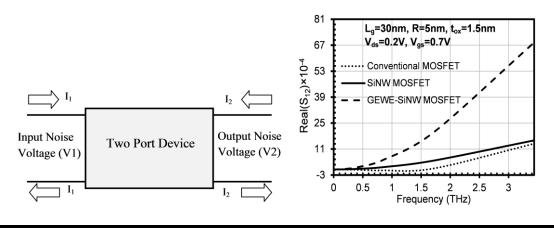

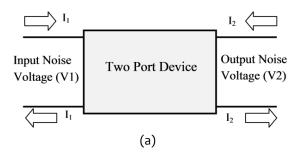

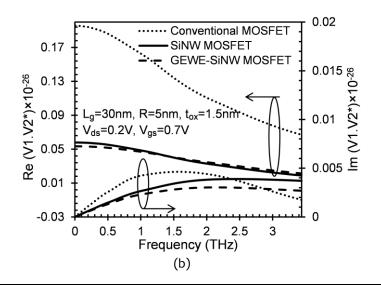

| <ul> <li>Figure 4.15: (a) MOSFET as a two port device where the input noise is replaced by a voltage V1 and the noise received at output is replaced by V2,</li> <li>(b) Cross correlation as a function of frequency for Conventional, SiNW and GEWE-SiNW MOSFET at V<sub>g</sub>s=0.7 V and V<sub>ds</sub>=0.2 V.</li> </ul> | 119 |

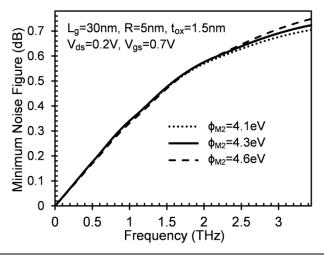

| Figure 4.16: Minimum Noise Figure as a function of frequency for GEWE-SiNW MOSFET for different gate metal workfunction values at drain end.                                                                                                                                                                                   | 120 |

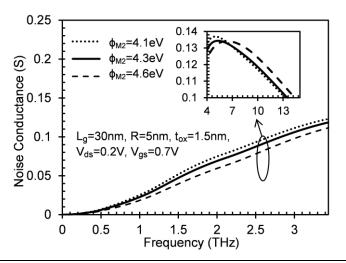

| Figure 4.17: Noise Conductance as a function of frequency for GEWE-SiNW MOSFET for different gate metal workfunction values at drain end.                                                                                                                                                                                      | 120 |

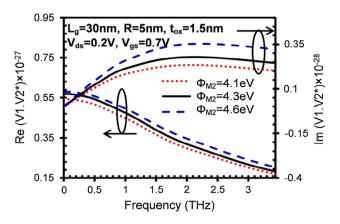

| Figure 4.18: Cross correlation as a function of frequency for GEWE-SiNW MOSFET for different gate metal workfunction values at drain end.                                                                                                                                                                                      | 121 |

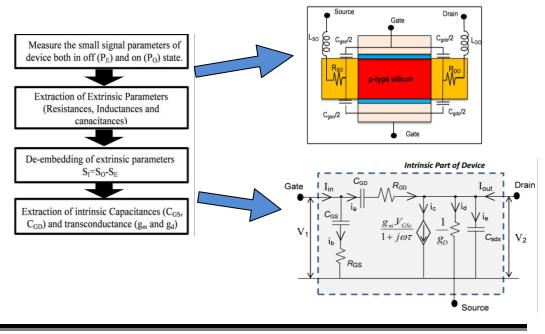

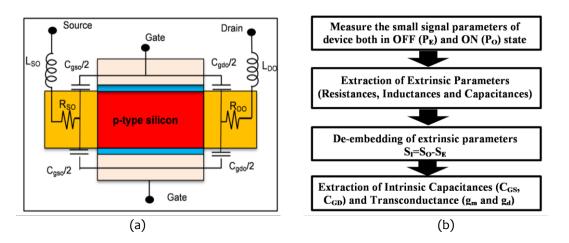

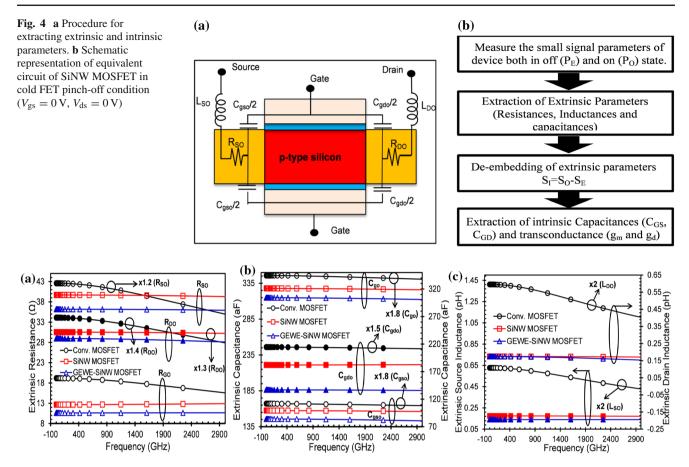

| Figure 5.01: | (a) Procedure of extracting extrinsic and intrinsic parameters. (b) Schematic representation of the Equivalent circuit of SiNW MOSFET in a cold FET pinch-off condition ( $V_{gs}$ =0V, $V_{ds}$ =0).                                                | 129 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

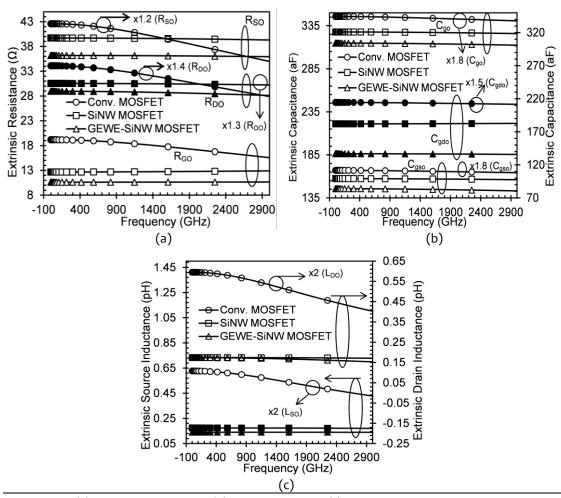

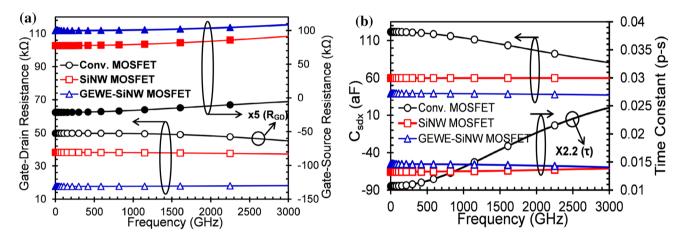

| Figure 5.02: | (a) Extrinsic Resistance, (b) Capacitance and (c) Inductance as a function of frequency for Conventional, SiNW and GEWE-SiNW MOSFET.                                                                                                                 | 130 |

| Figure 5.03: | Non-quasi-static (NQS) equivalent circuit model of SiNW MOSFET at RF region operating in the strong inversion region.                                                                                                                                | 131 |

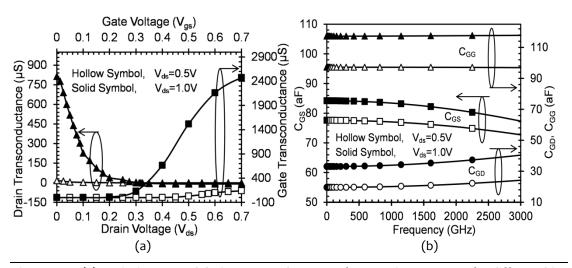

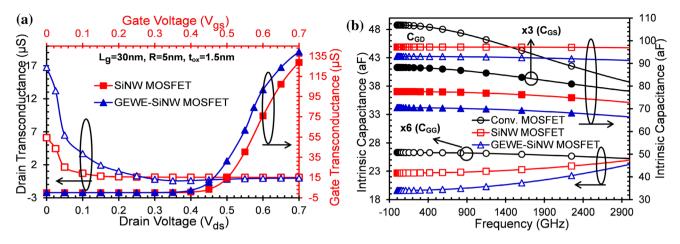

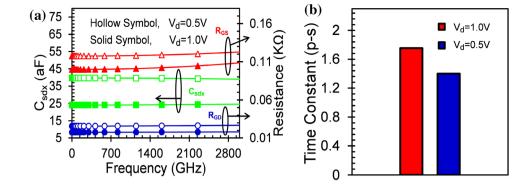

| Figure 5.04: | (a) Intrinsic gate and drain transconductance of Conventional, SiNW and GEWE-SiNW MOSFET as a function of bias voltage, (b) Intrinsic Capacitance as a function of the frequency of Conventional, SiNW and GEWE-SiNW MOSFET.                         | 132 |

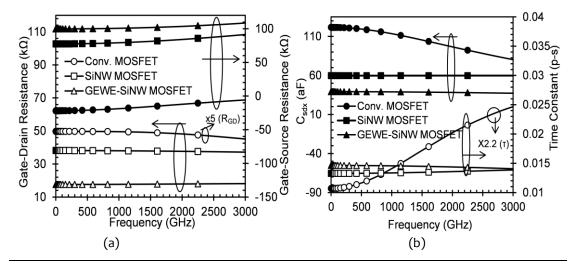

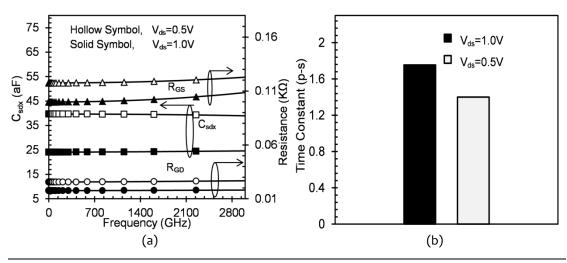

| Figure 5.05: | (a) Intrinsic gate to drain and gate to source resistance of Conventional, SiNW and GEWE-SiNW MOSFET as a function of frequency, (b) $C_{sdx}$ and Time Constant of Conventional, SiNW and GEWE-SiNW MOSFET respectively as a function of frequency. | 133 |

| Figure 5.06: | Intrinsic gate and drain transconductance of GEWE-SiNW MOSFET for different metal workfunctions.                                                                                                                                                     | 135 |

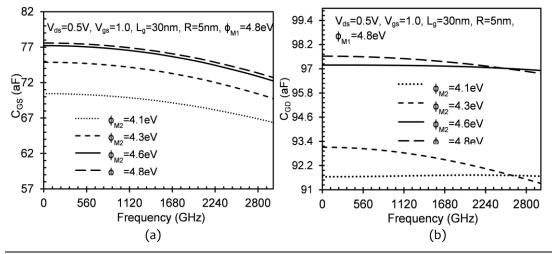

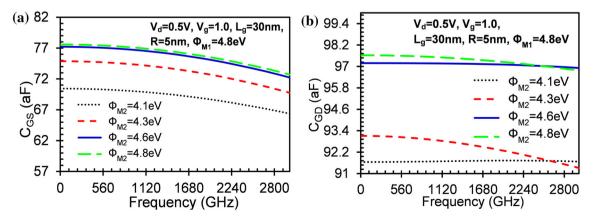

| Figure 5.07: | (a-b) Intrinsic Capacitance of GEWE-SiNW MOSFET as a function frequency for different gate metal workfunction.                                                                                                                                       | 136 |

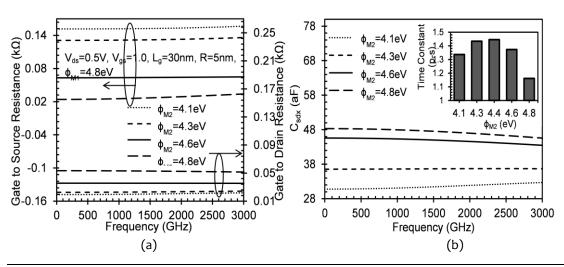

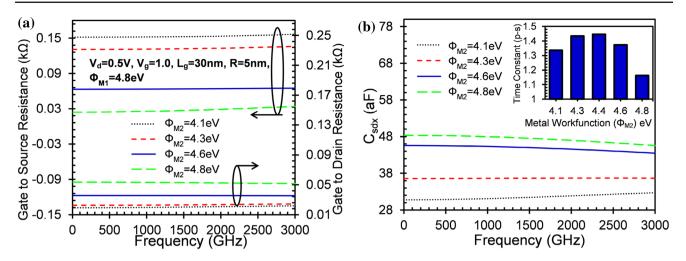

| Figure 5.08: | (a) Intrinsic gate to drain and gate to source resistance of GEWE-SiNW MOSFET for different metal workfunction, (b) $C_{sdx}$ and Time-Constant of GEWE-SiNW MOSFET for different metal workfunction.                                                | 136 |

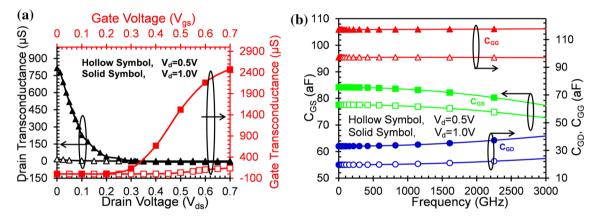

| Figure 5.09: | (a) Intrinsic gate and drain transconductance of GEWE-SiNW MOSFET for different bias value, (b) Intrinsic Bias dependent parasitic capacitance of GEWE-SiNW MOSFET.                                                                                  | 138 |

| Figure 5.10: | (a-b) $C_{sdx}$ and Distributed gate resistance; and time constant of GEWE-SiNW MOSFET respectively for different drain bias values.                                                                                                                 | 138 |

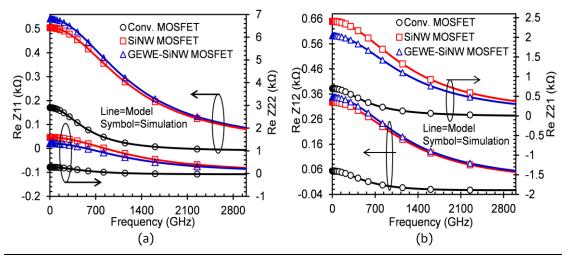

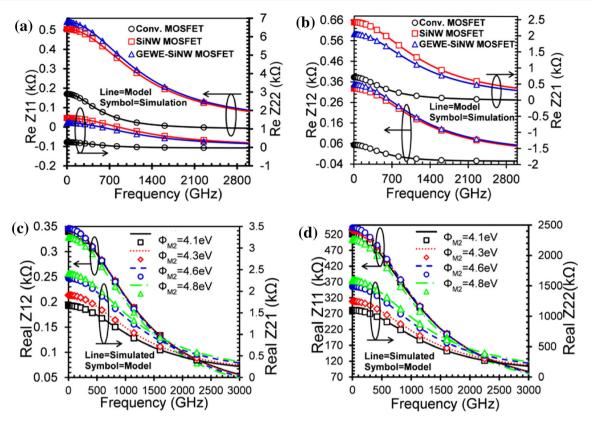

| Figure 5.11: | (a-b) Z-parameters of Conventional, SiNW and GEWE-SiNW MOSFET as a function of frequency at $V_{ds}$ =1.0V and $V_{gs}$ =0.5V.                                                                                                                       | 141 |

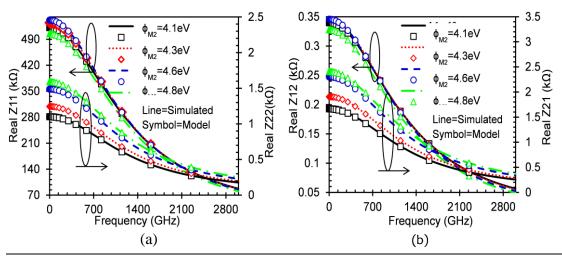

| Figure 5.12: | (a-b) Z-parameters of GEWE-SiNW MOSFET for different gate metal workfunction as a function of frequency at $V_{ds}$ =1.0V and $V_{gs}$ =0.5V.                                                                                                        | 142 |

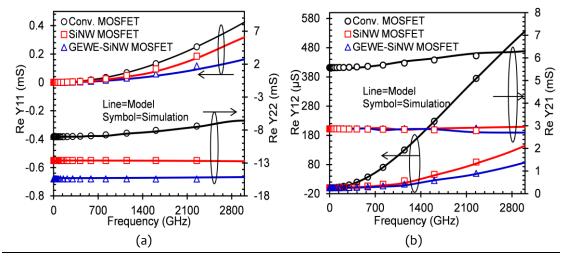

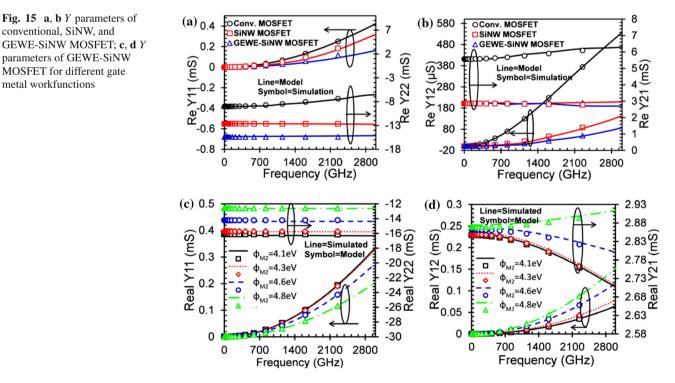

| Figure 5.13: | (a-b) Y-parameters of Conventional, SiNW and GEWE-SiNW MOSFET as a function of frequency at $V_{ds}$ =1.0V and $V_{gs}$ =0.5V.                                                                                                                       | 143 |

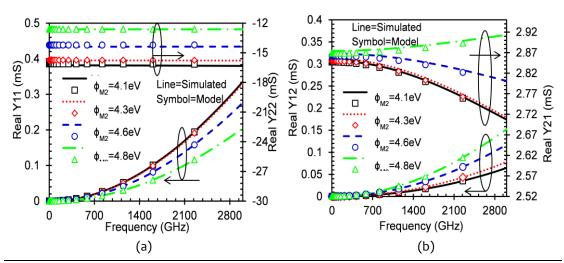

| Figure 5.14: | (a-b) Y-parameters of GEWE-SiNW MOSFET for different gate metal workfunction as a function of frequency at $V_{ds}$ =1.0V and $V_{gs}$ =0.5V.                                                                                                        | 143 |

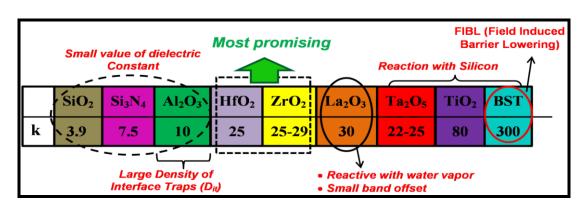

| Figure 6.01: | Dielectric constant of some high-k dielectrics.                                                                                                                                                                                                      | 153 |

| Figure 6.02: | (a) Simulated Device Structure of SG-GEWE-SiNW MOSFET, (b) 2-D schematic view of SG-GEWE-SiNW MOSFET.                                                                                                                                                | 157 |

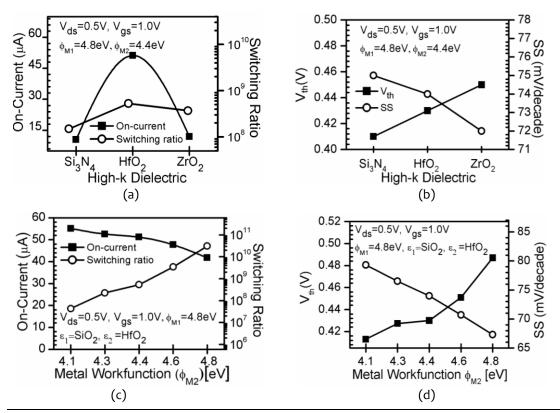

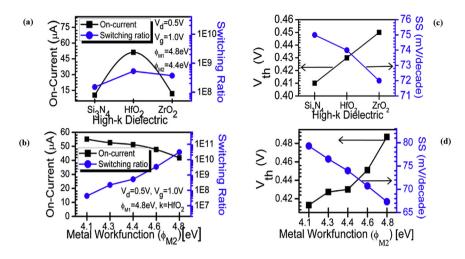

| Figure 6.03: (a-d) On-Current, switching ratio and Threshold Voltage, Sub-threshold<br>Swing for different high-dielectrics and metal gate workfunction ( $\Phi_{M2}$ ) at<br>$V_{ds}$ =0.5V and $V_{gs}$ =1.0V. | 160 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

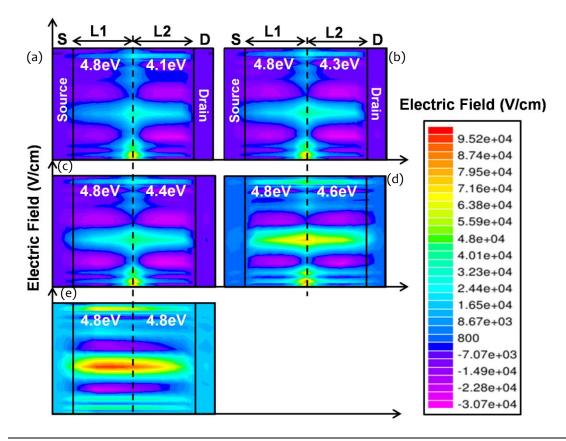

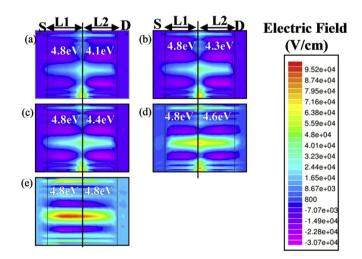

| Figure 6.04: (a-e) Electric Field Distribution for different metal gate workfunction ( $\Phi_{M2}$ )<br>at $V_{ds}$ =0.5V and $V_{gs}$ =1.0V.                                                                    | 161 |

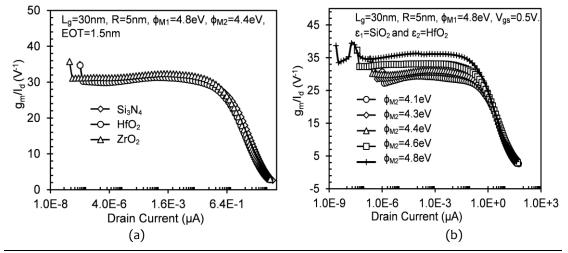

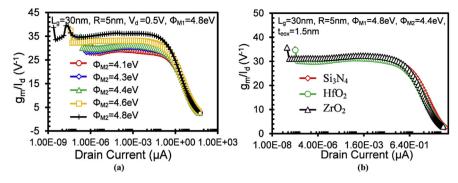

| Figure 6.05: (a-b) Device Efficiency as a function of drain current for different high-<br>dielectrics and metal gate workfunction ( $\Phi_{M2}$ ) at $V_{ds}$ =0.5V and $V_{gs}$ =1.0V.                         | 162 |

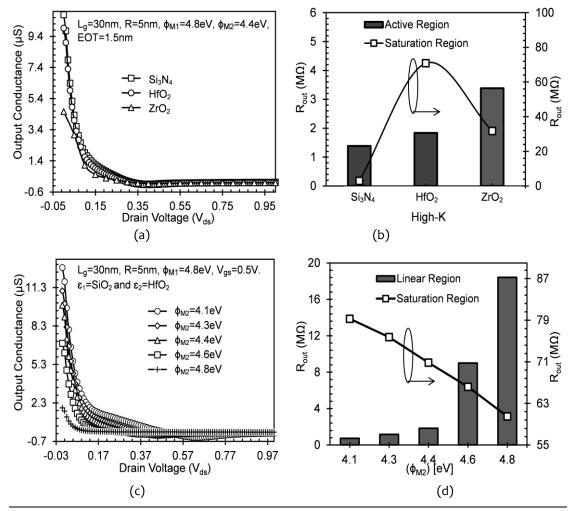

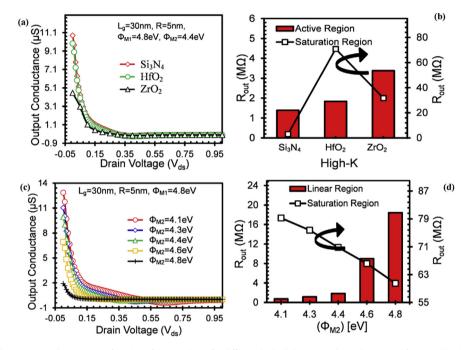

| Figure 6.06: (a-d) Output conductance and $R_{out}$ as a function of drain voltage for different high-dielectrics and metal gate workfunction ( $\Phi_{M2}$ ) at $V_{gs}$ =1.0V.                                 | 163 |

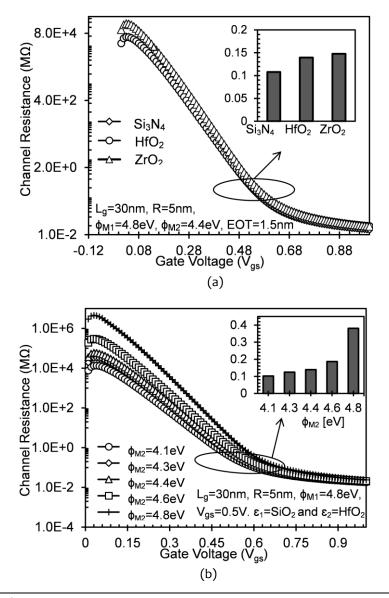

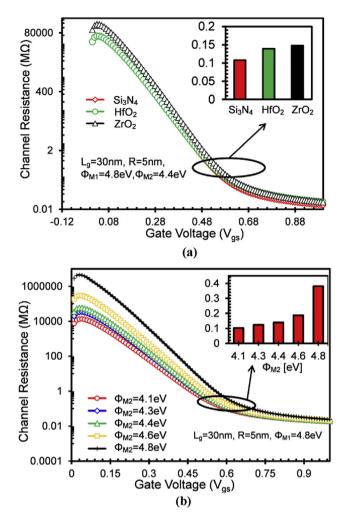

| Figure 6.07: (a-b) Channel Resistance as a function of gate voltage for different high-dielectrics at $V_{ds}$ =0.5V.                                                                                            | 164 |

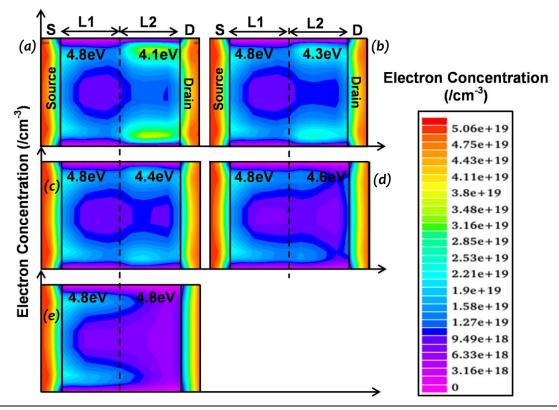

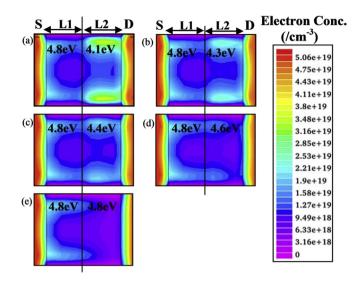

| Figure 6.08: (a-e) Electron Concentration Distribution for different metal gate workfunction ( $\Phi_{M2}$ ) at V <sub>ds</sub> =0.5V and V <sub>gs</sub> =1.0V.                                                 | 165 |

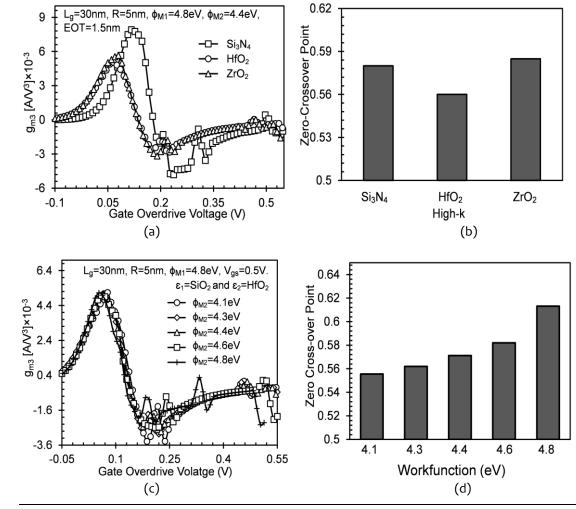

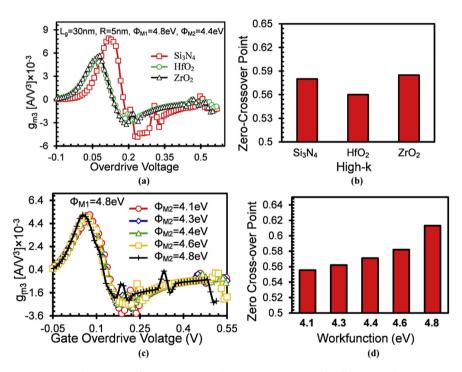

| Figure 6.09: (a-c) Higher order transconductance coefficients $g_{m3}$ , (b-d) Zero-Crossover<br>Point for different high-dielectric materials at $V_{ds}$ =0.5V.                                                | 167 |

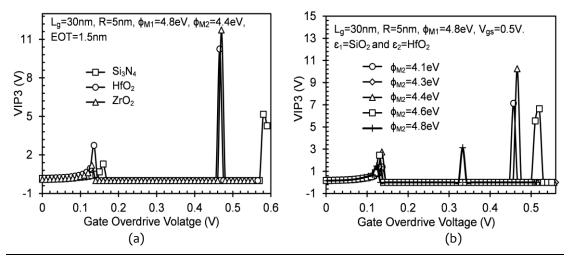

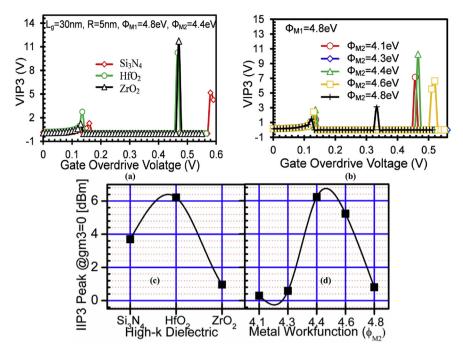

| Figure 6.10: (a-b) VIP3 as a function of gate overdrive voltage and VIP3 for different gate metal workfunction at the drain end ( $\Phi_{M2}$ ) at V <sub>ds</sub> =0.5V and V <sub>gs</sub> =1.0V.              | 168 |

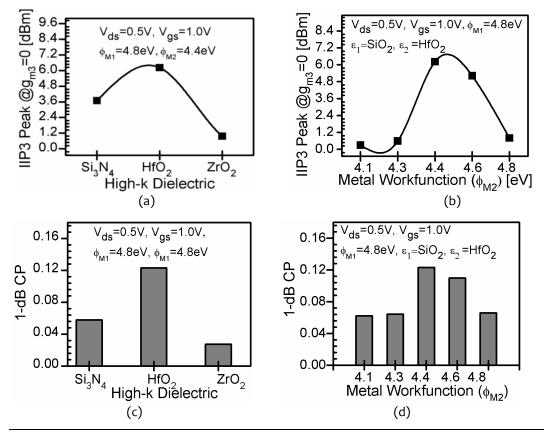

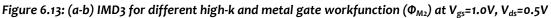

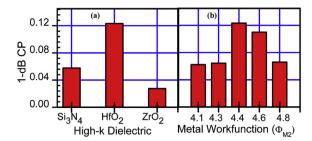

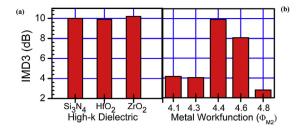

| Figure 6.11: (a-d) IIP3 and 1-dB Compression Point for different high-k dielectrics and metal gate workfunction ( $\Phi_{M2}$ ) at $V_{ds}$ =0.5V and $V_{gs}$ =1.0V.                                            | 169 |

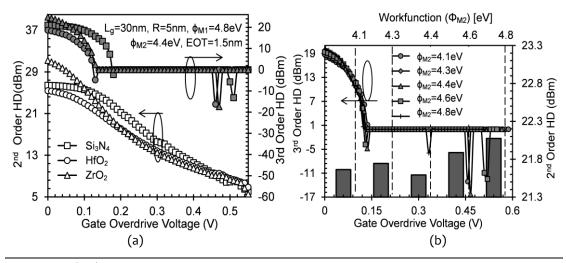

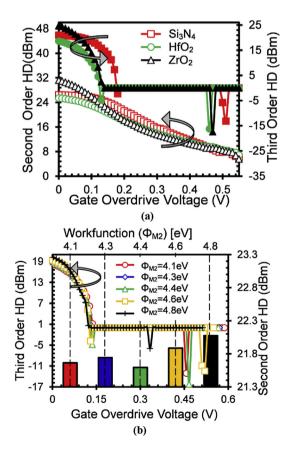

| Figure 6.12: (a-b) 2nd order Harmonic Distortion and 3rd Order Harmonic Distortion as a function of VGT for different high-k and metal gate workfunction ( $\Phi_{M2}$ ) at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V.      | 172 |

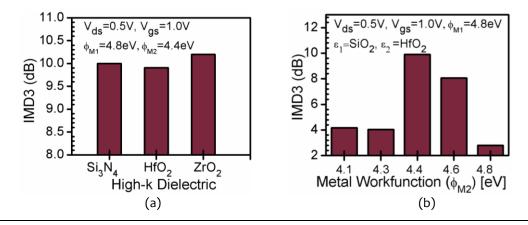

| Figure 6.13: (a-b) IMD3 for different high-k and metal gate workfunction ( $\Phi_{M2}$ ) at $V_{gs}$ =1.0V, $V_{ds}$ =0.5V.                                                                                      | 173 |

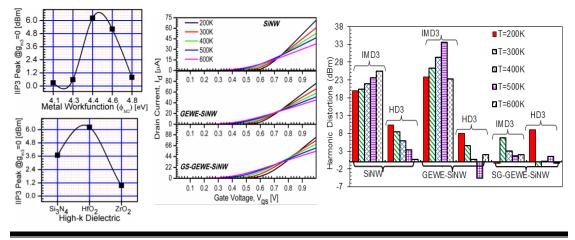

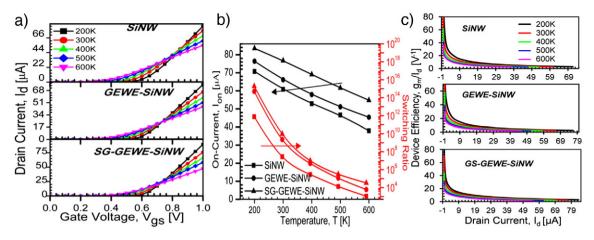

| Figure 6.14: (a) Transfer Characteristics, (b) Drain transconductance and (c) Device<br>Efficiency of SiNW, GEWE-SiNW and GS-GEWE-SiNW MOSFET for<br>different temperatures.                                     | 174 |

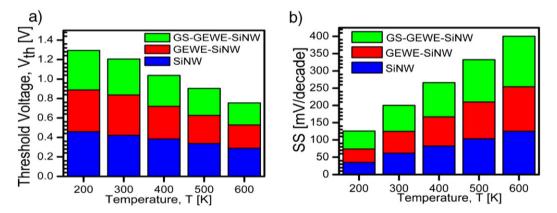

| Figure 6.15: (a) Threshold Voltage, (b) Sub-threshold Swing and of SiNW, GEWE-SiNW and GS-GEWE-SiNW MOSFET                                                                                                       | 175 |

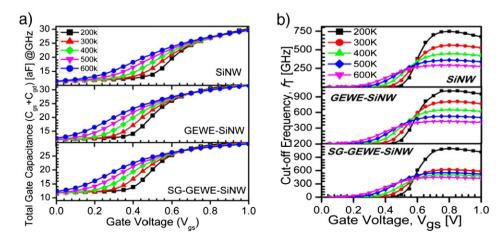

| Figure 6.16: (a) Total Gate Capacitance ( $C_g$ ) and (b) Cut-off frequency ( $f_T$ ) of SiNW, GEWE-SiNW and GS-GEWE-SiNW MOSFET at $V_{ds}$ =0.5V.                                                              | 176 |

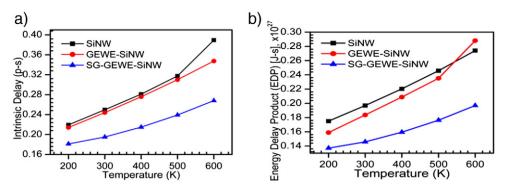

| Figure 6.17: (a) Intrinsic Delay and (b) Energy Delay Product (EDP) of SiNW, GEWE-SiNW and GS-GEWE-SiNW MOSFET at $V_{ds}$ =0.5V.                                                                                | 178 |

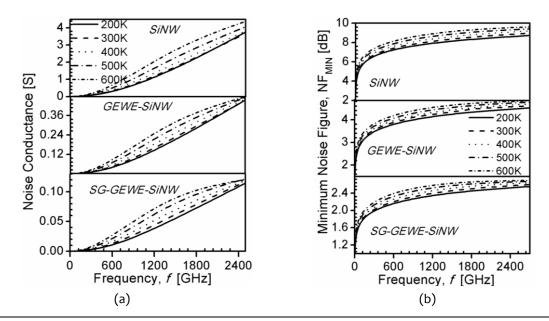

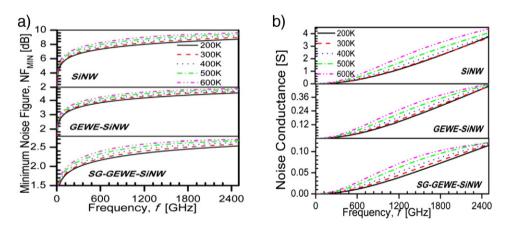

| Figure 6.18: (a) Minimum Noise Figure (NF <sub>MIN</sub> ) and (b) Noise Conductance as a function of frequency for SiNW, GEWE-SiNW and SG-GEWE-SiNW MOSFET at $V_{ds}$ =0.5V and $V_{gs}$ =1.0V.                | 179 |

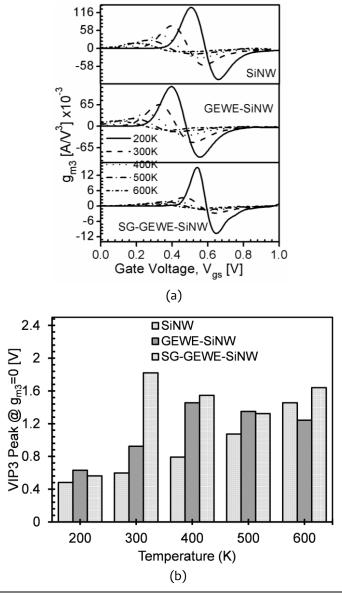

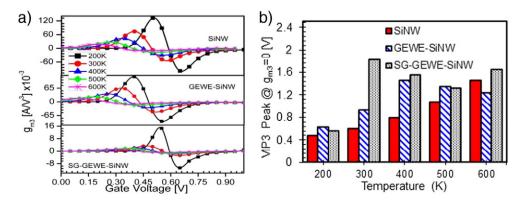

| Figure 6.19: (a) $g_{m3}$ and (b) VIP3 of SiNW, GEWE-SiNW and GS-GEWE-SiNW MOSFET for different temperatures at $V_{gs}$ =1.0V and $V_{ds}$ =0.5V.                                                               | 180 |

xv

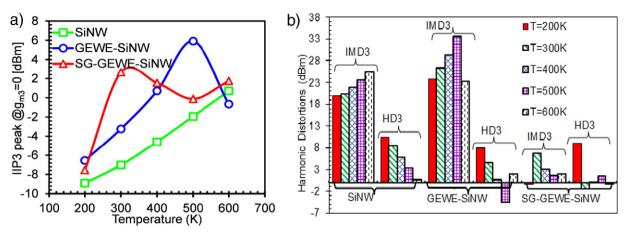

- Figure 6.20: VIP3 of SiNW, GEWE-SiNW and GS-GEWE-SiNW MOSFET for different temperatures at  $V_{gs}$ =1.0V and  $V_{ds}$ =0.5V.

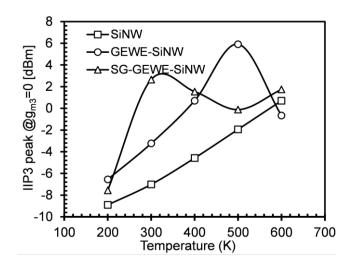

- Figure 6.21: IIP3 of SiNW, GEWE-SiNW and GS-GEWE-SiNW MOSFET for different temperatures at  $V_{gs}$ =1.0V and  $V_{ds}$ =0.5V. 182

### Page No.

\_

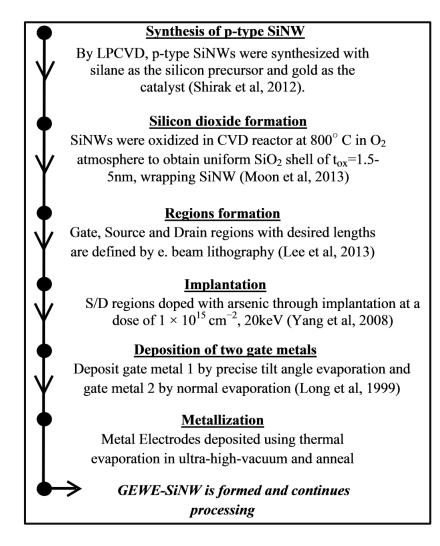

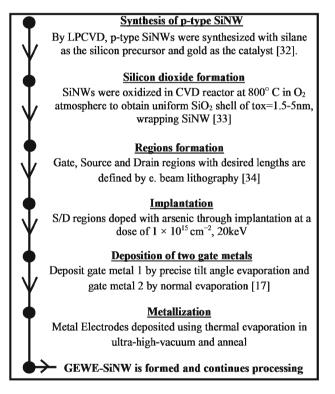

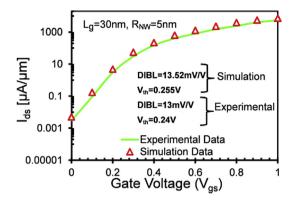

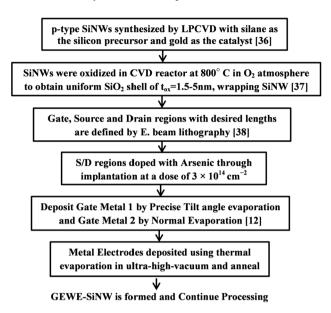

| Table 2.01: Summary of the Standard Process Flow of GEWE-SiNW                   | 46  |

|---------------------------------------------------------------------------------|-----|

| Table 2.02: Extracted parameters at different values of oxide thickness and     | 59  |

| high-k                                                                          |     |

| Table 3.01: Default design parameters used in the analysis                      | 71  |

| Table 3.02: Simulations Models                                                  | 72  |

| Table 4.01: Extracted S-parameters of GEWE-SiNW and SiNW MOSFET                 | 111 |

| Table 5.01: Extracted Parameters of all three devices for linear and saturation | 144 |

| region.                                                                         |     |

| Table 5.02: Extracted Parameters of GEWE-SiNW MOSFET for different metal        | 145 |

| workfunction ( $\Phi_{M2}$ ).                                                   |     |

| Table 6.01: Default Parameters of High-k                                        | 158 |

| Table 6.02: Default design parameters used in the analysis.                     | 158 |

| Table 6.03: Boundary Conditions                                                 | 158 |

#### IN INTERNATIONAL REFEREED JOURNALS (7)

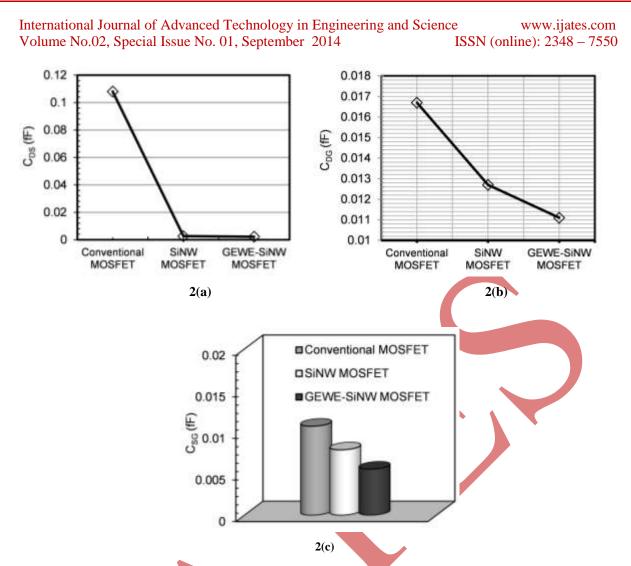

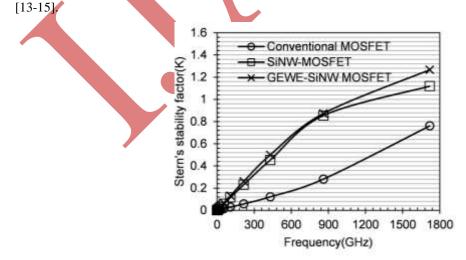

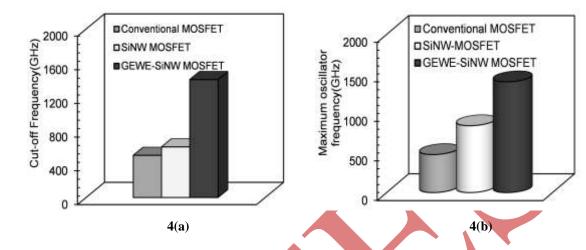

- Neha Gupta, Ajay Kumar and Rishu Chaujar, "Investigation of Frequency Dependent parameter of GEWE-SiNW MOSFET for Microwave and RF Applications", International Journal of Advanced Technology in Engineering and Science, Vol. 2, Sept. 2014, ISSN (Online): 2348 – 7550.

- Neha Gupta, Ajay Kumar and Rishu Chaujar," Oxide Bound Impact on Hot-Carrier Degradation for Gate Electrode Workfunction Engineered (GEWE) Silicon Nanowire MOSFET", in Microsystem Technologies, Springer, Vol. 22(11), pp. 2655-26642015. Doi: 10.1007/s00542-015-2557-9.

- **3. Neha Gupta**, Ajay Kumar and Rishu Chaujar, "Impact of Device Parameter Variation on RF performance of Gate Electrode Workfunction Engineered (GEWE)-Silicon Nanowire (SiNW) MOSFET", Journal of Computation Electronics, Springer, Vol. 14(3), pp. 798-810, 2015. Doi: 10.1007/s10825-015-0715-z

- 4. Neha Gupta and Rishu Chaujar, "Influence of Gate Metal Engineering on Small Signal and Noise Behaviour of Silicon Nanowire MOSFET for Low Noise Amplifiers" Applied Physics A, Springer, Vol.122(8), pp. 717 (1-9), 2016. Doi: 10.1007/s00339-016-0239-9

- 5. Neha Gupta and Rishu Chaujar, "Optimization of High-k and Gate Metal Workfunction for Improved Analog and Intermodulation Performance of Gate Stack (GS)-GEWE-SiNW MOSFET", Superlattices and Microstructures, Elsevier, Vol. 97, pp. 630-641, 2016. Doi: 10.1016/j.spmi.2016.07.021

- 6. Neha Gupta and Rishu Chaujar, "Effect of Temperature on Analog/RF Performance of Stacked Gate GEWE-Silicon Nanowire MOSFET", Microelectronics Reliability, Elsevier, Vol. 64, pp. 235-241, September 2016. Doi: 10.1016/j.microrel.2016.07.095.

- 7. Neha Gupta and Rishu Chaujar, "Quantum Simulation Based Extraction of Frequency Dependent Intrinsic and Extrinsic Parameters for GEWE-SiNW

MOSFET", Journal of Computational Electronics, Vol. 16 (1), pp. 61-73, Springer, 2016.

### **IN INTERNATIONAL CONFERENCES (9)**

- Neha Gupta and Rishu Chaujar, "Implications of transport models on the analog performance of Gate Electrode Workfunction Engineered (GEWE) Silicon Nanowire MOSFET", Devices, Circuits and Systems (ICDCS), 2014 2nd IEEE International Conference, pp.1-5, 6-8 March 2014. Doi: 10.1109/ICDCSyst.2014.6926154

- 2. Neha Gupta, Ajay Kumar and Rishu Chaujar, "Simulation analysis of Gate Electrode Workfunction Engineered (GEWE) Silicon Nanowire MOSFET for hot carrier reliability" IEEE 1st International Conference on Microelectronics, Circuits and Systems", Kolkata, pp. 150-153, 11-13th July, 2014.

- 3. Neha Gupta, Ajay Kumar and Rishu Chaujar, "TCAD Analysis of Noise and Small signal behaviour of Gate Electrode Workfunction Engineering (GEWE) Silicon Nanowire (SiNW) MOSFET", 3rd International Conference Nanocon-014, Pune, 14th-15th October, 2014.

- 4. Neha Gupta, Ajay Kumar and Rishu Chaujar, "Impact of Channel Doping and Gate Length on Small Signal Behaviour of Gate Electrode Workfunction Engineered Silicon Nanowire MOSFET at THz Frequency", Fifth International Symposium on Electronic System Design, Mangalore, Karnataka, 15-17th December, 2014. Doi 10.1109/ISED.2014.46

- 5. Neha Gupta, Ajay Kumar and Rishu Chaujar, "TCAD Analysis of Frequency Dependent Intrinsic and Extrinsic parameters of GEWE-SiNW MOSFET", Tech-Connect World Innovation Conference & Expo, 14-17th June 2015, Washington DC, USA.

- 6. Neha Gupta, Ajay Kumar and Rishu Chaujar, "TCAD AC Analysis of Gate Electrode Workfunction Engineered Silicon Nanowire MOSFET for High Frequency Applications", Tech-Connect World Innovation Conference & Expo, 14-17th June 2015, Washington DC, USA.

- 7. Neha Gupta, Ajay Kumar and Rishu Chaujar, "Effect of Dielectric Engineering on Analog and Linearity performance of Gate Electrode Workfunction Engineered (GEWE) Silicon Nanowire MOSFET", 15th IEEE International Conference on Nanotechnology, pp. 928-931, 27 - 30 July 2015, ROME, ITALY. Doi: 978-1-4673-8156-7/15/\$31

- 8. Neha Gupta, Ajay Kumar and Rishu Chaujar, "Gate Electrode Workfunction Engineered (GEWE) Silicon Nanowire (SiNW) MOSFET: A Solution for LNA at RF Frequency", 2nd International Conference on Microelectronics, Circuits and Systems MICRO-2015, Kolkata, 11-12th July, 2015.

- 9. Neha Gupta, Ajay Kumar and Rishu Chaujar, "Quantum Mechanical C-V Analysis of Gate Electrode Workfunction Engineered (GEWE) Silicon Nanowire MOSFET for HF Applications", 18th International Workshop on Physics of Semiconductor Devices (IWPSD-2015), Bangalore, 7-10 Dec 2015.

# CONTENTS

## Page No.

| Certificate          | í        |

|----------------------|----------|

| Acknowledgments      | ίί-ίν    |

| Abstract             | ν-νίίί   |

| List of Figures      | íx-xví   |

| List of Tables       | xvíí     |

| List of Publications | xvííí-xx |

## **CHAPTER-1: INTRODUCTION**

| 1.1 Overview: Growing of Nanoscale MOSFET | 2         |

|-------------------------------------------|-----------|

| 1.2 Literature Review                     | 3         |

| 1.2.1 Scaling of MOSFET                   | 3         |

| 1.2.2 Short Channel Effects               | 5         |

| A. Threshold Voltage (Vth) Roll-off       | 5         |

| B. Drain Induced Barrier Lowering (DIBL)  | 6         |

| C. Hot-Carrier Effects (HCEs)             | 7         |

| 1.2.3 Ways to overcome SCEs               | 7         |

| A. Engineering Schemes                    | 8         |

| í. Source/Draín Engíneeríng               | 8         |

| íí. Channel Engíneering                   | 9         |

| ííí. Gate Engineeríng                     | 10        |

| B. Novel Device Concepts                  | 13        |

| í. Sílícon On Insulator (SOI) MOSFET      | 14        |

| íí. Dual Gate MOSFET                      | 15        |

| iii. FinFTT                               | 15        |

| ív. Gate All Around (GAA) MOSFET          | 16        |

| 1.3 Research Gaps                         | 18        |

| 1.4 Possible Solutions                    | 19        |

| 1.4.1 Silicon Nanowires                   | 19        |

| A. Electronic Properties of SiNW          | 19        |

| B. Physical Properties of SiNW            | 20        |

| 1.4.2 Silicon Nanowire Transistors        | <b>21</b> |

| A. Advantages of SiNW MOSFET              | 22        |

| B. Drawbacks of SiNW MOSFET               | 23        |

| 1.5 Objectives of Thesis   | 23 |

|----------------------------|----|

| 1.6 Organization of Thesis | 26 |

| 1.7 References             | 30 |

## CHAPTER-2: INVESTIGATION OF HOT-CARRIER DEGRADATION IN GATE ELECTRODE WORKFUNCTION ENGINEERED (GEWE) SILICON NANOWIRE (SINW) MOSFET

| 2.1 Introduction                                             | 38        |

|--------------------------------------------------------------|-----------|

| 2.2 Device Structure and Its Parameters<br>2.2.1 Calibration |           |

| 2.3 Fabrication Feasibility                                  | <b>45</b> |

| 2.4 Results and Discussion                                   | 46        |

| 2.4.1 Effect of Gate Oxide Thickness                         | 51        |

| 2.4.2 Effect of Dielectric Constant (High-k)                 | 55        |

| 2.5 Summary                                                  | 60        |

| 2.6 References                                               | 62        |

## CHAPTER-3: IMPACT OF DEVICE PARAMETER VARIATION ON RF PERFORMANCE OF GATE ELECTRODE WORKFUNCTION ENGINEERED (GEWE) SILICON NANOWIRE (SINW) MOSFET

| 3.1 | Introduction                                                                                              | <b>68</b> |

|-----|-----------------------------------------------------------------------------------------------------------|-----------|

| 3.2 | <b>Device Structure: Parameters and Simulation Models</b><br>3.2.1 Simulation Methodology and Calibration |           |

| 3.3 | <b>RF Performance Metrics Inquisition</b>                                                                 | 76        |

|     | 3.3.1 Effect of Gate Metal Engineering                                                                    |           |

|     | 3.3.2 Effect of Oxide Thickness<br>3.3.3 Effect of Channel Length (L <sub>g</sub> )                       |           |

|     | 3.3.4 Effect of Radius of Nanowire                                                                        | 92        |

| 3.4 | Summary                                                                                                   | 94        |

| 3.5 | References                                                                                                | 96        |

### CHAPTER-4: INVESTIGATION OF SMALL SIGNAL AND NOISE BEHAVIOUR OF GEWE-SINW MOSFET FOR LOW-NOISE AMPLIFIERS

| <ul><li>4.1 Introduction</li><li>4.2 Device Structure and Physical Models</li></ul> | 102<br>105 |

|-------------------------------------------------------------------------------------|------------|

| 4.3 Results and Discussion                                                          | 108        |

| 4.3.1 Scattering Parameter Analysis                                                 | 109        |

| A. Effect of Gate Metal Workfunction ( $\Phi_{M2}$ )                                | 111        |

| B. Effect of Channel Length (Lg)                                                    | 113        |

| C. Effect of Channel Doping (N <sub>a</sub> )                                       | 115        |

| 4.3.2 Noise Metrics                                                                 | 116        |

| 4.4 Summary                                                                         |            |

| 4.5 References                                                                      | 123        |

### CHAPTER-5: EXTRACTION OF FREQUENCY DEPENDENT INTRINSIC AND EXTRINSIC PARAMETERS FOR GEWE-SINW MOSFET

| 5.1 Introduction                                 | 127 |

|--------------------------------------------------|-----|

| 5.2 Results and Discussion                       | 129 |

| 5.2.1 Extrinsic Parameters                       | 129 |

| 5.2.2 Intrinsic Parameters                       | 131 |

| A. Effect of Gate Metal Workfunction Engineering | 135 |

| B. Bias Dependent Intrinsic Parameters           | 137 |

| 5.2.3 Small Signal Model Parameters: Z and Y     | 139 |

| 5.3 Summary                                      | 145 |

| 5.4 References                                   | 147 |

#### CHAPTER-6: INFLUENCE OF STACKED GATE ON COMPREHENSIVE DEVICE PERFORMANCE OF GEWE-SINW MOSFET

| 6.1 Introduction                                       | 152 |

|--------------------------------------------------------|-----|

| 6.2 Device Structure                                   | 156 |

| 6.3 Simulation Methodology                             | 159 |

| 6.4 Results and Discussion                             | 159 |

| 6.4.1 Optimization of High-k Gate Stack and Gate Metal |     |

| Workfunction                                           | 159 |

| A. Analog Figure of Merits                             | 159 |

| i. Switching Ratio and Device Efficiency               | 159 |

| ii. Output Resistance and Channel Resistance    | 162 |

|-------------------------------------------------|-----|

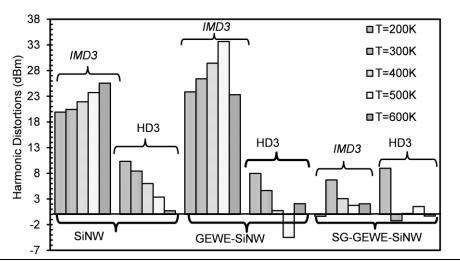

| B. Linearity and Harmonic Distortion Analysis   | 165 |

| i. VIP3/IIP3 and 1-dB Compression Point         | 168 |

| ií. Harmoníc Distortions                        | 170 |

| 6.4.2 Reliability Issues of SG-GEWE-SiNW MOSFET | 173 |

| A. Analog Performance                           | 173 |

| B. RF Noise Performance                         | 176 |

| C. Linearity and Harmonic Distortions           | 179 |

| 6.5 Summary                                     | 183 |

| 6.6 References                                  | 185 |

## CHAPTER-7: CONCLUSION AND FUTURE SCOPE

| 7.1 Conclusion                 | 190 |

|--------------------------------|-----|

| 7.2 Future Research Directions | 195 |

# Reprints of Publications

## **CHAPTER-1**

# **INTRODUCTION**

- This chapter gives a brief overview of Evolving of Nanoscale Metal Oxide Semiconductor Field Effect Transistor (MOSFET).

- <sup>©</sup> Various adverse effects arise due to the scaling of dimensions and to overcome these limitations, different engineering schemes have been discussed in this chapter.

- <sup>©</sup> Numerous device structures and innovative materials are reviewed and found silicon nanowire MOSFET as a suitable candidate for improved device performance.

- C Advantages and Disadvantages of Silicon Nanowire MOSFET along with its electrical properties are reviewed in this chapter

- <sup>©</sup> In addition, fabrication feasibility of Gate All Around SiNW MOSFET and gate metal workfunction engineering scheme for CMOS processes is presented.

- S In the end, the objectives and brief outline of the thesis are presented

<sup>1</sup>

#### **1.1 OVERVIEW: GROWING OF NANOSCALE MOSFET**

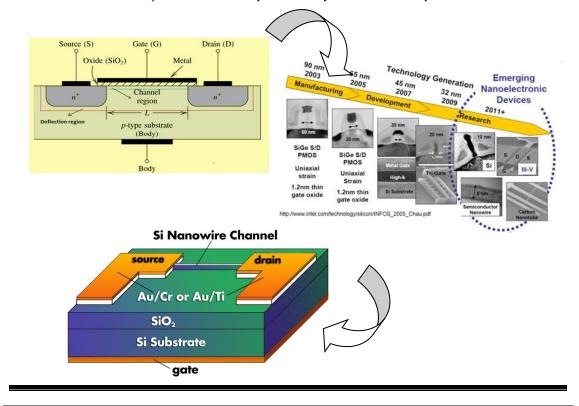

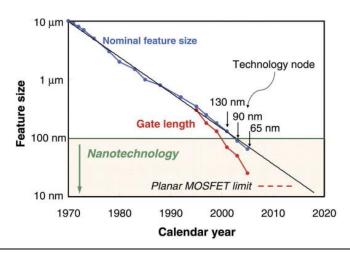

One of the essential developments in modern engineering history is monolithic integrated circuits (IC) technology. From last few decades, incredible improvement in IC technology has miraculously changed our lives and the whole world by providing a boost to Information technology (IT). The main reason behind this is downscaling of CMOS dimensions (the key component of IC), and increasing the package density (by increasing the total number of transistors in one chip). According to Moore's law (Bondyopadhyay, 1998), the number of transistors on one IC chip would duple every year which finally paraphrased as a doubling in transistor count every two years in 1975 (Moore, 2004) and thus efficaciously predicted the device scaling as evidently shown in Fig. 1.01.

For upholding consecutive improvements in IC technology, continuous device scaling is essential. However, as the channel length enters into nm-regime, the so-called short channel effects (SCEs) arises such as threshold voltage ( $V_{th}$ ) roll-off, drain induced barrier lowering (DIBL), hot-carrier effects (HCEs) and Punchthrough etc, which hinders the device performance and also restricts the scaling ability of conventional silicon MOSFET (Abuelma'atti, 2013; Khanna, 2016; Veeraraghavan & Fossum, 1989). To overcome such effects, various device engineering schemes have been proposed to alleviate the issue of SCEs which will be discussed in next section. In addition, lower carrier (electron) mobility of silicon in comparison to other semiconductor results in degradation of MOSFET's I-V characteristics which eventually hampers the device analog and RF performance. Therefore, novel device structure and materials such as Silicon Nanowire (SiNW) MOSFET (Shirak et al, 2012; Singh et al, 2006a; Wang et al, 2003), carbon nanotube FETs (Guo et al, 2002), molecular transistors (Reed, 1999), novel materials (e.g., strained silicon, pure germanium) to enhance the mobility and thus device performance (Lee et al, 2005; Leitz et al, 2001), are being widely investigated. Among all these promising CMOS candidates, SiNW MOSFET has its inimitable benefit, Firstly, the SiNW is based on silicon, which is abundant in nature and also IC industry has been working on it over last few decades. Also, from device and circuit developers, they have procured remarkable attention because of its potential for high performance and building highly dense electronic circuits and therefore emerge as a possible solution for future silicon based nano-devices (Bangsaruntip et al, 2009; Yang et al, 2004).

#### **1.2 LITERATURE REVIEW**

#### **1.2.1 Scaling of MOSFET**

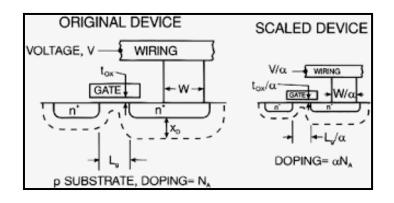

The main aim of the VLSI/ULSI electronics is to lower down the cost per logic function and simultaneously upsurge the switching speed of logic gates and this aim has been achieved by scaling down the device dimensions and thus resulted in new generations ICs (Nair, 2002). MOS transistors has been systematically scaled down in dimensions in order to achieve higher circuit density (more circuit functions in a given silicon area), higher switching speed and lower power dissipation etc. (Arora, 1993). Scaling was first proposed by Dennard et al. with the idea of reducing the device dimensions without affecting its voltage-current behavior of large devices (Dennard et al, 2007; Veeraraghavan & Fossum, 1989). Rules of scaling given by him are known as constant field scaling. In constant field scaling, all the dimensions and voltages are reduced by a scaling factor  $\alpha(>1)$ , that result constant electric field inside the device as those of an original device (Borkar, 1999; Davari et al, 1995) as shown in Fig. 1.02.

Figure 1.02: Principles of constant-electric-field scaling for MOSFETs and integrated circuits. (Frank et al, 2001)

When developed in 1960, the channel length of the MOSFET was around 10µm. Today most of the integrated circuits utilize CMOS technology with channel length around sub-nm range. Following are the advantages of scaling (Abuelma' atti, 2013):

- 1. *Low Cost*: Due to small size of transistor, more and more transistors can be integrated onto small wafer and thus leads to cheaper circuits.

- 2. *High Speed*: Smaller transistors and shorter interconnects lead to reduced capacitances and hence higher IC speed.

3. It also lead to reduced power supply voltages and little power consumption instead of rise in switching frequency.

However, downscaling has its own problem at very short gate length (sub-nm range)

(Hu, 2010). These are:

- Static and dynamic power consumption.

- > Overheating and possible evaporation become major concerns.

- ▶ Increased electric field within the oxide and increased leakage gate-current.

#### **1.2.2 Short Channel Effects (SCEs)**

To apprehend high circuit density and maximum operational frequency for future ICs, the channel length and width of device must be reduced. But, diminishing the channel length leads to short channel effects, whereas decreasing the width causes a reduction in current drive. MOSFET scaling thus results in increased SCEs, the most pronounced of which is threshold voltage ( $V_{th}$ ) roll-off, DIBL, HCEs.

#### A. Threshold Voltage (V<sub>th</sub>) Roll-off

The key parameter that characterizes SCE is the degradation of  $V_{th}$  with decrease in channel length. The shrinkage of threshold voltage with lessening in channel length is a well-known SCE called the "Threshold voltage roll-off". As the channel of the device is reduced to sub-nm range, then the charge sharing in the channel is influenced by the field originating from the source/drain. Consequently, the potential barrier at the source end is pull down, which causes increased flow of carriers, and thus results in higher sub-threshold drain current. Due to this, standby leakage power dissipation increases which is given by V×I<sub>off</sub> (V is the applied voltage and I<sub>off</sub> is the leakage current). Methodically, threshold voltage roll-off is the difference between the

threshold voltage of a short channel MOSFET and that of a long channel MOSFET (Arora, 1993; Taur & Ning, 2013).

#### B. Drain Induced Barrier Lowering (DIBL)

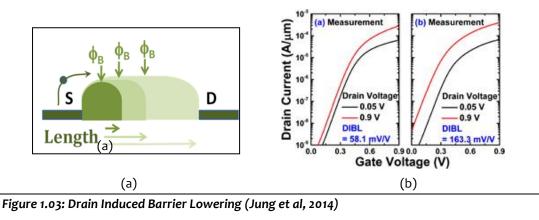

Kit Man Cham et.al reported that DIBL result an increase in the residual leakage current in short channel devices as the drain to source voltage is increased (Troutman, 1979).

In scaled MOSFETs, the potential barrier in inversion regime is controlled by both the bias voltage i.e., gate-to-source voltage ( $V_{gs}$ ) and the drain-to-source voltage ( $V_{ds}$ ). If  $V_{ds}$  is increased, the potential barrier in the channel decreases, which results increase in drain current. This effect is known as drain-induced barrier lowering (DIBL). The lowering of the barrier eventually allows more carriers to flow between the source and the drain, even if the  $V_{gs}$  is lesser than the threshold voltage as evidently reflected in Fig. 1.03(a). The drain current that flows under this situation ( $V_{gs}$ < $V_{th}$ ) is called the sub-threshold or leakage current which is not desirable (Chamberlain & Ramanan, 1986).

Mathematically, DIBL effect can be calculated by the lateral shift of the transfer curve  $(I_{ds}-V_{gs})$  in the weak inversion regime divided by the  $V_{ds}$  difference of the two curves and is given in units (mV/V) as reflected in Fig. 1.03(b).

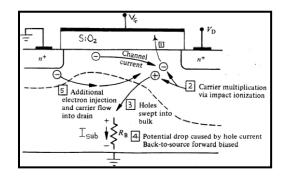

#### C. Hot-carrier effects (HCEs)

During scaling down the device dimensions, device voltages are not scale down properly and thus lead to high electric fields. Due to which, several hot-carrier effects appears in short channel MOSFET as shown in Fig. 1.04. High electric field at the drain junctions can lead to avalanche injection from channel region to drain depletion region and impact ionization which results in dislocating of e-h pairs. These holes contribute to substrate current (or leakage current) and some of them move towards source end, lower the potential barrier and results in electron injection from source to channel and thus loses the gate control from the drain current (Hu, 1989). In addition, some of the high-field electrons tunnel through the substrate-gate oxide barrier and get trapped into the oxide or at the interface. These trapped electrons degrade the subthreshold swing, modify the threshold voltage and transfer characteristics of the device (Takeda et al, 1995). Thus, they need to be controlled for sub-nm range devices.

Figure 1.04: Cross-Sectional View of n-channel MOSFET showing Injection of Hot-Carriers due to shortening of channel length (Wolf, 1995)

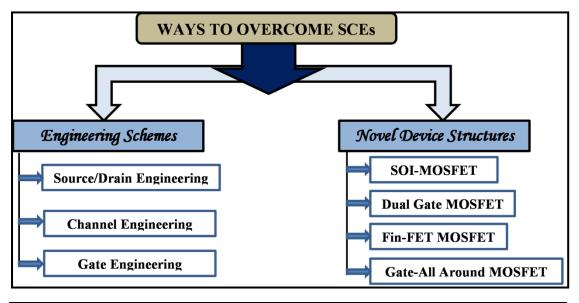

#### 1.2.3 Ways to Overcome SCEs

Since, short channel effects obstruct the device operation and degrade device characteristics, therefore these effects should be removed, so that physical short

7

channel device can preserve the electrical long channel behaviour. Numerous device engineering schemes have been reported in literature from last few years to get over these problems which are discussed below.

Figure 1.05: Different schemes to alleviate SCEs in nano-scale MOSFET

#### A. Engineering Schemes

#### i. Source/Drain Engineering

By decreasing the doping concentration in the source/drain regions, the junction fields become smaller and thus reduce HCEs. Conversely, lightly doped source/drain regions are incompatible with nm-range devices because of contact resistances and other similar problems. Fig. 1.06 depicts the compromise design of MOSFET, called *Lightly Doped Drain (LDD)* (Rubel et al, 2015), using two doping levels with heavy doping over most of the source and drain areas with light doping in a region adjacent to the channel. The LDD structure decreases the field between drain and channel regions, thereby reducing injection into the oxide, impact ionization and other hot electron effects (Bampi & Plummer, 1986; Kaga & Sakai, 1988).

8

Figure 1.06: Cross-Section of n-type MOSFET considering low doped extension from drain side. (Hower & Pendharkar, 2005)

#### ii. Channel engineering

When the channel length of the device is below 100 nm, it shows significant threshold  $V_{th}$  roll off and DIBL effects. These are the most daunting road block for future MOSFET design. It was found that  $V_{th}$  roll-off can be reduced or even reversed by locally raising the channel doping next to the drain or drain/source junctions (Mohankumar et al, 2010). In the past few years, the locally high doping concentration in the channel near source/drain junctions has been implemented via lateral channel engineering, e.g., halo (Ravindhran et al, 1995) or pocket implants (Nandakumar et al, 1999) as shown in Fig. 1.07. The two terms are used interchangeably here although a halo may indicate a pocket that is deeper than the drain. The implant can be either symmetric or asymmetric with respect to source and drain. The pocket, implant technology is very promising in the effort to *tailor* the short-channel performance of deep-submicron MOSFET's, although careful tradeoffs need to be made between and other device electrical parameters.

9

Figure 1.07: Schematic View of n-channel SOI-MOSFET showing graded channel doping (Galeti et al, 2006)

#### iii. Gate Engineering Scheme

#### > Gate dielectric material engineering (high-k gate dielectric materials)

As the dimension of the device decreases, the gate oxide thickness simultaneous decreases, causing an increase in tunneling current. Hence, gate-tunneling current is a concern in sub-nanometer regime. To surmount the limitation of gate oxide thickness, high-k materials in oxide could be helpful. However, the difficulties of adopting high-k dielectric in VLSI include chemical reaction between them and the silicon substrate and the gate (Frank et al, 2009). In addition, they also lack thermal stability. Moreover, the use of high- k dielectric gate materials may also result in dielectric thickness comparable to the device gate length and arises an increased fringing fields from gate to source/drain (Inani et al, 1999; Mohapatra et al, 2001). Thereby, affecting the sub-threshold characteristics and DIBL. Thus, high-k gate dielectric stacked with SiO<sub>2</sub> (gate stack engineering) is a possible candidate to replace thinner silicon-dioxide layer in a nanoscale MOSFETs (Lee et al, 2006) as depicted in Fig. 1.08.

Figure 1.08: Schematic structure of a gate stack with a high-k dielectric layer. A series capacitance has to be taken into account to evaluate the dielectric constant of the high-k material. (Moers et al, 2010)

An extremely thin interfacial oxide can be used to passivate the interface and minimize interface states when high-*K* gate materials are deposited. The concept of equivalent oxide thickness (EOT) is to provide a suitable alternative gate dielectric or gate stack dielectric structure having similar characteristics, when using  $SiO_2$  gate dielectric, but having greater physical thickness to improve gate control over the channel and limit the tunneling transport in sub-nm MOSFETs.

# > <u>D</u>ual <u>M</u>aterial <u>G</u>ate (DMG) Engineering