Dissertation on

# Dadda Multiplier based hardware for convolution operation

Submitted in partial fulfilment of the requirements

for the award of the degree of

# Master of Technology in VLSI Design and Embedded System

Submitted by:

### VinodMeena

(Roll No. 2K14/VLS/21)

Under the Guidance of

## Dr. S. Indu

(Associate Professor)

Department of Electronics and Communication Engineering Delhi Technological University Main Bawana Road Delhi-110042

# CERTIFICATE

This is to certify that the dissertation titled "**Dadda multiplier based hardware for convolution operation**" is a bonafide record of work done by **Vinod Meena**, Roll No. **2K14/VLS/21** at Delhi Technological University in partial fulfillment of the requirements for the award of degree of Master of Technology in VLSI Design and Embedded System. This project was carried out under my supervision and has not been submitted elsewhere, either in part or full, for the award of any other degree or diploma to the best of my knowledge and belief.

Date: .....

Dr. S. Indu Associate Professor Department of Electronics & Communication Engineering Delhi Technological University, Delhi

# ACKNOWLEDGEMENT

I would like to express my deep sense of respect and gratitude to my project supervisor **Dr. S. Indu**, Associate Professor, Department of Electronics and Communication Engineering, Delhi Technological University Delhi for providing the opportunity of carrying out this project and being the guiding force behind this work. I am deeply indebted to her for the support, advice and encouragement she provided without which the project could not have been a success.

A special thanks to all my friends especially Mr. Shobhit Shrivastava and Mr. Ashwani Goel for their knowledge and investigation has helped me unconditionally to solve various problems.

I would also like to acknowledge Delhi Technological University for providing the right academic resources and environment for this work to be carried out. Last but not the least I would like to express sincere gratitude to my parents for constantly encouraging me during the course of work.

#### Vinod Meena

University Roll no: 2K14/VLS/21

M.Tech. (VLSI Design and Embedded System)

Department of Electronics & Communication Engineering

Delhi Technological University, Delhi

# ABSTRACT

Multiplier is a central block in the Digital Signal Processor (DSP). In order to improve speed of processing, a hardware convolution unit is embedded in the design of multiplier. Convolution unit performs multiplication and addition process. Basic Convolution unit consists of multiplier, adder. Generally convolution unit is designed using different Multiplier and adder as Carry Save Adder (CSA). The proposed Convolution unit is designed using Dadda Multiplier (DM) and adder as Logically Optimized Full Adder (LOFA). However in the proposed model all traditional full adders are replaced by improved full adder. The performance analysis of Convolution unit models in terms of area, delay and power are compared. Various Convolution unit models are designed using Verilog HDL. Simulation and synthesis are done using Xilinx ISE 14.7 for Virtex-7 family 40nm technology device. The power is calculated using Lattice Diamond Design suite software.

# **TABLE OF CONTENTS**

| CERTIFICATE           | II   |

|-----------------------|------|

| ACKNOWLEDGEMENT       | III  |

| ABSTRACT              | IV   |

| TABLE OF CONTENTS     | V    |

| LIST OF TABLES        | VIII |

| LIST OF FIGURES       | IX   |

| LIST OF ABBREVIATIONS | XI   |

| CHAPTER 1 INTRODUCTION    | 1-2 |

|---------------------------|-----|

| 1.1 Introduction          | 1   |

| 1.2 Motivation            | 1   |

| 1.3 Applications          | 1   |

| 1.4 Outline of the Thesis | 2   |

#### **CHAPTER 2 LITERATURE SURVEY** 3-17 2.1 Digital System Design 3 2.1.1 Combinational and Sequential Circuits 3 2.2 Adders 4 2.2.1 Half adder 5 2.2.2 Full adder 6 2.2.3 Logically Optimized Full adder 7 2.2.4 Ripple Carry Adder 9

| 2.2.5 Carry Increment Adder                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2.6 Carry Save Adder                                           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Multipliers                                                      | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.3.1 Array Multiplier                                           | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.3.2 Ripple Carry Array Multiplier with Row Bypassing Technique | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.3.3 Wallace Tree Multiplier                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.3.4 Dadda Multiplier                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Conclusion                                                       | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| APTER 3 PROPOSED MODELS                                          | 18-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Proposed Convolution Model                                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IAPTER 4 RESULTS                                                 | 20-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Tabular output for 16 different input combinations used          | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2 Waveform output for 16 different input combinations used       | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Simulation Results for Adders                                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.3.1 Half Adder                                                 | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.3.2 Traditional Full Adder                                     | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.3.3 Logically Optimized Full Adder                             | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Simulation Results of Dadda Multipliers                          | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5 Simulation results of convolution                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5 Performance analysis of adders                                 | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Terrormance analysis of adders                                   | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                  | <ul> <li>2.2.6 Carry Save Adder</li> <li>Multipliers</li> <li>2.3.1 Array Multiplier</li> <li>2.3.2 Ripple Carry Array Multiplier with Row Bypassing Technique</li> <li>2.3.3 Wallace Tree Multiplier</li> <li>2.3.4 Dadda Multiplier</li> <li>2.3.4 Dadda Multiplier</li> <li>Conclusion</li> </ul> <b>Conclusion CAPTER 3 PROPOSED MODELS</b> Proposed Convolution Model <b>EXPETER 4 RESULTS</b> Tabular output for 16 different input combinations used Simulation Results for Adders <ul> <li>4.3.1 Half Adder</li> <li>4.3.2 Traditional Full Adder</li> <li>4.3.3 Logically Optimized Full Adder</li> </ul> |

| CHAPTER 5 CONCLUSION AND FUTURE | WORK 45 |

|---------------------------------|---------|

| 5.1 CONCLUSION                  | 45      |

| 5.2 FUTURE WORK                 | 45      |

| REFERENCES                      |         |

APPANDIX A

# **LIST OF TABLES**

| 2.1 Performance Comparison of Various Adders for 8 bit application | 4-5 |

|--------------------------------------------------------------------|-----|

| 2.2 Performance Comparison of Carry Save Adder and Carry Increment |     |

| adder for 16 bit application                                       | 5   |

| 2.3 Half Adder Truth Table                                         | 6   |

| 2.4 Full Adder Truth Table                                         | 7   |

| 2.5 Logical effort for inputs of static CMOS gates                 | 9   |

| 2.6 Carry Save Adder Computation Flow                              | 11  |

| 2.7 Performance Comparison of Various Multipliers                  | 12  |

| 4.1 Device Utilization Summary for Half Adder                      | 35  |

| 4.2 Device Utilization Summary for Traditional Full Adder          | 36  |

| 4.3 Device Utilization Summary for Logically Optimized Full Adder  | 37  |

| 4.4 Device Utilization Summary for Dadda Multiplier                | 39  |

| 4.5 Device Utilization Summary for Proposed Dadda Multiplier       | 41  |

| 4.6 Performance Analysis of Single Bit Adders                      | 41  |

| 4.7 Advanced HDL Synthesis Report                                  | 43  |

| 4.8 FPGA Results of Proposed Convolution Model                     | 43  |

| 4.9 Timing Summary of Proposed Convolution Model                   | 43  |

# **LIST OF FIGURES**

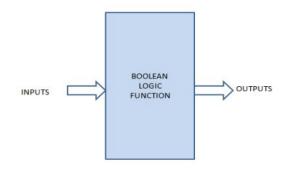

| 2.1 Block diagram for elementary combination circuits               | 3  |

|---------------------------------------------------------------------|----|

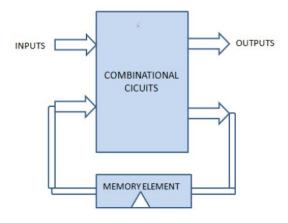

| 2.2 Block diagram for elementary sequential circuits                | 4  |

| 2.3 Half Adder(HA)                                                  | 6  |

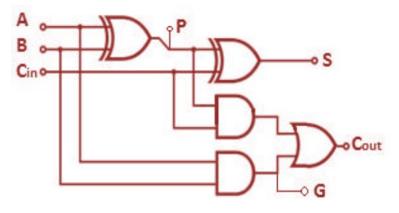

| 2.4 Full Adder(FA)                                                  | 7  |

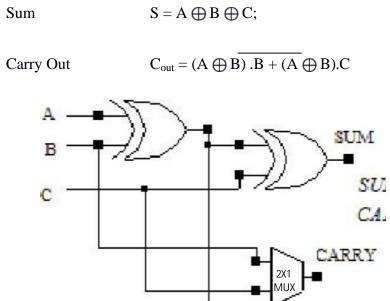

| 2.5 Logically Optimized Full Adder(LOFA)                            | 8  |

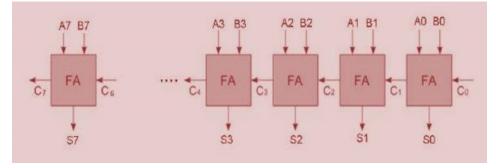

| 2.6 Ripple Carry Adder (RCA)                                        | 9  |

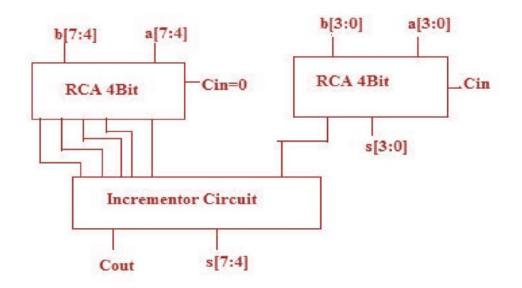

| 2.7 Carry Increment Adder (CIA)                                     | 10 |

| 2.8 Carry Save Adder (CSA)                                          | 11 |

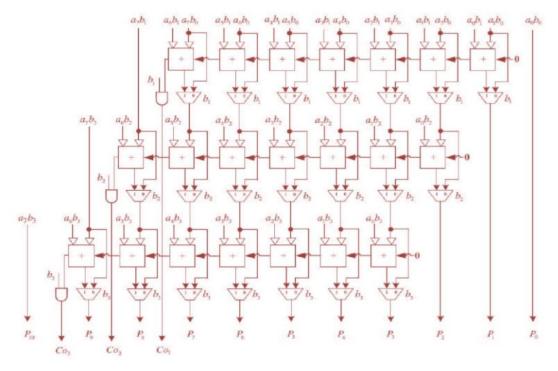

| 2.9 Array Multiplier (AM)                                           | 13 |

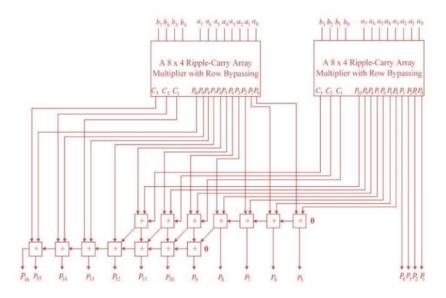

| 2.10 Structure of 8x4 Ripple Carry Array Multiplier with Row Bypass | 14 |

| 2.11 Structure of 8x8 Ripple Carry Array Multiplier with Row Bypass | 14 |

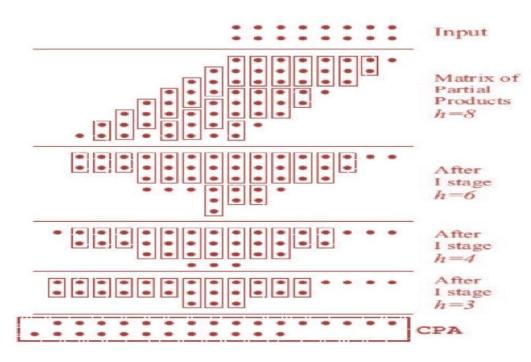

| 2.12 Wallace Tree Multiplier (WT)                                   | 15 |

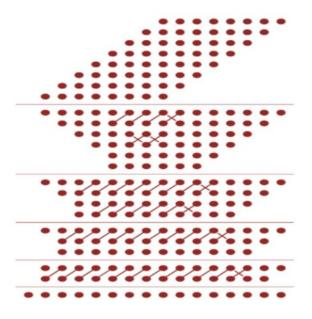

| 2.13 Dadda Multiplier Reduction                                     | 16 |

| 2.14 Dadda Multiplier (DM) Algorithm                                | 17 |

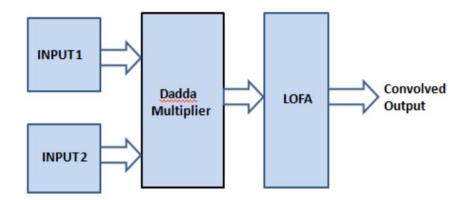

| 3.1 Block diagram for the Proposed Convolution Model                | 18 |

| 4.1 Timing waveform for x(n)=h(n)=[0 0 0 0 ]                        | 27 |

| 4.2 Timing waveform for x(n)=h(n)=[0 0 0 1 ]                        | 27 |

| 4.3 Timing waveform for $x(n)=h(n)=[0\ 0\ 1\ 0]$                    | 28 |

| 4.4 Timing waveform for $x(n)=h(n)=[0\ 0\ 1\ 1]$                    | 28 |

| 4.5 Timing waveform for $x(n)=h(n)=[0\ 1\ 0\ 0]$                    | 29 |

| 4.6 Timing waveform for $x(n)=h(n)=[0\ 1\ 0\ 1]$                    | 29 |

| 4.7 Timing waveform for $x(n)=h(n)=[0\ 1\ 1\ 0\ ]$                  | 30 |

| 4.8 Timing waveform for $x(n)=h(n)=[0\ 1\ 1\ 1\ ]$                  | 30 |

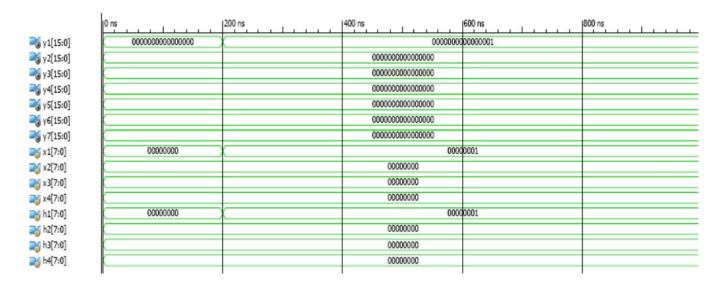

| 4.9 Timing waveform for x(n)=h(n)=[1 0 0 0 ]                        | 31 |

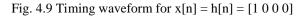

| 4.10 Timing waveform for $x(n)=h(n)=[1\ 0\ 0\ 1\ ]$                 | 31 |

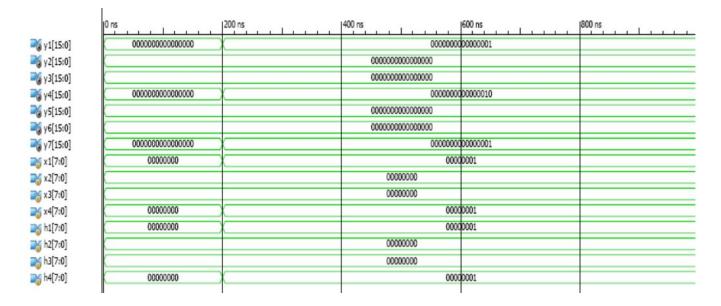

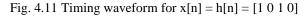

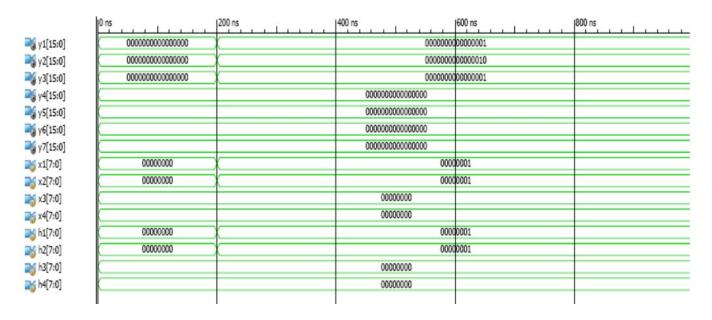

| 4.11 Timing waveform for $x(n)=h(n)=[1 \ 0 \ 1 \ 0]$                | 32 |

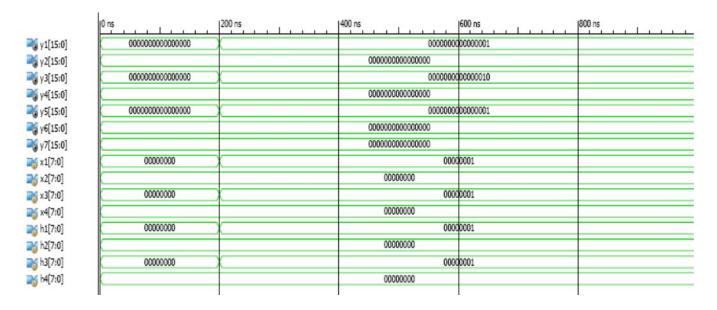

| 4.12 Timing waveform for $x(n)=h(n)=[1 \ 0 \ 1 \ 1 \ ]$             | 32 |

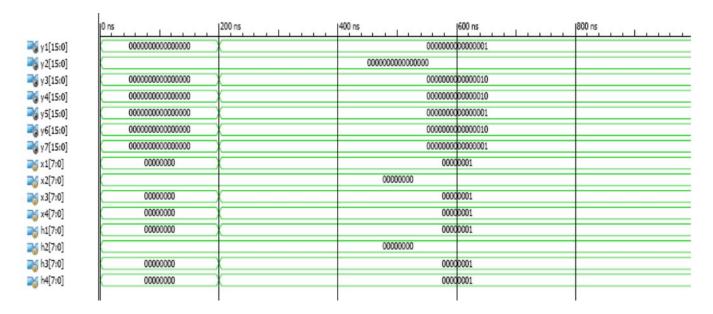

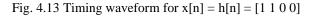

| 4.13 Timing waveform for $x(n)=h(n)=[1\ 1\ 0\ 0]$                        | 33 |

|--------------------------------------------------------------------------|----|

| 4.14 Timing waveform for x(n)=h(n)=[1 1 0 1 ]                            | 33 |

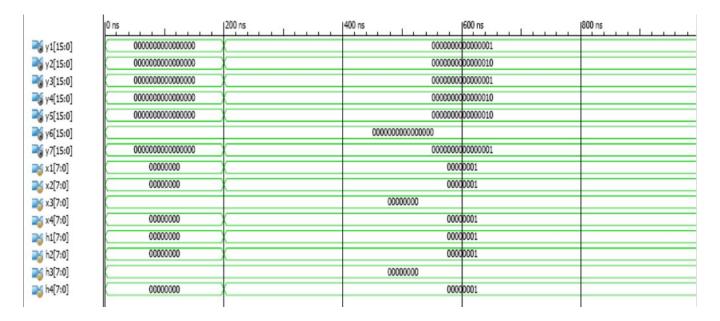

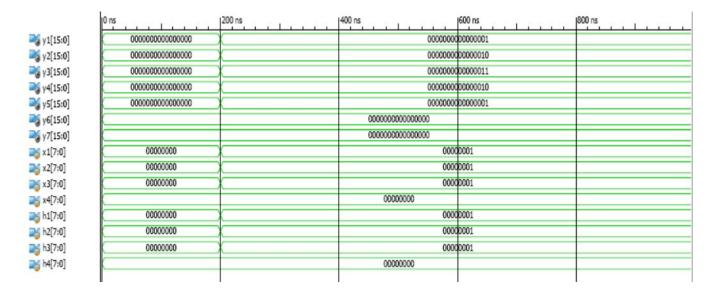

| 4.15 Timing waveform for x(n)=h(n)=[1 1 1 0 ]                            | 34 |

| 4.16 Timing waveform for x(n)=h(n)=[1 1 1 1 1]                           | 34 |

| 4.17 Technology View and RTL View of Half Adder                          | 35 |

| 4.18 Timing Waveform of Half Adder                                       | 35 |

| 4.19 Technology View and RTL View of Traditional Full Adder              | 36 |

| 4.20 Timing Waveform of Traditional Full Adder                           | 36 |

| 4.21 Technology View and RTL View of Logically Optimized Full Adder      | 37 |

| 4.22 Timing Waveform of Logically Optimized Full Adder                   | 37 |

| 4.23 Technology View and RTL View of Dadda Multiplier                    | 38 |

| 4.24 Timing Waveform of Dadda Multiplier                                 | 38 |

| 4.25 Technology View and RTL View of Proposed Convolution                | 39 |

| 4.26 Hardware implemented output for x[n]=h[n]=[1 1 1 1] for convolution | 40 |

|                                                                          |    |

# **ABBREVIATIONS**

| ADD     | Adder                                                   |

|---------|---------------------------------------------------------|

| RCA     | Ripple Carry Adder                                      |

| CIA     | Carry Increment Adder                                   |

| CLAA    | Carry Look Ahead Adder                                  |

| CSA     | Carry Save Adder                                        |

| CSIA    | Carry Select Adder                                      |

| CBA     | Carry Bypass Adder                                      |

| AM      | Array Multiplier                                        |

| WTM     | Wallace Tree Multiplier                                 |

| RCAM RB | Ripple Carry Array Multiplier with Row Bypass Technique |

| DM      | Dadda Multiplier                                        |

| VM      | Vedic Multiplier                                        |

| HA      | Half Adder                                              |

| FA      | Full Adder                                              |

| LOFA    | Logically Optimized Full Adder                          |

| ISE     | Integrated System Environment                           |

| HDL     | Hardware Description Language                           |

## **CHAPTER 1**

## **INTRODUCTION**

### **1.1 INTRODUCTION**

Convolution being an operation between two operands provides for mathematical framework in Digital Signal Processing (DSP). It is one the fundamental building block involved in DSP.

On receiving a signal, removal of less significant signal components is very important before further processing. Filtering, is a solution to remove unwanted insignificant signal components. This filtering is assisted by convolution. A large number of image processing options involve convolution filtering. Rotating or scaling an image is one such option.

### **1.2 MOTIVATION**

Rapid industrialization and technological advances have paved way for more and more digital systems to occupy spaces in all spheres of life. Ranging from day to day work to rigorous scientific researches digital systems have evolved a lot.

This in turn developed need for low power consuming efficient basic elements to serve the purpose. Recent researches implementing the Dadda multiplier or the logically optimized full adder (LOFA) reducing the power consumption during convolution motivated this research work towards introducing and speculating the performance of the convolution operation using both Dadda multiplier and LOFA.

### **1.3 APPLICATIONS**

Convolution finds itself involved in various applications such as

- As a convolution filter in digital image processing

- In digital data processing, for example in analytical chemistry for smoothing filters, the moving average etc.

- In acoustics, electrical engineering and physics

- In radiotherapy

• Convolutional neural networks too are proving advantageous in artificial intelligence (AI)

Thus, due to varied uses, a method for convolution with higher efficiency and minimal power usage is in demand.

### **1.4 OUTLINE OF THE THESIS**

In this thesis, we speculate the performance of the modified convolution scheme using LOFA and dada multiplier by implementing the same on the available Spartan kits. Preliminary knowledge and previously established information content about adders, multipliers and convolution are discussed in Chapter 2. Chapter 3 deals with the proposed modified convolution model as an introduction to it. Simulation and hardware implemented results are tabulated and shown in figures in Chapter 4. Chapter 5 discusses about the future possibilities and concludes the thesis.

# CHAPTER 2 LITERATURE SURVEY

This chapter provides details about the previously established work in this domain. As concern to this research topic, during research session the references of many important involvements were very helpful during research.

#### 2.1 DIGITAL SYSTEM DESIGN

Digital system design is the one which uses digital information in the form of alphabets, numbers and other information bits commonly termed as digital discrete inputs [2]. These inputs are then processed by a system designed to do a specific task or to multitask ranging from simple arithmetic to complex jobs. This results in output which is generally human interpretable. Such a system which processes this discrete information is a digital system.

Two common modes of circuits exist based on the use of memory, viz. combinational circuits and sequential circuits.

#### 2.1.1 COMBINATIONAL AND SEQUENTIAL CIRCUITS

Combinational circuits are the ones which do not involve memory element thus removing from the picture the effect of previous input on the present output. Thus at any point of time the output of such a circuit depends upon the inputs involved at that instant of time. It has 'm' inputs and 'n' outputs.

Examples:- decoders, encoders, multiplexers etc.

Fig. 2.1 Block diagram for elementary combinational circuits

Sequential Circuits are the ones which involves memory reflecting the effect of previous input on the output. In basic terms it is just a combinational circuit with a memory element involved. Examples- Flip Flops etc.

Fig. 2.2 Block diagram for elementary sequential circuits

#### **2.2 ADDERS**

Adders are the basic building blocks in Digital Design and are inseparable part of digital signal processing applications. Numerous advanced blocks like subtractor, multiplier, divider, and address calculator are obtained from Adders. As Addition is the base of all these operations. First three adders discussed here are single bit adders as they can perform addition of single bit numbers only therefore they are called single bit adders. After which only important parallel N bit adders namely Carry Save Adder (CSA), Carry Increment Adder (CIA), Ripple Carry Adder (RCA) are discussed in this section. Apart from this other parallel adder topologies are also available but we have not included them because their delay is higher than Ripple Carry Adder and there area is also same or higher [6].

| S.No. | Design                        | Area (LUT's) | Area (Slices) | Delay (ns) |

|-------|-------------------------------|--------------|---------------|------------|

| 1.    | Ripple Carry Adder (RCA)      | 8            | 5             | 2.191      |

| 2.    | Carry Skip Adder (CSkA)       | 8            | 6             | 2.267      |

| 3.    | Carry Increment Adder (CIA)   | 8            | 5             | 1.907      |

| 4.    | Carry Look Ahead Adder (CLAA) | 10           | 5             | 2.266      |

| 5.    | Carry Save Adder (CSA)        | 13           | 9             | 1.433      |

| 6. | Carry Select Adder (CSIA) | 8  | 5 | 2.588 |

|----|---------------------------|----|---|-------|

| 7. | Carry Bypass Adder (CBA)  | 12 | 6 | 3.160 |

Table 2.1 Performance Comparison of Various Adders for 8 bit application

| S.No. | Design                      | Area (Slices) | Delay (ns) |

|-------|-----------------------------|---------------|------------|

| 1     | Carry Increment Adder (CIA) | 22            | 14.32      |

| 2     | Carry Save Adder (CSA)      | 23            | 19.8       |

Table 2.2 Performance Comparison of Carry Save Adder and Carry Increment adder for 16 bit application

It is found that for 8 bit addition applications Carry Save Adder provides the least delay at cost of increase in area by roughly 50% whereas Carry Increment adder provides good speed without compromising with area. Whereas for 16 bit addition applications Carry Increment adder is better than Carry Save Adder [4]. The same results can be verified from the tables given above. Table 2.1 shows performance comparison of various adders for 8 bit application [5]. While performance comparison of Carry Save Adder and Carry Increment adder for 16 bit application [4] is described in Table 2.2.

#### **2.2.1 HALF ADDER**

The half-adder adds two single binary digits A and B. It has two outputs, sum (S) and carry (C). The carry signal represents an overflow into the next digit of an addition. The basic half-adder design using an XOR gate for S and an AND gate for C. The half adder adds two input bits and produces a carry and sum. The truth table and logic diagram for the half adder are shown in figure 2.1. The characteristic equations for half adder are as follows:

$Sum = A \bigoplus B$ Carry = A.B

Fig. 2.3: Half Adder

| Inputs |   | Output | S |

|--------|---|--------|---|

| А      | В | С      | S |

| 0      | 0 | 0      | 0 |

| 1      | 0 | 0      | 1 |

| 0      | 1 | 0      | 1 |

| 1      | 1 | 1      | 0 |

Table 2.3: Half Adder Truth Table

#### 2.2.2 FULL ADDER

A full adder adds three one-bit numbers, usually written as A, B, and  $C_{in}$ ; A and B are the operands, and  $C_{in}$  is a bit carried in from the previous less significant stage. The circuit produces a two-bit output, output carry and sum represented by the  $C_{out}$  and S. Here P and G are internal signals termed as propagate and generate signal respectively. The logic diagram and truth table for the full adder are shown in figure 2.2. The characteristic equations for traditional full adder are as follows:

| Propagate Signal | $\mathbf{P} = \mathbf{A} \bigoplus \mathbf{B};$ |

|------------------|-------------------------------------------------|

| Generate Signal  | G = A.B;                                        |

| Carry Out        | $C_{out} = A.B + (A \bigoplus B).(C_{in});$     |

| Sum              | $S = A \bigoplus B \bigoplus C$                 |

Fig. 2.4: Full Adder

|   | Inputs | 6               |   |   | Outputs          |   |

|---|--------|-----------------|---|---|------------------|---|

| А | В      | C <sub>in</sub> | G | Р | C <sub>out</sub> | S |

| 0 | 0      | 0               | 0 | 0 | 0                | 0 |

| 0 | 0      | 1               | 0 | 0 | 0                | 1 |

| 0 | 1      | 0               | 0 | 1 | 0                | 1 |

| 0 | 1      | 1               | 0 | 1 | 1                | 0 |

| 1 | 0      | 0               | 0 | 1 | 0                | 1 |

| 1 | 0      | 1               | 0 | 1 | 1                | 0 |

| 1 | 1      | 0               | 1 | 0 | 1                | 0 |

| 1 | 1      | 1               | 1 | 0 | 1                | 1 |

Table 2.4: Full Adder Truth Table

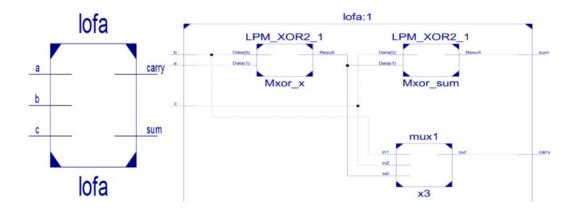

#### 2.2.3 LOGICALLY OPTIMIZED FULL ADDER

In [4] R.Uma and P.Dhavachelvan proposed a logically optimized full adder. This adder incorporates two XOR gates and one 2X1 Multiplexer. They have simulated 20 different Boolean expressions for the full adder operation. The performance of all the full adders has been analysed in terms of delay, transistor count and power dissipation. It is observed that adder designed with XOR and MUX has the least delay, transistor count and power dissipation when compared to other combinations of gate. So the adder realized with MUX and XOR is considered to be the optimized adder in terms of delay, transistor count and power dissipation. The logic diagram for this full adder is shown in figure 2.3.The characteristic equations for Logically Optimized Full adder are as follows:

Fig. 2.5 Logically Optimized Full Adder

**Reason:** This Full Adder architecture uses 2X1 Multiplexer for carry computation instead of two AND and one OR gate which optimizes adder in terms of delay, transistor count and power dissipation. Because logical effort of Multiplexer is 2 while logical effort of replaced carry circuit is higher.

The logical effort of a logic gate tells how much worse it is at producing output current than is an inverter, given that each of its inputs may contain only the same input capacitance as the inverter. Reduced output current means slower operation, and thus the logical effort number for a logic gate tells how much more slowly it will drive a load than an inverter would. Equivalently, logical effort is how much more input capacitance a gate presents to deliver the same output current as an inverter [1].

| Gate type    |   | Number of inputs |     |     |      |                     |  |  |

|--------------|---|------------------|-----|-----|------|---------------------|--|--|

|              | 1 | 2                | 3   | 4   | 5    | n                   |  |  |

| inverter     | 1 |                  |     |     |      |                     |  |  |

| NAND         |   | 4/3              | 5/3 | 6/3 | 7/3  | (n+2)/3             |  |  |

| NOR          |   | 5/3              | 7/3 | 9/3 | 11/3 | (n+2)/3<br>(2n+1)/3 |  |  |

| multiplexer  |   | 2                | 2   | 2   | 2    | 2                   |  |  |

| XOR (parity) |   | 4                | 12  | 32  |      |                     |  |  |

Table 2.5: Logical effort for inputs of static CMOS gates

It is interesting but not surprising to note from Table 1.1 that more complex logic functions have larger logical effort. Moreover, the logical effort of most logic gates grows with the number of inputs to the gate. Larger or more complex logic gates will thus exhibit greater delay.

#### 2.2.4 RIPPLE CARRY ADDER (RCA)

Half Adders can be used to add two one bit binary numbers. It is also possible to create a logical circuit using multiple full adders to add N-bit binary numbers. The full adder inputs a **Cin**, which is the **Cout** of the previous adder. This type of adder is a **Ripple Carry Adder** (**RCA**) [6], since each carry bit "ripples" to the next full adder. RCA contains series structure of Full Adders (FA); each FA is used to add two bits along with carry bit. Only the first full adder can be substituted by a half adder. The carry generated from each full adder is given to next full adder and so on. Hence, the carry is propagated in a serial computation. Hence, delay is more as the number of bits is increased in RCA. The 8bit RCA is shown in figure 2.4:

Fig.2.6: Ripple Carry Adder (RCA)

#### 2.2.5 CARRY INCREMENT ADDER (CIA)

The design of Carry Increment Adder (CIA) consists of RCA's and incremental circuitry [7]. The incremental circuit can be designed using HA's in ripple carry chain with a sequential order. The addition operation is done by dividing total number of bits in to group of 4bits and addition operation is done using several 4bit RCA's. The architecture of CIA is shown in Fig 2.3.

Fig.2.7: Carry Increment Adder (CIA)

#### 2.2.6 CARRY SAVE ADDER (CSA)

The carry-save adder reduces the addition of 3 numbers to the addition of 2 numbers. The propagation delay is 3 gates regardless of the number of bits. The carry-save unit consists of n full adders, each of which computes a single sum and carries bit based solely on the corresponding bits of the three input numbers. The entire sum can then be computed by shifting the carry sequence left by one place and appending a 0 to the front (most significant bit) of the partial sum sequence and adding this sequence with RCA produces the resulting n + 1-bit value. This process can be continued indefinitely, adding an input for each stage of full adders, without any intermediate carry propagation. The main application of carry save algorithm is, well known for multiplier architecture is used for efficient CMOS implementation of much wider variety of

algorithms for high speed digital signal processing. In this scheme, the carry is not propagated through the stages. Instead, carry is stored in present stage, and updated as addend value in the next stage. Hence, the delay due to the carry is reduced in this scheme. The architecture of CSA is shown in Fig 2.4.

Fig.2.8: Carry Save Adder (CSA)

| Х   |   | 1 | 0 | 0 | 1 | 1 |

|-----|---|---|---|---|---|---|

| Y   |   | 1 | 1 | 0 | 0 | 1 |

| S   |   | 0 | 1 | 0 | 1 | 0 |

| С   | 1 | 0 | 0 | 0 | 1 |   |

| SUM | 1 | 0 | 1 | 1 | 0 | 0 |

Table 2.6: Carry Save Adder Computation Flow

#### **2.3 MULTIPLIERS**

Multiplication is one of the simple functions which are used in digital signal processing applications (DSP). Multipliers requie more hardware resources and processing time compared to that of adders. In order to achieve the high speed and low power demand, the various multipliers has to design to meet requirements of current VLSI industry requirments. Multipliers are not only used in processor, but also used in other part of processor designs such as various data path

units. In general, two numbers such as multiplier and multiplicand are multiplied and generate a product value. All multipliers architectures are built with basic blocks such as Half Adders (HA), Full Adders (FA), and various complex adder architectures. In recent years, many researchers developed several multipliers for the current needs of VLSI industry. Here, a brief description of some traditional multipliers such as Array Multiplier (AM), Ripple Carry Array Multiplier using Row Bypass Technique (RCAM RB), Wallace Tree Multiplier (WTM), Dadda Multiplier (DM) and are discussed. Table 2.7 describes Performance Comparison of Various Multipliers [9] for 8 bit multiplication applications

| S.No. | Multiplier (8 Bit)                               | Area<br>(LUT's) | Delay(ns) |

|-------|--------------------------------------------------|-----------------|-----------|

| 1.    | Array Multiplier (AM)                            | 79              | 8.369     |

| 2.    | Ripple Carry Array Multiplier with Row Bypassing | 74              | 6.417     |

|       | (RCAM RB)                                        |                 |           |

| 3.    | Wallace Tree Multiplier (WTM)                    | 80              | 6.285     |

| 4.    | Dadda Multiplier (DM)                            | 86              | 3.862     |

| 5.    | Vedic Multiplier (VM)                            | 100             | 7.406     |

| 6.    | Modified Radix-2 Booth Multiplier (MRBM)         | 108             | 7.627     |

Table 2.7 Performance Comparison of Various Multipliers

From above performance comparison table, it is observed that Dadda Multiplier (DM) has optimized performance in terms of Area and Delay.

#### 2.3.1 ARRAY MULTIPLIERS (AM)

Array multiplier is one of the basic multiplier which comprises of partial products generated by AND Logic [10]. All partial products are added by the Half Adder (HA) and Full Adder (FA) [8] depending on the number of input bits. Architecture of array multiplier is shown in Fig.2.9.

Fig.2.9.Array Multiplier

# **2.3.2 RIPPLE CARRY ARRAY MULTIPLIER WITH ROW BYPASSING TECHNIQUE** (RCAM RB)

In ripple carry array multiplier with row bypassing technique [11], the multiplication method is similar to the array multiplier. But the partial product stages are bypassed from previous state to next state depending upon the carry value obtained in adder stage. An 8x8 Multiplier as shown in Fig.2.11 requires two 8x4 RCM multipliers and the architecture is shown in Fig.2.10.

Fig.2.10.Structure of 8x4 Ripple Carry Array Multiplier with Row Bypassing

Fig.2.11.Structure of 8 bit Ripple Carry Array Multiplier (RCM) with Row By passing

### 2.3.3 WALLACE TREE MULTIPLIER (WTM)

In Wallace tree multiplier, the carry save adder scheme is used to add partial products generated in each stage [12]. Hence, carry generated in the present state is saved and added in the

next state. Hence the delay due to carry will be reduced in a greater extent. The design of Wallace Tree Multiplier [13] is shown in Fig 2.12.

Fig.2.12.Wallace Tree Multiplier (WTM)

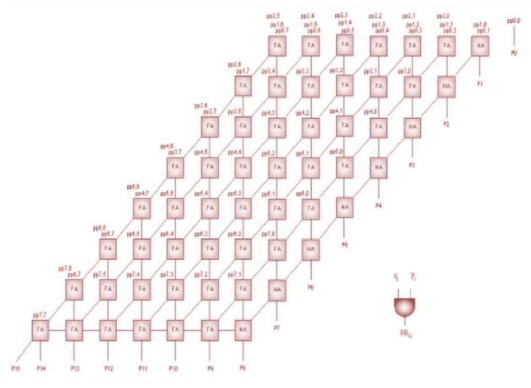

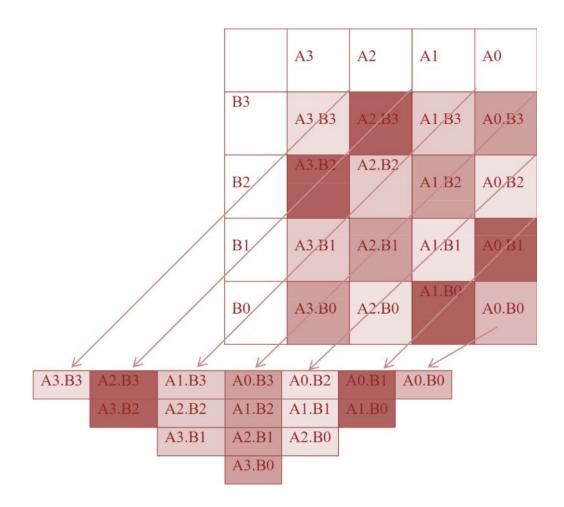

#### 2.3.4 DADDA MULTIPLIER (DM)

Dadda multipliers are the refinement of parallel multipliers first presented by Wallace in 1964. In contrast to the Wallace reduction Dadda multiplier perform the least reduction at each stage [14]. The maximum height of each stage is determined by working back from final stage which consists of two rows of partial products. The height of each stage should be in the order 2, 3, 4, 6, 9, 13, 19, 28, 42, 63 etc. An 8 bit Dadda multiplier reduction is shown in Fig 2.11. For Dadda multipliers the required number of full adders and half adders are depend on the value of N. An 8 bit Dadda multiplier reduction is shown in Fig 5. For Dadda multipliers the required number of full adders are depend on the value of N.

Fig.2.13.Dadda Multiplier Reduction

The principle behind Dadda Multiplier is discussed with the help of 4 bit multiplication example given below. Suppose we have to multiply tow 4 bit numbers A & B then the following algorithm is used in Dadda Multiplier. Figure 2.14 describes the algorithm used by Dadda Multiplier.

Fig.2.14.Dadda Multiplier Algorithm

### **2.4 CONCLUSION**

After thoroughly studying various research work we have reached to following conclusion

- Use of Half adder at possible instances could minimize the area, delay & power.

- Use of logically optimized full adder instead of Traditional Full adders at all possible instances could minimize the area, delay & power as well [5].

- Dadda Multiplier is best suitable for 8-bit Convolution unit compared to other general purpose multiplier Architectures [4].

## **CHAPTER 3**

### **PROPOSED MODEL FOR CONVOLUTION**

#### **3.1 PROPOSED CONVOLUTION MODEL**

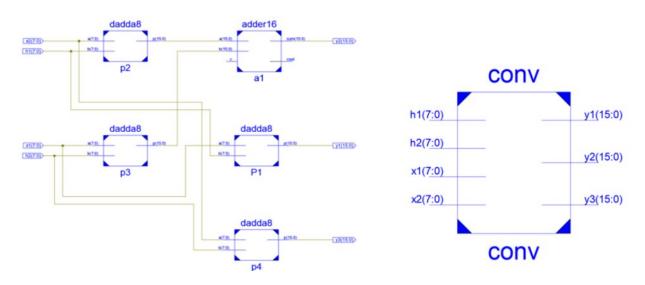

In this we are proposed a method to reduce to reduce the convolution processing time using hardware computing and implementation of discrete linear convolution of two finite length sequences (NXN). The proposed convolution model uses a modified hierarchical design approach, which is efficient and accurate to speed-up the computation, reduce power and hardware resources.

The circuit deals with two signals having N values each. We selected N=4 in this implementations which consider the two numbers like two arrays having four locations each to store values. The basic concept of convolution is to multiply and add. Now for two signals of four values each, we have to multiply and then add the values. Block diagram of convolution process is shown below.

Fig 3.1: Block diagram for the proposed convolution model

In this we did the change in our multiplier which we are using Dadda Multiplier (DM) and for addition we are using Logically Optimized Full Adder (LOFA). We implement this on hardware and apply different inputs x[n] and h[n]. Here we apply 16 different input and got the result on FPGA LCD Display. We are showing one of those results for input  $x[n] = h[n] = [1 \ 1 \ 1 \ 1]$  in result section.

Proposed Convolution in which for multiplication, we used Dadda Multiplier (DM) and Logically Optimized Full Adder (LOFA) is given below.

|    | A0    | A1    | A2    | A3    |

|----|-------|-------|-------|-------|

| B0 | A0xB0 | A1xB0 | A2xB0 | A3xB0 |

| B1 | A0xB1 | A1xB1 | A2xB1 | A3xB1 |

| B2 | A0xB2 | A1xB2 | A2xB2 | A3xB2 |

| В3 | A0xB3 | A1xB3 | A2xB3 | A3xB3 |

Y0 = A0xB0

Y1=A0xB1+A1xB0

Y2=A0xB2+A1xB1+A2xB0

$Y3{=}A0xB3{+}A2xB1{+}A2xB1{+}A3xB0$

Y4=A1xB3+A2xB2+A3xB1

Y5=A2xB3+A3xB2

Y6=A3xB3

## **CHAPTER 4**

## RESULTS

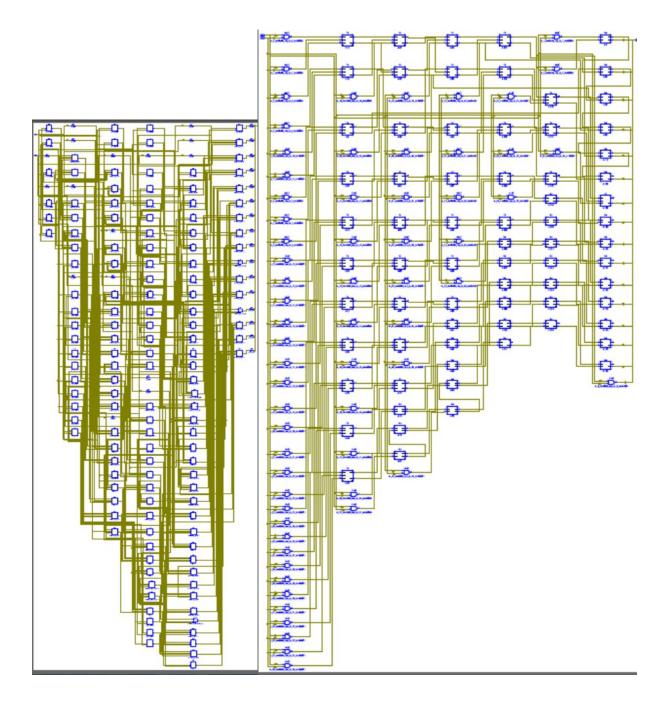

In simulation results, technolgy view[15] is a schematic representation of a design in terms of logic elements optimized to the target xilinx device or technology in terms of Look Up Tables (LUTs)[16], carry logic, I/O buffers and other technology specific components. A Look Up Table is basically just a small memory. A four input and one output LUT can genrate any four input Bollena function(AND/OR/XOR/NOT/Combination of these/etc). When FPGA has to be configured, it is required to be configured the contents of the LUTs, and thus the will be implemented.

RTL view is te schematic reperesentation of te pre-optimized design in terms of the genraic symbols that are independent of te targeted xilinx devices in terms of adders, multipliers, counters, AND gates, OR gates. Timing Wavefrom[15] is genrated by writing test bench program in verilog design which contents the possible number of inputs test vectors applied to the design.

# 4.1TABULAR OUTPUTS FOR 16 DIFFERENT INPUT COMBINATIONS USED

### Case 1 – when input x[n] = h[n] = [0 0 0 0]

| Case(1) | x[0]=0 | x[1]=0 | x[2]=0 | x[3]=0 |

|---------|--------|--------|--------|--------|

| h[0]=0  | 0      | 0      | 0      | 0      |

| h[1]=0  | 0      | 0      | 0      | 0      |

| h[2]=0  | 0      | 0      | 0      | 0      |

| h[3]=0  | 0      | 0      | 0      | 0      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 0 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 0 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 0 |

## Case 2 – when input x[n] = h[n] = [0 0 0 1]

| Case(2) | x[0]=0 | x[1]=0 | x[2]=0 | x[3]=1 |

|---------|--------|--------|--------|--------|

| h[0]=0  | 0      | 0      | 0      | 0      |

| h[1]=0  | 0      | 0      | 0      | 0      |

| h[2]=0  | 0      | 0      | 0      | 0      |

| h[3]=1  | 0      | 0      | 0      | 1      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 0 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 0 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 1 |

# Case 3 – when input x[n] = h[n] = [0 0 1 0]

| Case(3) | x[0]=0 | x[1]=0 | x[2]=1 | x[3]=0 |

|---------|--------|--------|--------|--------|

| h[0]=0  | 0      | 0      | 0      | 0      |

| h[1]=0  | 0      | 0      | 0      | 0      |

| h[2]=1  | 0      | 0      | 1      | 0      |

| h[3]=0  | 0      | 0      | 0      | 0      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 0 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 1 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 0 |

# Case 4 – when input x[n] = h[n] = [0 0 1 1]

| Case(3) | x[0]=0 | x[1]=0 | x[2]=1 | x[3]=1 |

|---------|--------|--------|--------|--------|

| h[0]=0  | 0      | 0      | 0      | 0      |

| h[1]=0  | 0      | 1      | 0      | 0      |

| h[2]=1  | 0      | 0      | 1      | 1      |

| h[3]=1  | 0      | 0      | 1      | 1      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 0 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 1 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 2 |

| Y[6]=x[4]*h[4]                               | 1 |

# Case 5 – when input x[n] = h[n] = [0 1 0 0]

| Case(1) | x[0]=0 | x[1]=1 | x[2]=0 | x[3]=0 |

|---------|--------|--------|--------|--------|

| h[0]=0  | 0      | 0      | 0      | 0      |

| h[1]=1  | 0      | 1      | 0      | 0      |

| h[2]=0  | 0      | 0      | 0      | 0      |

| h[3]=0  | 0      | 0      | 0      | 0      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 1 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 0 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 0 |

# Case 6 – when input x[n] = h[n] = [0 1 0 1]

| Case(2) | x[0]=0 | x[1]=1 | x[2]=0 | x[3]=1 |

|---------|--------|--------|--------|--------|

| h[0]=0  | 0      | 0      | 0      | 0      |

| h[1]=1  | 0      | 1      | 0      | 1      |

| h[2]=0  | 0      | 0      | 0      | 0      |

| h[3]=1  | 0      | 1      | 0      | 1      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 1 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 2 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 1 |

| Case 7 – when | input x[n] : | $= h[n] = [0 \ 1 \ 1 \ 0]$ |

|---------------|--------------|----------------------------|

|---------------|--------------|----------------------------|

| Case(3) | x[0]=0 | x[1]=1 | x[2]=1 | x[3]=0 |

|---------|--------|--------|--------|--------|

| h[0]=0  | 0      | 0      | 0      | 0      |

| h[1]=1  | 0      | 1      | 1      | 0      |

| h[2]=1  | 0      | 1      | 1      | 0      |

| h[3]=0  | 0      | 0      | 0      | 0      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 1 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 2 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 1 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 0 |

# Case 8 – when input x[n] = h[n] = [0 1 1 1]

| Case(3) | x[0]=0 | x[1]=1 | x[2]=1 | x[3]=1 |

|---------|--------|--------|--------|--------|

| h[0]=0  | 0      | 0      | 0      | 0      |

| h[1]=1  | 0      | 1      | 1      | 1      |

| h[2]=1  | 0      | 1      | 1      | 1      |

| h[3]=1  | 0      | 1      | 1      | 1      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 1 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 2 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 3 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 2 |

| Y[6]=x[4]*h[4]                               | 1 |

# Case 9 – when input x[n] = h[n] = [1 0 0 0]

| Case(2) | x[0]=1 | x[1]=0 | x[2]=0 | x[3]=0 |

|---------|--------|--------|--------|--------|

| h[0]=1  | 1      | 0      | 0      | 0      |

| h[1]=0  | 0      | 0      | 0      | 0      |

| h[2]=0  | 0      | 0      | 0      | 0      |

| h[3]=0  | 0      | 0      | 0      | 0      |

| Y[0]=x[0]*h[0]                               | 1 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 0 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 0 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 0 |

# Case 10 – when input x[n] = h[n] = [1 0 0 1]

| Case(2) | x[0]=1 | x[1]=0 | x[2]=0 | x[3]=1 |

|---------|--------|--------|--------|--------|

| h[0]=1  | 1      | 0      | 0      | 1      |

| h[1]=0  | 0      | 0      | 0      | 0      |

| h[2]=0  | 0      | 0      | 0      | 0      |

| h[3]=1  | 1      | 0      | 0      | 1      |

| Y[0]=x[0]*h[0]                               | 1 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 0 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 1 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 0 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 1 |

# Case 11 – when input x[n] = h[n] = [1 0 1 0]

| Case(3) | x[0]=1 | x[1]=0 | x[2]=1 | x[3]=0 |

|---------|--------|--------|--------|--------|

| h[0]=1  | 1      | 0      | 1      | 0      |

| h[1]=0  | 0      | 0      | 0      | 0      |

| h[2]=1  | 1      | 0      | 1      | 0      |

| h[3]=0  | 0      | 0      | 0      | 0      |

| Y[0]=x[0]*h[0]                               | 0 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 0 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 1 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 0 |

# Case 12 – when input x[n] = h[n] = [1 0 1 1]

| Case(3) | x[0]=1 | x[1]=0 | x[2]=1 | x[3]=1 |

|---------|--------|--------|--------|--------|

| h[0]=1  | 1      | 0      | 1      | 1      |

| h[1]=0  | 0      | 0      | 0      | 0      |

| h[2]=1  | 1      | 0      | 1      | 1      |

| h[3]=1  | 1      | 0      | 1      | 1      |

| Y[0]=x[0]*h[0]                               | 1 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 0 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 2 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 2 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 1 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 2 |

| Y[6]=x[4]*h[4]                               | 1 |

# Case 13 – when input x[n] = h[n] = [1 1 0 0]

| Case(1) | x[0]=1 | x[1]=1 | x[2]=0 | x[3]=0 |

|---------|--------|--------|--------|--------|

| h[0]=1  | 1      | 1      | 0      | 0      |

| h[1]=1  | 1      | 1      | 0      | 0      |

| h[2]=0  | 0      | 0      | 0      | 0      |

| h[3]=0  | 0      | 0      | 0      | 0      |

| Y[0]=x[0]*h[0]                               | 1 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 2 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 1 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 0 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 0 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 0 |

# Case 14 – when input x[n] = h[n] = [1 1 0 1]

| Case(2) | x[0]=1 | x[1]=1 | x[2]=0 | x[3]=1 |

|---------|--------|--------|--------|--------|

| h[0]=1  | 1      | 1      | 0      | 1      |

| h[1]=1  | 1      | 1      | 0      | 1      |

| h[2]=0  | 0      | 0      | 0      | 0      |

| h[3]=1  | 1      | 1      | 0      | 1      |

| Y[0]=x[0]*h[0]                               | 1 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 2 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 1 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 2 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 2 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 1 |

# Case 15 – when input x[n] = h[n] = [1 1 1 0]

| Case(3) | x[0]=1 | x[1]=1 | x[2]=1 | x[3]=0 |

|---------|--------|--------|--------|--------|

| h[0]=1  | 1      | 1      | 1      | 0      |

| h[1]=1  | 1      | 1      | 1      | 0      |

| h[2]=1  | 1      | 1      | 1      | 0      |

| h[3]=0  | 0      | 0      | 0      | 0      |

| Y[0]=x[0]*h[0]                               | 1 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 2 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 3 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 2 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 1 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 0 |

| Y[6]=x[4]*h[4]                               | 0 |

# Case 16 – when input x[n] = h[n] = [1 1 1 1]

| Case(3) | x[0]=1 | x[1]=1 | x[2]=1 | x[3]=1 |

|---------|--------|--------|--------|--------|

| h[0]=1  | 1      | 1      | 1      | 1      |

| h[1]=1  | 1      | 1      | 1      | 1      |

| h[2]=1  | 1      | 1      | 1      | 1      |

| h[3]=1  | 1      | 1      | 1      | 1      |

| Y[0]=x[0]*h[0]                               | 1 |

|----------------------------------------------|---|

| Y[1]=x[0]*h[1]+x[1]*h[0]                     | 2 |

| Y[2]=x[0]*h[2]+x[1]*h[1]+x[2]*h[0]           | 3 |

| Y[3]=x[0]*h[3]+x[1]*h[2]+x[2]*h[1]+x[3]*h[0] | 4 |

| Y[4]=x[1]*h[3]+x[2]*h[2]+x[3]*h[1]           | 3 |

| Y[5]=x[2]*h[3]+x[3]*h[2]                     | 2 |

| Y[6]=x[4]*h[4]                               | 1 |

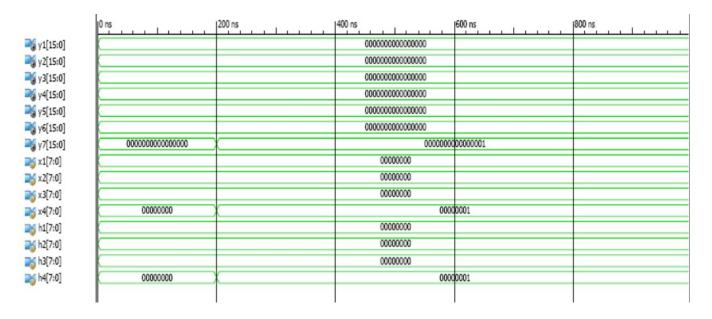

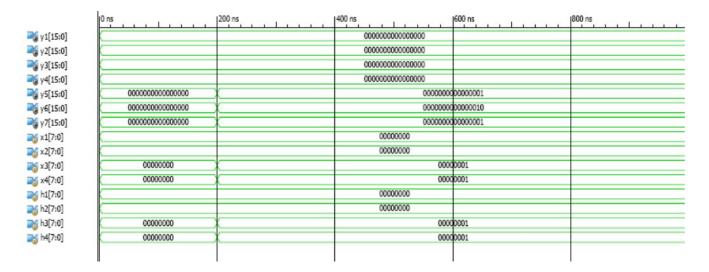

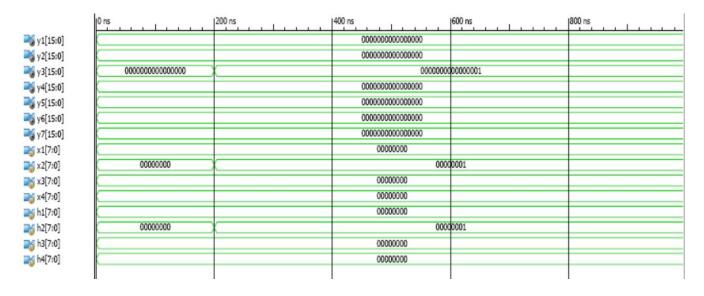

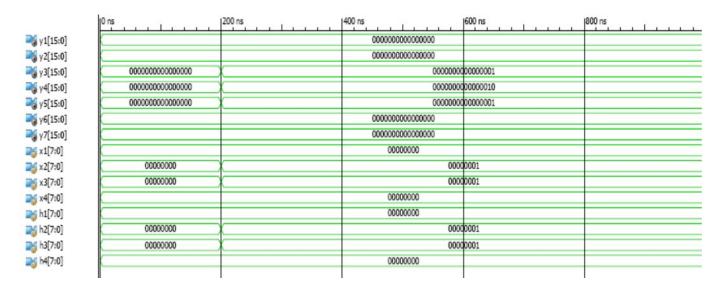

# 4.2 WAVEFORM OUTPUTS FOR 16 DIFFERENT INPUT COMBINATIONS USED

|             | 10 ns   | 200 ns | 1400 ns                                 | 600 ns | 1800 ns |

|-------------|---------|--------|-----------------------------------------|--------|---------|

| N 91[15:0]  | (       |        | 000000000000000000000000000000000000000 |        |         |

| N y2[15:0]  |         |        | 000000000000000000000000000000000000000 |        |         |

| N3[15:0]    | C       |        | 000000000000000000000000000000000000000 |        |         |

| Pi y4[15:0] | (       |        | 000000000000000000000000000000000000000 |        |         |

| Pi y5[15:0] |         |        | 000000000000000000000000000000000000000 |        |         |

| Pi y6[15:0] |         |        | 000000000000000000000000000000000000000 |        |         |

| 💐 y7[15:0]  |         |        | 000000000000000000000000000000000000000 |        |         |

| 📷 ×1[7:0]   |         |        | 00000000                                |        |         |

| ₩2[7:0]     |         |        | 00000000                                |        |         |

| 📷 ×3[7:0]   |         |        | 00000000                                |        |         |

| 📷 x4[7:0]   |         |        | 00000000                                |        |         |

| 📷 h1[7:0]   |         |        | 00000000                                |        |         |

| 📷 h2[7:0]   |         |        | 00000000                                |        |         |

| 📷 h3[7:0]   | <u></u> |        | 00000000                                |        |         |

| 📷 h4[7:0]   |         |        | 00000000                                |        |         |

|             |         |        |                                         |        |         |

#### Case 1 – when input $x[n] = h[n] = [0 \ 0 \ 0 \ 0]$

Fig. 4.1 Timing waveform for  $x[n] = h[n] = [0 \ 0 \ 0 \ 0]$

## Case 2 – when input x[n] = h[n] = [0 0 0 1]

Fig. 4.2 Timing waveform for  $x[n] = h[n] = [0 \ 0 \ 0 \ 1]$

## Case 3 – when input $x[n] = h[n] = [0 \ 0 \ 1 \ 0]$

Fig. 4.3 Timing waveform for  $x[n] = h[n] = [0 \ 0 \ 1 \ 0]$

#### Case 4 – when input x[n] = h[n] = [0 0 1 1]

Fig. 4.4 Timing waveform for  $x[n] = h[n] = [0 \ 0 \ 1 \ 1]$

Case 5 – when input x[n] = h[n] = [0 1 0 0]

Fig. 4.5 Timing waveform for  $x[n] = h[n] = [0 \ 1 \ 0 \ 0]$

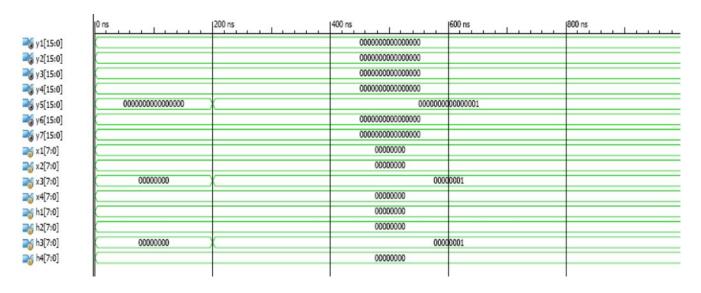

## Case 6 – when input x[n] = h[n] = [0 1 0 1]

ı

|             | 0 ns                                    | 200 ns | 400 ns                                  | 600 ns   | 1800 ns |

|-------------|-----------------------------------------|--------|-----------------------------------------|----------|---------|

| 💐 y1[15:0]  | (                                       |        | 000000000000000000000000000000000000000 |          |         |

| ₽¥ y2[15:0] |                                         |        | 000000000000000000000000000000000000000 |          |         |

| Pi y3[15:0] | 000000000000000000000000000000000000000 | X      | 0000000                                 | 00000001 |         |

| 💐 y4[15:0]  | (                                       |        | 000000000000000000000000000000000000000 |          |         |

| 💐 y5[15:0]  | 000000000000000000000000000000000000000 | X      | 0000000                                 | 00000010 |         |

| i y6[15:0]  | (                                       |        | 000000000000000000000000000000000000000 |          |         |

| ₩y7[15:0]   | 000000000000000000000000000000000000000 | X.     | 0000000                                 | 00000001 |         |

| ₩x1[7:0]    |                                         |        | 00000000                                |          |         |

| ₩2[7:0]     | 00000000                                | X      | 000                                     | 0001     |         |

| 📷 x3[7:0]   |                                         |        | 00000000                                |          |         |

| ₩¥4[7:0]    | 00000000                                | X      | 000                                     | 0001     |         |

| 📷 h1[7:0]   |                                         |        | 00000000                                |          |         |

| 📷 h2[7:0]   | 00000000                                |        | 000                                     | 0001     |         |

| 📷 h3[7:0]   | (                                       |        | 00000000                                |          |         |

| 📷 h4[7:0]   | 00000000                                | ×      | 000                                     | 0001     |         |

Fig. 4.6 Timing waveform for  $x[n] = h[n] = [0 \ 1 \ 0 \ 1]$

## Case 7 – when input x[n] = h[n] = [0 1 1 0]

Fig. 4.7 Timing waveform for  $x[n] = h[n] = [0 \ 1 \ 1 \ 0]$

#### Case 8 – when input $x[n] = h[n] = [0 \ 1 \ 1 \ 1]$

Fig. 4.8 Timing waveform for  $x[n] = h[n] = [0 \ 1 \ 1 \ 1]$

Case 9 – when input x[n] = h[n] = [1 0 0 0]

## Case 10 – when input x[n] = h[n] = [1 0 0 1]

Fig. 4.10 Timing waveform for  $x[n] = h[n] = [1 \ 0 \ 0 \ 1]$

Case 11 -when input  $x[n] = h[n] = [1 \ 0 \ 1 \ 0]$

#### Case 12 – when input x[n] = h[n] = [1 0 1 1]

Fig. 4.12 Timing waveform for  $x[n] = h[n] = [1 \ 0 \ 1 \ 1]$

#### Case 13 – when input x[n] = h[n] = [1 1 0 0]

#### Case 14 – when input x[n] = h[n] = [1 1 0 1]

Fig. 4.14 Timing waveform for  $x[n] = h[n] = [1 \ 1 \ 0 \ 1]$

## Case 15 – when input x[n] = h[n] = [1 1 1 0]

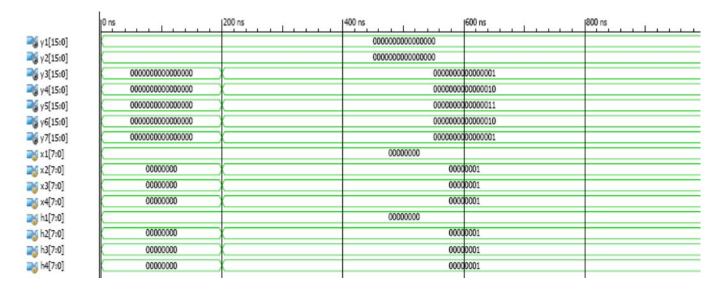

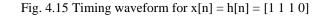

## Case 16 – when input x[n] = h[n] = [1 1 1 1]

|            | 10 ns                                   | 200 ns | 400 ns   | 600 ns   | 800 ns |

|------------|-----------------------------------------|--------|----------|----------|--------|

| 💐 y1[15:0] | 000000000000000000000000000000000000000 | X      | 0000000  | 00000001 |        |

| ¥ y2[15:0] | 000000000000000000000000000000000000000 | X      | 0000000  | 00000010 |        |

| ₩y3[15:0]  | 000000000000000000000000000000000000000 | X      | 0000000  | 00000011 |        |

| 💐 y4[15:0] | 000000000000000000000000000000000000000 | X      | 00000000 | 00000100 |        |

| ₩y5[15:0]  | 000000000000000000000000000000000000000 | X      | 00000000 | 00000011 |        |

| No[15:0]   | 000000000000000000000000000000000000000 | X      | 0000000  | 00000010 |        |

| 💐 y7[15:0] | 000000000000000000000000000000000000000 | X      | 0000000  | 00000001 |        |

| ₩x1[7:0]   | 00000000                                | X      | 0000     | 0001     |        |

| 📷 x2[7:0]  | 00000000                                | X      | 0000     | 0001     |        |

| 📷 x3[7:0]  | 00000000                                | X      | 0000     | 0001     |        |

| 📷 x4[7:0]  | 00000000                                | X      | 0000     | 0001     |        |

| 📷 h1[7:0]  | 00000000                                | X      | 0000     | 0001     |        |

| N2[7:0]    | 00000000                                | XX     | 0000     | 0001     |        |

| 📷 h3[7:0]  | 00000000                                | X      | 0000     | 0001     |        |

| 📷 h4[7:0]  | 00000000                                | X      | 0000     | 0001     |        |

| 1.1.70     |                                         |        |          |          |        |

Fig. 4.16 Timing waveform for  $x[n] = h[n] = [1 \ 1 \ 1 \ 1]$

# **4.3 SIMULATION RESULTS FOR ADDERS**

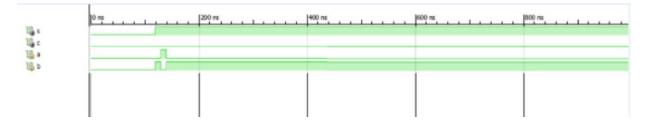

# 4.3.1 HALF ADDER

Fig. 4.17 RTL and Technology view of Half Adder

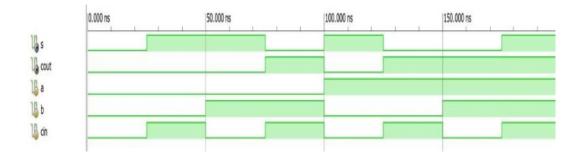

Fig. 4.18Timing waveform for Half Adder

| Logic Utilization                              | Used  |

|------------------------------------------------|-------|

| Number of Slice LUTs                           | 1     |

| Number of occupied Slices                      | 1     |

| Number of bonded IOBs                          | 4     |

| Average Fanout of Non-Clock Nets               | 4.00  |

| Maximum combinational path delay in nanosecond | 0.770 |

| Power in milliwatts (mW)                       | 90.6  |

Table 4.1 Device Utilization Summary for Half Adder

## 4.3.2 Full Adder

Fig. 4.19 RTL and Technology view of Full Adder

#### Fig. 4.20Timing waveform for Full Adder

| Logic Utilization                              | Used  |

|------------------------------------------------|-------|

| Number of Slice LUTs                           | 1     |

| Number of occupied Slices                      | 1     |

| Number of bonded IOBs                          | 5     |

| Average Fanout of Non-Clock Nets               | 3.50  |

| Maximum combinational path delay in Nanosecond | 0.923 |

| Power in milliwatts (mW)                       | 90.6  |

Table 4.2 Device Utilization Summary for Full Adder

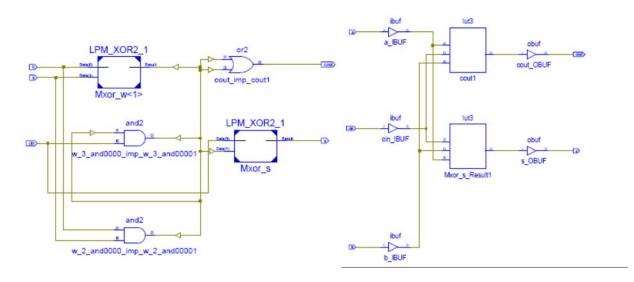

## 4.3.3 Logically Optimized Full Adder

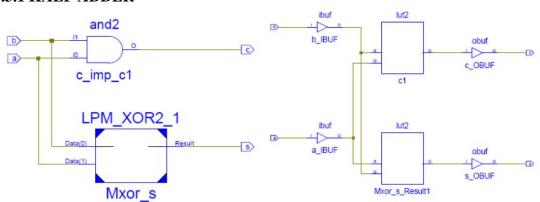

Technology view and RTL view of Logically Optimized Full Adder are given in fig

Fig. 4.21 RTL and Technology view of Logically Optimized Full Adder

Fig. 4.22 Timing waveform of Logically Optimized Full Adder

| Logic Utilization                              | Used  |

|------------------------------------------------|-------|

| Number of Slice LUTs                           | 1     |

| Number of occupied Slices                      | 1     |

| Number of bonded <u>IOBs</u>                   | 5     |

| Average Fanout of Non-Clock Nets               | 3.50  |

| Maximum combinational path delay in Nanosecond | 0.776 |

| Power in milliwatts (mW)                       | 90.6  |

Table 4.3 Device Utilization Summary for Logically Optimized Full Adder

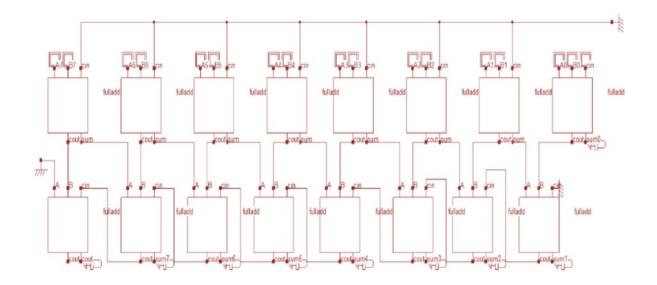

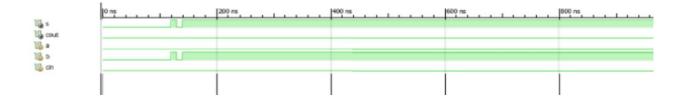

#### 4.4 SIMULATION RESULTS FOR DADDA MULTIPLIER

Fig. 4.23 RTL and Technology view of Dadda Multiplier

| <b>=</b> [15:0] | 0 ps     | 200,000 ps        | 1400,000 ps | 600,000 ps | 800,000 ps |

|-----------------|----------|-------------------|-------------|------------|------------|

| a[7:0]          | 00000000 | 00000100 00000101 | X           | 00000100   |            |

| ₩ b[7:0]        | 00000000 | 11111001 11111000 | ×           | 00000110   |            |

|                 |          |                   |             |            |            |

## Fig. 4.24 Timing waveform for Dadda Multiplier

| Logic Utilization                              | Used  |

|------------------------------------------------|-------|

| Number of Slice LUTs                           | 86    |

| Number of occupied Slices                      | 34    |

| Number of bonded IOBs                          | 32    |

| Average Fanout of Non-Clock Nets               | 3.93  |

| Maximum combinational path delay in Nanosecond | 4.395 |

| Power in milliwatts (mW)                       | 96.8  |

Table 4.4 Device Utilization Summary for Dadda8 Multiplier

# 4.5 SIMULATION RESULTS FOR CONVOLUTION

Fig. 4.25 RTL and Technology view for Convolution

Fig. 4.26 Figure showing hardware implemented output for x[n]=h[n]=[1 1 1 1] for convolution

| Logic Utilization                              | Used |

|------------------------------------------------|------|

| Number of Slice Flip Flops                     | 39   |

| Number of 4 input LUTs                         | 47   |

| Number of occupied Slices                      | 44   |

| Number of Slices containing only related logic | 44   |

| Number of Slices containing unrelated logic    | 0    |

| Total Number of 4 input LUTs                   | 73   |

| Number used as logic                           | 45   |