## MODELING OF PHOTONIC CRYSTAL BASED LOGIC GATES AND OPTICAL DEVICES

A THESIS Submitted to the Delhi Technological University For the Award of the Degree of

## DOCTOR OF PHILOSOPHY IN APPLIED PHYSICS

By PREETI RANI

DEPARTMENT OF APPLIED PHYSICS DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042 (INDIA) OCTOBER 2016

## MODELING OF PHOTONIC CRYSTAL BASED LOGIC GATES AND OPTICAL DEVICES

by

#### PREETI RANI

#### DEPARTMENT OF APPLIED PHYSICS

Submitted

in fulfilment of the requirements of the degree of

#### **DOCTOR OF PHILOSOPHY**

to the

# DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042 (INDIA) OCTOBER 2016

## ©DELHI TECHNOLOGICAL UNIVERSITY-2016 ALL RIGHTS RESERVED

This is to certify that this thesis entitled "MODELING OF PHOTONIC CRYSTAL BASED LOGIC GATES AND OPTICAL DEVICES", being submitted for the award of degree of Doctor of Philosophy to the Delhi Technological University, (Formerly Delhi College of Engineering) India, embodies the original research work carried out by me under the guidance of Dr. Yogita Kalra and Prof. Ravindra Kumar Sinha, Department of Applied Physics, Delhi Technological University, India. The results obtained in this thesis have not been submitted in part or in full to any other University or Institute for the award of any degree or diploma.

(Preeti Rani)

Candidate (Enrolment No: 2k11/PhD/AP/04) Place: Delhi

Date:

#### Dr. Yogita Kalra (Supervisor)

Assistant Professor Department of Applied Physics Delhi Technological University Delhi, India

#### Prof. Ravindra Kumar Sinha (Supervisor)

Director, CSIR-Central Scientific Instruments Organization Chandigarh, India Professor (on lien), Department of Applied Physics Delhi Technological University, Delhi, India

## **DELHI TECHNOLOGICAL UNIVERSITY**

### CERTIFICATE

This is to certify that the Ph.D. thesis entitled "MODELING OF PHOTONIC CRYSTAL BASED LOGIC GATES AND OPTICAL DEVICES" submitted to the Delhi Technological University (Formerly Delhi College of Engineering) India, for the award of degree of Doctor of Philosophy is based on the original research work carried out by me under the supervision of Dr. Yogita Kalra and Prof. Ravindra Kumar Sinha, Department of Applied Physics, Delhi Technological University, Delhi, India. It is further certified that the work embodied in this thesis have not been submitted in part or full to any other University or Institution for the award of any degree or diploma.

Preeti Rani (Enrolment No.: 2k11/PhD/AP/04)

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

#### Dr. Yogita Kalra (Supervisor)

Assistant Professor Department of Applied Physics Delhi Technological University Delhi, India

#### **Prof. Ravindra Kumar Sinha** (Supervisor) Director, CSIR-Central Scientific Instruments Organization Chandigarh, India Professor (on lien), Department of Applied Physics Delhi Technological University, Delhi, India

**Prof. Suresh C. Sharma** Head of the Department, Department of Applied Physics Delhi Technological University Delhi, India

# DEDICATED To Lord Krishna

&

## My Parents

#### Who have been my sources of Inspiration

# ACKNOWLEDGMENTS

It is a matter of great privilege for me to have this blessed opportunity to express my sincere appreciation and deepest gratitude to everyone who has contributed and supported my PhD work.

I would like to express my greatest gratitude to my supervisors **Dr. Yogita Kalra** and **Prof. R. K. Sinha** for their proficient guidance and continued encouragement for the fulfilment of this research work. I would like to express my thanks for their trust, help and support that helped me to get acquainted with the new environment, the new colleagues and the new field of research. I express my great pleasure for their advice, fruitful discussions, constructive criticism and constant support throughout the research work. They gave me many useful suggestions from choosing the topic of my PhD thesis to the detailed steps in the implementation of my ideas. I thank almighty to give me the opportunity to work under the guidance of Prof. Sinha and Dr. Kalra.

Beside my advisor I am grateful to Mr. James P. P. and Mr. Suresh for making available all laboratory facilities throughout the PhD work. All the computer systems always run well under their supervision.

I gratefully acknowledge the initiatives and support provided by the establishment of TIFAC Centre of Relevance and Excellence in Fibre Optics and Optical Communication at Delhi Technological University, Delhi through "MISSION REACH" program of Technology Vision-2020, Government of India. I am also thankful to Delhi Technological University for providing me the University fellowship during the entire PhD tenure.

I am grateful to my PhD colleagues (Venus Dillu, Reena Dalal, Rachna Sharma, Than Singh Saini, Nishant Shankhwar, Jiten Boruah and Neeraj Sharma) and friends (Saloni Rathee and Neha Gupta) at Delhi Technological University for their helping nature in academic and personal fronts and encouragement throughout the PhD work. I am also thankful to Dr. Ajeet Kumar, Dr. Kamal Kishor and Dr. Shruti for their suggestions and well wishes. I would like to thank SPIE (International Society for Optics and Photonics) and OSA (The Optical Society) for supporting and recognizing my research work. I am grateful to them for providing me the opportunity to attend workshops and conferences and to explore different cultures and traditions around the world.

I am greatly indebted to constant encouragement, emotional support and blessings of my parents **Mr. Vijender Singh** and **Mrs. Shila Devi**, who stood behind me through all the difficult moments of my life and grateful to my brothers **Sumit** and **Nitesh** for their love and support that has carried me through difficult times and helped me to reach my dreams. Their trust on my decisions and beliefs pushed me forward in any difficulty that I faced in my research and to reach my goals.

I am thankful to my husband **Jitender Kumar**, In-laws and my loved ones for their blessings and wishes.

Finally, I would like to thank Almighty God, creator of everything and all those whose names are not explicitly mentioned but who helped and supported me in this research work.

Date: Place: Delhi (Preeti Rani)

## ABSTRACT

Recently, light guidance in photonic crystal structures has become one of the most fascinating technologies for the design and development of various optoelectronic devices. These structures provide an interesting platform for building the photonic circuitry due to their unique possibilities of molding the flow of light. Analogous to the electronic band gap in atomic crystals, photonic crystals exhibit photonic band gap, which is a wavelength range over which electromagnetic radiations are inhibited. The density of photon states in the photonic band gap region goes to zero. The two dimensional (2D) photonic crystals have attracted considerable attention due to their on-chip applications and the comparative ease of fabrication. They are periodic along a plane and extruded in the third dimension i.e. they include either periodically arranged dielectric rods in air or equally spaced air holes in a dielectric block.

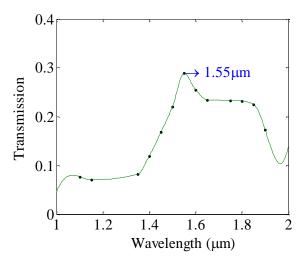

This thesis addresses the design of all optical photonic crystal (PhC) devices and circuits. In this thesis, some novel designs of all optical logic gates have been presented. The two dimensional PhC composed of hexagonal array of silicon rods in air has been used for devising ultra compact photonic crystal waveguide based AND optical logic gate. Further, the AND optical logic gates have been designed in the PhC consisting of hexagonal array of air holes in silicon with the material waveguide as well as with the air waveguide. The proposed gates are operational at a wavelength of 1.55µm as also indicated by their spectral response.

Further, all-optical logic gates such as AND, OR, NOT, NAND, NOR, XOR, XNOR have been designed by introducing an appropriate initial phase difference between the input waveguides and the reference waveguide in the photonic crystal air bridge structure working for single polarization. However, these structures are mechanically unstable and require specific polarization leading to their unsuitability for on-chip integration. To overcome these problems, polarization independent all-optical logic gates have been designed on silicon on insulator (SOI) substrate. The contrast ratio, response period and bit rate have been calculated for all the proposed designs. These devices have

high switching rates as they require low power consumption of about micro watts and response time less than few pico seconds. Moreover, these devices are easier to fabricate and could be a strong candidate for future polarization independent all optical integrated circuits.

Another unique property of the photonic crystal structures is their ability to slow down the group velocity of light due to the strong light matter interaction. Slow light in slotted photonic crystal waveguide with slow down factor of 18.50 and its application as an optical buffer without the use of nonlinear material has been investigated in the thesis. The structure has been analysed for its application as time and wavelength division demultiplexer.

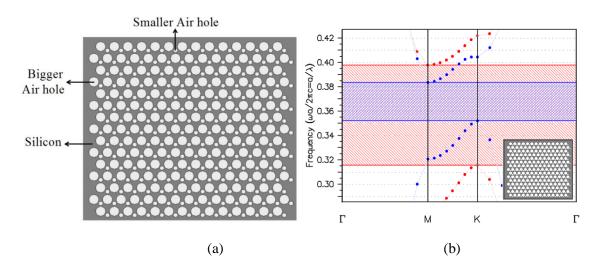

Complete photonic band gap is exhibited by a few specifically designed photonic crystal structures only. A photonic crystal with honey comb lattice arrangement of air holes of two different radii on SOI substrate exhibits complete photonic band gap for a narrow range of frequencies. This feature has been exploited to design a polarization beam splitter. The characteristics of the proposed polarization beam splitter such as extinction ratio, insertion loss, excess loss, coupling loss and degree of polarization indicate the separation of two polarizations.

Hence, a suitably tailored photonic crystal structure can have a broad spectrum of applications ranging from the development of all-optical logic families to slow light photonic devices and polarization splitters, operational at a wavelength of  $1.55 \mu m$ .

# **LIST OF PUBLICATIONS**

#### **Papers in Refereed International Journals**

Preeti Rani, Yogita Kalra, and R. K. Sinha (2013) 'Realization of AND gate in Y shaped photonic crystal waveguide', Optics Communications, 298–299, pp. 227– 231.

http://dx.doi.org/10.1016/j.optcom.2013.02.014

- Preeti Rani, Yogita Kalra, and R. K. Sinha (2015) 'Design of all optical logic gates in photonic crystal waveguides', Optik, 126, pp. 950–955. http://dx.doi.org/10.1016/j.ijleo.2015.03.003

- Preeti Rani, Yogita Kalra, and R. K. Sinha (2015) 'Slow light enabled time and wavelength division de-multiplexer in slotted photonic crystal waveguide', Journal of Nanophotonics, 9, pp. 093063-1. http://dx.doi.org/10.1117/1.JNP.9.093063

- 4. **Preeti Rani,** Yogita Kalra, and R. K. Sinha (2016) 'Design and analysis of polarization independent all-optical logic gates in silicon-on-insulator photonic crystal', Optics Communication, 374, pp. 148–155.

Doi:10.1016/j.optcom.2016.04.037

Preeti Rani, Yogita Kalra, and R. K. Sinha (2016) 'Complete photonic band gap based polarization splitter on silicon-on-insulator platform', Journal of Nanophotonics, 10(2), pp. 026023-1.

http://dx.doi.org/10.1117/1.JNP.10.026023

#### Papers in refereed conference proceedings

Preeti Rani, Yogita Kalra, and R. K. Sinha, (2013) 'Design of Photonic Crystal Architecture for Optical Logic AND Gates', SPIE Optics + Photonic 2013 (Photonic Fiber and Crystal Devices: Advances in Materials and Innovations in Device Applications VII), August 25-29, 2013, San Diego USA: SPIE, pp. 88470X. <u>http://dx.doi.org/10.1117/12.2023855</u>

- Preeti Rani, Yogita Kalra, and R. K. Sinha, (2013) 'Design of AND Optical Logic Gate in Photonic Crystal Waveguide', Frontiers in Optics 2013/Laser Science XXIX © OSA 2013, October 6-10, 2013, Orlando Florida, USA: Optical Society of America, pp. FTh4E.6. <u>http://dx.doi.org/10.1364/FIO.2013.FTh4E.6</u>

- Preeti Rani, Yogita Kalra, and R. K. Sinha, (2013) 'Design and Operation of Photonic Crystal based AND Optical Logic Gate', presented at WRAP, 17-18 December 2013, IIT Delhi. <u>Doi: 10.1109/WRAP.2013.6917637</u>

- Himanshu Chauhan, Preeti Rani, Yogita Kalra, and R. K. Sinha, (2013) 'Novel Design of a Highly Sensitive Micro-Displacement Sensor based on Photonic Crystal Waveguides', presented at WRAP, 17-18 December 2013, IIT Delhi. Doi: 10.1109/WRAP.2013.6917634

- 5. **Preeti Rani,** Yogita Kalra, and R. K. Sinha, (2014) 'Photonic crystal based highly sensitive displacement sensor', presented at ICOL 2014, Dehradun, Uttarakhand, India.

- Preeti Rani, Yogita Kalra, and R. K. Sinha, (2014) 'Refractive index sensor based on slow light in photonic crystal on SOI platform', Frontiers in Optics 2014/Laser Science XXIX © OSA 2014, October 19-23, 2014. Tucson, Arizona, USA: Optical Society of America, pp. JW3A.32.pdf.

Doi:10.1364/FIO.2014.JW3A.32

- Preeti Rani, Yogita Kalra, and R. K. Sinha, (2014) 'Photonic crystal based nanodisplacement sensor', SPIE Optics + Photonic 2014 (Photonic Fiber and Crystal Devices: Advances in Materials and Innovations in Device Applications VIII), August 17-21, 2014. San Diego USA: SPIE, pp. 92000Q. Doi: 10.1117/12.2061627

- Preeti Rani, Yogita Kalra, and R. K. Sinha, (2014) 'Slow light enhanced slotted photonic crystal waveguide', Photonics 2014: 12th International Conference on Fiber Optics and Photonics © OSA 2014, pp. M4A.75.pdf. <u>Doi: 10.1364/PHOTONICS.2014.M4A.75</u>

- Preeti Rani, Venus Dillu and R. K. Sinha (2014) 'Field enhanced plexitonic coupling between InAs quantum dots and silver film: Highly sensitive plasmonic composite', SPIE Optics + Photonics 2014 (Proc. SPIE 9163, Plasmonics:

Metallic Nanostructures and Their Optical Properties XII, 91630W) 10 September 2014, San Diego USA: SPIE, pp 9163. <u>Doi: 10.1117/12.2061914</u>

- Preeti Rani, Yogita Kalra, and R. K. Sinha, (2015) 'Slow Light effect in pinch waveguide in photonic crystal', SPIE Optics + Photonic 2015 (SPIE. Proc. SPIE 9586, Photonic Fiber and Crystal Devices: Advances in Materials and Innovations in Device Applications IX, 95860X) August 26, 2015, San Diego USA. <u>Doi: 10.1117/12.2187322</u>

- Preeti Rani, Reena Dalal, Yogita Kalra, and R. K. Sinha, (2015) 'Polarization splitter in silicon-on-insulator photonic crystal; design and simulation', Frontiers in Optics 2054/Laser Science XXIX © OSA 2014, October 18-22, 2015, San Jose, California, USA: Optical Society of America, pp. FTu2B.5.pdf. Doi: 10.1364/FIO.2015.FTu2B.5

- Reena Dalal, Preeti Rani, Yogita Kalra and R. K. Sinha, (2015) 'Zero back scattering by ellipsoidal single nanoparticle', Frontiers in Optics 2054/Laser Science XXIX © OSA 2014, October 18-22, 2015, San Jose, California, USA: Optical Society of America, pp. JW2A.77.pdf. <u>Doi: 10.1364/FIO.2015.JW2A.77</u>

- Ashwini Agrawal, Preeti Rani, Yogita Kalra, and R. K. Sinha, (2016) 'Enhanced imaged resolution in photonic crystal structure by modification of the surface structure', SPIE Optics + Photonic 2016 (SPIE. Proc. SPIE 9958, Photonic Fiber and Crystal Devices: Advances in Materials and Innovations in Device Applications X, 99580G) September 7, 2016, San Diego USA. Doi: 10.1117/12.2237767

- Shiba Fatima, Preeti Rani, Yogita Kalra, and R. K. Sinha, (2016) 'Design of AND optical logic gate using NAND gate in photonic crystal waveguides', SPIE Optics + Photonic 2016 (SPIE. Proc. SPIE 9958, Photonic Fiber and Crystal Devices: Advances in Materials and Innovations in Device Applications X, 99580U) September 7, 2016, San Diego USA. <u>Doi: 10.1117/12.2237777</u>

# CONTENTS

|                                                     | •     |

|-----------------------------------------------------|-------|

| Declaration                                         | i     |

| Certificate                                         | iii   |

| Acknowledgement                                     | vii   |

| Abstract                                            | ix    |

| List of Publications                                | xi    |

| Contents                                            | XV    |

| List of Figures                                     | xxi   |

| List of Tables                                      | xxvii |

| List of Acronyms                                    | xxix  |

|                                                     |       |

| 1. Introduction                                     | 1-14  |

| 1.1 Introduction                                    | 1     |

| 1.2 Literature review                               | 1     |

| 1.2.1 Photonic crystals                             | 1     |

| 1.2.2 Optical logic gates                           | 8     |

| 1.2.3 Slow light                                    | 8     |

| 1.3 Methods of fabrication                          | 9     |

| 1.4 Outline of thesis                               | 10    |

| 1.4.1 Computational methods                         | 11    |

| 1.4.1.1 Plane Wave Expansion (PWE) Method           | 11    |

| 1.4.1.2 Finite Difference Time Domain (FDTD) Method | 11    |

#### Contents

|    | 1.4.1.3 Finite Element Method (FEM)                                  | 12    |

|----|----------------------------------------------------------------------|-------|

| 2. | Design of optical logic AND gates in Y shaped photonic crystal       |       |

|    | Waveguides                                                           | 15-32 |

|    | 2.1 Introduction                                                     | 15    |

|    | 2.2 Design and analysis of AND logic gates                           | 16    |

|    | 2.2.1 AND logic gate based on AHS with material waveguide            | 17    |

|    | 2.2.1.1 Model and operating principle                                | 17    |

|    | 2.2.1.2 Optimization of the radius of the air hole at the            |       |

|    | centre of the three waveguides                                       | 20    |

|    | 2.2.1.3 Results and discussion for AHS with material                 |       |

|    | waveguide based AND optical logic gate                               | 21    |

|    | 2.2.2 AND logic gate based on AHS with air waveguide                 | 23    |

|    | 2.2.2.1 Model and operating principle                                | 23    |

|    | 2.2.2.2 Optimization of the radius of the air hole at the            |       |

|    | centre of the three air waveguides                                   | 24    |

|    | 2.2.2.3 Results and discussion for AHS with air                      |       |

|    | waveguide based AND optical logic gate                               | 25    |

|    | 2.2.3 AND logic gate based on SRA structure                          | 27    |

|    | 2.2.3.1 Model and operating principle                                | 27    |

|    | 2.2.3.2 Optimization of the radius of the Si rod at the              |       |

|    | centre of the three air waveguides                                   | 28    |

|    | 2.2.3.3 Results and discussion for SRA structure                     | 29    |

| 4  | 2.3 Comparison study of AND optical logic gates                      | 31    |

| 4  | 2.4 Conclusions                                                      | 32    |

| 3. | Realization of all-optical logic gates in photonic crystal waveguide | 33-47 |

|    | 3.1 Introduction                                                     | 33    |

#### Contents

|   | 3.2 Structure design and operating principle of all-optical logic gates                                                                                                                                                                                                                                                                                                                                                                          | 34                                        |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|   | 3.3 Optimization of the radius of the hole at the centre of the four                                                                                                                                                                                                                                                                                                                                                                             |                                           |

|   | waveguides                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37                                        |

|   | 3.4 Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                       | 37                                        |

|   | 3.4.1 For AND gate                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                        |

|   | 3.4.2 For OR gate                                                                                                                                                                                                                                                                                                                                                                                                                                | 39                                        |

|   | 3.4.3 For XOR gate                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                        |

|   | 3.4.4 For NOT gate                                                                                                                                                                                                                                                                                                                                                                                                                               | 42                                        |

|   | 3.4.5 For NAND gate                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                                        |

|   | 3.4.6 For NOR gate                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                                        |

|   | 3.4.7 For XNOR gate                                                                                                                                                                                                                                                                                                                                                                                                                              | 45                                        |

|   | 3.5 Response Time                                                                                                                                                                                                                                                                                                                                                                                                                                | 46                                        |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

|   | 3.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47                                        |

| 4 | 3.6 Conclusion<br>I. Polarization independent all-optical logic gates in silicon-on-                                                                                                                                                                                                                                                                                                                                                             | 47                                        |

| 4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47<br>49-67                               |

| 4 | I. Polarization independent all-optical logic gates in silicon-on-                                                                                                                                                                                                                                                                                                                                                                               |                                           |

| 4 | l. Polarization independent all-optical logic gates in silicon-on-<br>insulator photonic crystal                                                                                                                                                                                                                                                                                                                                                 | 49-67                                     |

| 4 | <ul> <li>Polarization independent all-optical logic gates in silicon-on-<br/>insulator photonic crystal</li> <li>4.1 Introduction</li> </ul>                                                                                                                                                                                                                                                                                                     | 49-67<br>49                               |

| 4 | <ul> <li>4. Polarization independent all-optical logic gates in silicon-on-<br/>insulator photonic crystal</li> <li>4.1 Introduction</li> <li>4.2 Device design, optimization and simulation results</li> </ul>                                                                                                                                                                                                                                  | 49-67<br>49<br>50                         |

| 4 | <ul> <li>A. Polarization independent all-optical logic gates in silicon-on-<br/>insulator photonic crystal</li> <li>4.1 Introduction</li> <li>4.2 Device design, optimization and simulation results</li> <li>4.2.1 For AND optical logic gate</li> </ul>                                                                                                                                                                                        | 49-67<br>49<br>50<br>51                   |

| 4 | <ul> <li>A. Polarization independent all-optical logic gates in silicon-on-<br/>insulator photonic crystal</li> <li>4.1 Introduction</li> <li>4.2 Device design, optimization and simulation results</li> <li>4.2.1 For AND optical logic gate</li> <li>4.2.1.1 Design</li> </ul>                                                                                                                                                                | 49-67<br>49<br>50<br>51                   |

| 4 | <ul> <li>A. Polarization independent all-optical logic gates in silicon-on-<br/>insulator photonic crystal</li> <li>4.1 Introduction</li> <li>4.2 Device design, optimization and simulation results</li> <li>4.2.1 For AND optical logic gate</li> <li>4.2.1.1 Design</li> <li>4.2.1.2 Optimization of the radius of the central hole for</li> </ul>                                                                                            | 49-67<br>49<br>50<br>51<br>51             |

| 4 | <ul> <li>A. Polarization independent all-optical logic gates in silicon-on-<br/>insulator photonic crystal</li> <li>4.1 Introduction</li> <li>4.2 Device design, optimization and simulation results</li> <li>4.2.1 For AND optical logic gate</li> <li>4.2.1.1 Design</li> <li>4.2.1.2 Optimization of the radius of the central hole for<br/>AND optical logic gate</li> </ul>                                                                 | 49-67<br>49<br>50<br>51<br>51<br>52       |

| 4 | <ul> <li>4. Polarization independent all-optical logic gates in silicon-on-<br/>insulator photonic crystal</li> <li>4.1 Introduction</li> <li>4.2 Device design, optimization and simulation results</li> <li>4.2.1 For AND optical logic gate</li> <li>4.2.1.1 Design</li> <li>4.2.1.2 Optimization of the radius of the central hole for<br/>AND optical logic gate</li> <li>4.2.1.3 Simulation results and discussion for AND gate</li> </ul> | 49-67<br>49<br>50<br>51<br>51<br>52<br>53 |

4.2.2.2 Optimization of the radius of the central hole for

#### Contents

| all optical logic gates                                           | 57    |

|-------------------------------------------------------------------|-------|

| 4.2.2.3 Results and discussion                                    | 57    |

| 4.2.2.3.1 AND gate                                                | 58    |

| 4.2.2.3.2 OR gate                                                 | 61    |

| 4.2.2.3.3 NOT gate                                                | 62    |

| 4.2.2.3.4 NAND gate                                               | 63    |

| 4.2.2.3.5 NOR gate                                                | 64    |

| 4.2.2.3.6 XOR gate                                                | 64    |

| 4.2.2.3.7 XNOR gate                                               | 65    |

| 4.3 Conclusion                                                    | 67    |

| 5. Time and wavelength de-multiplexer in slotted photonic         |       |

| crystal waveguide on SOI platform                                 | 69-81 |

| 5.1 Introduction                                                  | 69    |

| 5.2 Structure design                                              |       |

| 5.3 Optimization of slotted structure                             | 73    |

| 5.4 Results and discussion                                        | 74    |

| 5.4.1 Applications                                                | 76    |

| 5.4.1.1 Optical Buffer                                            | 76    |

| 5.4.1.2 Time and wavelength division de-multiplexer               | 79    |

| 5.5 Conclusion                                                    | 81    |

| 6. Polarization splitter on silicon-on-insulator photonic crystal |       |

| platform                                                          | 83-91 |

| 6.1 Introduction                                                  | 83    |

| 6.2 Structure design and analysis                                 | 84    |

| 6.3 Results and discussion                                        | 88    |

| 6.4 Conclusion                                                    | 91    |

# 7.1 Summary and Future Scope93-95References97-108Brief bio-data of the author109-110

Contents

# **LIST OF FIGURES**

| Figure 1.1 | Types of photonic crystals                                                                                                                        |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 | Schematic representation of point defect and line defect in photonic crystal                                                                      | 5  |

| Figure 1.3 | Dispersion relation showing defect mode within the band gap range                                                                                 | 6  |

| Figure 1.4 | Schematic filed distribution showing propagation of defect mode in photonic crystal waveguide                                                     | 6  |

| Figure 1.5 | Schematic representations of (a) dielectric cylinders in air and (b) air holes in dielectric medium                                               | 7  |

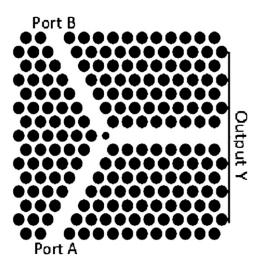

| Figure 2.1 | Schematic of all-optical AND logic gate based on AHS structure with material waveguide                                                            | 18 |

| Figure 2.2 | Band gap of the photonic crystal structure composed of air holes in silicon with material waveguide                                               | 19 |

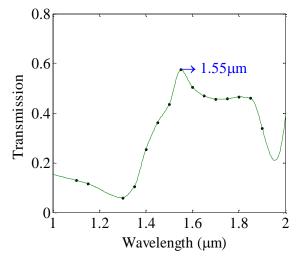

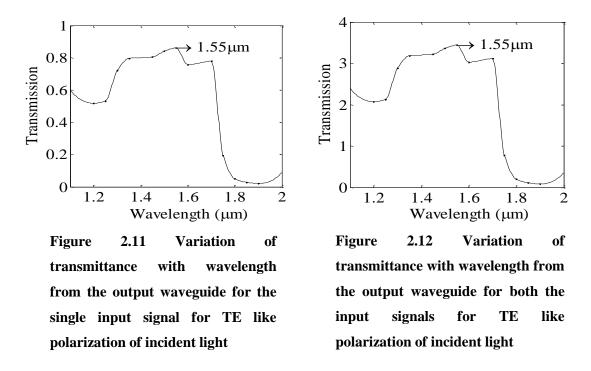

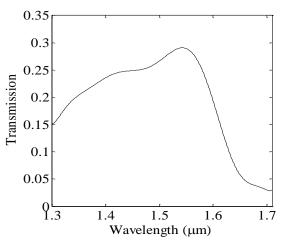

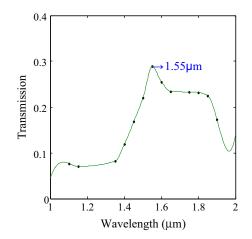

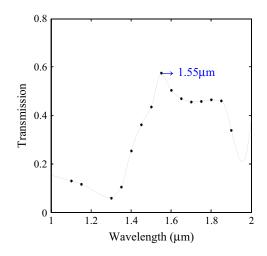

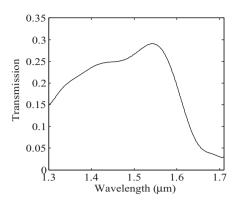

| Figure 2.3 | Variation of transmittance with wavelength from the output<br>waveguide for the single input signal for TE like polarization<br>of incident light | 19 |

| Figure 2.4 | Variation of transmittance with wavelength from the output<br>waveguide for both the input signals for TE like polarization of<br>incident light  | 19 |

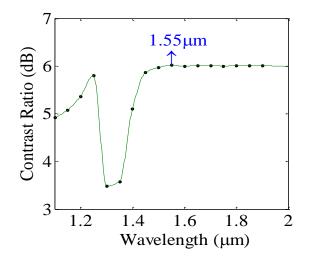

| Figure 2.5 | Contrast ratio versus the normalized operating wavelength                                                                                         | 20 |

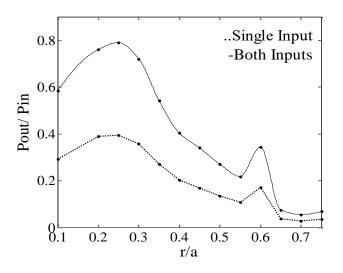

| Figure 2.6 | Power transmittance versus normalized radius of the central air<br>hole at the centre of the three material waveguides in AHS<br>structure        | 20 |

| Figure 2.7 | Field distributions at steady state of the AND logic gate based<br>on AHS structure with material waveguide for (a) A=1, B=0                      |    |

List of figures

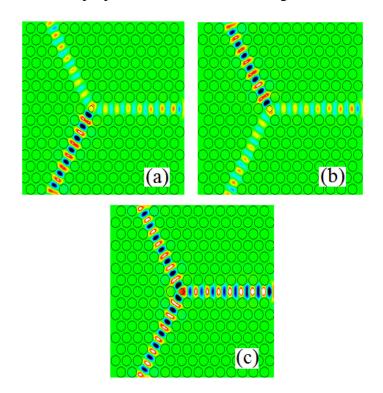

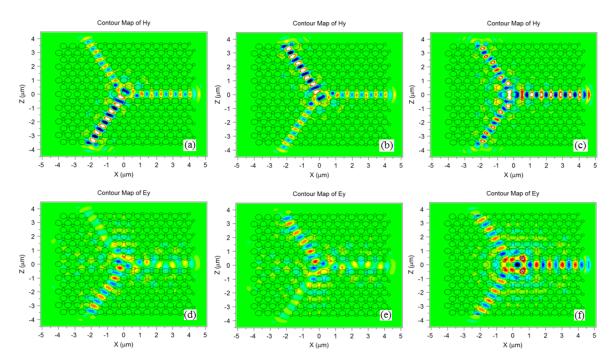

|             | (b) A=0, B=1 (c) A=1, B=1                                                                                                                                                                                                              | 22 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

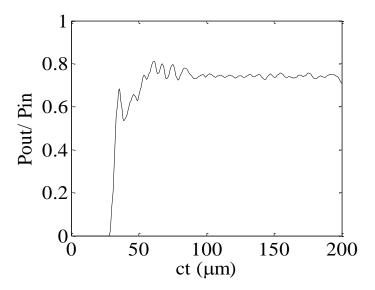

| Figure 2.8  | Time evolving curve of the output power for AHS structure with material waveguide                                                                                                                                                      | 23 |

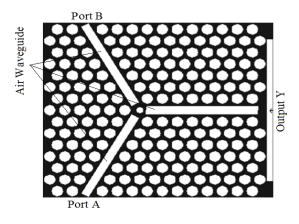

| Figure 2.9  | Schematic of all-optical AND logic gate for air holes in silicon with air waveguide                                                                                                                                                    | 23 |

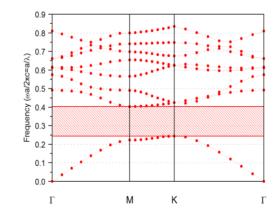

| Figure 2.10 | Band gap of the photonic crystal structure composed of air holes in silicon with air waveguide                                                                                                                                         | 23 |

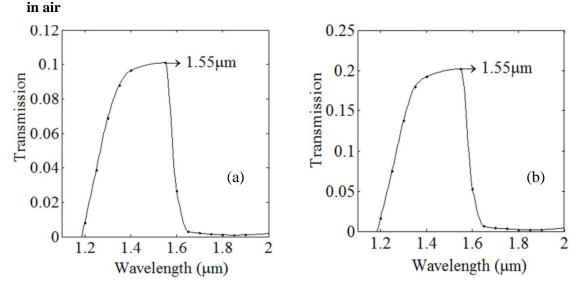

| Figure 2.11 | Variation of transmittance with wavelength from the output<br>waveguide for the single input signal for TE like polarization<br>of incident light                                                                                      | 24 |

| Figure 2.12 | Variation of transmittance with wavelength from the output<br>waveguide for both the input signals for TE like polarization of<br>incident light                                                                                       | 24 |

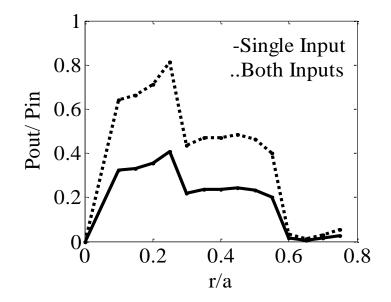

| Figure 2.13 | Power transmittance versus the normalized radius for air hole<br>at the centre of the three air waveguides in AHS structure                                                                                                            | 25 |

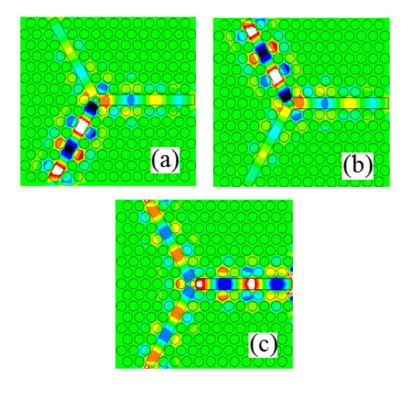

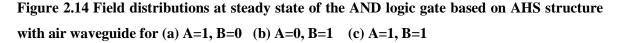

| Figure 2.14 | Field distributions at steady state of the AND logic gate based<br>on AHS structure with air waveguide for (a) A=1, B=0<br>(b) A=0, B=1 (c) A=1, B=1                                                                                   | 26 |

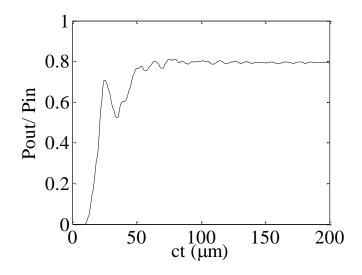

| Figure 2.15 | Time evolving curve of the output power for AHS structure with air waveguide                                                                                                                                                           | 27 |

| Figure 2.16 | Schematic of all-optical AND logic gate for Si rods in air                                                                                                                                                                             | 28 |

| Figure 2.17 | Band gap of the photonic crystal structure composed of Si rods in air                                                                                                                                                                  | 28 |

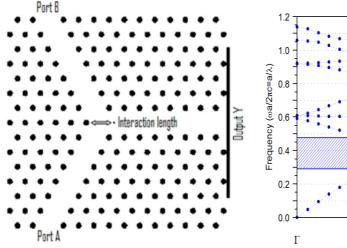

| Figure 2.18 | Variation of transmittance with wavelength from the output<br>waveguide for (a) the single input signal for TM like<br>polarization of incident light and (b) for both the input signals<br>for TM like polarization of incident light | 28 |

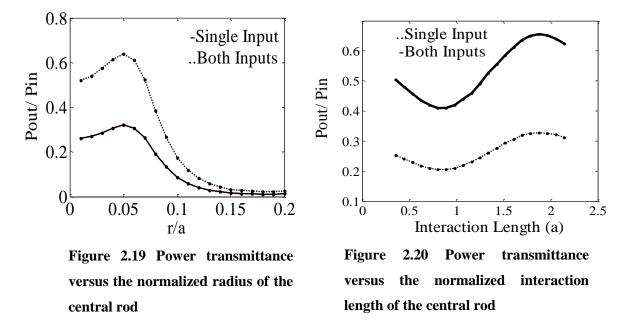

| Figure 2.19 | Power transmittance versus the normalized radius of the<br>central rod 29                                                                                                                                                                                             |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

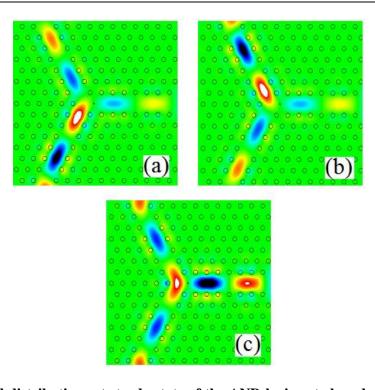

| Figure 2.20 | Power transmittance versus the normalized interaction length of the central rod                                                                                                                                                                                       | 29 |

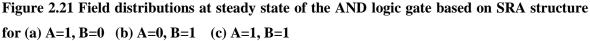

| Figure 2.21 | Field distributions at steady state of the AND logic gate based<br>on SRA structure for (a) A=1, B=0 (b) A=0, B=1 (c) A=1,<br>B=1                                                                                                                                     | 30 |

| Figure 2.22 | Time evolving curve of the output power for SRA structure                                                                                                                                                                                                             | 31 |

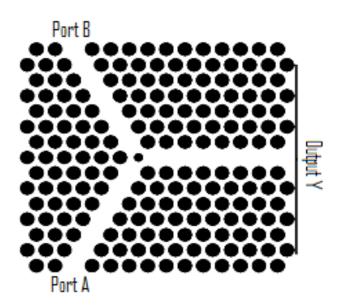

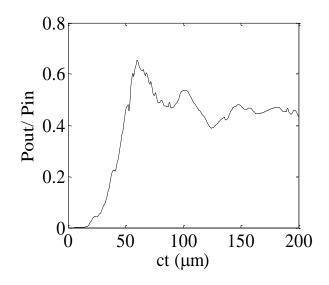

| Figure 3.1  | Schematic representation of all-optical logic gates                                                                                                                                                                                                                   | 35 |

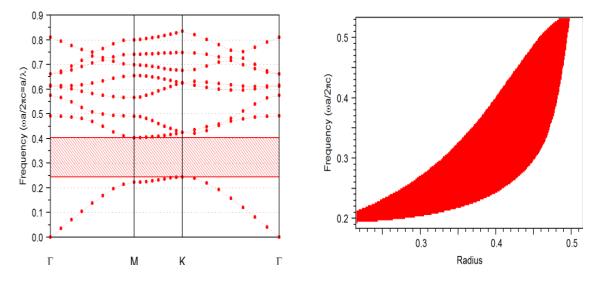

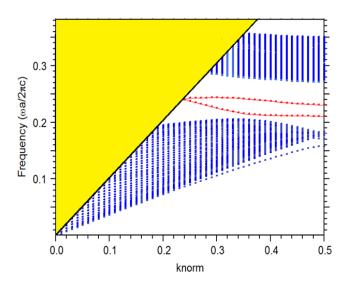

| Figure 3.2  | Band gap of the photonic crystal structure composed of air holes in silicon                                                                                                                                                                                           | 35 |

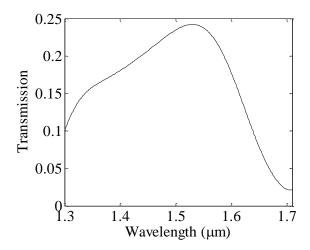

| Figure 3.3  | Variation of transmittance with wavelength from the output<br>waveguide for the single input signal along with the reference<br>signal for TE like polarization of incident light                                                                                     | 36 |

| Figure 3.4  | Variation of transmittance with wavelength from the output<br>waveguide for both the input signals along with the reference<br>signal for TE like polarization of incident light                                                                                      | 36 |

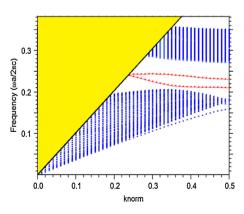

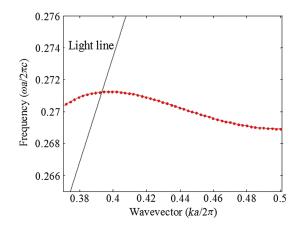

| Figure 3.5  | Dispersion relation for all the four involved PhC waveguides.<br>The black solid line corresponds to the light line and the red<br>dotted lines inside the band gap region correspond to the<br>respective guided modes for TE polarization in all the<br>waveguides. | 36 |

| Figure 3.6  | Normalized power transmittance versus the normalized radius<br>of the central hole at the centre of the four PhC waveguides                                                                                                                                           | 37 |

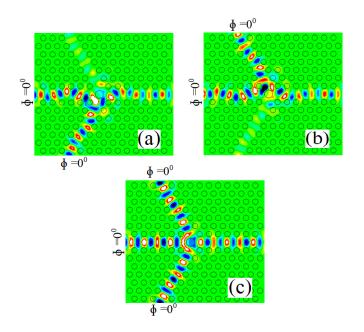

| Figure 3.7  | Field distributions at steady state of the AND logic gate for<br>(a) A=1, B=0, R=1 (b) A=0, B=1, R=1 (c) A=1, B=1, R=1                                                                                                                                                | 38 |

| Figure 3.8  | Field distributions at steady state of the OR logic gate for                                                                                                                                                                                                          |    |

xxiii

List of figures

(a)

$$A=1$$

,  $B=0$ ,  $R=1$  (b)  $A=0$ ,  $B=1$ ,  $R=1$  (c)  $A=1$ ,  $B=1$ ,  $R=1$  40

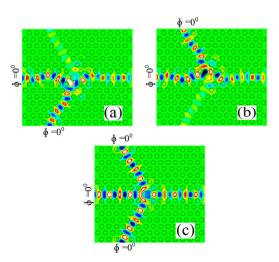

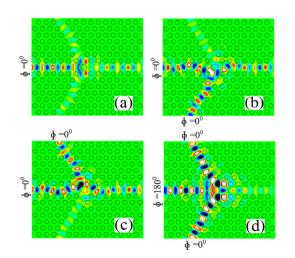

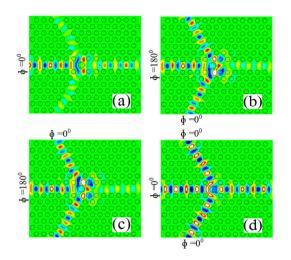

- Figure 3.9Field distributions at steady state of the XOR logic gate for(a) A=1, B=0, R=1(b) A=0, B=1, R=1(c) A=1, B=1, R=141

- Figure 3.10Field distributions at steady state of the NOT logic gate for<br/>(a) A=1, R=1<br/>(b) A=0, R=142

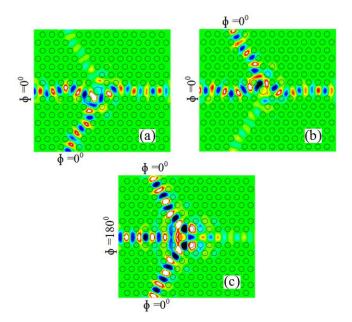

- Figure 3.11

Field distributions at steady state of the NAND logic gate for

(a) A=0, B=0, R=1

(b) A=1, B=0, R=1

(c) A=0, B=1, R=1

44

(d) A=1, B=1, R=1

44

- Figure 3.12 Field distributions at steady state of the NOR logic gate for (a) A=0, B=0, R=1 (b) A=1, B=0, R=1 (c) A=0, B=1, R=1 45 (d) A=1, B=1, R=1

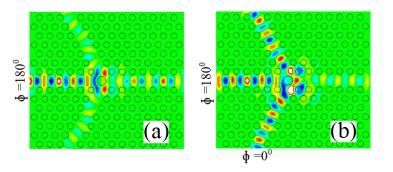

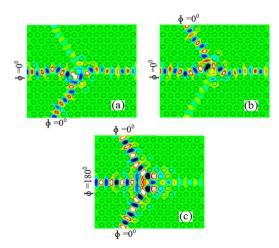

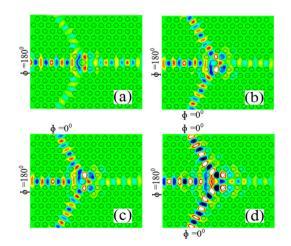

- Figure 3.13

Field distributions at steady state of the XNOR logic gate for

(a) A=0, B=0, R=1

(b) A=1, B=0, R=1

(c) A=0, B=1, R=1

46

(d) A=1, B=1, R=1

46

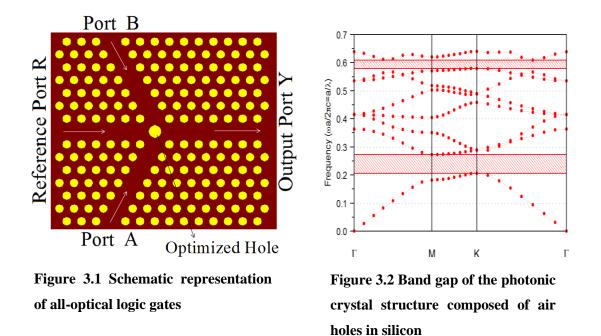

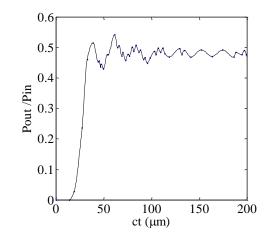

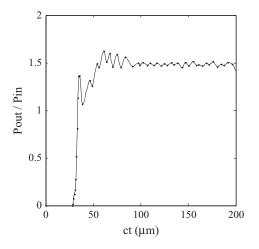

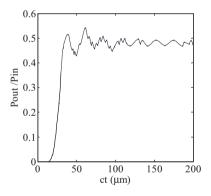

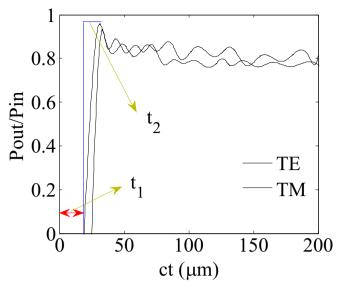

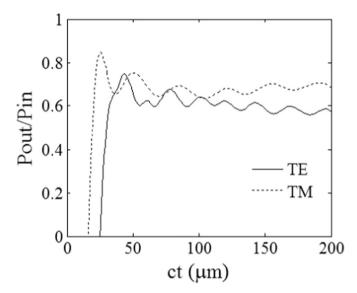

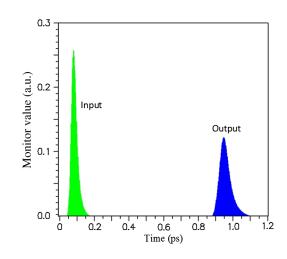

#### Figure 3.14Time evolution curve of the output power47

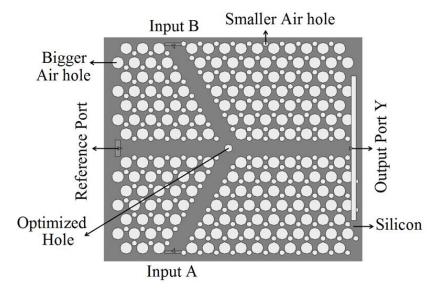

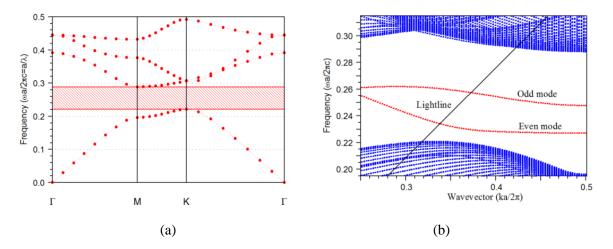

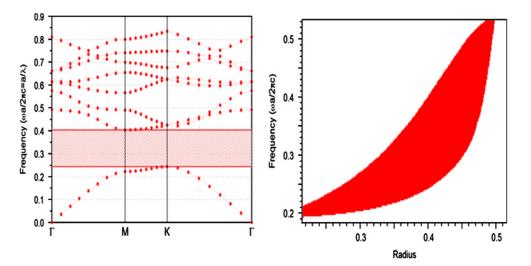

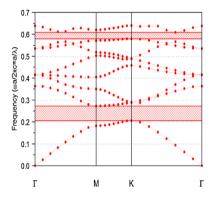

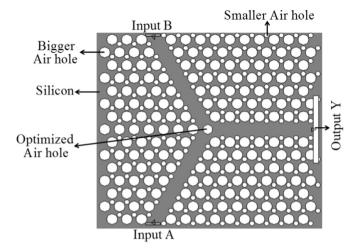

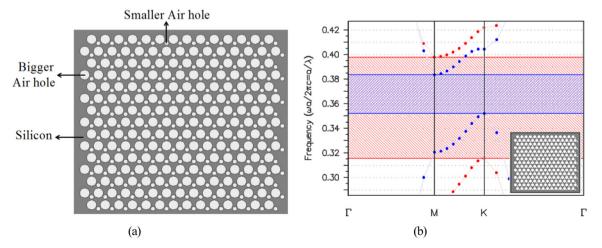

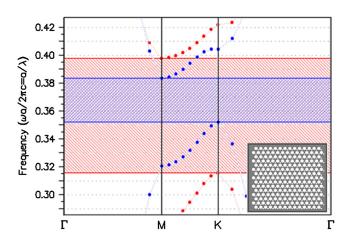

- Figure 4.1 (a)Schematic representation of honey comb photonic crystal (b) complete band gap for honey comb lattice arrangement 51 where red curves correspond to the TE modes and blue curves correspond to the TM modes

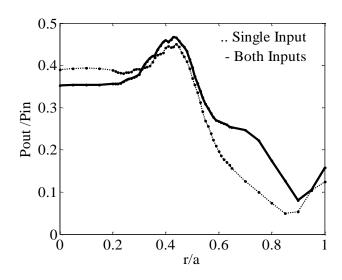

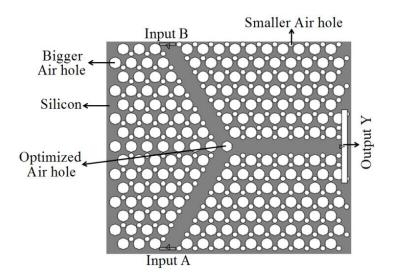

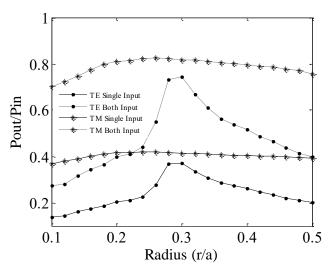

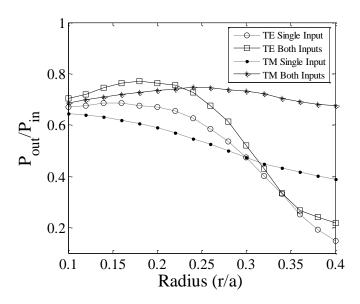

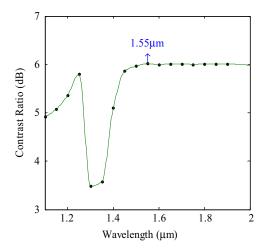

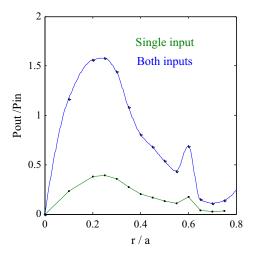

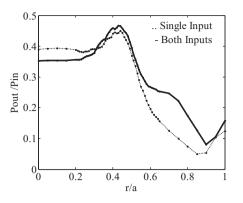

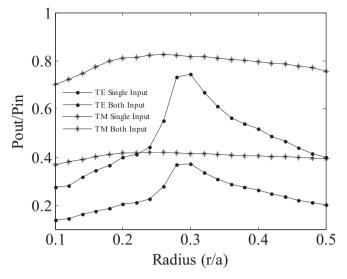

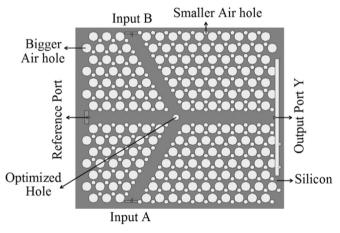

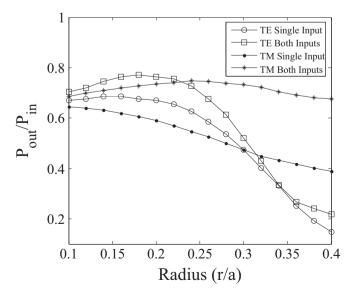

- Figure 4.2Schematic representation of AND optical logic gate52Figure 4.3Power transmittance with radius of central hole both for TEand TM much with memory to the single input and both input 52

and TM mode with respect to the single input and both inputs

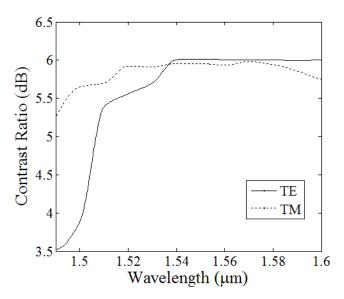

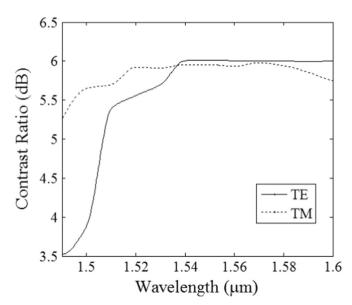

- Figure 4.4Contrast ratio for both TE and TM polarizations in the<br/>complete band gap range53

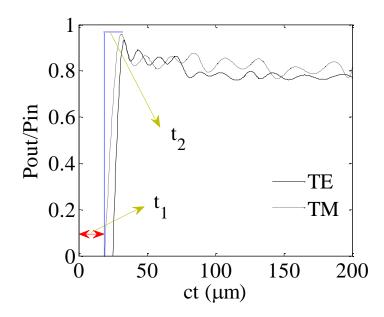

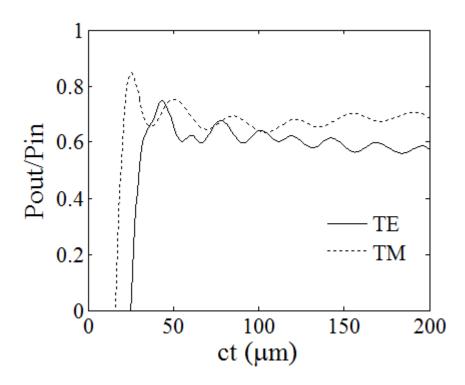

- Figure 4.5Response time in terms of time evolution of the output power<br/>for both TE and TM polarizations54

- Figure 4.6 Field distributions at steady state of the AND logic gate at

1.55

$$\mu$$

m wavelength for TE polarization at (a) A=1, B=0

(b) A=0, B=1 (c) A=1, B=1 and for TM polarization at

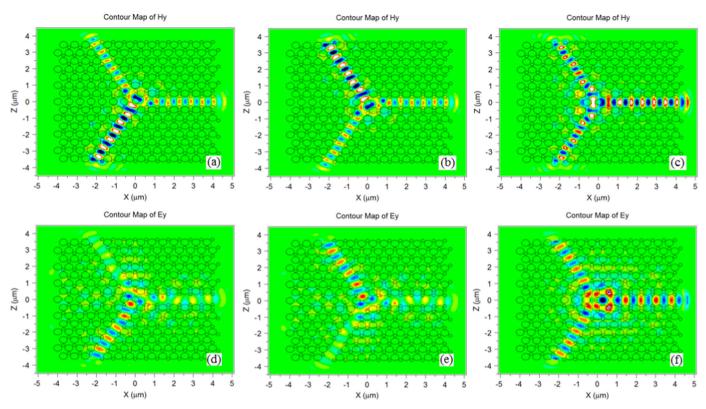

(d) A=1, B=0 (e) A=0, B=1 (f) A=1, B=1 55

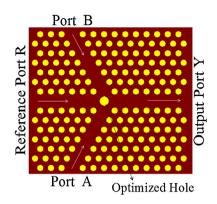

#### **Figure 4.7** Schematic representation of all optical logic gates

56

- Figure 4.8Power transmittance versus radius of central hole for all<br/>optical logic gates for both TE and TM polarized modes with<br/>respect to the single input and both inputs along with the<br/>reference/control signal

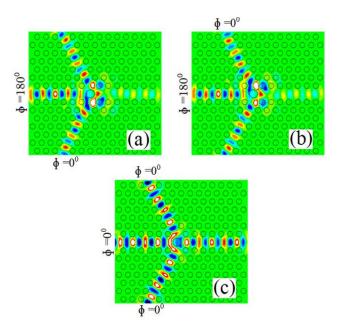

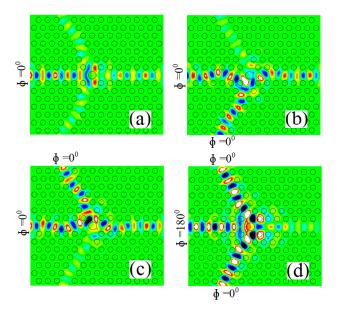

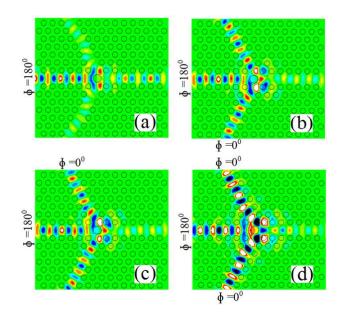

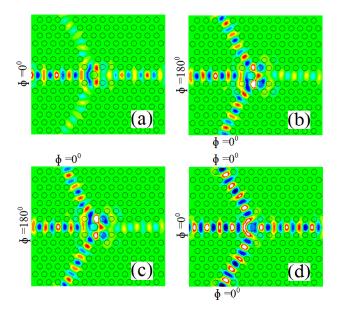

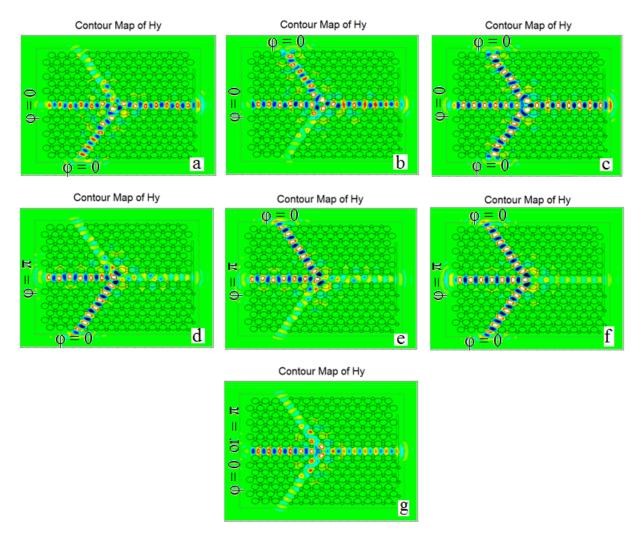

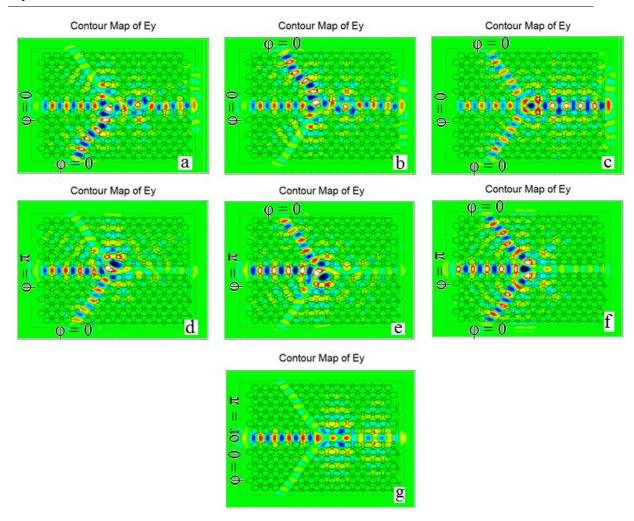

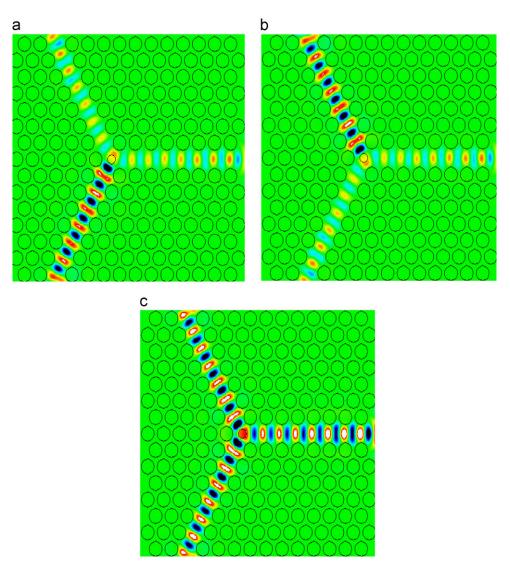

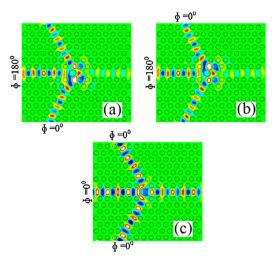

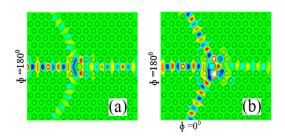

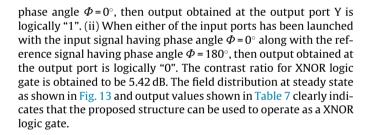

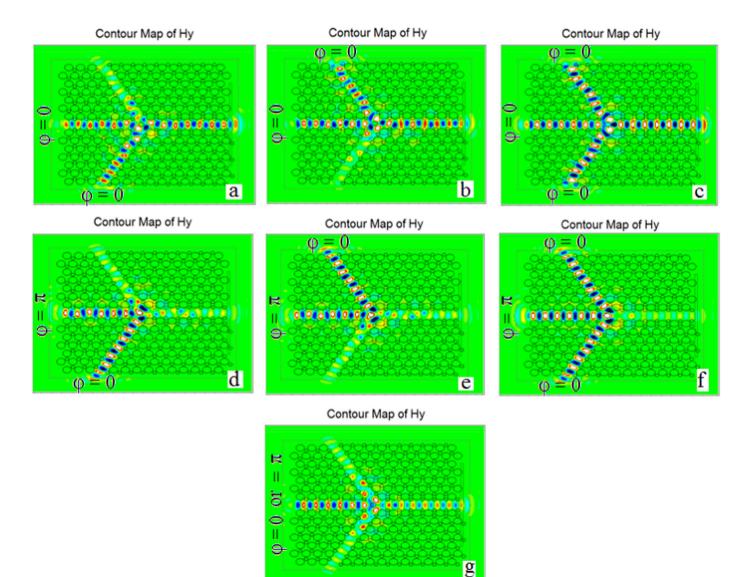

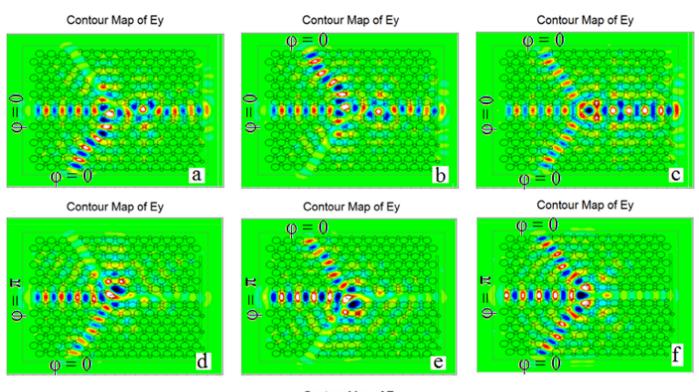

- **Figure 4.9** Field distributions at steady state for all optical logic gates at 1.55µm wavelength for TE like polarization at (a) A = 1, B = 0 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = 0^{\circ}$  (b) A = 0, B = 1 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = 0^{\circ}$  (c) A = 1, B = 1 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = 0^{\circ}$  (d) A = 1, 59 B = 0 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = \pi$  (e) A = 0, B = 1 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = \pi$  (f) A = 1, B = 1 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = \pi$ (g) A = 0, B = 0, R = 1 at  $\varphi = 0^{\circ} \text{ or } \pi$

- **Figure 4.10** Field distributions at steady state for all optical logic gates at 1.55µm wavelength for TM like polarization at (a) A = 1,B = 0at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = 0^{\circ}$  (b) A = 0, B = 1 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = 0^{\circ}$  (c) A = 1, B = 1 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = 0^{\circ}$  (d) A = 1, 60 B = 0 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = \pi$  (e) A = 0, B = 1 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = \pi$  (f) A = 1, B = 1 at  $\varphi = 0^{\circ}$ , R = 1 at  $\varphi = \pi$ (g) A = 0, B = 0, R = 1 at  $\varphi = 0^{\circ} or\pi$

- **Figure 4.11** Response time in terms of time evolution of the output power for all optical logic gate design for both TE and TM polarizations

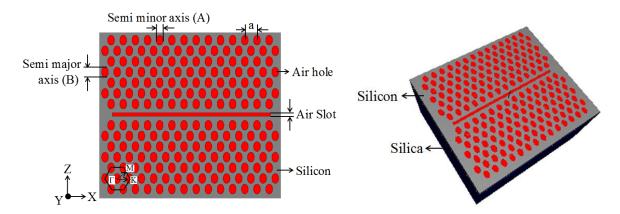

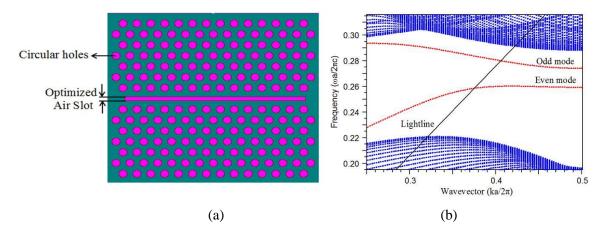

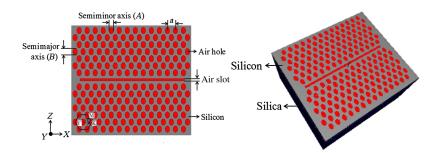

- Figure 5.1Schematic representation of the proposed optimized structure<br/>with an air slot and regular arrangement of elliptical air holes,

71

66

where A and B correspond to the radius of semi-minor axis and semi-major axis

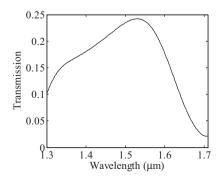

| Figure 5.2  | (a)Band gap for TE polarization (b) dispersion relation showing two modes (even and odd) below the light line lying within the band gap range for radius of air holes = $0.3a$ .                 | 72 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

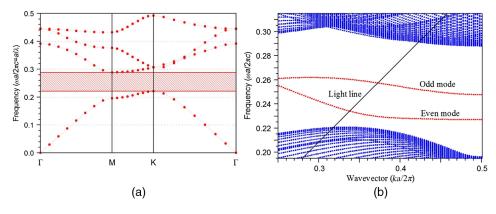

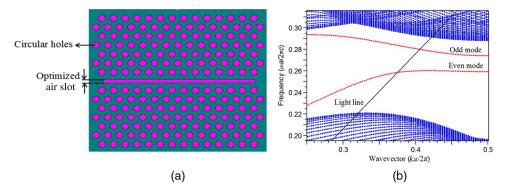

| Figure 5.3  | (a)Basic structure with optimized slot width in W1 PhC waveguide (b) dispersion relation showing two modes with flat band section below the light line for slotted waveguide of width $s = 0.3a$ | 72 |

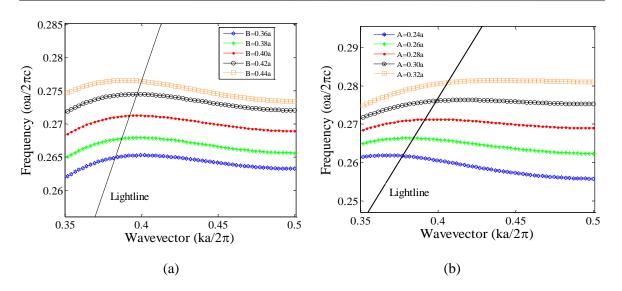

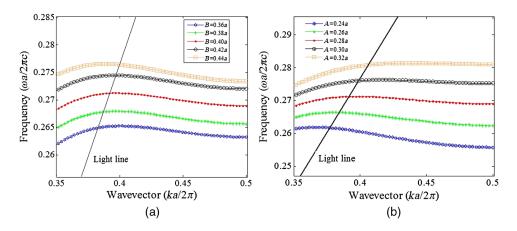

| Figure 5.4  | Variation of dispersion curve of slot even mode (a) when semi<br>minor axis A is fixed and semi major axis B is varied (b) when<br>semi major axis B is fixed and semi minor axis A is varied.   | 74 |

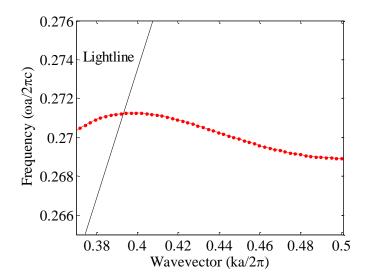

| Figure 5.5  | Dispersion relation representing the even mode for the optimized structure with values s=0.3a, A=0.28a and B=0.40a                                                                               | 74 |

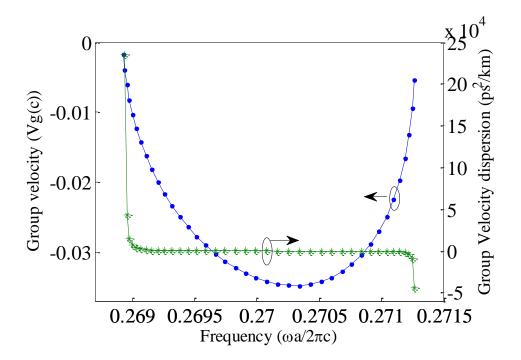

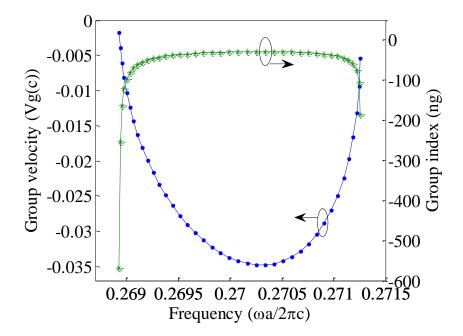

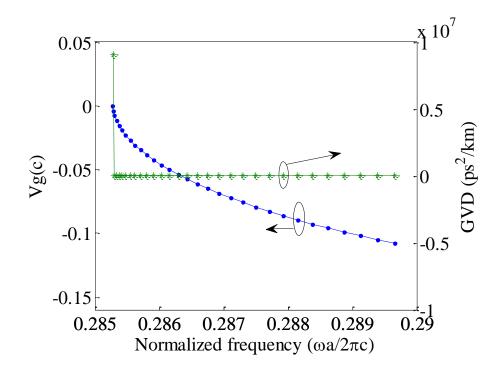

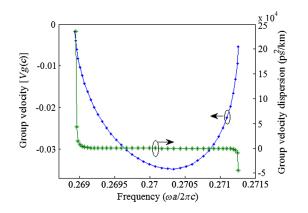

| Figure 5.6  | Variation of group velocity and group velocity dispersion with<br>respect to the normalized frequency of the optimized structure                                                                 | 76 |

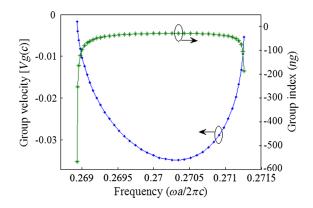

| Figure 5.7  | Variation of group velocity and group index with respect to the<br>normalized frequency of the optimized structure                                                                               | 78 |

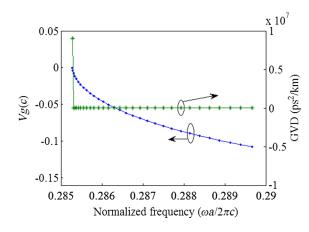

| Figure 5.8  | Variation of group velocity and group velocity dispersion with<br>respect to the normalized frequency of the optimized structure                                                                 | 79 |

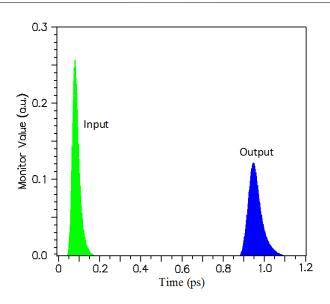

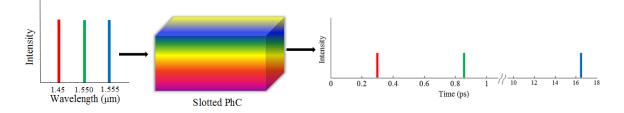

| Figure 5.9  | Time domain Gaussian optical pulse propagation in the slotted PhCW for $\lambda$ =1.55µm                                                                                                         | 80 |

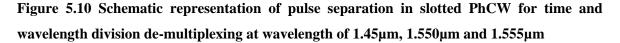

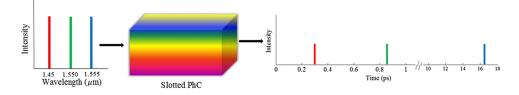

| Figure 5.10 | Schematic representation of pulse separation in slotted PhCW for time and wavelength division de-multiplexing at wavelength of $1.45\mu m$ , $1.550\mu m$ and $1.555\mu m$                       | 80 |

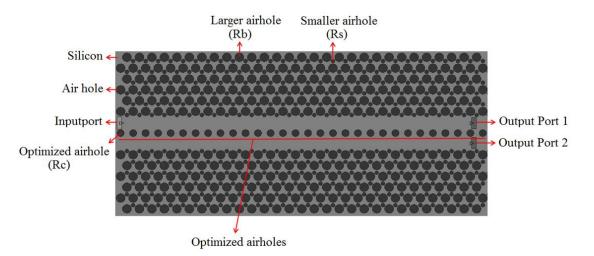

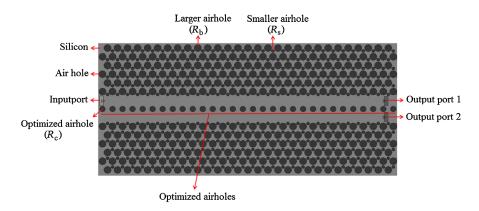

| Figure 6.1  | Schematic representation of the polarization splitter on SOI substrate where $R_b$ and $R_s$ represents the radius of the larger and smaller air holes and Rc represents the radius of the       | 84 |

optimized air holes separating the two waveguides

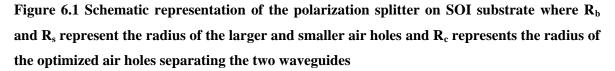

| Figure 6.2 | Photonic band diagram for the honey comb lattice                 |    |  |  |

|------------|------------------------------------------------------------------|----|--|--|

|            | arrangement, where red region corresponds to the TE              | 85 |  |  |

|            | polarization and blue region corresponds to the TM               |    |  |  |

|            | polarization                                                     |    |  |  |

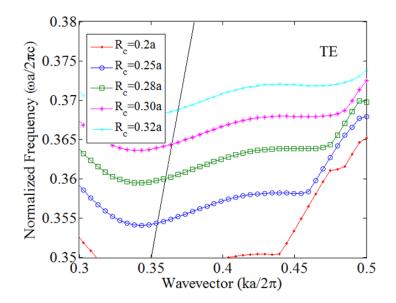

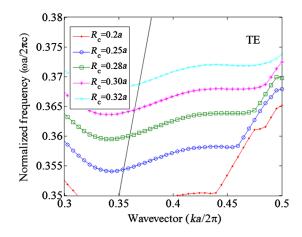

| Figure 6.3 | Dispersion relation of TE polarized modes with the radius of     |    |  |  |

|            | the central row of air holes separating the two waveguides 86    |    |  |  |

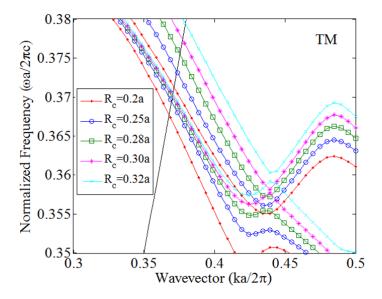

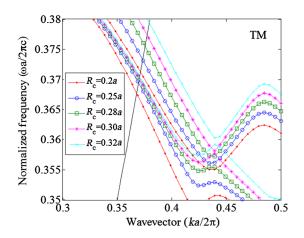

| Figure 6.4 | Dispersion relation of TM polarized modes with the radius of     |    |  |  |

|            | the central row of air holes separating the two waveguides       | 86 |  |  |

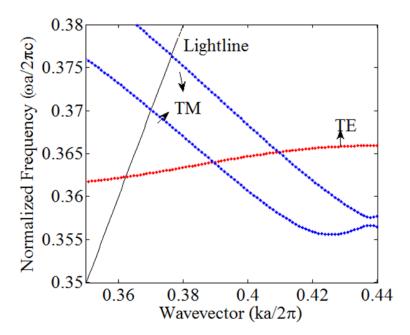

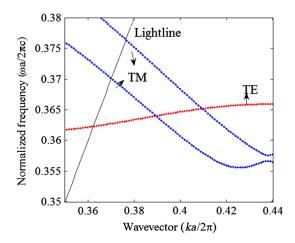

| Figure 6.5 | Dispersion relation at radius $Rc = 0.29a$ of the central row of |    |  |  |

|            | air holes separating the two waveguides for both the             |    |  |  |

|            | polarizations                                                    |    |  |  |

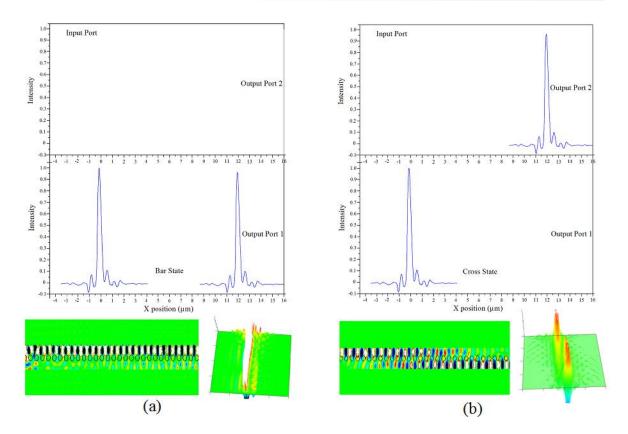

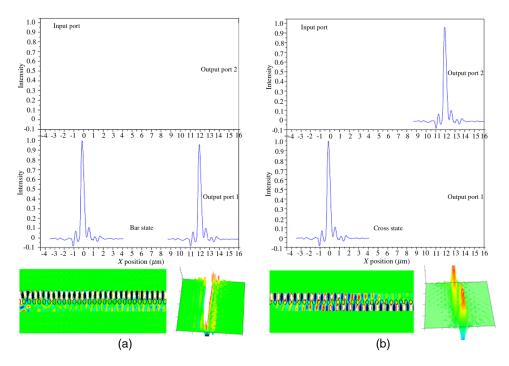

| Figure 6.6 | The intensity distribution at a distance of $12\mu m$ for (a) TE |    |  |  |

|            | polarization and (b) TM polarization                             | 88 |  |  |

xxvii

# **LIST OF TABLES**

| Table 2.1 | Truth table for AND logic gate based on AHS structure with material waveguide, where output Y is in terms of input power $P_a$                     | 21 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2 | Truth table for AND logic gate based on AHS structure with air waveguide, where output Y is in terms of input power $P_a$                          | 26 |

| Table 2.3 | Truth table for AND logic gate based on SRA structure where output Y is in terms of input power $P_a$                                              | 30 |

| Table 2.4 | Comparison between three structures                                                                                                                | 32 |

| Table 3.1 | Truth table for AND logic gate where output Y is in terms of input power $P_o$                                                                     | 39 |

| Table 3.2 | Truth table for OR logic gate where output Y is in terms of input power $P_{\rm o}$                                                                | 40 |

| Table 3.3 | Truth table for XOR logic gate where output Y is in terms of input power $P_o$                                                                     | 41 |

| Table 3.4 | Truth table for NOT logic gate where output Y is in terms of input power $P_o$                                                                     | 42 |

| Table 3.5 | Truth table for NAND logic gate where output Y is in terms of input power $P_o$                                                                    | 43 |

| Table 3.6 | Truth table for NOR logic gate where output Y is in terms of input power $P_o$                                                                     | 44 |

| Table 3.7 | Truth table for XNOR logic gate where output Y is in terms of input power $P_o$                                                                    | 46 |

| Table 4.1 | Truth table for AND optical logic gate for TE and TM polarizations at $1.55\mu m$ wavelength where output power Y is in terms of input power $P_a$ | 54 |

|           | in terms of input power 1 <sub>a</sub>                                                                                                             |    |

| Table 4.2 | Truth table for AND optical logic gate for TE and TM polarizations at $1.55\mu m$ wavelength where normalized output power Y is in terms of input power P <sub>a</sub>  | 61 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.3 | Truth table for OR optical logic gate for TE and TM polarizations at $1.55\mu m$ wavelength where normalized output power Y is in terms of input power P <sub>a</sub>   | 62 |

| Table 4.4 | Truth table for NOT optical logic gate for TE and TM polarizations at $1.55\mu m$ wavelength where normalized output power Y is in terms of input power P <sub>a</sub>  | 62 |

| Table 4.5 | Truth table for NAND optical logic gate for TE and TM polarizations at $1.55\mu m$ wavelength where normalized output power Y is in terms of input power P <sub>a</sub> | 63 |

| Table 4.6 | Truth table for NOR optical logic gate for TE and TM polarizations at $1.55\mu m$ wavelength where normalized output power Y is in terms of input power P <sub>a</sub>  | 64 |

| Table 4.7 | Truth table for XOR optical logic gate for TE and TM polarizations at $1.55\mu m$ wavelength where normalized output power Y is in terms of input power P <sub>a</sub>  | 65 |

| Table 4.8 | Truth table for XNOR optical logic gate for TE and TM polarizations at $1.55\mu m$ wavelength where normalized output power Y is in terms of input power P <sub>a</sub> | 66 |

| Table 5.1 | Comparison of time delay between two wavelengths at transmission length of 600µm                                                                                        | 81 |

| Table 6.1 | Comparison of the extinction ratio with wavelength for both TE and TM polarizations                                                                                     | 89 |

| Table 6.2 | Comparison of the insertion loss with wavelength for both TE and TM polarizations                                                                                       | 90 |

| Table 6.3 | Comparison of the excess loss with wavelength                                                                                                                           | 90 |

# LIST OF ACRONYMS

| AHS   | Air Holes in Silicon               |

|-------|------------------------------------|

| CAD   | Computer Aided Design              |

| CW    | Continuous Wave                    |

| DBP   | Delay Bandwidth Product            |

| FDTD  | Finite Difference Time Domain      |

| FEM   | Finite Element Method              |

| GVD   | Group Velocity Dispersion          |

| IL    | Insertion Loss                     |

| MZI   | Mach-Zehnder Interferometer        |

| NDBP  | Normalized Delay Bandwidth Product |

| PhCs  | Photonic crystals                  |

| PBG   | Photonic Band Gap                  |

| PWE   | Plane Wave Expansion               |

| PML   | Perfectly Matched Layer            |

| PhCW  | Photonic crystal waveguide         |

| SOI   | Silicon – on – Insulator           |

| Si    | Silicon                            |

| SPhCW | Slotted Photonic crystal waveguide |

| SRA   | Silicon Rods in Air                |

| SOA   | Semiconductor Optical Amplifier    |

|       | xxxi                               |

| SiO <sub>2</sub> | Silica                             |

|------------------|------------------------------------|

| S                | Slow Down Factor                   |

| TDM              | Time Division De-Multiplexer       |

| TE               | Transverse Electric                |

| TM               | Transverse Magnetic                |

| Т                | Transmittance                      |

| WDM              | Wavelength Division De-Multiplexer |

| 1D               | One Dimensional                    |

| 2D               | Two Dimensional                    |

| 3D               | Three Dimensional                  |

### **CHAPTER 1 Introduction**

#### **1.1 Introduction**

Photonics technology has become an attractive alternative to the electronic technology due to their several advantages over their counterparts. This includes larger bandwidth, high transmission, manipulation and storage of data using photons, low power consumption and reduced energy losses. The on-chip and chip-to-chip optical devices based on so called photonic crystals (PhCs) and quasi crystals pave a way towards faster signal processing. These highly periodic structures can be used to operate at the desired frequencies leading to the conception of all optical logic gates, switches, filters and transistors. The on-chip optical communication provides a path for transfer of information from one part of the microchip to another end by means of light propagation through optical waveguides, which in turn has improved the speed of optical communication. The highly developed micro and nano fabrication technology has now enabled the design and development of ultra compact on chip silicon integrated optical devices. In addition, a good progress has been made in the development of new technologies and techniques for producing controllable optical waveguides with slow group velocity. This also offers a robust platform for developing applications based on slow light techniques. The development of the subject and how it has convincingly become the platform of the present day technology has been briefly discussed below.

#### **1.2 Literature review**

#### **1.2.1 Photonic crystals**

Firstly, Lord Rayleigh in 1887 studied the propagation of electromagnetic waves in periodic media called as one dimensional (1D) photonic crystals. These structures exhibit a narrow band gap prohibiting light to propagate through the planes. About a century later, the designing of PhCs was proposed by Eli Yablonovitch and Sajeev John in 1987 [1, 2].

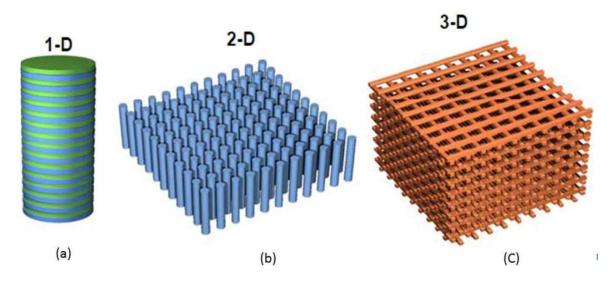

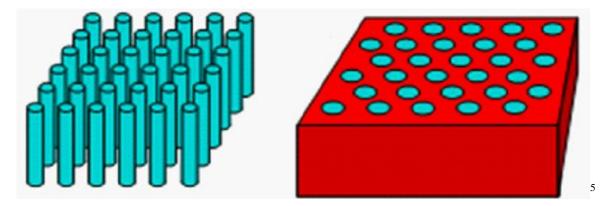

Photonic crystals [3] are the materials with refractive index periodicity that affect the propagation of electromagnetic waves in the same way as periodic potential in semiconductors affect the motion of electrons defined by allowed and forbidden energy bands. Depending on the periodicity they are categorized as one dimensional (1D), two dimensional (2D) and three dimensional (3D) PhCs as shown in figures 1.1(a), (b) and (c) respectively.

1D PhCs [4, 5] are alternating stacks of dielectric constants along the propagation direction and are useful in wide range of applications such as high reflection mirrors, stop band filters, anti reflecting coatings and cavities for distributed feedback lasers. A 2D PhCs are periodic array of dielectric constants along two directions while homogenous and infinite in a direction perpendicular to the plane of periodicity. A good example of 2D PhC is periodically arranged air holes in homogenous medium and dielectric rods in air. The 3D PhCs consist of regular periodicity of dielectric constants in all the three directions. PhCs also exist in nature, such as pattern on the wings of blue Morpho butterfly, feathers of peacock, fur of sea mouse and also occur in hard minerals (opals). Due to the difficulty in fabrication of 3D PhC structures more attention has been drawn on the development of 2D PhC slab structures. 2D PhCs are believed to be of great importance in integrated devices

<sup>&</sup>lt;sup>1</sup> Image: http://www.intechopen.com/books/advances-in-photonic-crystals/photonic-crystal-ring-resonator-based-optical-filters

with nanoscale features due to the existence of the photonic bandgap and easily available fabrication techniques. Photonic bandgap (PBG) is a band of frequencies within which light is prohibited from propagating inside the PhC. The band gap analysis and propagation of light in PhCs have been calculated by solving the Master equation [3] which is obtained by four Maxwell's equations in isotropic linear dielectric medium i.e.

$$\nabla \bullet \vec{B} = 0 \tag{1.1}$$

$$\vec{\nabla} \bullet \vec{D} = \rho \tag{1.2}$$

$$\vec{\nabla} \times \vec{E} = -\frac{\partial \vec{B}}{\partial t}$$

(1.3)

$$\vec{\nabla} \times \vec{H} = \frac{\partial \vec{D}}{\partial t} + \vec{J}$$

(1.4)

and the constitutive relations

$$\vec{J} = \sigma \vec{E} \tag{1.5}$$

$$\vec{D} = \varepsilon \vec{E}$$

(1.6)

$$\vec{B} = \mu \vec{H}$$

(1.7)

where,  $\vec{E}$  is the macroscopic electric field,  $\vec{H}$  is the magnetic field,  $\rho$  is the free charge density,  $\vec{J}$  is current density,  $\mathcal{E} = \mathcal{E}_0 \mathcal{E}_r$  is the permittivity in isotropic medium (where  $\mathcal{E}_0$  is the permittivity of vacuum and  $\mathcal{E}_r$  is the relative permittivity), and  $\mu = \mu_0 \mu_r$ , is the permeability (where  $\mu_0$  is the permeability in vacuum and  $\mu_r$  is the relative permeability).

The materials used in this work are non-magnetic insulators i.e.  $\rho = 0$ ,  $\vec{J} = 0$  and  $\sigma = 0$ , therefore equations (1.3) and (1.4) can be written as

$$\vec{\nabla} \times \vec{E}(r,t) = -\frac{\partial}{\partial t} \left[ \mu_0 \vec{H}(r,t) \right]$$

(1.8)

$$\vec{\nabla} \times \vec{H}(r,t) = \frac{\partial}{\partial t} \left[ \varepsilon_0 \varepsilon_r(r) \vec{E}(r,t) \right]$$

(1.9)

On taking curl of equation (1.9) and substituting the time derivative of equation (1.8) into it, equation (1.9) becomes:

$$\vec{\nabla} \times \left[ \frac{1}{\varepsilon_0 \varepsilon_r(r)} \vec{\nabla} \times \vec{H}(r, t) \right] = -\frac{\partial^2}{\partial t^2} \mu_0 \vec{H}(r, t)$$

(1.10)

The magnetic field in terms of harmonic modes can be written as:

$$\vec{H}(r,t) = \vec{H}(r)e^{-i\omega t}$$

(1.11)

Using equation (1.11), equation (1.10) becomes:

$$\vec{\nabla} \times \left[ \frac{1}{\varepsilon_0 \varepsilon_r(r)} \vec{\nabla} \times \vec{H}(r) \right] = \left( \frac{\omega}{c} \right)^2 \vec{H}(r)$$

(1.12)

where,  $c = \left\lfloor \frac{1}{\sqrt{\varepsilon_0 \mu_0}} \right\rfloor$  is the speed of light in vacuum. Equation (1.12) is known as the

master equation in terms of the magnetic field. The electric field can be calculated from

$$\vec{E}(r) = \frac{i}{\omega \varepsilon_0 \varepsilon_r} \vec{\nabla} \times \vec{H}(r)$$

(1.13)

The master equation can be analogously written in terms of electric field as:

$$\vec{\nabla} \times \vec{\nabla} \times \vec{E}(r) = \left(\frac{\omega}{c}\right)^2 \varepsilon_0 \varepsilon_r(r) \vec{E}(r)$$

(1.14)

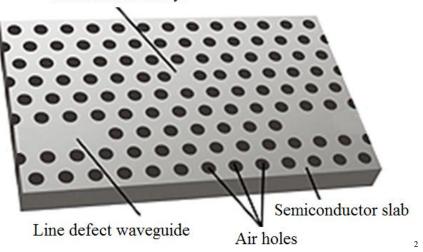

2D PhCs are of much interest not only due to the presence of photonic band gaps but due to the possibility of creation of localized defect states within the band gap region. The structural defects are classified as point defects i.e. cavity and extended defects/line defects i.e. waveguide [6-7] as shown in figure 1.2. The point defects can be created by locally modifying the refractive index, by changing the size of the patterns, by displacing one of the periodic patterns or by inserting a different pattern. The waveguides are alignment of identical point defects which are regularly spaced along the desired direction. Line defects

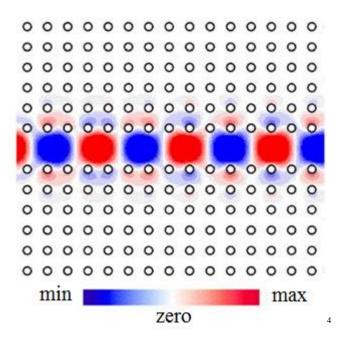

are sometimes called as defect doping (i.e. acceptor doping and donor doping) similar to impurity doping of semiconductors. In acceptor doping, the effective index at the lattice site is reduced either by replacing some higher index material with a lower index material or by increasing the size of air holes in a slab whereas, in donor doping the effective index at a lattice site is increased either by replacing some low index material with higher index material or by reducing the size of air holes in slab. These defect sites create defect associated photon states or defect modes in the band gap region as shown in figure 1.3. These defect modes are analogous to the impurity or dopant states between the conduction band and valence band of the semiconductor. A light wave with defect mode frequency does not leak out in the surrounding periodic medium and propagates inside the photonic crystal waveguide as shown in figure 1.4. The loss in the waveguide depends on its width approximately as  $1/(width)^2$ .

Point defect cavity

Fig.1.2 Schematic representation of point defect and line defect in photonic crystal

<sup>&</sup>lt;sup>2</sup> Image : https://www.ntt-review.jp/archive/ntttechnical.php?contents=ntr201108ra1.html

Fig. 1.3 Dispersion relation showing defect mode within the band gap range

Fig. 1.4 Schematic filed distribution showing propagation of defect mode in photonic crystal waveguide

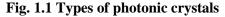

Basically, two types of 2D PhCs exist, one of which consist of disconnected dielectric cylinders and the other one is formed by air pores drilled in the dielectric matrix as shown in figure 1.5. These are symmetrical 2D PhC slab structures in which light is confined in the horizontal direction due to photonic band gap effect and in the vertical

<sup>&</sup>lt;sup>3</sup> Image: http://nanophotonics.spiedigitallibrary.org/article.aspx?articleid=1226536

<sup>&</sup>lt;sup>4</sup> Image: https://nanohub.org/resources/19417/watch?resid=19419

direction by total internal reflection due to the changes in the refractive index at the surface. The symmetrical structures are mechanically unstable from the fabrication point of view. An asymmetrical 2D PhC slab structure i.e. silicon on insulator (SOI) structure provides a new platform for planar integrated optics. In 2D PhC slab structures the propagating modes have been chosen with respect to the light line. The modes which lie below the light line are ideally not subject to propagation losses whereas the modes above the light line are called as leaky radiation modes and offer the propagation losses in the vertical direction.

Fig. 1.5 Schematic representation of (a) dielectric cylinders in air and (b) air holes in dielectric medium

2D PhCs could be developed into a direct continuation of planar integrated optics on employing the semi-infinite slab structures. These structures offer a tremendous advantage in terms of realization of compact optical devices as compared to the current status. These structures are assumed to be finite along the vertical direction and infinite along the horizontal directions. These PBG structures offer a wide variety of applications such as polarisers, splitters, multiplexers and de-multiplexers, couplers, resonators, lasers, modulators and logical devices [8-13].

<sup>&</sup>lt;sup>5</sup> Image: http://www.intechopen.com/books/advances-in-photonic-crystals/photonic-crystal-ring-resonatorbased-optical-filters

#### **1.2.2 Optical logic gates**

In recent years various techniques have been employed to design optical logic gates which are classified into two groups, one is band gap based and another is non band gap based. Band gap based logic gates have been designed using interferometers [14], modulators [11], filters [15], waveguides [16], multiplexers/de-multiplexers [17] and lasers [12], whereas non band gap based logic gates have been designed on the concept of self collimation effect [18] and dispersive prisms [19] that utilize the anisotropic dispersion exhibited by the photonic crystals. The main goal of designing and manufacturing optical logic gates is to increase the operational bandwidth, decrease power consumption, improve response time between the ON and OFF state, increase the contrast ratio between the high and low logical levels and integrate them to create all-optical logic circuits. Recently, photonic crystal based logic gates have received considerable attention to create optical processors because of the reduction in the size of the optical logic gate to the order of wavelength. Optical logic gates have low power consumption of about few microwatts and high switching speed with response time less than a few picoseconds. Optical logic gates have great influence in all-optical signal processors, optical computers and in high speed communication networks due to their numerous applications such as switching, computing, buffering, encoding, data signal regeneration, address recognition, data encryption/decryption, parity checking and de-multiplexing. The switching speed in optical logic gates is only limited by the speed of light passing through it.

#### 1.2.3 Slow light

The ultra high speed for the efficient data transmission between two points is advantageous but requires the control of optical signals in the time domain, which is a difficult task and to overcome this problem slow light technology has now been investigated as a new means. Recently engineers have been developing information networks for all-optical signal processing that avoid electro optic conversions and provide solutions for the loop holes in present mechanical approaches. The control on the group velocity of light with much faster response speed could be useful in the design of optical buffers and in various types of time domain processing techniques such as multiplexing, retiming and performing convolution integrals [20]. Control over group velocity improves the phase control in array

beam shapers and interferometric modulators. It is also helpful in compressing optical signals and optical energy in space. Recently, photonic crystal structures are being considered as promising candidates for generation of slow light, as they are compatible with on-chip integration and room temperature operations. They also provide wide bandwidth and dispersion free propagation [21-24]. A delay bandwidth product (DBP) which is defined as the extent up to which group velocity of light is reduced within the required bandwidth range below the light line is a desirable property for dispersion compensated slow light devices. Slow light in PhCs is motivated by the fact that it can be achieved by changing the structural parameters alone. The nearly flat band region in the dispersion diagram can be used to achieve slow light in photonic crystal structures. This can be obtained by various ways such as by chirping the waveguide properties, by changing the waveguide width, by changing the holes size and shape, by infiltrating holes with dielectric materials and by adjusting the position of the holes adjacent to the PhC waveguide. Some of these techniques may lead to multimode operation and others are difficult to control during on chip fabrication processes. However, the photonic crystal structures with low group velocity, low group velocity dispersion (GVD) and broad bandwidth [21, 25] can find applications in optical buffer (for storage of data) as well as time and wavelength division de-multiplexing (TDM and WDM) [26].

#### **1.3 Methods of fabrication**

The fabrication methods [27, 28] play an important role in the study and practical applications of PhCs. Due to the unavailability of natural PhCs for their commercial use, several attempts have been made for the design and fabrication of the artificially structured materials which show the properties of PhCs. Various techniques have been proposed to fabricate high quality PhCs which have revolutionized the optical integrated circuits. The templates for PhCs have been created using wide variety of methods such as 1D PhCs and can be fabricated using molecular beam epitaxy method, chemical vapor deposition method, pulsed layer deposition method, spin coating method and sol gel method. The 2D PhCs and 3D PhCs are more complicated in terms of fabrication and require expensive micro fabrication technologies such as laser holography lithography, self-assembly of colloidal particles and direct laser writing, etc. A number of techniques are available for

colloidal assembly fabrication and widely used techniques are gravity sedimentation and cell method introduced by Xia and co-workers [29, 30] which is useful for fabrication of polystyrene PhCs in water. The two photon lithography technique for the fabrication of 3D PhCs such as logpile type PhC utilizes the fact that certain materials are sensitive to two photon excitation to trigger chemical and physical changes in the material structure. The electron beam lithography is relatively a complicated method that enables one to create on chip PhCs with extremely high resolution. It uses a focused beam of electrons to drill holes in a given substrate. The beam position and intensity is computer controlled and are too focused to specific areas to get the desired pattern. After the exposition the samples are accompanied by etching procedures to get the final crystalline structure. The holographic method utilizes the concept of multiple beam interference technique in which initial laser beam is split into several beams and is allowed to overlap at angles predetermined by the desired periodicity. The holographic method can also be used to fabricate electrically switchable polymer-dispersed liquid crystal photonic band gap materials. In holographic method highly periodic structures can be fabricated in a single laser exposure, thus avoiding step by step fabrication process.

#### **1.4 Outline of the thesis**

The main focus of this thesis is to design and characterize all optical devices based on the photonic crystal waveguides. These devices include the design of optical logic gates, optical buffers and delay lines, and polarization splitter. This thesis also includes generation of slow light in slotted photonic crystal waveguide and its applications. The thesis is divided into seven chapters as per the following layout.

Chapter 1 defines the literature review about photonic crystals and how they are useful in the design of optical devices. Further, the design of all the proposed devices in the present thesis have been formulated using certain computation methods as discussed below:

#### **1.4.1 Computational methods**

Recently research has been oriented in a more focused way towards the analysis of distinct characteristics of photonic crystal for the optoelectronics. The analysis of PhCs require computer capabilities through the computer aided design (CAD) that can provide exact, fast and efficient solutions of Master equations shown above. The solution of most practical and complex structures requires efficient numerical methods such as Plane Wave Expansion (PWE) Method, Finite Difference Time Domain (FDTD) Method and Finite Element Method (FEM).

Here, the basic principle behind different numerical methods used for the theoretical analysis of the structures presented in this thesis work has been discussed.

#### 1.4.1.1 Plane Wave Expansion (PWE) Method

Plane Wave Expansion (PWE) method is a computational technique based on Fourier expansion of electromagnetic fields and dielectric function. PWE is an efficient method for obtaining the band structures of photonic crystals. PWE expansions are rigorous solutions and well suited for the model solutions of Maxwell's equations over an inhomogeneous or periodic geometry. This method solves Maxwell's equations by formulating an Eigen value problem out of the Master equation which gives rise to a set of Eigen values ' $\omega a/2\pi c$ ' for each value of 'k' i.e. optical modes solved in wave vector space or reciprocal space. In this thesis work the dispersion relations for periodic as well as for non periodic structures i.e. cavities and waveguides have been calculated using RSoft Bandsolve Software [31] by implementing a supercell of specific dimension.

#### 1.4.1.2 Finite Difference Time Domain (FDTD) Method