# Chapter 1 INTRODUCTION

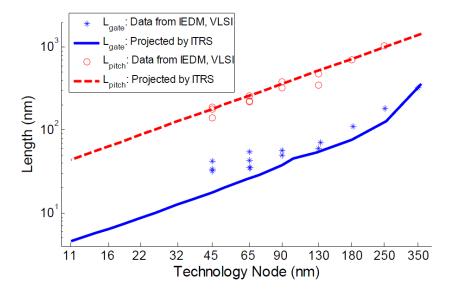

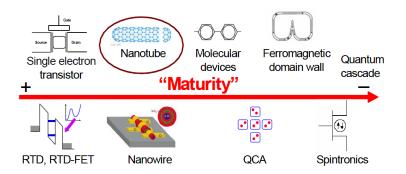

The major driving force for the semiconductor industry, the device contacted gate pitch (Lpitch) is scaled down by a factor of 0.7 every technology node [1]. Reasonable questions to ask are: Will the MOSFET scaling be stopped? Is there a way to extend the silicon technology roadmap? After silicon technology, or as a complement to silicon technology, is there any potential technology that may be used? The last few years witnessed a dramatic increase in nanotechnology research, especially the nano electronics. These technologies vary in their maturity, as illustrated by Figure 1.2. The exciting opportunity is to design complex electronic circuits using the cutting-edge silicon technology and/or the novel nanometer-scale transistors in the future.

Figure 1.1: The physical gate length (Lgate) and the contacted gate pitch (Lpitch) of the fabricated devices (denoted by symbols) and projected by ITRS (denoted by lines).

Figure 1.2: The novel nanoelectronic technologies in order of their maturity.

Carbon nanotubes (CNTs) are at the forefront of these new materials because of the unique mechanical and electronic properties. Carbon nanotube field effect transistor (CNTFET or CNFET) is the most promising technology to extend or complement traditional silicon technology due to three reasons: First, the operation principle and the device structure are similar to CMOS devices; we can reuse the established CMOS design infrastructure. Second, we can reuse CMOS fabrication process. And the most important reason is that CNTFET has the best experimentally demonstrated device current carrying ability to date [2,3].

The thesis is organized as follows:

Chapter 2: It describes the basic of carbon nanotube. In this chapter, firstly we will understand the bonding structure and fundamentals of the tube. Later is the summary of fundamental parameter definition and their relationship. It also explains the basics of energy band and tube conductivity dependency.

Chapter 3: This chapter is a brief literature survey of Carbon nanotube FET (CNFET).

Chapter 4: The complete device model of CNFET is divided into two parts. First part is the intrinsic channel behavior of the tube conductivity including some nonidealities, will be explained in this chapter.

Chapter 5: In this chapter, we will see the rest part of device model. Here, two different six and four capacitor model has been discussed, though the four capacitor model is implemented. We will also see the device behavior and performance via HSPICE simulations. A brief comparison between CMOS and CNFET has also been demonstrated here.

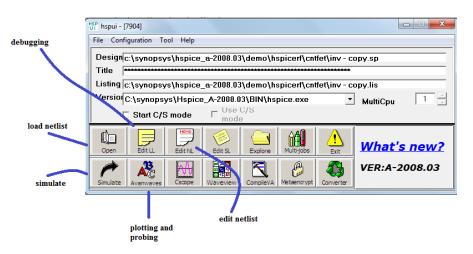

Chapter 6: This chapter is about the brief introduction of HSPICE and the useful tool (mathematical as well as simulation), that will be very helpful in the analog behavioral modeling of the device. Also, we will briefly overview the library files to understand the mechanics of the device design.

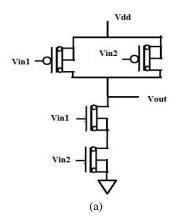

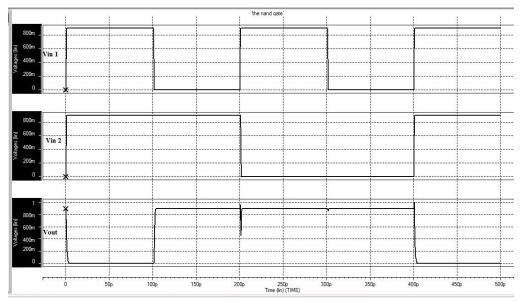

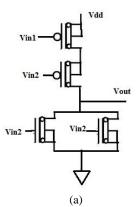

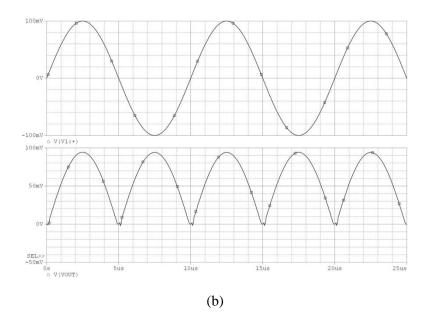

Chapter 7: In this chapter, we are going to implement some digital and analog application. In digital applications, gates like NAND and NOR is implement. The EXOR gate based on pass transistor design is implemented, so that the gate as well as the pass transistor performance could be demonstrated using CNTFET.

# Chapter 2 **THE CARBON NANOTUBE**

**Carbon nanotubes** (**CNTs**) are allotropes of carbon with a cylindrical nanostructure. Nanotubes have been constructed with length-to-diameter ratio of up to 132,000,000:1 [4], significantly larger than for any other material. These cylindrical carbon molecules have unusual properties, which are valuable for nanotechnology, electronics, optics and other fields of materials science and technology. In particular, owing to their extraordinary thermal conductivity and mechanical and electrical properties, carbon nanotubes find applications as additives to various structural materials. Nanotubes are members of the fullerene structural family. Their name is derived from their long, hollow structure with the walls formed by one-atom-thick sheets of carbon, called graphene. These sheets are rolled at specific and discrete ("chiral") angles, and the combination of the rolling angle and radius decides the nanotube properties; for example, whether the individual nanotube shell is a metal or semiconductor. Nanotubes are categorized as single-walled nanotubes(SWNTs) and multi-walled nanotubes (MWNTs).

#### 2.1 Atomic Bonding and Structure

Carbon atom has an electron configuration of 1s2 2s2 2p2 in its ground state. In graphene, sp2 hybridization occurs through covalent bonding of the two outermost shells. A carbon atom in graphene assembles in a single-sheet hexagonal lattice. The inter-carbon-atom distance within the hexagonal lattice (d) is approximately 1.44 Å, and the angle between carbon-carbon bonds ( $\sigma$ -bond) is 120 degrees. The lattice constant (a) is given by  $\sqrt{3} d = 2.49 \text{ Å}$ . The 2p electrons from all the atoms on a lattice form a delocalized  $\pi$ -orbital between the two adjacent sheets. The inter-layer spacing between the multiple sheets in graphene is about 3.35 Å. The weak electrostatic interactions between the sheets make it possible to assume the electrical characteristics of the graphite sheets are independent each other.

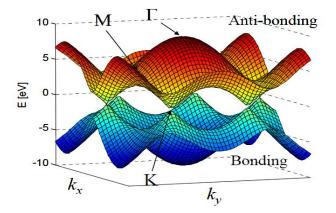

Figure 2.1: E-k dispersion relation for graphene, calculated using a nearest-neighbour tight-binding model. The three high-symmetry points are indicated by capital letters.

The dispersion relation for graphene, obtained by the Slater-Koster tight-binding scheme, considering only the  $\pi$ -orbital, is given by,

$$E_{g2D}(k_x, k_y) = \pm \sqrt{1 + 4\cos(\frac{\sqrt{3}k_x a}{2})\cos(\frac{\sqrt{3}k_y a}{2}) + 4\cos^2(\frac{k_y a}{2})}$$

(2.1)

Where  $(k_x, k_y)$  are wave vectors,  $V_{\pi}$  is the transfer integral (or the nearest-neighbour parameters). Figure 2.1 illustrates the band structure calculated with the above equation. The high-symmetry points are indicated by capital letters. *K*-points are degenerate, indicating the zero-bandgap (semi-metallic) characteristic of graphene sheet.

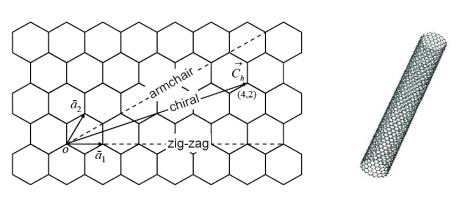

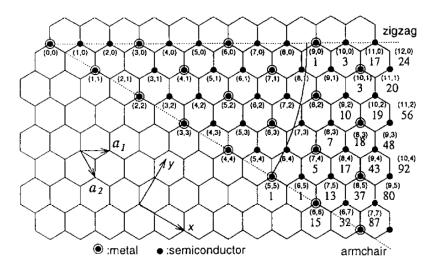

A single-walled carbon nanotube (SWCNT) can be visualized as a sheet of graphite which is rolled up and joined together along a wrapping vector  $C_h = n_1.\bar{a}_1 + n_2.\bar{a}_2$ , where  $[\bar{a}_1, \bar{a}_2]$  are lattice unit vectors as shown by Figure 2.2, and the indices  $(n_1, n_2)$  are positive integers that specify the chirality of the tube [5]. The length of  $C_h$  is thus the circumference of the CNT, which is given by,

$$C_h = a\sqrt{n_1^2 + n_2^2 + n_1 n_2}$$

(2.2)

Figure 2.2: Unrolled graphite sheet and the rolled carbon nanotube lattice structure.

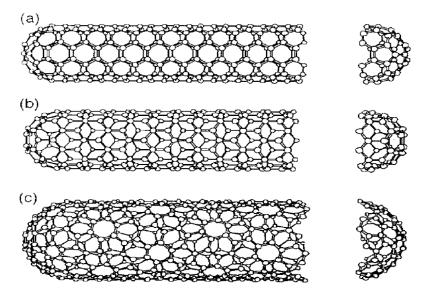

Single-walled CNTs are classified into one of their groups (Figure 2.2), depends on the chiral number  $(n_1, n_2)$ : (1) armchair  $(n_1 = n_2)$ , (2) zigzag  $(n_1 = 0 \text{ or } n_2 = 0)$ , and (3) chiral (all other indices). Figure 2.3 can give more easier look on the classification [5]. The diameter of the CNT is given by the formula  $DCNT = C_h / \pi$ . The typical diameters of CNTs are about several nanometers. Due to the small diameter of CNT, the quantization of wave vector in the circumferential direction occurs. A general analytic *E-k* dispersion relation for CNT is obtained by applying periodic boundary conditions in the circumferential direction to the 2D graphite sheet *E-k* dispersion relation. Pictorially, the dispersion of CNT is obtained by taking slices of the surface in Figure 2.1 with each cut determined by the circumferential quantization.

Figure 2.3: The 2D graphene sheet with different chiralities.

#### 2.2 Fundamental Parameters and Relationship for CNT

This section summarizes the fundamental parameters for the CNT, to give the basic relations governing these parameters [5], and list typical numerical values for these parameters.

In the theoretical carbon nanotube literature, the focus is on single-wall tubules, cylindrical in shape with caps at each ends as shown in Figure 2.4, such that the two caps can be joined together to form a fullerene. The cylindrical portions of the tubules consist of a single graphene sheet that is shaped to form the cylinder. Recent discoveries of method help to make it possible to test the predictions of the theoretical calculations.

It is convenient to specify a general carbon nanotubule in terms of the tubule diameter d and the chiral angle  $\theta$ . The chiral vector  $C_h$  is defined in table 2.1in terms of the integers  $(n_1, n_2)$  and the basis

vector  $a_1$  and  $a_2$  of the honeycomb lattice, which are also given in the table in terms of rectangular coordinates. The length *L* of the chiral vector  $C_h$  is directly related to the tubule diameter *d*. the chiral angle  $\theta$  between the  $C_h$  direction and the zigzag direction of the honeycomb lattice  $(n_1, \theta)$  is related in related in table 2.1 to the integers  $(n_1, n_2)$ .

Figure 2.4: fullerene-derived tubules.

| symbol                                        | name                                      | Formula                                                                                                                                      | value                           |

|-----------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| a <sub>C-C</sub>                              | carbon-carbon distance                    |                                                                                                                                              | 1.421 Å (graphite)              |

| a                                             | length of unit vector                     | $\sqrt{3} a_{C-C}$                                                                                                                           | 2.46 Å                          |

| <i>a</i> <sub>1</sub> , <i>a</i> <sub>2</sub> | unit vectors                              | $(\frac{\sqrt{3}}{2},\frac{1}{2})a,(\frac{\sqrt{3}}{2},-\frac{1}{2})a$                                                                       | in $(x, y)$ coordinate          |

| <i>b</i> <sub>1</sub> , <i>b</i> <sub>2</sub> | reciprocal lattice vectors                | $(\frac{1}{\sqrt{3}},1)\frac{2\pi}{a},(\frac{1}{\sqrt{3}},-1)\frac{2\pi}{a}$                                                                 | in $(x, y)$ coordinate          |

| $C_h$                                         | chiral vector                             | $C_h = n_1 a_1 + n_2 a_2 \equiv (n_1, n_2)$                                                                                                  | $n_1, n_2$ integers             |

| L                                             | circumference of nanotube                 | $L =  C_h  = a\sqrt{n_1^2 + n_2^2 + n_1 n_2}$                                                                                                | $0 \leq  n_2  \leq n_1$         |

| d                                             | diameter of nanotube                      | $d = \frac{L}{\pi} = \frac{a\sqrt{n_1^2 + n_2^2 + n_1 n_2}}{\pi}$ $\sin \theta = \frac{\sqrt{3}n_2}{2\sqrt{n_1^2 + n_2^2 + n_1 n_2}}$        |                                 |

|                                               |                                           | $\sin \theta = \frac{\sqrt{3}n_2}{2\sqrt{n_1^2 + n_2^2 + n_1 n_2}}$                                                                          | $0 \leq \theta \leq 30^{\circ}$ |

| θ                                             | chiral angle                              | $\cos\theta = \frac{2n_1 + n_2}{2\sqrt{n_1^2 + n_2^2 + n_1 n_2}}$                                                                            |                                 |

|                                               |                                           | $\tan \theta = \frac{\sqrt{3}n_2}{2n_1 + n_2}$                                                                                               |                                 |

| D                                             | highest common divisor<br>of(n1,n2)       |                                                                                                                                              |                                 |

| $D_R$                                         | highest common divisor of (2n1+n2,2n2+n1) | $D_{R} = \begin{cases} D & \text{if } n1 - n2 \text{ not multiple of } 3D \\ 3D & \text{if } n1 - n2 \text{ a multiple of } 3D. \end{cases}$ |                                 |

| Table 2.1: | parameters | of carbon | nanotube |

|------------|------------|-----------|----------|

|------------|------------|-----------|----------|

|   |                                        | $T = t_1 a_1 + t_2 a_2 \equiv (t_1, t_2)$                                            | t <sub>1</sub> ,t <sub>2</sub> integer |

|---|----------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------|

| Т | translational vector of 1D unit cell   | $t_1 = \frac{2n_2 + n_1}{D_R}$                                                       |                                        |

|   |                                        | $D_R$ $t_2 = -\frac{2n_1 + n_2}{D_R}$                                                |                                        |

| Ν | number of hexagons per 1D<br>unit cell | $N = \frac{2(n_1^2 + n_2^2 + n_1 n_2)}{D_R}$                                         | $2N \equiv n_c / unit cell$            |

| R | symmetry vector                        | $R = pa_1 + qa_2$                                                                    | p,q:integers                           |

| Λ |                                        | $D = n_2 p - n_1 q, 0 \le p \le n_1 / D, 0 \le q \le n_2 / D$                        |                                        |

| М | number of 2 $\pi$ revolutions          | $M = \left[ \left( 2n_1 + n_2 \right) p + \left( 2n_2 + n_1 \right) q \right] / D_R$ | M: integer                             |

| M |                                        | $N\mathbf{R} = MC_h + DT$                                                            |                                        |

| R | basic symmetry operation               | $R = (\psi / \tau)$                                                                  |                                        |

| Ψ | relation operation                     | $\psi = 2\pi \frac{M}{N}, \left(\chi = \frac{\psi L}{2\pi}\right)$                   | $\Psi$ in radians                      |

| τ | translation operation                  | $\tau = \frac{DT}{N}$                                                                | $\chi, 	au$ :length                    |

These parameters will be used in chapter 3 in the understanding and physical modeling of CNTFET. To be compatible with the quasi 1D structure of CNT, we convert the  $(k_x, k_y)$  coordinate to  $(k_t, m)$ , where the wave vector  $k_t$  is in the direction of transport, and m is quantization number in the circumferential direction. Analytically, the dispersion of CNT is given by the formula [5],

$$E_{CNT}(k_t, m) = \pm V_{\pi} \sqrt{1 + 4\cos t_1 \cos t_2 + 4\cos^2 t_2}$$

(2.3)

Where the parameters are given by

$$t_{1} = \frac{\sqrt{3}a}{4} \frac{n_{2} - n_{1}}{n} k_{t} + \frac{\pi}{2} \frac{n_{1} + 3n_{2}}{n^{2}} m$$

$$t_{2} = \frac{\sqrt{3}a}{4} \frac{n_{2} + n_{1}}{n} k_{t} + \frac{\pi}{2} \frac{3n_{1} - n_{2}}{n^{2}} m$$

$$n^{2} = n_{1}^{2} + n_{2}^{2} + n_{1}n_{2} \qquad (2.4)$$

$$-\frac{\pi D_{R}}{\sqrt{3}a.n} < k_{t} < \frac{\pi D_{R}}{\sqrt{3}a.n}$$

$$m = 0: \frac{2n}{D_{R}} - 1$$

### 2.3 Electrical Conductivity and Density of States in CNT

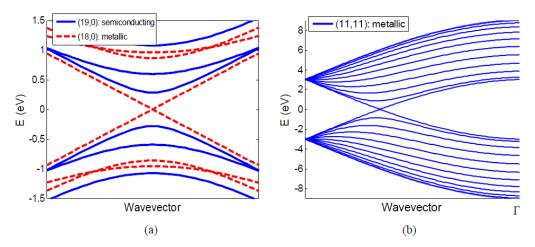

In terms of the electrical conductivity, SWCNT is either metallic (when  $|n_1-n_2|$  is a multiple of 3) with zero band gap or semiconducting with finite band gap. The band structure for both metallic CNTs

and semiconducting CNTs are illustrated by figure 2.5, using both armchair SWCNTs (single walled carbon nanotubes) and zigzag SWCNTs as examples. To be accurate, achiral armchair SWCNTs ( $n_1=n_2$ ) and zigzag SWCNTs ( $n_1n_2 = 0$ ) are metallic, and the others ( $|n_1-n_2|$  is a multiple of 3 but  $n_1 \neq n_2$  and  $n_1n_2 \neq 0$ ) are quasi-metallic with small band gap, calculated with equations (2.3, 2.4).

Figure 2.5: Energy dispersion relation for (a) (19,0), (18,0) zigzag CNTs, and (b) (11,11) armchair CNT.

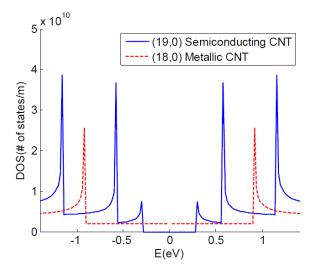

The density of states (DOS) can be obtained as,

$$g(E) = \frac{2}{\pi} \int \left| \frac{\partial E_{CNT}}{\partial k_t} \right|^{-1} dE_{CNT}$$

(2.5)

proposes an universal expression to describe CNT band structure and the density of states, which are valid for the energy range  $E_{CNT} \ll V\pi$  [6]. Figure 2.6 shows the DOS for (19,0) and (18,0) SWCNT with similar diameter (~ 1.5 nm).

Figure 2.6: The density of states for (19,0) semiconducting and (18,0) metallic CNT

The electrons in CNT are confined within the atomic plane of graphene. Due to the quasi-1D structure of CNT, the motion of the electrons in the nanotubes is strictly restricted. Electrons may only move freely along the tube axis direction. As a result, all wide angle scatterings are prohibited. Only forward scattering and backscattering due to electron-phonon interactions are possible for the carriers in nanotubes. The experimentally observed ultra-long elastic scattering mean-free-path (MFP) [2, 3, 7] (~ 1  $\mu$ m) implies ballistic or near-ballistic carrier transport. High mobility, typical in the range of  $10^3 \sim 10^4$  cm<sup>2</sup>/V·s which are derived from conductance experiments in transistors, has been reported by a variety of studies [8, 9]. Theoretical study also predicts a mobility of ~  $10^4$  cm<sup>2</sup>/V·s for semiconducting CNTs [10]. The current carrying capacity of multi-walled CNTs are demonstrated to be more than  $10^9$  A/ cm<sup>2</sup>, about 3 orders higher than the maximum current carrying capacity of copper which is limited by the electron migration effect, without performance degradation during operation well above room temperature [11]. The superior carrier transport and conduction characteristic makes CNTs desirable for nanoelectronics applications, e.g. interconnect and nanoscale devices.

Now at the end and of this chapter, we have understood some of important the basics of carbon nanotube such as the parameters to define the CNT structure, bonding model and the energy bands and density of states. In the coming chapters we will use the parameters to characterize the carbon nanotube field effect transistor (CNFET or CNTFET) and understand its modeling.

# Chapter 3 **THE CNTFET- A Literature Survey**

The operation principle of carbon nanotube field-effect transistor (CNTFET) is similar to that of traditional silicon devices. This three (or four) terminal device consists of a semiconducting nanotube, acting as conducting channel, bridging the source and drain contacts. The device is turned on or off electrostatically via the gate. The quasi-1D device structure provides better gate electrostatic control over the channel region than 3D device (e.g. bulk CMOS) and 2D device (e.g. fully depleted SOI) structures [12].

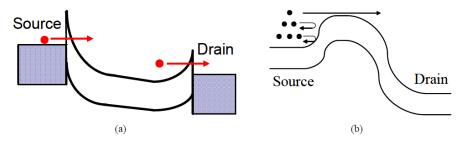

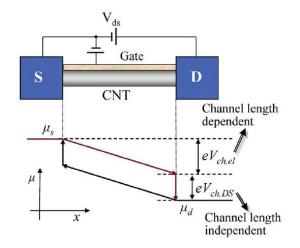

In terms of the device operation mechanism, CNFET can be categorized as either Schottky Barrier (SB) controlled FET (SB-CNFET) or MOSFET-like FET [2, 3, 13]. The conductivity of SB-CNFET is governed by the majority carriers tunneling through the SBs at the end contacts. The oncurrent and thereby device performance of SB-CNFET is determined by the contact resistance due to the presence of tunneling barriers at both or one of the source and drain contacts, instead of the channel conductance, as shown by Figure 3.1(a). The SBs at source/drain contacts are due to the Fermi-level alignment at the metal-semiconductor interface. Both the height and the width of the SBs, and therefore the conductivity, are modulated by the gate electrostatically. SB-CNFET shows ambipolar transport behavior [14]. The work function induced barriers at the end contacts can be made to enhance either electron or hole transport. Thus both the device polarity (n-type FET or p-type FET) and the device bias point can be adjusted by choosing the appropriate work function of source/drain contacts [15]. On the other hand, MOSFET like CNFET exhibits unipolar behavior by suppressing either electron (pFET) or hole (nFET) transport with heavily doped source/drain. The non-tunneling potential barrier in the channel region, and thereby the conductivity, is modulated by the gate-source bias (Figure 3.1(b)).

Figure 3.1: The energy band diagram for (a) SB-CNFET, and (b) MOSFET-like CNFET.

The first fabricated CNFET devices with Au or Pt source/drain metal contacts were reported in 1998 [16, 17]. The gate dielectric material was a thick SiO2 layer. A highly doped Si back gate was used to control the conductivity. The  $Al_2O_3$  gate dielectric was introduced to improve the gate controllability over the channel region. The front gate device structure, by placing the gate electrode over the thin gate oxide that covers CNT, was used to further improve the channel electrostatics. Better gate electrostatics was achieved by using high-k, e.g. HfO<sub>2</sub>, gate dielectric material [13]. The source/drain contacts using a variety of metals (Ti, Ni, Al, Pd, ...) were fabricated to study the effect of the work function difference between the metal contacts and CNT on device conductivity. Ti source/drain metallization was reported to be efficient on reducing the contact resistance [14]. The device fabricated with Pd source/drain metal contact, Al gate electrode, and HfO2 gate dielectric was reported to achieve excellent dc characteristics. Logic circuits with field-effect transistors based on single carbon nanotubes have been demonstrated in the past few years. In 2001, demonstrated one-, two-, and three transistor circuits that exhibit a range of digital logic operations, including an inverter, a logic NOR, a static random-access memory (SRAM) cell, and an three-stage ac ring oscillator operating at 5 Hz. A five-stage CMOS type nanotube ring oscillator using palladium p-type gates and aluminum n-type gates was reported in 2006. Owing to the compact device/circuit design, this ring oscillator works at a frequency of 72 MHz Regarding RF analog application using CNFET, the first demonstration of ac gain in a single-walled carbon nanotube common-source amplifier was reported in 2006. The low frequency gain was ~ 11.3 dB, and the unitygain frequency was about 560 kHz which was mostly limited by the parasitic load capacitance.

While the CNT synthesis / fabrication technique and the performance of CNFET devices and circuits have been significantly improved since the first fabricated device in 1998, CNFETs is still premature for very large scale integrated (VLSI) circuits design and commercial use. In order for CNFET to develop into a technology, first, we need tools to enable circuit design and performance benchmarking.

Efforts have been made in recent years on modeling semiconducting CNFET for digital logic applications and CNT for interconnects in order to evaluate the potential performance at the device level. This thesis will mostly focus on the device applications of CNT. A numerical model was reported in [18] to evaluate the dc current of SB-CNFET. The model reported in [19] predicts the dc performance of short channel SB-CNFET. Though good dc current can be achieved by SB-CNFET with the self-aligned structure, its ac performance is going to be poor due to the proximity of the gate electrode to the source/drain metal. The ambipolar behavior of SBCNFET also makes it undesirable for complementary logic design. Considering both the fabrication feasibility [20] and superior device performance of MOSFET-like CNFET as compared to SB-CNFET, we will focus on MOSFET-like CNFETs. To

evaluate the device/circuit performance as well as the performance dependence on device/geometry parameters, the requirements for a good device model include:

(1) Good scalability.

(2) Physics-based, or at least semi-physics based.

(3) Reasonable accuracy for both large signal and small signal analysis.

(4) Acceptable run time.

The reported compact models to date [21, 22] used one or more lumped static gate capacitances and assumed an ideal ballistic transport channel. These simplifications make it questionable when evaluating the transient response and device dynamic performance. The integral function used in [23] requires intensive calculation efforts and thereby makes it difficult to implement in circuit simulators, e.g. HSPICE [24]. The model in [22] improves the run time significantly by using a polynomial fitting approach. This methodology dilutes the physical meaning of the device model and makes evaluating CNFET performance with different device parameters (e.g. CNT chiralities, gate oxide thickness) inconvenient. The reported models to date [21, 22, 23] used a simple coaxial or planer gate structure that differs from the typical realistic CNFET gate structure that consists of high-k gate oxide on top of SiO2 insulating bulk [13]. For a CNFET with multiple parallel CNTs [3], these published models cannot examine the multiple CNT-to-CNT screening effect on both the driving current and the effective gate capacitance [25]. All the reported device models assumed CNFET devices with perfect and ideal CNT channel. Compared to the intrinsic performance of CNFET predicted by theoretical studies [23], the actual device and circuit level performance is mostly limited by various parasitic and process induced imperfections. The device parasitics and/or non-idealities include, but are not limited to: the channel length dependence of current drive, the finite scattering mean free path, the source/drain series resistance, the source/drain contacts (SBs) resistance, the geometry dependence of the gate to channel capacitance, and the interconnect wiring capacitance. To evaluate CNFET device/circuit performance with improved accuracy, a CNFET device model with a more complete circuit-compatible structure and also incorporating the typical device/circuit non-idealities is necessary. A good balance between the simulation run-time and accuracy is desired.

The circuit macro level performance is not only limited by the performance of one single device, but also limited by the device performance variations which are significant for nanometer scale devices. There are a variety of device parameter variations and imperfections caused by today's CNT synthesis/fabrication technique: (1) CNT diameter and chirality control; (2) Doping level control; (3) The probability of a CNT to be metallic; (4) Directed-CNT-growth. A reasonable question to ask is: considering these imperfections, what can be gained at the circuit-level using CNFET technology compared to cutting-edge Si CMOS?

# Chapter 4 COMPACT MODEL FOR INTRINSIC CHANNEL REGION OF CNFET

As one of the promising new transistors, carbon-nanotube field-effect transistor (CNFET) avoids most of the fundamental limitations for traditional silicon MOSFETs. With ultra-long ( $\sim 1 \mu m$ ) mean free path (MFP) for elastic scattering, a ballistic or near-ballistic transport can be obtained with an intrinsic carbon nanotube (CNT) under low voltage bias to achieve the ultimate device performance [7]. The quasi 1D structure provides better electrostatic control over the channel region than 3-D device (e.g., bulk CMOS) and 2D device (e.g., fully depleted SOI) structures [26]. Efforts have been made in recent years on modeling semiconducting CNFET for digital logic applications and CNT for interconnects, in order to evaluate the potential performance at the device level [21,27,28]. The reported compact models to date used one or more lumped static gate capacitances and an ideal ballistic transport model. These simplifications make it questionable when evaluating the transient response and device dynamic performance. The integral function [27,28] used in and requires intensive calculation efforts and thereby makes it difficult to implement in circuit simulators, e.g., HSPICE [24]. The polynomial fitting approach used in improves the runtime significantly [21], but it makes the evaluation of the CNTFET performance with different device parameters inconvenient. The simple coaxial or planer gate structures utilized in differ from the typical realistic CNFET gate structure that consists of high-k gate oxide on top of the SiO2 insulating bulk. For a CNFET with multiple parallel CNTs [2], these published models cannot examine the multiple CNT-to-CNT screening effects on both the driving current and the effective gate capacitance. To evaluate the CNFET circuit performance with an improved accuracy, a CNTFET device model with a more complete circuit-compatible structure and also incorporating the typical device/circuit nonidealities is necessary.

#### **4.1 Device Structure**

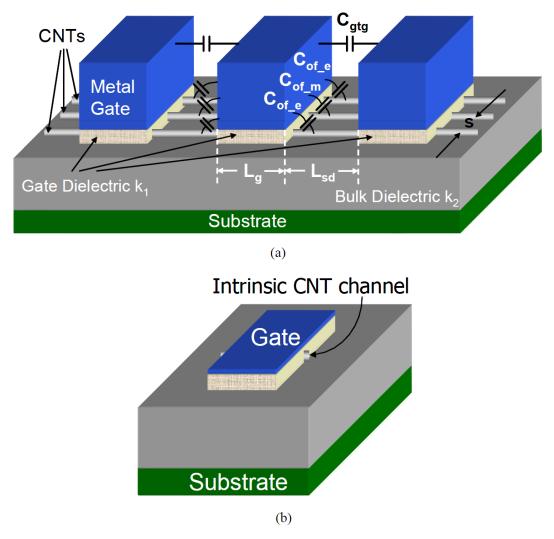

A typical layout of a MOSFET-like CNFET device is illustrated in Figure 4.1(a). One or multiple devices can be fabricated along a single CNT, and multiple CNTs may be placed under the same gate in order to improve the drive current. The CNT channel region is undoped, and the other regions are heavily

Figure 4.1: (a) The 3-D device structure of CNFETs with multiple channels, high-k gate dielectric material, and the related parasitic gate capacitances. In this example, three CNFETs are fabricated along one single CNT. The channel region of CNTs is un-doped, and the other regions of CNTs are heavily doped. (b) The 3D device structure of CNTFET that is modeled in this chapter, only with the intrinsic channel region.

acting as both the source/drain extension region and/or interconnects between two adjacent devices (uncontacted source-gate/gate-drain configurations). In order to account for the screening by the adjacent CNTs for the device with multiple CNTs, the nanotubes under the gate are grouped into (1) the two CNTs at the edges; (2) the other CNTs in the middle. The CNTs in each group are treated identically [25].

This chapter describes the modeling of one single intrinsic channel of CNFET, as shown in Figure 4.1(b), which is a starting point towards the complete device model reported in Chapter 5. For

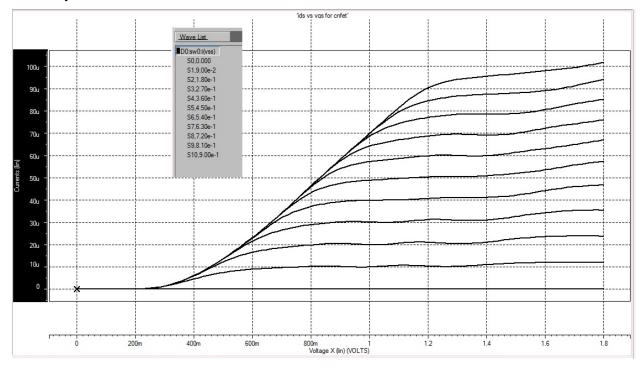

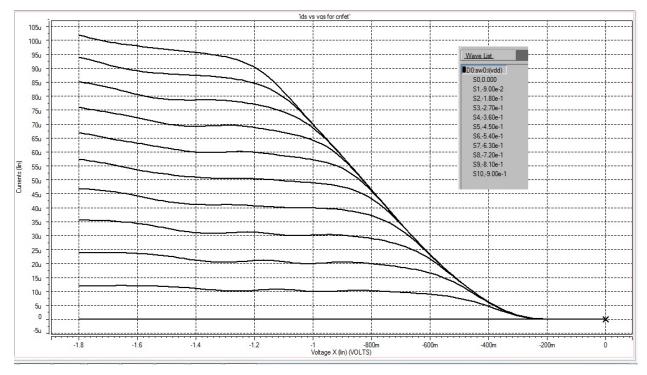

MOSFET-like CNFET, since pFET behavior is similar to nFET, we will only describe the equations for nFET in this chapter, though we implemented both nFET and pFET for the SPICE simulations.

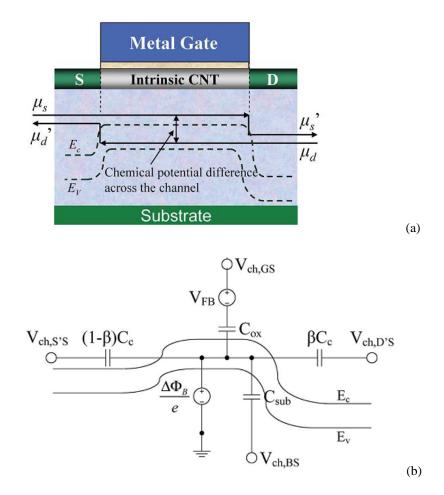

From the circuit point of view, the input / output signals can be defined as either current or potential, and the outputs (current or potential) are just the responses to the inputs (current or potential). The potential can be either electrostatic potential or chemical potential (referred as the "Fermi level" in the following). For macro scale circuits/devices, potential usually means electrostatic potential because the Fermi level profile follows the electrostatic potential profile around the contacts which are usually the input/output ports. For a 1-D quantum wire with two contacts (source and drain), the source Fermi level  $\mu_d$  will be split apart with finite drain bias ( $V_{ds}$ ) due to the finite density of states (DOS) [29]. Thus it becomes ambiguous to describe 1-D device behavior with electrostatic potential only, especially for the devices that are connected serially without an intermediate reservoir of electrons provided by a metal contact. In this work, we use both the Fermi level and the surface (electrostatic) potential to describe CNFET device behavior.

#### 4.2 Model of the Intrinsic Channel Region

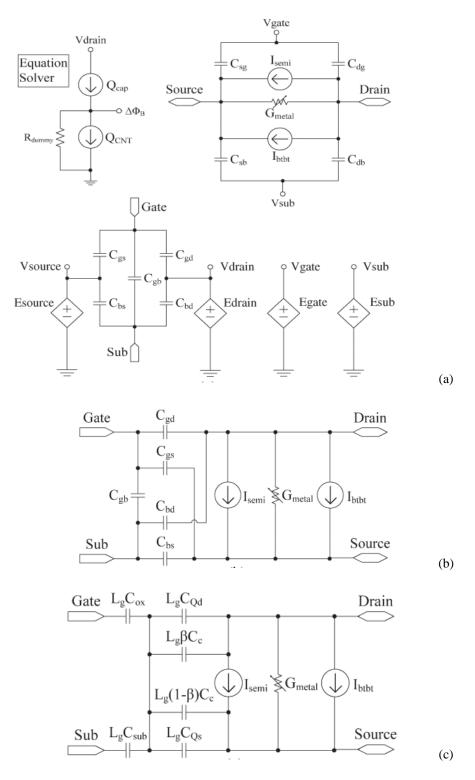

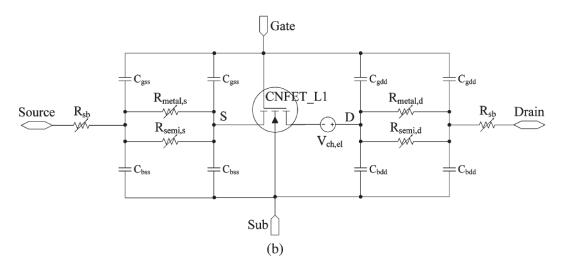

This part models the intrinsic channel region of CNFET with a near-ballistic transport and without any parasitic capacitance and parasitic resistance. The equivalent circuit model is shown as Figure 4.2. Figure 4.2(a) is the equivalent circuit implemented with HSPICE [24], and Figure 4.2(b) and (c) is the other two possible implementations for the trans-capacitance network, which will be discussed in the coming section.

Figure 4.2: Equivalent circuit model for the intrinsic channel region of CNFET. (a) Nine-capacitor model, assuming that the carrier distribution along the channel is uniform. Exxx is the voltage-controlled voltage source, and the potential of Vxxx is equal to the controlling voltage source. R<sub>dummy</sub> is a large-value (>1e15) resistor to keep the circuit stable. (b) Five-capacitor model and (c) six-capacitor model, assuming that all the carriers from +k branches are assigned to the source and that all the carriers from -k branches are assigned to the drain.

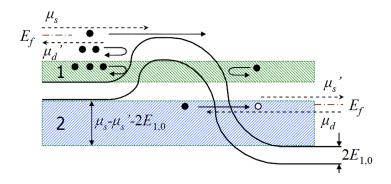

The Fermi-level profiles and the energy-band diagram in the channel region with a ballistic transport are shown in fig .The potential differences  $\mu_s - \mu'_s$  and  $\mu_d - \mu'_d$  are determined by both the applied bias and the property of the source/drain extension regions. We will treat the nonballistic transport and the potential drop at the source/drain extension region and the contacts in the complete device model. We assume near-ballistic transport and ideal (reflectionless) contacts in this chapter, i.e.,  $eV_{DS} \approx \mu_d - \mu_s$ ; thus,  $\mu_s(\mu_d)$  remains almost constant in the source-channel (drain-channel) region Figure 4.3(a).

Figure 4.3(a): Ideal CNFET with ballistic (intrinsic) channel. Superposed are the Fermi-level profiles (solid arrows) from source to drain and the energy-band diagram (dashed lines) with bias  $V_{DS}=(\mu_d-\mu_s)/e$ . (b) Electrostatic capacitor model used to calculate the channel surface-potential change  $\Delta\Phi_B$  before and after gate /source /drain /substrate bias. All the node potentials are referred to the input source Fermi level. Superposed is the energy-band diagram (only the first subband shown) from the external source nodes to the external drain node D'.

#### **4.3 Current Sources**

The single-walled CNT (SWCNT) is treated as a quasi-1D quantum wire in this chapter. For SWCNT with chiralities  $(n_1, n_2)$ , the diameter  $(D_{CNT})$  is given by (a=2.49 Å is the lattice constant) [5].

SWCNTs can be grouped as either metallic or semiconducting nanotubes. For SWCNT with a finite length (Lg) and a finite diameter ( $D_{CNT}$ ), applying the Born–von Karman boundary condition on both the circumferential direction and axial (channel length) directions, the E–k dispersion relation is quantized into discrete substates. We denote (m, l) as the l<sup>th</sup> substate at the  $m^{th}$  subband,  $k_m$  as the wavenumber of the m<sup>th</sup> subband in the circumferential direction, and  $k_1$  as the wavenumber of the l<sup>th</sup> substate in the current-flow direction [5]. We define the subbands with positive band gap as "semiconducting subbands," and the subbands with zero or negative band gap as "metallic subbands." Thus, the band structure of metallic nanotubes can be treated as a summation of the metallic and semiconducting subbands.

$$D_{CNT} = \frac{a\sqrt{n_1^2 + n_2^2 + n_1 n_2}}{\pi}$$

(4.1)

The wavenumbers related with semiconducting subbands are given by [29]

$$k_m = \frac{2\pi}{a\sqrt{n_1^2 + n_2^2 + n_1 n_2}} .\lambda$$

(4.2a)

$$\lambda = \begin{cases} \frac{6m - 3(-1)^m}{12}, & m = 1, 2, \dots, ; \mod(n_1 - n_2, 3) \neq 0. \\ m, & m = 0, 1, \dots, ; \min(n_1 - n_2, 3) = 0. \end{cases}$$

(4.2b)

$$k_l = \frac{2\pi}{L_g} l, \qquad l = 0, 1, 2, \dots.$$

(4.2c)

*m*=0 is reserved for the metallic subband.  $k_l$  approaches the continuous values for large  $L_g$ . Around the Fermi point with carrier energy  $E_{m,l} \ll V_{\pi} (\sim 3.033 \text{ eV})$ , the carbon  $\pi - \pi$  bond energy in the tight bonding model), CNT E - k dispersion relation can be approximated as

$$E_{m,l} \approx \frac{\sqrt{3}}{2} a V \pi \sqrt{k_m^2 + k_l^2}$$

(4.3)

We consider three current sources in the CNFET model: 1) the thermionic current contributed by the semiconducting subbands ( $I_{semi}$ ) with the classical band theory; 2) the current contributed by the metallic subbands( $I_{metal}$ ); and 3) the leakage current ( $I_{btbt}$ )caused by the band-to-band tunneling (BTBT) mechanism through the semiconducting subbands.

#### 4.3.1 Thermionic Current Contributed by Semiconducting Subbands

For semiconducting subbands, we only consider the electron current for the nFET because the hole current is sup-pressed by the n-type heavily doped source/drain. The current contributed by the substate (m, l) is given by

$$J_{m,l}(V_{xs}, \Delta \Phi_B) = 2env_F \tag{4.4}$$

Where  $V_{xs}$  is the potential difference between the node x and the source. The Fermi velocity  $v_F = l/\hbar \cdot \partial E/\partial k_l$ . The factor of two is due to electron spin degeneracy, e is the unit electronic charge, and n is the number of electrons that occupy the substate (m, l), which is given by

$$n = \frac{f_{FD}(E_{m,l} + eV_{xs} - \Delta\Phi_B)}{Lg}$$

(4.5a)

$$f_{FD} = \frac{1}{1 + e^{E/kT}} \tag{4.5b}$$

Where  $\Delta \Phi_B$  is the channel surface-potential change with gate/drain bias,  $f_{FD}(E)$  is the Fermi–Dirac distribution function, k is the Boltzmann constant, T is the temperature in kelvin, and  $E_{m,1}$  is the carrier energy at the substate (m, l).

With (4.4) and (4.5), we obtain

$$J_{m,l}(V_{xs}, \Delta \Phi_B) = \frac{2e}{h} \frac{\sqrt{3}a\pi V_{\pi}}{L_g} \frac{k_l}{\sqrt{k_m^2 + k_l^2}} \frac{1}{1 + e^{(E_{m,l} + eVxs - \Delta \Phi_B)/kT}}$$

(4.6)

The total current contributed by all substates is equal to the current flowing from the drain to the source (+k branch) minus the current flowing from the source to the drain (-k branch)

$$I_{semi}(V_{ch,DS}, V_{ch,GS}) = 2\sum_{\substack{k_m \\ m=1}}^{M} \sum_{\substack{l=1 \\ l=1}}^{L} \left[ T_{LR} J_{m,l}(0, \Delta \Phi_B) |_{+k} - T_{RL} J_{m,l}(V_{ch,DS}, \Delta \Phi_B) |_{-k} \right]$$

(4.7)

Where  $V_{ch,DS}$  and  $V_{ch,GS}$  denote the Fermi potential differences near the source side within the channel, the factor of two is due to the double degeneracy of the subband, and M and L are the numbers of subbands and substates, respectively.

For typical devices with appropriate diameter range( $D_{CNT}$ <3nm) and short gate length ( $L_g \leq 100$ nm), only the first two or three subbands and the first 10–15 substates have a significant impact on the current using a sub-1-V power supply. Including more subbands should be done with more caution due to two limitations: (1) The band-structure model used in this chapter requires  $E_{m,l} < < V_{\pi}$ , and (2) the complex phonon modes at high energy level. For long-channel devices (Lg>100 nm), one can either approximate the current for short device equation 4.7 by setting  $L_g=100$  nm in equations (4.2c), (4.5a), and (4.6) or use the long-channel model introduced in equation 4.14 in the succeeding part of this part.  $T_{LR}$  and  $T_{RL}$  are the transmission probability of the carriers at the substate (m,l) in +k and -k branches, respectively. We consider three typical scattering mechanisms in the channel region: 1) acoustic phonon scattering (near-elastic process [27]); 2) optical phonon scattering (inelastic process [30]); and 3) elastic scattering [30]. The elastic-scattering probability is assumed to be independent of the carrier energy and will be treated in the complete device modeling in coming chapter. Both the acoustic and optical phonon scatterings depend on the carrier energy. Only intraband scatterings are considered in this chapter. Random-angle scatterings are suppressed and only back and forward scatterings can occur in a 1D quantum wire due to the Pauli's exclusion principle and the confined k-space [5]. A scattering event from the substate  $(m, l_1)$  in +/-k branch to the substate  $(m, l_2)$  in -/+k branch can occur only if the two conditions are satisfied: 1) The substate  $(m, l_1)$  is filled with electrons, and 2) the substate  $(m, l_2)$  is empty so that it can accept the scattered carrier from  $(m,l_1)$ . Assuming that the optical phonon-scattering MFP ( $\lambda op \sim 15$  nm) and the acoustic phonon-scattering MFP ( $\lambda ap \sim 500$  nm [2]) are constant if both conditions are met, we normalize the effective acoustic phonon-scattering MFP  $(l_{ap})$  and the effective optical phonon-scattering MFP( $l_{op}$ ) of the semiconducting subbands to the available target empty states

$$l_{ap}(V_{xs}, m, l) = \frac{\lambda_{ap} D_o}{D(E_{m,l}) \Big[ 1 - f_{FD} \Big( E_{m,l} - \Delta \Phi_B + eV_{xs} \Big) \Big]}$$

(4.8a)

$$l_{op}(V_{xs}, m, l) = \frac{\lambda_{op}D_o}{D(E_{m,l} - \hbar\Omega) \Big[ 1 - f_{FD} \left( E_{m,l} - \hbar\Omega - \Delta\Phi_B + eV_{xs} \right) \Big]}$$

(4.8b)

Where  $\hbar\Omega(\sim 0.16 \text{ eV} [2])$  is the optical phonon energy that a carrier attains before an optical phonon scattering can occur.

Optical phonon scattering becomes more significant at high  $V_{ch,DSbias}$ . Do is a constant  $\delta/(3\pi V_{\pi} \cdot d)$ , where *d* is the carbon–carbon bond distance, which is about 0.144 nm. D(E) is the CNT universal DOS which is valid in the range  $E_{m,l} < V_{\pi}$ .

$$D(E) = \begin{cases} D_0 \cdot E / \sqrt{E^2 - E_{m,0}^2}, & E > E_{m,0} \\ 0, & E \le E_{m,0}. \end{cases}$$

(4.9)

The effective phonon-scattering MFP is in the form of

$$\frac{1}{l_{eff}(V_{xs},m,l)} = \frac{1}{l_{ap}(V_{xs},m,l)} + \frac{1}{l_{op}(V_{xs},m,l)}$$

(4.10)

It is reasonable to assume that the phonon backscattered carriers are not likely to be backscattered again due to the energy loss and/or the occupied states. Thus, the transmission probabilities in equation 4.7 are given by

$$T_{LR} = \frac{l_{eff}(V_{ch,DS}, m, l)}{l_{eff}(V_{ch,DS}, m, l) + L_g}$$

(4.11a)

$$T_{RL} = \frac{l_{eff}(0, m, l)}{l_{eff}(0, m, l) + L_g}$$

(4.11b)

The key parameter for evaluating CNFET current is  $\Delta \Phi_B$ , which is the channel surface-potential change in response to the changes in the gate and source/drain bias. As shown in Figure 4.3(b), there are three electrostatic coupling capacitors, assuming that the channel material is with an infinite DOS: the capacitance ( $C_{ax}$ ) between the gate and channel, the capacitance ( $C_{sub}$ ) between the channel and substrate, and the capacitance ( $C_c$ )between the channel and external drain (D')/source (S').  $\Delta \Phi_B$  is dynamically affected by the drain bias.  $\beta C_c$  is a fitting parameter that describes this effect due to the two mechanisms: 1) the surface-potential lowering due to the electrostatic coupling between the channel region and the external drain electrode through fringing electric field, and 2) the surface-potential lowering due to nonuniform channel surface-potential profile caused by the drain-induced barrier-lowering effect. Operationally, the parameters  $C_c$  and  $\beta$  are chosen to fit the subthreshold slope and the measured shortchannel effect. For a semiconducting channel with a finite DOS, the channel surface potential  $\Delta \Phi_B$ changes with the gate bias at a rate  $\Delta \Phi_B / \Delta V_{GS} < 1$ , a phenomenon known as the effect of quantum capacitance. We calculate  $\Delta \Phi_B$  using the charge conservation equations

$$Q_{cap} = Q_{CNT} \tag{4.12a}$$

$$Q_{cap} = C_{ox} \left( V_{ch,GS} - V_{FB} \right) + C_{sub} V_{ch,BS} + \beta C_{c} V_{ch,DS} + (1 - \beta) C_{c} V_{ch,s's} - (C_{ox} + C_{sub} + C_{c}) \frac{\Delta \Phi_{B}}{e}$$

(4.12b)

$$Q_{CNT} = \frac{4e}{L_g} \sum_{\substack{k_m \\ m=m_0}}^{M} \sum_{\substack{k_l \\ l=0}}^{L} \left[ \frac{1}{1 + e^{(E_{m,l} - \Delta\Phi_B)/KT}} + \frac{1}{1 + e^{(E_{m,l} - \Delta\Phi_B + eV_{DS})/KT}} \right]$$

(4.12c)

$$m_0 = \begin{cases} 1, & \mod(n_1 - n_2, 3) \neq 0\\ 0, & \mod(n_1 - n_2, 3) = 0. \end{cases}$$

(4.12d)

The factor of four includes both the spin degeneracy and the double degeneracy of the subband.  $V_{FB}$  is the flat-band voltage, and  $V_{BS}$  is the potential difference between the substrate and source.  $Q_{cap}$  is the charge induced by the electrodes, and  $Q_{CNT}$  is the total charge induced on the SWCNT surface. We solve iteratively using a construct in HSPICE [Fig. 4.2(a)].

The front-gate capacitance  $C_{ox}$  is modeled as a planar-gate structure with high-k*gate* dielectric on top of the SiO2 insulating layer (Figure 4.1). For the device with multiple SWCNTs in parallel, Cox is grouped into the capacitance between the gate and SWCNT at the two ends (*Cox\_e*) and the capacitance between the gate and SWCNT in the middle (*Cox\_m*) [20]. For SWCNT of 1.5 nm in diameter with 4*nm*-thick HfO<sub>2</sub> ( $k_1$ =16) and 5*nm* inter-CNT spacing, *Cox\_e*=246 aF/µm, and *Cox\_m*=186 aF/µm. The substrate-to-gate capacitance  $C_{sub}$  can either be calculated similarly if a doublegate device is desired or be calculated with the simple equation  $C_{sub} = 2\pi k_2 \varepsilon 0/ln(2H_{sub}/r)$ .

For a long-channel device (Lg >> 100 nm), the wavenumber  $k_1$  can be represented as a continuous variable. By replacing the inner summation with the integral function and assuming  $T_{LR} = T_{RL} = T_m$ , can be simplified as

$$I_{semi}(V_{ch,DS}, V_{ch,GS}) \approx \frac{4e^2}{h} \sum_{k_m \atop m=1}^{M} \left[ V_{ch,DS} + \frac{KT}{e} \ln \left( \frac{1 + e^{(E_{m,0} - \Delta \Phi_B)/KT}}{1 + e^{(E_{m,0} - \Delta \Phi_B + eV_{ch,DS})/KT}} \right) \right]$$

(4.13)

The previous equations utilize the approximated SWCNT band structure which is valid in the range  $E_{m,l} >> V_{\pi}$ . A more accurate model can be obtained by replacing the simplified band structure with the tight binding model at the cost of the more intensive calculations (approximately three times) or an exact analytical form valid only for achiral CNTs. Little difference is found for both the E–k relationship and the current drive in low-energy range. The chirality difference for SWCNTs with the same diameter can also be ignored, for our purpose, in the range where the carrier energy is less than 1.0eV.

#### 4.3.2 Current Contributed by Metallic Subbands

For metallic subbands of metallic nanotubes, the current includes both the electron and hole currents

$$I_{metal} = 2(1 - m_0)T_{metal} \sum_{\substack{k_l \\ l=1}}^{L} \left[ J_{ele_0, l} + J_{hole_0, l} \right]$$

(4.14a)

$$J_{ele_{0,l}} = \frac{2e}{h} \frac{\sqrt{3a\pi V_{\pi}}}{L_g} (f_{FD}(E_{0,l} - \Delta\Phi_B) - f_{FD}(E_{0,l} + eV_{ch,DS} - \Delta\Phi_B))$$

(4.14b)

$$J_{hole\_0,l} = \frac{2e}{h} \frac{\sqrt{3}a\pi V_{\pi}}{L_g} (f_{FD}(-E_{0,l} - \Delta\Phi_B) - f_{FD}(-E_{0,l} + eV_{ch,DS} - \Delta\Phi_B))$$

(4.14c)

The transmission probability  $T_{metal}$  is given by,

$$T_{metal} = \frac{\lambda_{ap}\lambda_{op}}{\lambda_{ap}\lambda_{op} + (\lambda_{ap} + \lambda_{op}).L_g}$$

(4.15)

If the summation function is replaced with an integral, can be simplified to

$$I_{metal} = (1 - m_0) \frac{4e^2}{h} T_{metal} V_{ch,DS}$$

(4.16)

Thus,  $I_{metal}$  is independent of the channel surface-potential change  $\Delta \Phi_B$  as expected because the DOS of metallic CNT is independent of the carrier energy. For metallic CNTs of less than 3 nm in diameter, the half band gap of the first semiconducting subband is larger than 0.43eV. Considering the large quantum capacitance of metallic CNT and the typical gate electrostatic capacitance discussed in Section following, the semiconducting subbands in a metallic CNT are not likely to be populated in and thereby contribute to the current with sub-1-V power supply.

#### 4.3.3 Band to Band Tunneling Current

In the sub-threshold region, especially with negative gate bias (nFET), the band-to-band tunneling (BTBT) current from drain to source becomes significant. We include a voltage controlled

current source  $I_{btbt}$  in the device model in order to evaluate the device sub-threshold behavior and the static power consumption.

Figure 4.4: Energy-band diagrams (only the first subband is shown) and the associated Fermi levels at the source/drain side for NFET with moderate gate/drain bias. There are two possible tunneling regions: regions 1 and 2, which are shaded on the plot. We only consider the tunneling through region 2 in this chapter.

As shown in Figure 4.3, there are two possible tunneling regions: the "n" shape region 1 and the "L" shape region 2. With  $V_{ch,DS} > E1,0$ , the tunneling through the drain junction in region 1 causes holes (electrons) pile up in the nFET (pFET) channel region because the source junction prohibits the holes (electrons) from escaping away. The hole (electron) pile up results in surface potential lowering and thereby a higher current and worse subthreshold behavior [32]. This mechanism depends on the drain junction electrical field and thereby the doping profile. A gradual drain junction doping profile helps relieve this effect by spreading the potential drop over a longer distance. Little such effect is observed for well-tempered devices. To simplify the modeling, we ignore this effect in this work. Because the tunneling through the source junction in region 1 is prohibited, we only consider the BTBT current through the drain junction in region 2. There are two prerequisites for tunneling to occur in region 2: First, the conduction band at the drain side is below the valance band at source side, i.e Vch,DS > 2Em,0where Em, 0 is the half band gap of the mth sub-band; and second, there are enough empty states at the drain side to accept the carriers that tunnel from the source/channel region. Assuming ballistic transport for the tunneling process, the BTBT current is approximated by the BTBT tunneling probability (Tbtbt) times the maximum possible tunneling current integrating from the conduction band at drain side up to the valance band at source side,

$$I_{btbt} \approx \sum_{\substack{k_m \\ m=1}}^{M} T_{btbt} \frac{4e}{h} \int_{E_{m,0}-E_f}^{V_{ch,DS}-E_{m,0}-E_f} (1 - f_{FD}(E)) dE$$

(4.17)

*Ef* is the Fermi level of the doped source/drain nanotube in units of eV. Applying the Fermi-Dirac function from equation 4.5b in the above equation, we obtain,

$$I_{btbt} = \frac{4e}{h} kT \cdot \sum_{\substack{k_m \\ m=1}}^{M} \left[ T_{btbt} \ln \left( \frac{1 + e^{(E_{ch,DS} - E_{m,0} - E_f)/kT}}{1 + e^{(E_{m,0} - E_f)/kT}} \right) \cdot \frac{\max \left( eV_{ch,DS} - 2E_{m,0}, 0 \right)}{eV_{ch,DS} - 2E_{m,0}} \right]$$

(4.18)

Following the work of Kane [24,25], the WKB-like transmission coefficient is given by,

$$I_{btbt} \approx \frac{\pi^2}{9} \exp\left(-\frac{\pi m^{*(1/2)} \left(\eta_m 2E_{m,0}\right)}{2^{3/2} e.\hbar.F}\right)$$

(4.19)

The "perpendicular energy" part in [25] is ignored in this case because the motion of the carriers in 1-D quantum wire is confined along the channel direction.  $2E_{m,0}$  is the band gap, and  $\eta_m$  is a fitting parameter, set to 0.5 in this work, which represents the band gap narrowing effect under high electrical field [26,27].  $m^*$  is the effective electron mass, defined as  $\hbar^2 / (\partial E_{m,l} / \partial k_l^2)$ . Applying equation (4.3) and approximating the effective mass near the bottom of the sub-bands, we obtain,

$$m^* \approx \frac{2\hbar k_m}{\sqrt{3.a.V_\pi}} \tag{4.20}$$

$m^*$  is about 0.05mo and 0.10mo for the carriers in the 1st and the 2nd (semiconducting) subband, respectively, where mo is the electron rest mass. F is the electrical field triggering the tunneling process near the drain side junction; we normalize the total potential drop across the channel-drain junction to a fitting parameter,  $l_{relax}$ , assuming the potential difference relaxes over the distance  $l_{relax}$ ,

$$F = \frac{V_{ch,DS} + E_f - \Delta \Phi_B}{l_{relax}}$$

(4.21)

$l_{relax}$  affects both BTBT current slope and its magnitude. The default value is set to 40 *nm* to match the BTBT current slope vs. Vgs of MOSFET-like CNFET in [2].

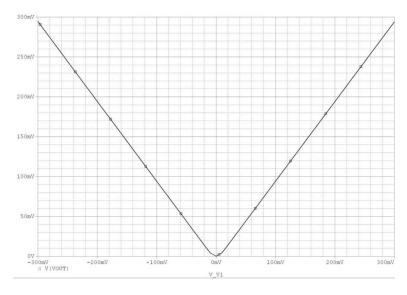

#### 4.4 Transcapacitance network

To model the intrinsic ac response of CNFET device, we use a controlled transcapacitance array among the four electrodes (G,S,D and B) with the Meyer capacitor model [28].  $C_{IJ}$  is the mathematically derived transcapacitance per unit gate length (*Lg*) between the nodes i and j, which is defined as  $|\partial Q_I / \partial V_J|$ . The actual transcapacitance in the channel region is  $C_{ij} = C_{IJ} L_g$  [Figure 4.2(a)].

First, we consider the source/drain capacitance with respect to the gate/substrate voltage variation. There are two methods to assign the charges in the channel region to the source and the drain: 1) Assuming a near-ballistic transport in the channel, the carrier distribution along the channel should be almost uniform, i.e.,  $Q_{s,ch} \approx Q_{d,ch} = Q_{cap}/2 = Q_{CNT}/2$ . 2) All the carriers from +k branches are assigned to the source, and all the carriers from -k branches are assigned to the drain. The first approach is more

reasonable in representing the physical meaning of the capacitor (a carrier reservoir which does not distinguish where the carriers come from), whereas it may result in  $C_{ij} \neq C_{ji}$ . We first discuss the former (charge separation) approach which results in the equivalent circuit model in Figure 4.2(a). All the carriers in both the channel region and the source/drain nodes [Fig. 4.3(b)] come from the (external) source and drain electrodes; thus  $Q_S = L_g \cdot (Q_{cap}/2 + (1 - \beta)C_c \cdot \Delta\Phi_B)$ , and  $Q_D = L_g \cdot (Q_{cap}/2 + \beta C_c(\Delta\Phi_B - V_{DS}))$ . We denote the total electrostatic coupling capacitance per unit length between the channel and other electrodes as  $C_{tot} = C_{ox} + C_{sub} + C_c$ . Taking the partial derivative of  $Q_S$  and  $Q_D$  over  $V_G$ , we obtain

$$C_{sg} = \frac{L_g}{2} \left( C_{ox} - \frac{1}{e} \frac{C_{tot} - 2(1 - \beta)C_c}{\partial V_G / \partial \Delta \Phi_B} \right)$$

(4.23a)

$$C_{g} = \frac{L_g}{2} \left( C_{ox} - \frac{1}{e} \frac{C_{tot} - 2\beta C_c}{\partial V_G / \partial \Delta \Phi_B} \right)$$

(4.23b)

$$C_{gd} = \frac{L_g}{2} \left( C_{ox} - \frac{1}{e} \frac{C_{tot} - 2\beta C_c}{\partial V_G / \partial \Delta \Phi_B} \right)$$

(4.23b)

where  $\partial V_G / \partial \Delta \Phi_B$  can be calculated by equating  $\partial Q_{cap} / \partial \Delta \Phi_B$  and  $\partial Q_{CNT} / \partial \Delta \Phi_B$  with fixed  $V_{ch,S}$ ,  $V_{ch,D}$ , and  $V_B$  using (4.12b) and (4.12c).

$$\frac{\partial V_G}{\partial \Delta \Phi_B} = \frac{1}{EC_{ox}} \left( C_{tot} + C_{Qs} + C_{Qd} \right)$$

(4.24a)

$$C_{Qs} = \frac{4e^2}{L_g.kT} \sum_{\substack{k_m \ m=0}}^{M} \sum_{\substack{k_l \ m=0}}^{L} \left[ \frac{e^{(E_{m,l} - \Delta \Phi_B)/kT}}{\left( 1 + e^{(E_{m,l} - \Delta \Phi_B)/kT} \right)^2} \right]$$

(4.24b)

$$C_{Qd} = \frac{4e^2}{L_g.kT} \sum_{\substack{k_m \ m=0}}^{M} \sum_{\substack{k_l \ m=0}}^{L} \left[ \frac{e^{(E_{m,l} - \Delta\Phi_B + eV_{ch,DS})/kT}}{\left(1 + e^{(E_{m,l} - \Delta\Phi_B + eV_{ch,DS})/kT}\right)^2} \right]$$

(4.24c)

We define  $C_{Qs}$  and  $C_{Qd}$  as the quantum capacitance due to the carriers from source (+k branch) and drain (-k branch), respectively. With small gate bias  $(E_{m,0} < \Delta \Phi_B)$ ,  $\partial V_G / \partial \Delta \Phi_B \approx C_{tot} / (eC_{ox})$ ; thus, the channel acts as a linear voltage divider which has little dependence on quantum capacitance. With large gate bias  $(E_{m,0} < \Delta \Phi_B)$ ,  $\partial V_G / \partial \Delta \Phi_B > C_{tot} / (eC_{ox})$ ; therefore, the surface potential will be limited by the quantum capacitance. With (23) and (24), we obtain

$$C_{sg} = \frac{L_g C_{ox}}{2} \frac{C_{Qs} + C_{Qd} + 2(1 - \beta)C_c}{C_{tot} + C_{Qs} + C_{Qd}}$$

(4.25a)

$$C_{dg} = \frac{L_g C_{ox}}{2} \frac{C_{Qs} + C_{Qd} + 2\beta C_c}{C_{tot} + C_{Qs} + C_{Qd}}$$

(4.25b)

We can follow a similar approach to calculate the capacitance  $C_{sb}$  and  $C_{db}$  as  $C_{sb} = C_{sg} \cdot (C_{sub}/C_{ox})$  and  $C_{db} = C_{dg} \cdot (C_{sub}/C_{ox})$ , respectively. The charges accumulated on the gate and substrate (back gate) electrodes

are given by  $Q_G = L_g \cdot C_{ox} \cdot (V_{GS} - V_{FB} - \Delta \Phi_B)$  and  $Q_B = L_g \cdot C_{sub} \cdot (V_{BS} - \Delta \Phi_B)$ , respectively. With a similar approach, the coupling capacitance between the gate and the substrate is derived as

$$C_{bg} = C_{gb} = \frac{L_g C_{sub} C_{ox}}{C_{tot} + C_{Qs} + C_{Qd}}$$

(2.26)

Next, we consider the gate/substrate capacitance due to source/drain voltage variation. With similar approach as the earlier one, we obtain

$$C_{gs} = \frac{L_g C_{ox} \left[ C_{Qs} + (1 - \beta) C_c \right]}{C_{tot} + C_{Qs} + C_{Qd}}$$

(4.27a)

$$C_{gd} = \frac{L_g C_{ox} \left[ C_{Qd} + \beta C_c \right]}{C_{tot} + C_{Qs} + C_{Qd}}$$

(4.27a)

$$C_{bs} = C_{gs} \frac{C_{sub}}{C_{ox}}$$

(4.27c)

$$C_{bd} = C_{gd} \frac{C_{sub}}{C_{ox}}$$

(4.27d)

The earlier equations give the values of the nine capacitors in Figure 4.2(a). If we use the second channel charge-separation approach (+k carriers for source and -k carriers for drain), reciprocality is guaranteed, and Csg = Cgs, Cdg = Cgd, Csb = Cbs, and Cdb = Cbd; thus, the gate-capacitance network can be simply represented by the five-capacitor model in Fig. 4.2(b), or by the six-capacitor model, as shown in Figure 4.2(c), which shows explicitly the electrostatic and quantum capacitances with the same transfer function as the five-capacitor model.

This chapter presented a circuit-compatible compact model of the intrinsic channel region of MOSFET-like SWCNFETs including some channel region nonidealities. Comparison with a more accurate device model using the tight binding band-structure model shows that this model is valid for CNFET with a wide range of chiralities and diameters. This model uses a substate summation approach, instead of the integral, to calculate the parameters. This approach makes the modeling methodology described in this chapter to be generally applicable to other 1-D devices, e.g., silicon nanowire FET, and requires less computation efforts, thereby making it more compatible with a circuit simulator. The complete dynamic gate-capacitance network makes the model suitable for both small- (analog) and large signal (digital) applications. This model serves as a starting point toward the complete CNFET-device model, including the device/circuit-level nonidealities and multiple CNTs, which is reported in the next chapter.

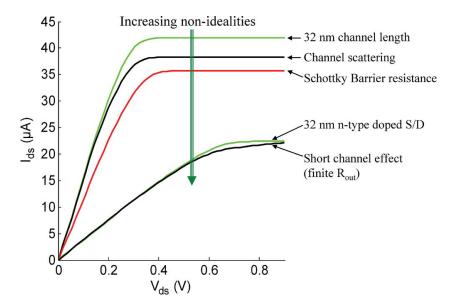

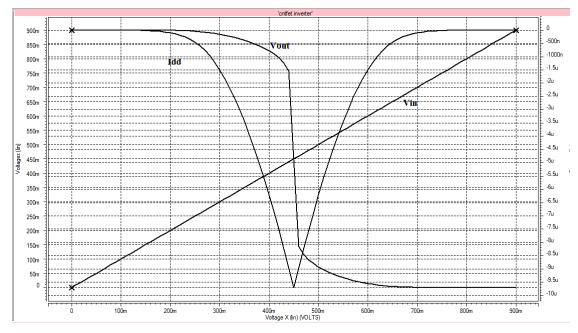

# Chapter 5 COMPLETE DEVICE MODEL AND CIRCUIT PERFORMANCE

In addition to the nonidealities included in the chapter 4, this chapter includes the elastic scattering in the channel region, the resistive source/drain (S/D), the Schottky-barrier resistance, and the parasitic gate capacitances. More than one nanotube per device can be modeled. Compared to silicon technology, the CNFETs show much better device performance based on the intrinsic *CV/I* gate-delay metric (six times for nFET and 14 times for pFET) than the MOSFET device at the 32-nm node, even with device nonidealities. This large speed improvement is significantly degraded (by a factor of five to eight) by interconnect capacitance in a real circuit environment. We performed circuit-performance comparison with all the standard digital library cells between CMOS random logic and CNFET random logic with HSPICE simulation. Compared to CMOS circuits, the CNFET circuits with one to ten carbon nanotubes per device is about two to ten times faster, the energy consumption per cycle is about seven to two times lower, and the energy-delay product is about 15–20 times lower, considering the realistic layout pattern and the interconnect wiring capacitance.

#### **5.1 Circuit Topology**

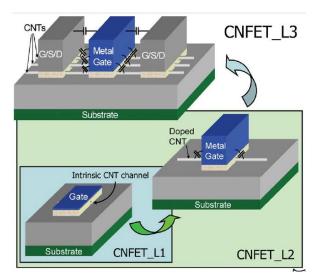

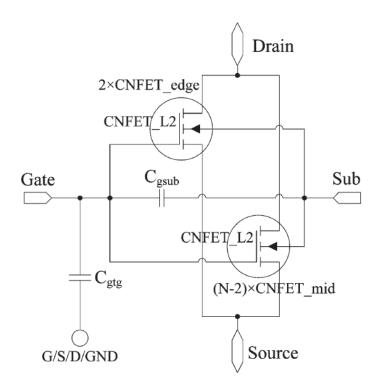

A MOSFET-like CNFET device structure (Figure 4.1a) is used for the modeling and this chapter because of both the fabrication feasibility and superior device performance of the MOSFET-like CNFET as compared to the Schottky Barrier (SB)-controlled FET. The complete CNFET device model is implemented hierarchically in three levels (Figure 5.1). Device nonidealities are included hierarchically at each level. Level 1, denoted as CNFET\_L1, models the intrinsic behavior of MOSFET like CNFET. The model at this level is similar to the device level models such as those in [27] and [28]. The second level, denoted as CNFET\_L2, includes the device nonidealities: the capacitance and resistance of the doped S/D CNT region, as well as the possible SB resistances of S/D contacts. The first two levels deal with only one CNT under the gate. The top level, denoted as CNFET\_L3, models the interface between the CNFET device and the CNFET circuits. This level deals with multiple CNTs per device and includes the parasitic gate capacitance and screening due to the adjacent CNTs. This chapter presents the secondand third-level model as an extension to the first-level model CNFET\_L1 in chapter 4.

Figure 5.1: Complete CNFET device model is implemented with hierarchical three levels. Level 1, CNFET\_L1, models the intrinsic behavior of CNFET. The second level, CNFET\_L2, includes the device nonidealities. The first two levels deal with only one CNT under the gate. The top level, CNFET\_L3, models the interface between the CNFET device and CNFET circuits. This level deals with multiple CNTs per device and includes the parasitic gate capacitance and screening due to adjacent CNTs.

#### 5.2 Device Model- The Second Level

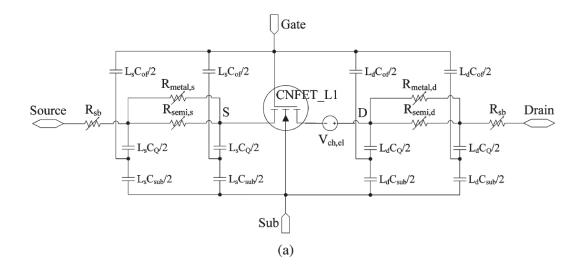

As an extension to the first-level CNFET model CNFET\_L1 of the intrinsic channel region in chapter 4, this level models the device nonidealities, including the elastic scattering in the channel region, the quantum/series resistance and the parasitic capacitance of the doped S/D region, as well as the SB resistance at the interface between the doped CNT and the S/D metal contacts. The equivalent circuit diagram is shown in Figure 5.2.

Figure 5.2: Second-level equivalent circuit model CNFET\_L2 for CNFET. (a) The six-capacitor model and (b) the four-capacitor model.

#### **5.2.1 Channel Resistance**

We consider three typical scattering mechanisms in the channel region: 1) acoustic phonon scattering (near elastic process [33]); 2) optical phonon scattering (inelastic process [33]); and 3) elastic scattering. Both the acoustic phonon scattering and optical phonon scattering are treated in the first-level device modeling [30]. The elastic-scattering rate and thereby the MFP are assumed to be independent of the carrier energy. We include the elastic scattering in this chapter in a computationally efficient way. Although the elastic-scattering MFP of the intrinsic CNT can be longer than 1  $\mu$ m, the fabricated CNTs often contain nonideal scattering centers (e.g., defects) which may degrade the MFP significantly and, in turn, cause additional potential drop along the channel region. The total potential drop  $(V_{DS})$  across the channel region is a summation of the potential drop ( $V_{ch,DS}$ ) due to the channel quantum resistance  $R_{ch,c}$ and the potential drop ( $V_{ch,el}$ ) over the channel resistance  $R_{ch,el}$  due to the elastic scattering (Figure 5.3), i.e.,  $V_{\text{DS}} = V_{\text{ch,DS}} + V_{\text{ch,el}}$ ,  $V_{\text{ch,DS}} = I_{\text{DS}}R_{\text{ch,c}}$ , and  $V_{\text{ch,el}} = I_{\text{DS}}R_{\text{ch,el}}$  is equal to  $(1 - T_{\text{ch}})/T_{\text{ch}} \cdot R_{\text{ch,c}}$ , where  $T_{\rm ch}$  is the transmission probability in the channel region,  $T_{\rm ch} = l_{\rm eff}/(L_g + l_{\rm eff})$ , and  $L_g$  and  $l_{\rm eff}$  are the channel length and the effective elastic-scattering MFP, respectively. We further assume that MFP  $l_{eff}$  is linearly proportional to the nanotube's diameter, i.e.,  $l_{eff} = D_{CNT}/(1.5 \text{ nm}) \cdot \lambda_{eff}$ , where  $D_{CNT}$  is the CNT diameter, and  $\lambda_{eff}$  (~200 nm [31]) is the elastic-scattering MFP for 1.5 nm in diameter CNT. With the aforementioned equations, we can represent the potential drop over  $R_{ch,el}$  as

$$V_{ch,el} = \frac{L_g}{L_g + \frac{D_{CNT}}{1.5nm} \cdot \lambda_{eff}} V_{DS}$$

(5.1)

Figure 5.3: Fermi-level profile for 1-D device with series resistance (finite MFP along CNT). The Fermi-level profile is approximated as a linear function of the position along the channel.

Representing the effect of the channel resistance due to elastic scattering as a voltage-controlled voltage source  $V_{ch,el}$  (Figure 5.2) can avoid calculating  $R_{ch,el}$  directly, thereby simplifying the computation.

#### 5.2.2 Doped S/D CNT

The heavily doped nanotube regions of the CNFET act as both the S/D extension region and the local interconnect between two adjacent devices.  $\pi$  model is used to represent the equivalent circuit of the doped S/D region (Figure 5.2).

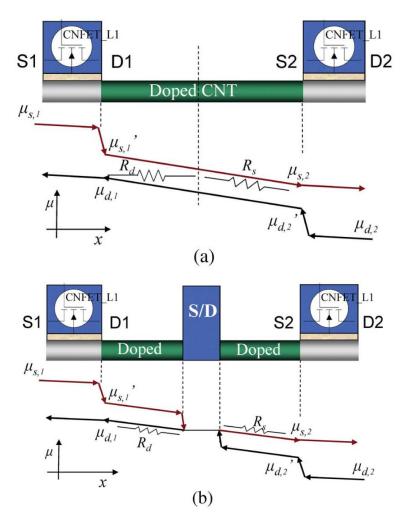

**Resistance:** First, we discuss the model for the resistance of the doped CNT region. Similar to the channel region, the CNT can be either metallic or semiconducting. The S/D resistance is modeled as two paralleled resistors:  $R_{\text{semi},d}$  ( $R_{\text{semi},d}$ ) due to the semiconducting subbands and  $R_{\text{metal},s}$  ( $R_{\text{metal},d}$ ) due to the metallic subbands of the metallic nanotubes. We consider two typical cases for device connectivity: 1) The drain of one CNFET is connected to the source of another CNFET, i.e., the doped CNT acts as interconnect between two devices in series [Figure 5.4(a)] without a metal contact in between, and 2) the S/D of one CNFET is connected to the metal contact, e.g., at the output node [Fig. 4(b)]. For the first case, the two segment doped nanotubes should be the same as one continuous doped nanotube in the model, i.e., the potential profile along the two segments is continuous [Fig. 4(a)]. Furthermore, we describe the device intrinsic behavior with S/D input Fermi levels ( $\mu s$ ,  $\mu d$ ) as mentioned earlier, whereas the input source Fermi level  $\mu s$  of one device is connected to the output port of the equivalent circuit model from  $\mu d$  to  $\mu s$  for this case. For the second case, the ideal metal contact is an electron reservoir that has infinite density of state (DOS) and acts as an infinite scattering center so that there is an additional

potential drop across the boundary between the doped CNT and the metal contact (called the quantum contact resistance) due to mode mismatch [Fig. 4(b)]. The device model is able to handle both cases correctly as described next. We define two parameters  $S_{out}$  ( $D_{out}$ ) representing the S/D connectivity: they are equal to 0 if source (drain) is connected to the doped CNT; otherwise, they are equal to 1. Consider the Fermi-level profiles for both cases in Figure 5.4. Now we obtain the total effective resistance of the doped S/D region [30].

Figure 5.4: Related Fermi-level profiles for (a) two CNFETs that are connected with a doped CNT and (b) two CNFETs that are connected by an ideal metal contact (without considering the SBs between the CNT and metal interface).Superposed are the equivalent S/D resistors.

$$R_{x,s} = L_s / (\lambda_{sd} G_{x,c}) \tag{5.2a}$$

$$R_{x,d} = \eta_{deff} / G_{x,c} \tag{5.2b}$$

$$\eta_{deff} = \begin{cases} \left( L_d - \lambda_{sd} \right) / \lambda_{sd}, & D_{out} = 0 \\ L_d / \lambda_{sd}, & D_{out} = 1 \end{cases}$$

(5.2c)

The subscript x denotes either "semi" or "metal". L<sub>s</sub> and L<sub>d</sub> are the lengths of the doped source and drain regions, respectively.  $\lambda_{sd}$  is the impurity scattering MFP, assumed a constant with a default value of 15 nm, which is a pessimistic estimation, for degenerately doped nanotubes. A longer MFP, 20–50 nm, can be derived from the work in [20] with charge-transfer doping.  $G_{x,c}$  is the quantum conductance of doped CNT.  $G_{x,c}$  depends on CNT diameter, the doping level (E<sub>f</sub>), and the S/D Fermi-level difference ( $eV_c =$  $|\mu_s - \mu_d|$ ).  $G_{x,c}$  expression is mentioned in [30], for semiconducting subband given as

$$G_{semi,c}(V_c) = \frac{4e^2}{h} \sum_{\substack{k_m \\ m=1}}^{2} \left[ 1 + \frac{kT}{eV_c} \ln\left(\frac{1 + e^{(E_{m,0} - E_f - \Delta\Phi_B)/kT}}{1 + e^{(E_{m,0} - E_f - \Delta\Phi_B + eV_c)/kT}}\right) \right]$$

(5.3)

With small drain bias ( $V_c < E_f - E_{1,0} + \Delta \Phi_{s,max}$ ),  $G_{semi,c}$  can be approximated as a constant,  $G_{semi,c} \approx 4e^2/(m \cdot h)$ , where *m* is the number of subbands below  $E_f$ . With large drain bias ( $V_c > E_f - E_{1,0} + \Delta \Phi_{s,max}$ ), e.g., in the saturation region, the maximum surface-potential change referred to  $\mu s$  will be pinned at  $\Delta \Phi_{s,max}$ , and the drain Fermi level will be pushed below the first subband, which causes a rapid increase in resistance. Therefore, the S/D resistance increases with an increasing current (drain bias). On the other hand, the quantum conductance of the metallic subbands is almost independent of bias because the DOS is constant,

$$G_{metal,c} = (1 - m_0) \frac{4e^2}{h}$$

(5.4)

where m0 = 0 if  $mod(n_1 - n_2, 3) = 0$  with  $(n_1, n_2)$  CNT; otherwise, it is equal to 1. The internal parameter  $V_c$  is related to the circuit parameter  $V_{series,s}$  or  $V_{series,d}$  (the potential drop over the series resistor at the source or drain side, respectively) by equation  $V_c = V_{series,d}/\eta_{deff} = V_{series,s}\lambda_{sd}/L_s$ . With the aforementioned equations, we are ready to calculate the S/D resistance as voltage-controlled resistors ( $R_{semi,s}$ ,  $R_{semi,d}$ ,  $R_{metal,s}$ , and  $R_{metal,d}$ ).

**Capacitance:** Similar to the channel region in chapter 4, there are two implementations for the extrinsic capacitor network: 1) the six capacitor model that consists of the electrostatic capacitance and quantum capacitance [Figure 5.2(a)] or 2) the four-capacitor model with four transcapacitances [Figure 5.2(b)]. The two implementations are equivalent in terms of ac response. The four equivalent capacitances can be expressed in terms of the six physical capacitors in Fig. 2(a) by

$$C_{gzz} = \frac{L_z \cdot C_{of} C_Q}{2(C_Q + C_{of} + C_{sub})}$$

(5.5a)

$$C_{bzz} = \frac{L_z \cdot C_{sub} C_Q}{2(C_Q + C_{of} + C_{sub})}$$

(5.5b)

The subscript "z" denotes either "s" or "d"; thus  $L_z$  is the length of either source or drain.  $C_Q$  is the quantum capacitance of the doped S/D region. For the channel region, we need to model  $C_Q$  accurately because the gate capacitance ( $C_{ox}$ ) is comparable with  $C_Q$ . However, for the heavily doped CNT region,  $C_Q$  (~400 aF/µm per subband) is typically much larger than the electrostatic capacitance ( $C_E$ ) between CNT and ground (typically100aF/µm). Thus, we approximate  $C_Q$  to the first order as  $C_Q = \left[\Theta(E_f - E_{1,0}) + \Theta(E_f - E_{2,0})\right] \times 400 aF / µm$  where  $\Theta$  (x) is a step function that is equal to 1 if x > 0; otherwise, it is equal to 0. For multiple CNTs per gate, the gate outer-fringe capacitances ( $C_{of}$ ) are grouped into the fringe capacitance between the gate and S/D CNT at the two edges ( $C_{of_e}$ ) and into the fringe capacitance between the gate and S/D CNT in the middle ( $C_{of_e}$ ) in this chapter, as described in [25].

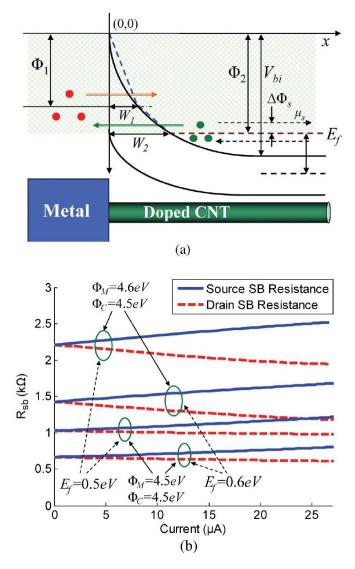

**SB Resistance:** SB may exist at the interface between CNT and metal contact [34] and in CNT hetero-junctions between metallic and semiconducting CNTs . In this chapter, we use a simplified model to describe SB resistance between doped CNT and metallic electrode to include some signature effects of SB on device performance. We made the following simplifying assumptions in this model: 1) The doped CNT region is long enough so that there is no surface-potential modification due to the quantum confinement within a short CNT; 2) dipole effects are ignored; 3) there are no pinning effects [35]; and 4) the depletion profile is steep. Figure 5.5(a) shows an example of the potential profile of SB at the source side. In this simple model, we only consider tunneling through the first subband, assuming that the carriers injecting from the metal contact can redistribute over all the subbands near the contact region. The potential barriers seen by the carriers at the metal contact side ( $\Phi_1$ ) and the doped CNT side ( $\Phi_2$ ) are given by

$$\Phi_1 = \Phi_M - \Phi_C + E_{1,0} \tag{5.6a}$$

$$\Phi_{2} = \begin{cases} \Phi_{1} + |V_{sb,s}| + \Delta \Phi_{s}, & Source - SB \\ \Phi_{1} - |V_{sb,d}| - V_{c} + \Delta \Phi_{s}, & Drain - SB \end{cases}$$

(5.6b)

*Vsb,s* and *Vsb,d* are the potential drops over the equivalent SB resistor at the source and drain sides, respectively, from the equivalent circuit point of view.  $\Phi_M$  and  $\Phi_C$  are the metal and CNT work functions, respectively. With positive bias  $V_{\text{DS}}$  and  $V_{\text{GS}}$ , the carriers of the source side see a higher SB,

whereas the carriers of the drain side see a lower SB. With doping level  $E_f$ , the normalized volume doping density is

$$N_D = \frac{32E_{1,0}^2}{3\pi^2 V_\pi^3 d^3} \sqrt{E_f^2 - E_{1,0}^2}$$

(5.7)

The depletion length is then approximately

$$W_d = \sqrt{\frac{2k_2\varepsilon_0}{eN_D}}V_{bi}$$

(5.9a)

Where

$$V_{bi} = E_f - E_{1,0} + \Phi_2 \tag{5.9b}$$

$V_{bi}$  is the build in potential with an applied bias. For low doping level (< 2 × 10-4), the depletion width for CNT is micrometers or so, precluding a nanoscale device [23]. At high doping (> 10-3), the length scale becomes small enough so that the contact is essentially ohmic through tunneling. The conductionband potential profile is

$$E_{C}(x) = \frac{eN_{D}(W_{d} - x)^{2}}{2k_{2}\varepsilon_{0}} + E_{1,0} - E_{f} - \Phi_{1} + \Phi_{2}$$

(5.10)

We approximate the potential profile with a triangular potential profile with the same classical turning points,  $0, W_1$  (before bias), and  $W_2$  (after bias) shown in the Figure 5.5(a).

$$W_{1} = \sqrt{\frac{2k_{2}\varepsilon_{0}}{eN_{D}}} \left( \sqrt{V_{bi}} - \sqrt{E_{f} - E_{1,0} + \Phi_{1} - \Phi_{2}} \right)$$

(5.11a)

$$W_{2} = \sqrt{\frac{2k_{2}\varepsilon_{0}}{eN_{D}}} \left( \sqrt{V_{bi}} - \sqrt{E_{f} - E_{1,0}} \right)$$

(5.11b)

Using the Wentzel–Kramer–Brillouin approximation, we obtain the tunneling probability through a triangular potential barrier with height v and width w

$$\ln T \simeq -2\int_{0}^{w} |k(x)| dx = -\frac{2\sqrt{2m} \times w\sqrt{v}}{3\hbar} - \frac{4w}{9r}\sqrt{\frac{2v}{E_{1,0}}}$$

(5.12)

The average transmission probability through the first subband is approximately

$$T_{SB} \approx \frac{\int_{\Phi_1}^{\Phi_2} T dE}{\Phi_2 - \Phi_1} \approx \frac{2}{3(\Phi_2 - \Phi_1)\tau^{2/3}} \left[ \Gamma\left(\frac{3}{2}, \tau \cdot \Phi_1^{3/2}\right) - \Gamma\left(\frac{3}{2}, \tau \cdot \Phi_2^{3/2}\right) \right]$$

(5.13a)

$$\tau \approx \frac{4\sqrt{2}W_2}{9r\sqrt{E_{1,0}.\Phi_2}}$$

(5.13b)

Figure 5.5: (a) The energy band diagram for the contacted metal and doped CNT with bias. The potential barrier in the tunneling region (shaded area) is approximated as a triangle potential barrier. (b) SB resistances as functions of the current, with different metal/CNT work functions and different CNT doping levels. Both smaller barrier height and higher CNT doping level help to reduce SB resistance significantly.

The potential barrier height  $\Phi 2$  and thickness  $W_2$  depend on the bias. With high degenerate doping which is satisfied in this chapter, to improve runtime, the prior equation can be approximated with

$$T_{SB} \approx 0.5 \times \left( \exp(-\tau . \Phi_1^{3/2}) + \exp(-\tau . \Phi_2^{3/2}) \right)$$

(5.14)

The equivalent SB series resistance is then given by

$$R_{sb} = \frac{1}{G_{semi,c}} \left( \frac{1}{T_{SB}} - 1 \right) (1 - X_{out})$$

(5.15)

The symbol "X" denotes either "S" (source-side SB) or "D" (drain-side SB), which are defined as either 0 or 1 in previous section. The SB resistance is modeled as a voltage controlled resistor (Figure 5.2). The equations in this section are highly simplified and only valid for the heavily doped CNT, i.e.,  $E_f > E_{1,0}$ ; otherwise, the performance of CNFET will be heavily limited by S/D resistance which is out of the. With this model, we can observe that the source (drain) SB resistance increases (decreases) with an increased S/D current (increased  $V_{DS}$  and  $V_{GS}$ ) due to the increased (reduced) SB seen by the carriers tunneling from the doped CNT to the metal contact shown in Figure 5.5(b). With high doping (~0.8%) and  $\Phi_M = \Phi_C = 4.5 \text{ eV}$ , the SB resistance can be suppressed to a small value (< 1 k $\Omega$ ) compared with the typical device resistance (~40 k $\Omega$ ); thus, it can be ignored in most applications if this high level of doping can be achieved experimentally.

#### **5.3 Device Model-The Third Level**

This level is the top level of the device model, which allows for multiple CNTs for each device (Fig. 5.6). Consider the case where there are NCNTs under the gate. The CNTs are grouped into 1) a number of min(N,2) CNTs at the two edges and 2) the other (N-min(N, 2)) CNTs in the middle. The direct coupling capacitance (Cgsub) between the gate and the substrate is simply expressed as  $C_{gsub} \approx 2\pi L_g k_2 \varepsilon_0 / \ln(4H_{sub} / H_{gate})$ , where Hsub is the insulating bulk thickness, and Hgate is the gate height. Cgsub is about 1 aF, about one-third of the gate intrinsic capacitance, assuming a 10-µm-thick SiO2 bulk, a 64-nm gate height and a 32-nm channel length, and an infinitely large substrate.

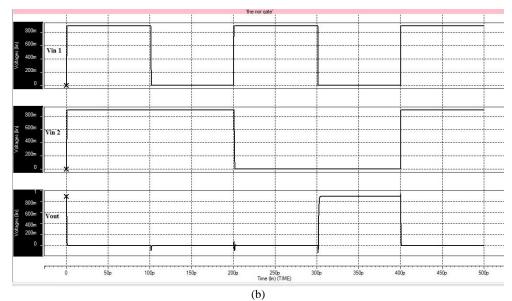

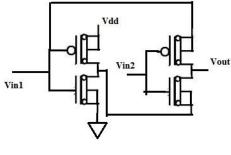

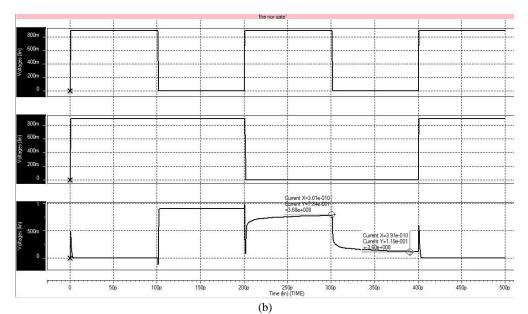

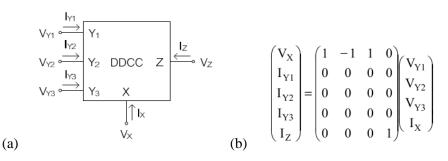

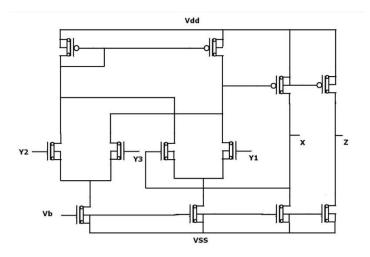

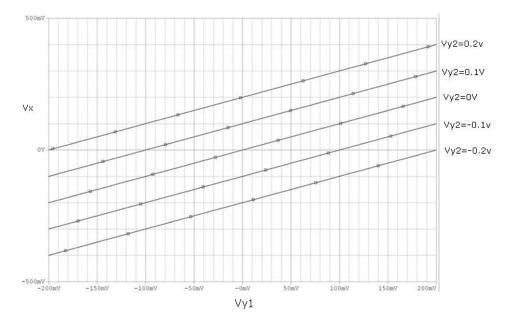

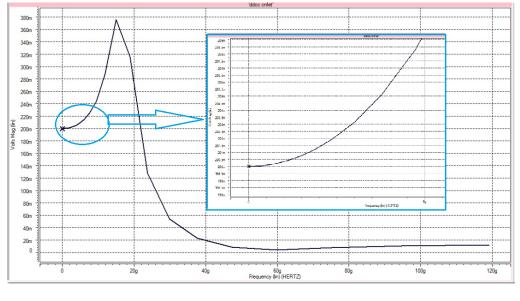

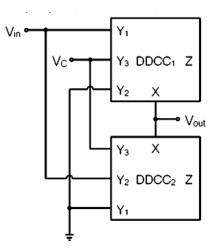

#### 5.4 Gate and Interconnect Parasitic Capacitances