# TCAD ANALYSIS OF HOT CARRIER RELIABILITY AND THERMAL BEHAVIOUR OF TRANSPARENT GATE RECESSED CHANNEL MOSFET

Thesis Submitted To Delhi Technological University For The Award Of Degree Of

MASTER OF TECHNOLOGY IN NANOSCIENCE & TECHNOLOGY

by

AJAY KUMAR

Under the Supervision of

Dr. Rishu Chaujar

Department of Applied Physics Delhi Technological University Delhi, India. JUNE-2014

# CERTIFICATE

This is certified that the thesis titled "TCAD ANALYSIS OF HOT CARRIER RELIABILITY AND THERMAL BEHAVIOUR OF TRANSPARENT GATE RECESSED CHANNEL MOSFET" is being submitted by me (Ajay Kumar–2K12/NST/01) towards partial fulfilment for the award of Master of Technology degree in Nanoscience & Technology in Delhi Technological University. This work is original and has not been submitted in part or fully to any other University or institute for the award of any degree or diploma.

#### Ajay Kumar

Candidate Department of Applied Physics Delhi Technological University Delhi, India

#### Dr. Rishu Chaujar

Supervisor Department of Engineering Physics Delhi Technological University Delhi, India.

#### Prof. S. C. Sharma

Head Department of Applied Physics Delhi Technological University Delhi, India.

# ACKNOWLEDGEMENT

I wish to express my deep sense of gratitude and veneration to my supervisor, *Dr. Rishu Chaujar*, Assistant Professor, Department of Engineering Physics, Delhi Technological University, Delhi, for her perpetual encouragement, constant guidance, valuable suggestions and continued motivation, which has enabled me to complete this work.

I am deeply indebted to *Prof. S. C. Sharma* Head, department of Applied Physics, and all faculty members for their constant guidance and facilities to carry out my thesis work.

### Ajay Kumar

M.Tech. (Nanoscience & Technology) Roll No. 2K12/NST/01

# ABSTRACT

# TCAD ANALYSIS OF HOT CARRIER Reliability and Thermal Behaviour of Transparent Gate Recessed Channel MOSFET

Ajay Kumar Microelectronocs Research Laboratory Department Of Engineering Physics Delhi Technological University Supervisor: Dr. Rishu Chaujar

In this thesis, a novel device structure called <u>T</u>ransparent <u>G</u>ate <u>R</u>ecessed <u>C</u>hannel MOSFET (TGRC-MOSFET) is proposed to alleviate the hot carrier effects for the advanced nanometer process. TGRC-MOSFET involving a recessed channel and incorporates Indium Tin Oxide as a transparent gate. TCAD analysis shows that performance of TGRC-MOSFET surpasses <u>C</u>onventional <u>R</u>ecessed <u>C</u>hannel (CRC)-MOSFET in terms of high  $I_{ON}/I_{OFF}$  ratio and better carrier transport efficiency in compare to <u>C</u>onventional <u>R</u>ecessed <u>C</u>hannel (CRC) MOSFET. This simulation divulges the reduction in hot-carrier-effects metrics like electron velocity, electron temperature, potential, and electron mobility. All the simulations have been done using DEVEDIT-3D and ATLAS device simulator. The work proposes the novel design for reduction in hot carrier and low power switching application.

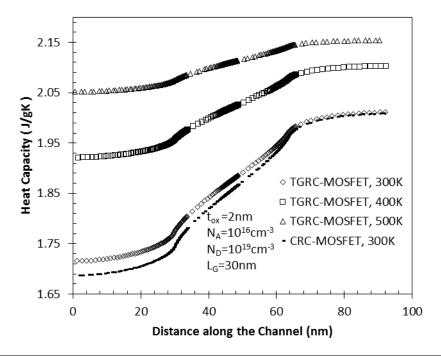

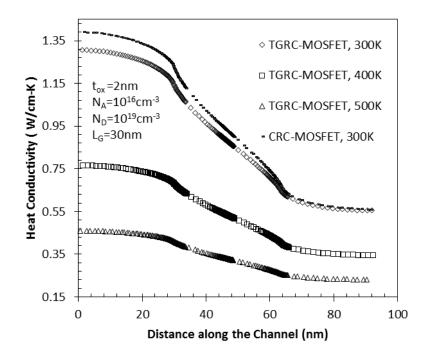

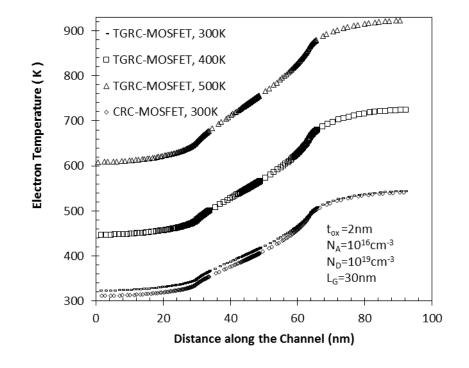

In thermal analysis of a novel design <u>T</u>ransparent <u>G</u>ate <u>R</u>ecessed <u>C</u>hannel MOSFET (TGRC-MOSFET) at 300K. TGRC- MOSFET involves a recessed channel and incorporates Indium Tin Oxide as a transparent gate. Simulation results show that performance of TGRC-MOSFET surpasses <u>C</u>onventional <u>R</u>ecessed <u>C</u>hannel (CRC)-MOSFET in terms of heat capacity, heat conductivity, lattice temperature and total heat power in comparison to CRC-MOSFET. All the simulations have been done using DEVEDIT-3D AND ATLAS device simulator. Indium tin oxide (ITO or tin-doped indium oxide) is a solid solution of indium oxide (In<sub>2</sub>O<sub>3</sub>) and tin oxide (SnO<sub>2</sub>). It is transparent and colourless in thin layers. Because of its two key properties, i.e. electrical conductivity and optical transparency, indium tin oxide is used as one of the most widely used transparent conductivity. Furthermore, with the reduction in transistor size, intrinsic self-heating effects have become unfavourable in low power applications. As the issue of heat becomes increasingly important in sub-micron MOSFETs, it becomes increasingly more important to accurately measure and model its thermal parameters to fully characterize its thermal performance.

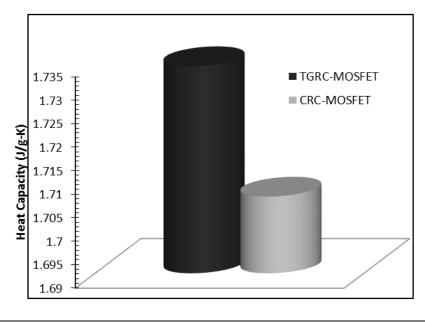

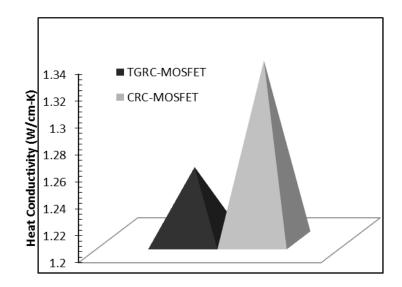

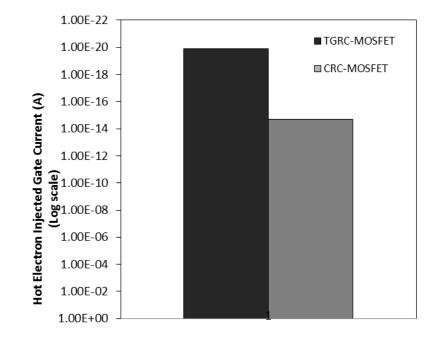

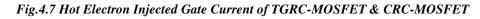

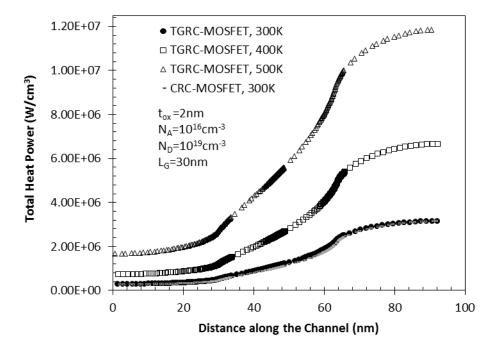

High heat capacity of TGRC-MOSFET device is favourable for high power applications as compared to CRC MOSFET. Furthermore, low thermal conductivity of a device, finding application as heat insulation. TGRC-MOSFET has lower thermal conductivity as shown in fig. 3. In addition, there is reduction in hot electron (HE) injection gate current and impact ionization (II) substrate current in TGRC-MOSFET compared to CRC MOSFET which improves the device speed performance and hence reduced the power dissipation as it is evident from results respectively. Since, there is appreciable reduction in electric field at the drain side in TGRC-MOSFET in comparison to CRC-MOSFET which results in lower leakage current.

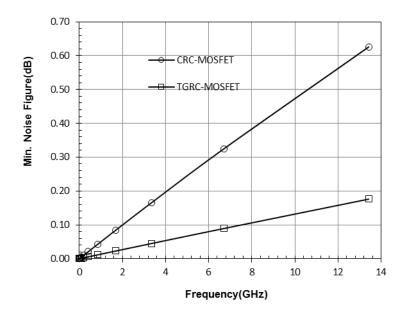

The noise assessment of Novel <u>Transparent Gate Recessed Channel MOSFET</u> has been investigated based on the simulated result from ATLAS device simulation. TCAD simulation results show TGRC-MOSFET divulges <u>Conventional Recessed Channel (CRC)-MOSFET</u> in terms of reduction in noise figure, noise conductance and parasitic capacitances. It also achieves higher optimum source impedance for high performance applications where noise immunity is a key factor. Here we accentuate our focus on Transparent Gate architecture incorporation onto the Conventional Recessed Channel MOSFET for superior noise performance of scaled MOS devices. Intensive TCAD device simulations have been performed to probe the internal transport conditions of CRC MOSFET and TGRC-MOSFET,

and substantial interpretation is given to the internal behaviours observed in all the devices investigated. TCAD simulation reveals the deterioration in minimum noise figure, noise conductance and parasitic capacitances. It also achieves higher optimum source impedance. This work presents a TGRC-MOSFET device which is reliable for RF applications and CMOS technology for the designing of multi-gigahertz communication circuits.

# TABLE OF CONTENTS

| CERTIFICATE                                                                    | •••••             | •••••        | •••••                                   |       | ••••• | i        |

|--------------------------------------------------------------------------------|-------------------|--------------|-----------------------------------------|-------|-------|----------|

| ACKNOWLEDGEME                                                                  | NT                | •••••        | ••••••                                  |       | ••••• | ii       |

| ABSTRACT                                                                       |                   | •••••        | • • • • • • • • • • • • • • • • • • • • | ••••• | ••••• | iii      |

|                                                                                |                   |              |                                         |       |       |          |

|                                                                                |                   |              |                                         |       |       |          |

| Chapter-1                                                                      |                   |              |                                         |       | (1    | -21)     |

| INTRODUCTION                                                                   |                   |              |                                         |       |       |          |

| 1.1 Conventional Mos                                                           | SFET              |              |                                         |       |       | 1        |

| 1.2 NEED OF RECESSED                                                           | CHANNEL ]         | MOSFETs      |                                         |       |       | 3        |

| 1.2.1. RECESSED CH                                                             | IANNEL <b>M</b> ( | OSFETS PERFO | RMANCE                                  |       |       | 3        |

| 1.3 TRANSPARENT<br>Performance                                                 |                   |              | CHANNEL                                 |       |       | Ітs<br>7 |

| 1.4 ATLAS-DEVICE SIM                                                           | ULATOR            |              |                                         |       |       | 10       |

| 1.4.1 MOBILITY MOI                                                             | DELS              |              |                                         |       |       | 10       |

| 1.4.2 CARRIER GENE                                                             | ERATION-R         | ECOMBINATION | MODELS                                  |       |       | 11       |

| 1.4.2 CARRIER GENERATION-RECOMBINATION MODELS   1.4.3 IMPACT IONIZATION MODELS |                   |              |                                         |       |       | 12       |

| 1.4.4 GATE CURREN                                                              | r Models.         |              |                                         |       |       | 12       |

| 1.4.5 DEVICE LEVEL                                                             | RELIABILI         | TY MODELING. |                                         |       |       | 13       |

| 1.4.6 Specifying The Initial Mesh   | 15 |

|-------------------------------------|----|

| 1.4.7 Specifying Regions & Materias | 15 |

| 1.4.8 Specifying Electrodes         | 16 |

| 1.4.9 Specifying Doping             | 16 |

| 1.4.10 Analytical Doping Profiles   | 16 |

|                                     |    |

| 1.5. SYNTAX AND PARAMETERS OF ATLAS | 17 |

| 1.5.1 THE ORDER OF ATLAS COMMANDS   | 17 |

| 1.5.2 Types Of Parameters           | 18 |

|                                     |    |

| 1.6. References                     | 19 |

| Chapter-2                                                  | (22-30) |

|------------------------------------------------------------|---------|

| TRANSPARENT CONDUCTING OXIDES-AN OVERVIEW                  |         |

| 2.1. INTRODUCTION.                                         |         |

| 2.2 TRANSPARENT CONDUCTING OXIDES (TCOS)                   | 23      |

| 2.2.1 TCOs In General.                                     |         |

| 2.2.2 Indium Tin Oxide (ITO)                               | 24      |

| 2.2.3 Aluminum Doped Zinc Oxide (Zno:Al)                   | 25      |

| 2.2.4 DELAFOSSITE AND MAYENITE TYPE TRANSPARENT CONDUCTING |         |

| Oxides                                                     |         |

|                                                            |         |

| 2.3 Summary     | 27 |

|-----------------|----|

| 2.4. References | 28 |

# TRANSPARENT GATE RECESSED CHANNEL MOSFET FOR IMPROVED HOT CARRIER Reliability Applications

| 3.1. | INTRODUCTION |  |  |  |  |  |

|------|--------------|--|--|--|--|--|

|------|--------------|--|--|--|--|--|

| 3.2 COMPUTER SIMULATION RESULTS OF TRANSPARENT GATE RECESSED CHANNEL |

|----------------------------------------------------------------------|

| MOSFET                                                               |

| 3.2.1 POTENTIAL                                                      |

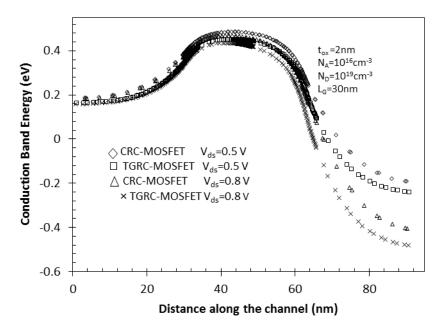

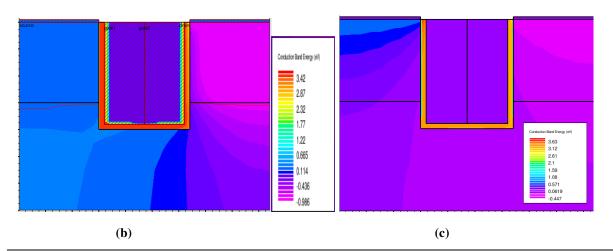

| 3.2.2 CONDUCTION BAND ENERGY                                         |

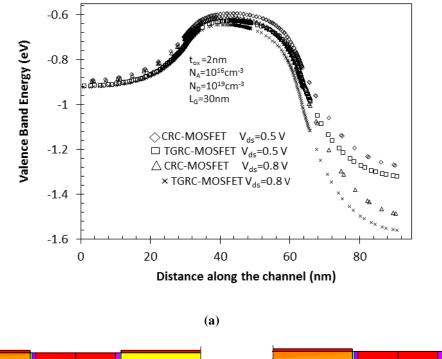

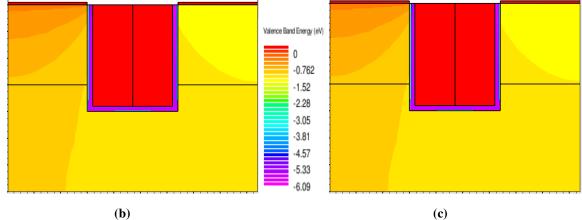

| 3.2.3 VALENCE BAND ENERGY                                            |

| 3.2.4 DRAIN INDUCED BARRIER LOWERING                                 |

| 3.2.5 ELECTRIC FIELD                                                 |

| 3.2.6 Electron Velocity                                              |

| 3.2.7 ON CURRENT                                                     |

| 3.2.8 Electron Mobility40                                            |

| 3.2.9 Electron Temperature                                           |

| 3 SUMMARY |

|-----------|

|-----------|

| 3.4. REFERENCES |

|-----------------|

|-----------------|

| THERMAL            | BEHAVIOR           | OF               | NOVEL        | TRANSPARENT        | GATE    |

|--------------------|--------------------|------------------|--------------|--------------------|---------|

| <b>RECESSED CH</b> | ANNEL (TGRC) M     | OSFET: T         | CAD Analysis |                    |         |

|                    |                    |                  |              |                    |         |

| 4.1. Introduc      | TION               |                  |              |                    | 46      |

|                    |                    |                  |              | E RECESSED CHANNEL |         |

| MOSFET             |                    | ••••••           | •••••        |                    | 48      |

| 4.2.1 H            | EAT CAPACITY       |                  | ·····        |                    |         |

| 4.2.2 Hi           | EAT CONDUCTIVITY   |                  |              |                    | 49      |

| 4.2.3 He           | OT-ELECTRON INJEC  | CTED GATE        | CURRENT      |                    | 51      |

| 4.2.4 IN           | IPACT IONIZATION S | UBSTRATE (       | CURRENT      |                    | 52      |

| 4.2.5 To           | DTAL HEAT POWER.   |                  |              |                    | 53      |

| 4.2.6 EI           | LECTRON TEMPERAT   | TURE             |              |                    | 54      |

| 4.3 SUMMARY.       |                    |                  |              |                    | 54      |

| 4.4. REFERENC      | ES                 |                  |              |                    | 55      |

| Chapter-5          |                    |                  |              |                    | (56-64) |

| Noise Analys       | SIS OF TARNSPAREI  | NT GATE <b>R</b> | ECESSED CHAN | NEL (TGRC) MOSFE'  | Г.      |

| 5.1. INTRODUC      | TION               |                  |              |                    | 56      |

| 5.2. DEVICE STRUCTURE & PARAMETERS |

|------------------------------------|

|------------------------------------|

| 5.3 COMPUTER SIMULATION RESULTS OF TRANSPARENT GATE RECESSED CHANNEL |    |

|----------------------------------------------------------------------|----|

| MOSFET                                                               | 58 |

| 5.3.1 Minimum Noise Figure                                           | 58 |

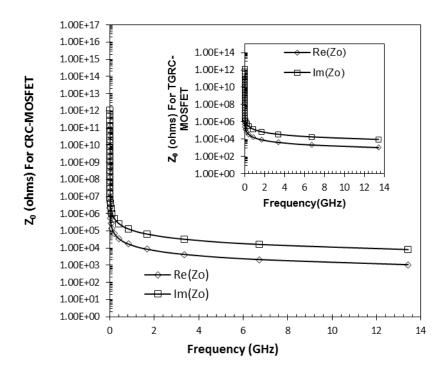

| 5.3.2 Optimum Source Impedance (Z <sub>0</sub> )                     | 59 |

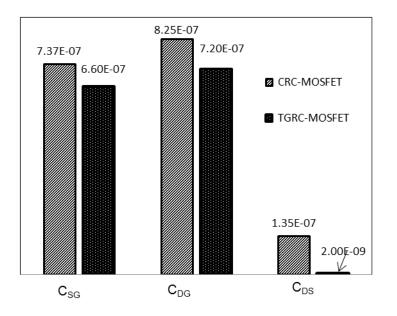

| 5.3.3 PARASITIC CAPACITANCES                                         | 60 |

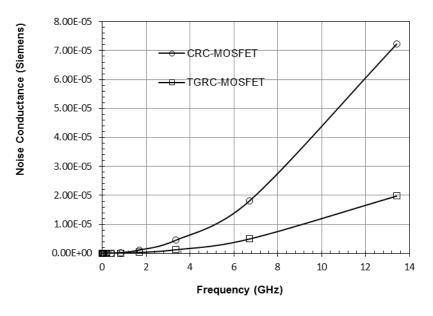

| 5.3.4 Noise Conductance                                              | 61 |

| 5.4 SUMMARY | 6 | 52 |

|-------------|---|----|

|-------------|---|----|

| 5.5. References |

|-----------------|

|-----------------|

# CHAPTER-6

# (65-69)

#### CONCLUSION, PERSPECTIVE & FUTURE RESEARCH

| 6.1. SUMMARY OF CONTRIBUTIONS       | 65 |

|-------------------------------------|----|

| 6.2. RECOMMENDATION FOR FUTURE WORK | 68 |

| 6.3 References                      | 69 |

# **CHAPTER 1**

# **INTRODUCTION**

#### **1.1 CONVENTIONAL MOSFET**

Having studied the junction diode, which is the most basic two-terminal semiconductor device, we now turn our attention to three-terminal semiconductor devices. Three-terminal devices are far more useful than two-terminal ones because they can be used in a multitude of applications, ranging from signal amplification to digital logic and memory [1]. The basic principle involved is the use of the voltage between two terminals to control the current flowing in the third terminal. In this way a three-terminal device can be used to realize a controlled source, which as we have learned is the basis for amplifier design. Also, in the extreme, the control signal can be used to cause the current in the third terminal to change from zero to a large value, thus allowing the device to act as a switch. The switch is the basis for the realization of the logic inverter, the basic element of digital circuits [2]. There are two major types of three-terminal semiconductor devices: the metal-oxide semiconductor fieldeffect transistor (MOSFET) and bipolar junction transistor (BJT). Although each of the two transistor types offers unique features and areas of application, the MOSFET has become by far the most widely used electronic device, especially in the design of integrated circuits (ICs), which are entire circuits fabricated on a single silicon chip. Compared to BJTs, MOSFETs can be made quite small (i.e., requiring a small area on the silicon IC chip), and their manufacturing process is relatively simple. Also, their operation requires comparatively little power. Furthermore, circuit designers have found ingenious ways to implement digital and analog functions utilizing MOSFETs almost exclusively [3]. All of these properties have made it possible to pack large numbers of MOSFETs (as many as 2 billion!) on a single IC chip to implement very sophisticated, very-large-scale-integrated (VLSI) digital circuits such as those for memory and microprocessors. Analog circuits such as amplifiers and filters can also be implemented in MOS technology, albeit in smaller, less-dense chips. Also, both analog and digital functions are increasingly being implemented on the same IC chip, in what is known as mixed-signal design. The objective of this chapter is to develop in the reader a high degree of familiarity with the MOSFET: its physical structure and operation, terminal characteristics, circuit models, and basic circuit applications. Although discrete MOS transistors exist, and the material studied in this chapter will enable the reader to design discrete MOS circuits, our

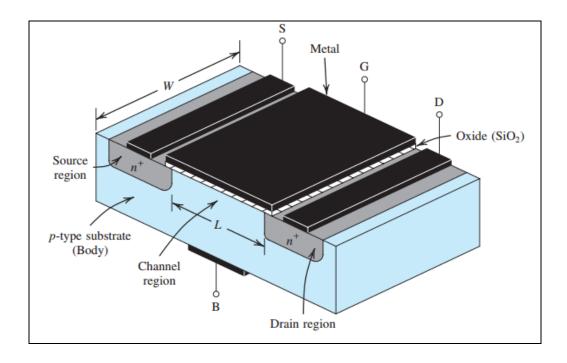

Fig. 1.1 Schematic structure of Conventional MOSFET [4].

study of the MOSFET is strongly influenced by the fact that most of its applications are in integrated-circuit design [1]. The high voltage power MOSFETs that are available today are N-channel, enhancement-mode, double diffused, Metal Oxide-Silicon, Field Effect Transistors. They perform the same function as NPN, bipolar junction transistors except the former are voltage controlled in contrast to the current controlled bi-polar devices. Today MOSFETs owe their ever-increasing popularity to their high input impedance and to the fact that being a majority carrier device, they do not suffer from minority carrier storage time effects, thermal runaway, or second breakdown [5].

## 1.2 NEED OF RECESSED CHANNEL MOSFETS

As mentioned, the supply voltage also scales down with device scaling, however, it cannot follow the speed of channel length reduction. Therefore, the maximum electric field for a minimum size MOS transistor rises to the tens of Volts/µm level. The carriers in the device are accelerated by this electric field and acquire excessive kinetic energy. These high energy carriers are called "hot carriers" because they have effective temperatures of several thousands of carrier temperatures. The hot-carriers occur at the drain junction where the electric field is highest in a MOS device. To lose this excessive kinetic energy from scattering, the carrier needs to travel tens of nanometers which is of the order of half the channel length of the smallest devices currently in mass production. This effect is also called velocity overshoot because the carriers travel at higher velocity than the scatter-limited saturation velocity. Therefore the carrier distribution along the channel is changed and more carriers are injected from the source. The high energy carriers also cause excess noise because of these high carrier temperatures and field modification along the channel. Moreover, the conventional planar MOSFETs also face the drawbacks of increase in the subthreshold swing due to high doping and increase in series resistance due to the shallow junction. Recent experimental studies on sub-100 nm MOSFET's [6-7] attempted to overcome the drawbacks faced by conventional planar MOSFET's, such as the increase in sub-threshold swing due to high doping and the increase in series resistance due to the shallow junction. High transconductance and excellent sub-threshold swing were attained by low-temperature operation and silicon-on-insulator structures, respectively. However, the problems of short channel effects were not fully addressed. The quickening pace of MOSFET scaling is accelerating the introduction of new technologies to extend CMOS beyond the 65 nm node. These technologies include both new materials and advanced MOSFET structures.

### 1.2.1. Recessed Channel MOSFET Performance

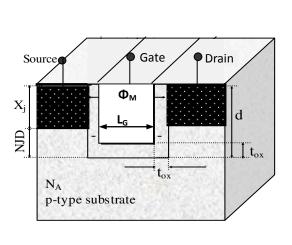

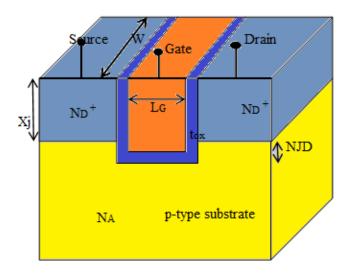

Recessed Channel (RC) MOSFET, as shown in Fig.1.2 is considered as a promising device for suppressing short channel effects and hot carrier effects because structures with shallow junctions or even negative junctions can be fabricated without any increase in the series resistance. These MOSFETs are, hence, good candidates for use in sub-100 nm regime. The optimization of the structure and technology is, however, important to obtain better gate control and hence, high drain current. The geometry of the device retained for the scaling of MOSFET down to the sub-100 nm range should not require too many additional and expensive process steps. This eliminates, for the moment, original structures as gate-all-around transistors [8], although very good performances in term of short-channel effects and current drive capabilities were demonstrated, due to the excellent control of the gate on the channel. In a review of the technology requirements for sub-100 nm MOSFET's, Fiegna et al. reported different conventional structures with uniform, buried or epitaxial channel and also single and double gate SOI devices, but overlooked the investigation of structures with elevated source and drain. These device architectures have recently attracted much attention for their low sensitivity to the short-channel effects and hot carrier effects [9-11].

Φ

Fig.1.2. Schematic cross-sectional view of Conventional Recessed Channel MOSFET. [12]

The "corner effect" or the potential barrier formed at each concave corner is found to be responsible for suppressing the short-channel effects, hot-carrier effects and punch-through. It is also responsible for the degradation of current capability [13]. The higher the potential barriers are, the larger the energy needed to surmount the potential barriers for carriers, so the threshold voltage is increased and the carrier velocity is reduced with the increase of the concave corner, which will bring about hot carrier-effect immunity and driving capability degradation.

When the carriers move to the drain electrode, they not only have to surmount the potential barriers formed at the two concave corners, but also have to change their moving direction. And the electric field at the region near the source is smaller in Recessed Channel than that in planar devices. Therefore the impact ionization generation rate is far smaller than that in planar devices. Low impact ionization rate brings small substrate and gate current consequentially, which means hot-carrier-effect immunity in Recessed Channel MOS devices is better than that in planar devices. Furthermore, as the concave corner increases, the hotcarrier effect is strongly suppressed due to noticeable corner effect. Carriers lose more energy when surmount the two potential barriers and their velocity becomes lower, therefore the hotcarrier effect is low [12]. As the negative junction depth (NJD) increases, the potential barriers increase, and the potential in the channel becomes lower. Besides that, as the negative junction depth increases, the flat portion of the channel shortens. Hence, the path in which carriers are accelerated is shortened and the energy gained by the carriers is lowered, so the probability of becoming the hot carrier becomes smaller and the hot-carrier-effect immunity is better. Studies by Chaujar et.al [14-15], Appenzeller et.al [16] prove that the capability of the hot-carrier-effect immunity in recessed channel MOSFET is intensely influenced by geometric structure. Due to the geometric structure, the electric field distribution and the corner effect in Recessed Channel MOSFETs are influenced strongly, so do the transportation of carriers and the hot-carrier-effect immunity.

The shape and dimensions of the gate of MOSFET transistors are generally the only device parameters controllable by the integrated-circuit design engineer once the process parameters have been specified. Typically the designer utilizes the rectangular-shaped gate whenever possible. This approach is commonplace since the rectangular geometry is convenient for layout, component density can be high, and good models for this device have been developed. Nonrectangular devices are (eg., trapezoidal, "L"-shaped, "V"-shaped, etc.), however, used occasionally [17-18]. These devices are particularly useful when it is of paramount importance to fit a given amount of circuitry into a predetermined region on the die or when extreme device lengths or widths are required. Unfortunately, utilization of these nonrectangular MOSFET's is limited by the unavailability of suitable device models. This dissertation, is hence, focused on the rectangular gate geometry recessed channel MOSFETs. This work can, thus, guide us to optimize the Recessed Channel (RC) structure and to obtain the most satisfactory hot-carrier reliability. It is clear that one potential barrier is formed at each concave corner for RC MOSFET. However, there is only one barrier observed in planar

devices [13]. The formation of these barriers is the basic reason for improvement in the shift of threshold voltage with a decrease in channel length in RC MOSFET. With increase of drain bias voltage, the surface potential distribution is affected directly by drain voltage using depleted area causing the potential in the channel to distort intensely; and the only potential barrier present in planar MOSFETs disappears. On the contrary, the potential barrier near drain decreases just a little and in addition, these two barriers also exist. Thus the effect of drain electric field on channel is diminished in these devices and the DIBL (Drain-Induced Barrier Lowering) is suppressed. In a planar device, the main reason for short channel effects (such as shift of threshold voltage, punch-through, DIBL etc.) is attributed to the severe impact of drain voltage on electric field in the channel; and as a result, the drain area potential extends to the source region [19]. In RC devices, however, the effect of drain voltage is almost shielded by the two barriers formed at each concave corner and the short channel effects are, hence, suppressed effectively. Because of the emergence of corner effect, the threshold voltage roll-off with the shortness of channel length is removed completely in RC MOSFETs even in sub-100 nm regions. It is possible to eliminate this threshold voltage shift against channel length variation by taking advantage of the corner effect. A number of structural parameters, such as the concave corner, junction depths, concave sidewall structure, and the channel doping concentration can be used to adjust the threshold voltage in RC MOSFET's, while only the channel doping concentration can be used in conventional planar MOSFET's. In addition, although the gate length of the conventional MOSFET is longer than the effective channel length due to the lateral diffusion of the source/drain regions, the gate length of the RC MOSFET is shorter than the effective channel length because the junction depths are less than the groove depth. Therefore, RC structure lends itself to higher packing density. This MOSFET design, thus, proves its efficacy for high performance applications where device and hot carrier reliability is a major concern.

For the fabrication feasibility of Recessed Channel MOSFET structure, several integration schemes have been suggested such as plasma etching and LOCOS isolation [20], reactive ion etching and LOCOS isolation technique [21], shallow trench isolation (STI) where gate oxide films were produced with a conventional furnace and the oxide films for gate electrode was deposited by LP-CVD at 850°C [22] and Self-Aligned Chemical Mechanical Polishing (CMP), where, the self-aligned process was defined by the groove etching and polysilicon CMP steps [23].

In order to overcome the shortcomings associated with Recessed Channel MOSFET such as driving current degradation, poor carrier transport efficiency and reduced gate controllability over the channel, Gate Dielectric Engineering and Gate Electrode Workfunction Engineering are carried out in order to overcome these drawbacks and enhance the device performance. The next section outlined the manifestation of these engineering schemes for betterment of the device characteristics and improved reliability and further, extends the lifespan of conventionally scaled MOSFET device. Hence a novel structure introduced, called Transparent Gate Recessed Channel (TGRC) MOSFET. In this device a transparent conducting material is introduced in place of Aluminium gate. By using of transparent conducting material and replacing gate material, transport efficiency, gate controllability, electron velocity, electric field, electron temperature and thermal parameters have been improved.

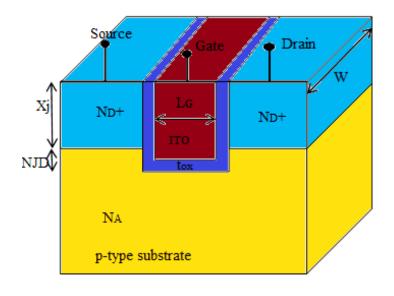

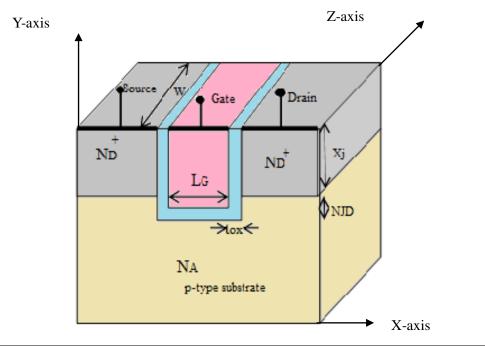

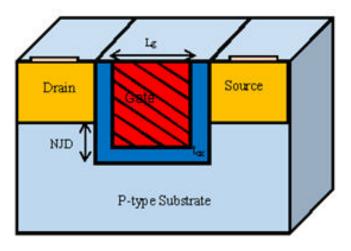

#### 1.3 TRANSPARENT GATE RECESSED CHANNEL (TGRC) MOSFET

Transparent Gate Recessed Channel MOSFET consists of gate which is made of transparent conducting material Indium Tin Oxide (ITO) as shown in Fig 1. Indium tin oxide (ITO or tindoped indium oxide) is a solid solution of indium oxide ( $In_2O_3$ ) and tin oxide ( $SnO_2$ ). It is transparent and colorless in thin layers. Indium tin oxide is one of the most widely used transparent conducting oxides because of its two chief properties, its electrical conductivity and optical transparency, as well as the ease with which it can be deposited as a thin film. By using ITO, we improve  $I_{ON}$  which causes the decrease in device power consumption. The  $In_2O_3$  phase itself contributes free electron for electrical conductivity [24].

When Tin (Sn) is diffused, then some of the oxygen vacancies may be created by  $SnO_2$  which creates free electrons to enhance the concentration of carriers and hence increase conductivity and decrease the resistivity with temperature. In the presence of indium tin oxide in TGRC-MOSFET which is effectively acting as a parallel oxide with  $SiO_2$  and hence effective permittivity is increased which eventually leads to increase in input impedance. It also decreases parasitic capacitances.

Fig.1.3 Schematic structure of Transparent Gate Recessed Channel (TGRC) MOSFET.

Hasten in semiconductor manufacturing techniques and more and more demand for high speed and more complicated Integrated Circuits (ICs) have driven the associated Metal Oxide Semiconductor Field Effect Transistor (MOSFET) sizes close to their physical limits. On the other hand, it is difficult to scale-down the supply voltage used to perform these ICs consistently due to compatibility problem with earlier generation circuits, power, noise margin and delay requirements, and not scaling the threshold voltage and sub-threshold slope.

While the successive increase in internal electric fields in aggressively scaled MOSFETs comes with the additional ameliorate of increased carrier velocities, and hence increased switching speed, it also presents higher reliability complications for the long period of operation of these devices.

As devices are scaled down, the benefits of higher electric fields saturate while the associated reliability problems get worse. The presence of large electric fields in MOSFETs implies the presence of high energy carriers, referred as "hot-carriers", in such devices [25]. The presence of this kind of mobile carriers in the oxide creates some physical damages which may change device characteristics for a long time. The aggregation of damage can ultimately be the reason of circuit failure . The aggregation damage of the hot carrier results in deterioration in device behavior [19,26]. The need of superior performance of ICs has led to the scaling of MOSFETs down to 30 nm and below.

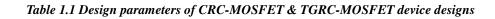

| Design parameters of CRC-MOSFET & TGRC-MOSFET<br>device designs |                                    |  |  |

|-----------------------------------------------------------------|------------------------------------|--|--|

| Channel Length (L <sub>G</sub> )                                | 30nm                               |  |  |

| Device Width                                                    | 200nm                              |  |  |

| Groove Depth                                                    | 38nm                               |  |  |

| Source/Drain Junction Depth                                     | 30nm                               |  |  |

| Negative Junction Depth (NJD)                                   | 10nm                               |  |  |

| Substrate Doping (N <sub>A</sub> )                              | $1 \times 10^{16} \text{ cm}^{-3}$ |  |  |

| Source/Drain Doping $(N_D^+)$                                   | $1 \times 10^{19} \text{ cm}^{-3}$ |  |  |

| Physical Oxide Thickness (tox)                                  | 2nm                                |  |  |

| Permittivity of SiO <sub>2</sub>                                | $\varepsilon_{\rm ox} = 3.9$       |  |  |

| Gate to Source Voltage $(V_{gs})$                               | 0.7V                               |  |  |

| Drain to Source Voltage $(V_{ds})$                              | 0.5V                               |  |  |

| Work function for TGRC-MOSFET ( $\Phi_{rro}$ )                  | 4.7 eV                             |  |  |

| Work function for CRC-MOSFET ( $\Phi_{M}$ )                     | 4.1 eV                             |  |  |

The hot-carrier dilapidation becomes a stringent limitation to the reliability of 100-nm devices and VLSI packing density [27]. Under the influence of high lateral fields in short-channel MOSFETs, carriers in the channel and pinch-off regions of the transistor reach non-equilibrium energy distributions. The generation of these hot-carriers is the primary source of several reliability problems. Hot-carriers can acquire sufficient energy to surmount the energy barrier at the Si-SiO<sub>2</sub> interface or tunnel into the oxide.

From the last several decades, the hot carrier reliability performance in a MOS device has been studied since MOS device is scaled and suffered from hot carrier effect which also pervert analog circuit desideratum. When we scaled the device, the ameliorates of higher electric fields impregnate while associated reliability problems get worse. When electric field will be large in MOSFETs, then carrier will have high energy and these carriers are hot carriers. To abate these hot-carrier effects in CRC-MOSFET, instead of metallic gate we are using Indium Tin Oxide.

#### **1.4 ATLAS-DEVICE SIMULATOR**

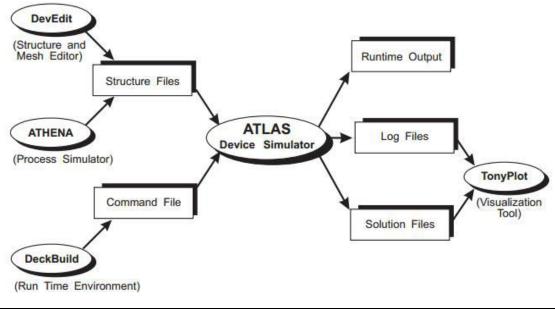

ATLAS provides general capabilities for physically-based two (2D) and three-dimensional (3D) simulation of semiconductor devices. ATLAS is designed to be used with the VWF INTERACTIVETOOLS. The VWF INTERACTIVE TOOLS are DECKBUILD, TONYPLOT, DEVEDIT, MASKVIEWS, and OPTIMIZER. See their respective manuals on how to use these products. ATLAS is supplied with numerous examples that can be accessed through DECKBUILD. These examples demonstrate most of ATLAS's capabilities. The input files that are provided with the examples are an excellent starting point for developing your own input files [29].

There are different physical models which are used in device simulation. These are:

### 1.4.1 MOBILITY MODELS

Electrons and holes are accelerated by electric fields, but lose momentum as a result of various scattering processes. These scattering mechanisms include lattice vibrations (phonons), impurity ions, other carriers, surfaces, and other material imperfections. Since the effects of all of these microscopic phenomena are lumped into the macroscopic mobilities introduced by the transport equations these mobilities are therefore functions of the local electric field, lattice temperature, doping concentration, and so on. Mobility modelling is normally divided into: (i) low-field behavior, (ii) high field behavior, (iii) bulk semiconductor regions and (iv) inversion layers [29].

The value of this mobility is dependent upon phonon and impurity scattering. Both of which act to decrease the low-field mobility. The high electric field behavior shows that the carrier mobility declines with electric field because the carriers that gain energy can take part in a wider range of scattering processes. The mean drift velocity no longer increases linearly with increasing electric field, but rises more slowly. Eventually, the velocity doesn't increase any more with increasing field but saturates at a constant velocity. Impurity scattering is relatively insignificant for energetic carriers, and so µsat is primarily a function of the lattice

temperature. Modeling mobility in bulk material involves: (i) characterizing  $\mu_{n0}$  and  $\mu_{p0}$  as a function of doping and lattice temperature, (ii) characterizing  $\mu$ sat as a function of lattice temperature, and (iii) describing the transition between the low-field mobility and saturated velocity regions. Modeling carrier mobilities in inversion layers introduces additional complications. Carriers in inversion layers are subject to surface scattering, extreme carrier-carrier scattering, and quantum mechanical size quantization effects. These effects must be accounted for in order to perform accurate simulation of MOS devices. The transverse electric field is often used as a parameter that indicates the strength of inversion layer phenomena. You can define multiple non-conflicting mobility models simultaneously. You also need to know which models are over-riding when conflicting models are defined [29].

#### 1.4.2 CARRIER GENERATION-RECOMBINATION MODELS

Carrier generation-recombination is the process through which the semiconductor material attempts to return to equilibrium after being disturbed from it. If we consider a homogeneously doped semiconductor with carrier concentrations n and p to the equilibrium concentrations  $n_0$  and  $p_0$  then at equilibrium a steady state balance exists according to:

#### $n_0 p_0 = n_i^2$

Semiconductors, however, are under continual excitation whereby n and p are disturbed from their equilibrium states:  $n_0$  and  $p_0$ . For instance, light shining on the surface of a p-type semiconductor causes generation of electron-hole pairs, disturbing greatly the minority carrier concentration. A net recombination results which attempts to return the semiconductor to equilibrium. The processes responsible for generation-recombination are known to fall into six main categories:

- phonon transitions

- photon transitions

- Auger transitions

- surface recombination

- impact ionization

- tunnelling

In addition to generation-recombination within the bulk of the semiconductor, electrons or holes may recombine or be generated at interfaces. The rate of surface recombination may be even greater than within the bulk. The standard method is to model interface recombination in a similar manner as the bulk generation-recombination rate [29].

#### 1.4.3 IMPACT IONIZATION MODELS

In any space charge region with a sufficiently high reverse bias, the electric field will be high enough to accelerate free carriers up to a point where they will have acquired sufficient energy to generate more free carriers when in collision with the atoms of the crystal. In order to acquire sufficient energy, two principle conditions must be met. First, the electric field must be sufficiently high. Then, the distance between the collisions of the free carrier must be enough to allow acceleration to a sufficiently high velocity. In other words, the carrier must gain the ionization energy  $E_i$  between collisions. If the generation rate of these free carriers is sufficiently high this process will eventually lead to avalanche breakdown. The general impact ionization process is described by-

$$G = \alpha_n |\vec{J}|_n + \alpha_p |\vec{J}|_p$$

Here, G is the local generation rate of electron-hole pairs,  $\alpha_{n,p}$  are the ionization coefficient for electrons and holes and  $J_{n,p}$  are their current densities. The ionization coefficient represents the number of electron-hole pairs generated by a carrier per unit distance travelled. The accurate calculation of this parameter has been researched because it is vital if the effects related to impact ionization, such as substrate current and device breakdown, are to be simulated. These models can be classified into two main types: local and non-local models. The former assume that ionization at any particular point within the device is a function only of the electric field at that position. Non-local models, however, perform a more rigorous approach by taking into account the energy that the carrier gains [29].

#### 1.4.4 GATE CURRENT MODELS

In devices that have a metal-insulator-semiconductor (MIS) formation, the conductance of the insulating film would ideally be considered as zero. But, for the sub 0.5um generation of MOS devices there is now considerable conductance being measured on the gate contacts.

This gate current has resulted in two major consequences, one negative and one positive. On the negative side, the gate current is responsible for the degradation in device operating characteristics with time. This reliability issue is important because the lifetime of electronic parts has to be guaranteed. You can simulate reliability within the Silvaco suite of tools for device level reliability which are described in a later chapter [29].

On the positive side, the existence of this gate current has caused the proliferation of the nonvolatile memory market. These devices use the existence of gate current to program and erase the charge on a "floating" contact. This concept has resulted in a variety of different devices such as FLASH, FLOTOX, and EEPROM. All such devices rely on the physics of the gate current process for their existence. There are a variety of different conduction mechanisms within an insulating layer, but in the case of non-volatile memory, only two mechanism are relevant: Fowler-Nordheim tunneling and hot carrier injection. Models for these two injection processes are described in the following sections. In the case of hot electron injection, two models are available: the lucky electron model and the Concannon gate current model [29].

#### 1.4.5 Device Level Reliability Modeling

The Hansch Reliability Model can be used to simulate MOS transistor degradation under stress conditions. The causes of device characteristic degradation are the hot electron (hole) injection into gate oxide, and the trapping of electron (hole) charge on the effective interface acceptor (donor) like traps. The model calculates hot electron (hole) injection current according to the lucky electron model. The arbitrary position-dependent distributions of acceptor and donor-like traps are specified on the oxide-semiconductor interface with corresponding capture cross sections. The device degradation is calculated as a function of stress time by performing transient calculations. The trap rate equation is solved on every time-step and thus the trapped electron (hole) concentration is calculated [29].

The results of stress simulation can be used to calculate the characteristics of the degraded device (the shift of the threshold voltage, transconductance degradation, and so on). You can view the distribution of traps, hot electron (hole) current density, and trapped electron (hole) distribution by using TONYPLOT.

ATLAS simulations use two input files. The first input file is a text file that contains commands for ATLAS to execute. The second input file is a structure file that defines the structure that will be simulated. ATLAS produces three types of output files. The first type of output file is the run-time output, which gives you the progress and the error and warning messages as the simulation proceeds. The second type of output file is the log file, which stores all terminal voltages and currents from the device analysis. The third type of output file is the solution file, which stores 2D and 3D data relating to the values of solution variables within the device at a given bias point. The ATLAS tool supports calculation of various AC parameters like Hybrid (H), Admittance(Y), Impedance (Z), Scattering(S) etc. The gain analysis can also be done as a part of small signal analysis. AC sinusoidal small-signal analysis should be performed after solving for a DC condition. The full Newton method must be used for this analysis. Frequency range of interest, device width and the method for ac analysis has to be selected. A direct parameter is included which is robust for all range of frequencies. The gate terminal is selected as input port where ac bias will be applied, while drain terminal is selected as output port indicating that device works in common source configuration.

Fig.1.4 Processing of ATLAS Device Simulation [28]

### 1.4.6 Specifying the Initial Mesh

The first statement must be:

```

MESH SPACE.MULT=<VALUE>

```

This is followed by a series of X.MESH and Y.MESH statements.

#### X.MESH LOCATION=<VALUE> SPACING=<VALUE>

#### Y.MESH LOCATION=<VALUE> SPACING=<VALUE>

The SPACE.MULT parameter value is used as a scaling factor for the mesh created by the X.MESH and Y.MESH statements. The default value is 1. Values greater than 1 will create a globally coarser mesh for fast simulation. Values less than 1 will create a globally finer mesh for increased accuracy. The X.MESH and Y.MESH statements are used to specify the locations in microns of vertical and horizontal lines, respectively, together with the vertical or horizontal spacing associated with that line. You must specify at least two mesh lines for each direction. ATLAS automatically inserts any new lines required to allow for gradual transitions in the spacing values between any adjacent lines. The X.MESH and Y.MESH statements must be listed in the order of increasing x and y. Both negative and positive values of x and y are allowed [29].

#### 1.4.7 Specifying Regions & Materials

Once the mesh is specified, every part of it must be assigned a material type. This is done with REGION statements. For example:

REGION number=<integer> <material\_type> <position parameters>

Region numbers must start at 1 and are increased for each subsequent region statement. You can have up to 200 different regions in ATLAS. A large number of materials is available. If a composition-dependent material type is defined, the x and y composition fractions can also be specified in the REGION statement.

The position parameters are specified in microns using the X.MIN, X.MAX, Y.MIN, and Y.MAX parameters. If the position parameters of a new statement overlap those of a previous REGION statement, the overlapped area is assigned as the material type of the new region. Make sure that materials are assigned to all mesh points in the structure. If this isn't done, error messages will appear and ATLAS won't run successfully [29].

### 1.4.8 Specifying Electrodes

Once you have specified the regions and materials, define at least one electrode that contacts a semiconductor material. This is done with the ELECTRODE statement. For example:

ELECTRODE NAME=<electrode name> <position\_parameters>

You can specify up to 50 electrodes. The position parameters are specified in microns using the X.MIN, X.MAX, Y.MIN, and Y.MAX parameters. Multiple electrode statements may have the same electrode name. Nodes that are associated with the same electrode name are treated as being electrically connected. Some shortcuts can be used when defining the location of an electrode. If no Y coordinate parameters are specified, the electrode is assumed to be located on the top of the structure [29].

You also can use the RIGHT, LEFT, TOP, and BOTTOM parameters to define the location. For example:

#### ELECTRODE NAME=SOURCE LEFT LENGTH=0.5

specifies the source electrode starts at the top left corner of the structure and extends to the right for the distance LENGTH.

#### **1.4.9** Specifying Doping

You can specify analytical doping distributions or have ATLAS read in profiles that come from either process simulation or experiment. You specify the doping using the DOPING statement. For example:

DOPING <distribution\_type> <dopant\_type> <position\_parameters>

#### 1.4.10 ANALYTICAL DOPING PROFILES

Analytical doping profiles can have uniform, gaussian, or complementary error function forms. The parameters defining the analytical distribution are specified in the DOPING statement. Two examples are shown below with their combined effect :

DOPING UNIFORM CONCENTRATION=1E16 N.TYPE REGION=1

DOPING GAUSSIAN CONCENTRATION=1E18 CHARACTERISTIC=0.05 P.TYPE \ X.LEFT=0.0 X.RIGHT=1.0 PEAK=0.1

The first DOPING statement specifies a uniform n-type doping density of 10^16 cm-3 in the region that was previously labelled as region #1. The position parameters X.MIN, X.MAX, Y.MIN, and Y.MAX can be used instead of a region number [29].

### 1.5 SYNTAX AND PARAMETERS OF ATLAS

#### 1.5.1 THE ORDER OF ATLAS COMMANDS

The order in which statements occur in an ATLAS input file is important. There are five groups of statements that must occur in the correct order (see Figure 1). Otherwise, an error message will appear which may cause incorrect operation or termination of the program. For example, if the material parameters or models are set in the wrong order, then they may not be used in the calculations. The order of statements within the mesh definition, structural definition, and solution groups is also important. Otherwise, it may also cause incorrect operation or termination of the program[29].

| Group                            | Statements                                 |

|----------------------------------|--------------------------------------------|

| 1. Structure Specification       | MESH<br>REGION<br>ELECTRODE<br>DOPING      |

| 2. Material Models Specification | MATERIAL<br>MODELS<br>CONTACT<br>INTERFACE |

| 3. Numerical Method Selection    | - METHOD                                   |

| 4. Solution Specification        | LOG<br>SOLVE<br>LOAD<br>SAVE               |

| 5. Results Analysis              | EXTRACT<br>TONYPLOT                        |

Fig.1.5 ATLAS Command Groups with the Primary Statements in each Group [26].

# 1.5.2 Types of Parameters

| Parameter | Description               | Value Req. | Example         |

|-----------|---------------------------|------------|-----------------|

| Character | Any character string      | Yes        | INFILE=NMOS.DOP |

| Integer   | Any whole number          | Yes        | REGION=2        |

| Logical   | A true or false condition | No         | GAUSSIAN        |

| Real      | Any real number           | Yes        | X.MIN=0.52      |

#### **1.6.** References

- [1] Sedra and Smith, Microelectronic Circuits, pp. 231-233.

- [2] J. Watts. "Advanced Compact Models for MOSFETs", (Invited Paper), NSTI Nanotech, 2005, pp. 3-12.

- [3] B. V. Zeghbroeck. "Principles of Semiconductor Devices" 2011.

- [4] Sedra and Smith, Microelectronic Circuits, pp. 233.

- [5] R. Locher. "Introduction to Power MOSFETs and Their Applications." National Semiconductor Application Note 558, 1988.

- [6] R. Chaujar, R. Kaur, M. Saxena, M. Gupta and R.S. Gupta. "Solution to CMOS Technology for high Performance Analog Applications: GEWE-RCMOSFET", ACMD 2008

- [7] S. Kumara, J. Tanaka, H. Noda, T. Toyabe, S. Ihara, "Short-channel effect suppressed sub-0.1µm grooved gate MOSFET's with W gate", IEEE Trans Electron Dev. Vol.42, pp. 94-100,1995.

- [8] J. P. Colinge, SOI Technology. Norwell, MA: Kluwer, 1991.

- [9] J. Lee, Y.S. Suh, H. Lazar, R. Jha, J. Gurganus et. Al., "Compatebolity og dual metal gate electrodes with high-k dielectrics for CMOS." In IEDM Tech. Dig., pp. 323-326,2006.

- [10] E. Takeda, H. Kume, and S. Asai, "New Grooved-gate MOSFET with Drain Separated from Channel Implanted Region (DSC)", IEEE Tran Electron De, vol. 30, pp. 681-686, 1983.

- [11] J. Tanaka, T. Toyabe, S. Ihara, S. Kumara, H. Noda and K. Itoh, "Simulation of sub-0.1µm MOSFET's with completely suppressed short channel effect", IEE Electron Device Lett, vol.14, pp.396-399, 1993.

- [12] R. Chaujar, R. Kaur, M. Saxena, M. Gupta and R.S. Gupta, "Two Dimensional Analutical Sub-Thresold Model of Multi Layered Gate Dielectric Recessed Channel (MLaG-RC) Nanoscale MOSFET", Semiconductor Science and Technology, vol.23, pp.1-10,2008.

- [13] R. Chaujar, R. Kaur, M. Saxena, M. Gupta and R.S. Gupta, "Laterally amalgamated Dual material Gate Concave (L-DUMGAC) MOSFET for ULSI", Microelectronic Engineering, vol.85, pp.566-576, 2008.

- [14] J. Appenzeller, R. Martel, P. Avouris, J. Knoch, J. Scholvin, J.A. del Alamo, P. Rice and P. Solomon, "Sub-40nm SOI V-groove n-MOSFETs", IEEE Electron Device Lett, Vol.23, pp. 100-102, 2002

- [15] E. Takeda, H. Kume and S.Asia, "New grooved-gate MOSFET with drain separated from channel implanted region (DSC)", IEEE Trans Electron Devices, vol.30, pp.681-686, 1983

- [16] K. Hieda, K. Sunouchi, H. Takato, A. Nitayama, F. Horiguchi, F. Masuoka, "Sub-halfmicrometer concave MOSFET with double LDD structutr", IEEE Trans Electron Dev, vol. 39, pp. 671-676, 1992.

- [17] P. Malik, R. Chaujar, M. Gupta and R.S. Gupta. "Exploring the Effect on Negative Junction Depth on Electrical Behaviour ofSub-50nm GME-TRC MOSFET: A Simulation Study". IEEE. pp,689-692, 2008.

- [18] P. Malik, R. Chaujar, M. Gupta and R.S. Gupta. "Evaluation of Multi-Layered Gate Design on GMETRC MOSFET for Wireless Applications". ICSE 2010 Proc. 2010.

- [19] R. Chaujar, R. Kaur, M. Saxena, M. Gupta and R. S. Gupta, "TCAD Assessment of Gate Electrode Workfunction Engineered Recessed Channel (GEWE-RC) MOSFET and Its Multilayered Gate Architecture—Part I: Hot-Carrier-Reliability Evaluation" IEEE Trans. Electron Devices, vol. 55, no. 10, pp 2602-2612, 2008.

- [20] J.Y. Seo, K.J. Lee, Y.S. Kim, S.Y. Lee, S.J. Hwang and C.K. Yoon, "Reliability for Recessed Channel Structure n-MOSFET ", Microelectronics Reliability, Vol. 45, pp. 1317-1320, 2005.

- [21] M. Xiao-Hua, H. Yue, S. Bao-Gang, G. Hai-Xia, R. Hong-Xia, R. Hong-Xia, "Fabrication and characterization of groove-gate MOSFETs based on a self-aligned CMOS process," Chin.Phys. Soc., Vol.15, No.1, pp.195-198, 2006.

- [22] N.arora "MOSFET models for VLSI circuit simulation theory and practice", Springer Verlag Wien New York, pp. 87-89.

- [23] A.A. Orouji, M.J. Kumar," Shielded channel double-gate MOSFET: a novel device for reliable nanoscale CMOS applications. IEEE Trans. Device and Material Reliab. vol. 5, pp. 509–514, 2005.

- [24] S. V. N. Pammi, Hyun-June Jung, and Soon-Gil Yoon. "Low-Temperature Nanocluster Deposition (NCD) for Improvement of the Structural, Electrical, and Optical Properties of ITO Thin Films".

- [25] Y. Pan, K.K. Ng, C.C. Wei, "Hot-carrier induced electron mobility and series resistance degradation in LDD NMOSFET's", IEEE Electron Device Lett., vol.15, pp. 499–501, 1994.

- [26] G. Krieger, R. Sikora, P.P. Cuevas, M.N. Misheloff, "Moderately doped NMOS (M-LDD)-hot electron and current drive optimization". IEEE Trans. Electron Devices, vol. 38, pp. 121–127, 2001.

- [27] R. Chaujar, R. Kaur, M. Saxena, M. Gupta and R.S. Gupta. "GEWE-RCMOSFET:A Solution to CMOS Technology for RFIC Design Based on the Concept of Intercept Point". Interactional Conference on Microwave, IEEE, pp 661-662, 2008.

- [28] ATLAS:3D Device Simulator SILVACO International (2002).

- [29] ATLAD User's Manual Device Simulation Software (2012).

# CHAPTER 2

# TRANSPARENT CONDUCTING OXIDES-AN OVERVIEW

#### **2.1.** INTRODUCTION

Transparent conducting oxides (TCOs) are electrical conductive materials with comparably low absorption of electromagnetic waves within the visible region of the spectrum. They are usually prepared with thin film technologies and used in opto-electrical apparatus such as solar cells, displays, opto-electrical interfaces and circuitries. Here, based on a modern database-system, aspects of up-to-date material selections and applications for transparent conducting oxides are sketched, and references for detailed information are given. As n-type TCOs are of special importance for thin film solar cell production, indium-tin oxide (ITO) and the reasonably priced aluminium-doped zinc oxide (ZnO:Al), are discussed with view on preparation, characterization and special occurrences. For completion, the recently frequently mentioned typical p-type delafossite TCOs are described as well, providing a variety of references, as a detailed discussion is not reasonable within an overview publication [1].

TCOs are electrical conductive materials with a comparably low absorption of light. They are usually prepared with thin film technologies and used in opto-electrical devices such as solar cells, displays, opto-electrical interfaces and circuitries. Glass fibres are nearly lossless conductors of light, but electrical insulators; silicon and compound semiconductors are wavelength dependent optical resistors (generating mobile electrons), but dopant dependent electrical conductors. Transparent conducting oxides are highly flexible intermediate states with both these characteristics. Their conductivity can be tuned from insulating via semiconducting to conducting as well as their transparency adjusted. As they can be produced as n-type and p-type conductive, they open a wide range of power saving opto-electrical circuitries and technological applications. A still valuable overview of transparent conductive oxides is given in [2], basics to material physics of TCOs are discussed in [3], some structural investigation of TCOs was made e.g., in [4], preparation of TCOs was discussed in [5] and substitutes for the most popular transparent conducting oxide, namely ITO are listed in [6]. Here, based on a modern database-system, aspects of up-to-date material selections and applications for transparent conducting oxides are sketched, and references for detailed information are given. As n-type TCOs are of special importance for thin film solar cell production, ITO and the reasonably priced aluminium-doped zinc oxide (ZnO:Al) are discussed with view on preparation, characterization and special occurrences. For completion, the recently frequently mentioned typical p-type delafossite TCOs are described as well, providing a variety of references, as a detailed discussion is not reasonable within an overview publication.

As transparent conducting oxides are usually compound semiconductors—where the nonmetal part is oxygen—they are discussed along their metal elements. Metals were used as compound materials or dopants (with just a few per cent content).

### 2.2 TRANSPARENT CONDUCTING OXIDES (TCOs)

### 2.2.1 TCOs IN GENERAL

In TCOs, the non-metal part, B, consists of oxygen. In combination with different metals or metal-combinations, A, they lead to compound semiconductors, Ay Bz, with different optoelectrical characteristics. These opto-electrical characteristics can be changed by doping, Ay Bz:D (D = dopant), with metals, metalloids or non-metals. Hence, metals can be part of the compound semiconductor itself, A, or can be a dopant, D. Scanning the periodic table of elements, with a view on the utilization of metals for TCOs, results in Table 1 (regarding just the 2nd and 3rd period, exclusively aluminium).

| Period of<br>the PE | Compound semiconductor                                                  | Dopant | Preparation                                                                  | Characterization            | Reference |

|---------------------|-------------------------------------------------------------------------|--------|------------------------------------------------------------------------------|-----------------------------|-----------|

| 2                   | NiO                                                                     | Li     | Pulsed Laser Deposition<br>(different Li-concentr.)<br>No TCO-Layers with Be | ?                           | [6]       |

| 3                   | ZnO                                                                     | Na, Al | Sol-gel, Annealing                                                           | SEM,<br>Photoluminescence   | [7–9]     |

|                     | $Cr_2O_3$                                                               | Mg, N  | Spray Pyrolysis                                                              | ?                           | [10]      |

|                     | CuCrO <sub>2</sub><br>(Delafossite)                                     | Mg     | Sol-gel Technique                                                            | ?                           | [11]      |

|                     | Mg <sub>1-x</sub> Zn <sub>x</sub> O                                     | In     | Pulsed Laser Deposition<br>(different substrates)<br>Radio Frequency         | X-ray diffraction,<br>HRTEM | [12]      |

|                     | Mg <sub>1-x</sub> Zn <sub>x</sub> O                                     | Al     | Magnetron Sputtering<br>(different substrates)                               | ?                           | [13]      |

|                     | Mg <sub>12</sub> Al <sub>14</sub> O <sub>33</sub><br>("Mayenite")<br>Al |        | ?                                                                            | ?                           | [14]      |

Table 1.Published results regarding transparent conducting oxide (TCO)-layers, containing metallic elements e.g., from the 2nd and 3rd period of the periodic table of the elements (PE, excluding aluminum), including examples for the later discussed ZnO's and delafaossites (mayenites)—research with the web of knowledge using "TCO < name of element > oxide".

Outstanding good optical characteristics have been provided by tin-, indium- and zinc oxides (A = tin, indium, zinc). Well known is, for example, indium tin oxide (ITO), and the doping of zinc oxide with less than 5% aluminium (ZnO:Al). Moreover, doped delafossite and mayenite compounds are of upcoming interest (see Table 1). A variety of preparation and characterization methods was applied to investigate their different chemical structures and physical characteristics. These shall be briefly discussed.

### 2.2.2 INDIUM TIN OXIDE (ITO)

ITO is a solid solution of indium (III) oxide  $(In_2O_3)$  and tin(IV) oxide  $(SnO_2)$ , with typically 90%wtIn<sub>2</sub>O<sub>3</sub>, 10%wtSnO2. It is transparent and colorless as a thin film and yellowish to grey as bulk material. Indium tin oxide is the most widely used transparent conducting oxide (TCO [15]) because of its two key properties, its electrical conductivity and optical transparency. ITO thin films are still deposited with ion assisted plasma evaporation [17], (low temperature) electron beam evaporation, direct current (DC), pulsed DC (PDC), high

power pulsed magnetron sputtering (HPPMS), radio frequency (RF) magnetron sputtering, thermal evaporation or pulsed laser deposition (PLD). Post process thermal annealing steps are discussed for the example in [17], oxygen-plasma treatments in and the influence of acids and bases on ITO thin films in. Investigations were made on electrical, optical and structural properties of this ternary compound semiconductor. According to structural investigations, the focus was set on the border between amorphous and crystal phases [18] and the growth mechanisms (Volmer-Weber, Frank-van der Merwe). Band structure and work function are analysed in.

#### 2.2.3 ALUMINIUM DOPED ZINC OXIDE (ZnO:Al)

Transparent conducting, aluminum doped zinc oxide thin films (AlxZnyOz, ZnO:Al) contain about 2%wtaluminum and can be produced with spray pyrolysis, sol gel technology, electro deposition, vapour phase deposition, magnetron DC sputtering, magnetron RF sputtering or a combination of both the sputter deposition methods. Moreover, high quality deposition methods using thermal plasmas, (low pressure (LP), metal organic (MO), plasma enhanced (PE)) chemical vapour deposition (CVD), electron beam evaporation, pulsed laser deposition and atomic layer deposition can be applied [19].

The underlying substrate—crystalline, amorphous or organic—may have an influence on the grown structure and the opto-electronic properties of the thin film [20], independent of the used deposition method. For example, in the case of solar cell production, an ultra-thin CdS buffer layer is usually the basis for ZnO:Al deposition. Even if the substrate is identical, the layer thickness (deposition time, position upon the substrate) itself influences the physical values of the deposited thin film [21]. A variation of the physical values from the grown thin films can also be reached by changing process parameters, as temperature or pressure, or by additions to the process gas, as oxygen or hydrogen. Commonly, pure zinc oxides are n-doped with aluminium. Alternatively, n-doping can be done with metals such as copper, Cu, silver, Ag, gallium, Ga, magnesium, Mg, cadmium, Cd, indium, In, tin, Sn, scandium, Sc, yttrium, Y, cobalt, Co, manganese, Mn, chrome, Cr, and boron, B. p-Doping of ZnO is technologically difficult, but apart from nitrogen, N, phosphorus, P, seems to be an adequate dopant [22]. The opto-electronic properties of these TCO thin films can be changed by post process thermal annealing in an inert gas or reactive gas atmosphere. Especially surface and interface states can be influenced. The deterioration of ZnO:Al thin films is discussed in [23].

#### 2.2.4 Delafossite And Mayenite Type Transparent Conducting Oxides

Commonly, ITO- and ZnO-based TCO thin films are n-doped, as p-doping has been shown to be technologically more difficult. Fortunately, for delafossite compound semiconductors this is vice versa. They typically show TCO properties with semiconducting p-type characteristics. Delafossites, CuxAyOz, are commonly ternary material combinations of copper, Cu, one (or more) further metal(s), A, (aboriginal iron, A = Fe) and oxygen, O. Copper may be replaced by silver, palladium or platinum. As further metal, A, iron, cobalt or chrome (without doping hardly transparent) may be used as well as elements of the 2nd group of the periodic table of the elements—strontium, barium—or the 3rd group—aluminium, gallium, indium, scandium, yttrium, lanthanum.

Moreover, other lanthanides such as praseodymium, neodymium samarium and europium have been applied [24], in order to get ternary semiconductor compounds. Quaternary semiconductors as for example the Sb-based CuA<sub>2</sub>/3Sb1/3O<sub>2</sub>(A = Mn, Co, Ni, Zn, Mg), respectively AgA<sub>2</sub>/3Sb1/3O<sub>2</sub>(A = Ni, Zn) or the Cr-based CuCr1–xAxO<sub>2</sub>(A = Mg, Ca, Al) delafossites have been investigated. Ag-Cu and Rh-Mg replacements were for example studied in the quaternary structure Cu1–xAgxRh1–y MgyO<sub>2</sub>. Oxygen off-stoichiometry, CuxAyO<sub>2+d</sub>, has been examined. Oxy-sulphide delafossite type TCOs, CuxAyOzS\alpha, were sputtered (CuLa1–xOS:Srx, x = 0%–5%) or already existing delafossites have been grown from a melt by a slow cooling-method in air.

They were deposited using low temperature hydro/solvothermal processes, the sol-gel technology and the spray pyrolysis technique. Moreover, advanced methods such as (direct current (DC), radio frequency (RF)) magnetron sputtering of prefabricated targets, with varying temperature, pressure, oxygen flow or sputter energies, pulsed laser deposition, with varying temperature and pressure [26], thermal evaporation, e-beam evaporation technique, and (low-pressure (LP), metal-organic (MO)) chemical vapor deposition (CVD) were applied. Annealing in N<sub>2</sub>, O<sub>2</sub>, air or argon was examined, showing for example a reduction in CuO resp. spinel CuCr<sub>2</sub>O<sub>4</sub> fraction and formation of highly crystalline films with single-phase delafossite CuCrO<sub>2</sub>structure. The CuA III O<sub>2</sub> group shows increasing band gap from A III= Al, Ga, to In. The largest gap CuInO<sub>2</sub>can be doped both n- and p-type but not the smaller

gaps  $CuAlO_2$  and  $CuGaO_2$  [27]. Therefore, doping  $CuInO_2$  with Ca results in p-type, doping with Sn inn-type semiconducting TCO thin films.

Bidirectional doping is possible for CuFeO<sub>2</sub>, too (p-type: Mg, n-type: Sn). In addition, the electronic structure of CuAO<sub>2</sub>(A = Al, Ga, Y) was discussed in and its luminescent properties in. Defect analyses have been made with the screened-hybrid density functional theory. Additional p-doping is usually performed with Ca, Mg or occasionally with K, in order to increase the conductivity resulting in e.g., CuInO<sub>2</sub>:Ca, Cu<sub>2</sub>In<sub>2</sub>O<sub>5</sub>:Ca, CuYO<sub>2</sub>:Ca, CuCrO<sub>2</sub>:Mg, CuScO2:Mg or Cu<sub>2</sub>SrO<sub>2</sub>:K. N-type doping of delafossite. TCO thin films is normally done with Sn, e.g., CuInO<sub>2</sub>:Sn or AgInO<sub>2</sub>:Sn.

Further discussion on doping of delafossite TCOs is shown in. Because of the structural anisotropy of the CuAlO<sub>2</sub>-crystal, anisotropic electrical conductivity was detected in. Ohmic contacts between CuInO<sub>2</sub>and Cu are reported in. The crystal structures and chemistries are by far the best investigated topics in delafossite (semi)conductor research and systematically discussed in; the according temperature dependency is shown in [28].

#### 2.3 SUMMARY

Based on a modern database-system aspects of up-to-date material selections and applications for transparent conducting oxides have been sketched; references for detailed information have been given for the interested reader. As n-type TCOs are of special importance for thin film solar cell production, indium-tin oxide (ITO) and the reasonably priced aluminium-doped zinc oxide (ZnO:Al) have been discussed with view on preparation, characterization and special occurrences. For completion, typical p-type delafossite TCOs have been described the same way, providing a variety of references, as a detailed discussion is not reasonable within an overview-publication. Moreover, absolutely unusual, novel TCO materials have been discussed and their presence and development in the world of science pointed out. Trends have been shown.

As transparent conducting oxides are usually compound semiconductors—where the nonmetal part is oxygen—they have been discussed along their metal elements. Metals were used as compound materials or dopants (with just a few per cent content).

#### **2.4.** References

- A. Stadler, "Transparent Conducting Oxides—An Up-To-Date Overview". ISSN 1996-1944Materials, pp. 661-683, 2012.

- [2] K.L. Chopra, S. Major, D.K. Pandya, Transparent conductors—A status review. Thin Solid Films 1983, 102, 1–46.

- [3] P.P. Edwards, A. Porch, M.O. Jones, D.V. Morgan, R.M. Perks, Basic materials physics of transparent conducting oxides. Dalton Trans. 2004, 19, 2995–3002.

- [4] H. Kawazoe, K. Ueda, Transparent conducting oxides based on the spinel structure. J. Am. Ceram. Soc. 1999, 82, 3330–3336.

- [5] Z.M. Jarzebski, Preparation and physical properties of transparent conducting oxide films. Phys. Stat. Sol. 1982, 71, 13–41.

- [6] T. Minami, Present status of transparent conducting oxide thin-film development for Indium-Tin-Oxide (ITO) substitutes. Thin Solid Films 2008, 516, 5822–5828.

- [7] U.S. Joshi, Y. Matsumoto, K. Itaka, M. Sumiya, H. Koinuma, Combinatorial synthesis of Li-doped NiO thin films and their transparent conducting properties. Appl. Surf. Sci. 2006, 252, 2524–2528.

- [8] T. Wang, Y. Liu,; Q. Fang, M. Wu, X. Sun, F. Lu, Low temperature synthesis wide optical band gap Al and (Al, Na) co-doped ZnO thin films. Appl. Surf. Sci. 2011, 257, 2341–2345.

- [9] M. Wang, Comment on "low temperature synthesis wideoptical band gap Al and (Al, Na) co-doped ZnO thin films". Appl. Surf. Sci. 2011, 257, 8752–8753.

- [10] T. Wang, Y. Liu, Response to the comment on "low temperature synthesis wide optical band gap Al and (Al, Na) co-doped ZnO thin films". Appl. Surf. Sci. 2011, 257, p. 8754.

- [11] E. Arca, K. Fleischer,; I.V. Shvets, Magnesium, nitrogen co-doped Cr2O3: A p-type transparent conducting oxide. Appl. Phys. Lett. 2011, 99, 111910.

- [12] S. Götzendörfer, P. Löbmann, Influence of single layer thickness on the performance of un doped and Mg-doped CuCrO2thin films by sol-gel processing. J. Sol-Gel Sci. Technol.2011, 57, 157–163.

- [13] C.H. Lau; L. Zhuang, K.H. Wong, In-doped transparent and conducting cubic magnesium zinc oxide thin films grown by pulsed laser deposition. Phys. Stat. Sol. B 2007, 244, 1533–1537.

- [14] K. Ellmer, G. Vollweiler, Electrical transport parameters of heavily-dope dzinc oxide and zinc magnesium oxide single and multilayer films hetero epitaxial grown on oxide single crystals. Thin Solid Films 2006, 496, 104–111.

- [15] B.J. Ingram, M.I. Bertoni, K.R. Poeppelmeier, K.R. Mason, Point defects and transport mechanisms in transparent conducting oxides of intermediate conductivity. Thin Solid Films2005, 486, 86–93.

- [16] H.L. Hartnagel, Semiconducting Transparent Thin Films; Institute of Physics Publishing: Bristol, UK, 1995, ISBN 978–0750303224.

- [17] S. Laux, N. Kaiser, A. Zöller, R. Götzelmann, H. Lauth, H. Bernitzki, Roomtemperature deposition of indium tin oxide thin films with plasma ion-assisted evaporation. Thin Solid Films1998, 335, 1–5.

- [18] D.C.Paine, T. Whitson, D. Janiac, R. Beresford,; C.O. Yang, B. Lewis, A study of low temperature crystallization of amorphous thin film indium-tin-oxide. J. Appl. Phys. 1999, 85, 8445–8450.

- [19] J.W. Elam, S.M. George, Growth of ZnO/Al<sub>2</sub>O<sub>3</sub> alloy films using atomic layer deposition techniques. Chem. Mater.2003, 15, 1020–1028.

- [20] T.L. Yang, D.H. Zhang; J. Ma, H.L. Ma, Y. Chen, Transparent conducting ZnO:Al films deposited on organic substrates deposited by RF magnetron-sputtering. Thin Solid Films 1998, 326, 60–62.

- [21] S.-S Lin, J.-L Huang. The effect of thickness on the properties of heavily Al-doped ZnO films by simultaneous rf and dc magnetron sputtering. Ceram. Int. 2004, 30, 497–501.

- [22] T. Yamamoto, Codoping for the fabrication of p-type ZnO. Thin Solid Films 2002, 420, 100–106.

- [23] S. Ibuki, H. Yanagi, K. Ueda, H. Kawazoe, H. Hosono, Preparation of n-type conductive transparent thin films of AgInO<sub>2</sub>:Sn with delafossite-type structure by pulsedlaser deposition, J. Appl. Phys. 2000, 88, 3067: 1–3067: 3.

- [24] R. Klenk, M. Linke, H. Angermann,; C. Kelch, M. Kirsch, J. Klaer, Ch. Köble, Die Stabilität von ZnO bei beschleunigter Alterung. In Proceedings of FVS Workshop (Session III), Berlin, Germany, 2005.

- [25] K. Isawa, Y. Yaegashi, M. Komatsu, M. Nagano, S. Sudo, Synthesis of delafossitederived phases, RCuO2+δwith R = Y, La, Pr, Nd, Sm, and Eu, and observation of spin-gap-like behavior. Phys. Rev. B1997, 56, 3457–3466.

- [26] K. Ueda, S. Inoue, S. Hirose, H. Kawazoe; H. Hosono, Transparent p-type semiconductor: LaCuOS layered oxysulfide. Appl. Phys. Lett. 2000, 77, 2701: 1– 2701: 3. Materials 2012, 5 681

- [27] X. Nie, S.-H. Wei, S. B. Zhang, Bipolar Doping and Band-Gap Anomalies in Delafossite Transparent Conductive Oxides. Phys. Rev. Lett. 2002, 88, 066405.

- [28] J. Li, A.W. Sleight, C.Y. Jones, B.H. Toby, Trends in negative thermal expansion behavior for AMO2(A = Cu or Ag; M = Al, Sc, In, or La) compounds with the delafossite structure. J. Solid State Chem. 2005, 178, 285–294.

## CHAPTER 3

# TRANSPARENTGATERECESSEDCHANNELMOSFETFORIMPROVEDCARRIERRELIABILITYAPPLICATIONS

#### **3.1.** INTRODUCTION

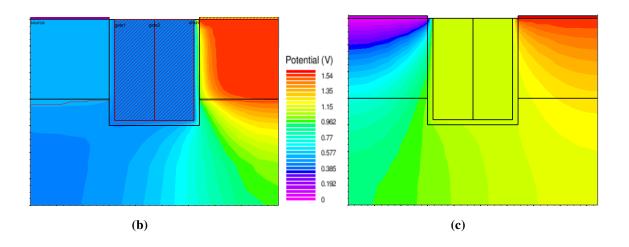

A novel device structure called <u>Transparent Gate Recessed Channel MOSFET</u> (TGRC-MOSFET) is proposed to alleviate the hot carrier effects for the advanced nanometer process. TGRC-MOSFET involves a recessed channel and incorporates Indium Tin Oxide as a transparent gate. TCAD analysis shows that the performance of TGRC-MOSFET surpasses <u>Conventional Recessed Channel (CRC)-MOSFET</u> in terms of high  $I_{ON}/I_{OFF}$  ratio and better carrier transport efficiency as compared to <u>Conventional Recessed Channel (CRC) MOSFET</u>.

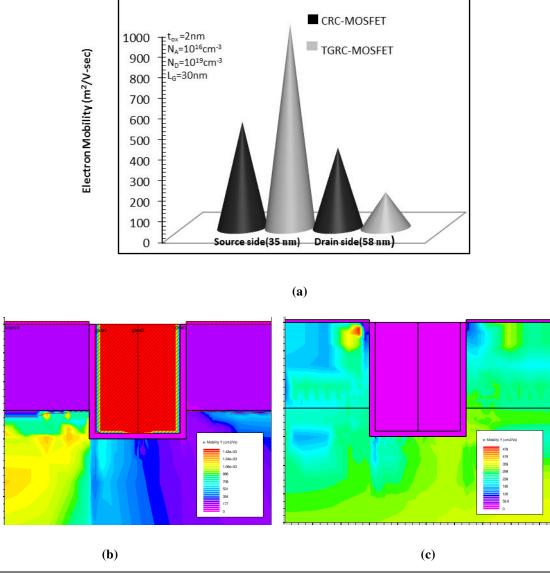

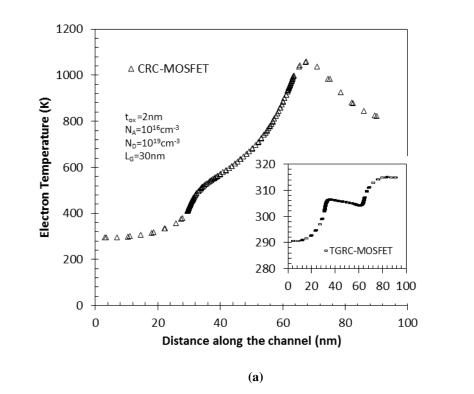

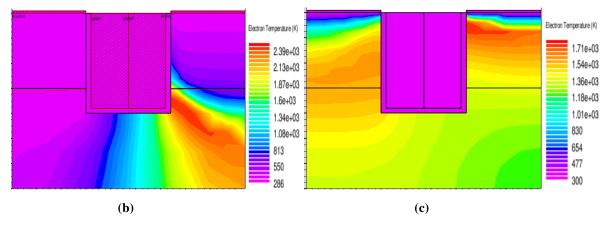

Fig. 3.1 Schematic structure of Transparent Gate Recessed Channel MOSFET.

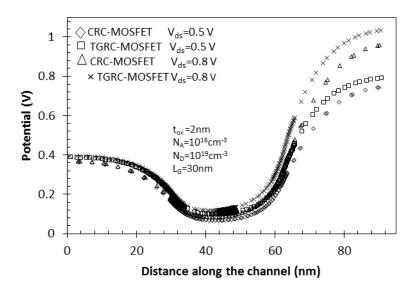

This simulation divulges the reduction in hot-carrier-effects metrics like electron velocity, electron temperature, potential, and electron mobility. All the simulations have been done using DEVEDIT-3D and ATLAS device simulator. The need of superior performance of ICs has led to the scaling of MOSFETs down to 30 nm and below. The hot-carrier dilapidation becomes a stringent limitation to the reliability of 100-nm devices and VLSI packing density [1-2].

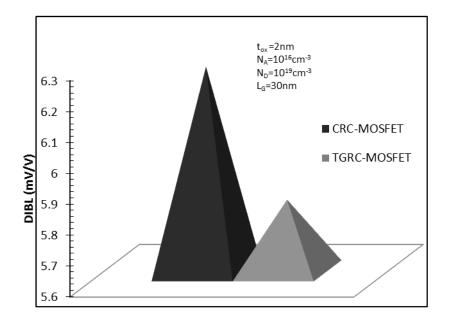

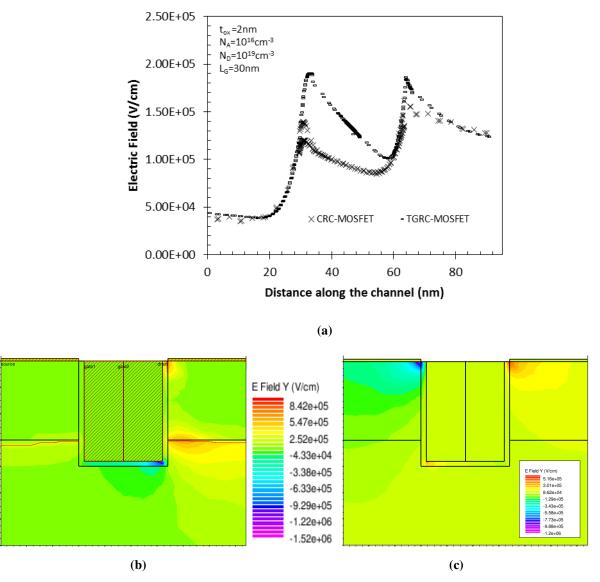

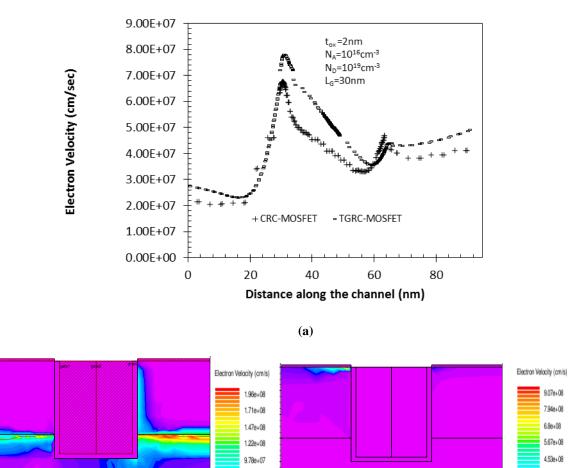

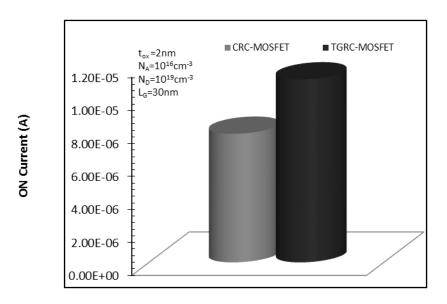

To abate these hot-carrier effects in CRC-MOSFET, instead of metallic gate we are using Indium Tin Oxide. Indium tin oxide (ITO or tin-doped indium oxide) is a solid solution of indium oxide ( $In_2O_3$ ) and tin oxide ( $SnO_2$ ). It is transparent and colorless in thin layers. Indium tin oxide is one of the most widely used transparent conducting oxides because of its two chief properties, its electrical conductivity and optical transparency, as well as the ease with which it can be deposited as a thin film. By using ITO, we improve  $I_{ON}$  which causes the decrease in device power consumption. The  $In_2O_3$  phase itself contributes free electron for electrical conductivity [3].