# ANALYSIS, DESIGN AND CONTROL OF DSTATCOM AND ITS APPLICATIONS

by

MANOJ BADONI Department of Electrical Engineering

Submitted

In fulfillment of the requirements of the degree of

## **DOCTOR OF PHILOSOPHY**

to the

### DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042, INDIA

**SEPTEMBER 2015**

© Delhi Technological University- 2015 All rights reserved

### CERTIFICATE

This is to certify that the thesis entitled "Analysis, Design and Control of DSTATCOM and its Applications" being submitted by Mr. Manoj Badoni for the award of degree of Doctor of Philosophy in the Department of Electrical Engineering, Delhi Technological University, Delhi, is the record of student's own work carried out by him under our supervision. The contents of this research work have not been submitted in part or full to any other university or institute for award of any degree.

Date\_\_/\_/\_\_\_

Prof. Bhim Singh Department of Electrical Engineering Indian Institute of Technology Delhi Hauz Khas, New Delhi-110016, India Dr. Alka Singh Department of Electrical Engineering Delhi Technological University Delhi Shahbad Daulatpur, Delhi-110042, India

#### ACKNOWLEDGEMENTS

I would like to express my deep and sincere gratitude to my supervisors **Prof. Bhim Singh** and **Dr. Alka Singh**, for their valuable guidance and continuous monitoring of my research work. It was great honor for me to pursue my research work under their supervision. Deep insight of Prof. Bhim Singh about the subject, enormous research experience, exposure in international forum and strong perception have enormously helped me to do this research work. Continuous monitoring of Dr. Alka Singh, valuable guidance and input have always been a driving force to complete my research work. It is a life time experience to work under both of my supervisors which I am cherished always.

My deepest thank to **Prof. Madhusudan Singh** for his immense support and valuable guidance as Head of the Department. I would like to convey my sincere gratitude to **Prof. Vishal Verma**, who has taught me relevant course work and allow me to work in simulation lab. I would like to thank the SRC members mainly **Prof. G. Bhuvaneswari** who have given me valuable guidance and advice to improve quality of my research work. I am extremely grateful to **Prof. Pragati Kumar**, **Dr. Mukhtiar Singh**, **Dr. M. Rizwan** and **Dr. M.M. Tripathi** for providing me valuable support and assistance. I am extremely thankful to staff members of Power System Lab, DTU Delhi for providing me immense facility and assistance to carry out my research work. I would like to thank others office staff, Central Library and Central Computer Centre for their valuable co-operation and support.

I would like my sincere thanks to **Dr. Sabha Raj Arya** who has guided me to develop hardware setup at initial stage and support me in many ways. His vast knowledge of control algorithms for shunt compensator and research publications guided me always to carry out my research work. I

am also grateful to Dr. Arun Kumar, Dr. Vashist Bist, Mr. Krishan Kant Bhalla, Dr. N. K. S. Naidu, Dr. M. Sandeep, Mr. Chinmay Jain and Mr. Ikhlaq Hussain, Research Scholars EE IITD, for their valuable support to drive my hardware setup. I am extremely grateful to my research group and friends Ravi Nath Tripathi, Sachin Kumar Kesharvani, Nitu Dhyani, Sandeep Kumar, Prakash Chittora, Ashutosh Trivedi, Girish Gowd Talapur, Amritesh Kumar, Ramesh Singh, Vivek Raiwani and Kuldeep for their valuable assistance, co-operation and great source of learning. I would like my sincere thanks to Chairman, Graphic Era University, Dehradun for encouraging me for research and allow me to avail study leave to pursue research work at DTU, Delhi.

If I get any success today for my research work, the entire credit should go to my mother Smt. Sumitra Devi, wife Akanksha and my sisters they were supporting me in various roles. I would like express my deep concern to my little son, Master Saksham Badoni for his consideration during the long hours of absence from home. I would like to thank other family members for supporting me directly or indirectly to carry out my research work.

I thank to almighty, the father of all, for their blessings to accomplish my research work successfully.

Date:\_/\_/\_\_

Place: Delhi

Manoj Badoni (2k11/Ph.D/EE/07)

#### ABSTRACT

The widespread use of power electronics based equipment is increasing these days. Poor power quality at power distribution level is attributed to a number of reasons and the increase in power electronics based loads is one of the major causes. These loads are nonlinear in nature and generate harmonic currents which propagate to other connected loads at the point of common coupling (PCC). Some other power quality problems viz. high reactive power demand, voltage regulation, load unbalancing and poor power factor cause concern to the electric utility and consumers of electric power supply. The current related power quality problems include harmonic currents, high reactive power burden, poor voltage regulation and unbalanced loads.

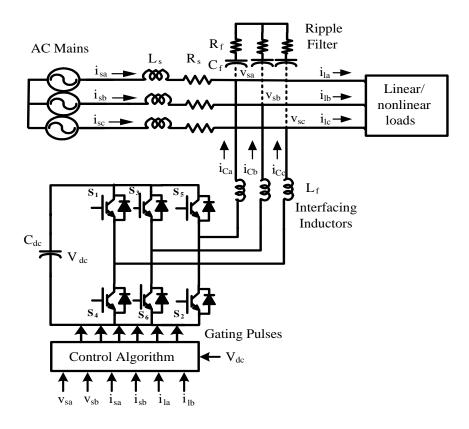

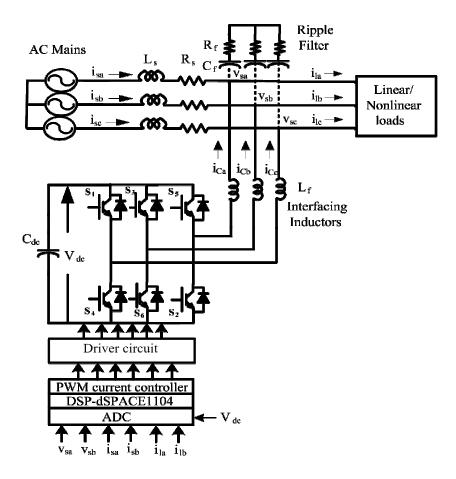

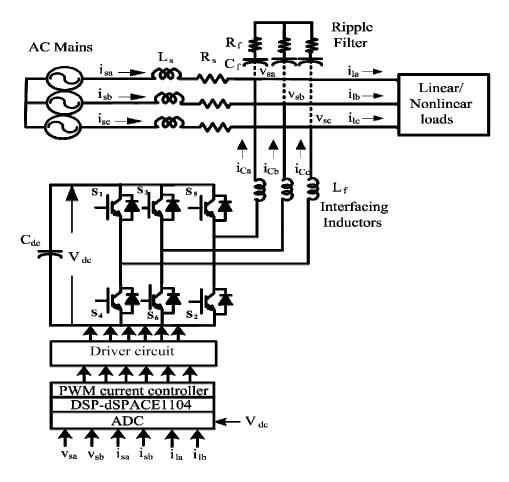

A number of power converter based solutions have been developed in the recent past due to the progress in speed and capacity of power semiconductor technology. The group of devices used for power quality improvement in distribution systems is referred to as custom power devices. A specific shunt connected custom power device used for the mitigation of current related power quality problems is widely known as a distribution static compensator (DSTATCOM). An implementation and control of DSTATCOM have become possible due to advancement in digital signal processing (DSP) and self-commutating semiconductor devices. The major components used for design of DSTATCOM include voltage source converter (VSC), interfacing inductors, ripple filters and DSP (Digital Signal Processor).

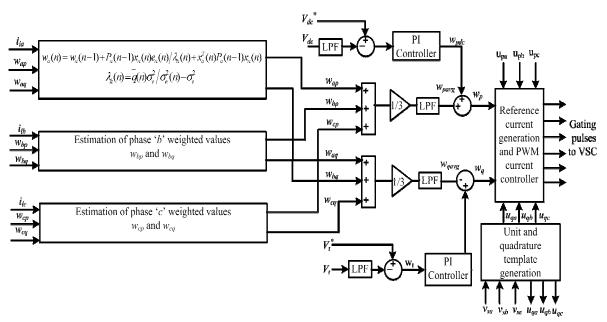

Performance of DSTATCOM mainly depends on the control algorithm used for the estimation of fundamental active and reactive components of reference currents. These reference currents are used for the generation of switching pulses for control of VSC used in DSTATCOM. The control algorithms for DSTATCOM have been divided into four categories in this proposed work. These

include the conventional control algorithms, adaptive theory based control algorithms, recursive theory based control algorithms and artificial intelligence based control algorithms.

The conventional control algorithms considered are based on power balance theory (PBT), instantaneous reactive power theory (IRPT), conductance based and instantaneous symmetrical component theory (ISCT). These control algorithms for the control of three-phase DSTATCOM, are used for harmonic currents reduction, reactive power compensation and load balancing in power factor correction (PFC) and voltage regulation modes. These algorithms are extended for voltage regulation operation, which are also required in various isolated power generation systems such as an isolated diesel generator, isolated micro hydro, biogas and biomass based generation systems.

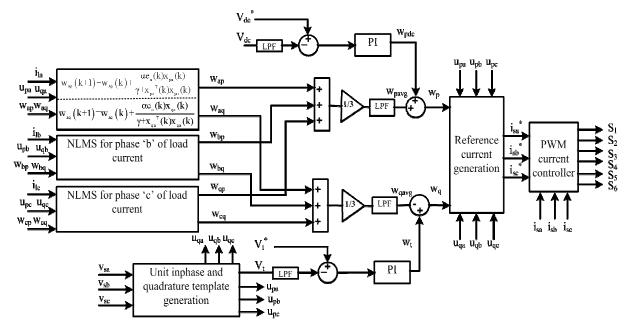

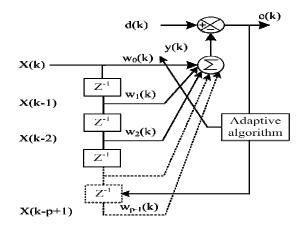

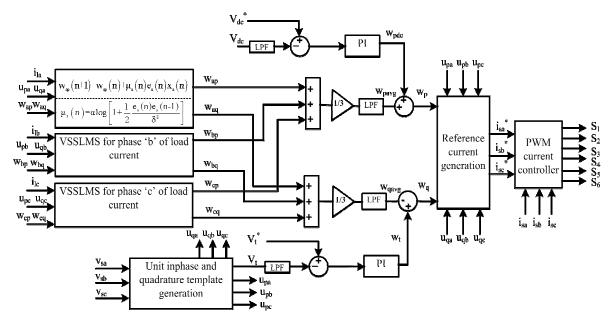

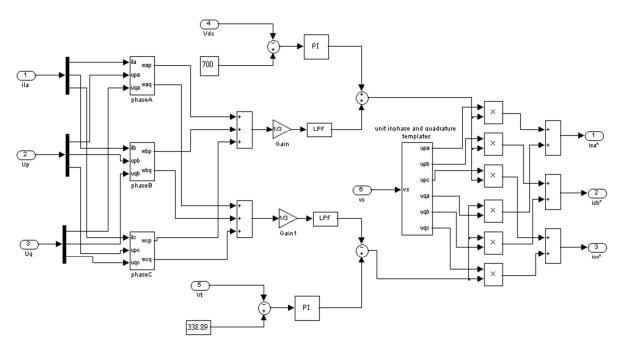

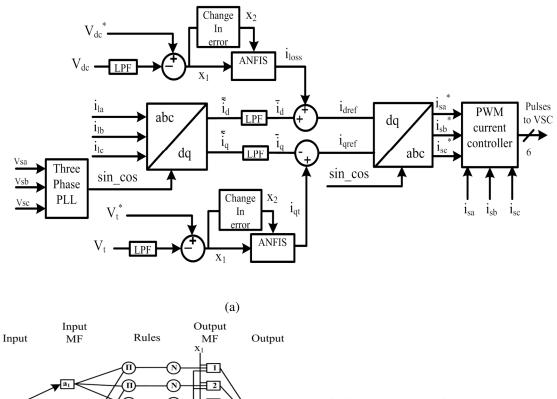

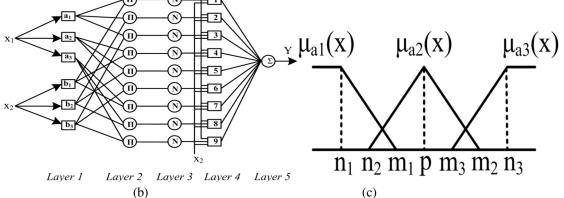

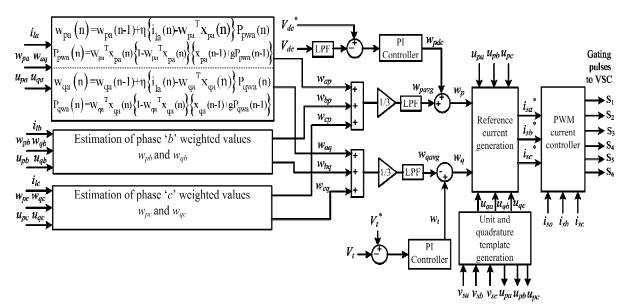

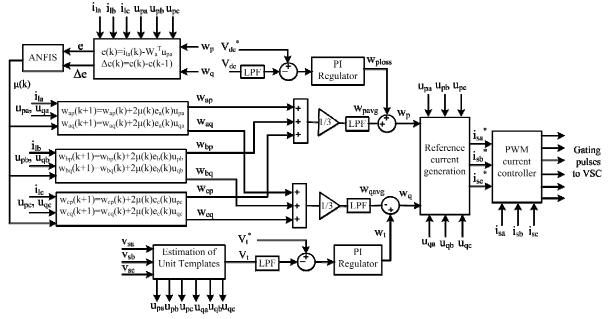

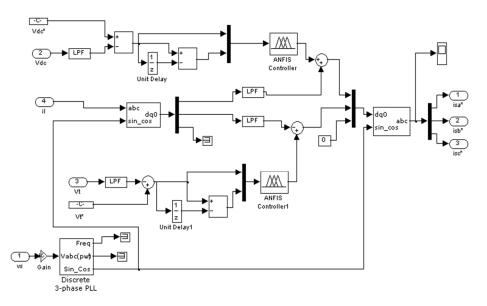

The control algorithms developed under adaptive theory are based on Wiener filter, fixed step size least mean square (FSSLMS) along with its variants and variable step size least mean square (VSSLMS). The control algorithms developed under the category of recursive theory are based on variable forgetting factor recursive least square (VFFRLS), recursive inverse (RI) and immune feedback principle. The category of artificial intelligence based algorithms includes adaptive neuro fuzzy inference system (ANFIS), real time recurrent learning (RTRL) and immune feedback based control algorithms.

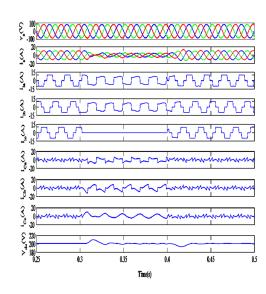

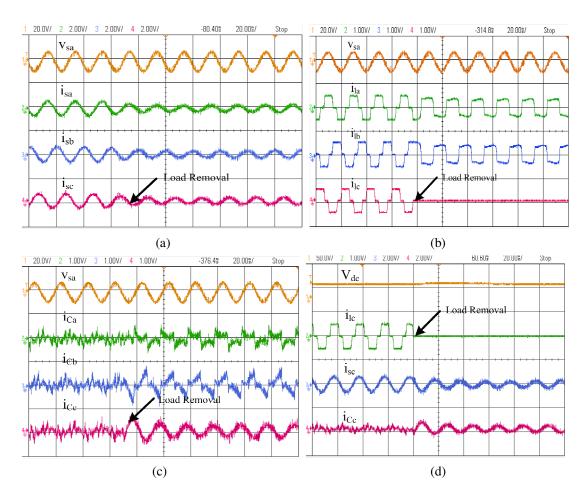

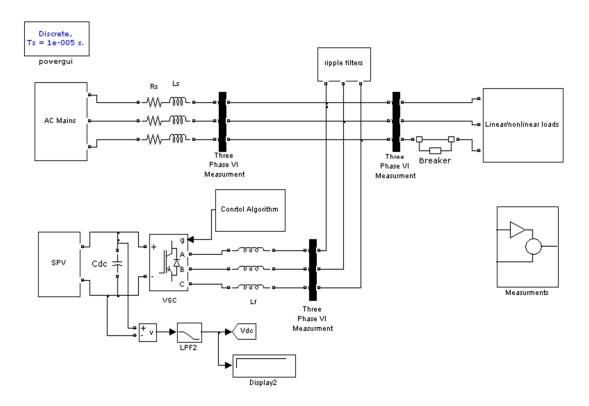

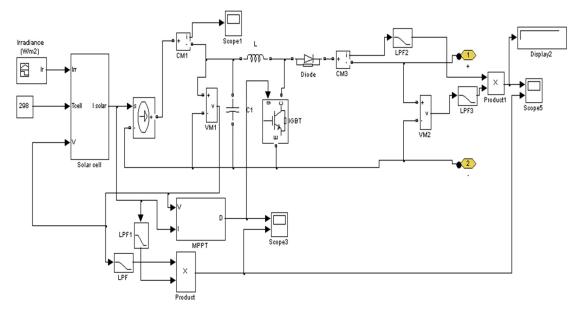

All these control algorithms are developed in MATLAB using SIMULINK and Sim-power system (SPS) tool boxes. Real time performance of these control algorithms for power quality improvement has been extensively tested using simulation studies and experimentally on the prototype of DSTATCOM developed in the laboratory.

v

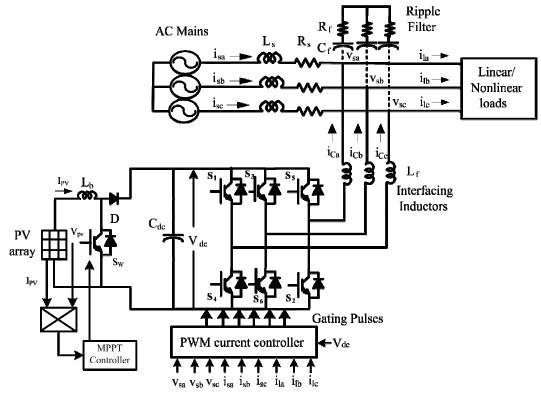

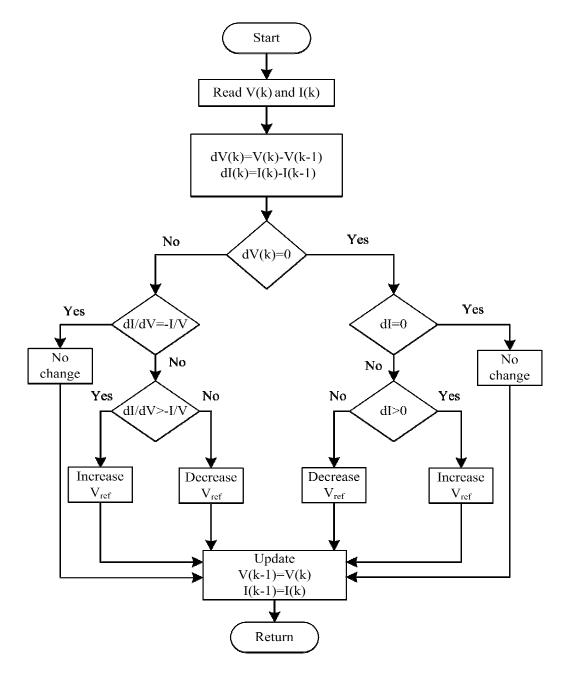

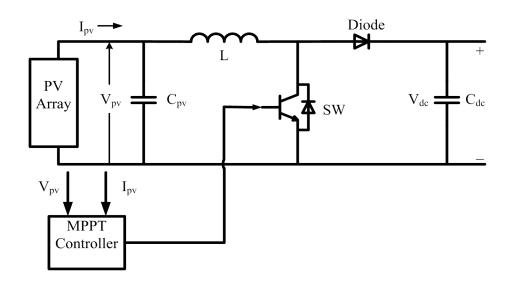

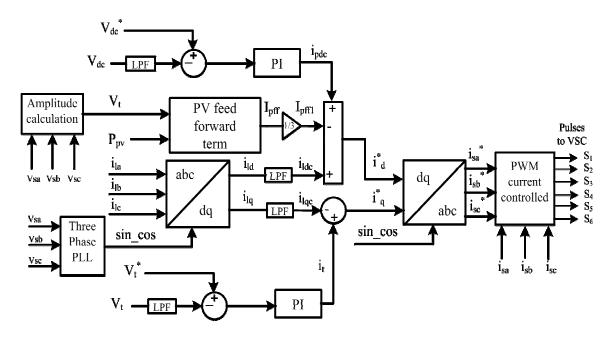

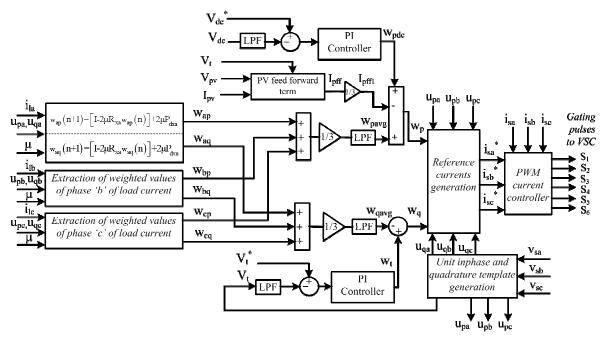

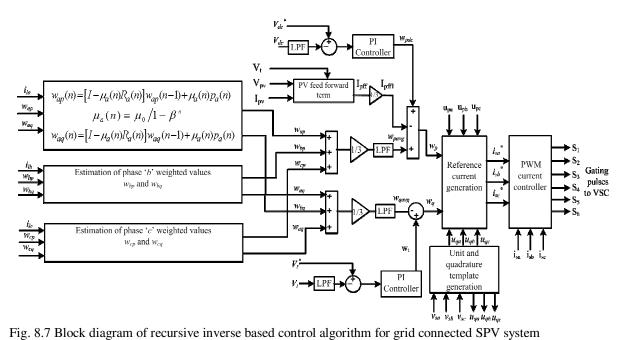

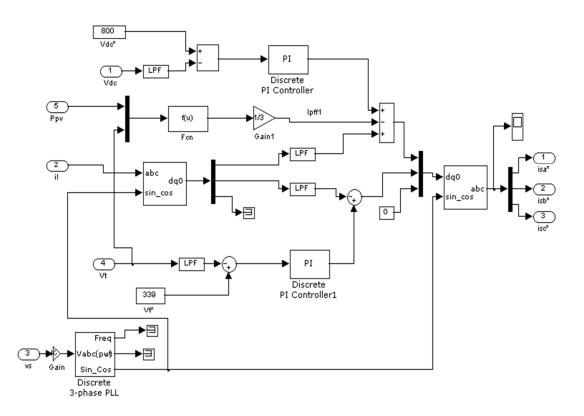

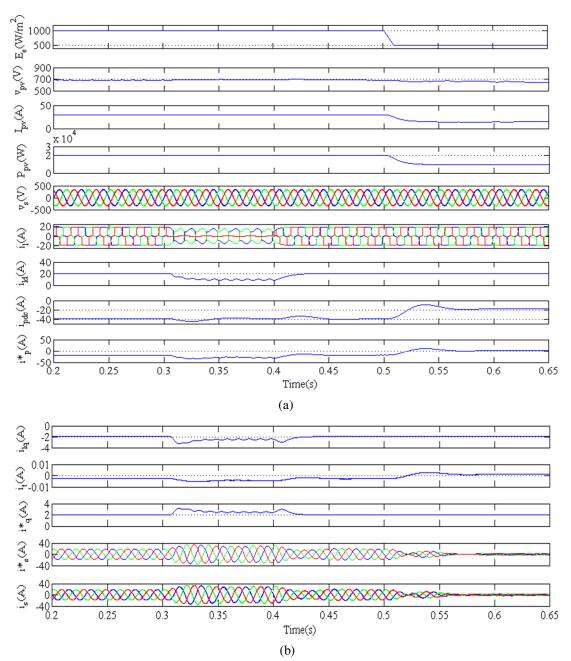

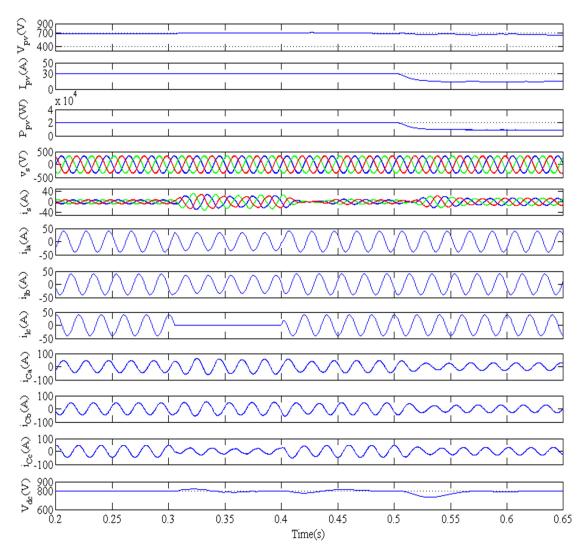

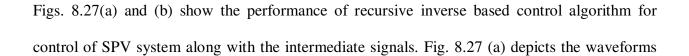

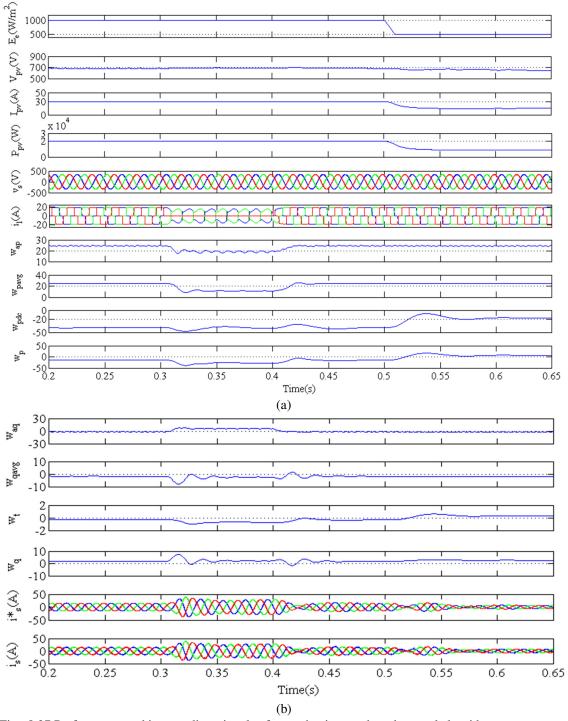

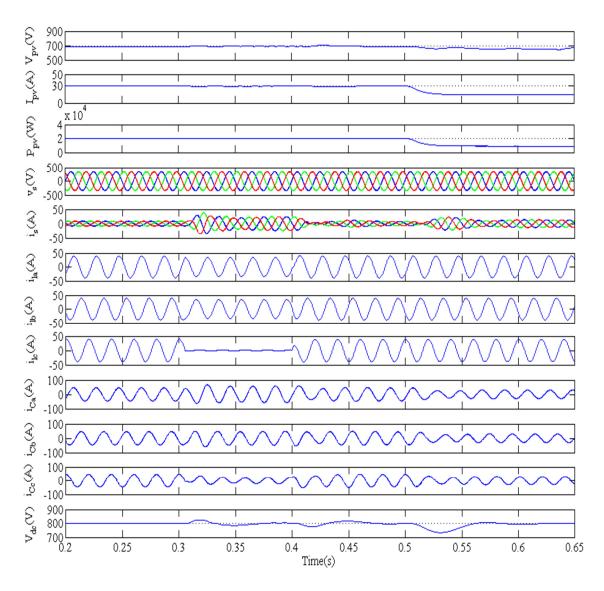

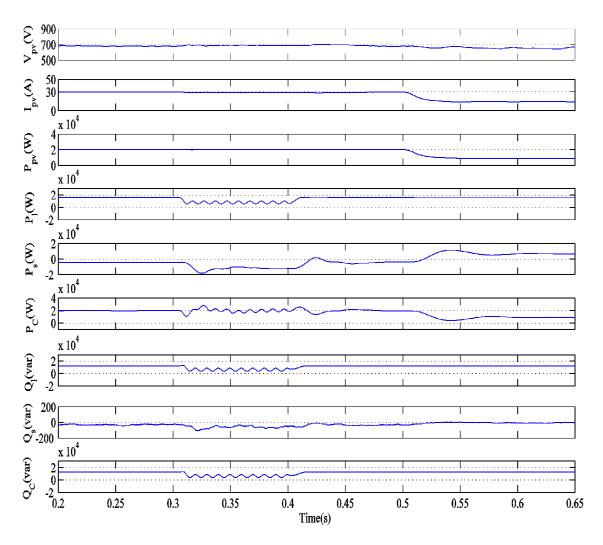

Additionally, the three phase DSTATCOM system is utilized for grid integration of solar photovoltaic (SPV) array. The VSC used in this system serves the purpose of power converter, which is used to transfer power generated from SPV array to the grid along with functions of power quality improvement such as harmonic currents elimination, reactive power compensation and load balancing in PFC and voltage regulation modes under linear and nonlinear loads. The performance of this system is studied with three control algorithms viz. synchronous reference frame theory (SRFT), Wiener filter and recursive inverse based control algorithms.

# **TABLE OF CONTENTS**

| Cert | tificate                                                           | i            |  |  |  |  |  |

|------|--------------------------------------------------------------------|--------------|--|--|--|--|--|

| Ack  | nowledgement                                                       | ii-iii       |  |  |  |  |  |

| Abs  | tract                                                              | iv-vi        |  |  |  |  |  |

| Tab  | Table of Contents                                                  |              |  |  |  |  |  |

| List | of Figures                                                         | xviii-xxviii |  |  |  |  |  |

| List | of Tables                                                          | xxix         |  |  |  |  |  |

| List | of Symbols                                                         | xxx-xxxi     |  |  |  |  |  |

| СНА  | PTER-I INTRODUCTION                                                | 1-11         |  |  |  |  |  |

| 1.1  | General                                                            | 1            |  |  |  |  |  |

| 1.2  | State of Art                                                       | 2            |  |  |  |  |  |

| 1.3  | Custom Power Devices                                               | 5            |  |  |  |  |  |

| 1.4  | Scope of Work                                                      | 6            |  |  |  |  |  |

|      | 1.4.1. Investigations on Three phase DSTATCOM                      | 6            |  |  |  |  |  |

|      | 1.4.2. Control Algorithms                                          | 7            |  |  |  |  |  |

|      | 1.4.2.1 Conventional Control Algorithms                            | 7            |  |  |  |  |  |

|      | 1.4.2.2 Adaptive Theory Based Control Algorithms                   | 8            |  |  |  |  |  |

|      | 1.4.2.3 Recursive Theory Based Control Algorithms                  | 8            |  |  |  |  |  |

|      | 1.4.2.4 Artificial intelligence Based Control Algorithms           | 9            |  |  |  |  |  |

|      | 1.4.3 DSTATCOM Application to Grid Integration of Solar PV Array   | 9            |  |  |  |  |  |

| 1.5  | Outline of Chapters                                                | 9            |  |  |  |  |  |

| CH   | APTER-II LITERATURE REVIEW                                         | 12-30        |  |  |  |  |  |

| 2.1  | General                                                            | 12           |  |  |  |  |  |

| 2.2  | Literature Survey on Power Quality Problems and Their Solutions 12 |              |  |  |  |  |  |

2.2.1Power Quality Problems122.2.2Power Quality Solutions14

| 2.3 | 3 Power Quality Standards                       |                                                                       |       |  |  |  |  |

|-----|-------------------------------------------------|-----------------------------------------------------------------------|-------|--|--|--|--|

| 2.4 | Literature Review on Power Quality Monitoring   |                                                                       |       |  |  |  |  |

| 2.5 | Literature Review on Configurations of DSTATCOM |                                                                       |       |  |  |  |  |

|     | 2.5.1                                           | Three Phase Three-Wire DSTATCOM Configuration                         | 19    |  |  |  |  |

|     | 2.5.2                                           | Three Phase Four- Wire DSTATCOM Configuration                         | 20    |  |  |  |  |

| 2.6 | Litera                                          | ture Review on Control Algorithms of DSTATCOM                         | 22    |  |  |  |  |

|     | 2.6.1                                           | Conventional Control Algorithms                                       | 22    |  |  |  |  |

|     | 2.6.2                                           | Adaptive Theory Based Control Algorithms                              | 23    |  |  |  |  |

|     | 2.6.3                                           | Recursive Theory Based Control Algorithms                             | 24    |  |  |  |  |

|     | 2.6.4                                           | Artificial Intelligence Based Control Algorithms                      | 25    |  |  |  |  |

| 2.7 | Litera                                          | ture Review on DSTATCOM Applications to Grid Integration of SPV Array | 26    |  |  |  |  |

| 2.8 | Identi                                          | fied Research Areas                                                   | 27    |  |  |  |  |

| 2.9 | Concl                                           | usions                                                                | 30    |  |  |  |  |

| CH  | APTER                                           | R-III DESIGN AND DEVELOPMENT OF DSTATCOM                              | 31-54 |  |  |  |  |

| 3.1 | Gener                                           | al                                                                    | 31    |  |  |  |  |

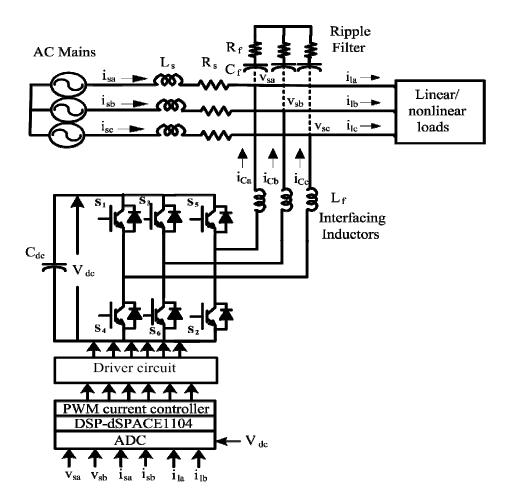

| 3.2 | Config                                          | guration of Three Phase DSTATCOM                                      | 31    |  |  |  |  |

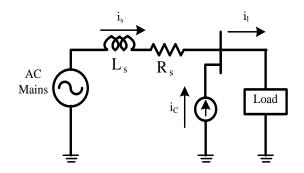

| 3.3 | Opera                                           | ting Principle and Features of DSTATCOM                               | 32    |  |  |  |  |

| 3.4 | Desig                                           | n of Components for Three Phase DSTATCOM                              | 34    |  |  |  |  |

|     | 3.4.1                                           | Design and Selection of Voltage Source Converter                      | 34    |  |  |  |  |

|     | 3.4.2                                           | Design and Selection of DC Bus Voltage                                | 34    |  |  |  |  |

|     | 3.4.3                                           | Design and Selection of DC Bus Capacitance                            | 35    |  |  |  |  |

|     | 3.4.4                                           | Design and Selection of AC Interfacing Inductors                      | 35    |  |  |  |  |

|     | 3.4.5                                           | Design and Selection of Ripple Filters                                | 36    |  |  |  |  |

|     | 3.4.6                                           | Design and Voltage and Current Rating of IGBTs                        | 36    |  |  |  |  |

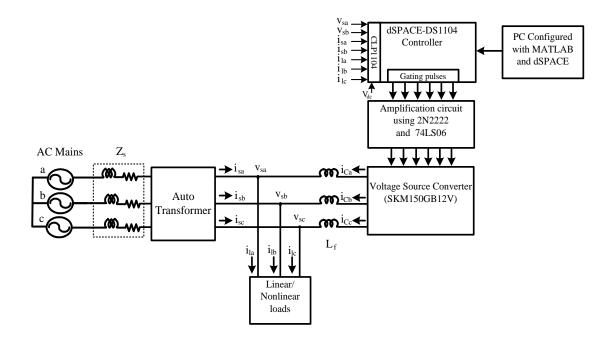

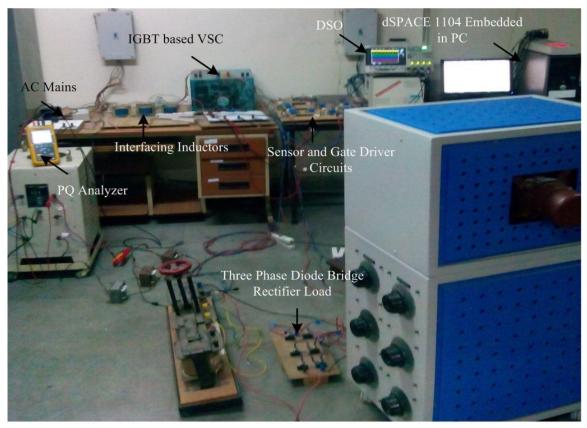

| 3.5 | Devel                                           | opment of Prototype of Three Phase DSTATCOM                           | 37    |  |  |  |  |

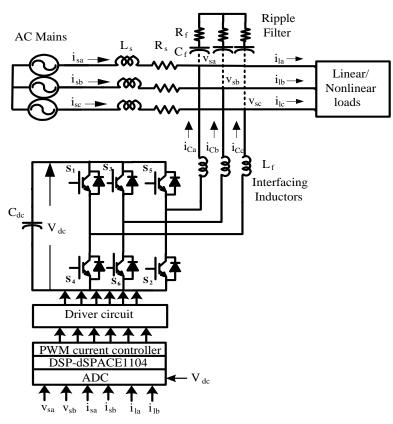

|     | 3.5.1                                           | Hardware Configuration of Prototype of DSTATCOM                       | 37    |  |  |  |  |

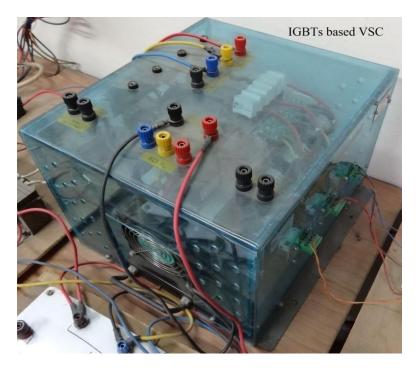

|     | 3.5.2                                           | Development of Voltage Source Converter                               | 39    |  |  |  |  |

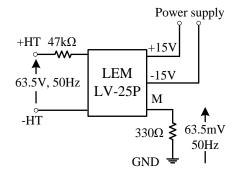

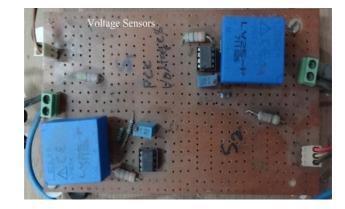

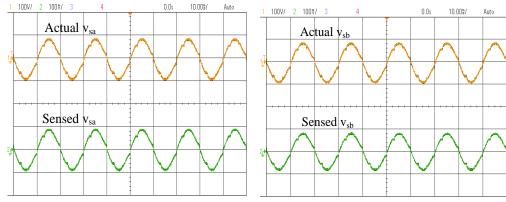

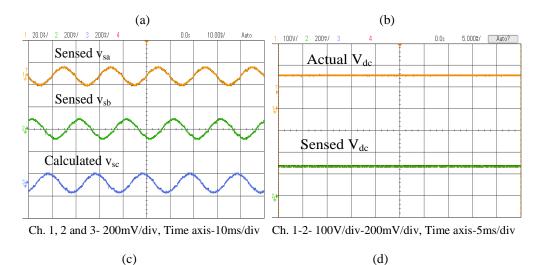

|     | 3.5.3                                           | Development of Voltage Sensor Circuit                                 | 41    |  |  |  |  |

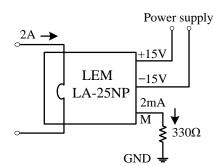

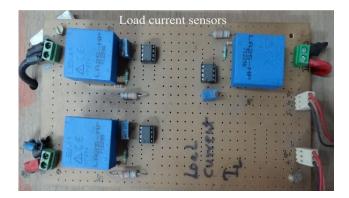

|     | 3.5.4                                           | Development of Current Sensor Circuit                                 | 42    |  |  |  |  |

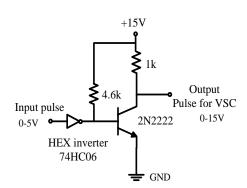

|      | 3.5.5                                      | Develop     | ment of Gating Circuit                                                              | 43     |  |

|------|--------------------------------------------|-------------|-------------------------------------------------------------------------------------|--------|--|

|      | 3.5.6 Development of Interfacing Inductors |             |                                                                                     |        |  |

|      | 3.5.7 Development of Ripple Filters        |             |                                                                                     |        |  |

| 3.6  | Result                                     | s and Dis   | cussion                                                                             | 46     |  |

|      | 3.6.1                                      | Results of  | of Design of DSTATCOM                                                               | 46     |  |

|      | 3.6.2                                      | Results of  | of Developed Prototype of DSTATCOM                                                  | 47     |  |

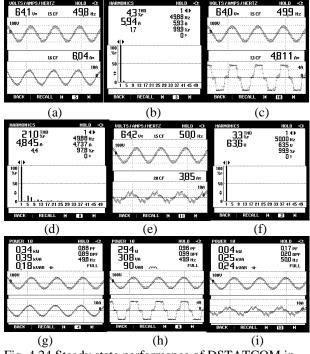

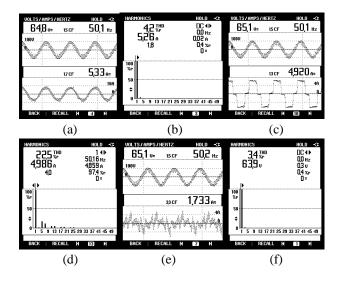

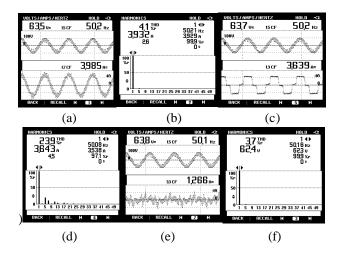

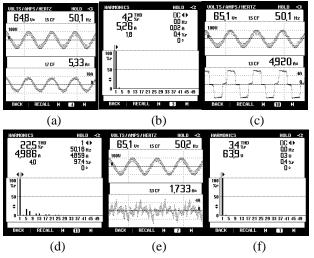

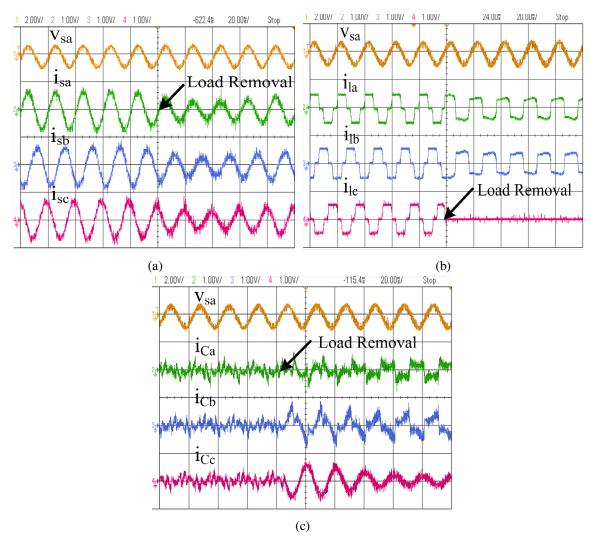

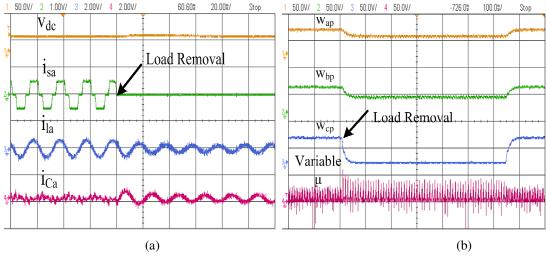

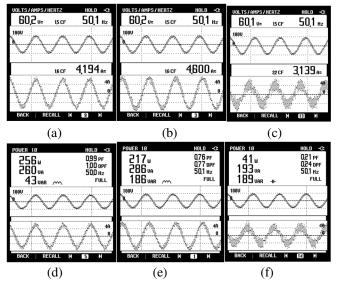

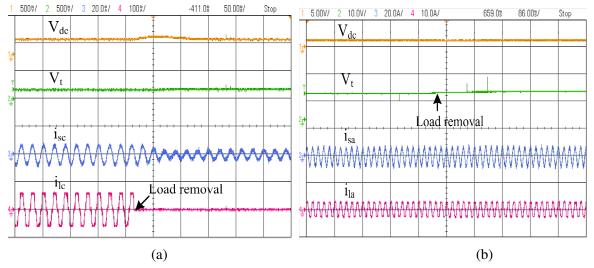

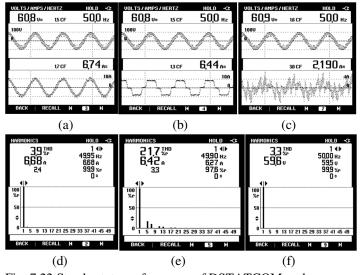

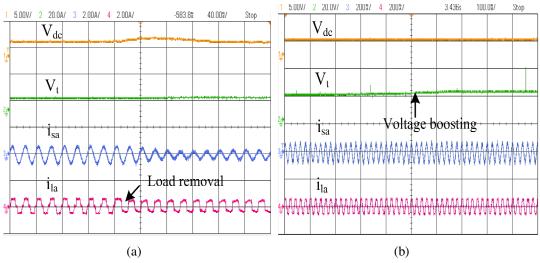

|      | 3.6.3                                      | Testing     | Results of Developed DSTATCOM                                                       | 48     |  |

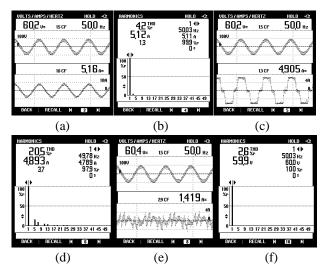

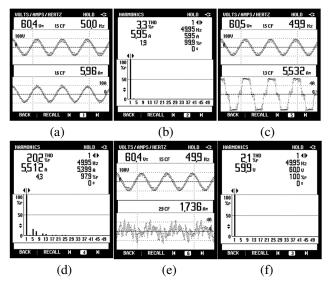

|      |                                            | 3.6.3.1     | Testing Results of Voltage Sensors                                                  | 48     |  |

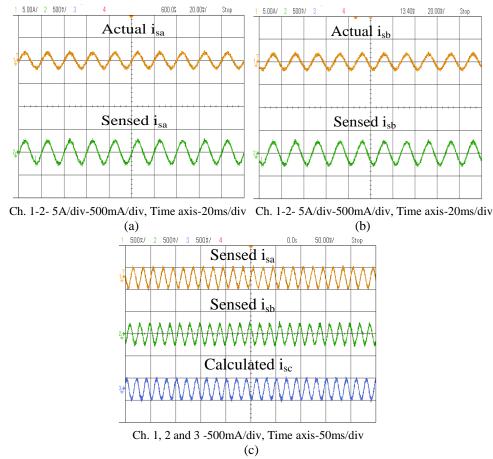

|      |                                            | 3.6.3.2     | Testing Results of Supply Current Sensors                                           | 48     |  |

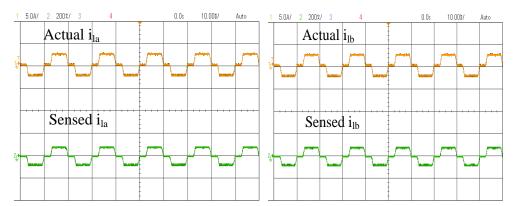

|      |                                            | 3.6.3.3     | Testing Results of Load Current Sensors                                             | 50     |  |

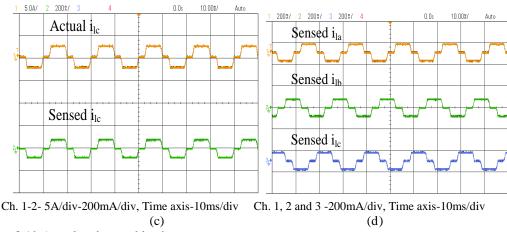

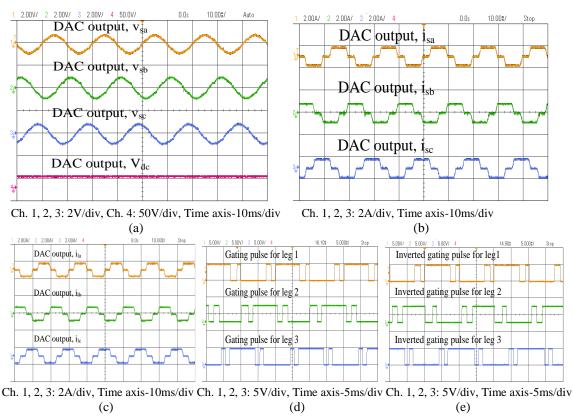

|      |                                            | 3.6.3.4     | Testing Results of Gating Circuit                                                   | 50     |  |

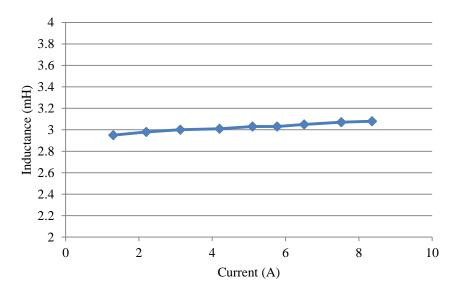

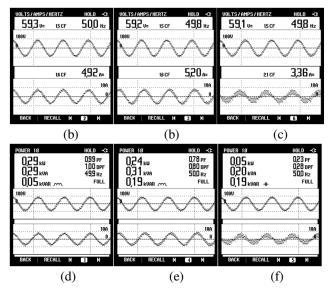

|      |                                            | 3.6.3.5     | Testing Results of Interfacing Inductor                                             | 51     |  |

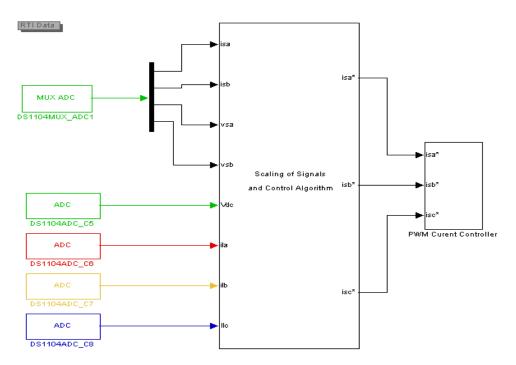

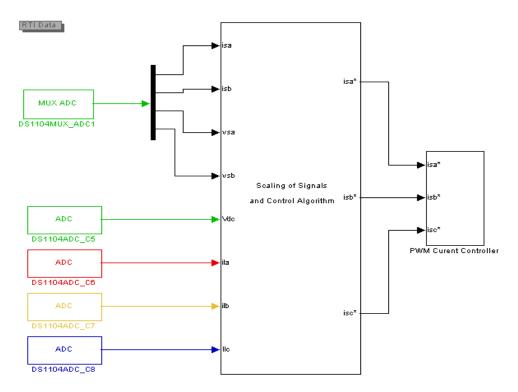

|      |                                            | 3.6.3.6     | Implementation Using DSP-dSPACE 1104                                                | 53     |  |

| 3.7  | 7 Conclusions                              |             |                                                                                     |        |  |

| CHA  | APTER                                      |             | ASSIFICATIONS OF CONTROL ALGORITHMS FOR<br>FATCOM                                   | 55-113 |  |

| 4.1. | Genera                                     | al          |                                                                                     | 55     |  |

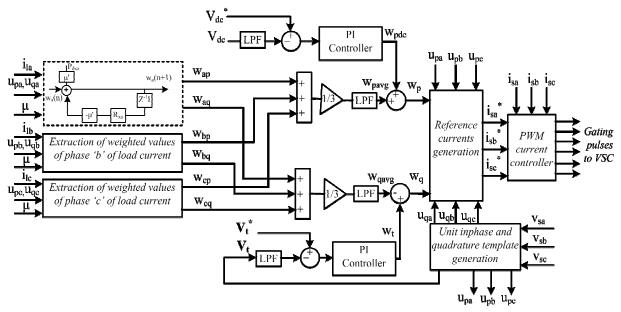

| 4.2. | Config                                     | guration a  | nd Operating Principle of DSTATCOM                                                  | 55     |  |

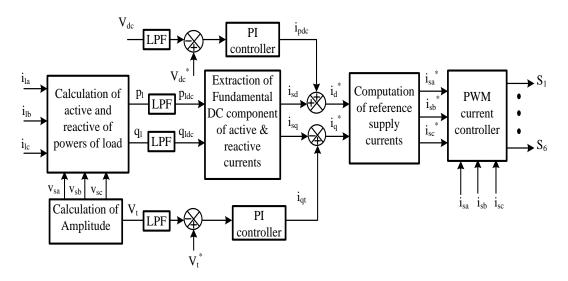

| 4.3. | Requi                                      | rement of   | Control Algorithm in DSTATCOM                                                       | 57     |  |

| 4.4. | Classi                                     | fication of | f Control Algorithms                                                                | 57     |  |

|      | 4.4.1                                      | Convent     | ional Control Algorithms                                                            | 57     |  |

|      | 4.4.2                                      | Adaptive    | e Theory Based Control Algorithms                                                   | 58     |  |

|      | 4.4.3                                      | Recursiv    | re Theory Based Control Algorithms                                                  | 58     |  |

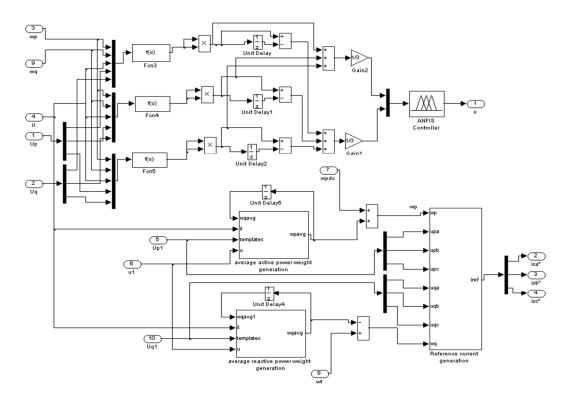

|      | 4.4.4                                      | Artificia   | l Intelligence Based Control Algorithms                                             | 59     |  |

| 4.5  | Basic                                      | Principle   | and Mathematical Formulation of Conventional Control Algorithms for                 |        |  |

|      | DSTA                                       | TCOM        |                                                                                     | 59     |  |

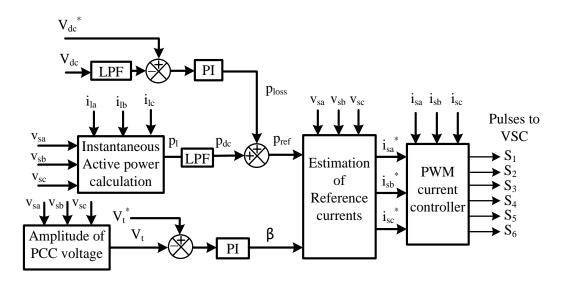

|      | 4.5.1                                      | Power B     | alance Theory Based Control Algorithm                                               | 59     |  |

|      |                                            | 4.5.1.1     | Estimation of Fundamental Active Power Components of Reference<br>Supply Currents   | 60     |  |

|      |                                            | 4.5.1.2     | Estimation of Fundamental Reactive Power Components of Reference<br>Supply Currents | 62     |  |

|        | 4.5.1.3 Generation of Reference Supply Currents and Switching Pulses                                                                                                                             | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

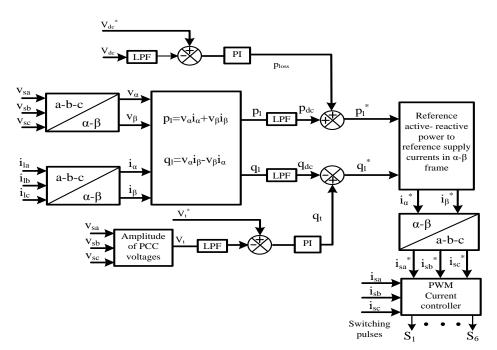

| 4.5.2  | Instantaneous Reactive Power Theory Based Control Algorithm                                                                                                                                      | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        | 4.5.2.1 Estimation of Reference Supply Currents                                                                                                                                                  | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        | 4.5.2.2 Generation of Switching Pulses                                                                                                                                                           | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

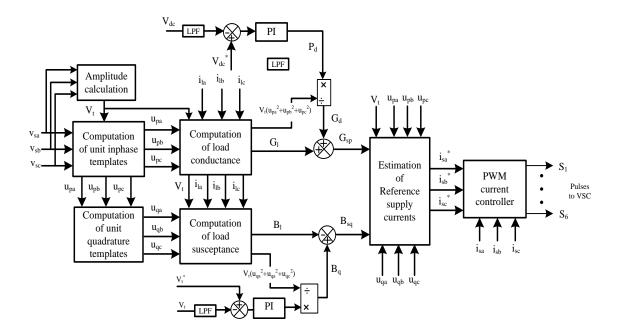

| 4.5.3  | Conductance Based Control Algorithm                                                                                                                                                              | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        | <ul> <li>4.5.3.1 Estimation of Fundamental Active Power Components of Reference<br/>Supply Currents</li> <li>4.5.3.2 Estimation of Fundamental Peactive Power Components of Reference</li> </ul> | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        | <ul><li>4.5.3.2 Estimation of Pundamental Reactive Fower Components of Reference Supply Currents</li><li>4.5.3.3 Generation of Reference Supply Currents and Switching Pulses</li></ul>          | 69<br>70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 4.5.4  | Symmetrical Component Theory Based Control Algorithm                                                                                                                                             | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        | 4.5.4.1 Estimation of Reference Supply Currents                                                                                                                                                  | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        | 4.5.4.2 Generation of Switching Pulses                                                                                                                                                           | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

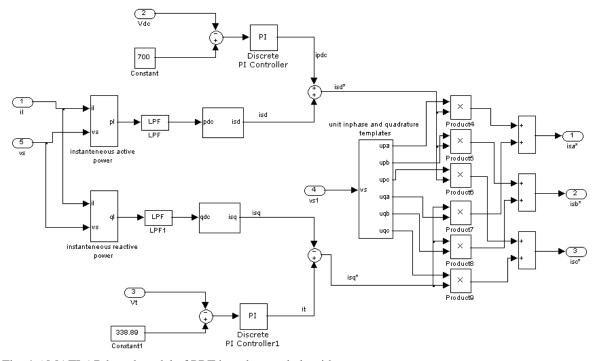

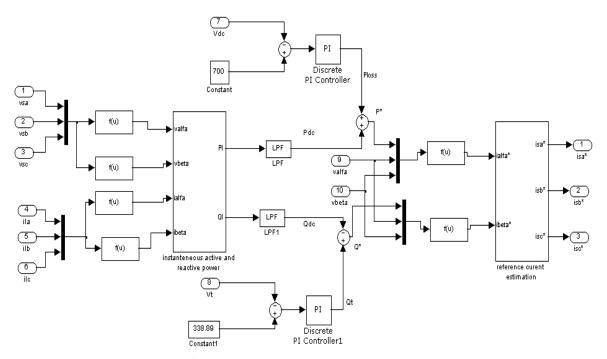

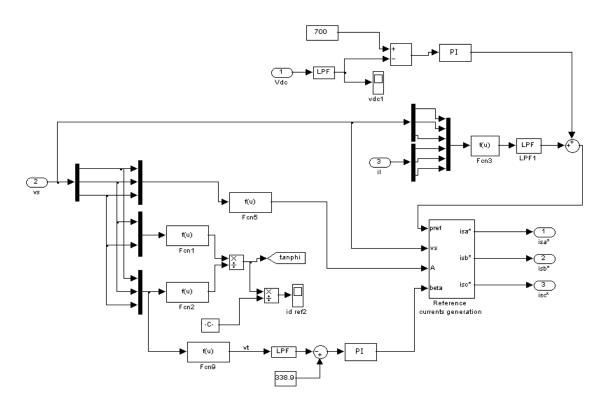

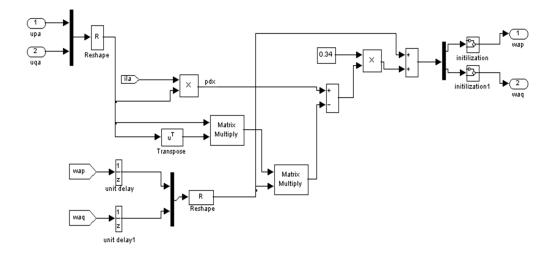

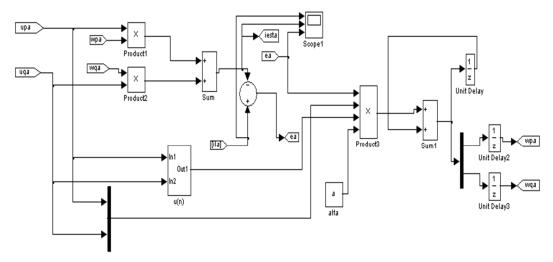

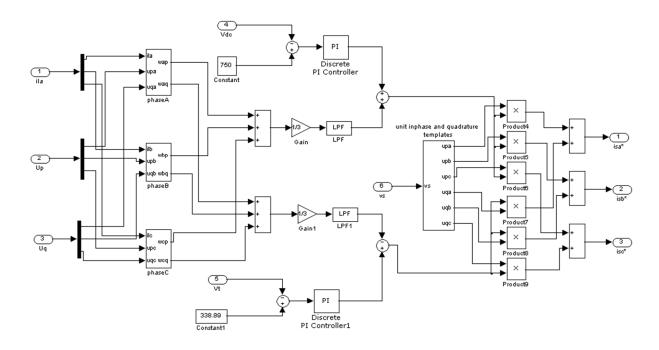

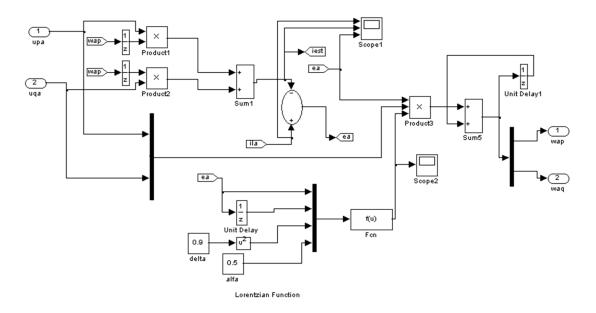

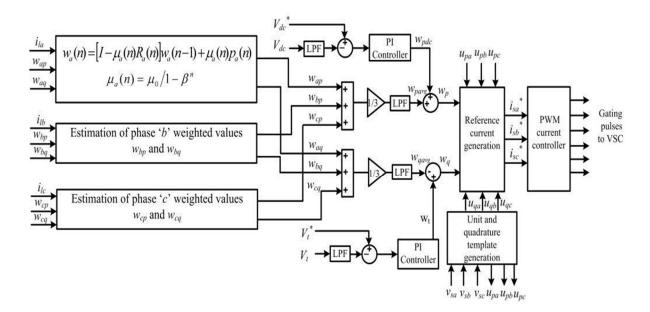

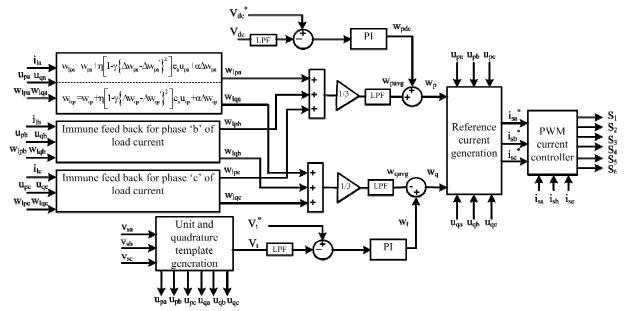

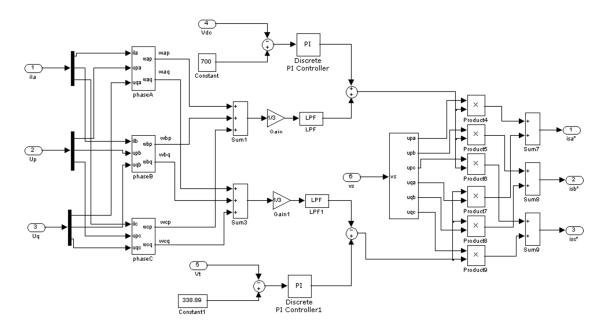

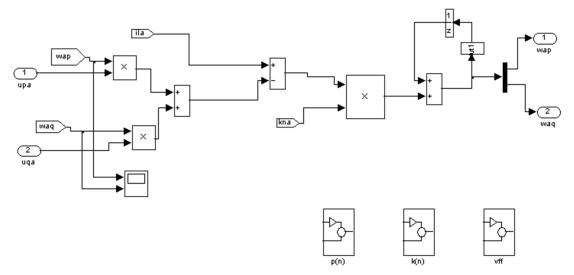

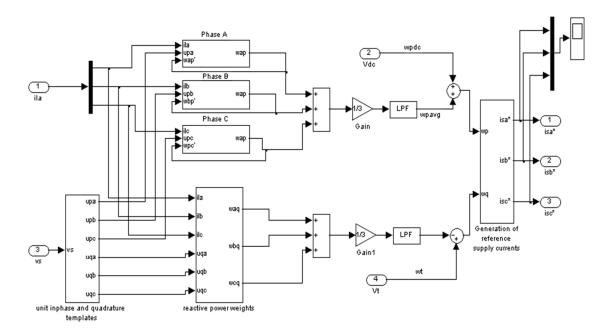

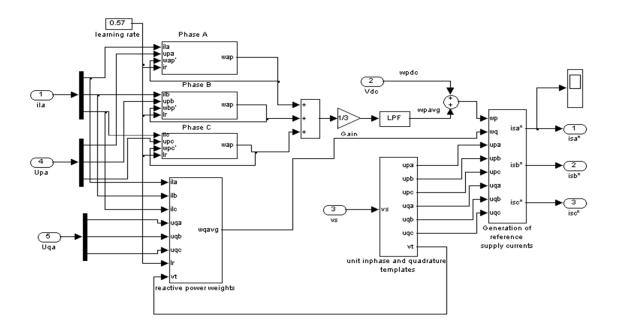

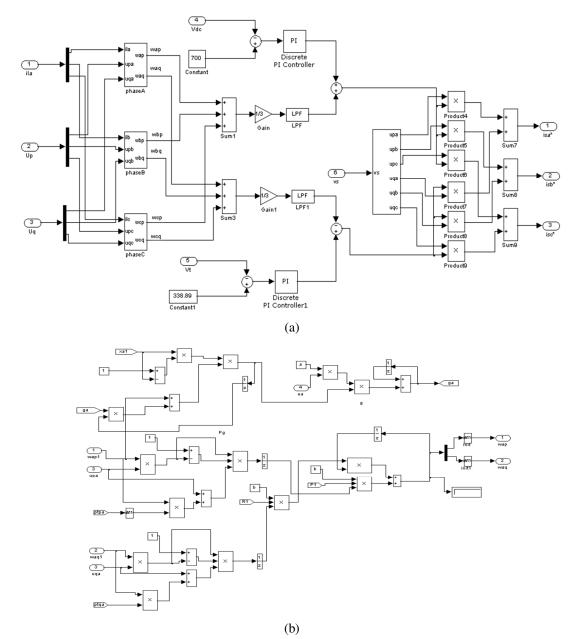

| MATI   | LAB Based Modeling of Conventional Control Algorithms                                                                                                                                            | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

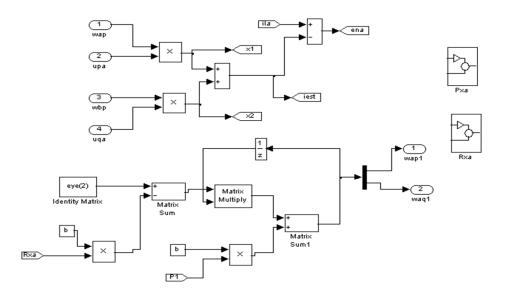

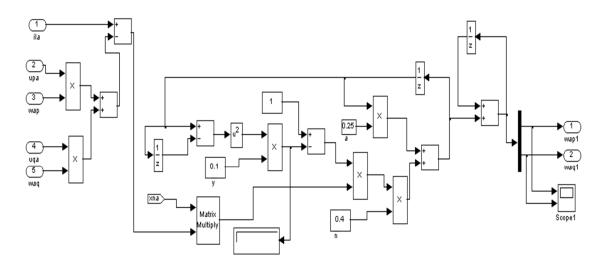

| 4.6.1  | Power Balance Theory Based Control Algorithm                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 4.6.2  | Instantaneous Reactive Power Theory Based Control Algorithm                                                                                                                                      | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

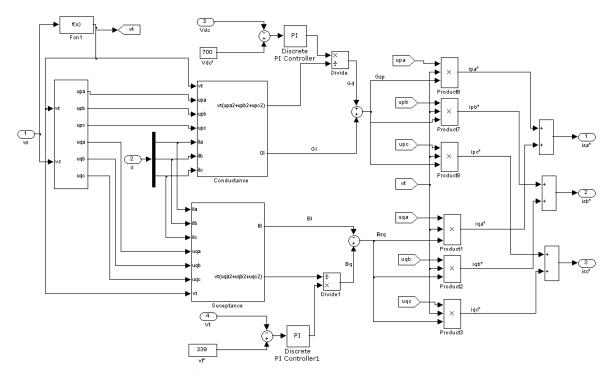

| 4.6.3  | Conductance Based Fryze Algorithm                                                                                                                                                                | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 4.6.4  | Instantaneous Symmetrical Component Theory Based Control Algorithm                                                                                                                               | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

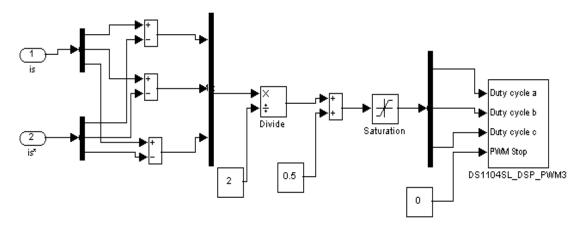

| DSP I  | implementation of Conventional Control Algorithms                                                                                                                                                | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

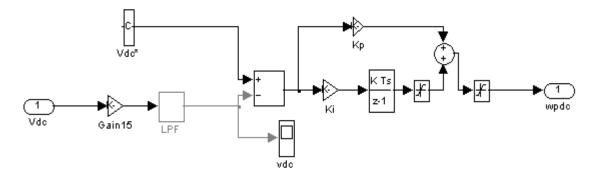

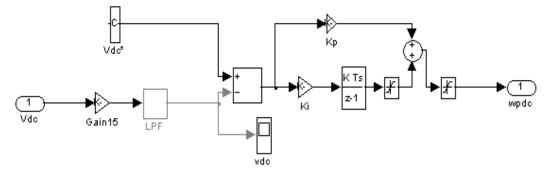

| 4.7.1  | Power Balance Theory Based Control Algorithm                                                                                                                                                     | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

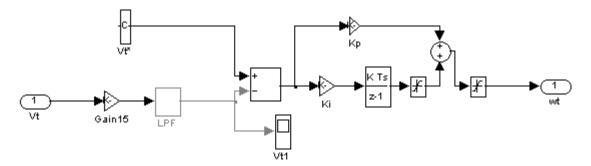

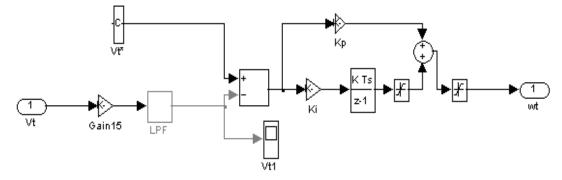

| 4.7.2  | Instantaneous Reactive Power Theory Based Control Algorithm                                                                                                                                      | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

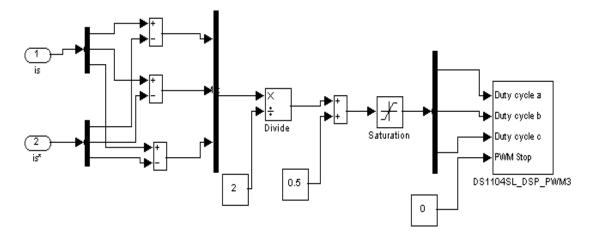

| 4.7.3  | Conductance Based Fryze Algorithm                                                                                                                                                                | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 4.7.4  | Symmetrical Component Theory Based Control Algorithm                                                                                                                                             | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Result | ts and Discussion                                                                                                                                                                                | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

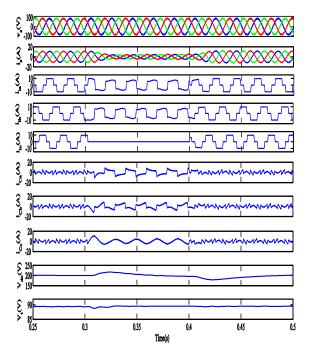

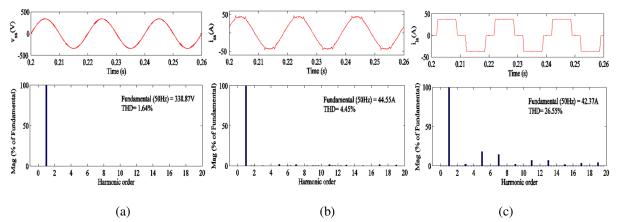

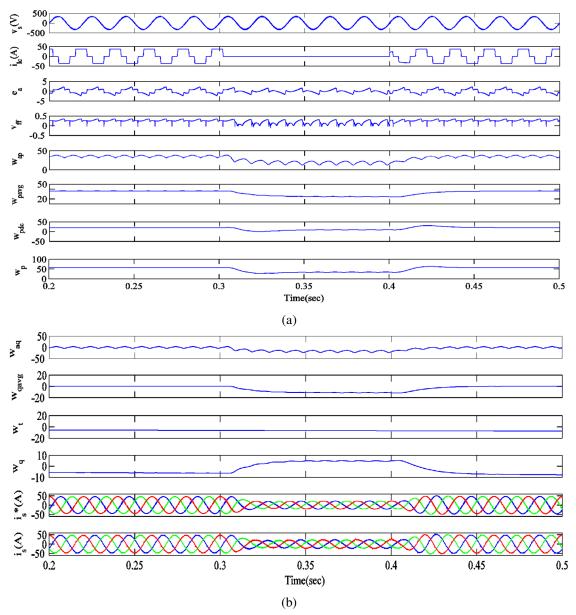

| 4.8.1. | Algorithm                                                                                                                                                                                        | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        |                                                                                                                                                                                                  | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        |                                                                                                                                                                                                  | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

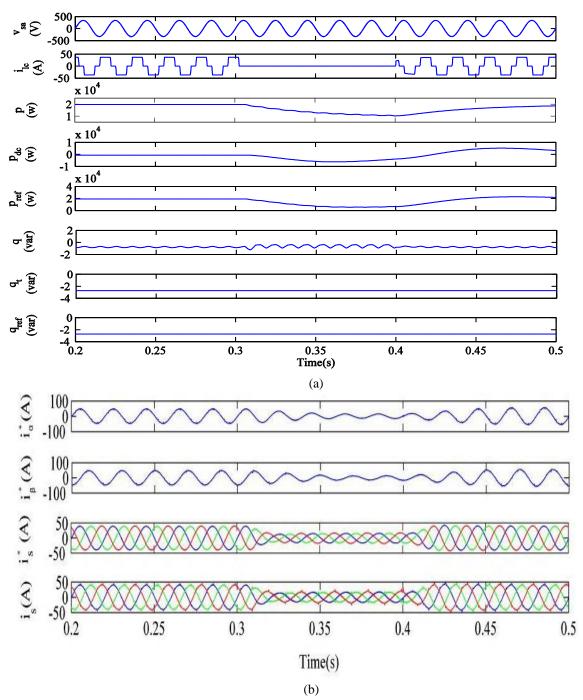

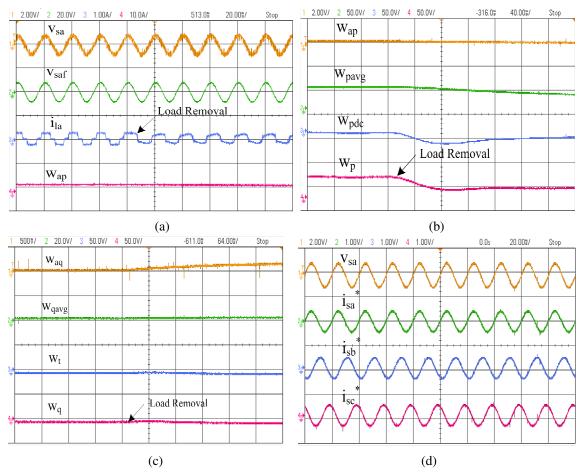

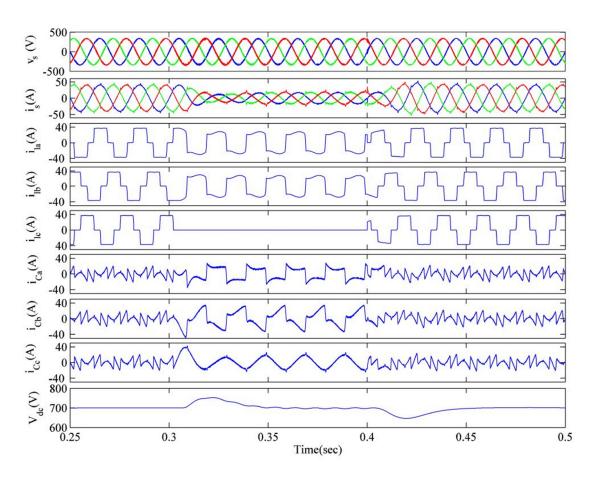

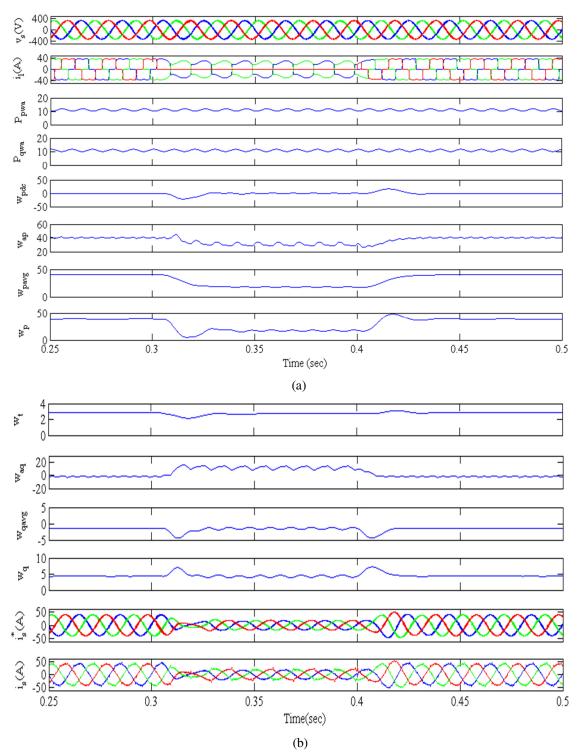

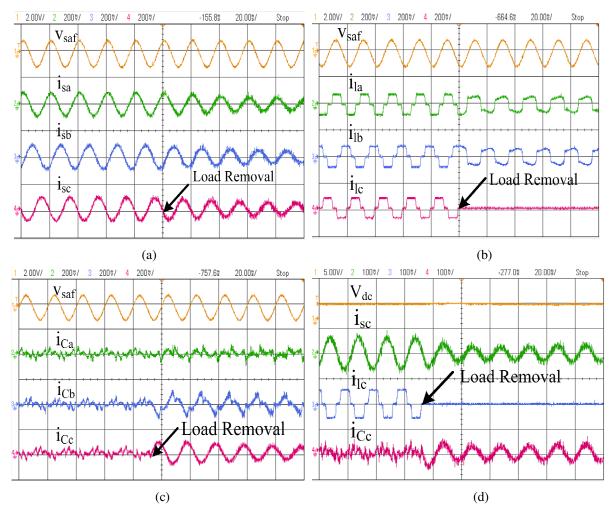

| 4.8.2  | •                                                                                                                                                                                                | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

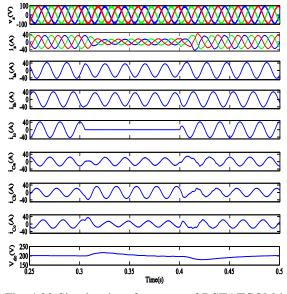

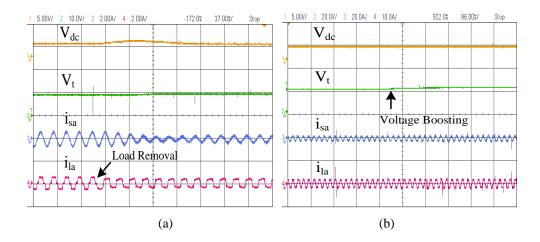

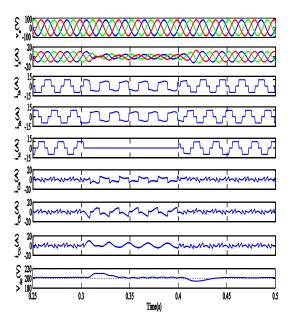

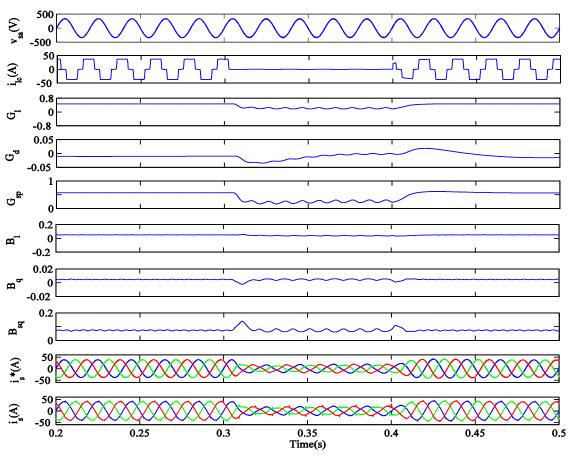

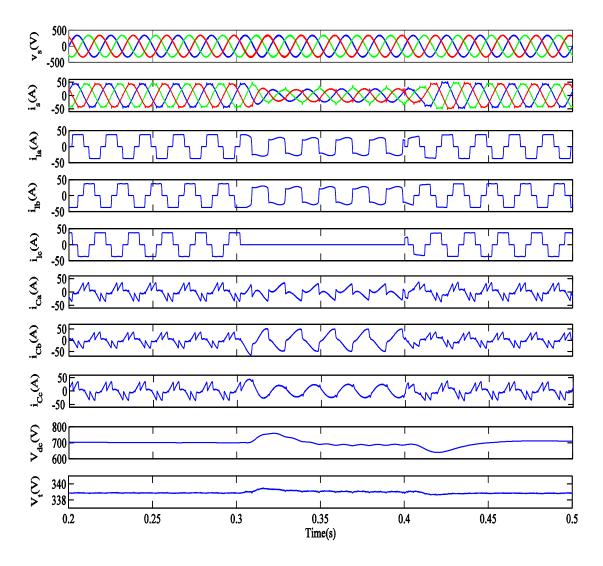

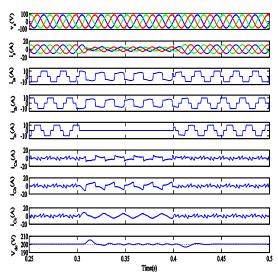

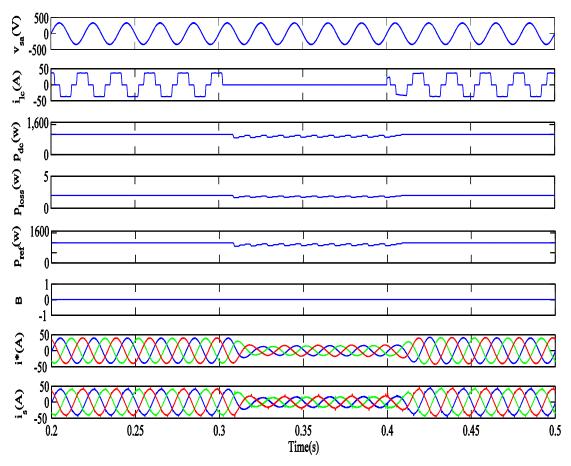

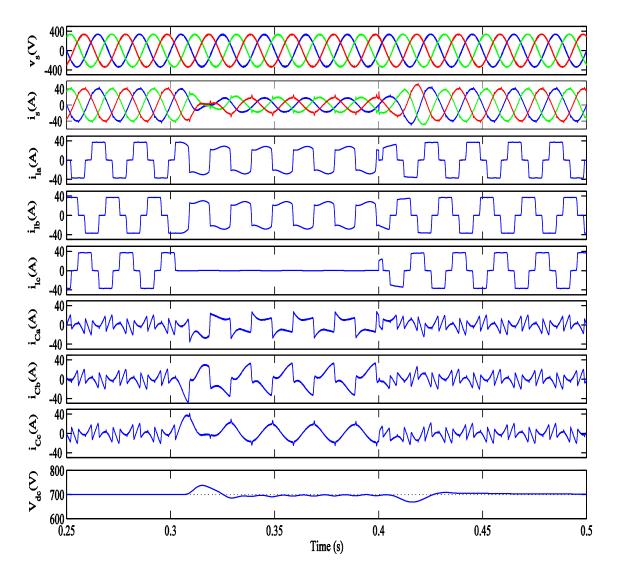

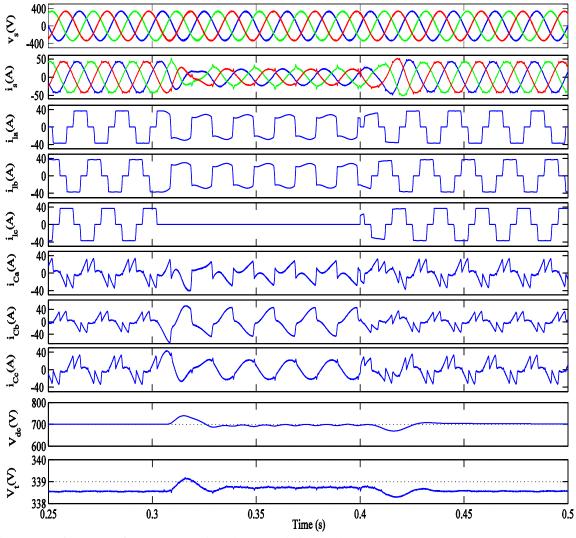

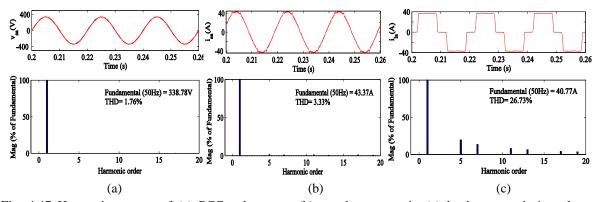

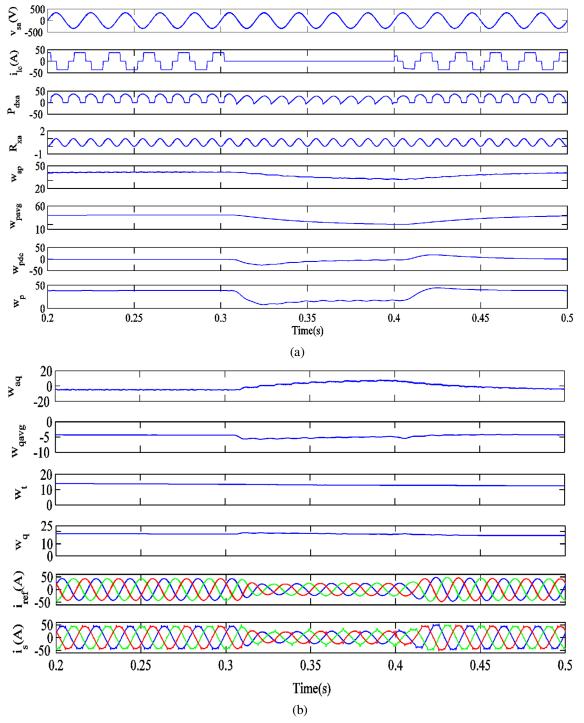

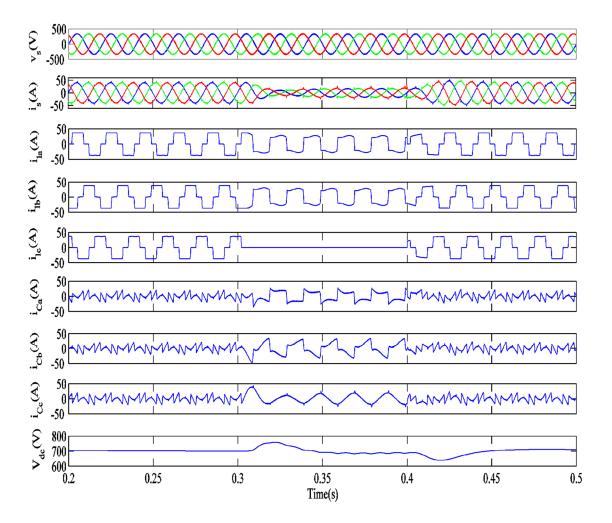

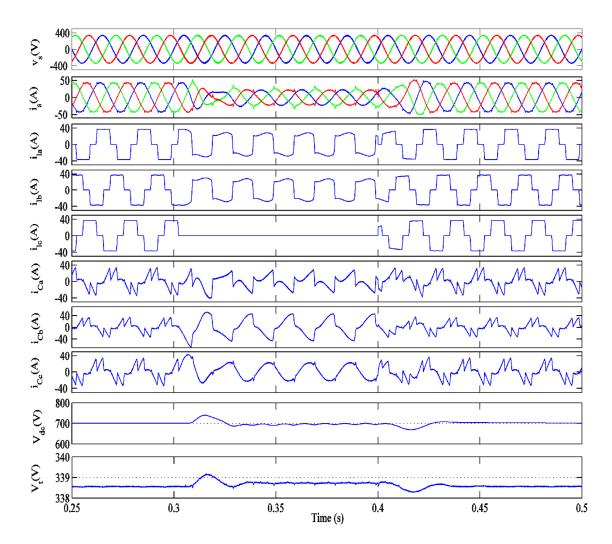

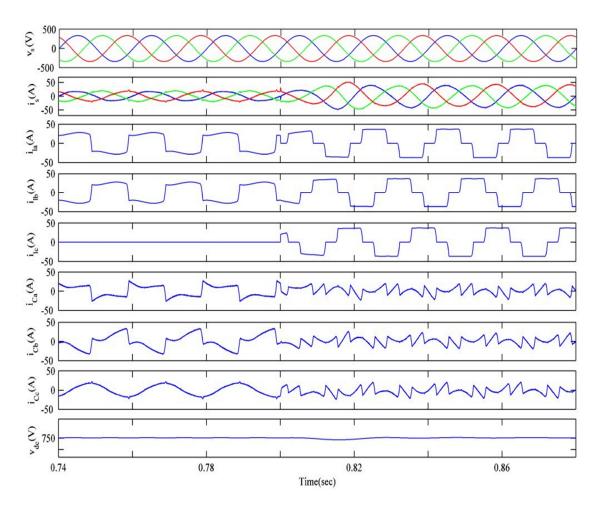

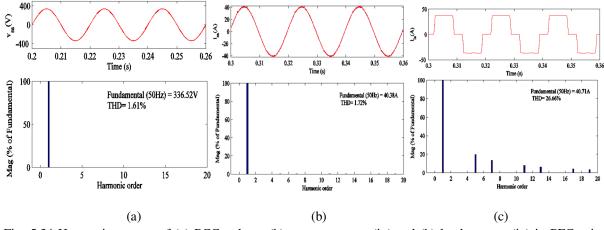

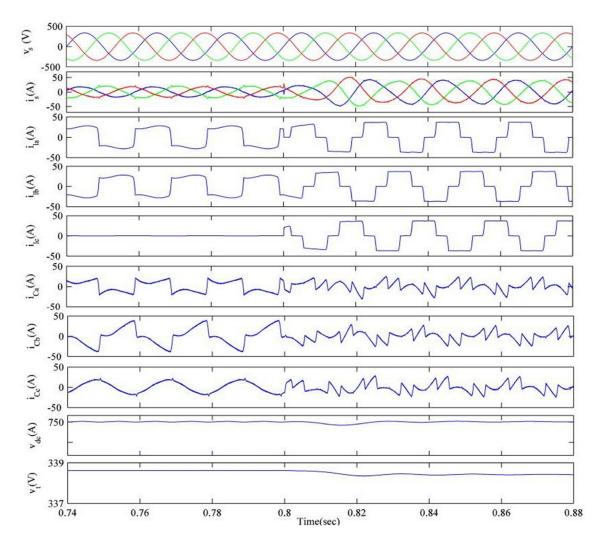

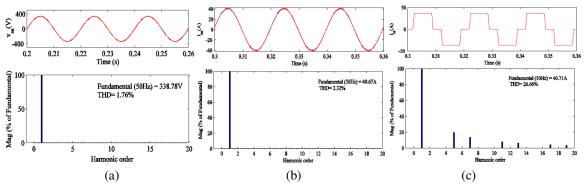

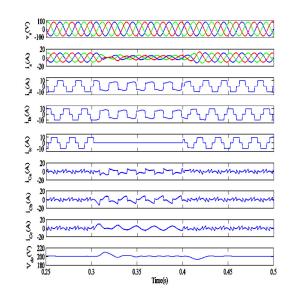

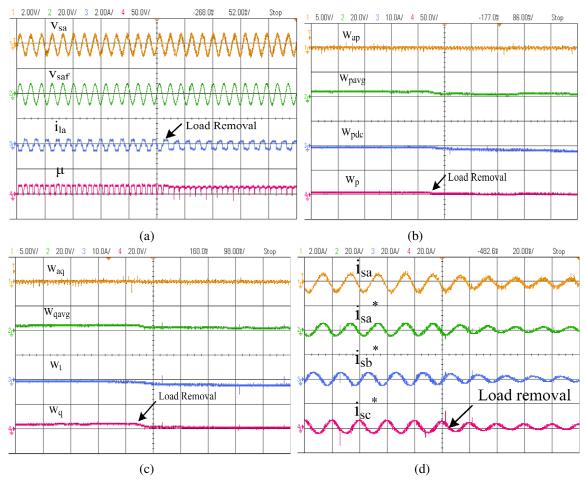

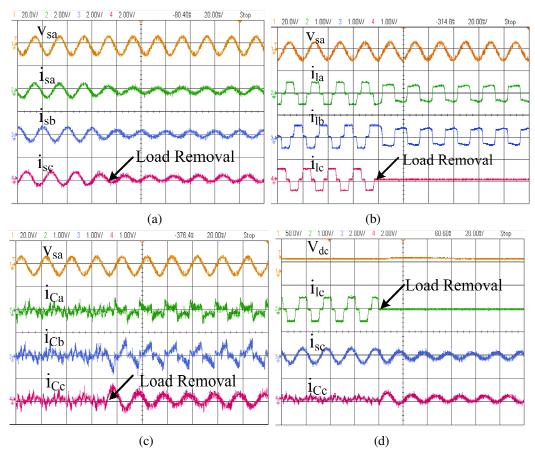

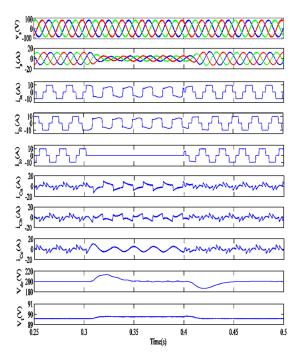

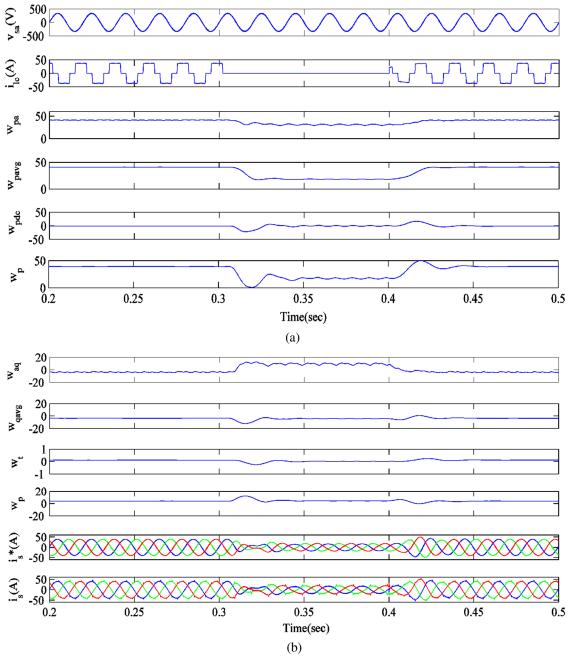

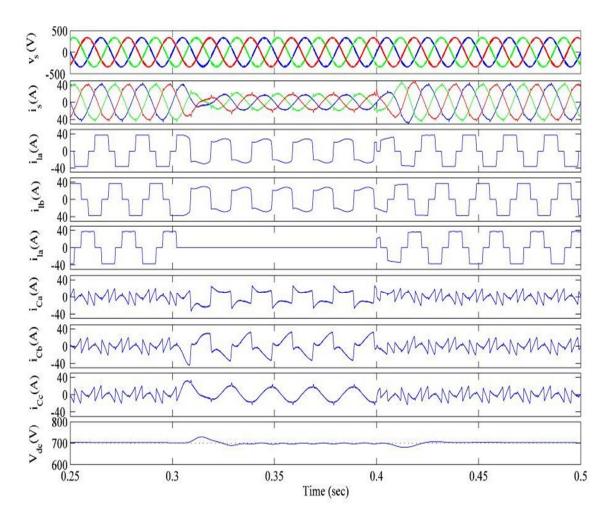

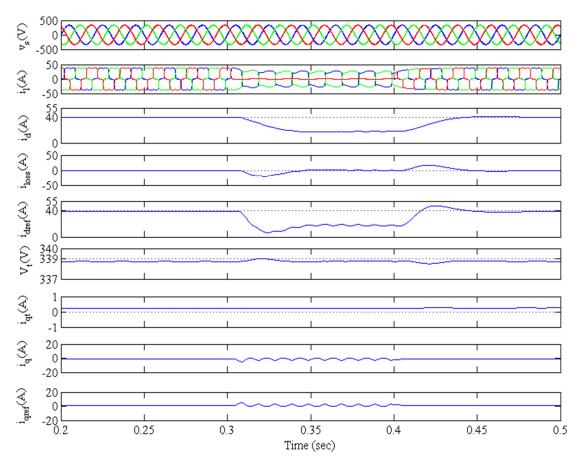

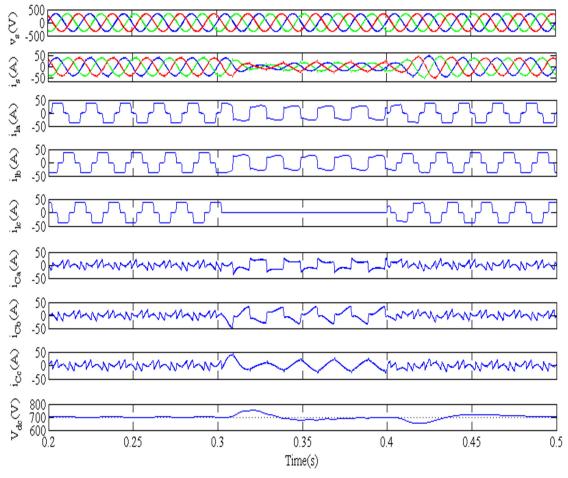

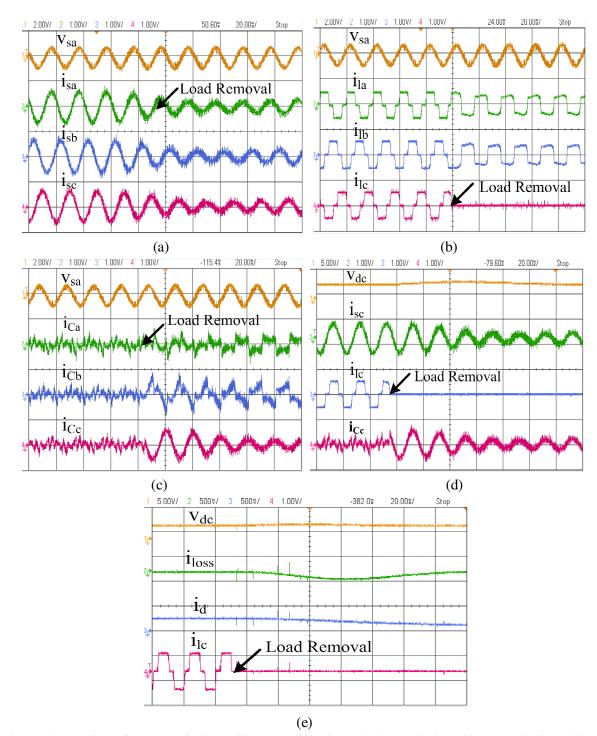

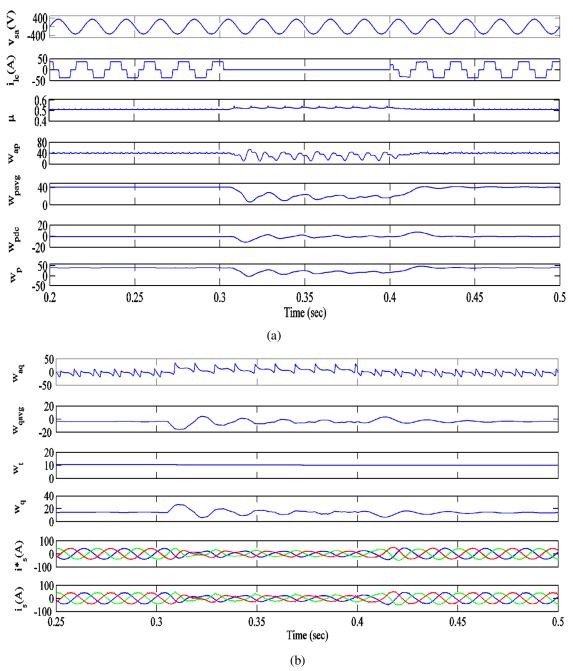

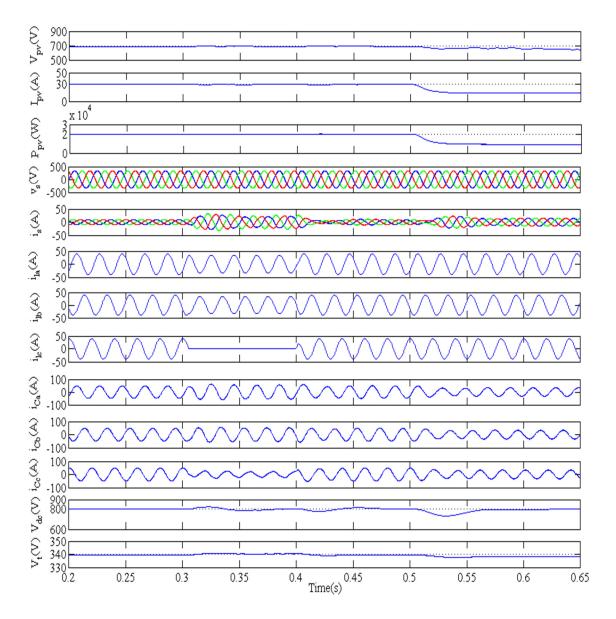

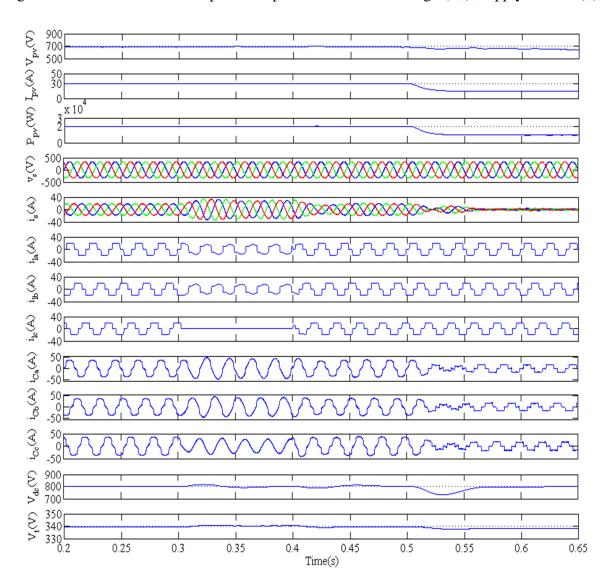

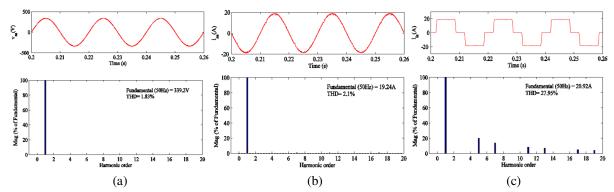

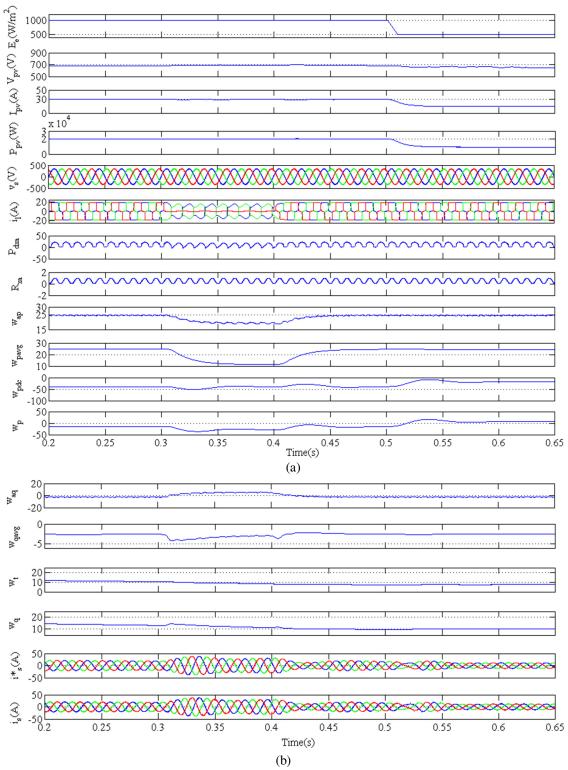

|        | 4.8.2.1 Simulated Performance of DSTATCOM in PFC and VR Modes                                                                                                                                    | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

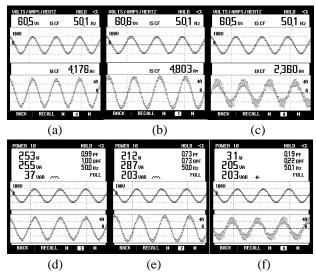

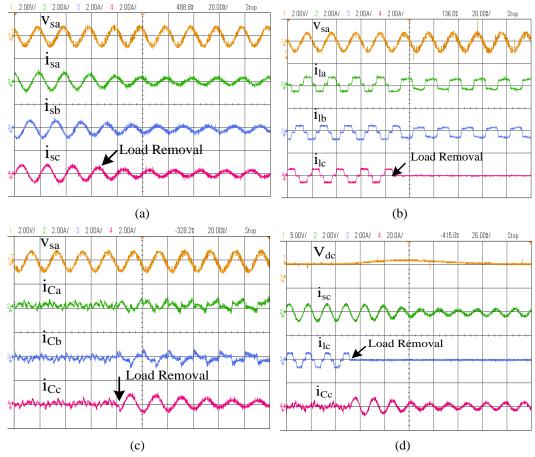

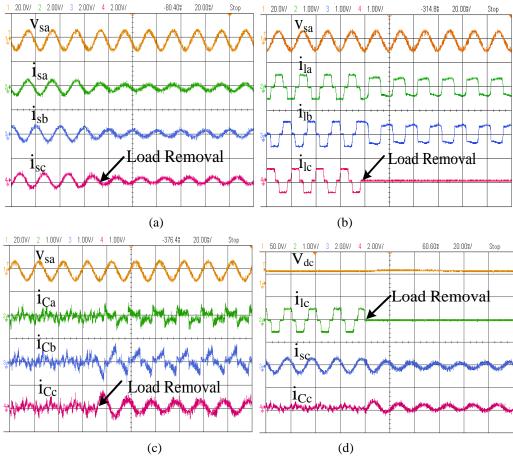

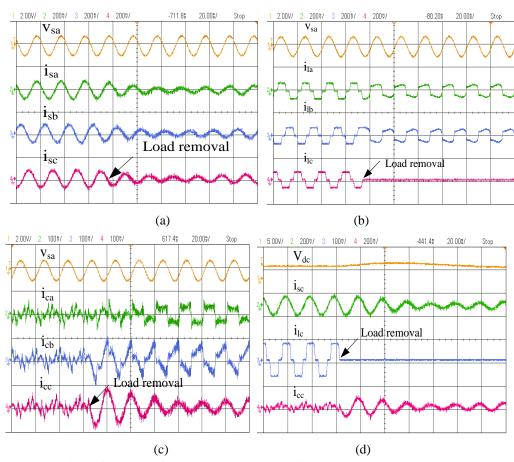

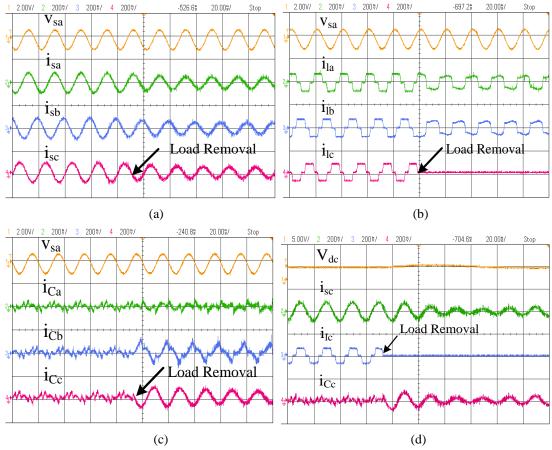

|        | 4.8.2.2 Experimental Performance of DSTATCOM in PFC Mode                                                                                                                                         | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

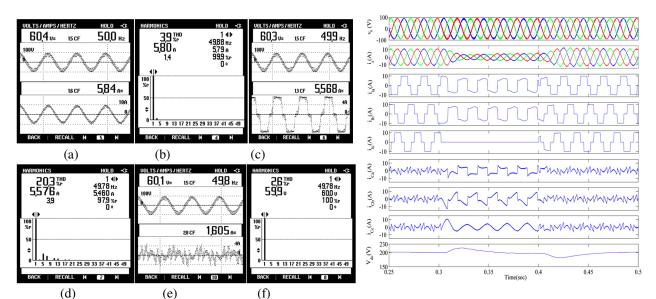

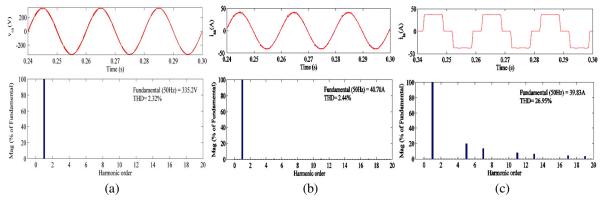

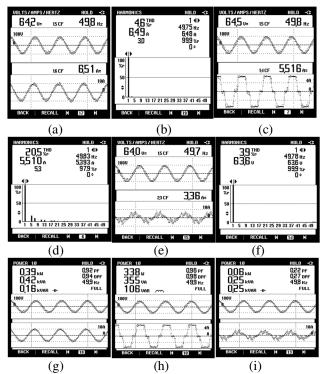

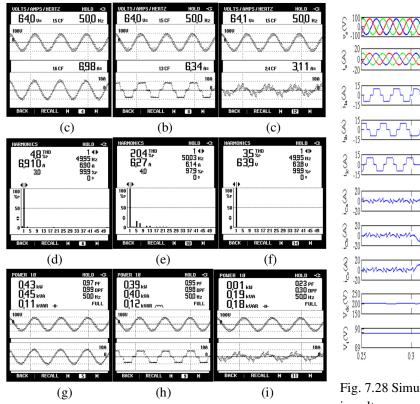

| 4.8.3  | Performance of DSTATCOM With Conductance Based Control Algorithm                                                                                                                                 | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|        | 4.5.3<br>4.5.4<br>MAT<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4<br>DSP I<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4<br>Result<br>4.8.1.<br>4.8.2                                                              | <ul> <li>4.5.2 Instantaneous Reactive Power Theory Based Control Algorithm</li> <li>4.5.2.1 Estimation of Reference Supply Currents</li> <li>4.5.2.2 Generation of Switching Pulses</li> <li>4.5.3 Conductance Based Control Algorithm</li> <li>4.5.3.1 Estimation of Fundamental Active Power Components of Reference Supply Currents</li> <li>4.5.3.2 Estimation of Fundamental Reactive Power Components of Reference Supply Currents</li> <li>4.5.3.3 Generation of Reference Supply Currents and Switching Pulses</li> <li>4.5.4 Symmetrical Component Theory Based Control Algorithm</li> <li>4.5.4.1 Estimation of Reference Supply Currents</li> <li>4.5.4.2 Generation of Reference Supply Currents</li> <li>4.5.4.2 Generation of Switching Pulses</li> </ul> MATLAB Based Modeling of Conventional Control Algorithms 4.6.1 Power Balance Theory Based Control Algorithm 4.6.2 Instantaneous Reactive Power Theory Based Control Algorithm 4.6.3 Conductance Based Fryze Algorithm 4.6.4 Instantaneous Symmetrical Component Theory Based Control Algorithm DSP Implementation of Conventional Control Algorithm 4.7.1 Power Balance Theory Based Control Algorithm 4.7.2 Instantaneous Reactive Power Theory Based Control Algorithm 4.7.3 Conductance Based Fryze Algorithm 4.7.4 Symmetrical Component Theory Based Control Algorithm 4.7.4 Symmetrical Component Theory Based Control Algorithm 4.8.1.1 Simulated Performance of DSTATCOM in PFC and VR Modes 4.8.2 Performance of DSTATCOM With Instantaneous Reactive Power Theory Based Control Algorithm 4.8.2.1 Simulated Performance of DSTATCOM in PFC and VR Modes 4.8.2.1 Simulated Performance of DSTATCOM in PFC and VR Modes 4.8.2.2 Experimental Performance of DSTATCOM in PFC Mode |  |  |

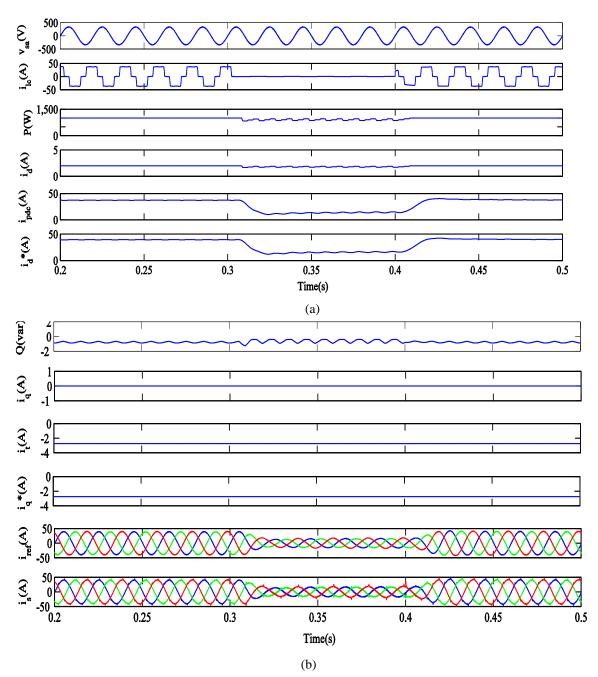

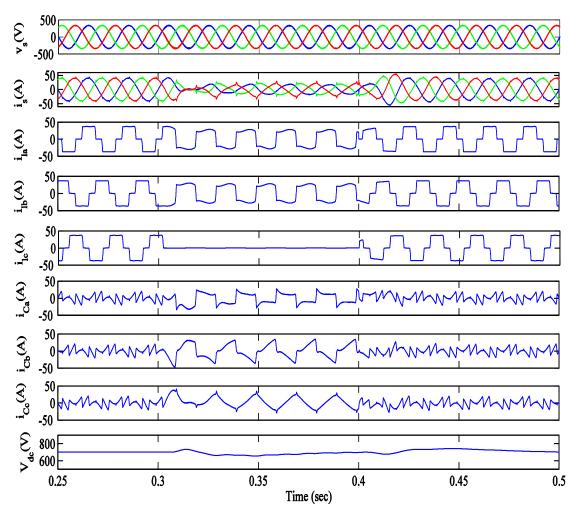

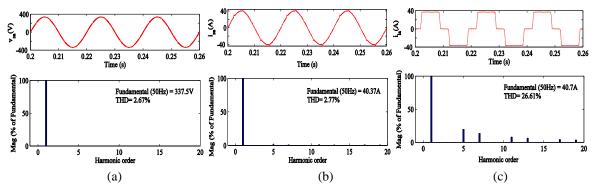

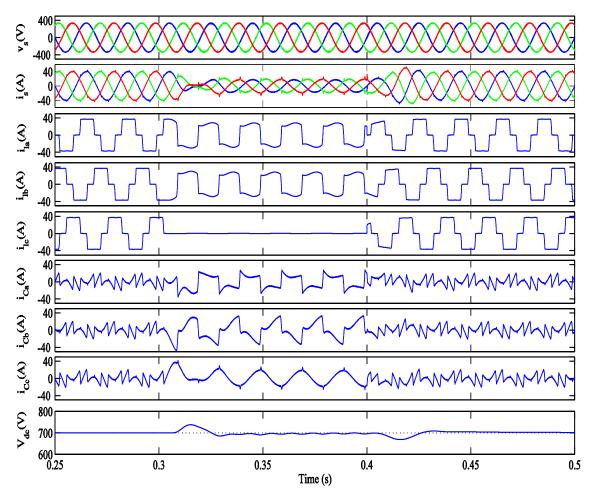

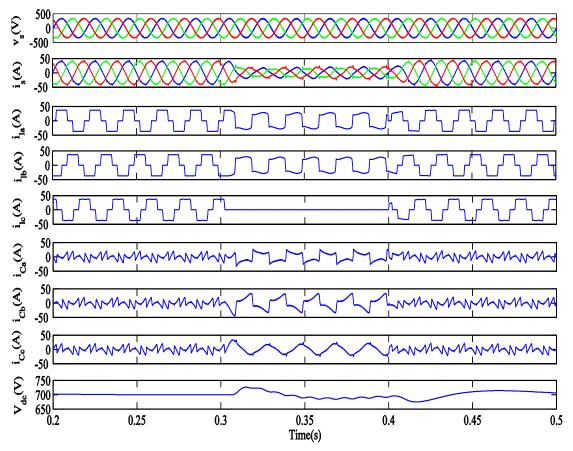

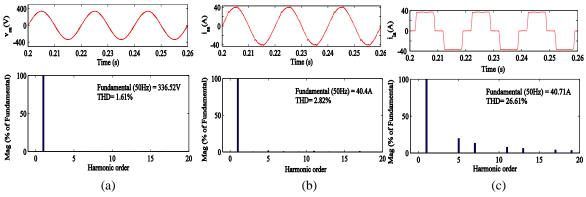

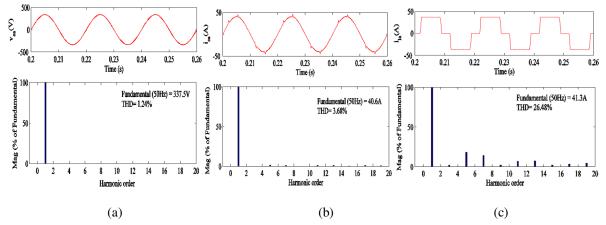

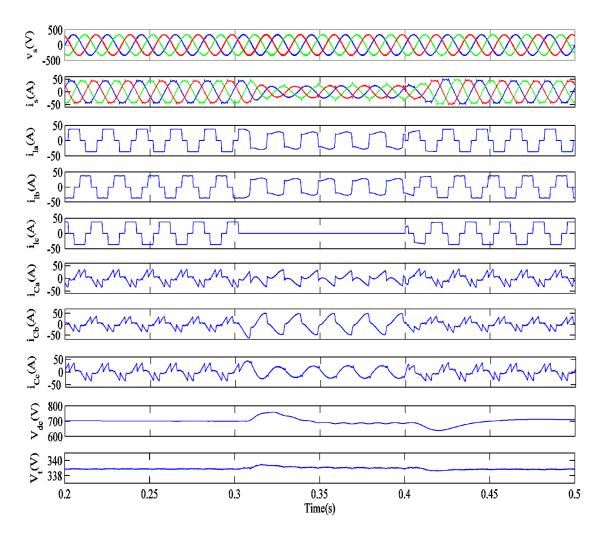

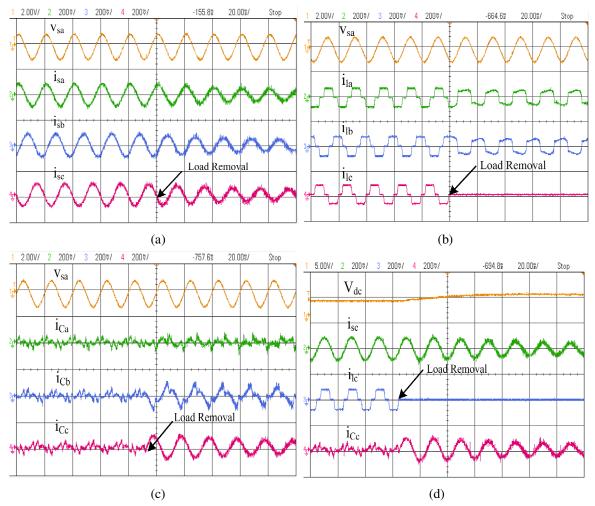

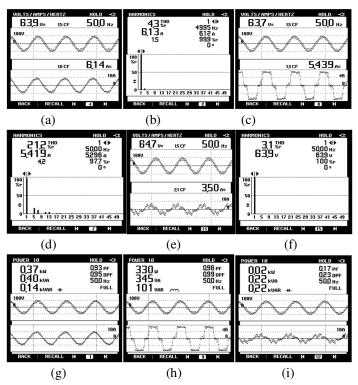

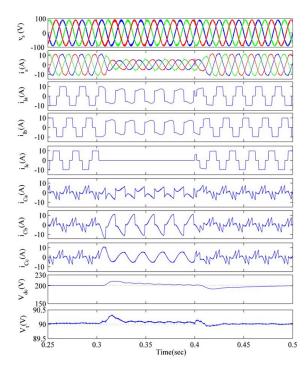

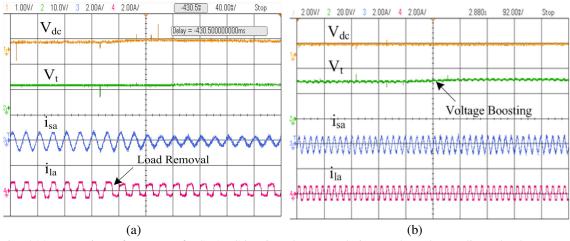

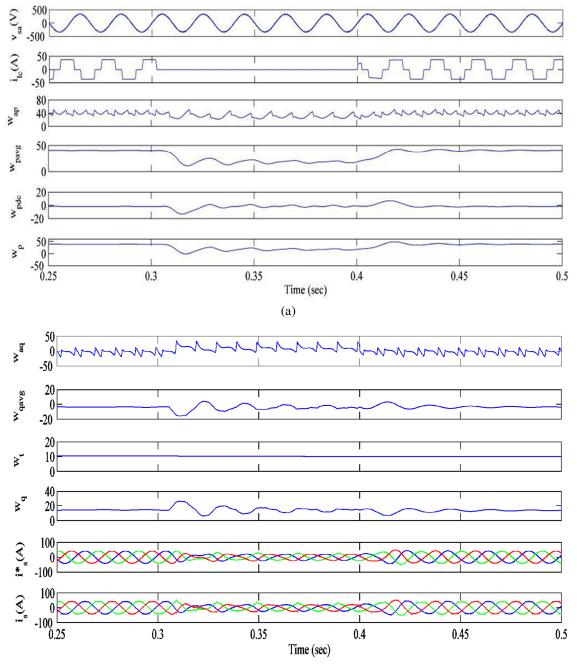

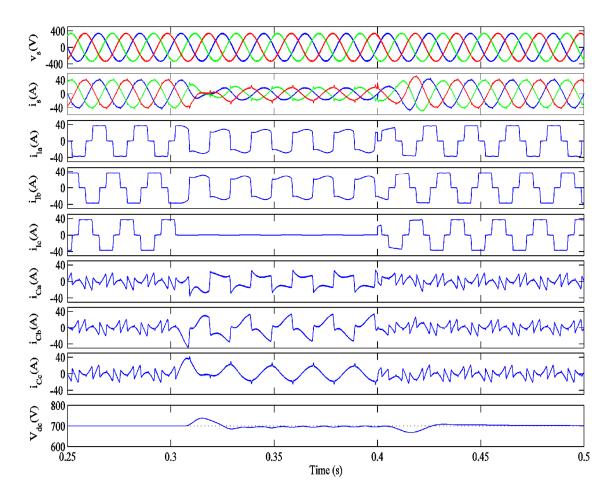

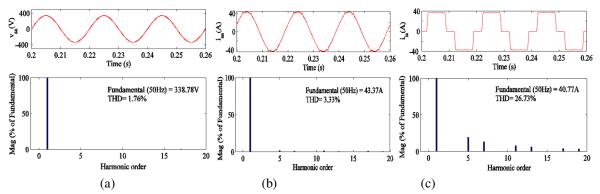

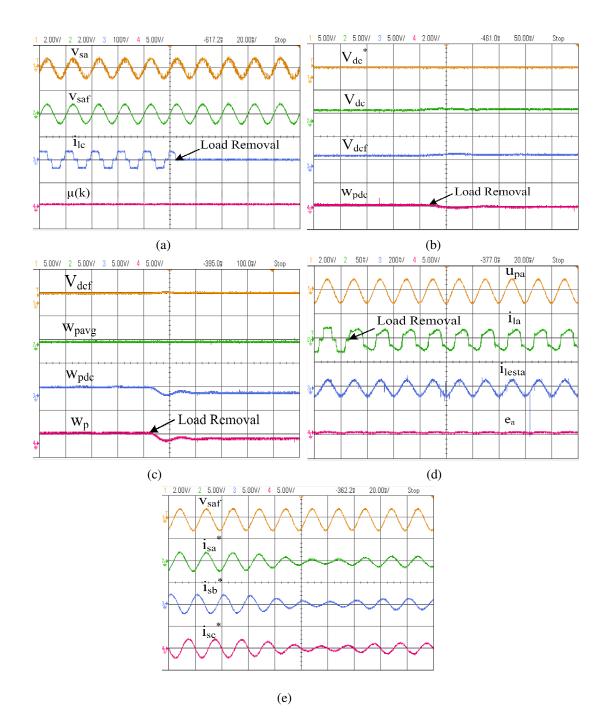

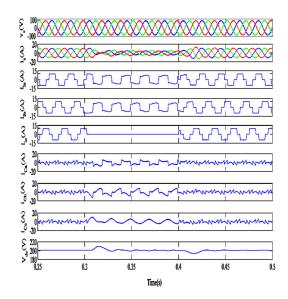

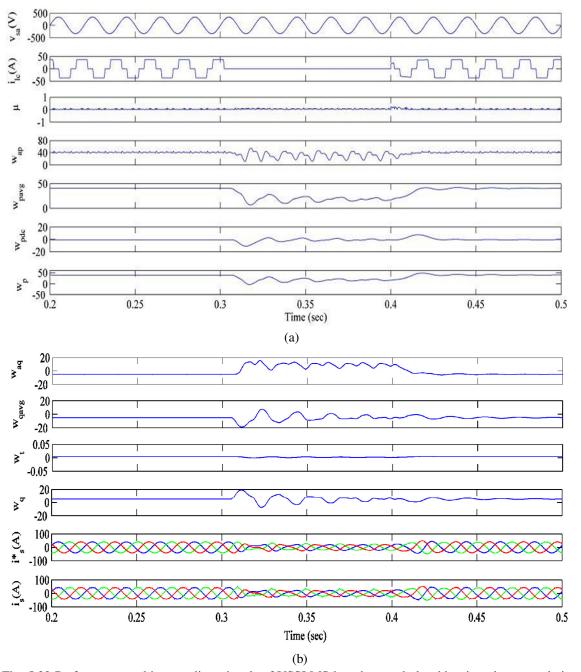

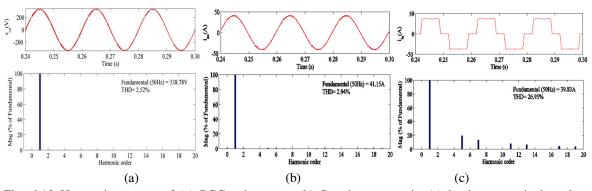

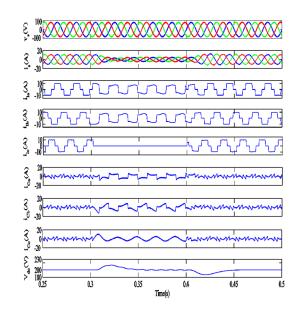

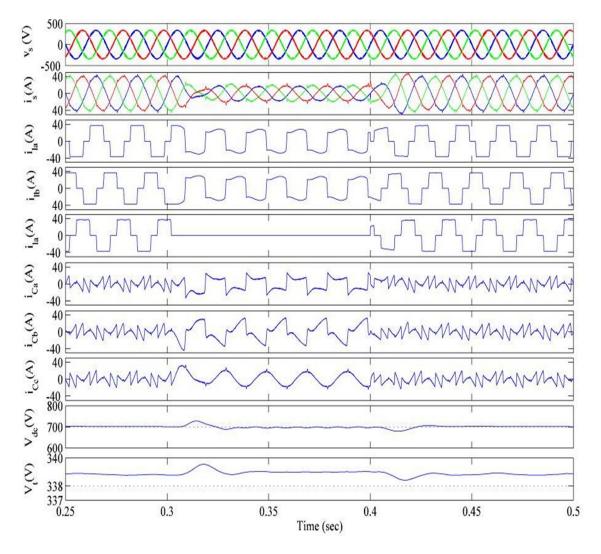

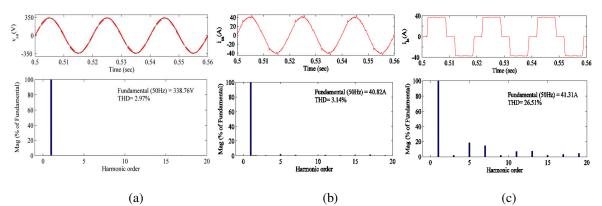

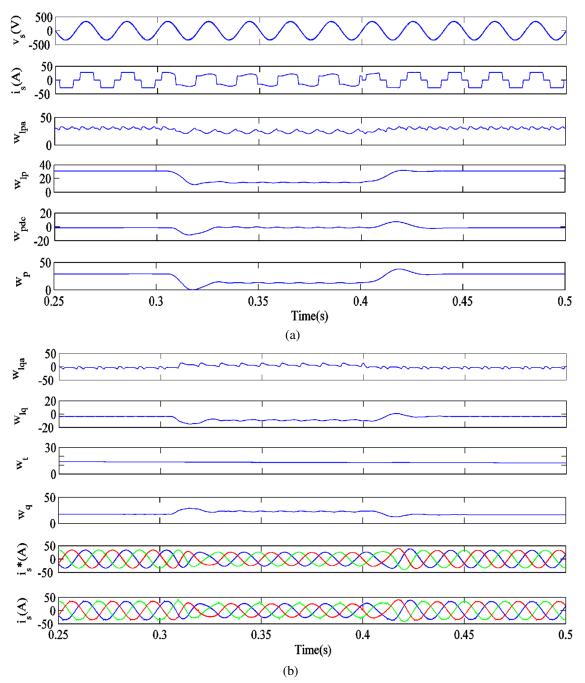

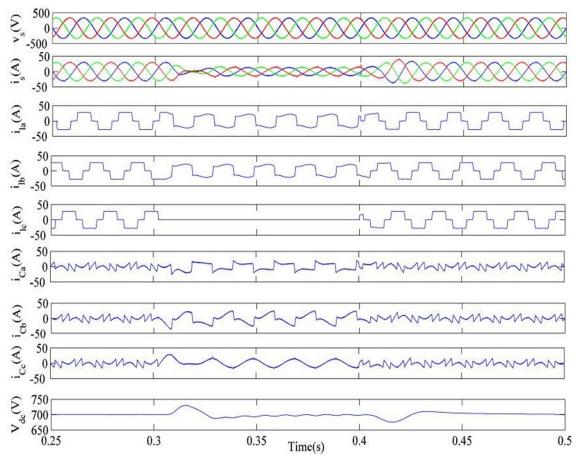

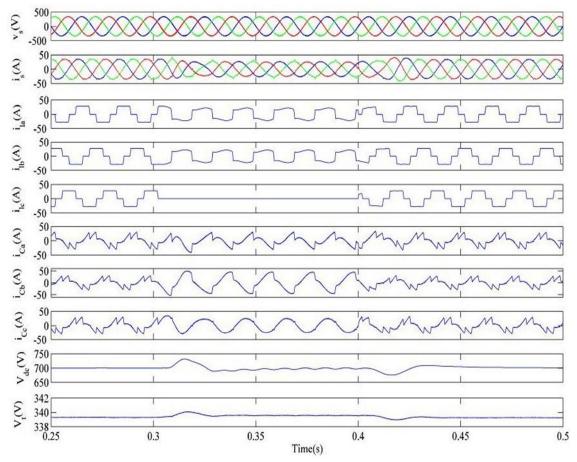

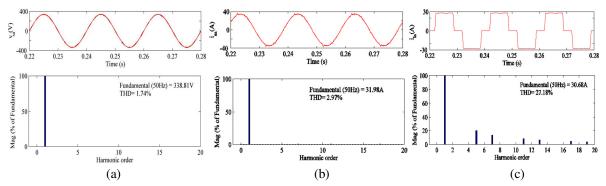

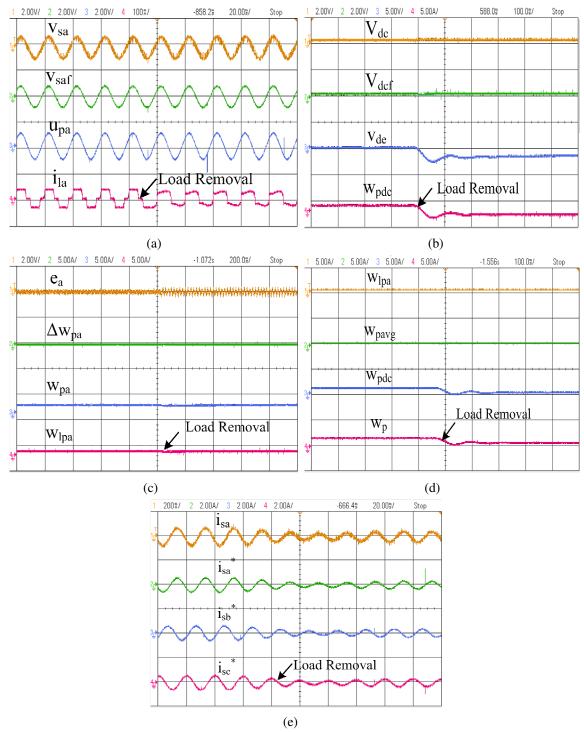

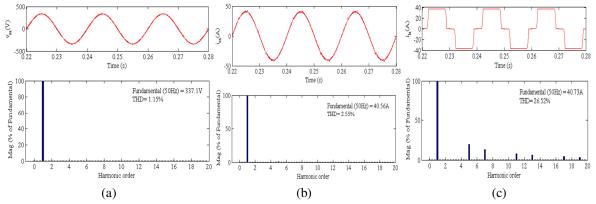

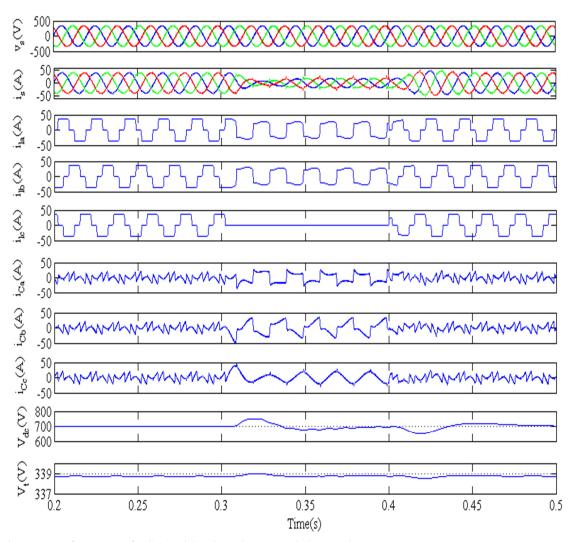

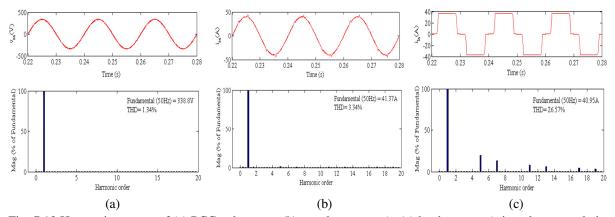

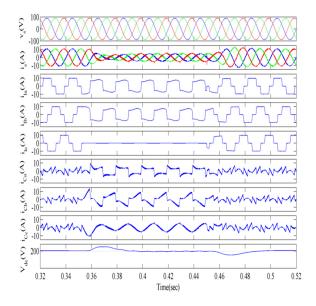

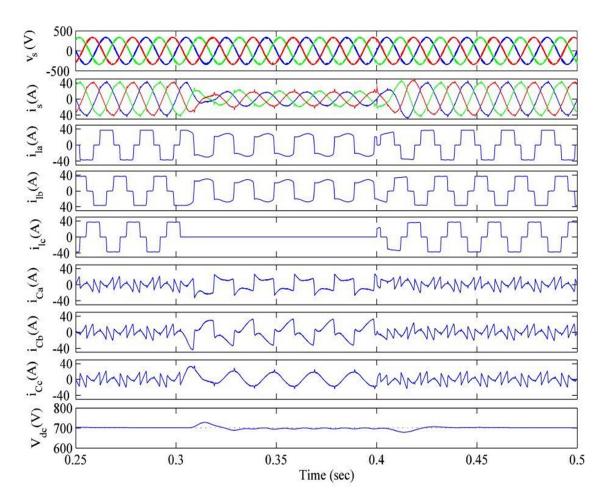

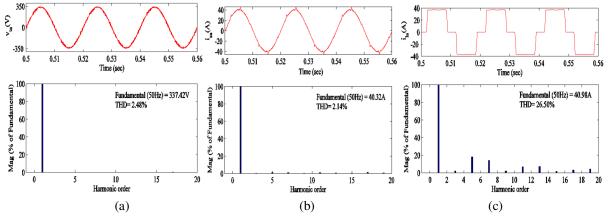

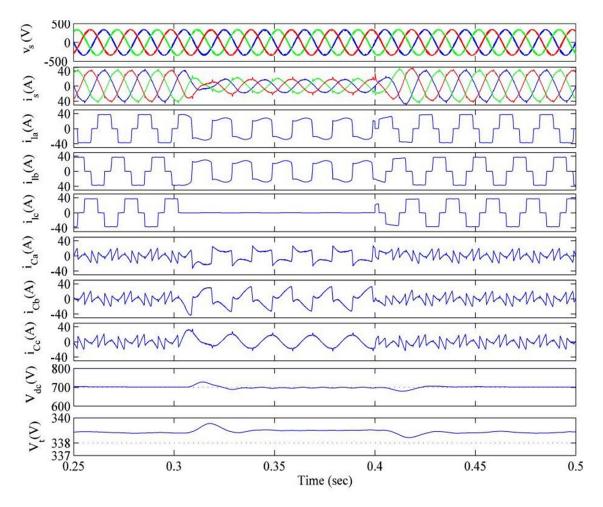

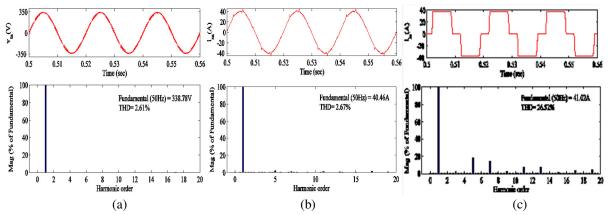

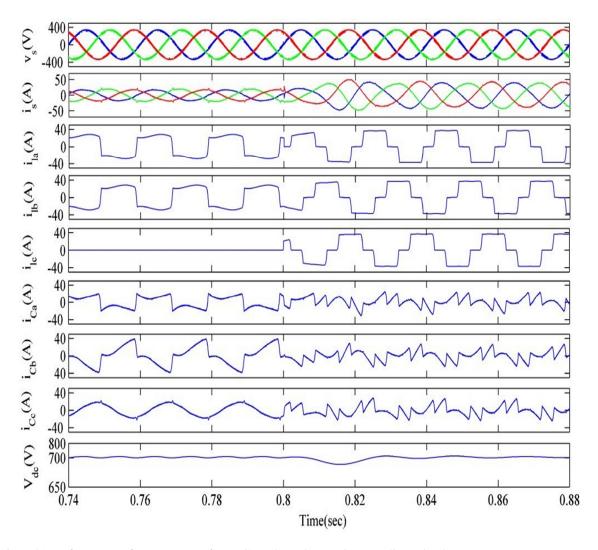

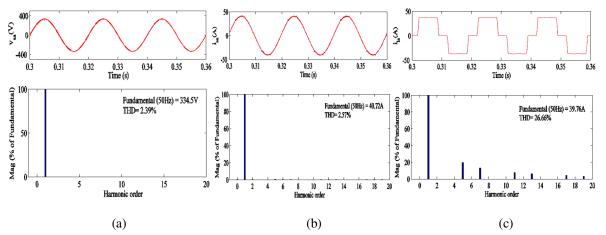

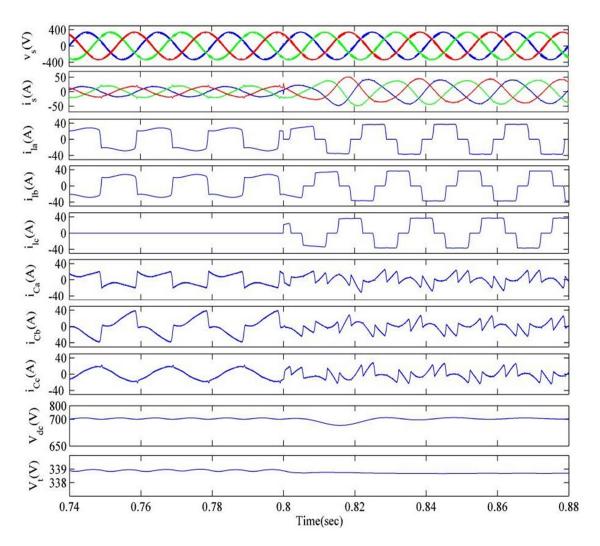

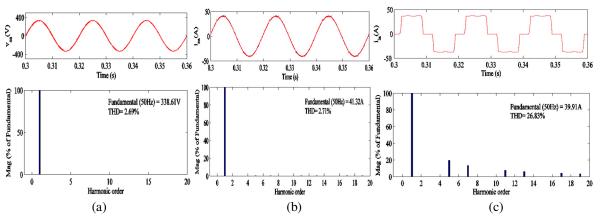

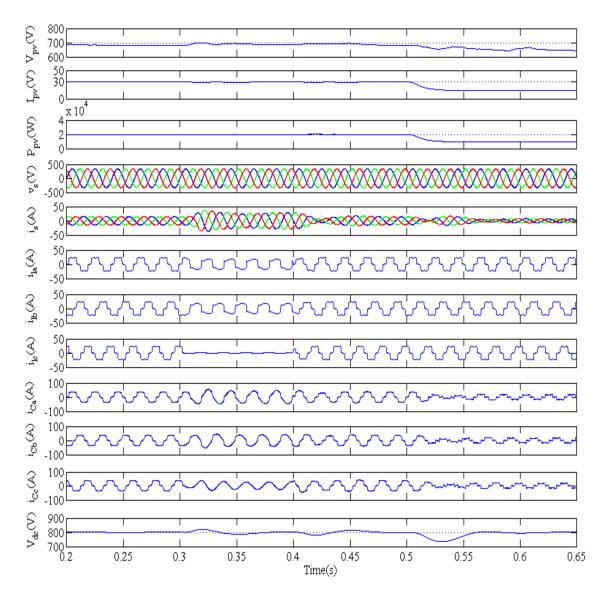

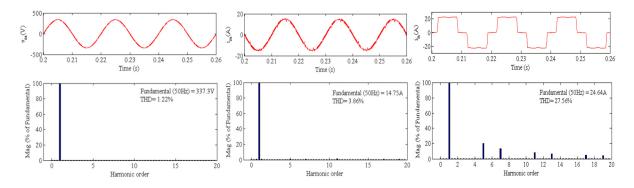

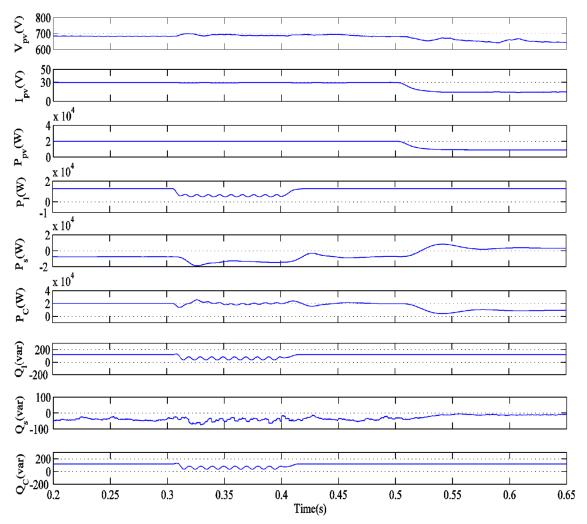

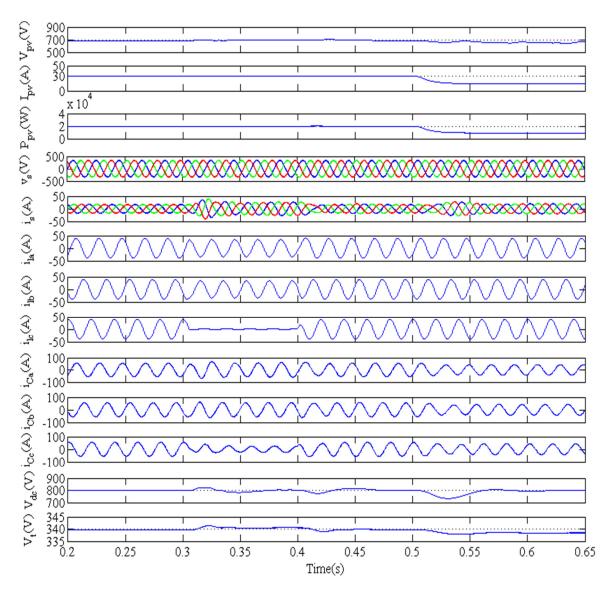

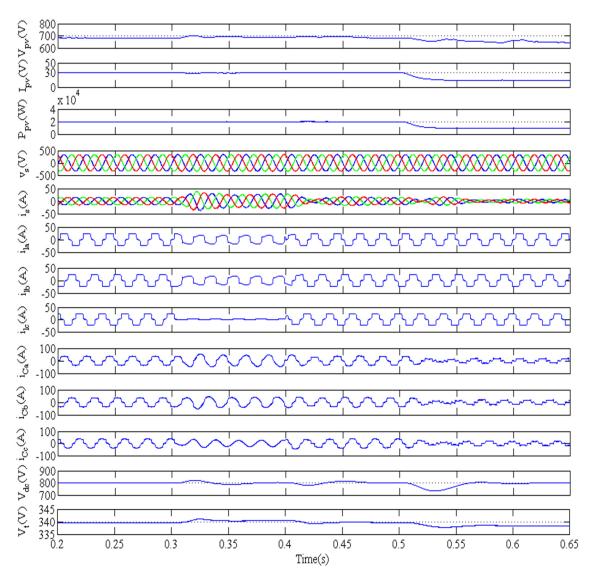

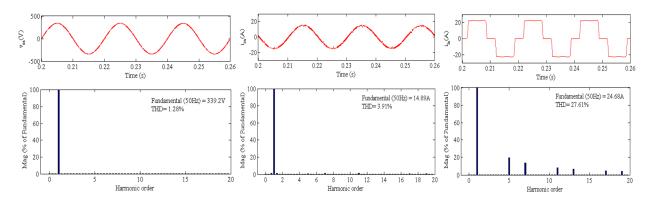

|     |                                                                               | 4.8.3.1            | Simulated Performance of DSTATCOM in PFC and VR Modes                                                                                                 | 99         |  |  |

|-----|-------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

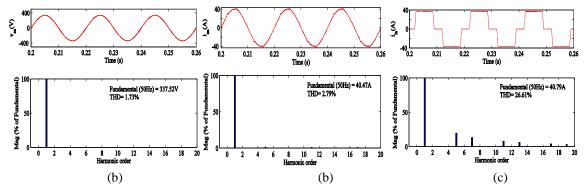

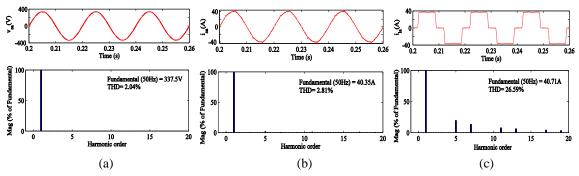

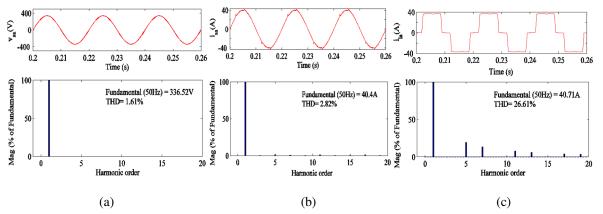

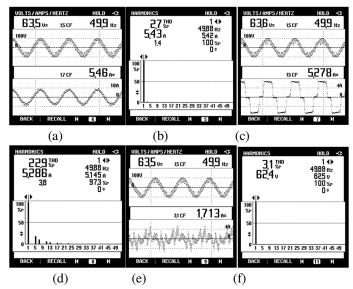

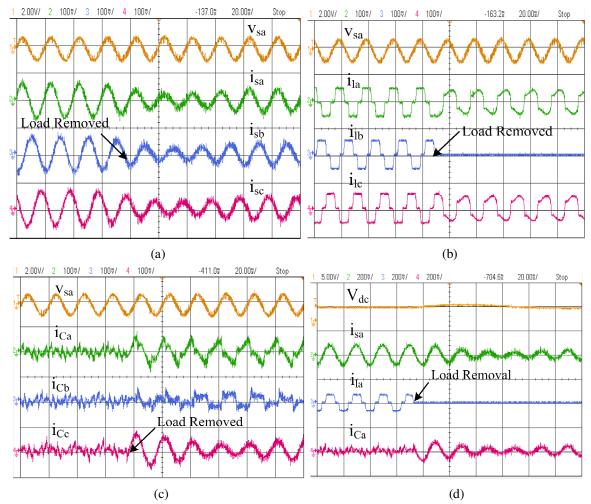

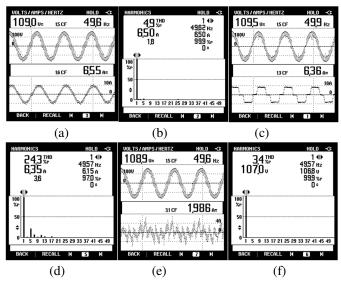

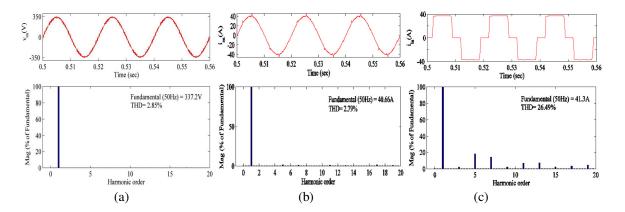

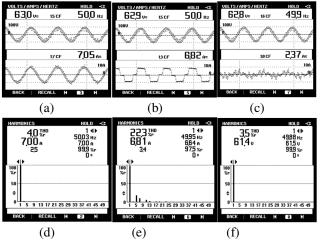

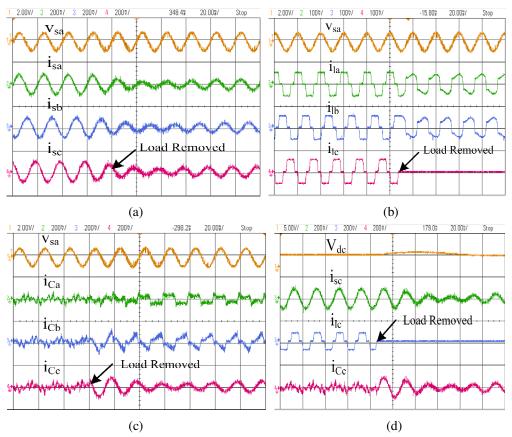

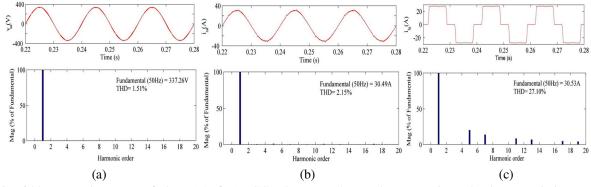

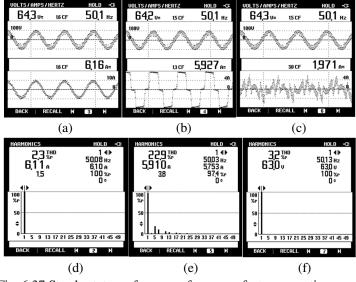

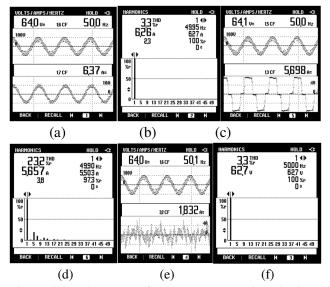

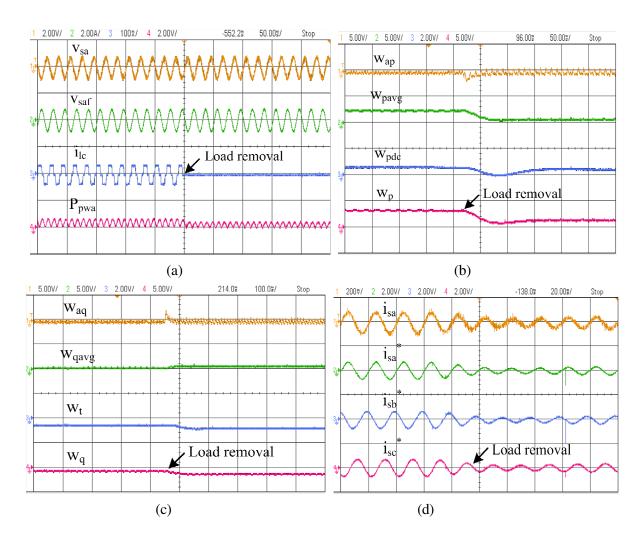

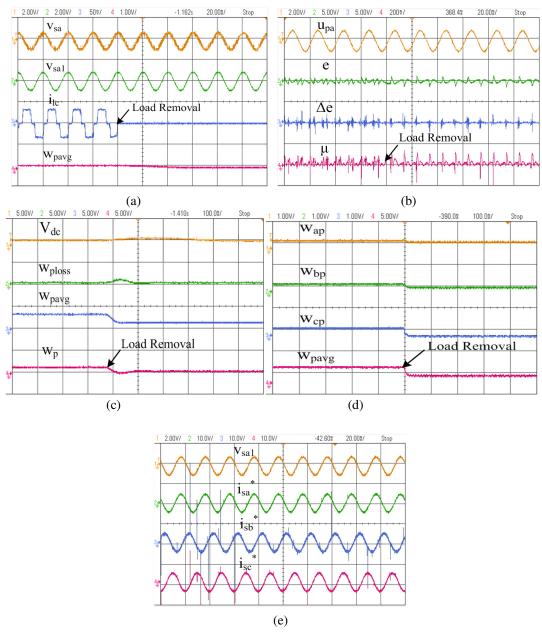

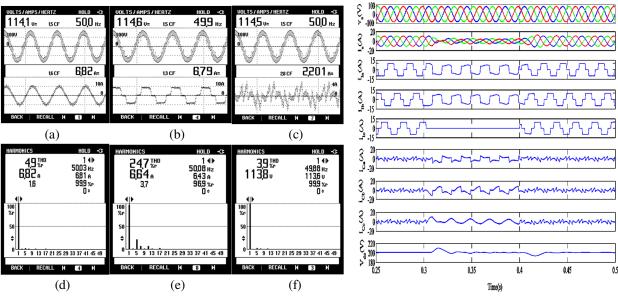

|     |                                                                               | 4.8.3.2            | Experimental Performance of DSTATCOM in PFC Mode                                                                                                      | 103        |  |  |

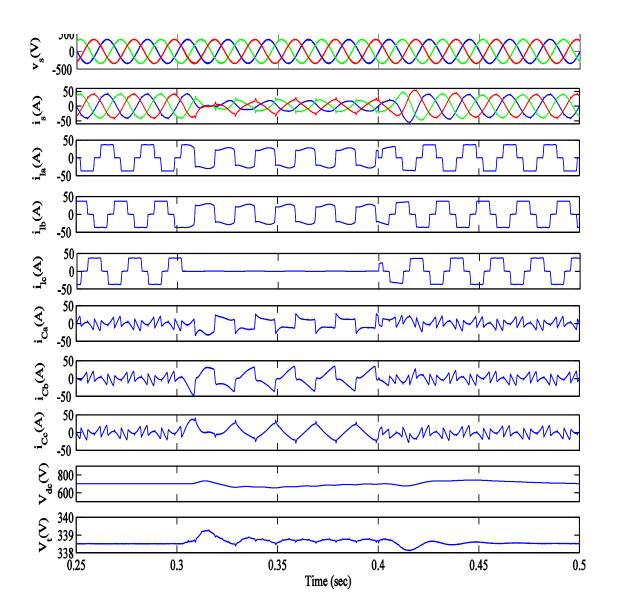

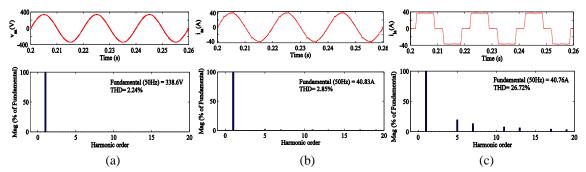

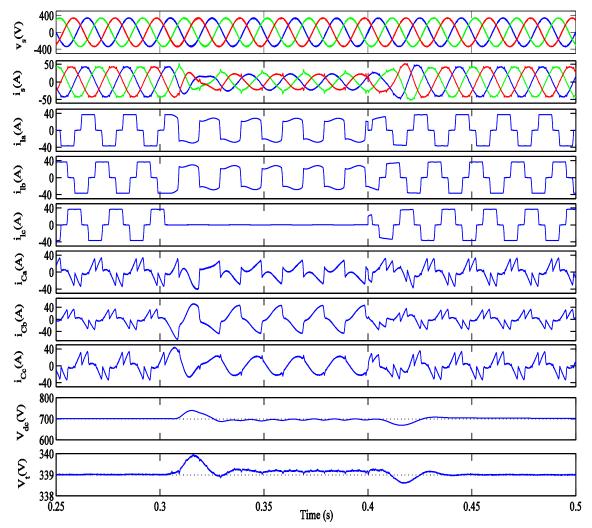

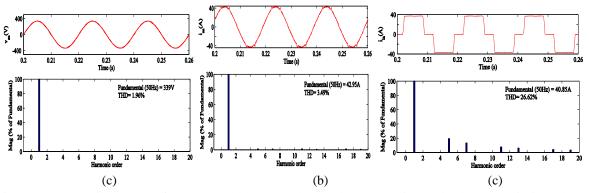

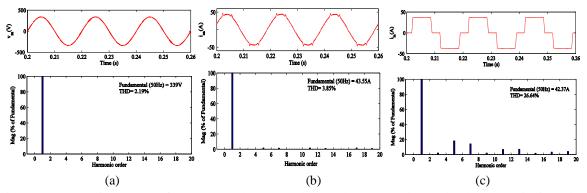

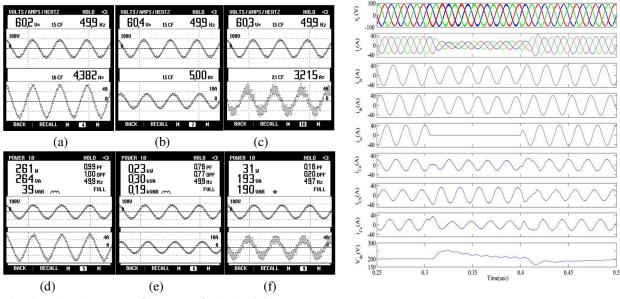

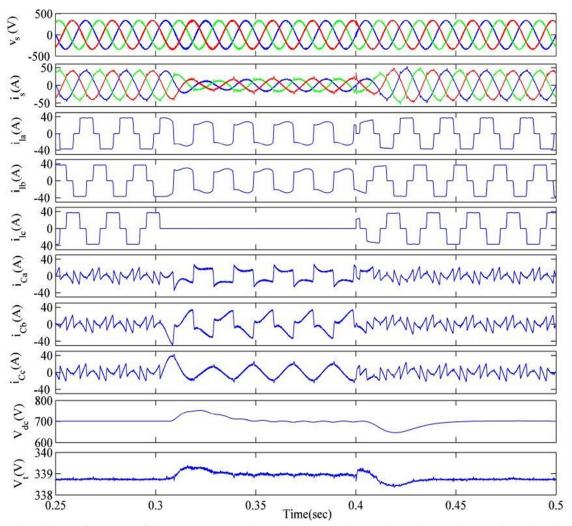

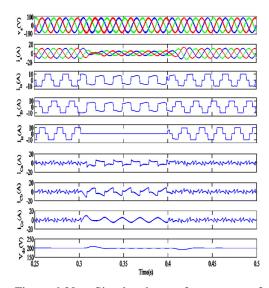

|     | 4.8.4                                                                         | Performa           | nce of DSTATCOM With Symmetrical Component Theory Based                                                                                               |            |  |  |