# DESIGN OF LOW POWER HIGH GAIN LNA USING MICROSTRIP LINES FOR WIRELESS APPLICATIONS

A Thesis submitted towards the partial fulfilment of the requirement for the award of the degree of

**Master of Technology**

in

**Microwave and Optical Communication**

Submitted by

Pappu Kumar Verma 2K12/MOC/12

Under the supervised of

Dr. Priyanka Jain Assistant Professor

Department of Electronics & Communication Engineering

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING AND APPLIED PHYSICS

DELHI TECHNOLOGICAL UNIVERSITY

(FORMERLY DELHI COLLEGE OF ENGINEERING)

DELHI-110042

JULY 2014

### **DELHI TECHNOLOGICAL UNIVERSITY**

Established by Govt. Of Delhi vide Act 6 of 2009

(Formerly Delhi College of Engineering)

SHAHBAD DAULATPUR, BAWANA ROAD, DELHI- 110042

### **CERTIFICATE**

This is to certify that the thesis report entitled, "Design of Low Power High Gain LNA Using Microstrip Lines for Wireless Applications" being submitted by Pappu Kumar Verma to the Department of Electronics and Communication Engineering and Applied Physics, Delhi Technological University, Delhi in partial fulfilment of the requirement for award of Master of Technology degree in Microwave and Optical Communication is a record of bona fide work carried out by him under the supervision and guidance of Dr. Priyanka Jain. The matter embodied in this report has not been submitted for the award of any other degree.

Dr. Priyanka Jain

Supervisor

**Assistant Professor**

Department of ECE

Delhi Technological University

Prof. Rajiv Kapoor

Head of Department

Department of ECE

Delhi Technological University

**DECLARATION**

I hereby declare that all the information in this document has been obtained and presented in

accordance with academic rules and ethical conduct. This report is my own, unaided work. I have

fully cited and referenced all material and results that are not original to this work. It is being

submitted for the degree of Master of Technology in Engineering at the Delhi Technological

University. It has not been submitted before for any degree or examination in any other university.

Signature

Name : Pappu Kuamr Verma

iii

### **ABSTRACT**

With the rapid development of the communication industry, more and more kinds of wireless communication apparatus are needed, such as small a low noise figure, low input/output return losses, a high IIP3, low power have been the main target of the businessman and the manufacturer of the wireless communication. In this condition, swift developmental radio frequency (RF) wireless communication technology has been widely used in all fields of the world. Low noise amplifier (LNA) which is in the RF front-end circuit has the great value in this field. LNAs are a crucial element of RF receivers. Their role is to amplify the RF signal to a level that meets the sensitivity requirements of the other components (e.g. Filter). In order to achieve the required gain it is essential to make sure that the reflection coefficients S11 and S22 are minimized. In addition, LNAs are usually the bottleneck in terms of Noise Figure and distortion.

Advanced Design System (ADS) tool was used for design and simulation, and each design was tuned to get the optimum value for noise figure, gain and input reflection coefficient. LNA standalone gives acceptable value of noise figure and gain but the bandwidth was too narrow compared to specification. The gain was almost flat over the whole band, i.e., 2.4-2.5 GHz compared to Low-Noise Amplifier designed

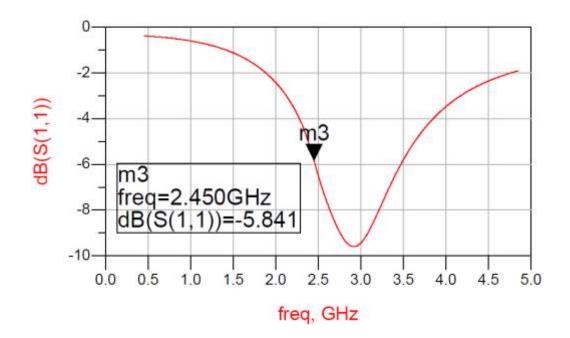

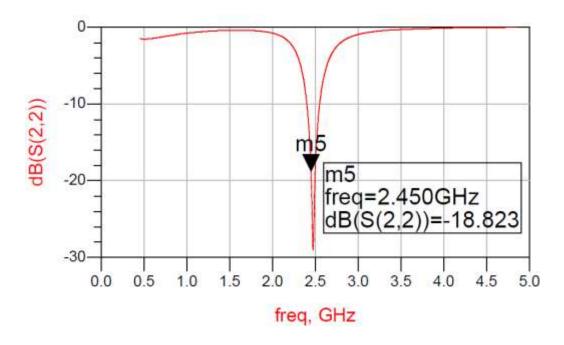

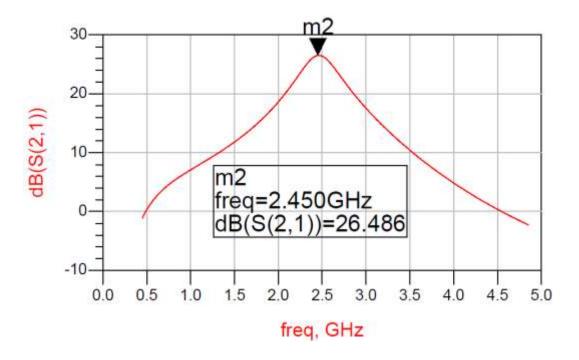

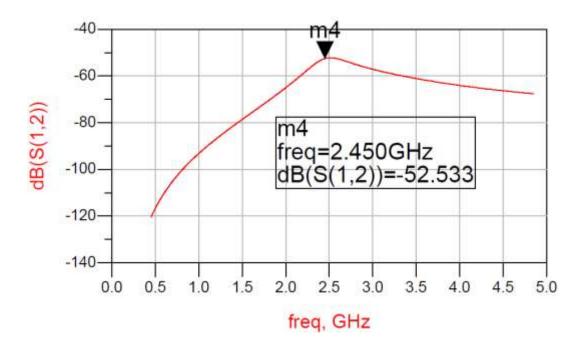

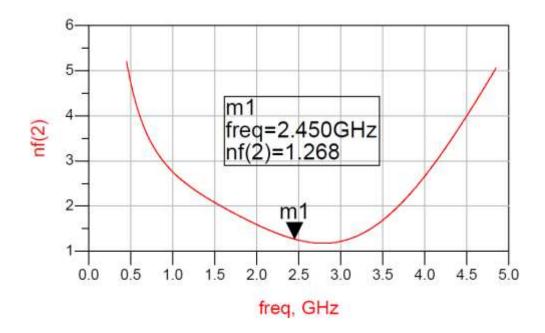

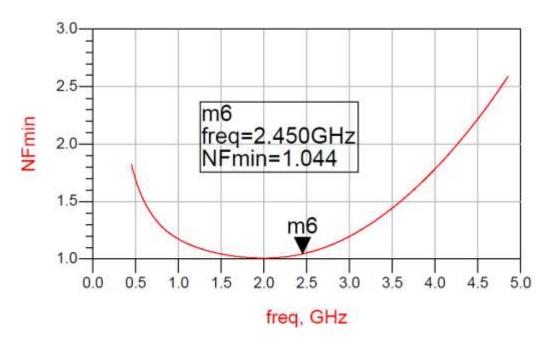

In this project report work, a new approach of design and performance analysis of A Low Power High Gain LNA for Wireless Applications is performed at 2.45 GHz. Performances of different designs are compared with respect to noise figure, gain, input and output reflection coefficient. In this design process, a single stage LNA using C-S LNA with a simple C-S stage added to the 'cascode' is design with CMOS Technology. After the simulation we got the simulated result of low noise amplifier as forward voltage gain (S<sub>21</sub>) of 26.486 dB, noise figure is 1.268 dB, input reflection coefficient (S<sub>11</sub>) is -5.841 dB, output reflection coefficient (S<sub>22</sub>) is -52.533 dB and S<sub>12</sub> is -18.823 dB. Power consumed by the design is 4.49 m W with supply voltage 1.2 V.

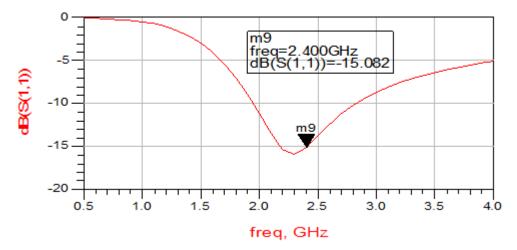

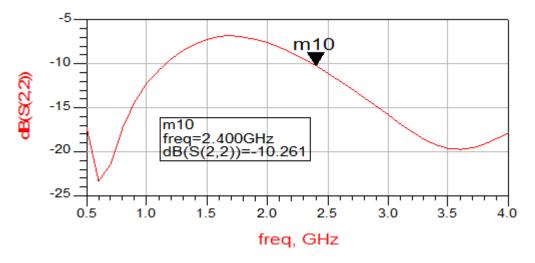

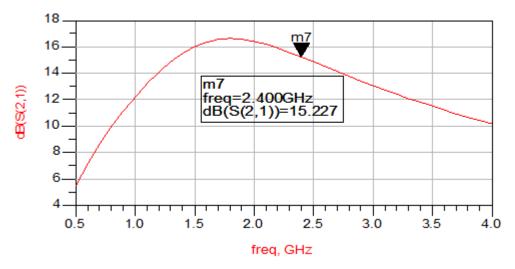

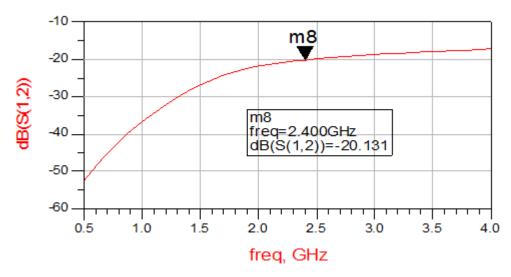

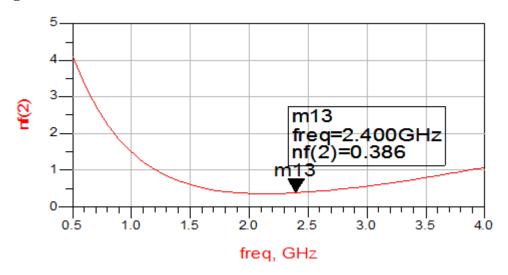

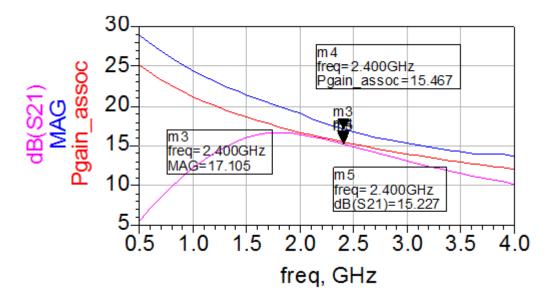

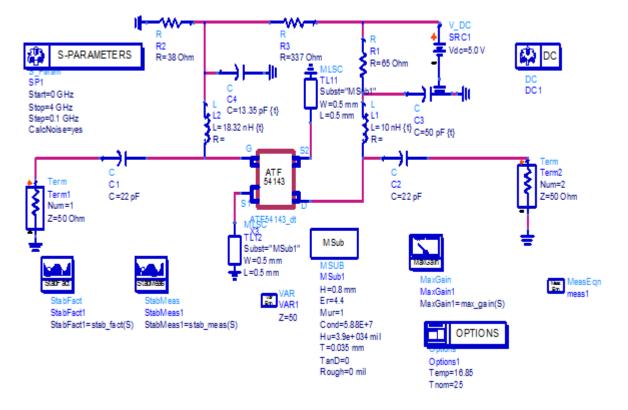

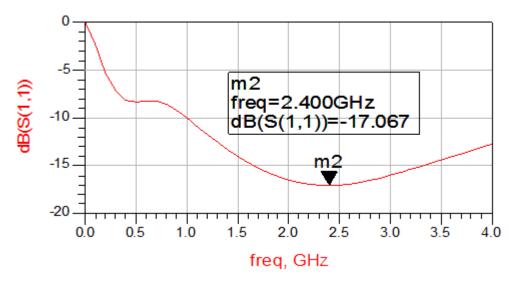

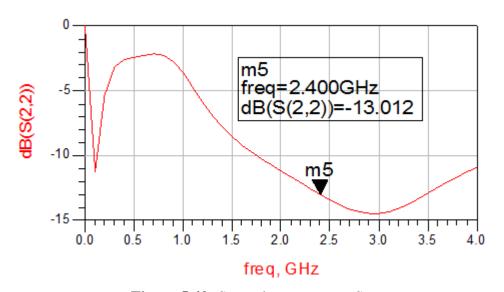

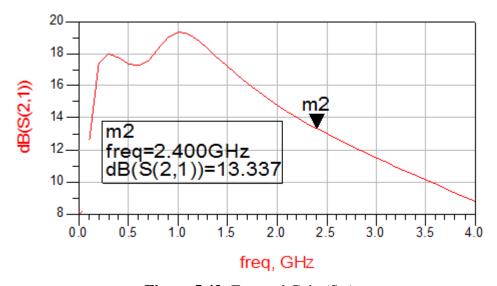

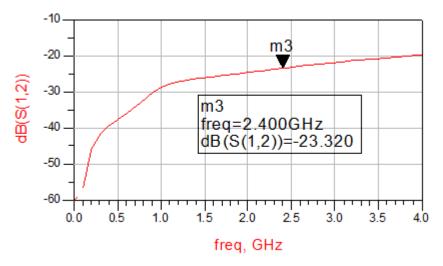

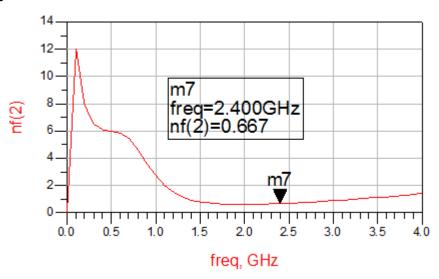

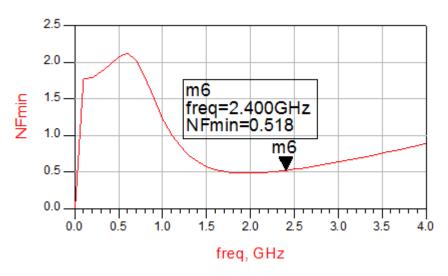

LNA designed using HEMT (using microstrip lines) at 2.4 GHz operating frequency, simulated by ADS designed by Agilent Technologies. After the simulation it has achieved the gain 13.33 dB, noise figure 0.667dB, minimum noise figure 0.518 dB, input reflection coefficient -17.06 dB, output reflection coefficient -13.02 dB, reverse isolation coefficient -23.32 dB, stability is greater than 1 with supply voltage 5 V using microstrip lines.

**ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my project supervisor, Asst. Professor Dr. Priyanka

Jain, for her supervision, invaluable guidance, motivation and support throughout the extent of the

project. I have benefitted immensely from her wealth of knowledge.

I would also like to thank Dr. Ajeet Kumar (Department of Applied Physics), Prof. R. K. Sinha

(Department of Applied Physics) and Dr. J. Panda (Department of ECE) for their precious

suggestions, support and technical help during the course of this project.

I am indebted to Prof. Rajiv Kapoor, Head of Department of Electronics and Communication

Engineering, Delhi Technological University, for his support and encouragement in carrying out

this project.

I wish to express my heart full thanks to Prof. S.C. Sharma, Head of Department of Applied

Physics, Delhi Technological University for his support that helped me a lot in successful

completion of this project.

I am also grateful to **Prof. P. B. Sharma**, Vice-Chancellor, Delhi Technological University for

providing the research environment in the institute.

My gratitude is extended to my colleagues and friends who have not been mentioned here

personally in making this project a success.

Last but not least, I take this opportunity to express my deepest thanks to my parents and my sister.

Without their support, love and encouragement, it would not have been possible to pursue M.Tech.

degree studies. I sincerely thank them.

Pappu Kumar Verma M.TECH. (MOC)

2K12/MOC/12

٧

# TABLE OF CONTENTS

| CERT | ΓIFICA | TE              |                                                   | ii   |

|------|--------|-----------------|---------------------------------------------------|------|

|      |        |                 |                                                   |      |

|      |        |                 |                                                   |      |

| ACK  | NOWL   | EDGEM           | MENTS                                             | v    |

| CON' | TENTS  | S               |                                                   | vi   |

| LIST | OF FIG | GURES           |                                                   | ix   |

| LIST | OF TA  | BLES .          |                                                   | xii  |

| LIST | OF SY  | MBOLS           | S                                                 | xiii |

| LIST | OF AF  | BREVI           | ATIONS                                            | xiv  |

|      |        |                 |                                                   |      |

| CHA  | PTER   | S               |                                                   |      |

| I.   | INT    | RODUC           | TION                                              | 1    |

|      |        |                 | 7                                                 |      |

|      |        |                 | low chart                                         |      |

|      |        | _               | on and Problem Statement                          |      |

|      |        |                 | ope of present work                               |      |

|      |        |                 | ructure                                           |      |

| II.  | LITI   | E <b>RATI</b> I | RE REVIEW                                         | 6    |

| 11.  |        |                 | ion                                               |      |

|      |        |                 | Survey                                            |      |

|      | 2,2 L  | 2.2.1           | Application Based LNAs                            |      |

|      |        |                 | High Gain LNAs                                    |      |

|      |        |                 | Different Matching Techniques for LNAs            |      |

|      |        |                 | Low Noise Techniques for LNAs                     |      |

|      | 2.3 P  |                 | Definitions                                       |      |

|      |        |                 |                                                   |      |

| III. | BAS    | IC PAR          | AMETERS OF LNA DESIGN                             | 12   |

|      | 3.1    | Two I           | Port Network                                      | 12   |

|      |        | 3.1.1           | Scattering Parameters                             | 13   |

|      | 3.2    | Gain            | of Two Port Network                               | 15   |

|      |        | 3.2.1           | Maximum Power Transfer Theorem                    | 15   |

|      |        | 3.2.2           | Different Gain Expression                         | 16   |

|      | 3.3    | Stabil          | ity                                               | 19   |

|      | 3.4    | Noise           |                                                   | 19   |

|      |        | 3.4.1           | Noise in MOSFET                                   | 20   |

|      |        |                 | 3.4.1.1 Input Equivalent Noise Source             | 20   |

|      |        |                 | 3.4.1.2 Input Equivalent Noise Source for MOS     | 21   |

|      |        |                 | 3.4.1.3 Absolute Value of Equivalent Noise Source | 22   |

|      | 3.5    | Noise           | Figure                                            | 23   |

|      | 3.6    |                 | Optimization Methods                              |      |

|      |        | 3.6.1           | Fixed Gm Optimization                             | 27   |

|     |     | 3.6.2  | Fixed Pd Optimization                                  | 28 |

|-----|-----|--------|--------------------------------------------------------|----|

|     | 3.7 | Linear | rity                                                   | 28 |

|     | 3.8 | Centre | e Frequency and Bandwidth                              | 29 |

| IV. | DIF | FEREN  | Γ TOPOLOGIES FOR LNA DESIGN                            | 30 |

|     | 4.1 | Introd | luction                                                | 30 |

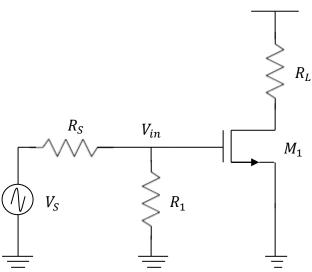

|     |     | 4.1.1  | Resistive Matching                                     | 31 |

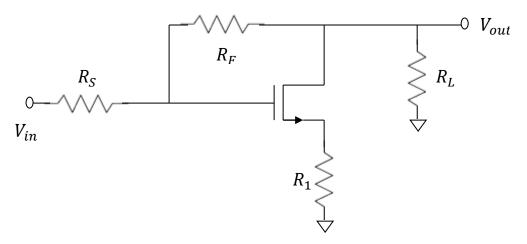

|     |     | 4.1.2  | Shunt- Series Feedback Amplifier                       |    |

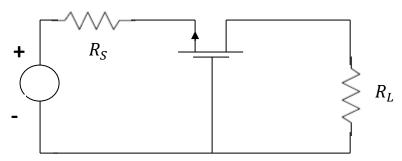

|     |     | 4.1.3  | Common Gate Amplifier                                  | 33 |

|     |     | 4.1.4  |                                                        |    |

|     |     | 4.1.5  | Cascode Inductive Source Degeneration                  |    |

| V.  | DES | IGN AN | ID SIMULATION                                          | 39 |

|     | 5.1 | Introd | luction                                                | 39 |

|     | 5.2 | Step o | of LNA Design                                          | 39 |

|     | 5.3 | Desig  | n Specifications                                       | 39 |

|     | 5.4 | Select | tion of Appropriate Components                         | 40 |

|     |     | 5.4.1  |                                                        |    |

|     |     | 5.4.2  | Inductor RF Models                                     | 41 |

|     |     | 5.4.3  | Capacitor RF Models                                    | 41 |

|     |     | 5.4.4  | Resistor RF Models                                     | 41 |

|     | 5.5 | LNA    | Design with Lumped Components Using MOS                | 42 |

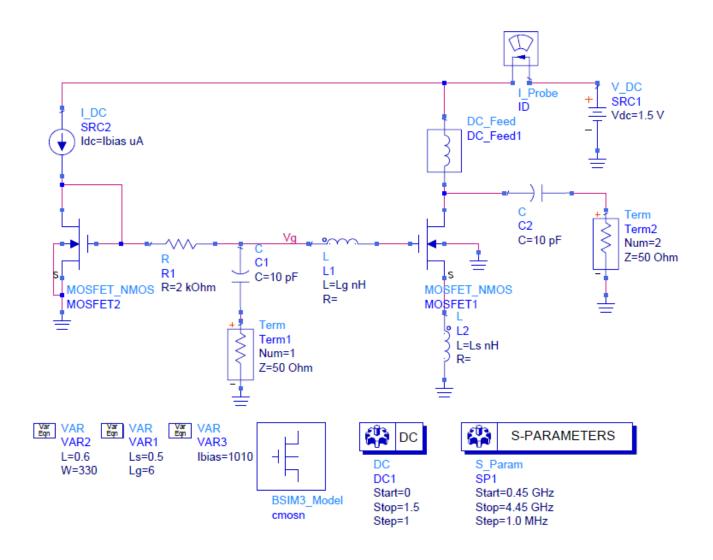

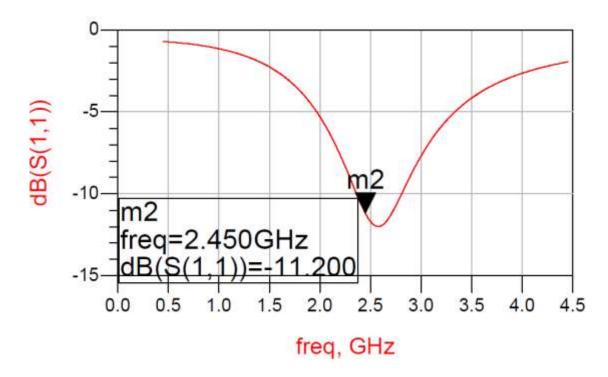

|     |     | 5.5.1  | Simulation of Basic LNA                                |    |

|     |     |        | 5.5.1.1 Simulation Results                             | 43 |

|     |     | 5.5.2  | Simulation of LNA with Additional Cascode Stage        | 47 |

|     |     |        | 5.5.2.1 Simulation Results                             | 48 |

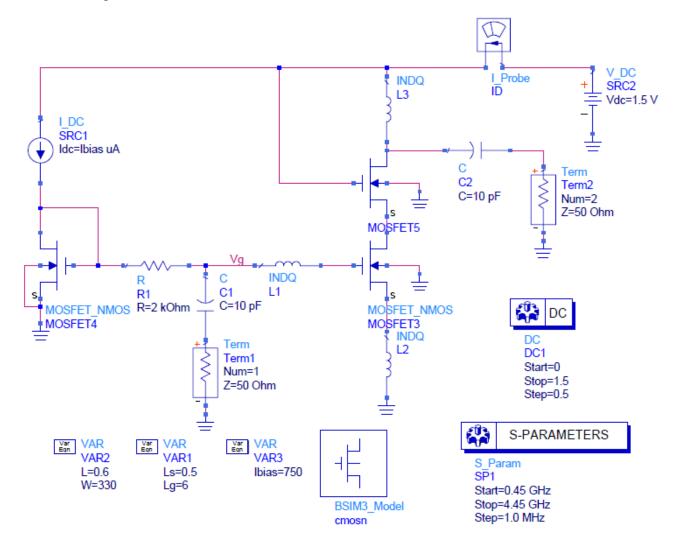

|     |     | 5.5.3  | Simulation of C-S LNA with a Simple C-S stage          | 51 |

|     |     |        | 5.5.3.1 Simulation Results                             | 52 |

|     |     | 5.5.4  | Results Obtained from Simulation                       | 55 |

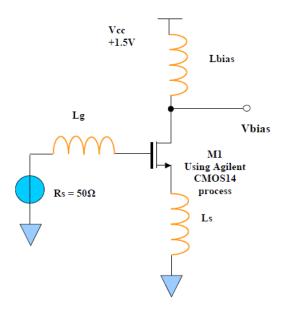

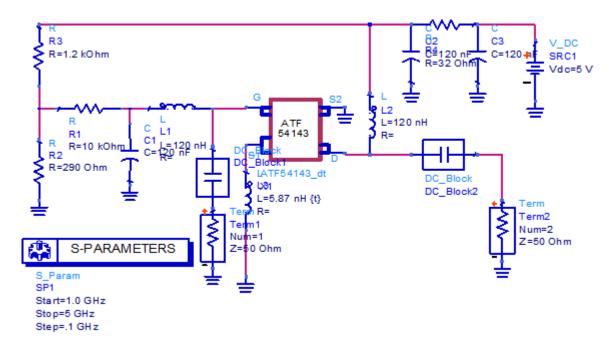

|     | 5.6 | LNA    | Design Using HEMT                                      | 56 |

|     |     | 5.6.1  | LNA Design with Lumped Components                      | 56 |

|     |     |        | 5.6.1.1 Stability Consideration                        | 58 |

|     |     |        | 5.6.1.2 Noise Figure                                   | 58 |

|     |     |        | 5.6.1.3 Matching Network                               | 59 |

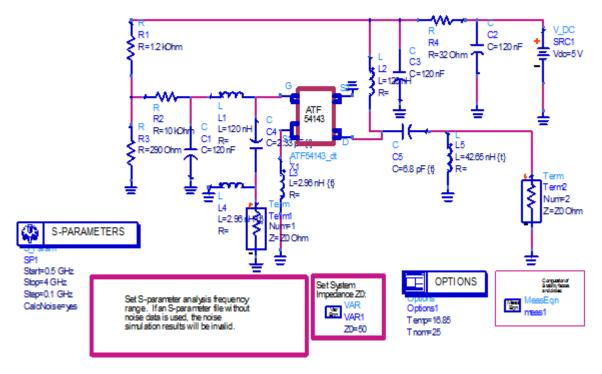

|     |     | 5.6.2  | Proposed Schematic Design of LNA using HEMT            | 60 |

|     |     |        | 5.6.2.1 Simulation Results                             | 61 |

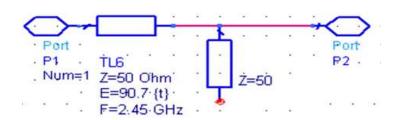

|     |     | 5.6.3  | LNA Design with Microstrip Lines Components using HEMT | 64 |

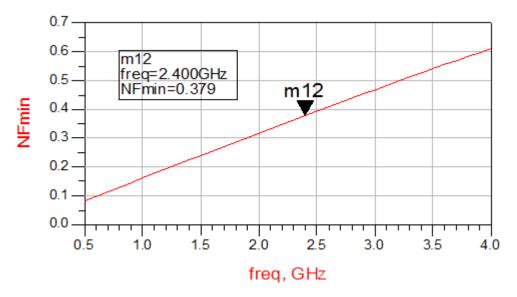

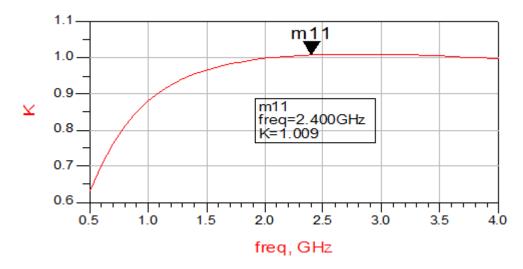

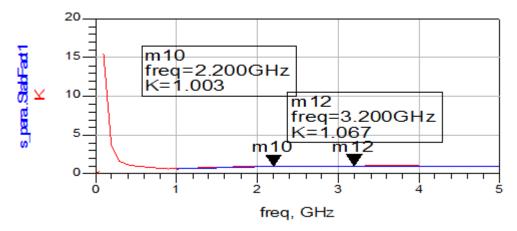

|     |     |        | 5.6.3.1 Stability of LNA                               | 65 |

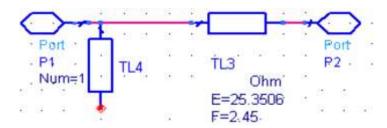

|     |     |        | 5.6.3.2 Design of Matching Network of Input Terminal   | 66 |

|     |     |        | 5.6.3.3 Design of Matching Network of Output Terminal  | 66 |

|     |     |        | 5.6.3.4 Determining the Size of Microstrip Line        | 67 |

|     |     |        | 5.6.3.4.1 Simulation Results                           | 67 |

|     |     | 561    | Pagulta Obtained from Simulation                       | 70 |

| VI.  | RES   | SULT                         | 71 |

|------|-------|------------------------------|----|

| VII. | CON   | NCLUSIONS                    | 72 |

|      | 7.1   | Conclusions                  | 72 |

|      | 7.2   | Future Scope of Present work | 73 |

| REFI | EREN  | CES                          | 74 |

| APPI | ENDIC | CES                          | 78 |

|      | Appe  | endix A HEMT Specifications  | 78 |

## LIST OF FIGURES

| FIGURES     |                                                                    |    |

|-------------|--------------------------------------------------------------------|----|

| Figure 1.1  | Disciplines requiring RF design                                    | 1  |

| Figure 1.2  | Flow chart of designing process for LNA                            | 3  |

| Figure 2.1  | Basic low noise amplifier                                          | 6  |

| Figure 3.1  | Two port network representation                                    | 12 |

| Figure 3.2  | Two port network showing incident and reflected wave               | 13 |

| Figure 3.3  | Source having complex impedance connected with complex load        | 15 |

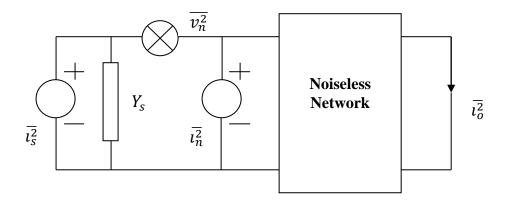

| Figure 3.4  | Input equivalent noise source                                      | 20 |

| Figure 3.5  | Input equivalent noise sources for MOS                             | 21 |

| Figure 3.6  | Noisy MOS replaced by noiseless source with input noise            | 22 |

| Figure 3.7  | Noiseless network with equivalent noise current and voltage        | 24 |

| Figure 3.8  | 1dB compression point                                              | 29 |

| Figure 3.9  | Third order intersect point                                        | 29 |

| Figure 3.10 | Illustration of centre frequency and bandwidth                     | 29 |

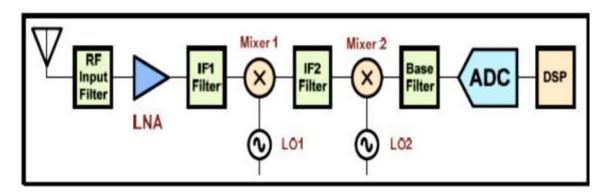

| Figure 4.1  | Basic heterodyne receiver architecture                             | 30 |

| Figure 4.2  | Resistive matching LNA                                             | 31 |

| Figure 4.3  | Shunt feedback amplifier                                           | 33 |

| Figure 4.4  | Common gate topology                                               | 34 |

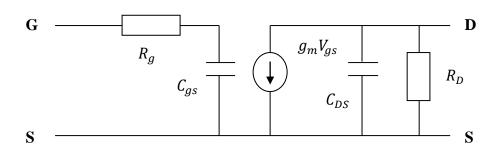

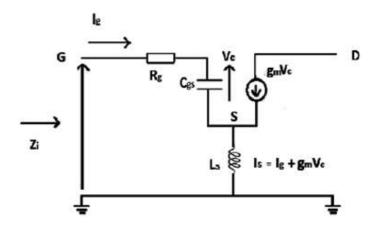

| Figure 4.5  | Equivalent model of MOSFET                                         | 34 |

| Figure 4.6  | Equivalent MOSFET model with inductive source degeneration         | 35 |

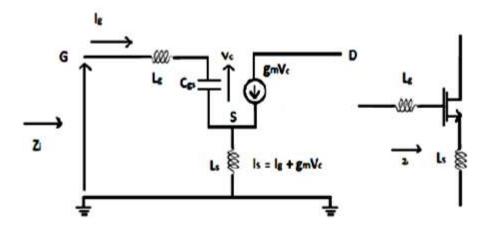

| Figure 4.7  | MOSFET model with inductive Gate and inductive source Degeneration | 35 |

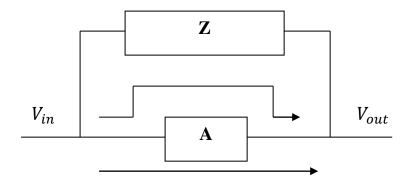

| Figure 4.8  | Typical Case for Miller's Theorem                                  | 36 |

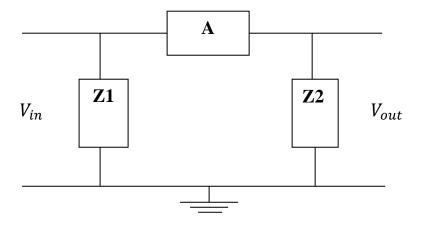

| Figure 4.9  | Application of Miller Theorem                                      | 36 |

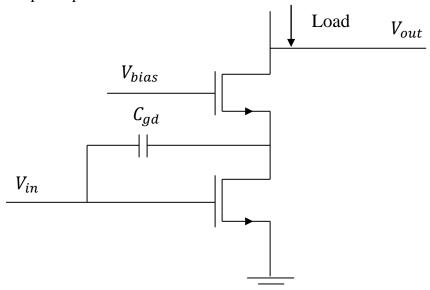

| Figure 4.10 | Cascode Configuration                                              |    |

| Figure 5.1  | Initial LNA Schematic                                              | 42 |

| Figure 5.2  | Schematic circuit of basic LNA design                              | 43 |

| Figure 5.3  | Scattering parameter S <sub>11</sub>                               | 44 |

| Figure 5.4  | Scattering parameter S <sub>22</sub>                                    | 44 |

|-------------|-------------------------------------------------------------------------|----|

| Figure 5.5  | Forward Gain S <sub>21</sub>                                            | 45 |

| Figure 5.6  | Scattering parameter S <sub>12</sub>                                    | 45 |

| Figure 5.7  | Noise Figure (NF)                                                       | 46 |

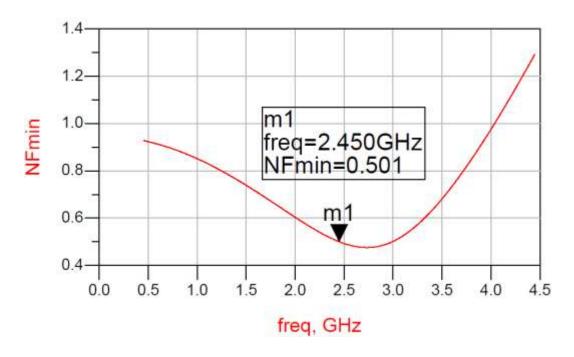

| Figure 5.8  | Minimum Noise Figure (NF <sub>min</sub> )                               | 46 |

| Figure 5.9  | Schematic circuit of LNA design with additional cacode stage            | 47 |

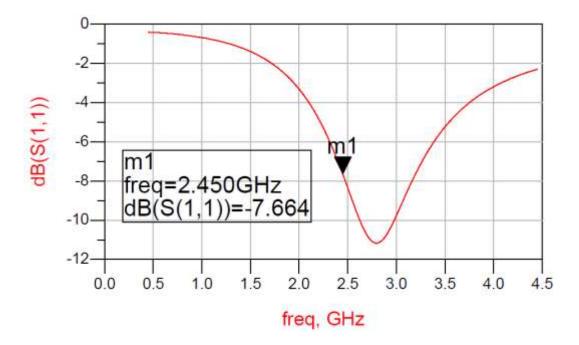

| Figure 5.10 | Scattering parameter S <sub>11</sub>                                    | 48 |

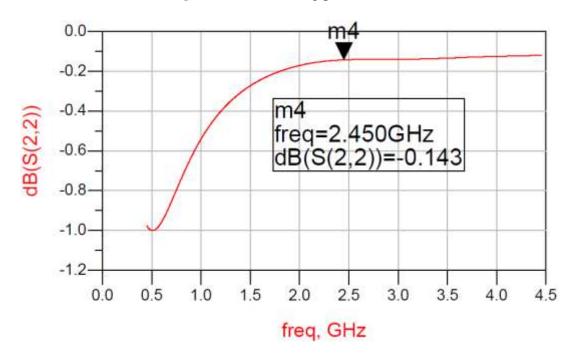

| Figure 5.11 | Scattering parameter S <sub>22</sub>                                    | 48 |

| Figure 5.12 | Forward Gain S <sub>21</sub>                                            | 49 |

| Figure 5.13 | Scattering parameter S <sub>12</sub>                                    | 49 |

| Figure 5.14 | Noise Figure (NF)                                                       | 50 |

| Figure 5.15 | Minimum Noise Figure (NF <sub>min</sub> )                               | 50 |

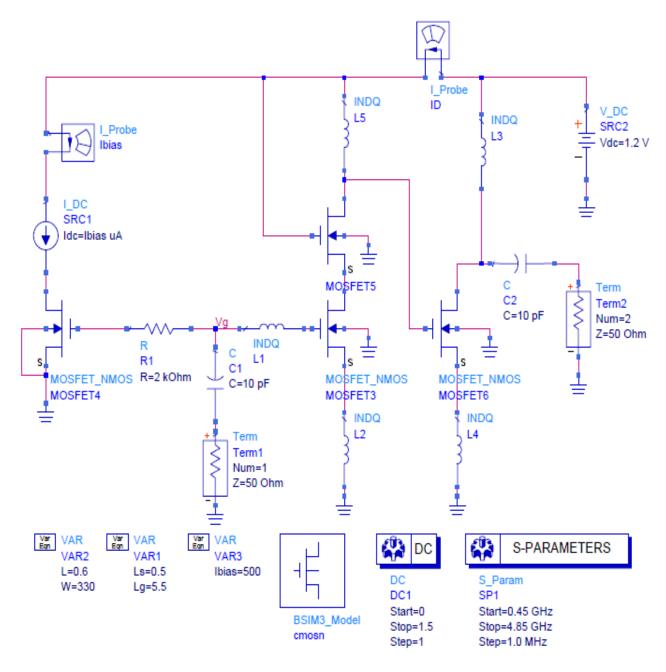

| Figure 5.16 | Schematic of the C-S LNA with a simple C-S stage added to the 'cascode' | 51 |

| Figure 5.17 | Scattering parameter S <sub>11</sub>                                    | 52 |

| Figure 5.18 | Scattering parameter S <sub>22</sub>                                    | 52 |

| Figure 5.19 | Forward Gain S <sub>21</sub>                                            | 53 |

| Figure 5.20 | Scattering parameter S <sub>12</sub>                                    | 53 |

| Figure 5.21 | Noise Figure (NF)                                                       | 54 |

| Figure 5.22 | Minimum Noise Figure (NF <sub>min</sub> )                               | 54 |

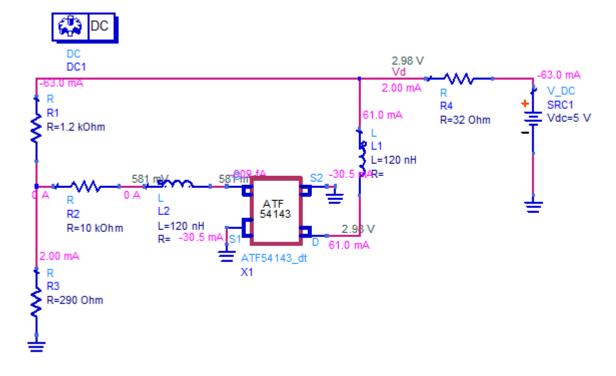

| Figure 5.23 | DC biasing Circuits                                                     | 56 |

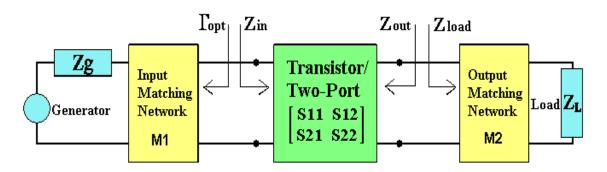

| Figure 5.24 | Block diagram of a single stage two port LNA model                      | 57 |

| Figure 5.25 | LNA circuit before matching network                                     | 59 |

| Figure 5.26 | Impedance matching network                                              | 59 |

| Figure 5.27 | Complete LNA circuit with input and output matching circuit             | 60 |

| Figure 5.28 | Scattering parameter S <sub>11</sub>                                    | 61 |

| Figure 5.29 | Scattering parameter S <sub>22</sub>                                    | 61 |

| Figure 5.30 | Forward Gain S <sub>21</sub>                                            | 62 |

| Figure 5.31 | Scattering parameter S <sub>12</sub>                                    | 62 |

| Figure 5.32 | Noise Figure (NF)                                                       | 62 |

| Figure 5.33 | Minimum Noise Figure (NF <sub>min</sub> )                               | 63 |

| Figure 5.34 | Stability factor                                                        | 63 |

| Figure 5.35 | Gain Comparison                                                         | 64 |

| Figure 5.36 | DC Bias circuit diagram                                                 | 64 |

| Figure 5.37 | Stability factor                                                        | 65 |

| Figure 5.38 | Matching network of input terminal        | 66 |

|-------------|-------------------------------------------|----|

| Figure 5.39 | Matching network of output terminal       | 66 |

| Figure 5.40 | Schematic of Microstrip LNA               | 67 |

| Figure 5.41 | Scattering parameter S <sub>11</sub>      | 68 |

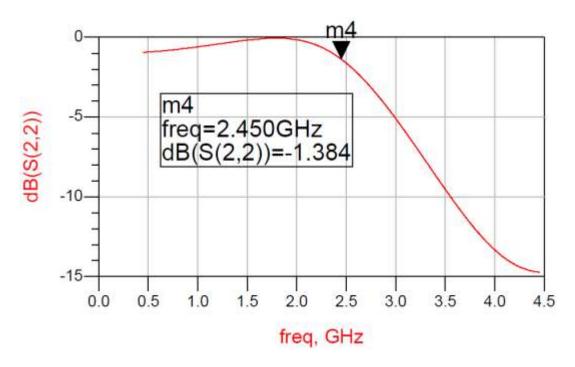

| Figure 5.42 | Scattering parameter S <sub>22</sub>      | 68 |

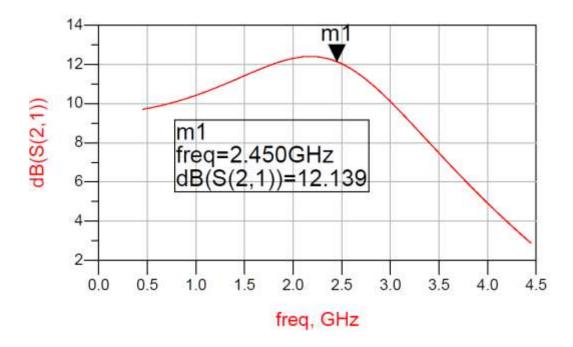

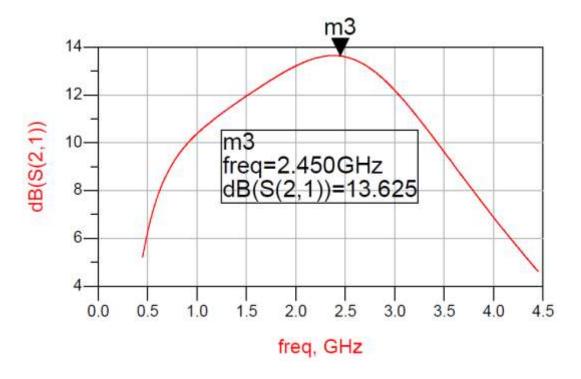

| Figure 5.43 | Forward Gain S <sub>21</sub>              | 68 |

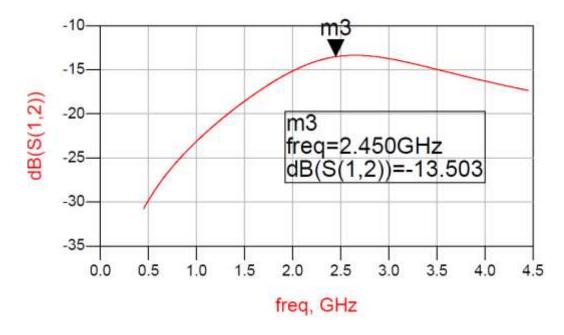

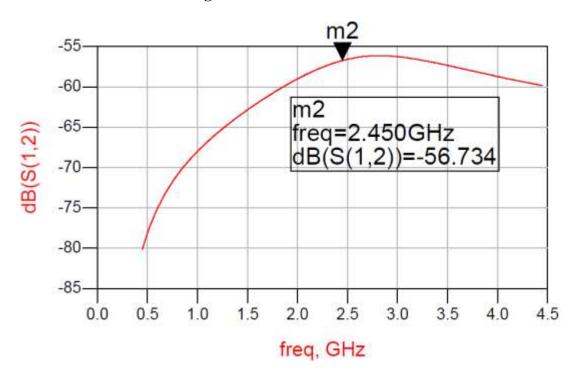

| Figure 5.44 | Scattering parameter S <sub>12</sub>      | 69 |

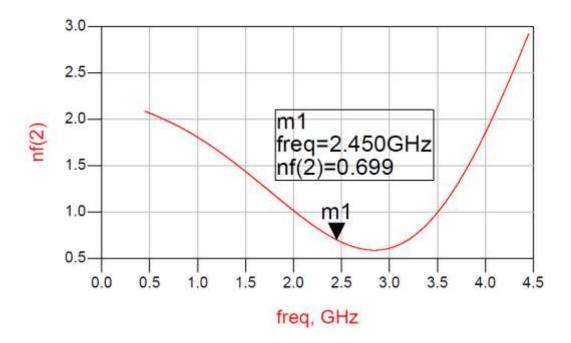

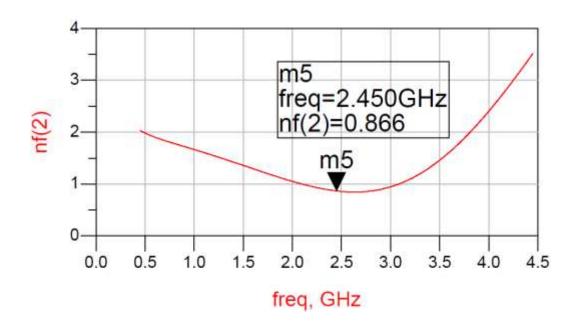

| Figure 5.45 | Noise Figure (NF)                         | 69 |

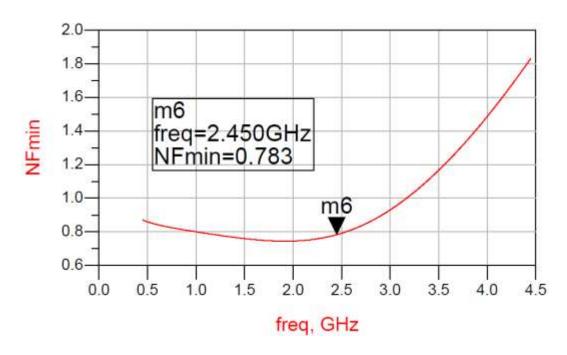

| Figure 5.46 | Minimum Noise Figure (NF <sub>min</sub> ) | 69 |

## LIST OF TABLES

| <b>TABLES</b> |                                                                     |    |

|---------------|---------------------------------------------------------------------|----|

| Table 2.1     | Summary of Application Based LNA's                                  | 8  |

| Table 2.2     | Summary of High Gain LNA's                                          | 9  |

| Table 2.3     | Summary of Different Matching Techniques for LNA's                  | 9  |

| Table 2.4     | Summary of Low Noise Techniques for LNA's                           | 10 |

| Table 4.1     | Advantages and Disadvantages of LNA topologies                      | 38 |

| Table 5.1     | Target Specification                                                | 40 |

| Table 5.2     | Current and Voltage value                                           | 47 |

| Table 5.3     | Current and Voltage value                                           | 50 |

| Table 5.4     | Current and Voltage value                                           | 54 |

| Table 5.5     | Performance Parameters                                              | 55 |

| Table 5.6     | Results differences in calculated and simulation before applying ma | •  |

| Table 5.7     | Performance Parameters                                              | 70 |

# LIST OF SYMBOLS

| $V_{out}$          | Output Voltage                |

|--------------------|-------------------------------|

| $V_{\text{in}} \\$ | Input Voltage                 |

| $\Gamma_s$         | Source Reflection Coefficient |

| $\Gamma_L$         | Load Reflection Coefficient   |

| K                  | Stability Factor              |

| Δf                 | Bandwidth                     |

| $f_{\rm o}$        | Centre Frequency              |

| $G_{\text{m}}$     | Transconductance              |

| $P_{D}$            | Power Dissipation             |

| C                  | Correlation coefficient       |

| Q                  | Quality Factor                |

| L                  | Chanel Length                 |

| $g_{\rm do}$       | Drain to Source Conductance   |

| γ                  | Drain Noise Coefficient       |

| δ                  | Gate Noise Coefficient        |

| $C_{gs}$           | Gate to Source Capacitance    |

| W                  | Width of MOSFET               |

| $I_D$              | Drain Current                 |

| L                  | Inductor                      |

| C                  | Capacitor                     |

| $G_{T}$            | Transducer Gain               |

| $G_{\mathbb{P}}$   | Operating Power Gain          |

Available Power Gain

$G_{A}$

### LIST OF ABBREVIATIONS

ISM Instruments Scientific and Medical

ADS Advance Design System

WLAN Wireless Local Area Network

LNA Low-Noise-Amplifier

BPF Band-Pass Filter

IMN Input Matching Network

OMN Output Matching Network

LPD433 Low Power Device, 433 MHz

PMR446 Private Mobile Radio, 446 MHz

ITU International Telecommunication Union

ITU-R The ITU Radio-communication Sector

FCC Federal Communications Commission

WDCT Digital Cordless Telecommunications

RFID Radio Frequency Identification

Hiper LAN High Performance Radio LAN

Wi-Fi Wireless Fidelity

PCB Printed Circuit Board

PCS Personal Communications Service

WCDMA Wideband CDMA

ADS Advanced Design System

WLL Wireless Local Loop

SMD Surface Mounted Device

### Introduction

### 1.1 Overview

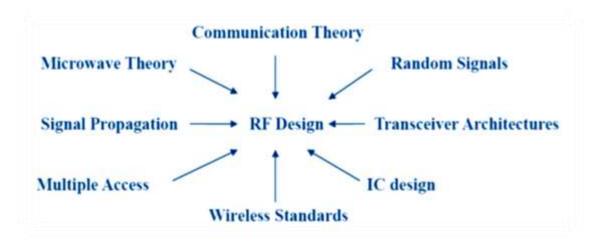

RF technology has changed quite a bit since the days of Marconi and Tesla-both the men who enabled radio communications. Modern radio frequency engineering is an exciting and dynamic field; due to the beneficial inter dependency between recent developments in electronic device technology and the increase in demand for voice, data, and video communication capacity. Prior to this revolution in communications, RF technology was the nearly exclusive domain of the defence industry but the recent increase in demand for communications systems with applications such as wireless paging, broadcast video, Bluetooth transceiver, Wi–Fi (WLAN), Wi-Max, CDMA, WCDMA, EGPRS, GSM and many more is revolutionizing the technology [1-2]. RF technology is important for these applications because these require high operational frequencies which allow both large numbers of independent channels as well as significant available bandwidth per channel for high speed communication. Figure 1.1 shows some disciplines that requires RF design.

Figure 1.1: Disciplines requiring RF design [1]

The field of design in the electronics system that employs RF and Microwave Engineering includes the frequencies ranging from 300kHz to over 100GHz. RF engineering refers to the circuits/device operating in the frequency range 300kHz to over 1GHz while the microwave engineering refers to the circuits/device operating in the frequency range between 300kHz or 1GHz to over 100GHz. Unfortunately, RFIC design is quite complex when tested results are obtained that differ drastically

from the simulation result. The reasons for this disparity may normally be traced to one of the following [2]:

- The frequency of operation is such that the circuit's elements display complex behaviour, not represented by the pure element definitions utilized during the design.

- The circuit layout includes coupling paths not accounted for in the design.

- > The ratio of transverse dimensions of transmission lines to wavelength is non-negligible thus, additional unwanted stored modes become available.

- > The package that houses the circuit becomes an energy storage cavity, thus absorbing some of the energy propagating through it.

- The perfect (ideally) dc bias source is not adequately decoupled from the circuit.

- ➤ The degree of impedance match among interconnected circuits is not good enough, so that large voltage standing wave ratio (VSWR) is present, which give rise to inefficient power transfer and to ripples in the frequency response.

### 1.2 Design Flowchart

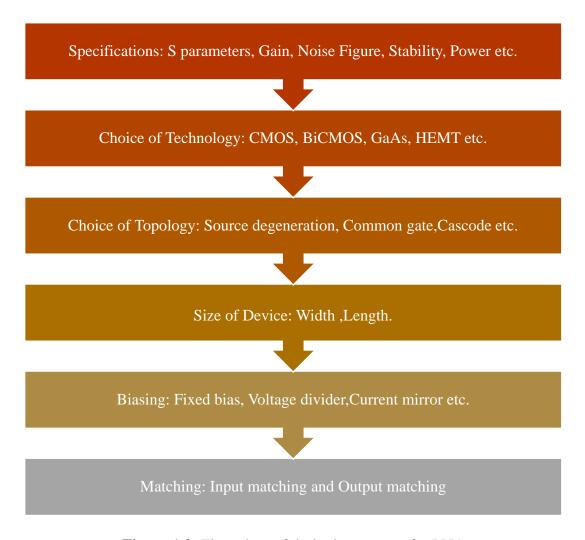

In the designing of low noise amplifier, some basic aspect of low noise amplifier should be kept in mind. Since in low noise amplifier there is trade-off between many factors i.e. gains, noise figure, stability, power consumption, and nonlinearity etc. And depending on these factors we have previously discussed different topology of low noise amplifier design. In this work we have chosen inductive source degeneration topology because this provides some beneficial advantages over other topologies as discussed in chapter 4. Inductive source degeneration topology is one of the most useful configurations for low noise amplifier design; because common source configuration provides low noise and solved the stability related problem.

Flow chart of LNA design is shown below that describes the design flow of low noise amplifier. The design starts from some basic specification means some standard output values that is desired for any circuits design these specification are scattering parameters, Gain, Noise Figure, Stability, Power, linearity etc. and our aim, tends to achieve these specified values. Second step in the design is choice of technology so here; HEMT technology has chosen for this design. Third step is choice the topology, there are different types of topologies and among them we can use topology depending on our design. Fourth step is some basic calculation like device width, gate to source capacitance and other things after that we can do the biasing to set the operating point and last if

there is some impedance mismatch so we have to do impedance matching by inserting a filter network.

Figure.1.2: Flow chart of designing process for LNA

### 1.3 Motivation and Problem Statement

Being the first block of the receiver chain LNA has to be able to receive the maximum signal without reflecting any part of it at the same time it has to ensure that it adds less noise to the signal component. The input impedance of the LNA should be  $50\Omega$  to match the source impedance, also the output stage should be able to give less noise, and more gain. Since any receiving block's performance depends mainly upon the LNA performance. It is the most important block for any communication system. So a LNA circuit with high gain and very low noise figure is highly needed for any modern receiver system, at the same time it should be less power consuming. In this work my aim to design a low noise amplifier at 2.4 GHz operating frequency for wireless communication because low noise amplifier is first block of receiver circuit and it is important to give more concentration to achieving high gain and low noise figure.

### 1.4 Objective/Scope of present work

The main objective of the research presented in this project is to design a low noise amplifier to be used in wireless communications operation. The goal of project is to understand the concepts of RF design such as gain, noise, matching networks, and linearity that are essential for amplifiers.

In the communication system, Low noise amplifier is the second element after antenna. LNA is used to boost up the received low energy and noisy signal to a desired energy level with noise suppression. So, noise figure (NF) is the key issue of concern in this design [3-5]. The receiver is the most power hungry block and the power consumption should be as low as possible. So, noise figure and power consumption are not less important issues than gain [6-7]. With the small power consumption, the LNA should amplify the weak receiving signal to the level suitable for processing and provide gain to overcome the noise of subsequent stages while adding small amount of noise as possible. Matching of each block of the receiver is also an important issue in order to provide maximum power transfer at a particular frequency the matching is required [8-9]. Furthermore, input and output matching to the source and load can maximize the gain. Input and output impedance matching is characterized by the input and output return loss. Since, it can affect the performance of the device. The gain should be large enough and the same time noise should be as less as possible [10]. The LNA should present specific impedance at the input, e.g.  $50\Omega$  to interface with the filter or antenna. Finding the delicate balance in all issues or parameters becomes the challenge more often than simply maximizing a single key parameter. The most recognizable tradeoff is between LNA gain and noise figure (NF). Linearity is also an important design issue. Third order intercept point, IP3 (Third order intercept point) has emerged as an important parameter in LNA design. The easiest way to improve the IP<sub>3</sub> performance for a given frequency is to increase the current density or current drawn of LNA. Input and output return losses, S<sub>11</sub> and S<sub>22</sub>, are also available for trading off to achieve improved gain and NF performance. Typically, the input and output matches are designed to afford good gain and NF performance. It is a balance of performance parameters. The approach for achieving this target is to design a low noise amplifier for wireless application at 2.4 GHz operating frequency range.

The next section describes the organization of chapters in the thesis.

### 1.5 Thesis Structure

The thesis report is divided into six chapters, each having ample information for comprehending the concept of this project.

Chapter 1 introduces the background history of RF technology and objective of research of low noise amplifier.

*Chapter 2* discussed the Low Noise Amplifier also deals the details about the research work carried out so far in the design of Low Noise Amplifier for different domain of RF.

*Chapter 3* provides the details about the different basic parameters of RF circuits design i.e. different type of Gain, noise in MOSFET, Noise Figure, Stability, linearity, Bandwidth etc.

*Chapters 4* presents different topology of Low Noise amplifier Design, based upon the Gain, Noise figure, and also discusses which topology is best suitable for Low Noise Amplifier.

*Chapter 5* discusses about the design, simulation, and analysis result of Low Noise amplifier, and some basic step for calculating the components parameters.

Chapter 6 summarizes detailed results of simulation analysis.

The Final chapter of the thesis (Chapter 7) presents the conclusions and future aspects of this project. The significance and contribution of this work is summarized.

### **Literature Review**

### 2.1 Introduction

The growth of wireless service and other telecom application has pushed the semiconductor industry towards complete system on chip solutions. Wireless system comprise of a front-end and a back end section. The front end section process analog signals in the high radio frequency range, while the back end section process analog and digital signals in the baseband low frequency range.

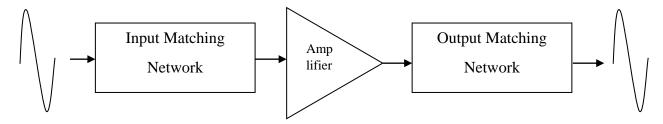

Figure 2.1: Basic low noise amplifier

The radio frequency signal received at the antenna is weak. Therefore an amplifier with high gain and good noise performance is needed to amplify this signal before it can be fed to others part of the receiver. Such an amplifier referred to as a low noise amplifier as shown in Figure 2.1. The first stage of the receiver is typically a low noise amplifier, whose main function is to provide enough gain to overcome the noise of subsequent stages (such as mixer). Aside from providing this gain while adding as little noise as possible, an LNA should accommodate large signals without distortion, and frequently must also present specific impedance. The general topology of low noise amplifier can be broken down into the three stages: input matching, amplifier and the output matching. Low noise amplifier used in various applications like ISM radio, cellular/PCS handsets, GPS receiver, cordless phone, wireless LAN, wireless data, satellite communication etc.

### 2.2 Literature Survey

Lot of research is being currently done in designing low noise amplifier. Some of the important papers related to this thesis work have been divided into four sub groups:

### 1. Application Based LNAs

- 2. High Gain LNAs

- 3. Different Matching Techniques for LNAs

- 4. Low Noise Techniques for LNAs

The discussions on the literature belonging to the above subgroup are given below:

### 2.2.1 Application Based LNAs

A low noise amplifier intended for use in a Global Positioning System (GPS) Receiver discussed by Derek K. Shaeffer et al. [11]. Inductive source degeneration topology has used for design of LNA.

A low noise amplifier, intended for use in a DECT (Digital Enhanced Cordless Communications) Receiver is presented by Jerome Le ny*et al.* [12], uses differential configuration with inductive source degeneration and constant g<sub>m</sub> bias for design of LNA.

The concept of Concurrent Multiband Low Noise Amplifiers is presented by Hussein Hashemi et al. [13]. They discuss the advantages of field effect transistors over bipolar junction transistor and concurrent dual band low noise amplifier in communication systems.

A low-noise amplifier for use in Ultra wideband wireless receiver is introduced by Andrea Bevilacqua et al. [14]. In the design it is discussed why the low noise amplifier is essential for UWB receiver. In their design they used multi-section Chebyshev filter at the input network and buffer stage at the output stage for design of LNA.

A low noise amplifier, intended for use in Ultra wideband wireless receiver is discussed by Che-Cheng Huang1 et al. [15] in which two stage cascode amplifiers with shunt-peaked load, two 2nd order notch filters, and an output buffer has been used for design of LNA.

A low noise amplifier intended for use in Ultra wideband wireless receiver front end is presented by Qiang Li et al. [16]. In which current-reuse topology, capacitive peaking is used for design of LNA. Inductors were not used in the design.

Zhe-Yang Huang et al. [17] has discussed low noise amplifier has been designed by using wideband input impedance matching network, a cascode amplifier with shunt-peaked load, a RLC impedance feedback loop. In another design Meng-Ping Chen et al. [18] used three LC-tank cascode amplifier and one output buffer for design of LNA.

A low-noise amplifier intended for use in Wi-Max system is discussed by Yu-Lin Wang [20]. They used differential, cascode configuration RC shunt feedback and shunt peak load for design of LNA.

A low noise amplifier intended for use in Ultra wideband Wireless Receiver is also provided by ShilaShamsadini et al. [21] with two-stage, common- gate in cascade with cascode for design of LNA. Table 2.1 shows the summary of application based LNA's.

Table 2.1: Summary of Application Based LNA's

| Parameters           | [11] | [12] | [14] | [15]  | [16] | [18] | [20]  | [21] |

|----------------------|------|------|------|-------|------|------|-------|------|

| Year                 | 1997 | 2002 | 2004 | 2007  | 2007 | 2008 | 2009  | 2010 |

| Technology(um)       | 0.18 | 0.25 | 0.18 | 0.18  | 0.13 |      | 0.18  | 0.18 |

| S <sub>11</sub> (dB) |      |      | -10  | -6.4  | -8.3 | -11  | -11   | -10  |

| S <sub>22</sub> (dB) |      |      |      | -10.1 |      |      | -10.9 |      |

| S <sub>21</sub> (dB) | 22   | 15   | 9.3  | 13.3  | 11   | 24.4 | 14.4  |      |

| Noise Figure(dB)     | 3.5  | 2    | 4    | 2.5   | 4.8  | 2.4  | 3.8   | 2.9  |

| Power consumed(mw)   | 30   | 25   | 9    | 21.9  | 19   | 9.2  | 14.8  | 10   |

### 2.2.2 High Gain LNAs

Bevin G.Perumana et al. [19] had used inductorless resistive feedback with current reuse topology and tuned resistive feedback for increase of gain in low noise amplifier for multiband applications.

Shila Shamsadini et al. [21] presented two-stage, common-gate in cascade with cascode for increase in gain low noise amplifier for Ultra Wideband applications. T. Hui Teo et al. [22] used fully integrated differential configuration for increase of gain in low noise amplifier for short-range radio in biomedical devices.

Jenn-Tzer et al. [23] used differential configuration and high-Q active inductor for design of low noise amplifier for multiband application. Table 2.2 shows the summary of high gain LNA's

Table 2.2: Summary of High Gain LNA's

| Parameters           | [19] | [22] | [21] |

|----------------------|------|------|------|

| Year                 | 2008 | 2008 | 2010 |

| Technology(um)       | 0.09 | 0.18 | 0.18 |

| S <sub>21</sub> (dB) | 22   | 26   | 25   |

### 2.2.3 Different Matching Techniques for LNAs

Derek K. Shaeffer et al. [11], discussed the different matching topologies at the input. It includes resistive termination, 1/gm termination, shunt-series feedback, inductive degeneration. For designing LNA inductive degeneration is used because of its advantage of providing low noise figure, high linearity, and high gain.

Andrea Bevilacqua et al. [14] used an inductively degenerated common-source amplifier by embedding the input network of the amplifying device in a multi-section reactive network so that the overall input reactance is resonated over a wider bandwidth.

Zhe-Yang Huang et al. [17], used wideband input impedance matching network, a cascade amplifier with shunt-peaked load, a RLC impedance feedback loop and an output buffer for input and output matching.

Meng-Ping Chen et al. [18], used input impedance matching network that included the conventional source degeneration input matching and an inductor shunted in a shunted resistor in RF signal path. The shunted resistor in RF path saved the three inductors used for design of Butterworth filter required earlier for the design in specified application. Table 3 shows the summary of different matching techniques for LNA's.

Table 2.3: Summary of Different Matching Techniques for LNA's

| Parameters     | [11] | [14] | [17] | [18] | [24] |

|----------------|------|------|------|------|------|

| Year           | 1997 | 2004 | 2007 | 2008 | 2007 |

| Technology(um) | 0.6  | 0.18 | 0.18 | 0.18 | 0.13 |

| S <sub>11</sub> (dB) | -10 | -10.1 | -6.8 | -44 |

|----------------------|-----|-------|------|-----|

| S22(dB)              | -7  | -9.76 | -9.5 | -12 |

### 2.2.4 Low Noise Techniques for LNAs

Derek K. Shaeffer et al. [11], had discussed the different matching topologies at the input. It includes resistive termination, 1/gm termination, shunt-series feedback, inductive degeneration. For designing they used inductive degeneration because of its advantage of providing low noise figure, high linearity, and high gain.

Michael T. Reiha et al. [24], presents the reactive (negative) feedback for design of low noise amplifier, reactive feedback reduces the noise figure by reducing the input insertion loss, flat group delay and lowering input referred noise.

Andries J. Scholten et al. [25], provided the noise modelling for RF CMOS circuits that included effect of drain current noise and gate noise for short channel MOSFETs. The results was modelled with a non-quasi- static RF model, based on channel segmentation, which is capable of predicting both drain and gate current noise accurately. Two additional noise mechanisms: avalanche noise associated with the avalanche current from drain to bulk and shot noise in the direct-tunnelling gate leakage current is also discussed.

Xiao-dong Wang et al. [26], added the capacitor between the gate and the source of the input MOSFET in cascode low noise inductive degeneration topology for reducing the noise figure in amplifiers.

Jenn-Tzer Yang et al. [17], used high-Q active inductor and differential configuration for lowering the noise figure. Table 4 shows the summary of low noise techniques for LNA's.

Table 2.4: Summary of Low Noise Techniques for LNA's

| Parameters     | [11] | [24] | [26] | [17]         |

|----------------|------|------|------|--------------|

| Year           | 1997 | 2007 | 2008 | 2007         |

| Technology(um) | 0.18 | 0.13 | 0.18 | 0.18         |

| NF(dB)         | 3.5  | .43  | .655 | 0.55 o 0.758 |

### 2.3 Problem Definitions

Design of Low Noise Amplifier for wireless communication with frequency range 2.4 GHz and some specific target has to be achieving i.e.

- (i) Gain should be greater than 15dB.

- (ii) Noise Figure should be lower than 2.0dB.

- (iii)Stability factor must be greater than 1.

- (iv)Power consumption should be low.

### **Basic Parameters of LNA Design**

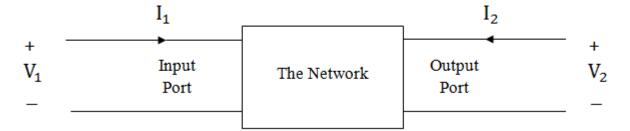

### 3.1 Two Port Network

The abstraction of the analogue block that is to be designed into a two port network is always useful in designing. So the characteristics and parameters of two port representation will be discussed. In a two port network, two port and four terminals are used to represent the characteristics of the circuit, especially in terms of current and voltage relations. The condition for any particular two terminals to be considered as a port is that current entering through one terminal must be equal to the current leaving through other terminal. And each port, two variables will be there out of them one will be independent and one will be dependent. At low frequency the two variables are voltage and current and the common two port representation are impedance matrix (Z parameter) and admittance matrix (Y parameter).

Figure 3.1: Two port network representation

The above figure shows a typical 2-port network, the impedance and admittance matrix are defined as shown in equations (3.1).and (3.2).

$$\begin{bmatrix} v_1 \\ v_2 \end{bmatrix} = \begin{bmatrix} z_{11} & z_{21} \\ z_{21} & z_{22} \end{bmatrix} \begin{bmatrix} i_1 \\ i_2 \end{bmatrix}$$

$$(3.1)$$

$$\begin{bmatrix} i_1 \\ i_2 \end{bmatrix} = \begin{bmatrix} y_{11} & y_{21} \\ y_{21} & y_{22} \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \end{bmatrix}$$

$$(3.2)$$

But it is to be noted that the concept of Y and Z parameters are useful only at low frequency because at low frequency these parameters can be determined by applying either current or voltage at one port and measuring other variable by shorting and opening other port respectively, but at

very high frequency it will be very difficult to open or short any port because it needs a broadband match at high frequency and also an active two port network might oscillate if one of its port is open or short circuited. That is why a new parameter has to be defined at RF, this parameter is called scattering parameter.

### 3.1.1 Scattering Parameters

Since the main problem with RF was that one has to rely on open and short circuiting the other port if one has to define Y and Z parameters for RF circuits therefore scattering parameter has the advantage that they can be measured by matching source and load impedance to the reference impedance. To represent a two-port network at microwave frequencies, scattering parameters(S - parameters) can be used. S-parameters themselves ( $S_{11}$ ,  $S_{12}$ ,  $S_{21}$ , and  $S_{22}$ ) represent reflection and transmission coefficients of the two-port under certain "matched" conditions.  $S_{11}$  is the reflection coefficient and  $S_{21}$  is the transmission coefficient at port 1 when port 2 is terminated in a load whose impedance is equal to that of the transmission line characteristic impedance. Likewise  $S_{22}$  is the reflection coefficient and  $S_{12}$  is the transmission coefficient at port 2 when port 1 is terminated in a matched load. The S parameter representation for two port network is as shown in Figure (3.2).

Figure 3.2: Two port network showing incident and reflected wave

Here in the above figure  $a_1$  is the normalized incident wave at port and  $b_1$  is the normalized reflected wave at the same port,  $v_1$  and  $i_1$  are voltage at port 1 and current entering into port 1. And the  $a_1$ ,  $b_1$ , the terminal current and terminal voltage relation is expressed in Equations (3.3) and (3.4),

$$a_i = \frac{v_i + z_0 i_i}{2\sqrt{z_0}} \tag{3.3}$$

$$b_i = \frac{v_i - z_0 i_i}{2\sqrt{z_0}} \tag{3.4}$$

Here  $Z_0$  is the reference impedance and it is taken as 50  $\Omega$  for all practical application. The overall scattering parameter in the matrix form can expressed as shown in Equation (3.5),

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} s_{11} & s_{12} \\ s_{21} & s_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \end{bmatrix}$$

$$(3.5)$$

But it is to be noted that the concept of Y and Z parameters are useful only at low frequency because at low frequency these parameters can be determined by applying either current or voltage at one port and measuring other variable by shorting and opening other port respectively, but at very high frequency it will be very difficult to open or short any port because it needs a broadband match at high frequency and also an active two port network might oscillate if one of its port is open or short circuited. That is why a new parameter has to be defined at RF, this parameter is called scattering parameter.

By expanding the scattering matrix the value of  $S_{11}$ ,  $S_{12}$ ,  $S_{21}$  and  $S_{22}$  can be expressed as shown below:

$$s_{11} = \frac{b_1}{a_1} \tag{3.6}$$

$$s_{12} = \frac{b_1}{a_2} \tag{3.7}$$

$$s_{21} = \frac{b_2}{a_1} \tag{3.8}$$

$$s_{22} = \frac{b_2}{a_2} \tag{3.9}$$

$S_{11}$  is input reflection coefficient,  $S_{12}$  is reverse transmission coefficient,  $S_{21}$  is forward transmission coefficient,  $S_{22}$  output reflection coefficient. Clearly  $S_{11}$  is the ratio of reflected wave to the incident wave at port 1 when port 2 is perfectly matched. Perfectly matched means the load impedance is equal to the value of characteristic impedance. Similarly  $S_{21}$  is the ratio of reflected wave at port 2 to the incident wave at port 1 when port 2 is properly matched, in other way it can be said that the ratio of value of voltage received at port 2 to the voltage on port 1 is  $S_{21}$ , so it is the Gain of the circuit.

### 3.2 Gain of Two Port Networks

For RF circuits designers prefer to express Gain in term of power, for any circuit the purpose is to maximize Gain and in order to get maximum gain the most important concept is that there should not be any power reflection means to say that all incident power should be applied to the circuit. The basic principle of this concept is based on maximum power transfer theorem, so it needs to be explained.

#### 3.2.1 Maximum Power Transfer Theorem

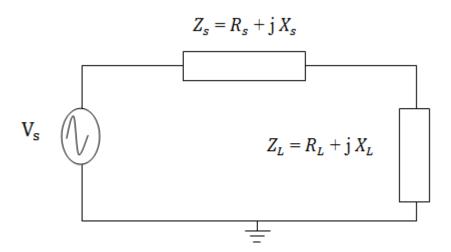

It is known that in order to the maximum power delivered by source going into the load the load impedance should be equal to the source impedance i.e.  $R_s = R_L$ . For the case of complex load it can be explained as follows –

**Figure 3.3:** Source having complex impedance connected with complex load From the above Figure (3.3), power delivered to the load RL is given as-

$$P_{L} = \frac{\left|V_{RL}\right|^{2}}{R_{L}} = \frac{R_{L}\left|V_{S}\right|^{2}}{\left|Z_{L} + Z_{S}\right|^{2}}$$

(3.10)

Now separating the real and imaginary part of Equation (3.10) we have

$$P_{L} = \frac{\left|V_{RL}\right|^{2}}{R_{L}} = \frac{R_{L}\left|V_{S}\right|^{2}}{\left(R_{L} + R_{S}\right)^{2} + \left(X_{L} + X_{S}\right)^{2}}$$

(3.11)

Now by differentiating the above equation with respect to  $X_s$  and  $R_s$  and equating to zero, the condition for maximum power transfer can be achieved. The condition for maximum power transfer is  $R_L$  should be equal to  $R_s$  and  $X_L + X_s$  should be equal to zero. In other words it can be said that for

maximum power transfer the real impedance of load should be equal to the real impedance of the source and summation of imaginary part load impedance and source impedance must be zero. So for maximum power transfer the load impedance  $Z_L$  should be the complex conjugate of source impedance  $Z_s$ . Also it is to be noted that even in case of maximum power source will deliver only half of the available power to the load.

### 3.2.2 Different Gain Expression

The gain of the device is its ability to amplify the amplitude or the power of the input signal. It is defined as the ratio of the output to the input signal and is often referred to in terms of decibels.

$$Voltage\ Gain = 20\log\frac{v_{out}}{v_{in}}$$

Power gain is generally defined as the ratio of the power actually delivered to the load to the power actually delivered by the source. Three power gains are commonly used in LNA design.

- (1) G<sub>T</sub>, transducer power gain

- (2) GP, operating power gain

- (3) GA, available power gain

Besides these three gain definitions, there are three additional gain definitions we can use to evaluate the LNA design.

- ➤ G<sub>umx</sub>, maximum unilateral transducer power gain

- ➤ G<sub>max</sub>, maximum transducer power gain

- ➤ G<sub>msg</sub>, maximum stability gain

Besides these six gain definitions, there are two gain circles that are helpful to the design of input and output matching networks.

- > GPC, power gain circle

- > GAC, available gain circle

### (1)Transducer Power Gain

Transducer power gain, GT is defined as the ratio between the power delivered to the load and the power available from the source [27].

$$G_{T} = \frac{1 - \left|\Gamma_{S}\right|^{2}}{\left|1 - S_{11}\Gamma_{S}\right|^{2}} \left|S_{21}\right|^{2} \frac{1 - \left|\Gamma_{L}\right|^{2}}{\left|1 - \Gamma_{out}\Gamma_{L}\right|^{2}}$$

(3.12)

The transducer gain expressions are too complex for manual design. To effect an approximate gain solution, let us ignore the feedback, that is assume that  $S_{12}=0$ . If an amplifier has no feedback, signals pass one way through it. Accordingly this is called unilateral gain. If  $S_{12}=0$ , then  $\Gamma_{in}=S_{11}$  and  $\Gamma_{out}=S_{22}$  and transducer gain becomes the unilateral gain.

### (2) Operating Power Gain

Operating power gain, G<sub>P</sub> is defined as the ratio between the power delivered to the load and the power input to the network.

$$G_{A} = \frac{1 - \left|\Gamma_{S}\right|^{2}}{\left|1 - S_{11}\Gamma_{S}\right|^{2}} \left|S_{21}\right|^{2} \frac{1}{1 - \left|\Gamma_{out}\right|^{2}}$$

(3.13)

The LNA scattering matrix is normalized in terms of the source and load resistance in Equation (3.14).

$$\Gamma_s = \Gamma_L = 0 \tag{3.14}$$

Thus, the input and output reflection coefficient are simply expressed in terms of Equation (3.15) and (3.16)

$$\Gamma_{in} = S_{11} \tag{3.15}$$

$$\Gamma_{out} = S_{22} \tag{3.16}$$

From these equations,

$$G_{P} = \frac{1}{1 - \left| S_{11} \right|^{2}} \left| S_{21} \right|^{2} \tag{3.17}$$

#### (3) Available Power Gain

Available power gain, G<sub>A</sub> is defined as the ratio between the power available from the network and the power available from the source [27].

$$G_{A} = \frac{1 - \left| \Gamma_{S} \right|^{2}}{\left| 1 - S_{11} \Gamma_{S} \right|^{2}} \left| S_{21} \right|^{2} \frac{1}{1 - \left| \Gamma_{out} \right|^{2}}$$

(3.18)

From Equations 3.15 and 3.16

$$G_{A} = |S_{21}|^{2} \frac{1}{1 - |S_{22}|^{2}}$$

(3.19)

The power available from the source is greater than the power input to the LNA network,  $G_P > G_T$ . The closer the two gains are the better the input matching. Similarly, because the power available from the LNA network is greater than the power delivered to the load,  $G_A > G_T$ .

### (4) Maximum Unilateral Transducer Power Gain

Maximum Unilateral transducer power gain  $G_{umx}$  is the transducer power gain when we assume that the reverse coupling of the LNA,  $S_{12}$  is zero, and the source and load impedances are conjugate matched to the LNA. That is  $\Gamma_S = S_{11}$  and  $\Gamma_L = S_{22}$ . If  $S_{12} = 0$  and the input and output reflection coefficient are  $\Gamma_{in} = S_{11}$  and  $\Gamma_{out} = S_{22}$ . Thus from Equation 3.13 we get Equation 3.20.

$$G_{umx} = \frac{1}{\left|1 - \left|S_{11}\right|^{2}\right|} |S_{21}|^{2} \frac{1}{\left|1 - \left|S_{22}\right|^{2}\right|}$$

(3.20)

#### (5) Maximum Transducer Power Gain

Maximum transducer power gain,  $G_{max}$  is the simultaneous conjugate matching power gain when both the input and output are conjugate matched. That is  $\Gamma_S=S_{11}$  and  $\Gamma_L=S_{22}$ . When the reverse coupling,  $S_{12}$  is small,  $G_{umx}$  is close to  $G_{max}$ .

$$G_{\text{max}} = \frac{\left|S_{21}\right|}{\left|S_{12}\right|} (k - \sqrt{k^2 - 1})$$

(3.21)

Where, K is stability factor

#### (6) Maximum Stability Gain

Maximum Stability gain,  $G_{msg}$  is the maximum of  $G_{max}$  when the stability condition K>1 is still satisfied.

$$G_{msg} = \frac{|S_{21}|}{|S_{12}|} \tag{3.22}$$

#### (7) Power Gain Circle

Power gain circle in short form is GPC. From Equation 3.13,  $G_p$ , is solely a function of the load reflection  $\Gamma_L$ . Thus we can draw power gain contours on the smith chart of  $\Gamma_L$ . The location for the peak of the contour corresponds to  $\Gamma_L$  producing the maximum  $G_P$ . We can move the peak location by changing the design of the output matching network. The best location for the contour peak is at the centre of the smith chart that is where,

$$\Gamma_L = 0$$

### (8) Available Gain Circle

Available gain circle in short form is GAC. From Equation 3.18, we can see that  $G_A$  is solely a function of the source reflection  $\Gamma_S$ . Thus we can draw available gain contours on the smith chart of  $\Gamma_S$ . The location for the peak of the contour corresponds to  $\Gamma_S$  producing the maximum  $G_A$ . we can move the peak location by changing the design of the input matching network. The best location for the contour peak is at the center of the smith chart that is where  $\Gamma_S = 0$ .

### 3.3 Stability

In the presence of feedback paths from the output to input, the circuits might become unstable for certain combination of source and load impedances. An LNA design that is normally stable might oscillate at the extremes of the manufacturing or voltage variations, and perhaps at unexpectedly high or low frequencies. The stability factor is given as in Equation 3.23

$$K = \frac{1 - \left| S_{11} \right|^2 - \left| S_{22} \right|^2 + \left| \Delta \right|^2}{2 \left| S_{12} S_{21} \right|}$$

(3.23)

Where

$$|\Delta| = |S_{11}S_{22} - S_{12}S_{21}| \tag{3.24}$$

Where K > 1 and  $\Delta < 1$ , the circuit is unconditionally stable. That is, the circuit does not oscillate with any combination of source and load impedance. We should perform the stability evaluation for the S parameters over a wide frequency range to ensure that K remains greater than one at all frequencies. As the coupling  $(S_{12})$  decrease, which is as reverse isolation increase, stability improves. Techniques such as resistive loading and neutralization are used to improve stability for LNA. Equation 3.23 is valid for small signal stability. If the circuit is unconditionally stable under small signal conditions, the circuit is less likely to be unstable when the input signal is large. Aside from the two metrics K and  $\Delta$ , the source and load stability circles cab be used to check LNA stability.

### 3.4 Noise

Noise is a random process means the value of the noise cannot be predicted at any time if the past value is known. Instantaneous value of noise cannot be predicted, a statistical model provides knowledge about some other important properties of the noise i.e. average power of noise that will be predictable.

#### 3.4.1 Noise in MOSFET

Design of LNA using CMOS will be discussed, therefore we will discuss the main source of noise and there expression in order to be able to express them both qualitatively and quantitively in the circuits. Several kinds of noise are discussed below:

#### (i) Thermal Noise

It is the random motion of electrons in a conductor introduces fluctuations in the voltage measured across the conductor even if the average current is zero. The thermal noise is proportional to the absolute temperature.

#### (ii) Flicker Noise

The interface between the gate oxide and the silicon substrate in a MOSFET entails an interesting phenomenon. Since silicon crystal reaches an end at this interface, many "dangling" bonds appear, giving raise to extra energy states. As charge carriers move at the interface, some are randomly trapped and later released by such energy states, introducing "flicker noise" in the drain current. Since LNA design for radio frequency and flicker noise is inversely proportional to frequency so it will be ignored. Noise due to gate resistance- the charge present in the channel fluctuates and it is capacitive coupled to gate and hence noise is produced and given as [28].

$$\frac{\hat{l}_{ng}^{2}}{\Delta f} = 4kTg_{g}\delta \tag{3.25}$$

Channel of MOSFET generates thermal noise and is given as-

$$\frac{\hat{l}_{ng}^{2}}{\Delta f} = 4kTg_{d_{o}}\delta \tag{3.26}$$

Where  $g_g$  is the gate conductance,  $g_{do}$  is open channel conductance [26].

#### 3.4.1.1 Input equivalent noise source

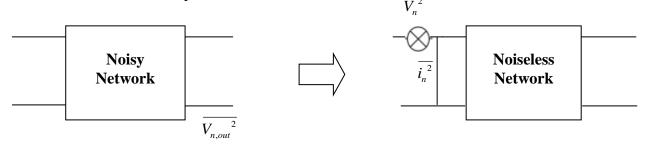

In order to able to explain the behaviour of the circuit a noisy circuit is expressed by a noiseless circuit and two sources at input.

Figure 3.4: Input equivalent noise source

Two noise sources one current and one voltage source is necessary because if Rs is zero(short) the noise current will flow out and only noise voltage will remain and similarly if Rs is infinite(open) only noise current will affect the circuit.

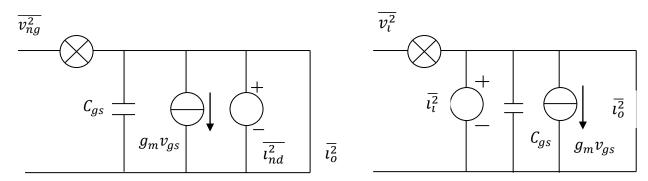

### 3.4.1.2 Input equivalent noise source for MOS

As shown in figure 3.5 input equivalents for noise source-

Figure 3.5: Input equivalent noise sources for MOS

By short circuiting the output of the actual circuit and equivalent circuit the relation between the equivalent current and voltage source with drain and gate noise current will be determined [27].

Case 1: when input is short circuited-

$$i_0 = g_m V_{ng} + i_{nd} (3.27)$$

It should be equal to the value of io from equivalent circuit i.e.

$$i_0 = g_m V_i \tag{3.28}$$

By equating the above two equations, Equation (3.29) is obtained.

$$V_i g_m = V_{ng} g_m + i_{nd} \tag{3.29}$$

Therefore it can be written as-

$$\overline{V_i^2} = \overline{V_{ng}^2} + \overline{i_{nd}^2} (\frac{1}{g_m})^2 \tag{3.30}$$

Case 2: when input is open circuited-

$$i_{o} = i_{nd} \tag{3.31}$$

And it should be equal to

$$i_0 = \left(\frac{i_i}{w_c g_s}\right) g_m \tag{3.32}$$

From the above two equations, it can also be written as-

$$\overline{\hat{\imath}_i^2} = \left(\frac{w_c g_s}{g_m}\right)^2 \overline{\hat{\imath}_{nd}^2} \tag{3.33}$$

So from Equations (3.30) and (3.33) equivalent noise source are defined, and it is to be noted that both the noise sources are correlated.

### 3.4.1.3 Absolute value of equivalent noise source

The correlation coefficient of the two thermal noise source is given by Equation (3.34)

$$c = \frac{\overline{\hat{l}_{ng} \, \dot{l}_{nd}}^*}{\sqrt{\hat{l}_{ng}^2} \sqrt{\hat{l}_{nd}^2}} \tag{3.34}$$

And value of c for long channel is 0.395j [5].

Figure 3.6: Noisy MOS replaced by noiseless source with input noise

Now again shorting the input and forcing equal current io in both the circuits, therefore

$$\overline{V_n^2} = \frac{\overline{\hat{\imath}_{nd}^2}}{g_m^2} = \frac{4kT\gamma g_{do}\Delta f}{g_m^2}$$

(3.35)

It is clear from the above equation that gate thermal noise does not contribute to this. The noise generated in Equation (3.35) can be expressed by the noise generated by a resistor of value  $R_n$  therefore

$$\overline{V_n^2} = 4KT\Delta f R_n \tag{3.36}$$

Where

$$R_n = \frac{\gamma g_{do}}{g_m^2} \tag{3.37}$$

$<sup>\</sup>overline{\hat{\imath}_{ng}^2}$  Will have contribution due to gate thermal noise  $\overline{\hat{\imath}_{ng}^2}$  in g2 and drain thermal noise  $\overline{\hat{\imath}_{ng}^2}$

$$\overline{i_{nl}^{2}} = \overline{i_{nd}^{2}} \frac{\left(\omega c_{gs}^{2}\right)}{g_{m}^{2}} = \frac{4kT\gamma g_{do}\left(\omega c_{gs}^{2}\right)\Delta f}{g_{m}^{2}}$$

(3.38)

From Equation 3.35

$$\overline{i_{nl}}^2 = \overline{v_{nl}}^2 \left( \omega c_{gs} \right) \tag{3.39}$$

$\overline{i_{ng}}^2$  has two components one correlated with  $\overline{v_n}^2$  and other not correlated with it

$$\overline{i_{ng}^{2}} = \overline{\left(i_{ngc} + i_{ngu}\right)^{2}} = 4KT\delta g_{g} \Delta f \left|c\right|^{2} + 4KT\delta g_{g} \Delta f \left(1 - \left|c\right|^{2}\right)$$

(3.40)

Therefore total equivalent noise current can be written into two parts-

(i) Uncorrelated term

$$\overline{\hat{\imath}_{nu}}^2 = \overline{\hat{\imath}_{ngu}}^2 \tag{3.41}$$

It can be represented by noise generated by Yu and value is given by-

$$Y_{u} = G_{u} = \frac{\overline{\hat{l}_{nu}^{2}}}{4KT\Delta f} = \delta g_{g} \left( 1 - \left| c \right|^{2} \right)$$

(3.42)

So

$$Y_{u} = G_{u} = \frac{\delta \omega^{2} c_{gs}^{2} g_{g} \left( 1 - |c|^{2} \right)}{5 g_{do}}$$

(3.43)

(ii) Correlated term

$$\overline{\hat{l}_{nc}^2} = \overline{\hat{l}_{ngc}^2} \tag{3.44}$$

It can be represented by noise generated by Yc and is given by the following equation.

$$Y_{c} = \frac{i_{nc}}{V_{n}} = \frac{g_{m}i_{nc}}{i_{nd}} + j\omega c_{gs}$$

(3.45)

Therefore, the model of MOS transistor as a noiseless system with two input noise sources is obtained and the noise sources can be characterized completely by  $Y_u$  and  $Y_c$ .

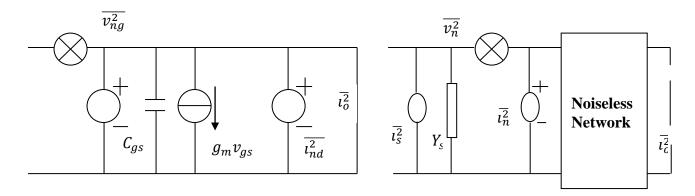

# 3.5 Noise Figure

Noise factor is defined as the ratio of signal to noise ratio at input to signal to noise ratio at output and also defined as the ratio of total output noise power to the output noise power due to source alone[29]. Decibel representation of noise factor is known as noise figure. Generally signal to noise ratio is the parameter that is being used for analog circuits but in RF design since the ultimate aim is to maximize the SNR therefore noise figure is defined [29].

Noise factor =

$$\frac{\text{SNRin}}{\text{SNRout}}$$

And

#### Noise figure = $10\log_{10}$ (Noise factor)

Now the expression for the noise factor of MOS transistor will be derived and also the condition for the noise factor to be minimum will be determined.

Figure 3.7: Noiseless network with equivalent noise current and voltage [30]

From the above circuit noise figure is-

$$F = \frac{\overline{\hat{\imath}_{s}^{2}} + \overline{(\hat{\imath}_{n} + Y_{s}V_{n})(\hat{\imath}_{n}^{*} + Y_{s}^{*}V_{n}^{*})}}{\overline{\hat{\imath}_{n}^{2}}}$$

(3.46)

It is known that the equivalent input current in is composed of two parts one is correlated with  $V_n$  and other is correlated with it. So considering correlated and uncorrelated terms-

$$i_n = i_{nu} + i_{nc} = i_{nu} + Y_c V_n \tag{3.47}$$

Therefore,

$$F = \frac{\overline{\hat{i}_{s}^{2}} + \overline{(i_{nu} + (Y_{c} + Y_{s})V_{n}(\hat{i}_{nu}^{*} + (Y_{c}^{*} + Y_{s}^{*})V_{n}^{*})}}{\hat{i}_{s}^{2}}$$

(3.48)

$$F = \frac{\overline{\hat{i}_s^2} + \overline{(i_{nu} + (Y_c + Y_s)V_n(\hat{i}_{nu}^* + (Y_c^* + Y_s^*)V_n^*)}}{\hat{i}_s^2}$$

(3.49)

And using above equation 3.49,

$$F = \frac{G_u + \left[ \left( G_c + G_s \right)^2 + \left( B_c + B_s \right)^2 \right] R_n}{Gs}$$

(3.50)

Here  $G_c+jB_c$  is used for  $Y_c$  and  $G_s+jB_s$  for  $G_s$ .

For MOS G<sub>c</sub>= 0 and above equation can be written as-

$$G_{u} = \frac{\delta c_{gs}^{2} \omega^{2} \left(1 - \left|c\right|^{2}\right)}{5 g_{do}} \qquad B_{c} = \omega c_{gs} \left(1 + \alpha \left|c\right| \sqrt{\frac{\delta}{5 \gamma}}\right)$$

And

$$R_n = \frac{\gamma}{\alpha g}$$

These values are putting in Equation 3.50

$$F = 1 + \frac{\delta \alpha \omega^{2} c_{gs} \left(1 - |c|^{2}\right)}{5g_{m}} + \left(\omega c_{gs} \left(1 + \alpha |c| \sqrt{\frac{\delta}{5\gamma}}\right) + B_{s}\right)^{2} \frac{\gamma}{\alpha g_{m}}$$

$$G_{s}$$

(3.51)

Now in order to optimize this noise figure, Equation 3.50 will be differentiated with respect to  $B_s$  and  $G_s$ , because these are the values which are coming from source and these values will have to be optimized in order to get minimum noise figure. So by taking differentiation with respect to  $B_s$  we have-

$$B_{s_{-}opt} = -B_{c} = -\omega c_{gs} \left( 1 + \alpha \left| c \right| \sqrt{\frac{\delta}{5\gamma}} \right)$$

(3.52)

Also by differentiating with respect to Gs-

$$G_{s\_opt} = \sqrt{\frac{G_u}{R_n}} = \alpha \omega c_{gs} \left( \sqrt{\frac{\delta \left( 1 - |c|^2 \right)}{5\gamma}} \right)$$

(3.53)

By using Equations 3.52 and 3.53

$$F_{\min} = 1 + \frac{2\omega}{\sqrt{5}w_n} \sqrt{\gamma \delta \left(1 - \left|c\right|^2\right)}$$

(3.54)

This is the expression for minimum noise figure.

Also from the maximum power transfer theorem the condition for maximum power transfer and the condition for minimum noise figure cannot be satisfied simultaneously. Therefore one will have to always look for the trade off in between noise and power gain.

# 3.6 Noise Optimization Methods

In low noise amplifier design, determination of the minimum noise figure is a common and Well-understood procedure. Typically, a small-signal model of the amplifier is assumed, an expression for F is formed, and differentiation leads to the unique conditions for optimized noise performance [30]. In the noise optimization techniques we seek the conditions that guarantee optimized noise performance for a specified fixed design parameter, such as gain or power consumption, under the condition of perfect input matching. Now, we fix the necessary design criteria and determine the appropriate small-signal model through the optimization procedure. Because the architecture

permits selection of Q<sub>L</sub> and L<sub>S</sub> independently, so we can optimize the noise performance that coincides with the input match. There are two approaches for the optimization of noise figure. The first assumes a fixed transconductance, G<sub>m</sub>, for the amplifier. The second assumes fixed power consumption. We know the equation of noise figure is [31].

$$F = 1 + \frac{R_l}{R_s} + \frac{R_g}{R_s} + \gamma \chi g_{do} R \left(\frac{\omega}{\omega_T}\right)^2$$

(3.55)

To illustrate these approaches the expression for the F in Equation 3.55 cab be recast to make its dependence on power dissipation. From equation 3.56 it is clear that condition for constant  $G_m$  is equivalent to the condition of constant  $\omega_T$ .

$$G_{m} = g_{m1}Q_{in} = \frac{g_{m1}}{\omega c_{gs} \left(R_{s} + w_{T}L_{s}\right)} = \frac{\omega_{T}}{\omega R_{s} \left(1 + \frac{w_{T}Ls}{R_{s}}\right)} = \frac{\omega_{T}}{2wR_{s}}$$

(3.56)

To maintain a fixed $\omega_T$ , we need only fix the value of  $\rho$ . Hence, we will reformulate F in terms of  $P_D$  and  $\rho$  to facilitate both optimizations. The equation of F in terms of  $P_D$  and  $\rho$  is given below [31].

$$F = 1 + \frac{\gamma \omega L}{3\nu_{ext}} P(\rho, P_D)$$

(3.57)

In this equation we have neglected the contribution of the gate resistance and inductor losses to the noise factor. In the Equation 3.57  $(\rho_1)$ , is a ratio of two sixth order polynomials of  $\rho$  given by

$$P(\rho, P_D) = \frac{\frac{P_D}{P_0} P_1(\rho) + P_2(\rho) + \frac{P_0}{P_D} P_3(\rho)}{\rho^3 \left(1 + \frac{\rho}{2}\right)^2 (1 + \rho)}$$

(3.58)

Where,

$$P_{1} = (1+\rho)^{2} + \frac{\delta}{5\gamma} (1+\rho)^{2} \left(1 + \frac{\rho}{2}\right)^{2}$$

$$P_{2}(\rho) = 2|c| \sqrt{\frac{\delta}{5\gamma}} (1+\rho)^{3} \left(1 + \frac{\rho}{2}\right)^{2}$$

$$P_{2}(\rho) = \frac{\delta}{5\gamma} \left(1 + \frac{\rho}{2}\right)^{2} \rho^{4}$$

Because F is a function of two variables, one can define contours of constant noise figure in  $\rho$  and P<sub>D</sub>. Equation (3.57) suggests that optimization of proceeds by minimizing with respect to one of its arguments, keeping the other one fixed.

## 3.6.1 Fixed G<sub>M</sub> Optimization

To fix the value of the transconductance, Gm, we need only assign a constant value to  $\rho$ . We know,

$$\omega_{T} \approx \frac{g_{m}}{c_{gs}} = \frac{g_{m}}{\frac{2}{3} wLc_{ox}} = \frac{3}{2} \frac{\alpha \mu_{eff} V_{od}}{L^{2}} = \frac{3\alpha \rho v_{sat}}{L}$$

(3.59)

The appropriate value for  $G_m$  is easily determined by substituting Equation (3.59) into the expression for as found in Equation (3.56). The value of  $G_m$  which relates to  $\rho$ , is

$$G_{m} = \frac{2v_{sat}\rho\left(1+\frac{\rho}{2}\right)}{2\omega R_{s}L(1+\rho)^{2}}$$

(3.60)

Once  $\rho$  is determined, we can minimize the noise factor by taking-

$$\frac{\delta P(\rho, P_D)}{\delta P_D} = 0$$

Which, after some algebraic manipulations result in

$$P_{D,opt.G_m} = P_0 \sqrt{\frac{P_3(\rho)}{P_1(\rho)}} = P_0 \frac{\rho^2}{1+\rho} \left[ 1 + \frac{5\gamma}{\delta\alpha^2} \right]^{\frac{1}{2}}$$

(3.61)

This expression gives the power dissipation which yields the best noise performance for a given  $G_m$  under the assumption of matched input impedance. We know  $Q_L$  is:

$$Q_{L} = \frac{P_{0}}{P_{D}} \frac{\rho^{2}}{1 + \rho} \tag{3.62}$$

By comparing Equations (3.61) and (3.62), we see immediately that this optimum occurs when [32]

$$Q_L = Q_{L,\text{opt},G_m} = \sqrt{1 + \frac{5\gamma}{\delta\alpha^2}} \ge 1.18$$

(3.63)

Hence, the best noise performance for a given transconductance is achieved at some specific input. Note that the value 1.87 is valid only for long-channel devices. For short-channel lengths, where  $\alpha$  < 1, we can expect the optimum Q<sub>L</sub> to be somewhat larger. By substituting (3.63) into (3.55), we determine that the minimum noise factor (neglecting inductor and gate losses) is

$$F_{\min,G_m} = 1 + \sqrt{\frac{4}{5}} \frac{\delta \gamma}{\delta \gamma} \left( \frac{\omega}{\omega_T} \right) \left\{ \left| c \right| + \sqrt{1 + \frac{5\gamma}{\delta \alpha^2}} \right\} \ge 1 + 1.33 \left( \frac{\omega}{\omega_T} \right)$$

(3.64)

The value 1.33 is only valid for long-channel devices; it may be three to four times larger in the presence of high electric fields.

## 3.6.2 Fixed P<sub>D</sub> Optimization

An alternate method of optimization fixes the power dissipation and adjusts  $\rho$  to find the minimum noise factor. If we assume that  $\alpha << 1$ , then P  $(\rho, P_D)$  can be simplified to:

$$P(\rho, P_D) \approx \frac{\frac{P_D}{P_0} \left( 1 + \frac{\delta}{5\gamma} \right) + 2|C| \sqrt{\frac{\delta}{5\gamma}} \rho^2 + \frac{P_0 \delta}{P_D 5\gamma} \rho^4}{\rho^3}$$

(3.65)

This expression is minimized for a fixed PD when  $\frac{\delta P(\rho, P_D)}{\delta \rho} = 0$

The solution of this equation, under the assumption that  $\alpha << 1$

$$\rho_{opt,P_{D}}^{2} = \frac{P_{D}}{P_{0}} |C| \sqrt{\frac{5\gamma}{\delta}} \left[ 1 + \sqrt{1 + \frac{3}{|C|^{2}} \left( 1 + \frac{\delta}{5\gamma} \right)} \right]$$

(3.66)

By comparing Equation (3.66) to Equation (3.65), it is clear that this value for  $\rho$  is equivalent to an optimum  $Q_L$  of

$$Q_{L,opt,P_D} \approx |C| \sqrt{\frac{5\gamma}{\delta}} \left[ 1 + \sqrt{1 + \frac{3}{|C|^2} \left( 1 + \frac{\delta}{5\gamma} \right)} \right]$$

(3.67)

So, it is clear that the optimum  $Q_L$  for fixed power dissipation  $P_D$  is larger than the optimum  $Q_L$  for a fixed Gm. from these equations

$$F_{\min,P_D} \approx 1 + 2.4 \frac{\gamma}{\alpha} \left(\frac{\omega}{\omega_T}\right) \ge 1 + 1.62 \frac{\omega}{\omega_T}$$

(3.68)

Where the value of 1.62 is valid only in the long-channel limit; the value will be somewhat larger for short-channel devices in velocity saturation.

# 3.7 Linearity

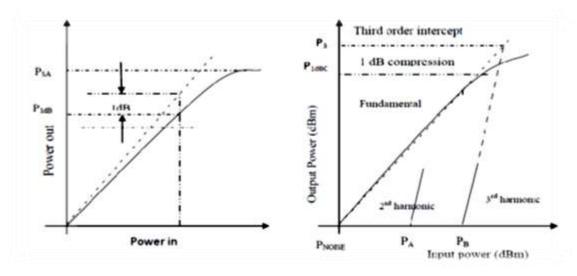

The linearity of the LNA is another concern that must be taken into account. Linear operation is crucial, particularly when the input signal is weak with a strong interfering signal in close proximity. This is because in such a scenario there is a possibility for undesired inter modulation distortion such as blocking and cross modulation. Third-order intercept (IP3) and 1-dB compression point (P1dB) are two measures of linearity. IP3 shows at what power level the third-order inter modulation product is equal to the power of the first-order output. IIP3 and OIP3 are the input power and output power respectively, that corresponds to IP3. P1dB shows at what power level the output power drops 1 dB, as a consequence of non-linearity, relative the theoretical linear power gain [29].

Figure 3.8: 1dB compression point

Figure 3.9: Third order intersect point

By knowing either IP3 or P1dB the other can be estimated with the following rule-of-thumb formula:

$$IP_3 = P_{1dB} + 10dB (3.69)$$

Third-order intercept point is shown in Figure 3.9. Both measurements indicate an upper distortion limit for the tolerable input power, whereas the noise figure sets a lower limit. The ratio of the two determines the dynamic range of the amplifier [10].

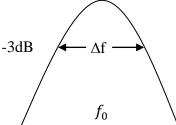

# 3.8 Centre Frequency and Bandwidth

As the LNA will operate with input signals of a particular frequency band, it is desired to design it with a centre frequency and bandwidth accordingly. Looking at the transfer function of the LNA, the differential of the two points around the centre frequency  $f_0$ , where the power gain is halved, is the bandwidth, denoted  $\Delta f$  in Figure 3.10. Although the target bandwidth should be specified numerically, by naming convention there are two options: narrowband and wideband. And  $\Delta f$  is called the bandwidth and it is difference between higher frequency component and lower frequency components and  $f_0$  is the operating frequency and this work operating frequency is 6GHz and bandwidth of system has to calculated by the simulation of circuit. We can also calculate the relative bandwidth that tells us system is wideband and narrow band.

Figure 3.10: Illustration of centre frequency and bandwidth

# **Different Topologies for LNA Design**

## 4.1 Introduction