# Investigation of Leakage Power in DCVS Logic Family

Dissertation submitted in Partial fulfilment of the requirement For the award of the degree of

### **Master of Technology**

*in* VLSI and Embedded System Design *by* Pratibha Bajpai

### University Roll No. 2K14/VLS/15

Under the guidance of

Mr. J. Panda Associate Professor, Electronics and Communication Engineering Department, DTU

2014-2016

### ELECTRONICS AND COMMUNICATION ENGINEERING DEPARTMENT

### DELHI TECHNOLOGICAL UNIVERSITY

#### DELHI-110042, INDIA

Electronics and Communication Engineering Department Delhi Technological University Delhi-110042 www.dce.edu

# CERTIFICATE

This is to certify that the dissertation titled "Investigation of Leakage Power in DCVS Logic Family" is a bonafide record of work done by Pratibha Bajpai, Roll No. 2K14/VLS/15 at Delhi Technological University for partial fulfilment of the requirements for the award of degree of Master of Technology in VLSI and Embedded systems Engineering. This project was carried out under my supervision and has not been submitted elsewhere, either in part or full, for the award of any other degree or diploma to the best of my knowledge and belief.

Date: \_\_\_\_\_

(Mr. J. Panda) Associate Professor Department of Electronics and Communication Engineering Delhi Technological University

## ACKNOWLEDGEMENT

First of all, I express my deepest gratitude to my project guide Mr. J.Panda, Associate Professor, Department of Electronics and Communication Engineering, DTU for providing the opportunity of carrying out this project and being the guiding force behind it. I am highly grateful to him for encouragement, guidance and support from the initial to the final level that enabled me to develop a well understanding of the subject.

Secondly, I would genuinely like to thank Dr. Neeta Pandey, Associate Professor, Department of Electronics and Communication Engineering, DTU for guiding and supporting at every step of the project without which the project could not have been a success. Her suggestions and ways of summarizing the things made me to go for independent studying and trying my best to get the maximum in my topic.

I am also grateful to Prof. Prem R. Chadha, HOD, Department of Electronics and Communication Engineering, DTU for his immense support. I would also acknowledge DTU for providing the right academic resources and environment for this work to be carried out.

Finally, I extend my deep appreciation to my family and friends, for all that they meant to me during the crucial times of the completion of my project.

(Pratibha Bajpai)

University Roll no: 2K14/VLS/15

M.Tech.(VLSI and Embedded System Design)

**Department of Electronics and Communication Engineering**

**Delhi Technological University**

# **TABLE OF CONTENTS**

| Certificateii                                                                   |

|---------------------------------------------------------------------------------|

| Acknowledgementiii                                                              |

| List of figuresvii                                                              |

| List of tablesxi                                                                |

| Abstractxv                                                                      |

| Chapter 1: Introduction1                                                        |

| 1.1 Motivation1                                                                 |

| 1.2 Research Objective                                                          |

| 1.3 Structure of Thesis                                                         |

| Chapter 2: Leakage Power Minimization Techniques5                               |

| 2.1 Introduction                                                                |

| 2.2. Power Dissipation in CMOS Circuits                                         |

| 2.2.1 Short-Circuit Power                                                       |

| 2.2.2 Dynamic Power                                                             |

| 2.2.3 Leakage Power                                                             |

| 2.3 Leakage Reduction Techniques11                                              |

| 2.3.1 Power Gating (Sleep Approach) with MTCMOS12                               |

| 2.3.2 Zigzag Approach                                                           |

| 2.3.3 Forced Stack Approach                                                     |

| 2.3.4 Sleepy Stack Approach15                                                   |

| 2.3.5 Leakage Feedback Approach17                                               |

| 2.3.6 Sleepy Keeper Approach                                                    |

| 2.3.7 LECTOR Technique                                                          |

| 2.3.8 GALEOR Technique                                                          |

| 2.4 Comparison of Various Techniques                                            |

| 2.5 Summary                                                                     |

| 2.6 Simulation results and discussions                                          |

| Chapter 3: Leakage Power Reduction in Differential Cascode Voltage Switch Logic |

| Family                                                                          |

| 3.1. Introduction                                                               |

| 3.2. Static DCVSL                                                                           |

|---------------------------------------------------------------------------------------------|

| 3.2.1 Operation of DCVSL                                                                    |

| 3.2.2 Advantages of DCVSL Logic Family over Conventional CMOS                               |

| Logic                                                                                       |

| 3.3. Idea of Leakage in DCVSL                                                               |

| 3.4. Application of Low Power Techniques to DCVSL Circuits                                  |

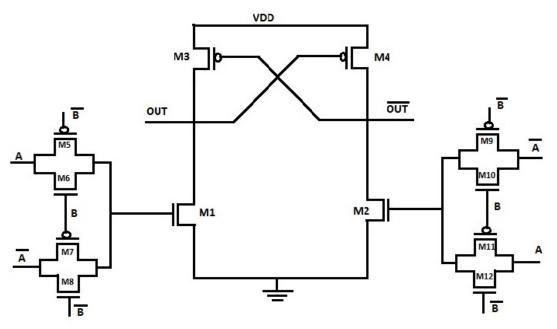

| 3.4.1 Existing Methodologies                                                                |

| A) MT-DCVS Design Methodology                                                               |

| B) Sleep Embedded DCVSL Methodology31                                                       |

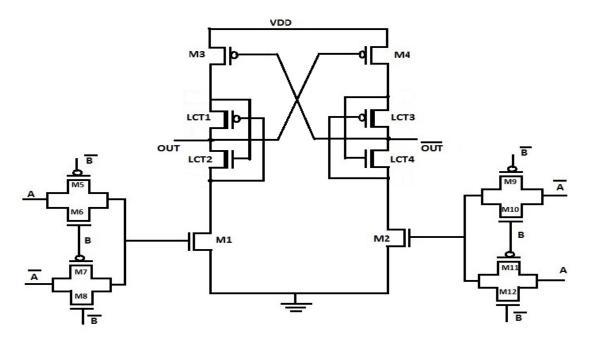

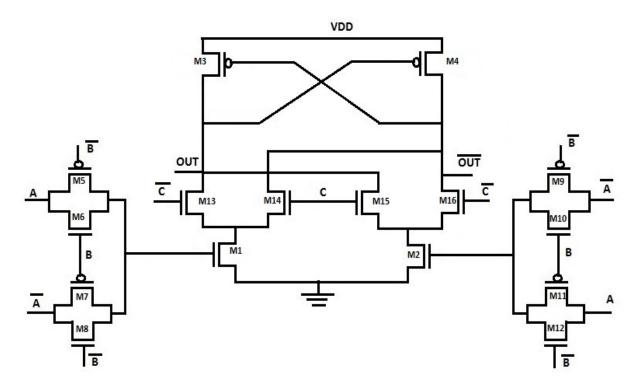

| 3.4.2 Proposed Methodology- Modified Lector Incorporated DCVSL<br>Approach                  |

| a) Concept Behind                                                                           |

| b) Architecture                                                                             |

| c) Leakage Control Mechanism In Modified DCVSL Circuit34                                    |

| d) Examples                                                                                 |

| i) Basic DCVSL 2-Input XOR Gate (2-Level Stacking)35                                        |

| <ul><li>ii) LECTOR Incorporated DCVSL 2-Input XOR Gate</li><li>(2-Level Stacking)</li></ul> |

| iii) Basic DCVSL 3-Input XOR Gate (3-Level Stacking)36                                      |

| iv) LECTOR Incorporated DCVSL 3-Input XOR Gate<br>(3-Level Stacking)                        |

| 3.5 Hybrid Static DCVSL (Hy-DCVSL)                                                          |

| 3.5.1 What are Transmission Gates?                                                          |

| 3.5.2 Proposed Hybrid Configuration                                                         |

| a) 2-Input XOR DCVSL Gate                                                                   |

| i) Basic hybrid DCVSL (all TG)                                                              |

| ii) LECTOR hybrid DCVSL (all TG)                                                            |

| b) 3-Input XOR DCVSL Gate40                                                                 |

| i) Basic Hybrid DCVSL TYPE 1 (TG+ two level stacking)40                                     |

| ii) LECTOR Hybrid DCVSL TYPE 1 (TG+ two level                                               |

| stacking)41                                                                                 |

| iii) Basic Hybrid DCVSL TYPE 2 (All TG)41                                                   |

| iv) LECTOR Hybrid DCVSL TYPE 2 (all TG)42                                     |   |

|-------------------------------------------------------------------------------|---|

| 3.6 Simulation results and discussions                                        |   |

|                                                                               |   |

| Chapter 4: Enhanced Differential Cascode Voltage Switch Logic (Dynamic DCVSL) |   |

| and Special Structures                                                        |   |

| 4.1 Introduction                                                              |   |

| 4.2 Dynamic DCVSL                                                             |   |

| 4.3 Enhanced Differential Cascode Voltage Switch Logic                        |   |

| 4.3.1 Architecture and Operation                                              |   |

| 4.3.2 Advantages of EDCVS logic design                                        |   |

| 4.3.3 Modified LECTOR incorporated EDCVSL approach                            |   |

| 4.4 Proposed Hybrid dynamic DCVSL and EDCVSL Configurations69                 |   |

| 4.4.1 Two-Input XOR EDCVSL Gate70                                             |   |

| a) Basic hybrid EDCVSL71                                                      |   |

| b) LECTOR hybrid EDCVSL71                                                     |   |

| 4.4.2 Three-Input XOR dynamic DCVSL Gate71                                    |   |

| a) Basic Hybrid dynamic DCVSL (TG+ two level stacking)72                      |   |

| b) LECTOR Hybrid dynamic DCVSL (TG+ two level stacking)72                     |   |

| 4.5 Special Configurations for DCVSL                                          |   |

| 4.5.1 NP mixed DCVSL                                                          |   |

| 4.5.2 Differential Static CMOS Logic (DSCL)74                                 |   |

| a) Problem with conventional DCVSL74                                          |   |

| b) DSCL configuration75                                                       |   |

| c) Proposed LECTOR incorporated DSCL configuration76                          |   |

| 4.6 Simulation results and discussions                                        |   |

| Chapter 5: Conclusion and Future Work102                                      |   |

| 5.1 Conclusion102                                                             | , |

| 5.2 Future Work                                                               |   |

| References104                                                                 |   |

# **LIST OF FIGURES**

| Fig. 1.1 Transistors in Intel microprocessors                                                |

|----------------------------------------------------------------------------------------------|

| Fig. 1.2 Power dissipated in various technologies                                            |

| Fig. 2.1 Short-circuit power                                                                 |

| Fig. 2.2 Clock frequencies of Intel microprocessors                                          |

| Fig. 2.3 Dynamic switching power                                                             |

| Fig. 2.4 Process generations                                                                 |

| Fig. 2.5 Leakage current components in an NMOS transistor                                    |

| Fig. 2.6 Subthreshold leakage current in an NMOS transistor10                                |

| Fig. 2.7 (a)Maximum subthreshold leakage current state. (b)Maximum gate oxide leakage        |

| current state. (c)Condition to avoid both subthreshold and gate oxide leakage                |

| current11                                                                                    |

| Fig. 2.8 Sleep Approach                                                                      |

| Fig. 2.9 Zigzag Approach                                                                     |

| Fig. 2.10 Natural stacking of NMOS transistors in a two input NAND gate14                    |

| Fig. 2.11 Stack Approach15                                                                   |

| Fig. 2.12 (a) Sleepy stack inverter with W=L of each transistor and active mode S, S'        |

| assertion. (b) Sleep mode S, S' assertion16                                                  |

| Fig. 2.13 Sleepy Stack Approach for general CMOS circuit16                                   |

| Fig. 2.14 (a) Forced stack technique inverter circuit schematic. (b) RC equivalent circuit17 |

| Fig. 2.15 (a) Sleepy stack technique inverter schematic. (b) RC equivalent circuit17         |

| Fig. 2.16 Leakage feedback approach    18                                                    |

| Fig. 2.17 Sleepy Keeper Approach                                                             |

| Fig. 2.18 Lector Technique Implementing NAND GATE                                      |

|----------------------------------------------------------------------------------------|

| Fig. 2.19 GALEOR Technique Implementing NAND Gate                                      |

| Fig. 2.20 Basic CMOS inverter                                                          |

| Fig. 2.21 LECTOR CMOS inverter                                                         |

| Fig. 2.22 Leakage current comparison for different supply voltages for basic DCVSL     |

| Inverter                                                                               |

| Fig. 2.23 Leakage current in CMOS inverter (in nA) at different technologies at 1.8V25 |

| Fig. 2.24 Leakage current in CMOS inverter (in nA) at different technologies at 1.2V26 |

| Fig. 2.25 Static current in CMOS inverter (in nA) at different technologies at 1.2V26  |

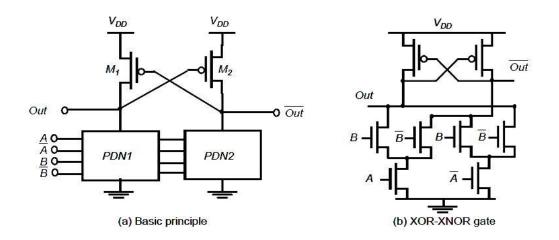

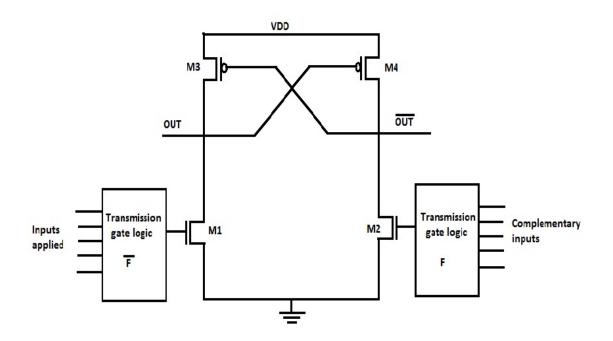

| Fig. 3.1 DCVSL logic gate                                                              |

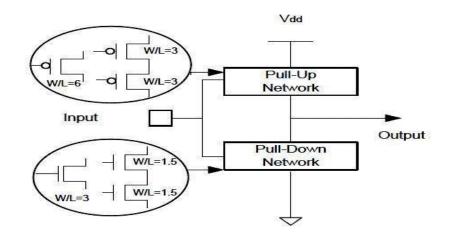

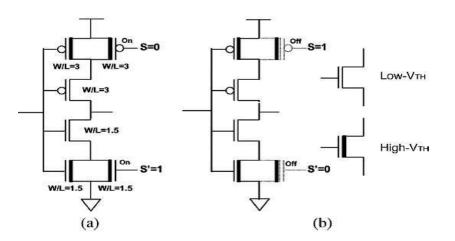

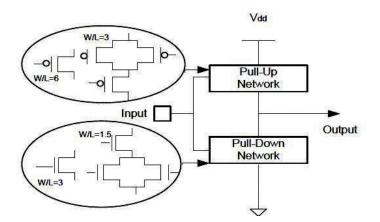

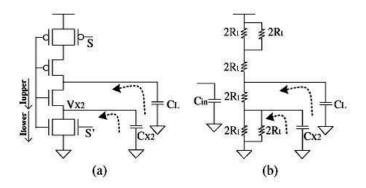

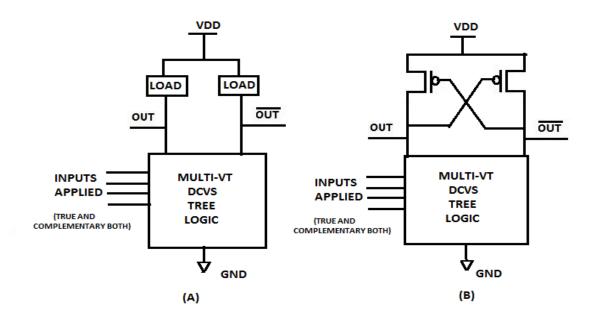

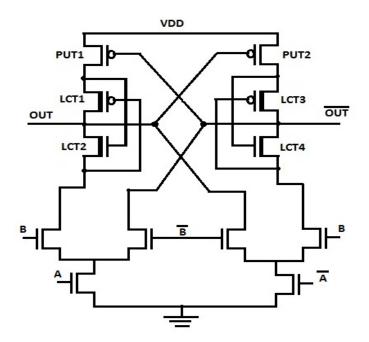

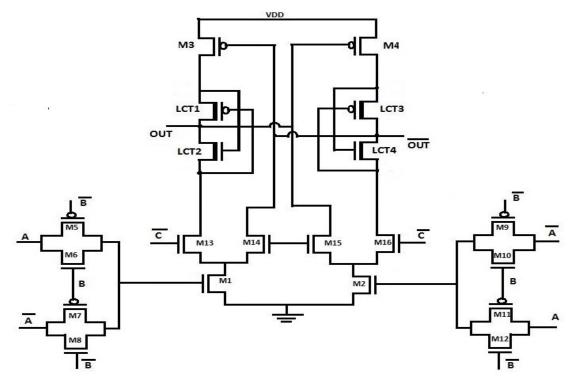

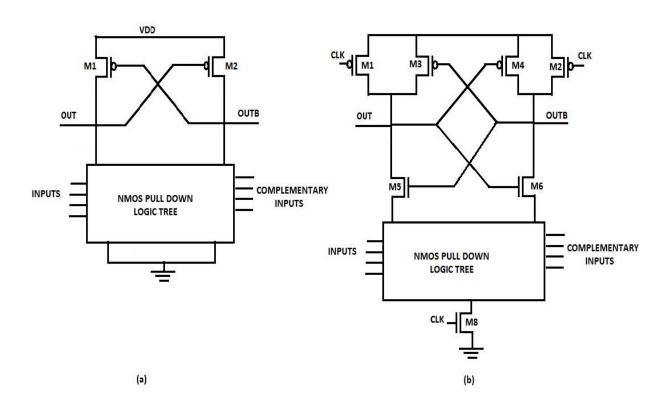

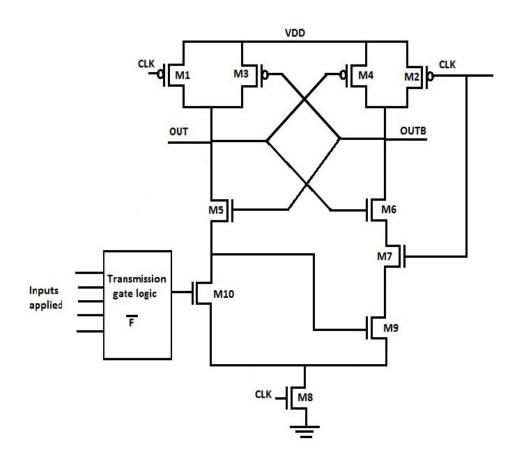

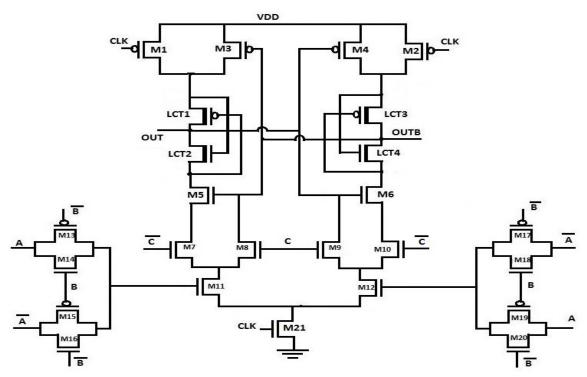

| Fig. 3.2 Schematic diagrams of (a) basic (b) static MT-DCVS circuit                    |

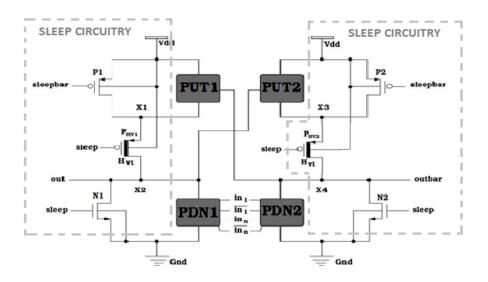

| Fig. 3.3 Generic sleep embedded DCVSL circuit                                          |

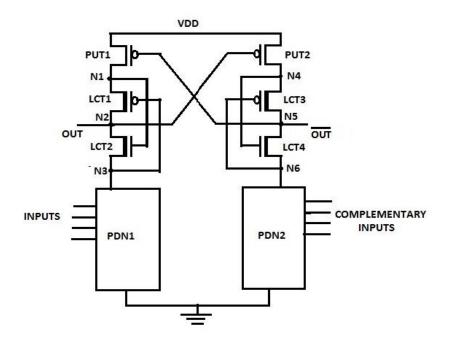

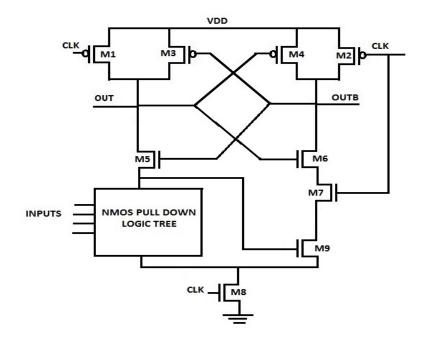

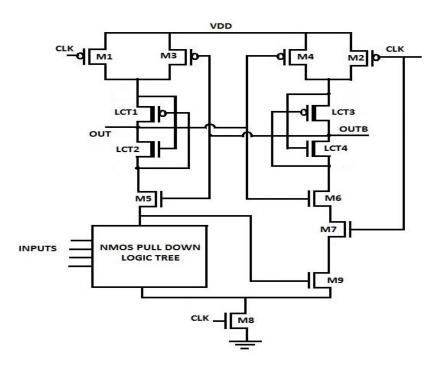

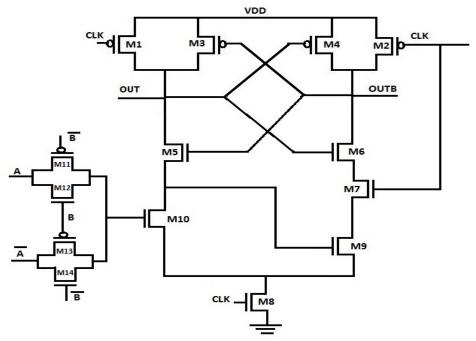

| Fig. 3.4 Modified LECTOR incorporated generic DCVSL circuit                            |

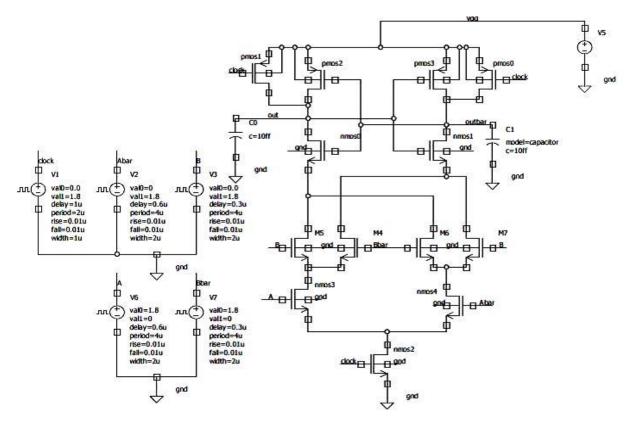

| Fig. 3.5 Two-input XOR gate                                                            |

| Fig. 3.6 Two-input LECTOR XOR gate                                                     |

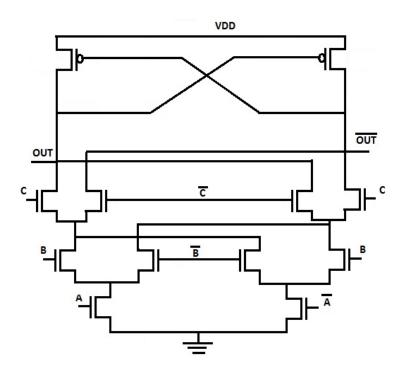

| Fig. 3.7 Three input XOR gate (all stacking)                                           |

| Fig. 3.8 Three-input LECTOR XOR gate                                                   |

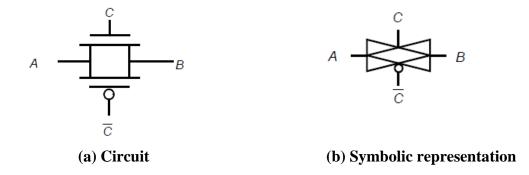

| Fig. 3.9 CMOS transmission gate (a) Circuit (b) Symbolic representation                |

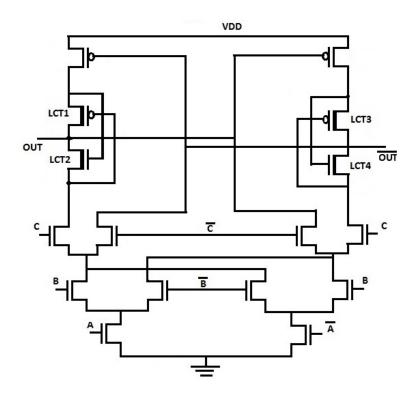

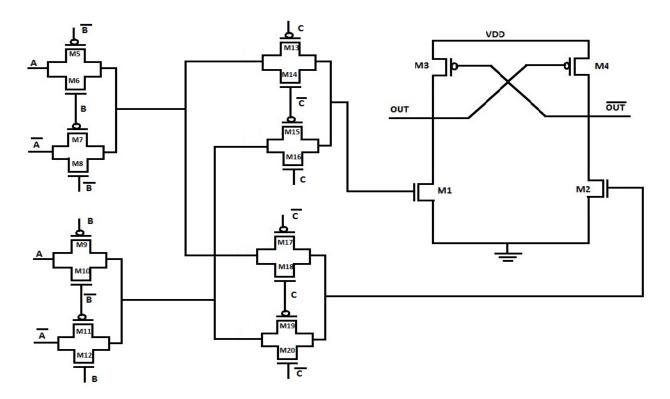

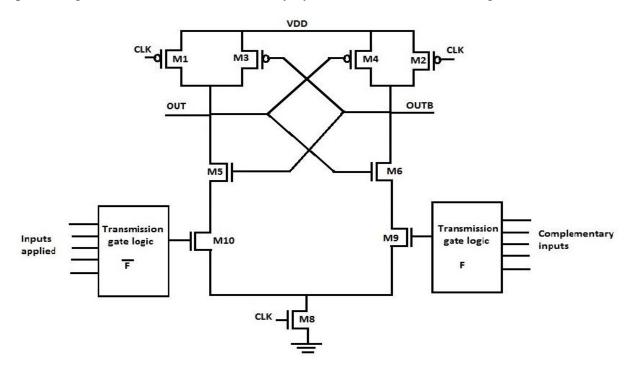

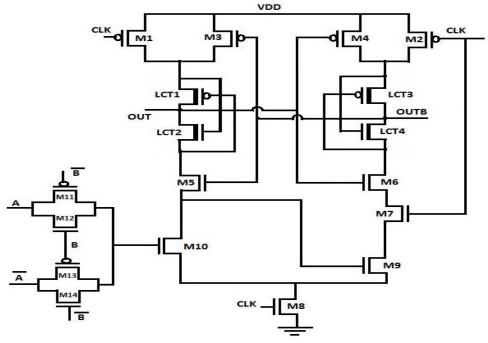

| Fig. 3.10 Basic architecture of a generic Hy-DCVSL circuit                             |

| Fig. 3.11 Basic hybrid DCVSL 2-input XOR gate                                          |

| Fig. 3.12 LECTOR hybrid DCVSL 2-input XOR gate                                         |

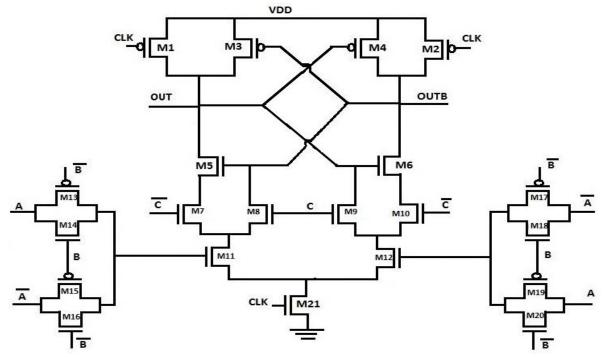

| Fig. 3.13 Basic Hybrid DCVSL 3-input XOR TYPE140                                       |

| Fig. 3.14 LECTOR Hybrid DCVSL 3-input XOR TYPE141                                      |

| Fig. 3.15 Basic Hybrid DCVSL 3-input XOR TYPE241                                       |

| Fig. 3.16 LECTOR Hybrid DCVSL 3-input XOR TYPE242                                      |

| Fig. 3.17 DCVSL inverter basic                                                         |

| Fig. 3.18 LECTOR incorporated DCVSL inverter                                           |

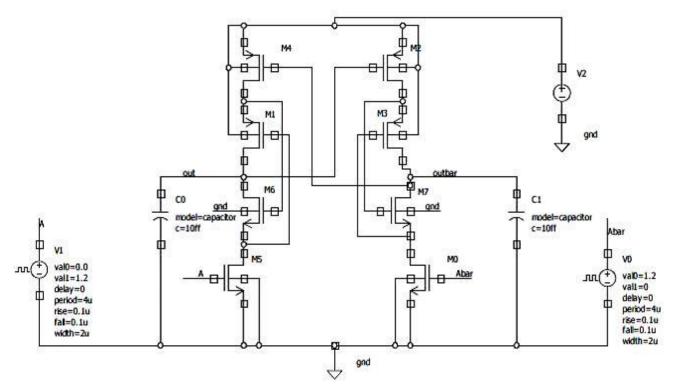

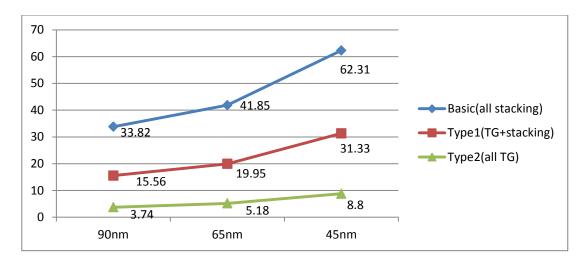

| Fig. 3.19 DCVSL NAND/AND.                                                           | 45  |

|-------------------------------------------------------------------------------------|-----|

| Fig. 3.20 LECTOR incorporated DCVSL NAND/AND                                        | .45 |

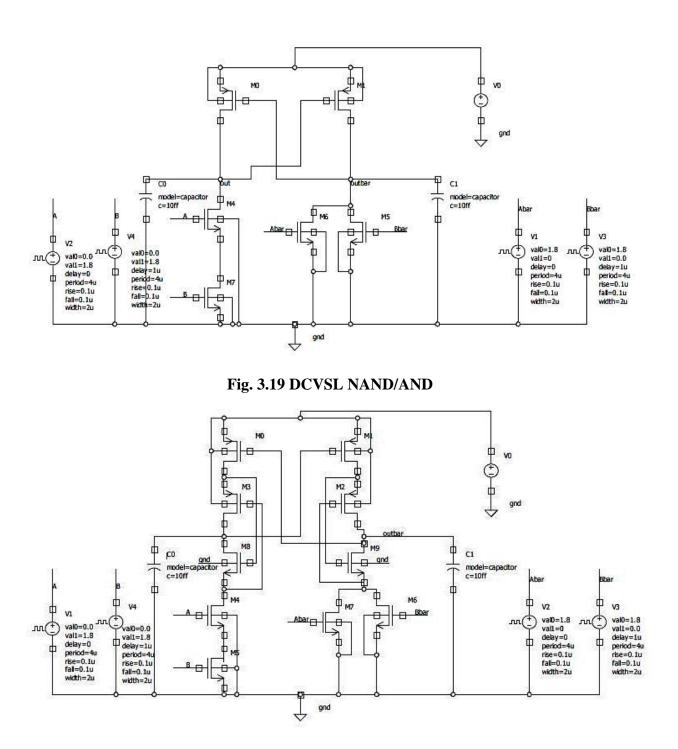

| Fig. 3.21 Leakage current (nA) comparison between Basic and Hybrid DCVSL            |     |

| configurations for 2-input XOR/XNOR at 1.2V                                         | 57  |

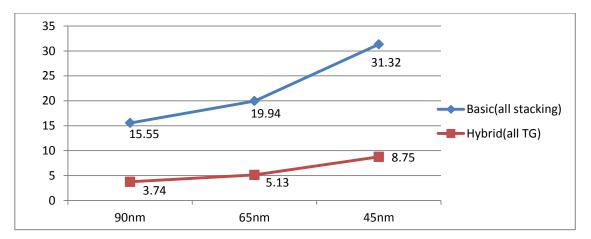

| Fig. 3.22 Leakage current (nA) comparison between Basic, Hybrid type1 (TG+stacking) |     |

| and hybrid Type2 (all TG) DCVSL configurations for 3-input XOR/XNOR                 |     |

| at 1.2V                                                                             | 58  |

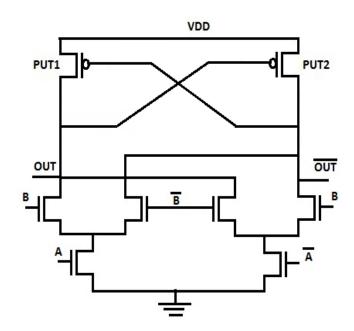

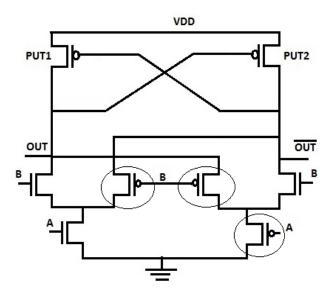

| Fig. 4.1 DCVSL: (a) Static version, and (b) Dynamic version                         | .66 |

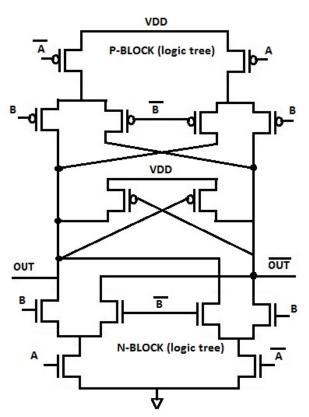

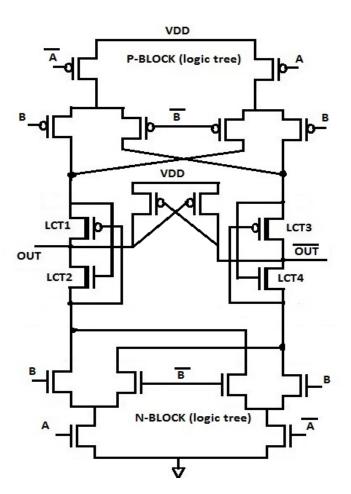

| Fig. 4.2 Basic architecture of EDCVSL                                               | 67  |

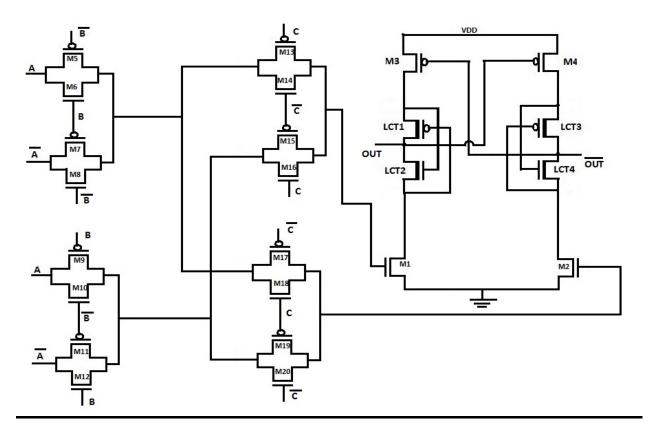

| Fig. 4.3 Modified LECTOR incorporated generic EDCVSL circuit                        | .68 |

| Fig. 4.4 Basic architecture of a generic Hy-DyDCVSL circuit                         | 69  |

| Fig. 4.5 Basic architecture of a generic Hy-EDCVSL circuit                          | 70  |

| Fig. 4.6 Basic hybrid EDCVSL 2-input XOR gate                                       | 71  |

| Fig. 4.7 LECTOR hybrid EDCVSL 2-input XOR gate                                      | .71 |

| Fig. 4.8 Basic Hybrid dynamic DCVSL 3-input XOR                                     | .72 |

| Fig. 4.9 LECTOR Hybrid dynamic DCVSL 3-input XOR                                    | 72  |

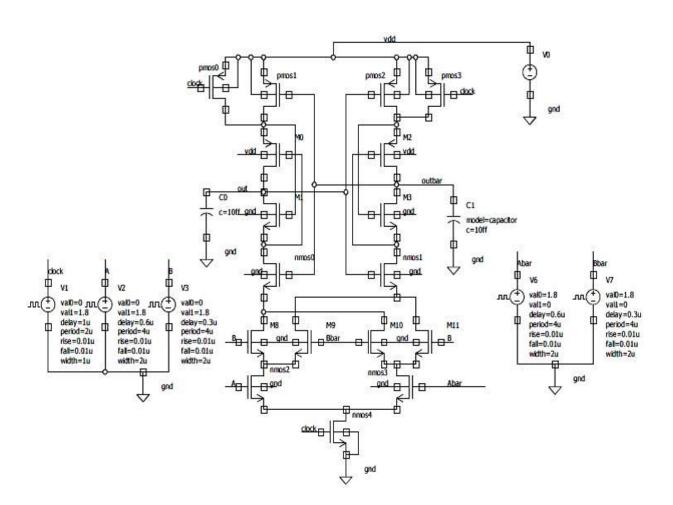

| Fig. 4.10 NP mixed DCVSL 2 input XOR gate                                           | 74  |

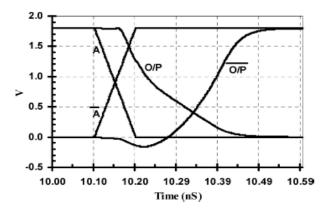

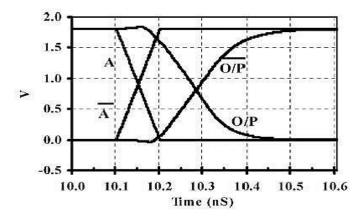

| Fig. 4.11 Input and output waveforms for DCVSL gate                                 | .74 |

| Fig. 4.12 Input and output waveforms for DSCL gate                                  | 75  |

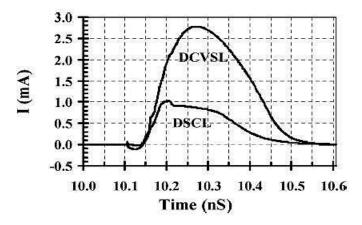

| Fig. 4.13 Peak supply currents for the DCVSL and the new DSCL while output          |     |

| Switching                                                                           | 76  |

| Fig. 4.14 Basic architecture for a 2-input XOR/XNOR DSCL gate                       | 76  |

| Fig. 4.15 Architecture of LECTOR incorporated 2-input XOR/XNOR DSCL gate            | 77  |

| Fig. 4.16 Basic EDCVSL Inverter/Buffer                                              | .78 |

| Fig. 4.17 LECTOR incorporated EDCVSL Inverter/Buffer                                | .79 |

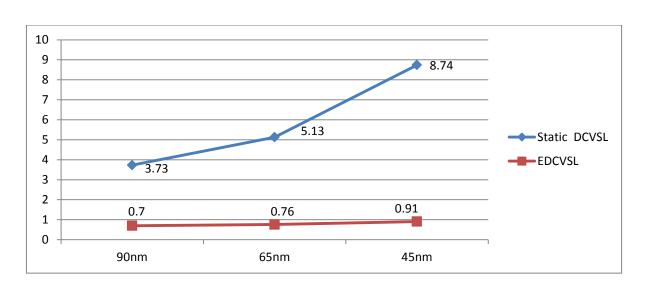

| Fig. 4.18 Average leakage current comparison for static DCVSL and dynamic EDCVSL    |     |

| inverter                                                                            | .81 |

| Fig. 4.19 Basic EDCVSL 2-input XOR gate (all stacking)                              | .81 |

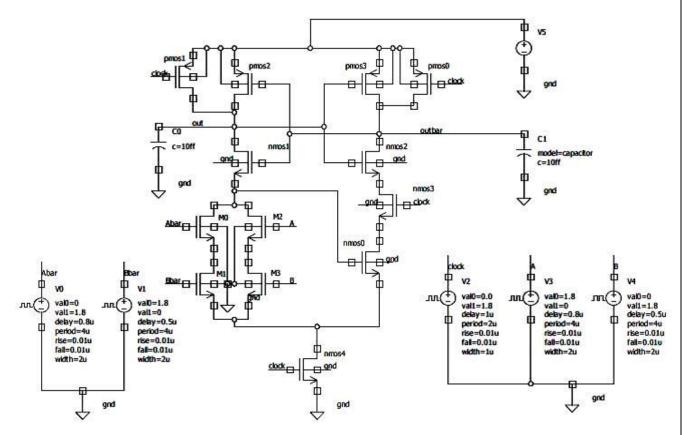

| Fig. 4.20 LECTOR incorporated EDCVSL 2-input XOR gate (all stacking)                 | 2  |

|--------------------------------------------------------------------------------------|----|

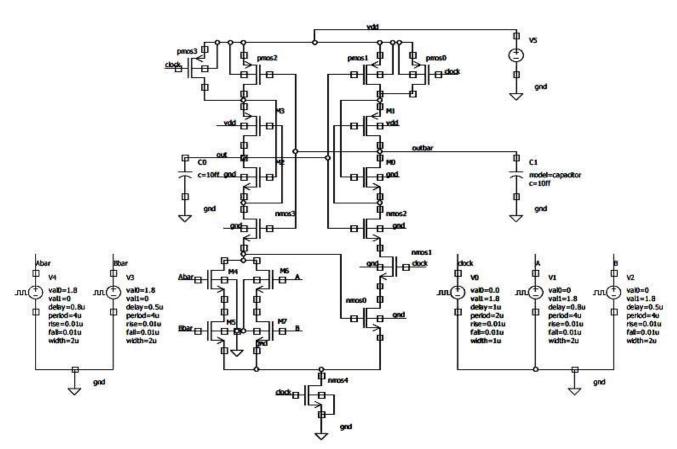

| Fig. 4.21 Basic Dynamic DCVSL 2-input XOR/XNOR gate (all stacking)                   | 7  |

| Fig. 4.22 LECTOR incorporated Dynamic DCVSL 2-input XOR/XNOR gate                    |    |

| (all stacking)                                                                       | 38 |

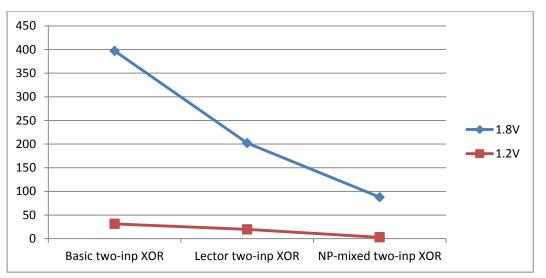

| Fig. 4.23 Leakage current comparison between basic, LECTOR incorporated and NP mixed |    |

| DCVSL 2-input XOR gate                                                               | 96 |

# LIST OF TABLES

| Table 2.1 Dependence of Subthreshold Leakage Current on MOS Transistor Parameters11 |

|-------------------------------------------------------------------------------------|

| Table 2.2 State Matrix of Two-Input LCT NAND Gate                                   |

| Table 2.3 Basic CMOS Inverter Leakage Current at Various Power Supplies             |

| Table 2.4 Leakage Current Measurement for Basic and LECTOR CMOS Inverter at         |

| VDD=1.8V25                                                                          |

| Table 2.5 Leakage Current Measurement for Basic and LECTOR CMOS Inverter at         |

| VDD=1.2V                                                                            |

| Table 2.6 Temperature Variation for CMOS Inverter                                   |

| Table 3.1 Leakage Current Measurement for Basic and LECTOR DCVSL Inverter at        |

| VDD=1.8V                                                                            |

| Table 3.2 Leakage Current Measurement for Basic and LECTOR DCVSL Inverter at        |

| VDD=1.2V                                                                            |

| Table 3.3 Leakage Current Measurement for Basic and LECTOR DCVSL NAND/AND           |

| Gate at VDD=1.8V46                                                                  |

| Table 3.4 Leakage Current Measurement for Basic and LECTOR DCVSL NAND/AND           |

| Gate at VDD=1.2V46                                                                  |

| Table 3.5 Leakage Current Measurement for Basic and LECTOR DCVSL 2-Input            |

| XOR/XNOR Gate at VDD=1.8V48                                                         |

| Table 3.6 Leakage Current Measurement for Basic and LECTOR DCVSL 2-Input            |

| XOR/XNOR Gate at VDD=1.2V48                                                         |

| Table 3.7 Leakage Current Measurement for Basic and LECTOR Hybrid 2-Input DCVSL     |

| XOR/XNOR Gate at VDD=1.8V49                                                         |

| Table 3.8 Leakage Current Measurement for Basic and LECTOR Hybrid 2-Input           |

| DCVSL XOR/XNOR Gate at VDD=1.2V50                                              |

|--------------------------------------------------------------------------------|

| Table 3.9 Leakage Current Measurement for Basic and LECTOR 3-Input DCVSL       |

| XOR/XNOR Gate at VDD=1.8V                                                      |

| Table 3.10 Leakage Current Measurement for Basic and LECTOR DCVSL 3-Input      |

| XOR/XNOR Gate at VDD=1.2V                                                      |

| Table 3.11 Leakage Current Measurement for Basic and LECTOR 3-Input Hybrid     |

| DCVSL XOR/XNOR Gate (Type 1) at VDD=1.8V53                                     |

| Table 3.12 Leakage Current Measurement for Basic and LECTOR 3-Input Hybrid     |

| DCVSL XOR/XNOR Gate (Type 1) at VDD=1.2V54                                     |

| Table 3.13 Leakage Current Measurement for Basic and LECTOR 3-Input Hybrid     |

| DCVSL XOR/XNOR Gate (Type 2) at VDD=1.8V55                                     |

| Table 3.14 Leakage Current Measurement for Basic and LECTOR 3-Input Hybrid     |

| DCVSL XOR/XNOR Gate (Type 2) at VDD=1.2V56                                     |

| Table 3.15 Delay Measurement for Basic DCVSL 2-Input XOR Gate                  |

| Table 3.16 Delay Measurement for LECTOR Incorporated DCVSL 2-Input XOR         |

| Gate60                                                                         |

| Table 3.17 Delay Measurement for 2-Input Basic Hybrid DCVSL XOR Gate61         |

| Table 3.18 Delay Measurement for 2-Input LECTOR Incorporated Hybrid DCVSL      |

| XOR Gate61                                                                     |

| Table 3.19 Delay Measurement for 3-Input Basic DCVSL XOR Gate (All Stacking)62 |

| Table 3.20 Delay Measurement for 3-Input LECTOR Incorporated DCVSL XOR         |

| Gate (All Stacking)62                                                          |

| Table 3.21 Delay Measurement for 3-Input Basic Hybrid DCVSL XOR Gate           |

| (Type1=>TG+Stacking)63                                                         |

| Table 3.22 Delay Measurement for 3-Input LECTOR Incorporated Hybrid DCVSL      |

| XOR Gate (Type1=>TG+ Stacking)63                                               |

| Table 3.23 Delay Measurement for 3-Input Basic Hybrid DCVSL XOR Gate           |

| (Type2=>Complete TG)63                                                           |

|----------------------------------------------------------------------------------|

| Table 3.24 Delay Measurement for 3-Input Lector Incorporated Hybrid DCVSL XOR    |

| Gate (Type2=> Complete TG)64                                                     |

| Table 4.1 Normalized Gate Oxide and Subthreshold Leakage Currents of the High-Vt |

| And Low-Vt Transistors at Different Temperatures                                 |

| Table 4.2 Leakage Current Measurement for Basic and LECTOR EDCVSL                |

| Inverter/Buffer at VDD=1.8V79                                                    |

| Table 4.3 Leakage Current Measurement for Basic and LECTOR EDCVSL                |

| Inverter/Buffer at VDD=1.2V80                                                    |

| Table 4.4 Leakage Current Measurement for Basic and LECTOR EDCVSL 2-Input        |

| XOR Gate (All Stacking) at VDD=1.8V                                              |

| Table 4.5 Leakage Current Measurement for Basic and LECTOR EDCVSL 2-Input        |

| XOR Gate (All Stacking) At VDD=1.2V                                              |

| Table 4.6 Leakage Current Measurement for Basic and Lector Hybrid EDCVSL         |

| 2-Input XOR/XNOR Gate (All TG) at VDD=1.8V                                       |

| Table 4.7 Leakage Current Measurement for Basic and LECTOR Hybrid EDCVSL         |

| 2-Input XOR/XNOR Gate (All TG) at VDD=1.2V                                       |

| Table 4.8 Leakage Current Measurement for Basic and LECTOR Incorporated Dynamic  |

| DCVSL 2-Input XOR/XNOR Gate (All Stacking) at VDD=1.8V                           |

| Table 4.9 Leakage Current Measurement for Basic and LECTOR Incorporated Dynamic  |

| DCVSL 2-Input XOR/XNOR Gate (All Stacking) at VDD=1.2V                           |

| Table 4.10 Leakage Current Measurement for Basic and LECTOR Incorporated Hybrid  |

| Dynamic DCVSL 3-Input XOR/XNOR Gate (TG+Stacking) at VDD=1.8V91                  |

| Table 4.11 Leakage Current Measurement for Basic and LECTOR Incorporated Hybrid  |

| Dynamic DCVSL 3-Input XOR/XNOR Gate (TG+Stacking) at VDD=1.2V92                  |

| Table 4.12 Leakage Current Measurement for Basic and LECTOR Incorporated DSCL    |

| 2-Input XOR/XNOR Gate at VDD=1.8V                                                |

| Table 4.13 Leakage Current Measurement for Basic and LECTOR Incorporated DSCL  |

|--------------------------------------------------------------------------------|

| 2-Input XOR/XNOR Gate at VDD=1.2V94                                            |

| Table 4.14 Leakage Current Measurement for NP-Mixed 2-Input XOR/XNOR Gate95    |

| Table 4.15 Delay Measurement for 2-Input Basic Hybrid EDCVSL XOR Gate          |

| (All TG)                                                                       |

| Table 4.16 Delay Measurement for 2-Input LECTOR Incorporated Hybrid EDCVSL     |

| XOR Gate (All TG)                                                              |

| Table 4.17 Delay Measurement for 3-Input Basic Hybrid Dynamic DCVSL XOR        |

| Gate (TG + Stacking)100                                                        |

| Table 4.18 Delay Measurement For 3-Input LECTOR Incorporated Hybrid Dynamic    |

| DCVSL XOR Gate (TG + Stacking)100                                              |

| Table 4.19 Delay Measurement For 2-Input Basic DSCL XOR Gate (All Stacking)101 |

| Table 4.20 Delay Measurement For 2-Input LECTOR Incorporated DSCL XOR          |

| Gate (All Stacking)101                                                         |

## ABSTRACT

Rapid scaling of transistor dimensions in accordance with Moore's law due to brisk demand of high speed portable electronic device has led to drastic upsurge in leakage currents in the device leading to unnecessary leakage power dissipation. The research in this thesis unfolds the rising gravity of the issue with continuous technology advancement and explores different ways to curtail the problem. Of late, a shift of trend from conventional CMOS logic to differential logic styles has been witnessed due to their in-built features of lower power consumption and high speed. DCVSL which is one of the differential logic families is an efficacious blend of the advantages of traditional CMOS logic and pseudo NMOS logic and offers a high speed, area effective and rail to rail swing logic design option. Henceforth, DCVS logic family has been explored in this thesis to exploit its inherent advantages and moreover its leakage power aspect has been dealt deeply to introduce low power DCVS logic which works well at lower technology nodes.

This thesis includes in depth study of causes of leakage power in devices and techniques to regulate leakage current at circuit level for CMOS logic circuits. Trends followed by leakage current with variation in supply and technology are studied and verified. LECTOR technique used for CMOS logic has been adapted and aptly applied to static, dynamic and enhanced DCVS logic which achieves a significant saving in leakage loss for DCVS logic circuits. Various basic logic circuits are implemented using DCVSL style and their low power versions are proposed by adapting studied methodologies which are leakage power efficient. Hybrid configurations involving combination of transmission gate logic and DCVS logic are proposed for two input and three input XOR gates for static, dynamic and enhanced DCVS logic. Hybrid configuration proves to be more efficient in terms of leakage power saving. Furthermore, LECTOR incorporated versions of hybrid configurations are introduced which achieves even more leakage saving when compared to basic DCVSL configuration. The functionality and effectiveness of all proposed architectures are confirmed through intensive simulations on SYMICA Development Environment at 90nm, 65nm and 45nm technology parameters (leakage effect is more predominant below 180nm). All the above introduced circuits are simulated with VDD=1.8V and 1.2V to analyse the pattern followed with supply variation. Similarly, temperature variation is performed for temperature values of -25°C, 27°C and 100°C at 45nm technology and VDD=1.2V. Effect of proposed configurations on the delay of the circuit has been analysed as well.

## **Chapter 1**

## Introduction

#### **1.1 MOTIVATION**

Earlier chief design constraints in VLSI design used to be the area, delay and cost of the device or system being designed. In recent years this trend has changed vividly and minimal power dissipation has been witnessed to emerge as the greatest challenge for designers relatively to other design metrics to avoid heating up and degradation of device [1]. Low power design has become the need of the hour of semiconductor industry due to steep increase in the demand of power efficient portable electronic devices. Portable devices have two modes of operation –active mode and standby mode. Cell phones, PCs and laptops sit in idle state most of the times and have burst mode type integrated circuits i.e. their idle time is quite higher than the time for which they are active[2]. There is a leakage power dissipation which takes place when the device is non-operational and drains out the battery worth of no use. This leakage power has come into main focus since the VLSI design industry has entered into deep submicron regime.

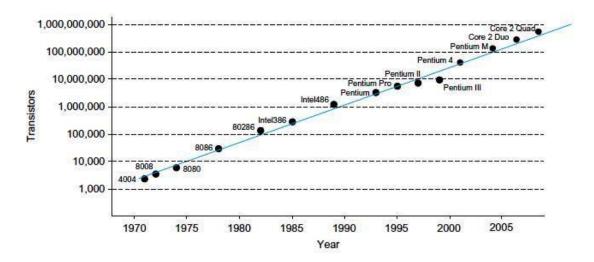

The demand of reduced overall power dissipation, higher speed and denser integration has commenced the scaling of MOS devices in every technology generations. Well known Moore's Law which is a phenomenological observation that every two years the number of transistors on an IC doubles is the practical realisation of scaling theory. A corollary of Moore's law is Dennard's Scaling Law [3]: as transistors shrink, they become speedier, consume less power, and are cheaper to manufacture. The multiplication in Transistor count in Intel microprocessors is shown in fig 1.1[3]

Fig 1.1 Transistors in Intel microprocessors[3]

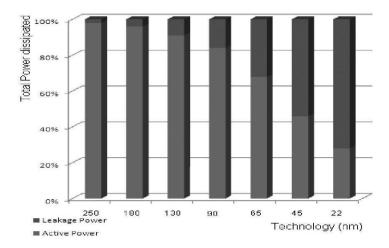

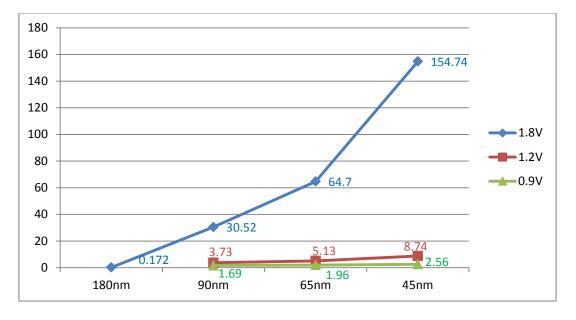

Undoubtedly progressing towards lower technology nodes is fulfilling above mentioned gainful features but unfortunately has resulted in a drastic increase in leakage currents while the device is inactive which gets even worse when multiplied with millions of transistors count on chip. The reasons behind the same are explained in the following chapters. We can observe the pattern followed by leakage power dissipation with decreasing channel length from fig 1.2[4]. It is an estimation based upon the present scenario that leakage power is going to increase 32 times per device as we touch year 2020 [5]. Fig 1.2 shows the percentage contribution of leakage power and active power in total power dissipated at various technology generations [4]. It should be noted that with every technology advancement leakage power for below 45nm technologies. Consequently, it has become extremely crucial to regulate the increasing leakage loss with shrinking device geometries.

Fig 1.2 Power dissipated in various technologies [4]

Design styles and logic family play a significant role in deciding the performance and

efficiency of the circuit based on various design constraints like area, speed, power dissipation, threshold voltage and supply voltage scalability of the circuit. Differential logic styles are gaining attention of researchers rapidly as they offer some very promising features like superior noise immunity, compact structure and implementation of both complemented and non-complemented functions together. There are several differential logic styles available like CPL, MCML etc. Differential cascode voltage switch logic or DCVSL is one of them which successfully combines the advantages of both conventional CMOS logic and pseudo NMOS logic and thereby provides a high speed, area efficient and rail to rail swing slogic design alternative. Our motive is to first to study various leakage reduction techniques available for CMOS logic circuits. Secondly, analyse DCVSL logic family in terms of its leakage power loss at various technology generations and develop a self-controlled circuit level methodology to minimise leakage currents for the same. Choice of logic family proves to be very crucial in accordance with what all design constraints are to be met and hence is a challenging task for VLSI designers.

### **1.2RESEARCH OBJECTIVE**

The basic motivation to proceed with this particular research is to perform a profound study of circuit level techniques to counteract the increasing leakage power losses with finer technologies and come up with a low power differential logic style by aptly applying those to DCVSL family. DCVSL being a differential logic style offers certain advantages over logic implementation using conventional CMOS logic style and hence is a part of high speed digital circuit designing. A lot of research has been performed in the field of leakage power reduction for traditional CMOS logic but leakage power aspect of DCVSL style is yet to be explored. This thesis is an attempt to unfold the leakage power losses in DCVSL logic circuits and propose different new low power structural configurations for the most frequently used logic circuit in digital VLSI design i.e. XOR gate which has minimal leakage power dissipation. The objectives of carrying out this research work are:

- To carefully study the trends followed by leakage power dissipation with rapid technology advancements.

- Study of various components contributing to leakage current and in depth analysis of several circuit-level leakage reduction techniques to gain control over it.

- Appropriately applying the knowledge of studied techniques to achieve DCVSL configuration incorporated with a self-controlled leakage reduction facility.

- Simulating basic static DCVSL, dynamic DCVSL and EDCVSL circuits along with proposing their low power, leakage controlled versions and comparing their leakage currents.

- To introduce new hybrid static and hybrid dynamic DCVSL architectures for two input and three input XOR gates and their reduced leakage configurations.

- To introduce new special structures (NP mixed DCVSL and DSCL) for two input XOR gate.

- Verification of proposed structures by performing intensive simulations on SYMICA development environment at 180nm, 90nm, 65nm and 45nm technologies.

- Performing voltage supply and temperature variations for the proposed structures.

### **1.3 STRUCTURE OF THESIS**

This thesis is framed in five chapters. First chapter discusses the basic motivation behind this work which explains that why this research has been taken up accompanied by the objectives of this thesis and also the literature regarding the leakage power reduction techniques in CMOS logic and in DCVS logic has been reviewed. Chapter 2 delineates about the trends followed by leakage power with scaling down of technology, types of power dissipation and different components of leakage current. It also discusses the various circuit level techniques to regulate leakage current through a CMOS logic circuit. Moreover, towards end it presents a comparison between various techniques. Chapter 3 is dedicated to static DCVSL which explains the advantages of DCVS logic style over traditional CMOS logic. It discusses the

operation of basic DCVSL, throws a light over existing leakage reduction techniques for DCVSL and proposes a new LECTOR incorporated structure of DCVSL which provides a self-controlled leakage reduction facility in DCVS logic circuits. It also presents an overview of transmission gate logic and finally proposes new hybrid configurations for 2 input and 3 input static DCVSL XOR gates combining transmission gate logic and DCVS logic which are then compared with existing fully stacked DCVSL structure of XOR gates for leakage currents. Chapter 4 describes the dynamic counterpart of DCVSL along with enhanced DCVSL. Hybrid dynamic DCVSL and EDCVSL architectures for 2 input and 3 input XOR gates have been proposed. In conjunction with this two special structures namely NP mixed DCVSL and LECTOR incorporated DSCL have been proposed. Voltage and temperature variations also have been performed for existing and proposed structures and the comparison is drawn. Chapter 5 comprises conclusion drawn from varied study and simulation, in accordance with the thesis objectives.

## **Chapter 2**

## Leakage Power Minimization Techniques

#### **2.1 INTRODUCTION**

With perpetual scaling of devices dimensions to stay on Moore's law is leading the electronics industry towards the path of denser and speedier integration. Henceforth it has provided a provision for catering the demand of complex functions with higher performance and lower power dissipation. Along with minimising device sizes supply voltage needs to be scaled as well to avoid high electric field effects (second order effects) and maintain the acceptable system functioning. Moreover voltage scaling is the most effective method to save dynamic power ( $C_{load} * F_{clk} * V_{dd}^2$ ) because of its square law dependence on supply voltage plus the reduction in parasitic capacitance due to scaling of device leads to lesser load capacitance and hence reduced dynamic power. Unfortunately voltage scaling degrades the performance of the circuit by reducing its speed due to decrease in overdrive voltage ( $V_{gs}$ - $V_{th}$ ). Generally, the ratio of the supply voltage to the threshold voltage of the device should be at least 5, in order to ensure that the performance of CMOS circuits is least affected [6]. Therefore, to counteract the performance degradation due to voltage scaling, we scale down threshold voltage of transistor to lessen the gate delays. Scaling V<sub>th</sub> is followed by an exponential increase in sub threshold leakage current. There are several other components as well contributing to leakage power dissipation in deep submicron and nanoscale technologies explained later in the chapter. But the most dominant phenomenon is subthreshold leakage which outdoes other leakage components.

Threshold voltage of transistors needs to be adjusted in digital circuits design for maximum saving in leakage loss while maintaining the desirable performance. Circuit level methodologies have a very important role to play in the motive of regulating the subthreshold leakage power dissipation in both active and sleep modes. Hence it has turned out to be indispensable for circuit designers to concede the importance of controlling leakage power consumption and saving energy efficiently at all levels of the design hierarchy, starting from the lower levels of abstraction. Various leakage minimisation techniques have been discussed in detail in the chapter.

#### 2.2. POWER DISSIPATION IN CMOS CIRCUITS

Average power dissipation  $(P_{avg})$  of CMOS digital circuits can be expressed as the sum of three key components which are given in the following equation, as

### $P_{avg} = P_{short-circuit} + P_{leakage} + P_{dynamic}$

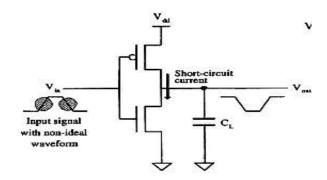

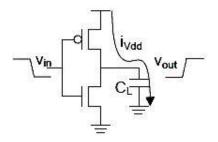

**2.2.1 Short-Circuit Power:** Short-Circuit Power is the power dissipation which takes place from stacked P and N device in a CMOS logic gate which get ON simultaneously. This happens for a brief period of time during which the input of the circuit switches. The most prominent way to control this type of power dissipation is the minimization of the transition times on nets. It typically accounts for 15%-20% of the overall power dissipation.

Fig 2.1 Short-circuit power

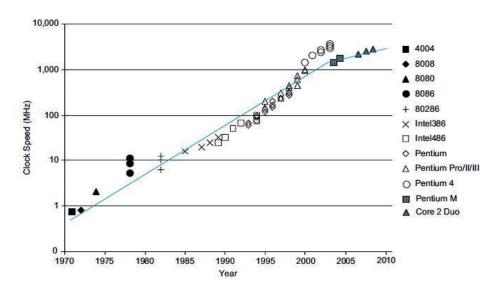

As the frequency of operation is being increased with every technology generation, the transition time signals are also getting reduced thus resulting in reduction of static power. Figure 2.2 shows that Intel microprocessor clock frequencies have doubled approximately every 34 months [4].

Fig 2.2 Clock frequencies of Intel microprocessors [4]

**2.2.2 Dynamic Power:** is the dynamic power dissipation, also called the switching power. This is the dominant source of power consumption in CMOS system-on-chip (SoC), accounting for roughly 75% of the total. It is generally represented by the following approximation,

$$\mathbf{P}_{\text{dynamic}} = \alpha \cdot \mathbf{C}_{\text{Load}} \cdot \mathbf{V}_{\text{dd}}^2 \cdot \mathbf{f}_{\text{clk}}$$

where ' $\alpha$ ' is the switching activity factor (also called transition probability) and it tends to increase as the need for bandwidth increases, ' $C_{Load}$ ' is the overall capacitance to be charged and discharged in a reference clock cycle.

Fig 2.3 Dynamic switching power

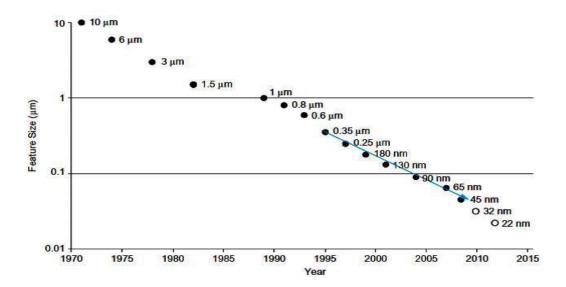

The power dissipation that results from switching activity proves to be the dominant component for technology processes having feature size greater than 1um [6]. The minimum dimension of a transistor that can be unfailingly manufactured is denoted by the feature size of a CMOS manufacturing process. With maturation of technology processes toward the deep-submicron and nanotech regime, the feature sizes of the transistors are getting reduced, and consequently reducing the load capacitances. Figure 2.4 shows the feature sizes for different process generations [4]. The reduction in feature size puts a constraint on supply voltage to avoid high electric field effects and hence forces its reduction. The voltage scaling technique taking the prominent benefit of the quadratic dependence of switching power on supply voltage contributes to dynamic power savings. It can be concluded that with reduction in feature size dynamic power dissipation is losing its dominance due to minimisation of parasitic capacitances and supply voltage.

Fig 2.4 Process generations [13]

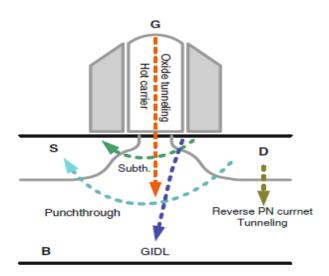

**2.2.3 Leakage Power:** A small amount of current is leaked even when transistors are supposedly OFF. Different leakage mechanisms comprise subthreshold conduction between source and drain, gate leakage from the gate to body, and junction leakage from source to body and drain to body, as shown in Fig 2.5. Thermal emission of carriers over the potential barrier set by the threshold causes subthreshold conduction. Tunnelling of charge carriers through the extremely thin gate dielectric causes a quantum mechanical effect called gate leakage. Junction leakage is the result of current through the reverse biased p-n junctions between the source/drain diffusions and the body. In technology with feature sizes greater than 180 nm, leakage was typically insignificant except in very low power applications. For 90 and 65 nm technologies, threshold voltage got reduced to the level that subthreshold leakage is raised from the levels of 1s to 10s of nA per transistor, which becomes significant when collectively seen for millions or billions of transistors on a chip. For 45 nm process technology, oxide thickness gets reduced to the extent that gate leakage becomes comparable to subthreshold leakage. Gate leakage can be reduced if high-k gate dielectrics are employed. On the whole, leakage has become a significant design concern in deep sub-micron and nanometre processes [3].

Leakage power also increases with increasing die area which means an increase in transistor count over the chip indicating the multiplication of leakage current.

Fig 2.5 Leakage current components in an NMOS transistor.

#### **Major Components of Leakage Power Dissipation**

The four major sources of leakage current flow in a MOS transistor are:

- i. Reverse-biased junction leakage current (IREV)

- ii. Gate induced drain leakage (IGIDL)

iii. Gate direct-tunnelling leakage (IG)

iv. Subthreshold (weak inversion) leakage (Isub)

which are discussed below.

#### i. Reverse-biased junction leakage current (*IREV*)

The reverse biased *junction leakage* current originates from the source or drain to the substrate through the reverse biased diodes formed between source/drain and substrate when a transistor is OFF. For instance, considering the case of an inverter with logic low input voltage, NMOS turns OFF, the PMOS turns ON, and the output voltage is logic high. Consequently, the drain-to-substrate voltage of the NMOS which is OFF transistor is equal to the supply voltage. As a result of it leakage current flows from the drain to the substrate through the reverse-biased diode (junction). The diode's leakage current magnitude depends on the drain diffusion area and the leakage current density, which is decided by the concentration of doping. The p-n junction leakage is dominated by band-to-band tunnelling (BTBT) if both n and p regions are heavily doped [7]. Junction reverse-bias leakage components are usually insignificant relating to the other three leakage components.

#### ii. Gate-Induced Drain Leakage

High field effect in the drain junction of MOS transistors causes gate induced drain leakage (GIDL). For an NMOS transistor having gate at ground potential and drain at VDD potential, band bending takes place in the drain which is very significant and allows electron-hole pair generation through avalanche multiplication and band-to-band tunnelling. A deep depletion condition arises as the holes are swiftly swept out to the substrate and simultaneously electrons get collected by the drain which results in GIDL current. This leakage mechanism even worsens by high drain to body voltage and high drain to gate voltage. Transistor scaling leads to progressively sharp halo implants, where the substrate doping at the junction interfaces is made higher, whereas the channel doping is kept low. This has been done primarily to avoid or control punch-through and drain-induced barrier lowering while having a very less effect on the carrier mobility in the channel. BTBT currents are increased as a result of steep doping profile at the drain edge, particularly as VDB is increased. GIDL current gets increased with thinner oxide and higher supply voltage [8].

#### iii. Gate Direct Tunnelling Leakage

The current flowing from the gate through the "leaky" oxide insulation to the substrate is the gate leakage current. For low Si-oxide thicknesses ( typically in 0.15um and even lower technology nodes), leading effect causing gate leakage is the direct tunnelling through the silicon oxide layer due to high electric field across the gate substrate for a high potential difference. There are several Mechanisms for direct tunnelling which include electron tunnelling in the conduction band (ECB), electron tunnelling in the valence band (EVB), and hole tunnelling in the valence band (HVB) and among all ECB proves to be the dominant one. The amount of the *gate direct tunnelling current gets* increased exponentially with the decrease in gate oxide thicknesses (of the order 2-3 nm), at a gate to source voltage (VGS) of 1V, every 0.2nm reduction in Tox results in a tenfold increase in gate leakage current IG [8]. It should be noted that the gate leakage for a NMOS device is

typically one order of magnitude higher than that of an PMOS device having identical  $T_{ox}$  and V<sub>DD</sub> when using SiO<sub>2</sub> as the gate dielectric. To maintain effective gate control over the channel region gate oxide thickness must also be reduced as transistor length and supply voltage are scaled down. As a consequence of it there is an exponential upsurge in the gate leakage due to direct tunnelling of electrons through the gate oxide [8]. An effective method to combat the gate leakage currents and maintaining excellent gate control as well is the replacement of the now used silicon dioxide gate insulator with high-K dielectric material such as TiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>.

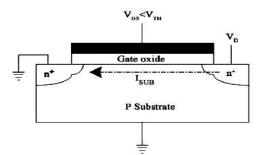

#### iv. Subthreshold (weak inversion) leakage (Isub)

There is a current flow between source and drain region in a MOS transistor when gate voltage,  $V_{GS}$  is below the threshold voltage,  $V_{TH}$  of the MOS transistor which is known as Subthreshold or weak inversion conduction current. It results due to the minority carrier drift from the drain to the source region through the channel in weak inversion region. The flow of subthreshold leakage current in an NMOS transistor has been shown in fig 2.6[5], when  $V_{GS}$  is less than  $V_{TH}$  of the transistor. The minority carriers' concentration in weak inversion region is rather small, but not actually zero. Subthreshold leakage power has become dominant among other leakage power components because of the inevitability to use low threshold voltage transistors in order to maintain the desired speed of the device. New and improved circuit design techniques should be devised to minimise this leakage power which is undesirable in digital circuit design.

Fig 2.6 Subthreshold leakage current in an NMOS transistor [5]

According to BSIM4 MOSFET model, the equation governing this subthreshold leakage current [5] can be expressed as

where,

$$I_o = \mu C_{ox} \left(\frac{W}{L}\right) V_T^2 e^{1.8}$$

and  $V_T = \frac{KT}{q}$

Here VGS, VDS and VBS are the gate to source, drain to source, and bulk to source voltages respectively,  $\mu$  denotes the carrier mobility, Cox is the gate oxide capacitance per

unit area, W and L denote the channel width and channel length of the transistor, K is the Boltzmann constant, T is the absolute temperature, q is the electrical charge of an electron, VT is the thermal voltage, VTH0 is the zero biased threshold voltage,  $\gamma$  is body effect coefficient,  $\eta$  denotes the drain induced barrier lowering coefficient, and n is the subthreshold swing coefficient. Table 2.1 [9] shows the dependence of subthreshold leakage current on MOS device parameters. Increasing the threshold voltage of the MOS transistor is an effective way to reduce sub- threshold leakage power dissipation.

#### TABLE 2.1 [9] DEPENDENCE OF SUBTHRESHOLD LEAKAGE CURRENT ON MOS TRANSISTOR PARAMETERS.

| TRANSISTOR<br>PARAMETER               | DEPENDENCE OF SUBTHRESHOLD<br>LEAKAGE                   |

|---------------------------------------|---------------------------------------------------------|

| Transistor width (W)                  | Directly proportional                                   |

| Transistor length (L)                 | Inversely proportional                                  |

| Temperature (T)                       | Exponential increase                                    |

| Transistor threshold<br>voltage (VTH) | Increases by an order of magnitude with 100 mV decrease |

| Input voltage (VGS)                   | Exponential increase                                    |

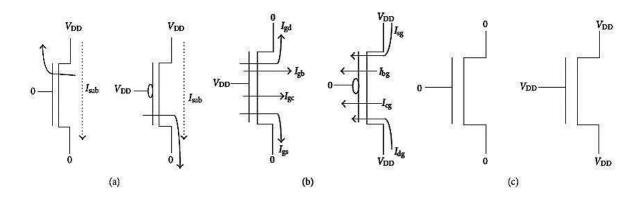

Fig 2.7 (a)Maximum subthreshold leakage current state. (b)Maximum gate oxide leakage current state. (c)Condition to avoid both subthreshold and gate oxide leakage current[10]

#### **2.3 LEAKAGE REDUCTION TECHNIQUES**

Continuous scaling down of CMOS technology has made leakage power comparable to dynamic switching power. Threshold voltage of transistors needs to be adjusted in digital circuits design for maximum saving in the leakage power dissipation while maintaining the desirable performance. To counteract the excessive leakage in CMOS circuit, many architectural techniques have been proposed over the years which achieve a significant saving in subthreshold leakage.

Various leakage power reduction techniques have been discussed below briefly:

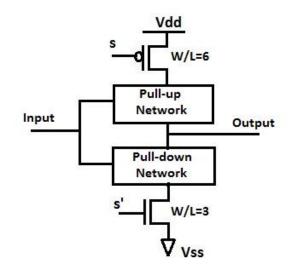

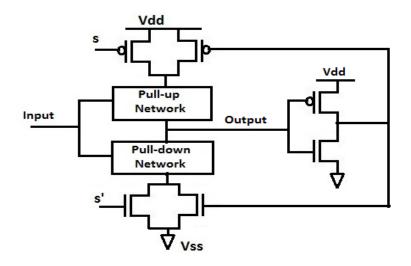

**2.3.1 Power Gating (Sleep Approach) with MTCMOS:** Sleep transistor technique [11] is the most widely known and conventional approach to achieve efficient leakage regulation in CMOS circuits. Sleep approach does two small changes in the basic circuitry of CMOS circuit (i) placement of an additional "sleep" PMOS transistor between power supply ( $V_{dd}$ ) and the pull-up network of a circuit and (ii) placement of an additional "sleep" NMOS transistor between the pull-down network and Gnd.

Fig 2.8 Sleep Approach

In standby mode when the circuit is sitting idle and is not supposed to work these sleep transistors turn off the circuit by cutting off the power rails. The circuit loses its connection from ground and V<sub>dd</sub>. The structure is shown in Fig 2.8 where transistors with input S and S' are sleep transistors. The sleep transistors are turned on when the circuit is active so that PUN is transparently connected to V<sub>dd</sub> through PMOS sleep transistor and PDN is connected to ground through NMOS sleep transistor so that normal operation takes place. And when the circuit is idle, the sleep transistors are turned-off. The power cut-off done by sleep transistor approach can reduce leakage power effectively. However, sleep technique results in some worth noticing drawback which are output destruction of state plus a floating output voltage after sleep mode. State-destructive techniques use sleep transistor to achieve cutting off of transistor (pull-up or pull-down or both) networks from supply voltage or ground. These techniques are also known as gated-V<sub>dd</sub> and gated- Gnd. Sleep transistors used are usually having high Vth to achieve effective leakage reduction. This technique is MTCMOS where sleep transistors are made high Vth while for maintaining fast switching speeds, transistors used in logic design are low-Vth. High Vth transistors suppress leakage manifold as compared to low Vth ones. Moreover, the state loss and floating values of the pull-up and pull-down networks during sleep mode has a significant impact on the wake up time and energy of the sleep technique because of the necessity to recharge transistors which suffered state loss during sleep.

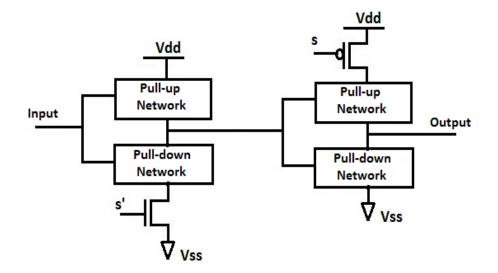

**2.3.2 Zigzag Approach:** One of the drawbacks of sleep technique was the floating state of output in sleep mode due to loss of connection from both  $V_{dd}$  and ground. The zigzag technique [11] shown in fig 2.9 is somewhat similar to sleep technique except it uses only one sleep transistor in each logic stage either in the pull-up or pull-down network depending upon a particular input pattern. Input pattern is a data vector which can achieve the lowest possible leakage power consumption for the concerned circuit. Sleep transistor is assigned to the pull-down network if the output of the circuit for the input vector corresponding to the lowest power is "1" so that the output node remains connected to V<sub>dd</sub> in sleep mode or else sleep transistor is assigned to the pull-up network if the output is "0" so that the output node remains connected to ground rail in sleep mode. For Fig 2.9, we have assumed that the output of the first stage turns out to be "1" and the output of the second stage turns out to be "0" when there is an assertion of minimum leakage inputs. Therefore, we insert a pull-down sleep transistor for the first stage between PDN and ground and a pull-up sleep transistor for the second stage between power supply and ground. Like the sleep transistor technique, here also size of the sleep transistors is determined by the size of the largest transistor in the network (pull-up or pull-down) connected to the sleep transistor. The configuration can be made dual-Vth with high-Vth transistors being used as are the sleep transistors and others as low Vth. The zigzag technique has been introduced in order to reduce the wake-up cost of the sleep transistor technique. The wake-up overhead is reduced by the zigzag technique by picking a particular circuit state (e.g., corresponding to a "reset") and then, for the specific circuit state chosen, the pull-down network for each gate whose output is high is turned off while on the other hand the pull-up network for each gate whose output is low are turned off. Henceforth the application of predetermined input pattern corresponding to lowest power dissipation, prior going to sleep, which directs the circuit output in sleep mode to some reset value and thus preventing the floating output problem.

Fig 2.9 Zigzag Approach

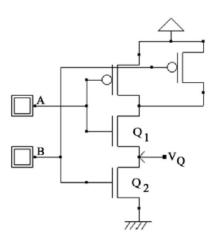

**2.3.3 Forced Stack Approach**: It has been observed that "a state with more than one transistor OFF in a path from supply voltage to ground is far less leaky than a state with only one transistor OFF in any supply to ground path"[9]. Another conventional technique to achieve leakage power reduction is the stacking of transistors approach. Stack effect or we can say Self-Reverse bias effect is the phenomenon where subthreshold leakage current diminishes due to series connection of two or more turned off transistors in the path from  $V_{dd}$  to ground. The process of stacking of transistor is done by replacement of transistor of width W with two series connected transistors of width W/2 thus maintaining equivalent input capacitance [12]. Two input NAND gate is an example of natural stacking of NMOS transistors in pull down network as shown in Fig.2.10. Suppose both NMOS transistors Q1 and Q2 are off corresponding to some input, then the intermediate node voltage, VQ is at a non-zero value due to the presence of a small drain current because of leakage. However, divided transistors adversely lead to increase in the delay and could impose a limitation on the usefulness of the approach.

Fig 2.10 Natural stacking of NMOS transistors in a two input NAND gate [5]

There are certain effects [5] of Positive potential Q at the intermediate node between two turned off stacked transistors which are discussed below:

1) VS for Q1 is positive, therefore VGS of Q1 becomes negative;

2) VBS of Q1 becomes negative, consequently causing a rise in threshold voltage of Q1 as body effect for Q1 comes in picture (relatively higher threshold transistor reduces leakage effectively);

3) VDS of Q1 decreases, which favourably aids in lessening the drain induced barrier lowering.

From the expression of subthreshold leakage current in chapter one, it can be observed that a negative VGS, an increase in the body effect (negative VBS), and a reduction in VDS (less drain induced barrier lowering) collectively reduce the subthreshold leakage current exponentially in standby mode.

Basic idea of the stacking approach for a generalised CMOS circuit is shown below in Fig2.11 where each of the transistors in PDN and PUN is replaced by two half sized transistors. From above discussion it can be inferred that stacking is an effective technique

which reduces leakage by increasing the effective threshold voltage of the stacked transistors but it has a serious drawback of delay overhead due to decrease in effective aspect ratio and due to the increased resistance offered by now two transistors in series rather than one. One of the advantages of stacking over sleep technique is that it is state saving.

Fig 2.11 Stack Approach [11]

**2.3.4 Sleepy Stack Approach:** The sleepy stack structure is basically a combination of structure of the forced stack and the sleep transistor techniques. The sleepy stack technique involves splitting up of existing transistors into two half size transistors similar to the stack technique. Then sleepy stack is finally obtained by addition of sleep transistors in parallel to one of the divided transistors. The structure is shown in fig 2.12. The sleep transistors of the sleepy stack have similar operation as that of the sleep transistors used in the sleep transistor technique in which sleep transistors turn on during active mode and turn off during sleep mode. This sleepy stack structure potentially cuts down circuit's delay in two possible ways. First, since the sleep transistor are virtually connected since sleep transistors remain on in active mode so, the value of voltage at the sleep transistor source is always readily existing at the sleep transistor drain, and thus, current flow can be immediately achieved to the low-Vth transistors which are connected to the gate output irrespective of the status of each transistor in parallel to the sleep transistors.

While in sleep mode, sleep transistors remain turned off and stacked transistors accomplish leakage current suppression along with state retention. Even though the sleep transistors are in off state, the sleepy stack structure preserves the exact logic state. The leakage reduction by sleepy stack structure is attained in two ways. First, leakage power is diminished by high-Vth sleep transistors and the transistors parallel to the sleep transistors. Second, series of stacked turned off transistors prompt the stack effect, which also causes

suppression of leakage power consumption. A reduction in delay during active mode is achieved due to reduced resistance of the path offered because of parallel arrangement of each sleep transistor to one of the stacked transistors [12]. However, area penalty to be paid for this approach is a noteworthy matter since each transistor has to be replaced by three transistors and extra controls wires are to be added for S and S<sup>\*\*</sup>, which are sleep signals.

Fig 2.12 (a) Sleepy stack inverter with W=L of each transistor and active mode S, S' assertion. (b) Sleep mode S, S' assertion [12]

Fig 2.13 Sleepy Stack Approach for general CMOS circuit [11]

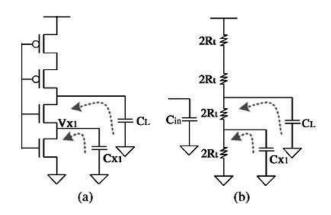

RC equivalent circuits for both forced stack and sleepy stack are shown below in Fig 2.14 and Fig 2.9 respectively. We can observe from the figures below that resistance experienced by the current in forced stack is  $4R_1$  for either side i.e. from Vdd to output node or output node to ground whereas for sleepy stack when same path resistance observed it comes out to be  $3R_1$  due to parallel combination of sleep transistor and one of the stacked transistors. This lower resistance through the path in sleepy stack enables the designer to use high Vth for sleep transistors as well as one of the stacked transistors parallel to it thereby achieving higher leakage suppression having the same performance.

Fig 2.14 (a) Forced stack technique inverter circuit schematic. (b) RC equivalent circuit [12]

Fig 2.15 (a) Sleepy stack technique inverter schematic. (b) RC equivalent circuit [12]

**2.3.5 Leakage Feedback Approach:** The leakage feedback technique is typically based on the sleep approach except the fact that leakage feedback approach makes use of two additional transistors to preserve the logic state during sleep mode, and the output of an inverter drives the two transistors which is in turn driven by output of the circuit implemented utilizing leakage feedback [11]. As shown in Fig 2.16, there is a PMOS transistor placed in parallel to the sleep transistor (S) in PUN and a NMOS transistor which is placed parallel to the sleep transistor (S') in PDN. These two transistors are being driven by the output of the inverter which is in turn being driven by the output of the implemented logic circuit. So while the circuit is in sleep mode, sleep transistors get turned off but one of the transistors in parallel to the sleep, zigzag, sleepy stack and leakage feedback approaches to gain higher leakage power reduction. High-Vth results in less leakage but lowers performance. Therefore high Vth is used just for sleep transistors and logic design transistors are kept low Vth to maintain the performance.

Fig 2.16 Leakage feedback approach

**2.3.6 Sleepy Keeper Approach:** Sleepy keeper [11] is basically a modification of leakage feedback technique. The structure of sleepy keeper as shown in Fig 2.17 is same as that of leakage feedback except that the inverter is not used at the output node to feed inverted output to the state retaining transistors instead PMOS parallel to PMOS sleep transistor in PUN is replaced by an NMOS and NMOS parallel to NMOS sleep transistor in PDN is replaced by a PMOS transistor. So when the output logic state just before going to sleep mode is '1', NMOS parallel to PMOS sleep transistor driven by the output turns on and output node is maintained at logic high state in sleep mode. Similarly when output is zero, PMOS parallel to NMOS sleep transistor turns on and connects the output node to ground to retain the logic in sleep mode. Hence the state is preserved in sleepy keeper along with effective leakage power reduction.

Fig 2.17 Sleepy Keeper Approach

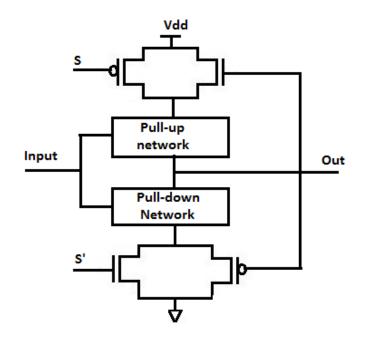

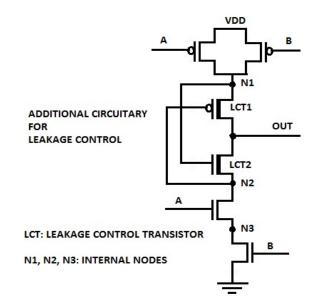

**2.3.7 LECTOR Technique:** The basic concept behind LECTOR technique for minimising leakage currents achieving effective stacking of transistors in the path from  $V_{dd}$  to ground. Above approach is based on the observation that "a circuit state with more than one turned OFF transistor in a path from supply voltage to ground is much less leakier than a circuit state with only one OFF transistor in any supply to ground path [9]". LECTOR introduces two leakage control transistors (a PMOS and a NMOS) in between the PUN and PDN of the logic gate where the gate terminal of each of the leakage control transistor (LCT) is controlled by the source of the other. This arrangement ensures that one of the LCTs is always in "near cut-off region" for any possible input combination. This results in effective increase in the resistance of the path from  $V_{DD}$  to ground, leading to substantial drop in leakage currents through the path [6]. The most noteworthy feature of LECTOR is that it manages to have leakage suppression in both active and idle states of the circuit effectively. Making LCTs high Vth contributes in achieving much more leakage control as high Vth transistors are far less leaky that low Vth transistors. This approach can be called as "dual Vth LECTOR technique".

Fig 2.18 Lector Technique Implementing NAND GATE

A CMOS NAND gate with the addition of two leakage control transistors LCT1 and LCT2 is shown in fig 2.18. Consider inputs (A, B) = (1, 0), M1 and M4 are turned OFF; M2 and M3 are turned ON. Status of LCT1 and LCT2 is determined by the voltages at nodes N1, N2, Out and N3. For input combination (1, 0) N1 is at VDD since M2 is on and PMOS passes strong VDD. Similarly LCT1 which is a PMOS passes good VDD to Output node so that Out is raised to VDD as well. LCT2 is an NMOS therefore it passes weak VDD and hence node N2 is at voltage VDD-Vth. Now voltage at node N2 (source voltage of LCT2) drives the gate of LCT1. VSG=Vth for LCT1 but the transistor is in "near cut-off" state because of no voltage difference between its drain (node N1) and source (output node). Similarly the voltage at node N1 (source voltage of LCT1) drives the gate of LCT2. LCT2 turns on as its VGS=Vth and VDS is also equal to Vth so there is a potential difference to allow current to flow through it turning it ON comfortably. Circuit can

analysed for other input combinations in the similar manner. Table 2.2[6] shown below gives the status of all the transistors for different input combinations.

| TRANSISTOR            | <b>INPUT VECTOR-</b> (A <sub>in</sub> , B <sub>in</sub> ) |              |              |              |

|-----------------------|-----------------------------------------------------------|--------------|--------------|--------------|

| REFERENCE             | (0,0)                                                     | (0,1)        | (1,0)        | (1,1)        |

| $M_1$                 | On state                                                  | On state     | Off state    | Off state    |

| $M_2$                 | On state                                                  | Off state    | On state     | Off state    |

| LCT <sub>1</sub>      | Near cut-Off                                              | Near cut-Off | Near cut-Off | On state     |

|                       | state                                                     | state        | state        |              |

| LCT <sub>2</sub>      | On state                                                  | On state     | On state     | Near cut-Off |

|                       |                                                           |              |              | state        |

| <b>M</b> <sub>3</sub> | Off state                                                 | Off state    | On state     | On state     |

| $M_4$                 | Off state                                                 | On state     | Off state    | On state     |

TABLE 2.2 [6]STATE MATRIX OF TWO-INPUT LCT NAND GATE

It can be very apparently observed from Table 2.2 that one of the leakage control transistor is always in near cut-off state. This cuts down the leakage by increasing resistance through the path.

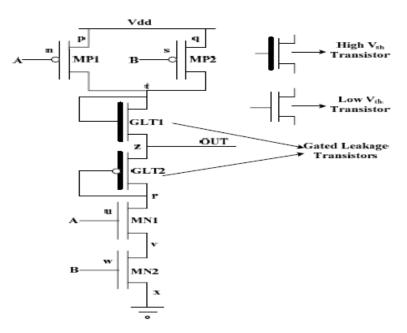

**2.3.8 GALEOR Technique:** GALEOR technique [13] has the exactly same structure as that of LECTOR except the fact that the locations of extra leakage control transistors (also known as Gated Leakage Transistors (GLTs)) are swapped. N-type GLT is placed between pull-up network and output and P-type GLT is placed between pull-down network and output. GLTs are usually made high Vth. GALEOR is also a self-controlled technique like LECTOR but has a limitation of one Vth drop in the logic high output and one Vth rise in logic low output.

Fig 2.19 GALEOR Technique Implementing NAND Gate [13]

### 2.4 COMPARISON OF VARIOUS TECHNIQUES

| TECHNIQUE |                                                       | ADVANTAGES                                                                                                                                                                        | DISADVANTAGES                                                                                                                                                                                                                                                                    |  |

|-----------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| •         | Sleep transistor<br>Approach<br>(power gating)        | • drastic reduction in<br>leakage current due<br>isolation from power<br>supply in sleep mode                                                                                     | <ul> <li>Additional signal required to<br/>drive sleep transistors</li> <li>Area and delay increased due<br/>to sleep transistors</li> <li>Unknown floating state in<br/>sleep mode</li> <li>High wake up time</li> <li>Energy requirement to<br/>recharge lost state</li> </ul> |  |

| •         | Zigzag technique                                      | <ul> <li>Circuit doesn't go into<br/>unknown state as<br/>connection is maintained<br/>either with Vdd or ground<br/>even in sleep mode.</li> <li>Wake up cost reduced</li> </ul> | <ul> <li>Area and delay increased due<br/>to sleep transistors</li> <li>Actual state still lost</li> </ul>                                                                                                                                                                       |  |

| •         | Leakage feedback<br>And<br>Sleepy keeper<br>Technique | • Actual state preserved                                                                                                                                                          | • Additional circuitry is needed<br>to monitor the circuit state and<br>control sleep transistors<br>despite the fact that the circuit<br>is in idle state                                                                                                                       |  |

| •         | Forced stack                                          | • Actual state preserved                                                                                                                                                          | <ul> <li>every transistor is replaced by<br/>two transistors</li> <li>Higher delay due to increase in<br/>resistance</li> </ul>                                                                                                                                                  |  |

| •         | Sleepy stack                                          | <ul> <li>Higher reduction in<br/>leakage current than<br/>forced stack</li> <li>state retention with<br/>smaller delay</li> </ul>                                                 | <ul> <li>Area penalty is a significant matter for this approach since every transistor is replaced by three transistors</li> <li>additional wires are added for Sleep control signal</li> </ul>                                                                                  |  |

| •         | LECTOR and<br>GALEOR                                  | <ul> <li>Self-controlled</li> <li>No additional circuitry required to control the LCTs and GLTs.</li> <li>Less area ,less power consumption</li> </ul>                            | <ul> <li>Vth drop in logic high output signal (V<sub>high</sub>=V<sub>dd</sub>-V<sub>th</sub>) and logic Low output signal is Vth higher than ground level (V<sub>low</sub>=V<sub>th</sub>) for GALEOR.</li> <li>Slight increase in delay for both LECTOR and GALEOR.</li> </ul> |  |

#### 2.5 SUMMARY

We can conclude from the above comparison table that maximum power saving is achieved in the case of sleep transistor approach but with a disadvantage of state loss and the need of external control signal (sleep signal). Forced stack provides reasonable power saving along with an advantage of state retention but increases the delay by breaking every transistor into half sized transistors and hence increasing the overall resistance of the path with significant transistor overhead. Sleepy stack technique somewhat tries to diminish the delay increased in forced stack by using high Vth sleep transistor in parallel to one of the stacked transistors which itself is taken as high Vth. Thus being able to use one of the transistors in stack as high Vth due to presence of parallel high Vth sleep transistors (parallel transistors reduce the resistance through the path thus using high Vth stack transistor would not affect delay much) further reduces the leakage current in addition stacking effect. Sleepy stack possess the same limitation of significant area and transistor count overhead along with the requirement of a sleep signal. Sleepy keeper is also a technique providing reasonable power saving along with state retention but still requires external signal to control the circuit. Finally we have a look at LECTOR technique which provides though low comparatively but sufficient leakage power saving has a lot of advantages which all the above techniques lack like state retention, low increase in delay, self-controlled (i.e. doesn't require external control signal to drive the circuit for leakage control) and requirement of only two extra stacked transistors for any circuit we wish to reduce leakage for. Thus, each technique has its own advantages and drawbacks. So it depends on our requirement which technique we use which suits the purpose best. Leakage increases with technology scaling hence the techniques will show even better performance efficiency as we move towards lower technology.

LECTOR proves to be an impressive approach for leakage regulation for logic circuits in terms of the advantages it offers, especially its self-controlled feature which makes it function efficiently both in active and standby mode. Leakage power loss aspect in DCVSL logic family and its variant configurations has been profoundly studied in the following chapters and careful application of LECTOR methodology has been done to achieve notable leakage power saving.

#### 2.6 SIMULATION RESULTS AND DISCUSSIONS

Simulations have been performed here for CMOS inverter to ascertain the effectiveness of application of LECTOR technique to CMOS logic circuits with lowering down of technology, supply voltage variation and temperature variation.

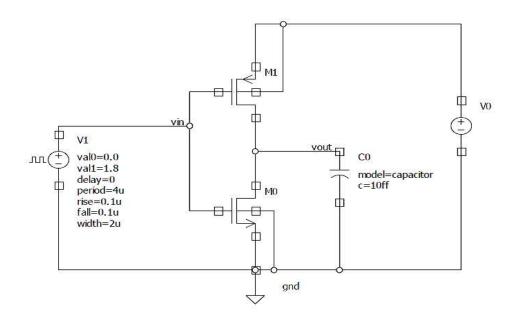

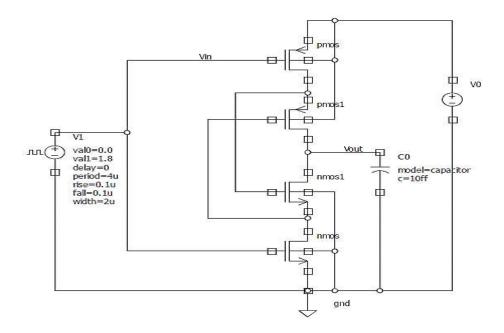

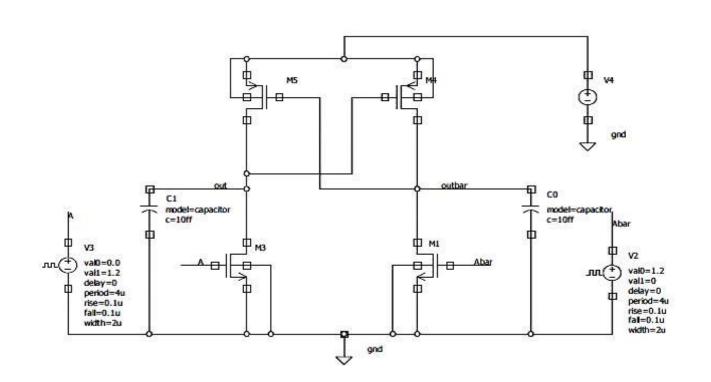

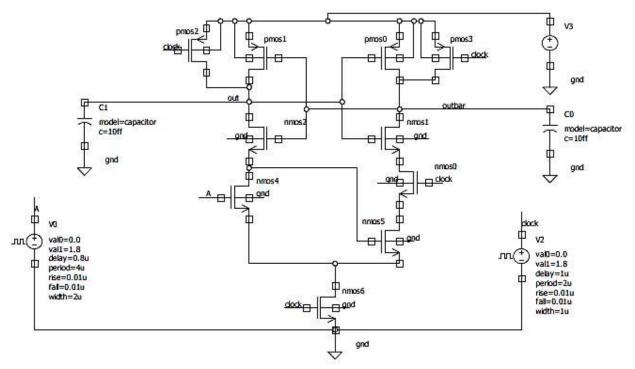

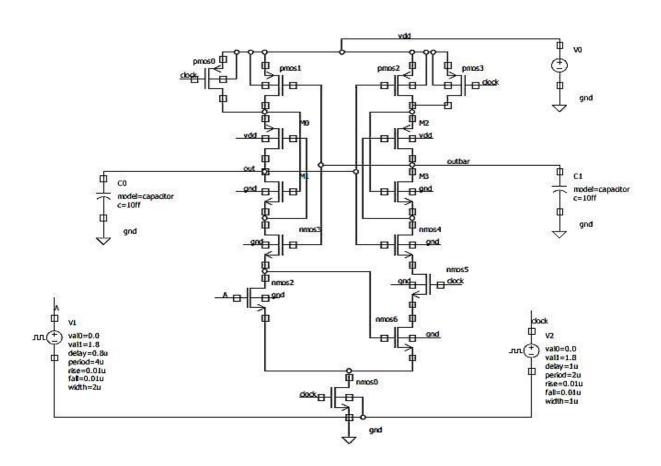

**CMOS INVERTER:** Basic and LECTOR CMOS inverters as shown in fig.2.20 and fig.2.21 respectively were designed and simulated to authenticate the efficacy of LECTOR technique in leakage current reduction on application to basic CMOS inverter.

Fig. 2.20 Basic CMOS inverter

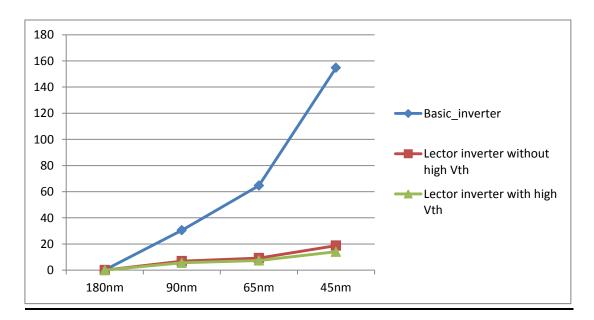

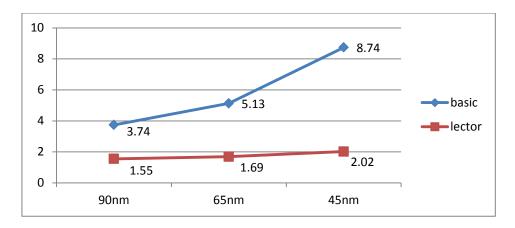

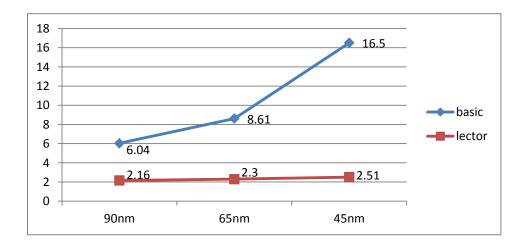

Fig. 2.21 LECTOR CMOS inverter