# Realization of Delay Locked Loop using VCDL in 180 nm CMOS Technology

A Project Report is Submitted in Partial Fulfillment of the Requirement for the

## MAJOR PROJECT 2

Under the guidance of

Dr. Neeta Pandey, Associate Professor, Department of Electronics and Communication Engineering, Delhi Technological University

Submitted by

Himanshu Daharia Roll No. : 2K13/VLSI/09 M.Tech. (VLSI Design & Embedded Systems) (2013-2015)

Department of Electronics and Communication Engineering, Delhi Technological University Shahbad Daulatpur, Main Bawana Road, Delhi-110042.

# CERTIFICATE

This is to certify that the. major project entitled "**Realization of Delay Locked Loop using VCDL in 180 nm CMOS Technology**" is submitted by Mr. **Himanshu Daharia (2K13/VLSI/09)**, in partial fulfilment of the requirements for the award of degree of **Masters in Technology** in **VLSI Design and Embedded Systems,** Delhi Technological university, Delhi.

Date:

Dr. Neeta Pandey Associate Professor Delhi Technological University

# DECLARATION

This is to certify that the. major project entitled "**Realization of Delay Locked Loop using VCDL in 180 nm CMOS Technology**" is submitted by me in partial fulfillment of the requirements for the award of degree of **Masters in Technology** in **VLSI Design and Embedded Systems,** Delhi Technological university, Delhi comprises of only my own work and due acknowledgement been made to all other materials used.

I, hereby, further declare that in case of any legal dispute in relation to my M.Tech. Major Project, will be solely responsible for the same.

Date:

Signature Himanshu Daharia (2K13/VLSI/09)

## ACKNOWLEDGEMENT

It gives me a great pleasure to express my profound gratitude to my supervisor and project guide Dr. Neeta Pandey, Associate Professor, Electronics and Communication Engineering Department, Delhi Technological University, for her invaluable guidance, encouragement and patient and thorough reviews throughout the progress of this dissertation. It has been a great experience to do research under her rich experience.

I would also like to extend my heartfelt gratitude to Prof. P. R. Chadha, Head of the department and all faculty members of Electronics and Communication Engineering Department, Delhi Technological University, for keeping the spirits high and clearing the visions to work on the project.

A note of heartiest gratitude goes to my friends and classmates for helping me out whenever I was stuck during my research work.

I am also thankful to my family for their constant support and motivation during this work.

#### Himanshu Daharia

University Roll no: 2K13/VLSI/09 M.TECH. (VLSI Design and Embedded System) Department of Electronics & Communication Engineering Delhi Technological University Delhi – 110042

## ABSTRACT

A proper operation of synchronous circuits requires tight control on clock signals which necessitated the use of clock synchronization circuits. Delay Locked Loop (DLL) is one among these circuits which has superior stability. The DLL uses a phase frequency detector to detect phase error between input reference clock and the output clock, a combination of charge pump and loop filter to generate control voltage and a Voltage Controlled Delay Line (VCDL) to delay the reference clock so that there is no skew between reference clock and output clock. The PFD block has been realized using NAND gates and inverters and C<sup>2</sup>MOS based register. Two modifications are also suggested in C<sup>2</sup>MOS based realization. This work aims at implementing a DLL and studies its performance.

## CONTENTS

| CHAPTER | 1 |  |

|---------|---|--|

|---------|---|--|

| 1.1 Introduction                                                                         | 1  |

|------------------------------------------------------------------------------------------|----|

| 1.2 DLL vs. PLL                                                                          | 4  |

| 1.3 Organization of Thesis                                                               | 5  |

| CHAPTER 2                                                                                |    |

| Delay Locked Loop                                                                        |    |

| 2.1 Introduction                                                                         | 6  |

| 2.2 Working Principle of Delay locked loop (DLL)                                         | 7  |

| 2.3 Systemic study of closed loop components of DLL                                      | 8  |

| 2.4 DLL Architectures                                                                    |    |

| 2.4.1 Analog DLLs                                                                        | 10 |

| 2.4.2 Digital DLLs                                                                       | 11 |

| 2.4.3 Dual Loop Delay Locked Loop                                                        | 12 |

| 2.4 Literature Review                                                                    | 14 |

| CHAPTER 3                                                                                |    |

| Phase Detector and Phase Frequency Detector                                              |    |

| 3.1 Introduction                                                                         | 20 |

| 3.2 XOR Gate based Phase Detector (PD)                                                   | 20 |

| 3.3 Flip-Flop based Phase Detector (PD) or Phase Frequency Detector (PFD)                | 23 |

| 3.4 CMOS Realization of PFD                                                              | 24 |

| 3.5 Simulation of CMOS PFD circuit                                                       | 25 |

| $3.6 \text{ C}^2 \text{MOS} - \text{Register based PFD}$                                 | 26 |

| 3.6.1 PFDs employing $C^2MOS - Register$                                                 | 28 |

| 3.7 Simulation of $C^2MOS - PFD$ circuit                                                 | 30 |

| 3.7.1 Simulation of type-1 PFD circuit                                                   | 31 |

| 3.7.2 Simulation of type-2 PFD circuit                                                   | 32 |

| 3.7.3 Simulation of type-3 PFD circuit                                                   | 33 |

| 3.8 Performance Comparison among CMOS – PFD and all three types C <sup>2</sup> MOS – PFD | 35 |

## **CHAPTER 4**

## **Charge Pump and Loop Filter**

| 4.1 Introduction                                              | 36 |

|---------------------------------------------------------------|----|

| 4.2 Charge Pumps                                              | 36 |

| 4.3 Practical implementation of the charge pump               | 38 |

| 4.4 Current mirrors                                           | 39 |

| 4.5 Loop filter                                               | 40 |

| 4.6 Simulation results                                        |    |

| 4.6.1 Simulation results of current mirror circuits           | 42 |

| 4.6.2 PFD and charge pump                                     | 43 |

| CHAPTER 5                                                     |    |

| Voltage Controlled Delay Line                                 |    |

| 5.1 Introduction                                              | 46 |

| 5.2 Variable Delay Element                                    | 47 |

| 5.3 Fully Differential Voltage Controlled Delay Line (VCDL)   | 48 |

| 5.4 Input Buffer                                              | 50 |

| 5.5 Implementation of VCDL with eight stage delay elements    | 51 |

| 5.5.1 V to I converter and Bias Circuit                       | 52 |

| 5.5.2 Performance of V to I converter and Bias Circuit        | 52 |

| 5.5.3 An eight stage VCDL                                     | 53 |

| 5.6 Transfer characteristic of VCDL                           |    |

| 5.6.1 Transfer Characteristic of RC delay cell VCDL           | 57 |

| 5.6.2 Transfer Characteristic of CSI delay cell VCDL          | 58 |

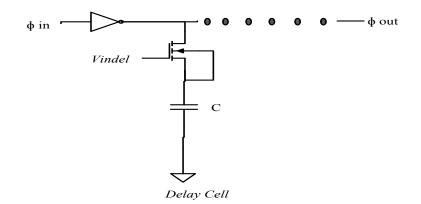

| 5.6.3 Transfer Characteristic of differential delay cell VCDL | 59 |

| CHAPTER 6                                                     |    |

| Results and Discussions                                       |    |

| 6.1 Simulation circuit                                        | 61 |

| 6.2 Operation of the DLL                                      |    |

| 6.2.1 DLL with CMOS – PFD                                     | 62 |

|                                                               |    |

- 6.2.2 DLL with type-1 PFD 63

- 6.2.3 DLL with type-2 PFD 64

| 6.2.4 DLL with type-3 PFD               | 65 |  |

|-----------------------------------------|----|--|

| 6.3 Jitter Performance                  |    |  |

| 6.3.1 Jitter in DLL with CMOS-PFD       | 66 |  |

| 6.3.2 Jitter in DLL with PFD type-1     | 66 |  |

| 6.3.3 Jitter in DLL with PFD type-2     | 67 |  |

| 6.3.4 Jitter in DLL with PFD type-3     | 67 |  |

| 6.4 Performance Summary and Comparisons | 68 |  |

| 6.5 Discussion                          |    |  |

| CHAPTER 7                               |    |  |

| Conclusions and Future Scope            | 69 |  |

| References                              | 71 |  |

| Appendix                                | 74 |  |

|                                         |    |  |

## LIST OF FIGURES

| 1.  | Fig. 1.1 Application of phase locked Lops(PLL)                                  | 1  |

|-----|---------------------------------------------------------------------------------|----|

| 2.  | Fig. 1.2 Functional composition of a phase locked loop (PLL)                    | 2  |

| 3.  | Fig. 1.3 Functional composition of a delay locked loop (DLL)                    | 3  |

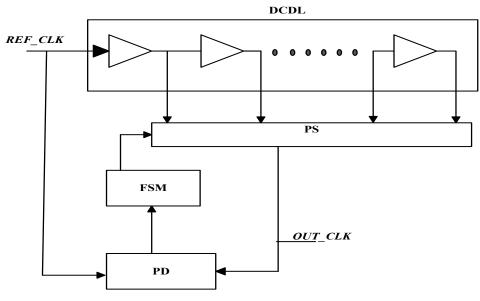

| 4.  | Fig. 2.1: Block diagram of DLL                                                  | 7  |

| 5.  | Fig. 2.2 Basic DLL timing                                                       | 8  |

| 6.  | Fig. 2.3: DLL control model                                                     | 8  |

| 7.  | Fig. 2.4 Simplified control model of DLL                                        | 9  |

| 8.  | Fig. 2.5 Analog type DLL                                                        | 11 |

| 9.  | Fig. 2.6 Digital DLL                                                            | 12 |

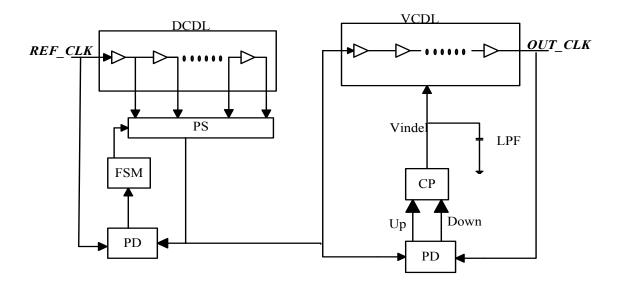

| 10. | Fig. 2.7 Dual-loop type DLL                                                     | 12 |

| 11. | Fig. 3.1: XOR Phase Detector                                                    | 20 |

| 12. | Fig. 3.2 when phase difference between the two signals is zero                  | 21 |

| 13. | Fig. 3.3 when phase difference between the two signals is $\pi/2$               | 21 |

| 14. | Fig. 3.4 when phase difference between the two signals is $\pi$                 | 21 |

| 15. | Fig. 3.5: XOR PD characteristic                                                 | 22 |

| 16. | Fig. 3.6 Output of XOR PD when inputs having different duty cycle               | 22 |

| 17. | Fig. 3.7 Block Diagram of Phase Frequency Detector                              | 23 |

| 18. | Fig. 3.8 Realization of PFD using NAND based D latch                            | 24 |

| 19. | Fig. 3.9 Simulation result of PFD when reference clock leads the output clock   | 25 |

| 20. | Fig. 3.10 Simulation result of PFD when reference signal lags the output signal | 25 |

| 21. | Fig. 3.10 Simulation result of PFD when phase difference is 0 or $2\pi$         | 26 |

| 22. | Fig. 3.11 Enlarged view of Up and Down signals                                  | 26 |

| 23. | Fig. 3.12 $C^2MOS-Register$                                                     | 27 |

| 24. | Fig. 3.13 Proposed $C^2MOS$ – Registers based PFD (Type-1)                      | 28 |

| 25. | Fig. 3.14 Proposed Type - 2 PFD                                                 | 29 |

| 26. | Fig. 3.15 Proposed Type - 3 PFD                                                 | 30 |

| 27. | Fig. 3.16 Simulation result of Type-1 PFD when reference clock                  |    |

|     | leads the output clock                                                          | 31 |

| 28. | Fig. 3.17 Simulation result of Type-1 PFD when output clock                     |    |

|     | leads the reference clock                                                       | 31 |

| 29. | Fig. 3.18 Simulation result of Type-1 PFD when phase difference is 0 or $2\pi$ | 31 |

|-----|--------------------------------------------------------------------------------|----|

| 30. | Fig. 3.19 Enlarged view of Up and Down signals                                 | 32 |

| 31. | Fig. 3.20 Simulation result of Type-2 PFD when reference clock                 |    |

|     | leads the output clock                                                         | 32 |

| 32. | Fig. 3.21 Simulation result of Type-2 PFD when reference clock                 |    |

|     | lags the output clock                                                          | 32 |

| 33. | Fig. 3.22 Simulation result of Type-2 PFD when phase difference is 0 or $2\pi$ | 33 |

| 34. | Fig. 3.23 Enlarged view of Up and Down signals                                 | 33 |

| 35. | Fig. 3.24 Simulation result of Type-3 PFD when reference clock                 |    |

|     | leads the output clock                                                         | 33 |

| 36. | Fig. 3.25 Simulation result of Type-3 PFD when reference clock                 |    |

|     | lags the output clock                                                          | 34 |

| 37. | Fig. 3.26 Simulation result of Type-2 PFD when                                 |    |

|     | phase difference is 0 or $2\pi$                                                | 34 |

| 38. | Fig. 3.27 Enlarged view of Up and Down signals                                 | 35 |

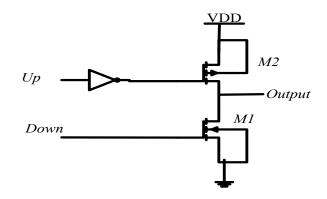

| 39. | Fig. 4.1 Tri –state charge pump                                                | 37 |

| 40. | Fig. 4.2 Charge Pump                                                           | 37 |

| 41. | Fig. 4.3 PFD with Charge Pump                                                  | 38 |

| 42. | Fig. 4.4 Practical Implementation of the Charge Pump                           | 38 |

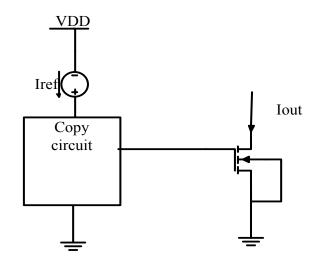

| 43. | Fig. 4.5 conceptual means of copying currents                                  | 39 |

| 44. | Fig. 4.7 Diode- connected device providing inverse function                    | 40 |

| 45. | Fig. 4.7 NMOS current mirror                                                   | 40 |

| 46. | Fig. 4.8 PMOS current mirror                                                   | 41 |

| 47. | Fig. 4.9 Simulation of PMOS current mirror shown in fig. 4.6                   | 42 |

| 48. | Fig. 4.10 Simulation of NMOS current mirror shown in fig. 4.7                  | 43 |

| 49. | Fig. 4.11 Circuit used for the simulation of Charge Pump with PFD              | 43 |

| 50. | Fig. 4.12 Simulation result of circuit shown in 4.11when reference clock       |    |

|     | leads the output clock                                                         | 44 |

| 51. | Fig. 4.13 Simulation result of circuit shown in 4.11when reference clock       |    |

|     | lags the output clock                                                          | 44 |

| 52. | Fig. 4.14 Simulation result of circuit shown in 4.11when reference clock       |    |

|-----|--------------------------------------------------------------------------------|----|

|     | and the output clock is synchronized                                           | 45 |

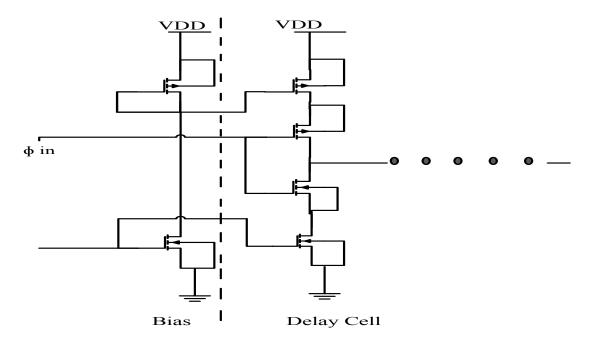

| 53. | Fig. 5.1 A typical VCDL configuration                                          | 46 |

| 54. | Fig. 5.2(a) VCDL made using inverter delay cells                               | 46 |

| 55. | Fig. 5.2(b) R –C delay cells                                                   | 47 |

| 56. | Fig. 5.2(c) Realization of C using NMOS in delay cell                          | 47 |

| 57. | Fig. 5.2(d) Current Starving Delay cell                                        | 47 |

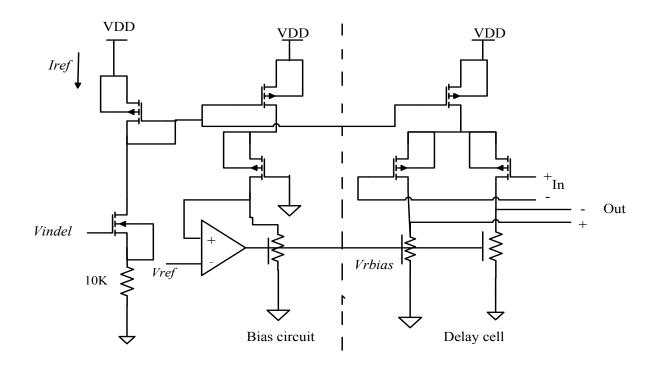

| 58. | Fig. 5.3 Block Diagram of a fully differential VCDL                            | 48 |

| 59. | Fig. 5.4 A differential delay element based on a voltage-controlled resistor   | 49 |

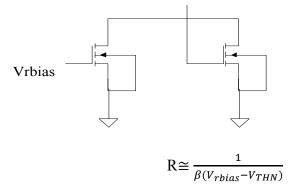

| 60. | Fig. 5.5 Voltage controlled resistor                                           | 49 |

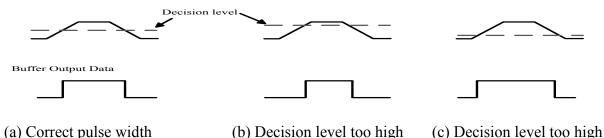

| 61. | Fig. 5.6 Timing errors in regenerating digital data                            | 50 |

| 62. | Fig. 5.7 A PMOS input buffer                                                   | 51 |

| 63. | Fig. 5.8 Transient response for buffer shown in fig. 5.7                       | 51 |

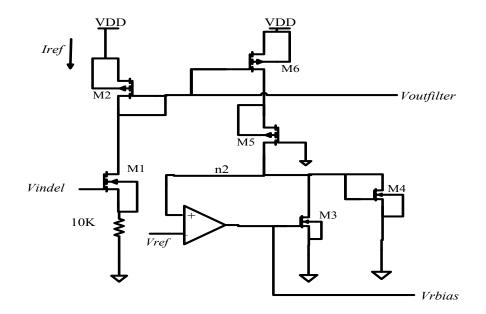

| 64. | Fig. 5.9 V to I converter and Bias circuit                                     | 52 |

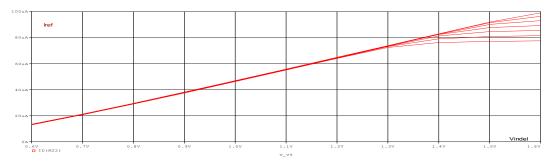

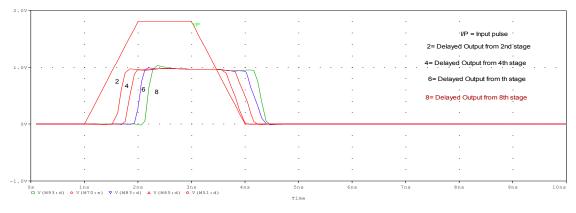

| 65. | Fig. 5.10 Plot of $I_{ref}$ vs. $V_{indel}$ and $V_{DD}$                       | 52 |

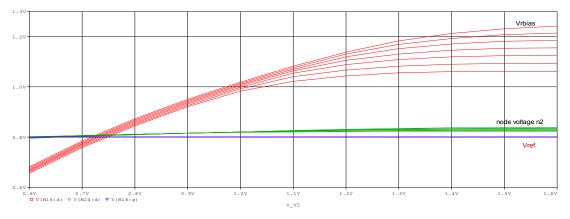

| 66. | Fig. 5.11 Plot of $V_{rbias}$ and node voltage n2 vs. $V_{indel}$ and $V_{DD}$ | 53 |

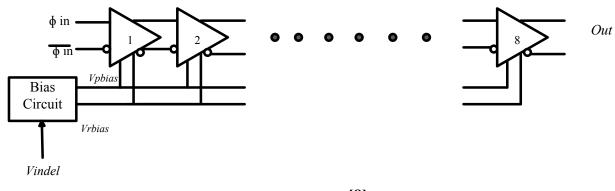

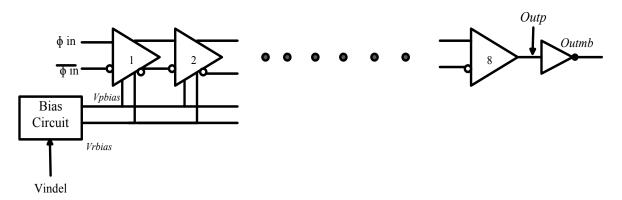

| 67. | Fig. 5.12 An eight stage VCDL                                                  | 54 |

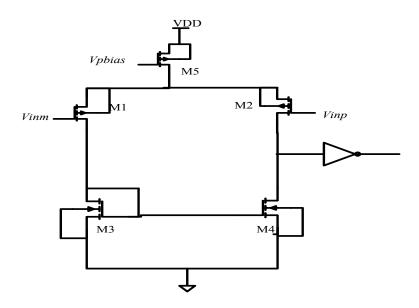

| 68. | Fig. 5.13 Differential Delay Cell                                              | 54 |

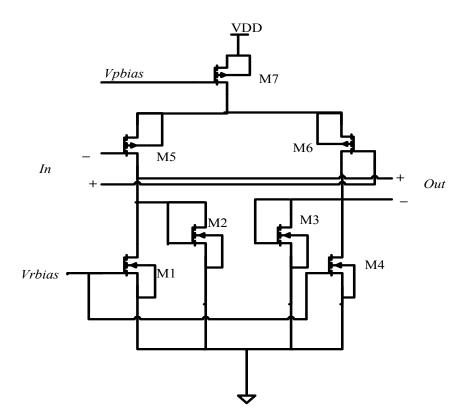

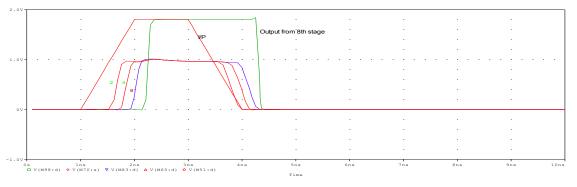

| 69. | Fig. 5.14 simulation of VCDL of fig. 5.12                                      | 55 |

| 70. | Fig. 5.15 Modified VCDL to generate full output logic levels                   | 55 |

| 71. | Fig. 5.16 Differential Amplifier used to generate full logic                   |    |

|     | levels at output of the VCDL                                                   | 56 |

| 72. | Fig. 5.17 Simulation for VCDL of fig.5.15                                      | 56 |

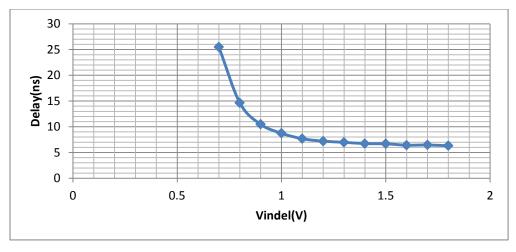

| 73. | Fig. 5.18 Plot between Delay and $V_{indel}$ of RC delay cell VCDL             | 58 |

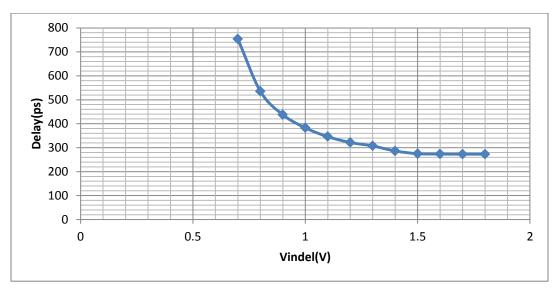

| 74. | Fig. 5.19 Plot between Delay and $V_{indel}$ of CSI delay cell VCDL            | 59 |

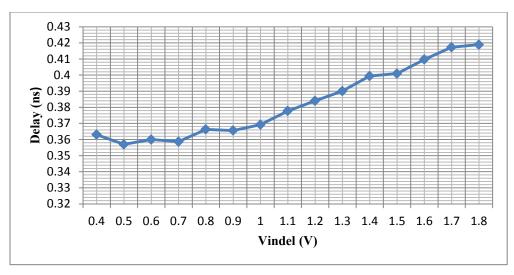

| 75. | Fig. 5.20 Plot between Delay and $V_{indel}$ of differential delay cell VCDL   | 60 |

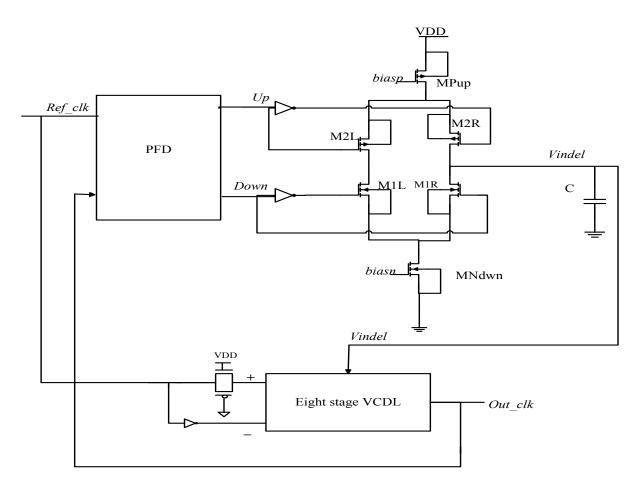

| 76. | Fig. 6.1 Complete DLL circuit for simulation                                   | 61 |

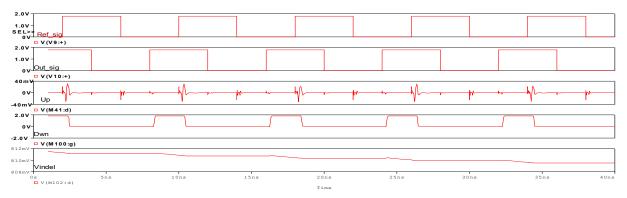

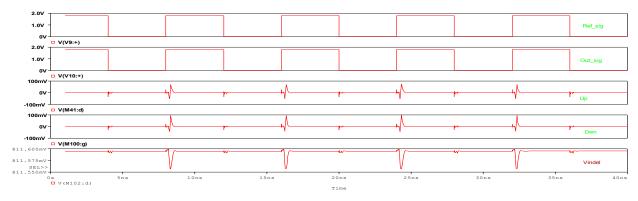

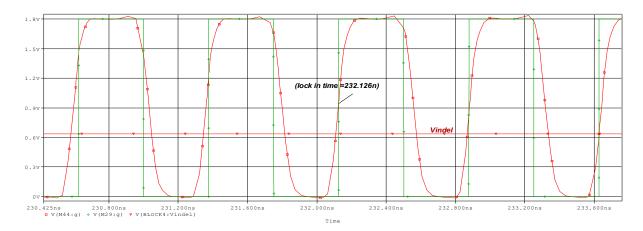

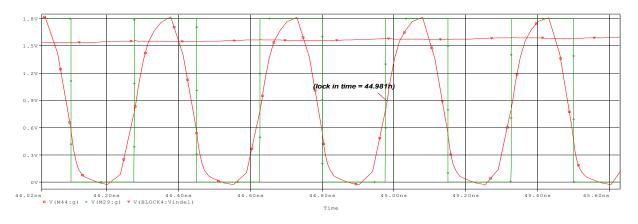

| 77. | Fig. 6.2 Locking of DLL with CMOS – PFD at 1.33GHz                             | 62 |

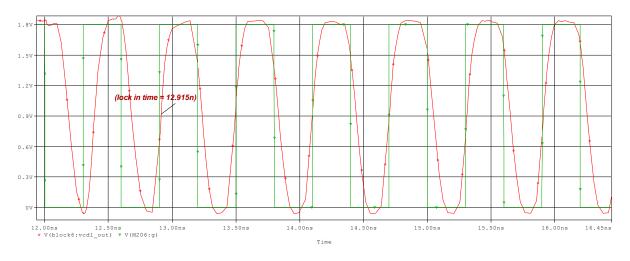

| 78. | Fig. 6.3 Locking of DLL with CMOS – PFD at 2.85 GHz                            | 62 |

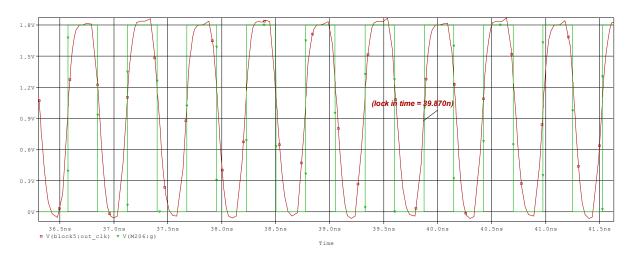

| 79. | Fig. 6.4 Locking of DLL with PFD type-1 at 1.8 GHz                             | 63 |

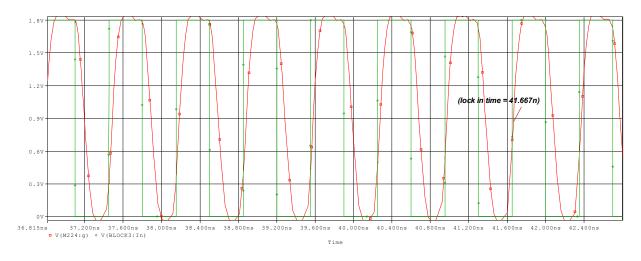

| 80. | Fig. 6.5 Locking of DLL with PFD type-1 at 2.08 GHz                            | 63 |

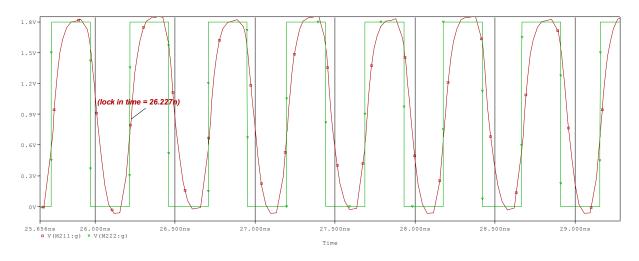

| 81. | Fig. 6.6 Locking of DLL with PFD type-2 at 1.4 GHz | 64 |

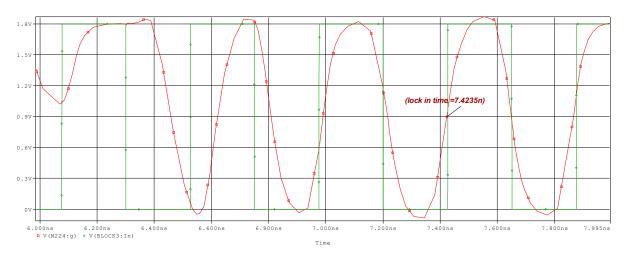

|-----|----------------------------------------------------|----|

| 82. | Fig. 6.7 Locking of DLL with PFD type-2 at 2.2 GHz | 64 |

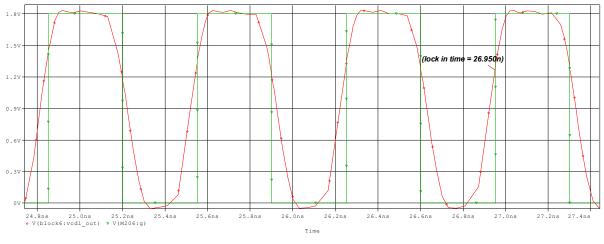

| 83. | Fig. 6.8 Locking of DLL with PFD type-3 at 1.4 GHz | 65 |

| 84. | Fig. 6.9 Locking of DLL with PFD type-3 at 2.2 GHz | 65 |

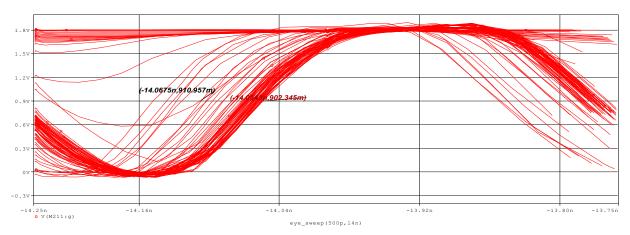

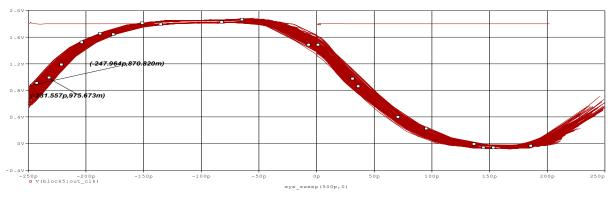

| 85. | Fig. 6.10 Eye diagram plot for DLL with CMOS-PFD   | 66 |

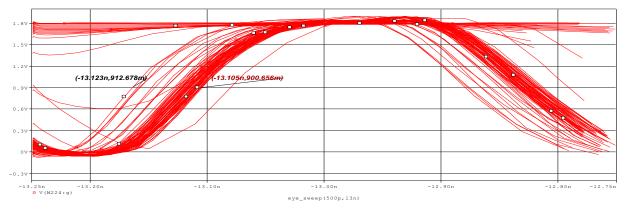

| 86. | Fig. 6.11 Eye diagram plot for DLL with PFD type-1 | 66 |

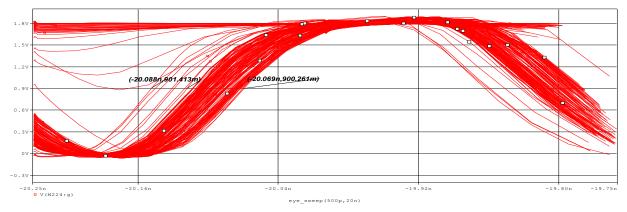

| 87. | Fig. 6.12 Eye diagram plot for DLL with PFD type-2 | 67 |

| 88. | Fig. 6.13 Eye diagram plot for DLL with PFD type-3 | 67 |

## LIST OF TABLES

| 1. | Table 3.1 Outputs of D flip flop based PFD                                           | 23 |

|----|--------------------------------------------------------------------------------------|----|

| 2. | Table 3.2 Performance Comparison among                                               |    |

|    | $CMOS - PFD$ and all three types $C^2MOS - PFD$                                      | 35 |

| 3. | Table 5.1 Values of Delay with change in $V_{indel}$ of RC delay cell VCDL           | 57 |

| 4. | Table 5.2 Values of Delay with change in $V_{indel}$ of CSI delay cell VCDL          | 58 |

| 5. | Table 5.3 Values of Delay with change in $V_{indel}$ of differential delay cell VCDL | 59 |

| 6. | Table 6.1 Performance Summary and Comparisons                                        | 60 |

## ABBREVIATIONS

| Abbreviations      | Full - Form                                | Abbreviations | Full - Form                      |

|--------------------|--------------------------------------------|---------------|----------------------------------|

| CMOS               | Complementary Metal<br>Oxide Semiconductor | LF            | Loop Filter                      |

| C <sup>2</sup> MOS | Clocked - CMOS                             | PD            | Phase Detector                   |

| CML                | Current Mode Logic                         | PFD           | Phase Frequency<br>Detector      |

| СР                 | Charge Pump                                | PLL           | Phase Locked Loop                |

| CSI                | Current Starving<br>Inverter               | RC            | Resistor - Capacitor             |

| DFF                | D Flip - Flop                              | VCDL          | Voltage Controlled<br>Delay Line |

| DLL                | Delay Locked Loop                          | VCO           | Voltage Controlled<br>Oscillator |

### **CHAPTER 1**

#### **1.1 INTRODUCTION**

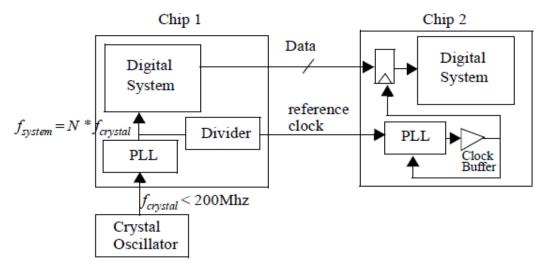

There are a number of digital ICs which require the on – chip periodic signal generation. Specially, the synchronous circuits need a global clock for synchronizing various events. Modern day microprocessors and other high- performance digital circuits work on very high frequencies that are in the range of gigahertz. Generally, crystal oscillators are accurate and provide less jitter, they can be used to generate reference clock signals for high performance digital circuits over a frequency range of 10's of MHz to 200's of MHz only. To generate higher frequency clocks from the low frequency crystal oscillator, a phase locked loop (PLL) is used. PLL takes the low frequency clock signals and multiplies it with a rational number N; along with generating high frequency clock signal, PLL also performs a function of synchronizing clocks among different chips. This is essential in communications between the chips. Application of PLL is shown in fig. 1.1.

Fig. 1.1 Application of phase locked loops (PLL) [6]

As shown in above fig. 1.1, a reference clock is being sent from chip 1 to chip 2 along with the parallel data during communication. The parallel data transfer from chip 1 to chip 2 requires lower clock reference as compared to system clock; so a reference clock signal is generated by dividing the system clock by a rational number N yet keeping it in phase with the system clock, and sent with the data to synchronize the input flip-flops present in chip 2. In case of wide data buses these flip-flops can give rise to clock loading. In such cases clock buffers are to be used for

avoiding the loading. But the problem with the clock buffers is that they introduce skew between the data and reference clock. A PLL is then used to synchronize the data and output of clock buffers. If any part in the chip 2 requires frequency higher than incoming reference clock, the PLL can provide it as well as by multiplying the incoming reference clock with a rational factor.

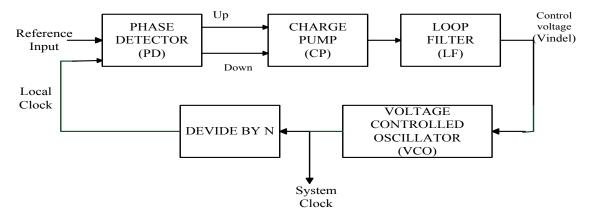

A PLL is complex, nonlinear feedback circuit. The basic working mechanism can be better understood by the following fig. 1.2 :

Fig. 1.2: Functional composition of a phase locked loop (PLL) [6]

As shown in the above fig. 1.2, a PLL mainly comprises of four blocks these are:

- 1. Phase Detector (PD)

- 2. Charge Pump (CP)

- 3. Loop Filter (LF) and;

- 4. Voltage Controlled Oscillator (VCO).

Note that an additional block "Divide by N" is placed also in feedback path, for multiplication of the reference signal. When a control voltage is applied to the VCO, it generates clock signal of desired frequency. The relation between control voltage ( $V_{indel}$ ) and output frequency is non-linear; hence to synthesize a particular frequency for system clock it is essential to set the control voltage at an appropriate value. This function is done by the rest of the blocks and the feedback loop in the PLL.

The reference clock is taken from outside the chip and generated by a crystal oscillator. Then it is compared with divided version of system clock (local clock), using a phase detector. The Phase detector generates its outputs depending upon the phase difference between the signals. It produces a high signal at 'Up' when reference clock leads the local clock and a high signal at '*Down*' when reference clock lags the local clock. These outputs are given to the charge pump which converts digitally encoded control information into an analog voltage. The value of this analog signal increases when *Up* signal goes high and it speeds up the VCO. On the other hand when '*Down*' is high, the value of analog voltage decreases which slows down the VCO. Providing this analog control voltage directly from charge pump to VCO can introduce jitters at the output of VCO. To avoid this situation a low pass filter is used which removes the high frequency components present in the control voltage and smoothens out the VCO output [6].

Two types of jitter occur in PLL. These are the input exhibited and the VCO generated jitter. PLL transfer function shows low- pass characteristic for the input exhibit jitter, it means fast variations in phase of the input is not tracked at output but slow variations in phase of the input is tracked at the output. In other words, fast jitter gets attenuated but slow jitter is propagated at output. At the same time for VCO generated jitter PLL transfer function shows high- pass characteristic which means slow jitter will be attenuated but fast one will be propagated [7].

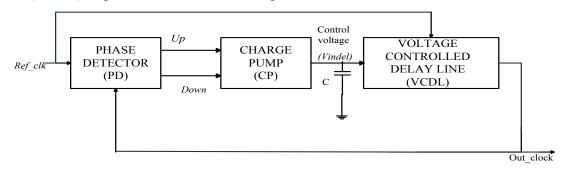

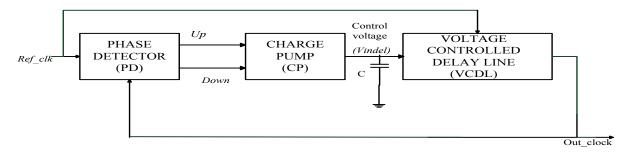

There are some techniques which can be used for reduction in jitter of PLL such as reducing the gain of the VCO and PD or reduction in the bandwidth of the loop filter, but it results in decrement of the overall gain of the forward loop. The problem associated with using small loop gain is reduction in lock-range and pull-in range along with increased pull-in and lock-range time. The alternative way to solve above problem is to use a Voltage Controlled Delay Line (VCDL) in place of VCO shown in fig. 1.3.

Fig. 1.3 Functional composition of a delay locked loop (DLL) [6]

The jitter in PLL output from the VCO output frequency, changing with a constant input voltage has led to the concept of DLL. At present, Delay Locked Loop (DLL), a variation of PLL structure is widely used in high- performance clocking. The working mechanism of DLL is similar to PLL as both employs feedback mechanism in their operation, but having some

differences as DLL consists of VCDL in place of VCO along with Loop Filter having a capacitor only. The main idea behind this VCDL is to delay the output clock such that it lines up perfectly with the reference. Since no signal generation takes place in VCDL as in VCO, it does not possess the problem of jitter as is the case with PLL [8].

#### **1.2 DLL versus PLL**

Some of the basic differences between DLL and PLL are as given below:

- The oscillator employed in PLL introduces phase errors and instability. This lowers the performance of the PLL when it is used for reduction in skew in clock distribution network. On the other hand, the unconditionally stable DLL architecture does not introduces phase errors.

- The DLL's closed loop transfer function is a single pole function. Thus, it is a naturally stable system. On the other hand PLL's closed loop transfer function may have two or three poles and sometimes might pose stability problems.

- At a given operating clock frequency a DLL can delay its input clock by an amount bounded by a minimum and maximum delay. However there is no hard boundary over the capture range of a PLL [9].

### **1.3 THESIS ORGANIZATION**

The primary goal of this thesis is to demonstrate a circuit level approach for a Delay Locked Loop which is used for clock synchronization. This thesis is organized into seven chapters as follows:

## **CHAPTER 2: DELAY LOCKED LOOPS**

This chapter explains the operating principle of DLL. Here various architectures of DLL and its specific applications along with the dynamic loop behavior of DLL is explained. Apart from this some relevant literature search is presented.

## **CHAPTER 3: PHASE DETECTOR AND PHASE FREQUNCY DETECTOR**

One of the most important components of a DLL is Phase Detector (PD). This chapter introduces the basic concept of working mechanisms of PD and PFD.

## **CHAPTER 4: CHARGE PUMP AND LOOP FILTER**

The PD generates Phase error and this error information has to be converted into a control voltage to control the delay of VCDL. This is done by using CP and LF. Working mechanism of CP and LF has been explained in this chapter

## **CHAPTER 5: VOLTAGE CONTROLLED DELAY LINE**

The heart of the DLL is Voltage Controlled Delay Line (VCDL). This Chapter explains the realization of delay elements and then an eight stage VCDL has been realized.

## **CHAPTER 6: RESULTS AND DISCUSSIONS**

This Chapter discusses all about performance summary of the DLL. All the realizations have performed in 180 nanometer CMOS process Technology and simulations performed on OrCAD PSPICE Capture.

## **CHAPTER 7: CONCLUSION AND FUTURE SCOPE**

This chapter summarizes the major accomplishments of this thesis and presents the scope for the future scope.

#### **CHAPTER 2**

### **DELAY LOCKED LOOP**

In this chapter working principle and systemic study of closed loop components of DLL is described. Thereafter, different DLL architectures and literature available on this is briefly reviewed.

#### **2.1 INTRODUCTION**

The DLL is a digital circuit used for clock synchronization in digital high-performance circuits. Similar to a PLL, DLL also employs feedback mechanism in its basic operation with only one difference i.e. DLL uses VCDL in place of VCO as in PLL. A DLL is desired to produce minimum possible phase difference phase difference between the reference clock and the output clock from last stage of the VCDL. Each VCDL delay stage is able to provide a clock signal which is phase shifted from the given reference input clock when the phase is matched between reference clock and output clock.

Nevertheless, today's rapidly improving technology offers difficulty in phase matching which works on very high frequencies. To accommodate this we need DLLs which locks the output clock to reference clock within less lock-in time, and have wide lock – in range. The increasing level of integration of integrated circuits introduces the problem of clock skew on chip. The clock skew is a time difference between the rising edges of global and local clocks on the chip. It is caused due to mismatch in clock path and variations in clock loading. This phenomenon strongly affects the function and performance of the sequential circuits. A DLL is used for clock distribution in order to remove the clock skew on chips [6].

The application area of DLL includes memory, clock synthesis, clock distribution, clock and data recovery and microprocessors in order to reduce on chip clock buffer delay.

#### **2.2 WORKING PRINCIPLE OF DLL**

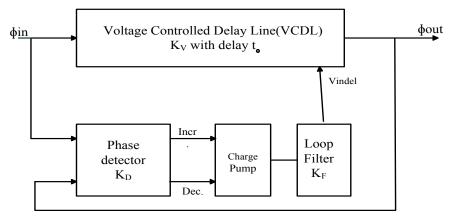

A DLL is a nonlinear negative feedback system. Figure 2.1 below shows the block diagram of DLL. As shown in fig. 2.1 it consists of mainly four basic components:

- (i) Phase Detector (PD)

- (ii) Charge Pump (CP)

- (iii) Loop Filter (LF)

- (iv) Voltage Controlled Delay Line (VCDL)

It works on an assumption that a reference clock of desired frequency is available and it is delayed until the reference clock and its delayed version is synchronized.

Fig. 2.1: Block diagram of DLL [6]

The overall mechanism of a DLL as follows:

PD takes reference clock and the output of VCDL as its inputs and provides information to CP either to charge or discharge the capacitor of loop filter is based on the relative phase between the two signals. The output of PD is then used to drive the charge pump whose function is to charge or discharge the capacitor of LF. If reference clock leads the VCDL's output which has been termed as  $Out\_Clk$ , Up signal goes high and CP charges the capacitor of LF and the value of  $V_{indel}$  increases. On the other hand if VCDL's output leads the reference clock, Down signal goes high and CP discharges the capacitor of LF and the value of  $V_{indel}$  decreases. The VCDL delays the input data in accordance with control voltage ( $V_{indel}$ ) and we get the required signal locking property. Owing to such a negative feedback mechanism, the phase error gradually decreases until it finally becomes zero.

A DLL finds its main application in removing clock skew in high- performance circuits. The DLL tries to remove the clock skew in between two clock signals by adding additional time delay as shown in fig. 2.2.

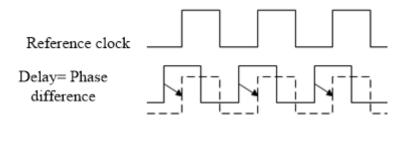

Output clock synchronized by adding delay (phase correction) Fig. 2.2 Basic DLL timing

For a DLL, Locking time, static phase error and lock range are the most important performance parameters. Locking time refers to the time duration a DLL requires to attain a stable locking state from an initial state. Generally, the amount of charging and discharging current flowing in Charge Pump, the overall delay loop bandwidth and the speed of the PD determines the lock time. The maximum and minimum delay of VCDL, is referred as Lock range within which the delay of the VCDL can be varied. A DLL is able to attain lock only in this range. The operating frequency range of a DLL is directly affected by Lock range. Static Phase error refers to the phase difference between the output signal of the last of the VCDL and the input reference signal. After a DLL is locked, the phase of these two signals should be perfectly matched in the ideal case.

### 2.2 SYSTEMIC STUDY OF CLOSED LOOP COMPONENTS OF DLL

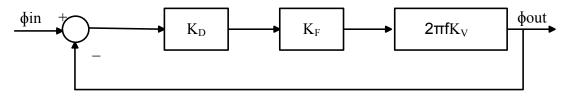

To analyze the dynamic behavior of DLL, its model shown in fig. 2.1 can be realized in terms of  $\phi_{in}$  and  $\phi_{out}$ , where  $\phi_{in}$  and  $\phi_{out}$  represent the phase of input and output clock respectively as shown below in fig. 2.3.

Fig. 2.3: DLL control model [9]

This model can be simplified by realizing the relationship between  $\phi_{in}$  and  $\phi_{out}$ . The phase (in radian) of the input clock is related to the phase of the output clock by following relation

$$\phi_{\text{out}} = \phi_{\text{in}} + t_0. \ (2\pi/T_{\text{clock}}) \ \dots \ (2.1)$$

Where  $T_{clock}$  is the period of the reference clock and  $t_0$  represents the time delay generated by the VCDL and is related to output voltage  $V_{indel}$  of loop filter by

$$\mathbf{t}_0 = \mathbf{K}_{\mathbf{V}} \cdot \mathbf{V}_{\text{indel}} \qquad (2.2)$$

here  $K_V$  denotes the gain of the VCDL. Its unit is seconds/V.

The expression 2.1 can be written as

$$\phi_{\text{out}} = \phi_{\text{in}} + t_0.2\pi f \qquad (2.3)$$

where  $f = 1/T_{clock}$ .

Since one of the performance metrics of a DLL is jitter, so for a good jitter performance a DLL should meet the following condition:

"Bandwidth of DLL (the rate at which the DLL will respond to a change in the input phase) should be less below the bandwidth (the rate at which a signal will propagate around the entire loop) by the factor of 10".

If above condition is met then the DLL model of fig. 2.3 can be further simplified as shown below in fig. 2.4.

Fig. 2.4 Simplified control model of DLL [9]

the overall transfer function is computed as

$$\phi_{\text{out}} = (\phi_{\text{in}} - \phi_{\text{out}}) K_{\text{D}} K_{\text{F}} K_{\text{V}} 2\pi f. \qquad (2.4)$$

$$\frac{\phi_{\text{out}}}{\phi_{\text{in}}} = \frac{K_D K_F K_V .2\pi f}{1 + K_D K_F K_V .2\pi f} \dots (2.5)$$

Since the term K<sub>F</sub> is gain of combination of charge pump and loop filter which can be expressed as

Putting the value of  $K_F$  in expression 2.6 we will obtain

$$\frac{\phi \text{out}}{\phi \text{in}} = \frac{1}{1 + \frac{s}{\omega_{Loop}}}.$$

(2.8)

$$\omega_{Loop} = K_D . K_L . K_V . 2\pi f. \qquad (2.9)$$

Generally the transfer function of PLL involves two poles that lead to less stability as compared to DLL which is a single pole system.

#### **2.3 DLL ARCHITECTURES**

The DLLs can be categorized on the basis of their phase shift generation and these are as follows:

#### 2.3.1 Analog DLLs

where

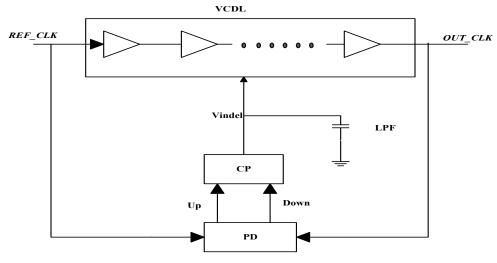

Figure 2.5 below is depicting the block diagram of Analog type DLL which comprises of Phase Detector (PD), Charge Pump (CP), first order Loop Filter (LF) and Voltage Controlled Delay Line (VCDL). The VCDL is a cascade connection of several variable delay elements. In order to maintain phase alignment in input and output clock signals, PD detects phase error by comparing their rising edges and the combination of CP and LF generates control voltage proportional to this phase error. The VCDL takes two inputs, one is reference input clock and the second is control voltage. This control voltage is utilized to produce delay in reference clock through VCDL. The DLL forces the phase of its input and output signal to be aligned. In locked condition the delay between input and output should be equal to one clock period of input signal.

From equation 2.8 we can observe that the transfer function of DLL has only one pole in sdomain, which suggests high stability of the system [9].

Fig. 2.5 Analog type DLL [12]

Analog type DLLs are most suitable where fine - grain delay variations are required. This type of architecture accumulates less jitter over digital DLLs because of its fine delay adjustments and this is important advantage of using analog DLLs but small delay steps limits locking range of the DLL.

#### 2.3.2 Digital DLLs

As in case of Analog type DLL, the delay was controlled by control voltage generated by the combination of CP and LF which was analog in nature. In Digital type DLLs delay is provided in fixed and quantized steps. The block diagram of Digital DLLs has been depicted in fig. 2.6 which consist of Phase Detector (PD), Phase selector (PS), Finite State Machine (FSM) and Digitally Controlled Delay Line (DCDL). The DCDL is composed of variable delay elements chain having different lengths. The amount of delay is determined by the number of delay elements in chain. The PS is realized as multiplexer. At the output of PS, pulse of defined phase – shift is selected. The amount of delay to be given is decided by the FSM. In this way the generation of phase shift takes place in digitally controlled manner.

Fig. 2.6 Digital DLL [12]

Time delay generated by delay elements are fixed and quantized, hence these are used where delay in steps of course – grain is required to lock a wide range of frequencies. Since the fixed and quantized time delay is used here, it leads to large jitter problem.

#### 2.3.3 Dual- Loop Delay Locked Loops

The architecture of Dual – Loop type DLLs consist of cascaded connection of Digital DLL and Analog DLL which has been depicted in fig. 2.7 below:

Fig. 2.7 Dual-loop type DLL [12]

On the basis of its architecture, these types of DLLs are also termed as hybrid DLLs. This type of DLLs can be used over wide range of frequencies. Jitter performance is not good as clock propagation involves two path cycles consisting of large number of delay elements. Implementation of this type of architecture is very complex and also requires more power dissipation [12].

#### **2.4 LITERATURE REVIEW**

#### 1. Analog DLLs

Most of the recent works have already been done in Analog type DLLs. A selection of the relevant literature has been presented below, where main focus was to expand operating range of the conventional DLL, DLL as frequency multiplier and to linearize the delay of VCDL etc. have been proposed.

Yongsam Moon, Jongsang Choi, Kyeongho Lee, Deog-Kyoon Jeong and Min-Kyu Kim [1] in their work proposed a method to expand the operating frequency range of the conventional DLL by attaching a replica delay line in parallel to it. The advantage of this architecture is that it keeps the benefits of conventional DLL such as good jitter performance and multiphase clock generation with small increments in chip area and power consumption. To provide duty cycle correction capability of dell cells which can be controlled by multiple voltages have been used here. The peak to peak jitter of this architecture is less than 30 ps in frequency range between 62.5 and 250 MHz with supply jitter sensitivity of 0.11ps/mV at 250 MHz. Implementation has been done in 0.35µm CMOS technology having chip area of 0.2 mm<sup>2</sup> with power dissipation of 42mW.

Hsiang-Hui Chang, Jyh-Woei Lin, Ching-Yuan Yang and Shen-Iuan Liu [2] have proposed an approach to dynamically change the number of delay cells to widen the operating frequency range of the DLL. This architecture uses a phase selection circuit to decide what number of delay cells should be employed. This phase selection circuit also controls the number of capacitors, in this way it can shift the bandwidth of the overall DLL. A new start controlled circuit has also been proposed to avoid false locking. Operating frequency range of this architecture is between 6MHz and 130 MHz with maximum r.m.s. jitter 25ps. Implementation has been done in 0.35µm CMOS technology having chip area of 880µm×515µm and maximum power dissipation is 132mW.

Hsun-Hsiang Chen, Zih-Hsiang Wong and Shen-Li Chen[3] have utilized the phase selection Circuit [7] but they used Frequency to Voltage Converter for the selection of capacitor. The operating frequency range of this architecture extends from 106 MHz  $\sim$  151 MHz to 54 MHz  $\sim$  250 MHz, and the power dissipation increases from 2.47 mW  $\sim$  3.33 mW to 6.7 mW  $\sim$  14 mW.

Kuo-Hsing Cheng, Yu-Lung Lo, Wen-Fang Yu and Shu-Yin Hung [4] have also proposed phase selection circuit based on Time to Digital conversion which reduces the locking time of this DLL architecture to only one clock cycle of reference signal's time period. For expansion of operating frequency range, multi-controlled VCDL has been employed in this architecture. This architecture does not possess the problem of false locking and accumulates less jitter. Simulations were based upon TSMC 0.25  $\mu$ m 1P5M N-well CMOS process. The locking range was 50MHz - 280MHz.

Chulwoo Kim, In-Chul Hwang, and Sung-Mo (Steve) Kang [5] have proposed DLL based clock generator. In this work they have proposed a phase detector with a reset circuitry and a new frequency multiplier to overcome the limited locking range and frequency multiplication problems of the conventional DLL – based systems. The operating frequency range of this architecture is from 120MHz to 1.1GHz with cycle to cycle jitter  $\pm 7.28$ ps at 1GHz. Implementation has been done in 0.35µm CMOS technology having chip area of 0.7mm<sup>2</sup> and the power dissipation is 42.9mW at 1GHz.

Ramin Farjad-Rad, William Dally, Hiok-Tiaq Ng, Ramesh Senthinathan, M.-J. Edward Lee, Rohit Rathi, and John Poulton [11] have proposed multiplying DLL by inserting a multiplexer and selected logic in conventional DLL for high speed on – chip clock generation. This architecture possesses characteristic of PLL for multi-rate frequency multiplication on the other hand it removed all other drawbacks of PLL – frequency multiplier such as jitter accumulation. Implementation has been done in  $0.18\mu$ m CMOS technology having chip area of  $0.05 \text{ mm}^2$ . The operating frequency range is 200MHz – 2GHz with multiplying ratios of 4, 5, 8 and 10. Its Power dissipation at 2GHz is 12mW. Peak to peak and rms jitters are 1.73ps and 13.1 ps respectively.

Goran Jovanovic, Mile Stojcev and Dragisa Krstic [12] have proposed a method to linearize the delay elements of conventional DLL. They modified the conventional Charge Pump and Bias circuit from single ended to differential input output kind of structure. This modified structure made DLL immune to power, process and temperature variations. Simulation has been done in 1.2µm double – poly and double – metal CMOS Technology.

Soh Lip-Kai, Mohd-Shahiman Sulaiman, and Zubaida Yusoff [13] have proposed a fast locking DLL with less jitter. They employed dual Charge Pump as Coarse charge pump and Fine Charge pump. Coarse charge pump made locking fast and Fine charge pump allowed fine adjustments

by reducing jitter. A modified Phase Frequency Detector with reduced reset time is also used in this structure. Implementation is done on the Silterra 0.18  $\mu$ m 1P6M CMOS process. The active area of the proposed DLL circuit is 327.46 $\mu$ m× 116.16 $\mu$ m.

Pin-Tseng Chen, Chia-Chen Chang, Han-Ying Liu, and Yu-Lung Lo [14] have proposed Dual slope technique to enhance the speed of DLL. As in the previous case, they used Dual charge pumps, here two types Phase Detectors have been employed. Accordingly, a modified charge pump has also been used in this architecture keeping small area cost and better jitter performance. Implementation has been done in 0.35  $\mu$ m CMOS process having core area of 0.069 mm<sup>2</sup>. Operating frequency range is 140 MHz – 270MHz. Peak to peak jitter is 3.2 ps and static phase error is 4.1ps at 230MHz. This architecture takes 88 cycles for locking and dissipates power of 10.8 mW.

B.Venkataramani, Karutharaja.V. and M.Bhaskar [15] have proposed a modified DLL which requires less cycles for locking. They employed charge pump with symmetric load and VCDL made of current starving inverters. Implementation has been done in UMC180 nm CMOS technology. Operating frequency range was 650MHz - 1.2GHz with a locking period of 4 to 8 cycles. Jitter of this structure was 10ps.

Pierre Maillard, W. Timothy Holman, T. Daniel Loveless, Bharat L. Bhuva and Lloyd W. Massengill[16] have proposed a radiation-hardened-by-design (RHBD) VCDL for single-event mitigation in DLLs. Single-event transients (SETs) have been identified as the primary failure mechanism behind several spacecraft malfunctions. A modified differential delay cells have been used to harden the VCDL that results in reduction of missing pulses generated by DLL after ion strike in space. The single event errors can be significantly reduced by increasing the W/L ratio of feedback transistor in delay cells of VCDL while keeping high operating frequency, wide tuning range and small area penalty.

Menka Sukhwani, V. B. Chandratre, Megha Thomas, C. K. Pithawa and Vangmayee Sharda [17] have proposed a 128-bit deep switched capacitor based analog waveform sampling memory ASIC "*Anusmriti*". The *Anusmriti* ASIC is designed specifically for pulse profile analysis of fast single shot events, occurring typically in High Energy Physics, Astronomy and Laser or accelerator based experiments without using high frequency sampling clocks. It samples and stores the randomly occurring fast exponential signals. The stored memory samples can be read and digitized subsequently at lower rate thereby relieving the need of high speed

digitization. Hence to provide accurate sampling interval this design is incorporated with 500 MHz DLL .Implementation is done in 0.7  $\mu$ m CMOS process occupying chip area of 5mm  $\times$  3.5mm.

Heedon Jang, Hyunggun Ma, Dongwook Seo, Jaeho Lee, Hyungsoo Lee and Franklin Bien[18] have proposed a low power receiver for medical implantable communication system (MICS) using DLL. As compare to its counterpart MICS using PLL, the MICS using DLL offers lesser power dissipation. Two channel DLL is employed in this design to generate 400MHz from 40MHz input signal. Power Dissipation of DLL is 4.8 mW and total occupied area by overall MICS is 3mm<sup>2</sup>.

#### 2. Digital DLLs

Ko-Chi Kuo and Chung-Yuan Chang and Si-Hsien Li [19] have proposed a DLL incorporated with Successive Approximation Register (SAR) in its architecture to make its locking fast. To reduce the power dissipation significantly Loop State Controller (LSC) is proposed which switches the mode of operation from tracking mode to sleeping mode and vice – versa. Phase Error Comparator (PEC) keeps the track for any variation in phase, supply, process, temperature and load. If PEC finds any error it informs the LSC to run in tracking mode and when it finds no error it informs the LSC to run in sleep mode deactivating PD and SAR. Implementation has been done in TSMC 180nm. It requires 6 cycles for locking and operating range is 150MHz – 900 MHz. The power dissipation is 15mW in tracking mode and 9mW in sleeping mode.

Bo Ye, Tianwang Li, Xingcheng Han, and Min Luo [20] have proposed Digital DLL incorporated with Delay Compensation Circuit (DCC). In this architecture, Shift Register (SR) has been employed to control the delay. It shifts the stream of bits either right or left according to input provided by the Phase Detector. This shifted bit stream decides the amount of delay to be generated. The function of DCC is to reset bits of SR when circuit is powered on. When some changes occur in SR due to any variation in supply, temperature and process, DCC takes care of it. The advantage of using DCC is that it has only one stable state. This design takes 16 cycles for locking.

Kai Huang, Zhikuang Cai, and Jun Yang [21] have proposed an all-digital delay-locked loop (ADDLL) with "reset in every step" (RES) delay line. Because of this reset mechanism in delay line this architecture has fast – locking and harmonic – free property. The locking time of

this architecture is N+1 where N is number of control bits for delay line. Simulation has been done on SMIC 180nm CMOS technology. The operating range was from 50 MHz to 250 MHz.

S. Moorthi, D. Meganathan, N. Krishna Prasad and J. Raja paul perinbam [22] have proposed a Modified Variable Successive Approximation Register controlled (MVSAR) algorithm based Digital DLL. This algorithm was used for fast-locking property, closed-loop operation and performing binary search without harmonic-locking issue. Implementation has been done in TSMC 0.18 $\mu$ m, six-metal technology. The operating frequency range of the ADDLL is 14MHz - 170 MHz and occupied an area of 142×142  $\mu$ m<sup>2</sup>.

#### 3. Dual Loop Delay Locked – Loops

Eunseok Song, Seung-Wook Lee, Jeong-Woo Lee, Joonbae Park, and Soo-Ik Chae [23] have proposed a DLL architecture incorporated with Replica Delay line and Cycle Period Detector (CPD) to remove the false lock problem of conventional DLLs. The CPD is placed in auxiliary loop of DLL. Whether the main loop of DLL is in correct locked state or not is decided by the CPD by estimating the cycle period of input clock. The auxiliary loop doesn't affects the main loop as it doesn't require any external signal. Duty Cycle Correction circuit has also been used. This was implemented in 0.25- µm CMOS technology and its operating frequency ranges from 30 to 200 MHz. Its cycle-to-cycle rms jitter is 12.8 ps at 133 MHz, and it dissipates 30 mW at 2.5 V supply.

Jinyeong Moon and Hye-young Lee [24] have proposed a dual-loop DLL for GHz DRAMs. This architecture has involved a conventional analog DLL in its reference loop and digital DLL in its main loop. Its main advantage is that it employs Multi – Digitally Controlled Delay Line (DCDL) which reduces the maximum operating frequency dependence of DLL on its unit time delay provided by Delay Line. The function of this reference loop in this architecture is to provide multi – phase input to the multiplexer present in main loop. For better jitter reduction, an extra invalidation system has also been employed in this architecture. The operating frequency range of this architecture is 500MHz- 3GHz. Its power dissipation is 12.5mW and the total jitter is 64.6ps at 1.6GHz.

Jacek Jasielski, Stanis\_aw Kuta, Witold Machowski, Wojciech Ko\_odziejski [25] have proposed an Analog Dual locked loop incorporated with cascaded course delay line and fine programmable delay line. The coarse delay line is to push the loop close to lock state, and a fine

programmable delay line to make small adjustments to the output phase. Both the delay lines have employed cascaded variable-delay elements based on single-ended Schmitt triggers. For the correction of a duty cycle of the delayed output signal, a duty cycle correction (DCC) has been used. It has been simulated using Spectre and BSIM3V3 device models for 1.8V 180nm CMOS technology from UMC.

S. Senthilnathan, S. Balaji and R. Prithviraj [26] have proposed a dual – loop DLL architecture for high accuracy Positron Emission tomography imaging with low power consumption. This proposed architecture has two control voltages to control delay of VCDL, in this way it has reduced jitter significantly. Two similar loops consisting of PD, CP and LF have been used to provide control voltages. This architecture is free from false – locking and further static D flip-flops have been employed for less power dissipation. It is operated at 1GHz with acquisition time of 19.5  $\mu$ s. Also its Capture range is 14 – 19.5  $\mu$ s and Lock – in range is 20 – 100  $\mu$ s.

## **CHAPTER 3**

### PHASE DETECTOR AND PHASE FREQUENCY DETECTOR

In this chapter working mechanism of the PD and PFD is detailed. After that realization of PFD using  $C^2MOS$  – register is proposed and their operation is verified with the help of simulations.

#### **3.1 INTRODUCTION**

The main purpose of the Phase Detector (PD) or Phase Frequency Detector (PFD) is to detect the phase difference between its input signals. The detected phase error signal is indicated as Up and Down signals. The input signals to PD or PFD are reference clock and output clock which is taken back from VCDL. The error signals Up and Down are voltage signals proportional to the phase error. This PD or PFD generates high on Up signal when reference signal leads to output signal. On the other hand Down signal goes high when reference signal lags behind output signal. When Up signal goes high, the value of control voltage increases through charge pump. On the contrary, if Down signal goes high it indicates the value of control voltage need to be decreased.

For detecting the phase error following is used:

- (1) XOR gate based Phase Detector

- (2) Flip- Flop based Phase Detector (also called Phase Frequency Detector)

#### **3.2 XOR based Phase Detector (PD)**

A XOR based PD is an example of a basic phase detector. It produces error pulses on both falling and rising edges.

Fig. 3.1: XOR Phase Detector

A detailed analysis of the XOR PD when the reference and output signals are out of phase by 0,  $\pi/2$ , and  $\pi$  respectively is shown in fig. 3.2.

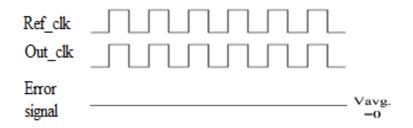

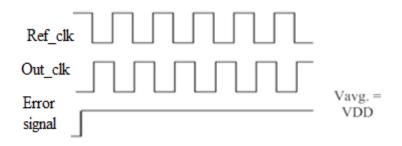

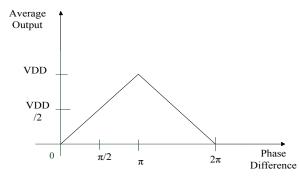

In fig. 3.2, the phase difference between the two signals is locked phase. The average output voltage is 0 in this case.

Fig. 3.2 when phase difference between the two signals is zero.

In fig. 3.3, the phase difference between the two signals is  $\pi/2$ . The average output voltage is VDD/2 in this case.

Fig. 3.3 when phase difference between the two signals is  $\pi/2$ .

In fig. 3.4, the phase difference between the two signals is  $\pi$ . The average output voltage is VDD in this case.

Fig. 3.4 when phase difference between the two signals is  $\pi$ .

Hence we can conclude that the DC value of the XOR based PD is linearly proportional to the difference between its two input signals. The XOR PD characteristic plot in fig. 3.5:

Fig. 3.5: XOR PD characteristic

XOR based PD has several drawbacks as

- 1. Only one output from the XOR PD makes it difficult to connect with subsequent circuit.

- 2. It is essentially a signal level detector, i.e. the output of the gate is dependent on duty cycle of its two input signals. Consequently XOR PD may generate incorrect phase error information unless duty cycle correction circuits are used.

The duty cycle problem of XOR phase detector can be understood by following fig. 3.6:

Fig. 3.6 Output of XOR PD when inputs having different duty cycle

As shown in the fig. 3.6, reference clock of 25% duty cycle and output clock with 50% duty cycle is given to XOR PD as inputs. Since both inputs have same frequency the output should be a zero level signal but XOR gate gives a high when both signals are of different levels, hence the output as shown in fig. 3.6 is obtained.

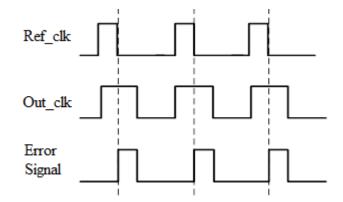

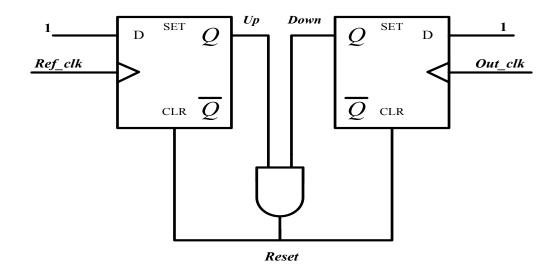

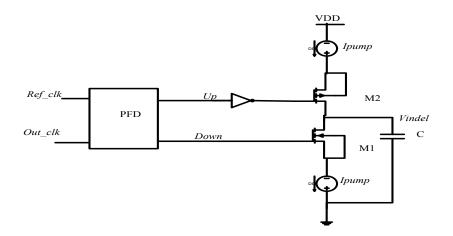

#### 3.3 Flip-Flop based PD or PFD

An improved PD is based on flip-flops which are also called Phase Frequency Detector (PFD). Since flip-flops works on the edges of clocks, the duty cycle dependence problem with XOR gate PD can be avoided. Figure 3.7 shows a flip-flop based PFD.

Fig. 3.7 Block Diagram of Phase Frequency Detector [8]

The PFD shown in fig. 3.7 consists of two resettable, edge triggered D-flip flops. The input D is kept at logic 1. The inputs, reference clock ( $Ref_clk$ ) and output clock ( $Out_clk$ ) are being provided as clock signals for these flip flops. The outputs have been denoted as Up and Down. At any point of time, the outputs of phase detector can be in one of the four states which are tabulated as:

| Up | Down | Reset |

|----|------|-------|

| 0  | 0    | 0     |

| 0  | 1    | 0     |

| 1  | 0    | 0     |

| 1  | 1    | 1     |

| Table | 3.1: | <b>Outputs</b> | of D flip | flop | based PFD |

|-------|------|----------------|-----------|------|-----------|

|-------|------|----------------|-----------|------|-----------|

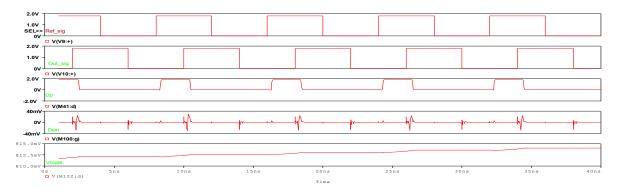

Here, the information related to phase error is coded at the output of a PFD with the use of two D flip-flops (DFF). The DFF outputs are denoted as *Up* and *Down*, individually. Expecting both outputs are at first low, a rising edge of reference clock causes the *Up* signal to go high. This

shows that the VCDL's delay should be expanded to match the reference signal. In any case, if Output of the VCDL leads the reference clock, *Down* signal goes high showing that the output of the VCDL should be delayed to match the reference signal. At the point when both outputs go high, the AND gate generates a reset signal giving back the PFD to the zero state. In this way, the "Up = Down = high" state is removed by the reset, and the PFD is basically a three-state device.

In any case, as the reference and output clock approach one another, the DFFs get reset before any charge is fed onto the capacitor by the CP; this characterizes the dead zone. The vicinity of the dead zone causes jitter in DLL. It can be reduced by inserting inverters into the reset path to increase the reset delay. On the other hand, enlarging the reset path delay expands the time duration in which the both PMOS and NMOS transistors turned on charge pump paths are simultaneously conducting. This short circuit alters the VCDL control voltage and results in increased phase noise. The DFFs also need to be matched. If one DFF resets earlier than the other, it can cause the reset signal to go to zero before the other DFF resets.

#### **3.4 CMOS REALIZATION OF PFD**

The PFD demonstrated in fig. 3.6 can be realized using inverters and NAND gates as shown in fig. 3.7.

Fig. 3.8 Realization of PFD using NAND based D latch [7]

#### **3.5 SIMULATION OF CMOS PFD CIRCUIT**

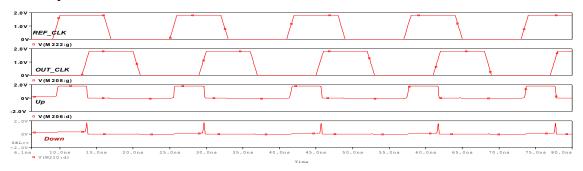

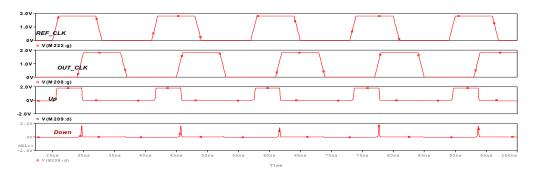

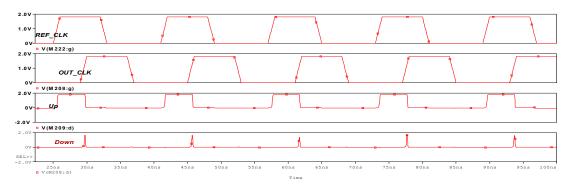

Realization of circuit shown in fig. 3.8 has been done in TSMC 180 nm CMOS process technology keeping device dimensions as  $W_p = 3600$  nm , $W_n = 1800$  nm and  $L_p = L_n = 180$  nm. Simulation Results for circuit shown in fig. 3.8 has been shown in fig. 3.9, fig. 3.10 and fig. 3.11. In fig. 3.9 and fig. 3.10 the phase difference between reference and output clock is  $\pi/2$ . Figure 3.9 shows the result when reference clock leads the output clock and in fig. 3.10 reference clock lags behind output clock.

Fig. 3.9 Simulation result of PFD when reference clock leads the output clock

From above simulation it can be observed that the width of the *Up* error signal is approximately equal to the duration between rising edges of both the pulses and the *Down* signals are glitches.

Fig. 3.10 Simulation result of PFD when reference signal lags the output signal

Here simulation has been done in opposite to previous one as reference clock lags the output clock. As a result, *Down* signal has width approximately equal to duration of rising edge of both the signals.

At the last in fig. 3.11 the situation when both clocks are synchronized or having phase difference of 0 or  $2\pi$  has been simulated.

Fig. 3.10 Simulation result of PFD when phase difference is 0 or  $2\pi$ .

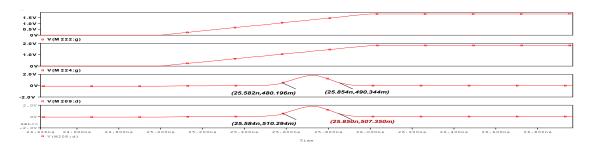

On the rising edges of both signals approaches each other or synchronizes the AND gate in reset path resets both the outputs of D flip-flops. Here some ripples are present at this moment, it's duration in actual is time taken by the overall circuit to give a stable zero at outputs of D flip-flops. In following fig. 3.11 enlarged view of *Up* and *Down* signals have been shown in to measure the reset time of the PFD. Reset time of CMOS-PFD is 0.133ns.

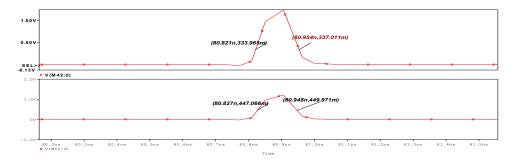

Fig. 3.11 Enlarged view of Up and Down signals

# 3.6 $C^2MOS$ – Register based PFD

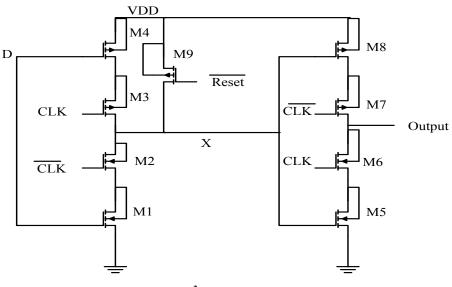

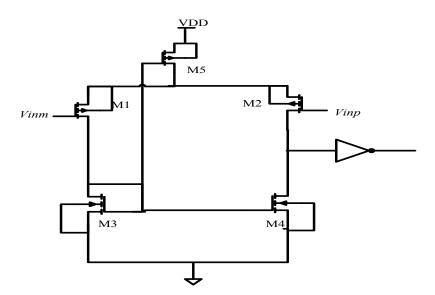

In order to design a PFD using C<sup>2</sup>MOS (Clocked CMOS) – Register, this register should have a reset arrangement in itself. Figure 3.12 below depicts the circuit of positive edge triggered C<sup>2</sup>MOS – Register based on master – slave configuration with an active low reset. Before going to design a PFD let's have a brief overview on working mechanism of  $C^2MOS$  – Register with an active low reset.

This  $C^2MOS$  (Clocked CMOS) – Register works on two phases:

- 1.  $CLK = \theta(\overline{CLK} = I)$ : Tristate driver in first stage is turned on and the master stage becomes inverter and the inverted version of D is stored at node X. At this moment master stage is in evaluation mode and slave stage is in hold mode. Transistors M<sub>7</sub> and M<sub>8</sub> are off, disconnecting input to output. Hence previous value of Q is hold at the output.

- 2.  $CLK = 1(\overline{CLK} = 0)$ : This time roles of master and slave stages are interchanged. The master stage is in hold (M<sub>3</sub> M<sub>4</sub> off) and the slave stage is in evaluation mode (M<sub>7</sub> M<sub>8</sub> on). The value stored at node X is propagated through second stage which is acting as inverter.

This circuit can be reset only in this second phase (CLK = 1, CLK = 0) on applying active low at reset. When reset = 0 is applied the output Q immediately becomes 0. This positive edge-triggered master – slave register offers benefit of insensitivity to clock overlap, provided rise and fall times of the clock edges are sufficiently small [6].

Fig. 3.12 C<sup>2</sup>MOS– Register [8]

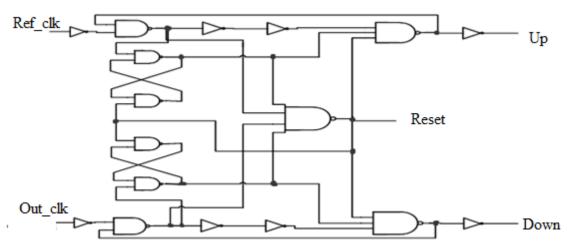

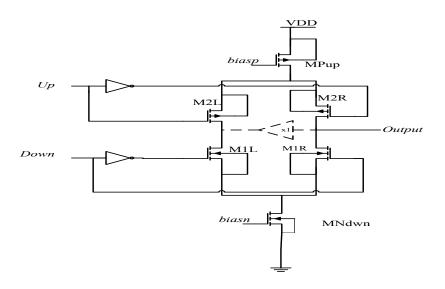

# 3.6.1 PFDs employing $C^2 MOS$ – Register

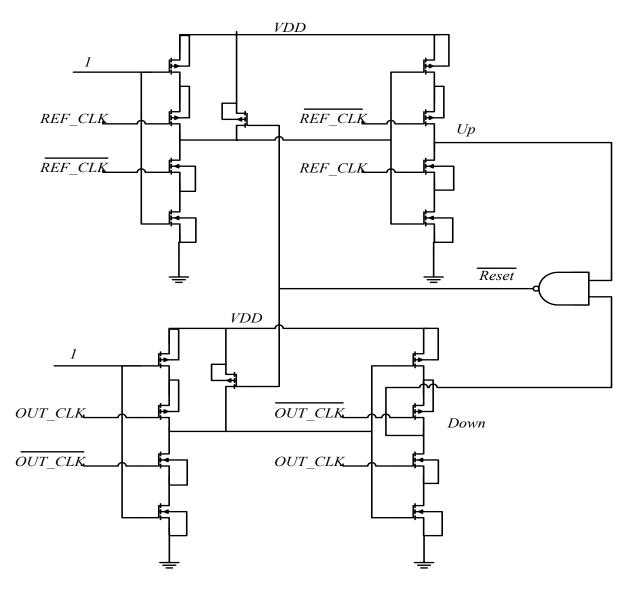

To propose PFDs which make use of  $C^2MOS$  – Register, we have used the concept of D flip-flop based PFD which has been described earlier in fig. 3.2. Here we simply replaced the D flip-flops with  $C^2MOS$  – Registers and the output of NAND is connected to reset of both registers. Figure 3.13 below is depicting the proposed PFD and it is termed as type-1.

Fig. 3.13 Proposed C<sup>2</sup>MOS – Registers based PFD (Type-1)

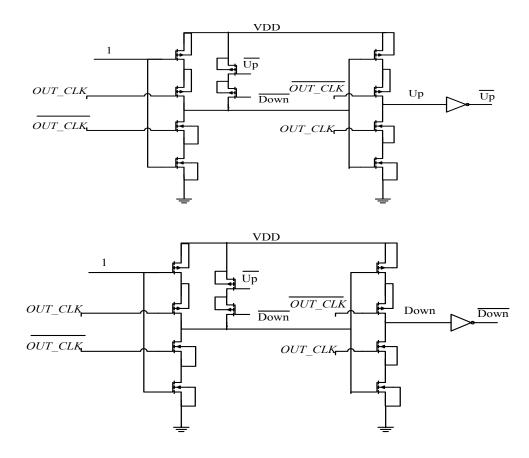

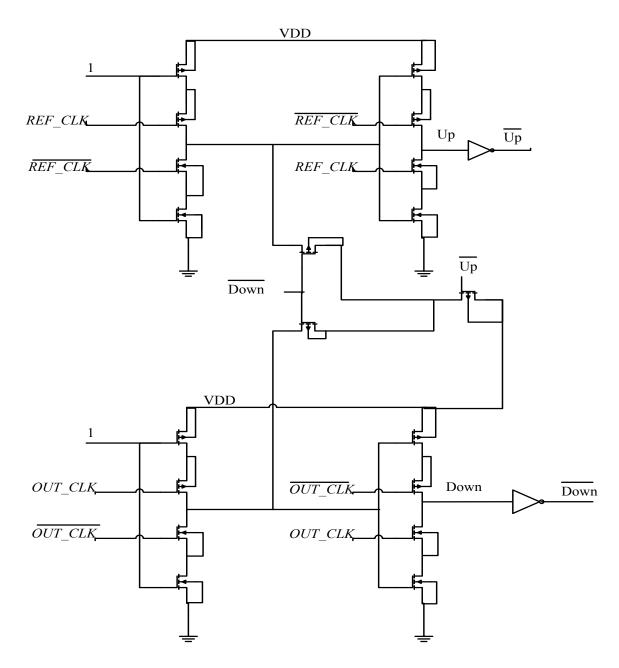

From the truth table1 of PFD we can conclude that reset is only activated when both the outputs *Up* and *Down* are high. So by utilizing this fact we can change the reset path of PFD shown in fig.3.13 as shown in fig.3.14. As evident in fig.3.14 we have employed two PMOS transistors for

reset in both  $C^2MOS - Registers$ . The inputs for these PMOS transistors are denoted as Up and  $\overline{Down}$  which are inverted versions of outputs Up and Down. The motive behind using this method is to reduce the number of transistors and we have effectively reduced two units of transistors in this circuit as compare to circuit shown in fig.3.13. Since Up and  $\overline{Down}$  require two inverters (total four transistors) for its generation and also NAND requires four transistors, so one can raise doubt whether we had reduced the number of transistors effectively. In DLL the PFD is followed by Charge Pump which requires four inputs these are Up,  $\overline{Up}$ , Down and  $\overline{Down}$ . Hence we can say that the architecture of Charge Pump employs two inverters to generate Up and  $\overline{Down}$  that can also be utilized to reset the PFD shown in fig. 3.13 and there is no need of extra inverters to be provided in design of PFD to reset. We have termed the PFDs of fig.3.13 and fig. 3.14 as type-1 and type-2 respectively. From PFD type-2 we have further reduced one more transistor which has been termed as type-3 shown in fig. 3.15. Three PMOS transistors have been employed here for reset effectively reducing the three transistors as compare to type-1 PFD.

Fig. 3.14 Proposed Type - 2 PFD

Fig. 3.15 Proposed Type - 3 PFD

# 3.7 SIMULATIONS OF C<sup>2</sup>MOS – PFD CIRCUIT

Realization of circuits shown in fig. 3.13, 3.14 and 3.15 has been done in TSMC 180 nm CMOS process technology keeping device dimensions as  $W_p = 3600$  nm , $W_n = 1800$  nm and  $L_p = L_n = 180$  nm. Simulations which were performed for CMOS-PFD, is performed for all three types of C<sup>2</sup>MOS – PFD.

# 3.7.1 Simulation results of Type 1 PFD

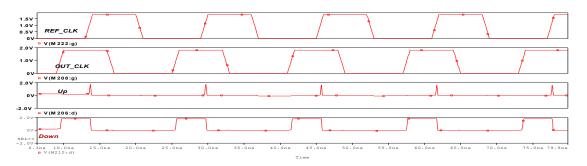

The functionality of the circuits of fig. 3.13 - 3.15 have been verified through time domain SPICE simulations using TSMC 180 nm while widths of 1800 nm and 3600 nm are used uniformly for all NMOS and PMOS transistors.

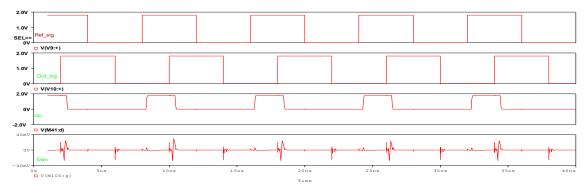

Fig. 3.16 Simulation result of Type-1 PFD when reference clock leads the output clock

Fig. 3.17 Simulation result of Type-1 PFD when output clock leads the reference clock

At the last in fig. 3.18 the situation when both clocks are synchronized or having phase difference of 0 or  $2\pi$  has been simulated.

Fig. 3.18 Simulation result of Type-1 PFD when phase difference is 0 or  $2\pi$ .

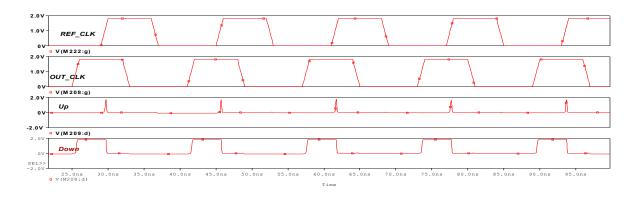

In all three simulations shown in fig. 3.16, 3.17 and 3.18, results show similarity with the simulation results of CMOS-PFD. Further in fig. 3.19 enlarged view of *Up* and *Down* signals has been shown to measure the reset timing. Reset time of Type-1 PFD is 0.257ns.

Fig. 3.19 Enlarged view of Up and Down signals

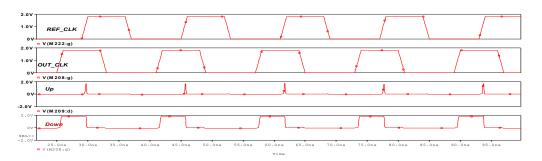

# 3.7.2 Simulation of Type 2 PFD circuit

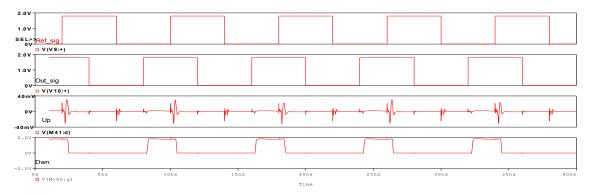

Simulations in all three cases which was done for Type-1 PFD, same has been performed for circuit shown in fig. 3.14 have been shown in from fig. 3.20 to fig. 3.23. Simulation results have found similar to simulation results of Type 1- PFD and CMOS-PFD except for reset time.

Fig. 3.20 Simulation result of Type-2 PFD when reference clock leads the output clock

Fig. 3.21 Simulation result of Type-2 PFD when reference clock lags the output clock

Fig. 3.22 Simulation result of Type-2 PFD when phase difference is 0 or  $2\pi$ .

Fig. 3.23 Enlarged view of Up and Down signals

Reset time of Type 2 PFD is 0.250ns.

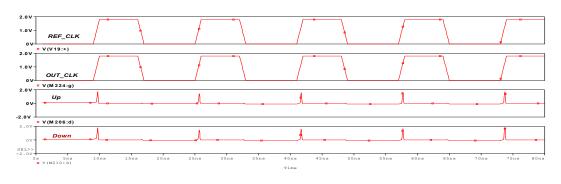

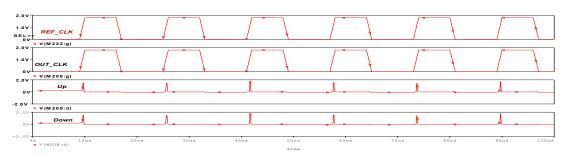

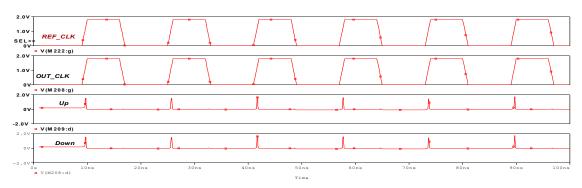

# 3.7.3 Simulation of Type 3 PFD circuit

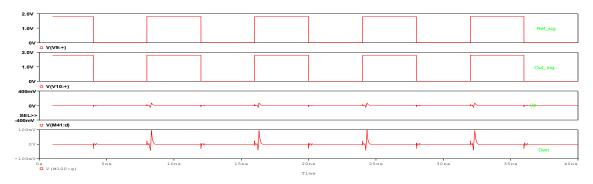

Simulations in all three cases which was done for Type-1 PFD, same has been performed for circuit shown in fig. 3.14 have been shown in from fig. 3.24 to fig. 3.27. Simulation results have found similar to simulation results of Type 1- PFD and CMOS-PFD except for reset time.

Fig. 3.24 Simulation result of Type-3 PFD when reference clock leads the output clock

Fig. 3.25 Simulation result of Type-3 PFD when reference clock lags the output clock

Fig. 3.26 Simulation result of Type-2 PFD when phase difference is 0 or  $2\pi$

Fig. 3.27 Enlarged view of Up and Down signals

Reset time for Type-3 PFD is 0.272ns.

# 3.8 Performance Comparison among CMOS – PFD and all three types C<sup>2</sup>MOS - PFD

The performance of all PFDs presented in this chapter is compared on the basis of transistor count, power consumption and reset time. The results are summarized in table 3.2.

| Sr.<br>No. | Parameter         | CMOS- PFD                         | C <sup>2</sup> MOS-PFD<br>Type-1 | C <sup>2</sup> MOS-PFD<br>Type-2 | C <sup>2</sup> MOS-PFD<br>Type-3 |

|------------|-------------------|-----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| 1.         | Transistor Count  | 60                                | 26                               | 24                               | 23                               |

| 2.         | Power dissipation | $3.64 \times 10^{-10} \mathrm{W}$ | 8.41×10 <sup>-5</sup> W          | 8.41×10 <sup>-5</sup> W          | 8.41×10 <sup>-5</sup> W          |

| 3.         | Reset time        | 0.133 ns                          | 0.257 ns                         | 0.250ns                          | 0.272ns                          |

Table 3.2. Performance Comparison among CMOS – PFD and all three types C<sup>2</sup>MOS – PFD.

It is found that CMOS-PFD shows most power efficient characteristic. On the other hand,  $C^2MOS$ -PFDs dissipate more power. Benefit involved in using the  $C^2MOS$ -PFDs is its less transistor count as compared to CMOS PFD's transistor count.

# **CHAPTER 4**

# **CHARGE PUMP AND LOOP FILTER**

This chapter focuses on the operation of charge pump and the role of capacitor in DLL. Since current mirrors are integral parts of the charge pump, these are also explained here.

# **4.1 INTRODUCTION**

The VCDL requires only one control signal but error signals generated by the PD or PFD are two in number, hence there is a requirement of combining the phase error signals into a single signal. This is accomplished by Charge Pump and a Loop filter. In a Delay Locked Loop, the phase error between the input reference signal and the VCDL output signal is detected by the PFD and transferred to the charge pump in the form of voltage pulses. The charge pump performs the function of adjusting the voltage of the loop filter and thereby altering the VCDL delay according to the phase error information provided from the Phase Frequency Detector.

As Charge Pump plays vital role in holding the control voltage of the VCDL in accordance with the phase error its proper designing is also important. We can provide higher values of current to loop filter through Charge Pump so that charging and discharging become fast, and this leads to better speed of the overall loop. The high value of current , however leads to higher power dissipation. Hence there are trade-offs, so a careful design approach is required here. Current mirror circuits are used as current sink and source in Charge Pump circuit depending upon *Up* and *Down* signals.

# 4.2 CHARGE PUMPs

The outputs of a Phase Frequency Detector are combined into a single input to drive the Loop Filter through a Charge Pump. There are two methods of doing this: The first method is called a tri-state output which is shown in fig. 4.1.

Fig. 4.1 Tri –state charge pump [8]

Both MOS devices in fig. 4.1 are functioning as switch which is used to connect the output terminal to either power supply  $V_{DD}$  or to the ground. When both Up and Down signals are low the output terminal will remain in high impedance state. A high signal at Up connects the output to the power supply and high at Down connects the output terminal to ground. The power supply variations affect its working as it modulates the output voltage.

Fig. 4.2 Charge Pump [8]

The second configuration shown is in fig. 4.2 is referred as Charge-Pump. MOS current sources are placed in series with NMOS and PMOS transistors of fig. 4.1. In this configuration both MOSFETS are working as switches, that connects or disconnects, the current sources to the output terminal. Because the current source can be made insensitive to supply variation, modulation of the VCDL control voltage doesn't take place [7].

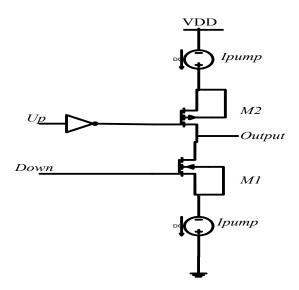

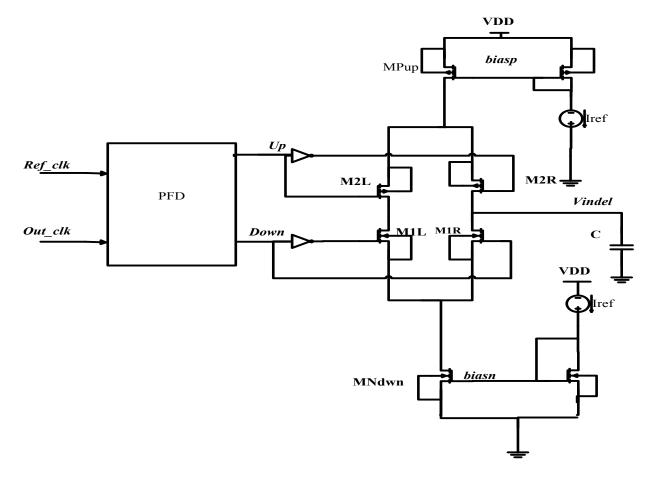

## **4.3 PRACTICAL IMPEMENTATION OF THE CHARGE PUMP**

The circuit of fig. 4.3 demonstrates the idea of the PFD with charge pump. Here in this circuit we come across some design issues that is when the sources of transistors M1 and M2 charge to *Ground* and *VDD* respectively, as when they are switched off. For example, assume that the source of M1 is released to ground when the *Down* signal goes high. At the point when M1 turns on, it doesn't supply the charge set by  $I_{pump}$  to the loop filter but instead, until the voltage over the current sink increases, carries on like a switch connecting the input of the filter to ground, which indicates we are not controlling the signal that is connected to the loop filter.

Fig. 4.3 PFD with Charge Pump [8]

To solve this problem, consider the circuit which is indicated in fig. 4.4.

Fig. 4.4 Practical Implementation of the Charge Pump [8]

At the point when Up and Down signals are low, M1L and M2L are on. The pump-up current source, MPup, is driving the pump-Down current source, MNdwn. At the point when either Up or Down signals goes high, the output is connected with one of the current sources. The MOSFETs M1L, M1R, M2L and M2R just direct the current to the loop filter. Another issue which we have with this topology is that when M1L and M2L are both on, the voltage on their drains will not be matched correctly with the voltage at the loop filter ( $V_{indel}$ ). It means, the voltage over each of the current sources (MPup and MNDwn) will not be the same as it is the point at which they are connected with the output node. It results in charge sharing between the parasitic capacitance on the drains of MPup and MNdwn and the capacitance utilized as loop filter causes a static phase error or jitter. To handle this difficulty, an amplifier (demonstrated in dashed lines in the fig. 4.4) can be inserted to keep the drain voltage of M1L and M2L to the same value  $V_{indel}$  [8].

#### 4.4 CURRENT MIRRORS

Current mirrors are integral part of the charge pump as they are used in this architecture to provide the bias voltages i.e. are *biasn* and *biasp*.

The Current Mirrors are active devices which are operated based on "copying" currents from a reference, with the assumption that one precisely – defined current source is already available. This "copying" of current from a reference current source to an active device is called "mirroring". The conceptual meaning has been shown in fig. 4.5.

Fig. 4.5 conceptual means of copying currents [7]

$I_{out} = I_{REF}$  is done in following way:

For a MOSFET the value of drain current  $I_D$  can be expressed as

$$I_{\rm D} = f(V_{\rm GS})$$

.....(4.5)

Where f(.) denotes the functionality of I<sub>D</sub> versus V<sub>GS</sub> (gate to source voltage).

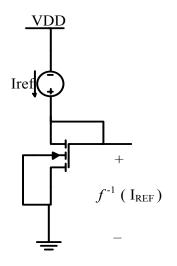

Then

$$V_{GS} = f^{-1} (I_D)$$

....(4.6)

It means if a transistor is biased at  $I_{REF}$ , then it gives  $V_{GS} = f^{-1}(I_{REF})$  as shown in fig. 4.6.

Fig. 4.7 Diode- connected device providing inverse function [7]

Hence, if same voltage is applied to the gate and source terminal of another MOSFET, the same current can be obtained in the second MOSFET. From fig. 4.7,  $I_{out} = ff^{-1}$  ( $I_{REF}$ ) =  $I_{REF}$ .

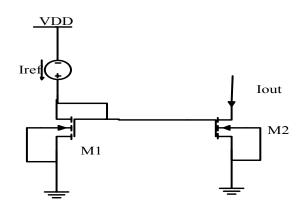

Fig. 4.7 NMOS current mirror [7]

In a simple way we can state the above phenomenon as two identical MOSFETs, are given equal gate to source voltages will have equal currents if they are operated in saturation (considering the channel length modulation is zero i.e.  $\lambda=0$ ).

From fig. 4.7, we can write

$$I_{\text{REF}} = \frac{1}{2} \,\mu_{\text{n}} \,C_{\text{ox}} \,(\frac{W}{L})_{1} \,(V_{\text{GS}} - V_{\text{TH}})^{2} \,\dots (4.7)$$

$$I_{out} = \frac{1}{2} \mu_n C_{ox} \left(\frac{W}{L}\right)_2 \left(V_{GS} - V_{TH}\right)^2 \dots (4.8)$$

While writing above equations of currents we have ignored the effect of channel length modulation means  $\lambda = 0$ .

From the equations 4.7 and 4.8 we can obtain the relation between  $I_{REF}$  and  $I_{out}$ , as

$$I_{out} = \frac{(W/L)2}{(W/L)1} I_{REF}$$

.....(4.9)

This topology allows the copying of current in a precise manner without depending upon process and temperature. The ratio of reference current and output current is completely in terms of device dimensions which can be controlled with reasonable accuracy [7].

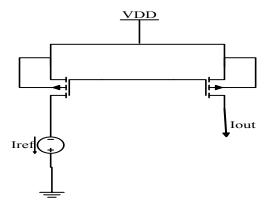

The PMOS version of fig. 4.7 is depicted in fig. 4.8

Fig. 4.8 PMOS current mirror [7]

## **4.5 LOOP FILTER**

The output from the combined blocks of PFD and charge pump has a large periodic content due to the repetitive phase detection. To remove the high frequency component, at the output of the

charge pump a loop filter is connected. This filter output is then used as control voltage for the VCDL

Typically a low pass filter is connected at the outputs of PFD as loop filter in PLL. A DLL uses simply a capacitor to integrate the phase error, which subsequently increases control voltage to VCDL. Though the lock time increases with increasing capacitor values, it improves bandwidth and ripples on control voltage.

A decrease in capacitor values result in lower lock time at the expense of increased ripples on control voltage.

## **4.6 SIMULATION RESULTS**

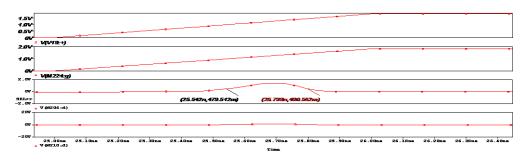

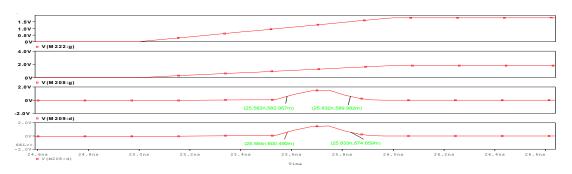

Simulations for NMOS current mirror (fig. 4.7), PMOS current mirror (fig.4.8) and the combination of charge pump (CP) and loop filter (LF) is shown in from fig.4.9 to fig. 4.10. All the circuits have been realized in TSMC 180 nm CMOS technology taking device dimensions as  $W_p = 3600$  nm,  $W_n = 1800$  nm and  $L_p = L_n = 180$  nm.

## 4.6.1 SIMULATION OF CURRENT MIRROR CIRCUITS

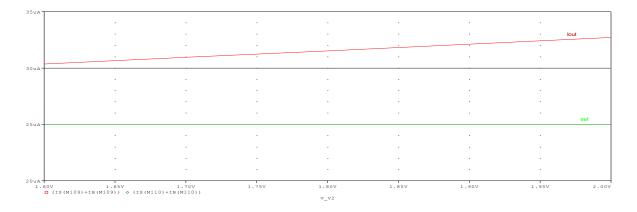

In fig. 4.9 the simulation for PMOS current mirror which is shown in fig. 4.8 has been shown. This simulation shows the variation of  $I_{out}$  with respect to change in supply voltage.

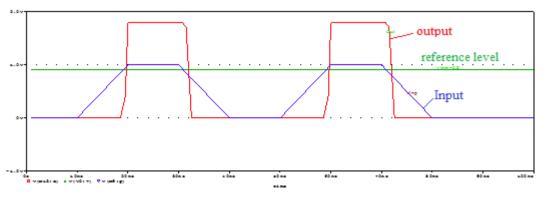

Fig. 4.9 Simulation of PMOS current mirror shown in fig. 4.6

Current  $I_{ref} = 25\mu A$  has been shown with green line and  $I_{out}$  with the red one which is trying to copy  $I_{ref}$ . It is evident from above simulation that the variation in supply doesn't affect too much the output  $I_{out}$ .

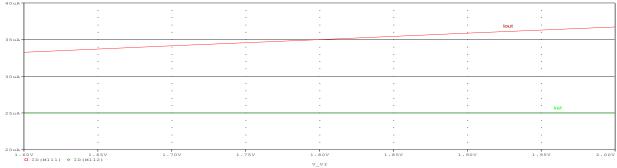

In fig. 4.10 the simulation for NMOS current mirror which is shown in fig. 4.7 has been shown. Here result is same as it was in previous case.

Fig. 4.10 Simulation of NMOS current mirror shown in fig. 4.7

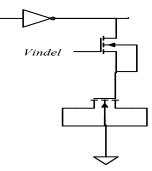

# 4.6.2 PFD and CHARGE PUMP