Α

Dissertation

on

# <u>"AN INVESTIGATING ON CDBA BASED CONTINOUS</u> <u>TIME CIRCUITS"</u>

Submitted in

partial fulfilment of the requirement for the award of the degree of

MASTER OF TECHNOLOGY

in

#### **VLSI DESIGN & EMBEDDED SYSTEMS**

Submitted by

#### VIKASH JARWAL

#### University Roll No: 2K13/VLSI/23

Under the guidance of

#### **Dr. RAJESHWARI PANDEY**

#### **Associate Professor**

Department of Electronics and Communication Engineering

Delhi Technological University

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY 2013-2015

## **CERTIFICATE**

This is to certify that the major project entitled "AN INVESTIGATION ON CDBA BASED CONTINUOUS TIME CIRCUITS" is submitted by Mr. Vikash Jarwal (2K13/VLSI/23), in partial fulfilment of the requirements for the award of degree of Masters in Technology in VLSI Design and Embedded Systems, Delhi Technological university, Delhi.

Mr. Prem R. Chadha Head of Department Department of ECE Delhi Technological University Dr. Rajeshwari pandey Associate Professor Delhi Technological University Delhi -110042

Delhi -110042

# **DECLARATION**

This is to certify that the. major project entitled "AN INVESTIGATION ON CDBA BASED CONTINUOUS TIME CIRCUITS" is submitted by me in partial fulfilment of the requirements for the award of degree of Masters in Technology in VLSI Design and Embedded Systems, Delhi Technological university, Delhi comprises of only my own work and due acknowledgement been made to all other materials used.

I, hereby, further declare that in case of any legal dispute in relation to my M.Tech. Major Project, will be solely responsible for the same.

Date:

Signature Vikash Jarwal (2K13/VLSI/23)

## **ACKNOWLEDGEMENT**

I express my deepest gratitude to my project guide **Dr. Rajeshwari Pandey**, associate professor department of Electronics and Communication Engineering, Delhi Technological University whose encouragement, guidance and support from the initial to the final level enabled me to develop an understanding of the subject. Her suggestions and ways of summarizing the things made me to go for independent studying and trying my best to get the maximum in my topic, this made circle of knowledge very vast. I am highly thankful to her for guiding me in this project.

I am grateful to **Prof. Prem R. Chadha**, HOD, Electronics and Communication Engineering department, DTU for his immense support in carrying out this work.

A Very special thanks to **Guru Murthy Komanapalli**, PhD scholar, (department of Electronics and Communication Engineering) and **Kapil Gehani** for their emotional support and technical help during my critical time.

I am also thankful to my family for their constant support and motivation during this work. Finally I would like to almighty God for his blessings without which nothing is possible in this world.

> Vikash Jarwal 2k13/VLSI/23

#### **ABSTRACT**

Over the year of time, the evolution of modern application of signal processing has followed the trends of so called current mode, when signals, representing the information being processed, are in the form of current. In contrast to the conventional mode which utilized electric voltage, the current mode circuit can exhibit higher bandwidth, better signal linearity, higher slew rate and lower power consumption. Since they are designed for lower voltage swings, smaller supply voltage can be used. The current differencing buffered (CDBA) amplifier can operate in both current mode and voltage mode, which provides flexibility.

This project discusses implementation of lossless grounded negative inductor circuits (and application thereof), and oscillator circuit, using single CDBA. CDBA is designed using AD844 IC.

# **CONTENTS**

## CERTIFICATE AND DECLARATION ACKNOWLEDGEMENT ABSTRACT CHAPTER1

### INTRODUCTION

| 1.1 Overview                                                               | 1 |

|----------------------------------------------------------------------------|---|

| 1.2 Motivation                                                             | 2 |

| 1.2.1 Development of active blocks                                         | 4 |

| 1.2.1.1 Development of Current Feedback Amplifier from Current Conveyor II | 4 |

| 1.2.1.2 FTFN                                                               | 5 |

| 1.2.1.3 generation of current Differencing Buffered Amplifier:             | 5 |

| 1.2.1.4 Design of Current Difference Trans conductance Amplifier (CDTA)    | 6 |

| 1.3 Research objective                                                     | 6 |

| 1.4 Thesis organization                                                    | 7 |

| REFERENCES                                                                 | 8 |

## **CHAPTER 2**

LITERATURE REVIEW

| 2.1 Reported work on CDBA realization                   | 9  |

|---------------------------------------------------------|----|

| 2.2 Reported work on CDBA Applications                  | 10 |

| 2.2.1 Linear application                                | 10 |

| 2.2.1.1 Filters                                         | 10 |

| 2.2.1.2 Oscillators                                     | 11 |

| 2.2.1.3 Immitance simulator                             | 12 |

| 2.2.1.4 Inverse filter                                  | 13 |

| 2.2.1.5 Nth order current transfer function realization | 13 |

| 2.2.2 Non-linear application                            | 13 |

| 2.2.2.1 Multi-vibrators                                 | 13 |

| 2.2.2.2 Multiplier                                      | 13 |

| REFERENCES                                              | 14 |

## CHAPTER 3

## CDBA ACTIVE BUILDING BLOCK

| 3.1. | CDBA T     | erminal Characteristics                           | 17 |

|------|------------|---------------------------------------------------|----|

| 3.2. | realizatio | on of CDBA                                        | 18 |

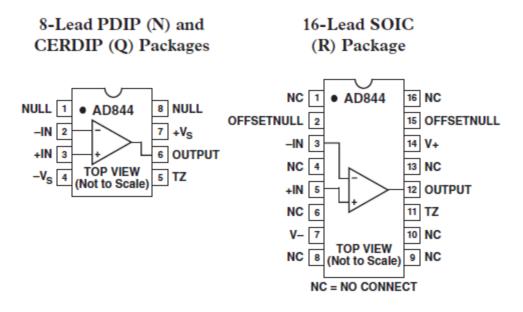

|      | 3.2.1.     | IC AD844 based Realization                        | 18 |

|      | 3.2.2.     | NPN Transistor based Realization                  | 19 |

|      | 3.2.2      | .1. Block Architecture                            | 19 |

|      | 3.2.2      | .2. Circuit description                           | 20 |

|      | 3          | .2.2.2.1. Current Differencing Circuit            | 20 |

|      | 3          | .2.2.2.2. Buffered Voltage Amplifier              | 22 |

|      | 3.2.3.     | CMOS based Realization                            | 22 |

|      | 3.2.4.     | Low Voltage Low Power CMOS based CDBA (LVLP CDBA) | 23 |

|      | 3.2.4      | .1. Block Architecture                            | 23 |

|      | 3.2.4      | .2. Circuit Description                           | 24 |

| 3.3. | Simulatio  | n Results                                         | 26 |

|      | 3.3.1.     | IC AD844 based Realization                        | 26 |

|      | 3.3.2.     | The LVLP CDBA                                     | 28 |

|      | 3.3.3.     | Comparison                                        | 30 |

|      |            |                                                   |    |

### REFERENCES

## **CHAPTER 4**

| FILTER REALIZATIONS              |    |

|----------------------------------|----|

| 4.1 Introduction                 | 32 |

| 1.2 CDBA based Filter Topologies |    |

| 4.2.1 Topology (A)               | 34 |

| 4.2.1.1 Low Pass Filter          | 35 |

| 4.2.1.2 High Pass Filter         | 36 |

| 4.2.1.3 Band Pass Filter         | 38 |

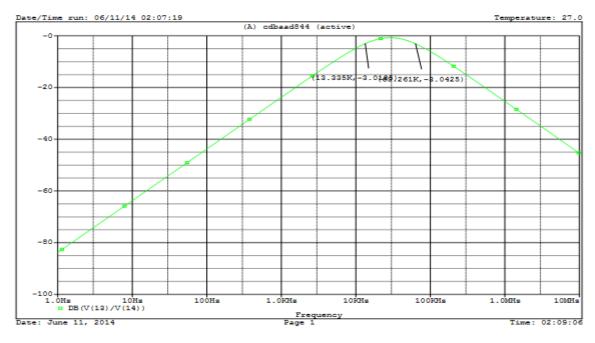

| 4.2.2 Topology (B)      | 40 |

|-------------------------|----|

| 4.2.2.1 All Pass Filter | 41 |

| 4.2.2.2 Notch Filter    | 43 |

| REFERENCES              | 45 |

## CHAPTER 5

## CDBA BASED OSCILLATORS

| 5.1 Introd | luction                                             | 46 |

|------------|-----------------------------------------------------|----|

| 5.2 Total  | .2 Total Harmonic Distortion                        |    |

| 5.3 Secon  | nd Order Quadrature Oscillator                      | 49 |

| 5.3.1      | Systematic approach to realize QO circuits          | 50 |

| 5.3.2      | Generation of various QO configurations using CDBAs | 51 |

| 5          | 3.2.1 PSPICE simulation results                     | 55 |

| 5.4 Multij | 5.4 Multiphase sinusoidal Oscillator56              |    |

| 5.4.1      | Approach to realize MSO Circuit                     | 57 |

| 5.4.2      | Simulation Using CDBA                               | 58 |

| REFERE     | REFERENCES                                          |    |

# CHAPTER 6

## **NEW PROPOSITIONS**

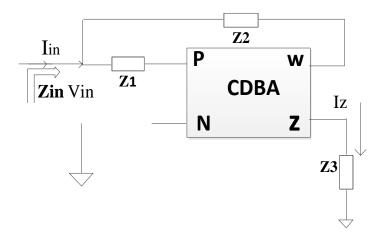

| 6.1 New topologies of lossless grounded negative inductor using single CDBA |    |  |

|-----------------------------------------------------------------------------|----|--|

| 6.1.1 Topology 1                                                            | 62 |  |

| <b>6.1.2</b> Topology 2                                                     | 64 |  |

| 6.1.3 simulations of proposed negative inductor                             | 65 |  |

| 6.2 Application example of proposed negative inductor and simulations       |    |  |

| 6.2.1 Second Order Sinusoidal Oscillator using negative inductor            | 67 |  |

| 6.2.1.1 Approach to realize SO Circuit using negative inductor              | 67 |  |

| 6.2.1.2 Simulation results                                                  | 69 |  |

| 6.3 new topologies of second order sinusoidal oscillator using single CDBA  |    |  |

| 6.3.1 Approach to realize sinusoidal oscillator Circuit using single CDBA   | 72 |  |

| 6.3.2 Simulation results:                                                   | 73 |  |

### REFERENCES

## **CHAPTER 7**

| CONCLUSIONS                                           | 81 |

|-------------------------------------------------------|----|

| APPENDIX (A)                                          |    |

| AD844 IC - 60 MHz, 2000 V/μs, Monolithic Op Amp       | 82 |

| APPENDIX (B)                                          |    |

| 0.18 μm, level 7 parameters provided by TSMC for NMOS | 85 |

| 0.18 μm, level 7 parameters provided by TSMC for PMOS | 86 |

# LIST OF FIGURES

| 1.  | Fig. 1.1 Development of Active Blocks                                         | 4  |

|-----|-------------------------------------------------------------------------------|----|

| 2.  | Fig. 1.2 symbol Current feedback amplifier                                    | 5  |

| 3.  | Fig. 1.3 (a) CDBA symbol (b) CDBA structure using AD844                       | 5  |

| 4.  | Fig. 1.4 Structure of CDTA                                                    | 6  |

| 5.  | Fig. 3.1 Symbol of CDBA                                                       | 17 |

| 6.  | Fig. 3.2 Equivalent circuit of CDBA                                           | 17 |

| 7.  | Fig. 3.3 Implementation of CDBA using CFOA (AD844 IC)                         | 18 |

| 8.  | Fig. 3.4 NPN transistors based CDBA circuit                                   | 20 |

| 9.  | Fig. 3.5 Unity gain current amplifier                                         | 21 |

| 10. | Fig. 3.6 Current differencing circuit                                         | 22 |

| 11. | Fig. 3.7 Buffer Voltage amplifier                                             | 22 |

| 12. | Fig. 3.8 CMOS implementation of CDBA                                          | 23 |

| 13. | Fig. 3.9 Low Power CMOS implementation                                        | 24 |

| 14. | Fig. 3.10 Flipped voltage follower current source (FVFCS)                     | 24 |

| 15. | Fig. 3.11 Current subtractor circuit                                          | 25 |

| 16. | Fig. 3.12 Differential flipped voltage follower (DFVF)                        | 26 |

| 17. | Fig. 3.13 Current transfer characteristics $I_z$ VS $I_p - I_n$ (AD844)       | 26 |

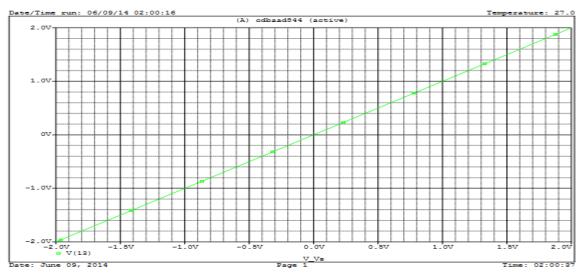

| 18. | Fig. 3.14 Voltage transfer characteristics $V_w$ VS $V_z$ (AD844)             | 27 |

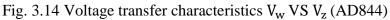

| 19. | Fig. 3.15 Current transfer ratio frequency response (AD844)                   | 27 |

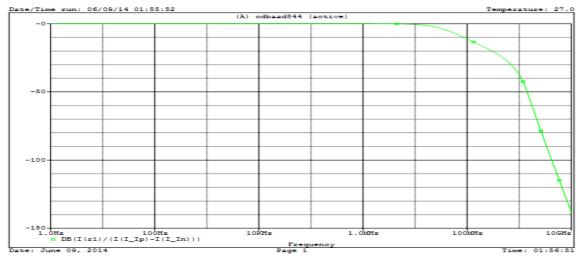

| 20. | Fig. 3.16 Voltage transfer ratio frequency response (AD844)                   | 28 |

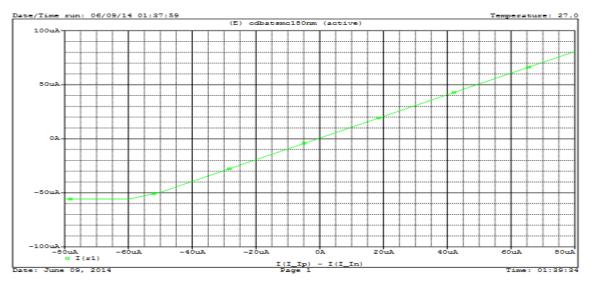

| 21. | Fig. 3.17 Current transfer characteristics $I_z$ VS $(I_p - I_n)$ (LVLP CDBA) | 29 |

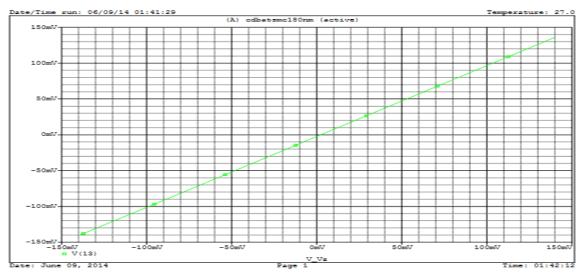

| 22. | Fig. 3.18 Voltage transfer characteristics $V_w$ VS $V_z$ (LVLP CDBA)         | 29 |

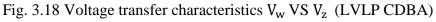

| 23. | Fig. 3.19 Current transfer ratio frequency response (LVLP CDBA)               | 29 |

| 24. | Fig. 3.20 Voltage transfer ratio frequency response (LVLP CDBA)               | 30 |

| 25. | Fig. 4.1 General filter topology (A) of CDBA                                  | 34 |

| 26. | Fig. 4.2 Low pass second order filter design using CDBA                       | 35 |

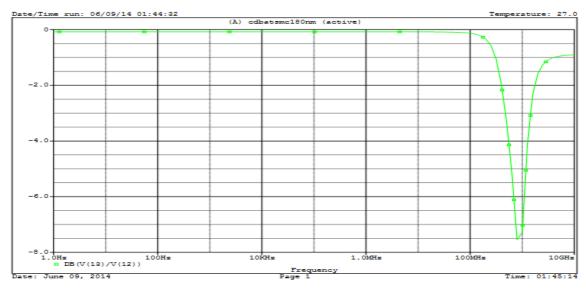

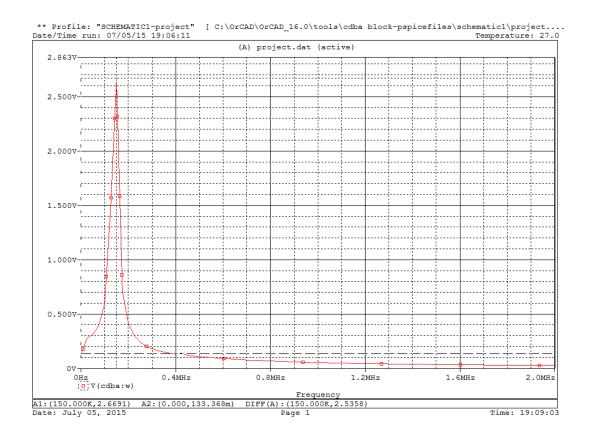

| 27. | Fig. 4.3 Frequency response of the low pass filter                            | 36 |

| 28. | Fig. 4.4 High pass second order filter design using CDBA                      | 37 |

| 29. | Fig. 4.5 Frequency response of the high pass filter                           | 38 |

| 30. | Fig. 4.6 Band pass second order filter design using CDBA                      | 38 |

|-----|-------------------------------------------------------------------------------|----|

| 31. | Fig. 4.7 Frequency response of the gain of band pass filter                   | 39 |

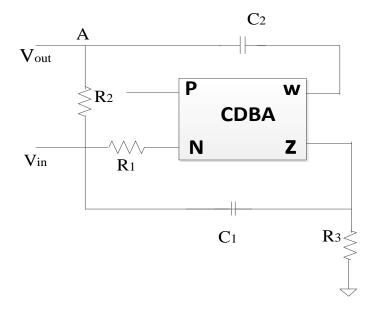

| 32. | Fig. 4.8 Filter topology (B) of CDBA                                          | 40 |

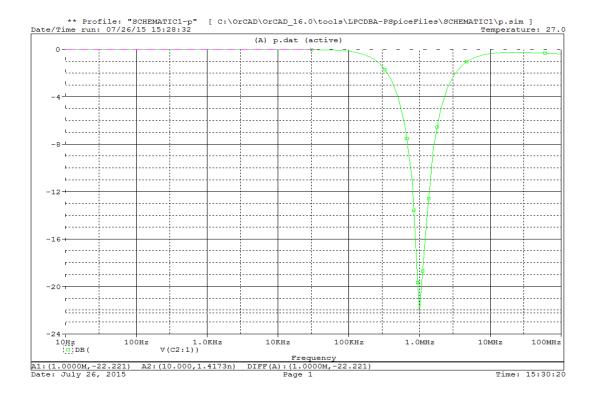

| 33. | Fig. 4.9 Frequency v/s gain response of all pass filter                       | 42 |

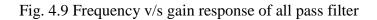

| 34. | Fig. 4.10 phase response of the all pass filter                               | 42 |

| 35. | Fig. 4.11 Frequency v/s gain response of the notch filter                     | 44 |

| 36. | Fig. 4.12 phase response of the notch filter                                  | 44 |

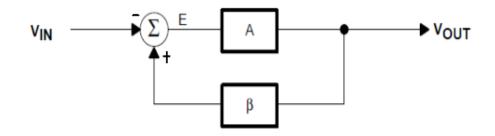

| 37. | Fig. 5.1 Basic structure of oscillator                                        | 46 |

| 38. | Fig. 5.2 AC source and an electrical load                                     | 48 |

| 39. | Fig 5.3 (a) Ideal Sine wave (b) Distorted Waveform                            | 48 |

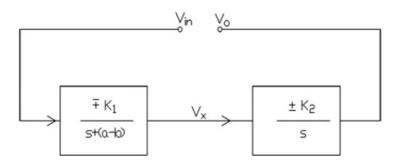

| 40. | Fig. 5.4 General scheme for QO realization                                    | 50 |

| 41. | Fig. 5.5 General configuration for LPF block                                  | 51 |

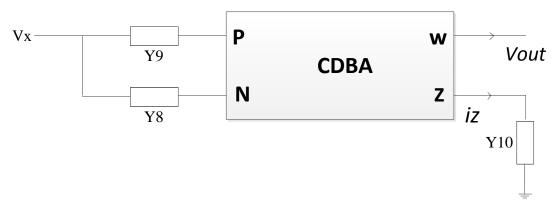

| 42. | Fig. 5.6 General configuration for integrator block                           | 51 |

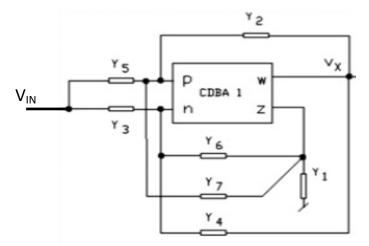

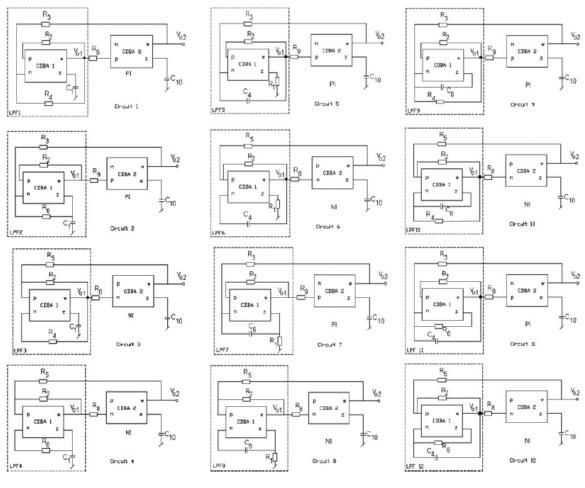

| 43. | Fig. 5.7 Various CDBA-based QO circuits                                       | 53 |

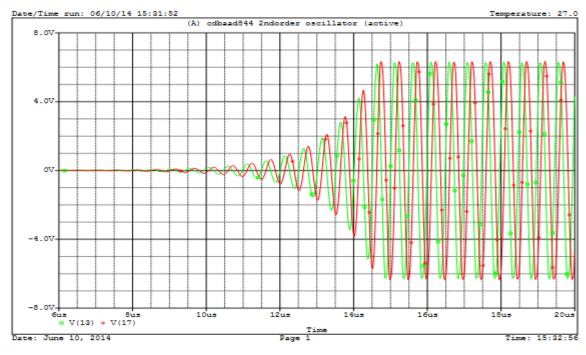

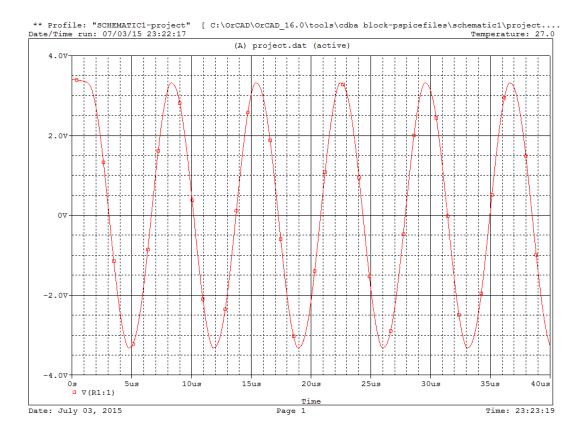

| 44. | Fig. 5.8 Transient waveform for oscillator circuit 1                          | 55 |

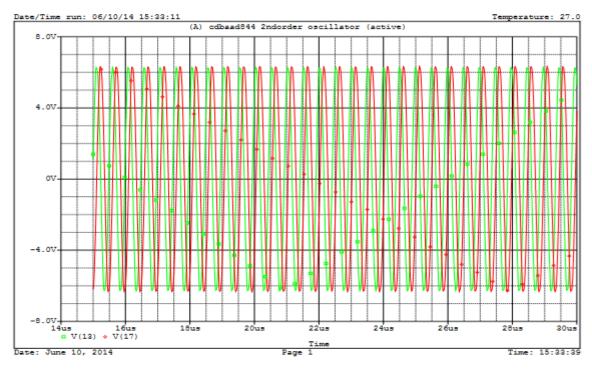

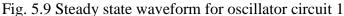

| 45. | Fig. 5.9 Steady state waveform for oscillator circuit 1                       | 56 |

| 46. | Fig. 5.10 Frequency spectrums for oscillator circuit 1                        | 56 |

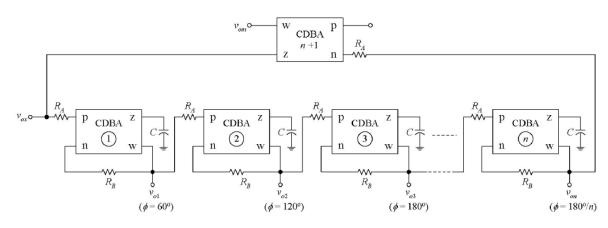

| 47. | Fig. 5.11 Scheme for MSO                                                      | 57 |

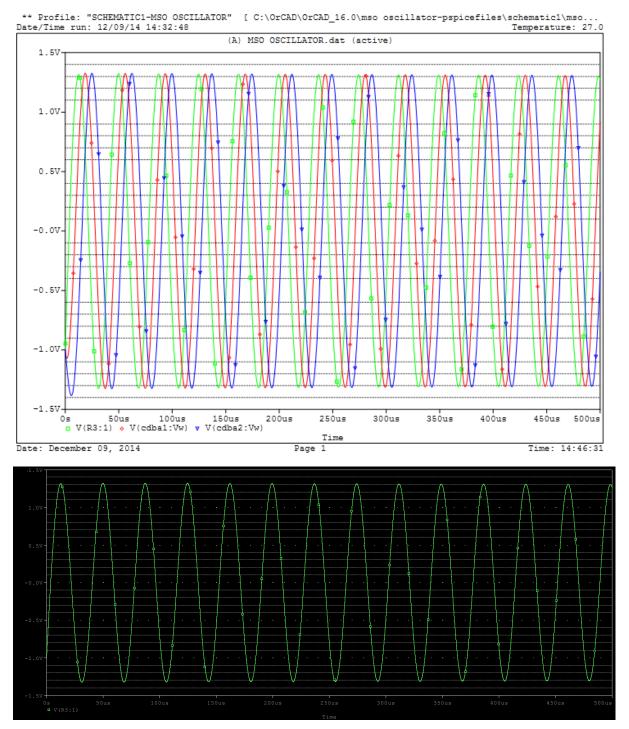

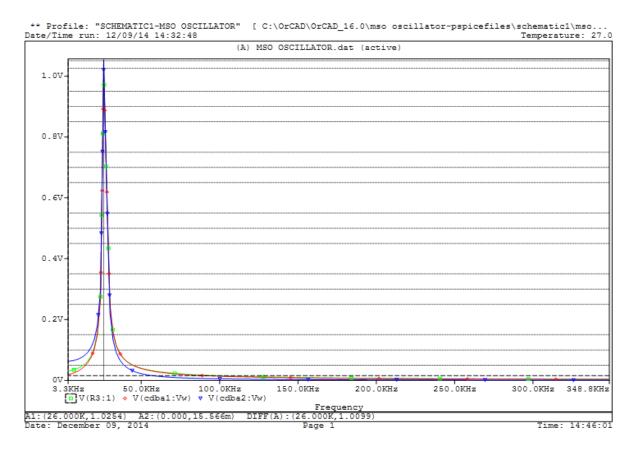

| 48. | Fig. 5.12 Output waveforms for MSO                                            | 59 |

| 49. | Fig. 5.13 Output spectrums for MSO                                            | 60 |

| 50. | Fig 6.1 Proposed lossless negative inductor topology I                        | 63 |

| 51. | Fig. 6.2 negative inductor circuit using topology 1                           | 64 |

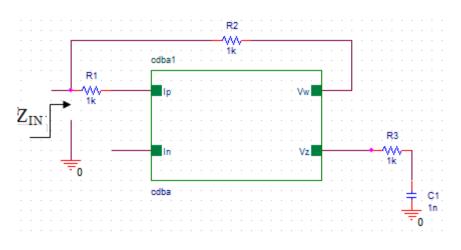

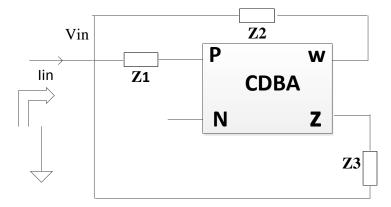

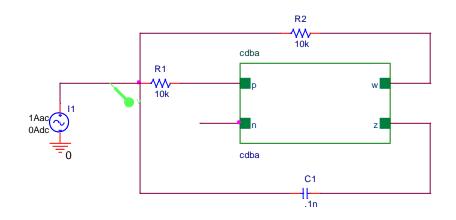

| 52. | Fig. 6.3 Lossless negative inductor topology II                               | 64 |

| 53. | Fig. 6.4 circuit diagram of negative inductor for topology 2 using CDBA       | 65 |

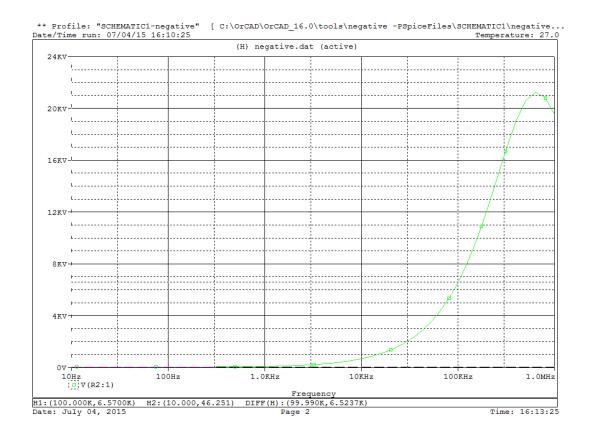

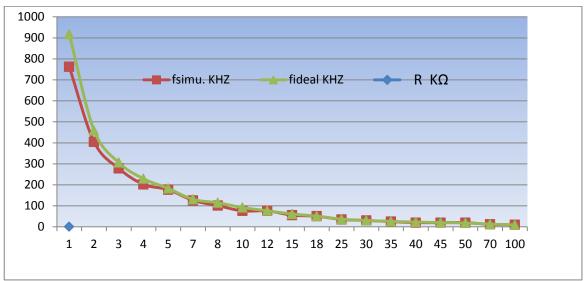

| 54. | Fig. 6.5 Impedance versus frequency response of proposed negative inductor in | 66 |

|     | kilo ohm = kilo volt                                                          | 66 |

| 55. | Fig. 6.6 Transient response for negative inductor for topology 2              | 66 |

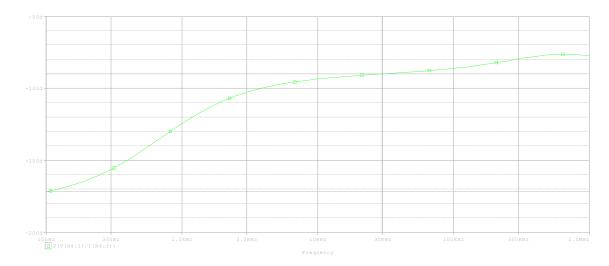

| 56. | Fig. 6.7 phase response of negative inductor for topology 2                   | 67 |

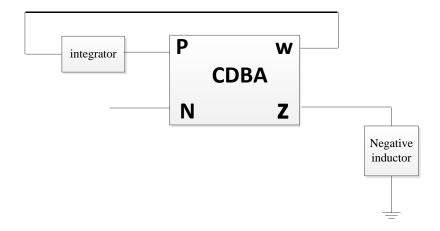

| 57. | Fig. 6.8 Approach to realize SO Circuit using negative inductor               | 68 |

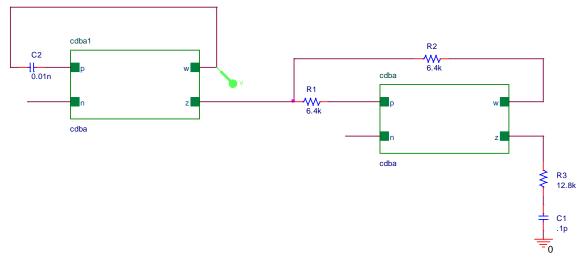

| 58. | Fig. 6.9: Circuit for unconditional QO realization                            | 69 |

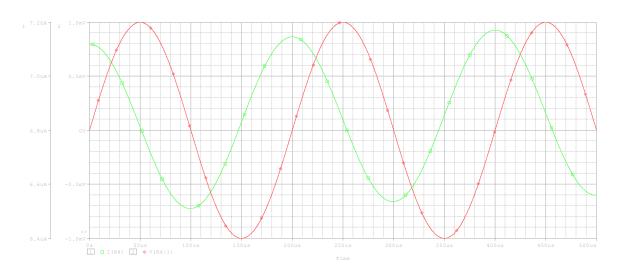

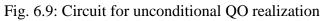

| 59. | Fig. 6.10 Output waveform of the unconditional QO circuit.                    | 69 |

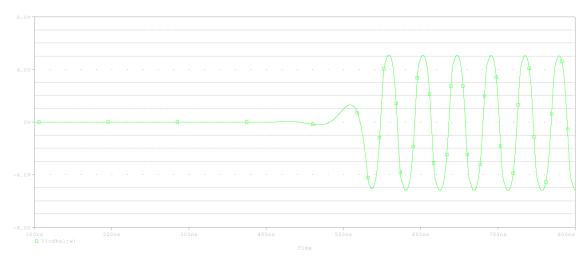

| <ul> <li>62. Fig 6.13 Configuration 1 to realize sinusoidal oscillator Circuit using single CDBA</li> <li>63. Fig. 6.14 frequency spectrum of circuit 6.16</li> <li>64. Fig. 6.15 transient response of circuit 6.16</li> </ul> | 60. | Fig. 6.11 frequency spectrum of circuit 6.12                                   | 70 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------|----|

| CDBA7463. Fig. 6.14 frequency spectrum of circuit 6.167464. Fig. 6.15 transient response of circuit 6.1675                                                                                                                      | 61. | Fig. 6.12 Approach to realize sinusoidal oscillator Circuit using single CDBA  | 72 |

| <b>63.</b> Fig. 6.14 frequency spectrum of circuit 6.1674 <b>64.</b> Fig. 6.15 transient response of circuit 6.1675                                                                                                             | 62. | Fig 6.13 Configuration 1 to realize sinusoidal oscillator Circuit using single |    |

| <b>64.</b> Fig. 6.15 transient response of circuit 6.1675                                                                                                                                                                       |     | CDBA                                                                           | 74 |

| $\mathcal{C}$                                                                                                                                                                                                                   | 63. | Fig. 6.14 frequency spectrum of circuit 6.16                                   | 74 |

| <b>65.</b> Fig. 6.16 freq. v/s R response of circuit 6.16 for $C_5=0.1nf$ 75                                                                                                                                                    | 64. | Fig. 6.15 transient response of circuit 6.16                                   | 75 |

|                                                                                                                                                                                                                                 | 65. | Fig. 6.16 freq. v/s R response of circuit 6.16 for $C_5=0.1nf$                 | 75 |

## LIST OF TABLES

| 1. | Table 3.1 MOS Transistor dimensions                                               | 28  |

|----|-----------------------------------------------------------------------------------|-----|

| 2. | Table 3.2 Performance of the CDBA realizations                                    | 31  |

| 3. | Table 5.1 Various LPF realizing T1(s) and integrator T2(s), which yield the requi | red |

|    | QOs                                                                               | 51  |

| 4. | Table 5.2 parameters of the various QO circuits                                   | 54  |

| 5. | Table 6.1 Total Harmonic Distortion For Circuit 6.12                              | 70  |

| 6. | Table 6.2 Total Harmonic Distortion For Circuit 6.17                              | 75  |

#### ABBREVIATIONS

| Abbreviations | Full - Form                                | Abbreviations | Full – Form                                          |

|---------------|--------------------------------------------|---------------|------------------------------------------------------|

| CMOS          | Complementary Metal<br>Oxide Semiconductor | LPF           | Low Pass Filter                                      |

| NI            | Non-inverting                              | CFA           | Current Feedback<br>Amplifier                        |

| CML           | Current Mode Logic                         | FTFN          | Four Terminal<br>Floating Nullor                     |

| QO            | Quadrature Oscillator                      | CDTA          | Current Difference<br>Trans conductance<br>Amplifier |

| SO            | Sinusoidal Oscillator                      | CDBA          | Current differencing<br>buffered amplifier           |

| MSO           | Multiphase Sinusoidal<br>Oscillator        | CCII          | Current Conveyor II                                  |

| SSB           | Single Side Band                           | VM            | Voltage mode                                         |

### **CHAPTER 1: INTRODUCTION**

#### **1.1 Overview**

Demand of low power microelectronic circuits requiring low supply voltage constitute long-term trends while developing advanced microelectronic design technologies. Speed and accuracy of data processing are very important factors to be considered. While satisfying one necessity another may have to be traded off which leads to non-fulfilment of all parameters at the same time. To overcome this problem a trade-off solution is utilized as a part of practice.

Over a span of time, the development of advanced applications of signal processing has accompanied the tendency of current mode [1], when signals, containing the useful information being refined, are in the form of electric currents. Counterpoint to the formal voltage mode, which utilizes electric voltages, the current mode microelectronic circuits can expose under particular conditions better linear signal and higher bandwidth. One more benefit is that they require low supply voltage as they are intended for lower voltage swings [1]. While developing advanced current mode applications, mixed mode microelectronic circuits are also examined to optimize the interface between sub-blocks which are playing different roles.

As the microelectronic circuit technology is getting advanced from the last two decades, circuit designers have become able to increase the efficiency of current-mode analog methodologies for producing refined and accurate solutions to several microelectronic circuit design problems. As a result, the current-mode signal processing methodology is always expected to offer one or more of the following benefits: consumption of less average power, higher operating frequency range, better linearity, higher slew rates and improved accuracy [2].

To overcome this problem of selecting either current mode or voltage mode technology, scientists Acar and Ozoguz have developed a current differencing buffered amplifier [3] which can work efficiently in both current-mode and voltage-mode technology for the flexible operation. This amplifier can operate at high frequency range and does not display many parasitic capacitances.

#### **1.2 Motivation**

Digital signal processing is a rapidly developing field and it is getting advanced further, as growth in microelectronic circuits technology demands dense and effective application of its algorithmic programs on silicon chips. Even though many digital techniques and circuits are available to process various forms of signal, but still many complex and high performance advanced devices require analog circuits. We know that analog signals occur naturally. That's why, analog circuits act as an interface between the actual world and the digital domain. Analog VLSI can deal with nearly all real world issues and has extended its range for new information processing applications in numerous fields like hand writing acknowledgement, integrated sensors, speech acknowledgement, image processing and so on.

As a result interest has been increased in the evolution process of active elements which are used for analog signal processing. The adaptation involved in their development included modification in basic circuits like current conveyors, Voltage Feedback Amplifier, Operational Trans-conductance Amplifier, Current Feedback Amplifier etc. Another direction of evolution is by inserting an entirely new element in the circuit which expands the original CC, VFA, OTA, CFA etc. The key motivation for performing such modifications is an attempt to raise the application prospective of active blocks. Concurrently, the internal structure of the element must be simple while consuming less power and operating at higher speed [4].

Advancement in IC technology in past two decades motivated VLSI designers to increase the efficiency of current mode methodologies. The CM provides various advantages over VM. CM approach includes high slew rates, better linearity, enhanced accuracy, broader bandwidth and reduced power consumption [4]. The traditional analog circuits are VM circuits wherein the voltage levels at various points along with the input and the output points determines the circuit parameters and performance, a simple example of such circuit is an operational amplifier. All these circuits cannot change its output voltage instantly in accordance with the abrupt transition occurred due to stray and parasitic capacitances in the input voltage. Due to the finite unity gain bandwidth product, bandwidth of circuits based on op amp becomes low. They require higher supply voltages to achieve better SNR and time constants of the circuits effect the slew rate. In this way, VM circuits are not fitting for their utilization at high frequency applications. In CM circuits, current form is used to display the input/output signals and the whole circuit

analysis is done in currents. Here, the voltage levels are not utilized for obtaining the circuit performance. CM circuits have low impedance internal nodes and voltage swings are small. The bandwidths of these circuits are higher and become low time constant circuits due to their low impedance. Higher slew rate can be obtained with the help of the higher rate of change in output signal. An easy architecture is used to design Current mode circuits and power supply voltage does not make any effect in the operation of these circuits.

The advantages of current mode has increased the evolution of many current-mode active building blocks for example, Differential Voltage Current Conveyor, Operational Trans-conductance Amplifiers, Differential Difference Current Conveyor, Current-Feedback Op-Amps, Current Controlled Current Conveyors, Dual X Current Conveyors, Voltage Differencing Trans-conductance Amplifier, Current Differencing Trans-conductance Amplifier. An advanced active building block named Current Differencing Buffered Amplifier incorporating the benefits of current mode was introduced in 1999 [3]. This block has gained popularity in past decade due to wide dynamic range and broad bandwidth. Also, it is suitable for high frequency operation as its internally grounded input terminals makes the circuit free from parasitic capacitances.

The growing interest in CDBA is mainly because of the flexibility and ease of implementation offered by this block. The block can be easily implemented by CMOS technology. Hardware implementation using IC AD844N can also be accomplished. Also, it offers broad range of linear and non-linear applications. These features of CDBA have captured the interest of analog designers towards it, thus motivating the designers to further explore this block to obtain satisfactory results through simulations and develop new applications using this active block.

## **1.2.1 Development of Active Blocks**

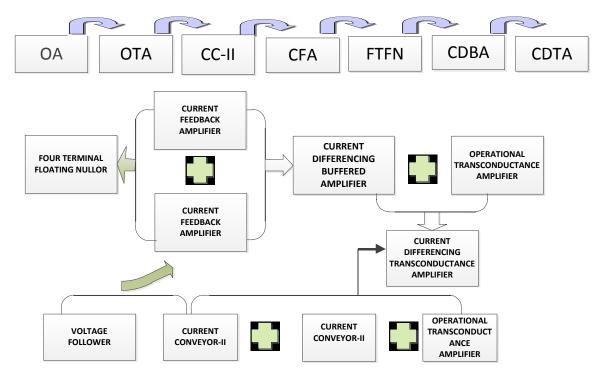

Fig.1.1 Development of Active Blocks [4]

Advancement in fundamental blocks like VFA, OTA, CC, CFA (full names are in fig.1.1) is being carried out for the development of active blocks. The internal structure of these element should be simple in order to have high-speed operation and low power consumption. Except the advancement in current ones, introducing of new elements is being carried out for the development of active elements, which expands the original VFA--OTA-CC-CFA active set.

A specialized pattern is followed in the process of development which has been going on.

# **1.2.1.1** Development of Current Feedback Amplifier from Current Conveyor II:

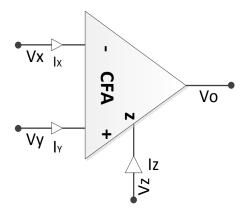

**Current Feedback Amplifier (CFA)** [4] was introduced over traditional voltage - feedback amplifier to enhance the limited finite gain-bandwidth product. Its functions are: to produce constant bandwidth unaffected by closed loop gain and to provide high slew rate capability. CFA acts as an operational Trans impedance amplifier and its internal structure contains a CCII+ followed by a voltage follower. CFA can be demonstrated as shown in fig 1.2

Fig.1.2 symbol Current feedback amplifier [4]

#### **1.2.1.2** Four Terminal Floating Nullor (FTFN)

FTFN was evolved after the development of Current Feedback amplifier. Due to its features of more flexibility and more versatility than operational amplifier or current conveyor, it was developed for the advancement in continuous-time circuits. It is designed by cascading CFAs.

#### **1.2.1.3** Generation of Current Differencing Buffered Amplifier:

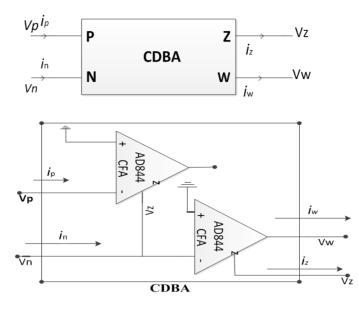

**Current Differencing Buffered Amplifier (CDBA),** advantages of current-mode circuit includes [3] absence of stray and parasitic capacitances, high slew rate, broad bandwidth, and easy implementation. It is used in current and voltage mode signal processing applications. CDBA comprises of a unity-gain voltage amplifier and a unity-gain current differential amplifier. Structure of CDBA is shown in Fig-1.3

Fig.1.3 (a) CDBA symbol (b) CDBA structure using AD844 [3]

## **1.2.1.4** Design of Current Difference Trans conductance Amplifier (CDTA)[4]

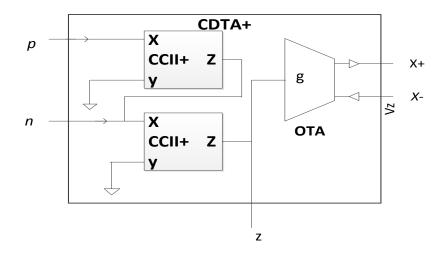

**Current Difference Trans conductance Amplifier** being compatible to the CDBA consists of different current inputs n and p [4]. Outside load obtains the difference of these currents from terminal z. We get voltage signal at the z terminal of CCII+ then this voltage is passed through the trans-conductance g block which is known as trans-conductance operational amplifier (OTA). Then we obtain the current pair at x terminals. The fact is, the trans-conductance can be controlled electronically through an auxiliary port. Output current pair at x terminals can flow in three combinations of directions:

1. Both currents flowing out of CDTA block.

2. The currents have opposite directions.

3. Both currents flowing inside the CDTA block.

In fig. 1.4 we can see that outside flow of current is shown by '+' and inside flow is shown by '-'sign. Therefore we can design three types of CDTA components viz. CDTA+-, CDTA-- and CDTA++.

Fig. 1.4 Structure of CDTA [4]

#### **1.3 Research objective**

The objectives of the research are listed below,

- To study and analyse the different methods of realizing CDBA active block.

- Comparative analysis of CDBA realizations in terms of various performance parameters.

- To study and analyse various applications based on CDBA

- To propose new circuit configurations which offer better performance.

• Verification of proposed circuits by functional simulations and/or by experimentation.

Initially the literature related to CDBA [3] and applications proposed using CDBA is reviewed which suggested the areas which could be explored to propose new designs. Signal generators such as oscillators and multi-vibrators are an important class of circuits and find wide application in electronic system design. It was observed that though, a large number of sinusoidal oscillators are available in literature, yet there is scope of further investigations. As a result two new negative inductor structures using single CDBA and two oscillator configurations are proposed. The first one is a second order sinusoidal oscillator (SO) configuration, designed using proposed negative inductor. Second proposition is a second order oscillator using single CDBA for minimizing chip area with better THD performance as compared to its second order counterpart. All the proposed designs are simulated using PSPICE to test their functionality.

#### 1.4 Thesis organization

The thesis is organized in 7 chapters as follows:

#### Chapter2:

Chapter 2 reviews the history and developments through the years in the block realization of CDBA and applications made out using the CDBA active block.

#### Chapter 3:

It describes the theory and various realizations of CDBA. Further for verification of CDBA active block simulation results, such as DC and AC analyses, are presented.

#### Chapter 4:

It describes theory of filters with all standard second order filters implementations using CDBA and their simulation results are verified.

#### Chapter 5:

It describes theory of oscillators and implementation of different configuration of QO and MSO using CDBA. The PSPICE simulations for functional verification of these implemented configurations are also presented.

#### Chapter 6:

Chapter 6 presents the CDBA based new propositions and their simulation results showing conformity with the proposed theory. This includes negative inductor using

single CDBA and its application, second order sinusoidal oscillator. Additionally, yet another second order sinusoidal oscillator using single CDBA is also proposed.

Chapter 7:

Chapter 7 summarizes the work presented in this dissertation followed by a concluding remark highlighting the objective achieved through this work.

#### **REFERENCES**

[1] Toumazou, C., Lidgey, F. J., & Haigh, D. G. (1990). Analogue IC design: The current-mode approach. London: Peter Peregrinus.

[2] D. Biolek, R. Senani, V. Biolková, Z. Kolka, "Active Elements For Analog Signal Processing: Classification, Review, And New Proposals "Radio engineering, Vol. 17, No. 4, December 2008

[3] Acar C. and Ozoguz S. "A new versatile building block: current differencing buffered amplifier" Microelectronics Journal, vol. 30, pp. 157-160, 1999.

[4] Sheikh ajaz basher, N.A. Shah "active device usage in filter design an overview" international journal of scientific and research publication, volume 2, Issue 6, June 2012 Issn 2250-3153.

#### **CHAPTER 2: LITERATURE REVIEW**

In past years, there has been trending shift to current mode design due to its various advantages over voltage mode. This lead to the development of various current mode active devices like second generation Current Conveyors (CCII), Operational Transconductance Amplifier (OTA), Current-Feedback Operational-Amplifiers (CFOA), Differential Voltage Current Conveyors (DVCC), third-generation Current Conveyors (CCIII), Differential Difference Current Conveyors (DDCC) etc. In 1999, a new building block called CDBA was proposed [1]. The block inherits all the properties of current mode circuits and therefore is suitable for high frequency applications. Designing of analog signal processing devices using CDBA has been an attractive task for many scholars and researchers and therefore a wide range of applications employing CDBA have been proposed in [2, 4, 8-28]. Numerous papers have been reported on CDBA in past one and a half decade. This includes various realizations of CDBA and broad range of signal processing and generation applications such as filters, oscillators, immitance simulator, multi-vibrator, multiplier, etc.

#### 2.1. Reported work on CDBA realization

C. Acar and S. Ozoguz in 1999 proposed a CDBA realization using CFOA (IC AD844) [1]. Two AD844IC's were used to design CDBA block and then filters were realized using it. In the same year, S. Ozoguz and C. Acar along with A. Toker, M. A. İbrahim also proposed CMOS realization of CDBA [2].

After two years, Kuntman and Tarim [3] presented a low power high performance CDBA using a voltage buffer and cascading of 2 second generation current conveyors (CCII). This configuration was implemented in CMOS technology incorporating only MOS transistors in it.

CDBA based on NPN transistor was proposed in 2006 by Sawangarom, Tangsrirat and Surakampontom [4] proposed. This CDBA could work at the power supply range of 2 to 5 volts. CDBA based on NPN transistors has been designed using two blocks called voltage follower and current differencing circuit. Cascading of 2 unity gain current amplifier is used to design the current differencing circuit and to reflect the current to output port, current mirror is used in the circuit. This circuit had the added advantage of using only NPN transistors which help to gain a maximum high frequency response which was earlier limited because of the use of PNP transistors. In the same year, K. Klahan, W.Tangsrirat, W. Surakampontorn and K. Kaewdang [5] presented a low supply voltage wide band NMOS based CDBA, which shows low resistance at the output-voltage node (w) and at the current-input nodes (p, n). The presented NMOS based CDBA could work more efficiently at the certain range of supply voltage and frequency. It can operate at minimum power supply voltage of  $\pm 1.25$  volts. This NMOS based CDBA was designed by altering low impedance second generation current conveyor circuit (CCII+) so that it can work as a voltage buffer circuit and a current differencing circuit also.

The existing CDBAs work on comparatively high supply voltage due to that they produce high input resistance, consume more average power and shows the problem of limited output voltage swing. To overcome this problem, scientists Oguzhan Cicekoglu and Cem Cakir [6] in 2008 introduced a high performance low voltage CDBA. Proposed circuit could work effectively consuming less average power at a maximum voltage of  $\pm 0.75$ V. A new approach based on flipped voltage follower current sources (FVFCS) used in the CDBA makes it more advantageous as it offers very low resistance at the input and output terminals. Moderate output voltage swing has been obtained from the output stage of this CDBA.

At that point after a year, Oguzhan Cicekoglu, Cem Cakir and Shahram Minaei [7] in 2009 invented an efficient low power low voltage CDBA based on CMOS. The circuit can function efficiently at the power supply voltage of  $\pm 0.6$  volts. This Low power CMOS CDBA circuit is made up of voltage buffer and current differencing circuit. It provides very low input resistance at n and p nodes and consumes less average power as compared to the other CDBA circuit designs existing in literature.

#### **2.2. Reported work on CDBA Applications**

#### 2.2.1 Linear Applications

#### 2.2.1.1 Filters

A design methodology to implement continuous-time current-mode filters employing CDBAs using minimum active components was presented by Worapong Tangsrira, Nobuo Fujii and Wanlop Surakampontorna [8] in 2002. They also implemented fifth-order Butterworth low-pass filter & a sixth-order Chebyshev band pass filter to describe the functionality of the techniques.

Visawa Sawangarom, Worapong Tangsrirat and Wanlop Surakampontom in 2006 proposed NPN based CDBA and realized all pass filter using it [4]. Likewise, in 2008

they realized Voltage mode universal biquad filter based on six passive components and two CDBA [9]. The configuration could realize all five types of filter with the same topology.

A. U. Keskin in 2008 presented voltage mode band pass filter based on single CDBA [10]. The filters were of High quality factor and used minimum number of components.

M. Sagbas, M. Koksal and S.E. Oner in 2009 presented another design of second order multi-function multi-mode filter [11]. This design utilizes one CDBA block and four to five passive components. Proposed topology was useful in implementing current, voltage, transadmittance and transconductance modes. It was also used in designing of band pass, low pass and high pass filters.

Firat Kacard and Yasin ozcelep in 2011 proposed five new configurations of first order all pass filter based on voltage mode using CDBA [12]. They used four to five passive elements while realizing the filter.

A current-mode linear transformation filter based on CDBA for realizing higher order filters was presented by Wen-Ta Lee, Yuh-Shyan Hwang, Jiann-Jong Chen and Zhao-Hong Huang [13] and also third order chebychev low pass filter was proposed by them to prove the functionality.

Shahram Minaei, Cem Cakir and Oguzhan Cicekoglu in 2010 presented a new CMOS realization of CDBA that operate at low voltage [14]. The circuit also consumed low power and offered high performance. Then they analyzed all pass and notch filter using the proposed topology to verify the performance of the new circuit. Also, ZC-CDBA performance was demonstrated on a new current mode filter topology proposed by Ersin Alaybey, Arda Güney and Hakan Kuntman in 2013 [15].

#### 2.2.1.2 Oscillators

CDBA based resistance controlled sinusoidal oscillators were first proposed in 2000 by S. O zcana, A. Tokera, C. Acara, H. Kuntmana and O. Cicekoglu [16]. They gave six configurations to design sinusoidal oscillator (SO). These oscillators are suitable for VCO implementations.

Another oscillator called multiphase sinusoidal oscillator employing CDBA as an active element was proposed by Sumaytee Pisitchalermpong, Worapong Tangsrirat and Wanlop Surakampontom in 2006 [17]. The circuit includes inverters and n cascaded

blocks of lossy integrators based on CDBA. N sinusoidal waves of phase difference  $\frac{180^{\circ}}{n}$  are obtained at the output of such oscillator.

A Quadrature oscillator (QO) consists of 2 capacitors and 3 CCCDBAs which is appropriate for IC architecture is proposed by Montree Siripruchyanum, Winai Jaikla and Phamorn Silapa in 2007 [18]. Here input bias current is used to electronically control the condition and frequency of oscillation.

CDBA based QO designed by 2 capacitors, 4 resistors and 2 CDBA blocks [9] is proposed in 2008 by Worapong Tangsrirat, Tattaya Pukkalanun, and Wanlop Surakampontorn. The virtually grounded resistors used in the circuit provide controllability on condition and frequency of oscillation independently.

In 2010, J.K. Pathak, R. Senani and A.K. Singh proposed a systematic approach to realise CDBA based QO [19]. They presented a general configuration designed using an integrator and low pass filter that yielded 12 different Quadrature oscillator circuits.

Abhirup Lehiri in 2011 also proposed a low frequency quadrature sinusoidal oscillator using CDBA [20]. His proposed circuits use reduced number of components and low frequency is obtained due to difference term in the oscillator's frequency.

Winyu Sonjoi, Worapong Tangsrirat and Wanlop Surakampontorn proposed another electronically tunable Quadrature oscillator made up of two CCCDBA and two grounded capacitors in 2009 [21]. This configuration provides two sinusoidal output having phase difference of 90°. Later in 2013, the performance of this oscillator was improved by using high performance CCCDBA by [22].

Ali Umit Keskin [23] proposed a design of CDBA based minimum Component Oscillators (MCO) in which Negative Impedance (NIC) approach was used. The steps in synthesis of NIC based oscillator are as follows: a) Initially a grounded NIC circuit structure of a particular type of active element is formed, b) then NIC is connected with a shunt branch so that, any real term can be eliminated from the complex plane & a symmetric pair of pole can be placed on the imaginary axis.

#### 2.2.1.3 Immitance Simulator

Ali Ümit Keskin and Erhan Hancioglu in 2005, proposed synthetic floating inductance circuits based on CDBA [24]. They presented two different configurations which uses grounded capacitor. The circuits were fully integrable and also electronically tunable.

Worapong Tangsrirat and Wanlop Surakampontorn in 2006 [25] proposed an electronically tunable lossless floating inductance simulator. The floating inductance circuit uses only three current controlled CDBAs (CC-CDBA) and a grounded capacitor. Equivalent inductance of this simulator can be adjusted by varying the external bias current of the current controlled CDBA. This floating inductance simulator is very useful in microelectronic circuit design as there is no requirement of external resistors.

#### 2.2.1.4 Inverse filter

CDBA based universal inverse filter configuration [26] was proposed by Rajeshwari Pandey, Neeta Pandey, Tushar Negi and Vivek Garg in 2013. The topology was use to design all five inverse filters namely inverse high pass, inverse low pass, inverse all pass, inverse band pass and inverse band reject filter.

#### 2.2.1.5 Nth order current transfer function realization

Cevdet Acar and Herman Sedef in 2003 proposed CDBA based two new configurations to realize high order current mode transfer function [31, 27]. One configuration was made of one CDBA block and four passive components and the other was designed with two CDBA blocks and four passive components. These topologies had reduced number of active elements in their realization.

#### 2.2.2. Non-linear Applications

#### 2.2.2.1 Multivibrators

Sajal K. Paul, Rajeshwari Pandey, Kashish Anand, Kranti Ghosh Gautam and Neeta Pandey [28] proposed three voltage mode astable multivibrator microelectronic circuit based on single CDBA. In this multivibrator design, first circuit outputs the square wave of fixed duty cycle and other two offer duty cycle controllability. One of the controllable square wave generators employ resistance to control the duty cycle, whereas the other makes use of voltage source to electronically control it.

#### 2.2.2.2 Multiplier

A new fully integrable fourth quadrant analog multiplier based on CDBA [29] was proposed by Ali Umit Keskin in 2003. The circuit gave good performance and featured reduce number of component and ease of implementation.

In 2007, Montree Siripruchyanun [30] designed an analog multiplier and divider using CCCDBA block. The circuits need only two CCCDBA for its construction and no passive element. The circuit also behaves as gain-controllable current amplifier. In same year, multiplier/divider circuit was designed using high performance Bi-CMOS CCCDBA [31]. The circuit can be used for analog signal processing based applications.

#### **REFERENCES**

[1] Acar C. and Ozoguz S. "A new versatile building block: current differencing buffered amplifier" Microelectronics Journal, vol. 30, pp. 157-160, 1999.

[2] S. Özoguz, A. Toker, M. A. İbrahim, C. Acar, "A new versatile building block: Current differencing amplifier and its applications", Proceedings of The European Conference on Circuit Theory and Design, pp. 90-93, 1999.

[3] N. Tarim and H. Kuntman, "A high performance current differencing buffered amplifier", Proceedings of the 13th International Conference on Microelectronics, Rabat, Morocco, pp. 153–156, 2001.

[4] VisawaSawangarom, WorapongTangsrirat and WanlopSurakampontom, "NPN-based Current Differencing Buffered Amplifier and Its Application" proceedings of IEEE international joint conference SICE-ICASE, pp. 5766-5769, 2006.

[5] W. Tangsrirat, K. Klahan, T. Dumawipata and W. Surakampontorn, "Low-voltage NMOS-based current differencing buffered amplifier and its application to current-mode ladder filter design", International Journal of Electronics, Volume 93, Number 11, pp. 777-791(15), 2006.

[6] Cakir C. and Cicekoglu O., "Low-voltage high-performance CMOS current differencing buffered amplifier (CDBA)", Proceedings of the IEEE 4<sup>th</sup> conference on Ph.D. research in microelectronics and electronics, Istanbul, Turkey, pp. 37–40., 2008.

[7] CemCakir, ShahramMinaei, and OguzhanCicekoglu, "Low-Voltage Low-Power and High-Swing Current Differencing Buffered Amplifier", proceedings of Joint IEEE North-East Workshop on circuits and systems and TAISA conference, pp. 1-4, 2009.

[8] WorapongTangsrira, Nobuo Fujii and WanlopSurakampontorna, "Current-Mode Leapfrog Ladder Filters Using CDBAs", proceedings of IEEE International symposium on circuits and system, vol.5, pp V57-V60, 2002.

[9] WorapongTangsrirat, TattayaPukkalanun, and WanlopSurakampontorn, "CDBA-Based Universal Biquad Filter and Quadrature Oscillator," Active and Passive Electronic Components, vol. 2008, Article ID 247171, 6 pages, 2008. [10] A. U. Keskin ,"Voltage-mode high-Q band-pass filters and oscillators employing single CDBA and minimum number of components", International Journal of Electronics, Vol. 92, No. 8, pp. 479–487, August 2005.

[11]M. Koksal, S.E. Oner and M. Sagbas, "A New Second-Order Multi-Mode Multi-Funtion Filter Using a Single CDBA", proceedings of IEEE European Conference on Circuit Theory and Design, pp. 699-702, 2009.

[12] FıratKacard and Yasinozcelep, "CDBA Based Voltage-Mode First-Order All-pass Filter Topologies", IU-Journal of Electrical and Electronics Engineering, Vol. 11, No. 1, 2011.

[13] Yuh-Shyan Hwang, Zhao-Hong Huang, Jiann-Jong Chen and Wen-Ta Lee, "High-Order Current-Mode Filters Based on Current Differencing Buffered Amplifiers", proceedings of IEEE International Conference on Communications, Circuits and Systems, pp. 999-1002, 2007.

[14] CemCakir, ShahramMinaei and OguzhanCicekoglu, "Low voltage low power CMOS current differencing buffered amplifier", Analog Integrated Circuits and Signal Processing, v.62 n.2, pp. 237-244, 2010.

[15] ErsinAlaybey, ArdaGüney and HakanKuntman, "A New CMOS ZC-CDBA Realization and Its New Filter Application", IEEE EUROCON, pp. 1814-1820, 2013.

[16] S. Ozcana, A. Tokera, C. Acara, H. Kuntmana and O. Cicekoglu, "Single resistancecontrolled sinusoidal oscillators employing current differencing buffered amplifier", Microelectronics Journal, vol. 31, pp. 169-174, 2000.

[17] SumayteePisitchalermpong, WorapongTangsrirat and WanlopSurakampontom, "CDBA-based Multiphase Sinusoidal Oscillator Using Grounded Capacitors", IEEE international joint conference SICE-ICASE, pp. 5762-5765, 2006.

[18] WinaiJaikla, PhamornSilapan, and MontreeSiripruchyanun, "A simple quadrature oscillator using only CCCDBAs and grounded capacitors," International Symposium on Communications and Information Technologies Proceedings, pp. 234–237, 2007.

[19] J.K. Pathak, A.K. Singh and R. Senani, "Systematic realization of quadrature oscillators using current differencing buffered amplifiers", IET Circuits devices and system, 5, pp. 203-211, 2011.

[20] AbhirupLehiri, "Low-frequency quadrature oscillators using current differencing buffered amplifiers" Indian journal of pure and applied science, Vol. 49, pp.423-428, June 2011.

[21] WinyuSonjoi, WorapongTangsrirat and WanlopSurakampontorn, "Current-Controlled Quadrature Oscillator Using Only CCCDBAs", IEEE proceedings of the 2009 12<sup>th</sup> International Symposium on Integrated Circuits, pp. 385-388, 2009.

[22] FabianKhateb, WinaiJaikla, David Kubanek and NabhanKhatib, "Electronically tunable voltage-mode quadrature oscillator based on high performance CCCDBA", Analog Integrated Circuits and Signal Processing, Vol. 74, pp. 499–505, 3013.

[23] Ali UmitKeskin,"Design of Minimum Component Oscillators Using Negative Impedance Approach Based On Different Single Active Elements", proceedings of 12<sup>th</sup> IEEE MediterranenElectrotechnical Conference, Vol. 1, pp. 83-86, 2004.

[24] Ali ÜmitKeskin and ErhanHancioglu," CDBA-Based Synthetic Floating Inductance Circuits with Electronic Tuning Properties", ETRI Journal, Volume 27, Number 2, April 2005.

[25] W. Tangsrirat and W. Surakampontorn, "Electronically Tunable Floating Inductance Simulation Based on Current- Controlled Current Differencing Buffered Amplifiers," Thammasat International Journal of Science and Technology, Vol. 11, No. 1, pp. 60-65, 2006.

[26] RajeshwariPandey, Neeta Pandey, Sajal K. Paul, KashishAnand, and KrantiGhoshGautam, "Voltage Mode AstableMultivibrator Using Single CDBA," ISRN Electronics, vol. 2013, Article ID 390160, 8 pages, 2013.

[27] Ali umitkeskin "A Four Quadrant Analog Multiplier Employing Single CDBA" Analog Integrated Circuits and Signal Processing, Vol. 40, pp. 99–101, 2004.

[28] MontreeSiripruchyanun, "A design of analog multiplier and divider using current controlled current differencing buffered amplifiers," International Symposium on Integrated Circuits, pp. 568–571, 2007.

[29] Silapan, Jaikla, and Siripruchyanun, "High-performance BiCMOS current controlled CDBA and application," International Symposium on Communications and Information Technologies Proceedings, pp. 40–43, 2007.

[30] RajeshwariPandey, Neeta Pandey, TusharNegi, and VivekGarg, "CDBA Based Universal Inverse Filter," ISRN Electronics, vol. 2013, Article ID 181869, 6 pages, 2013.

[31] Cevdet, Acar and Herman Sedef, "Realization of nth-order current transfer function using current-differencing buffered amplifiers", International Journal of Electronics, VOL. 90, NO. 4, pp. 277–283, 2003.

#### **CHAPTER 3: CDBA ACTIVE BUILDING BLOCK**

#### **3.1. CDBA Terminal Characteristics**

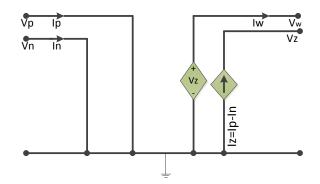

CDBA block can be designed using two fundamental blocks which are voltage follower block and current subtractor block. The symbol for the CDBA active block circuit is represented in Figure 3.1. The equivalent structure of circuit to the CDBA consists of dependent current and voltage sources and is shown in figure 3.2.

Fig. 3.1 Symbol of CDBA [1]

Fig. 3.2 Equivalent circuit of CDBA [2]

The characteristics of the ideal CDBA block can be modelled as [2]:

And for practical CDBA equation become

$$I_{Z} = \alpha_{p}I_{P} - \alpha_{n}I_{n}, V_{W} = \beta_{v}V_{Z}, V_{P} = V_{n} = 0$$

(3.2-3.4)

Where current gains are denoted by  $\alpha_p$  and  $\alpha_n$ , and voltage gain by  $\beta_v$ , which in the ideal case should be equal to unity.

In practice, they are expressed as

$$\alpha_p = 1 - \varepsilon_p, \alpha_n = 1 - \varepsilon_n, \beta_v = 1 - \varepsilon_v$$

(3.5-3.7)

With

$$\left| \varepsilon_{p} \right| \ll 1$$

,  $\left| \varepsilon_{n} \right| \ll 1$ ,  $\left| \varepsilon_{v} \right| \ll 1$

Here current-tracking errors are denoted by  $\varepsilon_p$  and  $\varepsilon_n$  and voltage-tracking error is denoted by  $\varepsilon_v$ .

If we observe the equivalent circuit and the above describing equations, we find that the z- terminal of circuit is showing the divergence of current through p terminal from current through n terminal that's why we name z as the current output node, which has typically infinite resistance. In this block p-terminal is called non-inverting terminal and n-terminal is called inverting terminal. These p and n terminals which act as inputs to the block are grounded thereby ideally having zero input impedances at these terminals internally. The w-terminal is termed as voltage output, as the voltage occurring at the wterminal is always same as that of the z-terminal due to the appearance of the voltage follower circuit between the two terminals. As w-terminal is used as a voltage output hence it should ideally have zero impedance.

#### **3.2. Realizations of CDBA**

#### 3.2.1. IC AD844 based Realization

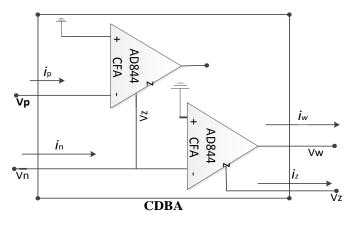

Fig. 3.3 Implementation of CDBA using CFOA (AD844 IC) [1]

Figure 3.3 presents the implementation of CDBA using two AD844 CFOA IC's

(see Appendix A). The current at the compensation node  $v_z$  of the CFOA is ideally equal to the difference of the current applied to the non-inverting and inverting terminals of the CFOA. Hence the current at the compensation node for first IC is given by:

$$i_{z1} = -i_p \tag{3.8}$$

thereby giving a resultant current of  $i_{n2}$  at the inverting terminal of second IC.

$$i_{n2} = i_n + i_{z1}$$

Or  $i_{n2} = i_n - i_p$  (3.9)

Therefore the current at the z-terminal (output node) of second IC is given by:

$$i_{z2} = i_p - i_n \tag{3.10}$$

Which is the required current at the z-terminal of CDBA, also the voltage at the wterminal called output voltage of the CFOA is same as that of the voltage at the z-terminal using a voltage follower circuit attached between the two terminals as can be seen in the CMOS implementation of the CFOA. The voltage at the z-terminal is formed by  $i_{z2}$ current and the impedance at the z-terminal.

#### **3.2.2.** NPN Transistor based Realization[3]

Various CDBA blocks has been proposed in literatures which are implemented using different technologies however, every implementation has some of its own limitations. There are certain limitations due to the use of PNP transistors in the implementation as they limit the high frequency operation of the circuit and this leads to a conclusion that CDBA should be designed in such a way that signals only pass through NPN transistors. Also due to the advances in large scale integration and increased use of complicated circuit systems and portable consumer electronics equipments, there has being a gradual increase in the need of a low voltage low power technique.

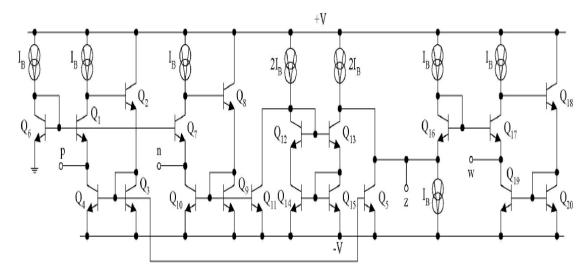

#### **3.2.2.1.** Block Architecture

In this section, a simple NPN based CDBA proposed in [3] is described which can work efficiently at power supply voltage up to 2 volts DC, and since the signal has only NPN transistors in its signal path this helps in achieving a maximum high frequency response. As shown in figure 3.4, the NPN based CDBA consists of two sub-circuits namely the current differencing circuits and a buffer voltage amplifier. We find from the circuit that when we traverse the path between the negative and positive supply voltages, the path has only one biased current source and two transistors. As a result this circuit can work at a low power supply voltage compared to other implementations with a minimum power supply voltage of  $(2 V_{be}+V_{cesat}) = 2 V$  (or +1 V to -1 V).

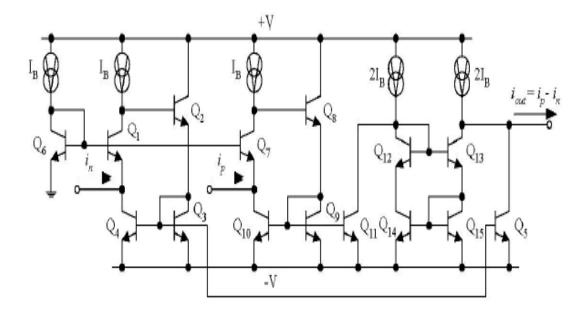

Fig. 3.4 NPN transistors based CDBA circuit [3]

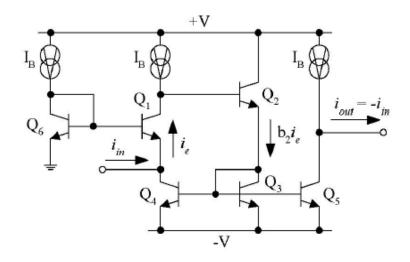

# 3.2.2.2.Circuit Description3.2.2.2.1.Current Differencing Circuit

This circuit can be designed by connecting 2 unity gain current amplifiers. Now if we consider figure 3.5 which depicts the circuit diagram of the unity gain current amplifier we can see that Q1 through Q4 transistors form a feedback loop. Let us assume that the emitter current passing through the Q1 transistor is $i_e$ , then the emitter current passing through the Q2 transistors will be equal to  $\beta_2 i_e$  which is also the emitter current for the Q3 transistor. Q3-Q4 transistors together form a current mirror and hence the current  $\beta_2 i_e$  is reflected to the collector of Q4 transistor. Therefore following relation can be obtained:

$$i_{in} = i_e + \beta_2 i_e \tag{3.11}$$

Or

$$i_e = \frac{i_{in}}{\beta_2 + 1} \tag{3.12}$$

Where,

$i_{in}$ - the input signal current  $\beta_2$ - the current gain of transistor Q2

Figure 3.5 Unity gain current amplifier [3]

For the circuit output current  $i_{out}$  can be given by:

$$i_{out} = -\beta_2 i_e = -\frac{\beta_2}{\beta_2 + 1} i_{in}$$

(3.13)

Generally the current gain  $\beta_2$  of the circuit is in several hundreds and is high enough to obtain the ratio ( $\beta_2/\beta_2+1$ ) nearly equal to 1; hence the output current of the circuit can be represented by:

$$i_{out} = -i_{in} \tag{3.14}$$

Because of the negative feedback applied Between the Q1 through Q4 transistors, the value of the input resistance  $r_{in}$  of the unity gain circuit is very low and is given by the following expression below:

$$r_{in} = \frac{r_{e_1}}{\beta_2} \tag{3.15}$$

Where,

$r_{e1} = V_T / I_B$  - the small signal emitter resistance

$V_T$  - the thermal voltage.

The two groups of transistors namely Q1-Q5 and Q7-Q11 form two current amplifiers which combine together to form the current differencing circuit as depicted in figure 3.6. Transistors Q1 through Q5 reflect current  $-i_n$  to the output port and second current amplifier Q7 through Q11 along with current mirror circuit Q12-Q15 represents  $i_p$  at the output terminal, Therefore the relation obtained for the output terminal of the circuit is:

$$i_{out} = i_p - i_n \tag{3.16}$$

Fig. 3.6 Current differencing circuit [3]

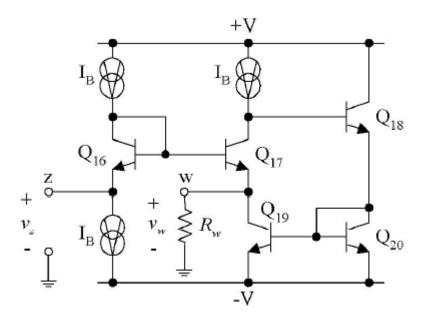

#### 3.2.2.2.2. Buffered Voltage Amplifier

The voltage at terminal W ( $V_w$ ) is forced to be equal to the voltage at terminal  $Z(V_Z)$  with the help of transistors Q16 through Q20 which together form the buffer voltage amplifier as shown in figure 3.7, i.e.  $V_w = V_Z$ .

Figure 3.7 Buffer Voltage amplifier [3]

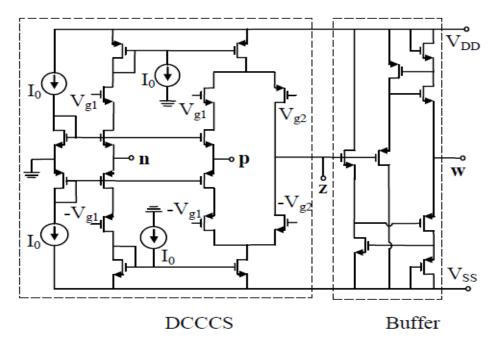

#### **3.2.3.** CMOS based Realization[4]

The DCCCS block which acts the current differencing circuit, followed by the voltage follower [5] block combine together to form the CMOS implementation of the CDBA active block as depicted in figure 3.8.

Fig. 3.8 CMOS implementation of CDBA [4]

The CCII configuration implemented by Bruun [6] is slightly modified to reach to the required DCCCS circuit which is used in current CDBA block.

# 3.2.4. Low Voltage Low Power CMOS based CDBA (LVLP CDBA) [2]

In the recent scenario, what we observe is a shift in the interest of researchers to low voltage circuit designs due to the advent of mobile communication systems and portable electronics and thus efforts are made to decrease the supply voltage of the circuit designs and hence minimize the power consumption. These low power capabilities were missing in the previously discussed implementations of CDBA.

Also in CMOS based CDBA, the terminal resistances are of the order of hundreds (high) of ohms and their transfer ratios for current and voltage are smaller than one. Hence, the main aim of discussing this implementation of CDBA based on the FVF technique is to overcome the disadvantages mentioned above.

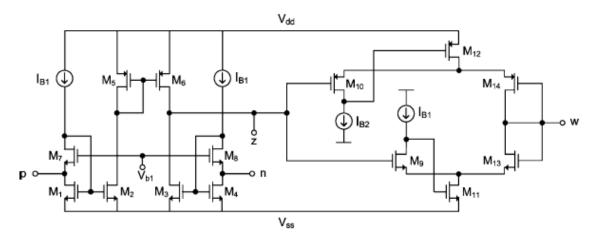

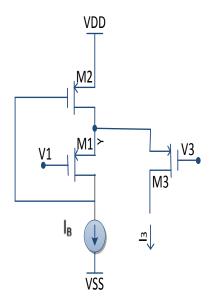

#### 3.2.4.1. Block Architecture

The low power low voltage CDBA circuit implementation can be separated into two blocks: first is the voltage buffer block and second is the current differencing block. Where first block works as a buffer between z and w terminals and second block replicates the divergence between the current passing through the P and N terminal obtained at z terminal and second block acts as a buffer between the Z and W terminals. The complete schematic of the block can be seen in figure 3.9, where M1-M8 transistors make up the current differencing block and M9-M14 make up the voltage buffer block.

Fig. 3.9 Low Power CMOS implementation [2]

#### **3.2.4.2.** Circuit Description

The resistances occurring at the input terminals (p & n) of the implemented CDBA block can be made very low by using FVFCS, hence the current subtraction circuit is so implemented thereby removing one of the disadvantage of other implementations.

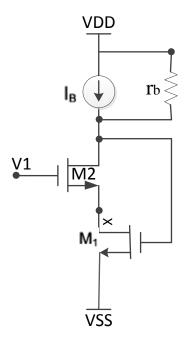

Fig. 3.10 Flipped voltage follower current source (FVFCS) [2]

The resistance occurring at input terminal of the FVFCS is shown in fig. 3.10, when seen at the node X can be found to be;

$$R \simeq \frac{\frac{1}{g_{m2}} \left(1 + \frac{r_b}{r_{02}}\right) / r_{01}}{g_{m1} (r_b / / g_{m2} r_{01} r_{02})}$$

(3.17)

Where,

$r_b$  - Output resistance of the current source

r<sub>o</sub>- Output resistance of the transistors

g<sub>m</sub> - trans conductance of the transistors

For a basic current source having  $r_b = r_{o2}$ , the node resistance can be found to be;

$$R \cong \frac{2}{g_{m1}g_{m2}r_{02}} \tag{3.18}$$

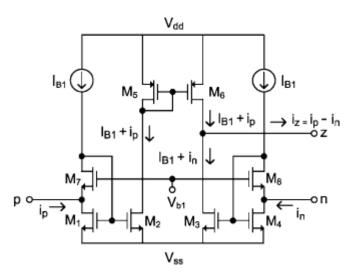

The current subtraction circuit comprises of M1 to M8 transistors is shown in fig. 3.11. The circuit can basically be understood as comprising of three current mirrors respectively constructed out of M1-M2, M3-M4 and M5-M6 transistors. Due to current mirror between M1-M2 the current flowing through M2 is  $I_{B1} + i_p$  and  $I_{B1} + i_n$  flows through M3 due to current mirror between M3-M4. Also the current mirror between M5-M6 leads to a current  $I_{B1} + i_p$  flowing through M6, thereby replicating the difference of the currents at the P and N terminals of the CDBA to the Z terminal.

Fig. 3.11 Current subtractor circuit [2]

Hence, terminal-z is labelled as current output node. The current at the output node can be represented as follows:

$$i_{z} = I_{B1} + i_{p} - (I_{B1} + i_{n}) = i_{p} - i_{n}$$

(3.19)

For the current implementation of CDBA, the output stage is based on DFVF. The circuit for DFVF is shown in figure 3.12, where for large currents through transistor M3 the voltage at node Y remains approximately constant and also the impedance of this node is very low.

Fig. 3.12 Differential flipped voltage follower (DFVF) [2]

This condition of constant voltage and very low impedance can be achieved if the transistors M1 and M3 are assumed to be of same sizes and the quiescent condition of V1=V3 is observed. DFVF has another important characteristic i.e. it can operate even for very low supply voltages. The supply voltage can be reduced up to a minimum level for satisfactory performance of the circuit given by,

$$V_{dd}(Min) = V_{Tp} + 2 V_{ds,sat}$$

(3.20)

The output stage circuit is a class AB voltage buffer, where M10, M12 and M9, M11 respectively form two complementary DFVF cells with current sources  $I_{B1}$  and  $I_{B2}$  as can be seen in figure 3.9. This circuit offers moderate output swing and low output impedance.

## **3.3.Simulation Results**

## 3.3.1. IC AD844 based Realization

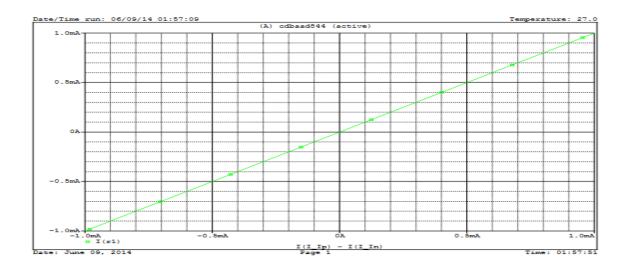

The proposed circuit is operated at the supply voltage of  $\pm 5$  V. To do the simulations, the PSPICE model file of AD844 IC (see Appendix A) supplied by Analog Devices is used.

Fig. 3.13 Current transfer characteristics  $I_z$  VS  $I_p - I_n$  (AD844)

Fig. 3.15 Current transfer ratio frequency response (AD844)

Fig. 3.16 Voltage transfer ratio frequency response (AD844)

The DC current characteristics and voltage transfer characteristics to realize the current are depicted in figure 3.13 and 3.14 respectively. It can be seen that these characteristics are linear for a large range. The current and voltage follow the given input current and voltages for as high as 1mA and 2V respectively and hence are found to be highly linear.

# 3.3.2. The LVLP CDBA

The supply voltage and the technology parameters used for the CDBA realization and its simulation are  $\pm 0.8$  V and TSMC 0.18µm respectively. The bias currents of 56 µA and 84 µA are chosen respectively for  $I_{B1}$  and  $I_{B2}$  and dimension of the gate channel of the transistors used are mentioned in Table 3.1.

| Transistor     | W/L ratio (µm/ µm) |

|----------------|--------------------|

| M1, M2, M3, M4 | 0.36/0.18          |

| M5, M6         | 0.18/0.18          |

| M7, M8         | 0.18/0.18          |

| M9             | 0.45/0.36          |

| M10            | 0.24/0.36          |

| M11            | 0.72/0.36          |

| M12            | 0.24/0.36          |

| M13            | 0.72/0.36          |

| M14            | 0.24/0.36          |

Table 3.1 MOS Transistor dimensions

For the current CDBA realization the DC current transfer characteristics are displayed in fig. 3.17. For the entire dynamic range at  $I_{B1} = 56\mu A$  the CDBA can be seen to be highly linear.

Fig. 3.17 Current transfer characteristics  $I_z$  VS  $(I_p - I_n)$  (LVLP CDBA)

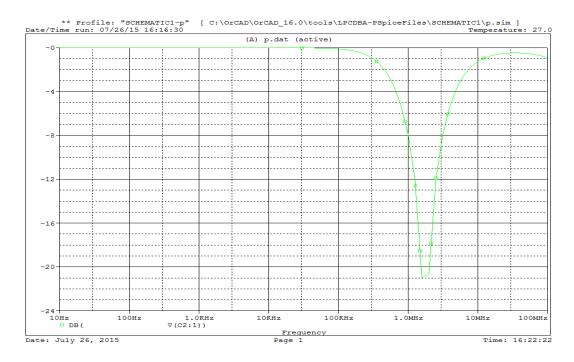

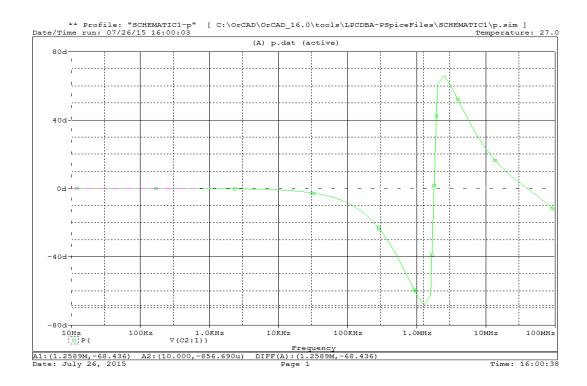

Fig. 3.19 Current transfer ratio frequency response (LVLP CDBA)

Fig. 3.20 Voltage transfer ratio frequency response (LVLP CDBA)

The output voltage,  $V_w$  which is proportional to  $V_z$  is shown by the DC voltage transfer characteristic, shown in figure 3.18. From figure 3.18 we can conclude that the voltage transfer error goes on increasing as the values of  $V_z$  starts to go beyond the range of  $\pm 100$  mV.

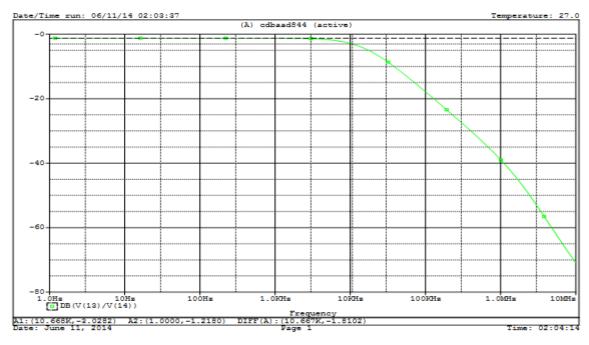

Figure 3.19 and Figure 3.20 are representing the frequency response of current and voltage transfer ratio respectively as the AC transfer characteristics of the simulated LVLP CDBA.

## 3.3.3. Comparison

Various parameters of both the simulated realizations of the CDBA are shown in Table 3.2. It can be clearly seen from table 3.2 that in AD844 based realization the voltage and current follow the required values more closely but LVLP CDBA has very less power dissipation, better voltage and current transfer bandwidths and hence can be used for higher frequency range.

| Parameter                                                     | AD844 Realization | LVLP CDBA<br>Realization |

|---------------------------------------------------------------|-------------------|--------------------------|

| Supply voltage (V)                                            | ±5                | $\pm 0.8$                |

| Current transfer ratio,<br>$\alpha = \frac{I_Z}{(I_P - I_n)}$ | 0.9996            | 0.9861                   |

| Current transfer BW<br>(MHz)                         | 28.81  | 30.47  |

|------------------------------------------------------|--------|--------|

| Voltage transfer ratio,<br>$\beta = \frac{V_w}{V_z}$ | 0.9998 | 0.9310 |

| Voltage transfer BW<br>(MHz)                         | 49     | 475    |

| Power Dissipation (mW)                               | 999.89 | 98.818 |

Table 3.2 Performance of the CDBA realizations

# **REFERENCES**

[1] Acar C. and Ozoguz S. "A new versatile building block: current differencing buffered amplifier" Microelectronics Journal, vol. 30, pp. 157-160, 1999.

[2] CemCakir, ShahramMinaei and OguzhanCicekoglu, "Low voltage low power CMOS current differencing buffered amplifier", Analog Integrated Circuits and Signal Processing, v.62 n.2, pp. 237-244, 2010.

[3] VisawaSawangarom, WorapongTangsrirat and WanlopSurakampontom, "NPN-based Current Differencing Buffered Amplifier and Its Application" proceedings of IEEE international joint conference SICE-ICASE, pp. 5766-5769, 2006.

[4] S. Özoguz, A. Toker, M. A. İbrahim, C. Acar, "A new versatile building block: Current differencing amplifier and its applications", Proceedings of The European Conference on Circuit Theory and Design, pp. 90-93, 1999.

[5] Manetakis K., Toumazou C., "Current-feedback opamp suitable for CMOS VLSI technology", Electronics Letters, v. 32, pp. 1090-1092, 1996.

[6] Bruun E., "CMOS high speed, high precision current conveyor and current feedback amplifier structures", International Journal of Electronics, v. 74, pp. 93-100,1993.

# **CHAPTER 4: FILTER REALIZATIONS**

## 4.1 Introduction

Filters are the electrical networks that process signal to modify its amplitude and/or phase characteristics in a frequency dependent manner. A filter never adds a new frequency neither it alters the component frequency of the input signal, it only varies the amplitude along with phase characteristics of the various frequency component present in the signal. Filters are often used in electronic systems to separate signals i.e. passing those of interest in certain frequency range and blocking the undesirable ones. The gain of such filters depends on signal frequency. Consider an example where the input signal comprises of desirable frequency  $F_1$  along with an undesirable one  $F_2$ . A filter having a very low gain at  $F_2$  and high gain at  $F_1$  will attenuate the frequency  $F_2$  and only useful frequency remains when the input signal is passed through it.

Analysis of filters is done in frequency domain, therefore to demonstrate its characteristics, generally phase vs. frequency and gain vs. frequency plots are used. Mathematically, Frequency domain behaviour of a filter is described with the term called Transfer Function which is represented as the ratio of the Laplace transform of the output signal to the input signal fed to the filter [1]. Therefore, the voltage transfer function is given by,

$$H(s) = \frac{V_{OUT}(s)}{V_{IN}(s)} \tag{4.1}$$

Where  $V_{OUT}(s)$  and  $V_{IN}(s)$  are the Laplace transform of the output and input signal voltages respectively.

The magnitude of the transfer function as a function of frequency is an important analysis as it shows the variation on the amplitudes of sinusoidal signals at different frequencies due to the presence of filter. The magnitude versus frequency of a transfer function is known as the amplitude response or frequency response. Also, the quantity of phase shift obtained in sinusoidal signals represented by a function of frequency is called its phase response. Since a variation in signal's phase also corresponds to a variation in time signal, hence the phase characteristics of a filter turn out to be essential while transacting with complex signals where the relationships between time and the signal components at different frequencies are critical. The effect of filter on the phase and magnitude of the input signal can be represented by replacing s with j $\omega$  in the transfer function. The magnitude is obtained by taking its absolute value i.e.

$$\left| H(j\omega) = \frac{V_{OUT}(j\omega)}{V_{IN}(j\omega)} \right|$$

(4.2)

And the phase is obtained as:

$$\arg H(j\omega) = \arg \frac{V_{OUT}(j\omega)}{V_{IN}(j\omega)}$$

(4.3)

An ideal filter has its amplitude response equal to one for the particular range of frequencies (pass band frequencies) and zero for any other frequency range (stop band frequencies). The frequency at which the response transits from pass band frequencies to stop band frequencies is known as the cut-off frequency  $f_c$ .

The two important parameters for consideration while designing filters are as follows: (i) 3 dB down frequency response from the pass band which is called cut-off frequency  $f_c$  (ii) quality factor (Q) which is shown as:

$$\alpha = \frac{1}{Q} \tag{4.4}$$

The highest power of the variable s in the transfer function (Laplace transform format) of the designed filter is called its order. It defines the steepness of the designed filter. It can also be determined by calculating the number of poles (existing either on real or imaginary axis) in the transfer function which is in x/y pattern. A pole and a zero are the root of the denominator (y) and numerator (x) respectively. Basically the total number of inductors and capacitors connected in the circuit determines the order of the filter. The Higher-order filters are therefore more costly to build as they are complicated and require more number of components. But increasing the order the filter enhances its signal discriminating power at different frequencies.

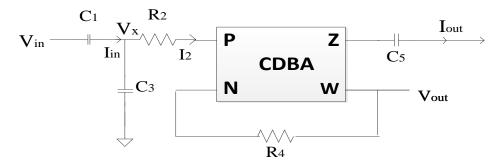

# 4.2 CDBA based Filter Topologies

The ancient forms of electronic filter circuits designed using combinations of Resistor (R), Capacitor (C) and Inductor (L) only are called passive filters. However, active filters are constructed using passive elements and active components (like transistors). The filtering performances of modern active filters are better compared to passive ones; also they are smaller in physical size and more flexible in application. The op-amps are widely used for designing active filter. There are various other active blocks, available in literatures which are used to implement active filters. CDBA is one among of them [2]. There are many CDBA topologies used to construct active filters, we are focusing on two of them namely topology (A) and topology (B) which are explained in

further sections. Filters are also classified according to their response characteristics as low pass, high pass, all pass, band pass and notch. These are described in detail in the subsequent sections of the chapter and designed using the CDBA topologies.

**4.2.1 Topology** (A)

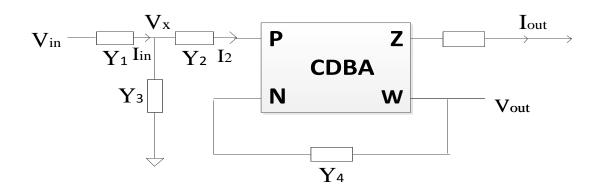

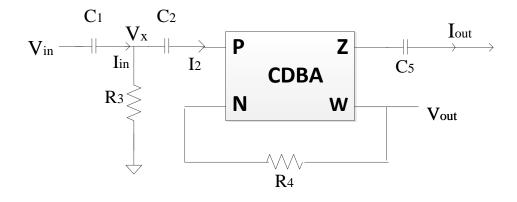

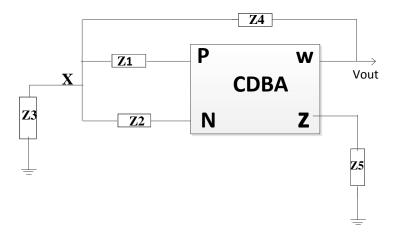

Fig. 4.1General filter topology (A) of CDBA [3]

Basic structure of multi-mode filter topology is shown in Fig.4.1 [3]. This structure consists of 4 or 5 passive elements and a single CDBA. Number of filter transfer functions calculated in CM, VM, TIM and TAM is 3 and is dependent on the passive elements used [3].

In the above topologies only VM topology is utilized to analyze the configuration for Filters. The voltage input  $V_{IN}$  is required to carry out VM analysis.

Using characteristic equations of CDBA given in chapter 3, the transfer function can be derived as follows:

Applying KCL at node  $V_X$ ,

$$(V_{IN} - V_X) Y_1 = V_X Y_3 + V_X Y_2 \tag{4.5}$$

$$\frac{V_X}{V_{IN}} = \frac{Y_1}{(Y_1 + Y_2 + Y_3)} \tag{4.6}$$

Using characteristic equations of CDBA,

$$V_{OUT}Y_5 = V_X Y_2 - V_{OUT}Y_4 (4.7)$$

$$\frac{V_{OUT}}{V_X} = \frac{Y_2}{(Y_4 + Y_5)} \tag{4.8}$$

Multiplying

$$\frac{V_X}{V_{IN}}$$

and  $\frac{V_{OUT}}{V_X}$ ,

$\frac{V_{OUT}}{V_{IN}} = \frac{Y_1 Y_2}{(Y_1 + Y_2 + Y_3)(Y_4 + Y_5)}$

(4.9)

Where  $Y_1$ ,  $Y_2$ ,  $Y_3$ ,  $Y_4$ ,  $Y_5$  are the admittance in the CDBA filter topology

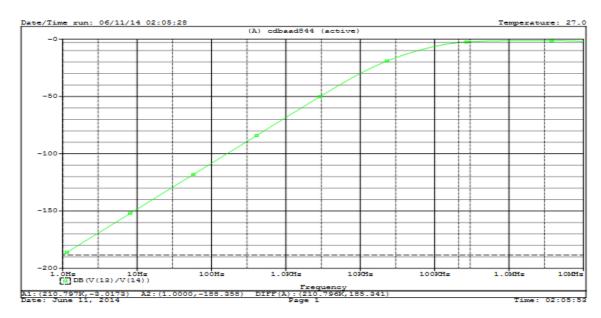

#### 4.2.1.1 Low Pass Filter

It gives a smooth passage to low frequency signals and rejects the high frequency signals more than the filter's cut off frequency  $(f_c)$ . They find their application in systems or part of the system where high frequency components are to be removed from the signal. In general the transfer function (in frequency domain) of the low pass filter is as follows,

$$H(s) = \frac{H_o}{s^2 + \frac{\omega_0}{Q}s + \omega_0^2}$$

(4.10)

Where  $H_o$  is pass band gain and  $\omega_0 = 2 \pi f_c$

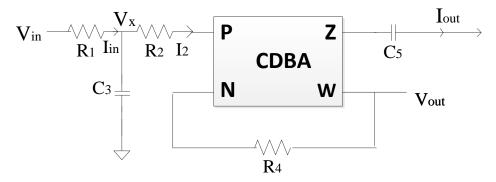

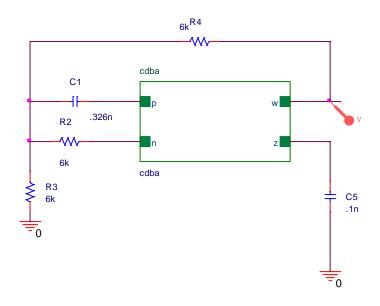

Low pass filter can be designed using topology (A) of CDBA by selecting the appropriate components. For that the following G and C replacements for the admittance of the transfer function given in section 4.2.1 are done,

$Y_1 = G_1, \ Y_2 = G_2, Y_3 = sC_3, \ Y_4 = G_4, \ Y_5 = sC_5$

Fig. 4.2 Low pass second order filter design using CDBA [3]

By putting the above replacements transfer function of topology (A), we get transfer function for low power filter,

$$\frac{V_{OUT}}{V_{IN}} = \frac{G_1 G_2}{(G_1 + G_2 + sC_3)(G_4 + sC_5)}$$

$$= \frac{G_1 G_2}{s^2 C_3 C_5 + s(C_3 G_4 + C_5 G_1 + C_5 G_2) + G_4 (G_1 + G_2)}$$

$$\frac{V_{OUT}}{V_{IN}} = \frac{\frac{G_1 G_2}{C_3 C_5}}{s^2 + s \frac{(C_3 G_4 + C_5 G_1 + C_5 G_2)}{C_3 C_5} + \frac{G_4 (G_1 + G_2)}{C_3 C_5}}$$

(4.11)

The natural frequency  $\omega_0$  and quality factor Q can be determined by the transfer function;

$$\omega_0 = \sqrt{\frac{G_4(G_1 + G_2)}{C_3 C_5}} \tag{4.12}$$

and