#### A DISSERTATION ON

## REALIZATION OF CURRENT CONTROLLED CONVEYOR MULTIMODE FILTERS

#### SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE AWARD OF THE DEGREE OF MASTER OF TECHNOLOGY (VLSI AND EMBEDDED SYSTEM DESIGN)

Submitted By: Mandeep Sheoran UNIVERSITY ROLL NO. 2K12/VLS/12

> Under the esteemed Guidance of: Dr. NEETA PANDEY

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION DELHI TECHNOLOGICAL UNIVERSITY

#### 2012-2014

#### **CERTIFICATE**

#### **DELHI TECHNOLOGICAL UNIVERSITY**

(Govt. of National Capital Territory of Delhi)

BAWANA ROAD, DELHI – 110042

Date: .....

This is certified that the dissertation entitled "**Realization of current controlled conveyor multimode filters**" is a work of **Mandeep Sheoran** (University Roll No.-2K12/VLS/12) a student of Delhi Technological University. This work is completed under my direct supervision and guidance and forms a part of Master of Technology (VLSI and Embedded System Design) course and curriculum. He has completed his work with utmost sincerity and diligence.

The work embodied in this major project has not been submitted for the award of any other Institute / University for the award of any other degree to the best of my knowledge.

Dr.Neeta Pandey (Project Guide) Associate Professor Department of Electronics & Communication Engg. Delhi Technological University, India

#### **ACKNOWLEDGEMENT**

It is distinct pleasure to express my deep sense of gratitude and indebtedness to my Project Guide **Dr. Neeta Pandey,** Associate Professor, Department of Electronics and communication, Delhi Technological University, for her invaluable guidance, encouragement and patient reviews. Her continuous inspiration only has made me complete this dissertation. Without her help and guidance, this dissertation would have been impossible. She remained a pillar of help throughout the project.

I am extremely thankful to **Prof. Rajiv Kapoor**, Head of the Department, Electronics and communication, Delhi College of Engineering Delhi for the motivation and inspiration. I would also like to take this opportunity to present my sincere regards to all my teachers those who came to my help in some way for marking the project successful. I am also thankful to all non-teaching staff of Electronics and communication Department for providing me unconditional and any time access to the resources.

My thanks and an appreciation also goes to my friend **Kamlesh Tanwer** for his kind cooperation and encouragement which helped me a lot in completing the project .I am grateful to my parents for their moral support all the time, they have been always around to cheer me up, in the odd times of this work. I am also thankful to my classmates for their unconditional support and motivation during this work.

Mandeep Sheoran Master of Technology (VLSI and Embedded System Design) University Roll No. – 2K12/VLS/12 Department of Electronics & communication Delhi Technological University, Delhi – 110042

#### **ABSTRACT**

Current mode circuits like current conveyors are getting significant attention in current analog ICs design due to their higher band-width, greater linearity, larger dynamic range, simpler circuitry, lower power consumption and less chip area. The second generation current controlled conveyor (CCCII) has the advantage of electronic tunability over the CCII. In CCCII adjustment of the X-terminal intrinsic resistance via a bias current is possible. The presented approach is based on the CMOS implementation of multiple output current controlled conveyor ( MO-CCCII) which is used to generate multiple loop feedback filter structure in transresistance mode , transadmittance mode and voltage mode . The circuit is used for its application in designing universal filter .

All the circuits have been designed and simulated on PSPICE software with  $0.35\mu$ m CMOS technology model parameters which is used to validate filter feasibility and operating frequency ranges using 2.5V supply voltage. Various simulations have been carried out to verify the valid filter expression . The outcomes show good agreement between expected and experimental results.

#### TABLE OF CONTENTS

| FITLE1            |

|-------------------|

| CERTIFICATE2      |

| ACKNOWLEDGEMENT3  |

| ABSTRACT4         |

| CONTENTS          |

| LIST OF FIGURES10 |

| LIST OF TABLE13   |

#### **CHAPTER 1**

#### INTRODUCTION

| 1.1 Comparison of current mode and voltage mode | 14 |

|-------------------------------------------------|----|

| 1.2 Current conveyor                            | 15 |

| 1.2.1 Advantages                                | 15 |

| 1.3 Objective                                   | 17 |

| 1.4 Organisation of thesis                      | 17 |

| References                                      | 19 |

#### **CHAPTER 2**

#### CURRENT MODE BUILDING BLOCKS

=

| 2.2 Current conveyor                                            |  |

|-----------------------------------------------------------------|--|

| 2.2.1 First current conveyor (CCI)                              |  |

| 2.2.2 Negative impedance converter                              |  |

| 2.2.3 The second generation current conveyor(CCII)              |  |

| 2.2.4 The third generation current conveyor(CCIII)              |  |

| 2.3 Differential voltage current conveyor ( DVCC )              |  |

| 2.4 Inverting current conveyor II (ICCII)                       |  |

| 2.5 Differential difference current conveyor (DDCC)             |  |

| 2.6 Differential difference current controlled conveyor (DDCCC) |  |

| 2.7 Differential current conveyor II (DCCII)                    |  |

| 2.8 Modified differential current conveyor (MDCC)               |  |

| 2.9 Dual – X current conveyor (DXCCII)                          |  |

| 2.10 Fully differential current conveyor II (FDCCII)            |  |

| 2.11 Operational floating conveyor ( OFC)                       |  |

| 2.12 Current gain conveyor II (CGC)                             |  |

| 2.13 Current controlled conveyor II (CCCII)                     |  |

| 2.13.1 Operation                                                |  |

| References                                                      |  |

#### MULTIPLE OUTPUT CURRENT CONTROLLED CONVEYOR II (MO-CCCII)

| 3.1 Theory                                               | 43 |

|----------------------------------------------------------|----|

| 3.2 Advantages                                           | 45 |

| 3.3 Multiple loop feedback current mode filter structure | 45 |

| 3.4 Simulation                                        |

|-------------------------------------------------------|

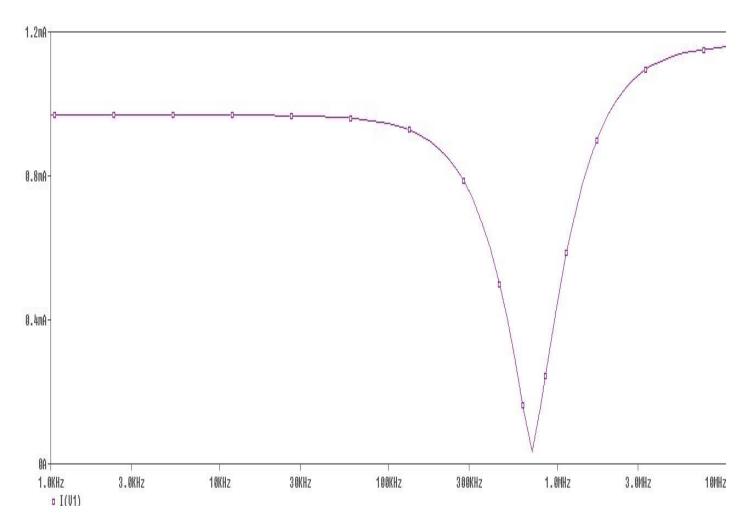

| 3.4.1 Transfer fuction of current mode filter (I/I)56 |

| 3.4.1.1. Low pass realization                         |

| 3.4.1.2 Band pass realization                         |

| 3.4.1.3 High pass realization60                       |

| 3.4.1.4 Notch filter realization                      |

| References62                                          |

#### TRANSRESISTANCE MODE FILTERS

| 4.1 Theory                                                                                | 64  |

|-------------------------------------------------------------------------------------------|-----|

| 4.2 General expression representing relation between $i_{in}$ and node voltage $V_{OUT1}$ | .65 |

| 4.3 Relation between different terminal currents and input current                        | 69  |

| 4.4 General expression representing relation between $i_{in}$ and node voltage $V_{OUT2}$ | .69 |

| 4.5 Coefficients and their characteristic                                                 | .71 |

| 4.5.1 Feedback coefficients (f <sub>ij</sub> )                                            | .71 |

| 4.5.2 Coefficient a <sub>i</sub>                                                          | 71  |

| 4.5.3 Coefficient b <sub>i</sub>                                                          | 72  |

| 4.5.4 Coefficients k <sub>im</sub>                                                        | 72  |

| 4.6 Filter synthesis                                                                      | .72 |

| 4.7 Filter characteristic and effect of non idealities                                    | .75 |

| 4.8 Simulation                                  |                   | 77                                      |

|-------------------------------------------------|-------------------|-----------------------------------------|

| 4.8.1 Transresistance 1 : Ratio of node voltage | V <sub>OUT1</sub> | to the input current i <sub>in</sub> 77 |

| 4.8.2 Transresistance 2 : Ratio of node voltage | V <sub>OUT2</sub> | to the input current i <sub>in</sub> 80 |

| References                                      |                   |                                         |

#### TRANSADMITTANCE MODE FILTERS

| 5.1 General expression between $I_{\text{OUT}}$ and $V_{\text{in2}}$           | 83  |

|--------------------------------------------------------------------------------|-----|

| 5.2 General expression between $I_{\text{OUT}}$ and $V_{\text{in3}}$           | .87 |

| 5.3 Filter synthesis                                                           | .89 |

| 5.4 Simulation                                                                 | .93 |

| 5.4.1 Transadmittance 1 : Ratio of $I_{OUT1}$ to the applied voltage $V_{in2}$ | 93  |

| 5.4.1.1 High pass realization                                                  | .94 |

| 5.4.1.2 Band pass realization                                                  | 96  |

| 5.4.2 Transadmittance 2 : Ratio of $I_{OUT1}$ to the applied voltage $V_{in3}$ | 98  |

| 5.4.2.1 High pass realization                                                  |     |

| 5.4.2.2 Band pass realization                                                  |     |

| References                                                                     | 102 |

#### CHAPTER 6

#### **VOLTAGE MODE FILTERS**

6.1 General expression representing relation between input voltage  $V_{\text{in2}}$  and different node

| voltages                                                                                   | 103  |

|--------------------------------------------------------------------------------------------|------|

| 6.2 General expression representing relation between input voltage $V_{in3}$ and different | node |

| Voltages                                                                                   | .106 |

| 6.3 Filter synthesis                                                                       | .108 |

| 6.4 Simulation                                                                             | 114  |

| References                                                                                 | 121  |

| CHAPTER 7                                                                                  |      |

| CONCLUSION                                                                                 | 122  |

|                                                                                            |      |

| APPENDIX |  |

|----------|--|

|          |  |

#### LIST OF FIGURES

| FIGURE    | TITLE PA                                                          | AGE  |

|-----------|-------------------------------------------------------------------|------|

| Fig 2.1   | Basic block diagram of CCI                                        | 22   |

| Fig 2.2   | Nullator-Norator representation of CCI                            | 23   |

| Fig 2.3   | CCI implementation of negative impedance converter (NIC) with – R | R at |

|           | terminal Y                                                        | .24  |

| Fig 2.4   | CCI implementation of negative impedance converter (NIC) with – H | R at |

|           | terminal X                                                        | 25   |

| Fig 2.5   | Basic block diagram of CCII2                                      | 26   |

| Fig 2.6   | Nullator-Norator representation of CCII                           | 27   |

| Fig 2.7   | A simplified representation of CCII                               | .27  |

| Fig 2.8   | Block diagram of DVCC                                             | .28  |

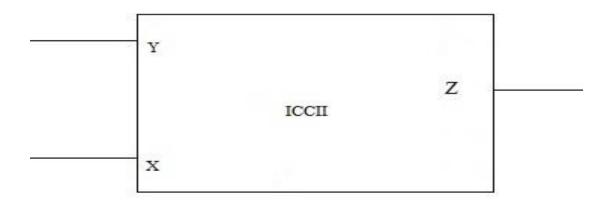

| Fig 2.9   | Block diagram of ICCII                                            | .29  |

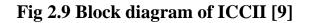

| Fig 2.10  | Block diagram of DDCC                                             | .30  |

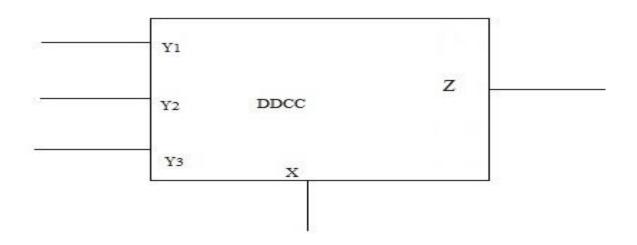

| Fig 2.11  | Block diagram of DDCCC                                            | .31  |

| Fig 2.12  | Block diagram of DCCII                                            | .32  |

| Fig 2.13  | Block diagram of MDCC                                             | .33  |

| Fig 2.14  | Block diagram of DXCCII                                           | .33  |

| Fig 2. 15 | Block diagram of FDCCII                                           | 34   |

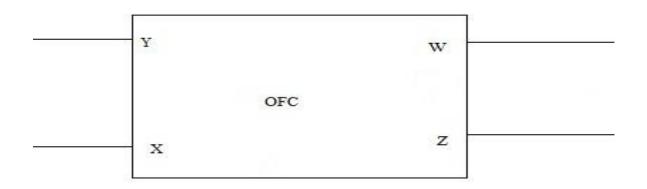

| Fig 2.16 | Block diagram of OFC                                                     |

|----------|--------------------------------------------------------------------------|

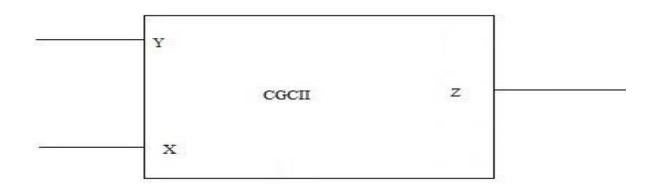

| Fig 2.17 | Block diagram of CGCII                                                   |

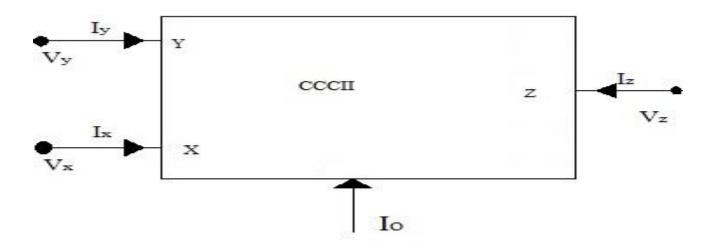

| Fig 2.18 | Block diagram of CCCII                                                   |

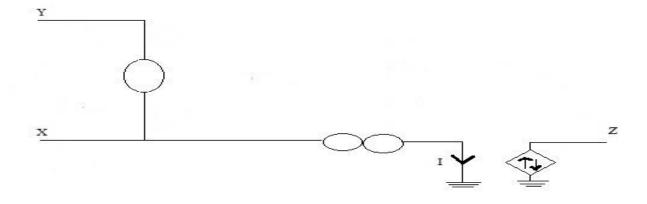

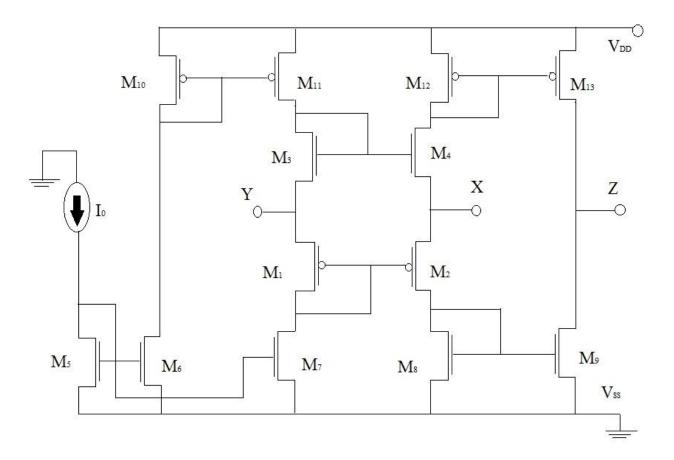

| Fig 2.19 | Internal circuit of CCCII                                                |

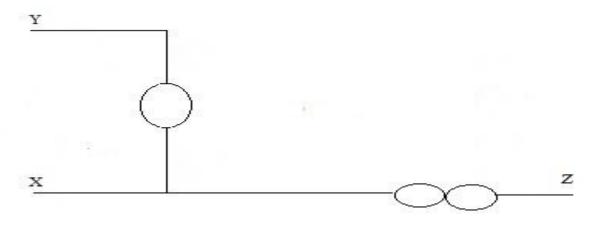

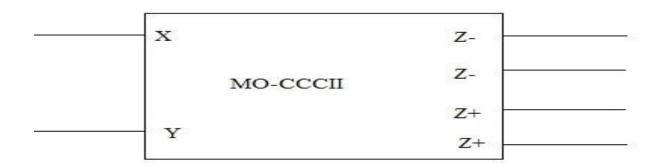

| Fig 3.1  | Block diagram of MO-CCCII43                                              |

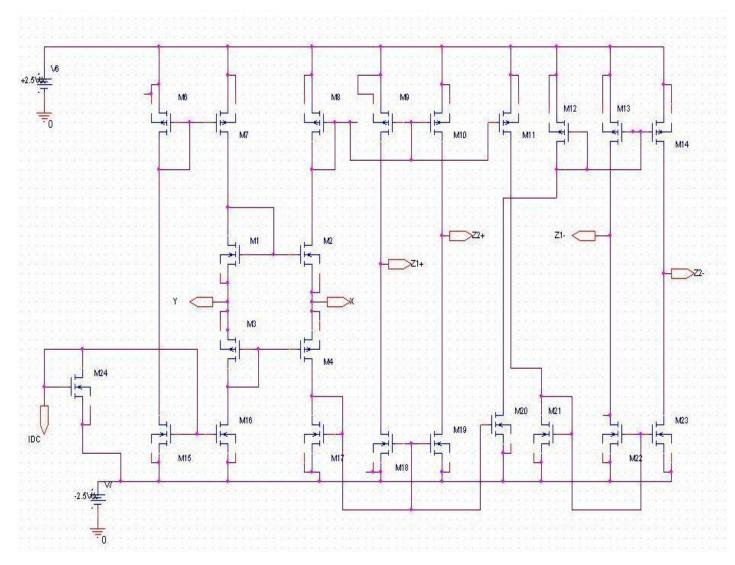

| Fig 3.2  | Internal circuit of MO-CCCII44                                           |

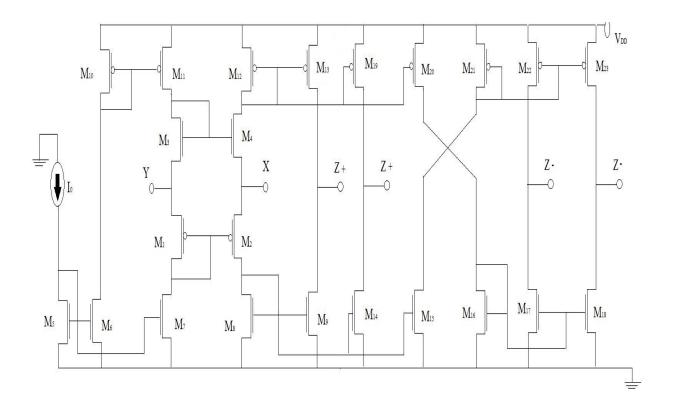

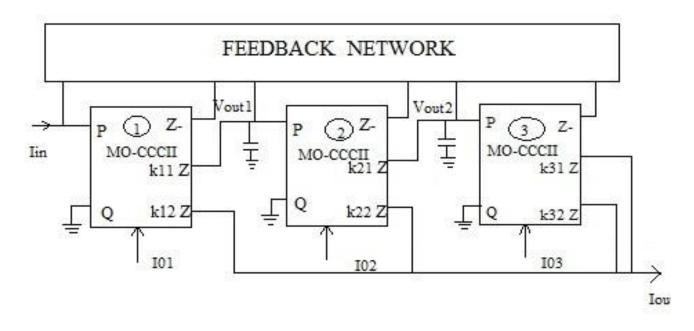

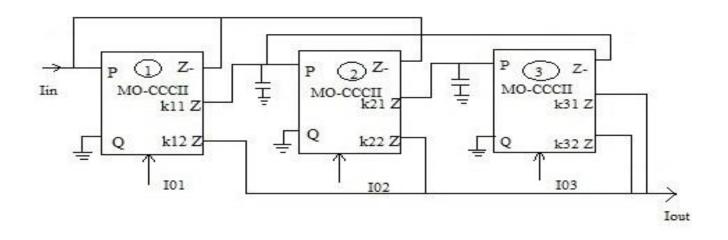

| Fig 3.3  | Multiple loop feedback current mode filter structure                     |

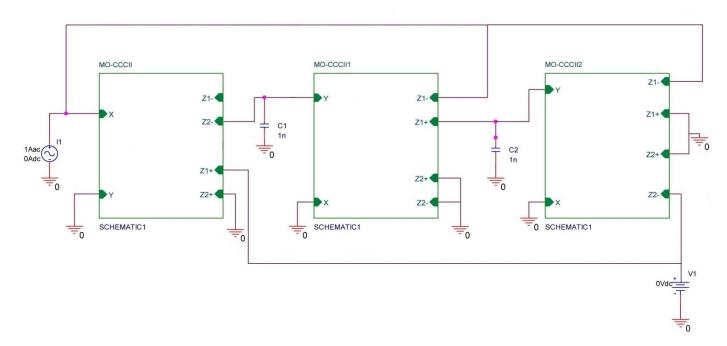

| Fig 3.4  | Schematic internal circuit of MO-CCCII                                   |

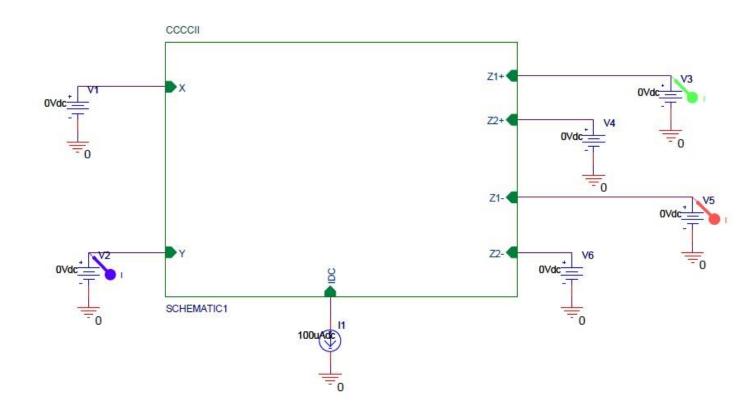

| Fig 3.5. | Schematic block diagram of MO-CCCII53                                    |

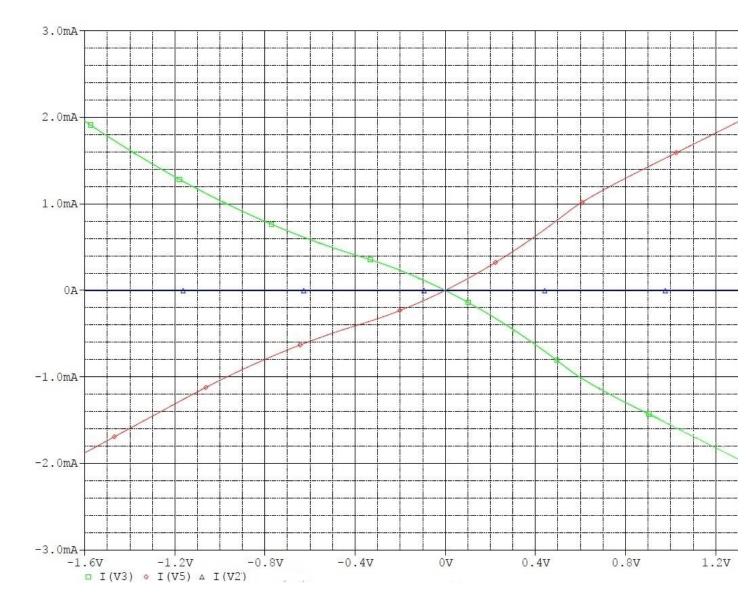

| Fig 3.6  | Simulated port relationship $I_Y = 0$ , $I_{Z=} - I_X$ , $I_{Z+} = I_X$  |

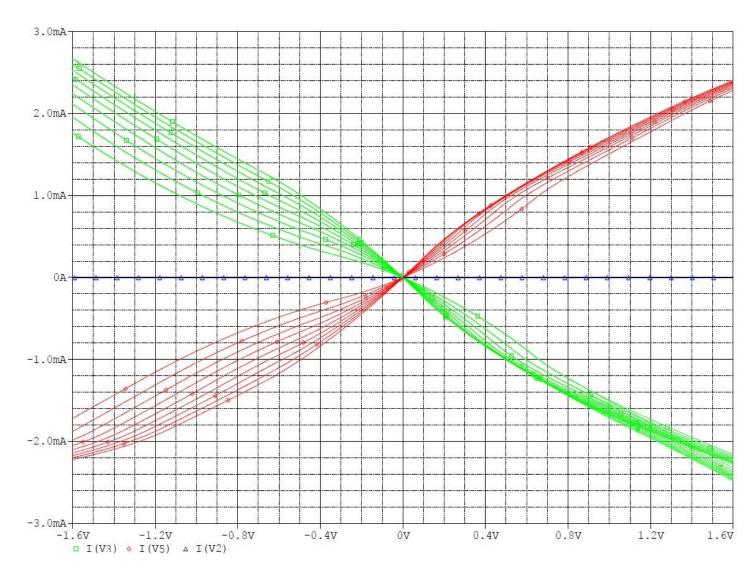

| Fig 3.7  | Simulated port relationship with varying biasing $current(I_0)$ 55       |

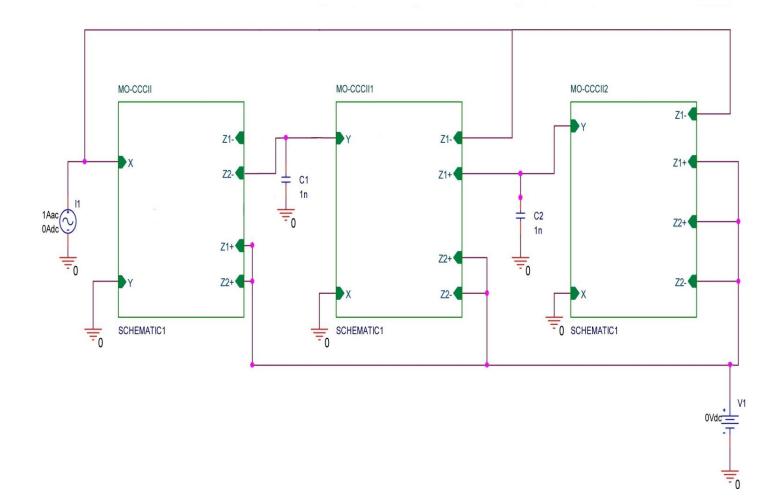

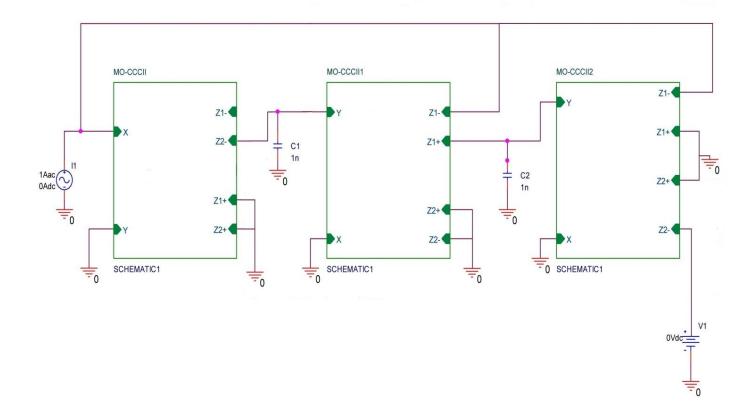

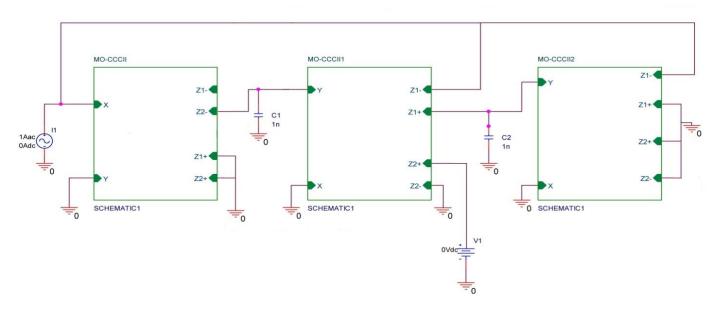

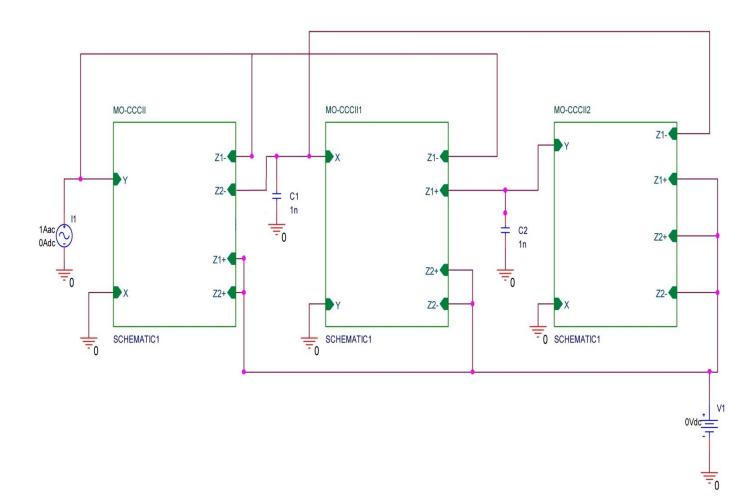

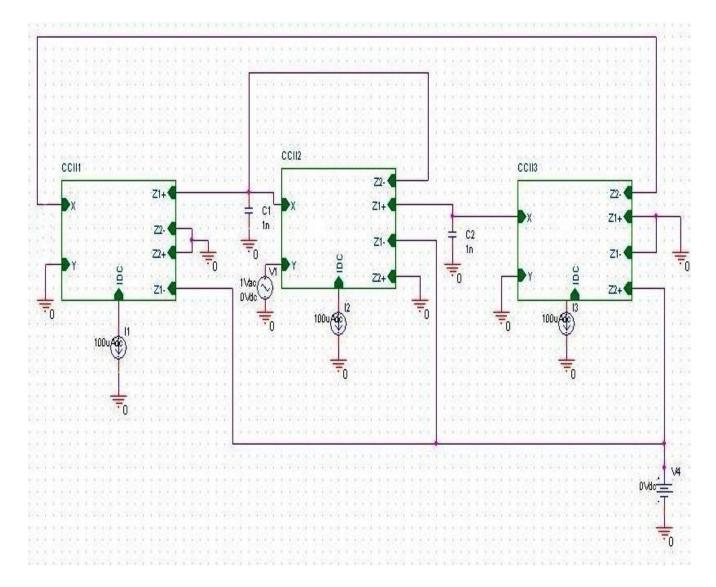

| Fig 3.8  | Schematic block diagram of structure I topology A57                      |

| Fig 3.9  | Schematic block diagram of structure I topology A for low pass filter58  |

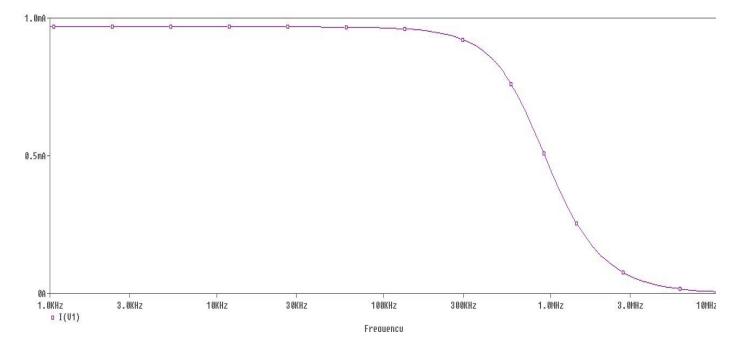

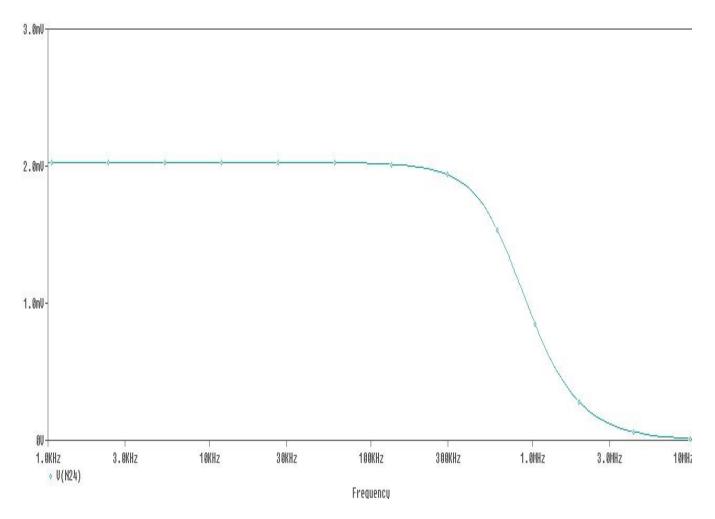

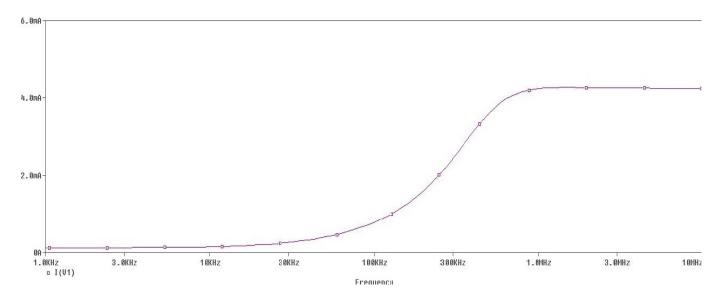

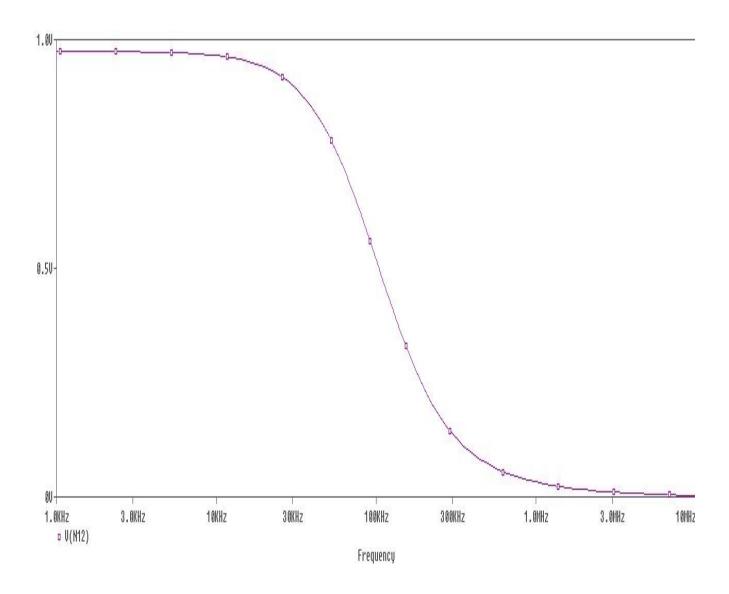

| Fig 3.10 | Graph of simulated structure showing low pass filter                     |

| Fig 3.11 | Schematic block diagram of structure I topology A for band pass filter59 |

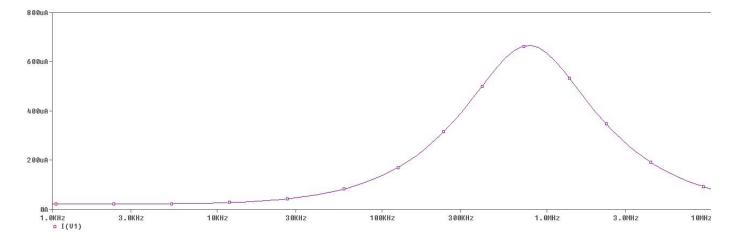

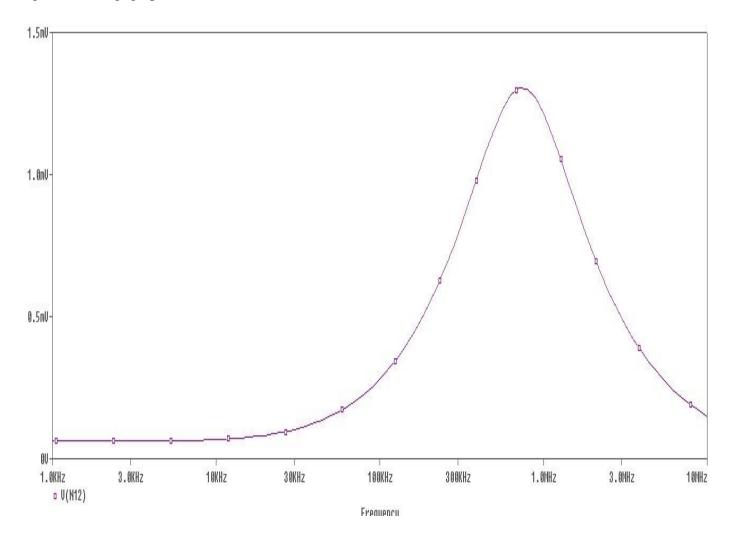

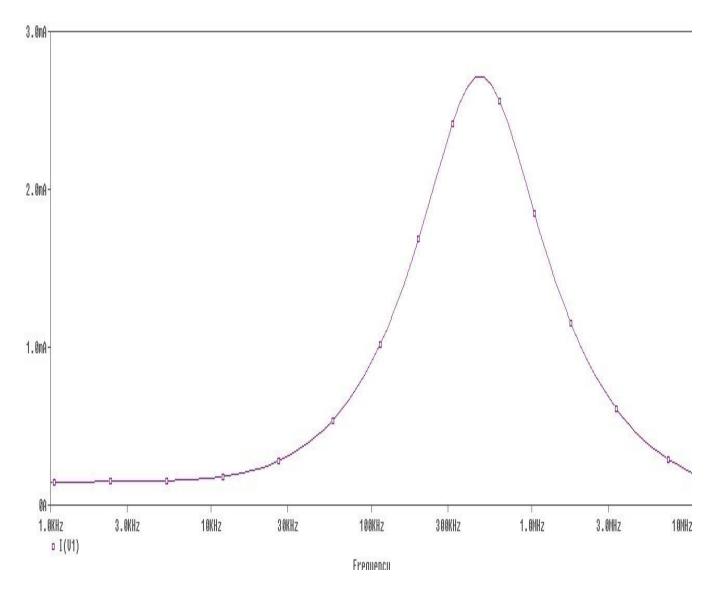

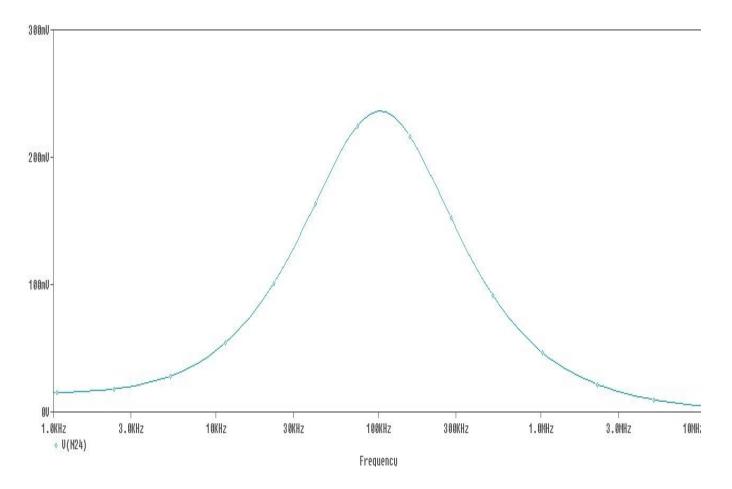

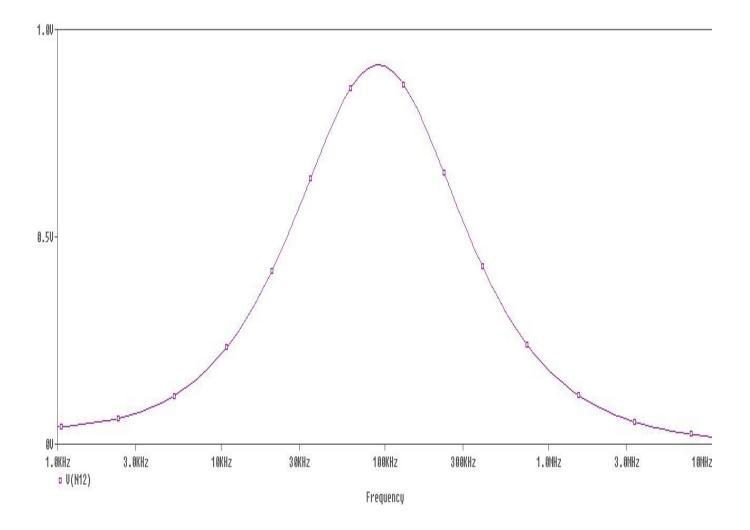

| Fig 3.12 | Graph of simulated structure showing band pass filter60                  |

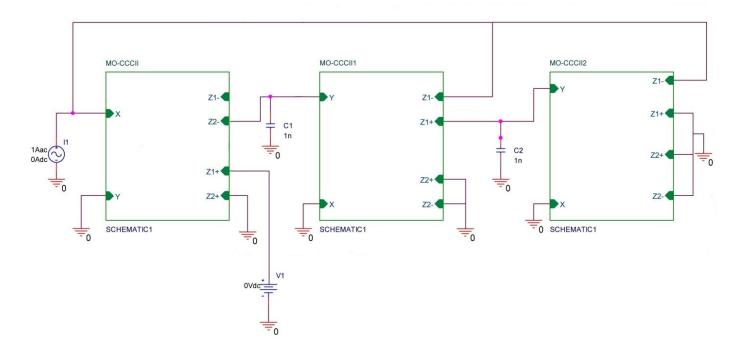

| Fig 3.13 | Schematic block diagram of structure I topology A for high pass filter60 |

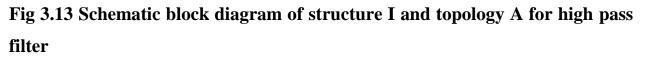

| Fig 3.14 | Graph of simulated structure showing high pass filter61                  |

| Fig 3.15 | Schematic block diagram of structure I topology A for notch filter62     |

| Fig 3.16 | Graph of simulated structure showing notch filter                        |

| Fig 4.1  | Multiple loop feedback transresistance mode filter structure65           |

| Fig 4. 2 | Block diagram of structure III                                              |

|----------|-----------------------------------------------------------------------------|

| Fig 4.3  | Schematic block diagram of structure III topology B78                       |

| Fig 4.4  | Graph of simulated structure III showing band pass filter                   |

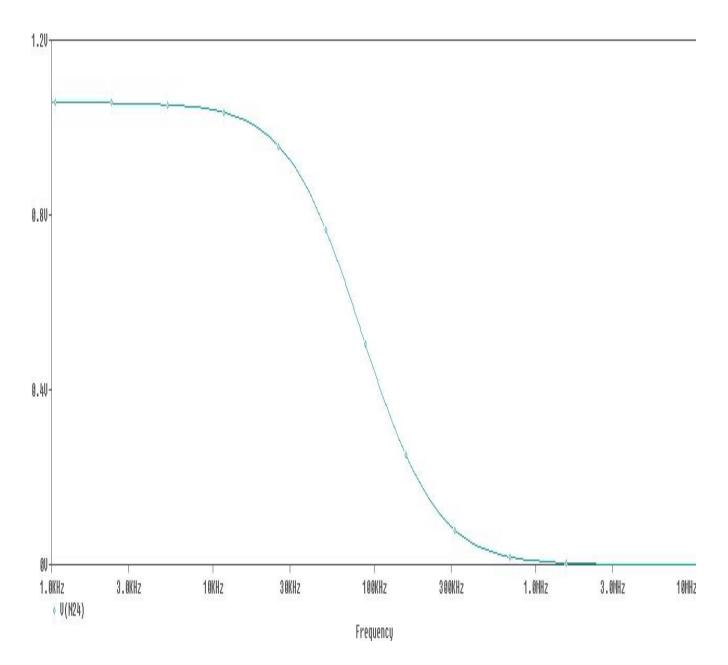

| Fig 4.5  | Graph of simulated structure III showing low pass filter                    |

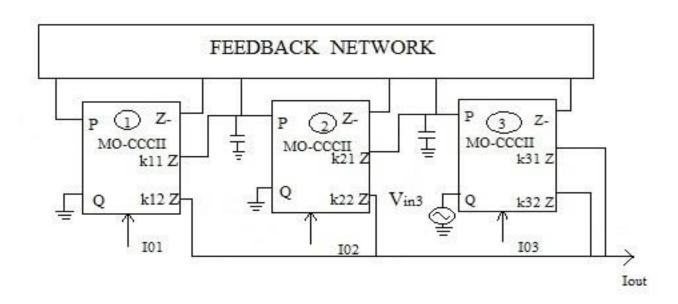

| Fig 5.1  | Multiple loop feedback transadmittance mode filter structure I              |

| Fig 5.2  | Multiple loop feedback transadmittance mode filter structure II             |

| Fig 5.3  | Block diagram of structure IV with input voltage V <sub>in2</sub>           |

| Fig 5.4  | Block diagram of structure VII with input voltage $V_{in3}$ 91              |

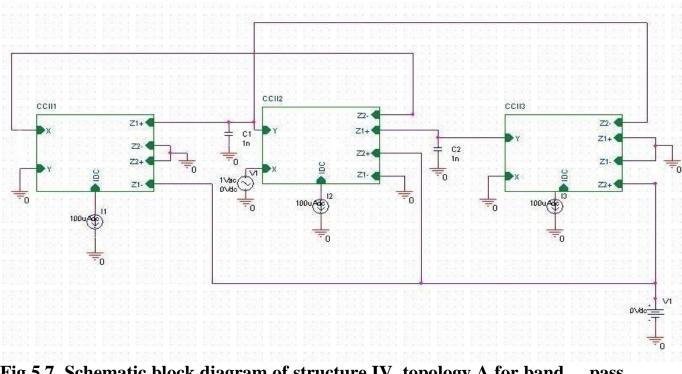

| Fig 5.5  | Schematic block diagram of structure IV topology A for high pass filter94   |

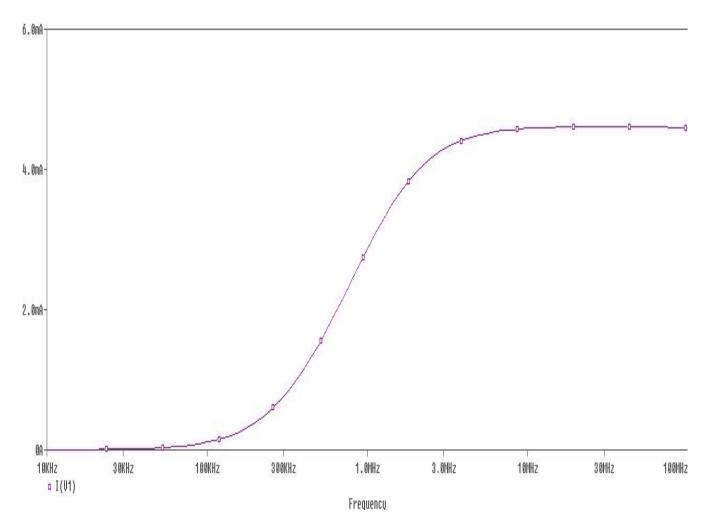

| Fig 5.6  | Graph of simulated structure IV showing high pass filter95                  |

| Fig 5.7  | Schematic block diagram of structure IV topology A for band pass filter96   |

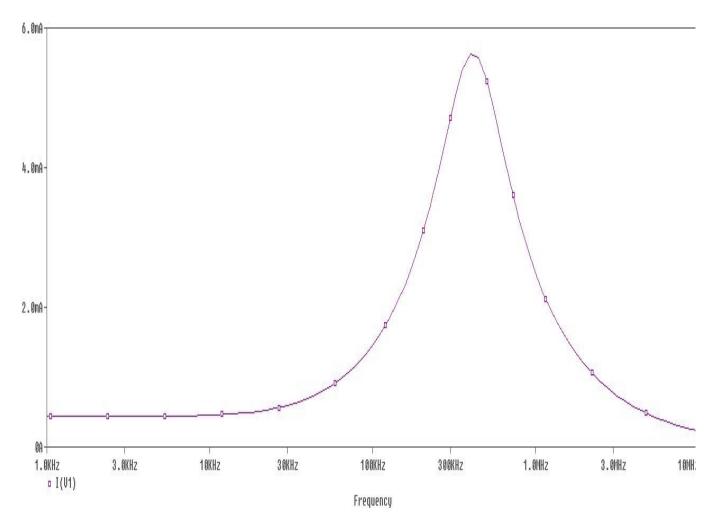

| Fig 5.8  | Graph of simulated structure IV showing band pass filter97                  |

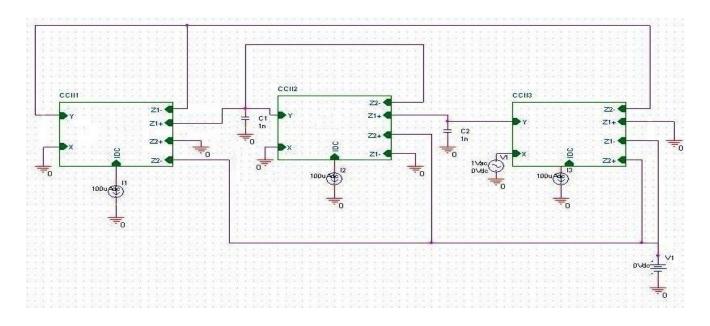

| Fig 5.9  | Schematic block diagram of structure VII topology A for high pass filter99  |

| Fig 5.10 | Graph of simulated structure VII showing high pass filter                   |

| Fig 5.11 | Schematic block diagram of structure VII topology A for band pass filter100 |

| Fig 5.12 | Graph of simulated structure VII showing band pass filter101                |

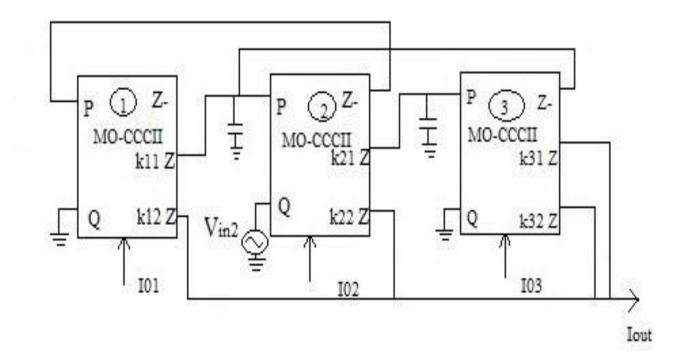

| Fig 6.1  | Multiple loop feedback voltage mode filter structure I103                   |

| Fig 6.2  | Multiple loop feedback voltage mode filter structure II                     |

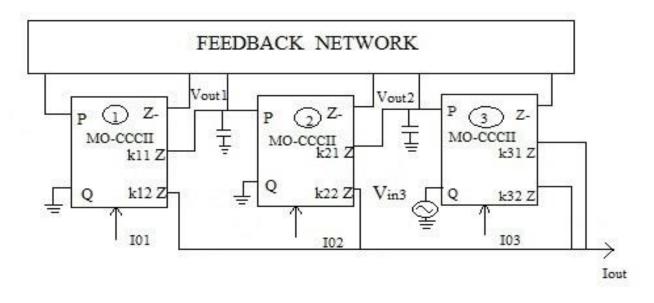

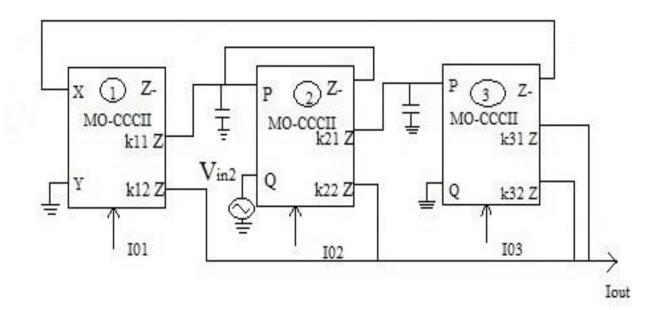

| Fig 6.3  | Block diagram of structure VIII with input voltage $V_{in2}$ 109            |

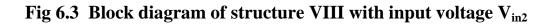

| Fig 6.4  | Block diagram of structure VIII with input voltage $V_{in3}$ 112            |

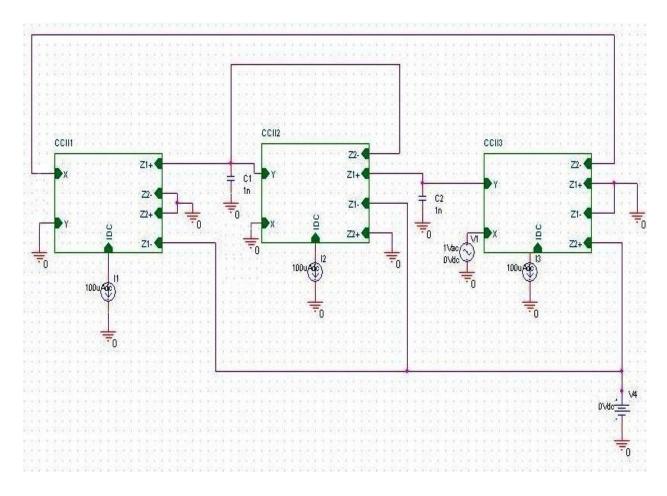

| Fig 6. 5 | Schematic block diagram of structure VIII topology D with applied input     |

|          | voltage V <sub>in2</sub> 115                                            |

|----------|-------------------------------------------------------------------------|

| Fig 6.6  | Graph of simulated structure VIII showing low pass filter               |

| Fig 6.7  | Graph of simulated structure VIII showing band pass filter117           |

| Fig 6.8  | Schematic block diagram of structure VIII topology A with applied input |

|          | voltage V <sub>in3</sub> 118                                            |

| Fig 6.9  | Graph of simulated structure VIII showing band pass filter119           |

| Fig 6.10 | Graph of simulated structure VIII showing low pass filter120            |

## **List of Tables**

| Table | TITLE                                                 | PAGE |

|-------|-------------------------------------------------------|------|

| no.   |                                                       |      |

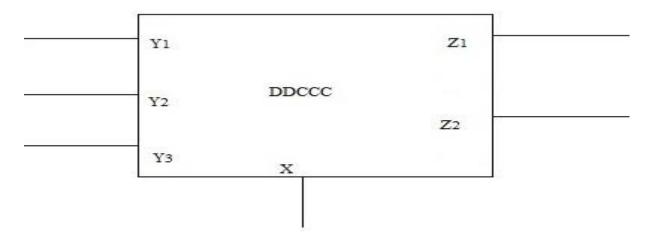

| 1     | Various Structures generated by Proposed Configration | 48   |

## **INTRODUCTION**

The prime requirements in today's microelectronics technologies are low supply voltages and low power consumption [1]. In addition to the above demands, there are other factors which are needed to be fulfilled in some applications, among them speed of signal processing is the first and efficiency or accuracy with which signal is proceesed is second factor. But fulfillment of above all conditions simultaneously is problematic. So from the last two decades, there are various applications which are now using the new technique for the analog signal proceesing called as current mode [2] which has features of both low power consumption and high speed. Earlier technologies made use of voltage mode which has some demerits as compared to the current mode.

#### **1.1 COMPARISON OF CURRENT MODE AND VOLTAGE MODE**

When voltage mode and current mode are compared, it is found that current mode has many advantages over voltage mode. First one is higher bandwidth and better signal linearity. Lower power consumption in current mode circuits constitute the second advantage. Also current mode circuits are designed for low voltage swings such that smaller supply voltage can be used. In the past, voltage mode were used in almost every applications, but now, with the development of current mode applications, there is third type of mode known as mixed mode was introduced, which can be used where there is requirement of interfacing between different sub blocks which are working in different modes [3]. Other than that, new circuits are developing for the processing of both analog and digital circuits which employs higher accuracy devices like current mirror, current copier and switched current filter. So the effect of these devices can only be calculated if system is working in current mode.

Higher slew rate and better accuracy is another merit of current mode . Also current mode circuits are not effected by noise and loop resistance which are present in long wire runs and

faulty connections. The only type of noise that can be present is electromagnetically induced noise which can be eliminated by employing shielded twisted pairs. Last but not the least, current-mode circuits does not need high voltage gain and high precision passive components, so they can be designed almost entirely with transistors. The only advantage of voltage mode signals over current mode signals is that they interface directly with D/A and A/D converters and analog multiplexing devices. So from above discussion it is clear that using current mode is more profitable and accurate choice over the voltage mode[3].

#### **1.2 CURRENT CONVEYOR :**

Current mode circuits proved to be more advantageous than voltage mode circuits which lead to vast development of various types of current mode building blocks . The current conveyor (CCII) is one among such blocks which has received significant attention. It is hybrid block and has basic construction containing a voltage follower interconnected with either current mirror or current follower. Current conveyors were introduced in the late sixties or early seventies by Smith and Sedra[5]. They were considered to be used not only as current sources, impedance converters and inverters, etc., but also as function generators, amplifiers, filters, etc., in current processing circuits in instrumentation and measurement applications.

In the initial years of its development , the performance of current conveyors was limited , as technologies available at that time are inflexible and did not allow well-matched devices on fabricated chips. But as the technology begin to progress , the current conveyors attracted the attention of analog designers ,which makes it very useful building blocks of analog electronics in today's technology. They are parts of a number of very often used circuits, like active filters, current feedback operational amplifiers, voltage and current operational amplifiers among others and their main application areas are in high-speed, high-frequency circuits for both voltage and current signal processing[6]. Current Conveyors represent the emerging class of high performance analog circuit design based on current-mode approach. They have simple structure, wide bandwidth and capability to operate at low voltages.

#### **<u>1.2.1</u> ADVANTAGES :**

Current conveyors are unity gain active elements exhibiting higher linearity, wider dynamic range and better high frequency performance.

Current conveyor has greater range of operating frequency which implies that higher voltage gain can be achieved at higher frequency also unlike OP-AMP which provide higher gain only at mid frequencies due to parasitic capictances at higher frequencies. So current conveyor has higher gain bandwidth product as compared to OP-AMP. If the comparison of its performance is done with the other active element like conventional bipolar operational transconductance amplifier (OTA), it is found that, the transconductance of the CCCII will be much higher than that of the bipolar OTA [3].

Then after the improvement in Current conveyor devices represented by CCI, CCII & CCIII , there is another type of current conveyor was introduced, which has the tuning capability such that parameters of current conveyor block can be tuned according to the bias current  $I_0$  [8-9], those current conveyor are called current controlled conveyor II (CCCII). The only difference between normal current conveyor and current controlled conveyor is that, the later will have the biasing current which is used to modify the parameters of current conveyor such as parasitic resistance. Now with that device multiple filters can be designed by cascading CCCII A device which is just the extension of CCCII is introduced ,which is called MO-CCCII stands for multiple output current controlled conveyor , which can be used for realization of multiple filter simultaneously.

MO-CCCII is same as CCCII but only difference is that , it has more than one output terminal unlike simple current controlled conveyor which has only one output terminal .Having multiple output has its benefits , that is , multiple output can be used for cascading one MO-CCCII with another , both feed forward and feedback at the same time which helps in realization of multiple filters simultaneously and if there is any modification required in feedback network for realization of different structure, it can be easily done without effecting the feed forward network . Input can be applied in form of both voltage and current , and there is common output which constitutes the connection from all the cascaded MO-CCCII .The node voltage and terminal currents at various points can be evaluated . Different node will have different transfer functions with respect to the input applied, which provides different filter expression simultaneously at every node , so that different filters can be realized at the same time . The detailed description of MO-CCCII are given in chapter 3.

#### **1.3 OBJECTIVE :**

The circuit was proposed cascading three MO-CCCII and two grounded capacitances and general expression for current gain was calculated for the 12 possible structure in the reference[8]. So extension of the proposed circuit is the main aim of the thesis, which includes

1. Calculation of generalized expression of transresistance i.e ratio of node voltages to the applied input current, at every node and verifying the derived expression on some structures(structure explained in chapter 3 in detail) by putting the values of different coefficients in the expression (coefficients explained in chapter 4 in detail) and verifying the results using PSPICE simulation for valid filter expression .

2. Calculation of generalized expression of transconductance i.e ratio of  $I_{OUT}$  to the applied input voltages, by applying the input in the form of voltage, at  $2^{ND}$  and  $3^{RD}$  MO-CCCII block and removing the main input node of 1st MO-CCCII. Then in the derived expression, different coefficients, whose value are structure dependent, are applied and checked for various valid filter expression and the result so obtained are verified using PSPICE simulation.

3. Calculation of generalized expression of transfer fuction in the form of V/V ratio i.e ratio of node voltages to the applied input voltages . The input voltages are applied at grounded terminal of  $2^{nd}$  and  $3^{rd}$  MO-CCCII block .The derived expression is applied on some structure and results are verified using PSPICE simulation

#### **1.4 ORGANIZATION OF THESIS :**

The thesis is organized as follows

**Chapter 2:** Literature survey of development of current conveyor including their history is described . The summary of different blocks of current conveyor and its derivatives including

current controlled conveyor (CCCII) which is used as basic active block for thesis , is introduced .

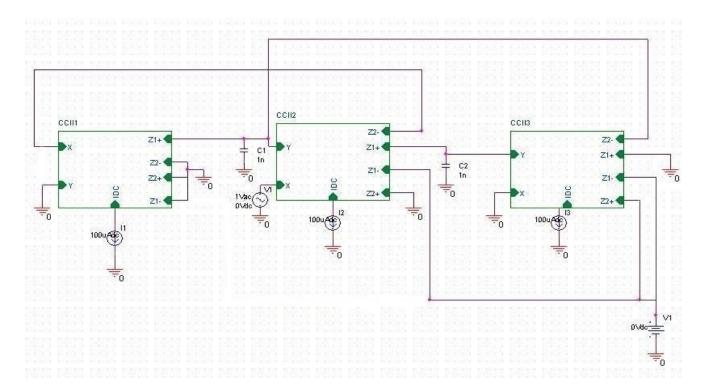

**Chapter 3:** This chapter describes the current controlled conveyor II in more detail with its internal circuit . Furthermore extension of CCCII , multiple output CCCII ( MO—CCCII), is explained in detail with its equations and internal circuit . Different structures possible(as proposed in reference[8]) with feedback and feed forward network of cascaded MO-CCCII is described in brief . The defining equations of basic block of MO-CCCII are verified using schematic Ppsice .

**Chapter 4:** In this chapter the generalized expression of transresistance for circuit proposed in [8] has been derived .In the reference [8], transfer fuction in the form of ratio of  $I_{OUT}$  to  $I_{IN}$  is calculated. In this chapter node voltages are considered. Furthermore different coefficient which are deciding factor in the realization of various filter are explained in detail. The derived generalized expression is verified on some structures of cascaded MO-CCCII using schematic Pspice.

**Chapter 5**: In this chapter generalized expression of transconductance i.e ratio of  $I_{OUT}$  to the applied input voltage, has been derived. The results are verified on structures of cascaded MO-CCCII using Pspice.

**Chapter 6**: In this chapter generalized expression of transfer function in the form of V/V ratio is derived . The results are verified on some structures of presented circuit using PSPICE simulation.

**Chapter 7:** In this section conclusion of the thesis work and future scope of the work are presented.

#### REFERENCES

[1] Giuseppe Ferri & Nicola C.Guerrini "Low Voltage Low power CMOS current conveyors" *Kluwer academic publishers*, 2003.

[2] Tommazau, C., Lindgey, F.J., Haigh, D.G "Analogue IC design : The current mode approach ". *IEEE Circuits and systems series 2. Peter Peregrinus Ltd.*, 1990.

[3] Nikhita Tripathi, Nikhil Saxena, Sonal Soni : Design of an Amplifier through Second Generation Current Conveyor ; *International Journal of Engineering Trends and Technology* (*IJETT*) - *Volume4 Issue5- May 2013*

[4] GUPTA, S.S., SENANI, R. Comments on "CMOS Differential difference current conveyors and their applications", *IEE Proc. Circuits*, *Devices and Systems*, *vol* 148, p. 335-336, 2001.

[5] K. C. Smith and A. Sedra, "The current conveyor-A new circuit building block," *Proc. IEE* (*Letters*), vol. 56, pp. 136B-1369A, August 1968.

[6] Ahmed M. Soliman "Current-Mode Universal Filters Using Current Conveyors: Classification and review". *Circuits, Systems & Signal Processing June 2008, Volume 27, Issue 3, pp 405-427 SPRINGER link*

[7] Pandey, N., Paul, A. and Jain, S. B ; A new electronically tunable current mode universal filter using MO-CCCII ; *Analog Integrated Circuits and Signal Processing February* 2009, *Volume 58, Issue 2, pp 171-178 Springer Link.*

[8] Pandey, N., Paul, A. and Jain, S. B : Systematic generation and design of multiple loop feedback current controlled conveyor – grounded capacitor filter . *Journal of Active & Passive Electronic Devices; october 2012, Vol. 7 Issue 4, p271*.

[9] Fabre, A., Saaid, O., Wiest F., and Boucheron, C.: High frequency applications based on a new current controlled conveyor. *IEEE Transactions on Circuit Systems-I* 43 (1996), 82 - 91.

### **CURRENT MODE BUILDING BLOCKS**

This chapter represents the literature survey of development of current conveyor from three decades . The hierarchy of current conveyor development are used in describing the application of the reference circuit . Various types of current conveyor building blocks are also discussed which includes current controlled conveyor II (CCCII) which is main active block of thesis..

#### 2.1 INTRODUCTION

The growth of analog IC design has been delayed by the process technologies that are mostly optimized for digital applications only. With the evolution of submicron technologies such as .18 micron and .13 micron , the supply voltage has been reduced to 3.3 volts and lower . This makes it difficult to design a voltage mode CMOS circuits with high linearity and wide dynamic range . Recently , current mode circuits have become viable alternative for future applications because of their inherit advantages over voltage mode circuits.

The main advantage of using the current mode technologies is because of the non linear characteristic exhibited by most field effect transistor. A small change in the input or controlling voltage results in the much larger change in the output current. Thus for a fixed supply voltage , the dynamic range of current mode circuit is much larger than that of a voltage circuit. If voltage supply voltage is lowered , one can still get the required signals represented by the current.

A second advantage of the current mode circuit is that they are much faster as compared to voltage mode circuits. The parasitic capacitances present in the analog circuits must be charged and discharged with the changing voltage levels. In the current mode circuits, a change in the current level is not necessary accompanied by a change in the voltage level.Hence, the parasitic capacitances will not effect the operating speed of the circuit by a significant amount. Other advantage of using the current mode circuits are that they do not require specially processed capacitances or resisitors, they are more compatible with digital CMOS technology making integration of mixed signal circuits more feasible.

#### 2.2 CURRENT CONVEYOR :

The current conveyor (CCII) is one among such blocks which has received significant attention. It is hybrid block and has basic construction containing a voltage follower interconnected with either current mirror or current follower. It is basic building block of a number of applications in current mode , voltage mode and the mixed mode. The principle of the current conveyor of the first generation was published by K.C Smith and A . S Sedra[2] .Two years later , today 's widely used second generation CCII was described and in 1995 , third generation CCIII was introduced[3] . However , initially , during that time , the current conveyor did not find many applications because its advantages as compared to the classical operational amplifier (OP AMP) and were not widely appreciated. An IC current conveyor , namely PA630 , was introduced by Wadsworth in 1989 ( mass produced by Phototronics Ltd . of Canada ) and about the same time the now well known AD844 ( operational trans impedance amplifier or more popularly known as current feedback opamp) was recognised to be internally as CCII+ followed by the voltage follower[4] .

An excellent review of state of art of current mode circuits prior to the 1990 was provided by the Wilson[5]. Today, the current conveyor is considered a universal building block with wide spread applications in the current mode , voltage mode and mixed mode signal processing. It features most of the applications in the current mode , when it so called voltage input voltage y is grounded and the current , flowing into the low impedance input x , is copied by simple current mirror into the z output. Since 1995 in particular , many successive modifications have been witnessed and generalisation of basic principle of CCII in order to use this circuit element more efficiently in various applications .

#### 2.2.1 FIRST CURRENT CONVEYOR (CCI):

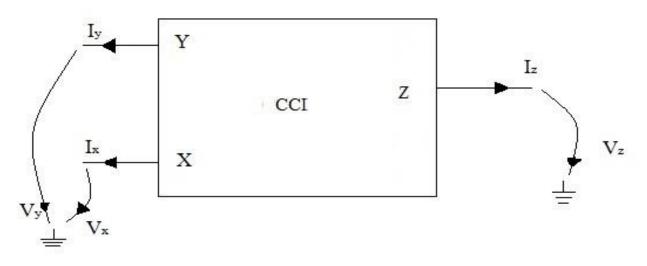

The current conveyor as initially introduced, is a 3-port device whose black box representation is as shown in fig 2.1.

Fig 2.1 Basic block diagram of CCI

The operation of this device is such that if voltage is applied to the terminal Y, an equal potential will appear on the terminal X. In a similar manner, if an input current is forced into terminal X will result into an equal amount of current flowing into terminal Y. Also the same current I will be conveyed to the output terminal Z such that terminal Z has the characteristic of a current source of value I, with high output impedance[2].

As it can be seen, the potential of X being set up by that of terminal Y, is independent of current being forced into port X. Similarly, the current through input Y, being fixed by that of X, is independent of the voltage applied at Y. Thus, the device exhibits a virtual short circuit input characteristic at port X and dual virtual open circuited input characteristic at port Y.

Mathematically, the input – output characteristic of CCI can be described by the following equation

$$I_{Y} = 0$$

$$V_{X} = V_{Y}$$

$$I_{Z} = \pm I_{X}$$

eq. (2.1)

Where the variables represents total instantaneous quantities. The + sign applies for the CCI in which both  $I_Z$  and  $I_X$  flow into the conveyor and it is denoted by CCI+. The - sign applies for the opposite polarity case denoted by CCI-. To visualize the interaction of the port voltages and currents described by the above matrix equations the nullator-norator representation as shown in fig 2.2.

Fig 2.2 Nullator - Norator representation of CCI

In the figure 2.2 shown on the previous page, single ellipse is used to represent the nullator element and two intersecting ellipses to represent the norator element. The nullator element has constitutive equation V = 0 and I = 0 whereas the norator has an arbitrary current voltage relationship. Clearly the nullator element is used to represents the virtual short circuit apparent between the X and Y terminal. Also included in the circuit are two dependent current sources. These are used to convey the current at port X to port Y and Z.

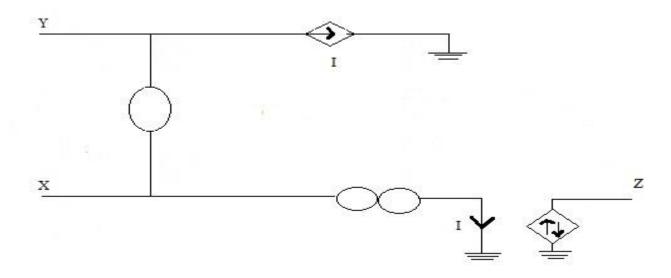

#### 2.2.2 NEGATIVE IMPEDANCE CONVERTER :

An early application of CCI was its use as a negative impedance converter (NIC). For this application terminal Z is grounded and the resistor is to be converted , is connected either between X and ground or between Y and ground . If resistor R is connected between X and ground , then looking into Y one sees a resistance –R that is short circuit stable[6]. Alternatively if R is connected between Y and ground then the input resistance at X is -R and is open circuit stable.

# Fig 2.3 CCI implementation of Negative Impedance Converter(NIC) with -R at terminal Y

Fig 2.4 CCI implementation of Negative Impedance Converter( NIC) with –R at terminal X

The major problem that hindered the fabrication of the CCI in IC form in the 1960s is its use of high quality PNP devices. Since complimentary devices are available in CMOS technology, it is easy to fabricate a CMOS current conveyor

#### 2.2.3 THE SECOND GENERATION CURRENT CONVEYOR (CCII):

To increase the versatility of current conveyor, a second version of current conveyor was introduced in which no current flows in terminal Y. The CCII is three-terminal devices with the terminals designated X, Y and Z. The potential at X equals whatever voltage is applied to Y. Whatever current flows into X is mirrored at Z with a high output impedance. No current flows through terminal Y. The block diagram of CCII is shown in Fig 2.5.

The ideal CCII can be seen as an ideal transistor, with perfected characteristics. No current flows into the gate which is represented by Y. There is no gate-source voltage drop, so the source voltage (at X) follows the voltage at Y. The gate has infinite input impedance (Y), while the source has zero input impedance (X). Any current out of the source (X) is reflected at the drain (Z) as a current in, but with infinite output impedance. Because of this reversal of sense between X and Z currents, this ideal field-effect transistor represents a CCII–[3]. If current

flowing out of X resulted in the same high-impedance current flowing out of Z, it would be a CCII+.

Fig 2.5 Block diagram of CCII

The relationship[3] between three terminals is defined as below:

$$I_y = 0$$

$$V_x = V_y \qquad \qquad \mbox{eq. (2.2)}$$

$$I_z = \pm I_x$$

The <u>+</u> sign indicates the  $I_x$  and  $I_z$  are in same direction or opposite.

According to above equations, as it is known that an ideal CCII is a combination of a voltage follower and a current follower. The voltage follower between Y and X terminals and the current follower between X and Z terminals. An ideal voltage follower has infinite input impedance and zero output impedance, and an ideal current follower has zero input impedance and infinite output impedance. In terms of nullator the port behavior of second generation current conveyor (positive or negative) can be depicted as in fig 2.6.

Fig 2.6 Nullator - Norator representation of CCII

The similarity and difference between CCI and CCII are clearly evident from their equivalent circuit. In the case of CCII-, the dependent current source is redundant, current flowing into terminal X must flow out of terminal Z. Hence the equivalent circuit of CCII- can be represented with single nullator element as shown in fig 2.7

Fig 2.7 A Simplified representation of CCII-

The first widely recognized applications of CCII were in the realization of controlled sources , impedance converters , impedance inverters , gyrators and various computation devices.

#### 2.2.4 THE THIRD GENERATION CURRENT CONVEYOR (CCIII):

This structure was published by Fabre in 1995. Structurally it is quiet similar to CCI with the exception that the current in port X and Y flow in the opposite direction. It is represented by push pull topology built from four simple CCIs. Its main application is current measurement[4].

Utilizing the same block diagram representation, CCIII is represented by

$$I_{y} = 0$$

$$V_{x} = V_{y}$$

eq. (2.3)

$$I_{z} = \pm I_{x}$$

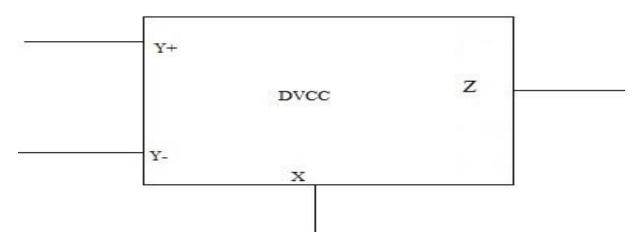

#### 2.3 <u>DIFFERENTIAL VOLTAGE CURRENT CONVEYOR (DVCC)</u>:

In this type of current conveyor, original input voltage is split into two pair of inputs Y+ and Y- [8]. There is another input terminal i.e X whose voltage is given by voltage difference of the voltages difference. This offers more freedom during the design of voltage and mixed mode applications[8]. The block diagram of DVCC is shown as below in fig 2.8.

Fig 2.8 Block diagram of DVCC [8]

Equations[8] satisfied by the above active block are

$$I_{Y+} = I_{Y-} = 0$$

$$V_X = V_{Y+} - V_{Y-}$$

eq. (2.4)

$$I_Z = I_X$$

#### 2.4 INVERTING CURRENT CONVEYOR II ( ICCII) :

In this current conveyor, the current at input terminal Y is zero and voltage at input terminal X and Y are equal but opposite in polarity. It is just the complementary type of current conveyor[9] whose block diagram is shown as fig 2.9

Equations[9] of above block can be represented as

$I_{\rm Y}=0$   $V_{\rm X}=-~V_{\rm Y}$  eq. (2.5)  $I_{\rm Z}=\pm I_{\rm X}$

#### 2.5 DIFFERENTIAL DIFFERENCE CURRENT CONVEYOR (DDCC) :

In this current conveyor, the input terminal is split into three terminal naming  $Y_{1,}Y_{2,}Y_{3}$  and input current at both the three terminal in zero[10]. There is another terminal X whose voltage is combination of three input terminal voltages of splited Y terminal.

Fig 2.10 Block diagram of DDCC[10]

Equation[10] of above block are

$I_{Y1} = I_{Y2} = I_{Y3} = 0$   $V_X = V_{Y1} - V_{Y2} + V_{Y3}$  eq. (2.6)  $I_Z = I_X$

## 2.6 <u>DIFFERENTIAL DIFFERENCE CURRENT CONTROLLED</u> <u>CONVEYOR (DDCCC) :</u>

This block is just extension of the previously described DDCC but only difference is just that , here, output terminal Z is also split into two terminal named as  $Z_1$  and  $Z_2[11]$  which is as shown in block diagram fig 2.11.

Fig 2.11 Block diagram of DDCCC [11]

Equations[11] representing the above blocks are

$$\begin{split} I_{Y1} &= I_{Y2} = I_{Y3} = 0 \\ V_X &= V_{Y1} - V_{Y2} + V_{Y3} + I_X \ R_X \qquad \qquad \text{eq. (2.7)} \\ I_{Z1} &= I_X \\ I_{Z2} &= - \ I_X \end{split}$$

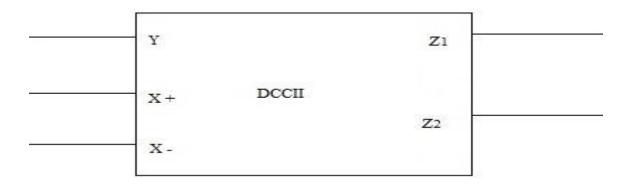

#### 2.7 DIFFERENTIAL CURRENT CONVEYOR II (DCCII) :

In this block of current conveyor[12], X input terminal is split into two terminal as  $X_+$  and X- and Z terminal as  $Z_1$  and  $Z_2$ , also in this current conveyor, the input terminal voltage at three terminal are equal and the output current at both terminal are equal but opposite in polarity and equivalent to the difference of current at terminal X+ and X-.

Fig 2.12 Block diagram of DCCII [12]

Equations[12] representing the above block are :

$I_{\rm Y}=0$   $V_{\rm X_{+}}=V_{\rm X_{-}}=V_{\rm Y}$  eq. (2.8)  $I_{\rm Z1}=-I_{\rm Z2}=I_{\rm X_{+}}-I_{\rm X_{-}}$

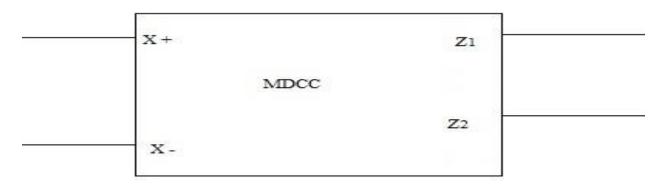

#### 2.8 MODIFIED DIFFERENTIAL CURRENT CONVEYOR (MDCC):

It is simplification of DCC on the assumption that signal voltage at terminal Y[12], is zero which implies that voltage at both the X terminal is also zero as the voltage is equal in three terminal i.e two terminal of X and one terminal of Y.

Fig 2.13 Block diagram of MDCC [12]

Equation[12] for the above defined block are :

$$V_{X+} = V_{X-} = V_Y = 0 \qquad \qquad \text{eq. (2.9)}$$

$$I_{Z1} = -I_{Z2} = I_{X+} - I_{X-}$$

#### 2.9 DUAL -X CURRENT CONVEYOR (DXCCII):

Dual –X current conveyor is proposed by Zeki and Toker[13]. It is combination of CCII and ICCII. Instead of single X terminal, DXCCII has two terminal  $X_P$  and  $X_N$  as outputs of non inverting and inverting unity gain amplifier with their inputs connected to y terminal[13]. Copies of  $X_P$  and  $X_N$  terminal currents are provided at  $Z_N$  and  $Z_P$  terminal[13]. The block diagram for above is as shown in fig 2.14

Fig 2.14 Block diagram of DXCCII [13]

Equation[13] representing the above block are :

$$I_{\rm Y}=0$$

$$V_{\rm XP}=-V_{\rm XN}=V_{\rm Y} \mbox{eq. (2.10)} \label{eq:XP}$$

$$I_{\rm ZP}=I_{\rm XP} \mbox{I}_{\rm ZN}=I_{\rm XN}$$

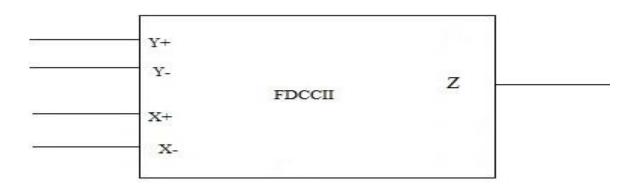

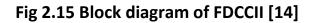

#### 2.10 FULLY DIFFERENTIAL CURRENT CONVEYOR II (FDCC II):

FDCC II is an important realization of the conventional CCII. The x, y, z terminal occurs here in pairs[14]. The basic circuit equation of CCII are now valid for differences of voltages or currents which corresponds to these pairs. It is thus designed for application with fully differential architecture for fast signal processing[15]. In this both X and Y terminal are splitted in two each which are shown as below in fig 2.15

Equation [14] for FDCC II are :

$$I_{Y\scriptscriptstyle +}=I_{Y\scriptscriptstyle -}=0$$

$$V_{X+} = V_{X-} = V_{Y+} - V_{Y-}$$

eq. (2.11)

$I_Z = \pm (I_{X+} - I_{X-})$

#### 2.11 OPERATIONAL FLOATING CONVEYOR (OFC) :

It is conveyor which is formed from joining of two current conveyor (CCII-)[16]. It is a universal differential input ,differential output building block enabling current and voltage and mixed mode applications[20]. In this voltage at both terminal X and Y are equal and current at Y terminal is zero[16], also the current at two output terminal W and Z are equal with opposite polarity which are shown as in fig 2.16

Fig 2.16 Block diagram of OFC [16]

Equations[20] are

$$I_{\rm Y}~=0$$

$$V_{\rm X}=V_{\rm Y}$$

eq. (2.12)

$$V_{\rm w}=Z_{\rm T}~I_{\rm X}$$

$$I_{\rm Z}=-~I_{\rm W}$$

#### 2.12 CURRENT GAIN CONVEYOR II (CGC):

This is another type of current conveyor which electronically control the parameters of applications .It has variable current gain  $I_Z/I_X$  [19]. The current conveyor of such type ,

concretely CCII- , was formerly manufactured by Elantec under the code EL2717[19] . The variable gain is implemented via transforming current  $I_Z$  into voltage by means of resistor and via back transformation of voltage into current by means of electronically gm controlled OTA. The most recent solution is characterized by digital control of the gain , utilizing the so called CDN[23] (current division network ) and DCCCF ( digitally controlled current follower). In this type of current conveyor current at terminal voltage Y is zero , voltage at two terminal X and Y are equal and most importantly the output current at terminal Z is current gain times the input current at terminal X [19]. Block diagram of above defined current conveyor is defined as follows in fig 2.17.

#### Fig 2.17 Block diagram of CGCII [17]

Equation [19] representing the above defined current conveyor are :

$I_{\rm Y}=0$   $V_{\rm X}=V_{\rm Y}\,,\ I_{\rm Z}=A\ I_{\rm X} \mbox{eq. (2.13)} \label{eq:VX}$

# 2.13 CURRENT CONTROLLED CONVEYOR II (CCCII) :

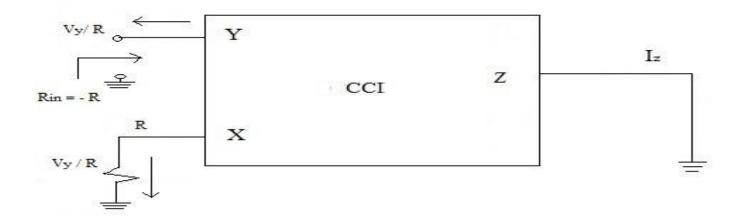

Current controlled conveyor was invented by Fabre in 1996, it was extension of earlier current conveyor, in which the input resistance can be altered using the biased current ( $I_0$ ) such that this current conveyor includes electronically tunable parameters and have high frequency range. In CCCII input impedance at terminal Y is very high such that no current flows through the terminal and at terminal X input impedance or value of parasitic resistance can adjustable according to the bias current so as value of resistance can be changed, so value of voltage at terminal X also indirectly depends on the biasing current[16] This can be shown , that this active device can be used in filters [18] whose parameters may be controlled electronically. Such a feature has been inherent in the so called  $g_mC$  filters i.e filters, compounded only of OTAs and capacitors. In this type of current controlled conveyor , current at Y terminal is zero[18] and current at output Z terminal is equal to  $\pm I_X$ . The CCCII based circuits doesnt require any external circuits, such that they can be used in the various analog applications, its property of electronic tunability can be used in the filters , CCCII based circuits can work in high frequency range operation. The basic block diagram of CCCII can be shown as below in fig 2.18

Fig 2.18 Basic block diagram of CCCII [21]

The defining equation for CCCII are

$$\begin{split} V_X \ &= \ V_Y + \ I_X |R_X(I_0)| \\ I_Y \ &= \ 0 \ , \ I_{Z-} = \ - \ I_X \ , \ I_{Z+} = \ I_X \ & \mbox{eq. (2.14)} \end{split}$$

Where  $R_X = \frac{V_T}{2I_0}$  is bias current dependence resistance ,  $V_T$  is thermal voltage,  $I_0$  is bias current of CCCII[23].

If non idealities is taken into the consideration the defining matrix for CCCII can be[23]

$$\begin{split} V_X &= \beta \; V_Y + \; I_X |R_X(I_0)| \\ I_Y &= \; 0 \;, \; I_{Z-} = - \; \alpha I_X \;, \; I_{Z+} = \; \alpha I_X \qquad \qquad \text{eq. (2.15)} \end{split}$$

where  $\alpha$  and  $\beta$  are respectively current and voltage gains which are all equal to unity in the ideal case. In practice, they can be expressed as  $\alpha = 1 - \varepsilon_i$ ,  $\beta = 1 - \varepsilon_V$  where  $|\varepsilon_i| <<1$  and  $|\varepsilon_v| <<1$ .  $\varepsilon_i$  denotes the current tracking error and  $\varepsilon_v$  denotes voltage tracking error[3]. The current controlled current conveyor (CCCII) exhibits the features of the CCII plus the controllability. It has been realized in different technologies, BJT, CMOS, and BICMOS[23]. The internal circuitry of CCCII can be shown with two input terminal i.e. X and Y and one output terminal Z using the CMOS can be shown as in fig 2.18 [21].

Fig 2.19 Internal Circuit of CCCII[18]

## 2.13.1 <u>OPERATION :</u>

The circuit in Fig 2.18 consists of one mixed trans-linear loop(transistors M1 to M4) as input cell. Two current mirrors (transistors M5, M7 and M10, M11) allow the mixed loop to be dc biased by the current I<sub>0</sub>, the input cell present a high input impedance input port (Y) and a low impedance output port(X)[25]. This cell act as a voltage follower. The output Z that copies the current flowing through port X is realized in the conventional manner using two complementary mirror . A current controlled conveyor with negative current transfer (CCCII-) will be obtained easily, by only adding two cross coupled current mirrors in order to reverse the sign of the current through  $i_z$ [25]. Now it can be said that the current controlled conveyor (CCCII) is a translinear CCII to which the possibility of changing the value of the DC bias current Io will increase the additional properties. All the other characteristics of the CCIIs are preserved. The above discussed CCCII have two input terminal and one output terminal, such that, it

applications can be extended if it is modified to the multiple output current controlled conveyor or MO-CCCII which is discussed in next chapter in detail .

# REFERENCES

[1] H.Wupper and K. Meerkotter, "New active filter synthesis based on scattering parameters", *IEEE Trans. CAS*, 22, 594-602, 1975

[2] SMITH, K.C., SEDRA, A. "The current conveyor : A new circuit building block ". *IEEE Proc. CAS*, vol. 56, no. 3, p. 1368-1369, 1968.

[3] SEDRA, A.S, SMITH, K.C "Second generation current conveyor and its application ". *IEEE Trans.*, CT-17, p. 132-134, 1970

[4] FABRE, A. "Third generation current conveyor : A new helpful active element ", *Electron*. *Lett.*, *vol 31*, *no. 5*, *p. 338-339*, *1995*.

[5] WILSON, B. "Recent developments in current conveyors and current mode circuits ". *IEEE Proc. G, vol. 132, p. 63-76, 1990*

[6] Giuseppe Ferri & Nicola C.Guerrini "Low Voltage Low power CMOS current conveyors" *Kluwer academic publishers*, 2003.

[7] IKEDA, K., TOMITA, Y,"Realization of current mode bi quadratic filter using CCIIs with current followers" *Electron*. *Commun. Jpn. Pt.2, Electron.,vol.* 71, no. 5, p. 809-815, 1991.

[8] ELWAN, H.O, SOLIMAN, A.M, "Novel CMOS differential voltage current conveyor and its application". *IEEE Proceedings : Circuits , devices and systems , vol. 144 , no. 3 , p. 195-200 , 1997.*

[9] AWAD , I.A. , SOLIMON , A.M . "Inverting second generation current conveyor : The missing building blocks" , CMOS realization and applications . *International Journal of Electronics* , vol. 86 , no.4 , p. 413-432 , 1999.

[10] CHIU, W., LIU, S.I., TSAO, H.W., CHEN, J.J. "CMOS differential difference current conveyors and their applications", *IEE Proc.*, *Circuits*, *Devices and Systems*, 1996, vol. 143, no. 2, p. 91-96.

[11] GUPTA, S.S., SENANI, R. Comments on "CMOS Differential difference current conveyors and their applications", *IEE Proc. Circuits*, *Devices and Systems*, *vol* 148, p. 335-336, 2001.

[12] ELWAN, H.O ,SOLIMAN, A.M, "CMOS differential current conveyor and its applications for analog VLSI" *Analog Integrated Circuits and Signal Processing*, vol. 11, p. 35-45, 1996

[13] ZEKI, A., TOKER, A. "The dual –X current conveyor (DXCCII) : A new active device for tunable continuos time filters", *Int J Electron*, *vol.* 89, *p.* 913-923, 2002.

[14] SOLOMON, A.M "New fully-differential CMOS second generation current conveyor". *ETRI Journal*, vol. 28, p. 495-501, 2006.

[15] HWANG, Y.S., LIN,J-F., WU,H-Y,CHEN,J-J. "A new FBCCII based pipelined ADC".In *conference on innovative applications of system prototyping and circuit design*. *Taiwan*, p. 16, 2007.

[16] FABRE, A., SAAID, O., WIEST, F., BOUCHERON, C. "Current controlled band pass filter based on translinear conveyor". *Electron. Lett., Circuits Syst. I, vol. 31, no.20*, p. 1727-1728,1995

[17] EL2082-CURRENT MODE MULTIPLIER

*http://www.datasheet4u.com/html/E/L/2/EL2082\_ElantecSemiconductor.pdf.html* [17] FABRE, [18] A., SAAID, O., WIEST, F., BOUCHERON, C. "High frequency applications based on new current controlled conveyor". *IEEE Trans, Circuits Syst. I, vol. 43, no.2 , p. 82-91,1996*

[19] BARTHELEMY, H. FABRE, A., "A second generation current controlled conveyor with negative intrinsic resistance". *IEEE Trans, Circuits Syst. I, vol. 49, no.1, p. 63-65,2002.*

[20] TOUMAZOU, C., PAYNE A. "OPERATIONAL FLOATING CONVEYOR". *ELECTRONICS LETTERS*, vol. 27, no. 8, p. 651-652, 1991.

[21] Shahram Minaei, Deniz Kaymak, Muhammed A. Ibrahim, Hakan Kuntman; New CMOS Configurations for Current-Controlled Conveyors (CCCIIs); *Circuits and Systems for Communications*, 2002. *Proceedings. ICCSC '02. IEEE International Conference*.

[22] Nikhita Tripathi, Nikhil Saxena, Sonal Soni: Design of an Amplifier through Second Generation Current Conveyor; International Journal of Engineering Trends and Technology (IJETT) - Volume4 Issue5- May 2013.

[23] Pandey, N., Paul, A. and Jain, S. B ; A new electronically tunable current mode universal filter using MO-CCCII ; Springer 2008.

[24] Ali toker, Ece Olcay Gunes, Serdar Ozoguz; New high-Q band-pass filter configuration using current controlled current conveyor based all-pass filters; *Electronics Circuits and Systems, 2001. ICECS 2001. The IEEE International Conference165 - 168 vol.1*.

[25] Fabre, A., Saaid, O., Wiest F., and Boucheron, C.: High frequency applications based on a new current controlled conveyor. *IEEE Transactions on Circuit Systems-I* 43 (1996), 82 - 91.

# CHAPTER 3

# Multiple Output - Current Controlled Conveyor II (MO-CCCII)

This chapter describes the internal circuit of multiple output current controlled conveyor II (MO-CCCII). It uses additional current mirrors in CCCII to provide current terminals. The block diagram of MO-CCCII are verified through simulation. A generalized current mode filter is reviewed first , which is subsequently used for deriving the generalized expression for transresistance mode filters , transadmittance mode filters and voltage mode filters .

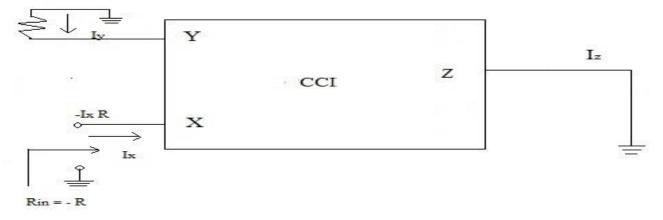

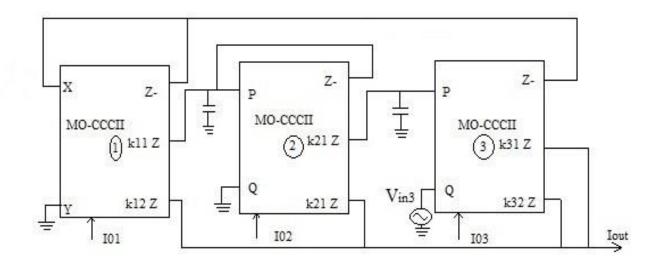

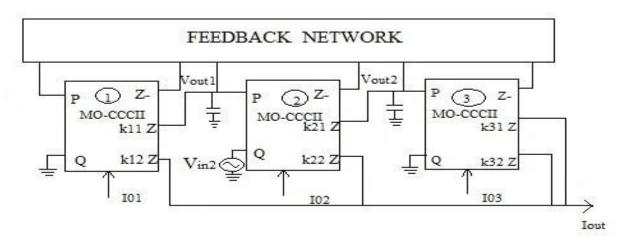

**3.1<u>THEORY</u>:** It is modified version of CCCII, as only difference between their block diagram is that MO-CCCII have multiple output i.e. two output terminal for Z+ and two output terminal for Z-, where sign represents the direction of the current. Sign positive stands for in the same direction of the current at terminal at X and negative sign means the direction of output current will be opposite to the direction of the current at terminal X. The MO-CCCII can be designed using CCCII by just employing the extra current mirrors. The advantage of having multiple output is that using the multiple ports, CCCII can be used for multi functionalities. Another beneficial of using MO-CCCII is that it helps in reducing the required number of current conveyor at the cost of a pair of transistor (current mirror). The block diagram of MO-CCCII is as shown in fig3.3.

# Fig 3.1 Basic block diagram of MO-CCCII [2]

It uses additional current output terminals for developing current feedback connected together for achieving useful filter function and makes structure more versatile and flexible. The filter exhibit low input impedance and also does not require any matching component criteria and current inversion for obtaining any filter response. The structure is also capable of generating all standard response of universal filters at high output impedance i.e low pass filter , band pass filter , high pass filter , notch and all pass[2]. The internal circuit of multiple output current controlled conveyor II (MO-CCCII) is as shown in fig 3.2.

Fig 3.2 Internal Circuit of MO-CCCII [2]

Port relationship of current conveyor shown in Fig 3.2 are

$$V_{X} = V_{Y} + I_{X} |R_{X}(I_{0})|$$

$$I_{Y} = 0, I_{Z\pm} = \pm I_{X}$$

## **3.2 ADVANTAGES:**

The MO-CCCII can be used for number of applications, when used as single block or when it is cascaded and there are multiple filters that can be generated, also it has many advantages over other current mode single input single output (SISO) structure[6].

First one is, when more than one MO-CCCII is realized by cascading them, so as to realize universal filters i.e low pass, high pass, band pass, notch filter, less number of current conveyor are required as compared to other multiple filter circuit generator. Secondly it uses grounded capacitor which allows absorption of parasitic capacitance[7] and also helps in minimizing chip area ,making the structure suitable for monolithic integration . Third advantage is, its verstality, as there is no or very little modification required for the realization of multiple filter fuction[8]. Fourth one is it got advantages of electronic tunability which are required in many applications such that filter coefficients can be tuned according to the demand, such that, it increase its adaptability ,also there are many structure which uses different type of current conveyors for achieving tunability ,some being variable gain CCIIs and rest being CCIIs which is not considered good for integrated circuit layout viewpoint but in this system only one type of current conveyor are used .Last but not the least , is it exhibits low active and passive sensitivities[7]. It is clear from above discussion that, MO-CCCII structure has many advantages and can be used for realization of filters, for which, more than one MO-CCCII are required and they should be cascaded so as to get multiple output at different node in the form of current or voltages

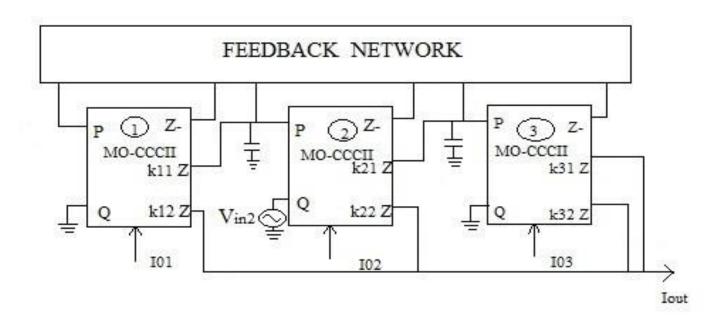

#### **3.3 MULTIPLE LOOP FEEDBACK CURRENT MODE FILTER STRUCTURE:**

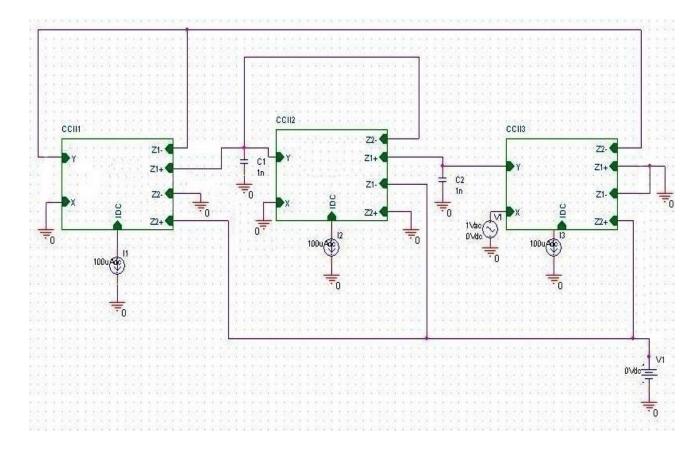

The structure of multiple loop feedback current mode filter which employs three MO-CCCII and two grounded capacitors was proposed in [7]. The MO-CCCII blocks in the structure are cascaded by both feed forward and feedback network simultaneously such that their structure can be changed by modifying the feedback network. Feedback is defined by feedback coefficients. Therefore a new generalized circuit was proposed in [7], which can be used for deriving the generalized expression for transresistance mode filters, transadmittance mode filters and voltage mode filters. A brief review is presented in the following subsection. The block diagram of discussed structure is shown in fig 3.3.

Fig3.3 Multiple loop feedback current mode filter structure[7]

Each block will satisfy the port relationship given below as

$$\begin{split} v_{X} &= v_{Y} + i_{X} |R_{Xi}(I_{0i})| \\ i_{Y} &= 0 \;,\; i_{Z} = \text{-}\; i_{X} \;,\; i_{K_{11}} = \; k_{i1} i_{X} \;,\; i_{k_{12}} = \; k_{i2} i_{X} \end{split}$$

where  $k_{i1}$  and  $k_{i2}=\pm 1$  and i=1, 2, 3 depending upon the number of block.  $R_{Xi} = \frac{V_T}{2I_{0i}}$  is bias current dependence resistance,  $V_T$  is thermal voltage,  $I_{0i}$  is bias current of i<sup>th</sup> MO-CCCII.

Apart from above port relationship, the above proposed structure will satisfy three feed forward equations also and depending on these three equations, different filters are realized by changing the value of different coefficients which will be defined in detail in next chapter.So three feed forward equation[7] are

$$i_i + i_{fl} = a_1 i_{xl}$$

(1)

$$k_{11}i_{x1} + sC_2V_{P2}(i = 2) + a_2i_{x2} = i_{f2}$$

(2)

$$k_{21}i_{x2} + sC_3V_{P3}(i=3) + a_3i_{x3} = i_{f3}$$

(3)

also there is one equation for node voltage also which is satisfied when either of terminal X or Y is grounded

$$V_{pi} = b_i i_{xi} R_{xi}$$

It is derived from equation

$$V_{X} = V_{Y} + i_{X} |R_{Xi}(I_{0i})|$$

Where  $f_{ij}$  is the current feedback coefficient from output of j<sup>th</sup> MO-CCCII to the input of i<sup>th</sup> MO-CCCII such that the value of  $f_{ij}$  can have zero or unity depending upon whether there is open circuited or direct feedback connection between i<sup>th</sup> and j<sup>th</sup> MOCCCII. It may be noted that  $f_{21} = f_{31} = f_{32} = 0$ , being non – feedback coefficients[7].

Notation  $a_i$  represents whether the current is flowing into the input of MO-CCCII or not So its value can be 0 or 1, zero if the input is Y terminal and 1 if the input terminal is X

Notation  $b_i$  can be either 1 or -1 depending on whether the input is connected to the X terminal or Y terminal which can be found out by the value of  $a_i$ .So if the value of  $a_i = 1$  means input is connected to terminal X and  $b_i = 1$  if  $a_i = 0$  then input to the MO-CCCII is connected to Y terminal means  $b_i = -1[7]$ .

Now by using the above three equations different structure can be formed, 12 such structures are possible and for each structure depending on the value of  $a_2$  and  $a_3$ , four different topologies are possible so total 48 expressions are possible. and then further taking different value of coefficient k, many filters expression are possible.

The transfer fuction of above structure in form of current gain can be expressed by[7]

$$\frac{I_{OUT}}{i_{in}} = -\frac{N(s)}{D(s)}$$

(1)

Where

$$\begin{split} N(s) &= k_{12}[(f_{33} - a_3 - b_3 \ sC_3R_{x3}) \ (f_{22} - a_2 - b_2sC_2R_{x3}) + f_{23}k_{21}] + k_{11}k_{22}(f_{33} - a_3 - b_3 \ sC_3R_{x3}) + k_{12}k_{21}(k_{31} + k_{32}) \\ D(s) &= (f_{11} - a_1)[(f_{33} - a_3 - b_3 \ sC_3R_{x3}) \ (f_{22} - a_2 - b_2sC_2R_{x3}) + f_{23}k_{21}] \\ &+ f_{12} \ k_{11}(f_{33} - a_3 - b_3 \ sC_3R_{x3}) \ + \ f_{13} \ k_{11}k_{21} \end{split}$$

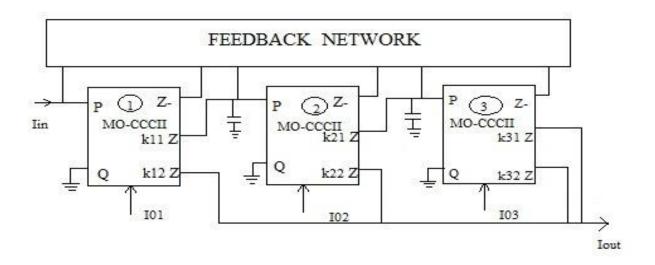

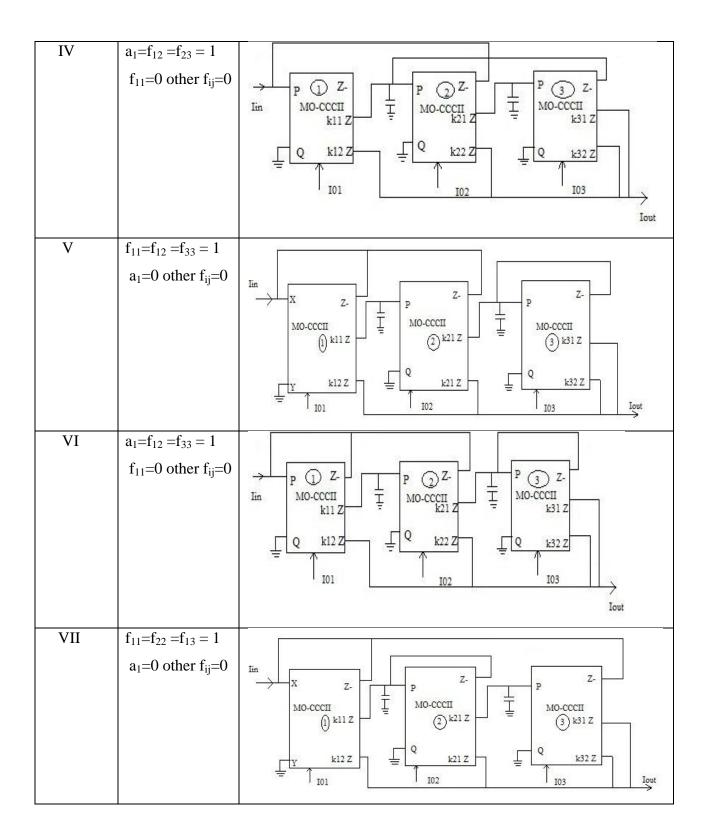

So that by putting value of coefficients  $f_{ij}$ ,  $a_i$ ,  $b_i$  and k, expression for different filters can be provided. The most important coefficients is feedback coefficient, which decides the feedback connection of the structure , also it should be noted that  $f_{11}$  and  $a_1$  cannot be simultaneously zero or 1 as it will reduce the first feed forward equation to zero . Value of  $f_{ij}$  can be found out by just observing the structure .So the 12 structure possible for the above multiple loop feedback current mode filter structure employing feedback and feed forward cascaded three MO-CCCII and two grounded capacitances shown in fig 3.3 which are taken from reference [7]. The below are the 12 structure possible , each structure having four possible topologies making it 48 structure in total are shown below with the structure number and condition on  $f_{ij}$  and  $a_1$  for each structure [7]

|           | Condition on $f_{ij}$                                                  | Schematic configration                                                                                                                                  |

|-----------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Structure | and a <sub>1</sub>                                                     |                                                                                                                                                         |

| Ι         | $a_1 = f_{12} = f_{13} = 1$<br>other $f_{ij} = 0$                      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                   |

| II        | $f_{11}=f_{12}=f_{13}=1$<br>$a_1=0$ other<br>$f_{ij}=0$                | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                   |

| III       | $f_{11}=f_{12}=f_{23}=1$<br>a <sub>1</sub> =0 other f <sub>ij</sub> =0 | $\begin{array}{c ccccc} & & & & & & \\ \hline & & & & & \\ Iin & & & MO-CCCII \\ & & & & I1Z \\ \hline & & & & & \\ \hline & & & & & \\ \hline & & & &$ |

# Table 1 Various Structures generated by Proposed Configration in[7]

| VIII | $a_1 = f_{22} = f_{13} = 1$                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | $f_{11}=0$ other $f_{ij}=0$                                    | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |