#### Dissertation

on

## Design of Ultra Low Voltage Low Noise Analog Front End for Bio-Potential Signals

submitted in partial fulfilment of the requirement for the award of the degree of

## **Master of Technology**

in

VLSI Design and Embedded System

Submitted by

Maheep Dwivedi University Roll No. 2K12/VLS/11

Under the Guidance of

Dr. Rajiv Kapoor Professor & Head, Department of Electronics and Communication Engineering Delhi Technological University

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

2012-2014

Electronics and Communication Engineering Department Delhi Technological University Delhi-110042 www.dce.edu

## **CERTIFICATE**

This is to certify that the dissertation titled "Design of Ultra Low Voltage Low Noise Analog Front End for Bio-Potential Signals" is a bonafide record of work done by Maheep Dwivedi, Roll No. 2K12/VLS/11 at Delhi Technological University for partial fulfilment of the requirements for the degree of Master of Technology in VLSI and Embedded System Design. This project was carried out under my supervision and has not been submitted elsewhere, either in part or full, for the award of any other degree or diploma to the best of my knowledge and belief.

Date: \_\_\_\_\_

Dr. Rajiv Kapoor Professor & Head Department of Electronics and Communication Engineering Delhi Technological University

## ACKNOWLEDGEMENTS

It would be a great pleasure to write a few words, which would although not suffice as the acknowledgement of this long cherished effort, but in the absence of which this report would necessarily be incomplete.

I would like to express deep gratitude towards Prof. Rajiv Kapoor (Head, Dept. of Electronics & Communication Engg. DTU, Delhi.). I take pride in availing our self of the opportunity to express our gratitude to my guide. He extended towards their valuable guidance, indispensable help and inspiration at times.in appreciation we offer him our sincere gratitude.

I am also highly indebted towards Prof. Ranjan Maheshwari (Director, National Institute of Electronics & IT, Aurangabad.) who expedited me throughout the project. I would like to thank Mr. Gaurav Agrawal (Research Scholar IIT Madras, Chennai) too. Without his key suggestion this project wouldn't have completed.

I would also like to acknowledge Delhi Technological University for providing the right academic resources and environment for this work to be carried out.

Last but not the least I would like to express sincere gratitude to my parents and my colleagues for constantly encouraging me during the completion of work.

Maheep Dwivedi University Roll no: 2K12/VLS/11 M.Tech (VLSI and Embedded System Design) Department of Electronics & Communication Engineering Delhi Technological University Delhi – 110042

## ABSTRACT

The information extracted from the bio-potential signals such as ECG, EEG, ECoG, ERG and ENG is extensively used for health care and medical treatment purposes. The use of bio-potential acquisition systems is not only limited to the hospitals but also extended to the homes for ubiquitous health care. Therefor the demand of portable bio-signal measurement system is increasing. The key constituent to this kind of systems is the analog front-end (AFE). The analog readout front-end extracts the bio-signals directly from human body through electrodes and defines the extracted signal quality.

The most critical block in an bio-potential acquisition system is the AFE as it is connected directly to the human body and the output this should be ready to feed the subsequent stages that are ADCs and DSPs. This block must operate under low power consumption with minimal added noise to ensure the better signal quality with enhanced battery life, when incorporated in portable bio-signal acquisition systems.

In this dissertation a novel multi-function Analog Front-End is proposed. This analog readout front end is oriented to be employed in flexible and portable bio-potential signal acquisition systems. The essential contribution of this work is the new Forward Body Biased Current Mode Amplifier (FBBCMA) based on convention forward body biased technique for low-voltage operation. The proposed FBBCMA achieves very low noise performance because of inherent properties of current mode topology. Forward body biasing of MOS devices further reduces the flicker noise that is a critical concern in circuits operating at low frequencies. Low power consumption and other advantages are achieved by the aid of the forward body biasing and current mode topology.

A complete analog readout front end is implemented and simulated using the standard TSMC 180nm parameters and P-Spice as simulator. This AFE consist of a pre amplifier followed by a band pass filter to enhance in band signals and reject the signals that are laying out of the band of interest. Tuneable bandwidth of AFE enables it to serve as the first stage in variety of bio-signal acquisition systems. The simulation results show that the designed circuits meet the basic requirements of the low power consumption under low noise operation for long time portable bio-potential recorders.

## TABLE OF CONTENTS

| CE | ERTIFICATE                                                                | i     |

|----|---------------------------------------------------------------------------|-------|

| AC | CKNOWLEDGEMENTS                                                           | ii    |

| AF | STRACT                                                                    | iii   |

| TA | ABLE OF CONTENTS                                                          | iv    |

| LI | ST OF FIGURES                                                             | vii   |

| 1. | INTRODUCTION                                                              | 1     |

|    | 1.1. Motivation                                                           | 1     |

|    | 1.2. Multi-Functional Bio-potential Analog Front Ends                     | 2     |

|    | 1.3. Bio-potential Signals                                                | 2     |

|    | 1.3.1. Electrocardiogram                                                  | 3     |

|    | 1.3.2. Electroencephalogram and Electrocorticogram                        | 6     |

|    | 1.3.3. Electroretinogram                                                  | 10    |

|    | 1.4. Objective and Scope of the Project                                   | 13    |

|    | 1.5. Organization of Thesis                                               | 13    |

| 2. | LOW VOLTAGE DESIGN TECHNIQUES FOR STANDARD                                | CMOS  |

|    | TECHNOLOGY                                                                | 15    |

|    | 2.1. Sub-Threshold MOS                                                    | 17    |

|    | 2.2. The Composite Transistor                                             | 19    |

|    | 2.3. The Lateral BJT                                                      | 19    |

|    | 2.4. Forward-Biased Bulk-Source                                           | 20    |

|    | 2.5. Bulk-Driven MOSFETs                                                  | 21    |

|    | 2.6. Limitations of circuits in strong-inversion working with low-voltage | power |

|    | supply                                                                    | 22    |

|    | 2.7. Voltage mode versus Current mode: A critical comparison              | 23    |

| 3. | FORWARD BODY-BIAS TECHNIQUE                                                | 26 |

|----|----------------------------------------------------------------------------|----|

|    | 3.1. Threshold Voltage of the MOSFET                                       | 27 |

|    | 3.2. Forward-Body Bias                                                     | 29 |

|    | 3.3. Noise of Forward Body-Bias MOSFETS                                    | 33 |

| 4. | DESIGN OF FORWARD BODY-BIASED CURRENT-MODE AMPLIFIER                       | 35 |

|    | 4.1. A Two-Stage CMOS Amplifier Topology                                   | 35 |

|    | 4.2. Low Voltage Current Mirror Design                                     | 36 |

|    | 4.3. Low Voltage Operational Amplifier Design                              | 39 |

|    | 4.3.1. Simulated Results                                                   | 45 |

|    | 4.4. Current Mode Amplifier Design Using FBB Op-Amp                        | 48 |

| 5. | NOISE ANALYSIS OF FBBCMA                                                   | 51 |

|    | 5.1. Thermal Noise                                                         | 51 |

|    | 5.2. Thermal noise in MOSFETs                                              | 52 |

|    | 5.3. Shot Noise                                                            | 52 |

|    | 5.4. Flicker Noise                                                         | 53 |

|    | 5.5. Noise in a Forward Body biased MOSFET                                 | 54 |

|    | 5.6. Noise Analysis of Proposed Forward Body Biased Current Mode Amplifier | 58 |

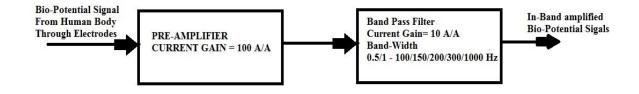

| 6. | AFE DESIGN USING FBBCMA                                                    | 62 |

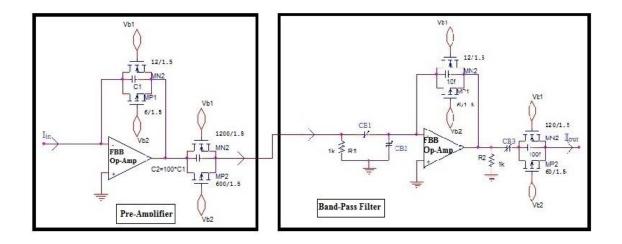

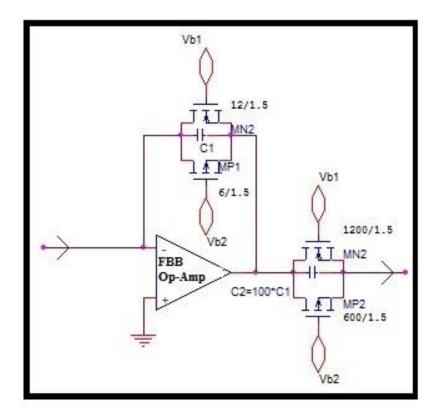

|    | 6.1. Pre-Amplifier                                                         | 63 |

|    | 6.2. Band-Pass Filter                                                      | 65 |

|    | 6.3. Frequency Responses of AFE                                            | 68 |

| 7. | CONCLUSION AND FUTURE WORK                                                 | 71 |

|    | 7.1. Conclusion                                                            | 71 |

|    | 7.2. Future Work                                                           | 72 |

|    | REFERENCES                                                                 | 73 |

|    | APPENDIX A                                                                 | 78 |

|    | APPENDIX B                                                                 | 80 |

## LIST OF FIGURES

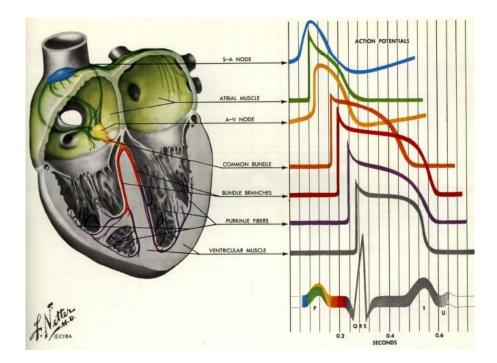

| Figure 1.1 | An ECG waveform is composed of action potentials originating in<br>different areas of the heart. The ECG waveform recorded at the skin is the<br>superposition of these different action potentials 5                                                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

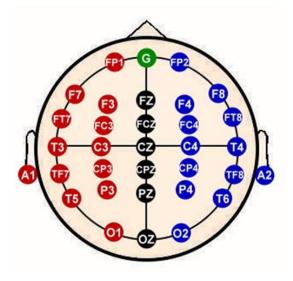

| Figure 1.2 | EEG electrode 10-20 system 8                                                                                                                                                                                                                                                                                                          |

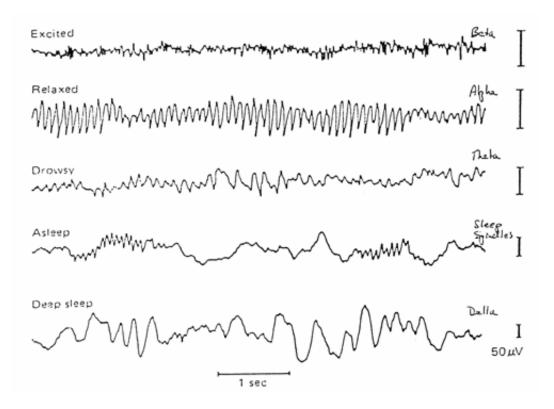

| Figure 1.3 | Various EEG traces 9                                                                                                                                                                                                                                                                                                                  |

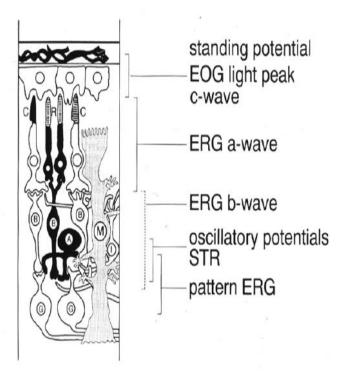

| Figure 1.4 | Simplified scheme of the human retina with the approximate sites of generation of electrophysiological signals 10                                                                                                                                                                                                                     |

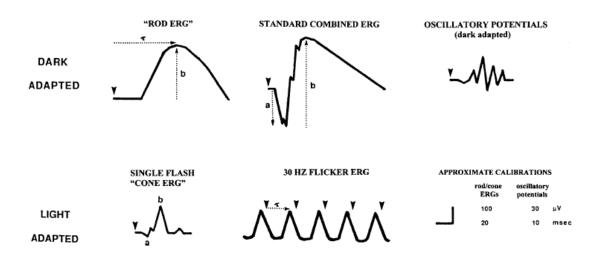

| Figure 1.5 | Diagram of the five basic ERGs defined by the Standard. These waveforms are exemplary only, and are not intended to indicate minimum, maximum or even average values. Large arrowheads indicate the stimulus flash. Dotted arrows exemplify how to measure time-to-peak (t, implicit time), as-wave amplitude and b-wave amplitude 11 |

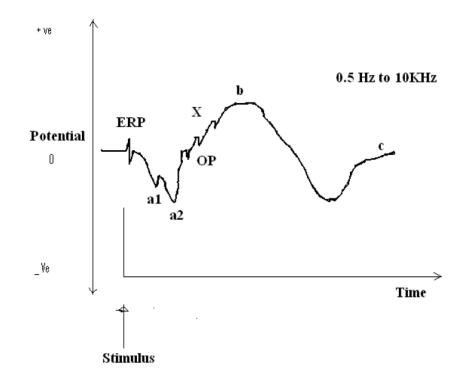

| Figure 1.6 | The Electoretinogram (ERG) Signal12                                                                                                                                                                                                                                                                                                   |

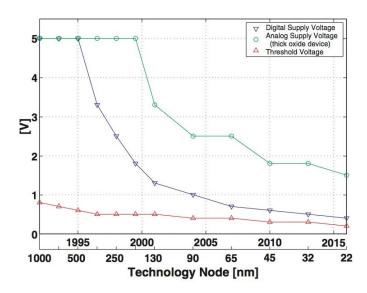

| Figure 2.1 | Supply voltage and threshold voltage of different technologies 15                                                                                                                                                                                                                                                                     |

| Figure 2.2 | Composite transistor 19                                                                                                                                                                                                                                                                                                               |

| Figure 2.3 | Cross-section of a NMOS transistor implemented in a p-well technology<br>and its symbol 20                                                                                                                                                                                                                                            |

| Figure 2.4 | Cross-section of forward bias NMOS transistor 21                                                                                                                                                                                                                                                                                      |

| Figure 2.5 | Cross-section of bulk-driven MOSFET 21                                                                                                                                                                                                                                                                                                |

| Figure 3.1 | CMOS inverter under (a) body-source short and (b) forward-body bias conditions. The VBS,N is the forward body-bias across the n-MOSFET and VSB,P is the forward body-bias across the p-MOSFET 26                                                                                                                                      |

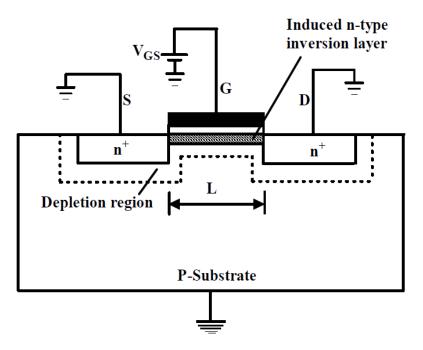

| Figure 3.2 | The cross-section of an n-MOS with positive gate voltage applied showing the depletion region and the inversion layer [1]. G is gate, D is drain and S is source 28                                                                                                                                                                   |

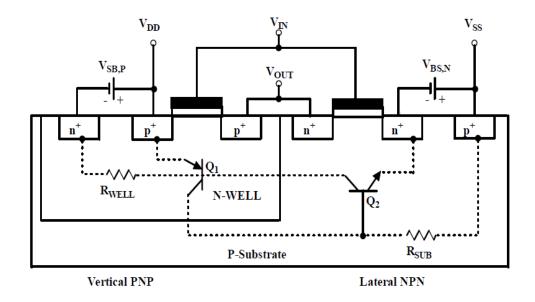

| Figure 3.3 | Vertical cross-section of an n-well CMOS showing parasitic bipolar<br>junction Transistors 30                                                                                                                                                                                                                                         |

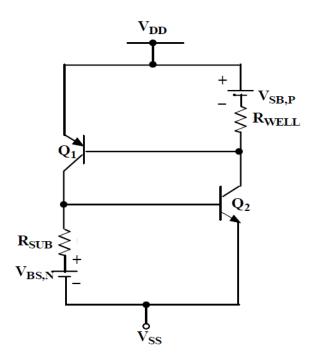

| Figure 3.4 | Extracted equivalent circuit of Figure 3.2 31                                                                                                                                                                                                                                                                                         |

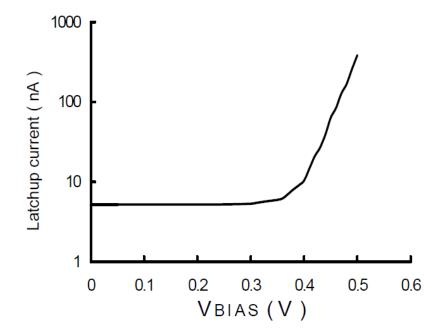

| Figure 3.5  | Latchup current under forward biased source-substrate condition for V <sub>DD</sub> =0.8V 31 |  |  |  |

|-------------|----------------------------------------------------------------------------------------------|--|--|--|

| Figure 3.6  | Current through forward biased source-substrate junction in an n-MOSFET 32                   |  |  |  |

| Figure 3.7  | variation of drain current and threshold voltages w.r.t. bulk-source                         |  |  |  |

|             | Potential 33                                                                                 |  |  |  |

| Figure 4.1  | A two-stage CMOS operational amplifier 36                                                    |  |  |  |

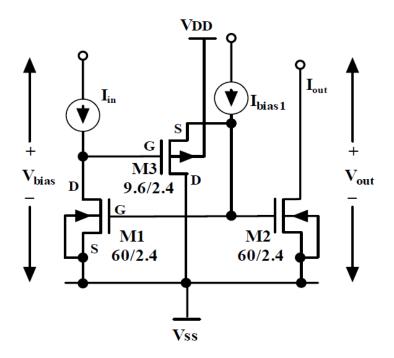

| Figure 4.2  | An n-MOS current mirror circuit in CMOS. The fraction indicate W/L                           |  |  |  |

|             | ratio of the corresponding transistors 37                                                    |  |  |  |

| Figure 4.3  | A CMOS level shift current mirror CMOS circuit. The fraction indicate                        |  |  |  |

|             | W/L ratio of the corresponding transistors38                                                 |  |  |  |

| Figure 4.4  | A new level shift current mirror CMOS circuit. The fraction indicate W/L                     |  |  |  |

|             | ratio of the corresponding transistors 38                                                    |  |  |  |

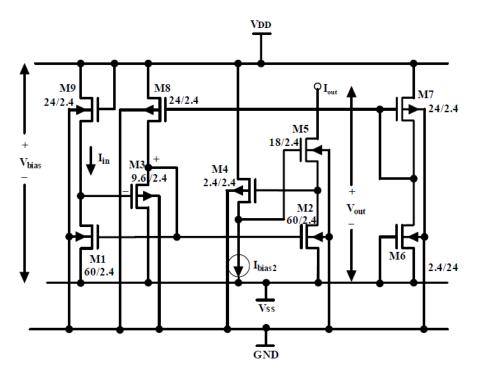

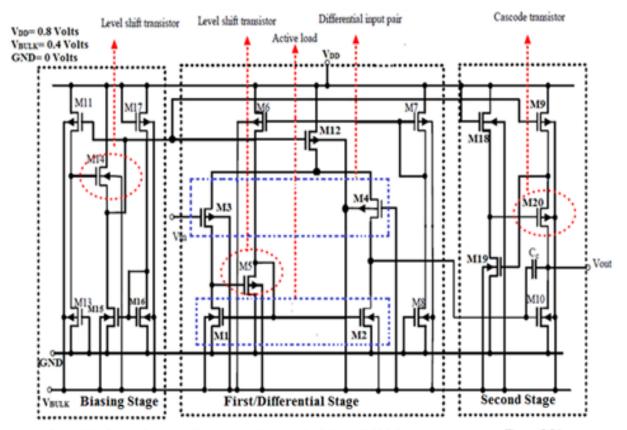

| Figure 4.5  | Circuit Design for Low Voltage Forward Body Bias CMOS Operational                            |  |  |  |

|             | Amplifier 41                                                                                 |  |  |  |

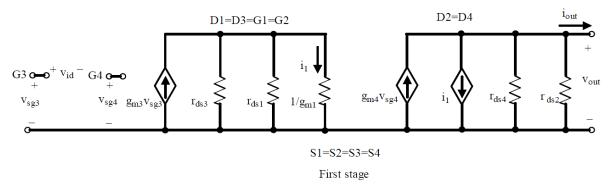

| Figure 4.6  | Simplified first stage circuit of amplifier circuit shown in Fig. 4.5 42                     |  |  |  |

| Figure 4.7  | Small signal equivalent circuit for the simplified first stage circuit of Fig.               |  |  |  |

|             | 4.6. vid is differential input voltage, i1 is current through M1 which is                    |  |  |  |

|             | mirrored to M2. DX is the drain of transistors and SX is the source of                       |  |  |  |

|             | transistors 42                                                                               |  |  |  |

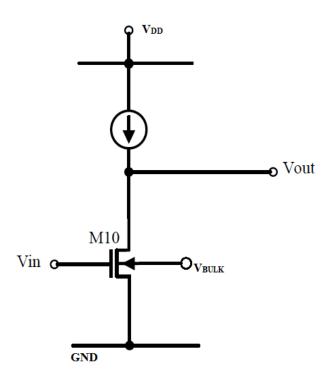

| Figure 4.8  | Simplified circuit for the second stage of the amplifier circuit shown in                    |  |  |  |

|             | Fig.4.5 44                                                                                   |  |  |  |

| Figure 4.9  | Small signal equivalent circuit of the second stage of the amplifier shown                   |  |  |  |

|             | in Fig.4.8. DX is the drain of transistors and SX is the source of                           |  |  |  |

|             | transistors. 44                                                                              |  |  |  |

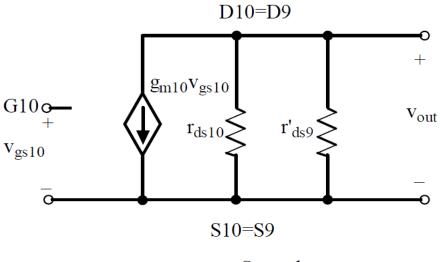

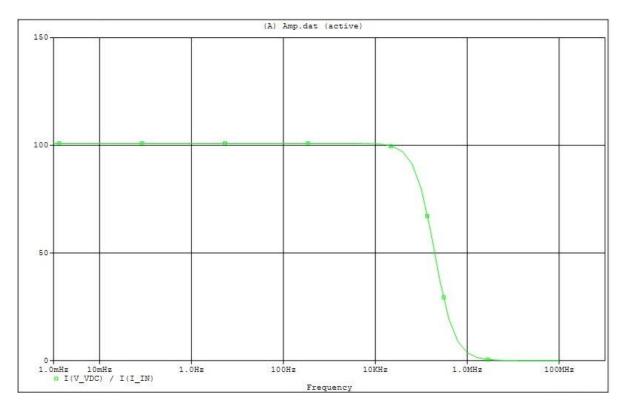

| Figure 4.10 | Simulated frequency response characteristics of the low power CMOS op-                       |  |  |  |

|             | amp circuit. Phase margin is 520 (-280+1800)46                                               |  |  |  |

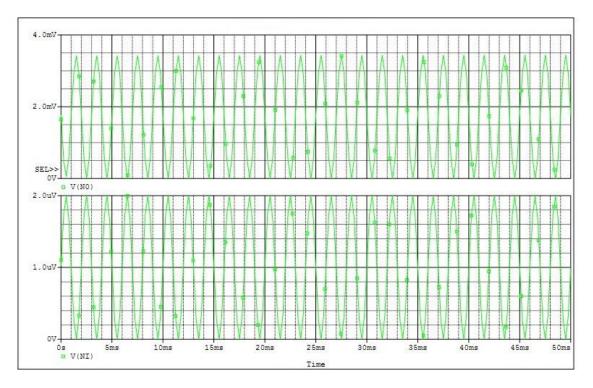

| Figure 4.11 | Transient Analysis of FBB CMOS op-amp48                                                      |  |  |  |

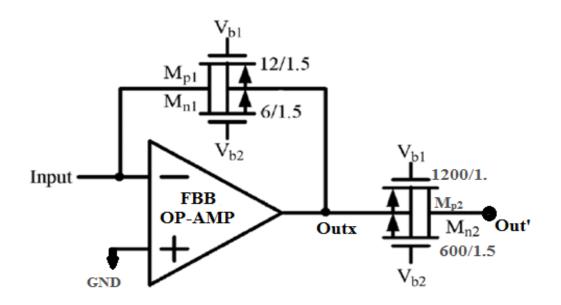

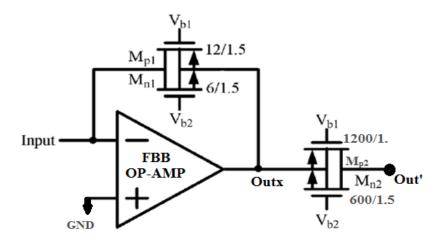

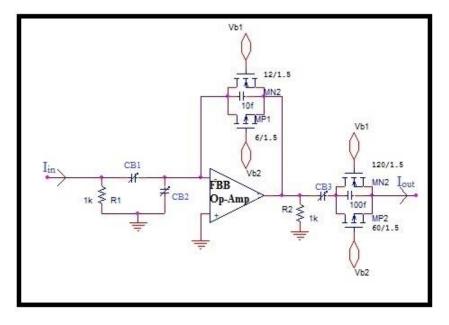

| Figure 4.12 | Structure of proposed current mode amplifier designed using forward                          |  |  |  |

|             | body biased op-amp proposed in figure 4.5 49                                                 |  |  |  |

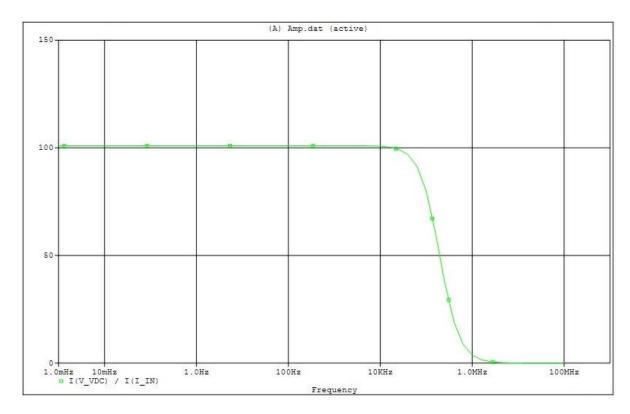

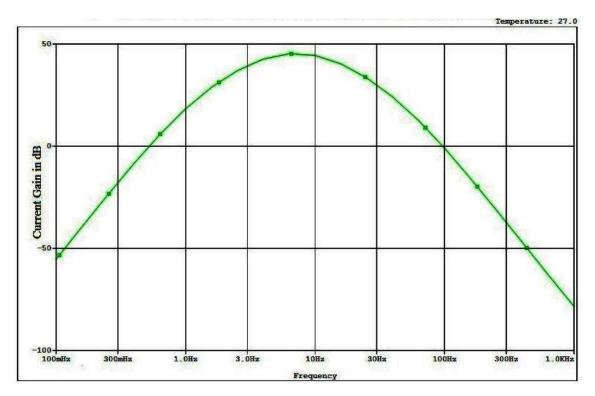

| Figure 4.13 | Frequency response of proposed FBBCMA with the gain of 100 A/A 50                            |  |  |  |

| Figure 5.1  | Thermal noise circuit model for a MOSFETs operating in saturation    | 52    |

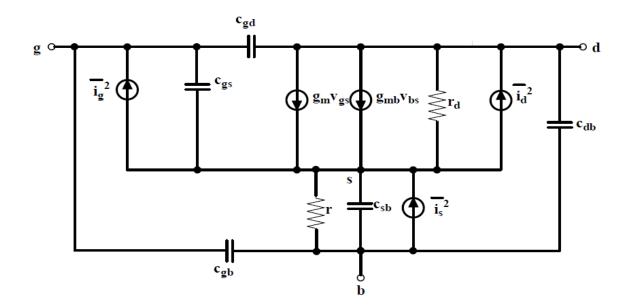

|-------------|----------------------------------------------------------------------|-------|

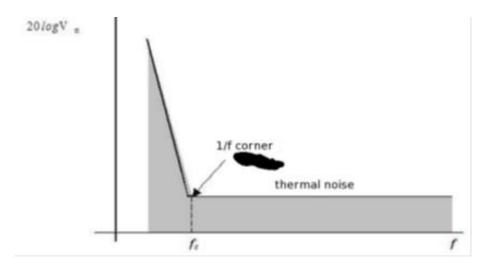

| Figure 5.2  | Flicker noise corner frequency                                       | 54    |

| Figure 5.3  | Small signal noise model of a forward body-biased n-MOSFET. So       | urce, |

|             | drain, gate and substrate are denoted by s, d, g and b, respectively | 56    |

| Figure 5.4  | Structure of proposed current mode amplifier designed using for      | ward  |

|             | body biased op-amp same as figure 4.12                               | 59    |

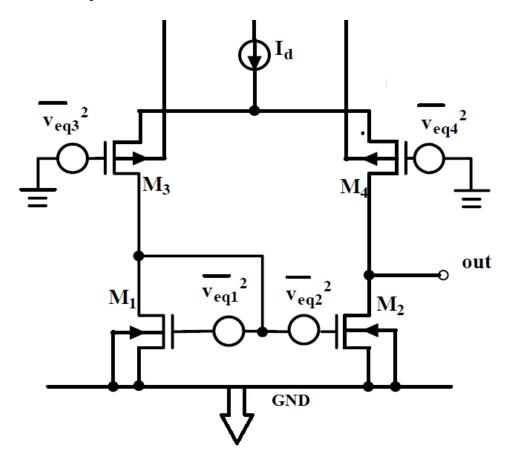

| Figure 5.5  | Circuit Diagram of low-voltage forward body bias CMOS Op-Amp         | 59    |

| Figure 5.6  | Noise model of a CMOS differential pair amplifier                    | 60    |

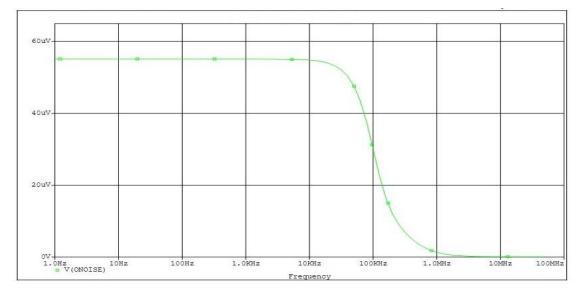

| Figure 5.7  | Output noise of forward body biased                                  | 61    |

| Figure 6.1  | Block Diagram of current mode multi-function analog readout front en | nd62  |

| Figure 6.2  | circuit diagram and interconnects of AFE shown in Fig. 6.1           | 63    |

| Figure 6.3  | Circuit diagram of Pre-amplifier                                     | 64    |

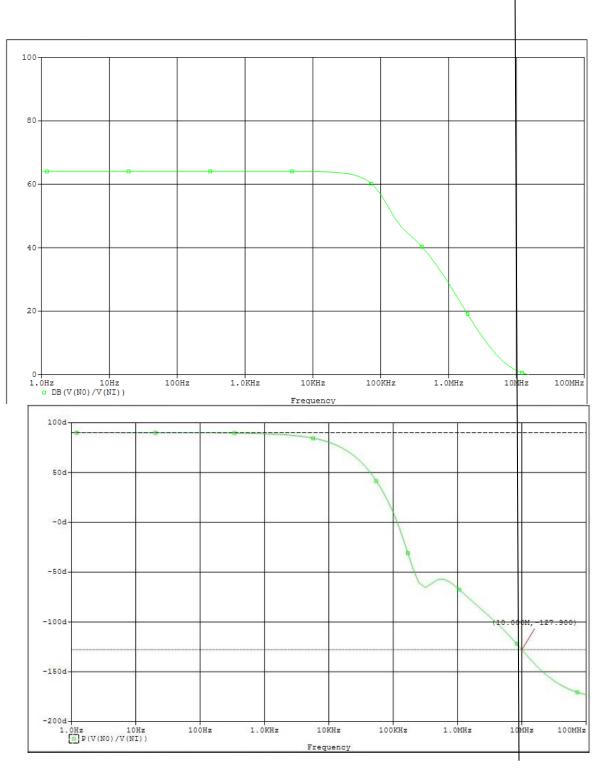

| Figure 6.4  | Frequency response of Pre-amplifier                                  | 65    |

| Figure 6.5  | Circuit diagram of band-pass filter                                  | 66    |

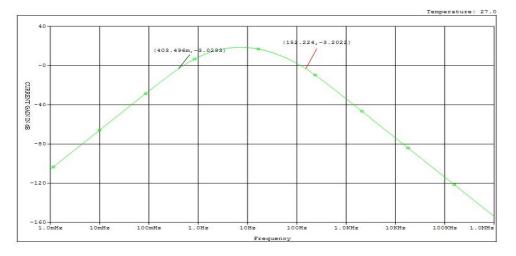

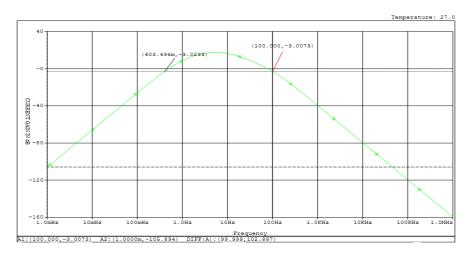

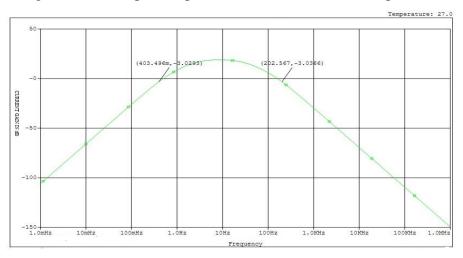

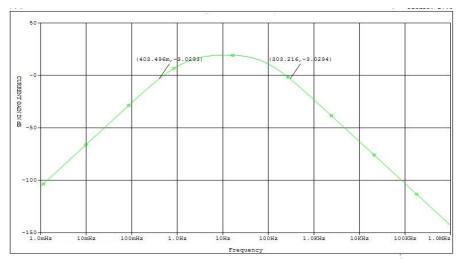

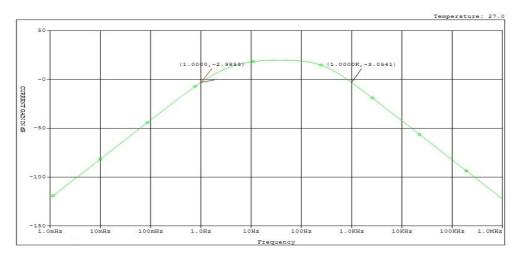

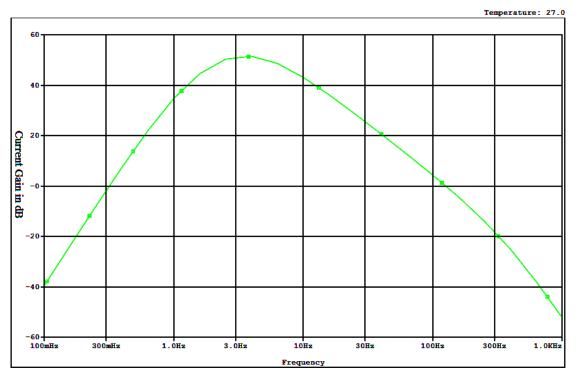

| Figure 6.6  | Band-pass response for ECG with cut-off frequencies                  | 66    |

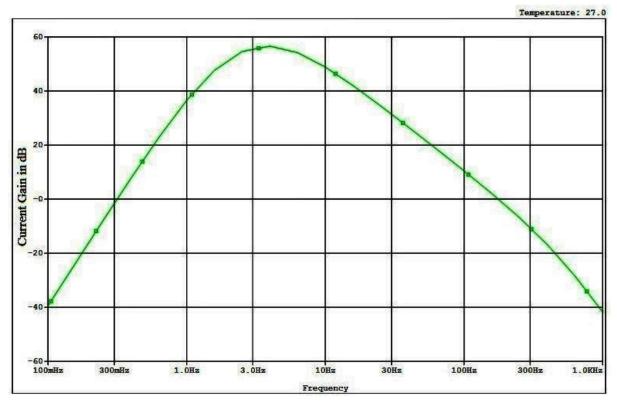

| Figure 6.7  | Band-pass response for EEG with cut-off frequencies                  | 67    |

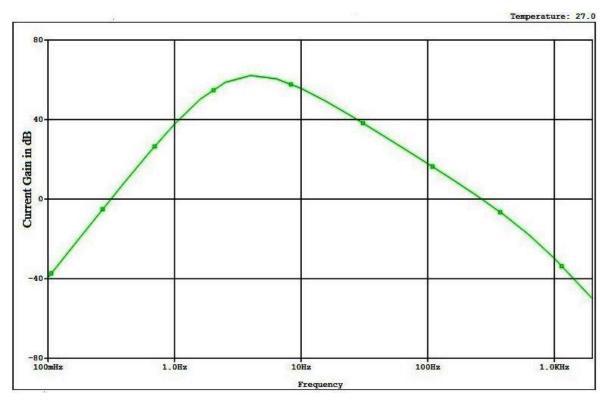

| Figure 6.8  | Band-pass response for ECoG with cut-off frequencies                 | 67    |

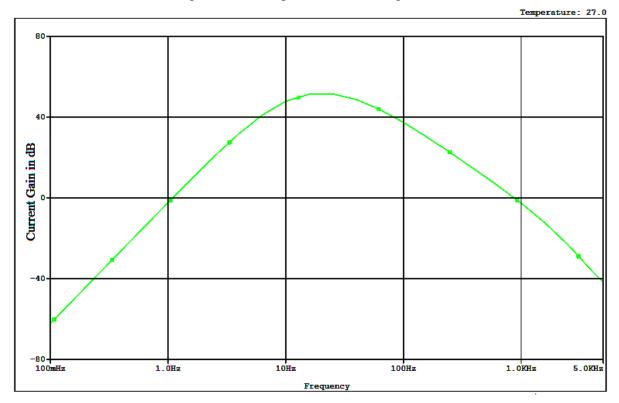

| Figure 6.9  | Band-pass response for ERG with cut-off frequencies                  | 67    |

| Figure 6.10 | Band-pass response for ENG with cut-off frequencies                  | 68    |

| Figure 6.11 | Response for EEG Signal.                                             | 68    |

| Figure 6.12 | Response for ECG Signal.                                             | 69    |

| Figure 6.13 | Response for ECoG Signal.                                            | 69    |

| Figure 6.14 | Response for ERG Signal.                                             | 70    |

| Figure 6.15 | Response for ENG Signal.                                             | 70    |

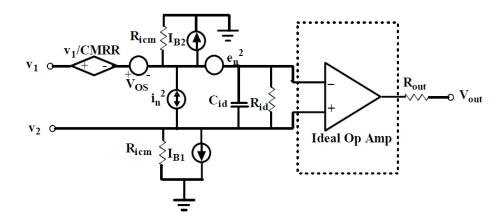

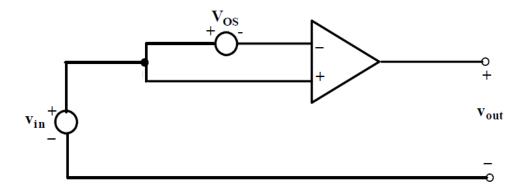

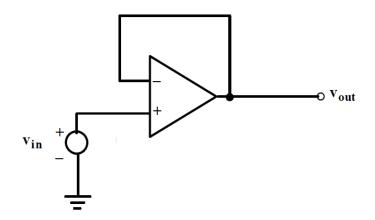

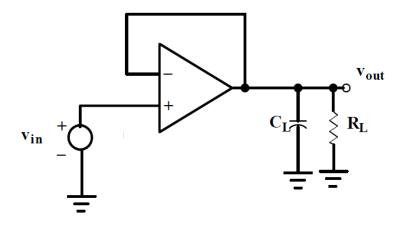

| Figure B.1  | Non ideal operational amplifier                                      | 78    |

| Figure B.2  | Common mode gain A <sub>CM</sub> measurement                         | 79    |

| Figure B.3  | PSRR measurement                                                     | 79    |

| Figure B.4  | ICMR measurement                                                     | 80    |

| Figure B.5  | Configuration of amplifier for measuring SR. RL and CL are included  | l for |

|             | the output loading during slew rate measurements                     | 81    |

## CHAPTER 1 INTRODUCTION

#### **1.1 Motivation**

The design methodologies of medical devices have evolved a lot with the expansion of integrated circuit over the last 40 years. Evolution of circuit technologies has facilitated the development of medical devices and the burgeoning need of health-care equipment has created a large demand for the new technology medical devices. In ubiquitous healthcare, acquisition and processing of bio-potential signals play a vital role. Bio-potential signals are commonly recorded in clinical centres for medical diagnosis and even at home for healthcare purpose. The most critical building block of such bio-signal acquisition systems is the analog front-end. This chapter introduces the challenges which occur while designing analog readout front-ends of bio-signals and the electrical characteristics of bio-potential signals with their associated acquisition system design.

Among the three categories of medical devices, implantable, in-vitro and external, designing of implantable devices is the most challenging task. The requirement of these devices to have low noise under low power consumption makes the design task cumbersome. Implantable medical devices include stimulatory devices, like pacemakers, implantable cardioverter defibrillators, neuro-stimulators and cochlea implants and measurement or control devices such as drug infusion, implanted diagnostic sensors and the very rapidly growing implanted diabetes monitor. Other than this, at medical and health-centres bio-potential signal acquisitions systems plays a critical role in diagnosis of various ailments.

While the bio-potential signals are being recorded from humans, the analog readout frontend circuits has to encounter various problems. These problems are because of extremely weak characteristics of bio-potential signals and the complex recording environments for different kinds of applications. In design perspective, despite the performance afforded by modern IC technology, electronic systems associated with implanted medical applications present formidable low power and low noise design challenges.

#### 1.2 <u>Multi-Functional Bio-potential Analog Front-ends:</u>

Nowadays, doctors can extract more and more information from bio-potential signals of human body for healthcare and diagnosis purposes. Electrocardiogram (ECG), Electroretinogram (ERG), Electroencephalogram (EEG), Electrocorticogram (ECoG) and neural signals are of utmost concern. The acquisition process of bio-signals signals is normally safe and efficient for patients, and doctors can examine the conditions prevailing inside the human body and perform possible treatments. Moreover , the growing demand for home healthcare applications makes Multi-functional bio-potential signal acquisition systems even more advantageous. These not only help in improving the quality of life but also extend applications to sports, entertainment and comfort monitoring [1].

In this dissertation a multi-functional analog readout front-end is proposed that measures cardiac, visual and all sort of neural signals. This single analog front-end can be tuned to measure ECG, EEG, ECoG, ERG and neural signals with low power consumption. Low power consumption makes it extremely useful for portable applications and in addition to this, these low power consumption circuits add very little noise which in turn maintains the signal quality. It is a Current-mode AFE (Analog Front End), the detailed discussion of advantages of current-mode circuits over voltage-mode circuits is presented in subsequent part of this chapter. The simulation results show that the proposed low power low noise current-mode AFE meets the basic requirements of the long-time portable biopotential acquisition system and is ready for connecting to next stages like ADC and DSP.

#### 1.3 **Bio-potential Signals:**

Bio-potential signals are electrical potentials between the membrane of certain cells of nervous, muscular and tissues. Generally, these cells exhibit resting potential when they are at rest and action potential when stimulated.

The mechanism of resting potential is , when there is a change in the concentrations of ions between the two sides of the membrane of cells. The diffusion of  $K^+$  from inner to outer membrane of the cell makes the concentration of free negative ions higher. This

increase in concentration of free negative ions causes the inner membrane to be more negative than the outer membrane. Thus the free negative ions attract  $K^+$  to prevent the diffusion and finally the cell reaches a steady state. The equilibrium is reached with a polarization voltage in the range from -20 mV to -100 mV and this value is usually between -70 mV to -90 mV.

When the cells are at resting potential, only  $K^+$  can diffuse freely through the membrane. After the stimulation of the cells once , the mobility of  $K^+$  and  $Na^+$  (also some  $Ca^{+2}$ ) change. Diffusion of  $Na^+$  ions into the cell makes it depolarized. When the depolarization of  $Na^+$  reaches the threshold value, the action potential is produced. At this moment, the mobility of  $K^+$  is enhanced on the depolarized membrane and that of  $Na^+$  reduces to resting state, and the potential eventually restores to resting potential level. To make the cell polarized, the conductivity of  $K^+$  is temporary increased and thereafter the cell restores to its resting state smoothly. This cycle of cellar potential is called action potential.

Bio-potential signals such as ECG, EEG, ECoG, ERG and neural signals are generated primarily due to combination of action potentials of different cells. The amplitude levels of bio-potential signals are very small practically and these are located at very low frequency band. They are prone to be affected by noise and common mode interference of human body, when extracted from surface placed electrodes. This may lead to false information about the physiology of the patient.

#### 1.3.1 <u>Electrocardiogram:</u>

ECG (also known as EKG, abbreviated from the German word), is a surface measurement of the electrical potential caused by electrical activity in cardiac tissue [2]. The contraction and dilation of the heart that leads the heart's pumping action causes a current flow, in the form of ions. The ECG has become a routine part of any complete medical evaluation because these signals help to diagnose many diseases. ECG is being used as a diagnostic test since its discovery. Many types of damages of heart tissues can be detected with an ECG because an ECG is a measure of the electricity that is conducted through the heart muscle (known as the myocardium). The ECG waveform allows one to

infer information about electrical activity associated with different aspects of a heart-beat and is therefore of particular value for assessing an individual's cardiac rhythm and heart health.

A normal cardiac rhythm is originated in the sino-atrial node (S-A node)so it is referred to as a "sinus" rhythm. When this sinus rhythm gets disrupted, the phenomenon that causes death, it is known as arrhythmia. "Pacemaker" cells present in S-A node triggers each heartbeat. These cells generate action potentials at the rate of 60 - 100 beats per minute (while at rest). Action potentials propagate throughout the myocardium in a predefined way and depolarize the tissues by contraction. After the departure of action potential from S-A node, The two upper chambers of heart depolarized by them, these two upper chambers of the heart are known as the atria. After this, these stimuli move to the atrio-ventricular node (A-V node). The A-V node sits between the atria and the ventricles (the two lower chambers of the heart). It performs action of a backup pacemaker at a lower rate of 40 - 60 beats per minute. Another function of A-V node is to delay the electrical impulses up to about 120ms. By slowing down these pulses A-V node gives the atria enough time to pump their blood into the ventricles before ventricles' contraction. After the action potentials leave the A-V node, they propagate to the area known as the "His" bundle. Now the ventricles are depolarized by conductive fibres known as Purkinje fibres, depolarization starts from the left ventricle and swings to the right. After the depolarization and contraction of ventricles, the cycle starts over with another impulse from the S-A node [3].

The Electrocardiogram is a representation of the electrical activity of an ensemble of cells in the myocardium. It is a vector measurement electrical potential across the surface of the body. A typical ECG waveform (as shown on the right side of Figure 1.1) is composed of three primary features: the P wave, the QRS complex, and the T wave. Each wave has its own significance in medical diagnosis as all of them correspond to the electrical activity in specific parts of the heart.

**P** wave: it comes first and represents the depolarization of the atria. It causes the contraction in the atria. As described earlier the delay produced by A-V node is present in the wave as the the delay between the P wave and the QRS complex, also known as the

PR interval. This interval gives the atria time to contract before depolarizing the ventricles.

**The QRS complex**: This represents the combined effect of re-polarization of the atria and depolarization of ventricles. The R spike represents the contraction of ventricles. QRS complex is usually the strongest wave in an ECG.

**T wave:** The last wave is the ECG is known as T and it represents the re-polarization of the ventricles. And *U wave* (if present) is generally considered as the result of after potential in the ventricular muscles. Taking a differential measurement of the electrical potential on the body surface at different locations generates different ECG vectors. In practice ECG signals has amplitude of order of few  $\mu$  Volts and lies between 300 mHz to 150 Hz

Figure 1.1: An ECG waveform is composed of action potentials originating in different areas of the heart. The ECG waveform recorded at the skin is the superposition of these different action potentials. [3]

| Amplitude: | P wave          | 0.25mV           |

|------------|-----------------|------------------|

|            | R wave          | 1.60mV           |

|            | Q wave          | 25% of Rwave     |

|            | T wave          | 0.1mV 0.5mV      |

| Duration:  | P-R interval    | 0.12 to 0.20 sec |

|            | Q-T interval    | 0.35 to 0.44 sec |

|            | S-T segment     | 0.05 to 0.15 sec |

|            | P wave interval | 0.11 sec         |

|            | QRS interval    | 0.09 sec         |

Ideal Amplitude and duration of all components of the ECG signals are as follows [2]:

#### 1.3.2 <u>Electroencephalogram and Electrocorticogram:</u>

The electroencephalography is a measurement of potential fluctuations of brain. It is firstly reported by a German psychiatrist Hanse Berger [3]. The EEG can help diagnose conditions such as epilepsy, brain tumours, brain injury, cerebral-palsy, stroke, liver kidney disease or brain death and helps to find many other physical problems [4].

Conventionally, there are three types of electrodes that are used to measure the electrical activity of brain- scalp, cortical and depth electrodes. When the electrodes are placed at exposed surface that is cortex of the brain, such recording is known as *Electrocorticogram (ECoG.)*. Another semi invasive method is to use insulated needles, in such case recording is referred to as a depth recording. In this kind of recording the insertion of appropriate size needle (electrode) causes little damage to brain tissue [3]. The EEG is typically 100  $\mu$ V in amplitude with a frequency response of 0.5 to 80 Hz [4]

In *Electrocorticogram (ECoG.)* a specific set of neurons (also known as motor) is selected and potential fluctuations are measured through these motors. An example of such case is measurement of the evoked potential, after measurement of evoked potential the wish of patient can be interpreted. This kind of measurement is used in brain computing interface (BCI). The study and description of BCI and calculations of ECoG are beyond the scope of this work.

| Signals                      | Bandwidth  | Amplitude |

|------------------------------|------------|-----------|

| Electrocortecography (Ecog)  | 0.5-200 Hz | < 100 µV  |

| Electroencephalography (EEG) | < 100 Hz   | 10-20 μV  |

| Neural                       | 1Hz-5KHz   | <500µV    |

**Recording system:** There is a slandered system for measurement of EEG recommended by the International Federation committee Society of Electroencephalography and Clinical Neurophysiology (IFSECN) that is known as a 10-20 system. The "10" and "20" refer to the fact that the actual distances between adjacent electrodes are either 10% or 20% of the total front-back or right-left distance of the skull. Another system is 20-21 system in same reference.

The American Society of Clinical Neurophysiology recommends the use of at least 21 electrodes for better resolutions. The electrodes with an even number are placed on the right and electrodes with a odd number are placed on the left side of the head. The letters specify an anatomical area; e.g. "F" means frontal, the electrodes between the ears are specified by "Cz". The electrodes T3 and T4 of this system are referenced as a T7 and T8 in extended systems; and the electrodes T5 and T6 are referred as a P7 and P8 in the new nomenclature. See figure 3.2. The EEG helps physicians to study and analyse electrical activity in the brain [3].

Figure 1.3: EEG electrode 10-20 system.

**EEG signals features:** The EEG signals are potential fluctuations with low frequencies recorded by scalp electrodes. The only required information about patient is his or her age and status, before starting the EEG. The status of the patient means the general clinical status of conscience in which the patient is. The analysis of EEG signal is pretty complex due the immense amount of information that is received by each electrode. The sorting criterion for different waves is their main frequency component and in some cases their shapes. There are six main groups that are defined as follows [5]:

**<u>Beta(β)</u>** activity: Beta activity is associated with signals having main frequency components between 13Hz and 30 Hz, and amplitudes between 5  $\mu$ V*pp* to 20  $\mu$ V*pp*. Figure 3.3 shows the β activity. β activity is associated with the reasoning, attention and focusing. It can reach 40Hz during the intense mental activity [5].

<u>Alpha( $\alpha$ ) activity:</u>  $\alpha$  activity is associated with signals having main frequency components from 8Hz to 13Hz, and amplitudes between 30 to 50 $\mu$ Vpp. The Alpha waves are associated with mental relaxation and poor interest in something [5].

Figure 1.3: Various EEG traces [4].

<u>Mu( $\mu$ ) activity:</u> Mu( $\mu$ ) activity can be defined as a spontaneous signal having frequency response around 8 to 10Hz and is the central rhythm of the Alpha activity. It can be measured in the motor cortex.

**Delta(\delta)** activity: The Delta activity produces signals that have frequencies between 0.5Hz and 4Hz, with variable amplitude. The Delta signals are associated to the dream activity and if they are found in an awake patient, then it indicates malfunctioning of the brain.

<u>Gamma( $\gamma$ ) activity</u>: This activity is associated with the frequencies range of 35Hz to 100 Hz. This activity is related to cognitive tasks such as attention, learning and memorization.

<u>Theta( $\theta$ ) activity</u>: Signals generated due to  $\theta$  activities have frequencies from 6 to 7Hz, with the amplitude of more than 20  $\mu$ V*pp*. The theta activity is reinforced by mental stress, like frustration in the frontal area of the brain. The Theta activity is also associated to the inspiration and depth meditation whose dominant frequency is 7Hz [5].

#### 1.3.3 <u>Electroretinogram:</u>

ERG is the recording of electrical potentials evoked by a flash of light and picked up at the cornea of the eye using contact lens electrode [6]. It is a measure of the electrical response of the eye's light-sensitive cells, called rods and cones. These cells are part of the retina (the back part of the eye). The electroretinogram (ERG) is an electrophysiological tool used to measure electrical activity originating in the outer part of retina in response to a light stimulus. Deficiencies occurring at different levels of the retina can be detected by ERG. ERG signal is composed of a sequence of components originated in various retinal layers and provides valuable physiological information about the photoreceptor behaviour in the human eye. Understanding the explicit features (onset, time delay, amplitude, line shape) of the ERG components and their relationship characterizes the principal aim of past and present research in the field of ocular electrophysiology.

Figure 1.4: Simplified scheme of the human retina with the approximate sites of generation of electrophysiological signals [6].

Furthermore, the shape of the ERG wave indicates the likely retinal cell type responsible for the deficit. It consists of various components (wavelets) which generates in different layers of the retina reflecting light evoked potentials caused by different cells shown in Figure: 1.4. in the figure 1.4 A- amacrine cells; B- bipolar cells; C- cone photoreceptors; G- ganglion cells, I- interplexiforme cells, M- Müller (glial) cells; R- rod photoreceptors. The amplitude of an ERG signal is of the order of few  $\mu$ Volts that lies between the frequency range of 0.3 to 300Hz (in special case upper range may change)

The five different kind of ERG recording as per standards is depicted in figure 1.5.

Figure 1.5: Diagram of the five basic ERGs defined by the Standard. These waveforms are exemplary only, and are not intended to indicate minimum, maximum or even average values. Large arrowheads indicate the stimulus flash. Dotted arrows exemplify how to measure time-to-peak (t, implicit time), as-wave amplitude and b-wave amplitude [7].

The *early receptor potential (ERP)* shown in figure 1.6 is a rapid discharge recorded with a very high intensity flash in a well dark adapted eye using high–frequency amplifiers. The *a*–*wave* is a negative potential produced extra-cellularly along the radial path from the cell body of the photoreceptors that hyperpolize in response to light, and it is an important component of the clinical ERG as a measure of photoreceptor activity. The a–

wave is made up of two components i.e., a1 and a2, generating from the cones and rods respectively.

Figure 1.6: The Electoretinogram (ERG) Signal [6]

The *b–wave* is the most readily recordable component of the clinical ERG. It reflects the postsynaptic summed neuronal activity of the inner nuclear layer and is thus an important measure. *B–wave* composed of two components, b1 and b2, representing the cone–mediated and rod–mediated responses like a-wave.

On the rising phase of the b-wave a rapid oscillation is evoked by a bright flash known as the *oscillatory potential (OP)*. The last oscillation, that is relatively well defined can be measured and is called the *x*-*wave* or b1. The amacrine cells, the inner plexiform layer and optic nerve fibres have all been suggested as possible generators of the oscillatory potential. The *c*-*wave* is a small, slow, positive deflection after the b-wave. Although it actually started slowly from the beginning of light stimulation but it appears after b-wave only. Briefly the integrity of the pigment epithelium and photoreceptors is an essential factor for the generation of the c-wave.

#### 1.4 Objective and Scope of the Project

The objective of this thesis is to a multi-function analog readout front end using P-spice Simulator. The parameter used in this work is TSMS standard 180nm level 7 parameter. The low-power and low noise analog front end is designed that produces a signal that is ready to use as an input to the ADC. The low power consumption makes it useful for portable applications while small amount of added noise ensures the signal quality.

This is a read out front end with tunable frequency, which ensures the utility of this AFE in variety of bio-signal recording systems. Multifunctioning along with low power consumption and low noise operation are key features of this analog readout front end.

#### **1.5 Organization of Dissertation**

The thesis outline is as follows:

**Chapter 2**: This chapter provides the well needed theoretical background for designing a low-voltage analog circuit. A comparison between the current mode and voltage mode topologies is illustrated.

**Chapter 3**: This chapter provides an insight to the forward body biased operation of the MOS devices. Along with the threshold voltage analysis, dependence of threshold voltage on forward body voltage is discussed.

**Chapter 4:** In this chapter detailed description of the proposed forward body biased current mode active block is presented. Large portion of the chapter deals with the design of forward body bias op-amp, last section describes the current mode amplifier architecture and working of the same, including the simulated results.

**Chapter 5:** This chapter gives an elaborated analysis of noise introduced by the active block in previous chapter. The noise added by the proposed active block is modeled and simulated in this chapter.

**Chapter 6:** This chapter provides the complete design of low-power low-noise analog read out front end for cardiac, visual and all kind of neural signals and simulation results for the same.

**Chapter 7:** This chapter deals with the conclusion from the interpreted results and explores the future work for this work.

## CHAPTER 2 THEORETICAL BACKGROUND

With the continuously expanding market for portable devices such as wireless communication devices, portable computers, consumer electronics and implantable medical devices, low power is becoming increasingly important in integrated circuits. The low power design enables to increase operation time and/or utilize a smaller size and lighter-weight battery.

The analog power supply must be at least the sum of the magnitudes of the n-channel and p-channel thresholds [8]. The threshold voltages of future CMOS technologies may not decrease much below the existing values of available nowadays. Low voltage circuits in the future will be incompatible with the standard CMOS technology. Consequently, low-voltage circuit design methodologies are required to make compatible future CMOS technologies with low-voltage requirements. Figure 2.1 shows the trends of the threshold voltage from the 1 $\mu$ m to the 22nm CMOS process.

Figure 2.1: Supply voltage and threshold voltage of different technologies [9].

In this Part, several design methodologies of low power complementary metal-oxidesemiconductor (CMOS) analog integrated circuit design are investigated.

| Node                            | Nm    | 250         | 180  | 130         | 90        | <i>65</i> | V  |

|---------------------------------|-------|-------------|------|-------------|-----------|-----------|----|

| L <sub>GATE</sub>               | Nm    | 180         | 130  | <i>92</i>   | <u>63</u> | 43        |    |

| t <sub>ox</sub> (inv.)          | Nm    | 6.2         | 4.45 | <i>3.12</i> | 2.2       | 1.8       | V  |

| Peak g <sub>m</sub>             | μS/μm | 335         | 500  | 720         | 1060      | 1400      | 1ì |

| <b>g</b> <sub>ds</sub> **       | μS/μm | 22          | 40   | 65          | 100       | 230       | 11 |

| g <sub>m</sub> ∕g <sub>ds</sub> | -     | <u>15.2</u> | 12.5 | 11.1        | 10.6      | 6.1       | V  |

| V <sub>DD</sub>                 | V     | 2.5         | 1.8  | 1.5         | 1.2       | 1         | VV |

| V <sub>TH</sub>                 | V     | 0.44        | 0.43 | 0.34        | 0.36      | 0.24      | V  |

| f <sub>T</sub>                  | GHz   | 35          | 53   | <i>9</i> 4  | 140       | 210*      |    |

Table 2.1 MOS device parameter trendz.

The low-voltage/low-power design can utilize a smaller size or a lighter-weight battery and increase operation time between battery recharging cycle. Among several available device technologies such as bipolar junction transistor (BJT), gallium arsenide (GaAs), complementary metal-oxide-semiconductor (CMOS), bipolar-CMOS (BiCMOS) [10-12], the CMOS technology is the dominant technology in the development of low power portable devices for wide-ranging applications. For more than 20 years, numerous low power CMOS design techniques have been investigated that includes basic circuit design modifications as well as new fabrication techniques. First one inhabits architecture changes for implementing desired functions using low threshold voltage devices, power down strategies, optimization of transistor size, supply voltage scaling, along with other possible techniques [13-15]. While new fabrication technologies comprises carbon neon technology field effect transistor (CNTFET) and FINNFET. In the following section, literature review and historic development of low-power analog CMOS design techniques are presented.

Low-power design drew attention in the early 1990s with expansion in portable consumer electronic market. A critical overview abut change in power dissipation of CMOS circuits changed since 1980 has been described by Kuroda and Sakurai [16]. There is a constant increase in the power dissipation of commercial CMOS chips because of increased clock frequency. For example, power dissipation of a 5 V DSP chip was 0.1 W in 1982, and

increased to 10 W in 1991. Power dissipation peaked in 1990-1991. After 1991, power dissipation of CMOS chips have reduced because of increasing demand of large number of portable systems.

Some of the standard low power techniques as discussed below.

#### 2.1 Sub-Threshold MOS

In the MOS devices gate to source voltage must be greater than a certain value known as threshold voltage  $(V_T)$  to turn on the device. When the VGS in the MOS transistor is less than the threshold voltage  $(V_T)$ , the device operates in sub threshold region or weak inversion. In the sub threshold region the ID depends exponentially on drain to source voltage unlike regular case where curve has quadratic behavior.

Some assumptions are considered in order to develop the model for sub-threshold operation. Channel length modulation effects are negligible. Generation currents in the drain, channel, and source depletion regions are almost negligible. Source and drain currents of MOSFET are equal, density of fast surface states and fluctuations of surface potentials are all negligible. Then the Barron's derivation [8] can easily be extended for case of nonzero source-to-substrate voltage. For an N-channel transistor:

$$I_{D} = S\mu U_{T}^{2} \sqrt{\left[\frac{1}{2}q\varepsilon_{s}n_{i}\right]} e^{-3\phi/2U_{T}} \frac{e^{\psi_{s}}/U_{T}}{\sqrt{\psi_{s}-U_{T}}} \left(e^{-V_{s}}/U_{T} - e^{-V_{D}}/U_{T}\right)$$

(2.1)

where S is the geometrical shape factor of the transistor (W/L),  $\mu$  is the mobility of carriers in the channel,  $\psi_S$  is the surface potential,  $U_T$  is the thermal voltage (kT/q),  $\varepsilon_s$  is the permittivity of the Silicon,  $V_S$  the source-to-substrate voltage,  $\varphi$  is the bulk Fermi potential,  $V_D$  the drain-to-substrate voltage,  $V_G$  is the gate-to-substrate voltage and  $I_D$  is the drain current.

Equation 2.1 is valid for:

$$4U_T + \emptyset + V_S < \psi_S < 2\emptyset + V_S \tag{2.2}$$

On the other hand, the depletion capacitance  $C_d$  can be expressed as:

$$C_d = \sqrt{\frac{\frac{1}{2}q \in_s n_i}{\psi_s - U_T}} e^{\emptyset/U_T}$$

(2.3)

Inserting (2.3) into (2.1), yields:

$$I_D = S \mu U_T^2 C_d \ e^{-2\phi/3U_T} \ e^{\psi_S/U_T} (e^{V_S/U_T} - e^{V_D/U_T})$$

(2.4)

Because of very slow variation of  $C_d$  with  $\psi_S,\,I_D$  shows an exponential behaviour on  $\psi_S/U_T\,.$

The relation between surface potential and gate voltage is given by:

$$\frac{\partial \psi_S}{\partial V_G} = \frac{c_{ox}}{c_{ox} + c_S} = 1 - \frac{c_G}{c_{ox}} \tag{2.5}$$

Where  $C_G$  is the gate-capacitance per unit area. According to (3.5),  $\psi_S$  is linearly depending on  $V_G$  in the range:

$$4U_T + \emptyset + V_S < \psi_S < 2\emptyset + V_S - 2U_T.$$

(2.6)

Then inside this range I<sub>D</sub> take the form of:

$$I_{DS} = I_{DO} \frac{W}{L} e^{V_G / n U_T} (e^{-V_S / U_T} - e^{-V_D / U_T}).$$

(2.7)

Where  $I_{DO}$  is the characteristic current, n is the slope factor, The above equation is also applicable for p-MOSFETs by just changing the signs of all the potential that areV<sub>G</sub>, V<sub>S</sub> and V<sub>D</sub>.

By definition, the gate trans-conductance can be found from equation (2.8):

$$g_{md} = \frac{\partial I_{DS}}{\partial V_{GS}} = \frac{1}{nU_T} I_{DS}$$

(2.8)

The small signal source conductance can be found from equation 3.17 as:

$$g_{ds} = \frac{\partial I_{DS}}{\partial V_{Ds}} = \frac{1}{U_T} I_{DO} \frac{W}{L} e^{V_G} / n U_T (e^{-V_S} / U_T - e^{-V_D} / U_T)$$

(2.9)

When  $V_{DS}$  is less than  $3U_T$  the device shows a poor linear behaviour. On the other hand when  $VDS >> 3U_T$  the conductance is almost constant [17].

#### 2.2 The Composite Transistor

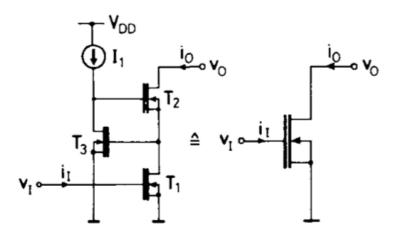

This is another technique for low power design which is based on the regulated-cascode current sink/source and is also known as the self-cascode technique and as the super-transistor [18]. It consists of a cascode configuration and a series feedback loop that upsurges the small signal output resistance without maximizing the voltage drop across the output of the current sink/source.

The composite transistor technique is depicted in the figure 3.1. The transistor T1 is input device that converts the input voltage V1 into drain current Io. The drain current of T1 flows through the drain to the source of the T2.  $V_{DS}$  of the transistor T1 is kept stable to reduce channel-length modulation; this is performed by a feedback that consists of an amplifier (transistor T3 and T1) and T2 is nothing but a follower [18].

Figure 2.2: Composite transistor. [18]

#### 2.3 The Lateral BJT

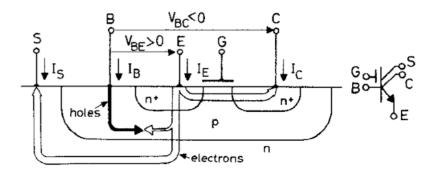

This technique overcomes the threshold limitation. When the voltage in the gate is negative enough (approximately  $-V_G > 0.6V$ ) the dependence of the  $I_D$  on  $V_G$  vanishes,  $I_D$  depends only on  $V_S$ , staying exponential up to much higher values of current, with a slope n equals to  $U_T$ . Figure 2.3 depicts the cross-section of a NMOS transistor and the current flow in bipolar operation.

Figure 2.3: Cross-section of a NMOS transistor implemented in a p-well technology and its symbol. [19].

The lateral BJT n-p-n is combined with the vertical n-p-n. Emitter current  $I_E$  is parted into a base current  $I_B$ , a lateral collector current  $I_C$ , and a substrate collector current  $I_S$ . To improve device performance the emitter area is minimized along with the lateral base width, and by having the emitter surrounded by the collector, the ratio  $I_C=I_S$  is incremented. The presence of the gate that pushes the flow of diffusion carriers away from the surface might even improve the device with respect to normal lateral bipolar [19].

This solution has supplementary advantage of much less 1/f noise because current flow in the bulk of the material. Moreover, another advantage of the lateral BJT is its low value of  $V_{CE}$  which is also important in low voltage analog circuits. The only disadvantage the lateral BJT is that it requires turn on voltages of 0.6V to 0.7V so it does not provide that much advantage over the MOSFET.

#### 2.4 Forward-Biased Bulk-Source

While operating the MOSFET at low voltage the only limitation is threshold voltage. This technique is based in reducing the threshold voltage by forward biasing on the bulksource junction. Threshold voltage of a MOS transistor is given by [20]:

$$V_t = V_{t0} + \gamma \left[ \sqrt{2\phi - V_{SB}} - \sqrt{2\phi} \right].$$

(2.10)

Where  $V_{t0}$  is the threshold voltage for zero substrate bias (VBS = 0V), is the bulk threshold parameter, and  $\phi$  is the strong inversion surface potential of the MOSFET.

Figure 3.4 depicted the cross-section of a CMOS device using this technique which also includes the parasitic vertical BJTs. This technique is further discussed in next section

Figure 2.4: Cross-section of forward bias NMOS transistor (Taken from [20]).

#### 2.5 Bulk-Driven MOSFETs

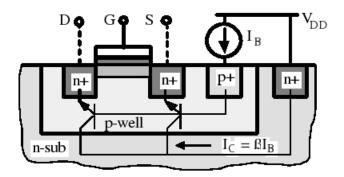

The bulk-driven MOSFET concept was proposed by A. Guzinski, et. al in 1987, as active components in an OTA differential input stage. The bulk driven differential pairs results in improved linearity and smaller trance-conductance. In 1998 a 1V op-amp was designed by P. E. Allen et al using the depletion characteristics of the bulk-driven MOSFET in order to achieve the low voltage requirements.[21]

Bulk-driven is the most significant solution to the threshold limitation in the MOS transistors. A CMOS cross section diagram illustrating this technique is shown in the figure 2.5.

Figure 2.5: Cross-section of bulk-driven MOSFET [21].

Generally, the bulk terminal of the MOSFET is tied to the source when using MOSFET as part of an amplifier and the signal is fed in the gate. In bulk-driven MOSFET, the gate

is tied to a bias voltage that is sufficient to turn it on while the signal is fed into the bulk terminal of the MOSFET.

The current flowing in the channel is modulated by the reverse bias voltage that is applied on the bulk-channel junction. Resultantly a junction field-effect transistor is formed with the bulk as the signal input. Consequently, the bulk driven configuration has a high-input impedance depletion device that requires no DC bulk-source voltage for current flow [21].

# 2.6 Limitations of circuits in strong-inversion working with low-voltage power supply

All the described low voltage techniques show good performance working in strong inversion region. Among all The techniques composite transistor has, the better performance again short channel modulation, while having low  $V_{DS}$ (composite), being a good candidate for low-voltage applications. However, to keep the feedback transistors in saturation larger  $V_{DS}$ (sat) is required. The lateral BJT could be a powerful device that reduces the amount of 1/f noise, while having high gain but, using higher gate voltages to turn it on is inevitable. The forward biased bulk is the dominant technique to reduce the threshold voltage ( $V_T$ ) of the transistor allowing lower  $V_{DS}$ (sat). Unfortunately, the  $V_{BS}$  activate a parasitic transistor producing undesired currents. The last technique discussed is the bulk-driven technique uses the MOSFET's bulk as input terminal avowing in some degree the threshold limitation. Though, to keep the transistors ON, the values of the  $V_{GS}$  must be at least the  $V_{TH}$  of the transistor.

All the presented techniques excluding the composite transistor, could work in both strong inversion and sub-threshold region. However, operating at low power supply voltages in strong-inversion brings some important constraints. The primary limitation is the threshold voltage. In CMOS technology, minimum power supply requirement is given by:  $V_{DD}+V_{SS}>V_{tN}+V_{tP}$  only in this condition the circuit works in strong inversion [20].

The other limitation is related to the decreased channel length of today and future submicron CMOS technologies. As discussed earlier the supply voltage is limited by the

threshold voltages of MOSFETs but the channel length keeps on decreasing so the resultant field across the channel mounts up. This phenomenon impacts in much larger channel length modulation effect. This results in poor signal gain because the small signal output resistance of the MOSFET has decreased [20].

The design of the low voltage analog circuits has become more challenging due to the lack of good analog models for deep submicron technologies and for low voltage operation. This limitation results in the use of longer channel lengths than necessary in order to have more reliable models. Subsequently, the full performance of submicron technologies is not utilized and more and more parasitic will be there [20].

Due to constant reduction in the device size such techniques are required that could operate supplies voltages as low as 0.5V. Therefore, most of the techniques presented here are not suitable to work in strong inversion region, as they require at least a supply voltage equal to the sum of the threshold voltages of the devices, in order to work properly. These limitations cause the obligation to work at sub-threshold region, allowing the reduction of the supply voltage.

In conclusion, circuits working in the sub-threshold region allow us to operate on reduced power supply voltage, while some of the presented techniques possibly will be used to improve the performance of the circuits.

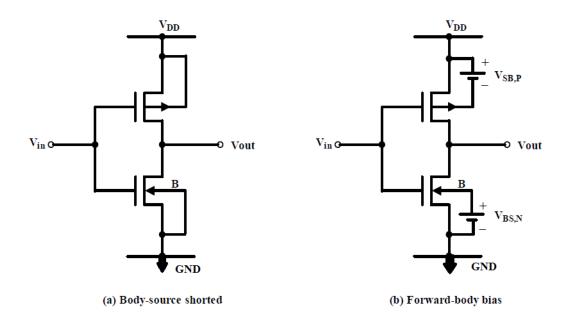

Figure 1.3: CMOS inverter under (a) body-source short and (b) forward-body bias conditions. The  $V_{BS,N}$  is the forward body-bias across the n-MOSFET and  $V_{SB,P}$  is the forward body-bias across the p-MOSFET.

#### 2.7 Voltage mode versus Current mode: A critical comparison

In any electrical network the information processed by lumped elements can be represented by either the branch current or nodal voltages. The latter are referred to as voltage-mode circuits whereas the former are known as current-mode circuits. To characterize complete behavior of any network both of the quantities are essential. However, Voltage-mode circuits are explored way too much and received a broader attention as compared with their current mode counterparts. Despite the fact that the concept of ideal current mode circuits, similar to that of ideal volt age-mode circuits, emerged approximately 40 years ago. This is reflected by countless texts on voltage mode circuits over a handful monographs on current-mode circuits. The reasons for such admiration and acceptance that voltage-mode circuits have been enjoying can be summarized as follows [22]:

- (i) In any electrical network Measurement of the nodal voltage is far more convenient than the measurement of the branch current of the networks. Nodal voltage can simply be measured using voltmeters without modifying the topology and altering the operation of the networks. On the contrary, the measurement of the branch current often needs a change of the configuration of the networks or supplementary circuitry,

- (ii) The inherent property of MOS devices having infinite input impedance makes these transistor an ideal choice for the realization of voltage-mode circuits, especially while designing cascade configurations, such as multi-stage amplifiers,

- (iii) The circuit design techniques, such as cascode and regulated cascodes make it easy to obtain a high voltage gain of voltage-mode circuits.

- (iv) In past low-voltage design was not of a critical concern because high voltage supply voltages are available,

- (v) High supply voltage makes the switching noise switching noise issue of least concern,

- (vi) Low speed requirements allow slow charging and discharging of nodal capacitors.

In past few years an aggressive reduction in the supply voltage of CMOS analog circuits has been observed, while there is only a moderate reduction in the device threshold voltage. The performance of the CMOS voltage-mode circuits has been greatly affected due to this diverse reduction, typically reflected by a decreased dynamic range, an enhanced propagation delay, and poor noise margins. The current mode circuits are advantageous over voltage mode circuits even after aggressive reduction of supply voltage. This is because the performance of current-mode circuits, however, is less severely affected as compared to voltage-mode circuits. The reason behind is the different

design methodologies are used in voltage and current mode circuits, the design emphasis of current-mode circuits is on branch currents rather than nodal voltages. The CMOS current-mode circuits are useful in dealing with the combined difficulties arising from the reduction of the supply voltage and the increase in the operation speed. The different design focuses of both the topologies are arising from the intrinsic characteristics of branch currents and nodal voltages, result in distinct design methodologies. The internal nodes of a current mode circuits have inherent characteristics like low impedance and low voltage swings, which make the supply voltage reduction possible without affecting the performance, unlike voltage mode circuits. To reduce the power consumption of a device the dc operating current should be low along with the supply voltage. The voltage noise is inversely proportional to dc operating current whereas the current noise is proportional to dc operating current whereas the current noise devices under low power consumption. While in current mode circuits both the low power and low noise performance can be obtained.

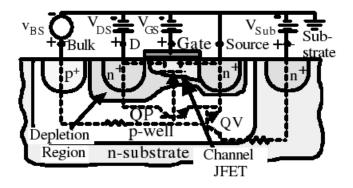

## CHAPTER 3 FORWARD BODY-BIAS TECHNIQUE

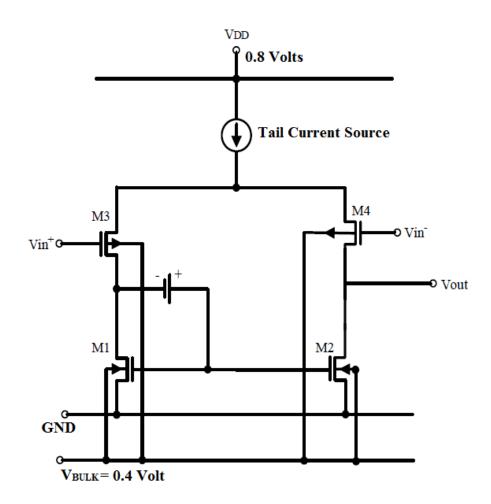

Transistors are treated as three terminal devices traditionally. While designing circuits the source and bulk terminal are shorted. It implies that the MOSFET operates as a zero bulk-biased threshold device. On the other hand, MOSFET can be used as a four terminal device forward or reverse bias can be applied between the bulk-source junctions of a MOSFET. As per the relation given in previous section under the reverse body-bias, the MOSFET threshold voltage is increased. Under the forward body-bias, the MOSFET threshold voltage is decreased. The detailed analysis of threshold voltage is discussed further. Figure 3.1 (a) depicts a standard CMOS inverter with zero body bias transistors. Figure 3.1 (b) depicts a CMOS inverter where MOS is used as a four terminal device under forward body-bias conditions.

# Figure 3.1: CMOS inverter under (a) body-source short and (b) forward-body bias conditions. The V<sub>BS,N</sub> is the forward body-bias across the n-MOSFET and V<sub>SB,P</sub> is the forward body-bias across the p-MOSFET.

In the design methodologies for ultra-low power, supply voltage scaling is a straight forward technique. Scaling down the supply voltage becomes more effective because of the fact that the power consumption has square relation with the supply voltage. However, operating the circuit with low supply voltage, results in low voltage drop across the gate and the source of a MOS transistor. Subsequently, low threshold MOSFETs are desired for operation at the low supply voltage. With the utilization of circuit design techniques and device models low threshold transistors can be obtained in current CMOS technologies. Lengthen the device decreases the threshold voltage considerably while forward body bias is a circuit design techniques that lowers device threshold values. In this chapter, using both of the techniques initially a low power and low voltage operational amplifier is designed.

#### 3.1 Threshold Voltage of the MOSFET

Threshold voltage modeling is elaborated in [10, 23]. The basic stages are presented in this section for completeness. Figure 3.2 depicts a long-channel enhancement mode n-MOSFET where bulk, source and drain terminals are connected to common reference termed as ground. A voltage,  $V_{GS}$  is applied to the gate and initially it is zero. As the gate voltage is increased to a positive magnitude from a zero value a depletion region is formed followed by weak inversion region close to the  $S_i$ - $S_iO_2$  interface. With further increment in gate voltage, a condition of strong inversion occurs where a p-type silicon is inverted to an n-type silicon. The certain value of the gate source voltage at which this condition occurs is called the threshold voltage,  $V_T$ .

There are three voltage components upon which threshold voltage,  $V_T$  of a MOSFET depends. These voltage components are the gate to bulk work function difference ( $\phi$ GC),  $-Q_{OX}/C_{OX}$  because of fixed oxide charge present at the Si-SiO2 interface and in the oxide, and a gate voltage ( $-2 \phi_F - Q_B/C_{OX}$ ) to alter the surface potential and to offset the  $Q_B$  that is the induced depletion region charge  $\phi F$  is Fermi energy and  $C_{OX}$  is the gate oxide capacitance per unit area.

Figure 3.2: The cross-section of an n-MOS with positive gate voltage applied showing the depletion region and the inversion layer [10]. G is gate, D is drain and S is source.

Mathematically,  $V_T$  can be expressed as follows:

$$V_T = \phi_{GC} - \frac{Q_{ox}}{c_{ox}} + (-2\phi_F - \frac{Q_B}{c_{ox}})$$

(3.1)

The first part  $\phi_{GC} - \frac{Q_{ox}}{c_{ox}}$  represents required voltage to attain flat-band (FB)

condition. The second part  $(-2\phi_F - \frac{Q_B}{c_{ox}})$  represents voltage required to bend the

bands in Si through a potential of  $2\phi_F$ .

The voltage that is required to attain the flat band condition is given by:

$$V_{FB} = \phi_{GC} - \frac{Q_{ox}}{c_{ox}} \tag{3.2}$$

For n-MOSFET Q<sub>B</sub> is given by:

$$Q_B = q N_A X_d = \sqrt{q N_A \varepsilon_{si} |\phi_s - \phi_F|} \quad for \ |\phi_s - \phi_F| \ge 0$$

(3.3)

In this equation N<sub>A</sub> represents the substrate doping density; X<sub>d</sub> is the thickness of the depletion region and  $\varepsilon_{si}$  represents the permittivity of silicon. The electrostatic surface potential of silicon with respect to Silicon substrate is  $\phi_s$ . In strong inversion region when  $V_{SB}=0$  (i.e. no body bias is applied) the depletion region charge  $Q_{BO}$  is given by

$$Q_B = \sqrt{-2qN_A\varepsilon_{si}|-2\phi_F|}.$$

(3.4)

While in the presence of body bias when  $V_{SB} \neq 0$  the required surface potential to produce strong inversion region is modified to  $|-2\phi_F| + V_{SB}$ .

The depletion region charge in such condition will be:

$$Q_B = \sqrt{-2qN_A\varepsilon_{si}|-2\phi_F + V_{SB}|}.$$

(3.5)

For n-MOS the threshold voltage in this condition will be:

$$V_T = \phi_{GC} - 2\phi_F - \frac{Q_{BO}}{c_{ox}} - \frac{Q_{OX}}{c_{ox}} - \frac{Q_B - Q_{BO}}{c_{ox}}, \text{ or}$$

(3.6)

$$V_T = V_{TO} \pm \gamma (\sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|}).$$

(3.7)

Where  $V_{TO}$  is the zero bias threshold voltage with bulk to source potential deference is zero. The  $\gamma$  parameter is known as body effect coefficient or body factor.

Generally,  $V_{SB} \leq 0$ , results in  $V_T \geq V_{TO}$  While with the substrate bias,  $V_{SB} \geq 0$ ,  $V_T$  is less than  $V_{TO}$ . Thus, a MOSFET can be designed to operate at a reduced threshold voltage by forward biasing the bulk source junction.

The separate equations for the n-MOS and p-MOS are given bellow:

For n-MOSFET

$$V_{TN} = V_{TNO} + \gamma (\sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|}).$$

(3.8)

Where the body factor is given by,  $\gamma = \frac{1}{c_{ox}} \sqrt{2q\varepsilon_{si}N_A}$ .

NA is the doping density in p-substrate.

For the p-MOSFET

$$V_{TP} = V_{TPO} - \gamma (\sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|}).$$

(3.9)

Where the body factor is given by,  $\gamma = \frac{1}{c_{ox}} \sqrt{2q\varepsilon_{si}N_D}.$

N<sub>D</sub> is the doping density in n-substrate.

#### **3.2 Forward Body-Bias**

With the upsurge in the use of battery-powered applications, design of low power circuit is enormously needed for portable devices like cellular phones, hand-held computers, healthcare equipment and personal assistant devices. As discussed earlier power supply reduction is the straightforward technique to achieve low power consumption. Forward body-bias technique is very beneficial in the low voltage CMOS circuits design. In reference [24], a low voltage inverter is designed using this technique. Using forward body bias MOSFETs a 0.8 V CMOS amplifier is designed and reported in [25].

Now the question arises is there any limit on the forward body bias voltage that reduces the threshold voltage of MOS transistors? The amount of  $V_{SB}$ , is limited by the phenomenon of CMOS latchup. Since large  $V_{SB}$  may trigger CMOS latchup. In [26] it is reported that the latchup action will not be triggered for the value of  $V_{SB} \leq 0.4$ volts. A brief investigation on CMOS latchup is presented here. Figure 3.3 depicts the vertical cross section of an n-well CMOS with parasitic *npn* and *pnp* bipolar junction transistors (BJTs). The corresponding equivalent circuit including both of the parasitic *npn* and *pnp* BJTs is shown in Figure 3.4 where source-bulk junctions are forward-biased and  $V_{DD}$  is 0.8 V. Figure 3.5 depicts the latchup current versus the forward body-bias voltage. It is apparent from Fig. 3.4 that the latchup action does not take place for the  $V_{SB} \leq 0.4$ V [25].

Figure 3.3: Vertical cross-section of an n-well CMOS showing parasitic bipolar junction transistors.[25]

Figure 3.4: Extracted equivalent circuit of Figure 3.2.

Figure 3.5: Latchup current under forward biased source-substrate condition for  $V_{DD}=0.8V$  [26].

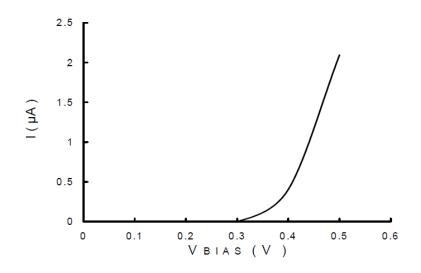

Figure 3.6 depicts the current trough bulk-source junction in a typical n-MOS while varying forward body bias is applied. It is clear that the current in a forward biased bulk-source n+-p junction is negligible till the junction is biased below 0.4 V.

Figure 3.6: Current through forward biased source-substrate junction in an n-MOSFET[25].

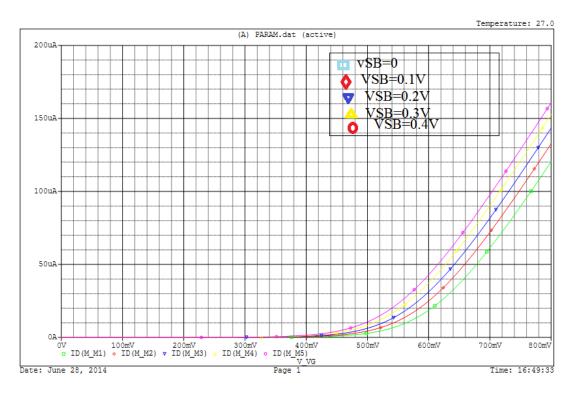

Figure 3.7 depicts how the threshold voltage is reduced for various values of bulk-source forward potential for a typical n- MOSFETs in a standard 180nm n-well CMOS process.

Figure 3.7: variation of drain current and threshold voltages w.r.t. bulk-source potential.

#### **3.3 Noise of Forward Body-Bias MOSFETS**

Noise is a major concern while designing analog circuits for low voltage applications.

Basically there are three types of noise in MOS transistors, Flicker noise, thermal noise and shot noise are associated with devices. Flicker noise also known as the 1/f noise. This noise is caused by trapped charge in Si-SiO<sub>2</sub> interface that is due to fluctuation in processing parameters and dominates at lower frequencies in a MOSFET. It is expressed as follows: [27]

$$\frac{v_{flucker}^2}{\Delta f} = \alpha \frac{I_D}{g_m^2 f}.$$

(3.10)

Where  $\frac{v_{flucker}^2}{\Delta f}$  is spectral density of the flicker noise voltage.  $\alpha$  is device specific constant. I<sub>D</sub>, *f* and g<sub>m</sub> are drain current, frequency of operation and trans-conductance of device respectively.

Other type of Noise is thermal noise that is caused by random motion of the electrons due to temperature variation in the channel of the MOSFET. It is given by [27]

$$\frac{\overline{v_{thermal}^2}}{\Delta f} = \frac{8}{3}kT\frac{1}{g_m}.$$

(3.11)

Where  $\frac{v_{thermal}^2}{\Delta f}$  is the spectral density of thermal noise voltage that is related to the V<sub>GS</sub> of the MOSFET that is being operated in the saturation region. *k*, *T* and *g<sub>m</sub>* are the

Boltzman's constant, absolute temperature and transconductance.

Shot noise is produced due to the transport phenomenon of charge carriers across the p-n junction. As each device has different energy and velocity transport is a random phenomenon. The shot noise is given by the following relation [27]:

$$\frac{i_{shot}^2}{\Delta f} = 2qI_{DC}.$$

(3.12)

Where  $\frac{\overline{u_{shot}^2}}{\Delta f}$  is the shot noise spectral density that is proportional to DC current  $I_{DC}$  in a pn junction.

Noise analysis of proposed active devise is will be discussed is subsequent section of this report.

# **CHAPTER 4**

# DESIGN OF FORWARD BODY-BIASED CURRENT-MODE AMPLIFIER

Amplifiers are the basic and widely used building block in analog and mixed- signal system design. In some of the previous works reported on low-voltage analog design wherein, bulk driven and current driven have been used [21, 28, 29]. In the previous one, the input is directly fed to the bulk and not the gate of the MOSFET. In the current driven topology, the source-bulk junction is forward biased by a bias current through another MOSFET connected to the bulk. A 0.8 V low power CMOS amplifier design using forward body-biased MOSFETs is reported in [25]. Several current mode amplifiers are also reported in [30], [31] that uses either pseudo resistors or other means to have low frequency path that increase power dissipation along with increased noise.

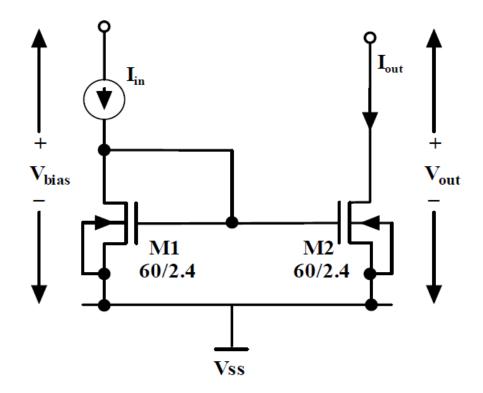

In this chapter a systematic approach to design a forward body-biased current-mode amplifier is presented. Starting with the design of a low voltage forward body bias current mirror, we are led to a FBB op-amp design and then it will be transformed to a current mode amplifier (reported in [32]).

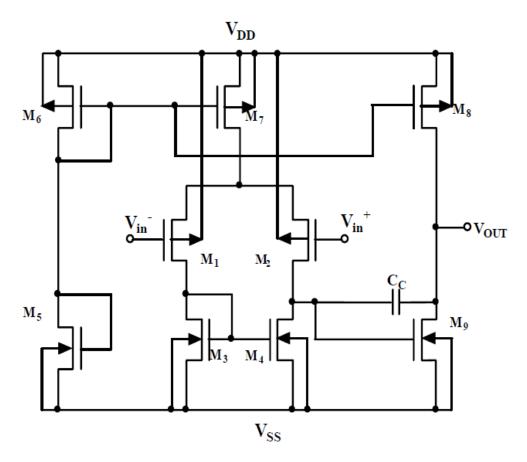

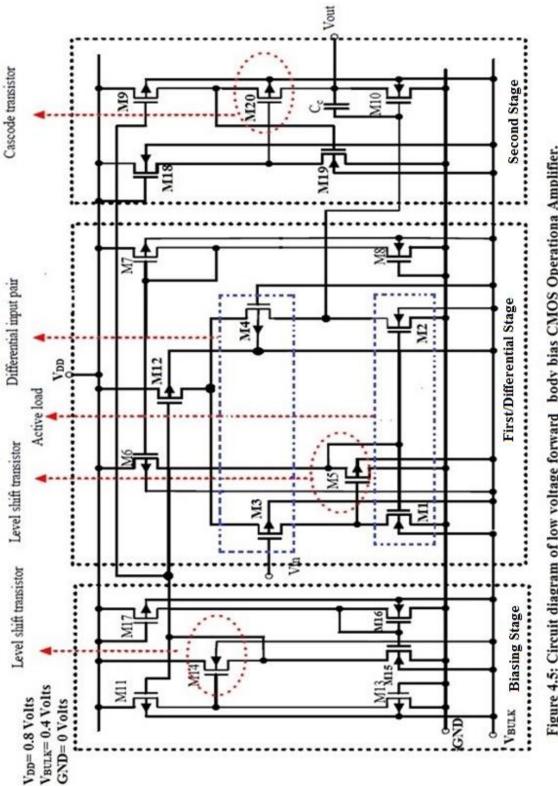

#### 4.1 A Two-Stage CMOS Amplifier Topology

Figure 4.1 depicts the circuit diagram of a two-stage CMOS operational-amplifier. The first stage consists of a p-MOS input differential pair,  $M_1$ - $M_2$  with an n-channel current mirror active load,  $M_3$ - $M_4$ . Transistors,  $M_5$  and  $M_6$  provide the bias current to  $M_7$  that biases the complete first stage. The second stage consists of an n-channel common source amplifier that level shifts the output voltage to enhance the gain.  $M_9$  is the n-MOS with a p-channel current-source load,  $M_8$ . Second stage is also biased by the current provided through  $M_5$  and  $M_6$  Transistors, and  $C_C$  is compensation (pole splitting) capacitor.

Figure 4.1: A two-stage CMOS operational amplifier.

#### 4.2 Low Voltage Current Mirror Design

Current mirrors are vital building blocks in design of analog integrated circuits. Current mirrors are used as an active load to enhance gain in op-amp as well as the serve as biasing circuits to also provide bias currents. Figure 4.2 depicts the basic CMOS current mirror circuit.

For the p-MOS current mirror, we can write:

$$\frac{I_{OUT}}{I_{IN}} = \frac{(W_2/L_2)}{(W_1/L_1)}$$

(4.1)

Where  $W_x$  and  $L_x$  is the channel width and length of transistor x respectively. In Fig. 4.2, to turn on the n-MOS transistor  $M_1$  it needs an input voltage greater than the threshold voltage,  $V_{TN}$ . The current mirror circuit of Fig. 4.2 is modified to a level shift current mirror as shown in Fig. 4.3, where the bias voltage  $V_{DS1}$  can be obtained through following circuit design equations:

$$V_{DS1} = V_{GS1} - V_{SG3} \tag{4.2}$$

The Eq. (4.2) defines that the bias voltage ( $V_{DS1}$ ) to transistor  $M_1$  is changed by the gate-source voltage of transistor  $M_3$  i.e.  $V_{SG3}$ . In this circuit,  $M_3$  is operated in the sub-threshold region ( $V_{SG3} < |V_{T,P}|$ ).

Figure 4.4 depicts a new level-shift current mirror design which combines the advantages of the level shift circuit for low voltage operation with the reduction in the threshold voltage of a forward body-biased MOSFET. It also includes output impedance enhanced architecture [33], which increases the output impedance of the current mirror, thereby enhancing the gain of the amplifier. This low voltage current mirror circuit of Fig. 4.4 operates as follows.  $I_{D1} = I_{D2}$ , since  $V_{GS1} = V_{GS2}$  where  $I_{Dx}$  is drain current of transistor x. The transistor M9 provides the bias current to the input transistor M1.

Figure 4.2: An n-MOS current mirror circuit in CMOS. The fraction indicate W/L ratio of the corresponding transistors.

Figure 4.3: A CMOS level shift current mirror CMOS circuit. The fraction indicate W/L ratio of the corresponding transistors. [25]