# INVESTIGATION OF DIFFERENT INTELLIGENT CONTROL ALGORITHM FOR D-STATCOM

#### DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE

OF

MASTER OF TECHNOLOGY

IN

Power SYSTEM

Submitted by:

Anuj Varshney (2K13/PSY/03)

*Under the supervision of*

Dr. Rachana Garg

# DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

2015

DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

**CERTIFICATE**

I, Anuj Varshney, Roll No. 2K13/PSY/03 student of M. Tech. (Power System), hereby

declare that the dissertation titled "Investigation of Different Intelligent control

Algorithm for D-STATCOM" under the supervision of Dr. Rachana Garg, Associate

Professor, Department of Electrical Engineering, Delhi Technological University in partial

fulfilment of the requirement for the award of the degree of Master of Technology has not

been submitted elsewhere for the award of any Degree.

Place: Delhi

cc. Denn

Date: 15.07.2015

Anuj Varshney

Dr. Rachana Garg

**Associate Professor**

Department of Electrical Engineering

Delhi Technological University

ACKNOWLEDGEMENT

I would like to express my sincere gratitude to Dr. Rachana Garg for her guidance and

assistance in the dissertation. The technical discussions with her were always been very

insightful, and I will always be indebted to her for all the knowledge she shared with me.

Her prompt responses and availability despite her constantly busy schedule were truly

appreciated. She always helped me in all the technical and non-technical issues during the

production of this dissertation. Without her consistent support, encouragement and

valuable inputs, this dissertation would not have become possible.

I would like to express my deep gratitude to Prof. Madhusudan Singh, Head of Department

of Electrical Engineering for providing his support during my project.

I would also like to thank my batch-mates and friends who encouraged and helped me in

completing the dissertation. A special mention to Saurabh, Astitva, Sidhant and Sanjeet

for their continued support and motivation.

Finally, I express my deep sincere thanks to my Parents and my brothers who motivated

and encouraged me for higher studies, without which it wouldn't have been possible.

Anuj Varshney

(2K13/PSY/03)

M.Tech (Power System)

3

# **ABSTRACT**

The presence of harmonics in power supply network poses a severe power quality problem that results in huge power losses in distribution system, causes interference in the parallel running communication lines and, sometimes, operational failures of electronic equipment. DSTATCOM are employed to feed the required reactive power demand, suppress the current harmonics, minimize the unbalancing in the line currents and reduce the total harmonic distortion (THD) in the load. The voltage source converter (VSC) is the core of a DSTATCOM. The hysteresis current control is an indirect method of controlling the VSC. In this work, Synchronous Reference Frame (SRF) theory with Proportional-Integral controller, Conductance based Fryze Algorithm, Fuzzy logic control technique, different topologies of fuzzy logic controller and Adaptive Neuro-Fuzzy Inference system technique has been implemented for the generation of reference current signals for the controller. This work investigates the effectiveness of the proposed model in mitigation of harmonics currents, feed reactive power demanded by the load and reduce unbalancing due to the different loads in each phase by modelling a 3-φ three-wire D-STATCOM. Simulation results indicate that the proposed D-STATCOM can restrain the unwanted component of current from reaching to source effectively.

All topologies are tested for different loads (non-linear load and unbalanced linear load). Performance comparison between the PI controller, PI-like FLC, PI gain scheduled FLC, Hybrid FLC-PI controller and ANFIS controller are made in terms of several performance criteria such as peak overshoot, settling time (t<sub>s</sub>) and rise time of the DC link voltage. Under all these topologies, THD of the grid side current is well within the IEEE standards and UPF at grid side is maintained.

# **Table of Contents**

| CER  | TIFICATE       | ••••••   |                                         | i   |

|------|----------------|----------|-----------------------------------------|-----|

| ACK  | NOWLEDGEN      | MENT     | *************************************** | II  |

| ABS' | TRACT          |          |                                         | iii |

| TAB  | LE OF CONT     | ENTS     |                                         | iv  |

|      |                |          |                                         |     |

| LIST | OF TABLES.     |          |                                         | xi  |

| LIST | OF ABBREV      | IATI(    | ONS                                     | xii |

| CHA  | PTER 1. INTE   | RODU     | CTION                                   | 1   |

| 1.1  | Introduction . |          |                                         | 1   |

| 1.2  | Power Scenar   | rio in I | ndia                                    | 2   |

| 1.3  | Power Qualit   | y        |                                         | 2   |

| 1.4  | Impact of Pov  | wer Qı   | nality Problems On Consumer             | 3   |

| 1.5  | Power Qualit   | y Stan   | dards                                   | 5   |

| 1.6  | Custom Powe    | er Dev   | ices                                    | 6   |

|      | 1.6.1          | Shur     | t Devices                               | 7   |

|      | 1.6.2          | Serie    | es Devices                              | 7   |

|      | 1.6.3          | Hybı     | rid Devices                             | 8   |

| CHA  | PTER 2. LITE   | CRATU    | URE REVIEW                              | 10  |

| 2.1  | GENERAL        |          |                                         | 10  |

| 2.2  | LITERATUR      | RE SUI   | RVEY                                    | 10  |

| CHA  | APTER 3. Mode  | elling a | and Design of D-STATCOM                 | 16  |

| 3.1  | Load Comper    | nsation  | using D-STATCOM                         | 16  |

|      | 3.1.1          | Oper     | ration Modes of D-STATCOM               | 19  |

| 3.2  | Proposed Sys   | tem      |                                         | 20  |

|      | 3.2.1          | Desi     | gn of D-STATCOM                         | 20  |

|      |                | i.       | DC Bus Voltage                          | 21  |

|      |                | ii.      | DC Bus Capacitor Rating                 | 22  |

|      |                | iii.     | Interfacing Inductance                  | 23  |

|      |                | iv.      | Ripple Filter                           | 23  |

| 3.3  | Synchronous    | Refere   | ence Frame Theory                       | 24  |

|      | 3.3.1          | Phas     | e Locked Loop                           | 26  |

|      | 3.3.2          | Hysteresis Current Controller       | 26       |

|------|----------------|-------------------------------------|----------|

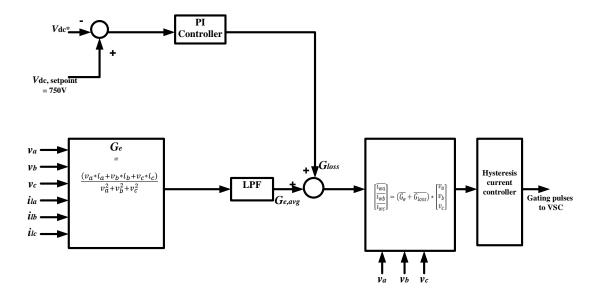

| 3.4  | Conductance    | based Fryze Algorithm               | 28       |

| CHA  | PTER 4. DIFF   | ERENT TOPOLOGIES OF FUZZY LOGIC CON | TROLLERS |

| FOR  | D-STATCOM      | [                                   | 31       |

| 4.1  | PI-like Fuzzy  | Logic Controller                    | 32       |

| 4.2  | PI Gain Scheo  | duling Using FLC                    | 35       |

| 4.3  | Hybrid Fuzzy   | -PI Controller                      | 36       |

| CHA  | PTER 5. ANFI   | IS control Scheme for D-STATCOM     | 38       |

| 5.1  | Architecture a | and Algorithm                       | 38       |

| 5.2  | Construction   | of Neuro-Fuzzy System               | 40       |

|      | 5.2.1          | Structure Identification Phase      | 41       |

|      |                | 5.2.1.1 Grid Type Partitioning      | 41       |

|      |                | 5.2.1.2 Clustering                  | 41       |

| 5.2  | Design of AN   | NFIS controller for proposed work   | 42       |

| CHA  | PTER 6. Resul  | lts and Discussion                  | 44       |

| 6.1  | System Confi   | iguration and System Modelling      | 44       |

| 6.2  | Synchronous    | Reference Frame Theory              | 48       |

| 6.3  | Conductance    | based Fryze Algorithm               | 52       |

| 6.4  | Different topo | ologies of FLC                      | 56       |

|      | 6.4.1          | PI-like FLC                         | 56       |

|      | 6.4.2          | PI Gain Scheduling using FLC        | 60       |

|      | 6.4.3          | Hybrid Fuzzy-PI Controller          | 63       |

| 6.5  | ANFIS based    | Control Scheme                      | 66       |

| CHA  | PTER 7. CON    | CLUSION AND FUTURE SCOPE            | 73       |

| 7.1  | Conclusion     |                                     | 73       |

| 7.2  | Future Scope   |                                     | 73       |

| REFI | ERENCES        |                                     | 75       |

| APPI | ENDIX          |                                     | 81       |

| PURI | LICATION       |                                     | 82       |

# LIST OF FIGURES

| Figure No. | Name                                                                                               | Page No |

|------------|----------------------------------------------------------------------------------------------------|---------|

| Fig 1.1    | Single line Diagram of a typical Power System                                                      | 3       |

| Fig 1.2    | Single line Diagram of DSTATCOM                                                                    | 7       |

| Fig 1.3    | Single Line diagram of DVR connection to AC Line                                                   | 8       |

| Fig 1.4    | Single line diagram of Hybrid Compensator                                                          | 9       |

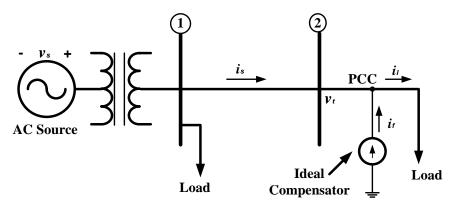

| Fig 3.1    | Single line diagram of ideal load compensation                                                     | 17      |

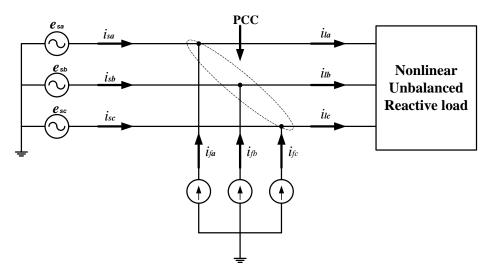

| Fig 3.2    | Schematic diagram of a 3-φ ideal shunt compensator connected to 3-φ three wire distribution system | 18      |

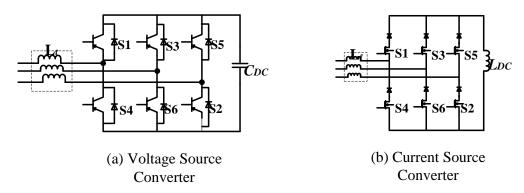

| Fig 3.3    | (a) Voltage source converter, (b) Current Source converter                                         | 19      |

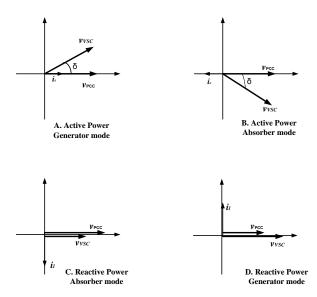

| Fig 3.4    | Different Modes of Operation of DSTATCOM                                                           | 20      |

| Fig 3.5    | Schematic diagram for shunt connected DSTACOM to an AC Three phase three wire distribution system  | 21      |

| Fig 3.6    | Principle of operation of DSTATCOM instantaneous active power and reactive power                   | 22      |

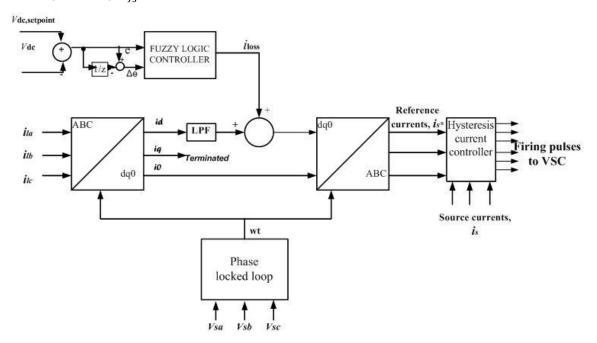

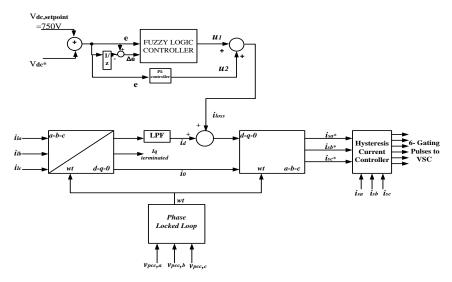

| Fig 3.7    | DSTATCOM Control Scheme Based on SRFT                                                              | 24      |

| Fig 3.8    | Schematic Diagram of 3-φ PLL                                                                       | 26      |

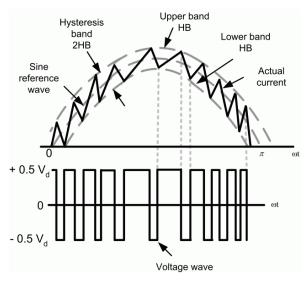

| Fig 3.9    | Hysteresis current control                                                                         | 27      |

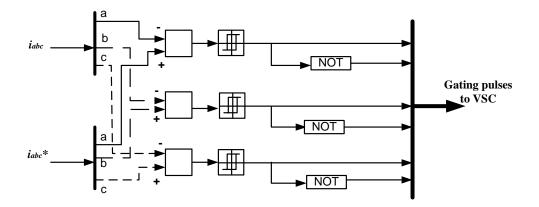

| Fig 3.10   | Schematic Diagram of Hysteresis Current Controller                                                 | 28      |

| Fig 3.11   | Control scheme for DSTATCOM using conductance based Fryze algorithm                                | 30      |

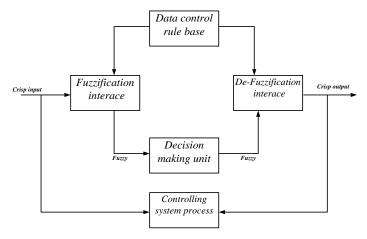

| Fig. 4.1   | Simple fuzzy logic control system block diagram                                                    | 31      |

| Fig. 4.2   | Schematic Diagram of Fuzzy Logic based control scheme for DSTATCOM                                 | 33      |

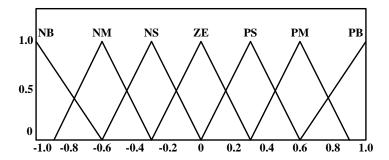

| Fig. 4.3   | Membership functions of $e$ , $\Delta e$ and $i_{loss}$                                            | 34      |

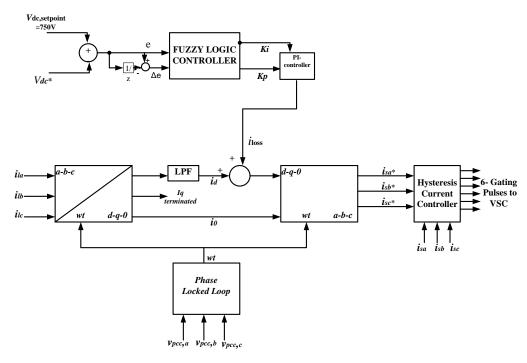

| Fig. 4.4      | Schematic Diagram of PI gain Scheduled FLC                                                                               | 35 |

|---------------|--------------------------------------------------------------------------------------------------------------------------|----|

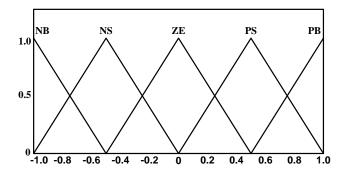

| Fig. 4.5      | Membership function $e$ , $\Delta e$ and $i_{loss}$                                                                      | 36 |

| Fig. 4.6      | Schematic Diagram of Hybrid Fuzzy-PI controller                                                                          | 37 |

| Fig. 5.1      | Five-layer ANFIS Feedforward Network                                                                                     | 39 |

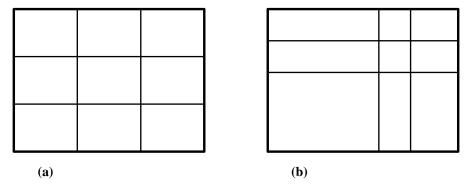

| Fig. 5.2      | (a) Fixed and (b) Adaptive Grid Partitioning                                                                             | 41 |

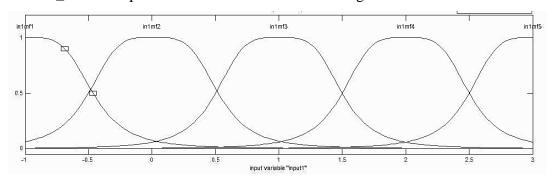

| Fig. 5.3      | Membership Functions plot for Input variables of ANFIS controller                                                        | 42 |

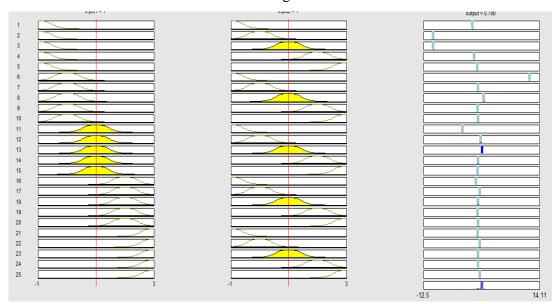

| Fig. 5.4      | Rule Base view from the toolbox                                                                                          | 43 |

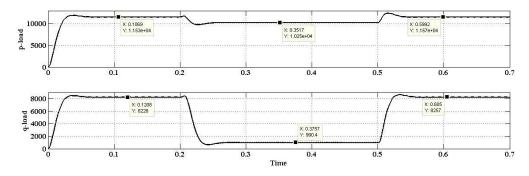

| Fig. 6.1      | Schematic diagram for shunt connected DSTACOM to an AC Three phase three wire distribution system                        | 44 |

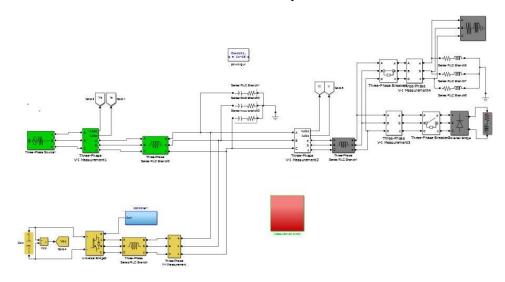

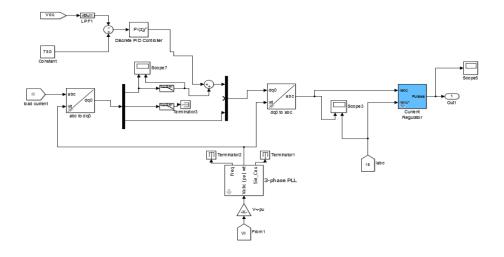

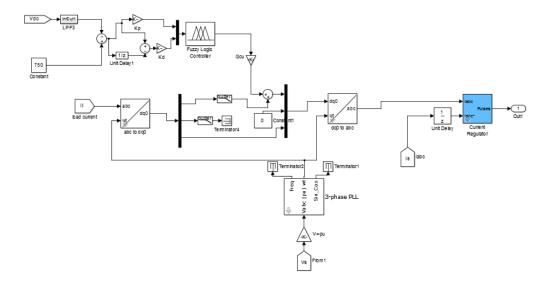

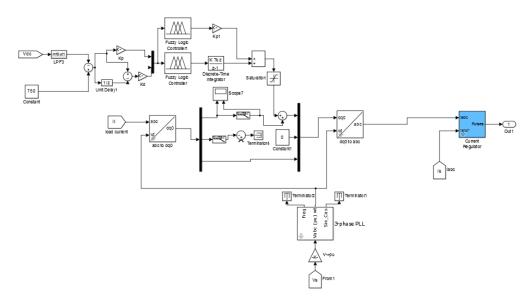

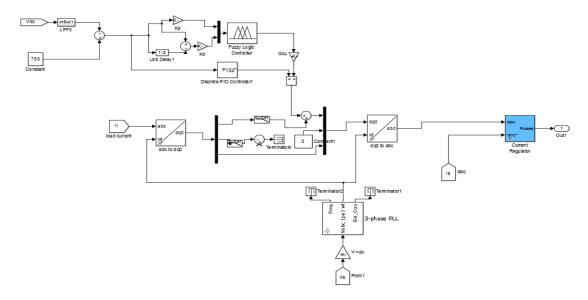

| Fig. 6.2      | Simulink model of the system with shunt connected DSTATCOM                                                               | 44 |

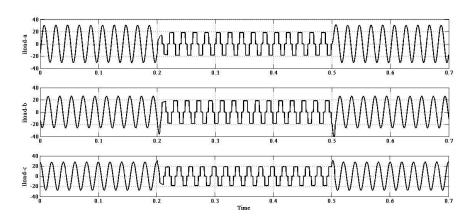

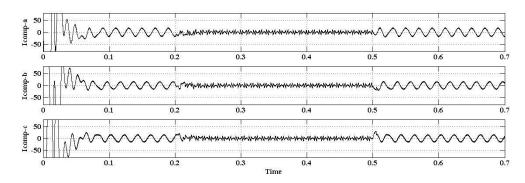

| Fig. 6.3      | Load current waveform in each phase                                                                                      | 45 |

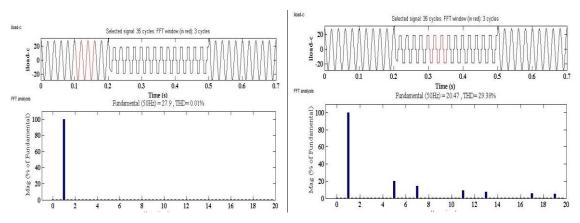

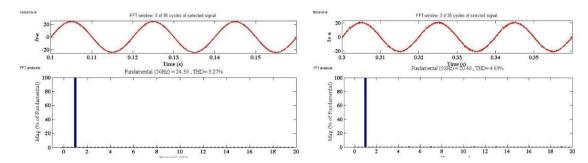

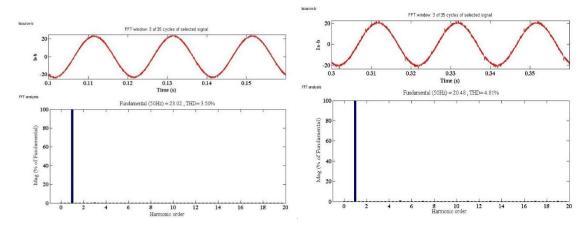

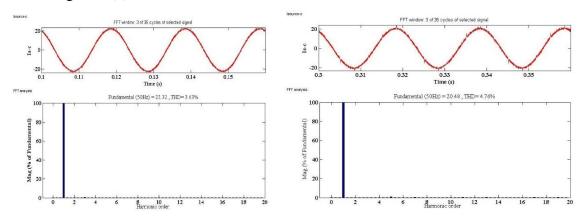

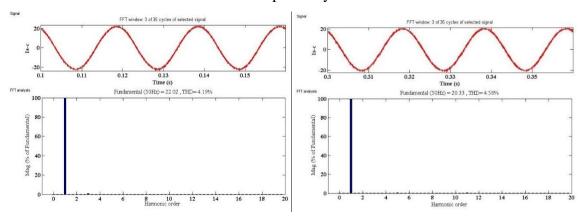

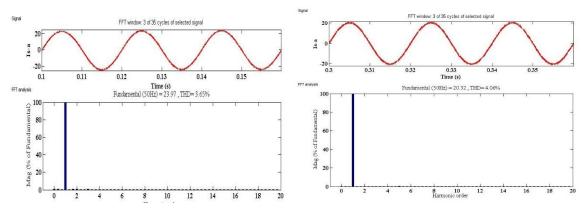

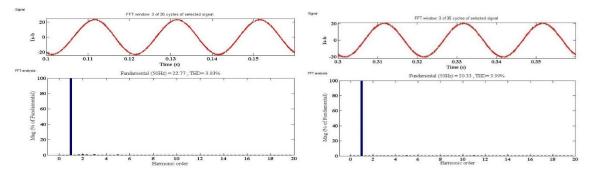

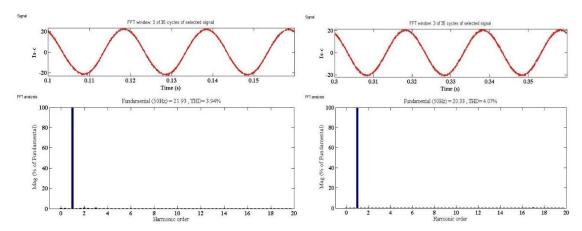

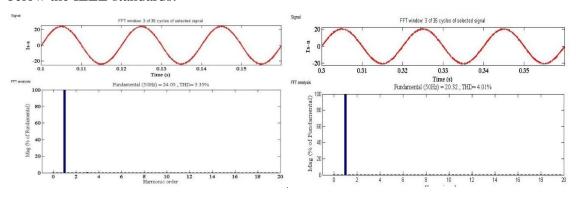

| Fig. 6.4      | FFT analysis for phase-a line current with (a) linear+unbalanced load and (b) non-linear load                            | 46 |

| Fig. 6.5      | FFT analysis for phase-b line current with (a) linear+unbalanced load and (b) non-linear load                            | 46 |

| Fig. 6.6      | FFT analysis for phase-c line current with (a) linear+unbalanced load and (b) non-linear load                            | 47 |

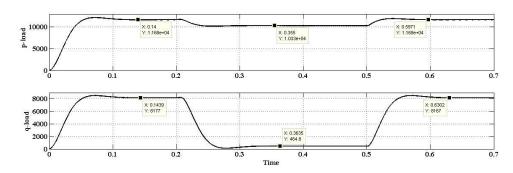

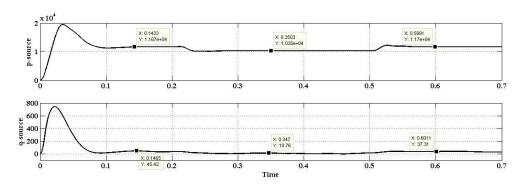

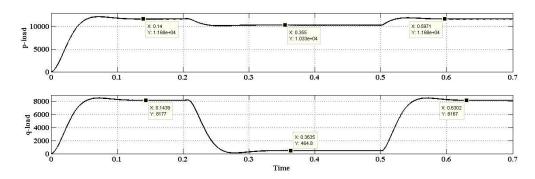

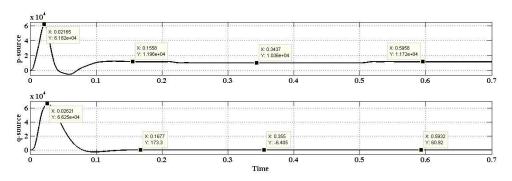

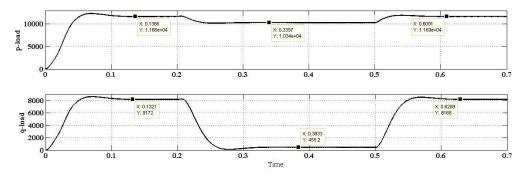

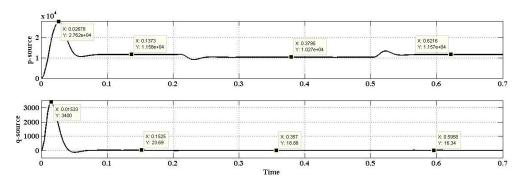

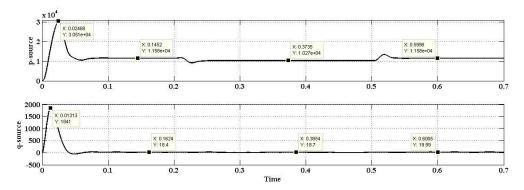

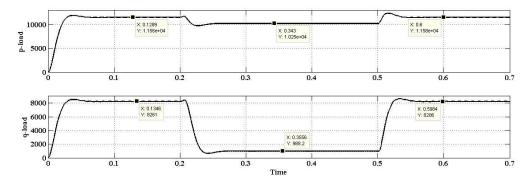

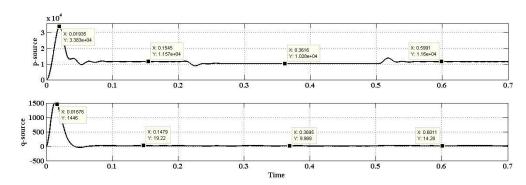

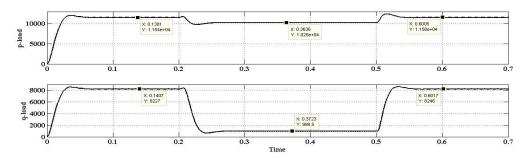

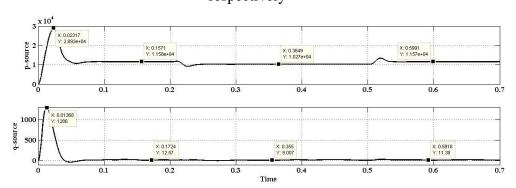

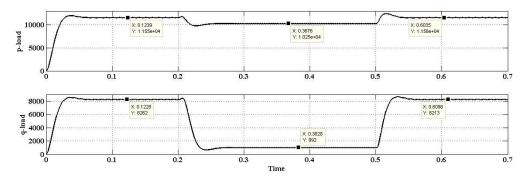

| Fig. 6.7      | Instantaneous active and reactive power demand of loads                                                                  | 47 |

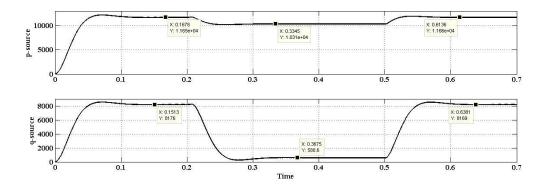

| Fig. 6.8      | Instantaneous active and reactive power supply from source                                                               | 48 |

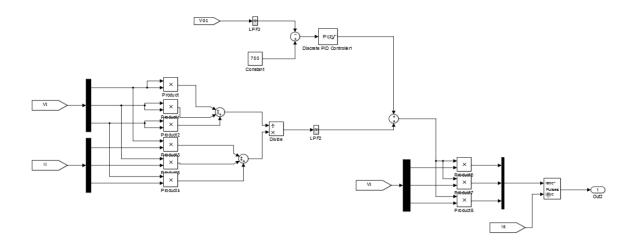

| Fig. 6.9      | Simulink Control model based on SRFT                                                                                     | 49 |

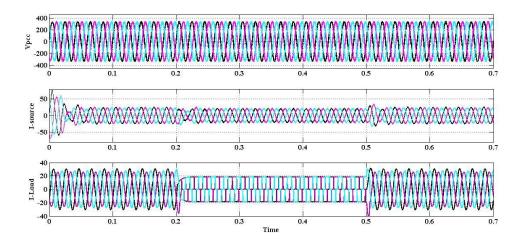

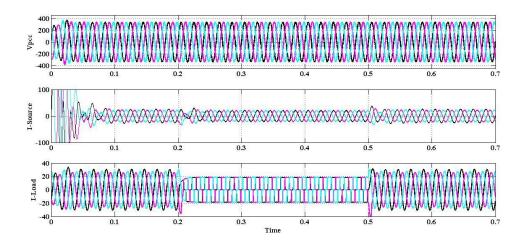

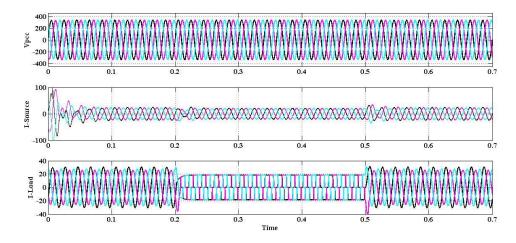

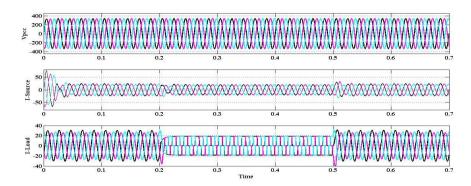

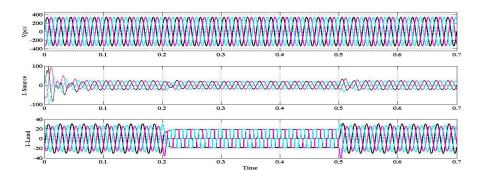

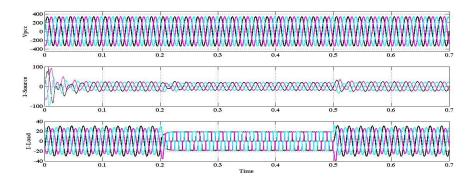

| Fig. 6.10     | Three phase waveform of voltage at PCC ( $v_{pcc}$ ), source current ( $i_{s-abc}$ ) and load current ( $i_{load-abc}$ ) | 49 |

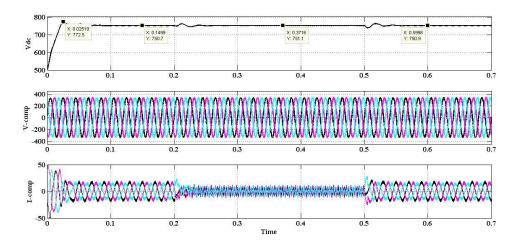

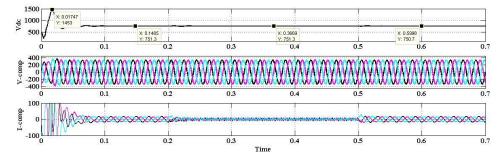

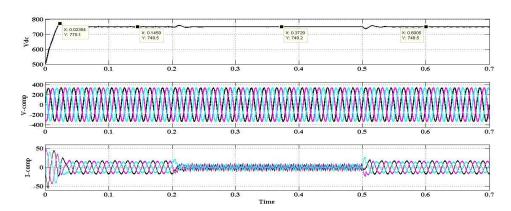

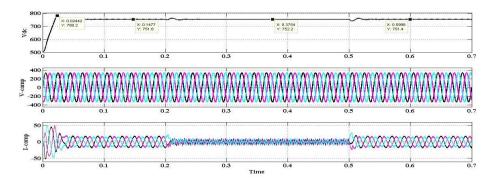

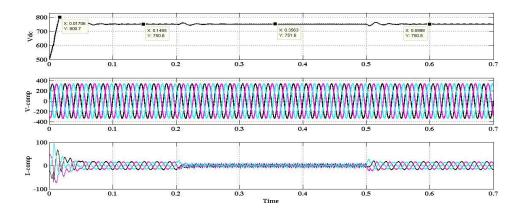

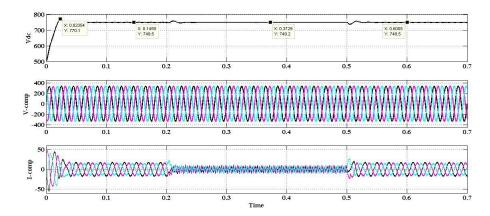

| Fig. 6.11     | Waveforms of DC terminal voltage, AC voltage and current generated by the DSTATCOM                                       | 49 |

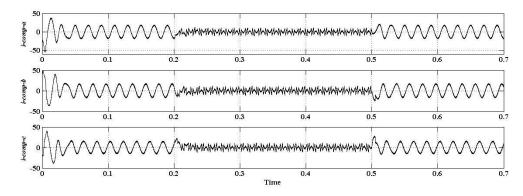

| Fig. 6.12     | Three phase current waveform generated by the DSTATCOM                                                                   | 50 |

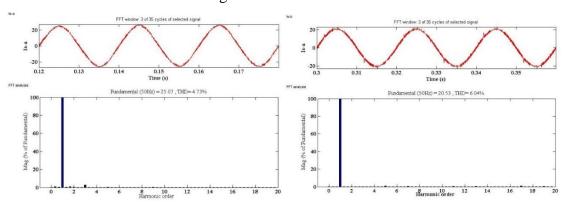

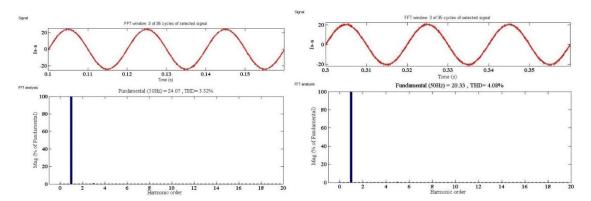

| Fig 6.13 (a)  | Source current waveform of Phase-a at time 0.1 sec and 0.3 sec                                                           | 50 |

| Fig. 6.13 (b) | Source current waveform of Phase- <i>b</i> at time 0.1 sec and 0.3 sec                                                   | 50 |

| Fig. 6.13 (c) | Source current waveform of Phase-c at time 0.1 sec and 0.3 sec                                                           | 51 |

| T' (11 ( )          |                                                                          |                |

|---------------------|--------------------------------------------------------------------------|----------------|

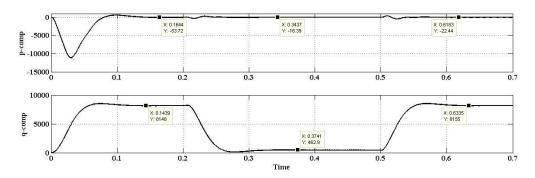

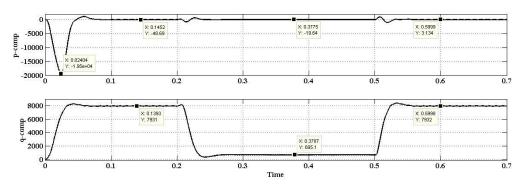

| Fig. 6.14 (a)       | Instantaneous active and reactive power delivered from source            | 51             |

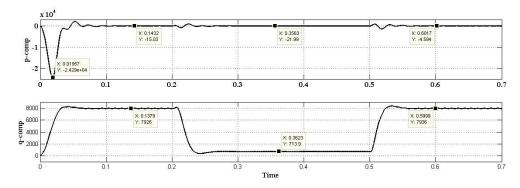

| Fig 6 14 (b)        |                                                                          | 52             |

| Fig 6.14 (b)        | Instantaneous active and reactive power delivered from DSTATCOM          | 32             |

| Fig. 6.14 (c)       | Instantaneous active and reactive power demand of                        | 52             |

|                     | load                                                                     |                |

| Fig. 6.15           | Simulink model of the Fryze algorithm based                              | 53             |

|                     | controller                                                               |                |

| Fig. 6.16           | Voltage at PCC ( $V_{pcc}$ ), source current ( $I$ -source) and          | 53             |

| 8                   | load current ( <i>I-load</i> )                                           |                |

| Fig. 6.17           | Voltage at DC terminal and at AC terminal, and                           | 53             |

| 115. 0.17           | Current generated from the DSTATCOM                                      | 23             |

| Fig. 6.18           | Three phase AC current generated from DSTATCOM                           | 54             |

| 11g. 0.16           | Three phase AC current generated from DSTATCOW                           | J <del>4</del> |

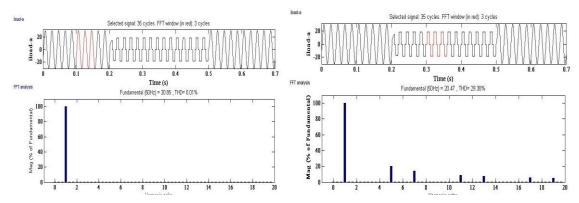

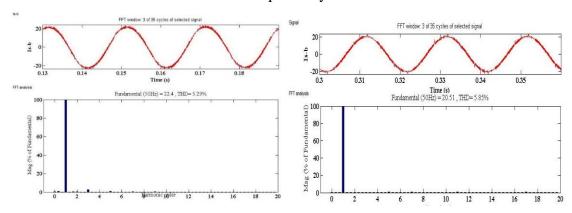

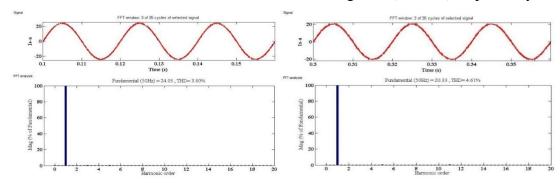

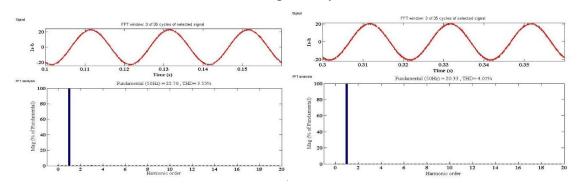

| Fig. 6.19 (a)       | THD of the line current of phase- $a$ at time $t = 0.1$ sec              | 54             |

|                     | and at $t = 0.3$ sec respectively                                        |                |

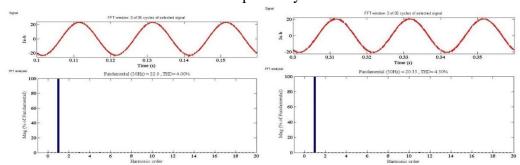

| Fig. 6.19 (b)       | THD of the line current of phase- <i>b</i> at time $t = 0.1 \text{ sec}$ | 54             |

| <i>B</i> , 1, 1 (1) | and at $t = 0.3$ sec respectively                                        | -              |

| Fig. 6.19 (c)       | THD of the line current of phase- $c$ at time $t = 0.1$ sec              | 55             |

| 8 (1)               | and at $t = 0.3$ sec respectively                                        |                |

| Fig. 6.20 (a)       | Instantaneous active and Reactive power supplied                         | 55             |

| 118. 0.20 (a)       | from source                                                              |                |

| Fig. 6.20 (b)       | Instantaneous active and Reactive power supplied                         | 55             |

| 118. 0.20 (0)       | from DSTATCOM                                                            |                |

| Fig. 6.20 (c)       | Instantaneous active and Reactive power demand of                        | 56             |

| 11g. 0.20 (c)       | load                                                                     | 20             |

| Fig. 6.21           | Simulink model of PI-like FLC controller for                             | 56             |

| 115. 0.21           |                                                                          | 30             |

|                     | DSTATCOM                                                                 |                |

| Fig. 6.22           | Three Phase Voltage at PCC ( $v_{pcc}$ ), source side current            | 57             |

|                     | $(i_{source})$ and Load side current $(I_{load})$                        |                |

| Fig 6.23            | Voltage at DC terminal ( $V_{dc}$ ), at AC terminal (V-                  | 57             |

| _                   | comp) and current (I-comp) generated by the                              |                |

|                     | compensator respectively                                                 |                |

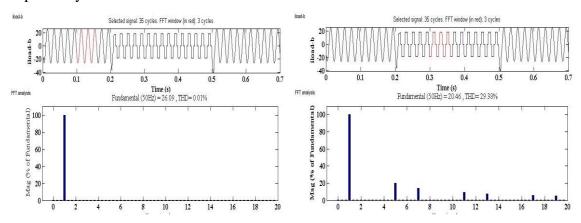

| Fig. 6.24 (a)       | THD of the line current of phase-a at time $t = 0.1$ sec                 | 58             |

|                     | and at $t = 0.3$ sec respectively                                        |                |

| Fig. 6.24 (b)       | THD of the line current of phase- <i>b</i> at time $t = 0.1 \text{ sec}$ | 58             |

|                     | and at $t = 0.3$ sec respectively                                        |                |

| Fig. 6.24 (c)       | THD of the line current of phase- $c$ at time $t = 0.1$ sec              | 58             |

|                     | and at $t = 0.3$ sec respectively                                        | -              |

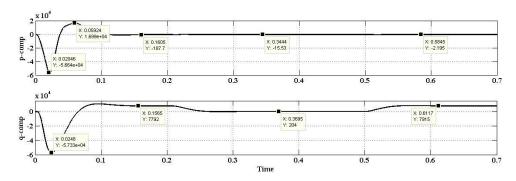

| Fig. 6.25 (a)       | Instantaneous active and reactive powers from source                     | 59             |

| <i>G. 21–2 (4)</i>  | respectively                                                             |                |

| <u> </u>            | I                                                                        |                |

| Fig. 6.25 (b)  | Instantaneous active and reactive powers from                                    | 59  |

|----------------|----------------------------------------------------------------------------------|-----|

|                | DSTATCOM respectively                                                            |     |

| Fig. 6.25 (c)  | Instantaneous active and reactive powers to load                                 | 59  |

| _              | respectively                                                                     |     |

|                | •                                                                                |     |

| Fig. 6.26      | Simulink model for PI gain scheduled type FLC                                    | 60  |

|                | controller                                                                       |     |

| Fig. 6.27      | Three phase waveform of Voltage at PCC (V <sub>pcc</sub> ),                      | 60  |

|                | Current at source side (I-source), current at load side                          |     |

|                | (I-load) respectively                                                            |     |

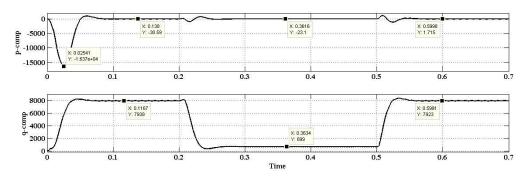

| Fig. 6.28      | DC terminal voltage (V <sub>dc</sub> ), three phase AC terminal                  | 61  |

|                | voltage $(V_{comp})$ and line currents $(I_{comp})$ from                         |     |

|                | DSTATCOM respectively                                                            |     |

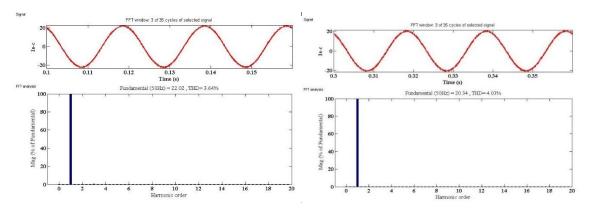

| Fig. 6.29 (a)  | THD of the line current of phase- $a$ at time $t = 0.1$ sec                      | 61  |

|                | and at $t = 0.3$ sec respectively                                                |     |

| Fig. 6.29 (b)  | THD of the line current of phase- $b$ at time $t = 0.1$ sec                      | 61  |

|                | and at $t = 0.3$ sec respectively                                                |     |

| Fig. 6.29 (c)  | THD of the line current of phase- $c$ at time $t = 0.1$ sec                      | 62  |

| _              | and at $t = 0.3$ sec respectively                                                |     |

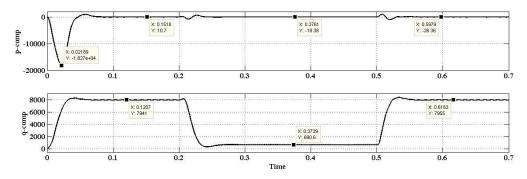

| Fig. 6.30 (a)  | Instantaneous active and reactive powers from source                             | 62  |

|                | respectively                                                                     |     |

| Fig. 6.30 (b)  | Instantaneous active and reactive powers from                                    | 62  |

|                | DSTATCOM respectively                                                            |     |

| Fig. 6.30 (c)  | Instantaneous active and reactive powers to the load                             | 63  |

|                | respectively                                                                     |     |

| Fig. 6.31      | Simulink model of Hybrid fuzzy-PI controller for                                 | 63  |

|                | DSTATCOM                                                                         |     |

| Fig. 6.32      | Three phase voltage at PCC (V <sub>pcc</sub> ), line current from                | 63  |

|                | source (I-source) and line current from load (I-Load)                            |     |

|                | respectively                                                                     |     |

| Fig. 6.33      | DC terminal voltage (V <sub>dc</sub> ), AC terminal voltage (V <sub>comp</sub> ) | 64  |

|                | and compensating currents (I <sub>comp</sub> ) respectively                      |     |

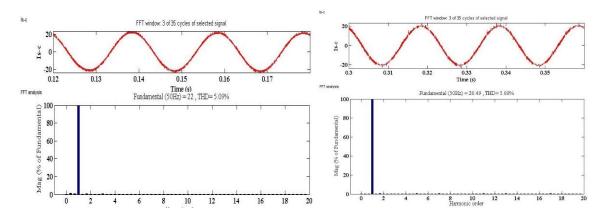

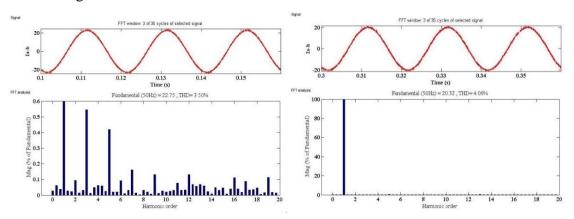

| Fig. 6.34 (a)  | THD of the line current of phase-a at time $t = 0.1$ sec                         | 64  |

|                | and at $t = 0.3$ sec respectively                                                |     |

| Fig. 6.34 (b)  | THD of the line current of phase- $b$ at time $t = 0.1$ sec                      | 64  |

|                | and at $t = 0.3$ sec respectively                                                |     |

| Fig. 6.34 (c)  | THD of the line current of phase- $c$ at time $t = 0.1$ sec                      | 65  |

|                | and at $t = 0.3$ sec respectively                                                | 0.5 |

| Fig. 6.35 (a)  | Instantaneous active and reactive powers from source                             | 65  |

| 116.0.33 (a)   | respectively                                                                     | 0.5 |

| Fig. 6.35 (b)  | Instantaneous active and reactive powers from                                    | 65  |

| 1 1g. 0.33 (0) | DSTATCOM respectively                                                            | 03  |

|                | DSTATEON TESPECTIVELY                                                            |     |

| Fig. 6.35 (c) | Instantaneous active and reactive powers to load respectively | 66 |

|---------------|---------------------------------------------------------------|----|

| Fig. 6.36     | Three phase voltage at PCC (Vpcc), line currents              | 66 |

|               | from source (I-source) and line currents to load (I-          |    |

|               | load) respectively                                            |    |

| Fig. 6.37     | DC terminal voltage, three phase AC terminal voltage          | 67 |

|               | and Compensating current generated from                       |    |

|               | DSTATCOM respectively                                         |    |

| Fig. 6.38 (a) | THD of the line current of phase- $a$ at time $t = 0.1$ sec   | 67 |

|               | and at $t = 0.3$ sec respectively                             |    |

| Fig. 6.38 (b) | THD of the line current of phase- $b$ at time $t = 0.1$ sec   | 67 |

|               | and at $t = 0.3$ sec respectively                             |    |

| Fig. 6.38 (c) | THD of the line current of phase- $c$ at time $t = 0.1$ sec   | 68 |

|               | and at $t = 0.3$ sec respectively                             |    |

| Fig. 6.39 (a) | Instantaneous active and reactive powers from source          | 68 |

|               | respectively                                                  |    |

| Fig. 6.39 (b) | Instantaneous active and reactive powers from D-              | 68 |

|               | STATCOM respectively                                          |    |

| Fig. 6.39 (c) | Instantaneous active and reactive powers to load              | 69 |

|               | respectively                                                  |    |

# LIST OF TABLES

| Table No. | Title                                                                                 | Page No. |

|-----------|---------------------------------------------------------------------------------------|----------|

| 1.1       | Power Quality problems and their causes                                               | 4        |

| 1.2       | Current distortion limits for General Distribution Systems                            | 6        |

| 3.1       | Comparison of VSC and CSC                                                             | 19       |

| 4.1       | FLCs rule base for computation of $i_{loss}$                                          | 34       |

| 4.2       | FLCs rule base for computation of $K_p$ and $K_i$                                     | 36       |

| 5.1       | Rule Base using ANFIS toolbox                                                         | 43       |

| 6.1       | Table. 6.1 List of Magnitude and THD % in three line currents after compensation      | 51       |

| 6.2 (a)   | List of THD % and Magnitude of current in line currents during linear+unbalanced load | 69       |

| 6.2 (b)   | List of THD % and Magnitude of current in line currents during Non-linear load        | 70       |

| 6.3 (a)   | Instantaneous active and Reactive powers magnitude during linear+unbalanced load      | 70       |

| 6.3 (b)   | Instantaneous active and Reactive powers magnitude during Non-linear load             | 71       |

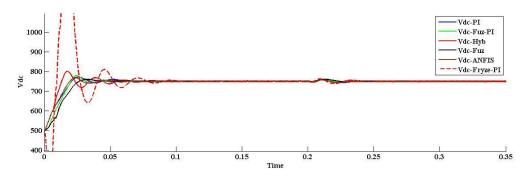

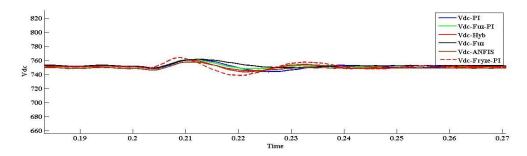

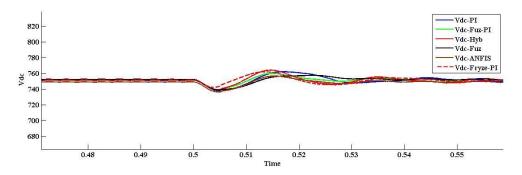

| 6.4       | Comparison of DC terminal voltage response due to different controllers               | 72       |

# LIST OF ABBREVIATION

| DC        | Direct Current                                  |

|-----------|-------------------------------------------------|

| AC        | Alternating Current                             |

| VSC       | Voltage Source Converter                        |

| PWM       | Pulse Width Modulation                          |

| HCC       | Hysteresis Current Controller                   |

| IGBT      | Insulated Gate Bipolar Transistor               |

| W         | Watts                                           |

| VAr       | Reactive Volt Ampere                            |

| THD       | Total Harmonic Distortions                      |

| PCC       | Point of Common Coupling                        |

| PID       | Proportional-Integral-Derivative                |

| PLL       | Phase Locked Loop                               |

| RMS       | Root Mean Square                                |

| DVR       | Dynamic Voltage Regulator                       |

| SVC       | Static VAR Compensator                          |

| FC-TCR    | Fixed Capacitor Thyristor Controlled<br>Reactor |

| SSSC      | Static Synchronous Series Compensator           |

| TCSC      | Thyristor Controlled Series Compensator         |

| D-STATCOM | Distribution Static Compensator                 |

| ANFIS     | Adaptive Neuro fuzzy Inference System           |

| FLC       | Fuzzy Logic Controller                          |

| SRFT      | Synchronous Reference Frame Theory              |

| CSC       | Current Source Converter                        |

## CHAPTER 1

## INTRODUCTION

## 1.1 Introduction

In present days, the increase in digital economy implies a distributed use of electronic equipment in each and every sectors (i.e. industrial, commercial and domestic). In literature various studies shows the data of the consumption share of electricity by the information and communication technology, and it has been concluded that nonresidential sector consumes 30-40% of annual electricity consumption. This shows greater demand of power and demand for high level of reliable quality power. The estimation suggests that the 30% power demand is from sensitive load equipment and continuously increasing day by day [1].

Now a days, number of factors decides the reliability of power supply, like non-linear loads, large switching loads and accidents can disrupt the electric power grid. The digital manufacturing assembly, information systems and our home appliances requires high grade of power [2]. The high power quality demand for electronic devices is due to the requirement of the semiconductor components which are highly sensitive to short power interruptions, low voltage direct current, require large amount of reactive power, sensitive to voltage surges/sags, current harmonics, and other waveform distortions [3].

Power system engineers and researchers are mostly concentrating on the idea of providing reliable, uninterrupted and high grade of power to the consumer. To achieve this, use of electronic equipment as a controller of power flow has been increased. Literature review in this area suggests different solutions for the problems related to high grade power and the idea of controlling different custom power devices using various evolutionary algorithms. Custom power devices include various FACTs devices like D-STATCOM, DVR, and UPQC etc [4].

This chapter highlights the power quality scenario in India, facts and figure related to different energy sources, installed capacity and contribution from renewable sources are provided. Problems due to distributed generation and problems due to different loads have been highlighted in this chapter. Various remedies to mitigate the power quality problems and how to increase the reliability and efficiency of the grid is explained in coming sections of this chapter.

## 1.2 Power Scenario in India

In India, the electricity sector has an installed capacity of 271.722 GW at the end of March 2015 [5]. Renewable power plants share 28% of total installed capacity and non-renewable energy plants shares the remaining 72%. India became the world's third largest manufacturer of electricity in 2013. During the year 2014-15, agriculture sector has recorded highest consumption of electricity. The per capita consumption suggests the standard of the society of the country and also its development. Despite the cheaper electricity tariff in India, the electricity per capita consumption in India is lower compared to many countries [6].

The demand of electricity in India is far more than can be met with the amount of installation at present. And as of alternative to the conventional energy sources, demand of renewable energy sources and different technologies to handle present load and to integrate new plants to the existing system has been increasing day by day. The integration of renewable energy based distribution generation will help in reduction of greenhouse gases and also help in meeting the demand of the country with cheaper form of electricity. But with the integration of the new technology to old power system, various technical problems arise in the area of power quality (i.e. voltage stability, harmonics, reliability, protection, and control) [7].

# 1.3 Power Quality

Power quality decides the wellness of electric energy to consumer loads. Synchronization of the voltage frequency and phase permits electrical systems to operate in their planned way without huge loss of performance. The term is utilized to depict electric power that drives an electrical burden and the load's capacity to work properly. Without the best possible power, an electrical load (or burden) may breakdown, fail to operate or not work at all. There are numerous causes in which electric power can be of low quality and numerous more reasons for such low quality power.

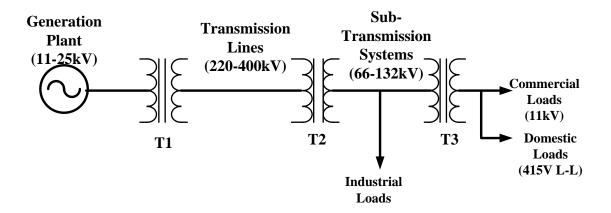

Now a days, integration of hundreds of generating plants and load center have made the power system circuit more complicated. The basic structure of typical power system is shown in Fig. 1.1. It shows a generating source, transmission line, sub transmission system and a distribution system [8, 9].

Fig. 1.1 Single line Diagram of a typical Power System

It can be seen from the Fig 1.1 that in between the generation and load point, various stages are there in power system. The correct operation of all the component is critical for reliable power system. There are many issues involved here such as the maintenance of power apparatus and system, the stability of the system, the operation of power distribution system, faults etc.

Few years back, consumers were mostly concerned about continuity of supply. Even though the generation is reliable, but distribution is not always so. Due to the exposure to the nature, the transmission systems also faces the problems (i.e. lightning, temperature etc.) [10]. But now a days, consumers wants continuity, with high grade of power. As there are various sensitive loads like hospital appliances, industries, air traffic control etc. connected to the same grid, and these all required uninterrupted clean power supply. Thus, in this changed scenario, where consumer is looking for high grade of power, 'Power Quality' term attains great significance. Literature suggests that power quality problems are distribution side problems but impact of transmission line problems is also significant on supply of high grade of power. Most of the transmission related problems arise due to the forces of nature or due to interconnection of grid, but individual consumer is mostly responsible for the distribution related problems [11].

# 1.4 Impact of Power Quality Problems on Consumer

Technically, the supply from utility should be pure sine wave of fundamental frequency (50/60 Hz) and the rated peak magnitude of the voltage wave. Unfortunately, the AC supply we receive from utility does not meet these specifications. Various problems associated to power quality, their characterization, methods and possible causes are listed [12] in Table 1.1.

Table 1.1 Power Quality problems and their causes

| Broad categories    | Specific categories | Methods of           | Typical causes         |

|---------------------|---------------------|----------------------|------------------------|

|                     |                     | characterization     |                        |

| Transients          | Impulsive           | Peak magnitude, rise | Lightning strike,      |

|                     |                     | time and duration    | transformer            |

|                     |                     |                      | energization and       |

|                     |                     |                      | capacitor switching    |

|                     | Oscillatory         | Peak magnitude and   | Line or capacitor or   |

|                     |                     | frequency            | load switching         |

|                     |                     | components           |                        |

| Short duration      | Sag                 | Magnitude and        | Ferro resonant         |

| voltage variation   |                     | duration             | transformers, L-G      |

|                     |                     |                      | faults                 |

|                     | Swell               | Magnitude and        | Ferro resonant X-mers, |

|                     |                     | duration             | L-G faults             |

| Long duration       | Under-voltage       | Magnitude and        | Switching on loads,    |

| voltage variation   |                     | duration             | capacitor de-          |

|                     |                     |                      | energization           |

|                     | Over-voltage        | Magnitude and        | Switching off loads,   |

|                     |                     | duration             | capacitor              |

|                     |                     |                      | energization           |

| Waveform distortion | Harmonic            | THD, Harmonic        | Adjustable speed       |

|                     |                     | spectrum             | drives and other       |

|                     |                     |                      | nonlinear loads        |

|                     | Notching            | THD, Harmonic        | Power electronic       |

|                     |                     | spectrum             | converters             |

|                     | DC offset           | Volts, Amps          | Geo-magnetic           |

|                     |                     |                      | disturbance, half      |

|                     |                     |                      | wave rectification     |

| Voltage flicker     |                     | Frequency of         | Arc furnaces, arc      |

|                     |                     | occurrence           | lamps                  |

The lack of quality power affects the customers in many ways. Impulsive transients do not travel too far but it can start an oscillatory transients which can cause transient overvoltage and damage the power line insulators. These are curbed using surge arresters.

Short duration voltage sags can cause loss of production in an automated industry by maloperating or tripping a motor, computer systems or data processing systems can crash. Voltage swell can put stress on home appliances and computer systems, consequently shortening their lives.

The effect of long duration voltage variations is more than short duration voltage variations. Voltage unbalance can cause temperature rise in machines and can even cause a large machine to trip. Voltage waveform is distorted by Harmonics, notching and DC offset. Unnecessary losses is caused due to unwanted current harmonics flowing through distribution network. Also it can affect the operation of traffic control or any other lifesaving appliance in a hospital badly.

A periodic transient that rides on the supply voltage is called "Notch". It can damage shunt capacitor due to high rate of rise of voltage at the notches. It is therefore required to provide high grade of power to the consumer [13].

# 1.5 Power Quality Standards

Various standards for power quality have been proposed by Geneva based IEC (international electro-technical commission) and IEEE (Institute of electrical and electronic engineers).

In these standards, mainly IEEE-519 [14] is the mostly followed in various research and literature regarding power quality and its improvement, and to decide the limits for disturbances to the distribution system that affects other equipment and communication. All type of power converters used in industries and commercial power systems produce harmonics and reactive power demand. Non-linear loads used in industry are made of static power converters, adjustable speed drives, UPS, arc discharge devices, and rotating machines. These devices are used in various conversions like ac to ac, dc to variable dc, dc to ac and vice-versa.

The sinusoidal nature of current waveform is altered by non-linear loads and therefore the ac voltage drop in the line, causing the flow of harmonic currents in ac power system, which produces interference with the communication lines and other neighboring equipment. The shunt capacitors used for improvement of the power factor, will start

resonating at some harmonic frequency with the nonlinear load, and this will cause high level of current distortion and harmonic voltage at PCC.

The harmonic distortion limits (recommended by IEEE-519 standards) establishes the maximum current distortion from a consumer.

**TDD:** Total Demand Distortion (TDD) gives the harmonic current distortion in percentage of maximum demand load current. And is an important index in defining the power quality. Table 1.2 lists all limits which should be used for designing a system for the worst case (conditions lasting longer than an hour). For shorter periods, during startups or unusual conditions, the limits may exceeded by 50%.

Table 1.2 Current distortion limits for General Distribution Systems

| A<br>B       |     |                                                                                                                                |                                                                                                |                                                                |                                |     |

|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------|-----|

| $I_{sc}/I_L$ | <11 | 11 <h<17< th=""><th>17<h<23< th=""><th>23<h<35< th=""><th>35<h< th=""><th>TDD</th></h<></th></h<35<></th></h<23<></th></h<17<> | 17 <h<23< th=""><th>23<h<35< th=""><th>35<h< th=""><th>TDD</th></h<></th></h<35<></th></h<23<> | 23 <h<35< th=""><th>35<h< th=""><th>TDD</th></h<></th></h<35<> | 35 <h< th=""><th>TDD</th></h<> | TDD |

| <20          | 4.0 | 2.0                                                                                                                            | 1.5                                                                                            | 0.6                                                            | 0.3                            | 5.0 |

| 20<50        | 7.0 | 3.5                                                                                                                            | 2.5                                                                                            | 1.0                                                            | 0.5                            | 8.0 |

Where,

$A = Maximum harmonic current distortion in % of <math>I_L$

B = Individual harmonic order (odd harmonics)

$I_{sc}$  = maximum short circuit current at PCC,

$I_L$  = maximum demand load current (fundamental frequency component) at PCC.

Even order harmonics are limited to 1/4<sup>th</sup> of the odd harmonic limits listed in the table above. Distortions in currents due to DC offset, e.g. half wave converters, are not allowed The percentage of harmonic current injection from a consumer depends upon the load demand and the size of the system it is connected. As the size of the consumer demand decreases with respect to the size of the system, the percentage of harmonic current injection will rise. This protects the other users and the utility, which aims to maintain a certain quality of voltage to its customer.

#### **1.6 Custom Power Devices**

The application of power electronic converter at power distribution level for the benefit of consumer and utility is categorized under custom power devices [15]. Family of custom power devices can be broadly classified into:

- Shunt device (e.g. DSTATCOM, SVC and FC-TCR etc.)

- Series devices (e.g. Dynamic Voltage Regulator (DVR), SSSC, TCSC etc.)

• Hybrid devices (e.g. Unified Power Quality Conditioner (UPQC), Interline power flow controller (IPFC) etc.)

#### 1.6.1 SHUNT DEVICES

Shunt devices are used to increase the limit for transmittable power and the voltage profile along the compensated line by controlling reactive power of the system. Various shunt devices have been suggested in literature (e.g. D-STATCOM, SVC, FC-TCR etc.). Shunt connected switched reactors are used to minimize overvoltage at load end during light load conditions and switched capacitors are used to maintain line voltage during heavy load conditions.

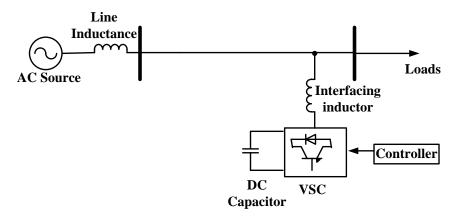

Fig 1.2 Single Line Diagram of DSTATCOM

The ideal single line diagram showing the connection of a D-STATCOM to an AC bus is shown in Fig 1.2. The use of D-STATCOM here is to maintain the PCC voltage magnitude constant irrespective of loads reactive power demand. Advancements in power electronics has produced fast switching devices using which a shunt connected device can be used to eliminate harmonics and at the same time can feed the required amount of reactive power to the system.

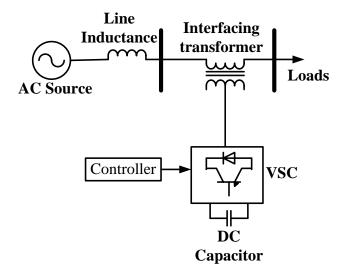

#### 1.6.2 SERIES DEVICES

These devices are connected in the series with the line. It is used for compensation of supply voltage by regulating if there are problems on the supply side of the distribution system e.g. DVR, SSSC and TCSC etc. Desired voltage of required amplitude, phase and frequency is injected by DVR between grid and load. It is a very powerful device, which has the ability to mitigate the voltage swells and sags at the PCC. The difference between DVR and D-STATCOM is in the way they are connected to the system. DVR employs a transformer in series with the ac system.

Some functions of DVR are,

- Reactive Power Compensation

- Voltage Regulation

- Compensation for Voltage sags and Swells

- Unbalance Voltage Compensation (for 3-phase systems)

Fig 1.3 Single Line diagram of DVR connection to AC Line

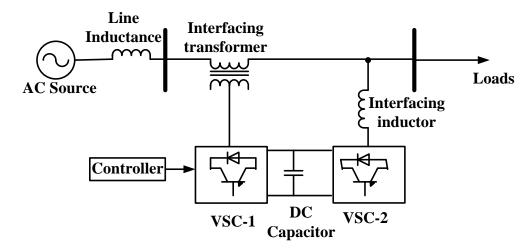

#### 1.6.3 HYBRID DEVICES

These type of devices are the combination of both series and shunt devices connected back to back. UPQC is a hybrid compensator having the capability to inject shunt currents and series voltage to the system. It consists of both series and shunt converters connected to the same DC link. It is a very powerful device which can mitigate both disturbances of current and voltage which may affect many sensitive loads. The basic structure of the UPQC is shown in Figure 1.4.

The UPQC has been used for real time control and dynamic compensation of AC transmission systems, providing multifunctional flexibility required to solve many of the problems faced by the power delivery industry. It can simultaneously or selectively control the flow of real and reactive power in the line.

Fig 1.4 Single line diagram of Hybrid Compensator

In the present work, modelling and simulation of D-STATCOM is done with different types of intelligent controllers and various loads to analyze and compare the response of the D-STATCOM.

# **CHAPTER 2**

# LITERATURE REVIEW

#### 2.1 GENERAL

In this chapter, many research papers and work related to D-STATCOM are reviewed. The review work is done for the areas given below,

- D-STATCOM Configuration

- SRFT and Fryze Algorithm

- FLC and different Topologies of PI-FLC

- ANFIS algorithm and control scheme

#### 2.2 LITERATURE SURVEY

**Arindam Ghosh and Gerard Ledwich** [4] have characterized the various problems related to the distribution system and their effect on generation, transmission and neighboring loads. Also the remedies to diminish these effects using DSTATCOM and controlling of DSTATCOM using SRF theory have been explained.

- **A. Van Zyl** et.al. [16] have shown power quality manager (PQM), a hybrid device comprising passive and active shunt filters. This topology has reduced the required rating of static VAR compensator, while reducing the harmonics and improving voltage regulation.

- **I. Wasiak** et.al. [17] have shown the problems due to distributed energy resources and used DSTATCOM to compensate the various problems related to radial distribution system. DSTATCOM is controlled in both current controlled and voltage controlled mode to mitigate current and voltage related problems respectively.

**Bhim singh** et.al. [18] have simulated a stand-alone alternator feeding a three phase three wire distribution network. The DSTATCOM with three leg VSC is used to mitigate the power quality related problems and hysteresis rule base gating signals are produced to control the output of the DSTATCOM.

- **D.** Nair et.al. [19] have explained the advantages of mitigating the power quality problems and used synchronous detection algorithm to control DSTATCOM for reactive power compensation and harmonic elimination.

- **P.** Jayapraksh et.al. [20] have proposed H-Bridge topology for VSC instead of conventional four leg converter for three phase four wire distribution network, decreasing

- the number of switches, while compensating the reactive power, elimination of harmonics, balancing load and neutral current compensation at point of common coupling (PCC).

- **G.O. Suvire** et.al. [21] have shown the wind energy generation and its advantages and disadvantages on grid. The inclusion of renewable source generates number of power quality problems so DSTACOM is used to minimize those effects.

- **C. Kumar** et.al. [22] have proposed the state space model of DSTATCOM with dead beat predictive controller for fast load voltage regulation during voltage disturbance. This proposed scheme is effective in eliminating the harmonics and power factor correction.

- **D.P. Kothari** et.al. [23] have proposed a T-connected transformer and three leg VSC based DSTATCOM for power quality improvement. Here two single phase transformers are connected in T-configuration for interfacing three phase four wire distribution system with three leg VSC.

- **T.R. Somayajulu** et.al. [24] have proposed a three leg VSC based DSTATCOM integrated with a zig-zag transformer for compensation of reactive power and elimination of harmonics at PCC.

- **J. Ramesh** et.al. [25] have shown the effect of load variation on grid and mitigated those effects using DSTATCOM. The controlling of DSTATCOM is done using instantaneous symmetrical component theory, DC link voltage is maintained at set point value using conventional controller (PI).

- **G. Sahu and K. Mahapatra** [26] have shown comparison of different reference current generation schemes viz. instantaneous p-q theory, synchronous reference frame theory (SRF), Modified SRF Theory, instantaneous symmetrical component theory and Average unit power factor theory to control DSTATCOM for different loads.

- **R.** Sharma et.al. [27] have shown the control algorithm for DSTATCOM based on Synchronous Reference Frame Theory (SRFT), used to extract the reference source currents for load balancing, power factor correction and harmonic elimination at PCC.

- **R.** Niwas and B. Singh [28] have proposed a distribution system with source of isolated diesel engine driven induction generator and mitigated the problems related to power quality using DSTATCOM, interfaced with a T-connected Transformer to the three phase four wire distribution system.

- **S. Bhowmick** et.al. [29] have shown the modelling and control of DSTATCOM and battery energy storage system (BESS). DSTACOM is used to compensate for wide variety of loads.

- **B. Singh** et.al. [30] have shown DSTACOM built with three single phase inverters interfaced to three phase four wire distribution system using three single phase inverters. This topology has the advantages of the use of "of the shelf" H-Bridge VSCs and optimum voltage ratings of VSCs.

- **P. Kumar** [31] has shown the compensation for linear and nonlinear loads connected to a distribution system. The reference currents are derived using SRFT for reactive power compensation, harmonic elimination and load balancing.

- **J. Solanki** et.al. [32] have shown three different reference current generation theory viz. instantaneous reactive power theory, synchronous reference frame theory and Adaline based algorithm, used to control DSTATCOM for linear and nonlinear loads.

- **A. Banerji** et.al. [33] have shown an autonomous grid along with a DSTATCOM and battery energy storage system for rural locations, while harnessing the renewable energy available at these locations. DSTATCOM is used to enhance the stability of the grid and maintaining the power quality to optimum.

- **Karuppanan P.** and **K. K. Mahapatra** [34] have presented shunt active filter for improving the power quality such as harmonics compensation and reactive power compensation because of non-linear loads. A novel compensation control scheme, generalized Fryze currents minimization based on positive sequence voltage detector is implemented and it is able to compensate harmonics and reactive power.

- **C.N. Rowe, T.J. Summers, R.E. Betz** and **D. Cornforth** [35] presented on control scheme to control power flow in a standalone micro-grid, which is Power frequency droop method. This paper compares the effect of instantaneous and Fryze power calculations on the operation of a three phase, two inverter micro-grid.

**Mauricio Aredes** and **Luis F. C. Monteiro** [36] described a novel control strategy i.e. the sinusoidal Fryze current control strategy based on minimization method equations, together with a robust synchronizing circuit (PLL circuit) for shunt active filters.

**Alexandru Bitoleanu** and **Mihaela Popescu** [37] presented paper on the Reference Current Methods Calculation and their Implementation for the shunt filters. Many control schemes have been described such as the Fryze's theory, the theory of Fryze-Buchholz-Depenbrock, the so-called generalized theory of instantaneous reactive and non-active powers, the Currents' Physical Components Theory (CPC) and the Conservative Power Theory (CPT).

**H. Suryanarayana** et.al. [38] have shown the variation in DC link voltage due to load variation and its effect on compensation. At the time of transient, Fuzzy logic controller is

used to supervise the proportional and integral gains of conventional control to maintain DC link voltage and for fast settling of the system.

- **M. Labeeb** et.al. [39] have proposed ANN based fuzzy logic controller to compensate reactive power, eliminate harmonics and load balancing is accomplished using DSTACOM.

- **R. Prajapati** et.al. [40] have proposed a fuzzy logic controller based on Takagi-Sugeno inference system to control DC link voltage of DSTATCOM for eliminate harmonics and control reactive power in three phase three wire distribution system.

- **Ji Liu** et.al. [41] have shown fuzzy PI control of DSTATCOM to maintain the DC link voltage constant. DSTATCOM is shunt connected at PCC to improve power factor and eliminate harmonics from the current.

- **P.P. Shimmeer** et.al. [42] have proposed a hybrid topology of DSTATCOM and zigzag transformer. Also an enhanced PLL (EPLL) is used to generate reference source current even under polluted utility voltage. DC link voltage is maintained using fuzzy logic controller.

- **P. Nijhawan** et.al. [43] have shown the effect of induction furnace load on neighboring loads and on system. DSTATCOM is used to compensate the harmonics produced from induction furnace operation and reactive power requirement of the loads.

- **Jan Jantzen** [44] has proposed tuning of fuzzy PID controllers. This paper has shown various fuzzy PID control techniques and their implementation for error minimization in various plant processes. Also gives idea about tuning of PID controller using Ziegler Nichols technique.

- **Z. W. Woo** et.al. [45] have proposed a PID type fuzzy controller with self-tuning scaling factors. This has improved the transient state and steady state performance of PID type controller. The scaling factors for PID type Fuzzy controllers are tuned on line.

- **W.Z. Qiao** et.al. [46] have shown a PID type Fuzzy controller with on line tuning of scaling factors, and also incorporating a parameter adaptive method to improve the performance of the controller at transient and steady state time of the process.

- **Yanan Zhao** et.al. [47] have proposed the control of industrial weigh belt feeder using a Fuzzy PI controller. In this paper fuzzy PID controllers are categorized in two parts; one category consists typical fuzzy logic controllers, while second category consists the combination of both PID and fuzzy controllers, named as 'Fuzzy PID controllers'.

- **Amit V. Sant** et.al. [48] have proposed a hybrid Fuzzy-PI control scheme with different weights assigned to the outputs of the two controllers. The paper presents the idea of stiff fuzzy control at transient time and stiff PID control at steady state time of the process.

- **R.K.** Mudi et.al. [49] have shown the self-tuning PI type Fuzzy logic controller. The proposed self-tuning controller is designed using a very simple rule base and the most natural and unbiased membership functions (MFs) i.e. symmetric triangles with equal base and 50% overlap with neighboring MFs.

- **K.A. Gopala Rao** et.al. [50] have presented the comparison of the fuzzy PI controller with fuzzy PID and conventional PID controllers.

- **T.B. Kumar** et.al. [51] have presented the pros and cons of wind energy generation on grid and different sensitive loads connected to it. The mitigation of these harmful effects have been done using STATCOM and STATCOM is controlled using artificial neuro fuzzy inference scheme (ANFIS).

- **S. Farid Torabi** et.al. [52] have shown the effects of low frequency oscillations on the power system, and STATCOM is used as a dynamic regulator to eliminate these oscillations. STATCOM is controlled using two intelligent control schemes fuzzy logic controller and ANFIS controller.

- **D. Nazarpour** et.al. [53] have studied the effects of sub synchronous resonance on generation and sensitive loads. These effects are eliminated using STATCOM, while controlling of STATCOM is done using Fuzzy logic controller and ANFIS controller, and results from these two controllers are compared.

In this chapter, a brief literature review related to the different topics of D-STATCOM configuration and its controllers have been presented.

# **CHAPTER 3**

# MODELLING AND DESIGN OF D-STATCOM

It is a shunt connected FACT device, having same configuration as of STATCOM (Static compensator). The STATCOM is a voltage source converter supplied by a DC capacitor. The converter consists of six IGBT switches with anti-parallel diodes which are switched on and off through a gate drive circuit. The D-STATCOM is used at PCC of the system to counterbalance the loads demand of unwanted component i.e. harmonic current components, reactive power demand, load balancing etc. Voltage regulation can also be achieved using D-STATCOM. In voltage control mode it can regulate the bus voltage constant and balanced against any kind of disturbance from supply side or load side. To counterbalance the unbalance or distortions in the load current or the supply voltage, DSTATCOM feeds equal and opposite unbalanced and harmonically distorted current or voltage to PCC.

There are two modes of operation of DSTATCOM:

- Load compensation in current control mode

- Voltage regulation in voltage control mode

In the load compensation mode, DSTATCOM is used to counteract the unwanted components due to the load current demand. To achieve this goal, current control mode is used to design the controller for DSTATCOM. This controller has to generate reference currents so that the DSTATCOM can compensate reactive current demand, harmonics and unbalancing due to load supply currents. DSTATCOM rating for the load compensation depends on reactive power, harmonic distortion and power requirement of the load to be compensated.

Voltage regulation mode of DSTATCOM uses voltage control mode. It means that controller has to generate reference voltages to compensate harmonics from voltage waveform and to feed reactive power to eliminate voltage sag and swell at PCC.

In the present work, D-STATCOM is used in load compensation mode.

#### 3.1 Load compensation using D-STATCOM

The single line diagram of a distribution system compensated by an ideal shunt compensator (DSTATCOM) is shown in Fig. 3.1.

Fig. 3.1 Single line diagram of ideal load compensation

It can be seen from the Fig 3.1 that DSTATCOM is working in current control mode. And it is denoted by an ideal current source  $(i_f)$ . It is assumed that load right to PCC is mixed i.e. reactive, non-linear and unbalanced. And in absence of the compensator the source current  $(i_s)$  will also be distorted and lagging in nature, consequently the bus-1 & 2 voltage will be distorted.

To make the source current fundamental and positive sequence only, the compensator has to feed the required amount of reactive, unbalance and harmonic compensating current to the PCC. This will cause the source current ( $i_s$ ) to be in phase to the PCC voltage ( $v_t$ ). Therefore, from utility side, it will look like a unity power factor load connected to PCC drawing harmonic free and balanced current from the grid.

The point at which the compensator is connected is called the utility-customer point of common coupling (PCC). The KCL at the PCC yields,

$$i_s + i_f = i_l \qquad \longleftrightarrow \qquad i_s = i_l - i_f \qquad \dots (3.1)$$

Where,  $i_l$  denotes the load current demand.

$i_f$  is the current generated by the compensator to counteract the reactive component, harmonic component and unbalance of the load current at PCC.

Consider a three phase three wire distribution network with an ideal shunt compensator shown in Fig 3.2. The 3- $\varphi$  source with grounded star point is connected to 3- $\varphi$  load (nonlinear, unbalanced and reactive in nature). At the point of common coupling the ideal three phase shunt compensator is feeding to all the unwanted components of the load current.

Fig 3.2 Schematic diagram of a 3-φ ideal shunt compensator connected to 3-φ three wire distribution system

.All the voltages and currents shown in the diagram are instantaneous quantities. Because the load currents may change frequently, and extracting the component to be compensated will be real time quantities. To extract the reference quantities various current segregation techniques have been suggested in literature such as synchronous reference frame theory (SRFT), instantaneous reactive power theory (IRPT), fryze current minimization algorithm etc.

The basic configuration of DSTATCOM consists of a voltage source converter and a DC capacitor at its DC terminals. Fig 3.3 (a) shows this configuration of DSTATCOM using VSC. The converter should have high switching frequency so that it can reproduce the compensating currents accurately. Normally,

$$f_{PWM} > 10 * f_{hmax}$$

... (3.2)

Where,  $f_{PWM}$  is the switching frequency of the converter,

$f_{hmax}$  is the frequency of the highest order harmonic current to be compensated.

Another method of realizing shunt active filter is by using current source converter. In VSC the DC side source is a capacitor, while in case of current source converter it is an inductor. It is to be noticed here that no power supply element is used at DC side of the converter because the principal function of the DSTATCOM is to behave as a compensator i.e. ideally, the average energy exchange between the DSTATCOM and the power system should be equal to zero.

A voltage source converter having six IGBTs with antiparallel diodes connected to them is shown in Fig 3.3(a) and in Fig 3.3(b) a current source converter is shown

Fig 3.3 (a) Voltage source converter, (b) Current Source converter

The comparison of VSC and CSC is tabulated in Table 3.1

Table 3.1 Comparison of VSC and CSC

| Voltage source converter                  | Current source converter                 |

|-------------------------------------------|------------------------------------------|

| 1. high efficiency                        | 1. robust in nature                      |

| 2. low initial cost                       | 2. series connection of IGBT and diode   |

|                                           | (for reverse blocking)                   |

| 3. smaller physical size                  | 3. complicated device design and         |

|                                           | fabrication                              |

| 4. due to anti-parallel diode no need for | 4. slightly worse device characteristics |

| reverse voltage blocking in IGBTs         | than conventional IGBTs                  |

## 3.1.1 Operation modes of D-STATCOM

D-STATCOM can work in four modes.

- A. Active power generator,

- B. Active Power absorber,

- C. Inductive mode or reactive power absorber,

- D. Capacitive mode or reactive power generator.

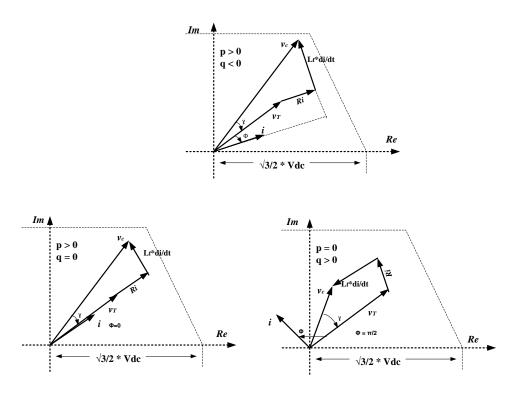

Fig 3.4 shows the vector diagrams for all four modes of operation of D-STATCOM. It can be seen that the relation of voltage generated by the D-STATCOM and voltage at PCC will decide the mode of operation of D-STATCOM. The magnitude of the VSC terminal voltage will decide the flow of reactive power, and the angle between the VSC voltage and the PCC voltage will decide the flow of active power in either direction.

Fig 3.4 Different Modes of Operation of D-STATCOM

Where,  $v_{pcc}$  is the instantaneous voltage at the point of common coupling.  $v_{vsc}$  is the instantaneous voltage generated by the ideal D-STATCOM,  $i_l$  is the instantaneous line current from system to load.

# 3.2 Proposed System

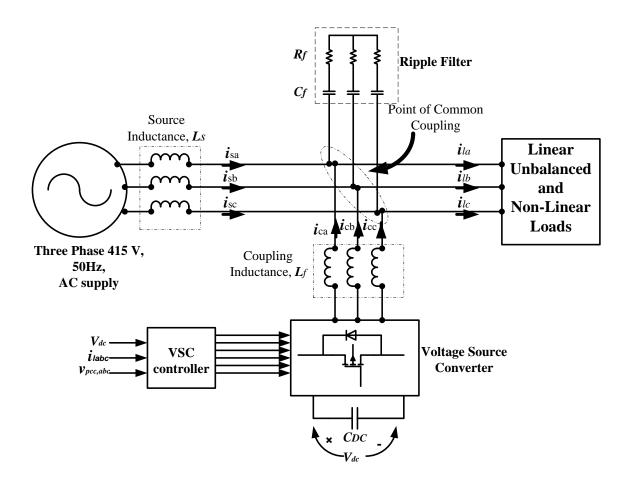

A three phase AC distribution system of 415V (line to line), 50Hz frequency is taken as power circuit to be studied under this project. Unbalanced linear loads (Star connected) and non-linear loads are connected to the system. The D-STATCOM is connected to the system in shunt at the point of common coupling with an interfacing inductor ( $L_f$ ). The proposed system diagram is shown in Fig 3.5. The D-STATCOM in this project is used to eliminate harmonics produced due to non-linear load connected to the system, reactive power demand of the loads and to minimize the unbalancing due to unbalanced nature of the loads. The control of D-STATCOM to compensate all unwanted component is done using SRF-theory with a conventional PI controller to maintain DC link voltage.

#### 3.2.1 Design of D-STATCOM [54]

Three leg VSC is used to design D-STATCOM, voltage source converter is having six IGBTs with anti-parallel diodes connected in a bridge formation. The ratings of IGBTs used are 2500kV and 1500A [55]. The selection and calculation for DC bus voltage to be maintained across the VSC, DC capacitor rating to maintain this voltage across the VSC terminals, interfacing inductor rating, and design of ripple filter is done as follows,

Fig 3.5 Schematic diagram for shunt connected DSTACOM to an AC Three phase three wire distribution system

#### i. DC Bus Voltage

The instantaneous energy fed to the D-STATCOM decides the DC terminal voltage magnitude. For a three leg VSC with a DC capacitor, the capacitor voltage is given by eqn. (3.3),

$$V_{dc} = 2\sqrt{2} * \frac{v_{ac}}{\sqrt{3}*m}$$

... (3.3)

Where, m is the modulation index and taken as 1, and  $v_{ac}$  is AC terminal voltage of D-STATCOM and is equal to 415 V (RMS line to line). With these values the calculated value of  $V_{dc}$  is 677.61V. The selected magnitude of dc terminal voltage is 750V in this project.

The principle of generating instantaneous active power and reactive powers by D-STATCOM is shown in Fig 3.6 using phasor diagram,

Fig 3.6 Principle of operation of D-STATCOM instantaneous active power and reactive power

It can be understood from the above figure that by generating a suitable AC voltage it is possible to produce arbitrary instantaneous vectors of both active and reactive power. The real component of currents is linked to the equivalent series resistance modelling losses on AC side. DSTATCOM can generate or absorb limited amount of active and reactive power. Circuit parameters and maximum ratings of VSC components are the reason behind this limitation. In Fig 3.6 a cautionary limit for AC voltage can be seen, it depends on VSC's DC side voltage ( $V_{dc}$ ). The operating region of DSTATCOM is defined by the limits of filter inductance ( $L_f$ ) and terminal voltage ( $v_T$ ). To increase this limit the DC terminal voltage is chosen more than the calculated value. Also VSC is a boost type converter i.e. in order to guarantee the controllability of the Hysteresis current control, the DC side voltage should be kept more than the peak value of the AC bus voltage.

# ii. DC Bus Capacitor Rating

The principle of energy conservation is given by eqn. (3.4),

$$\frac{1}{2}C_{dc}[(V_{dc})^2 - (V_{dc1})^2] = 3V_{ac}(\alpha I)t \qquad ... (3.4)$$

Where  $V_{dc}$  is the reference DC voltage,  $v_{ac}$  is the phase voltage (240 V<sub>rms</sub>),  $V_{dcl}$  is the minimum voltage level of DC bus, I is the phase current,  $\alpha$  is the overloading factor, and t is time up to when the DC voltage is to be recovered.

Considering 5% voltage ripple in the DC bus and taking the values of the quantities as  $V_{dc1}$  =740V,  $V_{dc}$  =750V,  $V_{ac}$  =240V, I = 55.64A, t = 350 $\mu$ sec and  $\alpha$  =1.2, the calculated value of  $C_{dc}$  is 2254  $\mu$ F and is selected as 2500  $\mu$ F.

In order to compensate for harmonic content of the current, the DC capacitor should be made large enough to behave as an energy storage element. So that it won't experience large voltage variations i.e. if DC voltage gets lower than the AC system's peak voltage, the VSC loses its inherent property of boost type converter and consequently loss of controllable compensation will not be achieved.

#### iii. Coupling Inductance $(L_f)$

The calculation of the coupling inductance ( $L_f$ ) for VSC depends on the current ripple  $\Delta i$ , DC bus voltage ( $V_{dc}$  =750V) and switching frequency fs =10 kHz, and  $L_f$  is given by eqn. (3.5),

$$L_f = \frac{\sqrt{3} * m * V_{dc}}{12 * h * f_s * \Delta i}$$

... (3.5)

Where,  $\Delta i = 5\%$  of 55.64(=I), h (=1.2) is overload factor and m (=1) is modulating index. The calculated value of  $L_f$  is 3.24 mH and  $L_f = 3.5$  mH is taken in this investigation.

The interfacing inductor is equivalent representation of the leakage reactance offered due to the transformer connected in between the AC system and the DSTATCOM. The transformer is connected to decrease the rating of the DSTATCOM to be used and to decrease the switching ripples at PCC.

#### iv. Ripple Filter

The switching of the VSC causes noise in PCC voltages. To remove those noises from the voltage waveform, a first order high pass filter is tuned at half of the switching frequency and the connection of the filter at PCC can be seen in Fig 3.5. A combination of capacitor and resistance in series connected to each phase is selected as a ripple filter with common ground point. The ratings of filter capacitance and resistance are taken as  $5\mu F$  and  $6.2~\Omega$  respectively. This combination offers high impedance( $636.65~\Omega$ ) at fundamental frequency and low impendence ( $8.88~\Omega$ ) at half of the switching frequency (here 5kHz) which forbids the flow of fundamental components at fundamental frequency in the filter branch and permits the flow of high frequency noises through the filter branch at higher than fundamental frequency.

The switching pulses for the VSC are generated using SRFT, Fryze current minimization Algorithm, Fuzzy logic controllers and ANFIS based controller. These switching schemes are explained in coming sections of the thesis.

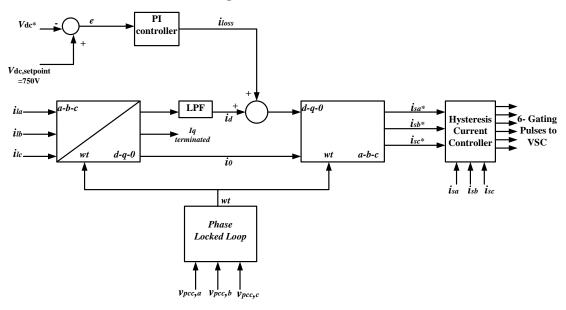

# **3.3 Synchronous Reference Frame Theory (SRFT)**

In this thesis, the SRFT-based indirect control technique [56] is used to generate gate pulses for controlling of D-STATCOM. The block diagram representation of control technique based on SRF theory is shown in Fig 3.7. As grid is supposed to feed only active power to load at PCC, but due to loads reactive or unbalanced or nonlinear nature, unwanted components flow in the line like reactive power, harmonic currents etc. but with the D-STATCOM connected in line, these unwanted components can be fed at PCC directly using DC capacitor connected VSC in shunt. As control technique is indirect in nature so the currents from load end are sensed and using Park's transformation, the 3- $\varphi$  load currents ( $i_{labc}$ ) are converted to d-q-0 frame [57].

Fig 3.7 DSTATCOM Control Scheme Based on SRFT

Firstly, the current components in  $\alpha$ – $\beta$ - $\theta$  co-ordinates are generated. 'a-b-c' phasors can then be transformed into  $\alpha$ – $\beta$ - $\theta$  coordinates using Clark's transformation as given by eqn. (3.6),

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \\ i_{0} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{\sqrt{3}}{2} & \frac{-\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} i_{la} \\ i_{lb} \\ i_{lc} \end{bmatrix} \dots (3.6)$$

Then using  $\omega t$  as the transformation angle, these currents can be transformed from  $\alpha - \beta - 0$  to d-q-0 frame using eqn. (3.7) (Park's transformation),

$$\begin{bmatrix} i_d \\ i_q \\ i_0 \end{bmatrix} = \begin{bmatrix} \sin \omega t & -\cos \omega t & 0 \\ \cos \omega t & \sin \omega t & 0 \\ 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} i_\alpha \\ i_\beta \\ i_0 \end{bmatrix} \dots (3.7)$$

It can be seen that the load's active power requirement and the power required to maintain constant DC voltage at VSC's DC terminals is to be fulfilled by the grid and therefore these two are added. To maintain DC voltage constant, the error between reference signal and sensed DC voltage is fed into a PI controller [12], thus generating an output current ( $i_{loss}$ ) equal to the loss in DC voltage and  $i_{loss}$  is given by eqn. (3.8),

$$i_{loss(n)} = i_{loss(n-1)} + k_p (V_{de(n)} - V_{de(n-1)}) + k_i * V_{de(n)}$$

... (3.8)

Where,  $V_{de(n)}$  is error in DC terminal voltage signal and reference DC voltage of 750V at  $n^{th}$  instant and given by eqn. (3.9),

and the direct component ( $i_d$ ) of current from d-q-0 transformation is then selected and filtered using a  $2^{nd}$  order Butterworth filter to eliminate unwanted signals ( $\tilde{i}$ ).

Therefore the total active power comprised in the grid current can be given by eqn. (3.10),

$$i_{active}^* = i_{ac} + i_{loss} \qquad \dots (3.10)$$

To eliminate unbalancing due to the load current, the zero component is calculated from the a-b-c to d-q-0 transformation and fed to the controller as shown in the block, as to eliminate the zero sequence components extra active power is needed, and this extra amount of power to be delivered from the grid.

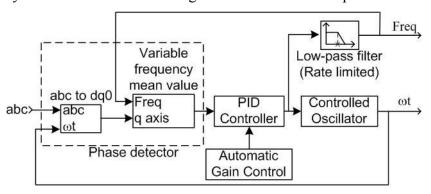

A 3- $\varphi$  PLL is used to synchronize these signals with the voltages at PCC. The angle  $\omega t$  of park's transformation in eqn. (3.7 & 3.11) is the synchronous angular position determined by the PLL. The resultant currents in the d-q-0 reference frame ( $i_d*=i_{active}*$ ,  $i_q*=0$ ,  $i_0*$ ) are reverse transformed into reference source current ( $i_{sa}*$ ,  $i_{sb}*$ ,  $i_{sc}*$ ) in a-b-c frame.