# DESIGN AND IMPLEMENTATION OF CURRENT MODE FILTERS USING LOG DOMAIN TECHNIQUES

А

DISSERTATION

#### SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

# MASTER OF TECHNOLOGY IN CONTROL & INSTRUMENTATION

Submitted by

# MOHIT SAXENA 2K13/C&I/06

Under the supervision of

# **PROF. PRAGATI KUMAR**

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# July 2015

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

# **CANDIDATE'S DECLARATION**

I Mohit Saxena Roll No. 2K13/C&I/06 student of M.Tech (Control and Instrumentation), hereby declare that the dissertation/project titled "Design and implementation of current mode filters using log domain techniques" under the supervision of Prof. Pragati Kumar of Electrical Engineering Department, Delhi Technological University in partial fulfillment of the requirement for the award of the degree of Master of Technology has not been submitted elsewhere for the award of any degree.

Place: Delhi Date: 28/07/15

(MOHIT SAXENA)

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

# CERTIFICATE

This is to certify that the dissertation "Design and implementation of current mode filters using log domain techniques" on Major Project-2 being submitted by Mohit Saxena (2K13/C&I/06) in partial fulfillment of the requirements for the degree of Master of Technology in Control and Instrumentation at Delhi Technological University is an authentic record of the work carried out by him under my supervision and guidance.

This is to certify that the above statement made by the candidate is correct to the best of my knowledge.

Place: Delhi Date: 28/07/2015

#### (PROF. PRAGATI KUMAR)

Professor, Electrical Department

# ACKNOWLEDGEMENT

I am thankful to the Almighty because without his blessings this work was not possible. It gives me a great pleasure to express my profound gratitude to my supervisor and project guide Prof. Pragati Kumar, Department of Electrical Engineering, Delhi Technological University (formerly Delhi College of Engineering), for his invaluable guidance, encouragement and patient reviews throughout the progress of this dissertation.

I would also like to extend my heartfelt thanks to Prof. Madhusudan Singh, head of the department, Assistant Prof. Ram Bhagat and all faculty members of Department of Electrical Engineering, Delhi Technological University, for keeping the spirits high and clearing the visions to work on the project.

Finally I am also thankful to my family and friends for their constant support and motivation during this work.

MOHIT SAXENA

# ABSTRACT

Due to the ongoing trends of lower power supply voltages and low power operation, the area of analog integrated filters is facing challenges. The maximal dynamic range achievable through conventional filter implementation techniques such as OA (Operational amplifier), MOSFET-C, transconductance-C etc. are restricted by the supply voltage. With log domain filters having signal swing of 100 mV, we can achieve 60-80 dB of dynamic range in circuits operating in the MHZ range using power supplies of 2.5V or less. These features make them an interesting choice in signal processing applications. Log-domain filters have emerged in recent years as a new and important class of Current-mode circuits. After presenting an overview of the log domain filtering, translinear principle for log domain filters, Bernoulli cell and its implementation to higher order filters have been presented. In the later part, design of log domain filters based on operational simulation of LC ladders and state space synthesis have been presented. All the circuits presented in the dissertation have been simulated in PSPICE.

# CONTENTS

| Acknowledgement<br>Abstract<br>Contents<br>List of figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                     |  |

| <ul><li>1.1 Introduction</li><li>1.2 A historical background</li><li>1.3 An overview of log domain filtering</li><li>1.4 Outline of the work presented in the dissertation</li></ul>                                                                                                                                                                                                                                                                                                                                              | 1<br>1<br>2<br>4                                      |  |

| Certificate<br>Acknowledgement<br>Abstract<br>Contents<br>List of figures<br>List of symbols and abbreviations<br>Chapter 1 Introduction<br>1.1 Introduction<br>1.2 A historical background<br>1.3 An overview of log domain filtering                                                                                                                                                                                                                                                                                            | 5                                                     |  |

| <ul> <li>2.2 Translinear circuit principle</li> <li>2.2.1 The bipolar translinear principle</li> <li>2.2.2 Principles of log domain design</li> <li>2.3 Synthesis of log domain block using translinear principle</li> <li>2.3.1 Log domain lossy integrator</li> <li>2.3.2 Simulation results</li> <li>2.3.3 First order log domain filter</li> <li>2.3.4 Simulation results</li> <li>2.4 A Bernoulli cell</li> <li>2.5 A Bernoulli cell in log domain structures</li> <li>2.5.1 A single input driven Bernoulli cell</li> </ul> | 5<br>6<br>8<br>10<br>10<br>11<br>13<br>14<br>17<br>19 |  |

| <ul> <li>2.5.2 Interconnection of Bernoulli cell</li> <li>2.6 Application of Bernoulli cell</li> <li>2.6.1 Log domain lossy integrator</li> <li>2.6.2 Simulation results</li> <li>2.6.3 Second order filter containing zero</li> </ul>                                                                                                                                                                                                                                                                                            | 19<br>23<br>23<br>24<br>25<br>27                      |  |

| <ul> <li>2.6.5 Third order low pass Butterworth filter</li> <li>2.6.6 Simulation results</li> <li>2.6.7 Proposed fourth order low pass Butterworth filter</li> <li>2.6.8 Simulation results</li> </ul>                                                                                                                                                                                                                                                                                                                            | 29<br>30<br>32<br>34<br>36                            |  |

| Chapter 3 Design of log domain filters based on LC ladders     | 37 |

|----------------------------------------------------------------|----|

| 3.1 Introduction                                               | 37 |

| 3.2 Basic of LC ladder filters                                 | 37 |

| 3.2.1 LC ladders                                               | 37 |

| 3.2.2 Signal flow graph representation of LC ladder            | 38 |

| 3.2.3 Components needed in signal flow graph for LC ladder     | 39 |

| 3.3 Introduction of Log and Exp operators                      | 39 |

| 3.4 Basic log domain building blocks                           | 42 |

| 3.4.1 Multiple input non inverting integrator                  | 42 |

| 3.4.2 Damped integrator                                        | 44 |

| 3.4.3 Input and output stages                                  | 45 |

| 3.5 Design of elliptic and chebyshev filter                    | 45 |

| 3.5.1 Design of third order elliptic filter                    | 46 |

| 3.5.2 Simulation results                                       | 48 |

| 3.5.3 Design of fifth order chebyshev filter                   | 50 |

| 3.5.4 Simulation results                                       | 52 |

| 3.6 Conclusion                                                 | 54 |

| Chapter 4 State space synthesis of log domain filters          | 55 |

| 4.1 Introduction                                               | 55 |

| 4.2 State space synthesis                                      | 55 |

| 4.3 Application of state space synthesis in log domain filters | 57 |

| 4.3.1 A first order log domain low pass filter                 | 57 |

| 4.3.2 Simulation results                                       | 59 |

| 4.3.3 A log domain lossless integrator                         | 61 |

| 4.3.4 Simulation results                                       | 62 |

| 4.3.5 Log domain band pass filter                              | 63 |

| 4.3.6 Simulation results                                       | 65 |

| 4.3.7 Proposed second order band pass filter                   | 67 |

| 4.3.8 Simulation results                                       | 68 |

| 4.4 Conclusion                                                 | 70 |

| Chapter 5 Conclusion and future scope                          | 71 |

| 5.1 Conclusion                                                 | 71 |

| 5.2 Scope for future work                                      | 71 |

| Appendices                                                     | 72 |

# LIST OF FIGURES

| Fig.1.1      | A simple log domain integrator                                                    | 3  |

|--------------|-----------------------------------------------------------------------------------|----|

| Fig.1.2      | Block diagram of log domain filter                                                | 4  |

| Fig.2.1      | Loop diagram using diodes                                                         | 6  |

| Fig.2.2      | Translinear loop with CB and CE configurations                                    | 8  |

| Fig.2.3      | Filter pole formed using a transconductor                                         | 9  |

| Fig.2.4      | Log domain lossy integrator                                                       | 10 |

| Fig.2.5 (a)  | Time response of lossy integrator                                                 | 11 |

| Fig.2.5 (b)  | Integrator output for frequency $(f_{in}) = 1$ MHZ of lossy                       | 12 |

| 0            | integrator                                                                        |    |

| Fig.2.5 (c)  | Frequency response of lossy integrator                                            | 12 |

| Fig.2.6      | Log domain high pass and low pass first order filter                              | 13 |

| Fig.2.7 (a)  | Time response of low pass filter                                                  | 14 |

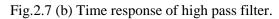

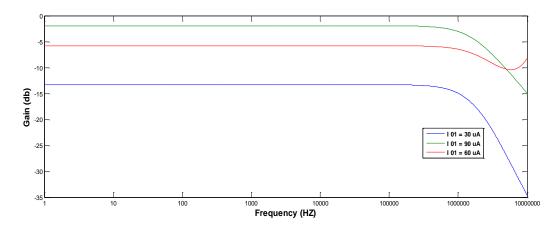

| Fig.2.7 (b)  | Time response of high pass filter                                                 | 15 |

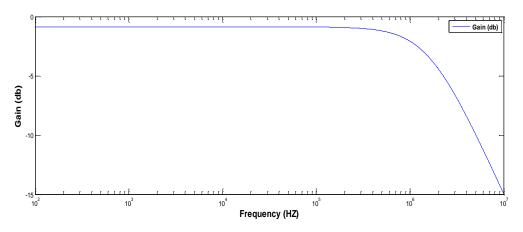

| Fig.2.7 (c)  | Frequency response of low pass filter                                             | 15 |

| Fig.2.7 (d)  | Frequency response of high pass filter                                            | 15 |

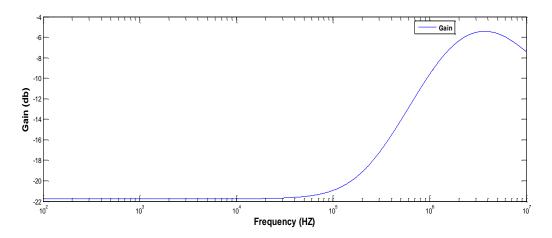

| Fig.2.7 (e)  | Variation of gain for different values of I <sub>01</sub> for low pass filter     | 16 |

| Fig.2.7 (f)  | Variation of gain for different values of $I_{02}$ for high pass filter           | 16 |

| Fig.2.7 (g)  | Variation of pole frequency for different values of $I_{03}$ for low              | 16 |

|              | pass filter                                                                       |    |

| Fig.2.7 (h)  | Variation of pole frequency for different values of $I_{03}$ for high             | 17 |

|              | pass filter                                                                       |    |

| Fig.2.8      | A Bernoulli cell                                                                  | 18 |

| Fig.2.9      | A single input driven Bernoulli cell                                              | 19 |

| Fig.2.10 (a) | Two interconnected Bernoulli cell                                                 | 21 |

| Fig.2.10 (b) | Cascaded Bernoulli cell                                                           | 21 |

| Fig.2.11     | Identification of variable $w_K(t)$ for a cascade of Bernoulli cell               | 22 |

| Fig.2.12     | A log domain lossy integrator                                                     | 23 |

| Fig.2.13 (a) | Input frequency of 10 MHZ for lossless integrator                                 | 24 |

| Fig.2.13 (b) | Integrator response for lossless integrator                                       | 24 |

| Fig.2.13 (c) | Frequency response for lossless integrator                                        | 25 |

| Fig.2.14     | Second order filter circuit containing zero                                       | 26 |

| Fig.2.15 (a) | Time response for input of second order filter                                    | 27 |

| Fig.2.15 (b) | Time response for output of second order filter                                   | 28 |

| Fig.2.15 (c) | Frequency response of second order filter for $f_0 = 4$ MHZ                       | 28 |

| Fig.2.15 (d) | Frequency response of second order filter for $f_0 = 4.4$ MHZ                     | 28 |

| Fig.2.16     | Third order Butterworth filter circuit                                            | 30 |

| Fig.2.17 (a) | Time response for input of third order Butterworth filter                         | 31 |

| Fig.2.17 (b) | Time response for output of third order Butterworth filter                        | 31 |

| Fig.2.17 (c) | Frequency response of third order Butterworth filter for $f_0 = 627 \text{ KHZ}$  | 32 |

| Fig.2.17 (d) | Frequency response of third order butterworth filter for $f_0 =$                  | 32 |

|              | 687 KHZ                                                                           |    |

| Fig.2.18     | Proposed fourth order Butterworth filter circuit                                  | 33 |

| Fig.2.19 (a) | Time response for input of fourth order Butterworth filter                        | 34 |

| Fig.2.19 (b) | Time response for output of fourth order Butterworth filter                       | 35 |

| Fig.2.19 (c) | Frequency response of fourth order Butterworth filter for $f_0 = 890 \text{ KHZ}$ | 35 |

| Fig.2.19 (d)    | Frequency response of fourth order butterworth filter for $f_0 = 970 \text{ KHZ}$ | 35 |

|-----------------|-----------------------------------------------------------------------------------|----|

| Fig.3.1 (a)     | A third order LC ladder                                                           | 38 |

| Fig.3.1 (b)     | Signal flow graph of Fig.3.1 (a)                                                  | 39 |

| Fig.3.2         | A basic log domain cell                                                           | 40 |

| Fig.3.3 (a)     | Linear system                                                                     | 40 |

| Fig.3.3 (b)     | Log domain structure of Fig.3.3 (a)                                               | 41 |

| Fig.3.4 (a)-(c) | Linearization of a log domain system                                              | 42 |

| Fig.3.5 (a)     | A multiple input non inverting integrator                                         | 43 |

| Fig.3.5 (b)     | Signal flow graph of multiple input non inverting integrator                      | 43 |

| Fig.3.6 (a)     | Damping using a current source                                                    | 44 |

| Fig.3.6 (b)     | Signal flow graph of damped integrator                                            | 44 |

| Fig.3.7 (a)     | Input and output stage of log domain system                                       | 45 |

| Fig.3.7 (b)     | Signal flow graph of Fig.3.7 (a)                                                  | 45 |

| Fig.3.8 (a)     | Signal flow graph of a simple ladder                                              | 46 |

| Fig.3.8 (b)     | Log domain equivalent of Fig.3.8 (a)                                              | 46 |

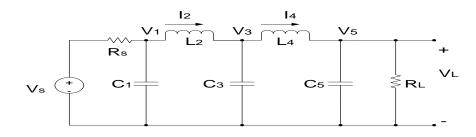

| Fig.3.9 (a)     | LC ladder of third order elliptic filter                                          | 46 |

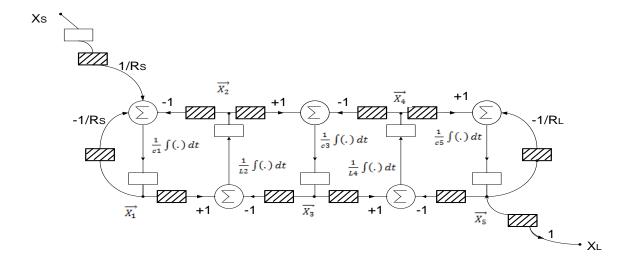

| Fig.3.9 (b)     | Signal flow graph of third order elliptic filter                                  | 47 |

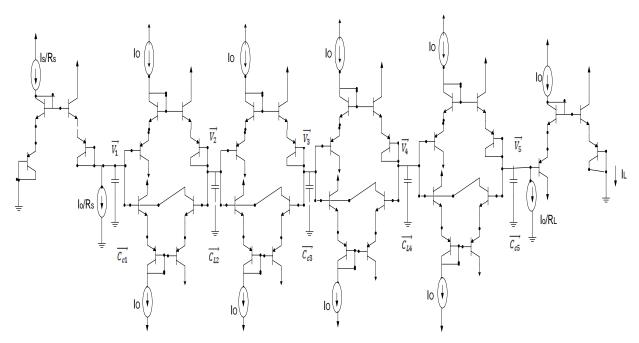

| Fig.3.9 (c)     | Circuit diagram of third order elliptic filter                                    | 48 |

| Fig.3.9 (d)     | Transient response of third order elliptic filter                                 | 49 |

| Fig.3.9 (e)     | Frequency response of third order elliptic filter for $I_0 = 90$ uA               | 49 |

| Fig.3.9 (f)     | Passband range of third order elliptic filter                                     | 49 |

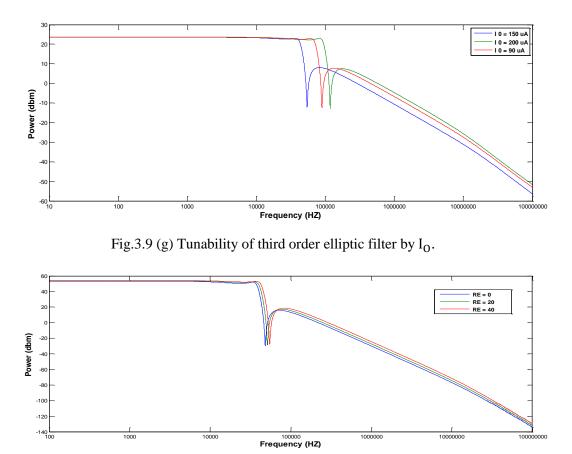

| Fig.3.9 (g)     | Tunability of third order elliptic filter by $I_0$                                | 50 |

| Fig.3.9 (h)     | Effect of different $R_E$ on frequency response of third order                    | 50 |

| 6               | elliptic filter                                                                   |    |

| Fig.3.10 (a)    | LC ladder of fifth order chebyshev filter                                         | 50 |

| Fig.3.10 (b)    | Signal flow graph of fifth order chebyshev filter                                 | 50 |

| Fig.3.10 (c)    | Circuit diagram of fifth order chebyshev filter                                   | 52 |

| Fig.3.10 (d)    | Transient response of fifth order chebyshev filter                                | 52 |

| Fig.3.10 (e)    | Frequency response of fifth order chebyshev filter for $I_0 = 220$                | 53 |

| -               | uA                                                                                |    |

| Fig.3.10 (f)    | Passband range of fifth order chebyshev filter                                    | 53 |

| Fig.3.10 (g)    | Tunability of fifth order chebyshev filter by I <sub>0</sub>                      | 53 |

| Fig.3.10 (h)    | Effect of different $R_E$ on frequency response of fifth order chebyshev filter   | 54 |

| Fig.4.1         | Log domain filter set up                                                          | 55 |

| Fig.4.2         | A first order log domain low pass filter                                          | 57 |

| Fig.4.3 (a)     | Time response for input of low pass filter                                        | 59 |

| Fig.4.3 (b)     | Time response for output of low pass filter                                       | 59 |

| Fig.4.3 (c)     | Gain response of low pass filter                                                  | 60 |

| Fig.4.3 (d)     | Phase response of low pass filter                                                 | 60 |

| Fig.4.4         | Circuit diagram of lossless integrator                                            | 61 |

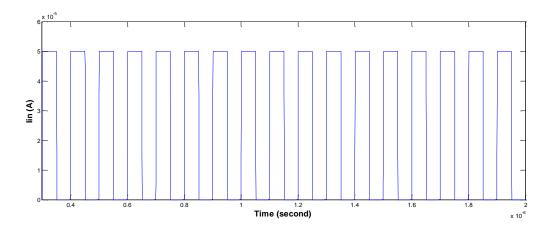

| Fig.4.5 (a)     | Input frequency of 100 KHZ for lossless integrator                                | 62 |

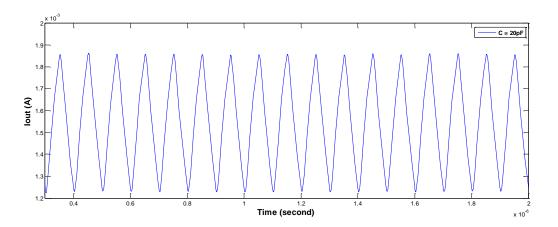

| Fig.4.5 (b)     | Integrator response for $C = 20 \text{ pF}$ for lossless integrator               | 62 |

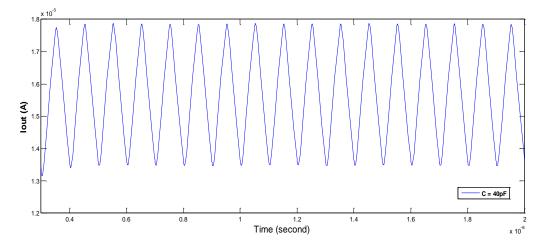

| Fig.4.5 (c)     | Integrator response for $C = 40 \text{ pF}$ for lossless integrator               | 63 |

| Fig.4.6         | Circuit diagram of band pass filter                                               | 64 |

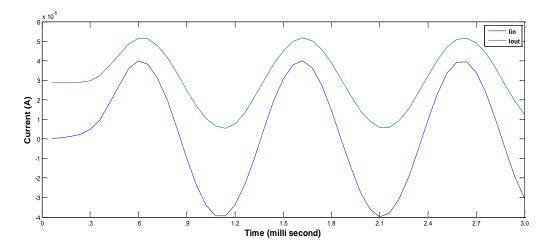

| Fig.4.7 (a)     | Transient response of band pass filter                                            | 65 |

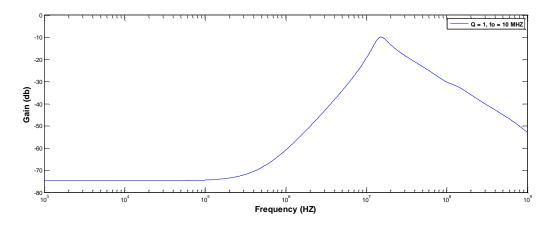

| Fig.4.7 (b)     | Frequency response of $f_0 = 10$ MHZ & Q = 1 for band pass                        | 66 |

|                 | filter                                                                            |    |

|                 |                                                                                   |    |

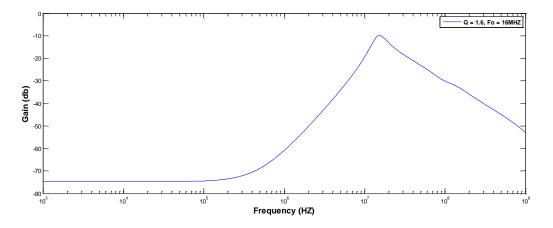

| Fig.4.7 (c) | Frequency response of $f_0 = 16$ MHZ & Q = 1.6 for band pass  | 66 |

|-------------|---------------------------------------------------------------|----|

|             | filter                                                        |    |

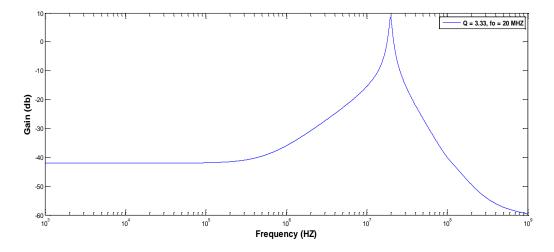

| Fig.4.7 (d) | Frequency response of $f_0 = 20$ MHZ & Q = 3.33 for band pass | 66 |

|             | filter                                                        |    |

| Fig.4.8     | Circuit diagram of second order low pass filter               | 67 |

| Fig.4.9 (a) | Transient response for input of low pass filter               | 68 |

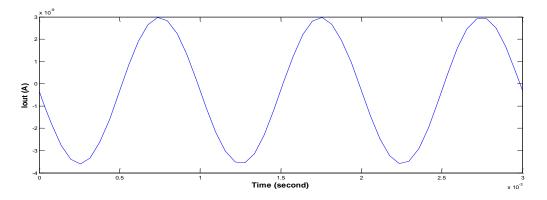

| Fig.4.9 (b) | Transient response for output of low pass filter              | 69 |

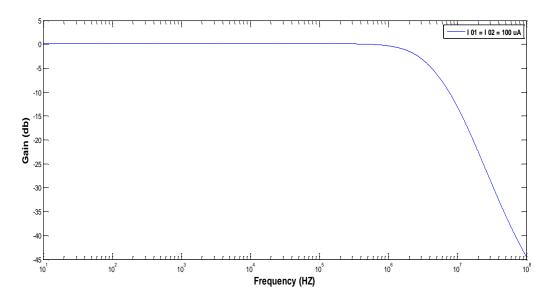

| Fig.4.9 (c) | Gain response of low pass filter                              | 69 |

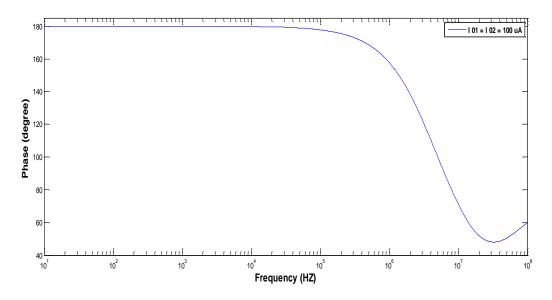

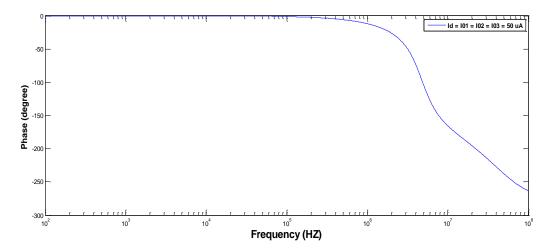

| Fig.4.9 (d) | Phase response of low pass filter                             | 69 |

| -           |                                                               |    |

# LIST OF SYMBOLS AND ABBREVIATIONS

| Symbols           | Descriptions                |

|-------------------|-----------------------------|

| I <sub>C</sub>    | Collector Current           |

| Is                | Reverse Saturation Current  |

| V <sub>T</sub>    | Thermal Voltage             |

| V <sub>c</sub>    | Collector Voltage           |

| V <sub>b</sub>    | Base Voltage                |

| V <sub>cc</sub>   | Source Supply Voltage       |

| I <sub>b</sub>    | Base current                |

| Io                | Bias Current                |

| I <sub>damp</sub> | Damping Current             |

| V <sub>be</sub>   | Base Emitter Voltage        |

| R <sub>E</sub>    | Emitter Resistance          |

| Wo                | Pole Frequency              |

| Q                 | Quality Factor              |

| BJT               | Bipolar Junction Transistor |

| KCL               | Kirchhoff 's Current Law    |

| KVL               | Kirchhoff 's Voltage Law    |

| TLP               | Translinear Principle       |

| CW                | Clockwise                   |

| CCW               | Counter clockwise           |

| ADC               | Analog to Digital Convertor |

| OA                | Operational Amplifier       |

# Chapter 1 Introduction

# **1.1 Introduction**

The present work deals with realization of current mode filters using log-domain techniques. Log domain filters exploit the non-linear relationship between the collector current and base-emitter voltage of bipolar transistors [1]. This relationship is an exponential relationship. In conventional RC-active filters, the active devices are used in their linear region of operations and the circuits are limited in their performance by temperature and dynamic range. The log domain filters do not suffer from both these problems as the temperature dependent terms in the design of the circuit cancel out. Similarly as the transistors non-linear characteristics is retained so there is theoretically no limitation on the amplitude of the input signals. Another noteworthy feature of the log domain circuits is the elimination of passive resistors thus making the circuits suitable for integration. As the parameters of the designed filters depends on the values of external DC currents these parameters can be varied by changing these DC bias currents thus making them electronically tunable.

In the following we present the evolution of the log-domain circuits followed by an introduction to log-domain filtering techniques. The outline of this chapter is as follows the first section will provide a description of the evolution of the log domain filter as it pertains to this work [2]. The next section will present an introduction to the concepts of log domain filtering, and will provide an overview of a log-domain filter structure and its implementation. The final section will discuss the organization of this thesis and provide an outline of its contents.

# 1.2 A historical background

The concept of the log-domain filter was originally proposed by Adams and introduced to the Audio Engineering Society in 1979 [3]. Adams had developed a method by which the resistor in an RC filter could be replaced with a diode, a nonlinear element. By controlling the bias Current of the diode, the cutoff frequency of the filter could be electronically tuned over several decades of frequency. Adams described the discovery as "a circuit composed of both linear and non-

linear elements, which when placed between a log converter and an anti-log converter, will cause the system to act as a linear filter".

The technique introduced by Adams did not receive significant attention until 1993, when Frey [1] proposed a formal procedure for synthesizing log-domain filter functions. The method developed by Frey introduced the state-space matrices as a means to explain the operation of the filter.

The Transistor level approach for Log-Domain Filtering was proposed by Emmanuel M. Drakakis, Alison J.Payne and Chris Toumazou in 1997[8]. The method introduced a continuoustime circuit element termed as Bernoulli cell which is composed of an npn BJT and an emitter connected grounded capacitor and is governed by the differential equation of the Bernoulli form. The Bernoulli cell can be utilized in both the analysis and synthesis of Log-Domain circuits.

Also, the more intuitive procedure for synthesizing log-domain filter functions was proposed by Perry and Roberts in 1995 [16]. The method introduced signal-flow graphs as a means to describe the operation of the filter, from which common filter design techniques, such as the operational simulation of LC ladders, could be applied. Such techniques can be used to simplify the filter design procedure, and can be applied to high-order systems.

#### 1.3 An overview of log domain filtering

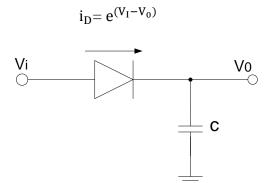

A simple explanation of the principle of log domain filtering can be understood in terms of the diode - capacitor circuit described by Adams [3], as shown in Fig.1.1. If we assume that the current flowing through the diode can be expressed by a simple exponential function, the differential equation describing the operation of this circuit can be expressed as

$$e^{(V_1 - V_0)} = C \frac{d}{dt} (V_0)$$

(1.1)

Where  $V_I$  is input voltage and  $V_0$  is output voltage.

Which can be written as

$$e^{\mathbf{V}_{\mathrm{I}}} = \mathrm{C}\frac{d}{dt}(e^{\mathbf{V}_{\mathrm{0}}}) \tag{1.2}$$

Or in integral form as

$$e^{V_0} = \frac{1}{c} \int (e^{V_1}) dt$$

(1.3)

2

This circuit does not implement a linear integrator in terms of the input and output voltages  $V_I$  and  $V_0$  [3]. However, if these variables were replaced by  $X_I$  and  $X_0$ , according to

$$V_{I} = \ln (X_{I}), V_{0} = \ln (X_{0}),$$

(1.4)

Which can be written as

$$X_0 = \frac{1}{c} \int (X_I) dt \tag{1.5}$$

Fig.1.1 A Simple log domain integrator

Therefore, by logarithmically compressing the signal  $X_I$  according to equation (1.4) to obtain  $V_I$  at the circuit input and by exponentially expanding  $V_0$  according to the inverse of equation (1.4) to obtain  $X_0$  at the circuit output, a linear integration can be realized. Such a means of expansion and compression is readily available in the form of the voltage to current relationship of the diode equation. In this case, the desired input and output signals,  $X_I$  and  $X_0$ , are in fact currents, and the integration which is taking place is performed on logarithmically compressed signals named as "logarithmic domain".

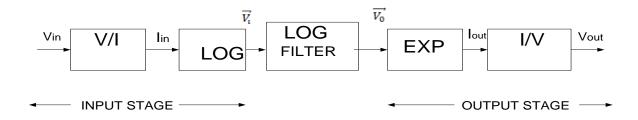

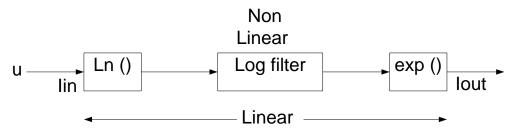

A generic block diagram for a log domain filter is shown in Fig.1.2. This filter is composed of three distinct sections an input compression stage, a filter stage, and an output expansion stage. Voltage to current conversion and logarithmic compression are performed in the first stage, as shown by the progression of the  $V_{in}$ ,  $I_{in}$  and  $\vec{V_l}$  signals in the figure. The V/I conversion ratio is represented as shown in Fig.1.2, and the logarithmic compression is performed by means of a bipolar transistor. Filtering (in the logarithmic domain) is performed in the second stage. The symbol for

Fig.1.2 Block diagram of log domain filter

the log-domain integrator, the basic building block for the filter, is drawn in the Fig.1.2. Exponential expansion and I/V conversion are performed in the final stage, as shown in the progression of  $\overrightarrow{V_0}$ ,  $I_{out}$  and  $V_{out}$  signals. Exponential expansion is once again performed by means of a bipolar transistor, and then the I/V conversion ratio is done.

## 1.4 Outline of the work presented in the dissertation

In this dissertation, chapter 1 covers the basic concepts of log domain filtering. The Basic log domain integrator and history of log domain is also discussed. Second chapter covers the basic description of Translinear circuits, design of log domain filters using translinear principle, and its general applications in analog signal processing. It also covers the basic concepts of Bernoulli cell and implementation of higher order filters have been verified by PSPICE simulation. In the third chapter, LC ladders and design of log domain filters based on simulation of LC ladders have been discussed. In fourth chapter, state space synthesis in linear circuits and corresponding log domain state space synthesis have been discussed. In the last and final chapter a summary of the work carried out has been presented alongwith some scope for future extension of the work.

# **Chapter 2**

# Log domain filters based on translinear circuits and the Bernoulli cell

## **2.1 Introduction**

In the present chapter, we will discuss the translinear circuit principle [5] and the Bernoulli cell [7]. Both translinear circuit principle and the Bernoulli cell have been used extensively in design of log domain filters, so it is worthwhile to present a review of these two in details. After the review we have also simulated simple first order, second order and higher order filter structures using these concepts.

The term translinear was first used by B. Gilbert in 1975 [7] though he had introduced these concepts as early as 1969. By translinear circuits he meant those circuits where the linear model of the transistor was not used to arrive at the input-output relations between the current input and current output in a circuit consisting of BJT's in which the base emitter junctions consists of an even number of transistors. He had proved that in such circuits (i) The input-output current relationships were independent of temperature. (ii) The relationships were not limited by the amplitude of the inputs (in contrast to the circuits in which a linear model of the transistor is used to arrive at the input-output relationships).

The Bernoulli cell comprises an npn transistor and an emitter-connected grounded capacitor. Its dynamic behavior is determined by a differential equation of the Bernoulli form [8]. The identification of the Bernoulli cell leads to the design of a system of linear differential equations which describe the dynamics of the derived log-domain state-variables. This approach can be used for the analysis of log-domain circuits. The collector current of the transistor have a form of Bernoulli's general non-linear differential equation [8]. By changing the suitable variables, Bernoulli's equation can be converted to a linear form and hence the Bernoulli cell can be used as a basic element for the synthesis of linear circuits.

In this chapter, a log domain lossy integrator, first order low pass and high pass filter circuits based on translinear principle and also the application of Bernoulli cells like first order lossy integrator, second order filter containing zero and a third order and proposed fourth order butterworth low-pass filter circuits have been constructed. Frequency domain and time domain responses have also been given to illustrate the performance of these circuits using PSPICE simulations.

## 2.2 Translinear circuit principle

#### 2.2.1 The bipolar translinear principle

The translinear principle uses the linear relationship between the transconductance and collector current in a bipolar transistor which is given by

$$I_C \cong I_S e^{(V_{be}/V_T)} \tag{2.1}$$

or

$V_{be} \cong V_T \ln(I_c/I_s)$

The transconductance is defined as

$$\frac{\partial I_c}{\partial V_{be}} = \frac{I_s \ e^{(V_{be}/V_T)}}{V_T} = \frac{I_c}{V_T}$$

(2.3)

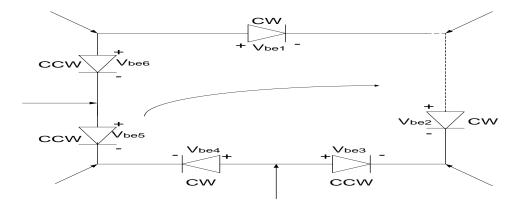

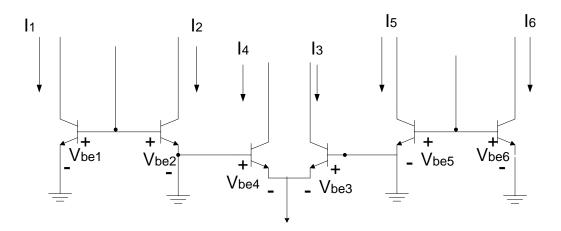

Where  $I_s$  is the saturation current of the device, and  $V_T$  is the device thermal voltage. The translinear principle applies to circuits in which a number of forward biased base-emitter ( $V_{be}$ ) junctions are connected in a continuous loop. The transistors within the loop can be identified as clockwise (CW) or counter clockwise (CCW), depending on the direction of current flow through the junction. The transistors may be npn or pnp but the complete loop must satisfy the following condition [6]

(i) The number of CW npn V<sub>be</sub> junctions is equal to the number of CCW npn V<sub>be</sub> junctions.

(ii) The number of CW pnp  $V_{be}$  junctions is equal to the number of CCW pnp  $V_{be}$  junctions

Fig.2.1 Loop diagram using diodes

(2.2)

By applying KVL in the circuit, we have

$$V_{be1} + V_{be2} + V_{be4} = V_{be3} + V_{be5} + V_{be6}$$

(2.4)

Using equation (2.2), the above relationship can be written as

$$V_T \ln\left(\frac{I_1}{I_S}\right) + V_T \ln\left(\frac{I_2}{I_S}\right) + V_T \ln\left(\frac{I_4}{I_S}\right) = V_T \ln\left(\frac{I_3}{I_S}\right) + V_T \ln\left(\frac{I_5}{I_S}\right) + V_T \ln\left(\frac{I_6}{I_S}\right)$$

(2.5)

$$V_T \ln \left[\frac{I_1}{I_S} \cdot \frac{I_2}{I_S} \cdot \frac{I_4}{I_S}\right] = V_T \ln \left[\frac{I_3}{I_S} \cdot \frac{I_5}{I_S} \cdot \frac{I_6}{I_S}\right]$$

(2.6)

or or

$$I_1. I_2 . I_4 = I_3. I_5 . I_6 \tag{2.7}$$

Let us Consider a loop where there are j numbers of npn  $V_{be}$  junctions in each direction and k numbers of pnp  $V_{be}$  junctions in each direction. By generalizing the result of equation (2.4), we can write

$$\sum_{CW_j} V_{bej} + \sum_{CW_k} V_{bek} = \sum_{CCW_j} V_{bej} + \sum_{CCW_k} V_{bek}$$

(2.8)

$$\sum_{CW_j} V_t \ln(I_{cj}/I_{sn}) + \sum_{CW_k} V_t \ln(I_{ck}/I_{sp}) = \sum_{CCW_j} V_t \ln(I_{cj}/I_{sn}) + \sum_{CCW_k} V_t \ln(I_{ck}/I_{sp})$$

(2.9)

where  $I_{cj}$  and  $I_{ck}$  represents the collector current associated with each of the  $V_{be}$  junctions within the loop.  $I_{sn}$  and  $I_{sp}$  represent the npn and pnp saturation currents respectively and can be expressed in terms of current densities ( $I_{sn} = J_{sn}A$ ,  $I_{sp} = J_{sp}A$ ), where  $J_{sn}$  and  $J_{sp}$  are process dependent.

$$\sum_{CW_j} \ln\left(\frac{I_{cj}}{J_{sn}A_j}\right) + \sum_{CW_k} \ln\left(\frac{I_{ck}}{J_{sp}A_p}\right) = \sum_{CCW_j} \ln\left(\frac{I_{cj}}{J_{sn}A_j}\right) + \sum_{CCW_k} \ln\left(\frac{I_{ck}}{J_{sp}A_p}\right)$$

(2.10)

$$\prod_{CW_{j,k}} \frac{I_{cj}I_{ck}}{J_{sn}{}^{j}A_{j}J_{sp}{}^{k}A_{k}} = \prod_{CCW_{j,k}} \frac{I_{cj}I_{ck}}{J_{sn}{}^{j}A_{j}J_{sp}{}^{k}A_{k}}$$

(2.11)

or

$$\prod_{CW_{j,k}} \frac{I_{cj}I_{ck}}{A_jA_k} = \prod_{CCW_{j,k}} \frac{I_{cj}I_{ck}}{A_jA_k}$$

(2.12)

If (j + k = m), then

$$\prod_{cw_m} \frac{I_{cm}}{A_m} = \prod_{ccw_m} \frac{I_{cm}}{A_m}$$

(2.13)

Hence, we can say that the above equation represents bipolar translinear principle in which the product of clockwise junction current densities is equal to the product of the counterclockwise junction current densities.

#### 2.2.2 Principles of log domain design

or

Translinear circuits are the fundamental structure of log-domain circuits. Fig.2.2 shows a translinear loop formed by the base-emitter junctions in bipolar transistors [6]. For the purpose of analysis, we consider all transistors to be ideal and perfectly matched having collector current given by

$$I_C \cong I_S e^{(V_{be}/V_T)} \tag{2.14}$$

where  $V_{be}$  is the base to emitter voltage,  $V_T$  is the thermal voltage (0.025V at room temperature) and  $I_s$  is the reverse saturation current.

$V_{be} \cong V_T \ln(I_c/I_s)$

Using the equation (2.13) (in which we have assumed equal emitter area for all the transistors), we get the following equation

$$I_1 \cdot I_3 \cdot I_5 = I_2 \cdot I_4 \cdot I_6 \tag{2.16}$$

Fig.2.2 Translinear loop with CB and CE configurations

(2.15)

The translinear principle gives a simple rule for computing products of currents. For designing filter circuits we need to find some equation which involves time-derivative of output current in the following form

$$I_{out} \propto I_{in}$$

(2.17)

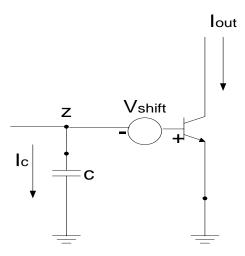

By grounding the emitter ( $V_e = 0$ ) and adding a capacitor C to the system yields an equation composed of current-mode variables [9]. Fig.2.3 shows such a system i.e. a basic building block of log-domain filters, in which a constant voltage  $V_{shift}$  is inserted between the capacitor node Z and the base without affecting the equation solution. Now the output current is given by

$$I_{out} = I_s \ e^{(V_{be}/V_T)}$$

(2.18)

$$I_{out} = I_s \ e^{(V_b - V_e/V_T)} \tag{2.19}$$

Fig.2.3 Filter pole formed using a transconductor.

On differentiating equation (2.19), we get

$$I_{out} = \frac{1}{V_T} I_{out} \frac{d}{dt} (V_b - V_e)$$

(2.20)

Since  $I_c = C V_{be}$ , we can write equation (2.20) as

$$\dot{I_{out}} = \frac{I_{out}I_c}{V_T c}$$

(2.21)

From this equation, we can find the derivative of a current by multiplying two currents together which can be done using a translinear loop circuit.

# 2.3 Synthesis of log domain blocks using translinear principle

In this section, we will discuss the applications based on translinear principle.

# 2.3.1 Log-domain lossy integrator

Fig.2.4 shows a log-domain lossy integrator based on the translinear principle [11]. Here we assume that each transistor has an ideal exponential characteristic. By applying KCL, the base-emitter voltage relations can be written as

Fig.2.4 Log domain lossy integrator.

$$V_{be1} + V_{be2} - V_{be3} - V_{be4} = 0 (2.22)$$

The collector current of the transistor is given by

$$I_C \cong I_S \ e^{(V_{be}/V_T)} \tag{2.23}$$

Now applying the translinear principle (TLP) to transistor Q1-Q4 as

$$I_{C1}I_{C2} = I_{C3}I_{C4} \tag{2.24}$$

If  $I_{C1} = I_i$ ,  $I_{C2} = I_2$ ,  $I_{C4} = I_0$ , then

$$I_i I_2 = I_{C3} I_0 \tag{2.25}$$

The collector current of Q3 can be expressed as

$$I_{C3} = I_3 + C_1 V_{C1} \tag{2.26}$$

The derivative of the voltage across the capacitor  $C_1$  is given by

$$\dot{V_{C1}} = \frac{dV_{C1}}{dt} = \frac{V_T}{I_0} \frac{dI_{out}}{dt} = \frac{V_T \dot{I_0}}{I_0}$$

(2.27)

The derivative of the output current based on equation (2.23) is given by

$$\dot{I_0} = \frac{dI_0}{dt} = \frac{I_S}{V_T} e^{(V_{C_1}/V_T)} \frac{dV_{C_1}}{dt} = \frac{I_0 \dot{V_{C_1}}}{V_T}$$

(2.28)

Substituting equation (2.26), (2.27) and (2.28) into equation (2.24) & (2.25), we get

$$I_1 I_2 = \left( I_3 + \frac{C_{1 I_0} V_T}{I_0} \right) I_0 \tag{2.29}$$

Let us assume  $I_2 = I_3 = I$ , then equation (2.29) become

$$I_i = I_o + \frac{c_{1 I_o} v_T}{I}$$

(2.30)

By taking the Laplace transform, the transfer function of the circuit of Fig.2.4 in s-domain can be written as

$$H(s) = \frac{I_O(s)}{I_i(s)} = \frac{1}{s\left(\frac{C_1V_T}{I}\right) + 1}$$

(2.31)

From equation (2.31), we can say that H(s) corresponds to the transfer function of a lossy integrator and the pole frequency can be controlled by the bias current I.

#### **2.3.2 Simulation results**

The translinear lossy integrator simulated in PSPICE is shown in Fig.2.4. The bias currents are taken as  $I_1 = I_2 = 50$  uA. The power supply voltage is taken as 2.5V and capacitance is taken as  $C_1 = 50$  pF.

The transient and frequency responses of the Fig.2.4 are shown in Fig.2.5 (a) to Fig.2.5(c).

Fig.2.5 (a) Time response of lossy integrator.

Fig.2.5 (b) Integrator output for frequency  $(f_{in}) = 1MHZ$  of lossy integrator.

Fig.2.5 (c) Frequency response of lossy integrator.

By PSPICE simulation, we get pole frequency = 5.7 MHZ which is close to the theoretically pole frequency = 6.1 MHZ.

# 2.3.3 First-order log domain filter

The dynamic translinear circuit principle has been used to realize first order log domain filters [12] .The circuit given below in Fig.2.6 has been used to realize this filter.

Fig. 2.6 Log domain high pass and low pass first order filter.

The current through the capacitor is given by

$$C\frac{dV_o}{dt} = I_O \ e^{\left[\frac{(V_{in} - V_o)}{2V_T}\right]}$$

(2.32)

From Fig.2.6 the current-mode transfer functions [9] is given by

$$T_{LP} = H \frac{w_o}{s + w_o} \tag{2.33}$$

$$T_{HP} = H \frac{s}{s + w_o} \tag{2.34}$$

The pole frequency  $(w_0)$  and gain (H) of the given filter in terms of bias current are given below

$$w_o = \frac{1}{2V_T C} \left( \frac{I_{03} I_{04}}{I_{02}} \right) \tag{2.35}$$

$$H_{HP} = \frac{I_{01}}{I_{02}} \tag{2.36}$$

$$H_{LP} = \frac{I_{01}}{I_{03}} \tag{2.37}$$

13

From equations (2.35) to (2.37), it is seen that the filter parameters are tunable through the respective biasing currents. The pole frequency ( $w_0$ ) can be adjusted by  $I_{02}$ ,  $I_{03}$  and  $I_{04}$  and also  $H_{LP}$  and  $H_{HP}$  can be tuned by  $I_{01}$  without disturbing  $w_0$ [12].

#### 2.3.4 Simulation results

The first order high pass and low pass filter is simulated in PSPICE to check the workability. The circuit is designed for a pole frequency of 1.59 MHZ, Q =1 and H=1. The value of parameters are selected as C = 200 pF and  $I_{01} = I_{02} = I_{03} = I_{04} = 100$  uA with  $V_{CC} = 3V$ . The current signal is taken across load resistor of 1 ohm. The time responses of low pass and high pass filter are shown in Fig.2.7 (a) and Fig.2.7 (b).

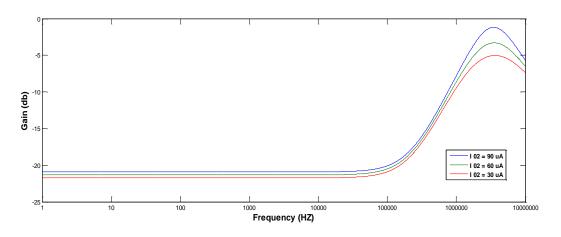

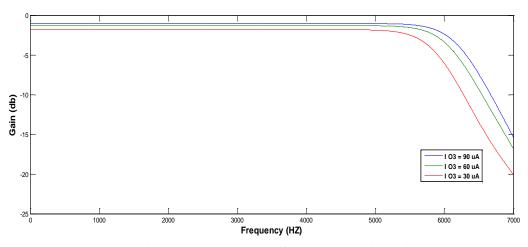

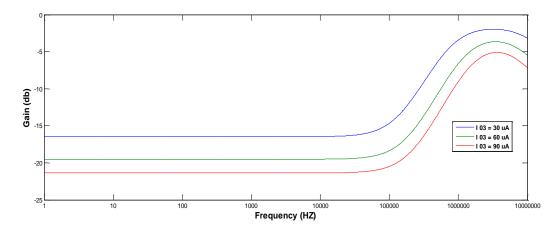

Fig.2.7 (c) and Fig.2.7 (d) shows the simulation results of low pass and high pass filter. The tuning characteristics for low pass and high pass filters are observed by varying respective bias currents. Fig.2.7 (e) and Fig.2.7 (f) shows the variation of gain and also Fig.2.7 (g) and Fig.2.7 (h) shows the variation of pole frequency. The pole frequency using PSPICE simulation for low pass and high pass filter comes out to be 1.78 MHZ and 1.23 MHZ respectively which is close to the theoretical pole frequency of 1.59 MHZ.

Fig.2.7 (a) Time response of low pass filter

Fig.2.7 (c) Frequency response of low pass filter.

Fig.2.7 (d) Frequency response of high pass filter.

Fig.2.7 (e) Variation of gain for different values of  $I_{01}$  for low pass filter.

Fig.2.7 (f) Variation of gain for different values of  $\ I_{02}$  for high pass filter.

Fig.2.7 (g) Variation of pole frequency for different values of  $I_{03}$  for low pass filter.

Fig.2.7 (h) Variation of pole frequency for different values of  $I_{03}$  for high pass filter.

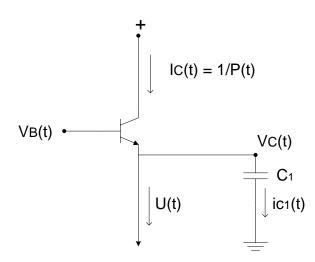

## 2.4 A Bernoulli cell

The Bernoulli cell is a nonlinear continuous-time circuit element. The Bernoulli cell comprises an npn transistor and an emitter-connected grounded capacitor and its dynamic behavior is determined by a differential equation. The collector current can be represented in form of Bernoulli's general non-linear differential equation. Bernoulli cell approach allows the transformation of a frequency domain transfer function into time domain transfer function which can be directly implemented by translinear (TL) loops [7]. By changing the suitable variables, Bernoulli's equation can be converted to a linear form and hence the Bernoulli cell can be used as a basic element for the synthesis of linear circuits.

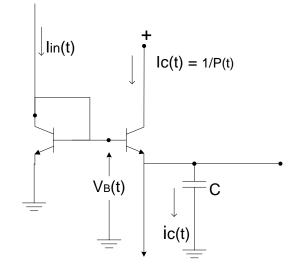

The Bernoulli cell is formed by connecting a grounded capacitor of value C at the emitter of a forward-biased npn BJT as shown in Fig.2.8. The collector current  $I_C$  obeys the exponential law given below

$$I_{C}(t) = I_{S} e^{\left[ (V_{B}(t) - V_{C}(t)/V_{T}] \right]}$$

(2.38)

Where  $I_S$  is reverse saturation current,  $V_B(t)$  is base voltage,  $V_C(t)$  is capacitor voltage and  $V_T$  is thermal voltage, then

$$\frac{dV_C(t)}{dt} = \dot{V_C}(t) = i_c(t)/C = [I_C(t) - u(t)]/C$$

(2.39)

Differentiation of (2.38) yields the following nonlinear differential equation

$$I_{C}(t) - \left(\frac{V_{B}(t)}{V_{T}} + \frac{u(t)}{CV_{T}}\right) I_{C}(t) + \frac{(I_{C}(t))^{2}}{CV_{T}} = 0$$

(2.40)

Equation (2.40) represents Bernoulli form and Fig.2.8 shows Bernoulli Cell. Equation (2.40) is nonlinear and can be linearized by a nonlinear substitution

$$I_{C}(t) = 1/P(t) \neq 0$$

(2.41)

Fig.2.8 A Bernoulli cell

Equation (2.40) reduces to

$$\frac{dP(t)}{dt} + \left(\frac{V_B(t)}{V_T} + \frac{u(t)}{CV_T}\right) P(t) - \frac{1}{CV_T} = 0$$

(2.42)

Equation (2.42) is a linear first order differential equation. Variables  $V_B$  (t) and u (t) are "free" parameters.

Let us considered a translinear loop of even number of 2m base emitter junctions (where emitter junction is forward biased).

$$CW \prod_{j=1}^{m} I_j(t) = CCW \prod_{j=1}^{m} \tilde{I}_j(t)$$

(2.43)

where  $I_j(t)$  represents the collector currents in clockwise (CW) direction and  $\tilde{I}_j(t)$  represents the collector currents in counter clockwise (CCW) direction [7]. If we assume  $I_C(t) = I_k(t)$ , then P(t) =  $\frac{1}{I_C(t)} = \frac{1}{I_k(t)}$ .

So, finally we can write

$$P(t) = \frac{1}{I_{C}(t)} = \frac{1}{I_{k}(t)} = \frac{CW \prod_{j=1}^{m,(j\neq k)} I_{j}(t)}{CCW \prod_{j=1}^{m} I_{j}(t)}$$

(2.44)

# 2.5 A Bernoulli cell in log domain structures

## 2.5.1 A single input-driven Bernoulli cell

A single input driven Bernoulli cell is shown in Fig.2.9. Input current  $I_{in}$  can be converted to a logarithmically compressed voltage  $V_B$  as

$$\dot{V}_B = V_T \frac{\dot{I}_{in}(t)}{I_{in}(t)} = V_T \frac{d}{dt} \left[ \ln(I_{in}(t)) \right]$$

(2.45)

By substituting equation (2.45) into (2.42) gives

$$CV_T \frac{d}{dt} \{ \ln[P(t) I_{in}(t)] \} + u(t) = \frac{1}{P(t)} = I_C(t)$$

(2.46)

Fig.2.9 A single input driven Bernoulli cell

The capacitor current can be written as

$$i_{C}(t) = C V_{T} \frac{d}{dt} \{ \ln[P(t) I_{in}(t)] \}$$

(2.47)

## 2.5.2 Interconnection of Bernoulli cell

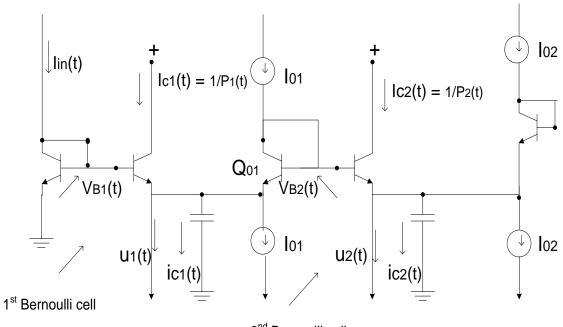

In Fig.2.10 (a), two Bernoulli cells are connected by a voltage level shifter  $Q_{01}[8]$ . For the first cell, we can write

$$C_1 V_T \frac{d}{dt} \{ \ln[P_1(t) I_{in}(t)] \} + u_1(t) = \frac{1}{P_1(t)} = I_{C1}(t)$$

(2.48)

The linearized expression for the second cell according to equation (2.42) is given by

$$\frac{dP_2(t)}{dt} + \left(\frac{V_{B_2}(t)}{V_T} + \frac{u_2(t)}{c_2 V_T}\right) P_2(t) - \frac{1}{c_2 V_T} = 0$$

(2.49)

where  $I_{C2}(t) = \frac{1}{P_2(t)}$ , and  $C_2$  is the capacitor value of the second Bernoulli Cell. From equation (2.47), we can write

$$\frac{dV_{C1}(t)}{dt} = V_T \frac{d}{dt} \{ \ln[P_1(t) I_{in}(t)] \}$$

(2.50)

From equation (2.49), we can write

$$C_2 V_T \frac{d}{dt} \{ \ln[P_2(t) P_1(t) I_{in}(t)] \} + u_2(t) = \frac{1}{P_2(t)} = I_{C2}(t)$$

(2.51)

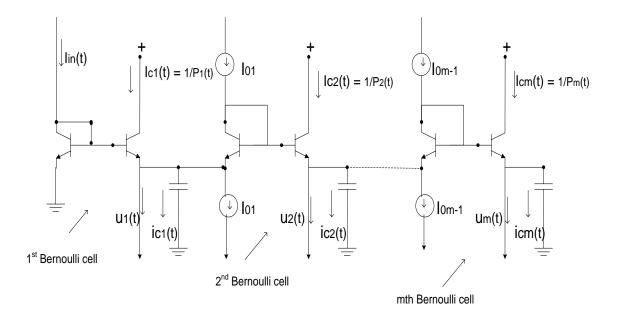

Hence, generalizing the equation (2.51) for mth cell, we can write

$$C_m V_T \frac{d}{dt} \{ \ln[P_m (t) P_{m-1}(t) \dots P_1 (t) I_{in}(t)] \} + u_m (t) = \frac{1}{P_m(t)} = I_{Cm}(t)$$

(2.52)

And capacitor currents of mth Bernoulli cell is given by

$$i_{C1}(t) = C_1 V_T \frac{d}{dt} \{ \ln[P_1(t) I_{in}(t)] \}$$

$$i_{C2}(t) = C_2 V_T \frac{d}{dt} \{ \ln[P_2(t)P_1(t) I_{in}(t)] \}$$

.....

$$i_{Cm}(t) = C_m V_T \frac{d}{dt} \{ \ln[P_m(t)....P_2(t)P_1(t) I_{in}(t)] \}$$

$$i_{Cm}(t) = C_m V_T \frac{d}{dt} \left\{ \ln \left[ \left[ \prod_{j=1}^m P(t) \right] I_{in}(t) \right] \right\}$$

(2.53)

Now, by substituting the products of  $P_k(t) \dots P_1(t)I_{in}(t)$ , a new variable  $w_k(t)$  is given by

$$w_k(t) = \left[\prod_{j=1}^k P_k(t)\right] I_{in}(t) = P_k(t) w_{k-1}(t)$$

(2.54)

From equation (2.53), we can write

$$i_{C1}(t) = C_1 V_T \frac{d}{dt} \{ \ln[w_1(t)] \}$$

$$i_{C2}(t) = C_2 V_T \frac{d}{dt} \{ \ln[w_2(t)] \}$$

.....

$$i_{Cm}(t) = C_m V_T \frac{d}{dt} \{ \ln[w_m(t)] \}$$

(2.55)

2<sup>nd</sup> Bernoulli cell

Fig.2.10 (a) Two interconnected Bernoulli cell

Fig.2.10 (b) Cascaded Bernoulli cell

The identification of the variable  $w_k(t)$  used for the analysis of higher order filter is given by

Fig.2.11 Identification of variable  $w_k(t)$  for a cascade of Bernoulli cell

Finally by equation (2.55), we can write

$$w_{1}(t) = u_{1} e^{(V_{C1}(t)/V_{T})}$$

$$w_{2}(t) = u_{2} e^{(V_{C2}(t)/V_{T})}$$

.....

$$w_{m}(t) = u_{m} e^{(V_{Cm}(t)/V_{T})}$$

(2.56)

where  $u_1, u_2, \dots, u_m$  are constant in time quantities and  $V_{C1}(t), V_{C2}(t), \dots, V_{Cm}(t)$  are the capacitor node voltages.  $u_1$  is dimensionless and the dimensions of  $u_m$  is  $[amp]^{-(m-1)}$ .

# 2.6 Applications of Bernoulli cell

In this section, we will discuss the application of Bernoulli cell in log domain filters.

# 2.6.1 Log domain lossy integrator

Let us assume that the desired lowpass frequency response is given by [13]

$$\frac{I_{out}(s)}{I_{in}(s)} = \frac{k}{s+w_0} \tag{2.57}$$

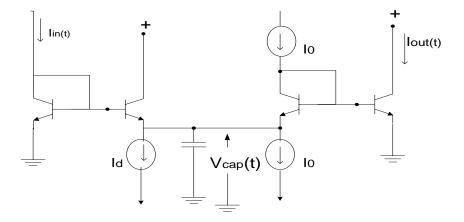

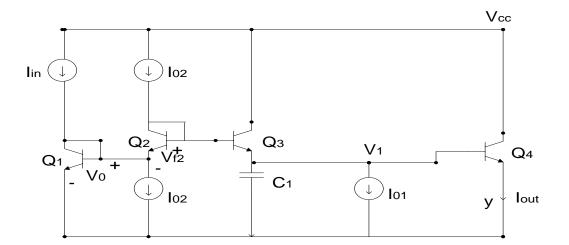

Lossy integrator is shown in Fig.2.12.

Fig.2.12 A log domain lossy integrator

In time domain, we can write

$$I_{out}(t) = I_S \ e^{\left[\frac{V_T \ln(I_O/I_S) + V_{cap}}{V_T}\right]} = I_O \ e^{\left(\frac{V_{cap}}{V_T}\right)}$$

(2.58)

or

$$I_{d} + C \dot{V_{cap}} = I_{S} e^{\left[\frac{V_{T} \ln(I_{in}/I_{S}) - V_{cap}}{V_{T}}\right]} = I_{in} e^{\left(\frac{-V_{cap}}{V_{T}}\right)}$$

(2.59)

From equation (2.58) and (2.59), we get

$$\frac{d}{dt}\left[e^{\left(\frac{V_{cap}}{V_T}\right)}\right] = e^{\left(\frac{V_{cap}}{V_T}\right)}\left(\frac{V_{cap}}{V_T}\right)$$

(2.60)

So, we can write

$$I_{d} \frac{I_{out}}{I_{0}} + (C V_{T}) \frac{I_{out}}{I_{0}} = I_{in}$$

(2.61)

So, in Laplace form, we can write

$$\frac{I_{out}(s)}{I_{in}(s)} = \frac{(I_O/C V_T)}{s + (I_d/C V_T)}$$

(2.62)

# 2.6.2 Simulation results

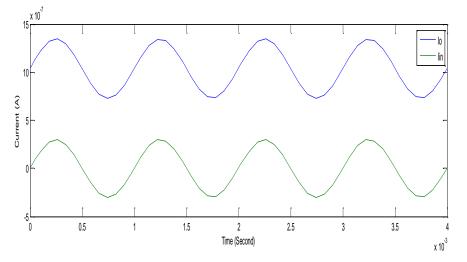

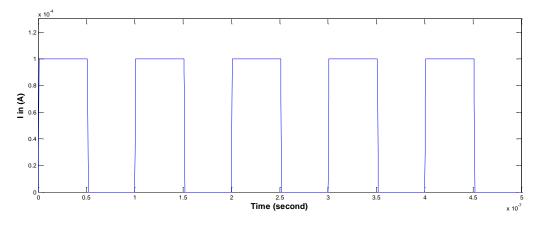

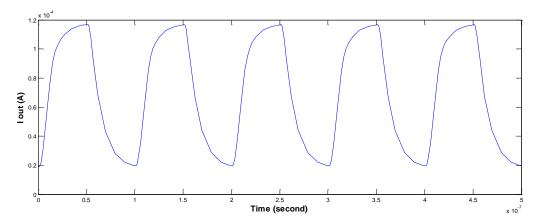

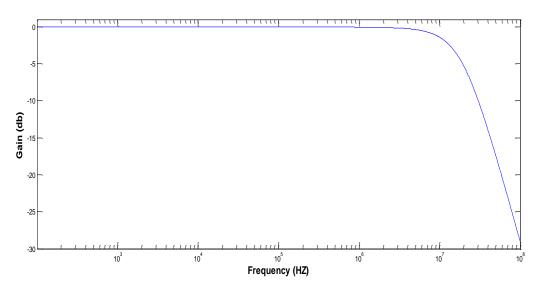

To prove the theoretical validity, lossy integrator of Fig.2.12 is simulated with PSPICE program. The coefficients were solved for C = 40 pF,  $I_d = I_0 = 100 \text{ uA}$  having cut off frequency of 14.8 MHZ which is close to the theoretical cut off frequency of 15.2 MHZ. The integrator response and frequency responses are shown in Fig.2.13 (a) to Fig.2.13 (c).

Fig.2.13 (a) Input frequency of 10 MHZ for lossy integrator.

Fig.2.13 (b) Integrator response for lossy integrator.

Fig.2.13 (c) Frequency response for lossy integrator

## 2.6.3 Second order filter containing zero

Let us assume that the desired Transfer function is given by [7]

$$\frac{I_{out}(s)}{I_{in}(s)} = \frac{ks + ak}{s^2 + as + b}$$

(2.63)

In time domain, we can write

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{k \frac{d}{dt} [\ln(I_{in})] + ak}{\frac{d}{dt} [\ln(I_{out})] \left\{ \frac{d}{dt} [\ln(I_{out})] \right\} + a \frac{d}{dt} [\ln(I_{out})] + b}$$

(2.64)

Here, after assuming  $\frac{d}{dt} [\ln(I_{out})] = \frac{i_{c2}}{cV_T}$  and  $\frac{d}{dt} [\ln(I_{out})] = \frac{i_{c1}}{cV_T}$ . The problem regarding wheather the term  $\frac{d}{dt} [\ln(I_{in})]$  would be substituted for  $\frac{i_{c2}}{cV_T}$  or  $\frac{i_{c1}}{cV_T}$  is solved by assigning a subscript j at each s-term converting it to s<sub>j</sub>.

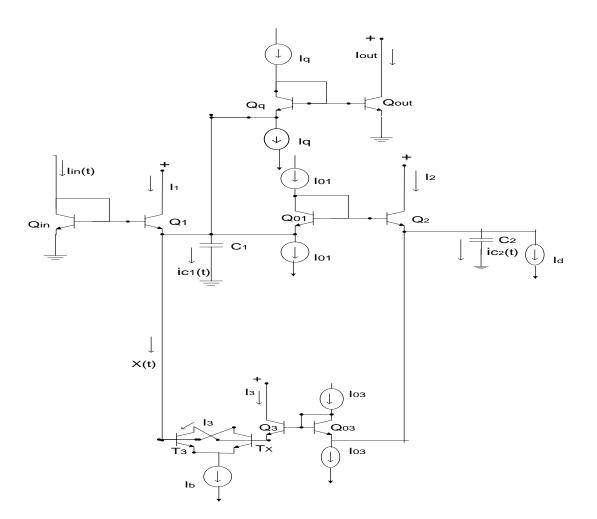

Fig.2.14 Second order filter circuit containing zero.

So, we can write

$$\frac{I_{out}(s)}{I_{in}(s)} = \frac{ks + ak}{s^2 + as + b} = \frac{k}{s + \frac{b}{s_2 + a}} = \frac{ks_2 + ak}{s_1 s_2 + as_1 + b}$$

(2.65)

Thus the terms  $\frac{d}{dt}[\ln(I_{in})]$  and  $\frac{d}{dt}[\ln(I_{out})]$  can be substituted for  $\frac{i_{c2}}{cV_T}$  if  $\frac{d}{dt}[\ln(I_{out})]$  is equal to  $\frac{i_{c1}}{cV_T}$ . So, the final time domain transfer function can be written as [10]

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{\dot{k} (i_{c2} + a CV_T)}{i_{c1} i_{c2} + i_{c1} (a CV_T) + b (CV_T)^2} = \frac{\dot{k}}{i_{c1} + \frac{b (CV_T)^2}{i_{c2} + (a CV_T)}}$$

(2.66)

Let us assume

$$\frac{b (CV_T)^2}{i_{c2} + (a CV_T)} = x (t)$$

(2.67)

So, time domain transfer function can be written as

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{\dot{k}}{i_{c1} + x(t)} = \frac{k (CV_T)}{i_{c1} + x(t)}$$

(2.68)

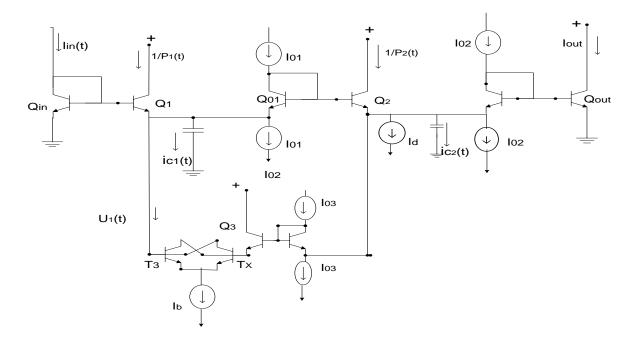

The second order circuit containing zero is shown in Fig.2.14.

Equation (2.67) corresponds to the translinear loop formed by  $Q_{01} T_3 T_X Q_3 Q_{03} Q_2$  and equation (2.68) corresponds to the translinear loop formed by  $Q_{in}Q_1 Q_q Q_{out}$ .

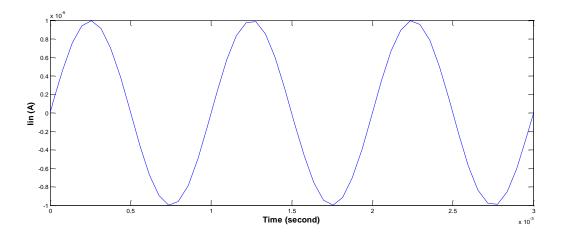

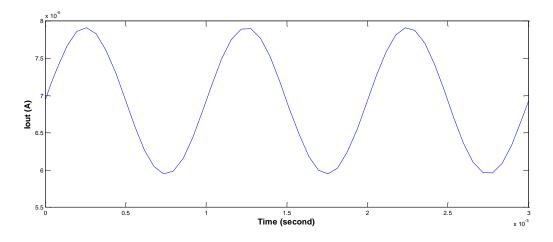

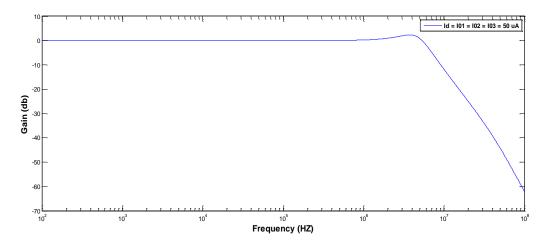

#### 2.6.4 Simulation results

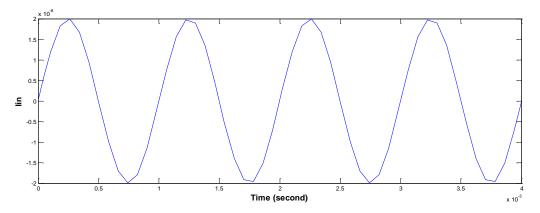

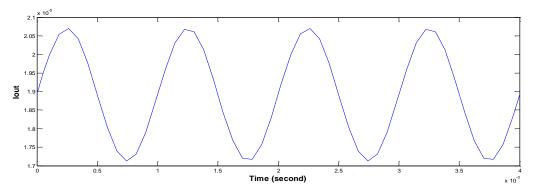

To prove the theoretical validity, Second order filter containing zero in Fig.2.14 is simulated with PSPICE program. The coefficients were solved for C = 5 pF having loss of 40db in next decade. The time response is shown in Fig.2.15 (a) and Fig.2.15 (b).

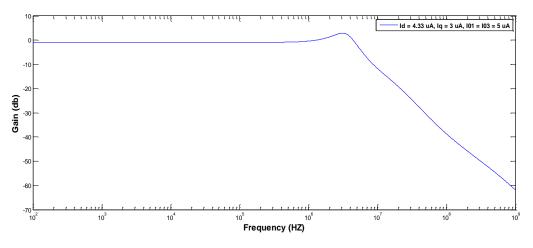

The frequency response of Second order filter containing zero for

- (a)  $I_d = 5 \text{ uA}$ ,  $I_q = 4.33 \text{ uA}$ ,  $I_{01} = I_{03} = 5 \text{uA}$  having Pole frequency = 4 MHZ is shown in Fig.2.15 (c).

- (b)  $I_d = 4.33 \text{ uA}$ ,  $I_q = I_{01} = I_{03} = 5 \text{ uA}$  having Pole frequency = 4.4 MHZ is shown in Fig.2.15 (d).

Fig.2.15 (a) Time response for input of second order filter.

Fig.2.15 (b) Time response for output of second order filter.

Fig.2.15 (c) Frequency response of second order filter for  $f_0 = 4$  MHZ.

Fig.2.15 (d) Frequency response of second order filter for  $f_0 = 4.4$  MHZ.

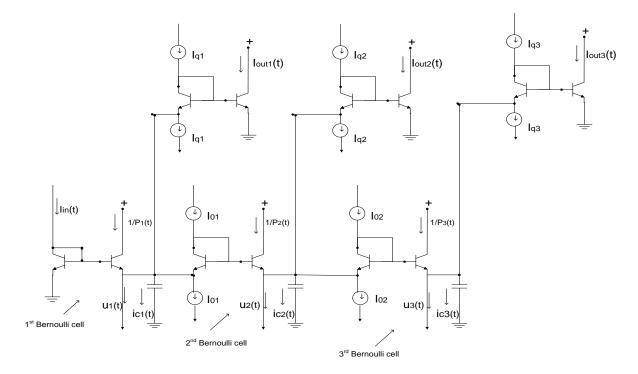

## 2.6.5 Third order low pass Butterworth filter

Let us assume that the desired lowpass frequency response is given by [7]

$$\frac{I_{out}(s)}{I_{in}(s)} = \frac{b_m}{s^3 + as^2 + bs + b_0}$$

(2.69)

In time domain, we can write

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{b_m}{b_0 + b \left\{ \frac{d}{dt} [\ln(I_{out})] \right\} + a \left\{ \frac{d}{dt} [\ln(I_{out})] \right\} \left\{ \frac{d}{dt} [\ln(I_{out})] \right\} + \left\{ \frac{d}{dt} [\ln(I_{out})] \right\} \left\{ \frac{d}{dt} [\ln(I_{out})] \right\} \left\{ \frac{d}{dt} [\ln(I_{out})] \right\}}$$

(2.70)

By expressing all term of form  $\frac{d}{dt}[\ln()]$  and using equation (2.55) and equation (2.69), we can write

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{b_m}{b_0 + b\frac{i_{c1}}{CV_T} + a\frac{i_{c1}i_{c2}}{(CV_T)^2} + \frac{i_{c1}i_{c2}i_{c3}}{(CV_T)^3}}$$

(2.71)

or in fraction form, we can write

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{\frac{\frac{b_m(CV_T)^3}{i_{C3} + (aCV_T)}}{\frac{b(CV_T)^2}{i_{C3} + (aCV_T)}}}{\frac{b_0(CV_T)^3}{i_{C3} + (aCV_T)}}$$

$$(2.72)$$

Let us assume

$$\frac{b(CV_T)^2}{i_{c3} + (aCV_T)} = x_3(t)$$

(2.73)

$\frac{(b_0/b)(CV_T)x_3}{i_{c2}+x_3} = x_2(t) \tag{2.74}$

Equation (2.72) can be written as

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{b_m}{b_0} \frac{x_2}{i_{c1} + x_2}$$

(2.75)

From equation (2.71), it is clear that dimensions of quantities  $b_m (CV_T)^3$ ,  $b_0 (CV_T)^3$ ,  $b(CV_T)^2$  and  $aCV_T$  are  $[amp]^3$ ,  $[amp]^3$ ,  $[amp]^2$  and [amp] respectively.

and

Fig.2.16 Third order Butterworth filter circuit.

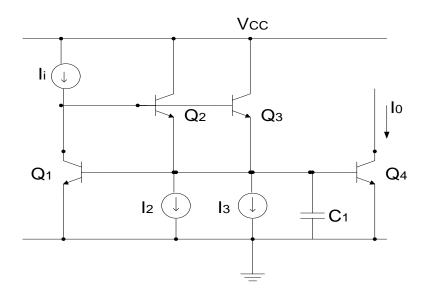

Let we assume  $u_1(t) = x_2(t)$ ,  $u_2(t) = x_3(t)$ ,  $u_3(t) = I_d = a \ CV_T$  and  $I_{01} \ I_{02} \ I_{03} = b_m (CV_T)^3$ .

The third order butterworth filter is shown in above Fig.2.16. Translinear loop formed by the equation (2.73) is  $Q_{02}Q_5T_{X3}Q_4Q_{q1}Q_3$  when  $I_{02}$   $I_{q1} = b(CV_T)^2$ , while equation (2.75) corresponds to loop formed by  $Q_{in}Q_1Q_7T_{X2}Q_6Q_{q2}Q_{03}Q_{out}$  when  $\frac{I_{03}}{I_{q2}} = \frac{b_m}{b_0}$ .

#### 2.6.6 Simulation Results

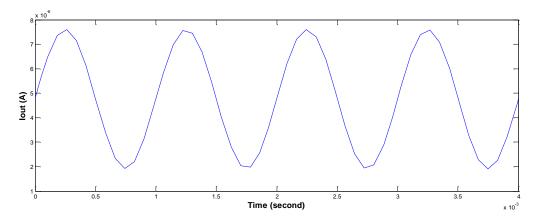

To prove the theoretical validity, Third order Butterworth filter in Fig.2.16 is simulated with PSPICE. The coefficients were solved for C = 40 pF having loss of 60 db in next decade. The values of the coefficients are  $I_d = aCV_T = 10.9 \text{ uA}$ ,  $I_{02}I_{q1} = b(CV_T)^2 = 59.3 \text{ (uA)}^2$ ,  $I_{01}I_{02}I_{03} = b_m(CV_T)^3 = 161.4(\text{uA})^3$  and  $\frac{I_{03}}{I_{q2}} = \frac{b_m}{b_0} = 1$ . The time response is shown in Fig.2.17 (a) and Fig.2.17 (b).

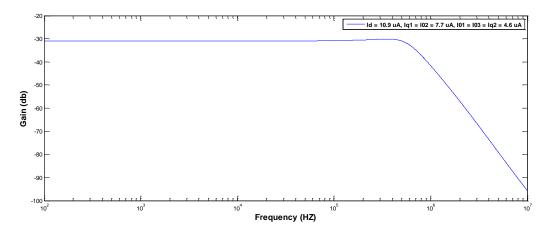

The frequency response of third order Butterworth filter for

- (a)  $I_d = 10.9 \text{ uA}$ ,  $I_{01} = I_{03} = I_{q2} = 4.4 \text{ uA}$ ,  $I_{02} = I_{q1} = 7.7 \text{ uA}$  having Pole frequency = 627 KHZ is shown in Fig.2.17 (c).

- (b)  $I_d = 10.9 \text{ uA}$ ,  $I_{03} = I_{q2} = 2.7 \text{ uA}$ ,  $I_{01} = I_{q1} = 5 \text{ uA}$ ,  $I_{02} = 11.9 \text{ uA}$  having Pole frequency = 687 KHZ is shown in Fig.2.17 (d).

Fig.2.17 (a) Time response for input of third order Butterworth filter.

Fig.2.17 (b) Time response for output of third order Butterworth filter.

Fig.2.17 (c) Frequency response of third order Butterworth filter for  $f_0 = 627$  KHZ.

Fig.2.17 (d) Frequency response of third order Butterworth filter for  $f_0 = 687$  KHZ.

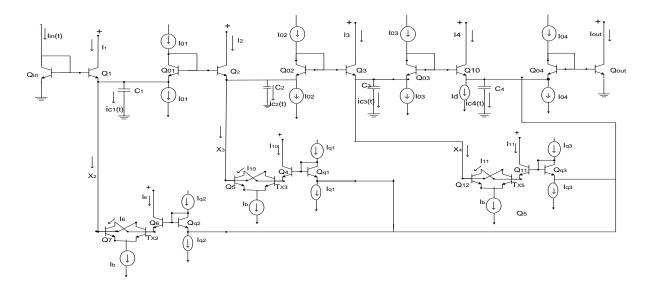

## 2.6.7 Proposed fourth order low pass Butterworth filter

Let us assume that the desired lowpass frequency response is given by

$$\frac{I_{out}(s)}{I_{in}(s)} = \frac{c_m}{s^4 + as^3 + bs^2 + cs + c_0}$$

(2.76)

In time domain, we can write

$\frac{I_{out}(t)}{I_{in}(t)} = \frac{c_m}{c_0 + c \left\{\frac{d}{dt}[\ln(I_{out})]\right\} + b \left\{\frac{d}{dt}[\ln(I_{out})]\right\} \left\{\frac{d}{dt}[\ln(I_{out})]\right\} + a \left\{\frac{d}{dt}[\ln(I_{out})]\right\} \left\{\frac{d}{dt}[\ln(I_{ou}$

(2.77)

By expressing all term of form  $\frac{d}{dt}[\ln()]$ , using equation (2.52) and equation (2.76), We can write

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{c_m}{c_0 + c\frac{i_{c1}}{CV_T} + b\frac{i_{c1}i_{c2}}{(CV_T)^2} + a\frac{i_{c1}i_{c2}i_{c3}}{(CV_T)^3} + \frac{i_{c1}i_{c2}i_{c3}i_{c4}}{(CV_T)^4}}$$

(2.78)

Let us assume

$$\frac{b(CV_T)^2}{i_{c4} + (aCV_T)} = x_4(t)$$

(2.79)

$$\frac{(c/b)(CV_T)x_4}{i_{C3}+x_4} = x_3(t)$$

(2.80)

and

$$\frac{(c_0/c)(CV_T)x_3}{i_{c_3}+x_3} = x_2(t)$$

(2.81)

So, we can write

$$\frac{I_{out}(t)}{I_{in}(t)} = \frac{c_m}{c_0} \frac{x_2}{i_{c1} + x_2}$$

(2.82)

It is clear that dimensions of quantities  $c_m (CV_T)^4$ ,  $c_0 (CV_T)^4$ ,  $c (CV_T)^3$ ,  $b (CV_T)^2$  and  $a CV_T$  are  $[amp]^4$ ,  $[amp]^4$ ,  $[amp]^3$ ,  $[amp]^2$  and [amp] respectively.

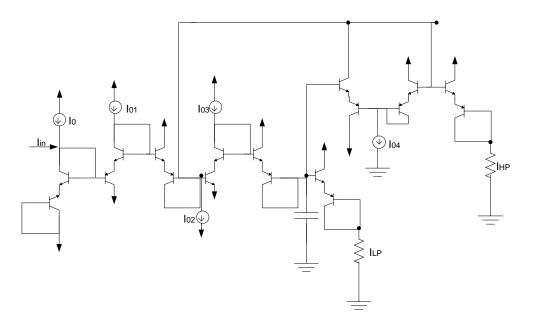

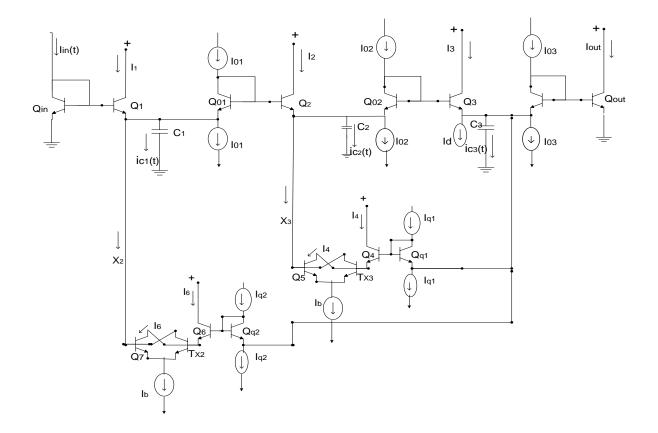

Fig.2.18 Proposed Fourth order Butterworth filter circuit.

Let us assume  $u_1(t) = x_2(t)$ ,  $u_2(t) = x_3(t)$ ,  $u_3(t) = x_4(t)$ ,  $u_3(t) = I_d = aCV_T$  and  $I_{01} I_{02} I_{03} I_{04} = c_m (CV_T)^4$ .

The fourth order butterworth filter is shown in above Fig2.18. Translinear loop formed by the equation (2.79) is  $Q_{03}Q_{12}T_{X5}Q_{11}Q_{q3}Q_{10}$  when  $I_{03}I_{q3}=b(CV_T)^2$ , while equation (2.82) corresponds to loop formed by  $Q_{in}Q_1Q_7T_{X2}Q_6Q_{q2}Q_4Q_{out}$  when  $\frac{I_{04}}{I_{q2}} = \frac{c_m}{c_0}$ .

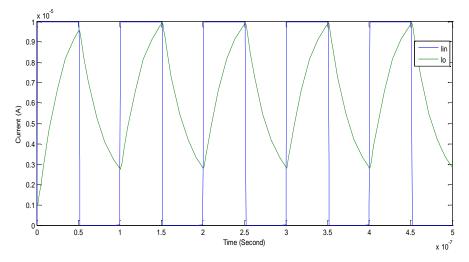

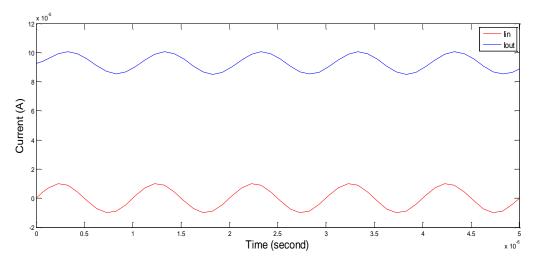

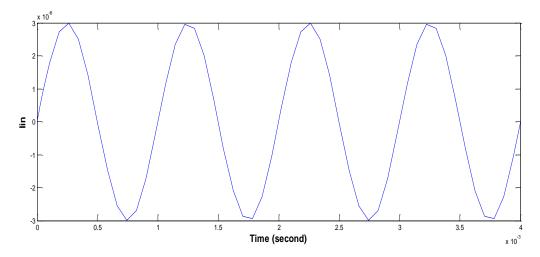

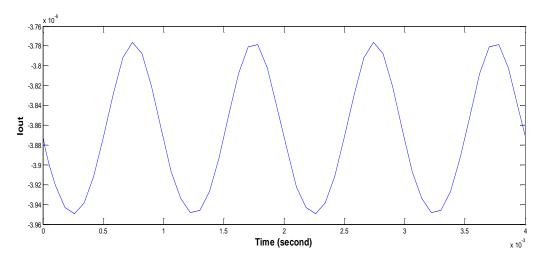

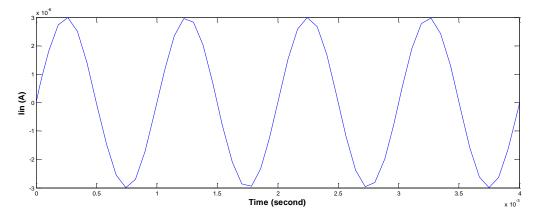

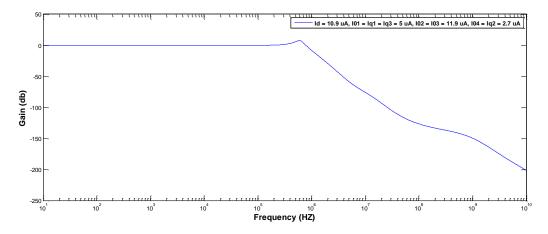

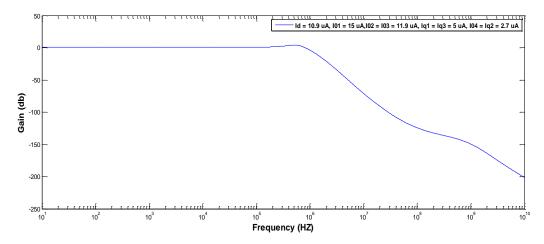

#### 2.6.8 Simulation results

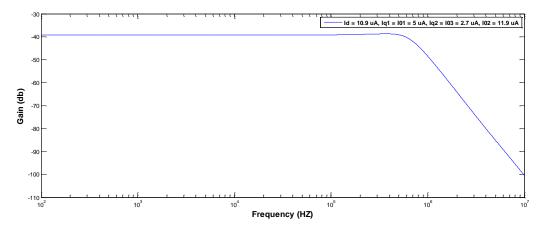

To prove the theoretical validity, Fourth order Butterworth filter in Fig.2.18 is simulated with PSPICE program. The coefficients were solved for C = 40 pF having loss of 80 db in next decade. The values of the coefficients are  $I_d = aCV_T = 10.9 \text{ uA}$ ,  $I_{03} I_{q1} = b(CV_T)^2 = 59.5 (uA)^2$ . The time response are shown in Fig.2.19 (a) and Fig.2.19 (b).

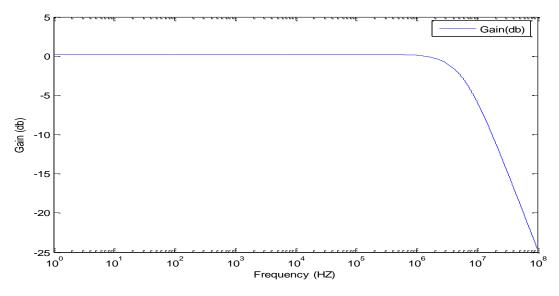

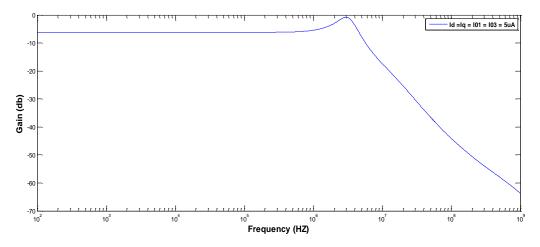

The frequency response of fourth order Butterworth filter for

- (a)  $I_d = 10.9 \text{ uA}$ ,  $I_{02} = I_{03} = 11.9 \text{ uA}$ ,  $I_{01} = I_{q1} = I_{q3} = 5 \text{ uA}$ ,  $I_{04} = I_{q2} = 2.7 \text{ uA}$  having Pole frequency = 890 KHZ is shown in Fig.2.19 (c).

- (b)  $I_d = 10.9 \text{ uA}$ ,  $I_{02} = I_{03} = 11.9 \text{ uA}$ ,  $I_{q1} = I_{q3} = 5 \text{ uA}$ ,  $I_{04} = I_{q2} = 2.7 \text{ uA}$ ,  $I_{01} = 15 \text{ uA}$ having Pole frequency = 970 KHZ is shown in Fig.2.19 (d).

Fig.2.19 (a) Time response for input of fourth order Butterworth filter.

Fig.2.19 (b) Time response for output of fourth order Butterworth filter.

Fig.2.19 (c) Frequency response of fourth order Butterworth filter for  $f_0 = 890$  KHZ.

Fig.2.19 (d) Frequency response of fourth order butterworth filter for  $f_0 = 970$  KHZ.

## **2.7 CONCLUSION**

In this chapter, we have discussed how first order systems can be synthesized using translinear principle. Also the basic structure of Bernoulli cell and its implementation to higher order filters is discussed. The Bernoulli cell relate Translinear loops and log domain structures and proves its utility in expressing a suitable time varying form of the Translinear principle. The basic applications using translinear principle such as lossy integrator and a first order low pass and high pass log domain filter is presented. The designed filter is based on integrator loops, current sources and grounded capacitors. The gain and pole frequency are independently and electronically tunable through the variation of bias currents. Applications of Bernoulli cell like lossy integrator, second order filter containing zero, third order filters have been presented. We have designed a new fourth order low pass filter with butterworth characteristics using the Bernoulli cell. All the circuits have been tested with PSPICE simulations using the parameters of transistor AT & T CBIC-R Transistor.

# **Chapter 3**

# Design of log domain filters based on simulation of LC ladders

## **3.1 Introduction**

Frequency shaping networks or filter is an electronic circuit that performs a frequency selection function passing the signals whose frequency spectrum lies within a specified range and stopping the signals whose frequency spectrum falls outside this range. In the previous chapters, we have discussed the log domain filters and their design by Bernoulli cell. Log domain filters can be designed by various methods. Operational simulation of LC ladder is one of these methods.

In this chapter, we will present a design of log domain filters which is based on the operational simulation of LC ladder networks [15]. The basic advantages of this method are the lowest component sensitivities over the passband and filter design at high frequency. Section 3.2 and Section 3.3 explains the basics of LC ladder filters and introduction of Log and Exp operator respectively. Section 3.4 explains the basic log domain building blocks and Section 3.5 demonstrates the design of two high-order log-domain filters i.e. third order elliptic filter and fifth order Chebyshev filter. Conclusions are drawn in Section 3.6.

## **3.2 Basic of LC ladder filters**

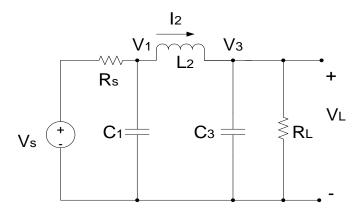

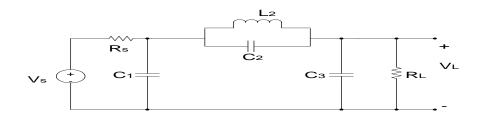

#### 3.2.1 LC ladders

LC ladders are the circuits where all components apart from source and load resistors are lossless i.e. they are capacitors and inductors that dissipate no energy [14]. LC ladders have an inherent advantage over active filters in terms of their low sensitivity to component tolerances. The basic third order LC ladder is shown in Fig.3.1 (a).

Fig.3.1 (a) A third order LC ladder

#### 3.2.2 Signal flow graph representation of LC ladder

There are different methods for active simulations of these LC ladders namely (i) Inductor simulation using GIC's (ii) Replacement of inductor by FDNR elements (iii) Operational simulation of the LC ladder. It is this method which we have used for simulation of LC ladders. In the following, development of this method is explained briefly.

Using KCL at all capacitor nodes and KVL around each inductor branch in Fig.3.1 (a), we have following equations

$$L_2 \frac{d}{dt} I_2 = V_1 - V_3 \tag{3.1}$$

$$C_1 \frac{d}{dt} V_1 = \frac{V_S}{R_S} - \frac{V_1}{R_S} - I_2$$

(3.2)

$$C_3 \frac{d}{dt} V_3 = I_2 - \frac{V_3}{R_L}$$

(3.3)

$$V_L = V_3 \tag{3.4}$$

Now, let us define a set of variables which will correspond to both voltages and currents.

$$X_{S} \leftrightarrow V_{S} , X_{1} \leftrightarrow V_{1} , X_{2} \leftrightarrow I_{2} , X_{3} \leftrightarrow V_{3} , X_{L} \leftrightarrow V_{L}$$

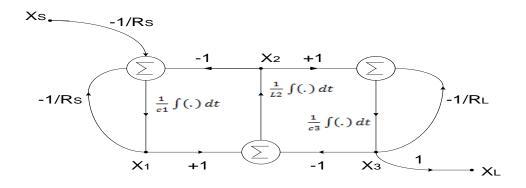

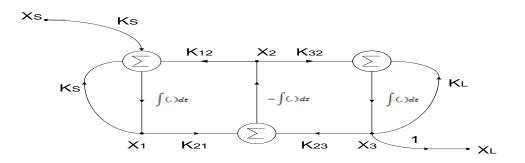

The signal flow graph corresponding to equations (3.1) to (3.4) is shown in Fig.3.1 (b).

Fig.3.1 (b) Signal flow graph of Fig.3.1 (a)

### 3.2.3 Components needed in signal flow graph for LC ladder

- (i) Summer Summer is the basic building block and can be used for addition and subtraction of the node voltages and currents.

- (ii) Inverter Inverter can be used for changing the sign of the scaling factor.

- (iii) **Nodes and branches -** Nodes represents the variables (i.e. voltage across capacitor and current in an inductor) and branch can be used for representing the transfer functions.

- (iv)**Integrator -** In LC ladder, integrator can be used for applying KCL and KVL equations around inductor and capacitor respectively.

## 3.3 Introduction of Log and Exp operators

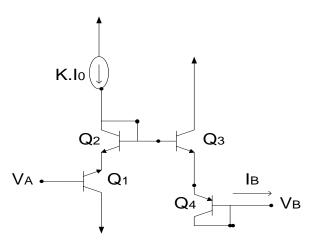

Log domain filters include two mathematical inverse operators i.e. Log and Exp [15]. Fig.3.2 shows a basic log domain cell in which we can write the equation which relates the voltage drop across the input-output terminals and the current  $I_B$  as

$$I_B = K. I_0 \cdot e^{(V_A - V_B)/2V_T}$$

(3.5)

Fig.3.2 A basic log domain cell

We define the Exp function as

$$\operatorname{Exp}(x) = I_0 \cdot e^{X/2V_T}$$

(3.6)

It will be equal to equation (3.5), if K = 1 and  $V_B$  is tied to ground, so

$$I_{B} = I_{0} \cdot e^{V_{A}/2V_{T}} \tag{3.7}$$

Let we assume, the Log function is defined as inverse of the Exp function

$$Log (Y) = 2 V_T \cdot ln \left(\frac{Y}{I_0}\right)$$

(3.8)

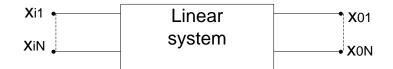

The block diagram of a linear system is shown in Fig.3.3 (a).

Fig.3.3 (a) Linear system

Fig.3.3 (b) Log domain structure of Fig.3.3 (a).

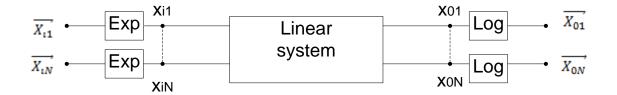

If in any system, Exp block appears at input and a Log block appears at output, then we have the system as shown in Fig.3.3(b).Variables marked with arrow ( $\rightarrow$ ) denotes the signals in log domain. It helps to easily track the signals in log domain.

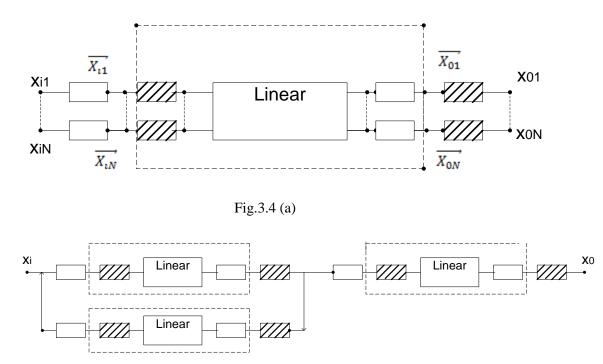

One possible way to make the non-linear system to linear is to place Log blocks preceding each input and Exp blocks after each output as shown in Fig.3.4 (a) to Fig.3.4 (c).

Fig.3.4 (b)

Fig.3.4 (a)-(c) Linearization of a log domain system.

## 3.4 Basic log domain building blocks

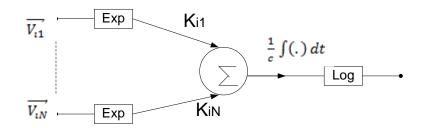

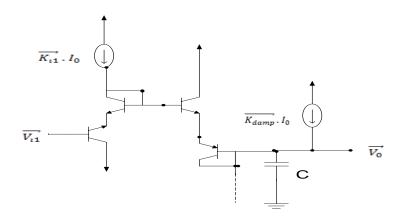

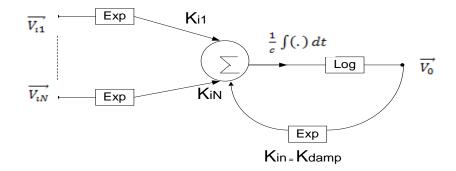

### 3.4.1 Multiple input non inverting integrator

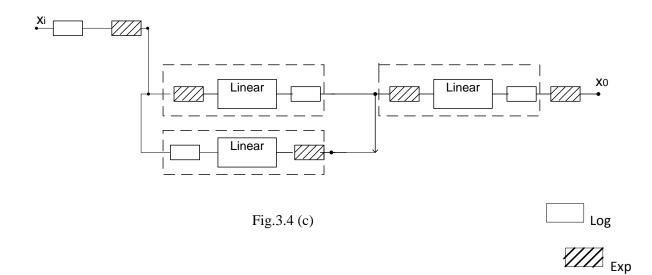

The circuit of multiple input non inverting integrator can be drawn using basic log domain cell [15] and is shown in Fig.3.5 (a) and its signal flow graph representation is shown in Fig.3.5 (b). Analysis of non-inverting integrator is given below

Using basic log domain equation and by applying KCL, we can write

$$C.\frac{d}{dt}\vec{V}_{0} = \vec{K}_{i1} \cdot I_{0} \cdot e^{(\vec{V}_{i1} - \vec{V}_{0})/2V_{T}} + \dots + \vec{K}_{iN} \cdot I_{0} \cdot e^{(\vec{V}_{iN} - \vec{V}_{0})/2V_{T}}$$

(3.9)

Multiplying by  $e^{\vec{V}_0/2V_T}$ , we get

C.

$$e^{\vec{V}_0/2V_T} \cdot \frac{d}{dt} \vec{V}_0 = \vec{K}_{i1} \cdot I_0 \cdot e^{(\vec{V}_{i1}/2V_T + \dots + \vec{K}_{iN} \cdot I_0 \cdot e^{\vec{V}_{iN}/2V_T}}$$

(3.10)

Finally, we can write

$$\frac{c.2V_T}{I_0} \cdot \frac{d}{dt} \left[ I_0 \cdot e^{\vec{V}_0/2V_T} \right] = \vec{K}_{i1} \cdot I_0 \cdot e^{\vec{V}_{i1}/2V_T} + \dots + \vec{K}_{iN} \cdot I_0 \cdot e^{\vec{V}_{iN}/2V_T}$$

(3.11)

We assign new constant K<sub>i</sub> as

Fig.3.5(a) A multiple input non inverting integrator.

Fig.3.5 (b) Signal flow graph of multiple input non inverting integrator

So, we can write

$$c \cdot \frac{d}{dt} \left[ I_0 \cdot e^{\vec{V}_0/2V_T} \right] = K_{i1} \cdot I_0 \cdot e^{\vec{V}_{i1}/2V_T} + \dots + K_{iN} \cdot I_0 \cdot e^{\vec{V}_{iN}/2V_T}$$

(3.13)

Using Exp operator, equation (3.13) becomes

$$c \cdot \frac{d}{dt} \left[ \exp(\vec{V}_0) \right] = K_{i1} \cdot \exp(\vec{V}_{i1}) + \dots + K_{iN} \cdot \exp(\vec{V}_{iN})$$

(3.14)

or

$$\vec{V}_0 = \log\left\{\frac{1}{c} \cdot \int \left[K_{i1} \cdot \exp(\vec{V}_{i1}) + \dots + K_{iN} \cdot \exp(\vec{V}_{iN})\right] dt\right\}$$

(3.15)

43

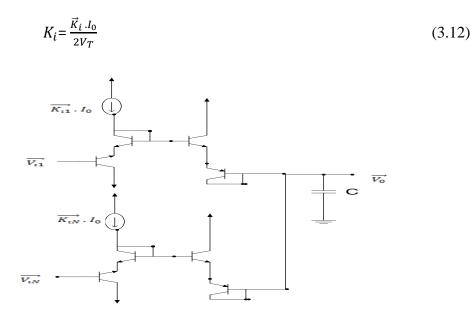

## 3.4.2 Damped integrator

The circuit of damped integrator can be obtained by giving the output back to its input as shown in Fig.3.6 (a) and the corresponding signal flow graph [15] is shown in Fig.3.6 (b).

Fig.3.6 (a) Damping using a current source

Fig.3.6 (b) Signal flow graph of damped integrator.

So, damping current can be expressed as

$$I_{damp} = \vec{K}_{damp} \cdot I_0 \cdot e^{(\vec{V}_0 - \vec{V}_0)/2V_T}$$

(3.16)

Which reduces to

$$I_{damp} = \vec{K}_{damp} \cdot I_0 \tag{3.17}$$

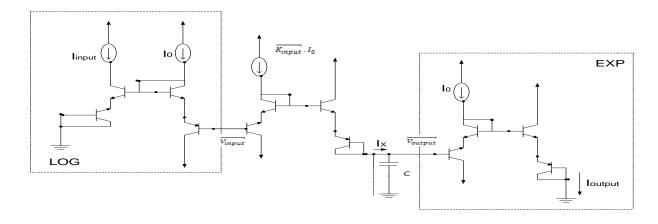

#### 3.4.3 Input and output stages

For linearization of a log domain system, a Log block should be placed at the input and Exp block at the output [15]. The corresponding circuit and the signal flow graph are shown in Fig.3.7 (a) and Fig.3.7 (b).

Fig.3.7 (a) Input and output stage of log domain system.

Fig.3.7 (b) Signal flow graph of Fig.3.7 (a).

## 3.5 Design of elliptic and chebyshev filters

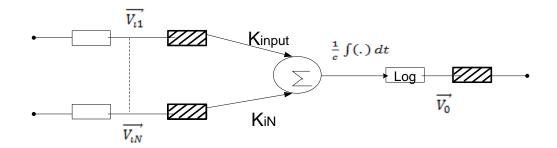

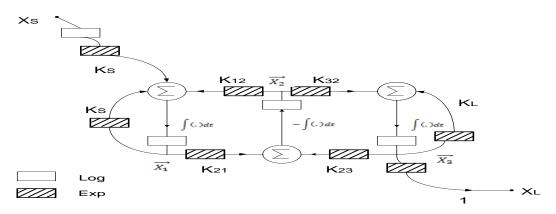

Operational simulation of the LC ladder has been used to realize higher order filters. For design of log domain filters, the signal flow graph of the LC ladder is converted to the form which is compatible with signal flow graph of log domain structures [15]. In the following, we will explain two exemplary filters i.e. elliptic and chebyshev filters. The rules for converting a linear signal flow graph into a log domain signal flow graph is given below.

- a) A Log block is placed after each integrator.

- b) An Exp block is placed at input to each summer.

- c) An Exp block is placed at output of the system.

- d) A Log block is placed at input to the system.

The signal flow graph of a simple third order LC ladder and its log domain equivalent is shown in Fig.3.8 (a) and Fig.3.8 (b).

Fig.3.8 (a) Signal flow graph of a simple ladder

Fig.3.8 (b) Log domain equivalent of Fig.3.8 (a)

## 3.5.1 Design of third order elliptic filter

The LC ladder which represents the third order elliptic filter is shown in Fig.3.9 (a).

Fig.3.9 (a) LC ladder of third order elliptic filter .

The signal flow graph and third order elliptic filter circuit [15] are shown in Fig.3.9 (b) and Fig.3.9 (c).

Fig.3.9 (b) Signal flow graph of third order elliptic filter.

Analysis of third order elliptic log domain filter is given below

Using basic log domain equation and by applying KCL, we can write

$$C_{C3} \cdot \frac{d}{dt} \overrightarrow{V_3} = \overrightarrow{K_{23}} \cdot I_0 \cdot e^{(\overrightarrow{V_2} - \ \overrightarrow{V_3})/2V_T} + \dots + C_{C2} \cdot \frac{d}{dt} (\overrightarrow{V_2} - \overrightarrow{V_3})$$

(3.18)

Multiplying by  $e^{\overrightarrow{V_3}/2V_T}$ , we get

$$C_{C3} \cdot e^{\overrightarrow{V_3}/2V_T} \cdot \frac{d}{dt} \overrightarrow{V_3} = \overrightarrow{K_{23}} \cdot I_0 \cdot e^{\overrightarrow{V_2}/2V_T} + \dots + C_{C2} \cdot e^{\overrightarrow{V_3}/2V_T} \cdot \frac{d}{dt} \overrightarrow{V_1} - C_{C2} \cdot e^{\overrightarrow{V_3}/2V_T} \cdot \frac{d}{dt} \overrightarrow{V_3}$$

(3.19)

Let

$$e^{\overrightarrow{V_1}/2V_T} = e^{\overrightarrow{V_3}/2V_T}$$

(3.20)

Finally, we can write

$$C_{C3} \cdot \frac{d}{dt} \left[ \operatorname{Exp}(\overrightarrow{V_3}) \right] = K_{23} \cdot \operatorname{Exp}(\overrightarrow{V_2}) + \dots + C_{C2} \cdot \frac{d}{dt} \left[ \operatorname{Exp}(\overrightarrow{V_1}) \right] - C_{C2} \cdot \frac{d}{dt} \left[ \operatorname{Exp}(\overrightarrow{V_3}) \right]$$

(3.21)

where

$$K_{23} = \frac{\overline{K_{23}} I_0}{2V_T} \tag{3.22}$$

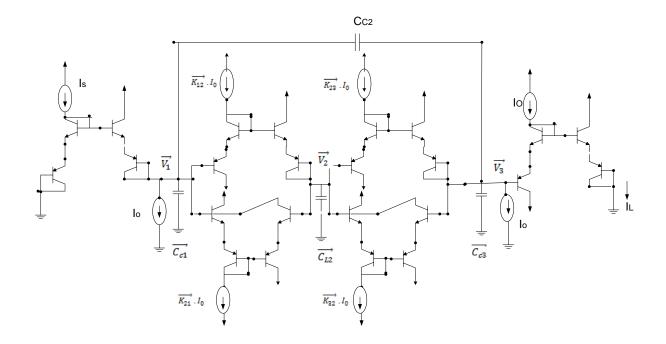

Fig.3.9 (c) Circuit diagram of third order elliptic filter.

So, equation (3.21) is given by

$$\overrightarrow{V_3} = \log\left\{\frac{1}{C_{C_3}} \cdot \int \left[K_{23} \cdot \operatorname{Exp}(\overrightarrow{V_2}) + \ldots + C_{C2} \cdot \frac{d}{dt} (\operatorname{Exp}(\overrightarrow{V_1}) - \operatorname{Exp}(\overrightarrow{V_3})\right] dt\right\}$$

(3.23)

### **3.5.2 Simulation results**

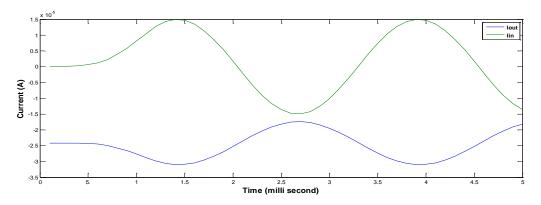

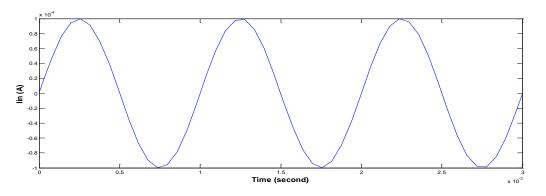

To prove the theoretical validity of third order elliptic log domain filter of Fig.3.9 (c), the filter is simulated with PSPICE. The passive elements are selected as  $C_{C1} = 6.79560$  nF,  $C_{L2} = 3.47308$  nF,  $C_{C3} = 9.55216$  nF. The supply voltages taken as  $V_{CC+} = 5V$  and  $V_{CC-} = -5V$ . The cut off frequency selected is 40 KHZ for bias current ( $I_0$ ) = 90 uA. The transient response, frequency response in full frequency range and passband is shown in Fig.3.9 (d) to Fig.3.9 (f).

Fig.3.9 (d) Transient response of third order elliptic filter

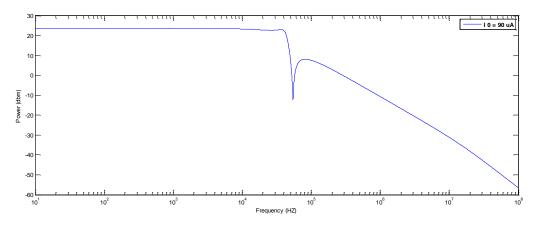

Fig.3.9 (e) Frequency response of third order elliptic filter for  $I_0 = 90 \text{ uA}$

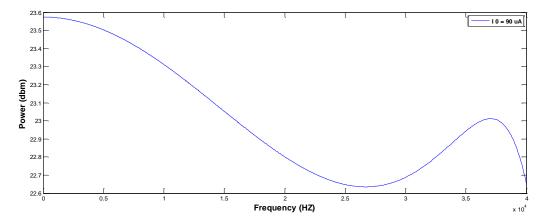

Fig.3.9 (f) Passband range of third order elliptic filter

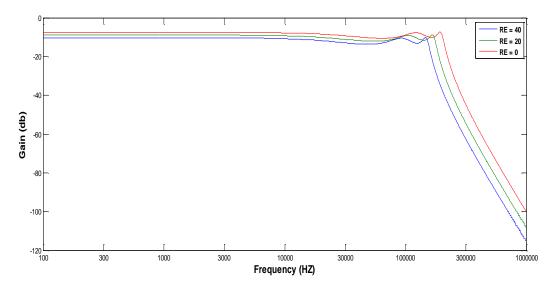

The tunability of this filter is controlled by biasing current ( $I_0$ ) having values 90 uA, 150 uA and 200 uA is shown in Fig.3.9 (g) and effect of emitter resistance ( $R_E$ ) having values 0, 20, 40 is shown in Fig.3.9 (h).

Fig.3.9 (h) Effect of different  $R_E$  on frequency response of third order elliptic filter

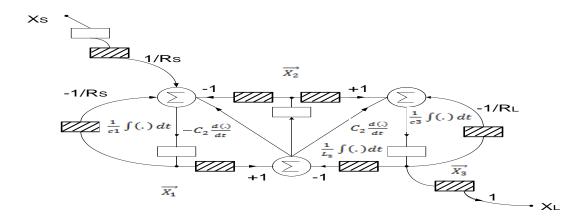

## 3.5.3 Design of fifth order chebyshev filter

The LC ladder which represents the fifth order [15] Chebyshev filter is shown in Fig.3.10 (a).

Fig.3.10 (a) LC ladder of fifth order chebyshev filter.

By applying KVL around each inductor branch and KCL at all capacitor nodes, we have following equations

$$L_2 \frac{d}{dt} I_2 = V_1 - V_3 \tag{3.24}$$

$$L_4 \frac{d}{dt} I_4 = V_3 - V_5 \tag{3.25}$$

$$C_1 \frac{d}{dt} V_1 = \frac{V_S}{R_S} - \frac{V_1}{R_S} - I_2$$

(3.26)

$$C_3 \frac{d}{dt} V_3 = I_2 - I_4 \tag{3.27}$$

$$C_5 \frac{d}{dt} V_5 = I_4 - \frac{V_5}{R_L} \tag{3.28}$$

$$V_L = V_5 \tag{3.29}$$

Now, let us define a set of variables which will correspond to both voltages and currents.

$X_S \leftrightarrow V_S \text{ , } X_1 \leftrightarrow V_1 \text{ , } X_2 \leftrightarrow I_2 \text{ , } X_3 \leftrightarrow V_3 \text{ , } X_4 \leftrightarrow I_4 \text{ , } X_5 \leftrightarrow V_5 \text{ , } X_L \leftrightarrow V_L$

The signal flow graph corresponds to LC ladder and fifth order Chebyshev filter circuit are shown in Fig.3.10 (b) and Fig.3.10 (c).

Fig.3.10 (b) Signal flow graph of fifth order Chebyshev filter.

Fig.3.10 (c) Circuit diagram of fifth order chebyshev filter.

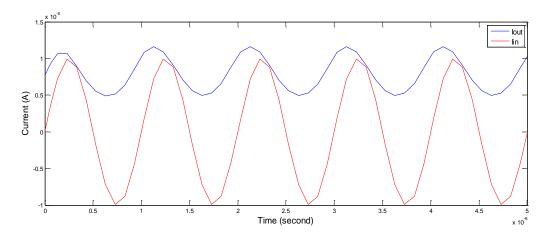

### 3.5.4 Simulation results

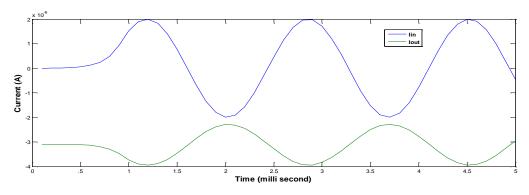

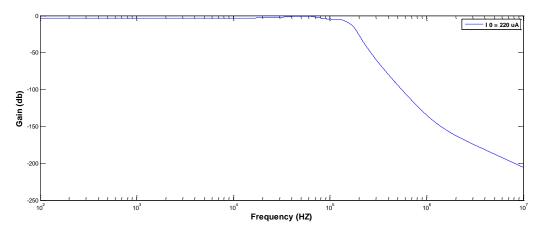

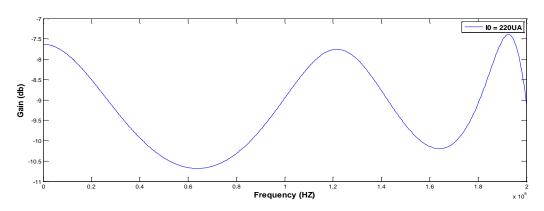

To prove the theoretical validity of fifth order chebyshev log domain filter of Fig. 3.10 (c), the filter is simulated with PSPICE. The passive elements are selected as  $R_S = 1 \Omega$ ,  $C_{C1} = 6.79560$  nF,  $C_{L2} = 3.47308$  nF,  $C_{C3} = 9.55216$  nF,  $C_{L4} = 3.47308$  nF,  $C_{C5} = 6.79560$  nF,  $R_L = 1 \Omega$ . The supply voltages are taken as  $V_{CC+} = 5V$  and  $V_{CC-} = -5V$ . The cut off frequency selected is 50 KHZ for bias current ( $I_0$ ) = 220 uA. The transient response, frequency response in full frequency range and passband are shown in Fig.3.10 (d) to Fig.3.10 (f).

Fig.3.10 (d) Transient response of fifth order chebyshev filter

Fig.3.10 (e) Frequency response of fifth order chebyshev filter for  $I_0 = 220$  uA

Fig.3.10 (f) Passband range of fifth order chebyshev filter

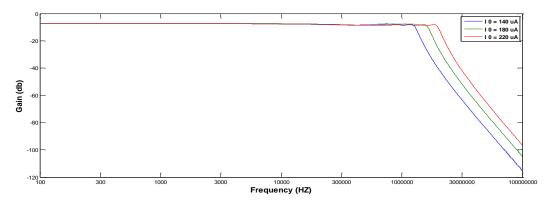

The tunability of this filter is controlled by biasing current ( $I_0$ ) having values 140 uA, 180 uA and 220 uA is shown in Fig.3.9 (g) and effect of emitter resistance ( $R_E$ ) having values 0, 20, 40 is shown in Fig.3.10 (h).

Fig.3.10 (g) Tunability of fifth order chebyshev filter by  $I_{\rm O}$  .

Fig.3.10 (h) Effect of different  $R_E$  on frequency response of fifth order chebyshev filter

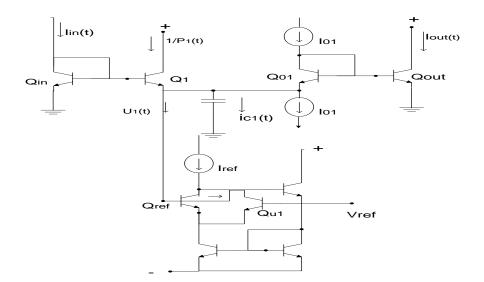

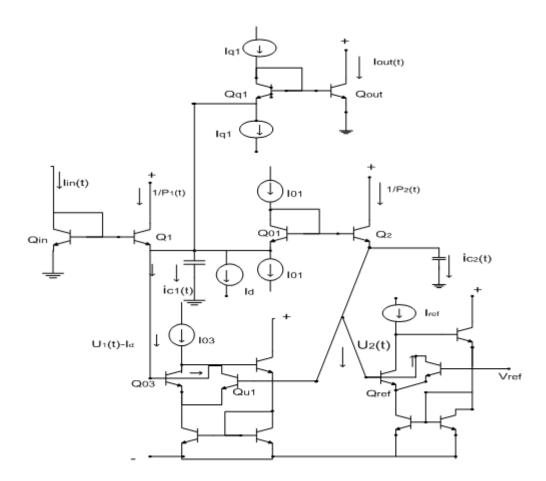

## **3.6 Conclusion**