A

Dissertation

on

# Performance Evaluation of CML based Serilalizer/Deserializer

Submitted in partial fulfillment of the requirement

for the award of the degree of

# **Master of Technology**

in

VLSI Design and Embedded System

Submitted

by

Garima Bhatia

#### University Roll No. 2K13/VLS/07

Under the Guidance of

Dr. Neeta Pandey Assistant Professor, Department of Electronics and Communication Engineering Delhi Technological University

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY 2013-2015

Department of Electronics and Communication Engineering Delhi Technological University Delhi-110042 www.dce.edu

### CERTIFICATE

This is to certify that the dissertation titled "Performance Evaluation of CML based Serilalizer/Deserializer" is a bonafide record of work done by Garima Bhatia, Roll No. 2K13/VLS/07 at Delhi Technological University for partial fulfilment of the requirements for the degree of Master of Technology in VLSI and Embedded System Design. This project was carried out under my supervision and has not been submitted anywhere else, either in part or full, for the award of any other degree or diploma to the best of my knowledge and belief.

Date: \_\_\_\_\_

(Dr. Neeta Pandey) Assistant Professor Department of Electronics and Communication Engineering Delhi Technological University

#### ACKNOWLEDGEMENT

This work would have not been possible without the support of many. First, it is my duty to thank God Almighty for making the completion of this research possible. Next, I would like to express my gratitude to my parents and my family for their continued support.

I would like to express my deep sense of respect and gratitude to my project supervisor **Dr Neeta Pandey,** Assistant Professor, Electronics and Communication Engineering Department, DTU for providing the opportunity of carrying out this project and being the guiding force behind this work. I am deeply indebted to her for the support, advice and encouragement she provided without which the project could not have been a success.

I am also grateful to **Prof. Prem R. Chadha**, HOD, Electronics and Communication Engineering Department, DTU for his immense support.

I would also like to express my gratitude to Mrs Kirti Gupta for her timely guidance and outstanding advice during this work.

I would also like to acknowledge Delhi Technological University for providing the right academic resources and environment for this work to be carried out.

Last but not the least I would like to express sincere gratitude to my friends and my colleagues for constantly encouraging me during the completion of work.

Garima Bhatia University Roll no: 2K13/VLS/07 M.TECH. (VLSI Design and Embedded System) Department of Electronics & Communication Engineering Delhi Technological University Delhi – 110042

#### ABSTRACT

In communication systems, serializers and deserializers are the common and important building blocks. They are used in optical networks for purpose of telecommunication for long distance as well as for high speed connections over small distance comparable to the length of circuit board, to meet higher data bandwidth. Since CMOS based circuits have this huge disadvantage of larger power dissipation at higher frequencies, this has led to a shift in trend to current mode circuits as they have innate advantage of higher speed performance because of reduced voltage swing and much less power consumption at higher frequencies, as compared to CMOS based circuits.

This thesis provides novel Serializers and deserializers for which triple-tail MCML cell based Dlatch with feedback resistors has been used as basic building block which is not only immune to various device mismatches caused by threshold voltage fluctuation and also operates at higher frequencies as compared to simple MCML based D-latch and triple-tail based MCML D–latch.

MCML D-latch uses two stacked transistors for logic implementation and puts a limit on minimum power supply that can be applied and hence have huge static power dissipation. This static power can be further reduced by decreasing the power supply, for which triple-tail MCML based D-latch, has come into picture, which uses one stack of transistors in PDN and hence can operate at low power supply as compared to traditional MCML D-latch. Despite of being shown that MCML circuits consumes less power as compared to CMOS at operation frequencies of very high in range, designers are showing reluctance to replace CMOS with MCML because its performance is greatly affected by the fluctuation of threshold voltages of the differential pair transistors of PDN network because of its differential nature.

For the basis of this thesis, first the study of basic MCML inverter, MCML based D-latch and triple-tail MCML based D-latch, their design parameters and static analysis have been

completed, also, how threshold voltage effects the circuit has been studied for both basic MCML circuit and triple-tail MCML based circuit, and the mathematical formulation of effect of threshold voltage among NMOS transistor has been studied and the mathematical formulation of effect of threshold voltage among PMOS transistor has been derived in this thesis.

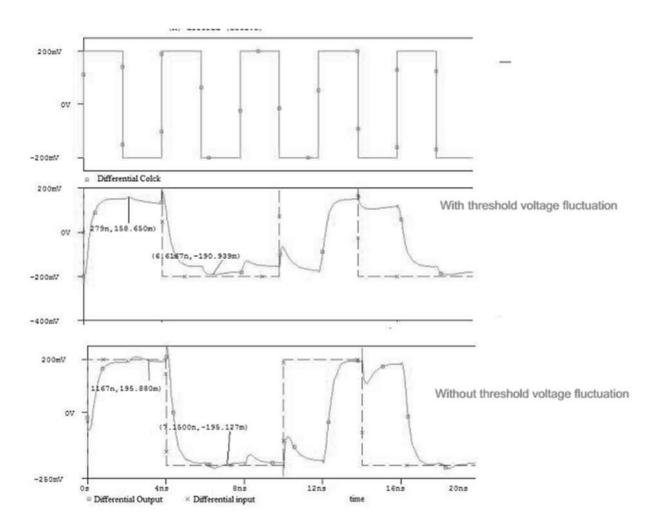

To overcome the problem of threshold voltage fluctuation, effect of using feedback resistance between input and output of MCML based circuits, a method to reduce the effect of threshold-voltage fluctuation has been analyzed for MCML inverters, and a significant improvement in their frequency i.e. 91% hike in cut-off frequency MCML inverters have been witnessed, and in our thesis, this scheme has been used in MCML based D-latch and triple-tail MCML based D-latch, for faster i.e. 74.7% speed improvement at the expense of reduced gain and robust D-latches, which later used as basic building blocks of our serializers and deserializer which are faster, more robust and more power efficient. Thus, the three performance parameters, i.e. power, area and speed are compared for Serializers and Deserializers whose building blocks are MCML based D-latch and triple-tail MCML based D-latch, and the latter is more efficient in all three performance parameters i.e. is more delay, power and area efficient.

# Contents

| CERTIFICATEii                                |

|----------------------------------------------|

| ACKNOWLEDGEMENTiii                           |

| ABSTRACTiv                                   |

| LIST OF FIGURES ix                           |

| LIST OF TABLES xii                           |

| Chapter 1 Introduction1                      |

| 1.1 Thesis Motivation                        |

| 1.2 Thesis Objectives                        |

| 1.3 Thesis Organization                      |

| Chapter 2 MCML Based D-Latch Design 4        |

| 2.1 Basics of MCML Operation                 |

| 2.2 MCML Design Parameters                   |

| 2.3 Design strategies of MCML based D-latch: |

| 2.4 Effect of process variation in MCML based D-latch: | . 21 |

|--------------------------------------------------------|------|

|                                                        |      |

| 2.5 Minimum Davier Sumply for MCML based D. Latah      | 22   |

| 2.5 Minimum Power Supply for MCML based D-Latch:       | . 22 |

| Chapter 3 Triple-Tail MCML based D-latch            |  |

|-----------------------------------------------------|--|

| 3.1 Analysis of the triple-tail MCML based D-latch: |  |

| 3.2 Design of triple-tail based MCML D-latch:       |  |

| apter 4 Threshold-Voltage Fluctuation and MCML circuits              |                      |

|----------------------------------------------------------------------|----------------------|

| .1 Effect of Vth Fluctuation among NMOS transistors in MCML          | inverter and MCML D- |

| atch:                                                                |                      |

| .2 Effect of <i>Vth</i> Fluctuation among PMOS transistors in MCMI   | inverter and MCML D- |

| atch:                                                                |                      |

| .3 Different cases of threshold voltage fluctuation:                 |                      |

| .4 Effect of threshold fluctuation in triple-tail MCML based D-Latch | h 54                 |

| .5 Feedback MCML Circuit                                             |                      |

| .6 Feedback In triple-Tail MCML Based D-Latch                        |                      |

| Chapter 5 Serializer and Deserializer                                      | 74 |

|----------------------------------------------------------------------------|----|

| 5.1 Serializer and deserializer overview:                                  | 74 |

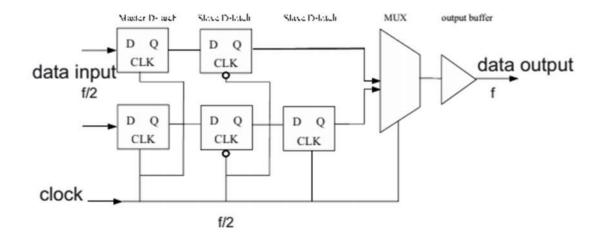

| 5.2 Implementation of Serializer/Deserializer Using MCML:                  | 76 |

| 5.2.1 1:8 DeMUX or Deserializer:                                           | 78 |

| 5.2.2 8:1 MUX or Serializer:                                               | 80 |

| 5.3 Proposed implementations of Deserializers:                             | 82 |

| 5.3.1 Deserializer employing triple-tail MCML based D-latch with feedback: | 82 |

| 5.3.2 Comparison between deserializers employing different D-latches:      | 82 |

| 5.4 Proposed implementations of Serializers:                               | 85 |

| 5.4.1 Serializer employing triple-tail MCML based D-latch with feedback:   | 85 |

| 5.3.2 Comparison between serializers employing different D-latches:        | 85 |

| Chapter 6 Conclusion And Future Work |  |

|--------------------------------------|--|

| 5.1 Conclusion                       |  |

| 5.2 Future Work                      |  |

| References | , 90 |

|------------|------|

|            | , 70 |

# **LIST OF FIGURES**

| Figure 2.1 Basic block of an MCML circuit.                                                              | 4   |

|---------------------------------------------------------------------------------------------------------|-----|

| Figure 2.2 Power vs. Frequency for MCML inverters[8]                                                    | 6   |

| Figure 2.3 MCML Inverter/Buffer[8]                                                                      | 8   |

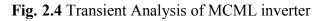

| Figure 2.4 Transient Analysis of MCML inverter                                                          | 9   |

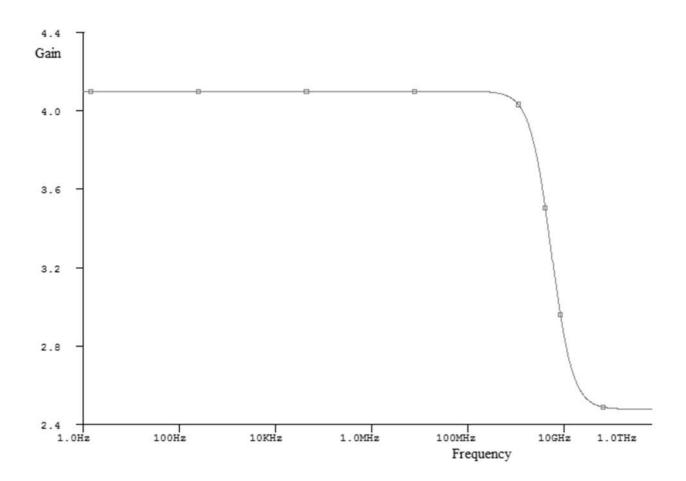

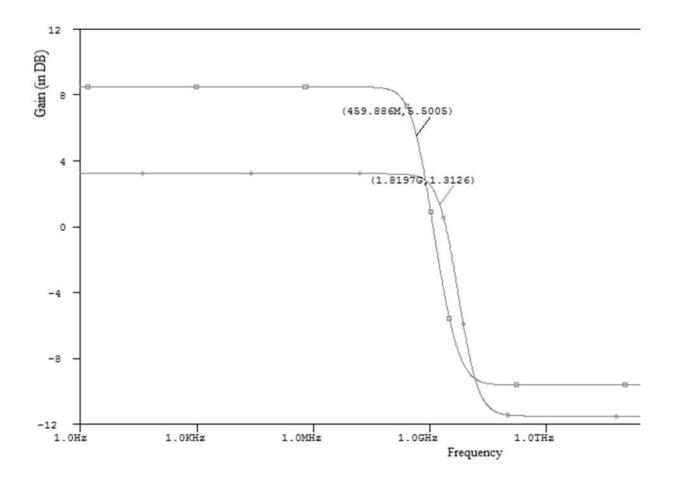

| Figure 2.5 AC Analysis of MCML inverter 1                                                               | . 1 |

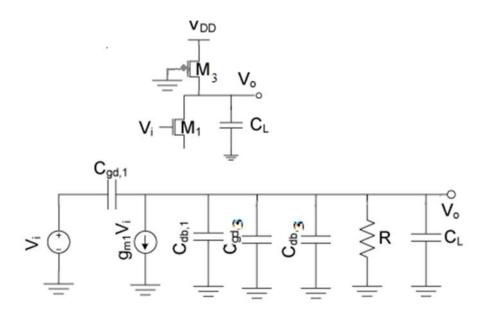

| Figure 2.6 Small-signal equivalent of MCML inverter 1                                                   | .2  |

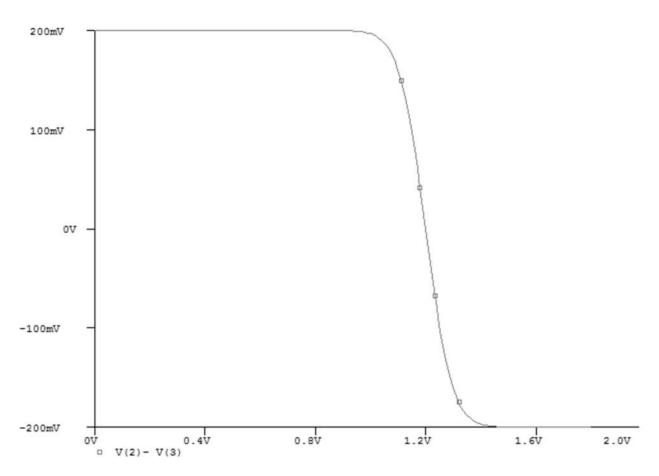

| Figure 2.7 Threshold Voltage characteristics of MCML inverter 1                                         | .4  |

| Figure 2.8 MCML based D-latch 1                                                                         | .6  |

| Figure 2.10 AC analysis of MCML based D-latch 1                                                         | .9  |

| Figure 2.11 Small-signal Half-circuit equivalent of MCML D-latch                                        | 20  |

| Figure 3.1 Triple-tail MCML based D-Latch                                                               | 26  |

| Figure 3.2 Output and voltage swing of triple-tail MCML based D-latch                                   | \$1 |

| Figure 3.3 AC analysis of triple-tail MCML D-Latch                                                      | \$2 |

| Figure 3.2 Linear Half-circuit (with low value of differential input A)                                 | 3   |

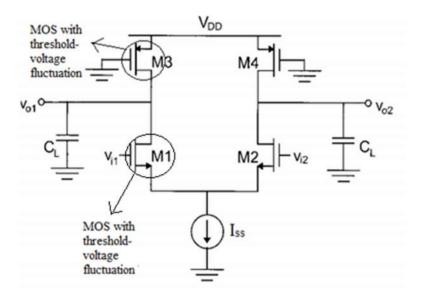

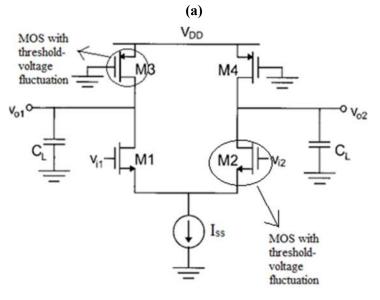

| Figure 4.1 Mismatching in NMOS transistors because of <i>Vth</i> Fluctuation (a) MCML inverte           | er  |

| (b) MCML based D-latch                                                                                  | \$8 |

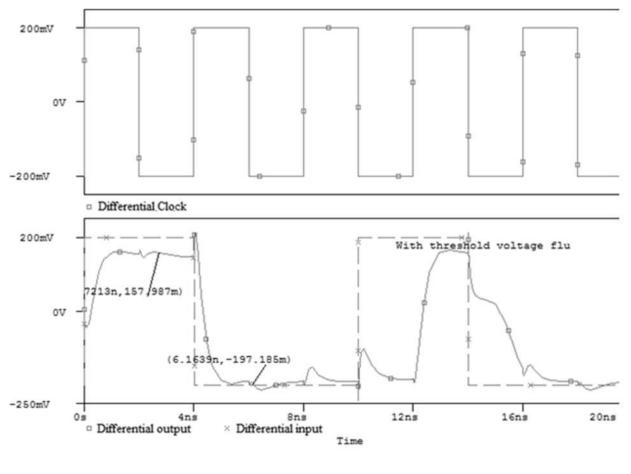

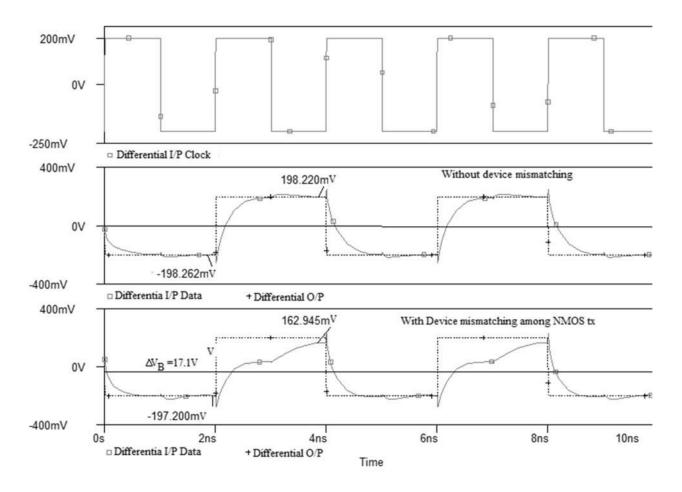

| Figure 4.2 MCML Inverter output waveforms (a) without threshold voltage fluctuation (b) with            | th  |

| threshold voltage fluctuation among NMOS transistors. MCML based D-latch output waveform                | 15  |

| (c) with and without threshold voltage fluctuation                                                      | 13  |

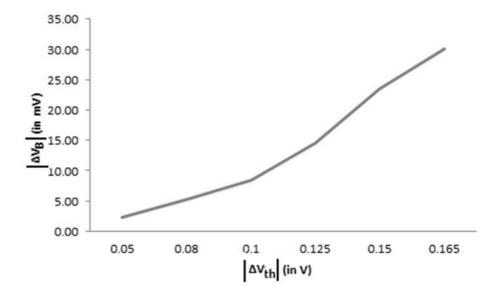

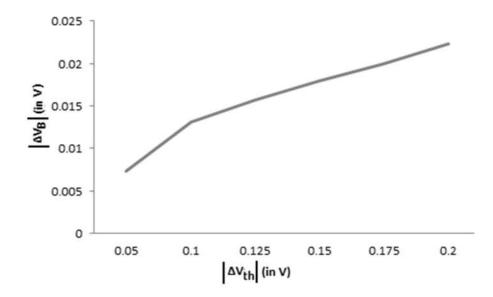

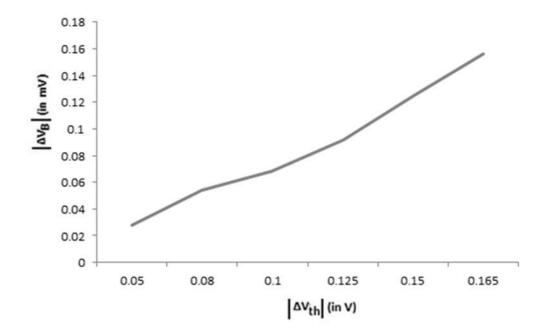

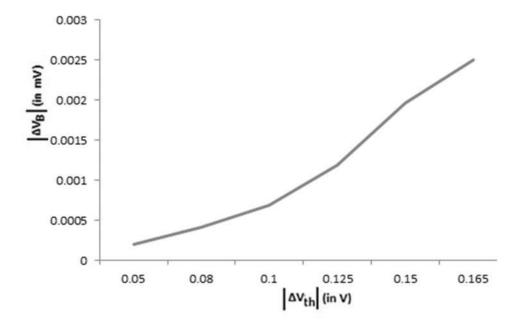

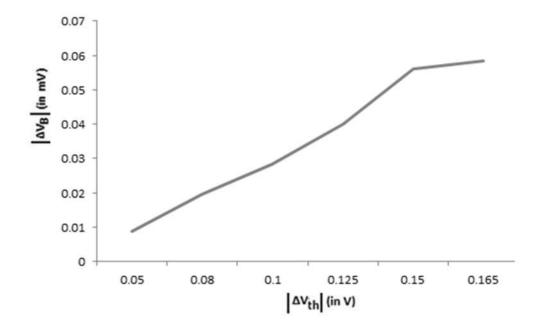

| Figure 4.3 Variations in $\Delta VB$ with respect to the threshold-voltage fluctuation ( $\Delta Vth$ ) | 4   |

| Figure 4.4 Device mismatching because of threshold-voltage fluctuation in PMOS transistor in                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) MCML inverter (b) MCML based D-latch                                                                                                                                                                                                                                                                                                                     |

| Figure 4.5 Output waveform with threshold voltage fluctuation among PMOS transistors in (a)                                                                                                                                                                                                                                                                  |

| MCML inverter (b) MCML based D-latch                                                                                                                                                                                                                                                                                                                         |

| Figure 4.6 Variations in $\Delta VB$ with respect to the threshold-voltage fluctuation ( $\Delta Vth$ )                                                                                                                                                                                                                                                      |

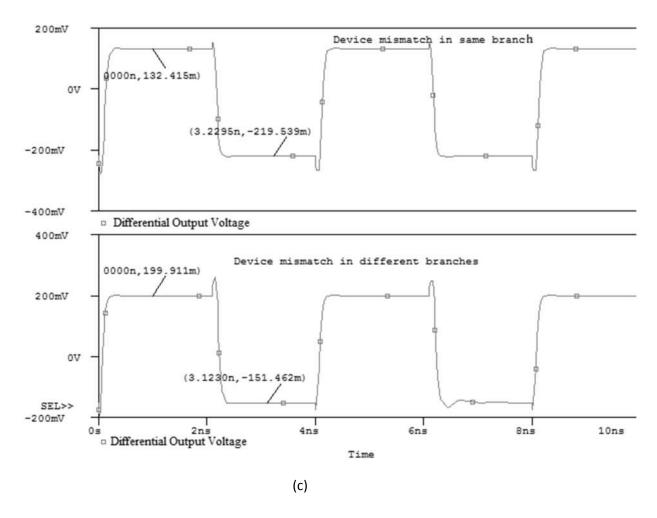

| Figure 4.7 Device mismatch among NMOS and PMOS transistors (a) in same branch of MCML                                                                                                                                                                                                                                                                        |

| inverter (b) in different branches of MCML inverter (c) output waveform of both cases 3 and 454                                                                                                                                                                                                                                                              |

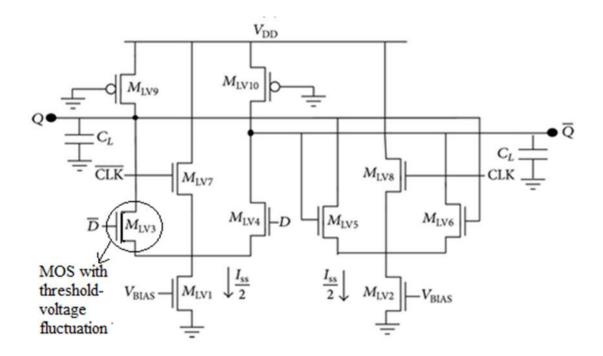

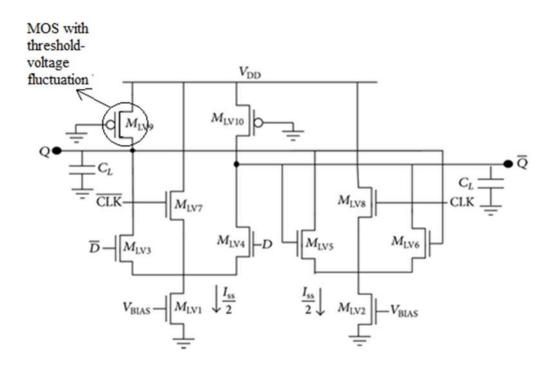

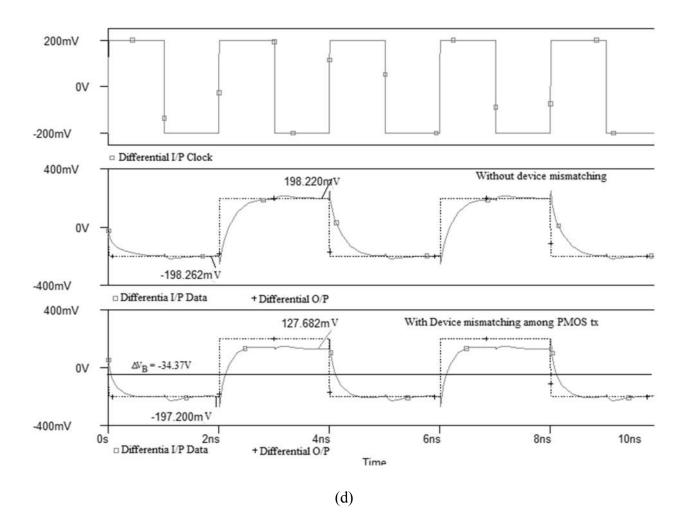

| Figure 4.8 Triple-tail MCML based D-latch with threshold-voltage fluctuation (a) among NMOS                                                                                                                                                                                                                                                                  |

| transistors (b) among PMOS transistors and Output waveforms of triple-tail MCML based D-                                                                                                                                                                                                                                                                     |

| latch (c) with threshold-voltage fluct fluctuations (among NMOS transistor) (d) with threshold-                                                                                                                                                                                                                                                              |

| voltage fluctuations (among PMOS transistor)                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                              |

| Figure 4.9 Variations in $\Delta VB$ with respect to the threshold-voltage fluctuation ( $\Delta Vth$ ) in triple-                                                                                                                                                                                                                                           |

| Figure 4.9 Variations in $\Delta VB$ with respect to the threshold-voltage fluctuation ( $\Delta Vth$ ) in triple-<br>tail MCML based D-latch. 60                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                              |

| tail MCML based D-latch                                                                                                                                                                                                                                                                                                                                      |

| tail MCML based D-latch                                                                                                                                                                                                                                                                                                                                      |

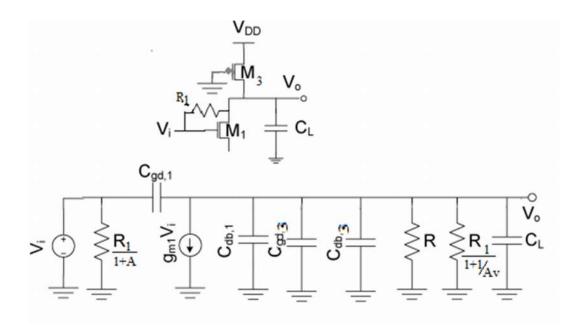

| tail MCML based D-latch.60Figure 4.10 Feedback MCML circuit                                                                                                                                                                                                                                                                                                  |

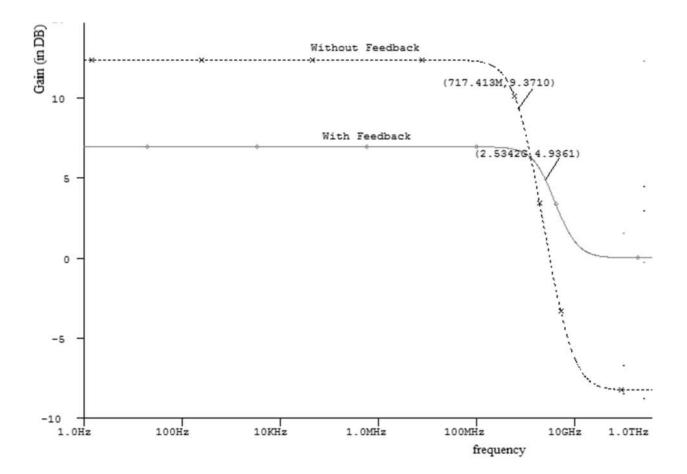

| tail MCML based D-latch.60Figure 4.10 Feedback MCML circuit61Figure 4.11 Small signal model of MCML inverter with feedback Resistor.63Figure 4.12 Simulation result of frequency response of traditional MCML and with feedback                                                                                                                              |

| tail MCML based D-latch.60Figure 4.10 Feedback MCML circuit61Figure 4.11 Small signal model of MCML inverter with feedback Resistor.63Figure 4.12 Simulation result of frequency response of traditional MCML and with feedback65                                                                                                                            |

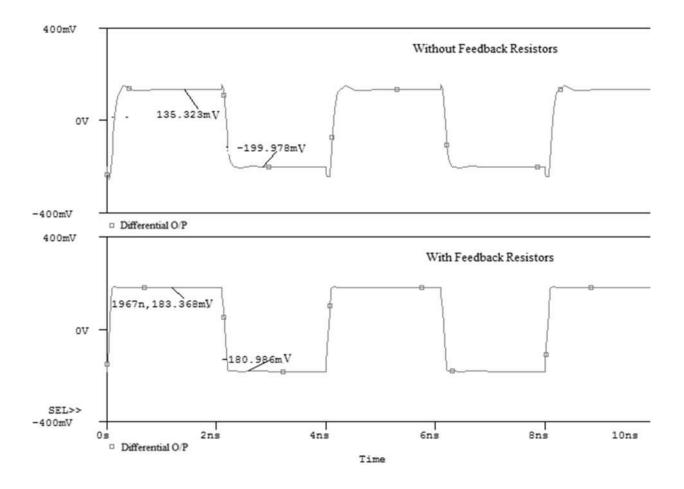

| tail MCML based D-latch.60Figure 4.10 Feedback MCML circuit61Figure 4.11 Small signal model of MCML inverter with feedback Resistor.63Figure 4.12 Simulation result of frequency response of traditional MCML and with feedback65Figure 4.13 Effect of feedback transistors on threshold-voltage fluctuation in (a) MCML inverter                            |

| tail MCML based D-latch.60Figure 4.10 Feedback MCML circuit61Figure 4.11 Small signal model of MCML inverter with feedback Resistor.63Figure 4.12 Simulation result of frequency response of traditional MCML and with feedback65Figure 4.13 Effect of feedback transistors on threshold-voltage fluctuation in (a) MCML inverter65(b) MCML based D-latch.67 |

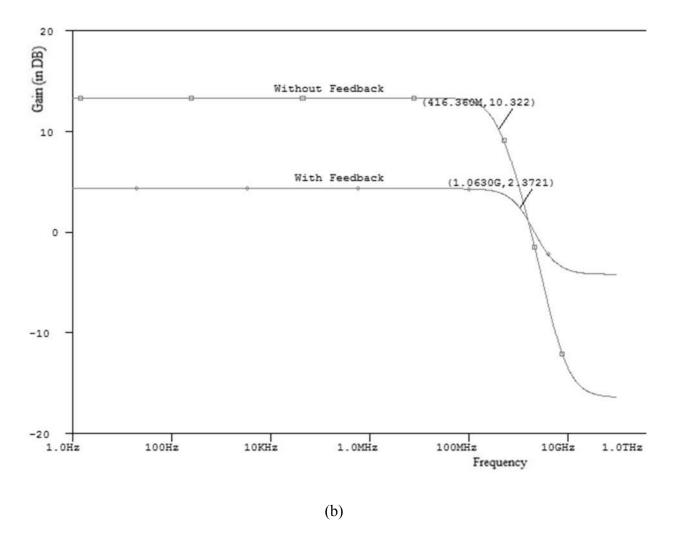

| Figure 4.16 Small signal model of triple-tail MCML based D-latch with feedback resistors                 | 70     |

|----------------------------------------------------------------------------------------------------------|--------|

| Figure 4.17 output waveform of effect of feedback transistors on triple-tail MCML bas                    | ed D-  |

| latch with threshold-voltage fluctuation                                                                 | 71     |

| Figure 4.18 Effect of feedback transistors on the frequency of operation of the triple-tail M            | 1CML   |

| based D-latch.                                                                                           | 72     |

| Figure 4.19 Variations in $\Delta VB$ with respect to the threshold-voltage fluctuation ( $\Delta Vth$ ) | ) with |

| feedback transistors in triple-tail MCML based D-latch.                                                  | 73     |

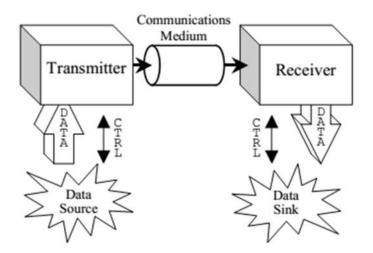

| Figure 5.1 Major components of communication system                                                      | 75     |

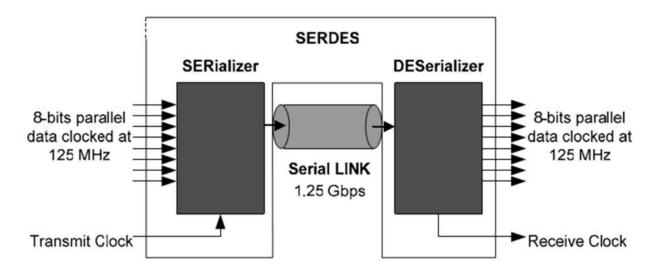

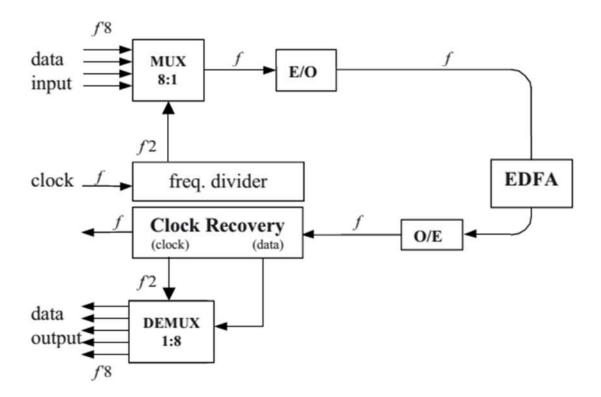

| Figure 5.2 Block diagram of SerDes transreceiver.                                                        | 76     |

| Figure 5.3 Fiber-optic link block diagram [16]                                                           | 77     |

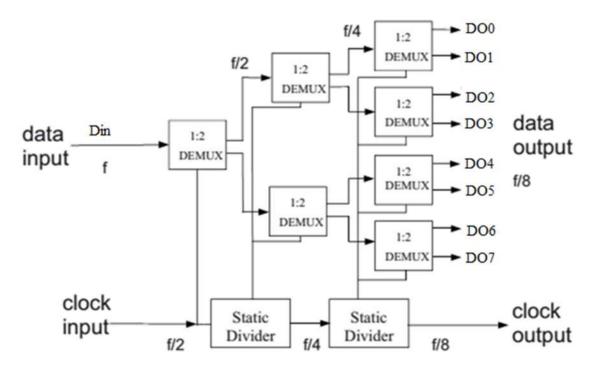

| Figure 5.4 Block Diagram of a 1:8 DEMUX [16]                                                             | 79     |

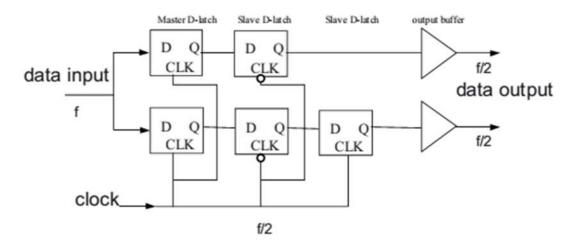

| Figure 5.5 Schematic of a 1:2 DEMUX [16]                                                                 | 79     |

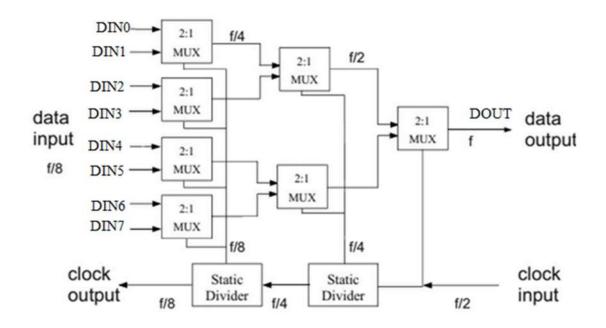

| Figure 5.6 Block diagram of 8:1 MUX [16]                                                                 | 81     |

| Figure 5.7 Implementation of 2:1 MUX [16]                                                                | 81     |

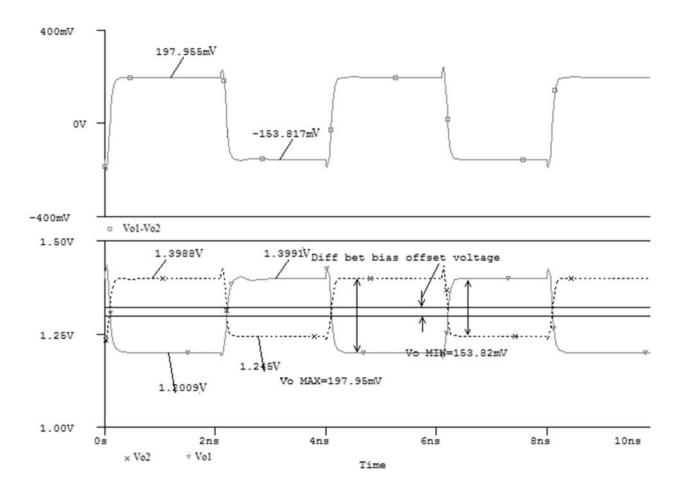

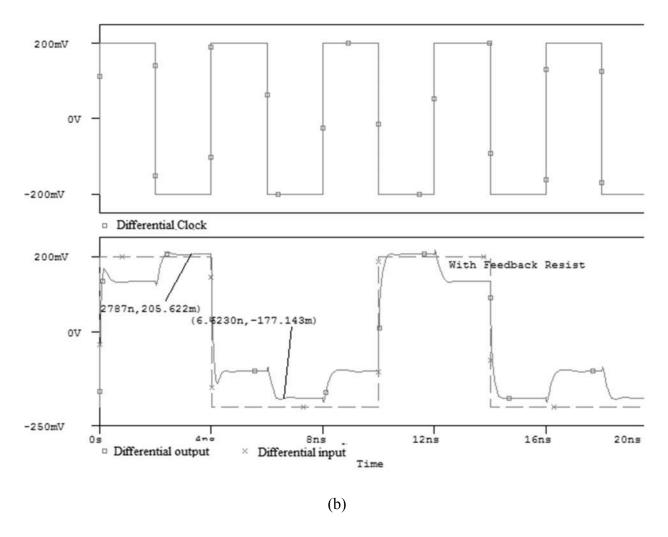

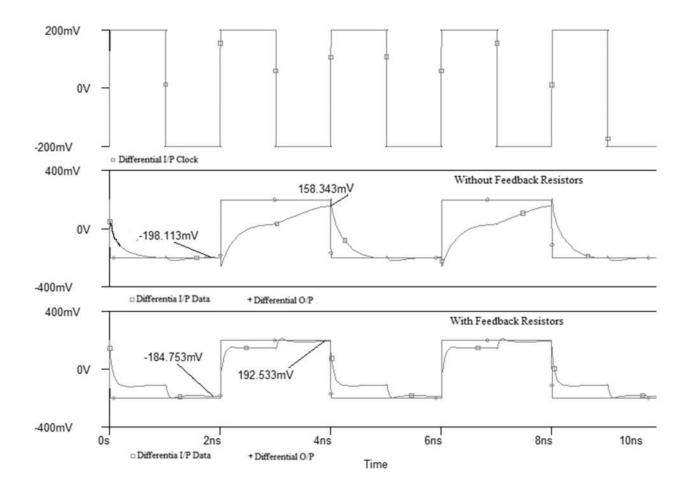

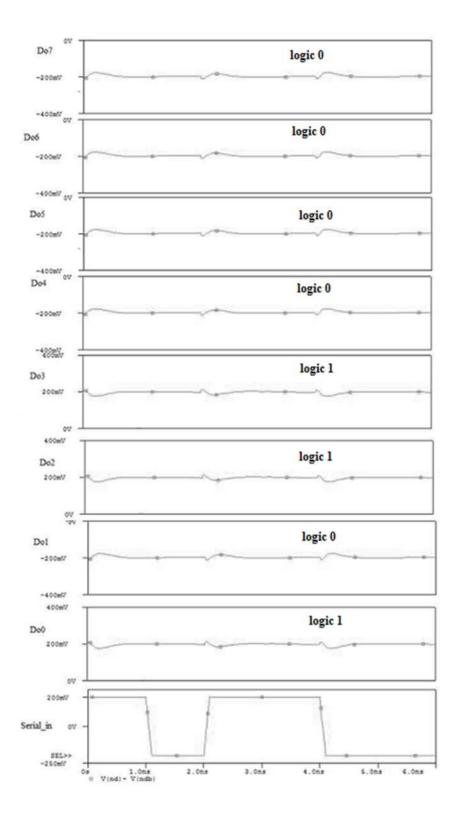

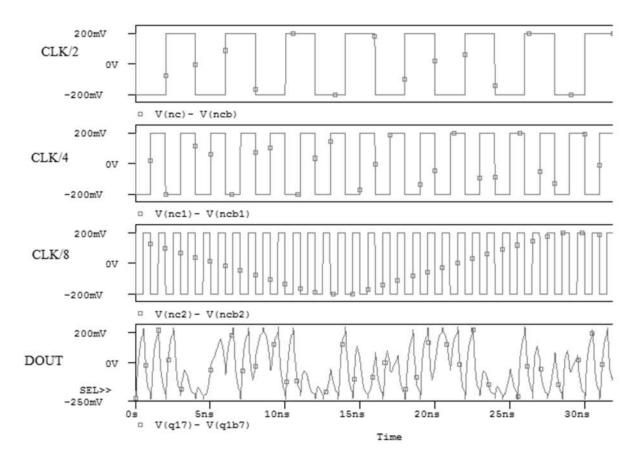

| Figure 5.8 Simulation result of the Deserializer for serial data input "10110000"                        | 84     |

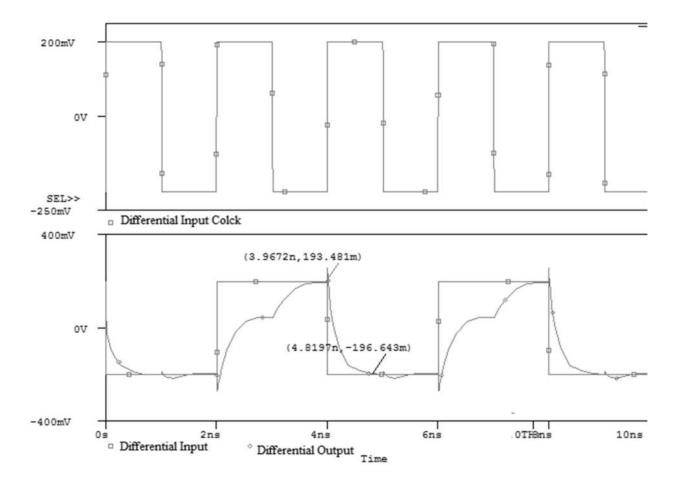

| Figure 5.9 Simulation result of the Serializer for parallel data input "1, 1, 1, 0, 0, 1, 1, 1"          | 87     |

# **LIST OF TABLES**

| Table 2.1 Voltage swing of MCML inverter simulated for different bias currents                    | 9    |

|---------------------------------------------------------------------------------------------------|------|

| Table 2.2 Delay between input and out for different bias current for MCML inverter                | . 12 |

| Table 2.3 Power Dissipation for different bias current for MCML inverter.                         | . 13 |

| Table 2.4 Delay between input and out for different bias current for MCML based D-latch           | . 21 |

| Table 2.5 Effect of process variation on static parameters the traditional MCML based D-latch     | ı 22 |

| Table 2.6 Effect of process variation on the delay of the traditional MCML based D-latch          | . 22 |

| Table 3.1 Output in the form of differential voltage for various input combination when appl      | lied |

| to triple-tail based MCML D-latch                                                                 | . 29 |

| Table 3.2Voltage swing of triple-tail MCML based D-Latch                                          | . 30 |

| Table 3.3 Sizing of transistors and load resistance for different bias current for triple-tail MC | ML   |

| based D-latch                                                                                     | . 35 |

| Table 4.1 Voltage swing ang bias offset voltage change for all the cases.                         | . 52 |

| Table 5.1 Comparison between deserializers employing different D-latches                          | . 82 |

| Table 5.2 Comparison between serializers employing different D-latches                            | . 85 |

# Chapter 1 Introduction

#### **1.1 Thesis Motivation**

This is the generation of portable mobile devices, and much recent advancement in VLSI technology has made possible the rapid growth in the area of hand-held electronic devices. PDAs, smart phones and portable laptops have all taken a substantial place in our daily life. Two main concerns while utilizing these devices are its speed and battery life. With the scaling down of the process technology, processing power demand is increasing also and hence, if architectural changes are not made now, the power consumption will increase over the time of future IC's[1]. The International Technology Road map for Semiconductors (ITRS) has stated in its 2005 report on Radio Frequency and Analog /Mixed-Signal Technologies for Wireless Communications that "As the integration density and the operation frequency increase, protection of noise sensitive analog circuits from noisy digital circuits will become increasingly difficult"[2]

New technologies and networks, including potent microprocessors, multimedia devices with vast bandwidth requirements are pushing the limits of system performances and data transfers in telecommunication area. The rapidly-increasing sizes of data in telecommunication networks have relighted interest in high-speed optical and electronics devices and systems. A digital logic style namely MOS Current Mode Logic (MCML) is a promising alternative to CMOS logic, in both reducing power consumption at high frequencies and providing high performance for mixed-signal applications [3-5]. In digital communication, because of high speed of MCML circuits, current-mode logic can be used in implementation of IC as a serializer(parallel to series converter converter) and deserializer(series to parallel converter), which is key component in gigahertz optical fiber link systems because of growing demand for high-speed communications. Also, static power can be further reduced by decreasing the power supply, but the traditional MCML D-latch have stacked transistor and puts a limit on minimum power supply that can be applied. And hence for power can be lowered by reducing the number of stacks, for which triple-tail MCML based has been introduced in [14].

Despite of being shown that MCML circuits consumes less power as compared to CMOS at operation frequencies of more than 300MHz[3], designers are showing unwillingness to replace CMOS with MCML because its performance is greatly affected by the fluctuation of threshold voltages of the differential pair transistors of PDN network because of its differential nature[5,10].

#### **1.2 Thesis Objectives**

The purpose of this work is to study the effect of threshold-voltage fluctuation in MCML circuits and triple-tail MCML D-latch. The method introduced in [10] to reduce the effect of threshold-voltage fluctuation has been studied and implemented on triple-tail based d-latch. Further, high speed serializer/ deserialzers are designed in this thesis using CMOS, traditional MCML and triple-tail MCML topology and comparative study has been done.

#### **1.3 Thesis Organization**

In next chapter a brief introduction of MCML and MCML based D-latch has been done. The discussion includes the general operation of the circuits, design parameters of both inverter and D-latch have been discussed. The requirements and problems associated with logic are also introduced in next chapter.

Chapter 3 discusses the triple-tail based D-latch. Its operation have been discussed Also, analysis of the circuit, and its technique to design the circuit with respect to its design parameters have also been studied in this chapter.

In chapter 4 how threshold voltage effects the circuit has been studied for both basic MCML circuit and triple-tail MCML based circuit, and the mathematical formulation of effect of threshold voltage among NMOS transistor has been studied and the mathematical formulation of effect of threshold voltage among PMOS transistor has been derived in this chapter of our thesis.

Also, a method to reduce the effect of threshold-voltage fluctuation introduced in [10] has been studied for MCML inverters and is also applied and varied using SPICE simulations for triple-tail based D-latch.

In chapter 5, an introduction has been done on how serializer and deserializer are designed using d-latch. Then serializer/ deserializers are designed in this chapter using CMOS, traditional MCML and triple-tail MCML topology and comparative study has been done.

# Chapter 2 MCML Based D-Latch Design

#### 2.1 Basics of MCML Operation

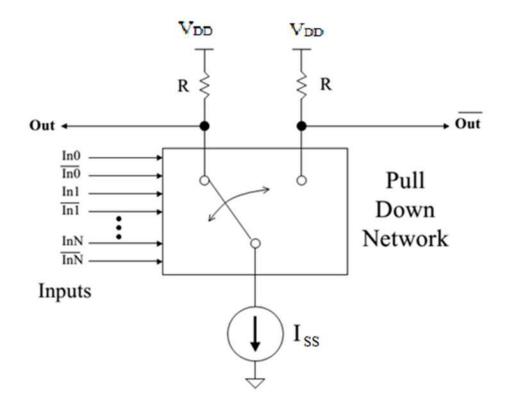

MOS Current-Mode Logic or MCML is a differential amplifier used in implementation of digital applications. Figure 2.1 shows a basic block of an MCML circuit. In Fig. 2.1, it can be observed that, by switching of current from one branch to another, the logic is comprehended, thus basically implements a voltage-controlled current switch.

Fig. 2.1 Basic block of an MCML circuit.

The circuit is composed of a set of differential-pair transistors, which are organized to steer the bias current,  $I_{SS}$  in one branch and switching off the other in a certain way, to realize the logic, according to the differential-inputs applied to the circuit. The voltages at corresponding output terminals are  $V_{DD}$  and  $V_{DD} - \Delta V$ , where  $\Delta V = I_{SS} \times R$ . Since the supply current required by the gate is almost constant, which in turn leads to static power dissipation and also the low-switching noise feature of MCML. An active load such as a PMOS transistor operating in the linear region can replace the load resistance and an NMOS transistor working in saturation region can control the tail-current  $I_{SS}$ .

For best performance, all the bias current,  $I_{SS}$  needs to flow though ON branch only, and the load resistance should be small to reduce the RC delay. This ensures the one output node of the circuit is at voltage  $V_{DD}$ , while other one is at the voltage  $V_{DD} - \Delta V$ , where  $\Delta V = I_{SS} \times R$ , where  $I_{SS}$  is the value of current flowing through the current source and R is load resistance implemented by PMOS transistors  $M_3$  and  $M_4$ . It is advantageous to have low voltage-swing because: (1) delay of the gate is reduced significantly and (2) results in reduction of cross-talk between the nearby signals. Also, another advantage of MCML is high immunity to common-mode noise because of its differential nature. Also the static current source in MCML provides a steady current irrespective of switching activity, thus MCML is a friendly alternative for mixed-signal applications as compared to CMOS.

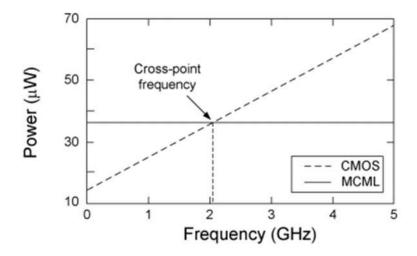

MCML has some major drawbacks. Firstly, due to constant current source, large static power is dissipated. But compared with CMOS circuits, using Power/MHz as a measure for power dissipation, it can be seen from Fig. 2.3 that MCML consumes less power at higher frequencies and more at lower frequencies. Thus, MCML is preferred in applications operating at high frequencies only, in order to reduce the overhead dissipation of static power. Also, the maximum operation frequency of the MCML, is greatly affected by the fluctuation of threshold voltages (V<sub>TH</sub>) of the differential pair transistors of the pull-down network[5] and this threshold voltage fluctuation increases as the gate length decreases, it turns out to be a serious problem for deep-submicron CMOS transistors. More details will be given in chapter 5, about how this threshold voltage fluctuation affects the working of MCML circuit and how it can be over-come this problem.

Fig. 2.2 Power vs. Frequency for MCML inverters[8]

#### 2.2 MCML Design Parameters

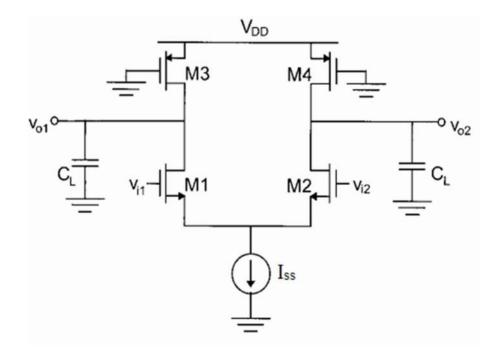

Let us consider an MCML inverter shown in Fig. 2.3. Here load capacitance  $C_L$  represents the loading effect of the wiring capacitance and following gates connected at the output. The NMOS differential transistor pair  $M_1 - M_2$ , which is driven by the differential input signal  $v_i = v_{i1} - v_{i2}$  and works in the saturation or the cut-off region and is biased by the constant current source  $I_{SS}$ , implemented by a NMOS transistor working in saturation region. When  $v_i$  is high, the bias current,  $I_{SS}$  flows through transistors  $M_1$  and  $M_3$ , and the differential output voltage  $v_o = v_{o1} - v_{o2}$  is at the low level and is equal to  $v_o = -\Delta V$ , where  $\Delta V$  is the voltage drop across  $M_3$  when its drain current is equal to  $I_{SS}$ . Similarly, if  $v_i$  is low, output voltage  $v_o = \Delta V$ , and hence the logic swing of the gate is equal to  $2\Delta V$ . To keep  $M_1$  out of the linear region,  $\Delta V = I_{SS} \times R$ , where R is the resistance implemented by PMOS transistors  $M_3$  and  $M_4$ , must be kept lower than the threshold voltage of NMOS transistor,  $V_{T,n}[6]$ .

In particular, assuming transistor operation in the saturation region, currents iD1 and iD2 of transistors  $M_1 - M_2$  differential pair shown in Fig. 2.2 can be expressed as a function of the differential input voltage  $v_i = v_{i1} - v_{i2}$  as

$$i_{D1}(\mathbf{v}_{i}) = \begin{cases} 0 & \text{if } \mathbf{v}_{i} \leq \sqrt{\frac{2I_{SS}}{\mu_{n}C_{0x}\frac{W_{n}}{L_{n}}}} \\ \frac{I_{SS}}{2} + \frac{\mathbf{v}_{i}}{2}\sqrt{\mu_{n}C_{0x}\frac{W_{n}}{L_{n}}} \mathbf{I}_{SS} - \left(\mu_{n}C_{0x}\frac{W_{n}}{L_{n}}\frac{\mathbf{v}_{i}}{2}\right)^{2}} & \text{if } |\mathbf{v}_{i}| \leq \sqrt{\frac{2I_{SS}}{\mu_{n}C_{0x}\frac{W_{n}}{L_{n}}}} \quad (2.1a) \\ I_{SS} & \text{if } \mathbf{v}_{i} \geq \sqrt{\frac{2I_{SS}}{\mu_{n}C_{0x}\frac{W_{n}}{L_{n}}}} \end{cases}$$

$$i_{D1}(v_i) = I_{SS} - i_{D1}(v_i)$$

(2.1b)

Where  $W_n$  and  $L_n$  are the effective width and length of NMOS differential pair shown in Fig. 2.2, respectively and  $C_{ox}$  is the oxide capacitance per unit area,  $\mu_n$  is the carrier mobility of NMOS transistor and  $I_{SS}$  is the bias current. For complete steering of bias current  $I_{SS}$  to the one

of the transistors, the input differential voltage should be greater than  $\sqrt{\frac{2I_{SS}}{\mu_n C_{ox} \frac{W_n}{L_n}}}$ . This steered

current is converted into differential output voltage through the PMOS transistors acting as active load  $M_3 - M_4$ .

Fig. 2.3 MCML Inverter/Buffer[8]

The design parameters of a typical MCML circuit are the circuit delay  $t_d$ , voltage swing  $\Delta V$ , voltage gain  $A_v$ , noise margin NM and total power dissipation  $P_D$ . And the design variables available to achieve the aforementioned parameters are the total bias current  $I_{SS}$ , transistor sizes of the differential pull-down network, load resistance and hence transistor sizes of PMOS transistors which implements the load resistances.[8]

(A) Voltage-Swing ( $\Delta V$ ):

As mentioned above, the voltage-swing of MCML circuits is expressed as,

$$V_{SWING} = 2\Delta V \tag{2.2a}$$

$$\Delta V = I_{SS} \times R \tag{2.2b}$$

It can be noted that, the circuit with same  $\Delta V$  and  $C_L$ , would require a larger bias current  $I_{SS}$ , in order to have a shorter  $t_d$ . Thus  $\Delta V$  is an important parameter that links

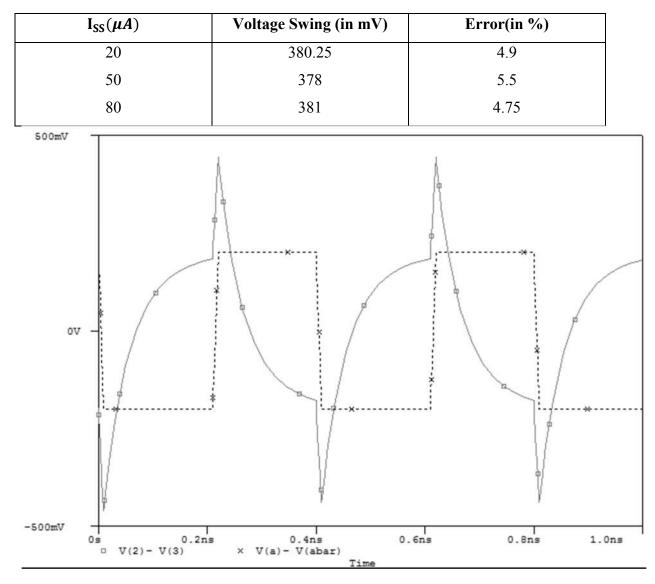

performance with power dissipation. Simulation results of transient analysis of MCML inverter has been shown in Fig. 2.4, for 400mV voltage swing and 80 $\mu$ A bias current. The voltage swing of the output came out to be 381mV with the error of 4.75%. Table 2.1 shows the voltage swing obtained for MCML inverter simulated for different bias currents and error between simulated and predicted values.

Table 2.1 Voltage swing of MCML inverter simulated for different bias currents

(B) Voltage gain  $(A_v)$ :

DC Voltage gain is defined as the voltage gain at common-mode voltage.  $A_v$  is a key parameter in regulating the stability and circuit regeneration. For MCML inverter,  $A_v$  can be expressed as

$$A_{v} = g_{m,1}R = R_{\sqrt{2\mu_{n}C_{ox}\frac{W_{n}I_{ss}}{L_{n}\frac{1}{2}}} = \Delta V_{\sqrt{\mu_{n}C_{ox}\frac{W_{n}I_{ss}}{L_{n}I_{ss}}}$$

(2.3)

where  $g_{m,1}$  is the tranconductance on the NMOS transistor  $M_1$  of MCML inverter shown in Fig. 2.3,  $\mu_n$  is the electron mobility,  $C_{ox}$  is the oxide capacitance and  $W_n$  and  $L_n$  are the effective width and length of  $M_1$ , respectively.

MCML inverter has been simulated for bias current value of  $50\mu$ A and gain 4, AC analysis of which is shown in Fig. 2.5. It can be seen that there is a close relation between simulated and predicted voltage gain.

Fig. 2.5 AC Analysis of MCML inverter

#### (C) Total circuit delay $(t_d)$ :

A small signal model can used to approximate the behavior of MCML circuits, as they experience small voltage swing[9]. Equivalent small-signal model of MCML inverters is shown in Fig. 2.6. Here,  $C_{db,1}$  and  $C_{gd,1}$  are the drain-bulk capacitance and gate-drain overlap capacitance of the NMOS transistor of the pull-down network, respectively, and,  $C_{db,2}$  and  $C_{gd,2}$  are the drain-bulk capacitance and gate-drain overlap capacitance of the PMOS transistor, respectively.  $C_L$  is the load capacitance which includes the loading effect of wiring capacitance and fan-out capacitances of the gates connected to the output of the circuit.

Fig. 2.6 Small-signal equivalent of MCML inverter

Using analysis of first-order circuits, delay of the inverter  $t_d$  can be approximated by

$$t_{d} = 0.69R(C_{gd,1} + C_{db,1} + C_{gd,3} + C_{db,3} + C_{L})$$

(2.4)

In table 2.2, simulated delay for different bias current values for 400mV voltage swing and for voltage gain equals to 4 with 50fF load capacitance has been tabulated. It can be seen that with increment in the value of bias current, delay keeps on decreasing, because for same voltage swing, value of load resistance is required less and hence, from eq. 2.4, with increment in current bias value, delay of the circuit decreases.

Table 2.2 Delay between input and out for different bias current for MCML inverter

| $I_{SS}(\mu A)$ | Delay (t <sub>d</sub> ) |

|-----------------|-------------------------|

| 20              | 54.7ps                  |

| 50              | 52.67ps                 |

| 80              | 43.37ps                 |

(D) Power Dissipation  $(P_D)$ :

Because of the use of constant current source, MCML circuits consume static power and compared to which dynamic power of the MCML circuits is ignorable [5].  $P_D$  in MCML is given by

$$P_{\rm D} = V_{\rm DD} \times I_{\rm SS} \tag{2.5}$$

Table 2.3 shows the simulated power dissipation of the MCML inverter for 1.4 supply voltage. As formulated, the power dissipation of the inverter has come out be their product. Thus, to minimize the dissipation, one has to reduce the power supply, such that all the transistors are in saturation for proper operation of the MCML based circuits.

| $I_{SS}(\mu A)$ | Power Dissipation(Watts) |  |  |

|-----------------|--------------------------|--|--|

| 20              | 2.80E-05                 |  |  |

| 50              | 7 E-05                   |  |  |

| 80              | 11.2 E-05                |  |  |

Table 2.3 Power Dissipation for different bias current for MCML inverter.

#### (E) Noise Margin (NM):

Because of reduced voltage swings, large noise margins can be achieved in MCML circuits. However, designers can accept small values of noise margins because of high noise immunity of MCML circuits which is result of differential nature of current-mode logic circuits. For MCML circuit, NM is given by [16]

$$NM = \Delta V \frac{\sqrt{4A_v^2 - 1 - \sqrt{8A_v^2 + 1}}}{A_v^2 \sqrt{2}} \times \left( \frac{\sqrt{4A_v^2 - 1 + \sqrt{8A_v^2 + 1}}}{2\sqrt{2}} - 1 \right)$$

(2.6)

which lead to following expression

$$NM = \Delta V \left( 1 - \frac{\sqrt{2}}{A_v} \sqrt{1 - \frac{1}{\sqrt{2}A_v}} \right) \cong \Delta V \left( 1 - \frac{\sqrt{2}}{A_v} \right)$$

(2.7)

The voltage transfer characteristics of the MCML inverter has been shown in Fig. 2.7 simulated for 400mV voltage swing,  $50\mu$ A bias current, 4 voltage gain and 130mV noise margin and the noise margin came out from simulation is 138.45 mV with the error of 6.5%.

Fig. 2.7 Threshold Voltage characteristics of MCML inverter.

### 2.3 Design strategies of MCML based D-latch:

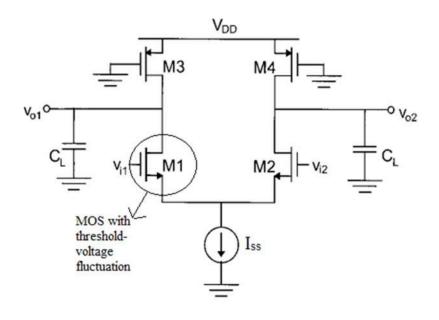

In literature, MCML gates have been explored in terms of delay modeling and noise margin. In this section, design strategies for MCML based D-latch has been studied. Since, MCML has superior power efficiency and speed at higher frequencies as compared to CMOS, hence they are more suitable for implementation of serializer/deserializer (also known by acronym SerDes), for which the fundamental gates that is used is D=latch, in the applications of digital broadband communications as the exhibit implementation of multiplexing/demultiplexing in the range of 10Gbps with much higher operating frequency and less power dissipation than static CMOS logic[10]. This strategy allows us to meet the speed constraint or aid us in optimizing the delay and power consumption by sizing the bias current transistor and aspect ratios of transistors of pull-down network and PMOS transistors which are used to implement resistors.

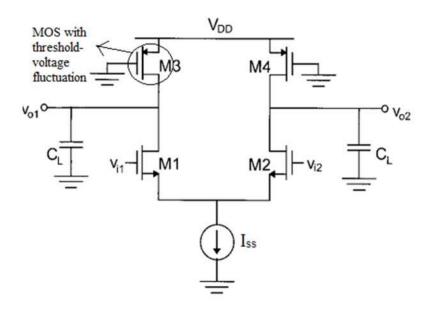

The circuit used to implement the MCML based D-latch has been shown in Fig. 2.8. In the circuit, according to the logic level of clock, new data carried by  $D - \overline{D}$  signal is conveyed at output or pervious output is restored. Indeed, static behavior of the circuit is not affected by other constant input.

Fig. 2.8 MCML based D-latch

(a) Voltage-swing:

As mentioned for MCML invertor shown in Fig. 2.2, the voltage-swing for D-latch can be expressed as

$$V_{SWING} = 2I_{SS}R_P \tag{2.8a}$$

Here,  $R_P$  is the resistance implemented by PMOS transistors working in linear region and by using the BSIM3v3 model[11], the expression  $R_P$  can be computed as

$$R_{P} = \frac{\frac{R_{int}}{(R_{DSW}^{*10^{-6}})/w_{P}}}{1 - \frac{R_{int}}{R_{int}}}$$

(2.8b)

where  $R_{DSW}$  is the empirical model parameter and the parameter  $R_{int}$  is the intrinsic resistance of the PMOS transistor in the linear region and is given as

$$R_{int} = [\mu_{eff,p} C_{ox} \frac{W_P}{L_P} (V_{DD} - |V_{TP}|)]^{-1}$$

(2.9)

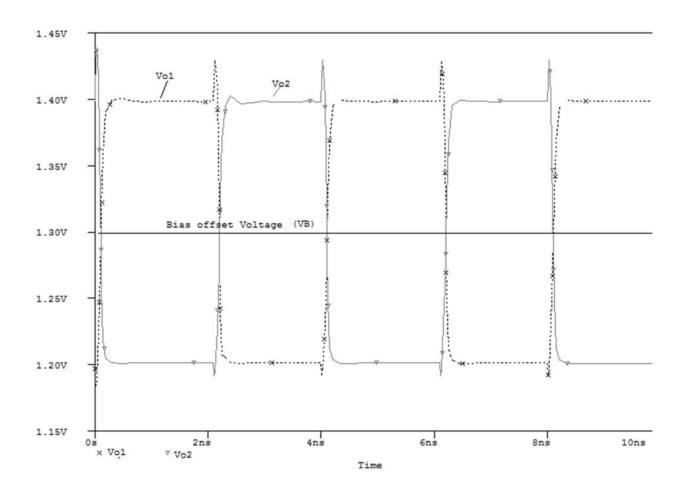

where  $C_{ox}$  is the oxide capacitance per unit area and the parameters  $\mu_{eff,p}$  is effective hole mobility,  $V_{TP}$  is the threshold voltage,  $W_P$  and  $L_P$  the effective channel width and effective channel length of the load transistor. For 400mV voltage swing, 20µA bias current and 4 voltage gain, transient analysis of MCML based D-latch is shown in Fig. 2.9, where when clock is 1, data is transferred at output and when clock is 0, previous output is maintained as current output of the latch, with the total simulated voltage swing came out to be 383.27mV with error of 4.2% between the predicted and simulated results.

Fig. 2.9 Transient analysis of MCML based D-Latch

(b) DC Voltage gain (A<sub>v</sub>):

As studied for MCML invertor shown in Fig. 2.2, when the logic threshold is zero i.e. at the common-mode input voltage, the small-signal voltage gain is resulted as

$$A_{v} = g_{m,n}R_{P} = R_{P}\sqrt{2\mu_{n}C_{ox}\frac{W_{n}I_{SS}}{L_{n}^{2}}} = \frac{V_{SWING}}{2}\sqrt{\mu_{n}C_{ox}\frac{W_{n}I_{n}}{L_{n}I_{SS}}}$$

(2.10)

Where  $g_{m,n}$  is the small-signal transconductance of NMOS transistors,  $W_n$  and  $L_n$  are the channel width and length of NMOS transistors shown in Fig.2.8 and  $\mu_n$  is the effective mobility which is given as [11]

$$\mu_{n} = \frac{\mu_{o}}{1 + (U_{A} + U_{C}V_{bseff}) \left(\frac{V_{gst} + 2V_{th}}{T_{ox}}\right) + U_{b} \left(\frac{V_{gst} + 2V_{th}}{T_{ox}}\right)^{2}}$$

(2.11)

Where  $V_{gst} = V_{gs} - V_{th}$ .

MCML inverter has been simulated for  $30\mu$ A bias current and gain 4, AC analysis of which is shown in Fig. 2.10. It can be seen that there is a close relation between simulated and predicted voltage gain

Fig. 2.10 AC analysis of MCML based D-latch

#### (c) Noise-Margin:

As studied for MCML invertor shown in Fig. 2.2, noise-margin can be expressed as[9]

$$NM = \frac{V_{SWING}}{2} \left( 1 - \frac{\sqrt{2}}{A_v} \sqrt{1 - \frac{1}{\sqrt{2}A_v}} \right) \cong \frac{V_{SWING}}{2} \left( 1 - \frac{\sqrt{2}}{A_v} \right)$$

(2.12)

#### (d) Delay model of D-latch:

As studied in [12], the worst case propagation delay is obtained by switching the clock signal applied to  $M_1$  and  $M_2$ , transistors shown in Fig. 2.8, keeping all the other inputs constant. Thus, the delay can be realized by analyzing the half-circuit of the MCML D-latch shown in Fig. 2.8, is shown in Fig. 2.11

Fig. 2.11 Small-signal Half-circuit equivalent of MCML D-latch

Using dominant pole concept, delay is obtained as

$$t_{d,latch} = 0.69 \left[ R_P (2C_{gd,3} + C_{db,3} + C_{gd,5} + C_{db,5} + C_{gd,P} + C_{db,P} + C_L) + \frac{1}{G_{M,n}} (C_{gd,1} + C_{db,1} + C_{gs,3} + C_{sb,3} + C_{sb,4} + C_{gs,4}) \right]$$

(2.13)

Here it's worth noting that  $G_{M,n}$  cannot be approximated by  $g_{m,n}$  i.e. its small-signal assessment in saturation region.  $G_{M,n}$  can be expressed as [12]

$$G_{M,n} = \sqrt{\frac{\mu_n C_{ox}}{2} \frac{W_{n3}}{L_{n3}} I_{SS}} = \frac{g_{m,n}}{2}$$

(2.14)

Hence, the delay can be expressed in terms of  $V_{SWING}$ ,  $I_{SS}$  and  $A_v$  as

$$t_{d,latch} = 0.69 \frac{V_{SWING}}{2I_{SS}} \left[ 3C_{gd,1} + 2C_{db,3} + C_{gd,P} + C_{db,P} + C_L + \frac{2}{A_v} \left( 2C_{gd,1} + 3C_{db,1} + C_{gs,3} \right) \right]$$

(2.15)

where all NMOS transistors have an equal aspect ratio.

In table 2.4, simulated delay for different bias current values for 400mV voltage swing and for voltage gain equals to 4 with 50fF load capacitance has been tabulated. It can be seen that with increment in the value of bias current, delay keeps on decreasing, because for same voltage swing, value of load resistance is required less and hence, from eq. 2.15, with increment in current bias value, delay of the circuit decreases.

Table 2.4 Delay between input and out for different bias current for MCML based D-latch

| $I_{SS}(\mu A)$ | Delay (t <sub>d</sub> ) |  |  |

|-----------------|-------------------------|--|--|

| 20              | 375.57ps                |  |  |

| 50              | 335.082ps               |  |  |

| 80              | 193.57ps                |  |  |

#### 2.4 Effect of process variation in MCML based D-latch:

The impact of parameter variation on traditional MCML based D-Latch performance is studied at different design corners. The findings for various operating conditions are given in Table 2.5. It is found that the voltage swing, small-signal voltage gain, and noise margin for the traditional MCML based D-Latch, the voltage swing, small-signal voltage gain, and noise margin varies by a factor of 1.12, 1.02, and 1.06 respectively between the best and the worst cases. Here, TT, FF, FS, SF and SS represents the different process corners, and are typical NMOS typical PMOS, fast NMOS fast PMOS, fast NMOS slow PMOS, slow NMOS fast PMOS and slow NMOS slow PMOS.

| Parameter                                                                                  | NMOS        | Т      | F      | S     | F     | S     |  |  |

|--------------------------------------------------------------------------------------------|-------------|--------|--------|-------|-------|-------|--|--|

|                                                                                            | PMOS        | Т      | F      | S     | S     | F     |  |  |

| Simulation Conditions: $A_v = 4$ , $V_{swing} = .4V$ , $C_L = 50$ fF, $I_{SS} = 100 \mu A$ |             |        |        |       |       |       |  |  |

| V <sub>swing</sub> (mV)                                                                    |             | 381    | 387    | 330   | 378   | 379   |  |  |

| $\mathbf{A_v}$                                                                             |             | 2.1    | 2.12   | 2.12  | 2.1   | 2.1   |  |  |

| NM(mV)                                                                                     |             | 139.6  | 139.5  | 139.6 | 141.2 | 140.7 |  |  |

| Simulation Conditions: $A_v = 4$ , $V_{swing} = .4V$ , $C_L = 50$ fF, $I_{SS} = 10\mu$     |             |        |        |       |       |       |  |  |

| V <sub>swing</sub> (mV)                                                                    |             | 384    | 381    | 342   | 380   | 377   |  |  |

| $A_v$                                                                                      |             | 2.09   | 2.12   | 2.13  | 2.1   | 2.1   |  |  |

| NM(mV)                                                                                     | Traditional | 139.57 | 142.28 | 140.1 | 135.4 | 137.8 |  |  |

|                                                                                            |             |        |        |       |       |       |  |  |

**Table 2.5** Effect of process variation on static parameters the traditional MCML based D-latch

Table 2.6 Effect of process variation on the delay of the traditional MCML based D-latch

| Parameter                                                                                    | NMOS | Т      | F      | S      | F      | S     |  |

|----------------------------------------------------------------------------------------------|------|--------|--------|--------|--------|-------|--|

|                                                                                              | PMOS | Т      | F      | S      | S      | F     |  |

| Simulation Conditions: $A_v = 4$ , $V_{swing} = .4V$ , $C_L = 50$ fF, $I_{SS} = 100 \ \mu A$ |      |        |        |        |        |       |  |

| t <sub>PD</sub> (ps)                                                                         |      | 142.3  | 113.4  | 172.5  | 127    | 138.6 |  |

| Simulation Conditions: $A_v = 4$ , $V_{swing} = .4V$ , $C_L = 50$ fF, $I_{SS} = 10\mu A$     |      |        |        |        |        |       |  |

| t <sub>PD</sub> (ps)                                                                         |      | 385.57 | 372.46 | 403.24 | 392.16 | 396.7 |  |

### 2.5 Minimum Power Supply for MCML based D-Latch:

This MCML based D-latch consist of two series stacked NMOS devices as shown in Fig. 2.8. Therefore, the main disadvantages of this scheme are

- The delay is also quite large as it includes load capacitance of both of the stacked transistors.

- This would require high voltage supply  $V_{DD}$  to keep both the stacks and bias current transistor in saturation for proper working. And hence, power dissipation is quite high in two series stacked D-Latch. The minimum supply required for proper working of D-latch can be calculated as[13]

$$V_{DD\_min} = V_{DS,source_{LVT}} + V_{DS,1_{LVT}} + V_{GS,3}$$

$$(2.16)$$

Where  $V_{DS,source_{LVT}}$ ,  $V_{DS,1_{LVT}}$  and  $V_{GS,3}$  represents drain-source saturation voltage of bias current transistor and  $M_1$  and gate-source voltage of the corresponding transistor  $M_3$  in Fig. 2.8, respectively. In general drain-source saturation voltage,  $V_{DS,LVT}$  is expressed as

$$V_{\rm DS_{LVT}} = V_{\rm GS} - V_{\rm th} \tag{2.17}$$

Where  $V_{th}$  represents the threshold voltage of the transistor. In the saturation region,  $V_{GS}$  can be expressed as

$$V_{GS} = \sqrt{\frac{I}{K}} + V_{th} \tag{2.18}$$

Where I is the current flowing through the transistor and K is the parameter in the process-transconductance and the aspect ratio of the device Thus,  $V_{DS_{LVT}}$  can be written as

$$V_{\rm DS_{\rm LVT}} = \sqrt{\frac{I}{\kappa}}$$

(2.19)

Taking  $I_{SS} = I_1 = I_3$  for the conducting case and  $K_1 = K_3 = K$ , and hence, using eq. (2.17-2.19) eq. (2.16) can be written as

$$V_{DD\_min} = \sqrt{\frac{I_{SS}}{K_{source}}} + \sqrt{\frac{I_1}{K_1}} + \sqrt{\frac{I_3}{K_3}} + V_{th,3}$$

(2.20)

$$= \sqrt{I_{SS}} \left( \frac{1}{\sqrt{K_{source}}} + \frac{2}{\sqrt{K}} \right) + V_{th,3}$$

$$= \sqrt{K_{source}(V_{bias} - V_{th})^2} \left( \frac{1}{\sqrt{K_{source}}} + \frac{2}{\sqrt{K}} \right) + V_{th,3}$$

$$= \left( V_{bias} - V_{th,source} \right) \left( 1 + \frac{2\sqrt{K_{source}}}{\sqrt{K}} \right) + V_{th,3}$$

$$\approx 3V_{bias} - 3V_{th,source} + V_{th,3}$$

(2.21)

Where  $V_{th,source}$  and  $V_{th,3}$ , are the threshold voltages of bias current source transistor and  $M_3$  respectively. Here, it can be seen from eq. (2.21), that if somehow we can reduce the stack of the transistor, we can decrease the minimum power supply and hence the power dissipation of the circuit. With this triple-tail MCML based D-latch comes into the scenario presented by K. Gupta et. al [14], which will be studied in next chapter.

### Chapter 3 Triple-tail MCML based D-latch

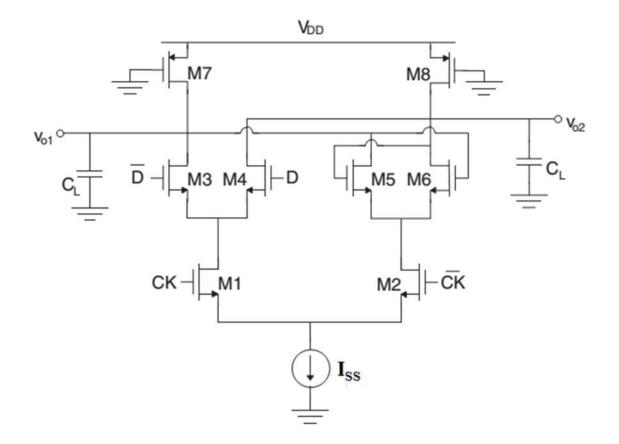

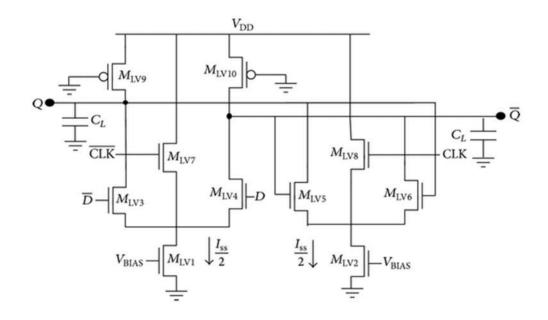

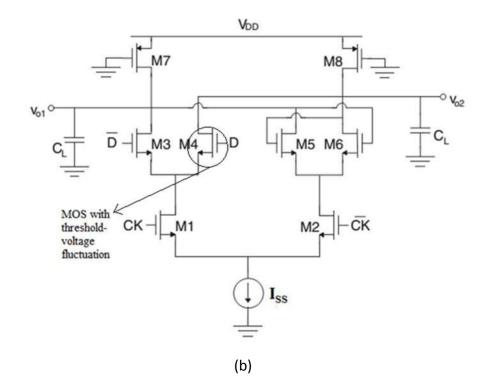

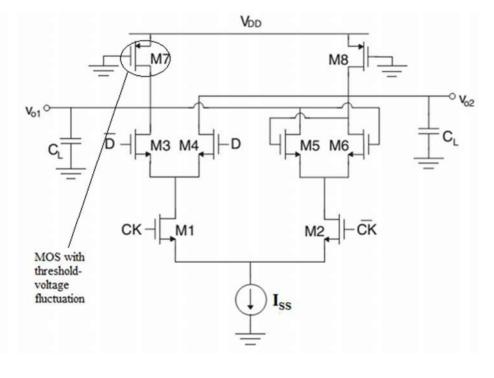

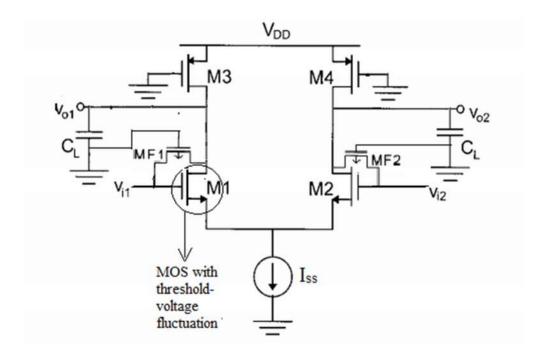

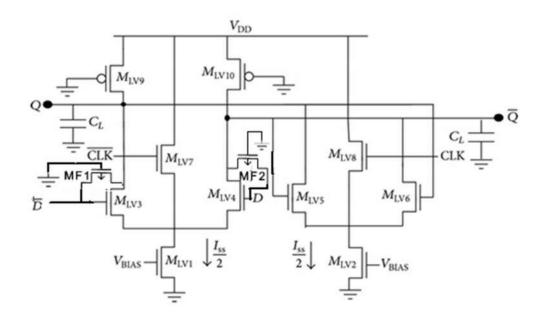

The triple-tail MCML based D-Latch proposed in [14] with differential inputs D and CLK is shown in Fig. 3.1. It consists of two current sources of  $I_{SS}/_2$  value biasing the two triple-tail

assembled by transistors ( $M_{LV4}$ , $M_{LV4}$ ,  $M_{LV7}$ ) and ( $M_{LV5}$ , $M_{LV6}$ ,  $M_{LV8}$ ). Differential CLK input drives the transistors  $M_{LV7}$  and  $M_{LV8}$  and are connected between the supply terminal and the common source terminal of transistor pairs  $M_{LV4} - M_{LV4}$  and  $M_{LV5} - M_{LV6}$  respectively. The transistor  $M_{LV8}$  is switched on by a high differential CLK voltage, and thus the transistor pair  $M_{LV5} - M_{LV6}$  is deactivated. At the same time, the transistor  $M_{LV7}$  turns off so that the output is generated by transistor pair  $M_{LV4} - M_{LV4}$  according to the differential input D. Similarly, the transistor pair  $M_{LV4} - M_{LV4}$  gets activated for low differential CLK voltage and restores the previous output and thus the latch, for low differential CLK, operates in hold stage. For proper operation, aspect ratios of transistors  $M_{LV7}$  and  $M_{LV8}$  is made larger (N times) than the other transistors [14].

Fig. 3.1 Triple-tail MCML based D-Latch

The minimum supply voltage,  $V_{DD_{MIN_{LV}}}$  for the triple-tail MCML based D-Latch is computed by the method outlined in [11] as

$$V_{DD_{MIN_{LV}}} = 2V_{BIAS} + V_{T1} - 2V_{T}$$

(3.1)

Where  $V_{T1}$  is the threshold voltage of transistors  $M_{LV4,4,5,6}$ ,  $V_T$  is the threshold voltage of  $M_{LV1}$ and  $V_{BIAS}$  is the biasing voltage of  $M_{LV1}$ . Here, we can see that the minimum supply voltage required for proper working of the latch is less than the supply voltage required (eq. 2.21). Hence, this scheme dissipates less power as compared to traditional MCML based D-Latch studied in chapter 2.

### **3.1 Analysis of the triple-tail MCML based D-latch:**

As it can be observed that if all the transistors in triple tail in Fig. 3.1 have equal aspect ratios, then the transistors  $M_{LV7}$  and  $M_{LV8}$  will not be able to completely switch off the transistor pair  $M_{LV4} - M_{LV4}$  and  $M_{LV5} - M_{LV6}$ . And hence for proper operation we have taken the aspect ratios of tail-transistors in Fig. 3.1 ( $M_{LV7,8}$ ) larger than the aspect ratios of other transistors of pull-down network ( $M_{LV4,4,5,6}$ ). The detailed analysis of impact of larger area of the tail transistors in Fig. 3.1, on the circuit operation, is studied in this section

#### 3.1.1 Static Analysis:

The static model is derived by modeling the load transistors  $M_{LV9}$ ,  $M_{LV10}$  by an equivalent linear resistance,  $R_P$  [6]. The linear resistance,  $R_P$  is computed by using the standard BSIM3v3 model, as

$$R_{\rm P} = \frac{R_{\rm int}}{1 - \frac{(R_{DSW} * 10^{-6})/W_{\rm P}}{R_{\rm int}}}$$

(3.2)

where  $R_{DSW}$  is the empirical model parameter and the parameter  $R_{int}$  is the intrinsic resistance of the PMOS transistor in the linear region and is given as

$$R_{int} = [\mu_{eff,p} C_{ox} \frac{W_P}{L_P} (V_{DD} - |V_{TP}|)]^{-1}$$

(3.3)

where  $C_{ox}$  is the oxide capacitance per unit area and the parameters  $\mu_{eff,p}$  is effective hole mobility,  $V_{TP}$  is the threshold voltage,  $W_P$  and  $L_P$  the effective channel width and effective channel length of the load transistor.

As it can be observed that if all the transistors in triple tail in Fig.3.1 have equal aspect ratios [14], then the transistors  $M_{LV7}$  and  $M_{LV8}$  will not be able to completely switch off the transistor pair  $M_{LV4} - M_{LV4}$  and  $M_{LV5} - M_{LV6}$ . Hence, the aspect ratios of transistors  $M_{LV7}$  and  $M_{LV8}$  is kept larger than other transistors' aspect ratios by a factor of *N* the linear resistance,

$R_P$  is computed. For, high differential input at D and low differential input at CLK, the transistors  $M_{LV4}$  and  $M_{LV7}$  have the same gate-source voltages, then for this input condition, currents flowing through  $M_{LV4}$  and  $M_{LV7}$  can be written as

$$i_{D,LV4} = \frac{\mu_{eff,n}C_{ox}}{2} \frac{W_N}{L_N} (V_{GS} - V_{T1})^2$$

(3.4a)

$$i_{D,LV7} = \frac{\mu_{eff,n} C_{ox} * N}{2} \frac{W_N}{L_N} (V_{GS} - V_{T1})^2$$

(3.4b)

Also, the sum of the drain currents of  $M_{LV4}$  and  $M_{LV7}$  will be constant i.e.

$$i_{D,LV4} + i_{D,LV7} = \frac{I_{SS}}{2}$$

(3.4c)

Solving the above equations for i<sub>D,LV4</sub> and i<sub>D,LV7</sub>, we get the following results

$$i_{D,LV4} = \frac{I_{SS}}{2} \frac{1}{N+1}$$

(3.5a)

$$i_{D,LV7} = \frac{I_{SS}}{2} \frac{N}{N+1}$$

(3.5b)

The current  $i_{D,LV4}$ , i.e. the current through transistor  $M_{LV4}$ , can be increased by increasing its area , that is by increasing the factor N. The input condition high differential input at D and high differential input at CLK , produces minimum output voltage, represent as  $V_{OL1}$  as

$$V_{0L1} = V_Q - \overline{V_Q}$$

=  $R_P[(i_{D,4} + i_{D,6}) - (i_{D,3} + i_{D,5})]$  (3.6)

=  $-\frac{R_P I_{SS}}{2} (1 + \frac{1}{N+1})$  (3.7)

For another input condition, when differential signals -clock signal CLK is low, D is high and previous state is low then

$$V_{0L2} = V_Q - \overline{V_Q}$$

= R<sub>P</sub>[(i<sub>D,4</sub> + i<sub>D,6</sub>) - (i<sub>D,3</sub> + i<sub>D,5</sub>)]

$$= -\frac{R_{\rm P}I_{\rm SS}}{2} \left(\frac{N}{N+1}\right) \tag{3.8}$$

Where  $i_{D,3}$ ,  $i_{D,4}$ ,  $i_{D,5}$  and  $i_{D,6}$  are the currents through transistors  $M_{LV3}$ ,  $M_{LV4}$ ,  $M_{LV5}$  and  $M_{LV6}$ , respectively. The Output in the form of differential voltage can be either  $V_{OH}$  or  $V_{OL}$ , depending for various input combination when applied to D-latch proposed in [14], which are enlisted in Table 3.1.

| State<br>Q | M <sub>LV3</sub>      |                                                                                          |                                                                                                             |                                                       |                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                         |

|------------|-----------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q          | $M_{1V2}$             |                                                                                          |                                                                                                             |                                                       |                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                         |

|            | 1 4 3                 | M <sub>LV4</sub>                                                                         | M <sub>LV5</sub>                                                                                            | M <sub>LV6</sub>                                      | M <sub>LV7</sub>                                                                                                                                                                            | M <sub>LV8</sub>                                                                                                                                                                                                                                                                                                                                                                                                            | $V_Q - \overline{V_Q}$                                                                                                                                                                                                                                                                                                  |

| L          | I <sub>3</sub>        | 0                                                                                        | $I_1$                                                                                                       | 0                                                     | I <sub>2</sub>                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>OL1</sub>                                                                                                                                                                                                                                                                                                        |

| н          | I <sub>3</sub>        | 0                                                                                        | 0                                                                                                           | $I_1$                                                 | $I_2$                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>OH2</sub>                                                                                                                                                                                                                                                                                                        |

| L          | 0                     | $I_3$                                                                                    | $I_1$                                                                                                       | 0                                                     | $I_2$                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>OL2</sub>                                                                                                                                                                                                                                                                                                        |

| Н          | 0                     | I <sub>3</sub>                                                                           | 0                                                                                                           | $I_1$                                                 | $I_2$                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>OH1</sub>                                                                                                                                                                                                                                                                                                        |

| L          | $I_1$                 | 0                                                                                        | $I_3$                                                                                                       | 0                                                     | 0                                                                                                                                                                                           | $I_2$                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>OL2</sub>                                                                                                                                                                                                                                                                                                        |

| Н          | $I_1$                 | 0                                                                                        | 0                                                                                                           | I <sub>3</sub>                                        | 0                                                                                                                                                                                           | $I_2$                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>OL2</sub>                                                                                                                                                                                                                                                                                                        |

| L          | 0                     | $I_1$                                                                                    | $I_3$                                                                                                       | 0                                                     | 0                                                                                                                                                                                           | $I_2$                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>OH2</sub>                                                                                                                                                                                                                                                                                                        |

| Н          | 0                     | $I_1$                                                                                    | 0                                                                                                           | $I_3$                                                 | 0                                                                                                                                                                                           | I <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>OH1</sub>                                                                                                                                                                                                                                                                                                        |

|            | H<br>L<br>H<br>L<br>H | $\begin{array}{ccc} H & & 0 \\ L & & I_1 \\ H & & I_1 \\ L & & 0 \\ H & & 0 \end{array}$ | $\begin{array}{c cccc} H & 0 & I_3 \\ L & I_1 & 0 \\ H & I_1 & 0 \\ L & 0 & I_1 \\ H & 0 & I_1 \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | H       0 $I_3$ 0 $I_1$ L $I_1$ 0 $I_3$ 0         H $I_1$ 0 $I_3$ 0         H $I_1$ 0       0 $I_3$ L       0 $I_1$ $I_3$ 0         H       0 $I_1$ $I_3$ 0         H       0 $I_1$ 0 $I_3$ | H       0       I_3       0       I_1       I_2         L       I_1       0       I_3       0       0         H       I_1       0       0       I_3       0       0 | H       0       I_3       0       I_1       I_2       0         L       I_1       0       I_3       0       0       I_2         H       I_1       0       0       I_3       0       I_2         H       I_1       0       0       I_3       0       I_2         L       0       I_1       I_3       0       0       I_2 |

**Table 3.1** Output in the form of differential voltage for various input combination when applied to triple-tail based MCML D-latch

Here  $I_1 = \frac{I_{SS}}{2}$ ,  $I_2 = \frac{I_{SS}}{2} \frac{N}{N+1}$  and  $I_3 = \frac{I_{SS}}{2} \frac{1}{N+1}$ .

(a) Voltage Swing:

Hence, from table 3.1 one voltage swing of the circuit, when input and output are same, can be expressed as

$$V_{SWING1} = V_{OH1} - V_{OL1} = R_P \left( 1 + \frac{1}{N+1} \right)$$

(3.9a)

Where  $V_{OH1}$  and  $V_{OL1}$ , for same input and output, are the maximum and minimum output voltage respectively. For different input and output, other voltage swing of the circuit can be calculated as

$$V_{SWING2} = V_{OH2} - V_{OL2} = R_P \left(\frac{N}{N+1}\right)$$

(3.9b)

Where  $V_{OH2}$  and  $V_{OL2}$ , for same input and output, are the maximum and minimum output voltage respectively.

As it can be seen that  $V_{SWING2} < V_{SWING1}$ , considering the pessimism here, we can consider the swing of the latch as  $V_{SWING2}$  i.e.

$$V_{SWING} = R_P\left(\frac{N}{N+1}\right)$$

(3.9c)

Table 3.2Voltage swing of triple-tail MCML based D-Latch

| $I_{SS}(\mu A)$ | Voltage Swing (in mV) | Error(in %) |

|-----------------|-----------------------|-------------|

| 20              | 380.25                | 4.93        |

| 50              | 390.12                | 2.47        |

| 80              | 387.24                | 3.15        |

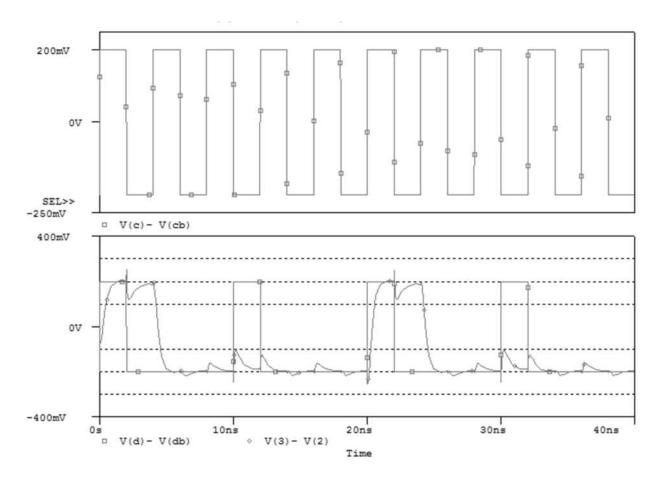

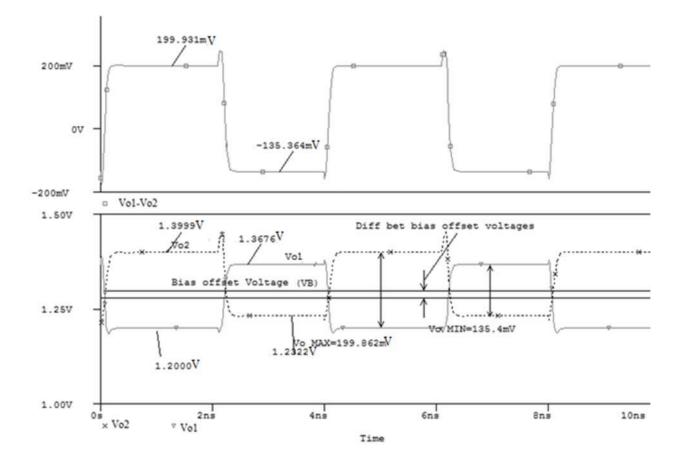

For 400mV voltage swing,  $50\mu$ A bias current, N=5, 400mC voltage swing and 4 voltage gain, transient analysis of triple-tail MCML based D-latch is shown in Fig. 3.2, where when clock is 1, data is transferred at output and when clock is 0, previous output is maintained as current output of the latch, with the total simulated voltage swing came out to be 390.124mV with error of 2.47% between the predicted and simulated results.

Fig. 3.2 Output and voltage swing of triple-tail MCML based D-latch

### (b) Voltage-Gain:

The small-signal voltage gain  $(A_v)$  and noise margin (NM) for the triple-tail MCML D-latch are computed as

$$A_{v} = g_{m,n} R_{P} = \frac{N+1}{N} \frac{V_{SWING}}{2} \sqrt{2\mu_{eff,n} C_{OX} \frac{W_{N}}{L_{N}} \cdot \frac{1}{I_{SS}}}$$

(3.10)

$$NM = \frac{V_{SWING}}{2} \left[ 1 - \frac{\sqrt{2}}{A_v} \right]$$

(3.11)

Where  $\mu_{eff,n}, g_{m,n}, W_N$  and  $L_N$  are the effective electron mobility, the transconductance, the effective channel width and length of transistors  $M_{LV4,4,5,6}$  respectively.

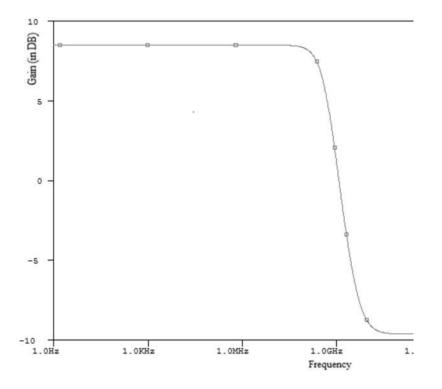

triple-tail MCML based D-latch has been simulated for  $50\mu$ A bias current, N=5, 400mV voltage swing and gain 4, AC analysis of which is shown in Fig. 3.3. It can be seen that there is a close relation between simulated and predicted voltage gain .

Fig. 3.3 AC analysis of triple-tail MCML D-Latch

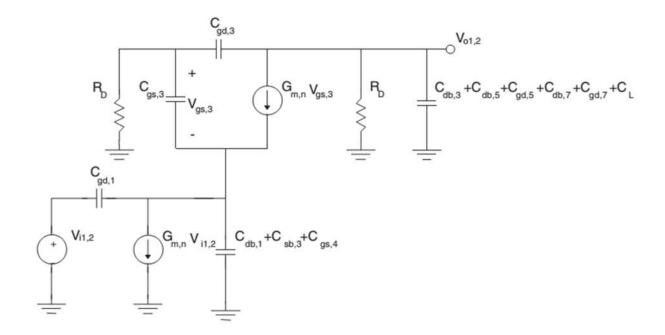

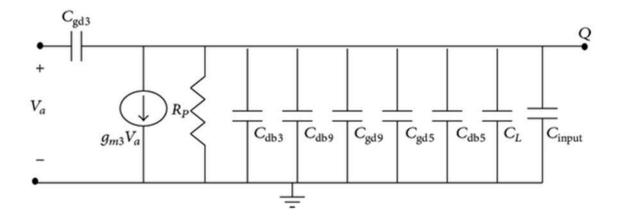

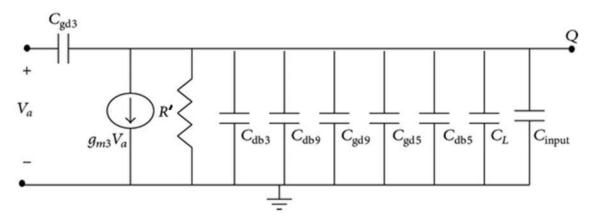

#### 3.1.2 Delay Model

In case of a low-to-high transition on CLK input that causes switching at the by activating (deactivating) the transistor pair  $M_{LV4} - M_{LV4} (M_{LV5} - M_{LV6})$ , and hence, the circuit reduces to a simple MCML inverter. The equivalent linear half circuit is shown in Fig. 3.4 where  $C_{gdi}$  and  $C_{dbi}$  represents the gate–drain capacitance and the drain–bulk junction capacitance of the ith

transistor. For NMOS transistors operating in saturation region,  $C_{gd}$  is equal to the overlap capacitance  $C_{gdo}W_n$  between the gate and the drain [6].  $C_{input}$  is the input capacitance of the source-coupled pair ( $M_{LV5} - M_{LV6}$ ). For the PMOS transistor operating in linear region,  $C_{gd}$  is evaluated as the sum of the overlap capacitance and the intrinsic contribution associated with its channel charge [6].

The delay of the triple-tail based MCML D-latch can be expressed as