A Dissertation work on

# DESIGN OF ANALOG GILBERT CELL MULTIPLIER USING CMOS TECHNOLOGY

Submitted in partial fulfillment of the requirement

for the award of the degree of

# **MASTER of ENGINEERING**

# (Electronics & Communication Engineering)

Submitted

by

# JAGDISH PRASAD

College Roll No: 11/ME/ECE/2K9

University Roll No: 13821

Under the supervision and guidance of:

Mr. Ajai Gautam Assistant Prof.

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

# DELHI COLLEGE OF ENGINEERING

UNIVERSITY OF DELHI

2009-2011

# **DEDICATION**

I would like to dedicate my work to my Father, Sh. Dharamvir Singh and my family members. I believe that I have made it possible merely due to the prayers and great moral support from my parents throughout my studies. Specially, my Father has been a source of great inspiration throughout this course work. My parents and family members have been always around to cheer me up and were always willing to partake in my sporadic study breaks.

As it is well said 'In every conceivable manner, the family is link to our past, bridge to our future.'

## **CERTIFICATE**

This is to certify that the work contained in this dissertation entitled "**Design of Analog Gilbert Cell Multiplier Using CMOS Technology**" submitted by Jagdish Prasad (11/E&C/09) of Delhi College of Engineering in partial fulfilment of the requirement for the degree of Master of Engineering in Electronics & Communication is a bonafide work carried out under my guidance and supervision in the academic year 2009-11.

The work embodied in this dissertation has not been submitted for the award of any other degree to the best of my knowledge.

Guided by:

# Mr. Ajai Gautam

**Assistant Professor**

Dept. of Electronics & Communication Delhi College of Engineering, Delhi.

## **ACKNOWLEDGEMENTS**

I feel very pleasant to extend my heartiest felt gratitude to everyone who helped me throughout the course of this project.

Firstly, I would like to express my sincere gratitude to my learned supervisor **Ajai Gautam** for giving me an opportunity to be one of his student. His skilfulness, academic guidance, technical insight and supervision as well as his pleasant personality are the main factors that empowered and encouraged this work. Without his continuous inspiration, it would not be possible to complete this dissertation.

I express my deep sense of gratitude and thanks to my Head of the department **Prof. Rajiv Kapoor** for his invaluable guidance, encouragement and enduring appraisals. He kept on boosting me time to time.

I would also like to extent my gratefulness to **Dr. Neeta Panday, Associate Professor** for her continuous guidance in understanding the basics and technical skills required throughout this work.

I would also like to take this opportunity to present my sincere regards to all the faculty members of the Department for their support and encouragement. I am also thankful to my classmates for their thorough support and motivation during this work.

#### JAGDISH PRASAD

M.E. (ECE) College Roll No. 11/E&C/09 University Roll No.: 13821 Electronics & Communication Engineering Delhi College of Engineering, Delhi-42

# Contents

| A        | cknov           | wledgments                                         | vi        |

|----------|-----------------|----------------------------------------------------|-----------|

| Li       | st of           | Tables                                             | ix        |

| Li       | st of           | Figures                                            | xi        |

| 1        | $\mathbf{Intr}$ | oduction                                           | 1         |

|          | 1.1             | Contributions                                      | 4         |

| <b>2</b> | Bac             | kground: The Bipolar Gilbert Cell Multiplier       | 5         |

|          | 2.1             | Introduction                                       | 5         |

|          | 2.2             | Bipolar Differential Pair                          | 7         |

|          | 2.3             | Bipolar Current-mode Amplifier                     | 8         |

|          | 2.4             | Bipolar Gilbert Cell Multiplier                    | 11        |

| 3        | The             | e CMOS Gilbert Cell Multiplier in Strong Inversion | <b>14</b> |

|          | 3.1             | Introduction                                       | 14        |

|          | 3.2             | CMOS Differential Pair                             | 14        |

|          | 3.3             | CMOS Current-mode Amplifier                        | 17        |

|          | 3.4             | CMOS Gilbert Cell Multiplier                       | 19        |

|          | 3.5             | Higher Order Effects                               | 22        |

| 4        | The             | e CMOS Gilbert Cell Multiplier in Subthreshold     | <b>24</b> |

|          | 4.1             | Introduction                                       | 24        |

|          | 4.2             | Subthreshold Biasing                               | 25        |

|          | 4.3             | The Inversion Coefficient                          | 29        |

|                                                             | 4.4                    | Highe                             | r Order Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29 |

|-------------------------------------------------------------|------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                             |                        | 4.4.1                             | $V_{ds}$ Term $\hfill \ldots \hfill \hfill \ldots \hfill \hfill$ | 30 |

|                                                             |                        | 4.4.2                             | Ideality Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31 |

|                                                             |                        | 4.4.3                             | Threshold Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36 |

|                                                             |                        | 4.4.4                             | Ideality Factor versus Threshold Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

|                                                             | 4.5                    | Biasin                            | g and Higher Order Effects on the Gilbert Cell Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39 |

|                                                             |                        | 4.5.1                             | The $V_{\rm ds}$ Term versus the Diode-connected Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40 |

|                                                             |                        | 4.5.2                             | Ideality Factor Mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42 |

|                                                             |                        | 4.5.3                             | Threshold Voltage Mismatch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45 |

|                                                             |                        | 4.5.4                             | Charging Parasitic Capacitances with Small Device Currents .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 48 |

| 5                                                           | $\mathbf{C}\mathbf{M}$ | os w                              | eak and Moderate Inversion Gilbert Cell Multiplier Cir-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|                                                             | cuit                   | s                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50 |

|                                                             | 5.1                    | Introd                            | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50 |

| <ul> <li>5.2 Deep Subthreshold Multiplier Circuit</li></ul> |                        | Subthreshold Multiplier Circuit   | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|                                                             |                        | w Subthreshold Multiplier Circuit | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|                                                             | 5.4                    | Super                             | threshold Multiplier Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58 |

| 6                                                           | Tes                    | t Resu                            | $\mathbf{lts}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65 |

| 7                                                           | Cor                    | nclusio                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72 |

|                                                             | 7.1                    | Sugge                             | stions for Further Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74 |

|                                                             |                        |                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

# List of Tables

| 4.1 | Subthreshold current range                                                       | 26 |

|-----|----------------------------------------------------------------------------------|----|

| 4.2 | Empirical versus simulated exponential current range                             | 28 |

| 4.3 | Inversion regions versus inversion coefficient (IC).                             | 29 |

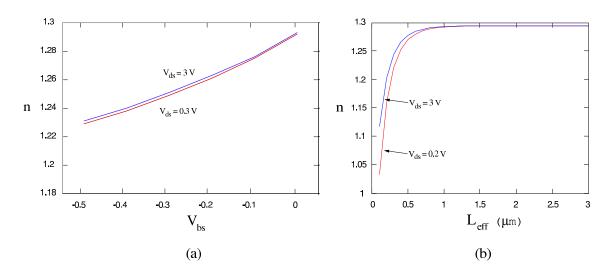

| 4.4 | $ \mathrm{V}_{bs} ,L_{eff},n$ relationship to $I_{ds}$                           | 35 |

| 4.5 | $ V_{\text{bs}} ,L_{\text{eff}},\text{and}V_{t}$ relationship to $I_{\text{ds}}$ | 38 |

| 4.6 | $ V_{\rm bs} ,L_{\rm eff},n,andV_{\rm t}$ relationship to $I_{\rm ds}$           | 39 |

| 4.7 | $\mathrm{V}_{bs},$ Leff, and n effects on slope distortion $\hdots$              | 45 |

| 5.1 | Deep subthreshold circuit, DC output nonlinearity.                               | 53 |

| 5.2 | Shallow subthreshold circuit, DC output nonlinearity                             | 57 |

| 5.3 | Superthreshold circuit, DC output nonlinearity.                                  | 63 |

| 6.1 | Final Results: % NL error at full scale opposite input                           | 70 |

| 7.1 | CMOS multiplier performance.                                                     | 73 |

# List of Figures

| 2.1  | Gilbert cell architecture block diagram                                   | 5  |

|------|---------------------------------------------------------------------------|----|

| 2.2  | Bipolar differential pair.                                                | 7  |

| 2.3  | Bipolar differential pair transfer characteristics.                       | 8  |

| 2.4  | Bipolar current-mode amplifier.                                           | 9  |

| 2.5  | Bipolar current-mode amplifier, linear transfer characteristics. $\ldots$ | 10 |

| 2.6  | Bipolar Gilbert cell multiplier                                           | 11 |

| 2.7  | Bipolar Gilbert cell multiplier linear transfer characteristics           | 12 |

| 3.1  | CMOS differential pair                                                    | 15 |

| 3.2  | CMOS differential pair transfer characteristics                           | 16 |

| 3.3  | CMOS current-mode amplifier.                                              | 17 |

| 3.4  | CMOS current-mode amplifier, linear transfer characteristics              | 19 |

| 3.5  | CMOS Gilbert cell multiplier                                              | 20 |

| 3.6  | Linear and nonlinear drain current characteristics                        | 21 |

| 3.7  | CMOS Gilbert cell multiplier transfer characteristic                      | 22 |

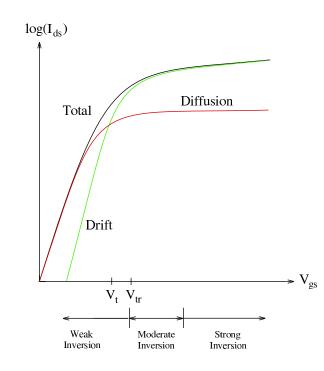

| 4.1  | Diffusion and drift components of the total device current. $\ldots$ .    | 25 |

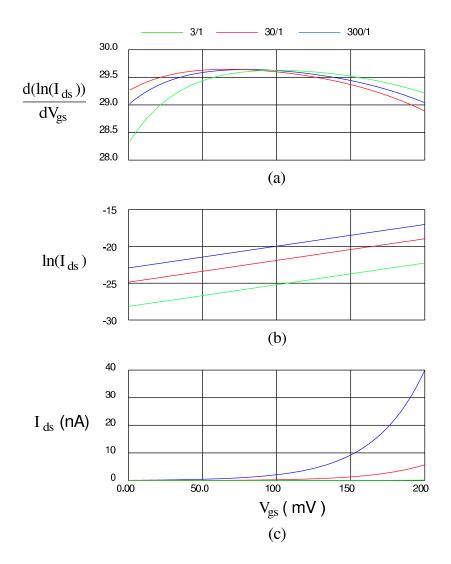

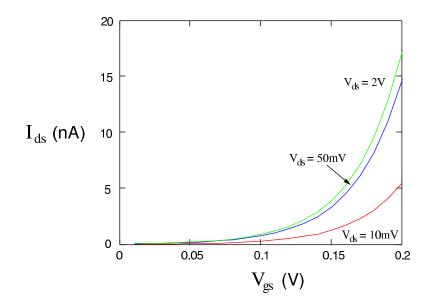

| 4.2  | $I_{exp}$ range                                                           | 27 |

| 4.3  | $\mathrm{V}_{ds}$ term effect on $\mathrm{I}_{ds}.$                       | 30 |

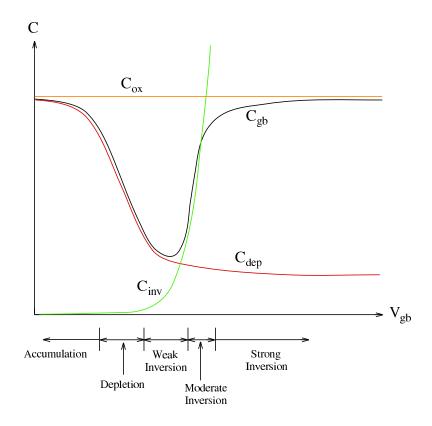

| 4.4  | Capacitive divider.                                                       | 31 |

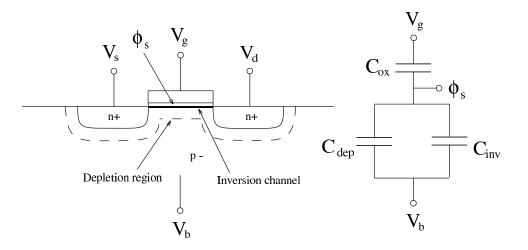

| 4.5  | MOSFET coupling capacitances.                                             | 32 |

| 4.6  | Ideality factor, n, versus $V_{bs}$ , $V_{ds}$ , and $L_{eff}$            | 34 |

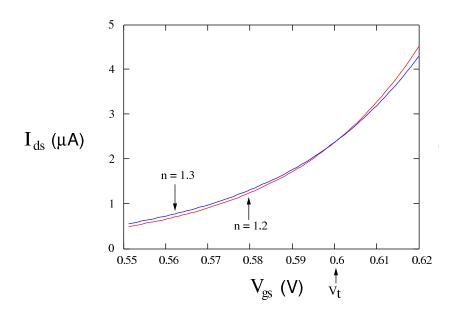

| 4.7  | n versus $I_{ds}$ around $V_{gs}=V_t.\ \ldots$                            | 35 |

| 4.8  | n versus $I_{ds}.$                                                        | 36 |

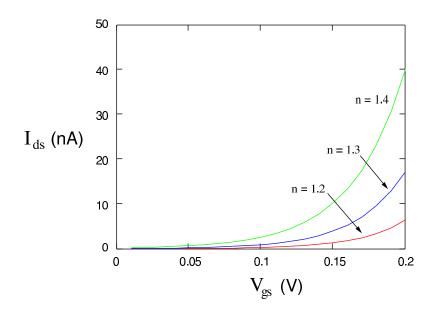

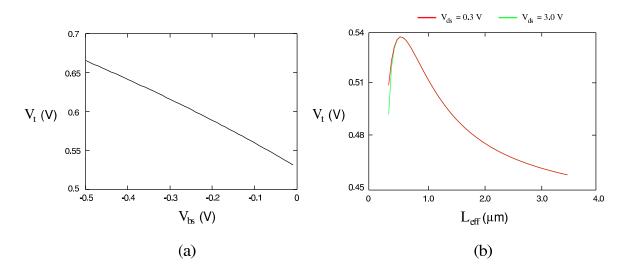

| 4.9  | $V_t,$ versus $V_{bs}$ and $L_{eff}.$                                     | 37 |

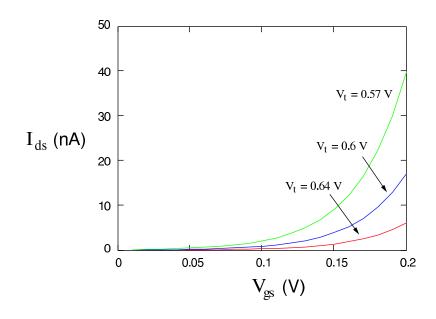

| 4.10 | $V_{\rm t}$ versus $I_{\rm ds}.$                                          | 38 |

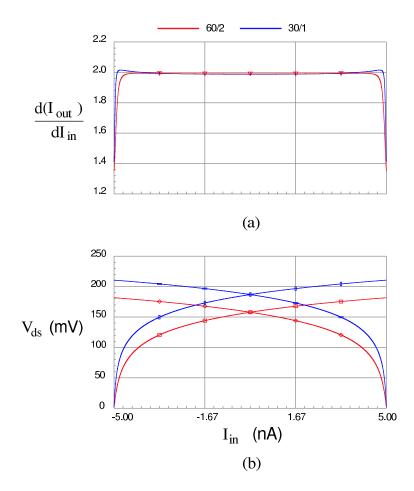

| 4.11 | Effects of the $V_{\rm ds}$ term on linearity                                                          | 41 |

|------|--------------------------------------------------------------------------------------------------------|----|

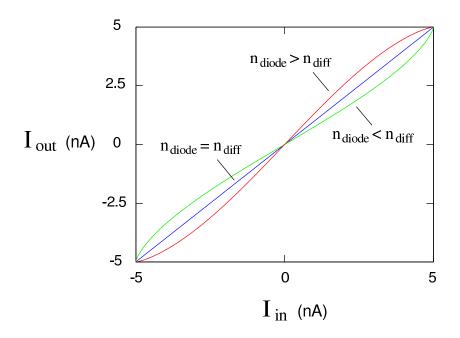

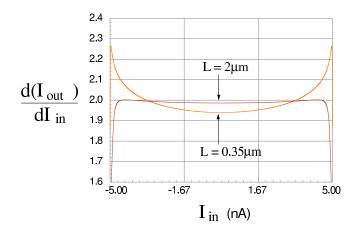

| 4.12 | Effects of n on $I_{out}.$                                                                             | 44 |

| 4.13 | Effects of $n$ on the slope of $I_{out}.$                                                              | 44 |

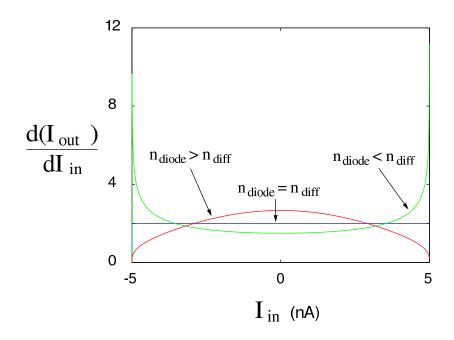

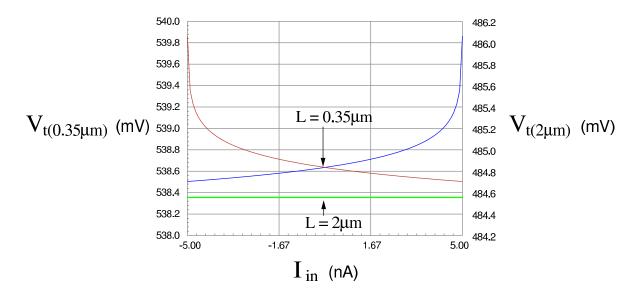

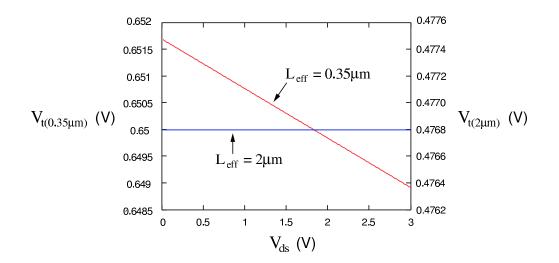

| 4.14 | Simulated V <sub>t</sub> values for L = 0.35 $\mu$ m and 2 $\mu$ m.                                    | 46 |

| 4.15 | Inverse relationship between V <sub>t</sub> and V <sub>ds</sub> for Leff = 0.35 $\mu$ m and 2 $\mu$ m. | 46 |

| 4.16 | Slope of $I_{out}$ for $L = 0.35 \mu m$ and $2 \mu m$                                                  | 47 |

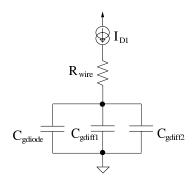

| 4.17 | RC circuit from gate capacitors                                                                        | 48 |

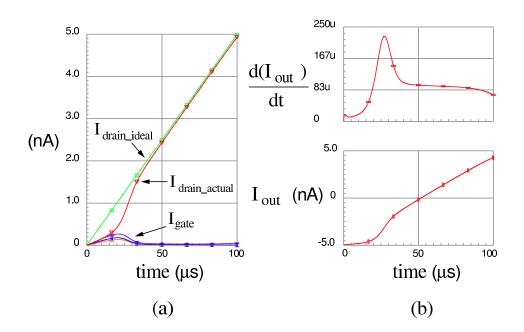

| 4.18 | Charging gate capacitor effects on linearity                                                           | 49 |

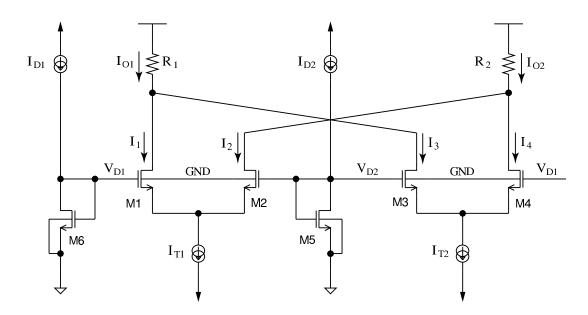

| 5.1  | PMOS Gilbert cell multiplier circuit.                                                                  | 51 |

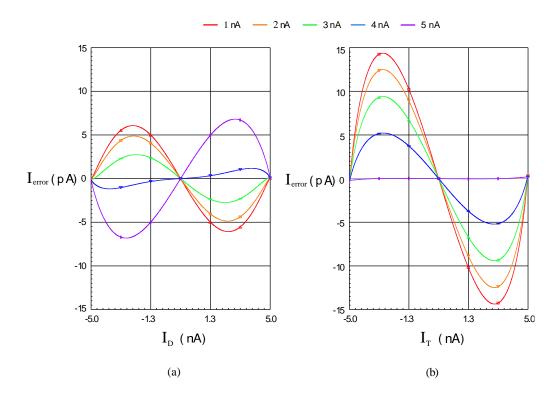

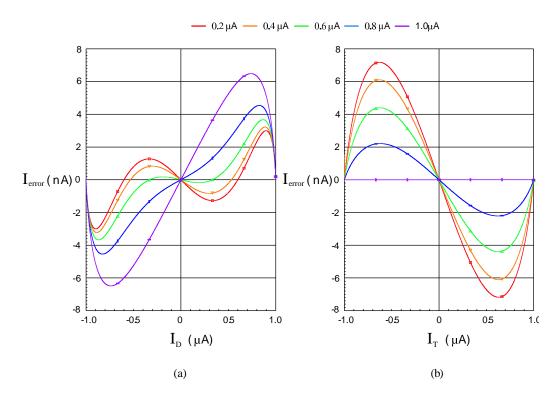

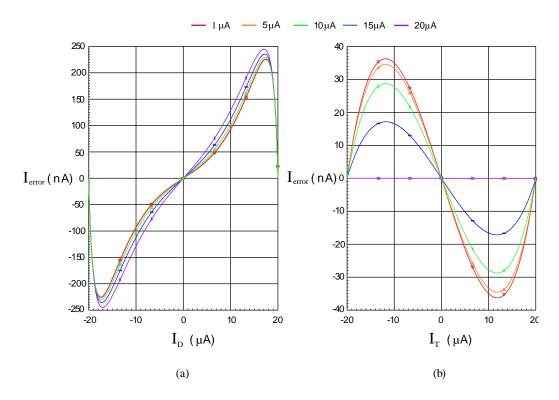

| 5.2  | Deep subthreshold DC linearity: $\mathrm{NL}_{\mathrm{error}}$ across input ranges                     | 52 |

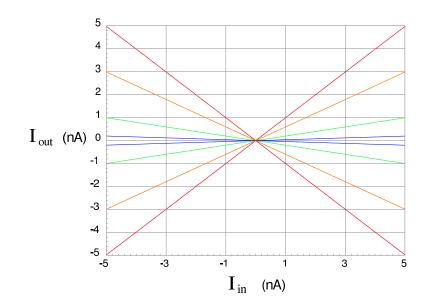

| 5.3  | $I_{out}$ DC linearity across full range of input currents                                             | 54 |

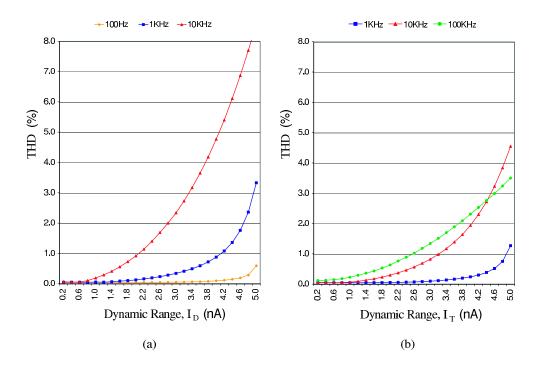

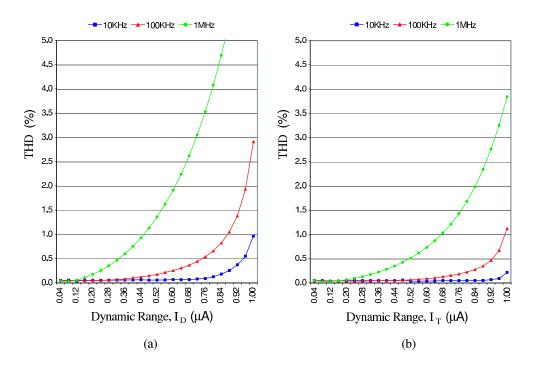

| 5.4  | THD for deep subthreshold circuit with distortion removed. $\ldots$ .                                  | 55 |

| 5.5  | Shallow subthreshold DC linearity: $\mathrm{NL}_{\mathrm{error}}$ across input ranges                  | 56 |

| 5.6  | THD for shallow subthreshold circuit                                                                   | 58 |

| 5.7  | NMOS Gilbert cell multiplier circuit.                                                                  | 59 |

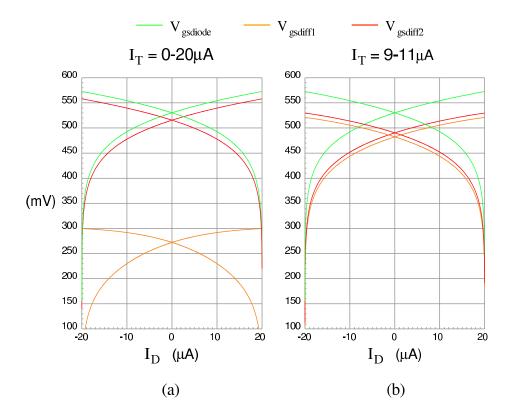

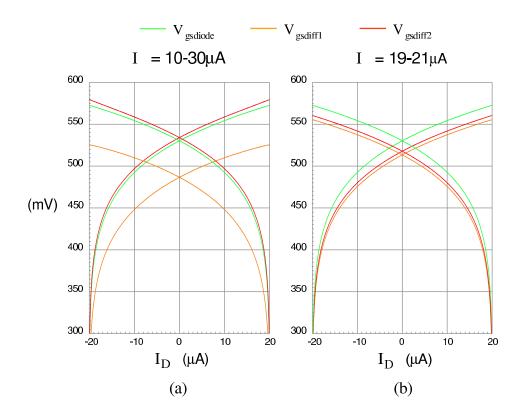

| 5.8  | $V_{\rm GS}$ Bias mismatch with no offset                                                              | 60 |

| 5.9  | $V_{GS}$ Bias mismatch with offset                                                                     | 61 |

| 5.10 | Superthreshold DC linearity: $\mathrm{NL}_{\mathrm{error}}$ across input ranges                        | 62 |

| 5.11 | THD for "Superthreshold" WI circuit.                                                                   | 63 |

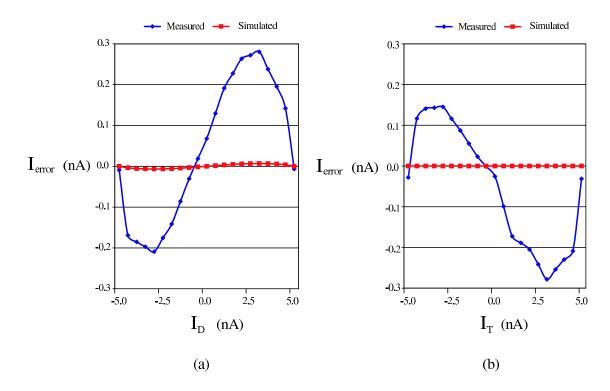

| 6.1  | Test results: Deep subthreshold DC linearity                                                           | 66 |

| 6.2  | Test results: Shallow subthreshold DC linearity                                                        | 67 |

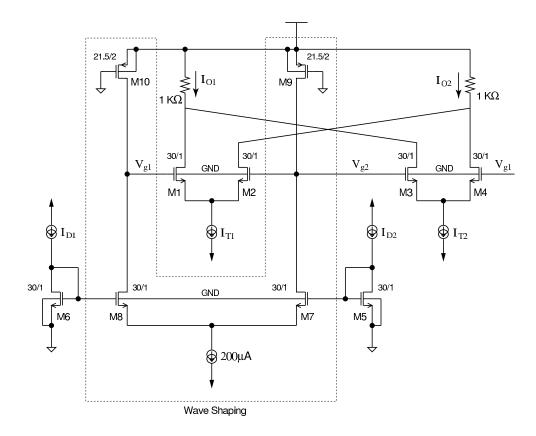

| 6.3  | "Wave-shaping" superthreshold circuit                                                                  | 68 |

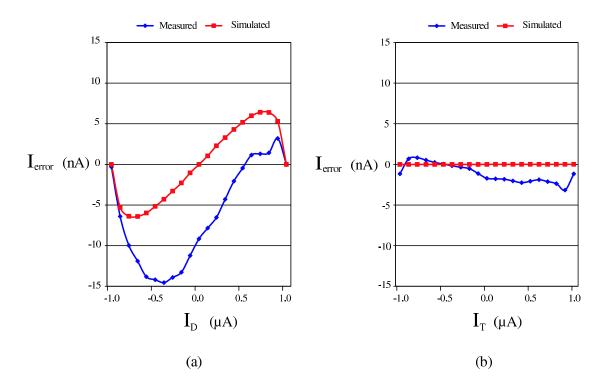

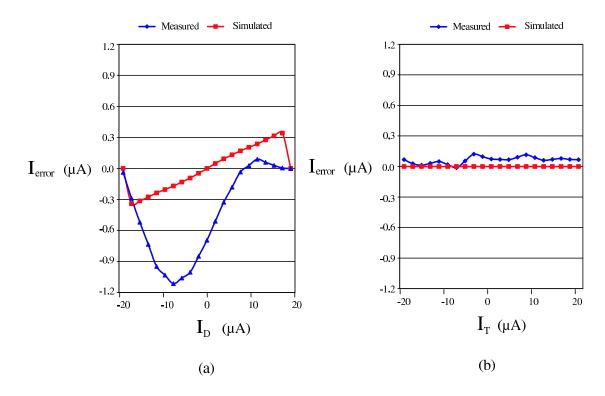

| 6.4  | Test results: Superthreshold DC linearity.                                                             | 69 |

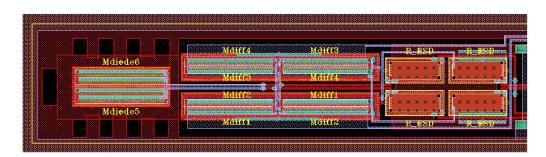

| 6.5  | Shallow subthreshold circuit physical layout                                                           | 71 |

# Chapter 1 Introduction

Analog multiplier is one of the fundamental building blocks in analog circuit design. Particularly the multiplier is important in communication and signal processing circuits where they are commonly used for modulation, mixing, phase detection, and adaptive filtering. Advancements in biomedical devices and increasing portability of signal measurement equipment, low power multipliers for portable battery power applications are also becoming increasingly important. For cost effectiveness, low power multiplier solutions are needed. In bipolar technology, most multiplier architectures were originally developed where signal distortion can be kept low across a wide range of frequencies [2]. As digital design has advanced, the ability to build analog and digital circuits with a single technology has become increasingly important. Development of CMOS multiplier architectures has evolved to meet mixed signal and low power needs. Due to its low processing cost and low power consumption CMOS technology is better suited for digital circuits than bipolar technology. However, reaching the level of nonlinear error that bipolar multipliers can achieve is difficult in CMOS technology.

The variable transconductance Gilbert cell multiplier architecture [2], which is the most common bipolar multiplier architecture, allows for linear operation due to the exponential **I**-**V** relationship of the BJT. Most CMOS multiplier architectures are biased in the active region of strong inversion, where the MOSFET **I**-**V** relationship is a square-law relationship. Due to the different **I**-**V** relationship between bipolar and CMOS,

1

traditional architectures used for bipolar multipliers cannot easily be implemented in CMOS.

Although difficult to build, limited and in their performance, many CMOS square-law multipliers have been built based on the bipolar Gilbert cell architecture [18]- [20]. To do this, various linearization techniques are used to compensate for the square-law nonlinearities. Other square-law CMOS architectures [21], multiplier use floating gates signal [17] of attenuation [18]. and other forms variable transconductance [12] [22], to achieve linearity. There are also CMOS architectures that implement bipolar characteristics, using lateral bipolar transistors [23], or the subthreshold region [24]. All of these architectures deviate from the traditional Gilbert cell architecture in implementation to achieve linear operation. This thesis will present CMOS multiplier architectures that more closely match the traditional bipolar Gilbert cell architecture. By doing so, some of the benefits of this architecture, such as low nonlinear error and higher bandwidths, can be taken advantage of. To evaluate analog multipliers it is important to understand some fundamental concepts. The function of a multiplier is just as its name implies, it multiplies two signals together. Ideal multipliers satisfy the fundamental multiplication expression.

$$\mathbf{Z} = (\mathbf{A}_0) \mathbf{X} \mathbf{Y}, \tag{1.1}$$

where output Z is the product of input signals X and Y, and  $A_0$ , the multiplier gain constant.

A key multiplier specification is linearity. The level of nonlinearity that is allowed is dependent on the multiplier application. An example of this is in audio communications,

where signal distortion introduced by the multiplier is very undesirable. Another application where linearity is important is in precision signal measurement equipment. A standard of less than 1 % nonlinear error is set for most bipolar analog multipliers [2].

Linearity is typically quantified by measuring the nonlinear error of the transfer function at unity gain. The % nonlinear error is defined by [12]

$$\% NLerror = \frac{Z-X}{Z_{FS}}.100$$

(1.2)

Referring to Equation (1.1), to measure the linearity on input X, input Y and the gain constant Ao, are set such that their product is equal to one (Ao·Y = 1). Then the difference between output Z and input X is taken across the full input range of X. This defines the nonlinear error, Z - X, which is the numerator of Equation 1.2. The % nonlinear error is then determined by dividing the nonlinear error by ZFS, which is the full scale output range when the multiplier is set at unity gain. This method of measuring linearity quantifies the output signal deviation from the ideal linear output signal characteristic when an input is swept across its full range. The same method is used to measure the multiplier linearity with regards to the Y input, where Ao·X = 1, and Y is swept and compared to Z.

Other key multiplier parameters are total harmonic distortion (THD), dynamic input range, bandwidth, DC offset and noise immunity. As with nonlinear error, the importance of each of these specifications depends on the application. All of these parameters, with exception of noise immunity, will be considered in this thesis.

Most multipliers can be classified as single-quadrant, twoquadrant, or fourquadrant

multipliers, depending on the possible polarities of the input signals. Single quadrant multipliers only allow positive input signals. Twoquadrant multipliers allow one signal to swing both positive and

3

negative. In four-quadrant multipliers, both input signals can be negative or positive.

The bipolar Gilbert cell multiplier architecture referred to above is also referred to as a "translinear" multiplier [5]. It is a fully differential fourquadrant current multiplier. Multiplying currents rather than voltages can offer better bandwidth performance, lower power operation and better noise immunity.

CMOS versions of the four-quadrant Gilbert cell multiplier is presented in this thesis.With a focus fully differential current-mode multipliers will be developed on linearity. High frequency operation (compared to other CMOS multiplier architecture) will also be addressed. All data is collected from Matlab, Mathcad and Cadence Spectre Spice simulations of circuits built in an AMIS *O.35-J.Im* process, with the exception of data presented in test results chapter (Chapter 6), where results from silicon are presented.

## **1.1 Contributions**

Contributions of this thesis are as follows:

• Developed design methods for multiplier circuits biased in weak and moderate inversion.

• Fabricated and tested three CMOS multiplier circuits biased in weak and moderate inversion. The correlation between simulation and silicon is shown.

• Developed a highly linear, low power CMOS multiplier circuit.

• Developed an analysis method to identify the contributions of distortion from ideality factor mismatch in a CMOS weak inversion Gilbert cell multiplier.

• Proposed distortion cancellation methods to improve CMOS Gilbert cell multiplier linearity in weak and moderate inversion.

4

## Chapter 2

## Background: The Bipolar Gilbert Cell Multiplier

#### 2.1 Introduction

The bipolar Gilbert cell was introduced by Barrie Gilbert in 1968. He started by developing a wide-band amplifier which consisted of a differential pair with diode connected I-V converters connected to each base terminal [1]. This wide-band amplifier configuration has a very linear transfer characteristic. The amplifier was then implemented into a four-quadrant multiplier configuration [2].

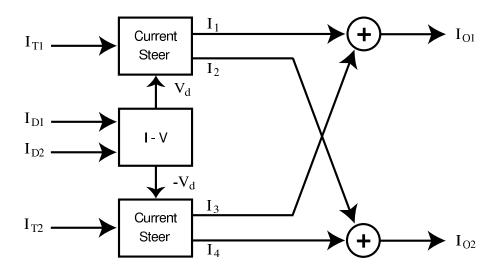

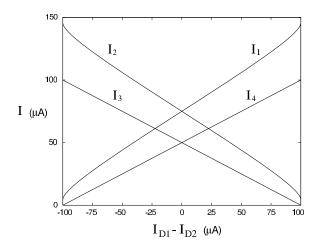

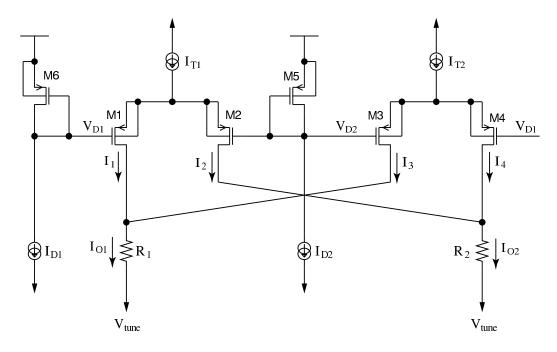

A block diagram of the Gilbert cell architecture is shown in Figure 2.1.  $I_{T1} - I_{T2}$ and  $I_{D1} - I_{D2}$  create the differential inputs,  $I_{Tin}$  and  $I_{Din}$ , respectively. These inputs are named with reference to their function,  $I_{T1}$  and  $I_{T2}$  being tail currents to differ-

Figure 2.1: Gilbert cell architecture block diagram.

entially coupled devices, and  $I_{D1}$  and  $I_{D2}$  being input currents to current-to-voltage converting diode connected devices. The diode input currents ( $I_{D1}$  and  $I_{D2}$ ) are first converted to voltages  $V_{D1}$  and  $V_{D2}$ . The difference of these voltages,  $V_d$ , is then applied to current steering devices, differentially controlling how tail input currents,  $I_{T1}$ and  $I_{T2}$ , are being split between currents  $I_1$  and  $I_2$ , and  $I_3$  and  $I_4$ , respectively. These currents are then cross-coupled and added. The output currents are  $I_{O1} = I_1 + I_3$ , and  $I_{O2} = I_2 + I_4$ . The final differential output current is then  $I_{out} = I_{O1} - I_{O2}$ .

If the full differential diode input current range is used at either positive or negative polarity, all of the tail currents will be steered to one output of each current steering block. This results in the full differential of the  $I_{Tin}$  input at the output, providing the maximum differential output current. Diode input currents that are smaller than the maximum will steer some of the tail current to the opposite output. Tail currents steered to the opposite output become common at the differential output puts and end up canceling when the final differential output current is taken. Thus, at  $[I_{Din}]_{min}$ , tail currents are divided equally, causing all current to be common at the output, and making  $I_{out} = 0$ .

An important point to note here is that the differential output current,  $I_{out}$ , can get no larger than the differential tail input current,  $I_{Tin}$ . This results in a maximum multiplier gain of unity. Based on this criterion, the gain constant,  $A_o$ , of the ideal multiplier expression (1.1) then becomes inverted maximum of one of the inputs, as shown in Equation (2.1),

$$Z = \left(\frac{1}{Y_{\text{max}}}\right) XY.$$

(2.1)

In the following sections, the design of the four-quadrant Gilbert cell multiplier will be evaluated by first analyzing the bipolar differential pair behavior. The effects of adding diode-connected devices to the inputs of the differential pair will then be evaluated. This configuration makes up a linear wide-band current amplifier, as discussed in [1]. Finally, two amplifiers will be combined into the multiplier configuration. This will result in a transfer characteristic that satisfies the ideal linear multiplier expression of Equation (2.1), where Z, X, and Y are differential signals.

#### 2.2 Bipolar Differential Pair

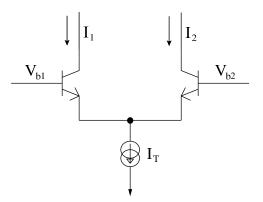

Figure 2.2: Bipolar differential pair.

To evaluate bipolar linear multiplication, the single differential pair of Figure 2.2 is first evaluated. The exponential I-V relationship applied to each transistor may be written

$$I_{c} = I_{S} e^{V_{be}/V_{T}}, \qquad (2.2)$$

where  $I_c$  is the collector current,  $I_S$  is the saturation current,  $V_T$  is the thermal voltage, and  $V_{be}$  is the base to emitter voltage. The differential relationship between the two transistors introduces the additional constraint

$$\mathbf{I}_1 + \mathbf{I}_2 = \alpha \mathbf{I}_{\mathrm{T}}.\tag{2.3}$$

Combining equations (2.2) and (2.3) gives [3]

$$I_1 = \frac{\alpha I_T}{1 + e^{(V_{b2} - V_{b1})/V_T}},$$

(2.4)

$$I_2 = \frac{\alpha I_T}{1 + e^{(V_{b1} - V_{b2})/V_T}}.$$

(2.5)

For the differential input voltage,  $V_d = V_{b1} - V_{b2}$ , the differential output current  $I_{out} = I_1 - I_2$  is

$$I_{out} = \alpha I_{T} \left( \frac{e^{V_{d}/V_{T}} - e^{-V_{d}/V_{T}}}{2 + e^{-V_{d}/V_{T}} + e^{V_{d}/V_{T}}} \right).$$

(2.6)

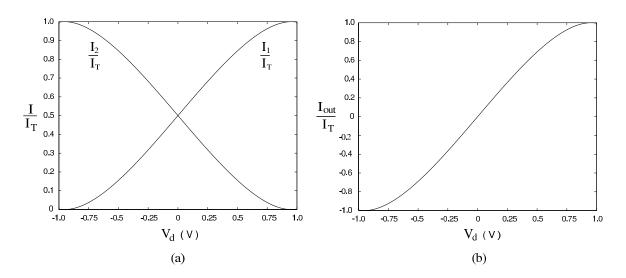

The transfer characteristics are shown in Figure 2.3. There is a small linear range around the middle of each characteristic that is typically used for linear amplification of small signals.

Figure 2.3: Bipolar differential pair transfer characteristics.

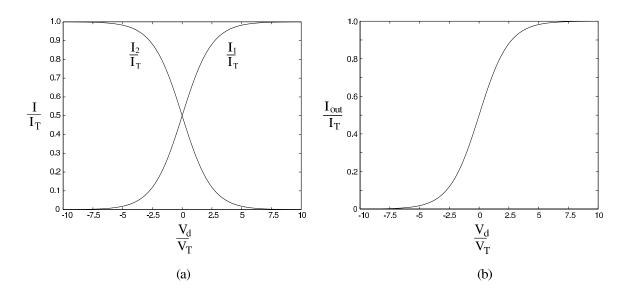

### 2.3 Bipolar Current-mode Amplifier

To increase the linear input range, diode connected devices can be added to the base terminals of the differential pair in the manner shown in Figure 2.4. If an input current is forced into the diode-connected devices, the input voltage from base to emitter becomes

$$V_{be} = V_{T} \ln \left(\frac{I_{D}}{I_{s}}\right).$$

(2.7)

The differential input voltage to the differential pair devices is now

$$V_{d} = V_{be1} - V_{be2} = V_{T} \left( \ln \left( \frac{I_{D1}}{I_{s}} \right) - \ln \left( \frac{I_{D2}}{I_{s}} \right) \right).$$

(2.8)

Figure 2.4: Bipolar current-mode amplifier.

Replacing  $V_{b1} - V_{b2}$  in equations (2.4) and (2.5) with  $V_d$  from Equation (2.8) and evaluating the exponential term, the logarithmic terms in  $V_d$  cancel the exponential terms,

$$e^{V_{d}/V_{T}} = e^{\frac{V_{T}[\ln(I_{D1}/I_{s}) - \ln(I_{D2}/I_{s})]}{V_{T}}} = \frac{e^{\ln(I_{D1}/I_{s})}}{e^{\ln(I_{D2}/I_{s})}} = \frac{I_{D1}}{I_{D2}}.$$

(2.9)

The collector currents then become

$$I_1 = \alpha I_T \left( \frac{I_{D2}}{I_{D1} + I_{D2}} \right),$$

(2.10)

$$I_2 = \alpha I_T \left( \frac{I_{D1}}{I_{D1} + I_{D2}} \right).$$

(2.11)

I<sub>out</sub> now becomes

$$I_{out} = \alpha I_{T} \left( \frac{I_{D2} - I_{D1}}{I_{D1} + I_{D2}} \right).$$

(2.12)

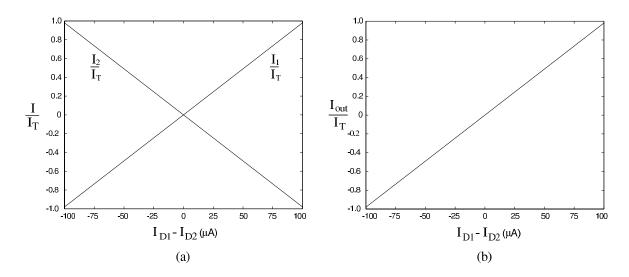

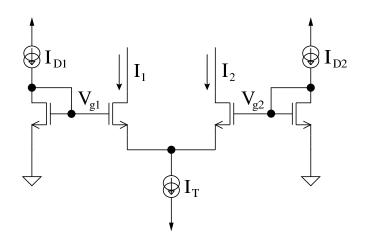

Plots of equations (2.10), (2.11), and (2.12) are shown in Figure 2.5.

Figure 2.5: Bipolar current-mode amplifier, linear transfer characteristics.

The amplifier input current is defined as the difference between  $I_{D1}$  and  $I_{D2}$ .  $I_{D1}$  and  $I_{D2}$  function differentially according to

$$\mathbf{I}_{\mathrm{D1}} = \mathbf{I}_{\mathrm{Q}} + \Delta \mathbf{I},\tag{2.13}$$

$$\mathbf{I}_{\mathrm{D2}} = \mathbf{I}_{\mathrm{Q}} - \Delta \mathbf{I},\tag{2.14}$$

where  $I_Q$  is a quiescent midpoint of the maximum input swing, and  $\Delta I$  is the deviation from that midpoint, having opposite polarity between  $I_{D1}$  and  $I_{D2}$ . For fully differential inputs,

$$\left[\frac{I_{D2} - I_{D1}}{I_{D1} + I_{D2}}\right]_{max} = 1.$$

(2.15)

Therefore, combining equations (2.12) and (2.15),

$$[I_{out}]_{max} = \alpha I_{T}.$$

(2.16)

It can be seen from the plots and equations that the linear input range has been increased to span the entire range of  $I_T$ . Due to the ratio in Equation (2.15), any differential input range can be used as long as all devices stay in the active region.

Figure 2.6: Bipolar Gilbert cell multiplier.

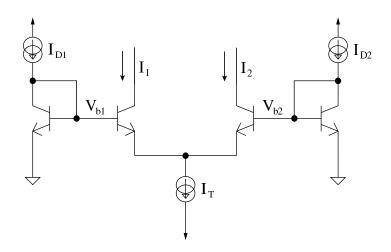

### 2.4 Bipolar Gilbert Cell Multiplier

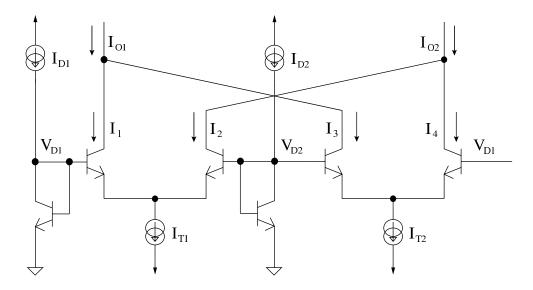

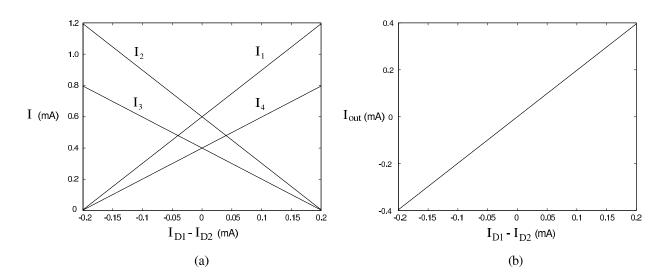

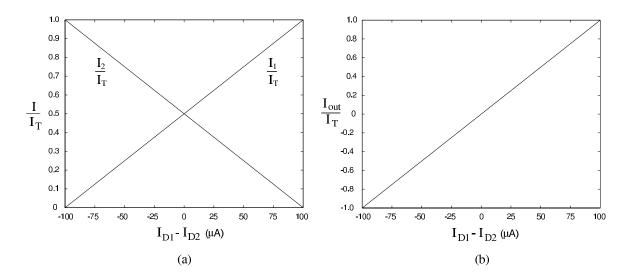

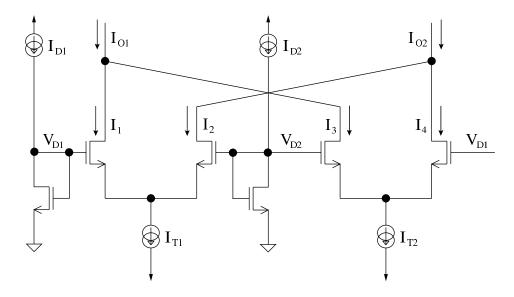

Combining two current-mode amplifiers as shown in Figure 2.6 creates the Gilbert cell current-mode multiplier. Comparing Figure 2.6 to the block diagram of Figure 2.1, each differential pair acts as a current steering device. Each diode-connected device acts as an I-V converter. Also, each device port matches the naming conventions at each block port in the block diagram.

The Gilbert cell collector currents can be defined as

$$I_1 = \frac{\alpha I_{T1}}{1 + e^{-V_d/V_T}},$$

(2.17)

$$I_2 = \frac{\alpha I_{\rm T1}}{1 + e^{V_{\rm d}/V_{\rm T}}},$$

(2.18)

$$I_3 = \frac{\alpha I_{T2}}{1 + e^{V_d/V_T}},$$

(2.19)

$$I_4 = \frac{\alpha I_{T2}}{1 + e^{-V_d/V_T}}.$$

(2.20)

Combining collector currents according to  $I_{O1} = I_1 + I_3$  and  $I_{O2} = I_2 + I_4$ , the differential output current,  $I_{out} = I_{O1} - I_{O2}$ , results in

$$I_{out} = \frac{\alpha (I_{T1} - I_{T2}) (e^{V_d/V_T} - e^{-V_d/V_T})}{2 + e^{-V_d/V_T} + e^{V_d/V_T}}.$$

(2.21)

Plugging  $V_d$  from (2.8) into (2.21) gives

$$I_{out} = \frac{\alpha (I_{T1} - I_{T2}) (I_{D2}/I_{D1} - I_{D1}/I_{D2})}{2 + I_{D2}/I_{D1} + I_{D1}/I_{D2}}.$$

(2.22)

Simplifying Equation (2.22) results in

$$I_{out} = \frac{\alpha}{(I_{D1} + I_{D2})} (I_{T1} - I_{T2}) (I_{D2} - I_{D1}).$$

(2.23)

Comparing Equation (2.23) to the ideal multiplier expression (2.1),  $I_{out} = Z$ ,  $I_{D2} - I_{D1} = X$ , and  $I_{T1} - I_{T2} = Y$ . Multiplying the common-base current gain,  $\alpha$ , to the right side, Equation (2.23) matches the ideal linear multiplier expression (2.1). This is only true with fully differential inputs.

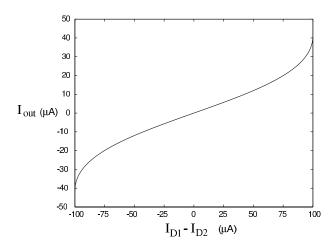

Figure 2.7: Bipolar Gilbert cell multiplier linear transfer characteristics.

Figure 2.7 shows the individual linear collector currents as well as the linear differential output current,  $I_{out}$ . Slightly different than the current-mode amplifier,

where the maximum output current is the whole range of  $I_T$ , the maximum multiplier output,  $I_{out}$ , is the maximum difference between tail currents,  $I_{T1} - I_{T2}$ . If Equation (2.23) is re-written as

$$I_{out} = \alpha (I_{T1} - I_{T2}) \frac{(I_{D2} - I_{D1})}{(I_{D1} + I_{D2})},$$

(2.24)

and for fully differential inputs,

$$\left[\frac{I_{D2} - I_{D1}}{I_{D1} + I_{D2}}\right]_{max} = 1,$$

(2.25)

combining equations (2.24) and (2.25) results in

$$[I_{out}]_{max} = \alpha [I_{T1} - I_{T2}]_{max}.$$

(2.26)

Regardless of input range used, the entire differential range of the tail current is utilized, maximizing input range. This ideal first order behavior neglects some higher order effects such as ohmic emitter resistance, finite beta, and device mismatch, which introduce some nonlinear effects. However, steps can be taken to minimize these effects [1][2].

### Chapter 3

## The CMOS Gilbert Cell Multiplier in Strong Inversion

#### 3.1 Introduction

The basic function of a CMOS Gilbert cell is the same as its bipolar equivalent. However, creating a linear CMOS multiplier is not nearly as straight forward due to the difference in bipolar and CMOS technologies. The fundamental I-V characteristic for a BJT is modeled by an exponential function. The fundamental I-V characteristic for a MOSFET is modeled by the square law. As will be shown in the following sections, this difference creates a significant challenge to linearizing the CMOS Gilbert cell. Simply adding a diode connected device to the gate terminals will not result in a linear Gilbert cell multiplier.

In the following sections, the CMOS Gilbert cell will be evaluated in the same manner as was done in Chapter 2, where the single differential pair is evaluated first, then the current-mode amplifier is presented, and finally the whole Gilbert cell is addressed. First order analysis will be used initially, then higher order effects of strong inversion will be considered.

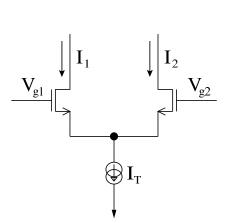

#### 3.2 CMOS Differential Pair

For a single MOSFET operating in the active region, the first order I-V characteristic behaves according to the square-law relationship

$$I_{d} = \frac{\mu C_{OX}}{2} \frac{W}{L} (V_{gs} - V_{t})^{2}, \qquad (3.1)$$

Figure 3.1: CMOS differential pair.

where  $I_d$  is the drain current,  $\mu$  is the mobility constant,  $C_{OX}$  is the oxide capacitance, W is the device channel width, L is the channel length,  $V_t$  is the threshold voltage, and  $V_{gs}$  is the gate to source voltage.

For a MOSFET differential pair, as shown in Figure 3.1, the devices share the tail current according to

$$I_1 + I_2 = I_T.$$

(3.2)

Combining equations (3.1) and (3.2), drain currents become

$$I_{1} = \frac{I_{T}}{2} + \sqrt{2KI_{T}} \left(\frac{V_{d}}{2}\right) \sqrt{1 - \frac{(V_{d}/2)^{2}}{(I_{T}/2K)}},$$

(3.3)

$$I_{2} = \frac{I_{T}}{2} - \sqrt{2KI_{T}} \left(\frac{V_{d}}{2}\right) \sqrt{1 - \frac{(V_{d}/2)^{2}}{(I_{T}/2K)}},$$

(3.4)

where  $K = \frac{\mu C_{ox}}{2} \frac{W}{L}$  and  $V_d = V_{g1} - V_{g2}$ , and  $V_{g1}$  and  $V_{g2}$  swing differentially [3]. This can also be written as

$$I_{1} = \frac{I_{T}}{2} + \frac{V_{d}}{2} \sqrt{K(2I_{T} - KV_{d}^{2})},$$

(3.5)

$$I_2 = \frac{I_T}{2} - \frac{V_d}{2} \sqrt{K(2I_T - KV_d^2)}.$$

(3.6)