## Design and Implementation of PID Controllers Using CM Building Blocks

A Dissertation Submitted In Partial Fulfillment of Requirements For the Award of the Degree of

#### MASTER OF TECHNOLOGY (CONTROL & INSTRUMENTATION) (2010-2012)

Submitted By RAKESH VERMA (06/C&I/2K10)

**Under the Supervision of**

Dr. PRAGATI KUMAR

Department of Electrical Engineering

Delhi Technological University

(Formerly Delhi College of Engineering)

### **Department of Electrical Engineering**

**Delhi Technological University**

(Formerly Delhi College of Engineering)

New Delhi-110042

**July 2012**

# Delhi Technological University (Formerly Delhi College of Engineering) New Delhi Department of Electrical Engineering

#### **CERTIFICATE**

This is to certify that Mr. Rakesh Verma, Roll No. 06/C&I/2K10, student of M.Tech, Control & Instrumentation, Department of Electrical Engineering, Delhi Technological University, has submitted the dissertation entitled "Design and Implementation of PID Controllers Using CM Building Blocks" under my supervision in partial fulfillment of the requirements for the award of the degree of Master of Technology in Electrical Engineering (Control & Instrumentation). This dissertation is a record of his work carried out by him under my guidance and supervision and has not been presented earlier for the award of any degree/diploma.

Dr. Pragati Kumar Associate Professor Department of Electrical Engineering Delhi Technological University Formerly Delhi College of Engineering Delhi-110042

#### **ACKNOWLEDGEMENT**

I am thankful to the Almighty because without his blessings this work was not possible. It gives me a great pleasure to express my profound gratitude to my supervision and project guide **Dr. Pragati Kumar,** Associate professor, Department of Electrical Engineering, Delhi Technological University (formerly Delhi College of Engineering), for his invaluable guidance, encouragement and patient reviews throughout the progress of this dissertation.

I would also like to extend my heartfelt thanks to **Prof. Narendra Kumar, Head of the Department** and all faculty members of Department of Electrical Engineering, Delhi Technological University, for keeping the spirits high and clearing the visions to work on the project.

Finally I am also thankful to my family and friends for their constant support and motivation during this work. I thank Almighty GOD for his countless blessings.

Rakesh Verma (06/C&I/2K10)

#### LIST OF FIGURES

| Fig.2.1.1    | OTA Block-Diagram                                                |

|--------------|------------------------------------------------------------------|

| Fig.2.1.2    | Nullor model of OTA                                              |

| Fig.2.1.3    | CMOS realization of OTA                                          |

| Fig.2.2.1    | Block-diagram of the first generation current-conveyor           |

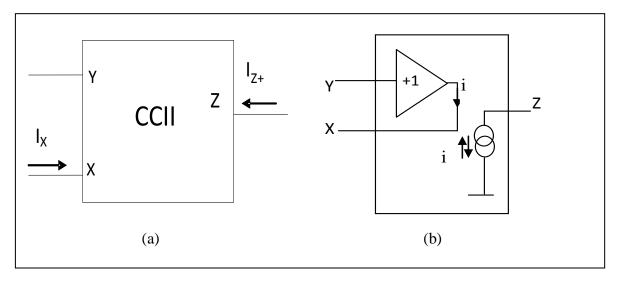

| Fig.2.2.2    | CCII: (a) Block-diagram, (b) Principal of operations             |

| Fig.2.2.3:   | Nullator-norator model of CCII                                   |

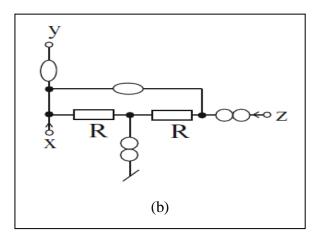

| Fig.2.2.3-1: | Novel circuit implementation of four forms of current conveyor,  |

|              | namely CCI +, CCI-, CCll+ & CCll- based on OA and OTA            |

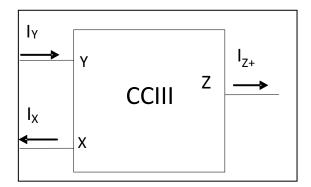

| Fig.2.2.4:   | Block-Diagram of CCIII                                           |

| Fig.2.2.5:   | (a) Symbol of CCCII, (b) Equivalent circuit of CCCII             |

| Fig.2.2.6:   | Block-Diagram of (a) DOCCII (b) DOCCIII                          |

| Fig.2.2.7:   | CCII circuit realization using CMOS vlsi process                 |

| Fig.2.2.8:   | CCIII circuit realization using CMOS vlsi process                |

| Fig.2.3.1:   | (a) Equivalent Block Diagram of CFOA                             |

| Fig.2.3.1:   | (b) Schematic symbol of CFOA                                     |

| Fig.2.3.2:   | CFOA circuit diagram using CMOS-bipolar technology               |

| Fig.2.4.1:   | (a) CDBA Block- Diagram, (b) CDBA equivalent circuit             |

| Fig.2.4.2:   | CMOS realization of CDBA                                         |

| Fig.3.1.1:   | Traditional PID controller constructed with op-amps              |

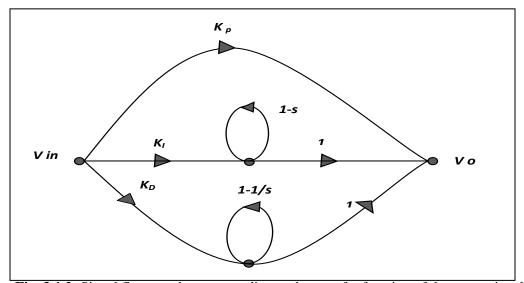

| Fig.3.1.2:   | Signal flow graph corresponding to the transfer function (PID    |

|              | Controller)                                                      |

| Fig.3.2.1:   | Basic building blocks using OTAs and corresponding signal flow   |

|              | graphs                                                           |

| Fig.3.2.2:   | An OTA-C based proportional-integral-derivative (PID) controller |

| Fig.3.3.1:   | Sub-graphs and corresponding active sub-circuits involve CCCII   |

| Fig.3.3.2:   | Proposed CCCII-based PID controller realization                  |

| Fig.3.4.1:   | Signal flow graph corresponding to the transfer function of PID  |

|              | Controller                                                       |

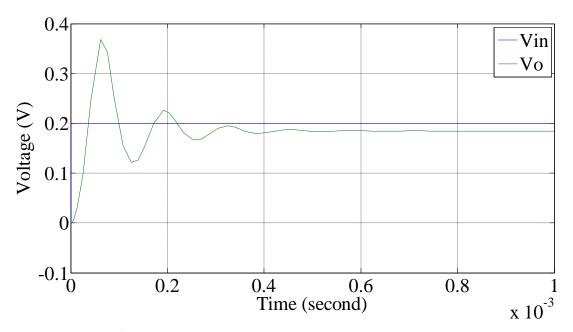

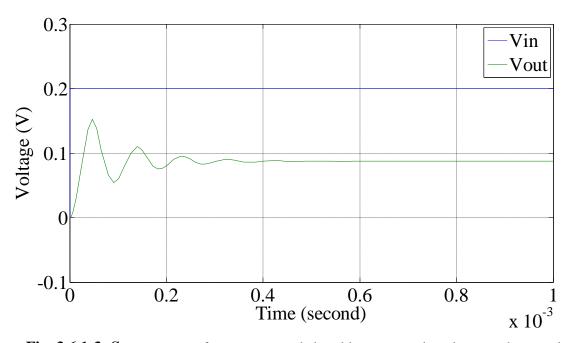

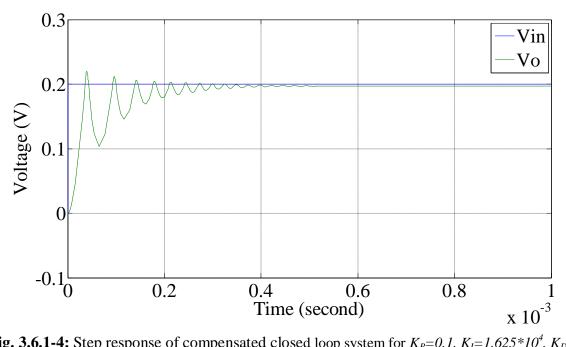

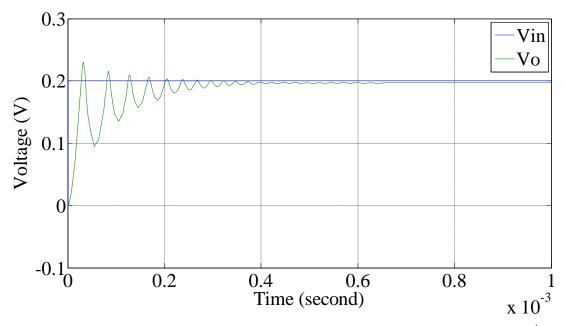

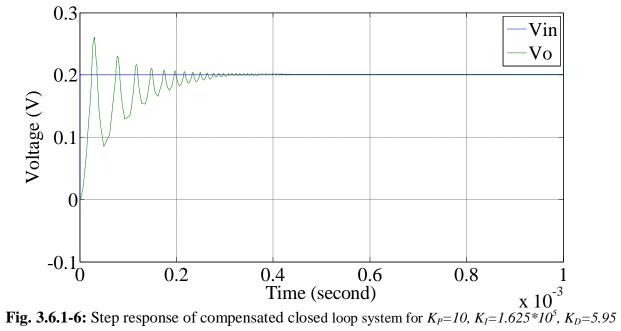

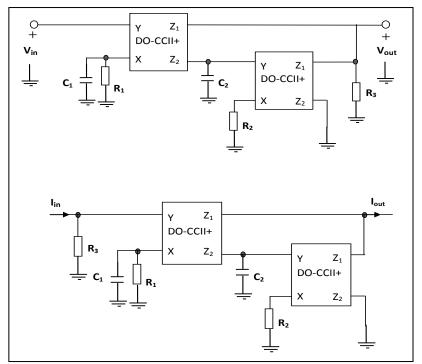

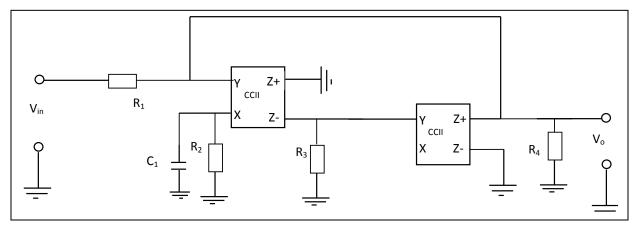

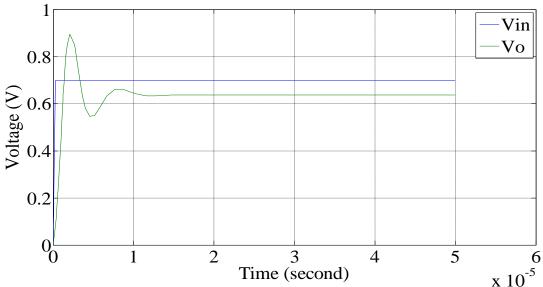

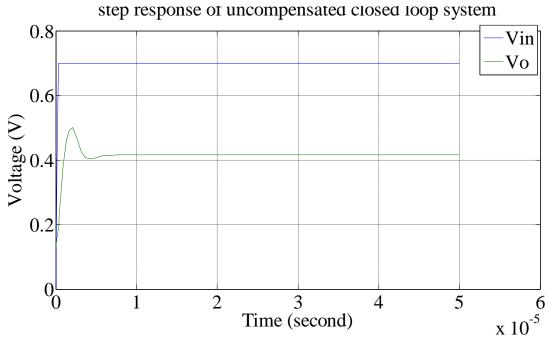

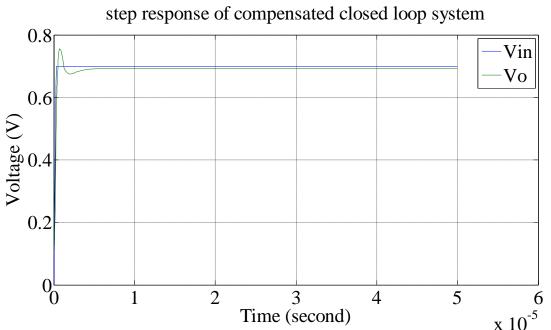

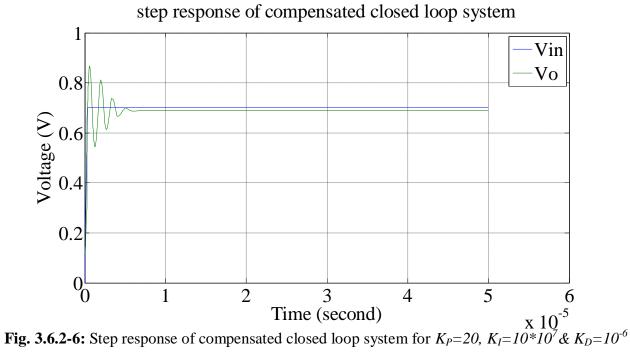

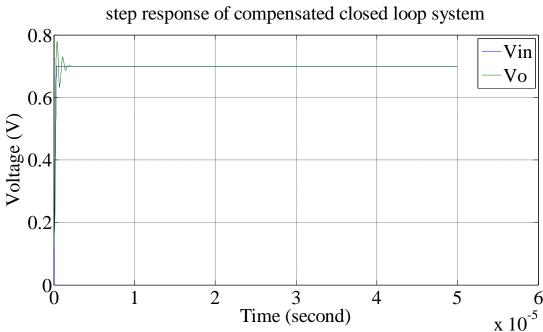

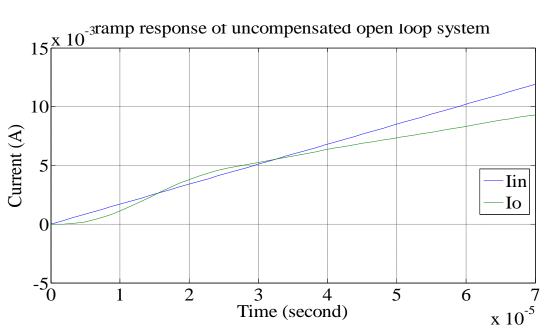

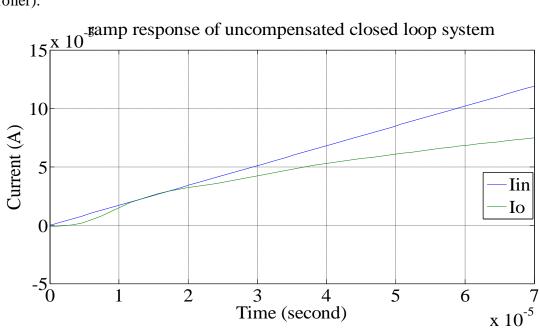

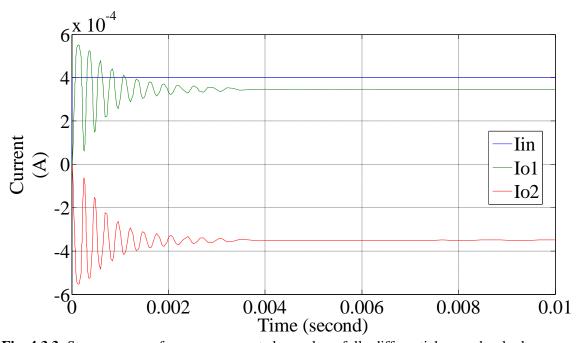

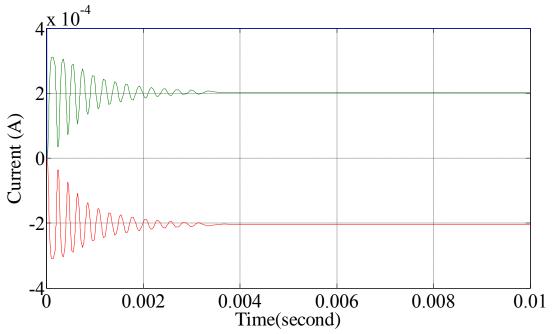

Fig.3.4.2: Basic building blocks using CFOAs with corresponding sub-graphs Fig.3.4.3: A CFA based PID controller corresponding to the signal flow graph Fig.3.5.1: Sub-graphs and sub-circuits for the PID controller using CDBA Fig.3.5.2: CDBA-based PID controller circuit Fig.3.6.1-1: OTA-C based voltage mode second order system Fig.3.6.1-2: Step response of uncompensated open loop system in voltage mode operation: OTA-C based system Fig.3.6.1-3: Step response of uncompensated closed loop system in voltage mode operation OTA-C based system Fig.3.6.1-4: Step response of compensated closed loop system for K<sub>P</sub>=0.1,  $K_I=1.625*10^4$ ,  $K_D=0.595$ Fig.3.6.1-5: Step response of compensated closed loop system for K<sub>P</sub>=1,  $K_I = 1.625 * 10^4$ ,  $K_D = 0.595$ Fig.3.6.1-6: Step response of compensated closed loop system for K<sub>P</sub>=10,  $K_I = 1.625 * 10^5, K_D = 5.95$ Fig.3.6.2-1: PID Controller: (a) Voltage Mode (b) Current Mode using DOCCII Fig.3.6.2-2: Block- diagram of a voltage- mode second order system Fig.3.6.2-3: STEP response of uncompensated open loop system operating in voltage mode: DOCCII based system Fig.3.6.2-4: STEP response of uncompensated closed loop system operating in voltage mode: DOCCII based system Fig.3.6.2-5: Step response of compensated closed loop system for K<sub>P</sub>=100,  $K_1=50*10^6$ ,  $K_D=50*10^{-6}$ Fig.3.6.2-6: Step response of compensated closed loop system for K<sub>P</sub>=20,  $K_1=10*10^7\& K_D=10^{-6}$ Fig.3.6.2-7: Step response of compensated closed loop system for K<sub>P</sub>=200,  $K_1=10*10^9\& K_D=10^{-6}$ Fig.3.6.2-8: Block- diagram of a current- mode second order system Fig.3.6.2-9: RAMP response of uncompensated open loop system operating in current mode: DOCCII based system Fig.3.6.2-10: RAMP response of uncompensated closed loop system operating in

#### current mode: DOCCII based system

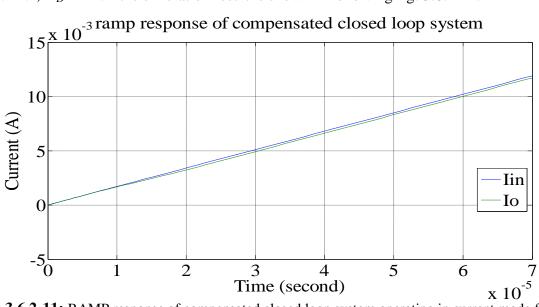

| Fig.3.6.2-11: | RAMP response of compensated closed loop system operating in                                |

|---------------|---------------------------------------------------------------------------------------------|

|               | current mode for $K_P = 20$ , $K_I = 10*10^6$ , $K_D = 1*10^{-5}$                           |

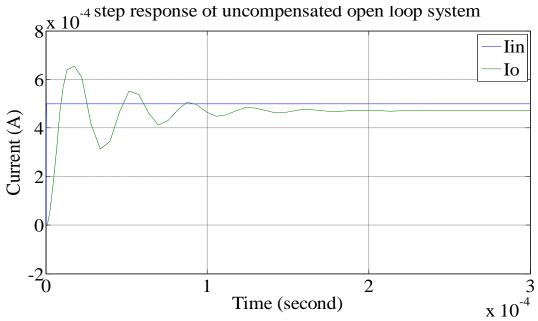

| Fig.3.6.2-12: | STEP response of uncompensated open loop system operating in                                |

|               | current mode: DOCCII based system                                                           |

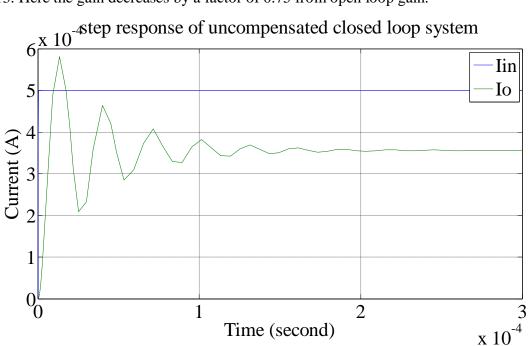

| Fig.3.6.2-13: | STEP response of uncompensated closed loop system operating in                              |

|               | current mode: DOCCII based system                                                           |

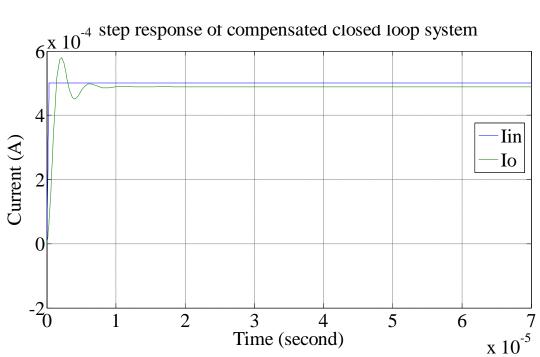

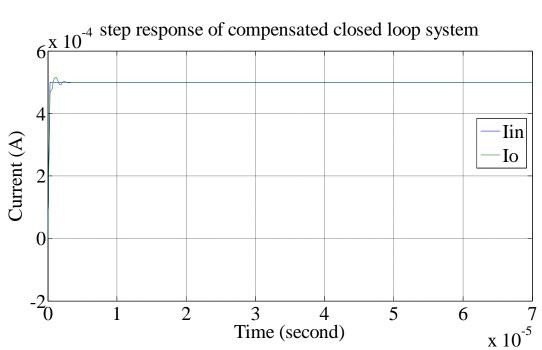

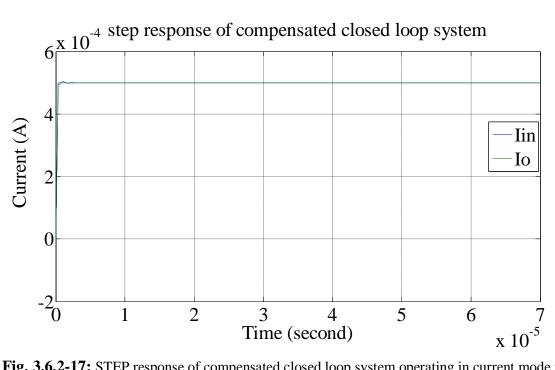

| Fig.3.6.2-14: | STEP response of compensated closed loop system operating in                                |

|               | current mode for $K_P=4$ , $K_I=2*10^{-6}$ and $K_D=2*10^6$                                 |

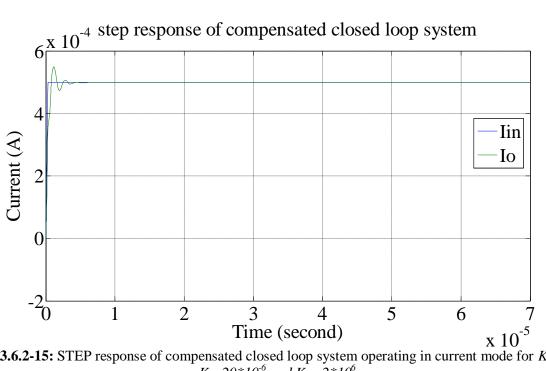

| Fig.3.6.2-15: | STEP response of compensated closed loop system operating in                                |

|               | current mode for $K_P$ =40, $K_I$ =20*10 <sup>-6</sup> and $K_D$ =2*10 <sup>6</sup>         |

| Fig.3.6.2-16: | STEP response of compensated closed loop system operating in                                |

|               | current mode for $K_P=200$ , $K_I=100*10^{-6}$ and $K_D=100*10^{6}$                         |

| Fig.3.6.2-17: | STEP response of compensated closed loop system operating in                                |

|               | current mode for $K_P=1000$ , $K_I=500*10^{-6}$ and $K_D=500*10^{6}$                        |

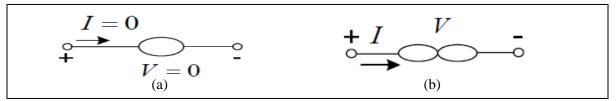

| Fig.4.2-1:    | (a) Nullator symbol representation (b) Norator symbol representation                        |

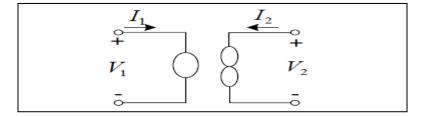

| Fig.4.2-2:    | Two-port nullor symbol                                                                      |

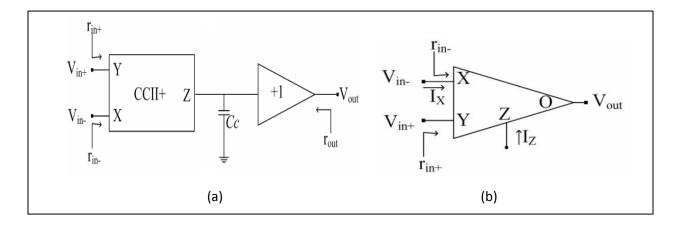

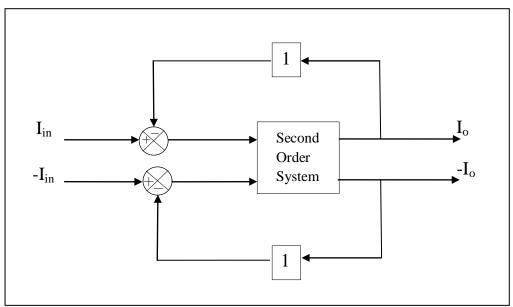

| Fig.4.2-3:    | Fully differential CM building block                                                        |

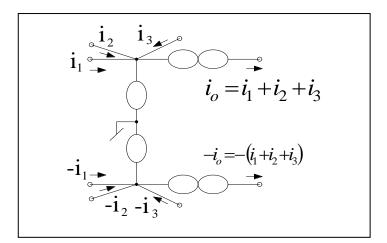

| Fig.4.2.1-1:  | Summing operation of PID controller with complementary CM                                   |

|               | outputs                                                                                     |

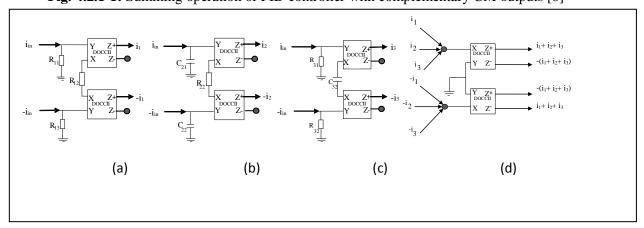

| Fig.4.2.1-2:  | CCII-based implementation of the sub-blocks of PID controller (a)                           |

|               | constant multiplication, (b) integration and (c) differentiation.                           |

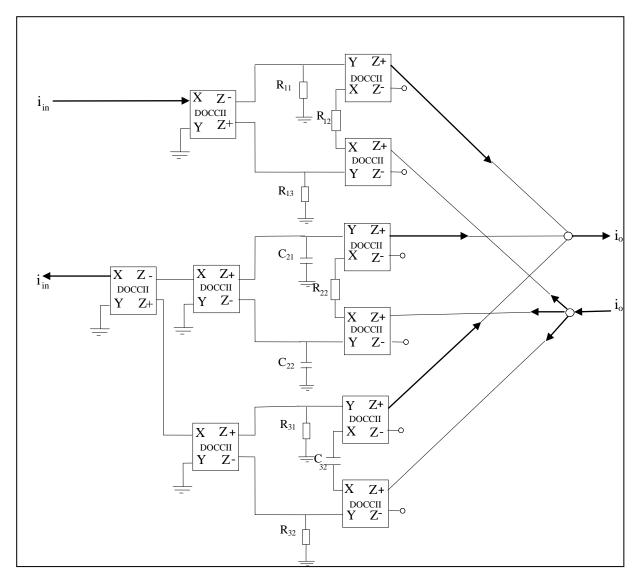

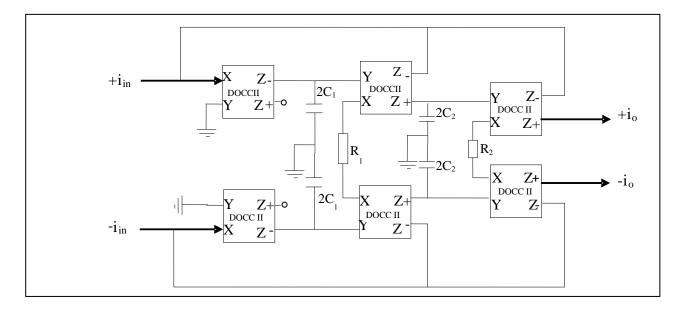

| Fig.4.2.1-3:  | A fully differential PID controller operating in current mode                               |

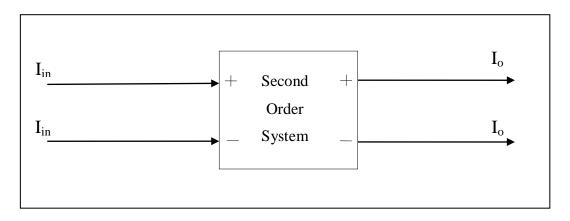

| Fig.4.2.2:    | A fully differential second order system employing DOCCII                                   |

| -             |                                                                                             |

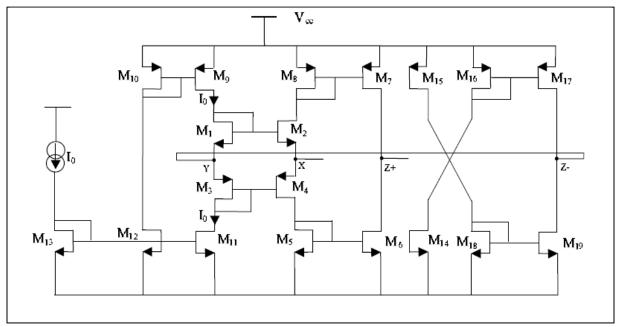

| Fig.4.3.1:    | CMOS implementation of DOCCII                                                               |

| Fig.4.3.2:    | Block-diagram of uncompensated closed loop system                                           |

| Fig.4.3.3:    | Step response of an uncompensated open loop fully differential second order low pass filter |

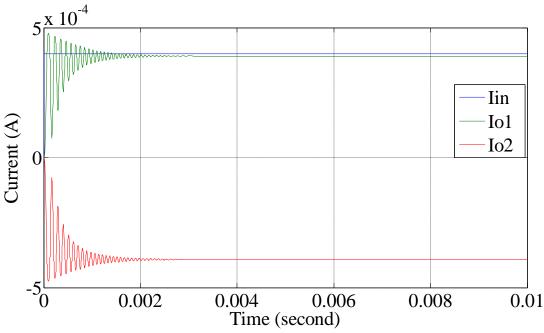

| Fig.4.3.4: | Block-diagram of uncompensated closed loop system                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Fig.4.3.5: | Step response of uncompensated closed loop second order low pass filter                                                               |

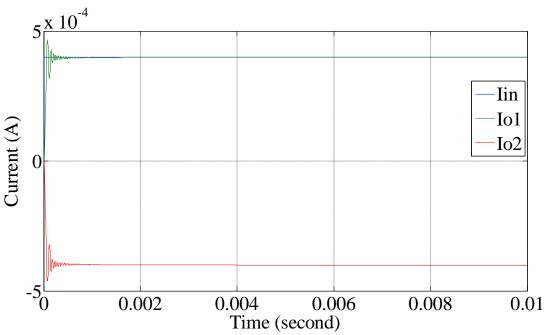

| Fig.4.3.6: | Block-diagram of a compensated fully differential low pass filter (LPF) with PID controller                                           |

| Fig.4.3.7: | Step response of a compensated fully differential second order low pass filter for $K_P$ =40, $K_I$ =20,000 and $K_D$ = $I0^{-5}$     |

| Fig.4.3.8: | Step response of a compensated fully differential second order low pass filter for $K_P$ =80, $K_I$ =2000 and $K_D$ =10 <sup>-3</sup> |

#### LIST OF SYMBOLS

| Symbols         | Descriptions                                                                                                                                                                                                                                                |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{\rm r}$     | Rise Time                                                                                                                                                                                                                                                   |

| $t_s$           | Settling Time                                                                                                                                                                                                                                               |

| e <sub>ss</sub> | Steady State Error                                                                                                                                                                                                                                          |

| $A_{o}$         | Open Loop Gain                                                                                                                                                                                                                                              |

| α               | Current Gain                                                                                                                                                                                                                                                |

| $\omega_{ m o}$ | Cut Off Frequency (in radian/sec.)                                                                                                                                                                                                                          |

| β               | Voltage Gain in Active Blocks                                                                                                                                                                                                                               |

| $A_{ m closed}$ | Closed Loop Gain                                                                                                                                                                                                                                            |

| ζ               | Damping Factor                                                                                                                                                                                                                                              |

| Т               | Time Constant                                                                                                                                                                                                                                               |

| K <sub>P</sub>  | Proportional Coefficient                                                                                                                                                                                                                                    |

| K <sub>I</sub>  | Integral Coefficient                                                                                                                                                                                                                                        |

| K <sub>D</sub>  | Derivative Coefficient                                                                                                                                                                                                                                      |

| g <sub>m</sub>  | Transconductance                                                                                                                                                                                                                                            |

| $Z_{i}$         | Input Impedance                                                                                                                                                                                                                                             |

| Z <sub>o</sub>  | Output Impedance                                                                                                                                                                                                                                            |

| V <sub>SS</sub> | Source Supply Voltage                                                                                                                                                                                                                                       |

| $V_{ m DD}$     | Drain Supply Voltage                                                                                                                                                                                                                                        |

| I <sub>o</sub>  | Bias Current                                                                                                                                                                                                                                                |

| I <sub>b</sub>  | Bias Current                                                                                                                                                                                                                                                |

|                 | $\begin{array}{c c} & t_{r} \\ & t_{s} \\ & e_{ss} \\ & A_{o} \\ & \alpha \\ & \omega_{o} \\ & \beta \\ & A_{closed} \\ & \zeta \\ & T \\ & K_{P} \\ & K_{I} \\ & K_{D} \\ & g_{m} \\ & Z_{i} \\ & Z_{o} \\ & V_{SS} \\ & V_{DD} \\ & I_{o} \\ \end{array}$ |

| 21 | w.r.t. | With respect to                            |

|----|--------|--------------------------------------------|

| 22 | OTA    | Operational Transconductance<br>Amplifier  |

| 23 | CC     | Current Conveyor                           |

| 24 | DOCC   | Dual Output Current<br>Conveyor            |

| 25 | CFA    | Current Feedback Amplifier                 |

| 26 | CFOA   | Current Feedback Operational Amplifier     |

| 27 | CDBA   | Current Differencing Buffer<br>Amplifier   |

| 28 | FTFN   | Four Terminal Floating<br>Nullors          |

| 29 | CMOS   | Complementary Metal Oxide<br>Semiconductor |

| 30 | OA     | Operational Amplifier                      |

| 31 | Op amp | Operational Amplifier                      |

| 32 | SFG    | Signal Flow Graph                          |

| 33 | SCSM   | Supply Current Sensing<br>Method           |

| 34 | VLSI   | Very Large Scale Integration               |

| 35 | VCO    | Voltage Controlled Oscillators             |

| 36 | WTA    | Wideband transconductance amplifier        |

| 37 | VCVS   | Voltage Controlled Voltage<br>Source       |

| 38 | VCCS   | Voltage Controlled Current<br>Source       |

| 39 | CCVS | Current Controlled Voltage<br>Source |

|----|------|--------------------------------------|

| 40 | CCCS | Current Controlled Current<br>Source |

| 41 | P    | Proportional                         |

| 42 | I    | Integral                             |

| 43 | D    | Derivative                           |

| 44 | W/L                | Transistor Aspect Ratio                                  |

|----|--------------------|----------------------------------------------------------|

| 45 | $\mu_n$            | Mobility of NMOS                                         |

| 46 | C <sub>ox</sub>    | Gate oxide capacitance per unit area                     |

| 47 | ВЈТ                | Bipolar Junction Transistor                              |

| 48 | CCCII              | Second Generation Current<br>Controlled Current Conveyor |

| 49 | H <sub>v</sub> (s) | Transfer Function for Voltage<br>Mode                    |

| 50 | $H_{i(s)}$         | Transfer Function for current Mode                       |

| 51 | T <sub>ii</sub>    | Integral Time Constant for Current Mode                  |

| 52 | $T_{iv}$           | Integral Time Constant for Voltage Mode                  |

| 53 | $T_{ m di}$        | Derivative Time Constant for Current Mode                |

| 54 | $T_{ m dv}$        | Derivative Time Constant for Voltage Mode                |

#### LIST OF TABLES

| Table 3.0: | Observation from the step response: Voltage Mode OTA based system    |

|------------|----------------------------------------------------------------------|

| Table 3.1: | Observation from the step response: Voltage Mode DOCCII based system |

| Table 3.2: | Observation from the step response: Current Mode OTA based system    |

Table 4.1: Observation from the step response: fully differential (DOCCII based) system

#### **ABSRACT**

Proportional plus Integral plus Derivative (PID) controllers are the mainstay of most of the control systems employed in different process industries. Traditional PID controllers have been implemented using the voltage mode operational amplifiers (VOA). Performance of these VOA based PID controller is limited by the performance of the traditional VOA.

In this dissertation, current mode (CM) and voltage mode (VM) analog PID controllers have been studied & implemented. The CM and VM building blocks chosen for study and implementation of the PID controllers are (i) OTA, (ii) DOCC-II, (iii) CFA and (iv) CDBA. The PID controllers have been implemented in PSPICE and closed loop performances of some prototype second order system have been studied to establish the workability of these PID controllers.

A novel fully differential current- mode PID controller has also been designed and implemented which uses a fully differential implementation of proportional, integral and differential terms.

#### **CONTENTS**

| CERT | 'IFICA' | ГЕ                                                                | ii   |

|------|---------|-------------------------------------------------------------------|------|

| ACKN | NOWL    | EDGEMENT                                                          | iii  |

| LIST | OF FIC  | GURES                                                             | iv   |

| LIST | OF SY   | MBOLS                                                             | viii |

| LIST | OF TA   | BLES                                                              | xi   |

| ABST | RACT    |                                                                   | xii  |

| CHAF | WEED I  | DITRODUCTION                                                      | 1-5  |

| CHAF | TER-I   | INTRODUCTION                                                      | 1-3  |

| 1.1  | Introd  | luction                                                           | 1    |

| 1.2  | PID c   | ontrollers using a new class of current mode active blocks        | 1    |

| 1.3  | Curre   | nt mode active blocks                                             | 2    |

| 1.4  | Organ   | nization of the Dissertation                                      | 3    |

| 1.5  | Refer   | ences                                                             | 4    |

| CAPT | ER-II   | CM/VM ACTIVE BUILDING BLOCKS USED FOR SYNTHESIS OF PID CONTROLLER | 6-26 |

| 2.1  | Opera   | ational Transconductance Amplifier (OTA)                          | 6-9  |

|      | 2.1.1   | History                                                           | 6    |

|      | 2.1.2   | Symbol and Characteristic Equation                                | 6    |

|      | 2.1.3   | CMOS/Bipolar Implementation                                       | 7    |

|      | 2.1.4   | Applications                                                      | 9    |

| 2.2  | Curre   | nt Conveyor (CC)                                                  | 9-15 |

|      | 2.2.1   | History                                                           | 9    |

|      | 2.2.2   | First Generation Current Conveyor: CCI                            | 9    |

|      | 223     | Second Generation Current Conveyor: CCII                          | 10   |

|      | 2.2.4 Third Generation Current Conveyor: CCIII                    | 12    |

|------|-------------------------------------------------------------------|-------|

|      | 2.2.5 Current Controlled Current Conveyor: CCCII                  | 12    |

|      | 2.2.6 DOCCII/DOCCIII                                              | 13    |

|      | 2.2.7 Applications                                                | 15    |

| 2.3  | Current Feedback Operational Amplifier (CFOA)                     | 15-19 |

|      | 2.3.1 History                                                     | 15    |

|      | 2.3.2 Symbol and Characteristic Equation                          | 16    |

|      | 2.3.3 CMOS/Bipolar Implementation                                 | 17    |

|      | 2.3.4 Circuit Description: Characteristics                        | 17    |

|      | 2.3.5 Applications                                                | 19    |

| 2.4  | Current Differencing Buffer Amplifier (CDBA)                      | 19-26 |

|      | 2.4.1 History                                                     | 19    |

|      | 2.4.2 Symbol and Characteristic Equation                          | 19    |

|      | 2.4.3 CMOS/Bipolar Implementation                                 | 20    |

| 2.5  | Conclusion                                                        | 21    |

| 2.6  | References                                                        | 22    |

|      |                                                                   |       |

|      |                                                                   |       |

| CAPT |                                                                   | 27-55 |

| 3.0  | ENDED PID CONTROLLERS Introduction                                | 27    |

| 3.1  | Traditional PID controller design based on operational amplifiers | 27    |

| 3.2  | OTA-C based PID controller                                        | 29    |

| 3.3  | Current Conveyor Conveyor-II based PID controller                 | 31    |

| 3.4  | CFA based PID controller                                          | 34    |

| 3.5  | CDBA based PID controller                                         | 37    |

| 3.6  | Simulation                                                        | 39-54 |

| 2.0  | 3.6.1 Implementation of OTA-C based PID controller                | 39    |

|      | 3.6.2 Implementation of DOCCII based PID controller               | 43    |

| 3.7  | Conclusion                                                        | 54    |

| 3.8  | References                                                        | 55    |

| ٥.٠  |                                                                   | 55    |

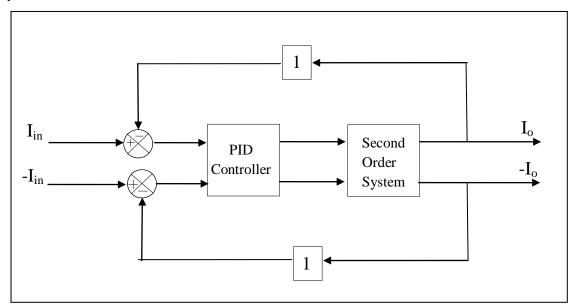

| CAPTER-IV CURF               | RENT MODE FULLY DIFFERENTIAL PID                                                                                                           | 56-66                            |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| (F.                          | DPID) CONTROLLER REALIZATION                                                                                                               |                                  |

| 4.2.1 Synthesis              | ly Differential Current Mode Active Block of Fully Differential PID (FDPID) controller of Fully Differential second order open loop system | 56<br>56<br>58<br>60<br>61<br>66 |

| CAPTER-V SUMN<br>5.1 Summary | MARY AND CONCLUSION                                                                                                                        | 67-68                            |

| J.1 Summary                  |                                                                                                                                            | 67                               |

| 5.2 Future Sc                | ope                                                                                                                                        | 68                               |

|                              | ENDIXES                                                                                                                                    | 69-70                            |

| 6.1 Appendix                 |                                                                                                                                            | 69                               |

| 6.2 Appendix                 | A D                                                                                                                                        | 70                               |

#### **CHAPTER I**

#### INTRODUCTION

#### 1.1 Introduction

This dissertation presents a study on designing and implementation of PID controllers using CM/VM active building blocks. The proportional-integral-derivative (PID) controller is one of the most important control elements used in the process control industry. A PID controller is composed of three terms namely: (1) proportional, (2) integral, and (3) derivative [1]. The proportional term adjusts the speed of response of the system; the integral term adjusts the steady-state error of the system, but may introduce instability in the system while the derivative term adjusts the degree of stability of the system, but might increase errors. By carefully tuning the various gains the closed-loop performance of a system can be improved significantly.

Traditionally, voltage operational amplifiers are largely used in analogue PID controllers. These op-amps (operational amplifiers) based controller have large number of active and passive components required for tuning the performance of closed loop control system [2]. Operational amplifiers have two major limitations viz. slew rate and constant product of gain & bandwidth. In the most traditional industrial problems, requirements on the selection of active components is not necessary, it depends on the general synthesis procedures [3]- [6] to perform operations of PID controller, so reduced number of parameters are required to be tuned for the closed loop control system.

#### 1.2 PID controllers using a new class of current mode active blocks

Generally, there are two modes to perform operations in any electronic circuit, they are: (i) voltage mode, and (ii) current mode operations. Several voltage and current mode continuous-time filters, oscillators, analog multipliers, inductance simulators and PID controllers have been developed using a new current mode active blocks in which circuits are driven by current carrying signals.

Current-mode signal processing techniques have received a wide attention due to wide bandwidth, low-voltage operation, better linearity and stability properties and simple implementations of signal operations such as addition and subtraction, and are often preferable to voltage-mode counterparts [2]. These components, such as current conveyors (CCs) [7], operational transconductance amplifiers (OTAs) [8], current feedback operational amplifiers (CFOAs) [9] and current differencing buffer amplifier (CDBAs) [10] are considered for PID applications where speed and/or large bandwidth are required.

#### 1.3 Current mode active blocks

The building blocks used for implementation of PID controllers can be implemented in both Bipolar as well as CMOS technology. These blocks in general fall into the categories of voltage controlled voltage source (VCVS), voltage controlled current source (VCCS), current controlled voltage source (CCCS) & current controlled current source (CCVS), or many a times into a combination of more than one of these blocks. The basic design of a voltage mode or current mode building block is guided by the signal processing functions it is supposed to perform. Nevertheless certain common features which may be found in most of the CM/VM building blocks are the presence of

- i. Voltage/Current differencing circuits

- ii. Current source biasing arrangements

- iii. Minimum number of passive components

- iv. Current mirrors of different types for copying of signal currents and/or bias currents from one part of the circuit to the other part.

OTA is a differential VCCS (Voltage Controlled Current Source) in which output current is controlled by input voltage source [8] and it is characterized by transconductance (g<sub>m</sub>). The second-generation current-conveyor [11] is a voltage-follower with input Y and output voltage terminal X, and a current-follower (or current-inverter) with a current input X and output Z. In third generation current conveyor [11], the input current flows into the Y-terminal and out from the X-terminal, it is assumed that a differential current input fed output in voltage form. A current feedback amplifier is equivalent to a plus type second-generation current conveyor with a voltage buffer [9]. The term current feedback is used because the signal entering at the feedback

node of op-amp is in the form of current signal. CDBA is a newly introduce active circuit; it is a combination of two fundamental building blocks i.e., current differencing block and voltage follower block. FTFN is a more general and flexible building block compared to other active elements. They are used to function more successfully in both voltage mode and current mode e.g., voltage mode op-amps and current conveyors.

The basic current-mode circuit of OTA configuration is obtained from a second-order integrator loop structure consisting of the loss-less integrators [8]. An implementation of the second generation current conveyor is done by using a mixed (NMOS and PMOS) translinear loop [12]. The circuit of CFOA allows almost a rail-to-rail input and output operation. The configuration of CDBA is same as that of a CMOS second-generation current conveyor (CCII) [7]. With the help of these devices several filters and oscillators are built. Generally most of these devices are made for current controlling operations in such a way that it provides a better performance by using biasing current.

#### 1.4 Organization of the Dissertation

In chapter II, a brief study of the characteristics, implementation and applications of various CM/VM active building blocks used for synthesizing PID controller has been presented. In chapter III, PID controllers are built through a general synthesis procedure with the help of signal flow graph (SFG). In order to test these PID controllers, implementation of CM/VM PID controller are done. In chapter IV, a new fully differential PID controller is made with the help of DO-CCII. In chapter V summary of the project has been presented along with suggestions for some future work on this topic.

#### 1.5 References

- [1] Kuo, "Automatic Control Systems", Prentice-Hall, Upper Saddle River, NJ, 1997.

- [2] E. Yuce, S. Tokat, S. Minaei, O. Cicekoglu, "Low-Component-Count Insensitive Current-Mode and Voltage-Mode PID, PI and PD Controllers" Frequenz, Vol. 60, No.3-4, pp. 29-33, 2006.

- [3] C. Erdal, A. Toker, and C. Acar, "Ota- C Based Proportional-Integral-Derivative (PID) Controller And Calculating Optimum Parameter Tolerances", Turkish Journal Of Electrical Engineering & Computer Sciences, Vol. 9, No.2, pp. 189-198, 2001.

- [4] C. Erdal, "A New Current- Feedback- Amplifiers (CFAs) Based Proportional- Integral-Derivative (PID) Controller Realization and Calculating Optimum Parameter Tolerances", Pakistan Journal of Applied Sciences, Vol. 2, No.1, pp. 56-59, 2002.

- [5] A. U. Keskin, "Design of a PID controller circuit employing CDBAs", International Journal of Electrical Engineering Education, 2006.

- [6] J. Ashraf, M. S. Alam & D. Rathee, "A New Proportional-integral-derivative (PID) Controller Realization by Using Current Conveyor", International Journal of Electronics Engineering, Vol. 3, No. 2, pp. 237–240, 2011.

- [7] A. Sedra, K. Smith, "A second-generation current-conveyor and its applications", IEEE Trans., vol. CT-17, pp. 132-134, 1970.

- [8] R. L. GEIGER, E. SANCHEZ-SINENCIO, "Active filter design using operational transconductance amplifiers: a tutorial", IEEE Circuits and Devices Magazine, Vol. 1, No. 2, pp. 20–32, 1985.

- [9] A.H. Madian, S. A. Mahmoud and A. M. Soliman, "New 1.5-V CMOS Current Feedback Operational Amplifier," 13<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems, 10-13 Dec. 2006.

- [10] A. U. Keskin, E. Hancioglu, "Current mode multifunction filter using two CDBAs," AEU INT. J. Electron. Commun., Vol. 56, pp.495-498, 2002.

- [11] N. B. El Feki and D. S. Masmoudi, "High Performance Dual-Output Second and Third Generation Current Conveyors and Current-Mode Multifunction Filter Application" The 6<sup>th</sup> International Multi- Conference on Systems, Signals and Devices, 2009.

- [12] N. HERENCSAR, K. VRBA, "Multifunction RF filters using OTA", In Proceedings of the 12th IFIP International Conference on Personal Wireless Communications PWC'07, Prague, Czech Republic, 2007, pp. 1–12.

#### **CHAPTER II**

## CM/VM ACTIVE BUILDING BLOCKS USED FOR SYNTHESIS OF PID CONTROLLER

In the present chapter, we present a brief description of various active building blocks used for implementation of the PID controllers. Though, a very large number of active building blocks have been proposed by various research groups in recent part [1]. In the present chapter, we have studied only those active building blocks which have been directly used for PID controller implementation.

#### 2.1 Operational Transconductance Amplifier (OTA)

#### **2.1.1** History

In 1969, RCA produced an integrated circuit, called OTA (Operational Transconductance Amplifier) for the purpose of commercial needs. The first publications with OTA came out in 1985, when the [4] presented to the new CMOS based OTA architectures and new filter realizations.

#### 2.1.2 Symbol and Characteristic Equation

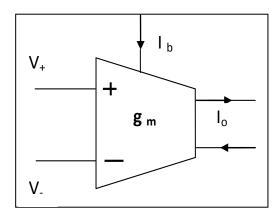

Fig. 2.1.1 OTA Block-Diagram

OTA is a differential VCCS (Voltage Controlled Current Source) in which output current is controlled by input voltage source and it is characterized by transconductance  $(g_m)$ . The output current of the OTA is given as follows [4]

$$I_o = g_m(V_+ - V_-),$$

where  $V_{+}$  and  $V_{-}$  are voltages on non-inverting and inverting input terminal of OTA.

Characteristics of ideal OTA can be summarized as below

Input impedance  $(Z_{in}) = \infty$ , Output Impedance  $(Z_0) = \infty$ , Bandwidth  $= \infty$ .

Fig. 2.1.2: Nullor model of OTA [3]

Nullor model of the OTA is given above in fig. 2.1.2 [3].

#### 2.1.3 CMOS/Bipolar Implementation

The Operational transconductance amplifier is basically a differential voltage controlled current source and several bipolar as well as CMOS implementations have appeared in literature. In the following we present a CMOS implementation of differential input differential output OTA given in [5]. The transconductance is taken as follows

$$g_m = \sqrt[2]{(\mu_n C_{ox} \frac{W}{L} I_b)}$$

<sup>&</sup>lt;sup>1</sup>The term "transconductance" (g<sub>m</sub>) comes because it is the ratio of the output current over the input voltage. Transconductance of an OTA is electronically tunable through an external DC bias voltage/ current.

Where  $\mu_n$ ,  $C_{ox}$ , W/L and  $I_b$  are the electron mobility of NMOS, gate oxide capacitance per unit area, transistor aspect ratio and bias current of the OTA, respectively. In above equation, it can observe that the transconductance  $g_m$  is adjustable by a supplied bias current  $I_b$ .

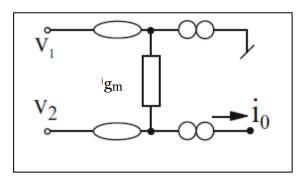

Fig. 2.1.3 shows the complete CMOS realization of OTA using MOS transistors [5].

Fig. 2.1.3: CMOS realization of OTA [5]

In [5], electronically tunable multiple-mode universal biquadratic circuits are introduced using some highly linear operational transconductance amplifiers (OTAs) and grounded capacitors. For realization of higher order circuit transfer function, a second-order function of biquadratic circuit is a very useful block. The basic current-mode circuit configuration is obtained from a second-order integrator loop structure consisting of loss-less integrators. The multiple-mode biquadratic circuits are constructed with additional OTAs to the current-mode one.

#### 2.1.4 Applications

In recent few years, OTA-C attracts more than OA (Operational Amplifier) IC, because it has several advantages e.g., it has a wider operational linear range, and this may possible with tuning of its transconductance (g<sub>m</sub>) also, it requires just a few or even no resistors for its circuitry and in addition, it is more reliable in high frequency operations as it imposes a current mode active circuitry. OTAs, have been used for the realization of OTA-C based filters [6]-[15], oscillators [16]-[18] in battery operated equipments. Currently, OTA elements are available in the market by many manufacturers [6]. A commercially available OTA element is the circuit LT1228 (Linear Technology) or MAX435 (MAXIM-Dallas Semiconductor), which is a high-speed wideband transconductance amplifier (WTA) with high-impedance inputs and output. The OTA is popular for implementing voltage controlled oscillators (VCO) and filters (VCF) for analog music synthesizers.

#### 2.2 Current Conveyor (CC)

#### **2.2.1 History**

Sedra and Smith introduced the first generation<sup>2</sup> and the second generation current conveyor<sup>3</sup>. The current-conveyor was presented in 1968 [23] and further developed a second-generation current-conveyor in 1970 [24]. The third generation current conveyor<sup>4</sup> was proposed in 1995 [25].

#### 2.2.2 First Generation Current Conveyor (CCI)

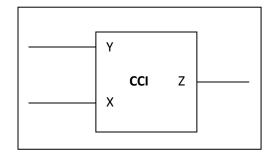

Fig. 2.2.1: Block-diagram of the first generation current-conveyor

<sup>&</sup>lt;sup>2, 3 & 4</sup> are popularly known as CCI, CCII and CCIII respectively.

Current-conveyor which is characterized by a three-port network has terminals X, Y and Z, as shown in fig. 2.2.1. The first generation current-conveyor CCI has been expressed in a matrix form as follows [23]

$$\begin{bmatrix} i_Y \\ v_X \\ i_Z \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} . \begin{bmatrix} v_Y \\ i_X \\ v_Z \end{bmatrix}$$

The first generation current conveyor (CCI) employs both currents and voltages in ports X and Y to be equal and a replica of the currents is conveyed to the output port Z.

#### 2.2.3 Second Generation Current Conveyor (CCII)

Fig. 2.2.2: CCII: (a) Block-diagram

**(b)** Principle of operations:  $i_{z+}=i_x$  [24]

The principle of operation of CCII+ is shown in fig. 2.2.2(b). The + sign indicates its positive gain. CCII is described in matrix form as follows [24]

$$\begin{bmatrix} i_Y \\ v_X \\ i_Z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} . \begin{bmatrix} v_Y \\ i_X \\ v_Z \end{bmatrix}$$

The second-generation current-conveyor is a voltage-follower with input voltage terminal Y and output voltage terminal X, and a current-follower (or current-inverter) with a current input X and a current output Z connected together. The second generation current conveyor has a high input impedance terminal in which no current is flowing in terminal Y, so it is used in many

applications by increasing the versatility of the current conveyor-I [24]. For these reasons, the second generation current-conveyor was developed. It has one high and one low impedance input rather than the two low impedance inputs of the CCI.

Fig. 2.2.3: Nullator-norator model of CCII [3]

CCII+ can be represented by nullators, norators and resistors; it requires two resistors in addition as shown in fig. 2.2.3 [3].

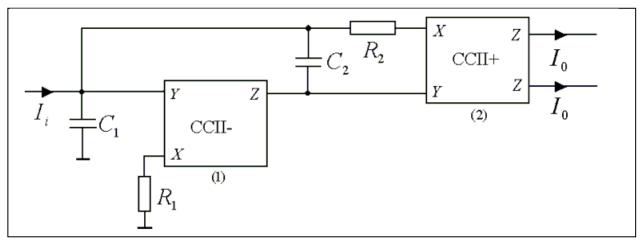

A variety of current conveyors (CCs) are implemented by Senani in [26]. The circuit configuration is shown in fig. 2.2.3-1. Here, the working applications of CCs viz. CCI+/- and CCII+/- depend on the proper connection adjustment of  $R_1$  &  $R_2$ .

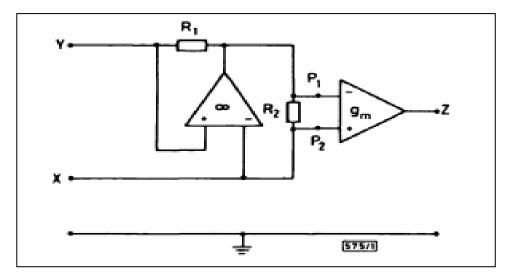

**Fig. 2.2.3-1:** Novel circuit implementation of four forms of current conveyor, namely CCI +, CCI-, CCIl+ & CCIl- based on OA and OTA [26]

#### 2.2.4 Third Generation Current Conveyor (CCIII)

Fig. 2.2.4: Block-Diagram of CCIII

CCIII is similar to CCI except there is opposite current transfer between X and Y terminal. The third generation current-conveyor CCIII is formulated in a matrix form as follows [25]

$$\begin{bmatrix} i_Y \\ v_X \\ i_Z \end{bmatrix} = \begin{bmatrix} 0 & -1 & 0 \\ 1 & 0 & 0 \\ 0 & +1 & 0 \end{bmatrix} . \begin{bmatrix} v_Y \\ i_X \\ v_Z \end{bmatrix}$$

The input current flows into the Y-terminal and out from the X-terminal, it is assumed that a differential current input could be realized with this amplifier. However, the CCIII has high input impedance with common-mode current signals, i.e. identical currents are fed both to terminal-Y and terminal-X.

#### 2.2.5 Current Controlled Current Conveyor (CCCII)

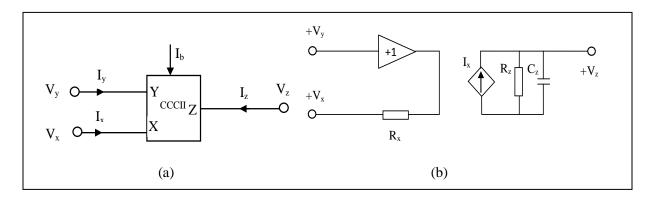

Fig. 2.2.5: (a) Symbol of CCCII (b) Equivalent circuit of CCCII

The ideal CCCII can be described as below [27]

$$I_y = 0$$

,  $V_x = V_y + R_x I_x$ ,  $I_z = \pm k I_x$

where  $V_y$  &  $V_x$  are the input terminal voltages and  $I_y$  &  $I_x$  are the input terminal currents of non-inverting and inverting input nodes, respectively.  $V_z$  and  $I_z$  are the voltage and current at output terminal respectively.

The positive k denotes a positive CCCII (CCCII+) and the negative k denotes a negative CCCII (CCCII-), and  $k=1-\epsilon$ ,  $|\epsilon| << 1$  represents the current tracking error.

$R_x$  is the input resistance at port X, which value is

$$R_{x} = \frac{V_{T}}{2I_{b}}$$

where  $V_T$  is the thermal voltage (25.8 mV at 27 °C) and  $I_b$  is the bias current of the CCCII. The equivalent circuit of CCCII is shown in fig. 2.2.5 (b), where  $R_x$  is the output resistance of the equivalent Thevenin generator seen from port X.  $R_z$  and  $C_z$  are the resistance and the capacitance of z-output, respectively.

#### 2.2.6 Dual Output CCII/CCIII (DOCCII/DOCCIII)

Fig. 2.2.6: Block-Diagram of (a) DOCCII (b) DOCCIII

Inputs and output terminals voltage and current relationship of DOCCII and DOCCIII are described in the following matrix form as described as bellow [28]

$$\begin{bmatrix} I_Y \\ V_X \\ I_{Z\pm} \end{bmatrix} = \begin{bmatrix} 0 & a & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} . \begin{bmatrix} V_Y \\ I_X \\ V_Z \end{bmatrix},$$

where  $I_{Z^{+}}$  is the positive-type and  $I_{Z^{-}}$  is the negative-type output current for both CCII± and CCIII±. For a=0, the circuit is called second generation current conveyor (CCII±). For a=-1, the circuit is called third generation current conveyor (CCIII±).

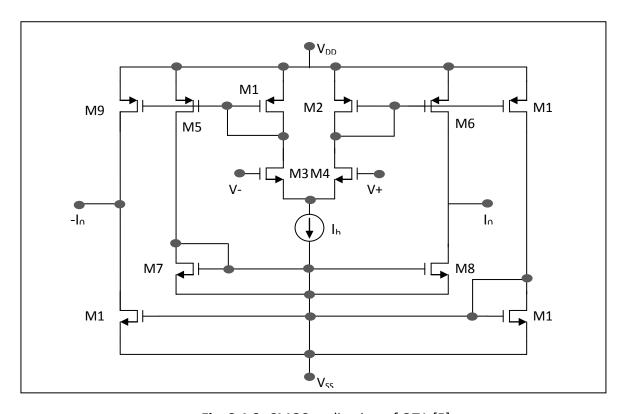

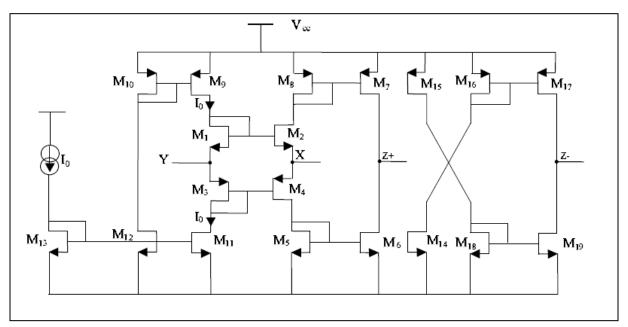

An implementation of the second generation current conveyor using a mixed (NMOS and PMOS) translinear loop is shown in fig. 2.2.6 [28], [29] & [30]. Nadhamia and Dorra proposed a multi-input multi-output filter, which contains two dual-output second-generation current conveyors (CCII±s) and one dual-output third-generation current conveyor (CCIII±) [28]. PSPICE simulations using CMOS 0.35 $\mu$ m technology parameters are included to demonstrate the results. Here it can be noticed that the bias current  $I_0$  directly affects the values of parasitic resistances  $R_X$ ,  $R_Y$  and  $R_Z$ .

Fig. 2.2.7 and 2.2.8 show CMOS realization of CCII and CCIII respectively, using translinear loop from [28].

Fig. 2.2.7: CCII circuit realization using CMOS vlsi process [28]

Fig. 2.2.8: CCIII circuit diagram using CMOS vlsi process [28]

#### 2.2.7 Applications

There are several applications of current conveyor since it has greater linearity and wider bandwidth over the voltage mode counterparts, op-amps [31]. Some applications are described in [24], [31], [37]. Despite, there is a lot of research papers published in as filters realizations [39]-[50], oscillatory circuit [38] (current mode Wein model oscillator) and in some papers some mathematical operations, like multiplication/division are introduced [35], [38]. The current conveyor active block derives several bipolar/cmos implemented circuits e.g., second generation current controlled current conveyor i.e., CCCII [32], dual output current conveyor i.e., DOCCII/DOCCIII $\pm$  [28], differential voltage i.e. DVCCII [32], [33], dual X current conveyor i.e., DXCC in which it has two X- terminals, these are non-inverting terminal  $X_p$  and inverting terminal  $X_p$  [34] reference cited therein.

#### 2.3 Current Feedback Operational Amplifier (CFOA)

#### **2.3.1** History

The CFA was invented by David Nelson at Comlinear Corporation, and first sold in 1982 as a hybrid amplifier, the CLC103. Now recently in few years, there are several CMOS realizations

for the CFOA which have been reported in the literature [52]-[58]. From beginning of the implementation of CFOA came out in existence with using only bipolar processes technology. It is well known for the current sensitivity so the techniques are intrinsically well suited to processing signals in the form of current which is given by the high bipolar junction transistor (BJT) transconductance.

#### 2.3.2 Symbol and Characteristic equation

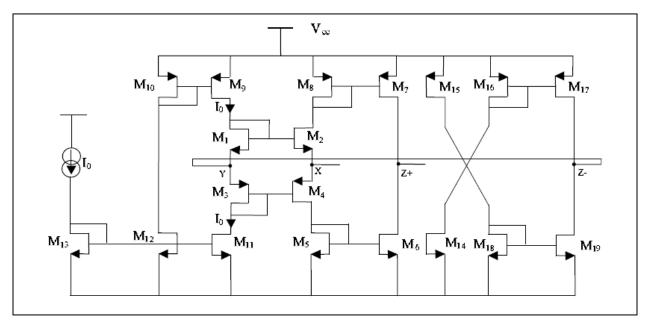

Fig. 2.3.1 (a) Equivalent Block Diagram of CFOA using current conveyor followed by a buffer

Fig. 2.3.1 (b) Schematic symbol of CFOA

CFOA can be expressed in matrix form, given as below

$$\begin{bmatrix} i_Y \\ v_X \\ i_Z \\ v_W \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_Y \\ i_X \\ v_Z \\ i_W \end{bmatrix}$$

A current feedback amplifier is equivalent to a plus type second-generation current conveyor with a voltage buffer as shown in fig. 2.3.1(a) [59]. The term current feedback is used because the signal entering at the feedback node of op-amp is in the form of current signal.

#### 2.3.3 CMOS/Bipolar Implementation

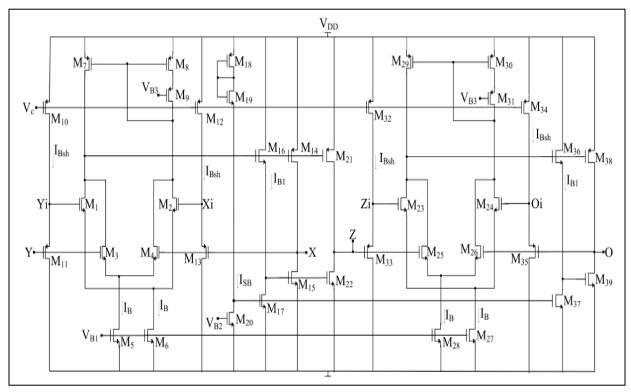

Fig. 2.3.2: CFOA circuit diagram using CMOS-bipolar technology [59]

In [59], a CMOS low-voltage current feedback operational amplifier (CFOA) is introduced. The design of this circuit is based on the MOS- transistor technology. The circuit allows almost a rail-to-rail input and output operation; also, it reduces the offset voltage and provides high driving current capabilities. The CFOA has been always seen as an extension of the CCII, therefore, the design approach was to cascade a CCII+ with a voltage follower to realize the complete circuit [60]. Fig. 2.3.2 shows the complete schematic circuit diagram of CFOA, using mos-bipolar technology.

#### 2.3.4 Circuit Descriptions: Characteristics

The X- terminal has low input impedance since the input stage of CFOA is a voltage follower. Transistors (M14-M20) designed to provide a buffering action with a rail-to-rail swing capability. Transistors M14 and M15 form the push pull output stage at the X terminal, so that they reduce the power dissipation in fig. 2.3.2. To prevent the cross over distortion, both transistors M14 and M15 must be ON when no current is withdrawn from the X terminal

(standby mode), this current should be small and controllable. This is achieved by using a suitable gate voltage of M20, which sets the voltage level shift between the gates of M14 and M15. The standby power consumption of the overall circuit for dual power supply is given by:

$$P_{SB} = 2V_{DD}(4I_{SB} + 4I_B + 4I_{BSh} + 2I_{B1})$$

In above equation, this is observed that power consumption can be reduced by varying  $I_{BI}$  as shown in fig. 2.3.2 and this current can be kept small by choosing small aspect ratio for transistors (M16 and M17). The proposed CFOA has a lot of advantages; the class AB output stage enables the circuit to drive the heavy resistive and capacitive load with low standby power dissipation and no slewing. There is important point that smaller miller compensation capacitors can be connected between the gate and drain of transistors M14 and M21 to ensure good transient response under all loads.

$$I_{M1} + I_{M3} = I_{M2} + I_{M4}$$

Since, transistors M7 and M8 force transistors M1 and M3 to equal currents in transistors M2 and M4. From above relation, the matched differential pair transistors are carrying equal currents. Therefore, it can be seen that,

$$V_X = V_Y$$

In Fig. 2.3.2, it can be seen that, transistors (M21, M22) are used to build a current follower stage. They are conveyed the X terminal current into the Z terminal current. Therefore,

$$I_Z = I_X$$

Finally, transistors M23 to M39 build a buffer between the Z and O terminals. It is similar to the buffer between the Y and X terminals. This buffer yields,

$$V_O = V_Z$$

Terminal-Y and terminal-X represent the non-inverting and inverting input terminals. Terminal-Z controls current in such a way producing equal voltage on terminal-W. The CFOA is capable to reduce the power dissipation and it can operate under a minimum supply voltage of  $(|V_{Tp}| + V_{DS,sat})$  [59]. It has also a high current drive capability and good power conversion

efficiency since it adds a new circuit design including a class AB output stage. In [59], also remarks one of things that a rail to rail input and output voltage operation is also achieved.

#### 2.3.5 Applications

One of the most popular CFOA namely, the AD844 from Analog Devices, is a 4-terminal building block. There is a growing interest employing CFOAs for the realization of active filters, immittance simulators, single frequency as well as single element controlled variable frequency sinusoidal oscillators and single/multiphase oscillators using CFOA pole. Recently, several current conveyor based and CFOA based [61], [62]–[64] oscillators are proposed in the literature.

#### 2.4 Current Differencing Buffered Amplifier (CDBA)

#### **2.4.1 History**

The current differencing buffered amplifier is initially introduced by Acar and Ozoguz [65]. It is a newly introduce active circuit that is a combination of two fundamental building blocks i.e., current differencing block and voltage follower block.

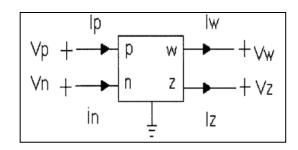

#### 2.4.2 Symbol and Characteristic Equation

Fig. 2.4.1: (a) CDBA Block- Diagram

(b) CDBA equivalent circuit [65]

It is a four terminal device; input terminals are assigned with p and n-terminal, and output terminals are assigned with w and z-terminal. The p-terminal shows, its non-inverting terminal and the n-terminal shows, its inverting terminal. The block-diagram of CDBA is shown in the

fig. 2.4.1 (a). CDBA equivalent circuit is shown in the fig. 2.4.1 (b.). It describes the conversion of the difference of input currents to the output voltage.

It can operate in both current-mode as well as voltage-mode, which provide flexibility and enable to have a variety of circuit design. Moreover, it is free from many parasitic capacitances and appropriate for high frequency operation.

The circuit can be described as under in matrix form,

Where current gains assigned by  $\alpha_p$  &  $\alpha_n$  and voltage gain  $\beta$  are ideally equal to one. Here, p and n-terminals are internally grounded.

The CDBA can be considered as a transimpedance amplifier that converts the difference of input currents  $I_p$  and  $I_n$  at the terminals p and n, respectively, into the output voltage  $V_w$  at the terminal w through an impedance connected at the terminal z.

Here, p and n terminals have ideally zero impedance and the current output at terminal-z which has ideally infinite impedance. Moreover, the voltage of terminal-w follows that of terminal-z. Hence, terminal-w is the voltage output that should have zero impedance.

#### 2.4.3 CMOS/Bipolar Implementation

In [66], Keskin and Hancioglu presented a current mode multi function using two CDBAs. In this paper they realized CDBA with the help of CMOS- bipolar technology.

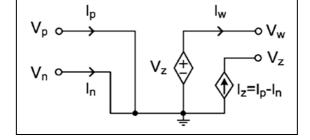

Fig. 2.4.2: CMOS realization of CDBA [66]

The CDBA used in this design is realized with CMOS technology using the topology illustrated in fig. 2.4.2 with supply voltages of  $V_{DD} = 2.5V$  and  $V_{SS} = -2.5 V$  and biasing currents of  $I_{BI} = I_{B2} = I_{B3} = 30\mu A$ . Fig. 2.4.2 shows the complete schematic of proposed CDBA, which is based on the use of current differencing circuit (M1-M12) and the voltage buffer circuit (M13-M20). The circuit simulation is done using 0.5 $\mu$  MIETEC level- 3 real transistor model parameters for all transistors in the circuit.

#### 2.5 Conclusion

In this chapter, history, characteristics, applications and CMOS/bipolar implementation of the current mode active building blocks used for implementation of PID controllers are briefly discussed. The devices described are

- (i) OTA-C

- (ii) DOCCII

- (iii)CFOA

- (iv)CDBA.

#### 2.6 References

- [1] D. Biolek, R. Senani, V. Biolkova and Z. Kolka, "Active Elements for Analog Signal Processing: Classification, Review, and New Proposals", Radioengineering, Vol. 17, No. 4, pp. 1532.

- [2] P. Kumar, R. Senani, "Bibliography on Nullors and Their Applications in Circuit Analysis, Senthsis and Design", Analog Integrated Circuits and Signal Processing, 33, 65-76, 2002.

- [3] Raj Senani, A.K. Singh, Pragati Kumar, and R.K. Sharma, "Integrated Circuits for Analog Signal Processing," Springer-Verlag New York Inc., Chapter 2, 2012.

- [4] R. L. Geiger, E. Sanchez-Sinencio, "Active filter design using operational transconductance amplifiers: a tutorial", IEEE Circuits and Devices Magazine, vol. 1, no. 2, pp. 20–32, 1985.

- [5] Y. Sumi, T. Tsukutani, H. Tsunetsugu and N. Yabuki, "Electrical Tunable Multiple-Mode Universal Biquadratic Circuits", 2010 International Conference on Computer Applications and Industrial Electronics (ICCAIE 2010), December 5-7, 2010.

- [6] N. Herencsar, K. Vrba, "Multifunction RF filters using OTA", In Proceedings of the 12th IFIP International Conference on Personal Wireless Communications PWC'07, Prague, Czech Republic, pp. 1–12, 2007.

- [7] V. K. Aatre, "Network Theory & Filter Design", 2nd Edition, New Age International (P) Ltd., 1980.

- [8] T. Deliyannis, "Active RC Filters Using an Operational Transconductance Amplifier and an Operational Amplifier", Int. J. Circuit Theory Appl., vol. 8, pp. 39-54, Jan. 1980.

- [9] A. Urbas and J. Osiwski, "High-Frequency Realization of C-OTA Second-Order Active Filters", Proc. IEEE/ISCAS, pp. 1106-1109, 1982.

- [10] H. S. Malvar, "Electronically Controlled Active Filters with Operational Transconductance Amplifiers", IEEE Trans. Circuits Syst., vol. CAS-29, pp. 333-336, May 1982.

- [11] R. L. Geiger and J. Ferrell, "Voltage Controlled Filter Design Using Operational Transconductance Amplifiers", Proc. IEEE/ISCAS, pp. 594-597, May 1983.

- [12] R. W. Newcomb and S. T. Liu, "A Voltage Tunable Active-R Filter", Proc. IEEE/ISCAS, pp. 409-412, May 1984.

- [13] H. S. Malvar, "Electronically Controlled Active-C Filters and Equalizers with Operational Transconductance Amplifiers", IEEE Trans. Circuits Syst., vol. CAS-31, pp. 645-649, July 1984.

- [14] 5. S. Franco, "Use of Transconductance Amplifier to make programmable active filters", Electronic Design, vol. 24, pp 98-101, Sep. 1976.

- [15] F. Krummenacher, "High-Voltage Gain CMOS OTA for Micropower SC Filters", Electron. Letters, vol. 17, pp. 160-162, Feb. 1981.

- [16] R. Senani, "New electronically tunable OTA-C sinusoidal oscillator", *Electron. Lett.*, vol. 25, no. 4, pp. 286-287, Feb. 1989.

- [17] R. Senani, M. P. Tripathi, D. R. Bhaskar and Amit Kumar Banerjee, 'Systematic generation of OTA-C sinusoidal oscillators', *Electron. Lett.*, vol. 26, no. 18, pp. 1457-1459, Aug. 1990.

- [18] D. R. Bhaskar, M. P. Tripathi and R. Senani, 'Systematic derivation of all possible canonic OTA-C sinusoidal oscillators', *J. Franklin Inst.*, vol. 330, no. 5, pp. 885-903, Sept. 1993.

- [19] C. F. Wheatley and H. A. Wittlinger, "OTA Obsoletes OP. AMP", P. Nat. Econ. Conf. pp. 152-157, Dec. 1969.

- [20] RCA Electronic Components, Linear Integrated Circuits, Model CA3060: Data File 404, Mar. 1970

- [21] National Semiconductor, Linear Applications Handbook, 1980.

- [22] RCA Solid-State Division, Data Book, Linear Integrated Circuits, File No. 475, Mar. 1975.

- [23] K. Smith, A. Sedra, "The current-conveyor a new circuit building block", IEEE Proc., vol. 56, pp. 1368-69, 1968.

- [24] A. Sedra, K. Smith, "A second-generation current-conveyor and its applications", IEEE Trans., vol. CT-17, pp. 132-134, 1970.

- [25] S. Sedra, G. W. Roberts and F. Gohh, "The current conveyor: history, progress and new results", IEEE Proc., Vol.137, 77-78, 1990.

- [26] R. Senani, "Novel circuit implementation of Current Conveyors using an OA and an OTA", Electronics Letters, IEE (UK), Vol. 16, no. 1, pp. 2-3, 1980.

- [27] C. Erdal, H. Kuntman, S. Kafali, "A Current Controlled Conveyor Based Proportional-Integral-Derivative (PID) Controller", Istanbul University Journal Of Electrical & Electronics Engineering, Vol. 4, No.2, 2004.

- [28] Nadhmia Bouaziz El Feki and Dorra Sellami Masmoudi, "High Performance Dual-Output Second and Third Generation Current Conveyors and Current-Mode Multifunction Filter Application" The 6<sup>th</sup> International Multi- Conference on Systems, Signals and Devices, 2009.

- [29] C.Thoumazou, F. Lidgey, and D.Haigh, "Analog Integrated Circuit Design: The Current mode approach", London, U.K.: IEE, 1990.

- [30] A. Fabre, "Third-generation current conveyor: a new helpful active element", Electronics Letters, vol. 31, pp. 338-339, 1995.

- [31] Giuseppe Ferri, Vincenzo Stornelli, and Mauro Fragnoli, "An integrated improved CCII topology for resistive sensor application," Analog Integr Circ Sig Process 48; 2006; pp. 247-250.

- [32] R. Chaisricharoen, B. Chipipop, and B. Sirinaovakul, "CMOS CCCII: Structures, characteristics, and considerations", Int. j. Electron. Comm. (AEO) 64, 2010, pp. 540-557.

- [33] H. Hamed and A. Khalaf, "± 1 V Supply Second Generation Current Conveyor in Standard CMOS Technology for Low Voltage Low Power Analog Circuits Applications", the 2003 46th MIDWEST Symposium on Circuits and Systems, Cairo, 2003; Vol. 1; pp. 257- 260.

- [34] S. Thankachan, M. Pattanaik, and S. S. Rajput, "A ±0.5V BiCMOS Class-A Current Conveyor," Proceedings Of World Academy Of Science, Engineering And Technology vol. 31; July 2008; ISSN 2070-3740; PWASET Volume, pp. 717-720.

- [35] J. Chant and D. Renault, "A CMOS Multiplier / Divider Based on Current Conveyor," IEEE; ISBN 0-7803-4455-3/98, 1998.

- [36] C. Premont, N. Abouchi, R. Grise and j. Chante, "A BiCMOS Current Conveyor Based Four Quadrant Analog Multiplier", Analog Integrated Circuits and Signal Processing, 19, 159-162, 1999.

- [37] H. Hamed, "Low voltage low power, highly linear CClls, and its applications," The International conference on microelectronics, ICM2003, Cairo, Egypt; pp. 59-62, Dec, 2003.

- [38] A. M. Soliman, "Novel Generation Method of Current Mode Wein Type Oscillators using Current Conveyors", Int. J. Of Electronics, vol. 85, pp. 737-747, 1998.

- [39] R. Senani, "New current-mode biquad filter", International Journal of Electronics, vol. 73, no. 4, pp. 735-742, 1992.

- [40] C. M. Chang, "Universal active current filter with single input and three outputs using CCIIs", Electronics. Letters, Vol. 29, No. 22, 1993, pp. 1932-1933.

- [41] C. M. Chang, "Novel universal current-mode filter with single input and three outputs using only five current conveyors", Electronics. Letters, Vol. 29, No. 23, 1993, pp. 2005-2007.

- [42] A. M. Soliman, "Current-mode universal filter", Electron. Lett., Vol. 31, No. 17, 1995, pp. 1420-1421, 1995.

- [43] M. T. Abuelma'atti, and M. K. Khan, "Low component current-mode universal filter", Electronics. Letters, Vol. 31, 1995, pp. 2160-2161.

- [44] S. Ozoguz, and C. Acar, "Universal current-mode filter with reduced number of active and passive components", Electronics. Letters, vol. 33, No. 11, pp. 948-949, 1997.

- [45] S. Ozoguz, A Toker, and O. Cicekoglu, "High output impedance current-mode multifunction filter with the minimum number of active elements and reduced number of passive elements", Electronics. Letters, Vol. 34, No. 19, pp. 1807-1809, 1998.

- [46] H. Y. Wang, and C. T. Lee, "Versatile insensitive current-mode universal biquad implementation using current conveyors", IEEE Transactions on Circuits and Systems-Part II, Vol. 48, No. 4, pp. 409-413, 2001.

- [47] A. Toker, and S. Ozoguz, "Insensitive current- mode universal filter using dual output current conveyors", Int. J. Electron., Vol. 87, No. 6, pp. 667-674, 2000.

- [48] S. H. Tu, C. M. Chang, and K. P. Liao, "Novel versatile insensitive universal current-mode biquad employing two second-generation current conveyors", International Journal of Electronics, Vol. 89, No. 12, pp. 897-903, 2002.

- [49] C. M. Chang, "Universal active current filters using single second-generation current conveyor", Electronics Letters, Vol. 27, No. 18, pp. 1614-1617, 1991.

- [50] C. M. Chang, C. C. Chien, and H. Y. Wang, "Universal active current filters using single second-generation current conveyor", Electronics Letters, Vol. 29, No. 13, pp. 1159-1160, 1993.

- [51] A. Toker, H. Kuntman, O. Cicecoglu and M.Disirgil, "New oscillator topologies using inverting second generation current conveyor". Turkj Elec. Engineering, vol. 10, No. 1, 2002.

- [52] A. Assi, M. Sawan, and J. Zhu, "An offset compensated and high-gain CMOS current feedback op-amp," IEEE Trans. Circuits and Systems, vol.45, no. 1, pp. 85-90, Jan. 1998.

- [53] A. M. Ismail and A. M. Soliman, "Novel CMOS current feedback opamp realization suitable for high frequency applications," IEEE Trans. Circuit Systems, vol. 47, pp. 918-921, 2000.

- [54] R. Mita, G. Palumbo, and S. Pennisi, "Low-voltage high-drive CMOS current feedback op-amp", IEEE Trans. Circuit Syst.-II, vol. 52, pp. 317- 321, 2005.

- [55] B. J. Maundy, I. G. Finvers, and P. Aronhime, "Alternative realizations of CMOS current-feedback amplifiers for low-voltage applications," Anal. Int. Circuits Signal Process., vol. 32, pp. 157-168, Dec. 2002.

- [56] K. Manetakis and C. Toumazou, "Current-feedback op amp suitable for CMOS VLSI technology," Elect. Letters, vol. 32, no. 12, pp. 1090–1092, Jun. 1996.

- [57] S. A. Mahmoud and A. M. Soliman, "Novel MOS-C oscillators using the current feedback opamp," Int. J. Electron., vol. 87, pp. 269-280, 2000.

- [58] E. Bruun, "A dual current feedback op amp in CMOS current Conveyor," Electron. Lett., vol. 34, pp. 2368-2369, 1998.

- [59] A.H. Madian, S. A. Mahmoud and A. M. Soliman, "New 1.5-V CMOS Current Feedback Operational Amplifier," 13<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems, 10-13 Dec. 2006.

- [60] S. A. Mahmoud and A. M. Soliman, "Novel MOS-C balanced-input balanced-output filter using the current feedback operational amplifier," Int. J. Electron., vol. 84, pp. 479-485, 1998.

- [61] A. Toker, O. Çiçekoğlu and H. Kuntman, "On the oscillator implementations using a single current feedback op-amp", Computers and Electrical Engineering, 28, No.5, 375-389, 2002.

- [62] P.A. Martinez, J. Sabadell, C.Aldea, "Grounded resistor controlled sinusoidal oscillator using CFOAs", Electron Letters, vol. 33, no.5, pp. 346–7, 1997.

- [63] R. Senani, V.K. Singh, "Novel single-resistance controlled- oscillator configuration using current feedback amplifiers", IEEE Trans. Circuits Systems-Fundamental Theory Appl., vol.43, no. 8, pp.698–700, 1996.

- [64] S.I. Liu, J.H. Tsay, "Single-resistance-controlled sinusoidal oscillator using current-feedback amplifiers", Inter. J. Electron, vol. 80, no. 5, pp. 661–664, 1996.

- [65] C. Acar & S. Ozoguz, "A new versatile building block: current differencing buffered amplifier suitable for analog signal processing filters," Microelectronics Journal, 30, 157–160, 1999.

- [66] Ali Umit Keskin, Erhan Hancioglu, "Current mode multifunction filter using two CDBAs," AEU INT. J. Electron. Comm., vol. 56, pp.495-498, 2002.

# **CHAPTER III**

# DESIGN AND IMPLEMENTATION OF SINGLE ENDED PID CONTROLLER

# 3.0 Introduction

In the present chapter, we present a review of the design of single ended PID controllers using current mode/voltage mode active building blocks. These controllers have been designed, based on the signal flow graph of a PID controller given in [2]-[5]. The current mode/voltage mode active building blocks used are OTA, CCCII, CFA and CDBA. The terminal equations characterizing these blocks have been used for designing a single ended PID controller. Detailed simulation results for OTA and DOCCII-based PID controllers are also presented.

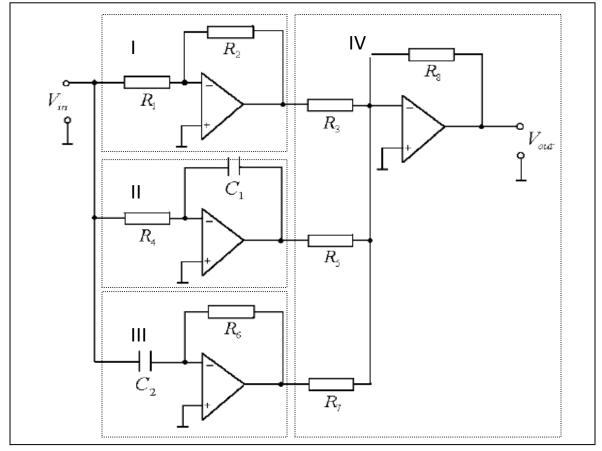

### 3.1 Traditional PID controller design based on operational-amplifier

Before we present the detailed design and simulation results of the single ended PID controllers based on other devices it is worthwhile to have a look at the traditional op-amp based PID controller which is presented in fig. 3.1.1[1].

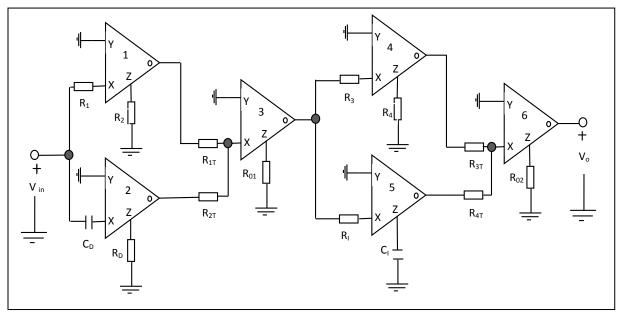

Fig. 3.1.1: Traditional PID controller constructed with op-amps

In this figure, P, I, D and summer operations are recognized by I, II, III and IV respectively. It can be seen that the circuit employs four op-amps and ten floating passive elements.

The transfer function of a PID controller can be written as follows (given in [1])

$$\frac{V_O(s)}{V_I(s)} = K_P + \frac{K_I}{s} + sK_D = \frac{K_D s^2 + K_P s + K_I}{s}$$

Here,

Proportional constant,

$$K_p = \frac{R_2 R_8}{R_1 R_3}$$

Integral constant,

$$K_I = \frac{R_8}{C_1 R_4 R_5}$$

Derivative constant,

$$K_D = \frac{R_6 C_2 R_8}{R_7}$$

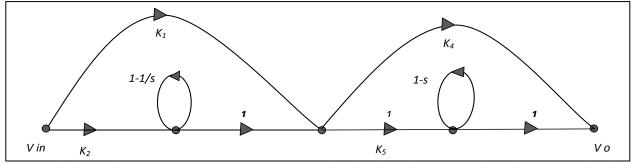

The signal flow graph representation of above equation is given in fig. 3.1.2 which is consisting of the sub-graphs for proportional, integral and derivative parts of the controllers.

**Fig. 3.1.2:** Signal flow graph corresponding to the transfer function of the proportional-integral-derivative (PID) Controller

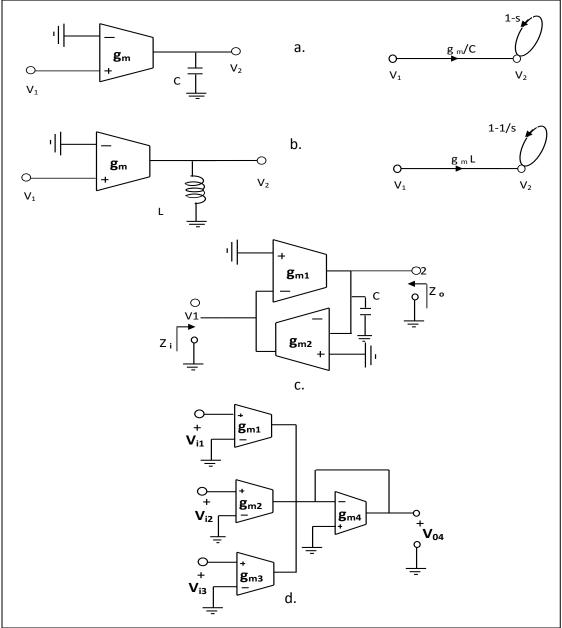

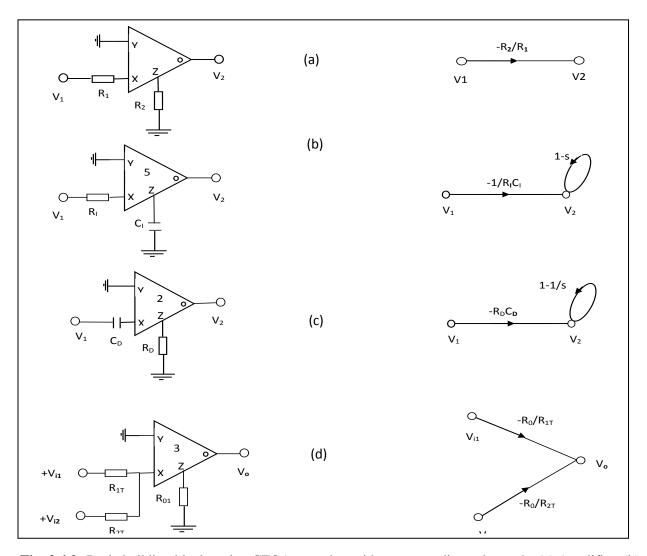

#### 3.2 OTA-C based PID controller

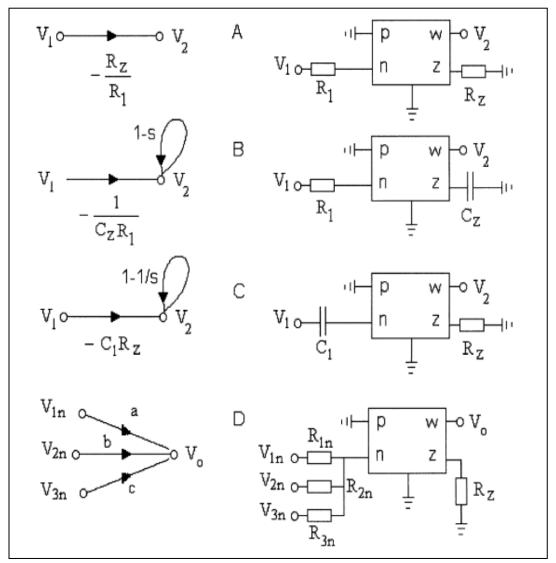

Based on the signal flow graph shown in fig. 3.1.2, the subgraphs and their corresponding blocks, using OTA-Cs are shown in following fig. 3.2.1 [2]. The circuit details of OTA-C are discussed in chapter 2. With the help of characteristics of the OTA-C circuit (defined in chapter 2), a voltage mode integrator is shown in fig. 3.2.1(a) and a voltage mode differentiator containing an inductor is shown in fig. 3.2.1(b), which is used for the realization of differentiator circuit as given in fig. 3.2.1(c). A summer circuit can be represented as shown in fig. 3.2.1(d) [2].

Fig. 3.2.1: Basic building blocks using OTAs and grounded capacitors together with corresponding signal flow graphs (a) Integrator circuit (b) Derivative circuit (c) Inductance element (d) Summing circuit

In fig. 3.2.1(c), OTA-C based gyrator circuit gives input impedance

$$Z_i = 1/g_{m1}g_{m2}Z_o = sC/g_{m1}g_{m2}$$

From above equation, it can be observed that  $Z_i$  is proportional to s, so this circuit behaves as an inductor. This inductance and the OTA build a derivative circuit. The capacitor C, together with the OTA (see fig. 3.2.1(a.)) forms the integration circuit. The OTAs, shown in above fig. 3.2.1(d), form the weighted summing circuit.

Connecting all these sub-circuits as shown in above fig. 3.2.1, into a single block as shown in fig. 3.2.2, performs the operation of a PID controller.

**Fig. 3.2.2:** An OTA-C based proportional-integral-derivative (PID) controller realization from [2] corresponding to the signal flow graph in Fig. 3.1.2.

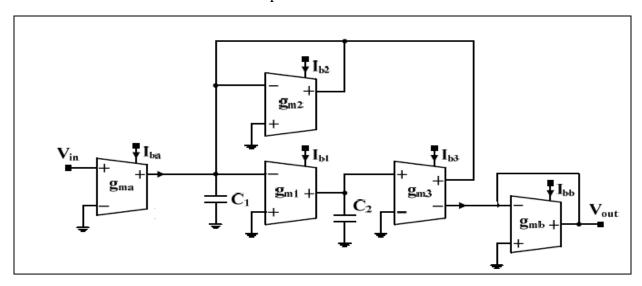

In fig. 3.2.2, the derivative circuit is configured by simulation of gyrator which is introduced by connecting two OTAs  $g_{m2}$  and  $g_{m3}$ , together with the capacitor C1 shown in fig. 3.2.2. The capacitor C2 and OTA  $g_{m4}$  form the integration circuit. The OTAs  $g_{m5}$ ,  $g_{m6}$ ,  $g_{m7}$  and  $g_{m8}$  form the weighted summing circuit. OTAs  $g_{m5}$  and  $g_{m8}$  form the proportional gain.

$$K_P = g_{m5}/g_{m8}$$

$K_I = \frac{g_{m4}}{C_2} \frac{g_{m7}}{g_{m8}}$

$K_D = \frac{g_{m1}C_1}{g_{m2}g_{m3}} \frac{g_{m6}}{g_{m8}}$

The controller gain can be assigned to the prescribed values by adjusting OTAs' transconductances,  $g_{mi}$ ; i = (1-8), by DC control voltages.

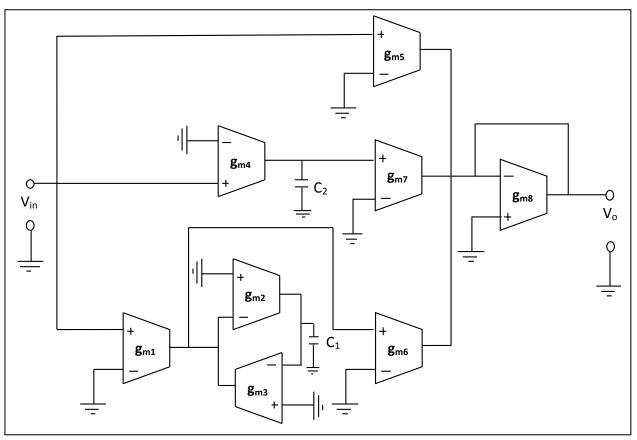

# 3. 3 Current-Controlled Conveyor based PID controller

Based on the signal flow graph as shown in fig. 3.1.2, the subgraphs and their corresponding blocks using current controlled current conveyors (CCCIIs) are shown in following fig. 3.3.1 [3]. The circuit details of CCCII are discussed in chapter 2. In fig. 3.3.1(a), block-diagram and signal flow graph of an amplifier circuit is shown. Fig. 3.3.1(b) and 3.3.1(c) represent the signal flow graphs and blocks of an integration circuit and of a derivative circuit, respectively. From the fig. 3.3.1(c), the value of derivative time constant is equal to  $L/R_x$  where Inductance L is realized through a routine analysis [3] and it gives the value of impedance for inductance simulation

$$Z_i = sR_{X1}R_{X2}C_D$$

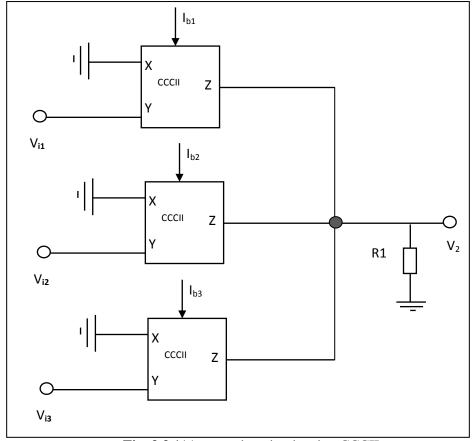

**Fig. 3.3.1:** Sub-graphs and corresponding active sub-circuits involve CCCII (a) Amplifier, (b) integrator, (c) derivative circuit, (d) inductance simulation

Fig. 3.3.1(e): summing circuit using CCCII

For the proportional gain in a PID controller, the CCCII is connected together with a resistor R1 as shown in the fig. 3.3.1(a). For the integration circuit, the CCCII is connected together with the capacitor C1 as shown in the fig. 3.3.1(b). For the derivative term in a PID controller, an inductance is connected together with the CCCII. This inductance, having a value of  $L=R_{x1}R_{x2}C_2$  is simulated through two CCCIIs (see fig. 3.3.1(c)), which is connected together with the capacitor  $C_2$  (see fig. 3.3.1(d)). In fig. 3.3.1(e), the weighted summing circuit is represented by three CCCIIs.

Connecting all these sub-circuits as shown in above fig. 3.3.1, into a single block as shown in fig. 3.3.2, gives the operation of a PID controller.

**Fig. 3.3.2:** Proposed CCCII-based PID controller realization from [3] corresponding to the signal-flow graph shown in fig. 3.1.2.

Taking ideal values, the circuit in fig. 3.3.2 gives the values of controller gains as follows

$$K_P = \frac{R_0 R_1}{R_{X1} R_{X6}}$$

$$K_I = \frac{R_0}{R_{X2} R_{X7} C_1}$$

$$K_D = \frac{R_{X4} R_{X5} R_0 C_2}{R_{X3} R_{X8}}$$

$R_{Xi}$  is the input resistance of  $i^{th}$  CCCII active element, here i=1; 2:::; 8. From above equations, it can be seen that the controller gains associated with X input resistances of CCCIIs and this can be adjusted by the control current,  $I_{bi}$  of a selected CCCII.

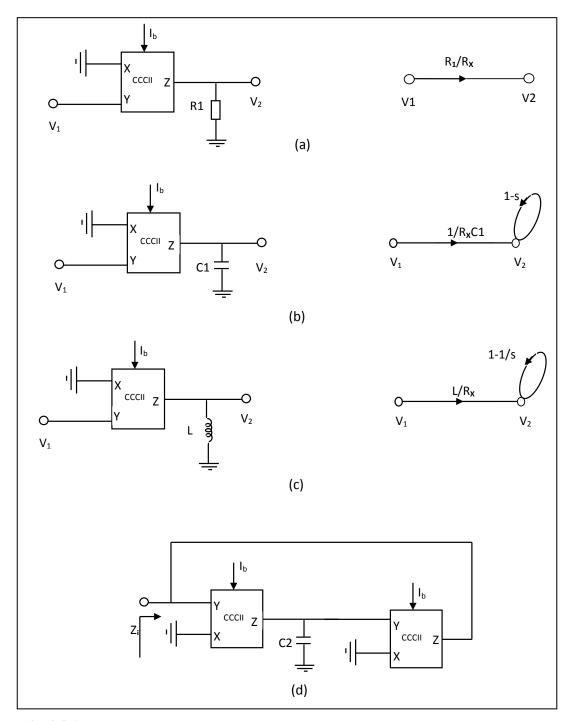

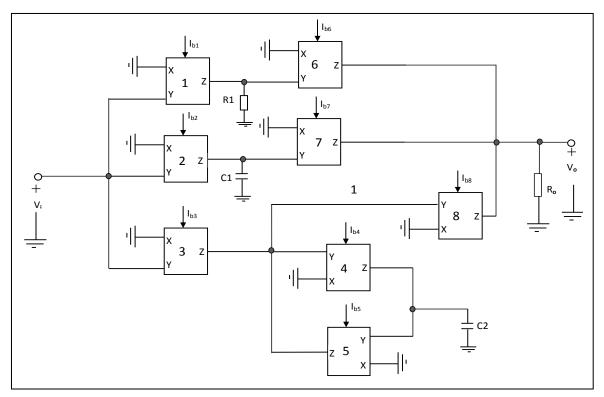

#### 3.4 CFA based PID controller

Based on the signal flow graphs as shown in fig. 3.4.1, the subgraphs and their corresponding blocks using active building blocks of CFAs, are shown in fig. 3.4.2 [4]. The circuit configuration of CFA is discussed in chapter 2. In fig. 3.4.2(a), block and signal flow graph of an amplifier circuit is shown. Fig. 3.4.2(b) and 3.4.2(c) represent the signal flow graph and block of

an integration circuit and of a derivative circuit, respectively. Fig. 3.4.2(d) represents block with corresponding signal flow graph of a summing circuit.

**Fig. 3.4.1:** Signal flow graph corresponding to the transfer function of the proportional-integral-derivative (PID) Controller

**Fig. 3.4.2:** Basic building blocks using CFOAs together with corresponding sub-graphs (a) Amplifier, (b) integrator, (c) derivative circuit, (d) summing circuit.

Fig. 3.4.2 (a) gives a value of  $-R_2/R_1$  for the proportional gain, fig. 3.4.2(b) & (c) give the value of  $1/R_1C_1$  for the time constant in the integrator circuit and of  $R_DC_D$  for the derivative time constant, respectively. Connecting all these blocks as shown in fig. 3.4.2, in such a way they can perform the operation of a PID controller as shown in fig. 3.4.3.

Fig. 3.4.3: A CFA based PID controller from [4] corresponding to the signal flow graph in fig. 3.4.1

Considering all ideal cases to adjust all gains as unity, the controller coefficients are given below

$$K_P = \frac{R_2 R_4}{R_1 R_3} + \frac{R_D C_D}{R_I C_I}$$

$$K_I = \frac{R_2}{R_1 C_I R_I}$$

$$K_D = \frac{R_D C_D R_4}{R_3}$$

# 3.5 CDBA based PID Controller:

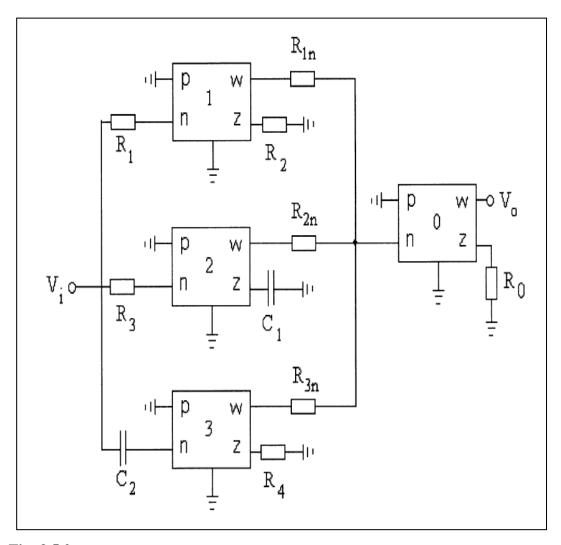

On the basis of a signal-flow graph as shown in fig. 3.1.2, the subgraphs and their corresponding blocks using CDBAs are shown in fig. 3.5.1 [5]. The circuit's details of CDBAs are discussed in chapter 2.

**Fig. 3.5.1:** Sub-graphs for the PID controller and their corresponding CDBA based sub-circuits. The coefficients in sub-graph D are  $a = -R_Z/R_{1n}$ ,  $b = -R_Z/R_{2n}$ ,  $c = -R_Z/R_{3n}$ .

Connecting all these blocks as shown in fig. 3.5.1, into a single block as shown in fig. 3.5.2, they perform the operation of a PID controller.

Fig. 3.5.2: CDBA-based PID controller circuit from [5]. All voltages are referred to ground.

Taking all ideal values, the coefficients of PID controllers are given below [5]

$$K_{P} = \frac{R_{0}R_{2}}{R_{1}R_{1n}}$$

$$K_{I} = \frac{R_{0}}{R_{3}C_{1}R_{2n}}$$

$$K_{D} = \frac{R_{0}C_{2}R_{4}}{R_{3n}}$$

# 3.6 Simulation

### 3.6.1 Implementation of OTA-C based PID controller

The voltage mode PID controller as shown in fig 3.2.2, was used to implement a closed loop system by cascading it with the following second order system and its open loop (without controller) and closed loop time (without/with controller) response was simulated in PSPICE. The details of the simulation results are presented below.

Fig. 3.6.1-1: OTA-C based voltage mode second order system [10]

The second order system [10] shown in fig. 3.6.1-1 gives the following transfer function

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{g_{m1}g_{m3}/C_1C_2}{s^2 + sg_{m2}/C_1 + g_{m1}g_{m3}/C_1C_2}$$