## "Managing Reactive Power Using Cascaded Multilevel D-STATCOM in

Sub-Transmission/11kV Distribution System"

A Dissertation Submitted in the Partial Fulfilment for the Degree of

**Master of Technology**

in

## **Power System Engineering**

Submitted By Tapesh Vishnoi Roll No. 11/P.Sy./09

Under the guidance of **Dr. Vishal Verma**

Department of Electrical Engineering Delhi Technological University (Formerly Delhi College of Engineering) Shahbad Daulatpur, Bawana Road New Delhi -110042 June 2011

#### CERTIFICATE

It is certified that **Mr. Tapesh Vishnoi** Roll No. **11/P.Sy./09**, student of **M.Tech. Power System Engineering**, Department of Electrical Engineering, Delhi Technological University, has submitted the dissertation entitled "Managing Reactive Power Using Cascaded **Multilevel D-STATCOM in Subtransmission/11kV Distribution System**" under my guidance towards partial fulfilment of the requirements for the award of the degree of Master of Technology (Power System Engineering).

The dissertation is a bonafide work record of project work carried out by him under my guidance and supervision. His work is found to be outstanding and his discipline impeccable during the course of the project.

I wish him success in all his endeavours.

Dr. Vishal Verma

Associate Professor

Department of Electrical Engineering

Delhi Technological University.

#### ACKNOWLEDGMENT

The completion of any project brings with it a sense of satisfaction, but it is never complete without thanking those people who made it possible and whom constant support has crowned my efforts with success.

One cannot even imagine the power of the force that guides us all and neither can we succeed without acknowledging it. My deepest gratitude to **Almighty God** for holding my hands and guiding me throughout my lives.

I would like to thank my beloved parents, who always give me strong inspirations, moral supports, and helpful suggestions. Without them, my study career would never have begun. It is only because of them, my life has always been full of abundant blessing.

I would like to devote my gratitude and thanks to my guide **Dr. Vishal Verma**, **Associate Professor**, **Department of Electrical Engineering**, **Delhi Technological University**, **Delhi** for his valuable guidance, constant encouragement and helpful discussions throughout the course of this work. Obviously, the progress I had now will be uncertain without his guidance.

I would also like to thank **Prof. Narendra Kumar**, **H.O.D. Electrical Engineering Department**, **Delhi Technological University**, **Delhi** for providing me better facilities and constant encouragement.

At last but not least I would like to express my vote of thanks to my brothers **Mr. Rajat Thapan** and **Mr. Vishesh Vishnoi** for their support and encouragement.

**TAPESH VISHNOI**

#### 11/P.Sy./09

#### ABSTRACT

This thesis investigates the problems associated with 11kV distribution system in terms of delivery of clean power and their solutions, in particular the reactive power compensation. The abnormalities in the distribution system has been modelled and analysed. Any deviation from the ideal condition has been computed in the time domain at every instant. The deviation so computed has been compensated by use of the D-STATCOM in the real time. A detailed model of 3-phase bridge D-STATCOM for line voltage upto 11kV has been developed using cascaded multilevel voltage source converter structure (VSCs). A same phase multilevel PWM control has been developed for the multilevel inverter for the medium voltage distribution system. The scheme has been replaced for the control of the D-STATCOM so that it maintains the reactive power and THD under control by keeping all the voltage and current waveforms as per their standard sinusoidal forms. The proposed system has been presented with the mathematical equations and block diagrams for detailed illustrations of the control loops. A SIMULINK model using MATLAB/SIMULINK platform has been used to present the proposed system. Simulation result for different operating condition has been obtained and analysed for viewing the merit of the proposed control technique. The obtained results corroborate the effectiveness of control scheme.

## **TABLE OF CONTENTS**

| COVI   | ER PA        | GE     |            |                                    | i        |

|--------|--------------|--------|------------|------------------------------------|----------|

| CERT   | <b>FIFIC</b> | ATE    |            |                                    | ii       |

| ACKI   | NOWI         | DEGEN  | MENT       |                                    | iii      |

| ABST   | [RAC         | Г      |            |                                    | iv       |

| CON    | ΓΕΝΤ         | S      |            |                                    | V        |

| LIST   | OF FI        | GURES  |            |                                    | viii     |

| LIST   | OF TA        | ABLES  |            |                                    | xi       |

| S. No. |              |        |            | CHAPTER NAME                       | Page No. |

| 1      | INT          | RODU   | ΓΙΟΝ       |                                    | 1-10     |

|        | 1.1          | Genera | ıl         |                                    | 2        |

|        | 1.2          | Power  | Quality Is | ssues                              | 2        |

|        |              | 1.2.1  | Poor Lo    | ad Factor                          | 3        |

|        |              | 1.2.2  | Harmon     | ic Contents in Loads               | 3        |

|        |              | 1.2.3  | Unbalan    | ced Loads                          | 3        |

|        |              | 1.2.4  | Notchin    | g in Load Voltage                  | 3        |

|        |              | 1.2.5  | DC Offs    | set in Load Voltage                | 4        |

|        |              | 1.2.6  | Voltage    | Sag/Swell                          | 4        |

|        |              | 1.2.7  | Short tir  | ne Overvoltage/Undervoltage        | 4        |

|        |              | 1.2.8  | Voltage    | Flicker                            | 4        |

|        |              | 1.2.9  | Power F    | Frequency Variation                | 4        |

|        | 1.3          | Custon | n Power (  | PQ Improvement Devices)            | 5        |

|        |              | 1.3.1  | Network    | c Configuration Type Devices       | 5        |

|        |              |        | 1.3.1.1    | Solid State Current Limiter (SSCL) | 5        |

|        |              |        | 1.3.1.2    | Solid State Circuit Breaker (SSCB) | 6        |

|        |              |        | 1.3.1.3    | Solid State Transfer Switch (SSTS) | 6        |

|        |              | 1.3.2  | Compen     | sating Devices                     | 7        |

|        |              |        | 1.3.2.1    | Distribution STATCOM (D-STATCOM)   | 7        |

|        |              |        | 1.3.2.2    | Dynamic Voltage Restorer (DVR)     | 8        |

|        |              |        | 1.3.2.3    | Unified Power Quality Conditioner  | 8        |

|   | 1.4 | Multilevel Structure for High/Medium Voltage System         | 9     |

|---|-----|-------------------------------------------------------------|-------|

|   | 1.5 | Organization of Dissertation                                | 10    |

| 2 | LIT | ERATURE SURVEY                                              | 11-38 |

|   | 2.1 | General                                                     | 12    |

|   | 2.2 | Literature Reviews                                          | 12    |

|   |     | 2.2.1 Survey for Multilevel Converter                       | 13    |

|   |     | 2.2.1.1 Diode Clamped Multilevel Inverter (DCMI)            | 13    |

|   |     | 2.2.1.2 Flying-Capacitor Multilevel Inverter (FCMI)         | 15    |

|   |     | 2.2.1.3 Cascaded H Bridge Inverters with Separated DC       | 17    |

|   |     | Sources                                                     |       |

|   |     | 2.2.2 Modulation Technique                                  | 19    |

|   |     | 2.2.2.1 Hysteresis Control                                  | 19    |

|   |     | 2.2.2.2 Multilevel carrier-based PWM                        | 20    |

|   |     | 2.2.3 Multilevel D-STATCOM                                  | 36    |

|   | 2.3 | Identified Research Areas                                   | 38    |

|   | 2.4 | Conclusion DELLECH                                          | 38    |

| 3 | МО  | DELLING OF THE MUTILEVEL D-STATCOM                          | 39-50 |

|   | 3.1 | General                                                     | 40    |

|   | 3.2 | Modelling of the CHBMI based Multilevel D-STATCOM           | 40    |

|   | 3.3 | Control Strategy for the D-STATCOM                          | 44    |

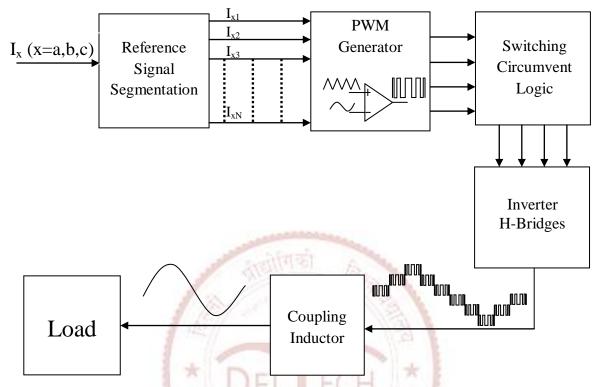

|   |     | 3.3.1 Control of the Cascaded H- Bridge Multilevel Inverter | 44    |

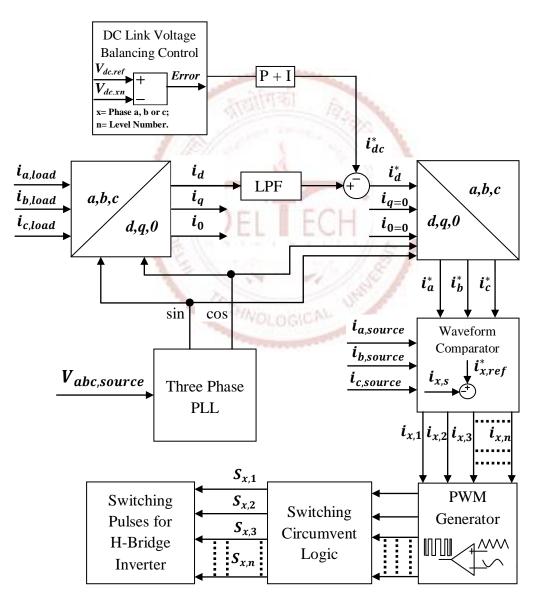

|   |     | 3.3.2 Control of the Multilevel D-STATCOM                   | 46    |

|   | 3.4 | Conclusion                                                  | 49    |

| 4 | PER | RFORMANCE EVALUATION OF THE PROPOSED SYSTEM                 | 51-81 |

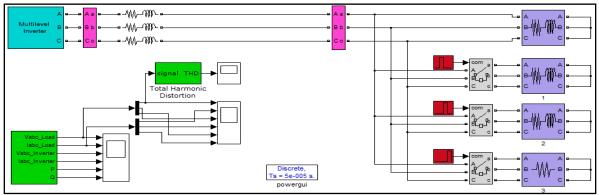

|   | 4.1 | General                                                     | 52    |

|   | 4.2 | Cascaded H- Bridge Multilevel Inverter (CHBMI)              | 52    |

|   |     | 4.2.1 Three Level Inverter                                  | 53    |

|   |     | 4.2.1.1 Model Description                                   | 53    |

|      |      |       | 4.2.1.2   | Results and Discussion                          | 54    |

|------|------|-------|-----------|-------------------------------------------------|-------|

|      |      | 4.2.2 | Five Lev  | vel Inverter                                    | 56    |

|      |      |       | 4.2.2.1   | Model Description                               | 56    |

|      |      |       | 4.2.2.2   | Results and Discussion                          | 56    |

|      |      | 4.2.3 | Seven L   | evel Inverter                                   | 59    |

|      |      |       | 4.2.3.1   | Model Description                               | 59    |

|      |      |       | 4.2.3.2   | Results and Discussion                          | 59    |

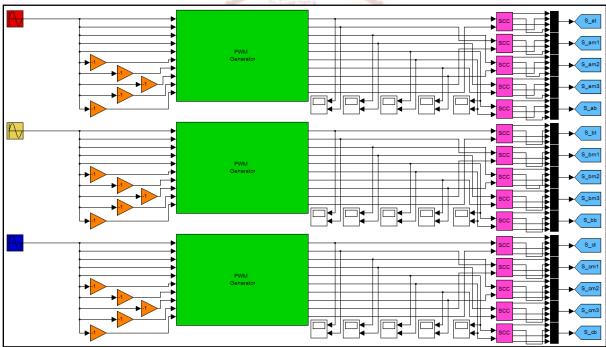

|      |      | 4.2.4 | Nine Le   | vel Inverter                                    | 62    |

|      |      |       | 4.2.4.1   | Model Description                               | 62    |

|      |      |       | 4.2.4.2   | Results and Discussion                          | 62    |

|      |      | 4.2.5 | Eleven I  | Level Inverter                                  | 65    |

|      |      |       | 4.2.5.1   | Model Description                               | 65    |

|      |      |       | 4.2.5.2   | Results and Discussion                          | 65    |

|      | 4.3  | Casca | ded H-Br  | idge Based Multilevel D-STATCOM                 | 69    |

|      |      | 4.3.1 | Applicat  | tion of D-STATCOM for Reactive Power Management | 70    |

|      |      |       | 4.3.1.1   | Control Strategy                                | 70    |

|      |      |       | 4.3.1.2   | Results and Discussion                          | 71    |

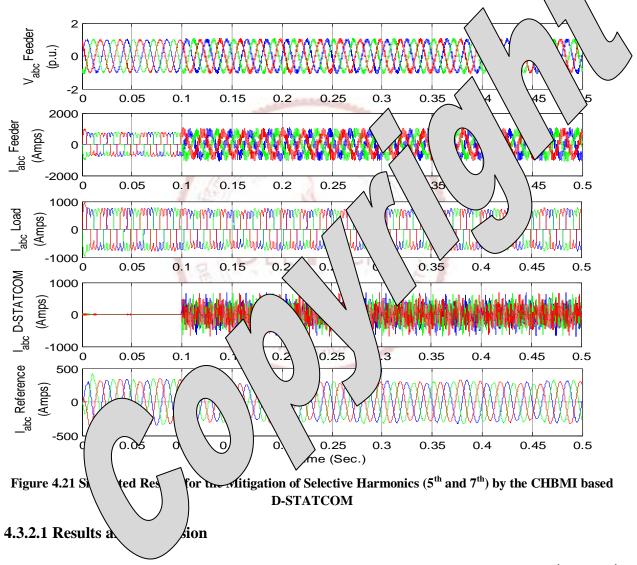

|      |      | 4.3.2 | Applicat  | tion of D-STATCOM for Selective Harmonic        | 78    |

|      |      |       | 4.3.2.1   | Control Strategy                                | 79    |

|      |      |       | 4.3.2.2   | Results and Discussion                          | 80    |

|      | 4.4  | Concl | usions    |                                                 | 81    |

| 5    | MAI  | N CON | CLUSIC    | ON AND FUTURE SCOPE OF THE WORK                 | 82-83 |

|      | 5.1  | Gener | al        |                                                 | 83    |

|      | 5.2  | Main  | Conclusio | Dn                                              | 83    |

|      | 5.3  | Sugge | stion For | Future Work                                     | 83    |

| REFE | RENC | CES   |           |                                                 | 85    |

## LIST OF FIGURES

| FIGURE | DESCRIPTION                                                                                              | Page No.  |

|--------|----------------------------------------------------------------------------------------------------------|-----------|

| 1.1    | Basic Configuration of SSCL.                                                                             | 6         |

| 1.2    | Basic Configuration of SSCB.                                                                             | 6         |

| 1.3    | Basic Configuration of SSTS.                                                                             | 6         |

| 1.4    | Schematic Diagram of D-STATCOM.                                                                          | 7         |

| 1.5    | Schematic Diagram of Capacitor Supported DVR.                                                            | 8         |

| 1.6    | Schematic Diagram of Right Shunt UPQC Configuration.                                                     | 9         |

| 2.1    | A Single Phase Five Level DCMI.                                                                          | 14        |

| 2.2    | A Single-Phase Five-Level Flying-Capacitor Inverter.                                                     | 16        |

| 2.3    | Single-Phase Structure of a Two-Cell Cascaded Inverter.                                                  | 18        |

| 2.4    | Classification of PWM Multilevel Converter Modulation Strategies.                                        | 20        |

| 2.5    | Simulation of Modulation Signals and Their Line-Line Output Voltage                                      | e 21      |

|        | Using Five Separate dc Sources (60 volts each dc Source) Cascaded                                        | L         |

|        | Multilevel Inverter With Three Major Conventional Carrier-Based PWM                                      | L         |

|        | Techniques at Unity Modulation Index and 2 kHz Switching Frequency. (a)                                  | 1         |

|        | SPWM, (b) THPWM, (c) SVM.                                                                                |           |

| 2.6    | Different Type of PWM Techniques.                                                                        | 22        |

| 2.7    | Multilevel Carrier-Based SH-PWM Showing Carrier Bands, Modulation                                        | a 24      |

|        | Waveform, and Inverter Output Waveform (m = 6, $m_f = 21$ , $m_a = 0.8$ ).                               |           |

| 2.8    | Multilevel Carrier-Based SFO-PWM Showing Carrier Bands and Inverter                                      | 25        |

|        | Output Waveform (m = 6, $m_f = 21$ , $m_a = 0.8$ ).                                                      |           |

| 2.9    | SFO-PWM where Carriers Have Different Showing Carrier Bands,                                             | , 25      |

|        | Modulation Waveform Frequencies ( $m_a = 0.85$ , $m_f = 15$ for Band <sub>2</sub> , Band <sub>-2</sub> ; | ,         |

|        | $m_f = 55$ for Band <sub>1</sub> , Band <sub>-1</sub> , Band <sub>0</sub> , $\phi = 0.10$ rad).          |           |

| 2.10   | Level Reductions in a Six-Level Inverter at Low Modulation Indices.                                      | 26        |

| 2.11   | Reference Rotation among Carrier Bands Rotation at Low Modulation                                        | <b>28</b> |

|        | Indices ( $m_a < 0.5$ ).                                                                                 |           |

| 2.12   | Preferred Method of Reference among Carrier Bands with 3× Carrier                                        | 29        |

|        | Frequency at Very Low Modulation Indices.                                                                |           |

| 2.13   | Alternate Method of Reference Rotation among Carrier Bands with $3\times$ | 29 |

|--------|---------------------------------------------------------------------------|----|

|        | Carrier Frequency at Very Low Modulation Indices.                         |    |

| 2.14   | Voltage Space Vector for a Six–Level Inverter.                            | 30 |

| 2.15   | Multiplexer Model of a Diode- Clamped Six-Level Inverter.                 | 30 |

| 2.16   | Sinusoidal Reference and Inverter Output Voltage States in d-q Plane.     | 33 |

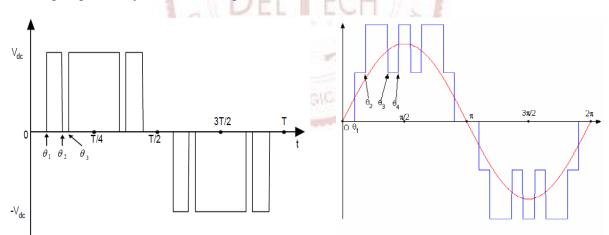

| 2.17   | Output Waveform of Virtual Stage PWM Control.                             | 34 |

| 2.18   | Unipolar Switching Output Waveform.                                       | 34 |

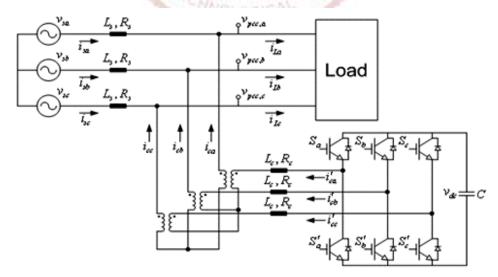

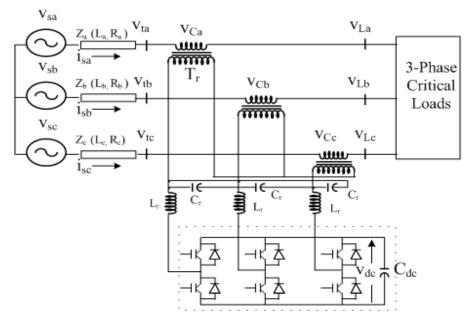

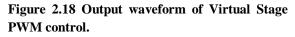

| 3.1    | Schematic Diagram of the Proposed DSTATCOM Based on Cascaded H-           | 41 |

|        | bridge Multilevel Inverter.                                               |    |

| 3.2    | Schematic Diagram of Control Module for the CHBMI.                        | 45 |

| 3.3    | Schematic Diagram of Control Module for CHBMI based D-STATCOM.            | 46 |

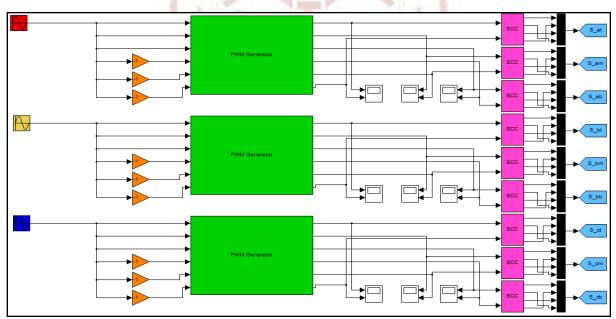

| 4.1    | SIMULINK Model for Multilevel Inverter.                                   | 52 |

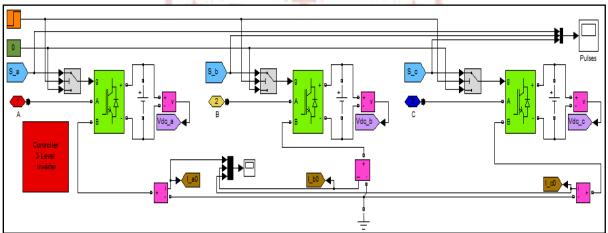

| 4.2.1  | SIMULINK Model of Three Level Cascaded H-Bridge Multilevel Inverter.      | 53 |

| 4.2.2  | Controller for Three Level Cascaded H-Bridge Multilevel Inverter.         | 54 |

| 4.3    | Simulated Results for Three Level Cascade H-Bridge Inverter.              | 55 |

| 4.4.1  | SIMULINK Model of Five Level Cascaded H-Bridge Multilevel Inverter.       | 56 |

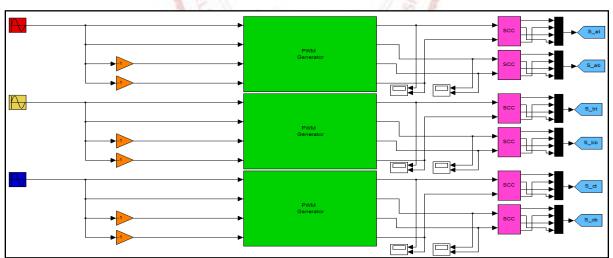

| 4.4.2  | Controller for Five Level Cascaded H-Bridge Multilevel Inverter.          | 57 |

| 4.5    | Simulated Results for Five Level Cascade H-Bridge Inverter.               | 58 |

| 4.6.1  | SIMULINK Model of Seven Level Cascaded H-Bridge Multilevel Inverter.      | 59 |

| 4.6.2  | Controller for Seven Level Cascaded H-Bridge Multilevel Inverter.         | 60 |

| 4.7    | Simulated Results for Seven Level Cascade H-Bridge Inverter.              | 61 |

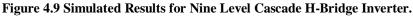

| 4.8.1  | SIMULINK Model of Nine Level Cascaded H-Bridge Multilevel Inverter.       | 62 |

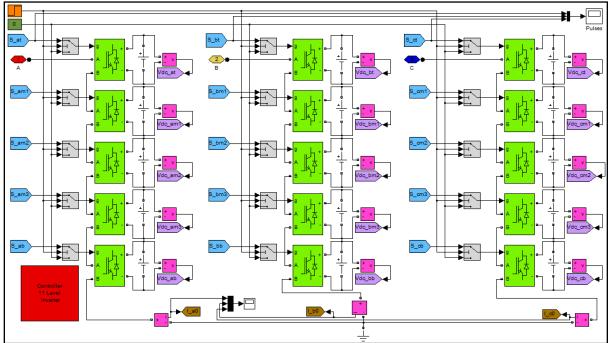

| 4.8.2  | Controller for Nine Level Cascaded H-Bridge Multilevel Inverter.          | 63 |

| 4.9    | Simulated Results for Nine Level Cascade H-Bridge Inverter.               | 64 |

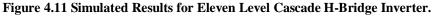

| 4.10.1 | SIMULINK Model of Eleven Level Cascaded H-Bridge Multilevel               | 65 |

|        | Inverter.                                                                 |    |

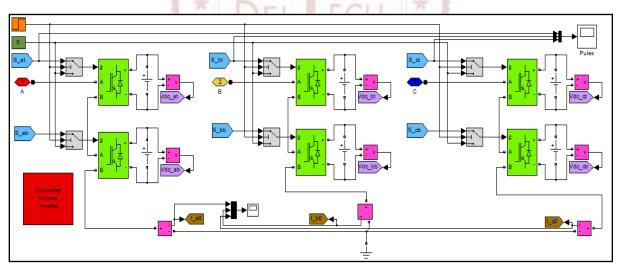

| 4.10.2 | Controller for Nine Level Cascaded H-Bridge Multilevel Inverter.          | 66 |

| 4.11   | Simulation Results for Eleven Level Cascade H-Bridge Inverter.            | 67 |

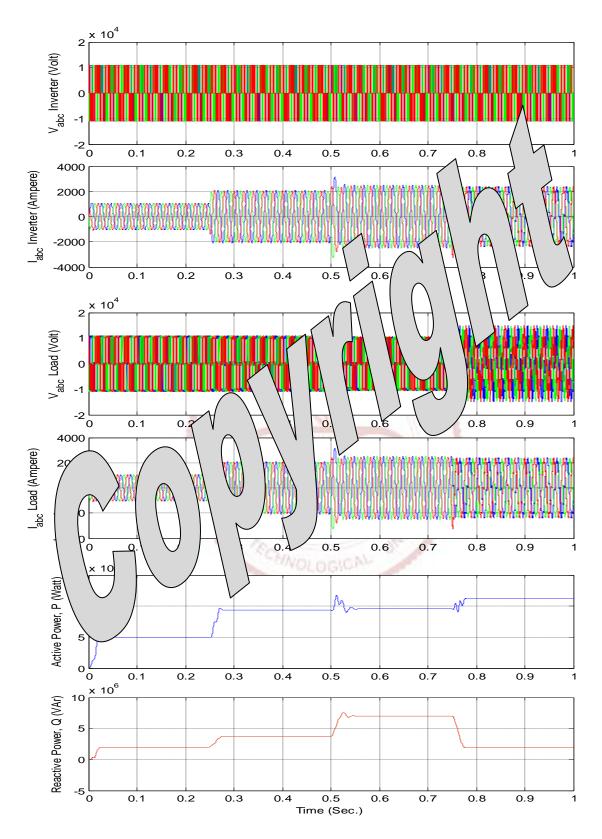

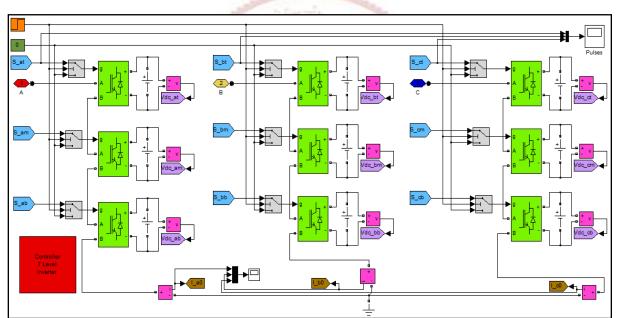

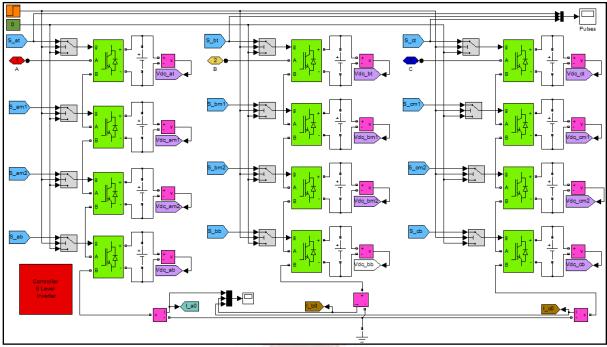

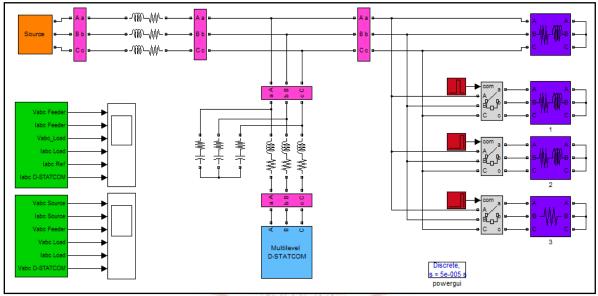

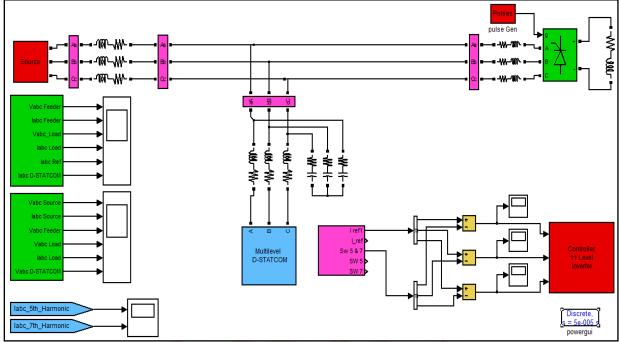

| 4.12.1 | SIMULINK Model of Distribution System Employed With 11-Level              | 70 |

|        | Cascaded H-Bridge Multilevel D-STATCOM.                                   |    |

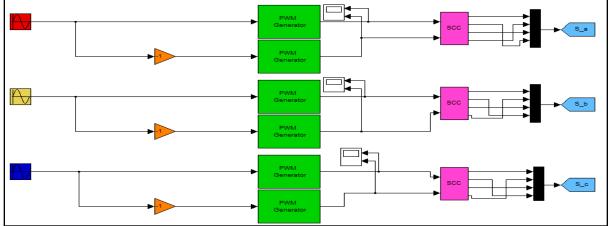

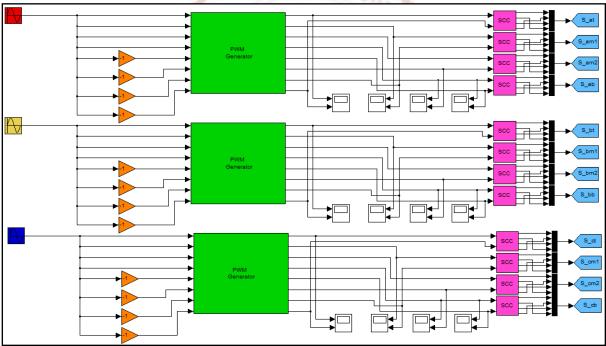

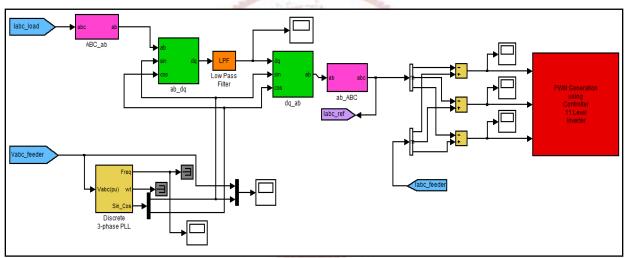

- 4.12.2 Controller of the Multilevel D-STATCOM for Reactive Power 71Compensation Having Controller for the 11 Level Inverter as a Subsystem.

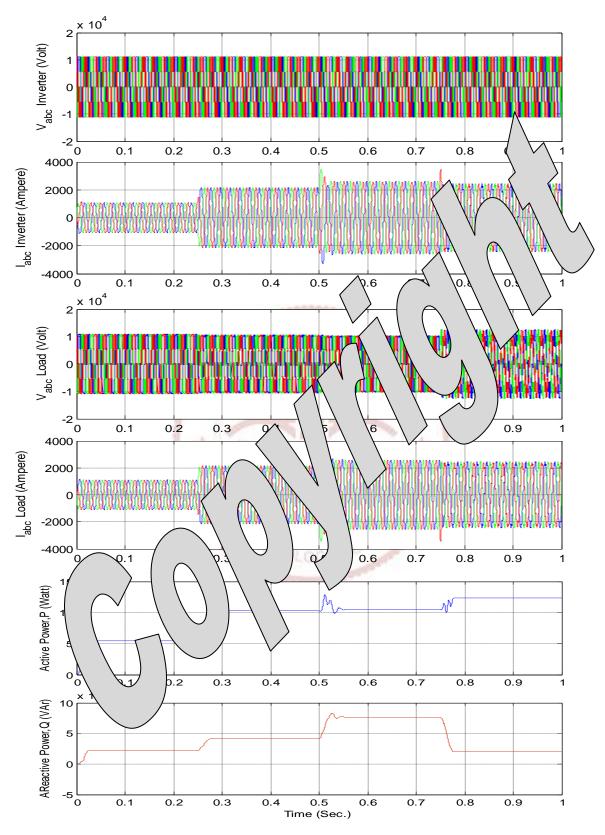

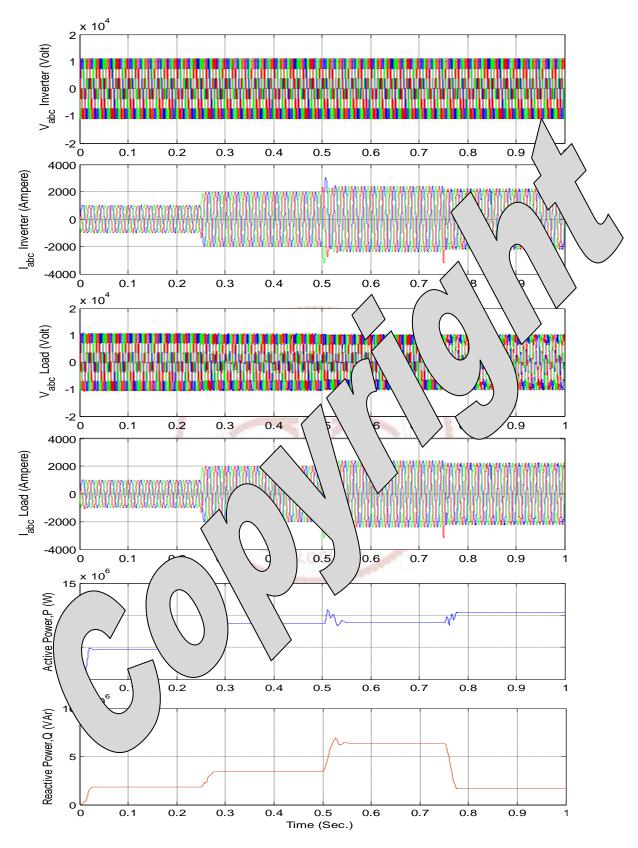

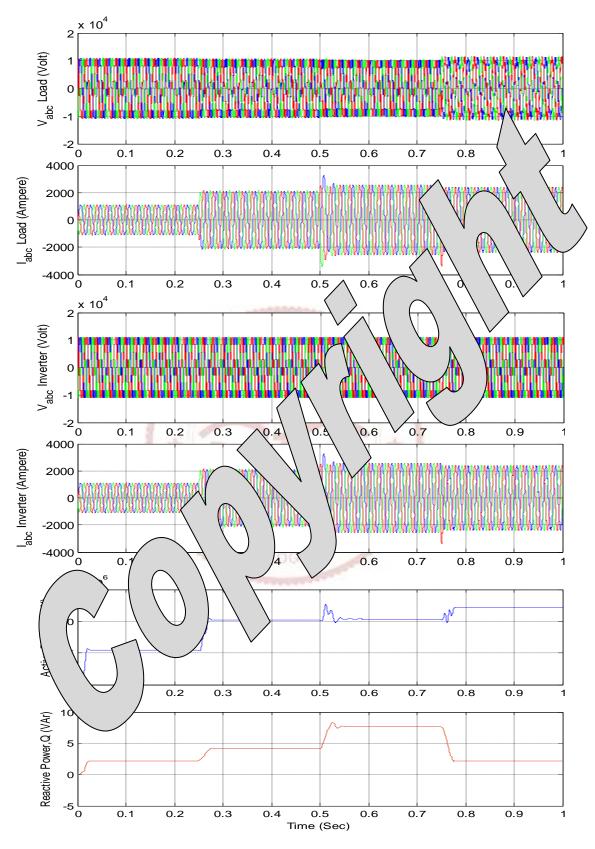

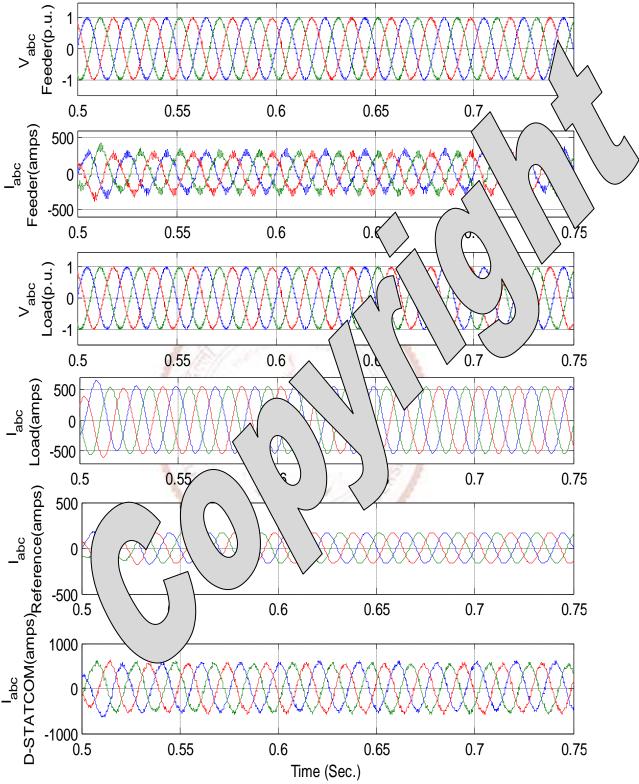

- 4.13 Simulated Results of the eleven level Cascaded Multilevel Inverter Based

73 D-STATCOM for Different Loads with Load switching instants t= 0.5,

0.75, 1.0 and 1.25 second and D-STATCOM Switching Instant = 0.2 Second.

- **4.14** Simulated Result for the Proposed CHBMI based D-STATCOM for load **74** impedance of  $10.2+j31.4 \Omega$  (Switching Instant of D-STATCOM = 0.2 Second).

- **4.15** Simulated Result for the Proposed CHBMI based D-STATCOM for load **75** impedance of  $5.1+j15.7 \Omega$ .

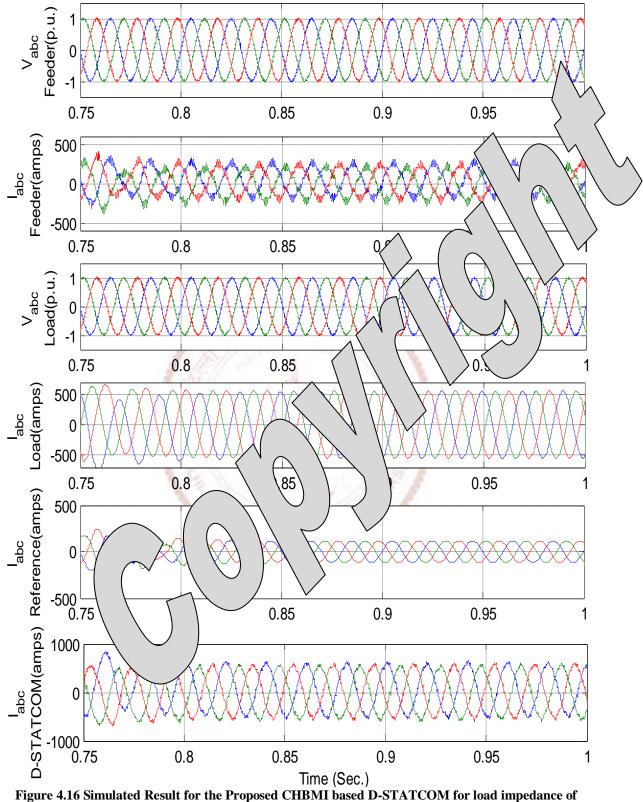

- **4.16** Simulated Result for the Proposed CHBMI based D-STATCOM for load **76** impedance of  $3.46+j15.84 \Omega$ .

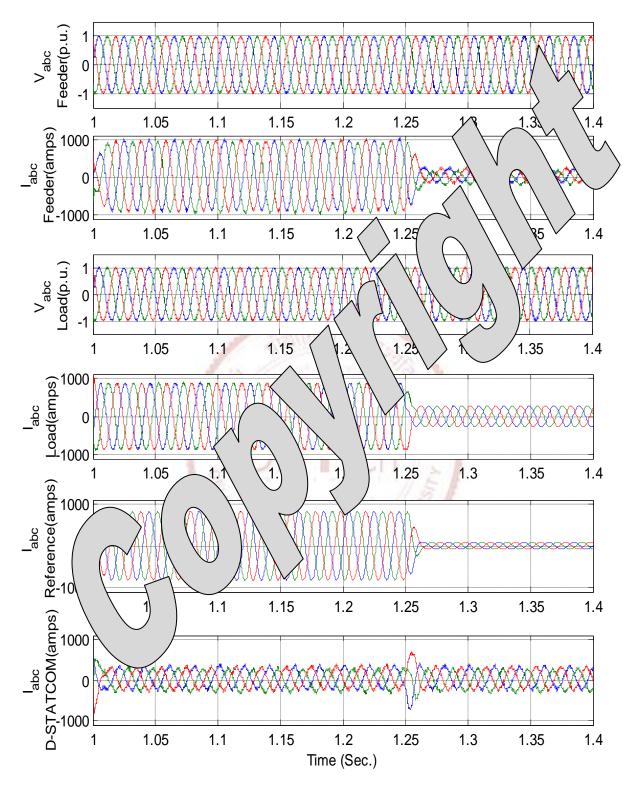

- **4.17** Simulated Result for the Proposed CHBMI based D-STATCOM for load impedance of  $9.84+j3.06\Omega$  and  $10.2+j31.4\Omega$  (Load Transition Instant = 1.25 Second).

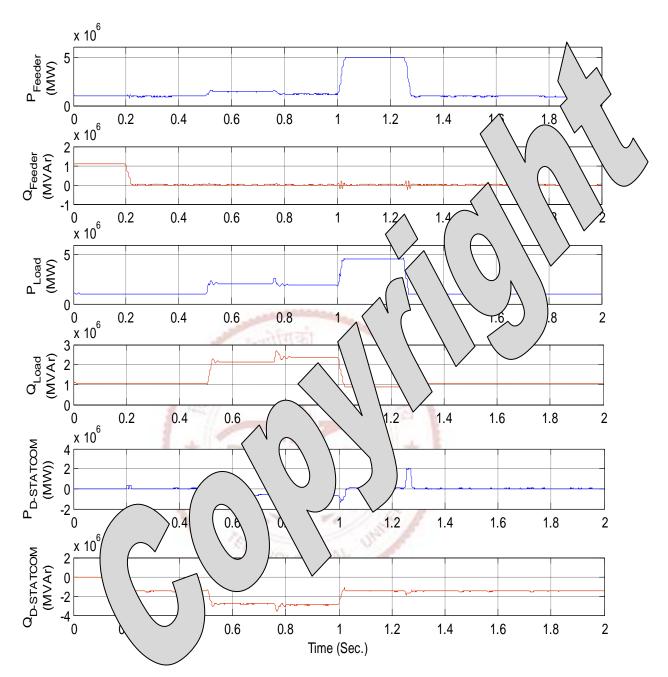

- 4.18 Active and Reactive Power Requirements for the Proposed System. 78

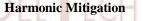

- 4.19 SIMULINK model of the CHBMI based D-STATCOM along with its79 controller for the Selective Harmonic Mitigation.

- 4.20 Controller for the CHBMI based D-STATCOM for Selective Harmonic 79 Mitigation.

- 4.21 Simulated Results for the Mitigation of Selective Harmonics (5th and 7th)80 by the CHBMI based D-STATCOM.

## LIST OF TABLES

| Table | Description                                                               | Page No. |

|-------|---------------------------------------------------------------------------|----------|

| 2.1   | Diode-Clamped Five-Level Inverter Voltage Levels and Their Switch States. | 14       |

| 2.2   | Switch Combination of the Voltage Levels and Their Corresponding Switch   | 16       |

|       | States.                                                                   |          |

| 2.3   | Two-Cell Cascade Inverter Voltage Levels and Their Switch States          | 18       |

| 2.4   | Comparison of Power Component Requirements Per Phase Leg Among Three      | 19       |

|       | Multilevel Inverters.                                                     |          |

| 2.5   | Different Arrangements of Carrier Wave for SPWM Technique.                | 23       |

| 2.6.  | Modulation Index Ranges Without Level Reduction (Min) or Pulse Dropping   | 26       |

|       | Because of Overmodulation (Max).                                          |          |

| 2.7   | Six-Level Inverter Line-Line Voltage Redundancies.                        | 27       |

| 2.8   | Increased Switching Frequency Possible at Lower Modulation Indices.       | 27       |

| 2.9   | Line-Line Redundancies of Six-Level Three-Phase Diode-Clamped Inverter.   | 32       |

| 4.1   | Comparison of %THD in Load Voltage (Phase A) of Different Cascaded H-     | 68       |

|       | Bridge Level Inverters for 11kV (Phase to Phase) Voltage.                 |          |

| 4.2   | Comparison of %THD in Load Current (Phase A) of Different Cascaded H-     | 68       |

|       | Bridge Level Inverters for 11kV (Phase to Phase) Voltage.                 |          |

| 4.3   | Comparison of %THD in Inverter Voltage (Phase A) of Different Cascaded    | 69       |

|       | H- Bridge Level Inverters for 11kV (Phase to Phase) Voltage.              |          |

| 4.4   | Percentage (%) Contamination of the Harmonics in Feeder Current (Phase A) | 81       |

|       | of the Proposed System in Case of Different Harmonic Mitigation.          |          |

# CHAPTER 1 INTRODUCTION

#### 1.1 General

An electric distribution system is part of a power system deriving power from the bulk power source and delivering power to the loads. Distribution systems are, in general, divided into six parts, namely, sub transmission circuits, distribution substations, distribution or primary feeders, distribution transformers, secondary circuits or secondary and consumer's service connections and meters or consumer's services. The present chapter discusses about the power quality issues associated with the distribution system, how their mitigation is done using custom power devices. With the advent of power electronics, the IGBT Switches have emerged as most promising candidate for customer power devices for power quality improvement. A single available such switch has as maximum of voltage 1.2 kV, where as the distributed system looks forwarded to 11kV distributed system. To provide compensation to such level of voltage a structure having multilevel structure is required. The following section deals with multilevel structure based VSI/D-STATCOM.

#### **1.2 Power Quality Issues**

Power Quality problems are referred as deviation of the electrical parameter such as current, voltage and frequency from their standard magnitude. These standards may vary from country to country but in general for power the current and voltage should be near sinusoidal and frequency of the oscillating supply should be constant. Along these factors a consumer should also get an uninterrupted supply. So, improved PQ power system can be defined as the uninterrupted distribution of supply following the standard waveform norms even in abnormal conditions caused by human or natural adversaries [1].

Many industrial loads such as semiconductor manufacturing industries, healthcare industries, financial organisation, air traffic control etc. are categorized as sensitive loads as a little

deviation from the standard supply can cause huge damages to the consumers [2]. So for these types of loads electric power quality is of high concern. However conventionally used distributed system faces many types of problems arise due to loading perturbations and abnormal switching conditions. Thus maintaining the power quality is apprehensive for the electric engineers.

The various power quality problems and their effects are as follows [3]:

**1.2.1 Poor Load Factor:** A load with high X/R ratio causes a poor load factor which makes the reactive component of the supply current high and the magnitude of the supply current also increases. This high reactive current causes a voltage drop in the system, also as the magnitude of supply current increases the ohmic loss ( $I^2R$  losses) also increases.

**1.2.2 Harmonic Contents in Loads:** The switching of nonlinear loads and power electronic equipments causes the generation of harmonics in the distributed system. These harmonics currents cause additional losses in the system in form of heating of the equipments which in long run can permanently damage the system. Some time these harmonics may also lead to maloperation of the system as various switching devices as the timer circuitry is disturbed by these harmonics.

17 81

**1.2.3 Unbalanced Loads:** In a healthy power system the 3-phases should be equal in magnitude and  $120^{0}$  degree spatial apart from each other. If the load connected to any of the phase is unbalanced, it causes the unbalance in the other phase also as the unbalanced supply current flows through the supply impedance. This imbalance causes the trouble in operation of the induction machine as the negative sequence voltage creates a flux in opposition of the main rotor flux and produces a negative torque. Also the decomposed zero sequence voltage can cause extra loss in the system.

**1.2.4 Notching in Load Voltage:** Notching is the periodic voltage distortion produced during the commutation of current from one phase to another in power electronic converter. The large phase controlled rectifiers cause notches in the phase voltage as they provide finite inductance in the supply. Due to this there are periods where line to line voltage falls to zero. Firing angle

of the rectifier does play a very important role in the place of notch in the waveform. This notching can cause abnormal operation of protective devices which can interrupt the whole system.

**1.2.5 DC Offset in Load Voltage:** Geomagnetic disturbances and half wave rectification produce the DC offset in the power system. The DC output of the power electronic loads such as rectifier cause the supply to have a DC offset. This offset can cause the flux excursion of the distribution transformer. DC current also enhances the corrosion of metallic structure as it causes the metallic ions to flow in the direction of the current flow which involve the earth as return path.

**1.2.6 Voltage Sag/Swell:** The short duration voltage variation caused by faults, energization of large loads that require large inrush current and intermittent loose connection produces voltage sag and swells in the system. As the name suggest voltage sag and swell are the decrement and increment of the fundamental frequency voltage from the standard value of the fundamental frequency voltage. These can cause the mal-operation of protective devices.

**1.2.7 Short time Overvoltage/Undervoltage:** Sustained transient usually oscillatory transient sustaining for more than one minute in the system can cause an increase or decrease in magnitude of the voltage. Switching on the large capacitive load pushes heavy reactive power to system which in turn causes the overvoltage. Undervoltage is the result of opposite events. Sustained overvoltages may damage the home appliances.

**1.2.8 Voltage Flicker:** Rapid variation in current magnitude as in the case of arc furnaces causes the rapid variation of the supply voltage. The term is referred as the voltage flicker. Due to this flicker the light intensity from the incandescent lamps vary rapidly which can have adverse effect on human health as it may lead to migraine and headache to the human observer.

**1.2.9 Power Frequency Variation:** As the load in the system changes very rapidly, the supply frequency of a system having low inertia system may also vary as according to torque, current and speed characteristics of the generation system. This change may throw the system out of synchronism and may lead to complete system failure.

The passive filters are included in the distribution system to filter out the distortions in the distributed system but their performance is restricted. However, load conditions are ever changing in the distribution system hence, a varying compensation is needed for the distribution system. The custom power devices are therefore required to be installed to provide active compensation.

#### 1.3 Custom Power (PQ Improvement Devices)

As the power electronics controller based shunt and series FACTS devices are used for the enhancing the transmission capabilities of the transmission system, similarly shunt and series power electronics devices can be used for addressing the power quality issues in distributed system which witness huge variety of problems [4]. The power electronic based devices work as compensating devices in distribution system. These custom power devices enhance the power quality while keeping the frequency, voltage and current under specific limits. The various operation performed by these controllers to improve the PQ problems includes the low phase unbalances, low flicker, low harmonic distortion and maintenance of the values of voltage, current and frequency within specified limits. These devices can also sustain the supply in case of power interruption if provided with DC power back up.

These compensating devices are connected in shunt, series or a combination of both. The controller of these devises can be implemented for the mitigation of one or many power quality issue. The custom power devices can be broadly classified in two types namely: (i) network reconfiguring type and, (ii) compensating type.

#### **1.3.1 Network Configuration Type Devices**

Network reconfiguring type custom powers are used for fast current limiting and current breaking during the faults. They can transfer the load to the alternate feeder in case of abnormalities in the system. The main devices belonging to this family are:

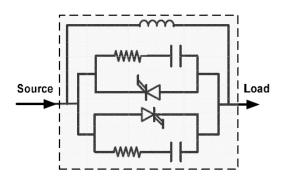

**1.3.1.1 Solid State Current Limiter (SSCL):** This GTO base device limits the fault current by inserting an inductor in the faulty line. As the system detects normal conditions the inductor is removed from the line.

Figure 1.1 Basic Configuration of SSCL.

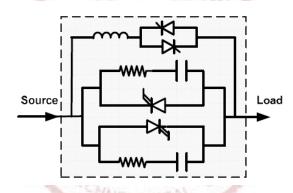

**1.3.1.2 Solid State Circuit Breaker (SSCB):** The fault current can be diverted from the healthy system very rapidly with the use of this devise. The system also incorporates the auto reclosing function to restore the supply in case of normal system condition is restored. This circuit consists of a combination of GTO and thyristor switches which performs very fast in comparison to its mechanical counterpart.

Figure 1.2 Basic Configuration of SSCB.

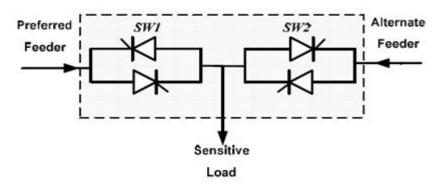

**1.3.1.3 Solid State Transfer Switch (SSTS):** This thyristor based device is used to transfer the load to an alternative feeder in case of any abnormalities. This device is usually employed to protect sensitive loads.

Figure 1.3 Basic Configuration of SSTS.

#### **1.3.2 Compensating Devices**

The compensating devices are used for the mitigation of power quality issues. They are used for active filtering, power factor correction, load balancing and voltage regulation to name a few. They can be installed as shunt, series or hybrid combination to compensate the power quality problems. Shunt devices are popular in those applications which demands greater ease of protection. These devices are operated in such manner that they provide balanced and harmonic free current to the upfront utility devices. They can also be controlled to correct the unbalance and distortion in the source currents in such a manner that it appears that a balance load is connected to the ac system. Similarly the series device work on improving the power quality issues related to voltages. These devices operate in such a way as to provide balance, undistorted and regulated voltage at the load end. These compensating devices family members with their specific function are presented in the following section:

**1.3.2.1 Distribution STATCOM (D-STATCOM):** This shunt connected device is the low level avatar of FACTS device STATic COMpensator (STATCOM). The opportunity to work at low voltage enable the device to perform harmonic filtering, power factor improvement, load balancing, reactive power compensation etc. when connected as load compensator. When connected to distribution system it can also perform the voltage regulation [5]. In this mode it can sustain the desired voltage against any demand of reactive power by the load connected to the distributed system.

Figure 1.4 Schematic Diagram of D-STATCOM.

The main difference in operating the D-STATCOM and STATCOM is that the STATCOM is required to inject a set of three balanced quasi-sinusoidal voltage which are phase displaced  $120^{\circ}$ . On the contrary a D-STATCOM can inject component of current to compensate reactive power, unbalance in currents and harmonic currents as per the requirement to eliminate power quality problems in the concerned system.

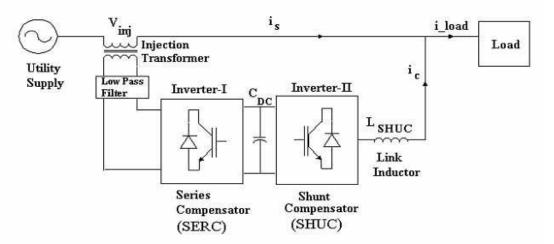

**1.3.2.2 Dynamic Voltage Restorer (DVR):** This device has the structure as that of static synchronous series compensator (SSSC) in the FACTS devices. This device injects a series voltage to compensate the voltage sag/swell in the supply side and also inject real or reactive power to regulate the voltage. The sensitive loads can be protected from any kind of voltage distortion with this device. The main difference between SSSC and DVR operation is that the former supplies a balance sinusoidal voltage in series; however the later is able to inject unbalance voltages and component corresponding to distortion. The DVR can also compensate the distorted voltage to clean the supply voltage.

Figure 1.5 Schematic Diagram of Capacitor Supported DVR.

**1.3.2.3 Unified Power Quality Conditioner:** This versatile device is able to compensate any of the power quality problems as it can inject current in shunt and voltage in series simultaneously as per the system requirement. The injected current or voltage can be of any shape or type, balanced or unbalanced as desired by the system.

Figure 1.6 Schematic Diagram of Right Shunt UPQC Configuration.

#### 1.4 Multilevel Structure for High/Medium Voltage System

In modern power system the power delivery is kept at a very high voltage (400kV or 765kV) to reduce the transmission losses. On the consumer side this voltage is brought down by the transformer as per the consumer requirements in two stages; sub-transmission and distribution level. Usually 66/33kV systems are termed as sub transmission systems while the systems below 33kV system are categorised as distribution system.

In present distribution system load shedding is inevitable as we have various types of loads and system requirements. With the advancement in distributed generation (DG) the distribution system requires different norms and regulations. The use of high voltage distribution not only ease the load shedding also it ensures the improved structure as there are less losses and theft of supply.

The main concern with the high/medium power distribution is the method to be adopted for improving the power quality. As the custom power requires a very fast switching for the harmonic reduction and compensating the distortion from the waveforms, the switch used in these power electronic based controllers should be of such grade that they should able to withstand high voltage and current conditions. In the present scenario the availability of such bidirectional switches is very restricted due to lack of research and manufacturing companies in this field.

This makes the multilevel structure of the power electronic based custom power a necessary requirement for mitigation of power quality issues. This multilevel structure can easily be employed with the switches of rather low ratings and provides a satisfactory performance in addressing the problems above mentioned. But the development of these converters is in initial phase and requires new methodologies for effective operation of these converters.

#### **1.5 Organization of Dissertation**

This dissertation is organised in five chapters which are arrange to give the comprehensive view of proposed work:

**Chapter 2** gives the record of literature surveyed in carrying out the proposed work. In this chapter different type of multilevel structure used in control of power flow and their control technique proposed by many researchers have been discussed. The main emphasis is given on the Cascades H-Bridge multilevel inverter (CHBMI) structure and multilevel D-STATCOM as custom power.

**Chapter 3** presents a mathematical model of PLL, an integral part of control schemes adopted for these power electronic based devices. A mathematical model for cascade H-bridge multilevel inverter is proposed for the system calculation. The inverter model is further enhanced to develop the multilevel D-STATCOM.

**Chapter 4** presents the SIMULINK model of 3-phase bridge D-STATCOM, multilevel inverter for different levels and multilevel D-STATCOM. The results for different load conditions are obtained in graphical form and detail analysis is done of the obtained results.

**Chapter 5** presents the main conclusions of dissertation and future scope of proposed work. This chapter extends the horizon for the further advancement that can be done in the related field.

In the last detailed information of all the references studied and used in forming the dissertation is given.

# CHAPTER 2

# LITERATURE SURVEY

CHNOLOGICAL

# CHAPTER 2 LITERATURE SURVEY

#### 2.1 General

Past few years have witnessed a substantial change in the electricity distribution system. The emphasis has been given on the reliable power system distribution which holds the key in improving the power quality along with reliability. Various industries which require quality supply of voltage and current, the office and household consumers who do not want to pay money for poor power and distribution companies (DisComs) who do not want their power to get wasted in the process of distribution have to properly understand the importance of power quality. Devices varying from the simple power factor correctors to UPQC are being installed for obtaining the pure power. The connectivity of Power Quality (PQ) compensator to the LT side distribution transformer attracts lots of problem which include frequent interruptions and reconnections, large bandwidth and rating of devices, improper utilization etc. Whereas, operation of PQ compensator at HT side/11kV distribution side offer longer time of connectivity, more depth of penetration and, such PQ compensators can serve various Distributed Power Generators (DPG) which forms microgrid and are connected to 11kV distribution system. A literature search is done to select the appropriate topology of multilevel converter in carrying out the proposed work and the area identified for further research.

#### 2.2 Literature Review

The concept of a unified converter theory [6] suggests that any power electronic converter can be observed as a matrix of switches which connects its input nodes to its output nodes. These nodes may be either DC or AC, and either inductive or capacitive; and the power flow can take place in either direction. However, basic laws of electricity enforce restrictions such as:

1) If one set of nodes (input or output) is inductive, the other set must be capacitive, so as not to create a cut set of voltage or current sources when the switches are closed.

**2**) The combination of open and closed switches should never open circuit an inductor, or short circuit a capacitor.

This unified set of converters is generally categorised into a number of different sets as according to their operation. In a rectifier the power flow is predominately from the AC side to

the DC side and in the inverter power flow is predominately from the DC side to the AC side. The term converter is used either when there is no predominant direction of power flow i.e. power flow is bidirectional. In general it encompasses both rectifiers and inverters [7].

#### 2.2.1. Survey for Multilevel Converter

A multilevel converter can switch either its input or output nodes (or both) between multiple (more than two) levels of voltage or current. The multilevel voltage source converter has found many industrial applications such as ac power supplies, static VAR compensators, drive systems, etc. Among the various advantages of multilevel configuration is the harmonic reduction in the output waveform without increasing switching frequency or decreasing the converter power output and also the stress of high power operating conditions is less on every switch [8], [9], [10]. The output voltage waveform of a multilevel converter is composed of the number of levels of voltages which are obtained either from battery or synthesized by capacitors which holds the voltage across them. We can build multilevel inverter to obtain the voltage level from 3 levels to any number of levels. As the number of levels increases, the output THD decreases. However, problems of voltage unbalancing, voltage clamping requirement, circuit layout, and packaging constraints restrict the number of the achievable voltage levels [8].

Three mostly used voltage synthesis-based multilevel inverters are introduced, i.e.

- 1. Diode Clamped Multilevel Inverter (DCMI) [8][9],

- 2. Flying Capacitor Multilevel Inverter (FCMI) [8],

- **3.** Cascade H-Bridge Multilevel Inverter (CHBMI) [8].

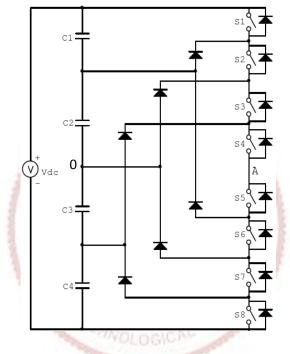

#### 2.2.1.1 Diode Clamped Multilevel Inverter (DCMI)

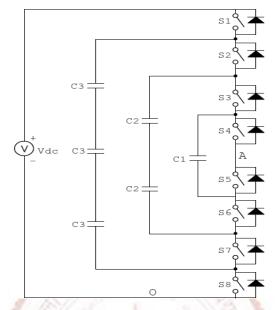

The diode-clamped multilevel inverter uses capacitors in series to divide the dc bus voltage into a set of voltage levels. An m-level diode-clamp inverter requires m-1 capacitors on the dc bus. The obtained output is m-level phase voltage. A single-phase five-level diode-clamped inverter, which can produce a nine-level phase to phase voltage waveform, is shown in Fig. 2.1.

The dc bus consists of four capacitors, i.e., C1, C2, C3, and C4. For dc bus voltage  $V_{dc}$ , the voltage across each capacitor is  $V_{dc}/4$ , and voltage stress on each device will be limited to one capacitor voltage level,  $V_{dc}/4$ , through clamping diodes. DCMI output voltage synthesis is relatively straightforward. To explain how the staircase voltage is synthesized, point O is considered as the output phase voltage reference point. Using the five-level inverter shown in Fig. 2.1, there are five switch combinations to generate two voltage level one above and below and other at zero level.

Figure 2.1 A Single Phase Five Level DCMI.

Table 2.1 shows the phase voltage level and their corresponding switch states. In the Table 1.1, state 1 represents that the switch is on and state 0 represents the switch is off. There exist four complementary switch pairs in each phase, i.e., S1-S5, S2-S6, S3-S7 and S4-S8.

| Output            |            | Switch State |            |    |            |            |            |            |

|-------------------|------------|--------------|------------|----|------------|------------|------------|------------|

| V <sub>AO</sub>   | <b>S</b> 1 | S2           | <b>S</b> 3 | S4 | <b>S</b> 5 | <b>S</b> 6 | <b>S</b> 7 | <b>S</b> 8 |

| $V_5 = -V_{dc}/4$ | 1          | 1            | 1          | 1  | 0          | 0          | 0          | 0          |

| $V_4 = -Vdc/2$    | 0          | 1            | 1          | 1  | 1          | 0          | 0          | 0          |

| $V_3 = 0$         | 0          | 0            | 1          | 1  | 1          | 1          | 0          | 0          |

| $V_2 = Vdc/2$     | 0          | 0            | 0          | 1  | 1          | 1          | 1          | 0          |

| $V_1 = Vdc/4$     | 0          | 0            | 0          | 0  | 1          | 1          | 1          | 1          |

However, due to the following disadvantages, the use of diode-clamped topology is limited to a maximum of five levels [8], [11], [14]:

- Although the transformer can be eliminated, extra components (diodes) are required to ensure load current continuity. As the number of levels increase, the number of extra components raises sharply. These extra components do not necessarily ensure equal voltage sharing for all switches.

- 2) Switch utilization is not equal as outer switches receive a lower average load. This problem becomes particularly apparent as the number of levels increase and the modulation depth is small. Similarly the power flow to and from the different capacitors in a capacitor string is not balanced.

- 3) All switch states are not allowed. The disallowed states must be remapped to their equivalent allowed states.

- 4) Different equivalent states show the capacitor voltages in different directions. This must be used to control the capacitor voltages.

For the above mentioned reasons, a dedicated modulation strategy must be used to control this topology. However these strategies are often complex even after specifically customized to the topology.

#### 2.2.1.2 Flying-Capacitor Multilevel Inverter (FCMI)

The flying capacitor inverter, or imbricated cells multilevel inverter topology was proposed in [12], [13]. A FCMI as shown in Fig. 2.2 uses a ladder structure of dc side capacitors where the voltage on each capacitor differs from that of the next capacitor. To generate m-level staircase output voltage, m-1similar capacitors are required in the dc bus. Each phase-leg has an identical structure. The size of the voltage increment between two capacitors determines the size of the voltage levels in the output waveform.

Here the switch pair-capacitor 'cell' is isolated and inserted within a similar cell – hence the term imbricated cells inverter. The inner pair of switches and their associated capacitor 'fly' as the outer pair of devices switch. The combination of conducting switches and capacitors ensures that the voltage across any blocking switch is always well defined. Table 2.2 shows the switch combination of the voltage levels and their corresponding switch states. In fact, there is

more than one combination to produce output voltages V2, V3, and V4, this provides the FCMI more flexibility than DCMI.

Figure 2.2 A Single-Phase Five-Level Flying-Capacitor Inverter.

| Table 2.2 Switch Combination of the | e Voltage Levels an | d Their Corresponding Switch State | es: |

|-------------------------------------|---------------------|------------------------------------|-----|

| 3.75                                |                     |                                    |     |

|                    |            | 2   |            |        | and a second |            |    |            |

|--------------------|------------|-----|------------|--------|--------------|------------|----|------------|

| Output             |            | a h |            | Switch | 1 State      |            |    |            |

| V <sub>AO</sub>    | <b>S</b> 1 | S2  | <b>S</b> 3 | S4     | S5           | <b>S</b> 6 | S7 | <b>S</b> 8 |

| $V_5 = -V_{dc}/2$  | 1          | 1   | 1          | - 1    | 0            | 0          | 0  | 0          |

| $V_4 = - V_{dc}/4$ | 1          | 1 ) | 1          | 0      | 0            | 0          | 0  | 1          |

|                    | 1          | 1   | 0          | 1      | 0            | 0          | 1  | 0          |

|                    | 1          | 0   | 1          | 1.00   | 0            | 1          | 0  | 0          |

|                    | 0          | 1   | 1          | 1      | 1            | 0          | 0  | 0          |

| $V_3 = 0$          | 1          | 1   | 0          | 0      | 0            | 0          | 1  | 1          |

|                    | 1          | 0   | 1          | 0      | 0            | 1          | 0  | 1          |

|                    | 1          | 0   | 0          | 1      | 0            | 1          | 1  | 0          |

|                    | 0          | 1   | 1          | 0      | 1            | 0          | 0  | 1          |

|                    | 0          | 1   | 0          | 1      | 1            | 0          | 1  | 0          |

|                    | 0          | 0   | 1          | 1      | 1            | 1          | 0  | 0          |

| $V_2 = V_{dc}/4$   | 1          | 0   | 0          | 0      | 0            | 1          | 1  | 1          |

|                    | 0          | 1   | 0          | 0      | 1            | 0          | 1  | 1          |

|                    | 0          | 0   | 1          | 0      | 1            | 1          | 0  | 1          |

|                    | 0          | 0   | 0          | 1      | 1            | 1          | 1  | 0          |

| $V_1 = V_{dc}/2$   | 0          | 0   | 0          | 0      | 1            | 1          | 1  | 1          |

The flying capacitor family of converters have many advantages as following [11],[12],[14]:

- This topology can be applied to a number of different converter types current or voltage source, DC-DC or DC-AC. For this purpose any switch combination can be adopted.

- As long as switch pairs receive complementary drive signals, voltage sharing is ensured. Any modulation strategy can be easily applied to this structure by phase shifting the drive signals.

- 3) There is no need of balancing voltages of the capacitors as conventional modulation strategy takes care of this problem, if required, the capacitor voltages can be actively controlled by an appropriate modification of the control signals.

- 4) This structure is not reliant on a transformer multilevel topology the switches equally shares the load by default.

However, this topology has certain limitation [11],[14]:

- This topology requires a lot of high voltage capacitors as compared to other topologies. These capacitors are essential as they conduct the full load current for at least part of the switching cycle. To reduce the value of capacitor used in the structure, the switch frequency has to be very high.

- 2) Starting the converter safely may be a non-trivial task as capacitors have zero voltage across them in the initial states.

- 3) The topology is not inherently fault tolerant. In case of even a single component burn out, the whole of the inverter is isolated making system inoperative.

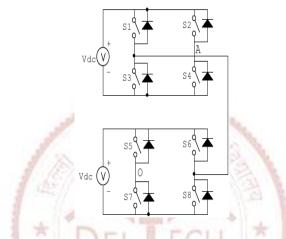

#### 2.2.1.3 Cascaded H Bridge Inverters with Separated DC Sources (SDCSs)

This topology is configured by cascading the identical single phase bridge rectifier. [8],[11].The multilevel inverter using cascaded-inverter with SDCSs synthesizes a desired voltage level from several independent sources of dc voltages, which are provided from either batteries, fuel cells or solar cells. This configuration is getting popularity in ac power supply and adjustable speed drive applications for its easy to upgrade structure. This new inverter can avoid extra clamping diodes or voltage balancing capacitors. A single-phase two-cell series configuration of such an inverter is shown in Fig. 2.3.

The ac terminal voltages of different level inverters are connected in series. Each inverter level generates three different voltage outputs,  $+V_{dc}$ ,  $-V_{dc}$ , and zero for the different firing combination of four switches, S1-S4. As the ac outputs of each level of full-bridge inverters are connected in series, the synthesized voltage waveform is the sum of the inverter outputs. In this topology, the number of output phase voltage levels is defined by m=2s+1, where s is the number of dc sources. Table 2.3 shows the switch combination of the voltage levels and their corresponding switch states.

Figure 2.3 Single-Phase Structure of a Two-Cell Cascaded Inverter.

| Output           |            | Switch State |            |    |            |            |    |            |

|------------------|------------|--------------|------------|----|------------|------------|----|------------|

| V <sub>AO</sub>  | <b>S</b> 1 | S2           | <b>S</b> 3 | S4 | <b>S</b> 5 | <b>S</b> 6 | S7 | <b>S</b> 8 |

| $V_5 = -2V_{dc}$ | 0          | 0            | 0          | 0  | 0          | 1          | 1  | 0          |

| $V_4 = -Vdc$     | 0          | 0            | 0          | 0  | 0          | 1          | 0  | 1          |

| $V_3 = 0$        | 0          | 1            | 1          | 0  | 0          | 0          | 0  | 0          |

| $V_2 = Vdc$      | 1          | 1            | 1          | 1  | 1          | 0          | 1  | 0          |

| $V_1 = 2Vdc$     | 1          | 1            | 1          | 1  | 1          | 0          | 0  | 1          |

Table 2.3 Two-Cell Cascaded-Inverter Voltage Levels and Their Switch States:

This multilevel converter structure has some very significant advantages, if its limitations are acceptable [11],[14]. Its advantages are:

- 1) It has perhaps the simplest architecture and the lowest component count. No transformer is needed, so capital costs are low.

- 2) Modularity is its main advantageous feature which makes the use of this topology in the ever expanding power system structure. This flexibility of modular structure is not only open to its component devices but the control for the system is also modular.

**3**) If a module fail (or be removed), it must fall short circuited, or be bypassed. The converter can continue to operate, at full current capacity, but at reduced voltage rating..

And the limitations of this topology are as follows:

- The access to DC bus capacitors is limited, which narrows its area of application to either those with only reactive power flow, or those where the power source or load can be both modular and isolated.

- 2) On the DC side if self supported system using the capacitors to be employed, the voltage balancing across all the capacitor is rather complex.

- **3**) Practically in case of module failure, or say, if fault tolerance is required, the converter will need a more conservative voltage rating a potential cost penalty.

Table 2.4 Comparison of Power Component Requirements Per Phase Leg Among Three Multilevel

Inverters[11][15]:

| Inverter Configuration | Diode – Clamp | Flying Capacitor | Cascade Inverter |

|------------------------|---------------|------------------|------------------|

| Main Switching Devices | 2(m-1)        | 2(m-1)           | 2(m-1)           |

| Main Diodes            | 2(m-1)        | 2(m-1)           | 2(m-1)           |

| Clamping Diodes        | (m-1)(m-2)    |                  | 0                |

| DC Bus Capacitors      | (m-1)         | (m-1)            | (m-1)/2          |

| Balancing Capacitors   | 0             | (m-1)(m-2)/2     | 0                |

#### 2.2.2 Modulation Technique

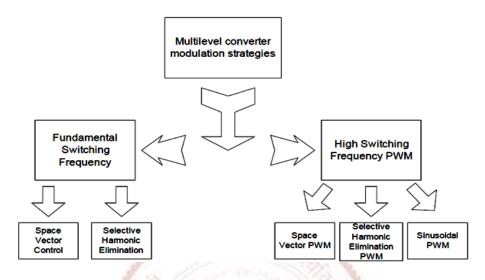

Pulse width modulation (PWM) strategies used in a conventional inverter can be modified to use in multilevel converters. The advent of the multilevel converter PWM modulation methodologies can be classified according to switching frequency as illustrated in Fig. 2.4. The three multilevel PWM methods most discussed in the literature have been multilevel carrier-based PWM, selective harmonic elimination, and multilevel space vector PWM; all are extensions of traditional two-level PWM strategies to several levels.

**2.2.2.1 Hysteresis Control**: In hysteresis band modulating scheme the pulses are obtained by calculating the error between the desired output and the measured output. As this error exceeds a certain bound (leaves the hysteresis band), the state of the switches is changed, so as to drive the error back within that bound. In this manner switching pulses are obtained to drive the inverter. This basic requirement of is to integrate the controlled output quantity of the inverter

by the load, or as part of the controller. As in a voltage source hysteretic inverter, the output current (the measured and subsequently controlled quantity) will be integrated by an inductive load.

Figure 2.4 Classification of PWM Multilevel Converter Modulation Strategies.

The advantages offered by this technique include simplicity to implement, closed loop nature and low distortion. This method gives bounded, predictable error and fast transient response to change at either the input or the output. But variable nature of switching period limits its usefulness to low power, high switching frequency applications as this variable nature causes a continuous and wide output spectra. Subharmonics can also be present as the switching instants are asynchronous or acyclic.

To eliminate sub-harmonics quarter wave symmetry is used at each zero crossing by resetting the error and forcing a switching, and hence a reflection of the pattern, at 90 degrees [16]. This method offers discrete spectra without sub-harmonics. Modulation of the width of the hysteresis band also restricts variation the switching frequency [17], [18]. This places upper and lower limits on the switching frequency, but does not address the problem of sub-harmonics.

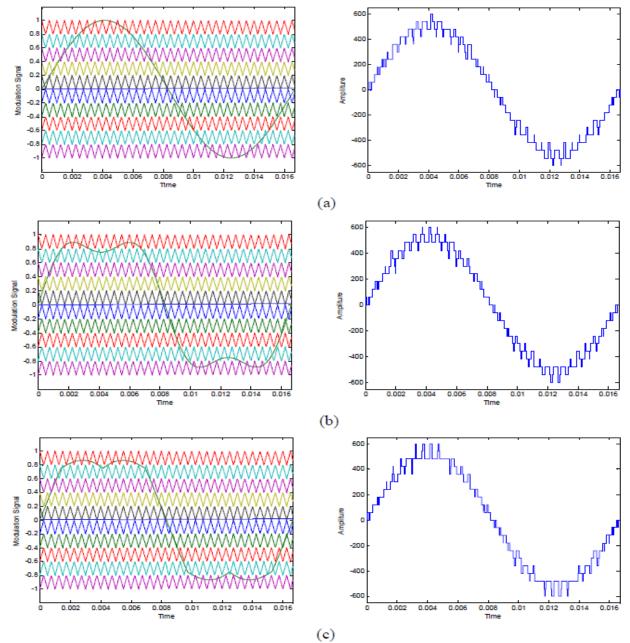

**2.2.2.2 Multilevel carrier-based PWM:** Many multilevel carrier-based PWM techniques as a means for controlling the active devices in a multilevel converter. The most popular and easiest technique to implement uses several triangle carrier signals and one reference, or modulation, signal per phase. Fig. 2.5 illustrates three major carrier-based techniques used in a conventional inverter that can be applied in a multilevel inverter: sinusoidal PWM (SPWM), third harmonic

injection PWM (THPWM), and space vector PWM (SVM). SPWM is a very popular method in industrial applications [11] [14][19].

Figure 2.5. Simulation of Modulation Signals and Their Line-Line Output Voltage Using Five Separate dc Sources (60 volts each dc source) Cascaded Multilevel Inverter with Three Major Conventional Carrier-Based PWM Techniques at Unity Modulation Index and 2 kHz Switching Frequency. (a) SPWM, (b) THPWM, (c) SVM.

In order to achieve better dc link utilization at high modulation indices, the sinusoidal reference signal can be injected by a third harmonic with a magnitude equal to 25% of the fundamental;

its line-line output voltage is shown in Fig. 2.5 (b). As can be seen in Fig. 2.5(b) and (c), the reference signals have some margin at unity amplitude modulation index. Obviously, the dc utilization i.e. the ratio of the output fundamental voltage to the dc link voltage of THPWM and SVM are better than SPWM in the linear modulation region [14][19].

A. Sinusoidal PWM (SPWM) Technique: The pulse width modulation schemes are simple to implement as well as the provide flexibility in control. This basic principle of this scheme is to compare the reference signal ( $V_r$ ) with a high frequency carrier wave ( $V_c$ ) i.e. usually triangular or Inverted U type. When  $V_r > V_c$ , the PWM output will be high (state +1) and, for  $V_r < V_c$  it will be low (state -1). In multilevel PWM generation the reference signal is compared by these carriers for definite bands. Thus, different SPWM can be achieved by different techniques of arranging carrier wave as shown in Fig. 2.6 and table 2.5 gives the description of carrier wave [19].

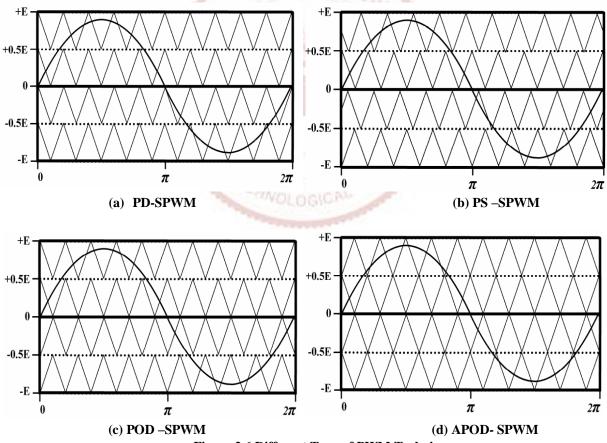

Figure 2.6 Different Type of PWM Techniques.

| Type of<br>SPWM | Meaning                                        | Description                                                                                                                                                                                 |

|-----------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD              | Phase Disposition                              | All carriers have same phase (Fig. 2.6 a)                                                                                                                                                   |

| PS              | Phase Shifted                                  | For each carrier, phase displacement equals $360/(N-1)^{0}$<br>and is successively added on the next carrier (Fig. 2.6 b)                                                                   |

| POD             | Phase Opposition<br>Disposition                | All carriers located above zero reference have the same<br>phase, but they have displaced 180 <sup>0</sup> phase displacement<br>respect to those located below zero reference (Fig. 2.6 c) |

| APOD            | Alternative Phase<br>Opposition<br>Disposition | A 180 <sup>°</sup> phase displacement is imposed between each carrier (Fig. 2.6 d)                                                                                                          |

Table 2.5 Different Arrangements of Carrier Wave for SPWM Technique:

**B.** Subharmonic PWM : Unlike SPWM which does not modulate the signal at zero crossing, the SH-PWM scheme modulates the signal even at zero crossings. SH-PWM for m multiple levels is extended as m-1 carriers with the same frequency  $f_c$  and the same amplitude  $A_C$  are disposed such that the occupied bands are contiguous [20]. The reference waveform has peak-to-peak amplitude  $A_m$ , a frequency  $f_m$ , and its zero centred in the middle of the carrier set. Continuously comparing the reference signal with each of the carrier signals, the active device corresponding to that carrier is switched on when the reference is greater than a carrier signal and it is switched off when the reference is less than a carrier signal. In multilevel inverters, the amplitude modulation index,  $m_a$ , and the frequency ratio,  $m_r$ , are defined as:

$$m_a = \frac{A_m}{(m-1)A_c} \tag{2.1}$$

$$m_f = \frac{f_c}{f_m} \tag{2.2}$$

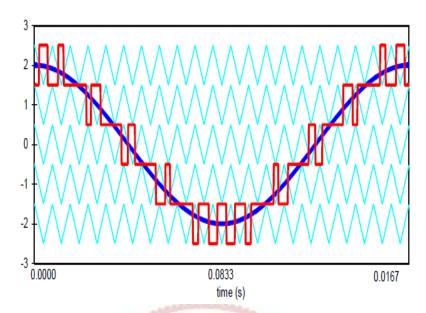

Fig. 2.7 demonstrates a set of carriers ( $m_f = 21$ ) for a six-level diode-clamped inverter and a sinusoidal reference, or modulation, waveform with an amplitude modulation index of 0.8. The resulting output voltage of the inverter is also shown in the same Fig. [24].

Figure 2.7 Multilevel Carrier-Based SH-PWM Showing Carrier Bands, Modulation Waveform, and Inverter Output Waveform (m = 6,  $m_r = 21$ ,  $m_s = 0.8$ ).

**C. Switching Frequency Optimal PWM:** One another method for multilevel inverter is switching frequency optimal PWM (SFO-PWM) which is similar to SH-PWM except that a zero sequence (triplen harmonic) voltage is added to each of the carrier waveforms [21]. In this method the instantaneous average of the maximum and minimum of the three reference voltages ( $V_a^*, V_b^*, V_c^*$ ) is obtained and, then this value is subtracted from each of the individual reference voltages i.e.

$$V_{offset} = \frac{\max(V_a^*, V_b^*, V_c^*) + \min(V_a^*, V_b^*, V_c^*)}{2}$$

(2.3)

$$V_{aSFO}^* = V_a^* - V_{offset} \tag{2.4}$$

$$V_{bSFO}^* = V_b^* - V_{offset}$$

(2.5)

$$V_{cSFO}^* = V_c^* - V_{offset}$$

(2.6)

All of the three reference waveforms in the carrier band are centred because of this addition of the triplen offset voltage which makes it equivalent to using space vector PWM [22, 23]. Fig. 2.8 and 2.9 depicts the SH- PWM and SFO- PWM generation which utilize different frequencies for different triangular wave carrier bands. This method is highly effective to balance the device switching for all the levels in a diode clamped inverter [24].

Figure 2.8 Multilevel Carrier-Based SFO-PWM Showing Carrier Bands, Modulation Waveform and Inverter Output Waveform (m = 6,  $m_f = 21$ ,  $m_a = 0.8$ ).

Figure 2.9 SFO-PWM where Carriers Have Different Frequencies ( $m_a = 0.85$ ,  $m_f = 15$  for Band<sub>2</sub>, Band<sub>-2</sub>;  $m_f = 55$  for Band<sub>1</sub>, Band<sub>-1</sub>, Band<sub>0</sub>,  $\phi = 0.10$  rad).

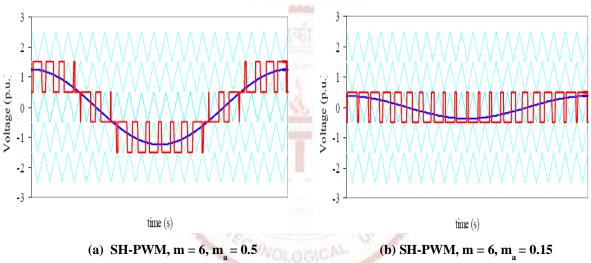

**D. Modulation Index Effect on Level Utilization:** A multilevel inverter is unable to make use of all of its levels at very low modulation indices [25]. Fig. 2.10 presents the simulation results of output voltage waveform at amplitude modulation indices of 0.5 and 0.15. Fig. 2.10 (a) clearly shows the unused band for amplitude modulation indices less than 0.6 in a six-level inverter which indicates that the switches in this band are not functioning. Fig. 2.10 (b) shows how at modulation index less than 0.2 a multilevel inverter operates as traditional two-level inverter as only the middle switches change state.

The minimum modulation index  $m_{amin}$  for which a multilevel inverter controlled with SH-PWM makes use of all of its levels, m, is

$$m_{amin} = \frac{m-3}{m-1} \tag{2.7}$$

Table 2.6 shows that the maximum modulation index before pulse dropping (overmodulation) occurs are 1.000 for SH-PWM and 1.155 for SFO-PWM [25]. Thus it can be observed whenever a multilevel inverter operates at modulation indices much less than 1.000, not all of its levels are utilized for the generation of the output voltage. Also as the number of levels in the inverter increases, level usage is also prone to suffer [14],[25].

|        | SH-F  | PWM   | SFO-PWM |       |  |

|--------|-------|-------|---------|-------|--|

| Levels | Min   | Max   | Min     | Max   |  |

| 3      | 0.000 | 1.000 | 0.000   | 1.155 |  |

| 4      | 0.333 | 1.000 | 0.385   | 1.155 |  |

| 5      | 0.500 | 1.000 | 0.578   | 1.155 |  |

| 6      | 0.600 | 1.000 | 0.693   | 1.155 |  |

| 7      | 0.667 | 1.000 | 0.770   | 1.155 |  |

| 8      | 0.714 | 1.000 | 0.825   | 1.155 |  |

| 9      | 0.750 | 1.000 | 0.866   | 1.155 |  |

| 10     | 0.778 | 1.000 | 0.898   | 1.155 |  |

| 11     | 0.800 | 1.000 | 0.924   | 1.155 |  |

| 12     | 0.818 | 1.000 | 0.945   | 1.155 |  |

| 13     | 0.833 | 1.000 | 0.962   | 1.155 |  |

Table 2.6. Modulation Index Ranges Without Level Reduction (Min) or Pulse Dropping Because of Overmodulation (Max):

Figure 2.10 Level Reductions in a Six-Level Inverter at Low Modulation Indices.

Even during low modulation periods, all multiple levels can be used by rotating level usage in the inverter after each modulation cycle. Taking advantage of the redundant output voltage states in such manner reduces the switching stresses on some of the inner levels by using the unused outer voltage levels [26].

For low modulation indices use of redundant line-line voltage states are available in a diode clamped inverters [26]. However these inverters do not have any phase redundancies. The available number of redundant states in an m-level diode-clamped inverter for an output voltage state (i, j, k) can be calculated as,

$$N_{redundancies} = m - 1 - [\max(i, j, k) - \min[i, j, k)]$$

available

$$(2.8)$$

As the modulation index is increased, more redundant states can be obtained. Table 2.7 shows the number of distinct and redundant line-line voltage states available in a six-level inverter for different output voltages [25],[26].

| $\max(i,j,k)$ -min $(i,j,k)$ | # Distinct States | # Redundancies per<br>Distinct State | Total # of States |

|------------------------------|-------------------|--------------------------------------|-------------------|

| 0                            | 1                 | 5                                    | 6                 |

| 1                            | 6                 | 4                                    | 30                |

| 2                            | 12                | 3                                    | 48                |

| 3                            | 18                | 2                                    | 54                |

| 4                            | 24                | 1                                    | 48                |

| 5                            | 30                | 0                                    | 30                |

| Total                        | 91                |                                      | 216               |

Table 2.7 Six-Level Inverter Line-Line Voltage Redundancies:

**E.** Increasing Switching Frequency at Low Modulation Indices: Even after making switching frequency double to sufficiently rotate the level usage in odd – level inverter in case of amplitude modulation indices less than 0.5, the thermal losses remain within the limits of the device. The modulation index at which frequency doubling can be accomplished varies with the levels in even level inverter [25]. As the switching frequency increases, inverter is able to compensate for higher frequency harmonics. This yields a waveform that follows reference more closely.

Table 2.8 Increased Switching Frequency Possible at Lower Modulation Indices [25]:

| KCON IN IN IN |            |        |            |  |  |  |

|---------------|------------|--------|------------|--|--|--|

| Inverter      | Modulation |        | Frequency  |  |  |  |

| Levels        | Min        | Max    | Multiplier |  |  |  |

| 3             | 0.000      | 0.500  | 2 <b>X</b> |  |  |  |

| 4             | 0.000      | 0.333  | 3X         |  |  |  |

| 5             | 0.250      | 0.500  | 2 <b>X</b> |  |  |  |

|               | 0.000      | 0.250  | 4X         |  |  |  |

| 6             | 0.200      | 0.400  | 2 <b>X</b> |  |  |  |

|               | 0.000      | 0.200  | 5 <b>X</b> |  |  |  |

| 7             | 0.333      | 0.500  | 2 <b>X</b> |  |  |  |

|               | 0.167      | 0.333  | 3X         |  |  |  |

|               | 0.000      | 0.167  | 6X         |  |  |  |

| 8             | 0.285      | 0.428  | 2X         |  |  |  |

|               | 0.142      | 0.285  | 3X         |  |  |  |

|               | 0.000      | 0.142  | 7X         |  |  |  |

| 9             | 0.25       | 0.500  | 2X         |  |  |  |

|               | 0.125      | 0.250  | 4X         |  |  |  |

|               | 0.000      | 0.125  | 8X         |  |  |  |

| 10            | 0.333      | 0.444  | 2 <b>X</b> |  |  |  |

|               | 0.222      | 0.333  | 3X         |  |  |  |

|               | 0.111      | 0.222  | 4X         |  |  |  |

|               | 0.000      | 0.111  | 9X         |  |  |  |

| 11            | 0.333      | 0.500  | 2 <b>X</b> |  |  |  |

|               | 0.200      | 0.333  | 3X         |  |  |  |

|               | 0.000      | 0.200  | 5X         |  |  |  |

| 12            | 0.272      | 0.454  | 2 <b>X</b> |  |  |  |

|               | 0.181      | 0.272  | 3X         |  |  |  |

|               | 0.090      | 0.181  | 5X         |  |  |  |

|               | 0.000      | 0.090  | 11X        |  |  |  |

| 13            | 0.333      | 0.500  | 2 <b>X</b> |  |  |  |

|               | 0.250      | 0.333  | 3X         |  |  |  |

|               | 0.167      | 0.250  | 4X         |  |  |  |

|               | 0.0833     | 0.167  | 6X         |  |  |  |

|               | 0.000      | 0.0833 | 12X        |  |  |  |

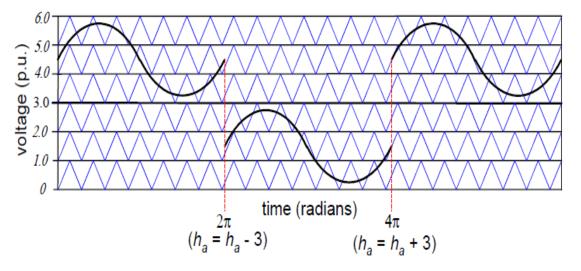

To accomplish this doubling of inverter frequency, a prototype of a seven-level diode-clamped inverter with an amplitude modulation index of 0.4 is switched such as that the reference waveform is centred in the upper three carrier bands and lower three carrier bands from one cycle to next cycle. Half of the switches "rest" in every other cycle and not endorse any switching losses. However, this method is limited to only three-wire systems as the diode-clamped inverter has line-line redundancies and no phase redundancies. Synchronization of transition for all three phases while moving from one carrier set to the next set is essential at the discontinuity. In this process of frequency doubling, all three phases add or subtract the following number of states (or levels) every other reference cycle [14],[25]:

$$h_a(j+1) = h_a(j) + (-1)^{j} \cdot \frac{[m-1]}{2}$$

(2.9)

At modulation indices closer to zero, even more increase in the switching frequency is possible by rotating the reference waveform among the carrier bands for a few cycles before returning to a previous set of switches for use. The switches are able to absorb higher losses as they "rest" for a few cycles. In redundant switching each of the three phases in the seven-level inverter will have three change states of switch pairs at the end of every reference cycle which results in additional switching losses. However, this redundant switching loss is around five percent of the total switching loss compared to the switching loss associated with the normal PWM switching [25].

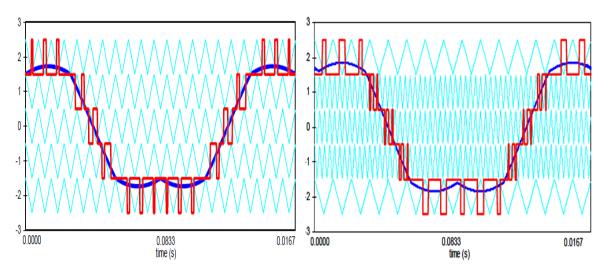

Figure 2.11 Reference Rotation among Carrier Bands Rotation at Low Modulation Indices (m<sub>a</sub>< 0.5).

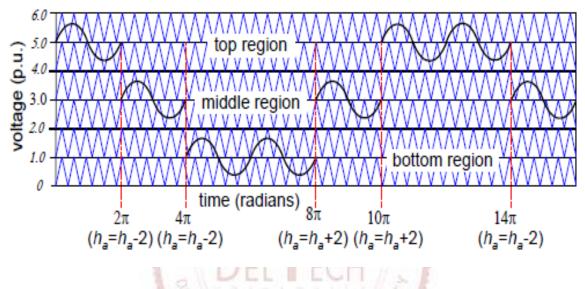

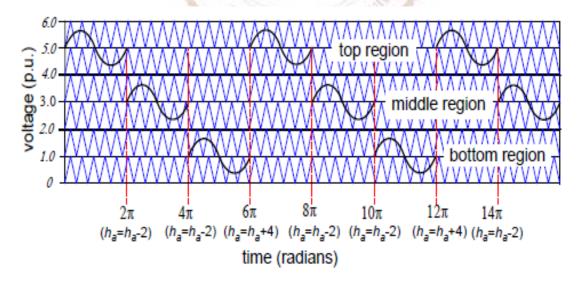

To increase the carrier frequency by a factor of three, two methods of rotating the reference waveform among three different regions (top, middle, and bottom) for modulation indices less than 0.333 in a seven-level inverter are shown in Fig. 2.12 and Fig. 2.13. Former is preferred to later as it requires only four redundant states switching as against of eight redundant states switching of later in every three reference cycles. In general preferred one will have ½ of the redundant switching losses that the alternate method would have.

Figure 2.12 Preferred Method of Reference among Carrier Bands with 3× Carrier Frequency at Very Low Modulation Indices.

Figure 2.13 Alternate Method of Reference Rotation among Carrier Bands with 3× Carrier Frequency at Very Low Modulation Indices.

The cascaded H-bridges inverter has phase redundancies in addition to the line-line redundancies [25][26]. As the output voltage in each phase of a three-phase inverter can be generated independently of the other two phases when only phase redundancies are used, phase redundancies can be easily exploited compared to line-line redundancies. In a cascaded inverter each active device's duty cycle is balanced over (m-1)/2 modulation waveform cycles regardless of the modulation index is obtained using these phase redundancies [27]. The pulse rotation technique with a PWM output voltage waveform represents a more effective means of controlling a driven motor at low speeds [28,29]. In this control the output waveform can have a high switching frequency even though individual levels can still switch at a constant switching frequency of 60 Hz.

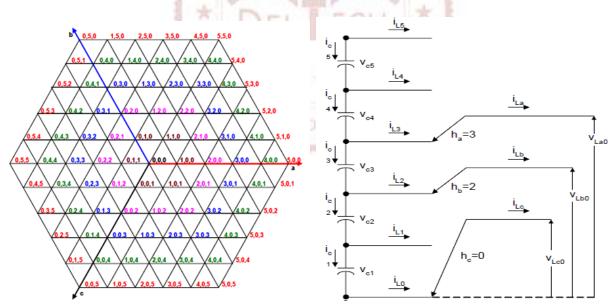

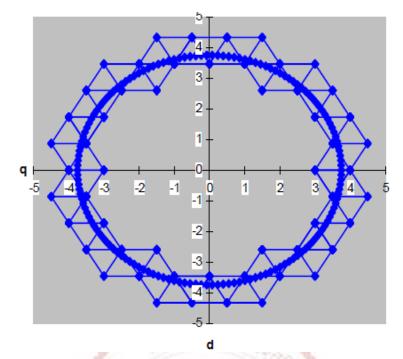

**F. Multilevel space vector PWM:** The two-level space vector pulse width modulation technique has been extended to more than three levels for the diode-clamped inverter [30]. Fig. 2.14 shows what the space vector d-q plane looks like for a six-level inverter. Fig. 2.15 represents the equivalent dc link of a six-level inverter as a multiplexer that connects each of the three output phase voltages to one of the dc link voltage tap points [31].

Figure 2.14 Voltage Space Vector for a Six–Level Inverter.

Figure 2.15 Multiplexer Model of a Diod-Clamped Six-Level Inverter.

A specific three-phase output voltage state of the inverter is represented with a specified point on the space vector plane. For example  $V_{an} = 3V_{dc}$ ,  $V_{bn} = 2V_{dc}$ , and  $V_{cn} = 0V_{dc}$  is represented with (3, 2, 0). Fig. 2.15 shows the corresponding connections between the dc link and the output lines for this point in a six-level inverter. An algebraic equation to represent the output voltages in terms of the switching states and dc link capacitors has been given as [32]. For n = m-1 where m is the number of levels in the inverter:

$$V_{abc0} = H_{abc} V_c , \qquad (2.10)$$

where

$$V_c = [V_{c1} V_{c2} V_{c3} \dots V_c]^T$$

,  $H_{abc} = \begin{bmatrix} h_{a1} & h_{a2} & h_{a3} \dots h_{an} \\ h_{b1} & h_{b2} & h_{b3} \dots h_{bn} \\ h_{c1} & h_{c2} & h_{c3} \dots h_{cn} \end{bmatrix}$ ,  $V_{abc0} = \begin{bmatrix} V_{a0} \\ V_{b0} \\ V_{c0} \end{bmatrix}$ , and

$h_{aj} = \sum_{j}^{n} \delta(h_a - j)$

where  $h_a$  is the switch state and j is an integer from 0 to n, and where  $\delta(x) = 1$  if  $x \ge 0$ ,  $\delta(x) = 0$  if x < 0.

The point (3, 2, 0) on the space vector plane can also represent the switching state of the converter. Each integer indicates the number of upper switches with state ON in each phase leg for a diode-clamped converter. As an example, for  $h_a = 3$ ,  $h_b = 2$ ,  $h_c = 0$ , the H<sub>abc</sub> matrix for his particular switching state of a six-level inverter would be

$$H_{abc} = \begin{bmatrix} 0 & 0 & 1 & 1 & 1 \\ 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$