A Dissertation on

# **REALIZATION OF P, PD, PI AND PID CONTROLLERS USING OTRA**

submitted in partial fulfillment of the requirements

for the award of degree of

Master of Technology

in

VLSI Design and Embedded System

Submitted By

Saurabh Chitransi (Roll no.:- 17/VLSI/09)

Under the guidance of

Mrs. Rajeshwari Pandey

(Associate Professor)

Department of Electronics and Communication Engineering Delhi Technological University (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042 (2009-2011)

$\mathbf{i}$

# **CERTIFICATE**

DELHITECHNOLOGICALUNIVERSITY,(FormerlyDelhiCollege of Engineering)BAWANAROAD, DELHI – 110042Departmentof Electronics & CommunicationEngineeringEngineeringEngineering

This is to certify that the report entitled "<u>Realization of P, PD, PI and PID Controllers using</u> <u>OTRA (Operational Transresistance Amplifier)</u>" submitted by Saurabh Chitransi, Roll. No. 17/VLSI/09, in partial fulfillment for the award of degree of Master of Technology in VLSI Design & Embedded System at **Delhi Technological University, Delhi**, is a bonafide record of student's own work carried out by him under my supervision and guidance in the academic session 2009-11. The matter embodied in dissertation has not been submitted for the award of any other degree or certificate in this or any other university or institute.

(Mrs. Rajeshwari Pandey)

ASSOCIATE PROFESSOR Department of Electronics & Communication Engineering Delhi Technological University, (Formerly Delhi College of Engineering) Delhi - 110042

# **ACKNOWLEDGEMENT**

It has been rightly said, "we are build on the shoulders of others" for everything we have achieved the credit goes to our faculty members.

I would like to express my immense gratitude to my advisor, **Asst. Prof. Rajeshwari Pandey**, for her enthusiasm, encouragement, patience, & timely support. It is my privilege to have worked under her supervision. Her invaluable guidance & helpful discussion at every stage of this project helped me in timely materialization & successful completion of this project.

My special thanks to Dr. Neeta Pandey for her support and guidance to understand the SPICE and to operate on OrCad PSpice tool.

I am thankful to my friends Chandra Shekhar, Piyush Gupta, and Praveen Kumar for valuable discussions.

I am grateful to my parents and my younger brothers Shivam and Pushkar for their moral support. They have been always around to cheer me up, in the odd times of this work. I am also thankful to my classmates for their unconditional support and motivation during this work.

Submitted by:

SAURABH CHITRANSI 17/VLSI/09 M. Tech. (VLSI DESIGN & EMBEDDED SYSTEM)

# **ABSTRACT**

Control engineering deals with understanding of plant under operation, and obtaining a desired output response in presence of system constraints. There has been an ever increasing demand of controllers in process industry for improving manufacturing processes and energy efficiency.

The evolution of submicron technologies has resulted in the requirement to use low power supply voltages which makes it difficult to design voltage mode circuits with high linearity and wide range. Also as signal processing extends to higher frequencies, the traditional design methods based on voltage operational amps are no longer adequate. However generally analog controllers are designed using operational amplifiers. To overcome these problems circuits operating in current mode, which have the inherent property of higher bandwidth, larger dynamic range and better linearity, are preferred. Various analog building blocks operating in the current mode such as various generations of current conveyor, CDBA, OTA, OTRA etc are available in literature. OTRA being a current mode device inherits all the advantages of current mode techniques, in addition it is free from parasitic input capacitances and resistances.

In this thesis OTRA based controllers i.e. P, PD, PI and PID with independent tuning of proportional  $K_p$ , derivative  $K_d$  and integral  $K_i$  constants are presented. These configurations can be made fully integrated by implementing the resistors using matched transistors operating in linear region. To observe the effect of controller on second order system a second order low pass filter is designed and simulated. In order to verify the functionality of proposed controller circuits, a closed loop control system using the proposed controllers and second order LPF is designed and simulated using SPICE.

# TABLE OF CONTENTS

| Certificate                                           | ii  |

|-------------------------------------------------------|-----|

| Acknowledgement                                       | iii |

| Abstract                                              | iv  |

| Table of Contents                                     | V   |

| List of Figures                                       | vii |

| List of Tables                                        | X   |

| Chapter 1 Introduction                                | 1   |

| 1.1 Motivation                                        | 1   |

| 1.2 Literature review                                 | 2   |

| 1.3 Objective and Scope of the Project                | 3   |

| 1.4 Organization of Thesis                            | 4   |

| Chapter 2 Operational Trans-Resistance Amplifier      | 5   |

| 2.1 Basics of OTRA                                    | 5   |

| 2.2 Differential OTRA                                 | 6   |

| 2.3 CMOS Realization of Differential OTRA             | 7   |

| 2.4 Simulation Results of Differential OTRA           | 8   |

| Chapter 3 Time Domain Analysis of Second Order System | 12  |

| 3.1 Standard Second Order System                      | 12  |

| 3.2 Unit Step Response of the Second Order System     | 13  |

| 3.3 Time Domain Specifications                        | 15  |

| 3.4 Proposed Second Order Low Pass Filter             | 17  |

| 3.5 Simulation Results of Second Order LPF            | 18  |

| Chapter 4 Proposed Controllers                        | 21  |

| 4.1 Proportional Controller                           | 21  |

| 4.1.1 Introduction                                    | 21  |

| 4.1.2 P-Controller with Second Order System           | 22  |

| 4.1.3 OTRA based P-Controller                         | 22  |

|         | 4.1.4 Non-ideality Analysis                  | 24  |

|---------|----------------------------------------------|-----|

|         | 4.2 PD Controller                            | 25  |

|         | 4.2.1 Introduction                           | 25  |

|         | 4.2.2 PD-Controller with Second Order System | 26  |

|         | 4.2.3 OTRA based Proposed PD-Controller      | 26  |

|         | 4.2.4 Non-ideality Analysis                  | 27  |

|         | 4.3 PI Controller                            | .29 |

|         | 4.3.1 Introduction                           | 29  |

|         | 4.3.2 PI-Controller with Second Order System | 30  |

|         | 4.3.3 OTRA based Proposed PI-Controller      | 30  |

|         | 4.3.4 Non-ideality Analysis                  | 31  |

| 4       | 4.4 PID Controller                           | 33  |

|         | 4.4.1 Introduction                           | 33  |

|         | 4.4.2 OTRA based Proposed PID-Controller     | 34  |

| Chapter | 5 Simulation Results                         | 36  |

| :       | 5.1 Simulation Results of P Controller       | 36  |

| :       | 5.2 Simulation Results of PD Controller      | 41  |

| :       | 5.3 Simulation Results of PI Controller      | 46  |

| :       | 5.4 Simulation Results of PID Controller     | 50  |

| :       | 5.5 Performance Comparison of Controllers    | 53  |

| Chapter | Conclusion and Future Work                   | 54  |

|         | 6.1 Conclusion                               | 54  |

|         | 6.2 Future Work                              | 54  |

| Referen | nces                                         | 56  |

| Append  | lix                                          | 60  |

# LIST OF FIGURES

| Fig. 2.1  | Symbol of OTRA5                                             |

|-----------|-------------------------------------------------------------|

| Fig. 2.2  | Small Signal AC Equivalent of OTRA6                         |

| Fig. 2.3  | Symbol of Differential OTRA [39]7                           |

| Fig. 2.4  | Small Signal AC Equivalent of Differential OTRA [39]7       |

| Fig. 2.5  | CMOS Realization of Differential OTRA Proposed in [9]7      |

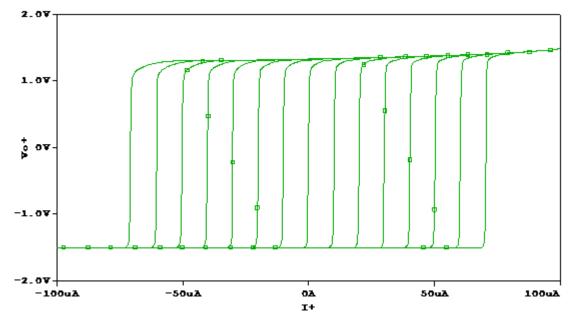

| Fig. 2.6a | Non-inverting DC Transfer Characteristics                   |

| Fig. 2.6b | Inverting DC Transfer Characteristics10                     |

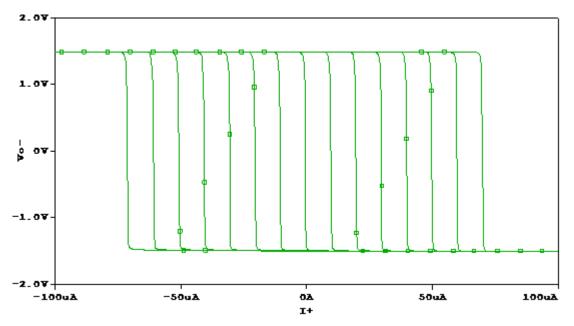

| Fig. 2.7  | Input Resistance of Differential Amplifier10                |

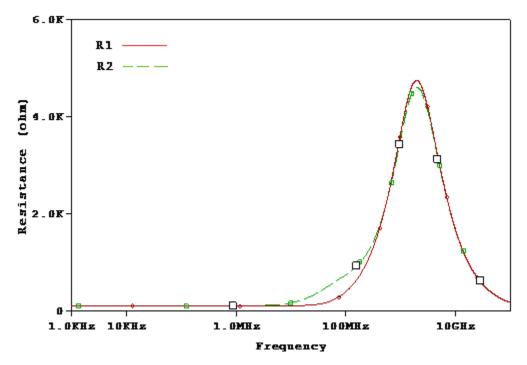

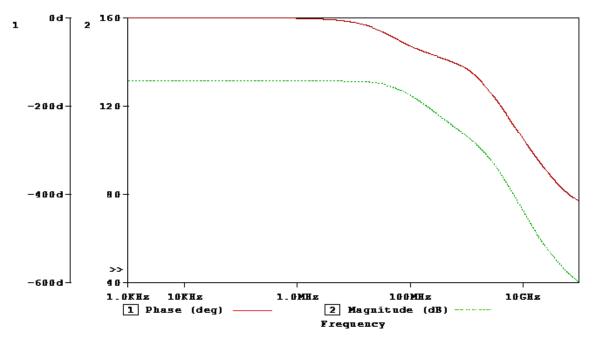

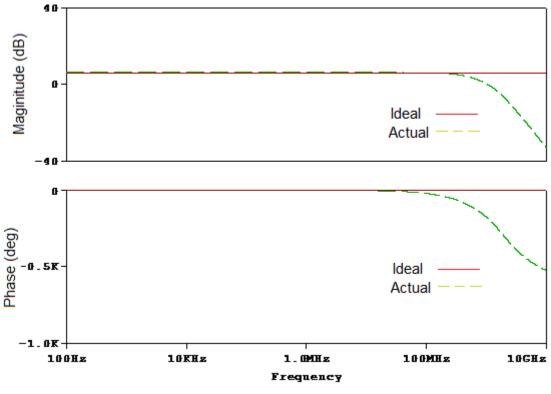

| Fig. 2.8  | Frequency Response of Differential OTRA11                   |

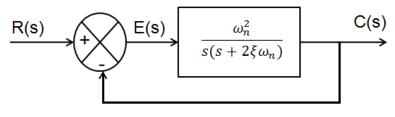

| Fig. 3.1  | Second Order System                                         |

| Fig. 3.2  | Step Response of an Underdamped Second Order System14       |

| Fig. 3.3  | Step Response of a Critically Damped Second Order System    |

| Fig. 3.4  | Step Response of an Over-damped Second Order System15       |

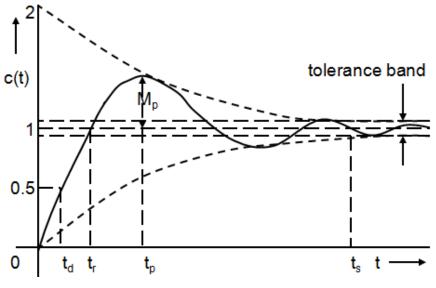

| Fig. 3.5  | Time Domain Specifications of a Second Order System15       |

| Fig. 3.6  | Proposed Second Order Low Pass Filter17                     |

| Fig. 3.7  | Step Response of the Proposed Second Order LPF              |

| Fig. 3.8  | Frequency Response of the Proposed Second Order LPF19       |

| Fig. 3.9  | Step Response of The Second Order LPF with varying $\xi$ 19 |

| Fig. 4.1  | Control System with P-controller                            |

| Fig. 4.2  | OTRA based P-Controller                                     |

| Fig. 4.3  | MOS implementation of a Linear resistance                   |

| Fig. 4.4  | MOS -C equivalent of P-Controller                           |

| Fig. 4.5  | P-Controller with Compensation                              |

| Fig. 4.6  | Control System with PD-controller                           |

|           |                                                             |

| Fig. 4.7   | OTRA based Proposed PD Controller                                                  | 26 |

|------------|------------------------------------------------------------------------------------|----|

| Fig. 4.8   | MOS-C equivalent of Proposed PD Controller                                         | 27 |

| Fig. 4.9   | Compensated PD Controller                                                          | 28 |

| Fig. 4.10  | Control System with PI-controller                                                  | 29 |

| Fig. 4.11  | OTRA based Proposed PI Controller                                                  | 30 |

| Fig. 4.12  | MOS-C equivalent of Proposed PI Controller                                         | 31 |

| Fig. 4.13  | Compensated PI Controller                                                          | 32 |

| Fig. 4.14  | Control System with PID-controller                                                 | 33 |

| Fig. 4.15  | OTRA based Proposed PID Controller                                                 | 34 |

| Fig. 4.16  | MOS-C equivalent of Proposed PI Controller                                         | 35 |

| Fig. 5.1   | Transient response of the P Controller                                             | 37 |

| Fig. 5.2   | Frequency and Phase Response of P controller                                       | 37 |

| Fig. 5.3   | Transient Response of MOS-C implementation of P Controller                         | 38 |

| Fig. 5.4   | Frequency and Phase Response of MOS-C implementation of P Controller               | 38 |

| Fig. 5.5   | Closed Loop Control System using P Controller                                      | 39 |

| Fig. 5.6a  | Step Response of a Second Order System without P Controller                        | 39 |

| Fig. 5.6b  | Step Response of a Second Order System with P Controller                           | 40 |

| Fig. 5.7   | Step Response of a Second Order System with P Controller with varying $K_p$        | 40 |

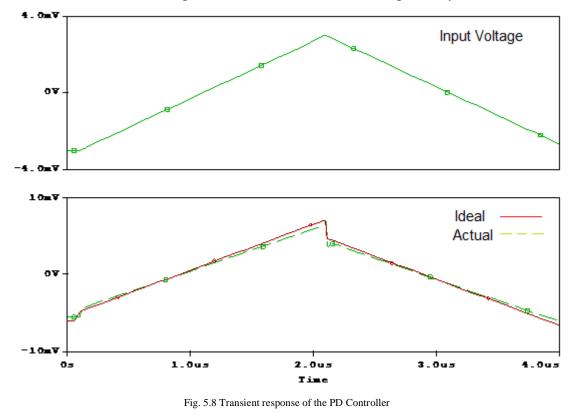

| Fig. 5.8   | Transient Response of PD Controller                                                | 41 |

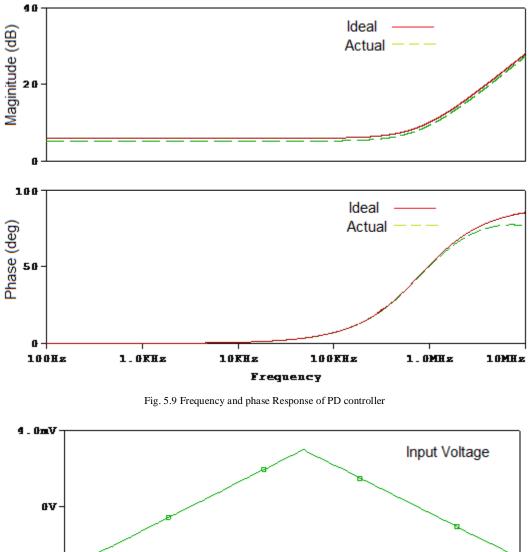

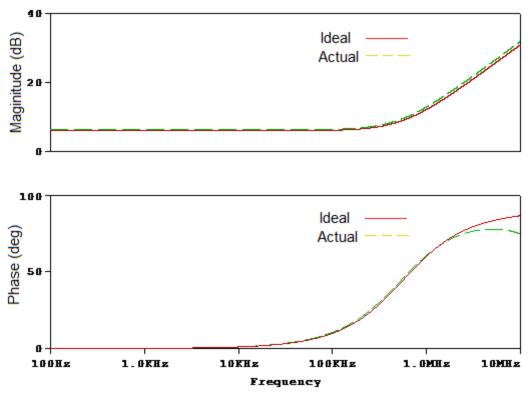

| Fig. 5.9   | Frequency and Phase Response of PD Controller                                      | 42 |

| Fig. 5.10  | Transient Response of MOS-C implemented PD Controller                              | 42 |

| Fig. 5.11  | Frequency and Phase Response of MOS-C implemented PD Controller                    | 43 |

| Fig. 5.12  | Closed Loop Control System using PD controller                                     | 44 |

| Fig. 5.13a | Step Response of a Second Order System without PD Controller                       | 44 |

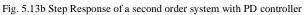

| Fig. 5.13b | Step Response of a Second Order System with PD Controller                          | 44 |

| Fig. 5.13c | Step Response of a Second Order System with PD Controller with varying $K_{\rm d}$ | 45 |

| Fig. 5.14  | Transient Response of PI Controller                                                | 46 |

| Fig. 5.15  | Frequency and Phase Response of PI Controller                                                | 47 |

|------------|----------------------------------------------------------------------------------------------|----|

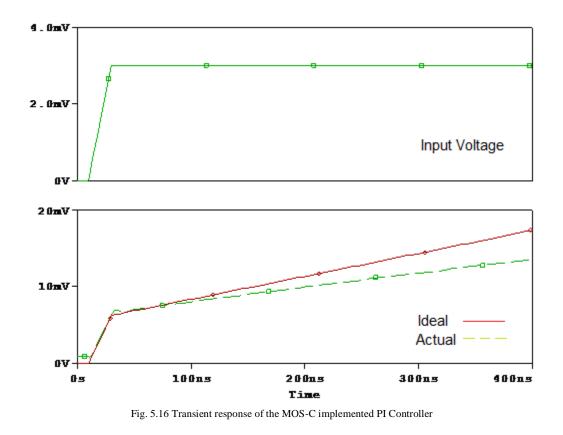

| Fig. 5.16  | Transient Response of MOS-C implemented PI Controller                                        | 47 |

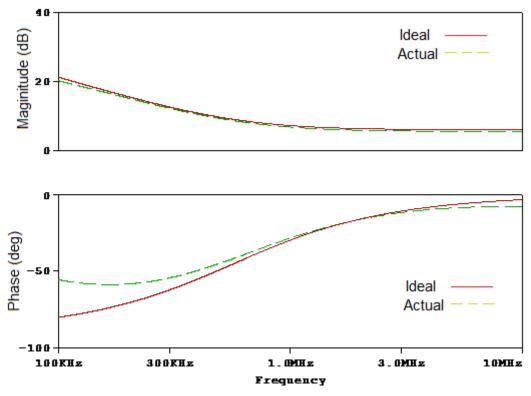

| Fig. 5.17  | Frequency and phase Response of MOS-C implemented PI Controller                              | 48 |

| Fig. 5.18  | Closed Loop Control System using PD Controller                                               | 48 |

| Fig. 5.19a | Step Response of a Second Order System with PI Controller                                    | 49 |

| Fig. 5.19b | Step Response of a Second Order System with PI Controller with varying $K_{i} \hdots \hdots$ | 49 |

| Fig. 5.20  | Transient Response of PID Controller                                                         | 51 |

| Fig. 5.21  | Transient Response of MOS-C implemented PID Controller                                       | 51 |

| Fig. 5.22  | Closed Loop Control System using PID Controller                                              | 52 |

| Fig. 5.23  | Step Response of a Second Order System with PID Controller                                   | 52 |

# LIST OF TABLES

| Table 2.1 | Transistors aspect ratios of the circuit shown in Fig.2.5                   | .8 |

|-----------|-----------------------------------------------------------------------------|----|

| Table 2.2 | Simulation results of the circuit shown in Fig. 2.5                         | .9 |

| Table 3.1 | Simulation results of the Proposed Second Order LPF2                        | 0  |

| Table 5.1 | Aspect ratios for MOS-C implementation of P Controller                      | 6  |

| Table 5.2 | Performance Comparison of closed loop system with and without P controller4 | 0  |

| Table 5.3 | Aspect ratios for MOS-C implementation of PD Controller4                    | -1 |

| Table 5.4 | Performance Comparison of closed loop system with and without PD            | 15 |

| Table 5.5 | Aspect ratios for MOS-C implementation of PI Controller4                    | 16 |

| Table 5.6 | Performance Comparison of closed loop system with and without PI4           | .9 |

| Table 5.7 | Aspect ratios for MOS-C implementation of PID Controller                    | 50 |

| Table 5.8 | Performance Comparison of closed loop system with and without PID           | 2  |

| Table 5.9 | Performance Comparison of closed loop system with and without controllers   | 53 |

# Chapter-1

# INTRODUCTION

# **1.1 Motivation**

Control engineering deals with understanding of plant under operation, and obtaining a desired output response in presence of system constraints. Controllers have applications in various sectors of industry, such as quality control of manufactured products, automated assembly lines, machine-tool control, space technology and weapon systems, computer control, transportation systems, power systems, robotics, Micro-Electro-Mechanical Systems (MEMS), nanotechnology etc [1]. There has been an ever increasing demand of controllers in process industry for improving manufacturing processes and energy efficiency [2]. Especially energy efficiency is the focus and controllers have a significant role to play. Hence there has been a significant endeavor to obtain effective controller designs.

Proportional-integral-derivative (PID) controllers are one of the most important control elements used in the process control industry. Generally operational amplifiers are used to design classical analog controllers. However the operational amplifiers, being voltage mode circuit, have their own limitation of constant gain bandwidth product and low slew rate. Current mode building blocks such as Current Conveyor, OTA, CDBA, CDTA, OTRA etc. have larger bandwidth, dynamic range, and also greater linearity than their voltage-mode counterparts, op-amps [3]. These active blocks therefore would be a better substitute of OPAMP for designing the analog controllers.

Operational Transresistance Amplifier (OTRA) is a high gain current input, voltage output amplifier [4]. OTRA being a current mode building block inherits the advantages of current mode processing as well as it is free from parasitic input capacitances and resistances as its input terminals are virtually grounded and hence, non-ideality problem is less in circuits implemented using OTRA. In literature, OTRA based controllers have not been reported so far.

In low power analog applications, the effect of noise is prominent. To reduce the effect of noise on the circuits, designers of analogue ICs usually build their circuitry as differential rather than single-ended structure.

In view of above, Differential Operational Transresistance Amplifier-based controllers are introduced in this dissertation. To verify the theoretical analysis of these controllers second order closed loop system using second order Low Pass Filter and the controllers are designed and simulated using SPICE.

#### **1.2 Literature Review**

OTRA is the basic building block of a number of applications both in current and voltage and mixed modes. The first CMOS circuit of OTRA was introduced in 1992 by J. J. Chen, H. W. Tsao & C. C. Chen [4]. Reference [5] 1995 shows that the input terminals of OTRA being virtually grounded, the circuits designed using OTRA were insensitive to stray capacitances [5]. In 1999 Salama and Ahmed M. Soliman introduced a simple CMOS realization of OTRA based on cascaded connection of modified differential current conveyor (MDCC) and a common source amplifier [6]. In [7] they proposed a new circuit based on same cascaded connection of modified differential current conveyor (MDCC) and a common source amplifier as in [6] but with improved performance and less number of transistors. The Circuit proposed in [8] is based on same input stage of OTRA proposed in [7] and a differential gain stage is used instead of the single common source amplifier and a compensation circuit is used to compensate difference between the two drain voltages of input transistors. The circuit proposed in [9] is another modification of circuit presented in [7] where differential gain stage is used instead of the single common source amplifier. Several other CMOS realizations of OTRA are also available in literature [10-12]. Circuit presented in [10] consists of a differential current controlled current source (DCCCS) followed by a voltage buffer whereas circuit reported in [11] is made of R<sub>m</sub> cell, feedback network and output driver. A low voltage regulated cascode current mirror with a low voltage regulated cascode load forms core of the circuit proposed in [12]. OTRA is commercially available from several manufacturers under the name current differencing or Norton amplifier, [13-15].

Various applications of OTRA also exist in literature. Filters using OTRA are proposed in [5-6, 16-21] and oscillators & multi vibrators are presented in [21-27] whereas Schmitt trigger is presented in [28]. Realizations of immittance using OTRA are reported in [29-31].

Further literature survey reveals that a number of circuits have been reported relating to proportional (P), proportional integral (PI), proportional derivative (PD), and proportional integral & derivative (PID) controllers in [32–38]. Circuits presented in [32, 33] are based on OpAmps and have their own limitation of finite gain bandwidth. [34] Presents OTA based controllers and [35] presents CDBA based controllers whereas CCII based controllers are proposed in [36-38]. However, no such OTRA based controllers have been reported in literature so far.

### **1.3 Objective and Scope of the Project**

The objective of the project is to design circuits of classical controllers i.e. P, PI, PD and PID using Operational Transresistance Amplifier, analyze their effect on Second Order Control System and design & simulate their MOS-C equivalent circuits for minimizing the chip area and for making these circuits electronically tunable.

These controllers are best suited for the systems where knowledge of the underlying process is absent. These OTRA based designs are best suited for the Low Power and High Speed applications like MEMS (Micro-electromechanical systems) and Low Power Medical Devices apart from its traditional field of application i.e. Process Industry.

### **1.4 Organization of thesis**

The thesis is organized as follows:

**Chapter 2:** It describes the basics of OTRA, and differential OTRA. It further describes their internal circuit structures. Terminal characteristics of these circuits have been verified through PSPICE simulations.

**Chapter 3:** This chapter describes the time domain analysis of standard second order system and time domain design specifications. A second order Low Pass Filter circuit using differential OTRA is proposed and it simulation results are also included.

**Chapter 4:** In this chapter detailed description of basic controllers i.e. P, PD, PI and PID and their effect on second order closed loop is given. Differential OTRA based PD, PI, and PID controllers are proposed and analyzed in this chapter. MOS-C equivalent of P, PD, PI and PID controllers are also discussed.

**Chapter 5:** This chapter analyzes the simulation results of the circuits proposed in this dissertation.

**Chapter 6:** In this section conclusion of the thesis work and future scope of the work are presented.

# Chapter-2

# OPERATIONAL TRANS-RESISTANCE AMPLIFIER

This chapter describes the basics of OTRA as well as Differential OTRA. Here, CMOS realization of Differential OTRA [9] is discussed and its simulation results are presented. This simulated Differential OTRA is used for designing of controllers proposed in this work.

### 2.1 Basics of OTRA

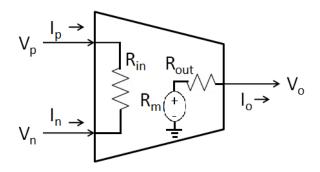

Operational Trans-resistance Amplifier (OTRA) is a high gain current input, voltage output amplifier [4]. Symbol of OTRA is illustrated in Fig.2.1. OTRA is a three terminal device described by matrix equation:

$$\begin{bmatrix} V_{p} \\ V_{n} \\ V_{o} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ R_{m} & -R_{m} & 0 & 0 \end{bmatrix} \begin{bmatrix} I_{p} \\ I_{n} \\ I_{o} \end{bmatrix}$$

$$V_{p} \xrightarrow{I_{p}} + R_{m}$$

$$V_{n} \xrightarrow{I_{n}} V_{o}$$

$$(2.1)$$

Fig. 2.1 Symbol of OTRA

From the above equation it is clear that both input and output terminals are characterized by low impedance, thereby eliminating response limitations incurred by capacitive time constants. The input terminals are virtually grounded leading to circuits that are insensitive to stray capacitances [5]. Ideally, the transresistance gain,  $R_m$ , approaches infinity, and external negative feedback must be used which forces the input currents,  $I_p$ and  $I_n$ , to be equal [6]. Thus OTRA must be used in a negative feedback configuration. Practically the Transresistance gain is finite and its effect should be considered. Also, the frequency limitations associated with OTRA should be considered. Considering a singlepole model for the transresistance gain,  $R_m$ [6], then:

$$\mathbf{R}_{\mathrm{m}}(\mathbf{s}) = \left(\frac{\mathbf{R}_{0}}{1 + s/\omega_{0}}\right) \tag{2.2}$$

For high frequency applications, the transresistance gain,  $R_{\rm m}(s)$ , can be expressed as:

$$R_{\rm m}(s) \approx \left(\frac{1}{sC_{\rm p}}\right)$$

(2.3a)

where

$$C_{p} = \frac{1}{R_{0}\omega_{0}}$$

(2.3b)

where,  $R_o$  is DC open loop transresistance gain and  $\omega_o$  is transresistance cut off frequency. The small signal ac equivalent of the OTRA is shown in the Fig. 2.2.

Fig. 2.2 Small Signal AC Equivalent of OTRA

### 2.2 Differential OTRA

Differential signal processing has higher dynamic range and power supply rejection compared to single-ended counterparts. These parameters are especially relevant in low power circuits. Other inherent advantages of differential circuits include immunity from common-mode noise signals and lower harmonic distortion.

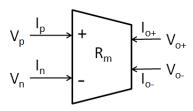

Differential OTRA is a four terminal device characterized by the matrix equation [39]:

$$\begin{bmatrix} V_{p} \\ V_{n} \\ V_{0+} \\ V_{0-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ R_{m} & -R_{m} & 0 & 0 \\ -R_{m} & R_{m} & 0 & 0 \end{bmatrix} \begin{bmatrix} I_{p} \\ I_{n} \\ I_{0+} \\ I_{0-} \end{bmatrix}$$

(2.4)

Fig. 2.3 and 2.4 show the symbol and small signal ac equivalent of differential OTRA respectively [39].

Fig. 2.3 Symbol of Differential OTRA [39]

Fig. 2.4 Small Signal AC Equivalent of Differential OTRA [39].

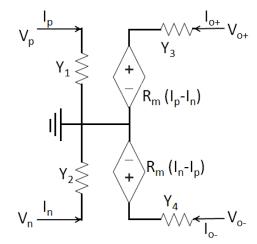

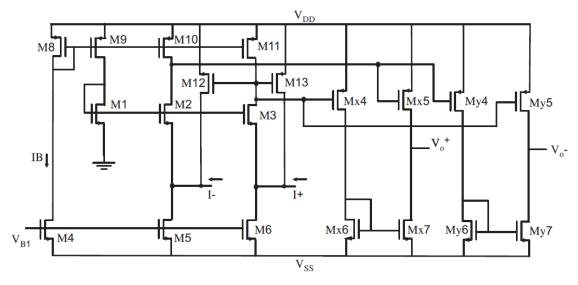

## 2.3 CMOS Realization of Differential OTRA

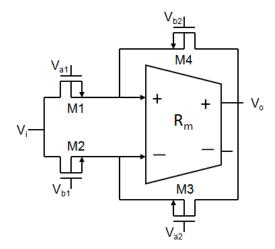

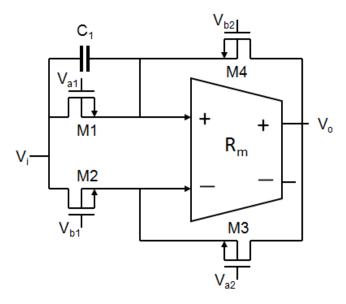

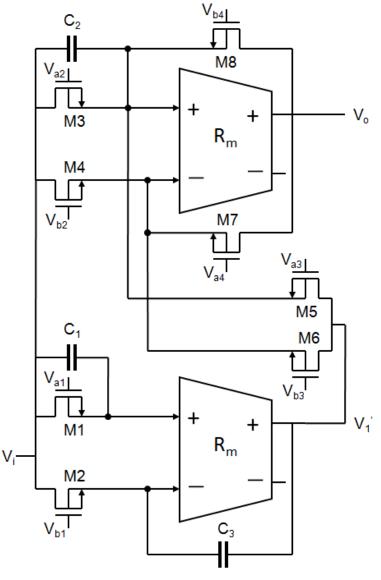

CMOS realization of differential OTRA proposed in [9] is shown in Fig. 2.5. It is based on cascaded connection of modified differential current conveyor (MDCC) [40] and a differential gain stage.

Fig. 2.5 CMOS Realization of Differential OTRA Proposed in [9]

Saurabh Chitransi, Dept. of Electronics and Communication Engineering, DTU, Delhi

Assuming that each of the groups of the transistors (M1-M3), (M5 and M6), (M9-M11) and (M12 and M13) are matched, and that all transistors operate in saturation region, the circuit operation can be explained as follows.

The current mirrors formed by (M8-M11) forces equal currents (IB) in the transistors M1, M2 and M3. This operation drives the gate to source voltages of M1, M2 and M3 to be equal and, consequently, forces the two input terminals to be virtually grounded.

Current mirrors formed by the transistor pairs (M10 and M11) and (M12 and M13) provide current differencing operation, whereas differential gain stage achieves the high gain stage. The transistors Mx4-Mx7 produce non-inverting output, while the transistors My4-My7 produce inverting output.

## 2.4 Simulation Results of Differential OTRA

For simulation CMOS implementation of differential OTRA proposed in [9] is used. The SPICE simulation is performed using 0.18 $\mu$ m, Level 7, CMOS process parameters provided by MOSIS (AGILENT) and supply voltages taken are ±1.5 V. Transistors aspect ratios are reported in Table 2.1.

| •                     |       |            |

|-----------------------|-------|------------|

| Transistors           | W(µm) | $L(\mu m)$ |

| M1-M3                 | 3.6   | 0.54       |

| M4                    | 5.4   | 0.18       |

| M5, M6                | 5.4   | 0.36       |

| M8                    | 5.4   | 0.18       |

| M9-M11                | 1.8   | 0.54       |

| M12, M13              | 3.6   | 0.54       |

| Mx4, Mx5, My4 and My5 | 0.18  | 0.18       |

| Mx6, My7              | 1.8   | 0.18       |

| My6, Mx7              | 0.18  | 0.18       |

|                       |       |            |

Table 2.1 Transistors aspect ratios of the circuit shown in Fig.2.5.

Biasing voltage VB1 = -0.798013V. Simulation results are tabulated in Table 2.2 and shown in Figs. 2.6, 2.7 and 2.8.

> 1. C .1 .

. .

**T 11 22**

. ..

| Table 2.2 Simulation results of the circuit shown in Fig. 2.5 |           |        |

|---------------------------------------------------------------|-----------|--------|

| Parameters                                                    | Results   | Unit   |

| Input current dynamic range                                   | -70 to 70 | μΑ     |

| Input resistances R1, R2                                      | 103.58    | Ω      |

| DC open loop transresistance                                  | 124.8     | dBΩ    |

| Gain bandwidth product                                        | 98.22     | THz. Ω |

| Transresistance gain B.W. (-3dB)                              | 56.52     | MHz    |

| Total power dissipation                                       | 2.12      | mW     |

| Capacitance C <sub>p</sub>                                    | 1.61      | fF     |

Fig. 2.6a Non-inverting DC Transfer Characteristics.

Fig. 2.6b Inverting DC Transfer Characteristics

Fig. 2.7 Input Resistances of Differential OTRA

Fig. 2.8 Frequency Response of Differential OTRA

# Chapter-3

# Time Domain Analysis of Second Order System

As time is the independent variable in most of the control systems, time domain analysis is a usual practice for evaluating the system. In this analysis, a reference input signal is applied to the system under test, and performance of the system is evaluated by analyzing system response in time domain [1].

In this chapter, standard second order system and its unit step response is discussed for various conditions of damping ratio. Time domain specifications are defined, which will be useful for evaluation of Controller circuits. Also, a second order Low Pass Filter is proposed and its step response is analyzed and simulation results are depicted. This LPF will be helpful in observing the effect of controllers on second order system.

### 3.1 Standard Second Order System

Standard transfer function of the second order control system is given as:

$$T(s) = \frac{C(s)}{R(s)} = \frac{\omega_n^2}{s^2 + 2\xi\omega_n s + \omega_n^2}$$

(3.1)

where,  $\omega_n$  = natural frequency of oscillations

$\xi$  = damping ratio or damping factor

Fig. 3.1 shows a standard form of a second order system in closed loop form.

Fig. 3.1 Second Order System

The transient response of any system depends on the poles of transfer function T(s) [41]. The roots of denominator polynomial in s of T(s) are poles of transfer function. Thus denominator polynomial of T(s), given by:

$$D(s) = s^2 + 2\xi\omega_n s + \omega_n^2 \tag{3.2}$$

is known as the characteristic polynomial of the system and D(s) = 0 is known as characteristic equation of the system. The poles of T(s), or, the roots of characteristic equation

$$s^{2} + 2\xi\omega_{n}s + \omega_{n}^{2} = 0$$

$$s_{1,2} = -\xi\omega_{n} \pm \omega_{n}\sqrt{(\xi^{2} - 1)}$$

If  $\xi < 1$

$$s_{1,2} = -\xi\omega_{n} \pm j\omega_{n}\sqrt{(1 - \xi^{2})} = -\xi\omega_{n} \pm j\omega_{d}$$

(3.3)

where,  $\omega_d$  is damped natural frequency of the system.

For

ξ<1, system is under damped</li>ξ>1, system is over damped and roots are real

$\xi = 1$ , system is critically damped and roots are real & equal.

## 3.2 Unit Step Response of Second Order System

For unit step response, R(s) = 1/s, from eq. 3.1

$$C(s) = T(s).R(s) = \frac{\omega_n^2}{s^2 + 2\xi\omega_n s + \omega_n^2} \cdot \frac{1}{s}$$

On solving it gives

$$C(t) = 1 - \frac{e^{\xi \omega_n t}}{\sqrt{1 - \xi^2}} \sin(\omega_d t + \Phi)$$

(3.4)

where,

$$\Phi = \tan^{-1} \frac{\sqrt{1-\xi^2}}{\xi}$$

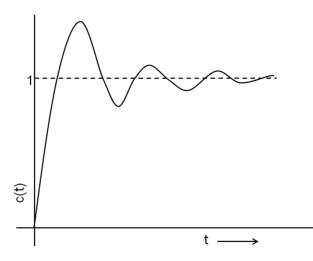

This response is plotted in Fig. 3.2. The response is oscillatory and as  $t \to \infty$ , it approaches unity.

Saurabh Chitransi, Dept. of Electronics and Communication Engineering, DTU, Delhi

Fig. 3.2 Step Response of An Underdamped Second Order System

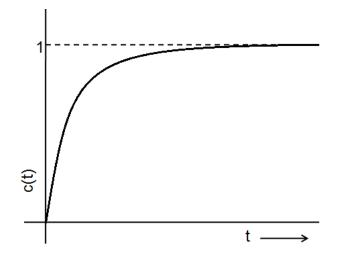

If  $\xi = 1$ , the two roots of the characteristic equations are  $s_1 = s_2 = -\omega_n$  and response is given by

$$C(s) = T(s).R(s) = \frac{\omega_n^2}{(s+\omega_n)^2} \cdot \frac{1}{s}$$

And

$$C(t) = 1 - e^{-\omega_n t} - t\omega_n e^{-\omega_n t}$$

(3.5)

This is plotted in Fig. 3.3.

Fig.3.3 Response of A Critically Damped Second Order System

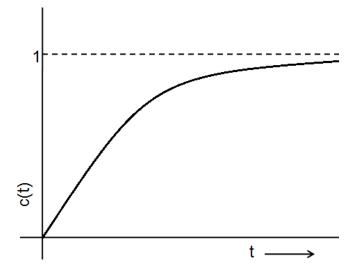

With increase in damping factor,  $\xi$  from a value less than to unity, oscillations decrease and just disappear [41]. If  $\xi$  increases beyond unity, roots of the characteristic equation become real and negative and hence, response approaches unity in an exponential way. This response is known as over-damped response and is shown in Fig. 3.4.

Fig. 3.4 Step Response of an Over-damped Second Order System

# **3.3 Time Domain specifications**

Time domain system performance is measured in terms of following qualities [41].

- 1. Time it takes to respond to input.

- 2. Time it takes to reach desired output.

- 3. Error between desired and actual output.

- 4. Oscillations around desired output.

For designing any system, certain design specifications are given based on underdamped step response of second order system as shown in Fig. 3.5.

Fig. 3.5 Time Domain Specifications of a Second Order System

*The design specifications are* [1, 41-42]:

1. *Delay time, t\_d:* It is the time taken by the output response to reach 50% of the steady state value for the first time. For second order system it is given by:

$$t_d = \frac{1+0.7\xi}{\omega_d} \tag{3.6}$$

2. *Rise time, t\_r:* It is the time taken by the output response to rise from 10% to 90% of its final value and for a second order system is given by:

$$t_r = \frac{\prod - \Phi}{\omega_d} = \frac{\prod - \cos^{-1}\xi}{\omega_n \sqrt{1 - \xi^2}}$$

(3.7)

3. *Peak time, t<sub>p</sub>*: Time at which the output response attains its maximum value is called peak time. For second order system it is given by:

$$t_p = \frac{\prod}{\omega_d} = \frac{\prod}{\omega_n \sqrt{1-\xi^2}} \tag{3.8}$$

4. *Peak overshoot*  $M_p$ : It is defined as the difference between the peak value of response and the steady state value. It is usually expressed in percent of the steady state value. If the peak time is  $t_p$ , peak overshoot percentage is given by,

Peak overshoot percentage,

$$M_p = \frac{c(t_p) - c(\infty)}{c(\infty)} \times 100$$

For second order system it is given by:

$$M_p = e^{-\Pi\xi} / \sqrt{1-\xi^2} \times 100 \tag{3.9}$$

Settling time t<sub>s</sub>: It is the taken by the output response to reach and remain within a specified tolerance limits (usually ± 2% or ± 5%) around the steady state value. For second order system it is given by:

$$t_s = \frac{4}{\xi \omega_n}, \qquad \text{for } \pm 2\% \tag{3.10a}$$

$$t_s = \frac{3}{\xi \omega_n}, \qquad \text{for } \pm 5\% \tag{3.10b}$$

6. *Steady state error*  $e_{ss}$ : It is the difference between desired and actual output as  $t \rightarrow \infty$  or under steady state conditions.

$$e_{ss} = \lim_{t \to \infty} [r(t) - c(t)] = \lim_{s \to 0} sR(s) \frac{1}{1 + G(s)H(s)}$$

(3.11)

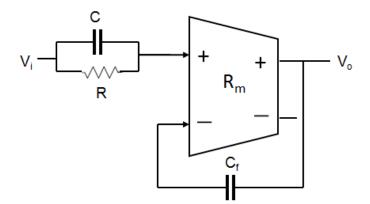

## 3.4 Proposed Second Order Low Pass Filter

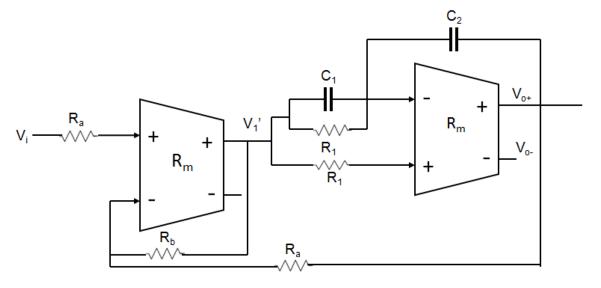

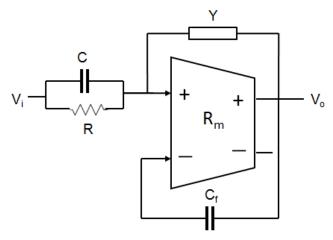

To verify the theoretical analysis of various controller circuits a second order Low pass filter is proposed and is shown in Fig. 3.6. It is designed using two differential OTRAs, two capacitors and five resistors. It is based on cascaded connection of the subtractor and the second order universal filter presented in [43]. From the Fig.3.6, the ratio  $V_0/V_1$  can be expressed as

$$V_1' = \frac{R_b}{R_a} (V_i - V_o)$$

(3.12a)

$$\frac{V_o(s)}{V_1^{I}(s)} = \frac{G_1^{2}}{sC_2(G_1 + sC_1)}$$

(3.12b)

From equations 3.12a and 3.12b the transfer function of the LPF can be derived as

$$\frac{V_0(s)}{V_i(s)} = \frac{KG_1^2}{s^2 C_1 C_2 + s C_2 G_1 + KG_1^2}$$

(3.13)

where,  $K = \frac{R_b}{R_a}$

On comparing with the standard equation of second order system, eq. 3.1, it is seen,

$$\omega_n = G_1 \sqrt{\frac{\kappa}{c_1 c_2}} \text{ and } \xi = \frac{1}{2\sqrt{\kappa}}$$

(3.14)

Hence,

$$\omega_d = \frac{G_1}{2} \sqrt{\frac{4K-1}{C_1 C_2}} \tag{3.15}$$

Fig. 3.6 Proposed Second Order Low Pass Filter

### 3.5 Simulation Results of Second Order LPF

For simulation of proposed second order low pass filter, differential OTRA simulated in  $2^{nd}$  chapter is used as an active component and values of passive element for the filters are selected as  $R_a=R_b=20k\Omega$ ,  $R_1=2k\Omega$ , and  $C_1=C_2=20pF$  which result in

$$\frac{V_0(s)}{V_i(s)} = \frac{6.25 \times 10^{14}}{s^2 + 25 \times 10^6 s + 6.25 \times 10^{14}}$$

$$(3.16)$$

$$f_n = 3.98 \text{ MHz}, \ \zeta = 0.5 \text{ and } f_d = 3.45 \text{ MHz}$$

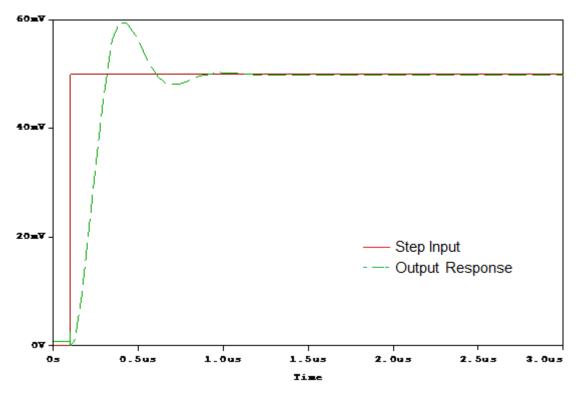

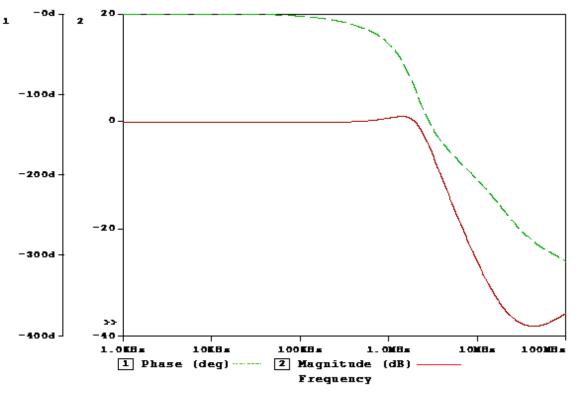

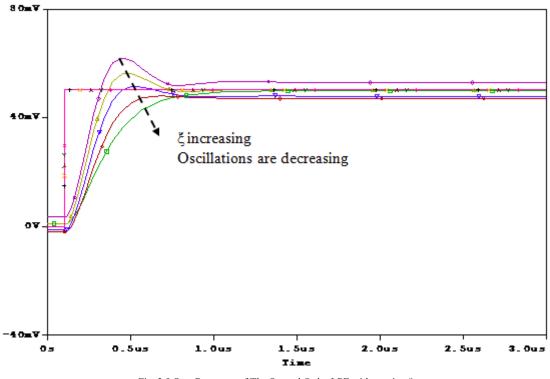

For time domain analysis a step signal of 50mV is applied and the simulated response is shown in Fig. 3.7 and the frequency response is shown in Fig. 3.8. Results are tabulated in table 3.1 and can be described as follow. Rise time of the system is 140ns and settling time is 303ns. Percentage of overshoot is 19.37% and cutoff bandwidth is 2.4MHz. Fig. 3.9 shows the effect of damping ratio,  $\xi$  on the step response of the second order LPF which follows the theoretical concept i.e. with the increase in damping ratio,  $\xi$  oscillations are decreasing.

Fig. 3.7 Step Response of the Proposed Second Order LPF

Fig. 3.8 Frequency Response of the Proposed Second Order LPF

Fig. 3.9 Step Response of The Second Order LPF with varying  $\boldsymbol{\xi}$

| Parameters              | Theoretical Values | Observed Values |

|-------------------------|--------------------|-----------------|

| Overshoot (%)           | 16.30              | 19.37           |

| Peak Voltage (V)        | 58.15m             | 59.49m          |

| Rise time (seconds)     | 96.74n             | 140.17n         |

| Settling Time (seconds) | 240n               | 302.89n         |

| Cutoff BW (-3dB) (Hz)   | 5.06M              | 2.41M           |

Table 3.1 Simulation results of the Proposed Second Order LPF

# Chapter-4

# **PROPOSED CONTROLLERS**

The performance of any control system can be improved by using different controllers in it. These controllers introduce poles and zeros for making the system response as desired. Major performance specifications are time response, steady state accuracy and stability. A **controller** is a device which monitors and modifies the operational conditions of a given dynamical system. The operational conditions are typically referred to as output variables of the system which can be modified by adjusting certain input variables.

In this chapter, classical controllers namely proportional (P), proportional-derivative (PD), Proportional Integrator (PI) and Proportional Integral and Derivative (PID), are discussed which is followed by their OTRA based realization. MOS-C implementations of all the controllers are also given which will help improve the chip area used in integration. Finally influence of controllers on performance of a second order system is also discussed.

## 4.1 Proportional Controller

#### 4.1.1 Introduction

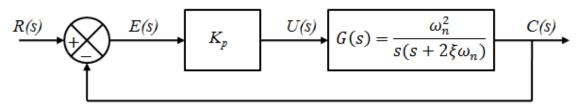

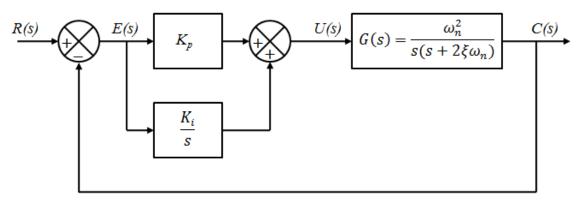

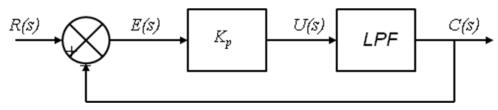

In proportional controller actuating signal, U(s) depends on the instantaneous value of the control error E(s) [42]. A proportional controller can control any stable plant, but it provides limited performance and nonzero steady state errors. This latter limitation is due to the fact that its frequency response is bounded for all frequencies. Fig. 4.1shows the block diagram of second order unity feedback control system using P-controller.

Fig. 4.1 Control System with P-controller

Mathematically,

$$U(s) = K_p E(s) \tag{4.1}$$

So, Transfer function

$$G_{c}(s) = K_{p}$$

where, K<sub>p</sub> is constant of proportionality.

#### 4.1.2 P-Controller with Second order system

From the Fig. 4.1 the transfer function of the complete system is,

$$T_p(s) = \frac{K_p \omega_n^2}{s^2 + 2\xi \omega_n s + K_p \omega_n^2}$$

$$\tag{4.2}$$

On comparing it with standard second order equation, eq. 3.1

$$\begin{split} \omega_n' &= \omega_n \sqrt{K_p} \\ \xi' &= \frac{\xi}{\sqrt{K_p}} \end{split}$$

From the above comparison, it is clear that natural frequency,  $\omega_n$  increases while damping ratio,  $\xi$  decreases by  $\sqrt{K_p}$ , this results in following merits and demerits:

- Rise time reduces.

- Peak time reduces.

- Maximum peak overshoot increases.

- Does not affect settling time.

- Reduces steady state error.

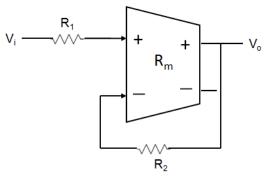

#### 4.1.3 OTRA based P-Controller

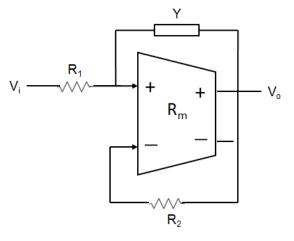

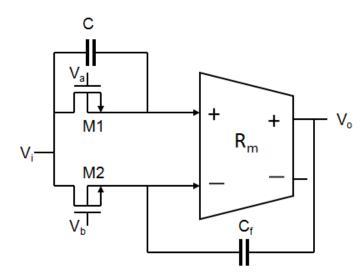

Proportional controller is shown in the Fig. 4.2. The circuit is basically a voltage controlled voltage source.

Fig. 4.2 OTRA based P-Controller

For Ideal case,  $R_m = \infty$

$$I_p = I_n$$

So, Transfer function will be

$$K_{p} = \frac{V_{0}(s)}{V_{i}(s)} = \frac{R_{2}}{R_{1}}$$

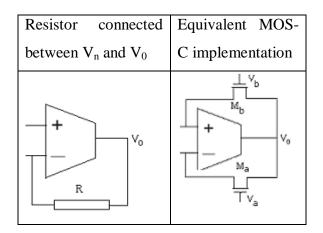

(4.3)

These parameters can be electronically tuned by implementing the linear passive resistors using MOS transistors operating in non-saturation region. The resistance value may be adjusted by appropriate choice of gate voltages. The resistors connected to the input terminals of OTRA can easily be implemented using MOS transistors with complete non-linearity cancellation [6]. Fig. 4.4 shows a typical MOS implementation of resistance connected between negative input and output terminals of OTRA.

Fig. 4.3 MOS implementation of a Linear resistance

The equivalent resistance value is given as

$$R = \frac{1}{\mu_n C_{ox}} (W_L) (V_a - V_b)$$

(4.6)

where  $\mu_{n,} C_{ox,}$  W and L are electron mobility, oxide capacitance per unit gate area, effective channel width, and effective channel length respectively which may be expressed as

$$\mu_n = \frac{\mu_0}{1 + \theta(V_{GS} - V_T)}$$

$$Cox = \frac{\varepsilon_{ox}}{T_{ox}}$$

$$W = W_{drawn} - 2W_D$$

$$L = L_{drawn} - 2L_D$$

$V_a$  and  $V_b$  are the gate voltages and other symbols have their usual meaning. Fig. 4.4 shows the MOS-C implementation of the circuit of Fig. 4.2.

Fig. 4.4 MOS-C realization of P-Controller

#### 4.1.4 Non-ideality Analysis

Taking the effect of the finite transresistance gain,  $R_m$  of OTRA into account  $K_p$  is given by:

$$K_p = \frac{R_2}{R_1} \in (s) \tag{4.4}$$

where,

$$\in (s) = \frac{1}{1 + \frac{R_2}{R_m}}$$

Using single pole model [2],

$$R_m = \frac{R_o}{1 + s/\omega_o} \tag{4.5a}$$

where,  $R_{\rm O}$  is dc transresistance gain.

Fig.4.5 P-Controller with Compensation

For high frequency applications the trans-resistance gain, reduces to

$$R_m \approx \frac{1}{sc_p}$$

(4.5b) where,

$$C_p = \frac{1}{R_o \omega_o}$$

Now from Fig. 4.5

$$\in (s) = \frac{1}{1 + R_2(sC_p - Y)}$$

(4.6)

by choosing:  $Y = s C_p$ ,  $\in$ (s) reduces to its ideal value of unity. Therefore, complete passive compensation of the P controller can be achieved by using a single capacitor connected between the output terminal and the non-inverting terminal.

#### 4.2 PD Controller

#### 4.2.1 Introduction

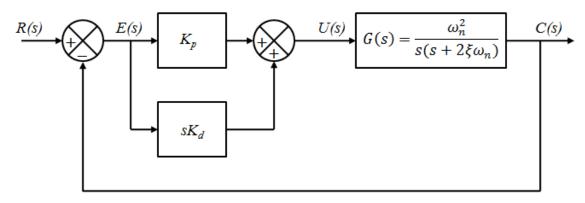

In PD controller the actuating signal U(s) is sum of proportional to the error signal E(s) and its rate of change. Therefore if the error is large or changing rapidly, the effect of the control will be an increase in the system response. It is a fast mode which ultimately disappears in the presence of constant errors. It is also known as predictive mode as it depends on the error trend. The main limitation of the derivative mode, viewed in isolation, is its tendency to yield large control signals in response to high frequency control errors, such as errors induced by set point changes or measurement noise [42]. Fig. 4.6 shows the block diagram of second order unity feedback control system using PD-controller.

Fig. 4.6 Control System with PD-controller

The controller is a proportional-derivative (PD) type with the transfer function.

$$G_c(s) = K_p + K_d s \tag{4.7}$$

where,  $K_p$  and  $K_d$  are the proportional and derivative constants, respectively.

### 4.2.2 PD-Controller with Second order system

From the Fig. 4.6 the transfer function of the complete system can be calculated as,

$$T_{pd}(s) = \frac{(K_p + sK_d)\omega_n^2}{s^2 + (2\xi\omega_n + K_d\omega_n^2)s + K_p\omega_n^2}$$

(4.8)

On comparing it with standard second order equation, eq. 3.1

For

$$K_p = 1$$

,

$\omega'_n = \omega_n$

$\xi' = \xi + \frac{K_d \omega_n}{2}$

From the above results, it is clear that natural frequency,  $\omega_n$  does not change while damping ratio,  $\xi$  increases, this result in following merits and demerits:

- Damping improves and peak overshoot reduces.

- Rise time reduces.

- Peak time reduces.

- Settling time reduces.

- Does not affect steady state error.

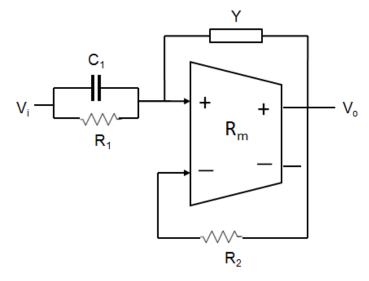

#### 4.2.3 OTRA based Proposed PD-Controller

Fig. 4.7 OTRA based Proposed PD Controller

The proposed PD-Controller is shown in Fig. 4.7. Routine analysis of this controller, using terminal equations of OTRA and assuming OTRA to be ideal, i.e.  $R_m = \infty$ , results in

$$V_i \left(\frac{1}{R} + sC\right) = \frac{V_{o^+}}{R_f}$$

$$\frac{V_{o^+}}{V_i} = \frac{R_f}{R} + sCR_f$$

(4.9)

comparison of equation 4.7 with equation 4.9 gives

$$K_p = \frac{R_f}{R}, \qquad K_D = CR_f \tag{4.10}$$

From 4.10 it is clear that by varying R,  $K_p$  value can be adjusted independent of  $K_d$  and by simultaneous variation of  $R_f$  and R,  $K_d$  can be independently controlled. Fig. 4.8 shows the MOS-C implementation of the circuit of Fig. 4.7.

Fig. 4.8 MOS-C realization of Proposed PD Controller

#### 4.2.4 Non-ideality Analysis

In this section the effect of finite trans-resistance gain  $(R_m)$  on PD controller is considered and for high frequency applications passive compensation is employed. Ideally,  $R_m$  is assumed to approach infinity. However, practically  $R_m$  is a frequency dependent finite value.

For low frequency applications the trans-resistance gain, reduces to

$$R_m \approx R_o$$

Taking this effect into account eq. 4.9 modifies to

$$\frac{V_{o^+}}{V_i} = \left(R_o \parallel R_f\right) \left(\frac{1}{R} + sC\right)$$

Since,  $R_o >> R_f$

$R_o \parallel R_f \approx R_f$

(4.11)

Hence eq. 4.11 reduces to eq. 4.9. The effect of  $R_o$  can thus be eliminated by choosing  $R_f \ll R_o$ .

For high frequency applications the trans-resistance gain, reduces to

$$R_{m}(s) \approx \left(\frac{1}{sC_{p}}\right)$$

Taking this effect into account eq. 4.9 modifies to

$$\frac{\mathbf{v}_{o^+}}{\mathbf{v}_i} = \frac{\mathbf{R}_f}{\mathbf{R}(1+\mathbf{s}\mathbf{C}_p\mathbf{R}_f)} + \mathbf{s}\mathbf{C}\frac{\mathbf{R}_f}{1+\mathbf{s}\mathbf{C}_p\mathbf{R}_f}$$

(4.12)

For high-frequency applications, compensation methods must be employed to account for the error introduced in eq. 4.9. Considering the circuit shown in Fig. 4.9, eq. 4.12 modifies to

$$\frac{\mathbf{v}_{o^+}}{\mathbf{v}_i} = \frac{\mathbf{R}_f}{\mathbf{R}(1 + \mathbf{R}_f(\mathbf{s}\mathbf{C}_p - \mathbf{s}\mathbf{Y}))} + \frac{\mathbf{s}\mathbf{C}\mathbf{R}_f}{1 + \mathbf{R}_f(\mathbf{s}\mathbf{C}_p - \mathbf{s}\mathbf{Y})}$$

(4.13)

Fig. 4.9 Compensated PD Controller

By taking  $Y = sC_p$ , eq. 4.13 reduces to eq. 4.9. The effect of  $R_m$  can thus be eliminated by connecting a single capacitor between the non inverting terminal and the output as shown in Fig. 4.9. Thus passive compensation has achieved for both low as well as high frequency.

#### 4.3 PI Controller

#### 4.3.1 Introduction

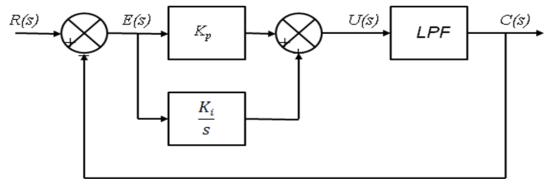

In PI Controller, actuating signal drives the plant to be controlled with a weighted sum of the error signal and the integral of that value which implies that it is a slow reaction control mode. This characteristic is also evident in its low pass frequency response. The integral mode plays a fundamental role in achieving perfect plant inversion at  $\omega = 0$ . This forces the steady state error to zero in the presence of a step reference and disturbance. The integral mode, viewed in isolation, has two major shortcomings: its pole at the origin is detrimental to loop stability and it also gives rise to the undesirable effect (in the presence of actuator saturation) known as wind-up [42]. Fig. 4.10 shows the block diagram of second order unity feedback control system using PI controller.

Fig. 4.10 Control System with PI-controller

The controller is a proportional-integrator (PI) type with the transfer function.

$$G_c(s) = K_p + \frac{K_i}{s} \tag{4.14}$$

where,  $K_p$  and  $K_i$  are the proportional and integral constants, respectively.

#### 4.3.2 PI-Controller with Second order system

From the Fig. 4.10 the transfer function of the complete system can be calculated as,

$$T_{pi}(s) = \frac{(K_i + sK_p)\omega_n^2}{s^3 + 2\xi \,\omega_n s^2 + K_p \omega_n^2 s + K_i \,\omega_n^2}$$

(4.15)

For  $K_p = 1$ , Error signal is given by

$$E(s) = R(s) \frac{s^2 (s+2\xi\omega_n)}{s^3 + 2\xi\omega_n s^2 + \omega_n^2 s + K_i \omega_n^2}$$

(4.16)

And the steady state error is given by

For step input,  $e_{ss} = 0$

For ramp input,  $e_{ss} = 0$

For parabolic input,  $e_{ss} = \frac{2\xi}{K_i \omega_n}$

Hence merits and demerits of PI-Controller can be described as

- It increases the type and order of the system.

- It improves steady state response by reducing the steady state error.

- Rise time increases

#### 4.3.3 OTRA based Proposed PI-Controller

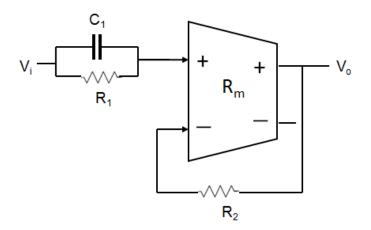

Proposed PI-Controller is shown in Fig. 4.11.

Fig. 4.11 OTRA based Proposed PI Controller

The routine analysis of this controller gives the following voltage transfer function

$$\frac{V_{o^+}}{V_i} = \frac{c}{c_f} + \frac{1}{sc_f R}$$

(4.17)

On comparing equations 4.14 and 4.17

$$K_p = \frac{c}{c_f}, \qquad K_i = \frac{1}{c_f R}$$

(4.18)

Saurabh Chitransi, Dept. of Electronics and Communication Engineering, DTU, Delhi

From the above equation it is clear that by varying C,  $K_p$  value can be adjusted independent of  $K_i$  and by simultaneous variation of  $C_f$  and C,  $K_i$  can be independently controlled. Fig. 4.12 shows the MOS-C implementation of the circuit of Fig. 4.11.

Fig. 4.12 MOS-C realization of Proposed PI Controller

#### 4.3.4 Non-ideality analysis

Here, effect of finite trans-resistance gain  $(R_m)$  on PI controller is considered and passive compensation is employed.

Taking the effect of R<sub>m</sub> into account, we get

$$\frac{V_{o^+}}{R_m} = V_i \left(\frac{1}{R} + sC\right) - sC_f V_{o^+}$$

Since

$$R_{m} = \frac{R_{o}}{1 + sR_{o}C_{o}}$$

$$V_{o}^{+}(\frac{1}{R_{o}} + s(C_{o} + C_{f})) = V_{i}(\frac{1}{R} + sC)$$

(4.19)

Since,

$$C_o \ll C_f$$

$$C_f + C_o \approx C_f$$

$$\therefore V_o + (\frac{1}{R_o} + sC_f) = V_i \left(\frac{1}{R} + sC\right) \qquad (4.20)$$

Now, for eliminating the effect of R<sub>o</sub>, circuit is modified as shown in Fig. 4.13

Fig. 4.13 Compensated PI Controller

Considering the circuit shown in Fig. 4.13, eq. 4.20 modifies to

$$V_{o^{+}}(\frac{1}{R_{o}} + sC_{f} - Y) = V_{i}\left(\frac{1}{R} + sC\right)$$

(4.21)

By taking Y =  $1/R_o$ , eq. 4.21 reduces to eq. 4.17. Hence the effect of finite  $R_m$  is completely eliminated.

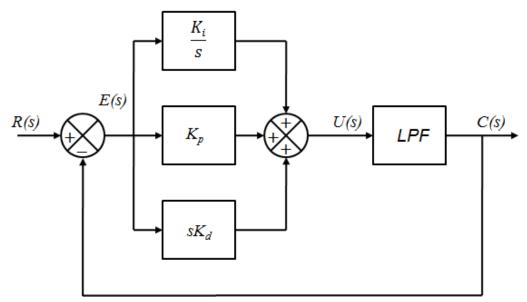

### 4.4 PID Controller

#### 4.4.1 Introduction

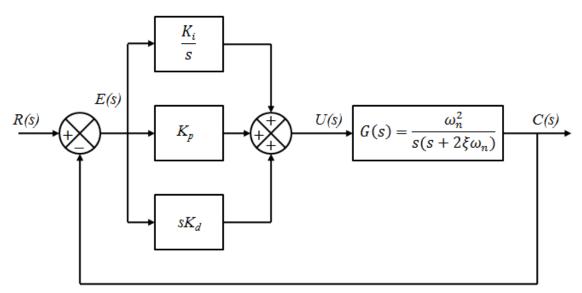

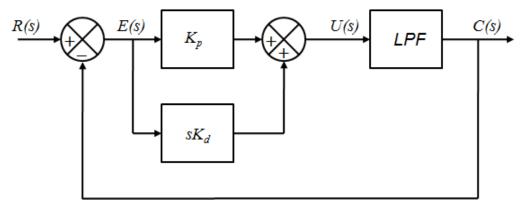

The PD controller improves damping of the system, but the steady-state response is not affected. The PI controller improves the relative stability and the steady-state error at the same time, but the rise time is increased [1]. So, none of them alone is capable of achieving the complete improvement in performance of a system. This leads to the motivation of using a PID controller so that the best features of each of the PI and PD controllers are utilized. Fig. 4.14 shows the block diagram of second order unity feedback control system using PID controller.

Fig. 4.14 Control System with PID-controller

Transfer function of PID Controller is given by

$G_c(s) = K_p + K_d s + \frac{K_i}{s}$  (4.22) where,  $K_p$ ,  $K_d$  and  $K_i$  are the proportional, derivative and integral constants, respectively.

Advantages of PID controller:

- High speed.

- High accuracy.

- High stability.

- No offset problem.

# 4.4.2 OTRA based Proposed PID-Controller

Proposed PID-Controller is shown in Fig. 4.15.

Fig. 4.15 OTRA based Proposed PID Controller

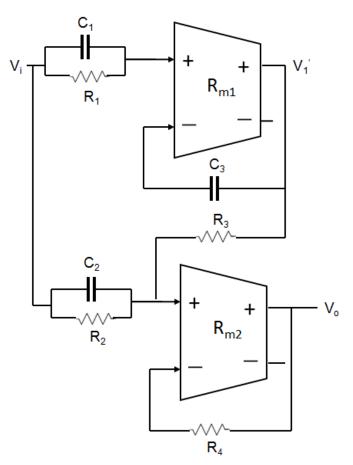

From Fig. 4.15 it is clear that PID is composed of PI and PD controllers. Here first OTRA works as PI controller while second is working as a PD controller as well as an adder. The analysis of the circuit reveals that

$$\frac{v_1'}{v_i} = \frac{c_1}{c_s} + \frac{1}{sc_s R_1}$$

(4.23)

$$V_o = V_i \left(\frac{R_4}{R_2} + sC_2R_4\right) + V_1' \frac{R_4}{R_3}$$

(4.24)

From eq. 4.23 & 4.24

$$\frac{V_o}{V_i} = \left(\frac{R_4}{R_2} + sC_2R_4\right) + \frac{R_4}{R_5}\left(\frac{C_1}{C_5} + \frac{1}{sC_5R_1}\right)$$

(4.25)

On comparing it with 4.22

$$K_{p} = \frac{R_{4}}{R_{s}} \times \frac{C_{1}}{C_{s}} + \frac{R_{4}}{R_{2}}, \quad K_{d} = C_{2}R_{4} \quad \& \quad K_{i} = \frac{R_{4}}{R_{s}} \times \frac{1}{C_{s}R_{1}}$$

(4.26a)

Saurabh Chitransi, Dept. of Electronics and Communication Engineering, DTU, Delhi

Component choice of  $R_4 = R_3$ ,  $R_2 = \infty$ , results in

$$K_{p} = \frac{C_{1}}{C_{s}}, \quad K_{d} = C_{2}R_{4} \quad \& \quad K_{i} = \frac{1}{C_{s}R_{1}}$$

(4.26b)

For  $R_{4} = R_{3}, C_{1} = 0$ , we get

$K_{p} = \frac{R_{4}}{R_{2}}, \quad K_{d} = C_{2}R_{4} \quad \& \quad K_{i} = \frac{1}{C_{s}R_{1}}$ (4.26c)

From the above equations it is clear that by varying  $R_2$  or  $C_1$  or both  $K_p$  can be adjusted independently, by variation of  $C_2$  or simultaneous variation of  $R_4$  &  $R_2$  K<sub>d</sub> can be varied independently, and K<sub>i</sub> can be independently controlled by varying  $R_1$  or simultaneously varying  $C_1$  &  $C_3$ . Fig. 4.16 shows the MOS-C implementation of the circuit of Fig. 4.15.

Fig. 4.16 MOS-C realization of Proposed PID Controller

# Chapter-5

# SIMULATION RESULTS

In order to verify the results of theoretical propositions, all controller circuits namely P, PD, PI and PID are simulated using PSICE program. 180nm, Level 7, CMOS process parameters provided by MOSIS (AGILENT) are used for simulation and supply voltages taken are  $\pm 1.5$ V. Further, to verify the influence of proposed circuits on second order system, a closed loop control system using proposed controllers and second order LPF is designed and simulated. The differential OTRA proposed in [9] is used as an active building block for all the controller circuits.

### 5.1 Simulation Results of P Controller

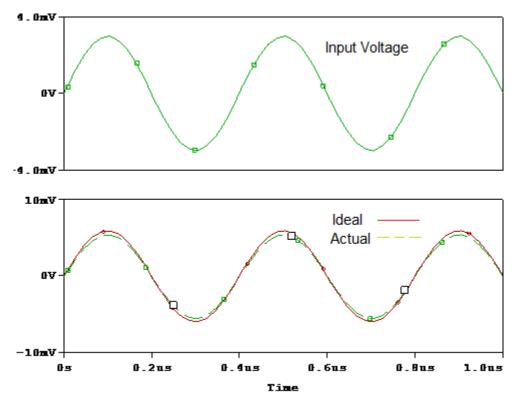

For the OTRA based P controller shown in Fig. 4.2, the values of the passive components are chosen as  $R_1$ =10K and  $R_2$ =20K. For time domain analysis, a 3mV, 2.5 MHz sinusoidal input voltage is applied. Both ideal and simulated results are presented in Fig. 5.1. Frequency domain characteristics are depicted in Fig. 5.2.

For MOS-C implemented P controller shown in Fig. 4.4 aspect ratios of the transistors used for implementing the resistances are listed in Table.5.1.

| Transistor | W(µm)/L(µm) |

|------------|-------------|

| M1,M2      | 0.18µ/.54µ  |

| M3,M4      | 0.18µ/1.08µ |

Table 5.1 Aspect ratios for MOS-C implementation of P Controller

Gate voltages are set as  $V_{a1} = V_{a2} = 1.2V$  and Vb1=0.59V, Vb2 =0.64V which result in resistance values as  $R_1 \approx 10K\Omega$  and  $R_2 \approx 20K\Omega$ . Fig. 5.3 shows the transient response and Fig. 5.4 shows frequency domain characteristics of MOS-C implementation of P controller.

Fig. 5.1 Transient response of the P Controller

Fig. 5.2 Frequency and phase Response of P controller

Fig. 5.3 Transient response of MOS-C implementation of P Controller

Fig. 5.4 Frequency and phase Response of MOS-C implementation of P controller

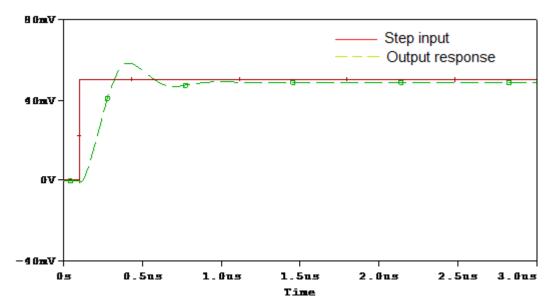

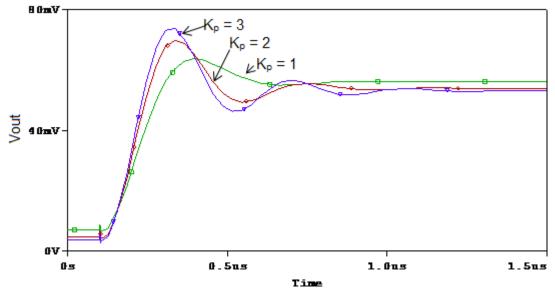

Fig. 5.5 shows a closed loop control system realized using the proposed P controller and a second order low-pass filter (LPF). Fig. 5.6a shows the step response of the LPF without P controller for a step input of 50mV whereas Fig.5.6b depicts the effect of P controller on step response of the closed loop system. Fig. 5.7 shows the effect of varying  $K_p$  on second order system and it is observed that with increase in  $K_p$ , rise time decreases while peak overshoot increases.

Fig. 5.5 Closed Loop Control System using P controller

Performance comparison of second order system with and without P controller is shown in Table. 5.2. It is clearly visible from table 5.2 that the response of the system has been improved with smaller rise time of 108.75ns, but Peak overshoot percentage is increased to 30.14%.

Fig. 5.6a Step Response of a second order system without P controller

Fig. 5.6b Step Response of a second order system with P controller

Table 5.2 Performance Comparison of closed loop system with and without P controller

| Parameter     | Without P Controller | With P Controller |

|---------------|----------------------|-------------------|

| Overshoot     | 19.56%               | 30.14%            |

| Peak output   | 58.26mV              | 62.64mV           |

| Rise time     | 140.43ns             | 108.75ns          |

| Settling time | 303.12ns             | 675.11ns          |

Fig. 5.7 Step Response of a second order system with P controller with varying  $K_p$

#### 5.2 Simulation Results of PD Controller

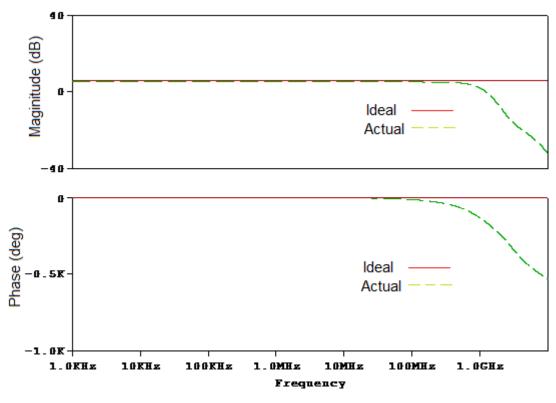

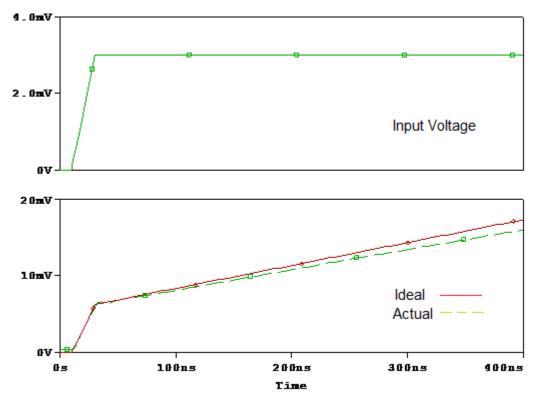

For OTRA based proposed PD controller shown in Fig. 4.7, the values of passive elements are chosen as  $R_1 = 10K\Omega$ ,  $R_2 = 20K\Omega$  and  $C_1 = 20pF$ . For time domain analysis, a 3mV peak triangular input voltage is applied and both ideal and simulated results are presented in Fig. 5.8. Frequency domain characteristics are depicted in Fig. 5.9.

For MOS-C implemented PD controller shown in Fig. 4.8 the aspect ratios of the transistors used for implementing the resistances are listed in Table.5.3.

| Transistor | $W(\mu M)/L(\mu M)$ |

|------------|---------------------|

| M1,M2      | 0.18µ/.54µ          |

| M3,M4      | 0.18µ/1.08µ         |

Table 5.3 Aspect ratios for MOS-C implementation of PD Controller

Gate voltages are set as  $V_{a1} = V_{a2} = 1.2V$  and Vb1=0.59V, Vb2 =0.64V which result in resistance values as  $R_1 \approx 10K\Omega$ ,  $R_2 \approx 20K\Omega$  and the chosen value of capacitance is  $C_1 = 20$ pF. Fig. 5.10 and Fig. 5.11 show the transient response and frequency domain characteristics of MOS-C implementation of PD controller respectively.

Fig. 5.10 Transient response of the MOS-C implemented PD Controller

Fig. 5.11 Frequency and phase Response of the MOS-C implemented PD Controller

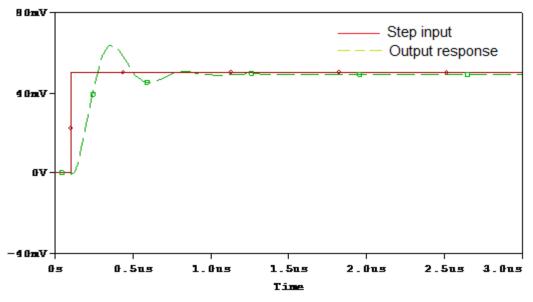

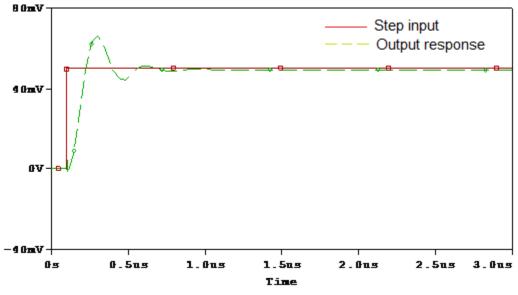

From the above results it is clear, that resistive components of PD controller can easily be replaced by MOS transistors working in linear region. Fig. 5.12 shows a closed loop control system realized using the proposed PD controller and a second order low-pass filter (LPF). Fig. 5.13a shows step response of the LPF without PD controller for a step input of 50mV whereas Fig.5.13b depicts the effect of PD controller on step response of the closed loop system.

Performance comparison of second order system with and without PD controller is shown in Table. 5.4. It is clearly visible from the table 5.4 that the response of the system has been improved with reduced overshoot percentage to 12.89% and smaller rise time of 124.27ns. Fig. 5.13c shows the step response with the variation in  $K_d$  and it shows that with increase in  $K_d$  peak overshoot decreases.

Fig. 5.12 Closed Loop Control System using PD controller

Fig. 5.13a Step Response of a second order system without PD controller

Saurabh Chitransi, Dept. of Electronics and Communication Engineering, DTU, Delhi

Fig. 5.13c Response of a second order system with PD controller with varying  $K_d$

Table 5.4 Performance Comparison of closed loop system with and without PD controller

| Parameter     | Without PD Controller | With PD Controller |

|---------------|-----------------------|--------------------|

| Overshoot     | 19.56%                | 12.89%             |

| Peak output   | 58.26m                | 56.53mV            |

| Rise time     | 140.43ns              | 124.27ns           |

| Settling time | 303.12ns              | 278.97ns           |

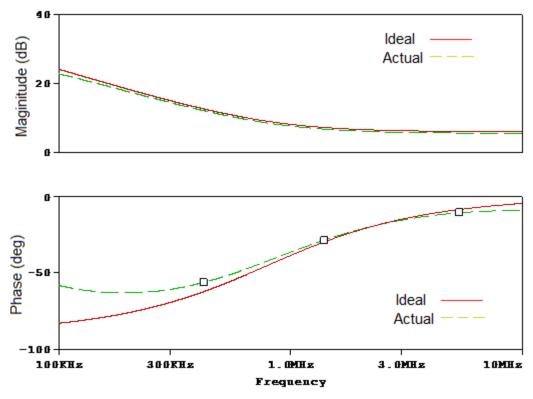

## 5.3 Simulation Results of PI Controller

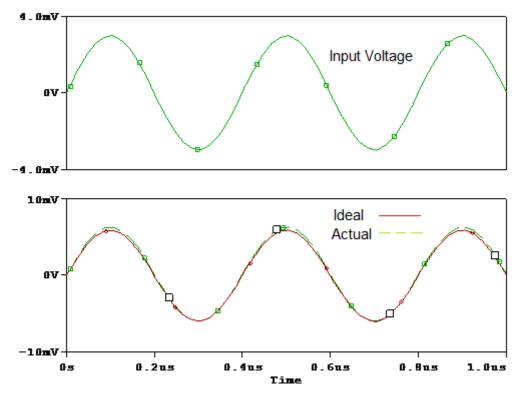

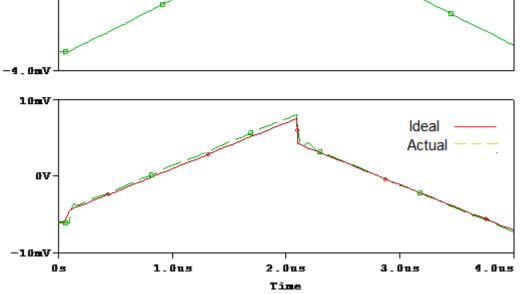

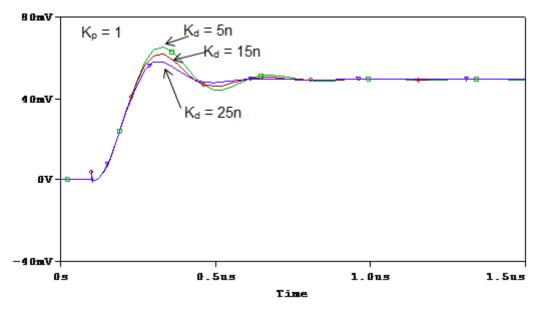

For the OTRA based proposed PI controller shown in Fig. 4.11, the values of passive element are chosen as  $R_1$ = 10K $\Omega$ ,  $R_2$  = 20K $\Omega$  and  $C_1$  = 20pF. For time domain analysis, a 3mV step input voltage with 20ns rise time is applied and both ideal and simulated results are presented in Fig. 5.14. Frequency domain characteristics are depicted in Fig. 5.15. For MOS-C implemented PI controller shown in Fig. 4.12 the aspect ratios of the transistors used for implementing the resistances are listed in Table.5.5.

| Transistor | $W(\mu M)/L(\mu M)$ |

|------------|---------------------|

| M1,M2      | 0.18µ/1.08µ         |

Table 5.5 Aspect ratios for MOS-C implementation of PI Controller

Gate voltages are set as  $V_{a1}$ = 1V and Vb1=0.5V which result in resistance value as  $R_1 \approx 50 \text{K}\Omega$  and the chosen values of capacitances are  $C_1 = 4\text{pF}$  and  $C_f = 2\text{pF}$ . Fig. 5.16 and Fig. 5.17 show the transient response and frequency domain characteristics of MOS-C implementation of PI controller respectively.

Fig. 5.14 Transient response of the PI Controller

Fig. 5.15 Frequency and phase Response of PI Controller

Fig. 5.17 Frequency and phase Response of the MOS-C implemented PI Controller

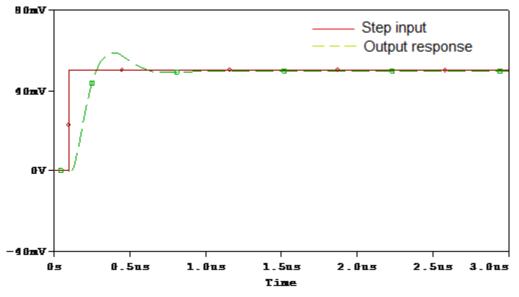

Fig. 5.18 shows a closed loop control system realized using the proposed PI controller and a second order low-pass filter (LPF). Fig. 5.19 depicts the effect of PI controller on step response of the closed loop system.

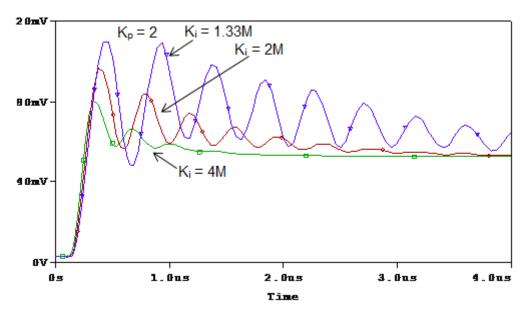

Performance comparison of second order system with and without PI controller is shown in Table. 5.6. From the table 5.6, the response of the system has been improved having smaller settling time of 266ns as well as smaller maximum peak amplitude of 57.8mV. Fig. 5.19b shows the step response with the variation in  $K_i$ .

Fig. 5.18 Closed Loop Control System using PD controller

Fig. 5.19a Step Response of a second order system with PI controller

Fig. 5.19b Response of a second order system with PI controller with varying  $K_{\mathrm{i}}$

| Parameter     | Without PI Controller | With PI Controller |

|---------------|-----------------------|--------------------|

| Overshoot     | 19.56%                | 18.76%             |

| Peak output   | 58.26mV               | 57.83mV            |

| Rise time     | 140.43ns              | 112.28ns           |

| Settling time | 303.12ns              | 266.11ns           |

#### **5.4 Simulation Results of PID Controller**

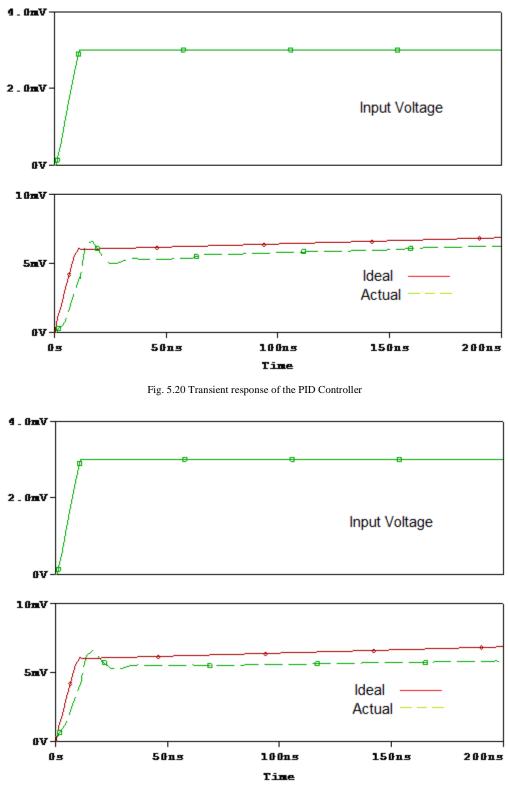

To simulate, differential OTRA based proposed PID controller shown in Fig. 4.15 values of passive elements are  $R_1 = R_2 = R_3 = R_4 = 50K$ ,  $C_1 = C_3 = 10pF$  and  $C_2 = 0.05pF$ . For time domain analysis, a 3mV step signal with 10ns rise time is applied and both ideal and simulated results are presented in Fig. 5.20.

For MOS-C implemented PID controller shown in Fig. 4.16 the aspect ratios of the transistors used for implementing the resistances are listed in Table.5.7. Gate voltages are set as  $V_{a1} = V_{a2} = V_{a3} = V_{a4} = 1V$  and  $Vb1 = V_{b2} = V_{b3} = V_{b4} = 0.5V$  which result in resistance values as  $R_1 = R_2 = R_3 = R_4 \approx 50K$  and the chosen value of capacitances are  $C_1 = C_3 = 10pF$  and  $C_2 = 0.05pF$ . Fig. 5.21 shows the transient response of MOS-C implementation of PID controller.

| Transistor | $W(\mu M)/L(\mu M)$                    |

|------------|----------------------------------------|

| M1,M2      | 0.18µ/1.8µ                             |

| M3,M4      | 0.18µ/1.8µ                             |

| M5,M6      | 0.18µ/1.8µ<br>0.18µ/1.8µ<br>0.18µ/1.8µ |

| M7,M8      | 0.18µ/1.8µ                             |

|            |                                        |

Table 5.7 Aspect ratios for MOS-C implementation of PID Controller

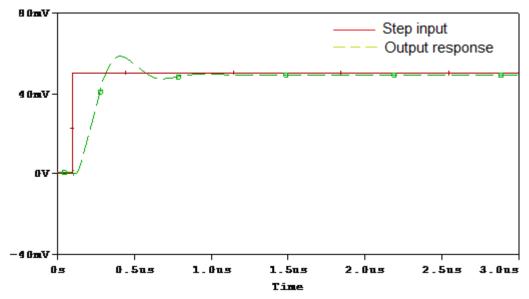

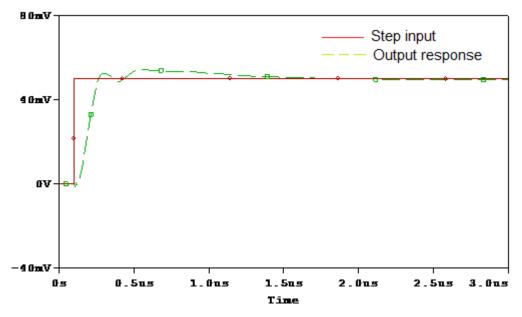

For verification of functionality of the proposed PID controller a closed loop control, system consisting of the proposed PID controller and a second order low-pass filter (LPF), as shown in Fig. 5.22 is realized. For simulation a step signal of 50mV is used. Fig. 5.23 depicts the effect of PID controller on step response of the closed loop system.

Performance comparison of second order system with and without PID controller is shown in Table. 5.8 which reveals that there is an overall improvement in the performance of the system with decreased overshoot, faster response with improved rise and settling time and smaller maximum peak amplitude.

Fig. 5.21 Transient response of the MOS-C implemented PID Controller

Fig. 5.22 Closed Loop Control System using PID controller

Fig. 5.23 Step Response of a second order system with PID controller

| Table 5.8 Performance Com | parison of closed loop system | with and without PID controller |

|---------------------------|-------------------------------|---------------------------------|

|                           |                               |                                 |

| Parameter     | Without PID Controller | With PID Controller |

|---------------|------------------------|---------------------|

| Overshoot     | 19.56%                 | 8.16%               |

| Peak output   | 58.26mV                | 52.59mV             |

| Rise time     | 140.43ns               | 99.75ns             |

| Settling time | 303.12ns               | 252.27ns            |

# 5.5 Performance Comparison of Controllers

Table 5.9 shows the performance comparison of controllers. This table clearly indicates with the help of controllers the performance of system is improved in a desired manner.

The effect of P controller is to make the system to respond faster i.e. improve rise time at the cost of overshoot but this is the simplest controller and can be easily designed.

The PD controller improves all the parameter, prominently overshoot and very small improvement in settling time is observed.

PI controller influences mainly the settling time as compared to all other parameter.

PID includes best features of all individual controllers and results in improvement of all the performance measure parameters.

| Parameter     | LPF      | With P     | With PD    | With PI    | With PID   |

|---------------|----------|------------|------------|------------|------------|

|               |          | Controller | Controller | Controller | Controller |

| Overshoot     | 19.56%   | 30.14%     | 12.89%     | 18.76%     | 8.16%      |

| Peak output   | 58.26mV  | 62.64mV    | 56.53mV    | 57.83mV    | 52.59mV    |

| Rise time     | 140.43ns | 108.75ns   | 124.27ns   | 112.28ns   | 99.75ns    |

| Settling time | 303.12ns | 675.11ns   | 278.97ns   | 266.11ns   | 252.27ns   |

Table 5.9 Performance Comparison of closed loop system with and without controllers

# Chapter-6 CONCLUSION AND FUTURE SCOPE

# 6.1 Conclusion

Differential Operational transresistance (OTRA) based proportional (P), proportionalderivative (PD), proportional integral (PI) and proportional integral derivative (PID) controllers have been presented which possess the feature of independent tuning of proportional ( $K_p$ ), derivative ( $K_d$ ) and integral ( $K_i$ ) constants.

Their MOS-C equivalent circuits were also designed. This is done by implementing the resistors using MOS transistors operating in linear region. Simulation results of these controllers are in close agreement with theoretical values. Implementing the resistors using MOS transistors results in lesser chip area consumption and therefore these controller designs are suitable for full integration.

As an application, a second order closed loop system was designed and simulated using SPICE program. The simulated results are in line with the proposed theory. The performance analysis reveals that P controller improves rise time at the cost of other performance parameter, PD controller enhances overshoot percentage specially, PI controller refines settling time while PID as a combination of P, I & D, enhances transient as well as steady state time response of the system.

### **6.2 Future Scope**

Time domain analysis of differential OTRA based controllers is presented in this thesis, but other analysis like stability analysis, noise analysis, effect of parameter variation, effect of power supply variation etc. are yet to be explored to make these controllers a market product. Various methods of parameter tuning like Ziegler–Nichols, Cohen-Coon, Skogestad, Process Reaction curve etc. can be further used.

In this work, step response of second order system with and without controller is analyzed for series (cascade) configuration of system. This analysis can be carried out for other system configurations like feedback, state-feedback, series-feedback, forward with series and feed-forward in which controllers are introduced for improving the system performance.

Further these controllers can be designed and simulated for multi input multi output (MIMO) system.

These OTRA based designs are best suited for the Low Power and High Speed applications so these can be used in MEMS (Micro-electromechanical systems) and Low Power Medical Devices.

# References

- Golnaraghi F. and Kuo B. C., Automatic Control Systems, 9<sup>th</sup> Edition, John Wiley & Sons, Inc., USA, ISBN-13 978-0470-04896-2.

- [2] Dorf, Richard C. and Robert H. Bishop, Modern Control Systems, 12<sup>th</sup> Edition, Prentice–Hall Inc., New Jersey-07458, USA, 2010.

- [3] Toumazou, C., Lidgey, F. J. and Haigh, D. G. Analogue IC Design: The Current Mode Approach. U.K., Peregrinus, 1990.

- [4] Chen, J. J., Tsao H. W., Chen, C. C. Operational transresistance amplifier Using CMOS Technology. Electronics Letters. 1992, vol. 28, no. 22, p. 2087–2088.

- [5] Chen J. J., Tsao H. W., Liu S. and Chui W., Parasitic-capacitance-insensitive current-mode filters using operational transresistance amplifiers, IEE Proc. Circuits Devices and Systems 1995, vol. 142, no. 3, p. 186–192.

- [6] Salama K. N., Soliman A. M., CMOS operational transresistance amplifier for analog signal processing. Microelectron J. 1999, vol. 30, issue 3, p. 235–45.

- [7] Mostafa H. and Soliman A.M., A modified CMOS realization of the operational transresistance amplifier Frequenz, 2006, vol. 60, p. 70-76.

- [8] Kafrawy A. K. and Soliman A. M., "New CMOS Operational Transresistance Amplifier", International Conference on Microelectronics, 2008, p. 31-34.

- [9] Kafrawy A. K. and Soliman A. M., A modified CMOS differential operational transresistance amplifier (OTRA), Int. J. Electron. Commun. 2009, (AEU) vol. 63, p. 1067-1071.

- [10] Toker A., Özo`guz S., Cicekoglu O. and Acar C., Current-mode allpass filters using current differencing buffered amplifier and new high-Q bandpass filter configuration, IEEE Tran. Circuits Syst. II, Analog Digital Signal Process. Sep. 2000, vol. 47, no. 9, p. 949–954.

- [11] Riewruja V., Parnklang J. and Julprapa A., Current Tunable Cmos Operational Transresistance Amplifier, ISIE 2001, vol. 2, p. 1328–1338.

- [12] Ravindran A., Salva A., Younus Md. I. and Ismail M., A 0.8V CMOS filter based on a novel low voltage OTRA, IEEE 2002, vol. III p. 368-371.

- [13] Brodie J., A notch filter employing current differencing operational amplifier, International Journal of Electronics, 1976, vol. 41, no. 5, p. 501–508.

- [14] National Semiconductor Corp., Designing with a New Super Fast Dual Norton Amplifier, Linear Applications Data Book, 1981.

- [15] National Semiconductor Corp., The LM3900: A New Current Differencing ^ Quad of the Input Amplifiers, Linear Applications Data Book, 1986.

- [16] Chen J. J., Tsao H. W. and Liu S. I., Voltage-mode MOSFET-C filters using operational transresistance amplifiers (OTRAs) with reduced parasitic capacitance effect, IEE Proc.-circuits Devices Sys., October 2001, vol. 148, no.5, p. 242-249.

- [17] Cam U., Cakri C. and Cicekoglu O., Novel Transmission Type First Order All- Pass Filter Using Single OTRA, Int. J. Electron. Commun. 2004 (AEU), vol. 58, p. 296-298.

- [18] Kiling S. and Cam U., Operational Transresistance Amplifier Based First-Order allpass Filter with an Application Example, the 47th IEEE International Midwest Symposium on Circuits and Systems, 2004, p. I-65 to I-68.

- [19] Kiling S. and Cam U., Transimpedance Type Fully Integrated Biquadratic Filters Using Operational Transresistance Amplifiers, Analog Integrated Circuits and Signal Processing, 2006, vol. 47, p. 193-198.

- [20] Gokcen A. and Cam U., MOS-C single amplifier biquads using the Operational Transresistance Amplifiers, Int. J. Electron. Commun. 2009, (AEU), vol. 63, p. 660-664.

- [21] Kaçar F., Operational Transresistance Amplifier Based Current-Mode All-pass Filter Topologies, Applied Electronics, 2009, p. 149–152.

- [22] Pandey R. and Bothra M., Multiphase Sinusoidal Oscillators Using Operational Trans-Resistance Amplifier, IEEE Symposium on Industrial Electronics and Applications, 2009, p. 371-376.

- [23] Cam U., A Novel Single-Resistance-Controlled Sinusoidal Oscillator Employing Single Operational Transresistance Amplifier, Analog Integrated Circuits and Signal Processing, 2002, vol. 32, p. 183–186.

- [24] Salama K. N. and Soliman A. M., Novel oscillators using the Operational Transresistance Amplifiers, Microelectronics Journal, 2000, vol. 31, p. 39-47.

- [25] Lo Y. K. and Chien H. C., Single OTRA-based current-mode monostable multivibrator with two triggering modes and a reduced recovery time, IET Circuits Devices Syst., 2007, vol. 1, no. 3, p. 257–261.

- [26] Lo Y. K. and Chien H. C., Current-Mode Monostable Multivibrators Using OTRAs, IEEE Transactions On Circuits And Systems, Nov. 2006, vol. 53, no. 11, p. 1274-1278.

- [27] Hou C.L., Chien H.C. and Lo Y.K., Square wave generators employing OTRAs, IEE Proc.-Circuits Devices Syst., Dec. 2005, vol. 152, no. 6, p. 718-722.

- [28] Lo Y. K., Chien H. C. and Chiu H. J., Current-input OTRA Schmitt trigger with dual hysteresis modes, Int. J. Circ. Theor. Appl., 2009.

- [29] Kacar F., Cam U., Cicekoglu O., Kuntman H. and Kuntman A., New parallel immittance simulator realizations using single OTRA. 2002,

- [30] Cam U., Kacar F., Cicekoglu O., Kuntman H. and Kuntman A., Novel Grounded Parallel Immittance Simulator Topologies Employing Single OTRA. 2003, Int. J.Electron. Commun. (AEU), vol. 57, no. 4, p. 287-290.

- [31] Cam U., Kacar F., Cicekoglu O., Kuntman H. and Kuntman A., Novel Two OTRA-Based Grounded Immittance Simulator Topologies. 2004, Analog Integrated Circuits and Processing, vol. 39, p.169-175.

- [32] Franco S., Design with operational amplifiers and analog integrated circuits. 2<sup>nd</sup> ed.

McGraw-Hill International Editions, 1998.

- [33] Kara M. T. and Rizkalla M. E. Single op-amp proportional-integral compensator with anti-windup. In Proceeding of the IEEE International Symposium on Circuits and System, Chicago (IL USA), 1993, p. 2260 - 2263.

- [34] Edral C., Toker A. and Acar C., OTA-C based proportional- Integral-derivative (PID) controller and calculating optimum parameter tolerances. Turkish journal of Elec., 2001, vol. 9, no. 2, p. 189 – 198.

- [35] Kesin A. U., Design of a PID controller circuit employing CDBAs, Int. J. of Electrical Engineering Education, 2006, vol. 43, no.1, p. 48 – 56.

- [36] Minaei S., Yuce E., Tokat S. and Cicekoglu O., Simple realization of current-mode and voltage mode PID, PI and PD controllers. In Proceeding of the IEEE International Symposium on Industrial Electronics. Dubrovnik (Croatia), 2005, vol.

1, p. 195 - 198.

- [37] Yuce E., Tokat S., Minaei S. and Cicekoglu O., Low-Component-Count Insensitive Current-Mode and Voltage-Mode PID, PI and PD Controllers. Frequenz, 2006, vol. 60, no. 3-4, p. 65-69.

- [38] Michal V., Prémont C., Pillonet G. and Abouchi N. Single Active Element PID Controllers. In Proceeding of 20th IEEE Radioelektronika International Conference. Brno (Czech Republic), 2010, p. 1 – 4.

- [39] Sánchez-López C., Fernández F.V. and Tlelo-Cuautle E., Generalized admittance matrix models of OTRAs and COAs. Microelectronics Journal, August 2010, vol. 41, issue 8, p. 502-505.

- [40] Elwan H.O. and Soliman A. M., CMOS Differential Current Conveyors and Applications for Analog VLSI, Analog Integrated Circuits and Signal Processing, 1996, vol. 11, p. 35-45.

- [41] Jagan N. C., Control Systems. Second Edition, BS Publications, Hyderabad, India, 2008, ISBN: 978-81-7800-177-2.

- [42] Goodwin G. C., Graebe S. F. and Salgado M. E., Control System Design. Valparaíso, Valparaíso Region, Chile January 2000.