# 'NANOSTRUCTURED SILICON SOLAR CELL'

### **SUBMITTED TO**

#### **DEPARTMENT OF APPLIED PHYSICS**

## DELHI TECHNOLOGICAL UNIVERSITY

## (FORMERLY DELHI COLLEGE OF ENGINEERING)

## NEW DELHI-110042

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE MASTER OF TECHNOLOGY IN NANOSCIENCE AND TECHNOLOGY

BY

# **SAURABH JAIN**

**UNDER THE SUPERVISION OF**

## DR. SANJAY KUMAR SRIVASTAVA

(NATIONAL PHYSICAL LABORATORY, NEW DELHI-110027)

## Certificate

This is to certify that Mr. Saurabh Jain has done a 1 year Research cum Project Work on the topic entitled '<u>NANOSTRUCTURED SILICON SOLAR CELL</u>' under my supervision. The present research work is being submitted to Department of Applied Physics, Delhi Technological University (Formerly Delhi College of Engineering), in partial fulfilment of the requirement for the award of the degree of Master of Technology in Nanoscience and Technology, embodies faithful record of research work carried out by Mr. Saurabh Jain. He has worked under my guidance and that this work has not been submitted, in part of full, for any other degree of Delhi Technological University or any other university.

(Dr. SANJAY KUMAR SRIVASTAVA) SCIENTIST SILICON AND SILICON DEVICES, NATIONAL PHYSICAL LABORARTORY (NPL), NEW DELHI-110027

Date: \_\_\_\_\_

# **Table of Contents**

| Table of Conte   | nt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Ι    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Lists of figures | ò                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IV   |

| Lists of Tables  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VII  |

| Acknowledgme     | ents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VIII |

| Chapter1: Intr   | ts of figures       IV         ts of Tables       VII         cnowledgments       VIII         apter1: Introduction       1         1.1 Background information       1         1.2 Motivation-Global climate change       2         1.3 High Aspect Ratio Structures for Solar Energy.       4         1.4 Silicon and silicon nanowire       5         1.4.1 Crystalline Silicon       7         1.4.2 Amorphous silicon       7         1.4.3 Polycrystalline Silicon       8         1.4.4 Microcrystalline Silicon       8         1.4.5 Nanocrystalline Silicon       8         1.4.5 Nanocrystalline Silicon       9         1.6 Growth Mechanism of silicon nanowire:       9         1.6.1 Vapour-Liquid-Solid (VLS) Growth Mechanism       9         1.6.2 The Solid Liquid Solid (SLS) Mechanism       11 |      |

| 1.1 Backgro      | ound information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1    |

| 1.2 Motivati     | ion-Global climate change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2    |

| 1.3 High As      | spect Ratio Structures for Solar Energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4    |

| 1.4 Silicon a    | and silicon nanowire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5    |

| 1.4.1 (          | Crystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5    |

| 1.4.2 A          | Amorphous silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7    |

| 1.4.3 H          | Polycrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8    |

| 1.4.4 N          | Microcrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 1.4.5 N          | Nanocrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|                  | 1.4.5.1 Quantum wire/Nanowires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9    |

| 1.5 The Pres     | ence of the Term 'Silicon Nanowires' in the Literatur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e9   |

| 1.6 Growth       | Mechanism of silicon nanowire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9    |

| 1.6.1 Va         | pour-Liquid-Solid (VLS) Growth Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9    |

| 1.6.2 Th         | e Solid Liquid Solid (SLS) Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11   |

| 1.6.3 Oth        | her Growth Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12   |

|      | 1.7 Properties of | f Silicon Nanowires         |                               | 12      |

|------|-------------------|-----------------------------|-------------------------------|---------|

|      | 1.8 Photovoltaic  | s (PV)                      |                               | 14      |

|      | 1.9 How Does a    | PN junction Solar Cell W    | /orks?                        | 14      |

|      | 1.10 Differen     | t Cell Types                |                               | 15      |

|      | 1.11 Natural      | Limits of Efficiency        |                               | 16      |

|      | 1.12 Characte     | eristic Current Voltage Cu  | rve for solar cell and its in | portant |

|      | parameters        |                             |                               | 17      |

|      | 1.13 Equivale     | ent circuit model of the so | lar cell                      |         |

|      | 1.14 PN Junc      | tion Silicon Solar cell     |                               | 21      |

| Chap | oter 2: Experin   | nental systems and t        | echniques                     | 22      |

|      | 2.1 Current Volt  | age (I-V) Characteristics.  |                               | 22      |

|      | 2.2 Scanning Ele  | ectron Microscopy (SEM)     |                               | 23      |

|      | 2.3 Metal Coatin  | ig systems                  |                               | 27      |

|      | 2.4 Sintering Un  | it (Rapid Thermal Proces    | sing)                         |         |

|      | 2.5 Diffusion fur | mace                        |                               |         |

| Chap | oter 3: Experin   | mental Methodology          |                               | 32      |

|      | 3.1 Silicon Wat   | fer details                 |                               |         |

|      | 3.2 Chemical P    | olishing                    |                               | 34      |

|      | 3.3 Cleaning of   | silicon Wafer               |                               | 34      |

|      | 3.4 Texturisatio  | on (Silicon Nanowires Ar    | ray Growth)                   |         |

|      | 3.5 Diffusion     |                             |                               | 37      |

|      | 3.6 Back surfac   | e field (BSF) Formation.    |                               | 40      |

| 3.7 Sintering                             | 41 |

|-------------------------------------------|----|

| 3.8 Metal Contact deposition              | 42 |

| 3.9 Firing the Contacts/Sintering         | 42 |

| 3.10 Edge                                 |    |

| isolation                                 |    |

| 3.11 Solar Cell Testing/ characterization | 43 |

| Chapter 4: Results and Discussion44                                     |

|-------------------------------------------------------------------------|

| 4.1 Samples Details44                                                   |

| 4.2 Results and discussion                                              |

| 4.2.1 Fabrication and Surface morphology of etched silicon samples (SEM |

| analysis); Silicon nanowires45                                          |

| 4.2.2 Chemical reaction involved in Si-NW Growth                        |

| 4.2.3 Mechanism Involved in Silicon nanowire (Si-NW) preparation50      |

| 4.2.4 Optical Property: Surface Reflectivity                            |

| 4.2.5 Solar cells performance53                                         |

| 4.2.5.1 I-V curves, Spectral Response graphs and Quantum efficiency     |

| (QE) graphs53                                                           |

| Chapter 5: Conclusion58                                                 |

| 5.1 Conclusion                                                          |

| Chapter 6: References                                                   |

# Lists of figures

| Figure 1.1: Solar spectrum for AM 0 and AM 1.5                                                           |

|----------------------------------------------------------------------------------------------------------|

| Figure 1.2: Schematic diagram of a traditional planar solar cell and the proposed wire array             |

| geometry. In the planar cell, the absorption length (~1/ $\alpha$ ) must be comparable to the minority   |

| carrier diffusion length (Lp). In the array cell, the absorption length (~1/ $\alpha$ ) independent to   |

| the minority carrier diffusion length (Lp)                                                               |

| <i>Figure 1.3: Photograph of crystalline silicon wafers</i>                                              |

| <b>Figure 1.4</b> : Face centered cubic crystal unit cell showing crystal planes and the [111] direction |

|                                                                                                          |

| <i>Figure 1.5</i> : <i>Representation of the structure of hydrogenated amorphous silicon8</i>            |

| <i>Figure 1.6</i> : Schematic diagram of silicon nanowires growth by VLS method10                        |

| <i>Figure 1.7</i> : Schematic diagram showing operation of basic p-n junction solar cell15               |

| <i>Figure 1.8: Limitation of efficiency with respect to band gap16</i>                                   |

| Figure 1.9: Typical voltage-current characteristics                                                      |

| Figure 1.10: Quantum Efficiency for the solar cell                                                       |

| <i>Figure 1.11</i> : Spectral Response for the solar cell                                                |

| Figure 1.12: A simplified equivalent circuit model of the solar cell                                     |

| <i>Figure 1.13:</i> Typical systematics p-n junction of silicon solar cell                               |

| <i>Figure 2.1:</i> Schematic of the Current-Voltage characterization system                              |

| Figure 2.2: Solar cell spectral response system at NPL, New Delhi                             | 23  |

|-----------------------------------------------------------------------------------------------|-----|

| Figure 2.3: Principal result of electron beam interaction with the sample                     | 24  |

| Figure 2.4: Simplified schematic of an SEM                                                    | 26  |

| Figure 2.5: Thermal evaporation unit at NPL, New Delhi                                        | 27  |

| Figure 2.6 Electron beam evaporation system at NPL, New Delhi                                 | 28  |

| <i>Figure 2.7</i> : Rapid thermal processing unit for firing contacts sintering and formation |     |

| Figure 2.8: Diffusion Furnaces, NPL, New Delhi                                                | 30  |

| <b>Figure 2.9</b> : P <sub>2</sub> O <sub>5</sub> disc dopant source                          | 31  |

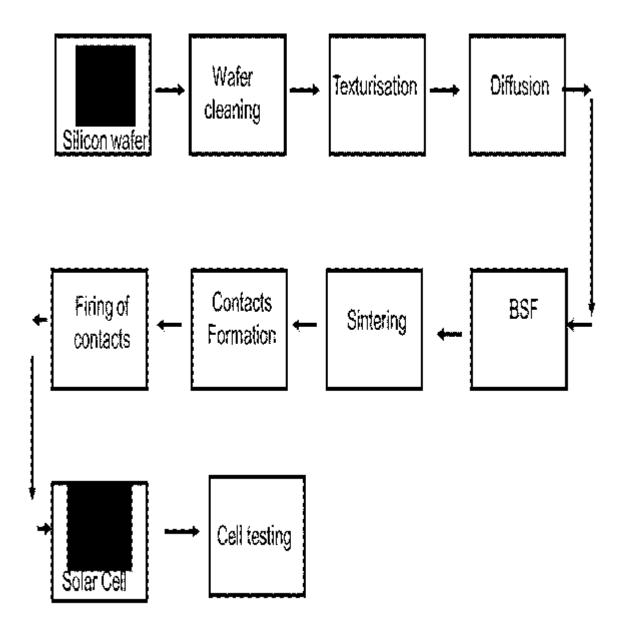

| Figure 3.1: Schematic of complete process sequence of typical solar cells fabrication         | 32  |

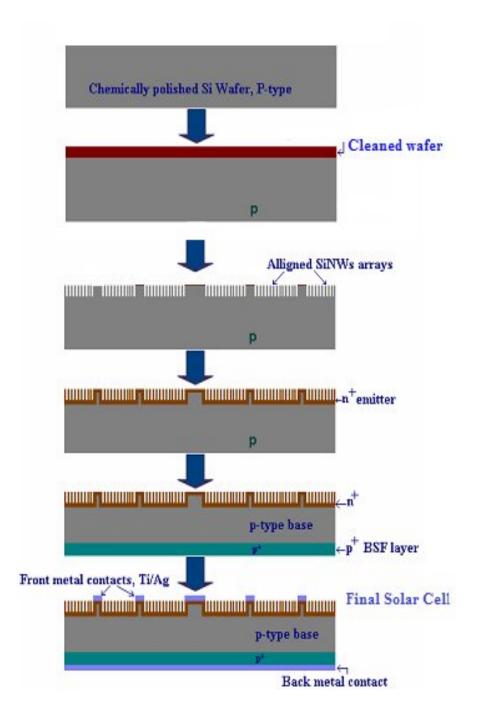

| Figure 3.2: Process sequence of silicon nanowires preparation followed by solar cell          |     |

| fabrication on it                                                                             | 33  |

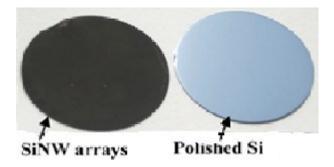

| Figure 3.3 Optical photograph of silicon nanowires array based wafer and polished             |     |

| wafer                                                                                         | 36  |

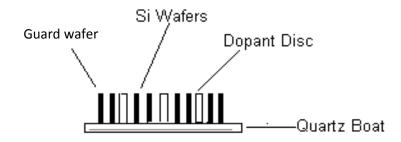

| Figure 3.4: Silicon wafer and dopant source arrangement in quartz boat for P-type             |     |

| diffusion                                                                                     | 38  |

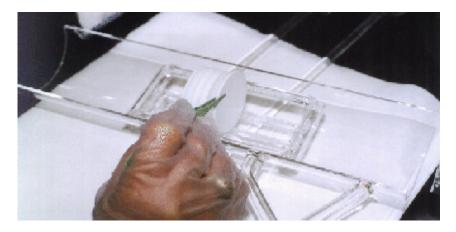

| Figure 3.5: Loading of source wafer                                                           | 39  |

| Figure 3.6: A view of the diffusion tube during the experiment                                | .39 |

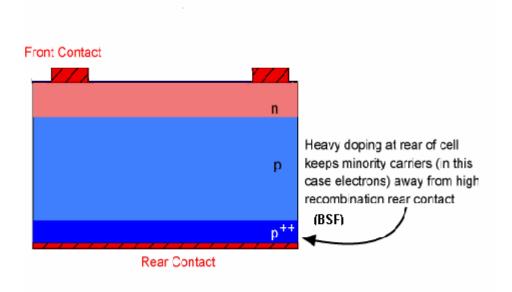

| Figure 3.7: Cross sectional view of conventional silicon solar cells with a BSF layer         | .40 |

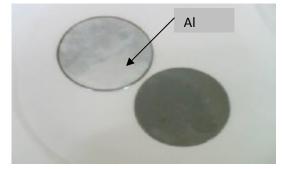

| Figure 3.8: Bare and aluminium coated silicon wafer                                           | .41 |

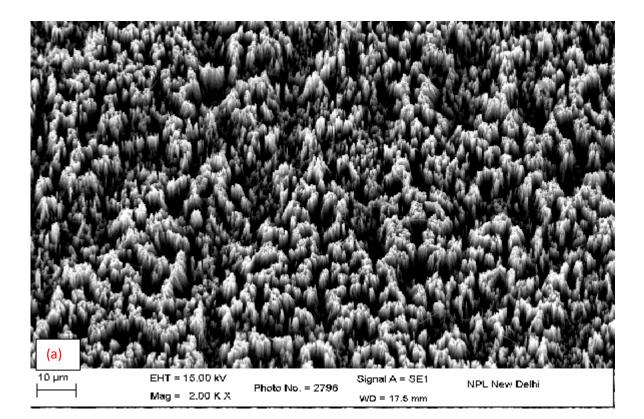

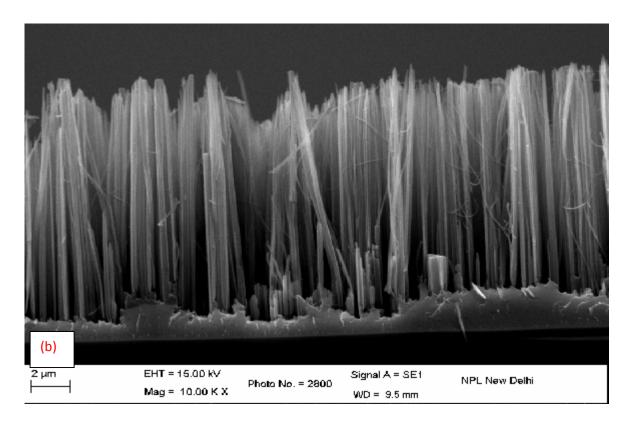

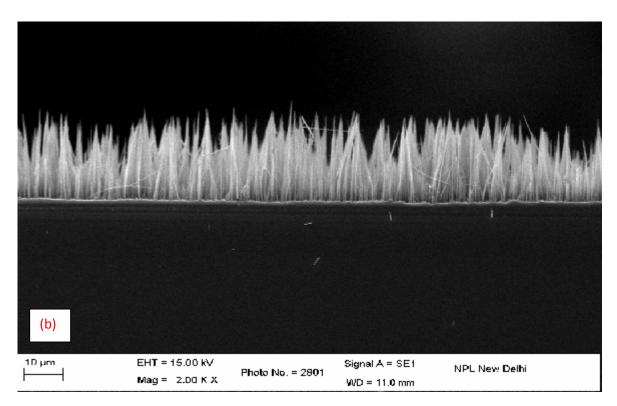

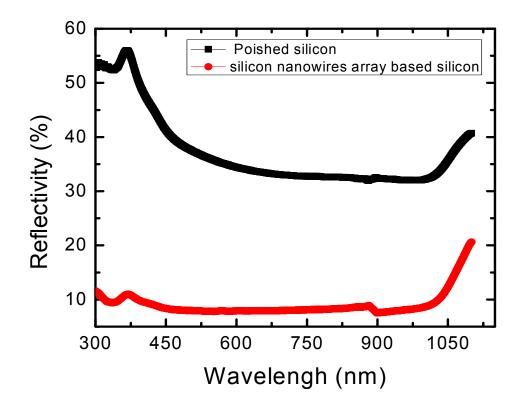

| Figure: 4.1 Scanning electron microscopy (SEM) pictures of Silicon nanowires with 0.02M                  |

|----------------------------------------------------------------------------------------------------------|

| $Ag_2O$ concentration with 1 hour etching (a) Top view (b) cross-sectional view with $10KX$              |

| magnification (c) cross-sectional view with 5K X magnification                                           |

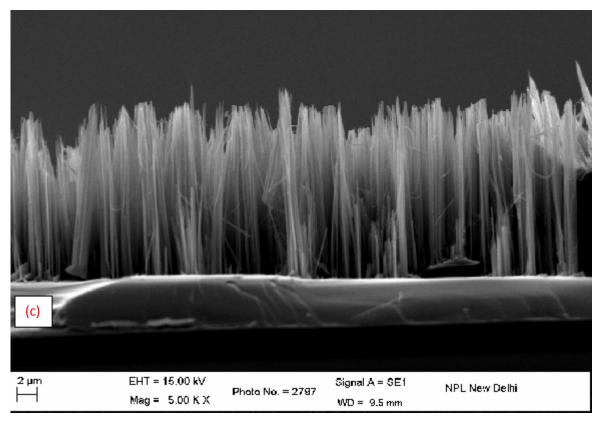

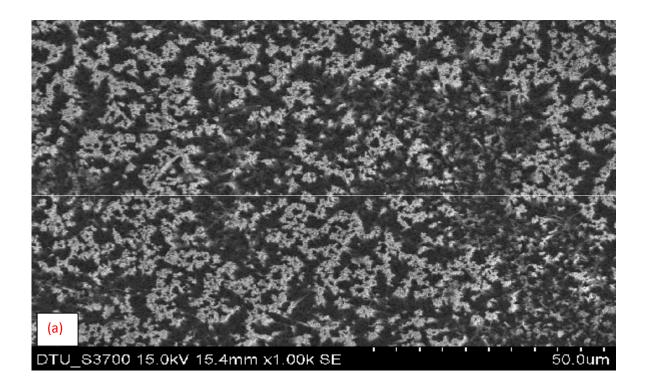

| Figure: 4.2 Scanning electron microscopy (SEM) pictures of Silicon nanowires with 0.05M                  |

| $Ag_2O$ concentration with 1 hour etching (a) Top view (b) cross-sectional view with $2KX$               |

| magnification (c) cross-sectional view with 5K X magnification                                           |

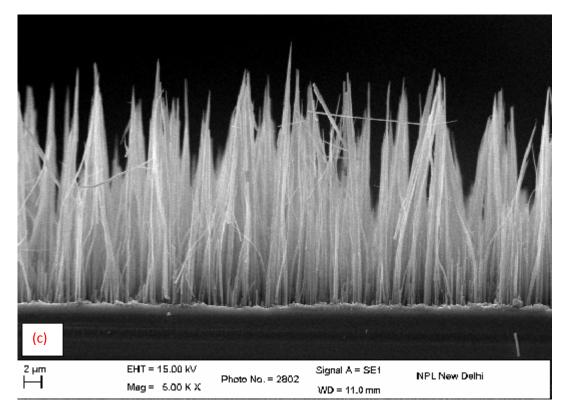

| Figure 4.3: Schematics of the Si-NWs growth mechanism by Ag-induced selective chemical                   |

| etching of silicon surface in HF-Ag <sub>2</sub> O solution via self-assembled Nano-electrochemical cell |

| model                                                                                                    |

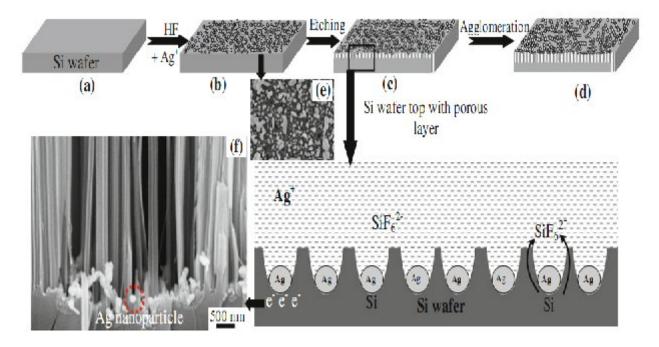

| Figure 4.4 Comparative spectral dependence surface reflectivity plots of silicon nanowires               |

| array based sample and polished silicon surface                                                          |

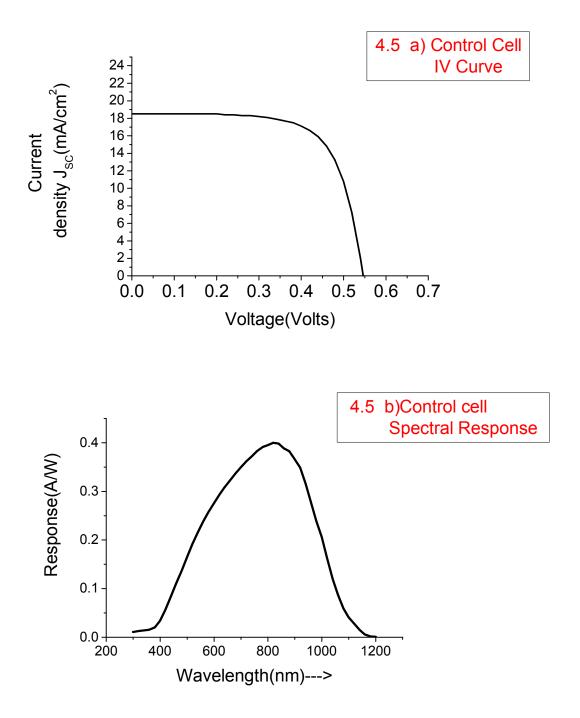

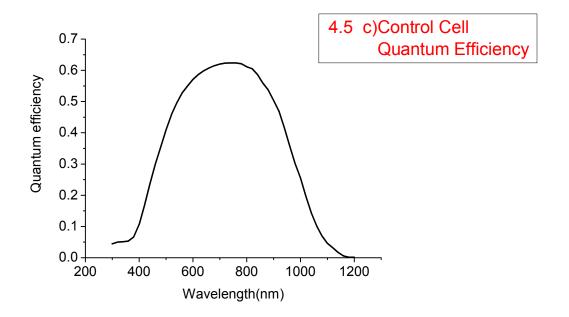

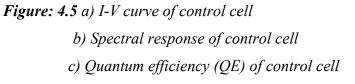

| Figure: 4.5 a) I-V curve of control cell                                                                 |

| b) Spectral response of control cell                                                                     |

| c) Quantum efficiency (QE) of control cel                                                                |

|                                                                                                          |

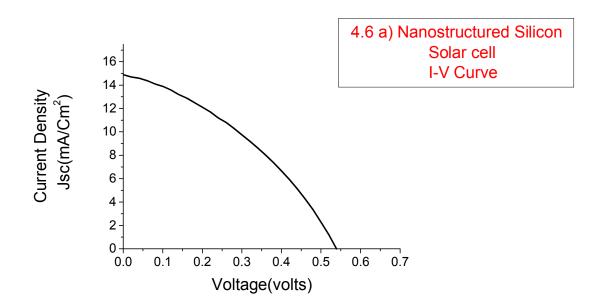

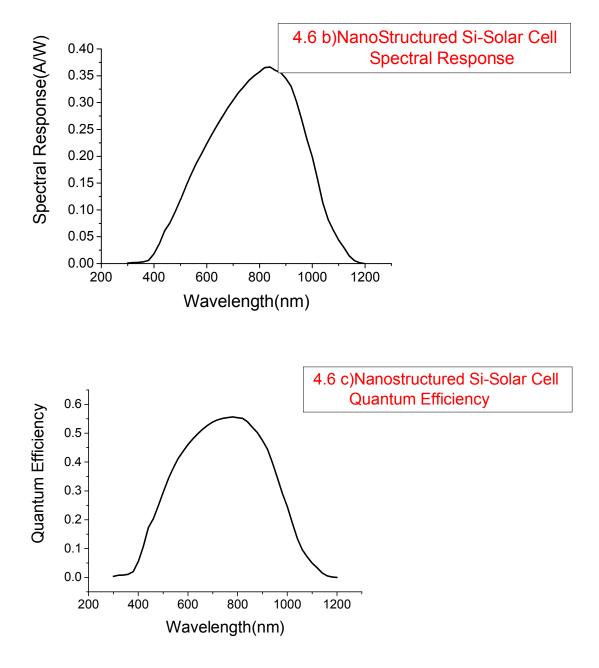

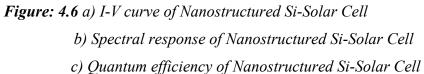

| Figure: 4.6 a) I-V curve of Nanostructured Si-Solar Cell |  |

|----------------------------------------------------------|--|

| b) Spectral response of Nanostructured Si-Solar Cell     |  |

| c) Quantum efficiency of Nanostructured Si-Solar Cell    |  |

# Lists of Tables

| Table 1.1: Comparison of efficiency of different types of silicon solar cells on the bas | es of |

|------------------------------------------------------------------------------------------|-------|

| material used                                                                            | 16    |

| Table 4.1 Samples details and preparation conditions                                     | 45    |

| Table 4.2 List of parameters of Control cell and Nanostructured Si-Solar cell            |       |

#### Acknowledgment

I would like to extend my sincere gratitude and thanks to my supervisors Dr. Sanjay Kumar Srivastava and Dr. P.K. Singh for their valuable guidance, support and words of wisdom throughout the course of this project. Without his advice and unique support this work would never had become a reality.

I would also like to express my gratitude to the members of the research group at National Physical Laboratory, New Delhi for their enthusiasm, support and suggestions. Their friendship has helped me get through this project and is greatly valued.

I would also like to thank Dr.R.K.Sinha, Head of Department of Applied physics, Delhi Technological University, Dr A.K. Jha, Delhi Technological University and Dr. P.K.Tyagi, Delhi Technological University for all their assistance and optimism regarding the future of nantechnological research in current and forth coming age.

I would like to thank the technical staff Miss. Pooja Sharma, Mr Ravi and Mr. Mukul Kumar Sharma at the National Physical Laboratory, New Delhi for their assistance and positive attitude. I would also like to thank Dr. A.K. Sood for taking the Scanning electron micrographs.

I would like to thank Mr. Firoz Khan, Mrs.Neha, Miss Amita and Miss Dazzy Verma for their help in the this work, and special thanks to Mr.Dinesh for the many discussions about the future of silicon solar cell in India and around the globe.

Finally, I wish to express my greatest thanks to my family, friends and colleagues, who have supported me.

Saurabh Jain

#### **CHAPTER 1: INTRODUCTION**

Considering the growing evidence that  $CO_2$  emissions from fossil fuels are a major contributor to anthropogenic global climate change, a source of carbon-neutral energy will be needed at the scale of our current global energy consumption. We propose to use solar energy due to its abundance and wide availability, but there are significant challenges to producing cost-competitive solar energy solutions. One of strategy to reduce the cost of current solar cells by using materials with high aspect ratios. This principle has been shown to improve the efficiency of low-quality and therefore inexpensive materials in simulations, but there are significant challenges and drawbacks associated with using highly structured materials. Some of these include the expected increase in surface and junction recombination, as well as the expected decrease in open circuit voltage due to reduced carrier flux per unit of junction area.

#### **1.1 Background Information**

Recently there has been a great deal of interest in the fabrication of semiconductor nanomaterials and nanostructures. These are structures or objects with dimensions on the nanoscale. One of the main reasons for this interest is that nanomaterials tend to have properties that differ from those of the bulk material. These properties, such as the large surface area of nanomaterials, can be exploited for various applications. Silicon-based nanostructures are attracting interest as the techniques used to produce them are largely compatible with existing semiconductor fabrication processes. Silicon nanostructures also have properties that differ from those of bulk silicon, such as a band-gap that is tunable by the size of the structure, which are of interest when producing semiconductor devices.

One silicon nanostructure is nano-crystalline silicon, which consists of array of nanometre-sized crystallites embedded in a silicon material. This material can be used in thin film solar cells [1] (Yue et al., 2006), the properties of which differ from crystalline and amorphous silicon based solar cells. The use of nanostructures in solar cells has several advantages over crystalline devices and amorphous thin films devices, including lower production costs, increased conversion efficiency and improved stability. Nanocrystalline silicon solar cells are predominantly produced as thin film devices ~500 nm thick, not including the substrate upon which they are grown. The production of these thin film devices uses much less material than crystalline-based devices allowing lower

production costs than those for crystalline silicon solar cells [2] (Green, 2004). Nanocrystalline silicon based solar cells, although having lower conversion efficiencies than crystalline solar cells; potentially have a higher efficiency than their amorphous counterparts.

Creating higher efficiency solar cells is the focus of much research effort. By producing higher efficiency solar cells, or producing efficient solar cells cheaply, the use of solar cells as an alternative energy source becomes more favourable. In an era of rising oil prices and great concern about the environmental impact of coal, oil-fired or nuclear power plants, the hunt is on for clean alternative energy sources. The use of silicon nanostructures would potentially allow for the reduced production and material costs associated with thin film photovoltaics while maintaining the higher efficiency and stability that are characteristic of crystalline solar cells.

A silicon nanowire is an elongated single crystal of silicon with a diameter of tens, to a few hundreds of nanometers and with a length of several micrometres. Silicon nanowires have been the focus of much recent interest due to their unique properties which often differ significantly from bulk silicon. The electronic band-gap of silicon nanowire is tunable with the adjustment of the nanowire diameter. The band-gap is known to increase as the diameter of the nanowire is decreased. It has been shown that array of silicon nanowires when applied to strong light yield high degree absorbance of applied light. Both of these properties would be of interest when producing solar cells [3] (Ma et al., 2003).

Controlling the band-gap allows the ability to tune the spectrum of light absorbed by the device. As a solar cell generates power by absorbing light, the demonstrated band-gap tuning and high absorbance bodes well for the use of silicon nanowires in solar cells. Both of these properties would be of interest when producing solar cells.

Recent results show that silicon nanowires can be used as anti-reflective coatings on crystalline solar cells [4], [19] (Peng et al., 2005). Peng and co-workers' (2005) have used a top down fabrication technique to prepare silicon nanowires on silicon wafer using silver nitrate (AgNO<sub>3</sub>) and hydrogen fluoride (HF). There has been some mention of silicon nanowire photovoltaics within the literature where nanowires are used as antireflective coatings [4], [19] (Peng et al., 2005). However, to date there has been little work done on incorporating silicon nanowires into thin film devices. Silicon nanowires have been produced by chemical vapour deposition and plasma enhanced chemical vapour deposition which is often used with catalysts like gold which is hindered for the silicon photovoltaics technology. Thus it would be of great interest to produce solar cells incorporating silicon nanowires into their design to take advantage of the properties of these silicon nanowires to improve the efficiency of the solar cell, without overly increasing cost of production.

#### **1.2 Motivation: --Global Climate Change**

The primary motivational force behind this work is the apparent onset of anthropogenic global climate change. Evidence is mounting that human actions have created circumstances in which the energy flux of the Earth is slightly out of balance, causing a rise in the global average temperature, and climate models predict that this temperature change may bring with it a host of sweeping changes in the weather patterns and coastlines of the world. The increased levels of  $CO_2$  and other greenhouse gases in the atmosphere are key contributors to global climate change, and the chief source of  $CO_2$  emissions is the burning of fossil fuels for energy. As a result, finding carbon-neutral alternatives to fossil fuels is an important and active area of research across the sciences, and the focus of this work has been on the understanding and development of silicon nanowire based devices for solar energy generation.

There are a number of possible choices to replace fossil fuels, but light from the sun is one of the most abundant sources of carbon-neutral energy available. Indeed, the fossil fuels currently used are essentially concentrated energy from the sun stored as chemical bonds. To understand the scale of the available solar energy resource, consider that the solar constant, the energy of incoming sunlight per unit area, is  $1.37 \text{ kW-m}^{-2}$ . The cross-sectional area of the Earth is about  $1.27 \times 1014 \text{ m}^2$  on average, giving a total incident power from the sun of about 174,000 TW. This is the flux outside the atmosphere of the Earth, so it must be corrected for the total amount of energy that is reflected, which is known as the Earth's albedo and is about 30% on average. This gives a total absorbed power from the sun of about 122,000 TW. This is a vast resource compared to the total global power consumption of only 15 TW currently. Taking this analysis one step further, we can calculate the total land area necessary to generate all of the world's power from the sun. Assuming 10% efficient energy conversion, and given that land mass accounts for only 29.2% of the total surface of the Earth, we find that 0.4% of the Earth's land area would be needed to be covered in solar energy conversion devices in order to power the

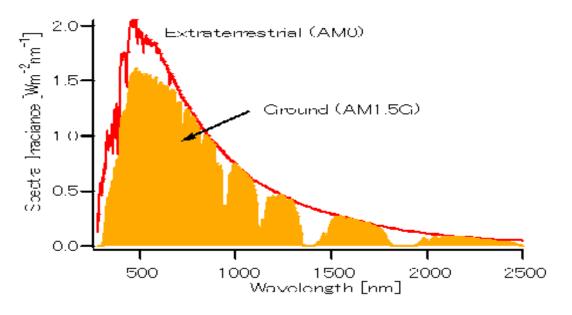

planet. In contrast, using all of the arable land to grow crops for biomass would only yield a power equivalent of  $\sim$ 8 TW, about half of what is currently being consumed, and there would also be fierce competition between land use for energy crops and for food crops. Thus, solar energy is clearly an attractive avenue for providing significant carbon-neutral energy. Solar energy spectrum for AM 0 and AM 1.5 is as shown in figure 1.1 below.

Figure 1.1: Solar spectrum for AM 0 and AM 1.5

#### 1.3 High Aspect Ratio Structures for Solar Energy

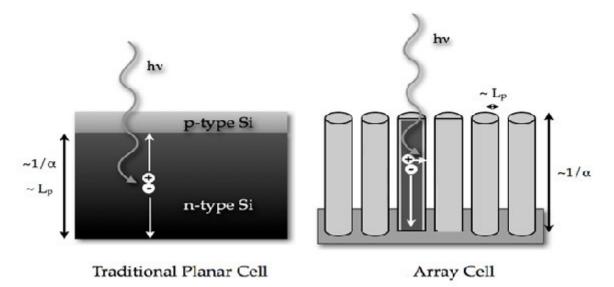

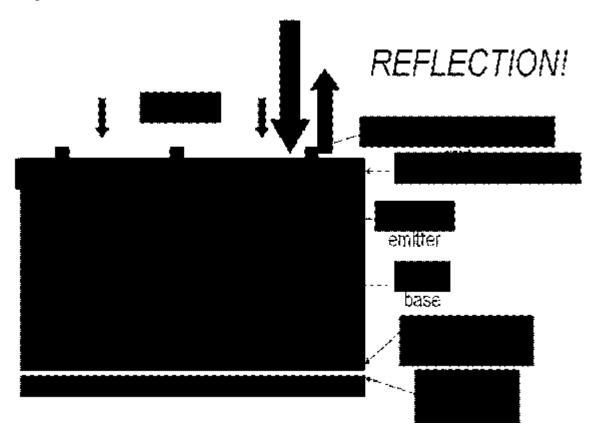

In order to take advantage of the vast solar energy resource in a meaningful way, it will be necessary to develop and manufacture solar energy conversion devices that are cost competitive with fossil fuels and nuclear fission. Although the price of conventional crystalline and multi-crystalline silicon solar cells continues to drop due to advances in manufacturing and due to economies of scale, a significant breakthrough in solar energy capture and conversion could lead to a step change in the cost of solar electricity. Furthermore, many groups are vigorously working toward the ultimate goal of a nanostructured fuel-producing device that could be manufactured cheaply at large scale. Photon capture and conversion will be an essential component of either photovoltaic or nanostructured photovoltaic energy conversion devices. For these reasons, this work focuses primarily on the nanostructured properties of high-aspect-ratio silicon structures with the goal of understanding the utility of these types of structures for low-cost solar energy capture and conversion. See Figure 1.2.

**Figure 1. 2:** Schematic diagram of a traditional planar solar cell and the proposed wire array geometry. In the planar cell, the absorption length ( $\sim 1/\alpha$ ) must be comparable to the minority carrier diffusion length (Lp). In the array cell, the absorption length ( $\sim 1/\alpha$ ) independent to the minority carrier diffusion length (Lp).

#### **1.4 SILICON AND SILICON NANOWIRES**

Question can be raised why only silicon is the preferred material for the solar cell development. Number of reasons for this are: ---

1. Silicon is one of the most abundant elements in the Earth's crust (25.7%) second only to oxygen.

2. Silicon is usually found in the form of oxides and silicates, such as sand and quartz. Arguably one of the more important and versatile elements, silicon can be used to produce everything from bricks to computer chips.

3. Strong technical backup from the micro-electronics industry.

- 4. Stable nature and non-toxic in nature.

- 5. Less complex process to produce solar cell.

#### 1.4.1 Crystalline Silicon

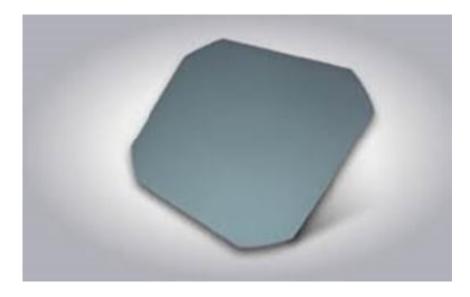

Crystalline silicon (c-Si) forms the basis of many of today's integrated circuits as it is a readily available semiconductor which is relatively easy to process and dope to form semiconductor devices. Crystalline silicon has a type of face centered cubic structure and is dark grey in colour with a slight bluish tinge. When cleaned and etched or polished, crystalline silicon is highly reflective. A photo of a sample of crystalline silicon is shown in Figure 1.3. Devices made from crystalline silicon include many integrated circuits, diodes and solar cells. High purity crystalline silicon is typically produced using the Czochralski process.

Figure 1.3: Photograph of crystalline silicon wafers

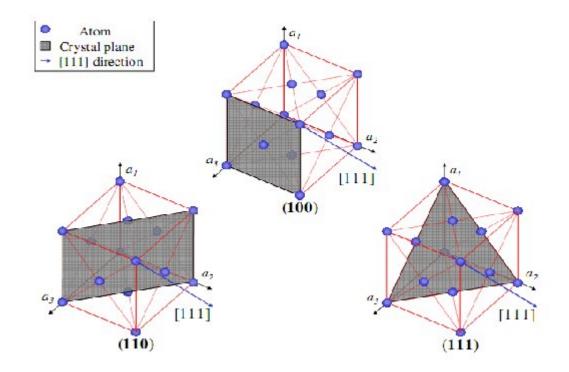

Silicon crystals/ingots are typically cut to produce wafers with different surface orientations such as (111), (100) and (110). The nomenclature (xyz) refers to the orientation of the crystal plane defined in terms of the axes (a1, a2, a3). This is illustrated in Figure 4 which shows a unit cell of the face-centered-cubic crystal structure with the different crystal planes. The nomenclature [xyz] refers to a direction as described by a vector where x, y and z are the components of the vector in terms of the axes (a1, a2, a3). An example [111] vector is shown in Figure1.4. Figure1.4 also shows the arrangement of the atoms in a face-centered-cubic unit cell, the basic unit of a crystal lattice. Silicon itself has a face-centered diamond cubic crystal structure.

*Figure 1.4*: Face centered cubic crystal unit cell showing crystal planes and the [111] direction. ([5] From Kittel)

#### 1.4.2 Amorphous silicon

Amorphous silicon (a-Si) is a glass-like material that structurally does not have long range structural order and is randomly oriented. Due to the random orientation of the material, the absorption coefficient of light in amorphous silicon tends to be higher than that of crystalline silicon [5] (from kittel).

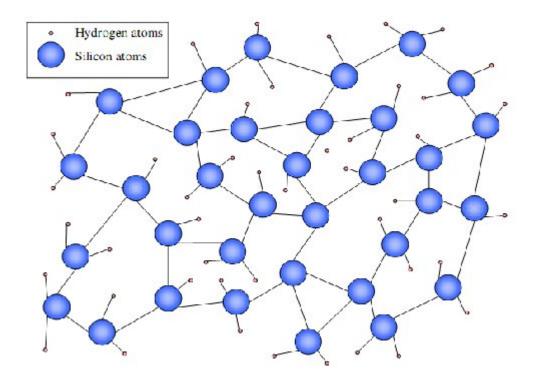

One of the main uses of a-Si silicon is in the solar cell industry for the fabrication of cost effective thin film solar cells. Amorphous materials are glass-like, randomly structured materials which gives amorphous solar cells some fairly unique properties and problems. An illustration of this glass like structure, hydrogenated amorphous silicon, is shown in Figure 1.5. Amorphous silicon by itself has many dangling bonds which trap charge carriers thereby reducing the efficiency of the cell. By creating hydrogenated amorphous silicon (a-Si:H), a hydrogen and silicon alloy, many of the traps can be eliminated [6] (Wilson, 1980). This allows it to be used in photovoltaic applications with useful efficiencies. In Figure 1.5 the dangling bonds have hydrogen atoms attached so as to passivate them and eliminate the traps.

*Figure 1.5*: Representation of the structure of hydrogenated amorphous silicon [6](Wilson, 1980)

#### 1.4.3 Polycrystalline Silicon

Typically, polycrystalline silicon is defined as having a grain size (crystallite diameter) of between 10-30 $\mu$ m and a crystalline fraction of close to 100%. Polycrystalline silicon can be doped and used to fabricate solar cells, amongst other devices [7] (Cabarrocas, 2004).

#### 1.4.4 Microcrystalline Silicon

Microcrystalline silicon is commonly defined as having a grain size between 10-20 nm and a crystalline fraction of between 10 and 100%. Microcrystalline silicon is an attractive material for electronic device applications due to its high carrier mobility and hence, high electrical conductivity. This variant of silicon is commonly used in the photovoltaic industry to produce single junction solar cells [7] (Cabarrocas, 2004).

#### 1.4.5 Nanocrystalline Silicon

Nanocrystalline silicon (nc-Si) is similar to microcrystalline silicon. Nanocrystalline silicon is commonly defined as having a grain size between 2 and 5nm and a crystalline fraction of between 10 and 80%. This form of silicon is an interesting material as it has

good optical and electronic properties [7] (Cabarrocas, 2004). It can be also be used to produce cheaper solar cells [8] (Yue et al., 2006).

#### 1.4.5.1 Quantum wire/Nanowires

There has been much recent interest in silicon-based quantum wires (nanowires). Crystalline silicon nanowires are a new form of semiconductor material, the properties of which differ from those of bulk silicon. A nanowire is a quasi-one-dimensional structure that has a nanoscale diameter, a length often in the micron range and a high aspect ratio. The aspect ratio refers to the ratio of the length to the diameter. Nanowires have diameters ranging between a few nanometers to the few hundreds of nanometers and lengths ranging up to a few millimeters. A nanowire usually has an approximately circular cross section. Nanowires can be bonded to, or embedded in, the surface of a substrate throughout their entire length. Or they can be freestanding, being attached to a substrate by only one end. Silicon nanowires can be fabricated using a range of different techniques and growth mechanisms, allowing their diverse potential applications.

#### 1.5 The Presence of the Term 'Silicon Nanowires' in the Literature

Many papers in the literature dealing with silicon nanowires and other semiconductor nanostructures begin with an introductory sentence similar to: 'Lately there has been a great deal of interest in silicon nanowires, silicon nanostructures and nanoscale semiconductors'. There are a number of variations but all express the same sentiment that (a) there has been an increase in interest in silicon nanowires and (b) that there is a large amount of recent interest. Silicon nanowires have been referred to as 'silicon filaments' or 'filamentary crystals' as far back as 1964 by Wagner and Ellis [9] (Wagner et al., 1964).

#### 1.6 Growth Mechanism of silicon nanowire

Many different growth mechanisms have been used to grow silicon nanowires. Each growth mechanism has its own defining characteristics to create nanowire.

#### 1.6.1 Vapour-Liquid-Solid (VLS) Growth Mechanism

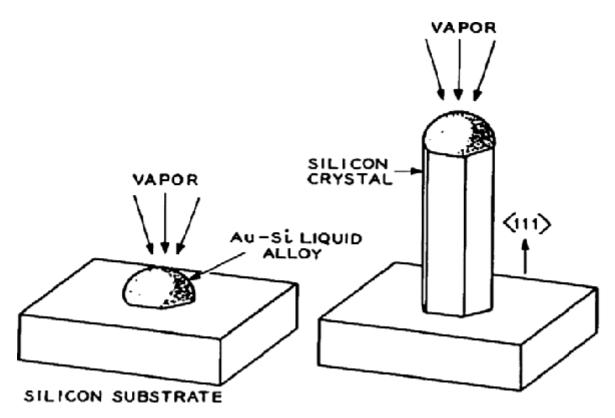

The most commonly used mechanism invoked to describe the growth of silicon nanowires is the Vapour Liquid Solid (VLS) mechanism. This was first proposed by Wagner and Ellis in 1964 to describe the growth of silicon filaments (Wagner and Ellis, 1964). The VLS mechanism uses a vapour phase reactant (SiCl<sub>4</sub>, SiI<sub>2</sub> or SiH<sub>4</sub>), a liquid

catalyst and a solid substrate to produce small diameter filaments or crystals of silicon [10] (Wagner and Ellis, 1964). The silicon comes from the disproportionation of  $SiI_2$  or the hydrogen reduction of  $SiH_4$ . The VLS mechanism can be used to produce silicon nanowires. See figure 1.6

*Figure 1.6*: Schematic diagram of silicon nanowires growth by VLS method [11] (McIlroy et al., 2004).

The VLS mechanism uses a liquid catalyst that absorbs material from the surrounding vapour, often SiCl<sub>4</sub>, SiI<sub>2</sub> or SiH4. Thin films of metallic catalysts are often used to grow silicon nanowires. A thin layer of metal catalyst is deposited onto a substrate under vacuum and is then placed in a deposition chamber which is also under vacuum. The substrate is heated until the metal catalyst melts. In the case of gold on a silicon substrate, a eutectic with silicon forms at 363°C. The liquid catalyst forms small droplets, or islands, on the surface of the substrate. The size of the island determines the size of the resulting nanowire. The gas source of silicon is then introduced and is thermally decomposed and absorbed by the liquid metal. When the catalyst becomes supersaturated with silicon, crystalline silicon is deposited underneath the metal droplet [11] (McIlroy et al., 2004).

The catalyst plays an important role in the growth of nanowires or filaments via the VLS mechanism. The choice of catalyst depends on the type of nanowire that is to be produced as the material to be used must be soluble in the catalyst. It

is also desirable that the catalyst produces a liquid alloy or eutectic droplet with a relatively low melting point. A liquid catalyst droplet acts as a preferred site for the deposition of material from the vapour phase reactants. To lower the melting point of the catalyst further, droplets or clusters with small diameters can be used as it is known that the melting point of droplets with a diameter below 200nm is lower than that of the bulk material. In the case of lead, for example, the melting point is decreased by about 200K for particles of a radius of 3nm. So where the catalyst particle size is below 200nm, the eutectic point of the nanoparticles and silicon will be reduced, allowing for lower temperature growth of silicon nanowires via the VLS mechanism. Silicon nanowires can be grown via thermal CVD at temperatures as low as 320°C using gold as a catalyst which is well below the eutectic point of gold and silicon [12] (Westwater and co-workers, 1998).

The morphology of the nanowire is also determined in part by the catalyst. The diameter of the catalyst droplet determines the size of the resulting nanowire. It has been shown using Au nanoclusters, which are nanoparticles of Au that the diameter of the grown nanowires increases proportionally with cluster diameter [13] (Cui et al., 2001).

#### 1.6.2 The Solid Liquid Solid (SLS) Mechanism

SLS mechanism is analogous to the VLS mechanism. Only difference is the use of a solid phase source of silicon rather than a vapour phase source. SLS mechanism can be used to produce silicon nanowires using a gold catalyst. In this technique nanowires produced involved the heating a gold coated silicon (c-Si (111)) substrate in a quartz-tube furnace under a flowing  $H_2$  atmosphere at 200 Torr for different time.

The SLS mechanism has three steps:-

- 1. Firstly Au-Si droplets form on the substrate when the substrate temperature is raised to the growth temperature. This forms a solid-liquid interface between the silicon substrate and the liquid catalyst droplet.

- 2. In the second phase, the  $H_2$  flowing over the surface of the droplets collides with and exchanges energy with the Si atoms on the surface of the droplets. The continual collision of the  $H_2$  with the droplets induces supersaturation at the surface of the droplets. Silicon atoms then precipitate out to nucleate the nanowires, forming a second solid-liquid interface between the liquid droplet and the nucleated nanowire.

3. The third and final phase of the SLS mechanism is the axial growth of the silicon nanowire. The compositional gradient between the two solid-liquid interfaces maintains the diffusion of Si atoms from the substrate to the growing nanowire, via the liquid catalyst droplet, allowing the growth of the silicon nanowire to continue.

#### 1.6.3 Other Growth Mechanisms

*Oxide Assisted Growth*, in this mechanism silicon nanowires are produced by thermal evaporation using an oxygen-assisted growth mechanism [14] (Pan, Lim and co-worker, 2005).

*Sulphide Assisted Growth (SAG),* silicon nanowires could be grown when sulphur powder is used as a catalyst in a low-vacuum CVD system [15] (Niu, Sha and Yang, 2004).

*Stress Driven Growth*, silicon nanowires also can be grown on a silicon substrate in a furnace without the presence of a silicon vapour or a metal catalyst. Nanowire growth would only occur if a native oxide layer was present on the silicon substrates and only after crack formation at the high temperatures used, as the nanowires were found to nucleate from the cracked regions. The different thermal expansion coefficients of  $SiO_x$  and crystalline silicon led to the creation of the cracks and a stress gradient in the sample. Prokes and Arnold (2005) proposed that this leads to the transport of silicon atoms from the stressed regions to the stress free regions resulting in the nucleation of nanowires out of the cracks [16].

#### **1.7 Properties of Silicon Nanowires**

One of the major points of interest in investigating nanostructured and nanoscale materials is how the properties of these materials differ from that of bulk silicon.

Several groups have performed Raman Spectroscopy (RS) on silicon nanowires and compared the results to bulk silicon. One of the main items of

interest is the diameter dependent downshift of the crystalline silicon peak that occurs in the Raman spectra for silicon nanowires. Silicon nanowires have been shown to have a Raman spectrum which exhibits a downshift in wavenumber of the transverse optical (TO) crystalline silicon peak in comparison to bulk crystalline silicon. This shift has been shown to be diameter dependent; there is a larger shift for smaller diameter nanowires while for larger diameters the value approaches that of bulk silicon [17] (Yu et al., 1998). This downshift has been attributed to the quantum confinement effect.

SiNWs arrays drastically suppress light reflection over a wide spectral bandwidth. The reflectance is less than 1.4% over the range of 300–600 nm for SiNWs fabricated on single-crystal Si wafers. This remarkably low reflectance of the SiNWs array is attributed to several distinct advantages associated with the wire geometry:

(1) The ultrahigh surface areas of high-density SiNWs;

(2) The sub-wavelength light-trapping effects of SiNWs arrays; and

(3) The collective light scattering interactions among SiNWs, which trap light and make it, travel many turns over distances much longer than the array thickness.

Therefore, SiNWs solar cells can have extremely low reflectance without any antireflection coatings [4] (Peng.et al., 2005).

The band-gap or energy-gap is an important property of silicon nanowires that has been shown to be dependent upon the diameter of the nanowire. The energy gap increases with decreasing diameter from 1.1eV for 7nm to 3.5eV for 1.3nm. The energy gap was found by using Scanning Tunnelling Spectroscopy (STS) measurements. The increase in band-gap is an indication of a quantum confinement effect within the silicon nanowires at low diameters [3] (Ma et al., 2003).

The properties of silicon nanowires as reported in the literature are strongly size dependant. For small diameters, properties such as the band-gap change greatly from that of bulk silicon. Larger diameter nanowires have properties that tend to approximate those of bulk silicon.

#### **1.8 Photovoltaics (PV)**

The word Photovoltaic is a combination of the Greek word for Light and the name of the physicist Allesandro Volta. It identifies the direct conversion of sunlight into energy by means of solar cells. The conversion process is based on the photoelectric effect discovered by Alexander Bequerel in 1839. The photoelectric effect describes the release of positive and negative charge carriers in a solid state when light strikes its surface. There are a number of different ways to produce solar cells and a range of materials from which they can be produced. Silicon is a commonly used semiconductor material for producing solid state solar cells. Solar cells produced using silicon have different properties when they are made using different types of silicon.

- ✤ PV benefits from a number of attractive features:

- Abundance of free fuel in the form of sunlight

- No moving parts low maintenance

- Totally noiseless, pollution free, benign source of energy

- ✤ However, it also suffers from a few limitations:

- Low energy density

- Requires storage in batteries

- Produces D.C. electricity that needs to be converted to A.C. for many applications.

#### 1.9 How Does a PN junction Solar Cell Work?

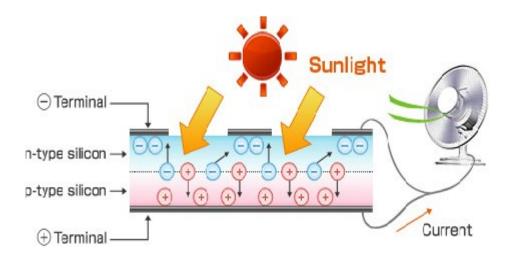

Solar cells are composed of various semiconducting materials. Semiconductors are materials, which become electrically conductive when supplied with light or heat, but which operate as insulators at low temperatures.

To produce a solar cell, the semiconductor is contaminated or "doped". "Doping" is the intentional introduction of chemical elements, with which one can obtain a surplus of either positive charge carriers (p-conducting semiconductor layer) or negative charge carriers (n-conducting semiconductor layer) from the semiconductor material. If two differently contaminated semiconductor layers are combined, then a so-called p-n-junction results on the boundary of the layers.

Figure 1.7: Schematic diagram showing operation of basic p-n junction solar cell

At this junction, an interior electric field is built up which leads to the separation of the charge carriers that are released by light. Through metal contacts, an electric charge can be tapped. If the outer circuit is closed, meaning a consumer is connected, then direct current flows. A transparent anti-reflection film protects the cell and decreases reflective loss on the cell surface. In the present study, an attempt is made to use the silicon nanowires array as anti-reflection surface in silicon solar cells. The main objectives of the work are as below:-

- 1. To develop the SiNWs on the silicon wafers with the electroless chemical deposition technique using Silver (Ag) as a catalyst.

- 2. To fabricate the silicon solar cell with the front surface as SiNW array.

- 3. To optimize the parameters of the SiNWs array solar cells, hence lowering the cost of solar cells and use them as antireflective coating.

- 4. To optimize the conditions for the growth of SiNWs.

#### 1.10 Different Cell Types

One can distinguish three cell types according to the type of crystal. This can be been seen in the table 1.1.

| Material                | Lab efficiency (%) | Production efficiency (%) |

|-------------------------|--------------------|---------------------------|

|                         |                    |                           |

|                         |                    |                           |

| Monocrystalline Silicon | approx. 24         | 14 to17                   |

| Polycrystalline Silicon | approx. 18         | 13 to15                   |

| Amorphous Silicon       | approx. 13         | 5 to7                     |

Table 1.1: Comparison of efficiencies of different types of silicon solar cells on the bases

of material used.

#### **1.11 Natural Limits of Efficiency**

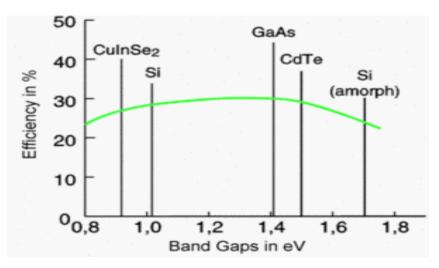

In addition to optimizing the production processes, work is also being done to increase the level of efficiency, in order to lower the costs of solar cells. However, different loss mechanisms are setting limits on these plans. Basically, the different semiconductor materials or combinations are suited only for specific spectral ranges. Therefore a specific portion of the radiant energy cannot be used, because the light quanta (photons) do not have enough energy to "activate" the charge carriers. On the other hand, a certain amount of surplus photon energy is transformed into heat rather than into electrical energy. In addition to that, there are optical losses, such as the shadowing of the cell surface through contact with the glass surface or reflection of incoming rays on the cell surface. Other loss mechanisms are electrical resistance losses in the semiconductor and the connecting cable.

Figure 1.8: Limitation of efficiency with respect to band gap

Single loss mechanisms (photons with too little energy are not absorbed, surplus photon energy is transformed into heat) cannot be further improved because of inherent physical limits imposed by the materials themselves. This leads to a theoretical maximum level of efficiency, i.e. approximately 29% for crystal silicon.

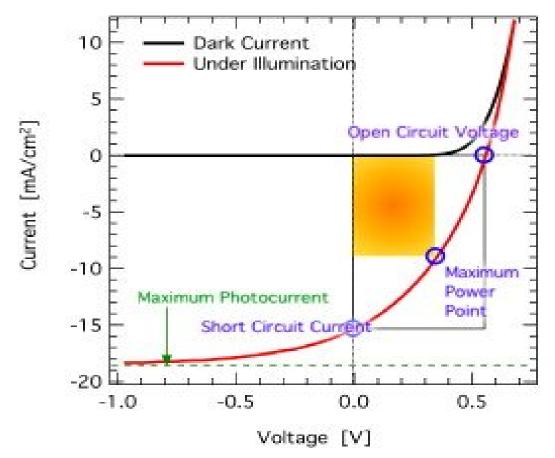

# 1.12 Characteristic Current Voltage Curve for solar cell and its important parameters

Typical voltage-current characteristics, known as the IV curve, of a diode without illumination is shown in black in Figure 1.9. The applied potential is in the forward bias direction. The curve shows the turn-on and the build-up of the forward bias current in the diode. Without illumination, no current flows through the diode unless there is external potential applied. With incident sunlight, the IV curve shifts to fourth quadrant and indicates that there is external current flow from the solar cell to a passive load i.e. power is being drawn from the device.

Figure 1.9: Typical voltage-current characteristics

*Short circuit current*,  $I_{sc}$ , flows with zero external resistance (V= 0) and is the maximum current delivered by the solar cell at any illumination level.

*Open circuit voltage*,  $V_{oc}$ , is the potential that develops across the terminals of the solar cell when the external load resistance is very large (ideally open).

The power delivered to the load is of course zero at both extremes and reaches a maximum  $(P_{max})$  at a finite load resistance value.  $P_{max}$  is shown as the area of the shaded rectangle in figure 1.9.

*Fill Factor*, FF, which is defined as the ratio of  $P_{max}$  to the area of the rectangle formed by  $V_{oc}$  and  $I_{sc}$ .

$$FF = \frac{P_{\max}}{(Voc)(Isc)}$$

*Efficiency*, $\eta$ , the efficiency of a solar cell is the ratio of the electrical power it delivers to the load, to the optical power incident on the cell (P<sub>in</sub>). Maximum efficiency is when power delivered to the load is  $P_{max}$ . Using expression of Fill Factor, maximum efficiency may be written as:

$$\eta_{\max} = \frac{P_{\max}}{P_{in}} = \frac{(Voc)(Isc)(FF)}{P_{in}}$$

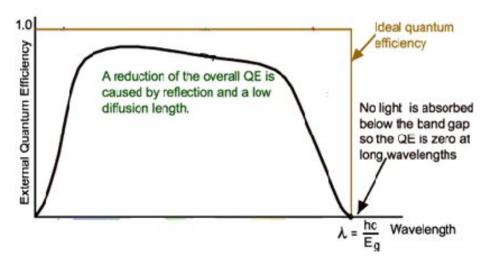

**Quantum efficiency,** QE, The "quantum efficiency" (Q.E.) is the ratio of the number of carriers collected by the solar cell to the number of photons of a given energy incident on the solar cell. The quantum efficiency may be given either as a function of wavelength or as energy. If all photons of a certain wavelength are absorbed and the resulting minority carriers are collected, then the quantum efficiency at that particular wavelength is unity .The quantum efficiency for photons with energy below the band gap is zero. A quantum efficiency curve for an ideal solar cell is shown in figure 1.10. While quantum efficiency for most

solar cells is reduced due to recombination effects. The same mechanisms which affect the collection probability also affect the quantum efficiency.

Figure 1.10: Quantum Efficiency for the solar cell[18]

Two types of quantum efficiency (QE) of a solar cell are often considered:

• External Quantum Efficiency (EQE) is the ratio of the number of charge carriers collected by the solar cell to the number of photons of a given energy shining on the solar cell from outside (incident photons i.e. without correction of photons lost due to reflection).

• Internal Quantum Efficiency (IQE) is the ratio of the number of charge carriers collected by the solar cell to the number of photons of a given energy that shine on the solar cell from outside and are absorbed by the cell (after correction of reflection loss).

The "external" quantum efficiency of a silicon solar cell includes the effect of optical losses such as transmission and reflection.

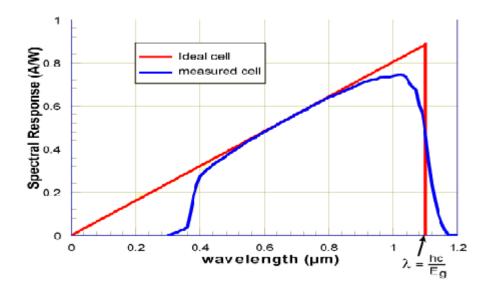

**Spectral Response of solar cell**, the spectral response is the ratio of the current generated by the solar cell to the power incident on the solar cell. A spectral response curve is shown in the figure 1.11.

Figure 1.11: Spectral Response for the solar cell [18]

The spectral response is conceptually similar to the quantum efficiency. The ideal spectral response is limited at long wavelengths by the inability of the semiconductor to absorb photons with energies below the band gap. This limit is the same as that encountered in quantum efficiency curves. However, unlike the square shape of QE curves, the spectral response decreases at small photon wavelengths. At these wavelengths, each photon has a large energy, and hence the ratio of photons to power is reduced. Any energy above the band gap energy is not utilised by the solar cell and instead goes to heating the solar cell.

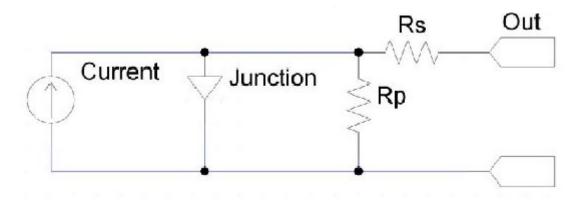

#### 1.13 Equivalent circuit model of the solar cell

Figure 1.12 shows the simplified equivalent circuit model of a solar cell. The value of the series resistance Rs, is typically much lower than the parallel resistance Rp (sometimes referred to as the shunt resistance Rsh). For the ideal solar cell, Rs would be zero, and Rp would be infinite.

Figure 1.12: A simplified equivalent circuit model of the solar cell

## 1.14 PN Junction Silicon Solar cell

The basic structure of a typical systematics p-n junction of silicon solar cell is shown in figure 1.13.

Figure 1.13: Typical systematics p-n junction of silicon solar cell

#### **Chapter 2: Experimental Systems and techniques**

#### 2.1 Current Voltage (IV) Characteristics

The Current Voltage (IV) characteristic, also known as a JV characteristic when referring to current density, is a commonly used tool for analyzing the electrical characteristics of a semiconductor device. IV characteristics simply show the current flow through a device as the voltage applied to it is varied. Information such as resistance and conductance can be gleaned using this technique. The characteristics of non-ohmic devices can also be examined.

This technique is often used to analyze solar cells. It gives information on the basic electrical properties of a solar cell including the fill-factor, series-resistance, shunt-resistance, short circuit current and open-circuit voltage, from which other factors such as the efficiency of the cell can be calculated.

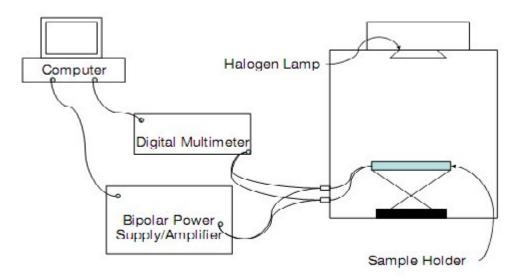

The IV characteristics of the nanowire based solar cell fabricated in this project were measured using an existing characterization system (model: Bunkoh-Keiki Co., CEP-25HS-50 SR) under AM 1.5 spectral irradiance (100 mW/cm<sup>2</sup> at 25°C) at NPL, New delhi. IV characteristics show the current flowing through a device as the voltage applied to it is varied, allowing information about the device to be gathered, as described in Chapter 1.

Figure 2.1: Schematic of the Current-Voltage characterization system.

The IV system was run in two modes. In the dark mode, the sample was isolated from any illumination. The data recorded by the computer could then be used to find the resistance of the material and the presence of any photo- conductance. A schematic diagram of the system can be seen in Figure 2.1.

As shown in figure 2.2 the samples were placed in a light-proof box to ensure they were exposed to the correct lighting conditions. For the photovoltaic devices produced the efficiency, fill factor, and current density were measured using *Solar cell Spectral Response System* (model Bunkoh-Keiki Co., Model: CEP-25HS-50 SR).

Figure 2.2: Solar cell spectral response system at NPL, New Delhi

#### 2.2 Scanning Electron Microscopy

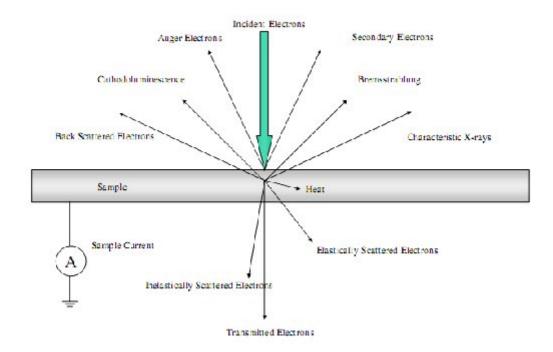

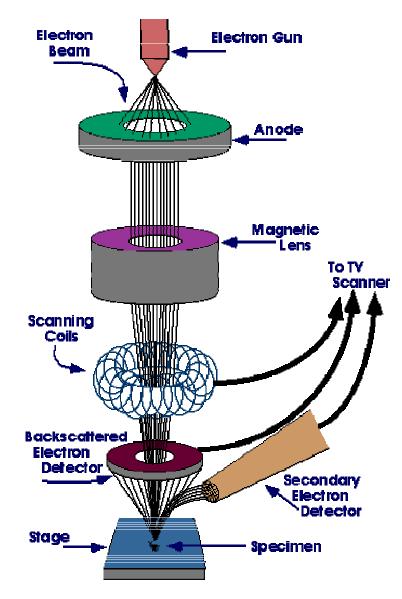

One of the major difficulties with nanotechnology and nanoscale materials arises in actually observing the material. How can the structure be observed if it is smaller than the wavelength of visible light? Electron microscopes are an answer to this question. There are two main types of electron microscopes, Scanning Electron Microscopes (SEM) and Transmission Electron Microscopes (TEM) and each has its own properties. While conventional light microscopes have a resolution in the order of  $\sim$ 200nm, the SEM has a resolution of  $\sim$ 1nm and TEM a resolution of  $\sim$ 0.1nm. Due to this vastly improved resolution, electron microscopes are commonly used to directly observe the morphology of nanostructured materials. Hence, Scanning electron microscopy is a popular and versatile characterization technique for a number of reasons.

Scanning electron microscopes function by firing a finely focused electron beam at a sample and then collecting information from the sample. The various signals emitted, and the results of electron beam interaction with the sample, are shown in Figure 2.3. The signals which are used to produce images are usually secondary electrons (SE) and back scattered electrons (BSE) for SEM.

#### Figure 2.3: Principal result of electron beam interaction with the sample

The primary mode of operation for the SEM is collecting the secondary electrons. These are loosely bound outer shell electrons that are provided with enough energy by the incident electron beam to be ejected from the material. When collected, these electrons provide topographical information about the sample. A second mode of operation involves back scattered electrons. Back scattered electrons originate in the incident electron beam. The electrons are fired at the sample and after many elastic scattering events some return to the surface and leave the sample. These can be collected to provide compositional information as the number of back scattered electrons is highly proportional to the atomic number of the material. The elements of an electron microscope are the electron source, a series of electromagnetic lenses, apertures, signal collectors and an image capture system. A simplified schematic is shown in Figure 2.4. The electrons are fired at the sample from an electron gun which can be one of several types depending on the instrument used. The most common electron gun used on older instruments is the tungsten filament which is relatively cheap but has a shorter lifetime than many other electron sources.

The accelerating voltage also helps to determine the resolution of the SEM. The resolution in the electron microscope is limited by the wave nature of electrons. The resolution and wavelength used are related through Abbe's equation

$$d = \frac{0.61\lambda}{n\sin\alpha}$$

where d is the resolution,  $\lambda$  is the wavelength, n is the refractive index of the medium through which the electrons are travelling and  $\alpha$  is the numerical aperture.

The wavelength of the electron is related to the accelerating voltage:

$$\lambda = \frac{h}{\sqrt{2mqV}}$$

where h is Planck's constant, m the mass of the electron, q the charge of the electron and V the accelerating voltage. From this it can be seen that a high accelerating voltage will produce electrons with a smaller wavelength and hence a finer resolution.

The electromagnetic lens system is used to de-magnify, direct and focus the e-beam onto the sample. A series of scan and deflection coils are used to raster the e-beam across the sample to form an image. The final aperture controls the depth of field of the micrograph. A smaller aperture allows a greater depth of field but reduces the current at the sample by physically blocking a portion of the e-beam. Another variable that alters the depth of field and image resolution is the working distance, or the distance between the sample and the final lens pole piece. With an increased working distance the image resolution decreases but the depth of field is improved. For smaller working distances the opposite holds. At times a larger working distance may need to be used to allow rotation of the sample within the specimen chamber. A larger working distance is used to avoid potentially damaging the back-scattered- electron detector when mounted on the final lens pole piece.

Figure 2.4: Simplified schematic of an SEM

The signals emitted from the sample are collected by several different types of collectors. For collecting secondary electrons an Everhart-Thornley detector is commonly used. The electrons are drawn to the detector by a metal grid with a positive bias on it. Back scattered electrons are often collected using a solid state detector (p-n junction) which is positioned around the pole piece of the objective lens. The signals from these detectors traditionally were used to display the image on a Cathode Ray Tube (CRT). In recent practice these signals have been captured by a computer which then manages the display and storage of the micrographs as image files. The micrographs can then be analyzed using analytical software to extract information, such as the size of morphological features, and printed out as required. In present work SEM

(Model: LEO 440 VP and Zeiss, EVO MA10) operating at 15 kV was used to examine the morphology of the nanostructured silicon surfaces.

# 2.3 Metal Coating systems

Two metal coating units are used during this project. One is thermal evaporation system, shown in Figure 2.5, was used for coating aluminium (Al) film at the rear surface of the silicon nanowire wafers required for back surface field (BSF) for solar cells and another metal deposition unit used is electron beam evaporation unit, as shown in figure 2.6, was used to deposit titanium and silver metal contacts of on the front and rear side of the silicon nanowire solar cells.

Figure 2.5: Thermal evaporation unit at NPL, New Delhi

For thermal evaporation unit, the required metal such as aluminium was placed in a tungsten filament basket which was attached to two electrodes within the system. Samples were placed on a framework above the filament. For the solar cells front metal grid pattern, a metal (Cu) mask, mask consisting of a series of equal-sized pattern is used for a metal coating. For deposition, the system was evacuated to a pressure in the order of  $10^{-6}$  Torr. Once the required pressure was achieved, the filament was heated resistively by passing high current using a low tension through the filament and therefore heating the metal (Al) to the evaporation temperature of Al. Al film of thickness ~ 2 µm was deposited.

Thereafter, current was slowly reduced and switched off and system was kept in high vacuum condition to allow the samples and filament to cool down to ambient temperature. Finally, vacuum system was switched off and vacuum chamber was vent by air to take out the samples.

Figure 2.6 Electron beam evaporation system at NPL, New Delhi

The process of metal deposition using electron beam evaporation system is similar to that of thermal evaporation of Al except that source of heating the metal was by e-beam rather than resistive heating by passing current through the filament. The metals such as silver (Ag) and titanium (Ti) were placed in two crucibles made of graphite. After creating high vacuum of the order  $\sim 2.0 \times 10^{-6}$  Torr, e-beam was focused at the centre of the respective crucible and heating of the metal takes place. The intensity of the e-beam was increased by increasing the e-gun current resulting into the melting and finally evaporation of the material. A shutter is located between the filament and the samples. Once the evaporation of the metal starts the shutter was then opened and the metal was deposited on the samples. The shutter is used to avoid the contamination, impurities (present in the evaporant) of the metal films adsorbed in the evaporant material which gets desorbed during heating to the evaporation temperature. Thickness of the film could be monitored in-situ by a quartz crystal based thickness monitor. After depositing the required film thickness of Ti, e-beam was switched off and crucible was allowed to cool for some time and then the crucible containing Ag was selected and process was repeated

to deposit the Ag film. In this way Ti/Ag layer was deposited (layer by layer) for front and rear metal contacts on the solar cells. Front surface contacts are usually made of grid pattern to allow light to fall on the cell surface. The metal covered area on the front surface should not be more than 10% of the cell surface. The back surface contact is simply a metal layer fully covering the back surface. Finally, the system was allowed to cool to room temperature, chamber was vent and sample was taken out for contact sintering.

# 2.4 Sintering Unit (Rapid Thermal Processing)

Sintering is a method for making objects from powder, by heating the material in a sintering furnace below its melting point (solid state sintering) until its particles adhere to each other. For the formation of back surface field (BSF) and metal contact sintering, Rapid thermal processing (RTP) unit (Model; Annelsys ASOne, France) was used. The optical photograph of the RTP system is shown in Figure 2.7 which is shown below.

Figure 2.7: Rapid thermal processing unit for firing contacts sintering and BSF formation.

The RTP system heating is done with set of 18 halogen lamps through a quartz window. RTP refers to a semiconductor manufacturing process which heats silicon wafers to high temperatures (850<sup>°</sup> C and above) on a timescale of several seconds or less. Unlike

conventional furnace sintering/annealing process, RTP is rapid, causing very low thermal budget, well controlled temperature profile etc. The present system can reach a maximum temperature up to 1200 °C and can accommodate a single wafer of 6 inch diameter or several wafers of smaller dimensions at a time. The BSF formation was carried out in Ar ambient at a temperature of 850 °C for a soaking period of 2 minutes and heating was achieved at a ramp rate of 25-30°C per sec. Metal contacts (Ti/Ag) sintering for both rear and front contacts, was carried out at an optimized soaking temperature of 650 °C for 2 minutes in nitrogen ambient. The required temperature was achieved at ramp rate of 20 °C.

## **2.5 Diffusion furnace**