## DESIGN AND ANALYSIS OF HIGH EFFICIENCY LDMOS POWER AMPLIFIER

A Dissertation Submitted towards the Partial Fulfillment of Award of Degree of

## MASTER OF TECHNOLOGY in MICROWAVE AND OPTICAL COMMUNICATION ENGINEERING

Submitted by

TUSHAR N. KHARBIKAR 2K09/MOC/15

Under the Supervision of

MR. AVINASH RATRE Asst. Professor Department of Electronics & Communication Engineering

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING IN ASSOCIATION WITH DEPARTMENT OF APPLIED PHYSICS

## DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)

Main Bawana Road, Shahabad Daulatapur, New Delhi – 110042 June-2011

## CERTIFICATE

This is to certify that the dissertation titled "Design and Analysis of High Efficiency LDMOS Power Amplifier" is the bonafide work of Tushar N. Kharbikar (2K09/MOC/15) under our guidance and supervision in partial fulfillment of requirement towards the degree of Master of Technology in Microwave and Optical Communication Engineering from Delhi Technological University, New Delhi.

Mr. Avinash Ratre Assistant Professor & Supervisor Electronics and Communication Engineering Delhi Technological University Delhi Date: /06/2011 Dr. Rajiv Kapoor Head of Department Electronics and Communication Engineering Delhi Technological University Delhi Date: /06/2011

## ACKNOWLEDGEMENT

I would like to take the opportunity to acknowledge my indebtedness towards all the people who have helped me in all my tasks and works.

My sincere gratitude is directed to my supervisor; Mr. Avinash Ratre. He actively involved himself in the project and offered useful support at every stage of my project, reviewed my schematics, answered my all questions and provided me with books and reading material.

I would like to acknowledge my friends and teachers at *Delhi Technological University, Delhi* who were kind enough to help me during my course work and teaching me with the best of their knowledge.

#### To the class of 2009-11, thank you for the very interesting and enjoyable two years!

I owe my loving thanks to my Parents, my brother, my sister and friends. They have supported me very much during my study and research. Without their encouragement and understanding it would have been impossible for me to finish this work.

Thank You all !!

Tushar N. Kharbikar 2K09/MOC/15 M.Tech (Microwave and Optical Communication Engineering) Department of Electronics and Communication Engineering Delhi Technological University

## Abstract

Linearity and efficiency are the two most important characteristics of RF power amplifier. Both these characteristics are complementary to each other. One characteristic must be achieved in order to achieve other one.

For future Worldwide Interoperability for Microwave Access (WiMAX) application which is intended to work on 3.5GHz frequency, linear power output is needed. To achieve high efficiency with the given output power requirement, Class AB is the only solution seen.

In class AB amplifier, all harmonics are shorted to achieve desired performance. In practice, to achieve shorts at all harmonic frequencies is almost impossible. The most obvious solution for this problem is to tune the harmonics to achieve the desired results.

Class J is one such topology of power amplifier. Here, second harmonic impedance is tuned so that fundamental and second harmonic assist each other to provide desired power output with increased efficiency.

Silicon is cheapest semiconductor material available. Now-a-days, compound semiconductors such as Gallium Nitride (GaN), Gallium Arsenide (GaAs), Silicon Carbide (SiC) are occupying the market of devices for applications in frequency range above 2GHz.

Si-LDMOS technology is promising technology emerged for design of power amplifiers below 1 GHz. Some recent research shows the usefulness of LDMOS technology at 2 GHz.

This work focuses on designing a high efficiency power amplifier for 3.5GHz applications using Si-LDMOS technology. For this, NXP semiconductors' BLF6G38S-25, a 25 W LDMOS power MOSFET is used. Two topologies are designed, Class AB and Class J.

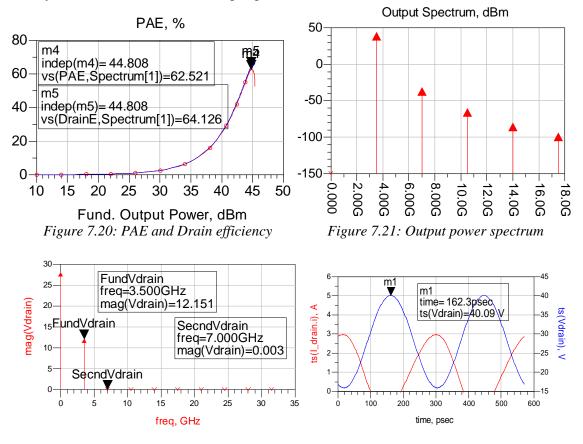

With Class AB amplifier, drain efficiency of 64% and power added efficiency (PAE) of 62.15% is achieved. The output power at this efficiency is 44.8dBm. Power back-off performance is good with PAE of 39.46%. Linearity of this power amplifier is in acceptable limit.

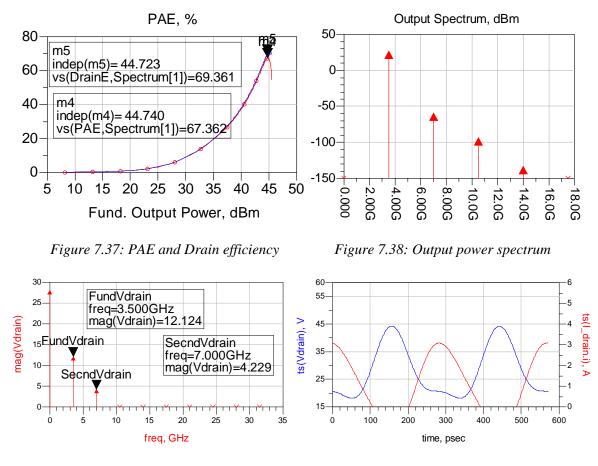

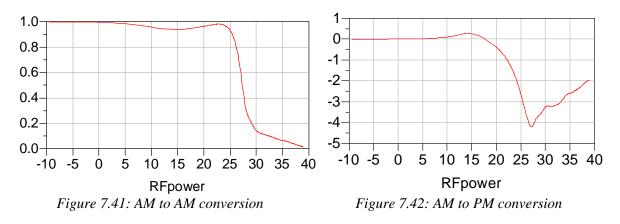

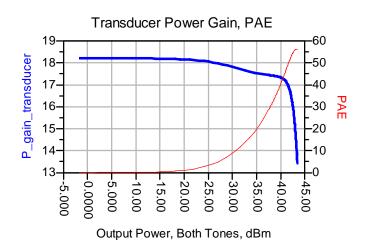

Class J amplifier gives superior performance at same biased level and input power level. Maximum drain efficiency is 69.36% and PAE is 67.36% with output power of 44.7dBm is achieved for input power level of 23dBm. Power back-off performance is also better than corresponding class AB power amplifier with 49.6% PAE at 3dB back-off.

Advanced Design System (ADS) v2008 Update 2 is used as platform for simulations.

## **Table of Content**

| Acknowledgement                                  | iii  |

|--------------------------------------------------|------|

| Abstract                                         | iv   |

| Table of content                                 | V    |

| List of figure                                   | viii |

| List of Table                                    | xii  |

| Chapter 1 Introduction                           | 1    |

| 1.1 Background                                   | 1    |

| 1.2 Motivation                                   | 2    |

| 1.3 Objective                                    | 2    |

| 1.4 Outline of Thesis                            | 3    |

| Chapter 2 Principle of class A/AB/B/C/D/E/F      | 4    |

| 2.1 Reduced conduction angle power amplifier     | 4    |

| 2.1.1 Class A                                    | 5    |

| 2.1.2 Class B                                    | 7    |

| 2.1.3 Class AB                                   | 8    |

| 2.1.4 Class C                                    | 8    |

| 2.2 Switching mode power amplifier               | 9    |

| 2.2.1 Class D                                    | 9    |

| 2.2.2 Class F                                    | 11   |

| 2.2.3 Class E                                    | 12   |

| Chapter 3 RF Power Amplifier Design Parameters   | 15   |

| 3.1 Power Output Capability (C)                  | 15   |

| 3.2 Power Added Efficiency (PAE)                 | 15   |

| 3.3 1-dB compression point (P)<br>$_{1-dB}$      | 16   |

| 3.4 Intermodulation Distortion (IMD)             | 16   |

| 3.5 Adjacent Channel Power Ratio (ACPR)          | 17   |

| 3.6 Intercept Point (IP)                         | 18   |

| 3.7 Amplitude Modulation to Phase Modulation     | 19   |

| (AM-PM) Conversion                               |      |

| Chapter 4 Harmonic Tuned Class-J Power Amplifier | 20   |

| 4.2 Sh       | provement of the efficiency of power amplifier<br>ort all the harmonics: Class-AB/B operation<br>ow the harmonics tune the fundamental frequency<br>waveform | 20<br>21<br>22 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.4 So       | lutions for class-J operation                                                                                                                                | 23             |

|              | b-optimum class-J operation                                                                                                                                  | 29             |

|              | onclusion                                                                                                                                                    | 34             |

| Chapter 5 Si | licon Lateral-Diffused MOSFETs                                                                                                                               | 35             |

| 5.1 De       | evice Cell Structure                                                                                                                                         | 36             |

| 5.2 RI       | F properties of Si-LDMOS                                                                                                                                     | 37             |

| Chapter 6    | Overview of Advanced Design System                                                                                                                           | 38             |

| 6.1 D0       | C Simulation                                                                                                                                                 | 38             |

|              | 6.1.1 DC Simulation Concept                                                                                                                                  |                |

|              | 6.1.2 Simulation Assumptions                                                                                                                                 |                |

| 6.2 A0       | C Simulation                                                                                                                                                 | 39             |

|              | 6.2.1 AC Simulation Concept                                                                                                                                  |                |

|              | Parameter Simulation                                                                                                                                         | 39             |

| 6.4 LS       | SSP Simulation                                                                                                                                               | 40             |

|              | 6.4.1 LSSP Simulation Concept                                                                                                                                |                |

|              | 6.4.2 LSSP Simulation Process                                                                                                                                |                |

|              | 6.4.3 Comparing LSSP and S-Parameter Simulations                                                                                                             |                |

| 6.5 Ha       | armonic Balance Simulation                                                                                                                                   | 41             |

| 6.6 XI       | OB Simulation                                                                                                                                                | 42             |

|              | 6.6.1 Gain Compression Concept                                                                                                                               |                |

|              | 6.6.2 Performing a Gain Compression Simulation                                                                                                               |                |

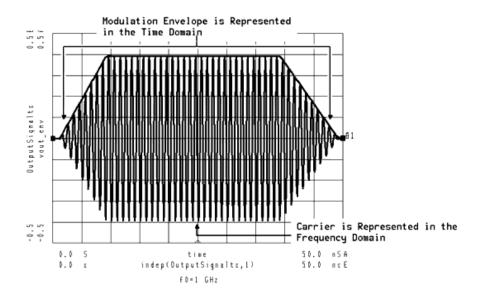

| 6.7 Er       | velope Simulation                                                                                                                                            | 43             |

|              | 6.7.1 Theory of Operation for Circuit Envelope                                                                                                               |                |

|              | Simulation                                                                                                                                                   |                |

|              | 6.7.2 When to Use Circuit Envelope Simulation                                                                                                                |                |

|              | 6.7.3 Advantage over Harmonic Balance:                                                                                                                       |                |

|              | 6.7.4 How to Use Circuit Envelope Simulation                                                                                                                 |                |

| Chapter 7 Si | mulation and Design                                                                                                                                          | 46             |

| 7.1 De       | evice Characterization                                                                                                                                       | 46             |

|              | 7.1.1 Device Model Used                                                                                                                                      |                |

|              | 7.1.2 DC Simulation                                                                                                                                          |                |

|              | 7.1.3 AC simulation                                                                                                                                          |                |

|              | 7.1.4 Small Signal S-Parameter Simulation                                                                                                                    |                |

| 7.1.5 Large Signal S-Parameter Simulation<br>7.1.6 Stability Analysis |    |

|-----------------------------------------------------------------------|----|

| • •                                                                   | 51 |

| 7.2.1 Input Bias Network                                              | 51 |

| 7.2.2 Input Matching Network Design                                   |    |

|                                                                       | 54 |

| 7.3.1 Load Pull Analysis                                              | 54 |

| 7.3.2 Output Matching Network                                         |    |

| 7.3.3 Overall Circuit and its Verification                            |    |

|                                                                       |    |

| 7.3.3.1 Overall Circuit Design<br>7.3.3.2 Verification                |    |

|                                                                       | 60 |

|                                                                       | 00 |

| 7.4.1 Load Pull Analysis                                              |    |

| 7.4.1.1 Fundamental Load Pull Simulation                              |    |

| 7.4.1.2 Second Harmonic Load Pull Simulation                          |    |

| 7.4.2 Output Matching Network                                         |    |

| 7.4.3 Overall Circuit and its Verification                            |    |

| 7.4.3.1 Overall Circuit Design                                        |    |

| 7.4.3.2 Verification                                                  |    |

| Chapter 8 Conclusion and Future Work                                  | 69 |

| 8.1 Conclusion                                                        | 69 |

| 8.2 Future Work                                                       | 69 |

|                                                                       |    |

| References                                                            | 70 |

| Appendix                                                              | 72 |

| A: Layout of Class AB amplifier                                       | 72 |

| 5 1                                                                   | 73 |

## **List of Figures**

| Figure 2.1: Reduced conduction angle                                                  | 4      |

|---------------------------------------------------------------------------------------|--------|

| Figure 2.2: Drain voltage and Drain current in class-A operation                      | 5      |

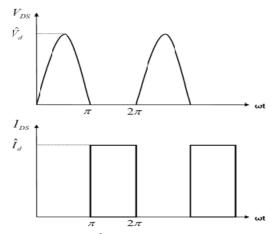

| Figure 2.3: Drain voltage and Drain current of class-B operation                      | 7      |

| Figure 2.4: Drain voltage and Drain current of class-C operation                      | 8      |

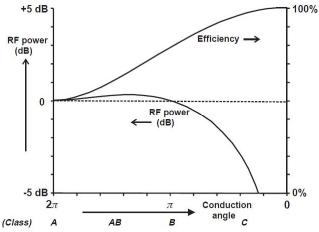

| Figure 2.5: The drain efficiency and output power versus conduction angle             | 8      |

| Figure 2.6: Class-D circuit topology.                                                 | 9      |

| Figure 2.7: Class-D voltage and current waveforms                                     | 9      |

| Figure 2.8: Class-D <sup>-1</sup> circuit topology                                    | 10     |

| Figure 2.9: Class-D <sup>-1</sup> voltage and current waveforms                       | 10     |

| Figure 2.10: Drain current and voltage of sub-optimum class-F power amplifier         | 11     |

| Figure 2.11: Third order harmonic shaped waveform                                     | 11     |

| Figure 2.12: Square waveform with different number of odd-order harmonics.            | 12     |

| Figure 2.13: Drain voltage waveform varies with different number of harmonics.        | 13     |

| Figure 2.14 Table of optimum load for class-E operation harmonics                     | 14     |

| Figure 3.1: 1-dB compression point                                                    | 16     |

| Figure 3.2: Intermodulation Distortion                                                | 17     |

| Figure 3.3 Plot of Adjacent Channel Power                                             | 18     |

| Figure 3.4 Plot showing Third Order Intercept Point                                   | 18     |

| Figure 4.1: Drain current and voltage of class-AB/B PA                                | 21     |

| Figure 4.2: Drain current and voltage of an ideal switching PA                        | 21     |

| Figure 4.3: Drain voltage and current of class-AB/B                                   | 22     |

| Figure 4.4 Phase relation of fundamental and second harmonic waveforms                | 23     |

| Figure 4.5: The drain current and voltage have reversed phase relation intrinsically. | 24     |

| Figure 4.6: The fundamental and second harmonic loads                                 | 27     |

| Figure 4.7: The loads of solution 2                                                   | 28     |

| Figure 4.8 (a) Drain voltage and current waveforms for solution 1of class-J operation | 28     |

| Figure 4.8 (b) Drain voltage and current waveforms for solution 2of class-J operation | 28     |

| Figure 4.9: the imaginary part of the load shift on the smith chart                   | 30     |

| Figure 4.10: Drain current and voltage waveforms for optimal load                     | 31     |

| Figure 4.11 (a): Drain current and voltage waveforms when the phase angle of fundam   | nental |

| harmonic load is $\frac{\pi}{5}$                                                             | 31                |

|----------------------------------------------------------------------------------------------|-------------------|

| Figure 4.11 (b): Drain current and voltage waveforms when the phase angle of fundamentation  | nental            |

| harmonic load is $\frac{\pi}{3}$                                                             | 31                |

| Figure 4.12 (a): The influence of amplitude ratio of fundamental and second harr             | nonic             |

| voltage. A/B=9.                                                                              | 32                |

| Figure 4.12 (b): The influence of amplitude ratio of fundamental and second hard             | nonic             |

| voltage. A/B=2.                                                                              | 33                |

| Figure 4.12 (c): The influence of amplitude ratio of fundamental and second harr             | nonic             |

| voltage. A/B=1.                                                                              | 33                |

| Figure 4.13: Imaginary part of load shifts with frequency (green arrow)                      | 34                |

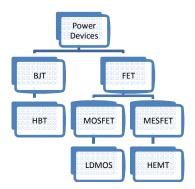

| Figure 5.1: Power Device family tree                                                         | 35                |

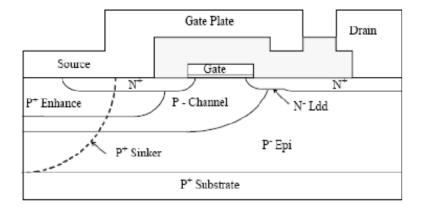

| Figure 5.2: Lateral-Diffused (LD) MOSFET Structure.                                          | 36                |

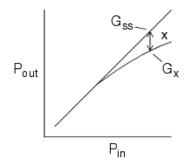

| Figure 6.1: Gain curve showing x dB compression                                              | 42                |

| Figure 6.2: Modulated signal in the time domain                                              | 43                |

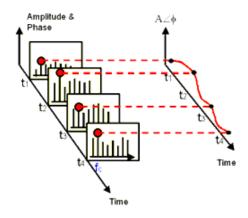

| Figure 6.3: Extraction of time domain data in frequency domain                               | 43                |

| Figure 6.4: Amplitude and Phase reconstruction                                               | 44                |

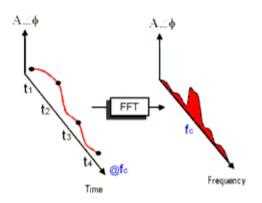

| Figure 6.5: Time domain to frequency domain conversion using FFT                             | 44                |

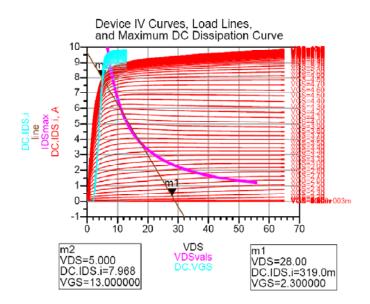

| Figure 7.1: I-V curve of BLF6G38S-25 with different drain and gate bias voltage              | 47                |

| Figure 7.2: Transconductance curve for various values of $V_{DS}$ and for $G_m$ vs $V_{CS}$  | <sub>3S</sub> for |

| particular V <sub>DS</sub>                                                                   | 48                |

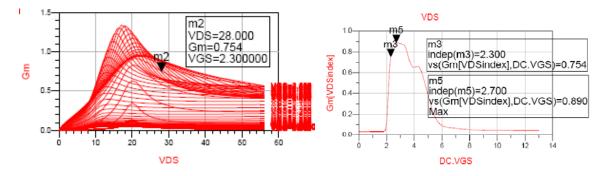

| Figure 7.3: Simulated S-parameter for frequency range of 3GHz to 4GHz                        | 48                |

| Figure 7.4: S-parameter at 3.5GHz                                                            | 49                |

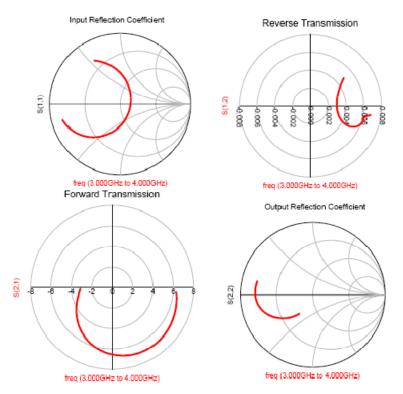

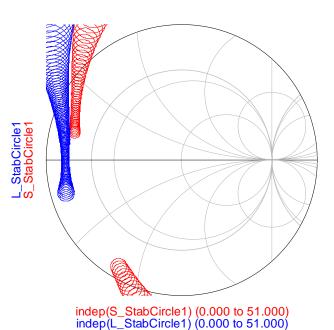

| Figure 7.5 Source (Red) and load stability (blue) circle for $V_{DS}$ =28V and frequency ran | nge of            |

| 3GHz to 4GHz                                                                                 | 50                |

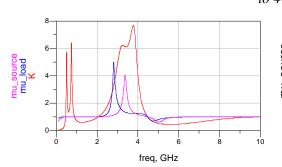

| Figure 7.6(a): Stability factor from DC to 10GHz                                             | 50                |

| Figure 7.6(b): Zoomed graph of stability factor from 3GHz to 4GHz                            | 50                |

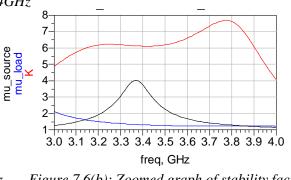

| Figure 7.7: MAG (blue), associated power gain (red) and transducer gain (pink)               | 51                |

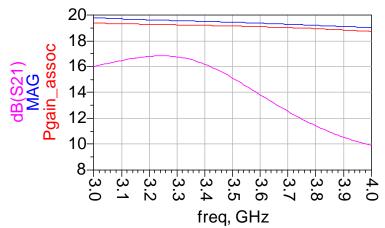

| Figure 7.8: Input bias network design                                                        | 52                |

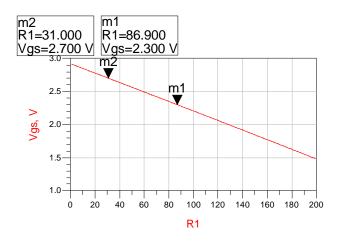

| Figure 7.9: $V_{GS}$ as function of potentiometer                                            | 52                |

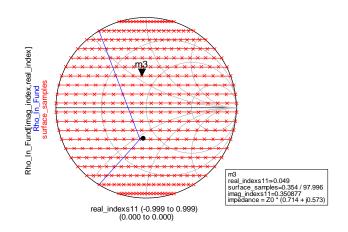

| Figure 7.10: Source pull simulation (marker m3 shows source matching point)                  | 53                |

| Figure 7.11 Input design network                                                             | 53                |

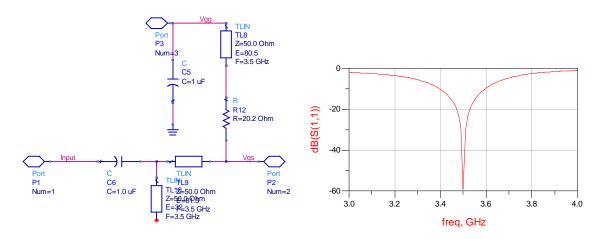

| Figure 7.12 Return loss of network of figure 7.11                                            | 53                |

| Figure 7.13: Input matching network implemented using microstrip line                        | 54                |

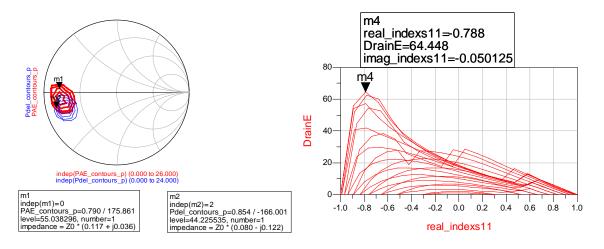

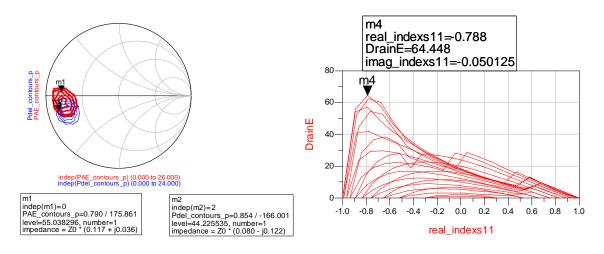

| Figure 7.14(a): PAE (red) and power (blue) contours                              | 55 |

|----------------------------------------------------------------------------------|----|

| Figure 7.14(b): Drain efficiency                                                 | 55 |

| Figure 7.14(c): Simulated load impedance from fundamental load pull simulation   | 55 |

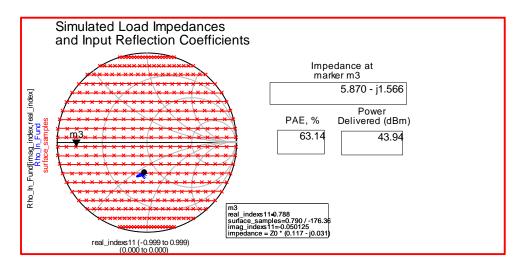

| Figure 7.15 Output matching network                                              | 56 |

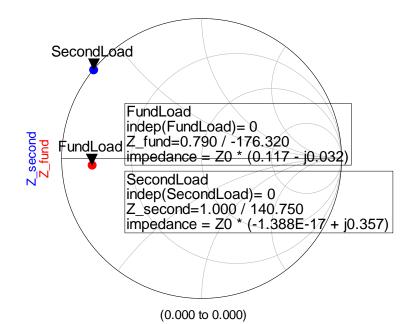

| Figure 7.16: Simulated load impedance. Fundamental (red), second harmonic (blue) | 56 |

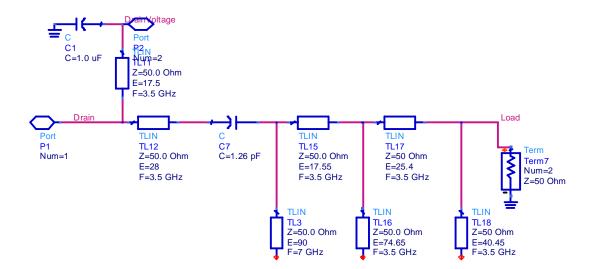

| Figure 7.17: Output matching network using microstrip line                       | 57 |

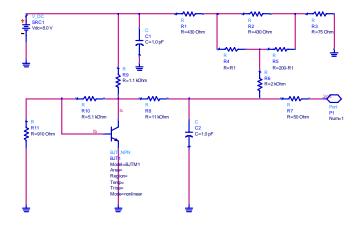

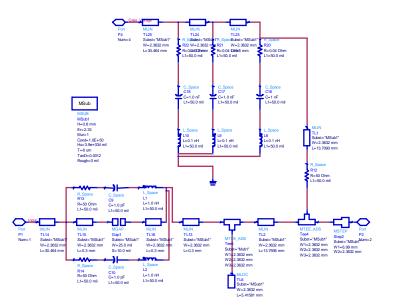

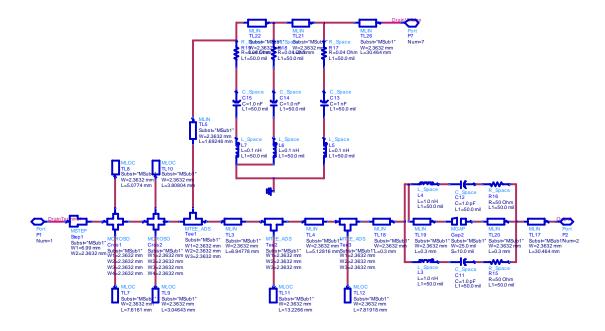

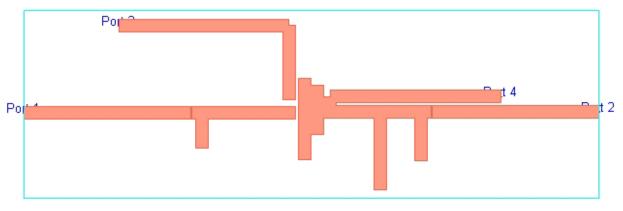

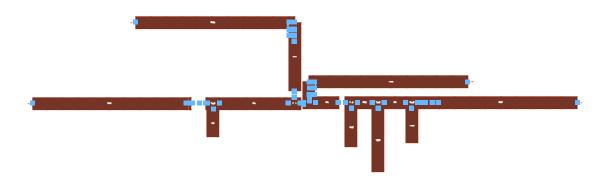

| Figure 7.18: Overall circuit of Class AB amplifier                               | 57 |

| Figure 7.19: Circuit implemented using microstrip line                           | 58 |

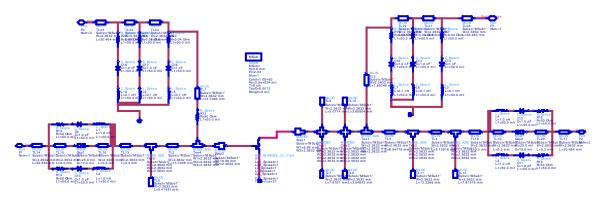

| Figure 7.20: PAE and Drain efficiency                                            | 58 |

| Figure 7.21: Output power spectrum                                               | 58 |

| Figure 7.22: Drain voltage spectrum                                              | 58 |

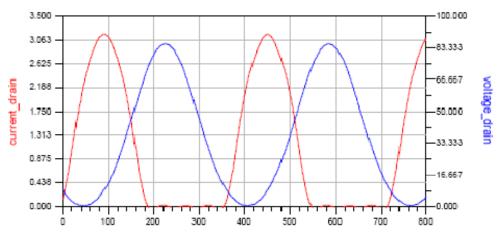

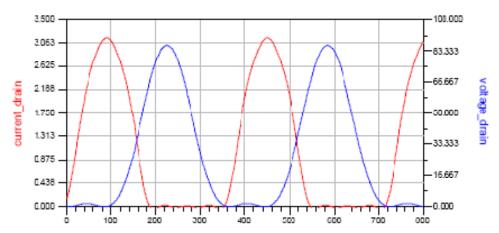

| Figure 7.23: Drain current (red) and voltage (blue)                              | 58 |

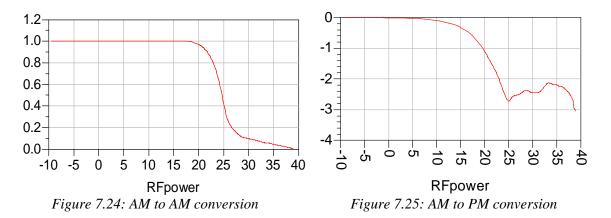

| Figure 7.24: AM to AM conversion                                                 | 59 |

| Figure 7.25: AM to PM conversion                                                 | 59 |

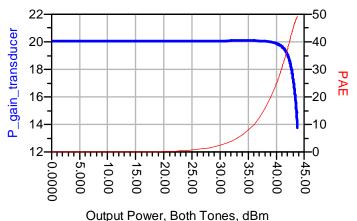

| Figure 7.26: PAE (red) and gain (blue) for both tones                            | 59 |

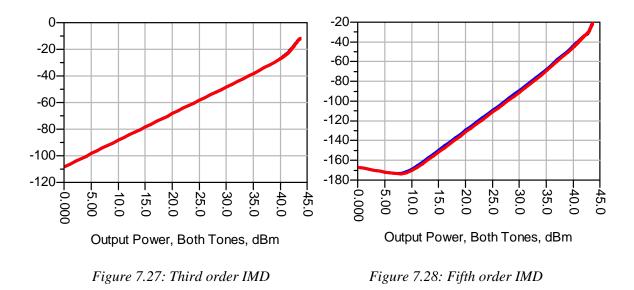

| Figure 7.27: Third order IMD                                                     | 60 |

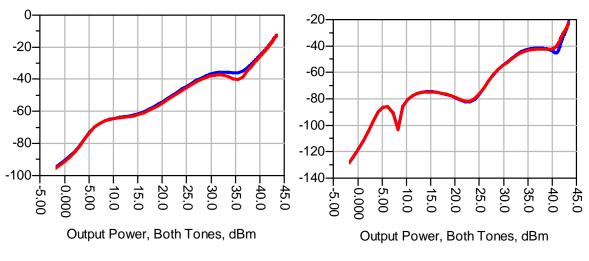

| Figure 7.28: Fifth order IMD                                                     | 60 |

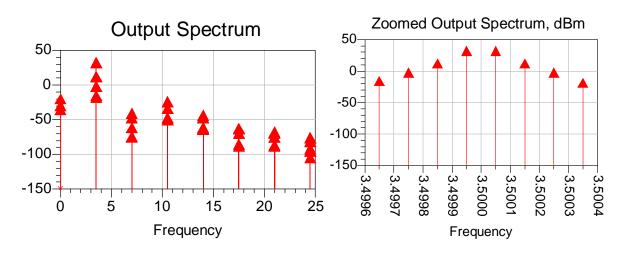

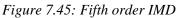

| Figure 7.29: Output spectrum and zoomed spectra for centre frequency of 3.5 GHz  | 60 |

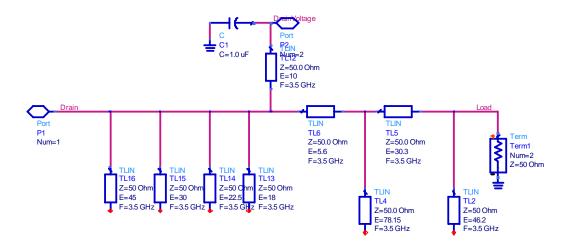

| Figure 7.30(a): PAE (red) and power (blue) contours                              | 61 |

| Figure 7.30(b): Drain efficiency                                                 | 61 |

| Figure 7.30(c): Simulated load impedance from fundamental load pull simulation   | 61 |

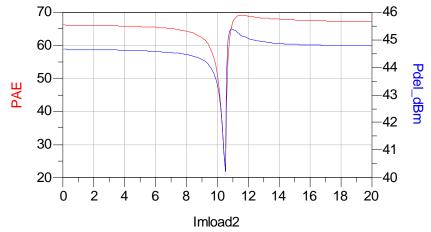

| Figure 7.31: PAE and Pdel as function of imaginary part of second harmonic load  | 62 |

| Figure 7.32: Output matching network                                             | 63 |

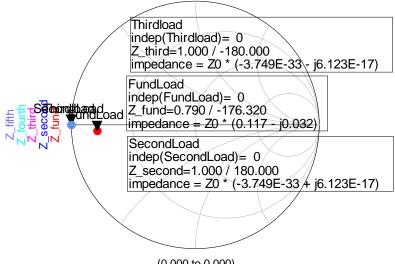

| Figure 7.33: Simulated load impedance. Fundamental (red), second harmonic (blue) | 64 |

| Figure 7.34: Output matching network using microstrip line                       | 64 |

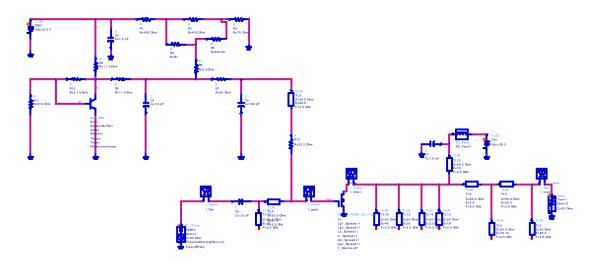

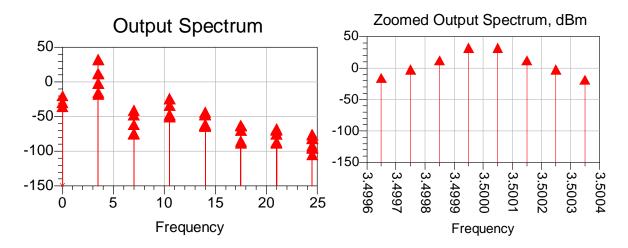

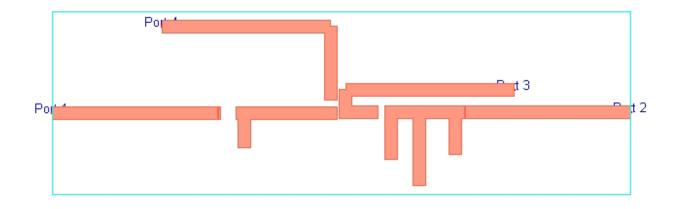

| Figure 7.35: Overall circuit of Class J amplifier                                | 65 |

| Figure 7.36: Circuit implemented using microstrip line                           | 65 |

| Figure 7.37: PAE and Drain efficiency                                            | 66 |

| Figure 7.38: Output power spectrum                                               | 66 |

| Figure 7.39: Drain voltage spectrum                                              | 66 |

| Figure 7.40: Drain current (red) and voltage (blue)                              | 66 |

| Figure 7.41: AM to AM conversion                                                 | 66 |

| Figure 7.42: AM to PM conversion                                                 | 66 |

| Figure 7.43: PAE (red) and gain (blue) for both tones                            | 67 |

| Figure 7.44: Third order IMD                                                    | 67 |

|---------------------------------------------------------------------------------|----|

| Figure 7.45: Fifth order IMD                                                    | 67 |

| Figure 7.46: Output spectrum and zoomed spectra for centre frequency of 3.5 GHz | 68 |

## List of Tables

| Table 1.1: Design goal                                             | 3  |

|--------------------------------------------------------------------|----|

| Table 2.1 Bias point and conduction angle of different classes     | 4  |

| Table 4.1: Phase angle of fundamental load versus drain efficiency | 32 |

| Table 4.2: Ratio of A/B versus drain efficiency                    | 33 |

| Table 7.1: Limiting values of NXP's BLF6G38S-25 model              | 46 |

| Table 7.2: Large signal S-parameter at 3.5GHz                      | 49 |

| Table 7.3: Small signal S-Parameter data                           | 52 |

| Table 7.4: Impedance presented by output matching network          | 56 |

| Table 7.5: Impedance presented by output matching network          | 64 |

# Dedicated to My Family

## **Chapter 1 Introduction**

## 1.1 Background

During last decade the phenomenal growth of personal wireless communications has made remarkable impacts to modern life. Nowadays billions of people use mobile cellular phones to communicate everyday with the coverage penetrating to massive areas around the whole world. Wireless data networking infrastructures are widely being deployed into public zones to offer wireless computing and internet services through laptops. Accordingly the revolution of communications has also been pushing the evolution of wireless systems and innovation of the internal radio frequency (RF) circuits, including the RF power amplifier (PA).

RF power amplifier is a circuit for converting DC supply power into a significant amount of RF output power. As a critical module in the transmit chain, it is typically the final stage of a wireless transmitter to drive the antenna. The modulated RF signal is amplified by the PA to a nominal power level and then sent through antenna to radiate for propagation.

RF power amplifiers are usually the most power-hungry building blocks in the transceivers (i.e. transmitter plus receiver) of wireless mobile terminals. For instance cellular handsets PA can consume more than 70% of the DC battery power during transmit period. There is increasing demand for highly efficient RF power amplifiers to meet the ever-growing need for power saving, compact and low cost solutions.

Indeed the higher the DC to RF conversion efficiency, the less amount of electrical charge is drawn from the battery for PA to transmit the same amount of RF power. That helps to considerably prolong the battery operation time to satisfy end users. High-efficiency RF PA also reduces the portion of battery power transformed into heat. The result is less stress for the active transistors inside PA and more importantly decreasing heat sink metal and its associated cost.

The ways of pursuing RF power amplifiers with high efficiency, are related to the modulation schemes of communication systems. Mainly there are two existing categories of modulation schemes for personal wireless applications: constant-envelope modulation and non-constant envelope modulation. The constant-envelope modulation schemes have been widely accepted by systems such as Globe System for Mobile Communications (GSM), Bluetooth and RFID. Linearity requirements of a PA are less stringent due to the usage of constant-envelope signals, e.g. GMSK (in GSM). In such a case, a non-linear PA with high efficiency can be considered: it maintains the modulated information while efficiently utilizing the limited battery power resource. In contrast to a linear PA (e.g. class A PA), where output signal amplitude presumably to be linearly controlled by the input signal amplitude, a non-linear PA's output signal is controlled by the phase and frequency information of its modulated input signal.

On the other hand, the non-constant envelope modulation applies to growing wireless systems such as wideband Code Division Multiple Access (WCDMA) and Worldwide

Interoperability for Microwave Access (WiMAX). The used shaped-pulse modulations (e.g. QAM, QPSK) or multiple carriers (OFDM) allow high data rate but occupy wider spectrum bandwidth and need highly linear components, particularly power amplifiers to transmit RF signals with time-varying envelope and phase. In such case a linear PA (typically controlled current sources) is required to lower the inter-modulation and adjacent channel interference of amplified signals. Oftentimes it operates at back-off for adequate linearity. Staying away from its peak input/output power in most of the time, however, wastes the supplied DC bias power designed for the maximum output capability and causes low PA efficiency.

## **1.2 Motivation**

Silicon LDMOS is the basic technology being used up to 1 GHz frequency for design of RF power amplifier. But upper band is captured by other solid state semiconductor technologies. At frequencies more than 2 GHz, compound materials are used to develop active devices. Various work shows successful working of GaN pHEMTs and GaAs HBT with efficiency more than 70% for output power of 2 to 10 W.

Since these technologies are very much costlier, use of these devices increases the cost of instruments where they are used. In order to provide cost effective solution of power amplifier for users, Silicon technology can be used. Silicon has developed base and many foundries are working on improving the properties.

WiMAX is developing technology. Three bands are released for WiMAX as 2.3GHz, 2.5GHz and 3.5GHz. In the USA, the biggest segment available is around 2.5 GHz, and is already assigned, primarily to Sprint Nextel and Clearwire. Elsewhere in the world, the most-likely bands used will be the Forum approved ones, with 2.3 GHz probably being most important in Asia. Some countries in Asia like India and Indonesia will use a mix of 2.5 GHz, and 3.5 GHz. Pakistan's Wateen Telecom uses 3.5 GHz.

Class AB amplifier provides good compromise between linearity and efficiency. But to achieve this, it is necessary to present short for all harmonics at drain terminal. This is difficult to achieve in practical design. The solution for this is to use harmonic tuned amplifier. Here, the harmonic impedance are tuned in such way to increase the efficiency while maintaining the linearity.

All these facts leads to the objective of this project work.

## **1.3 Objective**

The main objective of this project work is to design a highly efficient radio frequency power amplifier to be used in future WiMAX application. Two amplifiers are intended to design. One is Class AB amplifier and another is Class J amplifier

Si-LDMOS technology is used for active device. Another objective is to evaluate the possibility of using this technology at higher frequency band.

Table 1.1 shows the design goal established for this work

|                         | Class AB      | Class J       |

|-------------------------|---------------|---------------|

|                         |               |               |

| Output power            | 44dBm         | 44dBm         |

| Power Added Efficiency  | More than 60% | More than 65% |

| Drain efficiency        | More than 60% | More than 65% |

| Efficiency at 3dB power | More than 45% | More than 50% |

| back off                |               |               |

## **1.4 Outline of Thesis**

- Chapter 2 presents the working principle of different classes of power amplifier

- Chapter 3 gives brief overview of performance parameters on which power amplifier are characterized

- Chapter 4 gives detailed study of Class J amplifier

- Chapter 5 describes physical structure of Silicon Lateral Diffused MOSFET in detail with some description on RF properties of Si-LDMOS

- Chapter 6 presents description of simulation components present in Advanced Design System EM design software

- Chapter 7 contains the design of class AB and class J amplifier and simulation results

- Chapter 8 summarizes whole thesis with some points on future work.

## Chapter 2 Principle of class A/AB/B/C/D/E/F

In this chapter, the principles of some basic operation classes of power amplifiers.

### **Operation classes for power amplifiers:**

For different ways of device operation, people classify the power amplifiers to different classes. Class A/AB/B/C can be classified to one category. When the power amplifier operates at class A/B/C/AB, the transistor operates like a current source. Class D/E/F/J can be classified to another category. In these classes the transistor operates like a switch.

#### 2.1 Reduced conduction angle power amplifier

Let's first talk about the class A/B/C/AB power amplifier. The difference of these classes is the conduction angle (figure 2.1).

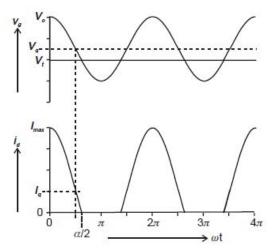

Figure 2.1: Reduced conduction angle when operating as a power amplifier' a' represents the conduction angle of power amplifier [1]

| Class | Gate bias<br>point | Current | Conduction angle |

|-------|--------------------|---------|------------------|

| Α     | 0.5                | 0.5     | 2pi              |

| AB    | 0-0.5              | 0-0.5   | Pi-2pi           |

| В     | 0                  | 0       | pi               |

| С     | <0                 | 0       | 0-pi             |

Table 2.1 Bias point and conduction angle of different classes (the signal voltage and current swing are normalized to 1) [1]

#### 2.1.1 Class A:

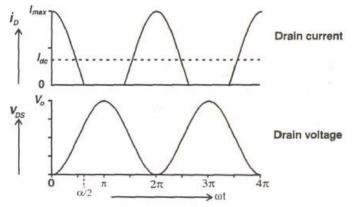

From these classes, class-A has the highest linearity and the transistor is equivalent to a current source. The drain current and voltage waveforms of class-A operation are given in figure 2.2:

Figure 2.2: Drain voltage and Drain current in class-A operation [1]

In order to enable the power amplifier operate in its linear region, the amplifier's gate and drain bias voltage should be chosen properly. The swing of the drain current for class-A operation should be between zero and Imax (with  $I_{max}$  being the saturation current of the transistor.). The swing of the drain voltage should be between zero and breakdown voltage of the device. The conduction angle is  $2\pi$  for class-A operation means the device is on all the times. It also means that the device loses power all the times.

Let's calculate the maximum efficiency and output power of class-A operation:

The drain current for an amplifier with reduced conduction angle:

$$i_{d}(\theta) = I_{q} + I_{pk} \cos \theta , -\alpha / 2 < \theta < \alpha / 2;$$

= 0, -\alpha < \theta < -\alpha / 2; -\alpha / 2 < \theta < \pi [1] (2.1)

where  $i_d(\theta)$  is the drain current,  $I_q$  is the quiescent current,  $I_{pk}$  is the amplitude of drain current,  $I_{max}$  is the peak value of drain current,  $\alpha$  is the conduction angle.

$$\cos(\alpha/2) = -\frac{I_q}{I_{pk}} \quad \text{and} \quad I_{pk} = I_{max} - I_q \tag{2.2}$$

So,

$$id(\theta) = \frac{l_{max}}{1 - \cos(\alpha/2)} \left(\cos\theta - \cos(\alpha/2)\right)$$

(2.3)

The DC component is as follows:

$$I_{dc} = \frac{1}{2\pi} \int_{-\alpha/2}^{\alpha/2} \frac{I_{max}}{1 - \cos(\alpha/2)} \left(\cos\theta - \cos(\alpha/2)\right) d\theta$$

#### DELHI TECHNOLOGICAL UNIVERSITY

$$=\frac{I_{max}}{2\pi}\frac{2\sin(\alpha/2)-\alpha\cos(\alpha/2)}{1-\cos(\alpha/2)}$$

(2.4)

The magnitude of nth harmonic is:

$$I_n = \frac{1}{\pi} \int_{-\alpha/2}^{\alpha/2} \frac{I_{max}}{1 - \cos(\alpha/2)} (\cos\theta - \cos(\alpha/2)) \cos n\theta \, d\theta \tag{2.5}$$

The fundamental harmonic component of drain current is:

$$I_1 = \frac{I_{max}}{2\pi} \frac{\alpha - \sin \alpha}{1 - \cos(\alpha/2)} \tag{2.6}$$

For class-A operation, the conduction angle is  $2\pi$ . So, the dc component of drain current is:

$$I_{dc}(class A) = \frac{I_{max}}{2}$$

(2.7)

The fundamental harmonic component of drain current:

$$I_1(class A) = \frac{V_{max}}{2} \tag{2.8}$$

The DC and fundamental harmonic component of drain voltage:

$$V_{dc}(class A) = \frac{V_{max}}{2}$$

(2.9)

$$V_1(class A) = \frac{V_{max}}{2} \tag{2.10}$$

The DC dissipation power of class-A operation power amplitude:

$$P_{dc} = V_{dc}I_{dc} = \frac{V_{max}I_{max}}{4}$$

(2.11)

The output power for class-A operation:

$$P_{out} = \frac{1}{2}V_1 I_1 = \frac{V_{max}I_{max}}{8}$$

(2.12)

The maximum drain efficiency of class-A operation:

$$\eta = \frac{P_{out}}{P_{dc}} = \frac{1}{2} = 50\%$$

[1] (2.13)

So, for class-A operation, the maximum drain efficiency 50%.

#### DELHI TECHNOLOGICAL UNIVERSITY

#### 2.1.2 Class B:

The class-B amplifier has half-sine drain current waveform and the drain voltage waveform is full-sine wave. Obviously, the overlap of the drain current and voltage is less, which means the dc power dissipation is less and therefore its efficiency is higher. However, the linearity of class-B operation is not as good as class-A operation.

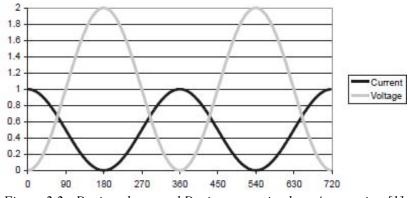

The voltage and current waveform of class-B amplifier is in figure 2.3:

Figure 2.3: Drain voltage and Drain current of class-B operation [1]

The efficiency of class-B operation:

From equations (2.4) to (2.6), we can obtain the dc and fundamental harmonic components of drain current. The conduction angle of class-B operation is  $\pi$ .

$$I_{dc}(class B) = \frac{I_{max}}{\pi}$$

[1] (2.14)

$$I_1(class B) = \frac{I_{max}}{2} \tag{2.15}$$

The dc and fundamental harmonic components of drain voltage:

$$V_{dc}(class B) = \frac{V_{max}}{2}$$

(2.16)

$$V_1(class B) = \frac{V_{max}}{2} \tag{2.17}$$

The dc and output power:

$$P_{dc} = V_{dc} I_{dc} \tag{2.18}$$

$$P_{out} = \frac{1}{2} I_1 V_1 \tag{2.19}$$

The maximum drain efficiency for class-B operation:

$$\eta = \frac{P_{out}}{P_{dc}} = \frac{\pi}{4} \approx 78.5\%$$

[1] (2.20)

The theoretical maximum class-B operation is 78.5%.

#### DELHI TECHNOLOGICAL UNIVERSITY

JUNE 2011

#### 2.1.3 Class AB:

Class-AB is a compromise between class A and B. The conduction angle for class-AB operation is between  $\pi$  and  $2\pi$ . The larger the conduction angle is typically the better the linearity is, but the lower the efficiency is, and vice versa. So, the theoretical maximum drain efficiency is between 50% and 78.5%.

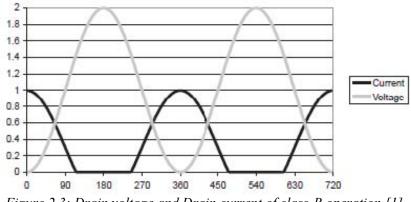

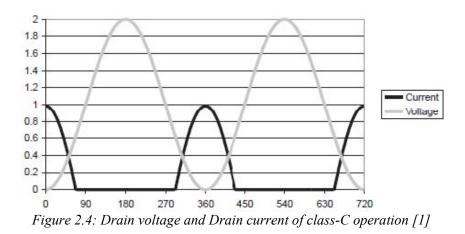

#### 2.1.4 Class C:

In class-C operation the conduction angle is between 0 and  $\pi$ . By using equation (2.4) to (2.6), we can calculate the drain efficiency of class-C operation. It isn't a constant and depends on the conduction angle. If the conduction angle is 0, theoretically we can obtain 100% drain efficiency. However, this also means that there is no power deliver to the load. So, 0° conduction angle is meaningless. In this class of operation we need to make a trade-off between efficiency and output power. The lower the conduction angle is, the higher the efficiency is and less output power is.

The waveforms of class-C operation:

The drain efficiency and output power versus conduction angle (figure 2.5):

*Figure 2.5: The drain efficiency and output power versus conduction angle [1]*

DELHI TECHNOLOGICAL UNIVERSITY

#### 2.2 Switching mode power amplifier

Class-D, class-E and class-F power amplifiers are switching mode power amplifier. The transistor acts like a switch. The theoretical maximum drain efficiency for these classes can be as high as 100%. However, due to the non-ideal conditions of device (limited switching time, parasitic and etc), 100% drain efficiency is difficult to reach [2]. Comparing with class-C operation, class-E and class-F power operation don't need to make a compromise between efficiency and output power.

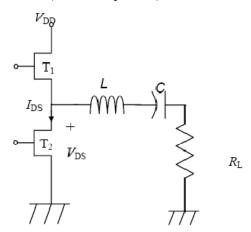

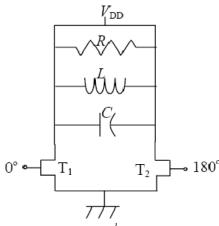

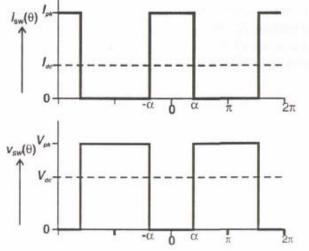

#### 2.2.1 Class D

The class-D power amplifier (or voltage mode class-D VMCD) is the only class which requires two transistors working out of phase 180°. The circuit topology is shown in figure 2.6; the load network has a series resonant circuit to pass the current at the fundamental frequency to the load and to block all other current components. Hence the voltage and current waveforms are a square (odd component) and sinusoidal (even component) waveforms, respectively, see figure 2.7.

Figure 2.6: Class-D circuit topology.

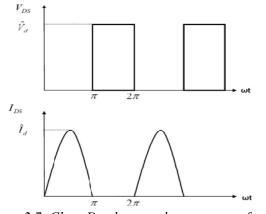

Figure 2.7: Class-D voltage and current waveforms.

There is another class which is complementary to class-D called  $D^{-1}$  (or current mode class-D CMCD). Its circuit topology could be as the circuit shown in figure 2.8. The class- $D^{-1}$  load network has a parallel resonant circuit with the load to pass the fundamental frequency and to short the odd harmonics. This topology allows the current to have square waveform and the voltage sinusoidal waveform as shown in figure 2.9. This class has an advantage over class-D, in that it can tune out the transistor output capacitance, which comes from grounding the source in both transistors, and include it as a part of the resonant circuit. Therefore, we can still achieve high efficiency, but not 100% due to the knee region. Also, class-D PA may exceed the breakdown voltage for T1 in figure 2.6, because its source terminal is not grounded

*Figure 2.8: Class-D<sup>-1</sup> circuit topology.*

*Figure 2.9: Class-D<sup>-1</sup> voltage and current waveforms.*

Another reason of degrading the efficiency from the theoretical value is the transistor output capacitance which is significant at high frequency, is large due to the size required for the high output power application. The susceptance of the output capacitance is very high for the high frequency and cannot be ignored (i.e.;  $Y=jB=j\omega Cds$ ). Also another reason of not achieving the theoretical efficiency is that the transistors do not work as ideal switches, which can be toggled between ON state and OFF state instantaneously. Within the finite turn-on and turn-off time, the voltage and the current overlap, and cause the transistor losses (switching loss). This drawback is addressed in the time domain design and analysis in Class-E amplifiers.

#### 2.2.2 Class F:

For an ideal class-F power amplifier, the voltage waveform should be an ideal square waveform. When the transistor on, the drain voltage is zero. In other words, the drain voltage is shaped to minimize the overlap of drain voltage and current. However, normally the ideal square waveform condition is hard to meet and drain voltage waveform is a sub-optimum square waveform. The waveforms of sub-optimum class-F power amplifier are:

Figure 2.10: Drain current and voltage of sub-optimum class-F power amplifier

The square waveform only contains odd-order harmonics. There are three factors which influent the shape of waveform.

1. The phase relations between fundamental and higher order harmonics. For ideal square waveform, the peak of fundamental and the valleys of higher order harmonics should be synchronized.

2. The amplitude relations of fundamental and higher order harmonics.

Figure 2.11: Third order harmonic shaped waveform (different amplitude of third harmonic) [1]

DELHI TECHNOLOGICAL UNIVERSITY

| The fundamental harmonic is: |     |        |

|------------------------------|-----|--------|

| $V_1 = \cos \theta$          | [1] | (2.21) |

| The third harmonic is:       |     |        |

|                              |     |        |

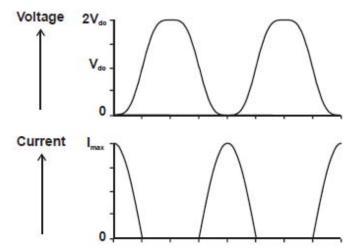

$-V_3 \cos(3\theta)$ (2.22) The superimposition of these two harmonics:  $V = \cos \theta - V_3 \cos(3\theta)$ (2.23)

The amplitude ratio of fundamental and third harmonic is very important too. As shown in figure 2.11, when the ratio is 1/6, the superimposition waveform is very flat. When the ratio is less than 1/9, the superimposition is still looks like a sinusoid.

3. The number of harmonics:

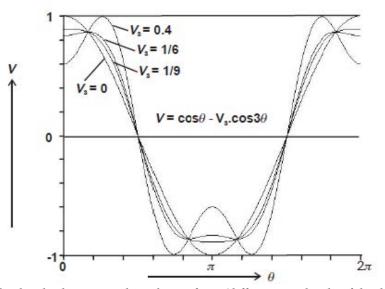

*Figure 2.12: Square waveform with different number of odd-order harmonics. m represents the number of odd-order harmonics [1]*

We can see from figure 2.8 that when the number of odd-order harmonics increases, the waveform becomes more and more like an ideal square waveform.

So, with finite number of harmonics or other non-ideal conditions, the efficiency of class-F power amplifier drops from theoretical value of 100%

#### 2.2.3 Class E:

Class-E power amplifier is also a kind of switching mode amplifier. For an ideal class-E operation, three requirements for drain voltage and current should be meet [2]:

1. The rise of the voltage cross the transistor at turn-off should be delayed until after the transistor is off.

- 2. The drain voltage should be brought back to zero at the time of transistor turn-on.

- 3. The slope of the drain voltage should be zero at the time of turn-on.

These conditions can only be met by controlling an infinite number of harmonics. When the number of harmonics is limit, the efficiency drops from theoretical value of 100% and we call that kind of operation sub-optimum class-E. The drain voltage waveform varies with different

number of harmonics are shown in figure 2.13.

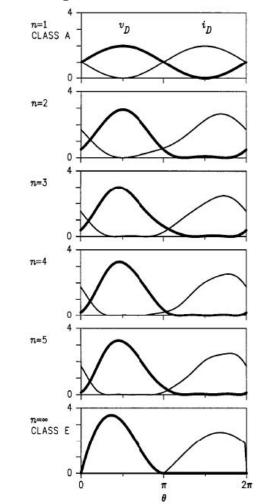

*Figure 2.13:* Drain voltage waveform varies with different number of harmonics. n represents the number of harmonics [3]

When the harmonic number is 2, the drain voltage only contains fundamental and second harmonic components. We call it class-J operation. The detail discussion on class-J operation is in later chapter. So, class-J is also a kind of sub-class E operation. When the number of harmonic increases to infinite, there is no overlap of drain voltage and current (figure 2.13) and 100% efficiency can be achieved. However, in practical situations, it's a very hard task due to the existence of on resistor or other parasitics of the transistors. Basically, the class-E power amplifier we call is in sub-class E operation.

The equations to calculate the optimum fundamental load for class-E operation:

$$R = \frac{0.58 \times V_{dd}^2}{P_{out}}$$

(2.24)

| k  | <i>v</i> _k     | 1 <sub>k</sub> | Z <sub>k</sub> for R=1     | $Z_k$ for $R_1 = 1$ |

|----|-----------------|----------------|----------------------------|---------------------|

| 0  | 1.000           | 0.5762         |                            |                     |

| 1  | 1.639           | 0.8691         | 1.5260 + j1.1064           | 1 + j0.725          |

| 2  | 0.8477          | 0.3120         | -12.7233                   | -11.7846            |

| 3  | 0.2222          | 0.1224         | -11.8155                   | -/1.1897            |

| 4  | 0.1433          | 0.1056         | 1.3616                     | -j0.8923            |

| 5  | 0.08001         | 0.07344        | -/1.0893                   | -j0.7138            |

| 6  | 0.05907         | 0.06536        | - 10.9038                  | -10.5923            |

| 7  | 0.04082         | 0.05246        | - 10.7781                  | -10.5099            |

| 8  | 0.03236         | 0.04774        | - 10.6778                  | -i0.4448            |

| 9  | 0.02470         | 0.04081        | - 10.6052                  | -10.3966            |

| 10 | 0.02045         | 0.03773        | -10.5420                   | -10.3552            |

|    | Figure 2.14 Tal | ble of optimum | load for class-E operation |                     |

The table of optimum harmonics load for ideal class-E operation [3]:

DELHI TECHNOLOGICAL UNIVERSITY

## Chapter 3

## **RF Power Amplifier Design Parameters**

### Overview

The RF power amplifier (PA), a critical element in transmitter units of communication systems, is expected to provide a suitable output power at a very good gain with high efficiency and linearity. The output power from a PA must be sufficient for reliable transmission. High gain reduces the number of amplifier stages required to deliver the desired output power and hence reduces the size and manufacturing cost. High efficiency improves thermal management, battery lifetime and operational costs. Good linearity is necessary for bandwidth efficient modulation. However these are contrasting requirements and a typical power amplifier design would require a certain level of compromise. There are several types of power amplifiers which differ from each other in terms of linearity, output power or efficiency. Parameters which quantify the various aspects of amplifier performance such as 1-dB compression point, input intercept point, intermodulation distortion, power output capability, power added efficiency and adjacent channel power ratio are discussed in this chapter.

## **3.1 Power Output Capability (C**)

The power output capability,  $C_p$ , is defined as the RF output power produced when the device has a peak drain voltage of 1 volt and a peak drain current of 1 ampere [3]. This is a unit less quantity. If the power amplifier uses two or more transistors, then the number of transistors is included in the denominator.

If  $P_0$  is the RF output power,  $I_{d, pk}$  is the peak drain current,  $V_{d, pk}$  is the peak drain voltage and N is the number of transistors, then

$$C_P = \frac{P_0}{NI_{d,pk}V_{d,pk}} \tag{3.1}$$

Usually the power output capability of a Class A amplifier is the highest since it is operated at the centre of the load line allowing room for maximum voltage and current swings. Based on this, another parameter called the power utilization factor (PUF) is defined as the ratio of RF power delivered by a device in a particular mode to the power delivered by operating the device as a Class A amplifier.

#### 3.2 Power Added Efficiency (PAE)

Efficiency or drain efficiency is simply defined as the ratio of output power at the drain to the input power supplied to the drain by the dc supply.

$$\eta_d = \frac{P_0}{P_{dc}} \tag{3.2}$$

Drain efficiency is usually not enough to characterize RF power amplifier performance. This is due to the substantial RF power at the input of the amplifier, especially in amplifiers with low gain. Power added efficiency (PAE) includes the effect of input drive power and is defined as:

$$PAE = \frac{P_0 - Pdrive}{P_{dc}}$$

(3.3)

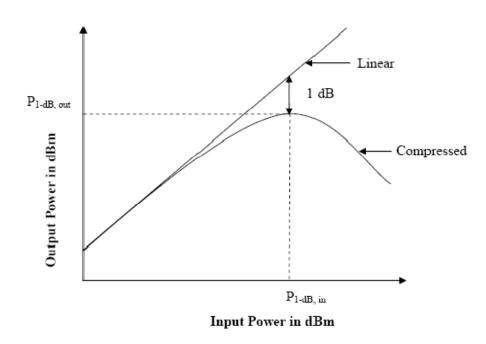

## **3.3 1-dB compression point** (P<sub>1-dB</sub>)

When a power amplifier is operated in its linear region, the gain is a constant for a given frequency. However when the input signal power is increased, there is a certain point beyond which the gain is seen to decrease. The input 1-dB compression point is defined as the power level for which the input signal is amplified 1 dB less than the linear gain. The 1-dB compression point can be input or output referred and is measured in terms of dBm. A rapid decrease in gain will be experienced after the 1-dB compression point is reached. This gain compression is due to the non-linear behaviour of the device and hence the 1-dB compression point is a measure of the linear range of operation.

Figure 3.1: 1-dB compression point

#### **3.4 Intermodulation Distortion (IMD)**

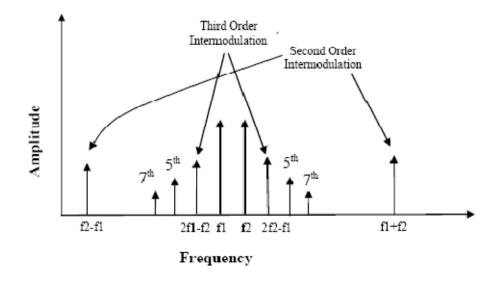

Intermodulation distortion is a nonlinear distortion characterized by the appearance, in the output of a device, of frequencies that are linear combinations of the fundamental frequencies and all harmonics present in the input signals [1]. A very common procedure to measure the

intermodulation distortion is by means of a two-tone test. In a two-tone test a nonlinear circuit is excited with two closely spaced input sinusoids. This would result in an output spectrum consisting of various intermodulation products in addition to the amplified version of the two fundamental tones and their harmonics. If  $f_1$  and  $f_2$  are the fundamental frequencies then the intermodulation products are seen at frequencies given by

$$f_{IMD} = mf_1 \pm nf_2 \tag{3.4}$$

where m and n are integers from 1 to  $\infty$ .

The ratio of power in the intermodulation product to the power in one of the fundamental tones is used to quantify intermodulation. Of all the possible intermodulation products usually the third order intermodulation products (at frequencies  $2f_1 - f_2$  and  $2f_2 - f_1$ ) are typically the most critical as they have the highest strength. Furthermore they often fall in the receiver pass band making it difficult to filter them out.

Figure 3.2: Intermodulation Distortion

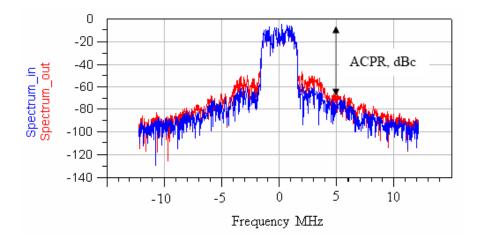

### 3.5 Adjacent Channel Power Ratio (ACPR)

In many modern communication systems, the RF signal typically has a modulation band that fills a prescribed bandwidth on either side of the carrier frequency. Similarly the intermodulation products also have a bandwidth associated with them. The IM bandwidth is three times the original modulation band limits for third order products, five times the band limits for fifth order products and so on. Thus the frequency band of the intermodulation products from the two tones stretches out, leading to leakage of power in the adjacent channel. This leakage power is referred to as adjacent channel power. The adjacent channel power ratio (ACPR) is the ratio of power in the adjacent channel to the power in the main channel. ACPR values are widely used in the design of power amplifiers to quantify the effects of intermodulation distortion and hence also serve as a measure of linearity.

Figure 3.3 Plot of Adjacent Channel Power

#### **3.6 Intercept Point (IP)**

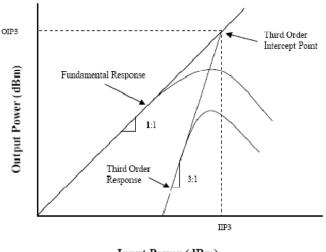

The intercept point is the point where the slope of the fundamental linear component meets the slope of the intermodulation products on a logarithmic chart of output power versus input power. Intercept point can be input or output referred. Input intercept point represents the input power level for which the fundamental and the intermodulation products have equal amplitude at the output of a nonlinear circuit. In most practical circuits, intermodulation products will never be equal to the fundamental linear term because both amplitudes will compress before reaching this point. In those cases intercept point is measured by a linear extrapolation of the output characteristics for small input amplitudes. Since the third order intermodulation products, among the IM products, are of greatest concern in power amplifier design, the corresponding intercept point called the third order intercept point (IP3) is an important tool to analyze the effects of third order nonlinearities. In fact intercept point serves as a better measure of linearity in comparison to intermodulation products as it can be specified independent of the input power level [1].

Input Power (dBm)

Figure 3.4 Plot showing Third Order Intercept Point

### **3.7** Amplitude Modulation to Phase Modulation (AM-PM) Conversion:

An amplifier driven under strongly nonlinear conditions produces phase distortion in addition to amplitude distortion. The phase distortion is a serious problem in systems with phase modulation such as QPSK. This phase distortion is characterized by AM-PM conversion which is defined as the change in phase of the output signal when the drive level at the input is increased toward and beyond the compression point. The AM-PM effects are usually caused by the storage elements in the circuit like the gate-source junction capacitances and parasitics associated with inductors under nonlinear conditions.

## Chapter 4 Harmonic Tuned Class-J Power Amplifier

In the previous chapters, the principles of operation of classes for power amplifiers and their performance parameters are discussed. In this chapter, the principles of class-J operation will be discussed. The definition of class-J operation is use of a second harmonic termination to tune the shape of drain voltage waveform. In this way, the performance of power amplifier can be improved. More details are discussed in following sections.

### 4.1 Improvement of the efficiency of power amplifier

When a power amplifier is designed, efficiency (drain efficiency, PAE) is an important performance. The equation for calculating the drain efficiency is:

$$Drain\_eff = \frac{P_{fund}}{P_{dc}}$$

(4.1)

*Drain\_eff* represents the drain efficiency.  $P_{fund}$  and  $P_{dc}$  represent fundamental harmonic power and DC power respectively.

From the equation 4.1, it can be found that there are two ways to improve the efficiency performance.

(1) One is to increase the fundamental harmonic power. This means that all the output power should be at the fundamental frequency and there is no power dissipation at higher order harmonics. So, even if the harmonics are used to tune the waveform of drain voltage or drain current, the higher order harmonics' loads (higher than order 2) should be pure reactive. However, because of some parasitic resistance of the device, there is always some loss of at these higher order harmonics. But, this loss is typically small compared with the fundamental harmonic power. So, what is needed to do is to keep all the higher order harmonics' loads reactive to minimize this loss.

(2) The second way to improve the efficiency is to minimize the dc power dissipation. The DC power is as follow:

$$P_{dc} = \frac{1}{\tau} \int I_d \times V_d dt \tag{4.2}$$

From equation 4.2, it can be deduced that to reduce the DC power dissipation, the product of current and voltage needs to be reduced, consequently the overlap of the drain current and voltage should be made as low as possible at all times (Figure 4.1 and 4.2):

Figure 4.1: Drain current and voltage of class-AB/B PA

Figure 4.2: Drain current and voltage of an ideal switching PA [1]

By applying the Fourier transform to the waveform in figure 4.1, the DC components of drain current and voltage is obtained. If the current and voltage are both high across the active device, DC components always exist at the same time and there will be power dissipation. Note that in figure 4.2, the ideal switching mode power amplifier has no drain current and voltage simultaneous, that means there is no power dissipation. All the DC power is transformed to signal power. For this ideal switching PA, the efficiency is 100%. But, this kind of PA is not easy to realize, so the harmonics can be used to tune the waveform in figure 4.1 and make the overlap of drain current and voltage as small as possible.

### 4.2 Short all the harmonics: Class-AB/B operation:

Before investing in the influence of harmonics on the efficiency performance of power amplifier, first study the operation of class-AB/B. For class-AB/B power amplifier, all the harmonics are shorted except the fundamental harmonic. The drain current and drain voltage of class-AB/B power amplifier are as follow:

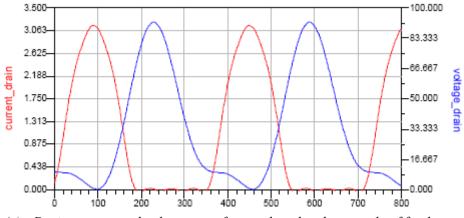

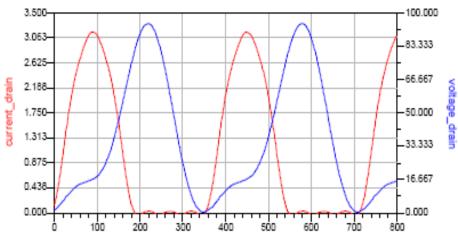

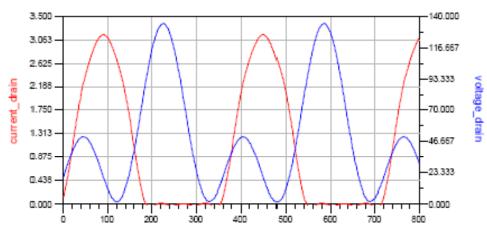

*Figure 4.3:* Drain voltage and current of class-AB/B operation (blue, drain voltage, red, drain current. X axis is phase of waveforms in degrees. Y axis is in Amperes and volts for current and voltage respectively)

The drain current of the class-AB/B power amplifier is half-sine wave. The equation for the half-sine wave is as follow:

$$half_{sin}(\theta) = 1 + \frac{\pi}{2} \times sin(\theta) + \sum_{n=1}^{\infty} -2 \times \frac{1}{n^2 - 1} \times cos(n\theta), n = 2K, \forall n, k \in \mathbb{N} [6]$$

(4.3)

Here all the currents are normalized to the DC component. So, the DC current equals 1, the amplitude of fundamental harmonic current will be  $\frac{\pi}{2}$ . The amplitudes for higher order harmonics are defined as  $\frac{-2}{n^2-1}$ . From the equation, it can be seen the half-sine wave contains only even-order harmonics and the fundamental harmonic.  $\Theta$  represents the phase angle. The drain voltage of class-AB/B operation contains only the fundamental harmonic since all harmonic sexcept the fundamental harmonic are shorted.

Obviously, if, to make the drain voltage sharper, can be used the harmonics, the overlap of the drain current and voltage can be reduced and the efficiency will increase.

### 4.3 How the harmonics tune the fundamental frequency waveform

For class-F operation, the odd order harmonics are used to shape the drain voltage to a square waveform. For class-E operation, the drain voltage waveform is shaped by the harmonics so that the drain voltage and the slope of drain voltage is zero when the transistor is on. However, the harmonic tune conditions for ideal class-E/F operations are difficult to meet. Due to the existence of output capacitance of transistor, higher order harmonics are therefore difficult to tune. So, typically just the second harmonic can be tuned in a practical matching network. This is main motivation for the use of class-J operation. The question is now how does the second harmonic affect the performance of PA. Let's discuss it step by step.

First, have a look on how the second harmonic affects the drain voltage waveform (figure 4.4):

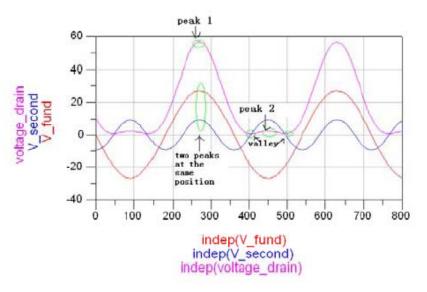

Figure 4.4 Phase relation of fundamental and second harmonic waveforms (x axis, phase angle in degree, y axis, voltage in V. Red, fundamental harmonic voltage. Blue, second harmonic voltage. Pink, superimposition of these two voltage)

Figure 4.4 shows us that the drain voltage becomes shaper after tuning by second harmonic. This is what is needed. For our first impression, the efficiency performance will be improved. However, is the problem really so simple? Let's calculate the theoretical efficiency of class-J operation.

### 4.4 Solutions for class-J operation

If the waveform only contains dc, fundamental and second harmonic components, it is called as pseudo half sinusoidal (PHS) [6]. The PHS of drain current is as follow:

$$PHS\_I_{sin}(\theta) = I_{dc} + I_{fund} + I_{second}$$

$$= I_{dc} \times \left(1 + \frac{\pi}{2} \times \sin(\theta) - \frac{2}{3} \times \cos(2\theta)\right) \quad [6] \quad (4.4)$$

PHS\_ $I_{sin}(\theta)$  is the drain current,  $I_{dc}$  is the dc current,  $I_{fund}$  is the fundamental harmonic current and  $I_{second}$  is the second harmonic current. For simplicity, the currents are normalized to DC current:

$$I_{dc} = 1 \tag{4.5}$$

$$I_{fund} = \frac{\pi}{2} \times \sin(\theta) \tag{4.6}$$

$$I_{second} = -\frac{2}{3} \times \cos(2\theta) \tag{4.7}$$

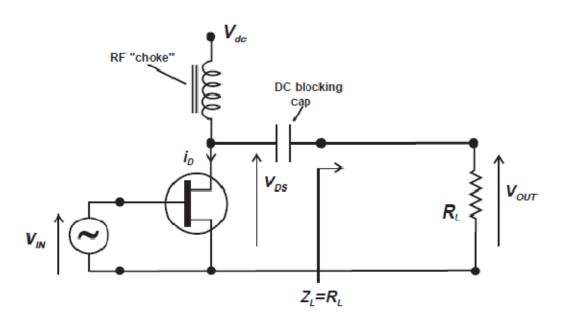

Now the composition of current is known, in order to obtain the loads, knowledge about the composition of voltage is also needed. From figure 4.8, it works out that the voltage waveform and current have reverse sign (fundamental component of drain voltage has a 180 degrees phase reversal with the drain current and the second harmonic component of drain voltage has a 360 degrees phase reversal of drain current), which is due to the nature of the schematic (see figure

4.5).

Figure 4.5: The drain current and voltage have reversed phase relation intrinsically. (see  $i_D$  and  $V_{DS}$  in the graph)

In the previous expressions of drain current and voltage, this phase reversal hasn't been taken into account yet.

The load for the second harmonic: on first sight it might seems that the second harmonic load can be arbitrary value. Actually, as discussed in section 1, in order to transform as much power from dc to fundamental frequency as more as possible, the power dissipation at higher order harmonics should be minimized. Therefore, the second harmonic load used, should be pure reactive. It can be inductive or capacitive. Inductive load means the second harmonic voltage will lead 90 degrees with the drain current. And a capacitive load means the second harmonic voltage will lag 90 degrees with the drain current. So, to synchronize the peak of the fundamental and second harmonic waveform like that in figure 4.4, the fundamental load should make the fundamental voltage lead or lag 45 degrees with the drain current. This also means that: for the typical class-J operation, there are two solutions for the fundamental and second harmonic loads. Let's discuss both of them.

The pseudo half sine (PHS) form of drain voltage:

$$PHS\_Vsin(\theta) = 1 + A \times sin(\theta) - B \times cos(2\theta)$$

[6] (4.8)

A and B is the amplitude of fundamental and second harmonic voltage respectively. All of the amplitudes are normalized to Vdc.

If we obtain the derivative of this equation and make it equal to zero, we can get the two peaks and two valleys of *PHS Vsin* [1]:

$$peak_{1,2} = 1 \pm A + B@\theta_1 = \frac{\pi}{2}, \theta_2 = \frac{3\pi}{2}$$

[6] (4.9)

Design and Analysis of High Efficiency LDMOS Power Amplifier

$$min_{1,2} = 1 - B - \frac{A^2}{8B} @\theta_1 = \pi + \arcsin\left(\frac{A}{4B}\right)$$

$$@\theta_2 = 2\pi - \arcsin\left(\frac{A}{4B}\right)$$

(4.10)

The minimum value of PHS waveform should be zero:

$$min_{1,2} = 0 \Longrightarrow 1 - B - \frac{A^2}{8B} = 0 \Longrightarrow A^2 = 8B(1 - B)$$

(4.11)

$$A^{2} = 8B(1-B) \Longrightarrow B = \frac{1}{2} + \frac{1}{2}\sqrt{1 - \frac{A^{2}}{2}}$$

(4.12)

From equation 4.12, the maximum and minimum values of A and B are obtained respectively:

$$1 - \frac{A^2}{2} \ge 0 \Longrightarrow \frac{A^2}{2} \le 1 \Longrightarrow A \le \sqrt{2}$$

(4.13)

$$A_{Max} = \sqrt{2} \& B_{min} = \frac{1}{2}$$

[6] (4.14)

**The first solution:** The first solution can be derived by checking the drain current and voltage relationship.

From equation 4.9, the drain current equation is given by:

$$I_{Drain}(\theta) = \frac{I_{peak}}{\pi} + \left(\frac{I_{peak}}{2}\right) \times \sin(\theta) - \frac{2 \times I_{peak}}{3 \times \pi} \times \cos(2\theta)$$

(4.15)

$$I_{dc} = \frac{I_{peak}}{\pi} \tag{4.16}$$

$$I_{fund} = \frac{I_{peak}}{2} \times \sin(\theta) \tag{4.17}$$

$$I_{second} = \frac{2 \times I_{peak}}{3 \times \pi} \times \cos(2\theta)$$

(4.18)

For the first solution, if the load for second harmonic is capacitive. The second harmonic voltage should lead 90 degrees with the phase of drain current :

$$V_{second} = -B\cos\left(2\theta + \pi - \frac{\pi}{2}\right) = -B\cos\left(2\left(\theta + \frac{\pi}{4}\right)\right)$$

(4.19)

B is amplitude of  $V_{second}$ , the  $\pi$  in the equation is caused by the reverse phase relation of drain current and voltage as shown in figure 4.5.

In order to synchronize the peaks of the fundamental and second harmonic voltage wave, the fundamental harmonic voltage waveform should lags 45 degrees with the phase of drain current:

$$V_{fund} = A \times \sin\left(\theta + \pi + \frac{\pi}{4}\right) \tag{4.20}$$

where A is the amplitude of  $V_{fund}$ . The  $\pi$  is caused by the reverse phase relation of drain current

and voltage as shown in figure 4.5.

Now the drain efficiency can be calculated. The output voltage on the load is  $V_{out}$  and  $I_{out}$  (see figure 4.5):

$$V_{out}(\theta) = V_{fund\_out} + V_{second\_out}$$

$$= A \times Vdc \times \sin\left(\theta + \frac{\pi}{4}\right) - B \times Vdc \times \cos\left(2\theta - \frac{\pi}{2}\right) (4.21)$$

$$I_{out}(\theta) = I_{fund\_out} + I_{second\_out}$$

$$= \left(\frac{l_{peak}}{2}\right) \times \sin(\theta) - \frac{2 \times l_{peak}}{3 \times \pi} \times \cos(2\theta)$$

(4.22)

The output voltage and the current flow into the load have in-phase relation and they don't contain DC component.

Now, calculate the output power and efficiency of class J operation. The DC power dissipation can be calculated from the DC components of drain voltage and current:

$$P_{dc} = I_{dc} \times V_{dc} = \frac{I_{peak}}{\pi} \times V_{dc}$$

(4.23)

The output power can be calculated from the output voltage and current on the load:

$$P_{out} = \frac{1}{2} \times Re\left[V_{fund_{out}} \times conj(I_{fund_{out}})\right]$$

$$= \frac{1}{2} \times Re\left[AV_{dc}e^{jw\left(\frac{\pi}{4}\right)} \times \frac{I_{peak}}{2}\right]$$

$$= \frac{I_{peak} \times V_{dc}}{4} \times \cos\left(\frac{\pi}{4}\right) \times A \qquad (4.24)$$

The drain efficiency:

$$\eta = \frac{P_{out}}{P_{dc}} = \frac{\pi}{4} \times \frac{1}{\sqrt{2}} \times A \tag{4.25}$$

The maximum efficiency can be obtained when A reaches its maximum value. As found previously, the maximum value for A is  $\sqrt{2}$ . So, the maximum efficiency is:

$$\eta_{max} = \frac{P_{out}}{P_{dc}} = \frac{\pi}{4} \times \frac{1}{\sqrt{2}} \times \sqrt{2} = \frac{\pi}{4} \approx 78.5\%$$

[6] (4.26)

So, the theoretical highest drain efficiency of class-J operation is 78.5% and if we want to achieve this peak efficiency, we need to choose A as  $\sqrt{2}$  and B as 1/2.

$$A = \sqrt{2} \qquad \qquad [6] \qquad (4.27)$$

$$B = \frac{1}{2} \tag{4.28}$$

Therefore, the drain voltage is:

$$V_{drain}(\theta) = V_{dc} + \sqrt{2} \times V_{dc} \times \sin\left(\theta + \pi + \frac{\pi}{4}\right) - \frac{1}{2} \times V_{dc} \times \cos\left(2\theta + \pi - \frac{\pi}{2}\right)$$

(4.29)

$$V_{fund} = \sqrt{2} \times V_{dc} \times \sin\left(\theta + \pi + \frac{\pi}{4}\right) \tag{4.30}$$

$$V_{second} = -\frac{1}{2} \times V_{dc} \times \cos\left(2\theta + \pi - \frac{\pi}{2}\right)$$

(4.31)

The  $\pi$  in equations (4.29) and (4.30) is due to the nature of schematic (see figure 4.5). So, it should be eliminated when the loads are calculated. From equations (4.16) to (4.17) and equations (4.30) to (4.31), the fundamental and second harmonic loads are calculated:

$$Zload_{fund} = \frac{2\sqrt{2} \times V_{dc}}{I_{peak}} \angle \frac{\pi}{4}$$

(4.32)

$$Zload_{second} = \frac{3 \times V_{dc} \times \pi}{4 \times I_{peak}} \angle -\frac{\pi}{2}$$

(4.33)

Let's choose the values of  $V_{dc}$  and  $I_{peak}$  to check the loads on the Smith chart.

Assume  $V_{dc}$ =30 V and  $I_{peak}$ =2.5 A.

$$Zload_{fund} = 34 \angle \frac{\pi}{4} \tag{4.34}$$

$$Zload_{second} = 28.3 \angle -\frac{\pi}{2}$$

[6] (4.35)

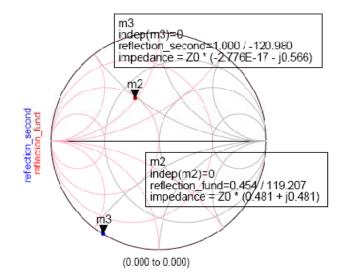

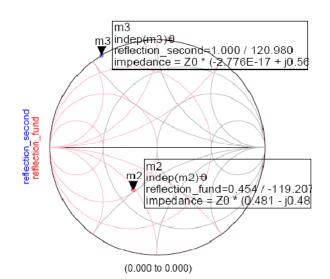

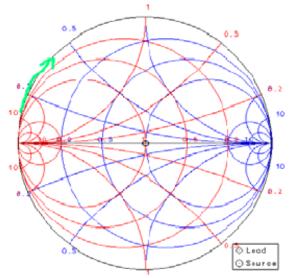

The loads on the Smith chart (figure 4.6):

*Figure 4.6: The fundamental and second harmonic loads (red, fundamental harmonic, blue, second harmonic, normalized to 50 Ohms)*

An alternative solution on the Smith chart, where the load for second harmonic of solution 2 is inductive (figure 4.7):

*Figure 4.7: The loads of solution 2 (red, fundamental harmonic, blue, second harmonic, normalized to 50 Ohms)*

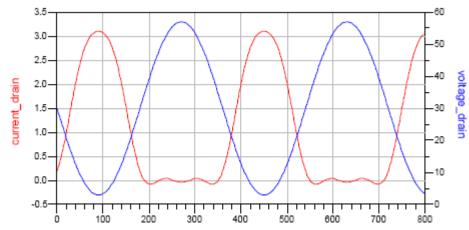

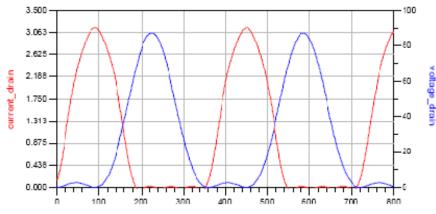

The drain voltage and current waveform for solution 1 and 2:

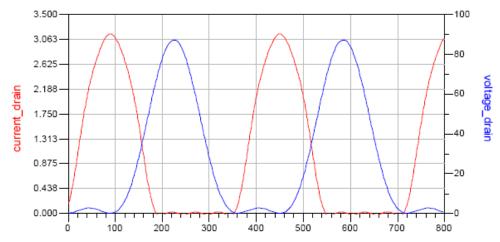

Figure 4.8 (a) Drain voltage (blue) and current (red) waveforms for solution 1 of class-J operation

Figure 4.8 (b) Drain voltage (blue) and current (red) waveforms for solution 2of class-J operation

So, the two solutions for class-J operation are:

$$Zload_{fund} = \frac{2\sqrt{2} \times V_{dc}}{I_{peak}} \angle \pm \frac{\pi}{4}$$

(4.36)

$$Zload_{second} = \frac{3 \times V_{dc} \times \pi}{4 \times I_{peak}} \angle \overline{+} \frac{\pi}{2}$$

(4.37)

$$P_{outpeak} = \frac{1}{4} \times V_{dc} \times I_{peak} \tag{4.38}$$

The loads in terms of peak power are:

$$Z_{fund} = \frac{V_{dc}^2}{\sqrt{2} \times P_{outpeak}} \angle \pm \frac{\pi}{4}$$

(4.39)

$$Z_{second} = \frac{3\pi \times V_{dc}^2}{16 \times P_{outpeak}} \angle \overline{+} \frac{\pi}{2}$$

[6] (4.40)

V<sub>dc</sub> is the dc voltage component of drain voltage and I<sub>peak</sub> is the peak amplitude of drain current.

In this section, the efficiency that class-J operation can provide together with the optimal loads for fundamental and second harmonics is discussed. This can be called as ideal class-J operation. For ideal class-J operation, the maximum drain efficiency is 78.5%, which is the same as that of class-B operation. However, this efficiency is reached without providing a perfect short for the second and higher order harmonics, something that is not always practical (for example, there is a series inductor of package) in wideband design. So, for single frequency design, we should test which class is works best for our device. While for wideband design, we can make use of the 2<sup>nd</sup> harmonic termination to achieve better results, when second harmonic shorts are not practical. In the next section, some practical considerations will be discussed.

#### 4.5 Sub-optimum class-J operation

In last section, the solutions for ideal class-J operation are obtained. From equations (4.36) to (4.40) we can see: for fixed values of dc voltage and  $I_{peak}$  or a peak output power, the optimal loads for fundamental and second harmonics are constants for a given operating frequency.

But if to design a wideband power amplifier, we will have constant values for the components of our matching network (for example, an fixed inductor, capacitor or transmission line). Use of these components will result in a not constant reactance versus frequency. For example, when we have an inductive load, the load is given by:

$$G_{loadfund} = g_{fund} + \frac{1}{jwL_{fund}}$$

(4.41)

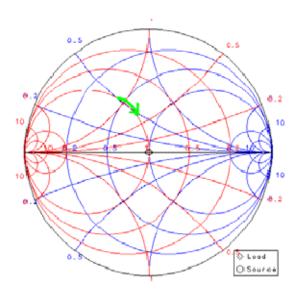

$g_{fund}$  is the conductance of the load, and with the frequency changes, the imaginary part  $\frac{1}{jwL_{fund}}$  will shift on the smith chart (figure 4.9):

*Figure 4.9:* With increasing frequency, the imaginary part of the load will shift on the smith chart in the direction of the green arrow

Another complication is that the reactance of parasitic output capacitance of the device  $j\omega C_{parasitic}$  will also change with frequency. Even worse this parasitic output capacitance is not a linear capacitor with supply voltage. In fact it is a very strong function of supply voltage, which will cause the optimum load shift on the Smith chart with supply voltage modulation as well. So, for a wideband power amplifier, it's almost impossible to match every load of different frequency to the optimum load. This is the reason why we discuss here sub-optimal class-J operation.

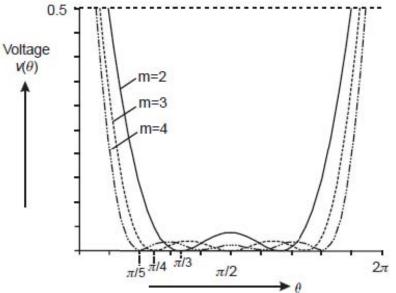

For optimum class-J, two conditions should be met:

- 1. The peak of the fundamental voltage waveform should synchronize with the second harmonic voltage waveform (as shown in figure 4.4). And only this condition is met, the superimposition of these two waveforms will have two peaks and two valleys.

- 2. The amplitude ratio of fundamental and second harmonic voltage should be a certain value. From equation (4.35) we know the amplitude ratio of fundamental and second harmonic voltage is A/B. For the optimal load,  $A=\sqrt{2}$ ,  $B = \frac{1}{2}$ . So,  $\frac{A}{B} = 2\sqrt{2} = 2.828$

For sub-optimal class-J operation, we indeed have used the second harmonic to tune the drain voltage waveform, but we don't meet the two conditions above exactly.

First, as we have discussed above, for wideband power amplifier, the fundamental loads for every frequency can't be matched to the optimal load. So, let's discuss how are the waveforms like, if the load deviates from the optimum value. For example:

When it's the optimum load is given by:

$$Zload_{fund} = \frac{2\sqrt{2} \times V_{dc}}{I_{peak}} \angle \frac{\pi}{4}$$

(4.42)

The waveform is:

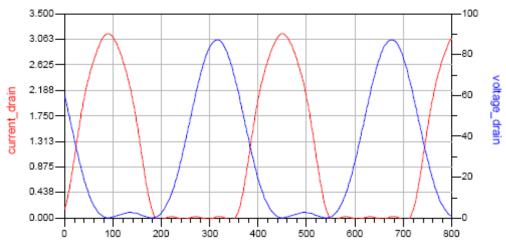

Figure 4.10: Drain current and voltage waveforms for optimal load

When the phase angle changes to  $\frac{\pi}{5}$  and  $\frac{\pi}{3}$ , the waveforms are:

*Figure 4.11 (a): Drain current and voltage waveforms when the phase angle of fundamental harmonic* load is  $\frac{\pi}{5}$

*Figure 4.11 (b): Drain current and voltage waveforms when the phase angle of fundamental harmonic* load is  $\frac{\pi}{3}$

| Phase angle of fundamental load | Drain efficiency |

|---------------------------------|------------------|

| Pi/5                            | 69.2%            |

| Pi/4                            | 78.5%            |

| Pi/3                            | 62.4%            |

Table 4.1: Phase angle of fundamental load versus drain efficiency