### **MAJOR PROJECT REPORT**

ON

# Implementation of SHA Algorithm using VHDL for Hardware Security

A Major Dissertation Submitted in Partial Fulfilment of the requirement for the award of degree of

#### **MASTER OF ENGINEERING**

in

#### ELECTRONICS AND COMMUNICATION ENGINEERING

By

Meenakshi

**Roll No. 2811**

Under the Guidance

of

Mrs. S. Indu

Senior Lecturer

Dept. of Electronics and Communication Engineering

Delhi University, Delhi

Department of Electronics and Communication Engineering Delhi College of Engineering June-2007

## **Acknowledgement**

I wish to express my deep sense of gratitude and indebtness to Mrs. S. Indu (Senior Lecturer, Dept. of Electronics And Communication Engineering) for her guidance and assistance without which completion of this project report would not have been possible.

I also express my sincere gratitude to the **Prof. Asok Bhattacharyya** (**Head of Department, Dept. of Electronics And Communication Engineering**) and faculty of Dept. of Electronics And Communication Engineering Department.

I also express my sincere gratitude to **Mrs. Mini Cherion** (Scientist 'F', Divisional Head, Integrated Hardware and Software Group, Defense avionics Research Establishment, DRDO)

Last but not the least, I am thankful to my parents, my Husband and friends for their encouragement and guidance.

Meenakshi Univ. roll no. 2811

# **Certificate**

This is to certify that **Ms. Meenakshi** student of Delhi College of Engineering, Delhi worked under my guidance on major project entitled **"Implementation of SHA Algorithm using VHDL for Hardware security"** being submitted in partial fulfilment of the requirement for the award of the degree of **"MASTER OF ENGINEERING"** to the Department of Electronics and Communication Engineering, Delhi College of Engineering, Bawana Road, Delhi-42.

Prof. Asok Bhattacharyya Head Of Division Dept. Electronics & Comm. Engg. Delhi University, Delhi Mrs. S.Indu Senior Lecturer, Dept. Of Electronics & Comm. Engg. Delhi University, Delhi

Department of Electronics and Communication Engineering Delhi College of Engineering Delhi-42

#### Abstract

With introduction of new technologies inventors are more concerned about the security of the new inventions they are bringing out. Data security is becoming ever more important in embedded and portable electronic devices. External interfaces to memory in digital devices and communication interfaces to other digital devices are more vulnerable to probing. The principal goal guiding the design of any encryption algorithm must be security against unauthorized attacks. These technique were sufficient to prevent the unauthorized access of the device but if the attack is at the device interface level not to access the system but to get the knowledge of complete architecture of device, algorithm used etc. This is very serious security threat from IP (intellectual property) point of view. So nowadays apart from the user authentication check device architecture information and algorithm are encrypted so as to avoid any kind of reverse engineering. The analysis techniques used by attackers are equally advanced. So the Defensive measures for protecting a device must be more sophisticated and robust.

This thesis presents an architecture that provides the security to the embedded application on a Field Programmable Gate Array (FPGA). The Identification Friend or Foe method is presented as the framework for creating a secure authentication system for the embedded system applications. It is shown that the Identification Friend or Foe method behaves like a secure wrapper around the user design and protects it from the leakage of the algorithm details of the device. The IFF concept is challenge and response based authentication scheme that protects the Intellectual Property from the threat of the cloning of the embedded application design. This scheme is capable of securing a variety of embedded applications. The cryptographic method used in the system is Secure Hash Algorithm. SHA is a standard specified in Federal Information Publication 180-1 and 180-2 (FIPS 180-1, FIPS 180-2). The SHA series hashes are currently the only FIPS-approved method. SHA-1 is also specified in ISO/IEC 10118-3.

# **Table of Contents**

| 1. Introduction                             | 1  |

|---------------------------------------------|----|

| 1.1 Motivation                              | 1  |

| 1.2 Overview                                | 3  |

| 1.3 Thesis Organization                     | 3  |

| 2. Background                               | 5  |

| 2.1 Need of Encryption                      | 5  |

| 2.2 Evolution Of Encryption Techniques      | 5  |

| 2.3 Security Threats                        | 7  |

| 2.2.1 Modern Encryption Techniques          | 8  |

| 2.2.1.1 Symmetric Key Algorithms            | 8  |

| 2.2.1.2 Asymmetric Key Algorithms           | 8  |

| 2.3 Requirement of Encryption Techniques    | 9  |

| 3. Algorithm Description                    | 10 |

| 3.1 Secure Hash Algorithm                   | 10 |

| 3.1.1 Introduction of Secure Hash Algorithm | 10 |

| 3.1.2 Properties of a Secure Hash Algorithm | 10 |

| 3.1.3 Terminology                           | 11 |

| 3.1.4 Message Padding                       | 11 |

| 3.1.4 Algorithm                             | 12 |

| 3.2 IFFTEST Concept                         | 16 |

| 4. Architecture                             | 18 |

| 4.1 Functional Blocks                       | 18 |

| 4.1.1 Wire Protocol                         | 18 |

| 4.1.2 LOADTEST                              | 21 |

| 4.1.3 IFFTEST                               | 26 |

| 4.1.4 CRC Generation                        | 29 |

| 4.1.5 3 To 8 Decoder                        | 31 |

| 5. Platform                                 | 32  |

|---------------------------------------------|-----|

| 5.1 Implementation                          | 32  |

| 5.2 Overview of DS2432                      | 34  |

| 5.2.1 64-Bit Lasered Rom                    | 34  |

| 5.2.2 Memory                                | 35  |

| 5.2.3 Address Registers and Transfer Status | 35  |

| 5.2.4 Writing with Verification             | 36  |

| 5.2.5 Memory and SHA Function Commands      | 36  |

| 5.2.6 Write Scratchpad [0Fh]                | 44  |

| 5.2.7 Read Scratchpad [AAh]                 | 44  |

| 5.2.8 Load First Secret [5Ah]               | 45  |

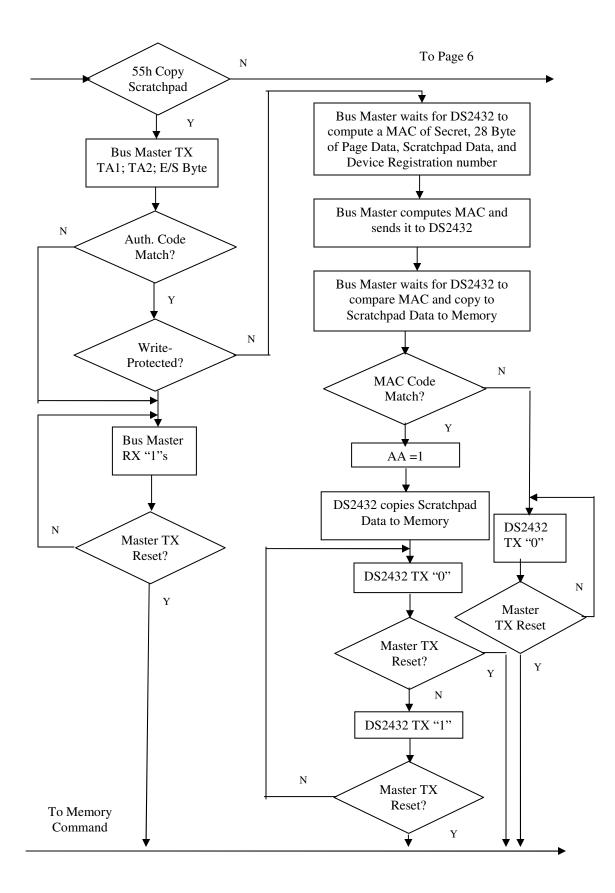

| 5.2.9 Copy Scratchpad [55h]                 | 45  |

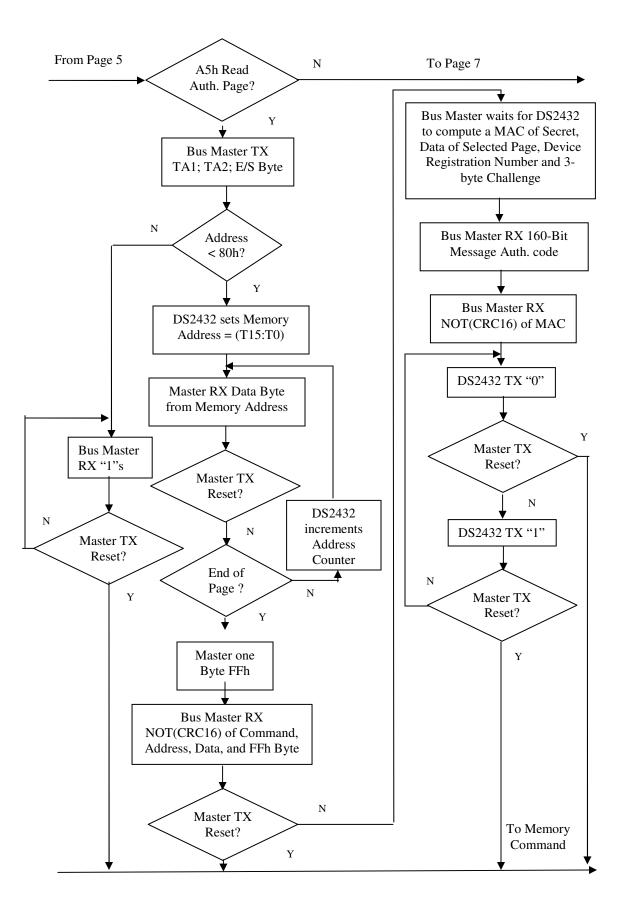

| 5.2.10 Read Authenticated Page [A5h]        | 47  |

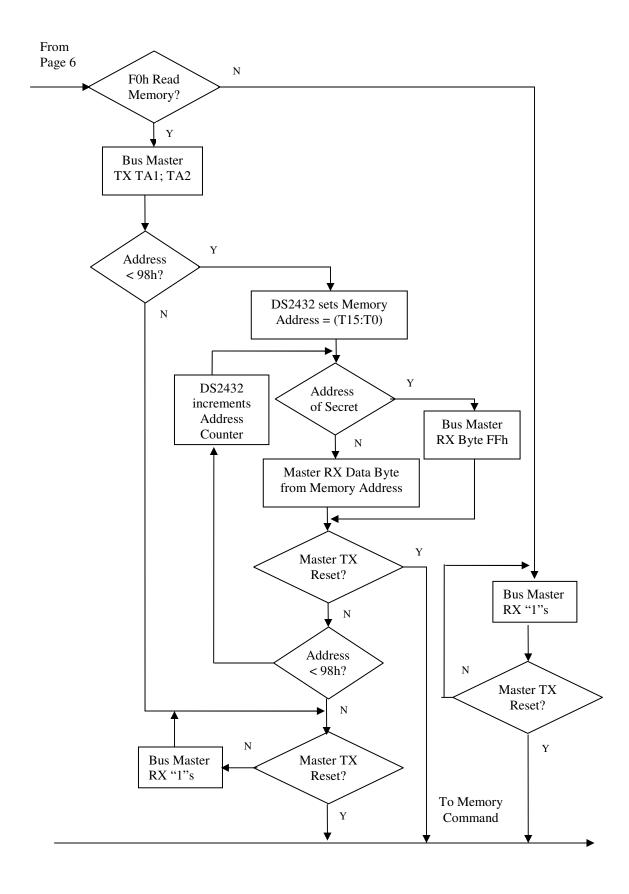

| 5.2.11 Read Memory [F0h]                    | 48  |

| 6. Source Code                              | 49  |

| 6.1 3 To 8 Decoder                          | 49  |

| 6.2 IFFTEST                                 | 50  |

| 6.3 LOADTEST                                | 61  |

| 6.4 Secure Hash Algorithm                   | 75  |

| 6.5 CRC Generation                          | 82  |

|                                             | 9.4 |

| 7. Results                                  | 84  |

| 8. Conclusion                               | 108 |

| 9. Bibliography                             | 109 |

# **Chapter 1**

### Introduction

#### **1.1 Motivation**

With the rapidly growing concerns of security in nearly every aspect of electronics system design, manufacturers and circuit designers are facing the challenges that never before existed. Companies are coming up with new technologies and ideas and countries are coming up with new devices and Weapons for Defense. With introduction of new technologies inventors are also concerned about the security of the idea they are bringing out. IP (Intellectual Property) security is becoming more and more important in today's competitive world. In the past security within electronic equipment was only faced by software related technologies, military and access control markets. This will face a change as designers will get set of new standard to meet in order to provide security.

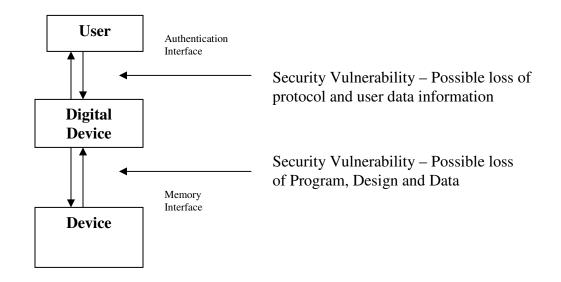

[10]In early days security was provided only at the user authentication level. This technique was sufficient to prevent the unauthorized access of the device but if the attack is at the device interface level no to access the system but to get the knowledge of complete architecture of device, algorithm used etc. This is very serious security threat from IP (intellectual property) point of view. So nowadays apart from the user authentication check device architecture information and algorithm are encrypted so as to avoid any kind of reverse engineering.

[2] The principal goal guiding the design of any encryption algorithm must be security against unauthorized attacks. However, for all practical applications, performance and the cost of implementation are also important concerns. A data encryption algorithm would not be of much use if it is secure enough but slow in performance because it is a common practice to embed encryption algorithms in other applications such as e-commerce,

banking, and online transaction processing applications. Embedding of encryption algorithms in other applications also precludes a hardware implementation, and is thus a major cause of degraded overall performance of the system.

Fig 1.1 Security Vulnerability at two difference interfaces

[1]In information security, message authentication is an essential technique to verify that received messages come from the alleged source and has not been altered. A key element of authentication schemes is the use of a message authentication code (MAC). One technique to produce a MAC is based on using a hash function and is referred' to as an HMAC. Secure Hash Algorithm 1 (SHA-I) is one of the algorithms, which has been specified for use in Internet Protocol Security (IPSEC), as the basis for an HMAC. As we shall show in the paper: it is reasonable to construct cryptographic accelerators using hardware implementations based on SHA-I hash algorithm

### **1.2 Overview**

To secure the digital applications, the IFF (Identification Friend or Foe) concept is implemented in FPGA. This architecture creates a wrapper around the FPGA based application and provides authentication interface for user design. As the wrapper doesn't allow revealing the information to the unauthenticated user, thus the FPGA is secured from unauthorized usage of the user design.

The IFF concept has been implemented using Virtex-2Pro Development Platform. This design utilizes the key management systems to secure user design on the FPGA, thus protecting its contents from discovery. The Maxim Dallas DS2432 1Kbit Protected 1-wire EEPROM with SHA-1 Engine is used to authenticate a user and establishes a secure channel to the FPGA. The communication between the DS2432 and the FPGA is through 1-wire protocol. The IFF test is designed to authenticate the system by using the knowledge of Secret key, serial number, page data, and challenge present in the FPGA. If EEPROM is valid the user design is activated, otherwise only limited functions are made operational.

The IFF test has been synthesized using Xilinx 8.1i Foundation Series and ChipScope Pro 8.1i has been used for the real time debugging and on-chip verification of FPGA at operating system speed.

#### **1.3 Thesis Organization**

Chapter 1 gives the introduction of the intention of this thesis work. Chapter 2 is about the discussion about the background of Encryption technique and brief introduction of different encryption techniques and requirement of encryption techniques. Chapter 3 is the description of Secure Hash Algorithm anf IFFTest in detail. Chapter 4 explains the functional blocks for IFF concept. Functional description consists of explanation of 1 Wire Protocol Loadtest, Ifftest, Crc Generation, 3 To 8 Decoder. Chapter 5 describes the hardware platform used for implementation of SHA algorithm which deals with the overview Of DS2432. Chapter 6 gives the selected blocks of the SHA algorithm. Chapter 7 and 8 is about the discussion and results conclusion.

### **Chapter 2**

### Background

#### 2.1 Need of Encryption

[4] Encryption is the process of obscuring information to make it unreadable without special knowledge. In cryptography, a *cipher* (or *cypher*) is an algorithm for performing encryption and decryption — a series of well-defined steps that can be followed as a procedure. Cipher is also called as *encipherment*. The concept of encryption is based on some Key value which changes the reception of data depending upon the correctness of the key.

The original in information/ message is known as plaintext and after encryption it is converted to ciphertext. As *ciphertext* is the encrypted form of the original message so it contains all the information as the original message but it can't be interpreted by a human or computer without some extra information which is called *key value*. The key value and *ciphertext* together are necessary and sufficient criteria to decrypt the plaintext.

The operation of a cipher usually depends on a piece of auxiliary information, called a key a *cryptovariable*. The encrypting procedure is varied depending on the key, which changes the detailed operation of the algorithm. A key must be selected before using a cipher to encrypt a message. Without knowledge of the key, it should be difficult, if not impossible, to decrypt the resulting *ciphertext* into readable plaintext.

### 2.2 Evolution of Encryption Techniques

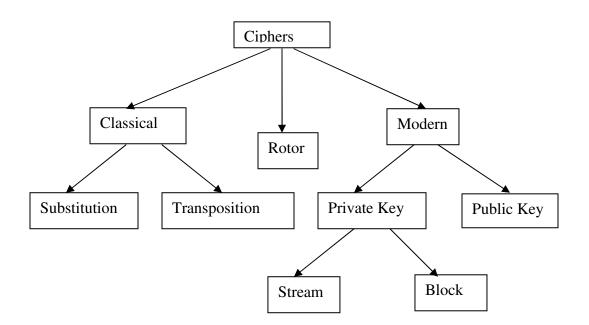

Encryption techniques can be broadly classified into two classes, tradition and modern encryption techniques. Traditional encryption techniques were developed when there were no computers, so these are pen and paper based. With the invention of computer the computer era started and encryption techniques underwent a major change and the idea of working on bits instead on alphabets was conceived.

Fig 2.1 Evolution of Encryption Techniques

[3]Chinese were the first to use the encryption concept and written language itself was used as encryption technique. Caesar Cipher is the most popular traditional encryption method which was developed by Julius Caesar between 50 and 60 BC. Principal of substitution was used, where a letter is substituted by another letter. In 1553 the idea of a password was first given by Giovan Belaso. Gilbert Vernam developed the Vernam Cipher in 1917 which is the oldest encryption technique still in use. It uses substitution where no pattern can arise.

[3]Encryption played a major role in the Second World War in 1942. Many encryption techniques came as a result of necessity of perfect encryption techniques for the information security. American military used spoken and written language as an encryption device known as Navajo windtalkers. US military used wheel Ciphers in the First World War. German government created TYPEX machine from Enigma machine and used in the Second World War.

Historical pen and paper ciphers used in the past are sometimes known as classical ciphers. They include simple substitution ciphers and transposition ciphers. For example MEENAKSHI may be encrypted as ODFMZLRIH where all the odd position alphabet is replaced by next alphabet and even position character is replaced with previous alphabet These simple ciphers are easy to crack, even without plaintext-ciphertext pairs.

With the invention of computer it became very easy to break the algorithms, which were once very difficult to solve, in a short time. Now, it was not possible to rely on pen paper techniques anymore and need for encryption techniques specific to computers re-invented the encryption field. At this time the use of bits was focused instead of written alphabets.

### **2.3 Security Threats**

[6] Attack is any malicious intent to subvert a system to defraud it. In other words attack is the intent to get access to a secure system. Few types of security are discussed here in short:

#### **Copy Attack**

Copy attack is done by copying the valid service data from a device which is part of the service to a device which is not part of the service. Purpose of this attack is to create an unauthenticated but technically valid copy of the service device to get any kind of advantage out of it.

#### **Eavesdrop Attack**

This technique is used where 1 wire communication is monitored to reveal the secret of a repeating pattern that could be replicated.

#### **Emulation Attack**

In this type of attack a microprocessor is used to emulate the behavior of a 1- Wire token. The emulator must be fast enough respond to a 1-Wre master as if it is a real device. This attack is not useful if authentication secret is not known. Risk can be further minimized by including a ROM ID as a component in the calculation.

#### Secret Brute Force Attack

The Secret Brute Force Attack tries all the possible combination until it gets the correct Service Identification code called MAC.A Token which is part of the service supplies the correct MAC. After getting the secret it can be used to try all possible options in few seconds.

#### Secret Microprobe Physical Attack

The physical attack is an attempt to probe the internal silicon chip to read the Unique Identification Secret.

### 2.2.1 Modern Encryption Techniques

**2.2.1.1 Symmetric key algorithms** (Private-key cryptography) - In a symmetric key algorithm (e.g., DES and AES), the sender and receiver must have a shared key set up in advance and kept secret from all other parties; the sender uses this key for encryption, and the receiver uses the same key for decryption.

Symmetric key ciphers can be distinguished into two types

- Block ciphers- work on blocks of symbols of fixed size

- Stream ciphers Work on a continuous stream of symbols.

**2.2.1.2** Asymmetric key algorithms (Public-key cryptography)- In an asymmetric key algorithm (e.g., RSA), there are two separate keys: a public key is published and enables any sender to perform encryption, while a private key is kept secret by the receiver and enables only him to perform decryption.

### 2.3 Requirement of Encription Techniques

Encryption Technique mush be able to provide/Ensure Integrity, Authenticity and Confidentiality of the information.

**Integrity** – It means that the receiver of data can detect any modification of the data on the way from the sender to the receiver.

Authenticity - Property that allows verifying that the data really originates from the alleged sender.

**Confidentiality** - Feature that enables the sender to transform the original data in a way that only the designated recipient can reconstruct it. No eavesdropper between sender and receiver can recover the original data.

# **Chapter 3**

### **Algorithm Description**

#### **3.1 Secure Hash Algorithm**

#### 3.1.1 Introduction of Secure Hash Algorithm

[5] SHA is a standard specified in Federal Information Publication 180-1 and 180-2 (FIPS 180-1, FIPS 180-2). The SHA series hashes are currently the only FIPS-approved method. SHA-1 is also specified in ISO/IEC 10118-3.

The Secure Hash Algorithm (SHA-1) is required for use with the Digital Signature Algorithm (DSA) as specified in the Digital Signature Standard (DSS) and whenever a secure hash algorithm is required for federal applications. For a message of length < 2^64 bits, the SHA-1 produces a 160-bit condensed representation of the message called a message digest. The message digest is used during generation of a signature for the message. The SHA-1 is also used to compute a message digest for the received version of the message during the process of verifying the signature. Any change to the message in transit will, with very high probability, result in a different message digest, and the signature will fail to verify.

#### **3.1.2 Properties of a Secure Hash Algorithm**

- 1. **Irreversibility** making it computationally infeasible to determine the input corresponding to a HASH result.

- Collision-resistance One Hash result should not produce more than one input message.

- 3. High avalanche effect Large change in Output for slight change in input.

The input bit string of length  $< 2^{64}$  is called as the *message* and the condensed output of 160 bits is called as *message digest*.

### 3.1.3 Terminology

Following terminologies related to the bit string will be used in this algorithm:

- 1. Message: The input string which can be of any length  $l < 2^{64}$ .

- 2. Message Digest: Condesed output of length 160 bits.

- 3. Word: A word is represented by a 32 bit string.

- 4. Block: A block is 512 bit string which may be represented by 16 words.

The following operations will be applied to the words:

- 1. X AND Y : Bitwise logical AND of X and Y.

- 2. X OR Y : Bitwise logical "inclusive OR" of X and Y.

- 3. X XOR Y : Bitwise logical "exclusive OR" of X and Y.

- 4. NOT X : Bitwise logical "complement " of X.

- 5.  $S^{n}(X)$  : Circular left shift of X by n positions to the left.

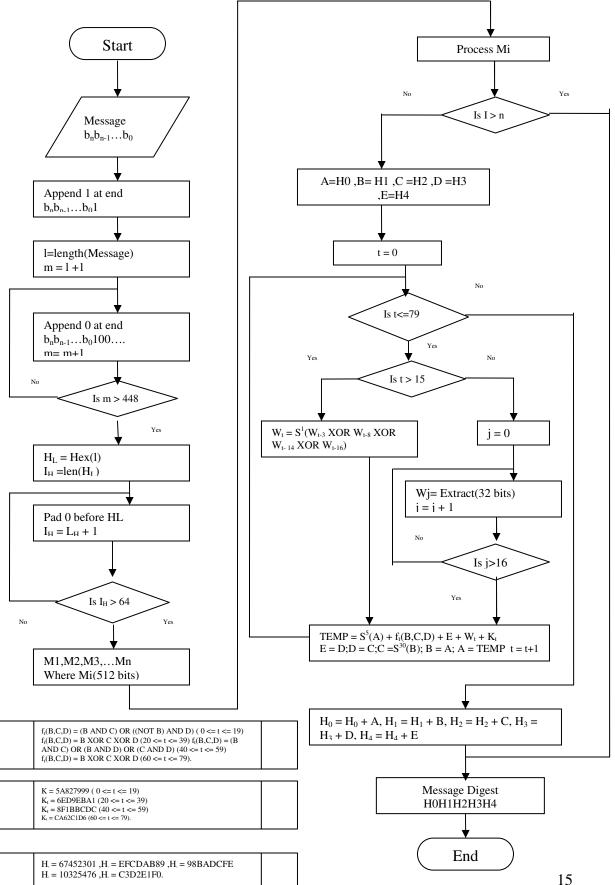

### 3.1.4 Message padding

SHA-1 computes the message digest for the input message bit string provided. The message is processed as 512 bits at a time. So message padding is done to make the length multiple of 512 bits. The SHA-1 processes the 512 bit blocks sequentially to compute the message digest of 160 bits. In this process 1 is appended at the end of the message and then enough zeros followed by 64-bit representation of the length of the original message so that the padded message is multiple of 512 bits.

The padded message can be represented as  $M_1$ ,  $M_2$ ,  $M_3$ ,..., $M_n$  where  $M_i$  is 16 words block and  $M_1$  contains the first character of the input message.

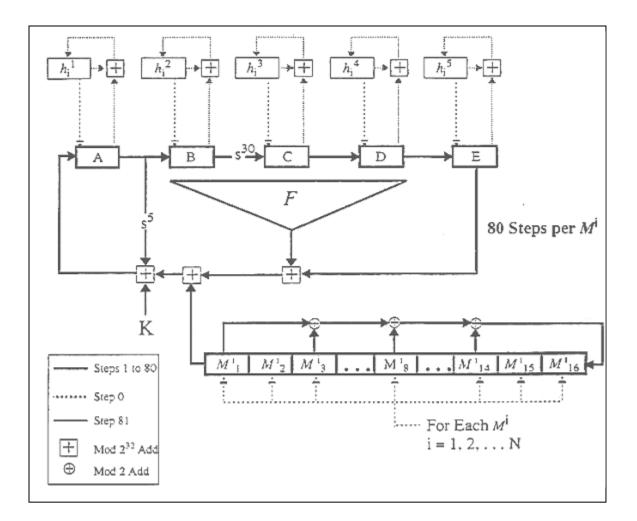

Fig 3.1 Secure Hash Algorithm

### 3.1.4 Algorithm

SHA-1 is based on a nonlinear function  $f_t$  which operates on 32-bit words B,C,D and produces a 32-bit word.  $f_t(B,C,D)$  is defined as follows:

$$f_{t}(B,C,D) = \begin{cases} (B \text{ AND C}) \text{ OR } ((\text{NOT B}) \text{ AND D}) & (0 \le t \le 19) \\ B \text{ XOR C XOR D} & (20 \le t \le 39) \\ (B \text{ AND C}) \text{ OR } (B \text{ AND D}) \text{ OR } (C \text{ AND D}) & (40 \le t \le 59) \\ B \text{ XOR C XOR D} & (60 \le t \le 79) \end{cases}$$

SHA-1 uses a sequence of constant words defined as:

$$K_{t} = \begin{cases} 0x5A827999 & (0 \le t \le 19) \\ 0x6ED9EBA1 & (20 \le t \le 39) \\ 0x8F1BBCDC & (40 \le t \le 59) \\ 0xCA62C1D6 & (60 \le t \le 79). \end{cases}$$

The 512-bit message block is broken into sixteen 32-bit words  $m_0,m_1,m_2,...,m_{15}$  which are used for the calculating the 80 words  $W_0, W_1, W_2, ..., W_{79}$  using formula :

$$W_{t} = \begin{cases} m_{t} & (0 \le t \le 15) \\ St(Wt-3 XOR Wt-8XOR Wt-14 XOR Wt-16) & (16 \le t \le 19) \end{cases}$$

In the beginning of the process five constant words are initialized as follows:

$H_0 = 0x67452301$   $H_1 = 0xEFCDAB89$   $H_2 = 0x98BADCFE$   $H_3 = 0x10325476$  $H_4 = 0xC3D2E1F0$

Before calculation starts five word variables A, B, C, D, E are initialized as:

$$A = H_0, B = H_1, C = H_2, D = H_3, E = H_4$$

SHA-1 algorithm is as follows:

For t = 0 to 79

TEMP =

$$S^5(A) + f_t(B,C,D) + E + W_t + K_t$$

;

E = D;

$$D = C;$$

$$C = S^{30}(B);$$

$$B = A;$$

$$A = TEMP$$

After all these calculations the values of H<sub>0</sub>, H<sub>1</sub>, H<sub>2</sub>, H<sub>3</sub> and H<sub>4</sub> are updated as follows

$$H_0 = H_0 + A;$$

$H_1 = H_1 + B;$

$H_2 = H_2 + C;$

$H_3 = H_3 + D;$

$H_4 = H_4 + E.$

If there are more 512-bit blocks then these are processed using the updated values of  $H_{0}$ ,  $H_{1}$ ,  $H_{2}$ ,  $H_{3}$  and  $H_{4}$ . After the processing of the last block the condensed 160-bit output, message digest, is the concatenation of the final values of  $H_{0}$ ,  $H_{1}$ ,  $H_{2}$ ,  $H_{3}$  and  $H_{4}$ :

Message digest =  $H_0H_1H_2H_3H_4$

### 3.1.5 Flow chart

### **3.2 IFFTEST Concept**

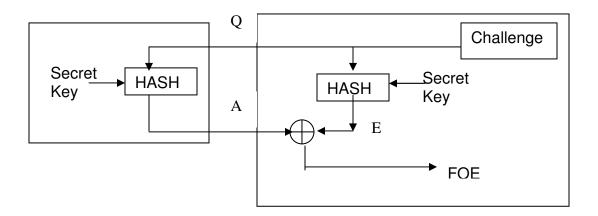

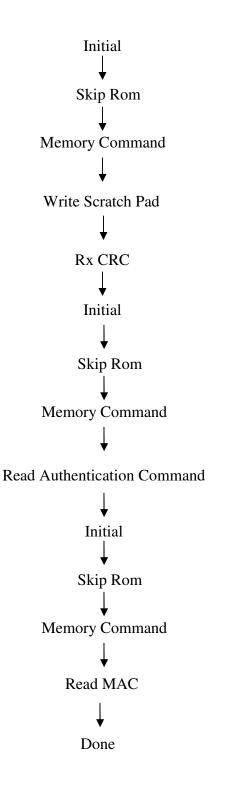

[7] Figure 3.2 shows the IFF concept. The following steps describe the concept of the Identification as Friend and Foe test for the authentication of the Secure EEPROM DS2432:

- 1. FPGA sends a Challenge 'Q' to DS2432.

- 2. The DS2432 uses a secret key programmed by the designer which is known only to the designer and SHA engine generates a 512-bit MAC, the actual response 'A' for the Challenge 'Q'.

Fig. 3.2 Identification Friend and Foe

- 3. The FPGA calculates the MAC, the expected response 'E' using the same key and compares it with the actual response A, produced by the DS2432.

- 4. Now expected and actual response is matched to determine whether the design is Friend or Foe. If it matches design is Friend, otherwise the design is Foe. It may occur because of the tampering.

5. FPGA application is designed in such a way that if design is detected as Foe, then either application does not operate or it operates with limited functionality. If the design is detected as Friend then it operates correctly and all features are operational.

# **Chapter 4**

# Architecture

### 4.1 Functional Blocks

The design includes six functional blocks:

- 1. **1-wire Protocol**: For the interfacing of EEPROM with the FPGA.

- 2. **IFFTEST**: To authenticate the user design in FPGA using EEPROM and the secret key written in the FPGA.

- 3. **LOADTEST**: To load the secret key in the EEPROM. It is not included in the user design.

- 4. **SHA (Secure Hash Algorithm)**: To generate unique 160-bit message digest using 512-bits as input.

- 5. **3 to 8 decoder**: It converts the decimal number from 0 to 7 into the binary equivalent. It is designed only for demonstration purpose.

- 6. **CRC** (**Cyclic Redundancy Check**): To determine whether the ROM data has been read without error or not.

# 4.1.1 Wire Protocol

[8] The DS2432 uses 1-wire protocol to communicate with host on single line. It consists of following type of signaling:

- Reset Sequence with Reset Pulse and Presence Pulse

- Write 0

- Write 1

- Read Data.

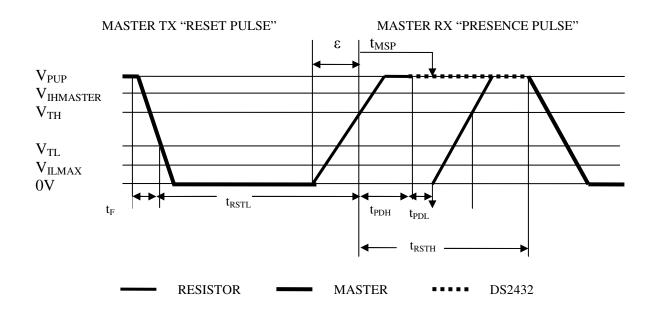

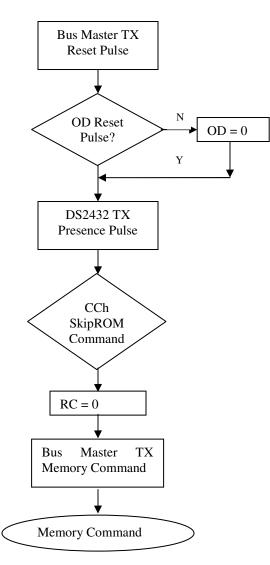

All these signals are initiated by the bus master except the presence pulse. The Fig. 4.1 shows the initialization process. DS2432 receives data when a reset pulse is followed by the Presence Pulse. If the device is in Overdrive mode then  $t_{RSTL}$  is less than 80µs and if

$t_{RSTL}$  is longer than 480µs it operates on standard speed. Speed is undetermined if  $t_{RSTL}$  is between 80µs and 480µs.

Once the bus master has released the line it goes into the receive mode. The pullup resistor pulls the 1-wire bus to  $V_{PUP}$ . The DS2432 waits for the  $t_{PDH}$  after the threshold  $V_{TH}$  is crossed and then transmits a Presence Pulse for  $t_{PDL}$  by pulling the line low.

Fig. 4.1 Initialization Procedure: Reset and Presence Pulse

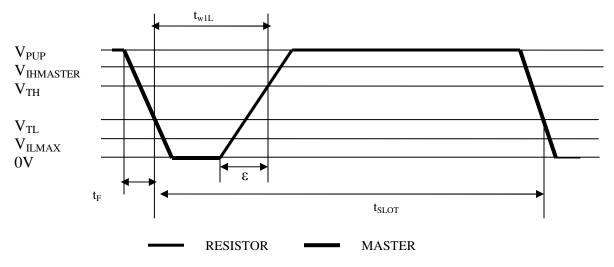

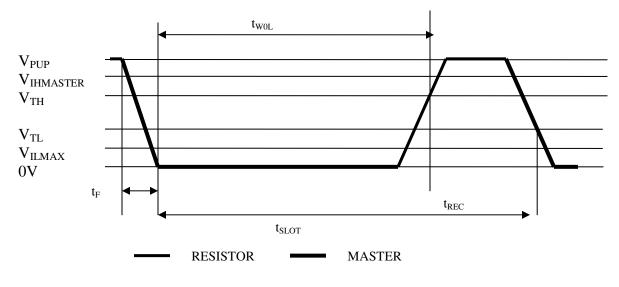

During data communication with DS2432 each time slot carries a single bit. During the Write time slots data is transferred from bus master to slave and during Read time slots data transfer takes place from slave to master. Master pulls the data line low to start communication. DS2432 starts its internal timing generator, when voltage on 1-Wire line falls below threshold  $V_{TH}$ , to determine when to sample the data line during a write time slot and how data is valid during Read time slot.

Fig. 4.3 Write-Zero Time Slot

In the Fig 4.2 write-One time slot the voltage on data line should cross the  $V_{TH}$  before expiration of write one low time  $t_{W1LMAX}$ . In the Fig. 4.3 write-zero time slot the voltage on data line should stay below  $V_{TH}$  before expiration of write one low time  $t_{W0LMIN}$ .

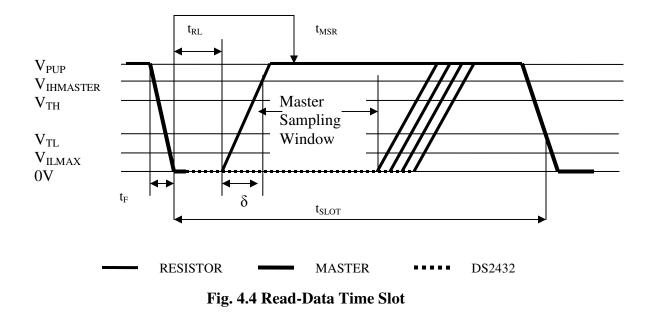

During the Read time slot (Fig 4.4) the data line voltage should remain low till expiration of read time low time  $t_{RL}$ . While responding to 0, the DS2432 pulls the data line low and its internal timing generator will determine when this pull down ends and the voltage starts rising again. While responding to 1, the voltage will rise again when  $t_{RL}$  is over.

The master should wait for  $t_{SLOT}$  to expire after reading from the data line. It ensures the recovery for DS2432 to start next time slot.

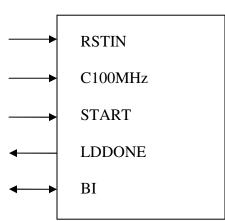

#### 4.1.2 LOADTEST

Loading of the key into the DS2432 device is done using the LOADTEST design. The 64-bit Secret key is loaded in a very secure environment and it is protected from the leakage of information. LOADTEST is not included in the final user design. The figure 4.5 shows the instantiation block diagram of the LOADTEST design. The inputs to the LODATEST design are:

- C100MHz: The available clock of 100MHz is used as input and it is divided by 100 to get the 1MHz frequency. It is done to met the timing specifications of the DS2432.

- 2. RSTIN: An active-Low RSTIN signal is provided for the initialization of the design process.

- 3. START: Start signal initiates the loading process of the Secret Key. It's an active-High signal.

- 4. BI: BI is single wire interface between the DS2432 and the FPGA. All communication between the two devices is possible through this signal only.

- 5. LDDONE: This signal shows the status of the LOADTEST design. This signal will be high only if the key is loaded successfully, otherwise it remains low. It's an active high signal.

LOADTEST

Fig. 4.5 LOADTEST Instantiation Block Diagram

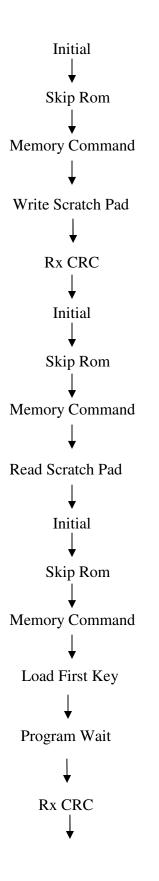

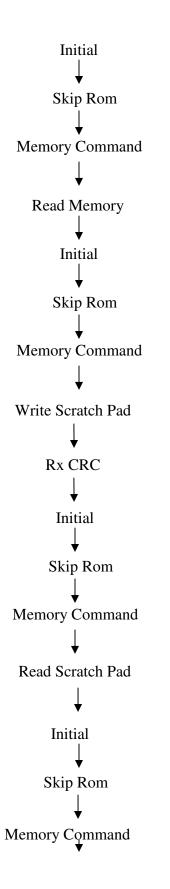

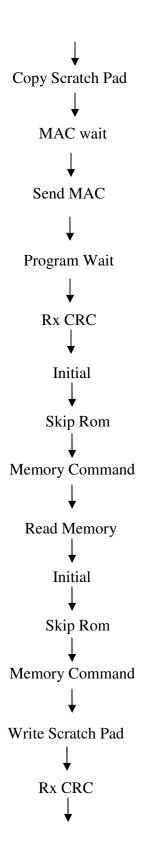

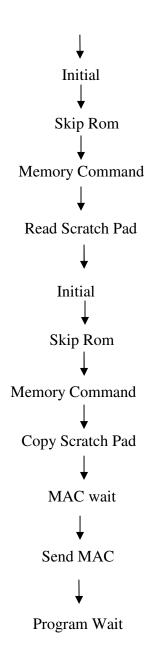

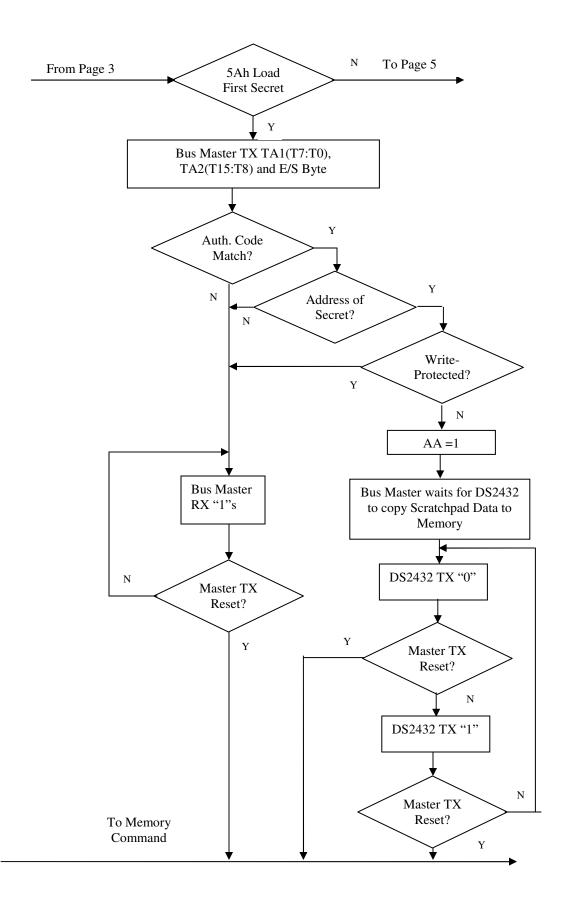

The Fig. 4.6 shows the data flow of the LOADTEST design.

Fig. 4.6 Load Test Flow diagram

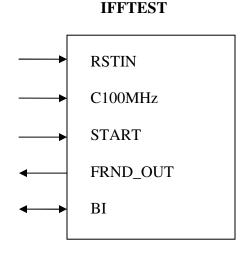

#### **4.1.3 IFFTEST**

IFFTEST is designed as a part of user design to authenticate the system. The DS2432 is used as the platform for the IFFTEST. The MAXIM-DALLAS DS2432 consists of a 64-bit secret key which can be rewritten by the user but can't be read back from the external interface. The DS2432 also consists a 64-bit serial number which is unique to all device,

no two devices can have same serial number. IFFTEST is designed in such a way that the user design is deactivated on power on. Upon power on the IFFTEST authenticate the system by using the knowledge of Secret key, serial number, page data, and challenge present in the FPGA. If EEPROM is valid the user design is activated, otherwise only limited functions are made operational. The Fig. 4.7 shows the instantiation block diagram of the IFFTEST design. The inputs to the IFFTEST design are:

- C100MHz: The available clock of 100MHz is used as input and it is divided by 100 to get the 1MHz frequency. It is done to met the timing specifications of the DS2432.

- RSTIN: An active-Low RSTIN signal is provided for the initialization of the design process.

- START: START signal initiates the authentication process of the DS2432, the Secret EEPROM device. It's an active-High signal.

- FRND\_OUT: This signal shows the status of the IFFTEST design. This signal will be high only if the secret EEPROM device is Friend i.e. authenticated and its low if the system integrity is altered.

- 5. BI: BI is single wire interface between the DS2432 and the FPGA. All communication between the two devices is possible through this signal only.

### Fig. 4.7 IFFTEST instantiation Block Diagram

The Fig. 4.8 describes the process of EEPROM authentication.

Fig. 4.8 IFF Test Flow diagram

### 4.1.4 CRC Generation

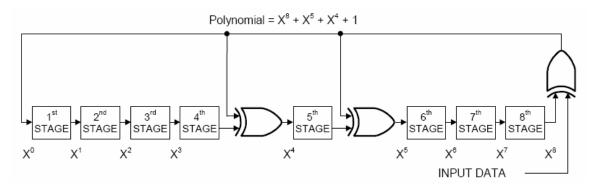

With the DS2432 there are two different types of CRCs (Cyclic Redundancy Checks). One CRC is an 8-bit type. It is computed at the factory and lasered into the most significant byte of the 64-bit ROM. The equivalent polynomial function of this CRC is  $X^8 + X^5 + X^4 + 1$ . To determine whether the ROM data has been read without error the bus master can compute the CRC value from the first 56 bits of the 64-bit ROM and compare it to the value read from the DS2432. This 8-bit CRC is received in the true form (non-inverted) when reading the ROM.

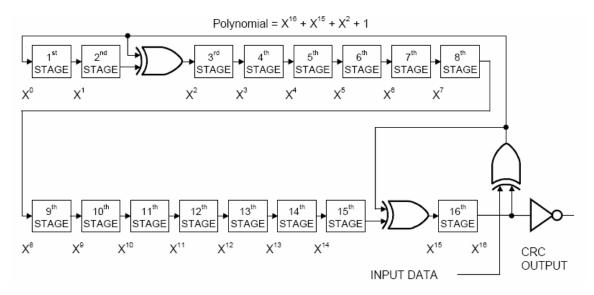

The other CRC is a 16-bit type, generated according to the standardized CRC16polynomial function  $X^{16} + X^{15} + X^2 + 1$ . This CRC is used for error detection with the Read Authenticated Page command, when reading the scratchpad and for fast verification of a data transfer when writing to the scratchpad. In contrast to the 8-bit CRC, the 16-bit CRC is always communicated in the inverted form. A CRC-generator inside the DS2432 chip calculates a new 16-bit CRC as shown in the command flow chart of Fig. 4.9 . The bus master may compare the CRC value read from the device to the one it calculates from the data and decide whether to continue with an operation or to re-read the portion of the data with the CRC error.

With the Write Scratchpad command the CRC is generated by first clearing the CRC generator and then shifting in the command code, the Target Addresses TA1 (with T2 to T0 set to 0) and TA2, and all data bytes as sent by the master. The DS2432 transmits this CRC only if the master has sent exactly eight bytes.

With the Read Scratchpad command the CRC is generated by first clearing the CRC generator and then shifting in the command code, the Target Addresses TA1 and TA2, the E/S byte, and the scratchpad data, which may have been modified by the DS2432.

The DS2432 will transmit this CRC only if the reading continues through the end of the scratchpad.

With the Read Authenticated Page command the 16-bit CRC value is the result of shifting the command byte into the cleared CRC generator, followed by the two address bytes, the data bytes, and the FFh byte. The CRC that follows the Message Authentication Code (MAC) results from clearing the CRC generator and then shifting in the 160-bit MAC in the same bit sequence as the master receives it.

Fig. 4.9 CRC-8 Hardware Description and Polynomial

Fig. 4.10 CRC-16 Hardware Description and Polynomial

### 4.1.5 3 to 8 Decoder

3 to 8 decoder has been implemented for the verification of the design. This functional block is the main application which is to be protected from the security attacks. This application is executed only when it is authenticated against the secure EEPROM DS2432. 3 to 8 decoder converts the decimal numbers from 0 to 7 into their equivalent binary value.

# Chapter 5

# Platform

## **5.1 Implementation**

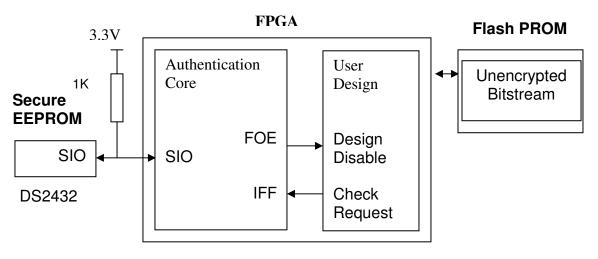

We have used DALLAS Semiconductor/ MAXIM DS2432 1KBit protected 1-Wire secure EEPROM with SHA Engine and VIRTEX-2PRO P4 development kit to implement the IFF concept.

The features of the DS2432 secure EEPROM include:

- 1. 64-bit read-only unique serial number (no two devices share the same ID).

- 2. 64-bit write-only secret key that can be rewritten at any time, but there is no way of reading it back.

- 3. Four 256-bit pages that can be write protected.

- 4. Five general purpose read/write registers.

- On-chip 512-bit SHA-1(ISO/IEC 10118-3) engine to compute 160-bit Message Authentication Codes (MAC)

- 6. Serial 1 wire interface for low pin count.

- 7. Reads and writes over a wide voltage range of 2.8V to 5.25V from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

The 1-wire PROTOCOL is implemented for interfacing FPGA and the secure EEPROM. LOADTEST loads the secret key into the EEPROM and its not included in the final user design. IFFTEST authenticates the EEPROM .It enables the design only when FPGA contains the valid key otherwise, the design is disabled. A 3 to 8 decoder is implemented for the verification purpose.

Fig. 5.1 DS2432 Secure EEPROM Connectivity to XILINX FPGA

The Fig 5.1 shows the connectivity diagram between the DS2432 secure EEPROM and FPGA to implement the copy protection scheme. First, the FPGA configures itself from a flash PROM. When the FPGA is configured, the user design is automatically disabled until it authenticates with the secure EEPROM using a secret key that is stored in the FPGA against the stored encrypted key in the secure EEPROM.

### 5.2 Overview of DS2432

[8] The DS2432 has five main data components:

- 1) 64-bit lasered ROM,

- 2) 64-bit scratchpad,

- 3) four 32-byte pages of EEPROM,

- 4) 64-bit register page,

- 5) 64-bit Secrets Memory, and

- 6) a 512-bit SHA-1 Engine

The bus master must first provide one of the seven ROM Function Commands:

- 1) Read ROM,

- 2) Match ROM,

- 3) Search ROM,

- 4) Skip ROM,

- 5) Resume Communication,

- 6) Overdrive-Skip ROM

- 7) Overdrive-Match ROM.

The protocol required for these ROM function commands is described in *Figure*. After a ROM function command is successfully executed, the memory and SHA-1 functions become accessible and the master can provide any one of the seven available function commands. The protocol for these memory function commands is described in *Figure*. All data is read and written least significant bit first.

#### 5.2.1 64-BIT LASERED ROM

Each DS2432 contains a unique ROM code that is 64 bits long. The first eight bits are a 1-Wire family code. The next 48 bits are a unique serial number. The last eight bits are a CRC of the first 56 bits. The 1-Wire CRC is generated using a polynomial generator consisting of a shift register and XOR gates as shown in *Figure*. The polynomial is  $X_8 + X_5 + X_4 + 1$ . The shift register bits are initialized to zero. Then starting with the least

significant bit of the family code, one bit at a time is shifted in. After the 8th bit of the family code has been entered, then the serial number is entered. After the 48th bit of the serial number has been entered, the shift register contains the CRC value. Shifting in the eight bits of CRC should return the shift register to all zeros.

#### 5.2.2 Memory

The DS2432 has four memory areas: data memory, secrets memory, register page with special function registers and user-bytes, and a scratchpad. The data memory is organized in pages of 32 bytes. Secret, register page and scratchpad are 8 bytes each. The scratchpad acts as a buffer when writing to the data memory, loading the initial secret or when writing to the register page.

The data memory and the register page have unrestricted read access. Writing to the data memory and the register page requires the knowledge of the secret .The secret can be installed either by copying data from the scratchpad to the secrets memory The secret cannot be read directly; only the SHA engine has access to it for computing message authentication codes.

#### 5.2.3 Address Registers and Transfer Status

The DS2432 employs three address registers: TA1, TA2 and E/S DS2432. Registers TA1 and TA2 must be loaded with the target address to which the data will be written or from which data will be read. Register E/S is a read-only transfer-status register, used to verify data integrity with write commands. Since the scratchpad of the DS2432 is designed to accept data in blocks of eight bytes only, the lower three bits of TA1 will be forced to 0 and the lower three bits of the E/S register (Ending Offset) will always read 1. This indicates that all the data in the scratchpad will be used for a subsequent copying into main memory or secret. is not an integer multiple of 8 or if the data in the scratchpad is not valid due to a loss of power. A valid write to the scratchpad will clear the PF bit. Bits 3, 4 and 6 have no function; they always read 1. The Partial Flag supports the master checking the data integrity after a Write command.

#### 5.2.4 Writing With Verification

To write data to the DS2432, the scratchpad has to be used as intermediate storage. First the master issues the Write Scratchpad command to specify the desired target address, followed by memory when commanded; therefore eight bytes of data should be written into the scratchpad to ensure that the data to be copied is known. Under certain conditions the master will receive an inverted CRC16 of the command, address and data at the end of the write scratchpad command sequence. Knowing this CRC value, the master can compare it to the value it has calculated itself to decide if the communication was successful and proceed to the Copy Scratchpad command. If the master could not receive the CRC16, it should send the Read Scratchpad command to verify data integrity. As preamble to the scratchpad data, the DS2432 repeats the target address TA1 and TA2 and sends the contents of the E/S register. If the PF flag is set, data did not arrive correctly in the scratchpad or there was a loss of power since data was last written to the scratchpad. The master does not need to continue reading; it can start a new trial to write data to the scratchpad. Similarly, a set AA flag together with a cleared PF flag indicates that the device did not recognize the Write command. If everything went correctly, both flags are cleared. Now the master can continue reading and verifying every data byte. After the master has verified the data, it can send the Copy Scratchpad command.

#### **5.2.5 Memory and SHA Function Commands**

The "Memory and SHA Function Flow Chart" (Fig. 5.2) describes the protocols necessary for accessing the memory and operating the SHA engine.

Fig 5.2 Memory and SHA Function Flow Chart

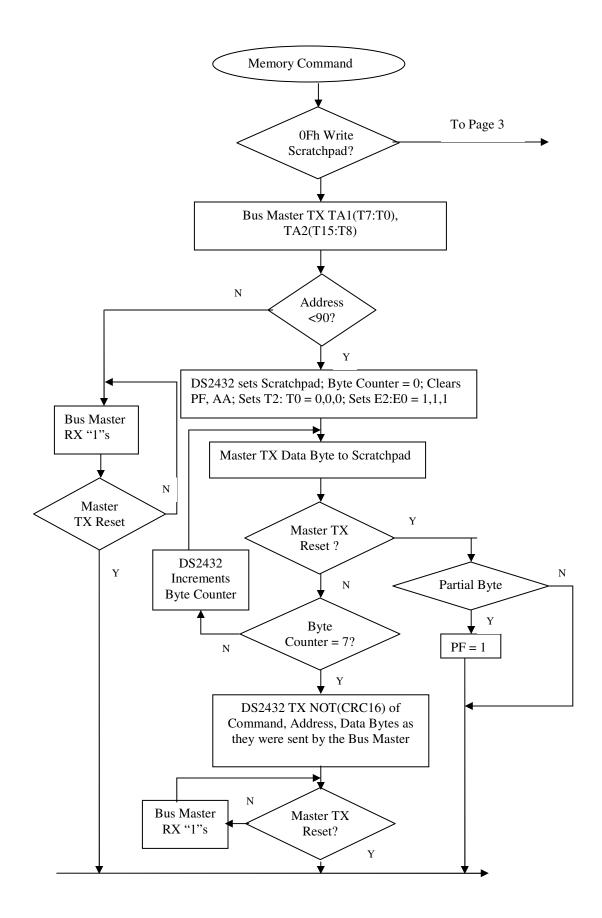

#### 5.2.6 Write Scratchpad [0Fh]

The Write Scratchpad command applies to the data memory, the secret and the writable addresses in the register page. If the bus master sends a target address higher than 90h, the command will not be executed. After issuing the write scratchpad command, the master must first provide the 2-byte target address, followed by the data to be written to the scratchpad. The data will be written to the scratchpad starting at the beginning of the scratchpad. the master should always send 8 bytes, especially if the data is to be loaded as a secret. If the master sends less than eight data bytes and does not read back the scratchpad for verification, parts of the new secret may be random data that is unknown to the master. Only full data bytes are accepted. If the last data byte is incomplete its content will be ignored and the partial byte flag PF will be set.

When executing the Write Scratchpad command the CRC generator inside the DS2432 (Figure) calculates a CRC of the entire data stream, starting at the command code and ending at the last data byte as sent by the master. This CRC is generated using the CRC16 polynomial by first clearing the CRC generator and then shifting in the command code (0FH) of the Write Scratchpad command, the Target Addresses (TA1 and TA2), and all the data bytes. The master may end the Write Scratchpad command at any time. However, if the scratchpad is filled to its capacity, the master may send 16 read time slots and will receive the CRC generated by the DS2432.

#### 5.2.7 Read Scratchpad [AAh]

The Read Scratchpad command allows verifying the target address and the integrity of the scratchpad data. After issuing the command code, the master begins reading. The first two bytes will be the target address with T2 to T0 = 0. The next byte will be the ending offset/data status byte (E/S) followed by the scratchpad data, which may be different from what the master has originally sent. This is of particular importance if the target address is the secret, the register page or page 1 in EPROM mode. The master should read through the end of the scratchpad after which it will receive the inverted CRC. This

is based on data as it was sent by the DS2432. If the master continues reading after the CRC all data will be logic 1's.

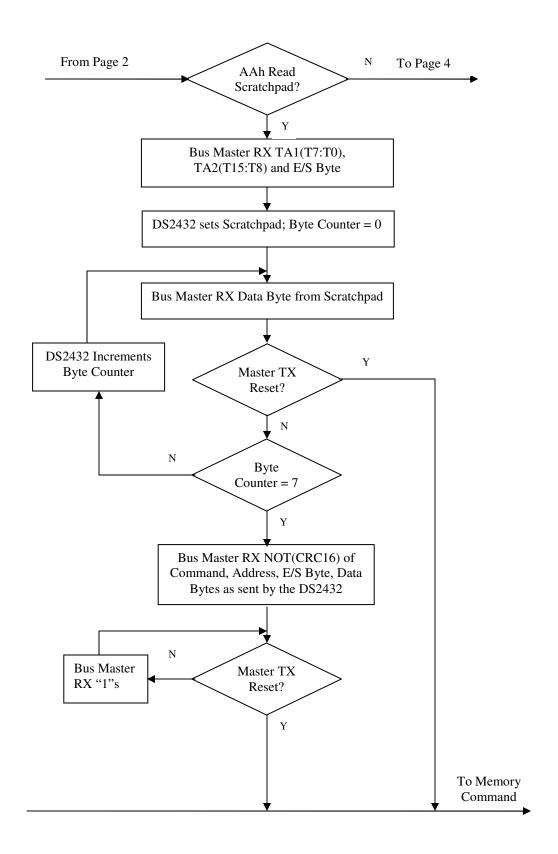

#### 5.2.8 Load First Secret [5Ah]

The Load First Secret command is used to replace the device's current secret with the contents of the scratchpad, provided that the secret is not write-protected. This command does not require the knowledge of the device's current secret. Before the Load First Secret command can be used the master must have written the new secret to the scratchpad using the starting address of the secret (0080h). After issuing the Load First Secret command, the master must provide a 3-byte authorization pattern, which should have been obtained by an immediately preceding Read Scratchpad command. This 3-byte pattern must exactly match the data contained in the three address registers (TA1, TA2, E/S, in that order). If the pattern matches and the secret is not write-protected, the AA (Authorization Accepted) flag will be set and the copy will begin. All eight bytes of scratchpad contents will be copied to the secret's memory location. Reading AAh indicates that the copy was successful, while reading FFh indicates that the copy was not successful.

#### 5.2.9 Copy Scratchpad [55h]

The data memory of the DS2432 can be read without any restrictions. Executing the Copy Scratchpad command to write new data to the memory or register page requires the knowledge of the device's secret and the ability to perform a SHA-1 computation to generate the 160-bit Message Authentication Code (MAC) to start the data transfer from the scratchpad to the memory. Table 5.1 Show how the various data components are entered into the SHA engine.

After issuing the Copy Scratchpad command, the master must provide a 3-byte authorization pattern, which should have been obtained by an immediately preceding Read Scratchpad command. If the authorization code matches and the target memory is

not write-protected, the DS2432 will start its SHA engine to compute a 160-bit MAC that is based on the current secret, all of the scratchpad data, the first 28 bytes of the addressed memory page, and the DS2432's registration number (without the CRC). Simultaneously the master computes a MAC from the same data and sends it to the DS2432 as evidence that it is authorized to write to the EEPROM. If the MAC generated by the DS2432 matches the MAC that the master computed, the DS2432 will set its AA (Authorization Accepted) flag, and copy the entire scratchpad contents to the data EEPROM. As indication for a successful copy the master will be able to read a pattern of alternating 1's and 0's until it issues a Reset Pulse. A pattern of all zeros tells the master

| M0[31:24] = (SS + 0)  | M0[23:16] = (SS + 1)  | M0[15:8] = (SS + 2)  | M0[7:0] = (SS + 3)  |

|-----------------------|-----------------------|----------------------|---------------------|

| M1[31:24] = (PP + 0)  | M1[23:16] = (PP + 1)  | M1[15:8] = (PP + 2)  | M1[7:0] = (PP + 3)  |

| M2[31:24] = (PP + 4)  | M2[23:16] = (PP + 5)  | M2[15:8] = (PP + 6)  | M2[7:0] = (PP + 7)  |

| M3[31:24] = (PP + 8)  | M3[23:16] = (PP + 9)  | M3[15:8] = (PP + 10) | M3[7:0] = (PP + 11) |

| M4[31:24] = (PP + 12) | M4[23:16] = (PP + 13) | M4[15:8] = (PP + 14) | M4[7:0] = (PP + 15) |

| M5[31:24] = (PP + 16) | M5[23:16] = (PP + 17) | M5[15:8] = (PP + 18) | M5[7:0] = (PP + 19) |

| M6[31:24] = (PP + 20) | M6[23:16] = (PP + 21) | M6[15:8] = (PP + 22) | M6[7:0] = (PP + 23) |

| M7[31:24] = (PP + 24) | M7[23:16] = (PP + 25) | M7[15:8] = (PP + 26) | M7[7:0] = (PP + 27) |

| M8[31:24] = (SP + 0)  | M8[23:16] = (SP + 1)  | M8[15:8] = (SP + 2)  | M8[7:0] = (SP + 3)  |

| M9[31:24] = (SP + 4)  | M9[23:16] = (SP + 5)  | M9[15:8] = (SP + 6)  | M9[7:0] = (SP + 7)  |

| M10[31:24] = MP       | M10[23:16] = (RN + 0) | M10[15:8] = (RN + 1) | M10[7:0] = (RN + 2) |

| M11[31:24] = (RN + 3) | M11[23:16] = (RN + 4) | M11[15:8] = (RN + 5) | M11[7:0] = (RN + 6) |

| M12[31:24] = (SS + 4) | M12[23:16] = (SS + 5) | M12[15:8] = (SS + 6) | M12[7:0] = (SS + 7) |

| M13[31:24] = FFh      | M13[23:16] = FFh      | M13[15:8] = FFh      | M13[7:0] = 80h      |

| M14[31:24] = 00h      | M14[23:16] = 00h      | M14[15:8] = 00h      | M14[7:0] = 00h      |

| M15[31:24] = 00h      | M15[23:16] = 00h      | M15[15:8] = 01h      | M15[7:0] = B8h      |

that the copy did not take place.

### Table 5.1 SHA-1 Input for Copy Scratchpad to a Data Memory Page

| Mt       | Input Buffer of SHA Engine; 0 <= t <= 15; 32-Bit Words             |

|----------|--------------------------------------------------------------------|

| (SS + N) | Byte N of Secret; Secret Begins at Address 80h                     |

| (PP + N) | Byte N of Memory Page; Memory Pages Begin at 00h, 20h, 40h and 60h |

| (SP + N) | Byte N of Scratchpad                                               |

| MP       | MP[7:4] = 0000b, MP[3:0] = T8:T5                                   |

| (RN + N) | Byte N of Registration Number                                      |

| (RP + N) | Byte N of Register Page; Page Begins at 88h                        |

|          | RP + 8 to RP + 15 is the location of the Registration Number.      |

Table 5.2 : Legends

Special attention is required when copying data to the register page. In order to prevent unintentional locking of a special function register or user byte it is recommended to first read the register page and then write it all with the intended modification to the scratchpad.

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |                       |                      |                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|----------------------|----------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | M0[31:24] = (SS + 0)  | M0[23:16] = (SS + 1)  | M0[15:8] = (SS + 2)  | M0[7:0] = (SS + 3)   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M1[31:24] = (SS + 0)  | M1[23:16] = (SS + 1)  | M1[15:8] = (SS + 2)  | M1[31:24] = (SS + 0) |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M2[31:24] = (SP + 4)  | M2[23:16] = (SP + 5)  | M2[15:8] = (SP + 6)  | M2[7:0] = (SP + 7)   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | M3[31:24] = (RP + 0)  | M3[23:16] = (RP + 1)  | M3[15:8] = (RP + 2)  | M3[7:0] = (RP + 3)   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M4[31:24] = (RP + 4)  | M4[23:16] = (RP + 5)  | M4[15:8] = (RP + 6)  | M4[7:0] = (RP + 7)   |

| M7[31:24] = FFh $M7[23:16] = FFh$ $M7[15:8] = FFh$ $M7[7:0] = FFh$ $M8[31:24] = (SP + 0)$ $M8[23:16] = (SP + 1)$ $M8[15:8] = (SP + 2)$ $M8[7:0] = (SP + 3)$ $M9[31:24] = (SP + 4)$ $M9[23:16] = (SP + 5)$ $M9[15:8] = (SP + 6)$ $M9[7:0] = (SP + 7)$ $M10[31:24] = MP$ $M10[23:16] = (RN + 0)$ $M10[15:8] = (RN + 1)$ $M10[7:0] = (RN + 2)$ $M11[31:24] = (RN + 3)$ $M11[23:16] = (RN + 4)$ $M11[15:8] = (RN + 5)$ $M11[7:0] = (RN + 6)$ $M12[31:24] = (SS + 4)$ $M12[23:16] = (SS + 5)$ $M12[15:8] = (SS + 6)$ $M12[7:0] = (SS + 7)$ | M5[31:24] = (RP + 8)  | M5[23:16] = (RP + 9)  | M5[15:8] = (RP + 10) | M5[7:0] = (RP + 11)  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | M6[31:24] = (RP + 12) | M6[23:16] = (RP + 13) | M6[15:8] = (RP + 14) | M6[7:0] = (RP + 15)  |

| M9[31:24] = (SP + 4) $M9[23:16] = (SP + 5)$ $M9[15:8] = (SP + 6)$ $M9[7:0] = (SP + 7)$ $M10[31:24] = MP$ $M10[23:16] = (RN + 0)$ $M10[15:8] = (RN + 1)$ $M10[7:0] = (RN + 2)$ $M11[31:24] = (RN + 3)$ $M11[23:16] = (RN + 4)$ $M11[15:8] = (RN + 5)$ $M11[7:0] = (RN + 6)$ $M12[31:24] = (SS + 4)$ $M12[23:16] = (SS + 5)$ $M12[15:8] = (SS + 6)$ $M12[7:0] = (SS + 7)$                                                                                                                                                               | M7[31:24] = FFh       | M7[23:16] = FFh       | M7[15:8] = FFh       | M7[7:0] = FFh        |

| M10[31:24] = MP $M10[23:16] = (RN + 0)$ $M10[15:8] = (RN + 1)$ $M10[7:0] = (RN + 2)$ $M11[31:24] = (RN + 3)$ $M11[23:16] = (RN + 4)$ $M11[15:8] = (RN + 5)$ $M11[7:0] = (RN + 6)$ $M12[31:24] = (SS + 4)$ $M12[23:16] = (SS + 5)$ $M12[15:8] = (SS + 6)$ $M12[7:0] = (SS + 7)$                                                                                                                                                                                                                                                        | M8[31:24] = (SP + 0)  | M8[23:16] = (SP + 1)  | M8[15:8] = (SP + 2)  | M8[7:0] = (SP + 3)   |

| M11[31:24] = (RN + 3) $M11[23:16] = (RN + 4)$ $M11[15:8] = (RN + 5)$ $M11[7:0] = (RN + 6)$ $M12[31:24] = (SS + 4)$ $M12[23:16] = (SS + 5)$ $M12[15:8] = (SS + 6)$ $M12[7:0] = (SS + 7)$                                                                                                                                                                                                                                                                                                                                               | M9[31:24] = (SP + 4)  | M9[23:16] = (SP + 5)  | M9[15:8] = (SP + 6)  | M9[7:0] = (SP + 7)   |

| $M12[31:24] = (SS + 4) \qquad M12[23:16] = (SS + 5) \qquad M12[15:8] = (SS + 6) \qquad M12[7:0] = (SS + 7)$                                                                                                                                                                                                                                                                                                                                                                                                                           | M10[31:24] = MP       | M10[23:16] = (RN + 0) | M10[15:8] = (RN + 1) | M10[7:0] = (RN + 2)  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | M11[31:24] = (RN + 3) | M11[23:16] = (RN + 4) | M11[15:8] = (RN + 5) | M11[7:0] = (RN + 6)  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | M12[31:24] = (SS + 4) | M12[23:16] = (SS + 5) | M12[15:8] = (SS + 6) | M12[7:0] = (SS + 7)  |

| M13[31:24] = FFh $M13[23:16] = FFh$ $M13[15:8] = FFh$ $M13[7:0] = 80h$                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M13[31:24] = FFh      | M13[23:16] = FFh      | M13[15:8] = FFh      | M13[7:0] = 80h       |

| $M14[31:24] = 00h \qquad M14[23:16] = 00h \qquad M14[15:8] = 00h \qquad M14[7:0] = 00h$                                                                                                                                                                                                                                                                                                                                                                                                                                               | M14[31:24] = 00h      | M14[23:16] = 00h      | M14[15:8] = 00h      | M14[7:0] = 00h       |

| $M15[31:24] = 00h \qquad M15[23:16] = 00h \qquad M15[15:8] = 01h \qquad M15[7:0] = B8h$                                                                                                                                                                                                                                                                                                                                                                                                                                               | M15[31:24] = 00h      | M15[23:16] = 00h      | M15[15:8] = 01h      | M15[7:0] = B8h       |

#### Table 5.3 SHA-1 Input for Copy Scratchpad to the Register Page

#### 5.2.10 Read Authenticated Page [A5h]

The Read Authenticated Page command provides the master with the data of a full or partial memory page plus a message authentication code (MAC). The MAC allows the master to determine whether the secret stored in the DS2432 is valid within the application. The DS2432 computes the MAC from its secret, all the data of the selected memory page, its registration number and a 3-byte challenge, which the master should write to the scratchpad prior to issuing the Read Authenticated Page command. The data input to the SHA engine as it applies to the Read Authenticated Page command is shown in Table 5.4. After the master has issued the command code and specified a valid target address it will receive the page data beginning at the target address through the end of the data page, one byte FFh and the inverted CRC of the command code, target address, transmitted page data and FFh byte. During this time the SHA engine of the DS2432

computes the message authentication code over the secret, all 32 data bytes of the selected page, the device's registration number (without the CRC) and the 3-byte challenge. Now the master reads the 160-bit MAC, which is followed by an inverted CRC.

| M0[31:24] = (SS + 0)  | M0[23:16] = (SS + 1)  | M0[15:8] = (SS + 2)  | M0[7:0] = (SS + 3)  |

|-----------------------|-----------------------|----------------------|---------------------|

| M1[31:24] = (PP + 0)  | M1[23:16] = (PP + 1)  | M1[15:8] = (PP + 2)  | M1[7:0] = (PP + 3)  |

| M2[31:24] = (PP + 4)  | M2[23:16] = (PP + 5)  | M2[15:8] = (PP + 6)  | M2[7:0] = (PP + 7)  |

| M3[31:24] = (PP + 8)  | M3[23:16] = (PP + 9)  | M3[15:8] = (PP + 10) | M3[7:0] = (PP + 11) |

| M4[31:24] = (PP + 12) | M4[23:16] = (PP + 13) | M4[15:8] = (PP + 14) | M4[7:0] = (PP + 15) |

| M5[31:24] = (PP + 16) | M5[23:16] = (PP + 17) | M5[15:8] = (PP + 18) | M5[7:0] = (PP + 19) |

| M6[31:24] = (PP + 20) | M6[23:16] = (PP + 21) | M6[15:8] = (PP + 22) | M6[7:0] = (PP + 23) |

| M7[31:24] = (PP + 24) | M7[23:16] = (PP + 25) | M7[15:8] = (PP + 26) | M7[7:0] = (PP + 27) |

| M8[31:24] = (PP + 28) | M8[23:16] = (PP + 29) | M8[15:8] = (PP + 30) | M8[7:0] = (PP + 31) |

| M9[31:24] = FFh       | M9[23:16] = FFh       | M9[15:8] = FFh       | M9[7:0] = FFh       |

| M10[31:24] = MP       | M10[23:16] = (RN + 0) | M10[15:8] = (RN + 1) | M10[7:0] = (RN + 2) |

| M11[31:24] = (RN + 3) | M11[23:16] = (RN + 4) | M11[15:8] = (RN + 5) | M11[7:0] = (RN + 6) |

| M12[31:24] = (SS + 4) | M12[23:16] = (SS + 5) | M12[15:8] = (SS + 6) | M12[7:0] = (SS + 7) |

| M13[31:24] = (SP + 4) | M13[23:16] = (SP + 5) | M13[15:8] = (SP + 6) | M13[7:0] = 80h      |

| M14[31:24] = 00h      | M14[23:16] = 00h      | M14[15:8] = 00h      | M14[7:0] = 00h      |

| M15[31:24] = 00h      | M15[23:16] = 00h      | M15[15:8] = 01h      | M15[7:0] = B8h      |

Table 5.4 SHA-1 Input for Read Authenticated Page

## 5.2.11 Read Memory [F0h]

The read memory command may be used to read all memory except for the secret. Attempting to read the secret will not reveal any data. After issuing the command, the master must provide the 2-byte target address. After these two bytes, the master reads data beginning from the target address and may continue until address 0097h. If the master continues reading the result will be logic 1's.

# **Chapter 6**

# **Source Code**

### 6.1 3 to 8 decoder

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

entity demo\_14\_11 is port ( C100MHz : in std\_logic;

> RSTIN : in std\_logic; IFF\_OUT : out std\_logic; dec\_in\_N : in std\_logic\_vector(7 downto 0); dig\_out\_N : out std\_logic\_vector(2 downto 0); BI : inout std\_logic

end demo\_14\_11;

architecture Behavioral of demo\_14\_11 is

);

component IFF\_TEST is Port ( C100MHz : in STD\_LOGIC; RSTIN : in STD\_LOGIC; FRND\_OUT : out std\_logic; BI : inout STD\_LOGIC);

end component;

signal IFF : std\_logic; signal dig\_out : std\_logic\_vector(2 downto 0); signal dec\_in : std\_logic\_vector(7 downto 0);

begin

IFF\_OUT <= IFF; X1: IFF\_TEST port map(C100MHz,RSTIN,IFF,BI); dig\_out\_N <= not dig\_out; dec\_in <= not dec\_in\_N;</pre>

process(dec\_in, C100MHz,IFF)

begin

```

if( IFF = '0') then

case dec_in is

when "00000001" => dig_out <= "000";

when "0000010" => dig_out <= "001";

when "00001000" => dig_out <= "010";

when "00010000" => dig_out <= "101";

when "00100000" => dig_out <= "100";

when "01000000" => dig_out <= "111";

when "10000000" => dig_out <= "111";

when others=>NULL;

end case;

```

else

dig\_out <= "111";

end if; end process;

end Behavioral;

### **6.2 IFFTEST**

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

entity IFF\_TEST is Port ( C100MHz : in STD\_LOGIC; RSTIN : in STD\_LOGIC; FRND\_OUT : out std\_logic; BI : inout STD\_LOGIC);

end IFF\_TEST;

architecture Behavioral of IFF\_TEST is

type q is array (0 to 11) of std\_logic\_vector(7 downto 0); type rr is array (0 to 3) of std\_logic\_vector(7 downto 0); --type s is array (0 to 11) of p;

-- (1byte command + 2byte address + 8byte secret + 1extra byte ) constant secret : q := ( X"0F",X"80",X"00",X"01",X"02",X"03",X"04",X"05",X"06",X"07",X"08",X"FF"); -- (1byte command + 2byte address + 8byte secret)

constant page\_01 : q := ( X"0F",X"00",X"00",X"11",X"12",X"13",X"14",X"15",X"16",X"17",X"18",X"FF"); constant page\_02 : q := ( X"0F",X"08",X"00",X"21",X"22",X"23",X"24",X"25",X"26",X"27",X"28",X"FF"); constant page\_03 : q := ( X"0F",X"10",X"00",X"31",X"32",X"33",X"34",X"35",X"36",X"37",X"38",X"FF"); constant page\_04 : q := ( X"0F",X"18",X"00",X"41",X"42",X"43",X"44",X"45",X"46",X"47",X"48",X"FF");

constant RDAUTH : rr := (X"A5",X"00",X"00",X"FF");

type stat\_typ is

(initial,skiprom,RXCRC,RDAUTH\_cmd,RDMAC,memcmd,wrscrpad,done);--

,rdscrpad,ldfkey,sendmac,progwait,macwait,rdmem,cpyscrpad);

signal pr\_stat, nx\_stat : stat\_typ ;

signal A,B,C,D,E : std\_logic\_vector(31 downto 0);

signal sflag : integer range 0 to 6 ;--std\_logic\_vector(2 downto 0);

signal c1, cnt, strtcnt, rdcnt, RDDATACNT : integer range 0 to 31;

signal waitcnt : integer;

signal j,mscnt : integer range 0 to 30;

signal CRCOK,cnten, RDDATACNT\_EN,mscnten : std\_logic;

signal CRCdata : std\_logic\_vector(87 downto 0);

signal CRCDATAld : std\_logic;

signal CCRC : std\_logic\_vector(15 downto 0);

\_\_\*\*\*\*\*\*\*\*\*\*

type state\_type is (IDEAL, RSTPLS, PRS, WRITE\_0, WRITE\_1, READ); signal pr\_state, nx\_state : state\_type; signal timer : std\_logic\_vector(9 downto 0);--integer range 0 to 1000;

signal clkcnt,rxcnt : integer range 0 to 62;

signal C1MHz,prsnt, rs,X, rxd, loaddone,r : std\_logic;

signal txsiftr : std logic vector(7 downto 0);

signal rxdata : std\_logic\_vector(31 downto 0);

signal flag, wr, rd : std\_logic;

\_\_\*\*\*\*\*\*\*\*\*\*\*\*\*

signal rden, wren, start : std\_logic; signal dbcnt : integer range 0 to 500005;

signal txdata : std\_logic\_vector(7 downto 0); signal start1,FRND : std\_logic; signal SRSTIN : std\_logic\_vector(10 downto 0);

```

signal rxdata_out : std_logic_vector(31 downto 0);

signal crcok_out,start_out,rstout,digest_vld_out,prsnt_out: std_logic;

component CRC is

Port ( clk, rst : in STD_LOGIC;

CRCDATAld : in std_logic;

datain : in std_logic_vector(87 downto 0);

CRC_out : out std_logic_vector(15 downto 0));

end component;

component MAC is

port(

clk : in std_logic;

reset : in std_logic;

m0i,m1i,m2i,m3i,m4i,m5i,m6i,m7i,m8i,m13i,m10i,m11i,m12i : in

std_logic_vector(31 downto 0);

message_vld : in std_logic;

digest : out std_logic_vector(159 downto 0);

digest_vld : out std_logic

);

end component;

signal m0,m1,m2,m3,m4,m5,m6,m7,m8,m13,m10,m11,m12 : std_logic_vector(31

downto 0);

signal message_vld, digest_vld, MACRST : std_logic;

signal digest,RXMAC : std logic vector(159 downto 0);

signal ldtsten : std logic;

begin

rstout \leq rst;

start out <= start;

prsnt_out <= prsnt;</pre>

crcok out <= not CRCOK;

digest_vld_out <= not digest_vld;</pre>

FRND_OUT <= not FRND;

inst_mac: MAC port map

(C1MHz,MACRST,m0,m1,m2,m3,m4,m5,m6,m7,m8,m13,m10,m11,m12,messag

e_vld,digest,digest_vld);

inst_CRC : CRC port map

(clk \Rightarrow C1MHz,

rst => rst,

```

CRCDATAld => CRCDATAld, datain => CRCdata, CRC\_out => CCRC);

```

process(C100MHz)

begin

if (C100MHz'event and C100MHz = '1') then

SRSTIN <= RSTIN & SRSTIN(10 downto 1);

if(SRSTIN(10) = '1' and SRSTIN(0) = '0') then

RST <= '0';

else

RST <= '1';

end if;

end if;

end process;

-- generate 1MHz clock from 50MHz system clock

process(RST,C100MHz)

begin

if(RST = '0') then

clkcnt \ll 0;

C1MHz <= '0';

elsif(C100MHz'event and C100MHz = '1') then

if(clkcnt = 49) then

C1MHz <= not C1MHz;

clkcnt \ll 0;

else

clkcnt \leq clkcnt + 1;

end if;

end if;

end process;

process(rst,C1MHz,rden)

begin

if(rst = '0') then

rxcnt \leq 0;

r <= '0';

```

```

elsif(rden = '0') then

```

```

r <= '1';

rxcnt \leq 0;

rd <= '0';

elsif(C1MHz'event and C1MHz = '1') then

if (rd = '0' and timer = 25) then

rxcnt \leq rxcnt + 1;

end if:

if (rxcnt > 23 and rd = '0' and RDDATACNT = 8) then

rd <= '1';

elsif (rxcnt \leq 31 and rd = '0') then

rd <= '0':

else

rd <= '1';

end if;

end if;

end process;

```

rxdata\_out <= rxdata and A and B and C and D and E;-- and digest(159 downto 128) and digest(127 downto 96) and digest(95 downto 64) and digest(63 downto 32) and digest(31 downto 0);--

--

```

process(RST,C1MHz)

begin

if(RST = '0') then

rxdata \le (others \implies '0');

flag <= '0';

txsiftr \le (others \implies '0');

elsif(C1MHz'event and C1MHz = '1') then

if (rd = '0' and timer = 25) then

rxdata <= RXd & rxdata(31 downto 1);</pre>

end if;

if(wren = '0') then

flag <= '1';

txsiftr <= txdata;

elsif(wr = '0' and timer = 10) then

txsiftr <= flag & txsiftr(7 downto 1);</pre>

flag <= '0';

end if;

end if;

```

end process;

```

-- process

process(rst,C1MHz)

begin

if(rst = '0') then

pr_state <= IDEAL;</pre>

elsif(C1MHz'event and C1MHz = '1') then

pr_state <= nx_state;

end if;

end process;

process(pr_state,timer,start,rs,rd,txsiftr,wr)

begin

case pr_state is

when IDEAL =>

if start = '0' then

nx_state <= RSTPLS;</pre>

elsif rs = '1' then

nx_state <= PRS;

elsif rd = '0' then

nx_state <= READ;</pre>

elsif(txsiftr(0) = '1' and wr = '0')then

nx_state <= WRITE_1;</pre>

elsif(txsiftr(0) = '0' and wr = '0')then

nx_state <= WRITE_0;</pre>

else

nx_state <= IDEAL;</pre>

end if;

when RSTPLS =>

if timer < 540 then

-- rst pulse is 480 < Trst > 640

nx_state <= RSTPLS;</pre>

else

nx_state <= IDEAL;</pre>

end if;

when PRS =>

if (timer < 100) then -- should be > [15us(Tpdh) + 60us (Tpdl) +

5us(Trec)]

nx_state <= PRS;

else

nx_state <= IDEAL;</pre>

end if;

```

```

when WRITE_0 =>

-- should be > Tslot(65us)

if(timer \leq 75) then

nx_state <= WRITE_0 ;</pre>

else

nx_state <= IDEAL;</pre>

end if;

when WRITE_1 =>

-- should be > Tslot(65us)

if(timer \leq 75) then

nx_state <= WRITE_1;</pre>

else

nx_state <= IDEAL;</pre>

end if;

when READ =>

-- should be >

Tslot(65us)

if(timer \leq 75) then

nx_state <= READ ;</pre>

else

nx_state <= IDEAL;</pre>

end if;

end case;

end process;

process(C1MHz,RST)

begin

if(RST = '0') then

timer <= (others => '0');

BI <= 'Z';

rs <= '0';

rxd <= '0';

prsnt <= '1';

elsif(C1MHz'event and C1MHz = '1') then

case pr_state is

when IDEAL =>

BI <= 'Z';

timer <= (others => '0');

prsnt <= '1';

when RSTPLS =>

BI <= '0';

```

rs  $\leq$  '1'; -- to indicate that next state is timer  $\leq$  timer + 1; when PRS => if (timer  $\geq 65$  and timer < 70) then prsnt <= BI;</pre> end if; rs <= '0'; timer  $\leq$  timer + 1; when WRITE\_0 => if (timer < 65) then -- Twol should be (>60us and < 120us) BI <= '0'; else BI <= 'Z'; end if; timer  $\leq$  timer + 1; when WRITE\_1 => -- Tw1l should be (>1us and <15us) -- should not exceed Trl(5us) if timer < 2 then BI <= '0'; else BI <= 'Z'; end if; timer  $\leq$  timer + 1; when READ => if (timer <= 5) then -- Trl (> 5us and < 15us) \*should use min BI <= '0'; else BI <= 'Z'; end if: if(timer > 8 and timer < 12)then --Tmsr ( > Trl and < 15us)  $rxd \leq BI;$ end if; timer  $\leq$  timer + 1; end case; end if; end process;

```

process(C1MHz,rst)

begin

if rst = 0' then

pr_stat <= initial;</pre>

elsif(C1MHz'event and C1MHz = '1') then

pr_stat <= nx_stat;</pre>

end if:

end process;

process(pr_stat,prsnt,cnt,wr,c1,j,rd,rdcnt,waitcnt,RDDATACNT,pr_state,CRCOK)

begin

case pr_stat is

when initial =>

if prsnt = '0' then

nx_stat <= skiprom;</pre>

else

nx_stat <= initial;</pre>

end if;

when skiprom =>

if (cnt > 5 and wr = '1') then

nx_stat <= memcmd;</pre>

else

nx_stat <= skiprom;

end if;

when memcmd =>

if(c1 = 1)then -- or C1=4 or c1=8 or c1=12 or c1=16)then

nx_stat <= wrscrpad; -- write

elsif(c1 = 2)then --or c1=5 or c1=9 or c1=13 or c1=17) then

nx_stat <= RDAUTH_cmd; --rdscrpad;</pre>

-- read

elsif(c1 = 3) then

nx_stat <= RDMAC; --ldfkey;</pre>

else

nx_stat <= memcmd;</pre>

end if;

when wrscrpad =>

if (j > 11 \text{ and } wr = '1') then -- if CRC\ = calculated CRC

nx_stat <= RXCRC;</pre>

else

nx_stat <= wrscrpad;</pre>

end if;

```

```

-- if rxdata = X"AAAAAAAA" at ldcnt = 3 then keydn '1'

when RXCRC =>

if(CRCOK = '1' and pr_state = ideal)then

nx_stat <= initial;</pre>

else

nx_stat <= RXCRC;</pre>

end if;

when RDAUTH_cmd =>

if(RDDATACNT > 8 and pr_state = ideal)then

nx_stat <= memcmd; --MACWAIT;</pre>

else

nx_stat <= RDAUTH_cmd;</pre>

end if;

when RDMAC =>

if (RDDATACNT > 6) then

nx_stat <= done;</pre>

else

nx_stat <= RDMAC;</pre>

end if;

when done =>

nx_stat <= done;</pre>

end case;

end process;

process(wr,rst)

if rst = '0' then

i <= 1;

elsif(wr'event and wr = '1') then

if (cnten = '1') then

j <= j + 1;

else

j <= 1;

end if;

end process;

process(rst,RDDATACNT_EN,rd)

if (rst = '0' \text{ or } RDDATACNT_EN = '0') then

RDDATACNT \leq 0;

```

begin

begin

```

elsif(rd'event and rd = '1') then

RDDATACNT <= RDDATACNT + 1;

end if:

end process;

process(C1MHz,RST)

begin

if(RST = '0') then

m0 \le secret(3) \& secret(4) \& secret(5) \& secret(6);

m12 \le secret(7) \& secret(8) \& secret(9) \& secret(10);

m1 \le (others \implies '0');

m2 \le (others \implies '0');

m3 \le (others \implies '0');

m4 \le (others \implies '0');

m5 \le (others \implies '0');

m6 \le (others \implies '0');

m7 \le (others \implies '0');

m8 \le (others \implies '0');

m13 \le (others => '0');

m10 \le (others => '0');

m11 \le (others => '0');

A \le (others => '0');

b \le (others => '0');

c \le (others => '0');

d \le (others => '0');

e \le (others \implies '0');

message vld \leq 0';

MACRST \leq 1';

elsif(C1MHz'event and C1MHz = '1') then

MACRST \leq 0';

m1 \le page_{01(3)} \& page_{01(4)} \& page_{01(5)} \& page_{01(6)};

m2 \le page_01(7) \& page_01(8) \& page_01(9) \& page_01(10);

m3 \le page_{02(3)} \& page_{02(4)} \& page_{02(5)} \& page_{02(6)};

m4 \le page_{02(7)} \& page_{02(8)} \& page_{02(9)} \& page_{02(10)};

m5 \le page_{03(3)} \& page_{03(4)} \& page_{03(5)} \& page_{03(6)};

m6 \le page 03(7) \& page 03(8) \& page 03(9) \& page 03(10);

m7 \le page_04(3) \& page_04(4) \& page_04(5) \& page_04(6);

m8 \le page 04(7) \& page 04(8) \& page 04(9) \& page 04(10);

m10 <= X"40" & X"33" & X"6D" & X"1F";

m11 <= X"25" & X"01" & X"00" & X"00";

m13 <= page_01(7) & page_01(8) & page_01(9) & X"80";

if(digest vld \leq 1') then

```

A <= digest(159 downto 128);

```

B \le digest(127 \text{ downto 96});

C \le digest(95 \text{ downto 64});

D \le digest(63 \text{ downto 32});

E \le digest(31 \text{ downto 0});

end if;

```

if(pr\_stat = wrscrpad) then

message\_vld <= '1';

end if;</pre>

end if;

end process;

end Behavioral;

# 6.3 LOADTEST

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

```

library UNISIM; use UNISIM.VComponents.all;

```

entity single_mod is

Port (

C100MHz : in STD_LOGIC;

RSTIN : in STD_LOGIC;

push3 : in std_logic;

rxdata_out : out std_logic_vector(31 downto 0);

lddone,crcok_out,start_out,rstout,keydn_out,

digest_vld_out,prsnt_out : out std_logic;

BI : inout STD_LOGIC);

```

end single\_mod;

architecture Behavioral of single\_mod is

\_\_\*\*\*\*\*\*\*\*\*\*\*

type q is array (0 to 11) of std\_logic\_vector(7 downto 0); type rr is array (0 to 3) of std\_logic\_vector(7 downto 0); --type s is array (0 to 11) of p;