# FPGA BASED SUPERVISORY CONTROL AND DATA ACQUISITION SYSTEM

## A DISSERTATION SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

## MASTER OF ENGINEERING

IN

## **CONTROL & INSTRUMENTATION**

SUBMITTED BY

## SHWETA SHARMA

### (Roll NO. 3344)

UNDER THE ESTEEMED GUIDANCE

### OF

## Dr. PARMOD KUMAR

(PROFESSOR & HEAD)

DEPARTMENT OF ELECTRICAL ENGINEERING DELHI COLLEGE OF ENGINEERING UNIVERSITY OF DELHI 2004-2005

## **CERTIFICATE**

It is certified that Shweta Sharma, Roll No.3344, student of M.E, Control and Instrumentation, Department of Electrical Engineering, Delhi College of Engineering, has submitted the dissertation entitled **"FPGA based Supervisory Control and Data Acquisition System"**, under my guidance towards partial fulfilment of the requirements for the award of the degree of Master of Engineering (Control & Instrumentation Engineering).

This dissertation is a bonafide record of project work carried out by her under my guidance and supervision. Her work is found to be excellent and her discipline impeccable during the course of the project.

I wish her success in all her endeavors.

Date:

(**Dr. Parmod Kumar**) Professor & Head Deptt. of Electrical Engineering Delhi College of Engineering Delhi -110042

## **ACKNOWLEDGEMENTS**

Any accomplishment requires the efforts of many people and this work is no exception. I appreciate the contribution and support, which various individuals have provided for the successful completion of this dissertation. It may not be possible to mention all by name but the following were singled out for their exceptional help.

My primary thanks goes to my project guide **Dr. Parmod Kumar**, Professor & Head, Department of Electrical Engineering, DCE, who provided me an opportunity to work under his guidance. His scholastic guidance and sagacious suggestions helped me to complete the project in this advanced field. His immense generosity and affection bestowed on me goes beyond his formal obligations as guide.

I would like to thank **Mr. Vishal Verma**, Assistant professor, Department of Electrical Engineering, DCE for his perpetual encouragement, generous help and inspiring guidance.

I express my gratitude to **Mrs. Rajeshwary Pandey**, Lecturer, Department of Electronics and Communication, DCE for her kind help and cooperation.

My sincere thanks to **Mr. Ajay J.**, Customer Support Engineer, Silicon Micro Systems (SIMS), for his initial help that eventually led to this project.

I am grateful to **Mr. Rajen Bhatt**, Research Scholar, IIT Delhi for his kind cooperation and guidance, whenever needed.

I want to express my regards to **Dr. Ashok De**, Head, Computer Centre, DCE for providing the internet access, without which everything could have been difficult.

I am thankful to **Mr. R.K Shukla**, Librarian, DCE, for facilitating me unconditionally with various literary resources.

I also want to say thanks to **Mr. Karan Singh**, Laboratory Assistant, Department of Electrical Engineering, DCE for his kind cooperation during the development of project.

I would like to extend my sincere appreciation to **Ms. Beena Antony** for reviewing this report and providing valuable comments and thoughtful criticism, which have resulted in an improved version.

I want to say thanks to my friends Sandeep Sharma, Zelalem Girma, Sunita Verma, Supriya Sharma, Shraddha Singhai, Payal Singla and Anshu Dev for their support in all my endeavors.

There are times in a project when the clock beats our time and we run out of energy, wishing to finish it once and forever. **My family** made me endure such times with their unconditional support, love and unfailing humour.

Date:

(Shweta Sharma)

## **ABSTRACT**

A prototype Supervisory Control and Data Acquisition (SCADA) System has been designed and programmed into the ACEX50K FPGA chip. The designed system provides the basic facilities of SCADA along with the advantages of great speed, high accuracy, negligible & predictable delay, no mechanical components, purely digitalized system facilitated by the FPGA. FPGA has excellent logic capabilities, enormous processing resources, and very high clock speed, therefore suitable for implementing data capture system.

The system is implemented using UVLSI-201 trainer kit and a general-purpose input-output board. The analog data is acquired from eight multiplexed external channels provided on the GPIO board. Selecting a particular channel and addressing it for reading data, is the responsibility of FPGA. As FPGA can deal only with digital information, the analog data is converted to the digital form by ADC 0808 provided on the GPIO board. This ADC is FPGA controlled and the digital data is stored in FPGA by programming the device.

The data is displayed on the GPIO board in hexadecimal form using multiplexed 4 digits, seven segment display. Data is processed and checked for any limit violation within the chip itself. If any limit violation is there, output LED glows, indicating a fault in the system. Also, a 5-volt analog control signal is generated to check the fault.

The system has been modeled using VHDL, a hardware description language.

## **CONTENTS**

| Page 1 | No. |

|--------|-----|

|--------|-----|

| LIST OF FIGURES                                | ix  |

|------------------------------------------------|-----|

| LIST OF TABLES                                 | xi  |

|                                                |     |

| <b>CHAPTER 1: INTRODUCTION</b>                 | 1   |

| 1.1 Introduction to SCADA                      | 1   |

| 1.2 Benefits of SCADA                          | 4   |

| 1.3 Introduction to FPGA                       | 5   |

| 1.4 Advantages of FPGA                         | 6   |

| 1.5 Scope of FPGA in SCADA                     | 7   |

| 1.6 FPGA based SCADA System Overview           | 8   |

| 1.7 Objectives of the study                    | 9   |

| 1.8 Dissection of Dissertation                 | 10  |

|                                                |     |

| <b>CHAPTER 2: LITERATURE REVIEW</b>            | 11  |

| 2.1 SCADA: A brief history                     | 11  |

| 2.2 FPGA: A brief history                      | 12  |

| CHADTED 2. DDOCDAMMADI E LOCIC DEVICES         | 1 - |

| CHAPTER 3: PROGRAMMABLE LOGIC DEVICES          | 15  |

| 3.1 Standard Logic ICs                         | 15  |

| 3.2 Application Specific ICs                   | 16  |

| 3.3 Programmable Logic Devices                 | 17  |

| 3.3.1 Types of PLDs                            | 18  |

| 3.3.2 Advantages & Disadvantages               | 19  |

|                                                |     |

| <b>CHAPTER 4: FIELD PROGRMMABLE GATE ARRAY</b> | 22  |

| 4.1 Introduction                               | 22  |

| 4.2 Technologies Used                          | 22  |

| 4.2.1 SRAM                                     | 22  |

|                                                |     |

| 4.2.2        | Anti-fuse                                        | 23 |

|--------------|--------------------------------------------------|----|

| 4.2.3        | EPROM/EEPROM                                     | 23 |

| 4.3 Applicat | ions                                             | 23 |

| 4.3.1        | Prototyping                                      | 23 |

| 4.3.2        | Embedded Cores                                   | 23 |

| 4.3.3        | Hybrid Chips                                     | 24 |

| 4.3.4        | Reconfigurable Computing                         | 24 |

| 4.3.5        | Other Applications                               | 24 |

| 4.4 ACEX50   | K Device                                         | 25 |

| 4.4.1        | Salient Features                                 | 25 |

| 4.4.2        | General Description                              | 27 |

| 4.4.3        | Functional Description                           | 29 |

|              | 4.4.3.1 Embedded Array Block                     | 31 |

|              | 4.4.3.2 Logic Array Block                        | 33 |

|              | 4.4.3.3 Logic Element                            | 34 |

|              | 4.4.3.4 FastTrack Interconnect Routing Structure | 39 |

|              | 4.4.3.5 I/O Element                              | 41 |

| 4.4.4        | ClockLock & ClockBoost Features                  | 43 |

| 4.4.5        | JTAG Boundary-Scan Support                       | 44 |

| 4.4.6        | Operating Conditions                             | 44 |

| 4.4.7        | Timing Model                                     | 44 |

| 4.4.8        | Power Consumption                                | 45 |

| 4.4.9        | Configuration & Operation                        | 46 |

|              | 4.4.9.1 Operating Modes                          | 46 |

|              | 4.4.9.2 Configuration Schemes                    | 47 |

| 4.4.10       | ) Device Pin-out                                 | 48 |

|              |                                                  |    |

| CHAPTEI      | R 5: SOFTWARE                                    | 53 |

| 5.1 Introduc | tion                                             | 53 |

| 5.2 QuartusI | I Software                                       | 53 |

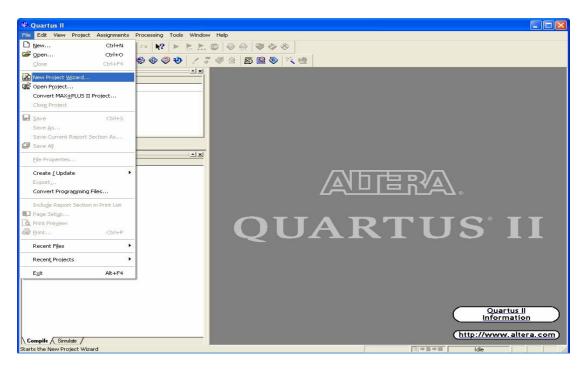

| 5.2.1        | Graphical User Interface Design Flow             | 53 |

| 5.2.2        | Procedure                                        | 54 |

| 5.3 VHDL                                      | 60 |

|-----------------------------------------------|----|

| 5.3.1 Introduction                            | 60 |

| 5.3.2 Salient Features                        | 60 |

|                                               |    |

| CHAPTER 6: UVLSI TRAINER                      | 63 |

| 6.1 Introduction                              | 63 |

| 6.1.1 Power Supply Unit                       | 63 |

| 6.1.2 Hardware Access Unit                    | 63 |

| 6.1.3 List of Cables                          | 64 |

| 6.2 Salient Features                          | 65 |

| 6.2.1 Connectors                              | 65 |

| 6.2.2 Switches                                | 66 |

| 6.2.3 LCD Display                             | 66 |

| 6.2.4 Daughter Board Connectors               | 66 |

| 6.2.5 Jumpers                                 | 66 |

| 6.2.6 On Board Programmer                     | 66 |

| 6.2.7 RS-232 Connector                        | 66 |

| CHAPTER 7: GPIO BOARD                         | 67 |

| 7.1 Introduction                              | 67 |

| 7.2 Details of GPIO board                     | 67 |

| 7.2.1 16 DIP Switch Inputs                    | 69 |

| 7.2.2 16 LED Outputs                          | 69 |

| 7.2.3 4-Key Interface                         | 69 |

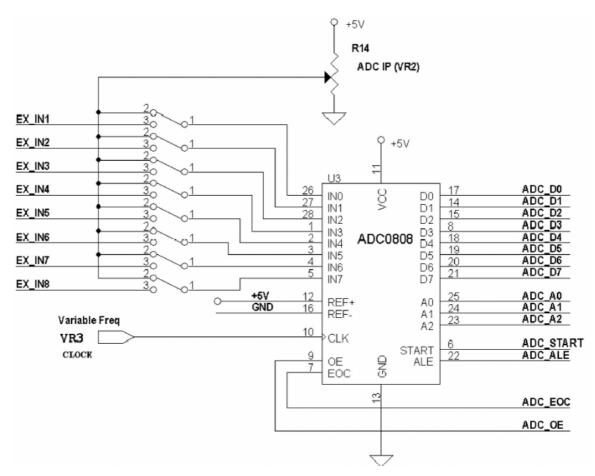

| 7.2.4 Multiplexed (4 digit) 7 Segment Display | 69 |

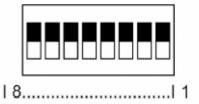

| 7.2.5 8-Bit ADC Interface                     | 69 |

| 7.2.6 8-Bit DAC Interface                     | 70 |

| CHAPTER 8: FPGA BASED SCADA SYSTEM            | 71 |

| 8.1 Introduction                              | 71 |

| 8.2 Data Acquisition                          | 72 |

| 8.2.1 Channel Scanning                        | 72 |

| 8.2.2 Analog to Digital Conversion            | 72 |

| 8.2.3 Seven Segment Display | 73        |

|-----------------------------|-----------|

| 8.3 Data Processing         | 74        |

| 8.4 Analysis and Control    | 75        |

| 8.5 Pin Locking in FPGA     |           |

|                             |           |

| Results and Discussion      | 79        |

| Conclusion                  | 88        |

| Scope for Further Work      |           |

| Appendix: Source Code       |           |

| References                  | <b>98</b> |

## **LIST OF FIGURES**

| Sr. No | Figure                                               | PageNo |

|--------|------------------------------------------------------|--------|

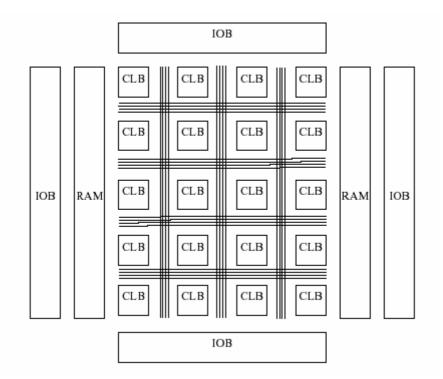

| 1      | General Architecture of FPGA                         | 6      |

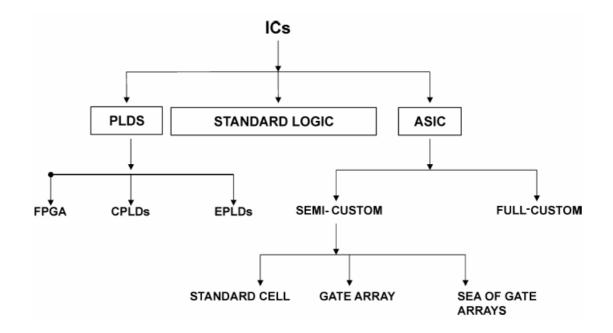

| 2      | ICs Classification                                   | 15     |

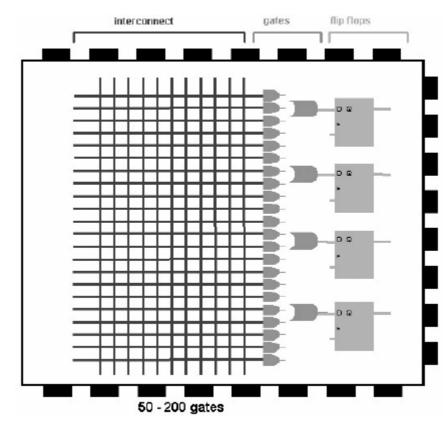

| 3      | Programmable Logic Device                            | 18     |

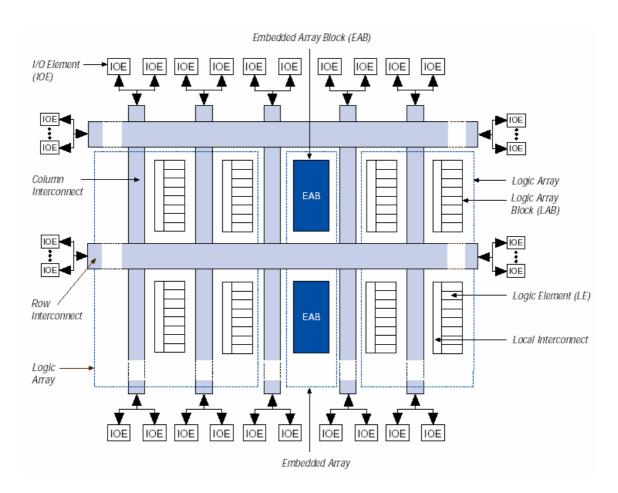

| 4      | ACEX50K Block Diagram                                | 30     |

| 5      | ACEX50K EAB in Dual-Port RAM Mode                    | 32     |

| 6      | ACEX50K EAB Memory Configurations                    | 32     |

| 7      | Examples of Combining EABs                           | 33     |

| 8      | ACEX50K Logic Array Block                            | 34     |

| 9      | ACEX50K Logic Element                                | 35     |

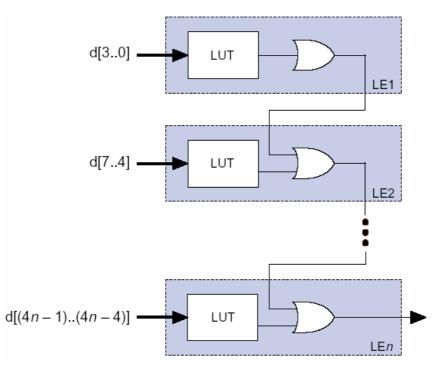

| 10     | ACEX50K Carry Chain Operation                        | 37     |

| 11     | ACEX50K AND Cascade Chain Operation                  | 38     |

| 12     | ACEX50K OR Cascade Chain Operation                   | 38     |

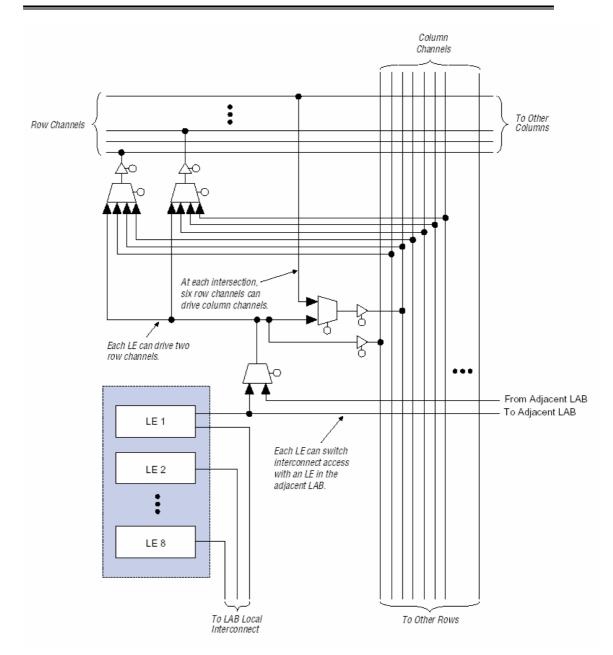

| 13     | ACEX50K LAB Connections to Row & Column Interconnect | 40     |

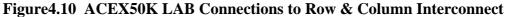

| 14     | ACEX50K Row-to-IOE Connections                       | 42     |

| 15     | ACEX50K Column-to-IOE Connections                    | 43     |

| 16     | ACEX50K Device Timing Model                          | 45     |

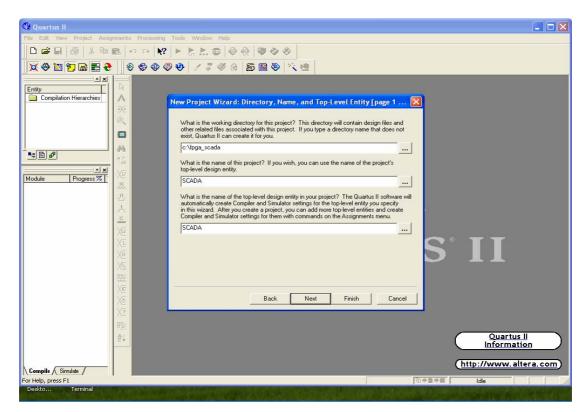

| 17     | Using Wizard Create New Project                      | 56     |

| 18     | Create Directory and Project Name                    | 56     |

| 19     | Select the Family of the Device                      | 57     |

| 20     | Summary of the New Project Wizard                    | 57     |

| 21     | Select the VHDL file                                 | 58     |

| 22     | Write the VHDL Code                                  | 58     |

| 23     | Compilation Process                                  | 59     |

| 24     | Assignment of Pins for the Device                    | 59     |

| Sr. No | Figure                          | Page No |

|--------|---------------------------------|---------|

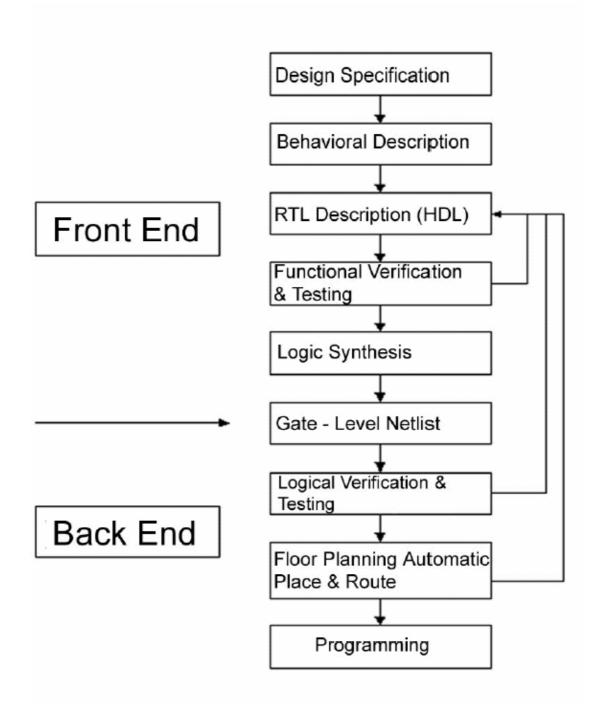

| 25     | VLSI Design Flow                | 62      |

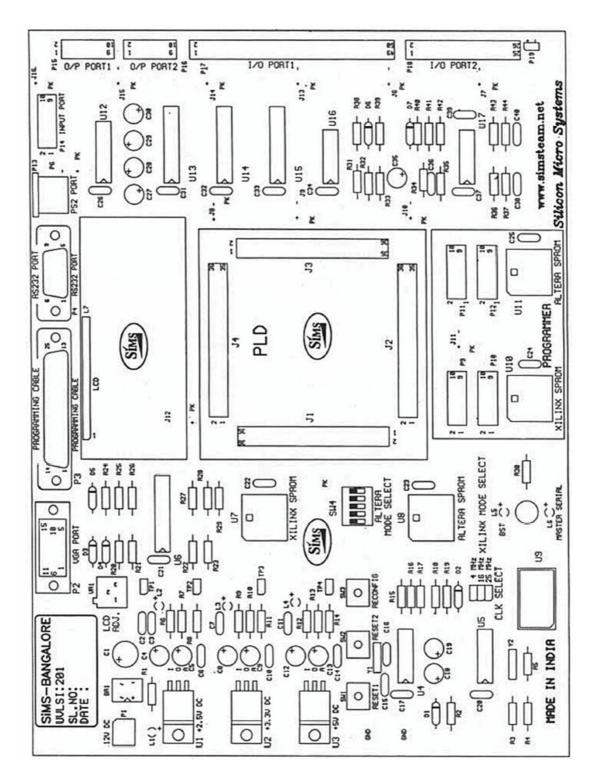

| 26     | Layout of UVLSI 201             | 64      |

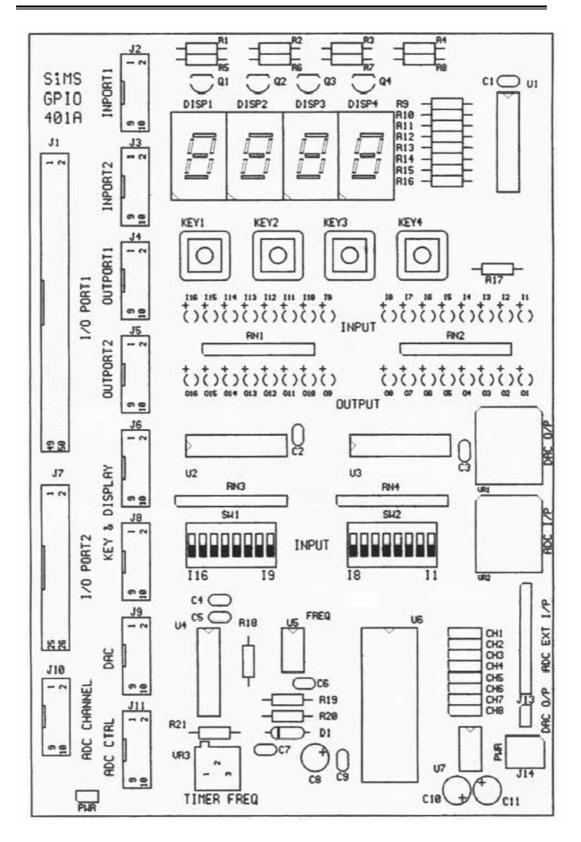

| 27     | GPIO401 Board Lay out           | 68      |

| 28     | Input DIP Switches              | 69      |

| 29     | Output LEDs                     | 69      |

| 30     | Block Diagram of ADC0808        | 73      |

| 31     | Seven Segment Display           | 74      |

| 32     | Block Diagram of DAC0800        | 76      |

| 33     | Compilation Process             | 81      |

| 34     | Flow Elapsed Time               | 81      |

| 35     | Floor Planning                  | 82      |

| 36     | Internal view of LABs           | 82      |

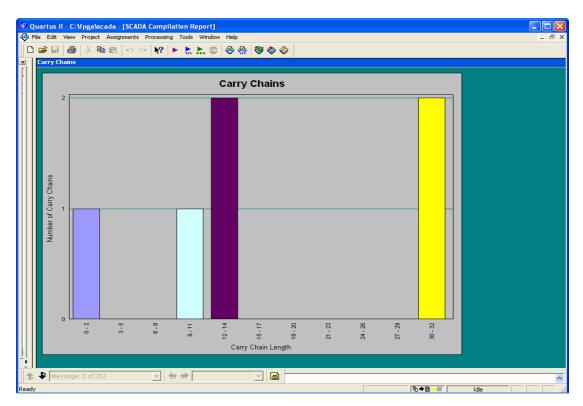

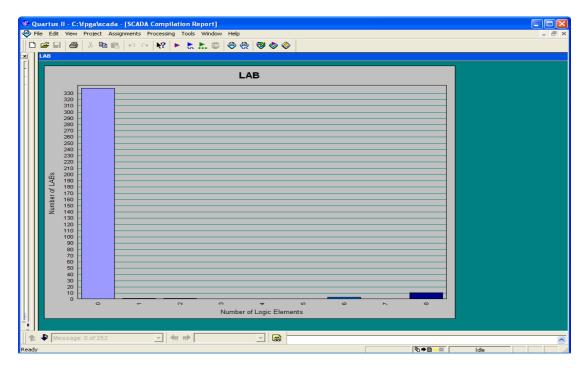

| 37     | Carry Chain Usage               | 83      |

| 38     | Logic Array Blocks Usage        | 83      |

| 39     | Resource Usage Summary          | 84      |

| 40     | Programming of FPGA             | 84      |

| 41     | No Limit Violation in Channel 0 | 85      |

| 42     | No Limit Violation in Channel 1 | 85      |

| 43     | Limit Violation in Channel 0    | 86      |

| 44     | Limit Violation in Channel 1    | 86      |

| 45     | Limit Violation in Channel 0    | 87      |

## **LIST OF TABLES**

| Sr. No | Table                                    | Page No |

|--------|------------------------------------------|---------|

| 1      | ACEX50K Features                         | 26      |

| 2      | ACEX50K Performance                      | 28      |

| 3      | ACEX50K FastTrack Interconnect Resources | 41      |

| 4      | ACEX50K Device Absolute Maximum Rating   | 44      |

| 5      | Data Sources for ACEX50K Configuration   | 47      |

| 6      | ACEX50K Pin-out                          | 48      |

| 7      | Pin Locking in FPGA                      | 77      |

## CHAPTER 1 INTRODUCTION

#### Introduction

SCADA (Supervisory Control and Data Acquisition) system is an intelligent system, which provides the facility of continuously monitoring, supervising and controlling the process plant. The main components of the SCADA system are [32]:

(1) Master Computer Station or Master Terminal Unit (MTU)

(2) Remote Terminal Unit (RTU)

(3) Communication Media

(4) Human Machine Interface (HMI)

Each component is discussed briefly below:

#### (1) Master Computer Station or Master Terminal Unit (MTU)

The main incentive for the process control is the optimization of the plant's economic performance. For performance analysis on the process plant, the information from the distributed RTUs should reach a central location where it can be consolidated and analyzed to generate the reports on the plant performance. The analysis may include histogram generation, standard deviation calculation, plotting one parameter with respect to another and so on. Software can be written depending on the type of analysis required.

Many times the human operator cannot find the best operating policy for a plant, which will minimize the operating cost. This deficiency is due to the enormous complexity of a typical process plant. Therefore, to analyze the situation and find out the best policy, the speed and the programmed intelligence of the digital computer is used; this computer is called Master Computer Station or Master Terminal Unit. It monitors, controls and coordinates the activities of various RTUs and provides the supervisory control facility to the process plant. The MTU is located at the operator's central control facility and provides a man-machine software interface, two-way data communication.

#### (2) Remote Terminal Unit (RTU)

RTU is a field interface device, which collects information from the machine that is to be monitored. The RTUs are basically nodes of the distributed SCADA system that are located at a remote site to gather data from field devices like pumps, valves, alarms etc. They should be rugged and able to work unattended for a long duration. Since these RTUs have to operate for a long duration unattended, the basic requirements would be that they consume minimum power and have considerable self diagnostic capability. There are two modes in which remote terminal units work: Under command from central computer and stand alone mode.

The RTUs should have some special software facilities, which are mentioned below:

(i) Quiescent Mode Operation: Since the transmitter consumes maximum power in RTU, especially in terrestrial and satellite communications, it is switched on only when the RTU has some information packets ready for sending. The RTU receives all the information from the central computer. Since the receiver is kept on all the time, this information is received and proper action is initiated. The quiescent mode saves considerable amount of power for RTUs.

(ii) Downloading of Limits from Central Computer: Generally the RTUs behave much like stand alone SCADA. They collect the data from various sensors, perform signal conditioning, filtering, conversion to engineering units and store them in the memory. They also perform the limit checking on these values and inform central computer on violation of limits, if any, immediately. Since these RTUs are at remote locations it should be possible to change these limits remotely from central computer. This is called downloading of limits. The central computer makes a special request to the RTU to change the limits. The RTU then enters in a special mode for the change of basic parameters and performs the function in an interactive way.

(iii) Exceptional Reporting: The RTUs normally have intelligence to perform all the functions including limit checking and when the limits are violated the central computer is informed. The other message that goes regularly is regarding all well condition of RTUs. Thus RTUs perform self diagnosis by executing different diagnostic software.

#### (3) Communication Media

Communication Media is an important component of the SCADA system and has the interface available with 2-wire/4-wire communication line. The communications media transmits the information from RTU to central computer or in the reverse direction. The way the MTU/RTU transmission network or topology is set up can vary, but the system must feature uninterrupted, bidirectional communication in order to properly function. Methods to accomplish this include private medium, where the end user owns, operates, licenses and services the medium or public medium, where the customer pays for a monthly, per time or volume use [32]. Following are the basic communication strategies that are used depending on the application need:

(i) Wireline Communications: The wireline communication may have a number of options and these options can be selected depending upon the distance between central computer and RTU. It is usually limited to low bandwidth applications. These options are enlisted below:

**RS232C/442:** RTU can support communication via standard RS232C/442. The I/O ports can select the average levels as well as the baud rates.

**Switch Line Modem:** When the user wants to use the existing telephone lines for communication, the switch line modem can be effective. In such cases, RTUs contain the facilities like auto answer, auto dial and auto select baud rates. The modem is ideal for data networks configured in time or event reporting RTUs.

**2-Wire or 4-Wire Communication:** The modem residing in the RTU can be configured to 2 or 4-wire communication on dedicated lines.

#### (ii) Wireless Communications:

**UHF/VHF radio:** The RTU may support a complete line of UHF/VHF terrestrial radios. UHF/VHF radio is an electromagnetic transmission with frequencies of 175MHz-450MHz-900MHz received by special antennas. Its coverage is limited to special geographical boundaries.

The communication protocol is transparent to the user and supports CRC intelligence, error checking, and packet protocol for error free data transmission.

**Microwave Radio:** Microwave Radio transmits at high frequencies through parabolic dishes mounted on towers or on top of buildings. This media uses point-

to-point, line-of-sight technology and communication may become interrupted sometimes due to misalignment and/or atmospheric conditions.

**Satellite Communications:** In the applications where wireline and terrestrial radio communications are impossible or cost prohibitive, the satellite communication may be desirable.

Some of the RTUs provide the facility to be interfaced to one-way or two way satellite communication using Very Small Aperture Terminal (VSAT). These terminals use one meter antennas and have data rates from 50 to 60 kbps. **Fiber-Optic Communications:** For applications where electromagnetic interferences or hazardous electrical potentials exist, the RTUs can be networked using fiber-optic cables.

#### (4) Human Machine Interface (HMI)

For efficient process monitoring and control, effective communication is necessary between the process operator and the process to be automated [4]. The man-machine dialogue between the process operator and the automation system is carried out with the Human Machine Interface. HMI allows operators to view the state of any part of the plant equipment.

The employment of an easy-to-use SCADA software package on PC, known as the human machine interface, provides a reliable representation of the real system at work [32]. An HMI allows the operator to view virtually all system alerts, warnings, urgent messages and functions as well as change set points and analyze, archive or present data trends. Some common HMI software packages are Cimplicity (GE-Fanuc), RSView (Rockwell Automation), IFIX (Intellution) and InTouch (Wonderware). Most of these software packages use standard data manipulation/presentation tools for reporting and archiving and integrate well with Microsoft Excel, Access and Word.

#### 1.2 Benefits of SCADA

SCADA is an industrial measurement and control system and has become the backbone for monitoring, controlling and meeting the desired objectives of the process plant. The major productivity issue facing the process industries today is plant automation i.e. the development of coordinated plant control system.

The process industries are going for automation to maintain their competitive edge. Some of the benefits provided with the SCADA are given below [26]:

- A properly designed SCADA system saves time and money by eliminating the need for service personnel to visit each site for inspection, data collection/ logging or make adjustments.

- Provides the facility of real-time monitoring, system modifications, troubleshooting, automatic report generating

- Reduces operational costs

- Provides immediate knowledge of system performance

- Improves system efficiency and performance

- Increases equipment life and reduces costly repairs

- Reduces the number of man-hours (labor costs) required for troubleshooting or service and frees up personnel for other important tasks

- Facilitates compliance with regulatory agencies through automated report generation

#### **1.3 Introduction to FPGA**

FPGAs are one of today's most important digital logic implementation options. An FPGA is a general purpose, multilevel, programmable logic device that is customized in the package by the end users. An FPGA consists of an array of programmable logic blocks and a programmable routing network. The programmable interconnect between blocks allows users to implement multi level logic, removing many of the size limitations of the PLD derived two level logic structure. This extensible architecture can currently support thousands of logic gates at system speed in the tens of megahertz [13].

The size, structure, number of logic blocks and connectivity of the interconnect vary considerably among the architectures. This difference in architectures is driven by different programming technologies and different target applications of the parts.

Figure 1.1. Basic Architecture of FPGA

FPGAs offer the benefits of both programmable logic arrays and gate arrays. They implement thousands of gates of logic in a single integrated circuit. FPGAs are programmable by designers at their site, eliminating the long delays and tooling costs. These advantages have made FPGAs very popular [13].

#### **1.4 Advantages of FPGAs**

#### 1) Low Tooling Costs

There is no custom tooling required for an FPGA, so there are no associated tooling costs, making FPGA cost effective for most logic designs.

#### 2) Rapid Turnaround

An FPGA can be programmed in a few minutes. On an FPGA, a modification to correct a design flaw or to address a late specification change can be made quickly and cheaply. Faster design turnaround leads to faster product development and shorter time to market for new FPGA products.

#### 3) Low Risks

The benefits of low initial Non Recurring Engineering (NRE) charges and rapid turnarounds mean that design iteration due to an error incurs neither a large expense nor a long delay. Low cost encourages early system integration and prototyping. The low cost of error encourages more aggressive logic design, which may yield better performance and more cost effective designs.

#### 4) Effective Design Verification

Instead of simulating large amounts of time, FPGA user may choose to use in circuit verification. Designers can implement the design and can use any functioning part as a prototype. The prototype operates at full speed and with excellent timing accuracy. A prototype can be inserted into the system to verify functionality of the system as a whole, eliminating a class of system errors early.

#### 5) Low Testing Cost

All ICs must be tested to verify proper manufacturing and packaging. The test program for FPGAs is the same for all design and test the FPGA for all users of the part. Because there is only one test program, it is reasonable to invest a considerable amount of effort in it and it can be continually improved over the lifetime of the FPGA. The resulting test program achieves excellent test coverage leading to high quality ICs. The manufacturer's test program verifies that every FPGA will be functional for all possible designs that may be implemented on it. FPGA users are not required to write design specific test for their designs. Therefore, designers need not built the testability into the design eliminating "design for testability" and the design effort and overhead associated with it.

#### 6) Life Cycle Advantages

The cost effectiveness of FPGAs in low volume and the flexibility provided by field programmability provide advantages over all phases of product lifetime. When introducing a product, an FPGA user may order a few parts at a time while testing the design for functionality and the product for market viability. During production, the FPGA user can accommodate rapid changes in sales easily because long lead times are not required. An FPGA user can make enhancements by shipping an upgraded design on the same FPGA device. This upgrade requires no inventory changes, no new hardware and does not interrupt production.

#### 1.5 Scope of FPGA in SCADA

Development in the field of FPGAs has provided great logic capabilities, enormous processing resources, significant on-chip independent RAM banks and very high clock speeds. FPGAs are therefore suitable for implementing data capture systems [23]. With the basic understanding of FPGA capabilities, I consider utilizing an FPGA based SCADA system [32] over a basic RTU or a proprietary system for the following reasons:

- FPGAs, like Master Terminal Units can continuously collect, process and store data, operating independently from the MTU through intelligent programming.

- FPGAs can provide security and monitoring of door switches, heat and motion detectors. Managers/operators can be informed 24 hours a day through automatic e-mail, paging and dial-up call features.

- Multiple users can easily be added and, if open architecture protocol is used, future equipment can easily be integrated. Since FPGAs have no moving parts, they are extremely reliable.

- FPGA based SCADA system can reduce the number of man-hours needed for on-site visual inspections, adjustments, data collection and logging. Continually monitoring and troubleshooting potential problems, increases equipment life, reduces service calls, reduces customer complaints and increases system efficiency. Simply put, FPGA based SCADA systems are an excellent means for process control facilities to save time and money.

- Redesigning of the SCADA system can be done easily according to the needs, as FPGA is reprogrammable.

- FPGA based SCADA system mainly consists of digital components and therefore it is more accurate and reliable.

Engineered SCADA systems today not only control processes but are also used for measuring, forecasting, billing, analyzing and planning [32]. Today's SCADA system must meet a whole new level of control automation while interfacing with yesterday's obsolete equipment yet remain flexible enough to adapt to tomorrow's developments.

### 1.6 FPGA based SCADA System Overview

FPGA are revolutionizing the way system designers implement logic [3]. FPGAs provide a new capability that facilitates simple and trouble free implementation of digital systems.

An FPGA based SCADA system has been designed in this project. The system utilizes the great logic capability and re-programmability of the FPGA to design the SCADA system. The project is divided into three parts; Data Acquisition, Processing and Control.

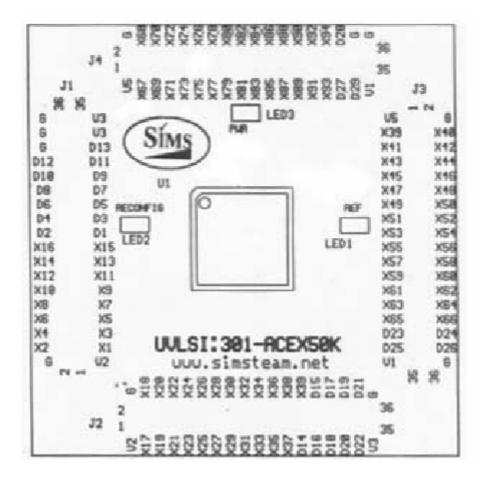

The system has been designed and implemented using the UVLSI 201 trainer. This universal PLD kit is an ideal trainer to implement and test simple and complex designs. It is possible to execute and verify digital experiments on this kit using VHDL, Verilog, AHDL, the standard hardware description languages. It is an assembled ready for various interfaces that include ADC/DAC, display, keyboard, serial communication, VGA, PS/2.

For data acquisition, general purpose input-output board is used. It has almost all the primary interfaces that a PLD may be used for. This board is designed to interface PLDs of any company, any gate count and any package. Input switches are provided to give steady state inputs and LEDs can indicate high or low outputs.

GPIO board has eight channels to communicate with outside world. Channels, from which data is to be captured, are interfaced with GPIO. FPGA is a digital device, it can handle only digital data; therefore the analog data is converted into the digital form by using a successive approximation ADC. SAR ADC0808 is provided on the GPIO board. It receives all its control signals e.g. start conversion, address latch enable etc. from the FPGA. The digital data is stored in the FPGA chip.

The data is processed for control purpose, in the chip itself. Software is written depending upon the type of analysis required in the system. Any fault in the system e.g. limit violation is indicated by an LED. FPGA is programmed using the VHDL, a hardware description language.

### 1.7 Objectives of the Study

The present study sets the following objectives:

- An exhaustive study of FPGA

- Scope of FPGA in SCADA

- Designing of FPGA based SCADA system

#### **1.8 Dissection of Dissertation**

**Chapter 2** presents the literature review. It explains the developments and advancements in SCADA systems in chronological order. Then it describes how FPGAs emerged and became the greatest logic implementation device.

**Chapter 3** describes the different types of ICs i.e. Standard Logic ICs, Application Specific ICs, PLDs and compares their architecture, functionality and applications. PLDs have been further classified into SPLDs, CPLDs, FPGAs and each is briefly covered. Advantages and disadvantages of PLDs are listed.

**Chapter 4** considers the FPGA in detail. Essential characteristics, different technologies and applications of FPGAs are explained.

ACEX50K device, used in this project is explained. Salient features, architecture, functionality, input-output capabilities, operating conditions, power consumption and pin configuration have been considered. Detailed functional description of Logic Array Block, Embedded Array Block, Logic Element, I/O Element is presented.

**Chapter 5** deals with the Altera QuartusII software used for programming the ACEX device. Steps to use this software for implementing any digital logic are defined. Salient features, design process and need of VHDL are explained.

**Chapter 7** introduces the features of UVLSI 201 trainer kit, which make it extremely convenient for testing and implementing the VLSI designs.

**Chapter 8** describes the features of the general-purpose input-output board (GPIO) and its capabilities to communicate with outside world.

**Chapter 9** A newer approach to the design and implementation of the Supervisory Control and Data Acquisition system has been discovered. It uses an FPGA for data acquisition, processing and control. The details of each stage; data acquisition, processing and control are presented.

#### **Results and Discussion**

Conclusion

#### **Scope for Future Work**

**Appendix:** VHDL source code to implement the FPGA based SCADA system **References**

## **CHAPTER 2**

### **Literature Review**

Supervisory Control and Data Acquisition (SCADA) is a process control system that enables a site operator to monitor and control processes distributed among various remote sites.

A properly designed SCADA system saves time and money by eliminating the need for service personnel to visit each site for inspection, data collection/logging or make adjustments. Real-time monitoring, system modifications, troubleshooting, increased equipment life and automatic report generating are just a few of the benefits that come with the SCADA systems [26].

### 2.1 SCADA: A brief history

SCADA began in the early 1960s as an electronic system operating as input/output transmissions between a master station and a remote station. The master station would receive the data from remote station through a telemetry network and then store the data on mainframe computers[32]. In the early 1970s, distributed control systems (DCS) were developed to control separate remote subsystems. They have similar functions to SCADA systems, but the field data gathering or control units are usually located within a more confined area. Communications may be via a local area network (LAN), normally reliable and high speed.

In 1977, John Muench, Chairman and Chief Executive Officer, Advanced Control Systems, delivered the industry's first microprocessor based master station and first microprocessor based RTU[28].

In the 1980s, with the development of the microcomputer, process control could be distributed among remote sites. Further development enabled DCS to use programmable logic controllers (PLC), which have the ability to control sites without taking direction from a master.

In the late 1990s, SCADA systems were built with DCS capabilities and systems were customized based on certain proprietary control features built in by the designer. With the internet being utilized more as a communication tool, SCADA and telemetry systems are using automated software with certain portals to download information or control a process.

In 1997, Advanced Control Systems delivered the first SCADA system with DNP implemented in Master Station and RTUs [28].

In 2000, F Morgan, T Bennett, A Shearer, M Redfern, Communications and Signal Processing Research Unit, Department of Electronic Engineering, National University of Ireland, Galway, implemented an "FPGA-based Time Resolved Data Acquisition System for Astronomical and Other Applications".

They described a programmable FPGA-based high-resolution, time resolved photon image capture system which supported current and future generations of astronomical photometry, biological and a range of SCADA applications. The system recorded and time stamped photon data arriving from a number of detectors and transmitted this data to an archive device for post processing. Time resolved data acquisition functionality was implemented and verified using the RC1000-PP Xilinx FPGA-based development platform and Handel-C programming environment [23].

#### 2.2 FPGA: A brief history

One of the most significant components in early digital computers was the magnetic core [16]. This tiny doughnut shaped ferrite material was used from the 1950s through the 1970s to construct the main memory of large computers. Each of these cores could store a binary bit of information by using the direction of magnetization of the core to indicate a 0 or a 1. The direction of the magnetic field inside the core could be changed by controlling the direction of current through the wires that were wound around a portion of the core. For many years, magnetic core storage was the dominant type of main memory for the computer.

As the technology for core storage was improved, the price continued to drop and some impressive computers became available. The IBM system 360 appeared in 1965 with one scientific model capable of storing about 64 million bits in its main memory. This system was sold for a price that varied between \$1,000,000 and \$2,000,000, depending on several options. The magnetic core cost about 1 to 2 cents per bit, wired into the memory. The 64-megabit storage system added approximately \$7,000,000 to the cost of the system. It was obvious that a reduction of the main memory costs would greatly reduce the overall cost of a computer. Furthermore, the core storage system required a set of high current

driver circuits that lead to high power dissipation and expensive circuit components.

Ironically, this same year (1965) saw the first proposal to use semiconductor memory. The obvious size benefits of integration led some engineers to believe that perhaps the integrated circuit might be used to produce low cost storage components. The first IC memories were more expensive and had much less storage capacity than the core memory and did not immediately replace this workhorse of the computer industry. One of the first commercial uses of a small semiconductor main memory was in IBM 360/85 in 1969.

As IC fabrication and design techniques improved over the years, the semiconductor memory became smaller and cheaper, leading to the demise of core storage. Without this development, it would be difficult to produce the highly capable personal computers and workstations that are now available.

Before the semiconductor memory was made large enough to replace the main memory of the computer, it became obvious that the small IC memory would be useful in circuit applications. Several companies implemented small memories such as 64 bit devices that were targeted for use in digital circuits rather than in computer memories. One of the first such devices was the read only memory (ROM). Small IC read write memories, called semiconductor RAMs also appeared at the same time. As the price dropped and the size increased, semiconductor memories began replacing core memories. In the late 1970s, the semiconductor memory was used almost exclusively in the personal computer. By the early 1980s, even large mainframe computers were produced with exclusively semiconductor main memories.

It became obvious in the late 1970s that the ROMs were also useful in logic function realization. As small ROMs were used for this purpose, the combinational PLA and PAL chips were developed to reduce the number of devices needed on a chip. Fabrication methods improved to allow the inclusion of the flip-flops on PLA and PAL chips in the 1980s. As industry looked for faster methods of developing digital products, the registered PLA and PAL, the PLS and the FPGA was conceived. In 1985, Xilinx company introduced the first FPGA. After this many companies like Actel, Altera launched their FPGAs in the market.

These devices became very popular in the late 1980s and continue to be significant in digital system logic design.

Today the worldwide market for programmable logic devices is about \$3.5 billion, according the market researcher Gartner/Dataquest. The market for fixed logic devices is about \$12 billion. However, in recent years, sales of PLDs have outpaced those of fixed logic devices built with older gate array technology. The high performance FPGAs, made with the more advanced standard cell technology are now beginning to take market share from fixed logic devices [35].

## **CHAPTER 3**

### **PROGRAMMABLE LOGIC DEVICES**

An electronic system designer has several options for implementing digital logic [13]. These options include Integrated Circuits (ICs), which can be broadly classified in the following categories:

- Standard logic ICs

- Application Specific ICs

- Programmable Logic Devices

Figure 3.1. ICs Classification

#### 3.1 Standard Logic ICs

Standard logic ICs have permanent circuits built in them, they perform one specific function or set of specified functions. Once manufactured, the function of standard ICs cannot be changed. A specific logic is contained in the IC package when it is purchased and it can never be changed. The operation of Standard Logic devices depends entirely on the IC chips used and the electrical connections between chips. The designer has no access to the internal interconnections of the IC chips. In designing a digital system we must specify each IC to be used and

indicate a wiring diagram to show how each circuit is to be connected. Once the design is completed, the system performs the function intended. If it is desired to modify the function of the circuit, the design must be modified. New circuits may be needed and some connections will certainly require changes. This type of system is often referred to as a Hardwired System [16].

Examples of standard ICs include ROMs, DRAM, SRAM, Microprocessors.

With fixed logic devices, the time required to go from design, to prototypes, to a final manufacturing run can take from several months to more than a year, depending on the complexity of the device. And, if the device does not work properly, or if the requirements change, a new design must be developed. The up-front work of designing and verifying fixed logic devices involves substantial "non-recurring engineering" costs, or NRE. NRE represents all the costs customers incur before the final fixed logic device emerges from a silicon foundry, including engineering resources, expensive software design tools, expensive photolithography mask sets for manufacturing the various metal layers of the chip, and the cost of initial prototype devices. These NRE costs can run from a few hundred to several million dollars [35].

### **3.2 Application Specific Integrated Circuits (ASICs)**

ASICs are the integrated circuits that are customized or tailored to a particular system or application rather than using standard ICs alone. These ASICs are specially designed to perform a function that cannot be done using standard components (Standard ICs). Microelectronic system design then can be done by implementing some functions using standard ICs and the remaining logic functions using one or more custom ICs [11].

Examples of ASICs include a chip for a toy bear that talks, a chip for a satellite, a chip designed to handle the interface between memory and a microprocessor for a workstation CPU and a chip containing microprocessor as a cell together with other logic.

ASICs are used in system design to improve the performance of a circuit, to reduce the volume, weight and power requirements so that it increases the reliability of a system by integrating a large number of functions on a single chip.

ASICs are classified into two types: Full Custom ASICs and Semi Custom ASICs. A full custom IC includes possibly all logic cells that are customized and all mask layers that are customized. A microprocessor is an example of a full custom IC. For semi custom ASICs all of the logic cells are pre designed and some (possibly all) of the mask layers are customized. Using pre-designed cells from a cell library makes design much easier [11].

There are many situations in which it is not appropriate to use a custom IC for each and every part of a microelectronic system. For example, if a large amount of memory is needed, it is still best to use standard memory ICs, either DRAM or SRAM, in conjunction with custom ICs.

#### **3.3 Programmable Logic Devices (PLDs)**

Programmable Logic Devices (PLDs) consist of an array of identical function cells. The cell array usually contains an AND-OR network and often includes a flip-flop. Some PLDs can perform only combinational logic functions, others can perform combinational and sequential functions.

In Programmable Logic Devices (PLDs), logic function is programmed by the user and in some cases, can be reprogrammed many times. Such a device includes array of logic elements on a chip and allows the user to specify or program many internal connections between the components on the chip. The logic elements could be various gates, inverters, buffers, flip-flops. A system configuration can be created on the chip simply by programming the chip or telling the chip where the interconnections are to be made.

A PLD can be defined as: A PLD is an IC chip that includes arrays of logic elements and allows a user to specify the connections among many of these elements [16].

Figure 3.2 shows the basic architecture of PLD.

Figure 3.2. Programmable Logic Device

With programmable logic devices, designers use inexpensive software tools to quickly develop, simulate, and test their designs. Then, a design can be quickly programmed into a device, and immediately tested in a live circuit. The PLD that is used for this prototyping is the exact same PLD that will be used in the final production of a piece of end equipment, such as a network router, a DSL modem, a DVD player, or an automotive navigation system. There are no NRE costs and the final design is completed much faster than that of a custom, fixed logic device [12].

#### 3.3.1) Types of PLDs

Programmable logic devices are divided into three broad categories [5]:

#### 3.3.1.1) Simple Programmable Logic Devices (SPLDs)

These are the least complex form of PLDs. An SPLD can replace several fixed function SSI or MSI devices and their interconnections. A few categories of SPLD are listed below:

- PAL (Programmable Array Logic)

- GAL (Generic Array Logic)

- PLA (Programmable Logic Array)

- PROM (Programmable Read only Memory)

#### 3.3.1.2) Complex Programmable Logic Devices (CPLDs)

These have a much higher capacity than SPLDs, permitting more complex logic circuits to be programmed into them. A typical CPLD is equivalent of from 2 to 64 SPLDs. CPLDs generally come in 44-pin to160-pin packages depending on the complexity [5].

CPLDs offer logic up to about 10,000 gates. CPLDs offer very predictable timing characteristics and are therefore ideal for critical control applications. CPLDs also require extremely low amounts of power and are very inexpensive, making them ideal for cost-sensitive, battery-operated, portable applications such as mobile phones and digital handheld assistants.

#### 3.3.1.3) Field Programmable Gate Arrays (FPGAs)

These are different from SPLDs and CPLDs in their internal organization and have greatest logic capability. FPGAs consist of an array of anywhere from 64 to thousands of logic gates groups that are called logic blocks.

Although the generalized architecture of the simpler PLDs is fairly standardized, that of FPGAs and CPLDs continues to evolve and differs considerably from one manufacturer to other [12]. The architecture has a mesh of horizontal and vertical interconnect tracks. At each junction, there is a fuse. With the aid of software tools, the user can select which junctions will not be connected, by blowing all unwanted fuses. This is done by a device programmer.

Input pins are connected to the vertical interconnect and the horizontal tracks are connected to AND-OR gates, also called product terms. These in turn connect to dedicated flip-flops whose outputs are connected to output pins.

All FPGA contain a regular structure of programmable basic logic cells surrounded by programmable interconnect. The exact type, size and the number of programmable basic logic cells varies tremendously.

#### 3.3.2) Advantages & Disadvantages of PLDs

Fixed logic devices and PLDs both have their advantages and disadvantages. Fixed logic devices, for example, are often more appropriate for large volume applications because they can be mass-produced more economically. For certain applications where the very highest performance is required, fixed logic devices may be the best choice [35].

However, programmable logic devices offer a number of important advantages over fixed logic devices [12]. It is desirable to use PLDs for the following reasons:

- To decrease PC board cost by reducing the package count; 15 to 20 SSI packages can be replaced by a single package. Many more logic circuits can be stuffed into a smaller area with PLDs.

- 2. To improve reliability, fewer packages mean less interconnection and thus greater reliability.

- To allow design changes as reprogramming the PLDs is less time consuming than re-designing a complete PC board using random logic or MSI logic devices.

- 4. During the design phase customers can change the circuitry as often as they want until the design operates to their satisfaction. That is because PLDs are based on re-writable memory technology; to change the design, the device is simply reprogrammed.

- 5. PLDs offer customers much more flexibility during the design cycle because design iterations are simply a matter of changing the programming file, and the results of design changes can be seen immediately in working parts.

- 6. To shorten design time; PLDs do not require long lead times for prototypes or production parts. The PLDs are already on a distributor's shelf and ready for shipment [12].

- 7. PLDs do not require customers to pay for large NRE costs and purchase expensive mask sets. PLDs suppliers incur those costs when they design their programmable devices and are able to amortize those costs over the multi-year lifespan of a given line of PLDs.

- 8. PLDs allow customers to order just the number of parts they need, when they need them, allowing them to control inventory. Customers who use fixed logic devices often end up with excess inventory which must be scrapped, or if demand for their product surges, they may be caught short of parts and face production delays.

- 9. PLDs can be reprogrammed even after a piece of equipment is shipped to a customer. Because of programmable logic devices, it is very easy to add new features or upgrade products that already are in the field. To do this, simply upload a new programming file to the PLD, via the internet, creating new hardware logic in the system.

- 10. Advanced process technologies help PLDs in a number of key areas: faster performance, integration of more features, reduced power consumption, and lower cost.

- 11. PLDs now have a growing library of intellectual property (IP) or cores. These are predefined and tested software modules that customer can use to create system functions instantly inside the PLD. Cores include everything from complex digital signal processing algorithms and memory controllers to bus interfaces and full-blown software-based microprocessors. Such cores save customers a lot of time and expense.

The disadvantage of PLDs is that the interconnections between elements on the chip must be specified or programmed [16]. Unlike conventional circuits, even after PLDs are wired into the system, they will not function properly unless they have been programmed.

## **CHAPTER 4**

## Field Programmable Gate Array (FPGA)

#### Introduction

Field Programmable Gate Array provides the next step in the Programmable Logic Devices hierarchy. The word Field in the name refers to the ability of the gate array to be programmed for a particular function by the user instead of by the manufacturer of the device [11]. The word array is used to denote a series of columns and rows of gates that can be configured by the end user.

All FPGAs contain a regular structure of programmable basic logic cells surrounded by programmable interconnects. The exact type, size and the number of programmable basic logic cells vary tremendously.

#### **Essential characteristics of FPGAs:**

- 1. None of the mask layers are customized.

- 2. A method for programming the basic logic cells and the interconnect is required.

- 3. The core is a regular array of programmable basic logic cells that can implement combinational as well as sequential logic.

- 4. A matrix of programmable interconnects surrounds the basic logic cells.

- 5. Programmable I/O cells surround the core.

#### 4.2 Technologies Used

In all FPGAs, the interconnections and how they are programmed vary. Depending upon the application, one FPGA technology may have features desirable for that application. Currently there are following technologies in use [12]:

#### 4.2.1) Static RAM Technology

In the Static RAM FPGAs, programmable connections are made using pass transistors, transmission gates or multiplexer that are controlled by SRAM cells. The advantage of this technology is that it allows fast in-circuit re-configuration. The major disadvantage is the size of the chip required by the RAM technology. The FPGAs are customized by loading configuration data into the internal memory cells. The FPGA can be programmed an unlimited number of times and

supports system clock rates up to 50 MHz. In the SRAM logic cell, instead of conventional gates there is a look-up-table (LUT), which determines the output based on the values of the inputs.

#### 4.2.2) Anti-Fuse Technology

An anti-fuse resides in a high-impedance state, and can be programmed into low impedance or fused state. A less expensive than the RAM technology, this device is a program once device.

#### 4.2.3) EPROM / EEPROM Technology

This method is the same as used in the EPROM memories. One advantage of this technology is that it can be reprogrammed without external storage of configuration, though the EPROM transistors cannot be re-programmed in-circuit. There are two basic types of FPGAs: SRAM based re-programmable and One-time programmable (OTP). These two types of FPGAs differ in the implementation of the logic cell and the mechanism used to make connections in the device.

#### **4.3 Applications**

Applications of FPGAs are so varied in embedded systems that it is impossible to generalize. Following are some instances [29]:

#### 4.3.1) Prototyping

Many times FPGAs are used in a prototype system. A small device may be present to allow the designers to change a board's glue logic more easily during product development and testing. Or a large device may be included to allow prototyping of a system-on-a-chip design that will eventually find its way into an ASIC. Either way, the basic idea is the same, allow the hardware to be flexible during product development. When the product is ready to ship in large quantities, the programmable device will be replaced with a less expensive, though functionally equivalent, hard-wired alternative.

#### 4.3.2) Embedded Cores

More and more vendors are selling or giving away their processors and peripherals in a form that is ready to be integrated into a programmable logic based design. They either recognize the potential for growth in the system-on-achip area and want a piece of the royalties or want to promote the use of their particular FPGA by providing libraries of ready-to-use building blocks. Either way, lower system costs and faster time-to-market are achieved. We can buy an equivalent piece of virtual silicon, so there is no need to develop own hardware.

The Intellectual Property (IP) market is growing rapidly. It is common to find microprocessors and microcontrollers for sale in this form, as well as complex peripherals like PCI controllers. Many of the IP cores are even configurable. We can find the entire usual supporting cast of simple peripherals like serial controllers and timer/counter units are available as well.

#### 4.3.3) Hybrid Chips

There is also been some movement in the direction of hybrid chips, which combine a dedicated processor core with an area of programmable logic. According to the vendors of hybrid chips, a processor core embedded within a programmable logic device will require far too many gates for typical applications. So they have created hybrid chips that are part fixed logic and part programmable logic. The fixed logic contains a fully functional processor and perhaps even some on-chip memory. This part of the chip also interfaces to dedicated address and data bus pins on the outside of the chip. Application-specific peripherals can be inserted into the programmable logic portion of the chip, either from a library of IP cores or the customer's own designs.

#### 4.3.4) Reconfigurable Computing

As mentioned earlier, an SRAM-based programmable device can have its internal design altered on-the-fly. This practice is known as reconfigurable computing. Though originally proposed in the late 1960's by a researcher at UCLA, this is still a relatively new field of study. The decades-long delay had mostly to do with a lack of acceptable reconfigurable hardware. On-the-fly reprogrammable logic chips have only recently reached gate densities making them suitable for anything more than academic research. But the future of reconfigurable computing is bright and it is already finding a niche in high-end communications, military, and intelligence applications.

#### **4.3.5)** Other Applications

Application Specific Integrated Circuits (ASICs) Implementation of random logic Replacement of SSI for random logic

Onsite configuration of hardware

# 4.4 ACEX50K Device

Altera is a leading company in the production and advancements of PLDs. Altera ACEX EP1K50, 144 pin, TQFP FPGA has been used in the development of this project. The general and functional characteristics of this device are discussed in detail below.

### 4.4.1) Salient Features

1. ACEX50K FPGAs provide low cost System-On-Programmable-Chip (SOPC) integration in a single device.

- Enhanced embedded array for implementing megafunctions such as efficient memory and specialized logic functions

- Dual-port capability with up to 16-bit width per embedded array block (EAB)

- Logic array for implementing general logic functions

- 2. High density

- 10,000 to 100,000 typical gates

- Up to 49,152 RAM bits, 4,096 bits per EAB, all of which can be used without reducing logic capacity

- 3. Cost-efficient programmable architecture for high-volume applications

- Cost-optimized process

- Low cost solution for high-performance communications applications

- 4. System-level features

- Multi Volt TM I/O pins can drive or be driven by 2.5V, 3.3V, or 5.0V devices

- Low power consumption

- Bidirectional I/O performance up to 250 MHz

- Fully compliant with the peripheral component interconnect

- 5. Extended temperature range

| Features              | EP1K10 | EP1K30  | EP1K50  | EP1K100 |

|-----------------------|--------|---------|---------|---------|

| Typical gates         | 10,000 | 30,000  | 50,000  | 100,000 |

| Max System Gates      | 56,000 | 119,000 | 199,000 | 257,000 |

| Logic elements        | 576    | 1,728   | 2,880   | 4,992   |

| EABs                  | 3      | 6       | 10      | 12      |

| Total RAM bits        | 12,288 | 24,576  | 40,960  | 49,152  |

| Maximum user I/O pins | 136    | 171     | 249     | 333     |

**Table4.1 ACEX Device Features**

6. Fully compliant with the peripheral component interconnect Special Interest Group (PCI SIG) PCI Local Bus Specification.

- -1 speed grade devices are compliant with PCI Local Bus Specification

- Built-in Joint Test Action Group (JTAG) boundary scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990, available without consuming additional device logic

- Operate with a 2.5V internal supply voltage

- In-circuit reconfigurability (ICR) via external configuration devices, intelligent controller or, JTAG port

- ClockLockTM and ClockBoostTM options for reduced clock delay, clock skew, and clock multiplication

- Built-in, low-skew clock distribution trees

- 100% functional testing of all devices, so test vectors or scan chains are not required

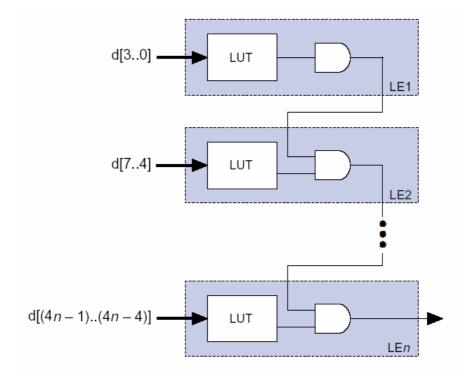

7. Flexible interconnect

- FastTrack Interconnect continuous routing structure for fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators, that are automatically used by software tools and megafunctions

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions, automatically used by software tools and megafunctions

- Tri-state emulation that implements internal tri-state buses

• Up to six global clock signals and four global clear signals

### 8. Powerful I/O pins

- Individual tri-state output enable control for each pin

- Open-drain option on each I/O pin

- Programmable output slew-rate control to reduce switching noise

- Clamp to  $V_{CCI/O}$  user-selectable on a pin-by-pin basis

- Supports hot-socketing

9. Software design support and automatic place-and-route provided by Altera development systems for Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations.

10. Additional design entry and simulation support provided by EDIF 200 and 300 netlist files, library of parameterized modules (LPM), DesignWare components, Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and Viewlogic [18].

### 4.4.2) General Description

Altera ACEX50K devices provide a die-efficient, low-cost architecture by combining look-up-table (LUT) architecture with EABs. LUT-based logic provides optimized performance and efficiency for data-path, register intensive, mathematical, or digital signal processing (DSP) designs, while EABs implement RAM, ROM, dual-port RAM, or first-in first-out (FIFO) functions. These elements make ACEX50K suitable for complex logic functions and memory functions such as digital signal processing, wide data path manipulation, data transformation and microcontrollers, as required in high-performance communications applications.

Based on reconfigurable CMOS SRAM elements, the ACEX50K architecture incorporates all features necessary to implement common gate array megafunctions, along with a high pin count to enable an effective interface with system components. The advanced process and the low voltage requirement of the 2.5V core allow ACEX 50K devices to meet the requirements of low cost, high-volume applications ranging from DSL modems to low-cost switches.

The ability to reconfigure ACEX50K devices enables complete testing prior to shipment and allows the designer to focus on simulation and design verification. Reconfigurability eliminates inventory management for gate array designs and test vector generation for fault coverage.

Table 4.2 shows ACEX50K device performance for some common designs. Special design techniques are not required to implement the applications, the designer simply infers or instantiates a function in a Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or schematic design file.

| Application                  | Res  | ources |             | Perfo | rmance    |

|------------------------------|------|--------|-------------|-------|-----------|

| Application                  | Used |        | Speed Grade |       |           |

|                              | LEs  | EABs   | -1          | -2    | -3 Units  |

| 16 Bit loadable Counter      | 16   | 0      | 285         | 232   | 185 (MHz) |

| 16 Bit Accumulator           | 16   | 0      | 285         | 232   | 185 (MHz) |

| 16 to 1 Multiplexer          | 10   | 0      | 3.5         | 4.5   | 6.6 (ns)  |

| 256*16 RAM read cycle speed  | 0    | 1      | 278         | 196   | 143 (MHz) |

| 256*16 RAM write cycle speed | 0    | 1      | 185         | 143   | 111 (MHz) |

Table4.2 ACEX50K Performance

Each ACEX50K device contains an embedded array and a logic array. The embedded array is used to implement a variety of memory functions or complex logic functions, such as digital signal processing (DSP), wide data-path manipulation, microcontroller applications, and data transformation functions. The logic array performs the same function as the sea-of-gates in the gate array and is used to implement general logic such as counters, adders, state machines, and multiplexers. The combination of embedded and logic arrays provides the high performance and high density of embedded gate arrays, enabling designers to implement an entire system on a single device.

ACEX50K devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers EPC16, EPC2, EPC1, and EPC1441 configuration devices, which configure ACEX50K devices via a serial data stream. Configuration data can also be

downloaded from system RAM via the Altera MasterBlasterTM, ByteBlasterMVTM, or BitBlasterTM download cables. After an ACEX50K device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Because reconfiguration requires less than 40 ms, real-time changes can be made during system operation [18].

ACEX50K devices are supported by Altera development systems, which are integrated packages that offer schematic, text (including AHDL), and waveform design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, and device configuration. The Altera software works easily with common gate array EDA tools for synthesis and simulation. For example, the Altera software can generate Verilog HDL files for simulation with tools such as Cadence Verilog XL. Additionally, the Altera software contains EDA libraries that use device specific features such as carry chains, which are used for fast counter and arithmetic functions. The Altera development systems run on Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations.

#### 4.4.3) Functional Description

Each ACEX50K device contains an enhanced embedded array that implements memory and specialized logic functions, and a logic array that implements general logic. The embedded array consists of a series of EABs. When implementing memory functions, each EAB provides 4,096 bits, which can be used to create RAM, ROM, dual-port RAM, or first-in first-out (FIFO) functions. When implementing logic, each EAB can contribute 100 to 600 gates towards complex logic functions such as multipliers, microcontrollers, state machines and DSP functions. EABs can be used independently or multiple EABs can be combined to implement larger functions.

The logic array consists of logic array blocks (LABs). Each LAB contains eight LEs and a local interconnect. An LE consists of a 4-input LUT, a programmable flip-flop, and dedicated signal paths for carry and cascade functions. The eight LEs can be used to create medium sized blocks of logic such as 8-bit counters, address decoders, or state machines or combined across LABs to create larger logic blocks. Each LAB represents about 96 usable logic gates.

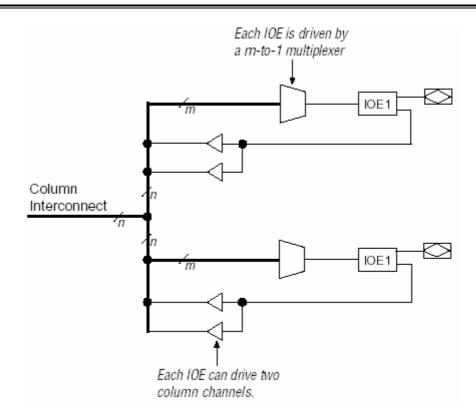

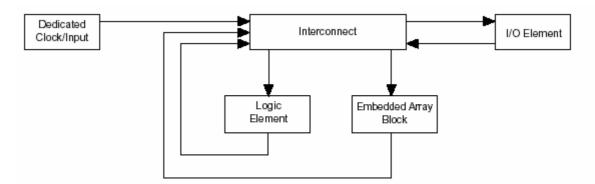

Signal interconnections within ACEX50K devices (as well as to and from device pins) are provided by the FastTrack Interconnect routing structure, which is a series of fast, continuous row and column channels that run the entire length and width of the device. Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect routing structure. Each IOE contains a bidirectional I/O buffer and a flip-flop that can be used as either an output or input register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. As inputs, they provide setup times as low as 1.1 ns and hold times of 0 ns. As outputs, these registers provide clock-to-output times as low as 2.5 ns. IOEs provide a variety of features such as JTAG BST support, slew-rate control, tristate buffers, and open-drain outputs.

Figure 4.1 shows the block diagram of the ACEX50K device.

Figure 4.1 ACEX50K Device Block Diagram

Each group of LEs is combined into an LAB; groups of LABs are arranged into rows and columns. Each row also contains a single EAB. The LABs and EABs are interconnected by the FastTrack Interconnect routing structure. IOEs are located at the end of each row and column of the FastTrack Interconnect routing structure. ACEX50K devices provide six dedicated inputs that drive the flip-flop's control inputs and ensure the efficient distribution of high-speed, low skew (less than 1.0 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect routing structure. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

### 4.4.3.1) Embedded Array Block (EAB)

The EAB is a flexible block of RAM, with registers on the input and output ports, that is used to implement common gate array megafunctions. Because it is large and flexible, the EAB is suitable for functions such as multipliers, vector scalars, and error correction circuits. These functions can be combined in applications such as digital filters and microcontrollers.

Logic functions are implemented by programming the EAB with a read only pattern during configuration, thereby creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of EABs.

The large capacity of EABs enables designers to implement complex functions in a single logic level without the routing delays associated with linked LEs. For example, a single EAB can implement any function with 8 inputs and 16 outputs. The ACEX50K enhanced EAB supports dual-port RAM. The dual-port structure is ideal for FIFO buffers with one or two clocks. The EAB can also support up to 16 bit wide RAM blocks. It can act in dual-port or single-port mode. When in dual-port mode, separate clocks may be used for read and write sections, allowing the EAB to be written and read at different rates. The EAB can also be used for bidirectional, dual-port memory applications where two ports read or write simultaneously. To implement this type of dual-port memory, two EABs are used to support two simultaneous reads or writes. Alternatively, one clock and clock enable can be used to control the input registers of the EAB, while a different clock and clock enable control the output registers.

Figure 4.2 ACEX50K EAB in Dual-Port RAM Mode

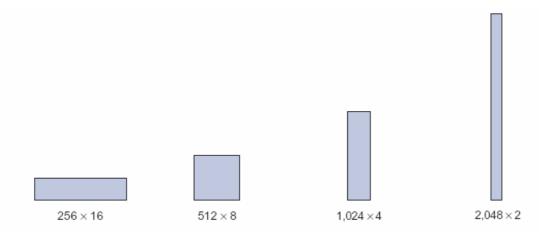

EABs can be used to implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the write enable signal. In contrast, the EAB's synchronous RAM generates its own write enable signal and is self-timed with respect to the input or write clock. When used as RAM, each EAB can be configured in any of the following sizes:  $256 \times 16$ ;  $512 \times 8$ ;  $1,024 \times 4$ ; or  $2,048 \times 2$ . Figure 4.3 shows the ACEX50K EAB memory configurations.

Figure 4.3 ACEX50K EAB Memory Configurations

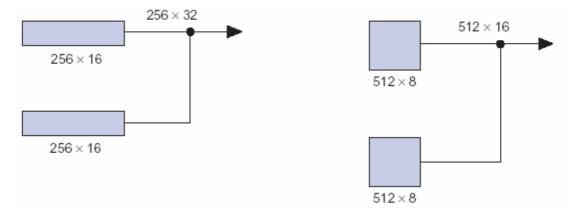

Larger blocks of RAM are created by combining multiple EABs. For example, two  $256 \times 16$  RAM blocks can be combined to form a  $256 \times 32$  block, and two  $512 \times 8$  RAM blocks can be combined to form a  $512 \times 16$  block Figure 4.4 shows examples of multiple EAB combination.

#### Figure 4.4 Examples of Combining EABs

Altera software automatically combines EABs to meet the designer's RAM specifications. An EAB is fed by a row interconnect and can drive out to row and column interconnects. Each EAB output can drive up to two row channels and up to two column channels; the unused row channel can be driven by other LEs. This feature increases the routing resources available for EAB outputs [18].

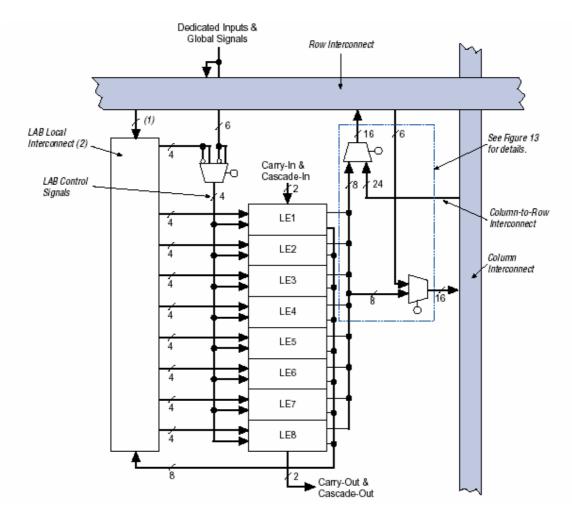

#### 4.4.3.2) Logic Array Block (LAB)

An LAB consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarsegrained structure to the ACEX50K architecture, facilitating efficient routing with optimum device utilization and high performance.

Each LAB provides four control signals with programmable inversion that can be used in all eight LEs. Two of these signals can be used as clocks; the other two can be used for clear/preset control. The LAB clocks can be driven by the dedicated clock input pins, global signals, I/O signals, or internal signals via the LAB local interconnect. The LAB preset and clear control signals can be driven by the global signals, I/O signals, or internal signals via the LAB local interconnect. The global control signals are typically used for global clock, clear, or preset signals because they provide asynchronous control with very low skew across the device. If logic is required on a control signal, it can be generated in one or more LEs in any LAB and driven into the local interconnect of the target LAB. In addition, the global control signals can be generated from LE outputs. Figure 4.5 shows the ACEX50K Logic Array Block.

Figure 4.5 ACEX50K Logic Array Block

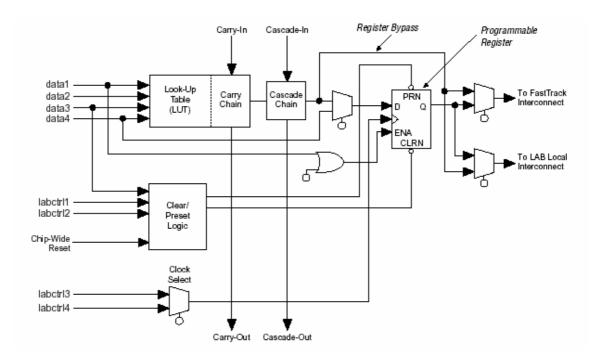

### 4.4.3.3) Logic Element

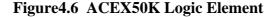

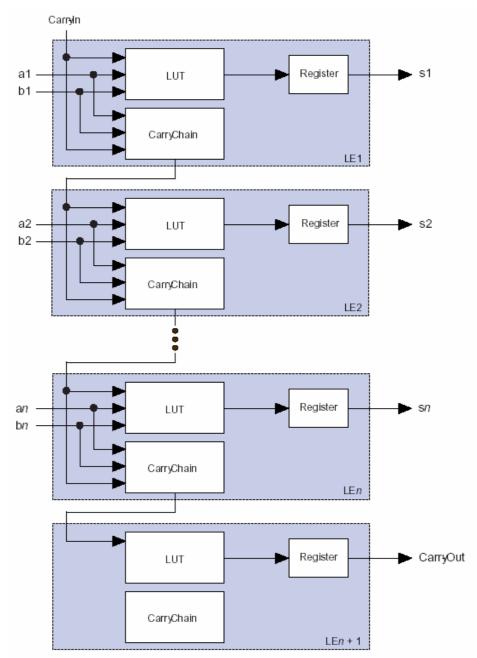

The LE, the smallest unit of logic in the ACEX50K architecture, has a compact size that provides efficient logic utilization. Each LE contains a 4-input LUT, which is a function generator that can quickly compute any function of four variables. In addition, each LE contains a programmable flip-flop with a synchronous clock enable, a carry chain, and a cascade chain. Each LE drives both the local and the FastTrack Interconnect routing structure.

The programmable flip-flop in the LE can be configured for D, T, JK, or SR operation. The clock, clear and preset control signals on the flip-flop can be driven

by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flip-flop is bypassed and the LUT's output drives the LE's output. The LE has two outputs that drive the interconnect: one drives the local interconnect, and the other drives either the row or column FastTrack Interconnect routing structure. The two outputs can be controlled independently. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, can improve LE utilization because the register and the LUT can be used for unrelated functions.

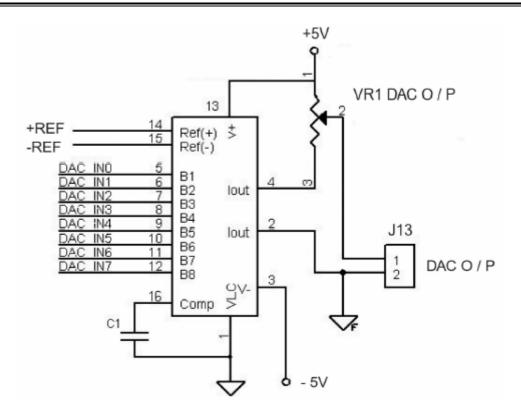

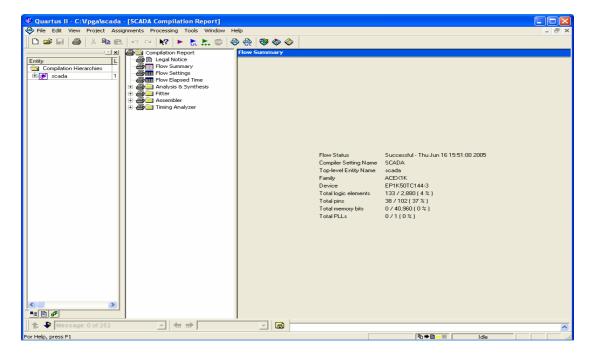

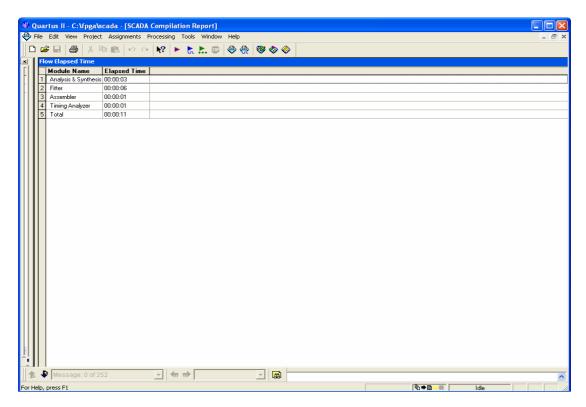

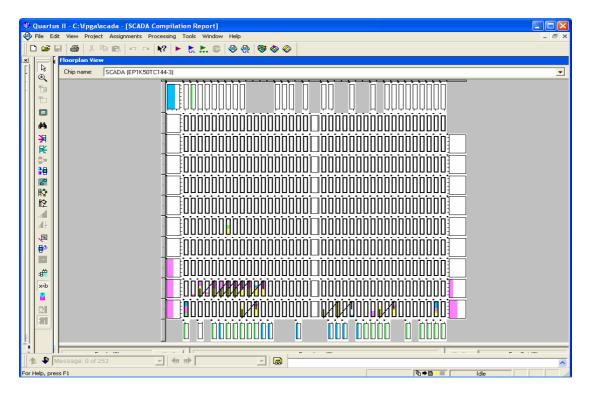

Figure 4.6 shows the ACEX50K Logic Element.