# Memory Architecture Design of a 32-bit Embedded Processor using VHDL

A Dissertation submitted to University of Delhi In partial fulfillment of the requirements for the award of the Master of Engineering in Electronics & Communication Engineering,

ΒY

MANOJ K N Roll No. 16/E&C/2001 University Roll No 4092

UNDER THE GUIDANCE OF

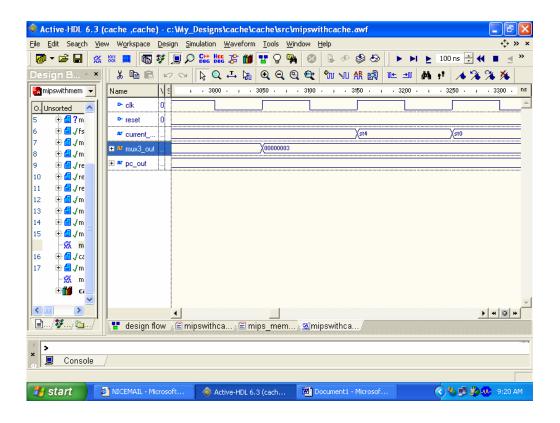

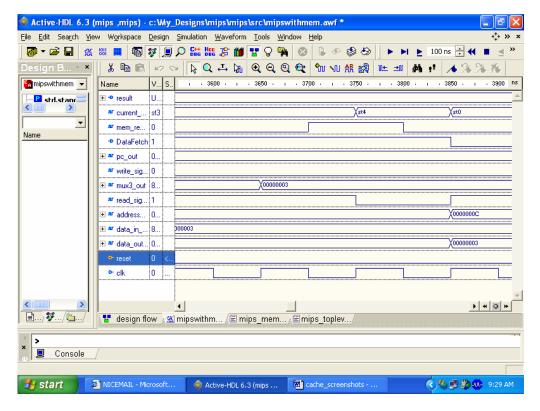

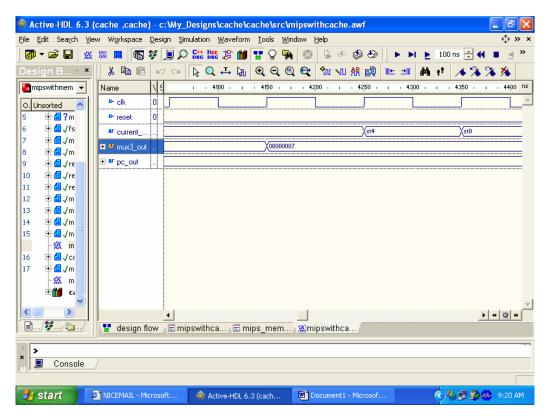

Prof. ASOK BHATTACHARYYA AND MRS. S. INDU

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING DELHI COLLEGE OF ENGINEERING DELHI UNIVERSITY

## **CERTIFICATE**

This is to certify that the dissertation entitled *Memory Architecture Design of a 32-bit Embedded Processor using VHDL* being submitted by Manoj K N for the degree of M E in Electronics & Communication is a record of his own work carried out under our supervision and guidance. The matter contained in this report has not been submitted for the award of any other degree or diploma.

Mrs. S INDU Lecturer Dept of ECE Delhi College of Engineering Dr. ASOK BHATTACHARYYA

Professor & H O D Dept of ECE Delhi College of Engineering

Department of Electronics & Communication Engineering Delhi College of Engineering Bawana Road, New Delhi – 110 042

#### ACKNOWLEDGMENT

With great pleasure, I express my sincere thanks to Dr. Asok Bhattacharyya, Professor & HOD, Department of Electronics & Communication Engineering, Delhi College of Engineering for his keen interest and encouragement in completing this project.

I am very much thankful and grateful to Mrs. S. Indu, Lecturer, Department of Electronics & Communication Engineering, for her valuable guidance during this project.

I am also thankful to other staff members of Delhi College of Engineering and all my fellow students, who helped me directly or indirectly in the completion of this project.

Manoj K N

#### ABSTRACT

Under this project entitled "*Memory Architecture Design of a 32-bit Embedded Processor using VHDL*", the following are modeled using VHDL.

1. A basic 32-bit embedded processor core using **VHDL.** It uses Register Transfer Level (**RTL**) description to model the processor. The processor modeled is based on MIPS Architecture. The design uses a 32 bit register file which is an array of thirty two 32-bit registers uses to store data, a 32bit register to store the instruction, 32-bit register to store operational data at various stage, an **ALU** for arithmetic and logic manipulation and an ALU control which decodes the function to be performed by **ALU**. Control is implemented using a Finite State Machine model. Multiplexers are used to select from different input signals in each functional blocks.

2. Behavioral model of a 32 bit Random Access Memory with burst transfer protocol implemented

3. Behavioral model of a Direct Mapped Write Through Cache Memory block which utilizes the burst transfer protocol while loading from the Random Access Memory.

The simulation is performed using **ACTIVE HDL Version 6.3** of **ALDEC Corporation**.

# CONTENTS

| 1. | Introduction                                   | 6  |

|----|------------------------------------------------|----|

|    | 1.1 MIPS32                                     | 6  |

|    | 1.2 Features                                   | 7  |

|    | 1.3 Applications                               | 7  |

| 2. | Introduction to VHDL                           | 9  |

|    | 2.1 VHDL Description of combinational networks | 9  |

|    | 2.2 Entity-Architecture Pair                   | 11 |

|    | 2.3 Compilation and Simulation of VHDL Codes   | 11 |

|    | 2.4 Variables, Signals and Constants           | 14 |

|    | 2.5 Arrays                                     | 15 |

|    | 2.6 VHDL Operators                             | 16 |

| 3. | Implementation                                 | 17 |

|    | 3.1 Single Cycle                               | 17 |

|    | 3.2 Multi Cycle                                | 17 |

|    | 3.3 Components of Data path                    | 17 |

|    | 3.4 Register File                              | 18 |

|    | 3.5 MIPS Instruction Format                    | 20 |

|    | 3.6 ALU Control                                | 22 |

|    | 3.7 Control Unit                               | 23 |

|    | 3.8 Breaking Instructions in to clock cycles   | 25 |

| 4. | Memory                                         | 28 |

| 5. | VHDL code and Simulation Results               | 31 |

| 6. | Conclusion                                     | 72 |

| 7. | Scope for further improvement                  | 73 |

| 8. | References                                     | 74 |

## 1. INTRODUCTION

We are living in a second age industrial revolution, when the availability and processing of information are causing untold changes in our lives. In 1971 Intel produced the first microprocessor, the 4004, which handled data as 4 bit numbers and contained 2250 transistors. It followed this soon with 8008, and within a few years number of companies were making their own microprocessor offerings. By the end of 1970s two trends were emerging for these remarkable devices. One was to scale down in size, if not computing power, the general purpose computer, this led quickly to the first desktop machines. The other, much more revolutionary was to place the microprocessor in products which apparently had nothing to do with computing. They began to find their way into photocopiers, washing machines, and a host of other products. While the first trend led to an inexorable demand for faster and bigger processors, the second placed lower demand on computational power and speed. It wanted physically small and cheap devices, with as much functionality of the system as possible squeezed on to one integrated circuit. Such microprocessors became known as micro controllers and the systems they controlled, embedded system.

**MIPS** architecture was chosen by Hennessey & Patterson [1] as a vehicle for teaching principle of Computer Architecture. It is a 32-bit Reduced Instruction Set Computer (**RISC**). Here we use the **MIPS** processor for developing a high level abstraction of in **VHDL** first. Then we develop a memory hierarchy to support this processor model to evaluate the importance of Cache Memory in improving the overall memory performance.

Developed more than 20 years ago at Stanford University, the MIPS architecture is a simple, streamlined, highly scalable RISC architecture. Its fundamental characteristics - such as the large number of registers, the number and the character of the instructions, and the visible pipeline delay slots - enable the MIPS architecture to deliver the highest performance per square millimeter and lowest energy consumption in today's SOC designs.

# 1.1 MIPS32

The MIPS32 Architecture sets a new performance standard for 32-bit embedded processors. The MIPS architecture is the leading embedded architecture because of its robust instruction set, scalability from 32-bits to 64-bits, broad-spectrum of software development tools. The MIPS32 architecture is a superset of the previous MIPS I and MIPS II Instruction Set Architectures (ISA) and incorporates powerful new instructions specifically for embedded applications, as well as proven memory management and privileged mode control mechanisms. By incorporating powerful new features, standardizing privileged mode instructions, and supporting past ISAs, the MIPS32 architecture provides a solid high-performance foundation for all future 32-bit MIPS processor-based development.

The MIPS32 architecture is based on a fixed-length, regularly encoded instruction set and uses a load/store data model. The architecture is streamlined to support optimized execution of high-level languages. Arithmetic and logic operations use a three-operand format, allowing compilers to optimize complex expressions formulation. Availability of 32 general-purpose registers enables compilers to further optimize code generation by keeping frequently accessed data in registers. Flexibility of its high-performance caches and memory management schemes continues to be a strength of the MIPS architecture. The MIPS32 architecture extends this advantage with well-defined cache control options. The size of the instruction and data caches can range from 256 bytes to 4Mbytes. The data cache can employ either a write-back or write-through policy. A no-cache option can also be specified.

# 1.2 Features

- Fully MIPS I and MIPS II ISA compatible

- Enhanced with conditional move and data-prefetch instructions

- Standardized DSP operations: multiply (MUL), multiply and add (MADD), and count leading 0/1s (CLZ/O)

- Privileged cache load/control operations

- Robust load/store RISC instruction set with 3-operand instructions in most formats (3 register, 2 registers + immediate), branch/jump options, and delayed jump instructions.

- 32 general purpose 32-bit registers (GPRs)

- Optional floating-point support:

- 32 single precision 32-bit or 16 double precision 64-bit floating point registers (FPRs)

- Floating-point condition code register

- Optional Memory Management Unit with:

- TLB or BAT address translation mechanisms

- Programmable page size

- o Optional caches:

- Instruction and or data cache options

- Write-back or write-through data-cache options

- Virtual or physical addressing

- Enhanced JTAG (EJTAG) support for non-intrusive debug support

MIPS32 compatible processors are intended for high performance, low-power, system-on-a-chip (SOC) embedded applications.

# 1.3 Applications

# **Security Devices**

- Smart cards

- Smart card readers

- Point of Deployment (POD) devices

# **Digital Consumer Devices**

- Digital Cameras

- Set-top Boxes

- Game Platforms

- DVD Players

# **Office Automation**

- Printers

- Copiers

- Scanners

- Multifunction Peripherals

## Other

- Industrial Controllers

- Mass Storage Systems

- Mass Storage Systems

Automotive Systems

Navigation (GPS)

PC Peripherals

Graphics Systems

Dedicated Terminals (POS, ATM, e-cash)

#### 2. INTRODUCTION TO VHDL

As integrated circuit technology has improved to allow more and more components on a chip, digital systems have continued to grow in complexity. As digital systems have become more complex, detailed design of the systems at the gate and flip-flop level has become very tedious and time consuming. For this reason, use of hardware description languages in the digital design process continues to grow in importance. A hardware description language allows a digital process continues to grow in importance. A hardware description language allows a digital system to be designed and debugged at a higher level before conversion to the gate and flip-flop Use of synthesis computer-aided design tools to do this conversion is level. becoming more widespread. This is analogous to writing software programs in a high-level language such as C and then using a compiler to convert the programs to machine language. The two most popular hardware description languages are VHDL and Verilog.

VHDL is a hardware description language used to describe the behavior and structure of digital systems. The acronym VHDL stands for VHSIC Hardware Description Language, and VHSIC in turn stands for very High Speed Integrated Circuit. However, VHDL is a general purpose hardware description language that can be used to describe and simulate the operation of a wide variety of digital systems, ranging in complexity from a few gates to an interconnection of many complex integrated circuits. VHDL was originally developed for the military to allow a uniform method for specifying digital systems. The VHDL language has since become and IEEE standard, and it is widely used in industry.

VHDL can describe a digital system at several different levels-behavioral, data flow, and structural. For example, a binary adder could be described at the behavioral level in terms of its function of adding two binary numbers, without giving any implementation details. The same adder could be described at the data flow level by giving the logic equations for the adder. Finally, the adder could be described at the structural level by specifying the interconnections of the gates that comprise the adder.

VHDL leads naturally to a top-down design methodology, in which the system is first specified at a high level and tested using a simulator. After the system is debugged at this level, the design can gradually be refined, eventually leading to a structural description closely related to the actual hardware implementation. VHDL was designed to be technology independent. If a design is described in VHDL and implemented in today's technology, the same VHDL description could be used as a starting point for a design in some future technology.

## 2.1 VHDL description of combinational networks

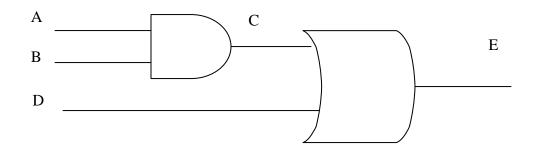

Below given is description of a simple gate network in VHDL. If each gate in the network of figure has a 5-ns propagation delay, the network can be described as follows:

| С | <= | A and  | B after 5 ns; |

|---|----|--------|---------------|

| E | <= | C or D | after 5 ns;   |

Where A, B, C, D and E are signals. A signal in VHDL usually corresponds to a signal in a physical system. The symbol "<=" is the signal assignment operator, which indicates the value computed on the right side is assigned to the signal on the left side. When these statements are simulated, the first statement will be evaluated any time A or B changes, and the second statement will be evaluated any time C or D changes. Suppose that initially A=1, and B=C=D=E=0. If B changes to 1 at time 0, C will change to 1 at time=5 ns. Then E will change to 1 at time = 10 ns.

## Fig. 2.1 GATE NETWORK

VHDL signal assignment statements, like the ones in the preceding example, are called concurrent statements when they are not contained in a VHDL process or block. The VHDL simulator monitors the right-hand side of each concurrent statement, and any time a signal changes, the expression on the right-hand side is immediately re-evaluated. The new value is assigned to the signal on the left-hand side after an appropriate delay.

When we initially describe a network, we may not be concerned about propagation delays. If we write

$C \le A$  and B;  $E \le C$  or D:

This implies that the propagation delays are 0 ns. In this case, the simulator will assume an infinitesimal delay referred to as (delta).

Unlike a sequential program, the order of the preceding statements is unimportant. If we write

The simulation results would be exactly the same as before. Even if a VHDL program has no explicit loops, concurrent statements may execute repeatedly as if they were in a loop. The VHDL statement

CLK <= not CLK;

Will cause a run-time error during simulation. Since there is 0 delay, the value of CLK will change at time 0 + 1, 0+2..., 0+3... etc., and real time will never advance.

In general, VHDL is not case sensitive; that is, capital and lowercase letters are treated the same by the compiler and simulator. Thus the statements

CLK <= NOT CLK After 10 NS;

And CLK <=NOT CLK after 10 ns;

Are treated exactly the same. Signal names and other VHDL identifiers may contain letters, numbers, and the underscore character (\_). An identifier must start with a letter, and it cannot end with an underscore. Thus C123 and ab\_23 are legal identifiers, but 1 ABC and ABC-are not. Every VHDL statement must be terminated with a semicolon.

#### 2.2 Entity-Architecture Pairs

To write a complete VHDL program, we must declare all the input and output signals and specify the type of each signal. As an example, we will describe the full adder of above figure. A complete description must include an entity declaration and an architecture declaration. The entity declaration specifies the inputs and outputs of the adder module:

Entity Full Adder is Port (X,Y, Cin: in bit; -- inputs Cout, Sum: out bit); -- outputs

End Full Adder;

The words entity, is port, in, out and end are reserved words (or keywords), which have a special meaning to the VHDL compiler. Anything that follows a double dash (--) is a VHDL comment. The port declaration specifies that X,Y and Cin are input signals of type bit, which means it can assume only values of '0' or '1'.

The operation of the full adder is specified by an architecture declaration:

architecture Equations of Full Adder is begin

Sum <=X xor Y xor Cin after 10 ns; Cout <= (X and Y) or (X and Cin) or (Y and Cin) after 10 ns;

end Equations;

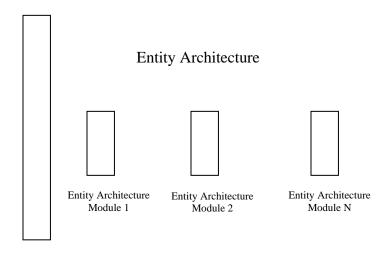

Fig. 2.2 VHDL Program Structure

In this example, the architecture name (Equations) is arbitrary; but the entity name (Full Adder) must match the name used in the associated entity declaration. The VHDL assignment statements for Sum and Cout represent the logic equations for the full adder. Several other architectural descriptions, such as a truth table or an interconnection of gates could have been used instead. In the Cout equation, parenthesis are required around (X and Y), since VDHL does not specify an order of precedence for the logic operators.

When we describe a system in VHDL, we must specify an entity and an architecture at the top level, and also specify an entity and architecture for each of the component modules that are part of the system. Each entity declaration includes a list of interface signals that can be used to connect to other modules or to the outside world. We will use entity declarations of the form

entity entity\_name is

[port (interface-signal-declaration);]

end [entity] [entity\_name];

The items enclosed in brackets are optional. The interface-signal-declaration normally has the following form;

list-of-interface-signals: mode type [:=initial-value]

Input signals are of mode in, output signals are of mode out, and bi-directional signals are of mode inout. The optional initial value is used to initialize the signals on the associated list; otherwise, the default initial value is used for the specified type. For example, the port declaration

Port (A, B: in integer := 2; C,D: out bit); Indicates that A and B are input signals of type integer, which are initially set to 2, and C and D are output signals of type bit, which are initialized by default to '0'.

Associated with each entity is one or more architecture declarations of the form

architecture architecture\_name of entity\_name is

(declaration)

begin

architecture body

end [architecture] [architecture\_name];

#### 2.3 Compilation and Simulation of VHDL code

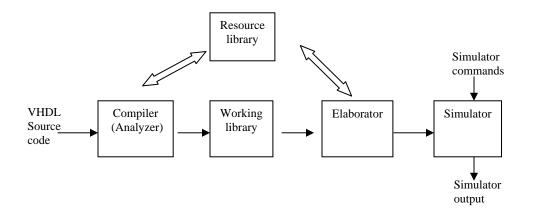

After describing a digital system in VHDL, simulation of the VHDL code is important for two reasons. First, we need to verify the VHDL code correctly implements the intended design; second, we need to verify that the design meets its specifications. Before the VHDL model of a digital system can be simulated, the VHDL code must first be compiled. The VHDL compiler, also called an analyzer, first checks the VHDL source code to see that it conforms to the syntax and semantic rules of VHDL. If there is a syntax error such as a missing semicolon, or if there is a semantic error such as trying to add two signals of incompatible types, the compiler will output an appropriate error message. The compiler also checks to see that references to libraries are correct. If the VHDL code confirms to all the rules, the compiler generates intermediate code, which can be used by a simulator or by a synthesizer.

In preparation for simulation, the VHDL intermediate code must be converted to a form that can be used by the simulator. This step is referred to as elaboration. During elaboration, ports are created for each instance of a component, memory storage is allocated for the required signals, the interconnections among the port signals are specified, and a mechanism is established for executing the VHDL processes in the proper sequence. The resulting data structure represents the digital

Fig. 2.3 Compilation, Elaboration, and Simulation of VHDL Code

system being simulated. After an initialization phase, the simulator enters the execution phase. The simulator accepts simulation commands, which control the simulation of the digital system and specify the desired simulator output.

#### 2.4 Variables, Signals and Constants

Variables may be used for local storage in process, procedures, and functions. A variable declaration has the form :

```

Variable list_of_variable_names : type_name [:=initial_value];

```

Variables must be declared within the process in which they are used and are local to that process. An exception to this rule is shared variables. Signals, on the other hand, must be declared outside of a process. Signals declared at the start of an architecture can be used anywhere within that architecture.

A signal declaration has the form

signal list\_of signal\_names : type\_name [:=initial\_value];

A common form of constant declaration is

constant constant\_name : type\_name : = constant\_value;

A constant delay of type time having the value of 5 ns can be defined as

constant delay : time : = 5 ns;

Constants declared at the start of an architecture can be used anywhere within that architecture, but constants declared within a process are local to that process.

Variables are updated using a variable assignment statement of the form

variable\_name : = expression;

When this statement is executed, the variable is instantaneously updated with no delay not even a delta delay. In contrast, consider a signal assignment of the form

```

signal_name<=expression [after delay];</pre>

```

The expression is evaluated when this statement is executed, and the signal is scheduled to change after delay. If no delay is specified, then the signal is scheduled to be updated after a delta delay.

#### 2.5 Arrays

In order to use an array in VHDL, we must first declare an array type and then declare an array object. For example, the following declaration defines a one-dimensional array type names SHORT\_WORD:

type SHORT\_WORD is array (15 down to 0) of bit;

An array of this type has an integer index with a range from 15 down to 0, and each element of the array is of type bit.

Next, we declare array objects of type SHORT\_WORD:

| signal DATA_WORD :  | SHORT_WORD;                       |

|---------------------|-----------------------------------|

| variable ALT_WORD : | SHORT_WORD: = "0101010101010101"; |

| constant ONE_WORD:  | SHORT_WORD := (others = '1');     |

DATA\_WORD is a signal array of 16 bits, indexed 15 down to 0, which is initialized (by default) to all '0' bits. ALT\_WORD is a variable array of 16 bits, which is initialized to alternating 0s and 1s. ONE\_WORD is a constant array of 16 bits, all bits are set to 1 by (others => '1'). We can reference individual elements of the array by specifying an index value. For example, ALT\_WORD (0) accesses the rightmost bit of ALT\_WORD. We can also specify a portion of the array by specifying an index range: ALT\_WORD (5 downto 0) accesses the low-order 6 bits of ALT\_WORD, which have an initial value of 010101.

The array type and array object declarations illustrated here have the general forms

type array\_type\_name is array index\_range of element\_type;

signal array\_name: array\_type\_name [: = initial\_values];

In the preceding declaration, signal may be replaced with variable or constant.

Multidimensional array types may also be defined with two or more dimensions. The following example defines a two-dimensional array variable, which is a matrix of integers with four rows and three columns:

type matrix\_4x3 is array (1 to 4, 1 to 3) of integer; variable matrix\_a : matrix\_4x3 := ((1,2,3), (4,5,6), (7,8,9), (10,11,12)); The variable matrix\_a, will be initialized to

1 2 3 4 5 6 7 8 9 10 11 12

The array element matrix A (3,2) references the element in the third row and second column, which has a value of 8.

## 2.6 VHDL Operators

Predefined VHDL operators can be grouped into seven classes:

- 1. Binary logical operators: and or nand nor xor xnor

- 2. Relational operators : =/ = < <= > >=

- 3. Shift operators: sll srl sla sra rol ror

- 4. Adding operators: + & (concatenation)

- 5. Unary sign operators : + -

- 6. Multiplying operators : \* / mod rem

- 7. Miscellaneous operators : not abs \*\*

When parentheses are not used, operators in class 7 have precedence and are applied first, followed by class 6, then class 5 etc. Class 1 operators have lowest precedence and are applied last. Operators in the same class have the same precedence and are applied from left to right in an expression. The precedence order can be changed by using parentheses.

## 3. IMPLEMENTATION

Any processor will two distinctive parts. One is Datapath and the other one being Control. MIPS datapath can be either single cycle or multicycle.

# 3.1 Single Cycle

Datapath executes all instructions in 1 clock cycle. This means that no datapath resource can be used more than once per instructions, so any element needed more than once must be duplicated. Inefficient because clock cycle is determined by the longest possible path in the machine (usually load instructions) so the overall performance of the single cycle instruction is not likely to be good as several of the instructions can be completed in a shorter cycle.

## 3.2 Multicycle

Each instruction is broken into several steps and each of such steps take one clock cycle to executes. This allows functional units to be used more than once per instruction as long as it is used in different clock cycle.

In this project we are modeling a multicycle datapath with finite state machine control for a 32-bit MIPS processor.

In a multicycle implementation, each step in the execution will take 1 clock cycle. The multicycle implementation allows a functional unit to be used more than once per instruction, as long as it is used on different clock cycles. This sharing can help reduce the amount of hardware required. The ability to allow instructions to take different numbers of clock cycles and the ability to share functional units within the execution of a single instruction are the major advantages of a multicycle design.

At the end of a clock cycle, all data that are used in subsequent clock cycles must be stored in a state element. Data used by subsequent instructions in a later clock cycle is stored into one of the programmer-visible state elements (i.e., the register file, the PC, or the memory). In contrast, data used by the same instruction in a later cycle must be stored into one of these additional registers.

Thus the position of the additional registers is determined by the two factors: what combinational units will fit in a clock cycle and what data are needed in later cycles implementing the instruction. In this multicycle design, we assume that the clock cycle can accommodate at most one of the following operations: a memory access, a register file access (two reads or one write), ore an ALU operation. Thus any data produced by one of these three functional units (the memory, the register file, or the ALU) must be saved into a temporary register for use on a later cycle.

# 3.3 Components of Datapath

A reasonable way to start a datapath design is to examine the major elements to required to execute each class of MIPS instruction. At the end of a clock cycle, all data that are used in subsequent clock cycles must be stored in a state element Data used by subsequent instructions in a Later Clock Cycle is stored into one of the programmer visible state elements (register file, the PC or the memory) where as

the data used by the same instruction in a later cycle is stored into one of the general purpose registers provided after each main functional unit.

The datapath will have the following two types of components.

Combinational Elements (Adder, MUX, ALU) Storage Elements (Register, Register File)

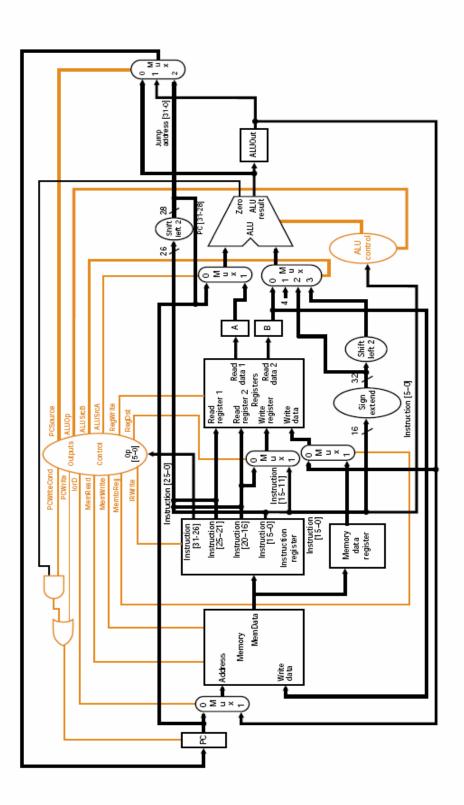

A multicycle datapath is shown in the figure 3.1. It contains the following

| (1) Register array                  | - 32 registers of 32- bit size                                                                    |  |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| (2) Register 32 bit                 | -Memory Data Register                                                                             |  |  |  |

|                                     | Register A                                                                                        |  |  |  |

|                                     | Register B                                                                                        |  |  |  |

|                                     | ALU Out Register                                                                                  |  |  |  |

| (3) Registers 32 bit with registers | - These are used where programmer visible                                                         |  |  |  |

| enable input                        | are needed                                                                                        |  |  |  |

|                                     | <ul><li>(i) Instruction Register (Write is controlled<br/>with IRWrite Signal from PSM)</li></ul> |  |  |  |

|                                     | (ii) Program Counter (32 bit) write is<br>controlled with PC Write control signal                 |  |  |  |

| (4) Multiplexers                    | All controlled with signals coming from PSM Control unit.                                         |  |  |  |

(5) Control Unit

## 3.4 Register file

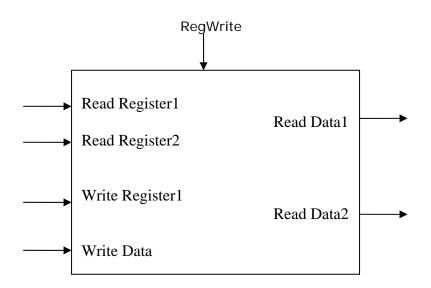

The processors 32 registers are stored in a structure called a register file. A register file is collection of register in which any register can be read or written by specifying the number of the register in the file. It has three inputs for selecting the register to be operated (2 for read operation and one in case of write operation)

Fig. 3.1 MIPS DATAPATH & CONTROL

**Register Files**

Fig. 3.2 Register File

To write data into the register file, we need 2 inputs one to specify the register number one to supply the data. The register file always outputs the contents of whatever register numbers are on the Read register inputs. Writes however are controlled by write control signal (Regwrite) which must be asserted for a write to occur at the clock cycle.

# 3.5 MIPS instruction format

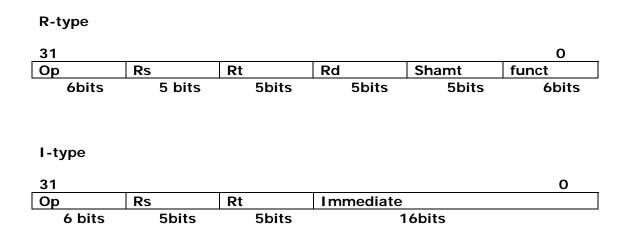

The layout of instruction is called the instruction format. MPIS instructions are classified into three types.

J TYPE

| 31    |                         | 0 |

|-------|-------------------------|---|

| Ор    | Target address (26bits) |   |

| 6bits |                         |   |

As it can be seen all **MIPS** instructions are 32 bit long.

The different fields are :

| ٠ | ор       | <ul> <li>operation of the instruction</li> </ul>     |

|---|----------|------------------------------------------------------|

| ٠ | rs,rt,rd | <ul> <li>source and destination registers</li> </ul> |

| ٠ | shamt    | - shift amount                                       |

| ٠ | funct    | - selects the variant of operation in Op field.      |

Here we will simulating MIPS datapath for R type (Arithmetic Operations) and I type (Load/Store Operations).

#### **R** Type Instructions

**R** type instructions have an **OP-code** of '0' always. These instructions have three register operands : **rs**, **rt** and **rd**. Field **rs** and **rt** are the source registers and **rd** is the destination. **ALU** function is in the **funct** field and is decoded by the **ALU** control. The **R** type instruction that we implement are **add**, **sub**, **and**, **or** and **slt** (**set on less than**). The **shamt** field is only used in shift instructions which we will ignore presently.

**R** type instructions implemented here are

| ADD rd, rs, rt | => rd = rs + rt               |

|----------------|-------------------------------|

| SUB rd, rs, rt | => rd = rs - rt               |

| AND rd, rs, rt | => rd = rs & rt               |

| OR rd, rs, rt  | => rd = rs    rt              |

| SLT rd, rs, rt | => if rs < rt, rd=1 else rd=0 |

Fields in the case of **ADD** instruction

As mentioned earlier, for and **R** type instruction the **OP** and **SHAMT** fields will be zero always (first and fifth fields). The second field gives the number of the register that is the first source operand (**rs**) and the third field indicates the second source operand (**rt**). Fourth field indicated the destination where the addition result will be stored (**rd**). Sixth filed defined the function to be performed, in this case it will be 100000 (32) for addition.

The above explanation is valid for other R type instructions as well. The only field that will change is that of function.

| R TYPE<br>INSTRUCTION | FUNCTION FIELD<br>ENTRY |

|-----------------------|-------------------------|

| ADD                   | 100000 (32)             |

| SUB                   | 100010 (34)             |

| AND                   | 100100 (36)             |

| OR                    | 100101 (37)             |

| SLT                   | 101010 (42)             |

## 3.6 ALU CONTROL

The control input to the data path are coming from several fields of Instruction Register and from the **FSM** controller. **ALU** has three control inputs. Only five of the possible eight input combinations are used.

| ALU CONTROL<br>INPUT | FUNCTION         |

|----------------------|------------------|

| 000                  | AND              |

| 001                  | OR               |

| 010                  | ADD              |

| 110                  | SUBTRACT         |

| 111                  | SET ON LESS THAN |

Depending on the instruction class the ALU will need to perform one of these five functions. For load word (LW) and store word (SW) instructions we use ALU to compute the memory address by addition. For R type instruction ALU needs to perform for the five functions (Addition, Subtraction, AND, OR and SLT) depending on the value of 6 bit function feed in the lower bits of the instruction.

We can generate the 3 bit ALU Control using a small control unit that has as inputs the function field of the instruction and a 2 bit control field which is ALUOp. Table

illustrates the way in which the ALU Control input is decided using ALUOp and function code.

| Instruction<br>OPCODE | ALUOp | Function Field | Desired ALU action | ALU control<br>input |

|-----------------------|-------|----------------|--------------------|----------------------|

| LW                    | 00    | XXXXXX         | ADD                | 010                  |

| SW                    | 00    | XXXXXX         | ADD                | 010                  |

| R - TYPE              | 10    | 100000         | ADD                | 010                  |

| R - TYPE              | 10    | 100010         | SUBTRACT           | 110                  |

| R - TYPE              | 10    | 100100         | AND                | 000                  |

| R - TYPE              | 10    | 100101         | OR                 | 001                  |

| R - TYPE              | 10    | 101010         | SET ON LESS THAN   | 111                  |

This style of using multiple levels of decoding (i.e. the main control unit generates the ALUOp bits, which then are used as inputs to the ALU control that generates the actual signal to control the ALU Control) can reduce the size of the main control unit which in turn increases the speed of control unit.

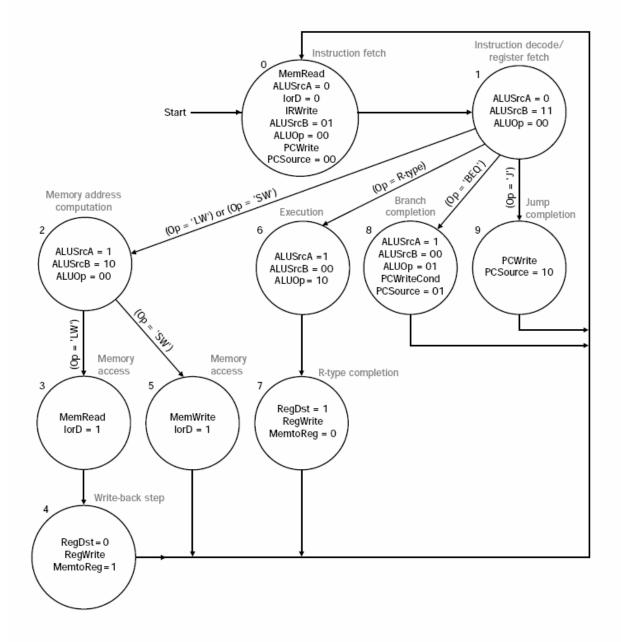

#### 3.7 CONTROL UNIT

The control is implemented using a finite state machine. A finite state machine consists of a set of states and directions on how to change states. The directions are defined by next-state functions, which maps the current state and the inputs to a new state. When we use a finite state machine, each state also specifies a set of outputs that are asserted when the machine is in that state. The implementation of a finite state machine usually assumes that all outputs are not explicitly asserted are deasserted. The correct operation of the datapath depends on the fact that a signal that is not explicitly asserted is reasserted, rather than acting as a don't care.

Multiplexer controls are slightly different, since they select one of the inputs whether they are 0 or 1. Thus in the finite state machine, we always specify the setting of all the multiplexer controls that we care about.

The finite state control essentially corresponds to the five steps of execution that will be discussed later. The finite state machine will consists of several parts. Since the first 2 states of FSM are identical for every instruction, the initial two states of the FSM will be common to all instructions. Step 3 through 5 differ, depending on the OPcode. After the execution of the last step for a particular instruction class, the FSM will return to the initial state to begin fetching the next instruction.

Figure 3.3 in the next page graphically represents the FSM used in the case. The signals that are asserted in each case state are shown within the circle representing the state. The arcs between the states define the next states and are labeled with conditions that select a specific next state when multiple states are possible. The process of branching to different states depending on the instruction

Fig 3.3 The Combined control unit

is called decoding, since the choice of next state and hence the actions that follow, depend on the instruction class.

For memory reference, the first state after fetching the instruction and registers computes the memory address (state 2). To compute the memory address, the ALU input multiplexers must be set so that the first input is the A register while the second is the sign extended displacement field, the result is written into the ALUOut register. After the memory address calculation the memory should be read or written, this requires two different states. If the instruction OPcode is LW, then state 3 does the memory read.

Output of memory is always written into MDR. If it is SW, state 5 does a memory write. In state 3 and 5, the signal IorD is set to 1 to force the memory address to come from the ALU. After performing a write, the SW instruction has completed execution, and next state is 0. If the instruction is a load, however another state (state 4) is needed to write the result from memory into the register file. After this state, corresponding to the memory read completion step, next state is 0.

To implement R type instruction requires two states corresponding to step 3 (execute) and 4 (R type completion). State 6 asserts ALUSrcA and ALUSrcB signal to 00, this forces the two registers that were read from the register file to be used as inputs to the ALU setting ALUOp to cause ALU control unit to use the function field to set the ALU control signed. In state 7, RegWrite signal is asserted to cause register file write.

#### 3.8 Breaking the instruction Execution into Clock Cycles

Given the datapath details, we now need to look at what should happened in each clock cycle of the multicycle execution, since this will determine what additional control signals may be needed, as well as the setting of the control signals.

All the operations listed in one steps occur in parallel within 1 clock cycle while successive steps operate in series in different clock cycles. The limitation of 1 ALU operations, one memory access, one register file access determines what can fit in one step.

## Step 1

Instruction Fetch step

IR = Memory (PC)PC = PC + 4

Operation : Send the PC to the memory as address perform a read and write the instruction into the Instruction Register (IR). Also increment PC BY 4.

To implement this the following control signals are needed

| Mem Read = 1   |                                                             |

|----------------|-------------------------------------------------------------|

| IR Write = 1   |                                                             |

| IorD = 0       | (to select PC as the source of address)                     |

| ALUSrcA = 0    | (sending PC to ALU)                                         |

| ALUSrcB = 01   | (sending 4 to ALU)                                          |

| ALUOp = 00     | (To make ALU add                                            |

| PC write = $1$ | (For storing the incremented instruction address back to PC |

The increment of PC and instruction memory access occur in parallel. The new value of PC is not visible until the next clock cycle.

#### Step 2

Only optimistic actions are performed in this step as the exact nature of instruction is not known yet. So, action performed in this step is access the register file to read register *rs* and *rt* and store the result into registers A and B.

A = Reg[IR(25-21)],

B = Reg [IR (20-16)];

#### Step 3

Execution, or Memory address computation.

This is the first cycle during which the datapath operation is determined by the instruction class. In all the cases, the ALU is operating on the operands prepared in the previous step, performing one of the following functions depending on the instruction class.

(i) Memory reference:

ALUOut = A + sign Extend [IR(15-0)]

To implement this the following control signals are needed

ALUSrcA = 1

ALUSrcB = 10

So that output of sign extension unit is used for second ALU input ALU output will be 00 causing ALU to Add.

(ii) Arithmetic – logic Unit (R-type)

ALUOut = A op B

ALU is performing the function specified by the function field on the two values read from the register file. ALUSrcA = 1 and ALUSrcB = 10 causing A & B to be used as

ALU inputs. ALUOp is set to '10' so that function field is used to determine the ALU control signal.

#### Step 4

Memory Access or R type Instruction completion step: During this step, a load or store instruction accesses memory and a arithmetic logic instruction writes its result when a value is stored into the memory data register (MDR), where it must be used on the next clock cycle.

MDR = Memory (ALUOut)

Or

Memory (ALUOut) = B

In either case, the address used, is the one computed during the previous step and stored in ALUOut.

The signal MemRead or MemWrite is asserted for loads, IorD is set to 1 to force memory address to come from the ALU

In the case of R-type instructions

Reg[IR(15-11)] = ALUOut

Place the content of ALUOut into result register. RegDst is set to 1 (to force rd 15-11) field to be used to select register file entry to write. RegWrite is asserted and MemtoReg is set to '0' so that ALUOut is written to the register file as opposed to the memory data output.

Step 5

Memory read completion step during this step, load complete by writing back the value from memory

Reg [IR(20-16)] = MDR

MemtoReg = 1 to write the result from memory

RegWrite = 1 (to cause a write)

RegOut = 0 to choose rt (20-16) as register

#### 4. MEMORY

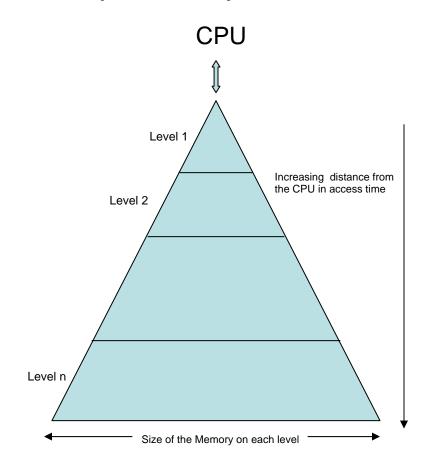

While designing memory we take advantage of principle of locality by implementing the memory of computer as a memory hierarchy. A memory hierarchy consist of multiple levels of memory with different speeds and sizes. Faster memories are more expensive per bit than the slower memories and thus are usually smaller.

Today there are three primary technologies used in building memory hierarchy. Main memory is implemented using DRAM ( Dynamic Random Access Memory ) while levels closer to the CPU are implemented using SRAM (Static Random Access Memory ). DRAM is less costly per bit than SRAM, although it is substantially slower. The price difference arises because DRAM uses significantly less area per bit of memory and DRAMs thus have larger capacity for the same amount of silicon. Because of the difference of cost and access time, it is advantageous to build memory as hierarchy of levels with faster memory closer to the CPU and slower less expansive memory below that as shown in figure 4.1

The memory system is organized as a hierarchy, a level closer to the process is a subset of any level further away and all data is stored in the lowest level.

Figure 4.1 Memory Hierarchies

A memory hierarchy can consists of multiple levels, but data is copied between only two adjacent levels at a time. If the data requested by the CPU appears in some block in the upper level, this is called a *hit* and if data is not present in the upper level the request is called a *miss*. Since performance is a major reason for having a memory hierarchy, the speed of hits and misses is important. Hit time is the time to access the upper level of memory which includes the time needed to determine whether the access is a hit or a miss. The miss penalty is the time to replace a block in the upper level with the corresponding block from the lower level plus the time to deliver this block to the CPU.

Program exhibit both temporal locality, the tendency to reuse recently accessed data items and spatial locality, the tendency to refer data items that are close to other recently accessed items. Memory hierarchy takes advantage of temporal locality by keeping more recently accessed data items closer to the CPU. Memory hierarchy takes advantage of spatial locality by moving blocks of multiple contiguous words in memory to upper level of hierarchy.

In our design a main memory is containing both data and instruction area. A write through direct mapped cache is designed for data memory. All instructions are maintained in the main memory itself. As soon as the first data access is initiated, data from adjacent locations are also copied to the cache memory using burst transfer.

#### 5. VHDL CODES & SIMULATION RESULTS

```

_____

-- **** simulation of mips processor *******

-- 32 bit instruction register

~

-----

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_bit.all;

_____

entity instreg is

port( A : IN std_logic_vector(31 downto 0);

clk : IN std_logic;

IRWrite : IN bit;

IR : OUT unsigned (31 downto 0));

end instreg;

-----

architecture a_instreg of instreg is

begin

process

begin

wait on clk until rising_edge(clk)and IRWrite ='1';

IR <= unsigned (to_bitvector(A));

end process;

end a_instreg;

-----

```

| Active-HDL 6.3 (misc ,alu) - c:\Wy_Designs\misc\misc1\src\instreg.awf      Elle Edit Search View Workspace Design Simulation Waveform Tools Window Help |                 |            |                     |                      |                  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------|---------------------|----------------------|------------------|--|--|

| 🗗 ▼ 🚔 🖶 👯 🐰 🔳 🚯                                                                                                                                         |                 |            |                     |                      |                  |  |  |

| Design Browser ×                                                                                                                                        | X 🖻 🖻 🕫 🛇       | ₿ Q        | ↓ 🍇 🍳 🍳             | 🔍 🐿 🗤 🤮              | 🖭 🏘 🕂 🦽          |  |  |

| 🖬 alu (a_alu) 📃                                                                                                                                         | Name 🗠 🛛 Vali   | ue Stimu   | ı - 50 - i          | · 100 · · · 150 ·    | 1 · 200 · 1 ns   |  |  |

| 0. Unsorted                                                                                                                                             | <b>±</b> ► A    | <= 011     | (00000001           |                      | <u>X00000003</u> |  |  |

| - 📆 mips_toplevel.awf<br>14 ⊕ 😫 / MIPSwithMEM.vhd                                                                                                       | P clk           | Clock      |                     |                      |                  |  |  |

| 14                                                                                                                                                      | ± • IR          |            | (UUUUUUUU X00000001 | <u></u>              |                  |  |  |

| 15 🕀 🛃? mips_mem1.vhd                                                                                                                                   | ► IRWrite       | Clock      |                     |                      |                  |  |  |

| -X MIPSwithMEM_gold<br>                                                                                                                                 |                 |            |                     |                      |                  |  |  |

|                                                                                                                                                         |                 |            |                     |                      |                  |  |  |

| - 📒 ? instreg. vhd 🛛 🗧                                                                                                                                  |                 |            |                     |                      |                  |  |  |

| -∰ instreg.awf<br>⊕fff misc1 library                                                                                                                    |                 |            |                     |                      |                  |  |  |

| ⊕t∰ mux_m1 🗸 🤍                                                                                                                                          |                 |            |                     |                      | _                |  |  |

|                                                                                                                                                         |                 |            | •                   |                      | × 0 + 4          |  |  |

| 📄 Files /¥Stru) 📬 Res/                                                                                                                                  | 🚏 design flow 🔬 | instreg.av | vf                  |                      |                  |  |  |

|                                                                                                                                                         | 1               |            |                     |                      |                  |  |  |

| <b>x</b> .                                                                                                                                              |                 |            |                     |                      |                  |  |  |

|                                                                                                                                                         |                 |            |                     |                      |                  |  |  |

|                                                                                                                                                         |                 |            |                     |                      | ~                |  |  |

| © <b>&gt;</b>                                                                                                                                           |                 |            |                     |                      |                  |  |  |

| Console /                                                                                                                                               |                 |            |                     |                      |                  |  |  |

| 1 signal(s) selected                                                                                                                                    |                 |            |                     |                      |                  |  |  |

| 🛃 start 🔰 📓 🍯 🕲 🐣                                                                                                                                       | 🚞 major_codes   |            | ode_word - Micro    | 🔷 Active-HDL 6.3 (mi | 🔇 🐠 🗊 🌮 4:59 PM  |  |  |

library IEEE; use IEEE.std\_logic\_1164.all;

entity reg\_32bit is

| port( |     |   |                                     |

|-------|-----|---|-------------------------------------|

|       | А   | : | IN std_logic_vector(31 downto 0);   |

|       | clk | : | IN std_logic;                       |

|       | Υ   | : | OUT std_logic_vector(31 downto 0)); |

end reg\_32bit;

-----

architecture a\_reg\_32bit of reg\_32bit is

begin

process begin wait until clk'event and clk= '1'; Y <= A; end process;

end a\_reg\_32bit;

-----

| Active-HDL 6.3 (mips ,mips) - C:\Wy_Designs\mips\mips\src\reg_32bit.awf          |                             |                              |               |            |      |              |              |         |          |    |

|----------------------------------------------------------------------------------|-----------------------------|------------------------------|---------------|------------|------|--------------|--------------|---------|----------|----|

| <u>File E</u> dit Sea <u>r</u> ch <u>V</u> iew W <u>o</u> rkspace <u>D</u> esign | Simulation <u>W</u> aveform | <u>T</u> ools <u>W</u> indov | ∾ <u>H</u> el | p          |      |              |              |         | ⇔ ≫      | x  |

| 🗗 • 🗳 🖶 💥 📖 🔳 🚯 💱 🔵                                                              | D 🛱 🛱 🕫 🖇 📶                 | ¥ 🖇 🉀                        | 8             | 🖡 🧇 🗳      | ا ⊗  | ► ► <u>►</u> | 100 ns 🗧     | •       | . ₹      | »  |

| Design Browser 🔷 🗙 🔺                                                             | 👗 🖻 💼 🖉 🗸                   | > 🖹 🔍 🕯                      | <u>r</u> , 🏹  | • Q        | ۹ 🗨  | ካ 🗤 🕯        | f 🕺 1        | ± ±1    | <b>#</b> |    |

| 📲 reg_32bit (a_reg_32bit)                                                        | Name                        | Value                        | Sti           | 1.1        | 50 - | ı <u>100</u> | - i - i 1    | 50 . 20 | 0 ns     | ns |

| 🗉 🕂 reg_32bit (a_reg_32bit)                                                      | ∎ • A                       | 00000001                     | <=            | (00000001  |      |              |              |         |          |    |

| Stristandard                                                                     | ► clk                       | 0                            | Clo           | ,          |      |              |              |         |          |    |

| Name Value                                                                       | <b>∃</b> ₽ Υ                | 00000001                     |               |            |      | 001          |              |         |          |    |

|                                                                                  |                             |                              |               |            |      |              |              |         |          |    |

|                                                                                  |                             |                              |               |            |      |              |              |         |          |    |

|                                                                                  |                             |                              |               |            |      |              |              |         |          |    |

|                                                                                  |                             |                              |               |            |      |              |              |         |          |    |

|                                                                                  |                             |                              |               |            |      |              |              |         |          |    |

|                                                                                  |                             |                              |               |            |      |              |              |         |          |    |

| <                                                                                |                             |                              |               | •          |      |              |              | +       | 0 #      |    |

| Files Structure/CResou/                                                          | 🚪 design flow 🛓             | reg_32bit.vh                 | 1 🔀 🔬 b       | eg_32bit.a | wf   |              |              |         |          | 1  |

|                                                                                  |                             |                              |               |            |      |              |              |         |          |    |

| <pre></pre>                                                                      |                             |                              |               |            |      |              |              |         |          | 2  |

| orun 100 ns                                                                      |                             |                              |               |            |      |              |              |         |          |    |

| e # KERNEL: stopped at time: 100 ns<br>• run 100 ns                              |                             |                              |               |            |      |              |              |         |          |    |

| 8 • # KERNEL: stopped at time: 200 ns                                            |                             |                              |               |            |      |              |              |         |          | ×  |

| >                                                                                |                             |                              |               |            |      |              |              |         |          |    |

| Console /                                                                        |                             |                              |               |            |      |              |              |         |          |    |

|                                                                                  |                             |                              |               |            |      |              | _            |         |          |    |

| Active-HDL 6.3 (mips                                                             | , 🛛 🕎 major-report -        | Micros                       |               |            |      |              | <b>\$</b> 9% | 60      | 7:38 PM  | 4  |

```

-----

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

____

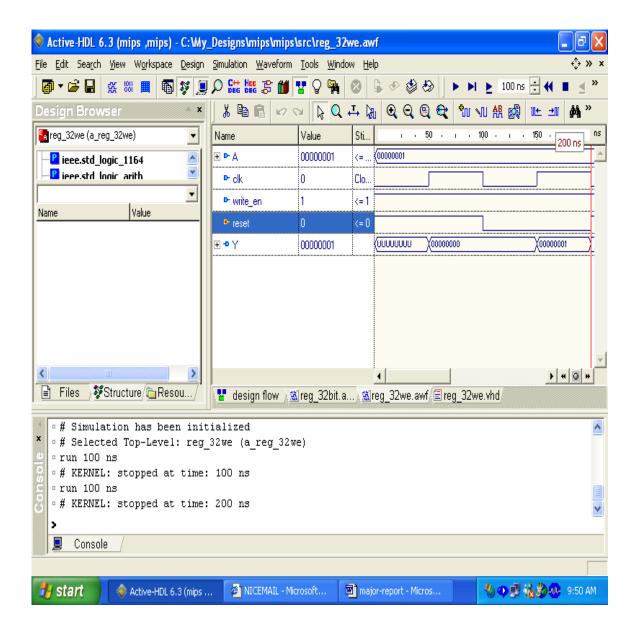

entity reg_32we is

A : in std_logic_vector(31 downto 0);

clk : in std_logic;

write_en : in bit;

reset : in bit;

Y : out std_logic_vector (31 downto 0));

end reg_32we;

-----

architecture a_reg_32we of reg_32we is

begin

process (clk)

begin

if clk = '1' and clk'event then

if reset = '1' then

Y <= x''0000_0000'';

elsif write_en ='1' then

Y < = A;

end if:

end if;

end process;

end a_reg_32we;

_____

```

----library IEEE; use IEEE.std\_logic\_1164.all; use IEEE.numeric\_bit.all; \_\_\_\_\_ entity register\_file is port( write\_en : in bit; rd\_reg1 : in unsigned (4 downto 0); rd\_reg2 : in unsigned (4 downto 0); wr\_reg : in unsigned (4 downto 0); data : in std\_logic\_vector(31 downto 0); reg1 : out std\_logic\_vector(31 downto 0); reg2 : out std\_logic\_vector(31 downto 0)); end register\_file; \_\_\_\_\_ architecture a\_register\_file of register\_file is begin regtag: process ( rd\_reg1, rd\_reg2, wr\_reg, data, write\_en) is type reg\_array is array (0 to 31) of std\_logic\_vector(31 downto 0); variable reg file : reg array; variable index1, index2, index3 : natural; begin  $reg_file(0) := X''00000001'';$ reg\_file(1) := X"0000002";  $req_file(2) := X''00000003'';$  $req_file(3) := X''00000004'';$  $reg_file(6) := X"00000000";$ --write port if write\_en = '1' then index3 := to\_integer(wr\_reg); reg\_file(index3) := data; end if; --read port1 index1 := to\_integer(rd\_reg1); req1 <= req\_file(index1) ;</pre> --read port2 index2 := to\_integer(rd\_reg2); reg2 <= reg\_file(index2) ;</pre> end process regtag; end a\_register\_file; \_\_\_\_\_

| ♦ Active-HDL 6.3 (misc ,mips_t<br>File Edit Search View Workspace          | = .             |            | \register_file\src\register_file.awf          |

|----------------------------------------------------------------------------|-----------------|------------|-----------------------------------------------|

|                                                                            | 💱 🧾 🔎 🔐 Hee 🍃   |            |                                               |

| Design Browser *                                                           |                 |            |                                               |

| nipswithmem (a_mipswithmem) 🔻                                              |                 | ue Stimu   |                                               |

| brted                                                                      | 🛨 🍨 data        |            |                                               |

| misc1                                                                      | ± ► rd_reg1     | <= 01      | (00 X01                                       |

| j mux_m1                                                                   | ± ► rd_reg2     | <= 011     | 00                                            |

| j mux_m2                                                                   |                 |            | (UUUUUUUU X0000001F                           |

| រ្យ៊ី mux_m3<br>រ្យ៊ី mux_m4                                               |                 |            |                                               |

| j reg_32                                                                   | ± ► wr_reg      | <= 00      | (01                                           |

| j reg_32WE                                                                 | P write_en      | <= 1       |                                               |

| register_file                                                              |                 |            |                                               |

| - 💥 register_file.awf                                                      |                 |            |                                               |

| €∰ register_file library                                                   |                 |            |                                               |

|                                                                            |                 | I          | ۲<br>۲<br>۲                                   |

| 📄 Files / 💱 Stru ) 📬 Res /                                                 | design 🗐 regist | e); 🐹 mip: | ps_t 🗟 fsm.awf 🗐 instreg 📓 mips 📓 mips 🕅 mips |

|                                                                            |                 |            |                                               |

| <ul> <li># ELBREAD: Elaboratio</li> <li>* # ELBREAD: Elaboratio</li> </ul> |                 |            |                                               |

|                                                                            |                 |            |                                               |

|                                                                            |                 |            |                                               |

| 8                                                                          |                 |            | <u>₩</u>                                      |

| 📮 Console /                                                                |                 |            |                                               |

| 1 signal(s) selected                                                       |                 |            |                                               |

|                                                                            |                 |            |                                               |

| 🛃 start 🔰 🗟 🙆 🦉                                                            | 🕘 3 Int 🝷 🧇     | Active     | 🖻 major 📓 code 🚺 fsm 🗾 🕏 🤣 6:31 PM            |

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_bit.all;

-----

entity mux_m1 is

port (

s : in bit;

d0 : in std_logic_vector (31 downto 0);

d1 : in std_logic_vector (31 downto 0);

y : out unsigned (31 downto 0));

;

end mux_m1;

-----

architecture a_mux_m1 of mux_m1 is

begin

process (s,d0,d1)

begin

case s is

when '0' =>

y <= unsigned (to_bitvector(d0));</pre>

when '1' =>

y <= unsigned (to_bitvector(d1));</pre>

end case;

end process;

end architecture a_mux_m1;

-----

```

| ♦ Active-HDL 6.3 (mips ,mips) - C:Wy_                                            | Designs\mips\mips                   | \src\mux_m1.a                | awf                   |                      |                   |

|----------------------------------------------------------------------------------|-------------------------------------|------------------------------|-----------------------|----------------------|-------------------|

| <u>File E</u> dit Sea <u>r</u> ch <u>V</u> iew W <u>o</u> rkspace <u>D</u> esign | <u>S</u> imulation <u>W</u> aveform | <u>T</u> ools <u>W</u> indow | <u>H</u> elp          |                      | ÷, ≫ ×            |

| 🗗 • 🖻 🖶 💥 🐘 🔳 🚯 💱 🔵                                                              | 🔎 🛱 Hee 🍃 🎁                         | ¥ 🛛 🙀 🖉                      | 6 6 4 4               | 🕨 🍋 👌 100 ns 🗧       | K ■ ⊴ *           |

| Design Browser 🔷 🗙                                                               | 👗 🖻 💼 🛷 <                           | 🖂 🔓 🔍 🕰                      | , 🕅 Q Q Q             | 🕻 🕅 🗤 🤼 🕅 🖿          | ±∎ 🏘 »            |

| mux_m1 (a_mux_m1)                                                                | Name                                | Value S                      | Sti 50 -              | ı i 100 i i 150      | 200 ns            |

| eee.std_logic_1164                                                               | • \$                                | 0                            |                       |                      |                   |

| ×                                                                                | 🛨 🖻 d0                              | 00000001 <                   | <= (00000001          |                      |                   |

| Name Value                                                                       | ± ► d1                              | 00000000 <                   | <= (00000000          |                      |                   |

| Value                                                                            | <b>+</b> ● y                        | 00000001                     | 00000001              |                      |                   |

|                                                                                  |                                     |                              |                       |                      |                   |

|                                                                                  |                                     |                              |                       |                      |                   |

|                                                                                  |                                     |                              |                       |                      |                   |

|                                                                                  |                                     |                              |                       |                      |                   |

|                                                                                  |                                     |                              |                       |                      |                   |

| <                                                                                |                                     |                              | 4                     |                      | <u>▼</u><br> +0+4 |

| Files Structure/CResou/                                                          | 🦉 design flow 🔡                     | reg_32bit.a                  |                       | reg_32we.vhd 🔊 mux_m |                   |

| • run 100 ns                                                                     |                                     |                              |                       |                      |                   |

| <pre>* # KERNEL: stopped at time:</pre>                                          | 100 ns                              |                              |                       |                      | <u> </u>          |

| • # KERNEL: Simulation has f                                                     | inished. There                      | are no more                  | e test vectors t      | o simulate.          |                   |

| • run 100 ns<br>• # KERNEL: stopped at time:                                     | 200 ns                              |                              |                       |                      |                   |

| 🖁 • # KERNEL: Simulation has f                                                   | inished. There                      | are no more                  | e test vectors t      | o simulate.          | ~                 |

| >                                                                                |                                     |                              |                       |                      |                   |

| Console /                                                                        |                                     |                              |                       |                      |                   |

|                                                                                  | _                                   | 7                            |                       |                      |                   |

| Active-HDL 6.3 (mips                                                             | . 🛛 🖉 NICEMAIL - Mic                | rosoft 🖻                     | major-report - Micros | <u> </u>             | 🤷 9:55 AM         |

----library IEEE; use IEEE.std\_logic\_1164.all; use IEEE.numeric\_bit.all; ----entity mux\_m2 is port (

s

:

in bit;

d0

:

in unsigned (4 downto 0);

d1

:

in unsigned (4 downto 0);

y

:

out unsigned (4 downto 0));

end mux\_m2; \_\_\_\_\_ ----architecture a\_mux\_m2 of mux\_m2 is begin process (s, d0,d1) begin case s is when '0' => y < = d0;when '1'=> y <= d1;end case; end process; end a\_mux\_m2; \_\_\_\_\_

----library IEEE; use IEEE.std\_logic\_1164.all; ----entity mux\_m3 is port ( s:in bit;d0:in std\_logic\_vector (31 downto 0);d1:in std\_logic\_vector (31 downto 0);y:out std\_logic\_vector (31 downto 0)); end mux\_m3; \_\_\_\_\_ architecture a\_mux\_m3 of mux\_m3 is begin process (s, d0, d1) begin case s is when '0' => y <= d0;when '1' => y <= d1;end case; end process; end a\_mux\_m3; -----

\_\_\_\_\_ library IEEE; use IEEE.std\_logic\_1164.all; \_\_\_\_\_ entity mux\_m4 is port ( s : d0 : d1 : d2 : d3 : in bit\_vector(1 downto 0); in std\_logic\_vector (31 downto 0); : out std\_logic\_vector (31 downto 0)); У end mux\_m4; \_\_\_\_\_ architecture a\_mux\_m4 of mux\_m4 is begin process (s, d0, d1, d2, d3) begin case s is when "00" => y <= d0;when "01" => y <= d1;when "10" => y <= d2;when "11" => y <= d3;end case; end process; end a\_mux\_m4;

-----

-- \*\*\*simulation of MIPS Processor \*\*\*\*\*\*\*\*\* -- Finite State Machine for MIPS Processor \_\_\_\_\_ LIBRARY ieee; USE IEEE.std\_logic\_1164.ALL; use IEEE.numeric\_bit.all; \_\_\_\_\_ ENTITY fsm IS PORT ( CIK: INstd\_logic;OP\_code: INunsigned (5 DOWNTO 0);Ready: INbit;RegDst: OUTbit;ALUSrcA: OUTbit;ALUSrcB: OUTbit\_vector (1 DOWNTO 0); MemtoReg : OUT bit; : OUT bit; IorD : OUT bit\_vector ( 1 DOWNTO 0 ); ALUOp PCSource : OUT bit\_vector (1 DOWNTO 0); RegWrite : OUT bit; MemRead : OUT bit; MemWrite : OUT bit; IRWrite : OUT bit; PCWrite : OUT bit); END fsm: \_\_\_\_\_ ARCHITECTURE a\_fsm OF fsm IS

TYPE state IS (ST0,ST1,ST2,ST3,ST4,ST5,ST6,ST7); SIGNAL current\_state,next\_state : state;

BEGIN

Proc1: PROCESS BEGIN CASE current\_state IS

## WHEN STO =>

| ALUOp    | <= "00";                 |

|----------|--------------------------|

| RegWrite | <= '0';                  |

| MemRead  | <= '1';                  |

| MemWrite | <= '0';                  |

| IRWrite  | <= '1';                  |

| PCWrite  | <= '1', '0' after 200ns; |

| ALUSrcB  | <= "01";                 |

| PCSource | <= "00";                 |

| ALUSrcA  | <= '0';                  |

lorD <= '0'; WAIT UNTIL ready'EVENT and ready = '1'; next\_state <= ST1;</pre> WHEN ST1 => ALUOp <= "00"; RegWrite <= '0'; MemRead <= '0'; MemWrite <= '0'; <= '0'; IRWrite PCWrite <= '0'; <= "11"; ALUSrcB ALUSrcA <= '0'; if OP\_code = "000000" then next\_state <= ST6;</pre> else if OP\_code = "100011" or OP\_code = "101011" then --LW(35) or SW(43) next\_state <= ST2;</pre> end if; end if; WHEN ST2 => ALUOp <= "00"; <= '0'; RegWrite MemRead <= '0'; MemWrite <= '0': IRWrite <= '0'; PCWrite <= '0'; <= "10"; ALUSrcB ALUSrcA <= '1'; if OP\_code = "100011" then --LW(35) next\_state <= ST3;</pre> else next\_state <= ST5; --SW(43)</pre> end if; WHEN ST3 => ALUOp <= "00"; RegWrite <= '0'; MemRead <= '1'; MemWrite <= '0'; IRWrite <= '0'; PCWrite <= '0'; IorD <= '1';

```

next_state <= ST4;</pre>

```

WHEN ST4 =>

| ALUOp    | <= "00"; |

|----------|----------|

| RegWrite | <= '1';  |

| MemRead  | <= '0';  |

| MemWrite | <= '0';  |

| IRWrite  | <= '0';  |

| PCWrite  | <= '0';  |

| MemtoReg | <= '1';  |

| RegDst   | <= '0';  |

|          |          |

next\_state <= ST0;

WHEN ST5 =>

| ALUOp    | <= "00"; |

|----------|----------|

| RegWrite | <= '0';  |

| MemRead  | <= '0';  |

| MemWrite | <= '1';  |

| IRWrit   | <= '0';  |

| PCWrit   | <= '0';  |

| IorD     | <= '1';  |

WAIT UNTIL ready'EVENT and ready = '1';

;

next\_state <= ST0;

WHEN ST6 =>

| ALUOp    | <= "10"; |

|----------|----------|

| RegWrite | <= '0';  |

| MemRead  | <= '0';  |

| MemWrite | <= '0';  |

| IRWrite  | <= '0';  |

| PCWrite  | <= '0';  |

| ALUSrcA  | <= '1';  |

| ALUSrcB  | <= "00"; |

next\_state <= ST7;</pre>

# WHEN ST7 =>

| ALUOp    | <= "00" |

|----------|---------|

| RegWrite | <= '1'; |

| MemRead  | <= '0'; |

| MemWrite | <= '0'; |

| IRWrite  | <= '0'; |

| PCWrite  | <= '0'; |

| RegDst   | <= '1'; |

|          |         |

END ARCHITECTURE a\_fsm;

| e Edit Search View<br>🗿 🕶 🗃 🔚 👯 |                                  | _     |           | -    |           |             | eip<br>🔒 🚸 🍪 🎝 | <b> </b> | 100 n    |         | ≽≫<br> |

|---------------------------------|----------------------------------|-------|-----------|------|-----------|-------------|----------------|----------|----------|---------|--------|

| esign Br ×                      |                                  | SH .  |           |      | ର୍ ପ୍     |             |                | 11       | <u>#</u> | <br>% % | -<br>% |

| a mipswithmem (a 👻              | Name 🗠                           | Value | Stimu     |      | 50        | 1.01        | iço i i 150    | 2        |          | 250 i   | ſ      |

| ted 🔼                           | <ul> <li>ALUSrcA</li> </ul>      |       |           |      |           |             |                |          |          |         |        |

| Workspace 'n                    |                                  |       |           | (1   |           |             | X3             |          |          | 2       |        |