# WAVELET TRANSFORM BASED ADAPTIVE IMAGE COMPRESSION ON FPGA

A minor project report submitted in partial fulfilment of the requirements for the award of the degree of

> Master of Engineering In Electronics and Communication Engineering

> > By

Manoj Sharma

Roll No. 8729

Department of Electronics and Communication Engineering, Delhi College of Engineering, University of Delhi Session 2004-2006

# ACKNOWLEDGEMENT

I wish to acknowledge our sincere thanks to my guide **Mrs. Rajeshwari Pandey** in Electronics and Communication Department and my co-guide **Mrs. Neeta Pandey** (Asst. Professor in Bhartiya Vidya Peetha) for there suggestions excellent guidance and timely advice which has made my project success.

I express my deep sense of gratitude to Dr. **Asok Bhattacharyya**, H.O.D. (Department of Electronics and Communication Engineering) for there inspirations and timely help in conducting our project. I am indebted to the entire faculty and non teaching staff of Electronics and communication department, who had very helpful and cooperative to me at all times.

Manoj Sharma (8729)

Department of Electronics and Communication Engineering Delhi College of Engineering, University of Delhi Session 2004-2006

# DEPARTMENT OF ELECTRONICSANDCOMMUNICATION DELHI COLLEGE OF ENGINEERING UNIVERSITY OF DELHI DELHI

CERTIFICATE

# Certified that the project work entitled

# WAVELET TRANSFORM BASED ADAPTIVE IMAGE COMPRESSION ON FPGA

is bonafied work carried by

Manoj Sharma (8729)

In partial fulfilment for the award of degree of Master of Engineering in Electronics and Communication Engineering of the University of Delhi during the year 2004-2006. It is certified that all corrections/suggestions indicated for internal assessment have been in corporate in the report deposited in the Departmental library. The project report has been approved as it satisfied the academic requirements in respect of minor project work prescribed for the Master of Engineering Degree.

Signature of Guide

Signature of HOD

Mrs Rajeshwari Pandey

Dr. Asok Bhattacharyya

# Abstract

Image processing systems can encode raw images with different degrees of precision, achieving varying levels of compression. Different encoders with different compression ratios can be built and used for different applications. The need to dynamically adjust the compression ratio of the encoder arises in many applications. One example involves the real-time transmission of encoded data over a packet switched network. To suitably adapt the encoder varying compression requirements, adaptive adjustments of the to compression parameters are required. This involves reconfiguring the encoder in an efficient manner. Our approach exploits the reconfigurable nature of Field Programmable Gate Arrays (FPGA), to adapt the encoder to the varying requirements in real time. A Wavelet transform based image compression scheme is implemented for encoding gray-scale frames of 512 by 512 pixels on FPGAs. By varying the zero thresholds, the encoder can achieve varying compression levels. The complete design of the encoder on FPGA is presented. Implementation details of the individual blocks are discussed in great detail. Finally, results from testing are reported and discussed.

# Contents

# 1 Introduction 1

| 1.1 Motivation                                                  |

|-----------------------------------------------------------------|

| 1.1.1 Scope of Field Programmable Gate Arrays                   |

| 1.1.2. Adaptive image compression 1                             |

| 1.2 Thesis Layout                                               |

| 1.3 Other Implementations                                       |

| 2 Wavelet Transform4                                            |

| 2.1 Wavelets                                                    |

| 2.1.1 A simple example - the Haar wavelet 5                     |

| 2.1.2 Lifting scheme                                            |

| 2.1.3 Wavelets that map Integer to Integer                      |

| 2.1.4 Compact support, Vanishing moments, and Smoothness. 5     |

| 2.1.5 Orthogonal and Bi-orthogonal Wavelets                     |

| 2.1.6 (2,2) Bi-orthogonal Cohen Daubechies Feauveau Wavelet . 7 |

| 2.1.7 Boundary treatment                                        |

| 2.1.8 Advantages of Wavelets                                    |

| <b>3 Design and Implementation 10</b>                           |

| 3.1 Hardware platform                                           |

| 3.2 Design parameters and constraints                           |

| 3.2.1 Memory read/write                                         |

| 3.2.2 Real time performance                                     |

| 3.2.3 Design partitioning 12                                    |

| 3.3 Stage 1: Discrete Wavelet Transform                         |

| 3.3.0.1 (2, 2) wavelet                                          |

| 3.3.0.2 DWT in X and Y directions                             |

|---------------------------------------------------------------|

| 3.3.0.3 3 stages of wave-letting 15                           |

| 3.3.0.4 Over all architecture of Stage 1 16                   |

| 3.4 Stage 2                                                   |

| 3.4.1 Dynamic quantization                                    |

| 3.4.2 Zero thresholding and RLE on zeroes                     |

| 3.4.3 Entropy encoding                                        |

| 3.4.3.1 Encoding scheme                                       |

| 3.4.3.2 Bit packing                                           |

| 3.4.3.3 Shifter                                               |

| 3.4.4 Output file format                                      |

| 3.4.5 Stage 2, Overall architecture                           |

| 4 Results 29                                                  |

| 4.1 Metrics for testing                                       |

| 4.1.1 Throughput                                              |

| 4.1.1.1 Embedded memory performance 29                        |

| 4.1.1.2 Effective throughput                                  |

| 4.1.2 Compression level Vs noise                              |

|                                                               |

| 4.1.3 Implementation costs on the hardware                    |

|                                                               |

| 4.1.3 Implementation costs on the hardware                    |

| <ul><li>4.1.3 Implementation costs on the hardware</li></ul>  |

| <ul> <li>4.1.3 Implementation costs on the hardware</li></ul> |

| <ul> <li>4.1.3 Implementation costs on the hardware</li></ul> |

| <ul> <li>4.1.3 Implementation costs on the hardware</li></ul> |

# **B** Source code listings 43

| B.1 Stage 1 - VHDL source code               |

|----------------------------------------------|

| B.1.1 waveletX.vhd                           |

| B.1.2 waveletY.vhd                           |

| B.1.3 pellca.vhd (top level for stage1)      |

| B.2 Stage 2 - VHDL source code               |

| B.2.1 quantizer.vhd                          |

| B.2.2 rle.vhd                                |

| B.2.3 huffman.vhd                            |

| B.2.4 shifter.vhd                            |

| B.2.5 pellca.vhd (top level for stage2)      |

| B.3 Control software - C source code listing |

| B.3.1 pgm.h                                  |

| B.3.2 wlt.h                                  |

| B.3.3 stage1.c                               |

| B.3.4 stage2.c                               |

# **List of Tables**

| 2.1 (2,2) CDF wavelet with lifting scheme                       |

|-----------------------------------------------------------------|

| 3.1 Bit range allocation for RLE 21                             |

| 4.1 Embedded memory access times from host computer 30          |

| 4.2 Delay along a single thread                                 |

| 4.3 PSNR and RMSE equations                                     |

| 4.4 Compression levels and noise neasurements for 'lena' 35     |

| 4.5 Compression levels and noise neasurements for 'barbara' 35  |

| 4.6 Compression levels and noise neasurements for 'goldhill' 35 |

| 4.7 Device usage and Timing statistics                          |

| A.1 Zero threshold levels for different configurations          |

| A.2 Throughput measured from the software encoder               |

# **List of Figures**

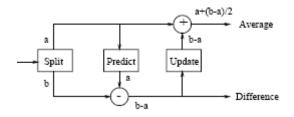

| 2.1 Lifting Scheme                                                 |

|--------------------------------------------------------------------|

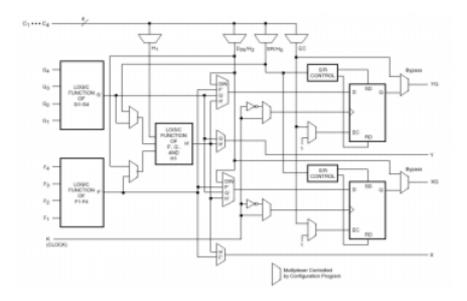

| 3.1 Configurable Logic Block (CLB) in XC4000 series FPGA 11        |

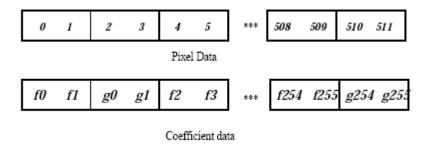

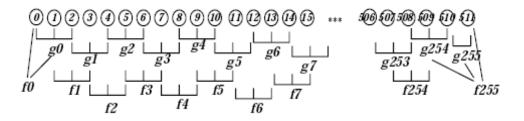

| 3.2 Coefficient ordering along X direction                         |

| 3.3 Coefficient ordering along Y direction                         |

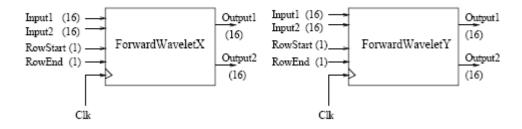

| 3.4 Fast Wavelet transform data flow blocks                        |

| 3.5 High pass and Low pass coefficients at stage 1, X direction 15 |

| 3.6 Mallot ordering along the 3 stages of wave-letting 16          |

| 3.7 Interleaved ordering along the 3 stages of wave-letting 17     |

| 3.8 Stage 1 architecture                                           |

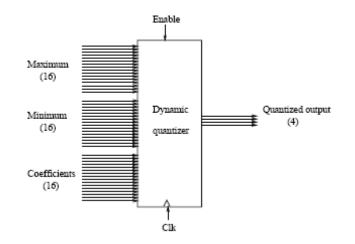

| 3.9 Dynamic Quantizer 19                                           |

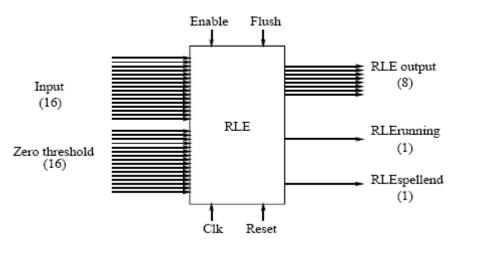

| 3.10 Run Length Encoder for continuous zeroes                      |

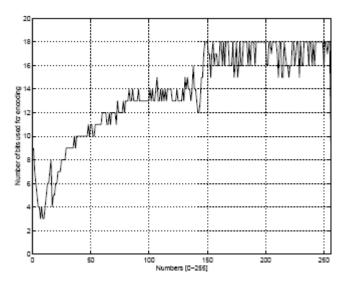

| 3.11 Entropy encoding, bit allocation                              |

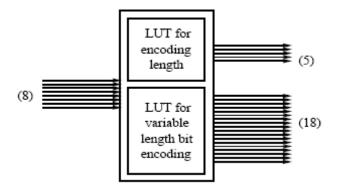

| 3.12 Entropy encoder                                               |

| 3.13 Binary Shifter for bit packing                                |

| 3.14 Outfile format                                                |

| 3.15 Stage 2, data flow diagram 27                                 |

| 3.16 Stage 2, control flow diagram                                 |

| 4.1 Original Images 32                                             |

| 4.2 Configuration 1, Minimum compression                           |

| 4.3 Configuration 2, Medium compression                            |

| 4.4 Configuration 3, Maximum compression                           |

| A.1 Design flow                                                    |

# Chapter 1 Introduction

#### 1.1 Adaptive Image Compression

With the use of more and more digital still and moving images, huge amount of disk space is required for storage and manipulation purpose. For example, a standard 35-mm photograph digitized at 12µm per pixel requires about 18Mbytes of storage and one second of NTSC-quality color video requires 23 Mbytes of storage. That is why image compression is very important in order to reduce storage need. Digital images can be compressed by eliminating redundant information present in the image, such as spatial redundancy, spectral redundancy and temporal redundancy. The removal of spatial and spectral redundancy is often Accomplished by transform coding, which uses some reversible linear transform to decorrelate the image data. JPEG is the most commonly used image compression standard in today's world. Joint Photographic Experts Group (JPEG) is an ISO standard committee with a mission on "Coding and compression of still images". It's jointly supported by ISO and ITU-T. But researchers have found that JPEG has many limitations. In order to overcome all those limitations and to add on new improved features, ISO and ITU-T has come up with new image compression standard, which is JPEG2000. The JPEG2000 is intended to provide a new image coding/decoding system using state of the art compression techniques, based on the use of wavelet technology. This thesis focuses on the adaptive image compression based on discrete wavelet transform.

Image processing systems can encode raw images with different degrees of Precision, achieving varying levels of compression. Encoding can be achieved with different encoders with varying compression ratios. The need to dynamically adjust the compression ratio of the encoder arises in many situations.One example involves the real-time transmission of encoded data over a packet switched network. On detecting network congestion, the encoder can cut down the precision and gain more compression, rather than waiting for some packets to be dropped. To suitably adapt the encoder to the varying compression requirements, adaptive adjustments of the compression parameters are required. This involves reconfiguring the encoder in some sense.

This thesis work presents the hardware design of a Forward Discrete Wavelet Transform (FDWT) processor using VHDL. The design utilises the *lossless* features of FDWT. This is a reversible algorithm, which means there is no loss of information while compressing and transmitting the image information. This work presents the hardware architecture of the processor as well as the design of its constituent components in VHDL. The architecture does not comprise any hardware multiplier unit and therefore suitable for development of highperformance image processors.

#### **1.2 Dissertation Layout**

The remainder of this document is organized as follows. Chapter one explains related work in this field. Chapter two describes Wavelet transform based image compression schemes. Next, chapter three explains the design and implementation of the encoder. Then, chapter four summarizes the results obtained. Finally, in chapter five conclusions and further scope of work has been discussed.

### **1.3** Other Implementations

There are many other implementations using ASICs and custom ICs. There have also been many software based image compression kits like [GEOFF], which utilizes wavelet based compression techniques. There have been other efforts to implement Wavelet transform based image Compression systems on FPGA. In one implementation [BRIAN], the discrete wavelet transform coefficients are computed for 256x256 grayscale frames. This implementation also supports a multiplierless quantizer and a run length encoder. The frame rates quoted are 20 frames/second on Xilinx 4008 FPGAs with on-board embedded memory. **Chapter 2** Wavelet Transform

#### **2.1 Wavelets**

The following introduction on wavelets is based on the paper by mathematician Gilbert Strang [STRANG]. A wavelet is a localized function in time (or space in the case of images) with mean zero. A wavelet basis is derived from the wavelet (small wave) by its own dilations and translations.

$$w_{i,k}(t) = 2^{\frac{-i}{2}}w(2^{-j}t - k)$$

Let the original wavelet start at t = 0 and end at t = N. The shifted wavelet  $w_{0,k}$ , starts at t = k and ends at t = k + N. The rescaled wavelet  $w_{j,0}$  starts at t = 0 and ends at  $t = N/2^{j}$  At a given resolution j, the basis functions are  $w_{j,k}(t)$ , and the time steps at that level are  $2^{-j}$ . At the next finer resolution, j+1, the time steps are  $2^{-(j+1)}$ . Frequencies shift upward by an octave, when time is rescaled by 2. Functionally, DiscreteWavelet Transform (DWT) is very much similar to the Discrete Fourier Transform, in that the transformation function is orthogonal. A signal passed twice through the orthogonal function is unchanged. As the input signal is a set of samples, both transforms are convolutions. While the basis function of the Fourier transform is a sinusoid, the wavelet basis is a set waves obtained by the dilations and translations of the mother wavelet.

### 2.1.1 A simple example - the Haar wavelet

One of the first wavelet was that of Haar. The Haar scaling function is shown below.

$$w(n) = \begin{cases} 1, 0 \le t \le 1\\ 0, \text{ otherwise} \end{cases}$$

Applying the Haar wavelet on a sequence of values computes its sums and differences. For example, a sequence of values a, b would be replaced by s = (a + b)/2 and d = (b - a). The values of a and b can be reconstructed as

$$a = s - d=2$$

and  $b = s + d=2$ .

The input signal with 2n samples is replaced with 2n-1 averages (s0(i)) and 2n-1 differences (d0(i)). The averages can be thought of as a coarser representation of the signal and the differences as the information needed to go back to the original resolution. The averages and differences are now computed on the coarser signal (so(i)) of length 2n-1. This gives (s1(i)) and (d1(i)) of length 2n-2 each. This operation can be performed n times, till we run out of samples. The inverse operation starts by computing  $s_{n-2}(j)$  from  $s_{n-1}(j)$  and  $d_{n-1}(j)$ .

#### 2.1.2 Lifting scheme

The above computation of the Haar wavelet needs intermediate storage to store the average and difference. The average computed, cannot be written back in place of a, till the difference has been computed. Lifting scheme on the other hand allows for an in place computation. In the first step, we compute only the difference d = (b-a) and store it in place of b. Next, the average value is computed in terms of a and the newly computed difference, b, as s = a + b=2. The inverse can be computed by reversing the order and flipping the signs. This is a simple instance of lifting. Split Predict Update

Figure 2.1: Lifting Scheme

A more general lifting scheme consists of three steps - split, predict and up-date, figure 2.1. The splitting stage splits the signal into two disjoint sets of samples. In the above example, it consists of even numbered samples and odd numbered samples. Each group contains half as many samples as the original signal. If the signal has a local correlation the consecutive samples will be highly correlated. In other words, given one set it should be able to predict the other. In the diagram, the even samples are used to predict the odd samples. Then the detail is the difference between the odd sample and its prediction. In the Haar case the prediction is simple, every even value is used to predict the next odd value. The order of the predictor in the Haar case is 1 and it eliminates zeroth order correlation. The reverse operation is done as undo-update, undo-predict and merge.

# 2.1.3 Wavelets that map Integer to Integer

We return to the Haar transform. Because of the division by 2 in the average computation, it is not an integer transform. A simple alternative is to calculate the sum instead of the average. Another solution known as the S (sequential) transform is to round off the average value to an integer value. The sum and difference of two integers are both even or both odd. So, the last bits of the difference and average should be identical. Hence the last bit from average can be omitted, with out

loosing information. In the general case, though rounding may add a non-linearity to the transform, it has been shown to be invertible, [CALDERBANK].

### 2.1.4 Compact support, Vanishing moments, and Smoothness

Wavelets are localized functions and zero outside a bounded interval. This compact support corresponds to an FIR implementation. Another way to characterize wavelets by the number of coefficients and the level of iteration. If the frequency response of the corresponding filter has p zeroes at  $\pi$ , the approximation order is p. In other words, a wavelet basis with p vanishing moments can give a pth order approximation for any signal. The smoothness of the transfer functions is measured by the number of its derivatives.

#### 2.1.5 Orthogonal and Bi-orthogonal Wavelets

The wavelet basis forms an orthogonal basis if the basis vectors are orthogonal to its own dialations and translations. A less stringent condition is that the vectors be bi-orthogonal. The DWT and inverse DWT can be implemented by filter banks. This includes an analysis filter and a synthesis filter. When the analysis and synthesis filters are transposes as well as inverses of each other, the whole filter bank is orthogonal. When they are inverses, but not necessarily transposes, the filter bank is bi-orthogonal.

### 2.1.6 (2, 2) Bi-orthogonal Cohen Daubechies Feauveau Wavelet

The main intent of wavelet transform is to decompose a signal f, in terms of its basis vectors.

To have an efficient representation of signal f using only a few coefficients  $a_i$ , the basis functions should match the features of the signal we want to represent. The (2, 2) Cohen Daubechies Feauveau Wavelet [COHEN] is widely used for image compression because of its good compression characteristics. The original filters have 5+3 = 8 filter coefficients, whereas an implementation with the lifting scheme has only 2+2 = 4 filter coefficients. The forward and reverse filters are shown in table 2.1. Fractional numbers are converted to integers at each stage. Though such an operation adds non-linearity to the transform, the transform is fully invertible as long as the rounding is deterministic. Forward transform

| Forward transf  | form                                 |

|-----------------|--------------------------------------|

| si              | $\leftarrow x_{2i}$                  |

| di              | $\leftarrow x_{2i+1}$                |

| di              | $\leftarrow d_i - (s_i + s_{i+1})/2$ |

| si              | $\leftarrow s_i + (d_{i-i} + d_i)/4$ |

| Inverse transfo | rm                                   |

| si              | $\leftarrow s_i - d_i/2$             |

| $d_i$           | $\leftarrow d_i + s_i$               |

| x <sub>2i</sub> | $\leftarrow s_i$                     |

| $x_{2i+1}$      | $\leftarrow d_i$                     |

Table 2.1: (2, 2) CDF wavelet with lifting scheme

# 2.1.7 Boundary treatment

Real world signals are limited to a finite interval. However filter bank algorithms assume infinite lengths. The computation of s and d coefficients refer to k signal

samples before and after the current sample, depending on the filter length k. Different methods of extending the signal at the boundaries has been suggested. One scheme that is widely used is the symmetric extension. It extends the finite signal by mirroring it around its boundaries.

#### 2.1.8 Advantages of Wavelets

Real time signals are both time-limited (or space limited in the case of images) and band-limited. Time-limited signals can be efficiently represented by a basis of block functions (Dirac delta functions for infinitesimal small blocks). But block functions are not band-limited. Band limited signals on the other hand can be efficiently represented by a Fourier basis. But sines and cosines are not time-limited. Wavelets are localized in both time (space) and frequency (scale) domains. Hence it is easy to capture local features in a signal. Another advantage of a wavelet basis is that it supports multi resolution. Consider the windowed Fourier transform. The effect of the window is to localize the signal being analyzed. Because a single window is used for all frequencies, the resolution of the analysis is same at all frequencies. To capture signal discontinuities (and spikes), one needs shorter windows, or shorter basis functions. At the same time, to analyze low frequency signal components, one needs longer basis functions. With wavelet based decomposition, the window sizes vary. Thus it allows analyzing the signal at different resolution levels.

# Chapter 3 Design and Implementation

#### **3.1 Hardware platform**

Xilinx 4000 series FPGAs [XC4000] are available and can be used for the implementation. These are look-up table based FPGAs. Each basic block called a CLB (Configurable Logic Block) consists of two 4 input look-up tables and one 3 input look-up table (figure A.1). Each CLB also has 2 flip flops. There are multiplexers within a CLB to achieve internal connectivity among the flip flops and look-up tables. The CLBs are arranged as a matrix. In addition to CLBs, these FPGAs have horizontal and vertical interconnects and switches (routing resources) to achieve connectivity between different ports of different CLBs. The look-up tables can be programmed with truth tables of 4 input or 3 input logic functions. The routing resources can be programmed to achieve the required connectivity between the CLBs. The hardware platform which can be used [WILDFORCE] is a PCI plug-in board with five Xilinx 4085 FPGAs, also referred to as PEs (Processing Elements). The board is stacked with five 1MB SRAM chips. Each of the five SRAM chips is directly connected to one of the five PEs. The embedded memory is accessible for read/write from both the host computer as well as from the corresponding PE. Each of the 1MB memory chip is organized as 262144 words of 32 bits each.

Figure 3.1: Configurable Logic Block (CLB) in XC4000 series FPGA

# 3.2 Design parameters and constraints

#### **3.2.1 Memory read/write**

The input image to the encoder is raw gray scale frames of 512 by 512 pixels. Each pixel is represented by 256 gray scale levels (8 bits). Input frames are loaded to the embedded memory by the host computer and results are read back, once the PE has processed it. The PE also uses the embedded memory as intermediate storage to hold results between different stages of processing.

The memory has a read latency of 2 cycles while memory writes are completed in the same cycle. Memory reads can be pipelined so that the effect of this latency is minimized. However, a clock cycle is wasted when there is a read to write turn around. The design concerns are to minimize memory read/write turn arounds and to allow longer spells of read or write cycles instead. Attempts have also been made to minimize memory operations.

### **3.2.2 Real time performance**

While the conventional television standards require 30 frames/second, many Multimedia applications like video conferencing run at much lower frame rates. In general, a good system clock ensures a good throughput. Other contributing factors to throughput include the time taken by the operating system driver routines to read/write from the embedded memory.

#### **3.2.3 Design partitioning**

The whole computation is partitioned into two stages. The first stage computes discrete wavelet transform coefficients of the input image frame and writes it back to the embedded memory. The second stage operates on this result to complete the rest of the processing. The second stage does dynamic quantization, zero thresholding, run length encoding for zeroes, and entropy encoding on the coefficients. The two stages are implemented on two separate FPGAs.

#### **3.3 Stage 1: DiscreteWavelet Transform**

Discrete Wavelet transform is implemented by filter banks. The filter used is the (2,2) Cohen-Debuchies-Feaveu wavelet filter. Though much longer filters are common for audio data, relatively short filters are used for video.

#### 3.3.0.1 (2, 2) wavelet

A modified form of the Bi-orthogonal (2,2) Cohen-Debuchies-Feaveu wavelet filter is used. The analysis filter equations are shown below.

High pass coefficients: g(k) = 2x(2k + 1) - x(2k) - x(2k + 2)Low pass coefficients: f(k) = x(2k) + (g(k-1) + g(k)=8

The boundary conditions are handled by symmetric extension of the coefficients as shown below:

x[2], x[1], [ x[0], x[1],....,x[n- 1], x[n] ], x[n- 1], x[n- 2]

The synthesis filter equations are shown below.

Even samples: x(2k) = f(k) - (g(k-1) + g(k+1))=8Odd samples: x(2k + 1) = (g(k) + f(k) + f(k+1))=2

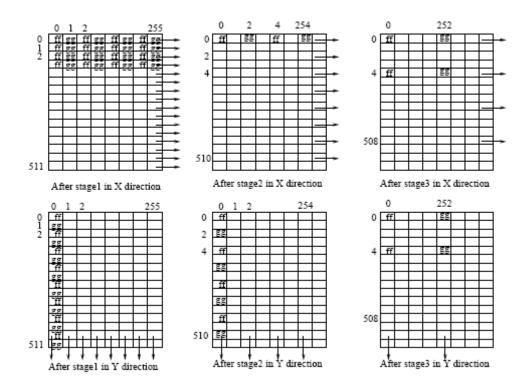

### 3.3.0.2 DWT in X and Y directions

Each pixel in the input frame is represented by 16 bits, accounting for 2 pixels per memory word. Thus, each memory read brings in two consecutive pixels of a row. Each clock cycle generates one value each of f and g coefficients. These have to be written back in place. The f coefficients are used again in the next stage of wave-letting. Two consecutive values of f are written back in one memory location (figure 3.2). This saves on memory reads of the f coefficients in the next stage. In the next stage, where only the fs are processed, only alternate memory words are

read from. Thus, the f and g coefficients are written back in an interleaved fashion. Another way to write back the coefficients is to put all the low frequency coefficients (f) ahead of the high frequency coefficients (g). This scheme of ordering the coefficients is called Mallot ordering. It allows progressive image transmission/reconstruction. The bulk of the 'average' information is ahead, followed by the minor 'difference' information. However, this ordering scheme requires temporary storage to hold the computed coefficients until the they can be written back. In our design, we use the in-place ordering scheme described above which is optimized for memory read/write operation. Once the three stages of wave-letting are done, we resort back to Mallot ordering.

Figure 3.2: Coefficient ordering along X direction

Once the filter has been applied along all rows in a stage, the same filter is applied along the columns. With the afore mentioned interleaved ordering scheme, alternate columns are all fs or all gs. Unlike the row traversal, the two values obtained in a memory read on a column traversal, are not consecutive values of the same column. Rather, they are corresponding values from two different vertically parallel streams (figure 3.3).

Figure 3.3: Coefficient ordering along Y direction

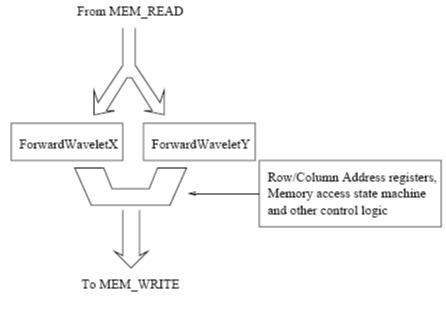

These differences along the row and column computations are accounted by having two separate data flow blocks along the two directions. The data flow block in X direction (ForwardWaveletX) accepts two successive values of the same row and outputs either two consecutive fs or two consecutive gs, in alternate fashion. The data flow block in Y direction (ForwardWaveletY) accepts one value each from two parallel streams and outputs either the fs for the two streams or the gs in an alternate manner, (figure 3.4). These blocks also need information on when a row/column starts/ends to handle the boundary conditions. They also have a pipeline latency of 3 cycles.

Figure 3.4: Fast Wavelet transform data flow blocks

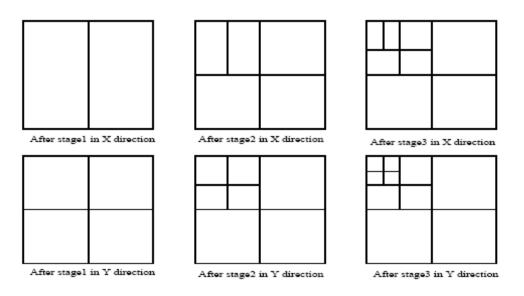

#### 3.3.0.3 3 stages of wave-letting

The 512 by 512 pixel input image frame is processed with three stages of waveletting. In the first stage, 512 pixels of each row are used to compute 256 high pass coefficients (g) and 256 low pass coefficients (f), figure 3.5. The coefficients are written back in place of the original row.

Figure 3.5: High pass and Low pass coefficients at stage 1, X direction

Once all the 512 rows are processed, the filters are applied in the Y direction. This completes the first stage of wave-letting. While conventional Mallot ordering scheme aggregates coefficients into the 4 quadrants, our ordering scheme interleaves the coefficients in the memory. The second stage of wave-letting only processes the low frequency coefficients from the first stage. This corresponds to the upper left hand quadrant in the Mallot scheme. Thus, second stage operates on row and columns of length 256, while the third stage operates on rows and columns of length 128. The aggregation of coefficients along the 3 stages under Mallot ordering is shown in figure 3.6. The memory map with the interleaved ordering is shown in figure 3.7.

Figure 3.6: Mallot ordering along the 3 stages of wave-letting

# 3.3.0.4 Over all architecture of Stage 1

Stage one starts with a raw frame and does three stages of wave-letting. The over all architecture is shown in figure 3.8. Memory addressing is done with a pair of address registers - read and write address registers. The difference between write and read registers is the latency of the pipelined data-flow blocks.

The maximum and minimum coefficient values for each block (each quadrant in the multi stage wave-letting) are maintained on the FPGA. These values are written back to a known location in the lower half (lower 0.5MB) of the embedded memory.

Figure 3.7: Interleaved ordering along the 3 stages of wave-letting

The second stage uses these values for the dynamic quantization of the coefficients. Row/Column Address registers, Memory access state machine and other control logic

Figure 3.8: Stage 1 architecture

#### 3.4 Stage 2

Stage 2 does the rest of the processing on the wavelet coefficients computed in the first stage. The coefficients, are quantized, zero-thresholded, zeroes run length encoded, and entropy encoded to get the final compressed image.

#### **3.4.1 Dynamic quantization**

The coefficients from different sub-bands (different quadrants with the Mallot ordering scheme) are quantized separately. The dynamic range of the coefficients for each sub-band (computed in first stage) is divided into 16 quantization levels. The coefficients are quantized into one of the 16 possible levels. The maximum and minimum value of the coefficients for each sub-band is also needed while decoding the image.

Figure 3.9: Dynamic Quantizer

The dynamic quantizer is implemented as a binary search tree look up in hardware (figure 3.9). A table look up based quantization scheme is not feasible since the range is dynamic - different for each sub-band, and different for each frame. The incoming stream of coefficients in the range [min:max] is translated to [0,max-min] by adding (or subtracting) the minimum. The shifted incoming value

is then compared with half the dynamic range (r/2) to determine whether it lies in the lower eight or upper eight quantization levels. The result forms the first bit (most significant bit) of the quantizer output. Depending on the outcome, the value is then compared with r/2 + r/4 or r/2 - r/4. This forms the second bit of the quantized output. The next two comparisons provide the remaining bits. The quantizer is a pipelined design, with 4 stages.

#### **3.4.2 Zero thresholding and RLE on zeroes**

Regions with abrupt changes will have larger wavelet coefficients while regions of little or no change would have smaller coefficients. Coefficients of small magnitude can be neglected without considerable distortion to the image. The error introduced is proportional to the magnitude of the coefficient being neglected. Coefficients are truncated to zero, based on a threshold. Different thresholds are used for different sub-bands, resulting in different resolution in different subbands. Further, different sets of thresholds are used to achieve different levels of compression. Three different set of thresholds are used for each sub-band to get three different variants of the encoder with different compression levels. The corresponding levels for the three configurations of the encoder are shown in the appendix. After the zero thresholding a large number of coefficients are truncated to zero. Long sequences of zeroes can be effectively compressed by run length encoding, which replaces each individual occurrence of a zero in a continuous spell with a count indicating the length of the spell. To decode a run length encoded stream, this count has to be distinguishable from other characters of the input data set. The other valid characters are the 4 bit output from the quantizer. Sixteen numbers 0 to 15 are reserved for the quantizer output values, while numbers 16 to

255 (240 numbers) are free. Thus, any continuous spell of zeroes ranging from 1 (represented by the number 16) to 240 (represented by the number 255) can be replaced by the corresponding count. Longer spells have to be broken down to fall within this range. Table 3.1 shows the bit range allocation. The run length encoder, might not have an output on every cycle. The succeeding block has to be signalled as to when to read the RLE count, and when to wait for a spell to finish. Whenever RLE detects a zero, it asserts 'RLErunning,'and starts counting the sequence of continuous zeroes. The current sum of zeroes is always available on 'RLEout.' When the continuous spell of zeroes end, 'RLErunning' is deasserted, and 'RLEspellEnd' is asserted for one cycle to allow the next block to read off the RLE count.

| 00000000 | 16 numbers allocated         |

|----------|------------------------------|

|          | for the output of quantizer, |

| 00001111 | 16 quantization levels.      |

| 00010000 | 256-16=240 numbers available |

|          | for RLE. RLE can count       |

| 11111111 | upto 240 continuous zeroes.  |

Table 3.1: Bit range allocation for RLE

The RLE counter is also reset to 15.In this set-up, there is look ahead problem. Before RLE can signal the end of a spell, it needs to see the next value is the stream. But, RLE is used in conjunction with the dynamic quantizer, (RLE and quantizer are connected in parallel) which is a 4 staged pipeline.RLE might face an arbitrarily long sequence of zeroes. RLE can count only upto a maximum of 240 zeroes. Thus, when RLE has seen 240 continuous zeroes and still more zeroes are arriving, 'RLEspellEnd' would be asserted for one Input Zero threshold.

Figure 3.10:

Run Length Encoder for continuous zeroes

Clock cycle and the internal counter are reset to 15. Here, 'RLErunning' would be high through out the spell. The logic followed by the succeeding block is as follows. If 'RLErunning' is asserted then wait till 'RLEspellEnd' is asserted and read the 'RLEout'. Else, read the output of the dynamic quantizer.

#### 3.4.3 Entropy encoding

Entropy encoding involves assigning a smaller length encoding for more frequently used characters in the data set and a larger length encoding for infrequently used characters in the data set. This involves variable length encoding of the input data. To efficiently retrieve the original data, an encoded word should not be a proper prefix of any other encoded word. Huffman trees are an efficient way of coming up with a variable length encoding for a set of characters, given the relative frequencies. Further, for a Huffman tree based encoding, decoding can be done in linear time (linear in the length of the encoded word).Various other schemes of encoding using different levels of context sensitive information exits. This might incur a costlier decoding function.

## **3.4.3.1 Encoding scheme**

In our implementation, we use an encoding scheme which is not a Huffman tree based code. The bit allocation is shown in figure 3.11. Eight bit inputs are variable length encoded between 3 to 18 bits. The complete encoding table is shown in the appendix. The encoding is implemented by two look-up tables on the FPGA. Given an eight bit input, the first look-up table (LUT), provides information about the size of encoding. The second LUT gives the actual encoding. Only the relevant bits from the second LUT should be used. The rest of the bits in the output are don't care and are either chosen as logic 0 or 1 during logic optimization. The VHDL description of the encoder can be found in the appendix, huffman.vhd.

Figure 3.11: Entropy encoding, bit allocation

Figure 3.12: Entropy encoder

# 3.4.3.2 Bit packing

The output of the entropy encoder varies from 3 to 18 bits. The bits need to be Packed into 32 bit words before being written back to the embedded memory. This is achieved by the shifter discussed below.

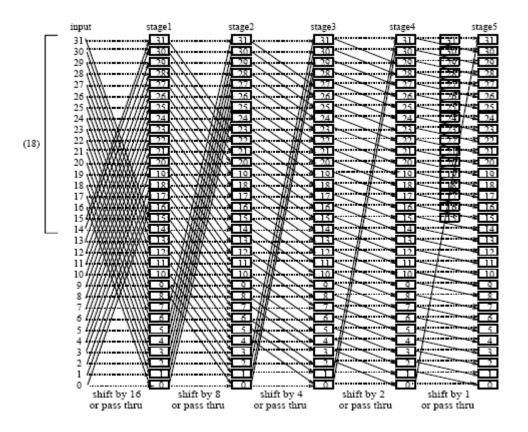

### 3.4.3.3 Shifter

The shifter consists of 5 register stages, each 32 bits wide. The input data can be shifted (rotated) by 16 or latched without shifting, to stage 1. The data can be shifted by 8 or passed on straight from stage 1 to stage 2. Similarly data can be shifted by 4, 2, and 1 when moving between the remaining stages. Data is shifted from stage to stage, and is accumulated at the last stage. When the last stage has 32 bits of data, a memory write is initiated and the last stage is flushed.

Figure 3.13: Binary Shifter for bit packing

The data is shifted to the right place over the 5 stages in order to complete a word at the last stage. The key decision is whether to shift or not at each stage. A 5 bit counter is maintained to store the length of the data currently held. For example, let the lengths of the words arriving at stage 1 be a1, a2, a3, etc. The counter will have values 0, a1, a1 + a2, etc. in the corresponding clock cycles. The counter is allowed to overflow once it reaches 31. Thus, the counter value indicates where the next word should start by the time it reaches the last stage. Different bits of the counter (delayed appropriately) are used to decide whether to shift or not at each stage. Part of the last stage needs double buffering. To determine the size of the double buffer needed, consider the worst case. The last stage already has 31 bits and the next data coming from stage 4 is of maximum size (18 bits). Only 1 out of the 18 bits can be added to the last stage and a memory write initiated. The rest of the 17 bits need to

be buffered for this cycle, and brought out in the next cycle. Thus, 17 out of the 32 bits in the last stage are double buffered. Thus, whenever an overflow is detected, the double buffer is loaded with the excess bits and taken out during the next cycle. The detailed hardware implementation may be found in the appendix in the file shifter.vhd.

### **3.4.4 Output file format**

At the end of the second stage, the upper memory (upper 0.5MB) contains the Packed bit stream. The total count of the bit stream approximated to the nearest WORD is written to memory location 0. To reconstruct the data from the bit stream, the following information is needed.

- The actual bit stream. On Huffman decoding, the actual 8 bit codes are retrieved. These codes are either the quantizer output, or the RLE count. On expanding the RLE count to the corresponding number of zeroes, we get the actual quantized stream.

- The four quadrants of the final stage of wave-letting can be located at the first four 128\*128 byte blocks. The three quadrants of the next stage can be located at at next three blocks sized at 256\*256 bytes each. Each quadrant (sub-band) is quantized separately. The dynamic range of each of the quadrant should be known to reconstruct the original stream.

The output file written has all the information needed to reconstruct the image. The format of the output file generated is shown in figure 3.14.

| Number of Bytes | (4 bytes)  |

|-----------------|------------|

| Block0 Min/Max  | (8 bytes)  |

| Block1 Min/Max  | (8 bytes)  |

| Block2 Min/Max  | (8 bytes)  |

| Block3 Min/Max  | (8 bytes)  |

| Block4 Min/Max  | (8 bytes)  |

| Block5 Min/Max  | (8 bytes)  |

| Block6 Min/Max  | (8 bytes)  |

| Block0 size     | (4 bytes)  |

| Block1 size     | (4 bytes)  |

| Block2 size     | (4 bytes)  |

| Block3 size     | (4 bytes)  |

| Block4 size     | (4 bytes)  |

| Block5 size     | (4 bytes)  |

| Block6 size     | (4 bytes)  |

| Bit stream      | (variable) |

Figure 3.14: Out file format

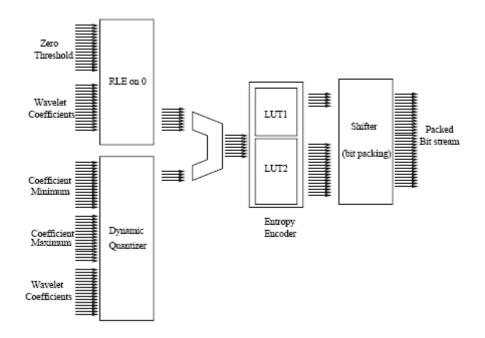

### 3.4.5 Stage 2, Overall architecture

The top level data flow diagram of the second stage is shown in figure 3.15. Wavelet coefficients from memory are read from the lower half of the embedded memory. The block (sub-band) minimum and maximum is also read from the memory. The packed bit stream output is written to the upper memory, and the bit stream length is written to memory location 0. The control software reads the embedded memory and generates the compressed image file.

Figure 3.15: Stage 2, data flow diagram

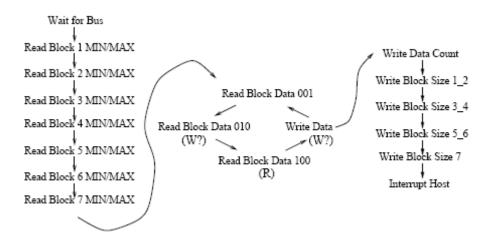

The control flow is show in figure 3.16. Before reading the wavelet coefficients, the maximum and minimum of coefficients in each sub-band are read from the lower memory. The coefficients are then read and processed for each sub-band, starting with the lowest frequency band. As shown in the state diagram, a memory read is fired in stage *Read 001*. Memory read has a latency of 2 clock cycles. The results of the read are finally available in state *Read 100*. Memory writes are completed in the same cycle. The two intermediate states, *Read 010* and *Write* can be used to write back the output, if output is available. Each memory read brings in two wavelet coefficients. Consider the worst case, where the two coefficients get expanded to 18 bits each. There are two memory write cycles before the next read. When ever a memory write is performed, the memory address register is incremented. The read address generators read each sub-band from the interleaved memory pattern. The address ranges for each sub-band with the interleaved ordering scheme is shown in appendix. The output is written as a continuous stream,

Figure 3.16: Stage 2, control flow diagram

Starting with the lowest sub-band. Thus the output is effectively in Mallot ordering and can be progressively transmitted/decoded.

# Chapter 4 Results

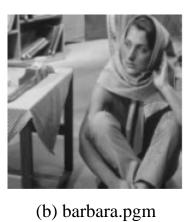

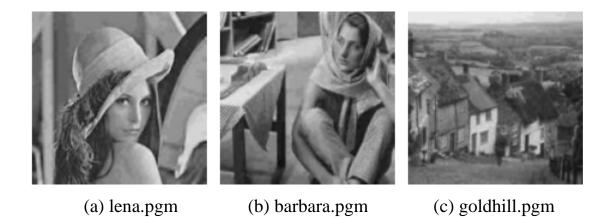

(c) goldhill.pgm

Figure 4.1: Original Images

(a) lena.pgm

(b) barbara.pgm

- (c) goldhill.pgm

- Figure 4.2: Configuration 1, Minimum compression

Figure 4.3: Configuration 2, Medium compression

(a) lena.pgm

(b) barbara.pgm

(c) goldhill.pgm

# **Chapter 5** Conclusions and Future Work

### **5.1 Conclusions**

We have designed a Wavelet transform based image encoder on re-programmable hardware - FPGA. The encoder has multiple configurations which support different compression levels. The effective frame rate achieved ranges between 10 and 12. The major conclusions are as follows:

- Wavelet based image compression is ideal for adaptive compression since it is inherently a multi-resolution scheme. Variable levels of compression can be easily achieved. The number of wave-letting stages can be varied, resulting in different number of sub bands. The zero thresholds for truncating coefficients of small magnitude can be varied. Different filter banks with different characteristics can be used. For example, audio data has much longer correlation and hence longer filter are used for audio, compared to video. Filters tuned to the nature of the data achieve much higher compression.

- Efficient fast algorithm (pyramidal computing scheme) for the computation of discrete wavelet coefficients makes a wavelet transform based encoder computationally efficient.

- Computationally intensive problems often require a hardware intensive solution. Unlike a microprocessor with a single MAC unit, a hardware implementation achieves greater parallelism, and hence higher throughput.

- Reconfigurable hardware is best suited for rapid prototyping applications where the lead time for implementation can be critical. It is an ideal development environment, since bugs can be fixed and multiple design

iterations can be done, with out incurring any non recurring engineering costs.

- Reconfigurable hardware is also suited for applications with rapidly changing requirements. In effect, the same piece of silicon can be reused.

- With respect to limitations, achieving good timing/area performance on these FPGAs is much harder, when compared to an ASIC or a custom IC implementation. There are two reasons for this. The first pertains to the fixed size look-up tables. This leads to under utilization of the device. The second reason is that the pre-fabricated routing resources run out fast with higher device utilization.

#### **5.2 Future work**

The lessons learned from this experience will help us enhance similar implementations in the future. Few of the improvements that we now foresee are listed below:

- Build a corresponding decoder on the FPGA and demonstrate the adaptability of the encoder-decoder pair. The encoder would need to signal the decoder on which codec is being used.

- Data movement from host to embedded memory and back to host takes a significant amount of the processing time. Data movement could have been minimized. By implementing both the stages of the encoder on a single FPGA, one read/write memory cycle could have been avoided. On the other side, when these FPGAs are utilized more than about 40%, the timing performance drops sharply. This is because it runs out of routing resources;

consequently many long and circuitous routes result. Hence the over all system clock drops. This tradeoff can be better optimized.

- An alternate architecture would be to use the two PEs for the two stages (to get good timing), but use the local bus on the board to transfer data from PE1 to PE2.

- A suggestion with respect to embedded memory architecture is to have two embedded memory chips attached to each PE, so that is can work as a double buffer. Here, the host can refill the next frame on one of the memory chips, while the PE is still working with the other chip.

- The metrics on which encoder can be graded include the compression ratio, throughput, Processing noise, and implementation costs. Further, the adaptively of the encoder to support different compression levels at different noise levels can also measured.

- The encoder runs in two stages. A raw frame of 512 by 512 pixels can loaded to the embedded memory. After stage 1 finishes its processing on this memory, the memory image can used as input for the second stage. The two hardware configurations, corresponding to the two stages, can be run at a system clock of 25MHz. The two hardware configurations are loaded onto two different FPGAs on the same board.

- The embedded memory can load and unloaded by the host computer using the operating system driver routines. The memory access times can be measured. List given below quantifies the time taken by the DMA based read/write APIs provided by the board vendor. The operating system running on the host computer is Linux, kernel version 2.2.5.

| Read from host<br>0.5 MB  | 4.244 ms |

|---------------------------|----------|

| Write from host<br>0.5 MB | 4.017 ms |

| Read from host<br>1.0 MB  | 8.398 ms |

| Write from host<br>1.0 MB | 7.981 ms |

Table 5.1: Embedded memory access times from host computer

- Different hardware configurations with different compression levels would build and tested. The characteristics of the three configurations over three different frames are displayed in tables (5.4, 5.5, and 5.6). A software decoder can be used to recontruct the encoded image in order to compare with the original.

- Noise figures from a software encoder can also quoted. The PSNR and RMSE metrics can compute as per the equation given below. Percentage compression is the ratio of compressed image size to the original image size (512x512 bytes). Bits per pixel (bpp) are the ratio of image size in bits to number of pixels.

$MSE = \frac{1}{512x512} \sum_{x=1}^{x=512} \sum_{y=1}^{y=512} [p(x, y) - p'(x, y)]^2$ RMSE =  $\sqrt{MSE}$ PSNR = 20log10(255/RMSE)

Table 4.3: PSNR and RMSE equations

| Configuration      | Compressed   | Compression | bpp   | PSNR     | RMS      |

|--------------------|--------------|-------------|-------|----------|----------|

|                    | size (bytes) | ratio       |       | (dB)     |          |

| Configuration 1,   | 28775        | 9.11        | 0.878 | 30.894   | 7.274    |

| Least compression  |              |             |       | (31.102) | (7.102)  |

| Configuration 2,   | 5556         | 47.18       | 0.169 | 29.530   | 8.511    |

| Medium compression |              |             |       | (30.015) | (8.049)  |

| Configuration 3,   | 3767         | 69.58       | 0.114 | 28.059   | 10.082   |

| Most compression   |              |             |       | (28.120) | (10.012) |

Table 5.4: Compression levels and noise measurements for 'lena'

| Configuration      | Compressed   | Compression | bpp   | PSNR     | RMS      |

|--------------------|--------------|-------------|-------|----------|----------|

|                    | size (bytes) | ratio       |       | (dB)     |          |

| Configuration 1,   | 29708        | 8.82        | 0.906 | 25.017   | 14.310   |

| Least compression  |              |             |       | (25.024) | (14.299) |

| Configuration 2,   | 8187         | 32.01       | 0.249 | 24.472   | 15.237   |

| Medium compression |              |             |       | (24.589) | (15.033) |

| Configuration 3,   | 4915         | 53.33       | 0.149 | 23.427   | 17.185   |

| Most compression   |              |             |       | (23.556) | (16.932) |

Table 5.5: Compression levels and noise measurements for 'barbara'

| Configuration      | Compressed   | Compression | bpp   | PSNR     | RMS      |

|--------------------|--------------|-------------|-------|----------|----------|

|                    | size (bytes) | ratio       |       | (dB)     |          |

| Configuration 1,   | 30024        | 8.7         | 0.916 | 30.038   | 8.027    |

| Least compression  |              |             |       | (30.045) | (8.021)  |

| Configuration 2,   | 6070         | 43.18       | 0.185 | 28.119   | 10.013   |

| Medium compression |              |             |       | (28.014) | (10.134) |

| Configuration 3,   | 3636         | 72.09       | 0.110 | 26.417   | 12.181   |

| Most compression   |              |             |       | (26.446) | (12.140) |

Table 5.6: Compression levels and noise neasurements for 'goldhill'

# Appendix

## Appendix A

### **Design parameters**

### A.1 Zero threshold levels for different codecs

| subband | Config. 1 | Config. 2 | Config. 3 |

|---------|-----------|-----------|-----------|

| 0       | 0         | 0         | 0         |

| 1       | 39        | 78        | 156       |

| 2       | 27        | 54        | 108       |

| 3       | 104       | 208       | 416       |

| 4       | 79        | 158       | 316       |

| 5       | 50        | 100       | 200       |

| 6       | 191       | 382       | 764       |

Table A.1: Zero threshold levels for different configurations

### A.2 Throughput comparison with a software encoder

The software encoder distributed as part of the ACS bench mark suite was used to obtain time stamps. The encoder was run on a Linux based computer with Pentium 2 processor, running at 333MHz, and having a main memory of 256MB.Time stamps were inserted at points which demarcate the 2 stages. As for the FPGA implementation, timing measurements do not include secondary storage media latencies.

| stage | time       |

|-------|------------|

| 1     | 181.046 ms |

| 2     | 132.331 ms |

Table A.2: Throughput measured from the software encoder

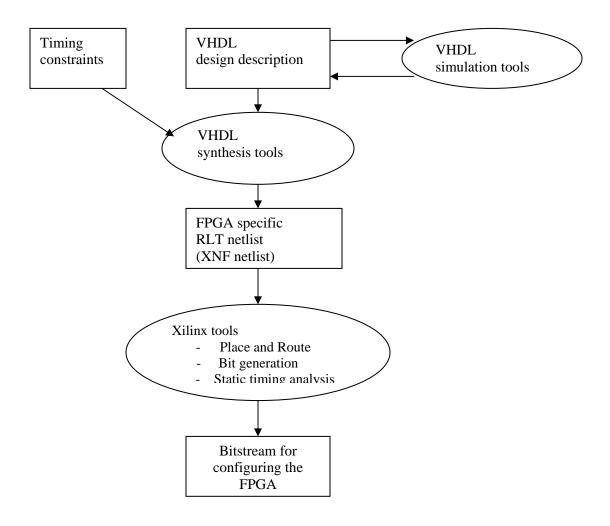

### A.3 Design flow

Figure A.1: Design flow

### **Appendix B**

### Source code listings

### **B.1 Stage 1 - VHDL source code**

#### B.1.1 waveletX.vhd

```

-- Stage1 - Forward Wavelet (in X direction)

- -

-- Input : A 512x512 pixel image, streamed row wise, two pixels at a time,

'p2' and 'p3'; two previous samples are held in 'p0' and 'p1'.

_ _

- -

-- Output : 'f' and 'g' are two weighted difference functions, The output is

256 values of 'f' and 256 values of 'g'. Note that 'f' and 'g' at the boundary are slightly different, due to which we need two

- -

- -

_ _

additional signals to signal row begining and ending.

_ _

-- Note that output is send back as 'f0', 'f1', 'q0', 'q1' ... instead of

--'f0', 'g0', 'f1', 'g1' ... This is because of the order it is written back

--into memory in the higher level module.

- -

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use ieee.std_logic_signed.all;

entity ForwardWaveletX is

port(

FwavClk

: in std logic;

FwavEnbl : in std_logic;

FwavStart : in std_logic;

FwavEnd : in std_logic;

: in std_logic_vector (15 downto 0);

: in std_logic_vector (15 downto 0);

: out std_logic_vector (15 downto 0);

Fwav p3

Fwav_p2

Fwav f

: out std_logic_vector (15 downto 0));

Fwav g

end ForwardWaveletX;

architecture structural of ForwardWaveletX is

constant prop_delay : time := 5 ns;

subtype std16 is std_logic_vector (15 downto 0);

signal p0, p1, g_out, g_prev1, g_prev2 : std16;

signal f_tmp1, f_tmp2, f_out, f_prev : std16;

signal ForG, FwavStart1, FwavEnd1 : std_lo

: std logic;

begin

run : process(FwavClk)

begin

if (rising edge (FwavClk)) then

if(FwavEnbl = '1') then

p0 <= Fwav p2 after prop delay;

```

p1 <= Fwav\_p3 after prop\_delay;</pre> if (ForG='1') then Fwav f <= f prev after prop delay;</pre> Fwav g <= f out after prop delay;</pre> else Fwav\_f <= g\_prev2 after prop\_delay;</pre> Fwav\_g <= g\_prev1 after prop\_delay;</pre> end if; if(FwavStart='1') then ForG <= '0' after prop delay;</pre> else ForG <= not(ForG) after prop delay;</pre> end if; g\_prev2 <= g\_prev1 after prop\_delay;</pre> g\_prev1 <= g\_out after prop\_delay;</pre> f\_prev <= f\_out after prop\_delay;</pre> FwavEnd1 <= FwavEnd after prop delay;</pre> FwavStart1 <= FwavStart after prop delay;</pre> end if; end if: end process; computeg : process(Fwav p3, p1, p0, FwavEnd1) begin if(FwavEnd1='1') then g\_out <= (p0(15) & p0(13 downto 0) & '0') - (p1(15) & p1(13 downto 0) & '0'); else q out <= (p0(15) & p0(13 downto 0) & '0') - (p1 + Fwav p3);end if; end process; computef : process(FwavStart1, g out, g prev1, f tmp1, f tmp2, p1) begin if(FwavStart1='1') then f tmp1 <= g out + g out;</pre> else f tmp1 <= g prev1 + g out;</pre> end if; f tmp2 <= (f tmp1(15) & f tmp1(15) & f tmp1(15) & f tmp1(15 downto 3));</pre> f out <= p1 + f tmp2;</pre> end process; end structural;

#### **B.1.2 waveletY.vhd**

```

-- Stage1 - Forward Wavelet (in Y direction)

--

-- Input : A 512x512 pixel image, streamed row wise, two pixels at a time,

-- 'p2' and 'p3'; two previous samples are held in 'p0' and 'p1'.

--

-- Output : 'f' and 'g' are two weighted difference functions, The output is

-- 256 values of 'f' and 256 values of 'g'.Note that 'f' and 'g' at

-- the boundary are slightly different, due to which we need two

```

```

- -

additional signals to signal row begining and ending.

_ _

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.std_logic_arith.all;

use ieee.std logic signed.all;

entity ForwardWaveletY is

port(

FwavClk

: in std logic;

FwavEnbl : in std logic;

FwavStart : in std logic;

FwavEnd

: in std_logic;

Fwav_a4 : in std_logic_vector (15 downto 0);

Fwav_b4 : in std_logic_vector (15 downto 0);

Fwav_a : out std_logic_vector (15 downto 0);

Fwav_b : out std_logic_vector (15 downto 0);

Fwav_Max : out std_logic);

end ForwardWaveletY;

architecture structural of ForwardWaveletY is

constant prop_delay : time := 5 ns;

subtype std1 is std_logic;

subtype std16 is std logic vector (15 downto 0);

-- 2 previous values of a4

signal a2, a3 : std16;

signal b2, b3 : std16;

-- 2 previous values of b4

signal a_g, b_g, a_gd : std16;

-- g outputs of 2 streams,

signal b gd, a gdd, b gdd: std16;

-- latched, double latched ...

signal a_f1, a_f2, a_f3, a_f3d : std16;

-- f, partial outputs

signal b_f1, b_f2, b_f3, b_f3d : std16;

-- f, partial outputs

signal FwavStart1, FwavStart2 : std1;

-- delayed FwavStart's

signal FwavEnd1, FwavEnd2 : std1;

-- and FwavEnd's

signal ForG : std1;

-- keep track of whether f or

--q is going out

begin

run : process(FwavClk)

begin

if(rising_edge(FwavClk)) then

if(\overline{F}wavEnbl = '1') then

a2 <= a3 after prop delay;

a3 <= Fwav_a4 after prop_delay;

b2 <= b3 after prop delay;

b3 <= Fwav_b4 after prop_delay;</pre>

FwavStart2<= FwavStart1 after prop delay;</pre>

FwavStart1<= FwavStart after prop delay;</pre>

FwavEnd1 <= FwavEnd after prop_delay;</pre>

FwavEnd2 <= FwavEnd1 after prop_delay;</pre>

a_gdd <= a_gd after prop_delay;</pre>

b_gdd <= b_gd after prop_delay;</pre>

a_gd <= a_g after prop_delay;</pre>

b gd <= b g after prop_delay;</pre>

a f3d <= a f3 after prop delay;

b f3d <= b f3 after prop delay;</pre>

if (FwavStart='1') then

ForG <= '0' after prop_delay;</pre>

else

ForG <= not(ForG) after prop delay;</pre>

end if;

```

vi

```

end if;

end if;

end process;

computeg : process(a2, a3, Fwav a4,b2, b3, Fwav b4, FwavEnd1)

begin

if(FwavEnd1='1') then

a g <= (a3(15) & a3(13 downto 0) & '0')-(a2(15) & a2(13 downto 0) & '0');

b g <= (b3(15) & b3(13 downto 0) & '0')-(b2(15) & b2(13 downto 0) & '0');

else

a g <= (a3(15) & a3(13 downto 0) & '0')-a2 -Fwav a4;

b g <= (b3(15) & b3(13 downto 0) & '0')-b2 -Fwav b4;

end if;

end process;

computef:process(FwavStart2, a2, b2, a g, b g, a gdd, b gdd, a f1, b f1, a f2, b f2)

begin

if(FwavStart2='1') then

a f1 <= a g + -- current g

a_g; -- current g

b_f1 <= b_g + -- current g

bg; -- current g

else

a_f1 <= a_gdd + -- prev g

ag; -- current g

b f1 <= b gdd + -- prev g

b g; -- current g

end if;

-- divide by 8 and drop fractional part,

-- because of two's compliment representation, if number is

-- negative and there is a non zero fractional value, we need to

-- add 1 after dropping the fractional part.

-- if ((a f1(15) = '1') and

-- ((a f1(2)='1') or (a f1(1)='1') or (a f1(0)='1'))) then

-- a f2 <= (a f1(15) & a f1(15) & a_f1(15) & a_f1(15 downto 3)) + 1;

-- else

a f2 <= (a f1(15) & a f1(15) & a f1(15) & a f1(15 downto 3));

-- end if;

-- if ((b f1(15) = '1') and

-- ((b f\overline{1}(2)='1') or (b f1(1)='1') or (b f1(0)='1'))) then

-- b f2 <= (b f1(15) & b f1(15) & b f1(15) & b f1(15 downto 3)) + 1;

-- else

b_f2 <= (b_f1(15) & b_f1(15) & b_f1(15) & b_f1(15 downto 3));

--end if;

a f3 <= a f2 + a2;

bf3 <= bf2 + b2;

end process;

out mux : process(ForG, a f3d, a gdd, b f3d, b gdd)

begin

```

```

if(ForG = '0') then

Fwav a <= a f3d;</pre>

Fwav b <= b f3d;</pre>

if(a_{\overline{f}3d} > b_{\overline{f}3d}) then

Fwav Max <= '0';

else

Fwav Max <= '1';</pre>

end if;

else

Fwav a <= a gdd;</pre>

Fwav_b <= b gdd;</pre>

if(a \ \overline{g}dd > b \ gdd) then

Fwav Max <= '0';

else

Fwav Max <= '1';</pre>

end if;

end if;

end process;

end structural;

```

#### B.1.3 top\_level\_for\_stage1.vhd

```

-- Description:

-- This file along with "waveletX.vhd" & "waveletY.vhd" implements DWT

-- (discrete wavelet transform)/multi resolution encoding of the input image.

- -

-- The input image is 512x512 pixels, with each memory WORD holding 2 pixels

-- (12 bits each) the input is a 512x256 memory array (0.5 MB).

- -

-- Stage 1: Process each row (512 pixels), extract 256 'f's and 256 'g's from

-- each row, write it back in place:

-- [pppppppp...pppp] => [fgfgfgfg...fgfg]

- -

-- Instead, it is actually written back as:

-- [ppppppppp] => [ffggffgg...ffgg].

_ _

-- Then same operation along Y direction.

- -

-- Stage 2: Only 'f's from first stage are input to second stage. Thus we have

-- rows of length 256.

-- (see why f/g outputs from stage1 was written back jumbled? need only 256

-- memory READS, else it would have taken 512 memory READS).

_ _

-- Stage 3: The third stage follows similarly, processing only the 'f's from

-- second stage. Each stage has to be done in both X and Y directions.

- -

-- It is smooth sailing in X direction with two pixels of a row arriving on

-- each memory READ and two values being written back in each memory WRITE.

- -

-- In Y direction, we have to perform two memory READs to get two consecutive

-- values of a stream (column). By then we also get two consecutive values

-- from the next (vertically parallel) stream.Hence, two different

-- ForwardWavelet blocks (ForwardWaveletX and ForwardWaveletY) are used for

-- the X and Y directions.

-- ForwardWaveletX: accepts two successive values of the same row and outputs

-- either two consecutive f's or two consecutive g's (alternately).

```

-- ForwardWaveletY: accepts one pixel each from two columns and outputs either -- one f each of the two columns or one g each of the two columns -- (alternately). library IEEE; use IEEE.std\_logic\_1164.all; use IEEE.std\_logic\_arith.all; use IEEE.std\_logic\_signed.all; architecture Memory Access of PE1 Logic Core is component ForwardWaveletX is port( : in std logic; FwavClk FwavEnbl : in std logic; FwavStart : in std logic; FwavEnd : in std logic; Fwav p3 : in std logic vector (15 downto 0); Fwav\_p2 : in std\_logic\_vector (15 downto 0); Fwav\_f : out std\_logic\_vector(15 downto 0); Fwav\_g : out std\_logic\_vector(15 downto 0)); end component; component ForwardWaveletY is port ( FwavClk : in std logic; FwavEnbl : in std logic; FwavStart : in std logic; FwavEnd : in std\_logic; : in std\_logic\_vector (15 downto 0); Fwav\_a4 Fwav\_b4 : in std\_logic\_vector (15 downto 0); Fwav\_a : out std\_logic\_vector (15 downto 0); Fwav\_b : out std\_logic\_vector (15 downto 0); Fwav\_Max : out std\_logic); end component; type MemoryStates is( MemWaitforBus, MemRead001, -- READ fired in this cycle, results later MemRead000, -- READ FILE MemRead100, -- READ result arrives -- normal coefficients -- READ fired last cycle, still waiting for results MemWriteMinMax1, -- coefficient min/max block1 (done at end of each stage) MemWriteMinMax2, -- coefficient min/max block2 MemWriteMinMax3, -- coefficient min/max block3 MemWriteMinMax4, -- coefficient min/max block4 MemInterrupt, MemDone); -- Black hole state! signal Mem PState : MemoryStates; -- Present state -- Next state signal Mem NState : MemoryStates; signal Enbl : std\_logic; signal nPass : std logic vector(1 downto 0); -- 00, 01, 10 signal ENDofROWx : std logic; -- Row BEGIN and END signals signal STARTofROWx : std logic; -- Col BEGIN and END signals signal ENDofROWy : std logic; signal STARTofROWy : std logic; -- 0=>row, 1=>col. signal ROWorCOL : std\_logic; signal ROWorCOL1 : std\_logic; -- delayed versions of signal ROWorCOL2 : std logic; -- ROWorCOL

signal ROWorCOL3 : std logic; signal cntrROW : std\_logic\_vector(8 downto 0); -- ROW, COL address

signal cntrCOL : std\_logic\_vector(7 downto 0); -- registers for READ signal cntrROW old1 : std logic vector(8 downto 0); signal cntrCOL\_old1 : std\_logic\_vector(7 downto 0); signal cntrROW\_old2 : std\_logic\_vector(% downto 0); signal cntrCOL\_old2 : std\_logic\_vector(% downto 0); signal cntrROW\_old3 : std\_logic\_vector(% downto 0); -- ROW, COL address signal cntrCOL\_old3 : std\_logic\_vector(% downto 0); -- registers for WRITE. signal ROW limit : std\_logic\_vector(8 downto 0); -- 511, 510, 508 signal COL\_limit : std logic vector(7 downto 0); -- 255, 254, 252 signal ROW\_skip : std\_logic\_vector(8 downto 0); signal COL\_skip : std\_logic\_vector(7 downto 0); -- 1, 2, 4 -- 1, 2, 4 -- Input, from mem READ signal userInputU : std\_logic\_vector(15 downto 0); signal userInputL : std\_logic\_vector(15 downto 0); signal userOutputUx : std\_logic\_vector(15 downto 0); -- Output from signal userOutputLx : std\_logic\_vector(15 downto 0); -- ForwardWaveletX signal userOutputUy : std\_logic\_vector(15 downto 0); -- Output from signal userOutputLy : std\_logic\_vector(15 downto 0); -- ForwardWaveletY signal normalCoeffU : std logic vector(15 downto 0); -signal normalCoeffL : std logic vector(15 downto 0); -signal Fwav MaxY : std logic; signal block1min : std\_logic\_vector(15 downto 0); -- Collect coefficient signal block1max : std\_logic\_vector(15 downto 0); -- MIN/MAX at each stage of signal block2min : std\_logic\_vector(15 downto 0); -- Waveletting, to be used signal block2max : std\_logic\_vector(15 downto 0); -- the next stage -- quantizer signal block3min : std logic vector(15 downto 0); signal block3max : std\_logic\_vector(15 downto 0); -- This saves an additional signal block4min : std logic\_vector(15 downto 0); -- pass over the data. signal block4max : std logic vector(15 downto 0); begin wlet x : ForwardWaveletX port map ( PE Pclk, -- here is the forward Wavelet Enbl, -- transform block for X direction STARTofROWx, ENDofROWx, userInputU, userInputL, userOutputUx, userOutputLx); wlet y : ForwardWaveletY port map ( PE Pclk, -- here is the forward Wavelet -- transform block for Y direction Enbl, STARTofROWy, ENDofROWy, userInputU, userInputL, userOutputUy, userOutputLy, Fwav MaxY);

memdata\_mux : process (ROWorCOL3, Mem\_PState,userOutputUx, userOutputLx, userOutputUy, userOutputLy,normalCoeffU, normalCoeffL,block1max, block1min) begin

```

if(ROWorCOL3='0') then

normalCoeffU <= userOutputUx;</pre>

normalCoeffL <= userOutputLx;</pre>

else

normalCoeffU <= userOutputUy;</pre>

normalCoeffL <= userOutputLy;</pre>

end if;

if (Mem PState=MemWrite) then

PE MemData OutReg(31 downto 16)<= normalCoeffU;</pre>

PE MemData OutReg(15 downto 0) <= normalCoeffL;</pre>

else

PE MemData OutReg(31 downto 16) <= block1max;</pre>

PE MemData OutReg(15 downto 0) <= block1min;

end if;

end process memdata mux;

st_update : process (PE_Pclk, PE_Reset)

variable xtest, ytest: std logic;

begin

if (PE Reset = '1') then

Mem_PState <= MemWaitforBus; -- Initialize current state</pre>

cntrROW <= "000000000"; -- Initialize ROW and COL

cntrCOL <= "000000000"; -- address registers.</pre>

cntrROW_old1 <= "000000000";

cntrCOL_old1 <= "00000000";

cntrROW_old2 <= "000000000";

cntrCOL_old2 <= "00000000";

cntrROW_old3 <= "000000000";</pre>

cntrCOL old3 <= "00000000";

ROWorCOL <= '0'; -- Initialize ROW / COL

ROWorCOL1 <= '0'; -- direction indicator

ROWorCOL2 <= '0'; -- to ROW

ROWOrCOL3 <= '0';

userInputU <= (others => '0');

userInputL <= (others => '0');

block1max <= (others => '0');

block1min <= (others => '0');

block2max <= (others => '0');

block2min <= (others => '0');

block3max <= (others => '0');

block3min <= (others => '0');

block4max <= (others => '0');

block4min <= (others => '0');

nPass <= "00";

ROW skip <= "000000001"; -- 1, 2, 4

COL skip <= "00000001"; -- 1, 2, 4

-- Pass 1 covers:

-- ROWS [0,1,2,3, ..., 511] and COLS [0,1,2,3, ..., 255]

- -

-- Pass 2 covers:

-- ROWS [0,2,4,6, ..., 510] and COLS [0,2,4,6, ..., 254]

- -

-- Pass 3 covers:

-- ROWS [0,4,8,12,..., 508] and COLS [0,4,8,12,..., 252]

ROW limit <= "111111111"; -- Initialize to 511

```

```

COL limit <= "11111111"; -- Initialize to 255

elsif (rising edge(PE Pclk)) then

Mem PState <= Mem NState;

-- Switch between X,Y directions

if (Mem PState = MemWrite) then

if((cntrROW = ROW limit) and (cntrCOL = COL limit)) then

ROWorCOL <= not(ROWorCOL); -- (ROWorCOL=0) => X,

-- (ROWorCOL=1) => Y.

if(ROWorCOL = '1') then

ROW_skip <= (ROW_skip(7 downto 0) & '0');</pre>

COL skip <= (COL skip(6 downto 0) & '0');

ROW limit <= (ROW limit(7 downto 0) & '0');

COL_limit <= (COL_limit(6 downto 0) & '0');

nPass <= UNSIGNED(nPass) + 1;</pre>

end if;

end if;

ROWorCOL1 <= ROWorCOL; -- update delayed

ROWorCOL2 <= ROWorCOL1; -- versions of</pre>

ROWorCOL3 <= ROWorCOL2; -- ROWorCOL

if(ROWorCOL = '0') then

cntrCOL <= UNSIGNED(cntrCOL) + UNSIGNED(COL skip);</pre>

if (cntrCOL = COL limit) then

cntrROW <= UNSIGNED(cntrROW) + UNSIGNED(ROW skip);</pre>

end if;

else

cntrROW <= UNSIGNED(cntrROW) + UNSIGNED(ROW skip);</pre>

if (cntrROW = ROW limit) then

cntrCOL <= UNSIGNED(cntrCOL) + UNSIGNED(COL skip);</pre>

end if;

end if;

cntrROW old1 <= cntrROW; -- 2 sets of address

cntrCOL old1 <= cntrCOL; -- regsisters, one for

-- memory READ and another

cntrROW_old2 <= cntrROW_old1; -- for memory WRITE.</pre>

cntrCOL old2 <= cntrCOL old1; --</pre>

-- WRITE lags the READ

cntrROW old3 <= cntrROW old2; -- by the latency of

cntrCOL_old3 <= cntrCOL_old2; -- ForwardWavelet.</pre>

end if;

if (Mem PState = MemRead100) then

userInputU <= PE MemData InReg(31 downto 16);</pre>

userInputL <= PE_MemData_InReg(15 downto 0);</pre>

end if;

if ((Mem PState= MemWriteMinMax1) or

(Mem PState = MemWriteMinMax2) or

(Mem PState = MemWriteMinMax3) or

(Mem PState = MemWriteMinMax4)) then

block1max <= block2max;</pre>

block1min <= block2min;</pre>

block2max <= block3max;</pre>

block2min <= block3min;</pre>

block3max <= block4max;</pre>

block3min <= block4min;</pre>

block4max <= (others => '0');

block4min <= (others => '0');

elsif (Mem_PState = MemWrite) then

if (nPass = "00") then

xtest := cntrROW old3(0);

ytest := cntrCOL old3(0);

elsif (nPass = "01") then

xtest := cntrROW old3(1);

ytest := cntrCOL_old3(1);

else

xtest := cntrROW old3(2);

```

```

ytest := cntrCOL old3(2);

end if;

if ((xtest = '0') and (ytest = '0') and (ROWorCOL3='1')) then

if (Fwav MaxY='0') then

if(SIGNED(block1max) < SIGNED(normalCoeffU)) then

block1max <= normalCoeffU;</pre>

end if;

if(SIGNED(block1min) > SIGNED(normalCoeffL)) then

block1min <= normalCoeffL;</pre>

end if:

else

if (SIGNED(block1max) < SIGNED(normalCoeffL)) then

block1max <= normalCoeffL;</pre>

end if;

if (SIGNED(block1min) > SIGNED(normalCoeffU)) then

block1min <= normalCoeffU;</pre>

end if;

end if;

end if;

if ((xtest = '0') and (ytest = '1') and (ROWorCOL3='1')) then

if(Fwav MaxY='0') then

if(SIGNED(block2max) < SIGNED(normalCoeffU)) then

block2max <= normalCoeffU;</pre>

end if;

if (SIGNED (block2min) > SIGNED (normalCoeffL)) then

block2min <= normalCoeffL;</pre>

end if;

else

if (SIGNED(block2max) < SIGNED(normalCoeffL)) then

block2max <= normalCoeffL;</pre>

end if;

if(SIGNED(block2min) > SIGNED(normalCoeffU)) then

block2min <= normalCoeffU;</pre>

end if;

end if;

end if;

if ((xtest = '1') and (ytest = '0') and (ROWorCOL3='1')) then

if(Fwav MaxY='0') then

if(SIGNED(block3max) < SIGNED(normalCoeffU)) then

block3max <= normalCoeffU;</pre>

end if;

if(SIGNED(block3min) > SIGNED(normalCoeffL)) then

block3min <= normalCoeffL;</pre>

end if;

else

if (SIGNED(block3max) < SIGNED(normalCoeffL)) then

block3max <= normalCoeffL;</pre>

end if;

if(SIGNED(block3min) > SIGNED(normalCoeffU)) then

block3min <= normalCoeffU;</pre>

end if;

end if;

end if;

if ((xtest = '1') and (ytest = '1') and (ROWorCOL3='1')) then

if(Fwav MaxY='0') then

if (SIGNED (block4max) < SIGNED (normalCoeffU)) then

block4max <= normalCoeffU;</pre>

end if;

if(SIGNED(block4min) > SIGNED(normalCoeffL)) then

block4min <= normalCoeffL;</pre>

end if;

```

```

else

if(SIGNED(block4max) < SIGNED(normalCoeffL)) then</pre>

block4max <= normalCoeffL;</pre>

end if;

if(SIGNED(block4min) > SIGNED(normalCoeffU)) then

block4min <= normalCoeffU;</pre>

end if;

end if;

end if;

end if;

end if;

end process st update;

start end : process (ROWorCOL, cntrCOL, cntrROW, ROW limit, COL limit)

begin

STARTofROWx <= '0';</pre>

ENDofROWx <= '0';</pre>

STARTofROWy <= '0';</pre>

ENDofROWy <= '0';</pre>

if (ROWorCOL = '0') then -- if X direction

if (cntrCOL = "00000000") then -- STARTofROW

STARTofROWx <= '1';</pre>

end if;

if (cntrCOL = COL limit) then -- ENDofROW

ENDofROWx <= '1';</pre>

end if;

else -- else if Y direction

if (cntrROW = "000000000") then -- STARTofROW

STARTofROWy <= '1';</pre>

end if;

if (cntrROW = ROW limit) then -- ENDofROW

ENDofROWy <= '1';</pre>

end if;

end if;

end process;

PE MemAddr OutReg(21 downto 18) <= (others => '0');

mem state: process(Mem PState, nPass, PE MemBusGrant n, ROWorCOL2, ROWorCOL3,

cntrROW, cntrCOL, cntrROW old3, cntrCOL old3, PE InterruptAck n)

begin

PE InterruptReq_n <= '1'; -- Default, do not interrupt host</pre>

PE_MemWriteSel_n <= '1'; -- read/write, default read</pre>

PE MemStrobe n <= '1'; -- No strobe, later

PE_MemBusReq_n <= '0'; -- Always request bus</pre>

Enbl <= '0';

PE MemAddr OutReg(17 downto 0) <= (others => 'X');

case Mem PState is

when MemWaitforBus => -- Wait for bus, when bus is

if (PE MemBusGrant n = '0') then -- available, fire READ in

Mem NState <= MemRead001; -- in next clock. Firing READ

else -- in same clock kills the

Mem NState <= MemWaitforBus;-- timing performance...</pre>

end if;

when MemRead001 => -- Fire READ, results of

```

```

PE MemStrobe n <= '0'; -- this will come later...

Mem NState <= MemRead010;</pre>

PE_MemAddr_OutReg(17) <= '0';</pre>

PE_MemAddr_OutReg(16 downto 8) <= cntrROW; -- Use cntrROW and</pre>

PE MemAddr OutReg( 7 downto 0) <= cntrCOL; -- cntrCOL for READ

when MemRead010 => -- Still waiting for

Mem NState <= MemRead100; -- READ results...</pre>

when MemRead100 => -- Got READ results here

Mem NState <= MemWrite;</pre>

when MemWrite =>

Enbl <= '1';

PE MemWriteSel n <= '0'; -- for writing

PE MemStrobe n <= '0';</pre>

PE MemAddr OutReg(17) <= '0';</pre>

PE MemAddr OutReg(16 downto 8) <= cntrROW old3; --Use cntrROW old3

PE_MemAddr_OutReg( 7 downto 0) <= cntrCOL_old3; --cntrCOL_old3 for</pre>

--WRITE

if((ROWorCOL3 = '1') and (ROWorCOL2 = '0')) then-- If COL->ROW switch

-- Write max/min statistics

Mem NState <= MemWriteMinMax1;</pre>

else