# **"VERIFICATION OF CONFIGURABLE IOB**

## ACCORDING TO JEDEC STANDARDS"

A dissertation submitted towards the partial fulfillment of the requirement for the Award of the Degree of

### Master of Engineering in

**Electronics & Communication**

Submitted by

Sanjib Deka University Roll No: 3313 College Roll No: 08/E&C/03

Under the guidance of

Dr. Asok Bhattacharyya

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING DELHI COLLEGE OF ENGINEERING UNIVERSITY OF DELHI 2003-2005

### CERTIFICATE

This is to certify that the project entitled "Verification of Configurable IOB According to JEDEC Standards", which is being submitted by Mr. Sanjib Deka, is a bonafide record of student's own work carried by him under my guidance and supervision in partial fulfillment of requirement for the award of the Degree of Master of Engineering in Electronic & Communication, Electronic & Communication Engineering Department, Delhi College of Engineering, University of Delhi. The matter embodied in this project has not been submitted for the award of any other degree.

#### Dr. Asok Bhattacharyya

#### **Project Guide**

Professor & Head of Department Department of Electronics & Communication Engineering Delhi College of Engineering Delhi - 110042

## ACKNOWLEDGEMENT

It is my pleasure to acknowledge and express my deep sense of gratitude towards my guide, Dr. Asok Bhattacharyya, project guide & HOD (Electronic & Communication Dept, DCE), who supervised the work reported in this thesis report. I sincerely thank him for providing me with opportunity to pursue my internship in ST Microelectronics, Noida & being a constant source of inspiration.

I would like to thank Mr.Hiten Advani, Sectional manager, FPGA dept, for giving me opportunity to work in STMicroelectronics and for his help during the course of this project.

I thank Mr. Puneet Suri and Ms Veena Krishnan, my Project Guide, in STMicroelectronics for providing me with their knowledgeable suggestions and valuable support. Also I thank members of the team Mr. Janit Kumar, Mr. Satinder Singh Malhi, Mr. Arun Mishra, Mr. Prashant Narang, Ms. Shobhna Tiwari, Mr. Varinder Kumar and Mr. Vikrant Singh for their continuous guidance and support for the project. I am greatly thankful to Mr. Rahul Bharti from HR for his help during training.

I also like to thank everyone who has helped me either directly or indirectly in the successful completion of this work.

Sanjib Deka College Roll No. 08/EC/2K3 University Roll No. 3103

### **"VERIFICATION OF CONFIGURABLE IOB**

### ACCORDING TO JEDEC STANDARDS"

BY

Sanjib Deka College Roll no: 08/EC/2K3 University Roll no: 3103

#### Abstract:

In this thesis Input Output block of FPGA is verified according to JEDEC standards. IOB's used in FPGA's are made configurable to support different applications. These IOB comply with electrical standard described by the JEDEC documents. In this thesis the postlay netlist of configurable IOB of FPGA is verified according to JEDEC standard. And the rise to rise delay, fall to fall delay and output duty cycle are also measured. Maximum frequency of operation of IOB was also verified. The simulations were carried out on EDA tools Eldo and Hspice. Measurements were done on the output waveforms. A relationship between rise delay, fall delay, input & output duty cycle was observed. An expression was derived which explains the behaviour observed, & this expression lets us calculate the maximum frequency when output is limited by duty cycle. The theoretical values found by the relation were confirmed with simulation results.

## **Table Of Contents**

| 1. Introduction1                 | 1  |  |  |

|----------------------------------|----|--|--|

| 1.1 Introduction                 | 2  |  |  |

| 1.2 FPGA                         | 3  |  |  |

| 1.3 Input Output Block(IOB)      | 3  |  |  |

| 1.4 JEDEC standards              | 4  |  |  |

| 1.5 Verification                 | 4  |  |  |

| 1.5.1 Schematic-Based Simulation | 4  |  |  |

| 1.5.2 Functional Simulation      | 4  |  |  |

| 1.5.3 Timing Simulation          | 4  |  |  |

| 1.6 Goals of the Project         | 5  |  |  |

| 1.7 Organisation of Thesis       | .5 |  |  |

##

| 2.1 Introduction                              | 7  |

|-----------------------------------------------|----|

| 2.2 FPGA                                      |    |

| 2.3 Basic Blocks of FPGA                      |    |

| 2.3.1 Logic blocks                            | 7  |

| 2.3.2 Interconnection resources.              | 8  |

| 2.4 Programming technologies                  | 8  |

| 2.4.1 Static RAM Programming Technology       | 9  |

| 2.4.2 Anti-fuse programming technology        |    |

| 2.4.3 EPROM and EEPROM programming technology | 12 |

| 2.5 Comparison of programmable technology     | 13 |

| 2.6 Applications of FPGAs                     | 13 |

| 2.7 Design Flow Overview                      | 13 |

| 2.7.1Design Entry and Synthesis               | 14 |

| 2.7.2 Design Verification                     |    |

| 2.7.2.1. Simulation                           | 17 |

| 2.7.2.2. Static Timing Analysis               | 18 |

| 2.7.2.3. In-Circuit Verification              |    |

| 2.8 Input output block                        | 19 |

| 2.8.1 Basic of I/O                            | 19 |

| 2.8.1.1 What is an I/O?                       | 19 |

| 2.8.1.2 I/O Logic Functions                   | 20 |

| 2.8.1.3 Specific functions of IO              | 21 |

=

| 2.8.2 Requirements of IO                          |    |

|---------------------------------------------------|----|

| 2.8.3 Electrical Interface Characteristics of IOB | 23 |

| 2.8.3.1 Input and output voltage level            |    |

| 2.8.3.3 Input and output current level            |    |

| 2.8.3.4 Rise, fall time and Propagation delay     | 24 |

| 2.8.3.5 Slew rate                                 | 25 |

| 2.8.4 Basic blocks of IOB.                        | 25 |

| 2.8.4.1 Input Stage of IOB                        |    |

| 2.8.4.2 Output stage of IOB                       |    |

| 2.9 ESD Protection in I/O.                        |    |

| 2.9.1 What is ESD?                                | 29 |

| 2.9.2 Effects of ESD                              |    |

| 2.9.3 ESD standard models                         |    |

| Human Body Model (HBD)                            |    |

| Machine Model (MM)                                | 32 |

| Charged Device Model (CDM)                        |    |

| 2.9.4 What to protect in silicon?                 |    |

| 2.9.5 High Speed ESD Protection                   |    |

| 2.9.5.1 Protection strategy                       |    |

| 2.9.5.2 ESD Protection Devices                    |    |

| 2.10 Latch up                                     |    |

| 2.10.1 Latch-up Model                             |    |

| 2.10.2 Latch-up Phenomenon                        |    |

| 2.10.3 Preventing Latch-up                        |    |

| 2.10.3.1 Causes of latch-up                       |    |

| 2.10.3.2 Latch-up prevention                      |    |

| 2.10.3.3 I/O Latch-up protection                  | 40 |

| 2.11 Jedec Standards                              | 41 |

| 2.11.1 Jedec Activities                           |    |

| 2.11.2 Standards Supported by IOB                 |    |

| 2.12 Summary                                      | 42 |

##

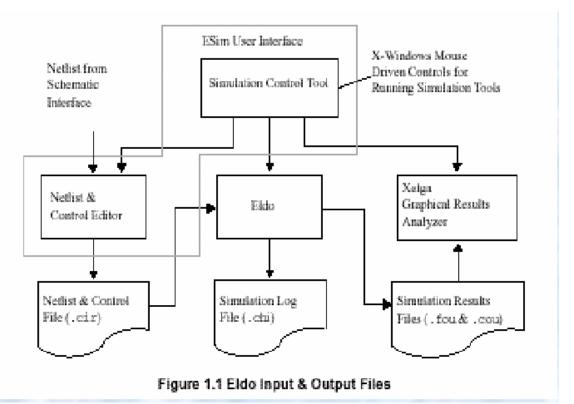

| 3.1 Introduction                   | 44 |

|------------------------------------|----|

| 3.2 Verification                   |    |

| 3.3 Verification plan for IOB      | 44 |

| 3.4 Simulation Information         |    |

| 3.5 . <i>cir</i> file              | 45 |

| 3.5.1 Description of .cir file     | 48 |

| 3.5.2 Parameters Measured          | 49 |

| 3.5.3 Maximum frequency            | 49 |

| 3.5 Method used to tabulate result |    |

| 3.6 Summary                        | 49 |

|                                    |    |

| 4. Results                                      |    |  |

|-------------------------------------------------|----|--|

| 4.1Introduction                                 | 51 |  |

| 4.2 Standards supported by IOB                  |    |  |

| 4.3 Specification of the Standard               |    |  |

| 4.3.1 Single Ended Standards                    |    |  |

| LVCMOS12                                        | 51 |  |

| LVCMOS15                                        | 52 |  |

| LVCMOS18                                        | 52 |  |

| LVCMOS25                                        | 53 |  |

| LVTTL                                           | 54 |  |

| 4.3.2 Pseudo-differential Standards             | 54 |  |

| HSTL 1.5                                        | 54 |  |

| HSTL 1.8                                        | 56 |  |

| SSTL 1.8                                        |    |  |

| SSTL 2.5                                        |    |  |

| SSTL 3.3                                        |    |  |

| GTL                                             |    |  |

| GTLP                                            |    |  |

| 4.3.3 Fully Differential Standards              |    |  |

| 4.5 Summary                                     | 61 |  |

| 5. Conclusion                                   | 62 |  |

| Reference                                       | 65 |  |

| Appendix                                        | 67 |  |

| A. Eldo Sytax Reference                         |    |  |

| B. Hspice Simulation & Syntax Reference         |    |  |

| C. Hsim Simulator Features & Syntax Summary     |    |  |

| D. Expression For Determining Maximum Frequency |    |  |

\_\_\_\_\_

# Chapter 1

# Introduction

#### **1.1 Introduction**

Very Large Scale Integration (VLSI) technology has opened the door implementation of powerful digital circuits at low cost. It has become possible to build chips with more than a million transistors, as exemplified by state-of-the-art microprocessors. Such chips are realized using the *full custom* approach, where all parts of a VLSI circuit are carefully tailored to meet a set of specific requirements. Semi-custom approaches such as Standard Cells and Mask-Programmed Gate Arrays (MPGAs) have provided an easier way of designing and manufacturing Application-Specific Integrated Circuits (ASICs).

Each of these techniques, however, requires extensive manufacturing effort, taking several months from beginning to end. This results in a high cost for each unit unless large volumes are produced, because the overhead to begin production of chips ranges from \$20,000 to \$200,000.

In the electronics industry it is vital to reach the market with new products in the shortest possible time and so reduced development and production time is essential. Furthermore, it is important that the financial risk incurred in the development of a new product be limited so that more new ideas can be prototyped. Field-Programmable gate Arrays (FPGAs) have emerged as the ultimate solution to these time-to-market and risk problems because they provide instant manufacturing and very low-cost prototypes. An FPGA can be manufactured in minutes, and prototype costs are of the order of \$100. A field-programmable device is a device in which the final logic structure can be directly configured by the end user, without the use of an integrated circuit fabrication facility.

Here's the general workflow when working with FPGAs:

- You use a computer to describe the "logic function" that you want. You might draw a schematic, or create a text file describing the function, doesn't matter.

- You compile the "logic function" on your computer, using a software provided by the FPGA vendor. That creates a binary file that can be downloaded into the FPGA.

- You connect a cable from your computer to the FPGA, and download the binary file to the FPGA.

- That's it! Your FPGA behaves according to your "logic function".

Keep in mind that

- You can download FPGAs as many time as you want no limit with different functionalities every time if you want. If you make a mistake in your design, just fix your "logic function", re-compile and re-download it. No PCB, solder or component to change.

- The designs can run much faster than if you were to design a board with discrete components, since everything runs within the FPGA, on its silicon die.

- FPGAs loose their functionality when the power goes away (like RAM in a computer that looses its content). You have to re-download them when power goes back up to restore the functionality.

#### 1.2 FPGA

*FPGAs (Field Programmable Gate Arrays)* are arrays of logic blocks which can be linked together to form complex logic implementations. A bit more flexible and complex than CPLDs and PALs, FPGAs can be separated into two categories; Fine Grained and Coarse grained. Fine grained being made up of a sea of gates or transistors or small macro cells, while coarse grained being made up of bigger macro cells which are often made up of flip flops and Look up Tables (LUTs) which make up the combinatorial logic functions. Inside the macro cell are often switches or multiplexers which allow for differing uses of the macro cell. The individual macro cells are connected together with a combination of switch matrixes and metal line matrixes which can be implemented with pass transistors, fuses/antifuses or multiplexers.

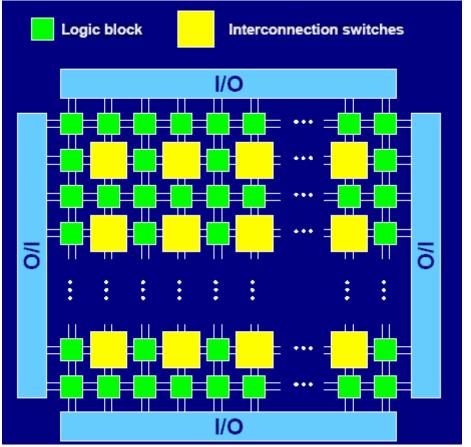

A typical FPGA consists of a two-dimensional array of logic blocks that can be connected by general interconnection resources. These arrays of logic block and interconnection resources are surrounded by Input output blocks.

#### **1.3 Input Output Block (IOB)**

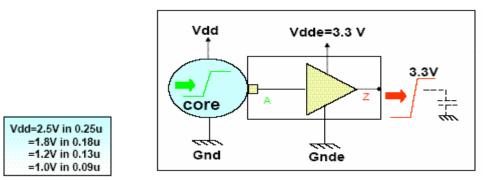

Any integrated circuit when looked inside package body can be broadly seen as two parts, i.e. core and IOB. Core is the silicon part where input signal provided by the IOB are processed and given back to IOB as output. IOB is the cell that allows interface between the logic inside the chip and external system components. In other words IOB protects the silicon from factors that may either damage the chip or hinder with chips functionality and performance. I/O Logic Functions

An I/O can have three basic logic functions:

A). *Input*: The I/O receives and adapts the signal to the core. Since core and I/O work at different voltage levels. Signal has to be level shifted to core voltage level. This function can be selected from control bits.

B). *Output*: The IO amplifies and adapts the signal from the core to the outside load. Since core voltage is less than IO voltage IOB amplifies the signal and supply it to the load.

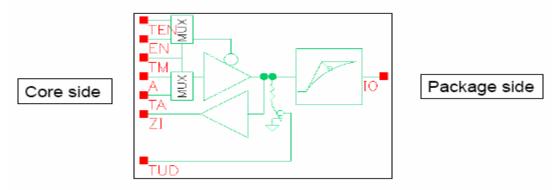

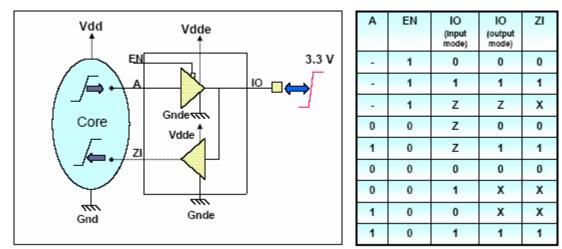

C). *Bidirectional:* IO can both work as input or output path. As shown in figure 3.5 this block has both input and output path. These blocks are selected from control signal from the core. In figure EN signal shown is active low. When EN is high block acts as input path, therefore ZI follows IO. And when EN is low this block acts as output path.

#### Specific functions of IO

A). *Pull-up and pull-down:* The optional pull-up and pull-down resistors are intended to establish High and Low levels, respectively, at unused I/Os.

B). *Hysteresis*: This feature is included, make core more immune to noise. There are two level of voltage known as trim points.

C). *Analog IO's*: These IO's are designed to carry analog signal e.g. oscillators, ADC. They have different current and voltage requirements thus have different design.

D). *Power Supply IO's*: These IO's are designed to carry supply for core and IO. They have inbuilt ESD protection circuitry.

E). Latch -up: The IO structure is more susceptible to latch-up. So the layout are made keeping this mind

#### **1.4 JEDEC standards**

JEDEC is the leading developer of standards for the solid-state industry. Almost 2400 participants, appointed by some 270 companies work together in 50 JEDEC committees meet the needs of every segment of the industry, manufacturers and consumers alike. The publications and standards that they generate are accepted throughout the world

JEDEC committees hold frequent meetings throughout the year in domestic and international venues. All standardization work takes place at these meetings and companies must be a member to participate. Surveys are also often taken to find out what companies are doing in important areas that often leads to ballots.

In this thesis the IOB which will be verified follow JEDEC standard.

#### **1.5 Verification**

#### 1.5.1 Schematic-Based Simulation

Design simulation involves testing of design using software models. It is most effective when testing the functionality of the design and its performance under worst-case conditions. We can easily probe internal nodes to check your circuit's behaviour, and then use these results to make changes in your schematic.

Simulation is performed using third-party tools that are linked to the Xilinx Development System. The software models provided for the simulation tools are designed to perform detailed characterization of your design. We can perform functional or timing simulation, as described follows:

#### 1.5.2 Functional Simulation

Functional simulation determines if the logic in the design is correct before it is implemented in a device. Functional simulation can take place at the earliest stages of the design flow. Because timing information for the implemented design is not available at this stage, the simulator tests the logic in the design using unit delays.

It is usually faster and easier to correct design errors if you perform functional simulation early in the design flow.

#### 1.5.3 Timing Simulation

Timing simulation verifies that the design runs at the desired speed for the device under worst-case conditions. This process is performed after your design is mapped, placed, and routed for FPGAs. At this time, all design delays are known. Timing simulation is valuable because it can verify timing relationships and determine the critical paths for the design under worst-case conditions. It can also determine whether or not the design contains set-up or hold violations.

#### 1.6 Goals of the Project

This project was done in STMicroelectronics pvt ltd, circuit made by the design team needs to be verified before tape-out. The circuit was designed according to the JEDEC standards, therefore it needs to be verified that it is behaving according to the JEDEC standard

The goals of the project this is to verify that the circuit designed by the design team, behaves electrically according to standard. The following are the things to be verified

- ★ It follows electrical standards as specified by the JEDEC standard.

- Verify working of the circuit under the maximum frequency.

- Check whether the output waveform have distortion or not.

- ✤ Give feedback to the design team.

\* Suggest changes if there is some problem in the circuit.

The following is the list of parameters measured for verification purpose.

- Input on time.

- Input off time.

- Input time period.

- Output on time.

- Output off time.

- Output time period.

- Rise to rise delay.

- Fall to fall delay.

- Output voltage low level (VOL).

- Output voltage high level (VOH).

- Peak to peak value of output.

- Output Duty cycle.

#### 1.7 Organisation of Thesis

Report title is 'Verification of configurable IOB'. Configurable IOBs are one of the basic blocks of FPGA. These blocks give electrical isolation to the core.

Chapter 2 gives the literature review of the topics which are directly or indirectly related to this project. The function of this chapter is to give reader all the introductory information needed to understand the project. First we discuss about FPGAs, FPGA architecture, building blocks, programming technologies and Applications of FPGA. Then a block of FPGA known as IOB is taken up. This block is explained extensively. Basic blocks of IOB, their importance and protection circuits are discussed. Issues like latch-up, EMC and ESD and method to prevent IOB from these issues are examined. In this project IOB were verified against a standard known as JEDEC standards. Information on JEDEC is provided in the end of the chapter.

Chapter 3 discusses about verification procedure followed. Details of parameter that were measured and cir file are given in this chapter.

Chapter 4 tells how verification was done on the postlay netlist of IOB.

Chapter 5 discusses result and conclusion of the project.

In Appendix syntax of simulators used are added for reference.

# Chapter 2

Literature Review

#### 2.1 Introduction

This chapter covers the literature background needed to understand the project. In this chapter FPGA, its architecture, & IOB are discussed. And issues like ESD, Latch-up are also discussed. Reader can skip these issues if the like, this will not hinder in flow of the thesis.

#### 2.2 Field Programmable Gate Array

A programmable logic device is a device whose logic characteristics can be changed and manipulated or stored through programming. The most common simple device which falls into this category is the *PAL (Programmable Array Logic)*. The internals of simple PALs consist simply of an array of AND gates and an array of OR gates. The AND array is programmable while the OR array is relatively fixed. A switch matrix selects which of the PALs inputs will be connected to the AND inputs which are then connect to the fixed OR matrix. The outputs can often times be rerouted to the input matrixes.

*FPGAs (Field Programmable Gate Arrays)* are arrays of logic blocks which can be linked together to form complex logic implementations. A bit more flexible and complex than CPLDs and PALs, FPGAs can be separated into two categories; Fine Grained and Coarse grained. Fine grained being made up of a sea of gates or transistors or small macro cells, while coarse grained being made up of bigger macro cells which are often made up of flip flops and Look up Tables (LUTs) which make up the combinatorial logic functions. Inside the macro cell are often switches or multiplexers which allow for differing uses of the macro cell. The individual macro cells are connected together with a combination of switch matrixes and metal line matrixes which can be implemented with pass transistors, fuses/antifuses or multiplexers.

#### 2.3 Basic Blocks of FPGA

A typical FPGA consists of a two-dimensional array of logic blocks that can be connected by general interconnection resources. The *interconnection resources* comprise of segments of wire, where the segments may be of various lengths. Programmable switches present in interconnect serve to connect the logic blocks to the wire segments, or one wire segment to another. Logic circuits are implemented in the FPGA by partitioning the logic into individual logic blocks and then interconnecting the blocks as required via the switches.

To facilitate the implementation of a wide variety of circuits, it is important that the FPGA be as versatile as possible. This means that the design of the logic block, coupled with that with of the interconnection resources, should facilitate the implementation of a large number of digital logic circuits.

#### 2.3.1 Logic blocks

Logic block can be designed in many different ways. Some FPGA logic blocks are as simple as 2-input NAND gates, other blocks have more complex structure, such as multiplexer or look-up tables. In some FPGA's, a logic block correspond to an entire PAL like structure. Most logic block also contains some type of flip-flop, to aid in the implementation of sequential circuits.

Fig 2.1 Block diagram of FPGA

#### 2.3.2 Interconnection resources

The structure and content of interconnect in a FPGA is called its routing architecture. The routing architecture consists of both wire segments and programmable switches. The programmable switches can be constructed in many ways, including: pass transistor controlled by static RAM cells, anti fuses, EPROM transistors and EEPROM transistors.

#### 2.4 Programming technologies

The term 'switch' generally used in FPGA's refers to the entity that allows programmable connections between wire segments. A more precise term for such an entity is programming element. This programming element can be implemented using different programming technologies. In this section programming technologies will be briefly explained.

Programmable technologies that are currently in use in commercial products are: static RAM cells, anti-fuses, EPROM transistors, and EEPROM transistors. The programming connections are used to implement the programmable connection among the FPGAs logic blocks.

The elements should have following properties:

- The programming element should consume as little chip area as possible.

- The programming element should have a low ON resistance and a very high OFF resistance.

- The programming element should contribute low parasitic capacitance to the wiring resources to which it is attached.

- It should be possible to reliably fabricate a large number of programming elements on a single chip.

#### 2.4.1 Static RAM Programming Technology

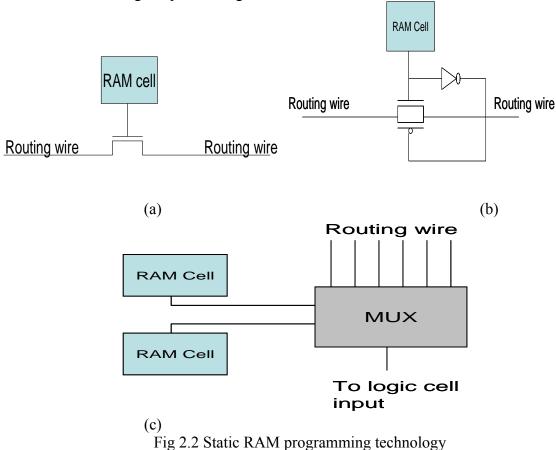

The static RAM programming technology is used in FPGA's produced by several companies: Algotronix, Concurrent logic, Plessey Semiconductors, and Xilinx. In these FPGA's, programmable connection are made using pass-transistors, transmission gates, or multiplexer that are all controlled by SRAM cells.

In case of pass-transistor approaches in figure 2.2a and 2.2b RAM cell controls whether RAM cell controls whether the pass gate is on or off. When off, the pass gate present a very high resistance between the two wires to which it is attached. When pass gate is turned on, it forms a relatively low resistance connection between the wires. For multiplexer approach in figure 2.2c, the RAM cells control which of the multiplexer's input should be connected to its output. This option would typically be used to optionally connect one of several wires to a single input of a logic block.

In an FPGA that uses SRAM programming technology, the logic blocks may be interconnected using a combination of pass-gates and multiplexers. Since the static RAM is volatile, these FPGAs must be configured each time the power is applied to the chip.

This requires external permanent memory to provide programming bits such as PROM, EPROM, EEPROM or magnetic disk.

A major disadvantage of SRAM programming technology is its large area. It takes at least five transistors to implement each SRAM cell, plus at least one transistor to serve as a programmable switch. However, SRAM programming technology two major advantages: fast re-programmability and that it require only standard integrated circuit process technology.

#### 2.4.2 Anti-fuse programming technology

Anti-fuse programming technology is used in FPGAs by Actel Corp., Quicklogic, and Crosspoint Solutions. While the anti-fuse used in each of these FPGAs differs in construction, their function is the same. A anti-fuse normally resides in a high-impedance state but can be 'fused' into a low-impedance state when programmed by a high voltage.

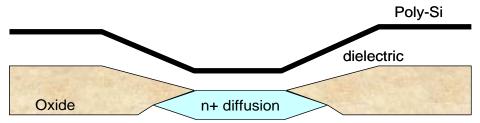

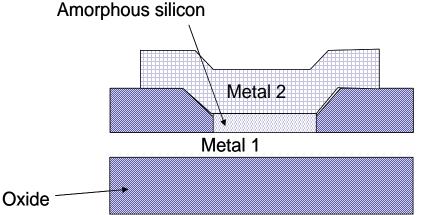

The Actel anti-fuse, called PLICE, can be described as a square structure that consists of three layers: the bottom layer is composed of positively-doped silicon (n+ diffusion), the middle layer is a dielectric (oxygen-nitrogen-oxygen insulator), and the top layer is made of poly-silicon. This construction is illustrated in figure 2.3.

Fig 2.3 Cross section of PLICE Anti-fuse programming technology

The PLICE anti-fuse is programmed by placing a relatively high voltage (18V) across the anti-fuse terminals and driving a current of about 5mA through the device. This procedure generates enough heat I the dielectric to cause it to melt and form a conductive link between the poly-Si and the n+ diffusion. Special high voltage transistors are fabricated within the FPGA to accommodate the necessary large voltages and currents.

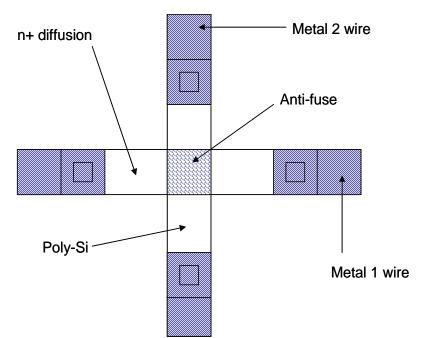

Both the bottom layer and the top layer of the anti-fuse are connected to metal wires, so that, when programmed, the anti-fuse forms a low resistance connection (from 300 to 500 ohms) between the two metal wires. This arrangement is depicted in figure 2.4. The PLICE anti-fuse is manufactured by adding three specialized mask to a normal CMOS process.

The anti-fuse used by Quicklogic is called Vialink. It is similar to the PLICE anti-fuse in that it consists of three layers. However, a Vialink anti fuse uses one level of metal for its bottom layer, an alloy of amorphous silicon fir its middle layer, and a second level of metal for the top layer.

Fig 2.4 Structure of PLICE anti-fuse programming technology

This structure is illustrated I figure 2.5. When in un-programmed state, the anti-fuse presents over a giga ohm of resistance, but when programmed it forms a low resistance path of about 80 ohms between the two metal wires. The anti-fuse is manufactured using three extra masks above a normal CMOS process. Here, a normal via is created for the anti-fuse, but the via si filled with the amorphous silicon alloy instead of metal.

Fig 2.5 Vialink anti-fuse programming technology

The Vialink anti-fuse is programmed by placing about 10 volts across its terminals. When sufficient current is supplied, this results in a change of state in the amorphous silicon and creates a conductive link between the bottom and the top layers of metal.

The chip area required by an anti-fuse (either PLICE or Vialink) is very small compared to the other programming technologies. However, this is somewhat offset by the large space required for the high-voltage transistors that are needed to handle the high programming voltages and currents. A disadvantage of anti-fuses is that their manufacture requires modifications to the basic CMOS process.

#### 2.4.3 EPROM and EEPROM programming technology

EPROM programming technology is used in the FPGAs manufactured by Altera Corp. and Plus logic. This technology is the same as that used in EPROM memories.

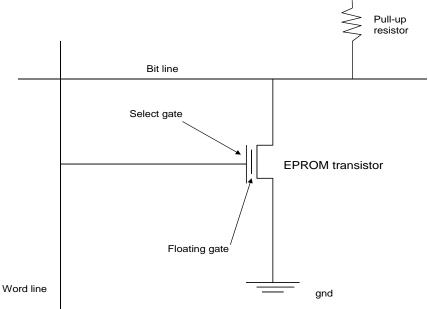

Unlike a simple MOS transistor, an EPROM transistor consists of two gates, a floating gate and a select gate. The floating gate, positioned between the select gate and the transistor channel, is so named because it is not electrically connected to any circuitry. In its normal (unprogrammed) state, no charge exists on the floating gate and the transistor can be turned ON in the normal fashion using the select gate.

However when the transistor is programmed by causing a large current to flow between the source and drain, a charge has the effect of permanently turning the transistor OFF. I this way, the EPROM transistor can function as a programmable element. An EPROM transistor can be re-programmed by first removing the trapped charge from the floating gate. Exposing the gate to ultraviolet light excites the trapped electron to the point where they can pass through the gate oxide into the substrate.

EPROM transistors are used in FPGAs in a different manner than are static RAM cells or anti-fuses. That is, rather than serving to programmably connect two wires, EPROM transistors are used as "pull down" devices for logic block inputs. This arrangement is shown in fig 2.5. One wire is called the word line, and is connected to the select gate of the EPROM transistor. As long as the transistor has not been programmed into OFF state, the word line can cause the "bit line", which is connected to a logic block input to be pulled to logic zero. Since a pull-up resistor is present on the bit line, this scheme allows the EPROM transistors to not only implement connections but also to realize wired-AND logic functions.

Fig 2.6 EPROM programming technology

A disadvantage of this approach is that the resistor consumes static power. One advantage of EPROM transistors is that they are re-programmable but do not require external voltage.

The EEPROM approach (used in AMD FPGAs) is similar to the EPROM technology except that EEPROM transistors can be re-programmed in-circuit. The disadvantage of using

EEPROM transistors is that they consume about twice chip area as EPROM transistor and they require multiple voltage sources (for re-programming) which might not otherwise be required.

| Programming<br>Technology | Volatile | Re-Prog.       | Chip Area                                  | R (ohm) | C(ff)    | Extra<br>FAB<br>Steps |

|---------------------------|----------|----------------|--------------------------------------------|---------|----------|-----------------------|

| Static RAM<br>Cells       | yes      | In-circuit     | large                                      | 1 – 2 K | 10–20 ff | 0                     |

| PLICE<br>Anti-fuse        | No       | No             | Small anti-<br>fuse, large<br>prog. trans  | 300-500 | 3 – 5 ff | 3                     |

| Via-Link<br>Anti-fuse     | No       | No             | Small anti-<br>fuse, large<br>prog. trans. | 50-80   | 1.3 ff   | 3                     |

| EPROM                     | No       | Out of circuit | Small                                      | 2 – 4 K | 10–20 ff | 3                     |

| EEPROM                    | No       | In-circuit     | 2x EPROM                                   | 2 – 4 K | 10–20 ff | >5                    |

#### 2.5 Comparison of programmable technology

Table 2.1 characteristic of programming technologies

#### 2.6 Applications of FPGAs

FPGAs can be used in almost all of the applications that currently use Mask-Programmable Gate Arrays, PLDs and small scale integration (SSI) logic chips. Below we present a few categories of such designs.

- Application-Specific Integrated Circuits (ASICs)

- Implementation of Random Logic

- Replacement of SSI Chips for Random Logic

- Prototyping

- FPGA-Based Compute Engines

- On-Site Re-configuration of Hardware

#### 2.7 Design Flow Overview

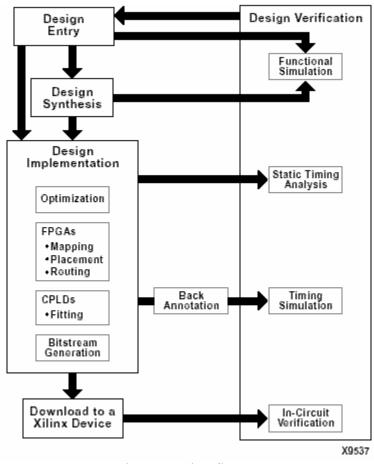

The standard design flow consists of the following steps:

#### Design Entry and Synthesis

In this step of the design flow, you create your design using a Xilinx-supported schematic editor, a Hardware Description Language (HDL) for text-based entry, or both. If you use an HDL for text-based entry, you must synthesize the HDL file into an EDIF or XNF file or, if you are using the Xilinx Synthesis Technology (XST) GUI, into an NGC file.

#### Design Implementation

By implementing to a specific Xilinx architecture, you convert the logical design file format, such as EDIF, that you created in the design entry or synthesis stage into a physical file format. The physical information is contained in the Native Circuit Description (NCD) file for FPGAs and the VM6 file for CPLDs. Then you create a bitstream file from these files and optionally program a PROM or EPROM for subsequent programming of your Xilinx device.

#### Design Verification

Using a gate-level simulator or cable, you ensure that your design meets your timing requirements and functions properly.

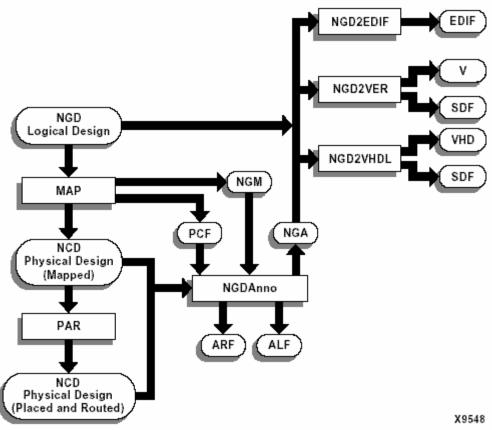

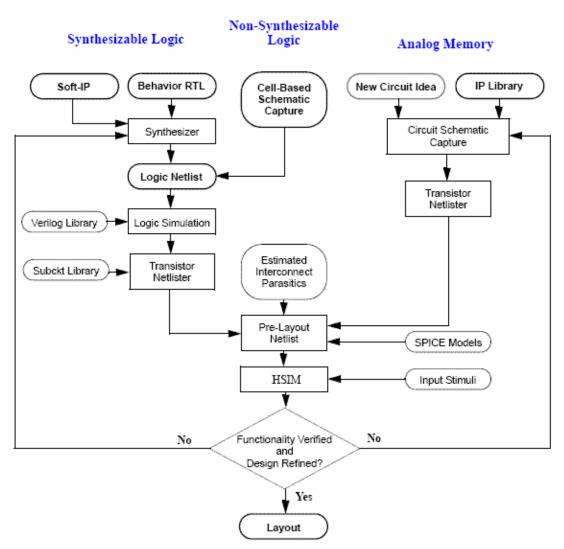

Fig 2.7 Design flow

The full design flow is an iterative process of entering, implementing, and verifying your design until it is correct and complete. The Xilinx Development System allows quick design iterations through the design flow cycle. Because Xilinx devices permit unlimited reprogramming, we do not need to discard devices when debugging the design in circuit.

#### 2.7.1 Design Entry and Synthesis

You can enter a design with a schematic editor or a text-based tool. Design entry begins with a design concept, expressed as a drawing or functional description. From the original design, a netlist is created, then synthesized and translated into a Native Generic Object (NGO) file. This file is fed into a program called NGDBuild, which produces a logical Native Generic Database (NGD) file.

#### Xilinx Development System Hierarchical Design

Design hierarchy is important in both schematic and HDL entry for the following reasons:

- Helps to conceptualize your design.

- Adds structure to the design.

- Promotes easier design debugging.

- Makes it easier to combine different design entry methods (schematic, HDL, or state editor) for different parts of your design

- Makes it easier to design incrementally, which consists of designing, implementing, and verifying individual parts of a design in stages Design Flow.

- Reduces optimization time.

- Facilitates concurrent design, which is the process of dividing a design among a number of people who develop different parts of the design in parallel, such as in Modular Design.

#### Schematic Entry Overview

Schematic tools provide a graphic interface for design entry. One can use these tools to connect symbols representing the logic components in your design. We can build our own design with individual gates, or can combine gates to create functional blocks.

#### Library Elements

Primitives and macros are the building blocks of component libraries. Xilinx libraries provide primitives as well as common high-level macro functions. Primitives are basic circuit elements, such as AND and OR gates. Each primitive has a unique library name, symbol, and description.

#### HDL Entry and Synthesis

A typical Hardware Description Language (HDL) supports a mixed level description in which gate and netlist constructs are used with functional descriptions. This mixed-level capability enables us to describe system architectures at a high level of abstraction, then incrementally refine a design s detailed gate-level implementation.

HDL descriptions offer the following advantages:

- We can verify design functionality early in the design process. A design written as an HDL description can be simulated immediately. Design simulation at this high level, at the gate level before implementation, allows us to evaluate architectural and design decisions.

- An HDL description is more easily read and understood than a netlist or schematic description. HDL descriptions provide technology-independent documentation of a design and its functionality. Because the initial HDL design description is technology independent, we can use it again to generate the design in a different technology, without having to translate it from the original technology.

- Large designs are easier to handle with HDL tools than schematic tools.

After creating our HDL design, we must synthesize it. During synthesis, behavioural information in the HDL file is translated into a structural netlist, and the design is optimized for a Xilinx device. Xilinx supports HDL synthesis tools for several third-party synthesis

vendor partners. In addition, Xilinx offers its own synthesis tool, *Xilinx Synthesis Technology* (*XST*).

#### Functional Simulation

After we enter the design, we can simulate it. Functional simulation tests the logic in the design to determine if it works properly.

#### Constraints

If we want to want to constrain your design within certain timing or placement parameters, we can specify mapping, block placement, and timing specifications. One can also enter constraints by hand or use the Constraints Editor, Floor planner, or FPGA Editor. We can also use the Timing Analyzer Graphical User Interface (GUI).

#### 2.7.2 Design Verification

Design verification is the process of testing the functionality and performance of your design. You can verify Xilinx designs in the following ways:

- Simulation (functional and timing)

- Static timing analysis

- In-circuit verification

Design verification procedures should occur throughout your design process, as shown in the following figures.

#### Simulation

Fig 2.8 Design verification

#### 2.7.2.1. Simulation

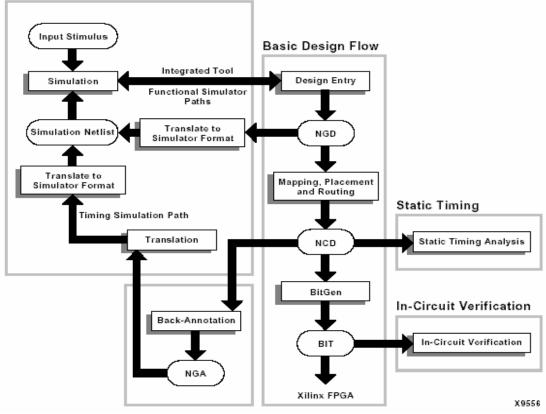

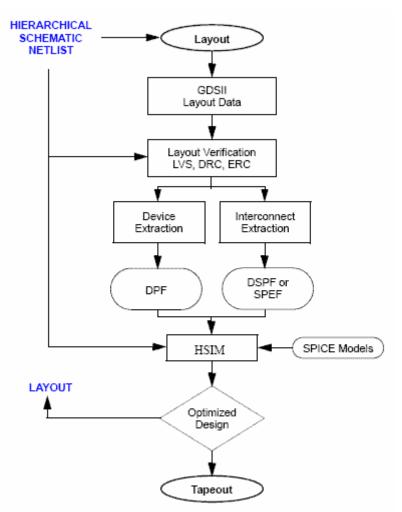

We can run functional or timing simulation to verify our design. A back-annotation process must occur prior to timing simulation.

<u>Back-Annotation</u>: Before timing simulation can occur, the physical design information must be translated and distributed back to the logical design. For FPGAs, this back-annotation process is done with a program called NGDAnno. These programs create a database for the netlist writers, which translate the back-annotated information into a netlist format that can be used for timing simulation. The following figures show the back-annotation flows.

<u>NGDAnno</u>: NGDAnno is a command line program that distributes information about delays, setup and hold times, clock to out, and pulse widths found in the physical NCD design file back to the logical NGD file. NGDAnno reads an NCD file as input. The NCD file can be a mapped-only design or a partial or fully placed and routed design.

An NGM file, created by MAP, is an optional source of input. NGDAnno merges mapping information from the NGM file with placement, routing, and timing information from the NCD file. NGDAnno outputs a Native Generic Annotated (NGA) file, which is a back-annotated NGD file. This file is input to the appropriate netlist writer, which converts the binary Xilinx database format back to an ASCII netlist.

Fig 2.9 Simulation block diagram

<u>Netlist Writers</u>: Netlist writers (NGD2EDIF, NGD2VER, or NGD2VHDL) take the output of NGDAnno and create a simulation netlist in the specified format. An NGD or NGA file is input to each of the netlist writers. The NGD file is a logical design file containing primitive components, while the NGA file is a back-annotated logical design file. NGD2VER translates an NGD or NGA file into a Verilog netlist (V) file. If the input is an NGA file, NGD2VER also generates an SDF (Standard Delay Format) file. The resulting V and SDF files have the same root name as the NGD or NGA file unless you specify otherwise.

<u>Schematic-Based Simulation</u>: Design simulation involves testing of design using software models. It is most effective when testing the functionality of the design and its performance under worst-case conditions. We can easily probe internal nodes to check your circuit's behaviour, and then use these results to make changes in your schematic.

Simulation is performed using third-party tools that are linked to the Xilinx Development System. The software models provided for the simulation tools are designed to perform detailed characterization of your design. We can perform functional or timing simulation, as described follows:

<u>Functional Simulation</u>: Functional simulation determines if the logic in the design is correct before it is implemented in a device. Functional simulation can take place at the earliest stages of the design flow. Because timing information for the implemented design is not available at this stage, the simulator tests the logic in the design using unit delays.

It is usually faster and easier to correct design errors if you perform functional simulation early in the design flow.

<u>Timing Simulation</u>: Timing simulation verifies that the design runs at the desired speed for the device under worst-case conditions. This process is performed after your design is mapped, placed, and routed for FPGAs. At this time, all design delays are known.

Timing simulation is valuable because it can verify timing relationships and determine the critical paths for the design under worst-case conditions. It can also determine whether or not the design contains set-up or hold violations.

#### 2.7.2.2. Static Timing Analysis

Static timing analysis is best for quick timing checks of a design after it is placed and routed. It also allows you to determine path delays in your design. Following are the two major goals of static timing analysis:

<u>Timing verification</u>: This is the process of verifying that the design meets your timing constraints.

<u>Reporting</u>: This is the process of enumerating input constraint violations and placing them into an accessible file. We can analyze partially or completely placed and routed designs. The timing information depends on the placement and routing of the input design.

#### 2.7.2.3. In-Circuit Verification

As a final test, we can verify how the design performs in the target application. In-circuit verification tests the circuit under typical operating conditions. Because we can program our Xilinx devices repeatedly, we can easily load different iterations of the design into the device

and test it in-circuit. To verify our design in-circuit, we should download the design bitstream into a device with the Parallel Cable III.

<u>Design Rule Checker</u>: Before generating the final bitstream, it is important to use the DRC option in BitGen to evaluate the NCD file for problems that could prevent the design from functioning properly.

#### 2.8 Input Output Block (IOB)

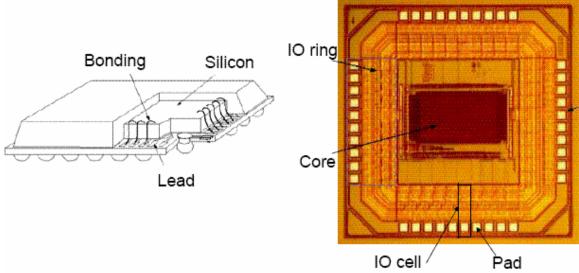

Any integrated circuit when looked inside package body can be broadly seen as two parts, i.e. core and IOB. Core is the silicon part where input signal provided by the IOB are processed and given back to IOB as output. IOB is the cell that allows interface between the logic inside the chip and external system components. In other words IOB protects the silicon from factors that may either damage the chip or hinder with chips functionality and performance. In this chapter IOB's are discussed in detail.

Fig 2.10 Cross section view of an IC at package level and at silicon level

#### 2.8.1 Basic of I/O

#### 2.8.1.1 What is an I/O?

IOB is the cell that allows interface between the logic inside the chip and external system components. As shown in figure this cell has two paths for signal.

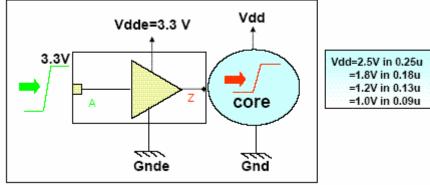

Fig 2.11 Basic block diagram of I/O

One path is for input whereas the other is for output. There are some additional bits known as control bits, which are used by core to configure IOB. IOB and core have different power supply. Core voltage is dependent upon technology being used. I/O voltage complies with IO standard, which in turn is selected according to interface voltage level of external system to which the chip is interfaced.

#### 2.8.1.2 I/O Logic Functions

An I/O can have three basic logic functions:

A). <u>Input</u>: The I/O receives and adapts the signal to the core. Since core and I/O work at different voltage levels. Signal has to be level shifted to core voltage level. This function can be selected from control bits.

Fig 2.12 Block representation of Input path

B). <u>*Output*</u>: The IO amplifies and adapts the signal from the core to the outside load. Since core voltage is less than IO voltage IOB amplifies the signal and supply it to the load.

Fig 2.13 Block representation of output path

C). *Bidirectional:* IO can both work as input or output path. As shown in figure 3.5 this block has both input and output path. These blocks are selected from control signal from the core. In figure EN signal shown is active low. When EN is high block acts as input path, therefore ZI follows IO. And when EN is low this block acts as output path.

Fig 2.14 Block representation of bidirectional block 2.8.1.2 Specific functions of IO.

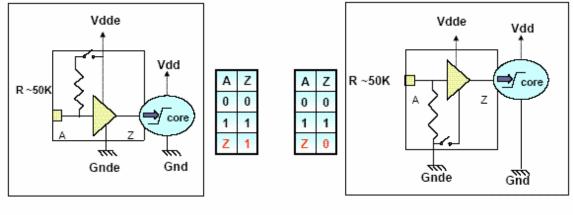

A). <u>Pull-up and pull-down</u>: The optional pull-up and pull-down resistors are intended to establish High and Low levels, respectively, at unused I/Os. The pull-up resistor optionally connects each IOB pad to VCCO. A pull-down resistor optionally connects each pad to GND. These resistors are placed in a design using the PULLUP and PULLDOWN symbols in a schematic, respectively. They can also be instantiated as components, set as constraints or passed as attributes in HDL code.

If there is no signal on the bus, a resistive load pulls up or pulls-down the bus. In case of pullup when there is no signal present at input, 'A' gets pulled up to Vdde so output becomes high. Same is the case with pull-down load; it pulls down the signal to ground if there is no signal present.

# Input with pull-Up Input with pull-Down Fig 2.15 Block diagram representing pull-up and pull-down

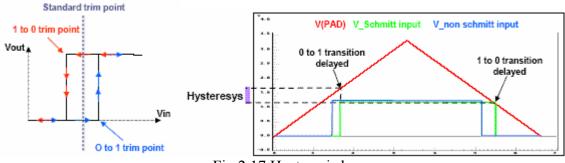

B). <u>Hysteresis</u>: This feature is included, make core more immune to noise. There are two level of voltage known as trim points. Let us assume output voltage is low at the moment, slowly if we increase the input voltage. Without hysteresis, the output would have gone high as input would have crossed the standard trim point. But with hysteresis, output goes high when input crosses 0 to 1 trim point. Now if some noise interferes with input signal and input

voltage fluctuates as long as input voltage does not go below 1 to 0 trim point output will remain high. This phenomenon is graphed in figure 3.8. The loop formed is known as hysteresis loop.

Fig 2.16 Block representation of hysteresis block

Fig 2.17 Hysteresis loop

C). <u>Analog IO's</u>: These IO's are designed to carry analog signal e.g. oscillators, ADC. They have different current and voltage requirements thus have different design.

D). *Power Supply IO's*: These IO's are designed to carry supply for core and IO. They have inbuilt ESD protection circuitry.

#### 2.8.2 Requirements of IO

All IC or programmable ASIC/FPGA contain some type of input/output cell (I/O cell). These I/O cells handle driving logic signals off-chip, receiving and conditioning external inputs, as well as handling such things as electrostatic protection.

The following are different types of I/O requirements.

- <u>DC output</u>. Driving a resistive load at DC or low frequency (less than 1 MHz). Example loads are light-emitting diodes (LEDs), relays, small motors, and such. Can we supply an output signal with enough voltage, current, power, or energy?

- <u>AC output</u>. Driving a capacitive load with a high-speed (greater than 1 MHz) logic signals off-chip. Example loads are other logic chips, a data or address bus, ribbon cable. Can we supply a valid signal fast enough?

- <u>DC input</u>. Example sources are a switch, sensor, or another logic chip. Can we correctly interpret the digital value of the input?

- <u>AC input</u>. Example sources are high-speed logic signals (higher than 1 MHz) from another chip. Can we correctly interpret the input quickly enough?

- <u>Clock input</u>. Examples are system clocks or signals on a synchronous bus. Can we transfer the timing information from the input to the appropriate places on the chip correctly and quickly enough?

- <u>Power input</u>. We need to supply power to the I/O cells and the logic in the core, without introducing voltage drops or noise. We may also need a separate power supply to program the chip.

#### 2.8.3 Electrical Interface Characteristics of IOB.

The following parameters characterizes electrical interface of IOB:

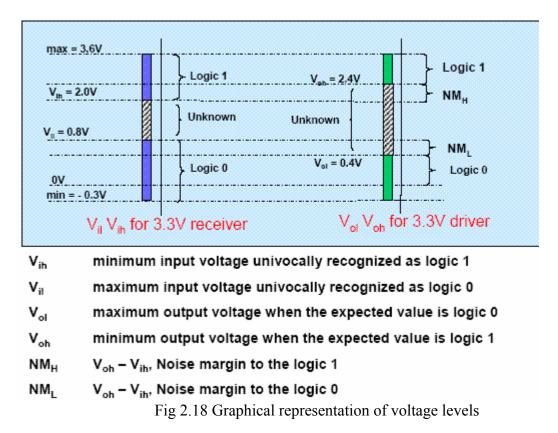

2.8.3.1 Input and output voltage level.

VIL: It is the value of voltage which is taken as logic '0' at the input. VIH: It is the value of voltage which is taken as logic '1' at the input. VOL: It is the value of voltage which is taken as logic '0' at the output. VOH: It is the value of voltage which is taken as logic '1' at the output.

#### 2.8.3.2 Input and output current level.

IIL: It is the value of injected current on logic state '0' to reach VIL value.IIH: It is the value of injected current on logic state '1' to reach VIH value.IOL: It is the value of injected current on logic state '0' to reach VOL value.IOH: It is the value of injected current on logic state '1' to reach VOH value.III, Iih, Iol and Ioh are not specification criteria in standard CMOS I/O.These parameters represent the buffer drive capability used to reach Vil, Vih, Vol and Voh criteria.

Fig 2.19 Current level

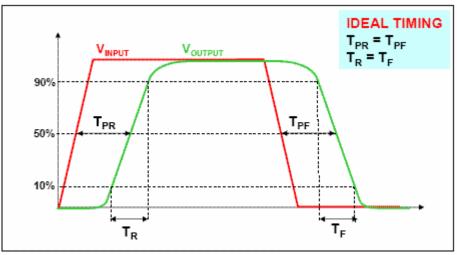

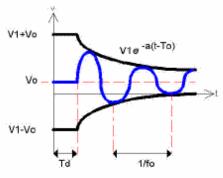

2.8.3.3 Rise, fall time and Propagation delay.

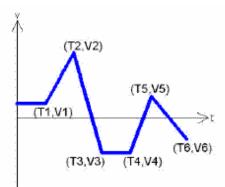

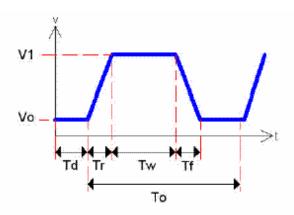

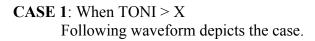

<u>Rising Time (TR)</u>: Output switching time from the 10% to the 90% of the IO supply. <u>Falling Time (TF)</u>: Output switching time from the 90% to the 10% of the IO supply. <u>Rising Propagation Time (TPR)</u>: Delay time between the Input, calculated at the 50% of the core supply value, and the Output calculated at the 50% of the IO supply value. <u>Falling Propagation Time (TPF)</u>: Delay time between the Output, calculated at the 50% of the core supply value, and the Output, calculated at the 50% of the IO supply value.

Fig 2.20 Waveform depicting rise, fall time and propagation delay

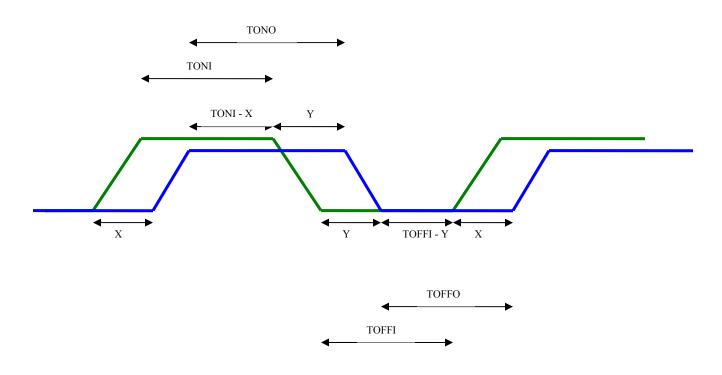

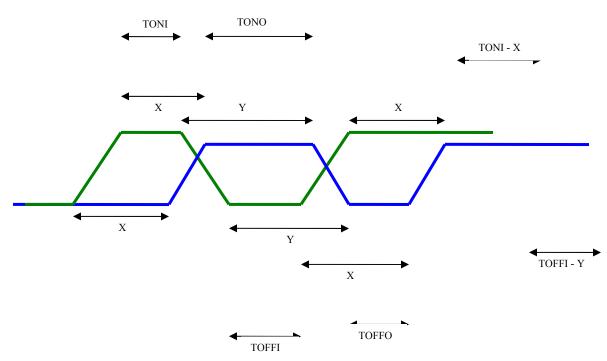

Ideally TPR should be equal to TPF and TR to TF. If they are not equal then output waveform distorts. For example if TPR< TPF, then duty cycle of output tend to increase with input frequency. And if TPR>TPF, then duty cycle of output decrease with increase in input frequency. A relationship depicting above mentioned phenomenon has been derived and included in the appendix.

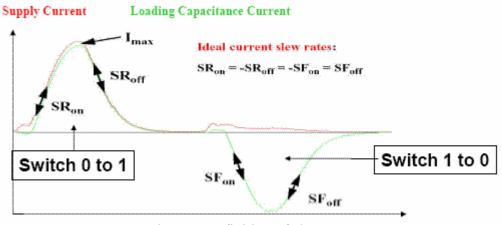

#### 2.8.3.4 Slew rate.

IMAX: Peak current on the IO supply

<u>SRON</u>: Switch on slew rate during capacitance charge, measured between 25% and 50% of the positive supply current peak. Positive

<u>SROFF</u>: Switch off slew rate during capacitance charge, measured between the 75% and 50% of the positive supply current peak. Negative

<u>SFON</u>: Switch on slew rate during capacitance charge, measured between 25% and 50% of the negative ground current peak. Negative

<u>SFOFF</u>: Switch off slew rate during capacitance charge, measured between 75% and 50% of the negative ground current peak. Positive

Fig 2.21 Definition of slew rate

#### 2.8.4 Basic blocks of IOB

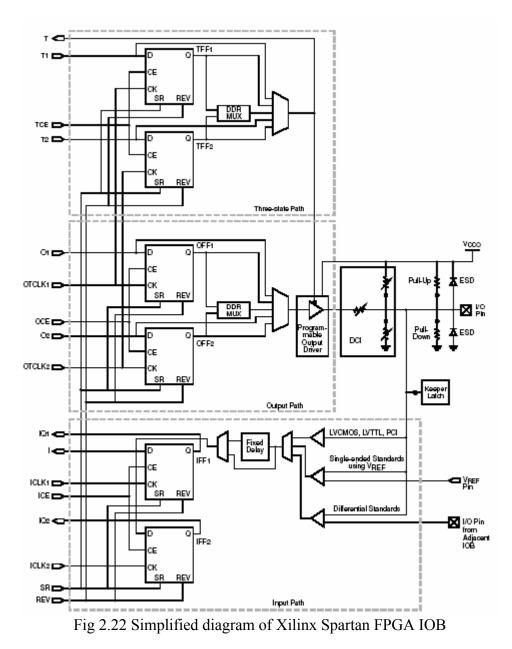

The Input/Output Block (IOB) provides a programmable, bidirectional interface between an I/O pin and the FPGA's internal logic. A simplified diagram of the IOB's internal structure appears in Figure 3.11. There are three main signal paths within the IOB: the output path, input path, and 3-state path and an ESD protection circuitry. Each path has its own pair of storage elements that can act as either registers or latches. The three main signal paths are as follows:

- The input path carries data from the pad, which is bonded to a package pin, through an optional programmable delay element directly to the I line. The IOB outputs lead to the FPGA's internal logic. The delay element can be set to ensure a hold time of zero.

- The output path, starting with the O1 and O2 lines, carries data from the FPGA's internal logic through a multiplexer and then a three-state driver to the IOB pad. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- Tri-state: The 3-state path determines when the output driver is high impedance. The T1 and T2 lines carry data from the FPGA's internal logic through a multiplexer to the output driver. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- Keeper Circuit: Each I/O has an optional keeper circuit that retains the last logic level on a line after all drivers have been turned off. This is useful to keep bus lines from floating when all connected drivers are in a high-impedance state. This function is placed in a design using the KEEPER symbol. Pull-up and pull-down resistors override the keeper circuit.

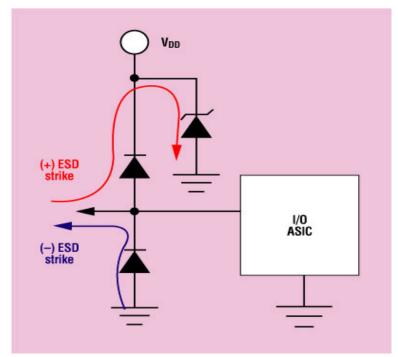

- ESD Protection: Clamp diodes protect all device pads against damage from Electro-Static Discharge (ESD) as well as excessive voltage transients. Each I/O has two clamp diodes: One diode extends P-to-N from the pad to VCCO and a second diode extends N-to-P from the pad to GND. During operation, these diodes are normally biased in the off state. These clamp diodes are always connected to the pad, regardless of the signal standard selected. The presence of diodes limits the ability of I/Os to tolerate high signal voltages.

Digitally Controlled Impedance (DCI): When the round-trip delay of an output signal i.e., from output to input and back again — exceeds rise and fall times, it is common practice to add termination resistors to the line carrying the signal. These resistors effectively match the impedance of a device's I/O to the characteristic impedance of the transmission line, thereby preventing reflections that adversely affect signal integrity. However, with the high I/O counts supported by modern devices, adding resistors requires significantly more components and board area. Furthermore, for some packages - e.g., ball grid arrays — it may not always be possible to place resistors close to pins. DCI answers these concerns by providing two kinds of on-chip terminations: Parallel terminations make use of an integrated resistor network. Series terminations result from controlling the impedance of output drivers. DCI actively adjusts both parallel and series terminations to accurately match the characteristic impedance of the transmission line. This adjustment process compensates for differences in I/O impedance that can result from normal variation in the ambient temperature, the supply voltage and the manufacturing process. When the output driver turns off, the series termination, by definition, approaches very high impedance; in contrast, parallel termination resistors remain at the targeted values. DCI is available only for certain I/O standards

#### 2.8.4.1 Input Stage of IOB

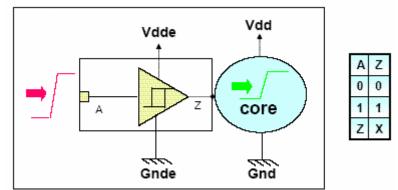

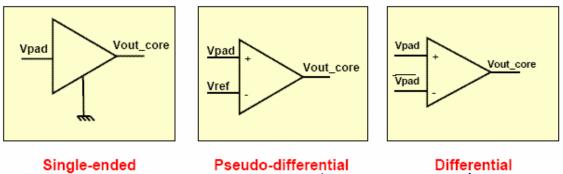

The input stage of IOB is of different configuration. They are of three basic types of input stage namely:

*A).* <u>Single ended</u>: Signal w.r.t. ground is taken, level shifted and amplified and fed to next block. E.g. LVCMOS, LVTTL are single ended standards.

*B).* <u>*Pseudo-differential:*</u> In this type of stage signal is compared with respect to reference voltage (Vref). VIL and VIH are defined with respect to Vref voltage. E.g. for SSTL18, VIL=Vref – 0.25 & VIH=Vref + 0.25.

*C).* <u>Differential I/O</u>: There is two signal lines carrying data. As shown in figure one signal is Vpad while other is inverted value of Vpad. Differential amplifier is used to amplify two input signals. In differential standards, electrical interface is defined by common mode voltage (VICM) and differential voltage (VID) specification.

Fig 2.23 Three type of input stages.

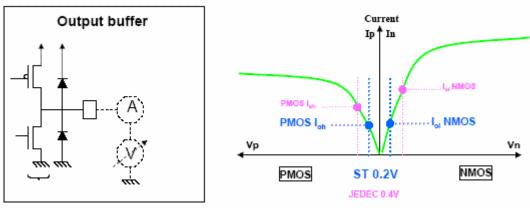

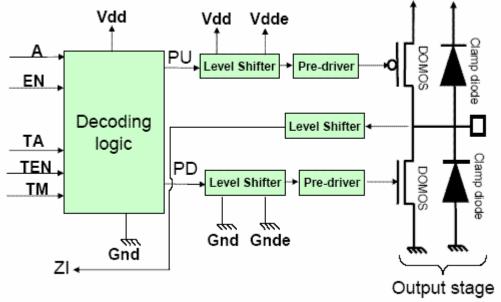

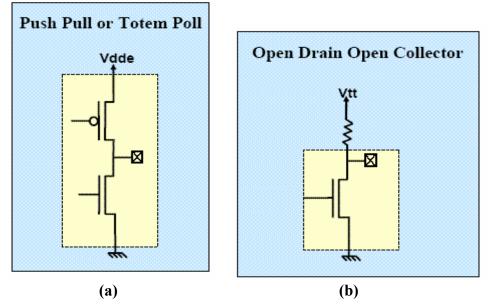

#### 2.8.4.2 Output stage of IOB

First and foremost, an output pad must have sufficient drive capability to achieve adequate rise and fall times into a given capacitive load. If the pad drives non-CMOS loads, then they should comply with different DC characteristic.

Fig 2.24 an output block

Basically output block contains:

*Decoding logic:* It is needed to configure output pad in different mode. It may be used to set output pad to a specific standard.

Level Shifter: It converts the signal from core voltage level to the IO voltage level.

*Output Stage:* It can also be referred as driver stage. It drives the load it should comply to rise, fall time and current requirement of the load. Output stage can be of different types.

#### 2.9 ESD Protection in I/O

An integrated circuit (IC) connected to external ports is susceptible to damaging electrostatic discharge (ESD) pulses from the operating environment and peripherals. The same ever-shrinking IC process technology that enables such high-port interconnects data rates can also suffer from higher ESD susceptibility because of its smaller fabrication geometry. Additional external protection devices can violate stringent signalling requirements, leaving design engineers with the need to balance performance and reliability.

#### 2.9.1 What is ESD?

An ESD event is the transfer of energy between two bodies at different electrostatic potentials, either through contact or via an ionized ambient discharge (a spark). This transfer has been modelled in various standard circuit models for testing the compliance of device targets.

*Static electricity* is defined as an electrical charge caused by an imbalance of electrons on the surface of a material. This imbalance of electrons produces an electric field that can be measured and that can influence other objects at a distance. *Electrostatic discharge* is defined as the transfer of charge between bodies at different electrical potentials.

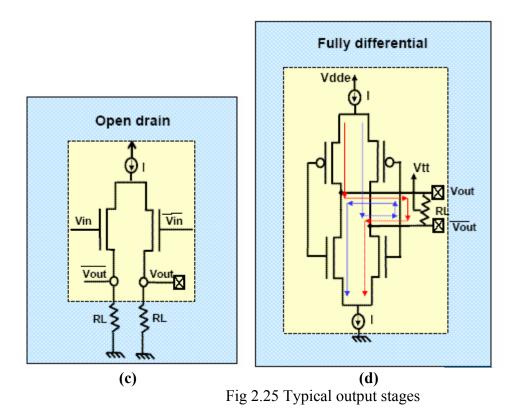

Creating electrostatic charge by contact and separation of materials is known as "triboelectric charging." It involves the transfer of electrons between materials. The atoms of a material with no static charge have an equal number of positive (+) protons in their nucleus and negative (-) electrons orbiting the nucleus.

In Figure 3.13, Material "A" consists of atoms with equal numbers of protons and electrons. Material B also consists of atoms with equal (though perhaps different) numbers of protons and electrons. Both materials are electrically neutral.

# **Triboelectric Charge**

Fig 2.26 The Triboelectric Charge, Materials Make Intimate Contact

When the two materials are placed in contact and then separated, negatively charged electrons are transferred from the surface of one material to the surface of the other material. Which material loses electrons and which gains electrons will depend on the nature of the two materials. The material that loses electrons becomes positively charged, while the material that gains electrons is

negatively charged. This is shown in Figure 3.14.

#

Fig 2.27 The Triboelectric Charge - Separation

The position inside the table points out charge polarity and amplitude.

- The first material takes positive charge and the other a negative one.

- Two materials far away from each other generate a stronger charge than the one generated when they are close.

# 2.9.2 Effects of ESD

- Electrostatic discharge can change the electrical characteristics of a semiconductor device, degrading or destroying it.

- Electrostatic discharge also may upset the normal operation of an electronic system, causing equipment malfunction or failure.

- In clean rooms charged surfaces can attract and hold contaminants, making removal from the environment difficult. When attracted to the surface of a silicon wafer or a device's electrical circuitry, these particulates can cause random wafer defects and reduce product yields.

- Induces latch-up in device. It triggers the regenerative action of current amplification in parasitic transistor.

# 2.9.3 ESD standard models

Within the semiconductors world, there are three principle sources of electrostatic discharges. Three standards were developed to model these events.

- Human Body Model (HBD).

- Machine Model (MM).

- Charged Device Model (CDM).

# Human Body Model (HBD)

- Represents the discharge of a standing people through a pointing finger.

- Ability to reproduce the field failures caused by human handling.

- Oldest model often considered as the ESD model.

- Discharge occurs in very short duration (100ns), current ranging from 1A to 4A.

Fig 2.28 Human Body Model

International standards distinguish different classes depending on the last stress level passed.

| Classes | Stress level (V)               |

|---------|--------------------------------|

|         |                                |

| 0       | <250                           |

| 1A      | 250 <x<500< td=""></x<500<>    |

| 1B      | 500 <x<1000< td=""></x<1000<>  |

| 1C      | 1000 <x<2000< td=""></x<2000<> |

| 2       | 2000 <x<4000< td=""></x<4000<> |

| 3A      | 4000 <x<8000< td=""></x<8000<> |

| 3B      | >8000                          |

Table 2.2 Class level of HBD Model

Machine Model (MM)

- Represents the discharge of improper grounding equipment through the IC when it is picked up for placement in the socket.

- Ability to reproduce the field failures caused by machine handling

- Parasitic elements easily detected.

- Shorter duration, higher current than HBM.

Fig 2.29 Equivalent circuit of MM

International standards distinguish different classes depending on the last stress level passed.

| Classes       | Stress level (V)            |

|---------------|-----------------------------|

| M1            | <100                        |

| M2            | 100 <x<200< td=""></x<200<> |

| мМЗ столько с | 200 <x<400< td=""></x<400<> |

| M4            | 400 <x< td=""></x<>         |

| Table 2.3 | Classes | for | Machine | Model |

|-----------|---------|-----|---------|-------|

|-----------|---------|-----|---------|-------|

# Charged Device Model (CDM)

- Represents the discharge of a charged device to ground through a single pin device.

- Ability to reproduce the real world ESD events.

- Parasitic components and environmental conditions play a very important role.

- Very short duration (10ns, very high current (10A and more).

Fig 2.30 Equivalent of CDM

A classification is given to determine if devices are sensitive or not to ESD and to help for defining a specification.

|                | Class | CDM Stress Level<br>(V)C1      |

|----------------|-------|--------------------------------|

| Very Sensitive | C1    | <125                           |

|                | C2    | 125 <x<250< th=""></x<250<>    |

|                | C3    | 250 <x<500< th=""></x<500<>    |

| Becomes safe   | C4    | 500 <x<1000< th=""></x<1000<>  |

|                | C5    | 1000 <x<1500< th=""></x<1500<> |

| Robust         | C6    | 1500 <x<2000< th=""></x<2000<> |

| Robust         | C7    | >2000                          |

Table 2.4 Class level for Capacitor Device Model

# 2.9.4 What to protect in silicon?

- All the pins (inputs, outputs, powers) of a circuit are directly connected to the real world as a result they might be destroyed by a discharge.

- Some part of the circuit are more sensitive than others:

- CMOS inputs: avoid gate oxide failure.

- Gate outputs: Avoid the drain/substrate junction breakdown of the MOS.

- Bipolar circuits: Avoid base-emitter junction breakdown.

# 2.9.5 High Speed ESD Protection

As IC manufacturers have achieved higher frequencies of input/output (I/O) interconnects, they have continued to decrease the minimum dimensions of the transistors, interconnections, and the silicon dioxide (SiO<sub>2</sub>) insulation layers in their devices. This decrease results in smaller structures for higher-speed devices that are more susceptible to

breakdown damage at lower energy levels. SiO<sub>2</sub> layers are more likely to rupture, and metal traces are more likely to open or bridge during an ESD event.

# 2.9.5.1 Protection strategy

- Protect the circuit without impacting its functionality.

- Protection devices are placed in parallel. They act like a switch: open during normal operation and closed during ESD event.

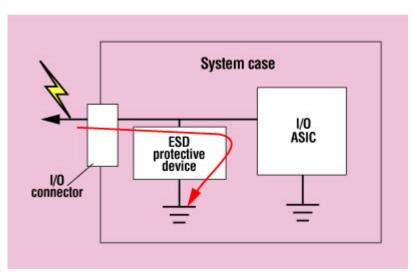

Fig 2.31 Basic ESD protection circuitry

# 2.9.5.2 ESD Protection Devices.

Basic protection strategy is to put the protective device in parallel to core as shown in figure 3.26

Figure 2.32. ESD protection devices attempt to divert a potentially damaging charge away from sensitive circuitry and protect the system from permanent damage.

A variety of technologies are used in devices for ESD protection. These are discussed below.

# Zener Diodes

One traditional device, the zener diode, is generally poorly suited for very high-speed I/O interfaces because the lowest capacitance of existing devices is about 30 pF (shown as a parasitic capacitor in Figure 3.27). This capacitance is too high to pass high-frequency signals without significant distortion. This distortion results in unreliable detection of the signals and increased high-frequency roll-off. Zener diodes could be made with lower capacitances, but this would result in ESD voltages insufficient to meet the 6–8-kV protection levels necessary.

# TVS Diodes

There are some TVS devices on the market that add a regular diode in series with the zener diode to effectively lower the net capacitance. To handle positive- and negative-polarity ESD pulses, a second zener and series diode pair (in the opposite polarity) must be placed in parallel with the first pair of diodes. Unfortunately, the resulting capacitance of 5-6 pF is still not low enough to avoid distortion of high-speed I/O signals.

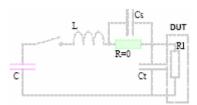

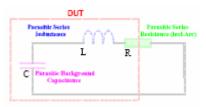

Figure 2.33. A parasitic capacitor here is too high to pass high-frequency signals without significant distortion.

## MOVs

MOVs can achieve slightly lower capacitances than TVS devices, but currently the lowest-capacitance MOV device available has a capacitance of 3 pF, which can still exceed the allowable load on high-speed interconnects.

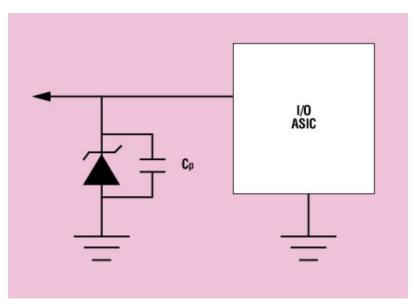

# Dual-Rail Clamp Diodes

Zener diode capacitances are high because their structures must be sufficiently robust to tolerate reverse breakdown phenomena. To eliminate the need for the zener's breakdown, regular diodes can be used to clamp the ESD pulses to the power or ground rail. Using this solution, the current flow is always in the diode's forward direction, as shown in Figure 3.28. This setup allows the use of smaller, and therefore lower, capacitance diodes. Positive ESD pulses are clamped to the positive supply rail, and negative ESD pulses are clamped to ground. (The system-bypass capacitors and power supply are responsible for shunting this extra energy on the positive rail back to ground. This can sometimes be aided by also adding a local zener diode, which does not affect the signal load.).

However, this capacitance is relatively high, and an examination of the data sheets reveals that they were not designed for high-current ESD pulses. These diodes have no specifications that guarantee their use with the high current and voltages of ESD pulses or with repetitive high-current ESD pulses. Some will degrade and eventually fail at high ESD voltage and currents.

Figure 2.34 Regular diodes can be used to clamp the ESD pulses to the power or ground rail so the current flow is always in the diode's forward direction.

# Polymer Devices

The polymer devices symbolized in Figure 3.28 have resistances that are voltage dependent. With a low voltage (e.g., 5 V), the impedance is in the Giga ohm realm. When a high voltage is applied across the polymer device, the resistance drops to a very low value, so that tens of amperes can be shunted to ground. What makes these polymers attractive for high-frequency applications is their sub-pico farad capacitance (0.05–1.0 pF). This low capacitance, however, comes with some not-so-attractive side effects. Unlike zener diodes that break down at the same voltage that they clamp to, a polymer device does not break down until it reaches a voltage that is much higher than the final clamping voltage. A typical polymeric ESD device does not break down until as much as 1000 V is reached. Then it snaps back to a clamping voltage of up to 150 V. After the charge is dissipated, the polymer returns to its high-impedance state.

Consequently, polymer devices can be used only in applications in which the ICs that are supposed to be protected must have their own built-in ESD protection that can tolerate the breakdown or trigger voltage of the polymer device (trigger voltages vary from 300 to 1000 V; clamping voltages vary from 60 to 150 V). These devices can be difficult to accurately characterize in manufacturing, so their data sheets often contain only typical specifications without guaranteed minimums and maximums.

# Metal Oxide Silicon (MOS) Devices

A new technology uses a dual-rail clamp configuration as shown in Figure 3.28. The process technology to make the diodes, however, is fundamentally different. PicoGuard technology is derived from a MOS process that is optimized for minimum capacitance. Traditional diode structures are derived from simple bipolar technologies and tend to have higher capacitance levels. The new technology is the first to combine low capacitance with low-voltage clamping levels and high ESD tolerance.

These diodes provide ESD protection beyond IEC 61000-4-2 ( $\pm$ 8-kV-and-above contact) with a capacitance of <1.3 pF maximum (~1.0 pF typical). They have a low insertion loss (virtually zero up to 3 GHz) and a clamping voltage below 15 V (V<sub>CC</sub>+10 V, ground -10 V) with no higher trigger voltages. Other specifications include a sub-nanosecond response time, durability of more than 1000 ESD pulses, and a leakage current of 1.0  $\mu$ A.

# 2.10 Latch up

Latch-up is a mechanism establishing a low resistance path between VDD and VSS. Very high current flows through the circuit, device doesn't work properly or it is destroyed. Latch-up activation causes must be characterized in order to determine some rules to prevent it.

Latch-up is a failure mechanism of CMOS integrated circuits characterized by excessive current drain coupled with functional failure, parametric failure and/or device destruction. It may be a temporary condition that terminates upon removal of the exciting stimulus, a catastrophic condition that requires the shutdown of the system to clear or a fatal condition that requires replacement of damaged parts. Regardless of the severity of the condition, latch-up is an undesirable but controllable phenomenon. In many cases, latch-up is avoidable.

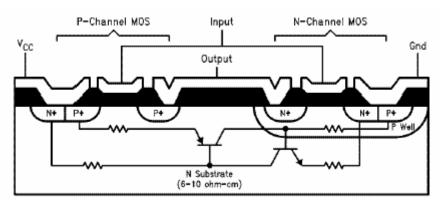

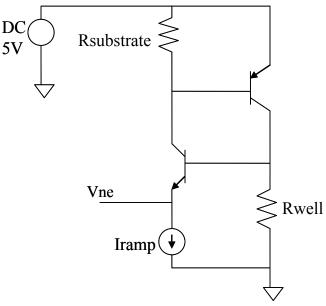

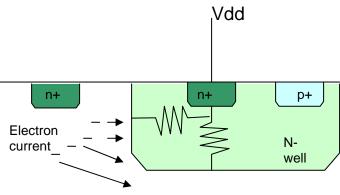

# 2.10.1 Latch-up Model

The cause of the latch-up exists in all junction-isolated or bulk CMOS processes: parasitic PNPN paths. Figure 3.29, a basic N-substrate CMOS cross section, shows the parasitic NPN and PNP bipolar transistors which most frequently participate in latch-up. The P+ sources and drains of the P channel MOS devices act as the emitters (and sometimes collectors) of lateral PNP devices; the N-substrate is the base of this device and collector of a vertical NPN device. The P-well acts as the collector of the PNP and the base of the NPN. Finally, the N+ sources and drains of the N-channel MOS devices serve as the emitter of the NPN. The substrate is normally connected to VCC, the most positive circuit voltage, via an N+ diffusion tap while the P-well is terminated at GND, the most negative circuit voltage, through a P+ diffusion. These power supply connections involve bulk or spreading resistance to all points of the substrate and P-well.

Fig 2.35 Basic CMOS inverter cross-section with Latch-up circuit model

### 2.10.2 Latch-up Phenomenon

Normally, only a small leakage current flows between the substrate and P-well causing only a minute bias to be built up across the bulk due to the resistivity of the material. In this case the depletion layer formed around the reverse biased PN junction between P-well and the substrate supports the majority of the VCC-GND voltage drop. As long as the MOS source and drain junctions remain reverse biased, CMOS is well behaved.

In the presence of intense ionizing radiation, thermal or over-voltage stress, however, current can be injected into the PNP emitter-base junction, forward-biasing it and causing current to flow through the substrate and into the P-well. At this point, the NPN device turns on, increasing the base drive to the PNP. The circuit next enters a regenerative phase and begins to draw significant current from the external network thus causing most of the undesirable consequences of latch-up. Once established, a latch-up site, through the fields generated by the currents being conducted, may trigger similar action in both elements of the IC.

Fig 2.36 Circuit formed during latch-up

# 2.10.3 Preventing Latch-up

In the loop of positive current feedback formed by the parasitic PNP and NPN transistors of the latch-up structures, regenerative switching may result if sufficient loop gain is available. One must remember, though, that three conditions are necessary for latch-up to occur.

1. Both parasitic bipolars must be biased into the active state.

2. The product of the parasitic bipolar transistor current gains (Bnpn•Bpnp) must be sufficient to allow regeneration, i.e., greater than or equal to one;

3. The terminal network must be capable of supplying a current greater than the holding current required by the PNPN path. In processes utilizing epitaxial silicon, this current is usually in excess of 1A.

If any of these conditions is not met both during the initiation and in the steady state, then the latch-up condition is either non-sustaining or cannot be initiated. If the current to the latched structure is not limited, permanent damage may result.

## 2.10.3.1 Causes of latch-up

- Capacitive effect during the switching.

- Current injection on the output.

- Over-voltages on VDD or Input/Output.

- Avalanche of the Nwell/Substrate junction.

- Punch through between Nwell and N+.

## 2.10.3.2 Latch-up prevention

Basically by reducing the resistor values and reducing the gain of the parasitic transistors are the basis for eliminating latch up. Latch-up may be eliminated in two basic ways:

- Latch-up resistant CMOS processes.

- Layout Techniques.

Some ways to eliminate latch-up are listed below

- Reduce the current gain

- NPN emitter and collector separated

- Reduction of the minor carriers 'life time'

- Reduction of the emitter efficiency

- Reduce Rnwell and Rpwell

- Low resistive substrate (HCMOS8D) = latch-up free

- Epi layer on substrate highly doped

- Retrograde implants

- Remove the npnp structure

- Deep trench isolation

- SOI

- Architecture with 3 wells

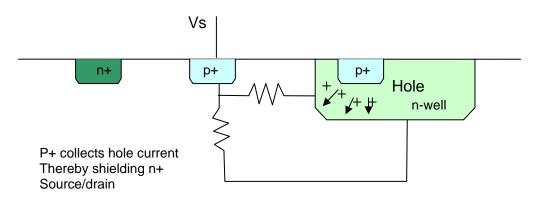

## 2.10.3.3 I/O Latch-up protection

Most likely place for latch-up to occur is in I/O structures where large currents flow, large parasitic may be present and abnormal circuit voltage may be encountered.

In these structures two options can be taken. The first is to use proven I/O structures designed by the experts who understand the process at detailed level. Second, rules may be applied to the design of these structures that minimize the possibility of latch-up. Typical rules (n-well process) include:

- Physically separate the n- and p- driver transistors (i.e. with the bonding pad).