# DESIGNING AND FABRICATION OF AT89S52 & AT89S8252 BASED KIT

A Project Report submitted by in the partial fulfillment of the requirement for award of Degree of

> Master of Science in Applied Physics

> > by

SANJEEV KUMAR (ROLL NO. – 6481)

Under the Guidance of

## MR. D.V. Chaure

DEPARTMENT OF APPLIED PHYSICS DELHI COLLEGE OF ENGINRRGING FACULTY OF TECHNOLOGY UNIVERSITY OF DELHI

DELHI - 110007

**JUNE - 2005**

## CERTIFICATE

This is to certify that the thesis entitled **"Deigning and Fabrication of AT89S52 & AT89S8252 based Kit**" submitted by **Mr. SANJEEV KUMAR** in partial fulfillment of requirements for the award of the degree of Master of Science in Applied Physics at Delhi College of Engineering, Faculty of Technology, University of Delhi, Delhi, India.

This project has been carried out under my supervision and guidance. I approve it for submission to the college for the award of Master of Science in Applied Physics.

MR. D.V.Chaure Department Of Applied Physics Delhi College of Engineering Bawana Road Delhi - 110042

## ACKNOWLEDGEMENT

No student has enough good ideas for a project such as this or the perseverance to see it through without help form other is the story of this project and the people who helped me turn it into reality.

First, I would heartily thank to **Prof. K.L.Deori**, **Professor and Head**, Department of Applied Physics, Delhi College of Engineering, Delhi for her inspiration to this project. It is my privilege to record my deep sense of gratitude and unbound reverence to **Mr. D.V. Chaure**, Department of Applied Physics, DCE, Delhi for his constant encouragement and inspiration throughout the project. I am greatly indebted to **Dr. R. K. Sinha** and **Dr. A.K. Jha**, Faculties, Department of Applied Physics, DCE, Delhi for their valuable advices.

I would like to thank **Mrs. Rajeshwari Pandey**, Lecturer, Electronics Dept., DCE, and **Mr. Anil Rathi**, Sylvania Limited, Gurgoan, without his help in preparation of board, and writing program, project would not have take the shape. I would also like to thank all the departmental laboratory staff of Applied physics and Electronics Dept. particularly **Mr. I. D. Kapoor** and **Mr. Rajender**.

Finally I want to express my heart-felt gratitude to my Parents and brother for their cheerful encouragement, immeasurable patience and inspiration.

Sanjeev Kumar

## CONTENTS

Acknowledgement Contents List of Tables List of Figures

## Chapter 1: 8-bit Microcontroller with 8K Bytes In-System Programmable Flash AT89S52.

- 1.1 Description

- 1.2 Pin Configurations

- 1.3 Block Diagram

- 1.4 Pin Description

- 1.5 Special Function Registers

- 1.6 Memory Organization

- 1.6.1 Program Memory

- 1.6.2 Data Memory

- 1.7 Watchdog Timer

- 1.7.1 Using the WDT

- 1.7.2 WDT During Power-down and Idle

- 1.8 UART

- 1.9 Timer 0 and 1

- 1.10 Timer 2

- 1.10.1 Capture Mode

- 1.10.2 Auto-reload

- 1.11. Baud Rate Generator

- 1.12. Programmable Clock Out

- 1.13. Interrupts

- 1.14. Oscillator Characteristics

- 1.15. Idle Mode

- 1.16. Power-down Mode

- 1.17. Program Memory Lock Bits

- 1.18. Programming the Flash Parallel Mode

- 1.19. Programming the Flash Serial Mode

- 1.20. Serial Programming Algorithm

## Chapter 2: Capture and Layout.

- 2.1. Introduction

- 2.2. Designs and Schematics

- 2.3. Navigating Designs

- 2.4. Editing a schematic page

- 2.5. Making Connections

- 2.6. Editing properties

- 2.7. Managing Parts of Libraries

- 2.8. Making parts

- 2.9. Processing our design

- 2.10. Introduction of Layout

- 2.11. Creating a new design

- 2.12. Autoroting

- 2.13. Finishing the design

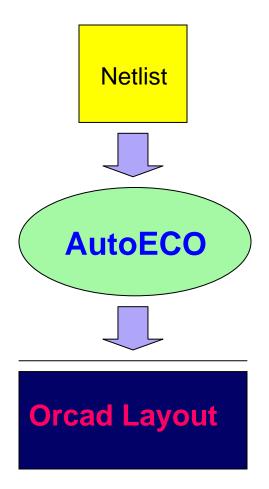

- 2.14. Using AutoECO

- 2.15. Autoplacement

## Chapter 3: Description of Designing and Fabrication of AT89S52 & AT89S8252 Based Kit.

- 3.1. Circuit Description

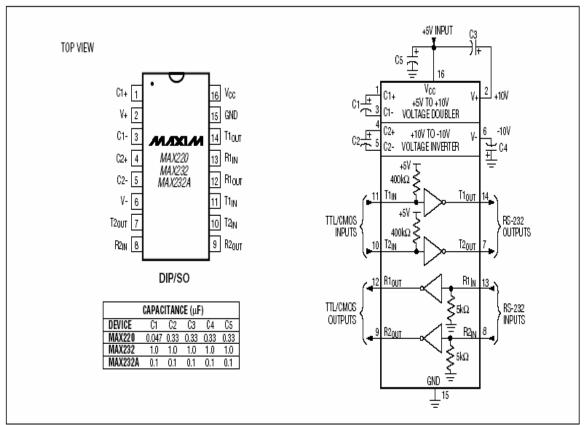

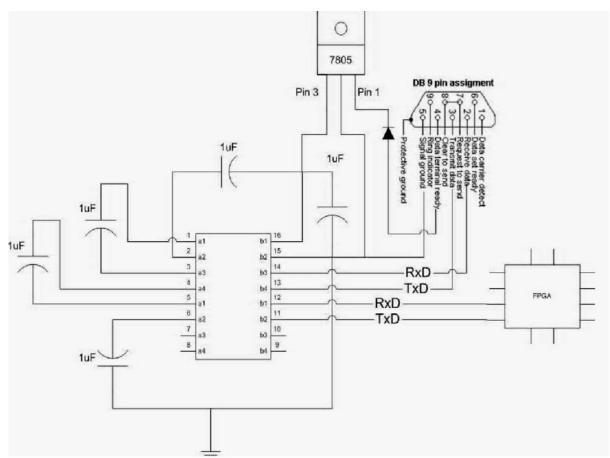

- 3.2. MAX 232

- 3.3. Connections for MAX232:

- 3.4. Testing Procedure:

- 3.5. Description of different Software

- 3.5.1. Atmel Microcontroller ISP Software

- 3.5.2. Description of ASEM 51

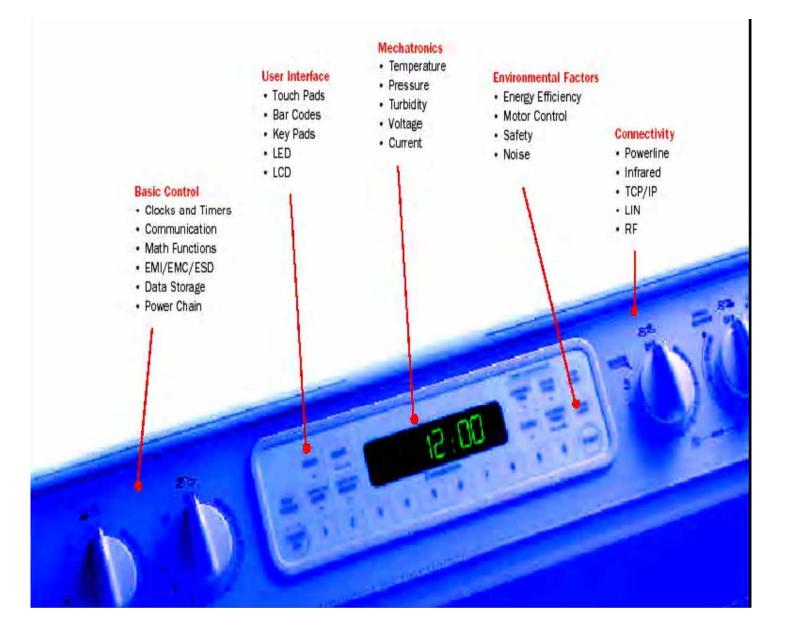

## 3.6. Application

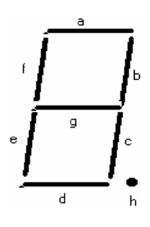

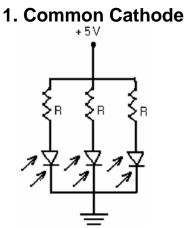

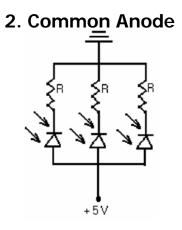

- 3.6.1. Seven Segment LED Display

- 3.6.2. Types of LEDs

- 3.6.3. Driving it with a micro-controller

## List of Figure

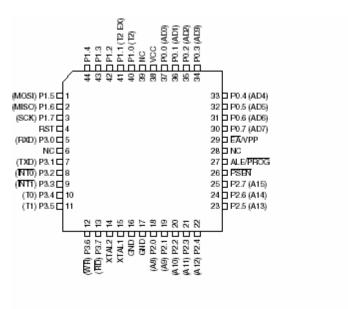

- Figure 1.1: Pin Configurations of AT89S52 Chip

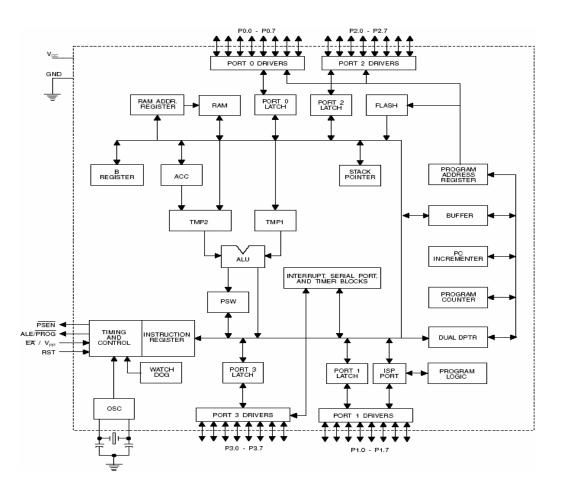

- Figure 1.2: Block Diagram of AT89S52

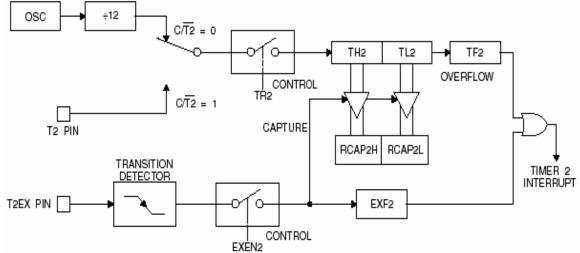

- Figure 1.3: Timer in Capture Mode

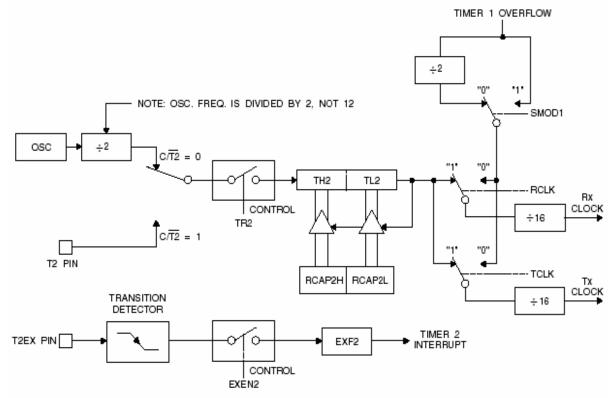

- Figure 1.4: Timer 2 in Baud Rate Generator Mode

- Figure 1.5: Timer 2 in Clock-Out Mode

- Figure 1.6: Interrupt Sources

- Figure 1.7: Oscillator Connections

- Figure 1.8: External Clock Drive Configuration

- Figure 2.1: Capture's session frame

- Figure 2.2: New project manager window

- Figure 2.3: File tab

- Figure 2.4: Hierarchy tab

- Figure 2.5: The Edit Obstacle dialog box

- Figure 2.6: A board prior to component placement

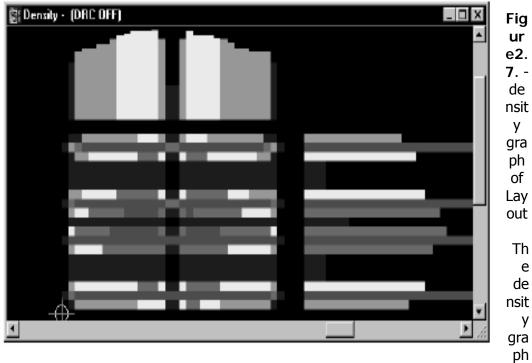

- Figure 2.7: density graph of Layout

- Figure 2.8: Link Footprint to Component

- Figure 2.9: Component placed in autoplacement

- Figure 2.10: The Edit Net dialog box

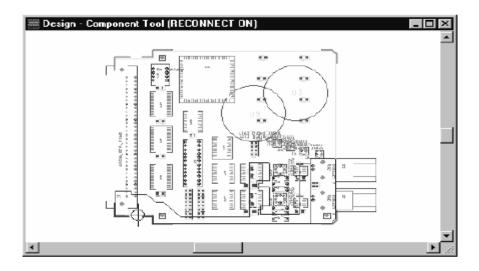

- Figure 3.1: Circuit Diagram of AT89S52 & AT89S8252 Based Micro-Controller

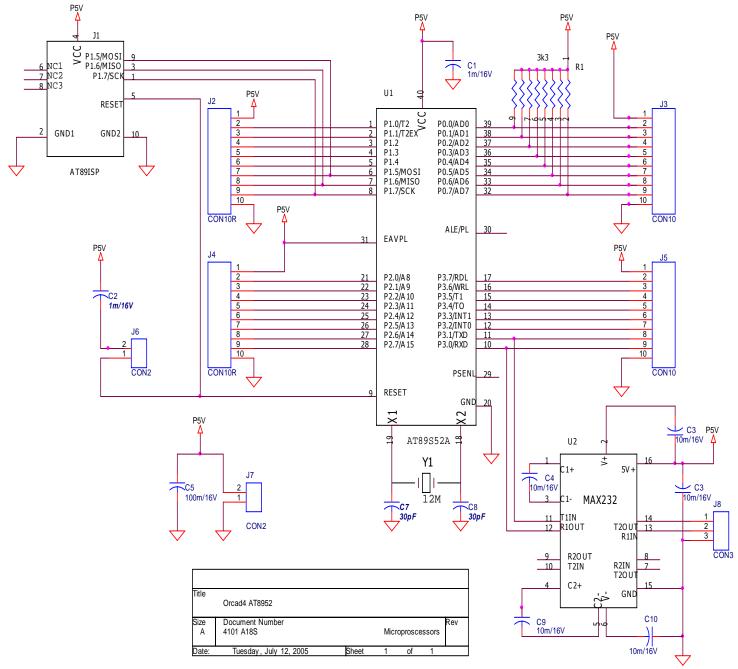

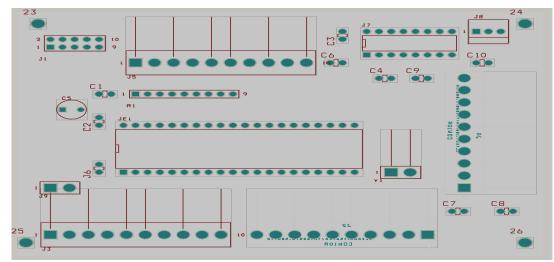

- Figure 3.2: Components layout for the PCB

- Figure 3.3: MAX220/MAX232/MAX232A Pin Configuration and Typical Operating Circuit

- Figure 3.4: MAX220/MAX232/MAX232A Pin Configuration and Typical Operating Circuit

- Figure 3.5: Interfacing of PC to MAX-232 pin out on a DB-9 pin used for Asynchronous Data

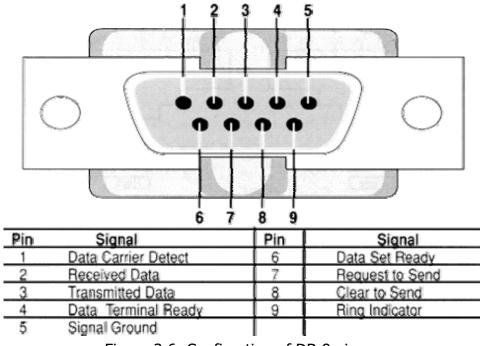

- Figure 3.6: Configuration of DB-9 pin

## List of Table

- Table 1.1:Port Pin Alternate Functions

- Table 1.2:Port Pin Alternate Functions

- Table 1.3: AT89S52 SFR Map and Reset Values

- Table 1.4: T2CON Timer/Counter 2 Control Register

- Table 1.5: T2MOD Timer 2 Mode Control Register

- Table 1.6: AUXR: Auxiliary Register

- Table 1.7:

AUXR1: Auxiliary Register 1

- Table 1.8: Timer 2 Operating Modes

- Table 1.9:

Interrupt Enable (IE) Register

- Table 1.10: Status of External Pins during Idle and Power-down Modes

- Table 1.11: Lock Bit Protection Modes

- Table 1.12: Flash Programming Modes

## Chapter – 1

## 8-bit Microcontroller with 8K Bytes In-System Programmable Flash AT89S52

## 1.1 Description

The AT89S52 is a low-power, high-performance CMOS 8-bit microcontroller with 8K bytes of in-system programmable Flash memory. The device is Atmel's high-density nonvolatile memory technology and is compatible with the standard 80C51 instruction set and Pinout. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with in-system programmable Flash on a monolithic chip, The AT89S52 provides the following standard features:

- 8K bytes of Flash,

- 256 bytes of RAM,

- 32 I/O lines,

- Watchdog timer,

- 5 two data pointers,

- three 16-bit timer/counters,

- a six-vector two-level interrupt architecture,

- a full duplex serial port,

- on-chip oscillator,

- and clock circuitry.

In addition, the AT89S52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes.

- The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning.

- The Power-down mode saves the RAM contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset.

## 1.2. Pin Configurations

#### 1. 40-lead PDIP

|               |    | <u></u> | 1          |

|---------------|----|---------|------------|

| (T2) P1.0     | 1  | ~ 40    | - vcc      |

| (T2 EX) P1.1  | 2  | 39      | P0.0 (ADO) |

| P1.2          | -  |         |            |

|               |    | 38      | - ' '      |

| P1.3          |    | 37      | P0.2 (AD2) |

| P1.4 🗆        | 5  | 36      | P0.3 (AD3) |

| (MOSI) P1.5   | 6  | 35      | P0.4 (AD4) |

| (MISO) P1.6   | 7  | 34      | P0.5 (AD5) |

| (SCK) P1.7    | 8  | 33      | P0.6 (AD6) |

| RST C         | 9  | 32      | P0.7 (AD7) |

| (RXD) P3.0    | 10 | 31      | EAVPP      |

| (TXD) P3.1    | 11 | 30      | ALE/PROG   |

| (INTO) P3.2 🗆 | 12 | 29      | D PSEN     |

| (INT1) P3.3 🗆 | 13 | 28      | P2.7 (A15) |

| (To) P3.4 🗆   | 14 | 27      | P2.6 (A14) |

| (T1) P3.5 🗆   | 15 | 26      | P2.5 (A13) |

| (WR) P3.6 🗆   | 16 | 25      | P2.4 (A12) |

| (RD) P3.7 🗆   | 17 | 24      | P2.3 (A11) |

| XTAL2         | 18 | 23      | P2.2 (A10) |

| XTAL1         | 19 | 22      | P2.1 (A9)  |

| GND E         |    | 21      | P2.0 (A8)  |

| 0.10          |    |         |            |

|               |    |         |            |

#### 2. 42-lead PDIP

Figure 1.1 : Pin Configurations of AT89S52 Chip

#### 3. 44-lead PLCC

|              | 6D P1.4          | 6 D P1.3 | ¢ри.2 | 3 🗖 P1.1 (T2 EX) | 2 D P1.0(T2) | Š | п  | 1000 (AD0) | 2 PO.1 (ADI) | 1 D PO.2 (AD2) |                 | 1 |      |      |    |

|--------------|------------------|----------|-------|------------------|--------------|---|----|------------|--------------|----------------|-----------------|---|------|------|----|

| (MOSI) P1.5  | 7                | -        |       |                  |              | à | ł  | 4          | 4            | 4              | 육<br>39         | Ь | P0.4 | (AD4 | a. |

| (MISO) P1.6  | 8                |          |       |                  |              |   |    |            |              |                | 38              |   |      | ADE  |    |

| (SCK) P1.7 C | 9                |          |       |                  |              |   |    |            |              |                | 37              |   |      | (AD6 |    |

| BST          | 10               |          |       |                  |              |   |    |            |              |                | 36              |   |      | AD7  |    |

| (RXD) P3.0   | 11               |          |       |                  |              |   |    |            |              |                | 35              |   | ΕĀΛ  |      |    |

|              | 12               |          |       |                  |              |   |    |            |              |                | 34              | þ | NC   |      |    |

| (TXD) P3.1   | 13               |          |       |                  |              |   |    |            |              |                | 33              | þ | ALE/ | PRO  | G  |

| (INTO) P3.2  | 14               |          |       |                  |              |   |    |            |              |                | 32              | þ | PSE  | 2    |    |

| (INT1) P3.3  | 15               |          |       |                  |              |   |    |            |              |                | 31              | Ь | P2.7 | (A15 | )  |

| (T0) P3.4    | 16               |          |       |                  |              |   |    |            |              |                | 30              | þ | P2.6 | (A14 | )  |

| (T1) P3.5    | 17 <sub></sub> ∞ | ₽        | ន     | ы                | ន            | ន | 24 | ĸ          | R            | 2              | ສ <sup>29</sup> | þ | P2.5 | (A13 | )  |

|              |                  | П        | П     |                  | П            |   | П  |            |              |                | U.              |   |      |      |    |

|              | 23.6             | 22       | 5     | 5                | 层            | Ş | 20 | Ę.         | 22           | 23             | 23.4            |   |      |      |    |

|              | Ē                | ē.       | MTX   | XIAL             | U            |   | 5  | 5          | ŝ            | ÷              | Ē.              |   |      |      |    |

|              | E.               | €        |       |                  |              |   | 5  | ŝ          | Ĕ            | Ē.             | ₩.              |   |      |      |    |

#### 4. 44-lead TQFP

|               | <u> </u> |    | 1            |

|---------------|----------|----|--------------|

| RST C         | 1        | 42 | P1.7 (SCK)   |

| (RXD) P3.0    | 2        | 41 | P1.6 (MISO)  |

| (TXD) P3.1    | з        | 40 | P1.5 (MOSI)  |

| (INTO) P3.2 C | 4        | 39 | DP1.4        |

| (INT1) P3.3 C | 5        | 38 | DP1.3        |

| (T0) P3.4 🗆   | 6        | 37 | DP1.2        |

| (T1) P3.5 🗆   | 7        | 36 | P1.1 (T2EX)  |

| (WR) P3.6 🗆   | 8        | 35 | P1.0 (T2)    |

| (RD) P3.7 🗆   | 9        | 34 |              |

| XTAL2         | 10       | 33 | PWRVDD       |

| XTAL1         | 11       | 32 | P0.0 (ADO)   |

| GND           | 12       | 31 | P0.1 (AD1)   |

| PWRGND        | 13       | 30 | P0.2 (AD2)   |

| (A8) P2.0 🗆   | 14       | 29 | P0.3 (AD3)   |

| (A9) P2.1 🗆   | 15       | 28 | P0.4 (AD4)   |

| (A10) P2.2 🗆  | 16       | 27 | P0.5 (AD5)   |

| (A11) P2.3 🗆  | 17       | 26 | D P0.6 (AD6) |

| (A12) P2.4 🗆  | 18       | 25 | P0.7 (AD7)   |

| (A13) P2.5 🗆  | 19       | 24 | EA/VPP       |

| (A14) P2.6 🗆  | 20       | 23 | ALE/PROG     |

| (A15) P2.7 🗆  | 21       | 22 | ] PSEN       |

|               |          |    |              |

Figure 1.2 : Block Diagram of AT89S52

## 1.4. Pin Description

**1**. **VCC**: Supply voltage.

#### 2. GND:

Ground.

#### 3. Port 0:

Port 0 is an 8-bit bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high-impedance inputs. Port 0 can also be configured to be the multiplexed low-order address/data bus during accesses to external program and data memory. In this mode, P0 has internal pull-ups. Port0 also receives the code bytes during Flash programming and outputs the code bytes during program verification. **External pull-ups are required during program verification**.

4. Port 1:

Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. When 1s are written to Port 1 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. Port 1 also receives the low-order address bytes during Flash programming and verification.

| P1.0 T2   | (external count input to Timer/Counter 2), clock-out           |

|-----------|----------------------------------------------------------------|

| P1.1 T2EX | (Timer/Counter 2 capture/reload trigger and direction control) |

| P1.5 MOSI | (used for In-System Programming)                               |

| P1.6 MISO | (used for In-System Programming)                               |

| P1.7 SCK  | (used for In-System Programming)                               |

Table 1.1 : Port Pin Alternate Functions

#### 5. Port 2:

Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. When 1s are written to Port 2 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @ DPTR). Port 2 emits the contents of the P2 Special Function Register. Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.

#### 6. Port 3:

Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. When 1s are written to Port 3 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (IIL) because of the pull-ups. Port 3 receives some control signals for Flash programming and verification. Port 3 also serves the functions of various special features of the AT89S52, as shown in the following table 2.

| P3.0 RXD  | (serial input port)                     |

|-----------|-----------------------------------------|

| P3.1 TXD  | (serial output port)                    |

| P3.2 INT0 | (external interrupt 0)                  |

| P3.3 INT1 | (external interrupt 1)                  |

| P3.4 T0   | (timer 0 external input)                |

| P3.5 T1   | (timer 1 external input)                |

| P3.6 WR   | (external data memory writes strobe)    |

| P3.7 RD   | (external data memory read strobe)      |

|           | Table 1.2. Dort Din Altornata Functions |

Table 1.2 : Port Pin Alternate Functions

7. RST:

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives high for 98 oscillator periods after the Watchdog times out. The DISRTO bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of bit DISRTO, the RESET HIGH out feature is enabled.

#### 8. ALE/PROG:

Address Latch Enable (ALE) is an output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming. If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.

#### 9. PSEN:

Program Store Enable (PSEN) is the read strobe to external program memory. When the AT89S52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.

#### 10. EA/VPP:

External Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH. Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. EA should be strapped to VCC for internal program executions. This pin also receives the 12-volt programming enable voltage (VPP) during Flash programming.

#### 11. XTAL1:

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

#### 12. XTAL2:

Output from the inverting oscillator amplifier. Capture/Reload registers for Timer 2 in 16-bit capture mode or 16-bit auto-reload mode.

## **1.5. Special Function Registers**

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in (Table 1.3)

| 0F8H |                   |                   |                    |                    |                  |                  |                     |                   | OFFH |

|------|-------------------|-------------------|--------------------|--------------------|------------------|------------------|---------------------|-------------------|------|

| OFOH | 8<br>0000000      |                   |                    |                    |                  |                  |                     |                   | OF7H |

| OEBH |                   |                   |                    |                    |                  |                  |                     |                   | OEFH |

| OGDH | 0000000           |                   |                    |                    |                  |                  |                     |                   | 067N |

| od8H |                   |                   |                    |                    |                  |                  |                     |                   | ODFB |

| ODOH | PSW 0000000       |                   |                    |                    |                  |                  |                     |                   | OD7N |

| 0C8H | T2CON<br>00000000 | T2MOD<br>XXXXXX00 | RCAP2L<br>00000000 | RCA926<br>00000000 | TL2<br>00000000  | TH2<br>00000000  |                     |                   | OCFR |

| 0C0H |                   |                   |                    |                    |                  |                  |                     |                   | 0C7H |

| OBSH | 1P<br>XX000000    |                   |                    |                    |                  |                  |                     |                   | OBFH |

| OBOH | P3<br>111111111   |                   |                    |                    |                  |                  |                     |                   | 087H |

| OÁBH | Ш<br>80080008     |                   |                    |                    |                  |                  |                     |                   | OAFH |

| OADH | P2<br>11111111    |                   | AUXR1<br>XXXXXXX0  |                    |                  |                  | WDTRST<br>XXXXXXXXX |                   | QA7H |

| 98H  | SCON<br>00000000  | SBUF<br>XXXXXXXXX |                    |                    |                  |                  |                     |                   | 9FH  |

| 90H  | P1<br>111111111   |                   |                    |                    |                  |                  |                     |                   | 97%  |

| 88H  | TCON<br>00000000  | TMOD<br>00000000  | TL0<br>00000000    | TL1<br>00000000    | TNO<br>0000000   | TH1<br>00000000  | RIKUA<br>DXXXODXXX  |                   | 8FN  |

| 80H  | Po<br>111111111   | SP<br>00000111    | DIPOL.<br>00000000 | DP0H<br>00000000   | DP1L<br>00000000 | 021H<br>00000000 |                     | PCON<br>0)0€X0000 | 87%  |

Table -1. 3. AT89S52 SFR Map and Reset Values

\*\*\* Here not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

**Timer 2 Registers**: Control and status bits are contained in registers T2CON (shown in Table -1.4) and T2MOD (shown in Table – 1.5) for Timer 2. The register pair (RCAP2H, RCAP2L) are the Capture/Reload registers for Timer 2 in 16-bit capture mode or 16-bit auto-reload mode.

| T2C0   | ON Address = 00                                                                                                                                                                                                                                                                                                                             | C8H             |                         |                 |                | F                | Reset Value = | 0000 0000B       |             |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|-----------------|----------------|------------------|---------------|------------------|-------------|--|

| Bit Ad | ddressable                                                                                                                                                                                                                                                                                                                                  |                 |                         |                 |                |                  |               |                  |             |  |

| Bit    | TF2                                                                                                                                                                                                                                                                                                                                         | EXF2            | RCLK                    | TCLK            | EXEN2          | TR2              | C/T2          | CP/RL2           |             |  |

| Dit    | 7                                                                                                                                                                                                                                                                                                                                           | 6               | 5                       | 4               | 3              | 2                | 1             | 0                |             |  |

| Symbol | Function                                                                                                                                                                                                                                                                                                                                    |                 |                         |                 |                |                  |               |                  |             |  |

| TF2    | Timer 2 overflow flag set by a Timer 2 overflow and must be cleared by software. TF2 will not be set when either RCLK = 1 or TCLK = 1.                                                                                                                                                                                                      |                 |                         |                 |                |                  |               |                  |             |  |

| EXF2   | Timer 2 external flag set when either a capture or reload is caused by a negative transition on T2EX and EXEN2 = 1.<br>When Timer 2 interrupt is enabled, EXF2 = 1 will cause the CPU to vector to the Timer 2 interrupt routine. EXF2 must be<br>cleared by software. EXF2 does not cause an interrupt in up/down counter mode (DCEN = 1). |                 |                         |                 |                |                  |               |                  |             |  |

| RCLK   | Receive clock enable. When set, causes the serial port to use Timer 2 overflow pulses for its receive clock in serial port<br>Modes 1 and 3. RCLK = 0 causes Timer 1 overflow to be used for the receive clock.                                                                                                                             |                 |                         |                 |                |                  |               |                  |             |  |

| TCLK   | Transmit clock<br>Modes 1 and 3                                                                                                                                                                                                                                                                                                             |                 |                         |                 |                |                  |               | an smit clock in | serial port |  |

| EXEN2  | Timer 2 extern<br>2 is not being                                                                                                                                                                                                                                                                                                            |                 |                         |                 |                |                  |               |                  | EX if Timer |  |

| TR2    | Start/Stop con                                                                                                                                                                                                                                                                                                                              | trol for Timer  | 2. TR2 = 1 sta          | arts the timer. |                |                  |               |                  |             |  |

| C/T2   | Timer or counter select for Timer 2. C/T2 = 0 for timer function. C/T2 = 1 for external event counter (falling edge triggered).                                                                                                                                                                                                             |                 |                         |                 |                |                  |               |                  |             |  |

| CP/RL2 | Capture/Reloa<br>causes automa<br>either RCLK o                                                                                                                                                                                                                                                                                             | atic reloads to | occur when <sup>1</sup> | Fimer 2 overfl  | ows or negativ | /e transitions ( | occur at T2EX | (when EXEN2      |             |  |

Table 1.4. T2CON – Timer/Counter 2 Control Register

| T2MOD Address = 0C9H Reset Value = XXXX XX00B |                                |                   |                |               |                |             |  |  |  |  |  |

|-----------------------------------------------|--------------------------------|-------------------|----------------|---------------|----------------|-------------|--|--|--|--|--|

| Not Bit Addressable                           |                                |                   |                |               |                |             |  |  |  |  |  |

|                                               | T20E DCEN                      |                   |                |               |                |             |  |  |  |  |  |

| Bit                                           | 7                              | 7 6 5 4 3 2 1 0   |                |               |                |             |  |  |  |  |  |

| Symbol                                        | Functi                         | on                |                |               |                |             |  |  |  |  |  |

| -                                             | Not im                         | olemented, rea    | served for fut | ire           |                |             |  |  |  |  |  |

| T2OE                                          | T2OE Timer 2 Output Enable bit |                   |                |               |                |             |  |  |  |  |  |

| DCEN                                          | When                           | set, this bit all | ows Timer 2 t  | obe configure | ed as an up/do | own counter |  |  |  |  |  |

Table 1.5. T2MOD – Timer 2 Mode Control Register

**Interrupt Registers:** The individual interrupt enable bits are in the IE register. Two priorities can be set for each of the six interrupt sources in the IP register.

**Dual Data Pointer Registers:** Accessing both internal and external data memory, two banks of 16-bit Data Pointer Registers are provided: DP0 at SFR address locations 82H-83H and DP1 at 84H-85H. Bit DPS = 0 in SFR AUXR1 selects DP0 and DPS = 1 selects DP1.

| AUXR   | Address                       | s = 8EH                                                             |               |               |             |           | Res | et Value = X) | KX00XX0B |  |  |  |

|--------|-------------------------------|---------------------------------------------------------------------|---------------|---------------|-------------|-----------|-----|---------------|----------|--|--|--|

|        | Not Bit /                     | Addressable                                                         |               |               |             |           |     |               |          |  |  |  |

|        |                               | -                                                                   | -             | -             | WDIDLE      | DISRTO    | -   | -             | DISALE   |  |  |  |

|        | Bit                           | Bit 7 6 5 4 3 2 1                                                   |               |               |             |           |     |               |          |  |  |  |

|        |                               |                                                                     |               |               |             |           |     |               |          |  |  |  |

| -      | Reserved for future expansion |                                                                     |               |               |             |           |     |               |          |  |  |  |

| DISALE | Disable/Ena                   | Disable/Enable ALE                                                  |               |               |             |           |     |               |          |  |  |  |

|        | DISALE                        | DISALE Operating Mode                                               |               |               |             |           |     |               |          |  |  |  |

|        | 0                             | 0 ALE is emitted at a constant rate of 1/6 the oscillator frequency |               |               |             |           |     |               |          |  |  |  |

|        | 1                             | ALE is act                                                          | ive only dur  | ing a MOV)    | or MOVC in  | struction |     |               |          |  |  |  |

| DISRTO | Disable/Ena                   | ble Reset ou                                                        | ıt            |               |             |           |     |               |          |  |  |  |

|        | DISRTO                        |                                                                     |               |               |             |           |     |               |          |  |  |  |

|        | 0                             | Reset pin                                                           | is driven Hi  | gh after WD   | T times out |           |     |               |          |  |  |  |

|        | 1                             | Reset pin                                                           | is input only | /             |             |           |     |               |          |  |  |  |

| WDIDLE | Disable/Ena                   | ble WDT in l                                                        | DLE mode      |               |             |           |     |               |          |  |  |  |

|        | WDIDLE                        |                                                                     |               |               |             |           |     |               |          |  |  |  |

|        | 0                             | WDT cont                                                            | inues to cou  | unt in IDLE i | mode        |           |     |               |          |  |  |  |

|        | 1                             | WDT halts                                                           | ₀ ∞unting ir  | IDLE mod      | e           |           |     |               |          |  |  |  |

Table 1.6. AUXR: Auxiliary Register

**Power Off Flag**: The Power Off Flag (POF) is located at bit 4 (PCON.4) in the PCON SFR. POF is set to "1" during power up. It can be set and rest under software control and is not affected by reset.

| AUXR1    | Address                      | Address = A2H Reset Value = XXXXXX0B |            |            |                                                                            |   |     |   |   |  |  |  |  |  |  |  |

|----------|------------------------------|--------------------------------------|------------|------------|----------------------------------------------------------------------------|---|-----|---|---|--|--|--|--|--|--|--|

|          | Not Bit Addressable          |                                      |            |            |                                                                            |   |     |   |   |  |  |  |  |  |  |  |

|          |                              | -                                    | -          | -          | -                                                                          | - | DPS |   |   |  |  |  |  |  |  |  |

|          | Bit                          | 7                                    | 6          | 5          | 4                                                                          | 3 | 2   | 1 | 0 |  |  |  |  |  |  |  |

| -<br>DPS | Reserved for<br>Data Pointer |                                      |            |            |                                                                            |   |     |   |   |  |  |  |  |  |  |  |

|          | DPS                          |                                      |            |            |                                                                            |   |     |   |   |  |  |  |  |  |  |  |

|          | 0                            | 0 Selects DPTR Registers DP0L, DP0H  |            |            |                                                                            |   |     |   |   |  |  |  |  |  |  |  |

|          | 1                            | Selects D                            | PTR Regist | are DD1L D | 0 Selects DPTR Registers DP0L, DP0H<br>1 Selects DPTR Registers DP1L, DP1H |   |     |   |   |  |  |  |  |  |  |  |

Table 1.7. AUXR1: Auxiliary Register 1

## 1.6. Memory Organization

MCS-51 devices have a separate address space for Program and Data Memory. Up to 64K bytes each of external Program and Data Memory can be addressed.

#### 1.6.1 Program Memory

If the EA pin is connected to GND, all program fetches are directed to external memory. On the AT89S52, if EA is connected to VCC, program fetches to addresses 0000H through 1FFFH are directed to internal memory and fetches to addresses 2000H through FFFFH are to external memory.

#### 1.6.2 Data Memory

The AT89S52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel address space to the Special Function Registers. When an instruction accesses an internal location above address 7FH, the address mode used in the instruction specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions which use direct addressing access the SFR space.

## 1.7. Watchdog Timer (One-time Enabled with Reset-out)

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upsets.

#### 1.7.1 Using the WDT

To enable the WDT, we write 01EH and 0E1H in sequence to the WDTRST register (SFR location 0A6H). When the WDT is enabled, we needs to service it by writing 01EH and 0E1H to WDTRST to avoid a WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH), and this will reset the device. When the WDT is enabled, it will increment every machine cycle while the oscillator is running. This means we must reset the WDT at least every 16383 machine cycles. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write-only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST pin.

#### 1.7.2 WDT During Power-down and Idle

In Power-down mode the oscillator stops, which means the WDT also stops. While in Power down mode, we do not need to service the WDT. There are two methods of exiting Power-down mode:

1. By hardware reset or via a level-activated external interrupt which is enabled prior to entering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally does whenever the AT89S52 is reset.

2. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service for the interrupt used to exit Power-down mode.

To ensure that the WDT does not overflow within a few states of exiting Powerdown, it is best to reset the WDT just before entering Power-down mode. Before going into the IDLE mode, the WDIDLE bit in SFR AUXR is used to determine whether the WDT continues to count if enabled. The WDT keeps counting during IDLE (WDIDLE bit = 0) as the default state. To prevent the WDT from resetting the AT89S52 while in IDLE mode, we should always set up a timer that will periodically exit IDLE, service the WDT, and reenter IDLE mode. With WDIDLE bit enabled, the WDT will stop to count in IDLE mode and resumes the count upon exit from IDLE.

## 1.8. UART

The UART in the AT89S52 operates the same way as the UART in the AT89C51 and AT89C52.

## 1.9. Timer 0 and 1

Timer 0 and Timer 1 in the AT89S52 operate the same way as Timer 0 and Timer 1 in the AT89S52

## 1.10. Timer 2

Timer 2 is a 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit C/T2 in the SFR T2CON (shown in Table 4). Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON, as shown in Table 8. Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

| RCLK +TCLK | CP/RL2 | TR2                  | MODE                |  |

|------------|--------|----------------------|---------------------|--|

| 0          | 0      | 1 16-bit Auto-reload |                     |  |

| 0          | 1      | 1                    | 16-bit Capture      |  |

| 1          | х      | 1                    | Baud Rate Generator |  |

| Х          | х      | 0                    | (Off)               |  |

Table 1.8. Timer 2 Operating Modes

In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency. To ensure that a given level is sampled at least once before it changes, the level should be held for at least one full machine cycle.

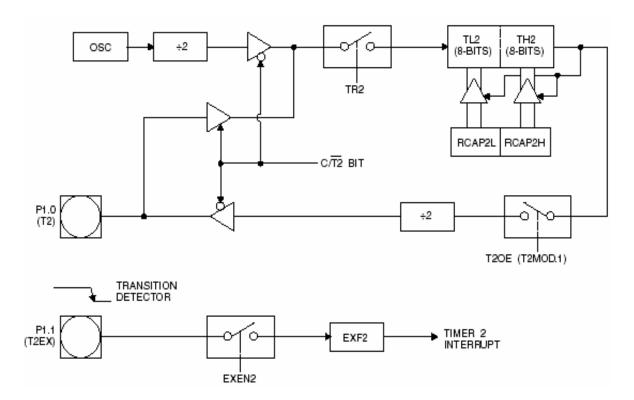

#### 1.10.1 Capture Mode

In the capture mode, two options are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 is a 16-bit timer or counter which upon overflow sets bit TF2 in T2CON. This bit can then be used to generate an interrupt. If EXEN2 = 1, Timer 2 performs the same operation, but a 1-to-0 transition at external input T2EX also causes the current value in TH2 and TL2 to be captured into RCAP2H and RCAP2L, respectively.

In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. The EXF2 bit, like TF2, can generate an interrupt.

Figure 1.3. Timer in Capture Mode

#### 1.10.2 Auto-reload (Up or Down Counter)

Timer 2 can be programmed to count up or down when configured in its 16-bit autoreload mode. This feature is invoked by the DCEN (Down Counter Enable) bit located in the SFR T2MOD (in Table 10-2). Upon reset, the DCEN bit is set to 0 so that timer 2 will default to count up. When DCEN is set, Timer 2 can count up or down, depending on the value of the T2EX pin.

## 1.11. Baud Rate Generator

Timer 2 is selected as the baud rate generator by setting TCLK and/or RCLK in T2CON (Table 1.4). Baud rates for transmit and receive can be different if Timer 2 is used for the receiver or transmitter and Timer 1 is used for the other function. The baud rate generator mode is similar to the auto-reload mode, in that a rollover in TH2 causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2H and RCAP2L, which are preset by software.

The baud rates in Modes 1 and 3 are determined by Timer 2's overflow rate as following Equation.

Modes 1 and 3 Baud Rates = Timer 2 Overflow Rate/16

Normally, as a timer, it increments every machine cycle (at 1/12 the oscillator frequency). As a baud rate generator, however, it increments every state time (at 1/2 the oscillator frequency). The baud rate formula is given below.

Modes 1 and 3 Baud Rate = Oscillator Frequency 32 x [65536-RCAP2H,RCAP2L)] Where (RCAP2H, RCAP2L) is the content of RCAP2H and RCAP2L taken as a 16bit unsigned integer. Timer 2 as a baud rate generator is shown in Figure 4.

Figure 1.4. Timer 2 in Baud Rate Generator Mode

#### 1.12. Programmable Clock Out

A 50% duty cycle clock can be programmed to come out on P1.0, as shown in Figure 1.5. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed to input the external clock for Timer/Counter 2 or to output a 50% duty cycle clock ranging from 61 Hz to 4 MHz (for a 16-MHz operating frequency). To configure the Timer/Counter 2 as a clock generator, bit C/T2 (T2CON.1) must be cleared and bit T2OE (T2MOD.1) must be set. Bit TR2 (T2CON.2) starts and stops the timer. The clock-out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L), as following equation.

Clock-Out Frequency =  $\frac{\text{Oscillator Frequency}}{4 \times [65536-(\text{RCAP2H}, \text{RCAP2L})]}$

In the clock-out mode, Timer 2 roll-overs will not generate an interrupt. This behavior is similar to when Timer 2 is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and clock-out frequencies cannot be determined independently from one another since they both use RCAP2H and RCAP2L.

Figure 1.5. Timer 2 in Clock-Out Mode

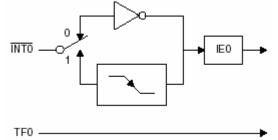

#### 1.13. Interrupts

The AT89S52 has a total of six interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (Timers 0, 1, and 2), and the serial port interrupt. These interrupts are all shown in Figure 1.6. Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Register IE. IE also contains a global disable bit, EA, which disables all interrupts at once. Timer 2 interrupt is generated by the logical OR of bits TF2 and EXF2 in register T2CON. Neither of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine may have to determine whether it was TF2 or EXF2 that generated the interrupt, and that bit will have to be cleared in software. The Timer 0 and Timer 1 flags, TF0 and TF1, are set at S5P2 of the cycle in which the timers overflow. The values are then polled by the circuitry in the next cycle. However, the Timer 2 flag, TF2, is set at S2P2 and is polled in the same cycle in which the timer overflows.

Figure 1.6. Interrupt Sources

| (MSB)                                  |                                         |                                                                                                                                                                                  | (LSB)                         |                  |                 |        |     |  |  |  |

|----------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|-----------------|--------|-----|--|--|--|

| EA                                     | -                                       | ET2                                                                                                                                                                              | ES                            | ET1              | EX1             | ET0    | EX0 |  |  |  |

| Enable Bit = 1 ena                     | ables the interrupt.                    |                                                                                                                                                                                  |                               |                  |                 |        |     |  |  |  |

| Enable Bit = 0 disables the interrupt. |                                         |                                                                                                                                                                                  |                               |                  |                 |        |     |  |  |  |

| Symbol Position Function               |                                         |                                                                                                                                                                                  |                               |                  |                 |        |     |  |  |  |

| EA                                     | IE.7                                    | Disables all interrupts. If EA = 0, no interrupt is acknowledged. If EA = 1, each<br>interrupt source is individually enabled or disabled by setting or clearing its enable bit. |                               |                  |                 |        |     |  |  |  |

| -                                      | IE.6                                    | Reserved.                                                                                                                                                                        |                               |                  |                 |        |     |  |  |  |

| ET2                                    | IE.5                                    | Time                                                                                                                                                                             | er 2 interrupt ena            | able bit.        |                 |        |     |  |  |  |

| ES                                     | IE.4                                    | Seria                                                                                                                                                                            | al Port interrupt             | enable bit.      |                 |        |     |  |  |  |

| ET1                                    | IE.3                                    | Time                                                                                                                                                                             | er 1 interrupt ena            | able bit.        |                 |        |     |  |  |  |

| EX1                                    | IE.2                                    | Exte                                                                                                                                                                             | rnal interrupt 1 (            | enable bit.      |                 |        |     |  |  |  |

| ET0                                    | IE.1                                    | Time                                                                                                                                                                             | Timer 0 interrupt enable bit. |                  |                 |        |     |  |  |  |

| EX0                                    | 0 IE.0 External interrupt 0 enable bit. |                                                                                                                                                                                  |                               |                  |                 |        |     |  |  |  |

| User software shou                     | ld never write 1s to                    | reserved bits,                                                                                                                                                                   | because they n                | nay be used in f | uture AT89 prod | ducts. |     |  |  |  |

Table 1.9. Interrupt Enable (IE) Register

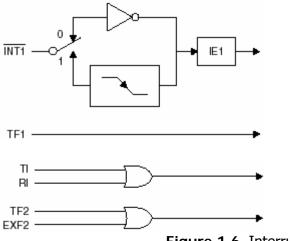

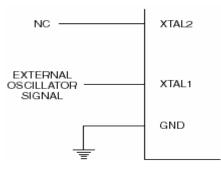

#### 1.14. Oscillator Characteristics

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator, as in Figure 1.7. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven, as shown in Figure 8. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two

flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

#### 1.15. Idle Mode

In idle mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.

When idle mode is terminated by a hardware reset, the device normally resumes program execution from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when idle mode is terminated by a reset, the instruction following the one that invokes idle mode should not write to a port pin or to external memory.

#### 1.16. Power-down Mode

In the Power-down mode, the oscillator is stopped, and the instruction that invokes Power-down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the Power-down mode is terminated. Exit from Power-down mode can be initiated either by a hardware reset or by an enabled external interrupt. Reset redefines the SFRs but does not change the on-chip RAM.

Figure 1.7. Oscillator Connections

Note: 1. C1, C2 = 30 pF  $\therefore$  10 pF for Crystals = 40 pF 10 pF for Ceramic Resonators

| Mode       | Program<br>Memory | ALE | PSEN | PORT0 | PORT1 | PORT2   | PORT3 |

|------------|-------------------|-----|------|-------|-------|---------|-------|

| Idle       | Internal          | 1   | 1    | Data  | Data  | Data    | Data  |

| Idle       | External          | 1   | 1    | Float | Data  | Address | Data  |

| Power-down | Internal          | 0   | 0    | Data  | Data  | Data    | Data  |

| Power-down | External          | 0   | 0    | Float | Data  | Data    | Data  |

Figure 1.8. External Clock Drive Configuration

Table 10. Status of External Pins during Idle and Power-down Modes

## 1.17. Program Memory Lock Bits

The AT89S52 has three lock bits that can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in Table1.11.

| Program Lock Bits |     |     |     |                                                                                                                                                                                                                              |

|-------------------|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | LB1 | LB2 | LB3 | Protection Type                                                                                                                                                                                                              |

| 1                 | U   | U   | U   | No program lock features                                                                                                                                                                                                     |

| 2                 | Ρ   | U   | U   | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset, and further programming of the Flash memory is disabled |

| 3                 | Р   | Р   | U   | Same as mode 2, but verify is also disabled                                                                                                                                                                                  |

| 4                 | Р   | Ρ   | Р   | Same as mode 3, but external execution is also disabled                                                                                                                                                                      |

#### Table 1.11. Lock Bit Protection Modes

When lock bit 1 is programmed, the logic level at the EA pin is sampled and latched during reset. If the device is powered up without a reset, the latch initializes to a random value and holds that value until reset is activated. The latched value of EA must agree with the current logic level at that pin in order for the device to function properly.

## 1.18. Programming the Flash – Parallel Mode

The AT89S52 is shipped with the on-chip Flash memory array ready to be programmed. The programming interface needs a high-voltage (12-volt) program enable signal and is compatible with conventional third-party Flash or EPROM programmers. The AT89S52 code memory array is programmed byte-by-byte.

**Programming Algorithm**: when we programming the AT89S52, the address, data, and control signals should be set up according to the "**Flash Programming Modes**" (Table 12). To program the AT89S52, we are following the steps:

- 1. Input the desired memory location on the address lines.

- 2. Input the appropriate data byte on the data lines.

3. Activate the correct combination of control signals.

4. Raise EA/VPP to 12V.

5. Pulse ALE/PROG once to program a byte in the Flash array or the lock bits. The bytewrite cycle is self-timed and typically takes no more than 50  $\mu$ s. Repeat steps 1 through 5, changing the address and data for the entire.

**Data Polling:** The AT89S52 features Data Polling to indicate the end of a byte write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written data on P0.7. Once the write cycle has been completed, true data is valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.

**Ready/Busy**: The progress of byte programming can also be monitored by the RDY/BSY output signal. P3.0 is pulled low after ALE goes high during programming to indicate BUSY. P3.0 is pulled high again when programming is done to indicate READY.

**Program Verify:** If lock bits LB1 and LB2 have not been programmed, the programmed code data can be read back via the address and data lines for verification.

The status of the individual lock bits can be verified directly by reading them back.

**Reading the Signature Bytes:** The signature bytes are read by the same procedure as a normal verification of locations 000H, 100H, and 200H, except that P3.6 and P3.7 must be pulled to a logic low. The values returned are as follows.

(000H) = 1EH indicates manufactured by Atmel

(100H) = 52H indicates AT89S52

(200H) = 06H

**Chip Erase:** In the parallel programming mode, a chip erase operation is initiated by using the proper combination of control signals and by pulsing ALE/PROG low for duration of 200 ns - 500 ns.

In the serial programming mode, a chip erase operation is initiated by issuing the Chip Erase instruction. During chip erase, a serial read from any address location will return 00H at the data output.

#### 1.19. Programming the Flash – Serial Mode

The Code memory array can be programmed using the serial ISP interface while RST is pulled to VCC. The serial interface consists of pins SCK, MOSI (input) and MISO (output). After RST is set high, the Programming Enable instruction needs to be executed first before other operations can be executed. Before a reprogramming sequence can occur, a Chip Erase operation is required. The Chip Erase operation turns the content of every memory location in the Code array into FFH. Either an external system clock can be supplied at pin XTAL1 or a crystal needs to be connected across pins XTAL1 and XTAL2. The maximum serial clock (SCK) frequency should be less than 1/16 of the crystal frequency. With a 33 MHz oscillator clock, the maximum SCK frequency is 2 MHz.

#### 1.20. Serial Programming Algorithm

To program and verify the AT89S52 in the serial programming mode, the following sequence is recommended:

1. Power-up sequence:

a. Apply power between VCC and GND pins.

b. Set RST pin to "H".

If a crystal is not connected across pins XTAL1 and XTAL2, apply a 3 MHz to 33 MHz clock to XTAL1 pin and wait for at least 10 milliseconds.

2. Enable serial programming by sending the Programming Enable serial instruction to pin

MOSI/P1.5. The frequency of the shift clock supplied at pin SCK/P1.7 needs to be less

Than the CPU clock at XTAL1 divided by 16.

3. The Code array is programmed one byte at a time in either the Byte or Page mode. The write cycle is self-timed and typically takes less than 0.5 ms at 5V.

4. Any memory location can be verified by using the Read instruction which returns the Content at the selected address at serial output MISO/P1.6.

5. At the end of a programming session, RST can be set low to commence normal device Operation.

Power-off sequence (if needed):

1. Set XTAL1 to "L" (if a crystal is not used).

- 2. Set RST to "L".

- 3. Turn VCC power off.

**Data Polling:** The Data Polling feature is also available in the serial mode. In this mode, during a write cycle an attempted read of the last byte written will result in the complement of the MSB of the serial output byte on MISO.

|                           |     |     |      |                   |                 | <u> </u> | <del>'</del> |      |      |      |                        |         |        |

|---------------------------|-----|-----|------|-------------------|-----------------|----------|--------------|------|------|------|------------------------|---------|--------|

|                           |     |     |      | ALE/              | EA/             |          |              |      |      |      | P0.7-0                 | P2.4-0  | P1.7-0 |

| Mode                      | Vcc | RST | PSEN | PROG              | V <sub>PP</sub> | P2.6     | P2.7         | P3.3 | P3.6 | P3.7 | Data                   | Address |        |

| Write Code Data           | 5V  | н   | L    | ζ <u>.</u>        | 12V             | L        | Н            | Н    | н    | н    | D <sub>IN</sub>        | A12-8   | A7-0   |

| Read Code Data            | 5V  | Н   | L    | Н                 | Н               | L        | L            | L    | Н    | н    | D <sub>OUT</sub>       | A12-8   | A7-0   |

| Write Lock Bit 1          | 5V  | Н   | L    | < _               | 12V             | Н        | н            | н    | Н    | н    | х                      | х       | х      |

| Write Lock Bit 2          | 5V  | н   | L    | $\langle \rangle$ | 12V             | н        | н            | н    | L    | L    | х                      | х       | х      |

| Write Lock Bit 3          | 5V  | н   | L    | ~                 | 12V             | н        | L            | н    | н    | L    | х                      | х       | х      |

| Read Lock Bits<br>1, 2, 3 | 5V  | н   | L    | н                 | н               | н        | н            | L    | н    | L    | P0.2,<br>P0.3,<br>P0.4 | x       | х      |

| Chip Erase                | 5V  | н   | L    | $\sim^{(1)}$      | 12V             | н        | L            | н    | L    | L    | х                      | х       | х      |

| Read Atmel ID             | 5V  | н   | L    | Н                 | Н               | L        | L            | L    | L    | L    | 1EH                    | X 0000  | ooH    |

| Read Device ID            | 5V  | н   | L    | н                 | Н               | L        | L            | L    | L    | L    | 52H                    | X 0001  | ooH    |

| Read Device ID            | 5V  | Н   | L    | Н                 | Н               | L        | L            | L    | L    | L    | 06H                    | X 0010  | ooH    |

#### Table 1.12. Flash Programming Modes

Notes: 1. Each PROG pulse is 200 ns - 500 ns for Chip Erase.

- 2. Each PROG pulse is 200 ns 500 ns for Write Code Data.

- 3. Each PROG pulse is 200 ns 500 ns for Write Lock Bits.

- 4. RDY/BSY signal is output on P3.0 during programming.

- 5. X = don't care.

## Chapter 2

## **Capture and Layout**

## 2.1. Introduction

Orcad family products offer a total solution for our core design tasks: schematic and VHDL-based design entry; digital, analog, and mixed-signal simulation; and printed circuit board layout. Orcad family products are a suite of applications built around an engineer's design flow-not just a collection of independently developed point tools.

Capture is a versatile design entry product you can use to create schematics for analog or mixed signal designs, printed circuit board layout designs, and programmable logic designs. First, create your flat or hierarchical design in the schematic page editor, and then use Capture's tools to Quickly annotate it and prepare it for the next stage of development.

Figure 2.1. Capture's session frame

. When we start capture, the session frame appears. We initially open or create a design or library from the session frame, the minimized session log appears log contains a log of events or errors that occur during the Capture session, If we update part references or properties, create a netlist, or check design rules, information is recorded in the session log. Click the restore button to open the window. After the session log is reviewed, it can be minimized again. The session log continues to record events even when it's minimized.

5. \*\*\* Information that appears in the status bar when we work on a schematic page.

## 2.2. Designs and Schematics

Capture stores all of a design's schematics, schematic pages, and parts in a single file. This makes it easy to handle our designs. When we open a capture design, it displays in a project manager window.

Figure 2.2. New project manager window

A Capture design contains one or more schematic folders, and each schematic folder contains one or more schematic pages. So even the simplest design contains one schematic folder with one schematic page, and a complicated design could many schematic pages. Designs include a design cache, which serves as an embedded archive of each unique part and symbol used in the design. We can set up your schematic page to be any size that our printer or plotter can handle. A schematic folder is simply a collection of schematic pages, which are logically connected by off-page connectors or hierarchical ports and pins. A design is a collection of related schematic folders. It contains hierarchy and back annotation information, as well as the design cache. Wire segments and off-page connectors on the same schematic page are electrically connected if they have the same name.

\*\*\* Design Rules Check process warns we a schematic folder contains two unconnected objects with the same name.

## 2.3. Navigating Designs

Capture's project manager provides a familiar graphical view of our design structure. We easily locate a single schematic page and see how it fits into the whole design. We can display our design structure in two different ways: as a file view or as hierarchy view.

Figure 2.3. File tab

| REFULLADD              |

|------------------------|

| PC8                    |

| E File R. Hierarchy    |

|                        |

| 🛱 - 🔂 HALFADD_A (EX5B) |

| 🗗 U1C (74LS 32)        |

| 🗗 U2C (74LS 04)        |

| 🖸 UZD (74LS04)         |

| B U3D (74LSOB)         |

| 🗗 U4A (74L508)         |

|                        |

|                        |

|                        |

| 🔂 U2C (74LSD4)         |

|                        |

|                        |

|                        |

|                        |

| 🔂 U1A (74LS32)         |

Figure 2.4. *Hierarchy tab*

Clicking the File tab displays the file view, which shows a list of all project files organized in folders. Clicking the Hierarchy tab display the hierarchy view, this shows a hierarchical relationship among the project components. For example this hierarchical design includes the FULLADD and HALFADD schematic folders. The file view of the design shows each schematic folder and its schematic pages, but doesn't show any hierarchical relationships. Either double-click on a schematic folder or click on the plus sign next to the schematic folder to show or hide its schematic pages. Double-click on a schematic page to open it in the schematic page editor. For a hierarchical design, you're asked which schematic page occurrence to open. The hierarchy view of the design shows the relationship of the schematic pages in a hierarchical design. Now you can see that there are actually two instances of the HALFADD schematic page in this design, Double clicking on a schematic page or clicking on its plus sign shows or hides the parts used on the schematic page. Select a part in the hierarchy view, and then click Edit from the pop-up menu. The HALFADD schematic page opens and the part is selected. Any changes made on one instance of HALFADD are reflected on every instance of HALFADD in the design.

From the project manager, we can selectively browse objects on one or more selected schematic pages. We can sort the list various ways by clicking one of the buttons at the top of the columns. If we double-click on an item's part reference, the schematic page containing the item opens and the item is selected. We can also use the browse results to edit multiple parts in one easy step by using the Edit Properties dialog box. Use the standard Windows selection methods-including the SHIFT and CTRL keys-to select the parts we want to edit. From the Edit menu, click Properties (CTRL+ E) to display the Browse Spreadsheet dialog box. The Browse Spreadsheet dialog box lists the objects selected in the browse window. As an example, let's specify a PCB footprint for all the selected parts. Click the PCB Footprint cell for any one of the parts, type the footprint name, and press ENTER. Double-click on the cell again, and then click the Copy button. This set is applying in the next step. Click the PCB Footprint button at the top of the column, and then click the Paste button. All the cells the columns get the pasted text. To add a property to the parts in the spreadsheet, click the new button and enter a name and value. Click OK to record our changes.

Capture adds the new property and its property value to all the parts listed in the Browse Spreadsheet dialog box. We can also browse nets, hierarchical ports, off-page connectors, titleblocks, bookmarks, and DRC markers.

**2.4. Editing a schematic page:** Capture's pulldown menus and shortcut keys make editing a schematic page an easy task-and the right mouse button makes it even easier. The right mouse button provides fast access to all the editing functions for the selected objects. We select an objects by clicking the select tool from the tool palette, placing the pointer on a part, then either clicking the left mouse button or pressing the SPACE BAR. Now click the right mouse button to display a pop-up menu of editing commands for the selected object. For example, the selected part be mirrored, rotated 90 degrees, or deleted. We can edit the part's properties and zoom in or out. We can add to the selection set by holding down the CTRL key and clicking on additional objects.

Or hold the CTRL key down and click on a selected object to remove it from the selection set. To select a block of objects, click the select tool on the palette and enclose the objects in a selection rectangle. Hold down the left mouse button, drag the pointer diagonally across the objects you want to select and release the mouse button. To move a wire or bus segment place the pointer on it and hold down the left mouse button to select it.

Hold the SHIFT key while moving the mouse to 'rubberband' any connecting wires or buses. You can separate a segment from the rest of the wire by holding down the ATL key while you drag the wire. Now the wire segment is separated from its original connections. We can move several objects at the same time by enclosing them within a selection rectangle, and clicking Group from the Edit menu (ATL, E, G). Now we can move the group as a single object. Ungroup it when we finish moving it by clicking Ungroup from the Edit menu. Capture uses the Windows Clipboard to support standard cut, copy, and paste actions. Select an object and press CTR+C to copy it, then select another schematic page and press CTRL+V to paste the object. Or open another Windows application and paste the object into the appropriate location.

## 2.5. Making Connections

Capture makes it easy to place the parts for our design. After we place the parts, we electrically connect them. All the electrical information is stored in the design, making it easy to progress from placing parts to creating a Netlist. When we place a part on a schematic page, the part can be placed without a referenced designator assigned to it, or it has one automatically assigned. To specify either automatic reference designators, click Preferences from the Options menu. The Preferences dialog box appears. Click the Miscellaneous tab, then either select or clear the checkbox for the automatically reference place parts option and click OK. To place a part click the Place part tool on the tool palette, or click Part from the Place menu. The parts for all selected libraries display in the list box. To exclude the parts in a selected library from being listed, press CTRL as we select the library again to deselect the library. Click the Add Library button to add the contents of another part library. We can type a selective search string to instantly locate a specific part or set of parts. We need to edit the selected part click the Edit Part button. Click OK to place the part. Click the left mouse button to place the resistor. We can continue placing resistors, then quit placing them by clicking End Mode from the

pop-up menu or by pressing ESC. Click the Place part tool on the tool palette again to place a different part. You've placed the parts, now click the Place wire tool on the tool palette to create the electrical create the electrical connections between them. Place the pointer on the pin where we want to start, and then click the left mouse button. Move the pointer and click the left mouse button again to change the wire direction. we can cross wires without connecting them, or click on a wire as you intersect it to automatically place a junction. To end a wire, just click on a pin. The unconnected pin box disappears, indicating the connection with the wire has been made. We can also place junctions on previously placed wires. Click the Place junction tool on the tool palette, and then press the left mouse button over two crossing wires. Now the wires are connected. We can also remove junctions using the same tool. Just place a new junction on an existing one to delete the placed junction. We place buses just like wires. Click the Place bus tool on the tool palette and draw a bus, and then click the Place bus entry tool on the tool palette to make the connections. Just place the first bus entry by hand, now hold down the CTRL key and drag a copy of the bus entry to where we want the second one, and then click Repeat Place from the Edit menu to place addition bus entries. To finish, click the Place wire tool on the tool palette to connect the bus to individual signals. If a pin is defined as a bus pin, you can connect the bus to it directly.