# MAJOR THESIS ON

# "DESIGN AND IMPLEMENTATION OF SYNCHRONIZATION AND SWITCHING COMPONENTS IN DIGITAL NETWORKS, WITH FPGA "

A dissertation submitted in partial fulfillment of the requirement for the degree of

> MASTER OF ENGINEERING in

# **ELECTRONICS AND COMMUNICATION**

Submitted by :

PRAVEEN KUMAR College Roll No. 16/EC/03 University Roll No. 9113 M.E. (ELECTRONICS AND COMMUNICATION) VI<sup>th</sup> SEMESTER

UNDER THE GUIDANCE OF

DR. ASOK BHATTACHARYYA PROFESSOR & HEAD ELECTRONICS AND COMMUNICATION DEPTT. DELHI COLLEGE OF ENGINEERING

#### CERTIFICATE

This is to certify that the thesis entitled "Design and Implementation of Synchronization and Switching components, in Digital Networks, with FPGA", " being submitted by Praveen Kumar in the partial fulfillment of the requirement for the degree of Master of Engineering in Electronics and Communication in the Department of Electronics and Communication, Delhi College of Engineering, University of Delhi is a record of bonafide work done by him under my supervision and guidance. It is also certified that the dissertation has not been submitted elsewhere for any other degree.

(Prof. A. BHATTACHARYYA) Head of Department, Project Guide Department of Electronics & Communication Delhi College of Engineering Delhi - 110042

## ACKNOWLEDGEMENT

The satisfaction and euphoria that accompanies the successful completion of any task would be incomplete without a mention of the people who made it possible, whose constant guidance and encouragement crown all the efforts with success.

I am grateful to **Prof. A. BHATTACHARYYA** (HOD, ECE Deptt.) for providing us an opportunity to undertake this project and for being my project guide for taking keen interest in my work and for his constant monitoring and invaluable guidance and support through out the course of my project. I profusely thank him for having patience to clear my doubts and channelise my efforts. His cheerful disposition made my work all the more enjoyable.

#### **PRAVEEN KUMAR**

College Roll No. 16/EC/03 University Roll No. 9113 Delhi College of Engineering University of Delhi, Delhi.

# INDEX

# CONTENTS PAGE NO.

| 1. S    | YNCHRONIZATION                        | 1  |

|---------|---------------------------------------|----|

| 1.1     | SYNCHRONIZATION INTRODUCTION          | 1  |

| 1.2     | HISTORICAL PERSPECTIVE                | 1  |

| 1.3     | SYNCHRONIZATION IN TELECOMMUNICATION  | 3  |

| 1.4     | NETWORK SYNCHRONIZATION ARCHITECTURES | 4  |

| 1.5     | NETWORK SYNCHRONIZATION STRATEGIES    | 5  |

| 1.6     | SYNCHRONIZATION AND DIGITAL SWITCHING | 7  |

| 2. PH   | IASE LOCKED LOOPS                     | 9  |

| 2.1     | PHASE LOCKED LOOPS                    | 9  |

| 2.2     | TYPES OF PHASE LOCKED LOOPS           | 9  |

| 2.3     | FUNDAMENTAL BLOCKS                    | 9  |

| 2.4     | BRIEF HISTORY                         | 10 |

| 2.5     | PLL APPLICATION                       | 10 |

| 2.6     | THE LINEAR PHASE LOCKED LOOP (LPLL)   | 12 |

| 2.6.1   | BUILDING BLOCKS OF LPLL               | 12 |

| 2.6.2   | LPLL PERFORMACE IN LOCKED STATE       | 13 |

| 2.7     | KEY PARAMETERS OF THE LPLL            | 16 |

| 2.7.1   | THE HOLD RANGE                        | 17 |

| 2.7.2   | THE LOCK RANGE                        | 17 |

| 2.7.3   | PULL IN RANGE                         | 17 |

| 2.7.4   | PULL OUT RANGE                        | 19 |

| 2.8     | THE CLASSICAL DIGITAL PLL (DPLL)      | 19 |

| 2.8.1   | DIGITAL PHASE DETECTORS               | 20 |

| 2.8.1.  | EXOR GATE PHASE DETECTOR              | 20 |

| 2.8.1.2 | 2 JK FLIP FLOP PHASE DETECTOR         | 21 |

| 2.8.1.3 | 3 PHASE FREQUENCY DETECTOR (PFD)      | 22 |

| 2.8.2   | DYNAMIC PERFORMANCE                   | 26 |

| 2.8.3   | PARAMETERS                            | 26 |

| 2.8.3.  | I THE HOLD RANGE                      | 27 |

| 2.8.3.2 | 2 THE LOCK RANGE                      | 28 |

| 2.8.3.3 | 3 PULL IN RANGE                       | 29 |

| 2.8.3.4 | 4 PULL OUT RANGE                      | 32 |

| 2.8.4        | DPLL DESIGN                           | 33 |

|--------------|---------------------------------------|----|

| 2.9          | ALL DIGITAL PHASE LOCKED LOOP (ADPLL) | 33 |

| 2.9.1        | DIGITAL PHASE DETECTOR                | 34 |

| 2.9.1.1      | FLIP FLOP COUNTER PHASE DETECTOR      | 34 |

| 2.9.2        | DIGITAL LOOP FILTERS                  | 35 |

| 2.9.2.1      | UP/DOWN COUNTER FILTER                | 35 |

| 2.9.2.2      | N-BFORE-M COUNTER FILTER              | 36 |

| 2.9.3        | DIGITAL CONTROLLED OSCILLATORS        | 36 |

| 2.9.4        | EXAMPLE OF AN IMPLEMENTED ADPLL       | 37 |

| 3. AD        | PLL IMPLEMENTATION                    | 40 |

| 3.1          | BLOCK DIAGRAM                         | 40 |

| 3.2          | SAMPLING PHASE DETECTOR               | 40 |

| 3.3          | LOOP FILTER AND DCO CONTROL UNIT      | 44 |

| 3.4          | DCO CIRCUIT                           | 45 |

| 3.5          | VHDL CODE                             | 45 |

| 3.6          | VHDL TESTBENCH                        | 50 |

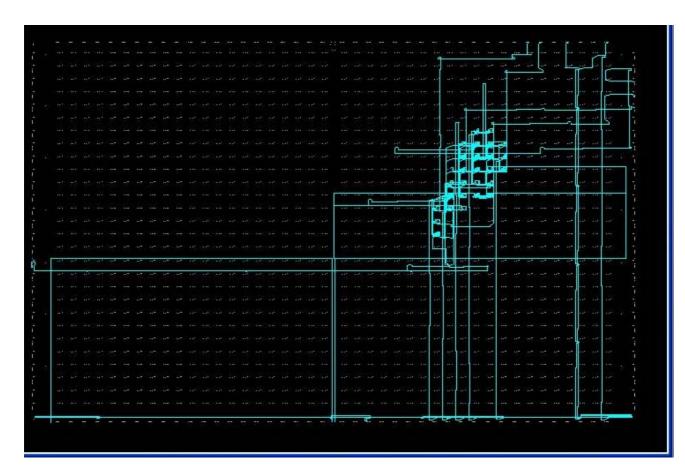

| 3.7          | SCHEMATICS                            | 51 |

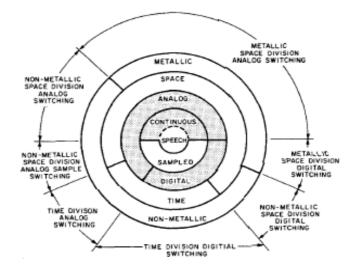

| 4. SWITCHING |                                       | 57 |

| 4.1          | SWITCHING BACKGROUND                  | 57 |

| 4.2          | ELECTRONICS IN SWITCHING              | 57 |

| 4.3          | DEFINITION                            | 58 |

| 4.4          | DIGITAL SWITCHING FUNDAMENTALS        | 59 |

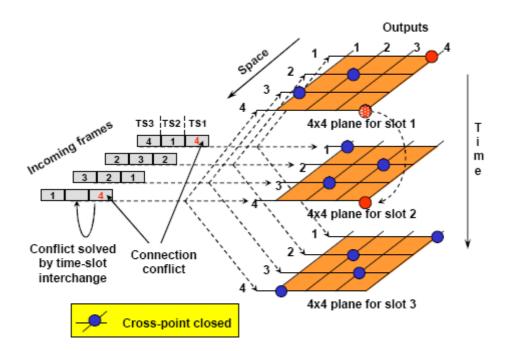

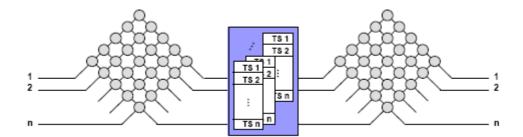

| 4.5          | TIME MULTIPLEXED SPACE SWITCHING      | 62 |

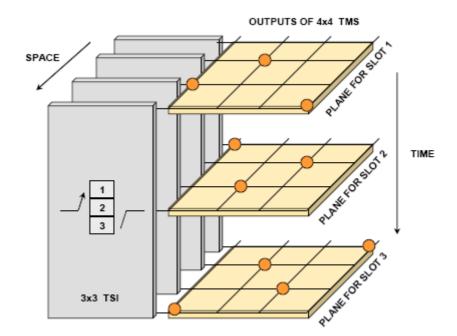

| 4.6          | TIME MULTIPLEXED TIME SWITCHING       | 63 |

| 4.7          | SWITCH FABRICS                        | 65 |

| 4.7.1        | BASIC CONCEPTS                        | 65 |

| 4.7.1.1      | ACCESSIBILITY                         | 66 |

| 4.7.1.2      | BLOCKING                              | 66 |

| 4.7.1.3      | COMPLEXITY                            | 67 |

| 4.7.1.4      | SCALABILITY                           | 67 |

| 4.7.1.5      | RELIABILITY                           | 68 |

| 4.7.1.6      | THROUGHPUT                            | 68 |

| 4.7.2        | TIME AND SPACE SWITCHING              | 68 |

| 4.7.2.1      | SPACE DIVISION SWITCHING              | 69 |

| 4.7.2.2      | TIME DIVISION SWITCHING               | 70 |

| 4.7.2.3      | PROPERTIES OF SPACE AND TIME SWITCHES | 72 |

| 4.7.3   | TWO STAGE SWITCHES                      | 73 |

|---------|-----------------------------------------|----|

| 4.7.3.1 | TIME MULTIPLEXED SPACE SWICTH           | 73 |

| 4.7.3.2 | 2 TS SWITCH INTERCONNECTING TDM LINK    | 74 |

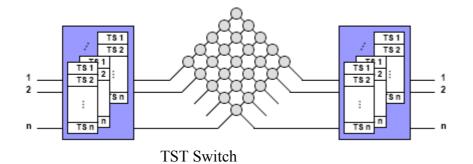

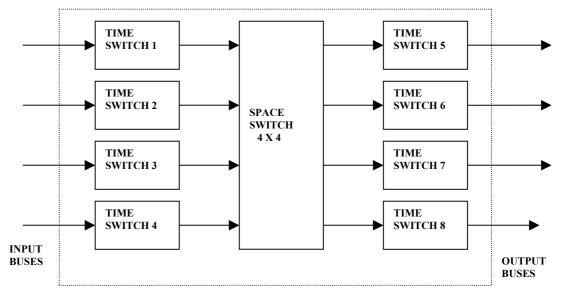

| 4.7.4   | THREE STAGE SWITCH                      | 75 |

| 4.7.4.1 | THREE STAGE SWITCH COMBINATIONS         | 75 |

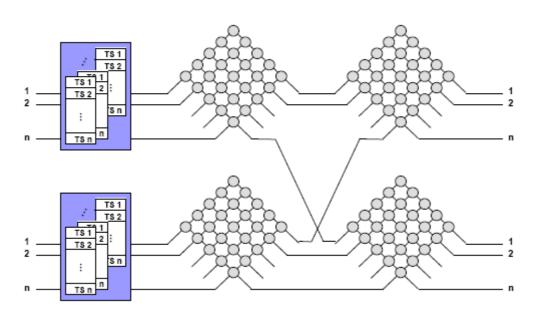

| 4.7.4.2 | 2 TIME-SPACE-SPACE SWITCH               | 76 |

| 4.7.4.3 | 3 SPACE-TIME-TIME SWITCH                | 76 |

| 5. IM   | IPLEMENTATION OF TIME AND SPACE SWITCH  | 77 |

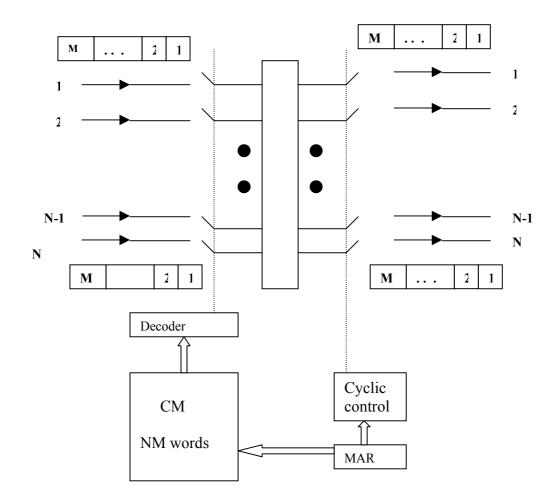

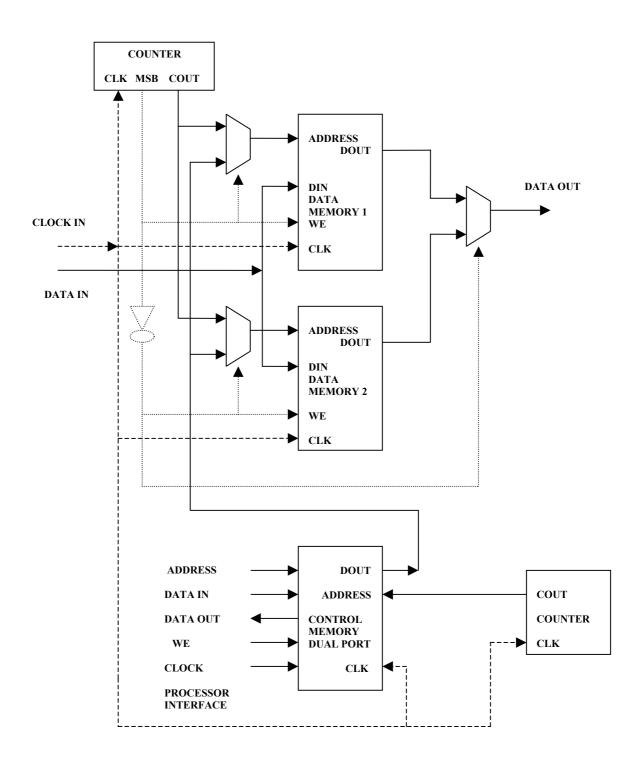

| 5.1     | IMPLEMENTATION OF TIME SWITCH           | 77 |

| 5.1.1   | FUNCTINAL DIAGRAM OF TIME SWITCH        | 77 |

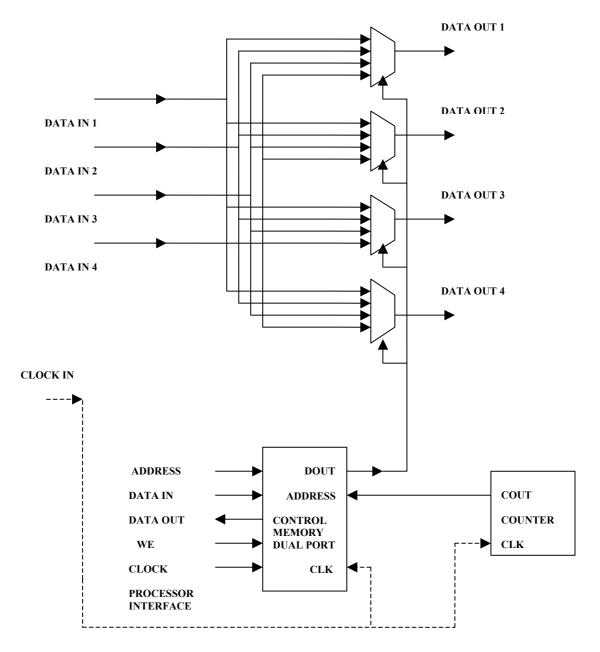

| 5.2     | IMPLEMENTATION OF SPACE SWITCH          | 78 |

| 5.2.1   | FUNCTINAL DIAGRAM OF TIME SWITCH        | 79 |

| 5.3     | VHDL CODES                              | 80 |

| 5.3.1   | PROJECT HIERARCHY                       | 80 |

| 5.3.2   | VHDL CODE OF TST SWITCH                 | 80 |

| 5.3.3   | VHDL CODE OF TIME SWITCH                | 84 |

| 5.3.4   | VHDL CODE OF SPACE SWITCH               | 86 |

| 5.4     | SIMULATION RESULTS                      | 88 |

| 6. PR   | ACTICAL UTILITY AND FUTURE ENHANCEMENTS | 97 |

| 6.1     | IMPLEMENTED ADPLL                       | 97 |

| 6.2     | IMPLEMENTED TST SWITCH                  | 97 |

|         |                                         |    |

BIBLIOGRAPHY

99

## **1.1 SYNCHRONIZATION INTRODUCTION**

Synchronization is *the act of synchronizing* (Webster's Ninth New Collegiate Dictionary) i.e. making synchronous (cf. the Greek etymon  $\sigma \dot{\nu} \gamma \chi \rho \upsilon \upsilon \sigma \zeta$ ) the operation of different devices or the evolving of different processes by aligning their time scales.

Many operations in digital systems must obey a precedence relationship. If two operations obey some precedence, then synchronization ensures that operation follow in the correct order. At the hardware level, synchronization is accomplished by distributing a common timing signal to all the modules of the system. At a higher level of abstraction, software processes synchronize by exchanging messages.

Depending on the application field, different systems of *abstractions* are adopted usefully, structured in a hierarchical fashion, where each level of abstraction relies on the features of the abstraction level below and hides unnecessary details to the higher level. Abstractions enable the designers to ignore such unnecessary details and focus on essential features, thus making easier achieving a greater complexity of the system designed.

In digital hardware systems, a common approach is to structure the system representation in abstraction levels such as the *physical level*, in which the designer is concerned about physical laws governing semi conductor properties; the *circuit level*, where he deals with transistor, resistor etc.; the *element level* focused on gates, logical ports etc.; the *module level*, where elements are grouped to form more complex entities, such as memories, logic units, CPUs etc.

Whichever is the abstraction criterion adopted in describing hardware and software systems, many are the entities mutually correlated, at any level, whose correct operation relies on temporal coordination. Though, entities of different abstraction levels, both in hardware and software systems, usually require different and independent 'synchronization' functions. Elliptical term synchronization is adopted to refer to whole set of heterogeneous issues where temporal coordination is essential.

# **1.2 HITORICAL PERSPECTIVE**

The modern telecommunication networks result from along evolution process, started since the end of the 19<sup>th</sup> century:

Network synchronization, at first an unknown issue as not relevant to network operation and performance, has played a role of increasing importance in telecommunication throughout this evolution process, especially since transmission and switching turned digital.

Transmission and switching are the two basic functions of any telecommunication network, and in particular telephone networks.

Transmission is the action of conveying information point-to-point, for example from one node in a network to another one directly linked to it by a physical channel. Moreover, transmission can also be from one point to multiple points (multicast) or even from one point to all listeners on the medium (broadcast).

Switching, on the other hand, is the function of connecting a given input-output pair in nodes where multiple transmission links are terminated. It deals thus with the dynamic assignment of the transmission channels available in a network, on the basis of user connection requests.

To make an analogy with railways, transmission systems are the tracks and switching nodes are the shunts. Transmission and switching are the complementary foundations on which all the telecommunication services are based. Both Transmission and Switching were analog first and then one after the other turned to digital technology.

The evolution of digital transmission and switching technology for the public telephones with isolated digital transmission links between analog switching machines or analog radio transmission systems. The fact that digital technology was used was transparent to the interfaces. Thus there was no need to relate internal clock rate of one system to the internal clock rate of another system.

Even as higher level multiplexing systems were developed there was no need (nor viable means) of relating the clock rates of the higher rate multiplexed signals with the clock rates of lower rate tributaries. Indeed the transmission equipment based on PDH technology does not need to be synchronized, since the bit justification technique allows the multiplexing of asynchronous tributaries with substantial frequency offsets.

Problems began to arise wit such asynchronous architecture when digital technology moved to switching machines too. Digital switching equipment requires to be synchronized in order to avoid slips at input elastic stores. And while slips do not significantly affect normal phone conversations, they may be troublesome indeed on some data services! The introduction of circuit switched data networks and of ISDN, therefore, yielded first the need for more stringent synchronization requirements.

The ongoing spread of SDH/SONET technology in transmission network has really made synchronization a hot topic in standard bodies since 1990s. The need for adequate network synchronization facilities has become more and more stringent in order to fully exploit SDH/SONET capabilities; it is widely recognized that SDH/SONET transmission may rely on a suitable

dependable timing distribution to fully meet all its benefits, in particular because pointer action may yield excess jitter on transported tributaries.

Beyond SDH/SONET needs, anyway, nowadays network synchronization facilities are unanimously considered as profitable network resource, allowing slip free digital switching, enhancing the performance of ATM based transport services and serviceable for improving the quality of a variety of services (e.g. ISDN, mobile cellular telephony, etc.). For this reason, most major network operators have set up national synchronization networks, in order to distribute a common timing reference to each node of the telecommunication network, On the standardization side, ITU-T and ETSI bodies released new synchronization standards, suitable for operation of modern digital communication network, specifying more stringent and complex requirements for jitter and wander at synchronization interfaces, for clock accuracy and stability and for the synchronization network architecture.

Most modern synchronization networks are provided with management systems. The main management functions relevant to synchronization network management lie in the areas of fault, configuration, performance and security management.

Most advanced synchronization networks are provided with monitoring systems that allows to verify continuously, in real time, the performance achieved in timing distribution. The rationale of synchronization performance monitoring is the need to be proactive, i.e. to detect timing degradations well before they impact service.

# **1.3 SYNCHRONIZATION IN TELECOMMUNICATION**

The term synchronization is familiar in a somewhat restricted sense, meaning only acquisition and tracking of a clock in a receiver, with reference to the periodic timing information contained in the receive signal. More properly speaking this should be referred to as carrier or symbol synchronization. On the contrary, synchronization plays an essential role in several other areas in telecommunications, at different level of abstraction and in different context too.

At different abstraction levels, the main contexts in which the word synchronization is used in telecommunication are the following:

- *Carrier synchronization*, i.e. the extraction of the carrier from a modulated signal in coherent demodulation;

- *Symbol synchronization*, i.e. the identification of sampling and decision times in digital demodulation, in order to extract the logical information from the received analog signal;

- *Word and frame synchronization*, i.e. the identification of start and end of code words or of group of code words(frames), or also the delineation of the frames in the raw and undifferentiated stream of received bits;

- *Packet synchronization*, i.e. the delay equalization of packet arrival times in order to reconstruct a user circuit with constant bit rate over a packet switched network;

- *Network synchronization*, i.e. the distribution of a common timing over a network of clocks, spread over an even wider geographical area;

- *Multimedia synchronization*, i.e. the orchestration of heterogeneous elements ( images, text, audio, video, etc.) in a multimedia communication at different (e.g. physical and human interface) levels of integration;

- *Synchronization of real-time clocks*, i.e. a substantially different kind of network synchronization in which the distribution of the absolute time (e.g. the national standard time) across a telecommunication network is concerned, mainly to network management purposes.

# **1.4 NETWORK SYNCHRONIZATION ARCHITECTURES**

Network synchronization is a comprehensive expression that addresses in a wide sense any distribution of time and frequency over a network of clocks. Its goal may be either

- 1. To align the absolute time scales of network nodes, thus aiming for instance at aligning local clocks to the Universal Time Coordinated (UTC)

- 2. To align the timing signals (or more precisely, their significant instants) generated by local clocks, independently from a constant phase offset among them. Thus aiming at minimizing phase fluctuations around such average phase offset (example : synchronization of synchronous digital multiplexers or digital switching exchanges in order to avoid slips at input elastic stores);

- 3. To equalize the frequencies of local clocks, without controlling their phase relationship (example: the distribution of a standard signal to PLL based slave clocks).

In a network synchronized as in case (1), local timing signals are synchronous and their total phases are aligned. Therefore, this network synchronization requires estimation and compensation of transmission delays on synchronization signals directed to each node.

In a network synchronized as in case (2), local timing signals are synchronous but there is no need to estimate transmission average delays of synchronization signals.

In a network synchronized as in case (3), finally, timing signals are just mesochronous.

In most cases network synchronization is intended as in case (2) and is achieved by transferring chrono signals (i.e.some pseudo-periodic signals such as sine or square waves), which carry a timing information with the uncertainty of the integer number of periods elapsed since the signal was generated (total transmission delay).

A synchronization network is the facility implementing network synchronization. It is able to provide all telecommunication networks with reference timing signals of required quality. Most

modern telecommunication operators have set up one synchronization network to synchronize their switching and transmission networks.

Basic elements of synchronization network are the nodes (autonomous and slave clocks) and links interconnecting them. An autonomous clock is a stand-alone device able to generate a timing signal, starting from some periodic physical phenomenon. A slave clock on the other hand, generates a timing signal having phase locked to a reference timing signal at its input. Slave clocks are usually implemented as PLLs (Phase Locked Loops).

Time and frequency are distributed by using the communication capacity of the links interconnecting the clocks (e.g. copper cables, optical fibres, radio links). However, network nodes may be many and spread over a wide geographical area. Therefore two distinct issues must be faced:

- How to transfer timing from one node to the other (the tactics of point-to-point timing transfer);

- How to organize timing distribution among all nodes of the network (the strategy of network synchronization).

# **1.5 NETWORK SYNCHRONIZATION STRATEGIES**

Network synchronization plays a central role in modern digital telecommunications, determining the quality of most services offered by network provider to its customers. To this purpose many different network synchronization strategies have been conceived. Among them following three have found wide application throughout the last decades: full plesiochrony, hierarchical master-slave (HMS) synchronization, and mutual synchronization. The main feature of these strategies are as follows.

#### **Full Plesiochrony (Anarchy):**

It is actually no synchronization strategy (i.e., it does not involve any synchronization distribution). Each network node is equipped with an independent clock. Anarchy is the easiest form of government, but it relies on good behavior of the single elements. Due to lack of any timing

distribution, the synchronization of the operation of different nodes is entrusted to accuracy of network clocks, which therefore must feature excellent performance.

Hierarchical Master – Slave Synchronization (Depotism):

The principal of master slave strategies is based on the distribution of the timing reference from a clock (master) to all other clocks of the network (slaves), directly or indirectly. Depotism is generally considered unethical, but it is certainly effective in ensuring very tight control of the slaves: an MS network is synchronous with the master clock and stable by definition. The HMS strategy is currently the most widely adopted to synchronize modern digital telecommunication networks, due to the excellent timing performance and reliability that can be achieved at limited cost.

#### **Mutual Synchronization (Democracy):**

Mutual synchronization is based on direct mutual control among the clocks so that output frequency of each is the result of the "suggestions" of the others. Such a pure democracy looks appealing: there are no masters and no slaves, but mutual cooperation. However, the behavior of the mutually controlled elements is hard to govern. Modeling the behavior of such networks, or even ensuring the stability of the control algorithms, can be very complex task. Network so designed thus tend to be quite expensive, but extremely reliable. Therefore, until now the field of application of mutual synchronization has been mostly limited to special cases (e.g., military networks).

Timing Relation ship between digital signals:

*Isochronous* : Digital signal in which time intervals between significant instants have, at least on the average, the same duration or durations which are integer multiples of shortest one.

Two *synchronous* digital signals are isochronous digital signals whose respective timing signal have the same frequency, at least on the average, and a phase relationship controlled precisely.

Two *mesochronous* digital signals are isochronous, asynchronous digital signals, whose respective timing signals have the same frequency, at least on the average, but no control on phase relationship. Two *plesiochronous* digital signals are isochronous, asynchronous digital signals, whose respective timing signals have the same frequency values only nominally, but actually different within a given tolerance range.

Two *heterochronous* digital signals are isochronous, asynchronous digital signals, whose respective timing signals have different nominal frequencies.

To give sound examples of above abstract concepts, a locked Phase Locked Loop (PLL) outputs a timing signal which is synchronous with the input signal, owing to the feedback control on the phase error between them. A Frequency Locked Loop (FLL), i.e., a feedback system operating like a PLL but instead controlling the frequency error between the input and the output signals, outputs a signal which is mesochronous with the input. Two oscillators, even if designed and built as equal by the same supplier, output two plesiochronous timing signals, owing to unavoidable manufacturing tolerances. Finally, two digital signals with different rates (e.g., 2.048 Mb/s and 8.448Mb/s signals) are heterochronous.

# 1.6 SYNCHRONISATION AND DIGITAL SWITCHING

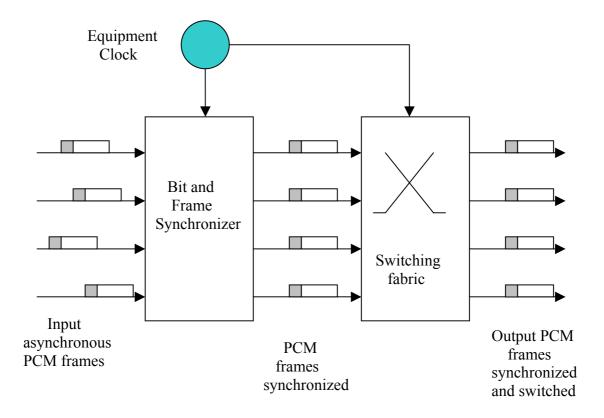

The advent of digital TDM techniques yielded a progressive integration of transmission and switching, since the PCM primary multiplex frame structure allows exploiting of the TDM principle for digital switching of circuit connections as well.

Digital Switching Requires Time Alignment Of The Input PCM Frames:

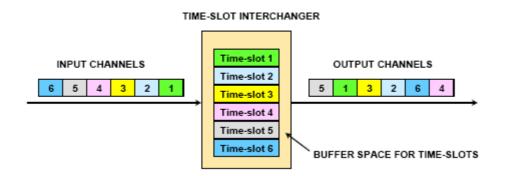

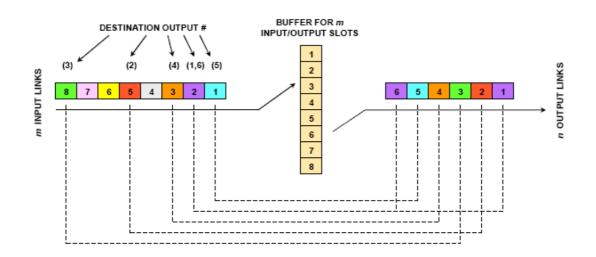

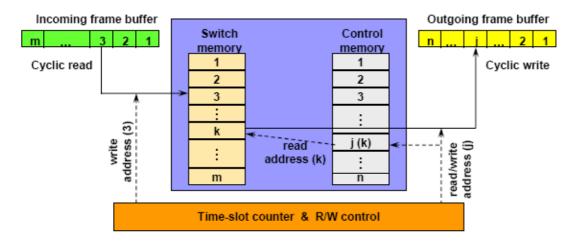

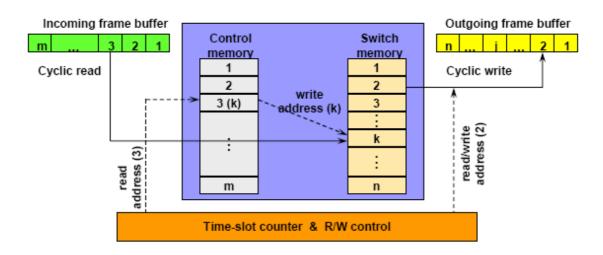

The European 2.048 Mb/s PCM frame is made of 32 octets (time slots), 30 of which carry single 64 Kb/s telephone channels, while the North American 1.544 Mb/s PCM frame is made of 24 slots. Digital switching is based on moving octets (speech samples) from one time slot to another, from one input signal to another output signal. Time slot exchanging is basically done by delaying, by a

suitable time interval, the incoming octets before retransmitting them in the output frame at the right place (time).

It clearly appears that digital switching can take place only if incoming frames (asynchronous since they can be generated by different pieces of equipment with different clocks) are made synchronous, with frame starts aligned, so that correspondent time slots at different inputs are perfectly time aligned. Therefore, one of the tasks of the input line units of a digital switching exchange is to synchronize bits and frames of incoming PCM signals before feeding them into the switching fabric, as outlined in figure. In this figure, for the sake of simplicity, only one frame per line is depicted (with alignment word shaded), and the time slot interchanging in the PCM frames is not pointed out.

Thus, for synchronization to be achieved Phase Locked Loops (PLLs) are to be used and hence are vital components for any synchronized network.

The main task of these PLLs is, on the one hand, to ensure adequate short-term stability by filtering phase fluctuations accumulated by pilots along the transmission links, and on the other to provide in any case an output reference frequency, even under loss of input pilot, by *free running* operation of the local oscillator. Free-run frequency accuracy requested to limit distortion in the demodulated signals is in order of 10<sup>-7</sup>. Such a frequency accuracy is enough to ensure an adequate transmission quality of telephone channels, even under pilot frequency losses lasting for the mean time for restoring.

## 2.1 PHASE LOCKED LOOPS

A phase-locked loop (PLL) is a circuit which causes a particular system to track with another one. More precisely, a PLL is a circuit synchronizing an output signal (generated by an oscillator) wit a reference or input signal in frequency as well as in phase. In the synchronized –often called *locked* – state the phase error between the oscillator's output signal and the reference signal is zero, or very small.

If a phase error builds up, a control mechanism acts on the oscillator in such a way that the phase error is again reduced to minimum. In such a control system the phase of output signal is actually locked to the phase of input signal. This is why it is referred to as *phase-locked loop*.

## 2.2 TYPES OF PLL

- 1. Linear PLL (LPLL)

- 2. Digital PLL (DPLL)

- 3. All Digital PLL (ADPLL)

- 4. Software PLL (SPLL)

## 2.3 FUNDAMENTAL BLOCKS

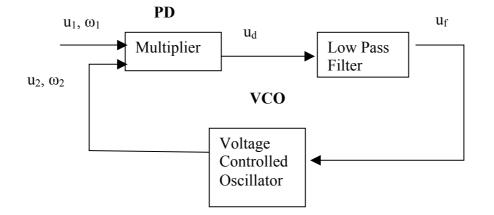

The PLL consists of three basic fundamental blocks:

- 1. A Phase Detector (PD)

- 2. A voltage controlled oscillator (VCO)

- 3. A loop filter (LF)

The signals of interest within the PLL circuit are defined as follows:

- The reference (or input ) signal u<sub>1</sub>(t)

- The angular frequency  $\omega_1$  of the reference signal

- The output signal u<sub>2</sub>(t) of the VCO

- The angular frequency  $\omega_2$  of the output signal

- The output signal u<sub>d</sub>(t) of the phase detector

- The output signal  $u_f(t)$  of the loop filter

- The phase error  $\theta_e$ , defined as the phase difference between signals  $u_1(t)$  and  $u_2(t)$

# 2.4 BRIEF HISTORY

The very first (PLL) were implemented as early as 1932 by de Bellesize; this French engineer is considered inventor the "coherent communication". The PLL found broad industrial applications only when it became available as an integrated circuit. The first PLL IC's appeared around 1965 and were purely analog devices.

An analog multiplier (four quadrant multiplier) was used as phase detector, the loop filter was build from a passive or RC filter and the well known voltage controlled oscillator was used to generate the output signal of PLL. This type of PLL is referred to as linear PLL today. In the following years the PLL drifted slowly but steadily into digital territory. The very first digital PLL (DPLL) which appeared around 1970, was in effect a hybrid device; only the phase detector was build from digital circuit, e.g., from an EXOR gate or a JK flip flop, but the remaining blocks still were analog. A few years later the "all-digital PLL (ADPLL)" was invented. The ADPLL is exclusively build from digital functional blocks hence doesn't contain any passive components like resistors and capacitors. In analogy to filters, PLL's can also be implemented "by software". In this case the function of PLL is no longer performed by a piece of specialized hardware, but rather by a computer program. This last type if PLL is referred to as SPLL.

Unfortunately, LPLLs, DPLLs, and ADPLLs behave differently, so there is no common theory which covers all of these types. Consequently we must treat the various types of PLLs separately.

# 2.5 PLL APPLICATIONS

A Sample of PLL Applications :

The reason that PLLs are so ubiquitous is that they are so useful in so many applications.

- Carrier Recovery

- Clock/Data Recovery

- Frequency Synthesis

- Modulation/Demodulation

- PLL Applications in Control Problems

- -- Disk Drive Control

- -- Harmonic Compensation

- -- Motor Control

EXAMPLES :

1. Carrier Recovery

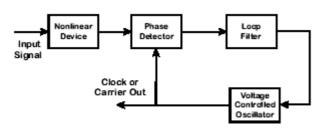

General block diagram of frequency recovery from a modulated signal.

Squaring loop to recover carrier from a BPSK modulated signal.

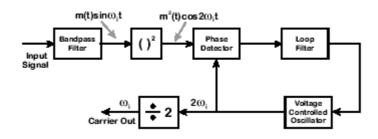

#### 2. Frequency Synthesis

To lock a clock with an input signal of a different frequency synthesize a clock frequency from a lower frequency input. Harmonic locking loop generates a clock at N times input frequency (non-integer N is possible). Example from storage industry is DVD+RW format uses a high frequency wobble embedded in the groove walls to synthesize a write clock frequency.

## 2.6 THE LINEAR PHASE LOCKED LOOP (LPLL)

#### 2.6.1 Building Blocks of LPLL

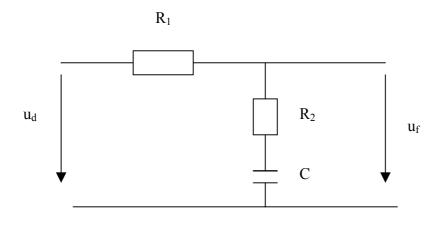

In linear PLLs, the fourth quadrant multiplier is used as phase detector. In most cases the input signal  $u_1(t)$  is a sine wave with angular frequency  $\omega_1$ , whereas output signal  $u_2(t)$  is a symmetrical square wave with angular frequency  $\omega_2$ , In the locked state the two frequencies are equal. The output signal  $u_d(t)$  of the phase detector then consist of a number of terms; the first of these is a "dc" component and is roughly proportional to the phase error  $\theta_e$ ; the remaining terms are "ac" components having frequencies of 2  $\omega_1$ , 4  $\omega_1$  ...Because these higher frequencies are unwanted signals, they are filtered out by the loop filter (which is a low pass filter). Fig below shows a passive lag filter having one pole and one zero.

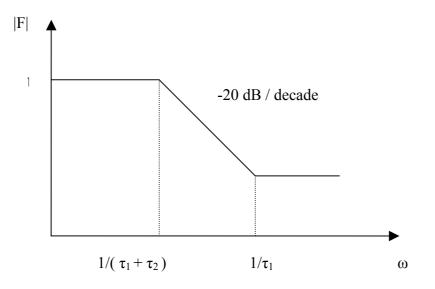

Its transfer function is given by  $F(s) = 1 + s \tau_2 / 1 + s(\tau_1 + \tau_2)$

Where  $\tau_1 = R_1C$  and  $\tau_2 = R_2C$

Its amplitude response is shown in figure below:

Higher order low-pass filters could be used instead of simple one-pole filters; this is done in some applications. Because each additional filter pole introduces phase shift, it is much more difficult to maintain stability in higher order systems.

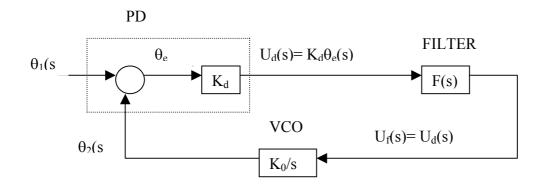

#### 2.6.2 LPLL performance in Locked State

Assuming PLL to be locked and remain locked in near future a mathematical model can be developed for phase transfer function H(s) which relates the phase  $\theta_1$  of the input signal to the phase  $\theta_2$  of the output signal.

$H(s) = \theta_2 (s) / \theta_1(s)$

Where  $\theta_1(s)$  and  $\theta_2(s)$  are the Laplace Transforms of the phase signals  $\theta_1(s)$  and  $\theta_2(s)$  respectively.

To get an expression for H(s) we must know the transfer functions of the individual blocks in block diagram of LPLL. Let us start with phase detector.

Input signal of an LPLL is usually a sine wave.

$$u_1(t) = U_{10} \sin \left( \omega_1 t + \theta_1 \right)$$

whereas output signal is usually a square wave and can therefore be written as a Walsh function

$$\mathbf{u}_2(\mathbf{t}) = \mathbf{U}_{20} \boldsymbol{\omega} \left( \boldsymbol{\omega}_2 \mathbf{t} + \boldsymbol{\theta}_2 \right)$$

The output signal of the four quadrant multiplier is obtained by multiplying the signals  $u_1$  and  $u_2$ . To simplify the analysis the Walsh function is replaced by its fourier series.

For  $u_2(t)$  we then get

$u_{2}(t) = U_{20} \left[ 4/\pi \cos (\omega_{2}t + \theta_{2}) + 4/3\pi \cos (3\omega_{2}t + \theta_{2}) + \dots \right]$

First term in square bracket is fundamental component the remaining terms are odd harmonics. For output signal  $u_2(t)$  therefore we get

$u_d(t) = u_1(t) u_2(t) = U_{10} U_{20} \sin (\omega_1 t + \theta_1)$

x  $[4/\pi \cos(\omega_2 t + \theta_2) + 4/3\pi \cos(3\omega_2 t + \theta_2) + ...]$

When PLL is locked, the frequencies  $\omega_1$  and  $\,\omega_2\,$  are identical and  $u_d(t)\,$  become

$u_d(t) = U_{10} U_{20} [2/\pi \sin \theta_e) + .... ]$

where  $\theta_e = \theta_1 - \theta_2$  is the phase error. The first term in the series is the wanted "dc" term, whereas the higher frequency terms will be eliminated by the loop filter. Setting

$K_d = 2 U_{10} U_{20} / \pi$  and neglecting higher frequency terms we get

$$u_d(t) = K_d \sin \theta_e$$

where  $K_d$  is called detector gain. When the phase error is small, the sine function can be replaced by its argument, and we have

$u_d(t) \approx K_d \theta_e$

In locked state of LPLL the Phase Detector represents a zero order block having a gain of  $K_d$ . Transfer function of a Passive Lag Filter having one pole and one zero is

$F(s) = 1 + s \tau_2 / 1 + s(\tau_1 + \tau_2)$

Where  $\tau_1 = R_1C$  and  $\tau_2 = R_2C$

Angular frequency of VCO is given by

$\omega_2(t) = \omega_0 + \Delta \omega_2(t) = \omega_0 + K_0 u_f(t)$

where  $K_0$  is called VCO gain (dimension : rad s<sup>-1</sup>V<sup>-1</sup>)

The model should yield the output phase  $\theta_2$  and not the output frequency  $\omega_2$ .

By definition

$\theta_2$  (t) =  $\int \Delta \omega_2 dt = K_0 \int u_f dt$

Laplace transform

$$\theta_2$$

(s) = (K<sub>0</sub>/s) U<sub>f</sub>(s)

The transfer function of the VCO is given by

$\theta_2$  (s) / U<sub>f</sub> (s) = K<sub>0</sub>/s

For phase signals the VCO simply represents an integrator.

From above equations a simplified linear model of a LPLL can be drawn :

From the model Phase Transfer Function H(s) is computed. We get

$H(s) = \theta_{2}(s) / \theta_{1}(s) = K_{0} K_{d} F(s) / s + K_{0} K_{d} F(s)$

In addition to the phase transfer function, an error transfer function  $H_e(s)$  is defined by  $H_e(s) = \theta_e(s) / \theta_1(s) = s / s + K_0 K_d F(s)$

Replacing F(s) by LPF transfer function we get, for passive lag filter :

$$H(s) = (\underline{K_0}\underline{K_d}) (1 + s \tau_2 / 1 + s(\tau_1 + \tau_2))$$

$$s^2 + s (1 + K_0 K_d \tau_2) / (\tau_1 + \tau_2) + (K_0 K_d) / (\tau_1 + \tau_2)$$

writing the denominator in normalized form i.e.,

Denominator =  $s^2 + 2\xi \omega_n s + \omega_n^2$

Where  $\omega_n$  is natural frequency and  $\xi$  is the damping factor.

For passive lag filter :

$\omega_n = \sqrt{(K_0 K_d)} / (\tau_1 + \tau_2)$   $\xi = \omega_n / 2 (\tau_2 + 1 / K_0 K_d)$  $K_0 K_d$ : Loop Gain

# 2.7 KEY PARAMETERS OF THE LPLL

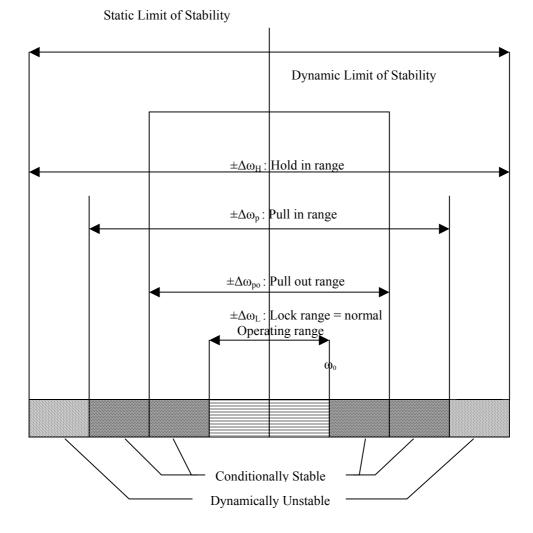

Hold range,  $\Delta \omega_H$  \_\_\_\_\_ LLPL can statically maintain phase tracking, conditionally stable.

Pull out range,  $\Delta \omega_{po}$ : Dynamic limit for stability, normally locked again. Pull in range,  $\Delta \omega_{p}$ : Lock again but process is slow. Lock range,  $\Delta \omega_{L}$ : Lock within single beat note between reference frequency & output frequency.

#### 2.7.1 The Hold Range

It is the frequency range in which a PLL is able to maintain the lock statically. The LPLL locks out for ever when the frequency of the input signal exceeds the hold range.

Magnitude is calculated by frequency offset at reference input which causes phase error  $\theta_e$  of  $\pi/2$ .

$\omega_1 = \omega_0 + \Delta \omega_H$

where is the hold range. For the phase signal we get

$\theta_1(t) = \Delta \omega_H t$

Laplace transform

$\theta_1(s) = \Delta \omega / s^2$

Phase error :

$\theta_{e}(s) = \theta_{1}(s) H_{e}(s) = (\Delta \omega / s^{2}) / (s / s + K_{d}K_{0}F(s))$

using final value theorem, final phase error in time domain :

$\lim_{t \to \infty} \theta_{e}(t) = \lim_{s \to 0} s\theta_{e}(s) = \Delta \omega / K_{d}K_{0}F(0)$

this is for small values of  $\theta_e$  only, for greater values :

$\lim \sin \theta_{e}(t) = \Delta \omega_{H} / K_{d} K_{0} F(0)$

$$t \rightarrow \infty$$

at the limit of hold range  $\theta_e = \pi/2 \sin \theta_e = 1$ , therefore expression for hold range :

$\Delta \omega_{\rm H} = K_{\rm d} K_0 F(0)$

for passive lag filter :

$\Delta \omega_{\rm H} = K_{\rm d} K_0$

#### 2.7.2 The Lock Range

Assume that the LPLL is initially not locked and that the reference frequency is

$\omega_1 = \omega_0 + \Delta \omega$ . The reference signal of the LPLL is then given by

$u_1(t) = U_{10} \sin (\omega_0 t + \Delta \omega t)$  and the output signal by

$$\mathbf{u}_2(\mathbf{t}) = \mathbf{U}_{20} \,\omega \,(\omega_0 \mathbf{t})$$

Phase Detector will deliver an output signal given by

$u_d(t) = K_d \sin(\Delta \omega t) + \text{higher frequency terms}$

The higher frequency terms can be filtered out by loop filter. The output of loop filter can be written as

$u_{f}(t) \approx K_{d} |F(\Delta \omega)| \sin (\Delta \omega t)$

this is an AC signal causing frequency modulation of the VCO. The peak frequency deviation is equal to  $K_d K_0 |F(\Delta \omega)|$ .

If this frequency deviation is less than the frequency offset  $\Delta \omega$  then lock in process will either not take place or is at least very slow. When frequency deviation is large so that  $\omega_2$  exactly meets the reference frequency  $\omega_1$ , PLL locks within the single beat note between the reference and the output frequencies.

The condition for locking is therefore

$K_d K_0 |F(\Delta \omega)| \ge \Delta \omega$

Lock Range itself is given by

$\Delta \omega_{\rm L} = K_{\rm d} K_0 \left| F \left( \Delta \omega_{\rm L} \right) \right|$

Approximating that lock range is much greater then corner frequencies  $1/\tau_1$  and  $1/\tau_2$  of the loop filter and also assuming  $\tau_2$  to be much smaller than  $\tau_1$  we can use

$F\left(\Delta\omega_L\right)|\approx \ \tau_2\ /\ \tau_1 \qquad \text{for passive lag filter}$

Assuming high gain loops and making substitutions we get

$\Delta \omega_L \approx 2\zeta \omega_n$  ------ for all types of loop filters

When LPLL locks quickly (  $\zeta < 1$ , damped oscillations, transients die out in one clock cycle), it is reasonable to state lock-in time as

$T_L \approx 2 \pi / \omega_n$  (settling time).

#### **2.7.3** Pull in Range $\Delta \omega_p$

Assume again that LPLL is not locked initially, that the frequency of the reference signal is  $\omega_1 = \omega_0 + \Delta \omega$ , and the VCO operates at the centre frequency  $\omega_0$ . Consequently the output signal  $u_d$  of the phase detector is a sine wave having the frequency  $\Delta \omega$ .

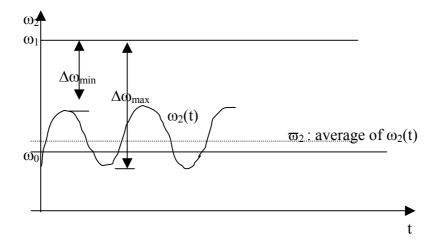

The difference  $\Delta\omega$  between reference frequency  $\omega_1$  and output frequency  $\omega_2(t)$  is not a constant; it is also varied by the frequency modulation of the VCO output signal. If the frequency  $\omega_2(t)$  is modulated in the positive direction, the difference  $\Delta\omega$  becomes smaller and reaches some minimum value  $\Delta\omega_{min}$ ; if  $\omega_2(t)$  is modulated in negative direction, however,  $\Delta\omega$  becomes greater and reaches some maximum value  $\Delta\omega_{max}$ , Because  $\Delta\omega(t)$  is not a constant, the VCO frequency is modulated non harmonically, that is, the duration of the half-period in which  $\omega_2(t)$  is modulated in the negative sense. As a consequence the average frequency  $\varpi_2$  of the VCO is now higher than it was without any modulation, i.e., the VCO frequency is pulled in the direction of the reference signal. The asymmetry of the waveform  $\omega_2(t)$  is greatly dependent on the value of the average offset  $\Delta \omega$ ; the asymmetry becomes more marked as  $\Delta \omega$  is decreased. If the average value of  $\omega_2(t)$  is pulled somewhat in the direction of  $\omega_1$  (which is assumed to be greater than  $\varpi_2$ ), the asymmetry of the  $\omega_2(t)$  waveform becomes stronger. This in turn causes  $\varpi_2$  to be pulled even more in the positive direction. This process is regenerative under certain conditions, so that the output frequency  $\omega_2$ finally reaches the reference frequency  $\omega_1$ . This phenomenon is called the *pull-in* process. Mathematical analysis shows that a pull-in process occurs whenever the initial frequency offset  $\Delta \omega$ is smaller than a critical value, the *pull-in range*  $\Delta \omega_p$ . If , on the other hand, the initial frequency offset  $\Delta \omega$  is larger than  $\Delta \omega_p$ , a pull-in process does not take place because the pulling effect is not then regenerative.

In the unlocked state of the PLL the frequency modulation of the VCO output signal is non harmonic . This causes the average value of the VCO output frequency to be pulled in the direction of the reference frequency.

The Pull-in process

The pull-in range also depends on loop filter.

For passive lag filter:

$\Delta \omega_{\rm p} = 4/\pi \sqrt{(2\zeta \omega_{\rm n} K_0 K_d - \omega_{\rm n}^2)}$

For active PI filter :

$\Delta \omega_p \rightarrow$  infinity (because high, theoretically infinite, DC gain)

#### 2.7.4 Pull Out Range $\Delta \omega_{po}$

The pull out range is by definition that frequency step which causes a lock-out if applied to the reference input of the PLL.

An exact calculation of the pullout range is not possible for the linear PLL. However, simulations on an analog computer have led to an approximation:

$\Delta \omega_{\rm PO} = 1.8 \, \omega_{\rm n} (\xi + 1)$

In most practical cases the pull out range is between the lock range and the pull in range

$\Delta \omega_L < \Delta \omega_{PO} < \Delta \omega_P$

# 2.8 THE CALSSICAL DIGITAL PLL (DPLL)

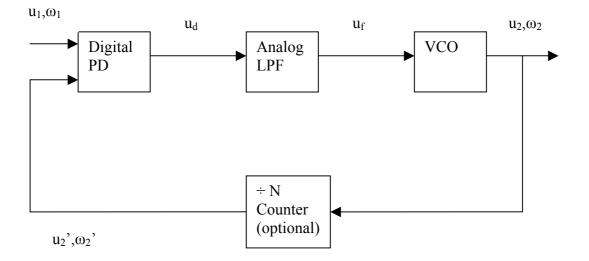

The classical DPLL is actually a hybrid system built from analog and digital functional blocks. The only part of the DPLL that is really digital is phase detector. In many aspects the DPLL performs similar to the LPLL, so some part of PLL theory can be adopted; in some particular aspects, however, DPLL behavior is completely different.

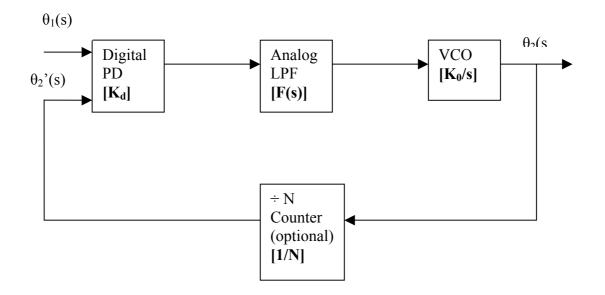

Block diagram of the DPLL

The block diagram of DPLL is shown in figure above, like the LPLL, consists of the three known function blocks phase detector, loop filter and voltage controlled oscillator. In many DPLL

applications (e.g.,PLL frequency synthesizers) a divide-by-N counter is inserted between VCO and phase detector. When such a counter is used, the VCO generates a frequency which is N times the reference frequency.

# 2.8.1 DIGITAL PHASE DETECTORS

Three most important logical circuits for phase detector are :

- The EXOR gate

- The (edge triggered) JK flip-flop

- The "phase frequency detector" (PFD)

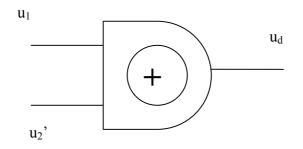

### 2.8.1.1 EXOR Phase detector

The operation of EXOR phase detector is most similar to that of the liner multiplier. The signals in DPLLs are always binary signals, i.e., square waves. We assume for the moment that both signals  $u_1$  and  $u_2$  are symmetric square waves.

At zero phase error the signals  $u_1$  and  $u_2$  are out of phase by exactly 90°. Then the output signal  $u_d$  is a square wave whose frequency is twice the reference frequency; the duty cycle of the  $u_d$  signal is exactly 50%. Because the high frequency component of this signal will be filtered out by loop filter, we consider only the average value of  $u_d$ , as shown by dashed line. The average value is arithmatic mean of the two logical levels.

When the output signal  $u_2$ ' lags the reference signal  $u_1$ , the phase error  $\theta_e$  becomes positive, the duty cycle of  $u_d$  becomes larger than 50% i.e., average value of  $u_d$  is considered positive. Clearly the mean of  $u_d$  reaches its maximum value for a phase error of  $\theta_e = 90^\circ$  and its minimum value for  $\theta_e = -90^\circ$ . Whereas the output signal of the four quadrant multiplier varied with the sine of phase error, the average output of  $\bar{u}_d$  of the EXOR is a triangular function of the phase error. Within a phase error range of  $-\pi/2 < \theta_e < \pi/2$ ,  $u_d$  is exactly proportional to  $\theta_e$  and can be written as

$\bar{u}_d = K_d \theta_e$ .

$K_d$  : constant.

When supply voltage to EXOR are  $U_B$  and 0, and when we assume logic levels are  $U_B$  and 0.  $K_d$  is given by

$K_d = U_B/\pi$

The performance of the EXOR phase detector becomes severely impaired if the signals  $u_1$  and  $u_2$ ' become asymmetrical. If this happens, the output signal  $\bar{u}_d$  gets clipped at some intermediate level, this reduces loop gain of the DPLL and results in smaller lock range and pull out range, etc.

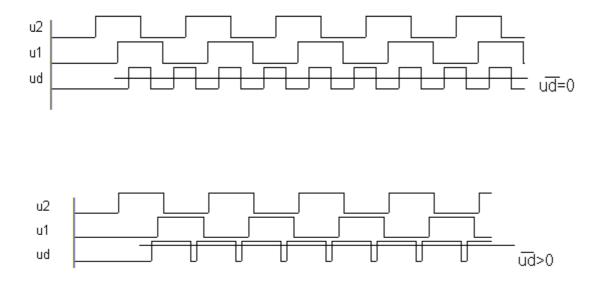

#### 2.8.1.2 J-K Flipflop Phase Detector

Waveform symmetry is unimportant; however the JK-flipflop is used as phase detector. This JK-flipflop differs from conventional JK-flipflops, because it is edge-triggered. A positive edge

appearing at the J input triggers the flipflop into its "high" state (Q = 1), a positive edge at the K input into its "low" state (Q = 0).

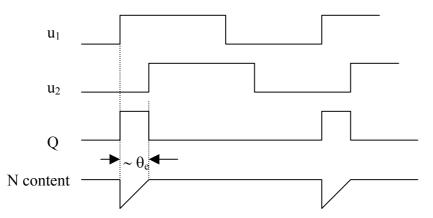

Figure above shows the waveforms of the JK-flipflop phase detector for the case  $\theta_e = 0$ . With no phase error,  $u_1$  and  $u_2$  have opposite phase. The output signal  $u_d$  then represents a symmetrical square wave whose frequency is identical with the reference frequency (and not twice the reference frequency). This condition is considered as  $\bar{u}_d$  being zero. If the phase error become positive, the duty cycle of the  $u_d$  signal becomes greater than 50 percent, i.e.,  $\bar{u}_d$  becomes positive. Clearly,  $\bar{u}_d$  becomes maximum when phase error reaches 180° and minimum when the phase error is -180°. If the mean value of  $\bar{u}_d$  is plotted vs phase error  $\theta_e$  the saw tooth characteristic is obtained. Within a phase error range of  $-\pi < \theta_e < \pi$  the average signal  $u_d$  is proportional to  $\theta_e$  and is given by

$$\bar{u}_d = K_d \; \theta e$$

Obviously the JK-flipflop phase detector is able to maintain phase tracking for phase errors within the range

$-\pi < \theta_e < \pi$

By analogous consideration, the phase detector gain of the JK flip flop phase detector is given by  $K_d = U_B/2\pi$ .

In contrast to EXOR gate , the symmetry of the  $u_1$  and  $u_2$ ' signals is irrelevant, because the state of the JK flip flop is altered only by the positive transitions of these signals.

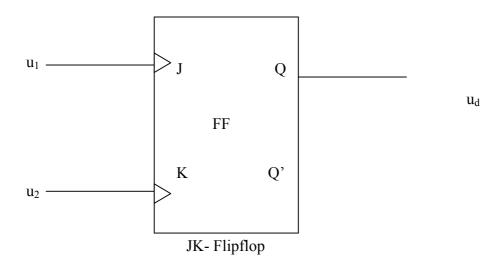

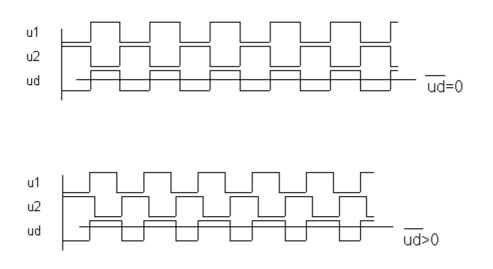

#### 2.8.1.3 **PFD (Phase Frequency Detector)**

As its name implies, its output signal depends not only on phase error  $\theta_e$  but also on frequency error  $\Delta \omega = \omega_1 - \omega_2$ , when the DPLL has not yet acquired lock. Fig above shows the schematic diagram of

the PFD. It is built from two D-flip flops, whose outputs are denoted "UP" and "DN"(down) respectively. The PFD can be in one of the four states

- UP=0, DN=0,

- UP=1, DN=0,

- UP=0, DN=1,

- UP=1, DN=1

The fourth state is inhibited, however, by an additional AND gate whose output goes to clear direct (CD) pin which resets both flip-flops.

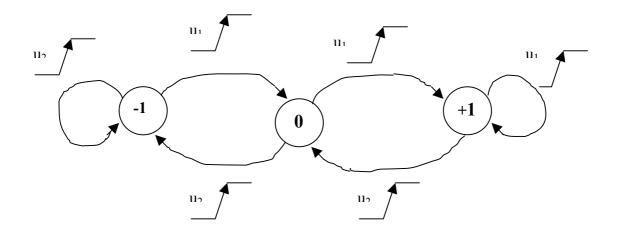

We assign symbols -1, 0, 1 to these states:

- DN = 1, UP = 0  $\rightarrow$  state = -1

- UP = 0, DN = 0  $\rightarrow$  state = 0

- UP = 1, DN = 0  $\rightarrow$  state = +1

The actual state of PFD is determined by the positive going transients of the signals  $u_1$  and  $u_2$ ', as explained by state diagram in fig below. A positive transition of  $u_1$  forces PFD to go into its next higher state unless it is already in +1 state. In analogy, a positive edge of  $u_2$ ' forces the PFD into its next lower stae, unless it is already in the -1 state. When PFD is in +1 state,  $u_d$  must be positive;

when it is in -1 state,  $u_d$  must be negative; and when it is in 0 state,  $u_d$  must be zero. Theoritically  $u_d$  is a ternary signal. Third state can be substituted by a high impedance state.

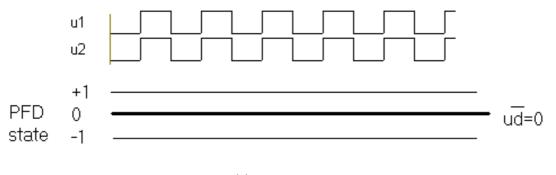

When the UP signal is high, the P channel MOS transistor conducts, so  $u_d$  equals the positive supply voltage  $U_B$ . When the DN signal is high, the N channel MOS transistor conducts, so  $u_d$  is on the ground potential. If neither signal is high, both MOS transistors are off, and the output signal floats i.e., is in the high impedance state. Consequently the output signal  $u_d$  represents a tristate signal. Fig (a) shows the case where the phase error is zero. It is assumed that the PFD has been in 0 state

initially. The signals  $u_1$  and  $u_2$ ' are exactly in phase here; both positive edges of

(a)

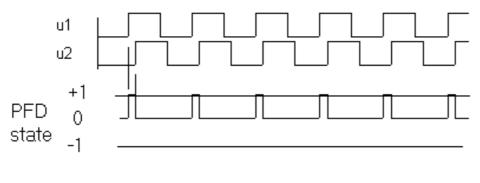

$u_1$  and  $u_2$ ' occur "at the same time"; hence their effects will cancel. The PFD will stay in 0 state for ever. Fig (b) shows the case where  $u_1$  leads  $u_2$ '.

(b)

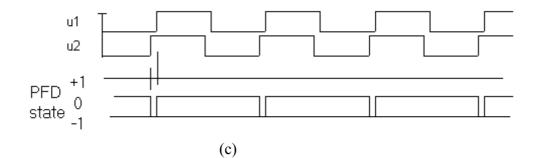

The PFD now toggles between the states 0 and +1. If  $u_1$  lags  $u_2$ ' as shown in Fig (c),

the PFD toggles between states -1 and 0. It is easily seen from the waveforms in fig (b) and fig(c) that  $u_d$  becomes largest when the phase error is positive and approaches 360° and smallest when the phase error is negative and approaches -360°. When the phase error  $\theta_e$  exceeds  $2\pi$ , the PFD behaves as if the phase error is recycled at zero; hence the characteristic curve of PFD becomes periodic with period  $2\pi$ . An analogous consideration can be made for phase errors smaller then  $-2\pi$ . When the phase error is restricted to the range  $-2\pi < \theta_e < 2\pi$ , the average of  $u_d$  becomes

$$\bar{u}_d = K_d \theta_d$$

In analogy to JK flip-flop, phase detector gain is computed by

$$K_d = U_B/4\pi$$

When the logic levels are  $U_B$  or 0 respectively.

To recognize the bonus offered by the PFD, we must assume that the DPLL is unlocked initially. Furthermore we make the assumption that the reference frequency  $\omega_1$  is higher than the output frequency  $\omega_2$ '. The  $u_1$  signal then generates more positive transitions per unit of time then the signal  $u_2$ '. Looking at fig(b) above we see that the PFD can toggle only between the states 0 and +1 under this condition but will never go into the -1 state. If  $\omega_1$  is much higher than  $\omega_2$ ' furthermore, the PFD will be in +1 state most of the time. When  $\omega_1$  is smaller than  $\omega_2$ ' however, the PFD will toggle between the states -1 and 0. If  $\omega_1$  is much lower than  $\omega_2$ ' , the PFD will be in -1 state most of the time. We conclude therefore that the average output signal  $\bar{u}_d$  of the PFD varies monotonically with

the frequency error  $\Delta \omega = \omega_1 - \omega_2$  when the DPLL is out of lock. This leads to the term phase-frequency detector.

For the case  $\omega_1 < \omega_2$  the duty cycle  $\delta$  is defined the average fraction of time the PFD is in the -1 state ; for  $\omega_1 > \omega_2$ ,  $\delta$  is by definition minus the average fraction of time the PFD is in the +1 state. As expected,  $\delta$  approaches -1 when  $\omega_1 \ll \omega_2$  and +1 when  $\omega_1 \gg \omega_2$ .

Because the output signal  $\bar{u}_d$  of the PFD depends on phase error in the locked state of the DPLL and on frequency error in the unlocked state, a DPLL which uses the PFD will lock under any condition, irrespective of the type of loop filter used. For this reason the PFD is the preferred phase detectors in DPLLs.

#### 2.8.2 DYNAMIC PERFORMANCE

When the DPLL has acquired lock and is not pulled out by large phase steps, frequency steps, or phase noise applied to its reference input, its performance can be analyzed by a linear model, as done for the LPLL.

Knowing the transfer functions of all building blocks of the DPLL, we are able to drive the phase-transfer function H(s), the natural frequency  $\omega_n$  and damping factor  $\xi$ . For  $\omega_n$  and  $\xi$ , expressions similar to those for the LPLL are obtained.

#### 2.8.3 PARAMETERS

- The Hold Range

- The Lock Range

- Pull in Range

- Pull out Range

#### 2.8.3.1 The Hold Range

The hold range  $\Delta \omega_{\rm H}$  is the frequency range within which PLL operation can be statically stable. Under normal operating conditions the PLL never operates at the limits of the hold range. To reach this limit of stability it would be necessary to weep the reference frequency slowly upward ( or downward). If the reference frequency is increased and the dc gain of the loop filter is finite, the phase error increases in proportion. When it attains the maximum value for which the phase detector operates linearly, the hold range is reached.

If an EXOR gate is used as phase detector, the maximum phase error is  $\pi/2$ . Based on the procedure as was adopted in LPLL case, we obtain for hold range

$\Delta \omega_{\rm H} = \frac{K_0 K_{\rm d} F(0)(\pi/2)}{N}$

Where F(0) is dc gain of the loop filter.

DC gain is 1 for passive lag,

For EXOR phase detector and passive lag filter, hold range:

$$\Delta \omega_{\rm H} = \frac{K_0 K_{\rm d}(\pi/2)}{N}$$

If the JK flip flop is used as phase detector, the maximum phase error becomes  $\pi$ , so hold range :  $\Delta \omega_{\rm H} = \underbrace{K_0 K_d \pi}_{N}$

The situation changes drastically, however, when the PFD is used as phase detector. Because its output is in the high-impedance state when none of the UP or DN outputs is active, the charge on the capacitor(s) of the loop filter remains unchanged when the PFD is in the 0 state. Consequently the output signal  $u_f$  of the loop filter can have a non-zero value even if the average  $u_d$  signal is 0. When driven by a tri-state source the loop filter acts like an integrator i.e., filter whose transfer function F(s) has a pole at s = 0.

The hold range of a DPLL using the PFD becomes infinite.

#### 2.8.3.2 The Lock Range

By definition lock range is the offset between the reference and (scaled down) VCO frequency which causes the DPLL to acquire lock within one beat note between reference and (scaled down) output frequencies. The lock range of the DPLL can be determined by considerations analog to those made in LPLL case we assume DPLL is initially out of lock and that the VCO oscillates on its center frequency N $\omega_0$ . The reference frequency is offset by  $\Delta\omega$  from its center value  $\omega_0$ , i.e.,  $\omega_1 = \omega_0 + \Delta\omega$ . The signals  $u_1$  and  $u_2$  can then be replaced by the walsh functions

$u_1(t) = U_{10}\omega[(\omega_0 + \Delta\omega)t]$

and

$u_{2}(t) = U_{20}\omega(\omega_{0})t$

respectively, where  $U_{10}$  and  $U_{20}$  are the amplitudes of the square wave signals. The phase error  $\theta_e$  is the difference of the phases of these two signals, i.e.,

$\theta_{e}(t) = \omega_0 t$  : which is a ramp function.

Case of EXOR phase detector :

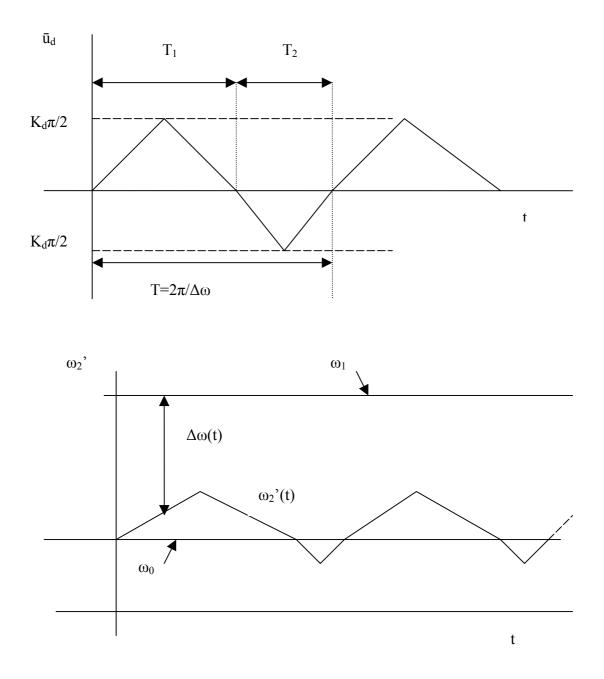

Average output signal  $\bar{u}_d$  (t) of the EXOR is a triangular function of phase error,  $\bar{u}_d(t)$  becomes triangular function of time. The shape of  $u_f$  signal is also triangular, therefore frequency of VCO is modulated by this triangular function. When the frequency offset  $\Delta \omega$  is chosen such that the peak of the  $\omega_2$ ' curve just reaches the reference frequency  $\omega_1$ ,  $\Delta \omega$  equals the lock range  $\Delta \omega_L$ . Using mathematical model developed in LPLL case, we obtain lock range

$\Delta \omega_L \approx \pi \xi \omega_n$

The lock range of the DPLL using the EXOR phase detector is greater than the lock range of the LPLL by a factor of approximately  $\pi/2$ . This is easily explained by the fact that the maximum output signal of the four quadrant multiplier is K<sub>d</sub>, whereas the maximum output signal of the EXOR is  $K_d\pi/2$ .

Case of JK flip-flop phase detector :

Average output signal  $\bar{u}_d(t)$  of the JK flip-flop varies in a saw-tooth-like fashion with phase error,  $\bar{u}_d(t)$  will also be a saw-tooth function. The frequency of VCO is modulated in a saw tooth like manner. When the frequency offset  $\Delta \omega$  is chosen such that the peak of the  $\omega_2$ ' curve just reaches the reference frequency  $\omega_1$ ,  $\Delta \omega$  equals the lock range  $\Delta \omega_L$ . By analog consideration we get the approximation

$\Delta \omega_L \approx \ 2\pi \xi \omega_n$

Case of PFD phase detector :

A similar procedure can be applied to the PFD. For a DPLL using the PFD the lock range becomes approximately

$\Delta \omega_L \thickapprox \ 2\pi \xi \omega_n$

The lock-in time can be calculated by analog consideration as made for the linear PLL. The lock process is completed within one cycle of the damped oscillation at most, so it is reasonable approximation to state that  $T_L$  is one period of the damped oscillation:

$T_L \approx 2\pi/\omega_n$

#### 2.8.3.3 Pull-in range

Pull-in process is a nonlinear phenomenon and is very hard to calculate. Analysis is different for different phase detectors.

Let us assume first EXOR gate phase detector.

We assume DPLL is initially out of lock and that the VCO oscillates on its center frequency N $\omega_0$ . The reference frequency is offset by  $\Delta\omega$  from its center value  $\omega_0$ , i.e.,  $\omega_1 = \omega_0 + \Delta\omega$ . The signals  $u_1$  and  $u_2$  can then be replaced by the walsh functions

$u_1(t) = U_{10}\omega[(\omega_0 + \Delta\omega)t]$

and

$u_{2}(t) = U_{20}\omega(\omega_{0})t$

respectively, where  $U_{10}$  and  $U_{20}$  are the amplitudes of the square wave signals. The phase error  $\theta_e$  is the difference of the phases of these two signals ,i.e.,

$\theta_{e}(t) = \omega_0 t$  : which is a ramp function.

Average output signal  $\bar{u}_d(t)$  of the EXOR is a triangular function of phase error,  $\bar{u}_d(t)$  becomes triangular function of time. The shape of  $u_f$  signal is also triangular, therefore frequency of VCO is modulated by this triangular function. If the triangular waveform were symmetrical the average frequency  $\omega_2$ ' would remain constant and is equal to  $\omega_0$ . However the frequency offset  $\Delta \omega$  is not constant but is given by the difference between reference frequency  $\omega_1$  and instantaneous frequency  $\omega_2$ '. Consequently,  $\Delta \omega(t)$  becomes smaller during the positive half of the  $\bar{u}_d$  signal and larger during the negative half-wave. Therefore, the waveform of  $\bar{u}_d$  becomes asymmetrical. When the  $\bar{u}_d$ waveform is asymmetrical, its mean value is no longer zero but becomes slightly positive. This causes the average frequency of the VCO to be pulled up. If the loop gain is high, pull in process becomes regenerative and the VCO frequency will be pulled up until it becomes close to the reference frequency. Then a locking process will take place. A pull-in process is initiated whenever the initial frequency offset  $\Delta \omega$  is smaller than the pull-in range  $\Delta \omega_p$ .

#### **Final results:**

For passive lag low gain loops

$\Delta \omega_{\rm p} = (\pi/2) \sqrt{(2\xi \omega_{\rm n} K_0 K_d - \omega_{\rm n}^2)}$

For passive lag high gain loops

$$\Delta \omega_{\rm p} = (\pi/\sqrt{2}) \sqrt{(\xi \omega_{\rm n} K_0 K_d)}$$

Final result for approximate pull-in time  $\mathrm{T}_{\mathrm{P}}$  :

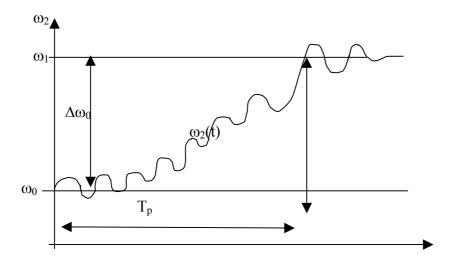

$$T_{\rm P} = 4\Delta\omega_0^2 / (\pi^2 \xi \omega_n^3)$$

Pull in time varies with square of initial frequency offset. Pull in time becomes infinite when initial frequency offset equals the pull-in range.

In case of JK flip-flop phase detector, the waveforms of average  $\bar{u}_d(t)$  signal is saw tooth instead of triangular. Performing analog computation as above, we get for the pull-in range :

For passive lag low gain loops

$\Delta \omega_{\rm p} = \pi \sqrt{(2\xi \omega_{\rm n} K_0 K_d - \omega_{\rm n}^2)}$

For passive lag high gain loops

$$\Delta \omega_{\rm p} = (\pi/\sqrt{2}) \sqrt{(\xi \omega_{\rm n} K_0 K_d)}$$

Pull in time

$$T_{\rm P} = \Delta \omega_0^2 / (\pi^2 \xi \omega_n^3)$$

Consider the case where PFD is used as phase detector:

The pull-in range becomes infinite now, because the loop filter is driven by a tri-state source. The charge on the filter capacitor remains unchanged when the output of the PFD is in the high impedance state, Hence even a passive lag filter works like a real integrator.

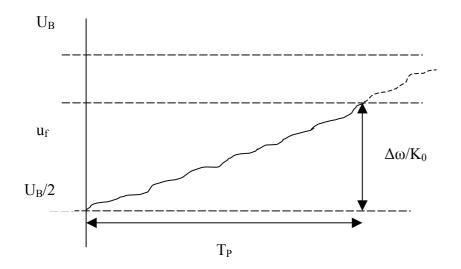

We assume again that the DPLL is initially out of lock and that the frequency  $\omega_1$  of the reference signal  $u_1$  is marked higher than the (down scaled) output frequency  $\omega_2$ . The output signal  $u_d$  of the PFD then toggles between the states 0 and +1. The average  $u_d$  signal has the shape of saw-tooth signal. It periodically ramps up from 0 to 1 and is a saw-tooth function as well. The average duty cycle of  $u_d$ is 50%. Because the time constant  $\tau_1$  of the loop filter is much larger than the period of the  $u_1$  signal, an equivalent  $u_{eq}$  having a constant duty cycle of 50% would have the same effect on the loop filter (neglecting  $\tau_2$  because  $\tau_2 \ll \tau_1$ ). Because the duty cycle is only 50%, however the capacitor needs twice as much time to charge. Therefore the loop filter acts like a simple RC filter whose time constant is not  $\tau_1$  but  $2\tau_1$ . After some time,  $u_f$  will have reached a level which causes the VCO to generate just the "right" frequency.

This occurs when the voltage on the capacitor has been increased by the amount  $\Delta\omega/K_0$ . When this happens, the pull-in process terminates, and a lock-in process takes place.

For passive lag loop filter pull-in time (time required for the capacitor to increase its voltage by  $\Delta\omega/K_0$ ):

$T_P = 2\tau_1 \ln ((K_0 U_B/2)/K_0 U_B/2 - \Delta \omega_p)$

Where  $\Delta \omega_p$  is the initial frequency offset,  $\Delta \omega_p = \omega_1 - \omega_p$

Major difference of the pull-in process for different types of phase detectors :

If the phase detector is an EXOR gate, the instantaneous frequency of the VCO is modulated in both directions around its average value. Provided a pull-in process starts, the frequency of the VCO is slowly "pumped up" as in case of LPLL. A similar pumping is observed when the phase detector is a JK flip-flop. No pumping occurs when the PFD is used, the VCO "knows where to go" at every time. The instantaneous frequency of the VCO approaches the final value from one side only. When the pull-in process is completed, a lock-in process follows.

### 2.8.3.4 Pull-out range

Pull out range is the size of the frequency step applied to the reference input which causes the PLL to loose phase tracking.

In case of LPLL the output signal of four quadrant multiplier varies with sine of the phase error, it is triangular function in case of EXOR which is quite similar. We expect, however, that the pull-out range would be slightly greater for the DPLL, because the output signal of the EXOR is linear over the full range  $-\pi/2 < \theta_e < \pi/2$  and does not flatten out at phase errors approaching  $\pi/2$ .

By simulations, using damping factors in the range of  $0.1 < \xi < 3$ , then a least squares fit gave the approximation

$\Delta \omega_{\rm PO} = 2.46 \, \omega_{\rm n} ( \xi + 0.65 )$

In case of the JK flip-flop, the pull-out range is the frequency step causing the peak phase error to exceed  $\pi$ ; in case of PFD, the pull-out range is the frequency step leading to a peak phase error of  $2\pi$ . Least square fit gives :

For JK flip flop phase detector  $\Delta \omega_{PO} = 5.78 \omega_n (\xi + 0.5)$  and

For PFD phase detector

$\Delta \omega_{PO} = 11.55 \, \omega_n ( \xi + 0.5 )$

#### 2.8.4 DPLL DESIGN

- Step 1. The input and output frequencies of the DPLL must be specified.

- Step 2. The scalar ratio must be determined.

- Step 3. Determination of damping factor  $\xi$ .(0.7 preferred for butterworth response)

- Step 4. Choice of Phase Detector (PFD preferred)

- Step 5. Characteristic of VCO is determined.  $\omega_0$  and N are decided, range for  $\omega$  is generated, VCO gain K<sub>0</sub> is determined

- Step 6. Specify type of loop filter.(passive lag filter is preferred with PFD for infinite hold and pull-in range)

- Step 7. Determining dynamic properties of DPLL. How the DPLL is used,  $T_P$  should be key parameter (goto step 8) or  $\Delta \omega_{po}$  should be key parameter (goto step 12) or  $T_L$  should be key parameter (goto step 13). User must resort to specification which makes as much sense as possible.

- Step 8. With  $T_P$  known  $\tau_1$  is calculated.

- Step 9. With  $\tau_1$  known  $\xi$  is calculated.

- Step 10. With  $\omega_n$  and  $\xi$  known  $\tau_2$  is calculated.

- Step 11. With  $\tau_1$  and  $\tau_2$  (plus eventually  $K_0$ ), the components of loop filter can be determined.

- Step 12. Given  $\Delta \omega_{po}$  and damping factor  $\xi$ , natural frequency  $\omega_n$  is calculated. Proceed to step 14.

- Step 13.  $\omega_n$  is calculated from T<sub>L</sub>, proceed to step 14

- Step 14. With  $\omega_n$  and  $\xi$  known  $\tau_1$  is calculated.

## 2.9 ALL DIGITAL PLL (ADPLL)

The Classical DPLL is a semi analog circuit. Because it always needs a couple of external components, its key parameters will vary because of parts spread. Even worse, the center frequency of a DPLL is influenced by parasitic capacitors on the DPLL chip. Its variation can be so large that trimming can become necessary in critical applications. Many parameters are also subject to temperature drift.

The all-digital PLL does away with these analog-circuitry headaches. In contrast to the DPLL, it is an entirely *digital* system. Let us know first that the term "digital" is used here for a number of different things. First of all, "digital" means that the system consists exclusively of logical devices. But "digital" also signifies that the signals within the system are digital too. Hence it can be a binary signal (or "bit" signal) as was the case with the classical DPLL, but it can as well be a "word" signal, i.e., a digital code word coming from a data register, from the parallel outputs of a computer, and the like. When discussing the various types of ADPLL, we find the whole palette of such digital signals. To realize an ADPLL, all function blocks of the system must be implemented by purely digital circuits.

#### 2.9.1 DIGITAL PHASE DETECTORS

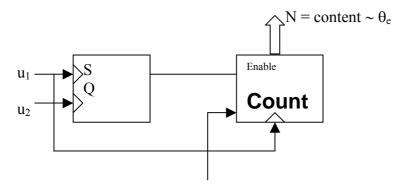

#### 2.9.1.1 Flip-Flop counter phase detector

High Frequency Clock

The reference (input) signal  $u_1$  and the output (or scaled down output) signal  $u_2$  of the DCO (or VCO) are binary valued signals. They are used to set or rest an edge triggered RS flip flop. The time period in which the Q output of the flip flop is a logic 1 is proportional to the phase error  $\theta_e$ . The Q signal is used to gate the high frequency clock signal into the upward counter. Note that the counter is reset on every positive edge of the  $u_1$  signal.

The content N of counter is also proportional to the phase error  $\theta_e$ , where N is n-bit output of this type of phase detector. The frequency of the high frequency clock is usually Mf<sub>0</sub> where f<sub>0</sub> is the frequency of reference signal and M is large positive integer.

#### 2.9.2 DIGITAL LOOP FILTERS

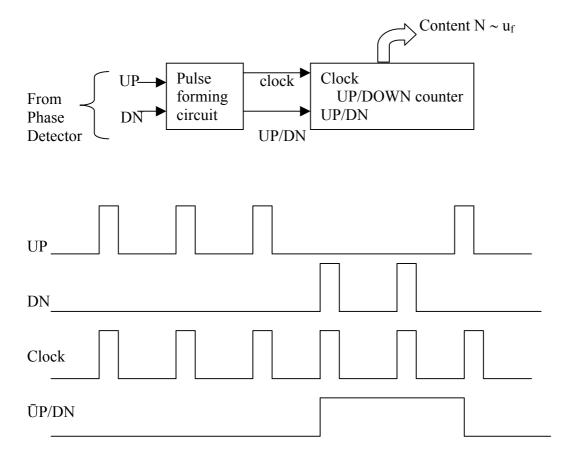

#### 2.9.2.1 UP/DOWN counter filter

Probably the simplest loop filter is built from an ordinary UP/DOWN counter. The UP/DOWN counter loop filter preferably operates in combination with a phase detector delivering UP or DN (DOWN) pulses, such as the PFD. It is easily adapted, however, to operate in conjunction with the XOR or JK flip flop phase detectors and others, as shown in figure. A pulse-forming network is first needed which converts the incoming UP and DN pulses into a counting clock and a direction (ŪP/DN) signal as explained by waveforms in figure.

On each UP pulse generated by the phase detector, the content N of UP/DOWN counter is incremented by 1. A DOWN pulse will decrement N in same manner. The content N is given by the n-bit parallel output signal  $u_f$  of the loop filter. Because the content N is the weighted sum of the UP and DN pulses — the UP pulses have an assigned weight of +1, the DN pulses, -1 — this filter can roughly be considered an integrator having the transfer function

$H(s) = 1/sT_I$

where  $u_1$  is the integrator time constant. This is however, a very crude approximation, since the UP and DN pulses do not carry any information about the actual size of the phase error; they only tell whether the phase of  $u_1$  is leading or lagging  $u_2$ .

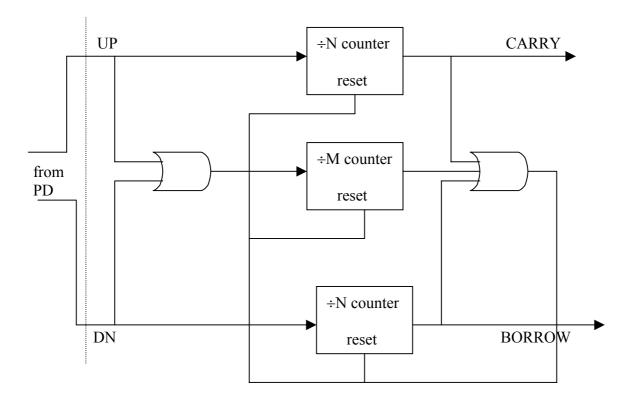

#### 2.9.2.2 N-before-M counter filter

Another digital loop filter is the so called N-before-M counter (shown in figure below). The performance of this filter is very non-linear. It is suggested that N-before-M filter operates in conjunction with a phase detector generating UP and DOWN pulses, as was the case with the PFD. The N-before-M filter uses two frequency counters scaling down the input signal by a factor N and one counter scaling down by M, where M > N always. The  $\div M$  counter counts the incoming UP and DN pulses. The upper  $\div N$  counter will produce one carry output when it has received N UP pulses. But it will generate this CARRY only when the  $\div M$  counter does not receive M pulses. Otherwise the  $\div N$  counter would have been reset. We can say the upper  $\div N$  counter will produce a carry pulse whenever more than N pulses of an ensemble of M pulses have been UP pulses. A similar statement can be made for the lower  $\div N$  counter in figure, which will output BORROW pulses only when the majority of incoming pulses are DN pulses.

The outputs of the N-before-M filter can be used in a similar way to control a DCO, as indicated for the K counter.

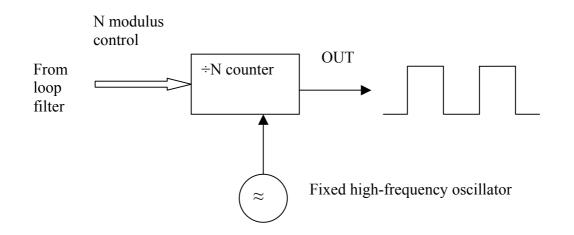

### 2.9.3 DIGITAL CONTROLLED OSCILLATORS

A variety of DCO's can be designed; they can be implemented by hardware or software. Probably the simplest solution is the ÷N counter DCO. A ÷N counter is used to scale down the signal generated by a high frequency oscillator operating at a fixed frequency. The N-bit parallel output signal of a digital loop filter is used to control the scaling factor N of the ÷N counter.

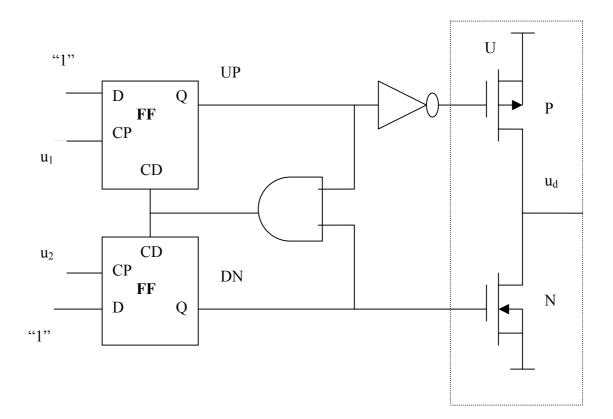

#### 2.9.4 EXAMPLE OF AN IMPLEMENTED ADPLL

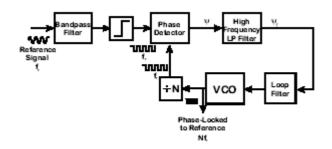

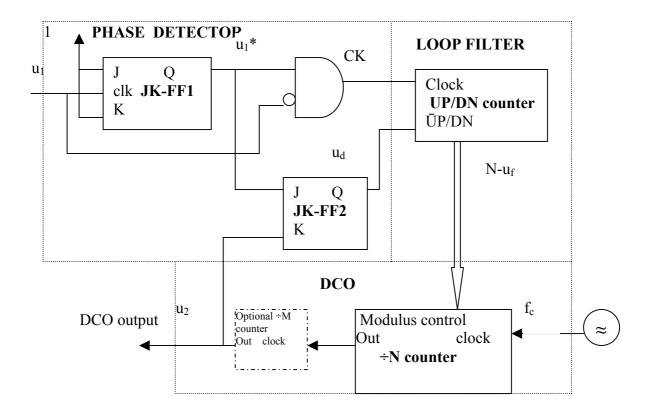

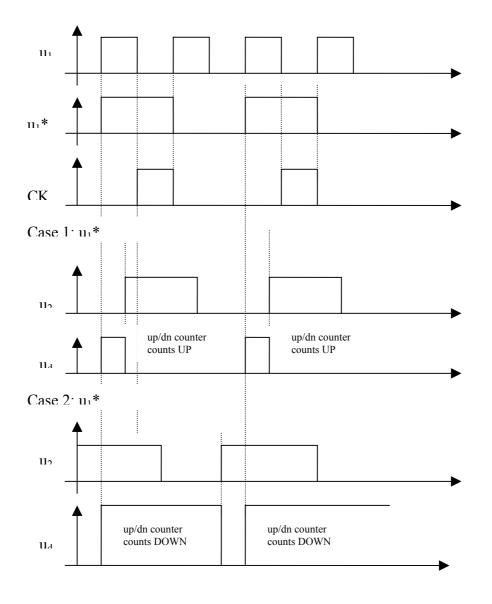

The Example depicted in Figure below, a JK flip-flop (JK-FF2) is used as a phase detector. The Phase detector block has been extended, however, by a pulse forming network consisting of another JK flip flop (JK-FF1) and an AND gate. The loop filter is built from an UP/DOWN counter.  $\div$ N counter is used as DCO. The pulse forming network generates the counting clock (CK) for the UP/DOWN counter.

(a) Block Diagram

The waveforms in figure (b) explain the operating principle of the PD. The JK-FF<sub>1</sub> scales down the input signal  $u_1$  by a factor of 2; the scaled down input signal is designated  $u_1^*$ . The reconstructed signal  $u_2$  has the same frequency as  $u_1^*$  not  $u_1$ . The waveforms in have been drawn for two cases:

- 1.  $u_1^*$  leading  $u_2$

- 2.  $u_1^*$  lagging  $u_2$

(b) Waveforms

The JK-FF2 is an edge-triggered flip-flop. The positive transitions of  $u_1^*$  set this flip flop; the positive transition of  $u_2$  reset it. The counting clock CK for the UP/DOWN counter occurs at a time when the output signal  $u_d$  or JK-FF2 is stable, that is, high when  $u_1^*$  lags  $u_2$  or low when  $u_1^*$  leads  $u_2$ . Consequently the phase-detector output signal  $u_d$  is used as the direction input  $\overline{UP}/DOWN$  for the UP/DOWN counter. If the frequencies of  $u_1^*$  and  $u_2$  are not identical, the UP/DOWN counter will

count upward or downward until N has reached the value that causes  $\div$ N counter to generate the correct output frequency.

Because N can only be varied in steps of 1, the frequency of signal  $u_2$  will normally be slightly too high or too low. This will force the contents of N to jitter continuously around the values of N and N+1 if the reference frequency  $f_1$  is constant. At equilibrium  $f_1$  will be equal to  $f_c/(N-M)$ , where M is the scaling factor of the optional  $\div M$  counter. ADPLL implemented by VHDL ,synthesized and tested on Xilinx FPGA.

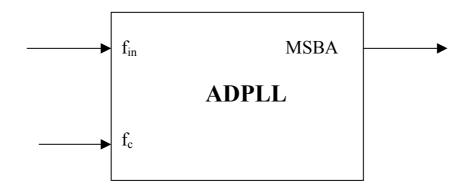

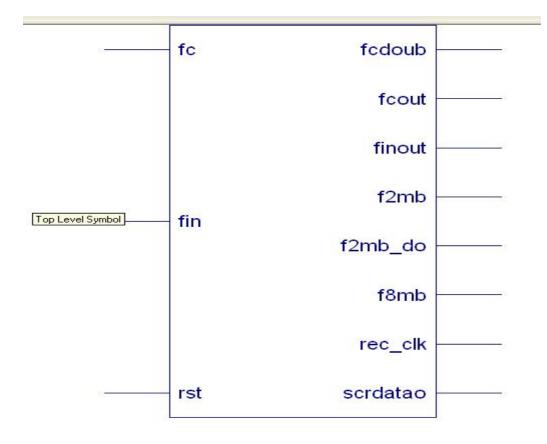

### **3.1 BLOCK DIAGRAM**

### **ADPLL**:

This is the symbol of ADPLL synthesized on xilinx FPGA and tested on PCB.

$f_{\text{in}}\,$  is the input reference signal and MSBA is output clock signal locked to input.

f<sub>c</sub> is standard high frequency clock from any independent clock source.

The ADPLL comprises of following components:

- Sampling Phase detector

- Loop filter and DCO control unit

- DCO circuit

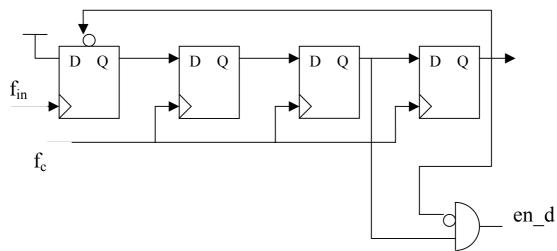

## 3.2 SAMPLING PHASE DETECTOR

This is the logical diagram of 'Sampling Phase Detector' . In this case input reference fin

is sampled by a high frequency (32 or 64 times)  $f_c$ . It produces a pulse whenever a positve edge of input reference is sensed.

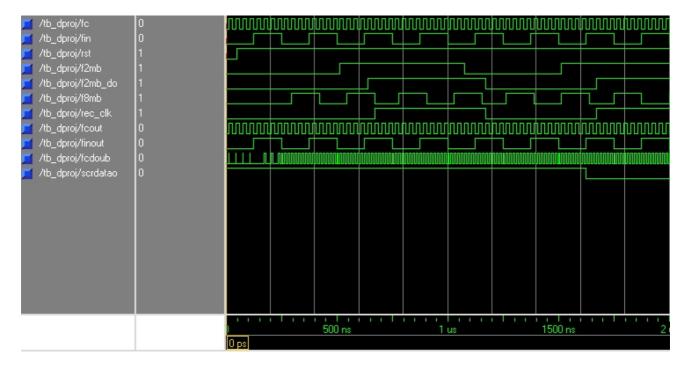

The circuit was implemented by VHDL and simulated on Altera's MaxPlus-II tool for various conditions i.e., when  $f_c$  is leading  $f_{in}$  or when  $f_c$  is lagging  $f_{in}$  or when  $f_c$  is in phase with  $f_{in}$  etc.

Following is the VHDL code and simulation results for various cases. An output pulse is generated on every positive edge of  $f_{in}$ .

```

library IEEE;

use IEEE.std_logic_1164.all;

-- use IEEE.std_logic_misc.all ;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity adpll is

port(

fc : in std_logic;

fin : in std_logic;

rst : in std_logic;

en_d : out std_logic

);

end adpll;

architecture RTL of adpll is

signal flout : std_logic;

signal f2out : std_logic;

signal f3out

: std logic;

: std logic;

signal en

begin

process(en, rst, fin)

begin

if (rst='0' or en='1') then

flout <= '0';

elsif fin'event and fin = '1' then

flout <= '1';

end if;

end process;

process(flout, f2out, f3out, fc, rst)

begin

if rst = '0' then

f2out <= '0'; f3out <= '0'; en <= '0';

elsif fc'event and fc = '1' then

f2out <= f1out ; f3out <= f2out ; en <= f3out ;</pre>

end if;

end process;

en_d <= f3out and (not en);</pre>

end RTL;

```

#### PHASE DETECTOR SIMULATIONS :

| mAX+plus II - e:\users                               | s\pkumar\proj\ad                      | pll - [adpll1.scf - Wavef | orm Editor] |         |       | _ 8 ×      |

|------------------------------------------------------|---------------------------------------|---------------------------|-------------|---------|-------|------------|

| Karata <u>M</u> AX+plus II <u>F</u> ile <u>E</u> dit | <u>⊻</u> iew <u>N</u> ode <u>A</u> ss |                           |             |         |       | <u>_8×</u> |

|                                                      |                                       | 🛆 🗟 🖻 🖻 🥭                 |             |         |       |            |

| Ref. 0.0ns                                           | + +                                   | Time: 2.036us             | Interval:   | 2.036us |       | *          |

| A<br>∋ Name:                                         | 1                                     |                           |             |         |       |            |

| 🔆 Name:                                              | Value:                                | 500.0ns                   | 1.0us       | 1.5us   | 2.0us | 2.5us      |

| rst                                                  | T 1 ]                                 |                           |             |         |       |            |

| 🗊 – fin                                              | 1                                     |                           |             |         |       |            |

| fc                                                   |                                       |                           |             |         |       |            |

| Q en_d                                               | 0                                     |                           |             |         |       |            |

|                                                      |                                       |                           |             |         |       |            |

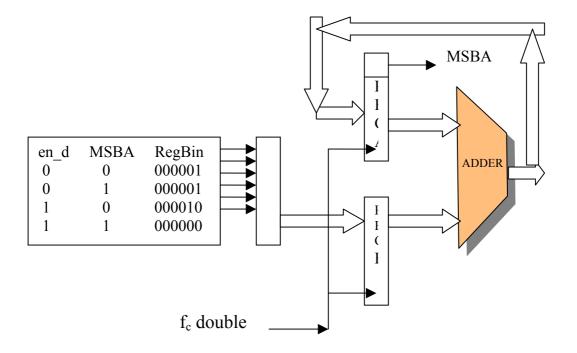

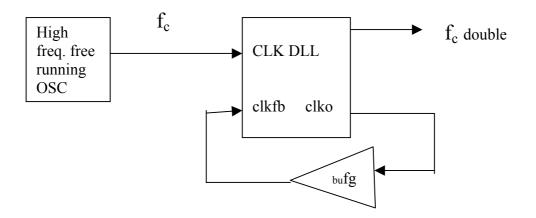

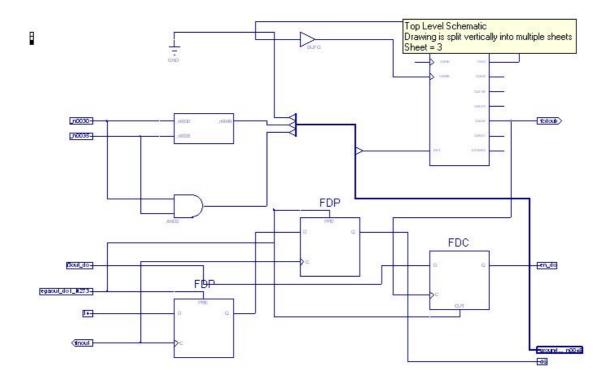

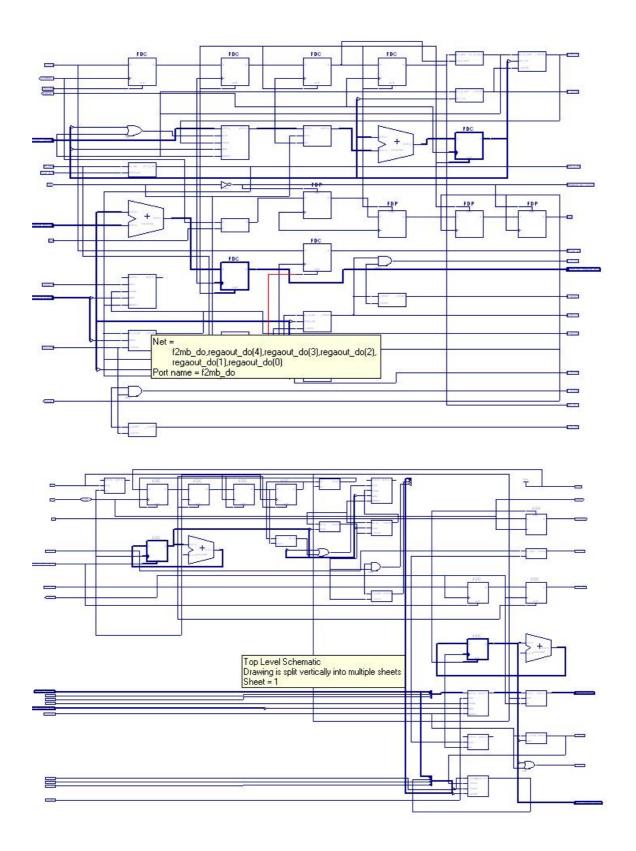

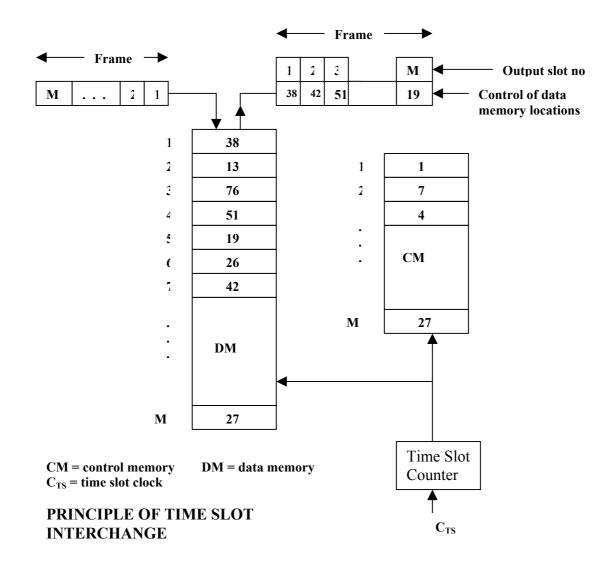

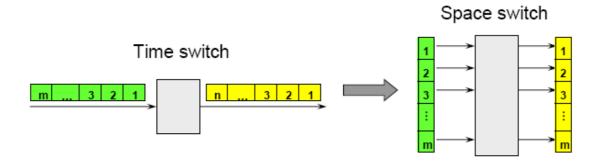

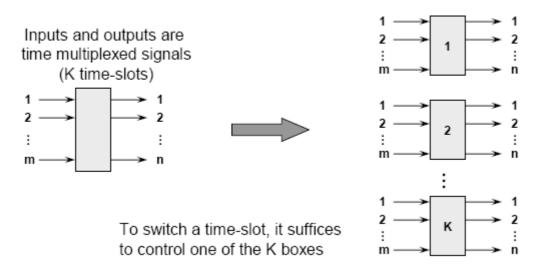

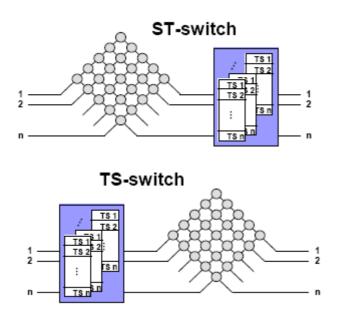

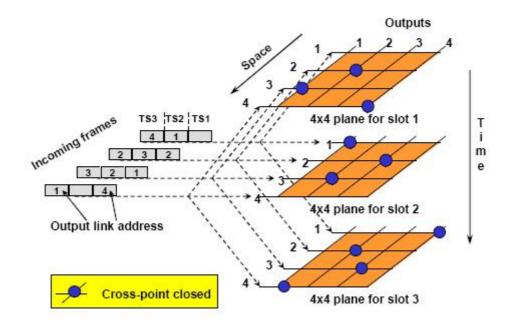

|                                                      |                                       |                           |             |         |       |            |